Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

48results about How to "High impurity concentration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

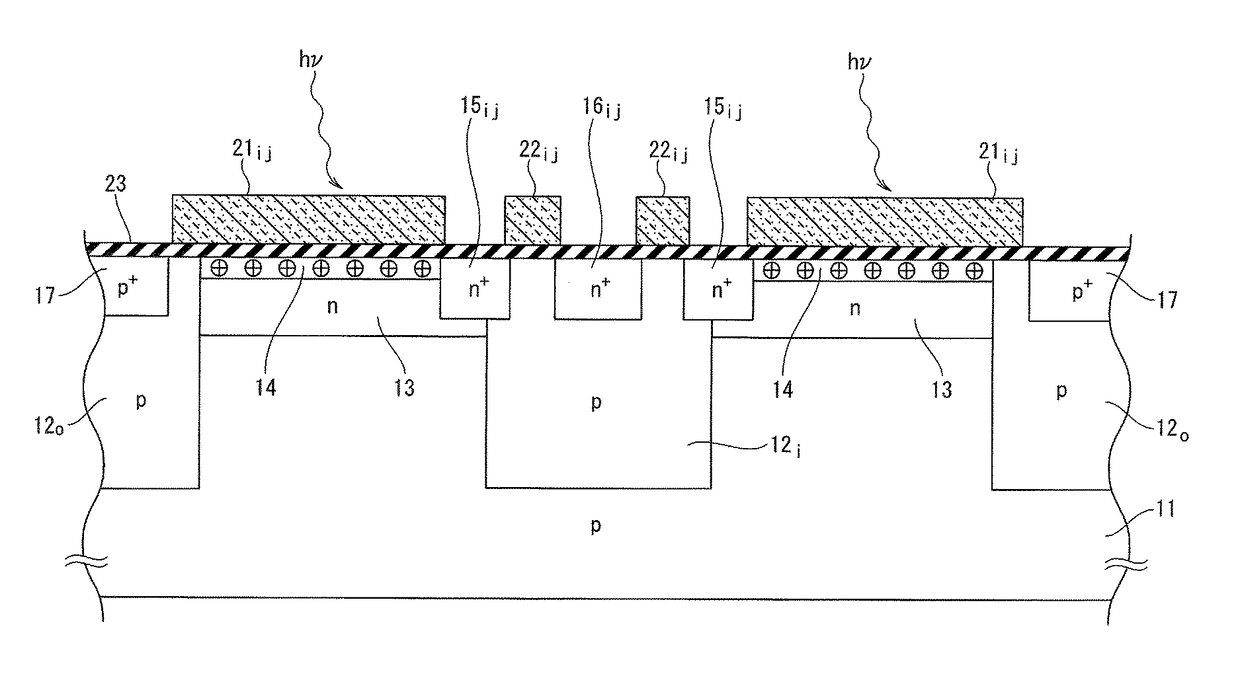

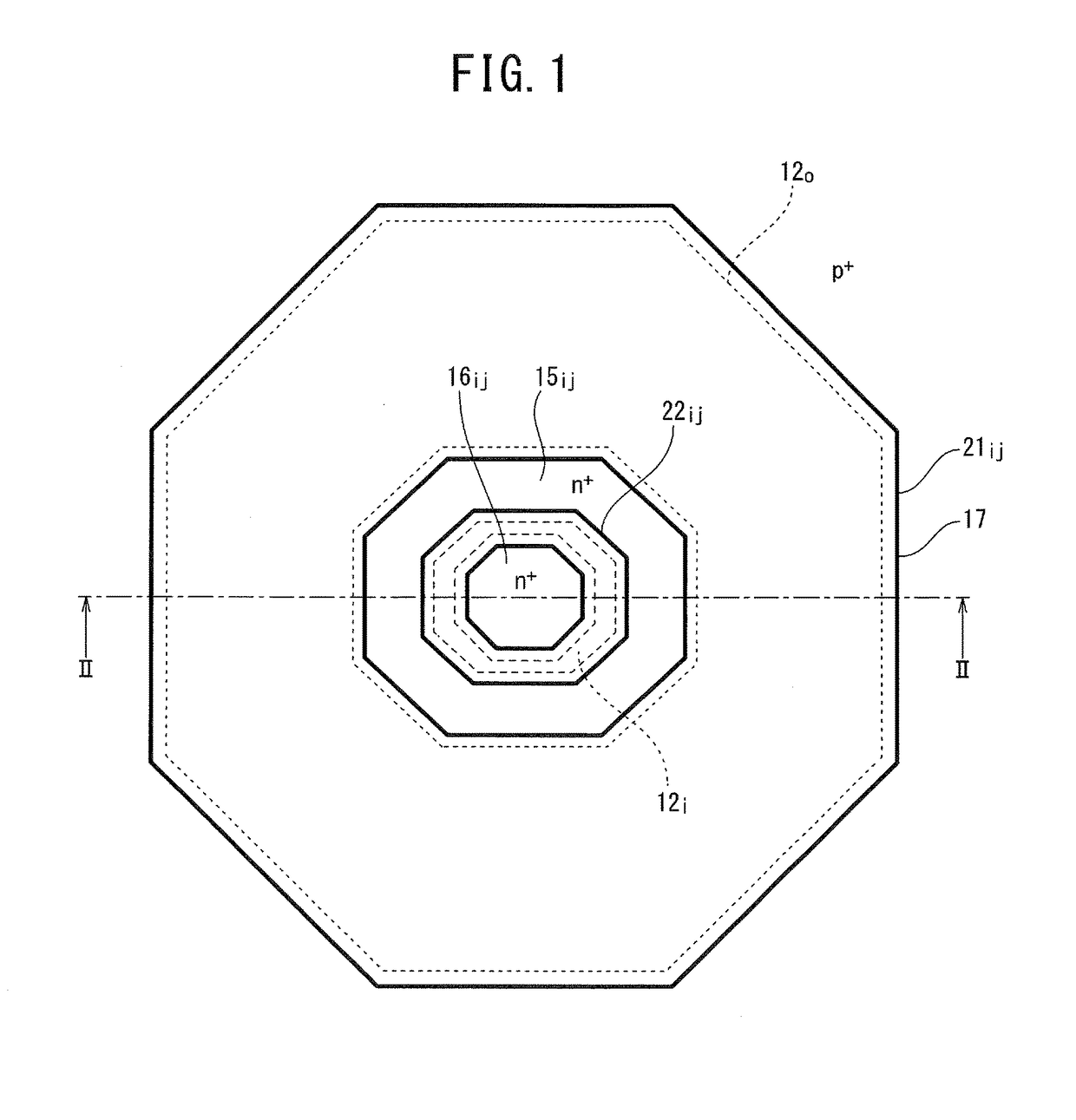

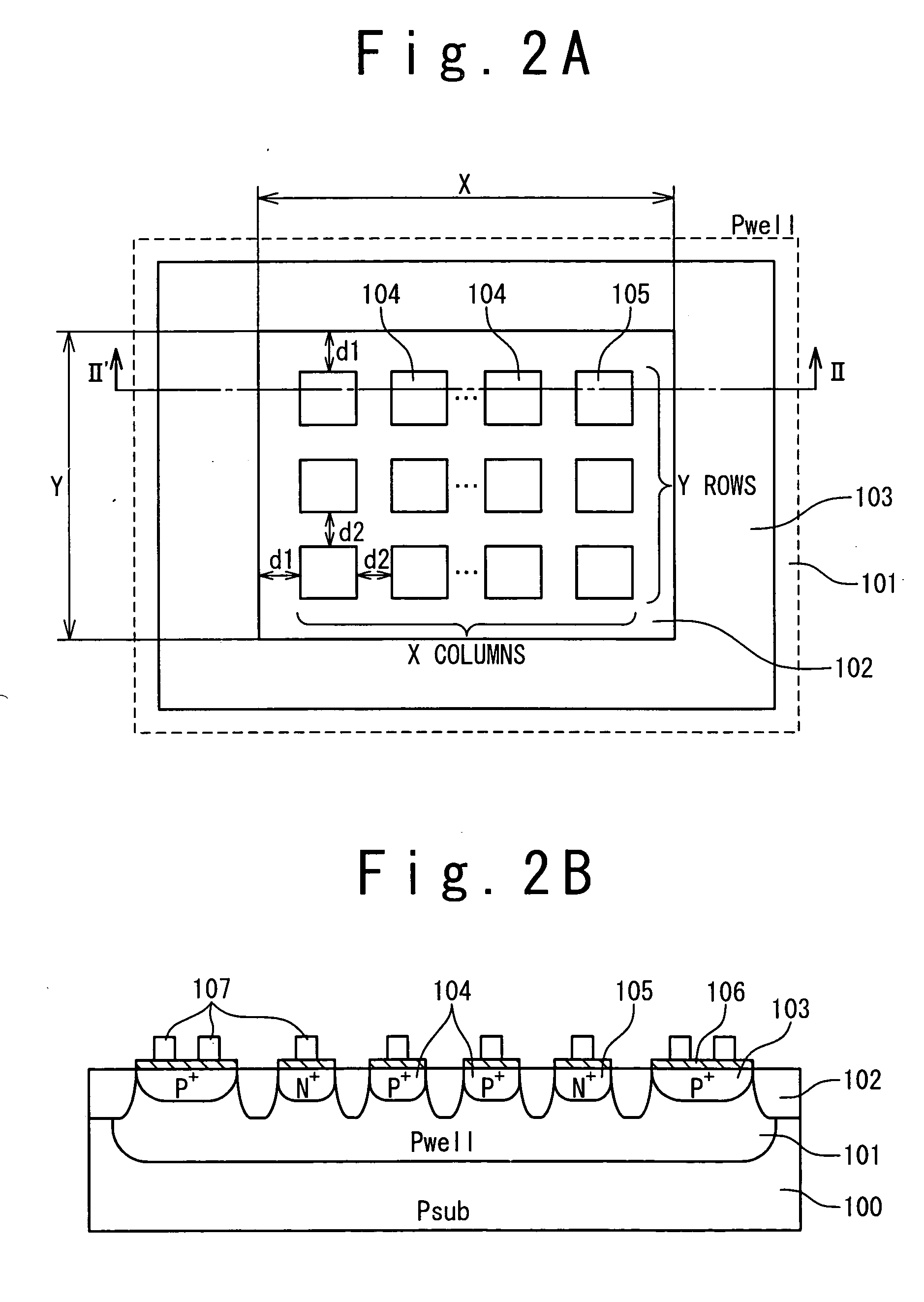

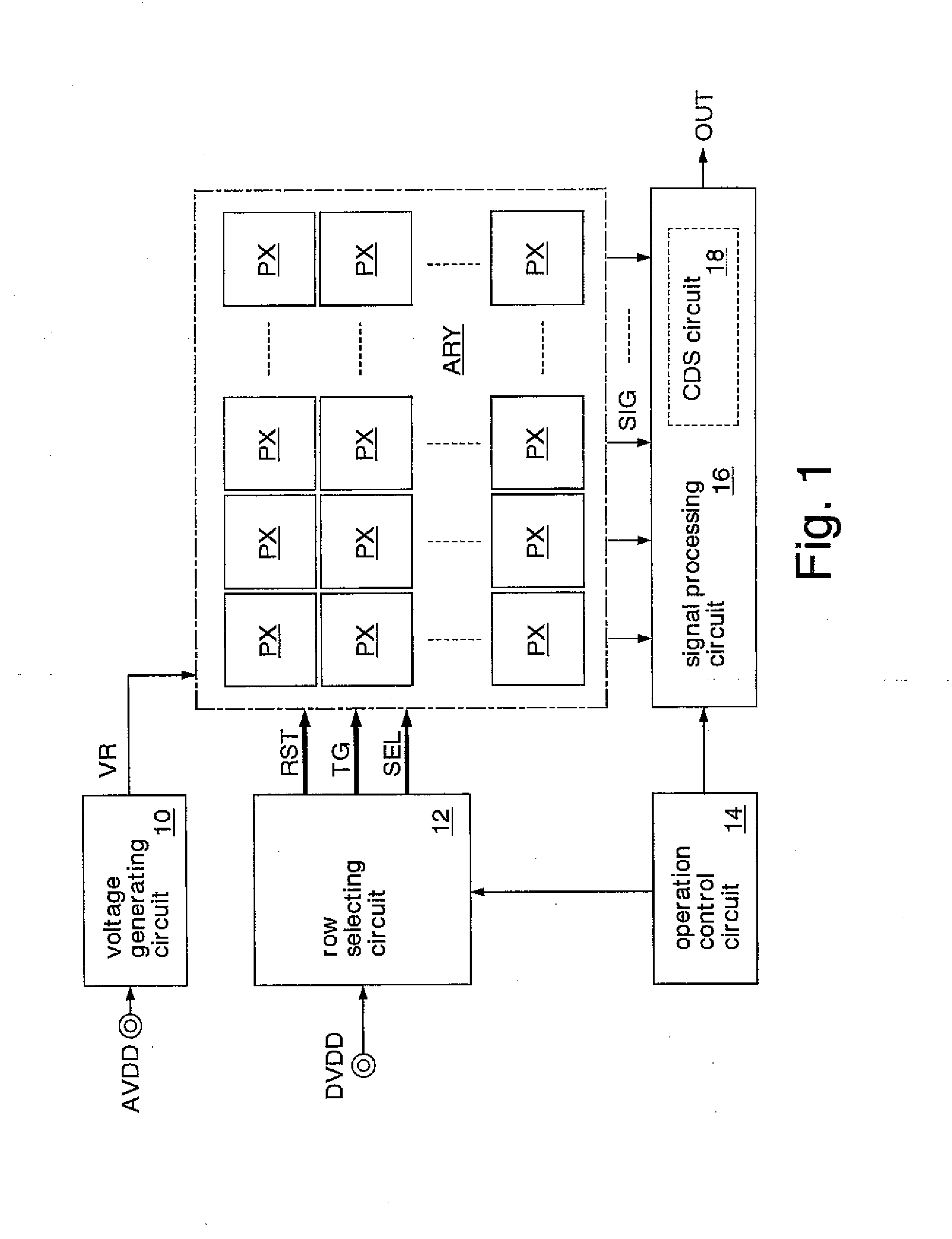

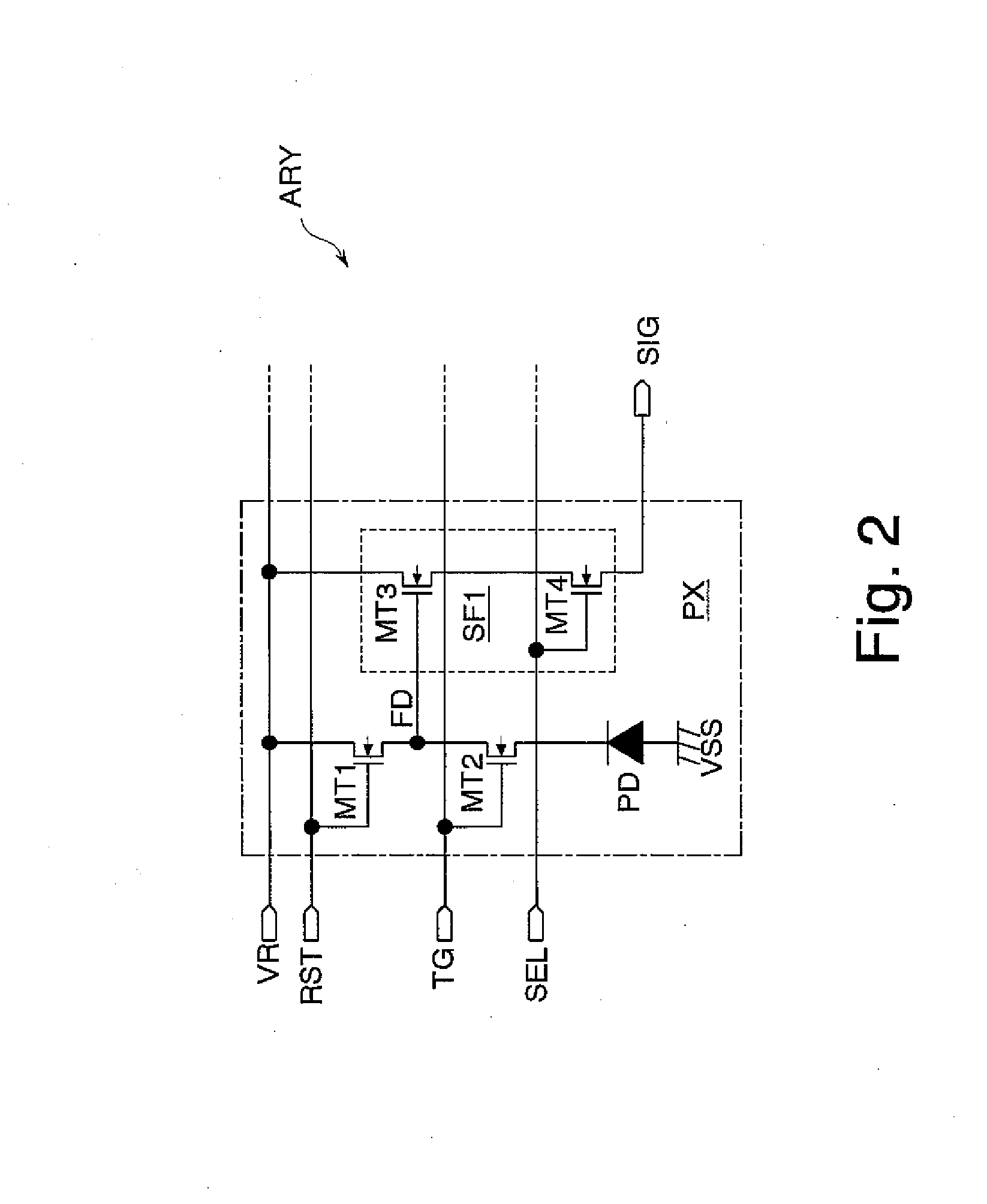

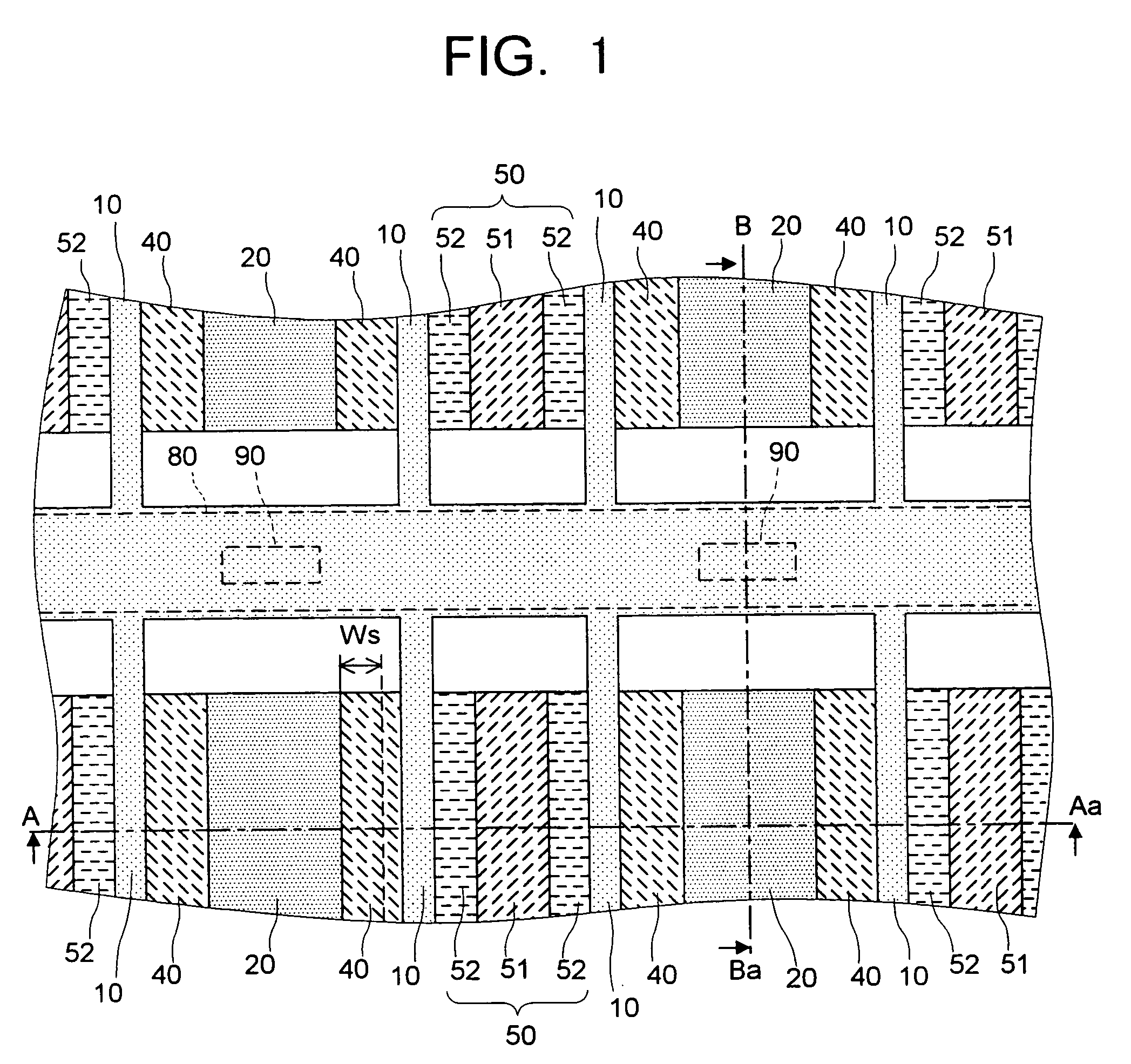

Image pickup device

InactiveUS20050269604A1High impurity concentrationSolid-state devicesRadiation controlled devicesEngineeringPhotoelectric conversion

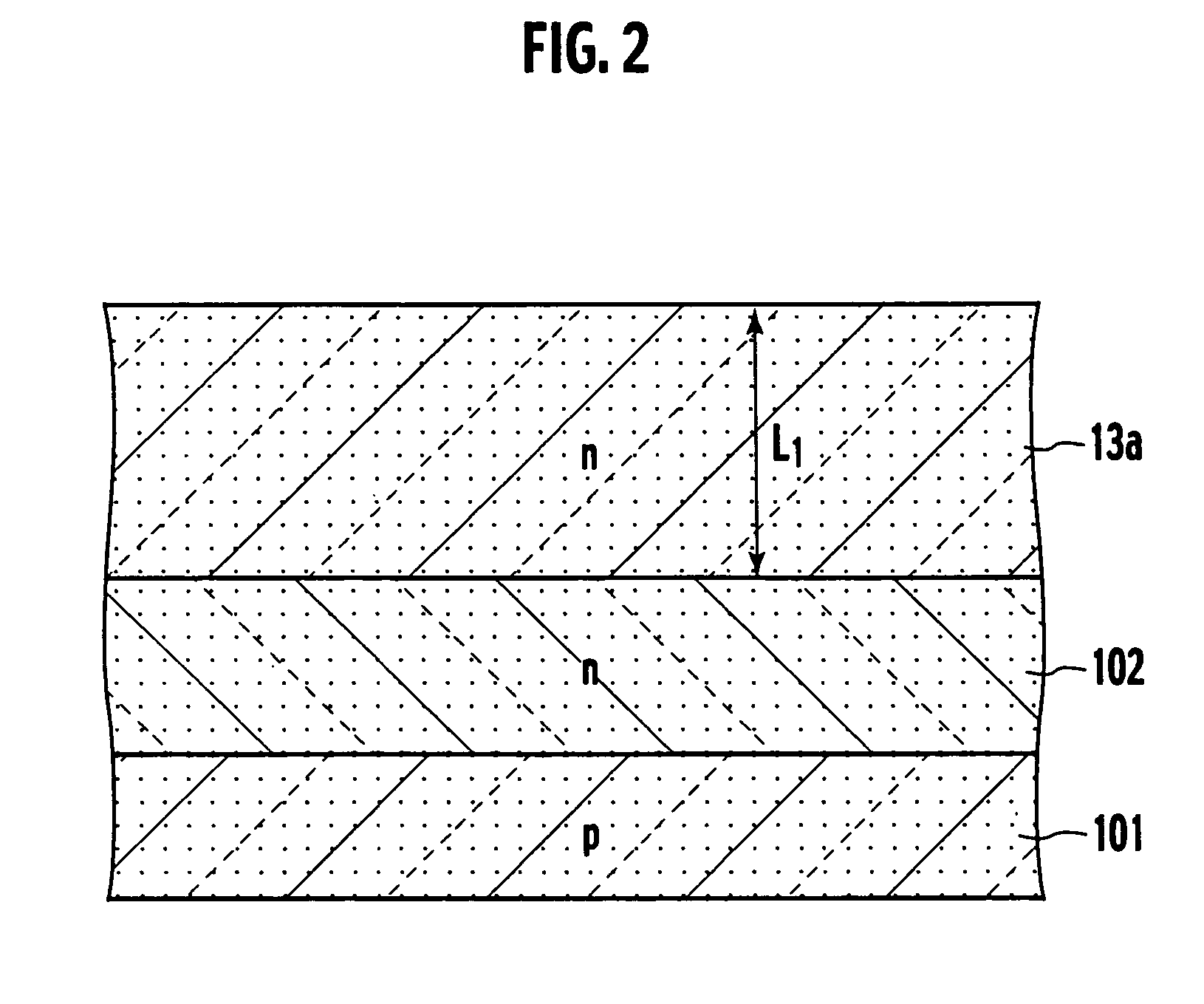

The present invention uses an image pickup device comprising a plurality of pixels respectively including a photoelectric conversion unit for converting incoming light into a signal charge, an amplifying unit for amplifying the signal charge generated by the photoelectric conversion unit and a transfer unit for transferring the signal charge from the photoelectric conversion unit to the amplifying unit, in which the photoelectric conversion unit is formed of a first-conductivity-type first semiconductor region and a second-conductivity-type second semiconductor region and a second-conductivity-type third semiconductor region is formed on at least a part of the gap between a photoelectric conversion unit of a first pixel and a photoelectric conversion unit of a second pixel adjacent to the first pixel, a first-conductivity-type fourth semiconductor region having an impurity concentration higher than that of the first semiconductor region is formed between the photoelectric conversion unit and the third semiconductor region and a first-conductivity-type fifth semiconductor region formed at a position deeper than the fourth semiconductor region and having an impurity concentration higher than that of the first semiconductor region is included between the photoelectric conversion unit and the third semiconductor region.

Owner:CANON KK

Semiconductor device

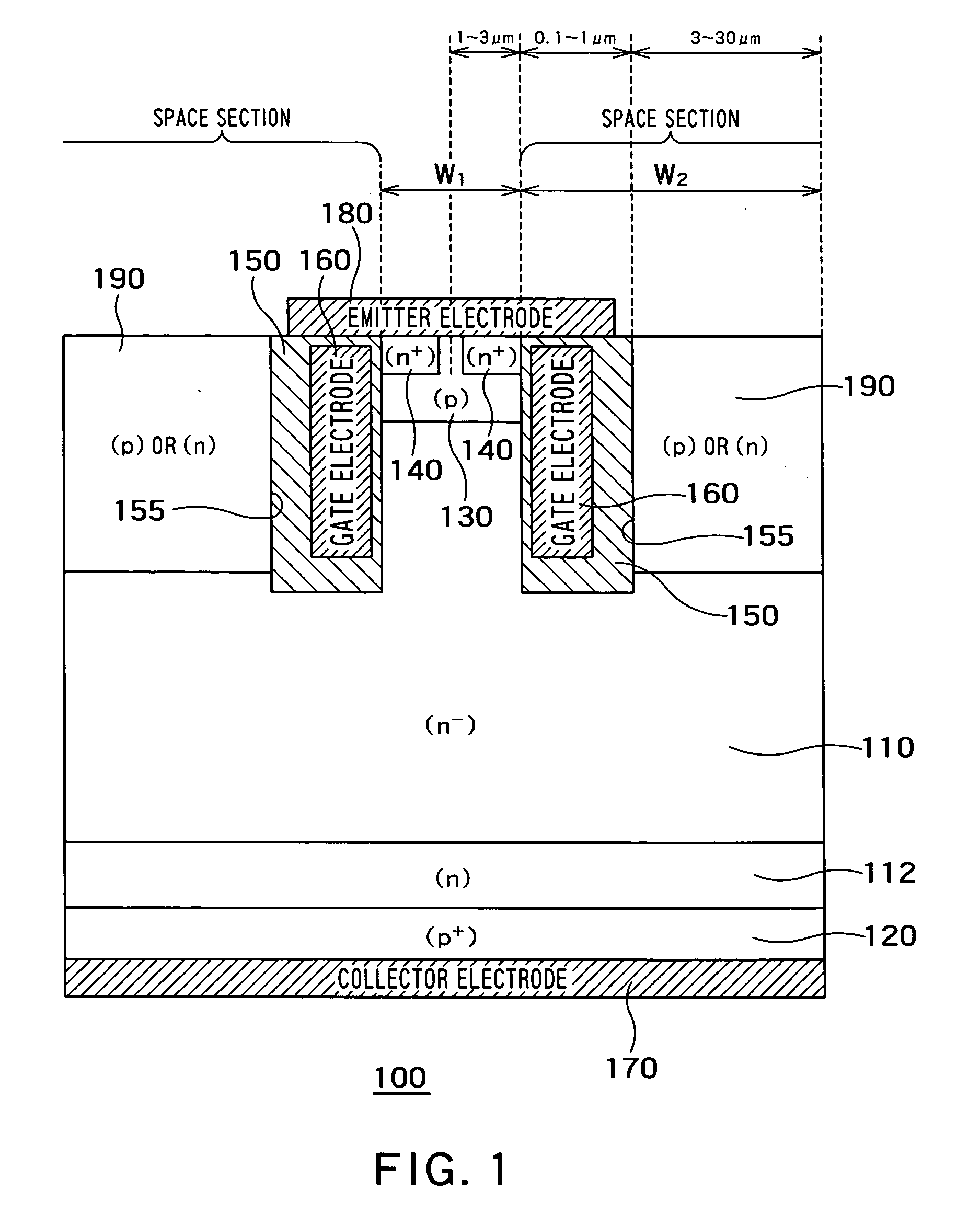

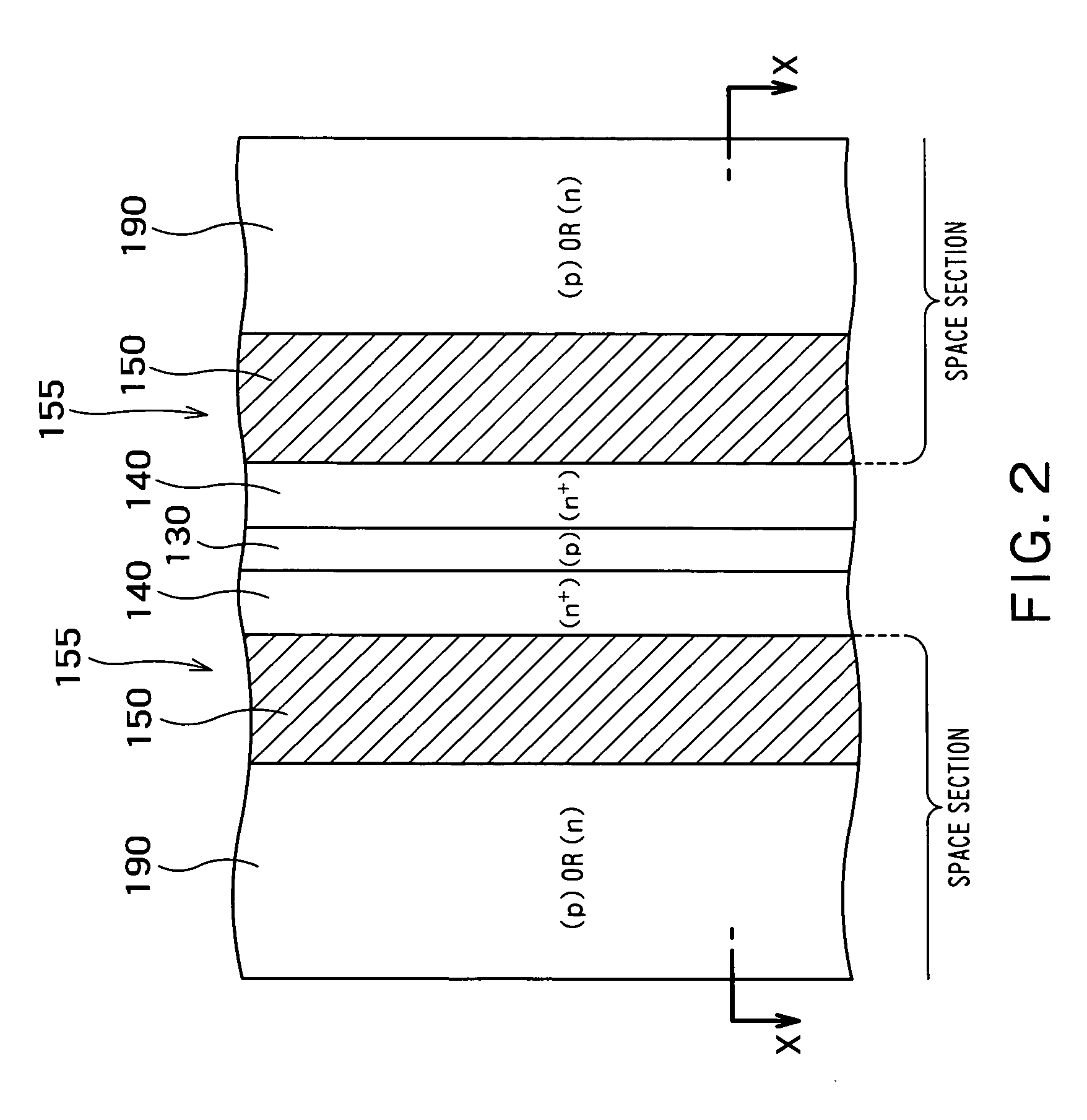

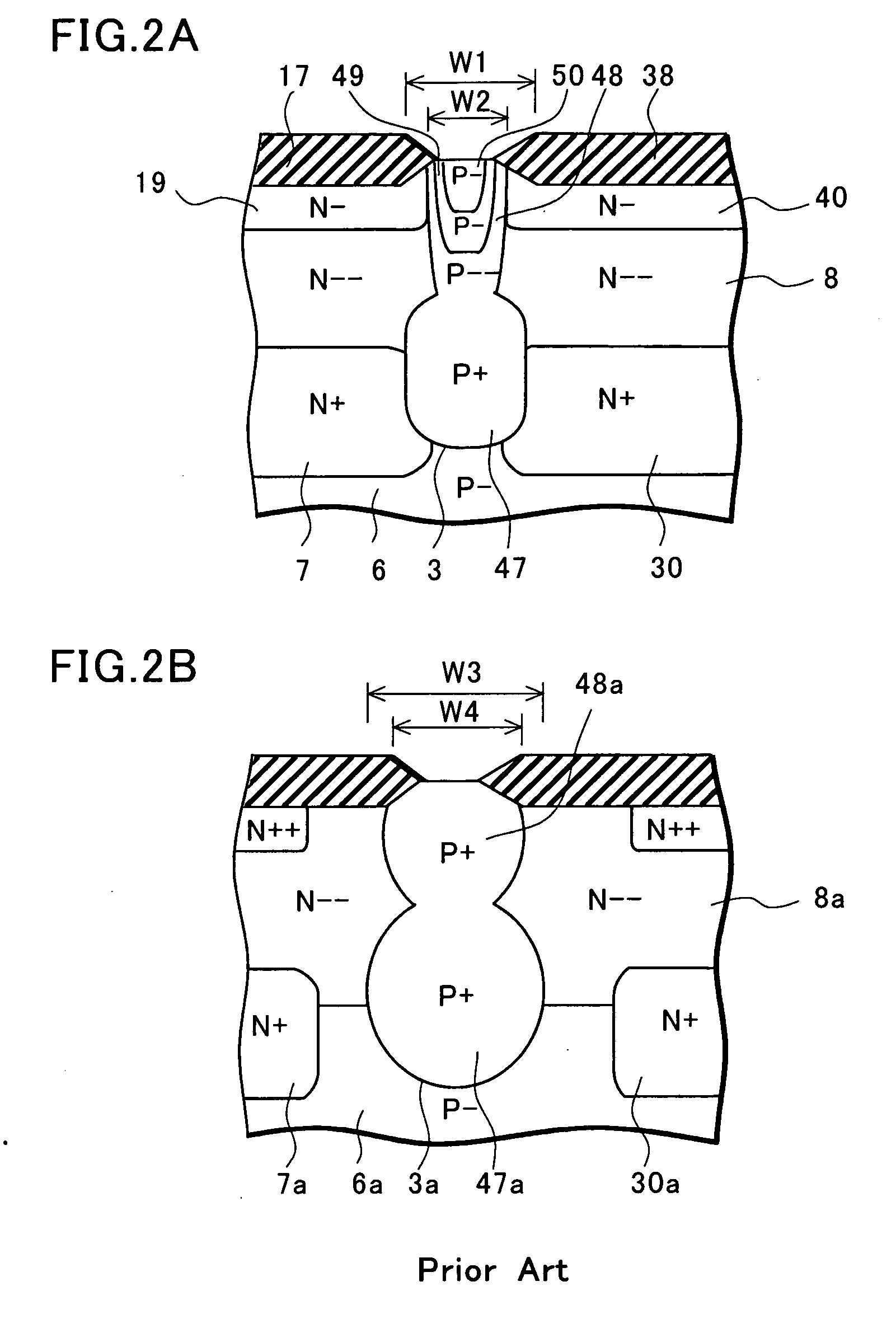

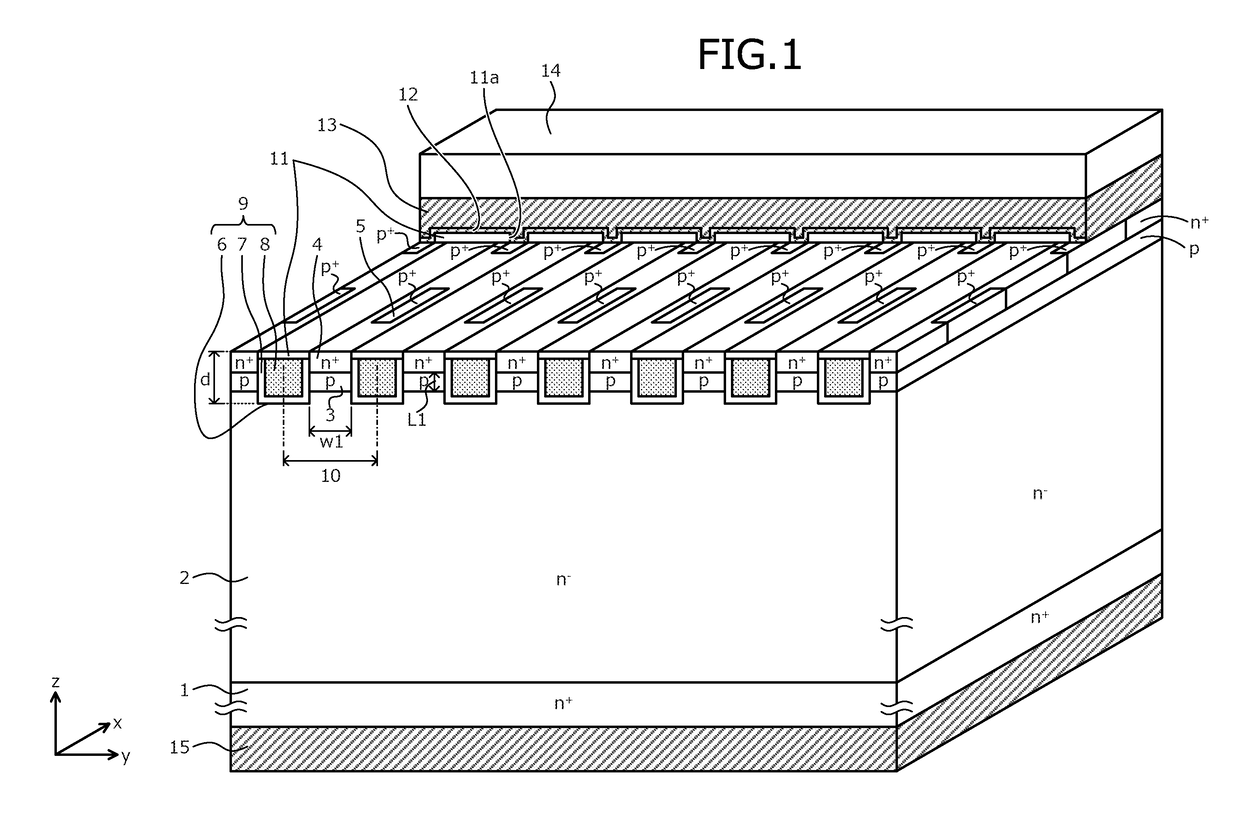

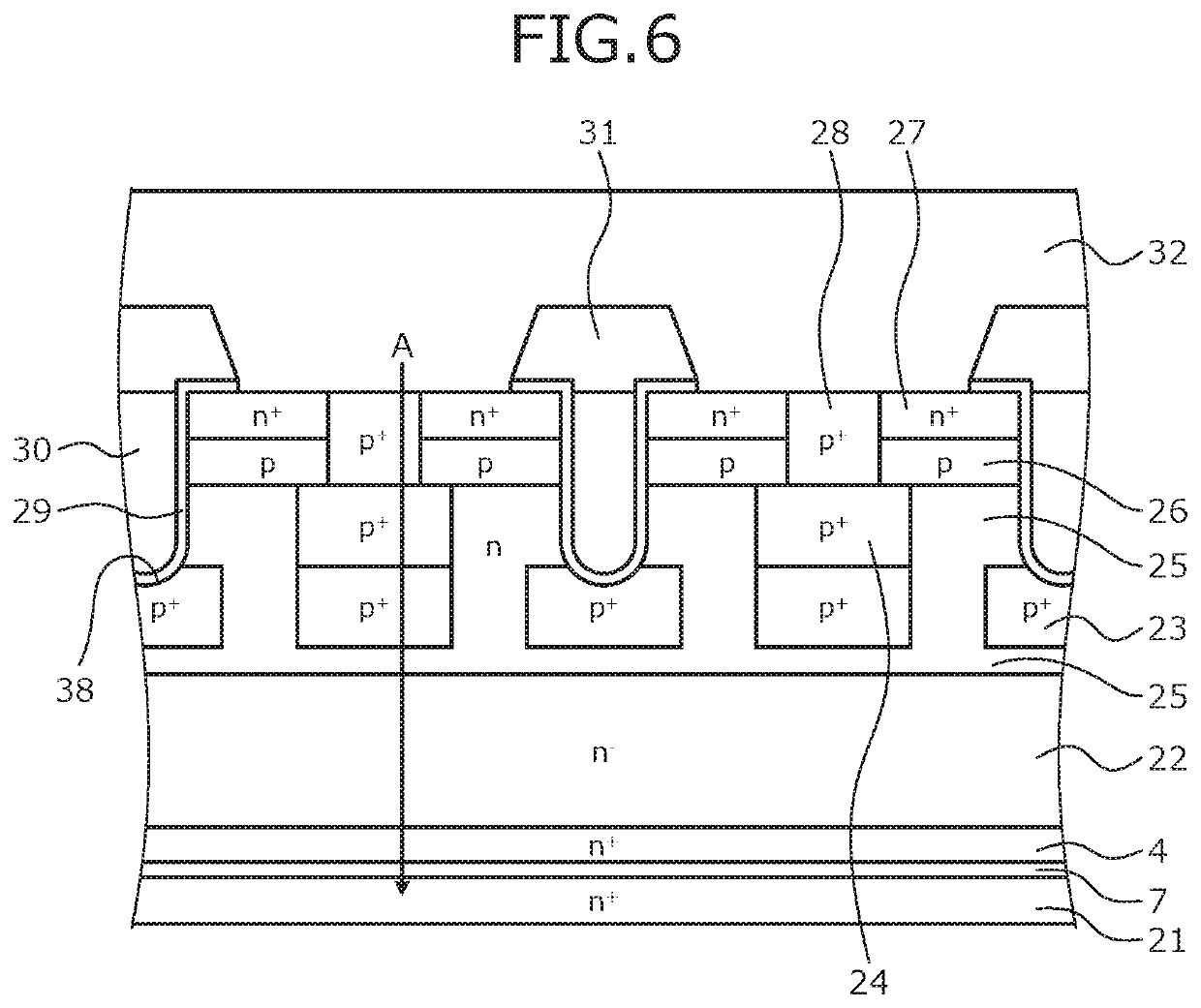

ActiveUS20050263852A1High impurity concentrationTransistorSolid-state devicesDevice materialSemiconductor

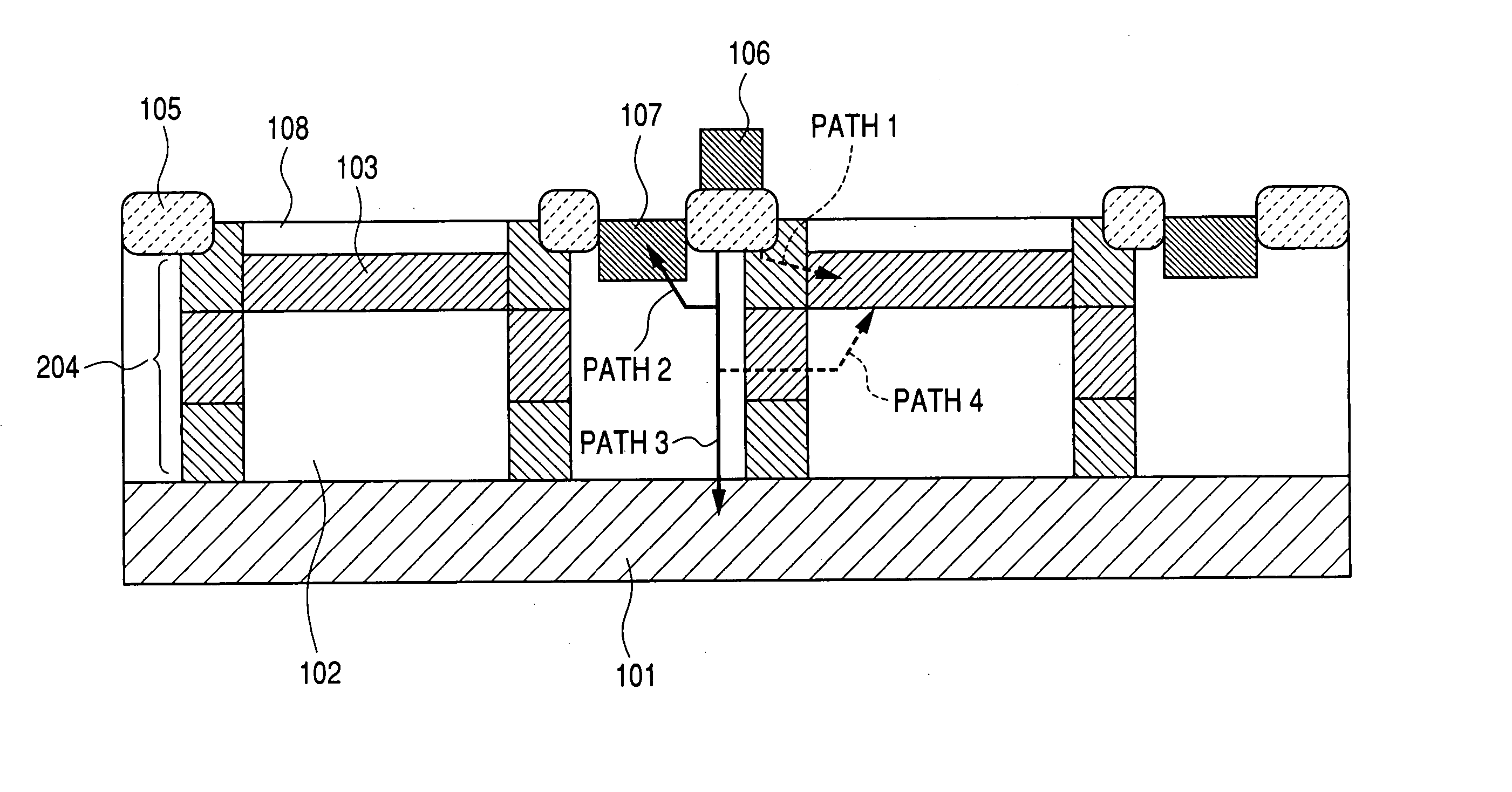

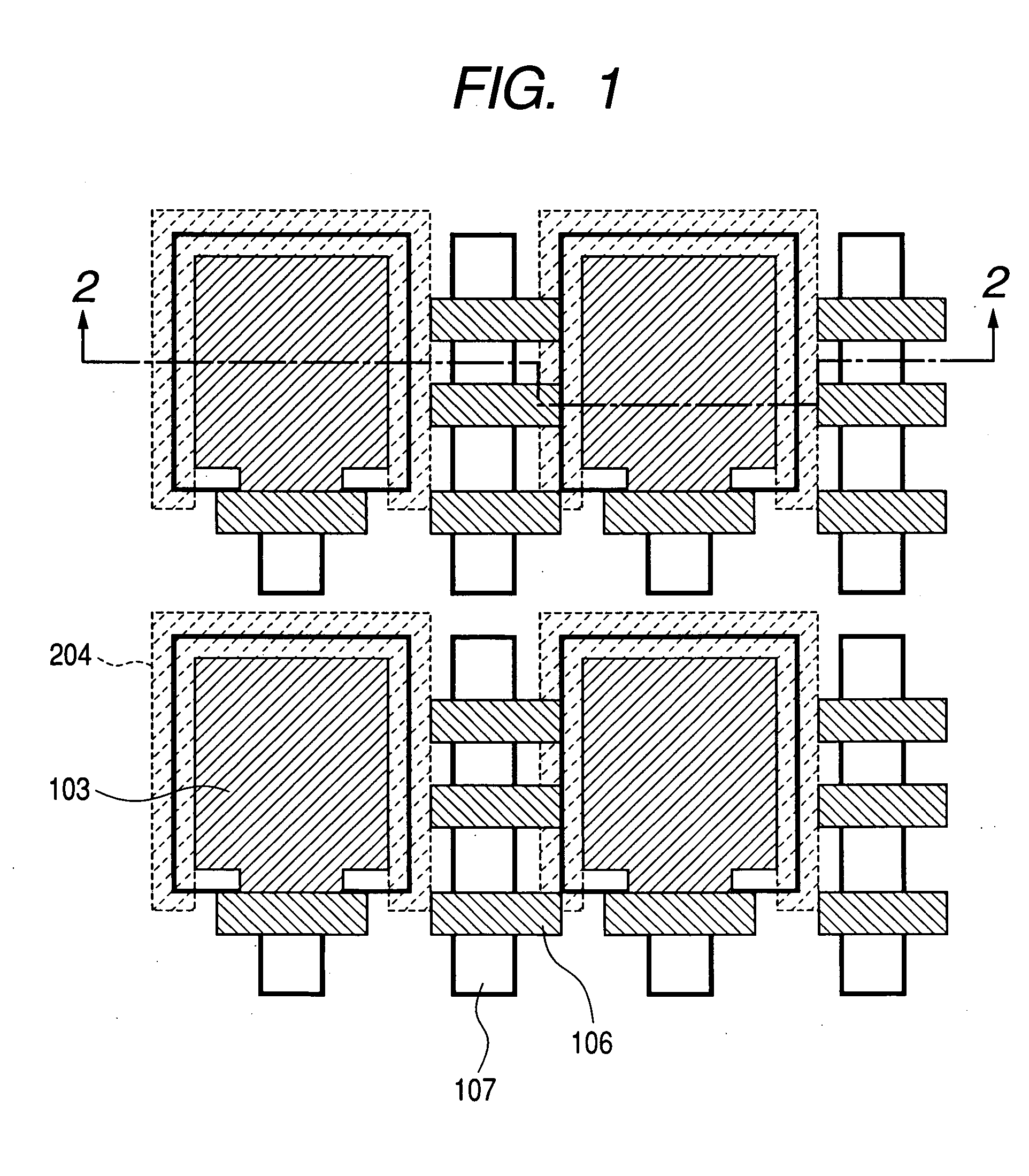

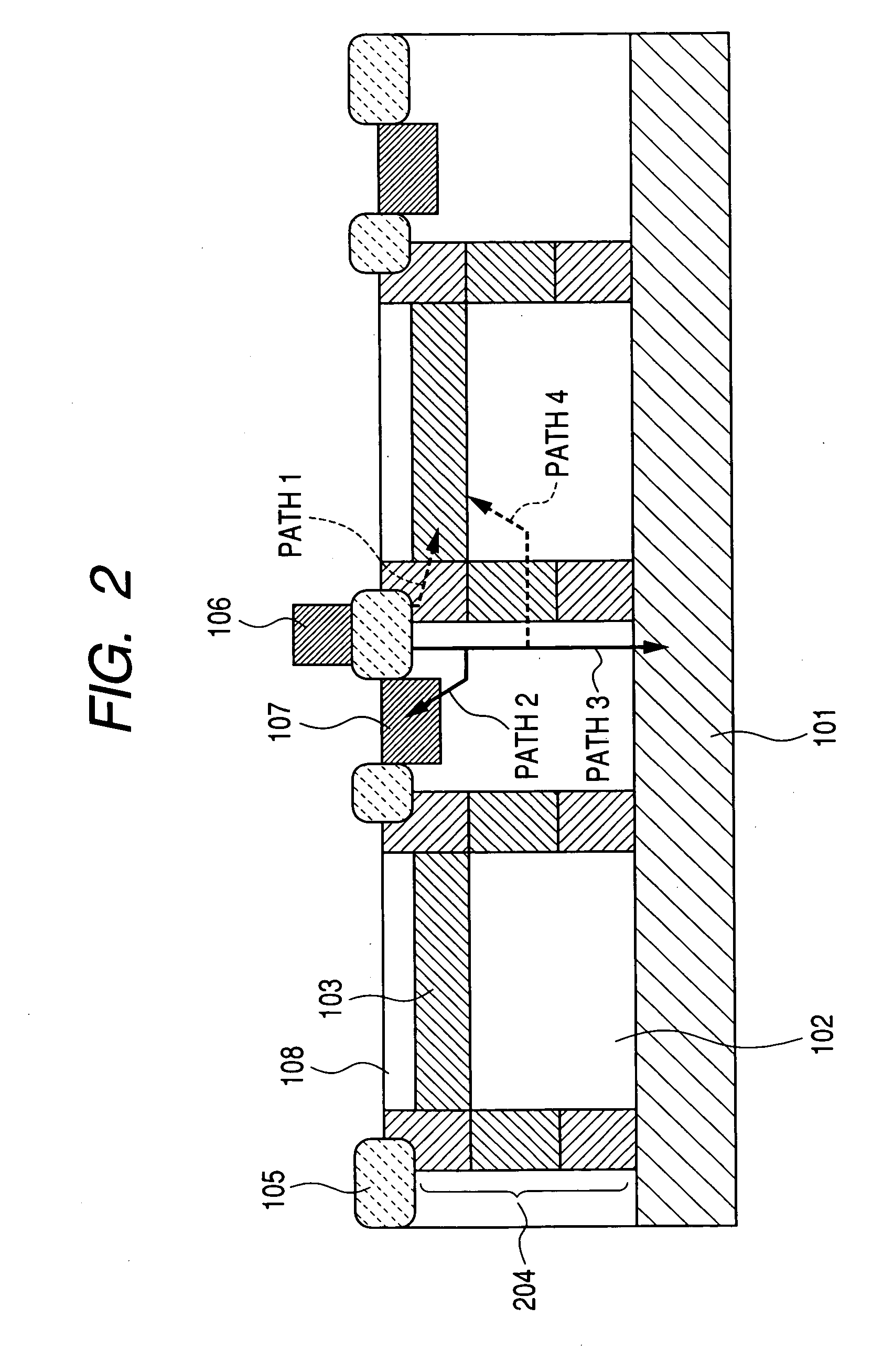

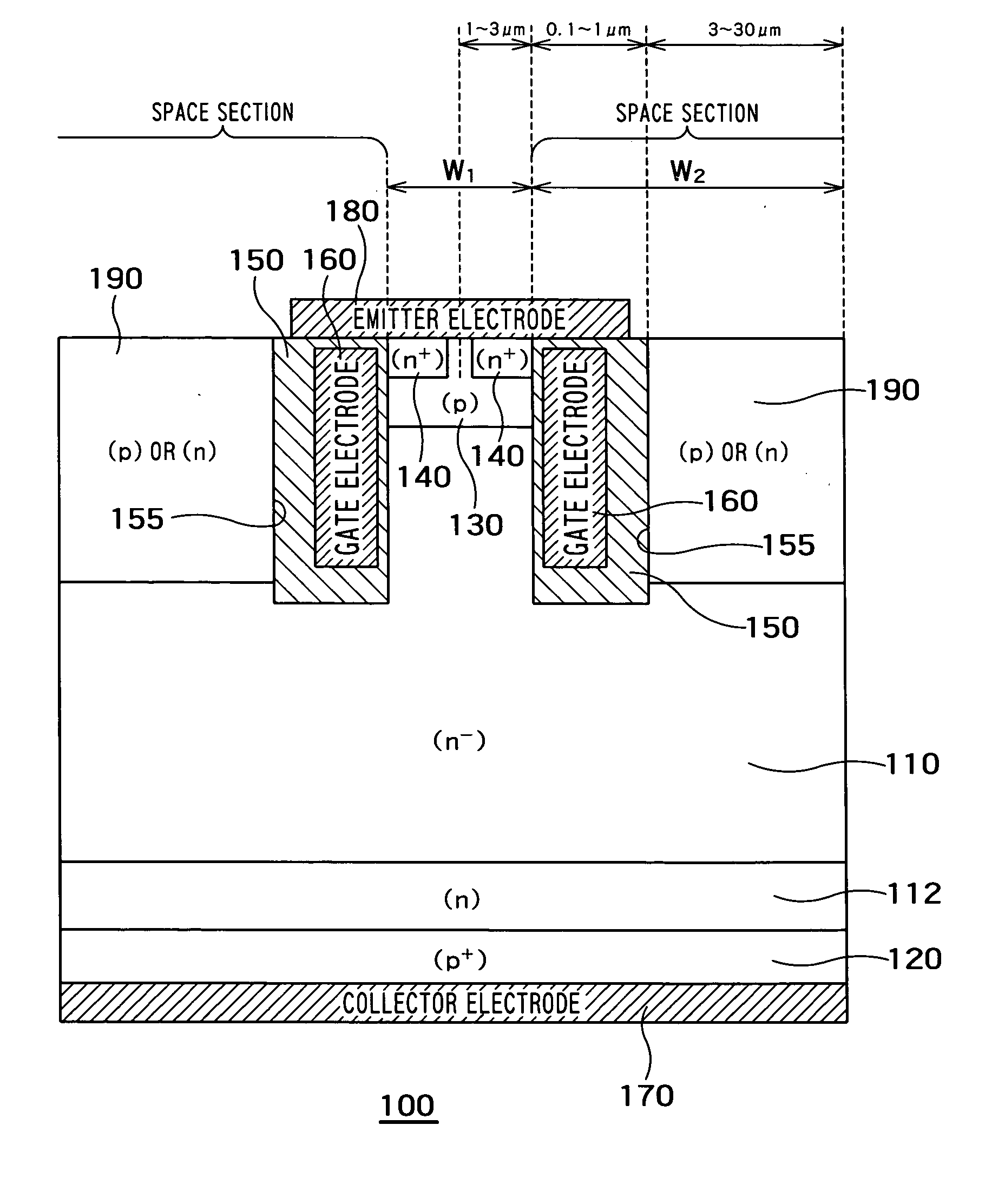

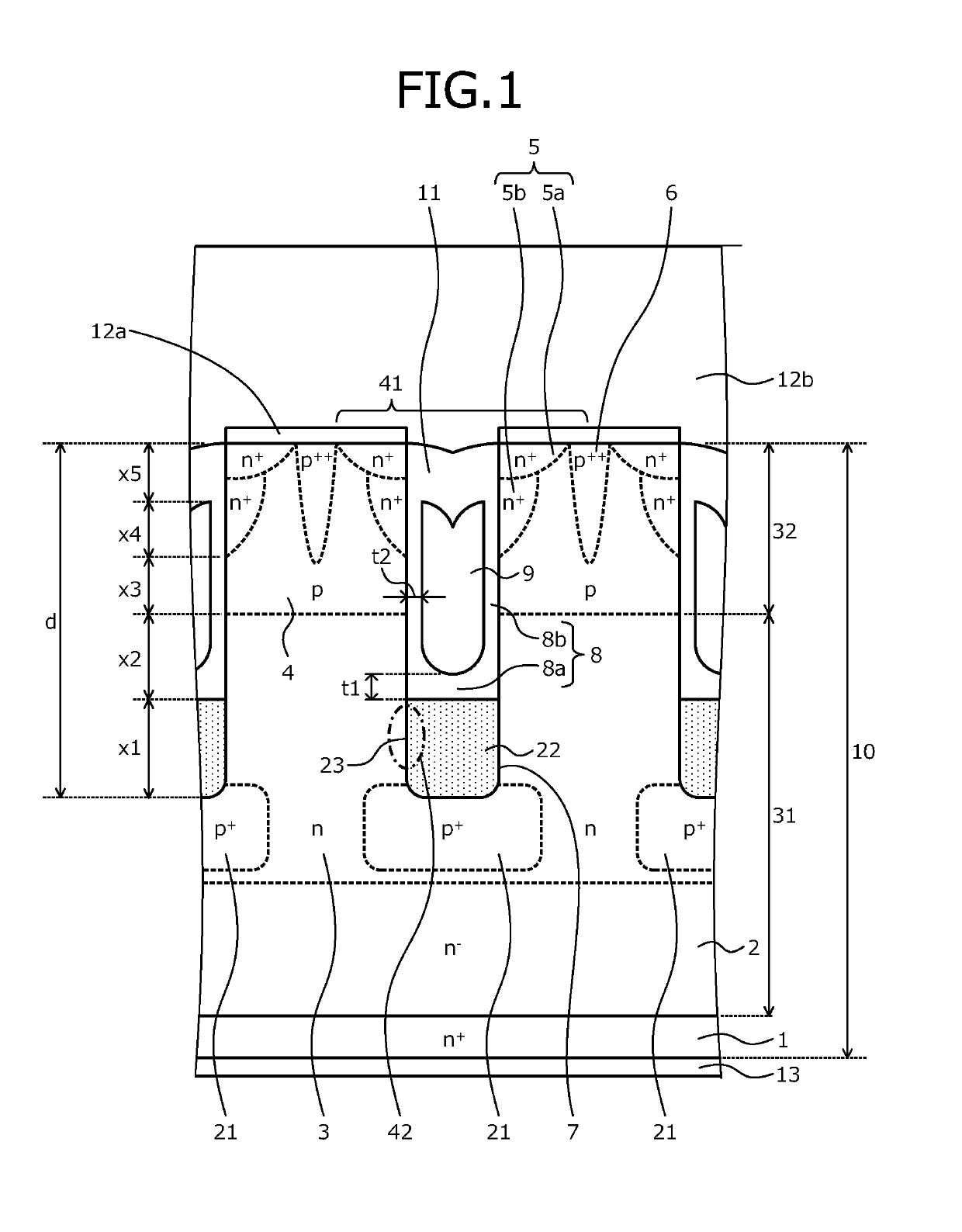

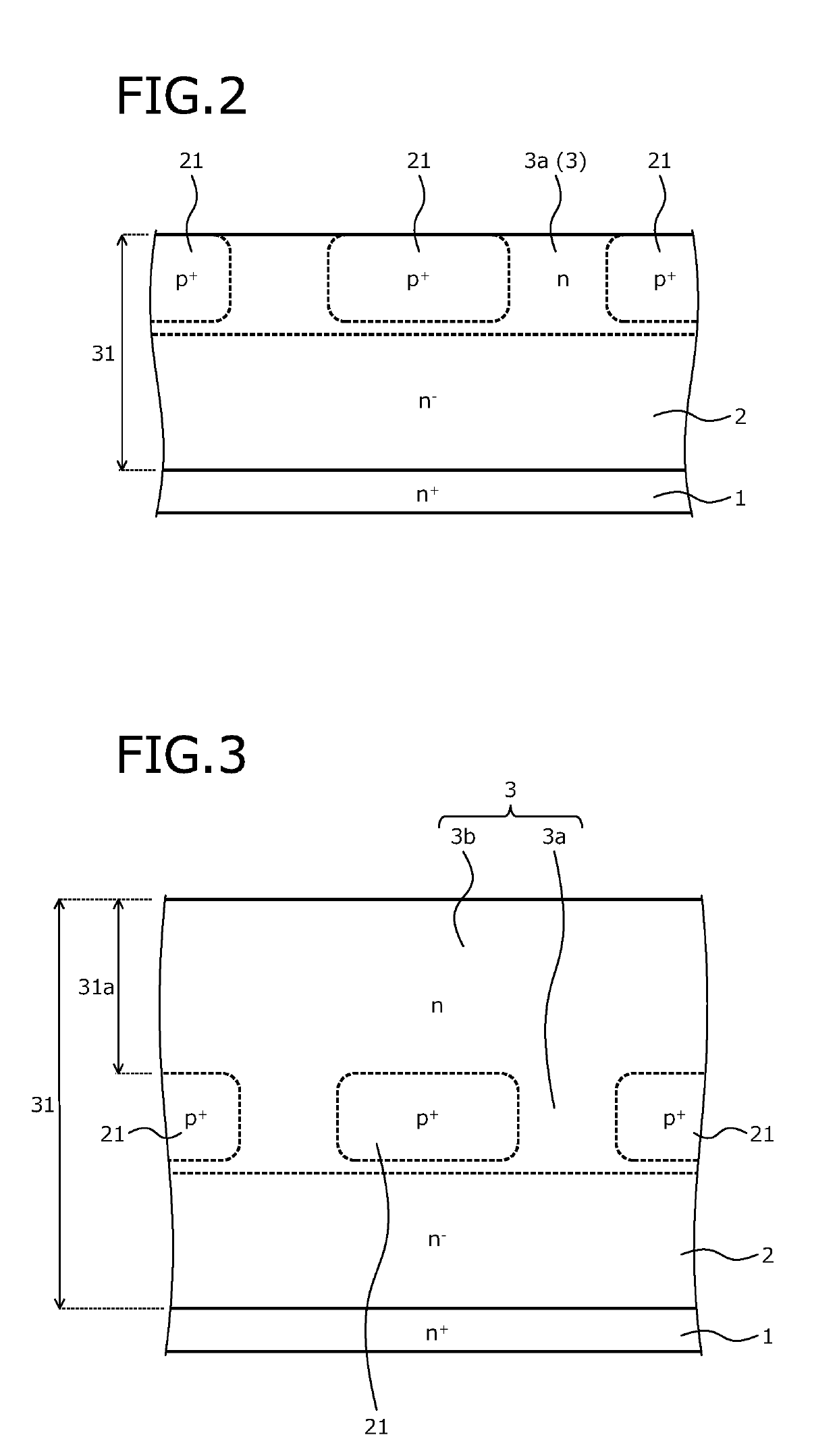

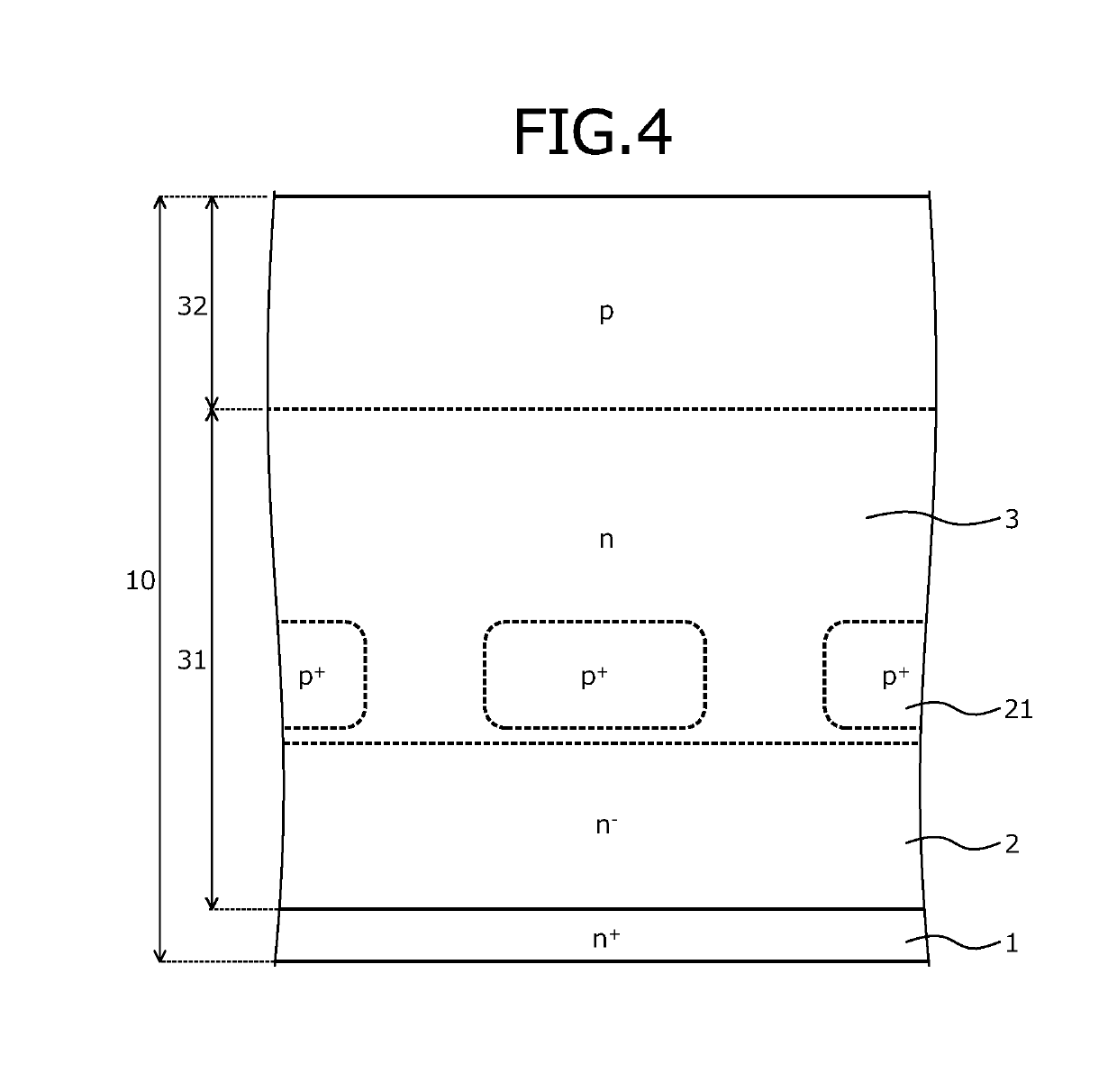

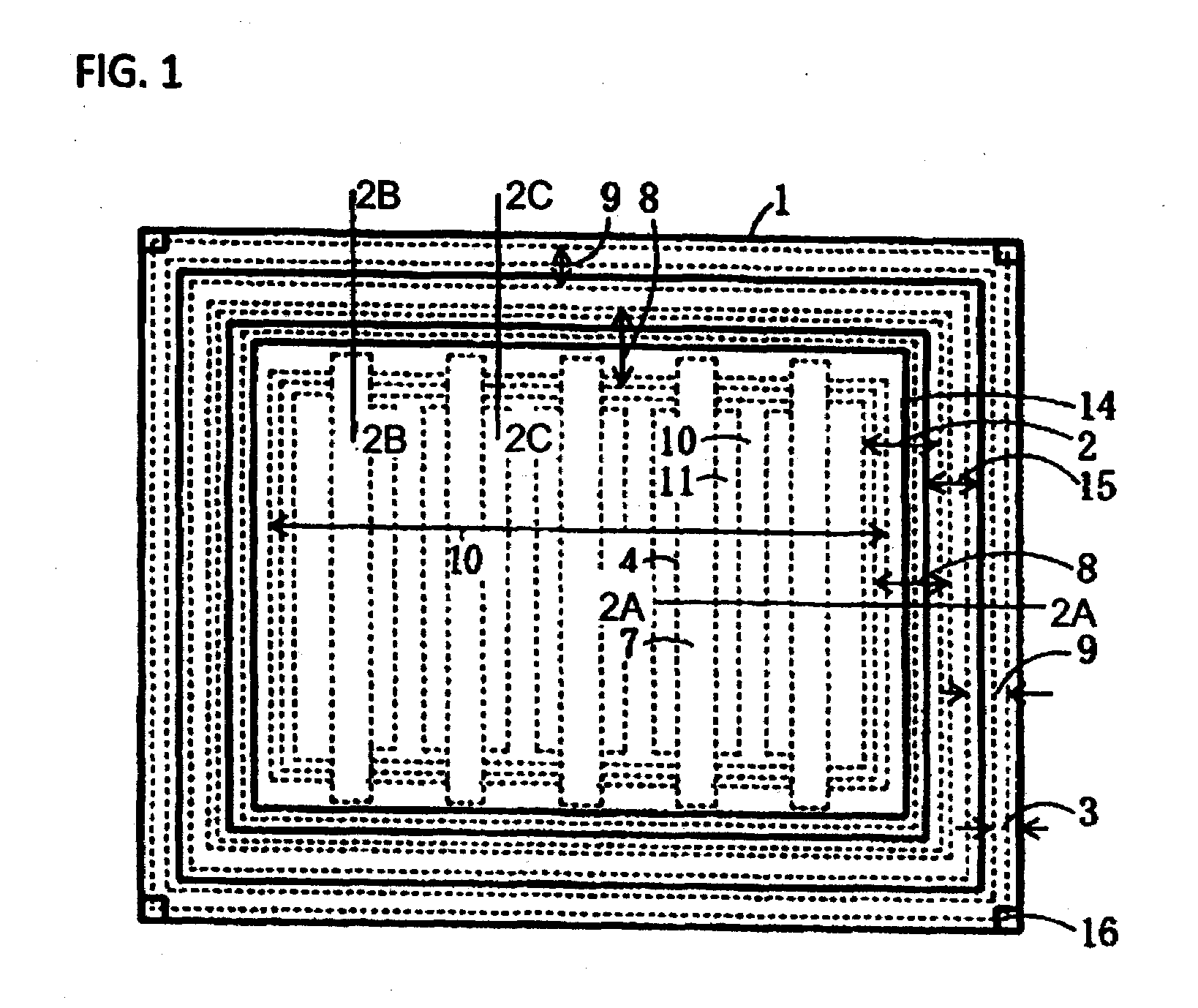

A semiconductor device comprises a first base layer of a first conductivity type; a plurality of second base layers of a second conductivity type, provided on a part of a first surface of the first base layer; trenches formed on each side of the second base layers, and formed to be deeper than the second base layers; an emitter layer formed along the trench on a surface of the second base layers; a collector layer of the second conductivity type, provided on a second surface of the first base layer opposite to the first surface; an insulating film formed on an inner wall of the trench, the insulating film being thicker on a bottom of the trench than on a side surface of the trench; a gate electrode formed within the trench, and isolated from the second base layers and the emitter layer by the insulating film; and a space section provided between the second base layers adjacent to each other, the space section being deeper than the second base layers and being electrically isolated from the emitter layer and the second base layers.

Owner:KK TOSHIBA

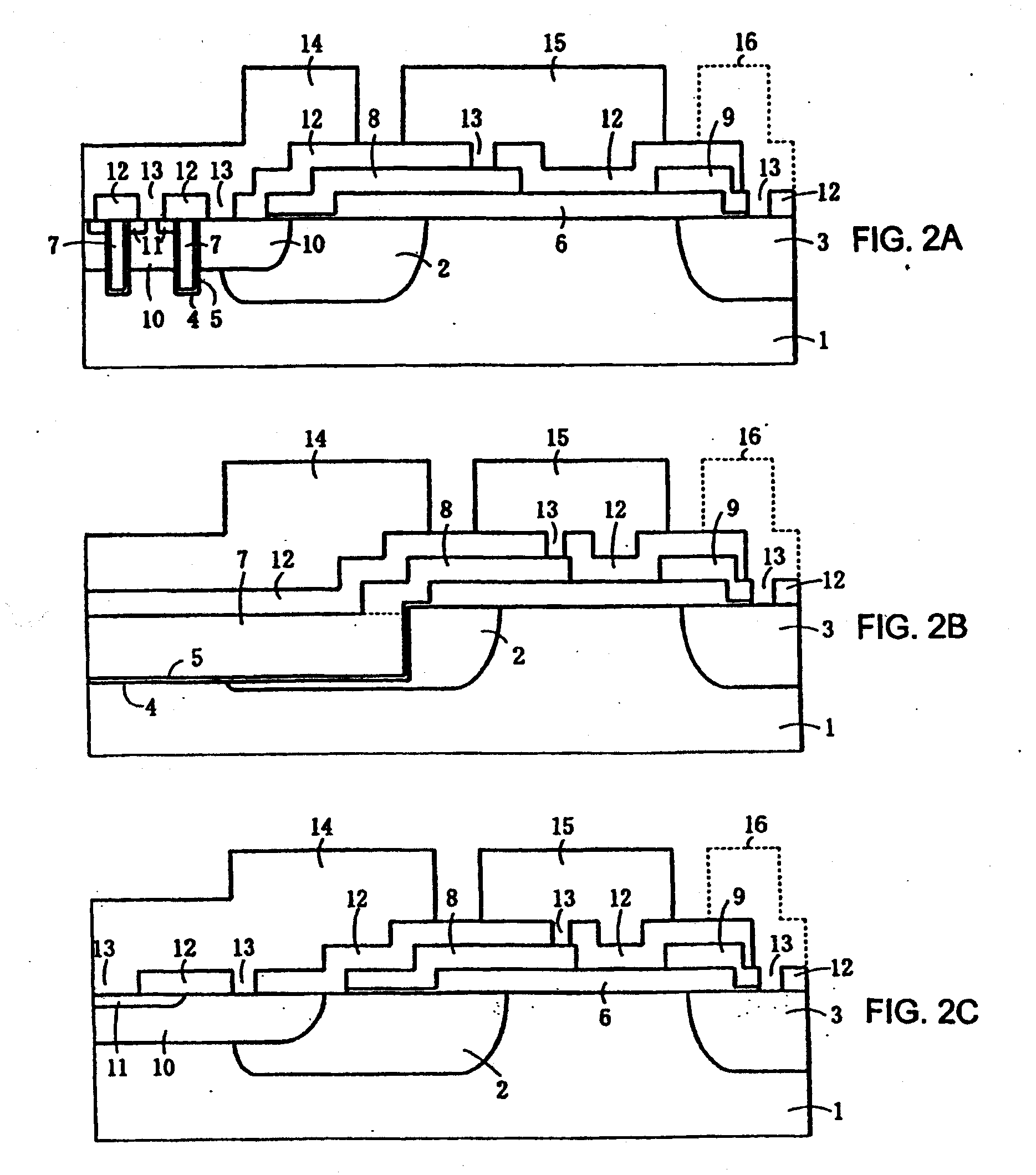

Semiconductor device and the method of manufacturing the same

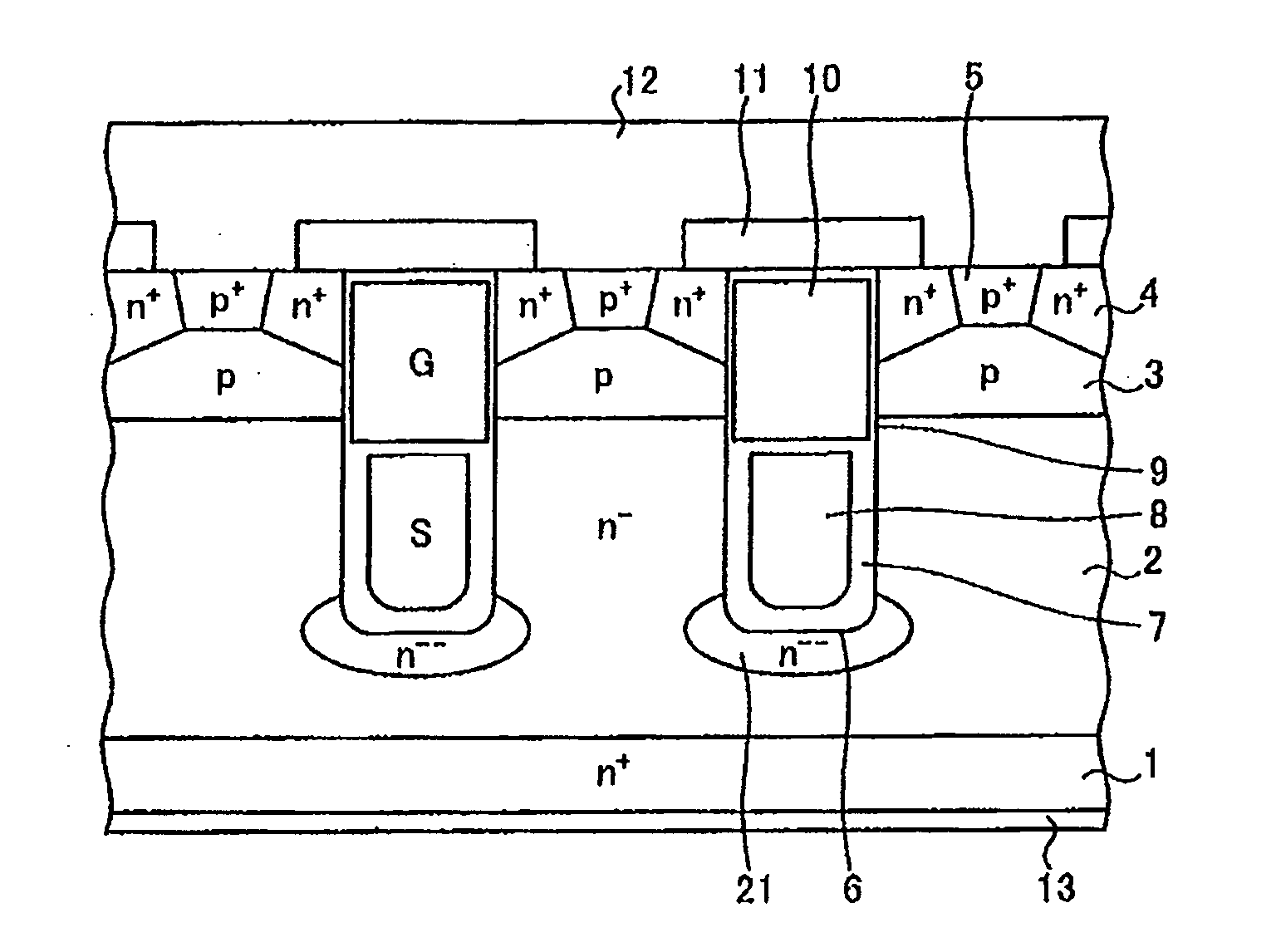

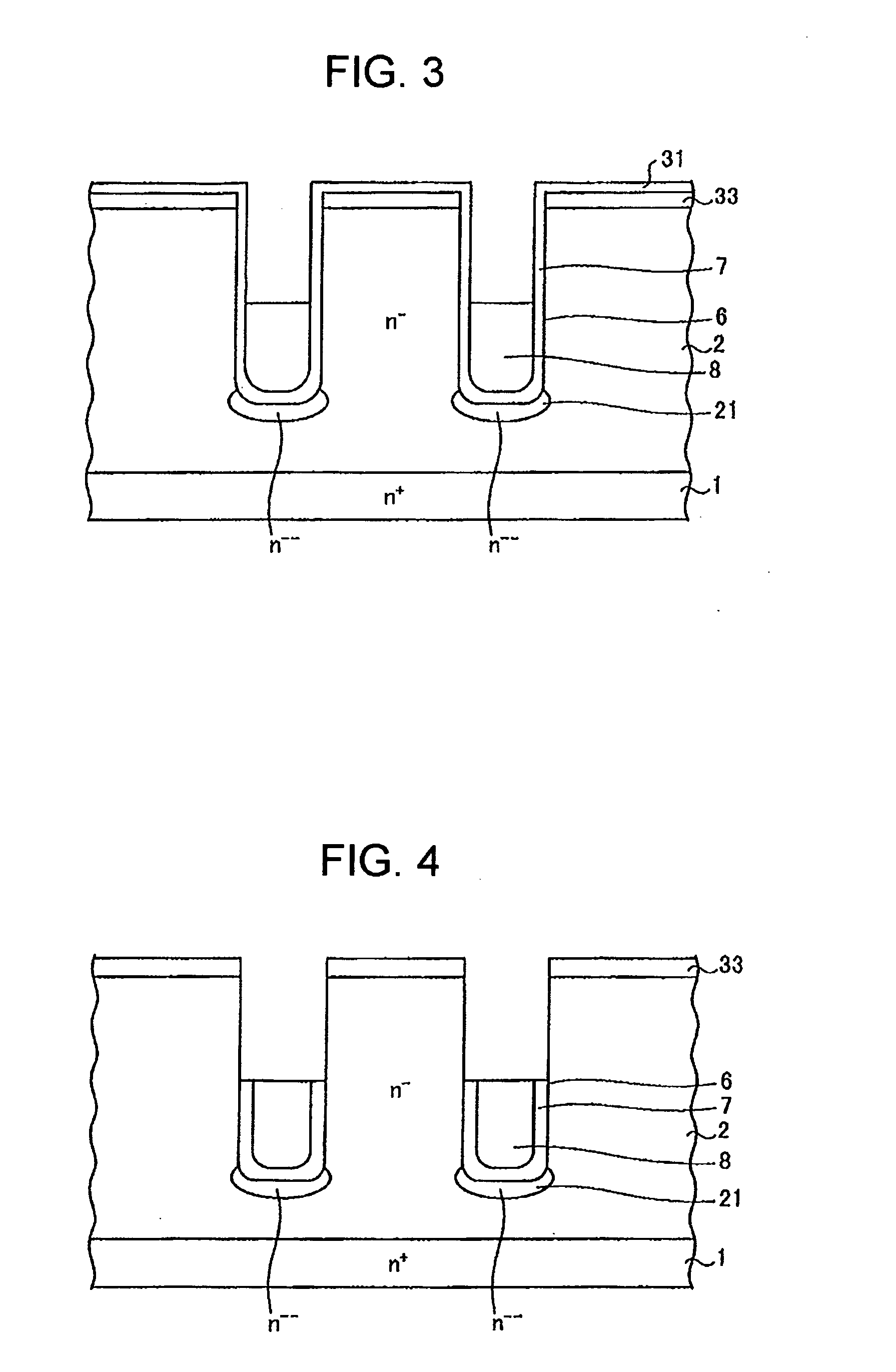

ActiveUS20110303925A1Lower on-state resistanceLow impurity concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing cost reductionPower semiconductor device

A semiconductor device according to the invention includes p-type well region 3 and n+ source region 4, both formed selectively in the surface portion of n− drift region 2; trench 6 in contact with n+ source region 4 and extending through p-type well region 3 into n− drift region 2; field plate 8 formed in trench 6 with first insulator film 7 interposed between the trench 6 inner surface and field plate 8; gate electrode 10 formed in trench 6 with second insulator film 9 interposed between the trench 6 side wall and gate electrode 10, gate electrode 10 being formed above field plate 8; first insulator film 7 being thicker than second insulator film 9; and n−− lightly doped region 21 in n− drift region 2, n−− lightly doped region 21 crossing under the bottom surface of trench 6 from the corner portion thereof, n−− lightly doped region 21 covering the bottom surface of trench 6.The semiconductor device according to the invention and the method of manufacturing the semiconductor device according to the invention facilitate lowering the ON-state voltage, preventing the breakdown voltage from lowering, lowering the gate capacitance, and reducing the manufacturing costs.

Owner:FUJI ELECTRIC CO LTD

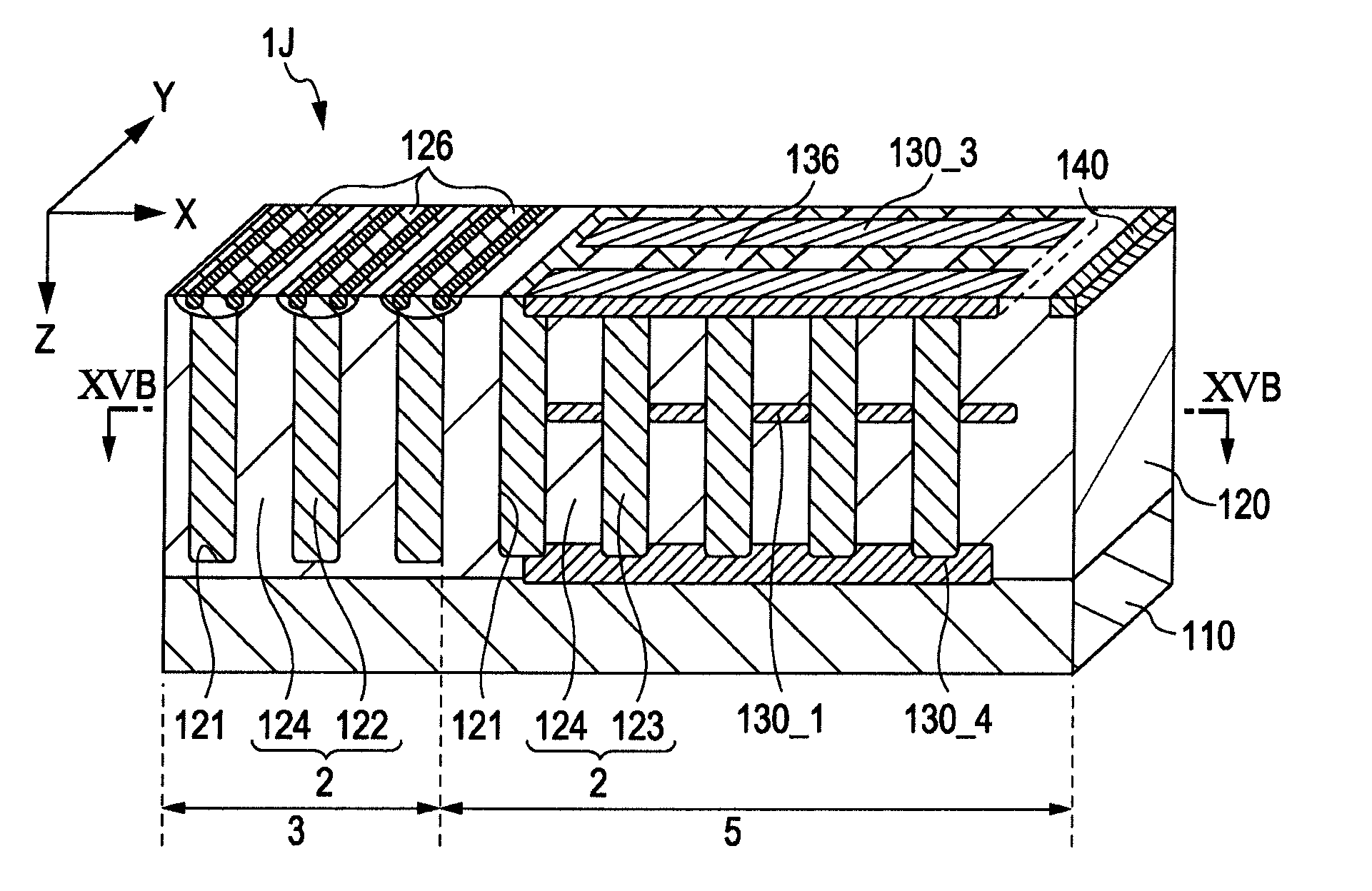

Semiconductor device and manufacturing method for the same

InactiveUS20100059818A1Improve breakdown voltageSimple processSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

A semiconductor device includes a first conductive type first semiconductor region, a second semiconductor region, and a second conductive type lateral RESURF region. The first semiconductor region is arranged on a first electrode side. The second semiconductor region includes first conductive type first pillar regions and a terminal part. The second pillar regions are alternately arranged on an element part. The terminal part is formed around the element part along a surface of the first semiconductor region on a second electrode side opposite to the first electrode side of the first semiconductor region. Furthermore, the second conductive type lateral RESURF region is formed in the second semiconductor region on the terminal part.

Owner:SONY CORP

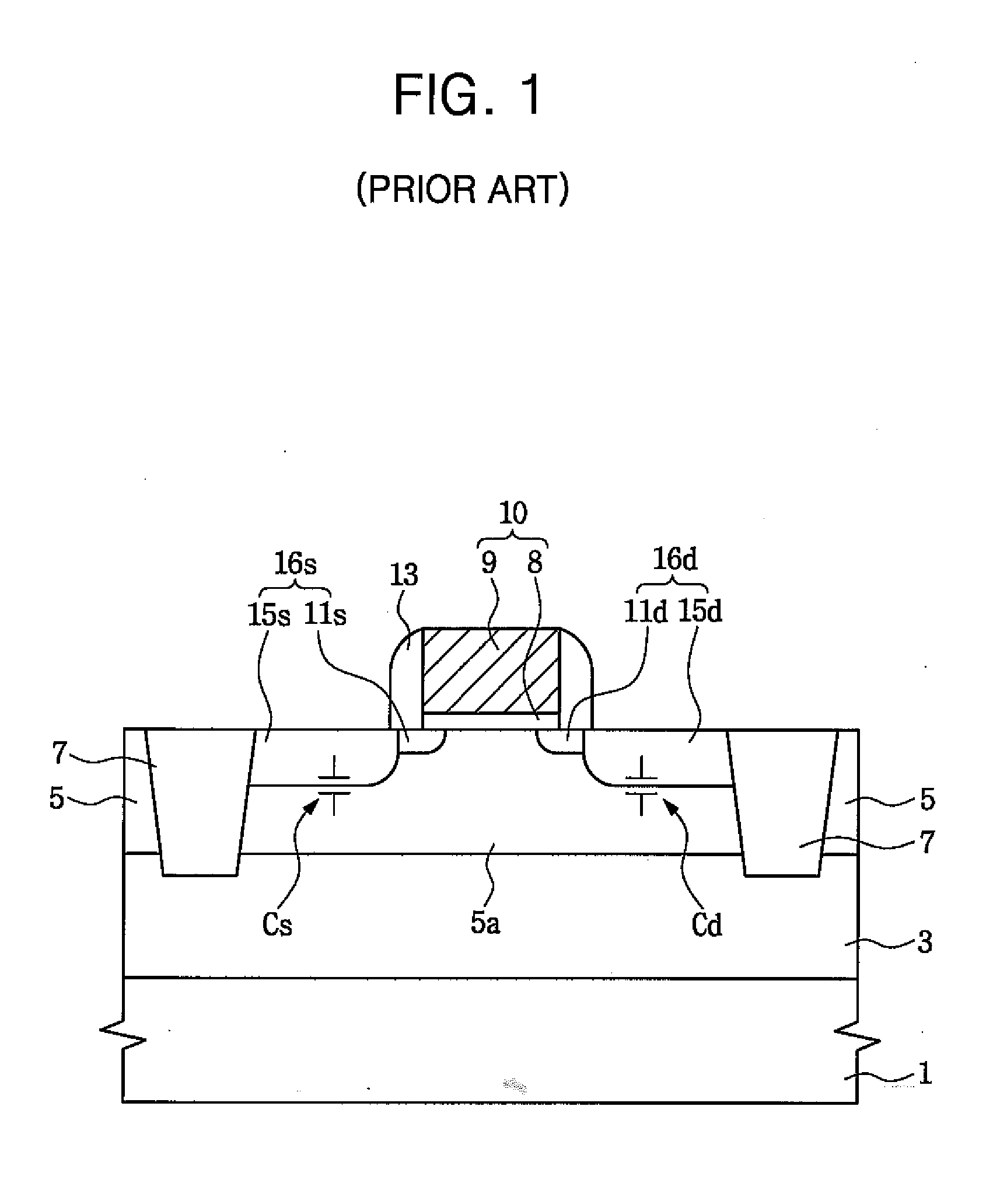

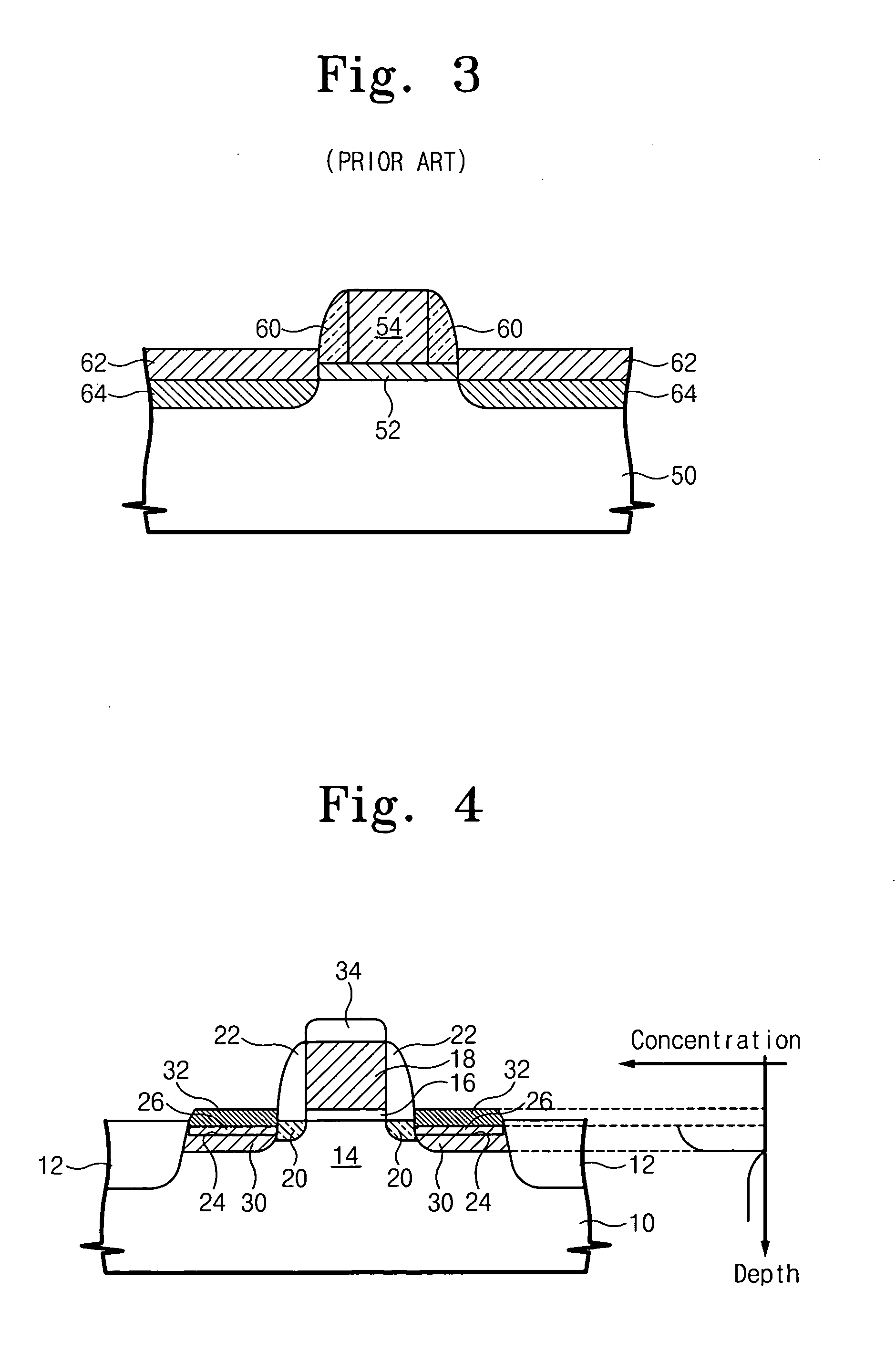

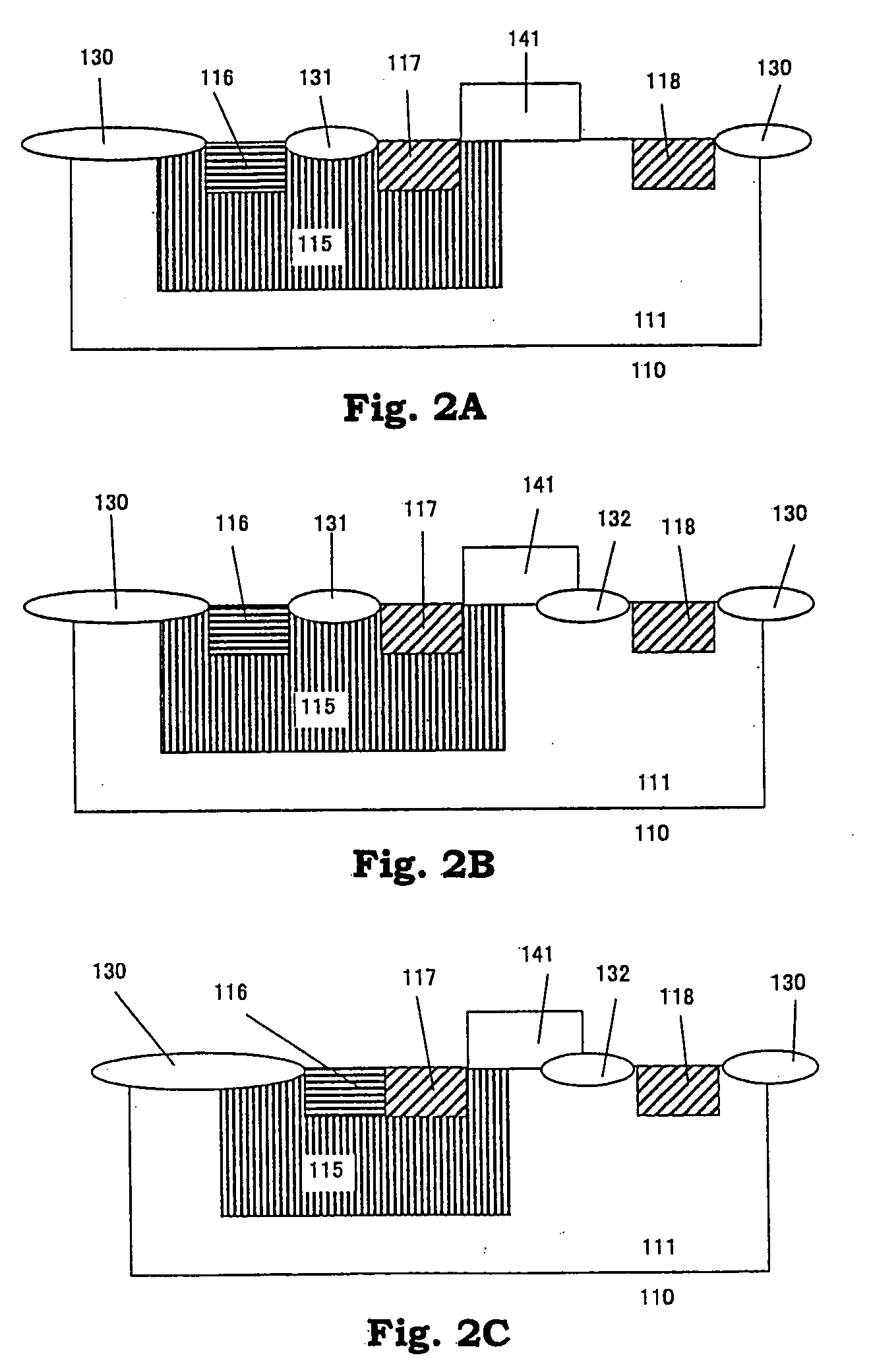

Single transistor memory device having source and drain insulating regions and method of fabricating the same

ActiveUS20080099811A1High impurity concentrationTransistorSolid-state devicesRandom access memoryEngineering

A single transistor floating-body dynamic random access memory (DRAM) device includes a floating body located on a semiconductor substrate and a gate electrode located on the floating body, the floating body including an excess carrier storage region. The DRAM device further includes source and drain regions respectively located at both sides of the gate electrode, and leakage shielding patterns located between the floating body and the source and drain regions. Each of the source and drain regions contact the floating body, which may be positioned between the source and drain regions. The floating body may also laterally extend under the leakage shielding patterns, which may be arranged at outer sides of the gate electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

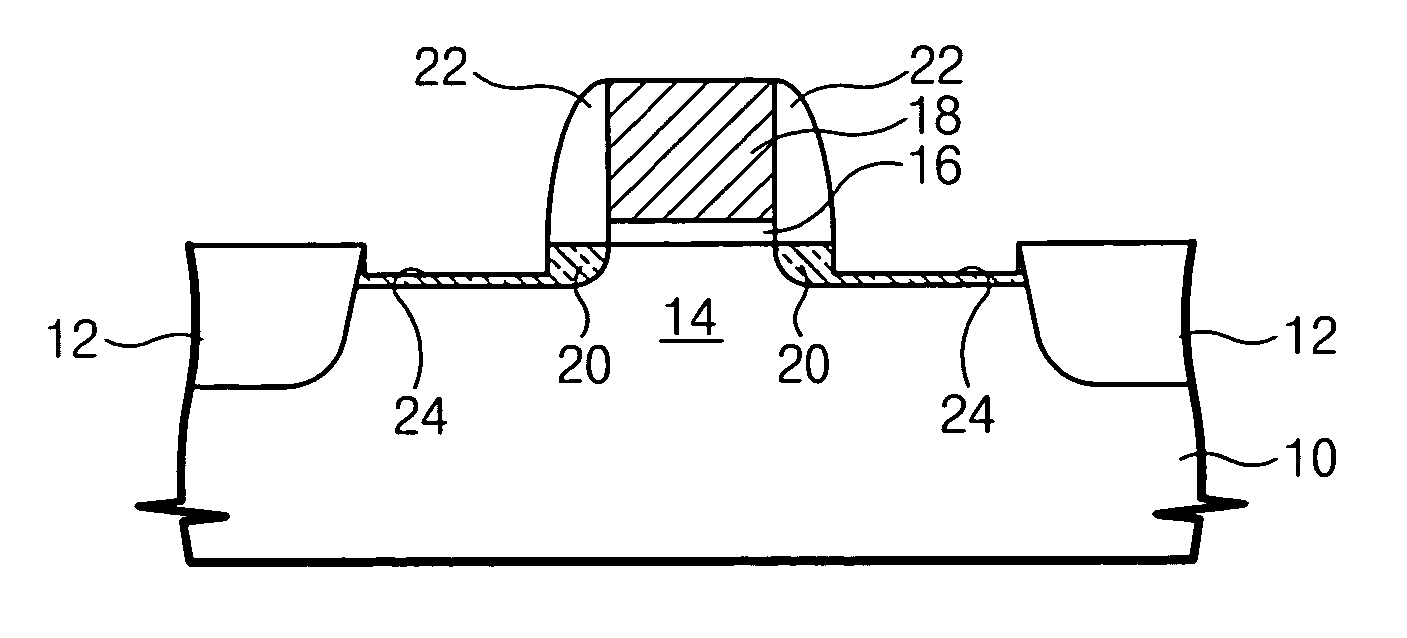

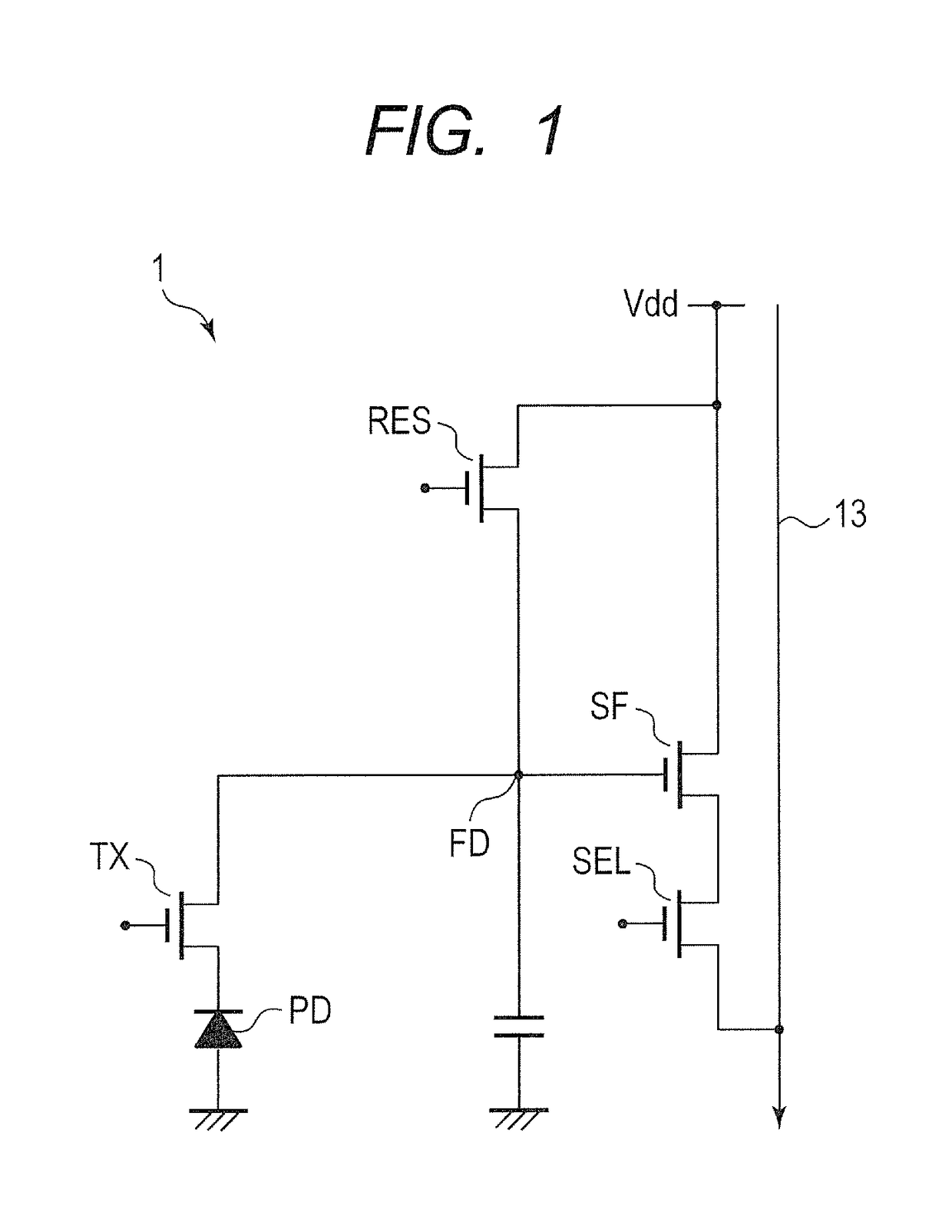

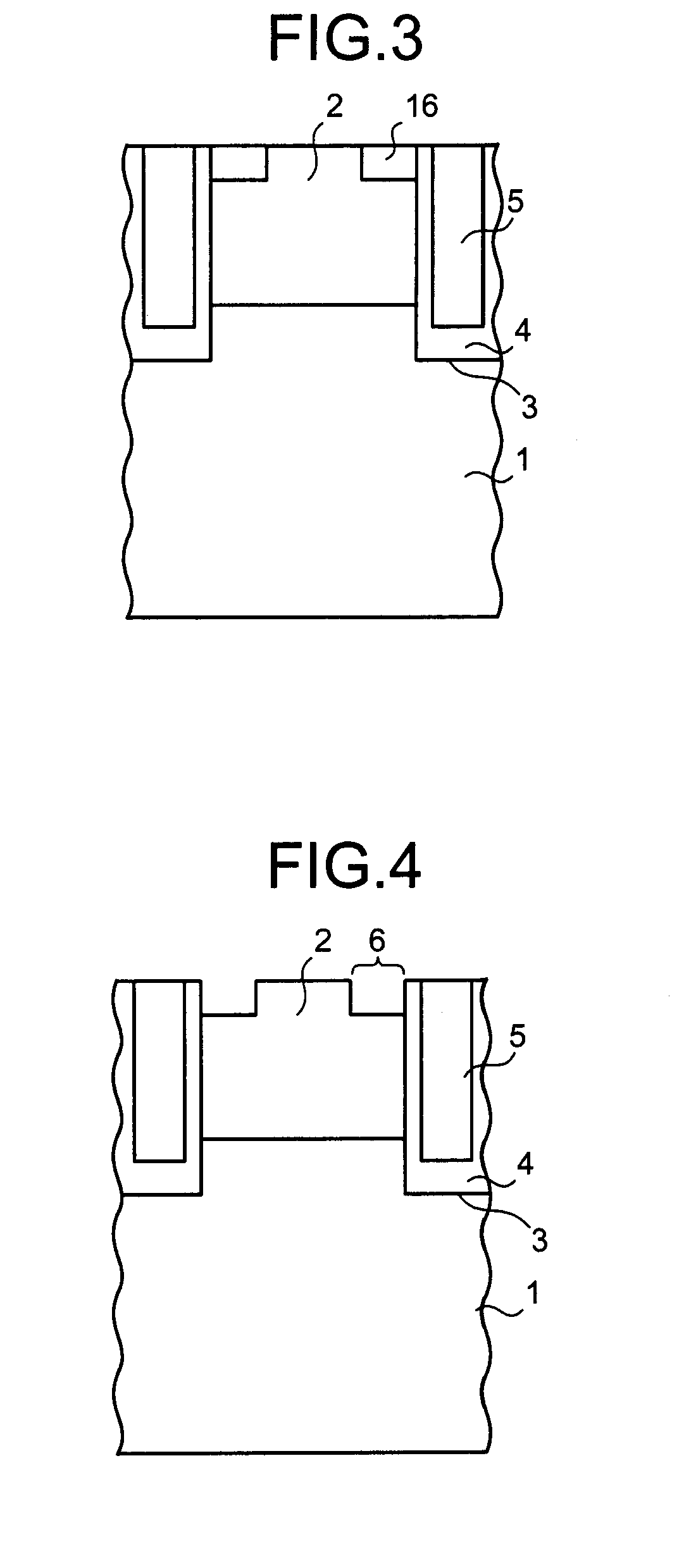

MOS transistors having recesses with elevated source/drain regions and methods of fabricating such transistors

ActiveUS20050095795A1High impurity concentrationIncrease concentrationTransistorSemiconductor/solid-state device manufacturingHigh concentrationCompound (substance)

Metal-oxide-semiconductor (MOS) transistors having elevated source / drain regions and methods of fabricating the same are provided. The MOS transistors may include a gate pattern formed to cross over a predetermined region of a substrate. Recessed regions are provided in the substrate adjacent to the gate pattern. Epitaxial layers are provided on bottom surfaces of the recessed regions. High concentration impurity regions are provided in the epitaxial layers. The recessed regions may be formed using a chemical dry etching techniques.

Owner:SAMSUNG ELECTRONICS CO LTD

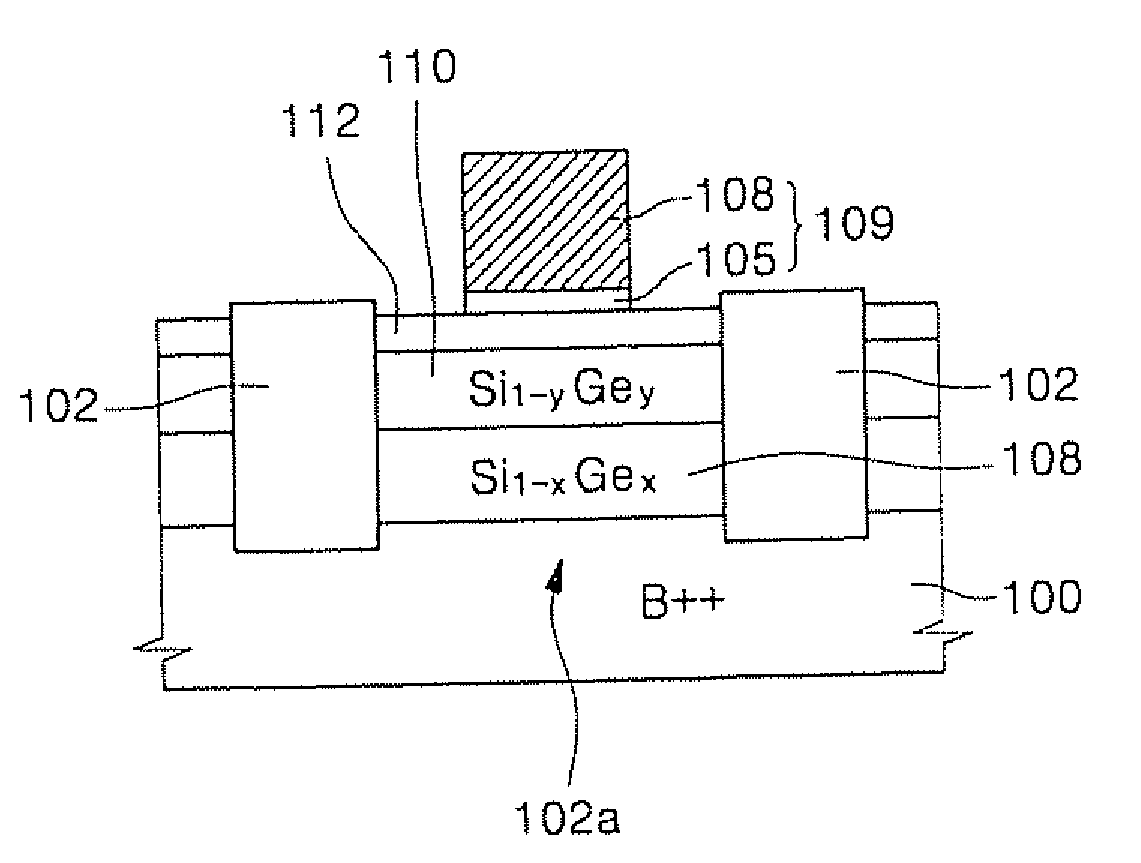

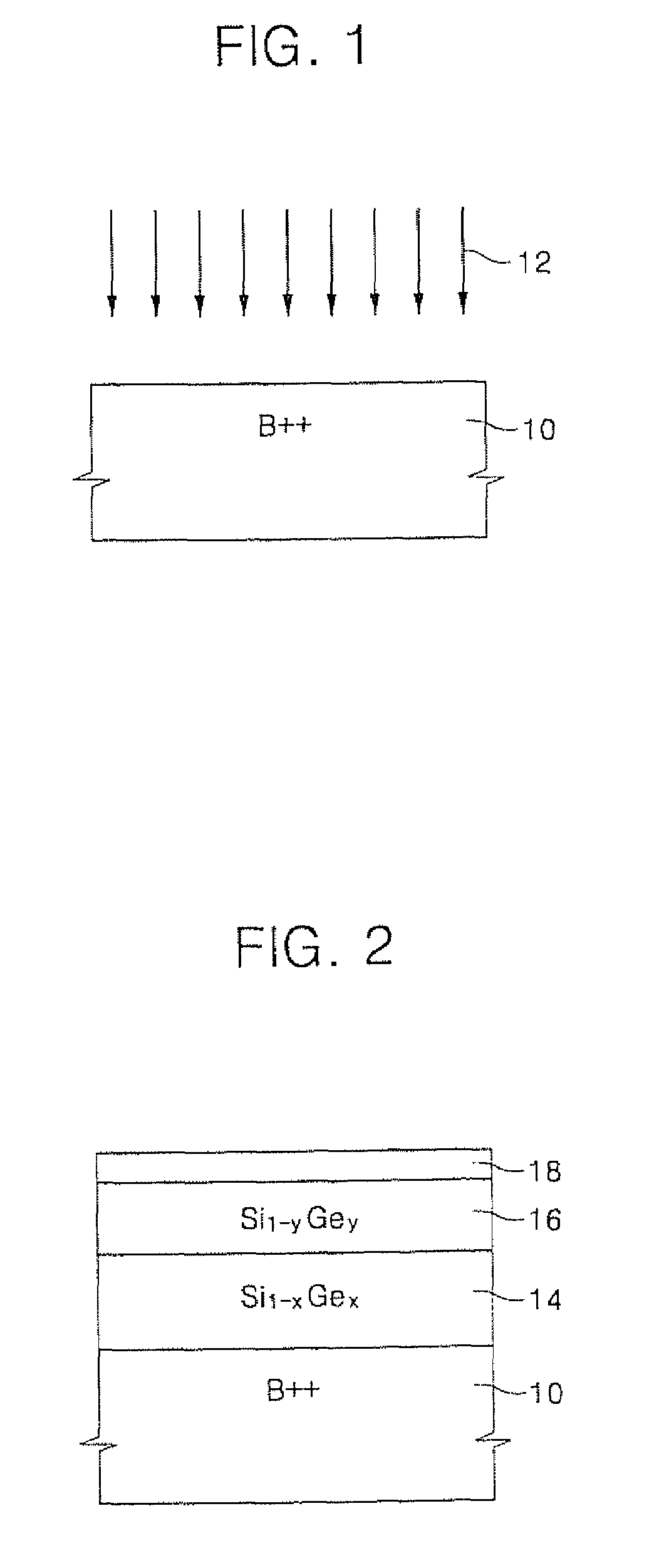

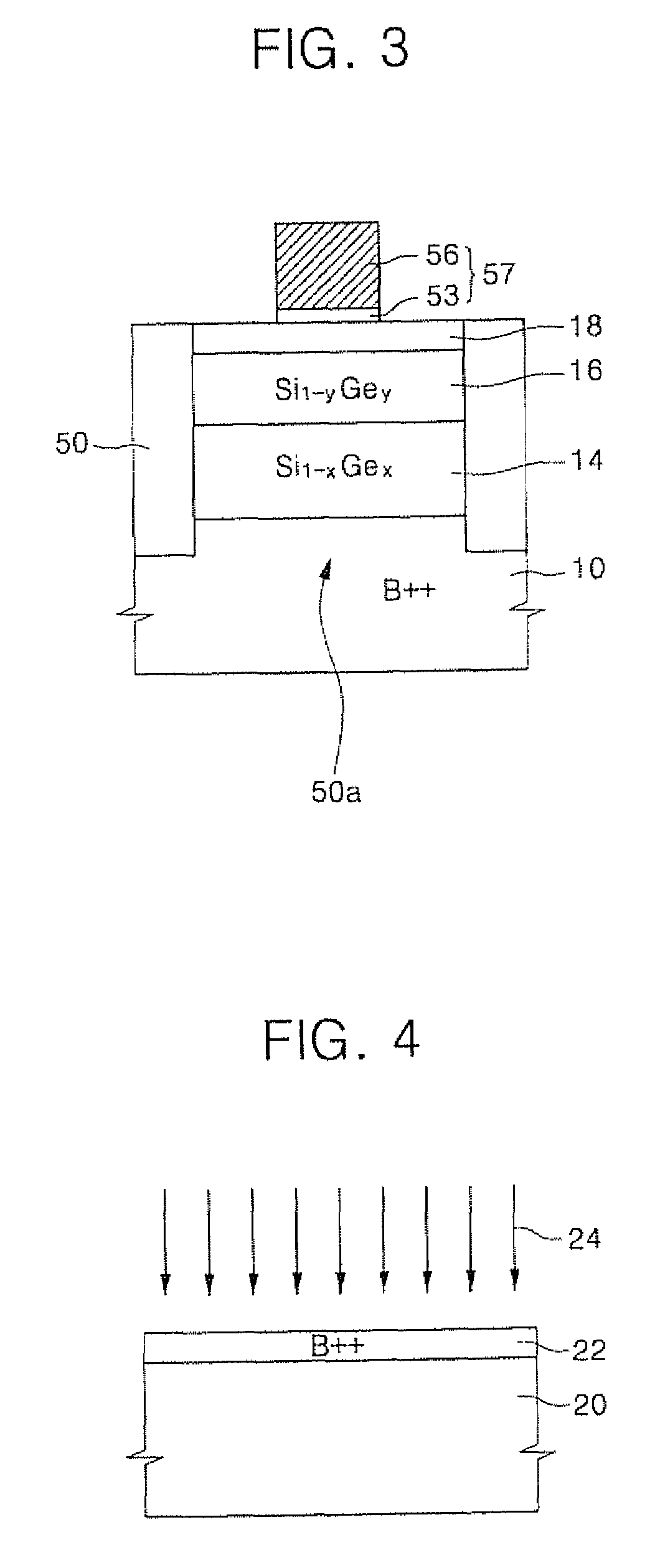

Method of Forming a Semiconductor Device Having a Strained Silicon Layer on a Silicon-Germanium Layer

InactiveUS20090130826A1High impurity concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialDislocation

A method of forming a semiconductor device having a strained silicon (Si) layer on a silicon germanium (SiGe) layer is provided. The method includes preparing a silicon substrate. A SiGe layer is formed on the silicon substrate. At least a part of the SiGe layer has a first dislocation density. A strained Si layer having a second dislocation density lower than the first dislocation density is formed on the SiGe layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device

ActiveUS20190109227A1High impurity concentrationReduce resistanceTransistorSemiconductor/solid-state device manufacturingPhysicsMOSFET

At bottom of a gate trench, a conductive layer is provided. A Schottky junction is formed along a side wall of the gate trench by the conductive layer and the n-type current spreading region. The Schottky junction constitutes one unit cell of a trench-type SBD. In the gate trench, a gate electrode is provided on the conductive layer, via an insulating layer. The gate electrode constitutes one unit cell of a trench-gate-type vertical MOSFET. In other words, one unit cell of the trench gate MOSFET and one unit cell of the trench-type SBD are disposed built into a single gate trench and oppose each other in a depth direction.

Owner:FUJI ELECTRIC CO LTD

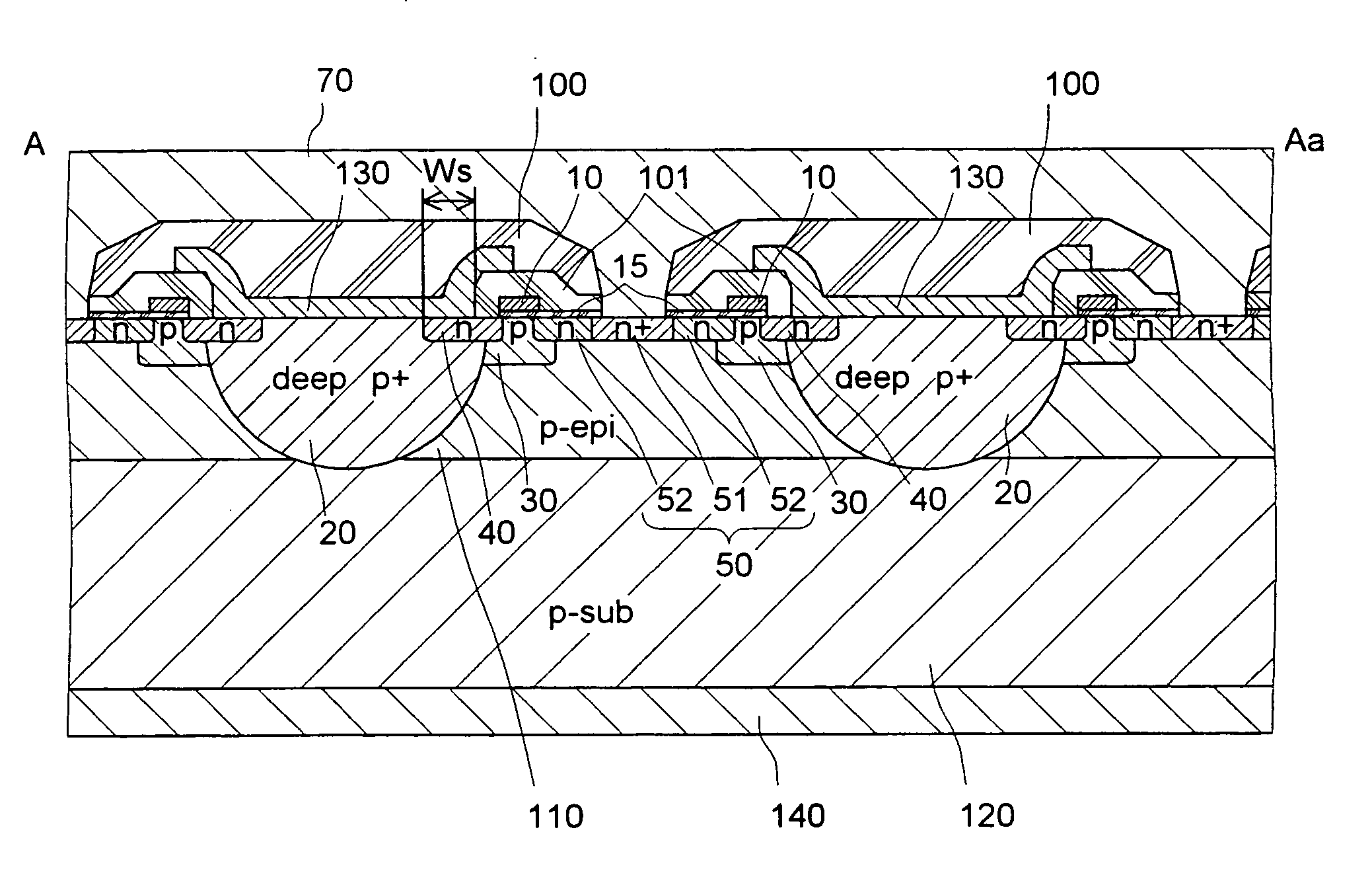

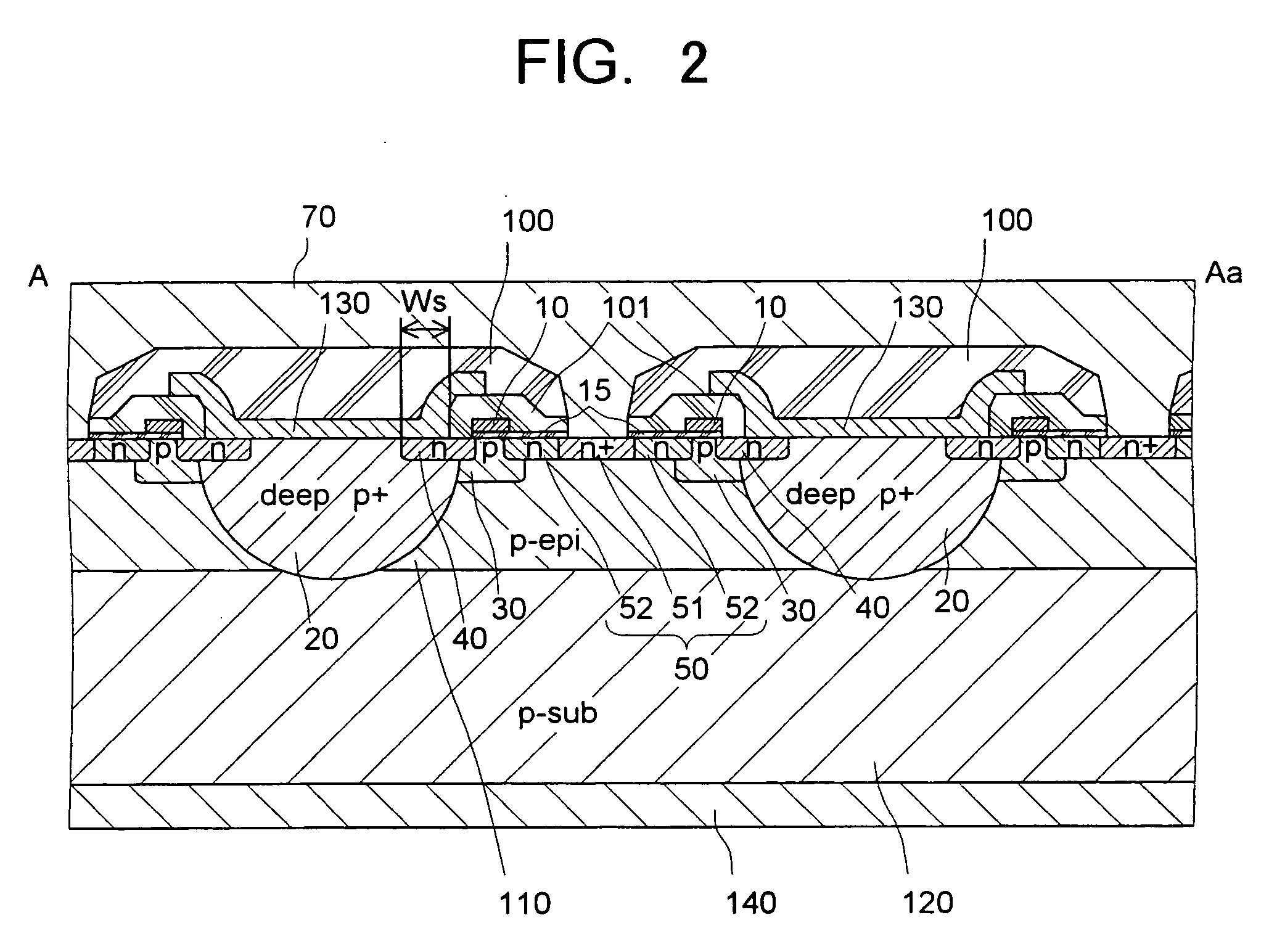

Semiconductor device and method of manufacturing the same

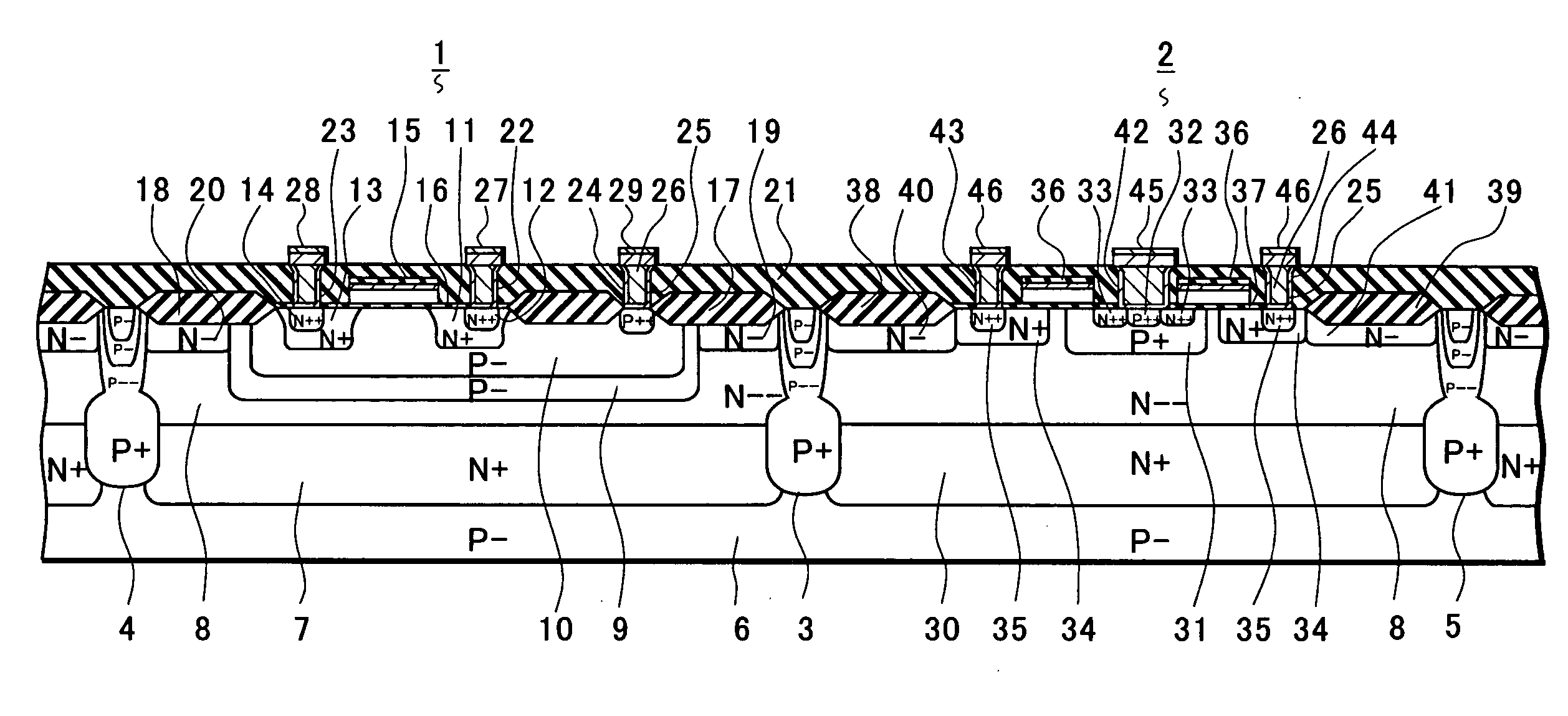

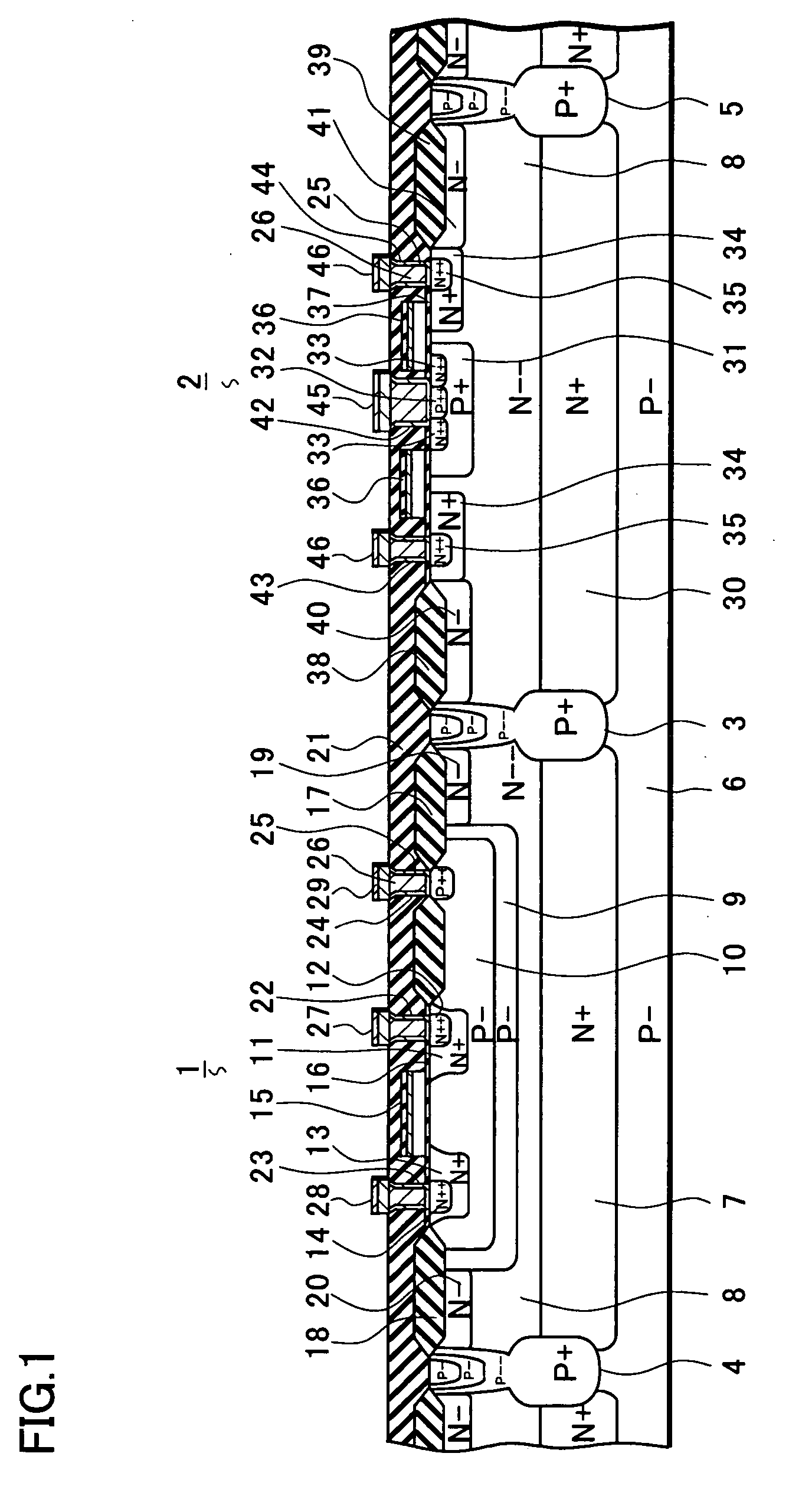

ActiveUS20070075363A1Reduce device sizeImprove withstand voltage characteristicsTransistorSemiconductor/solid-state device manufacturingDevice materialDiffusion layer

In a semiconductor device of the present invention, an N type epitaxial layer is formed on a P type single crystal silicon substrate. The substrate and the epitaxial layer are partitioned into a plurality of element formation regions by isolation regions. Each of the isolation regions is formed of a P type buried diffusion layer and a P type diffusion layer coupled thereto. The P type buried diffusion layer is joined to N type buried diffusion layers on both sides thereof to form PN junction regions. On the other hand, the P type diffusion layer is joined to N type diffusion layers on both sides thereof to form PN junction regions. This structure suppresses extension of widthwise diffusion of the P type buried diffusion layer and the P type diffusion layer, thus making it possible to reduce the device size.

Owner:SEMICON COMPONENTS IND LLC

Semiconductor device and method for manufacturing semiconductor device

InactiveUS20050035431A1High impurity concentrationTransistorSemiconductor/solid-state device manufacturingDevice materialEngineering

A semiconductor device includes: a collector region having a first conductivity type; an intrinsic base region having a second conductivity type provided on the collector region; an emitter region having the first conductivity type formed in an upper section of the intrinsic base region; an isolation region provided on a side of the collector region directly under the intrinsic base region; an extrinsic base region having the second conductivity type provided adjacent to the intrinsic base region, and having a higher impurity concentration than the intrinsic base region; and a base electrode region provided on the isolation region, and contacting a side of the extrinsic base region so as to have a region at the same level as the intrinsic base region.

Owner:KK TOSHIBA

Device for continuous filtration of material blends

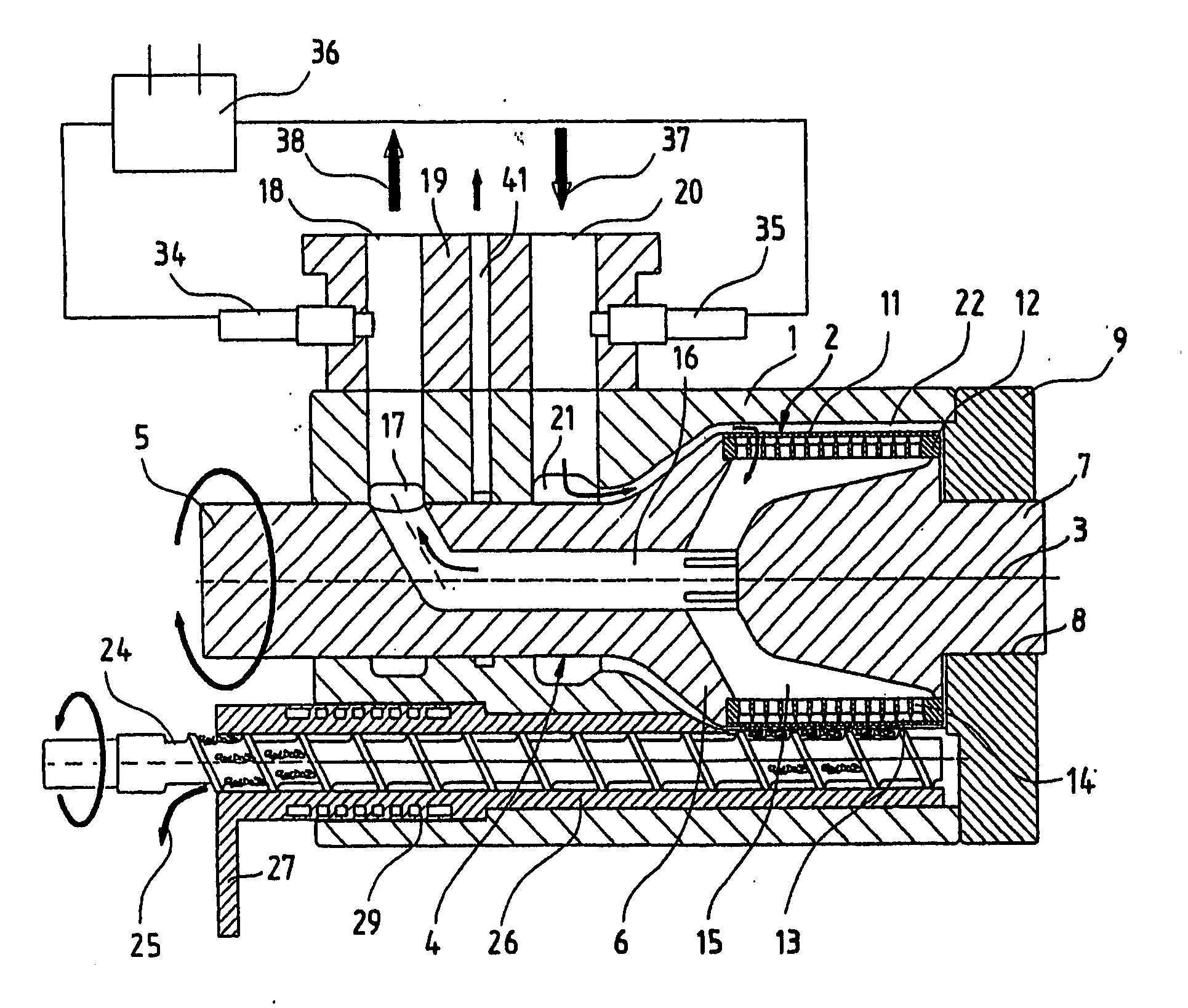

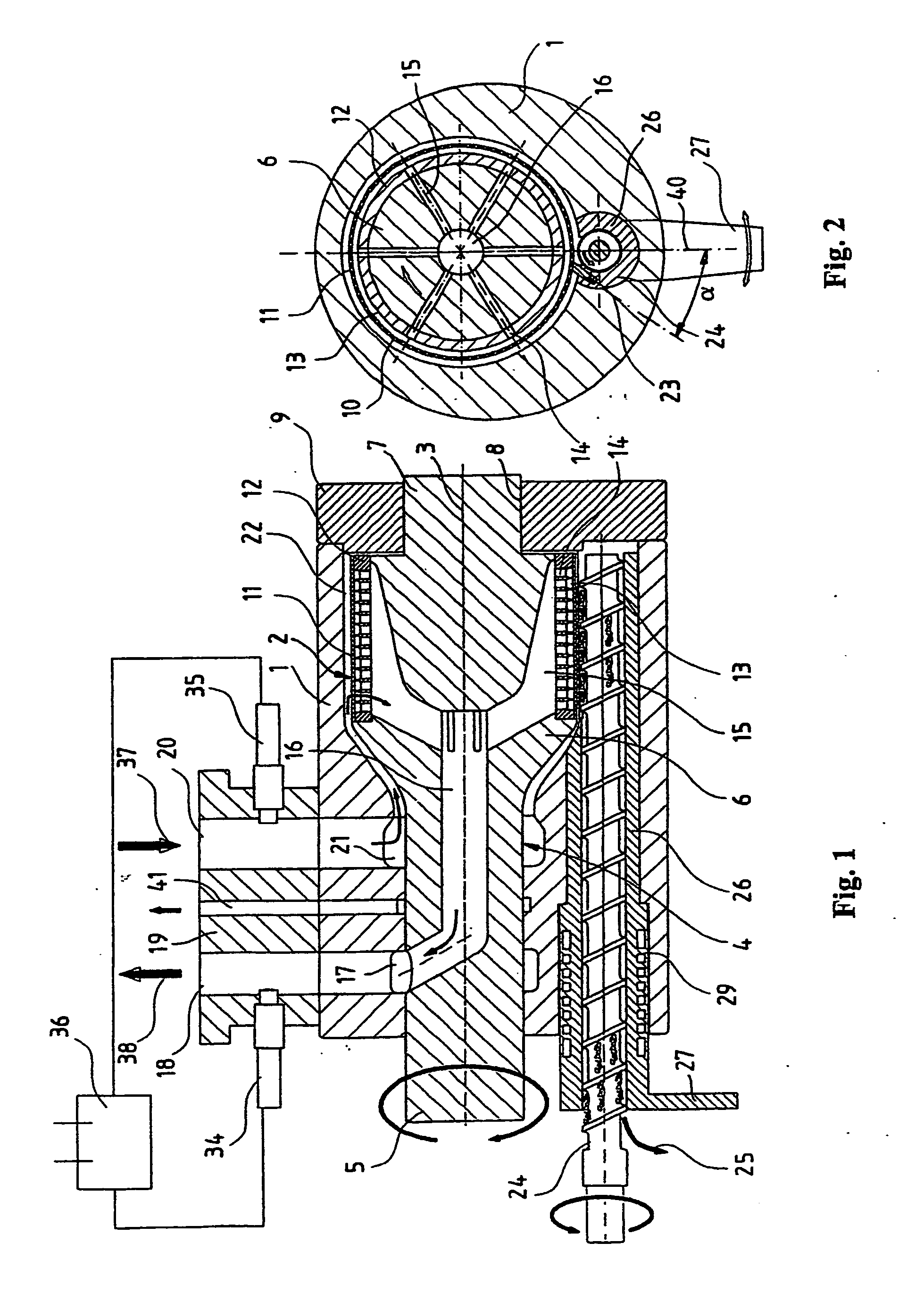

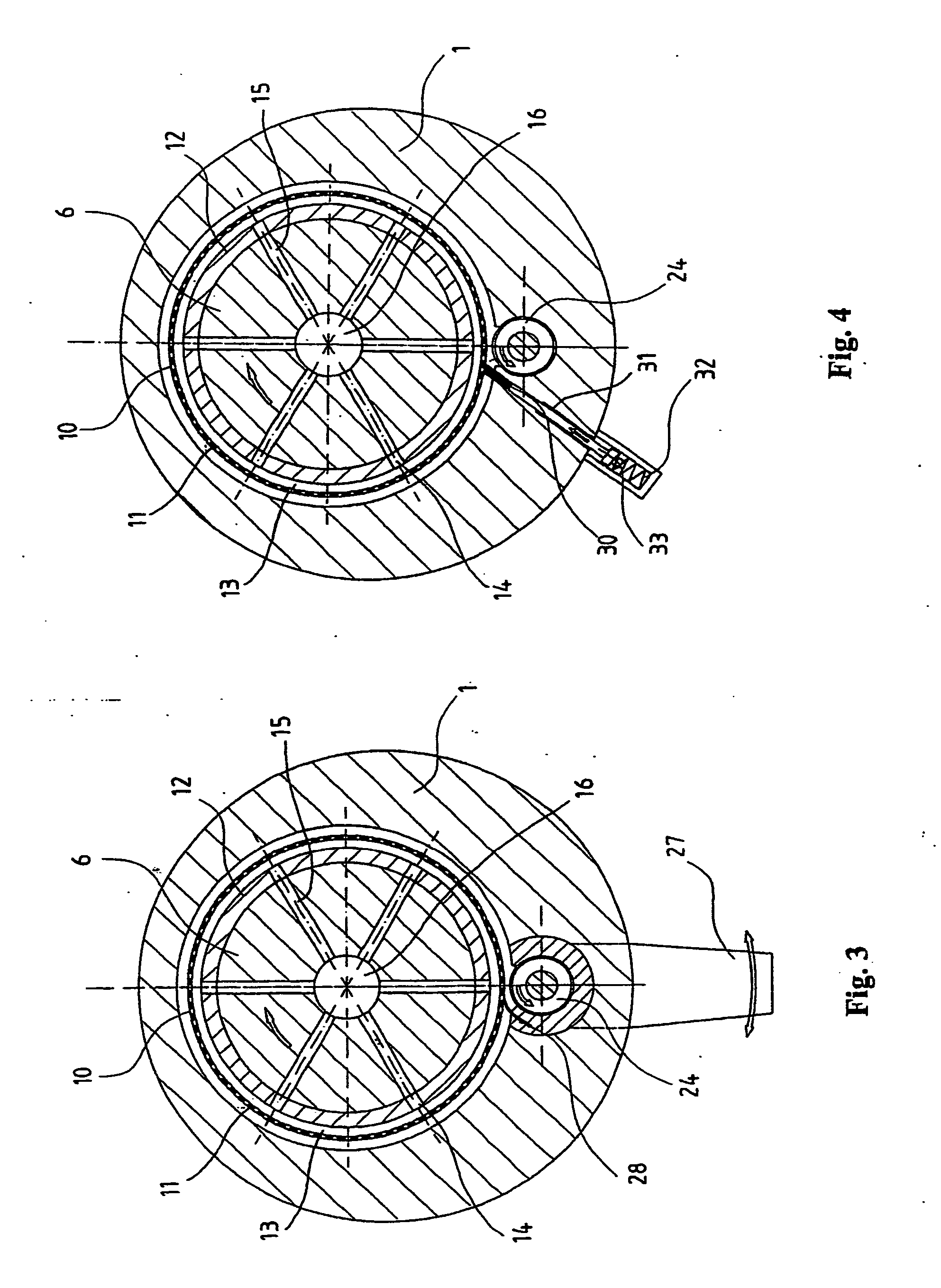

ActiveUS20050161391A1Reduce wearReduce tearingWrappingMoving filtering element filtersMotor driveFiltration

A device for the continuous filtration of material blends, in particular for separating impurities from plastic melts. A housing has a hollow cylindrical filter disposed inside. An inside chamber is disposed inside the filter. An annular chamber is defined by the outer surface of the filter and an inside wall of the housing. A cleaning device removes the impurities retained on the filter by a motor driving about an axis coupled to pivot the filter inside the housing. The cleaning device has at least one wiper for removing in the radial direction impurities retained on the filter. A conveying device transports off the impurities removed from the filter by the wiper. The motor-driven filter and the conveying device are driven separately of each other.

Owner:ETTLINGER KUNSTSTOFFMANSCHINEN GMBH

Semiconductor device

ActiveUS20110115020A1High impurity concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationSemiconductor

A semiconductor device includes a second conductive-type deep well configured above a substrate. The deep well includes an ion implantation region and a diffusion region. A first conductive-type first well is formed in the diffusion region. A gate electrode extends over portions of the ion implantation region and of the diffusion region, and partially overlaps the first well. The ion implantation region has a uniform impurity concentration whereas the impurity concentration of the diffusion region varies from being the highest concentration at the boundary interface between the ion implantation region and the diffusion region to being the lowest at the portion of the diffusion region that is the farthest away from the boundary interface.

Owner:KEY FOUNDRY CO LTD

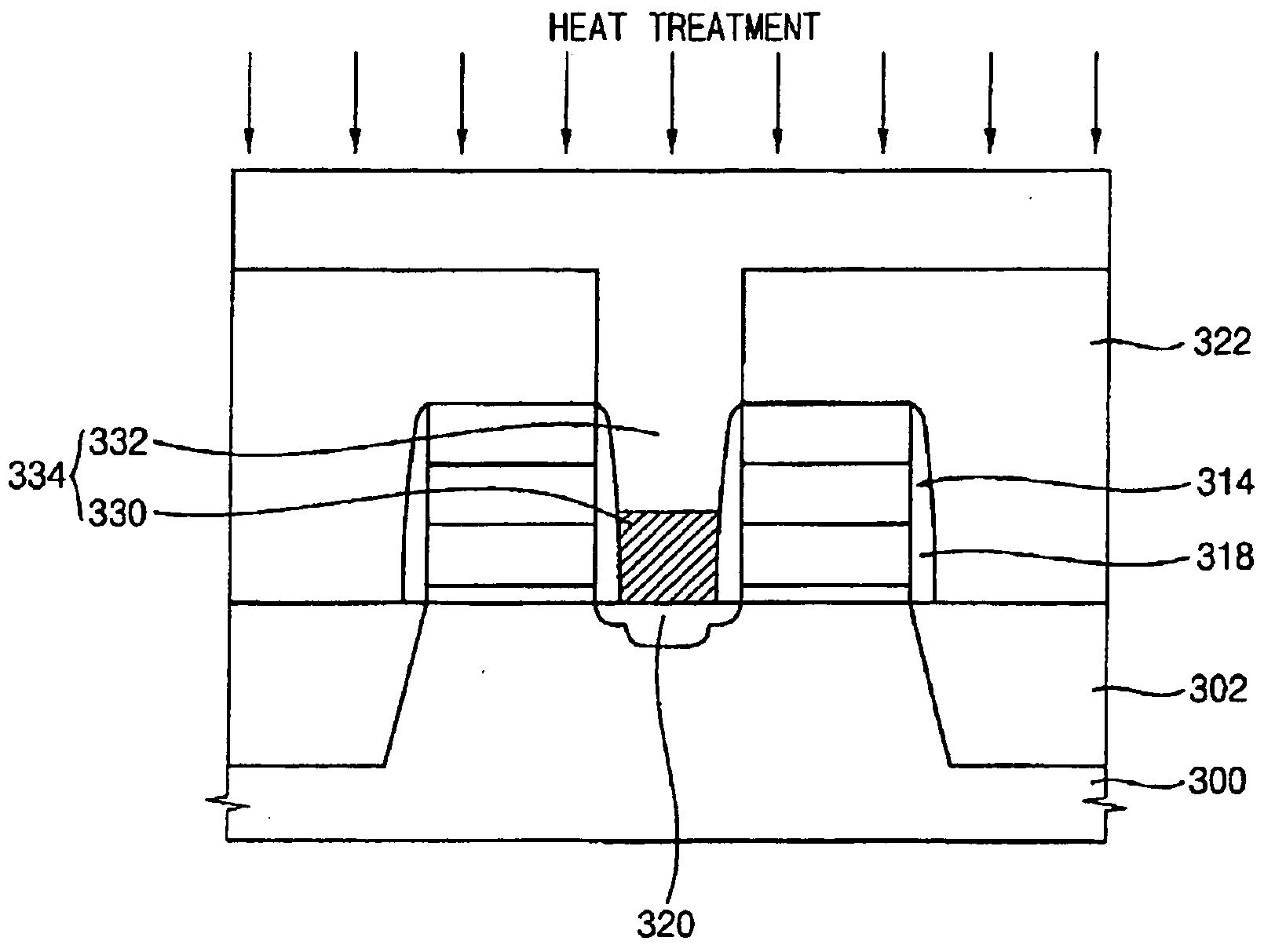

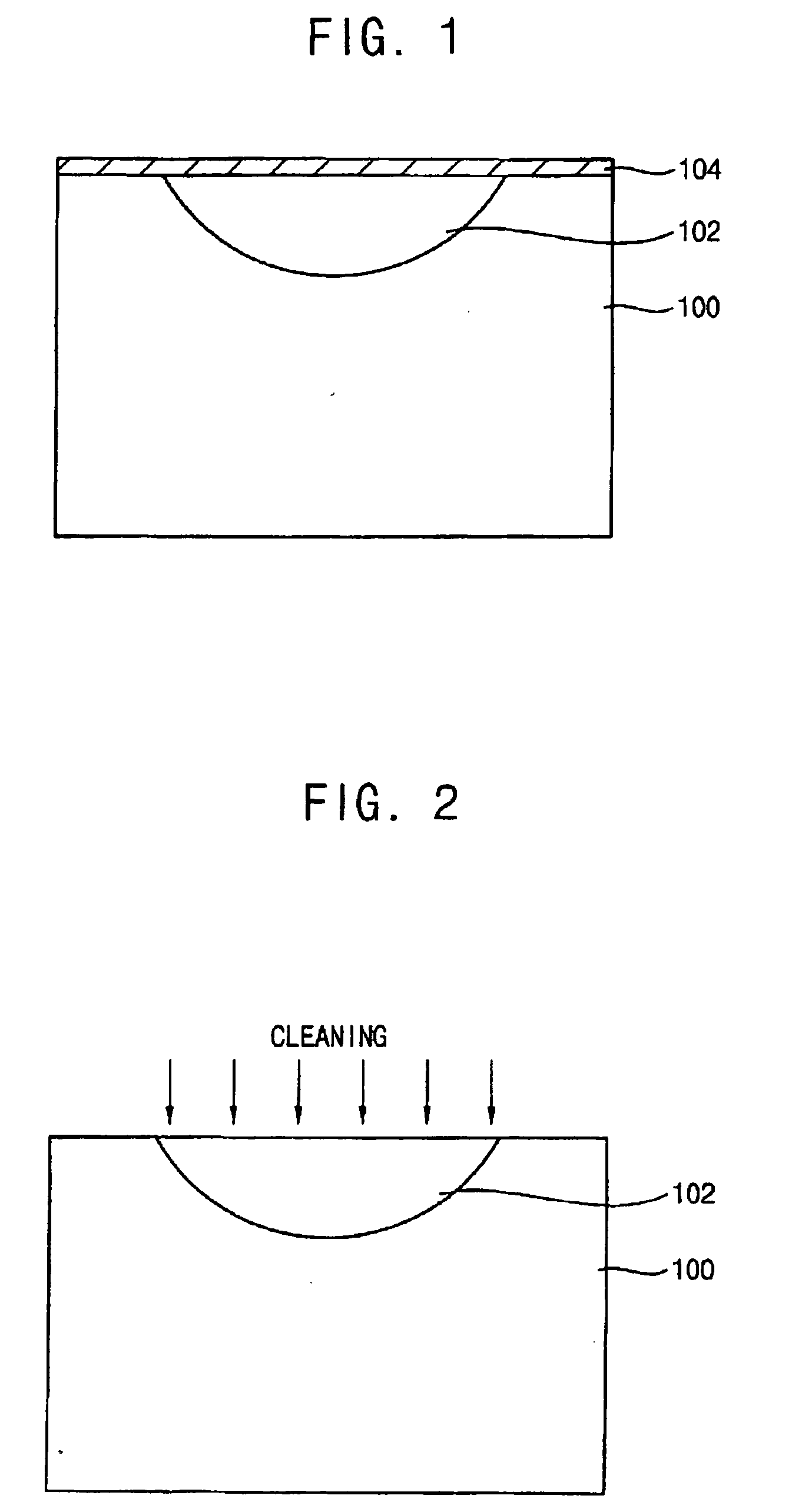

Method of forming a layer and method of manufacturing a semiconductor device using the same

InactiveUS20070022941A1High impurity concentrationLower resistancePolycrystalline material growthFrom solid stateElectrical resistance and conductanceDevice material

In a method of forming a layer having a lower electrical resistance and a method of manufacturing a semiconductor device, a first layer may be formed on a single crystalline substrate using amorphous silicon doped with impurities. A heat treatment may be performed on the single crystalline substrate at a temperature of about 550° C. to about 600° C. to convert the first layer into a second layer including a single crystalline silicon film transformed from a lower portion of the first layer contacting the single crystalline substrate and a polysilicon film transformed from an upper portion of the first layer. The layer may be formed at a relatively low temperature by a selective epitaxial growth process, and thus degradation or damage to a semiconductor device, which may be generated in a high temperature process, may be reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

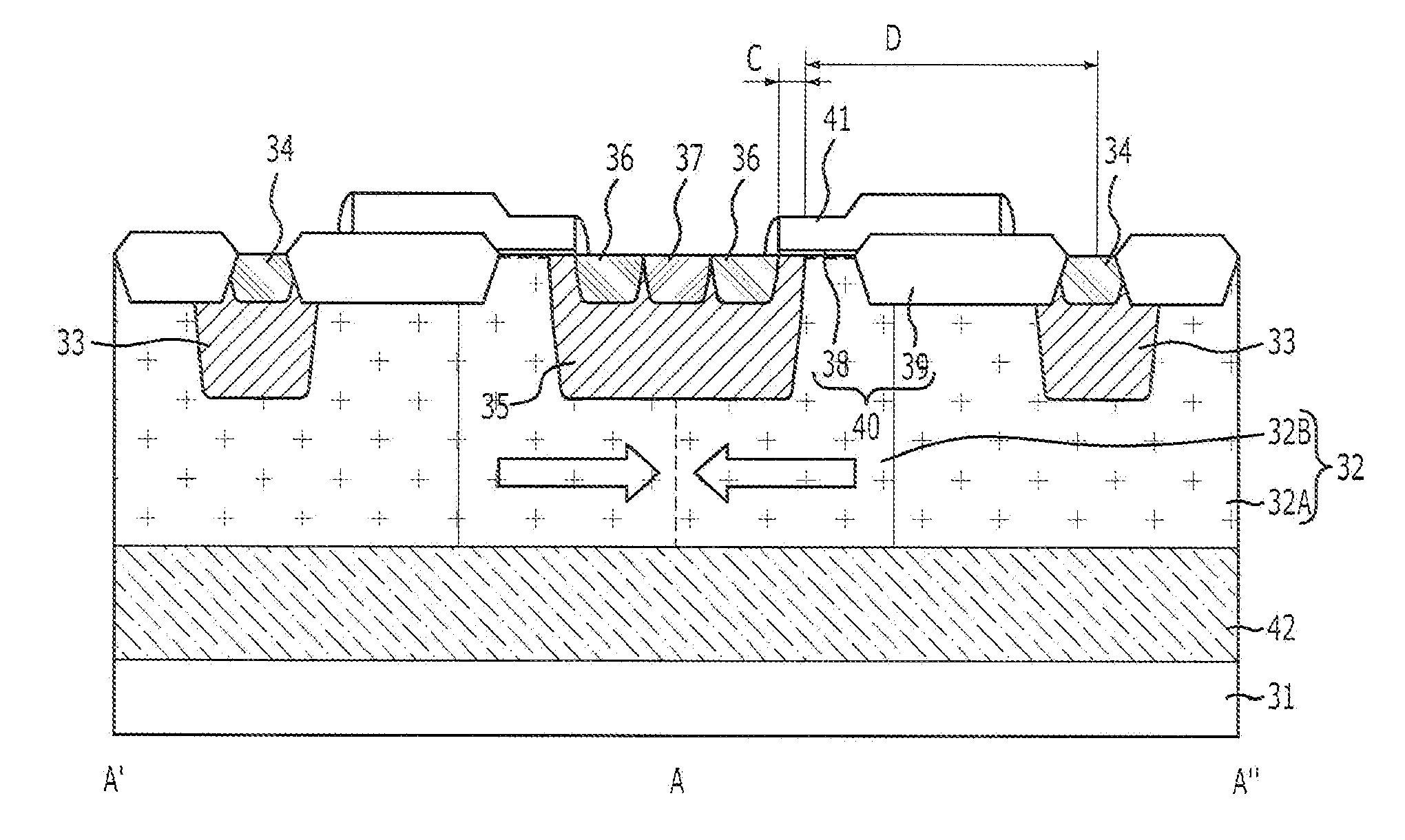

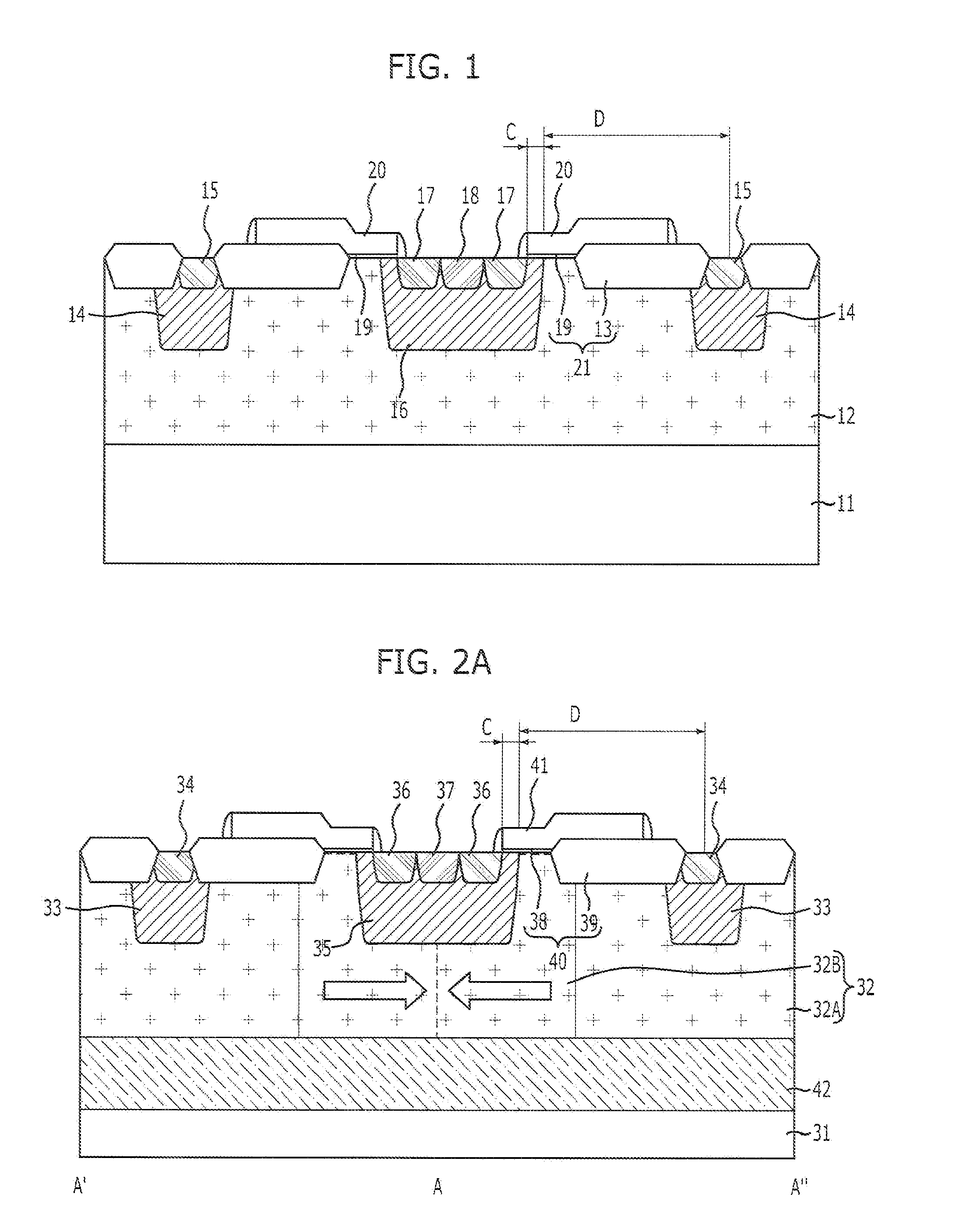

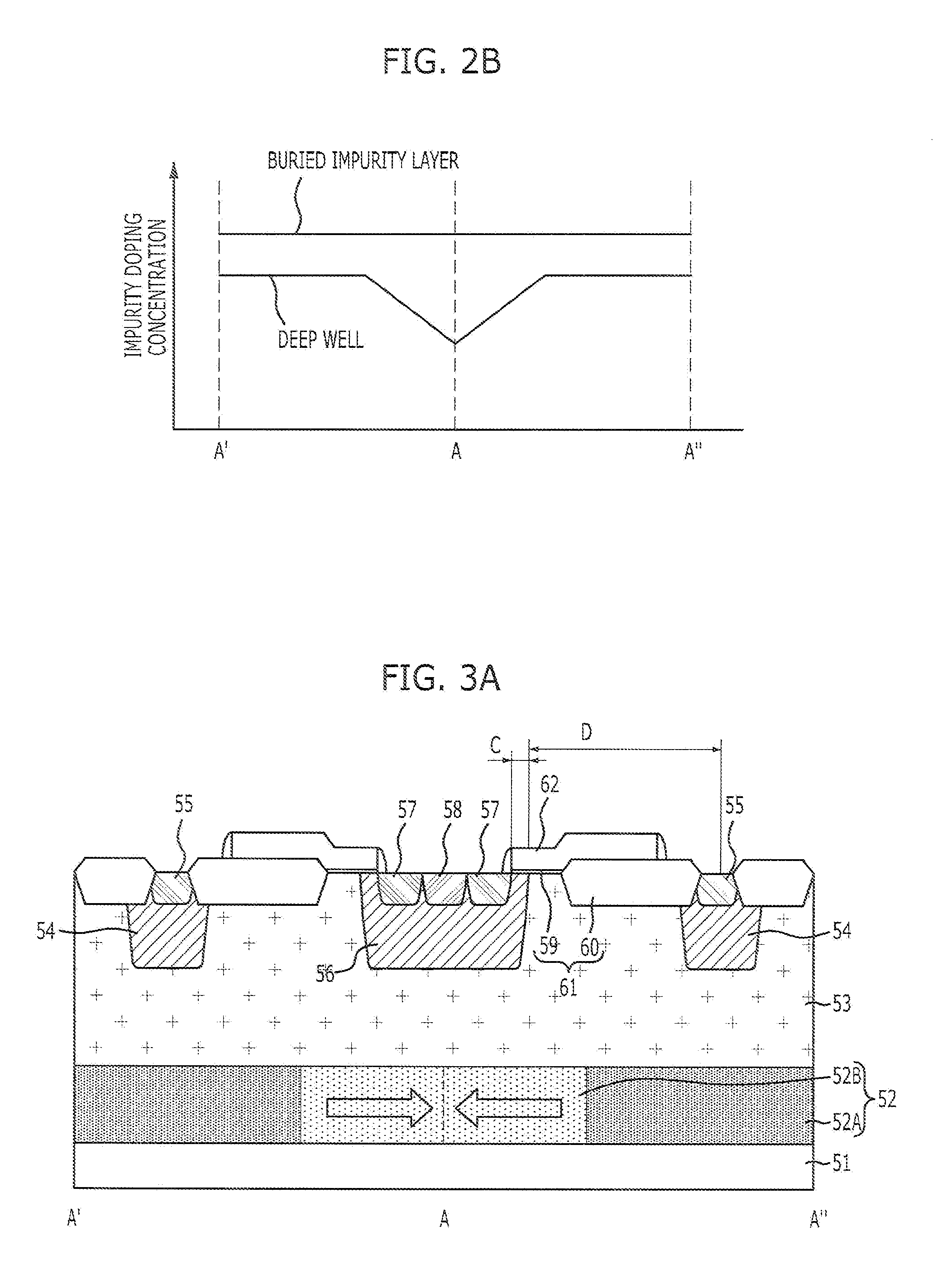

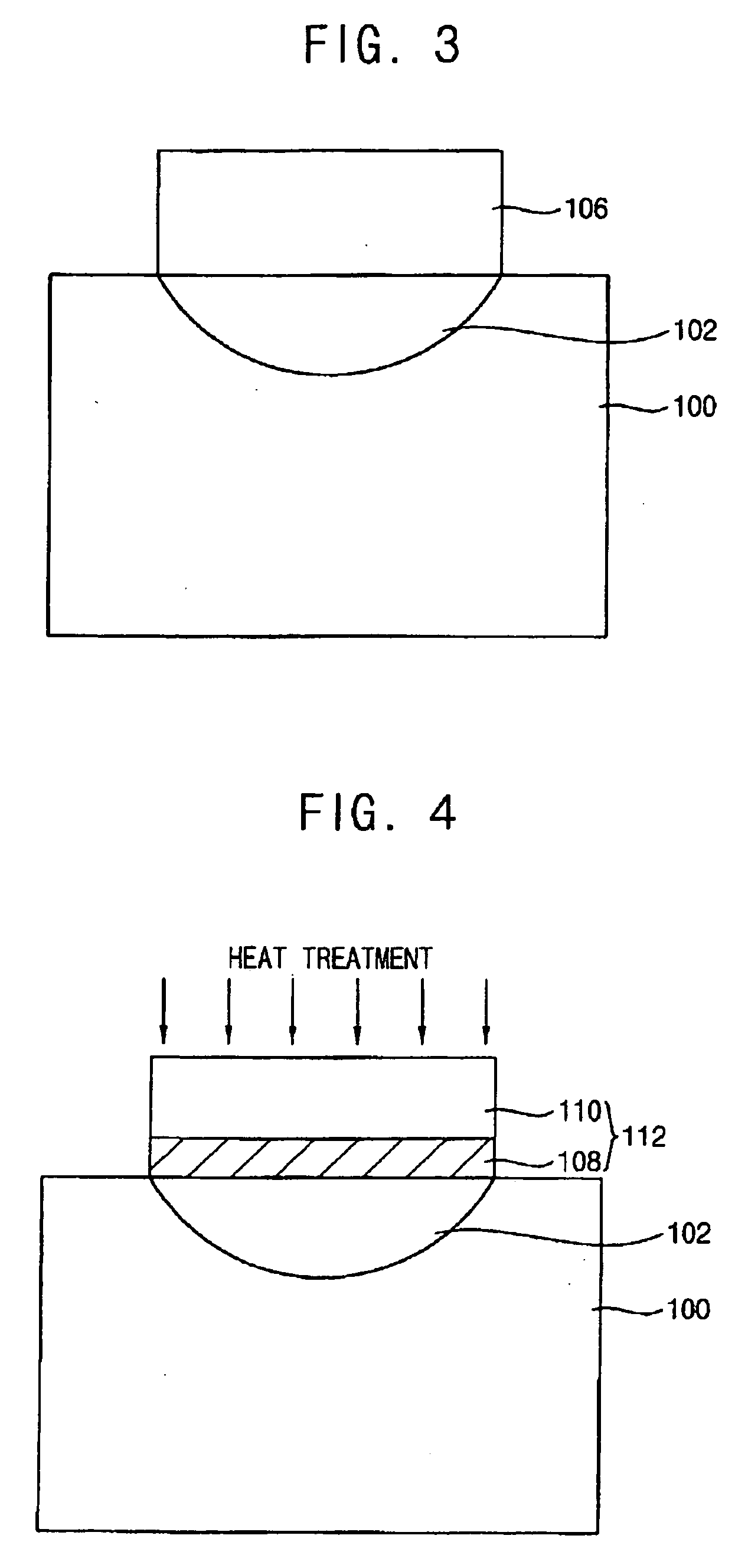

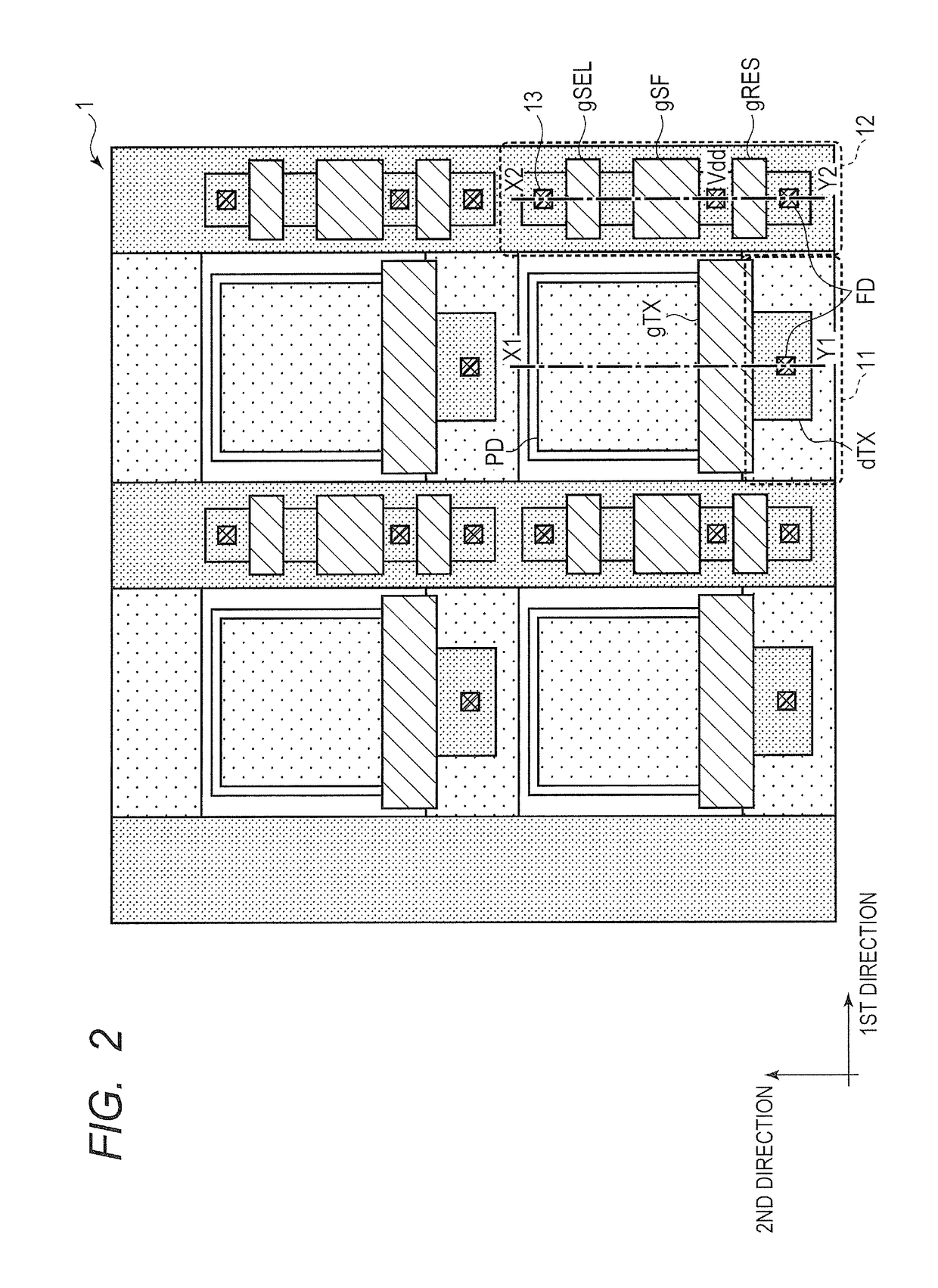

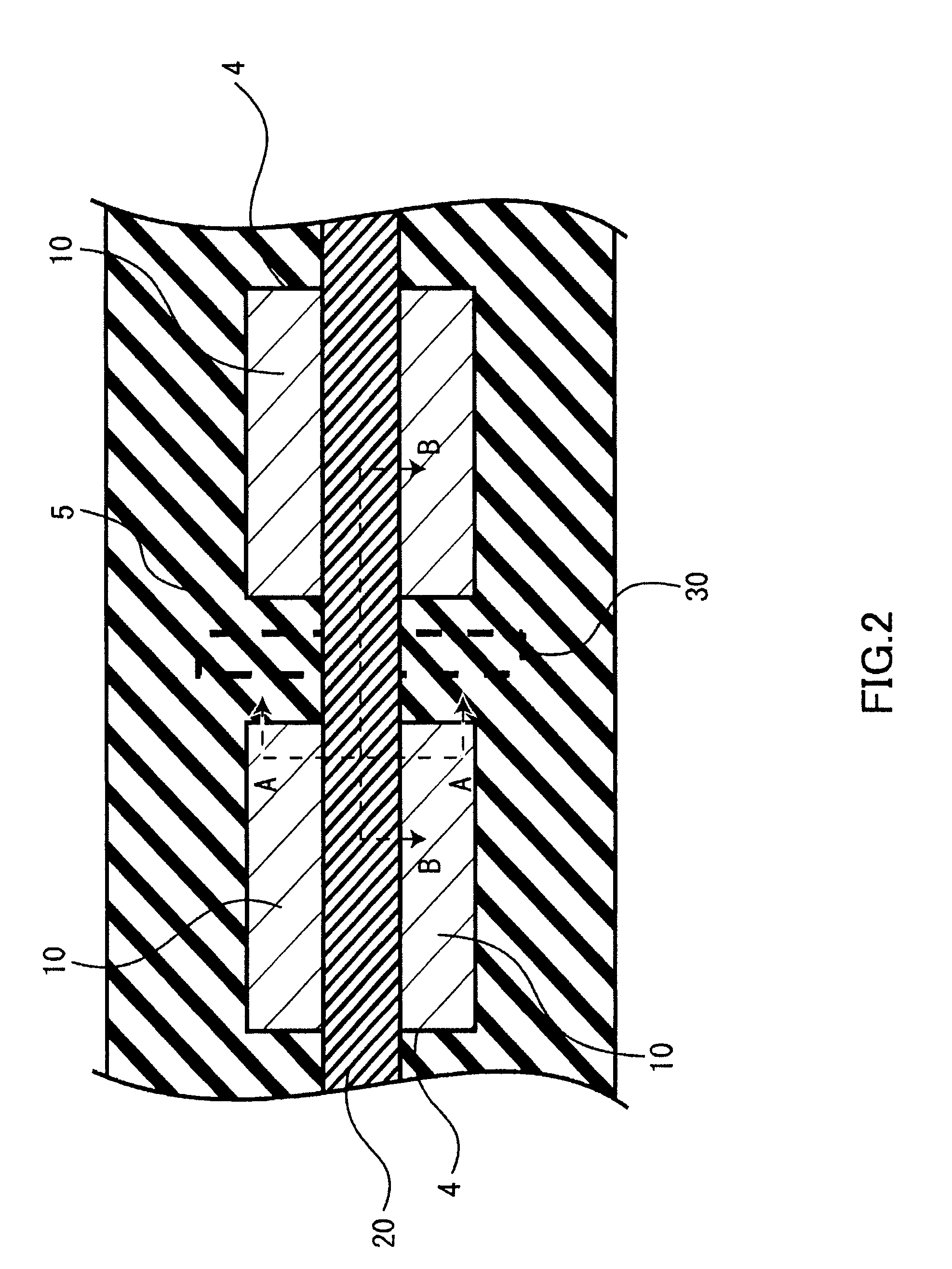

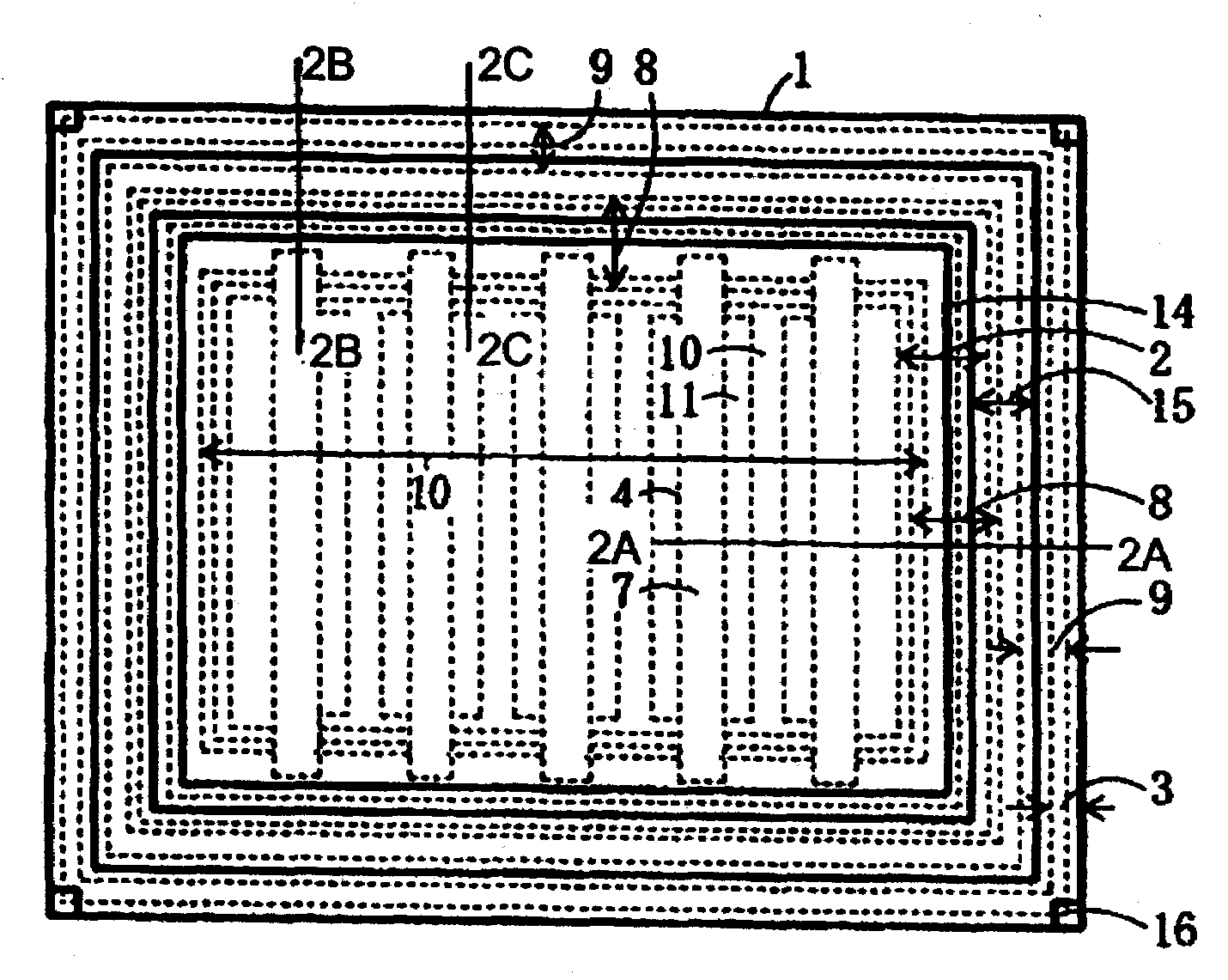

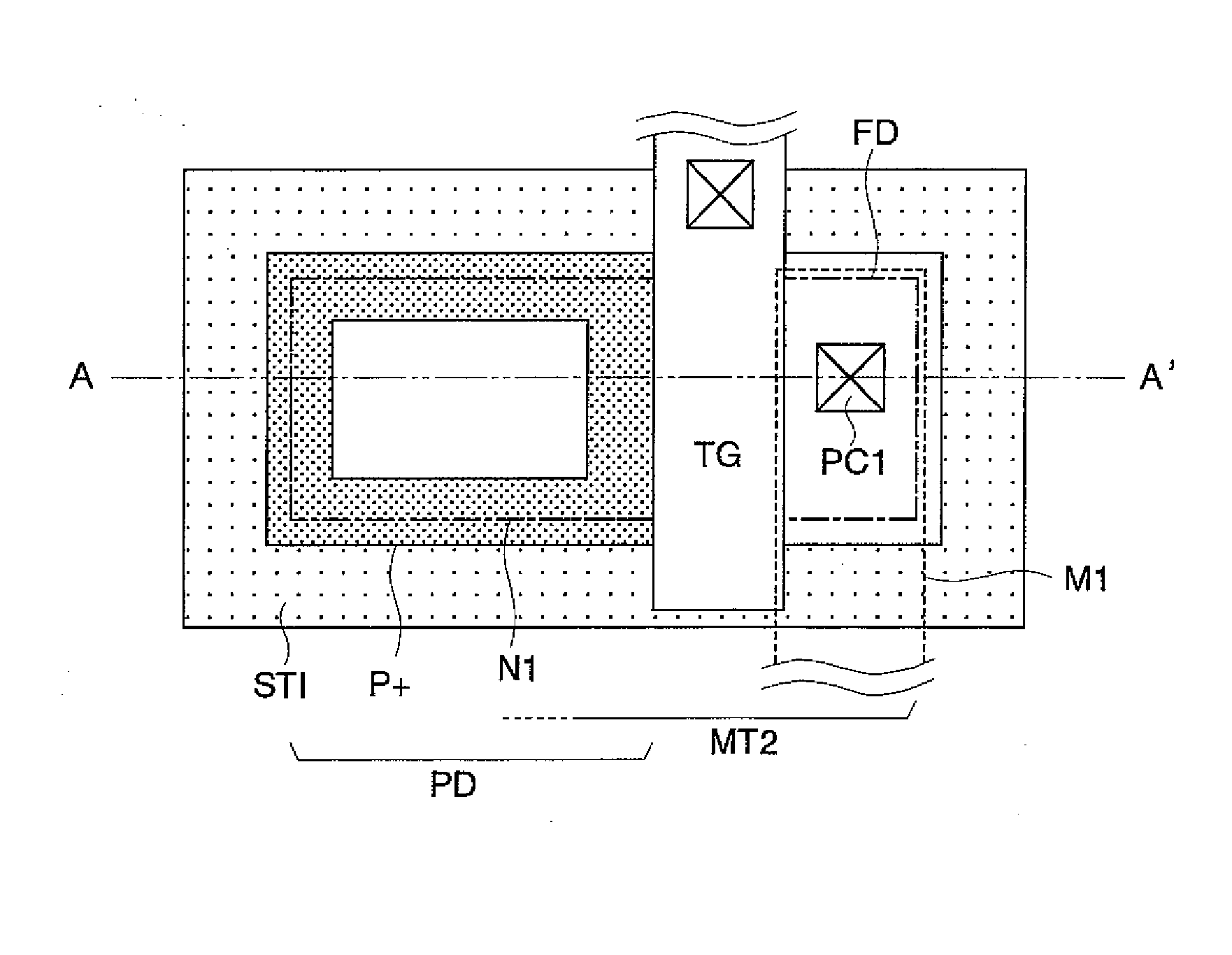

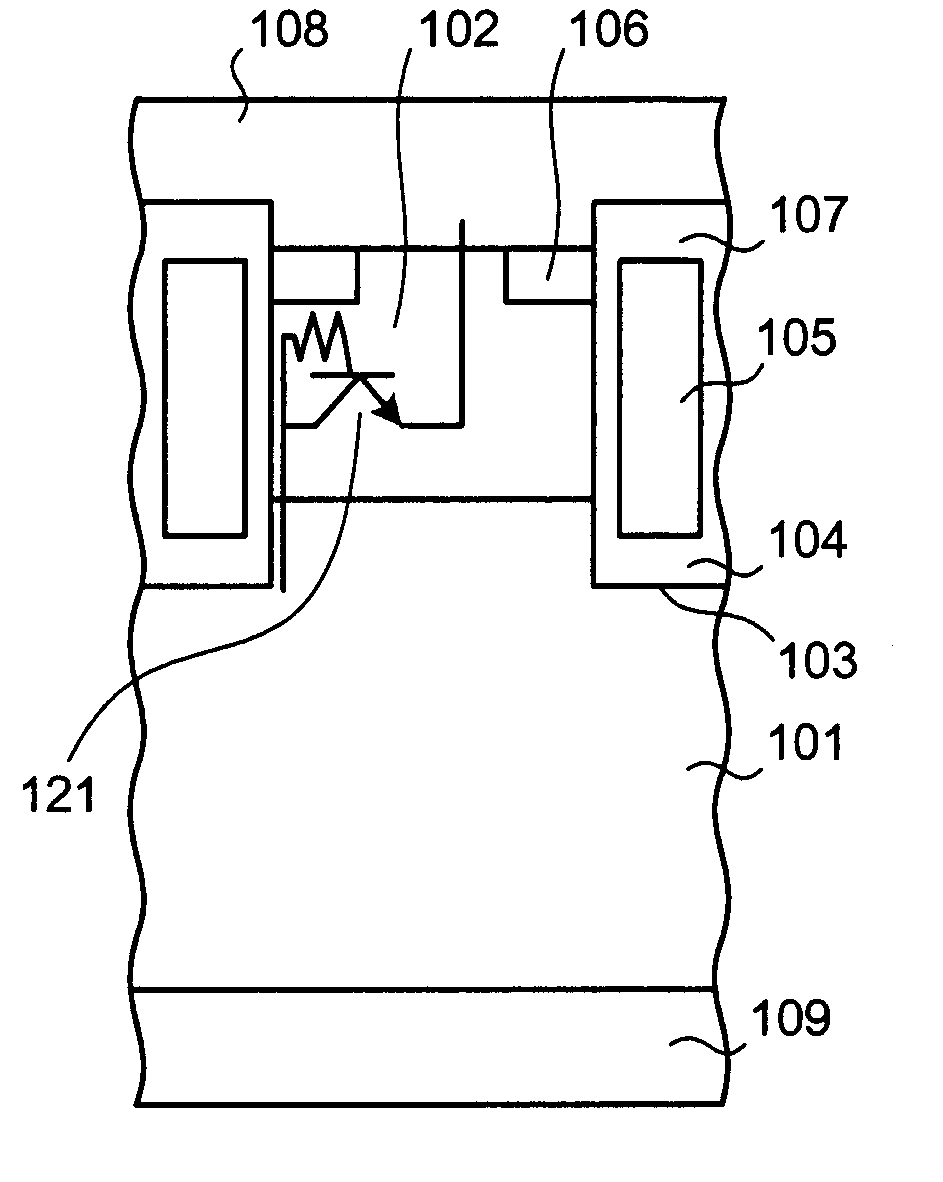

Solid-state imaging device, manufacturing method of solid-state imaging device, and imaging system

ActiveUS20180026073A1High impurity concentrationSolid-state devicesRadiation controlled devicesSolid-stateEngineering

A solid-state imaging device has: a counter dope region of a first conductivity type which is formed so as to surround a drain region of a transfer transistor of the solid-state imaging device and in which impurity concentration of the first conductivity type is lower than that of the drain region; and an isolating region of a second conductivity type which is formed in a deep region below channel regions of a plurality of transistors and in which impurity concentration of the second conductivity type is higher than that of a well region, wherein a depth position of a lower surface of the counter dope region is deeper than a depth position of a lower surface of a buried channel region.

Owner:CANON KK

Semiconductor device including resistor and method of fabricating the same

InactiveUS20060194436A1High impurity concentrationReduce areaSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

Owner:SAMSUNG ELECTRONICS CO LTD

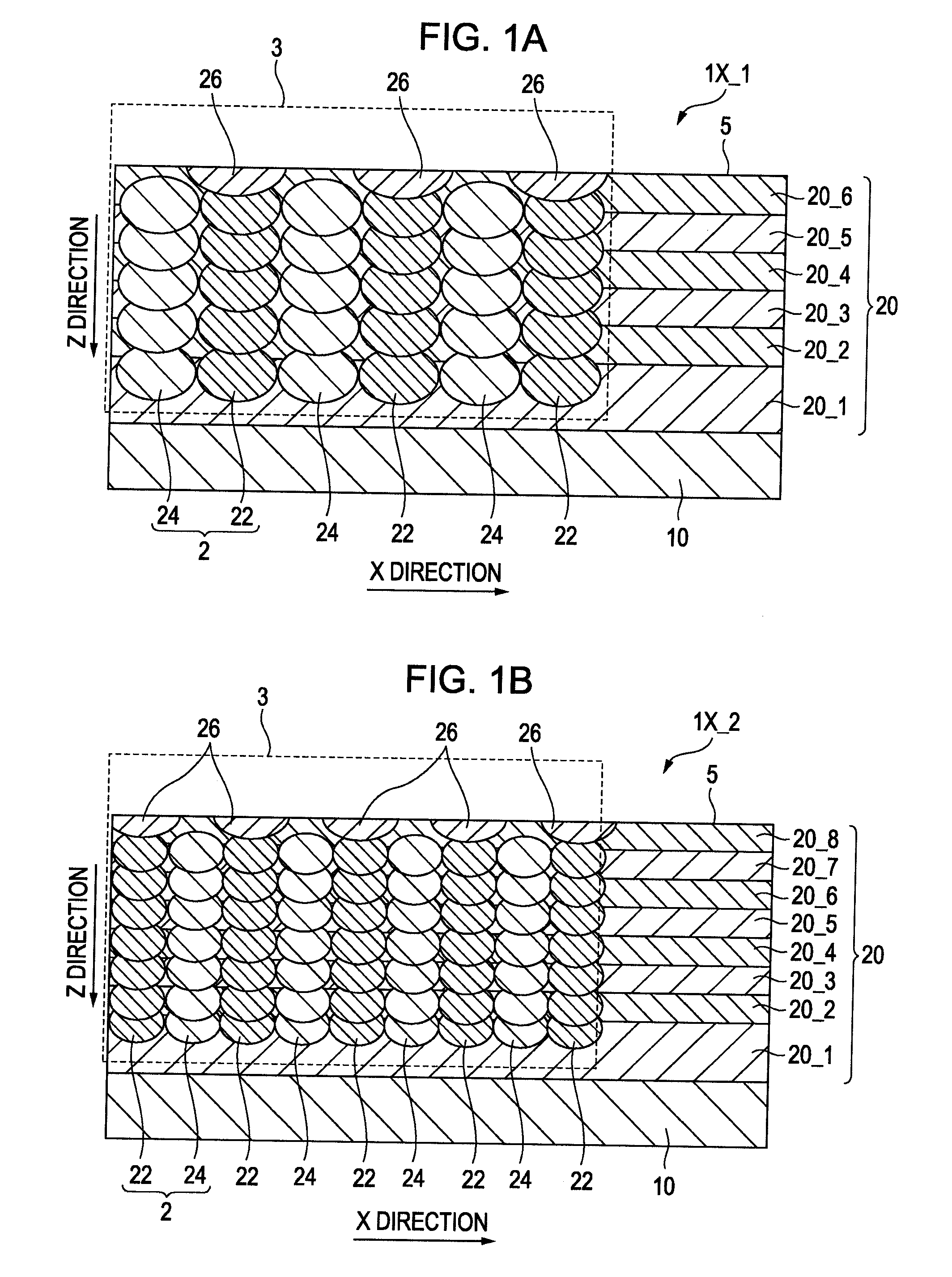

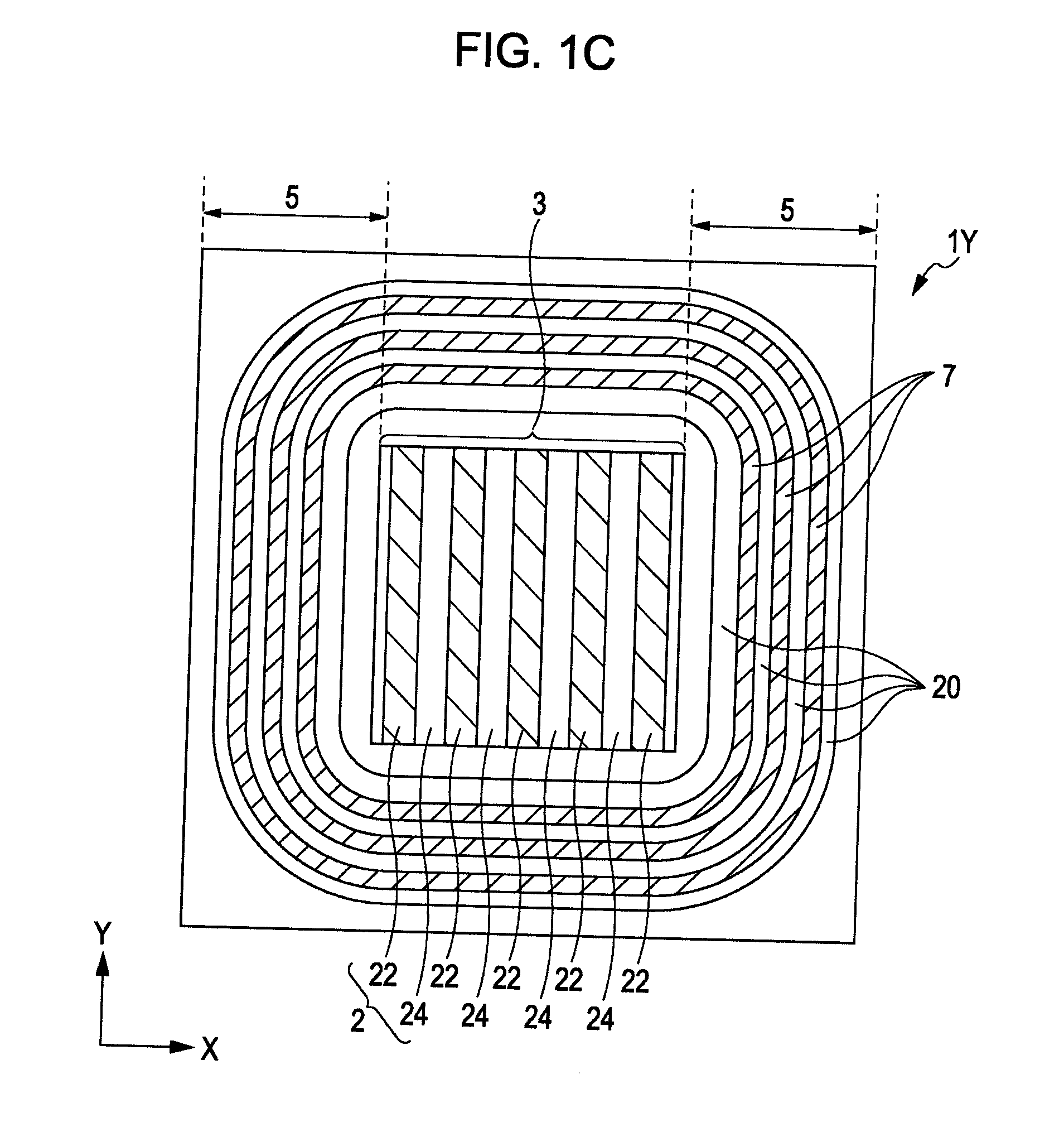

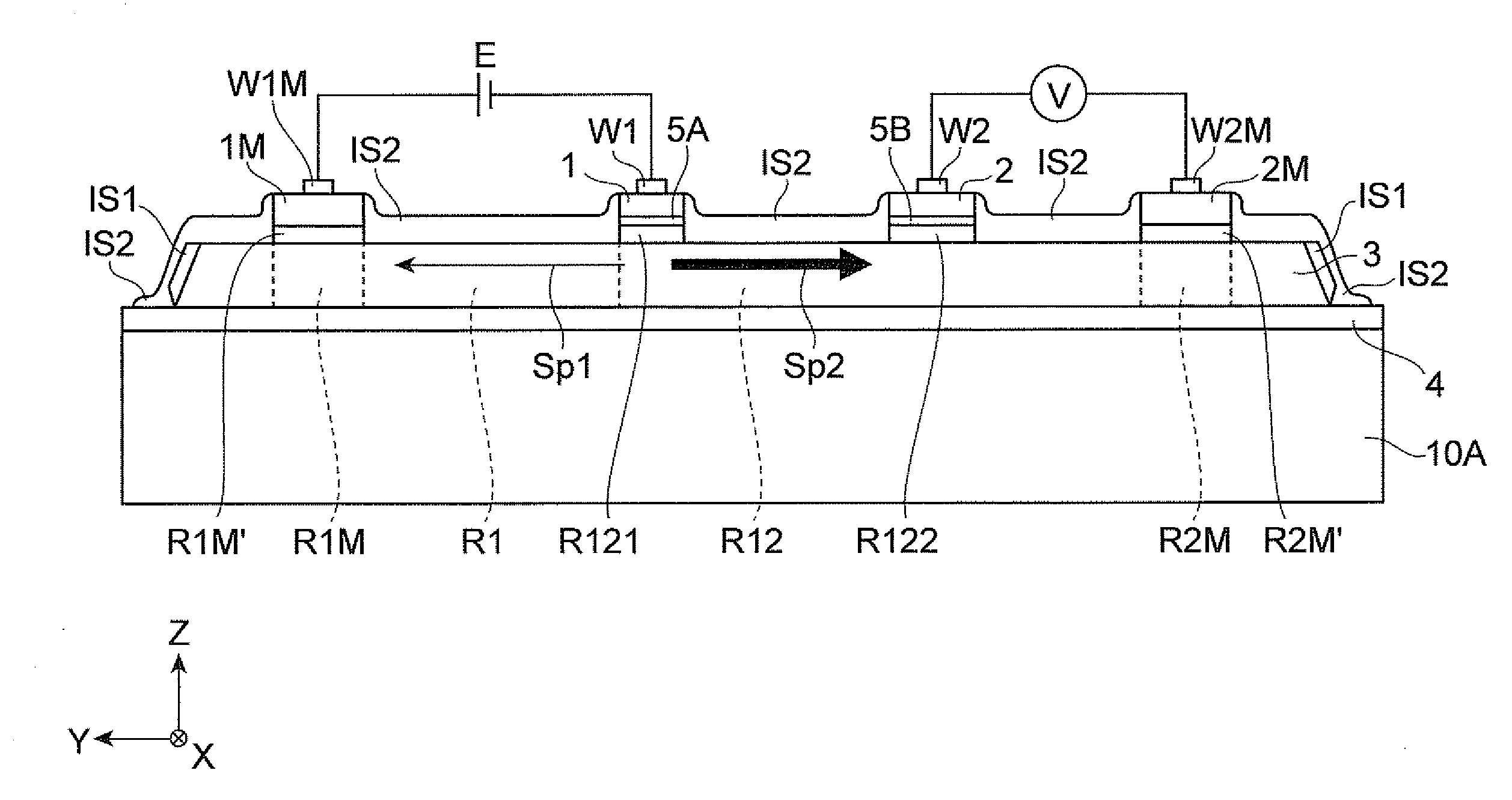

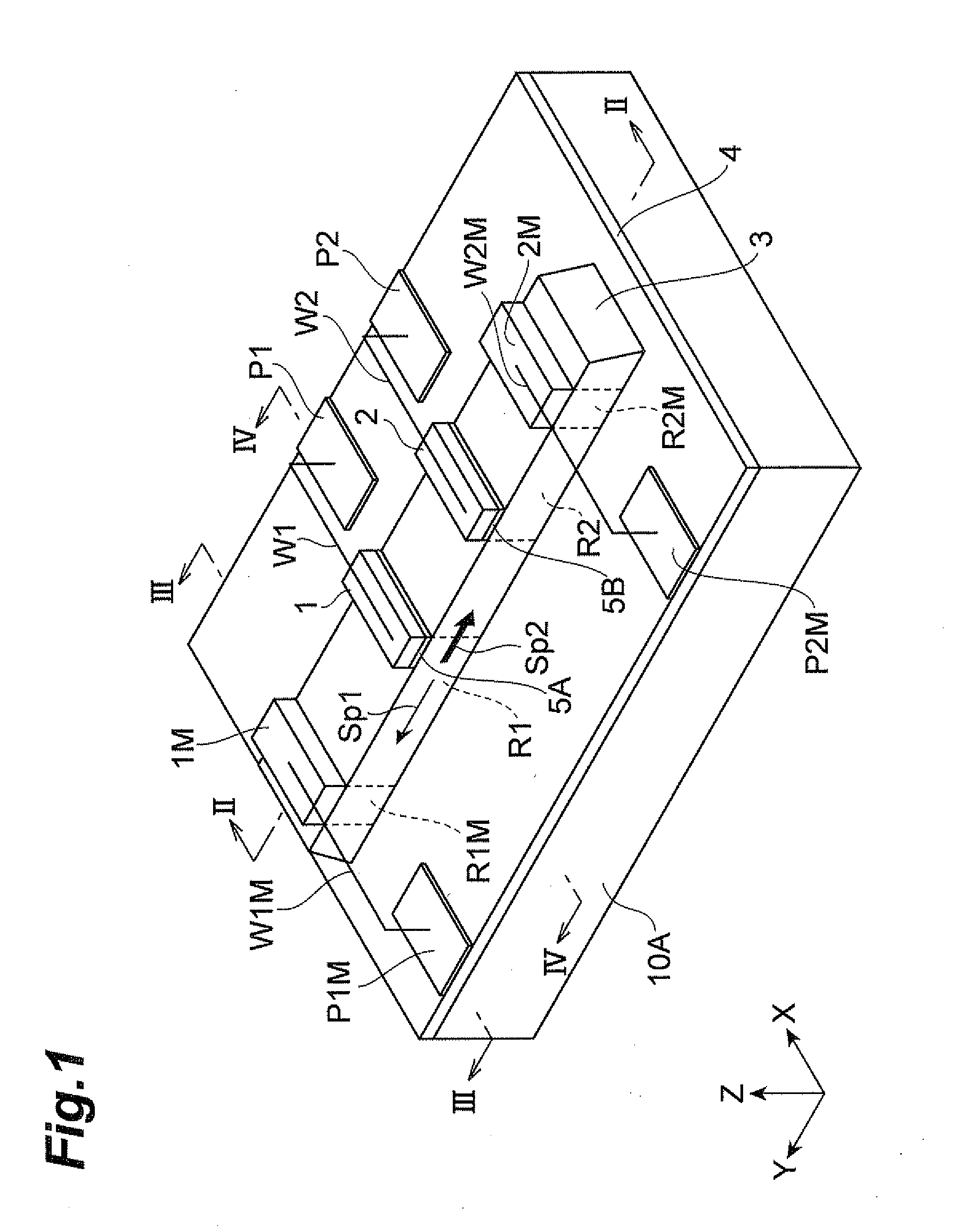

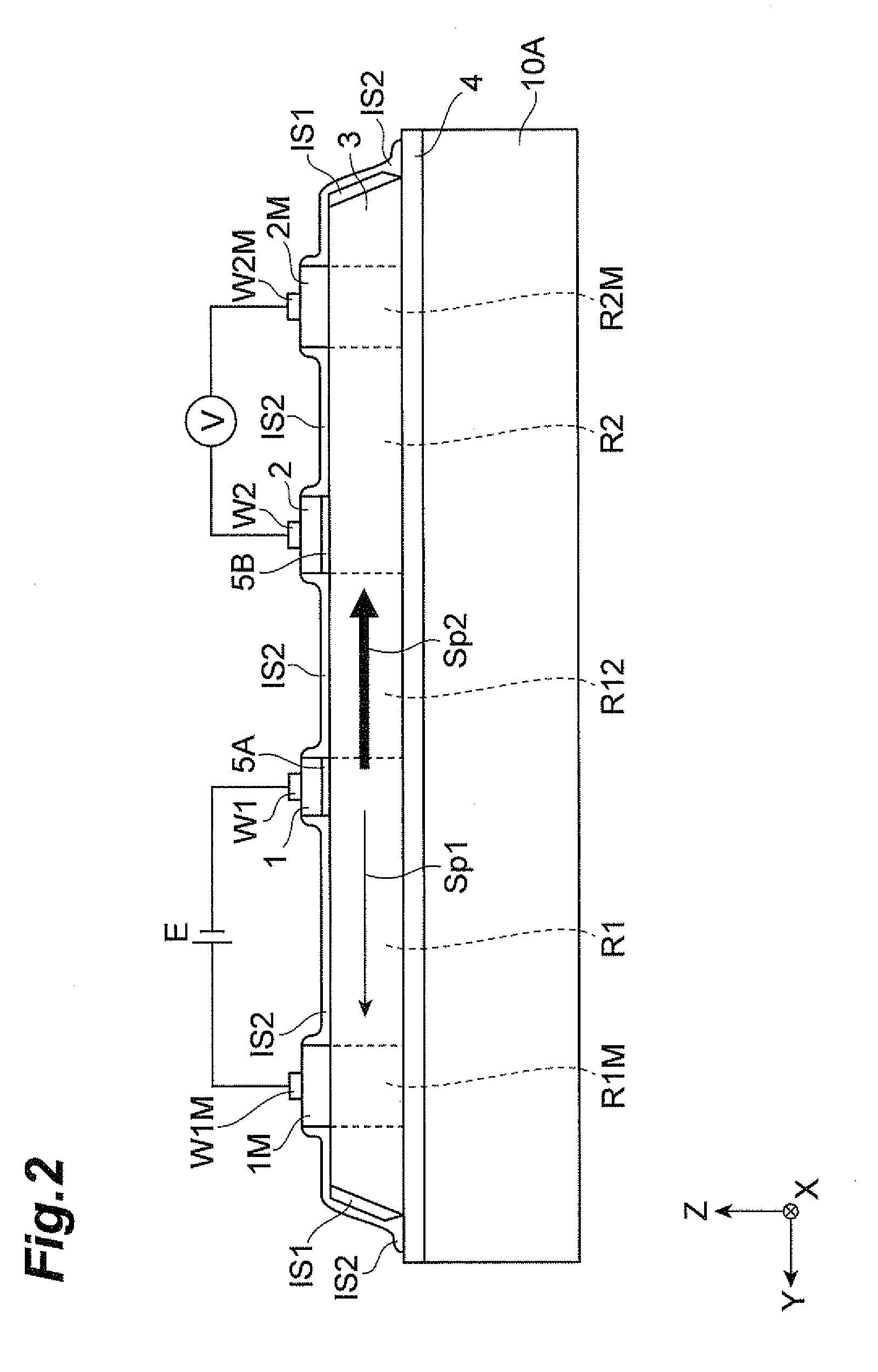

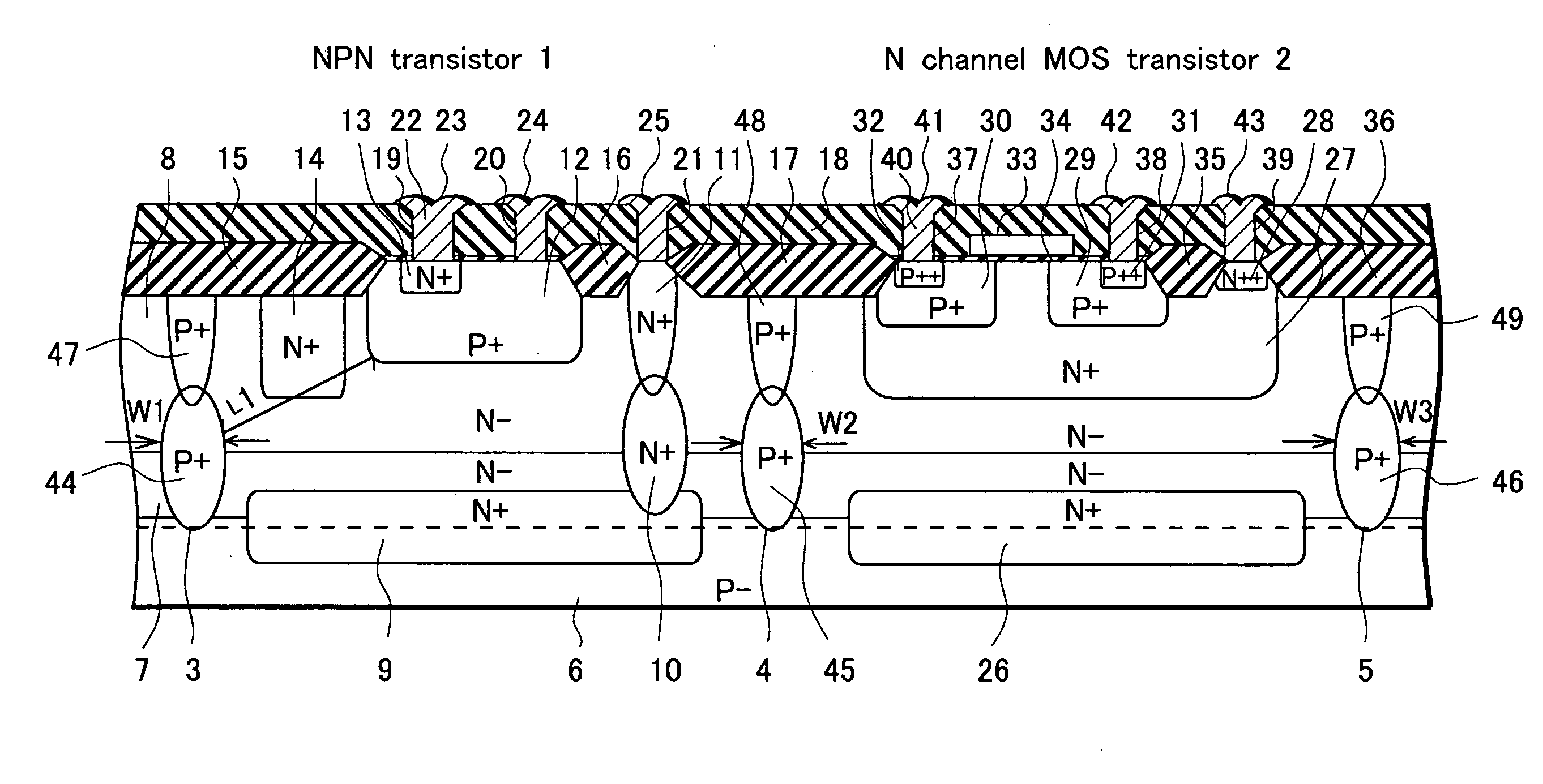

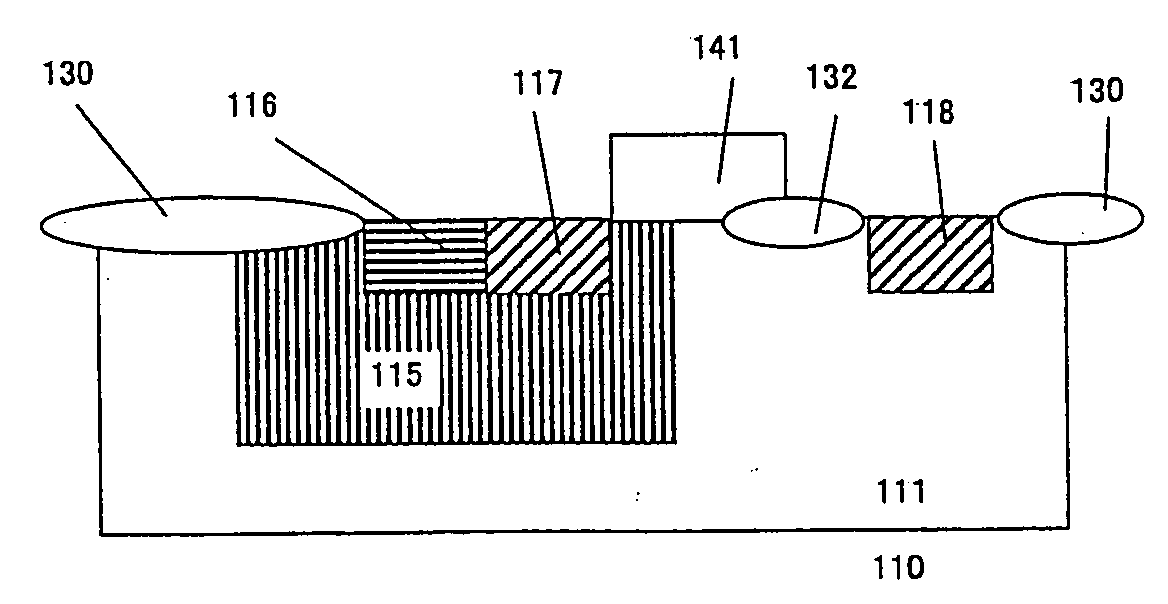

Spin transport device

ActiveUS20120267734A1High impurity concentrationEasy to detectSemiconductor devicesSpinsSemiconductor

A spin transport device includes a semiconductor layer 3, a first ferromagnetic layer 1 provided on the semiconductor layer 3 via a first tunnel barrier layer 5A, and a second ferromagnetic layer 2 provided on the semiconductor layer 3 via a second tunnel barrier layer 5B to be spaced from the first ferromagnetic layer 1, and the semiconductor layer 3 includes a first region RI broadening in a direction away from the first ferromagnetic layer 1 along a direction orthogonal to a thickness direction from the first ferromagnetic layer 1, and a second region R12 extending in a direction toward the second ferromagnetic layer 2 along the direction orthogonal to the thickness direction from the first ferromagnetic layer 1. The second region R12 has a relatively higher impurity concentration than the first region R1.

Owner:TDK CORPARATION

Semiconductor device and manufacturing method of the same

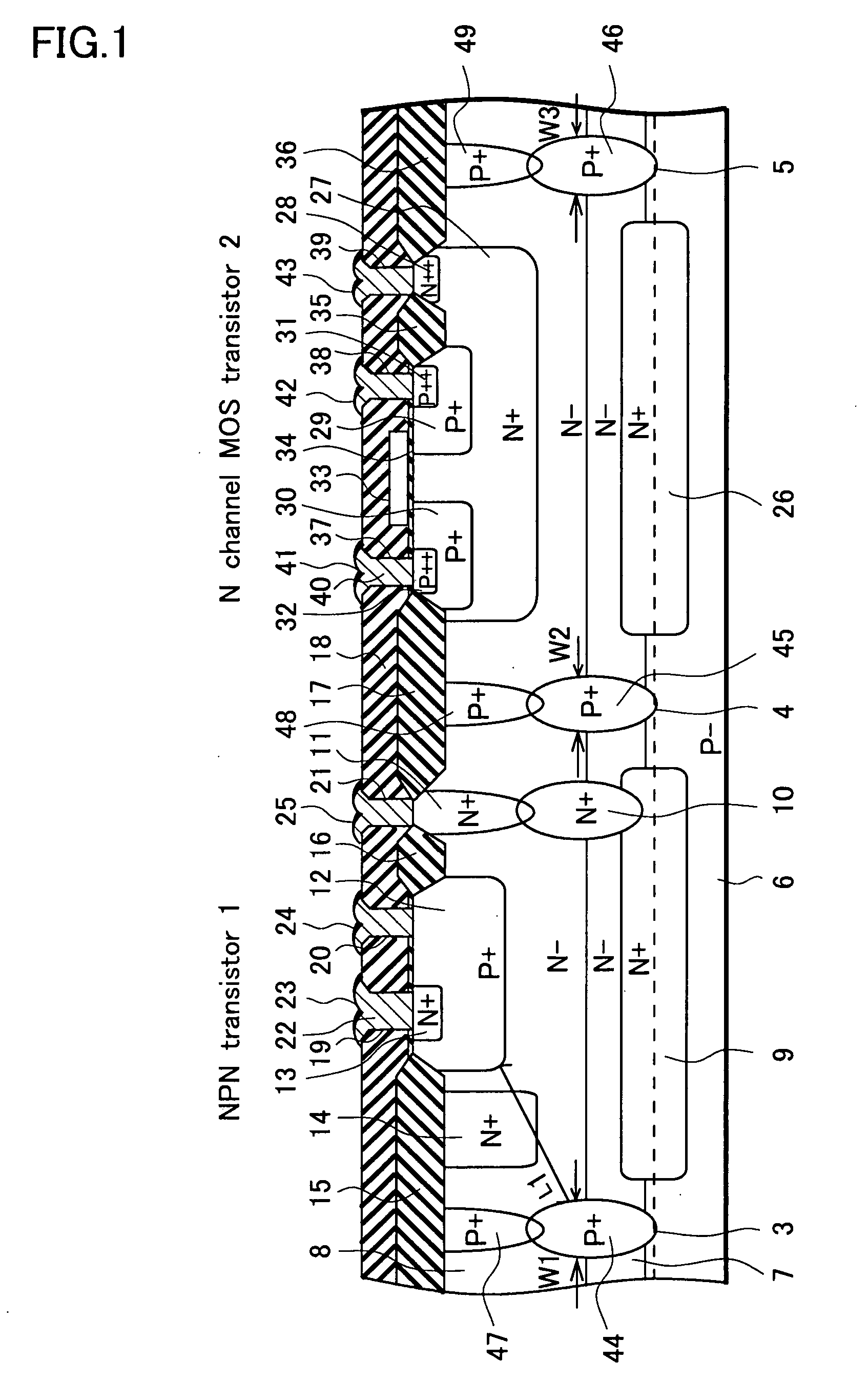

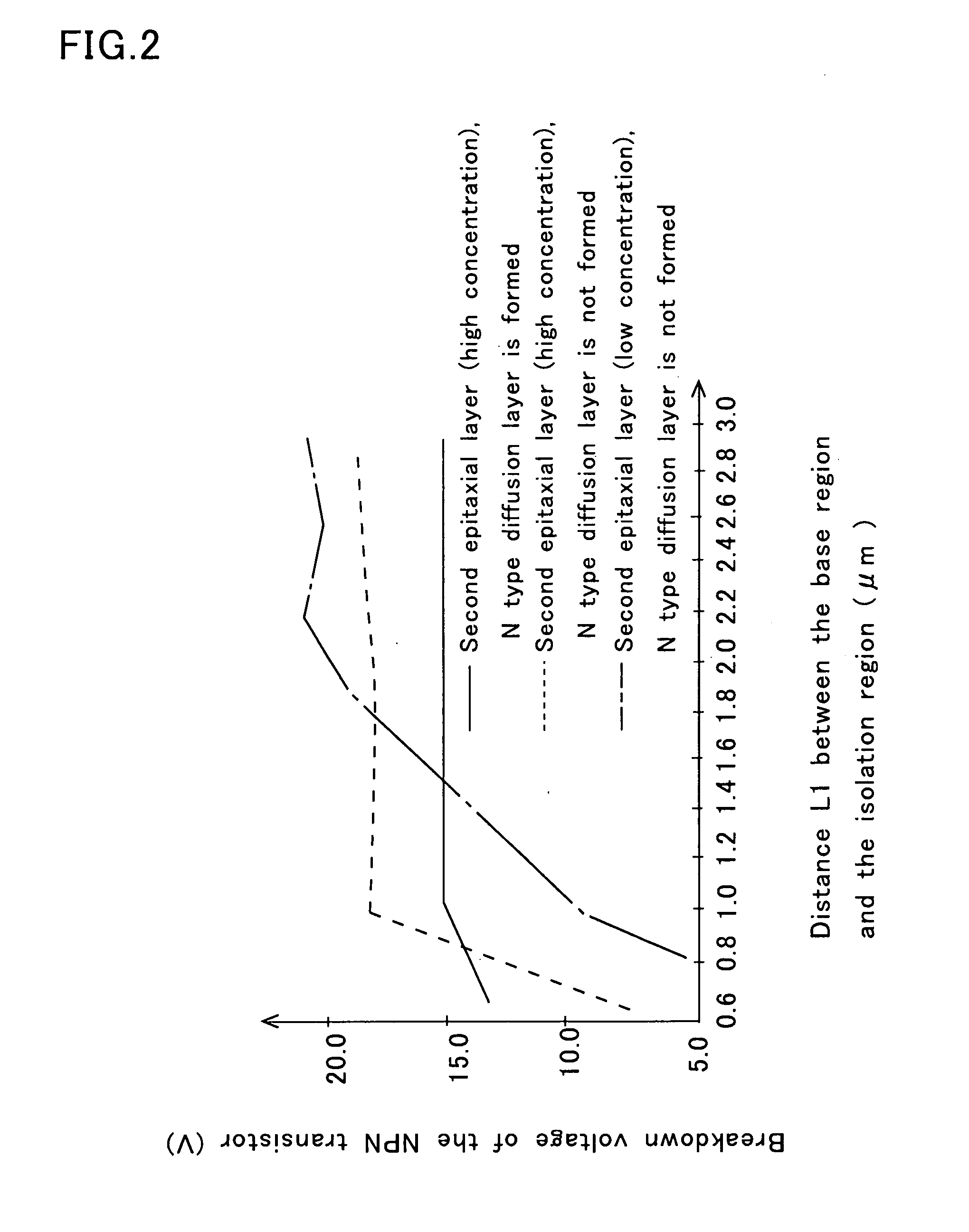

InactiveUS20070145520A1Improved breakdown voltage characteristicsDifficulty occurTransistorSemiconductor/solid-state device manufacturingDevice materialSemiconductor

In a semiconductor device of the present invention, two epitaxial layers are formed on a P type single crystal silicon substrate. One of the epitaxial layers has an impurity concentration higher than that of the other epitaxial layer. The epitaxial layers are divided into a plurality of element formation regions by isolation regions. In one of the element formation regions, an NPN transistor is formed. Moreover, between a P type diffusion layer, which is used as a base region of the NPN transistor, and a P type isolation region, an N type diffusion layer is formed. Use of this structure makes it hard for a short-circuit to occur between the base region and the isolation region. Thus, the breakdown voltage characteristics of the NPN transistor can be improved.

Owner:SEMICON COMPONENTS IND LLC

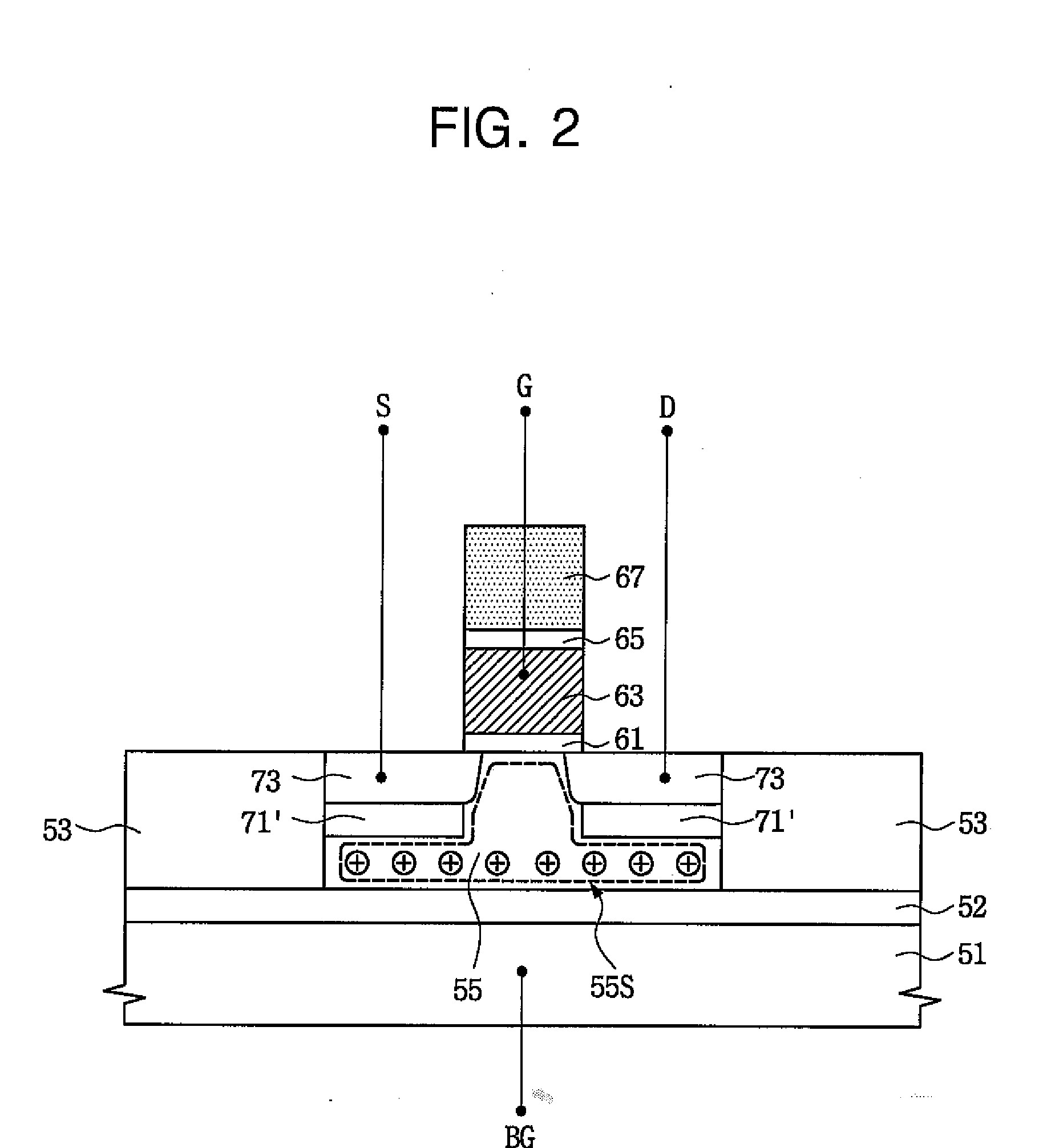

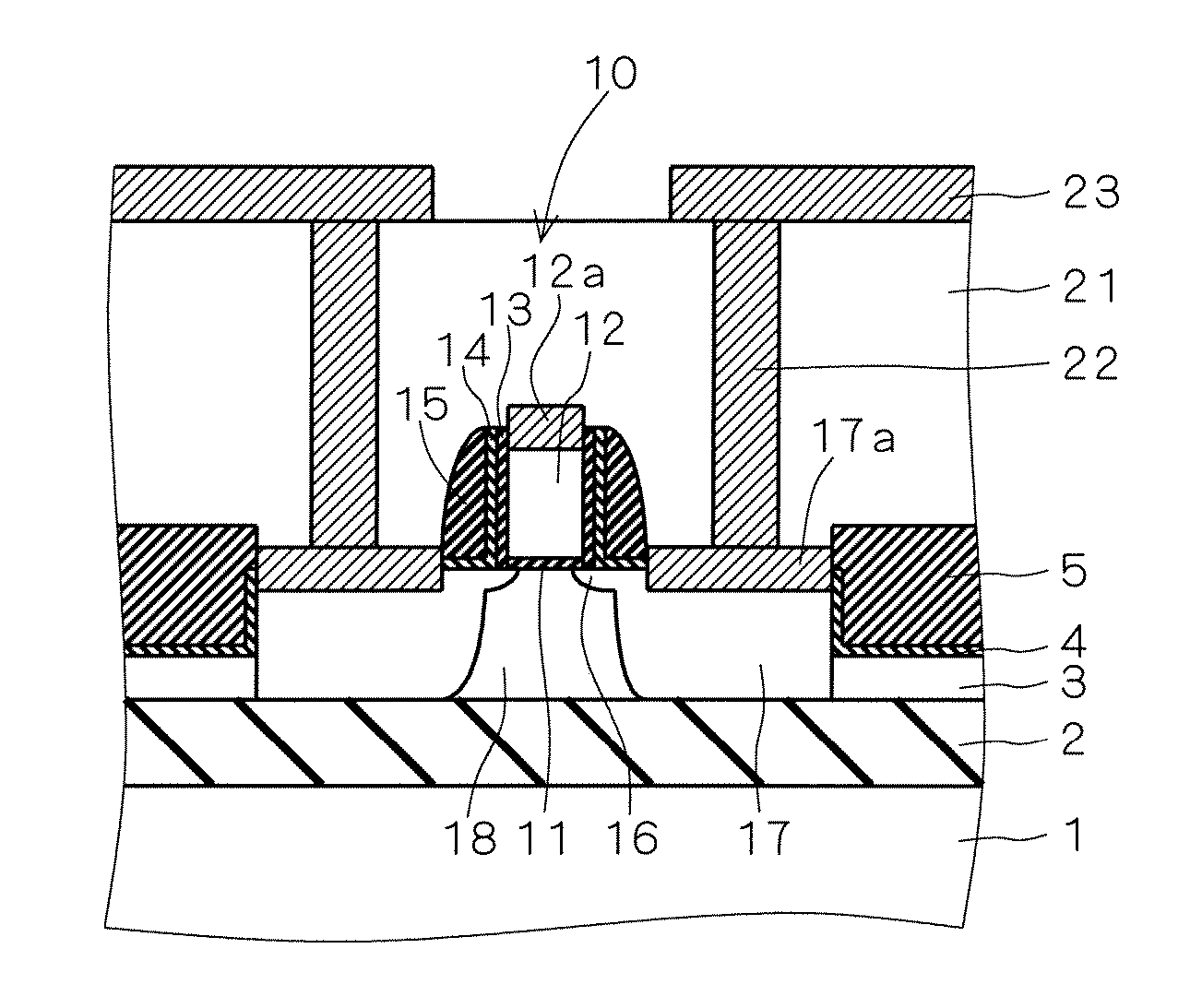

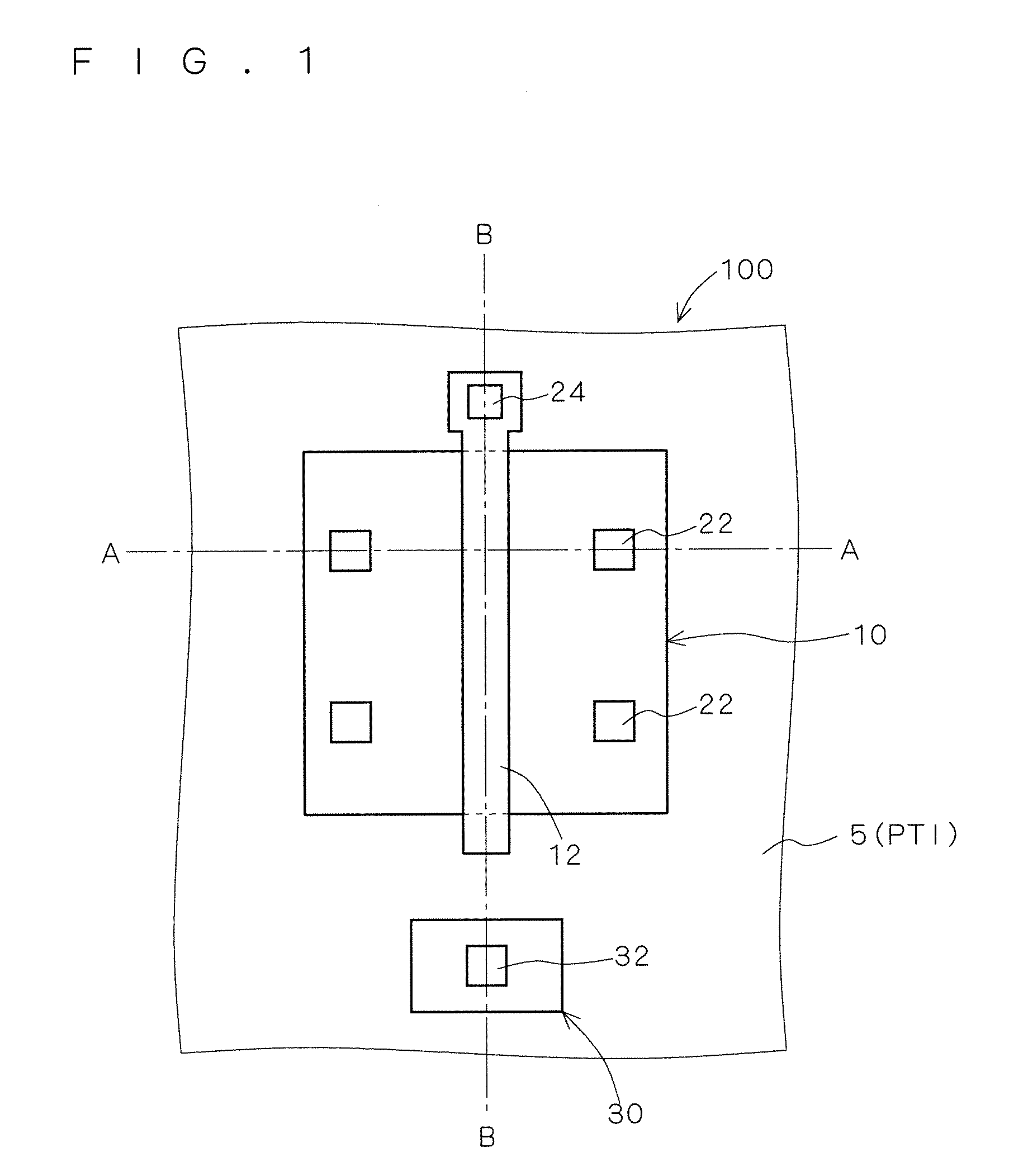

Semiconductor device and method of manufacturing the same

InactiveUS20060289904A1Reduce leakage currentReduce resistanceSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

In the semiconductor device which has partial trench isolation as isolation between elements formed in an SOI substrate, resistance reduction of the source drain of a transistor and reduction of leakage current are aimed at. A MOS transistor is formed in the active region specified by the isolation insulating layer in the SOI layer formed on the buried oxide film layer (BOX layer). An isolation insulating layer is a partial trench isolation which has not reached a BOX layer, and source and drain regions include the first and the second impurity ion which differs in a mass number mutually.

Owner:RENESAS TECH CORP

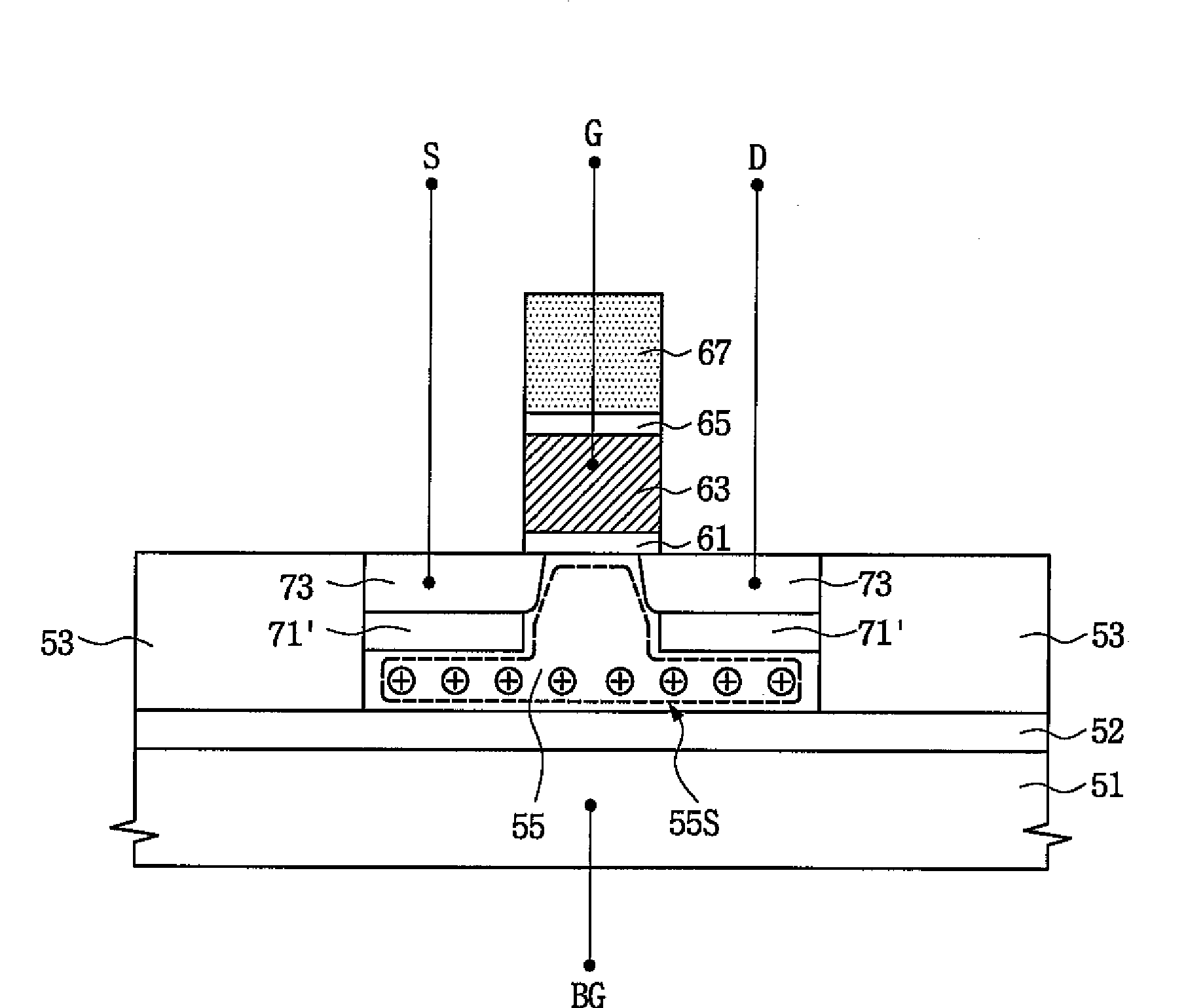

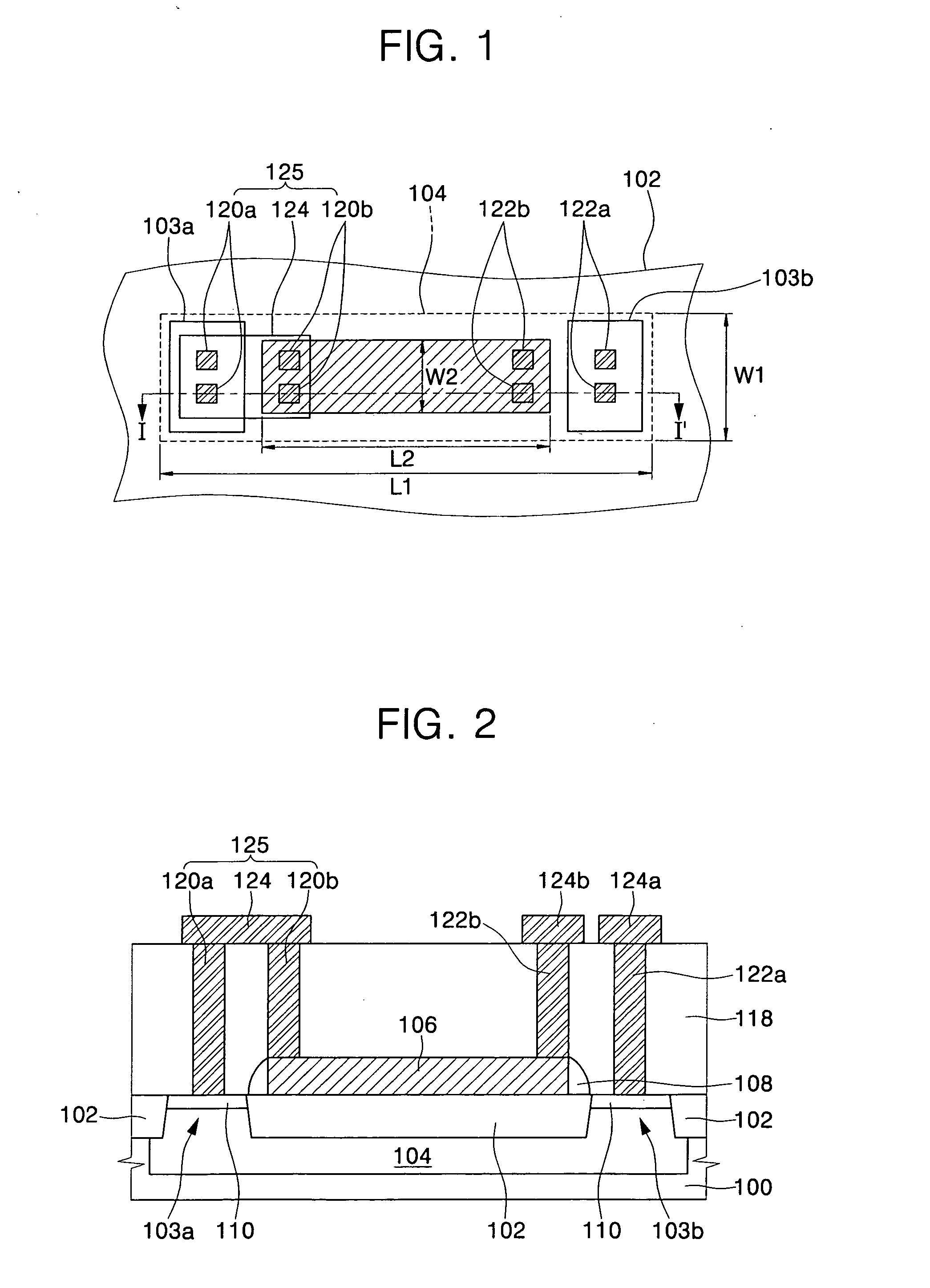

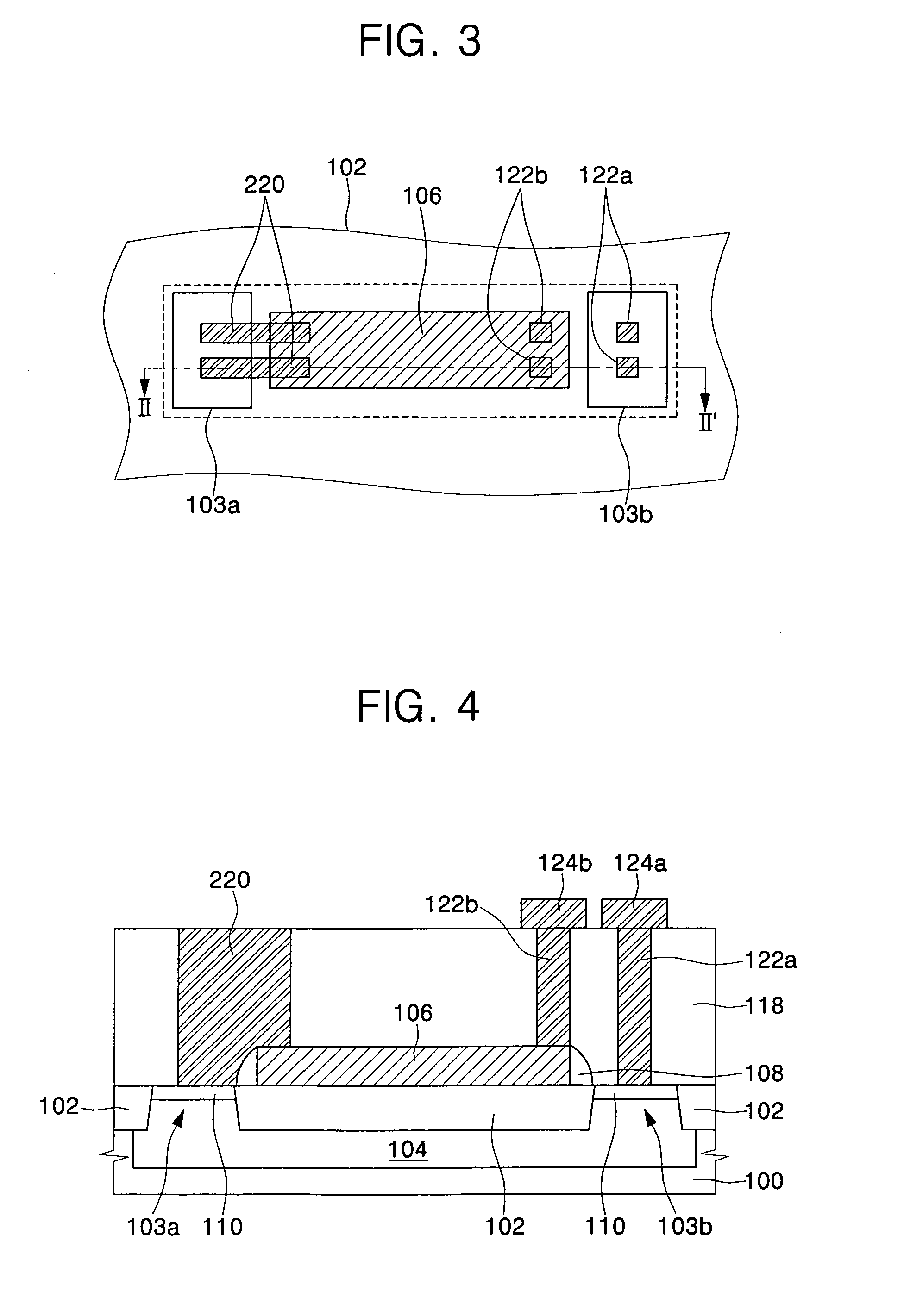

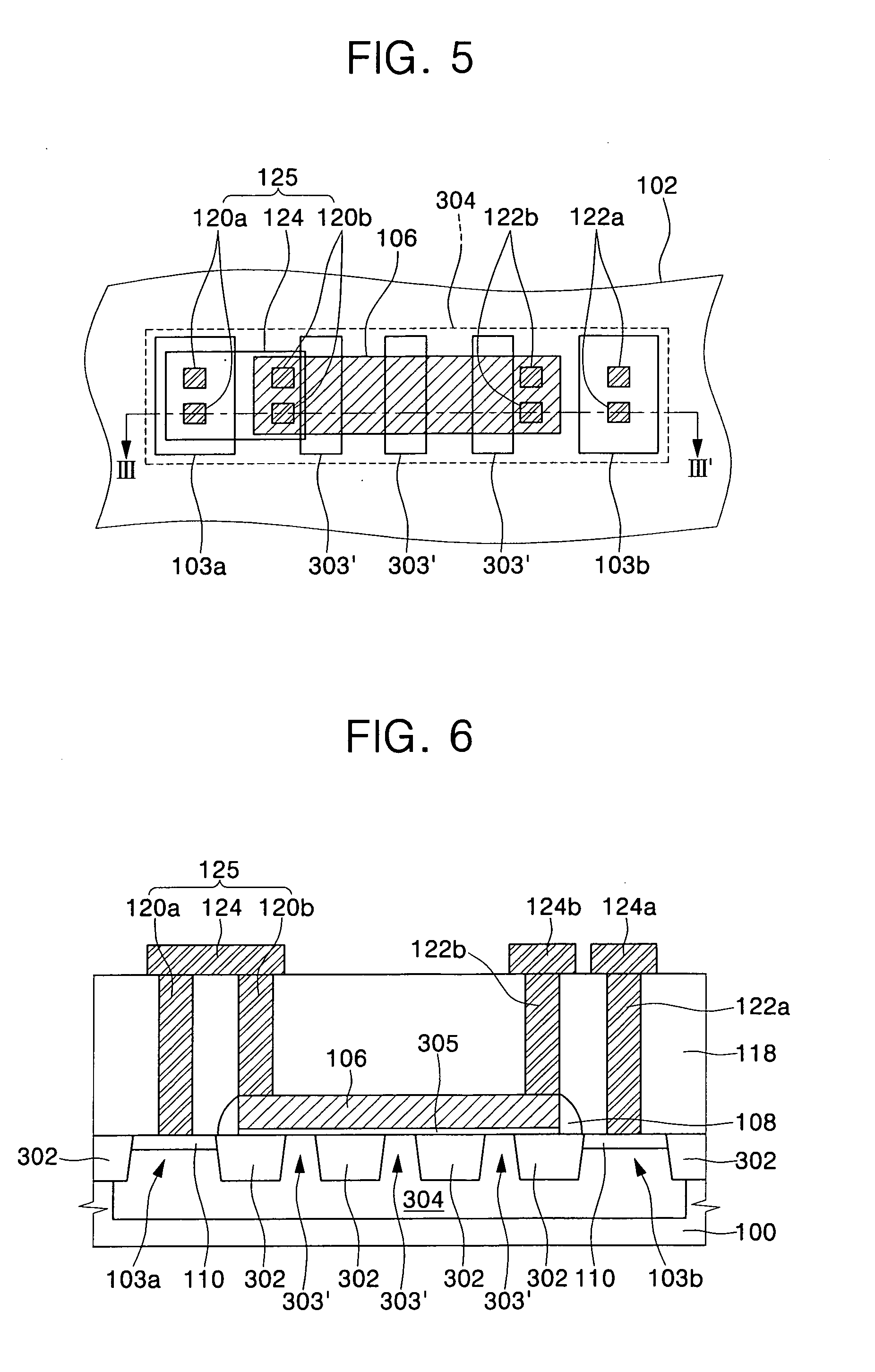

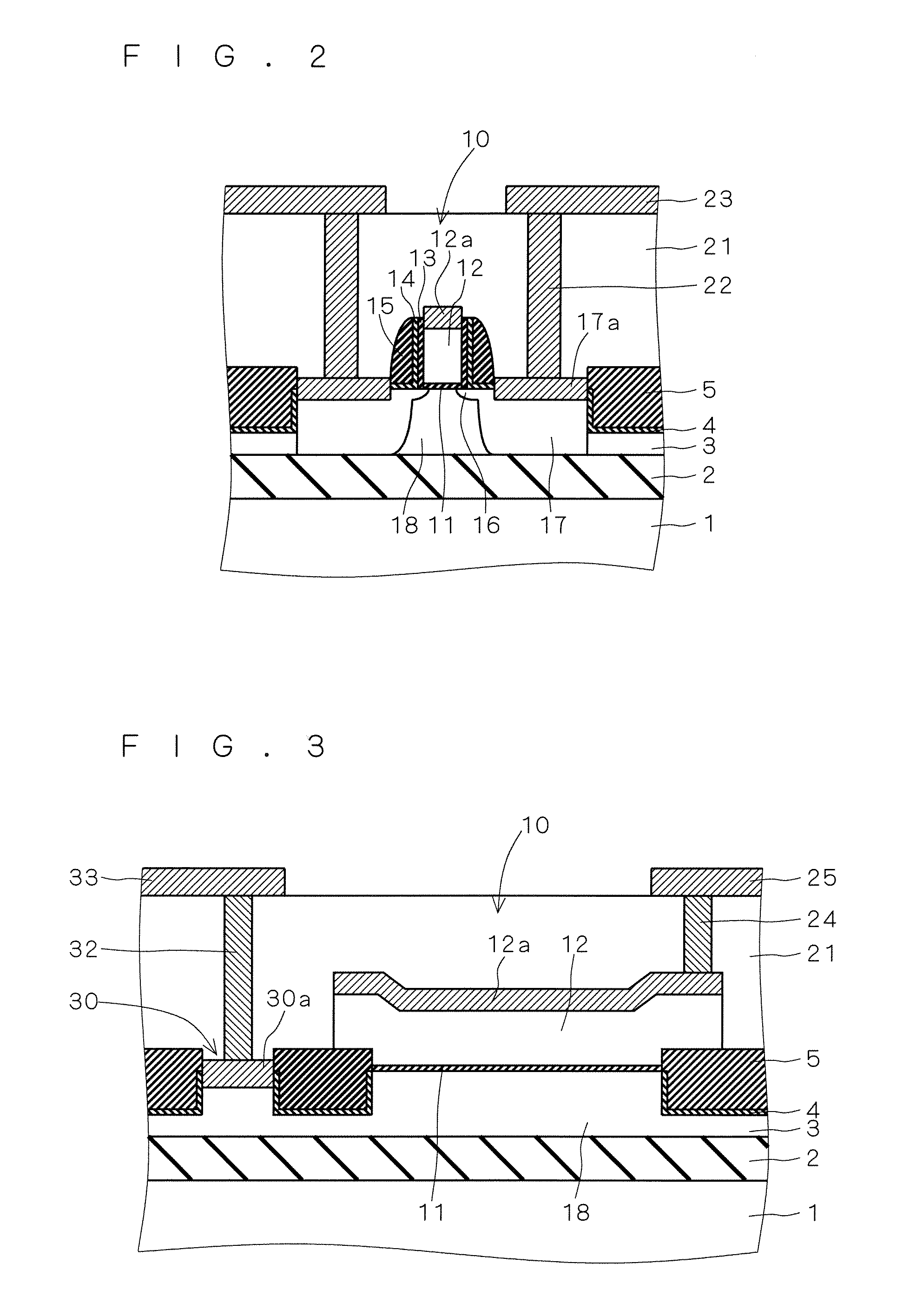

Optical detection element and solid-state image pickup device

ActiveUS20170133419A1Improve voltage sensitivityImprove toleranceSolid-state devicesDiodeEngineeringCharge generation

A radiation tolerant optical detection element includes: a p-type base-body region; a gate insulating film provided on an upper surface of the base-body region; an n-type buried charge-generation region buried in an upper portion of the base-body region; an n-type charge-readout region buried in an upper portion of the base-body region on the inner-contour side of the buried charge-generation region; an n-type reset-drain region buried on the inner-contour side of the charge-readout region; a transparent electrode provided on the gate insulating film above the buried charge-generation region; and a reset-gate electrode provided on a portion of the gate insulating film between the charge-readout region and the reset-drain region.

Owner:BROOKMAN TECH +2

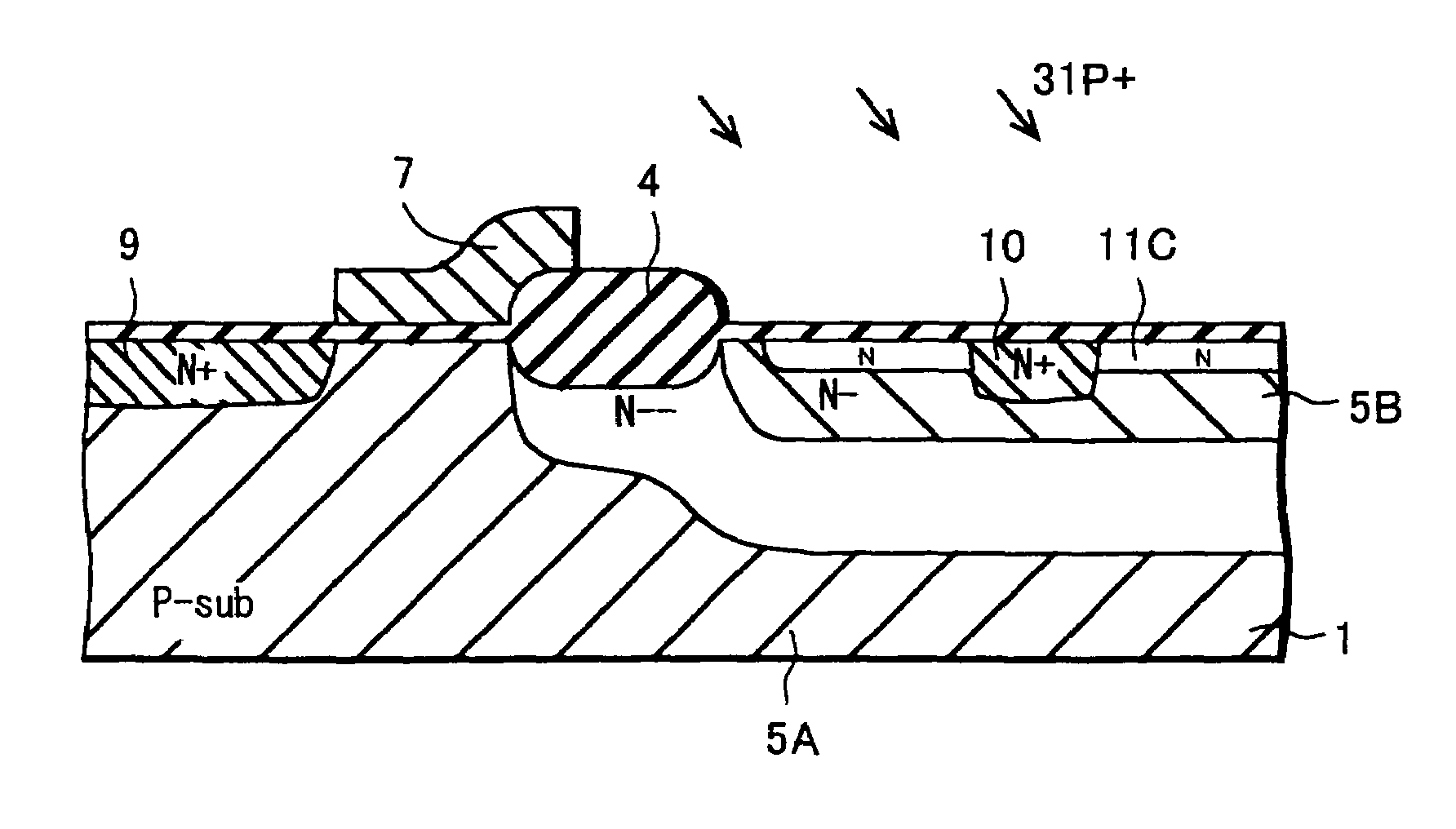

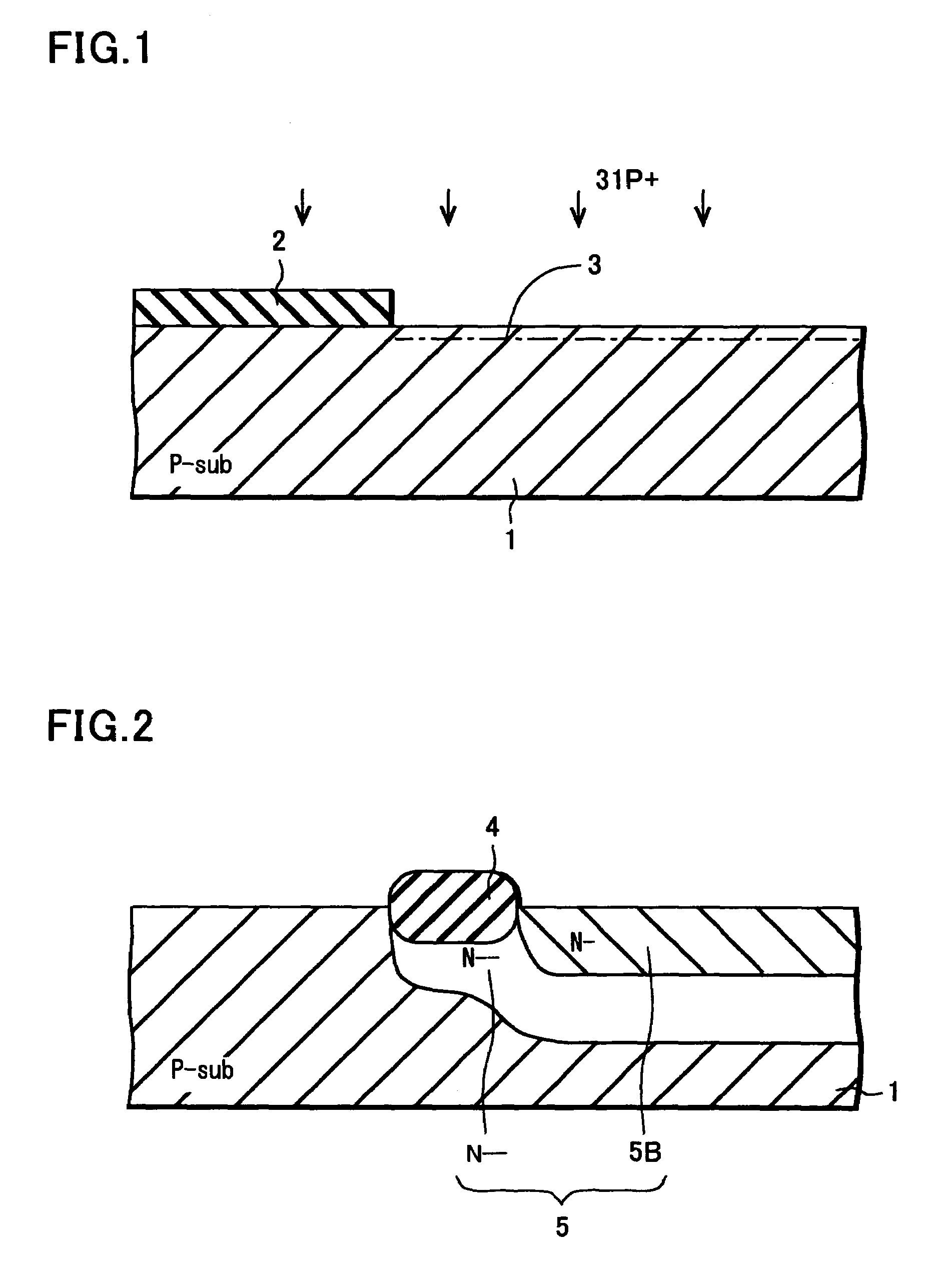

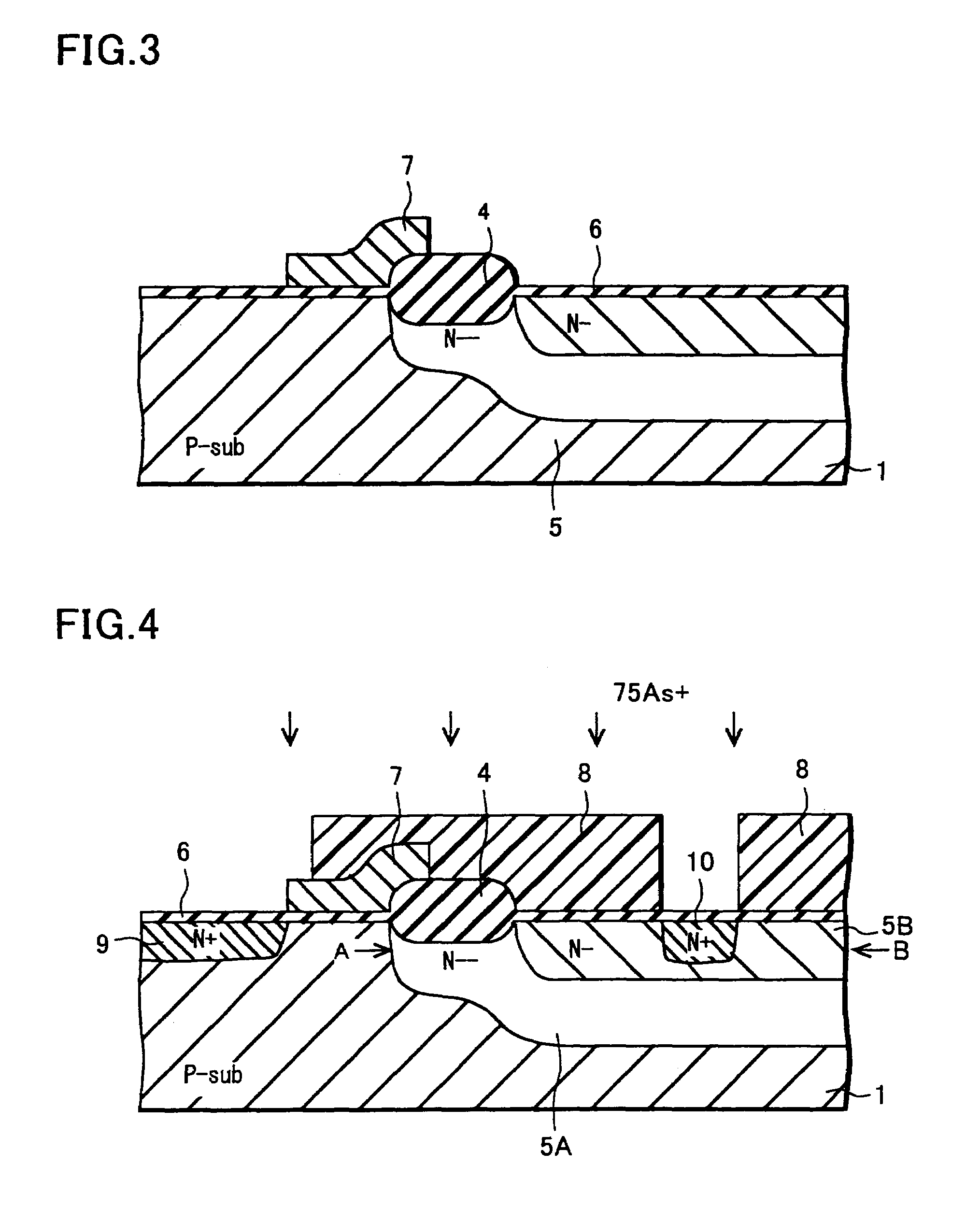

Semiconductor device and method of manufacturing the same

InactiveUS7056797B2High impurity concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesPeak valueSemiconductor

A semiconductor device has a gate electrode formed extending on a first and second gate insulation films formed on P type semiconductor substrate, an N+ type source region adjacent to one end of the gate electrode, an N− type drain region facing said source region through a channel region, having high impurity concentration peak at a position of the predetermined depth at least in said substrate under said first gate insulation film, and formed so that high impurity concentration becomes low at a region near surface of the substrate, an N− type drain region formed so as to range to the N− type drain region, an N+ type drain region separated from the other end of said gate electrode and included in said N− type drain region, and an N type layer formed so as to span from one end portion of said first gate insulation film to said N+ type drain region.

Owner:SEMICON COMPONENTS IND LLC

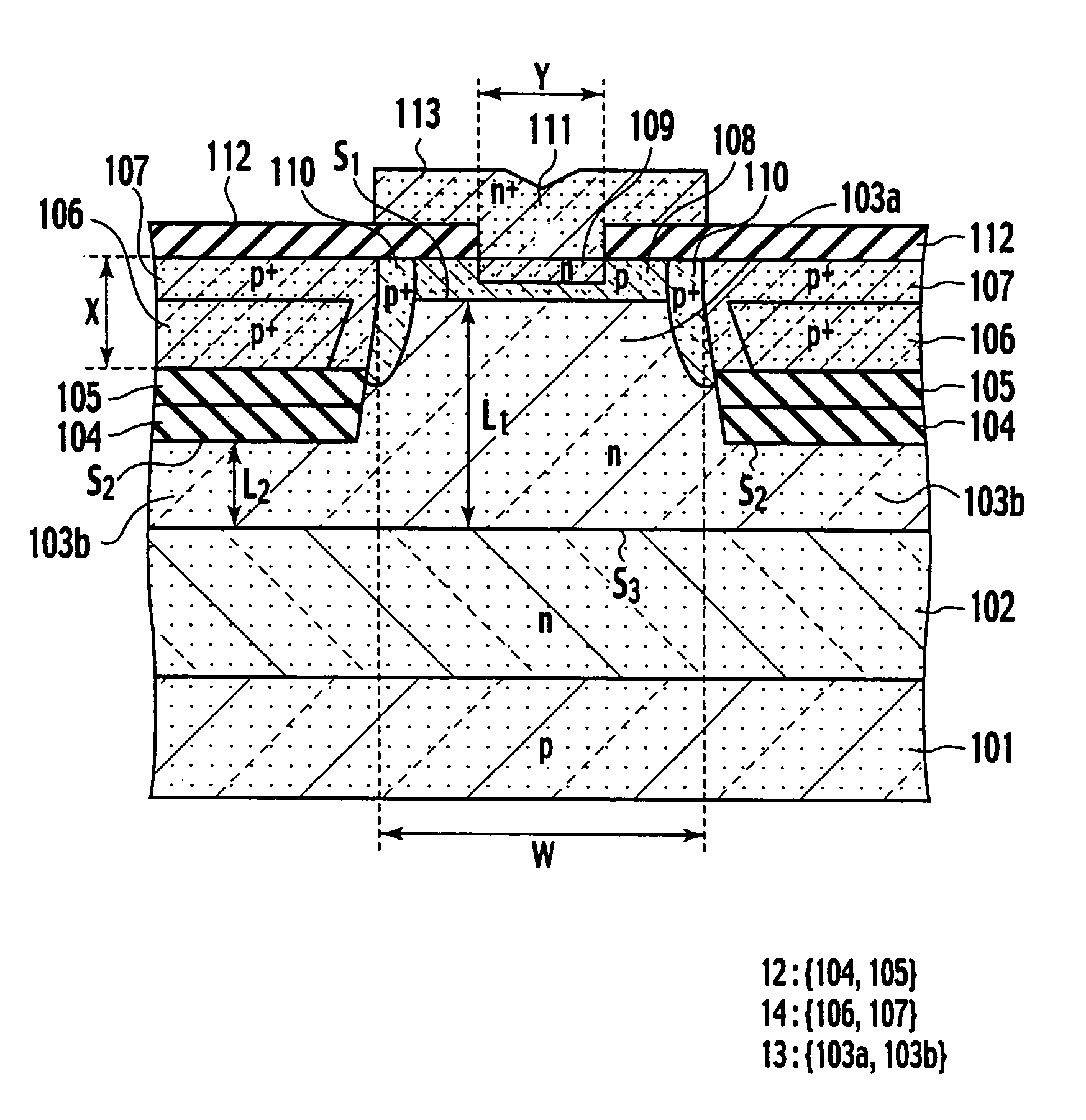

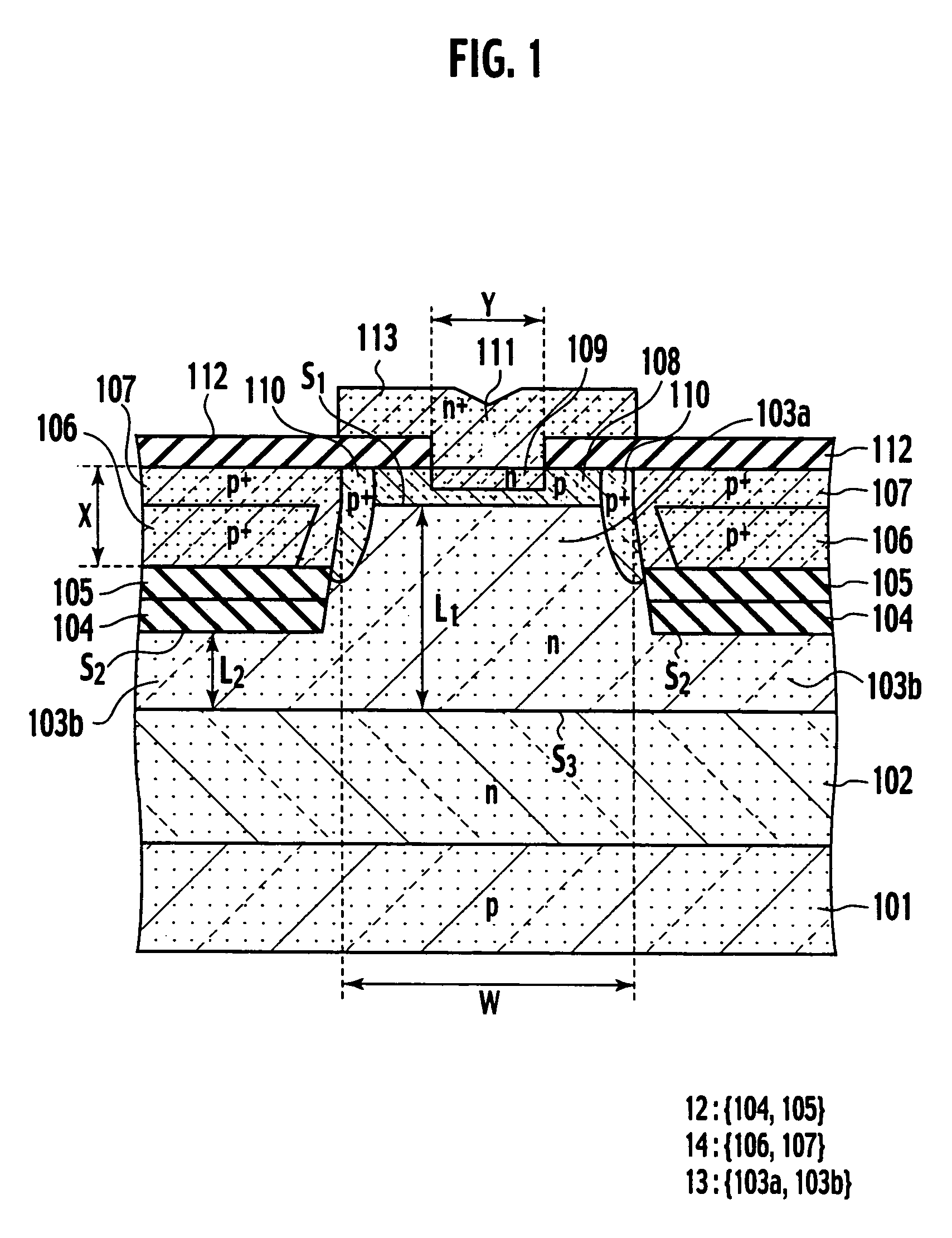

Semiconductor device and manufacturing method for the same

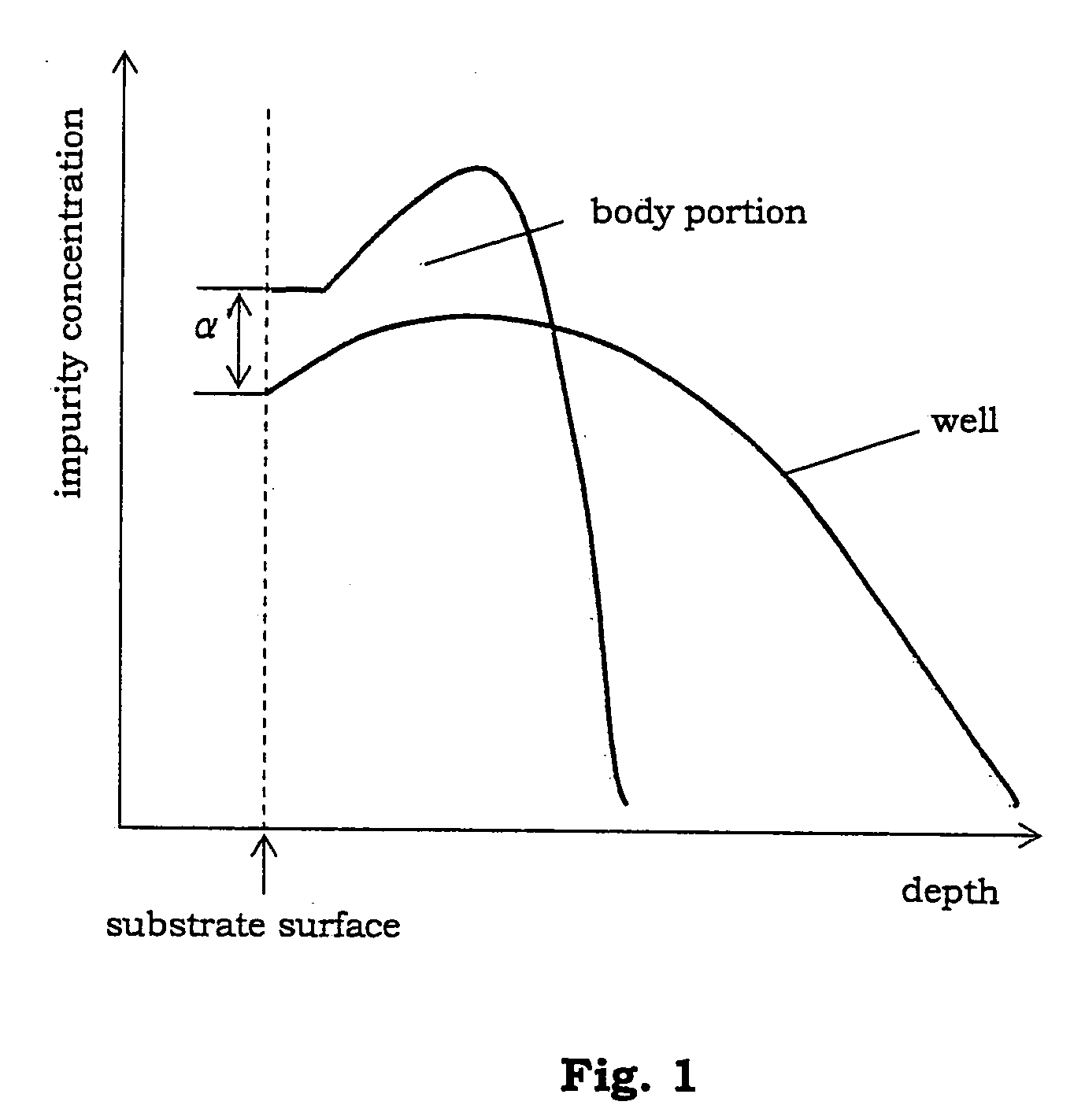

InactiveUS20060011975A1High impurity concentrationSemiconductor devicesGate dielectricDevice material

A manufacturing method for a semiconductor device, comprising the steps of: (a) forming a body portion of a DMOS by implanting impurity ions of a second conductive type into a predetermined region of a well of a first conductive type that has been formed in a main surface of a semiconductor substrate a plurality of times while changing an implantation amount or an implantation energy or both of them; (b) forming a gate dielectric film on the semiconductor substrate in a gate electrode formation region at least within the well, followed by a gate electrode on the gate dielectric film so as to cross an end of the body portion; (c) forming diffusion layers of the first conductive type on both sides of the gate electrode by implanting impurity ions of the first conductive type (provided that at least one of the diffusion layers is formed within the body portion); and (d) forming a contact layer of the second conductive type by implanting impurities of the second conductive type into the body portion with a impurity concentration higher than the impurity concentration in the body portion.

Owner:SHARP KK

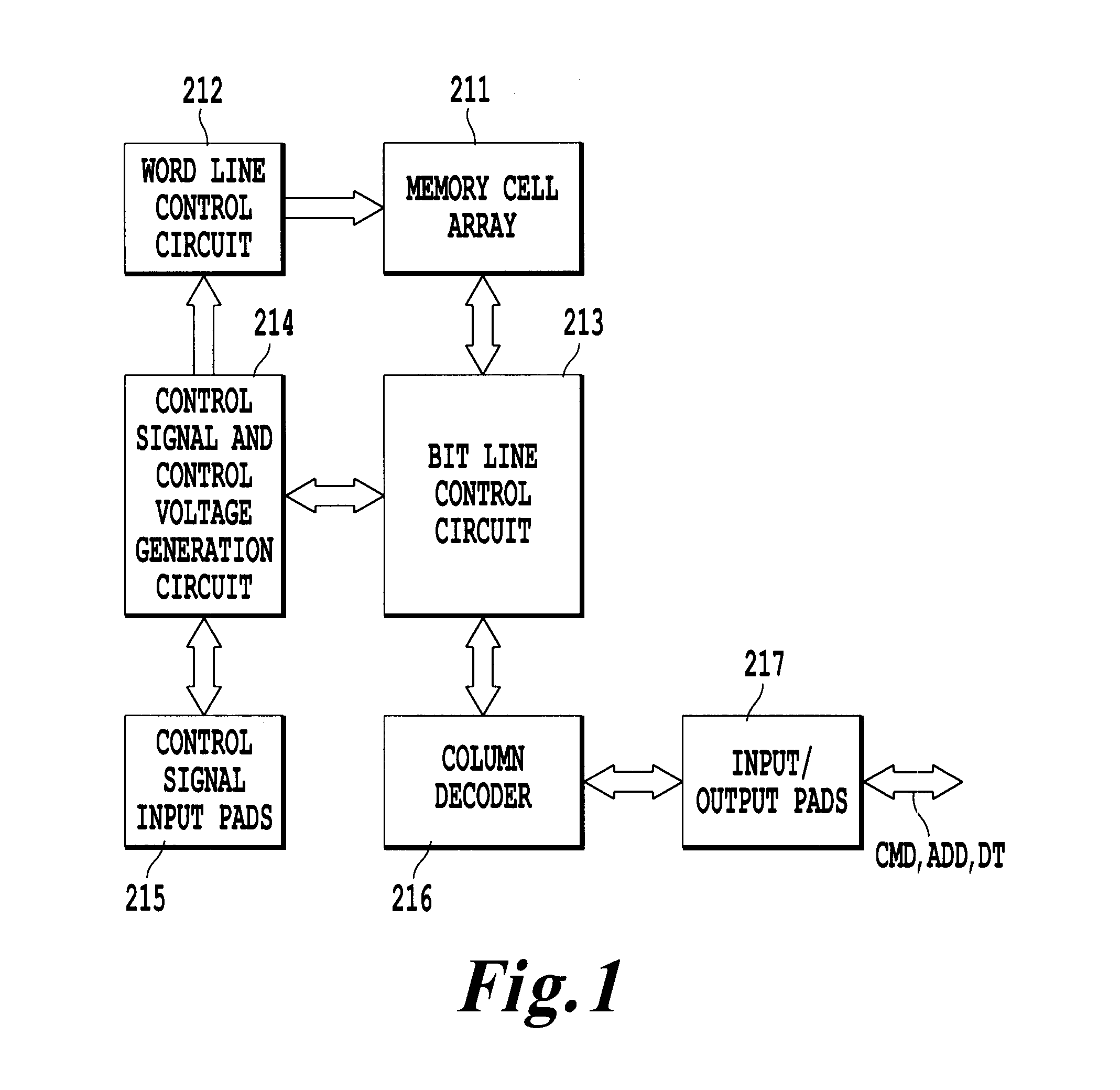

Semiconductor device and manufacturing method thereof

InactiveUS20100102375A1High impurity concentrationTransistorSolid-state devicesDiffusion layerSemiconductor

This semiconductor device comprises a semiconductor substrate with a first impurity type; a plurality of active areas formed in the semiconductor substrate; an element isolation trench including a first trench part and a second trench part surrounding the plurality of active areas, the first trench part being extended from a surface of the semiconductor substrate to a depth direction, the second trench part being extended from the center of a bottom surface of the first trench part to the depth direction with a narrower width than the width of the first trench part in a width direction; an element isolation insulator film filled in the element isolation trench; a gate electrode formed on the plurality of active areas via a gate insulator film; a plurality of diffusion layers with a second impurity type formed in a surface of the plurality of active areas, the plurality of diffusion layers being located on each side of the element isolation trench and separated each other on each side of the gate electrode; and a channel stop region extended from the bottom surface of the second trench part to the depth direction in a predetermined depth with the first impurity type, the channel stop region having a higher impurity concentration than the impurity concentration of the semiconductor substrate.

Owner:KK TOSHIBA

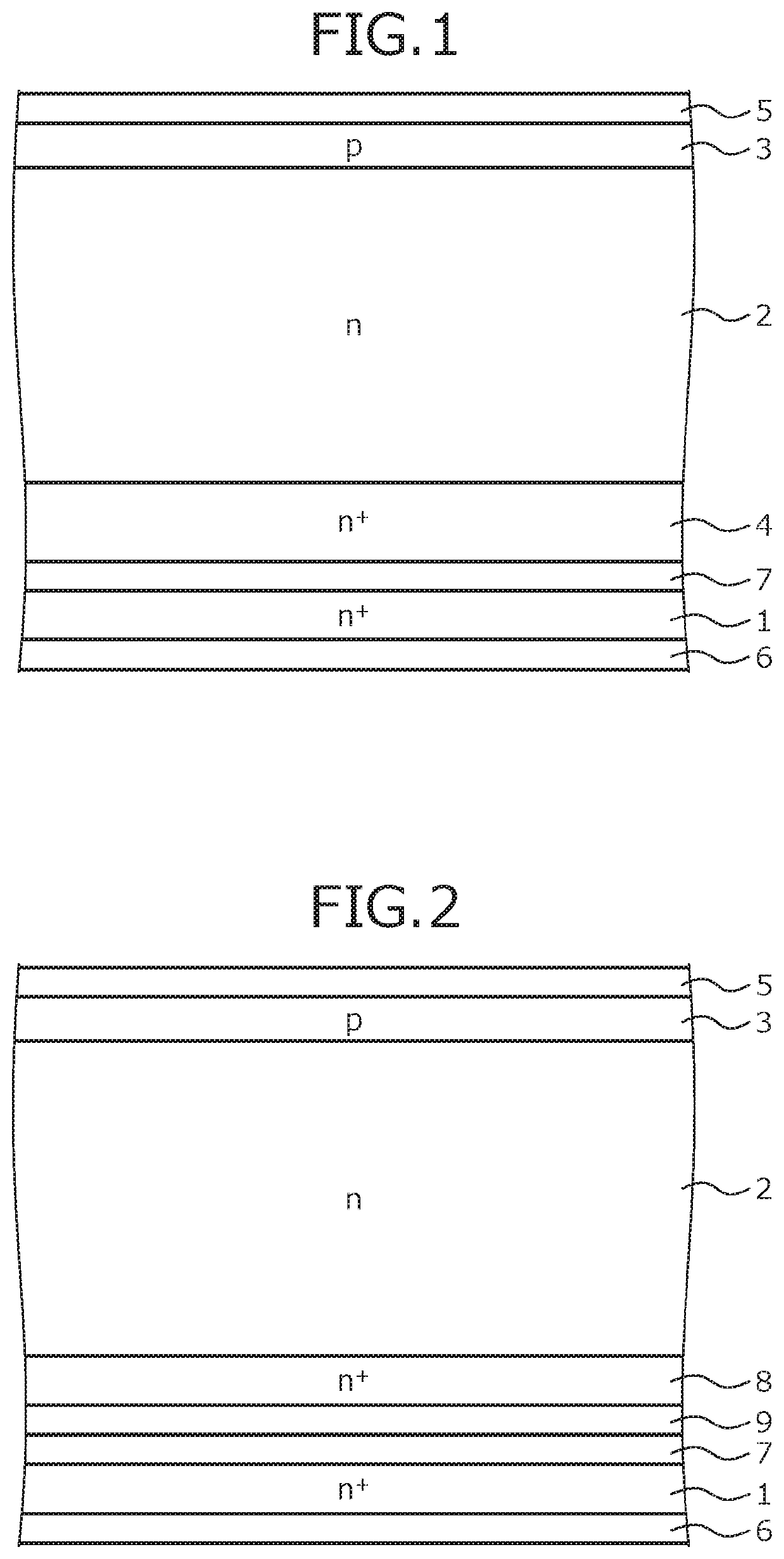

Method of manufacturing semiconductor device

ActiveUS20090111230A1High impurity concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceSurface layer

Owner:FUJI ELECTRIC CO LTD

Semiconductor device

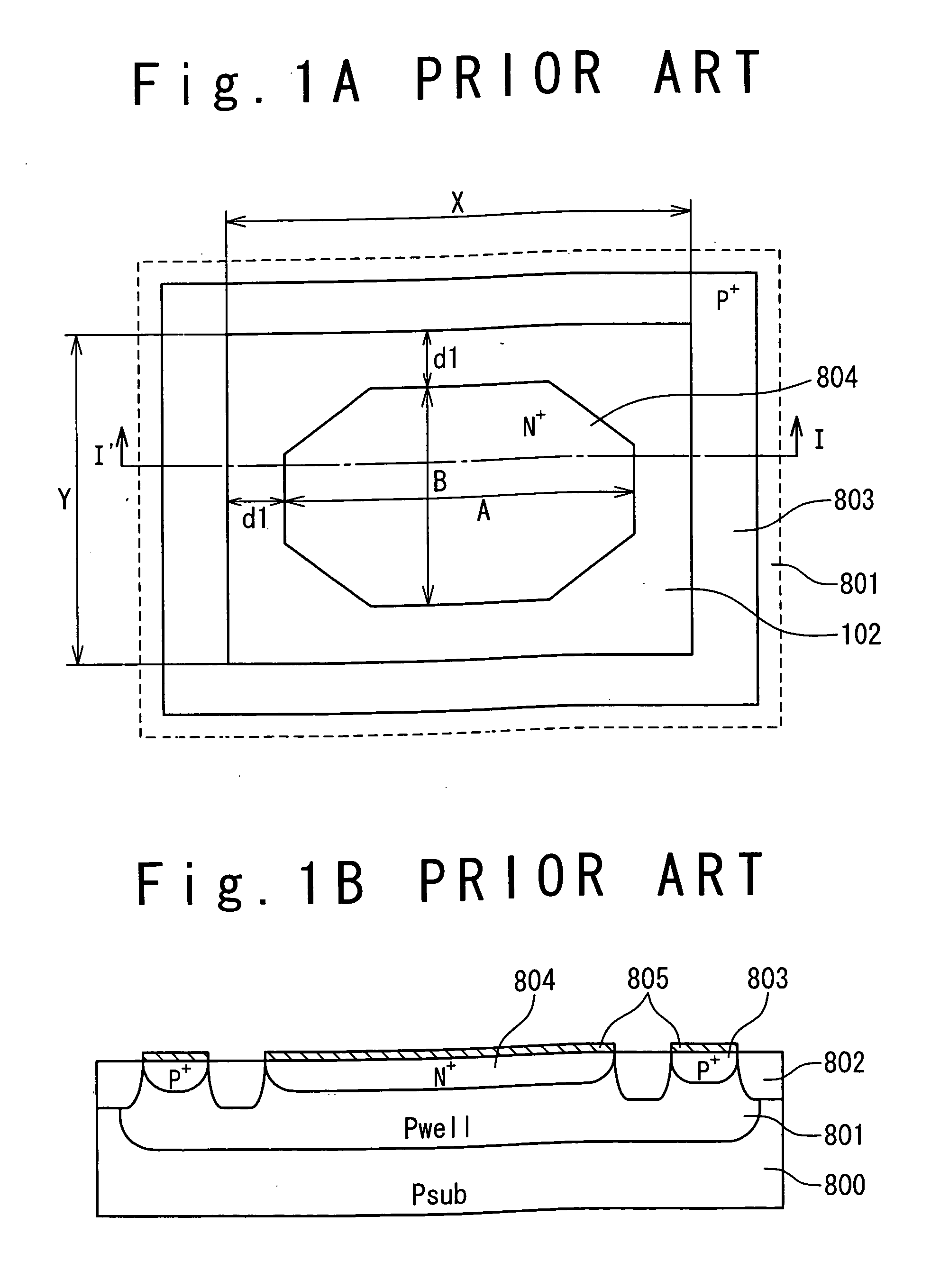

InactiveUS20050067657A1High breakdown voltageHigh impurity concentrationSemiconductor/solid-state device detailsSolid-state devicesDiffusion layerSemiconductor

In a semiconductor device, a plurality of first diffusion regions of a first conductive type are formed on a diffusion layer well of the first conductive type. A plurality of second diffusion regions of a second conductive type are formed on the diffusion layer well of the first conductive type. An impurity concentration of each of the plurality of first and second diffusion regions is desirably higher than that of the diffusion layer well. The plurality of first diffusion regions are connected to a first common node as an anode and the plurality of second diffusion regions are connected to a second common node as a cathode.

Owner:RENESAS ELECTRONICS CORP

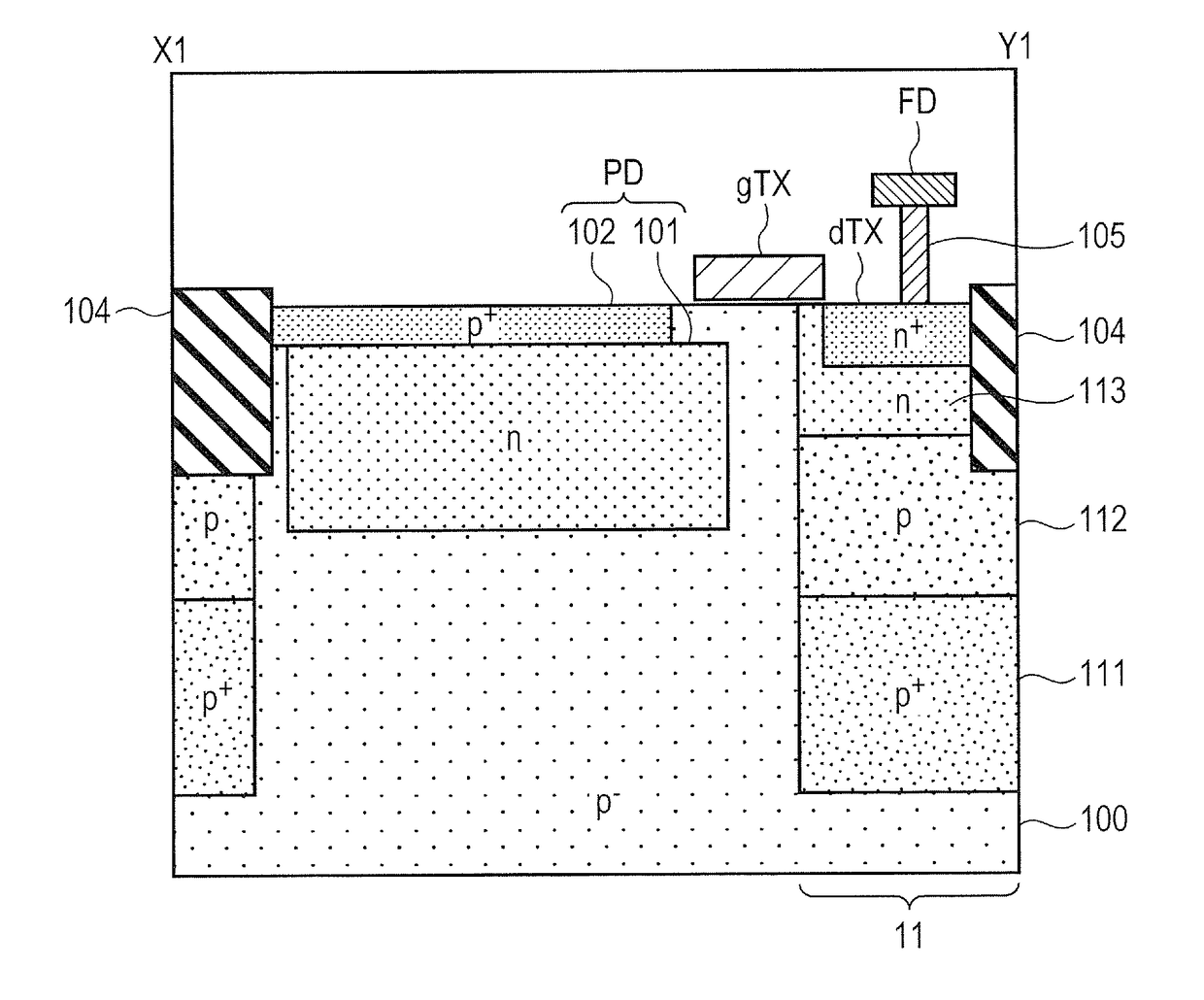

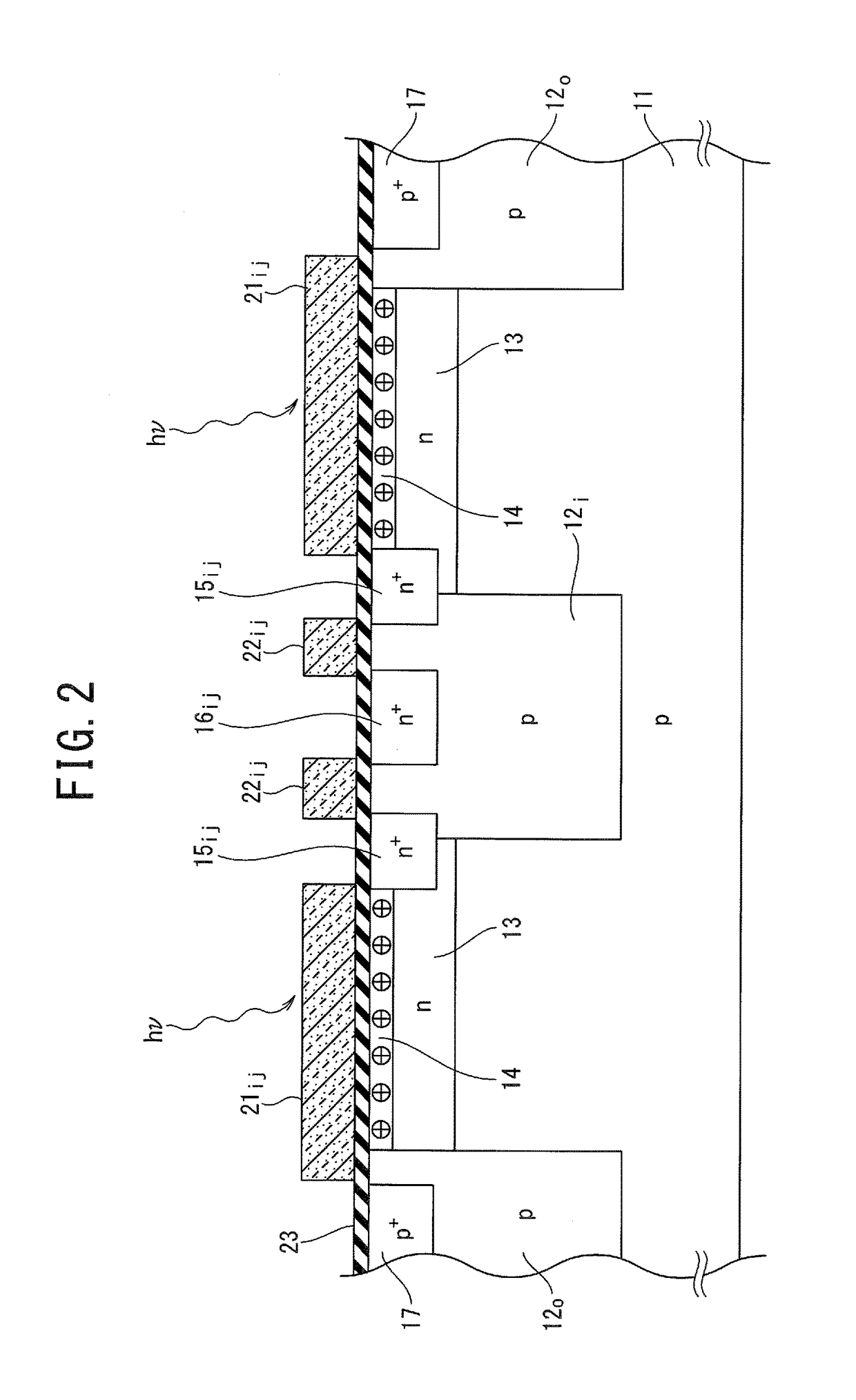

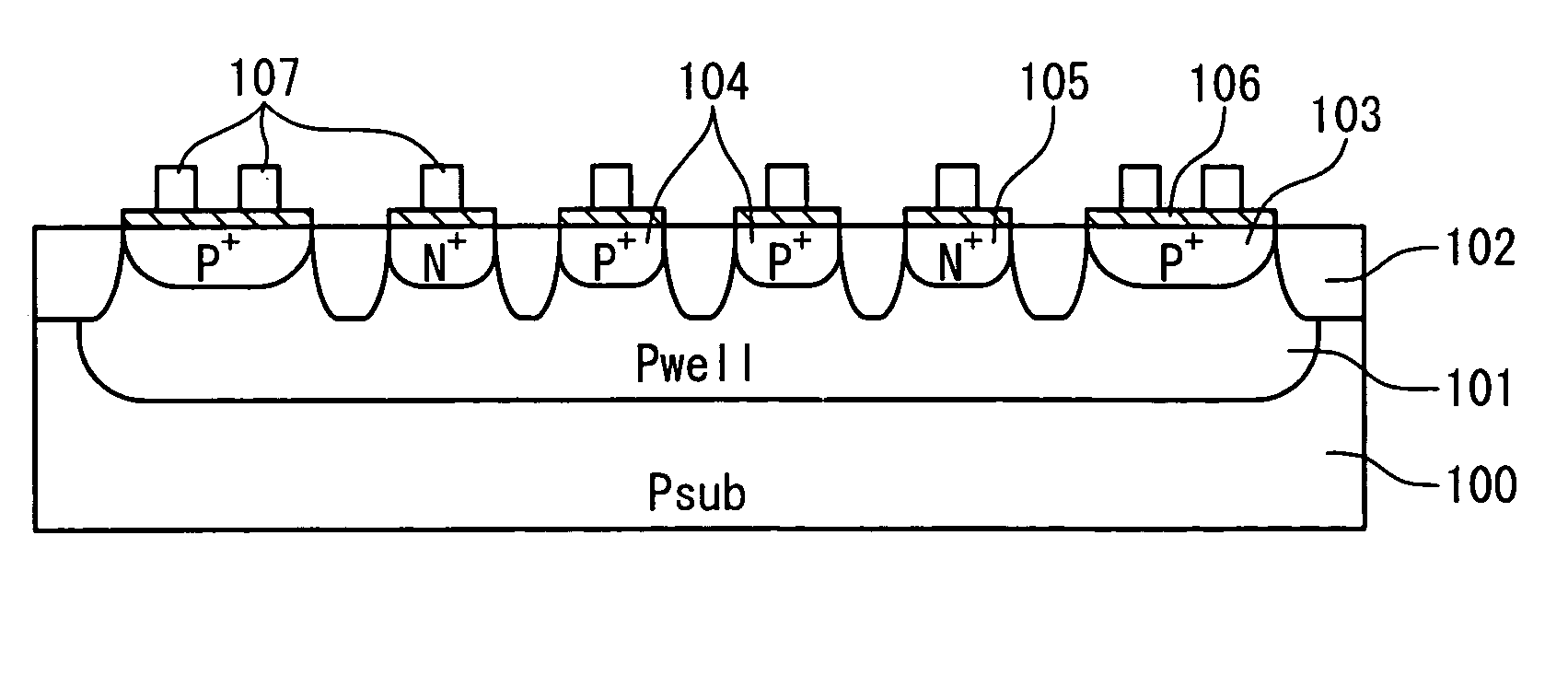

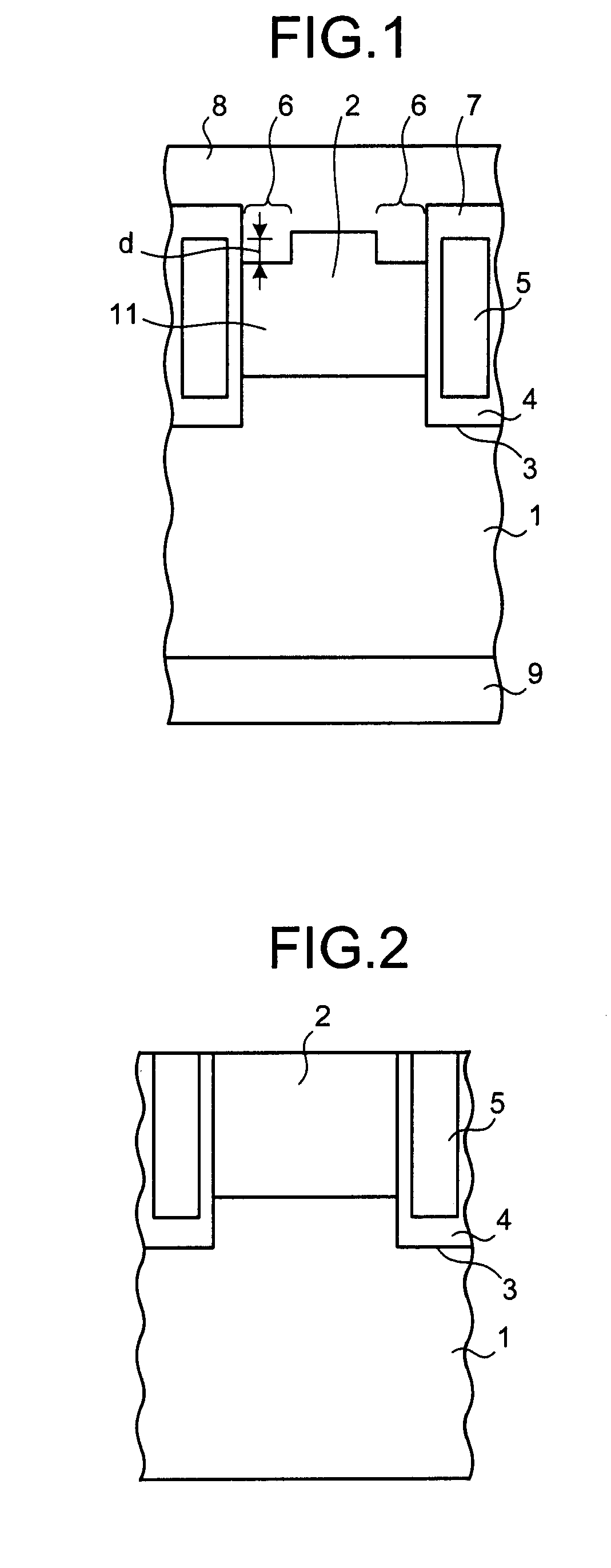

Imaging device

InactiveUS20080029788A1Improve transmission efficiencyHigh impurity concentrationTelevision system detailsTelevision system scanning detailsDiffusionCrystallographic defect

First diffusion region constituting a photodiode in each pixel stores carriers generated according to incident light. Second diffusion region is formed at a surface of the first diffusion region to cover a peripheral part of the first diffusion region. In the peripheral part of the first diffusion region, crystal defects tend to occur by a process of forming an isolation region and a gate electrode, so that dark current noise tends to occur. The second diffusion region functioning as a protection layer prevents crystal defects in a manufacturing process. The second diffusion region isn't formed on a center of the surface of the first diffusion region where crystal defects don't tend to occur. In the first diffusion region where the second diffusion region isn't formed, the thickness of a depletion layer increases, which improves light detection sensitivity. This improves detection sensitivity of the photodiode without increasing the dark current noise.

Owner:SOCIONEXT INC

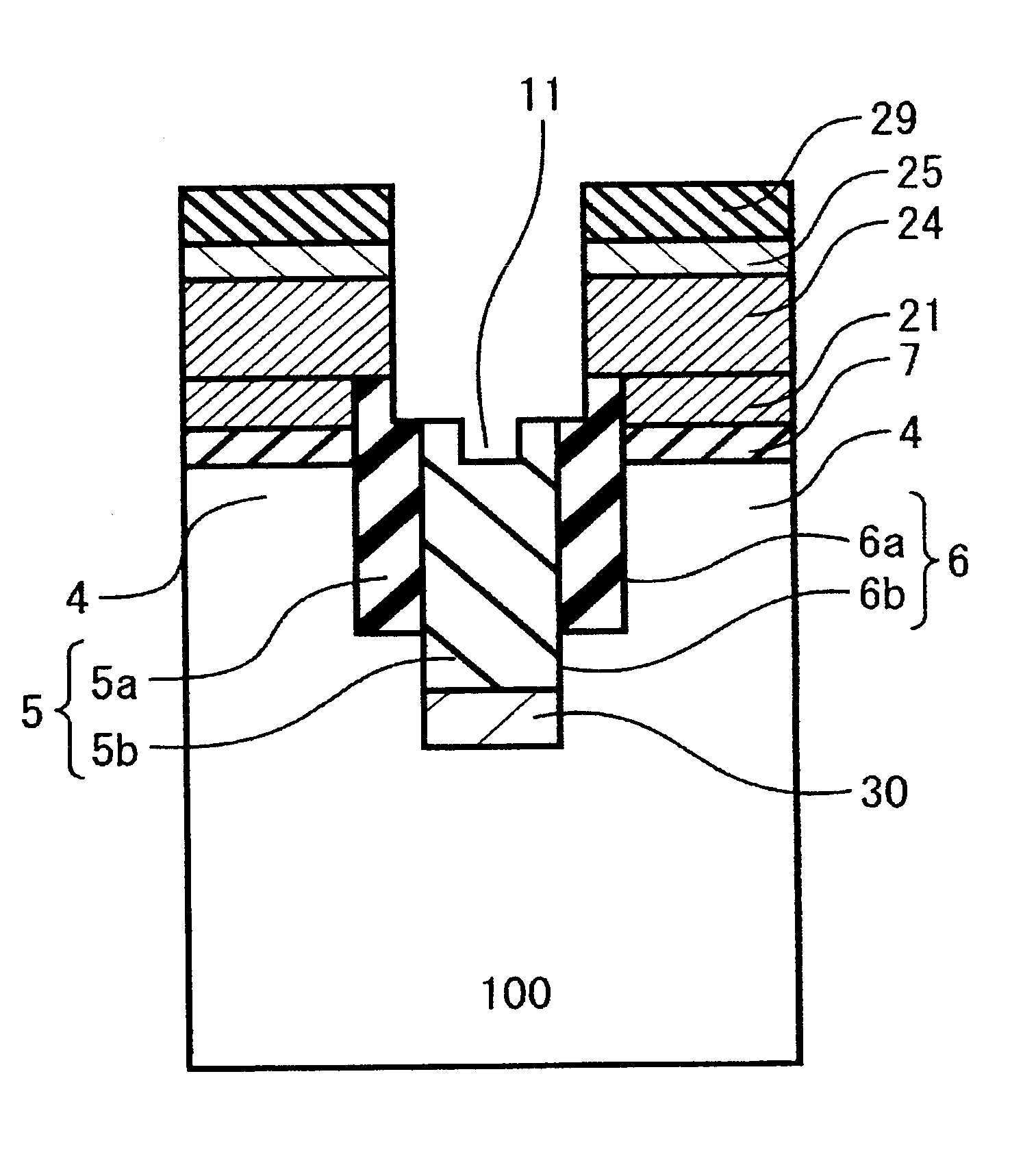

Semiconductor device and fabrication method of semiconductor device

ActiveUS20110204485A1High impurity concentrationInhibition effectSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorSemiconductor device

A semiconductor device includes a first semiconductor region of a first conductivity type; a second semiconductor region of a second conductivity type, disposed on a surface of the first semiconductor region, and having an impurity concentration higher than that of the first semiconductor region; a trench that penetrates the second semiconductor region to reach the first semiconductor region; a first electrode disposed inside the trench via an insulating film; a first recess portion disposed deeper than an upper end of the first electrode, in a surface layer of the second semiconductor region, so as to be in contact with the trench; and a second electrode embedded in the first recess portion.

Owner:DENSO CORP +1

Semiconductor device

InactiveUS20070034986A1High impurity concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialSemiconductor

Disclosed is a semiconductor device including a base region having a first conductive type, a drain region and a source region having a second conductive type, a gate insulation film and a gate electrode formed on a channel formation region and on a part of the drain region and the source region, a short electrode formed to include a top of another part of the source region, with contact length being 0.4 μm to 0.8 μm in a part of maximum length with the source region in a direction in which the source region is opposed to the drain region, and a fourth region having the first conductive type and a higher impurity concentration than the base region, provided at an opposite side of the source region from a side opposed to the drain region and at an underside of the short electrode to be adjacent to the base region.

Owner:KK TOSHIBA

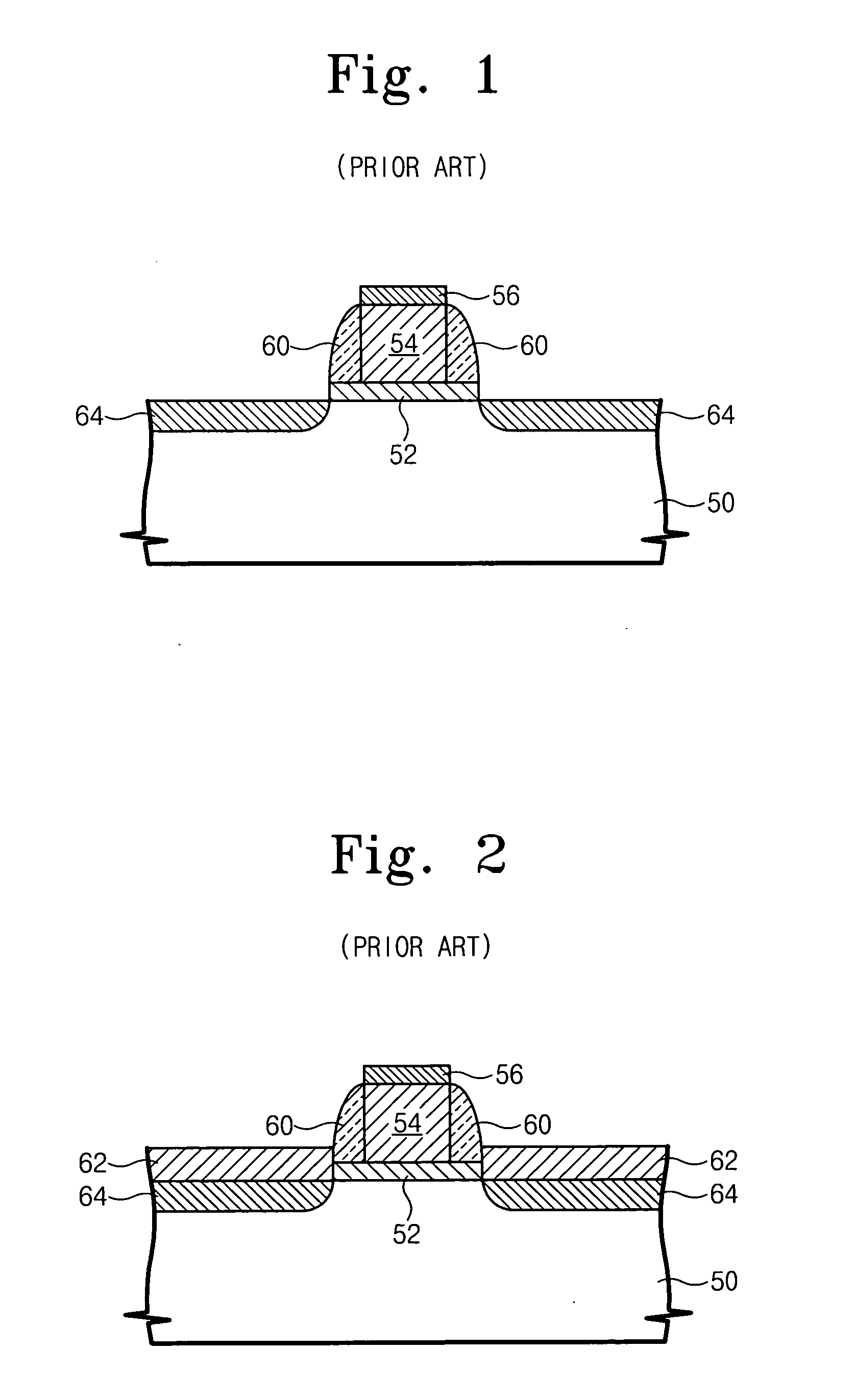

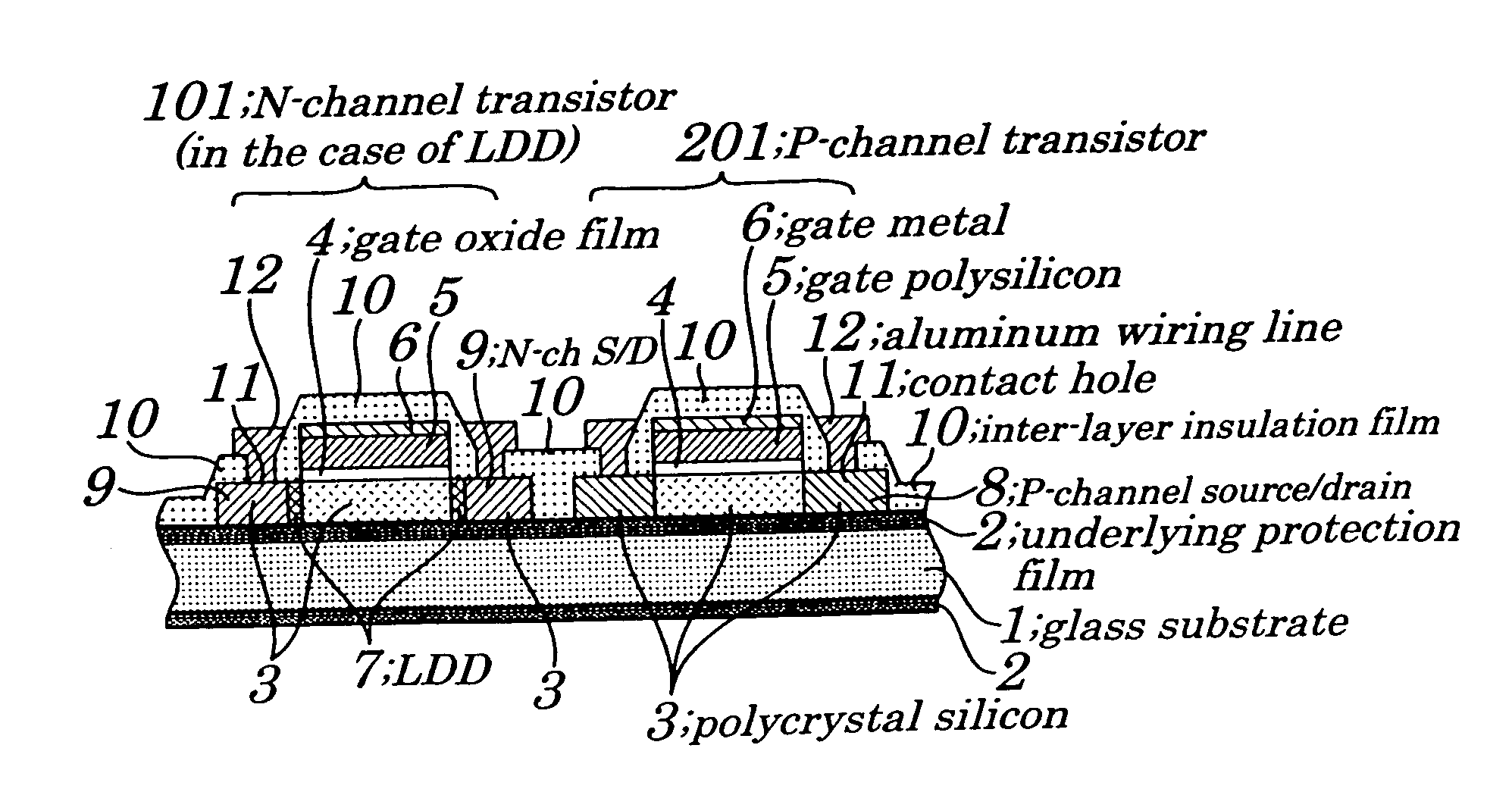

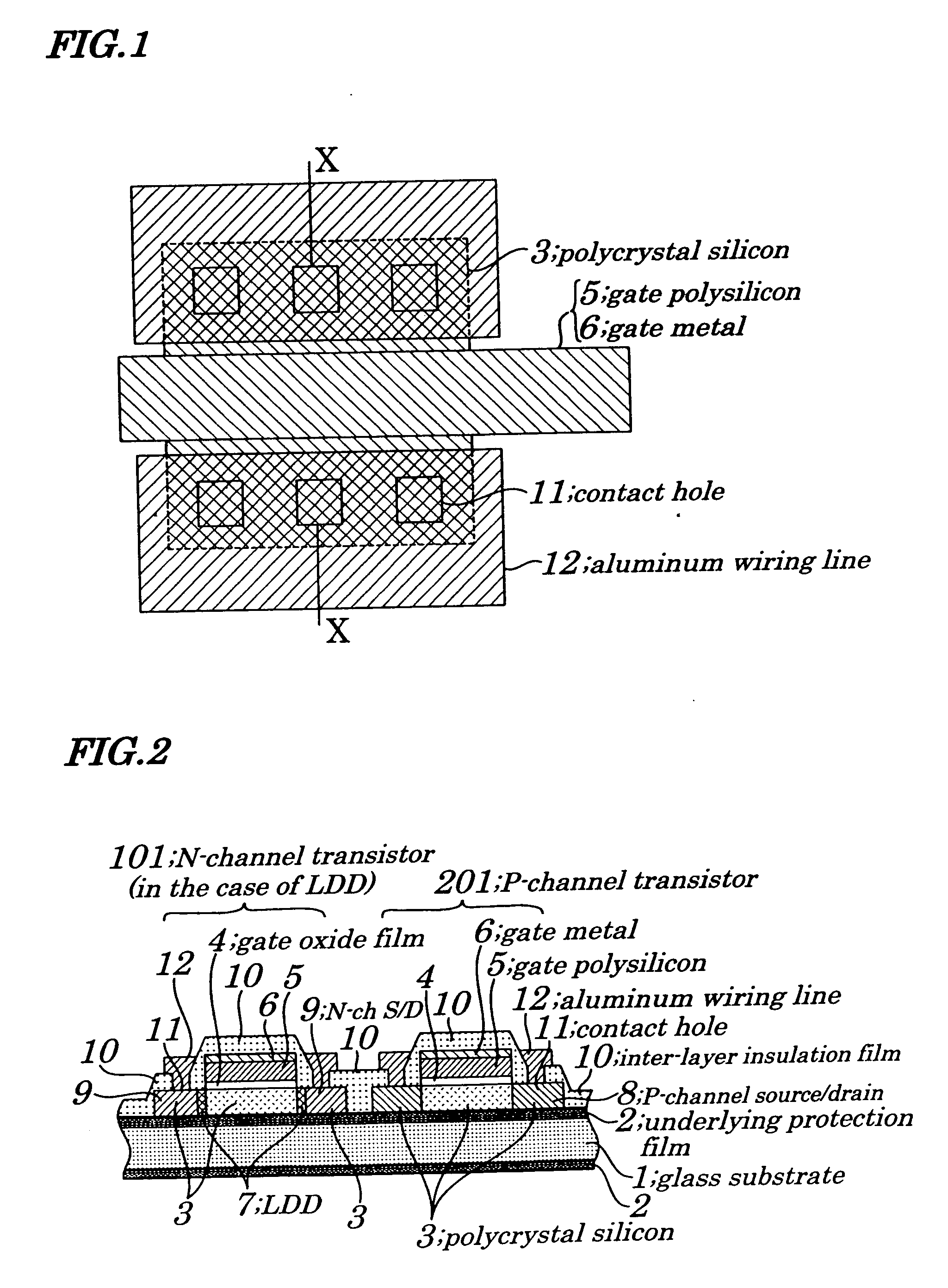

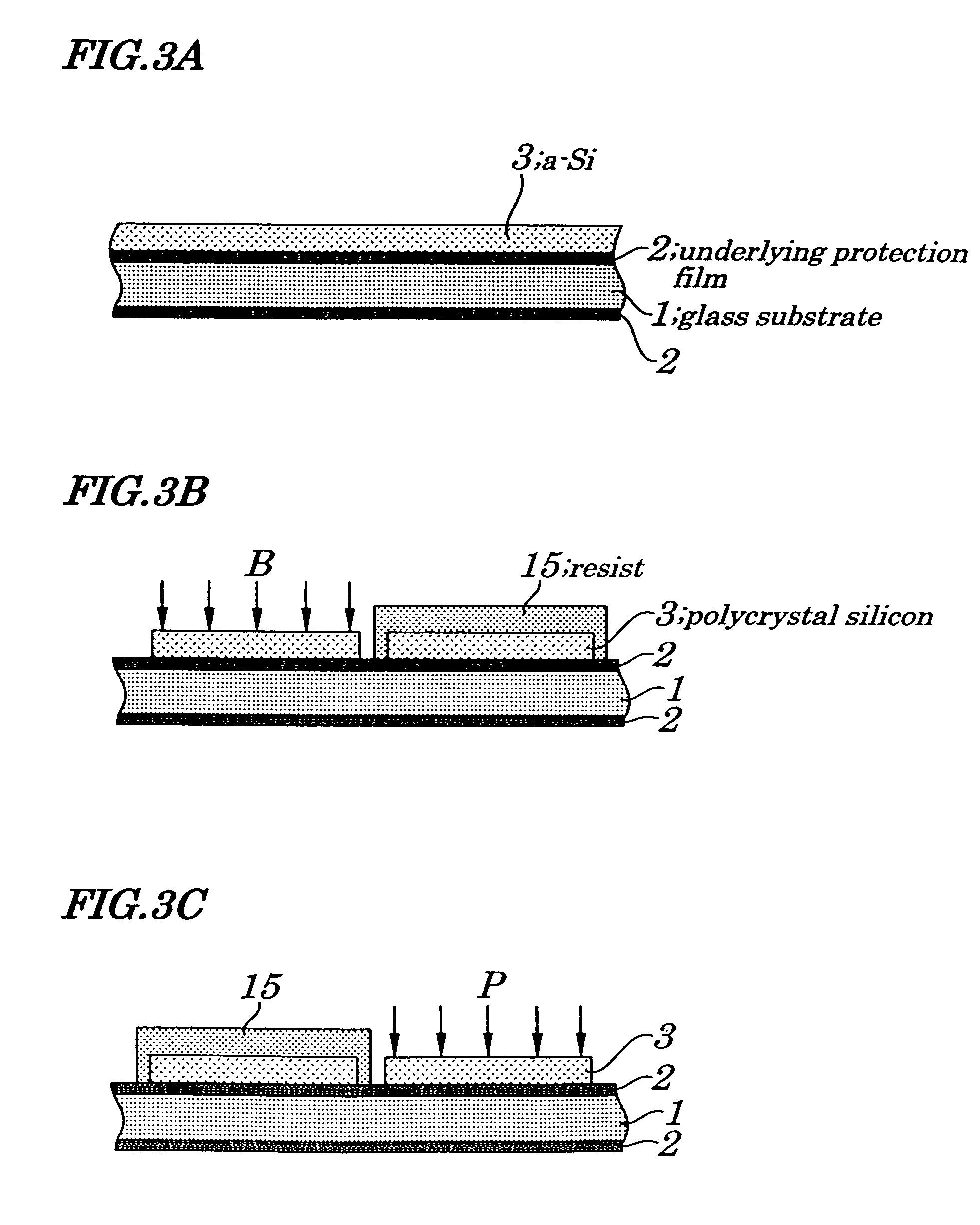

Thin film semiconductor device and method for manufacturing same

InactiveUS20050045883A1Reduce volatilitySolution value is not highTransistorSolid-state devicesLow voltageDevice material

In a semiconductor device having an N-channel MOS transistor and a P-channel MOS transistor, each of the N-channel and P-channel MOS transistors is made up of a polycrystal silicon layer, a gate insulating film, and a gate electrode containing a gate polysilicon on a glass substrate. A method of manufacturing the semiconductor device includes the steps of injecting an impurity into the gate polysilicon at a same time as or in a different step of impurity injection at a time of formation of source / drains of the MOS transistors or formation of an LDD (Lightly Doped Drain), to make an N-type of a gate polysilicon in the N-channel MOS transistor and make a P-type of a gate polysilicon in the P-channel MOS transistor and, furthermore, setting a thickness of the polycrystal silicon layer less than the width of a depletion layer which occurs when an inversion channel is formed. Thus, fluctuations in values of threshold voltages of the MOS transistors are reduced to realize low-voltage driving.

Owner:VISTA PEAK VENTURES LLC

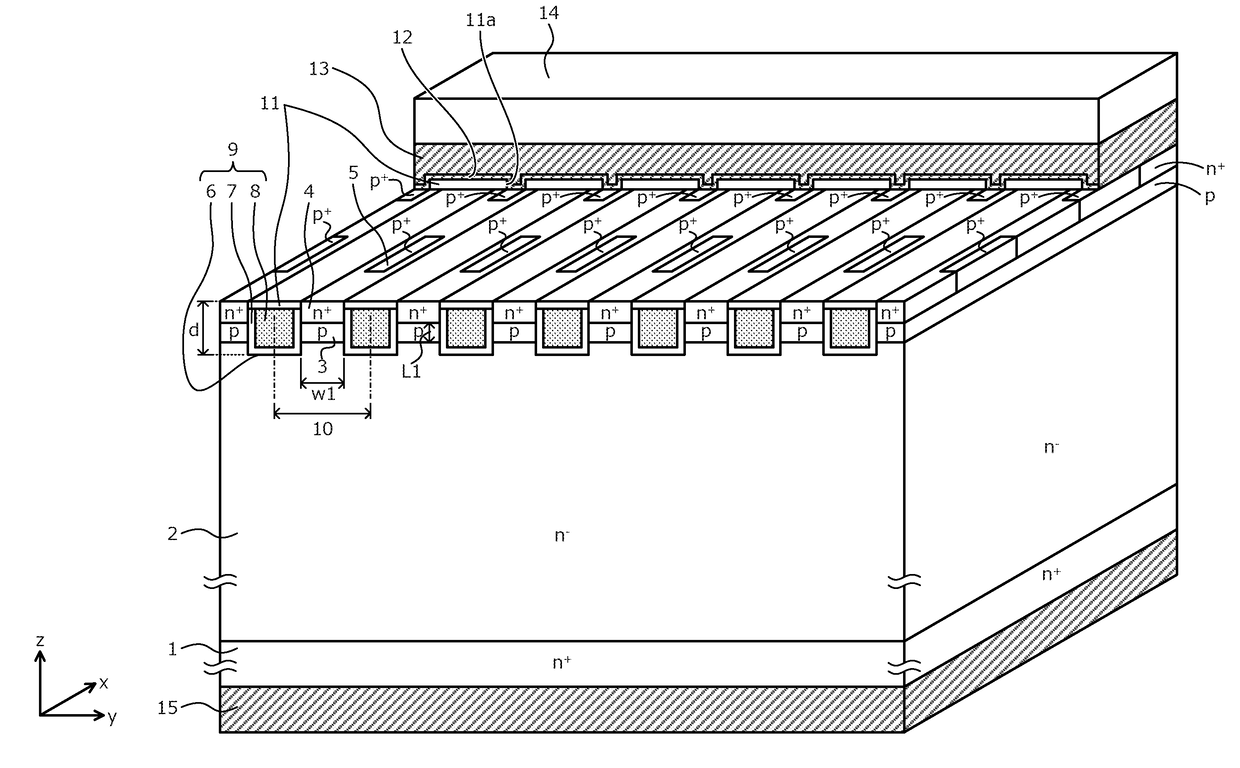

Semiconductor device

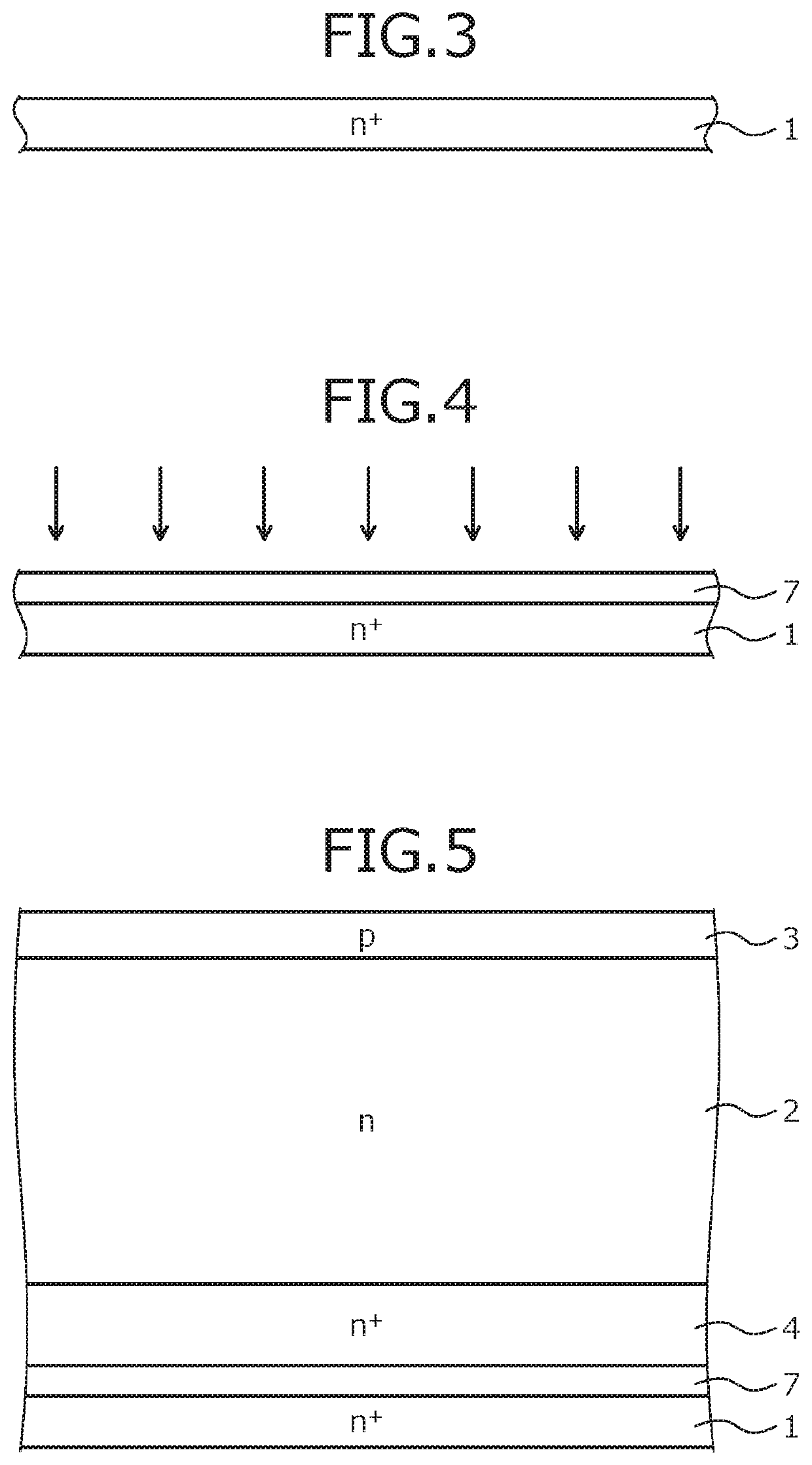

ActiveUS20170365665A1High impurity concentrationLower Reliability RequirementsSemiconductor devicesDepth directionSemiconductor

On a front surface of an n+-type SiC substrate becoming a drain region, an n−-type drift layer, a p-type base layer, and an n+-type source layer are sequentially formed by epitaxial growth. In the n+-type source layer, the p+-type contact region is selectively provided. A trench is provided penetrating the n+-type source layer and the p-type base layer in the depth direction and reaching the n−-type drift layer. In the trench, a gate electrode is provided via a gate insulating film. A width between adjacent trenches is, for example, 1 μm or less. A depth of the trench is, for example, 1 μm or less. The width is narrow whereby substantially the entire p-type base layer forms a channel. A cell includes a FinFET structure in which one channel is sandwiched between MOS gates on both side. Thus, ON resistance may be reduced and decreased reliability may be prevented.

Owner:FUJI ELECTRIC CO LTD

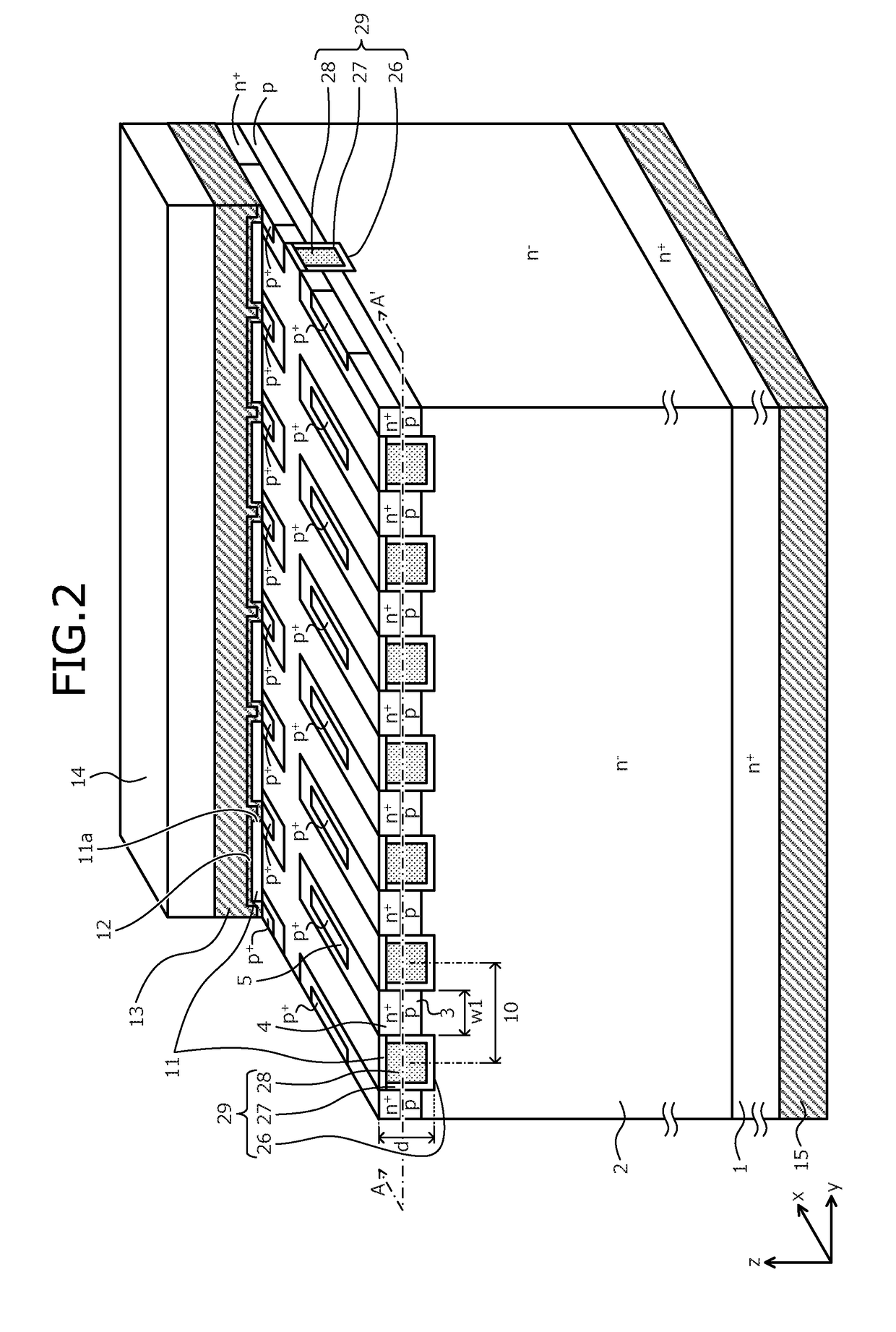

Silicon carbide semiconductor device and method of manufacturing silicon carbide semiconductor device

ActiveUS20200144371A1High impurity concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsElectrically conductive

A silicon carbide semiconductor device includes, sequentially, a first semiconductor layer of a first conductivity type, a second semiconductor layer of the first conductivity type provided on the first semiconductor layer, a third semiconductor layer of the first conductivity type provided on the second semiconductor layer, and a fourth semiconductor layer of a second conductivity type provided on the third semiconductor layer. A first electrode is provided on the first semiconductor layer, and a second electrode is provided on the fourth semiconductor layer. An impurity concentration of the second semiconductor layer is higher than that of the first semiconductor layer, and an impurity concentration of the third semiconductor layer is lower than that of the second semiconductor layer. The first semiconductor layer also contains, at a surface thereof in contact with the second semiconductor layer, a second impurity different from a first impurity that determines a conductivity type of the first semiconductor layer.

Owner:FUJI ELECTRIC CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com