Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

821 results about "Crystallographic defect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Crystallographic defects are interruptions of regular patterns in crystalline solids. They are common because positions of atoms or molecules at repeating fixed distances determined by the unit cell parameters in crystals, which exhibit a periodic crystal structure, are usually imperfect.

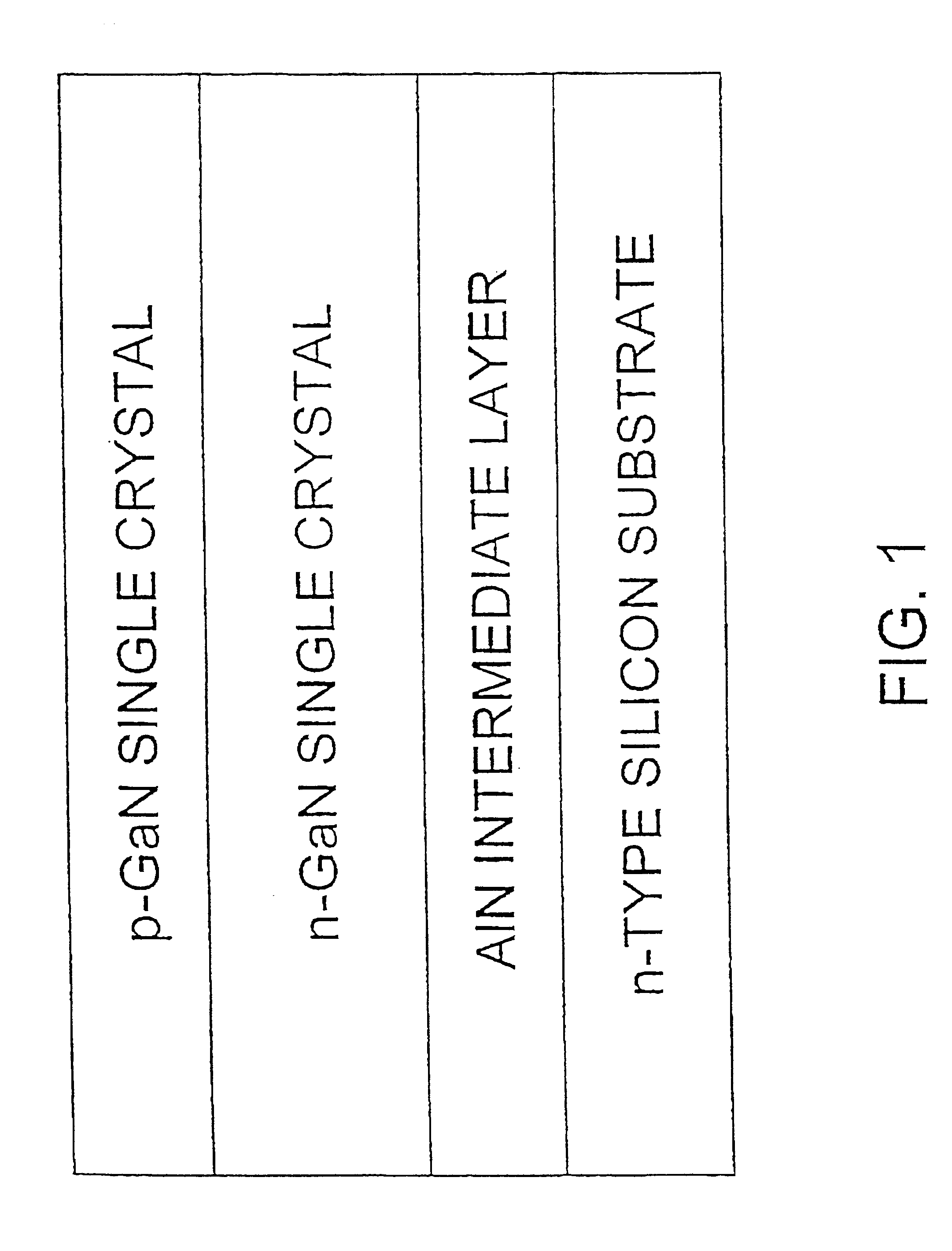

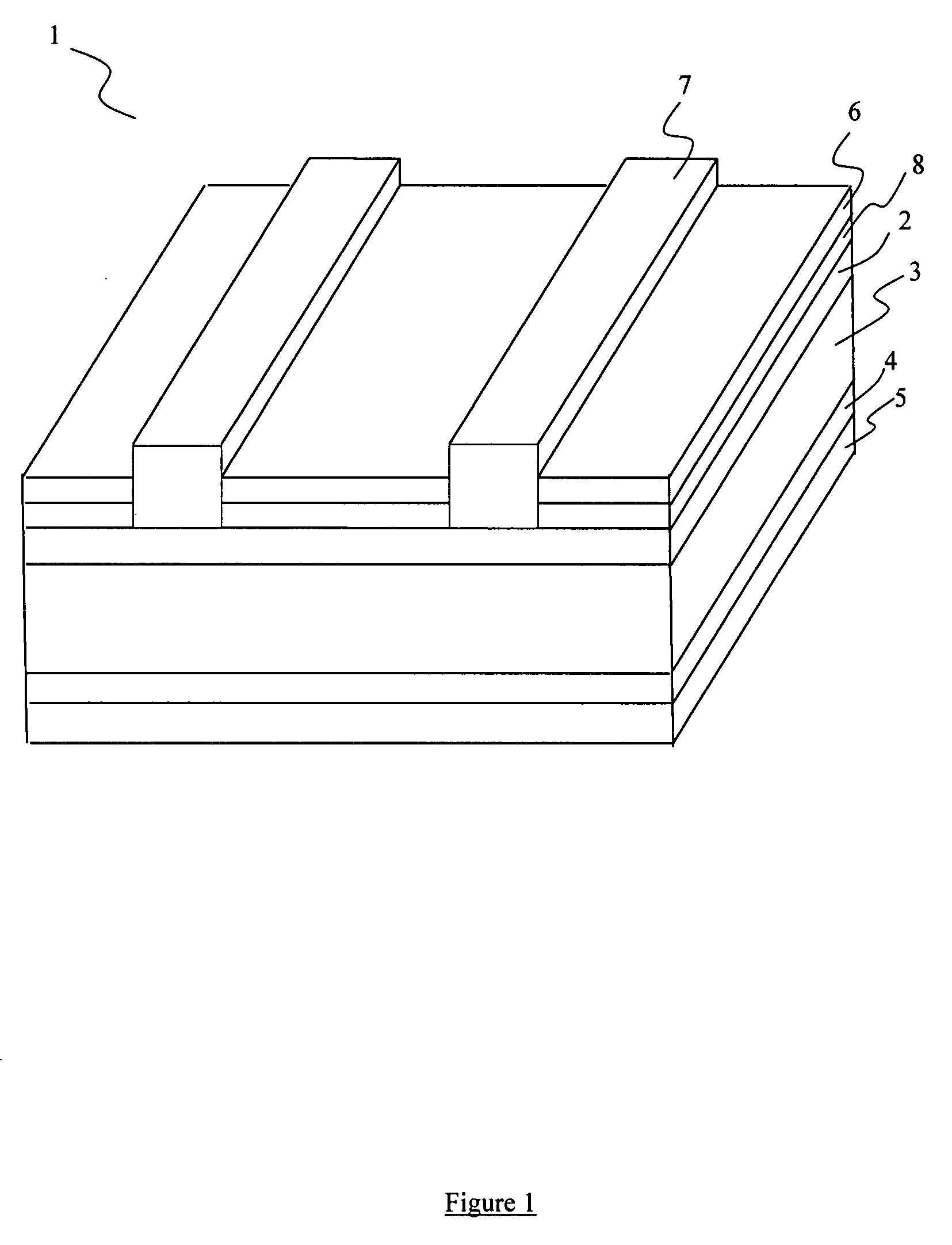

Method of growing nitride semiconductors, nitride semiconductor substrate and nitride semiconductor device

InactiveUS6153010APolycrystalline material growthLaser detailsNitrogen sourceCrystallographic defect

PCT No. PCT / JP98 / 01640 Sec. 371 Date Dec. 9, 1998 Sec. 102(e) Date Dec. 9, 1998 PCT Filed Apr. 9, 1998 PCT Pub. No. WO98 / 47170 PCT Pub. Date Oct. 22, 1998A method of growing a nitride semiconductor crystal which has very few crystal defects and can be used as a substrate is disclosed. This invention includes the step of forming a first selective growth mask on a support member including a dissimilar substrate having a major surface and made of a material different from a nitride semiconductor, the first selective growth mask having a plurality of first windows for selectively exposing the upper surface of the support member, and the step of growing nitride semiconductor portions from the upper surface, of the support member, which is exposed from the windows, by using a gaseous Group 3 element source and a gaseous nitrogen source, until the nitride semiconductor portions grown in the adjacent windows combine with each other on the upper surface of the selective growth mask.

Owner:NICHIA CORP

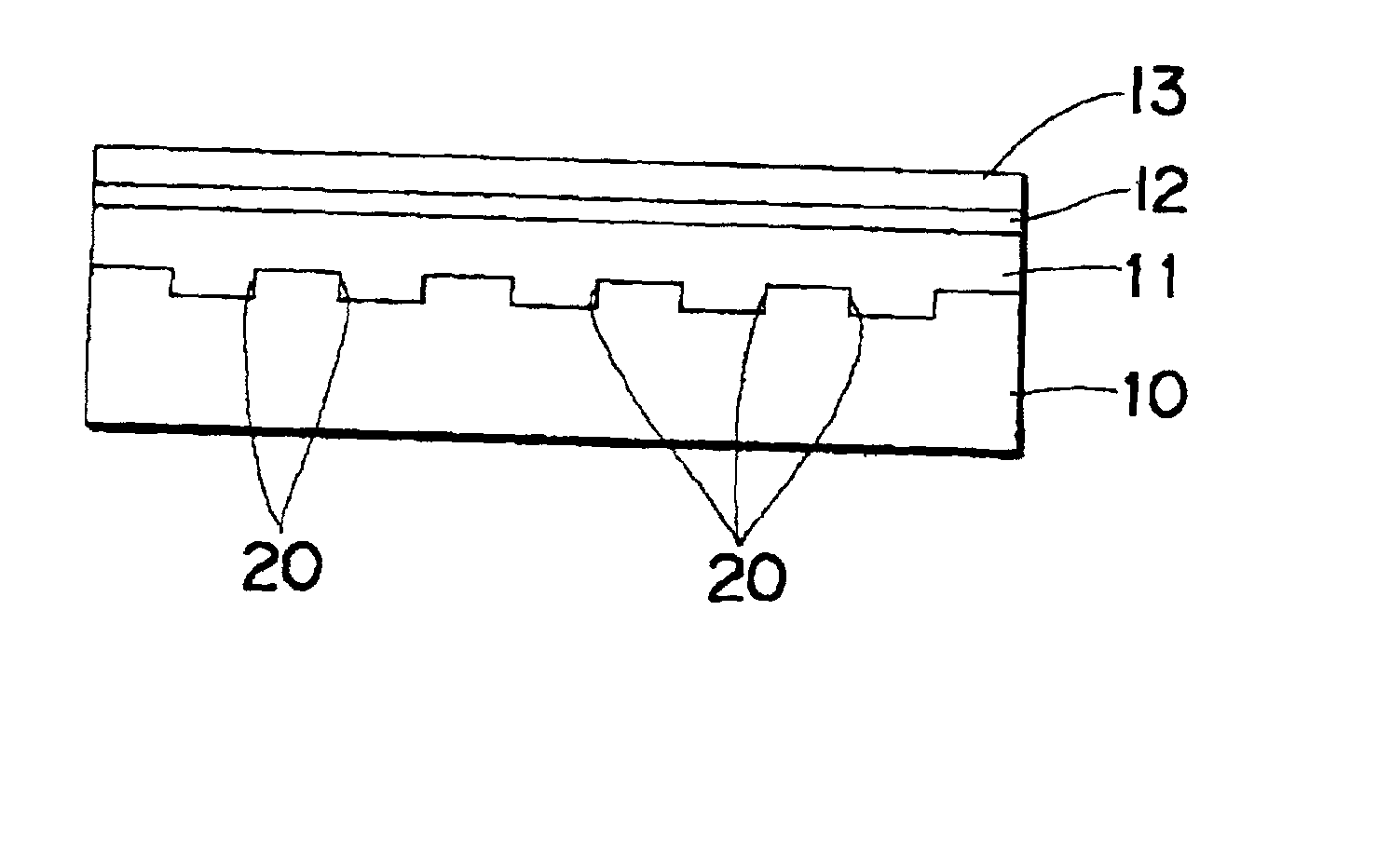

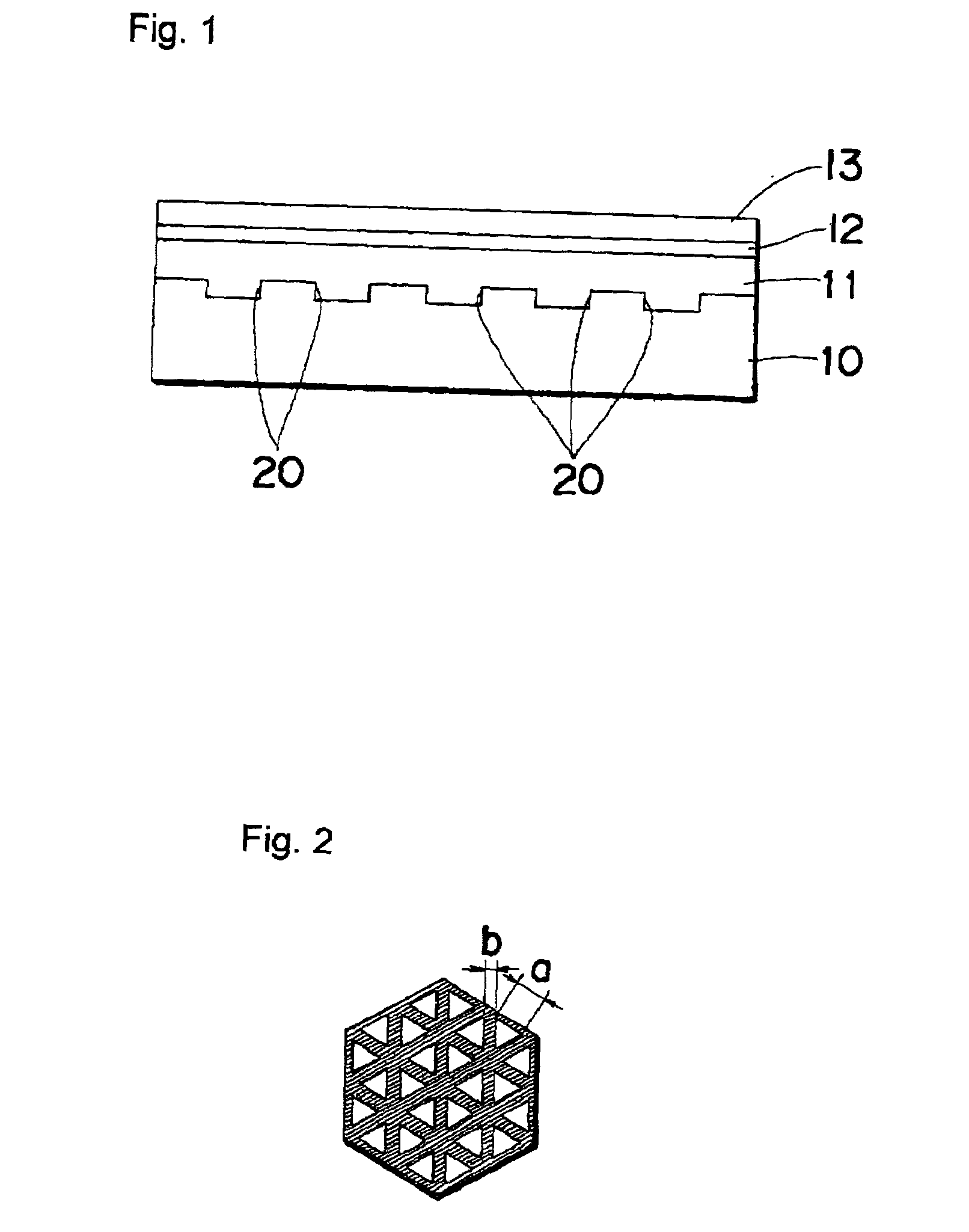

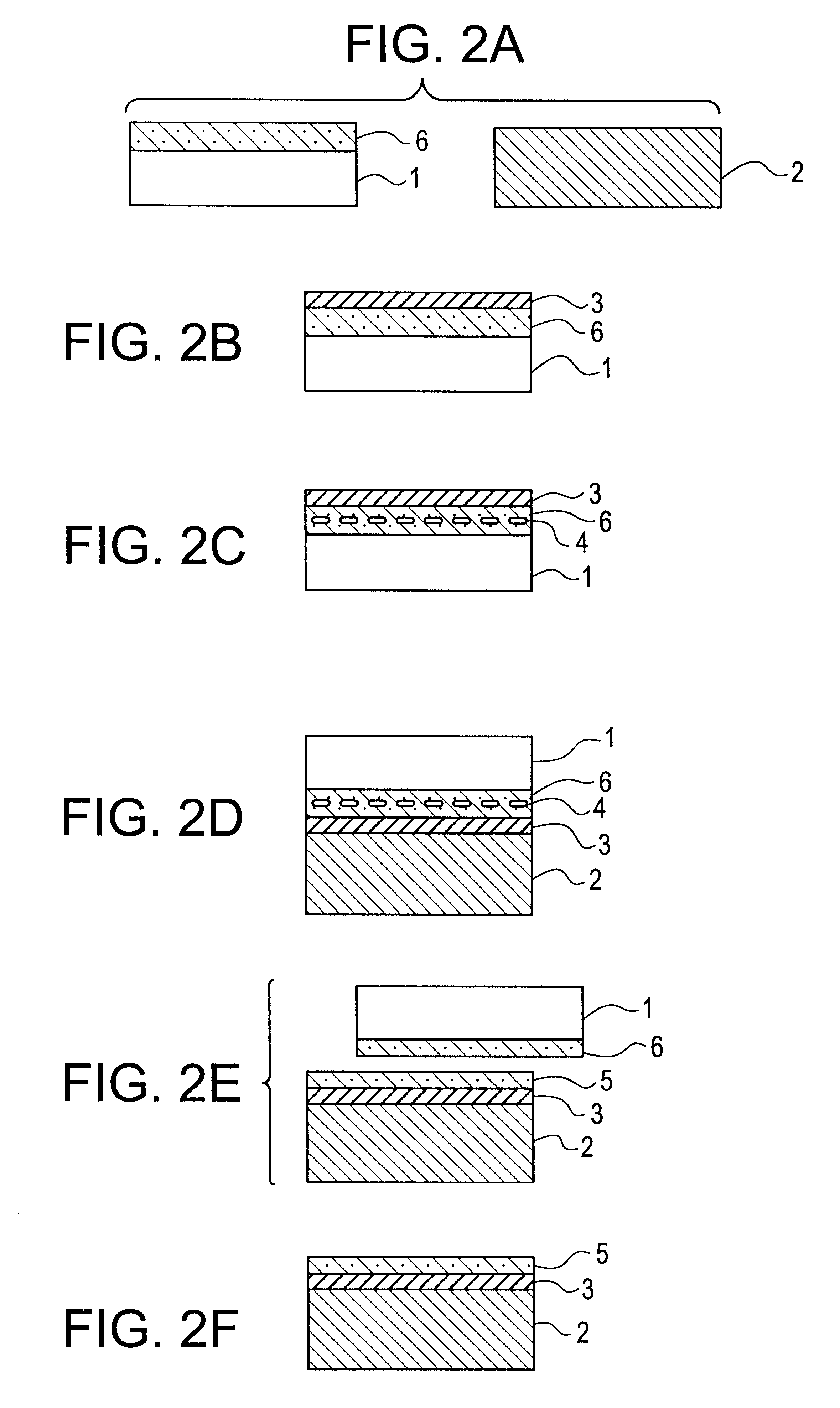

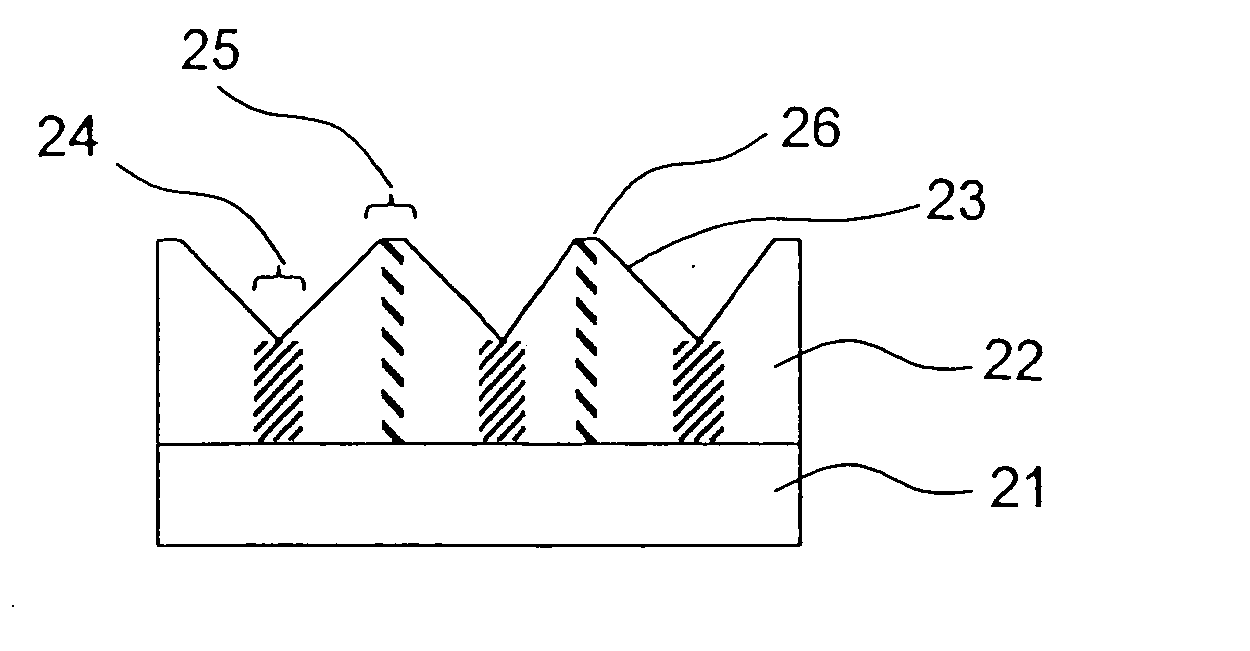

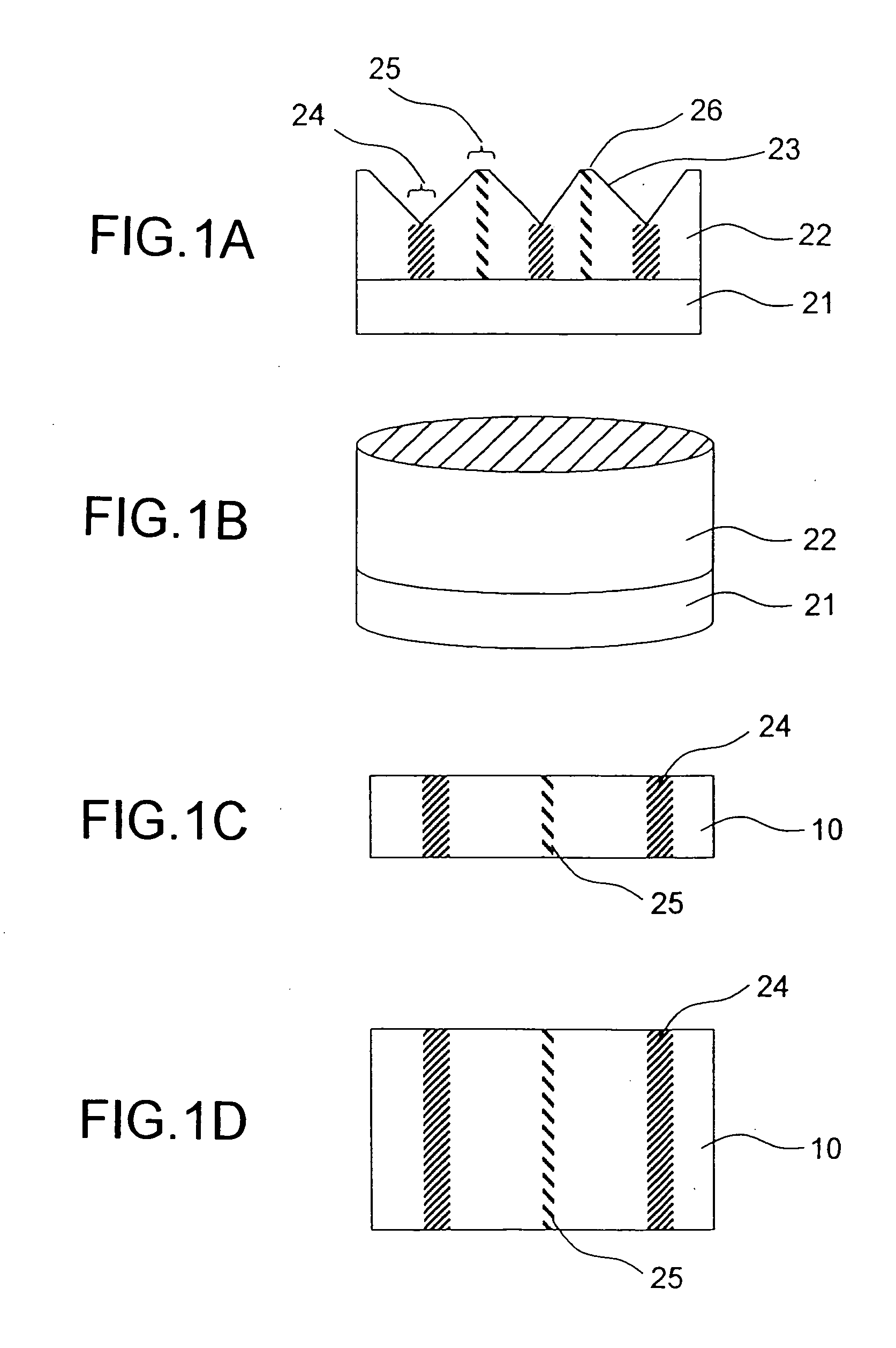

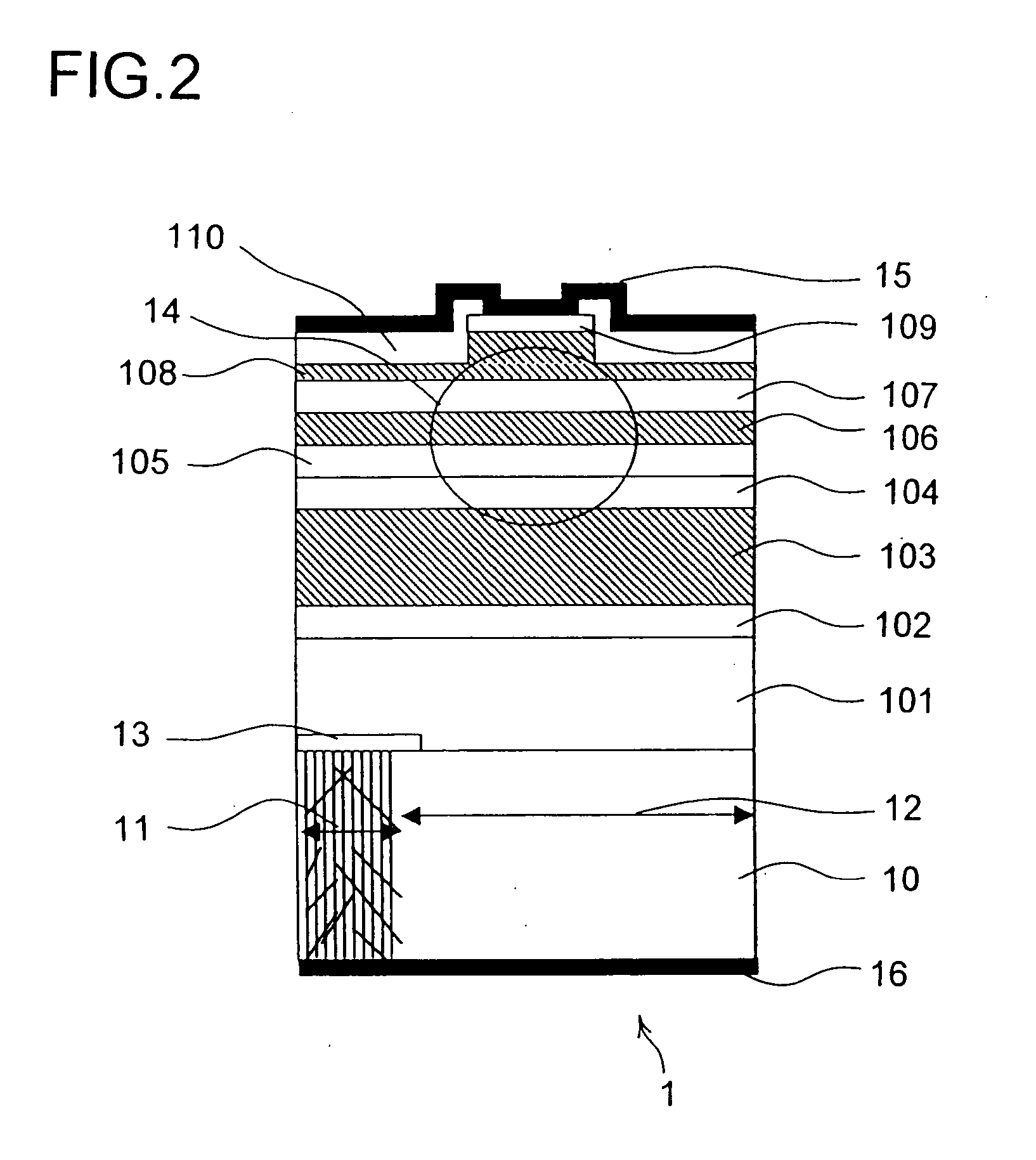

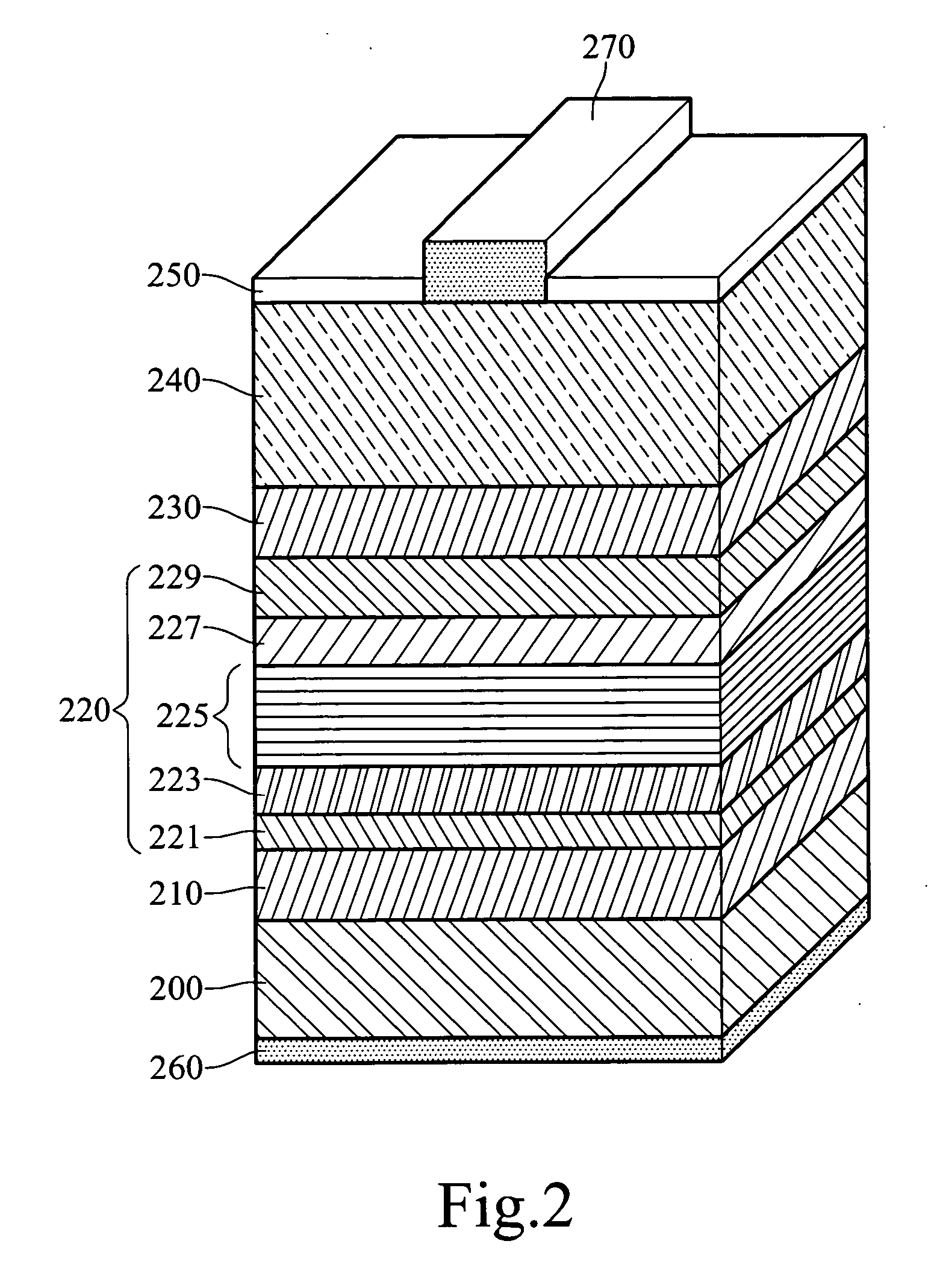

Semiconductor device

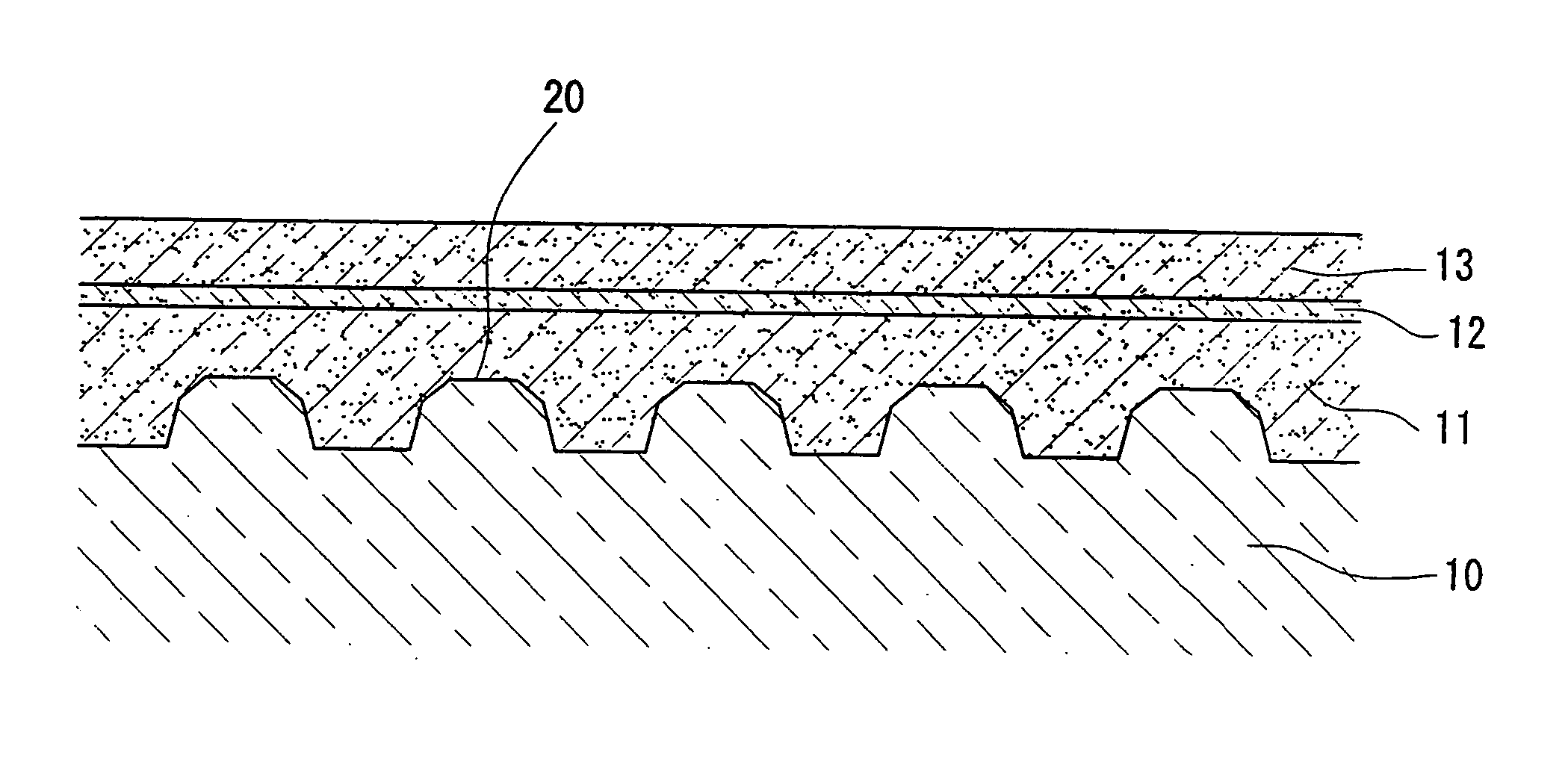

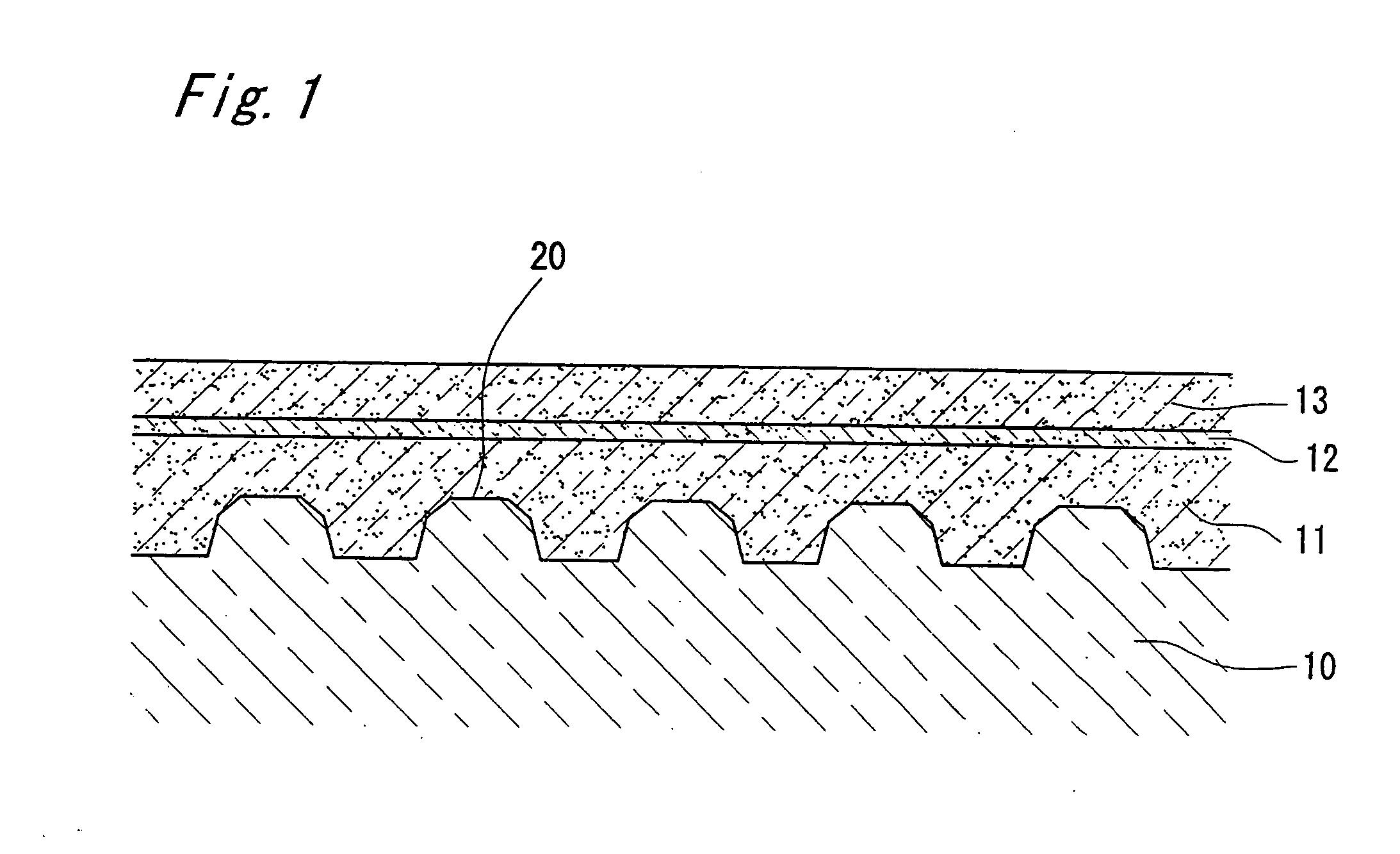

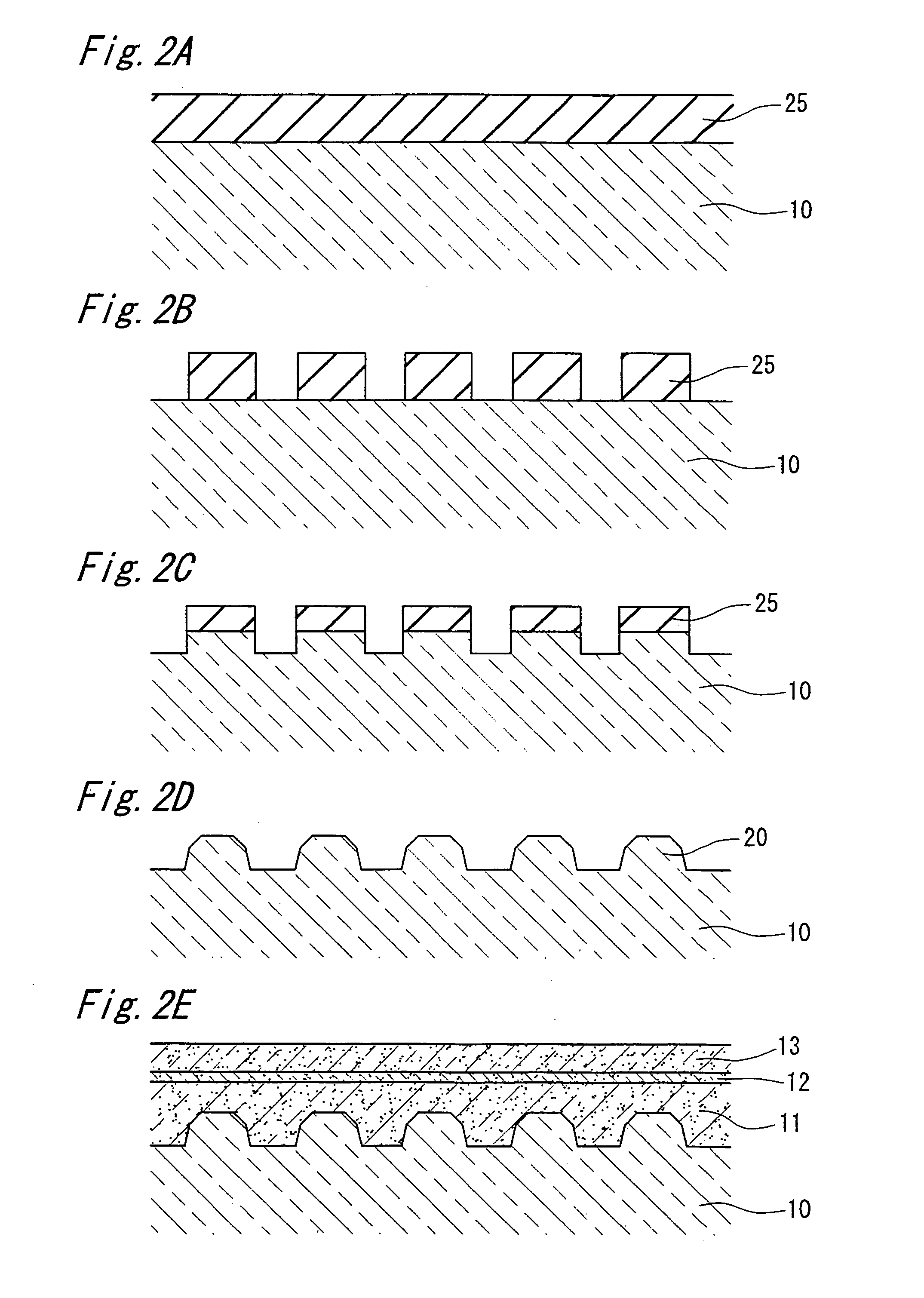

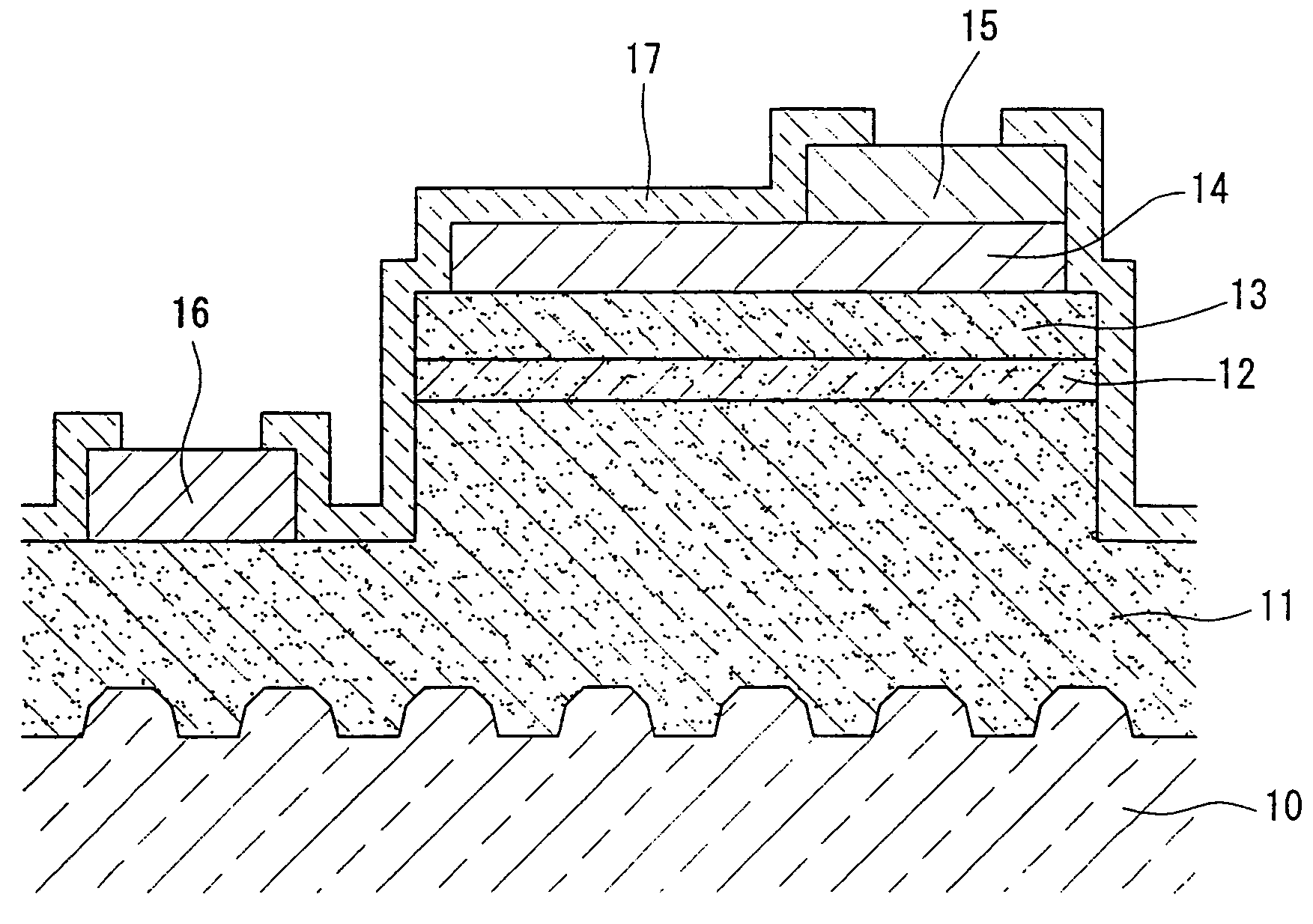

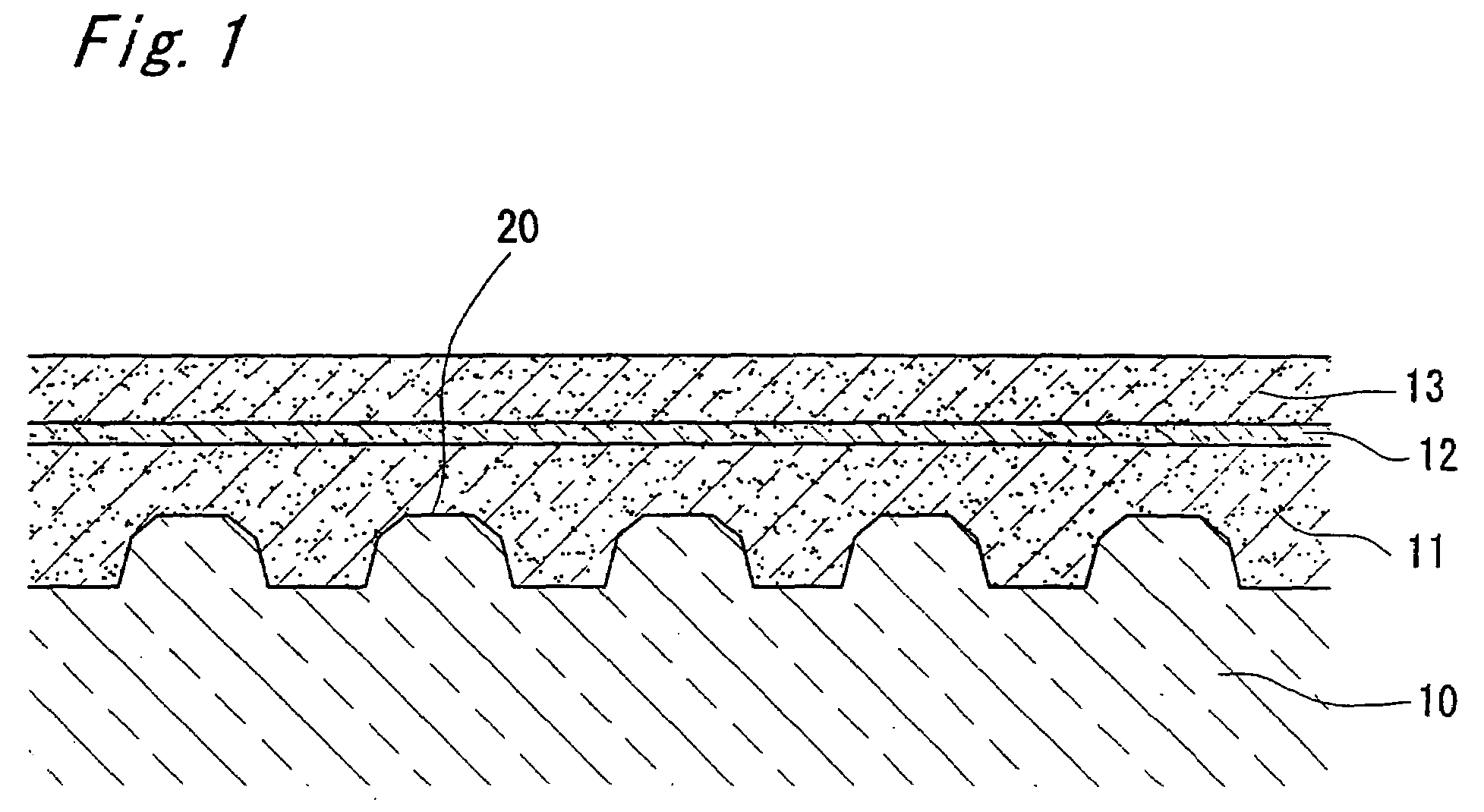

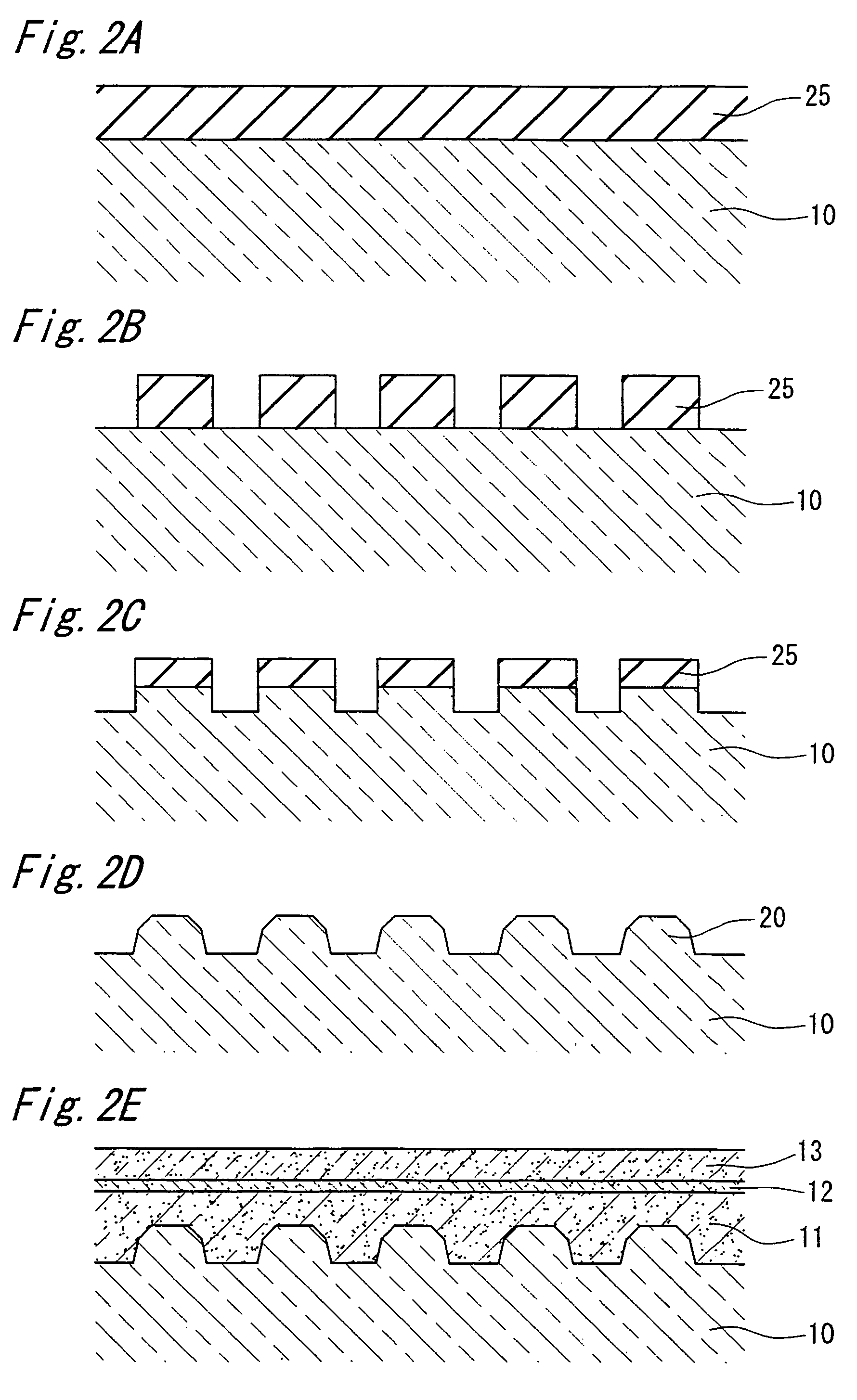

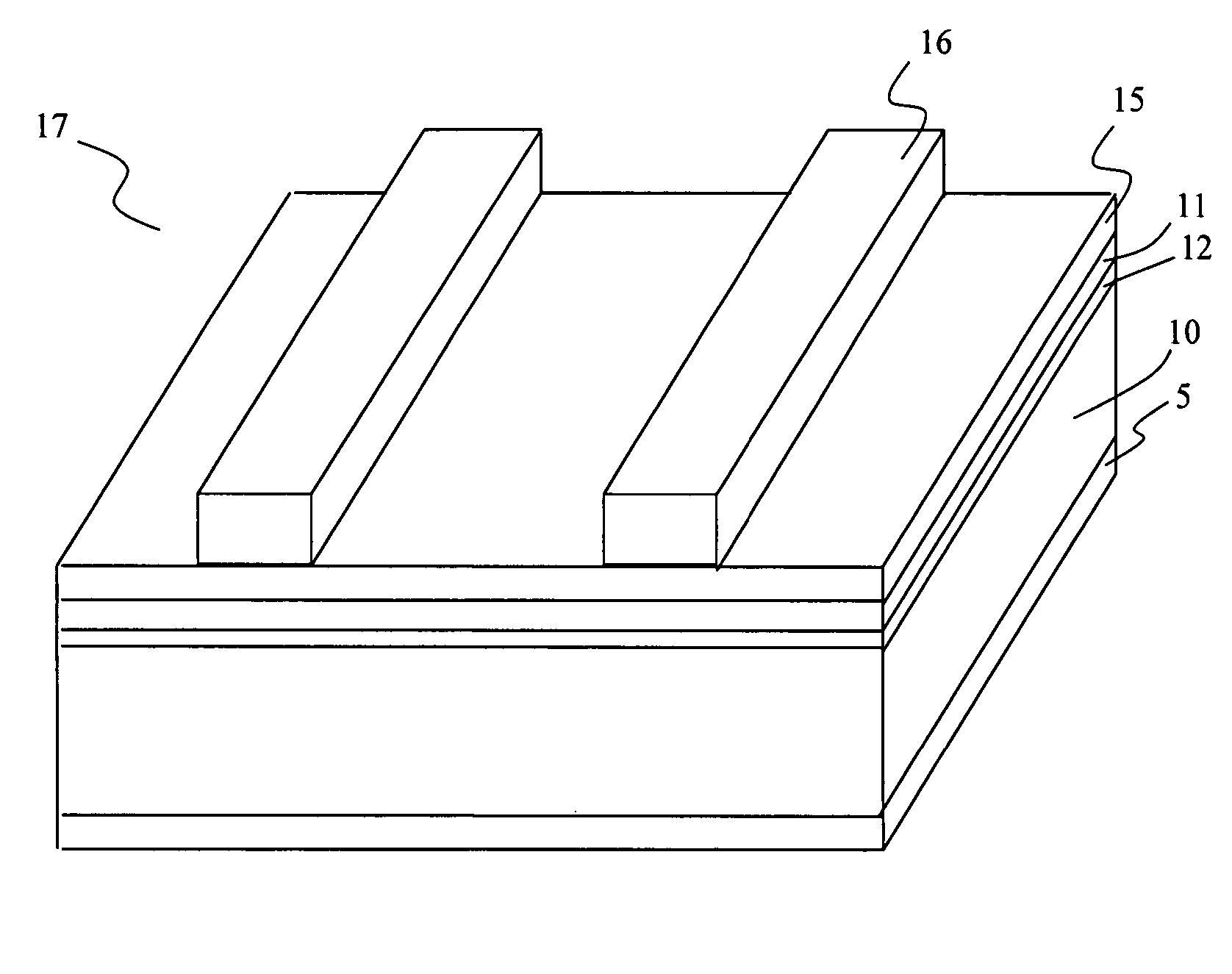

ActiveUS20050179130A1Easy to produceReduce crystallinitySemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A substrate (10) has at least one recess (20) and / or protrusion (21) formed on the surface thereof so as to scatter or diffract the light generated in an active layer (12). The recess and / or protrusion is formed in such a shape that can reduce crystalline defect in semiconductor layers (11, 13).

Owner:NICHIA CORP

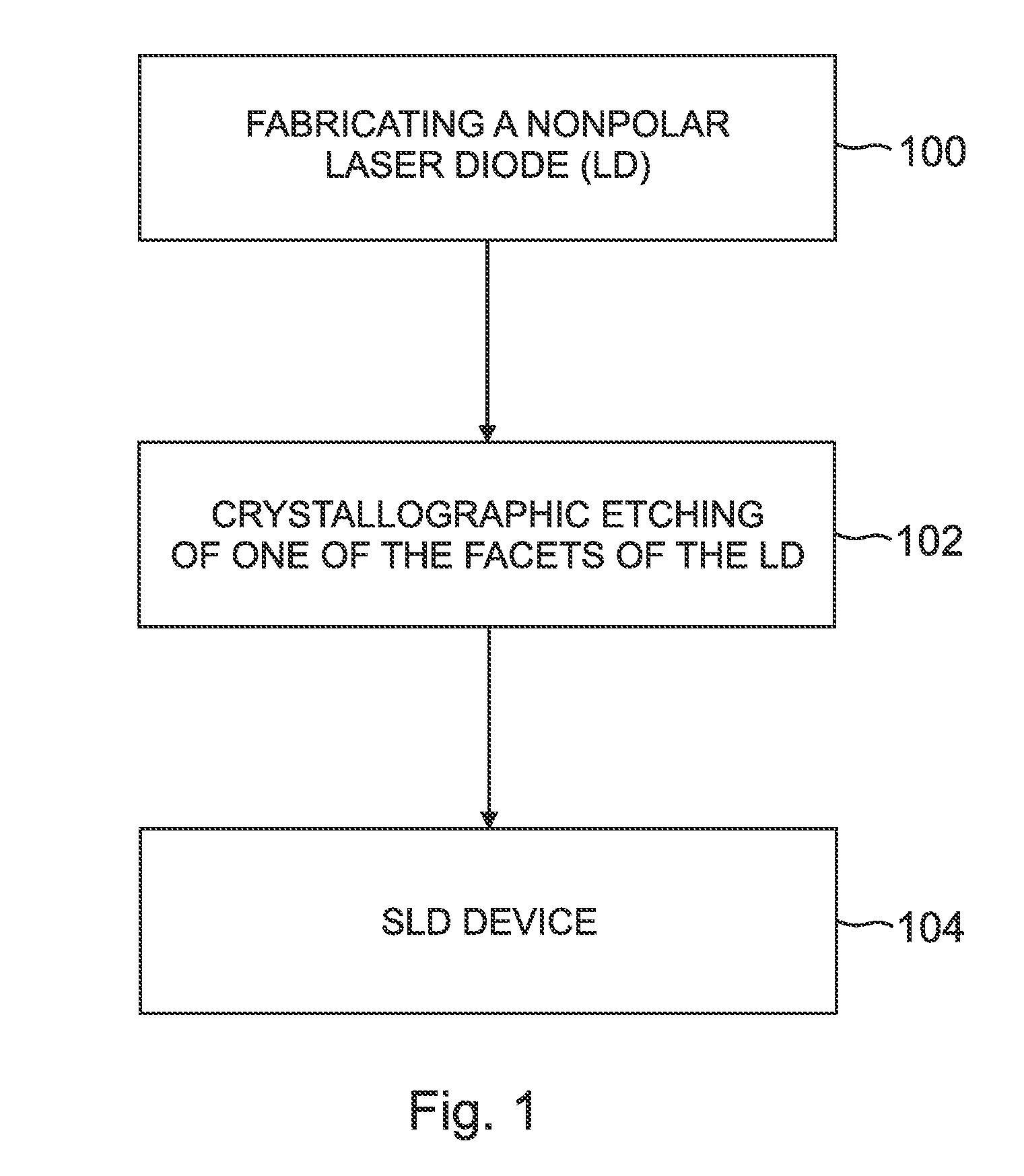

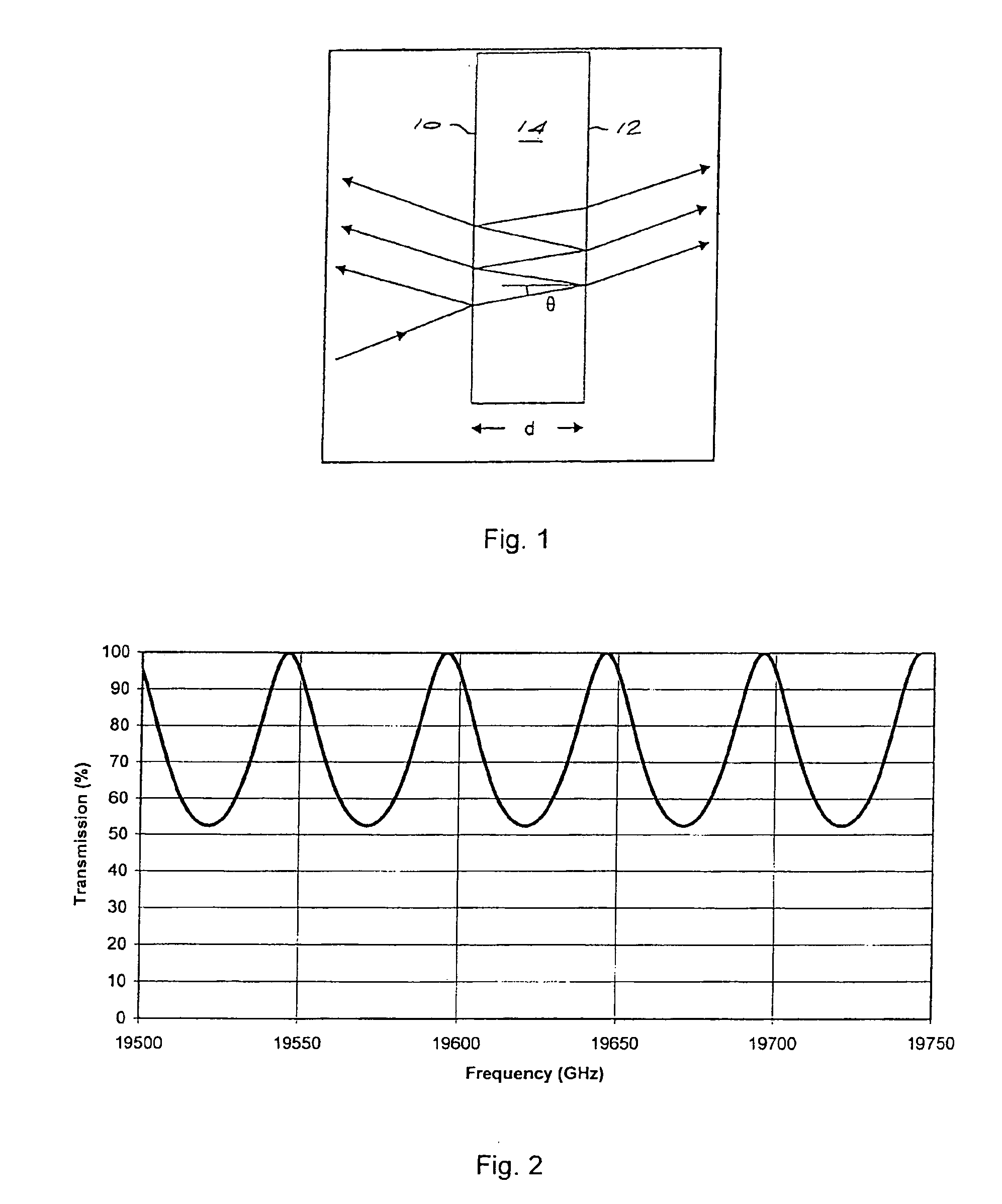

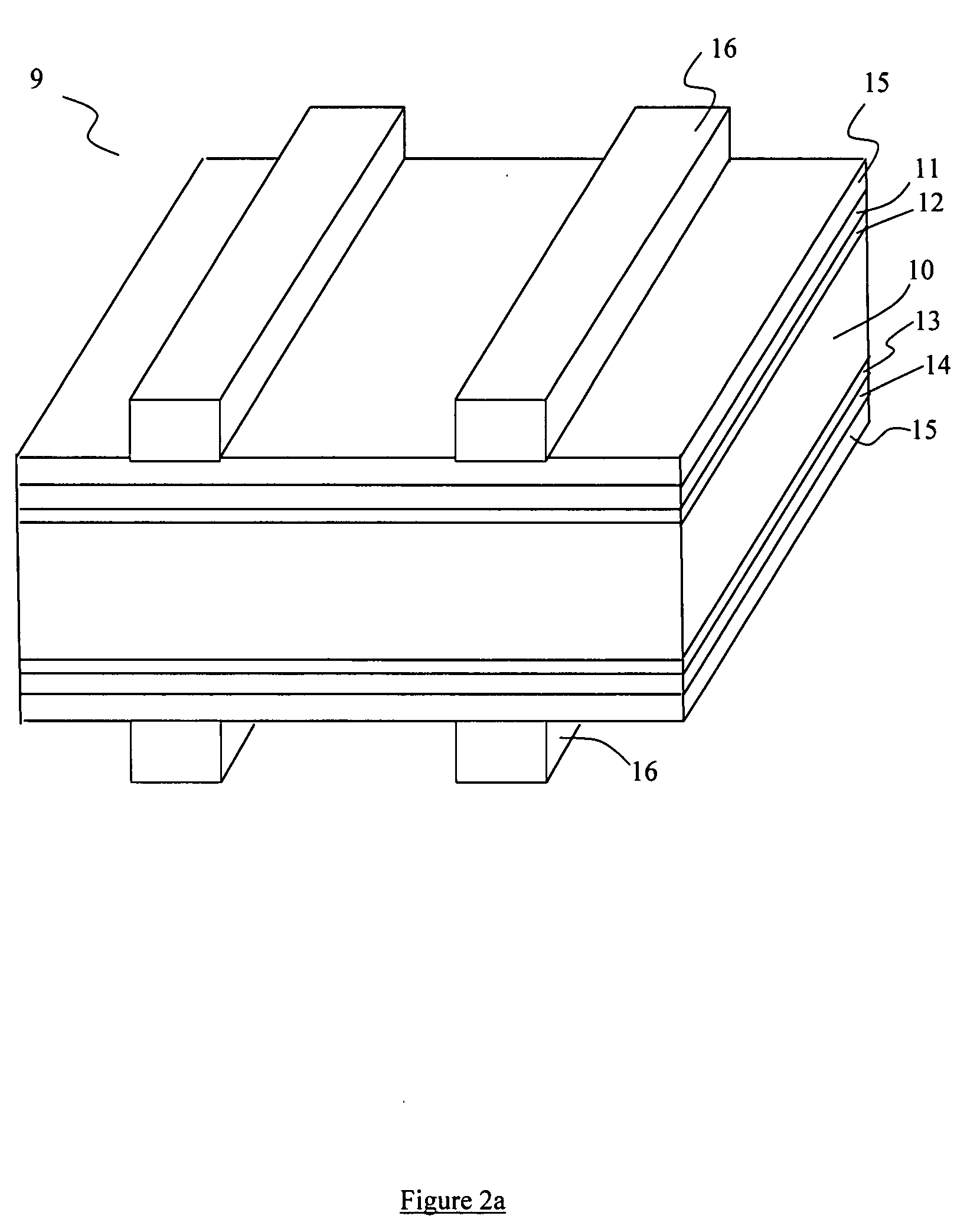

Superluminescent diodes by crystallographic etching

InactiveUS20110103418A1Reduce internal lossSignificant contributionOptical wave guidanceLaser detailsSuperluminescent diodeEtching

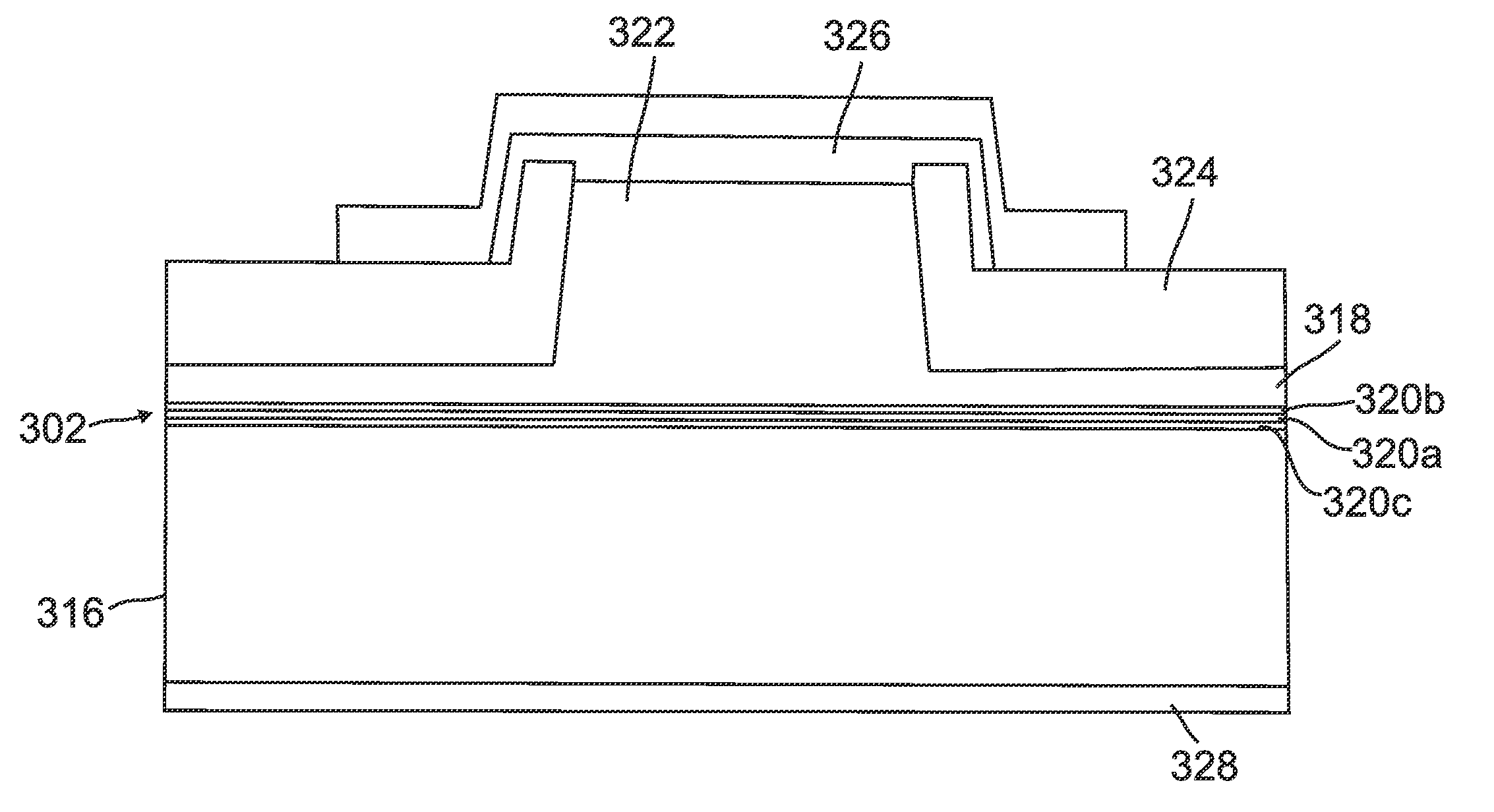

An optoelectronic device, comprising an active region and a waveguide structure to provide optical confinement of light emitted from the active region; a pair of facets on opposite ends of the device, having opposite surface polarity; and one of the facets which has been roughened by a crystallographic chemical etching process, wherein the device is a nonpolar or semipolar (Ga,In,Al,B)N based device.

Owner:RGT UNIV OF CALIFORNIA

Semiconductor light emitting device

InactiveUS20030057444A1Blocking may occurAvoid defectsSemiconductor/solid-state device detailsSolid-state devicesQuantum efficiencyCrystallographic defect

A high external quantum efficiency is stably secured in a semiconductor light emitting device. At least one recess and / or protruding portion is created on the surface portion of a substrate for scattering or diffracting light generated in a light emitting region. The recess and / or protruding portion has a shape that prevents crystal defects from occurring in semiconductor layers.

Owner:NICHIA CORP

Semiconductor device and a method of manufacturing the same

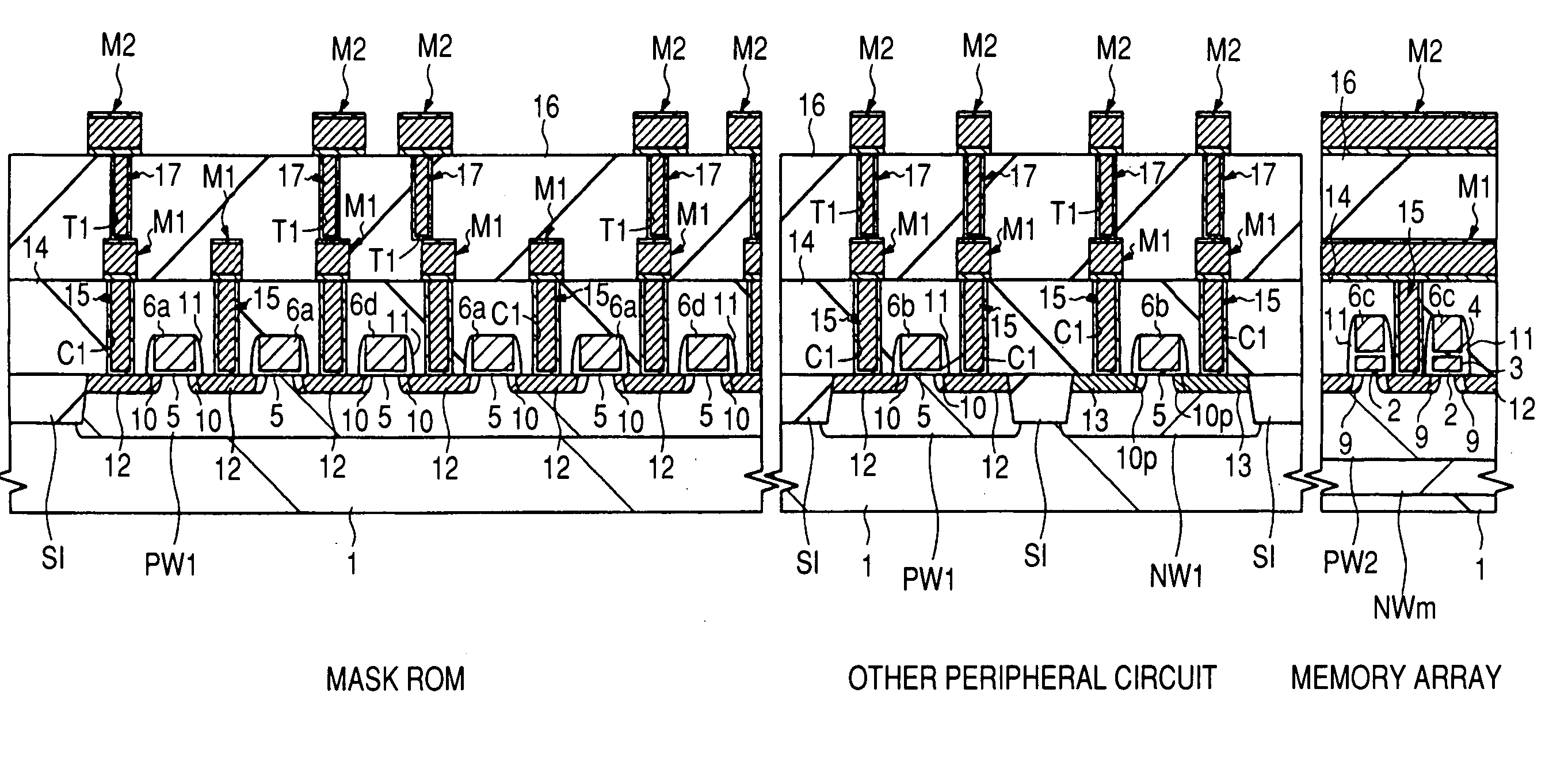

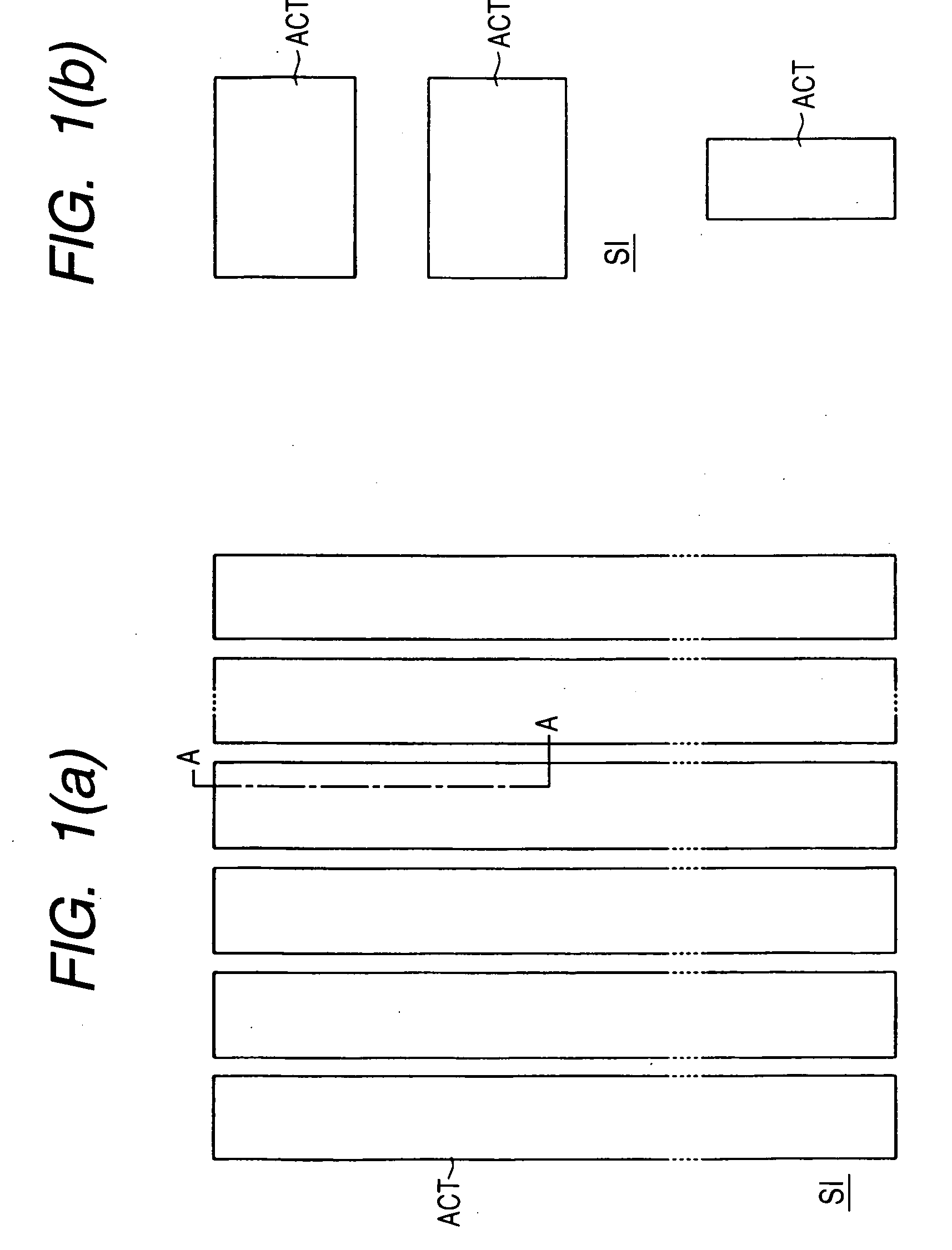

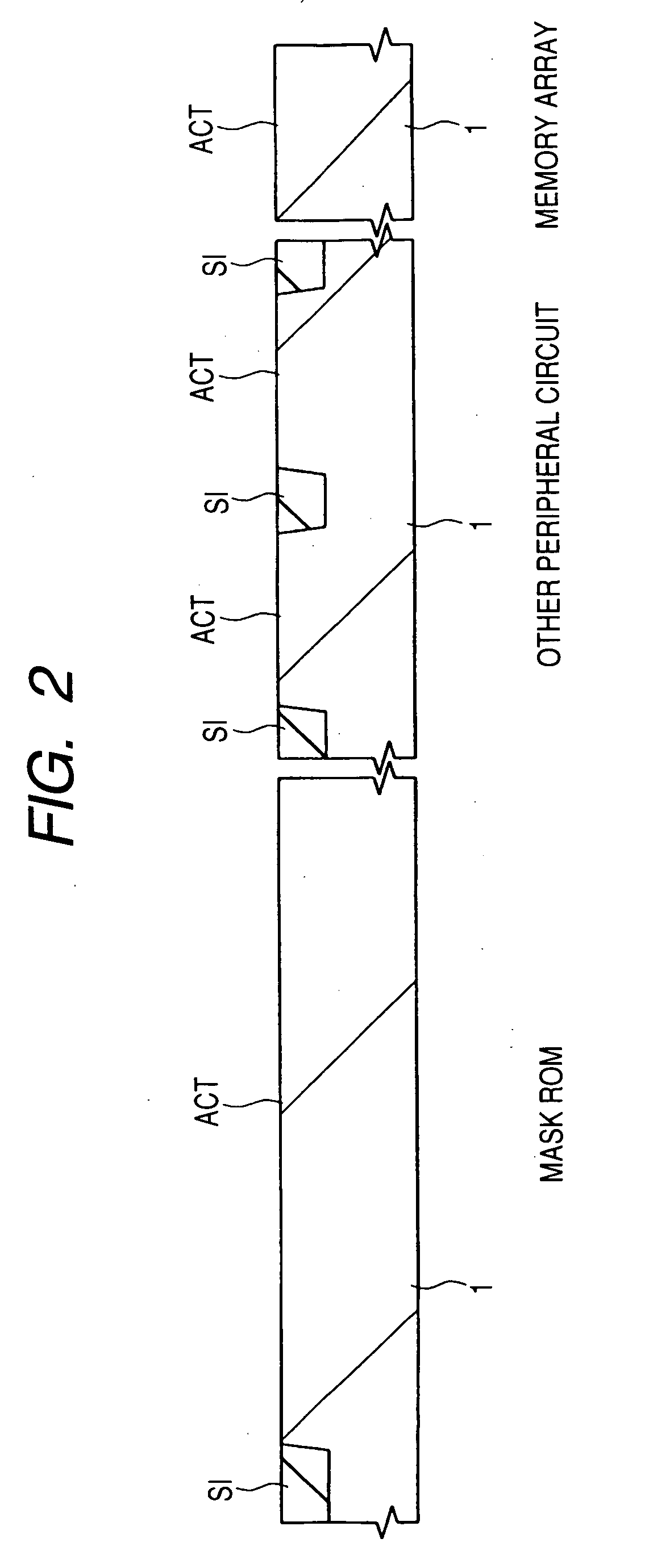

InactiveUS20060125024A1Improve reliabilityGood effectSolid-state devicesSemiconductor/solid-state device manufacturingMask ROMDevice material

To improve reliability of FETs having element isolation regions for electrically isolating field effect transistors adjacent to each other in the gate length direction in a mask ROM region, the isolation regions are each constructed by field plate isolation formed simultaneously with gate electrodes of the field effect transistors. This relatively lessens a stress generated in an active region ACT sandwiched by the element isolation regions even if the isolation width of each element isolation region is made relatively small, specifically, less than 0.3 μm. It is therefore possible to relax or prevent the generation of crystal defects resulting from the stress, thereby reducing occurrence of an undesired leak current between the source and drain of each field effect transistor.

Owner:RENESAS TECH CORP

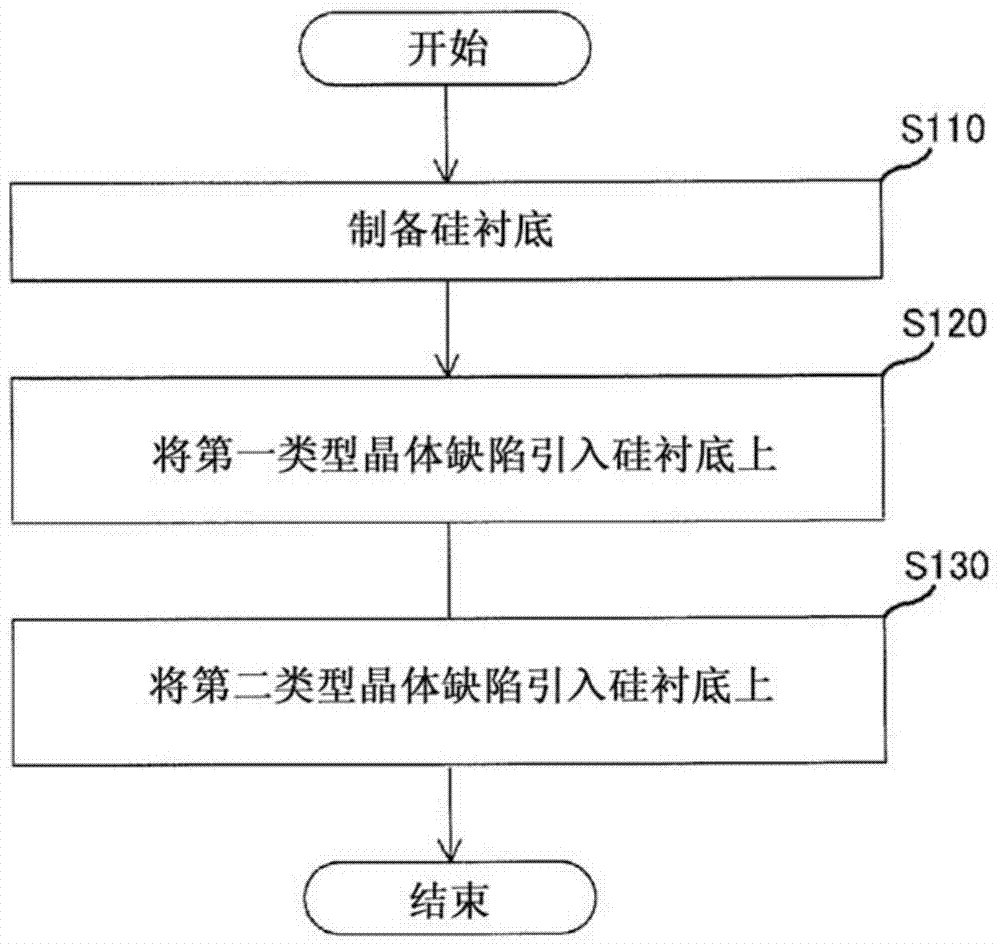

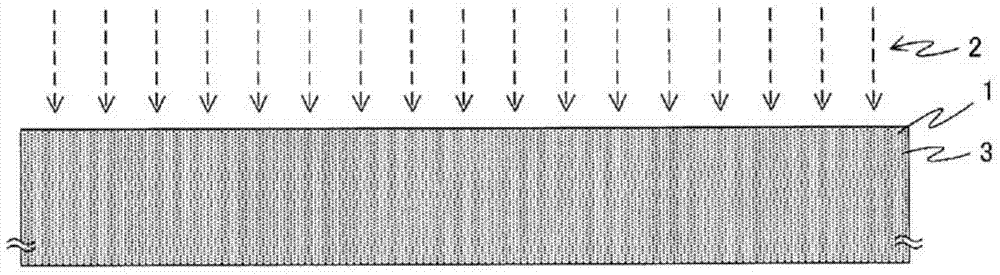

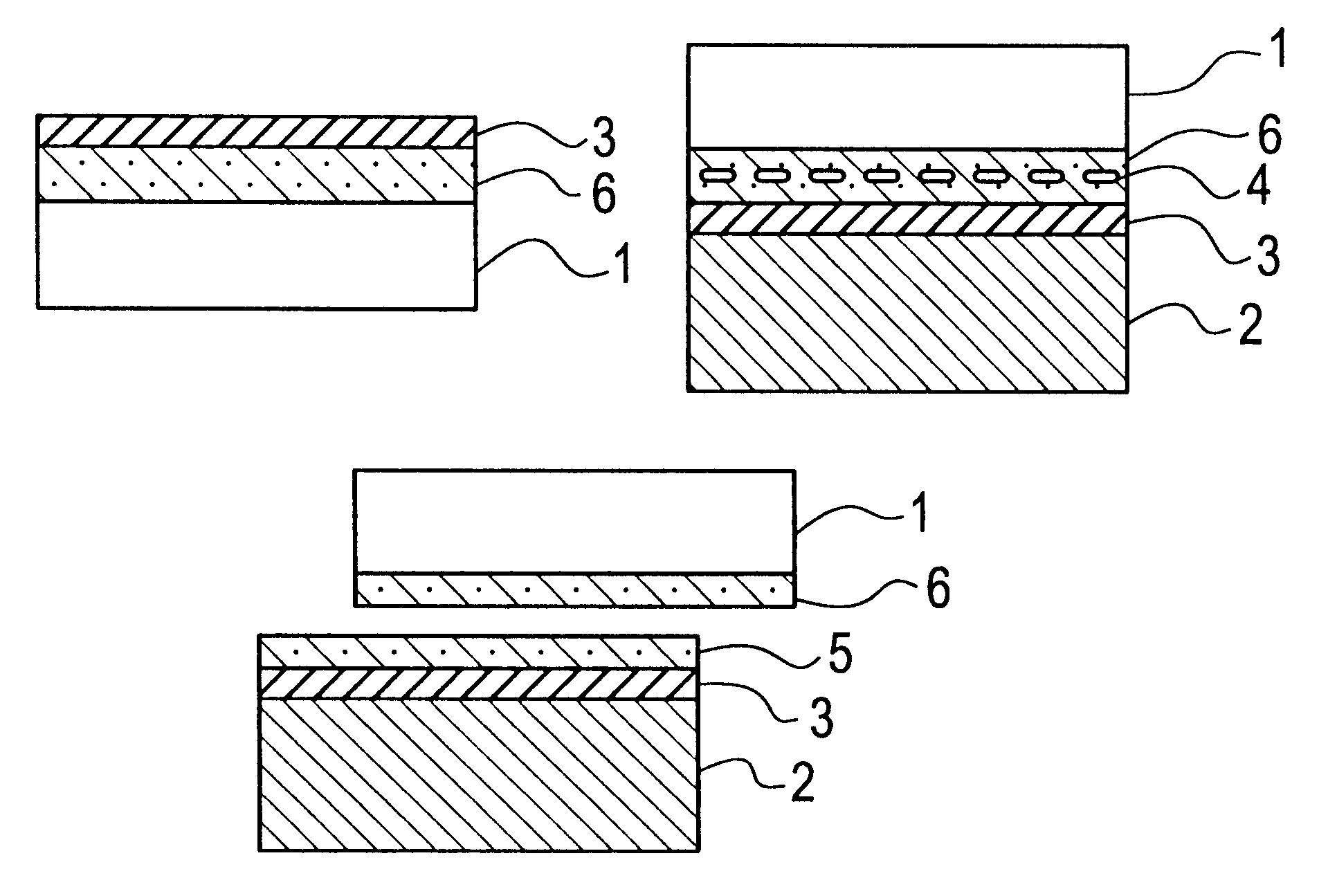

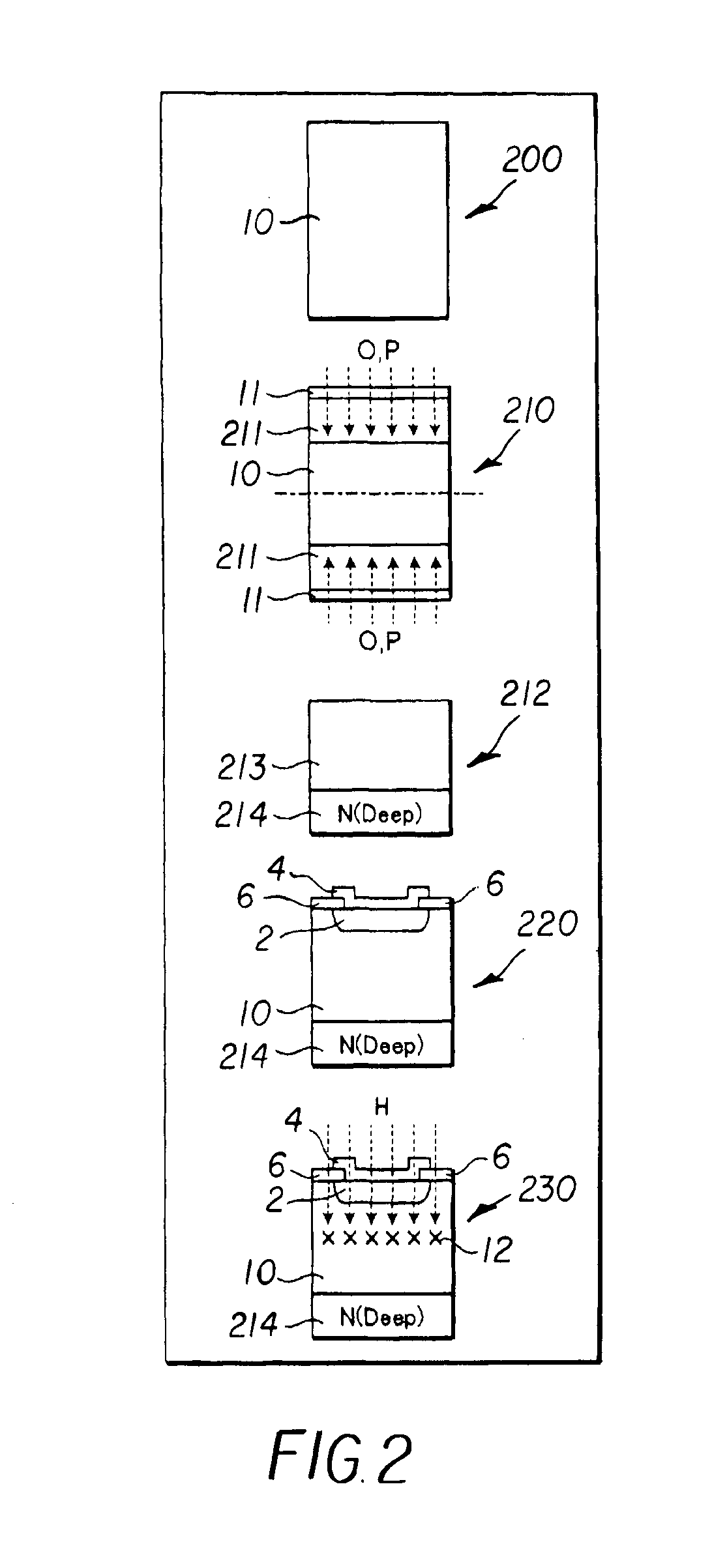

Semiconductor device, method of manufacturing semiconductor device, and antenna switch module

ActiveCN103811474ASemiconductor/solid-state device detailsSolid-state devicesEngineeringCrystallographic defect

The invention relates to a semiconductor device, a method of manufacturing semiconductor device, and an antenna switch module. Disclosed is a semiconductor device having a radio frequency switch. Also disclosed are an antenna switch module and a method of manufacturing the semiconductor device. The semiconductor device includes a metal wiring insulating film bonded to a silicon substrate. In the semiconductor device, a crystal defect layer extends into the silicon substrate from a surface of the silicon substrate. Crystal defects are throughout the crystal defect layer. The semiconductor device and an integrated circuit are in the antenna switch module. The integrated circuit in the antenna switch module is mounted with the radio-frequency switch device and the silicon substrate. The method of manufacturing the semiconductor device includes a step of forming crystal defects throughout a silicon substrate. Radiation or a diffusion is used to form the crystal defects. After the step of forming the crystal defects, the method includes a step of implanting ions into a surface of the silicon substrate to form a crystal defect layer.

Owner:SONY CORP

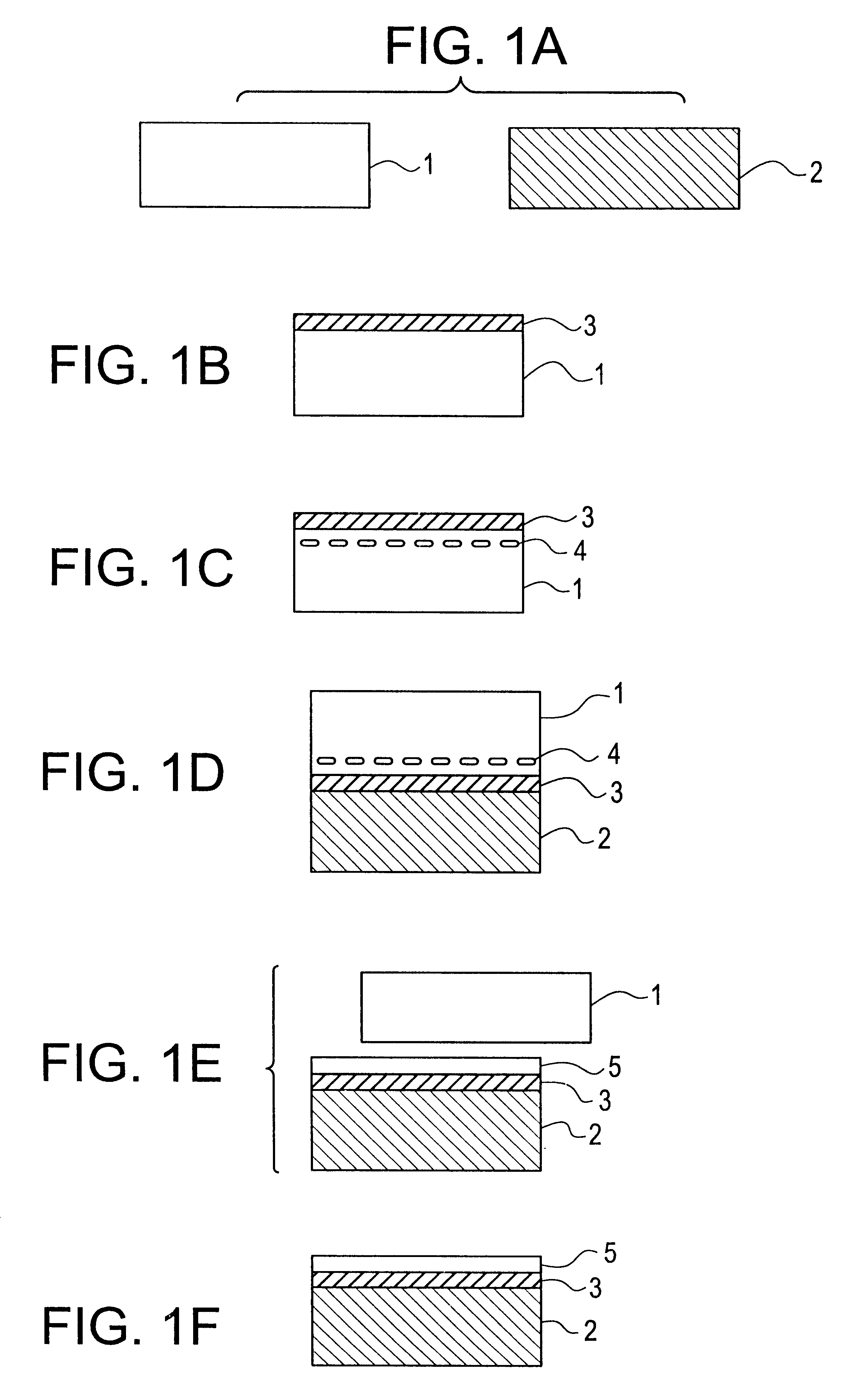

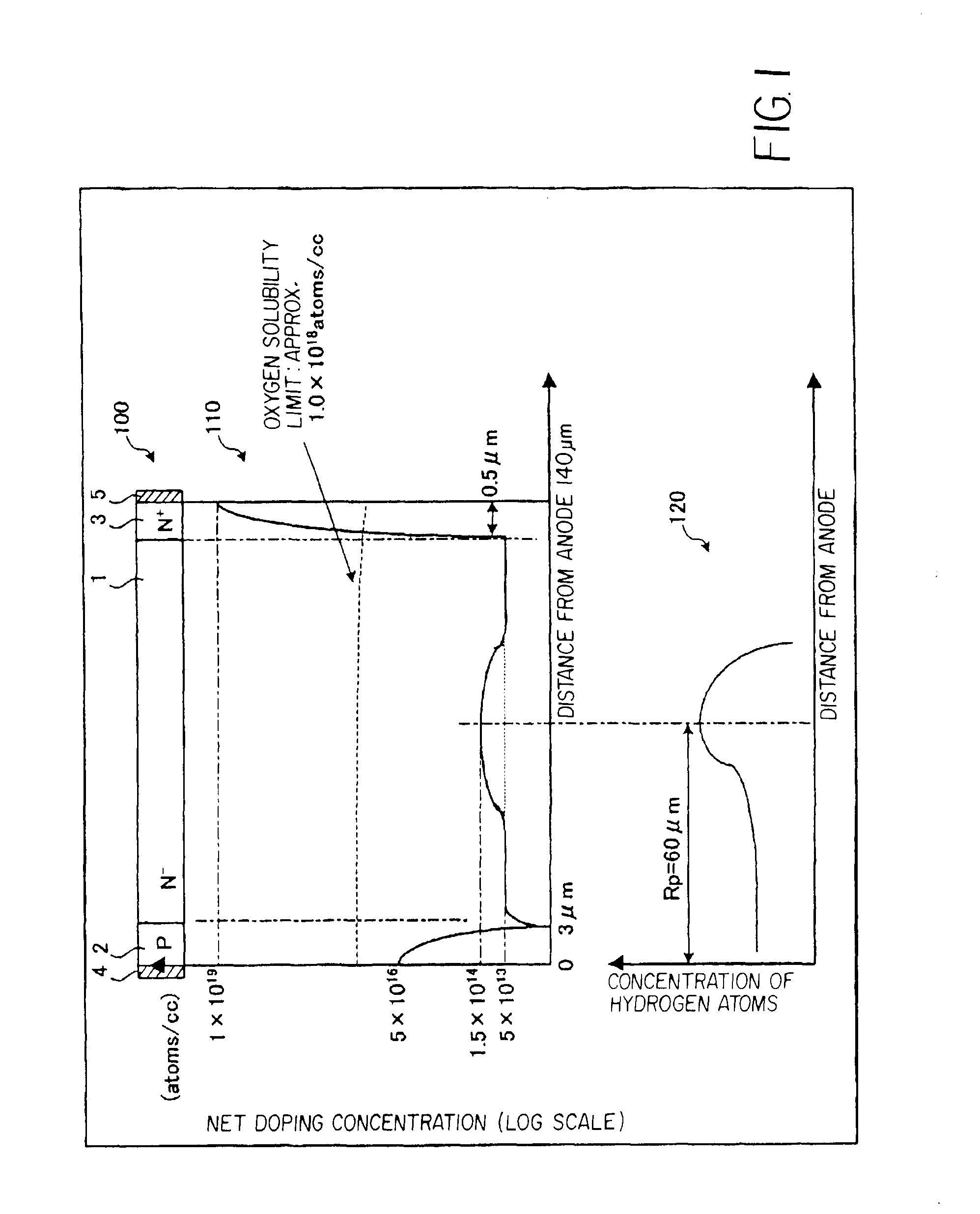

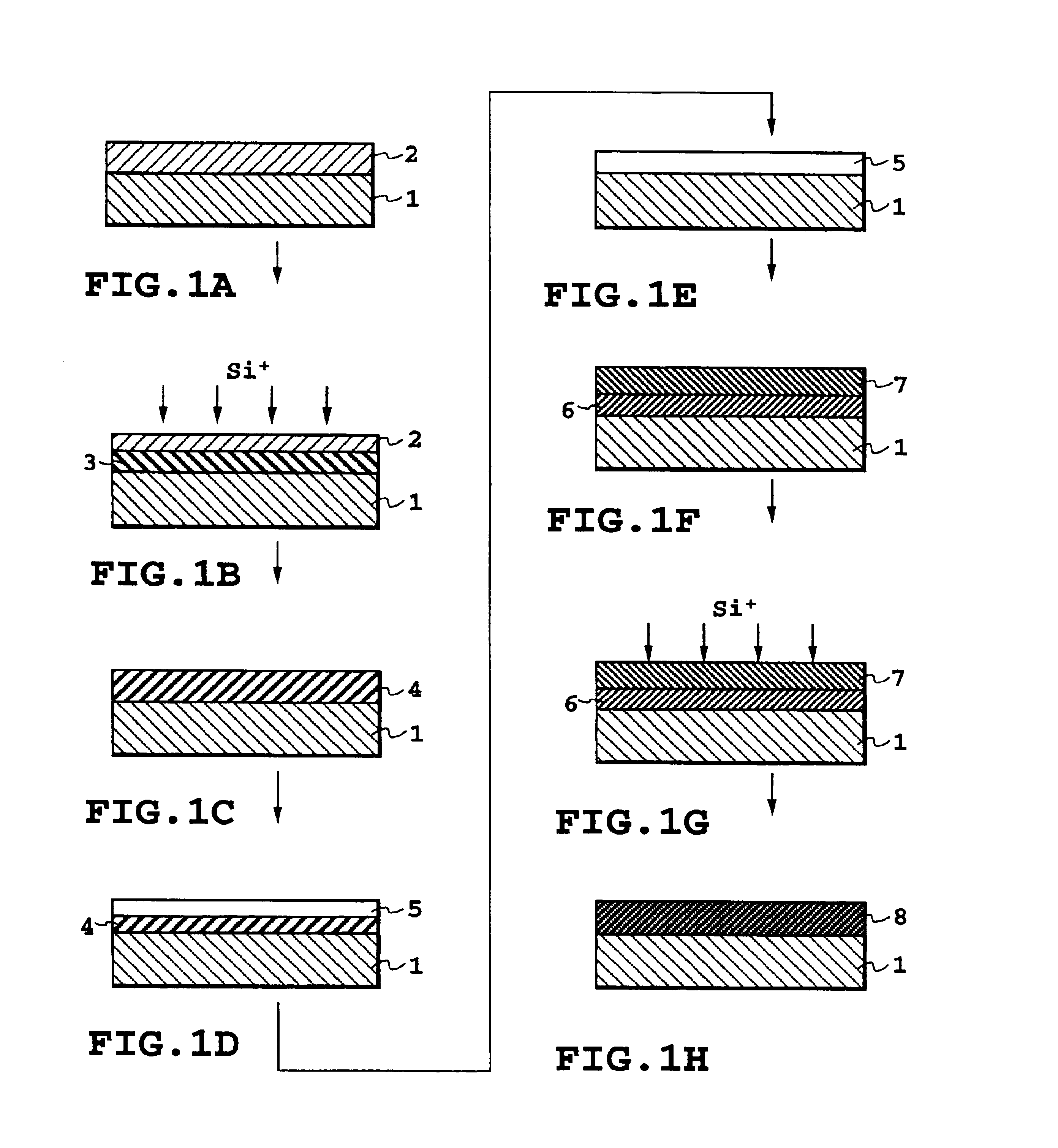

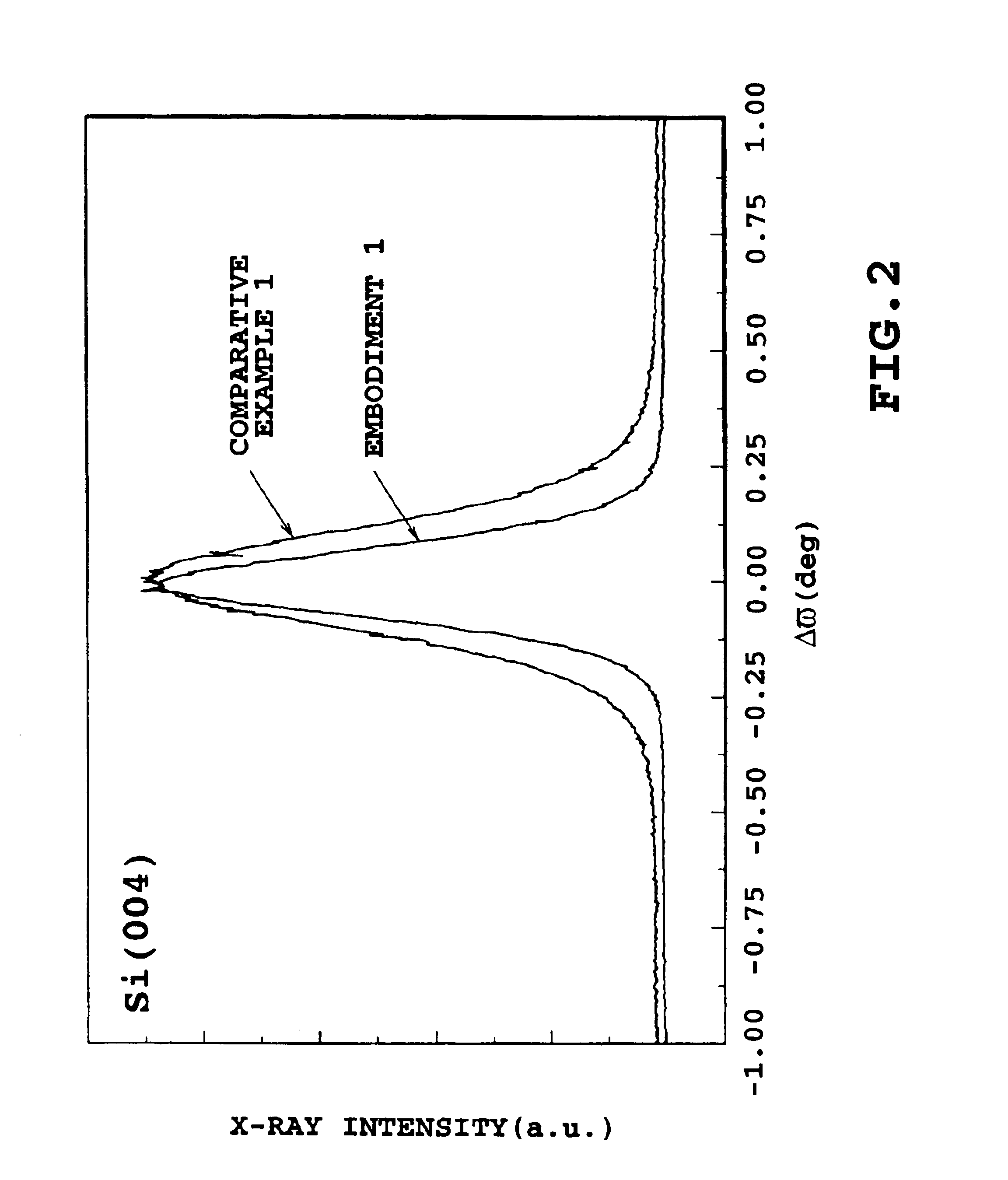

Silicon-on-insulator (SOI) substrate and method of fabricating the same

InactiveUS6211041B1Solid-state devicesSemiconductor/solid-state device manufacturingHydrogenSilicon oxide

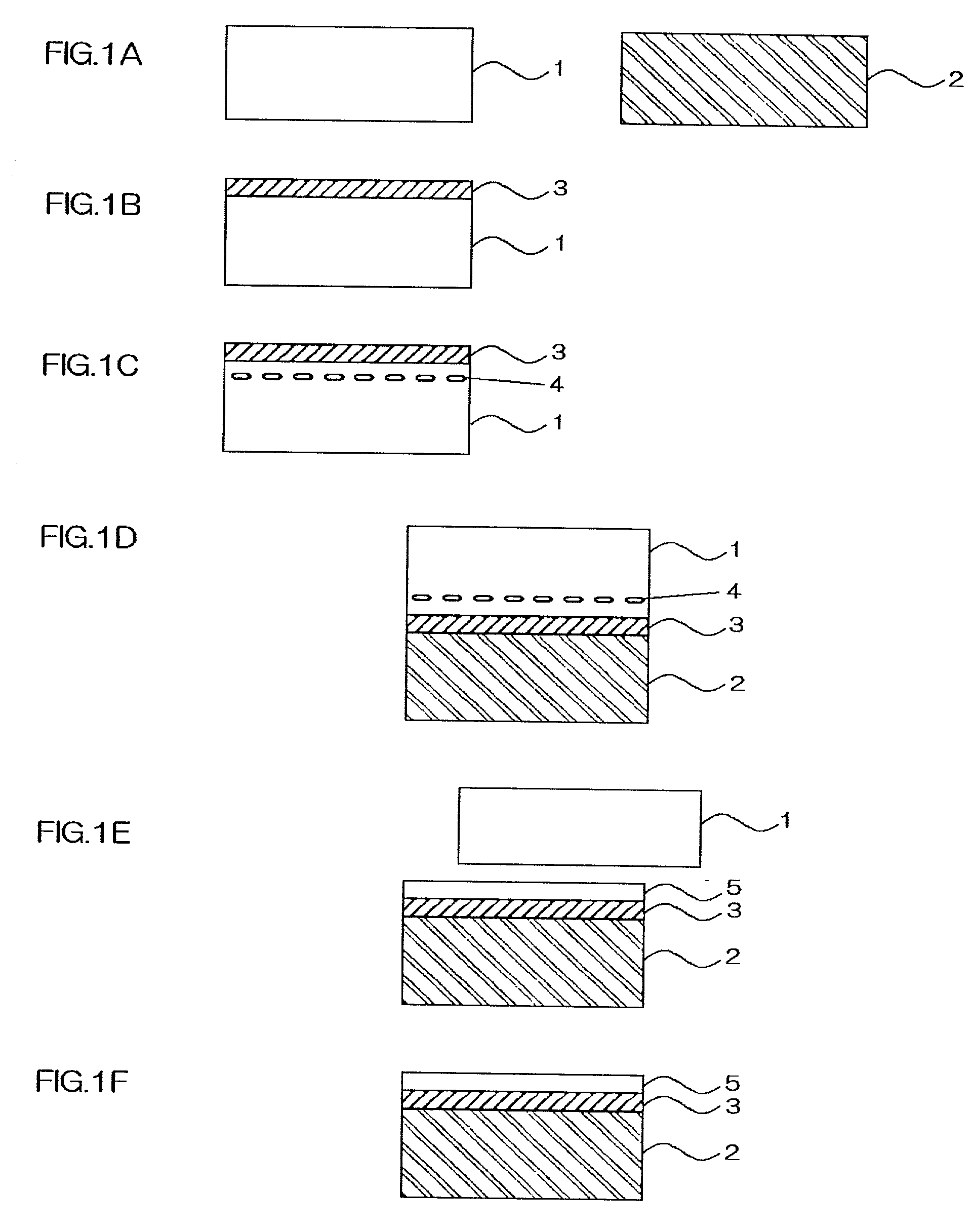

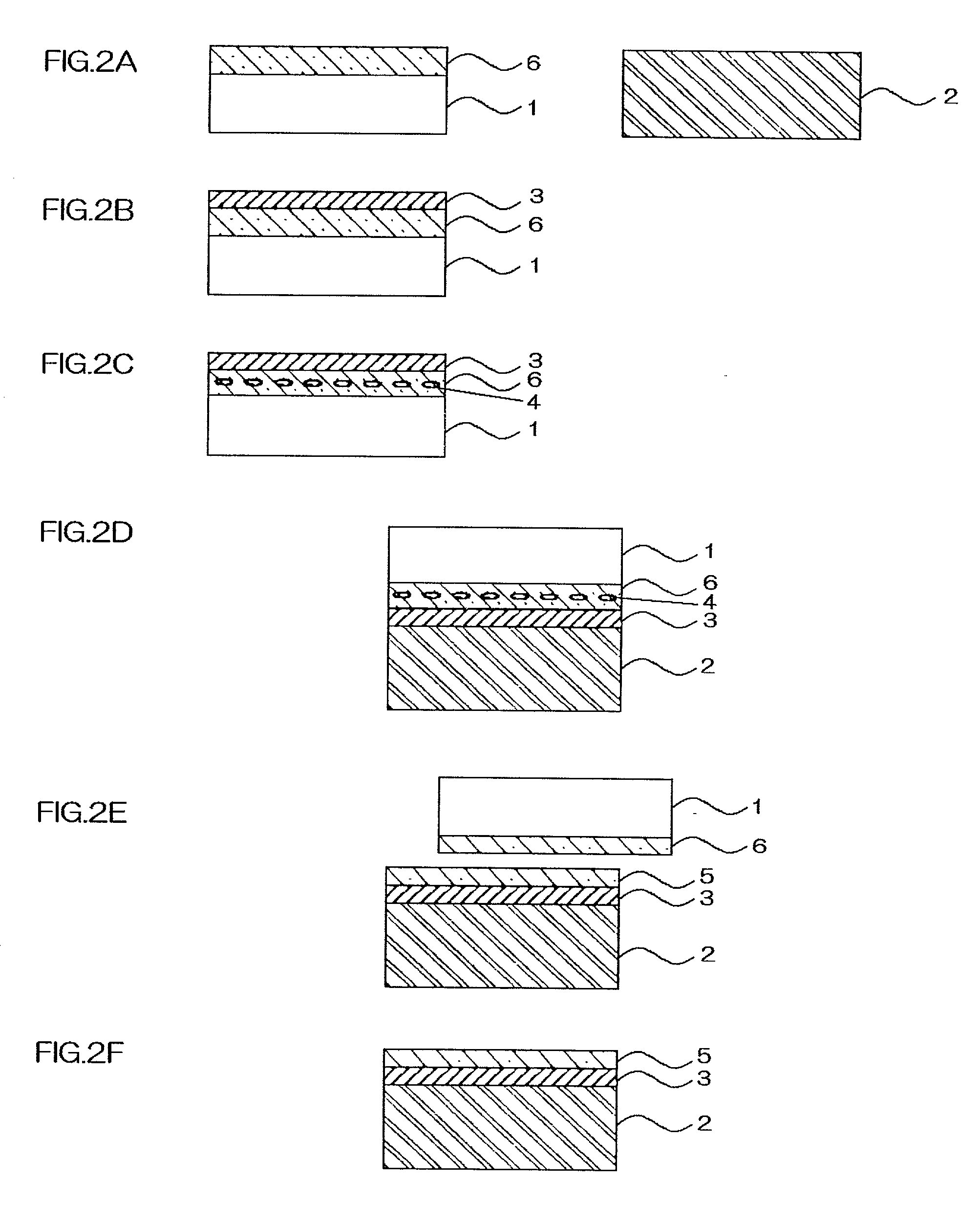

There is provided a method of fabricating a silicon-on-insulator substrate, including the steps of (a) forming a silicon substrate at a surface thereof with an oxygen-containing region containing oxygen at such a concentration that oxygen is not precipitated in the oxygen-containing region in later mentioned heat treatment, (b) forming a silicon oxide film at a surface of the silicon substrate, (c) implanting hydrogen ions into the silicon substrate through the silicon oxide film, (d) overlapping the silicon substrate and a support substrate each other so that the silicon oxide film makes contact with the support substrate, and (e) applying heat treatment to the thus overlapped silicon substrate and support substrate to thereby separate the silicon substrate into two pieces at a region into which the hydrogen ions have been implanted, one of the two pieces remaining on the silicon oxide film as a silicon-on-insulator active layer. The support substrate, the silicon oxide film located on the support substrate, and the silicon-on-insulator active layer formed on the silicon oxide film defines a silicon-on-insulator structure. The method makes it possible to significantly reduce crystal defect density in the silicon-on-insulator active layer, which ensures that a substrate made in accordance with the method can be used for fabricating electronic devices thereon.

Owner:NEC CORP

Semiconductor light-emitting device

InactiveUS20050001227A1Improve external quantum efficiencyImprove efficiencySemiconductor/solid-state device detailsSolid-state devicesQuantum efficiencyCrystallographic defect

Owner:NICHIA CORP

High surface quality GaN wafer and method of fabricating same

InactiveUS6951695B2Improve surface qualityPolycrystalline material growthAfter-treatment detailsSurface roughnessHigh surface

AlxGayInzN, wherein 0≦x≦1, 0≦y≦1, 0≦z≦1, and x+y+z=1, characterized by a root mean square surface roughness of less than 1 nm in a 10×10 μm2 area. The AlxGayInzN may be in the form of a wafer, which is chemically mechanically polished (CMP) using a CMP slurry comprising abrasive particles, such as silica or alumina, and an acid or a base. High quality AlxGayInzN wafers can be fabricated by steps including lapping, mechanical polishing, and reducing internal stress of said wafer by thermal annealing or chemical etching for further enhancement of its surface quality. CMP processing may be usefully employed to highlight crystal defects of an AlxGayInzN wafer.

Owner:WOLFSPEED INC

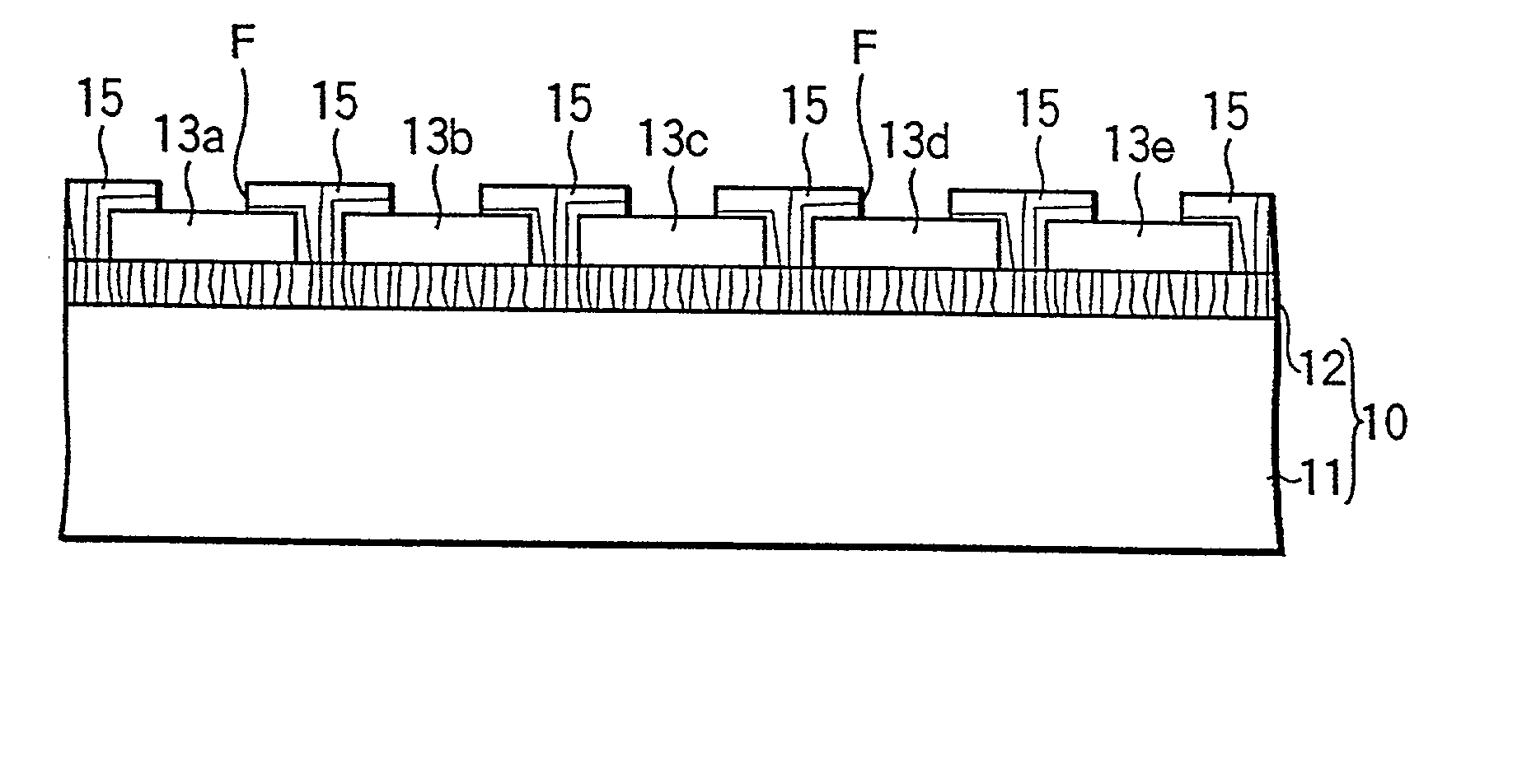

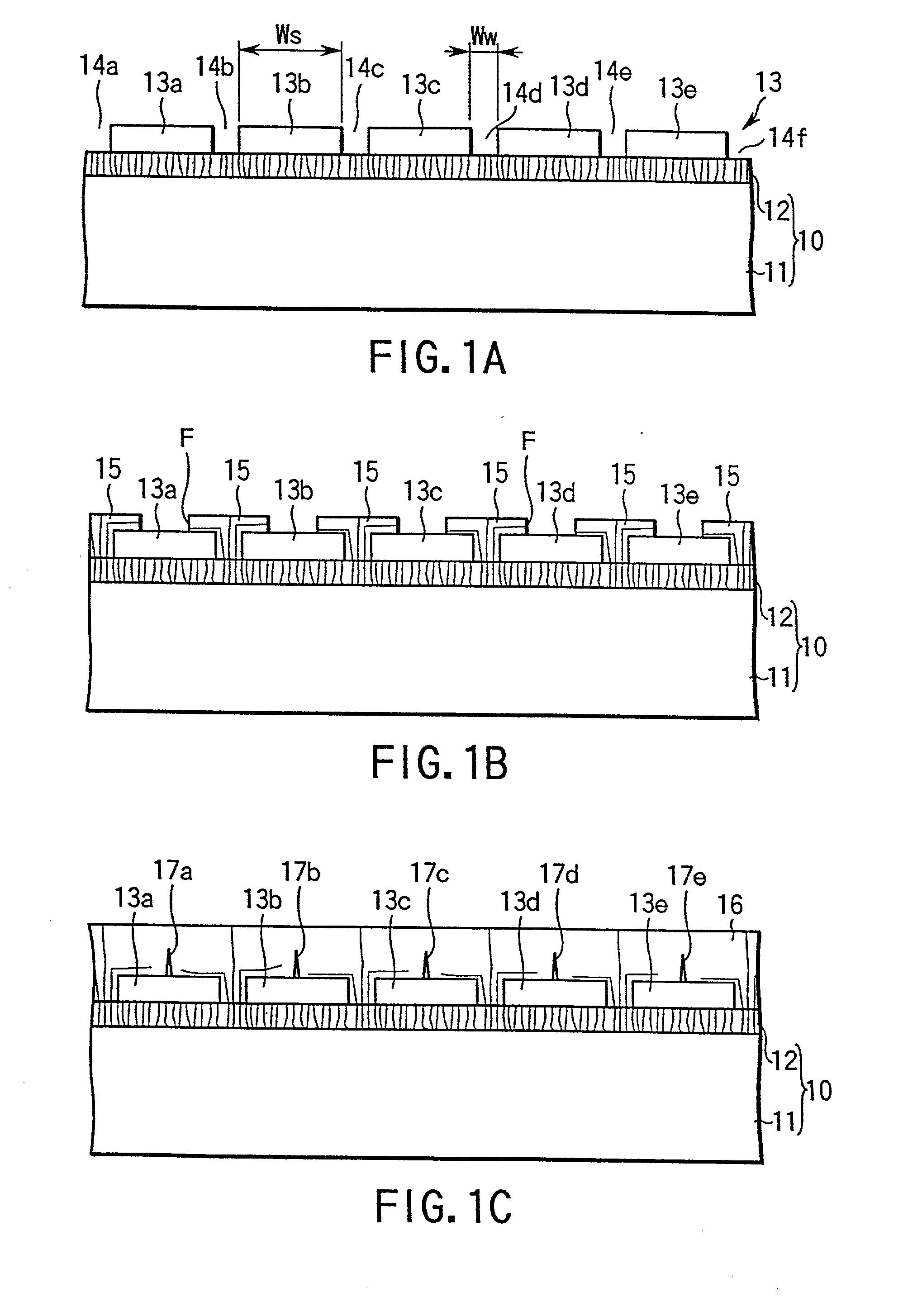

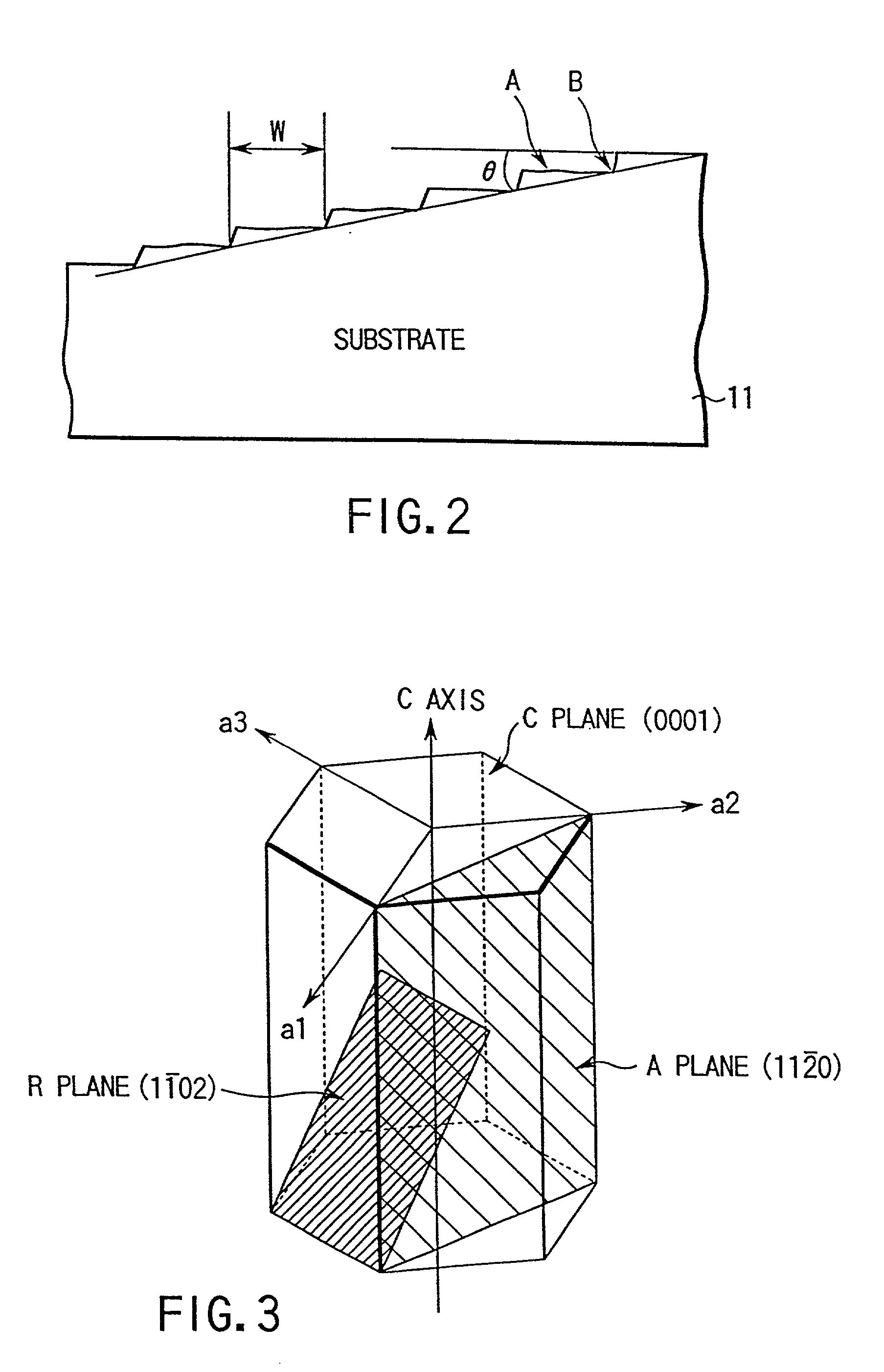

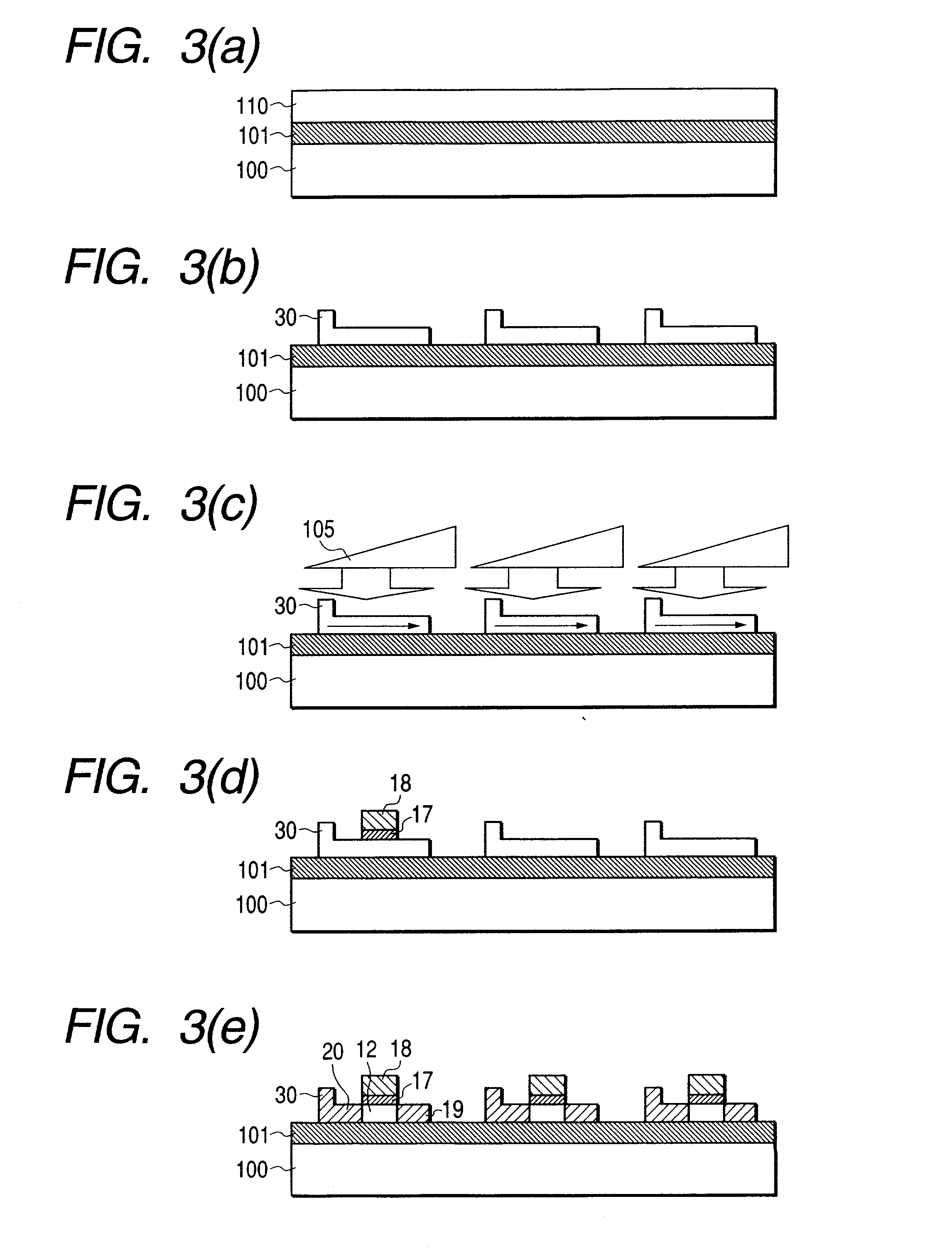

Nitride semiconductor growth method, nitride semiconductor substrate, and nitride semiconductor device

InactiveUS20020046693A1From gel statePolycrystalline material growthCrystallographic defectNitride semiconductors

A method of growing a nitride semiconductor crystal which has very few crystal defects and can be used as a substrate is disclosed. This invention includes the step of forming a first selective growth mask on a support member including a dissimilar substrate having a major surface and made of a material different from a nitride semiconductor, the first selective growth mask having a plurality of first windows for selectively exposing the upper surface of the support member, and the step of growing nitride semiconductor portions from the upper surface, of the support member, which is exposed from the windows, by using a gaseous Group 3 element source and a gaseous nitrogen source, until the nitride semiconductor portions grown in the adjacent windows combine with each other on the upper surface of the selective growth mask.

Owner:NICHIA CORP

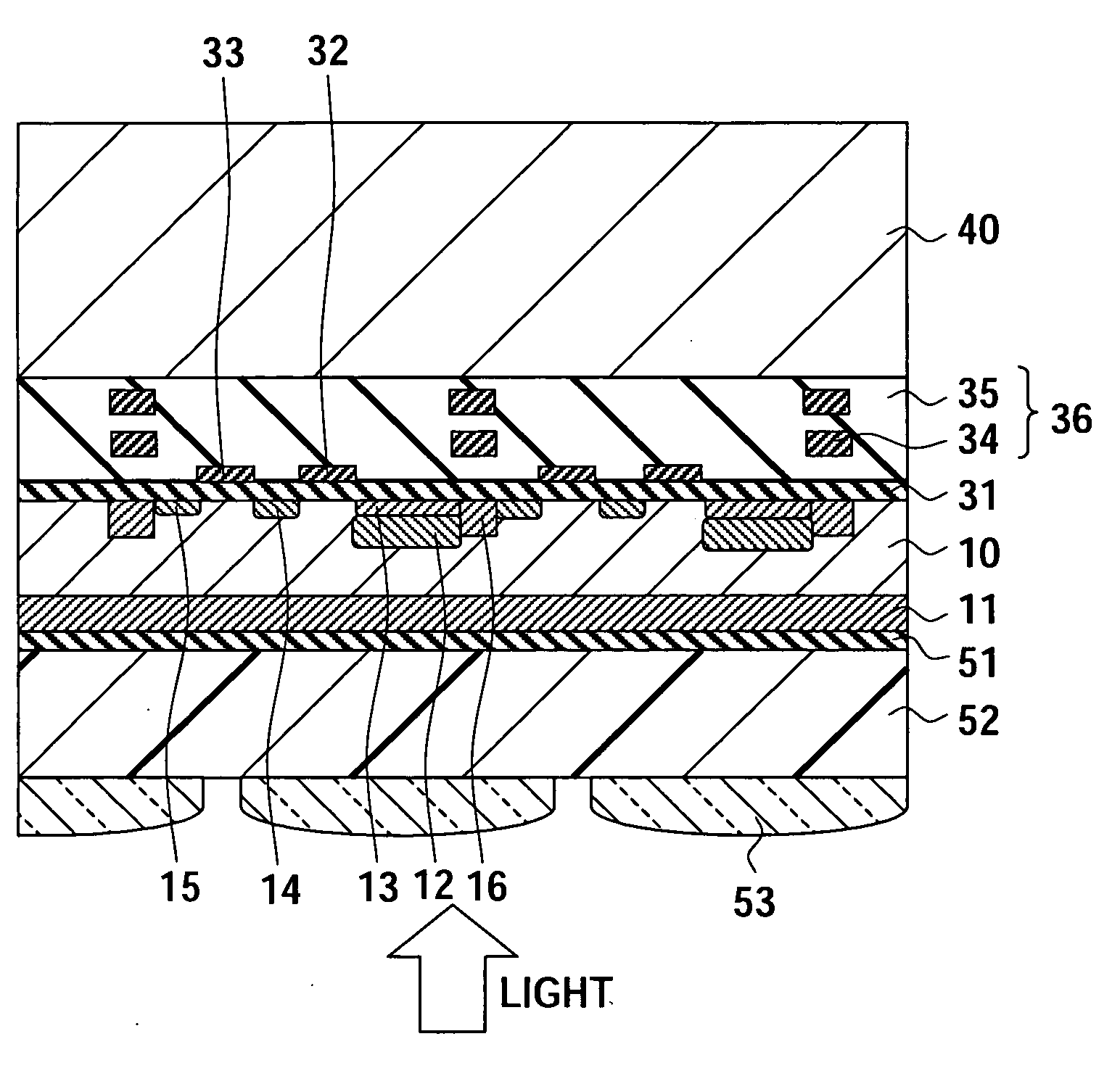

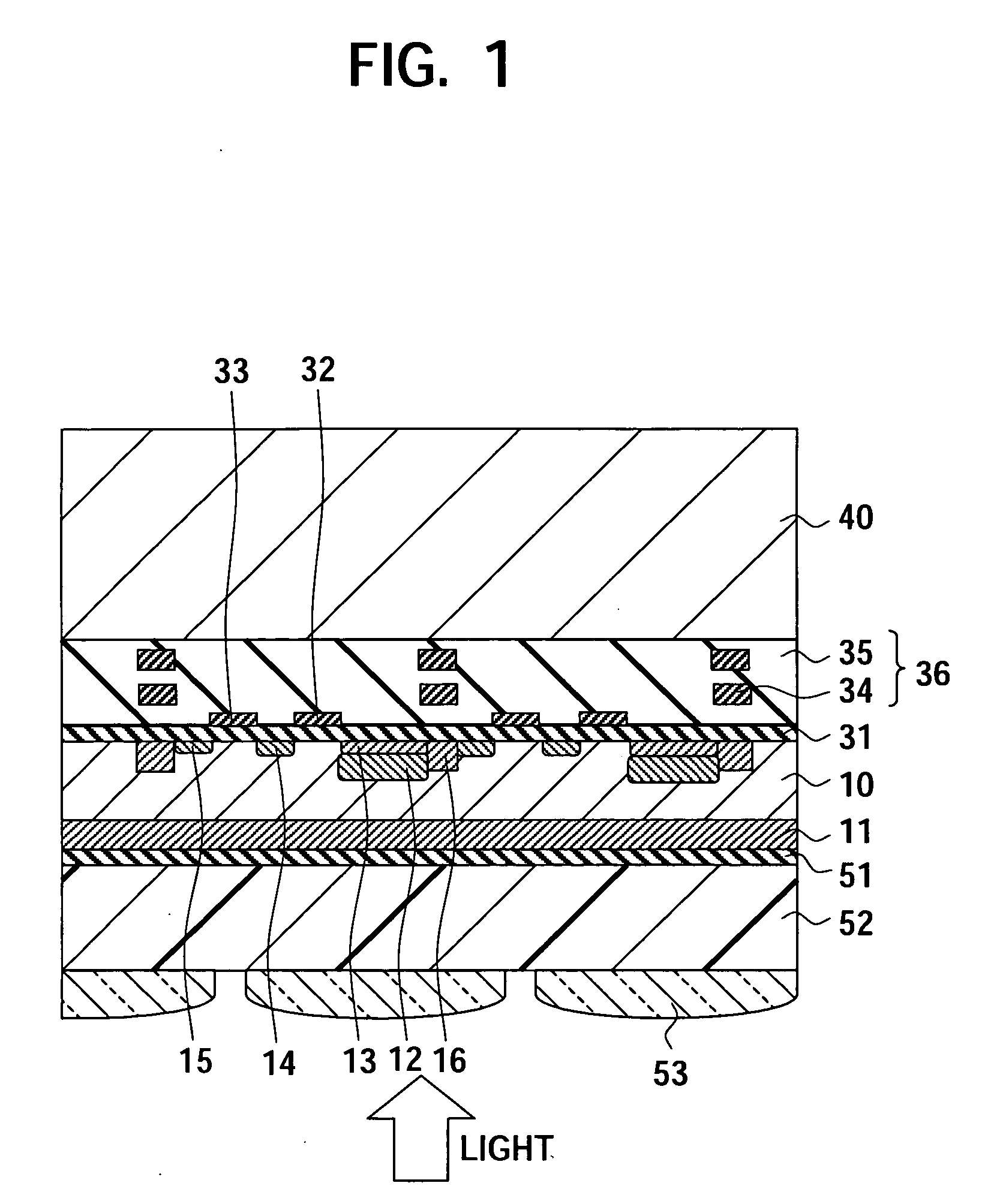

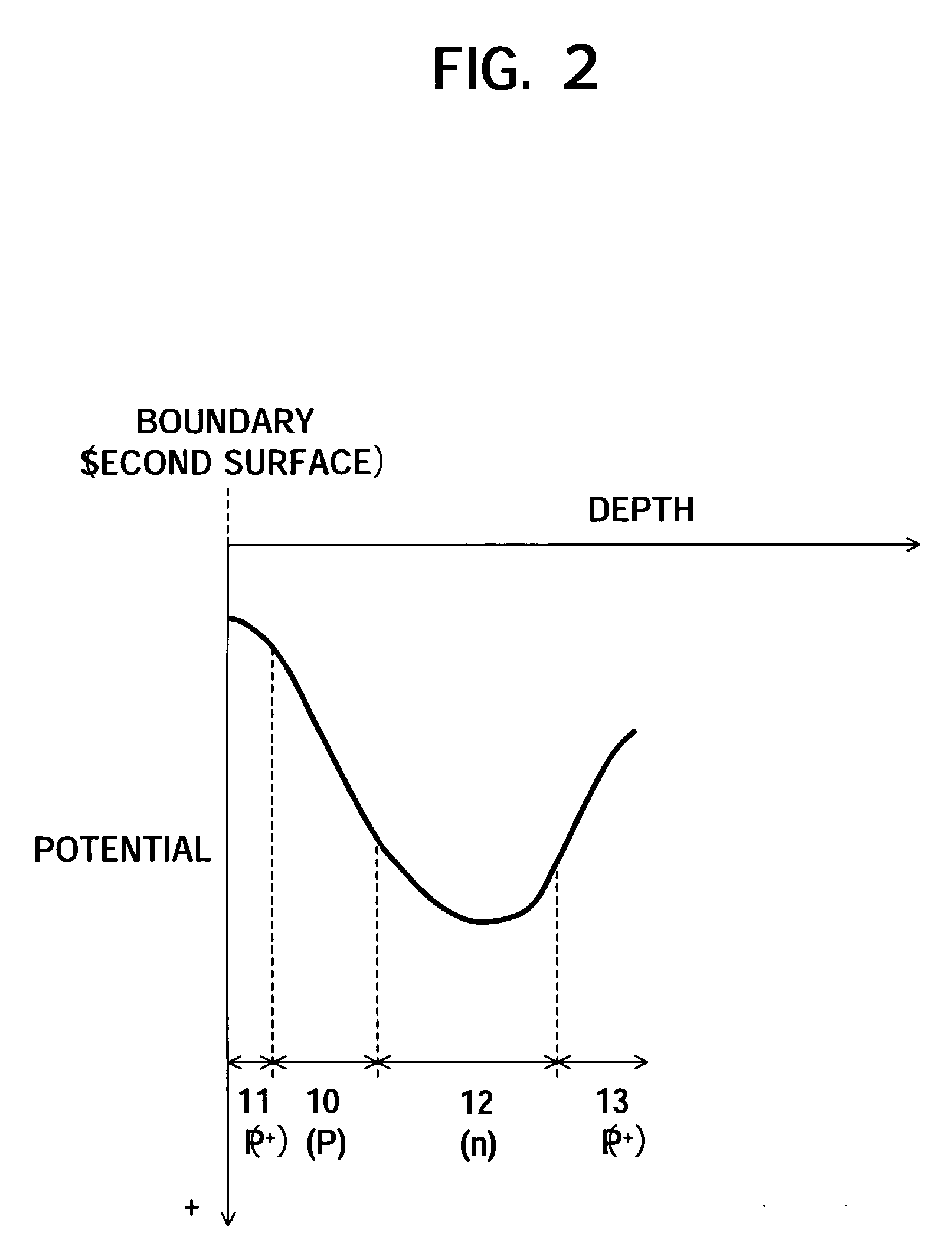

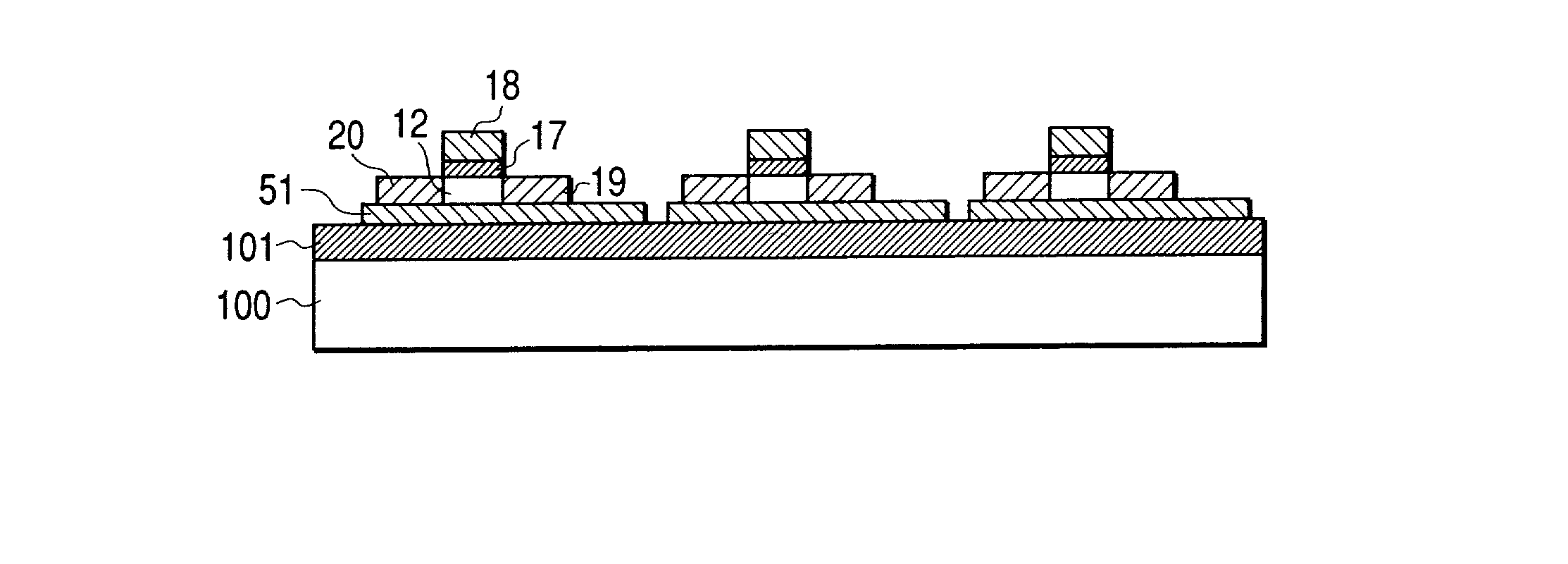

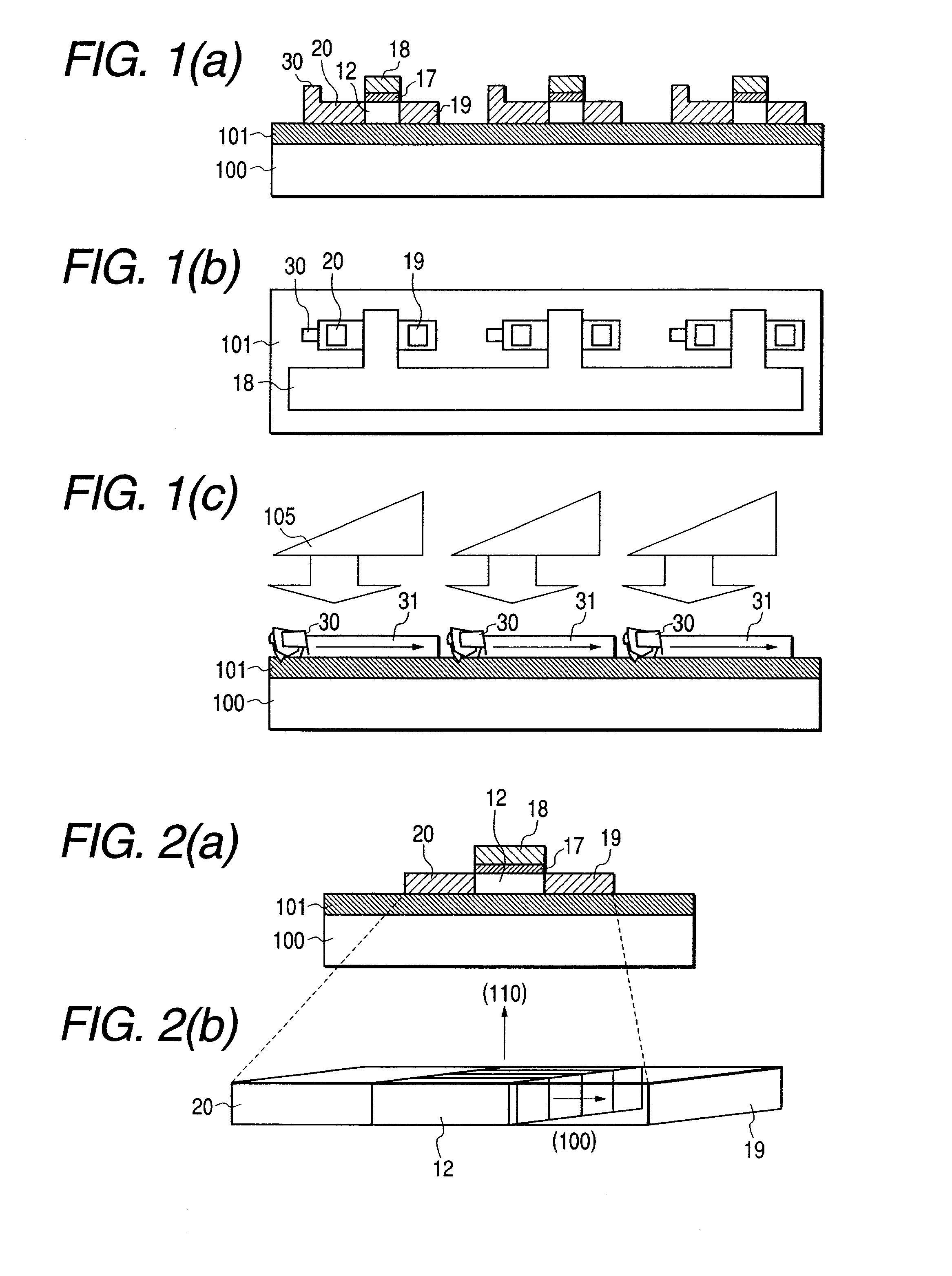

Solid-state imaging device, camera and method of producing the solid-state imaging device

InactiveUS20060006488A1High sensitivityInhibit currentTelevision system detailsSolid-state devicesQuantum efficiencyInterconnection

To provide a back-illuminated solid-state imaging device able to suppress a crystal defect caused by a metal contamination in a process and to suppress a dark current to improve quantum efficiency, a camera including the same and a method of producing the same, having the steps of forming a structure including a substrate, a first conductive type epitaxial layer and a first conductive type impurity layer, the first conductive type epitaxial layer being formed on the substrate to have a first impurity concentration, and the first conductive type impurity layer being formed in a boundary region to have a second impurity concentration higher than the first impurity concentration of the epitaxial layer; forming a second conductive type region storing a charge generated by a photoelectric conversion in the epitaxial layer; forming an interconnection layer on the epitaxial layer; and removing the substrate.

Owner:SONY CORP

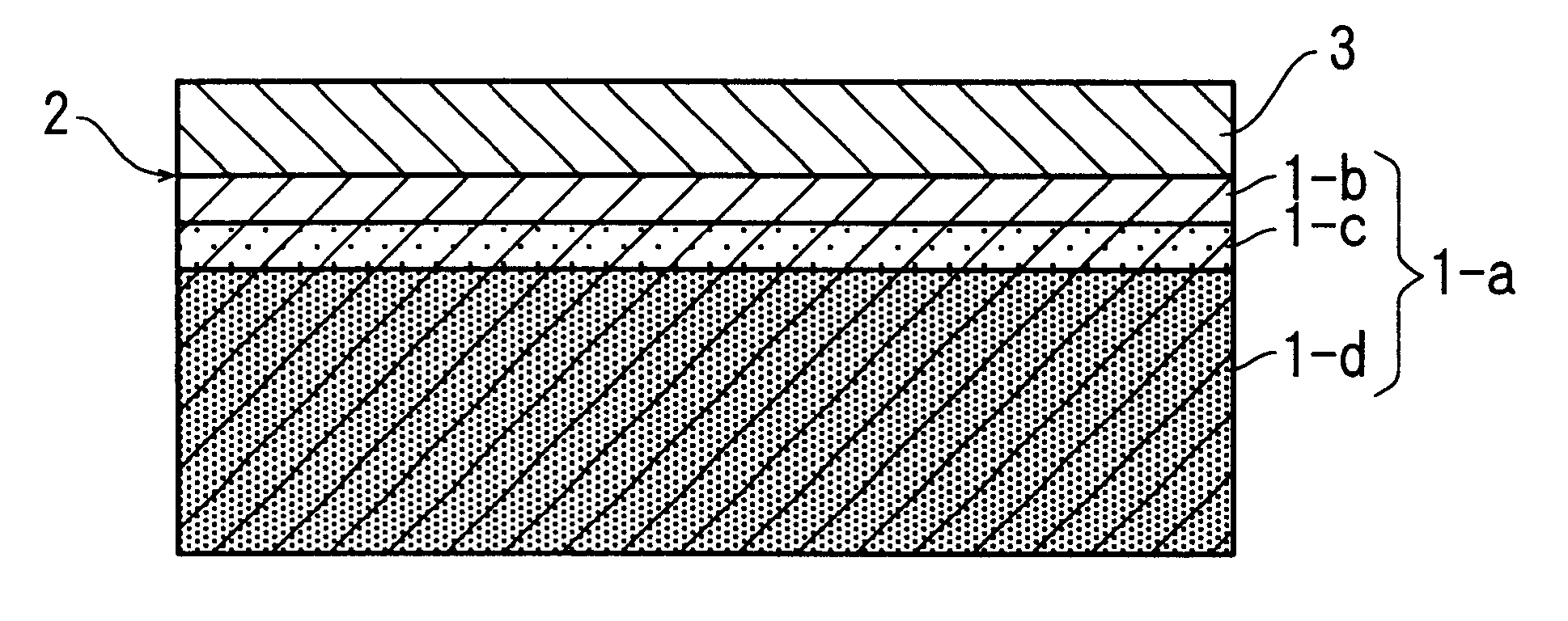

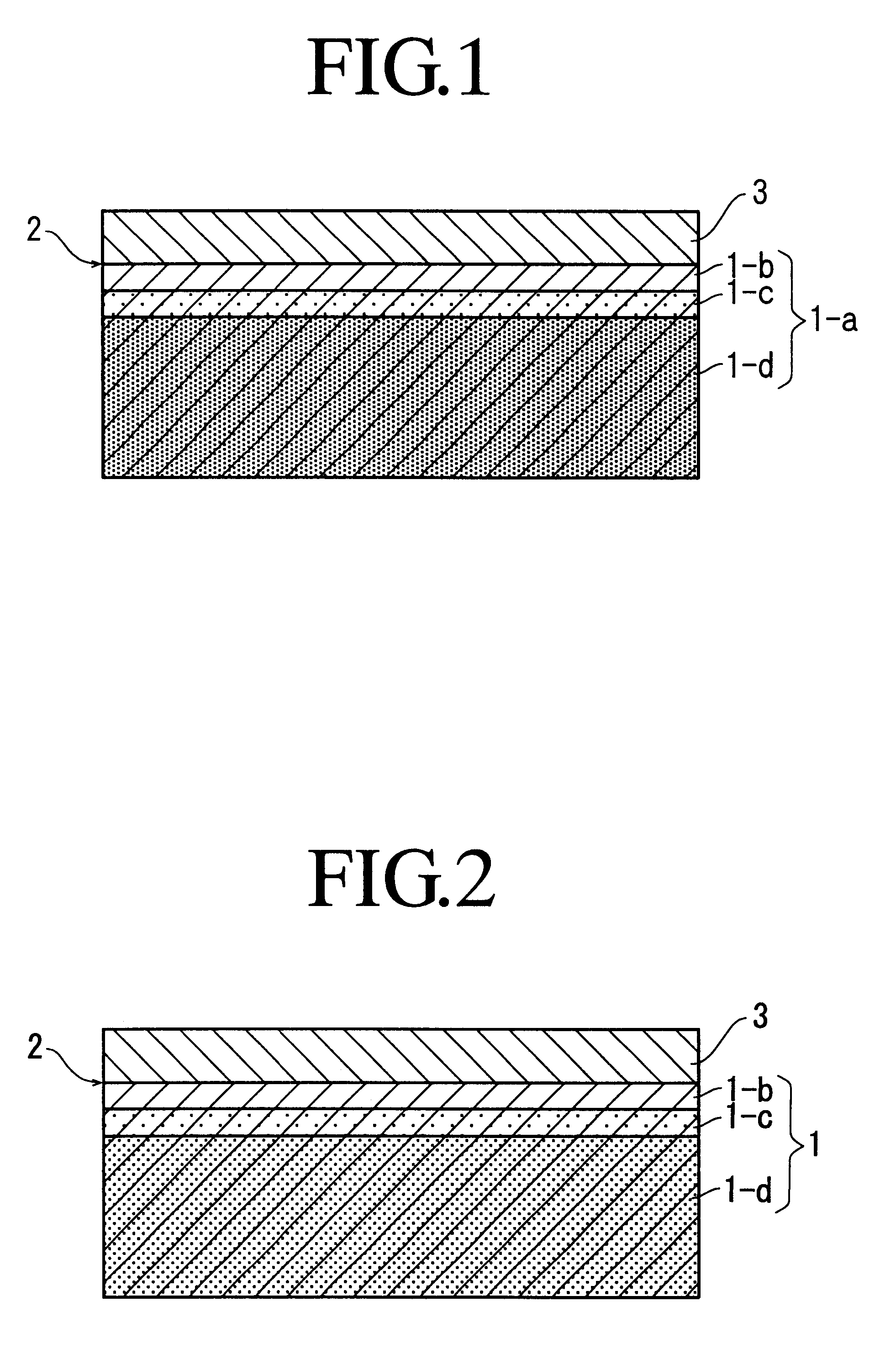

Thin film semiconductor device, polycrystalline semiconductor thin film production process and production apparatus

InactiveUS20020119609A1Reduce in quantityQuality improvementTransistorFrom solid stateElectrical conductorCrystal orientation

In an MIS field effect transistor having a gate electrode formed on a first semiconductor layer which is a polycrystalline silicon film on an insulating substrate through a gate insulating film, a channel region formed in the semiconductor layer and a source region and a drain region arranged on both sides of the channel region, a thin film semiconductor device has a main orientation of at least the channel region of {110} with respect to the surface of the gate insulating film. Further, a polycrystalline semiconductor film having a main orientation of the surface almost perpendicular to a direction for connecting the source and drain regions of {100} is preferably used in the channel of a semiconductor device. According to the present invention, a semiconductor device having a high-quality polycrystalline semiconductor film whose grain boundary, grain size and crystal orientation can be controlled and whose film roughness and crystal defects formed by crystallization have been reduced can be obtained on the insulating substrate.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

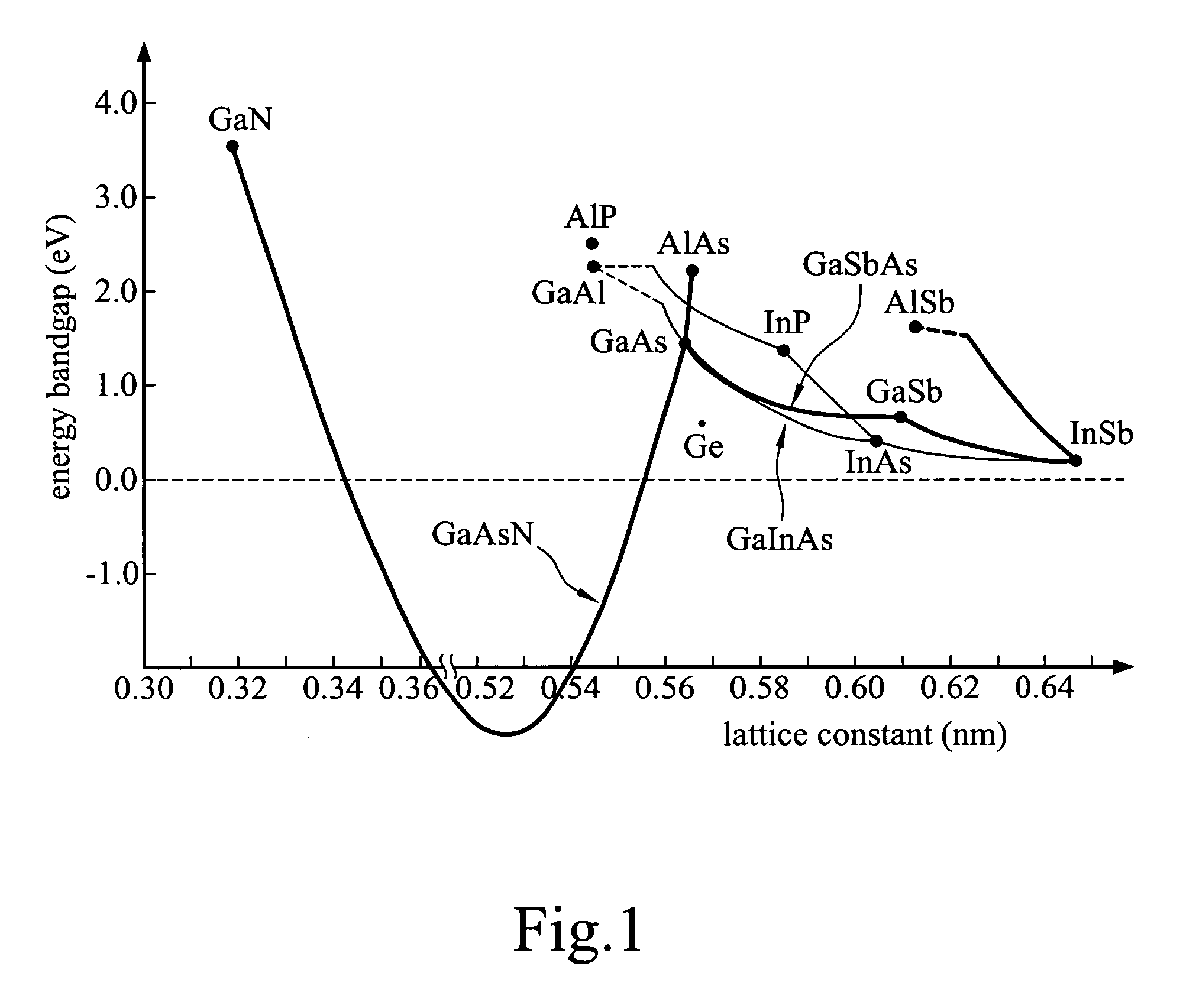

Nitride semiconductor device, its manufacturing method, and semiconductor optical apparatus

InactiveUS20050042787A1Stress minimizationRelaxation stressLaser detailsSemiconductor laser structural detailsHigh densityCrystallographic defect

A nitride semiconductor laser device with a reduction in internal crystal defects and an alleviation in stress, and a semiconductor optical apparatus comprising this nitride semiconductor laser device. First, a growth suppressing film against GaN crystal growth is formed on the surface of an n-type GaN substrate equipped with alternate stripes of dislocation concentrated regions showing a high density of crystal defects and low-dislocation regions so as to coat the dislocation concentrate regions. Next, the n-type GaN substrate coated with the growth suppressing film is overlaid with a nitride semiconductor layer by the epitaxial growth of GaN crystals. Further, the growth suppressing film is removed to adjust the lateral distance between a laser waveguide region and the closest dislocation concentrated region to 40 μm or more.

Owner:SHARP KK +1

Semiconductor light emitting device with protrusions to improve external efficiency and crystal growth

ActiveUS7683386B2Easy to produceReduce crystallinitySemiconductor/solid-state device detailsSolid-state devicesCrystallographic defectActive layer

Owner:NICHIA CORP

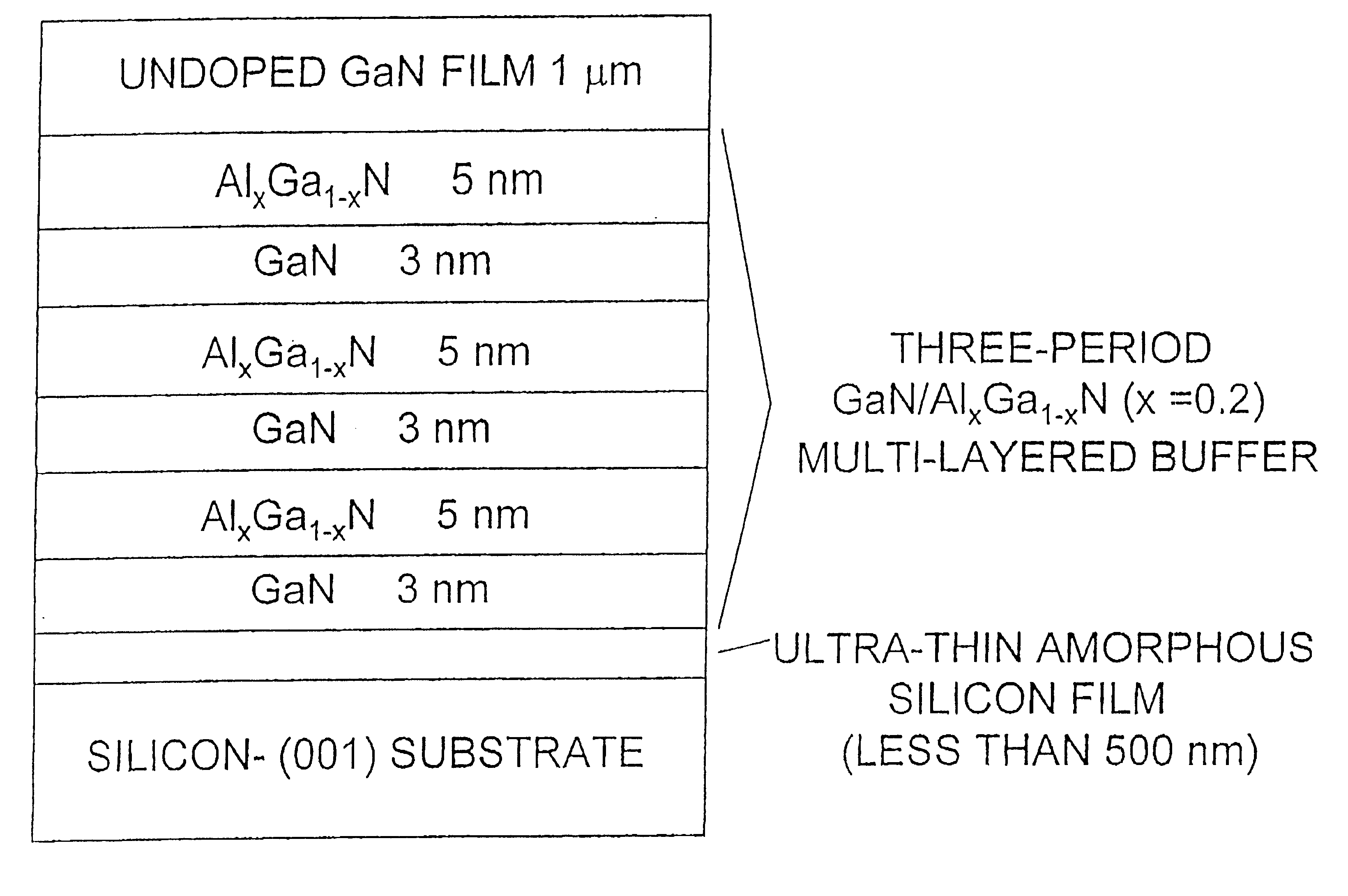

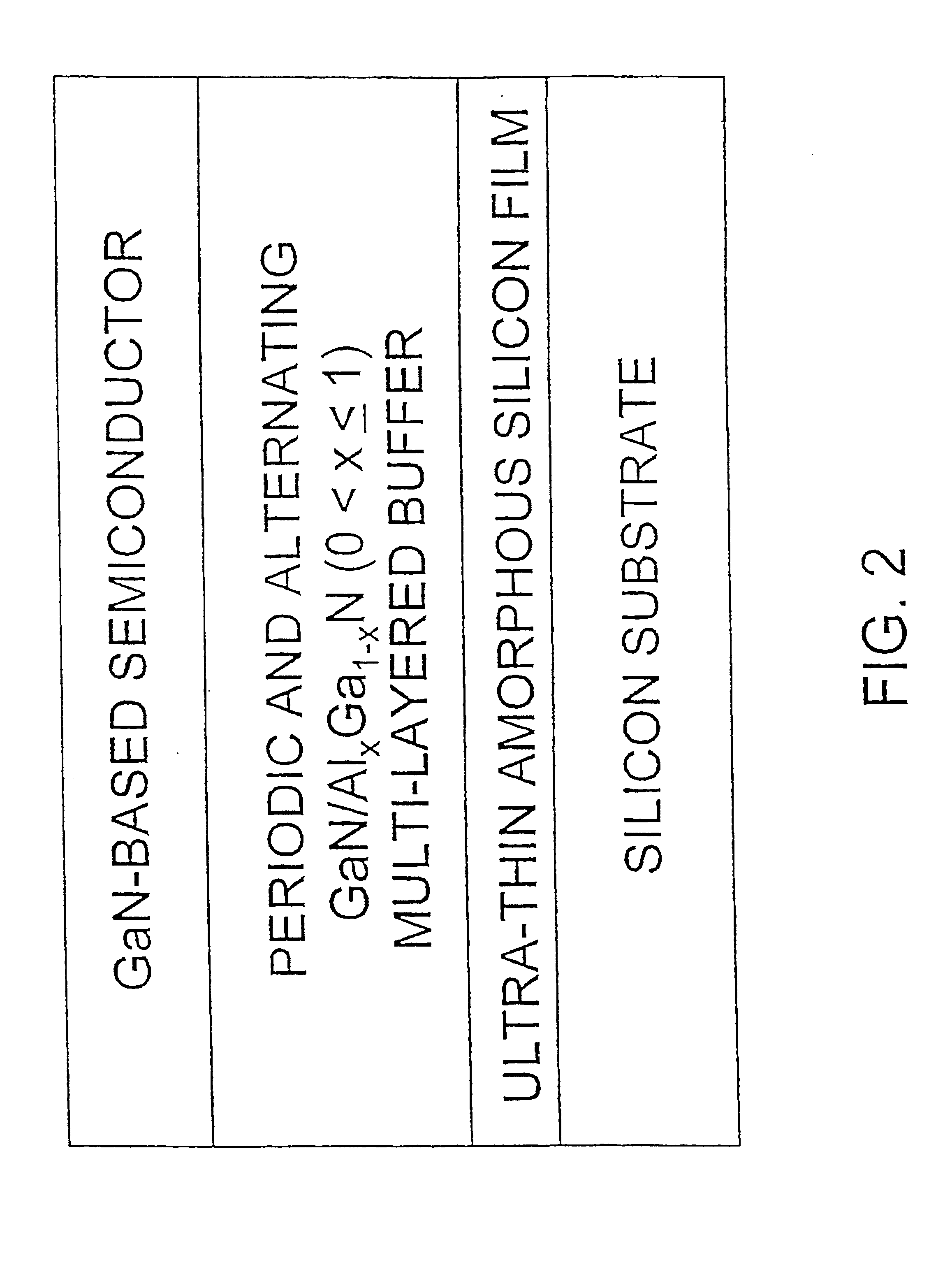

Method of fabricating group-III nitride-based semiconductor device

InactiveUS6524932B1Semiconductor/solid-state device manufacturingSemiconductor devicesInter layerLattice mismatch

Disclosed are a group-III nitride-based semiconductor device that is grown over the surface of a composite intermediate layers consisting of a thin amorphous silicon film or any stress-relief film or a combination of them and at least one multi-layered buffer on silicon substrate, and a method of fabricating the same device. The intermediate layers that suppress the occurrence of crystal defects and propagation of misfit dislocations induced by the lattice mismatch between the epitaxial layer and substrate, ca n be grown on a part or the entirety of the surface of a silicon (001) or (111) substrate which can be single crystal or coated with a thin amorphous silicon film. Then at least one layer or multiple layers of high quality group-III nitride-based semiconductors are grown over the composite intermediate layers.

Owner:NAT UNIV OF SINGAPORE

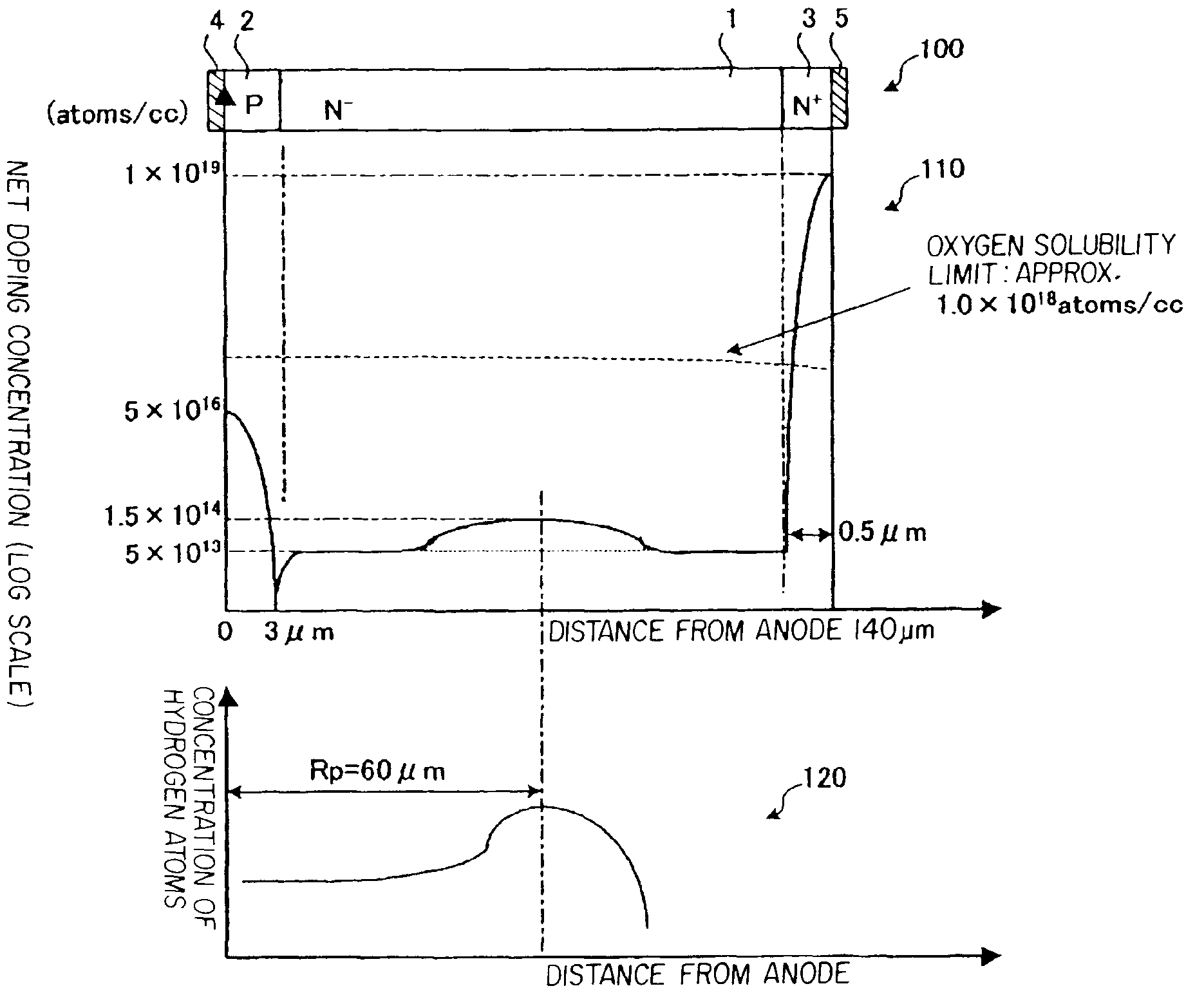

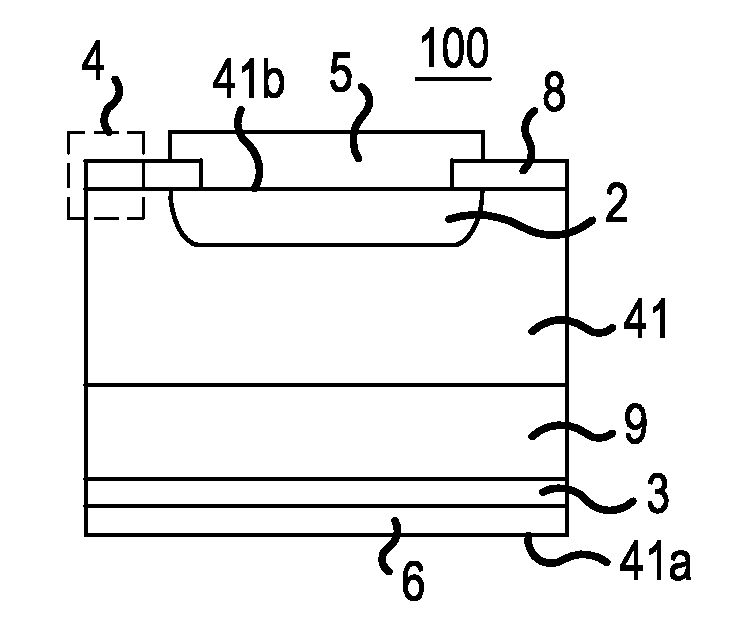

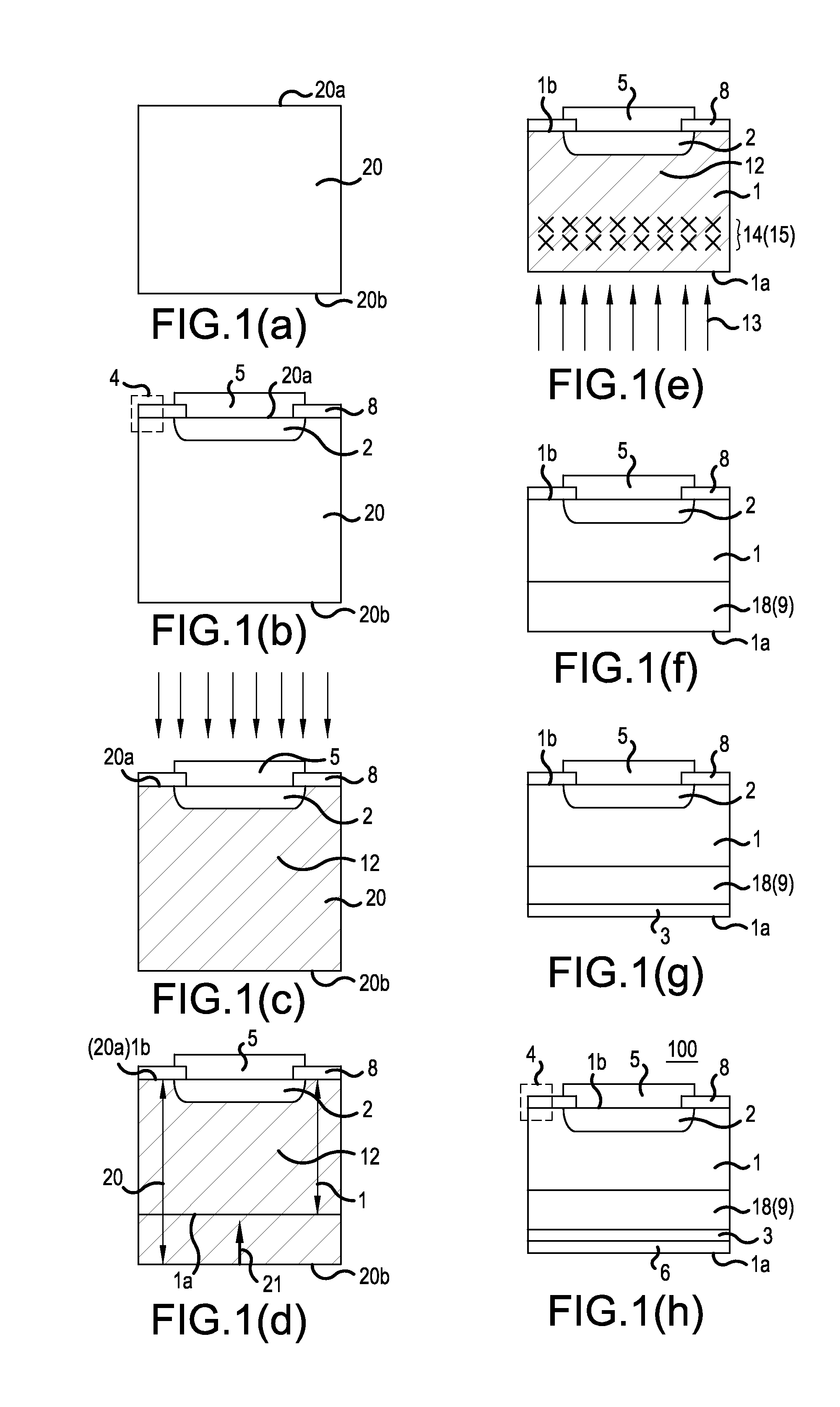

Semiconductor device and manufacturing method for same

ActiveUS20080315364A1Easy to operateReduce lossSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSoft switching

After introducing oxygen into an N− type FZ wafer serving as an N− type first semiconductor layer, a P type second semiconductor layer and an anode are formed on a surface of the FZ wafer. The FZ wafer is irradiated with protons from the side of the anode, introducing crystal defects into the FZ wafer. By performing heat treatment to recover the crystal defects in the FZ wafer, the net doping concentration of a portion within the first semiconductor layer is made higher than the initial net doping concentration of the FZ wafer, and a desired broad buffer structure is formed. Accordingly, a semiconductor device with fast operation and low losses, and having soft switching characteristics, can be manufactured inexpensively using FZ bulk wafers, with good controllability and yields.

Owner:FUJI ELECTRIC CO LTD

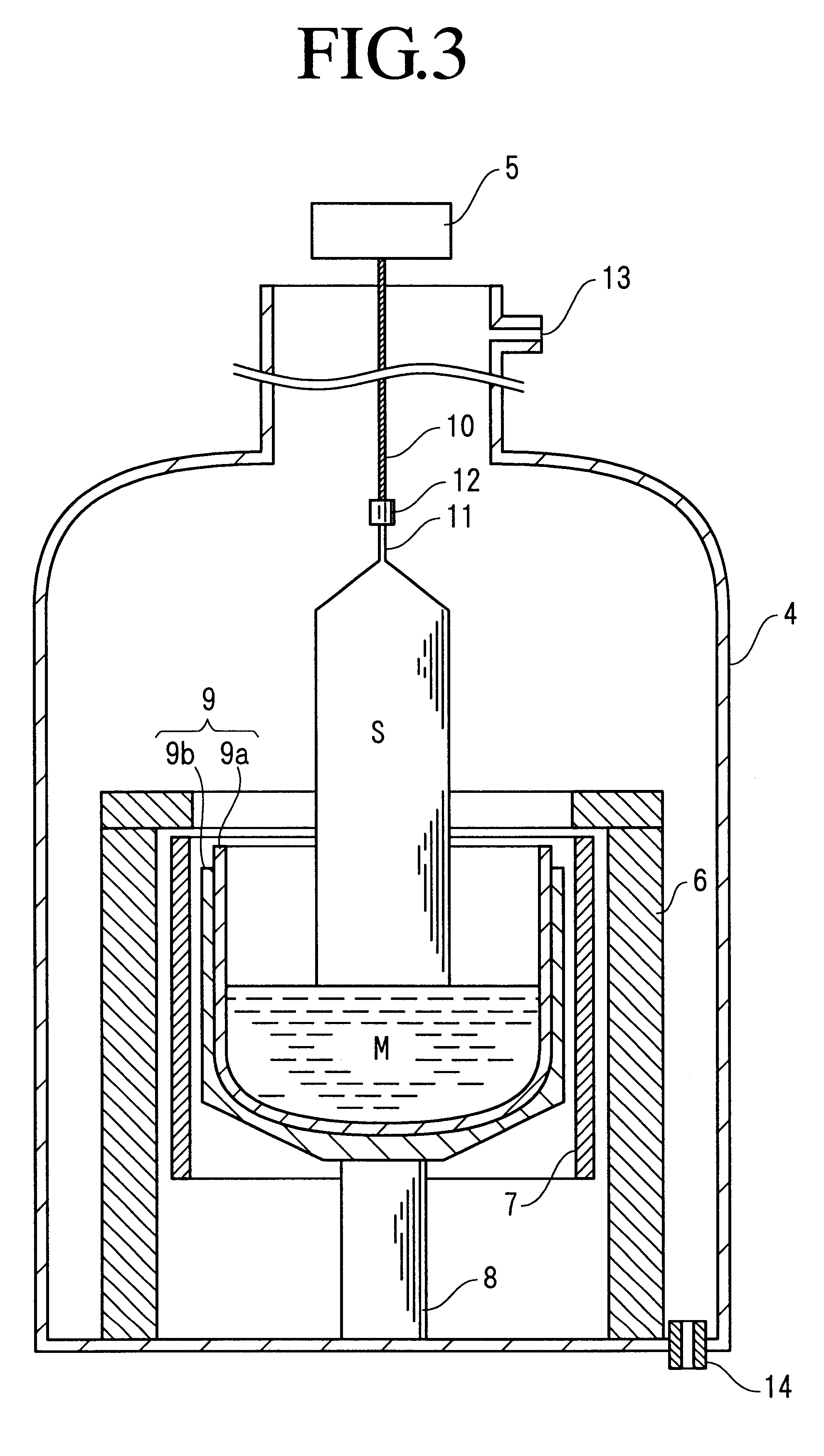

Silicon semiconductor wafer and method for producing the same

InactiveUS6548886B1Quality improvementLow costPolycrystalline material growthSemiconductor/solid-state device manufacturingCzochralski methodNitrogen

A silicon semiconductor substrate is obtained by deriving a silicon semiconductor substrate from a silicon single crystal grown by the Czochralski method from a molten silicon containing not less than 1x1016 atoms / cm3 and not more than 1.5x1019 atoms / cm3 of nitrogen and heat-treating the silicon semiconductor substrate at a temperature of not less than 1000° C. and not more than 1300° C. for not less than one hour and is characterized by the fact that the density of crystal defects measuring not less than 0.1 mum as reduced to diameter is not more than 104 pieces / cm3 at least in the region reaching a depth of 1 mum from the surface of the substrate and the nitrogen content at the center of thickness of the silicon semiconductor substrate is not less than 1x1013 atoms / cm3 and not more than 1x1016 atoms / cm3.

Owner:SILTRONIC AG

High surface quality GaN wafer and method of fabricating same

InactiveUS20060029832A1Improve surface qualityPolycrystalline material growthAfter-treatment detailsSurface roughnessCompound (substance)

Owner:XU XUEPING +1

Semiconductor substrate and its production method, semiconductor device comprising the same and its production method

InactiveUS6768175B1High crystallinityFew defectSemiconductor/solid-state device testing/measurementSolid-state devicesSilicon oxideSoi substrate

When a SOI substrate is produced a first silicon layer epitaxially grown on the insulating underlay is ion implanted to make deep part of interface of the silicon layer amorphous, and then annealed to recrystallize. Next, the silicon layer is heat treated to oxidize part of the surface side, and after the silicon oxide is removed by etching, a silicon layer is epitaxially grown on the remaining first silicon layer to form a second silicon layer. Subsequently, the second silicon layer is again ion implanted to make deep part of interface amorphous, then annealing is performed to recrystallize. With this method, a SOI substrate, which is very small in crystal defect density of the silicon layer and good in surface flatness, can be produced. Therefore, on the semiconductor substrate an electronic device or optical device having high device performance and reliability can be realized.

Owner:ASAHI KASEI KK

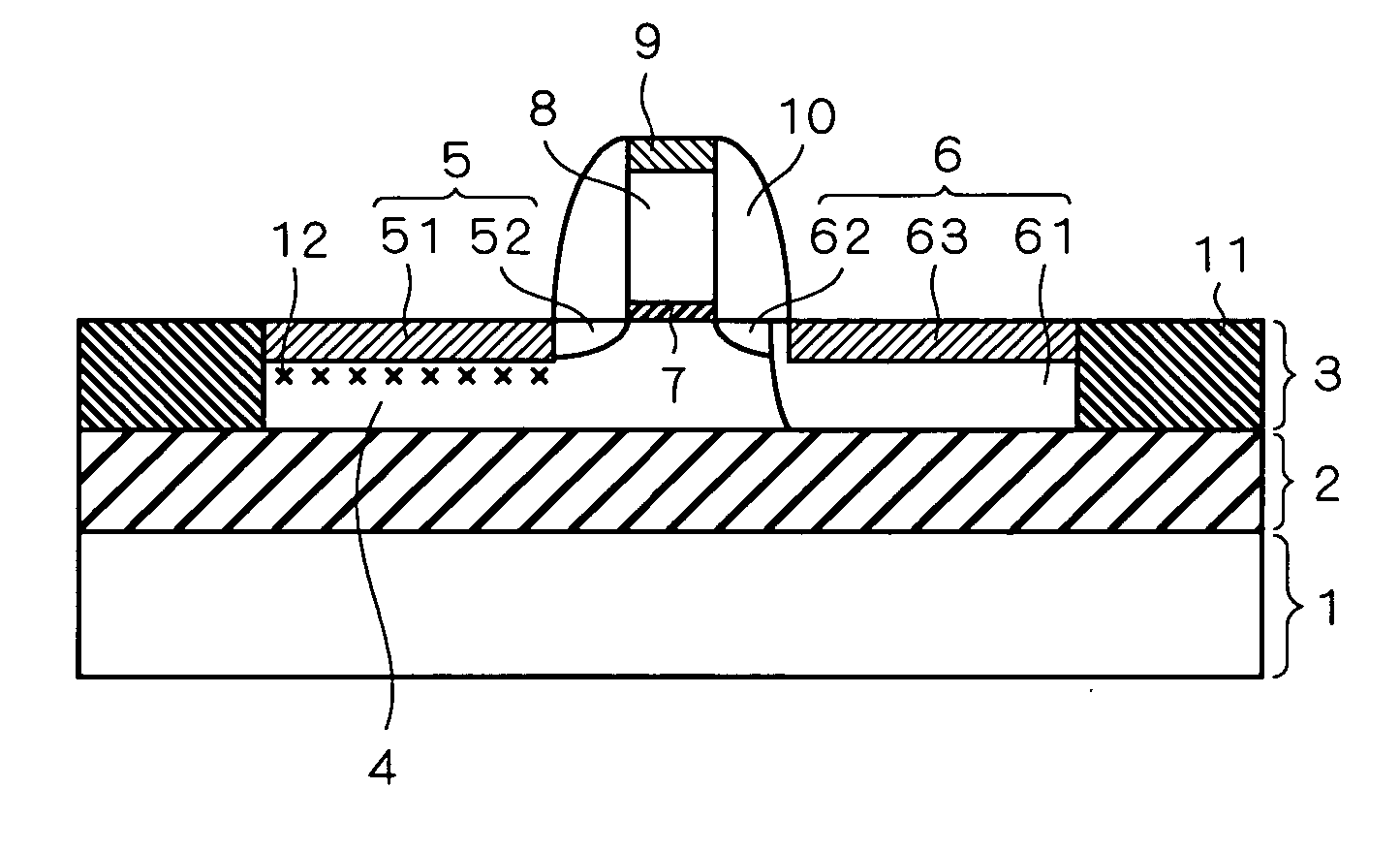

Semiconductor device, manufacturing method thereof, and memory circuit

InactiveUS20060081930A1Guaranteed uptimeTransistorSolid-state devicesSemiconductor packageMemory circuits

The present invention provides a semiconductor device capable of suppressing a body floating effect, and a manufacturing method thereof. A semiconductor device having an SOI structure includes a silicon substrate, a buried insulating layer formed on the silicon substrate, and a semiconductor layer formed on the buried insulating layer. The semiconductor layer has a body region of a first conduction type, a source region of a second conduction type and a drain region of the second conduction type, and a gate electrode is formed on the body region between the source region and the drain region via a gate oxide film. The source region includes an extension layer of the second conduction type, and a silicide layer which makes contact with the extension layer at its side face, and a crystal defect region is formed on a region of a depletion layer generated in a boundary portion between the silicide layer and the body region.

Owner:RENESAS ELECTRONICS CORP

Optical quality diamond material

ActiveUS7740824B2Prevent or reduce local strain generating defectsPrevent and reduce absorptionPolycrystalline material growthAfter-treatment detailsOptical reflectionGrating

Owner:ELEMENT SIX TECH LTD

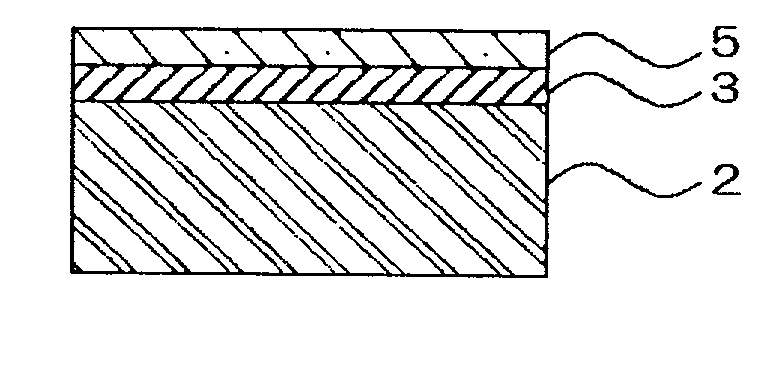

Low-temperature doping processes for silicon wafer devices

InactiveUS20080000521A1Quality improvementImprove concentrationPolycrystalline material growthFinal product manufactureGas phaseSystem configuration

A low temperature method and system configuration for depositing a doped silicon layer on a silicon substrate of a selected grade. The silicon substrate for functioning as a light absorber and the doped silicon layer for functioning as an emitter. The method comprises the acts of: positioning the silicon substrate in a chamber suitable for chemical vapour deposition of the doped silicon layer on the silicon substrate, an external surface of the silicon substrate suitable for promoting crystalline film growth; using a plurality of process parameters for adjusting growth of the doped silicon layer, the plurality of process parameters including a first process parameter of a process temperature for inhibiting diffusion of dopant atoms into the external surface of the silicon substrate, and a second process parameter of a hydrogen dilution level for providing excess hydrogen atoms to affect a layer crystallinity of the atomic structure of the doped silicon layer; exposing the external surface of the silicon substrate in the chamber to a vapour at appropriate ambient chemical vapour deposition conditions, the vapour including silicon atoms, dopant atoms and the excess hydrogen atoms, the atoms for use in growing the doped silicon layer; and originating growth of the doped silicon layer on the external surface to form an interface between the doped silicon layer and the silicon substrate, such that the doped silicon layer includes first atomic structural regions having a higher quality of the layer crystallinity next to the interface with adjacent second atomic structural regions having a lower quality of the layer crystallinity with increasing concentrations of crystal defects for increasing thickness of the doped silicon layer from the interface. The resultant silicon substrate and doped layer (or thin film) can be used in solar cell manufacturing.

Owner:SIVOTHTHAMAN SIVA +1

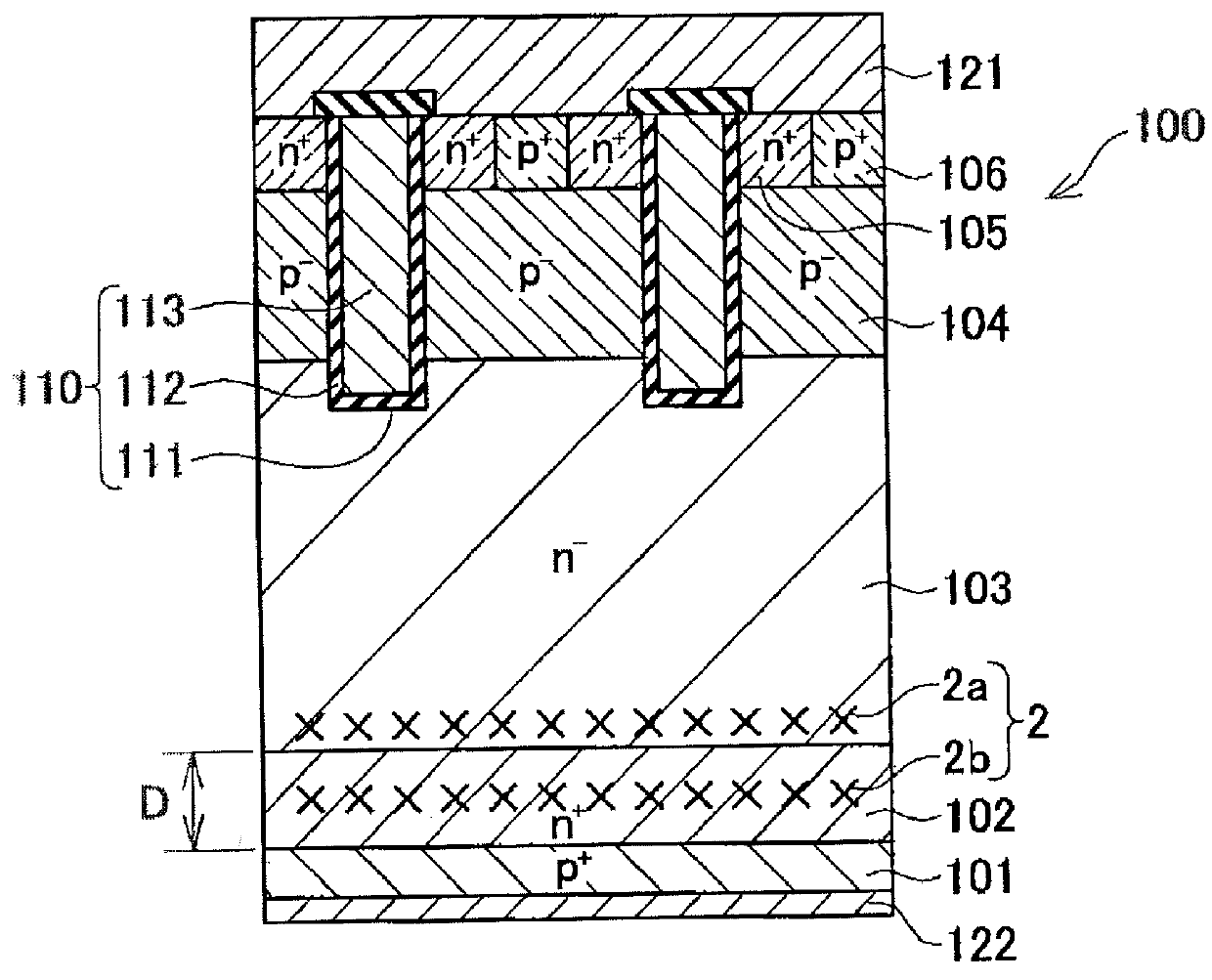

Semiconductor device and method for manufacturing the same

InactiveUS20130075783A1Improve featuresSemiconductor/solid-state device manufacturingSemiconductor devicesDopantHydrogen Ion Donors

A semiconductor device includes: a semiconductor substrate, the semiconductor substrate comprising; an n type drift layer, a p type body layer on an upper surface side of the drift layer, and a high impurity n layer on a lower surface side of the drift layer. The high impurity n layer includes hydrogen ion donors as a dopant, and has a higher density of n type impurities than the drift layer. A lifetime control region including crystal defects as a lifetime killer is formed in the high impurity n layer and a part of the drift layer. A donor peak position is adjacent or identical to a defect peak position, at which a crystal defect density is highest in the lifetime control region in the depth direction of the semiconductor substrate. The crystal defect density in the defect peak position of the lifetime control region is 1×1012 atoms / cm3 or more.

Owner:TOYOTA JIDOSHA KK

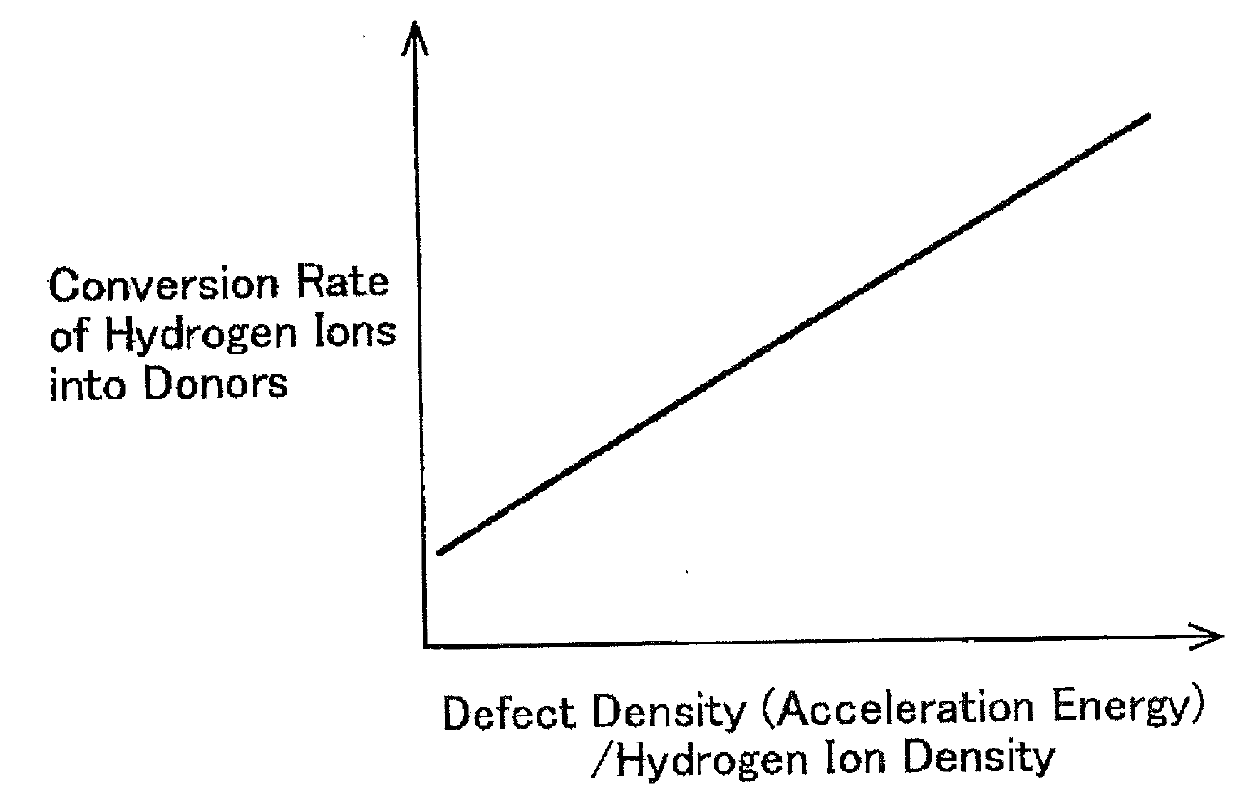

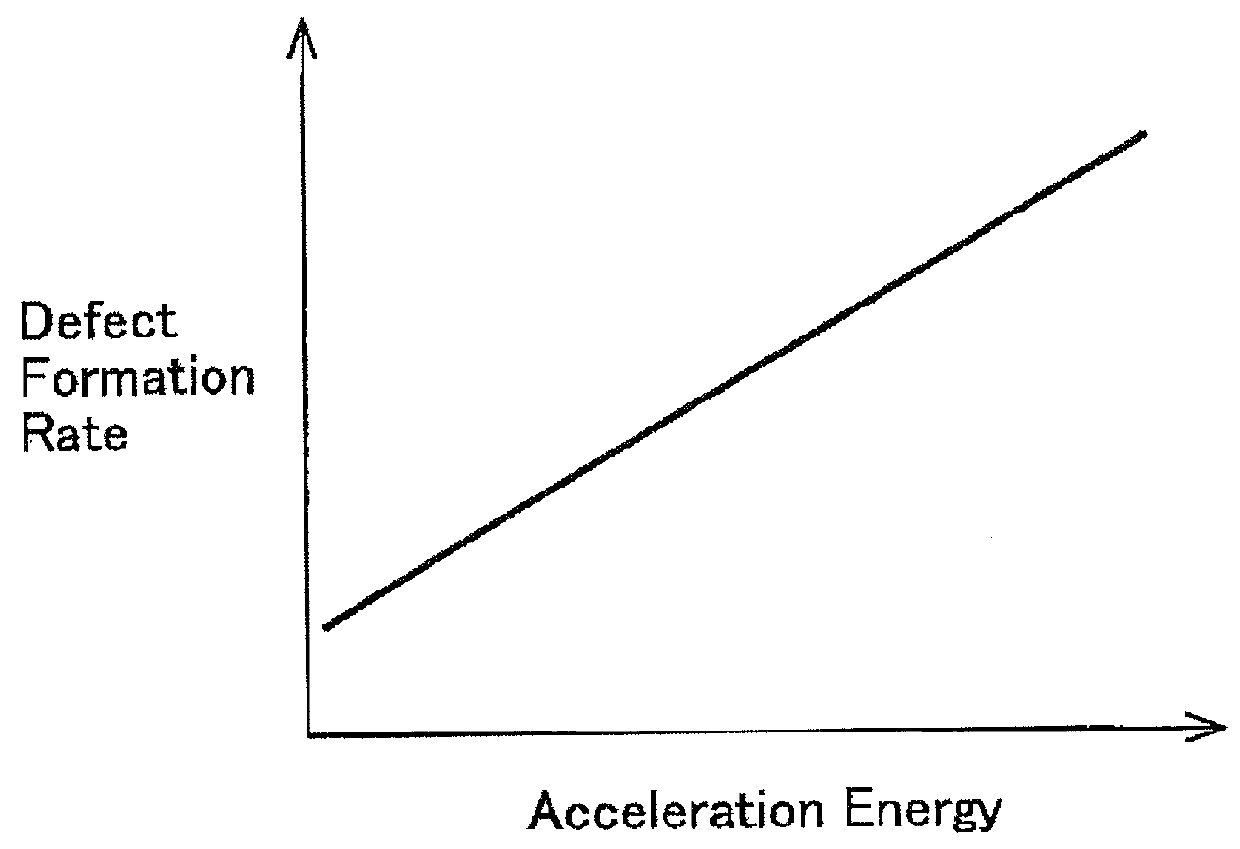

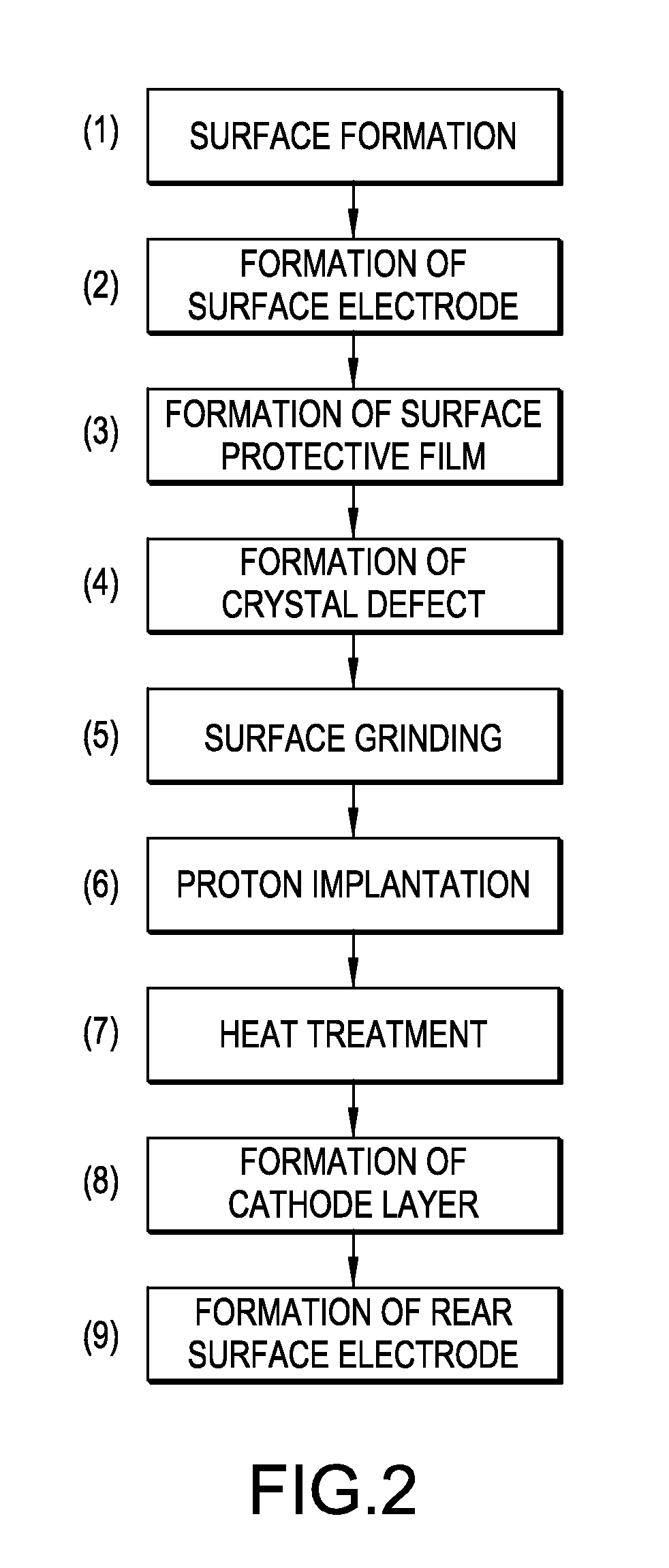

Semiconductor device and method for producing semiconductor device

ActiveUS20140246755A1Limited amountIncrease spawn rateSemiconductor/solid-state device manufacturingSemiconductor devicesProton implantationGeneration rate

Hydrogen atoms and crystal defects are introduced into an n− semiconductor substrate by proton implantation. The crystal defects are generated in the n− semiconductor substrate by electron beam irradiation before or after the proton implantation. Then, a heat treatment for generating donors is performed. The amount of crystal defects is appropriately controlled during the heat treatment for generating donors to increase a donor generation rate. In addition, when the heat treatment for generating donors ends, the crystal defects formed by the electron beam irradiation and the proton implantation are recovered and controlled to an appropriate amount of crystal defects. Therefore, for example, it is possible to improve a breakdown voltage and reduce a leakage current.

Owner:FUJI ELECTRIC CO LTD

Process for manufacturing a semiconductor integrated circuit device

InactiveUS6165873ASolid-state devicesSemiconductor/solid-state device manufacturingDevice PropertiesCrystallographic defect

This invention relates to a process for manufacturing a semiconductor integrated circuit device comprising hydrogen annealing where a silicon substrate on which a device structure is formed and an interlayer insulating film is deposited is annealed in an atmosphere of hydrogen, comprising removing a substrate material on a substrate surface opposite to the surface on which a device structure is formed (substrate rear face), to make the substrate thinner before the hydrogen annealing; and processing the rear face for removing damages due to crystal defects and scratches generated on the rear face. According to this invention, hydrogen annealing can improve device properties and reliability, regardless of a device structure on the substrate surface, and a semiconductor integrated circuit device can be manufactured in a higher yield.

Owner:NEC ELECTRONICS CORP

Silicon-on-insulator(SOI)substrate

InactiveUS20020153563A1Semiconductor/solid-state device detailsSolid-state devicesHydrogenSilicon oxide

There is provided a method of fabricating a silicon-on-insulator substrate, including the steps of (a) forming a silicon substrate at a surface thereof with an oxygen-containing region containing oxygen at such a concentration that oxygen is not precipitated in the oxygen-containing region in later mentioned heat treatment, (b) forming a silicon oxide film at a surface of the silicon substrate, (c) implanting hydrogen ions into the silicon substrate through the silicon oxide film, (d) overlapping the silicon substrate and a support substrate each other so that the silicon oxide film makes contact with the support substrate, and (e) applying heat treatment to the thus overlapped silicon substrate and support substrate to thereby separate the silicon substrate into two pieces at a region into which the hydrogen ions have been implanted, one of the two pieces remaining on the silicon oxide film as a silicon-on-insulator active layer. The support substrate, the silicon oxide film located on the support substrate, and the silicon-on-insulator active layer formed on the silicon oxide film defines a silicon-on-insulator structure. The method makes it possible to significantly reduce crystal defect density in the silicon-on-insulator active layer, which ensures that a substrate made in accordance with the method can be used for fabricating electronic devices thereon.

Owner:NEC CORP

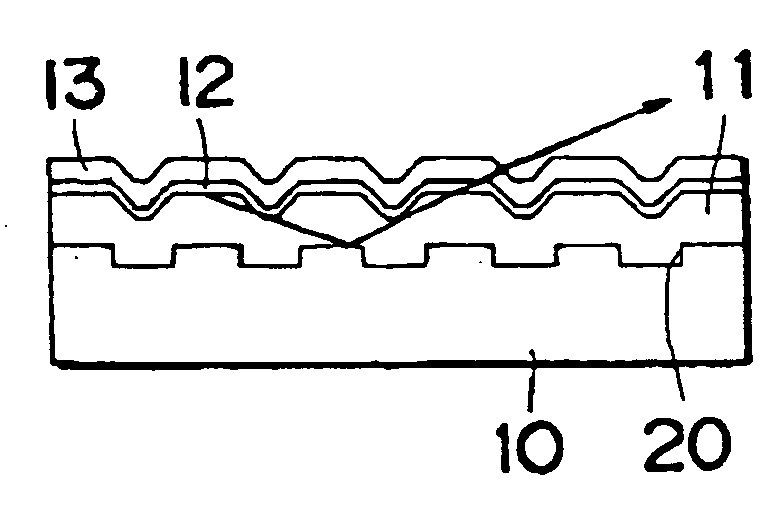

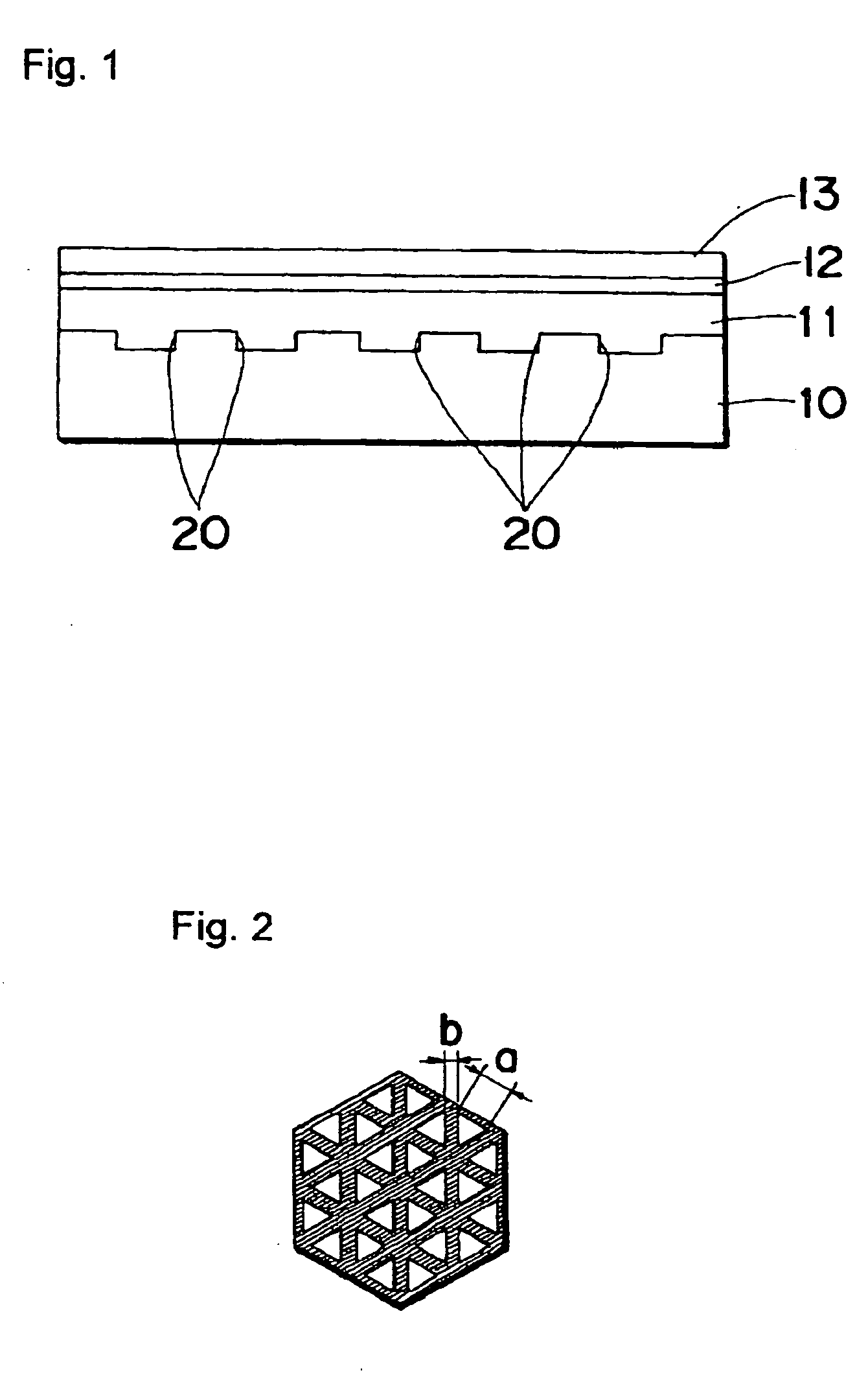

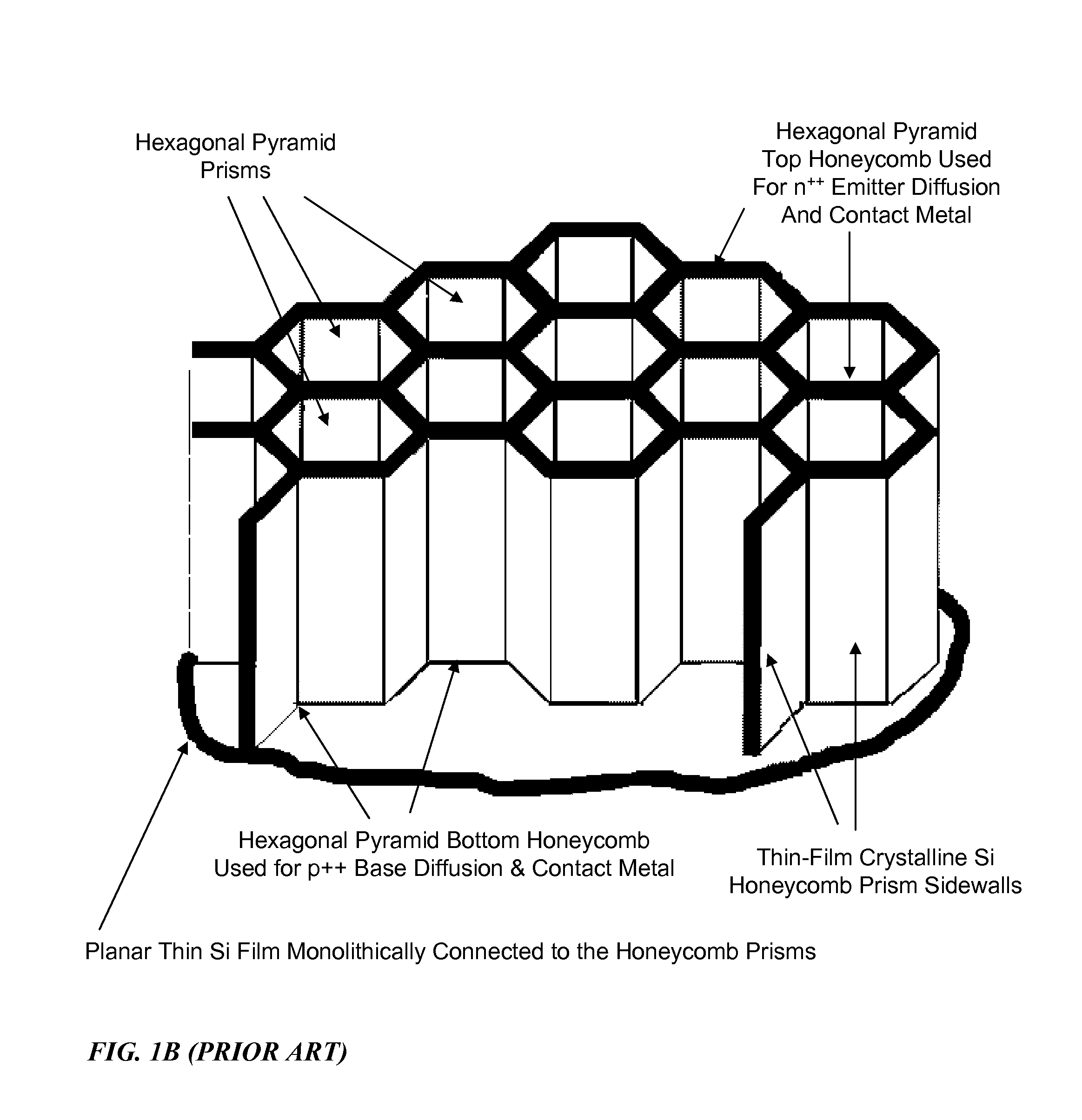

Three-Dimensional Semiconductor Template for Making High Efficiency Thin-Film Solar Cells

InactiveUS20100148318A1Eliminates and reduces disadvantageEliminates and reduces and problemFinal product manufactureSemiconductor/solid-state device manufacturingCrystallographic defectSilicon

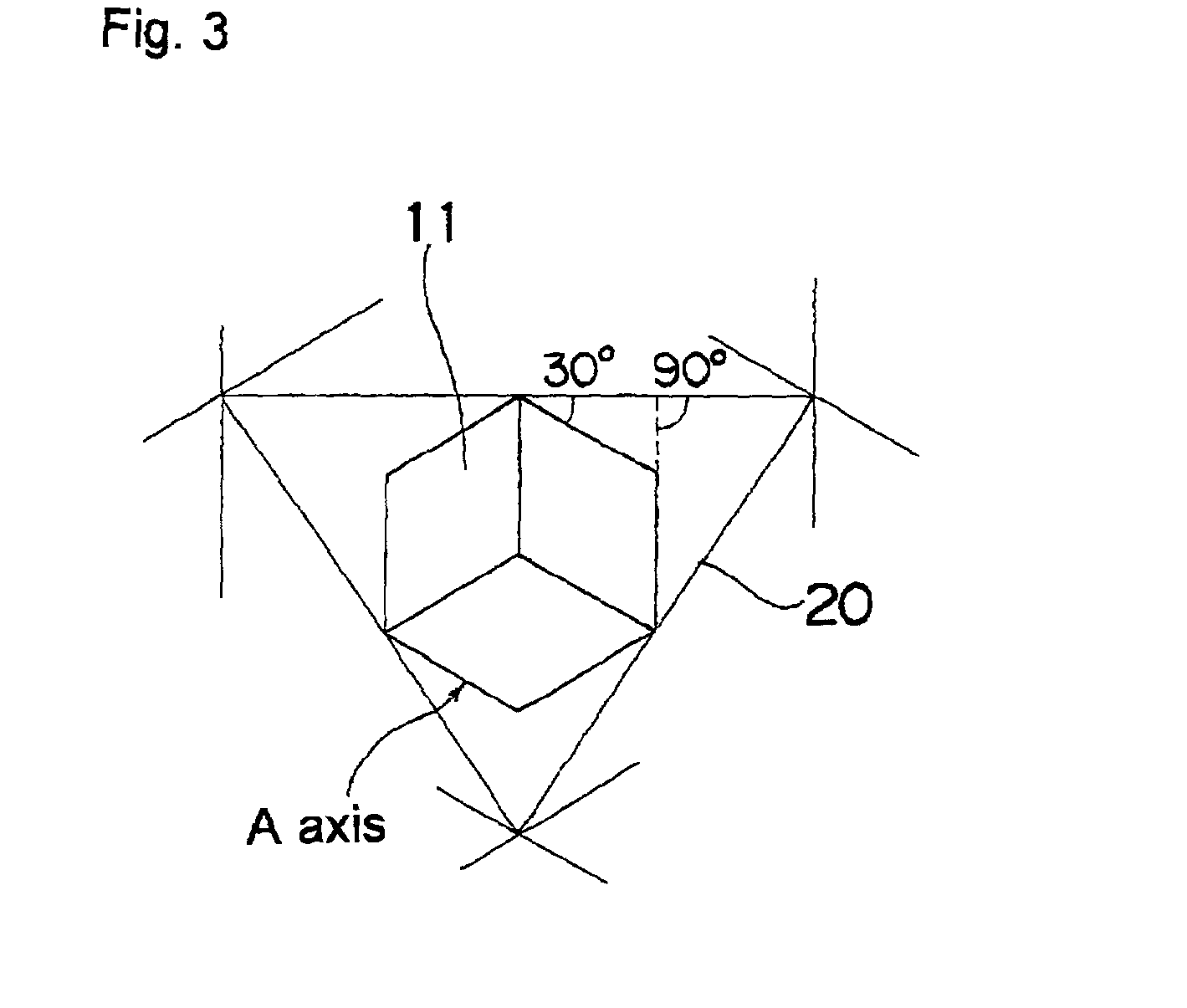

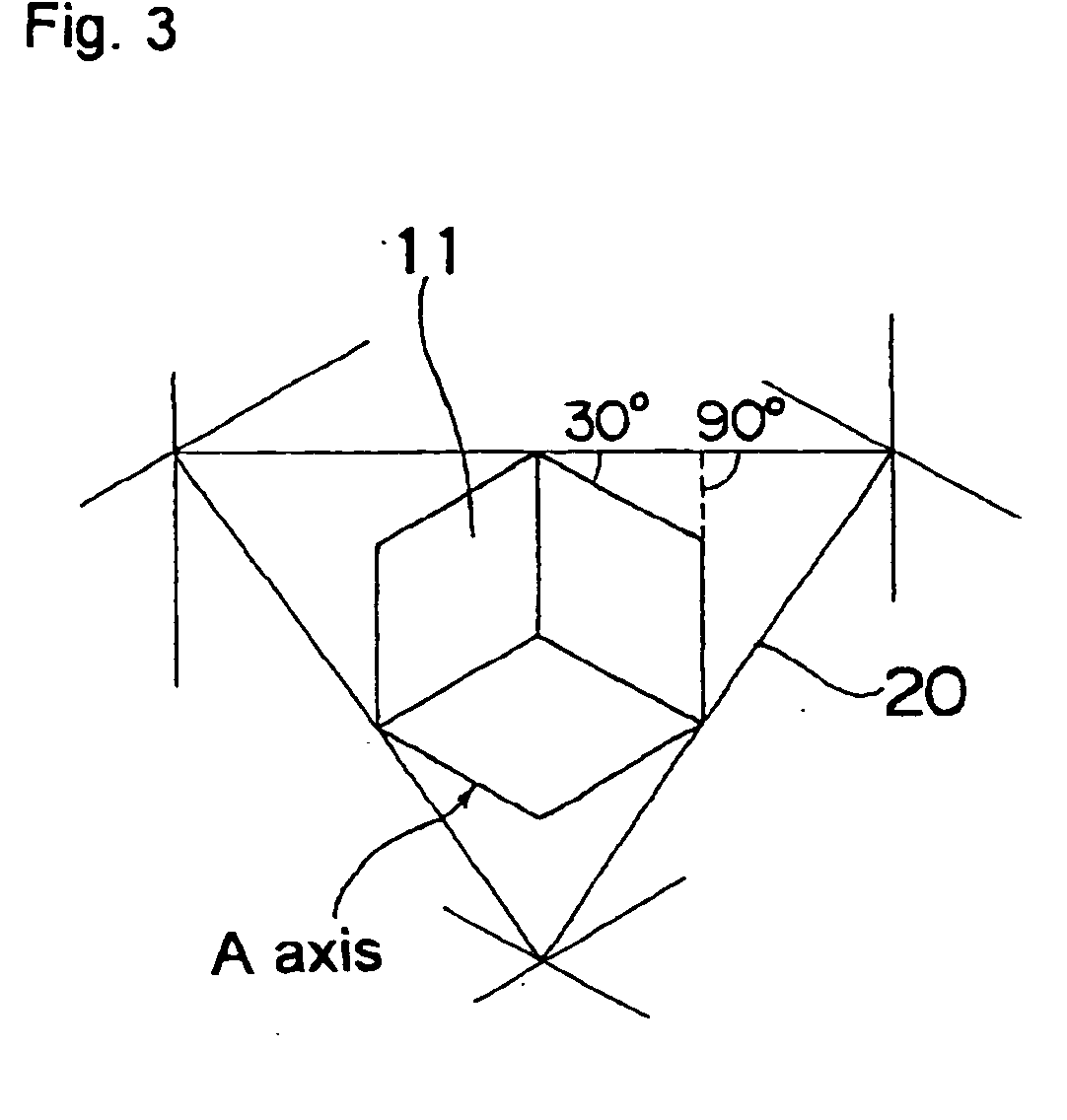

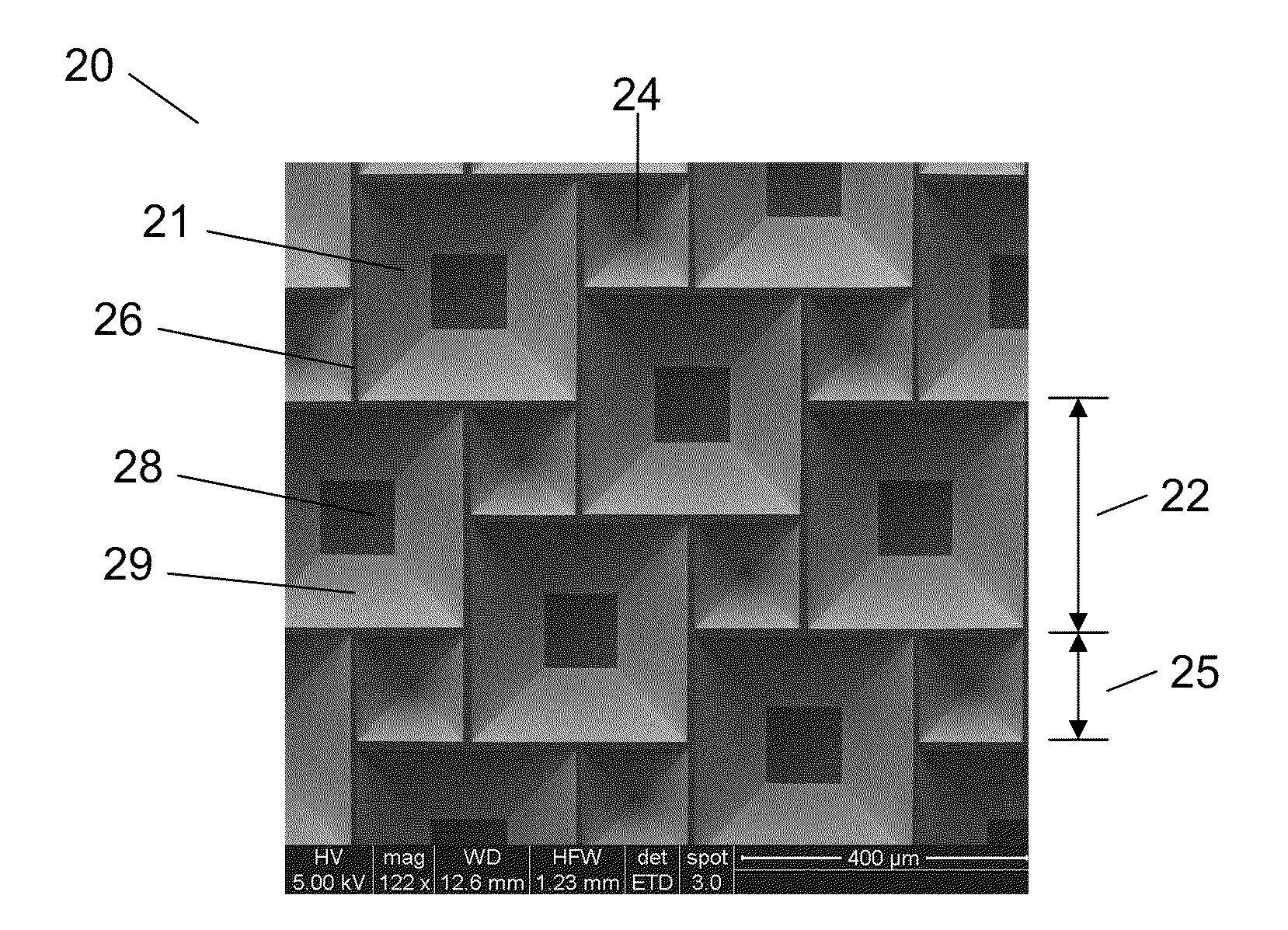

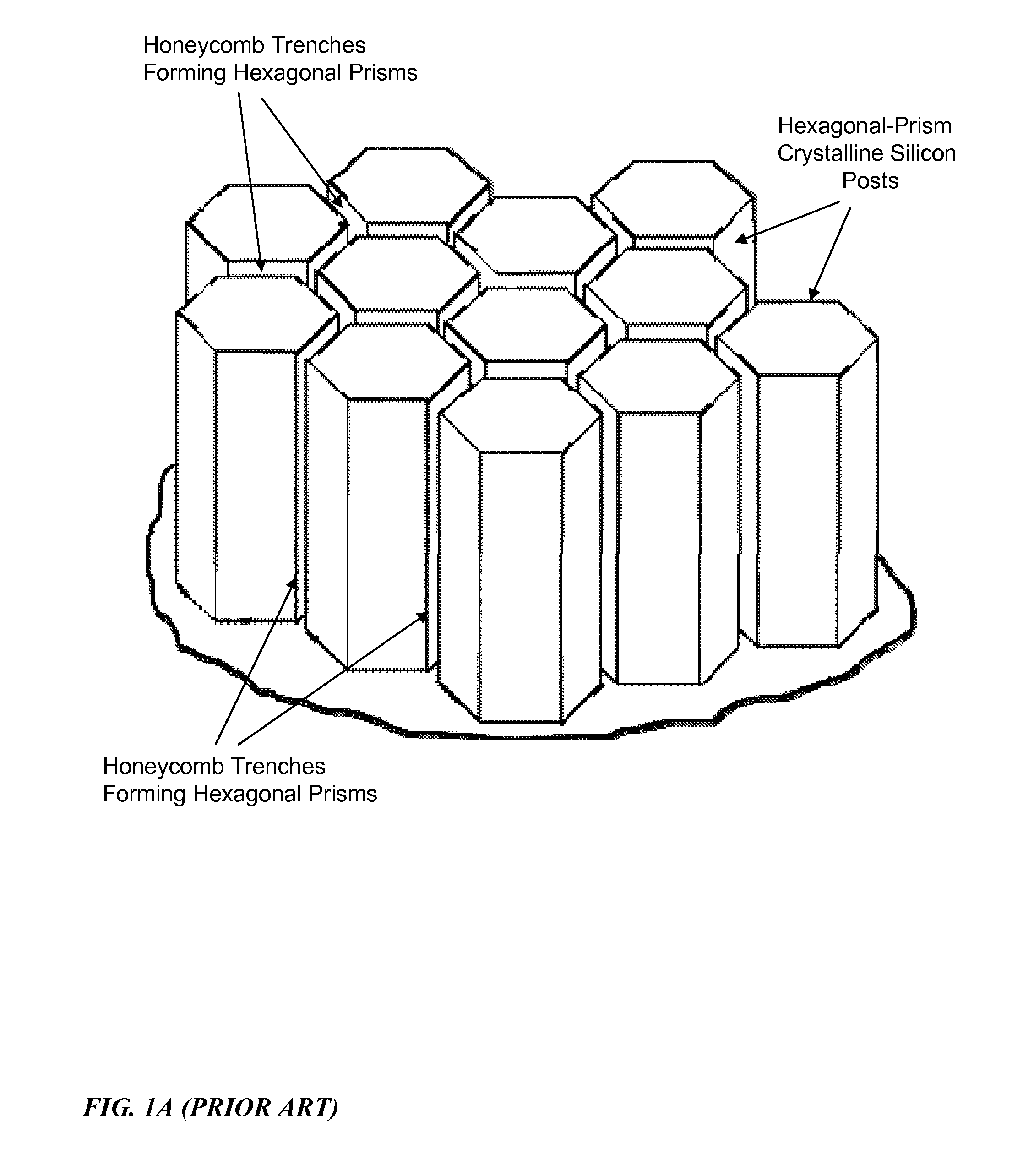

A semiconductor template having a top surface aligned along a (100) crystallographic orientation plane and an inverted pyramidal cavity defined by a plurality of walls aligned along a (111) crystallographic orientation plane. A method for manufacturing a semiconductor template by selectively removing silicon material from a silicon template to form a top surface aligned along a (100) crystallographic plane of the silicon template and a plurality of walls defining an inverted pyramidal cavity each aligned along a (111) crystallographic plane of the silicon template.

Owner:BEAMREACH SOLAR INC

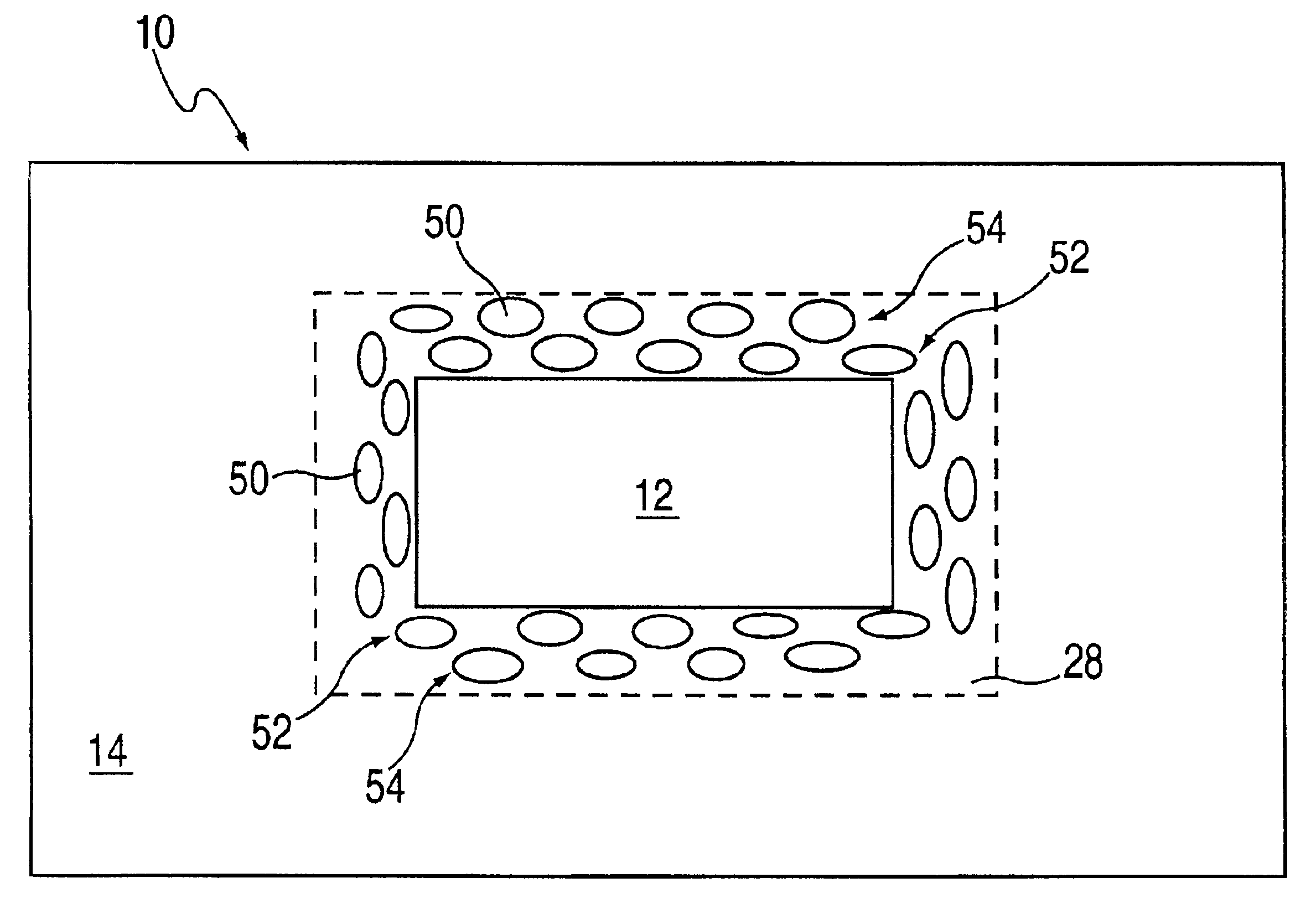

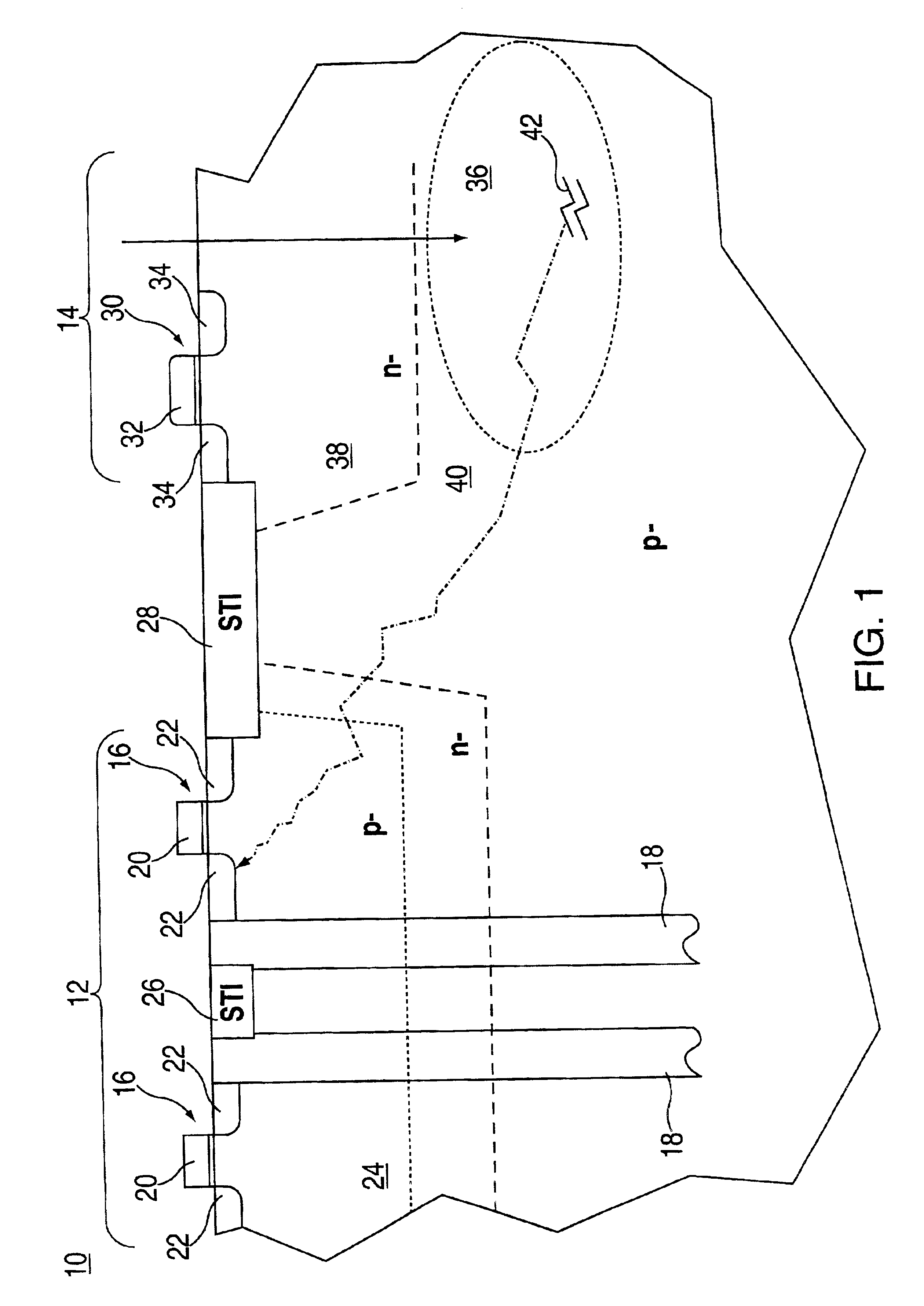

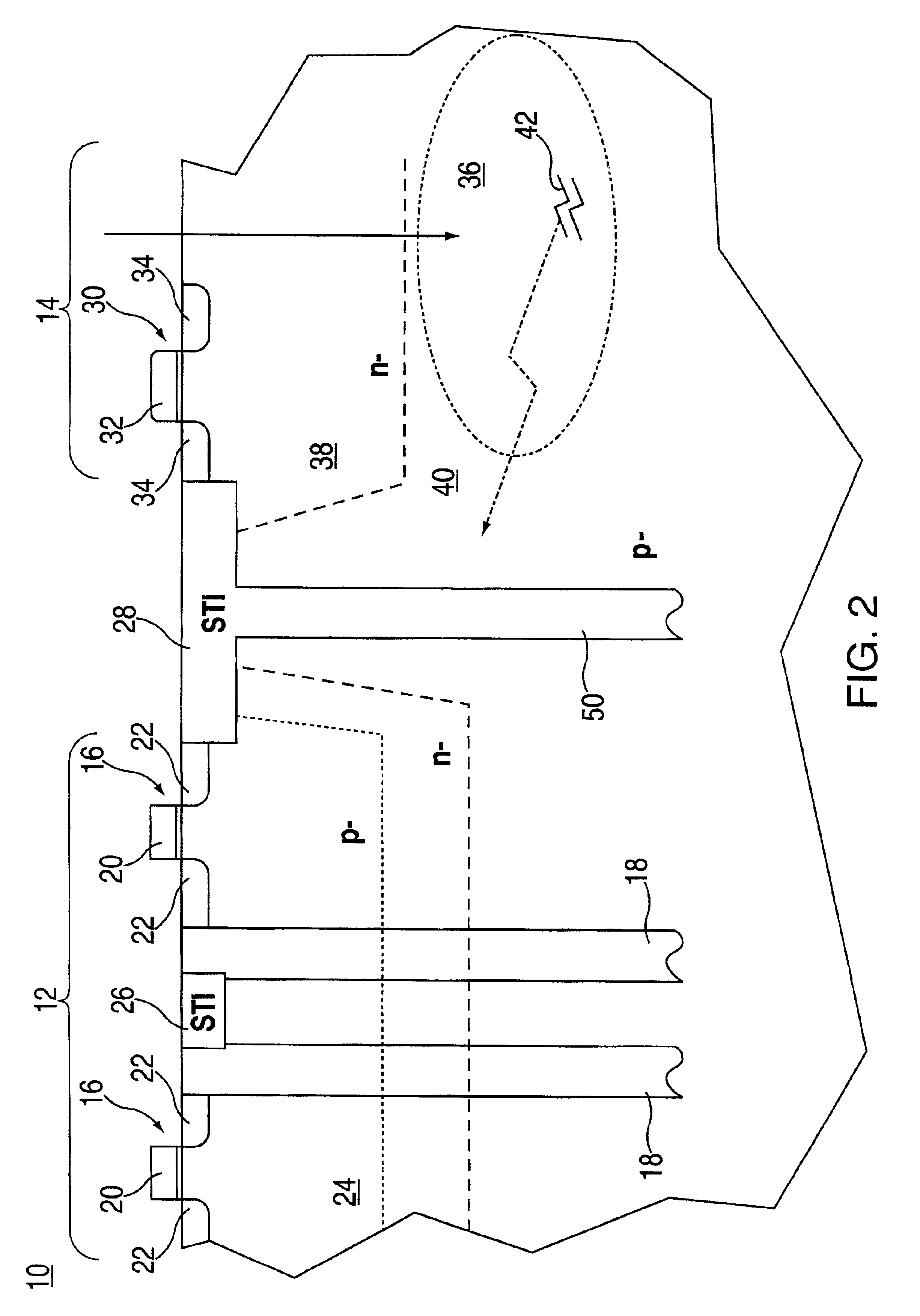

Deep trench isolation of embedded DRAM for improved latch-up immunity

A protective structure for blocking the propagation of defects generated in a semiconductor device is disclosed. In an exemplary embodiment, the structure includes a deep trench isolation formed between a memory storage region of the semiconductor device and a logic circuit region of the semiconductor device, the deep trench isolation being filled with an insulative material. The deep trench isolation thereby prevents the propagation of crystal defects generated in the logic circuit region from propagating into the memory storage region.

Owner:ELPIS TECH INC

Solar cell with superlattice structure and fabricating method thereof

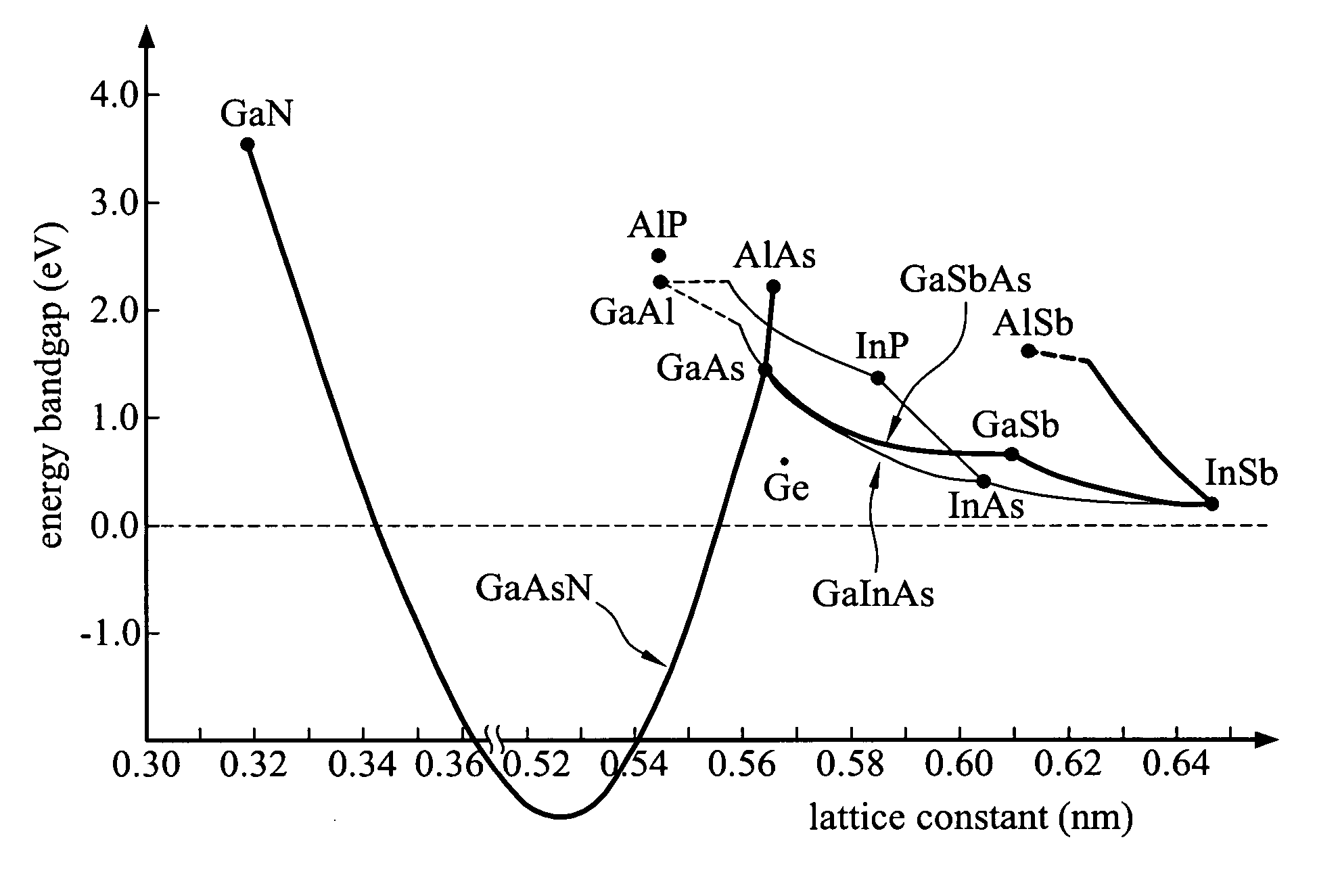

InactiveUS20070151595A1High carrier mobilityPreferable advantageSemiconductor/solid-state device manufacturingNanoopticsEngineeringCritical thickness

A solar cell with a superlattice structure and a fabricating method thereof are provided, which includes fabricating a superlattice structure of GaAsN / GaInAs, GaAsN / GaSbAs, or GaAsN / GaInSbAs between a base and an emitter of a middle cell of a triple junction solar cell by a strain-compensation technology. The provided solar cell not only decreases crystalline defects and increases the critical thickness of the crystal, but also makes the energy bandgap of GaAsN and GaInAs reach around the energy of 1.0 eV (electron volt). Hence, the absorption region can be raised to around the energy of 1.0 eV to enhance the efficiency of the solar cell.

Owner:IND TECH RES INST +1

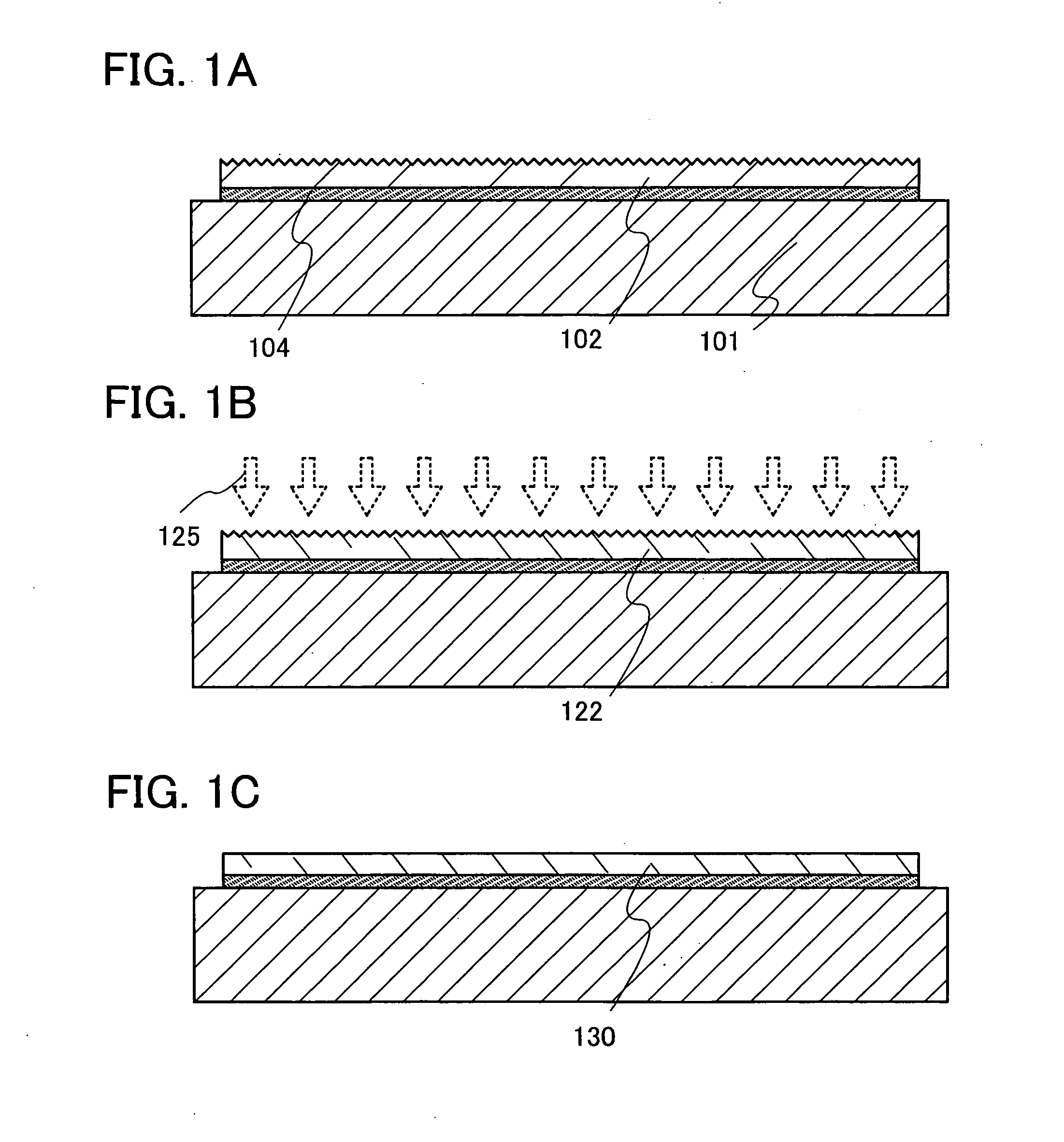

Method for manufacturing SOI substrate and method for manufacturing semiconductor device

InactiveUS20090004764A1Good planarityImprove performanceTransistorElectroluminescent light sourcesHigh energySingle crystal

To provide a method for manufacturing an SOI substrate provided with a single-crystal semiconductor layer which is suitable for practical use even when a substrate of which heat-resistant temperature is low, such as a glass substrate, is used, and to manufacture a highly reliable semiconductor device using such an SOI substrate. A semiconductor layer, which is separated from a semiconductor substrate and bonded to a supporting substrate having an insulating surface, is heated by supplying high energy by using at least one kind of particles having the high energy, and polishing treatment is performed on the heated surface of the semiconductor layer. At least part of a region of the semiconductor layer can be melted by the heat treatment by supplying high energy to reduce crystal defects in the semiconductor layer. Further, the surface of the semiconductor layer can be polished and planarized by the polishing treatment.

Owner:SEMICON ENERGY LAB CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com