Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

193 results about "Critical thickness" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The thickness upto which heat flow increases and after which heat flow decreases is termed as critical thickness. In the case of cylinders and spheres it is called critical radius.

Substrate for growing a III-V light emitting device

ActiveUS20070072324A1Relieve pressurePolycrystalline material growthLight-sensitive devicesSemiconductor structureCritical thickness

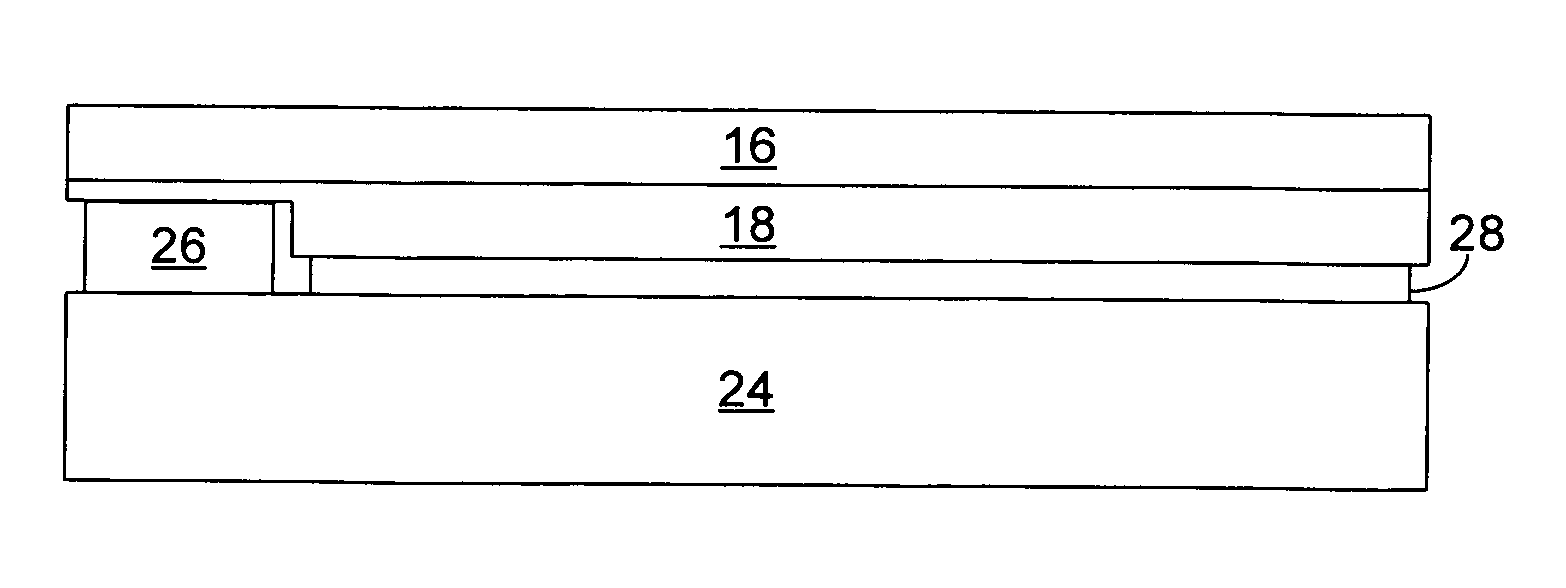

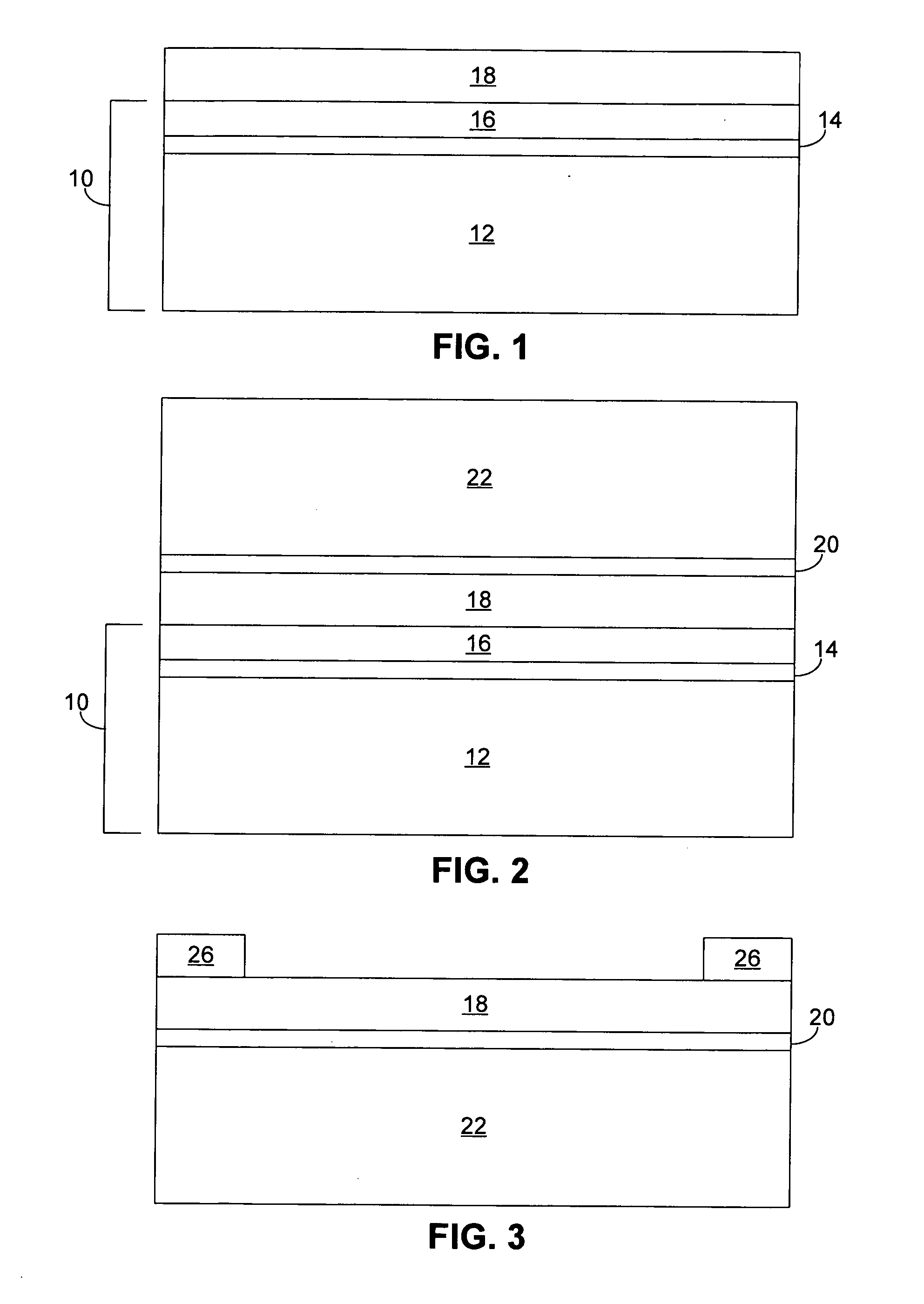

A substrate including a host and a seed layer bonded to the host is provided, then a semiconductor structure including a light emitting layer disposed between an n-type region and a p-type region is grown on the seed layer. In some embodiments, a bonding layer bonds the host to the seed layer. The seed layer may be thinner than a critical thickness for relaxation of strain in the semiconductor structure, such that strain in the semiconductor structure is relieved by dislocations formed in the seed layer, or by gliding between the seed layer and the bonding layer an interface between the two layers. In some embodiments, the host may be separated from the semiconductor structure and seed layer by etching away the bonding layer.

Owner:LUMILEDS

Dielectric layer for semiconductor device and method of manufacturing the same

InactiveUS6844604B2Improving interface characteristicReduce maintenanceTransistorSolid-state devicesDevice materialInterface layer

A multi-layer dielectric layer structure for a semiconductor device. The multi-layer dielectric layer structure comprises a silicate interface layer having a dielectric constant greater than that of silicon nitride and a high-k dielectric layer overlying the silicate interface layer. The high-k dielectric layer comprises one or more ordered pairs of first and second layers. With the present invention, the dielectric constant of the high-k dielectric layer can be optimized while improving interface characteristics. With a higher crystallization temperature realized by forming the multi-layer structure, each of whose layers is not more than the critical thickness, leakage current can be reduced, thereby improving device performance.

Owner:SAMSUNG ELECTRONICS CO LTD

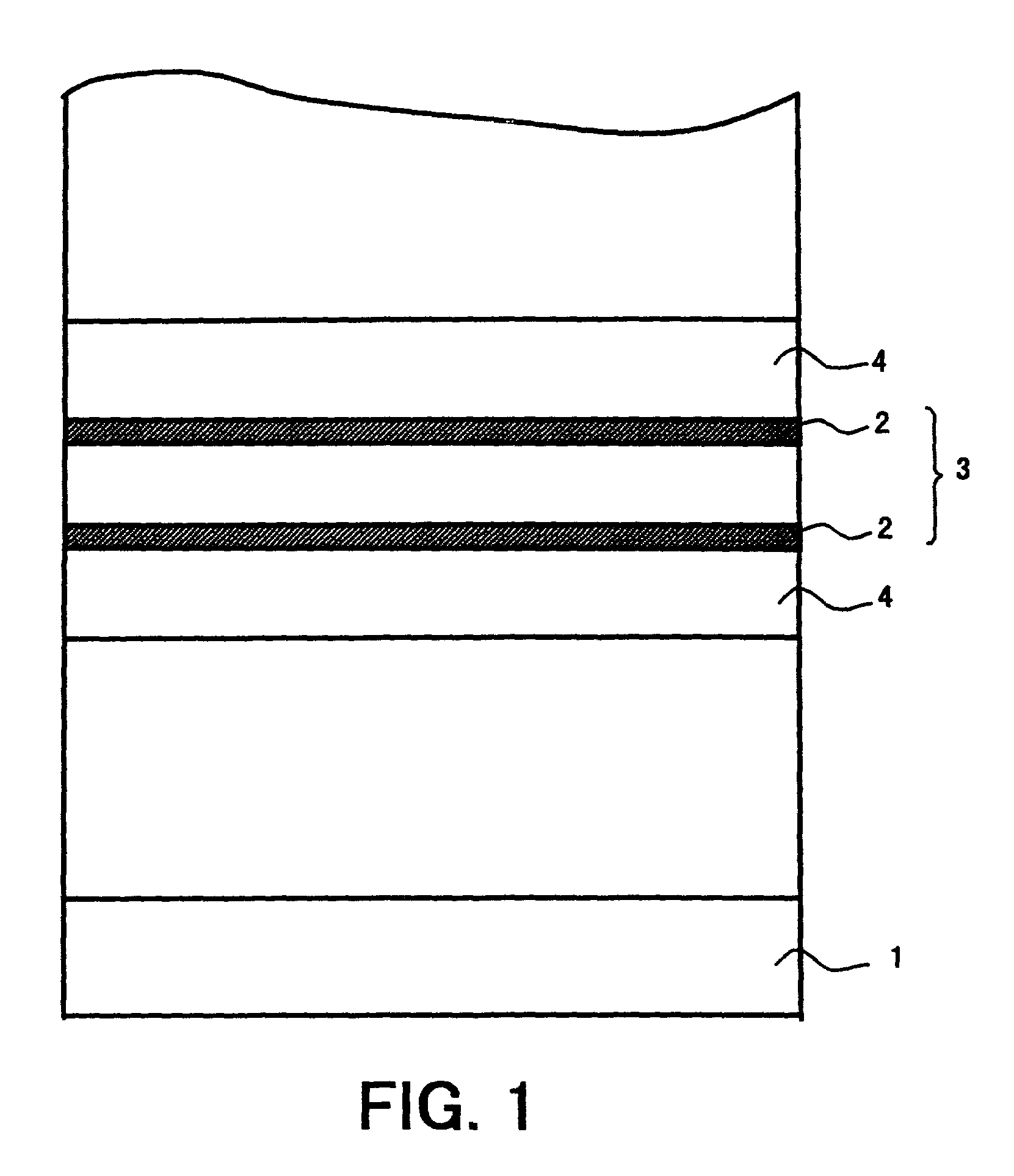

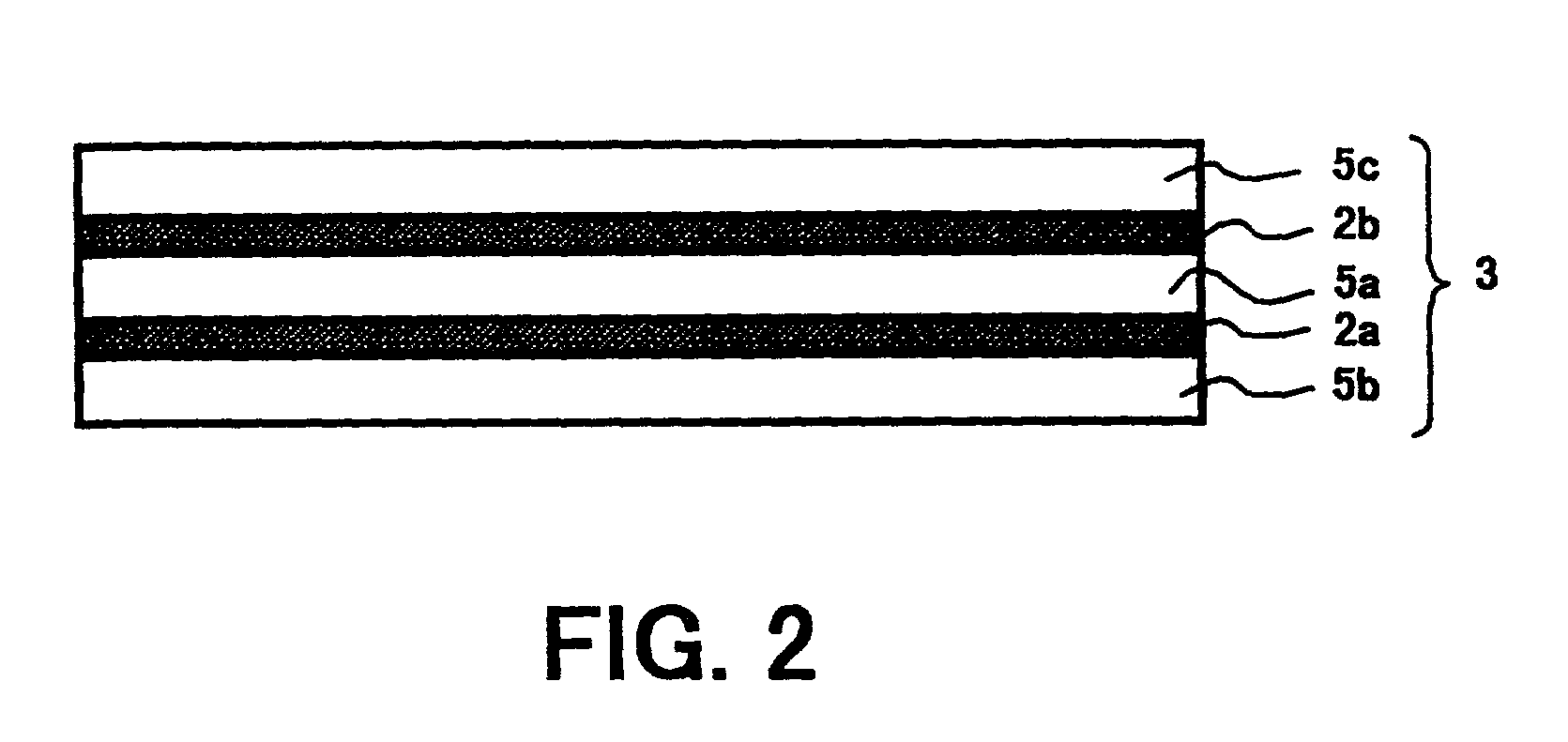

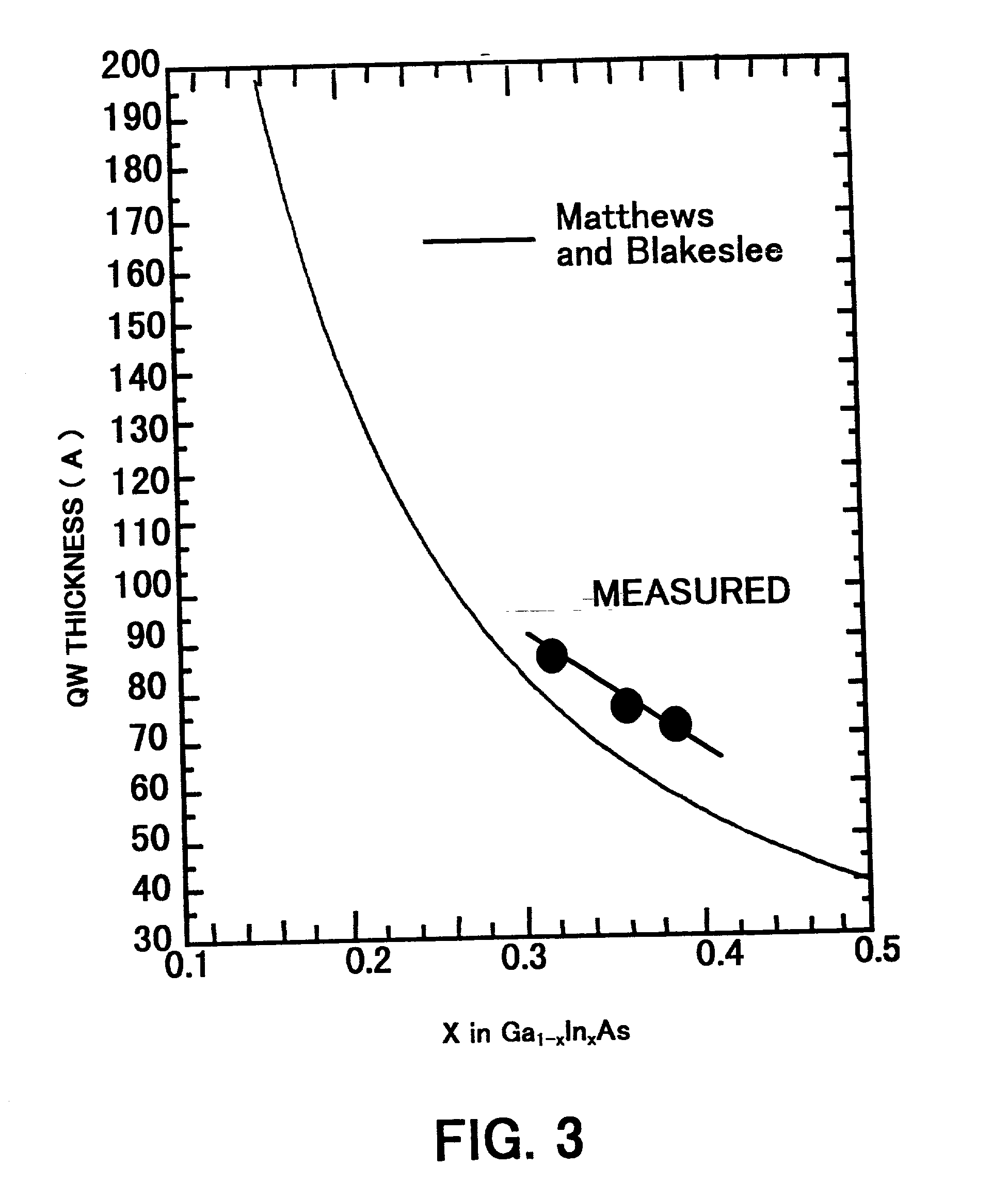

Light emitting devices with layered III-V semiconductor structures

InactiveUS6207973B1Improve crystal qualityFacilitates layerLaser detailsLaser active region structureCharge carrierSemiconductor structure

A semiconductor light emitting device is disclosed, including a semiconductor substrate, an active region comprising a strained quantum well layer, and a cladding layer for confining carriers and light emissions, wherein the amount of lattice strains in the quantum well layer is in excess of 2% against either the semiconductor substrate or cladding layer and, alternately, the thickness of the quantum well layer is in excess of the critical thickness calculated after Matthews and Blakeslee.

Owner:RICOH KK

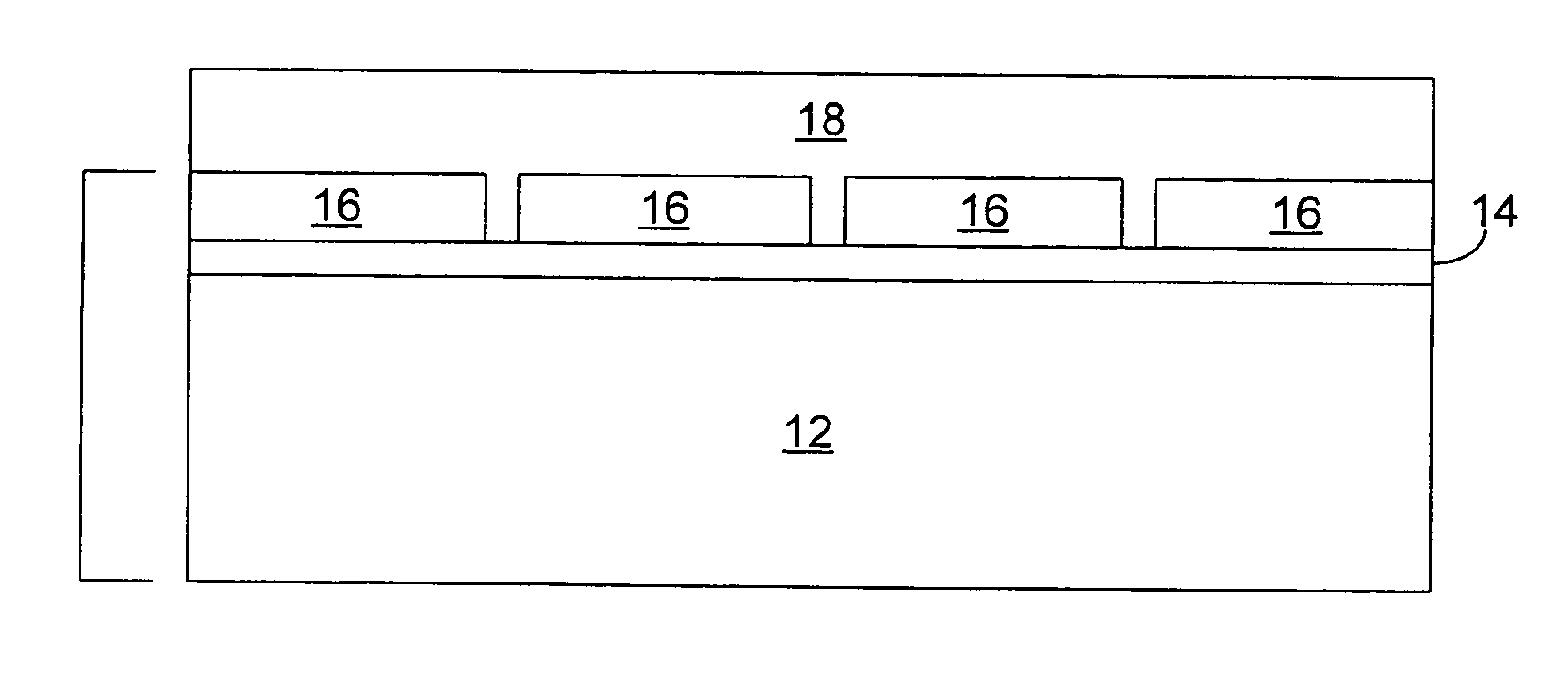

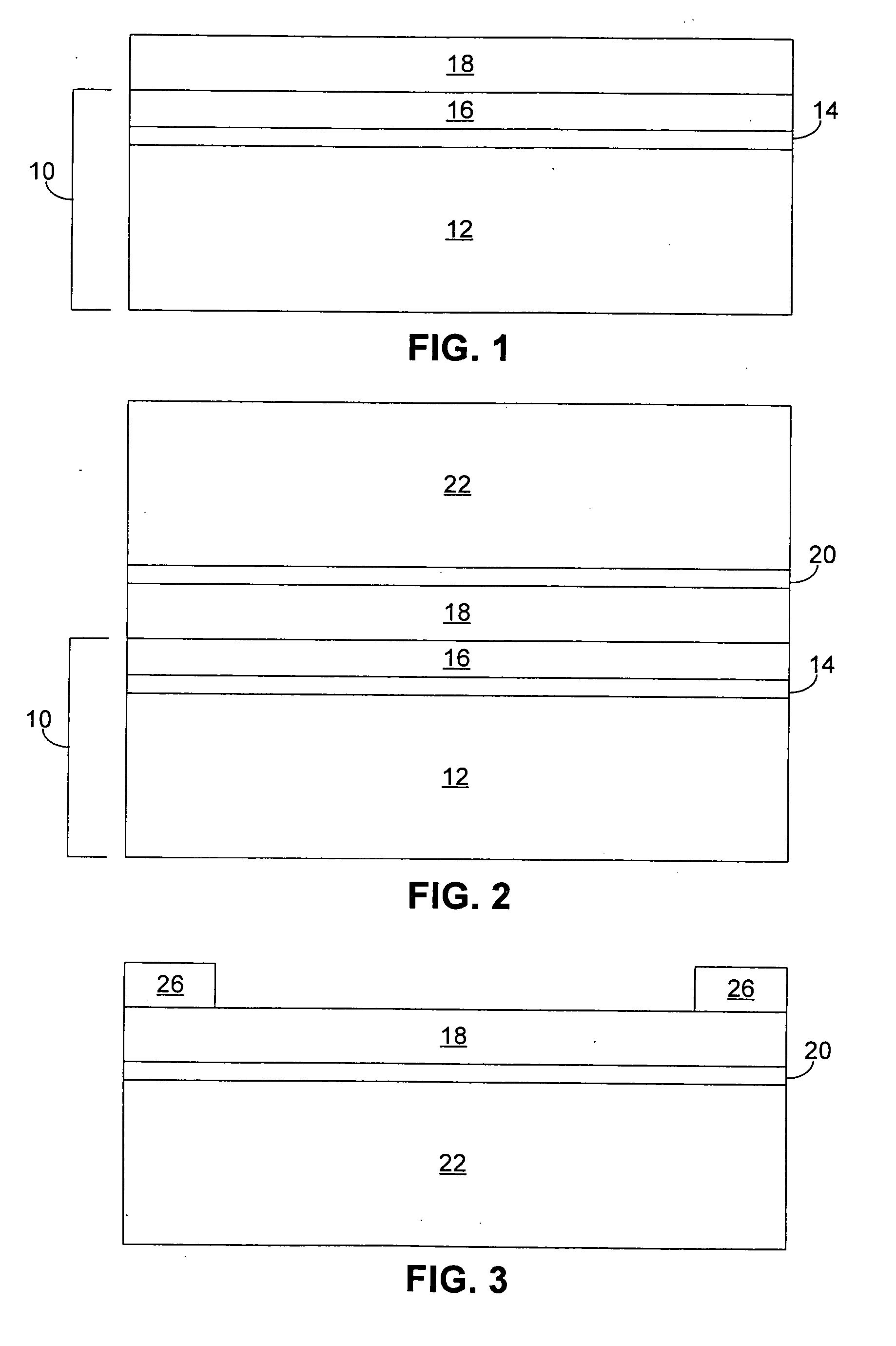

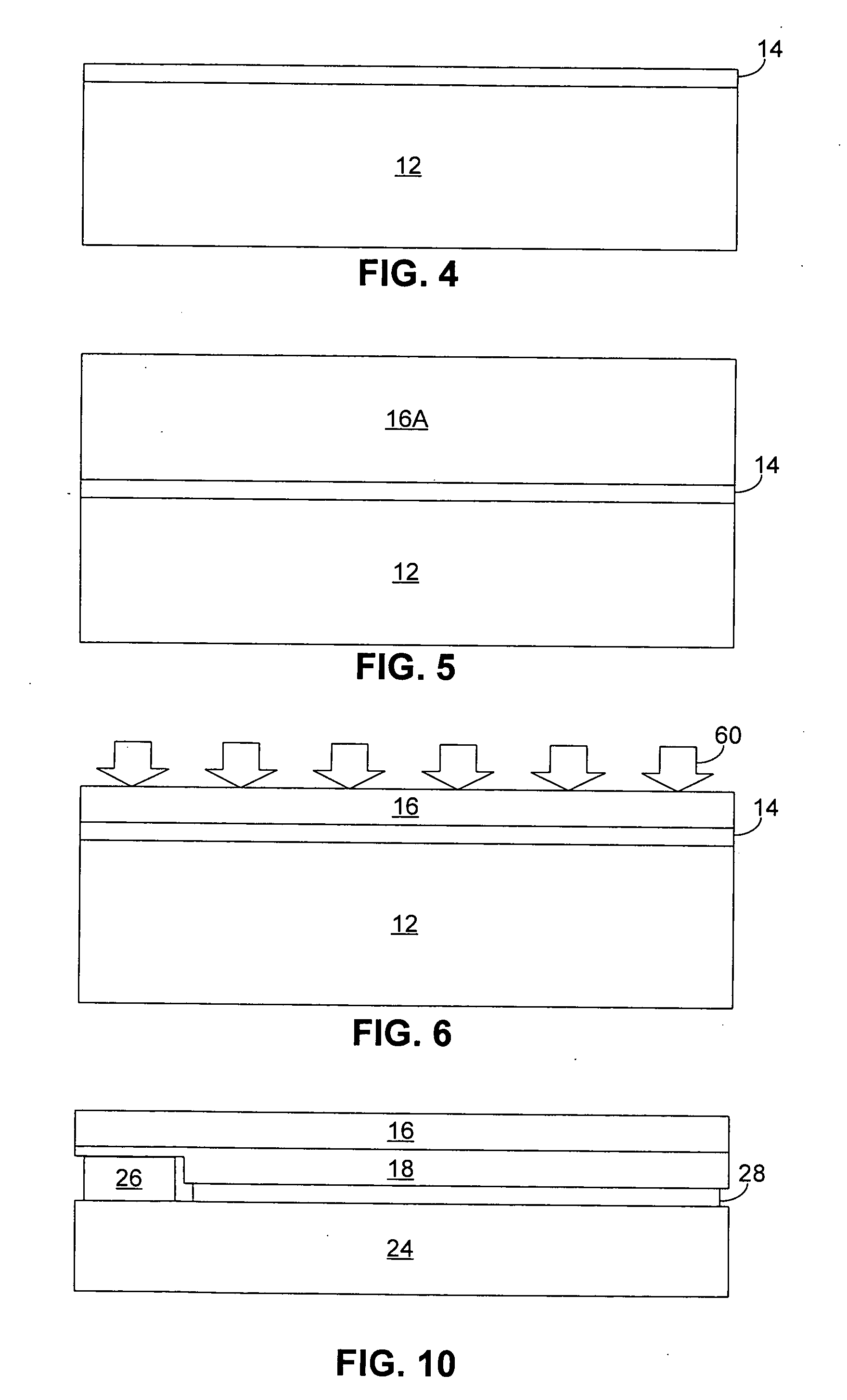

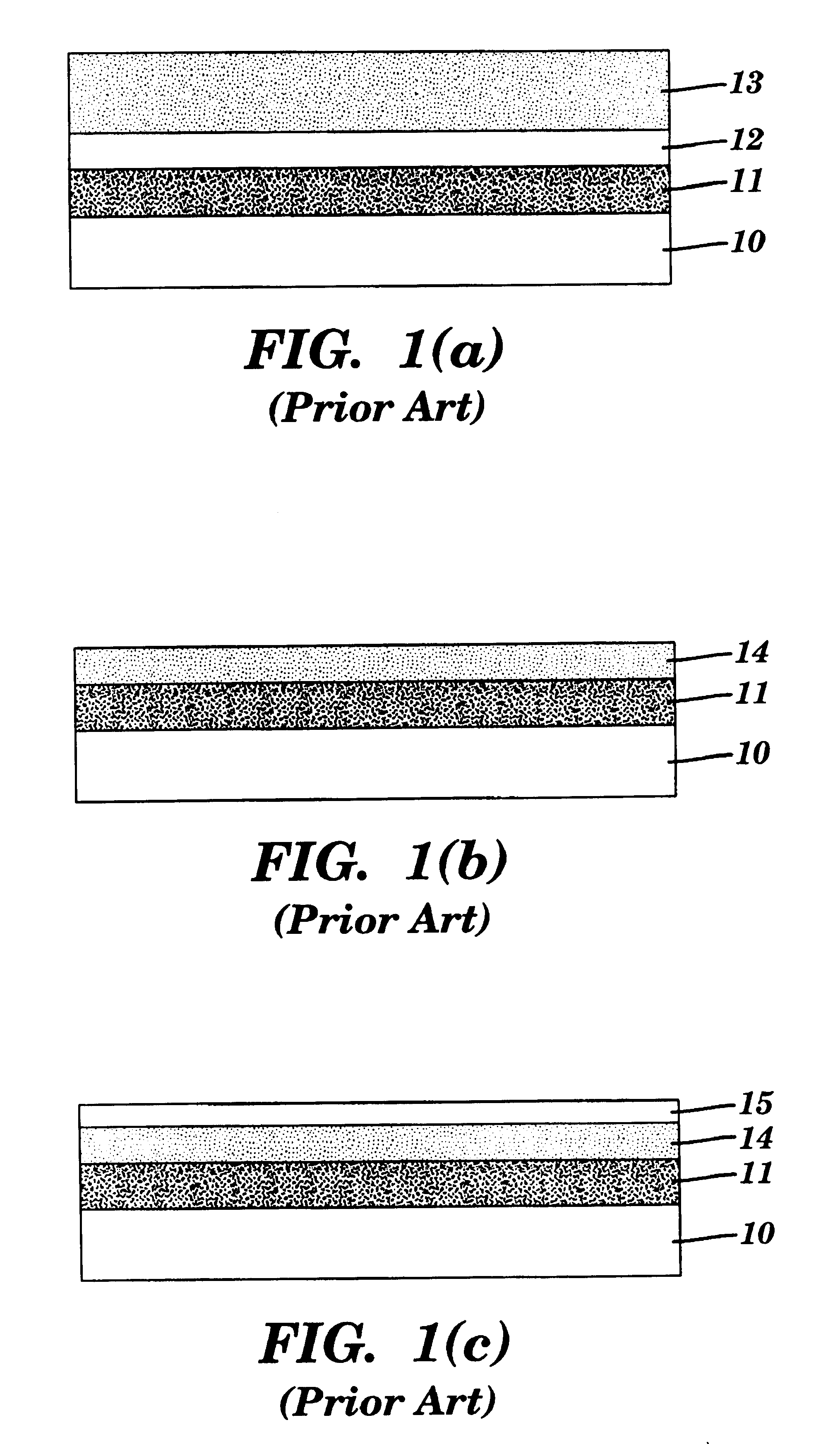

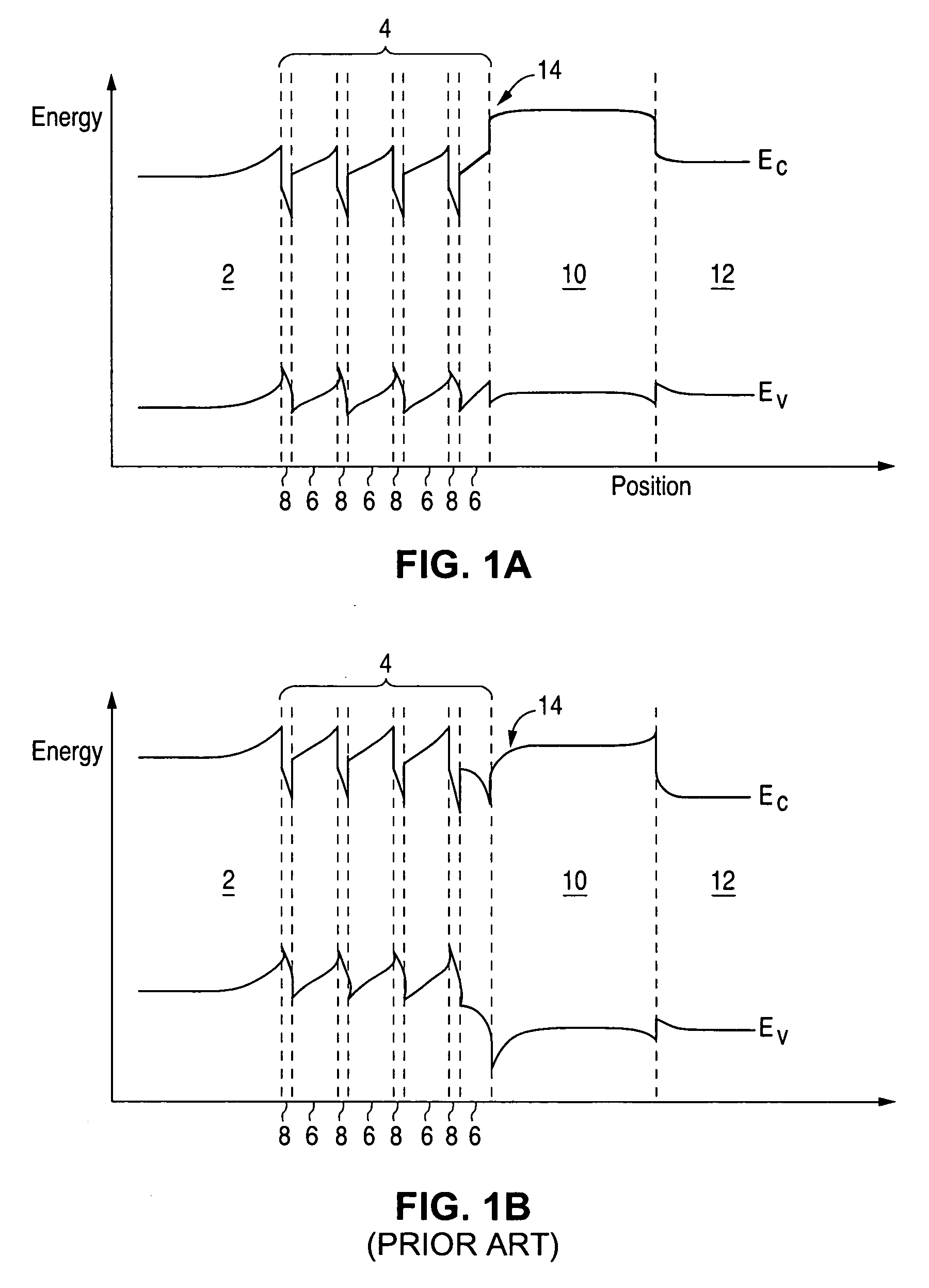

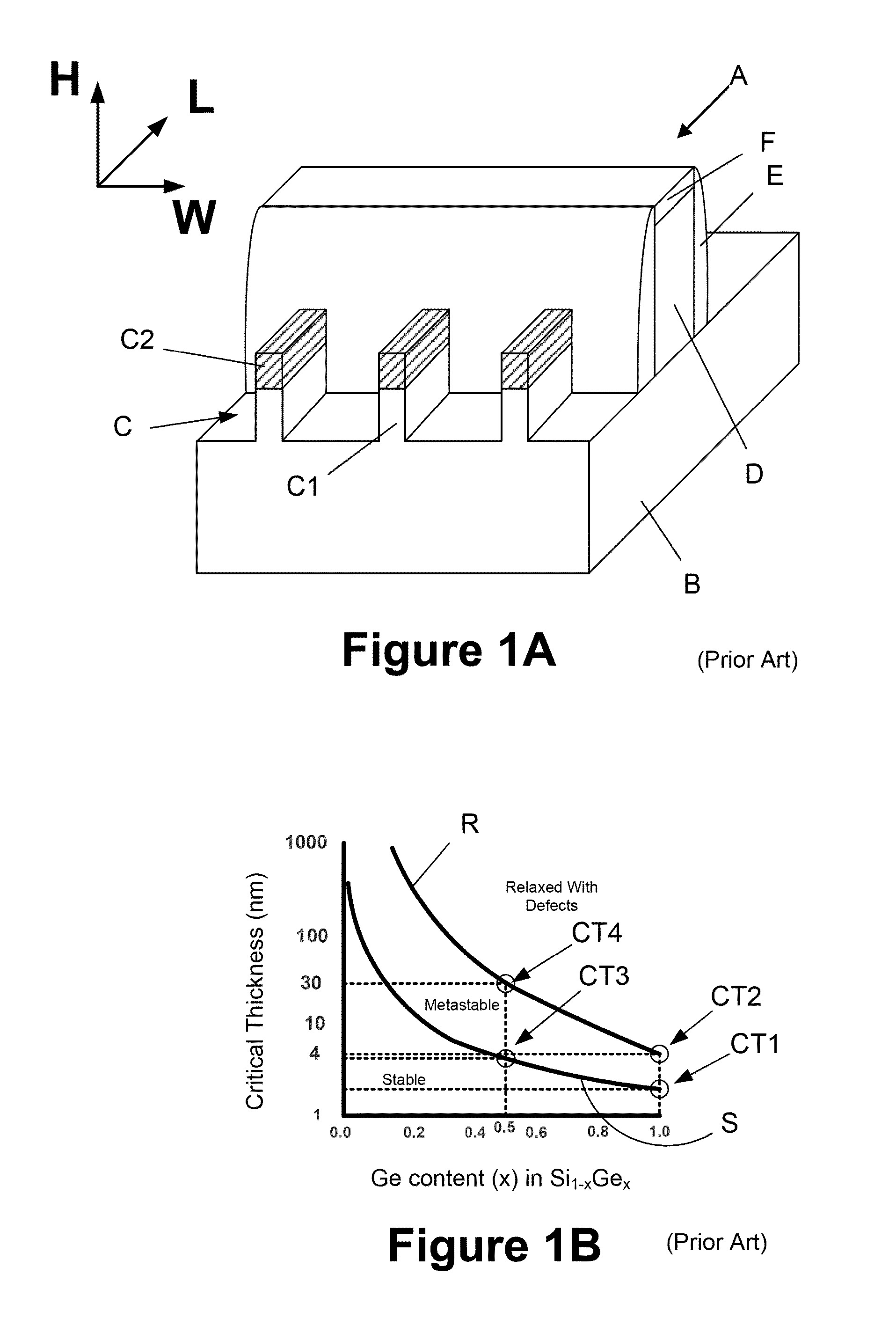

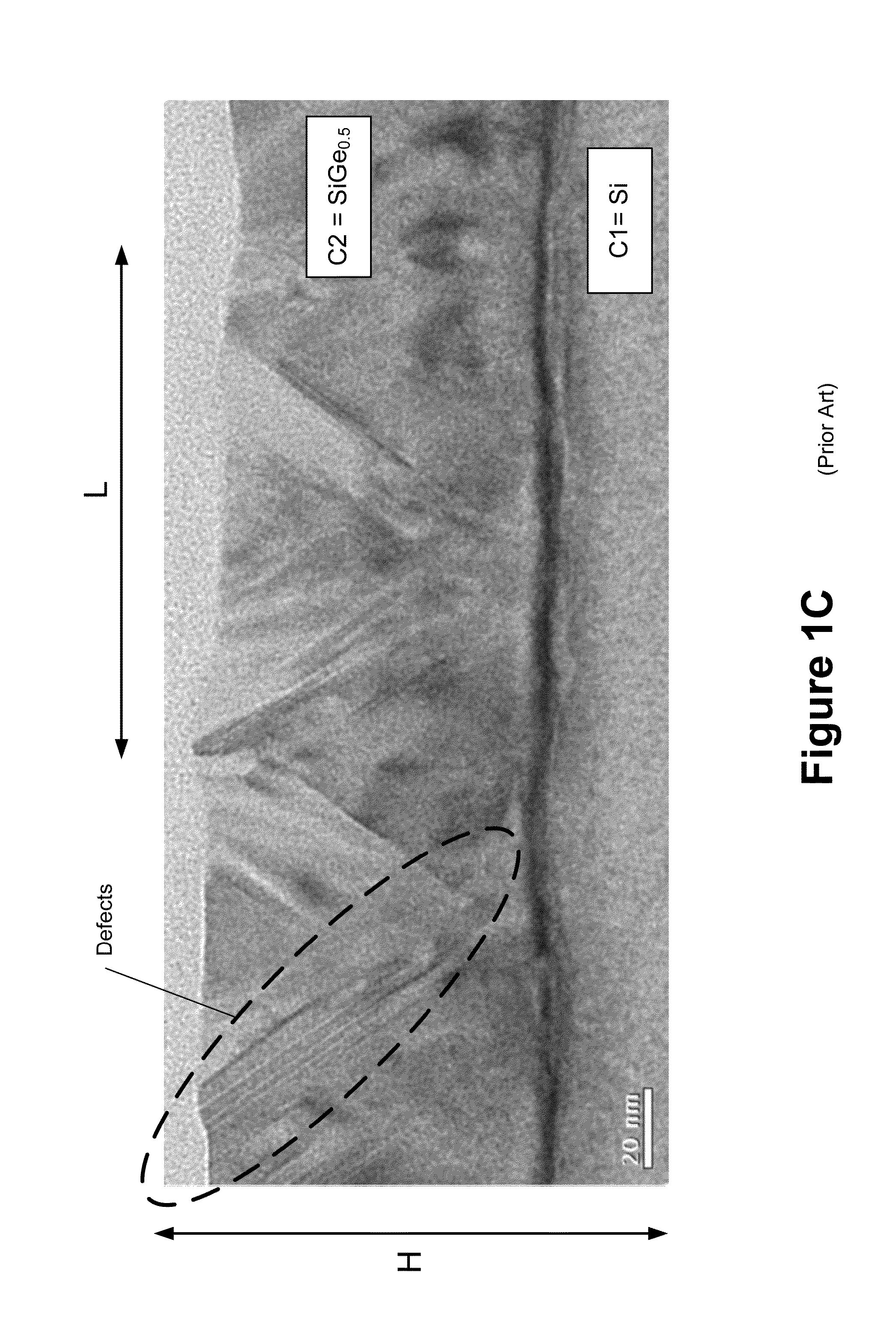

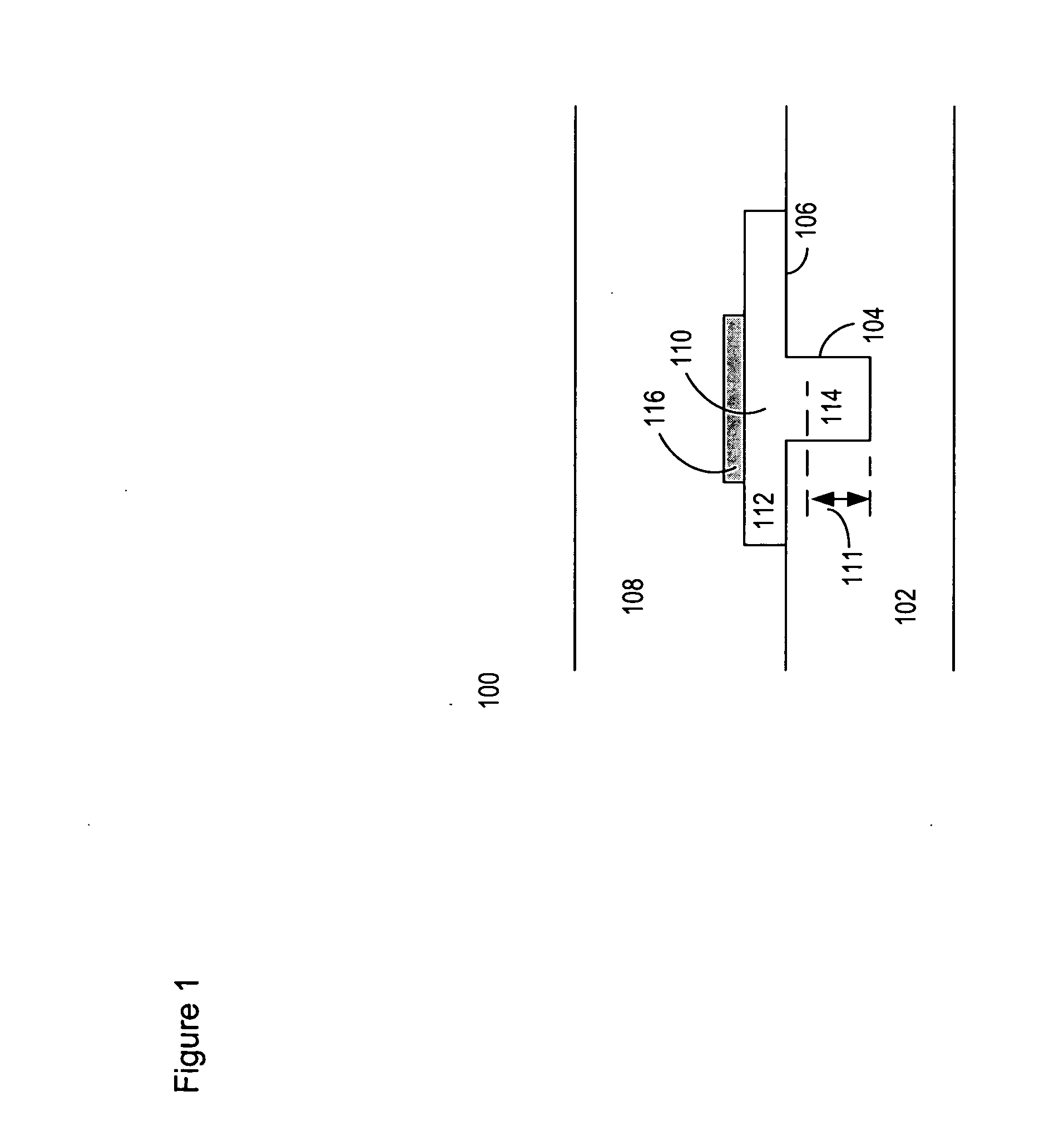

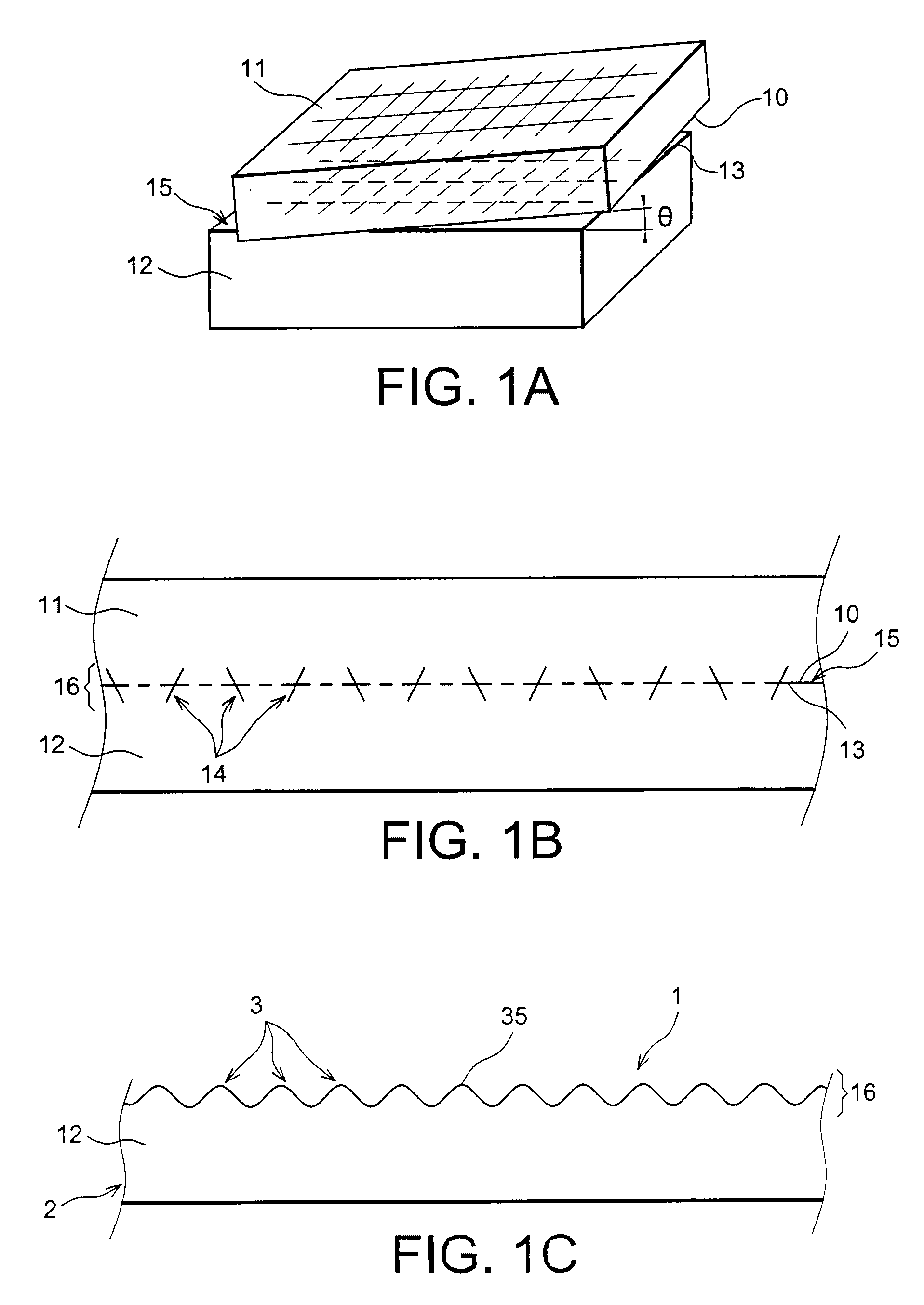

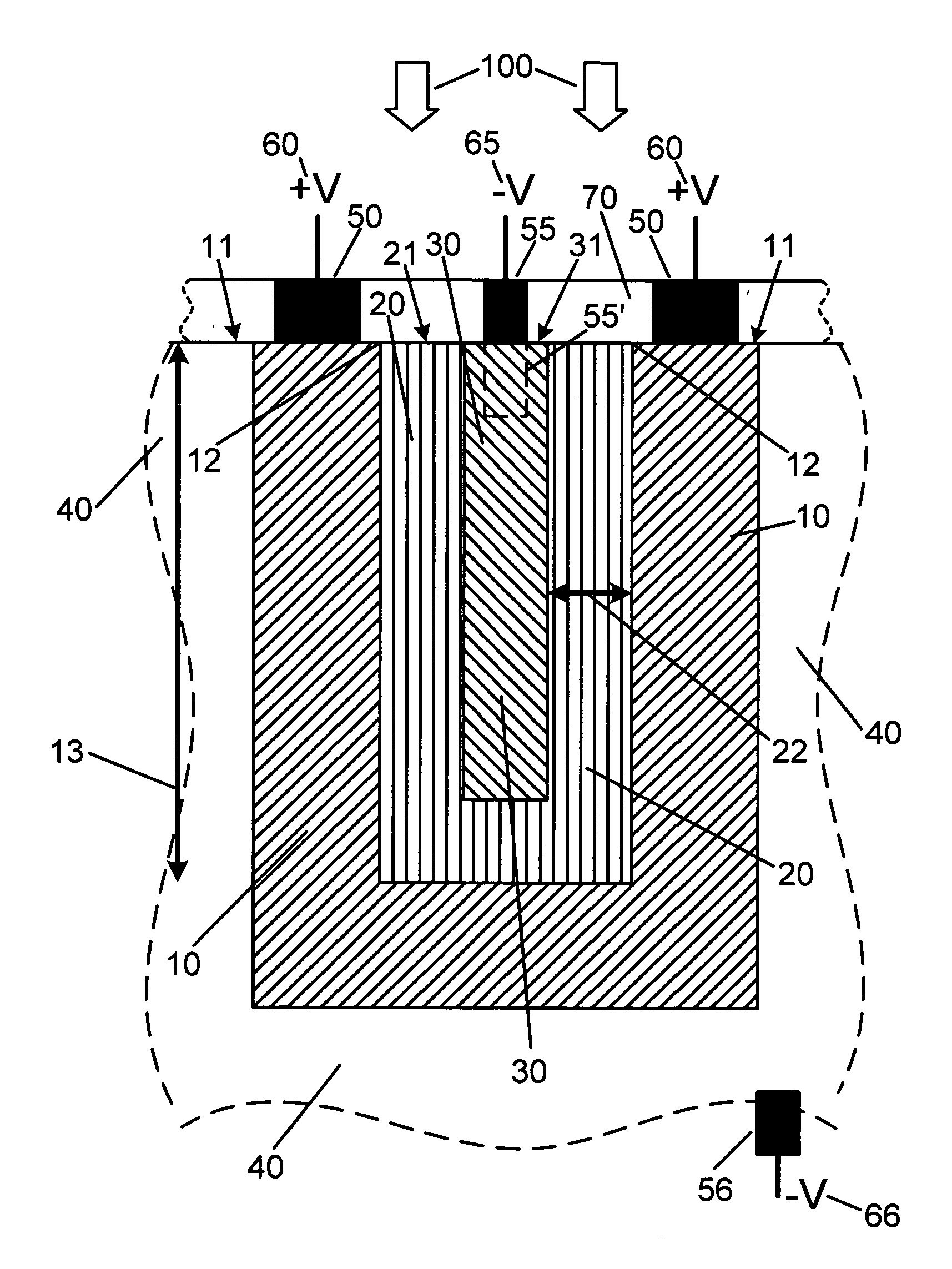

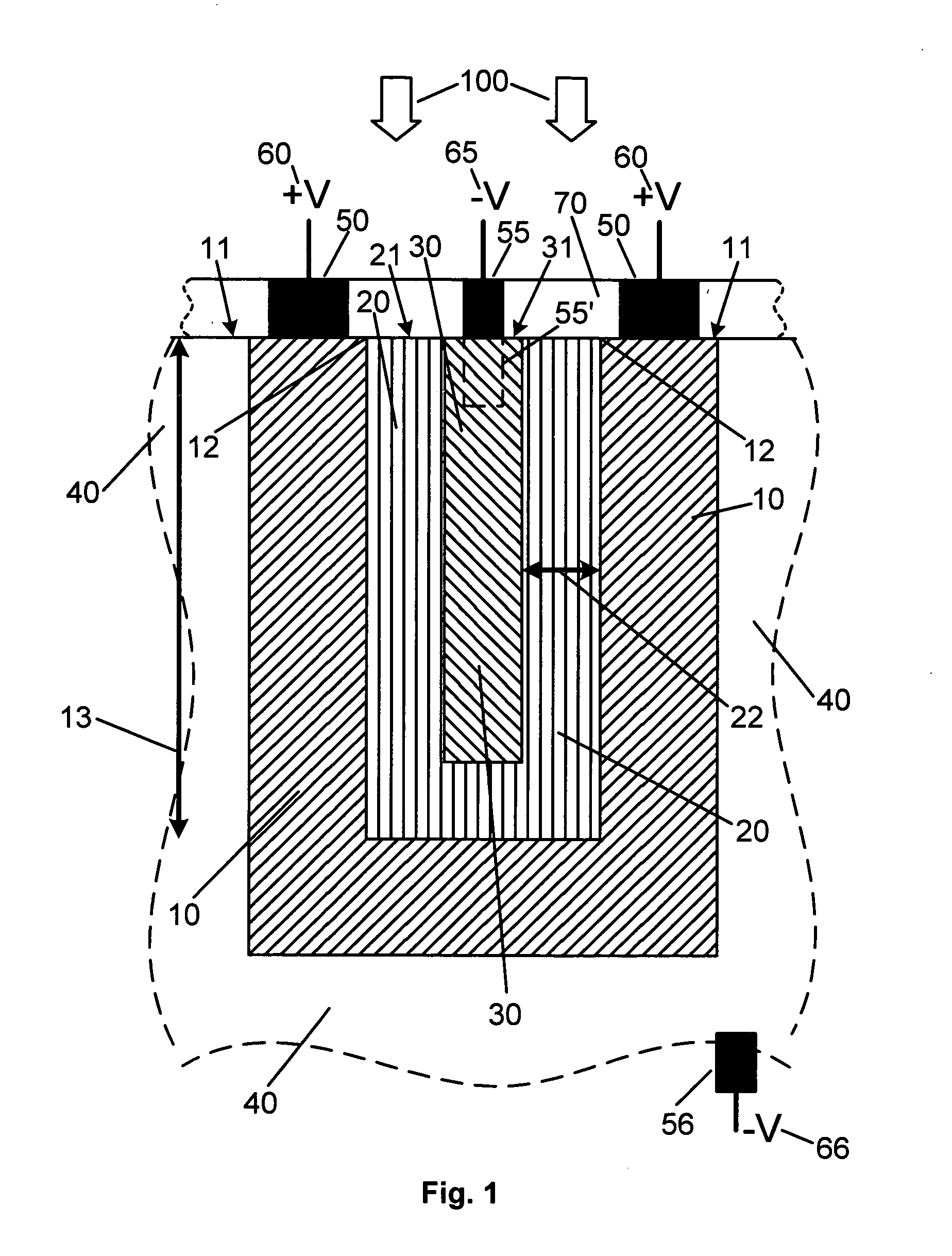

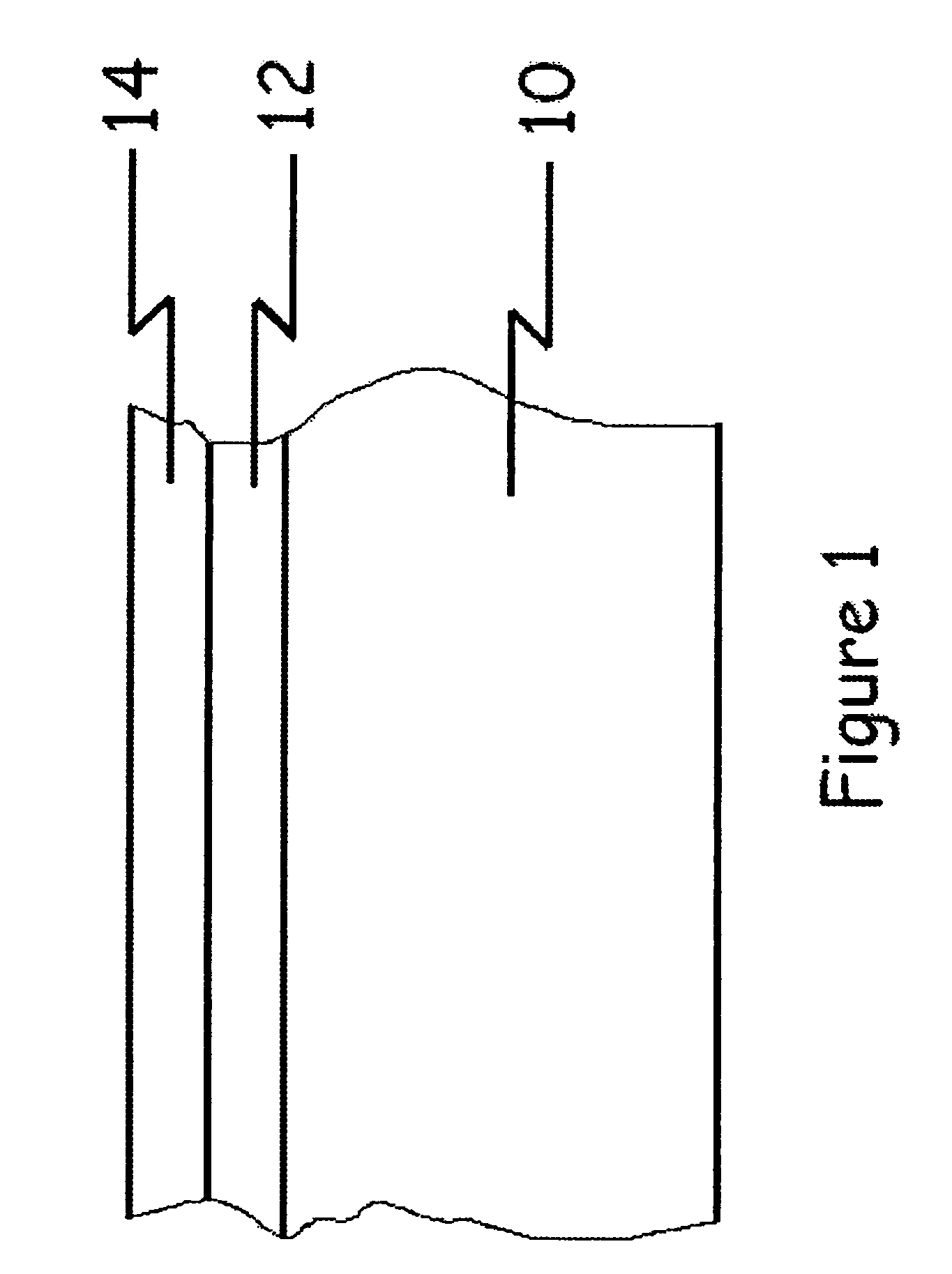

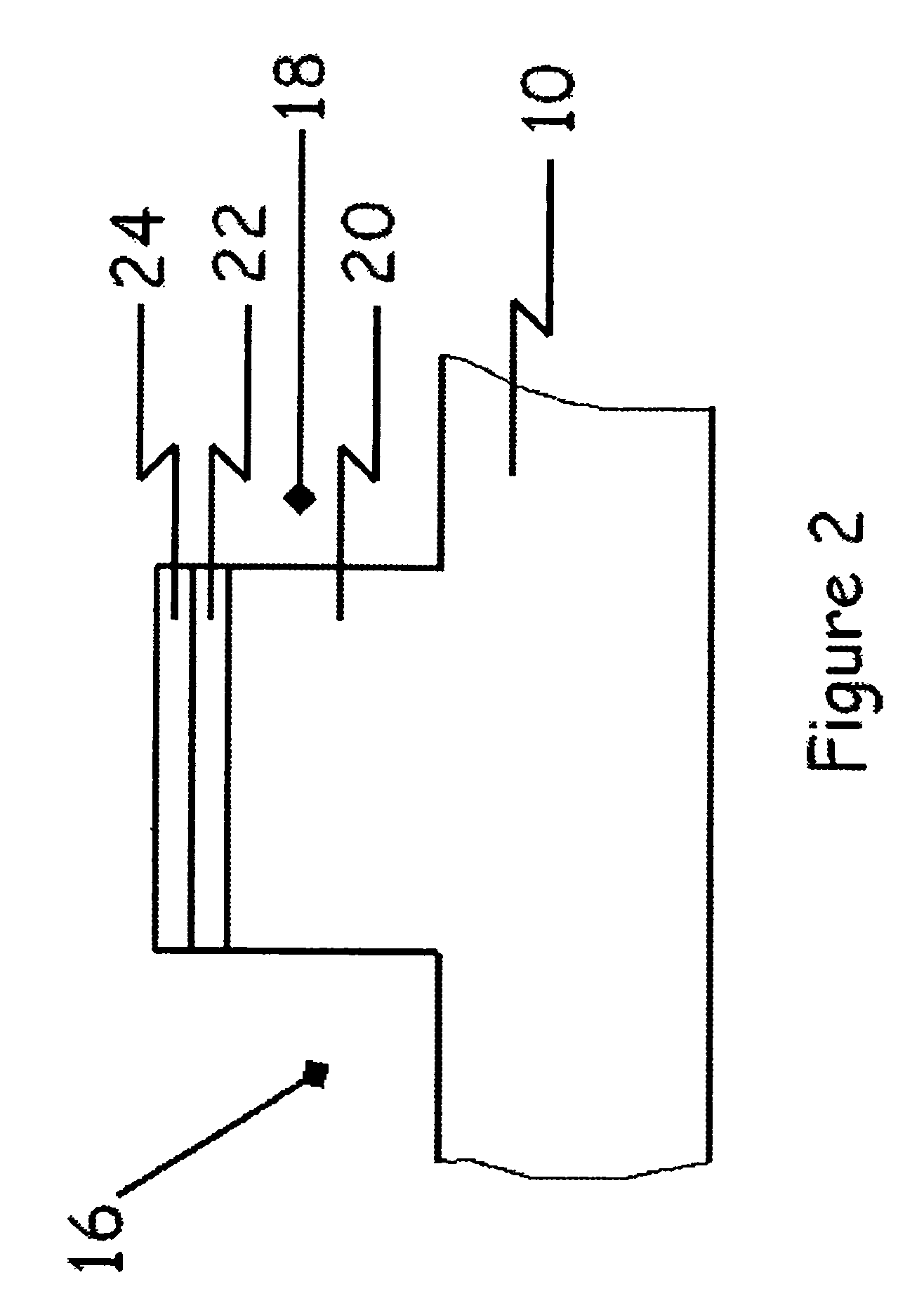

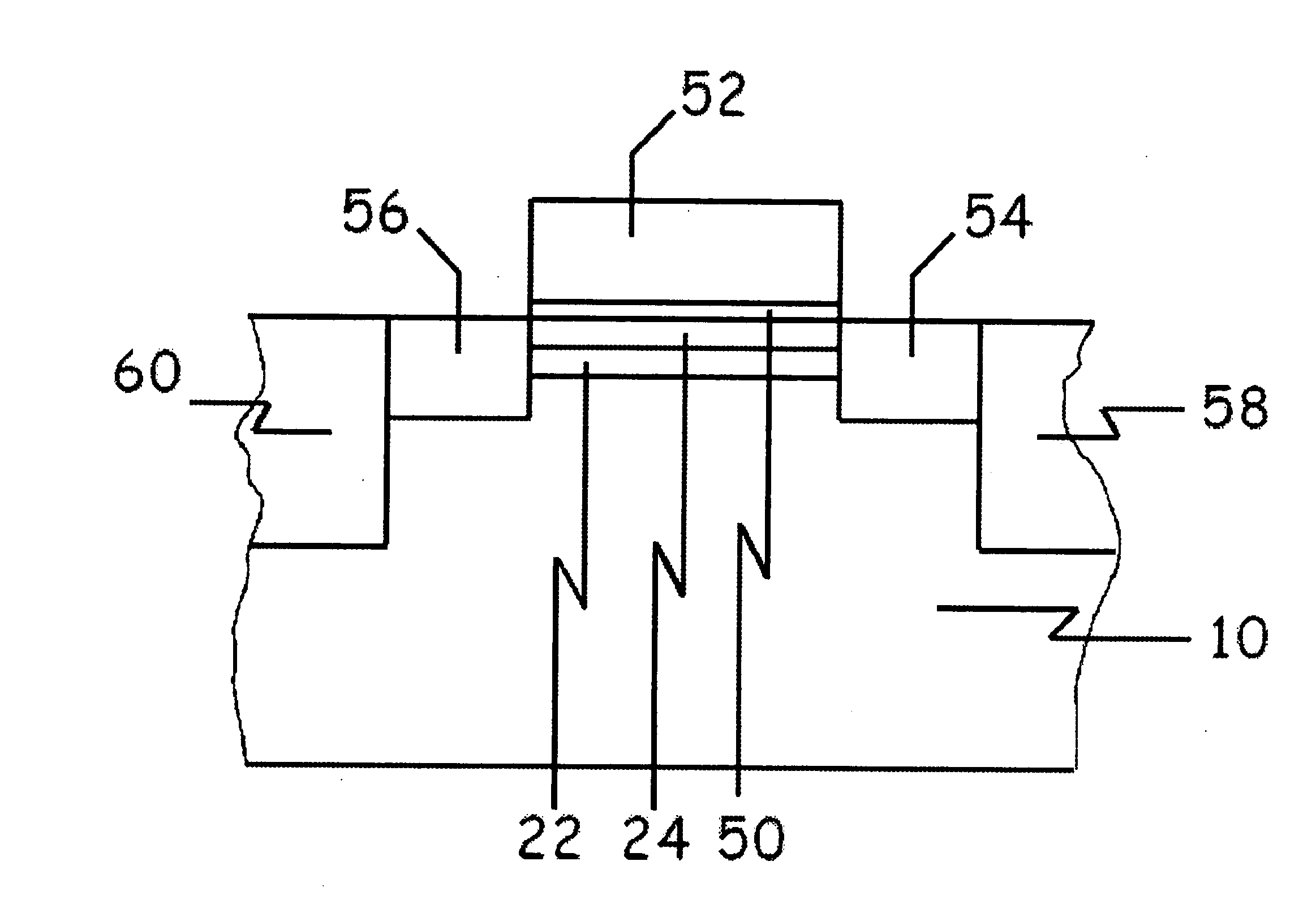

High mobility heterojunction complementary field effect transistors and methods thereof

InactiveUS7057216B2High hole mobilitySimilar current carrying capabilityTransistorSolid-state devicesHeterojunctionPresent day

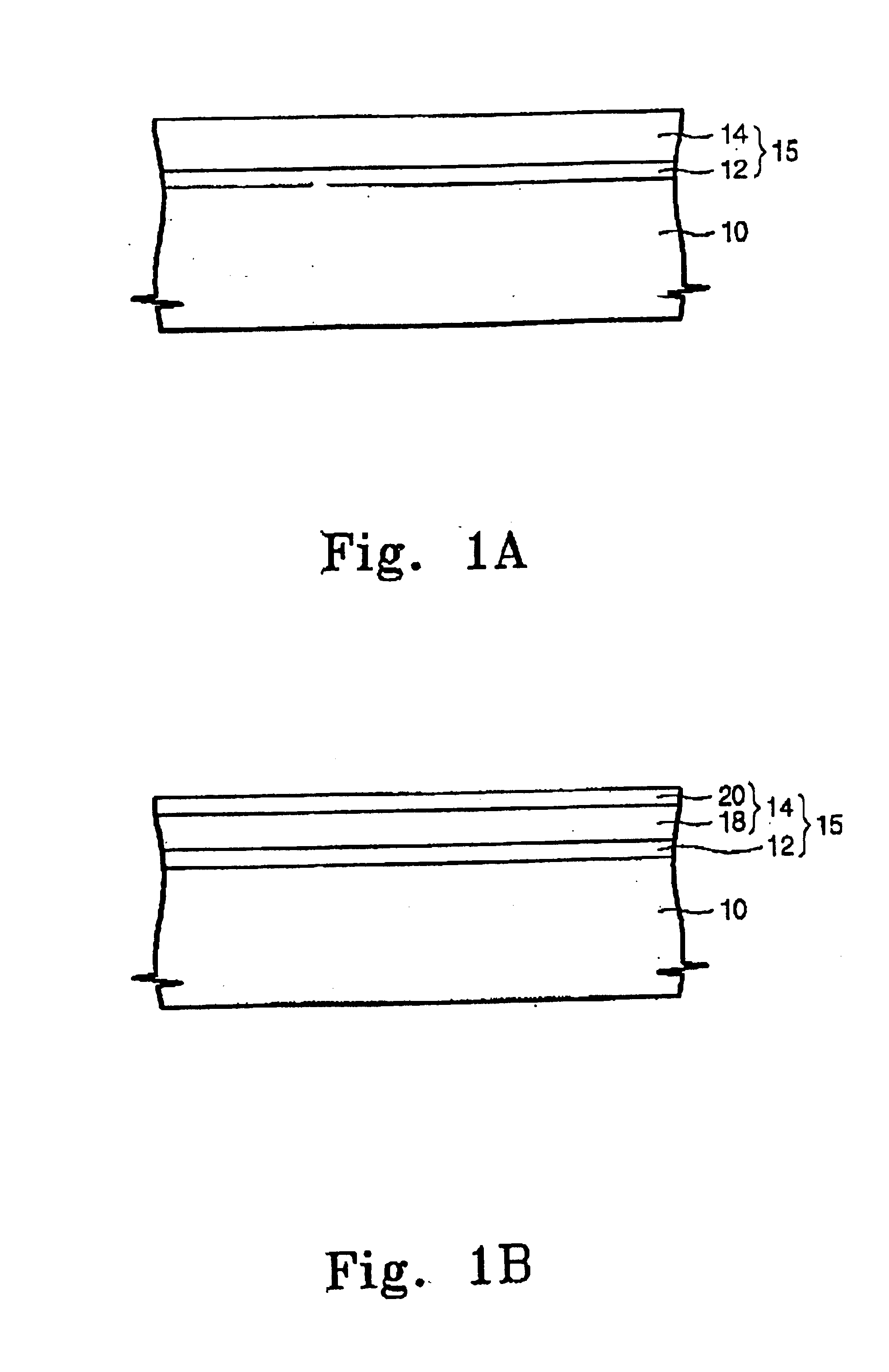

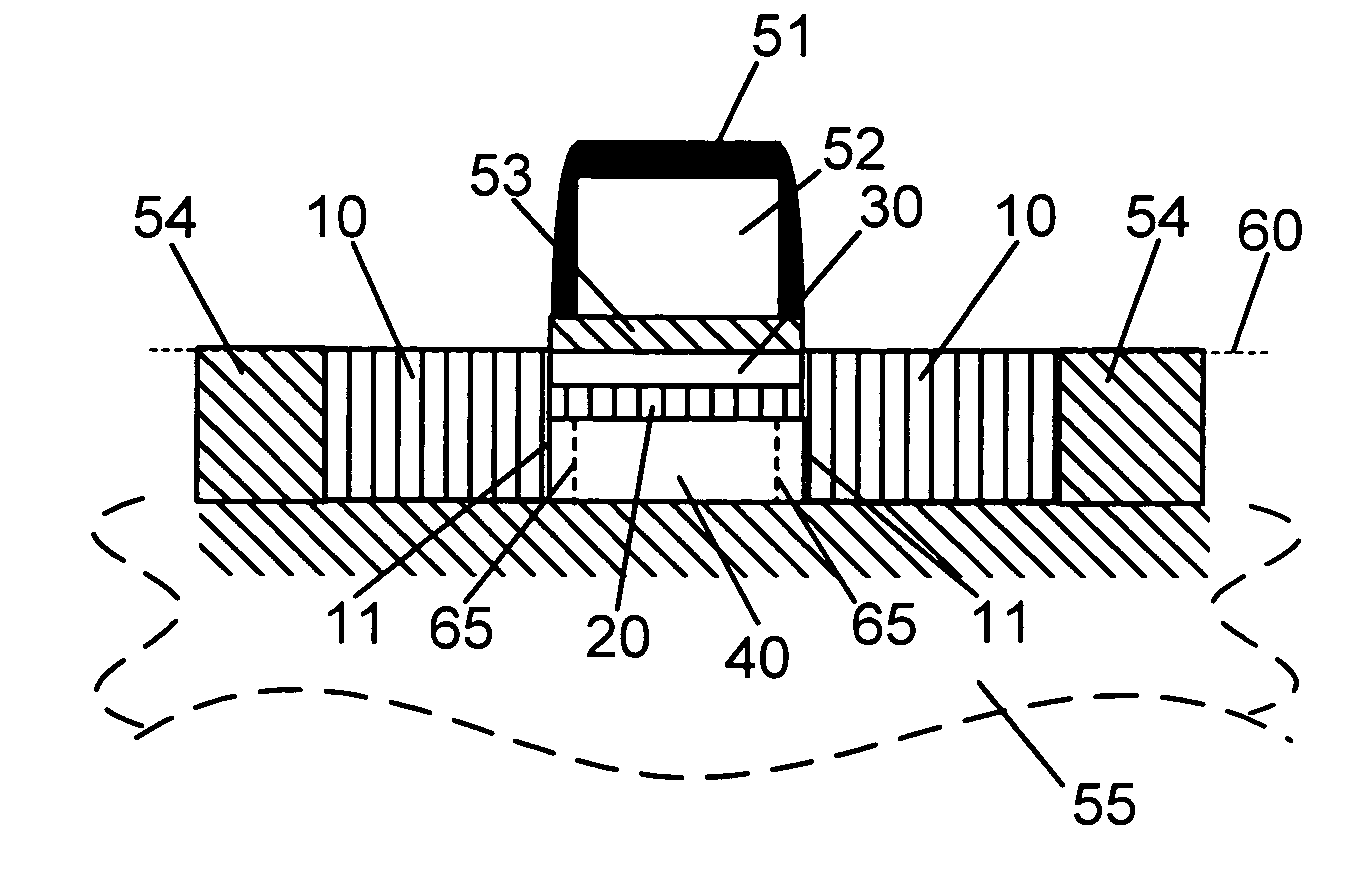

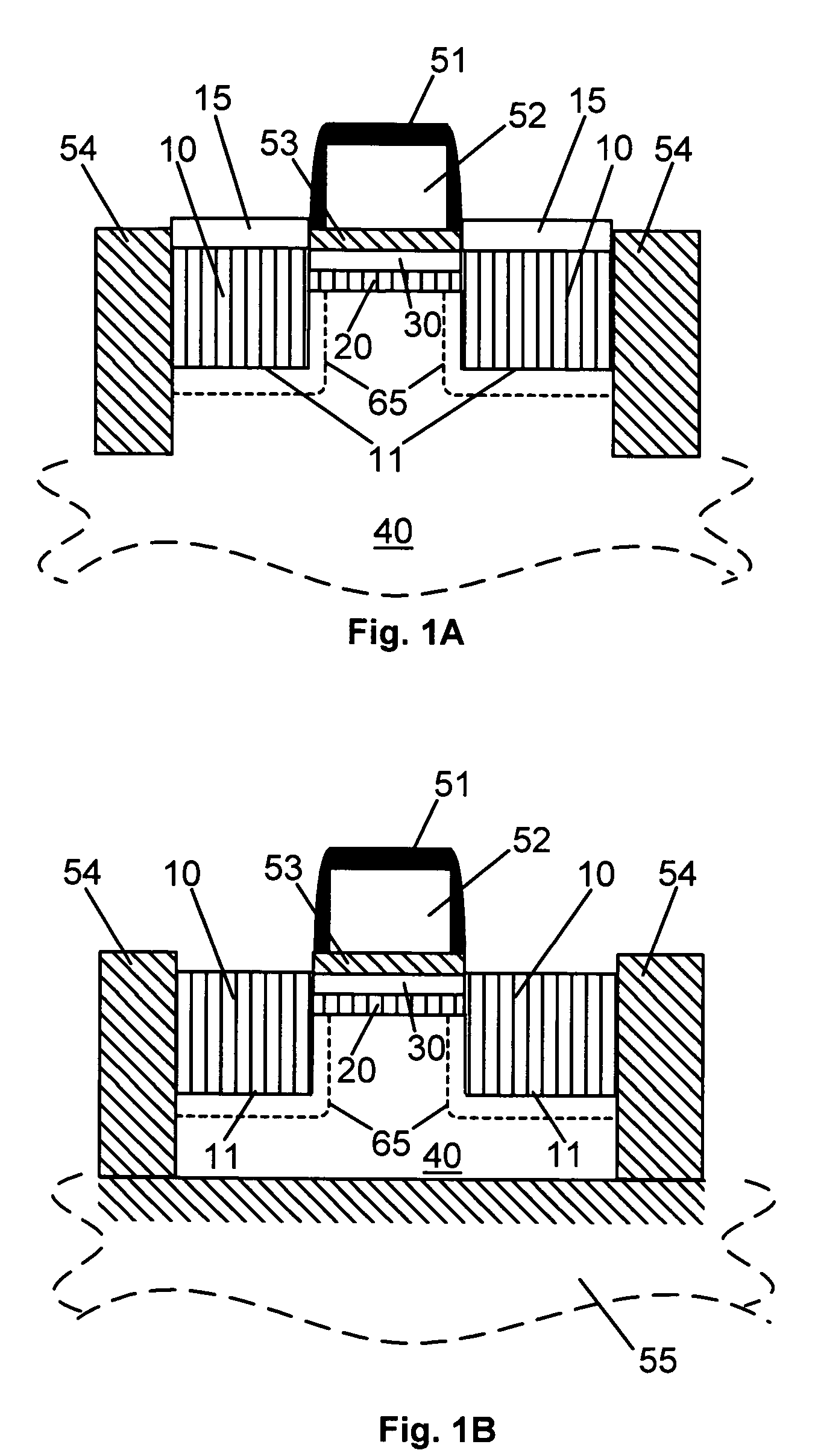

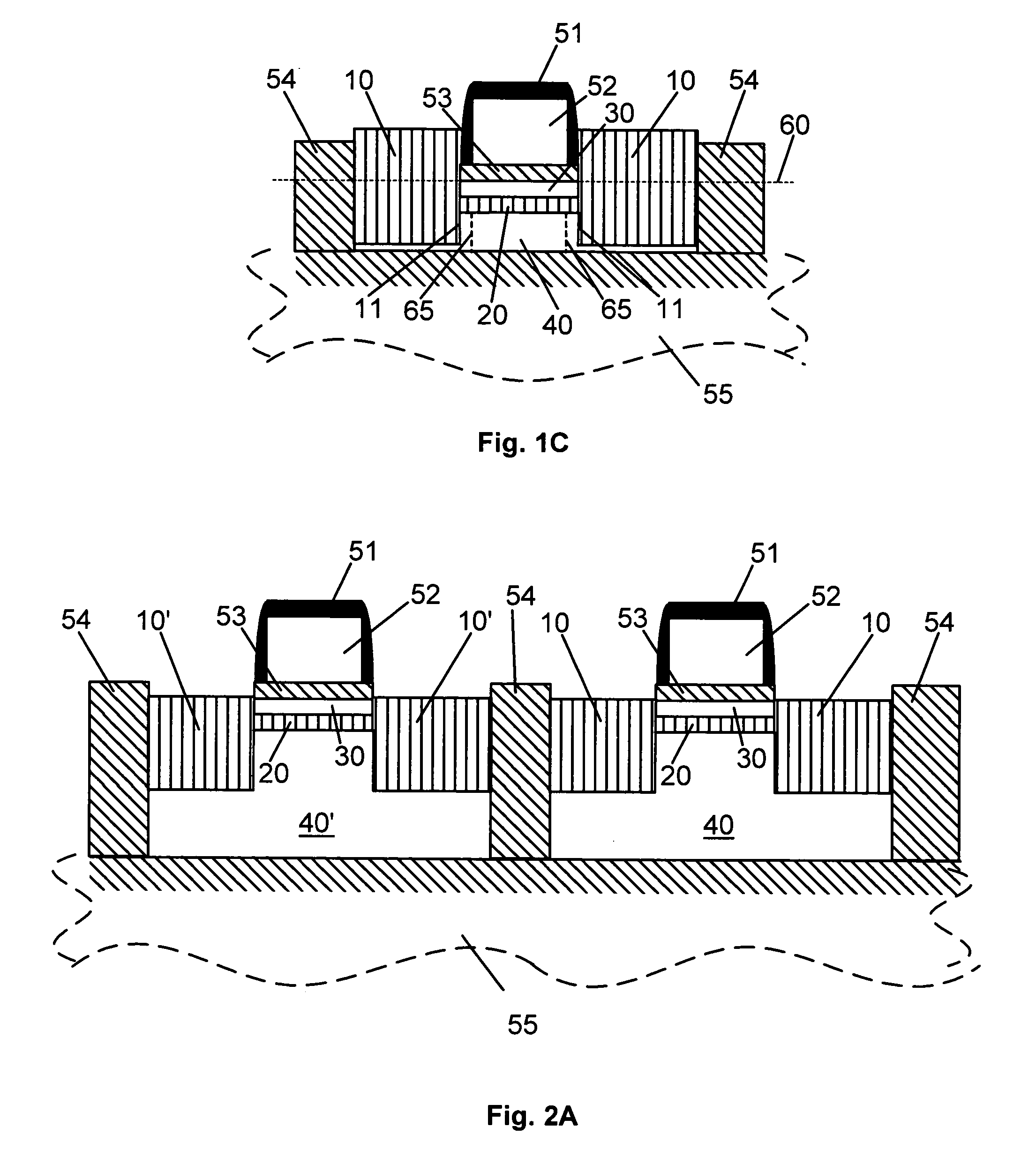

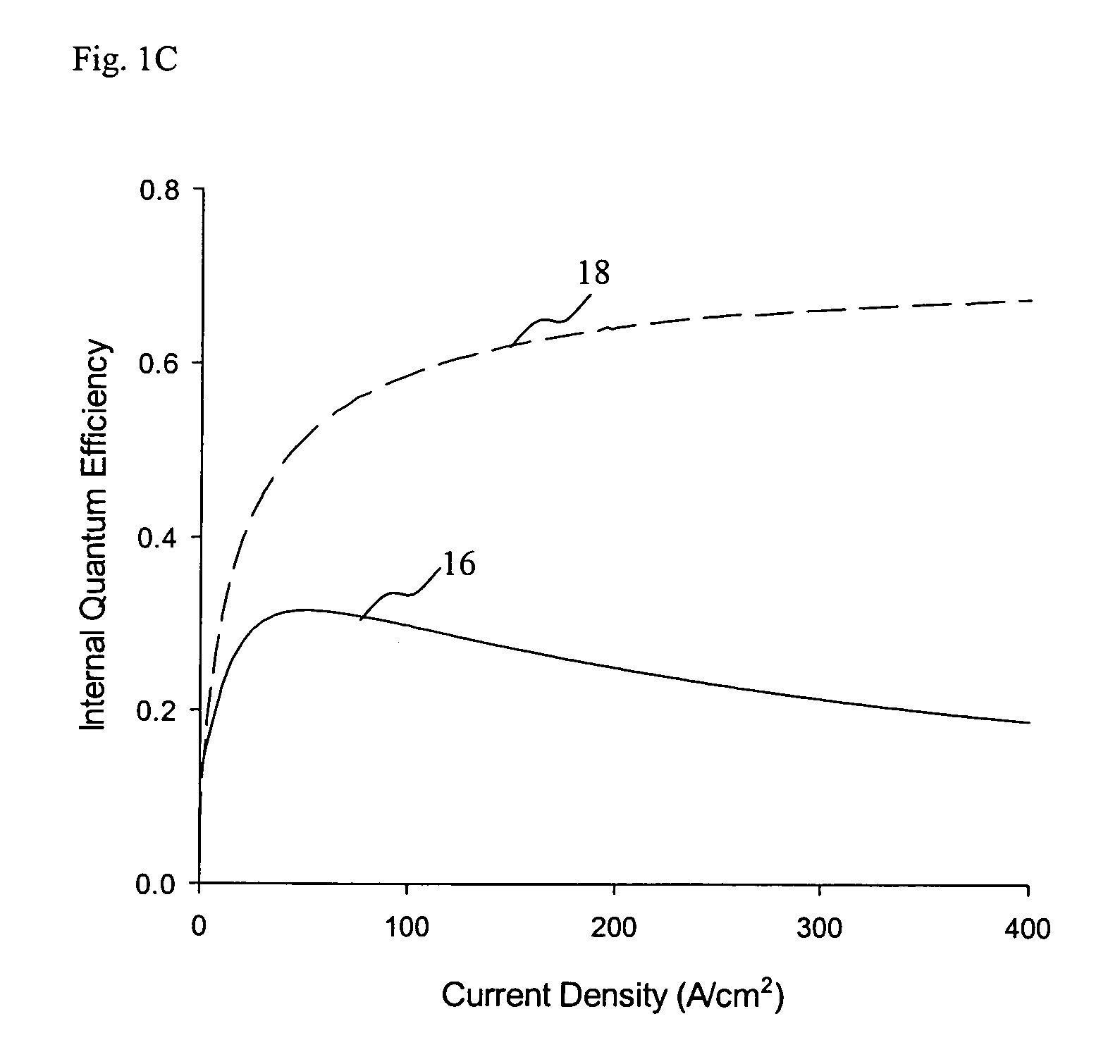

In all representative embodiments presented, the Ge concentration in the source and drain 10 and the SiGe epitaxial channel layer 20 is in the 15% to 50% range, preferably between about 20% to 40%. The SiGe thicknesses in the source / drain 10 are staying below the critical thickness for the given Ge concentration. The critical thickness is defined such that above it the SiGe will relax and defects and dislocations will form. The thickness of the SiGe epitaxial layer 20 typically is between about 5nm and 15nm. The thickness of the epitaxial Si layer 30 is typically between about 5nm and 15nm. FIG. 1A shows an embodiment where the body is bulk Si. These type of devices are the most common devices in present day microelectronics. FIGS. 1B and 1C show representative embodiment of the heterojunction source / drain FET device when the Si body 40 is disposed on top of an insulating material 55. This type of technology is commonly referred to as silicon on insulator (SOI) technology. The insulator material 55 usually, and preferably, is SiO2. FIG. 1B shows an SOI embodiment where the body 40 has enough volume to contain mobile charges. Such SOI devices are called partially depleted devices. FIG. 1C shows an SOI embodiment where the volume of the body 40 is insufficient to contain mobile charges. Such SOI devices are called fully depleted devices. For devices shown in FIG. 1B and 1C there is, at least a thin, layer of body underneath the source and drain 10. This body material serves as the seed material onto which the epitaxial SiGe source and drain 10 are grown. In an alternate embodiment, shown in FIG. 1D. for extremely thin fully depleted SOI devices, one could grow the source and drain 10 laterally, from a lateral seeding, in which case the source and drain 10 would penetrate all the way down to the insulating layer 55.

Owner:GLOBALFOUNDRIES US INC

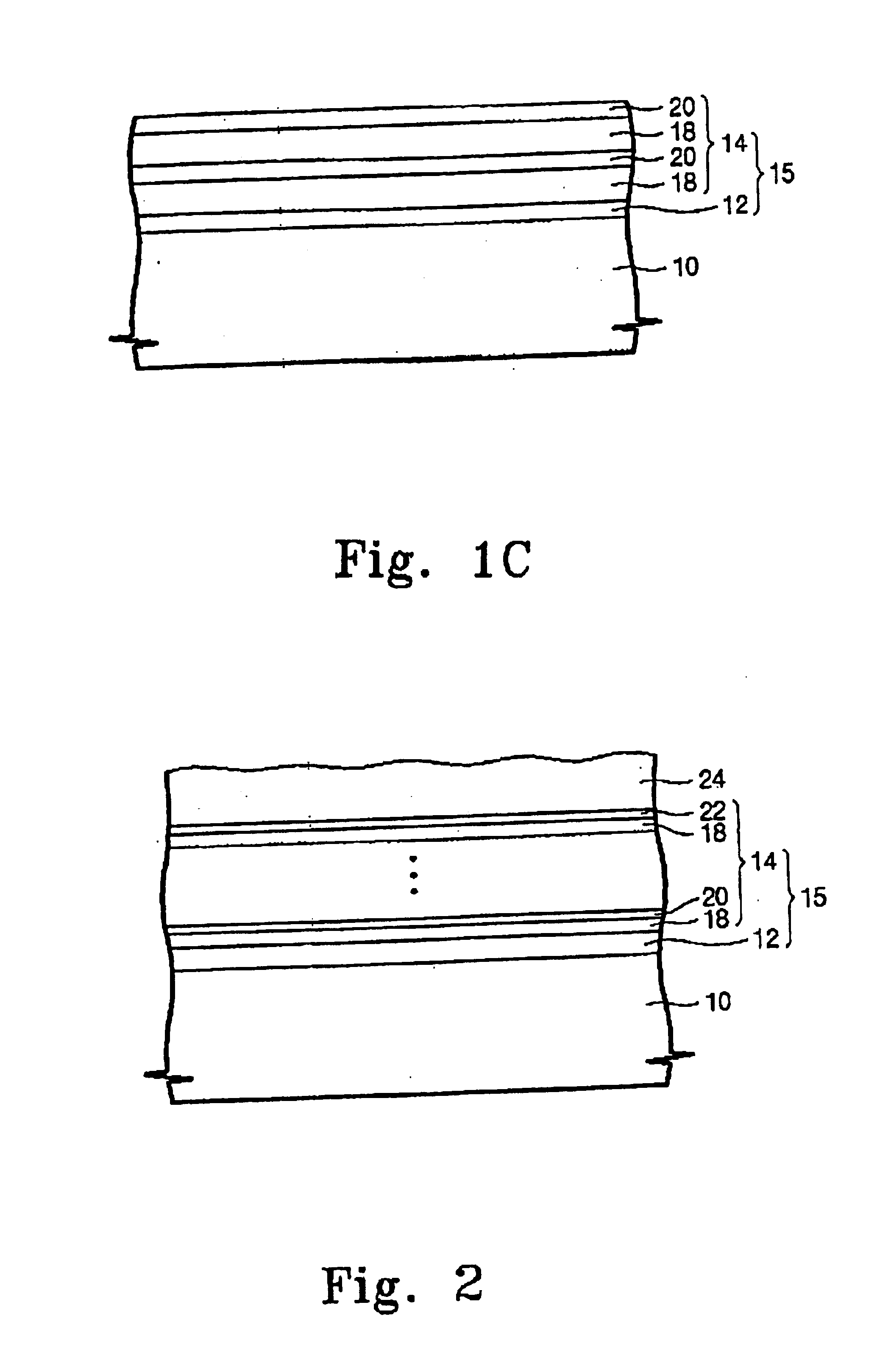

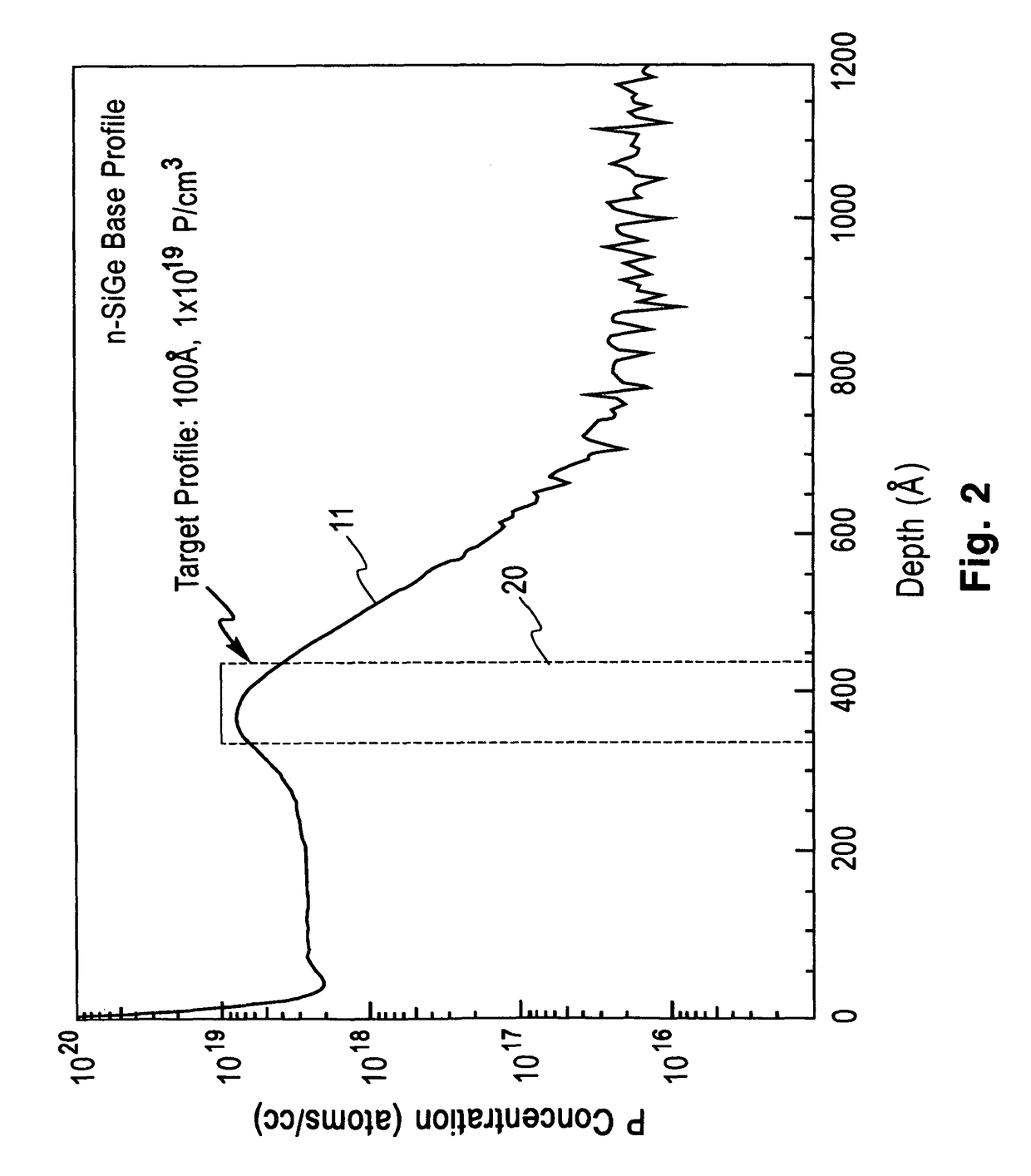

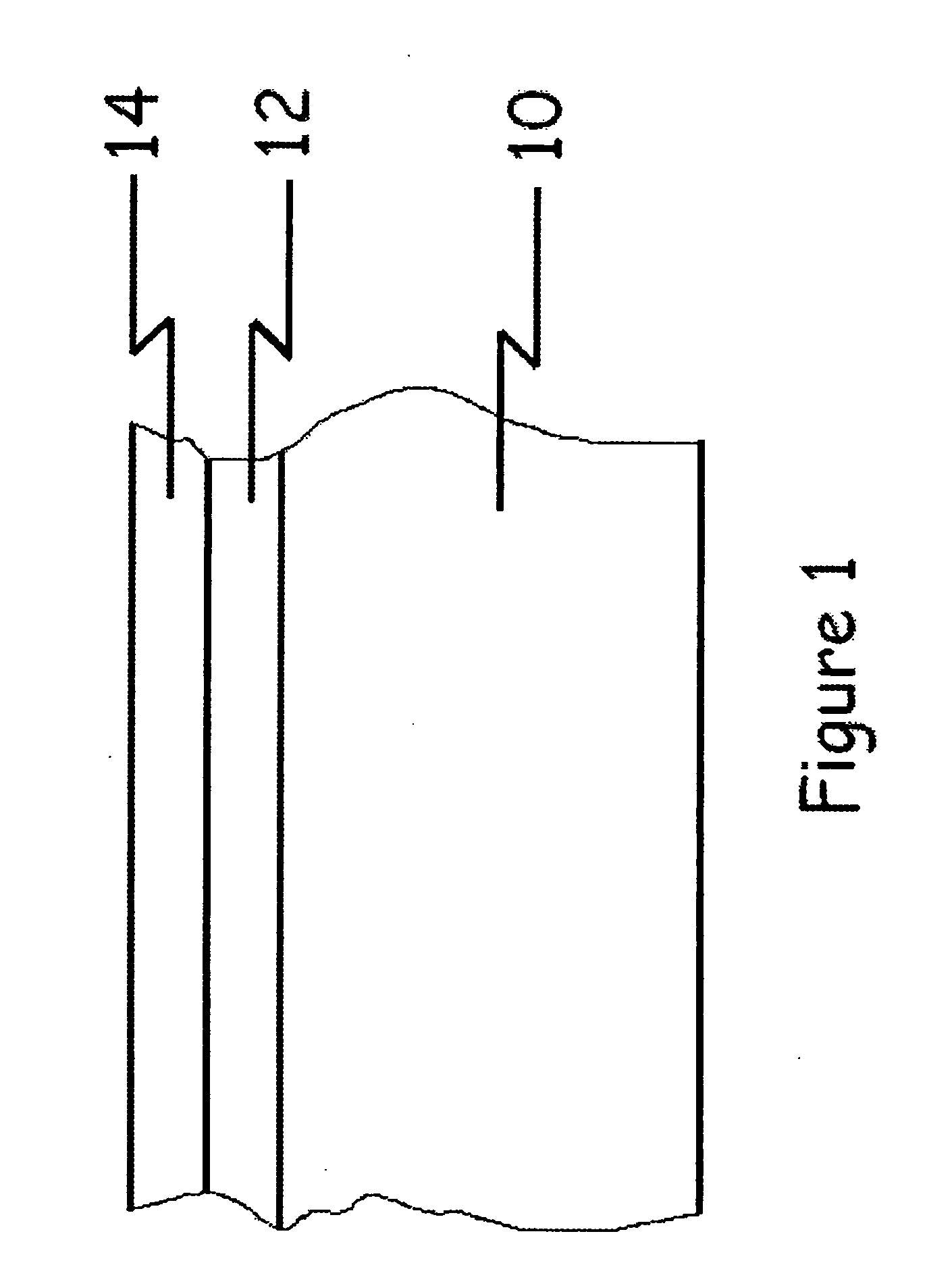

Abrupt “delta-like” doping in Si and SiGe films by UHV-CVD

InactiveUS7906413B2Eliminating the slow transient behaviorEliminate the effects ofTransistorPolycrystalline material growthCMOSSemiconductor structure

A structure and method of forming an abrupt doping profile is described incorporating a substrate, a first epitaxial layer of Ge less than the critical thickness having a P or As concentration greater than 5×1019 atoms / cc, and a second epitaxial layer having a change in concentration in its first 40 from the first layer of greater than 1×1019 P atoms / cc. Alternatively, a layer of SiGe having a Ge content greater than 0.5 may be selectively amorphized and recrystalized with respect to other layers in a layered structure. The invention overcomes the problem of forming abrupt phosphorus profiles in Si and SiGe layers or films in semiconductor structures such as CMOS, MODFET's, and HBT's.

Owner:GLOBALFOUNDRIES INC

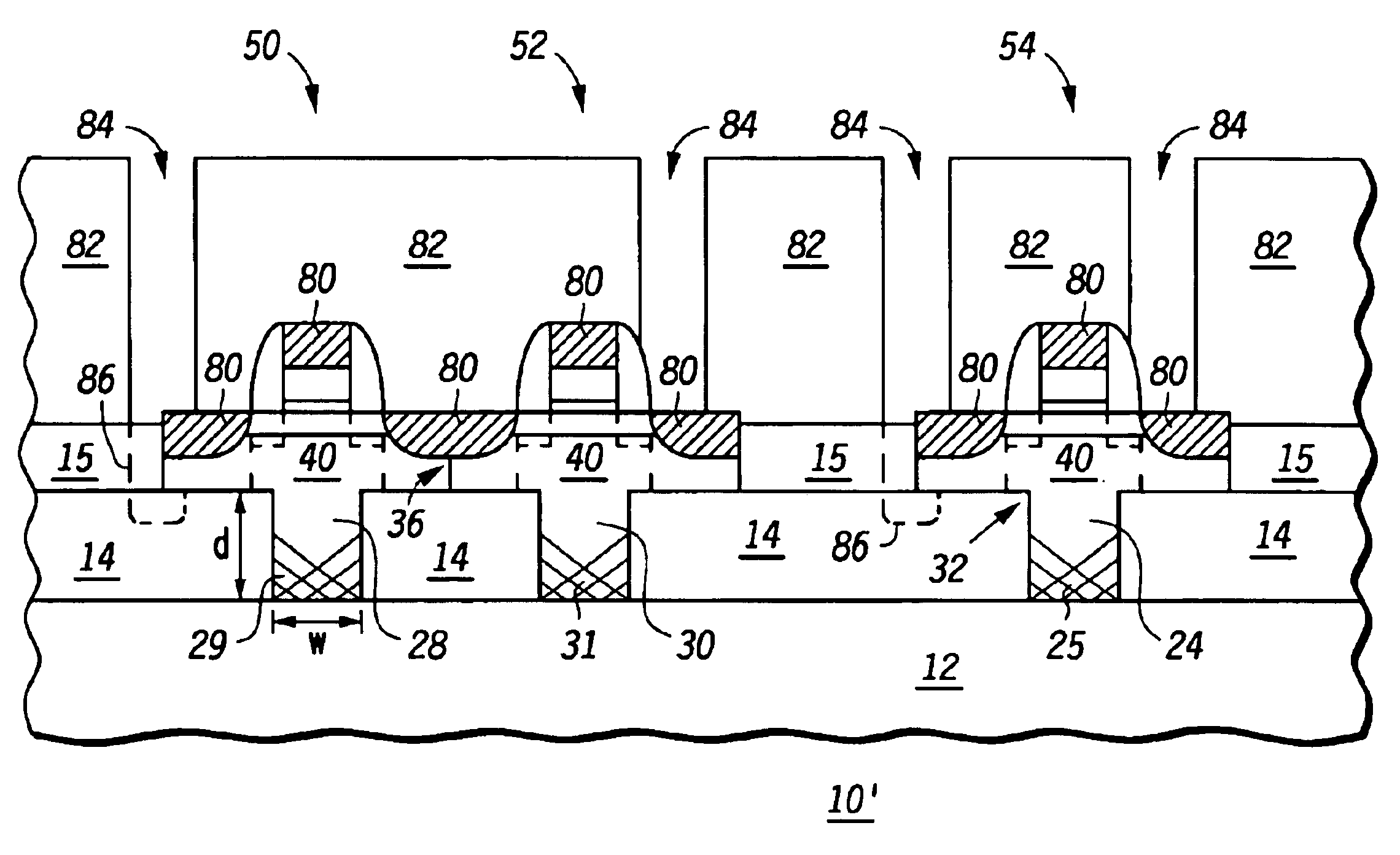

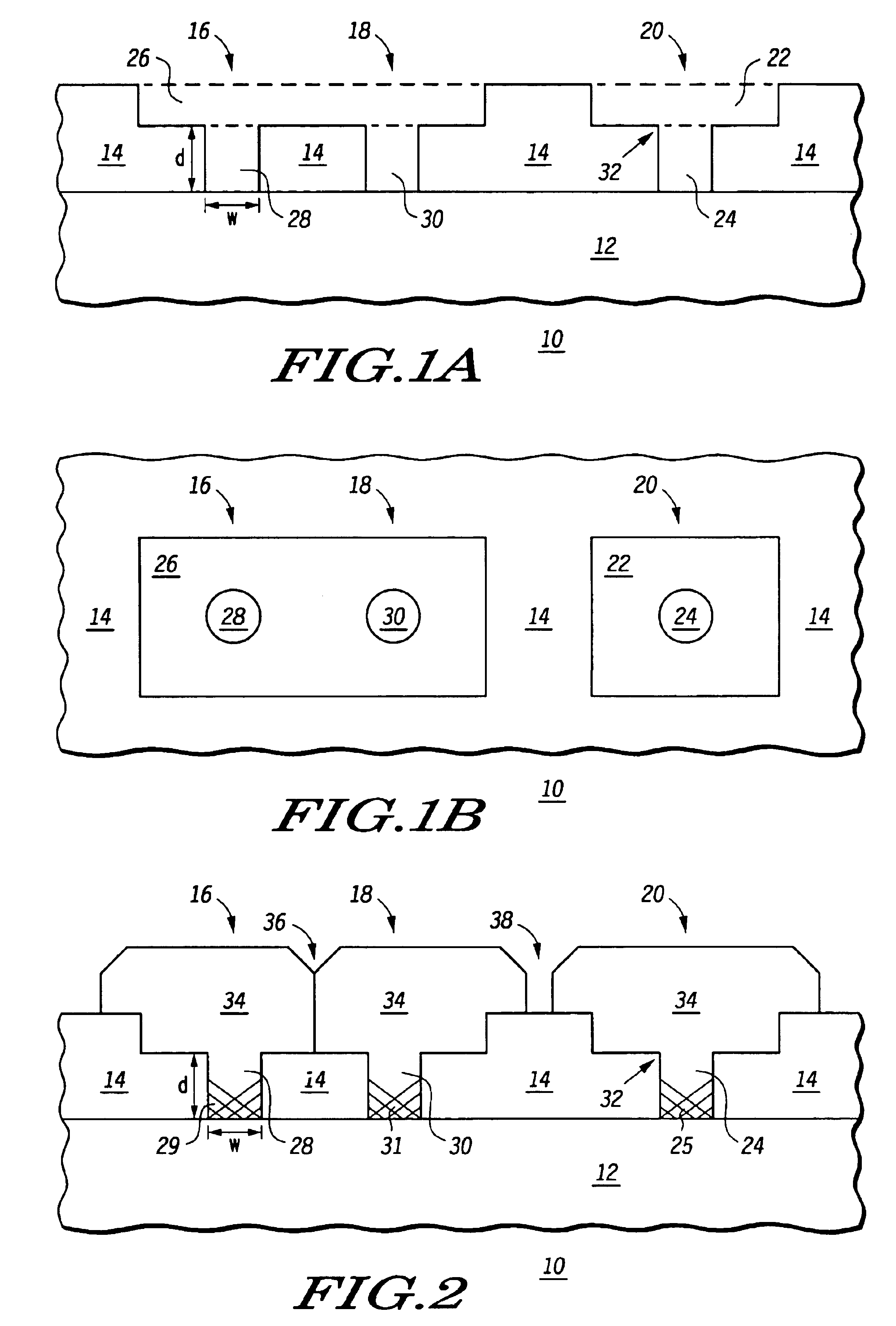

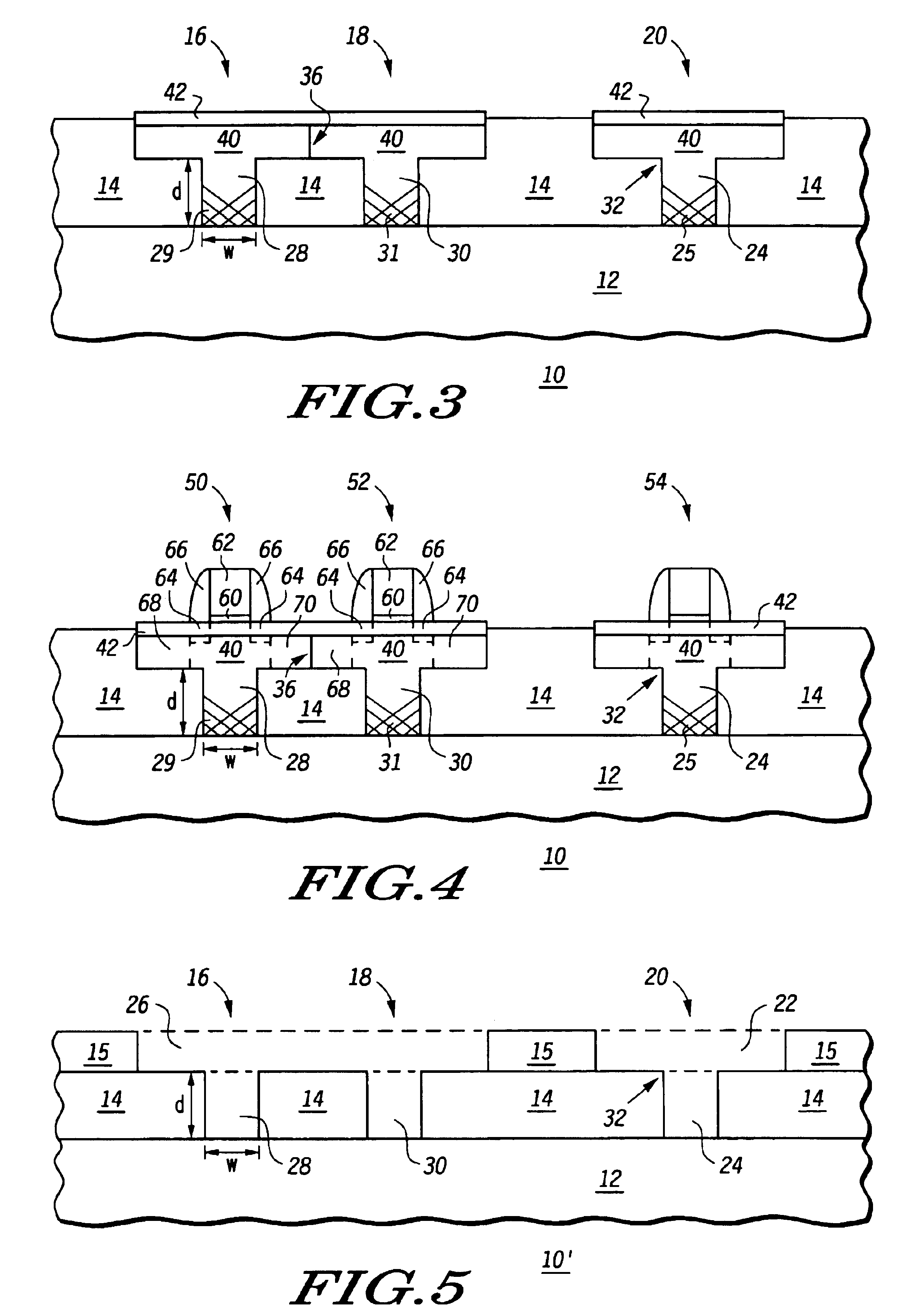

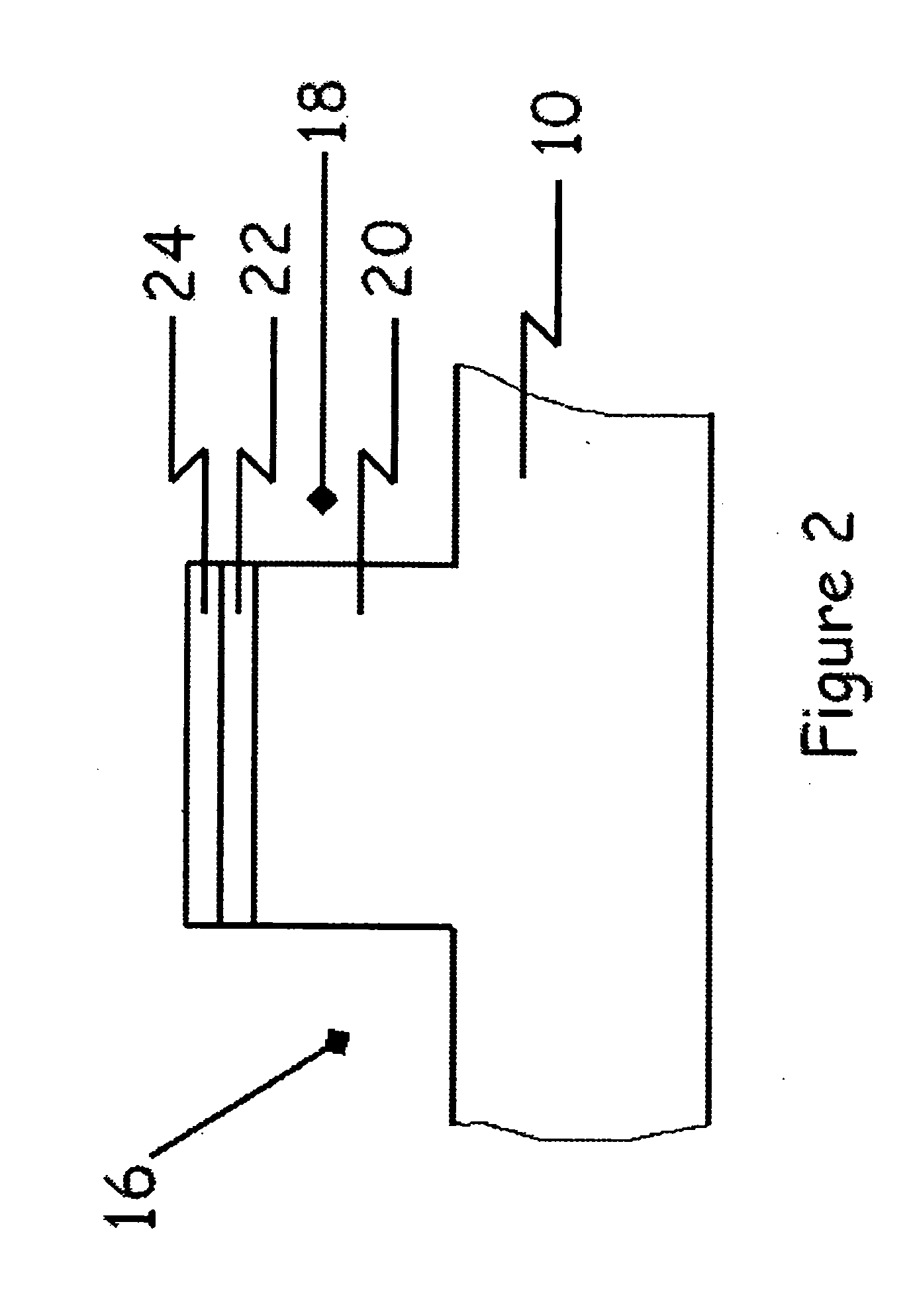

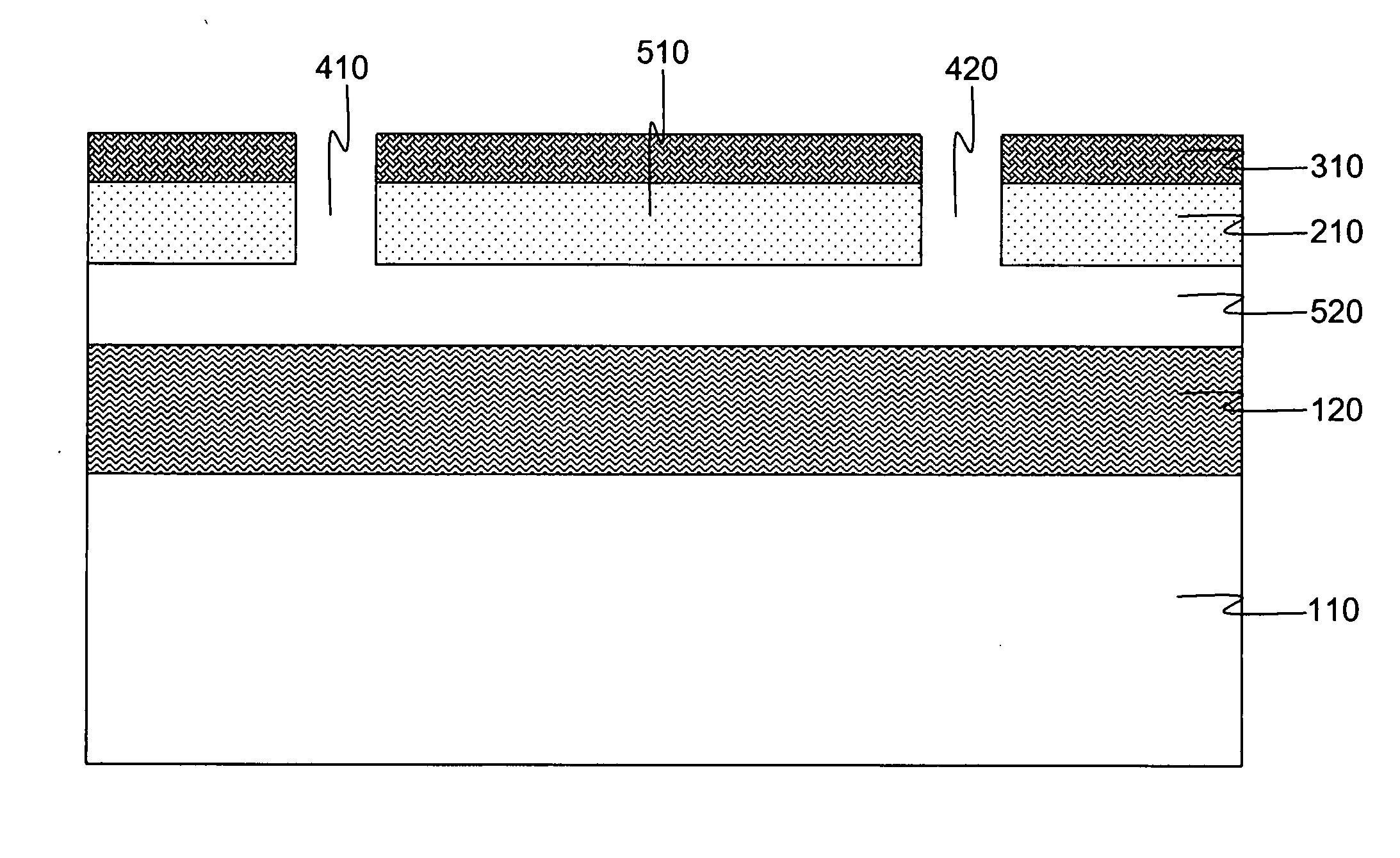

Semiconductor device incorporating a defect controlled strained channel structure and method of making the same

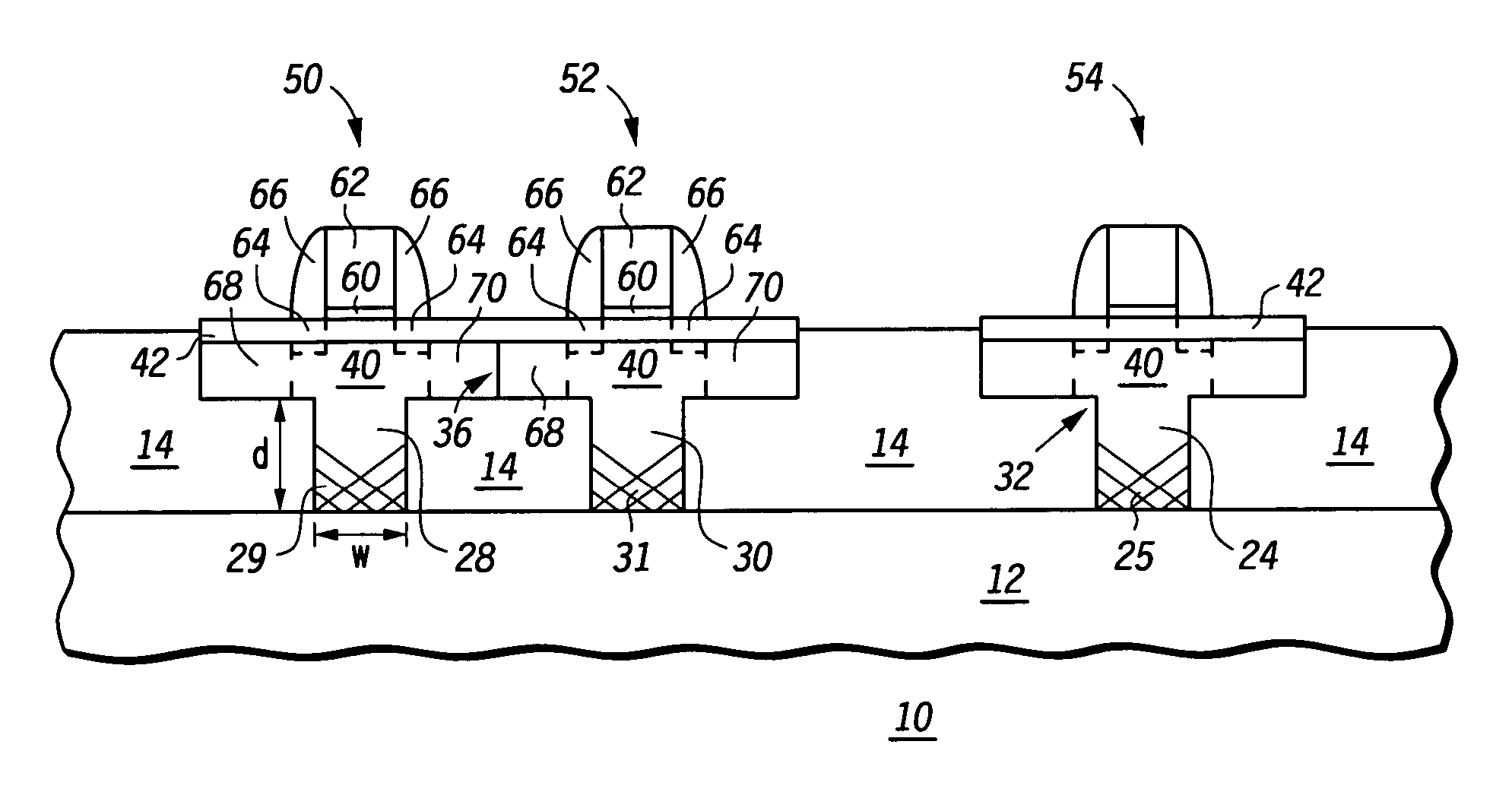

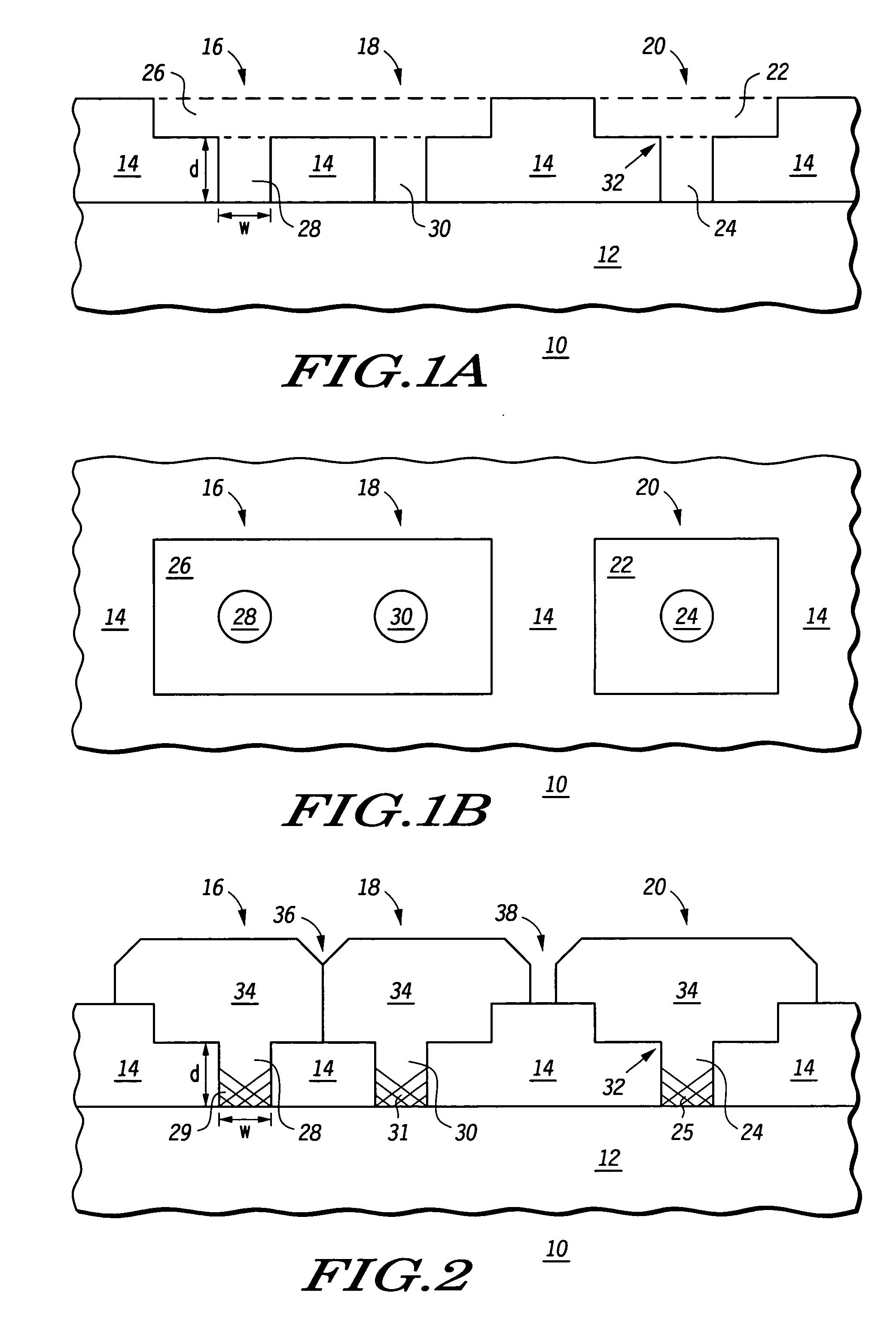

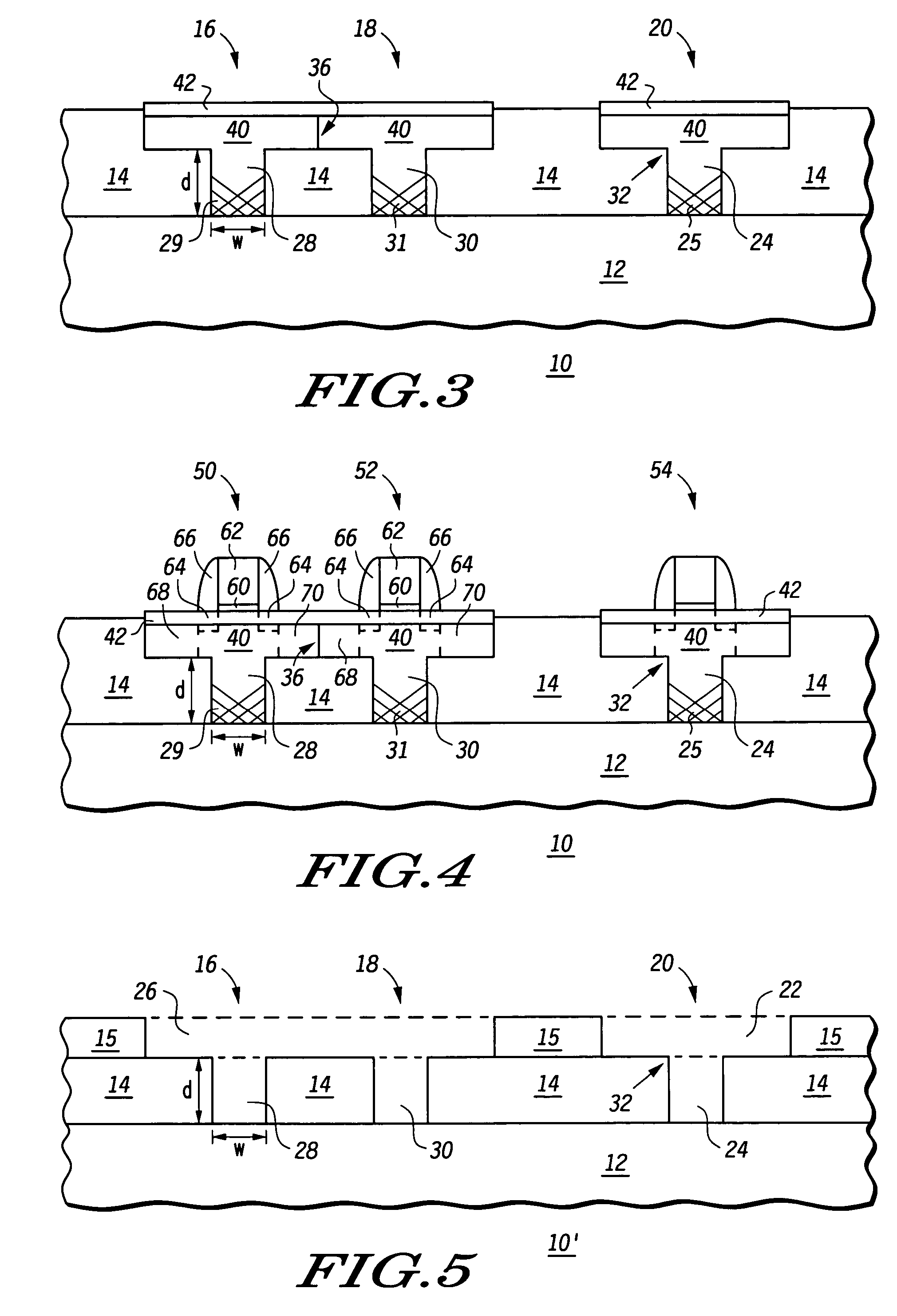

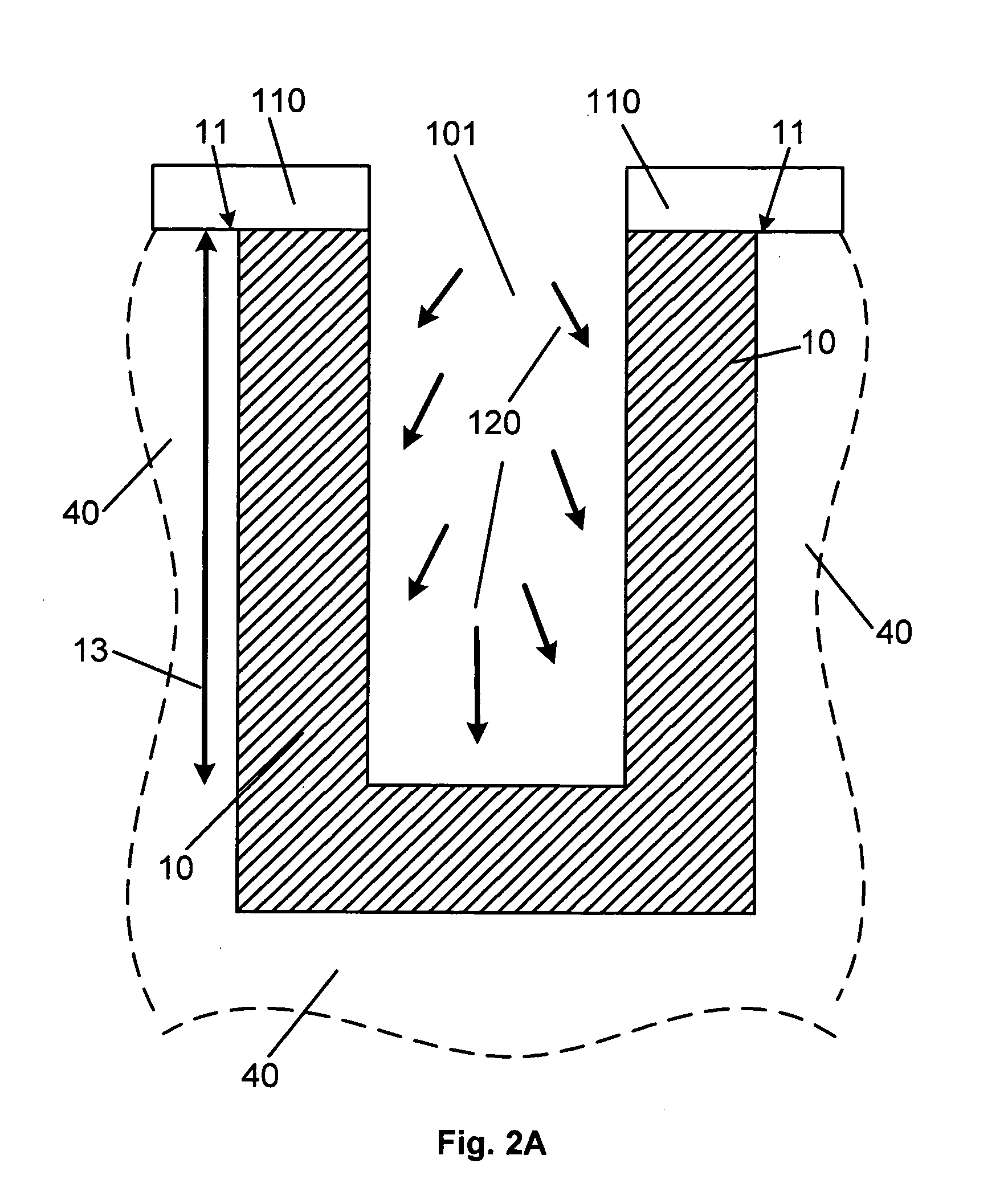

InactiveUS6919258B2Semiconductor/solid-state device manufacturingSemiconductor devicesCharge carrierSingle crystal substrate

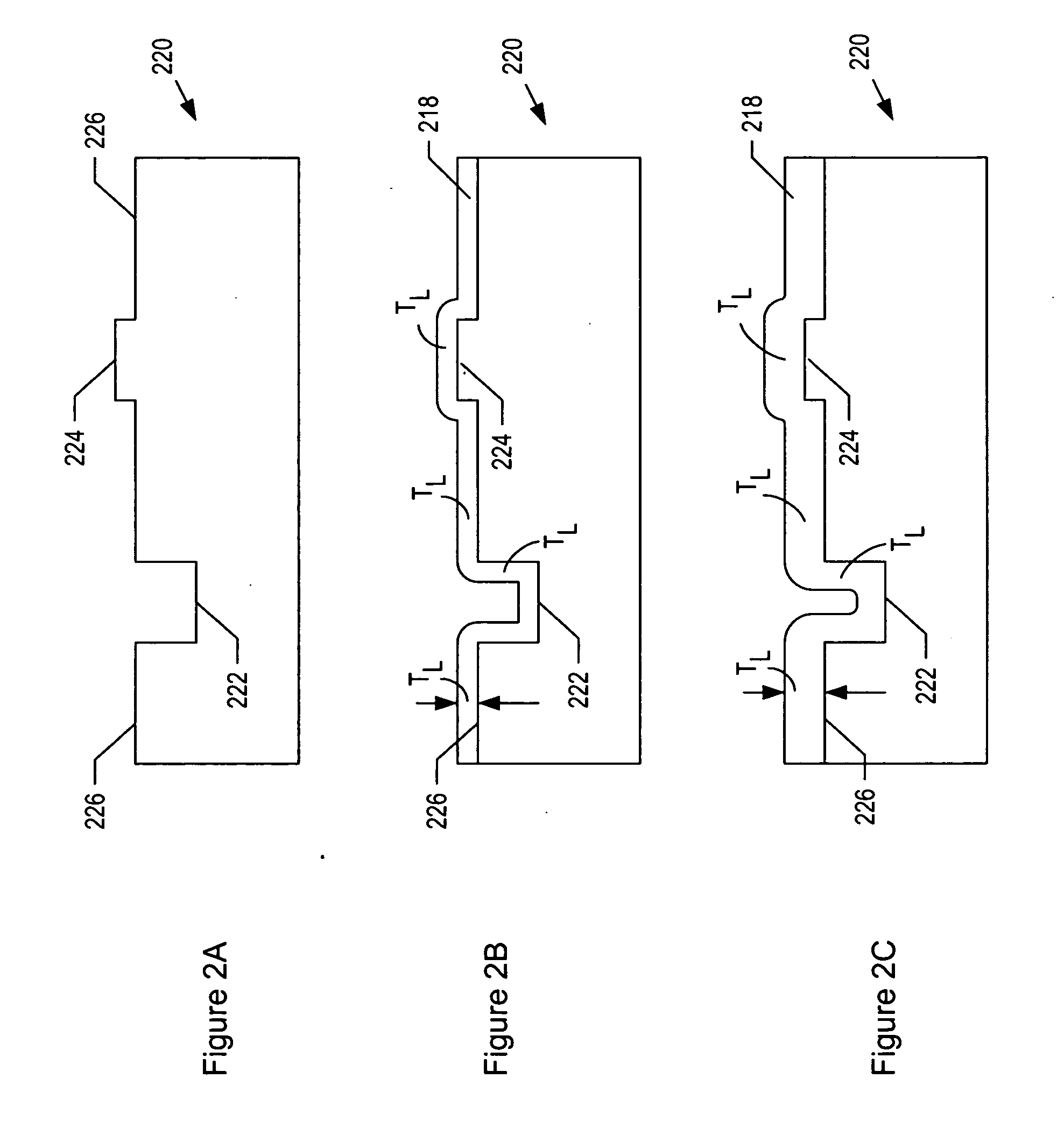

A semiconductor device includes a single crystal substrate and a dielectric layer overlying the substrate. The dielectric layer includes at least one opening having a first portion and an overlying second portion. The first portion has a depth and width, such that an aspect ratio of the depth to width is greater than one. The semiconductor device further includes a first material having a first portion and a second portion, the first portion of the first material filling the first portion of the at least one opening. Defects for relaxing strain at an interface between the first material and the substrate material exist only within the first portion of the first material due to the aspect ratio being greater than one. The second portion of the first material is substantially defect free. Furthermore, the second portion of the first material and an overlying second material different than the first material fill the overlying second portion of the at least one opening. The second material has a thickness which is less than a critical thickness to maintain the second material in a strained state. The strained second material functions as a channel for charge carriers.

Owner:MOTOROLA INC +1

Semiconductor device incorporating a defect controlled strained channel structure and method of making the same

ActiveUS20050073028A1Free from defectSemiconductor/solid-state device manufacturingSemiconductor devicesCharge carrierDevice material

A semiconductor device includes a single crystal substrate and a dielectric layer overlying the substrate. The dielectric layer includes at least one opening having a first portion and an overlying second portion. The first portion has a depth and width, such that an aspect ratio of the depth to width is greater than one. The semiconductor device further includes a first material having a first portion and a second portion, the first portion of the first material filling the first portion of the at least one opening. Defects for relaxing strain at an interface between the first material and the substrate material exist only within the first portion of the first material due to the aspect ratio being greater than one. The second portion of the first material is substantially defect free. Furthermore, the second portion of the first material and an overlying second material different than the first material fill the overlying second portion of the at least one opening. The second material has a thickness which is less than a critical thickness to maintain the second material in a strained state. The strained second material functions as a channel for charge carriers.

Owner:MOTOROLA INC +1

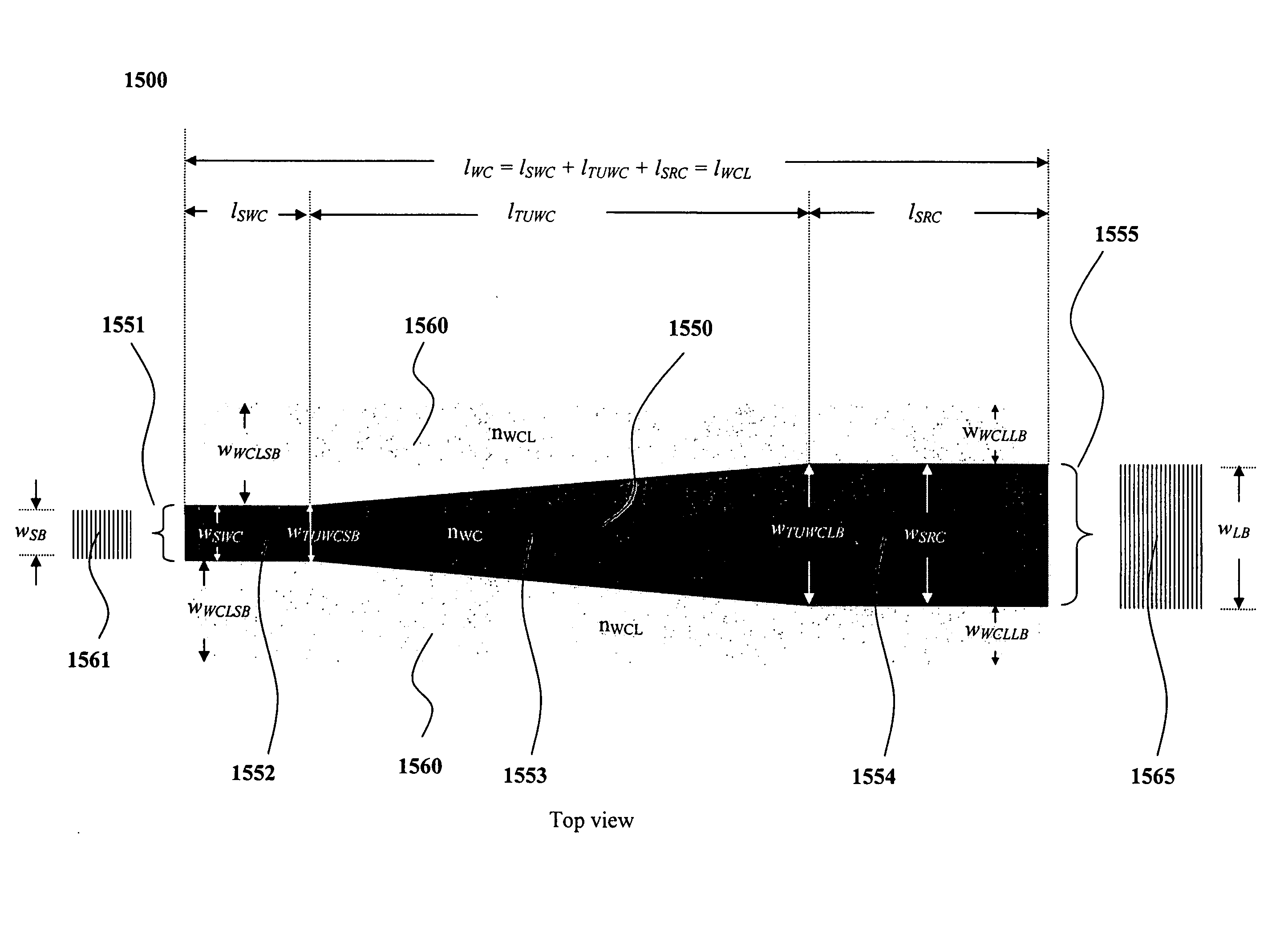

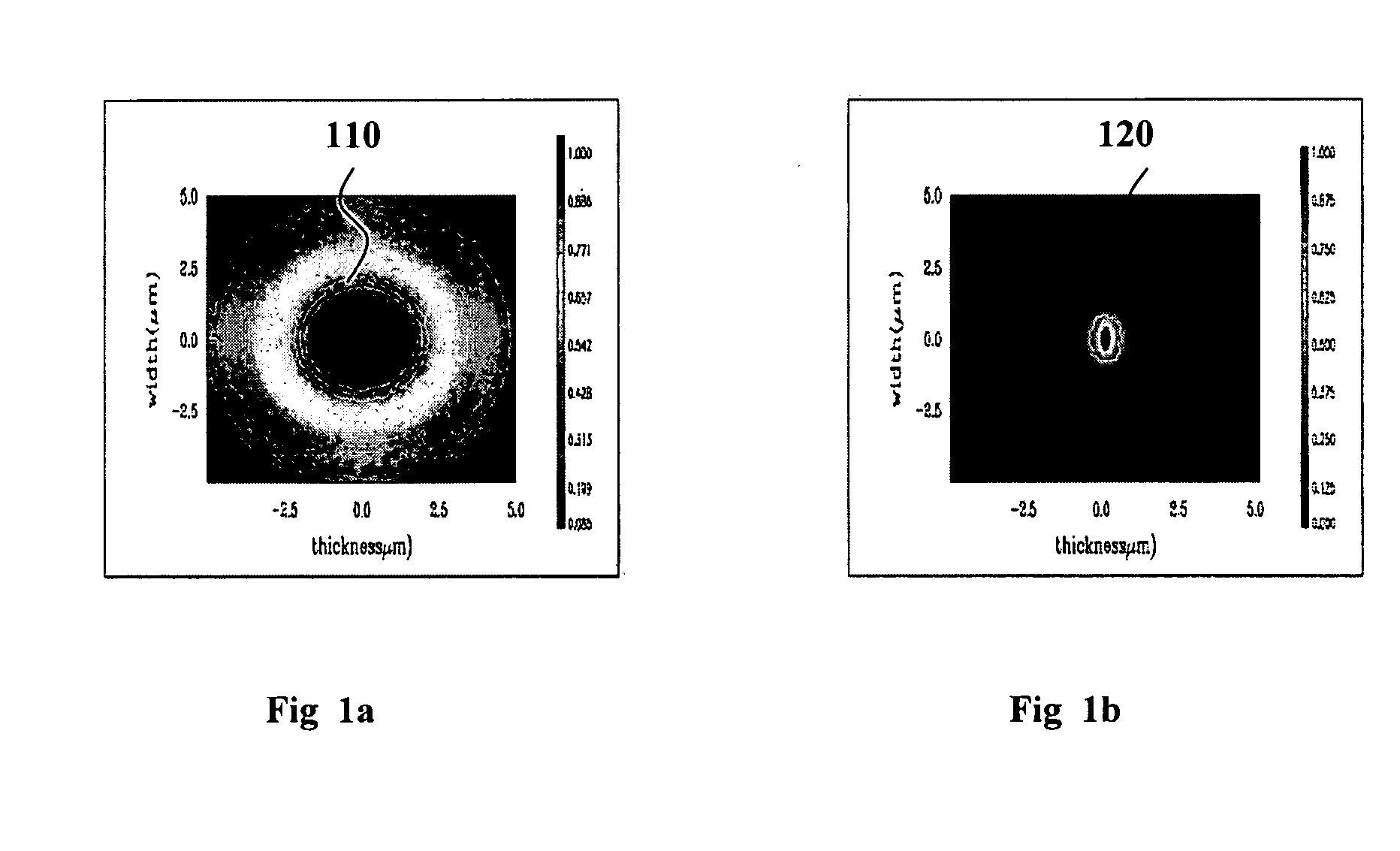

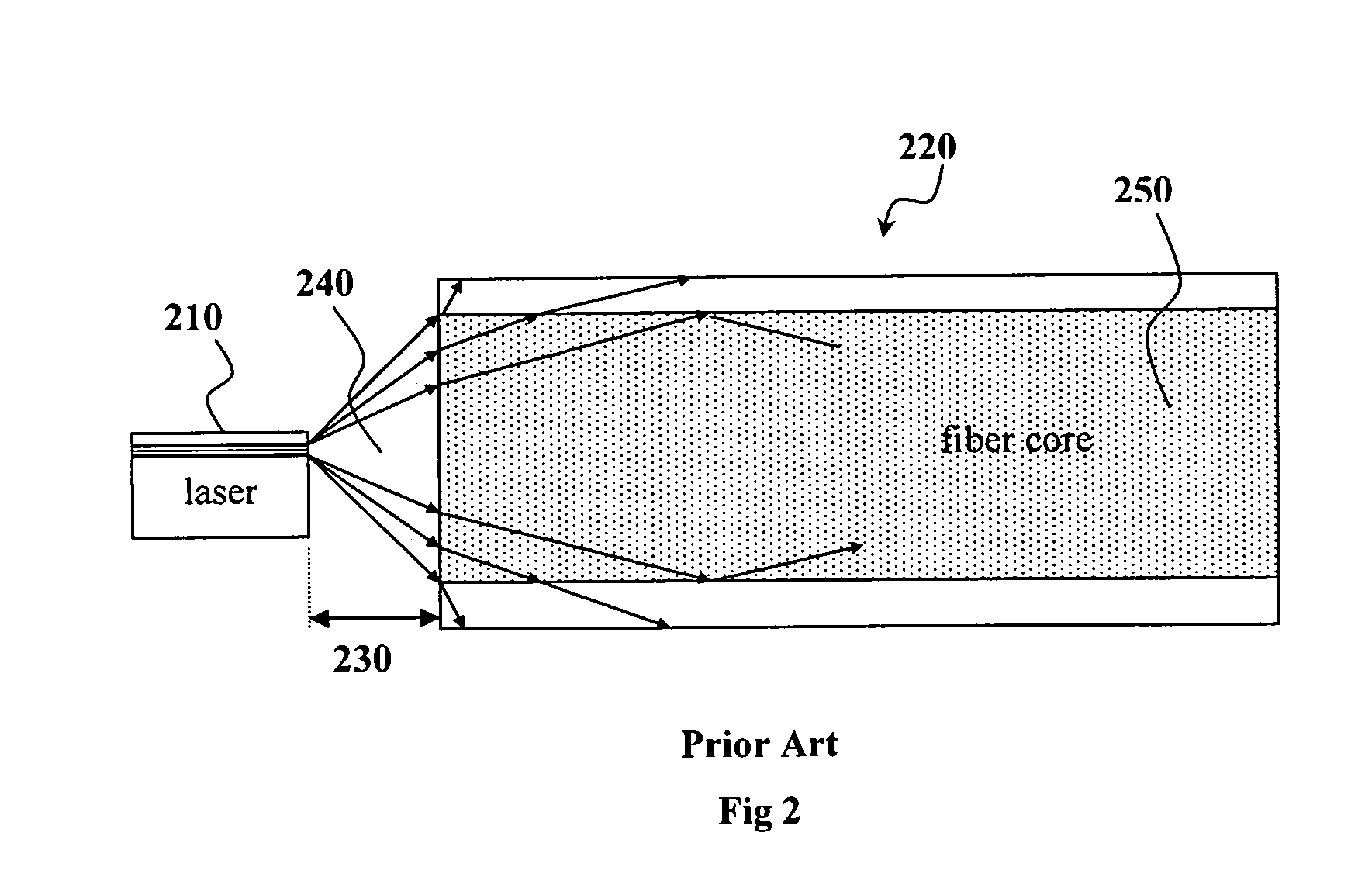

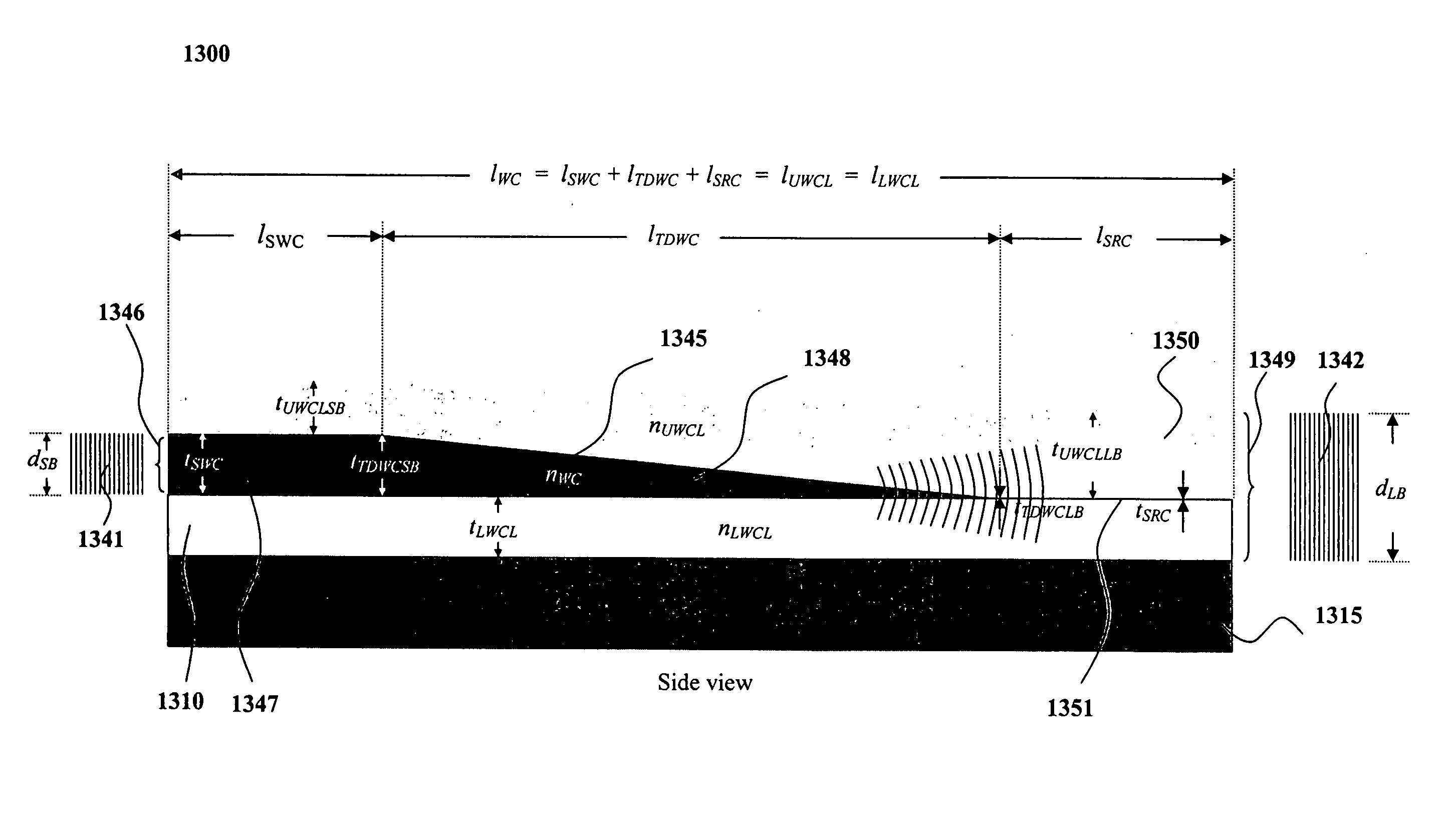

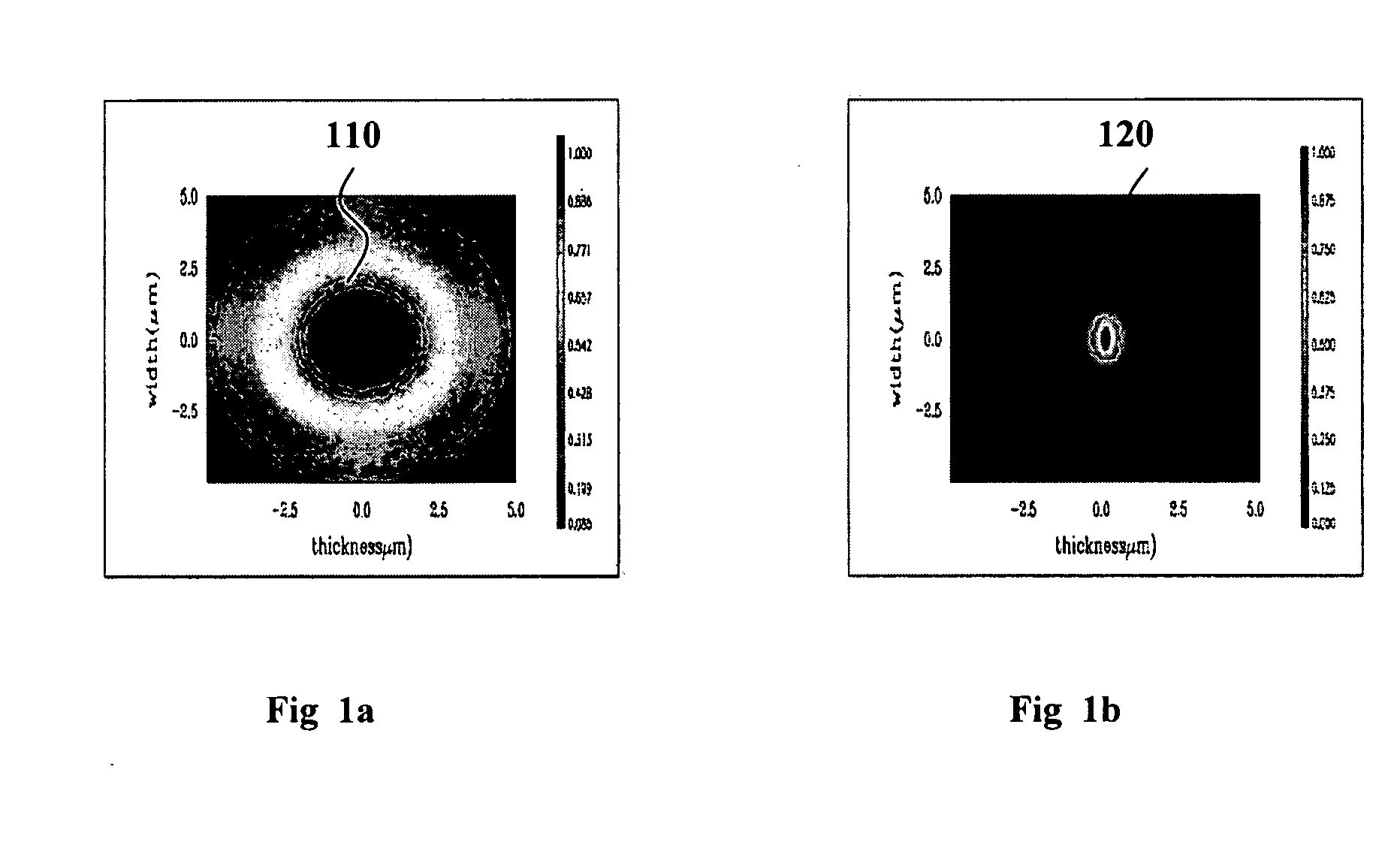

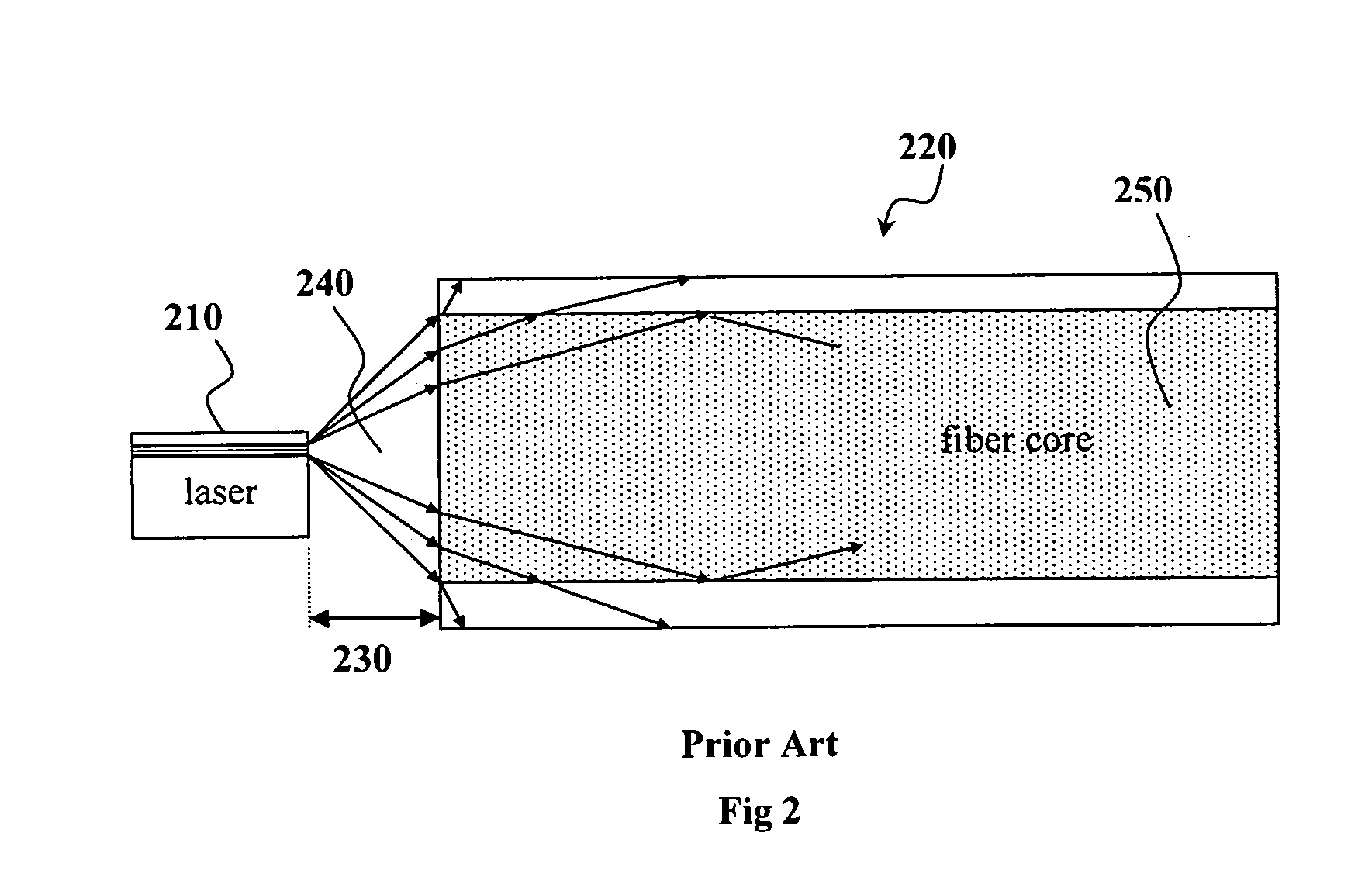

Integrated planar composite coupling structures for bi-directional light beam transformation between a small mode size waveguide and a large mode size waveguide

InactiveUS7218809B2Reduce manufacturing costReduce sensitivityCoupling light guidesOptical waveguide light guideFiberRefractive index contrast

Composite optical waveguide structures or mode transformers and their methods of fabrication and integration are disclosed, wherein the structures or mode transformers are capable of bi-directional light beam transformation between a small mode size waveguide and a large mode size waveguide. One aspect of the present invention is directed to an optical mode transformer comprising a waveguide core having a high refractive index contrast between the waveguide core and the cladding, the optical mode transformer being configured such that the waveguide core has a taper wherein a thickness of the waveguide core tapers down to a critical thickness value, the critical thickness value being defined as a thickness value below which a significant portion of the energy of a light beam penetrates into the cladding layers surrounding the taper structure thereby enlarging the small mode size. This primary tapered core structure may be present in either a vertical or horizontal direction and may be combined with further up taper or down taper structures in the directions transverse to the primary taper direction. Another aspect of the present invention is directed to a non-cylindrical graduated refractive index (GRID) lens structure. The non-cylindrical GRIN structure has a graded refractive index having a maximum value at its core and a minimum value at its outer edges. The grading of the refractive index is provided in a either the vertical or horizontal directions and may have either a fixed refractive index or a graded refractive index in the transverse directions. Yet another aspect of the present invention is directed to composite optical mode transformers that are combinations of the taper waveguide structures and the non-cylindrical graduated refractive index structures. Yet another aspect of the present invention is the further integration of the mode transformers with V-grooves for multiple input / output fibers and alignment platform for multiple input / output photonic chips or devices.

Owner:HO SENG TIONG

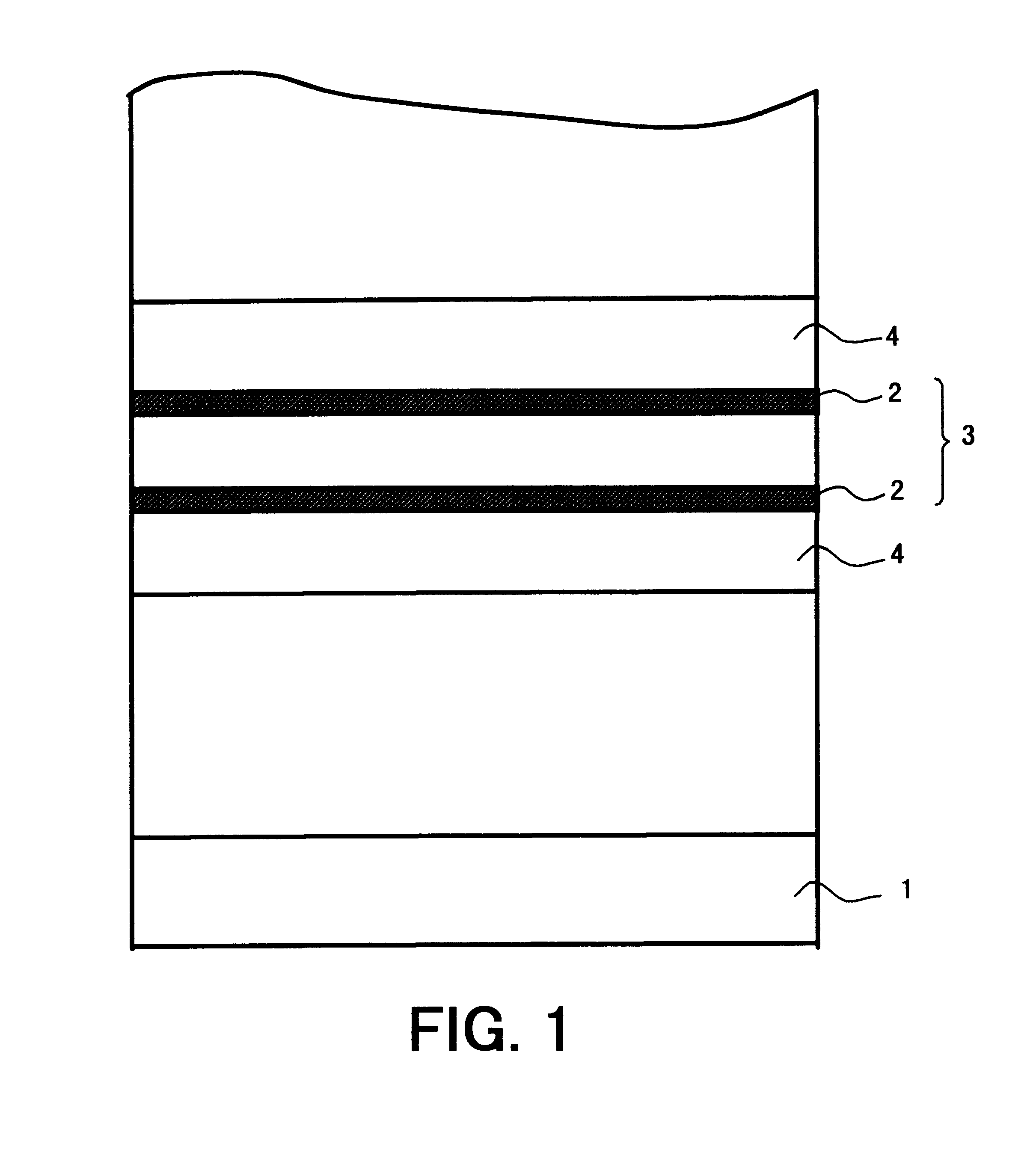

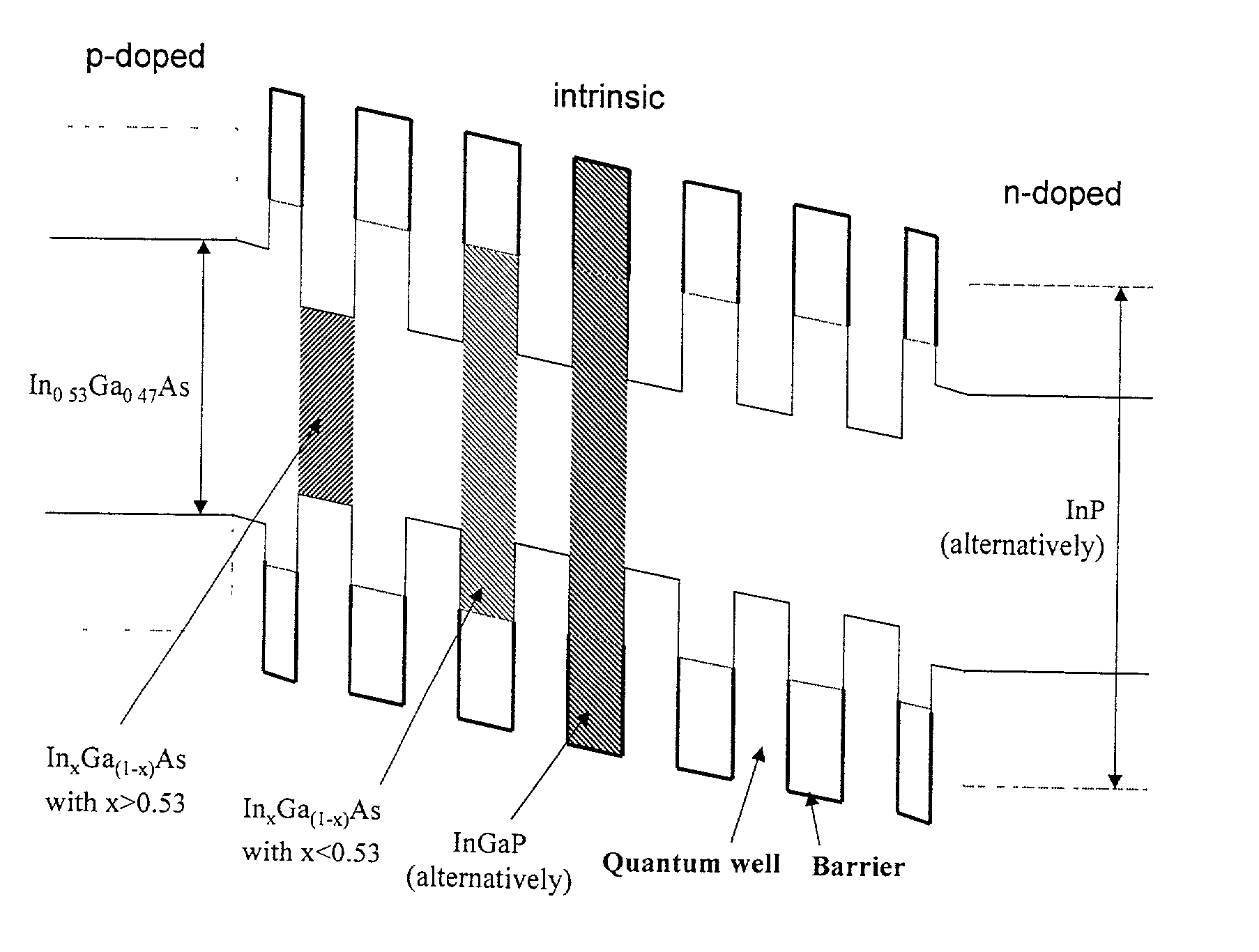

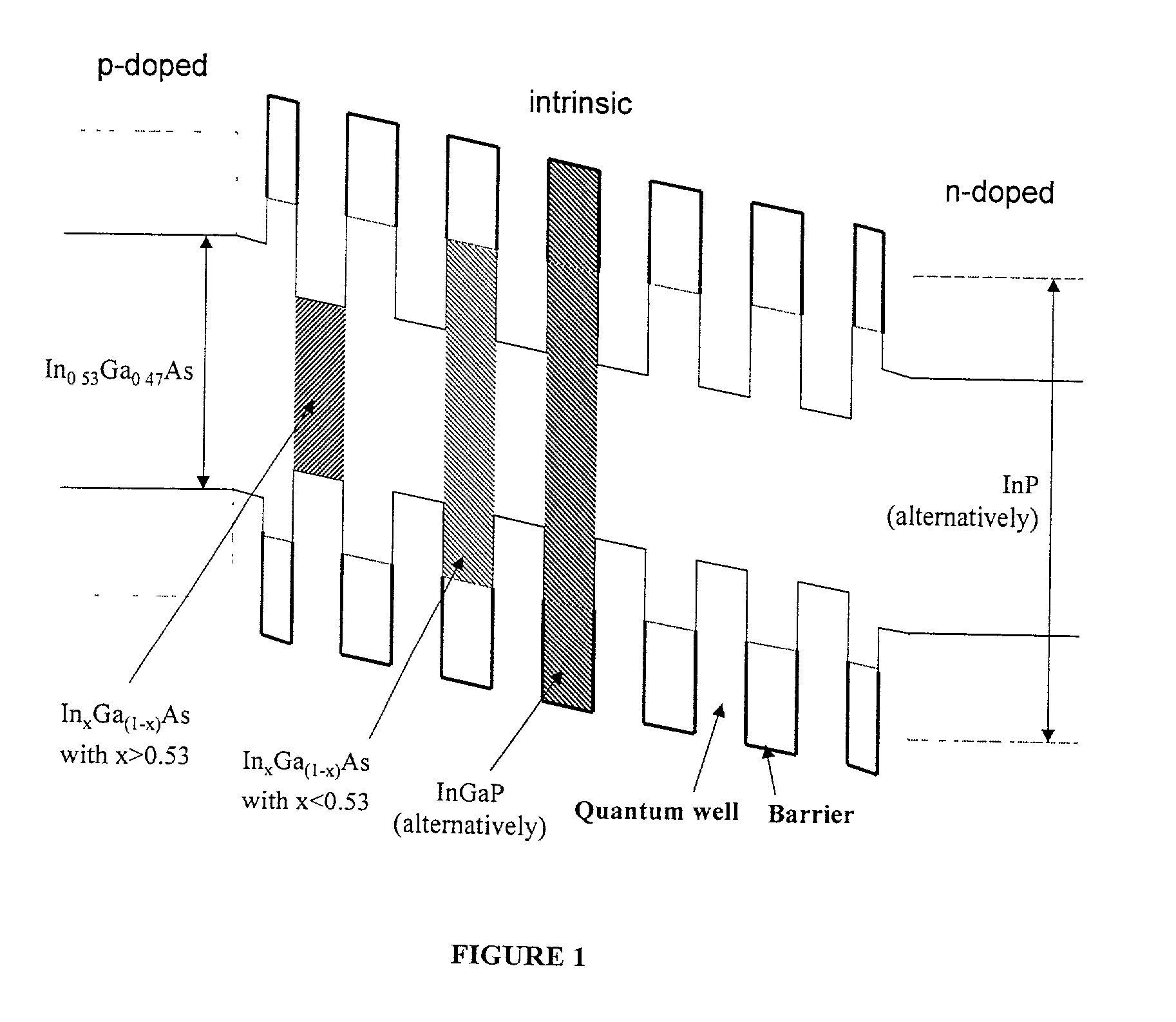

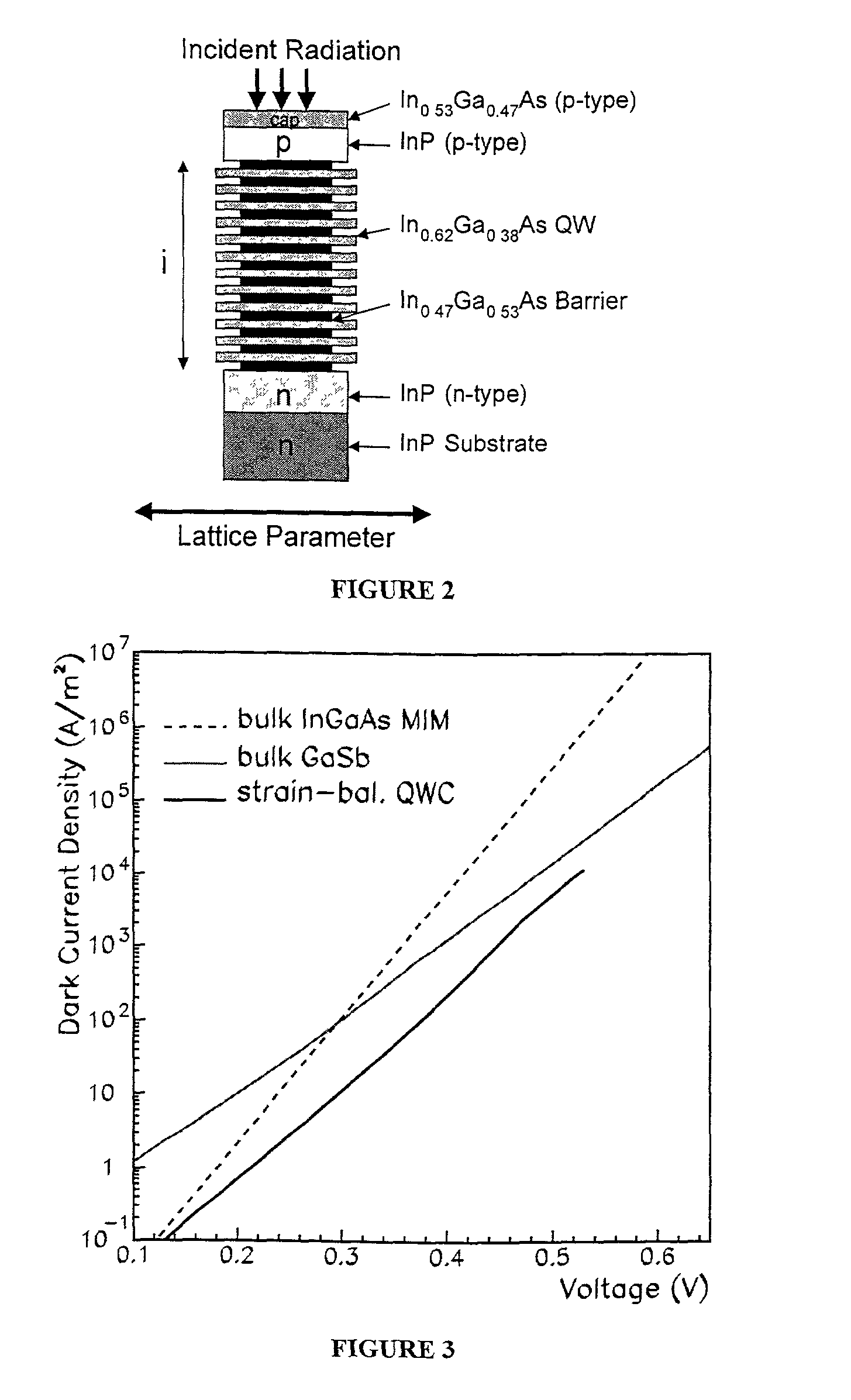

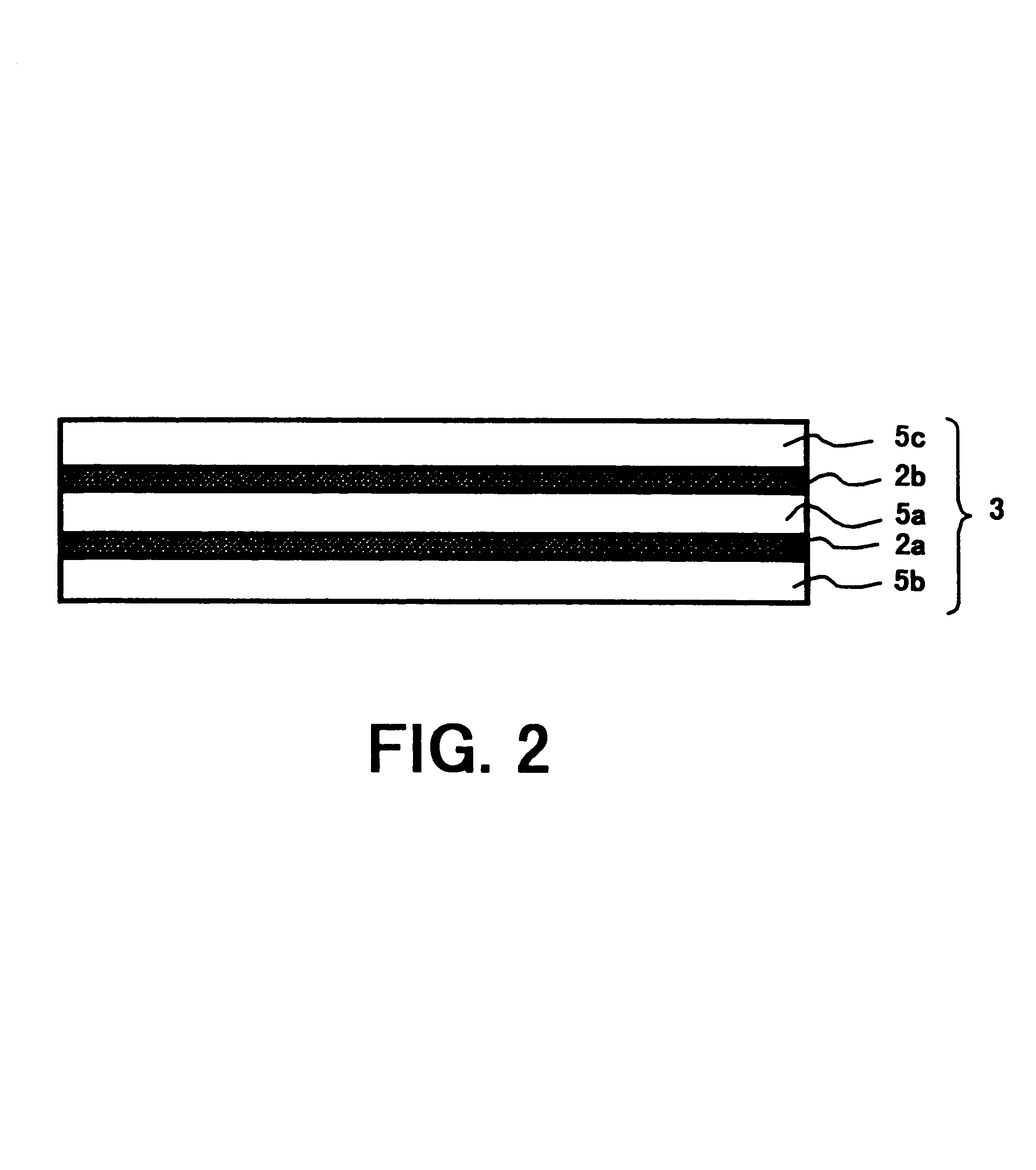

Photovoltaic device

InactiveUS20030089392A1Promote absorptionHigh bandgap barriersPV power plantsNanoopticsQuantum wellActive cell

A photovoltaic cell to convert low energy photons is described, consisting of a p-i-n diode with a strain-balanced multi-quantum-well system incorporated in the intrinsic region. The bandgap of the quantum wells is lower than that of the lattice-matched material, while the barriers have a much higher bandgap. Hence the absorption can be extended to longer wavelengths, while maintaining a low dark current as a result of the higher barriers. This leads to greatly improved conversion efficiencies, particularly for low energy photons from low temperature sources. This can be achieved by strain-balancing the quantum wells and barriers, where each individual layer is below the critical thickness and the strain is compensated by quantum wells and barriers being strained in opposite directions minimizing the stress. The absorption can be further extended to longer wavelengths by introducing a strain-relaxed layer (virtual substrate) between the substrate and the active cell.

Owner:IMPERIAL INNOVATIONS LTD

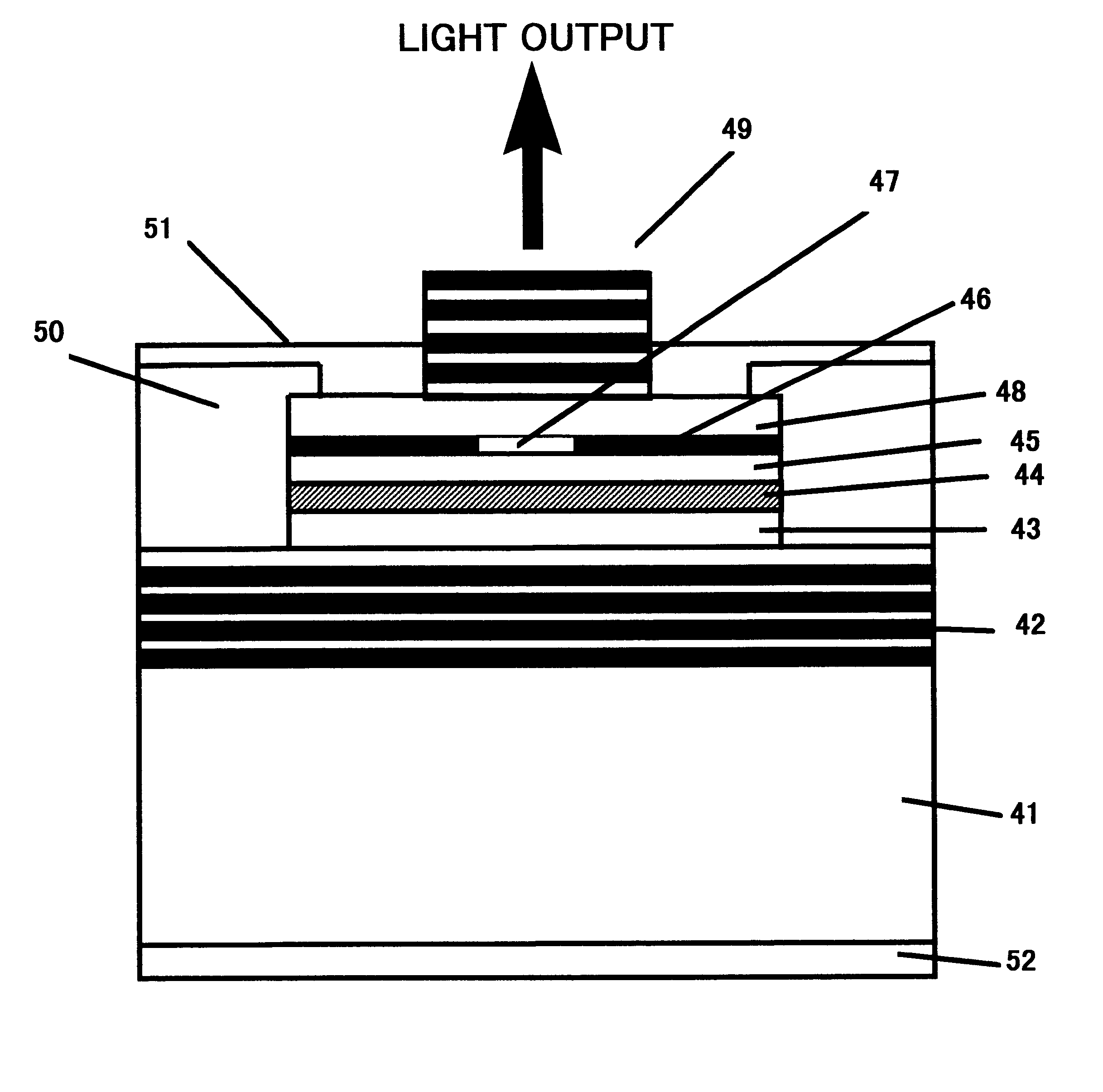

III-V light emitting device

InactiveUS20070069225A1Relieve pressureSemiconductor/solid-state device manufacturingSemiconductor lasersSemiconductor structureCritical thickness

A semiconductor structure includes an n-type region, a p-type region, and a III-nitride light emitting layer disposed between the n-type region and the p-type region. The III-nitride light emitting layer has a lattice constant greater than 3.19 Å. Such a semiconductor structure may be grown on a substrate including a host and a seed layer bonded to the host. In some embodiments, a bonding layer bonds the host to the seed layer. The seed layer may be thinner than a critical thickness for relaxation of strain in the semiconductor structure, such that strain in the semiconductor structure is relieved by dislocations formed in the seed layer, or by gliding between the seed layer and the bonding layer an interface between the two layers. In some embodiments, the host may be separated from the semiconductor structure and seed layer by etching away the bonding layer.

Owner:LUMILEDS

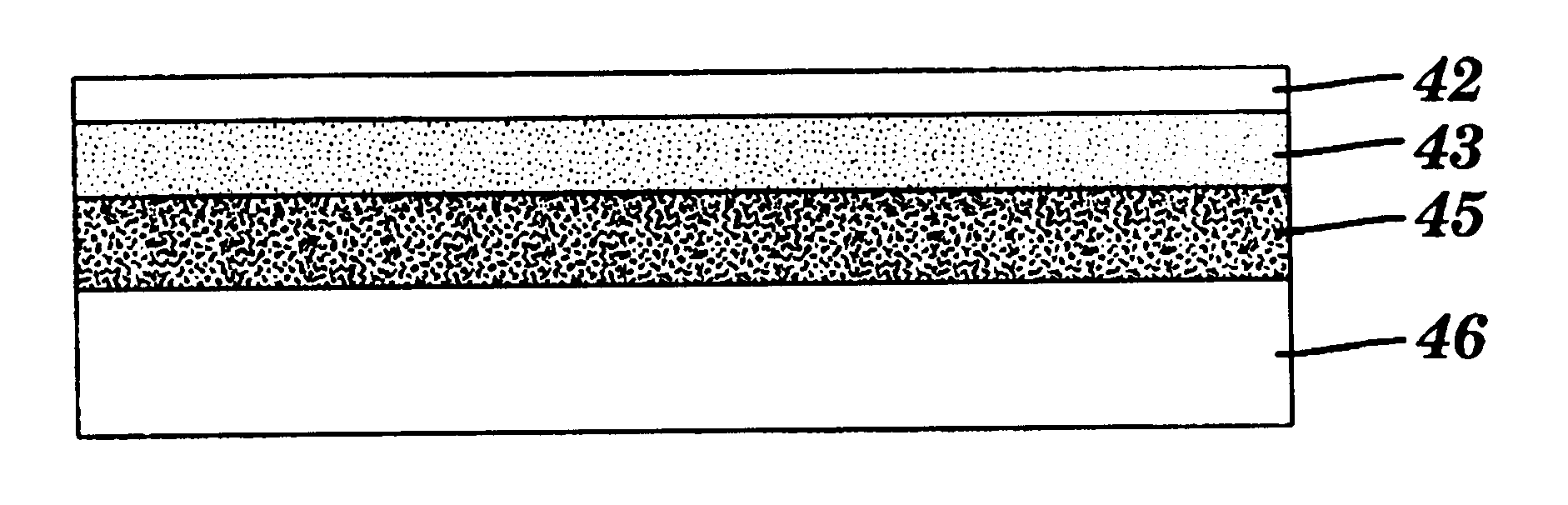

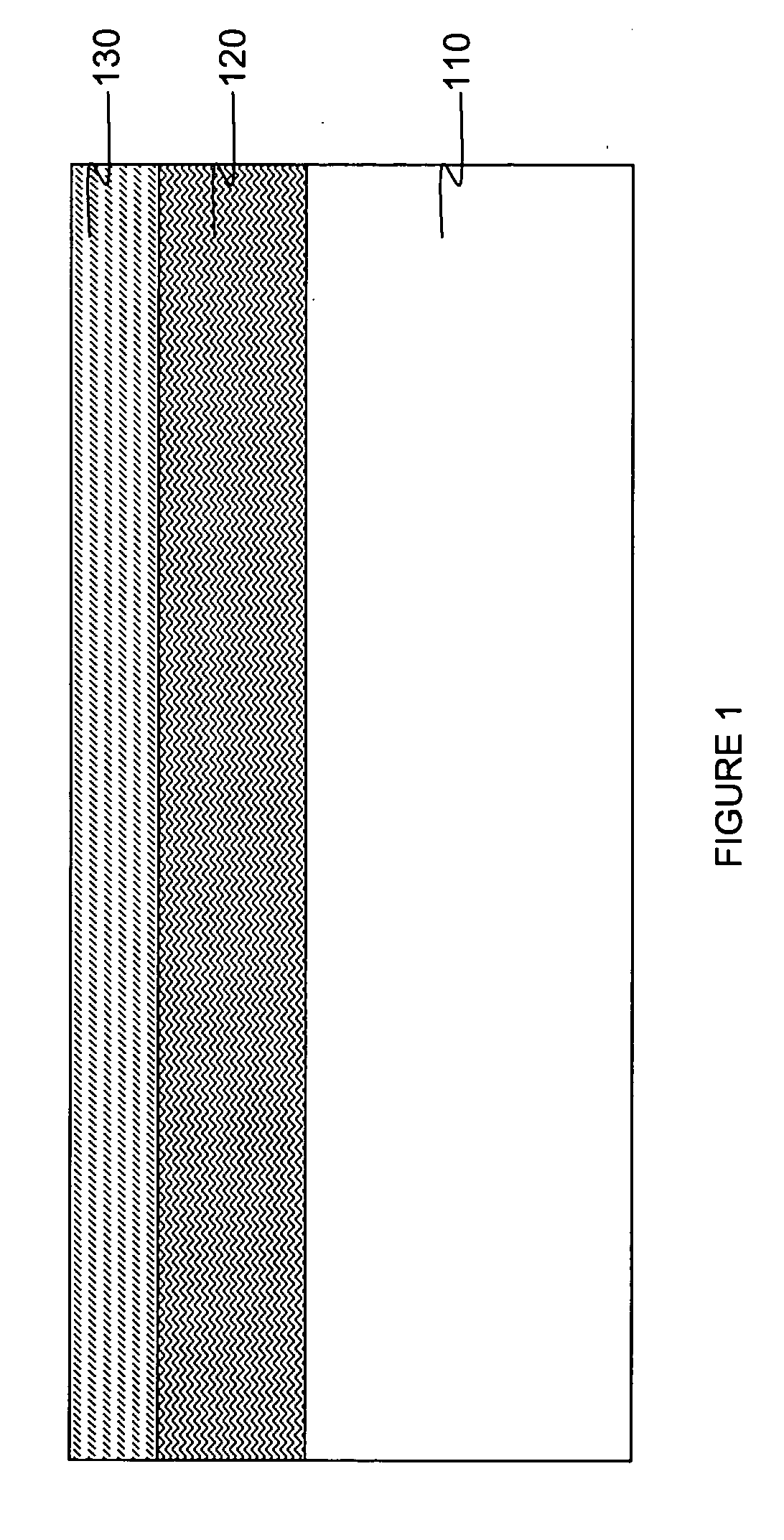

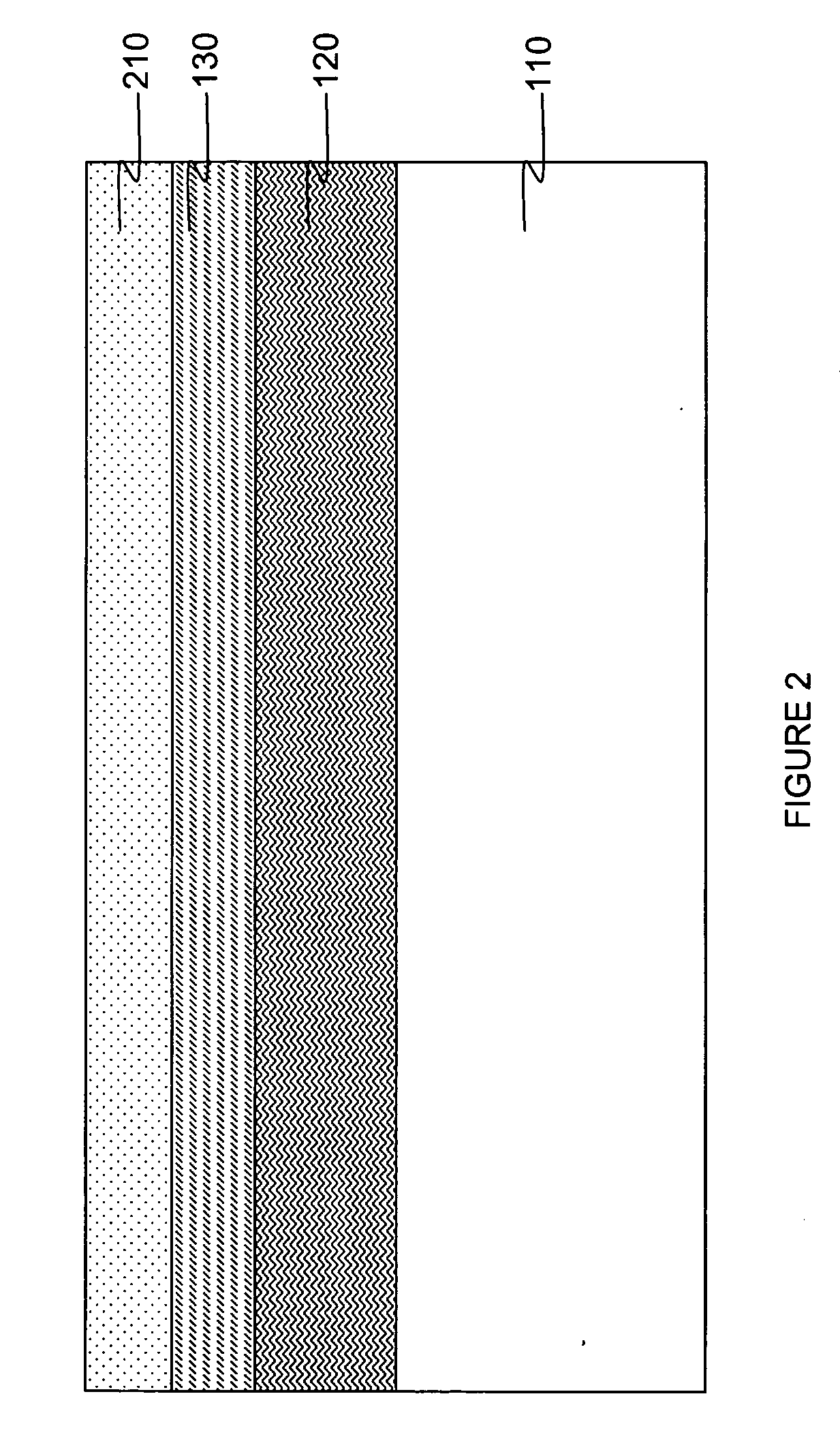

Method of Forming strained SI/SIGE on insulator with silicon germanium buffer

InactiveUS6893936B1Solid-state devicesSemiconductor/solid-state device manufacturingCritical thicknessTotal thickness

A method is disclosed for forming a semiconductor wafer having a strained Si or SiGe layer on an insulator layer. The method produces a structure having a SiGe buffer layer between the insulator layer and the strained Si or SiGe layer, but eliminates the need for Si epitaxy after bonding. The method also eliminates interfacial contamination between strained Si and SiGe buffer layer, and allows the formation of Si / SiGe layers having a total thickness exceeding the critical thickness of the strained Si layer.

Owner:GLOBALFOUNDRIES INC

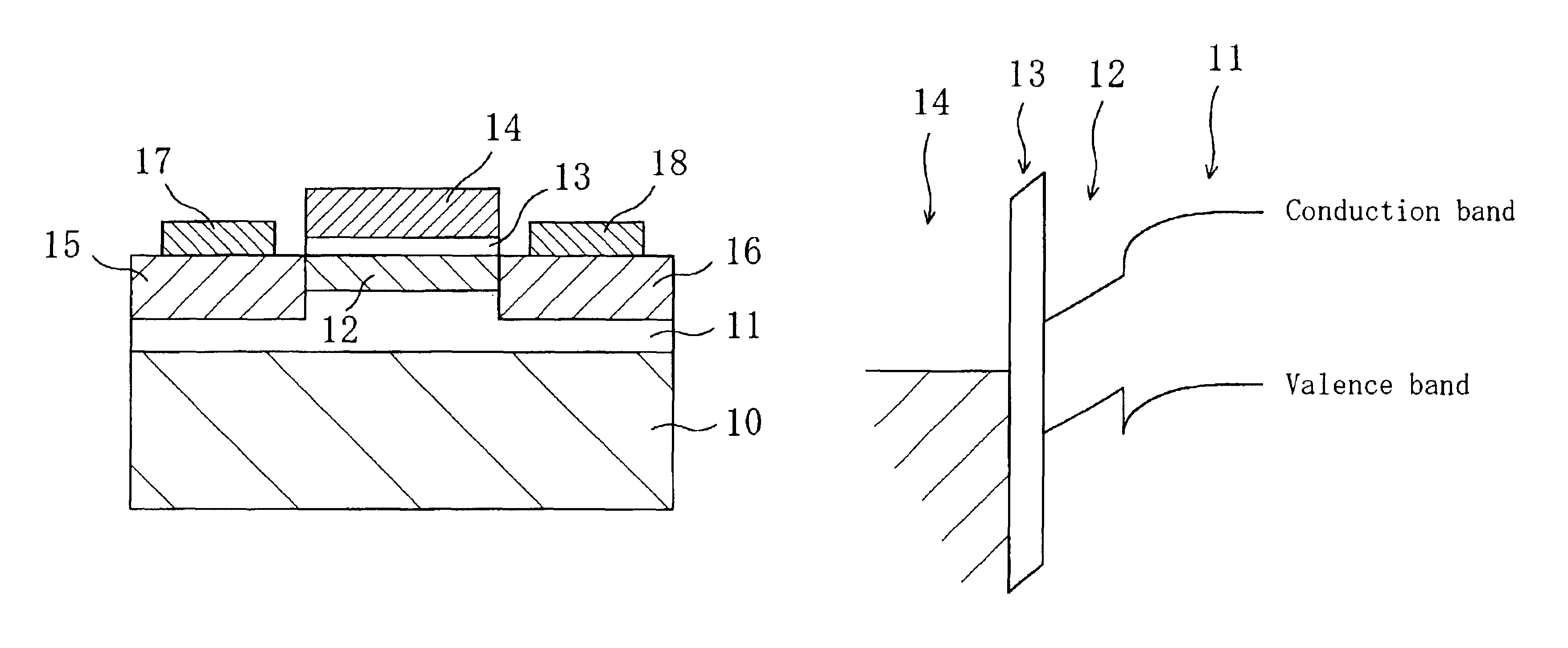

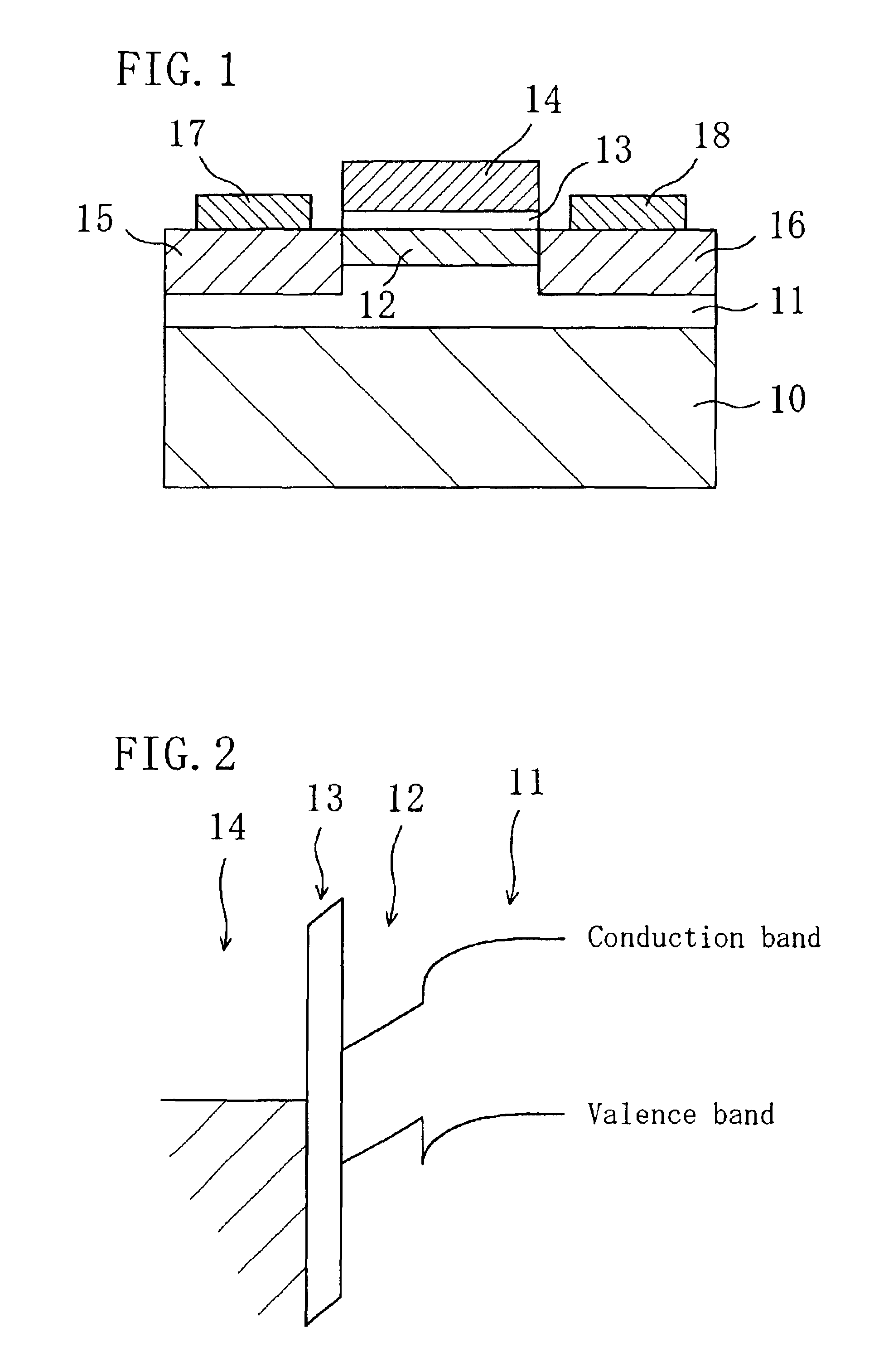

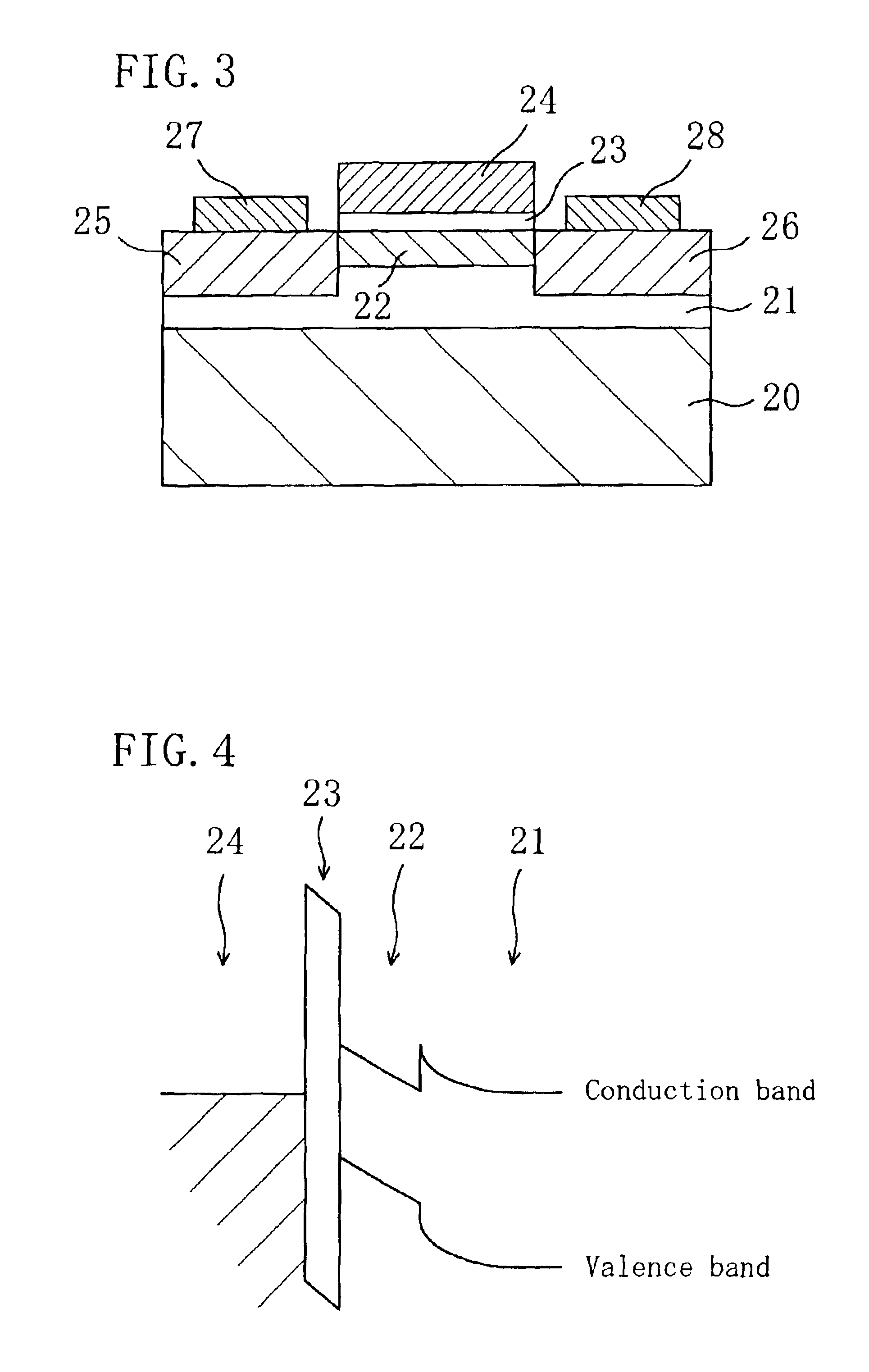

Semiconductor devices and method for manufacturing the same

InactiveUS6844227B2Improve featuresSufficient reliabilityTransistorSolid-state devicesDevice materialCarbon nitride

In a field effect transistor, an Si layer, an SiC (Si1-yCy) channel layer, a CN gate insulating film made of a carbon nitride layer (CN) and a gate electrode are deposited in this order on an Si substrate. The thickness of the SiC channel layer is set to a value that is less than or equal to the critical thickness so that a dislocation due to a strain does not occur according to the carbon content. A source region and a drain region are formed on opposite sides of the SiC channel layer, and a source electrode and a drain electrode are provided on the source region and the drain region, respectively.

Owner:PANASONIC CORP

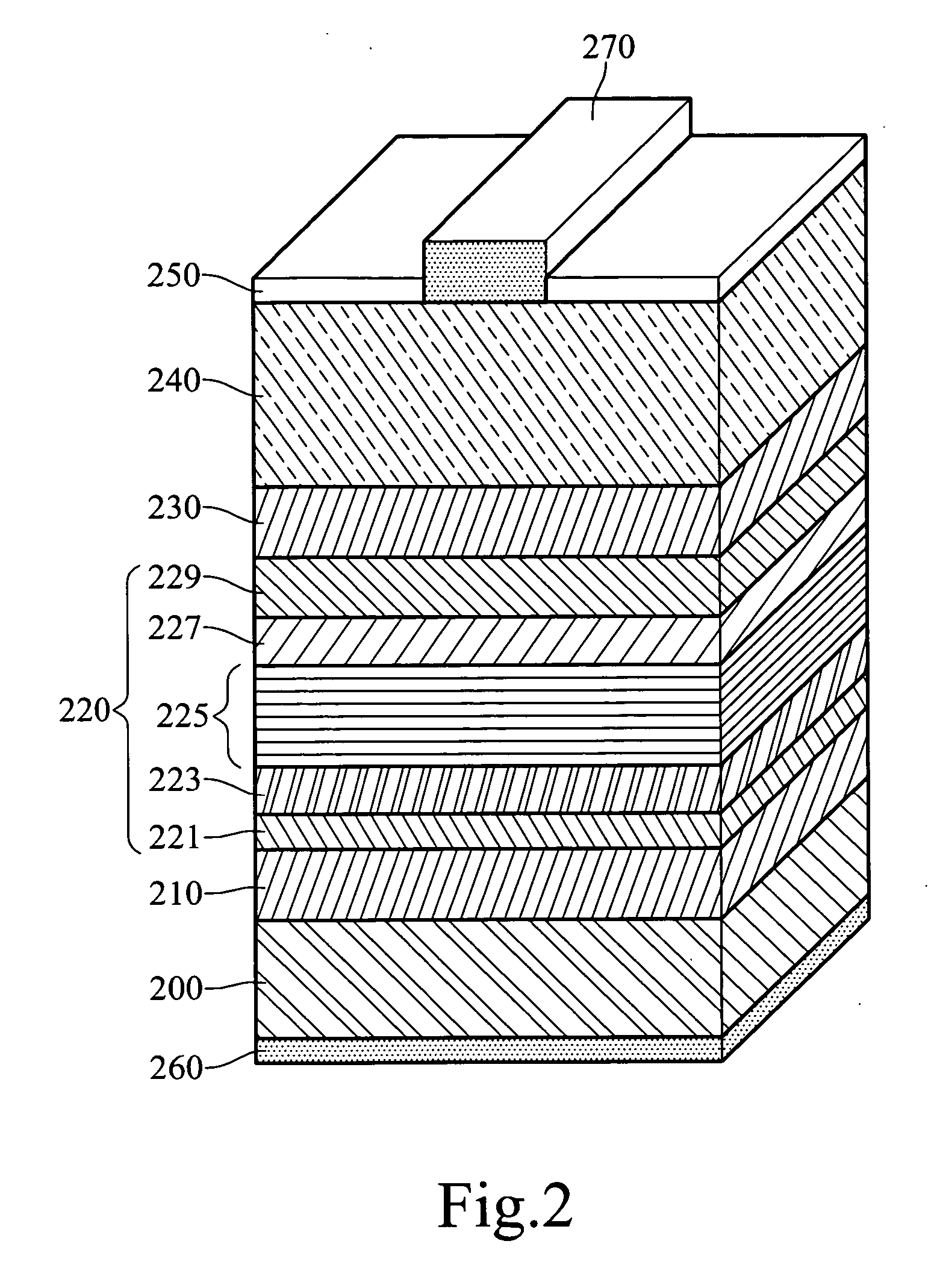

III-nitride light-emitting devices with improved high-current efficiency

ActiveUS6943381B2Improve efficiencyReduce layeringSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialCritical thickness

A light-emitting semiconductor device comprises a III-Nitride active region and a III-Nitride layer formed proximate to the active region and having a thickness that exceeds a critical thickness for relaxation of strain in the III-Nitride layer. The III-Nitride layer may be a carrier confinement layer, for example. In another aspect of the invention, a light-emitting semiconductor device comprises a III-Nitride light emitting layer, an InxAlyGa1-x-yN (0≦x≦1, 0≦y≦1, x+y≦1), and a spacer layer interposing the light emitting layer and the InxAlyGa1-x-yN layer. The spacer layer may advantageously space the InxAlyGa1-x-yN layer and any contaminants therein apart from the light emitting layer. The composition of the III-Nitride layer may be advantageously selected to determine a strength of an electric field in the III-Nitride layer and thereby increase the efficiency with which the device emits light.

Owner:LUMILEDS

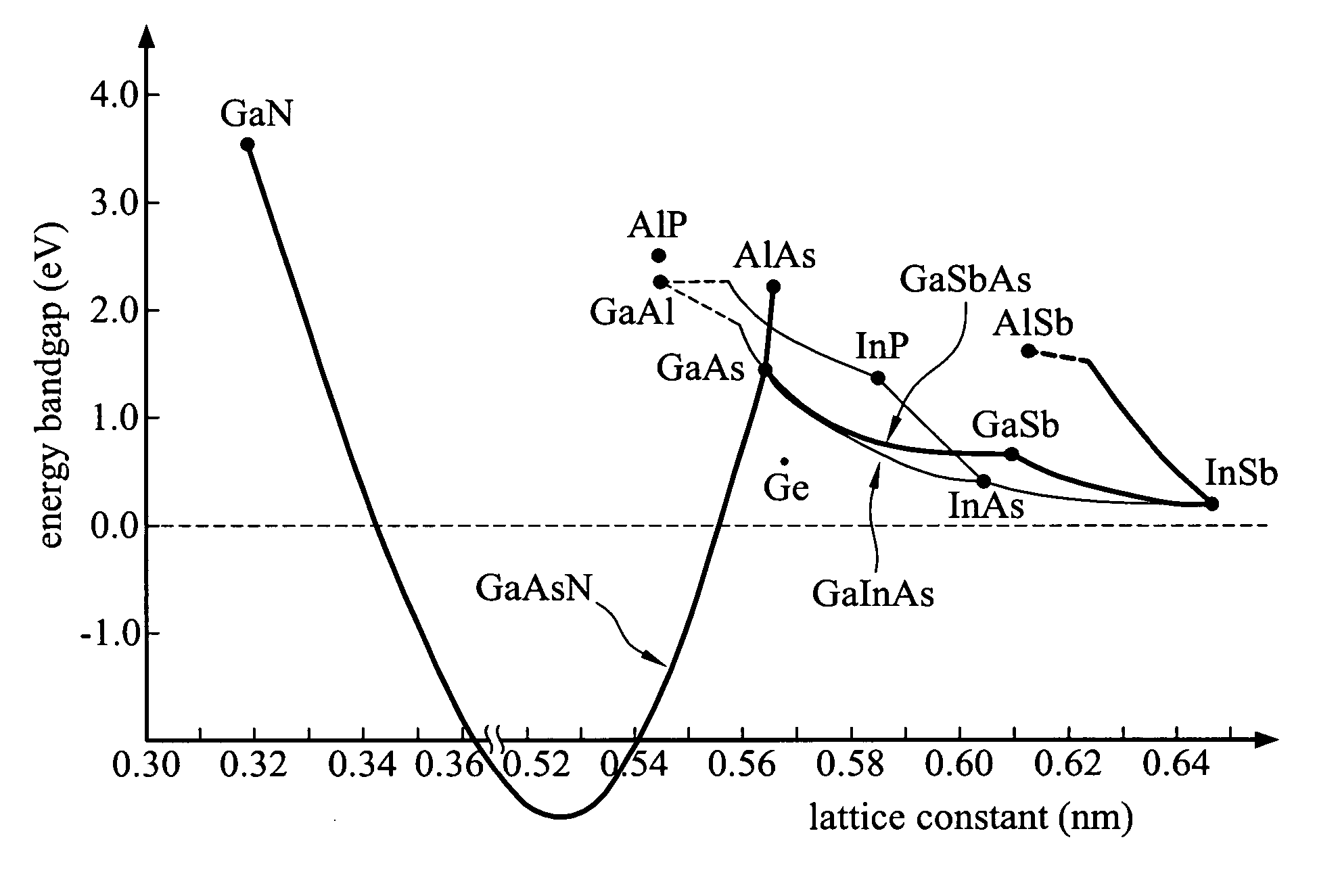

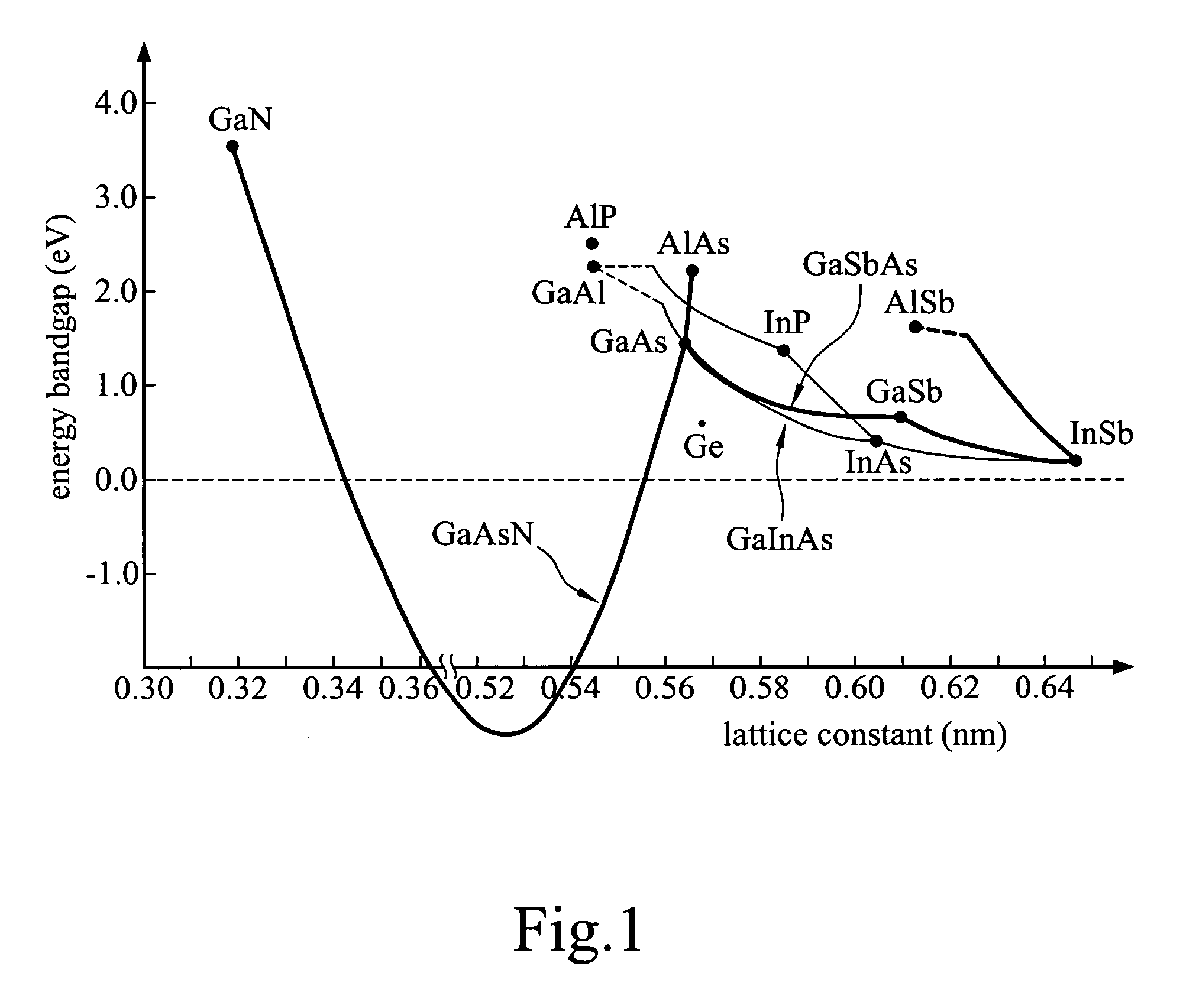

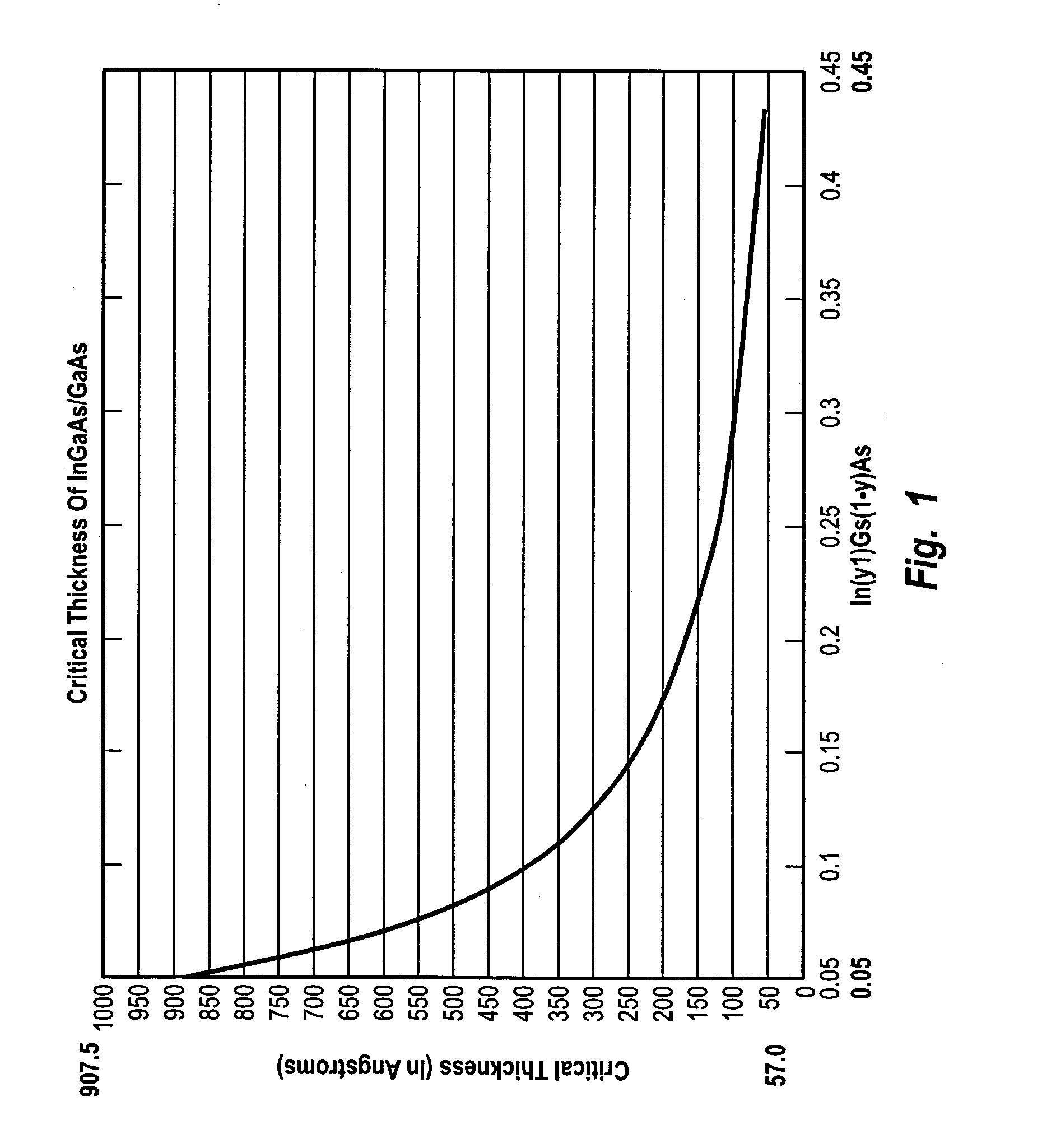

Solar cell with superlattice structure and fabricating method thereof

InactiveUS20070151595A1High carrier mobilityPreferable advantageSemiconductor/solid-state device manufacturingNanoopticsEngineeringCritical thickness

A solar cell with a superlattice structure and a fabricating method thereof are provided, which includes fabricating a superlattice structure of GaAsN / GaInAs, GaAsN / GaSbAs, or GaAsN / GaInSbAs between a base and an emitter of a middle cell of a triple junction solar cell by a strain-compensation technology. The provided solar cell not only decreases crystalline defects and increases the critical thickness of the crystal, but also makes the energy bandgap of GaAsN and GaInAs reach around the energy of 1.0 eV (electron volt). Hence, the absorption region can be raised to around the energy of 1.0 eV to enhance the efficiency of the solar cell.

Owner:IND TECH RES INST +1

Methods of forming replacement fins for a finfet semiconductor device by performing a replacement growth process

InactiveUS20150024573A1Well formedSolid-state devicesSemiconductor/solid-state device manufacturingCritical thicknessBiomedical engineering

Various methods are disclosed herein for forming alternative fin materials that are in a stable or metastable condition. In one case, a stable replacement fin is grown to a height that is greater than an unconfined stable critical thickness of the replacement fin material and it has a defect density of 104 defects / cm2 or less throughout its entire height. In another case, a metastable replacement fin is grown to a height that is greater than an unconfined metastable critical thickness of the replacement fin material and it has a defect density of 105 defects / cm2 or less throughout at least 90% of its entire height.

Owner:GLOBALFOUNDRIES INC

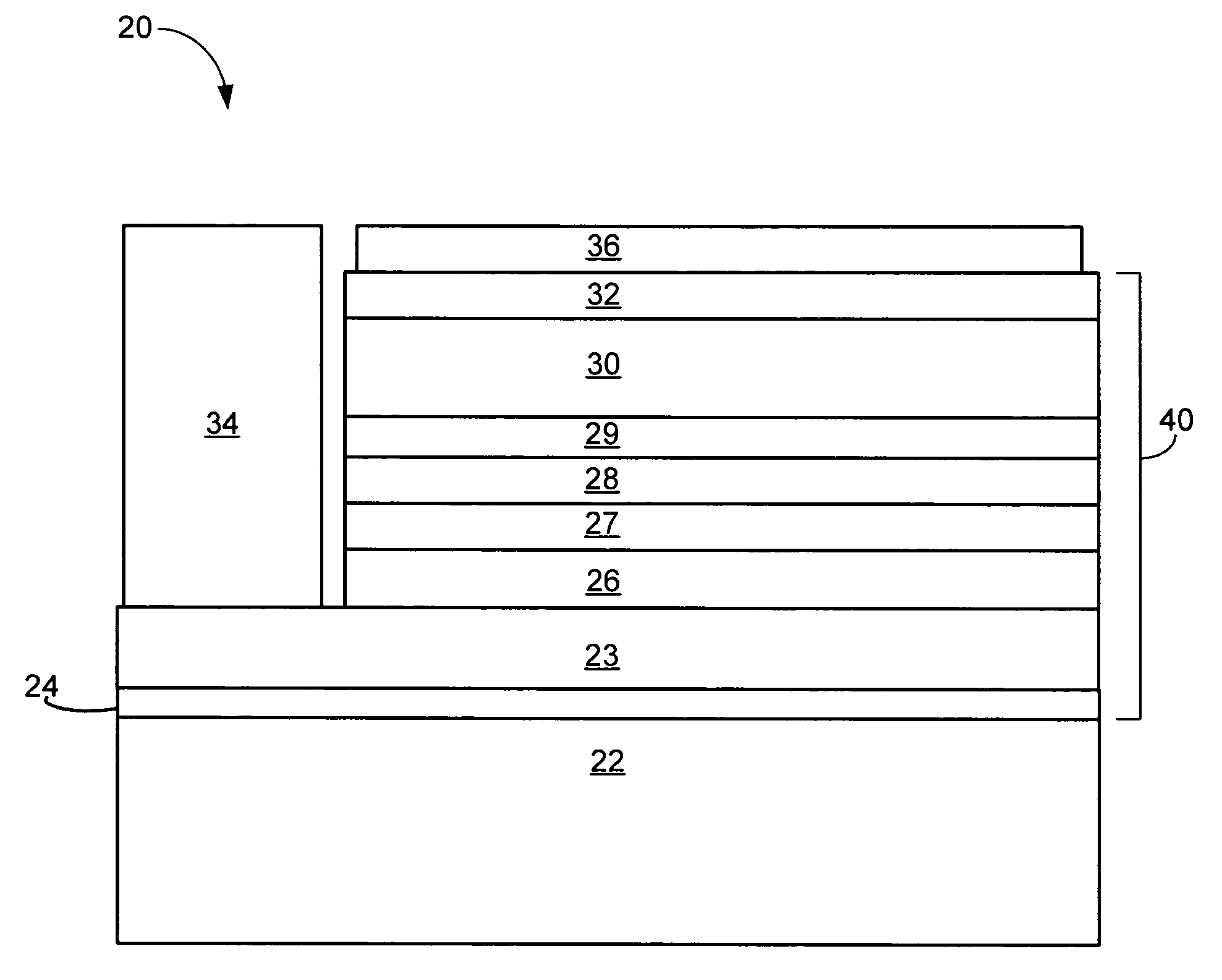

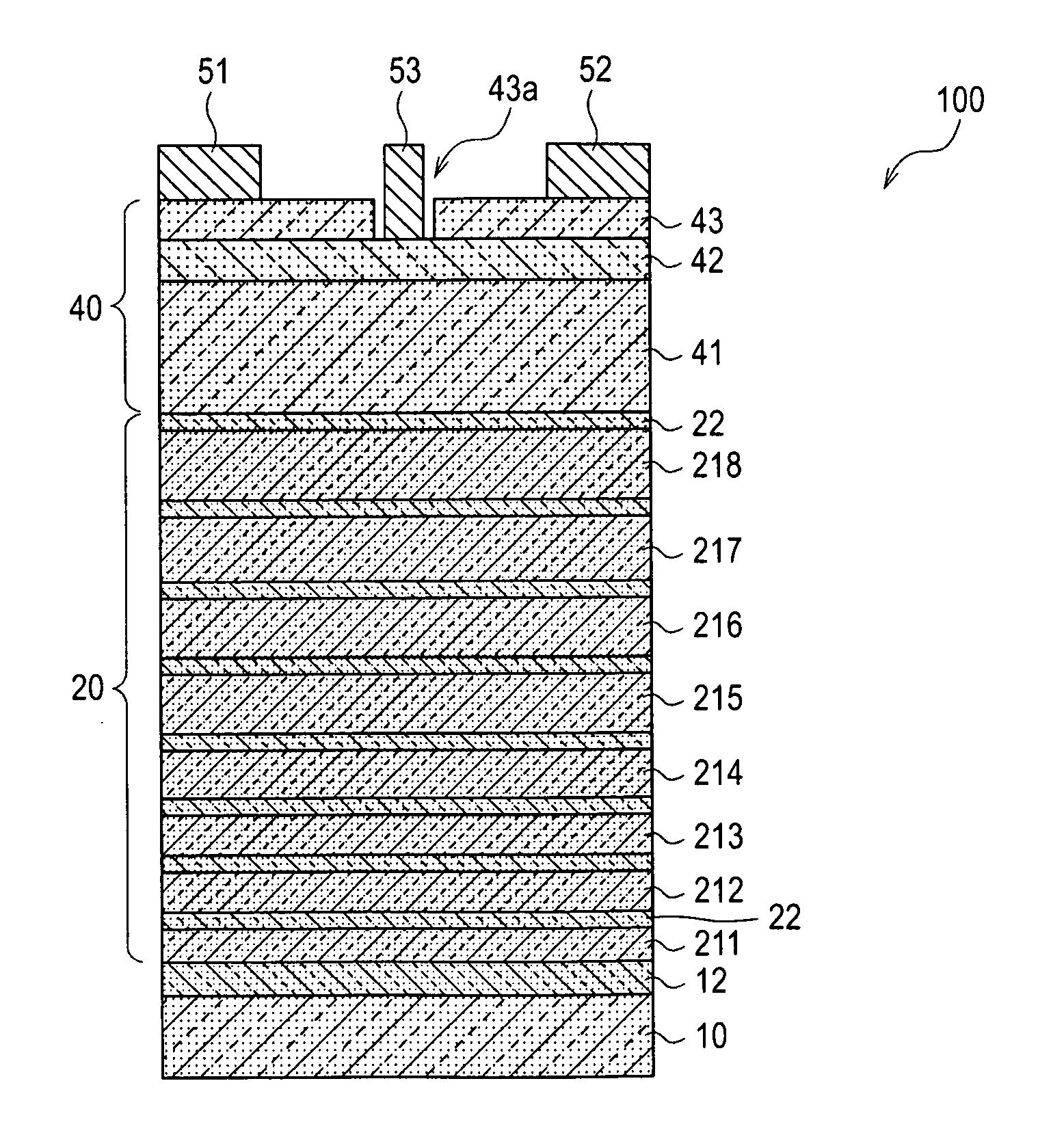

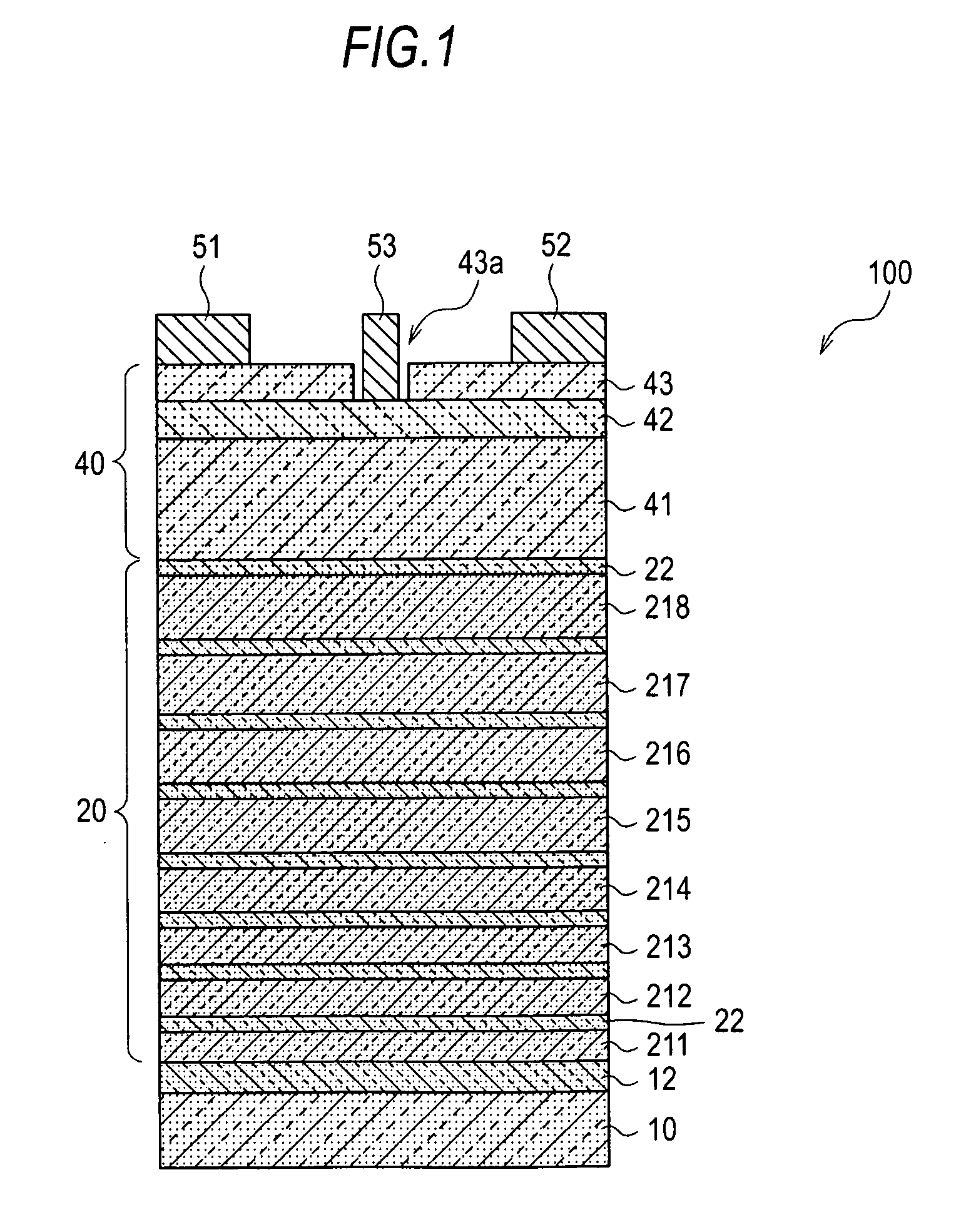

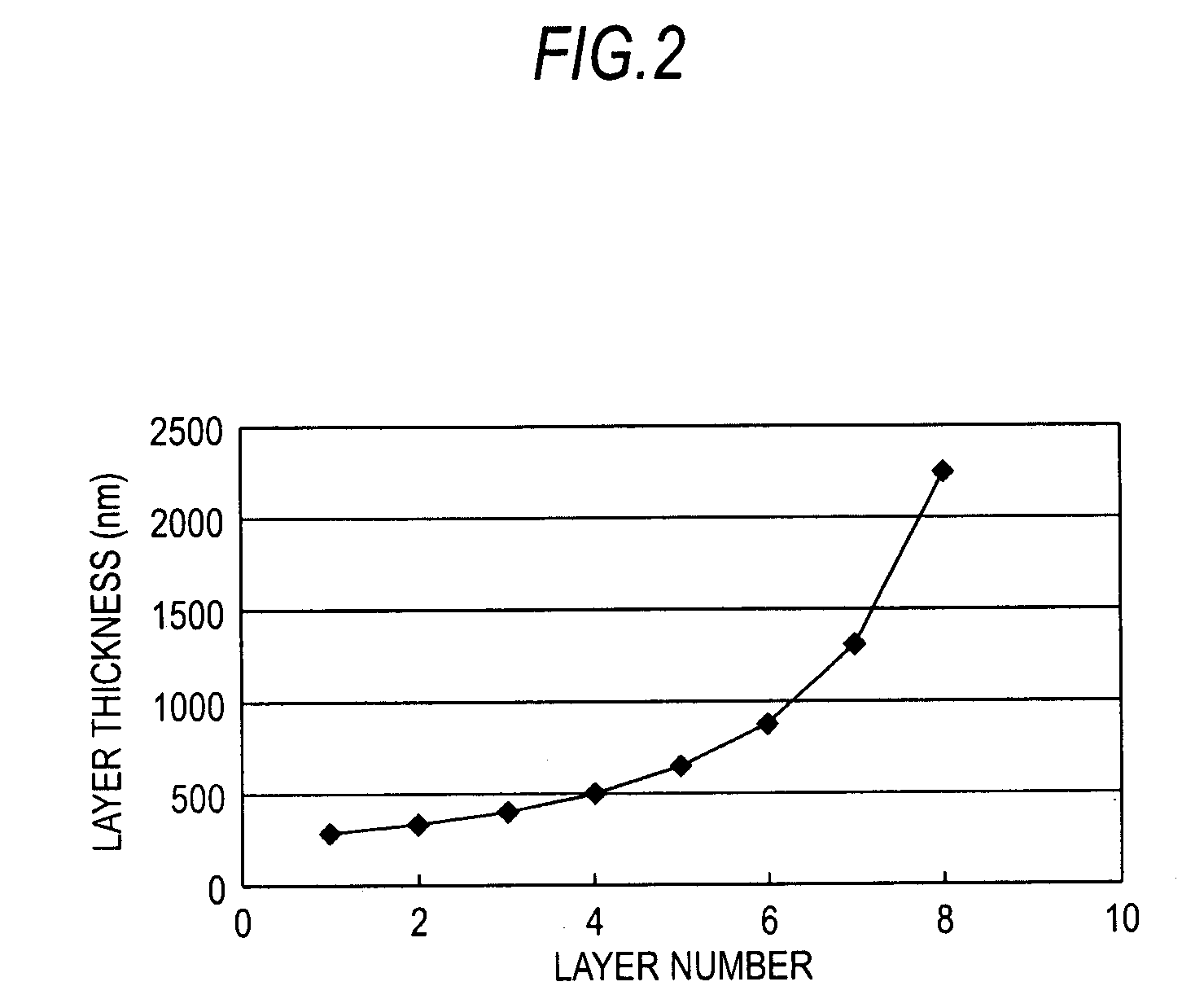

Semiconductor electronic device

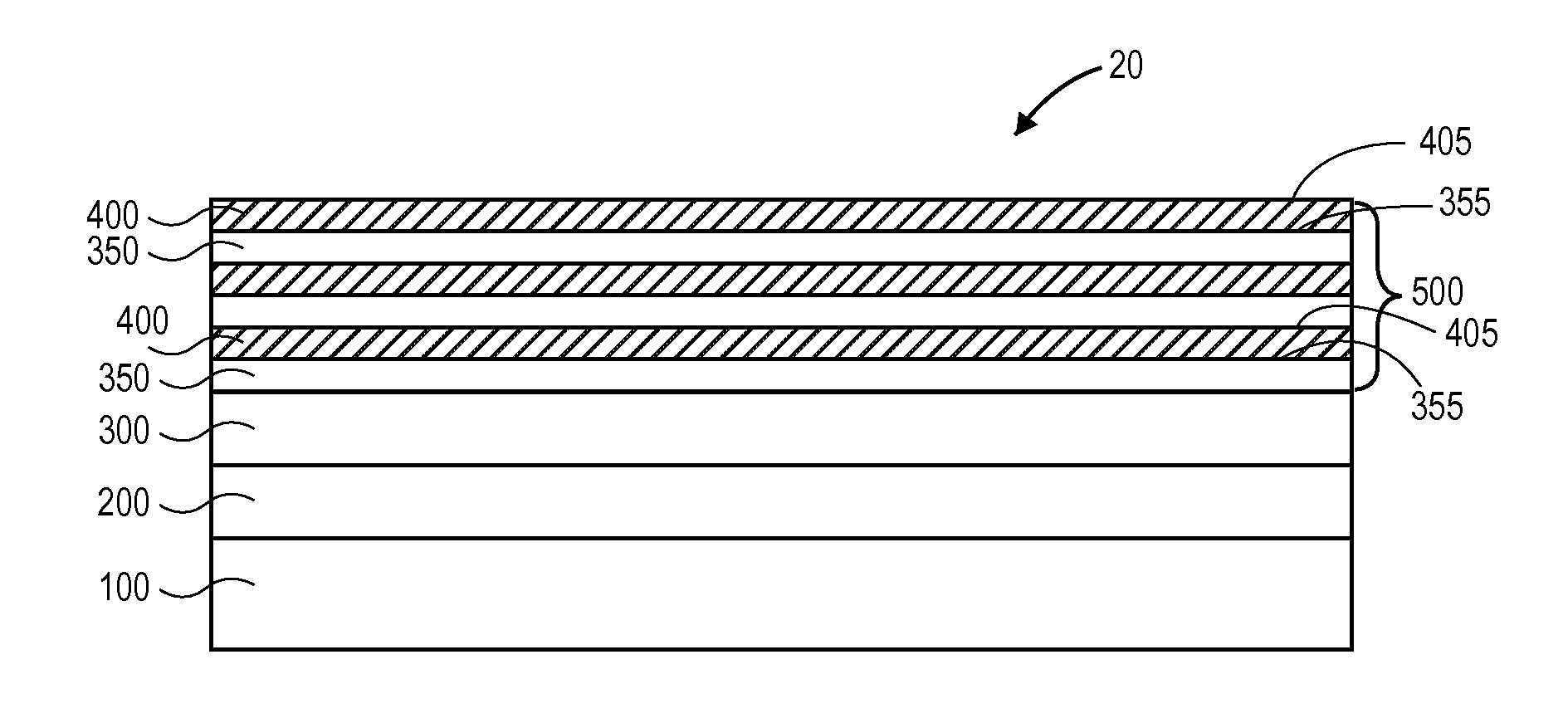

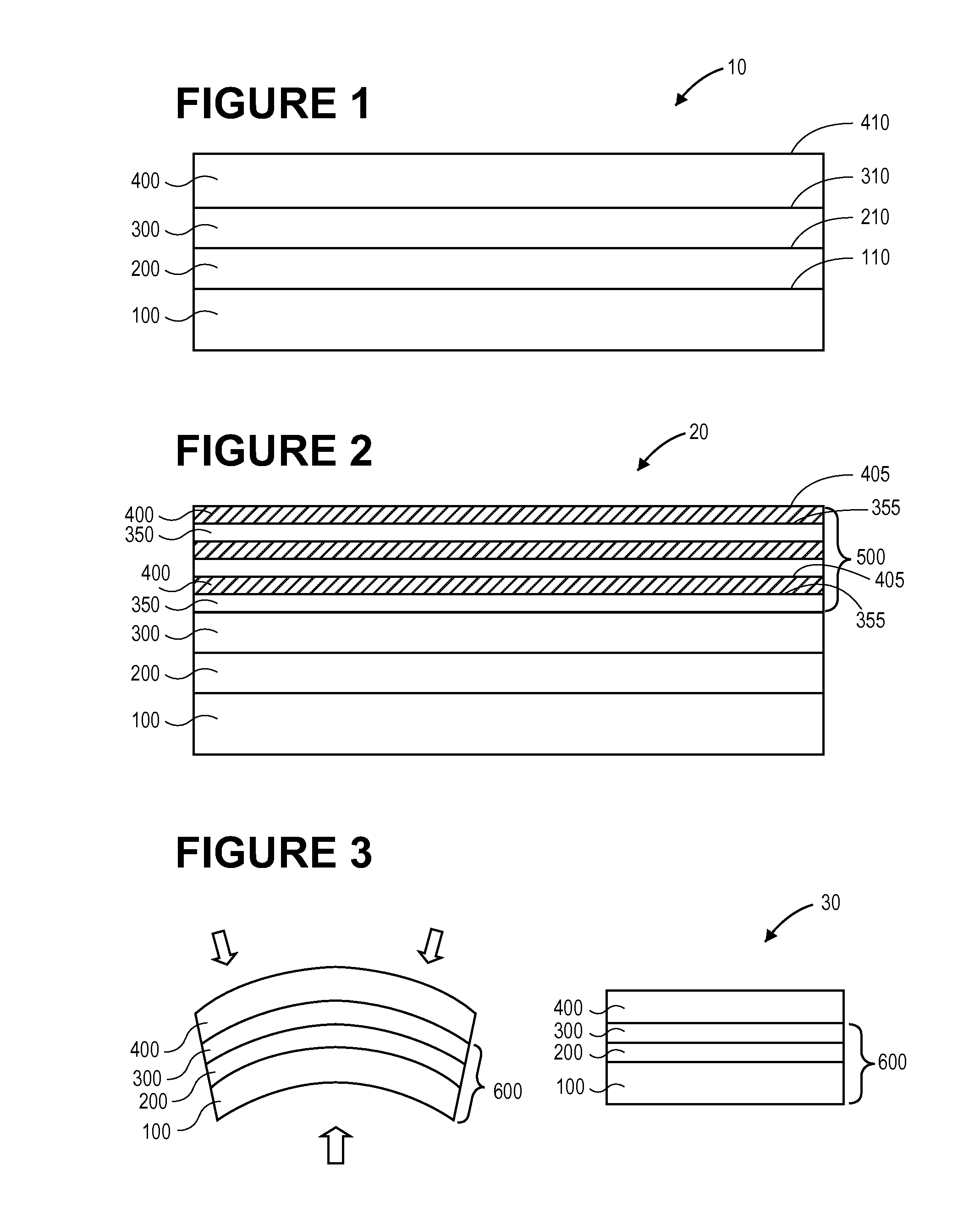

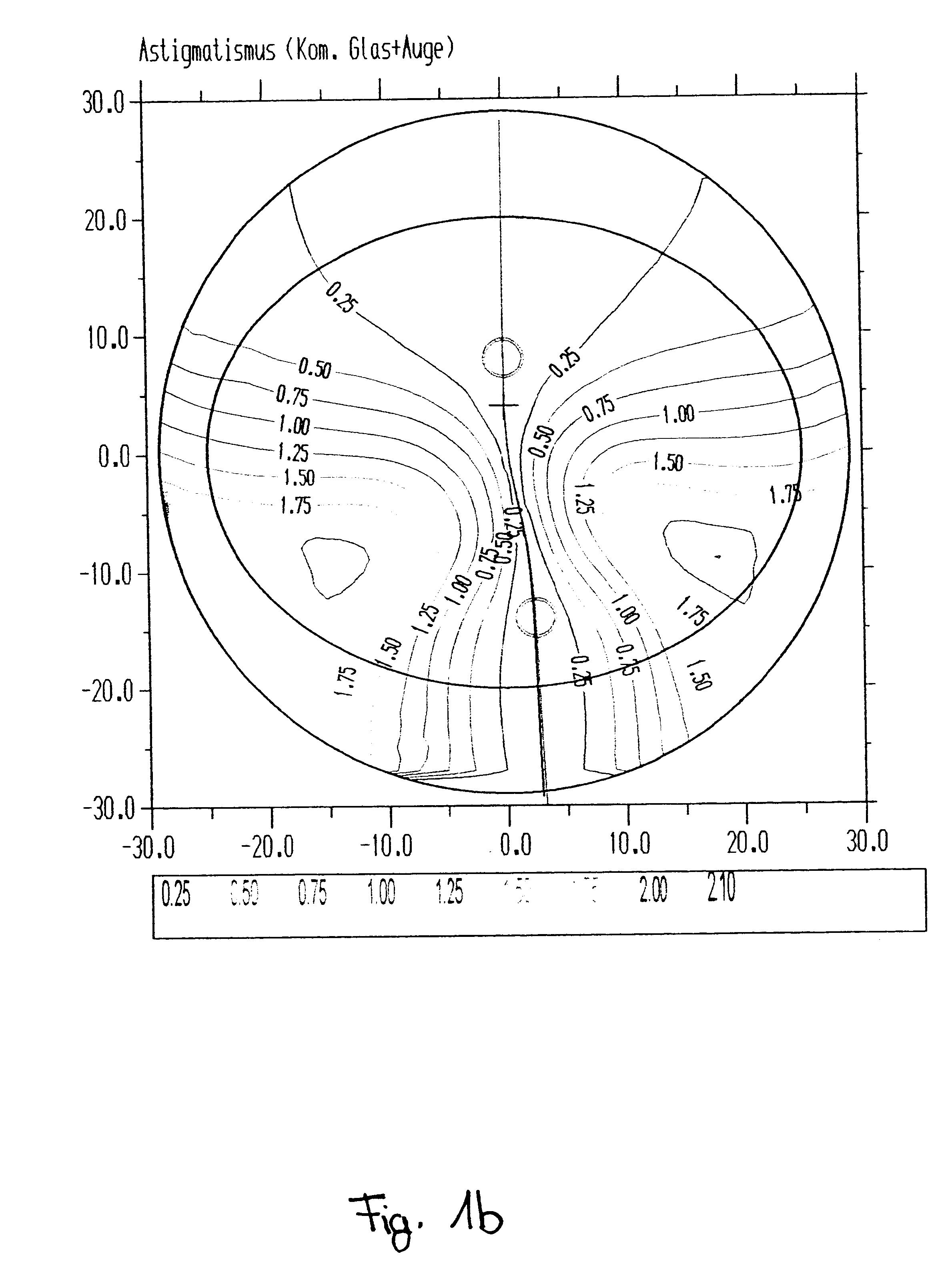

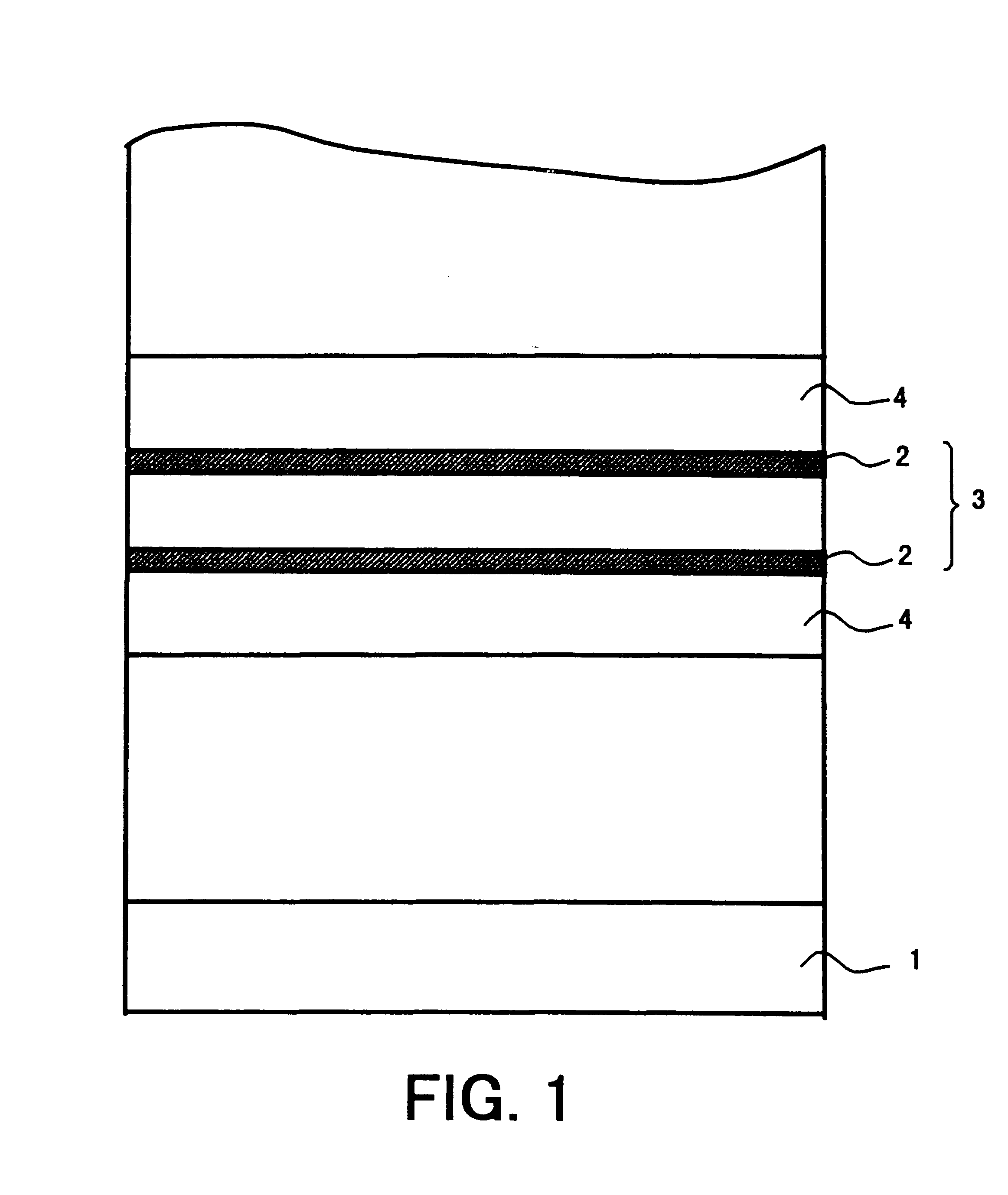

ActiveUS20090200645A1Reduce warpageLarge breakdown voltageSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorInter layer

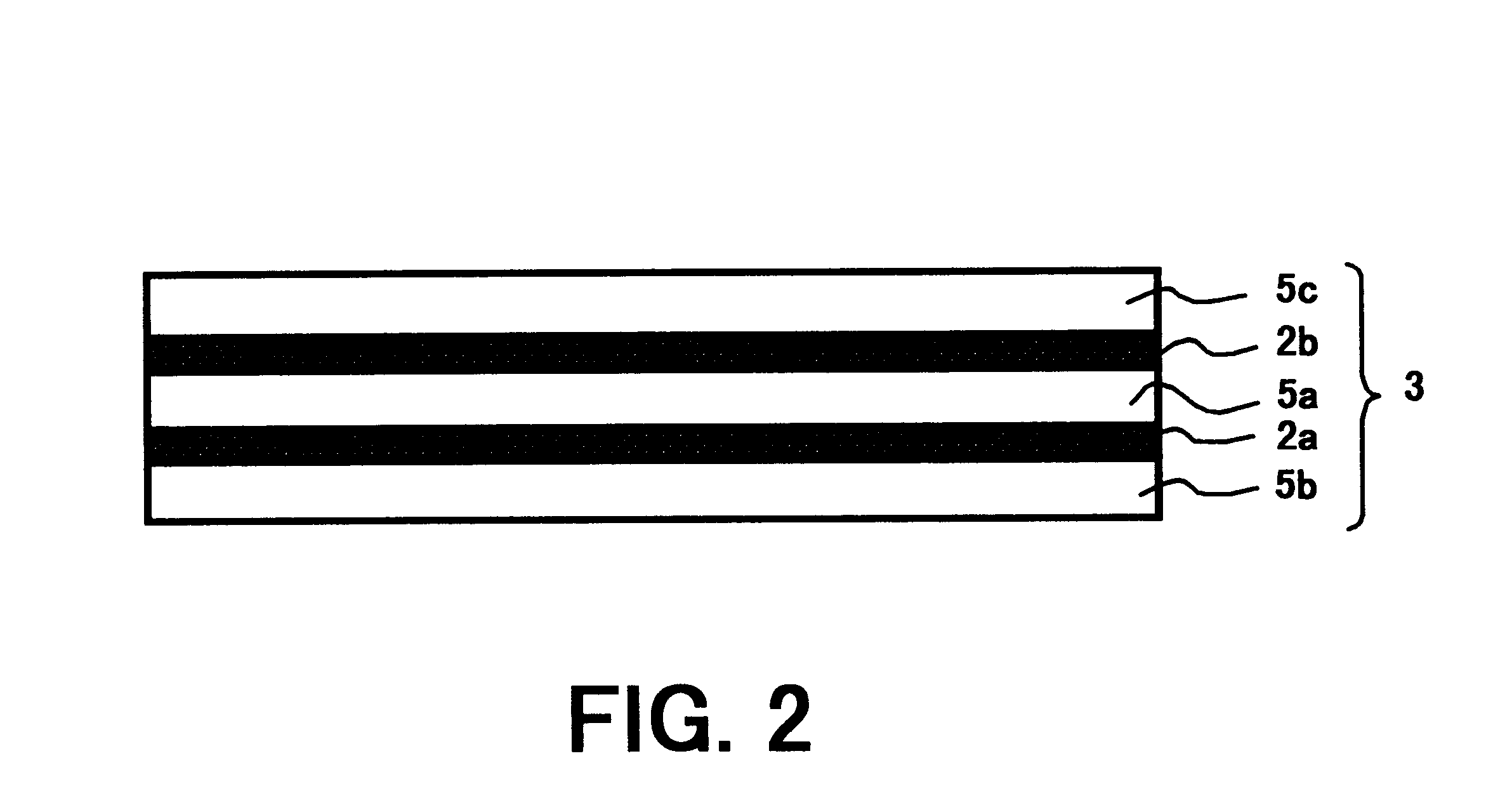

A semiconductor electronic device comprises a substrate; a buffer layer formed on the substrate, the buffer layer including not less than two layers of composite layer in which a first semiconductor layer formed of a nitride-based compound semiconductor layer having a lattice constant smaller than a lattice constant of the substrate and a thermal expansion coefficient larger than a thermal expansion coefficient of the substrate and a second semiconductor layer formed of a nitride-based compound semiconductor having a lattice constant smaller than a lattice constant of the first semiconductor layer and a thermal expansion coefficient larger than a thermal expansion coefficient of the substrate are alternately laminated; an intermediate layer provided between the substrate and the buffer layer, the intermediate layer being formed of a nitride-based compound semiconductor having a lattice constant smaller than a lattice constant of the first semiconductor layer and a thermal expansion coefficient larger than a thermal expansion coefficient of the substrate; and a semiconductor active layer formed on the buffer layer, the semiconductor active layer being formed of a nitride-based compound semiconductor, wherein: thicknesses of the first semiconductor layers in the buffer layer are non-uniform thereamong, and at least one of the first semiconductor layer has a thickness greater than a critical thickness, the critical thickness being a thickness above which a direction of warp caused by the first semiconductor layer to the substrate is inverted.

Owner:FURUKAWA ELECTRIC CO LTD

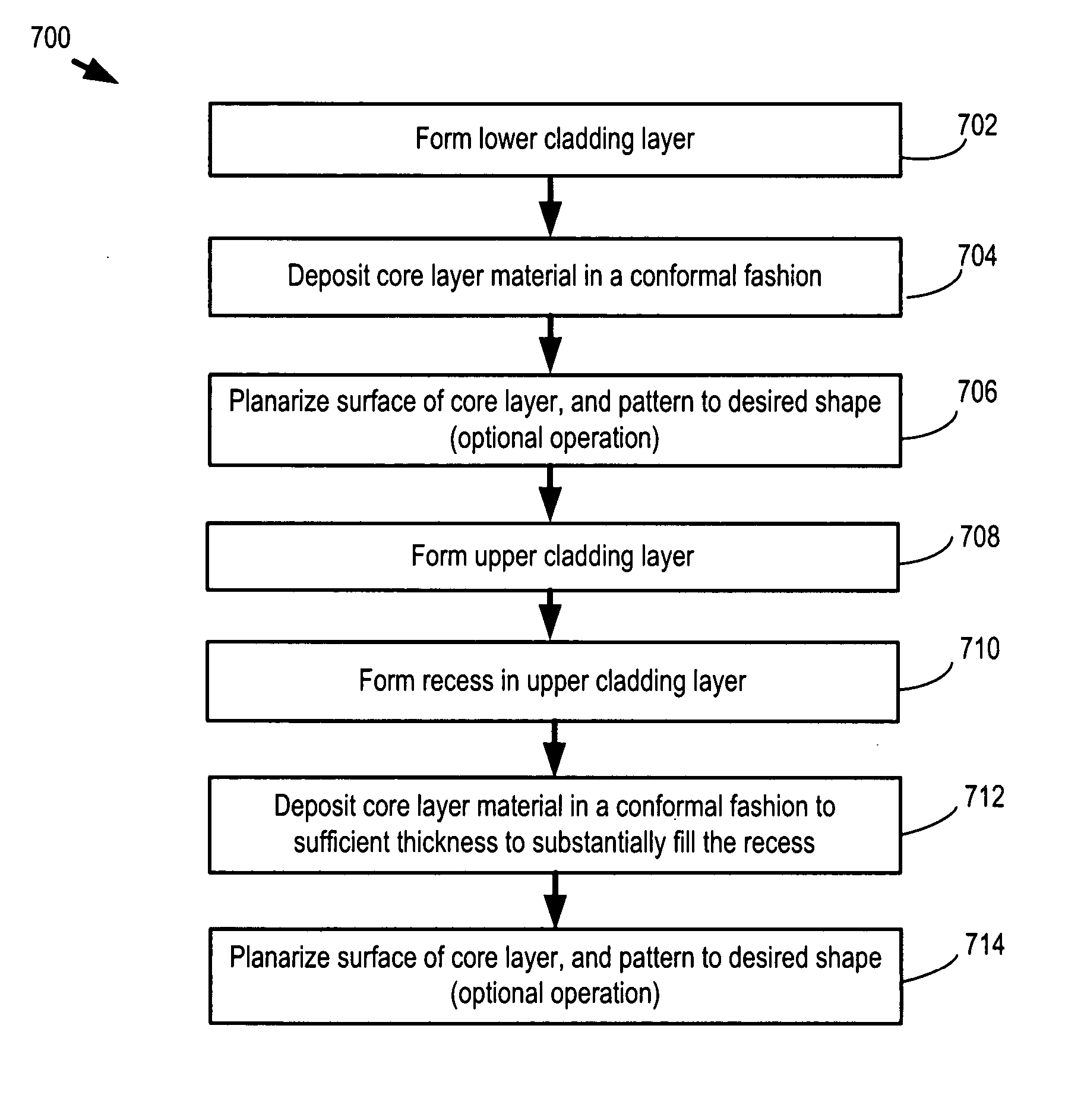

Surface waveguide and method of manufacture

A surface waveguide is disclosed. In the illustrative embodiment, the waveguide has a core and an upper and lower cladding. The core has a thickness that is greater than the critical thickness of the material that composes the core. This is achieved by depositing / growing the core as a conformal layer within a region that is recessed from the planar surface of the lower cladding, wherein the recessed region has a width that is no more than twice the critical thickness of the core material.

Owner:OCTROLIX

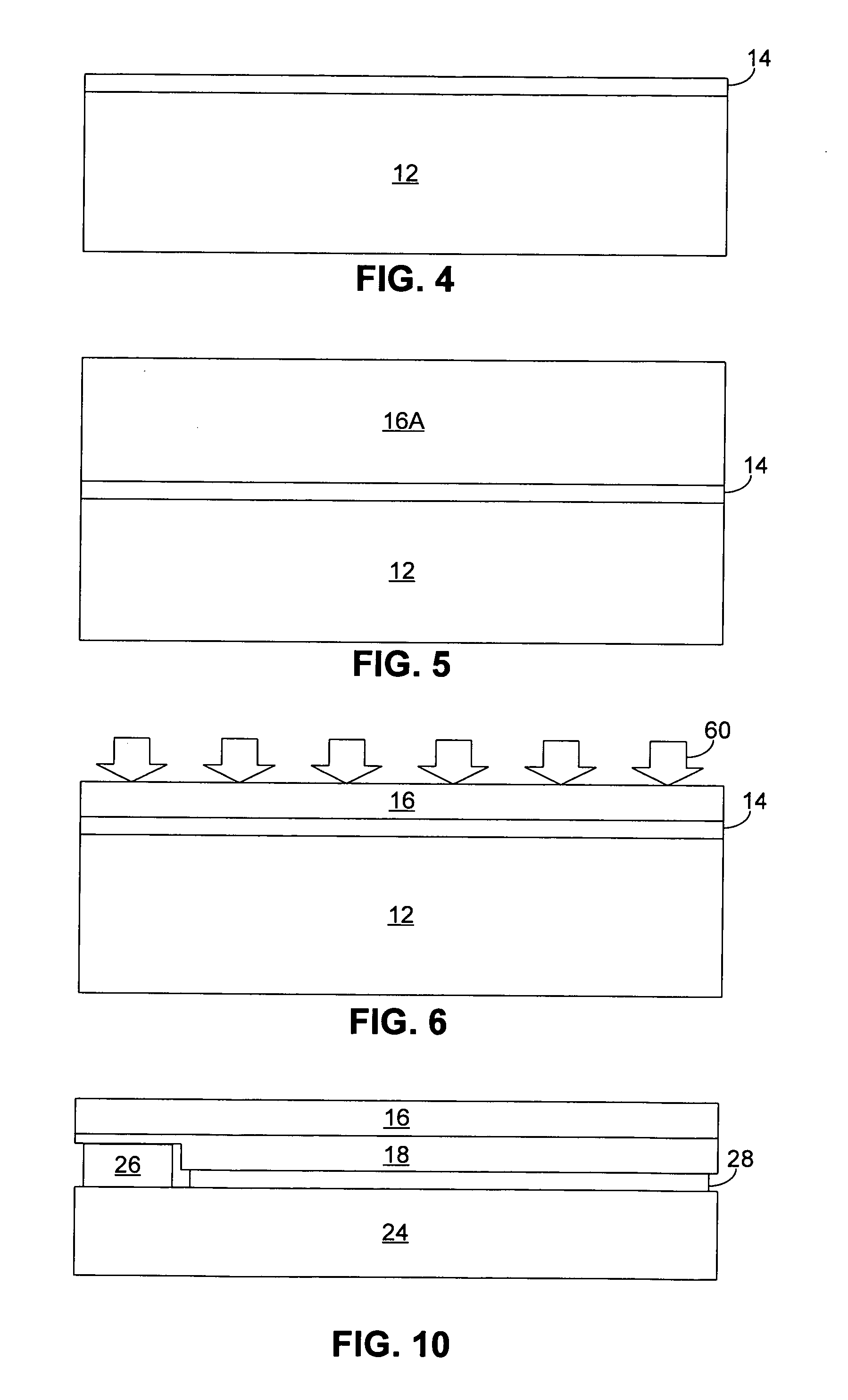

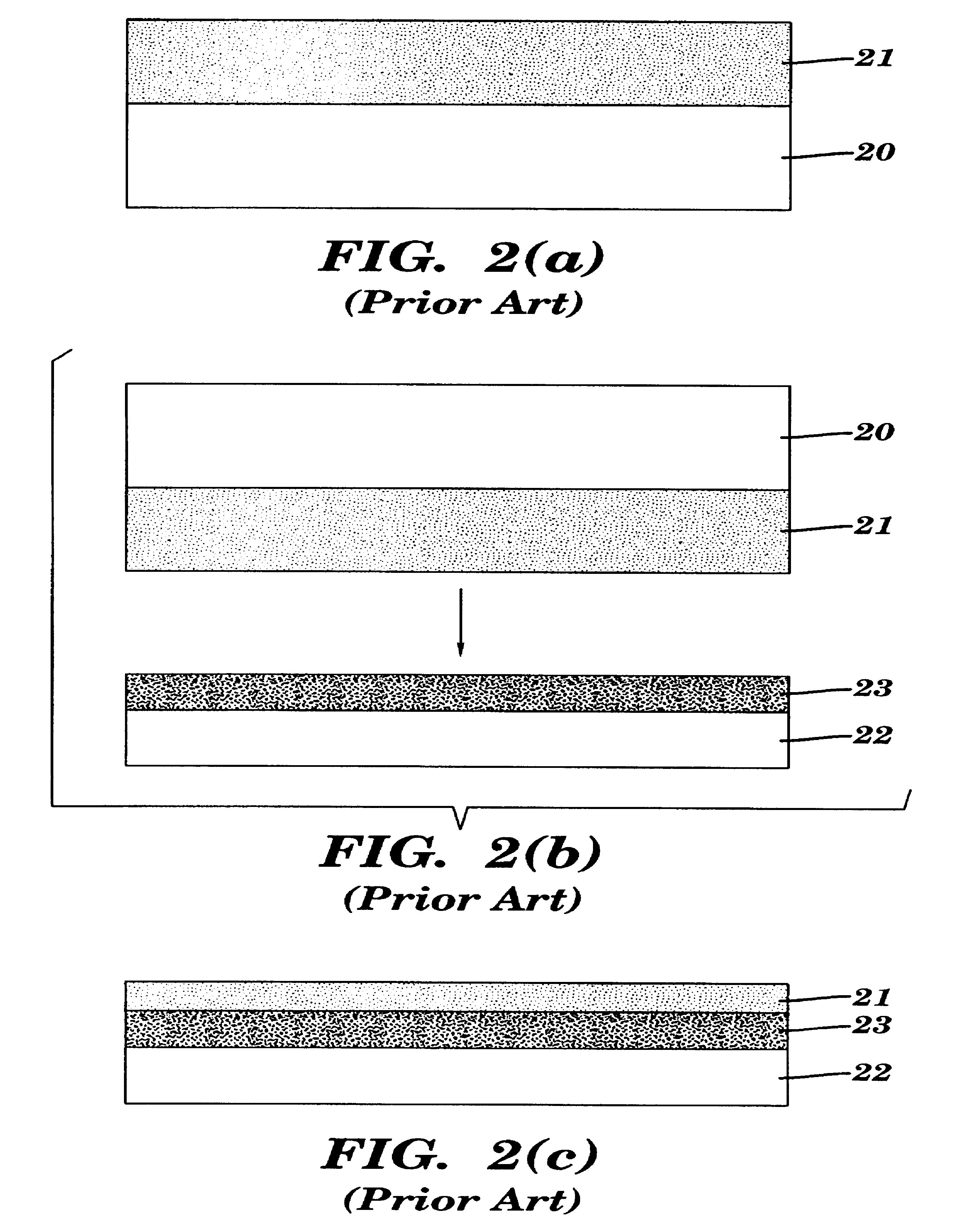

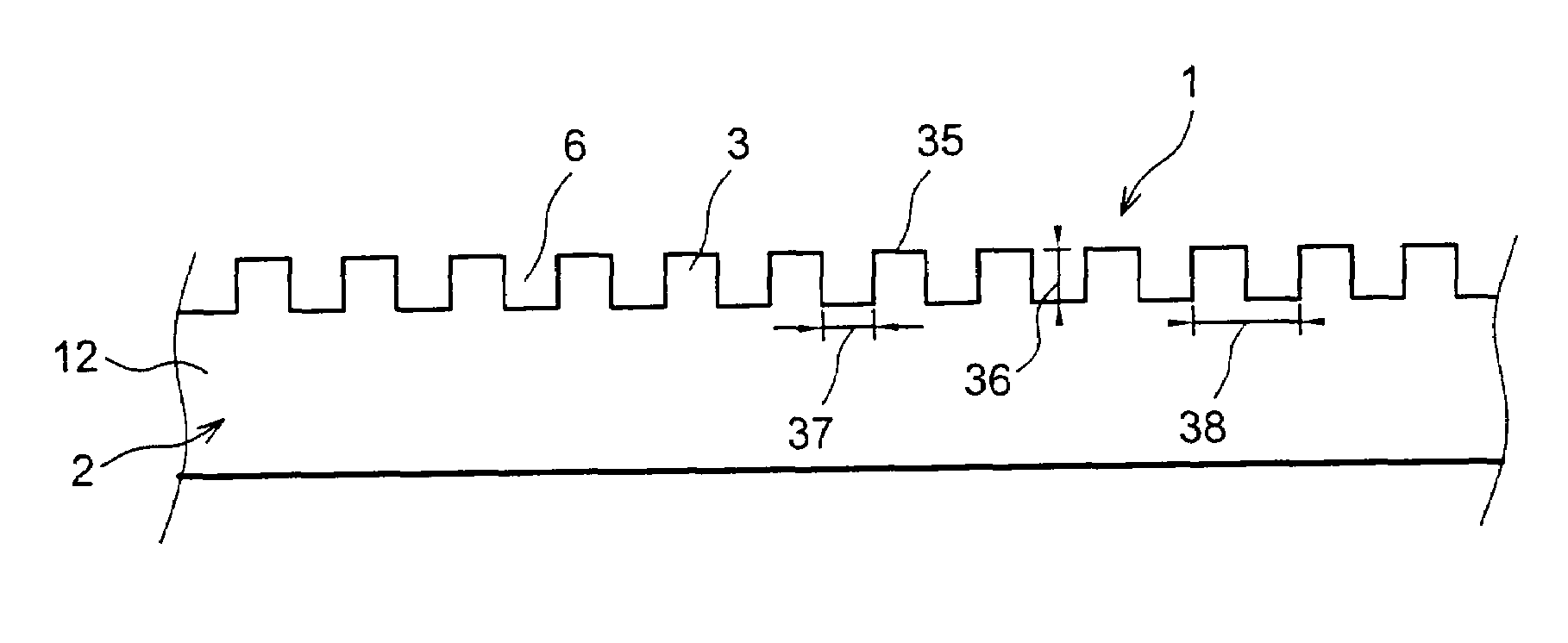

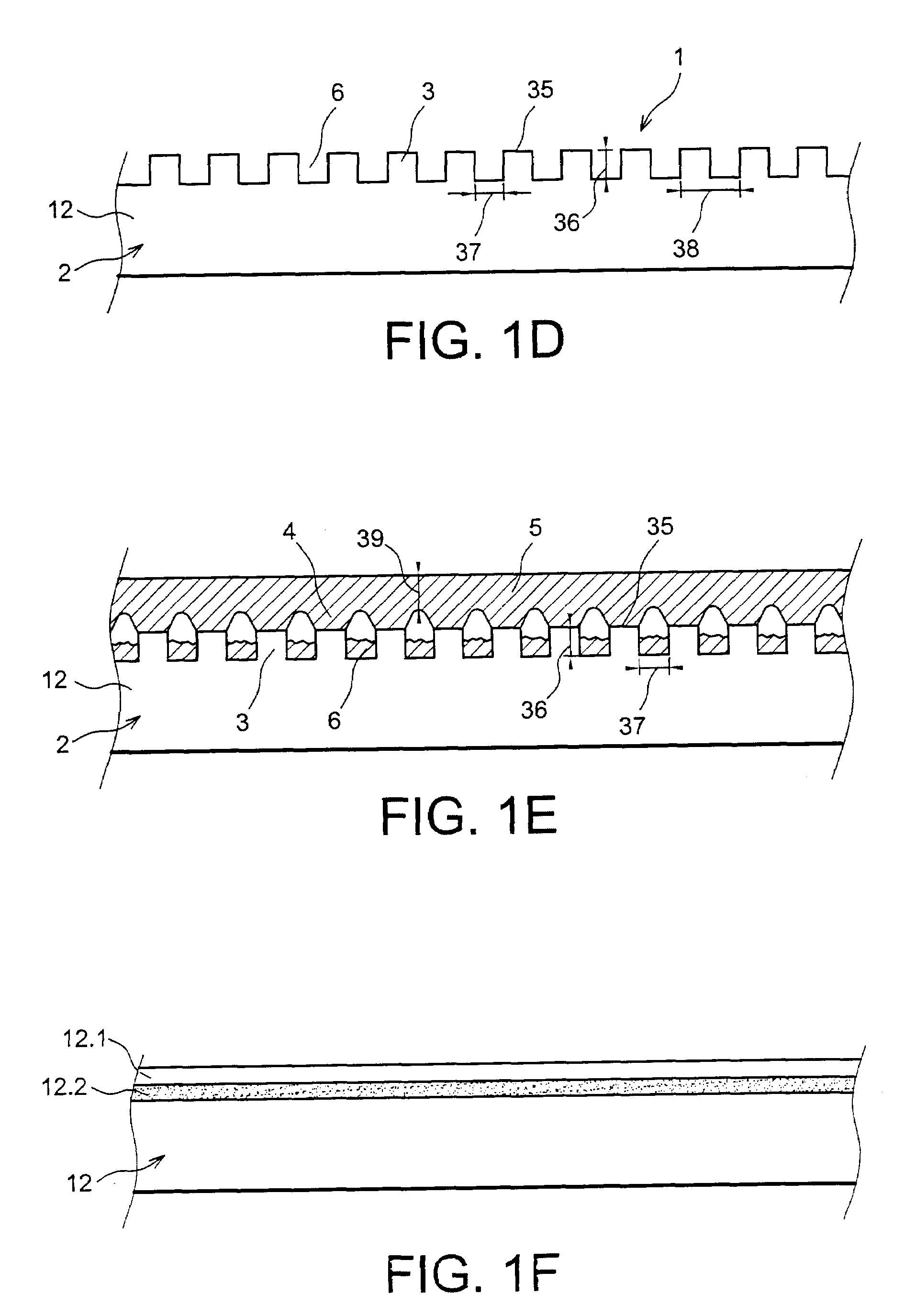

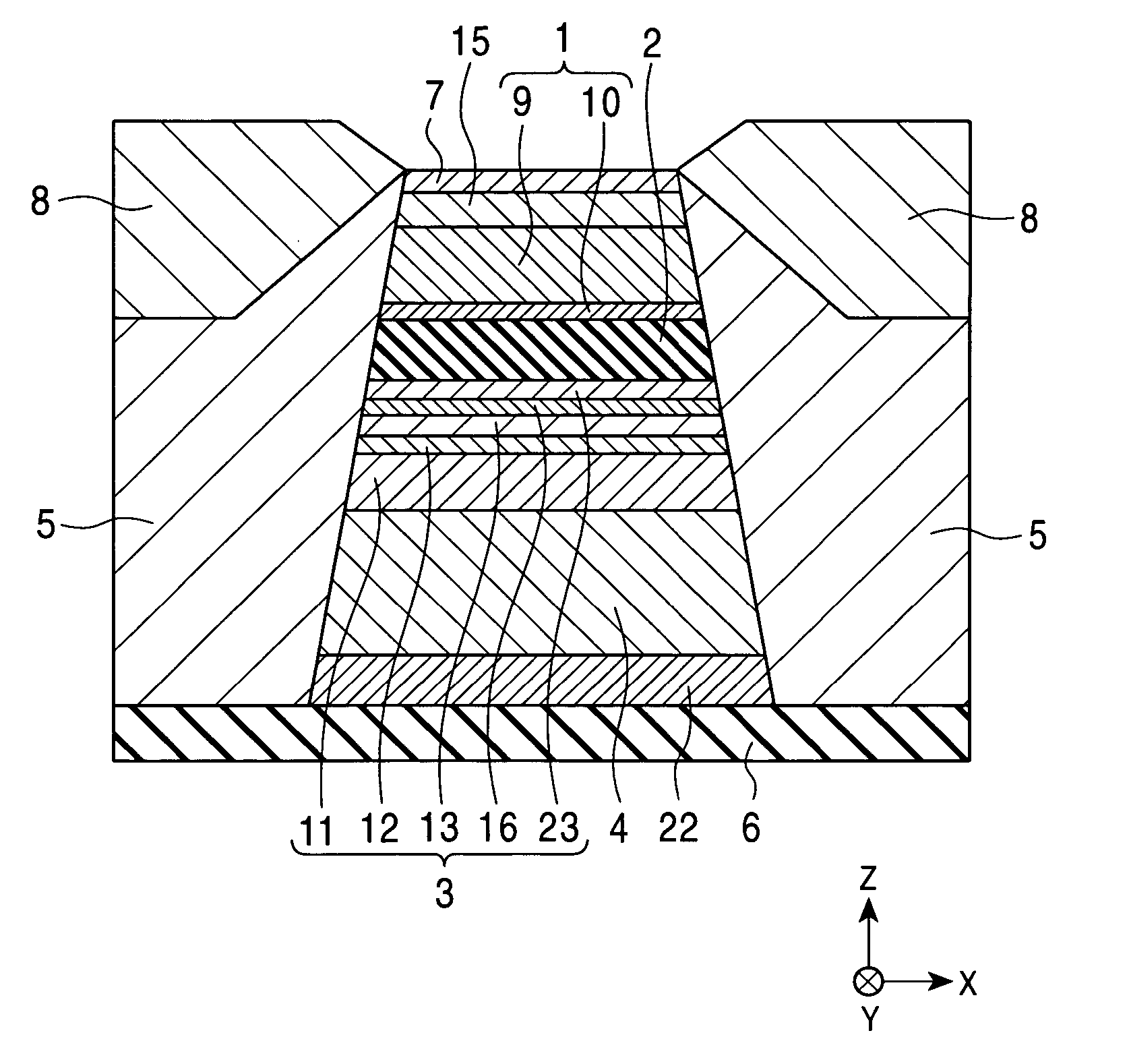

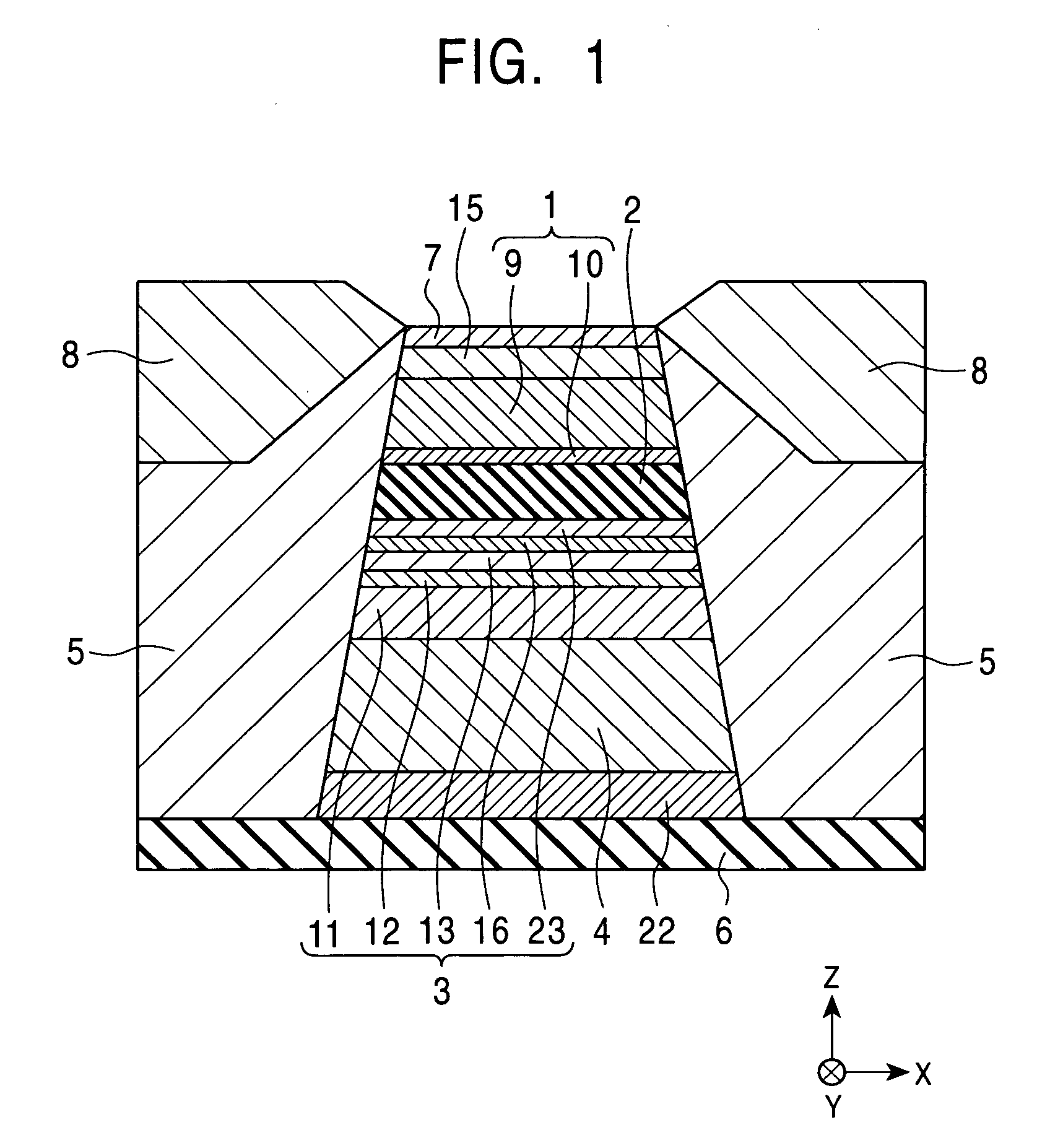

Simplified Method of Producing an Epitaxially Grown Structure

InactiveUS20080272396A1Increase surface areaObtained economicallyAfter-treatment detailsSemiconductor/solid-state device manufacturingBond interfaceLattice mismatch

Method to produce a structure consisting of depositing a material by columnar epitaxy on a crystalline face of a substrate (2), of continuing so that the columns (4) give a continuous layer (5). The surface is provided with a period array of bumps (3) on a nanometric scale, each bump (3) having a support zone (35) and being obtained from an array of crystalline defects and / or strain fields created within a crystalline region (16) located in the vicinity of a bonding interface (15) between two crystalline elements (11, 12) whose crystalline lattices have a twist and / or tilt angle and / or have interfacial lattice mismatch, able to condition the period (38) of the array of bumps (3). The period (38) of the array, the height (36) of the bumps and the size of their support zone (35) being adjusted so that the continuous layer (40) has a critical thickness that is greater than that obtained using epitaxy without the bumps.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

Ferroelectric layer with domains stabilized by strain

ActiveUS20090155931A1Polycrystalline material growthFerroelectric carrier recordingRoom temperatureCritical thickness

The present invention describes a method including: providing a substrate; forming an underlying layer over the substrate; heating the substrate; forming a ferroelectric layer over the underlying layer, the ferroelectric layer having a thickness below a critical thickness, the underlying layer having a smaller lattice constant than the ferroelectric layer; cooling the substrate to room temperature; and inducing a compressive strain in the ferroelectric layer.

Owner:INTEL CORP

Photodetector with hetero-structure using lateral growth

InactiveUS20050127275A1Increase speedRapid responseFinal product manufactureMaterial analysis by optical meansPhotovoltaic detectorsPhotodetector

A structure and method of fabrication for a Si based material p-i-n photodetector is disclosed. The light is absorbed in an undoped layer containing SiGe or Ge in such a manner that the absorption length is not limited by a critical thickness of the SiGe or Ge layer. The result is achieved by growing the SiGe or Ge layer from the walls of a trench in monocrystalline Si using lateral epitaxial. A second, doped material is disposed over the undoped layer for biasing and photocarrier collection in the p-i-n diode.

Owner:IBM CORP

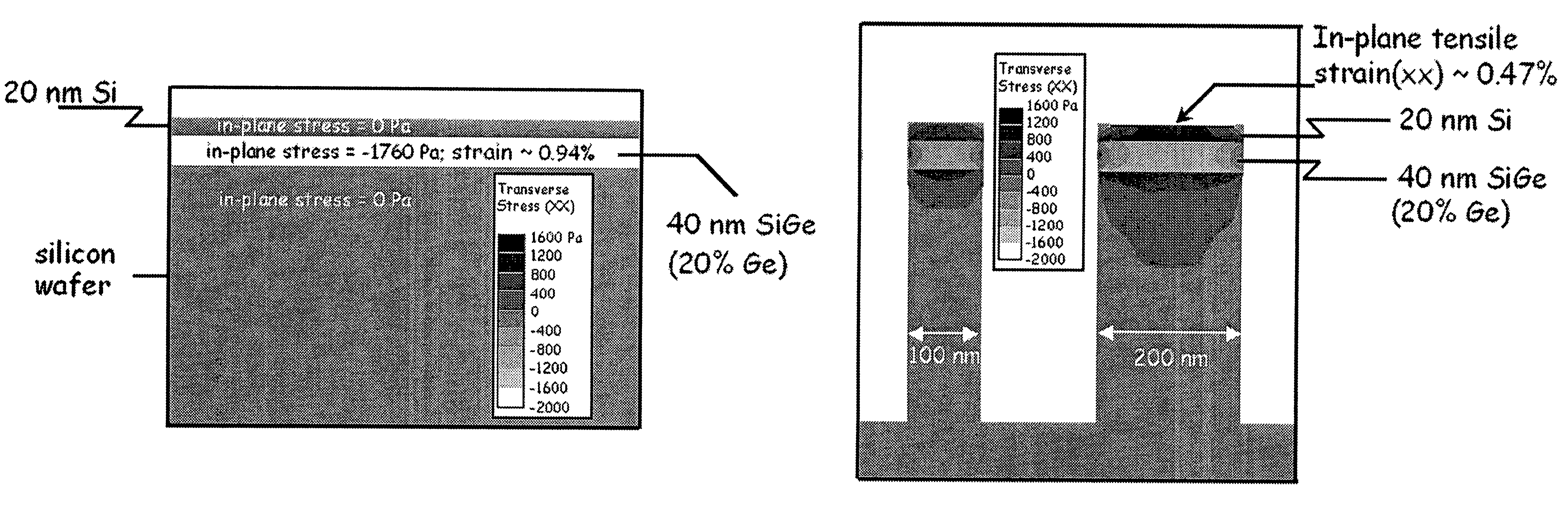

Strained silicon with elastic edge relaxation

ActiveUS7338834B2Semiconductor/solid-state device manufacturingSemiconductor devicesTensile strainStrain energy

A thin blanket epitaxial layer of SiGe is grown on a silicon substrate to have a biaxial compressive stress in the growth plane. A thin epitaxial layer of silicon is deposited on the SiGe layer, with the SiGe layer having a thickness less than its critical thicknesses. Shallow trenches are subsequently fabricated through the epitaxial layers, so that the strain energy is redistributed such that the compressive strain in the SiGe layer is partially relaxed elastically and a degree of tensile strain is induced to the neighboring layers of silicon. Because this process for inducing tensile strain in a silicon over-layer is elastic in nature, the desired strain may be achieved without formation of misfit dislocations.

Owner:ACORN TECH INC

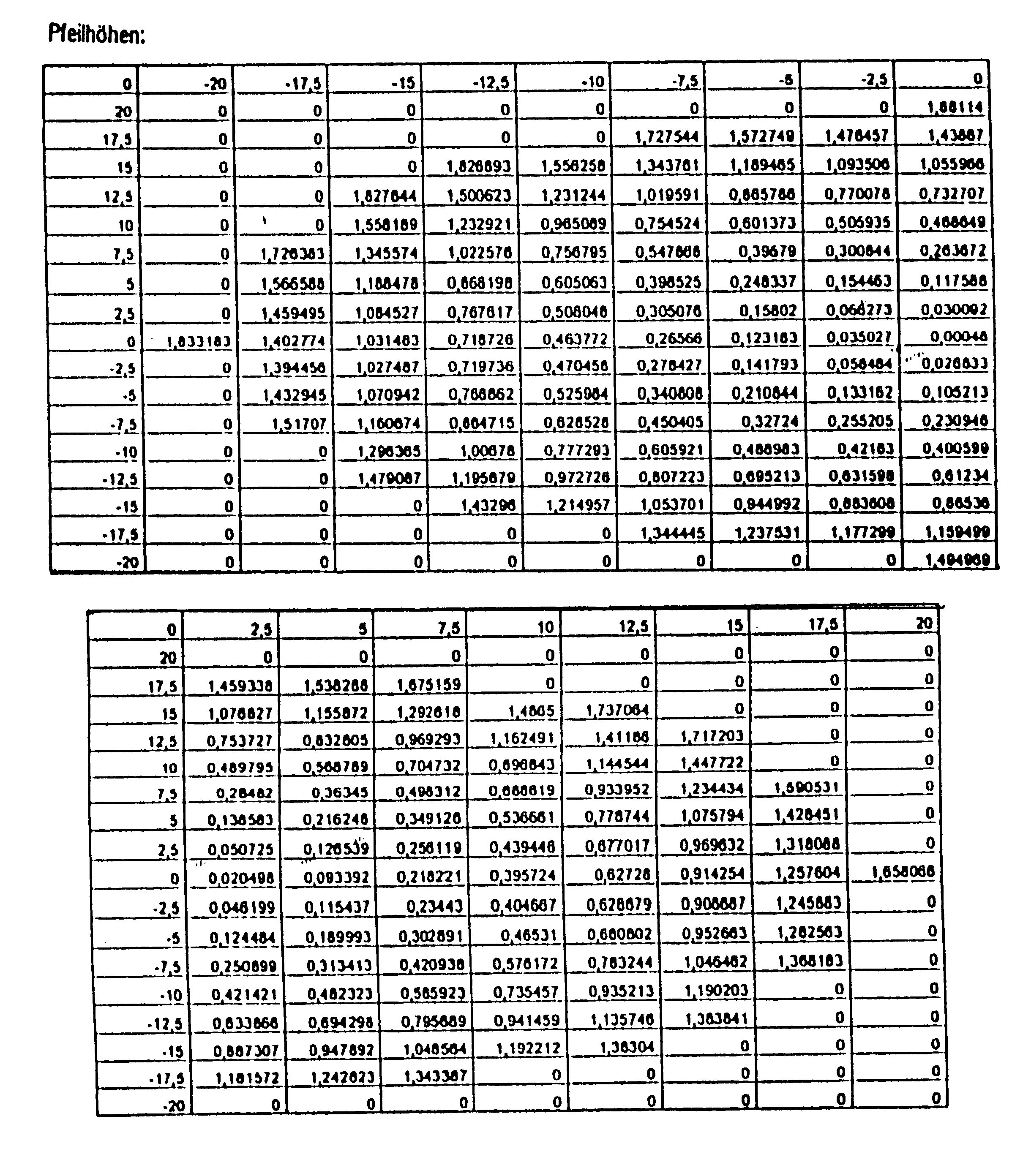

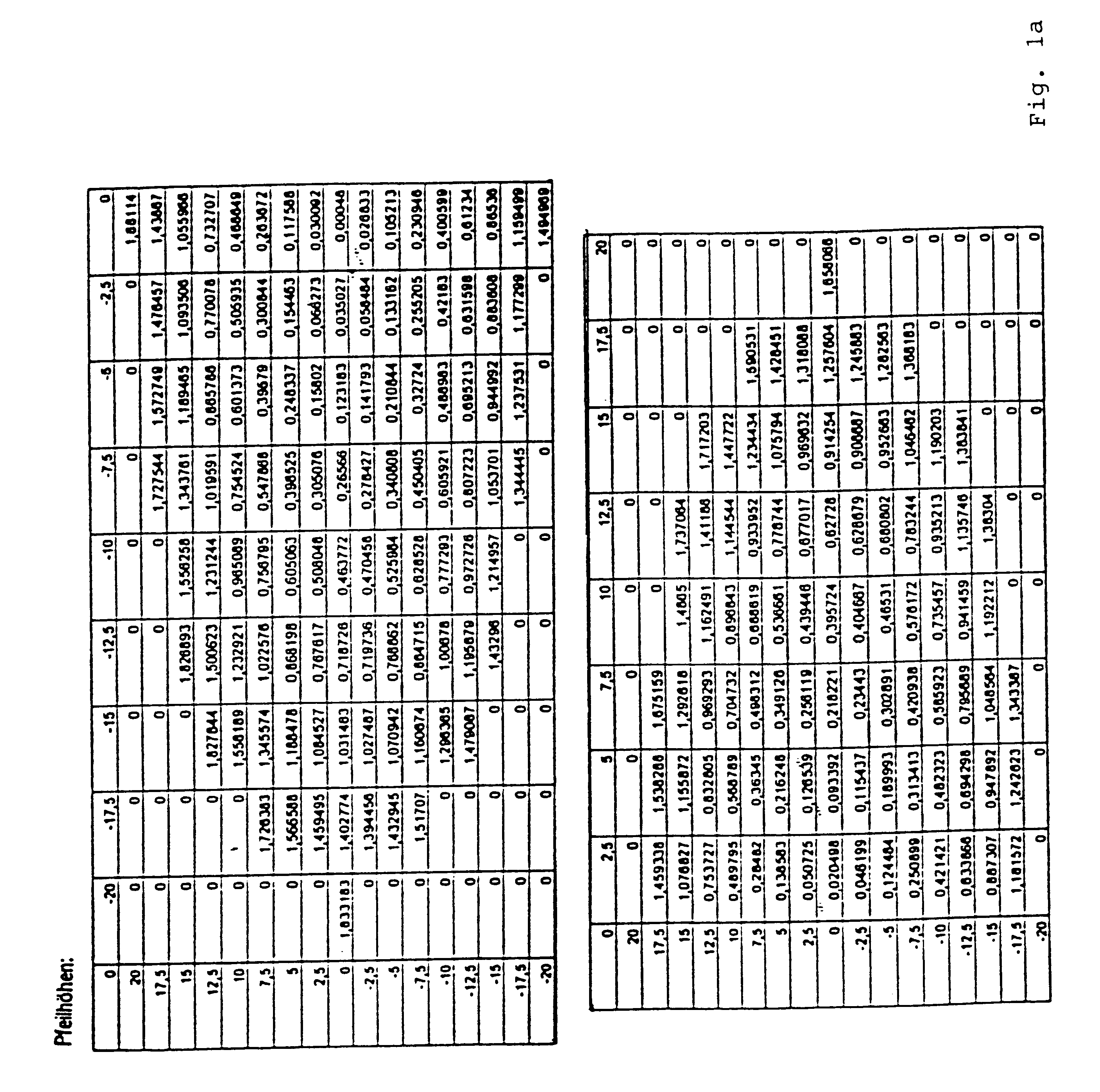

Method for producing eyeglasses

What is described here is a method of manufacturing spectacles comprising individual progressive ophthalmic lenses, including the following steps:selection of a spectacle frame,detection of the shape of the lens rings with a precision better than ±0.5 mm in the x- and y-directions (data set 1),detecting the intersection points of the lines of sight through the plane of the lens rings for at least two design distances of the progressive ophthalmic lenses with a precision better than ±1 mm (data set 2)selection and positioning relative to the lens rings of a spherical or non-spherical surface in view of the prescription data, using the data sets 1 and 2 (data set 3),computing and positioning the progressive surface relative to the selected surface, with minimization of the critical thickness of the ophthalmic lens, using the data sets 1 to 3 (data set 4),manufacturing the progressive surfaces as well as edges of the ophthalmic lenses from a non-edged semi-finished product finished on one side, using the data sets 1 to 4.

Owner:RODENSTOCK GMBH

Light emitting devices with layered III-V semiconductor structures, and modules and systems for computer, network and optical communication, using such device

InactiveUS6657233B2Improve crystal qualityFacilitates layerLaser detailsLaser active region structureQuantum wellCharge carrier

A semiconductor light emitting device is disclosed, including a semiconductor substrate, an active region comprising a strained quantum well layer, and a cladding layer for confining carriers and light emissions, wherein the amount of lattice strains in the quantum well layer is in excess of 2% against either the semiconductor substrate or cladding layer and, alternately, the thickness of the quantum well layer is in excess of the critical thickness calculated after Matthews and Blakeslee.

Owner:RICOH KK

Strained silicon with elastic edge relaxation

ActiveUS20070215859A1Less thicknessSemiconductor/solid-state device manufacturingSemiconductor devicesTensile strainStrain energy

A thin blanket epitaxial layer of SiGe is grown on a silicon substrate to have a biaxial compressive stress in the growth plane. A thin epitaxial layer of silicon is deposited on the SiGe layer, with the SiGe layer having a thickness less than its critical thicknesses. Shallow trenches are subsequently fabricated through the epitaxial layers, so that the strain energy is redistributed such that the compressive strain in the SiGe layer is partially relaxed elastically and a degree of tensile strain is induced to the neighboring layers of silicon. Because this process for inducing tensile strain in a silicon over-layer is elastic in nature, the desired strain may be achieved without formation of misfit dislocations.

Owner:ACORN TECH INC

Light emitting devices with layered III-V semiconductor structures, and modules and systems for computer, network and optical communication, using such device

InactiveUS20010030319A1Improve crystal qualityGood temperature characteristicsLaser detailsLaser active region structureSemiconductor structureQuantum well

A semiconductor light emitting device is disclosed, including a semiconductor substrate, an active region comprising a strained quantum well layer, and a cladding layer for confining carriers and light emissions, wherein the amount of lattice strains in the quantum well layer is in excess of 2% against either the semiconductor substrate or cladding layer and, alternately, the thickness of the quantum well layer is in excess of the critical thickness calculated after Matthews and Blakeslee.

Owner:RICOH KK

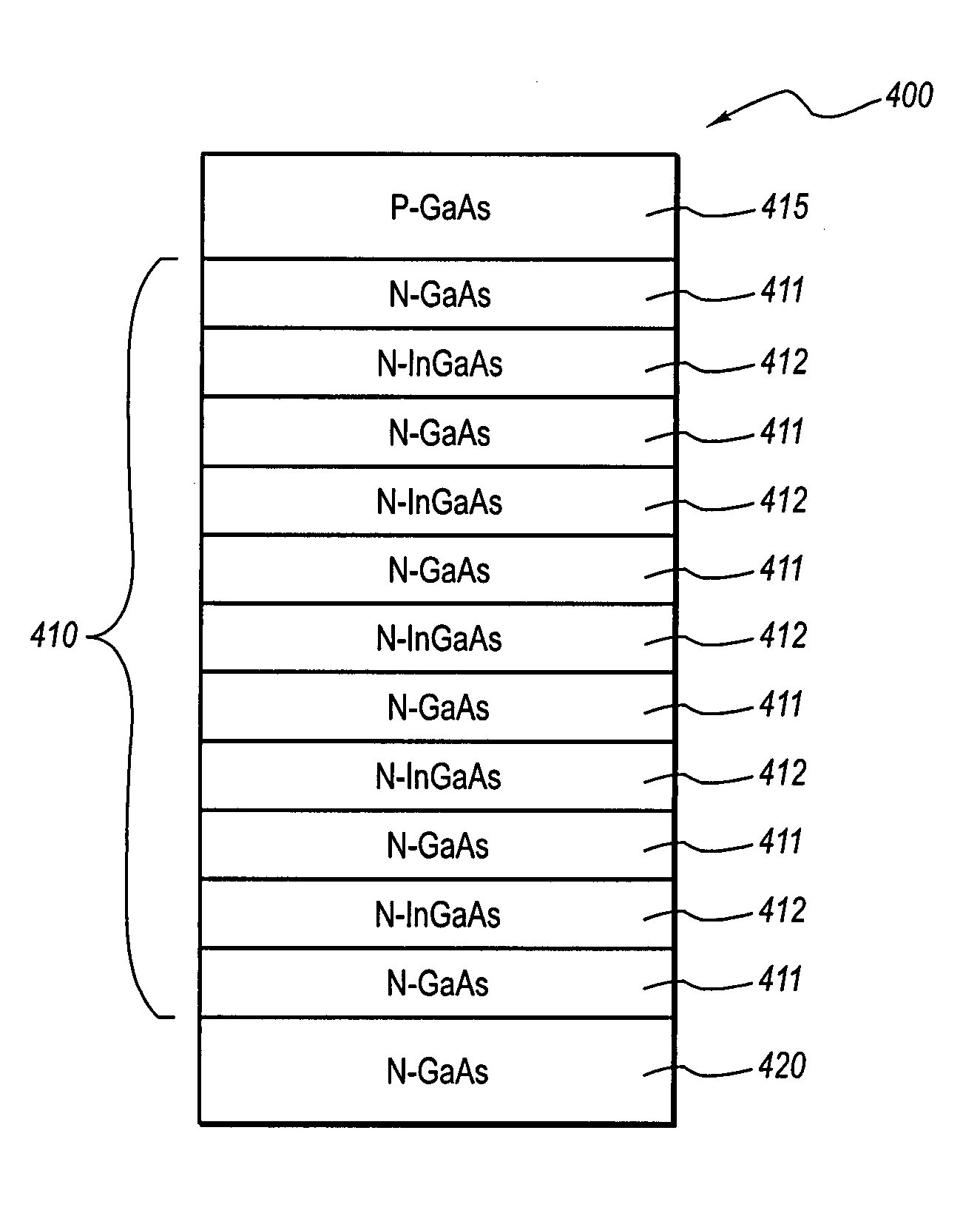

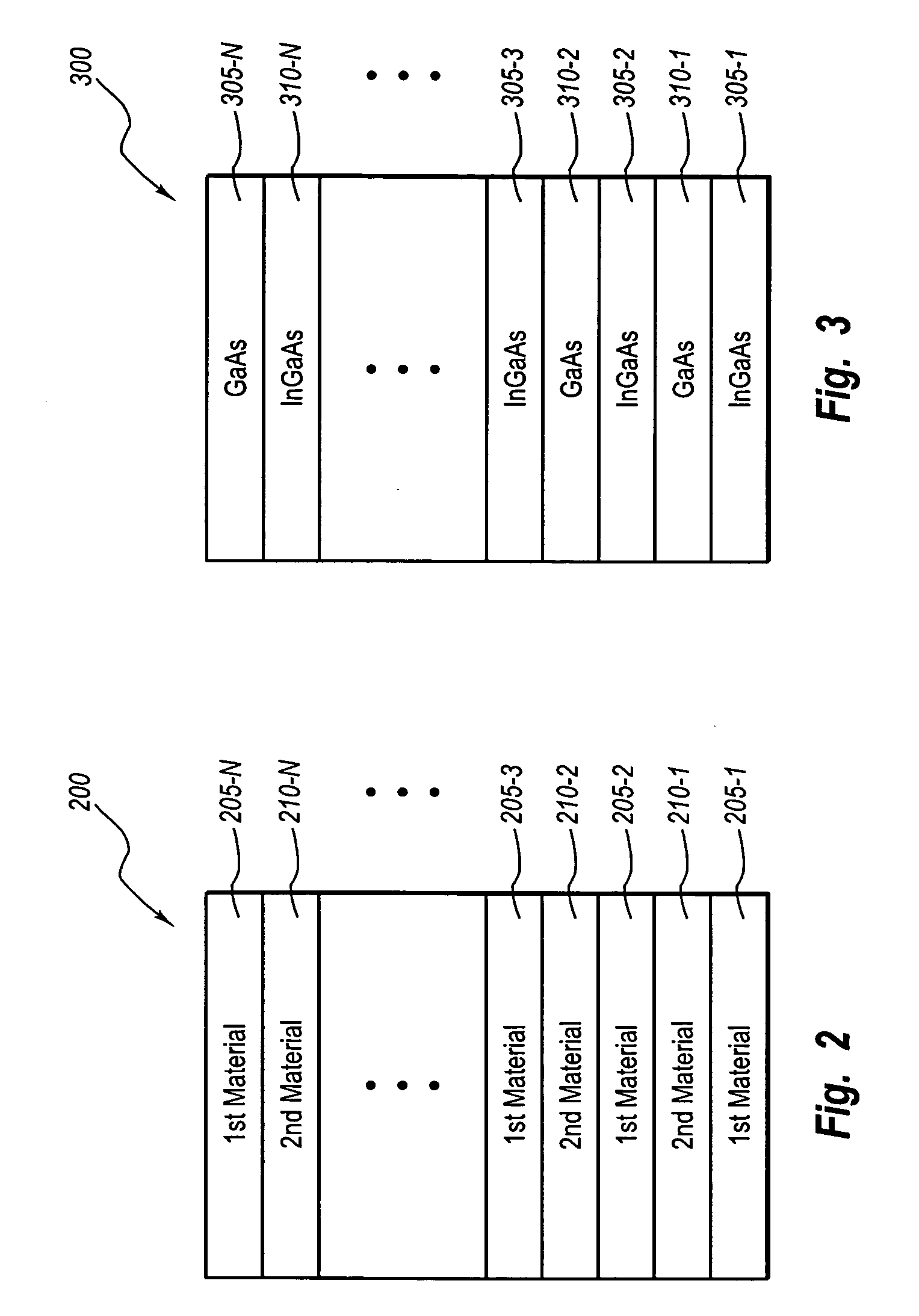

Super lattice tunnel junctions

InactiveUS20060011938A1Smooth connectionLower resistanceLaser detailsSemiconductor lasersSemiconductor materialsCritical thickness

Super lattice structures in conjunction with a tunnel junction to provide an improved contact for multiple components. The tunnel junctions can include a first semiconductor material having a resistance parameter for conducting a current and a second semiconductor material having a resistance parameter that is more restrictive to conduction of a current than the resistance parameter of the first semiconductor material. The first semiconductor material can have a critical thickness at which lattice matching of the first semiconductor material causes dislocation. The second semiconductor material can have a critical thickness at which lattice matching of the second semiconductor material causes dislocation that is thicker than the critical thickness of the first semiconductor material. The tunnel junction can be used in a monolithically manufactured photo transmitter and receiver design.

Owner:II VI DELAWARE INC

Integrated planar composite coupling structures for bi-directional light beam transformation between a small mode size waveguide and a large mode size waveguide

InactiveUS20060062521A1Reduce manufacturing costReduce sensitivityCoupling light guidesOptical waveguide light guideRefractive index contrastTransformer

Composite optical waveguide structures or mode transformers and their methods of fabrication and integration are disclosed, wherein the structures or mode transformers are capable of bidirectional light beam transformation between a small mode size waveguide and a large mode size waveguide. One aspect of the present invention is directed to an optical mode transformer comprising a waveguide core having a high refractive index contrast between the waveguide core and the cladding, the optical mode transformer being configured such that the waveguide core has a taper wherein a thickness of the waveguide core tapers down to a critical thickness value, the critical thickness value being defined as a thickness value below which a significant portion of the energy of a light beam penetrates into the cladding layers surrounding the taper structure thereby enlarging the small mode size.

Owner:HO SENG TIONG

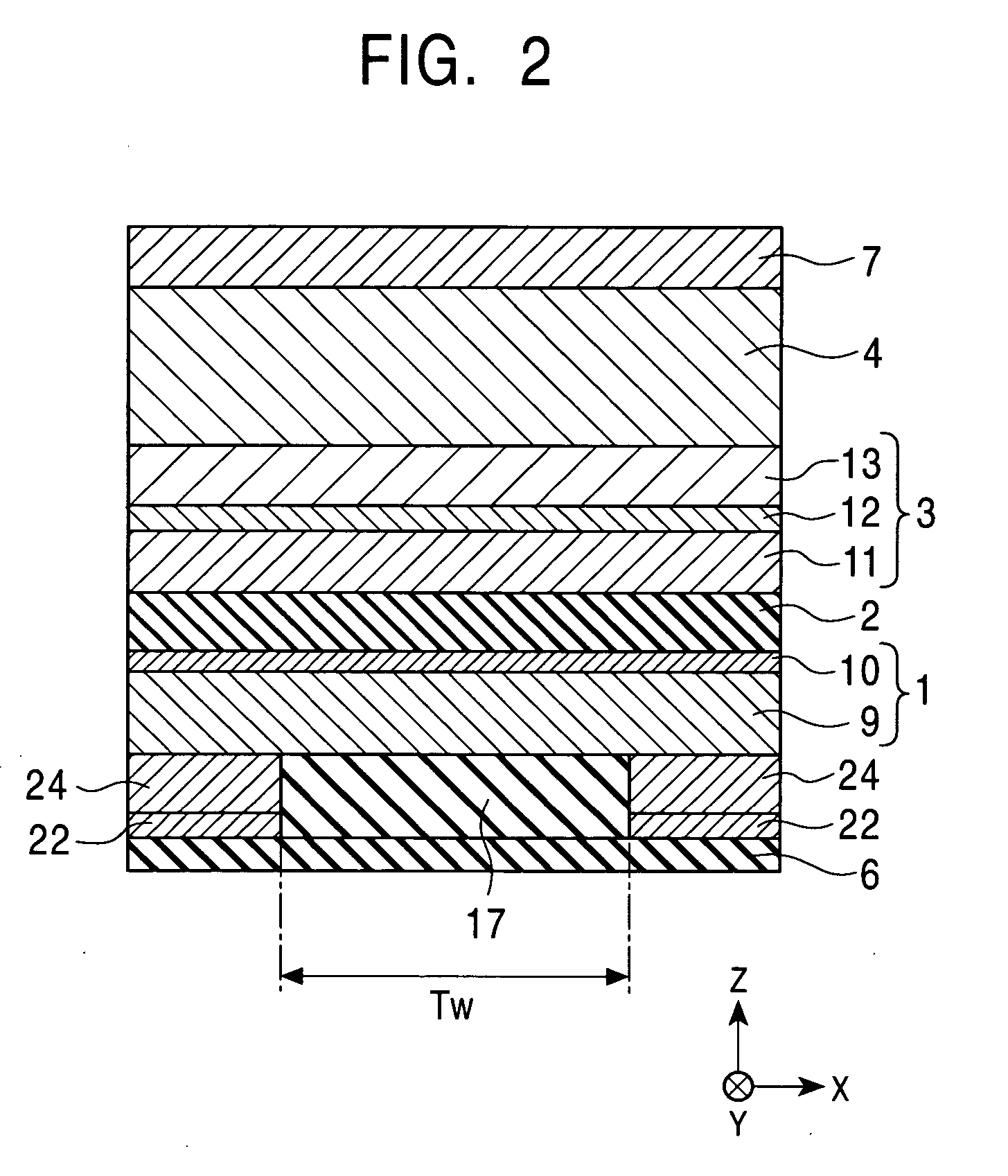

Exchange-coupled film, method for making exchange-coupled film, and magnetic sensing element including exchange-coupled film

InactiveUS20050024793A1Improve surface wettabilityImprove wettabilityNanostructure applicationNanomagnetismCritical thicknessOptoelectronics

An exchange-coupled film includes a seed layer, an antiferromagnetic layer, and a ferromagnetic layer. The seed layer is formed at a thickness that is larger than the critical thickness, and the thickness of the seed layer is then decreased by etching so as to be smaller than or equal to the critical thickness. Thereby, a crystalline phase which extends through the seed layer from the upper surface to the lower surface can be formed, and / or the average size, in a direction parallel to the layer surface, of the crystal grains in the seed layer can be set to be larger than the thickness of the seed layer. Consequently, a large exchange coupling magnetic field Hex can be generated between the antiferromagnetic layer and the ferromagnetic layer.

Strained silicon on a SiGe on SOI substrate

ActiveUS20050106790A1Solve the real problemTransistorSemiconductor/solid-state device manufacturingCapacitanceSoi substrate

A semiconductor device with an undercut relaxed SiGe layer having voids beneath the SiGe layer. The voids may be filled with a dielectric such as SiO2. A strained Si layer may be epitaxially grown on the relaxed SiGe layer to combine the benefits of a defect-free strained Si surface and a silicon-on-insulator substrate. The relaxed SiGe layer may be relatively thin, with a thickness below the critical thickness. Thus, the structure accommodates shallow junctions, which exhibit reduced junction capacitance.

Owner:GLOBALFOUNDRIES US INC

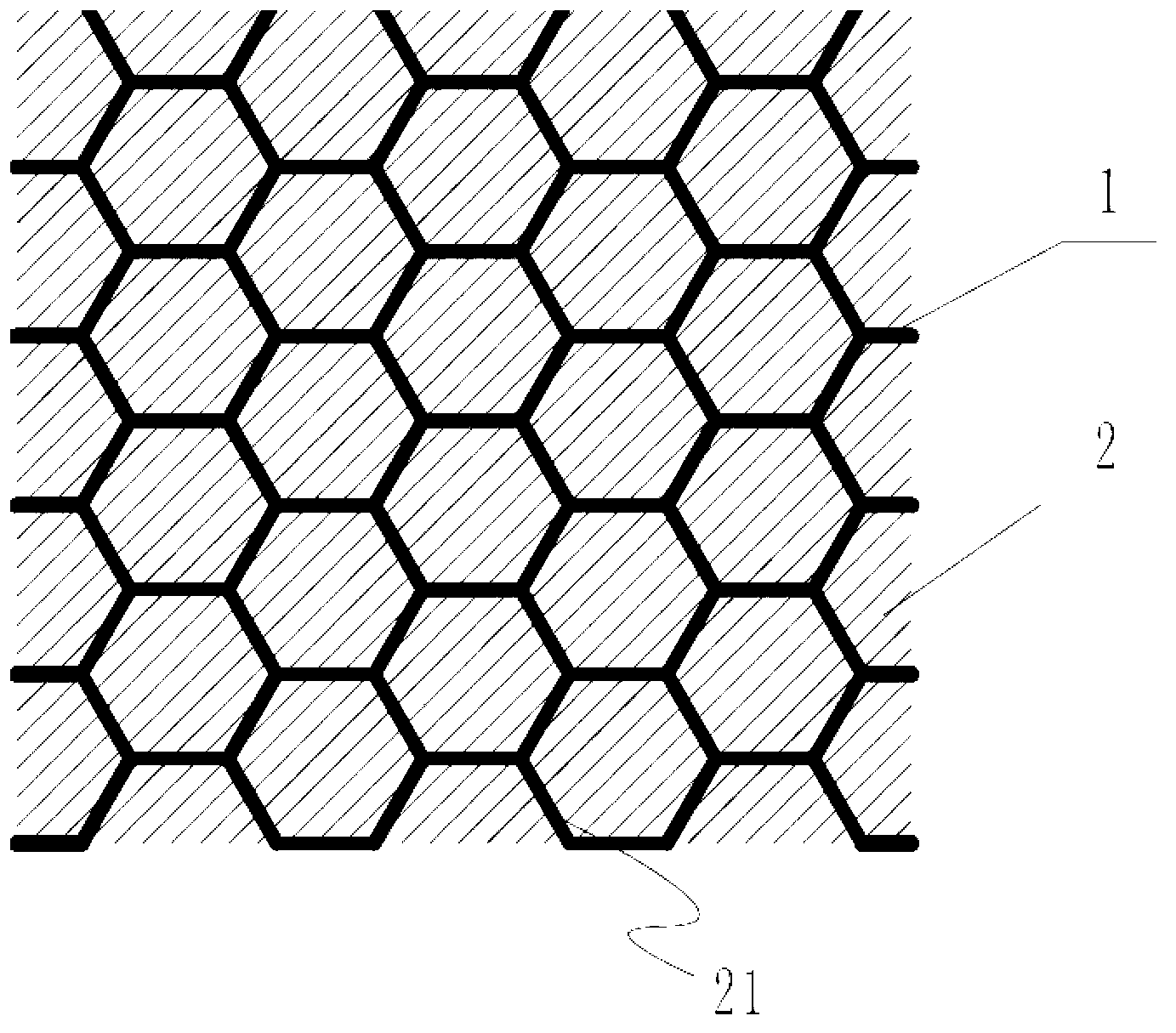

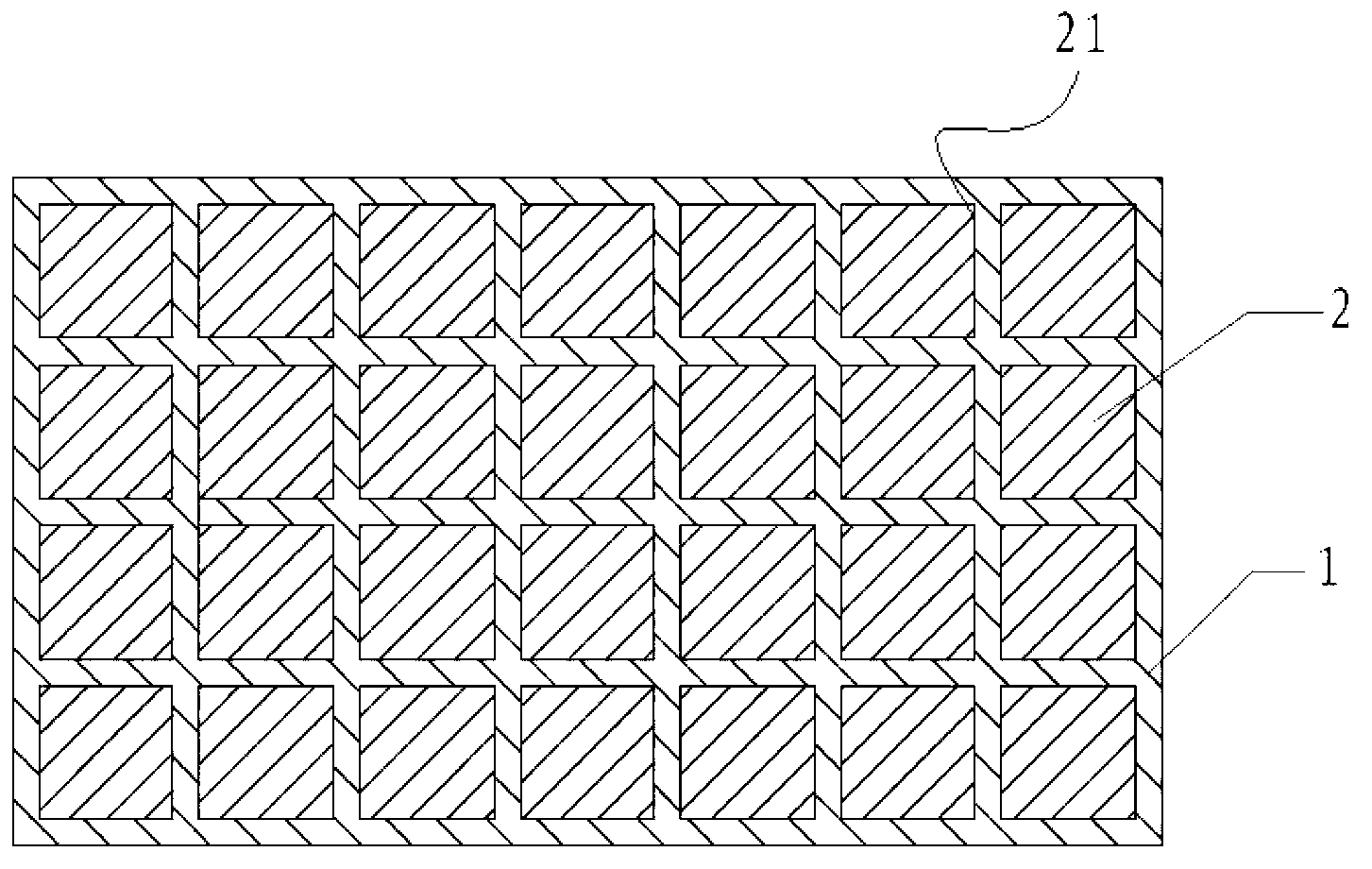

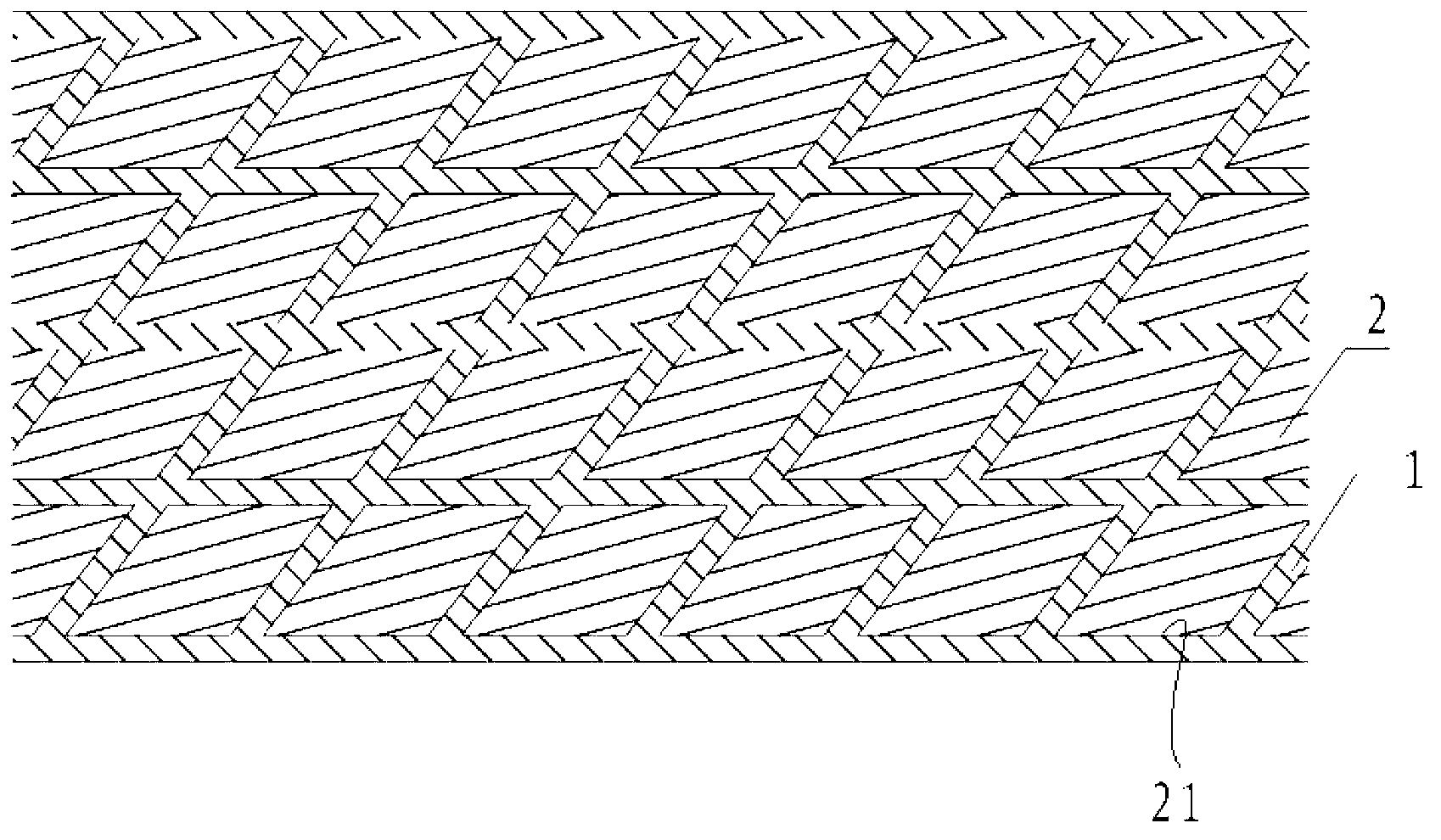

Special structural explosive for explosive cladding, explosive cladding method and explosive cladding device

ActiveCN103317222ASave explosivesReduce critical thicknessNon-electric welding apparatusShock waveExplosive cladding

The invention discloses special structural explosive for explosive cladding, an explosive cladding method and an explosive cladding device. The structural explosive comprises a filling plate, a plurality of cavities filled with the explosive are formed in the filling plate and distributed in a matrix. The special structural explosive for explosive cladding is formed by filling or injecting the explosive in the cavities of the filling plate. A layer of composite plate is mounted on each of two sides of the structural explosive, and the two composite plates are driven to move reversely after explosion to composite with two base plates in reserve directions. By the aid of an explosive filling method, explosive filling quality is guaranteed, critical thickness of stable explosive detonation is reduced, and energy utilization rate of explosive explosion is improved. The special structural explosive is convenient to use, and mechanized batch production can be realized. By the aid of the explosive cladding device, usage amount of the explosive is lowered, production cost is reduced, shock wave and noise pollution are reduced, and working environment of workers is improved.

Owner:UNIV OF SCI & TECH OF CHINA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com