Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

825 results about "Defect free" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

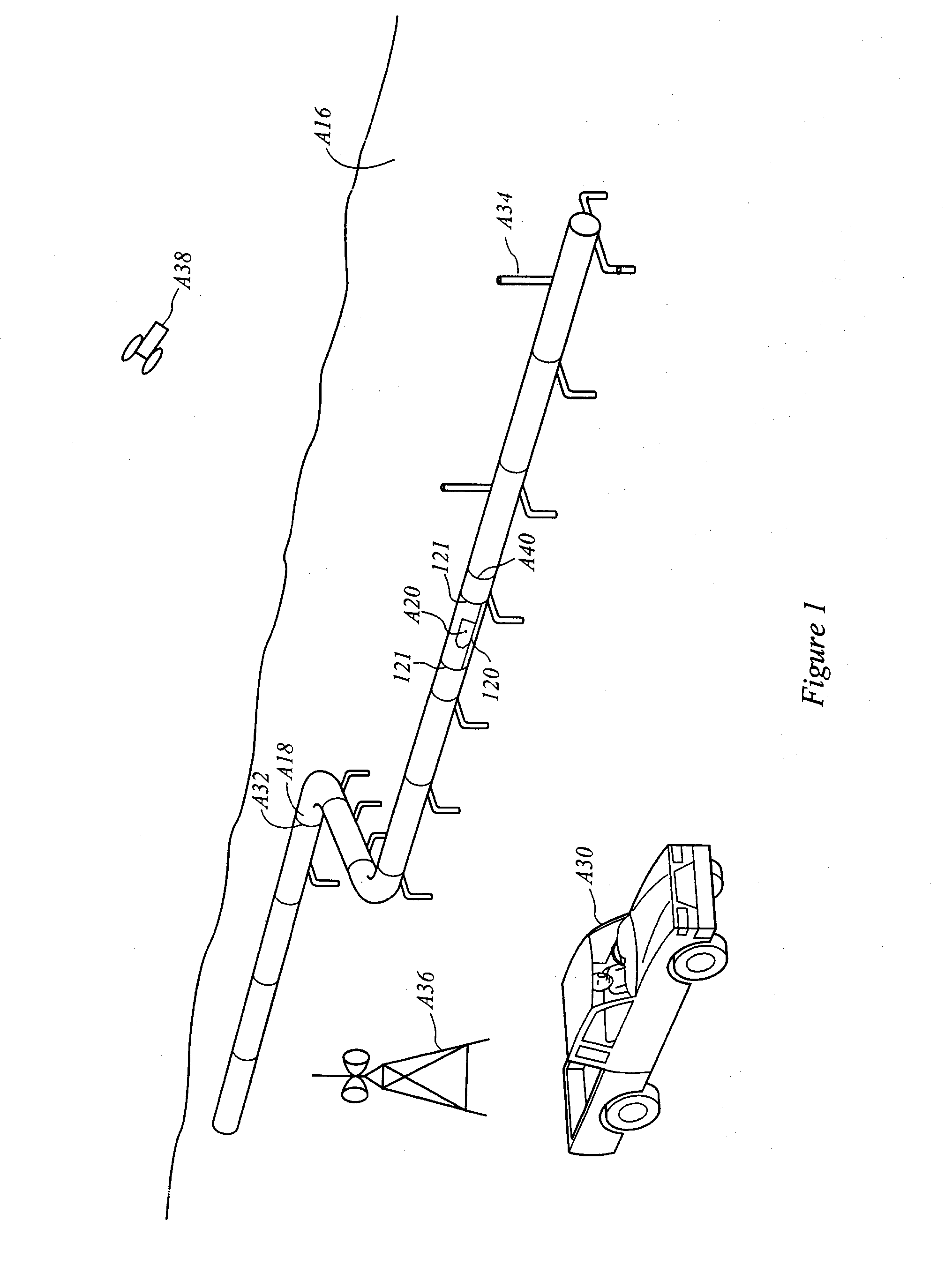

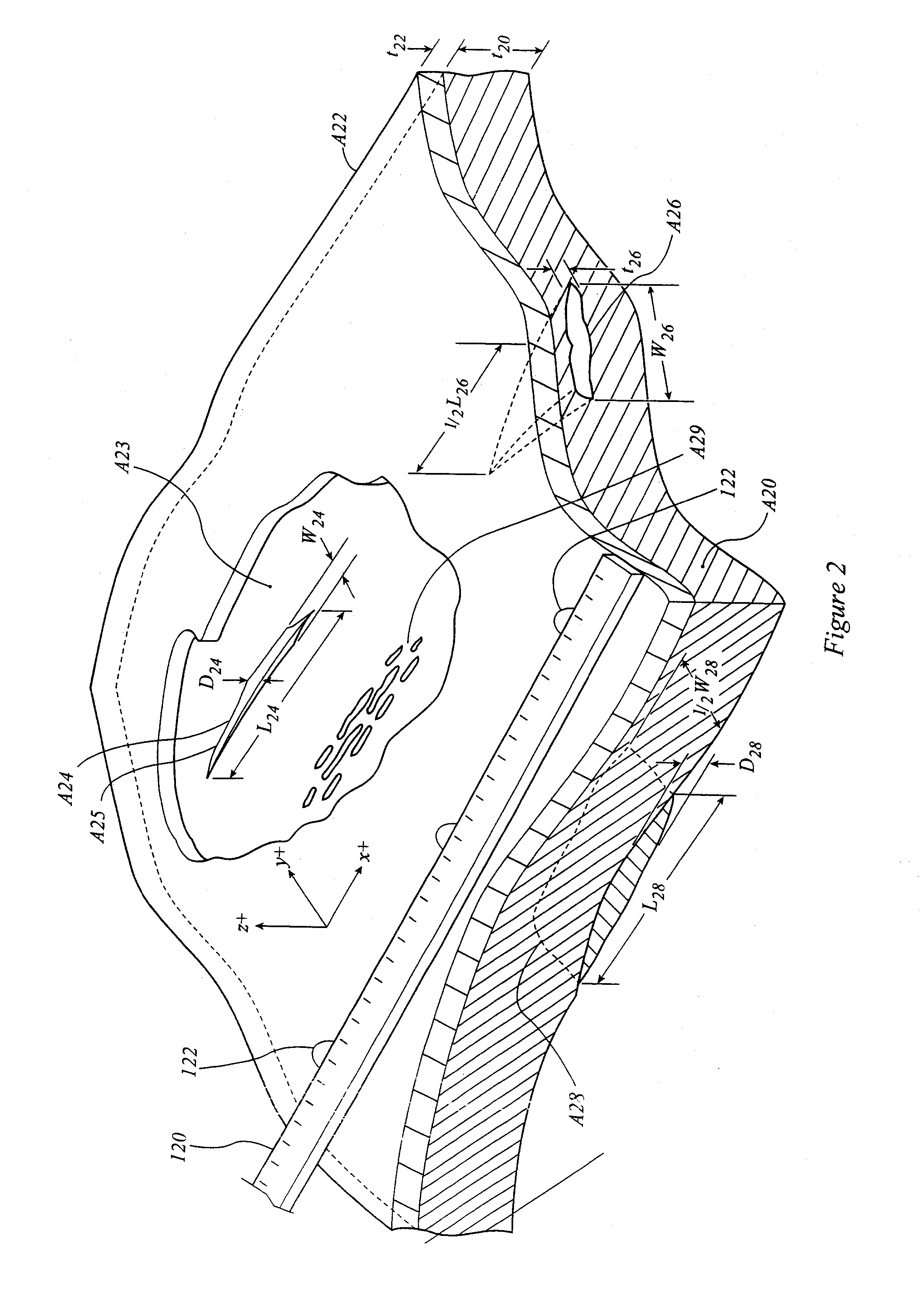

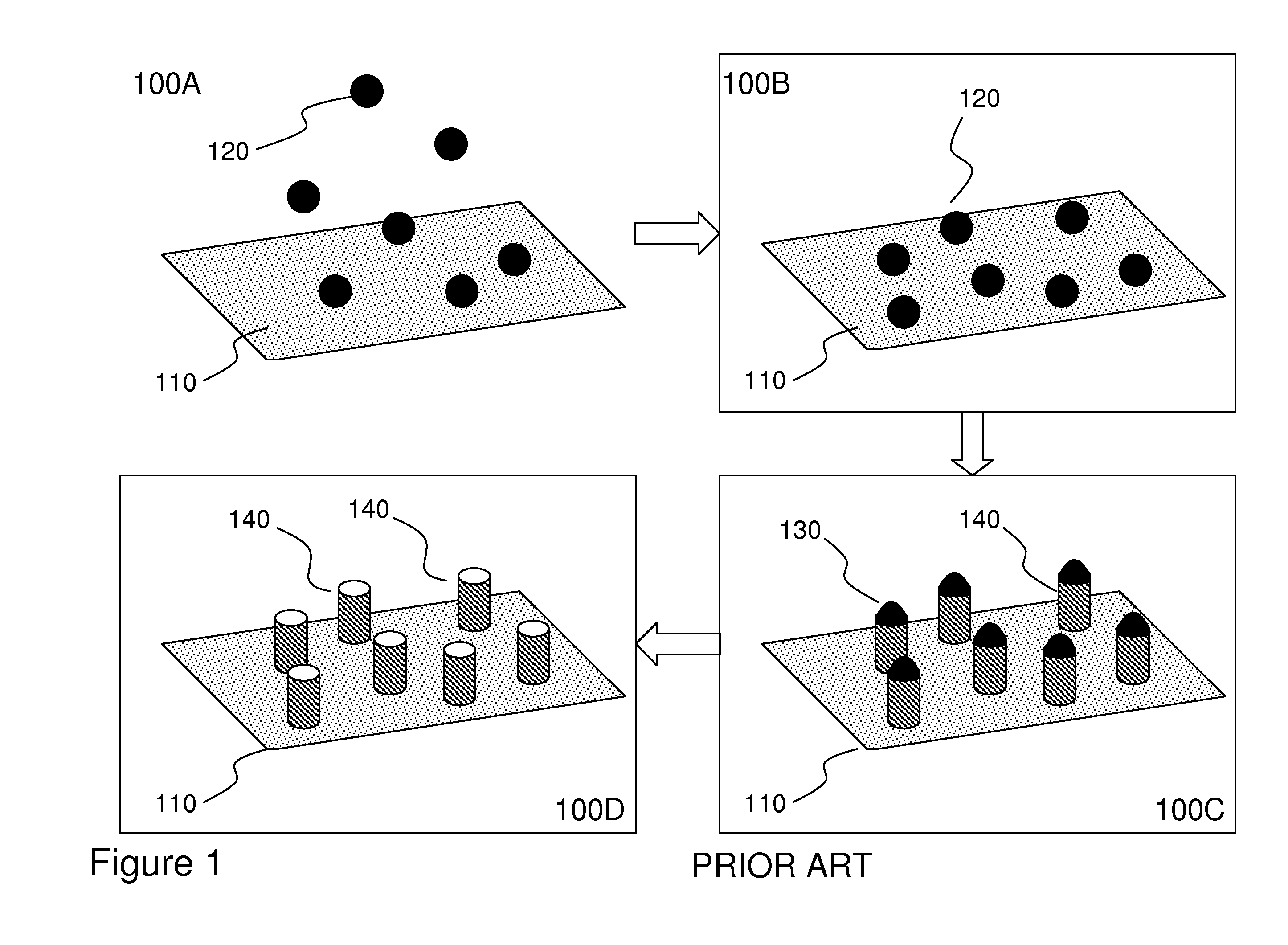

Systems and methods for additive manufacturing and repair of metal components

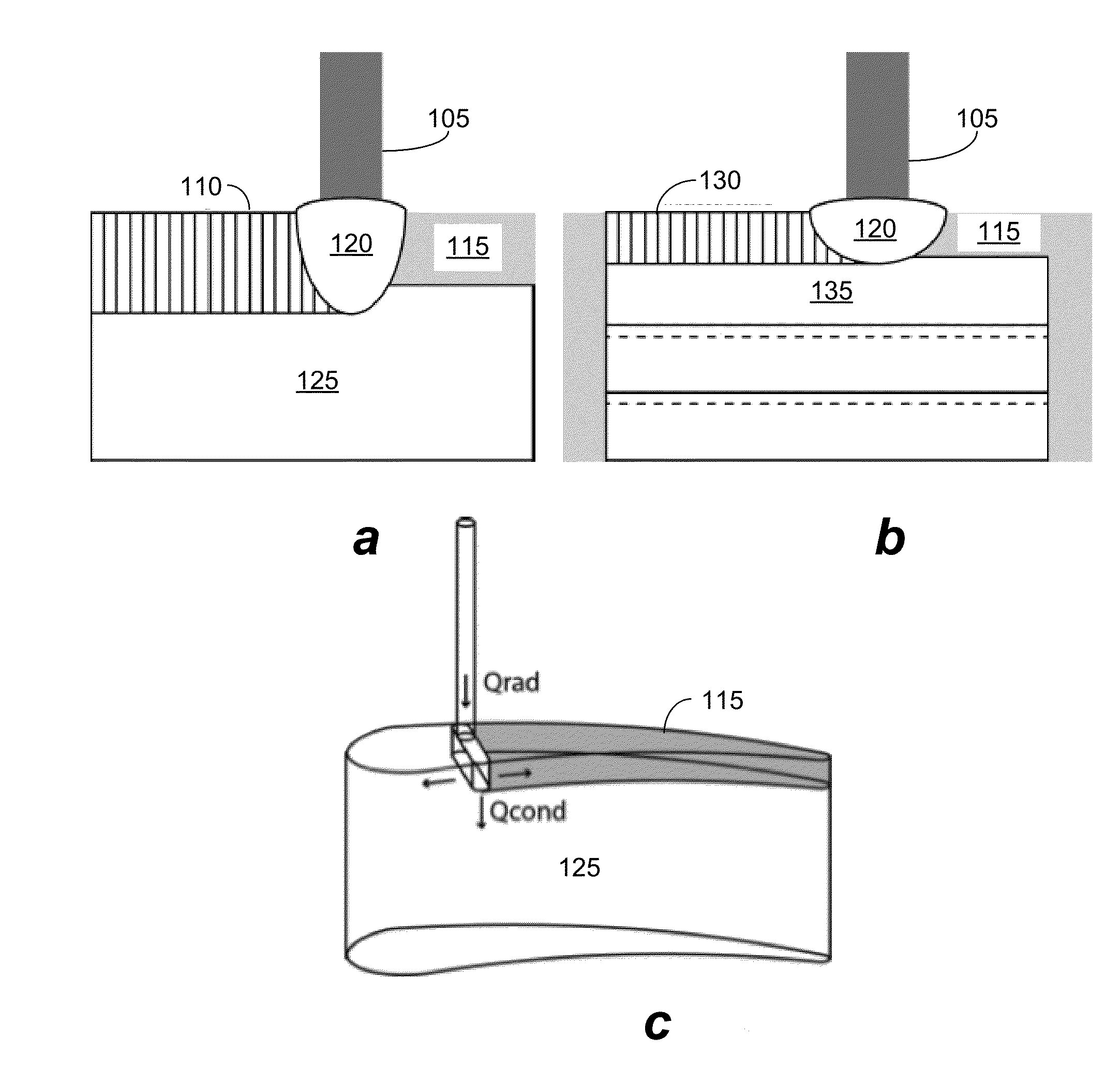

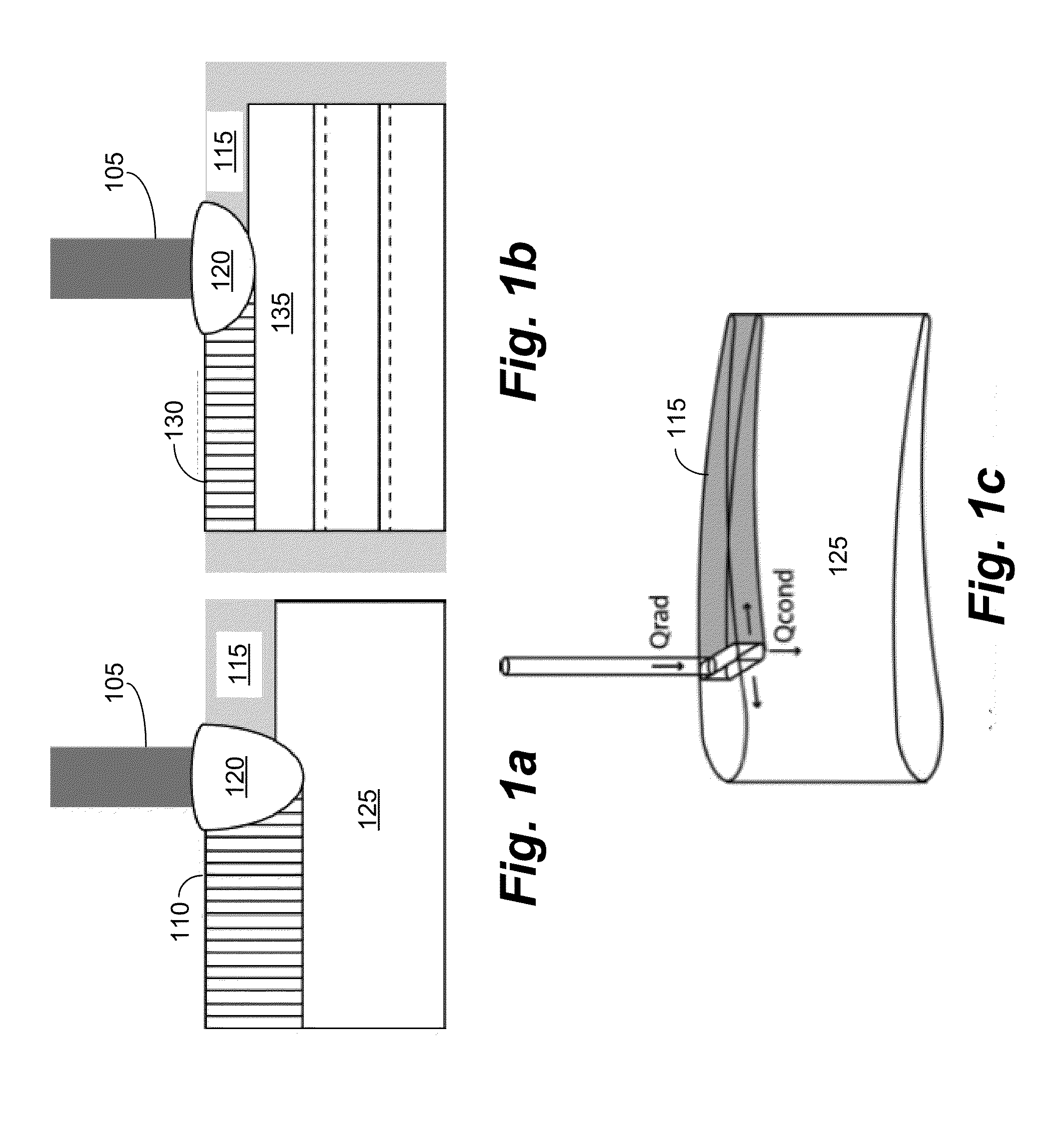

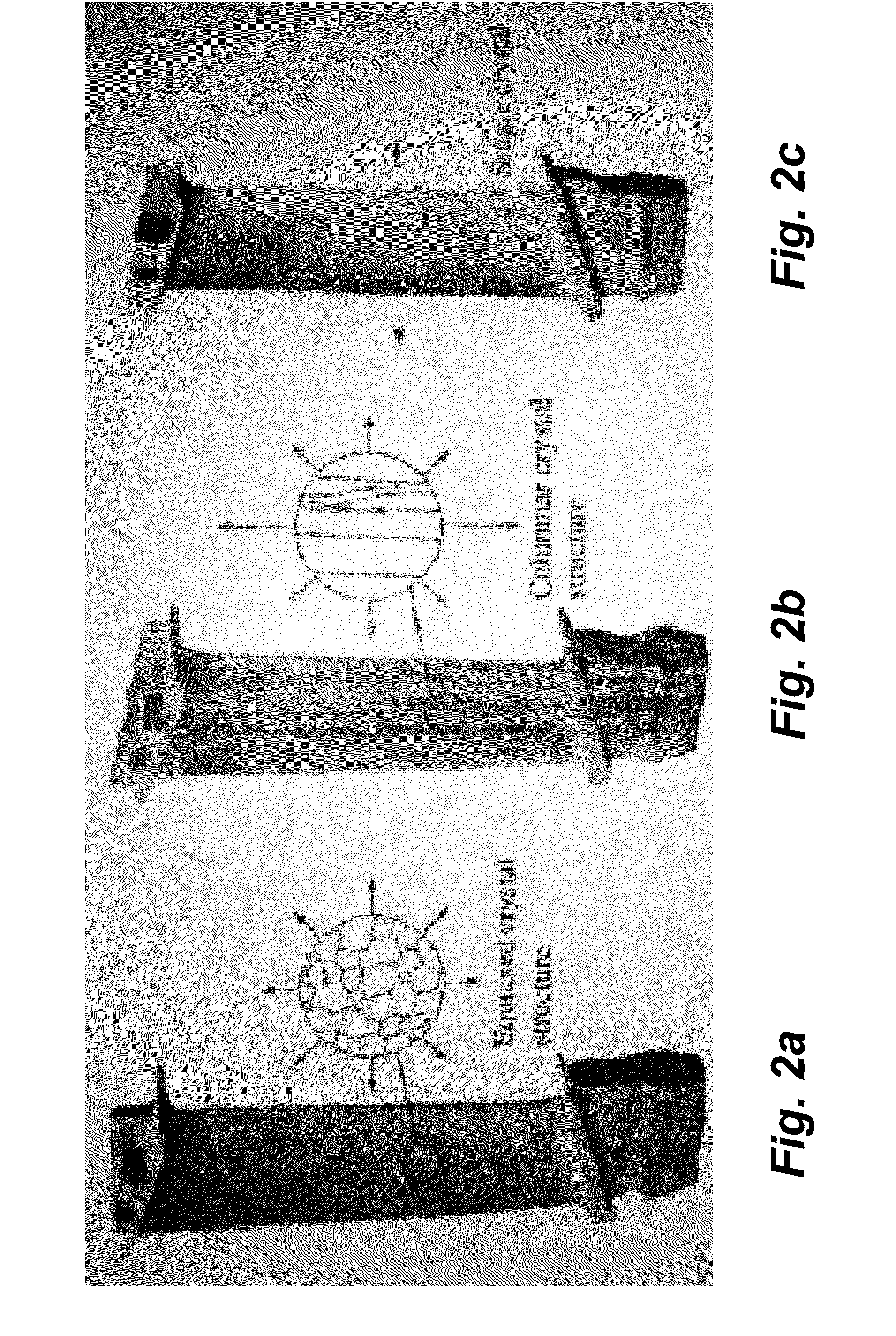

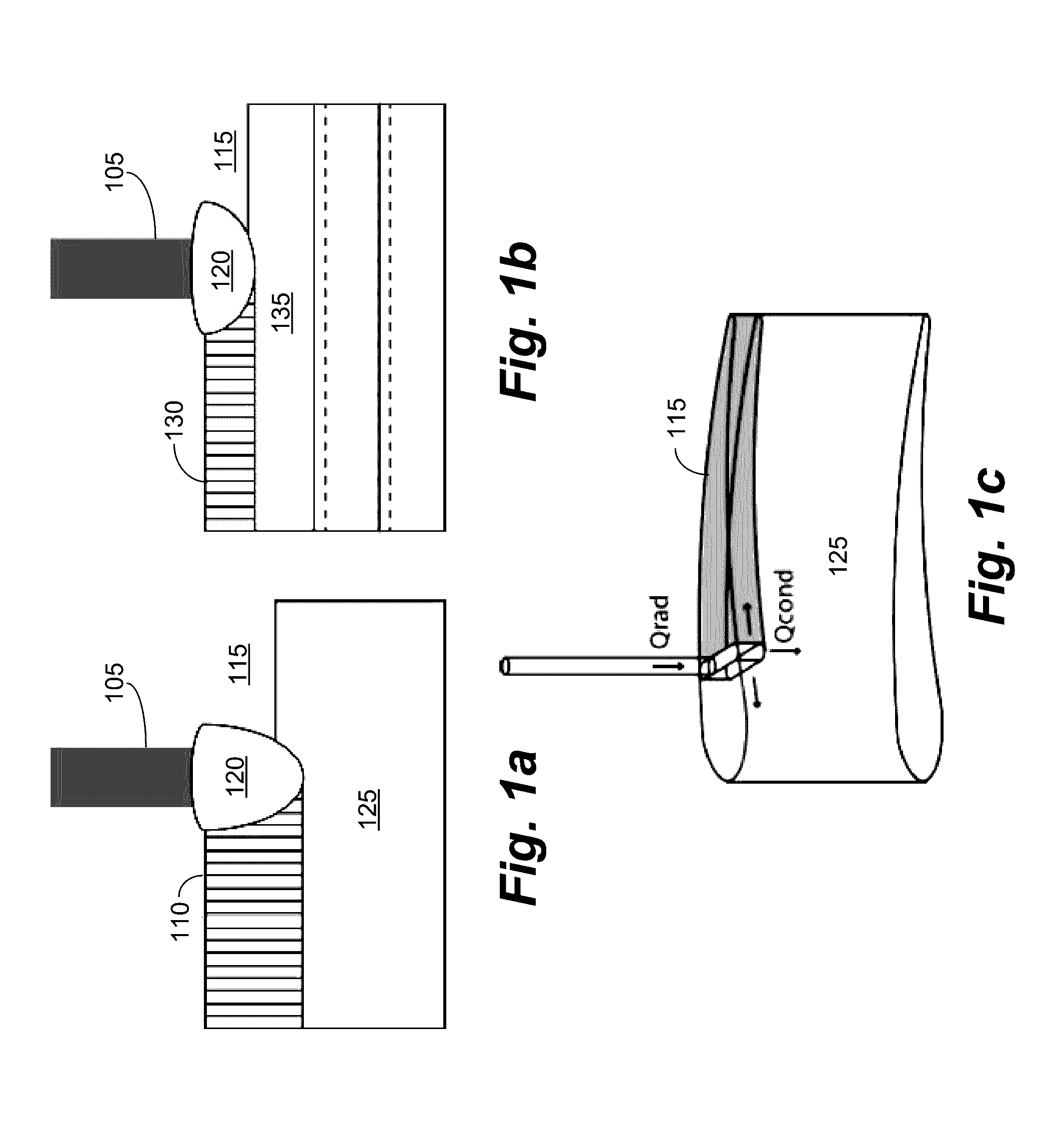

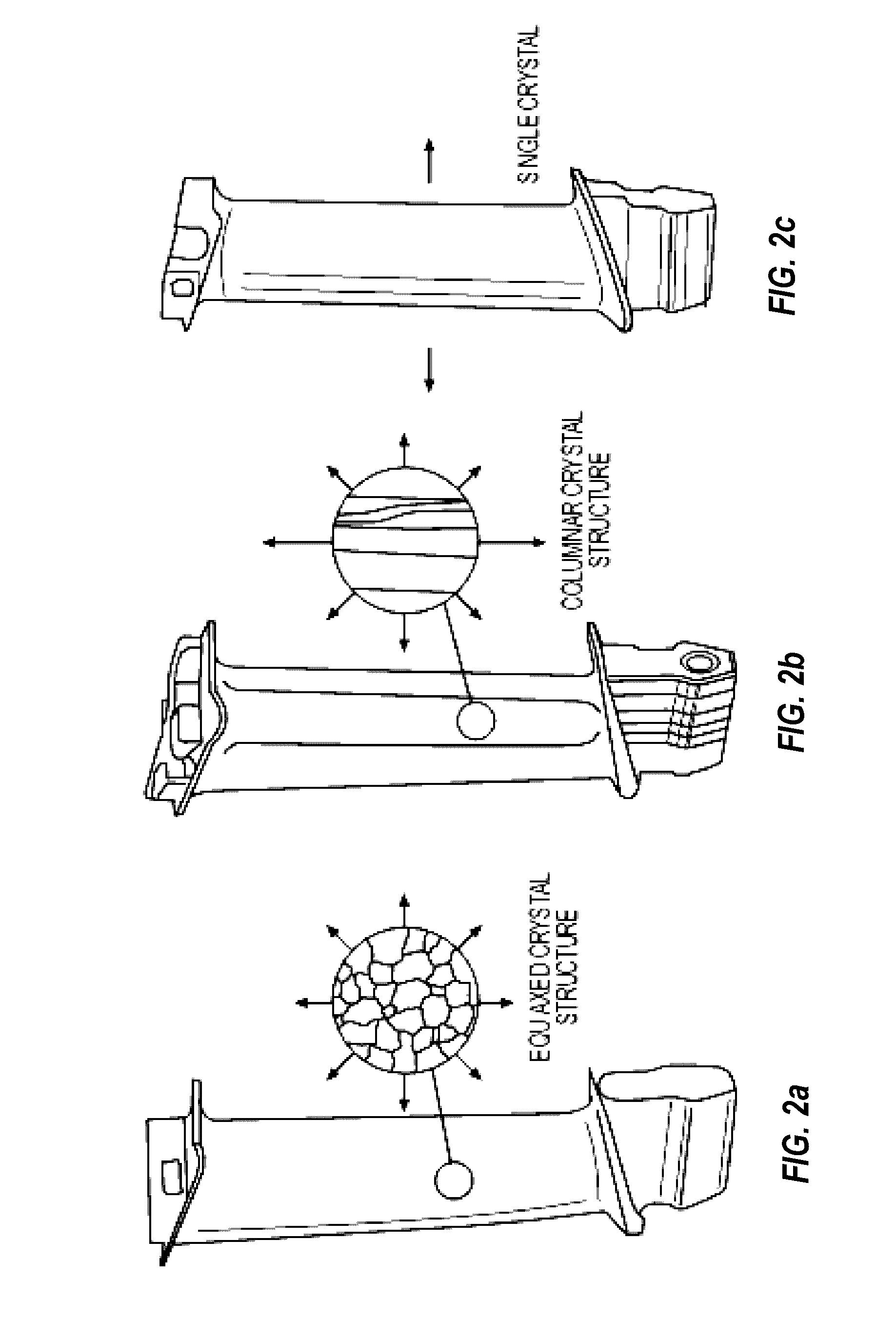

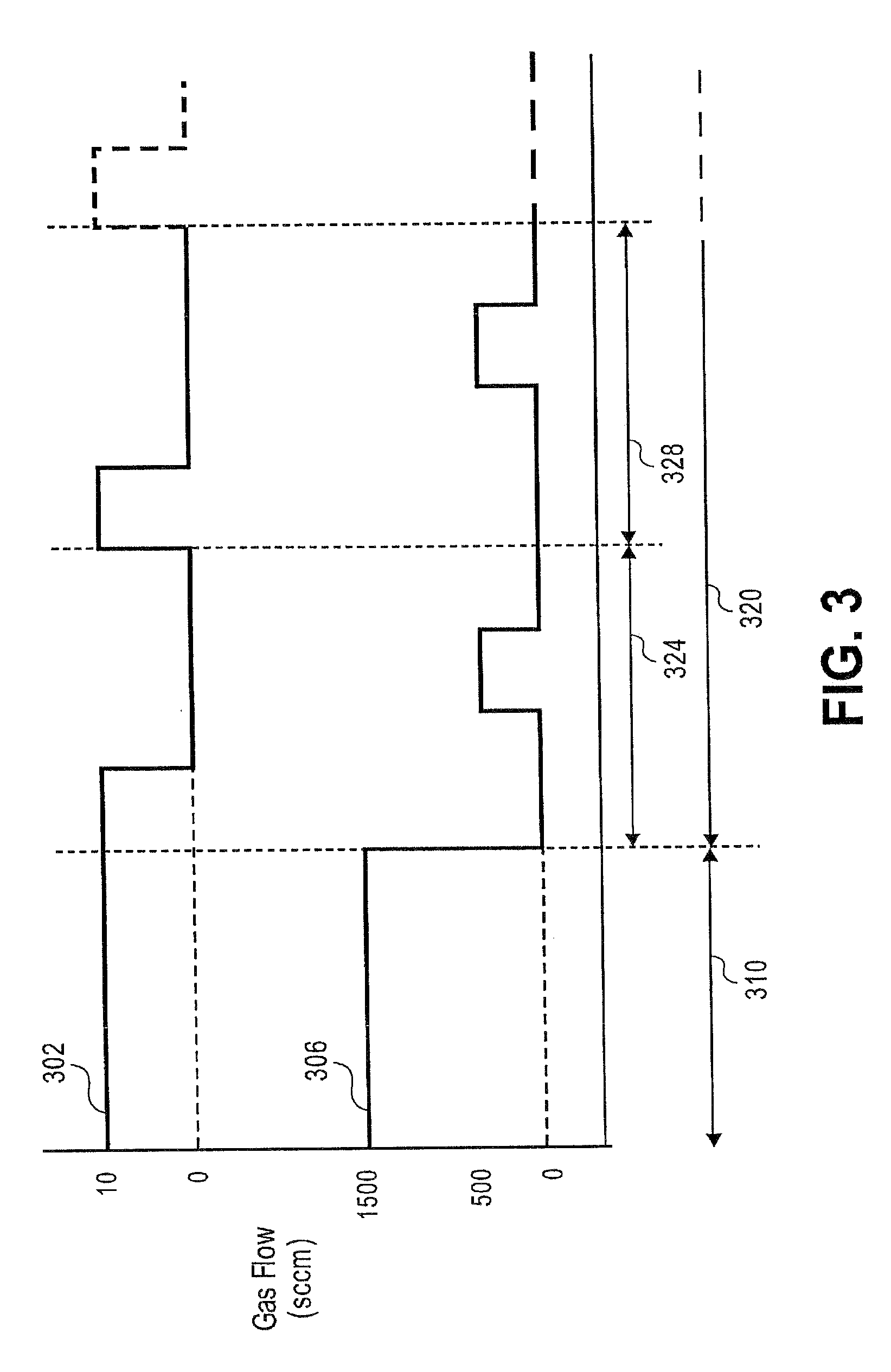

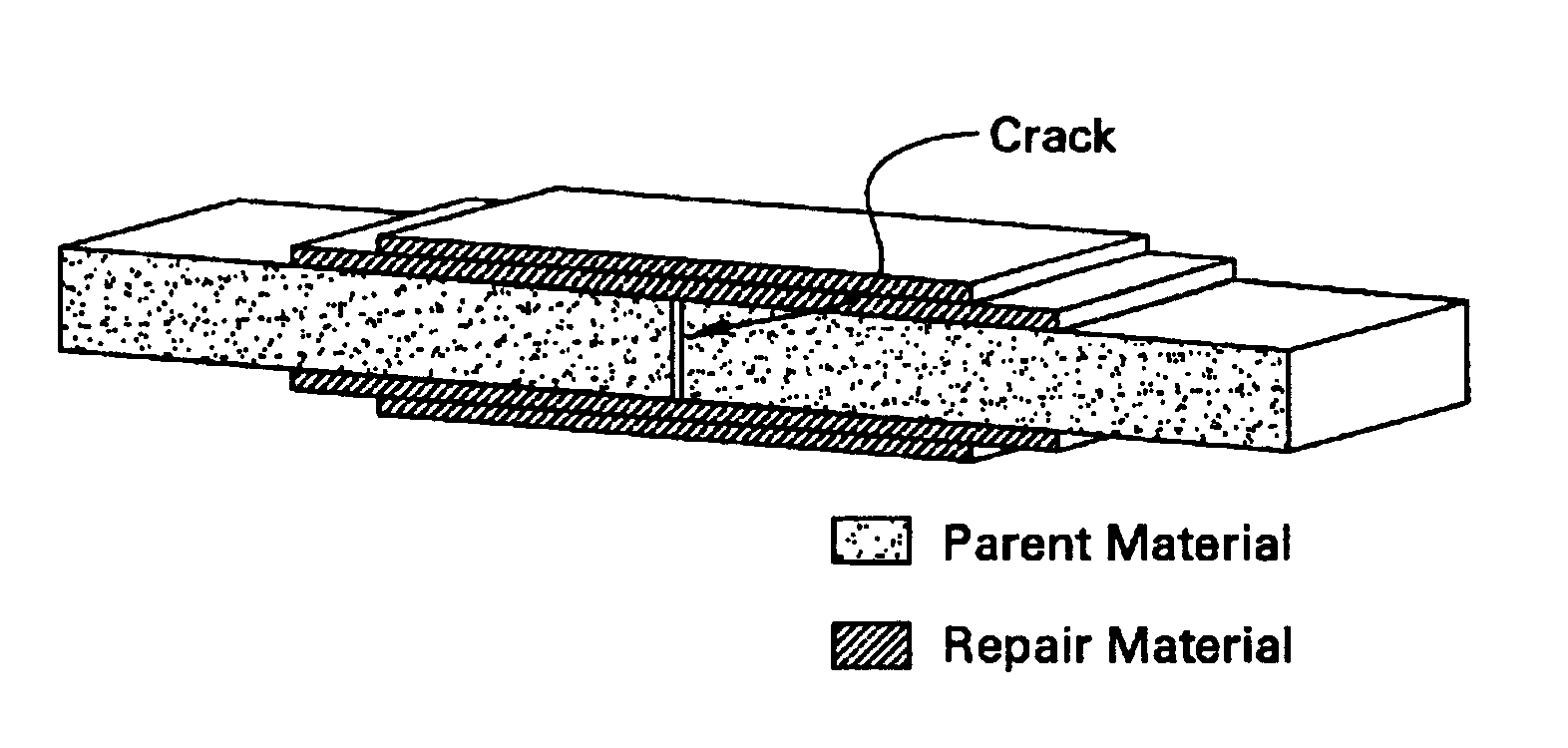

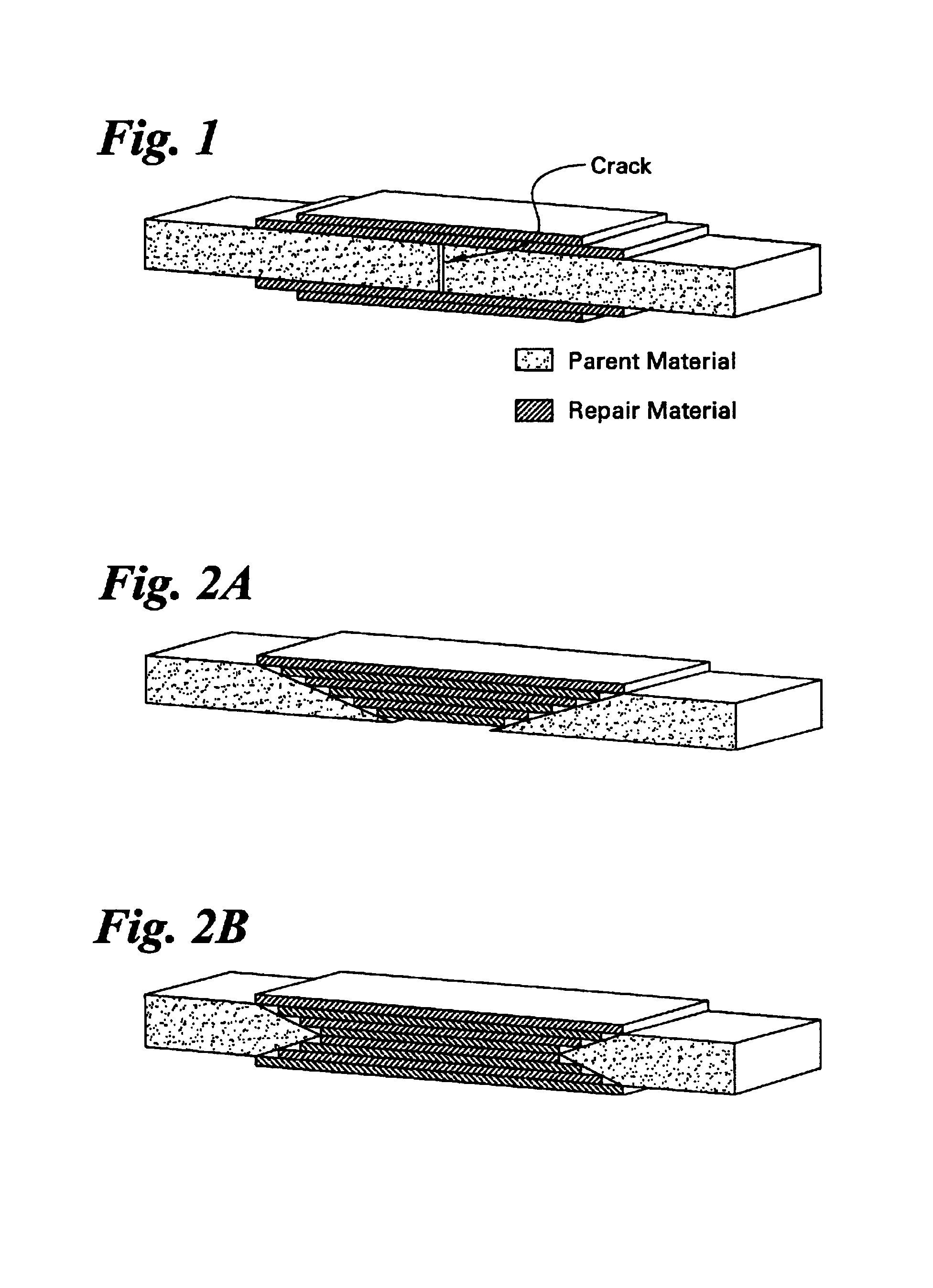

Scanning Laser Epitaxy (SLE) is a layer-by-layer additive manufacturing process that allows for the fabrication of three-dimensional objects with specified microstructure through the controlled melting and re-solidification of a metal powders placed atop a base substrate. SLE can be used to repair single crystal (SX) turbine airfoils, for example, as well as the manufacture functionally graded turbine components. The SLE process is capable of creating equiaxed, directionally solidified, and SX structures. Real-time feedback control schemes based upon an offline model can be used both to create specified defect free microstructures and to improve the repeatability of the process. Control schemes can be used based upon temperature data feedback provided at high frame rate by a thermal imaging camera as well as a melt-pool viewing video microscope. A real-time control scheme can deliver the capability of creating engine ready net shape turbine components from raw powder material.

Owner:GEORGIA TECH RES CORP

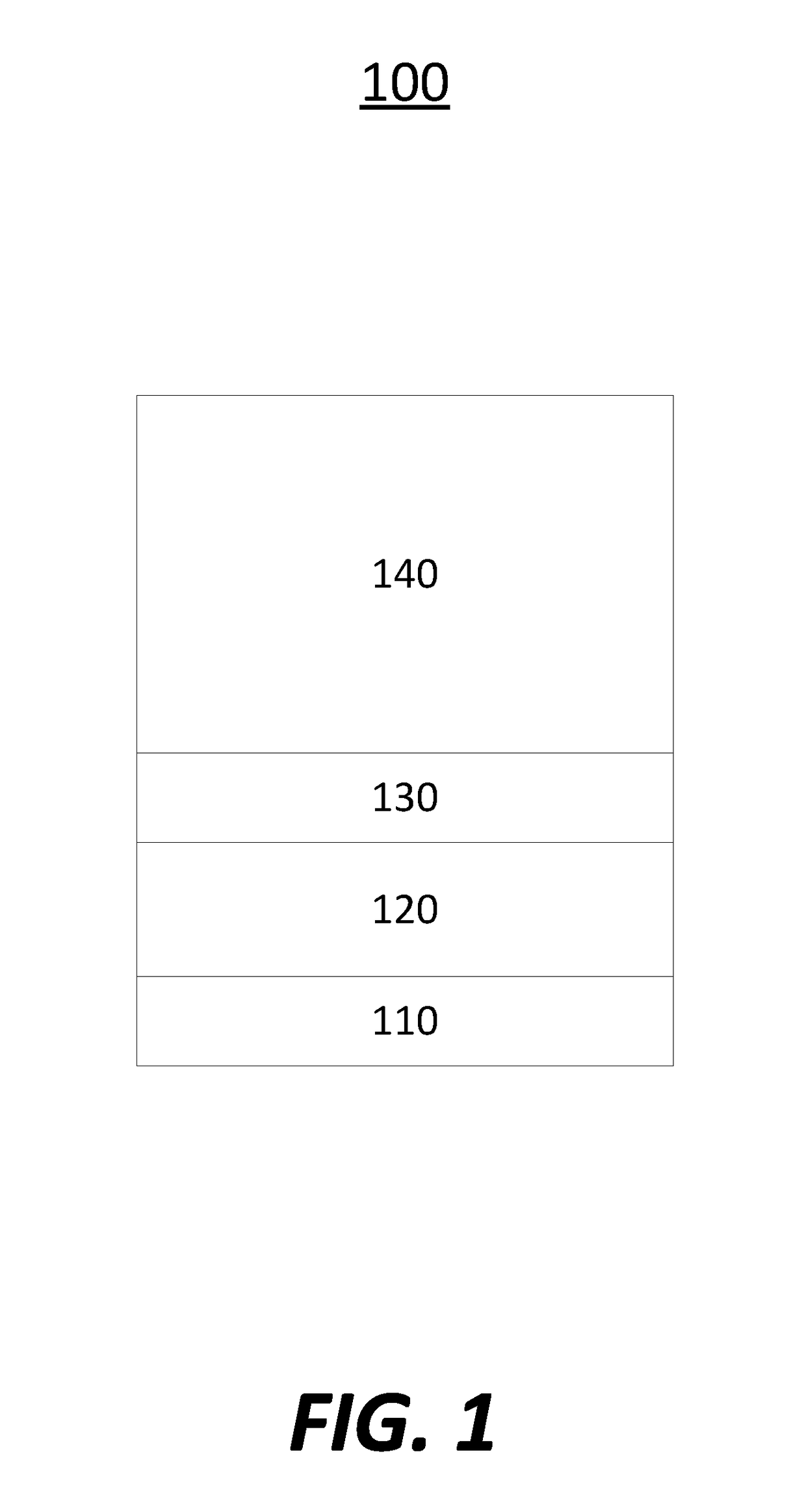

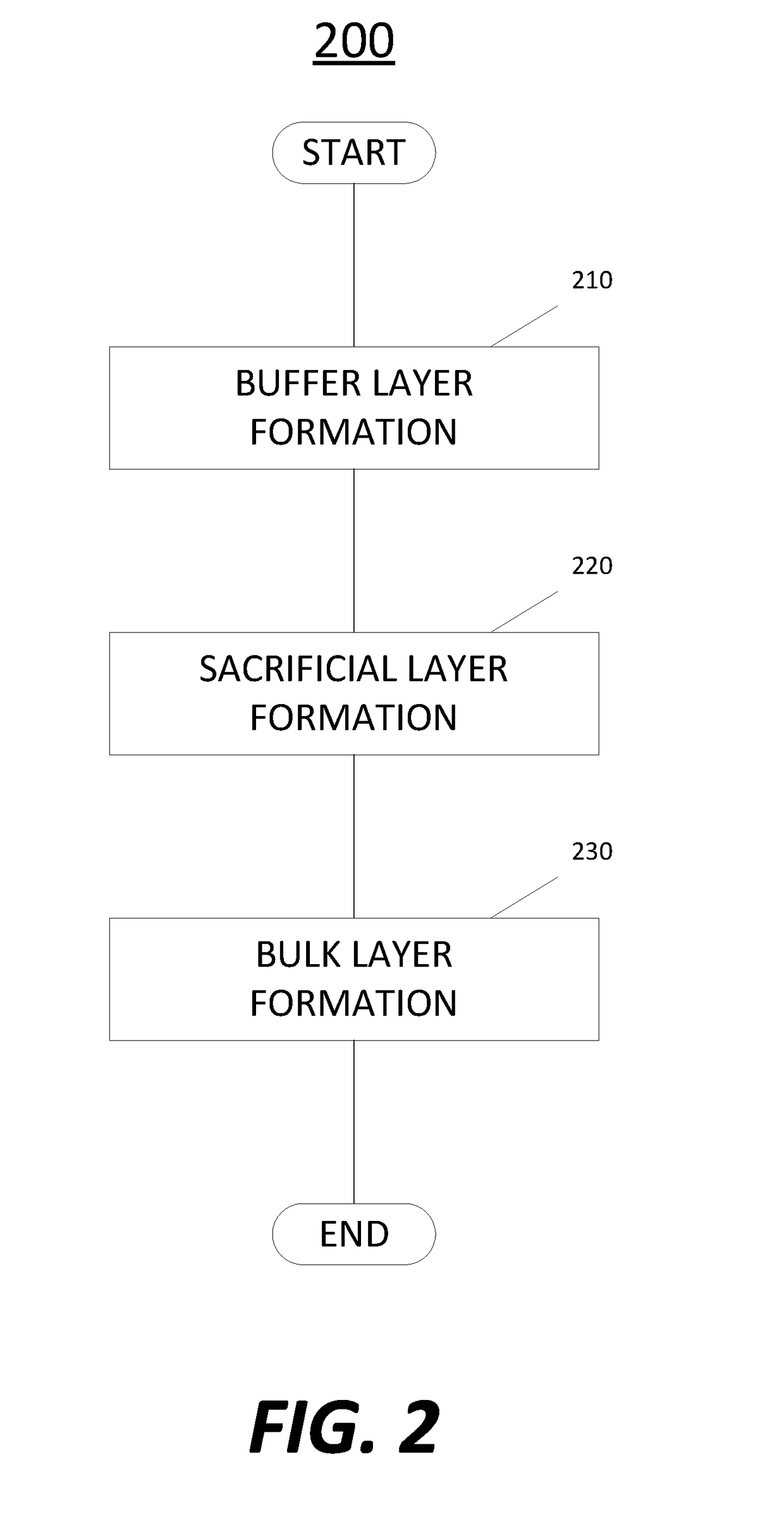

Formation of epitaxial layers via dislocation filtering

ActiveUS20170372884A1Semiconductor/solid-state device manufacturingSemiconductor devicesProcess conditionsDislocation

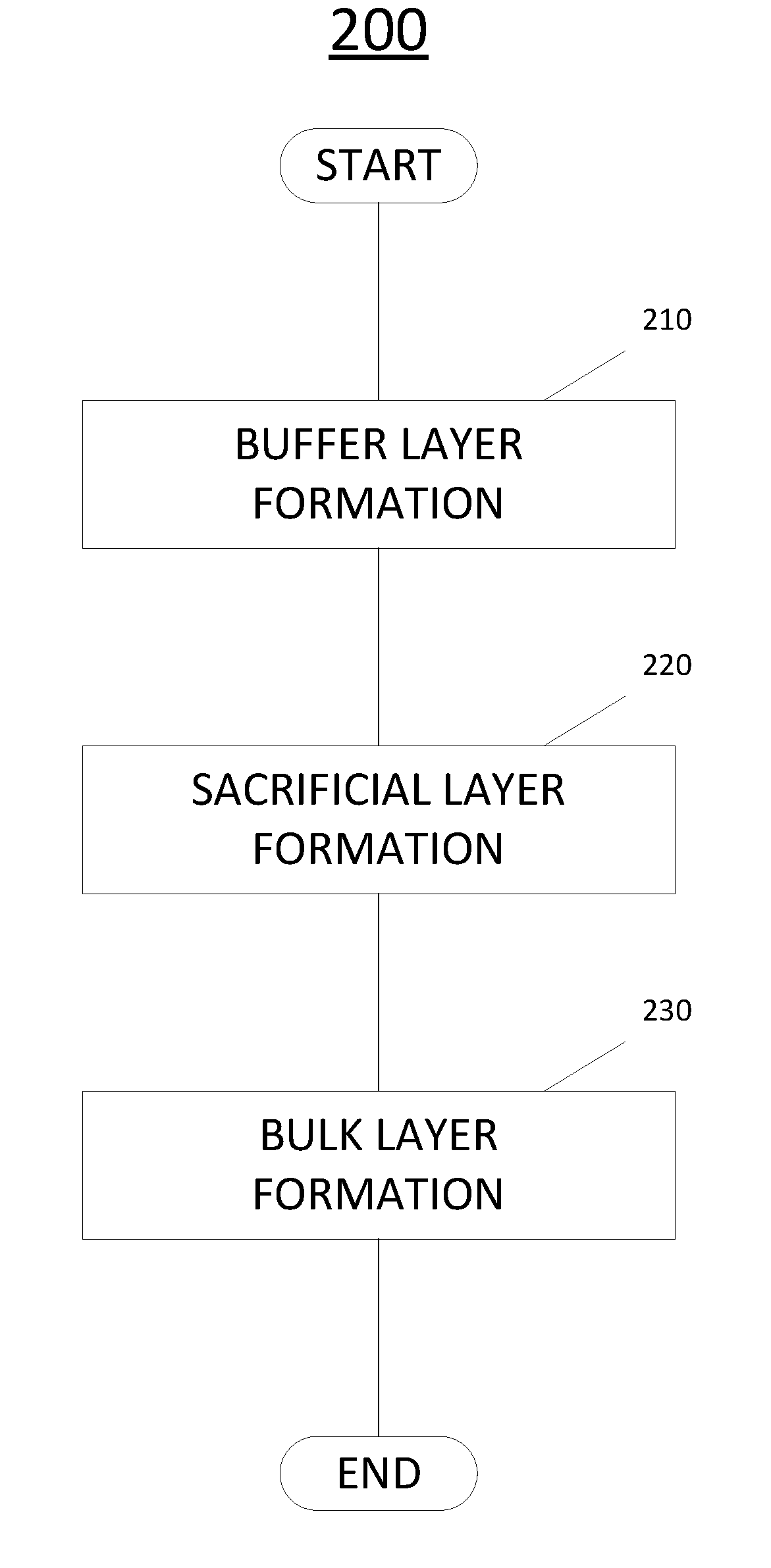

A process for forming a thick defect-free epitaxial layer is disclosed. The process may comprise forming a buffer layer and a sacrificial layer prior to forming the thick defect-free epitaxial layer. The sacrificial layer and the thick defect-free epitaxial layer may be formed of the same material and at the same process conditions.

Owner:ASM IP HLDG BV

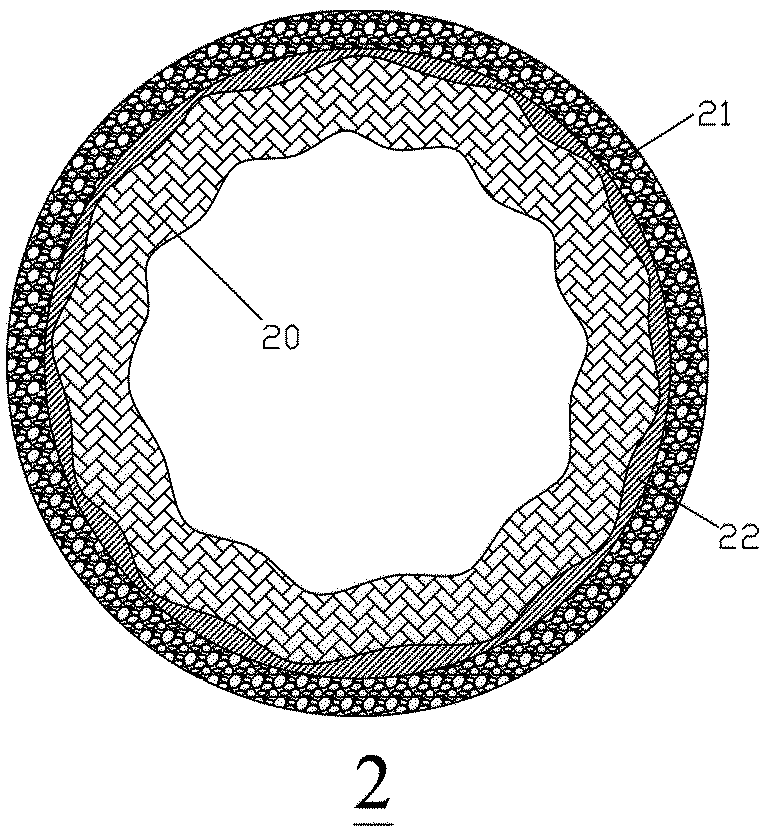

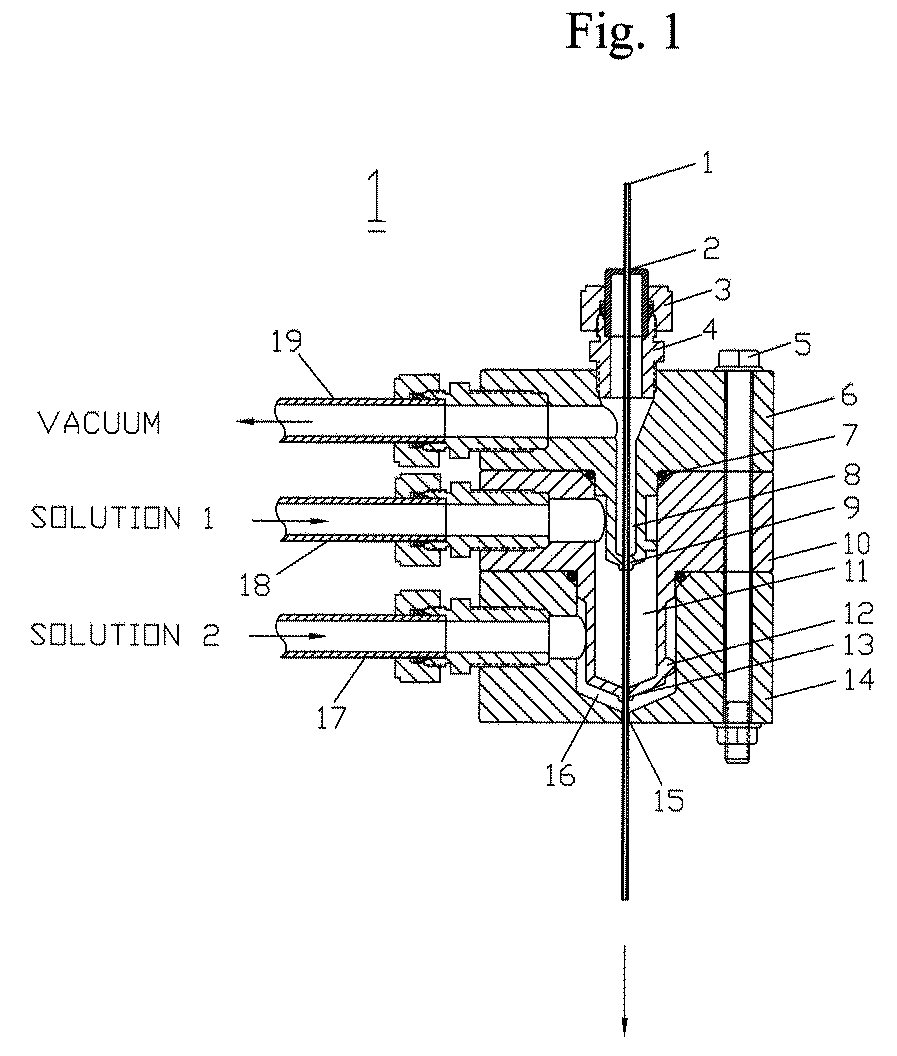

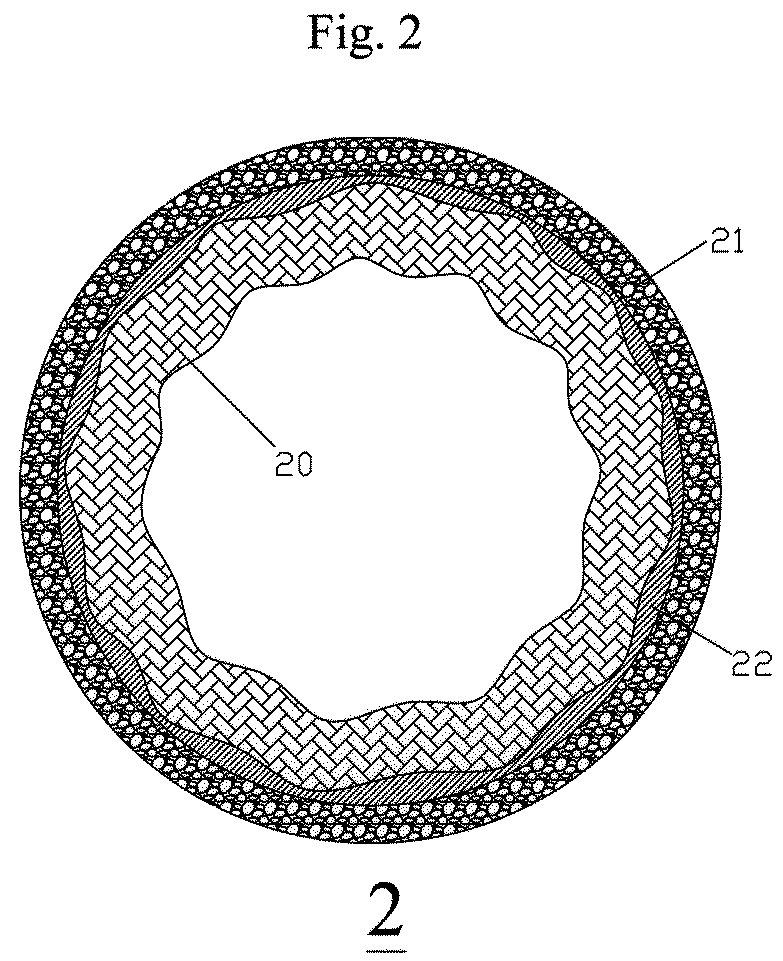

Defect free composite membranes, method for producing said membranes and use of the same

InactiveUS7172075B1Good water permeabilityStrong physical adhesionSemi-permeable membranesSynthetic resin layered productsFruit juiceChemical composition

Owner:ACCORD PARTNER

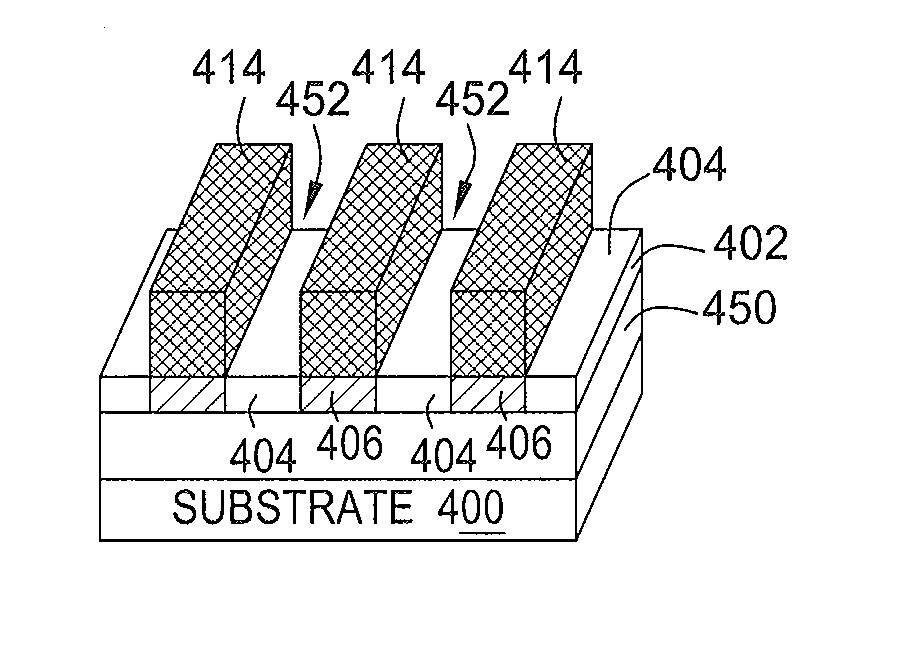

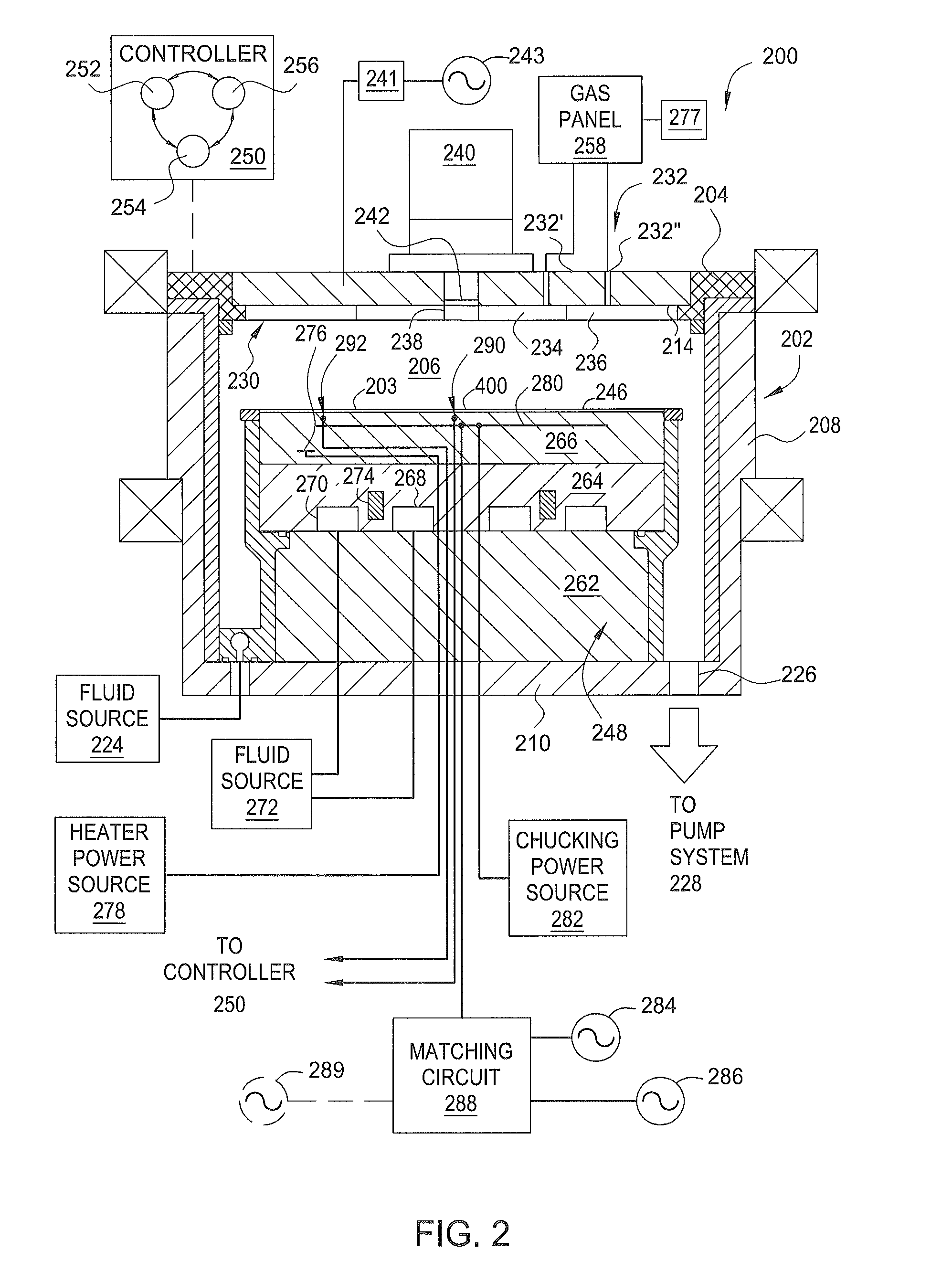

Directed block copolymer self-assembly patterns for advanced photolithography applications

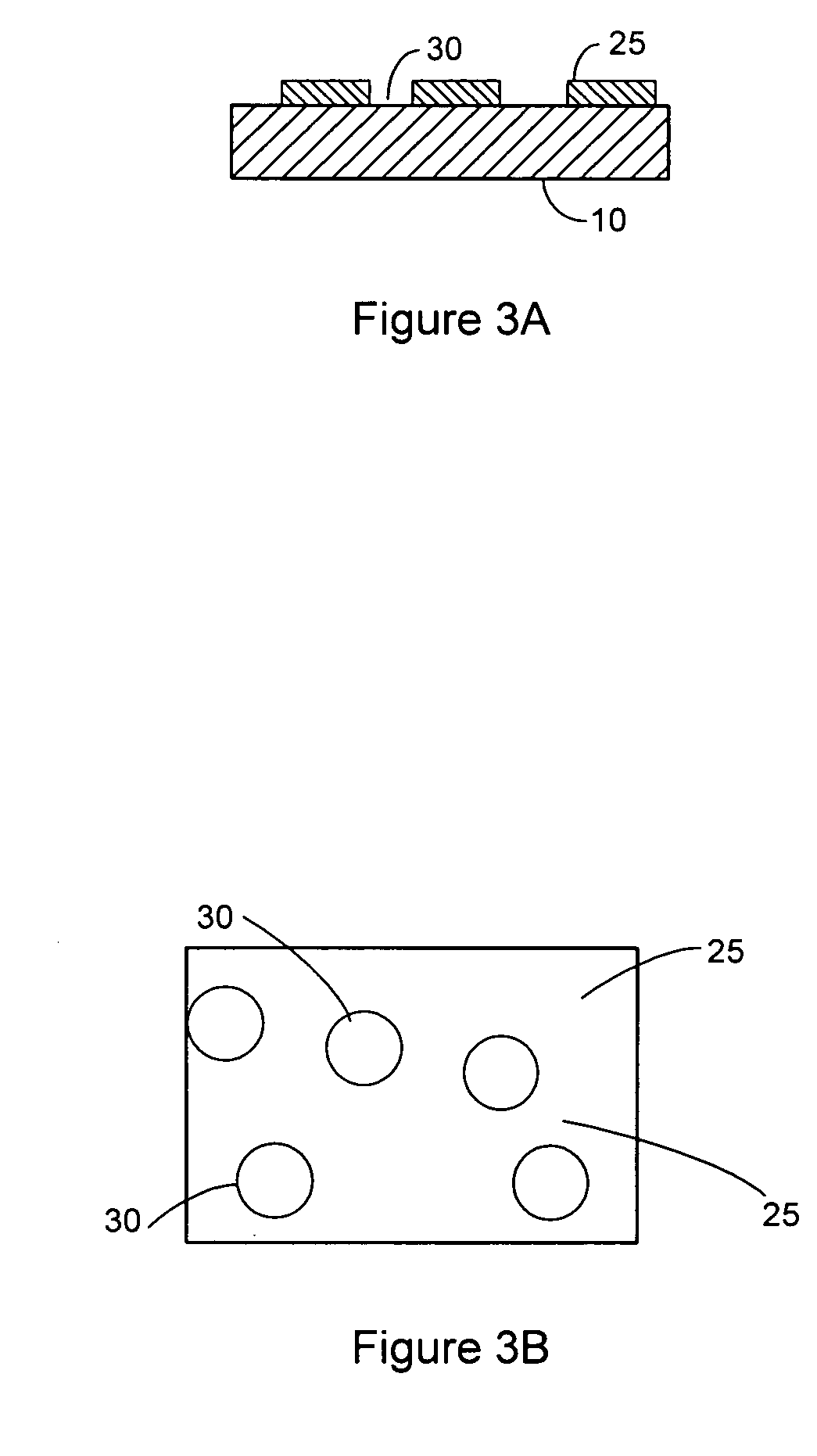

InactiveUS20140357083A1Electric discharge tubesSemiconductor/solid-state device manufacturingPhotoresistSelf-assembly

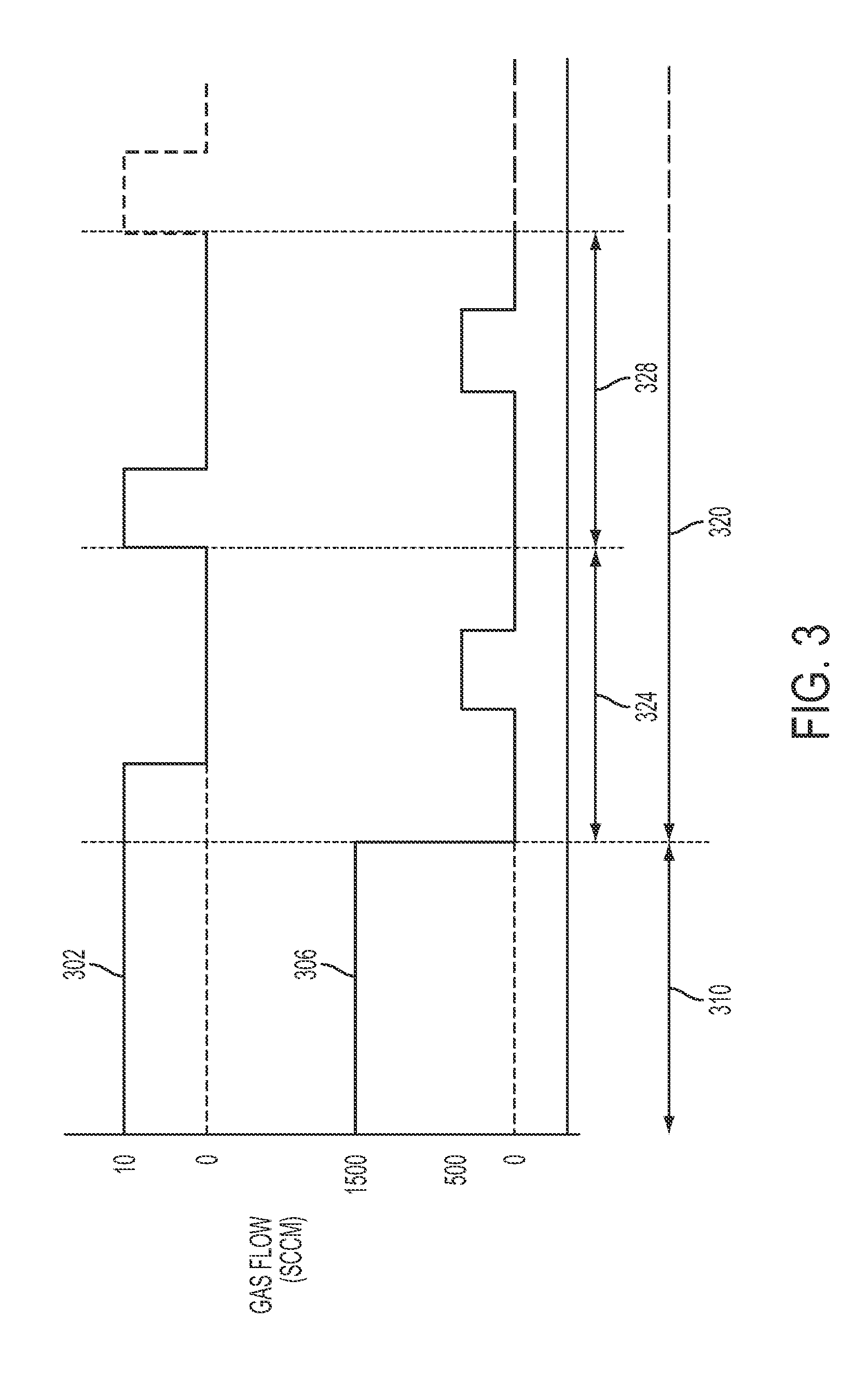

Embodiments of methods and an apparatus for utilizing a directed self-assembly (DSA) process on block copolymers (BCPs) to form a defect-free photoresist layer for feature transfer onto a substrate are provided. In one embodiment, a method for performing a dry development process includes transferring a substrate having a layer of block copolymers disposed thereon into an etching processing chamber, wherein at least a first type and a second type of polymers comprising the block copolymers are aggregated into a first group of regions and a second group of regions on the substrate, supplying an etching gas mixture including at least a carbon containing gas into the etching processing chamber, and predominately etching the second type of the polymers disposed on the second groups of regions on the substrate in the presence of the etching gas mixture.

Owner:APPLIED MATERIALS INC

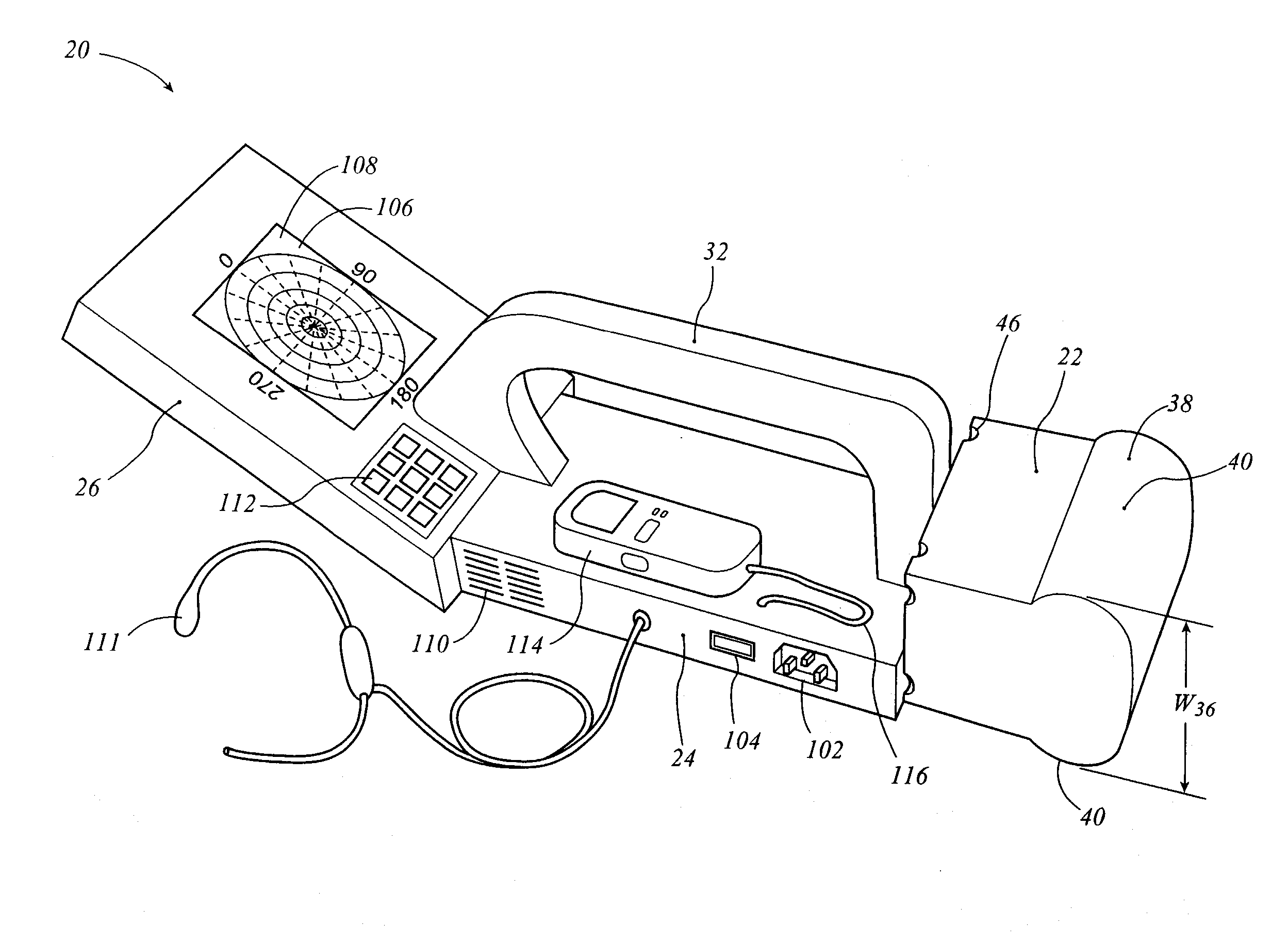

Inspection apparatus and method

ActiveUS20100207620A1Current/voltage measurementMagnetic property measurementsCounter-electromotive forceEddy-current testing

An apparatus and method are disclosed for detecting flaws in electrically conductive materials by observing properties of the back-EMF of the eddy current field generated by driving magnetic flux through the object to be examined. The input signal may include sweeps at several frequencies, and may do so at one time under the principle of wave superposition. The sectorial observations of eddy currents summations may be compared to a known datum for a defect free material, the presence of anomalies in eddy field back EMF divergence tending to provide an indication of an irregularity in the underlying eddy field, and hence in the underlying material itself. The portable unit may have a number of different configurations depending on the nature of the object to be examined, be it a flat or large radius plate, a flange, a rail, or some other structural element.

Owner:ATHENA IND TECH

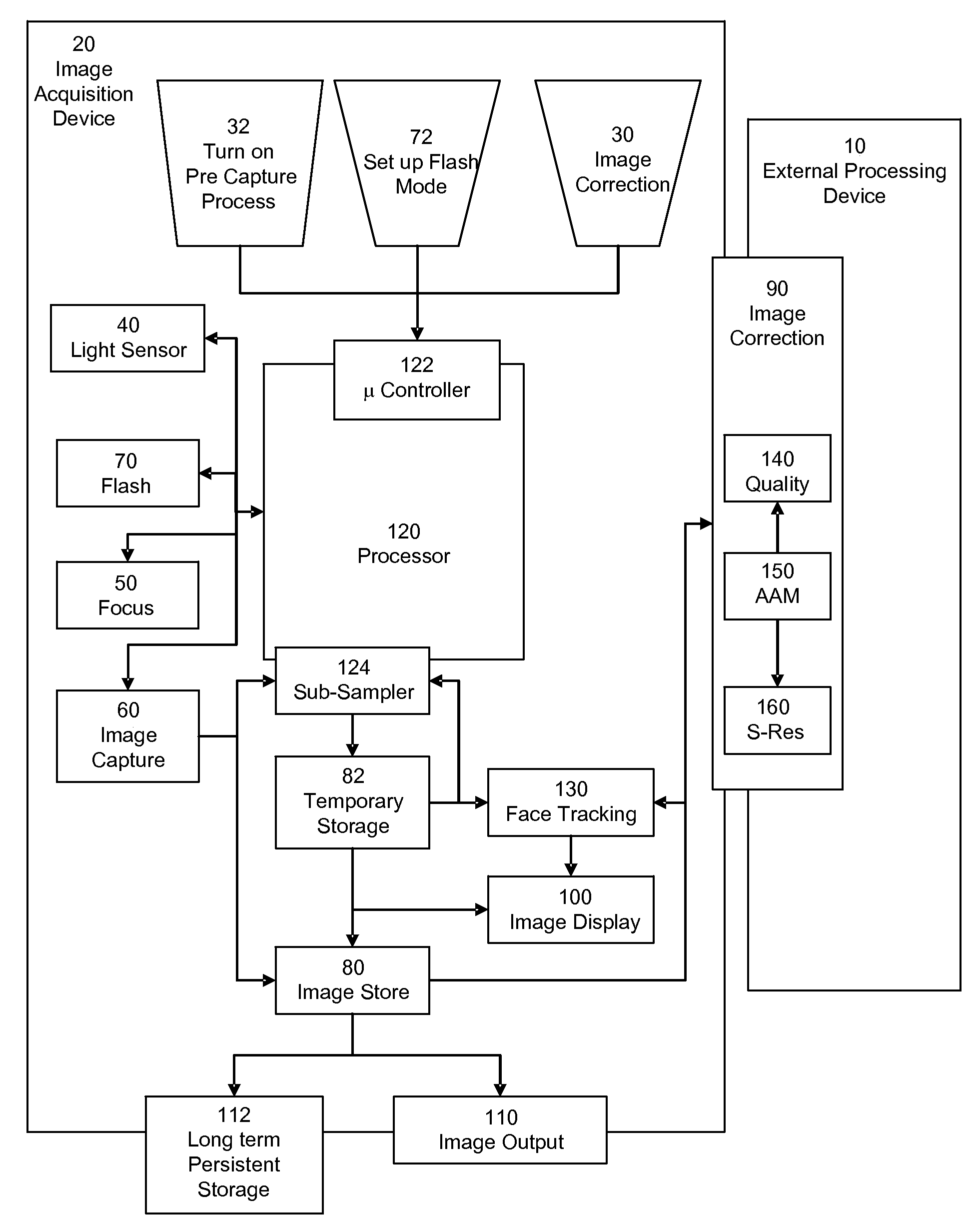

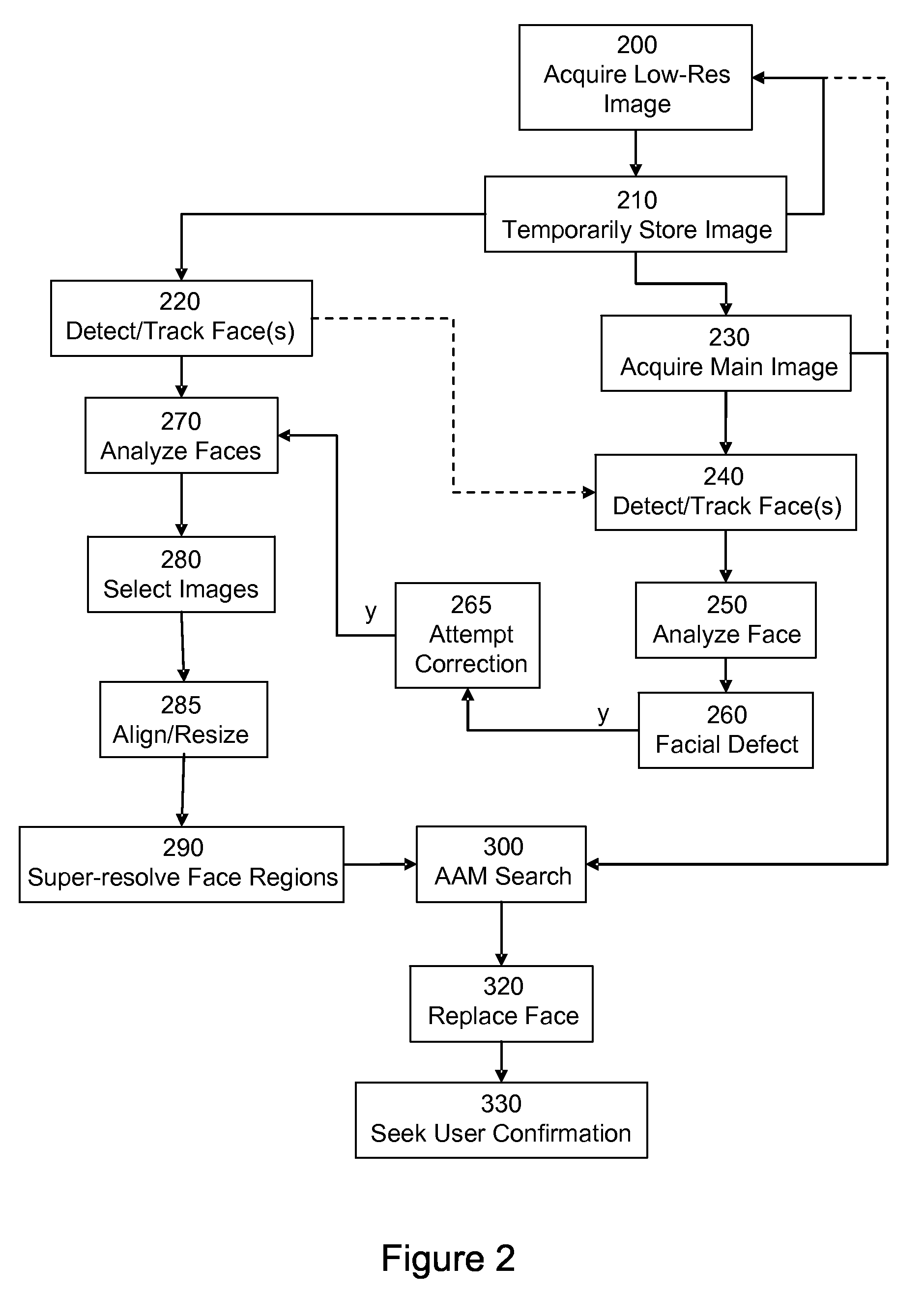

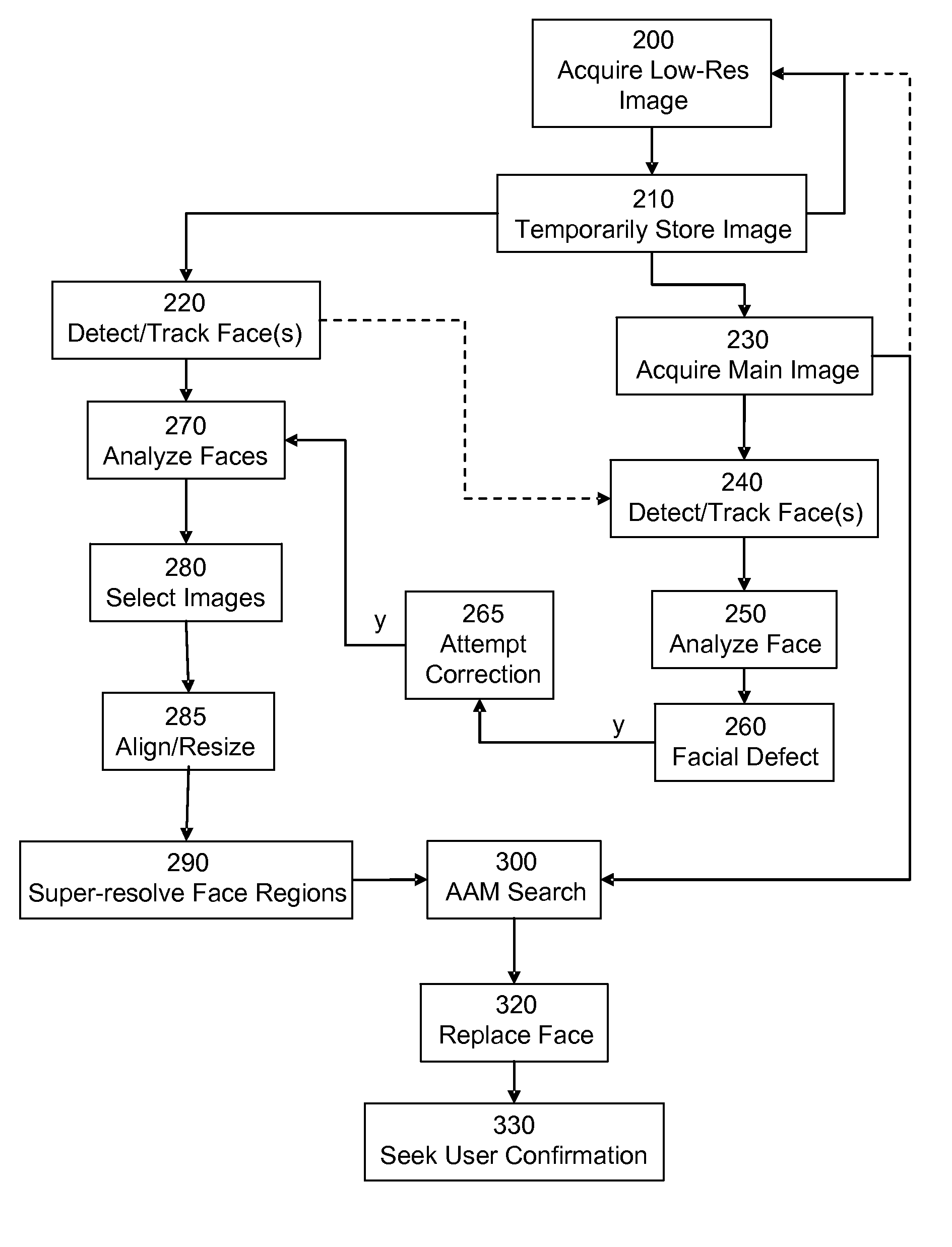

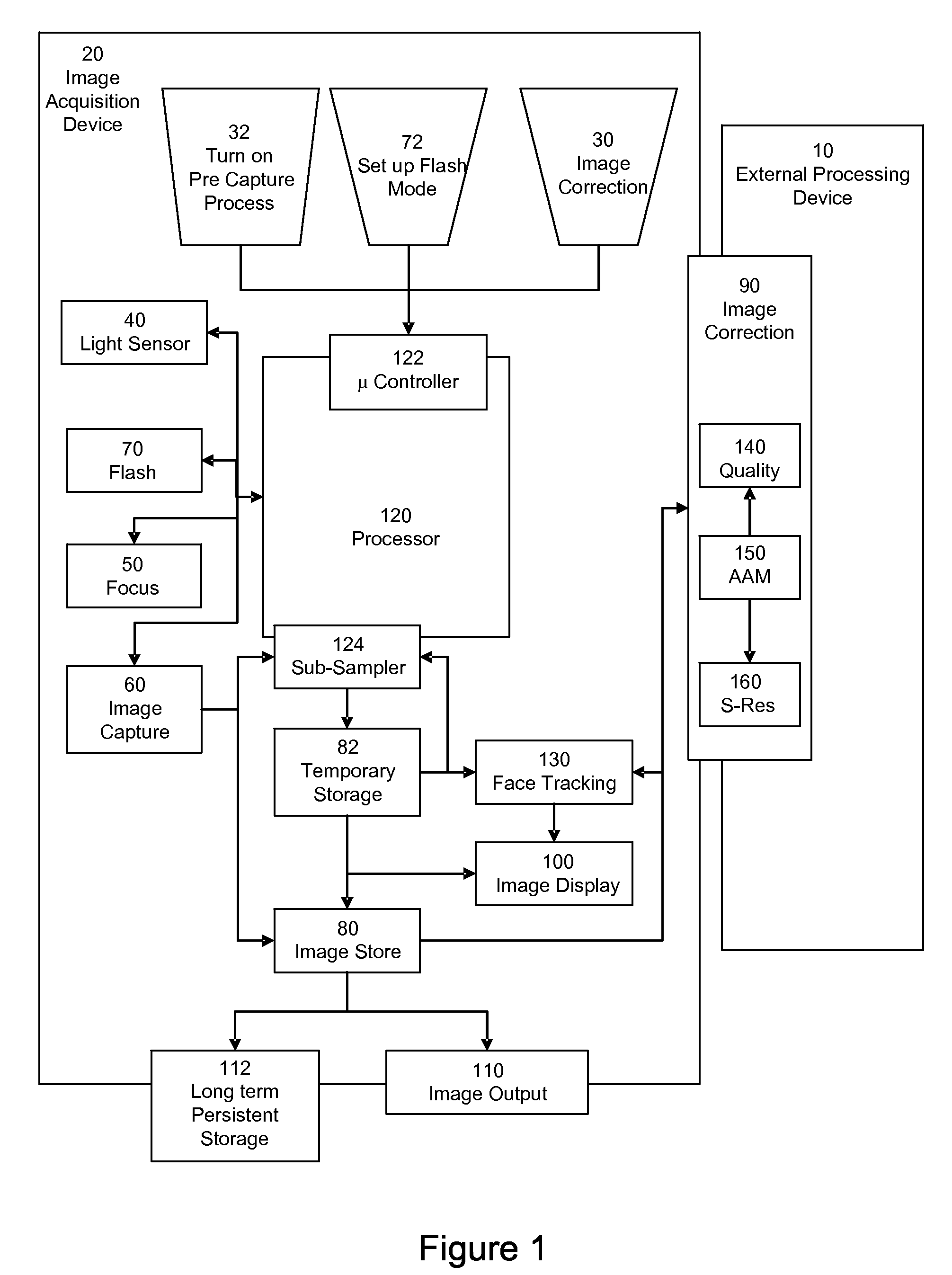

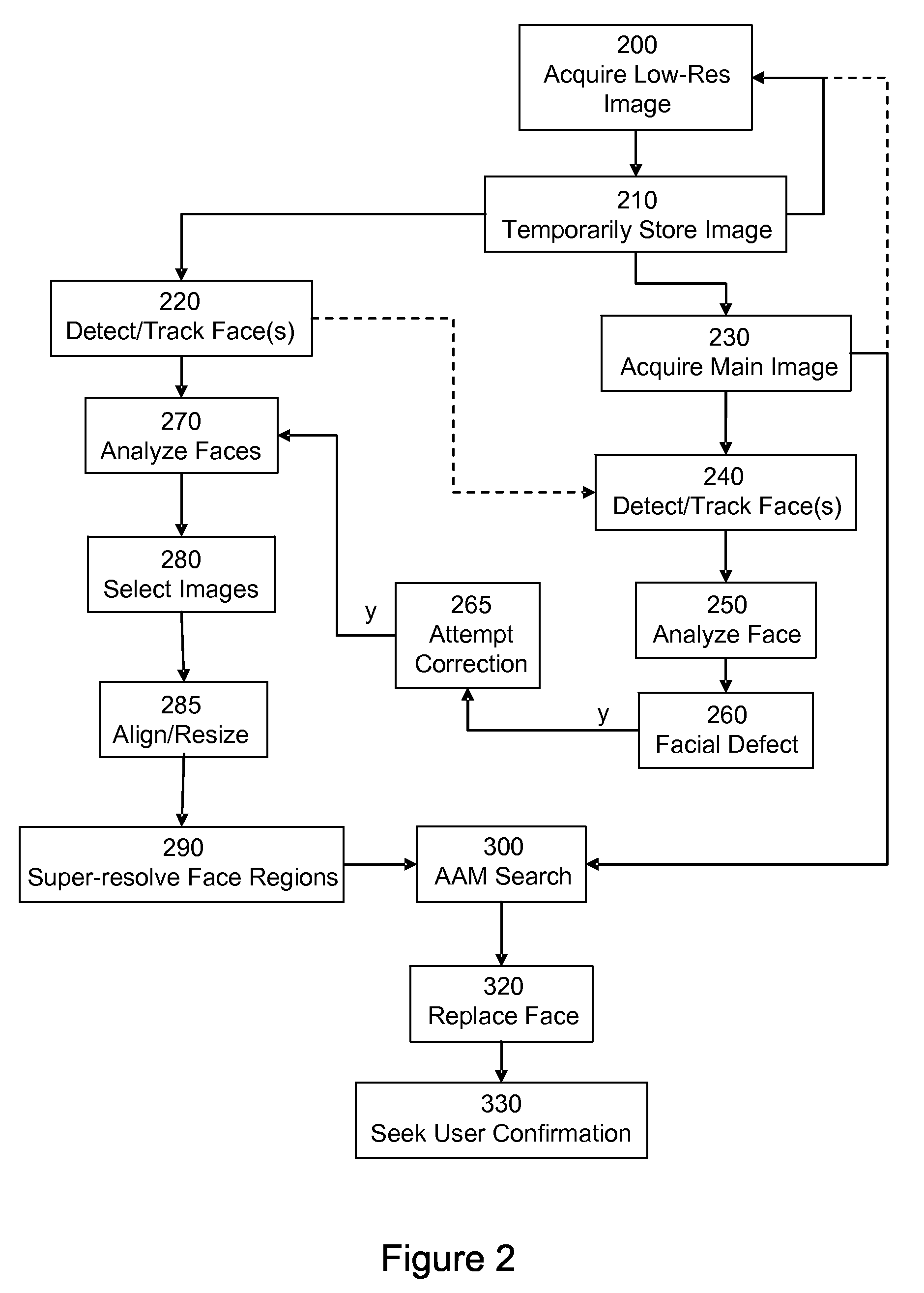

Image Processing Method and Apparatus

ActiveUS20080292193A1Television system detailsCharacter and pattern recognitionImaging processingImage resolution

An image processing technique includes acquiring a main image of a scene and determining one or more facial regions in the main image. The facial regions are analysed to determine if any of the facial regions includes a defect. A sequence of relatively low resolution images nominally of the same scene is also acquired. One or more sets of low resolution facial regions in the sequence of low resolution images are determined and analysed for defects. Defect free facial regions of a set are combined to provide a high quality defect free facial region. At least a portion of any defective facial regions of the main image are corrected with image information from a corresponding high quality defect free facial region.

Owner:FOTONATION LTD

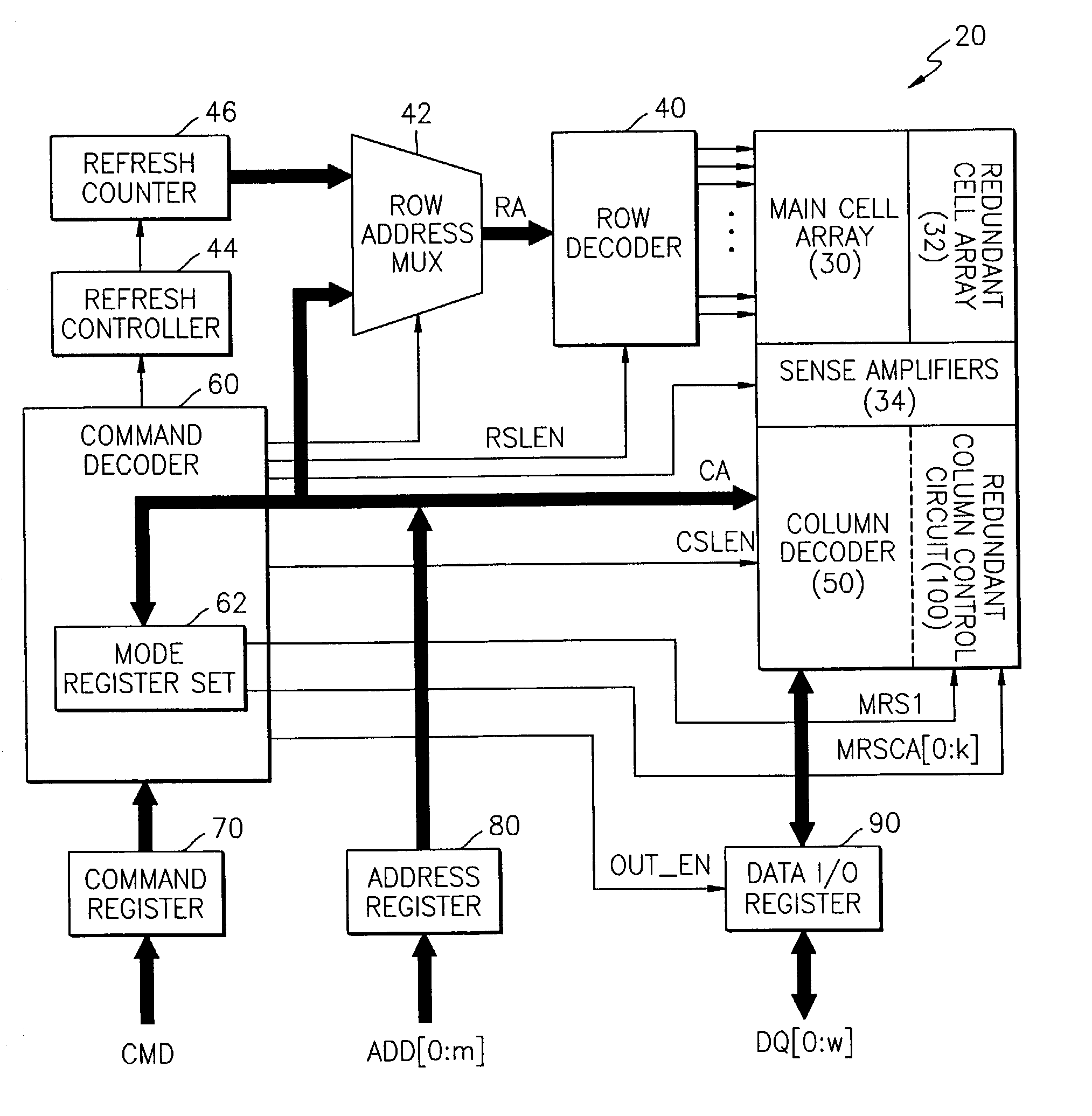

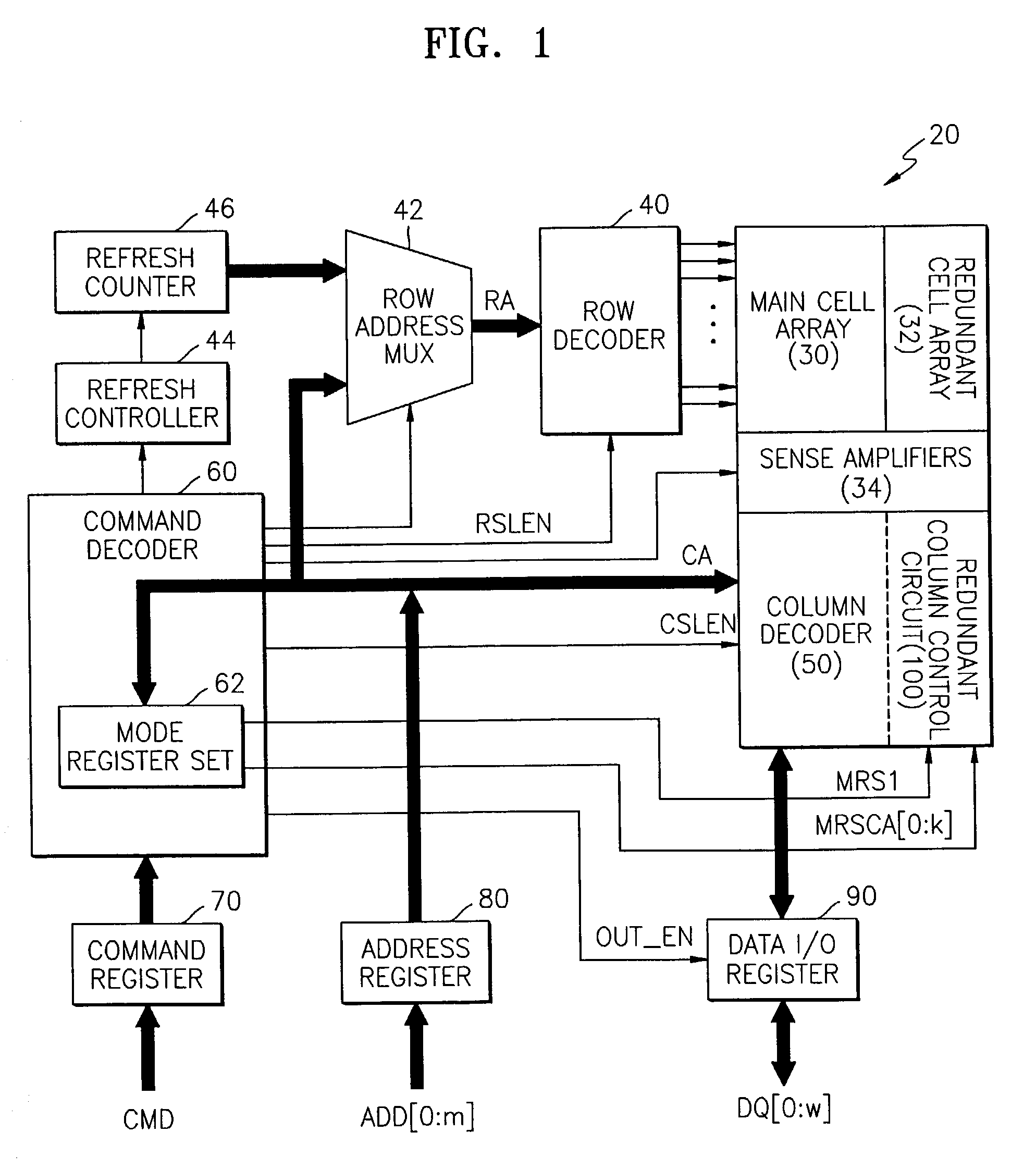

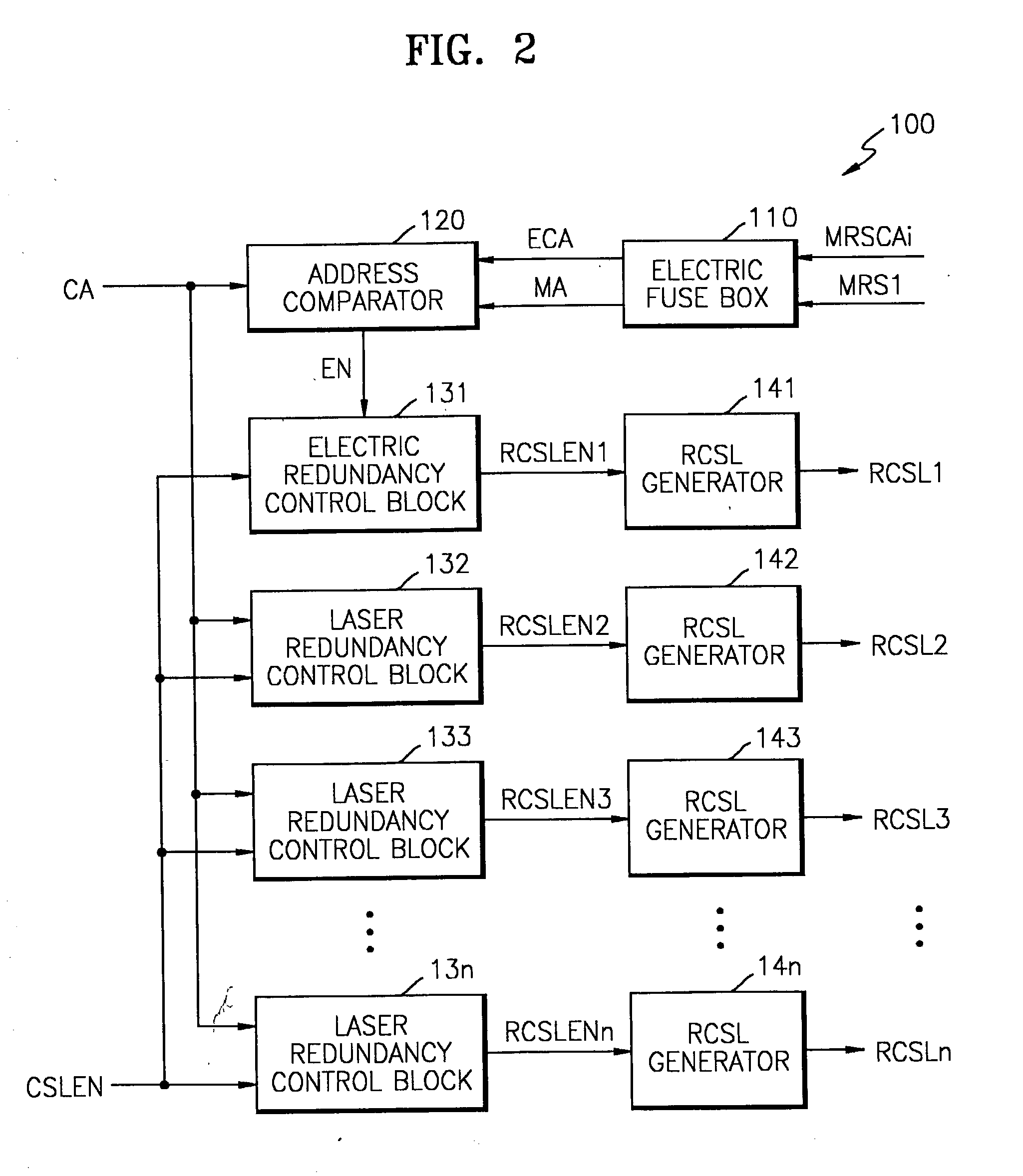

Semiconductor memory device post-repair circuit and method

The ability to repair defective cells in a memory array, by replacing those cells with redundant cells, is improved using a redundant memory line control circuit that employs two types of redundancy programming. Most, or all, redundant memory lines can be programmed while the memory array is in a wafer state by, e.g., cutting laser fuses. But at least one memory line can be programmed subsequent to device packaging ("post repair") using, e.g., commands that cut electric fuses. Preferably, the redundant memory line(s) that are reserved for post repair are selectable among the same redundant memory lines that can be programmed using laser fuses. This allows all redundant memory lines to be available for laser repair, if needed, but also allows a redundant memory line to be selected for post repair after it has been determined that that redundant memory line is defect-free. This increases the likelihood that a device will be repairable, and yet does not unnecessarily waste redundant memory lines by pre-dedicating them to laser or post repair.

Owner:SAMSUNG ELECTRONICS CO LTD

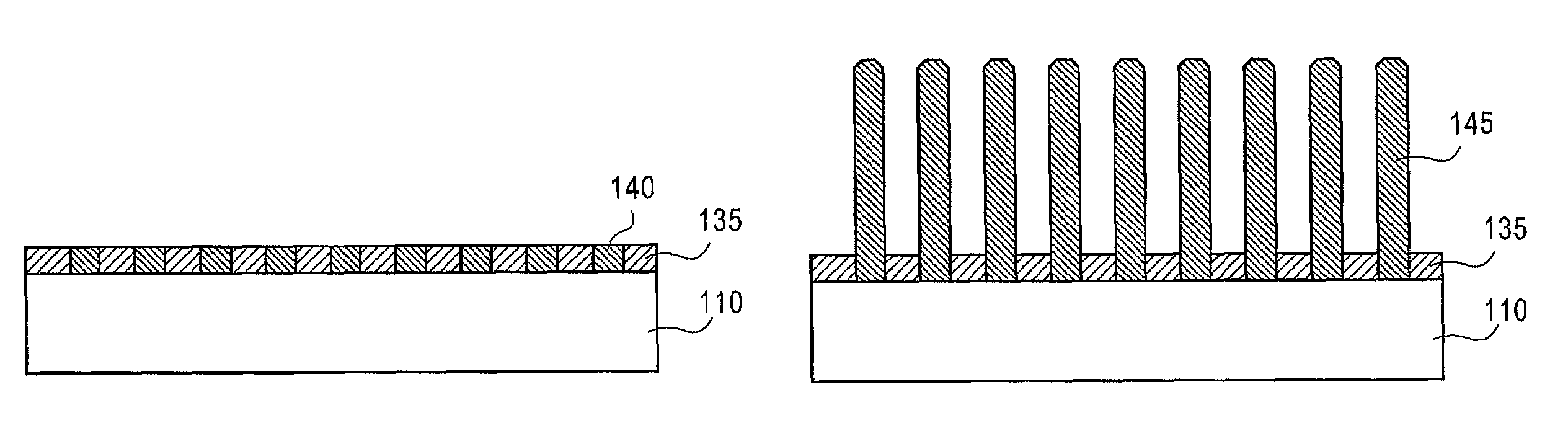

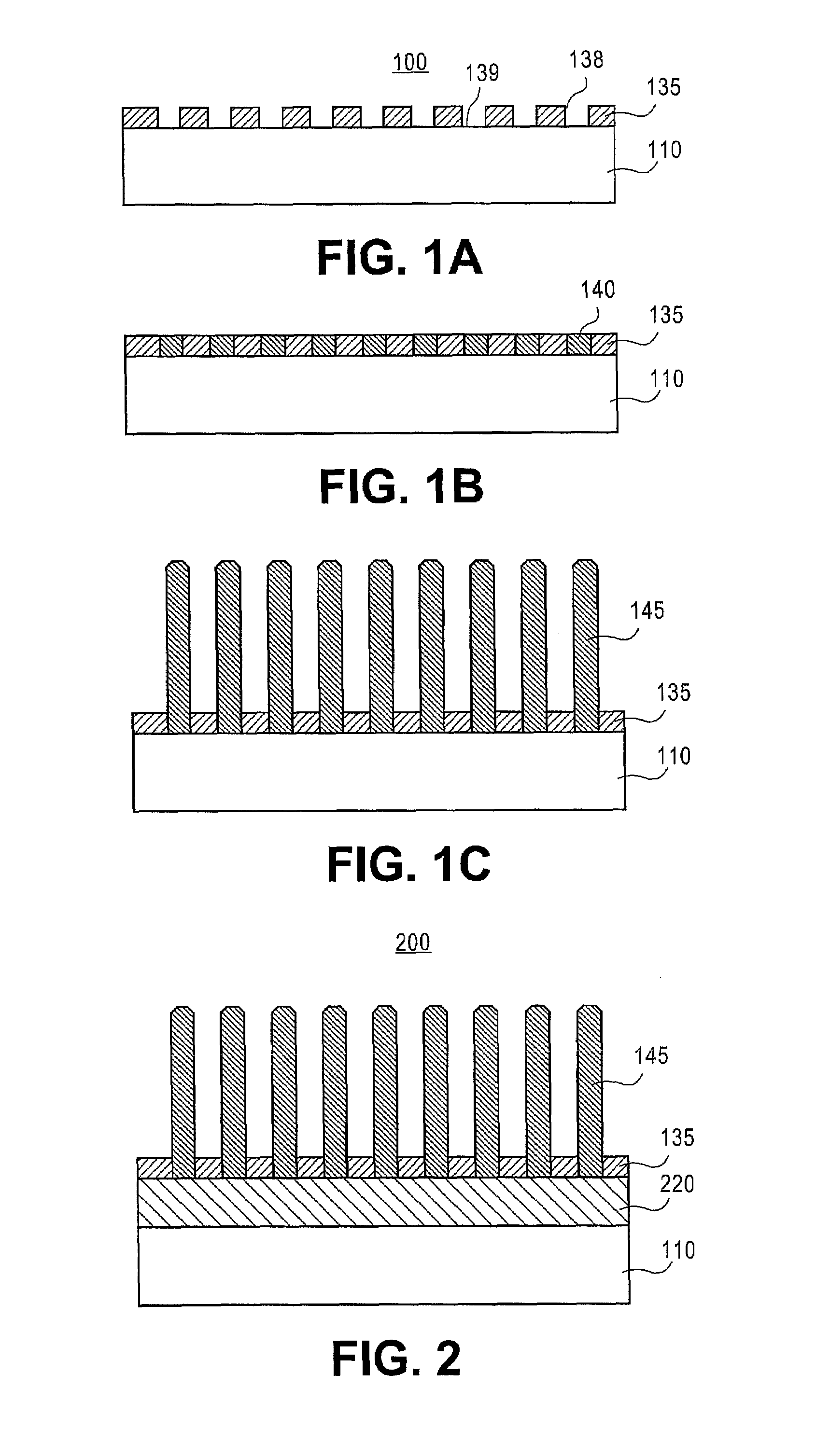

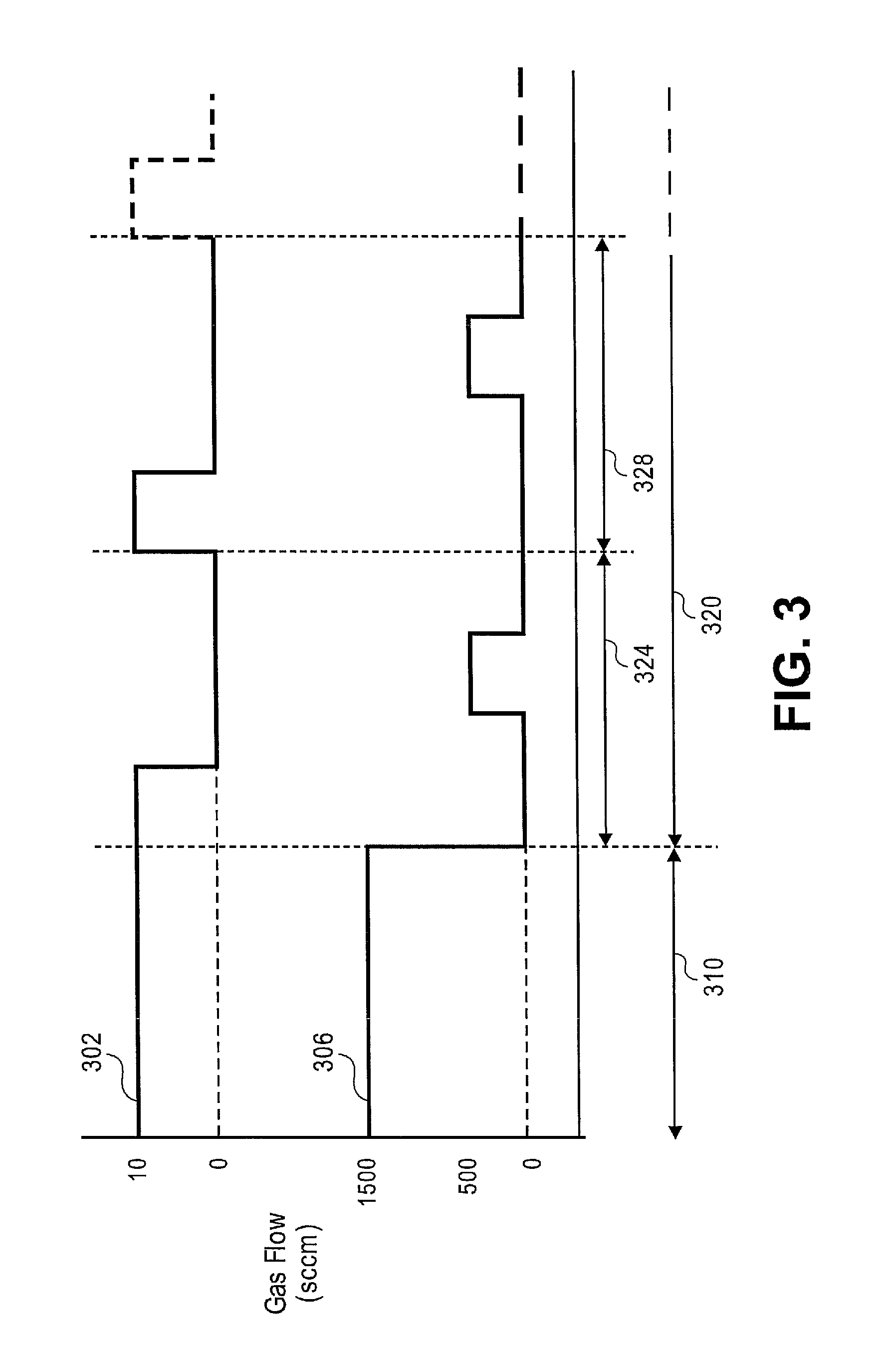

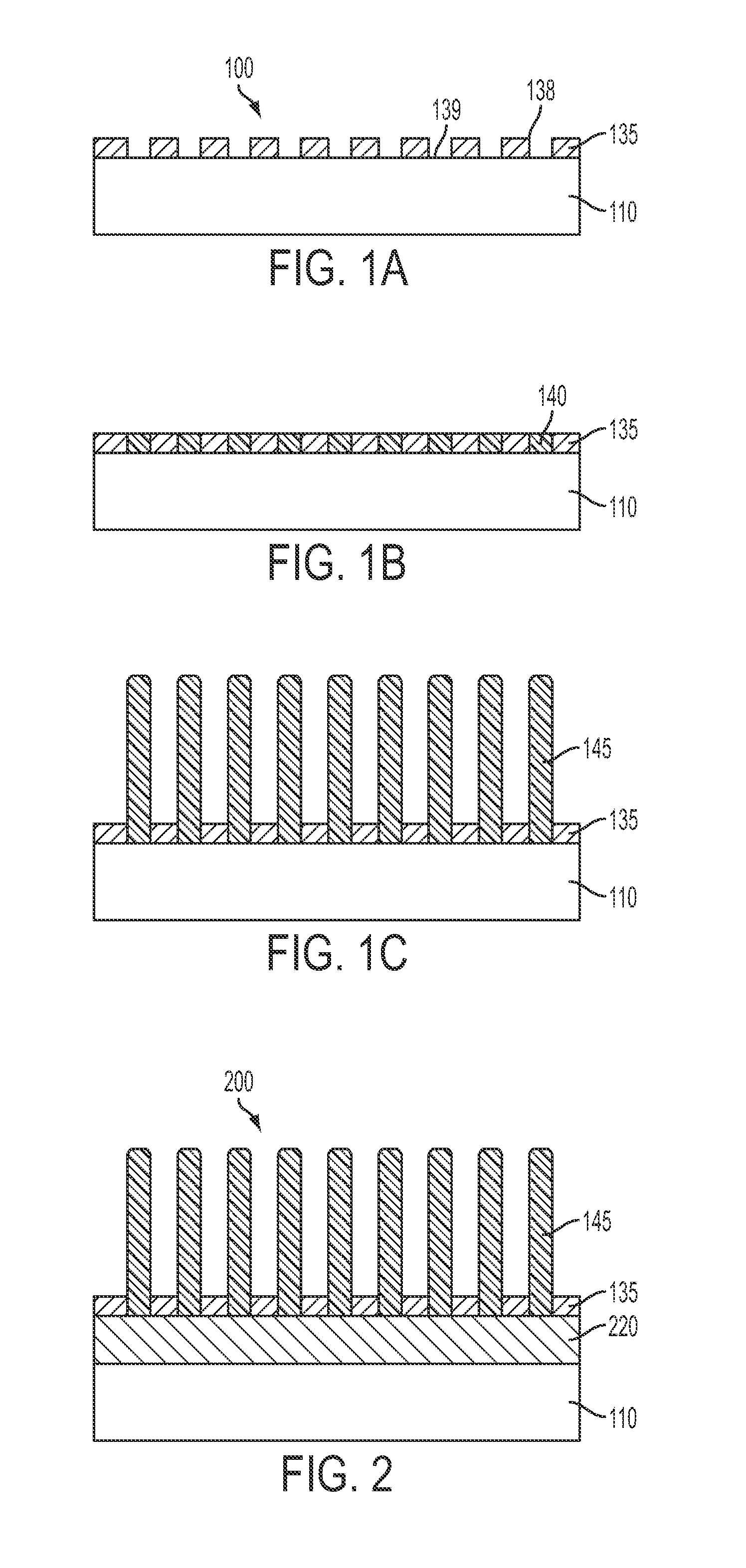

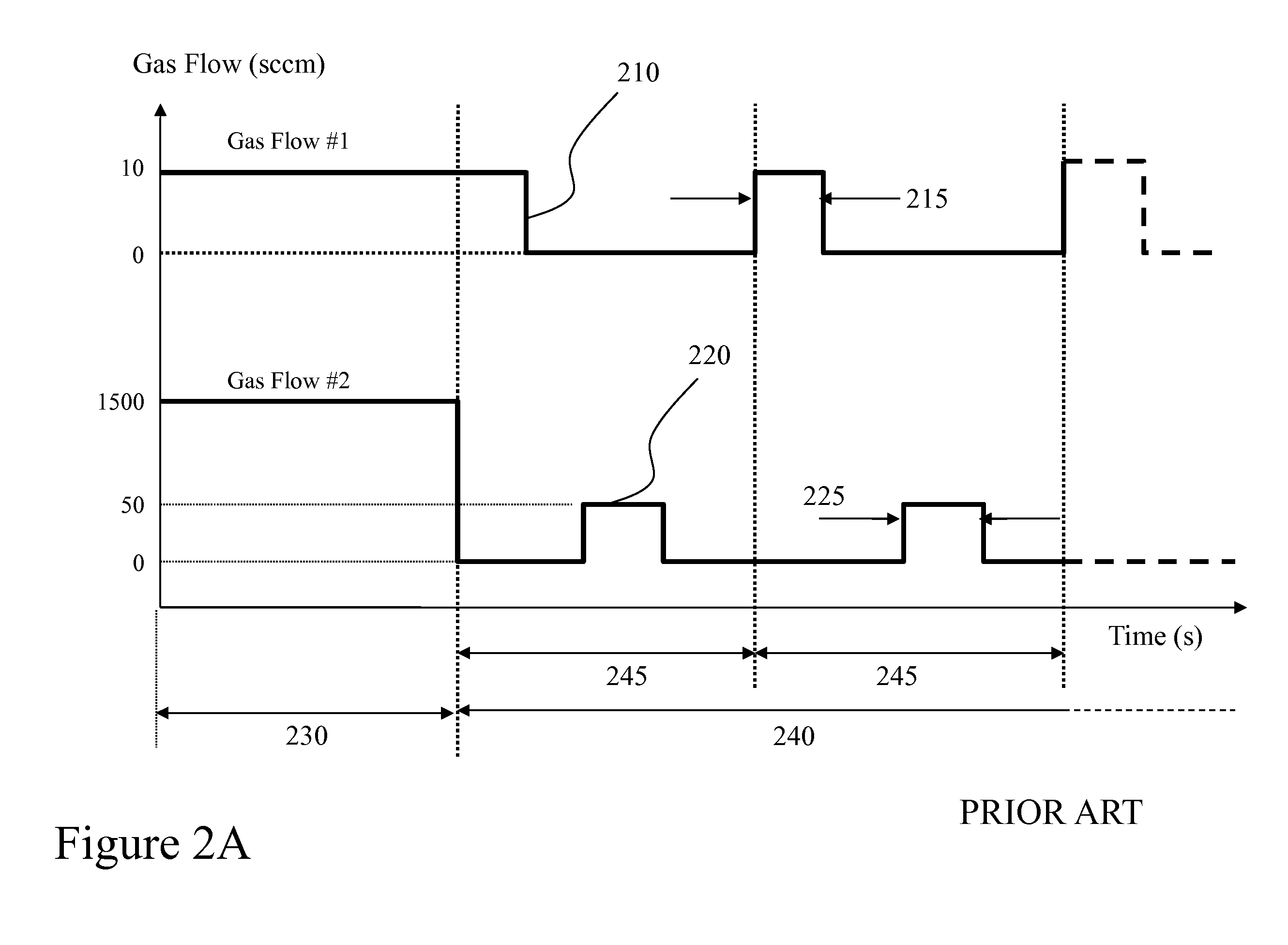

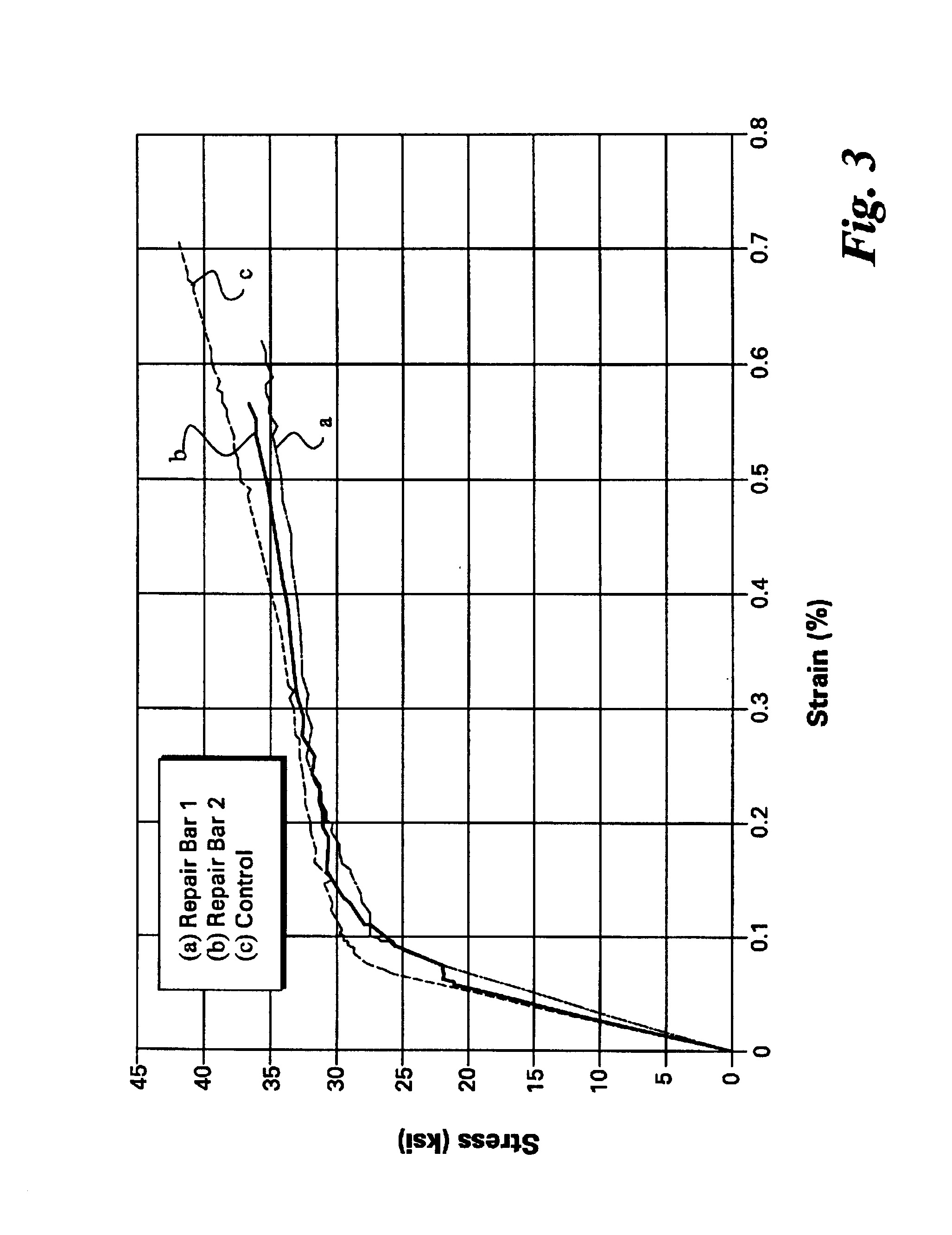

Pulsed growth of catalyst-free growth of GaN nanowires and application in group III nitride semiconductor bulk material

Exemplary embodiments provide semiconductor devices including high-quality (i.e., defect free) group III-N nanowires and uniform group III-N nanowire arrays as well as their scalable processes for manufacturing, where the position, orientation, cross-sectional features, length and the crystallinity of each nanowire can be precisely controlled. A pulsed growth mode can be used to fabricate the disclosed group III-N nanowires and / or nanowire arrays providing a uniform length of about 10 nm to about 1000 microns with constant cross-sectional features including an exemplary diameter of about 10-1000 nm. In addition, high-quality GaN substrate structures can be formed by coalescing the plurality of GaN nanowires and / or nanowire arrays to facilitate the fabrication of visible LEDs and lasers. Furthermore, core-shell nanowire / MQW active structures can be formed by a core-shell growth on the nonpolar sidewalls of each nanowire.

Owner:STC UNM

Systems and methods for additive manufacturing and repair of metal components

Scanning Laser Epitaxy (SLE) is a layer-by-layer additive manufacturing process that allows for the fabrication of three-dimensional objects with specified microstructure through the controlled melting and re-solidification of a metal powders placed atop a base substrate. SLE can be used to repair single crystal (SX) turbine airfoils, for example, as well as the manufacture functionally graded turbine components. The SLE process is capable of creating equiaxed, directionally solidified, and SX structures. Real-time feedback control schemes based upon an offline model can be used both to create specified defect free microstructures and to improve the repeatability of the process. Control schemes can be used based upon temperature data feedback provided at high frame rate by a thermal imaging camera as well as a melt-pool viewing video microscope. A real-time control scheme can deliver the capability of creating engine ready net shape turbine components from raw powder material.

Owner:GEORGIA TECH RES CORP

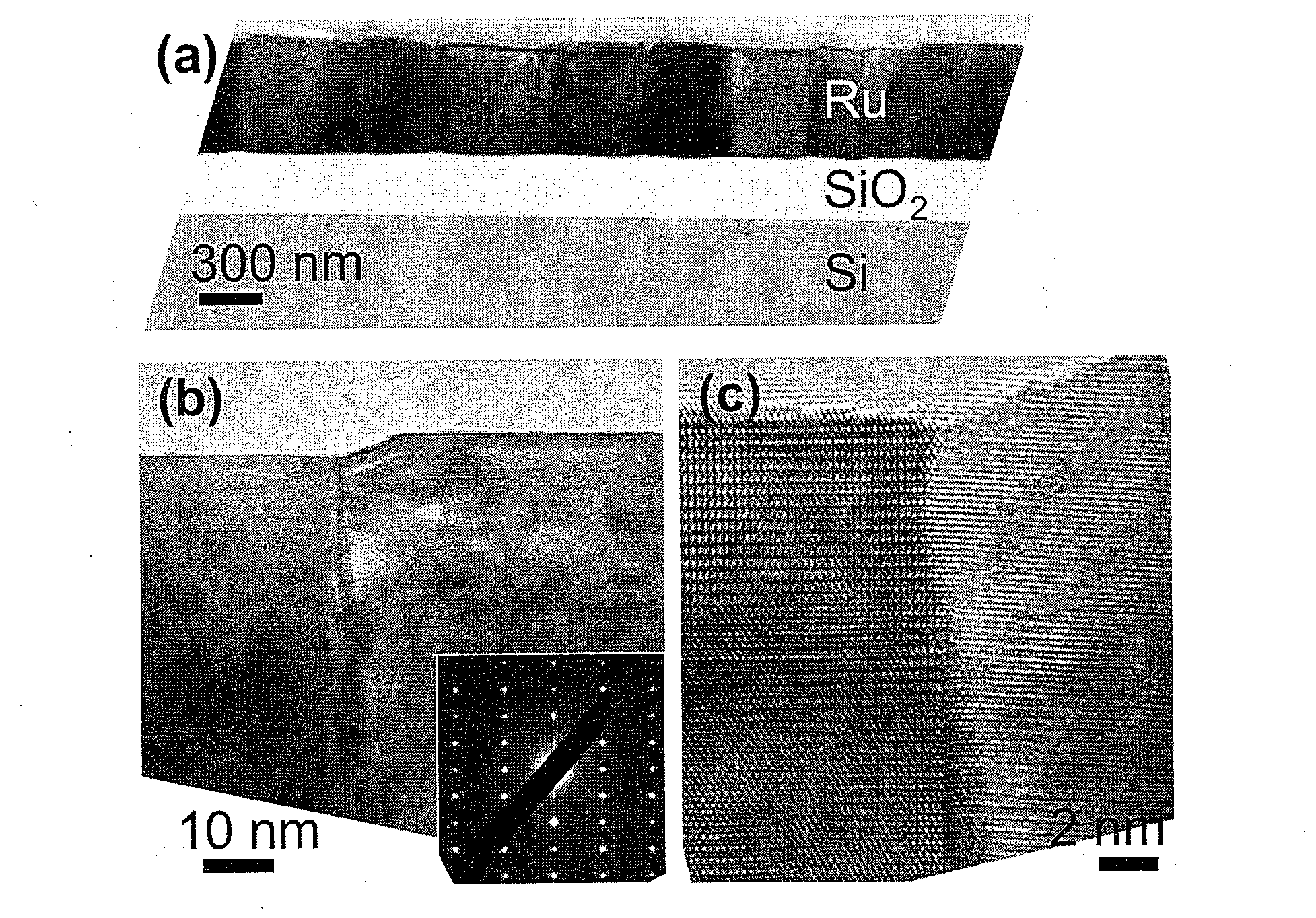

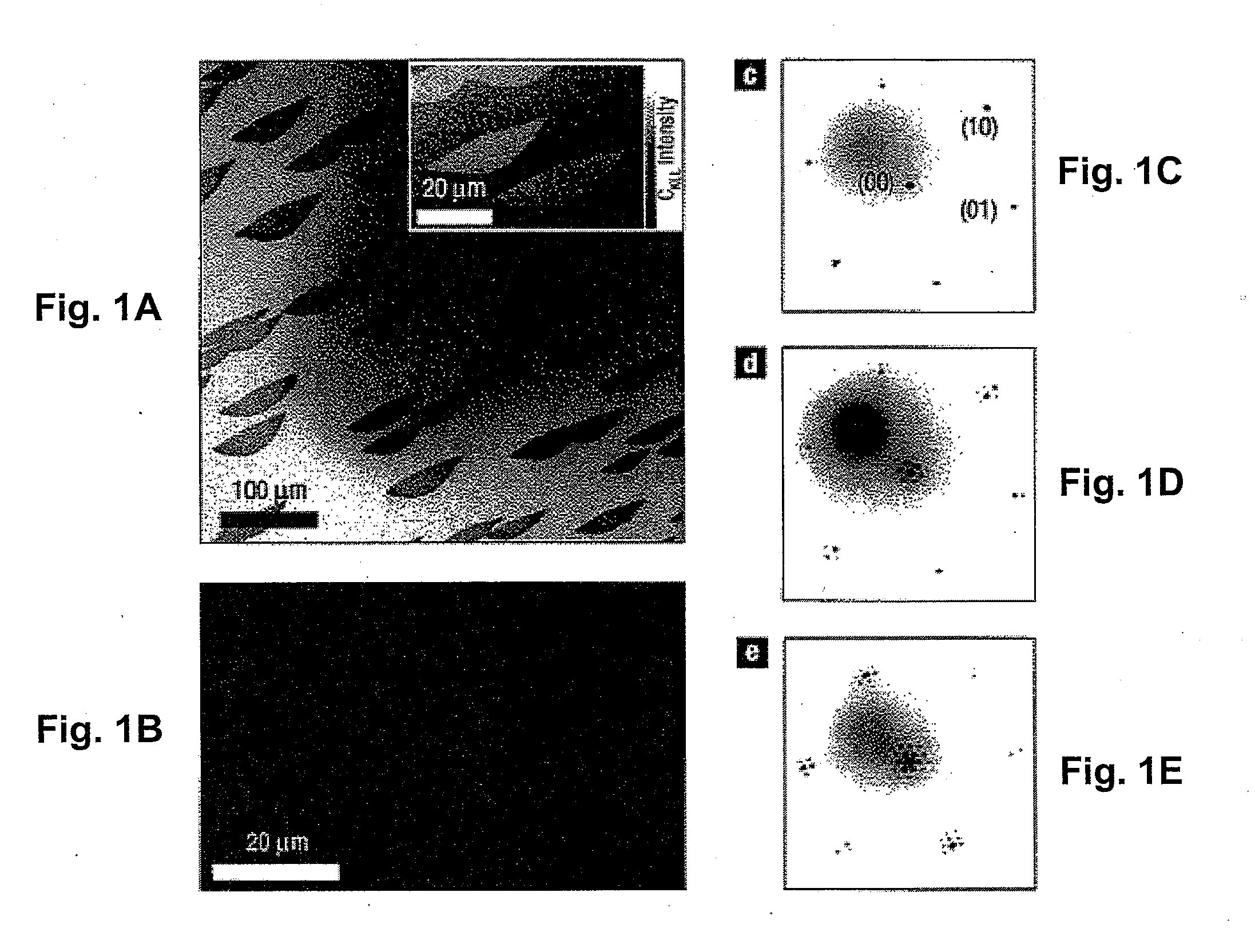

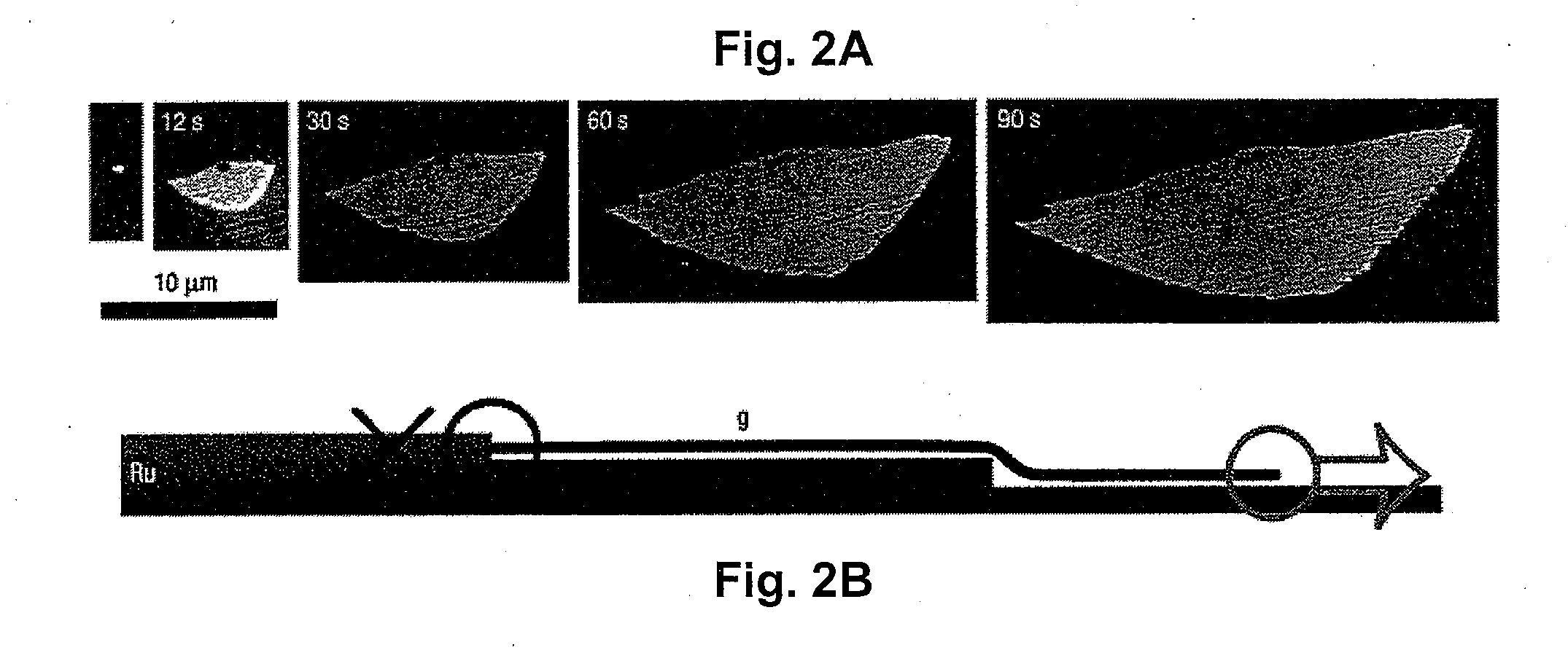

Monolayer and/or Few-Layer Graphene On Metal or Metal-Coated Substrates

InactiveUS20100255984A1Easy to disassembleMaterial nanotechnologyParticle separator tubesHigh concentrationIn plane

Graphene is a single atomic layer of sp2-bonded C atoms densely packed into a two-dimensional honeycomb crystal lattice. A method of forming structurally perfect and defect-free graphene films comprising individual mono crystalline domains with in-plane lateral dimensions of up to 200 μm or more is presented. This is accomplished by controlling the temperature-dependent solubility of interstitial C of a transition metal substrate having a suitable surface structure. At elevated temperatures, C is incorporated into the bulk at higher concentrations. As the substrate is cooled, a lowering of the interstitial C solubility drives a significant amount of C atoms to the surface where graphene islands nucleate and gradually increase in size with continued cooling. Ru(0001) is selected as a model system and electron microscopy is used to observe graphene growth during cooling from elevated temperatures. With controlled cooling, large arrays of macroscopic single-crystalline graphene domains covering the entire transition metal surface are produced. As the graphene domains coalesce to a complete layer, a second graphene layer is formed, etc. By controlling the interstitial C concentration and the cooling rate, graphene layers with thickness up to 10 atomic layers or more are formed in a controlled, layer-by-layer fashion.

Owner:BROOKHAVEN SCI ASSOCS

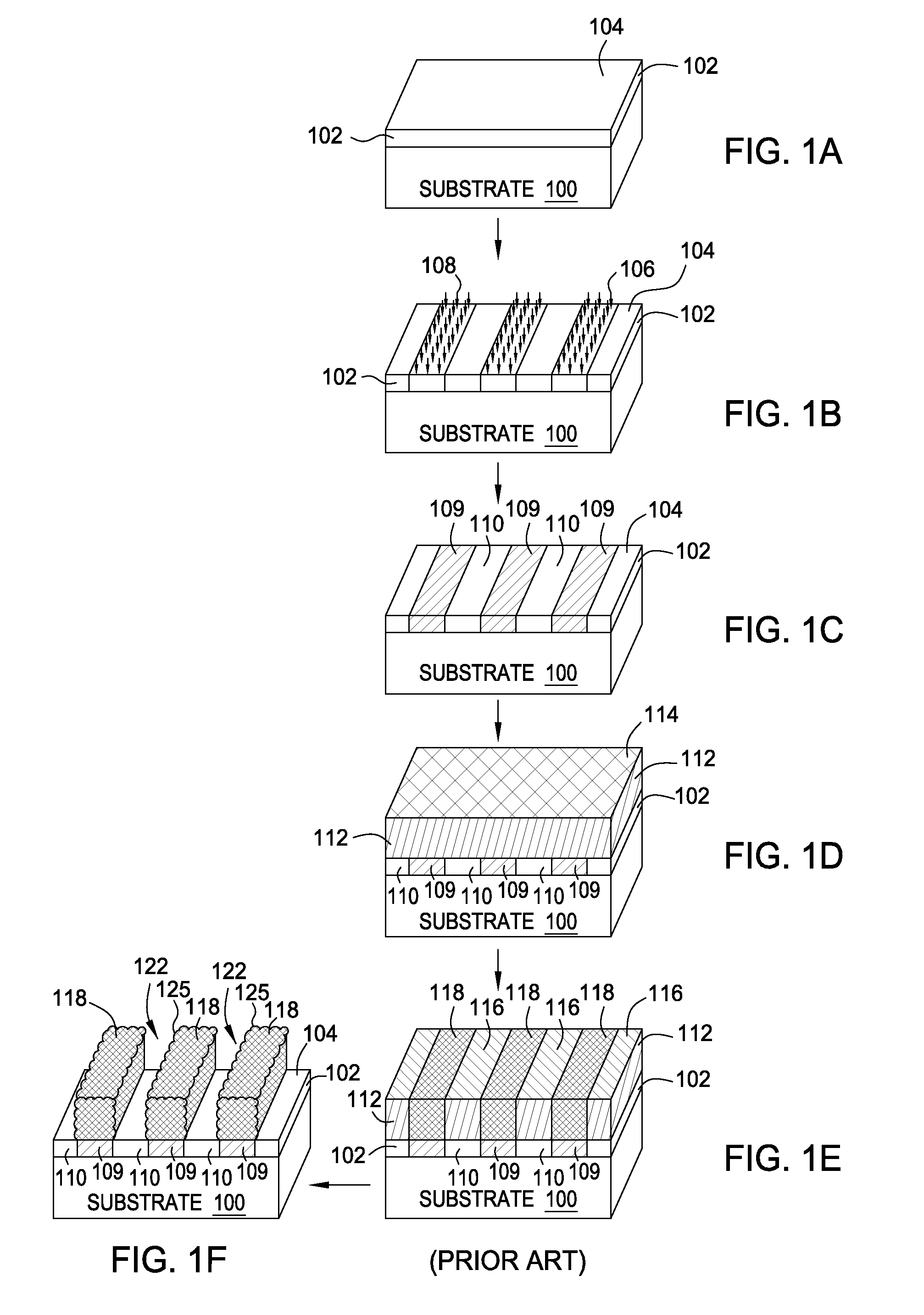

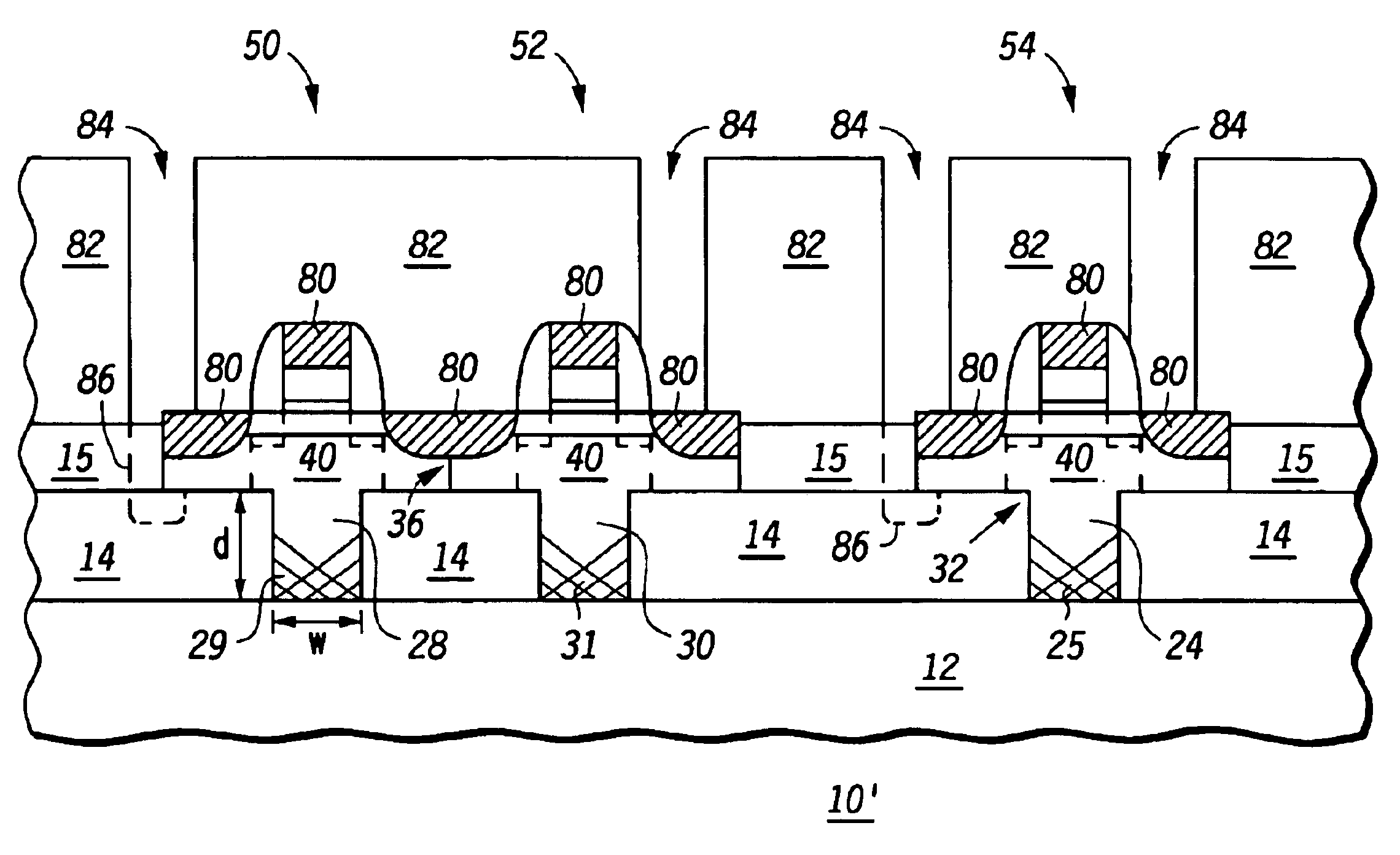

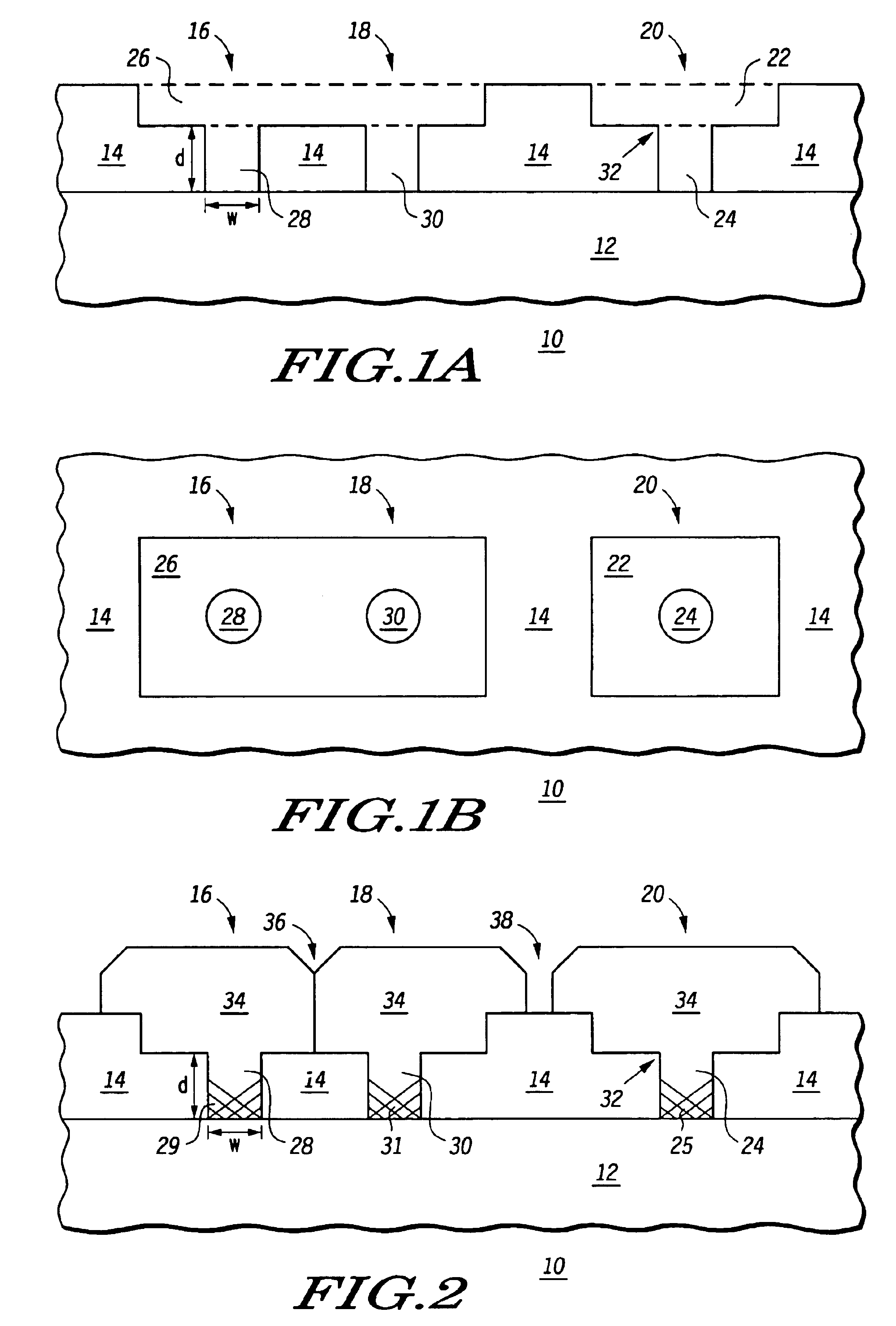

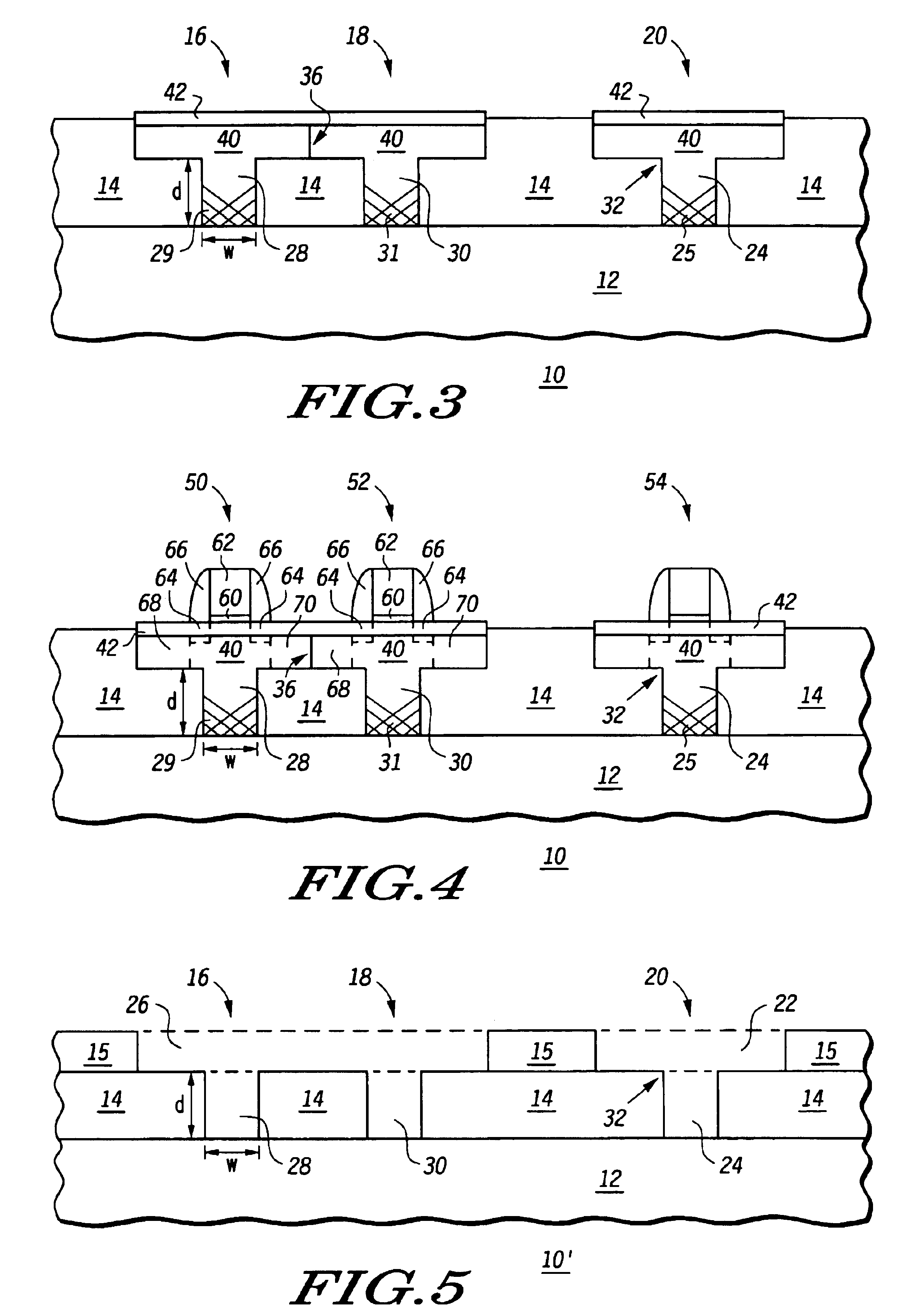

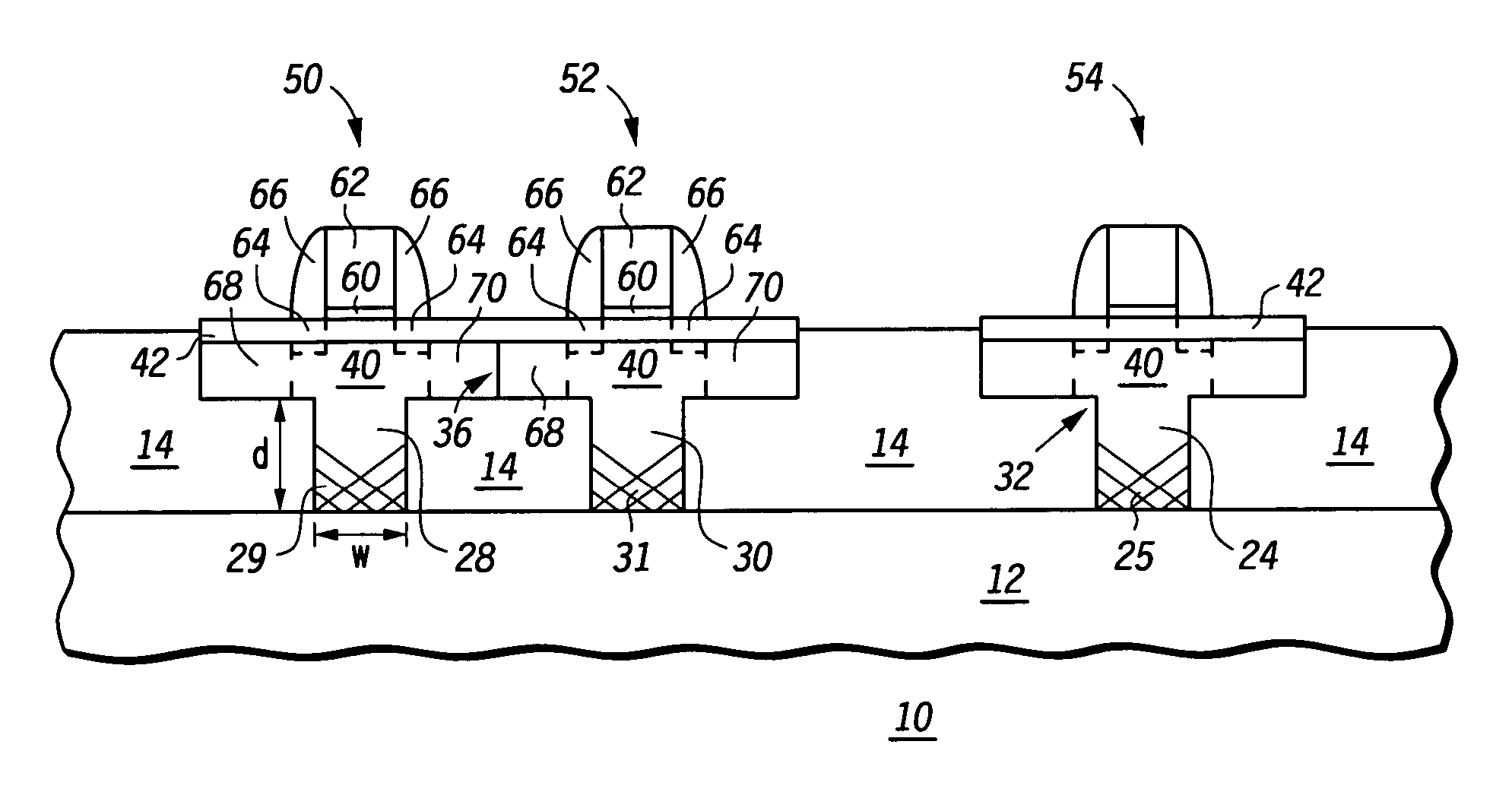

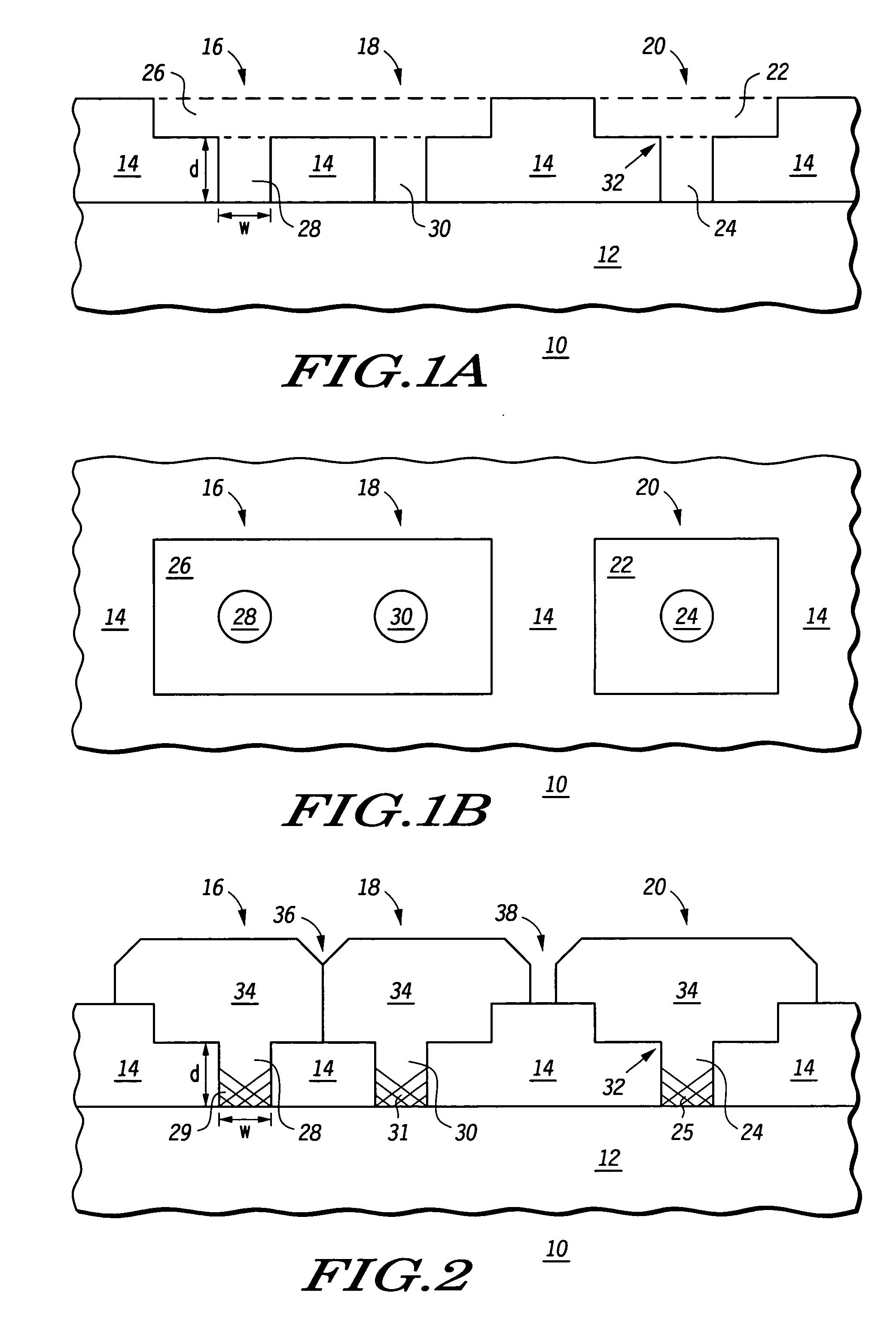

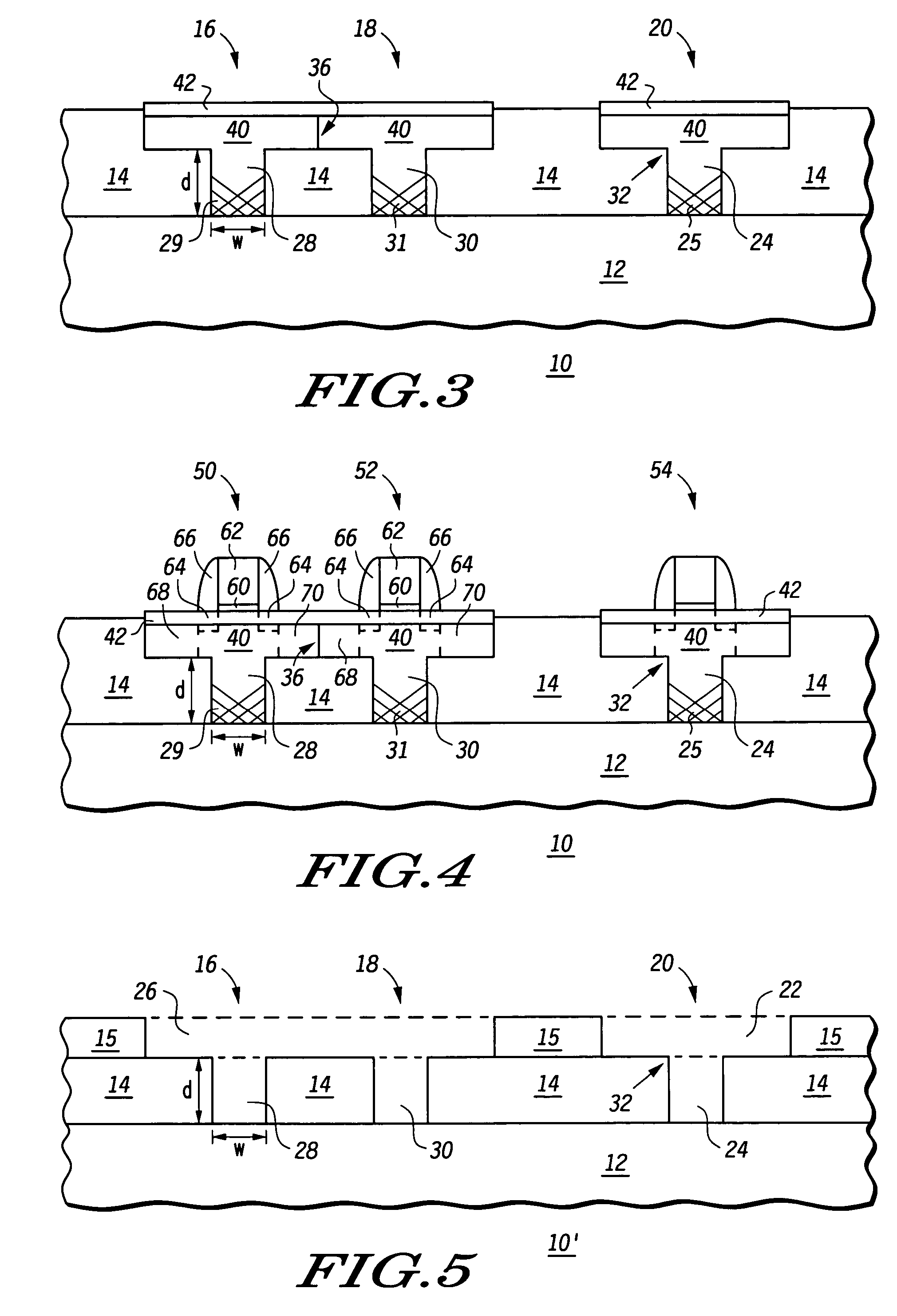

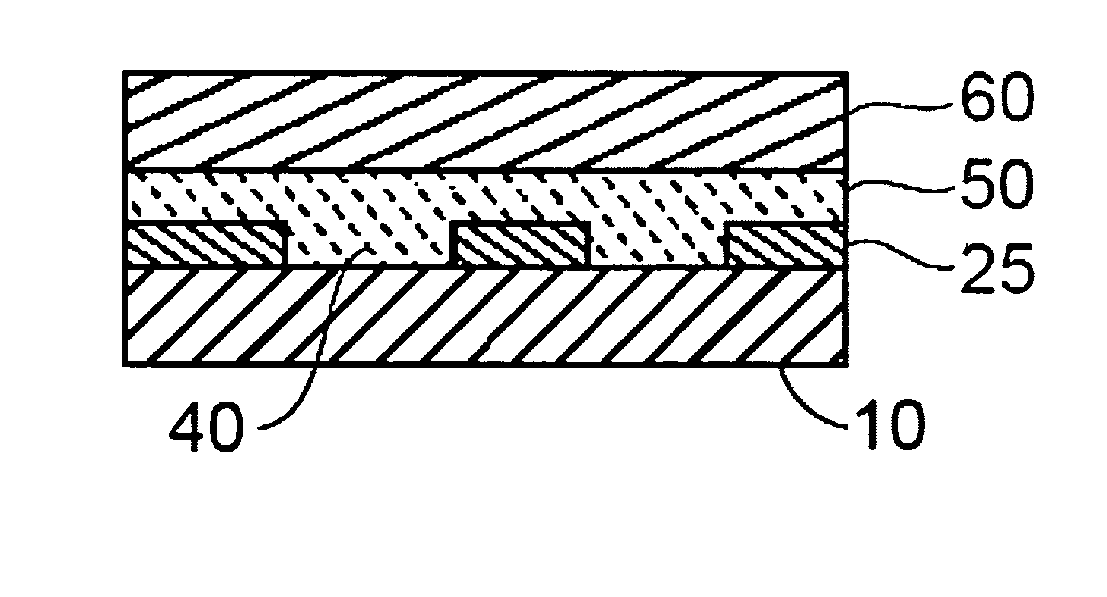

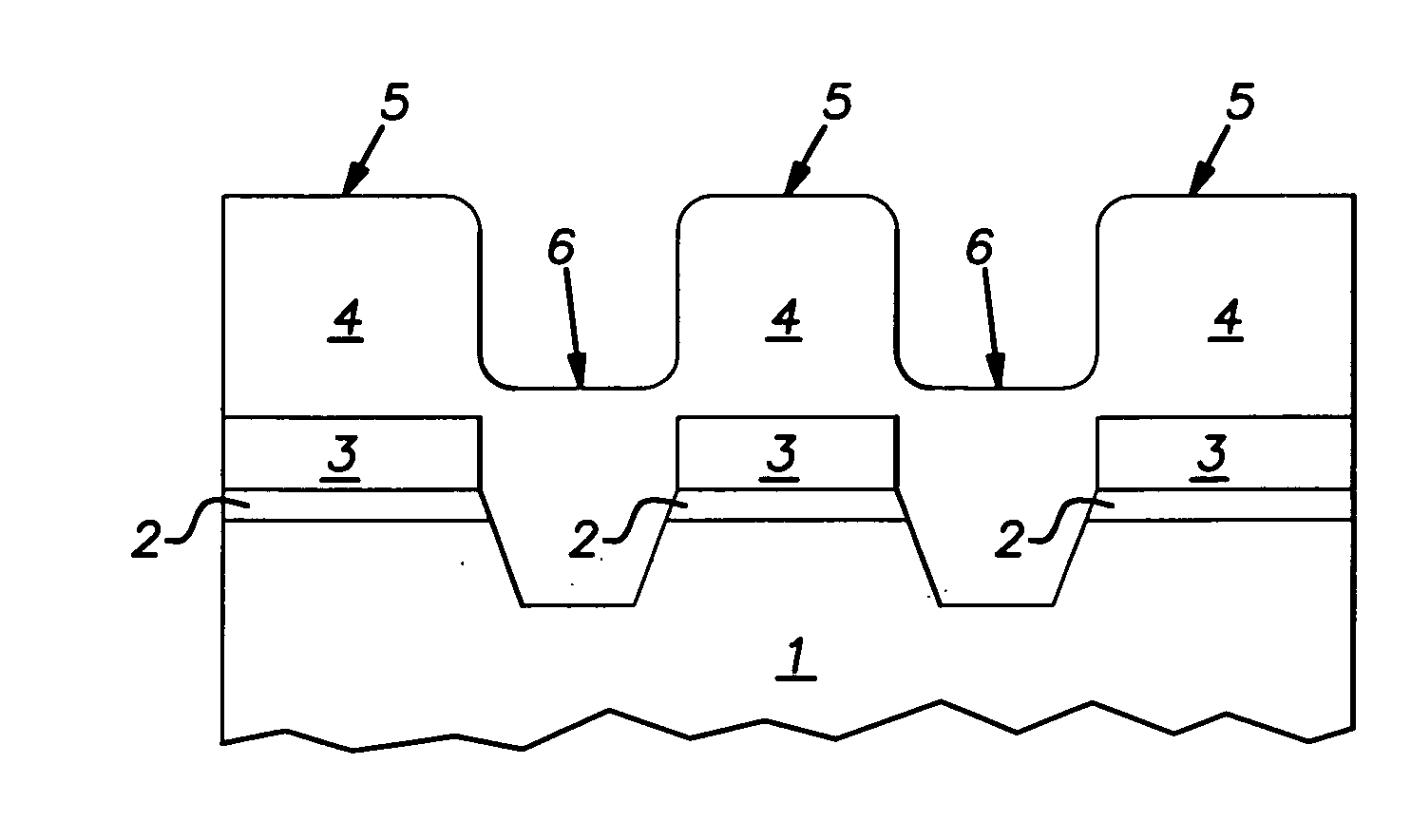

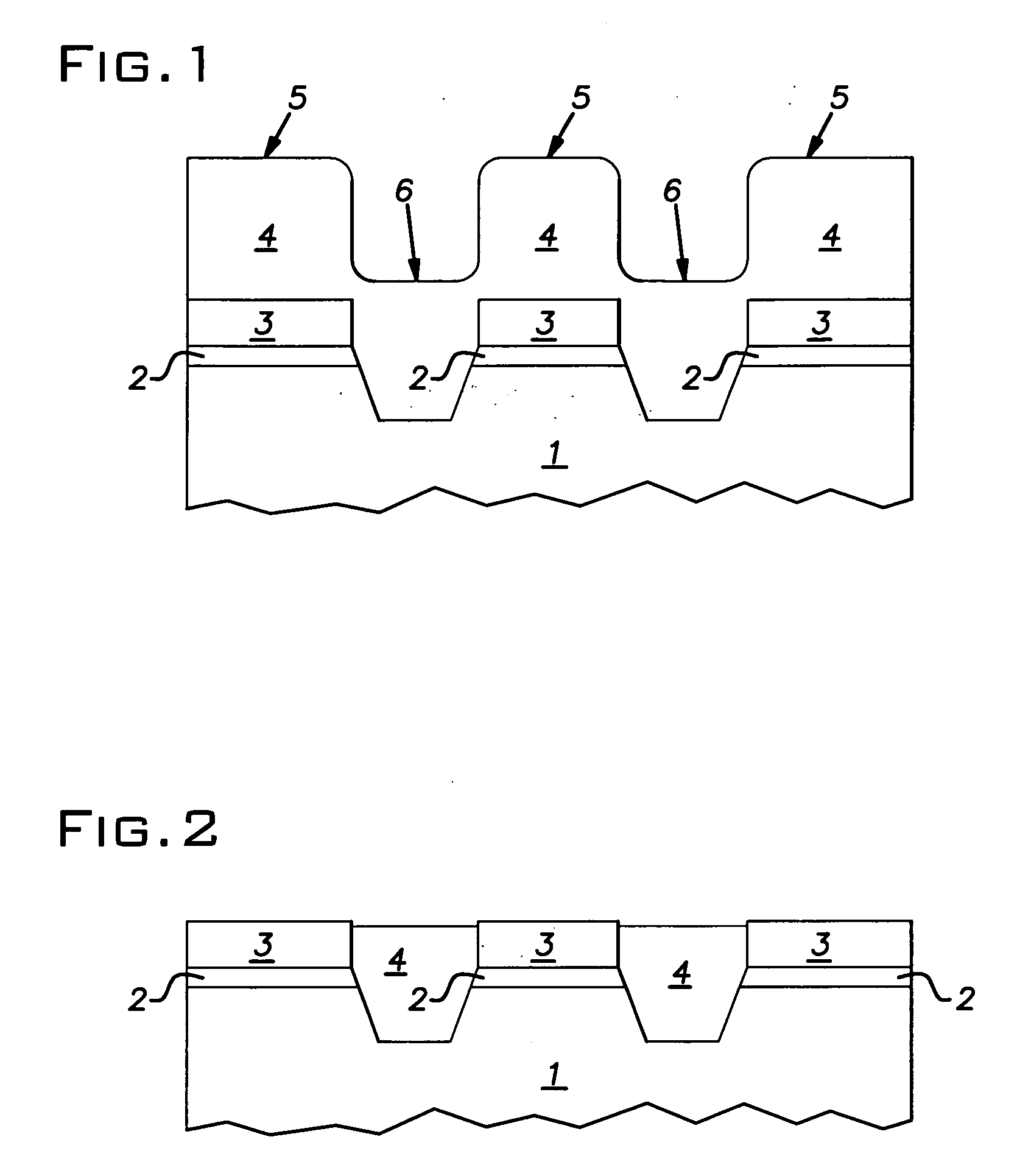

Semiconductor device incorporating a defect controlled strained channel structure and method of making the same

InactiveUS6919258B2Semiconductor/solid-state device manufacturingSemiconductor devicesCharge carrierSingle crystal substrate

A semiconductor device includes a single crystal substrate and a dielectric layer overlying the substrate. The dielectric layer includes at least one opening having a first portion and an overlying second portion. The first portion has a depth and width, such that an aspect ratio of the depth to width is greater than one. The semiconductor device further includes a first material having a first portion and a second portion, the first portion of the first material filling the first portion of the at least one opening. Defects for relaxing strain at an interface between the first material and the substrate material exist only within the first portion of the first material due to the aspect ratio being greater than one. The second portion of the first material is substantially defect free. Furthermore, the second portion of the first material and an overlying second material different than the first material fill the overlying second portion of the at least one opening. The second material has a thickness which is less than a critical thickness to maintain the second material in a strained state. The strained second material functions as a channel for charge carriers.

Owner:MOTOROLA INC +1

Semiconductor device incorporating a defect controlled strained channel structure and method of making the same

ActiveUS20050073028A1Free from defectSemiconductor/solid-state device manufacturingSemiconductor devicesCharge carrierDevice material

A semiconductor device includes a single crystal substrate and a dielectric layer overlying the substrate. The dielectric layer includes at least one opening having a first portion and an overlying second portion. The first portion has a depth and width, such that an aspect ratio of the depth to width is greater than one. The semiconductor device further includes a first material having a first portion and a second portion, the first portion of the first material filling the first portion of the at least one opening. Defects for relaxing strain at an interface between the first material and the substrate material exist only within the first portion of the first material due to the aspect ratio being greater than one. The second portion of the first material is substantially defect free. Furthermore, the second portion of the first material and an overlying second material different than the first material fill the overlying second portion of the at least one opening. The second material has a thickness which is less than a critical thickness to maintain the second material in a strained state. The strained second material functions as a channel for charge carriers.

Owner:MOTOROLA INC +1

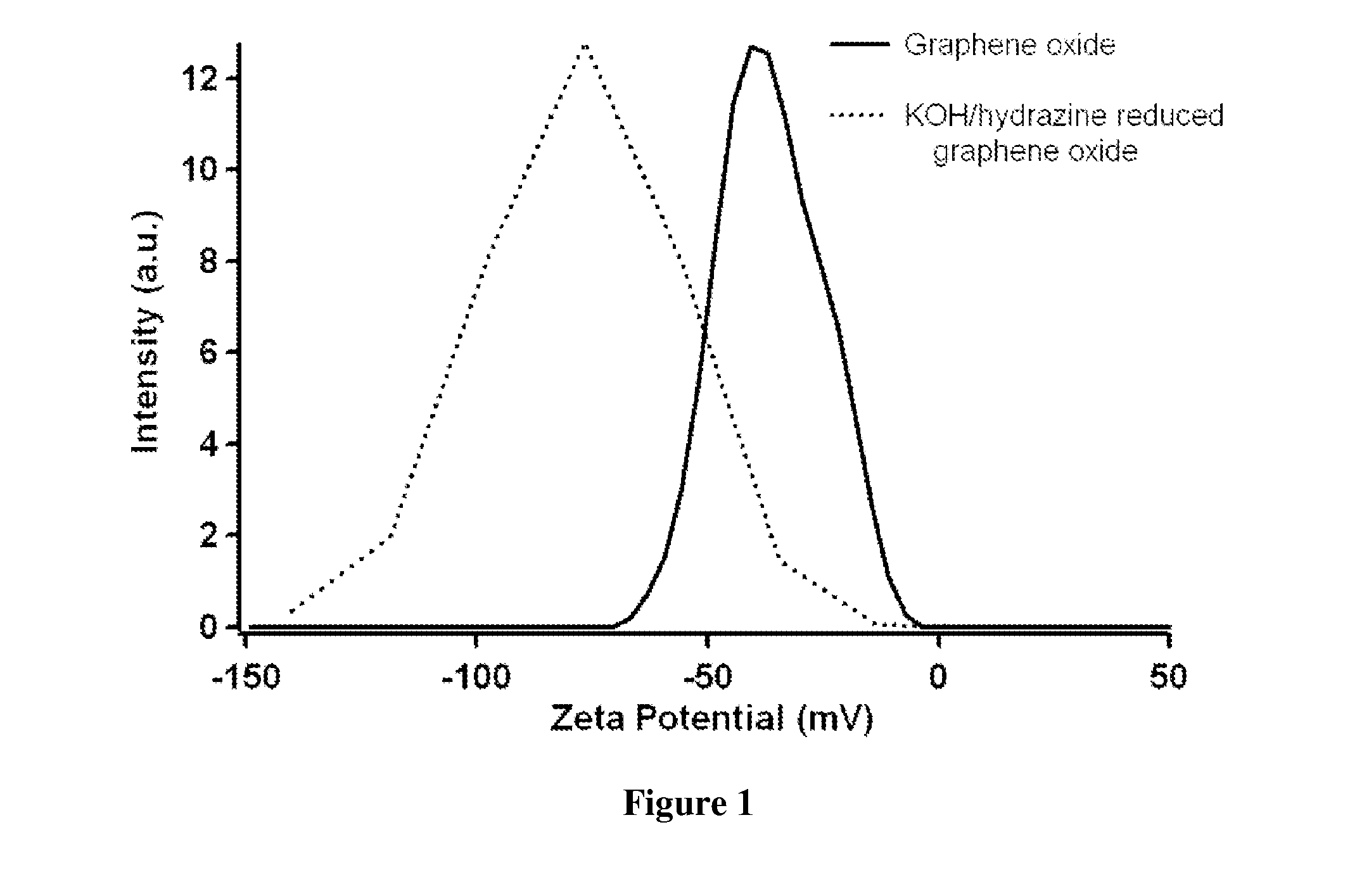

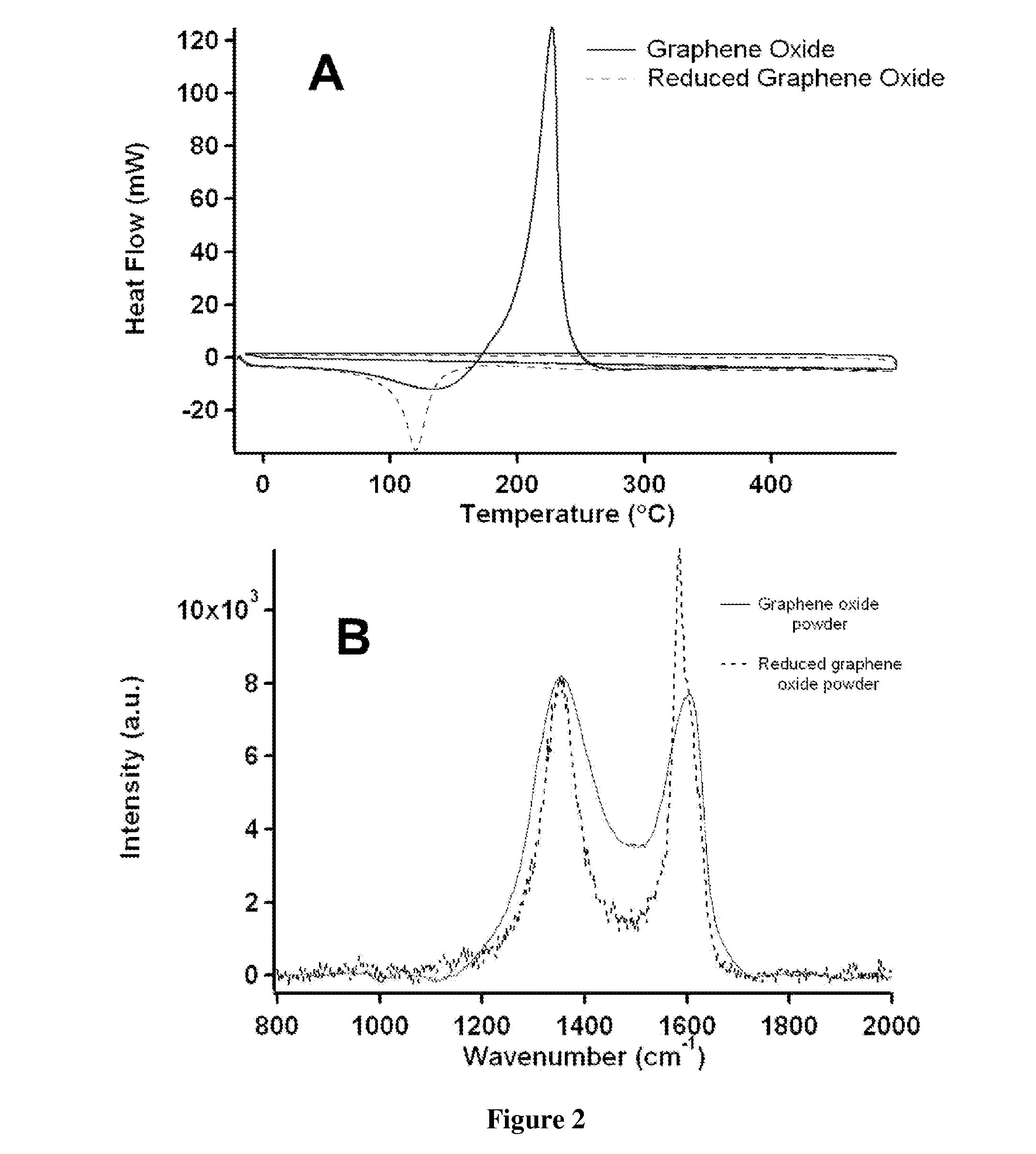

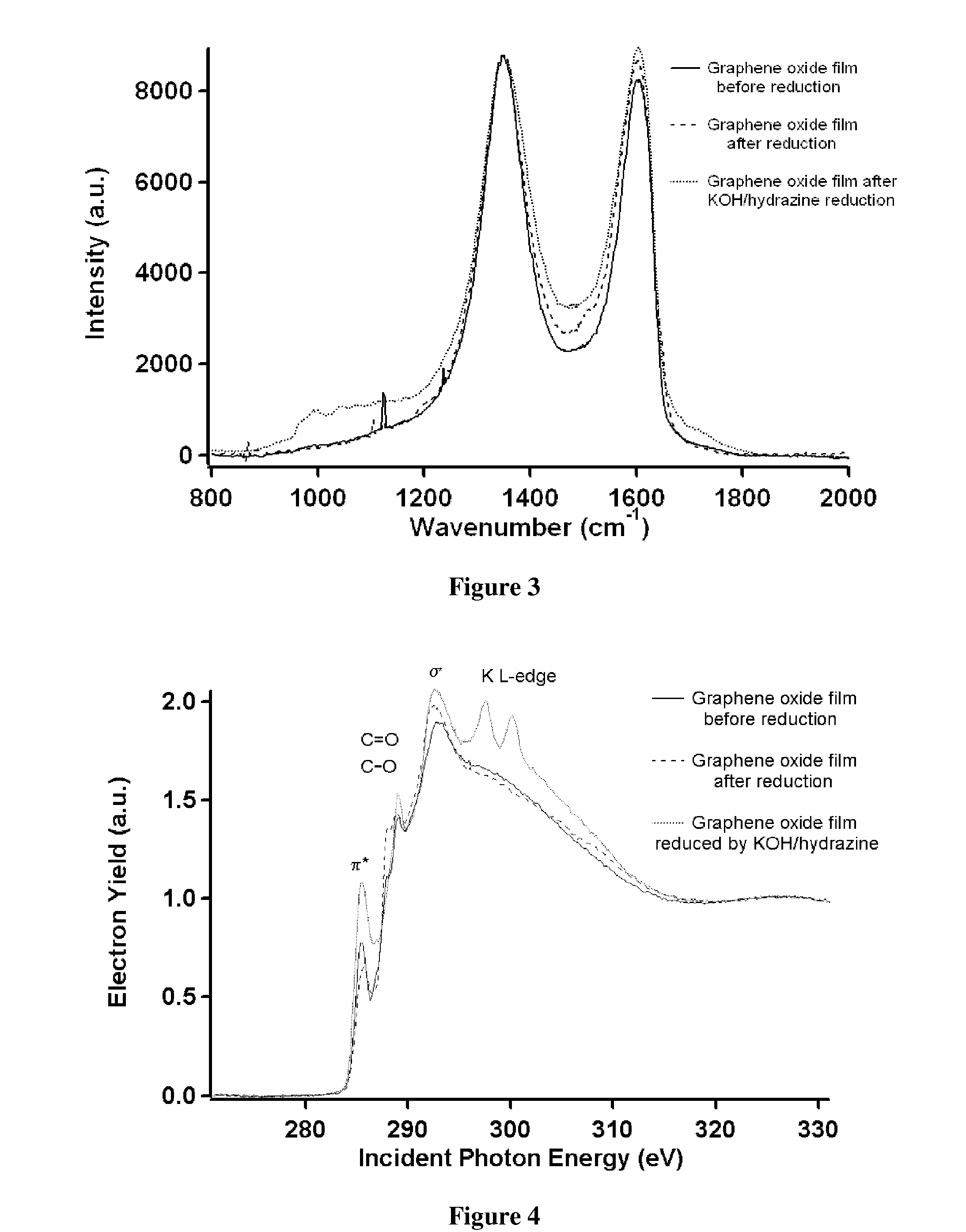

Graphene Films and Methods of Making Thereof

ActiveUS20130156678A1Material nanotechnologyElectrolysis componentsPlanar substrateConformal coating

Provided are methods for forming graphene or functionalized graphene thin films. Also provided are graphene and functionalized graphene thin films formed by the methods. For example, electrophoretic deposition methods and stamping methods are used. Defect-free thin films can be formed. Patterned films can be formed. The methods can provide conformal coatings on non-planar substrates.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK

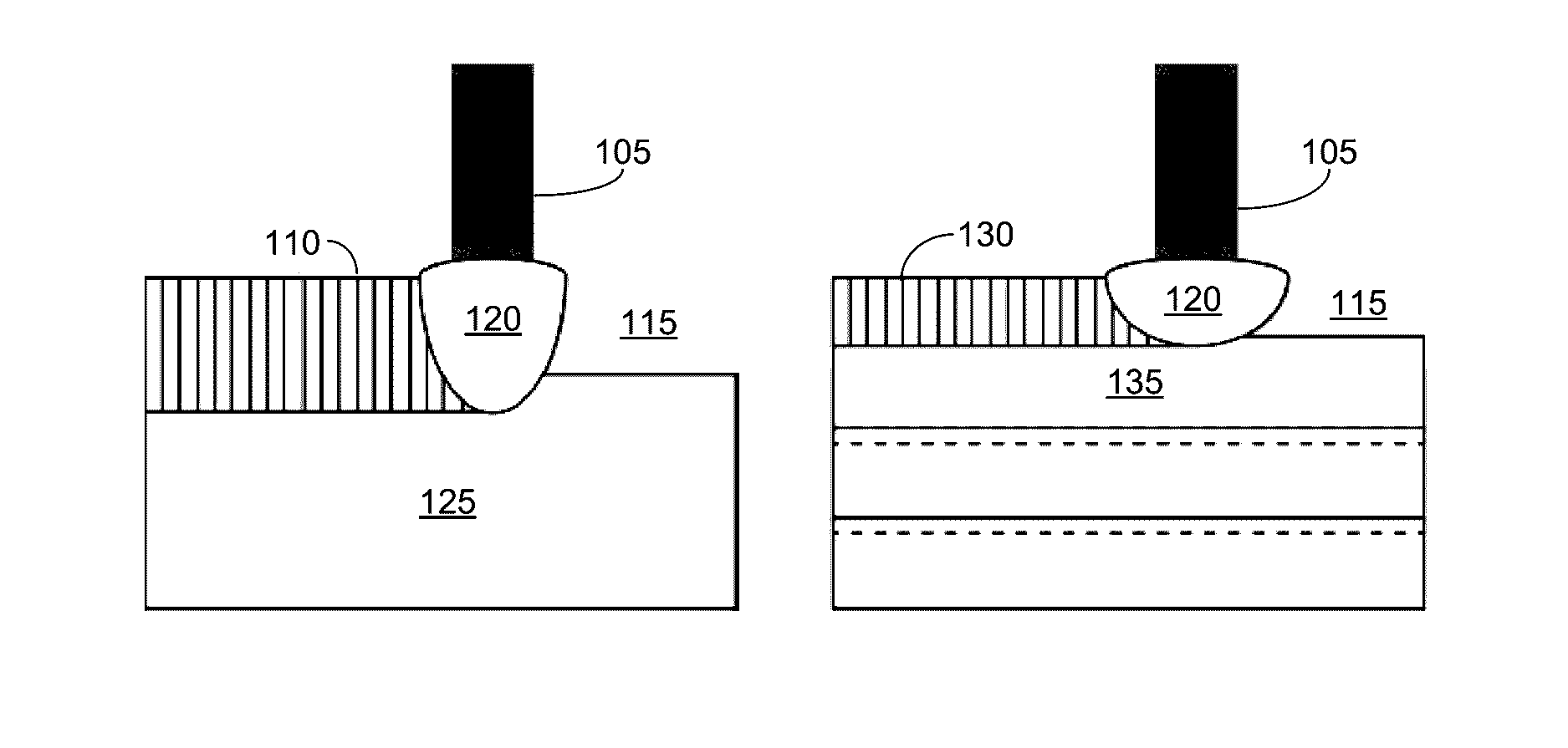

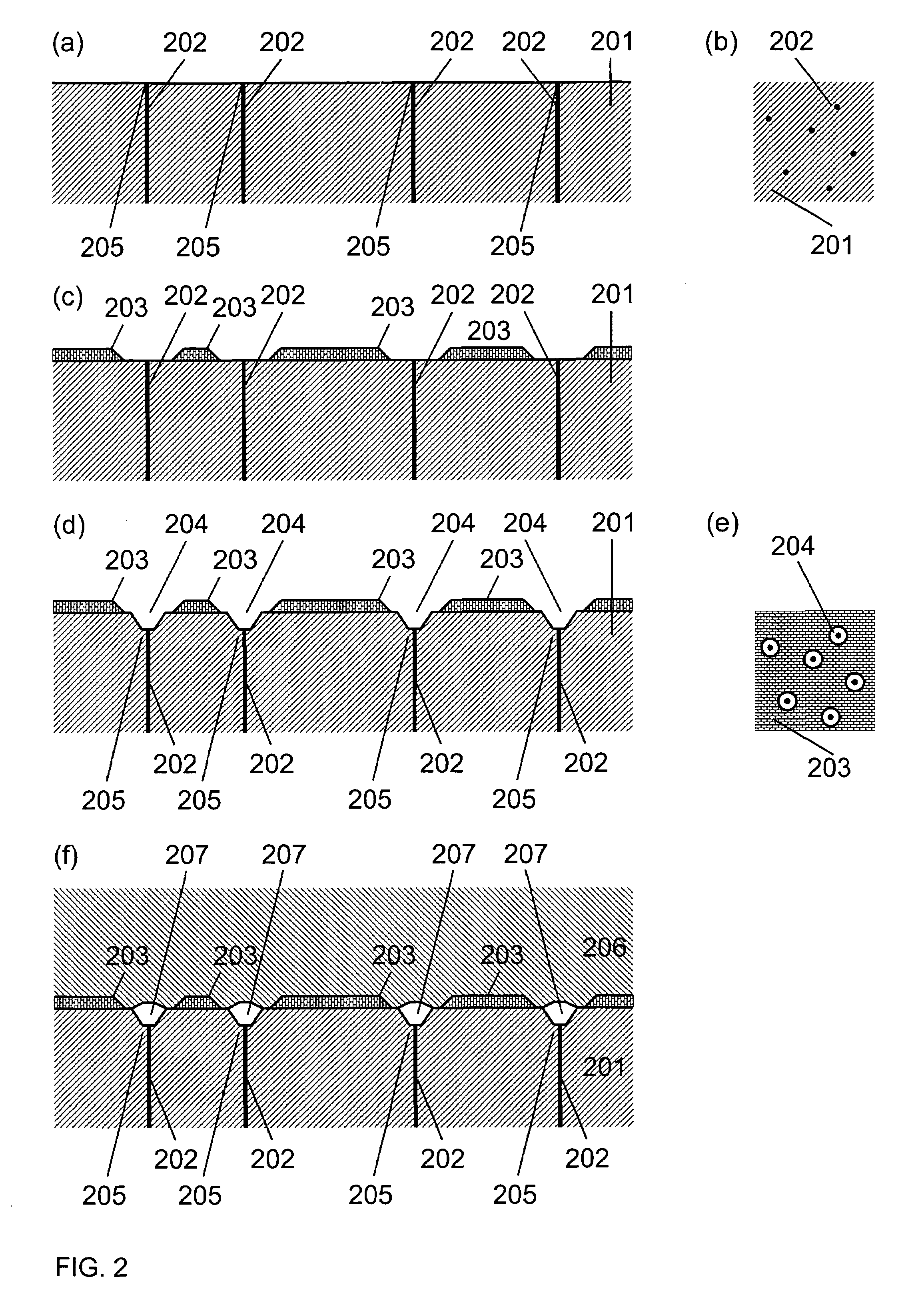

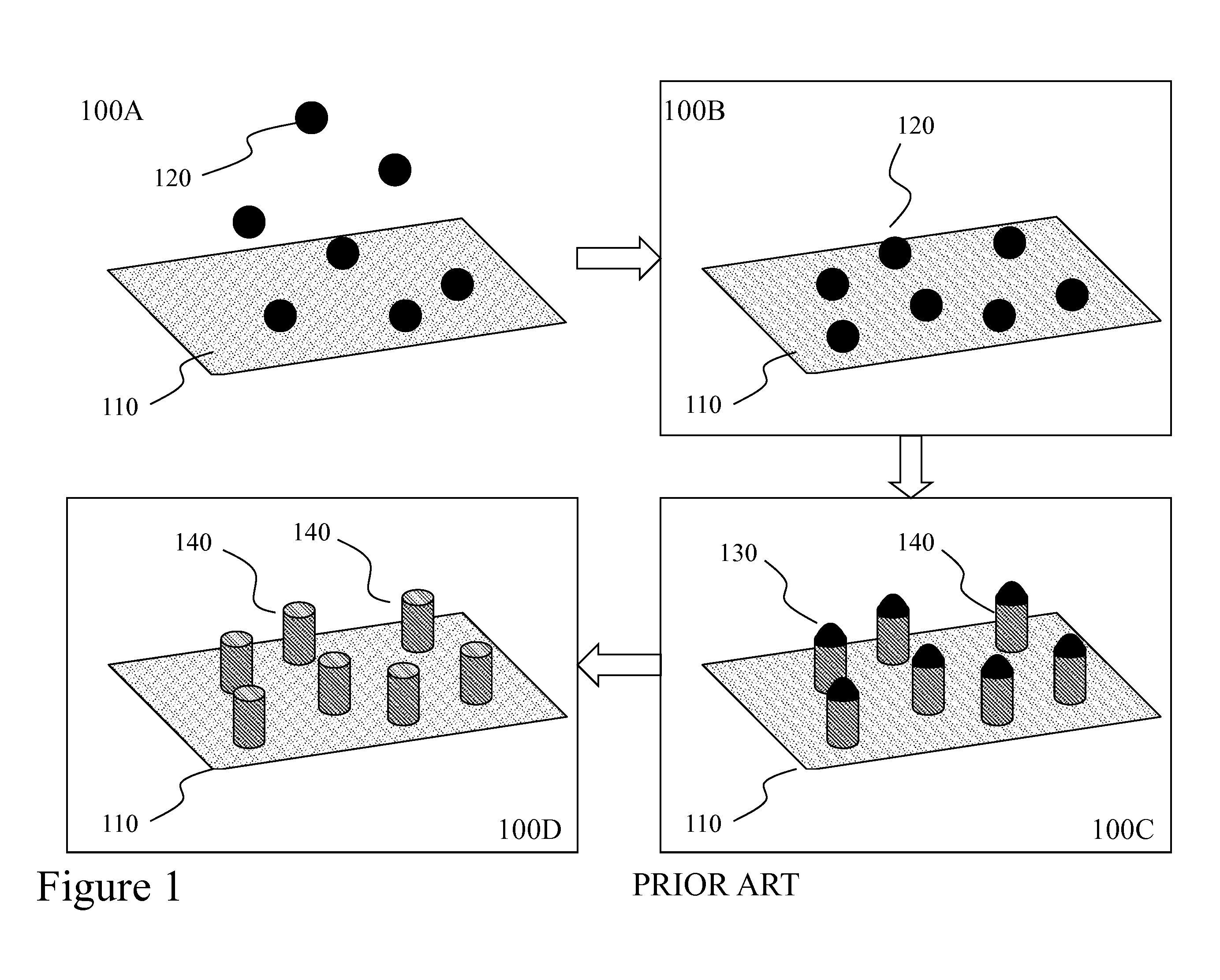

Threading-dislocation-free nanoheteroepitaxy of Ge on Si using self-directed touch-down of Ge through a thin SiO2 layer

ActiveUS20050054180A1Polycrystalline material growthSolid-state devicesThreading dislocationsDirect touch

A method of forming a virtually defect free lattice mismatched nanoheteroepitaxial layer is disclosed. The method includes forming an interface layer on a portion of a substrate. A plurality of seed pads are then formed by self-directed touchdown by exposing the interface layer to a material comprising a semiconductor material. The plurality of seed pads, having an average width of about 1 nm to 10 nm, are interspersed within the interface layer and contact the substrate. An epitaxial layer is then formed by lateral growth of the seed pads over the interface layer.

Owner:STC UNM

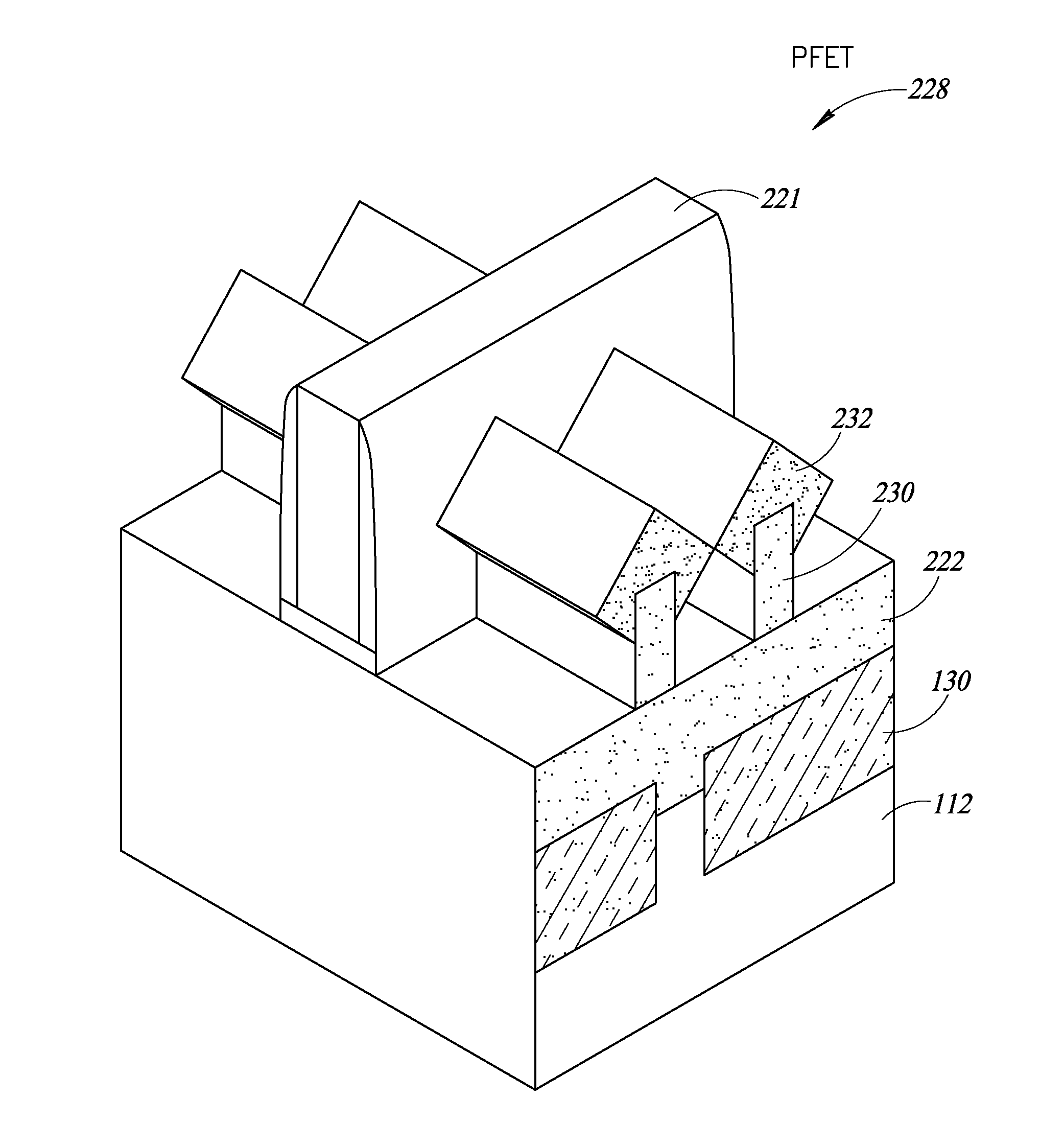

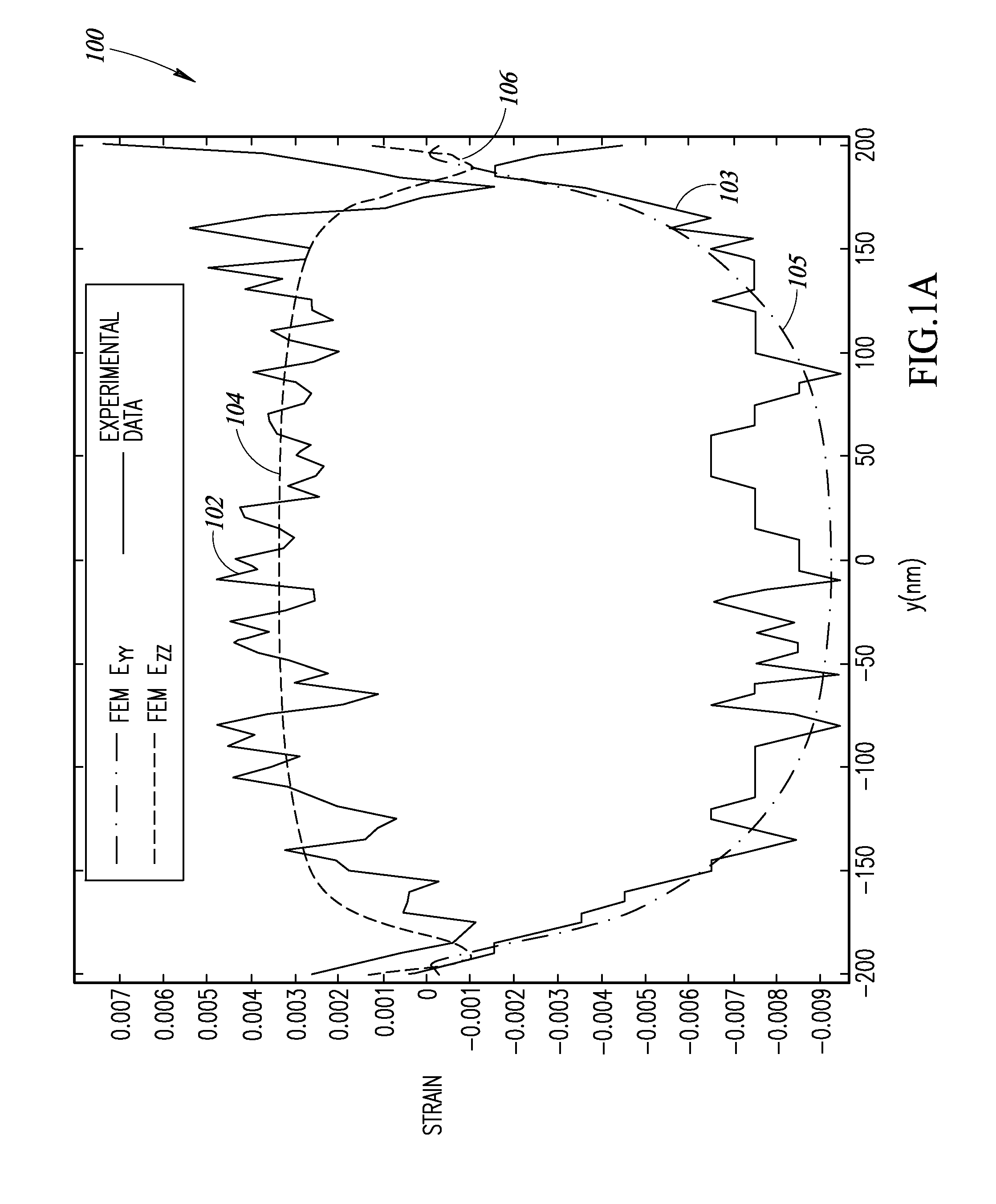

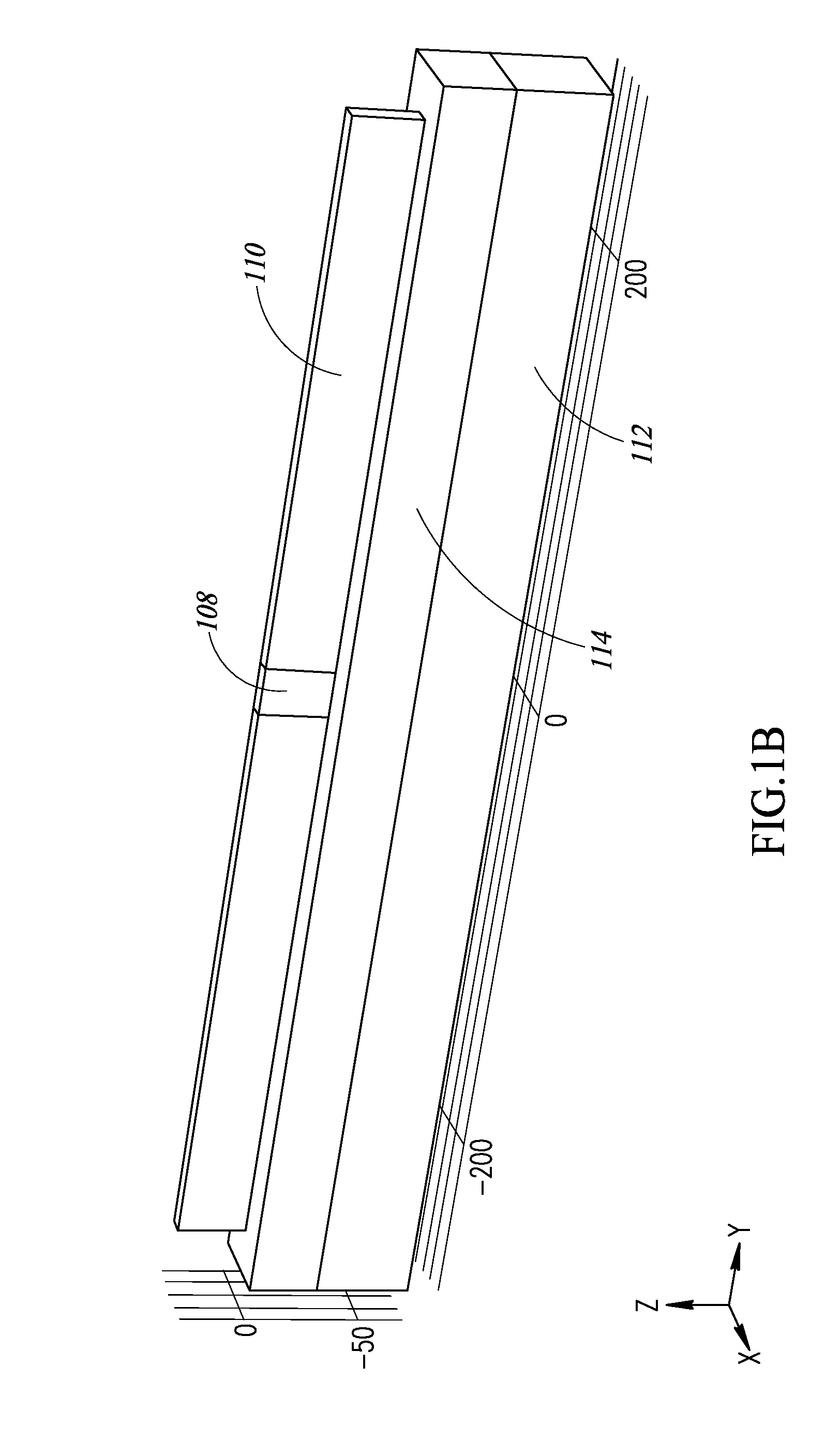

Defect-free strain relaxed buffer layer

ActiveUS20160190304A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringDislocation

A modified silicon substrate having a substantially defect-free strain relaxed buffer layer of SiGe is suitable for use as a foundation on which to construct a high performance CMOS FinFET device. The substantially defect-free SiGe strain-relaxed buffer layer can be formed by making cuts in, or segmenting, a strained epitaxial film, causing edges of the film segments to experience an elastic strain relaxation. When the segments are small enough, the overall film is relaxed so that the film is substantially without dislocation defects. Once the substantially defect-free strain-relaxed buffer layer is formed, strained channel layers can be grown epitaxially from the relaxed SRB layer. The strained channel layers are then patterned to create fins for a FinFET device. In one embodiment, dual strained channel layers are formed—a tensilely strained layer for NFET devices, and a compressively strained layer for PFET devices.

Owner:GLOBALFOUNDRIES US INC +2

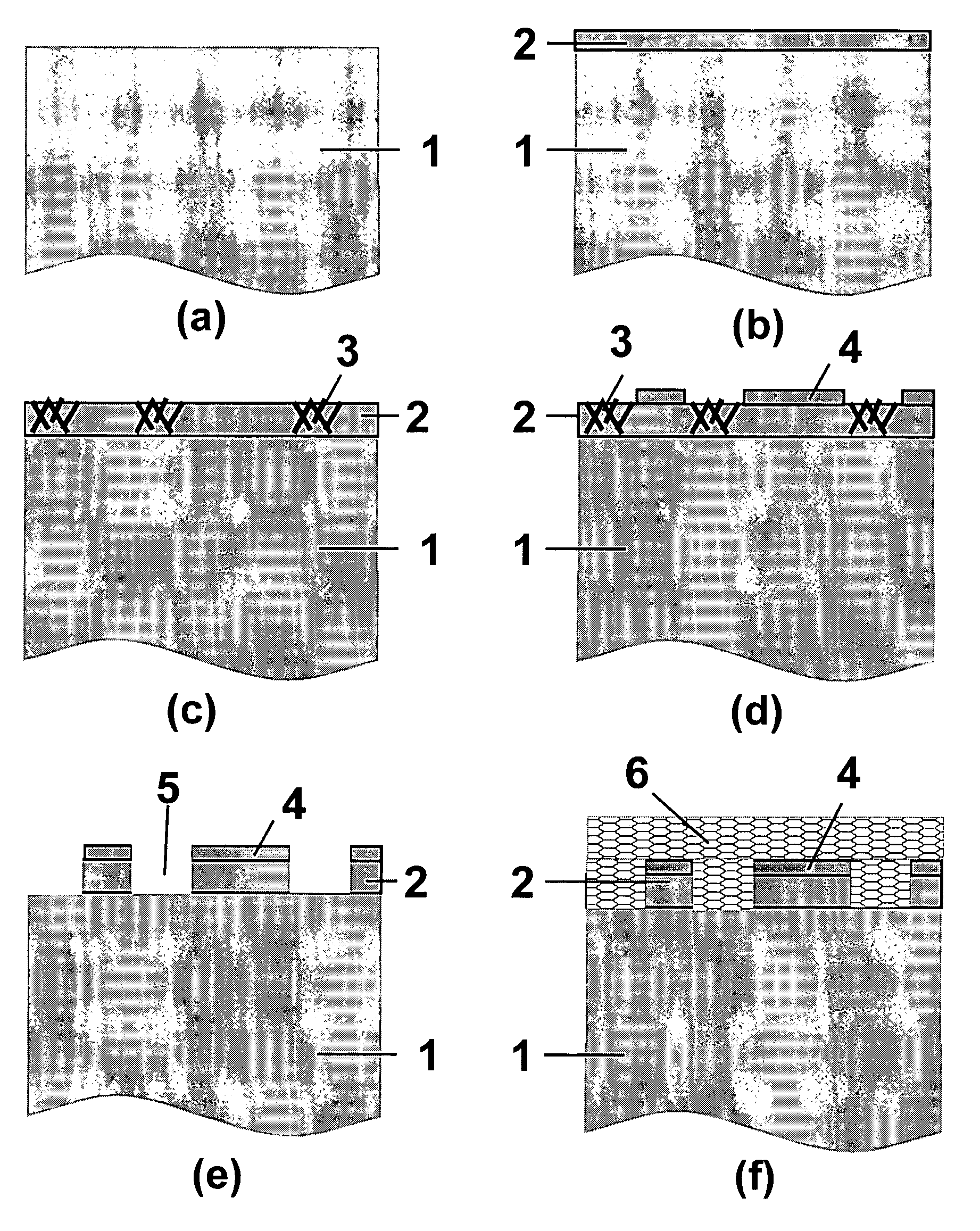

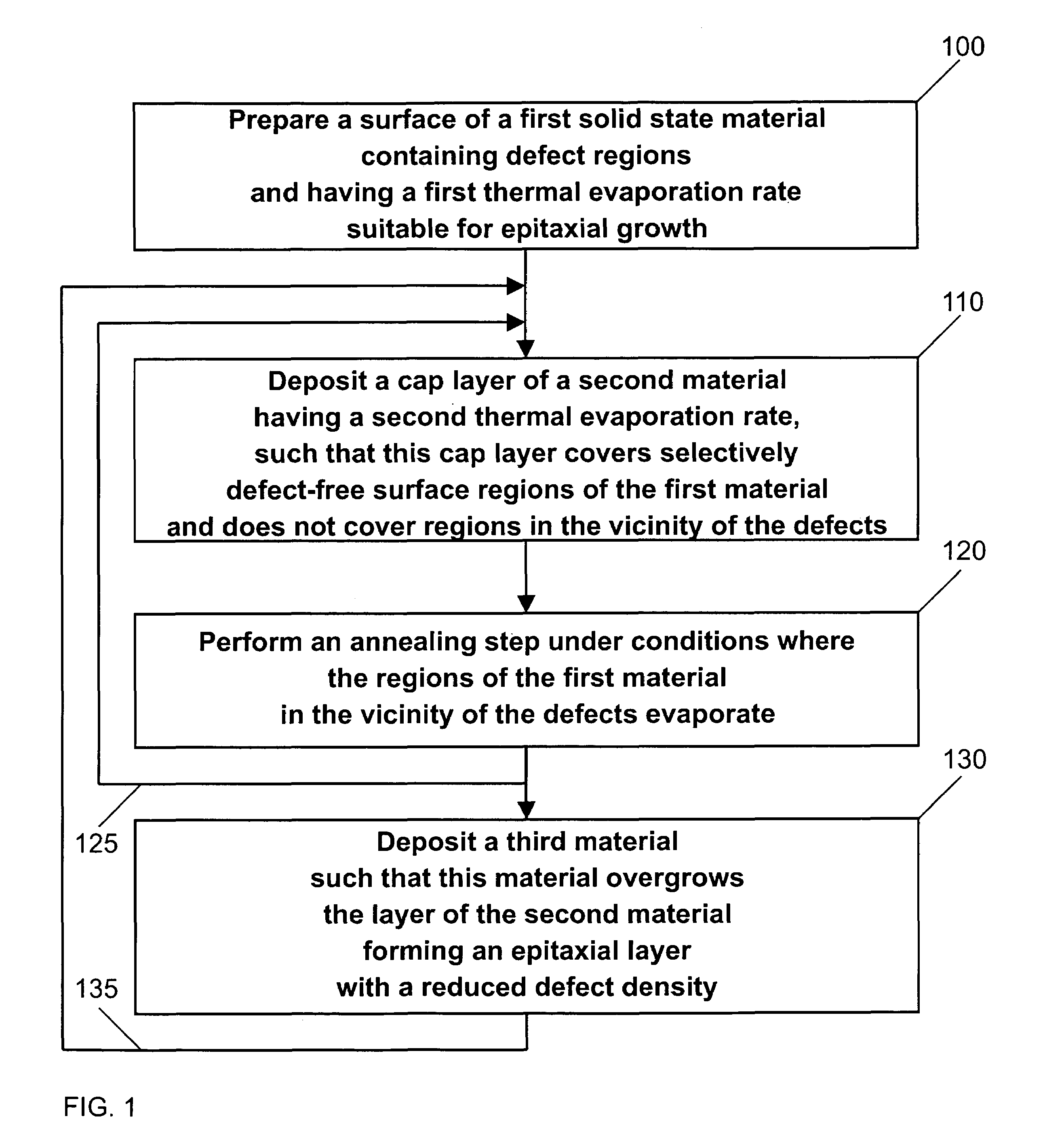

Defect-free semiconductor templates for epitaxial growth

InactiveUS7101444B2Improve high temperature stabilityMaterial nanotechnologyLaser detailsSelective depositionSemiconductor

A semiconductor device includes at least one defect-free epitaxial layer. At least a part of the device is manufactured by a method of fabrication of defect-free epitaxial layers on top of a surface of a first solid state material having a first thermal evaporation rate and a plurality of defects, where the surface comprises at least one defect-free surface region, and at least one surface region in a vicinity of the defects, the method including the steps of selective deposition of a second material, having a high temperature stability, on defect-free regions of the first solid state material, followed by subsequent evaporation of the regions in the vicinity of the defects, and subsequent overgrowth by a third material forming a defect-free layer.

Owner:INNOLUME

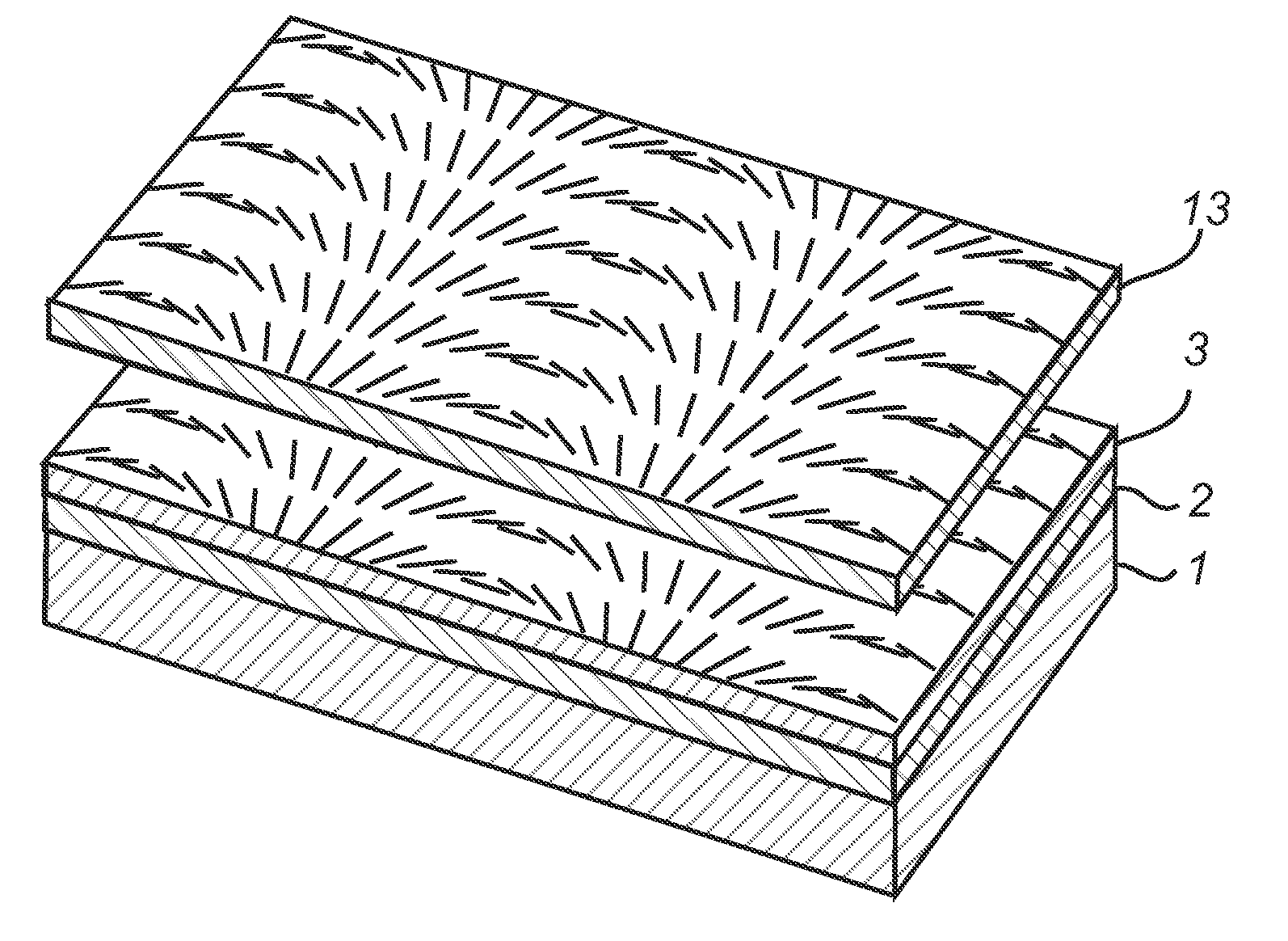

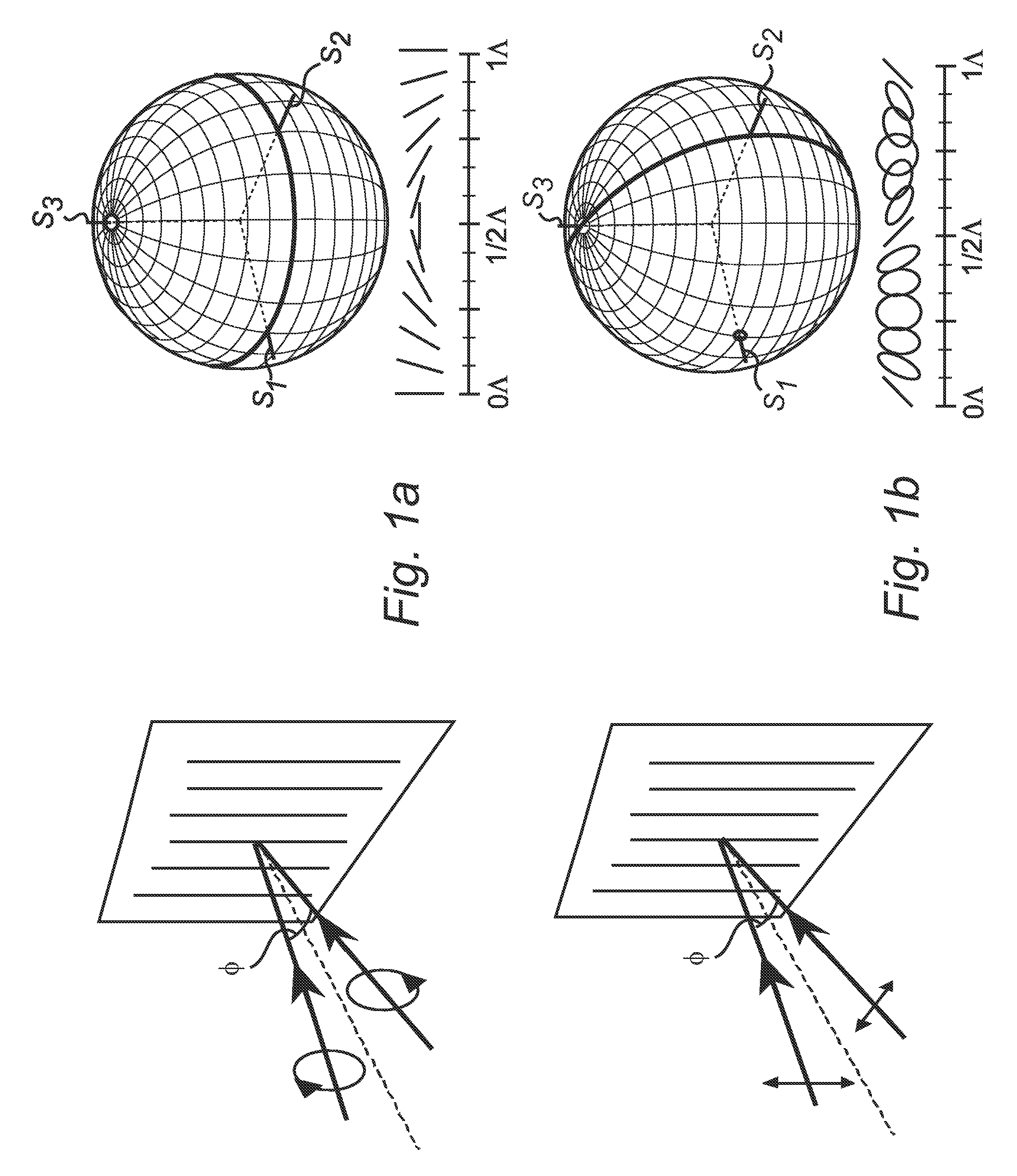

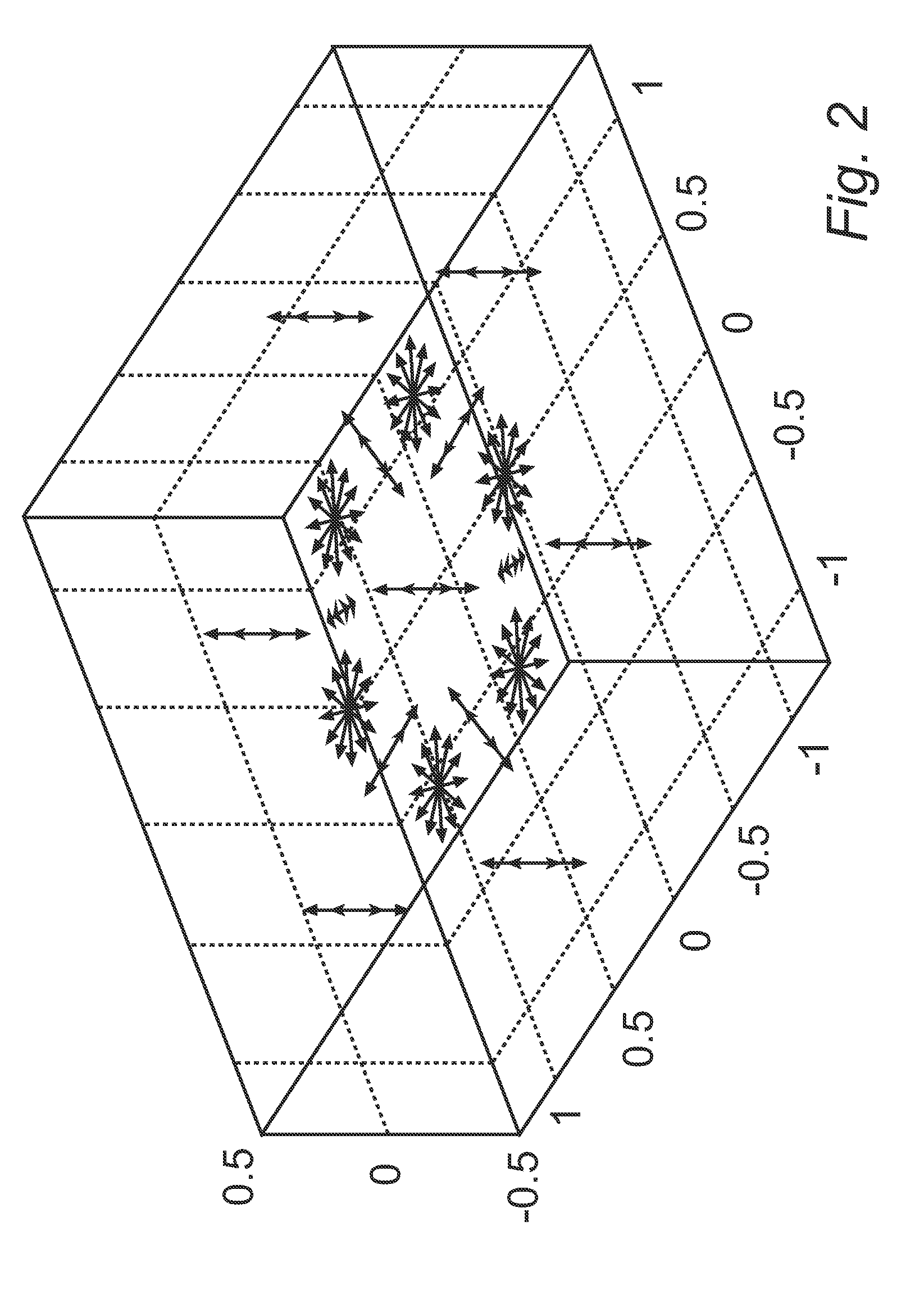

Polarization gratings in mesogenic films

A polarization grating comprising a polarization sensitive photo-alignment layer (2) and a liquid crystal composition (3) arranged on said photo-alignment layer is provided. An alignment pattern, corresponding to the polarization pattern of a hologram, is recorded in the photo-alignment layer, and the liquid crystal composition is aligned on the photo-alignment layer. As the origin for the alignment of the liquid crystal composition is a polarization hologram recorded in a photo-alignment layer, an essentially defect-free pattern can be obtained with this approach.

Owner:STICHTING DUTCH POLYMER INST

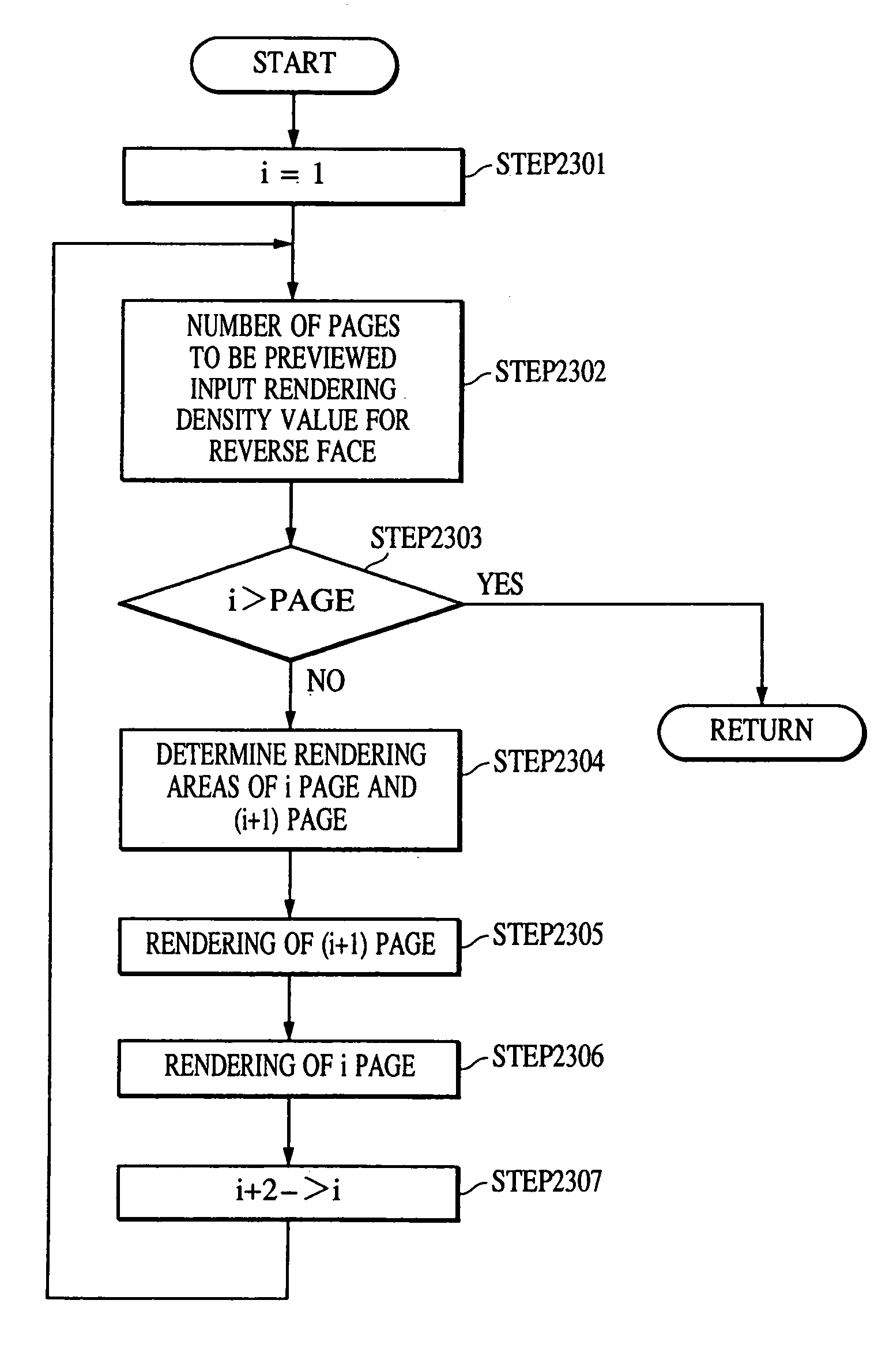

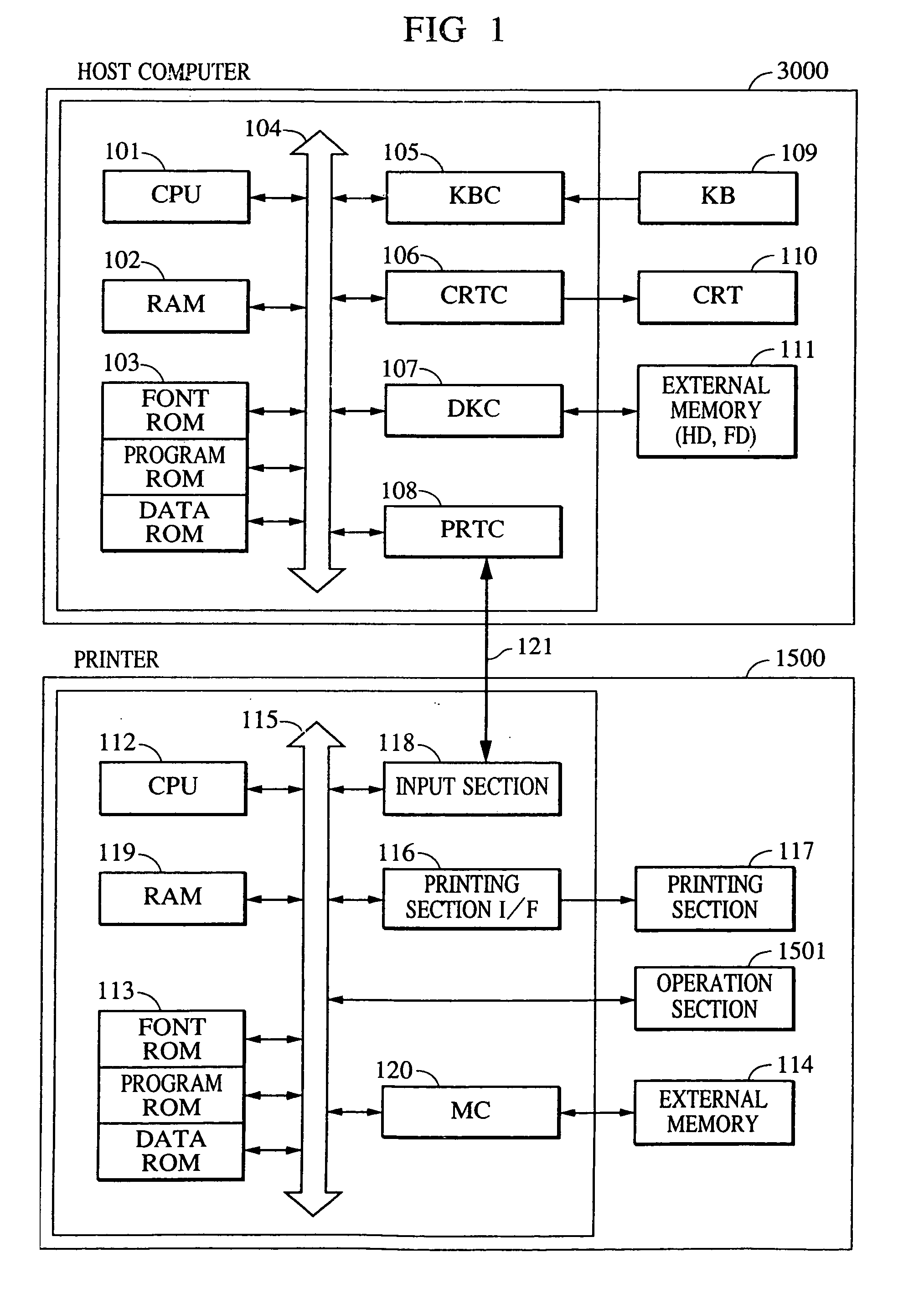

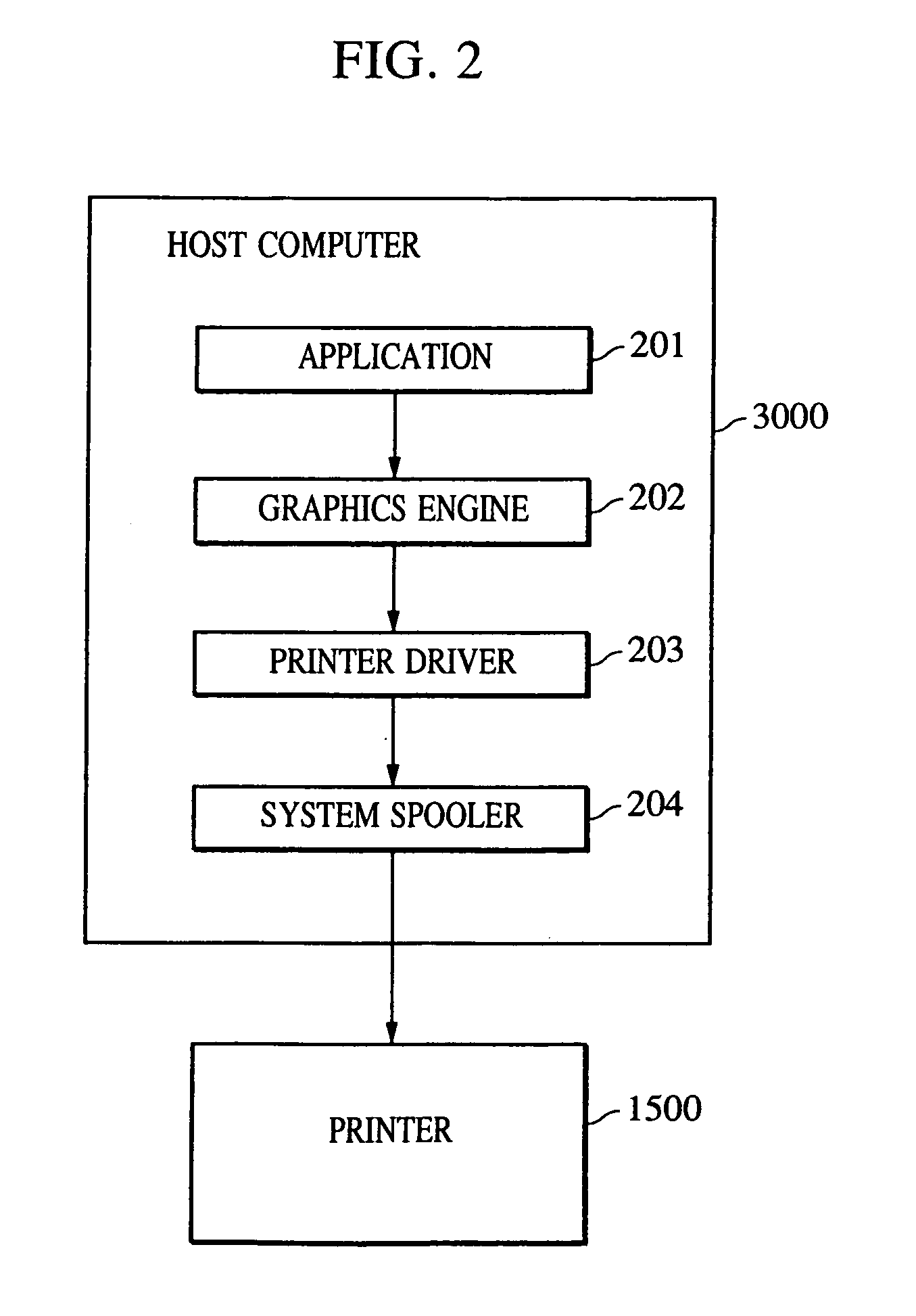

Information processing apparatus and method utilizing print previews, and computer-readable storage medium

InactiveUS6927865B1Digitally marking record carriersDigital computer detailsInformation processingDisplay device

Owner:CANON KK

Method of Growing Uniform Semiconductor Nanowires without Foreign Metal Catalyst and Devices Thereof

ActiveUS20110127490A1NanoinformaticsSemiconductor/solid-state device manufacturingNanowireMetal catalyst

Amongst the candidates for very high efficiency solid state lights sources and full solar spectrum solar cells are devices based upon InGaN nanowires. Additionally these nanowires typically require heterostructures, quantum dots, etc which all place requirements for these structures to be grown with relatively few defects. Further manufacturing requirements demand reproducible nanowire diameter, length etc to allow these nanowires to be embedded within device structures. Additionally flexibility according to the device design requires that the nanowire at the substrate may be either InN or GaN. According to the invention a method of growing relatively defect free nanowires and associated structures for group III—nitrides is presented without the requirement for foreign metal catalysts and overcoming the non-uniform growth of prior art non-catalyst growth techniques. The technique also allows for unique dot-within-a-dot nanowire structures.

Owner:MCGILL UNIV

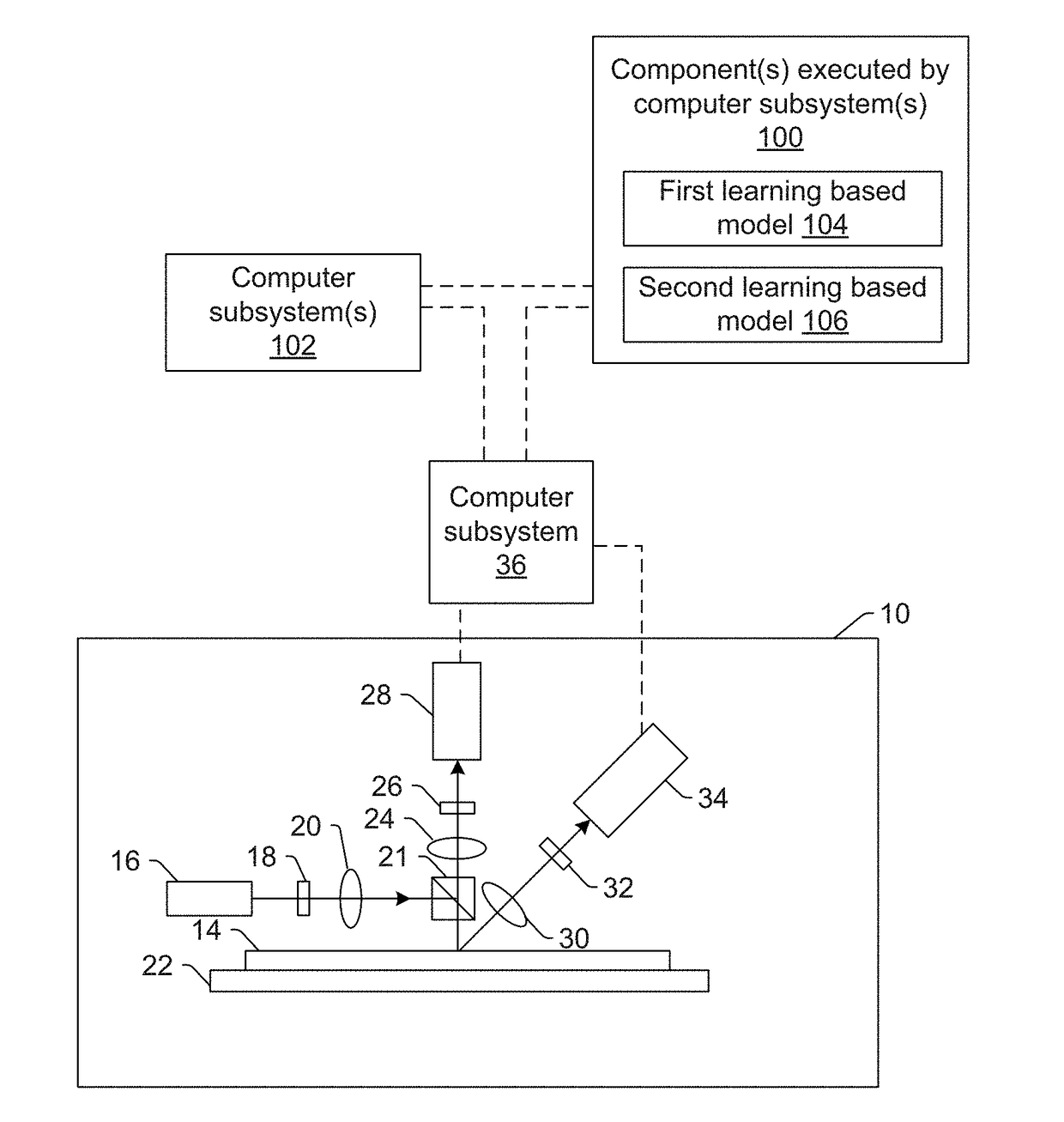

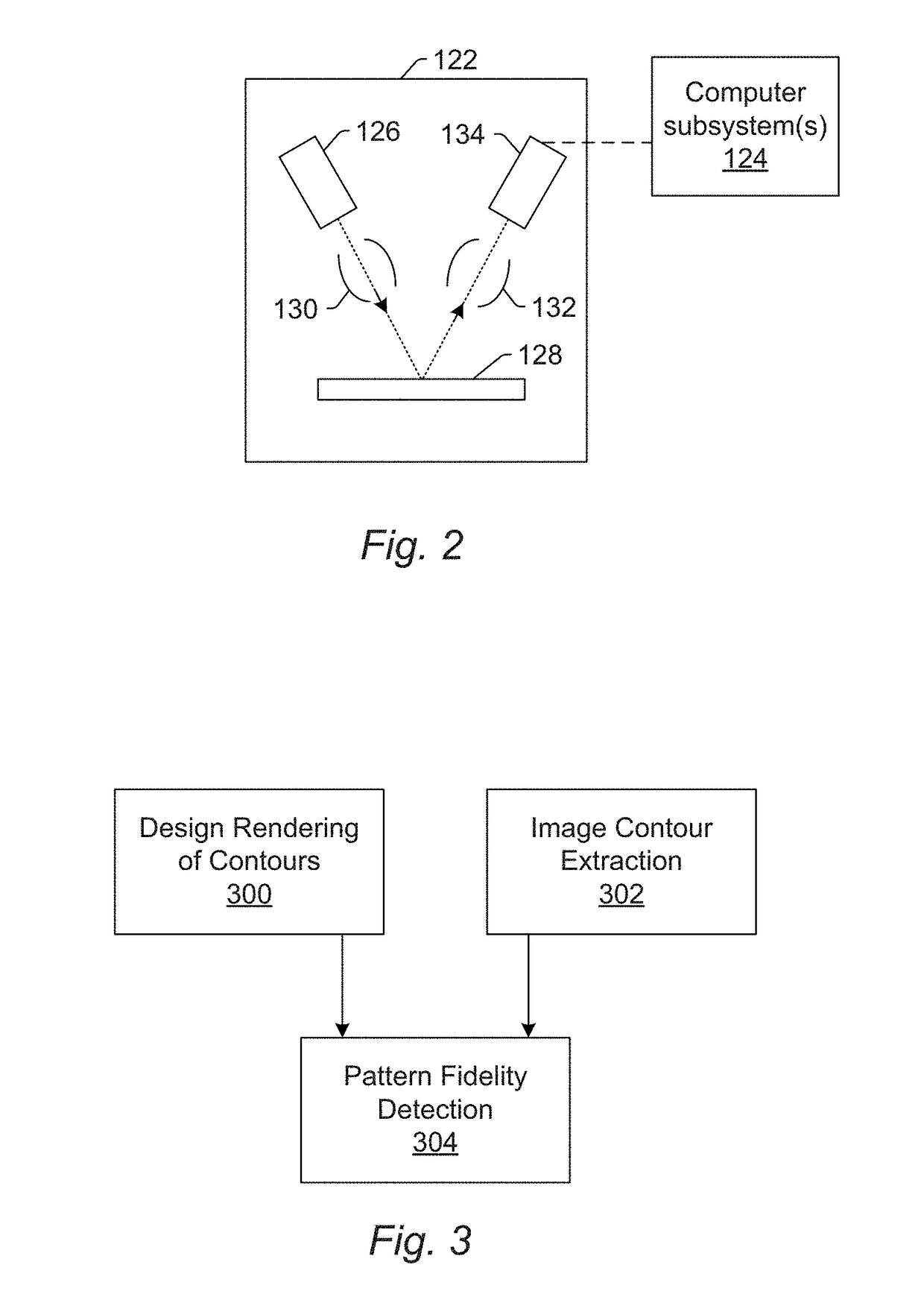

Contour based defect detection

Methods and systems for detecting defects in patterns formed on a specimen are provided. One system includes one or more components executed by one or more computer subsystems, and the component(s) include first and second learning based models. The first learning based model generates simulated contours for the patterns based on a design for the specimen, and the simulated contours are expected contours of a defect free version of the patterns in images of the specimen generated by an imaging subsystem. The second learning based model is configured for generating actual contours for the patterns in at least one acquired image of the patterns formed on the specimen. The computer subsystem(s) are configured for comparing the actual contours to the simulated contours and detecting defects in the patterns formed on the specimen based on results of the comparing.

Owner:KLA TENCOR TECH CORP

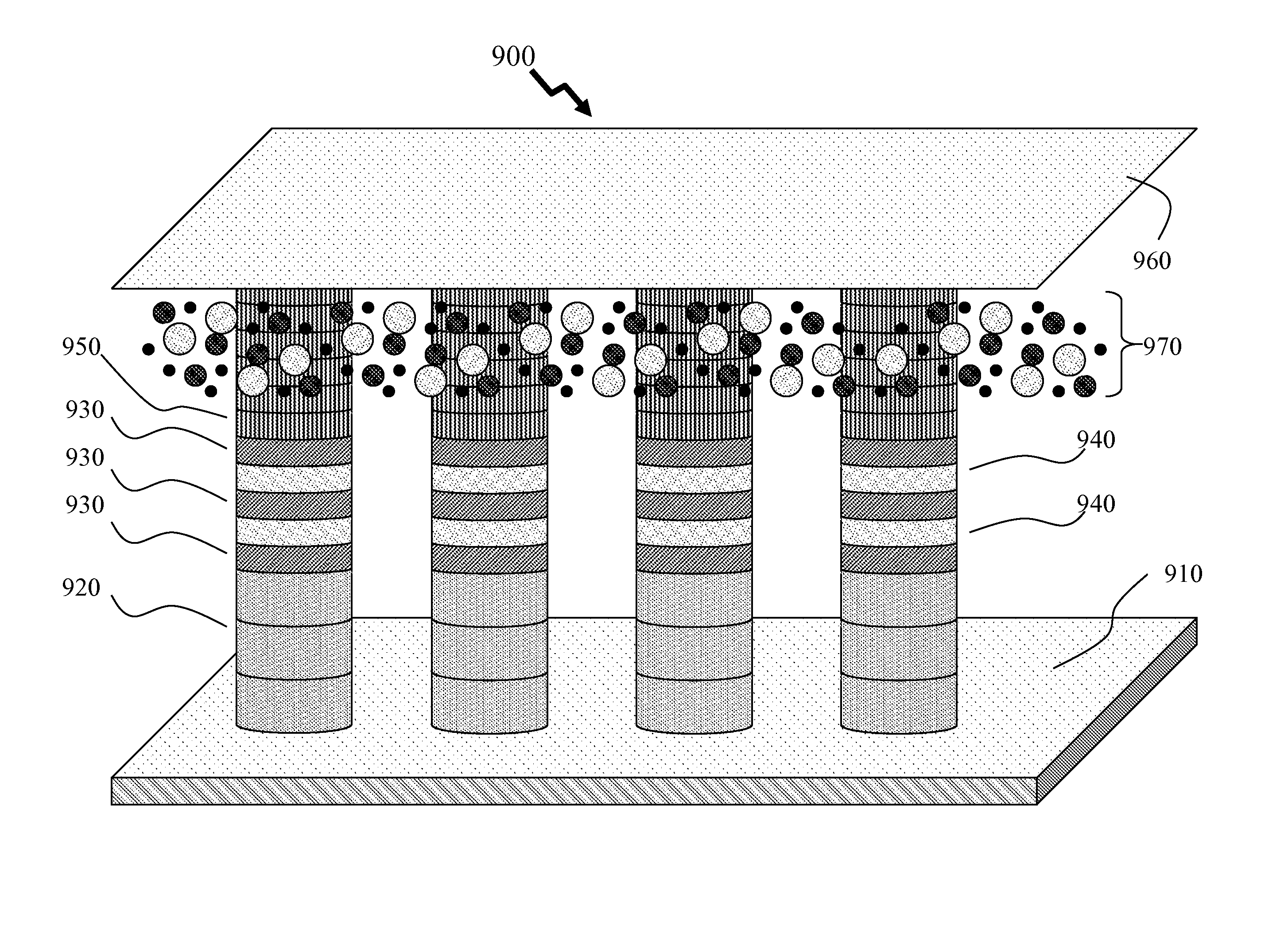

Pulsed growth of gan nanowires and applications in group III nitride semiconductor substrate materials and devices

Exemplary embodiments provide semiconductor devices including high-quality (i.e., defect free) group III-N nanowires and uniform group III-N nanowire arrays as well as their scalable processes for manufacturing, where the position, orientation, cross-sectional features, length and the crystallinity of each nanowire can be precisely controlled. A pulsed growth mode can be used to fabricate the disclosed group III-N nanowires and / or nanowire arrays providing a uniform length of about 10 nm to about 1000 microns with constant cross-sectional features including an exemplary diameter of about 10-1000 nm. In addition, high-quality GaN substrate structures can be formed by coalescing the plurality of GaN nanowires and / or nanowire arrays to facilitate the fabrication of visible LEDs and lasers. Furthermore, core-shell nanowire / MQW active structures can be formed by a core-shell growth on the nonpolar sidewalls of each nanowire.

Owner:新墨西哥大学雨林创新公司

Defect-free group iii - nitride nanostructures and devices using pulsed and non-pulsed growth techniques

InactiveUS20110140072A1Laser optical resonator constructionSemiconductor/solid-state device manufacturingDevice materialCrystallinity

Exemplary embodiments provide semiconductor devices including high-quality (i.e., defect free) Group III—Nitride nanostructures and uniform Group III—Nitride nanostructure arrays as well as their scalable processes for manufacturing, where the position, orientation, cross-sectional features, length and the crystallinity of each nanostructure can be precisely controlled. A pulsed growth mode can be used to fabricate the disclosed Group III—Nitride nanostructures and / or nanostructure arrays providing a uniform length of about 0.01-20 micrometers (μm) with constant cross-sectional features including an exemplary diameter of about 10 nanometers (nm)-500 micrometers (μm). Furthermore, core-shell nanostructure / MQW active structures can be formed by a core-shell growth on the non-polar sidewalls of each nanostructure and can be configured in nanoscale photoelectronic devices such as nanostructure LEDs and / or nanostructure lasers to provide tremendously-high efficiencies. Additional growth mode transitions from the pulsed to the non-pulsed growth mode and subsequent transitions from non-pulsed to pulsed growth mode are employed in order to incorporate certain group III—Nitride compounds more efficiently into the nanostructures and form devices of the designed shape, morphology and stochiometric composition. In addition, high-quality group III—Nitride substrate structures can be formed by coalescing the plurality of group III—Nitride nanostructures and / or nanostructure arrays to facilitate the fabrication of visible LEDs and lasers.

Owner:NANOCRYSTAL CORP

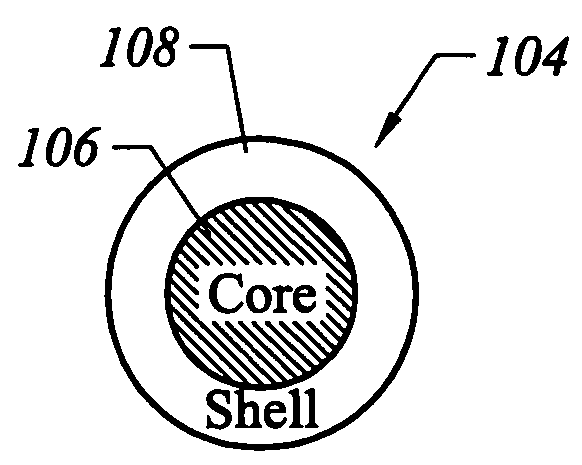

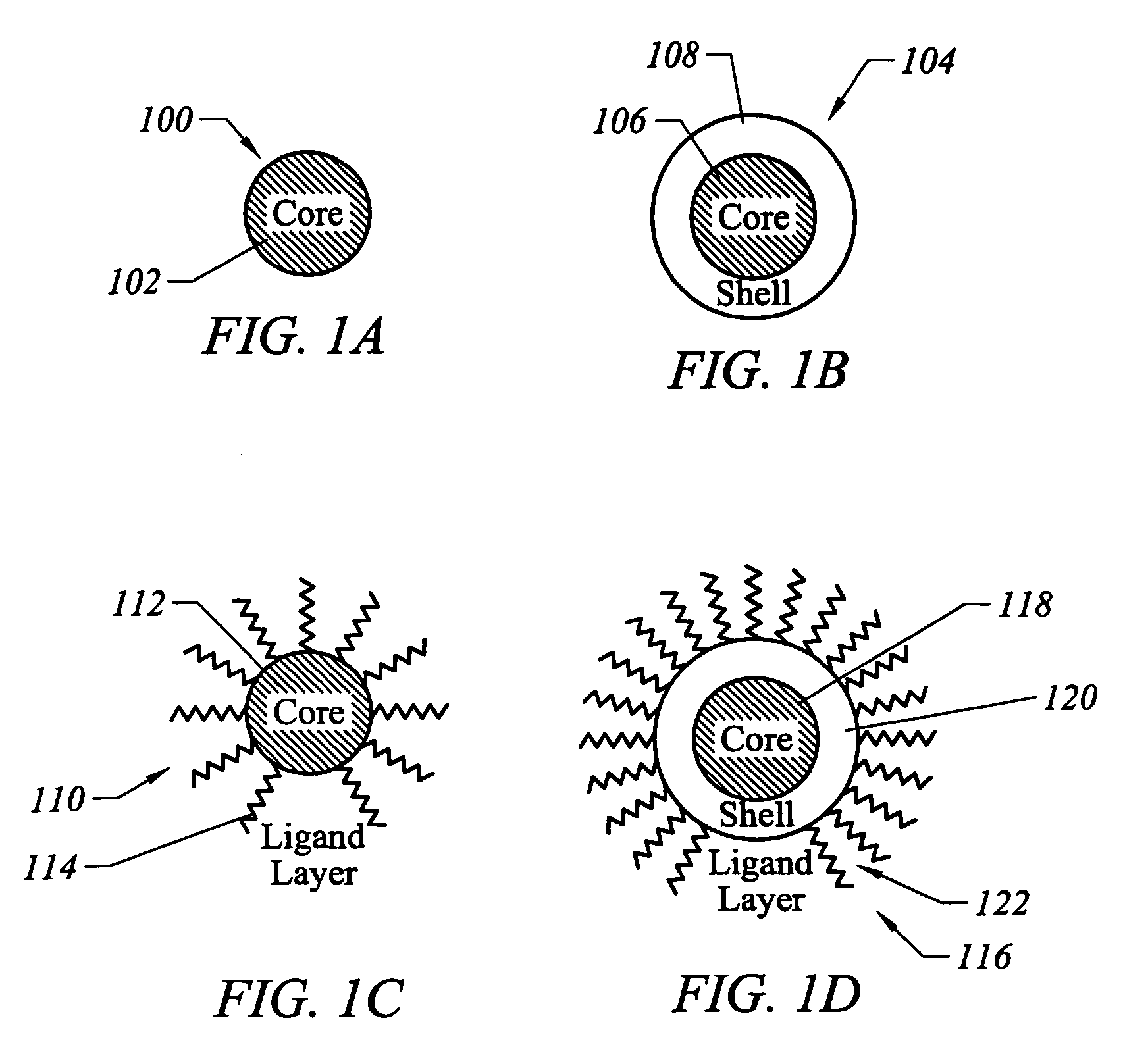

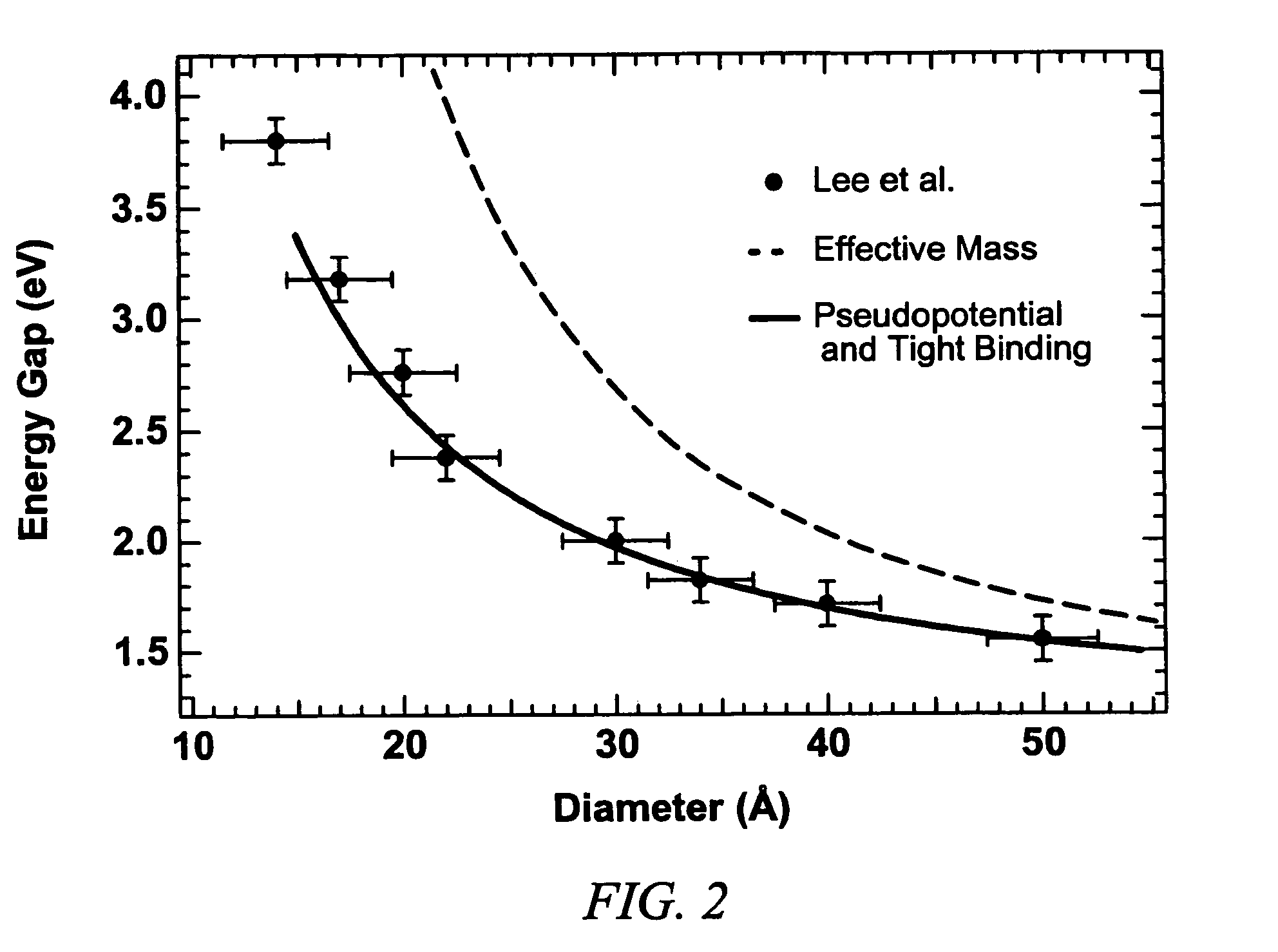

Quantum dots of group IV semiconductor materials

InactiveUS7358525B2NanoinformaticsSemiconductor/solid-state device manufacturingQuantum efficiencySemiconductor materials

The invention relates to a quantum dot. The quantum dot comprises a core including a semiconductor material Y selected from the group consisting of Si and Ge. The quantum dot also comprises a shell surrounding the core. The quantum dot is substantially defect free such that the quantum dot exhibits photoluminescence with a quantum efficiency that is greater than 10 percent.

Owner:SAMSUNG ELECTRONICS CO LTD

High Efficiency Broadband Semiconductor Nanowire Devices

Amongst the candidates for very high efficiency electronics, solid state light sources, photovoltaics, and photoelectrochemical devices, and photobiological devices are those based upon metal-nitride nanowires. Enhanced nanowire performance typically require heterostructures, quantum dots, etc which requirement that these structures are grown with relatively few defects and in a controllable reproducible manner. Additionally flexibility according to the device design requires that the nanowire at the substrate may be either InN or GaN. Methods of growing relatively defect free nanowires and associated structures for group IIIA-nitrides are presented without the requirement for foreign metal catalysts, overcoming the non-uniform growth of prior art techniques and allowing self-organizing quantum dot, quantum well and quantum dot-in-a-dot structures to be formed. Such metal-nitride nanowires and quantum structure embedded nanowires support a variety of devices including but not limited to very high efficiency electronics, solid state light sources, photovoltaics, and photoelectrochemical devices, and photobiological devices.

Owner:MCGILL UNIV

Composition for oxide CMP in CMOS device fabrication

InactiveUS20060216935A1Easy to polishSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingCMOSSilicon oxide

The present invention provides an oxide CMP slurry composition for use in planarizing silicon oxide-containing films via CMP during CMOS device fabrication, and a method of planarizing silicon oxide-containing films via CMP using the slurry composition. The oxide CMP slurry composition according to the invention includes: (i) proline, lysine and / or arginine; (ii) a pyrrolidone compound; and (iii) abrasive particles. Proline is presently most preferred for use in the invention. In the STI sub-process of the CMOS device fabrication process, the oxide CMP slurry composition according to the present invention acts to aggressively remove only the silicon dioxide overburden on the processed wafer that is in contact with a polishing pad, which results in the formation of a substantially planar, defect-free surface. The oxide CMP slurry composition according to the invention does not aggressively remove trench silicon dioxide thereby allowing for extended polishing beyond the end point without substantially increasing the minimum step height.

Owner:FERRO CORP

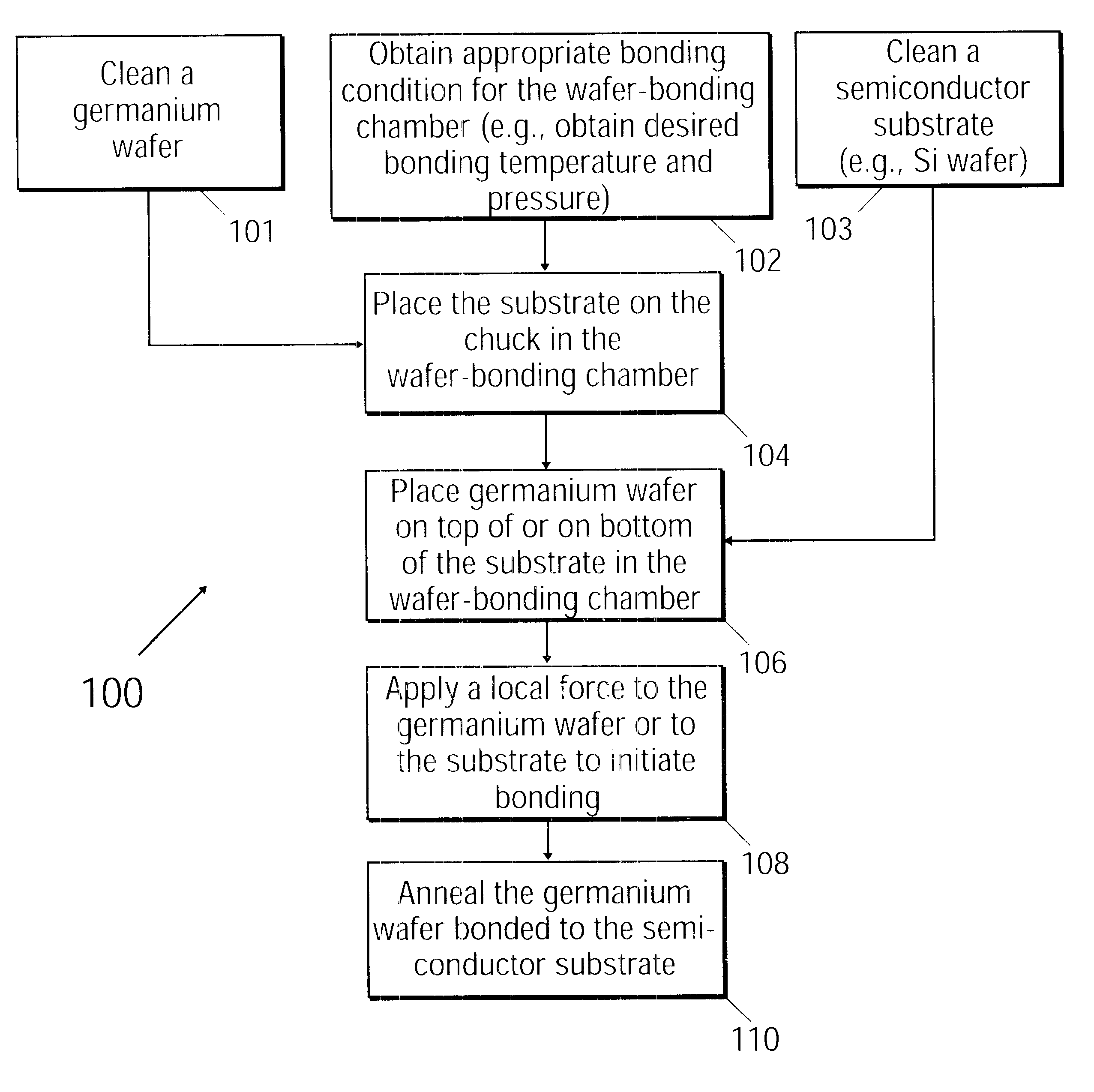

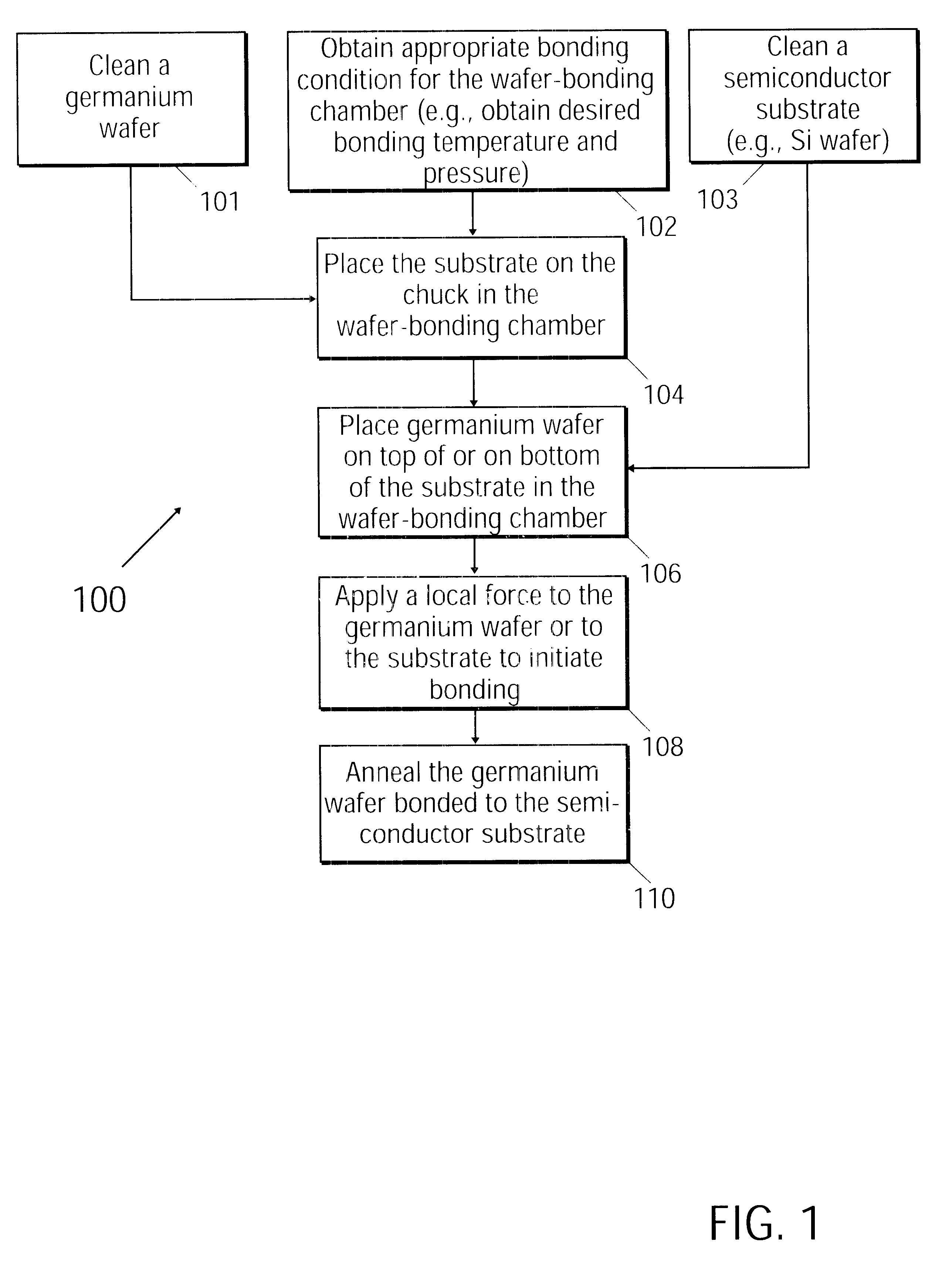

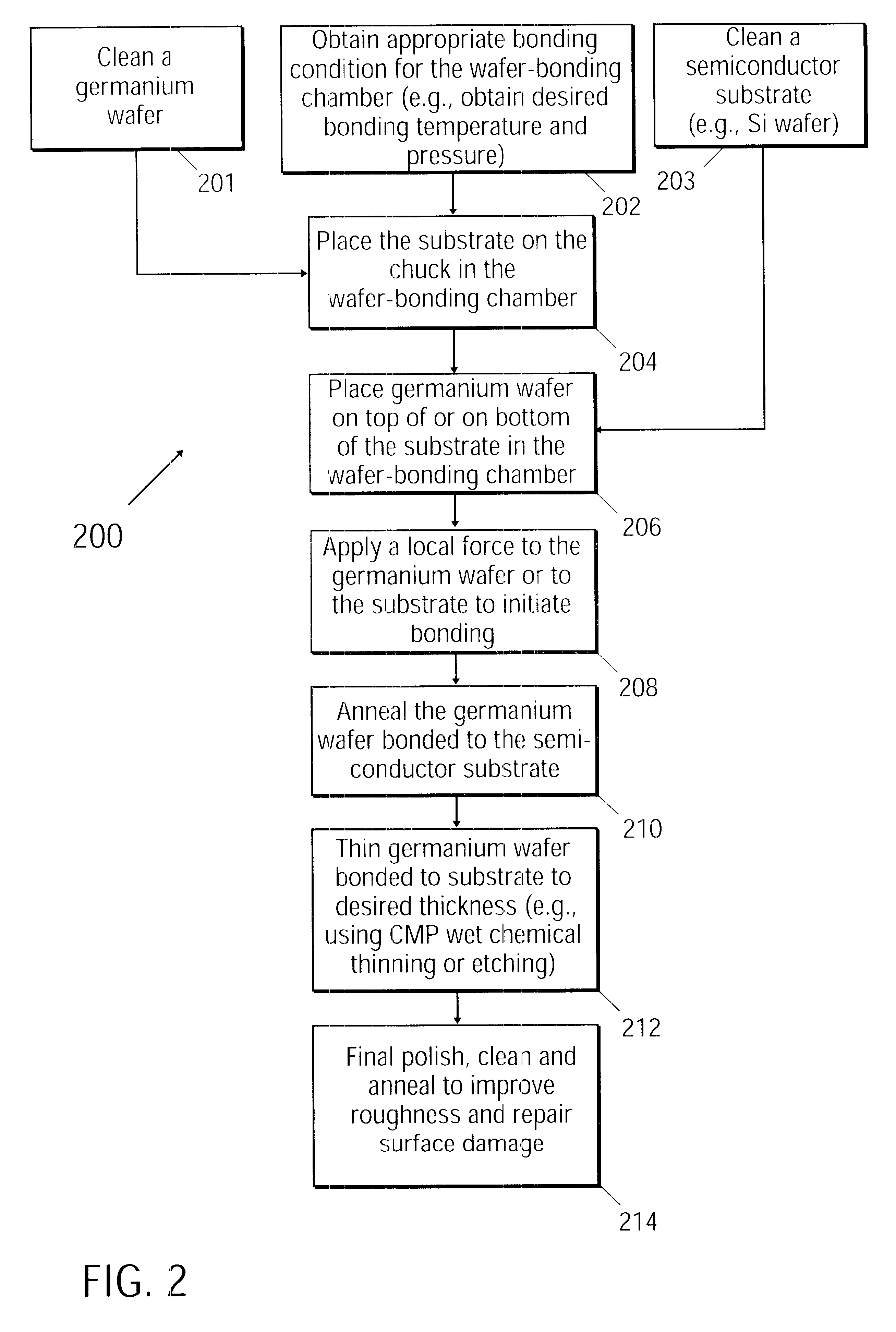

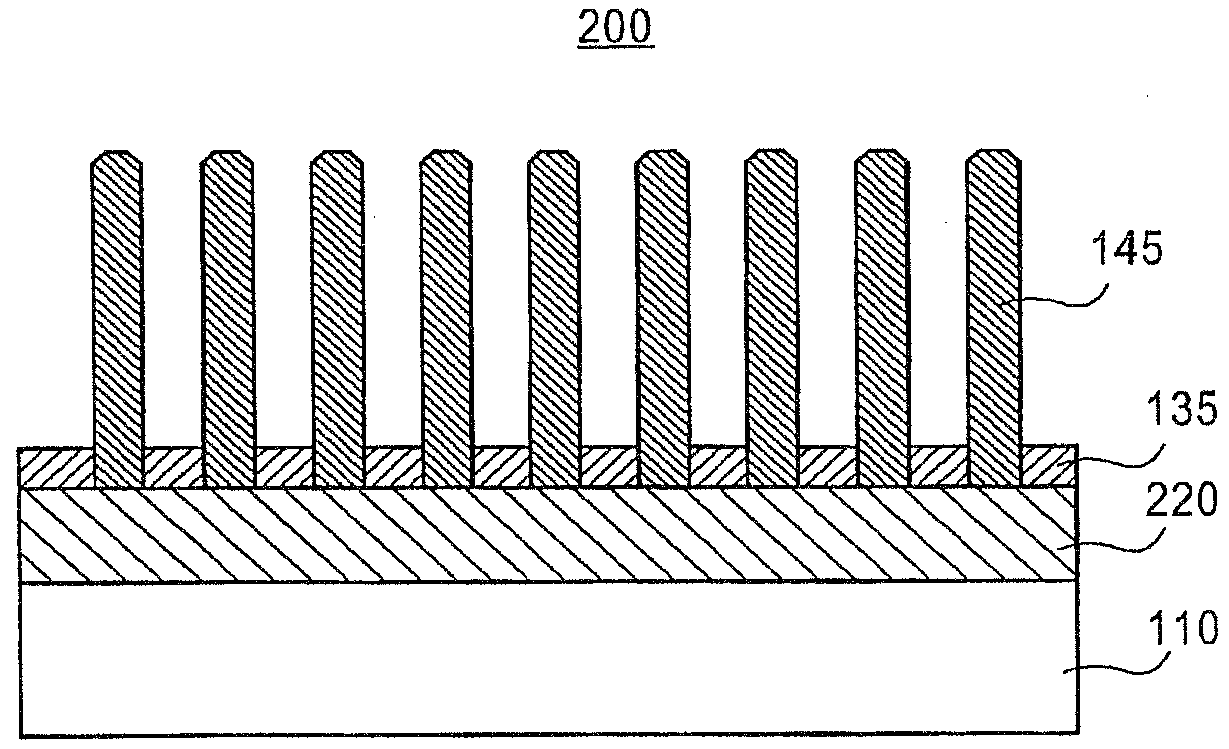

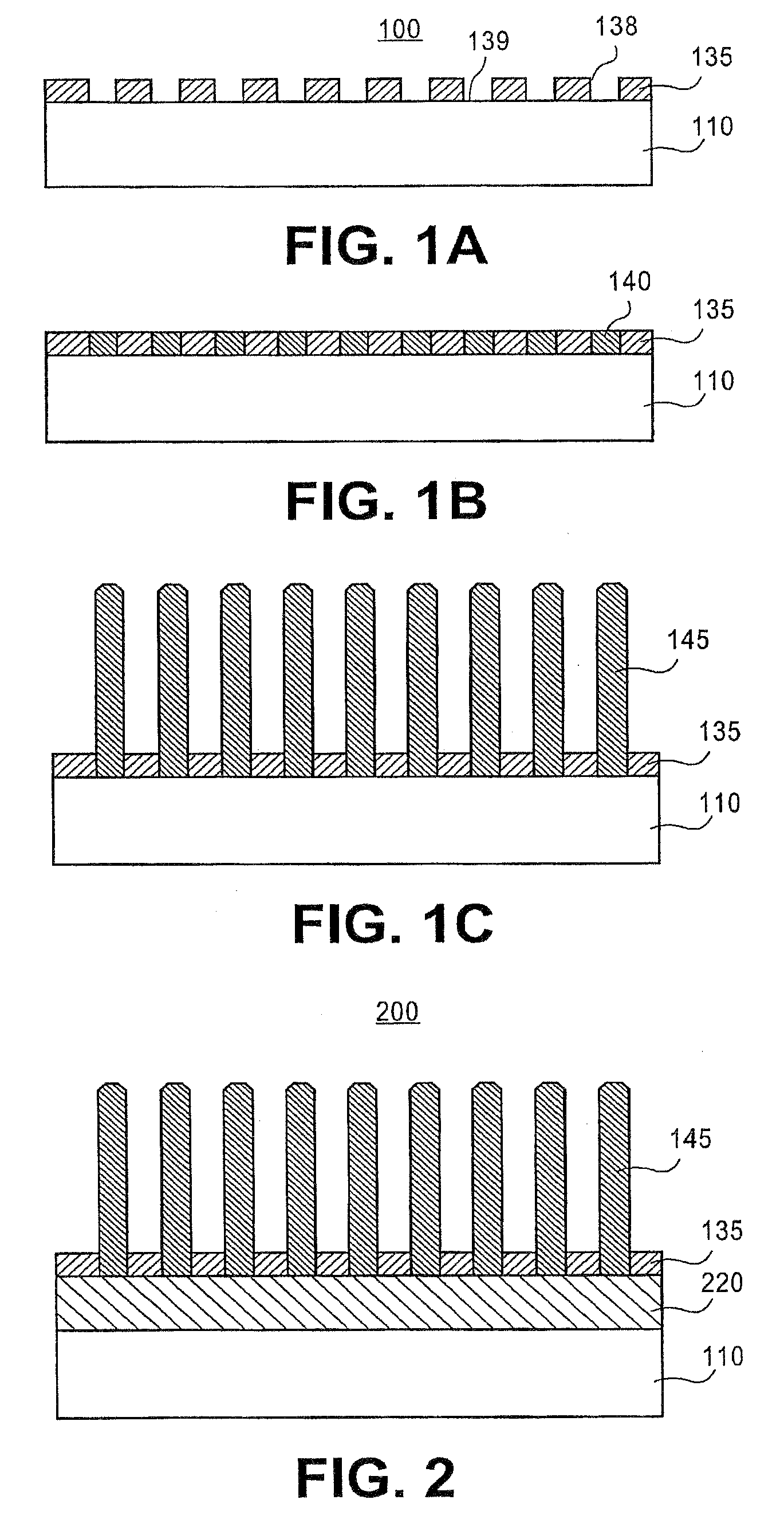

Thermally stable crystalline defect-free germanium bonded to silicon and silicon dioxide

InactiveUS6645831B1Semiconductor/solid-state device manufacturingSemiconductor devicesWaferingEngineering

A wafer pair comprising a substantially defect-free germanium wafer and methods of making the same. The wafer pair comprises the substantially defect-free germanium wafer directly bonded to a silicon wafer. The method of making the wafer pair comprises placing the silicon wafer in a wafer-bonding chamber, placing the germanium wafer on top or on bottom of the silicon wafer, and applying a local force to either the germanium wafer or to the silicon wafer to initiate bonding of the germanium wafer to the silicon wafer. The bonding occurs under a temperature ranging from about 23° C. to about 600° C. and under a vacuum condition inside a wafer-bonding chamber.

Owner:INTEL CORP

PULSED GROWTH OF CATALYST-FREE GROWTH OF GaN NANOWIRES AND APPLICATION IN GROUP III NITRIDE SEMICONDUCTOR BULK MATERIAL

Exemplary embodiments provide semiconductor devices including high-quality (i.e., defect free) group III-N nanowires and uniform group III-N nanowire arrays as well as their scalable processes for manufacturing, where the position, orientation, cross-sectional features, length and the crystallinity of each nanowire can be precisely controlled. A pulsed growth mode can be used to fabricate the disclosed group III-N nanowires and / or nanowire arrays providing a uniform length of about 10 nm to about 1000 microns with constant cross-sectional features including an exemplary diameter of about 10-1000 nm. In addition, high-quality GaN substrate structures can be formed by coalescing the plurality of GaN nanowires and / or nanowire arrays to facilitate the fabrication of visible LEDs and lasers. Furthermore, core-shell nanowire / MQW active structures can be formed by a core-shell growth on the nonpolar sidewalls of each nanowire.

Owner:STC UNM

Method for repairing articles of ceramic composites

InactiveUS6820334B2Prolong lifeReduce in quantityBlade accessoriesEfficient propulsion technologiesCeramic compositeMetallurgy

Owner:GENERAL ELECTRIC CO

Image processing method and apparatus

An image processing technique includes acquiring a main image of a scene and determining one or more facial regions in the main image. The facial regions are analysed to determine if any of the facial regions includes a defect. A sequence of relatively low resolution images nominally of the same scene is also acquired. One or more sets of low resolution facial regions in the sequence of low resolution images are determined and analysed for defects. Defect free facial regions of a set are combined to provide a high quality defect free facial region. At least a portion of any defective facial regions of the main image are corrected with image information from a corresponding high quality defect free facial region.

Owner:FOTONATION LTD

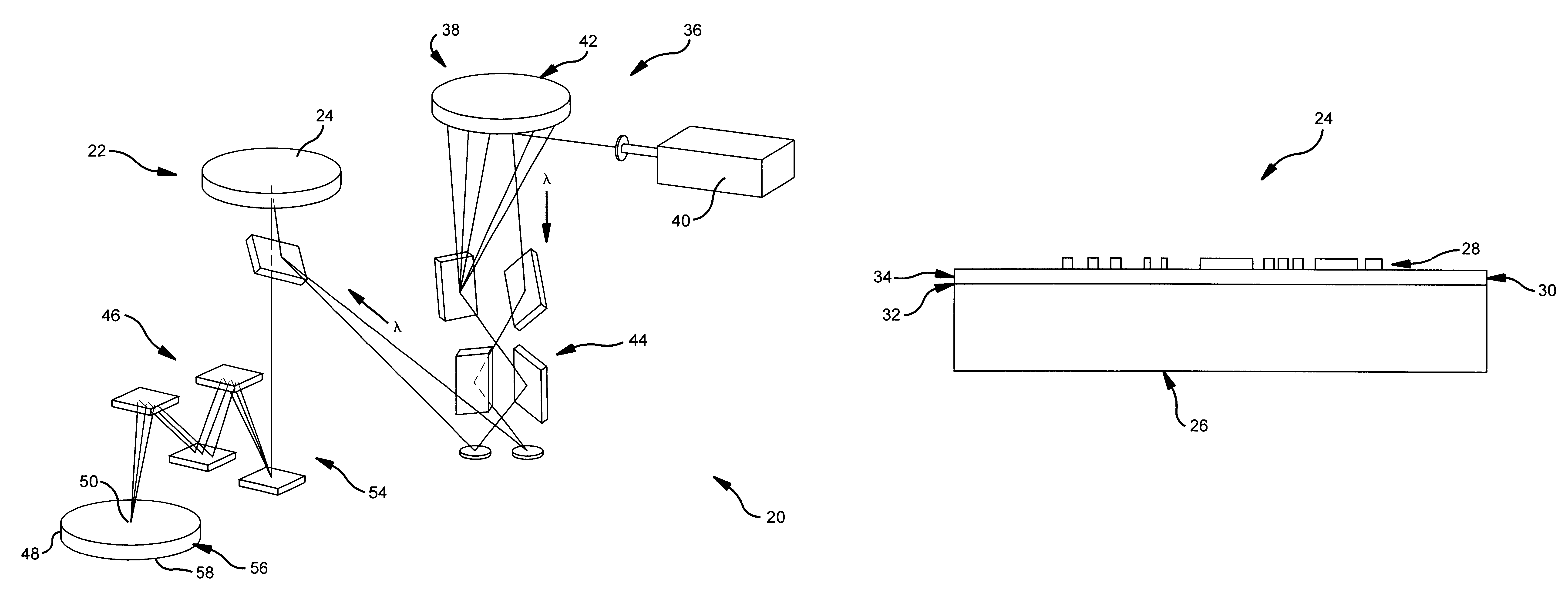

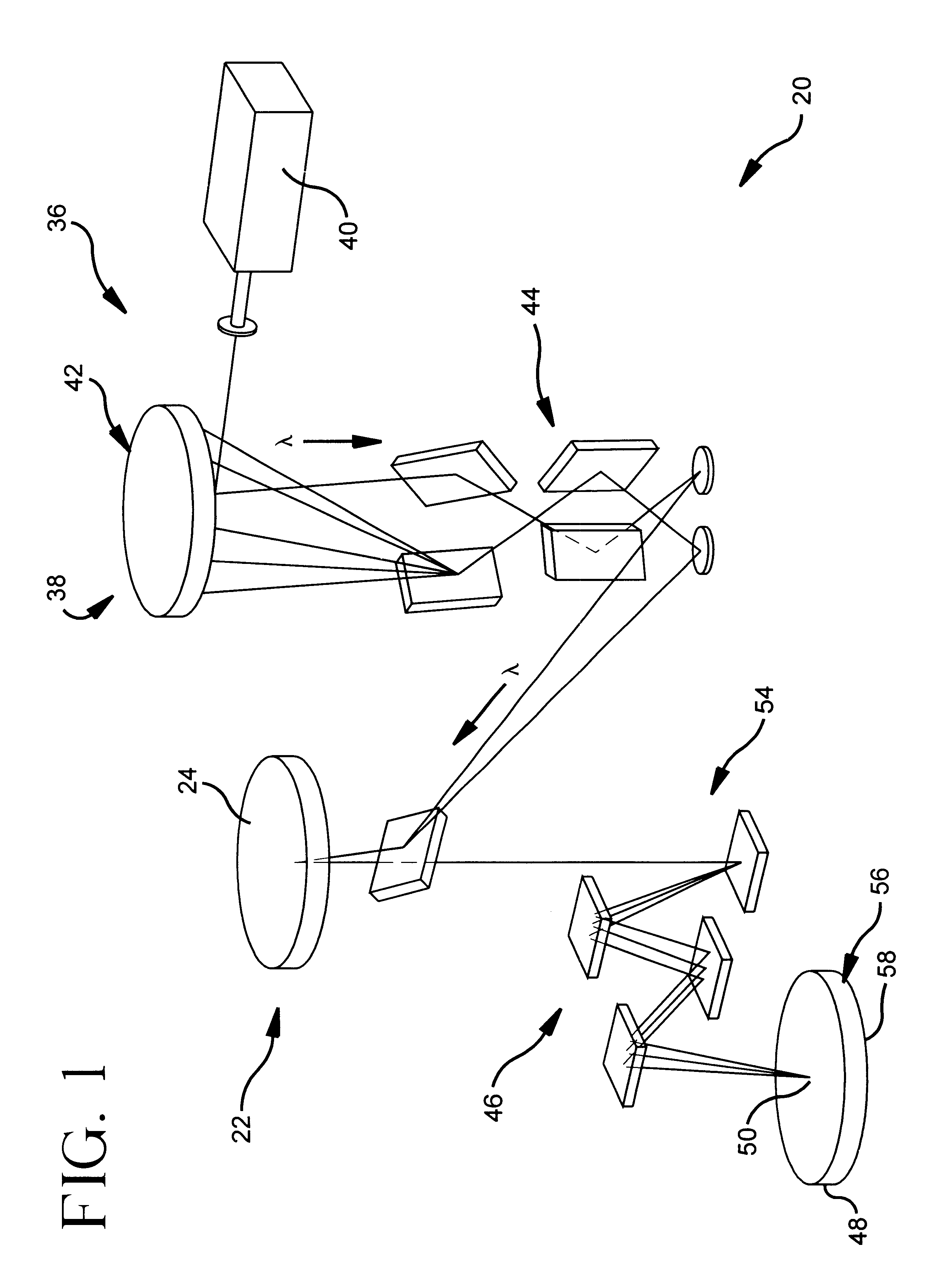

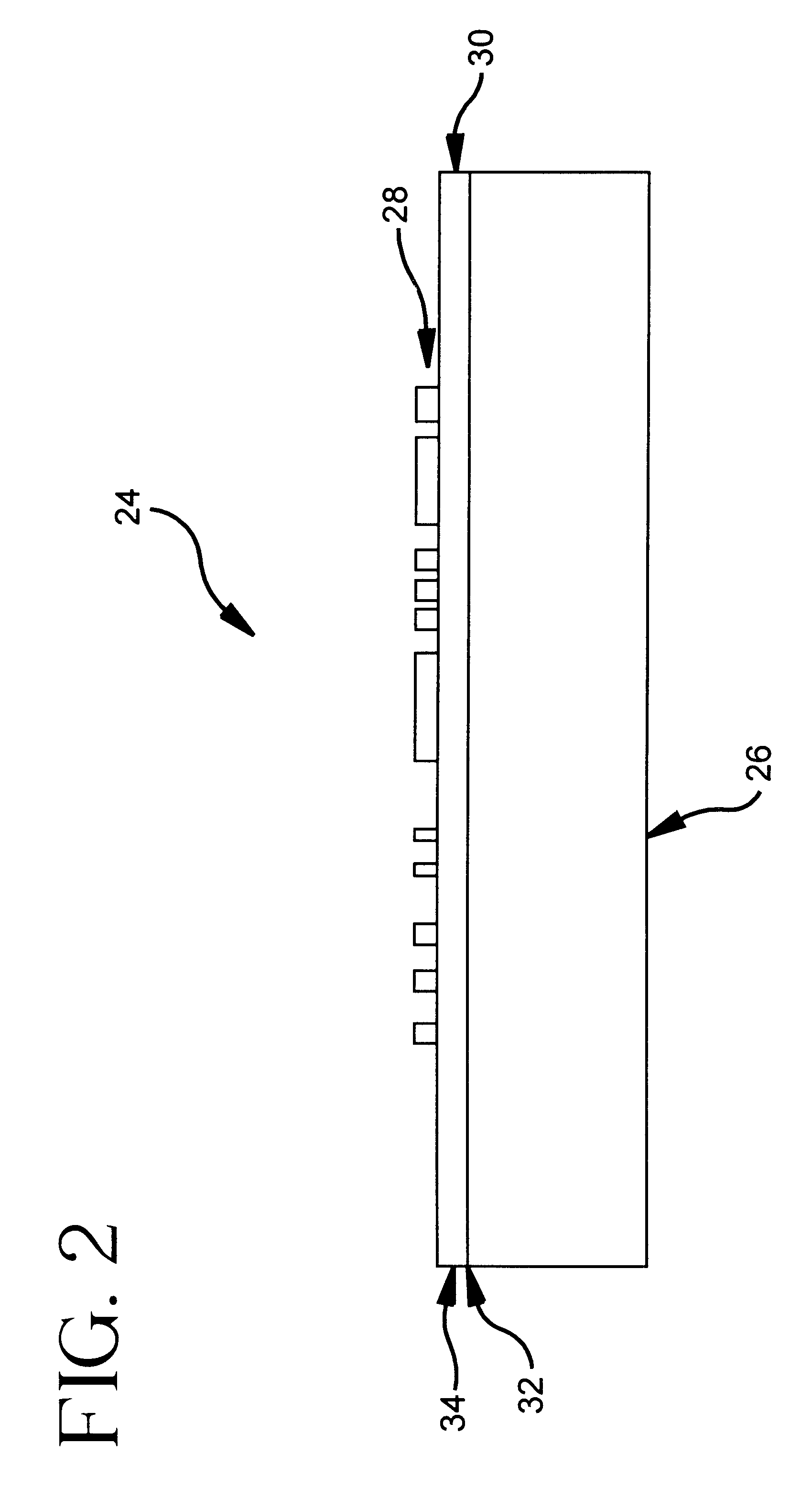

Extreme ultraviolet soft x-ray projection lithographic method and mask devices

InactiveUS6465272B1NanoinformaticsHandling using diffraction/refraction/reflectionTi dopingSoft x ray

The present invention relates to reflective masks and their use for reflecting extreme ultraviolet soft x-ray photons to enable the use of extreme ultraviolet soft x-ray radiation projection lithographic methods and systems for producing integrated circuits and forming patterns with extremely small feature dimensions. The projection lithographic method includes providing an illumination sub-system for producing and directing an extreme ultraviolet soft x-ray radiation lambd from an extreme ultraviolet soft x-ray source; providing a mask sub-system illuminated by the extreme ultraviolet soft x-ray radiation lambd produced by the illumination sub-system and providing the mask sub-system includes providing a patterned reflective mask for forming a projected mask pattern when illuminated by radiation lambd. Providing the patterned reflective mask includes providing a Ti doped high purity SiO2 glass wafer with a patterned absorbing overlay overlaying the reflective multilayer coated Ti doped high purity SiO2 glass defect free wafer surface that has an Ra roughness<=0.15 nm. The method includes providing a projection sub-system and a print media subject wafer which has a radiation sensitive wafer surface wherein the projection sub-system projects the projected mask pattern from the patterned reflective mask onto the radiation sensitive wafer surface.

Owner:CORNING INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com