Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

243results about How to "Relaxation stress" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

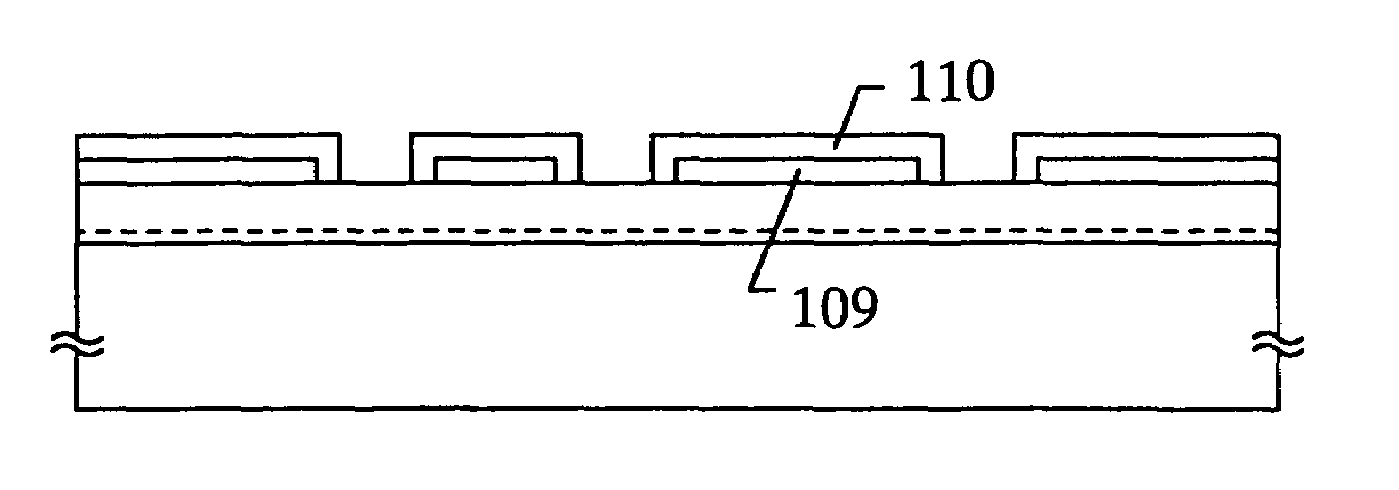

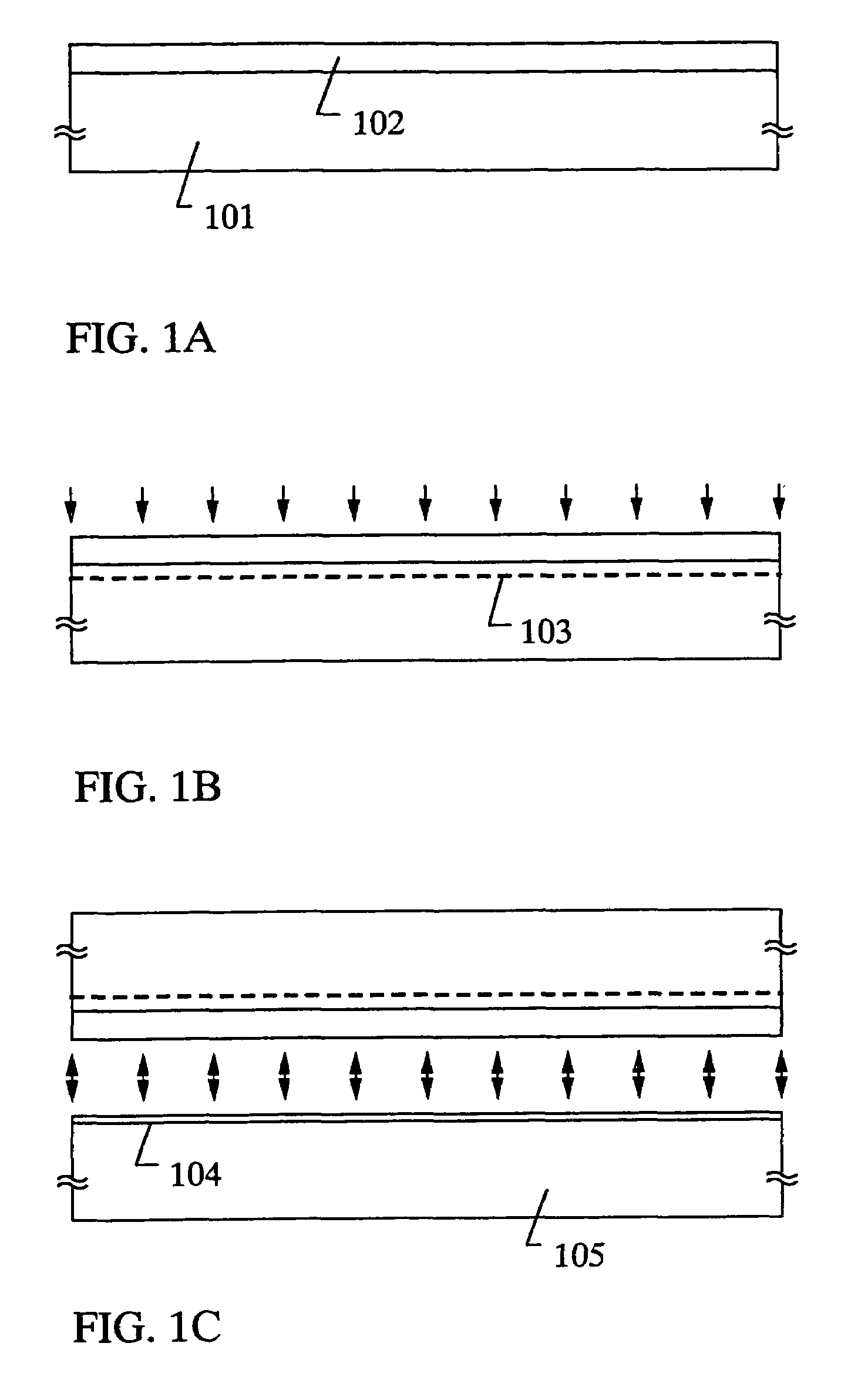

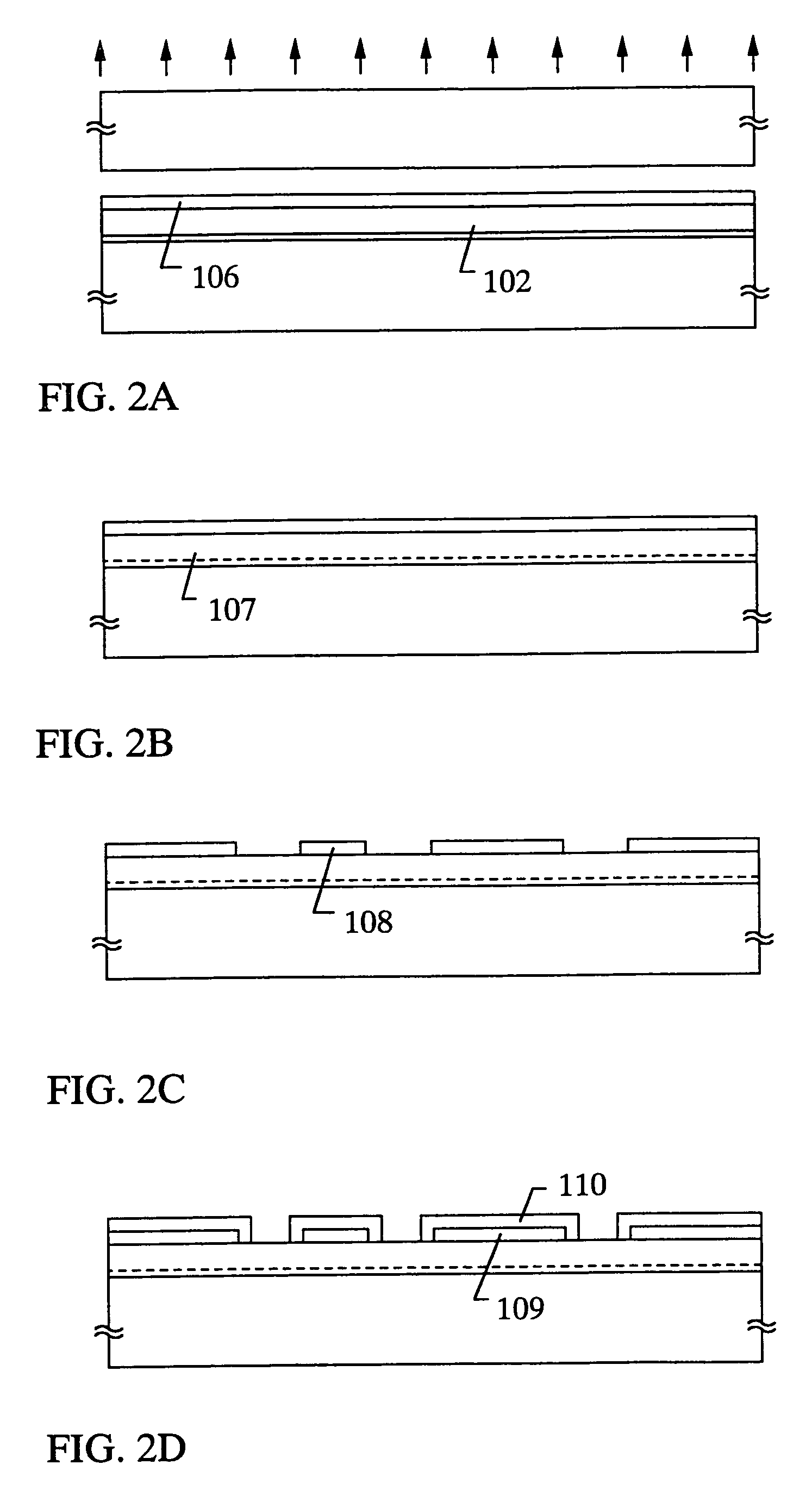

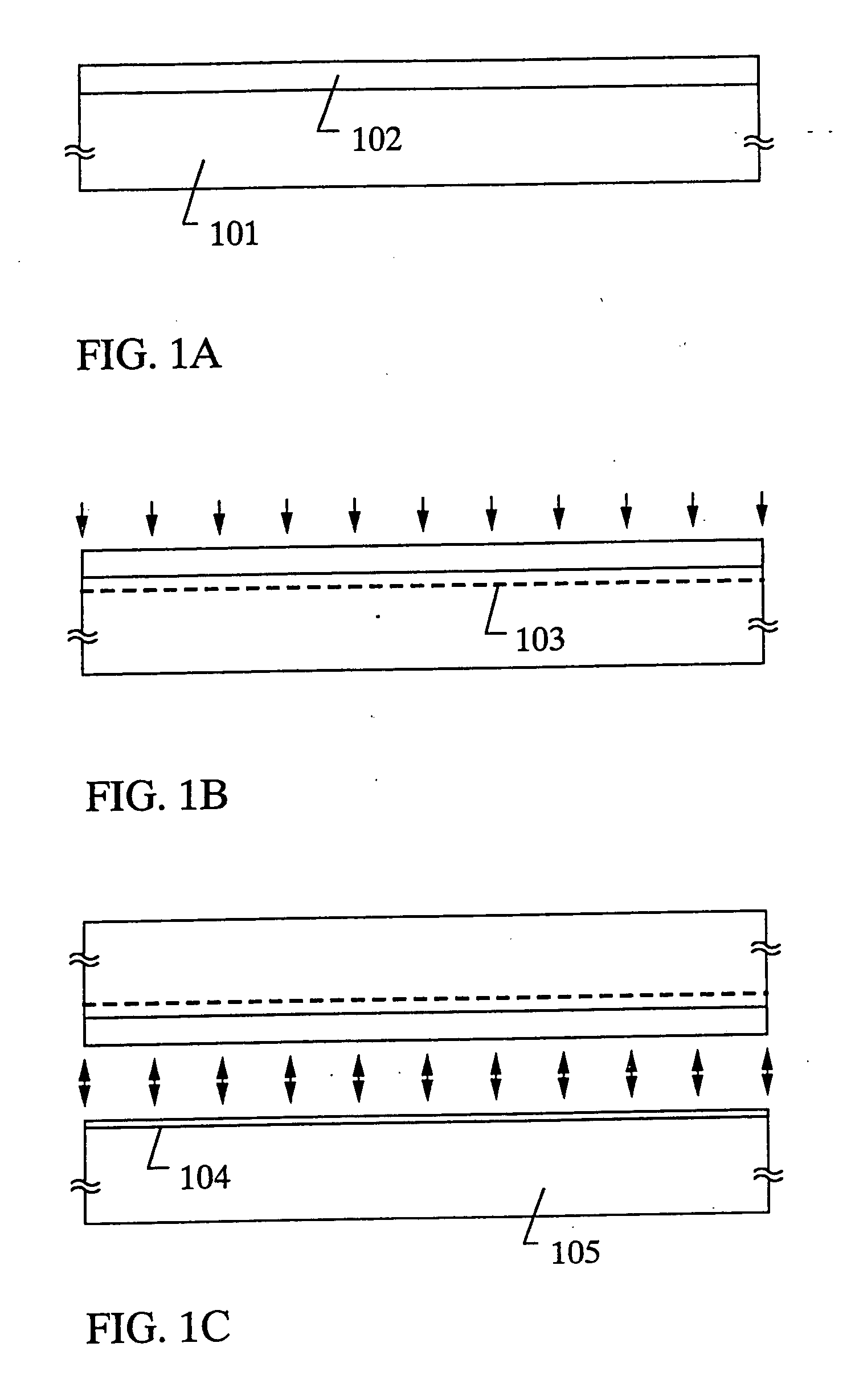

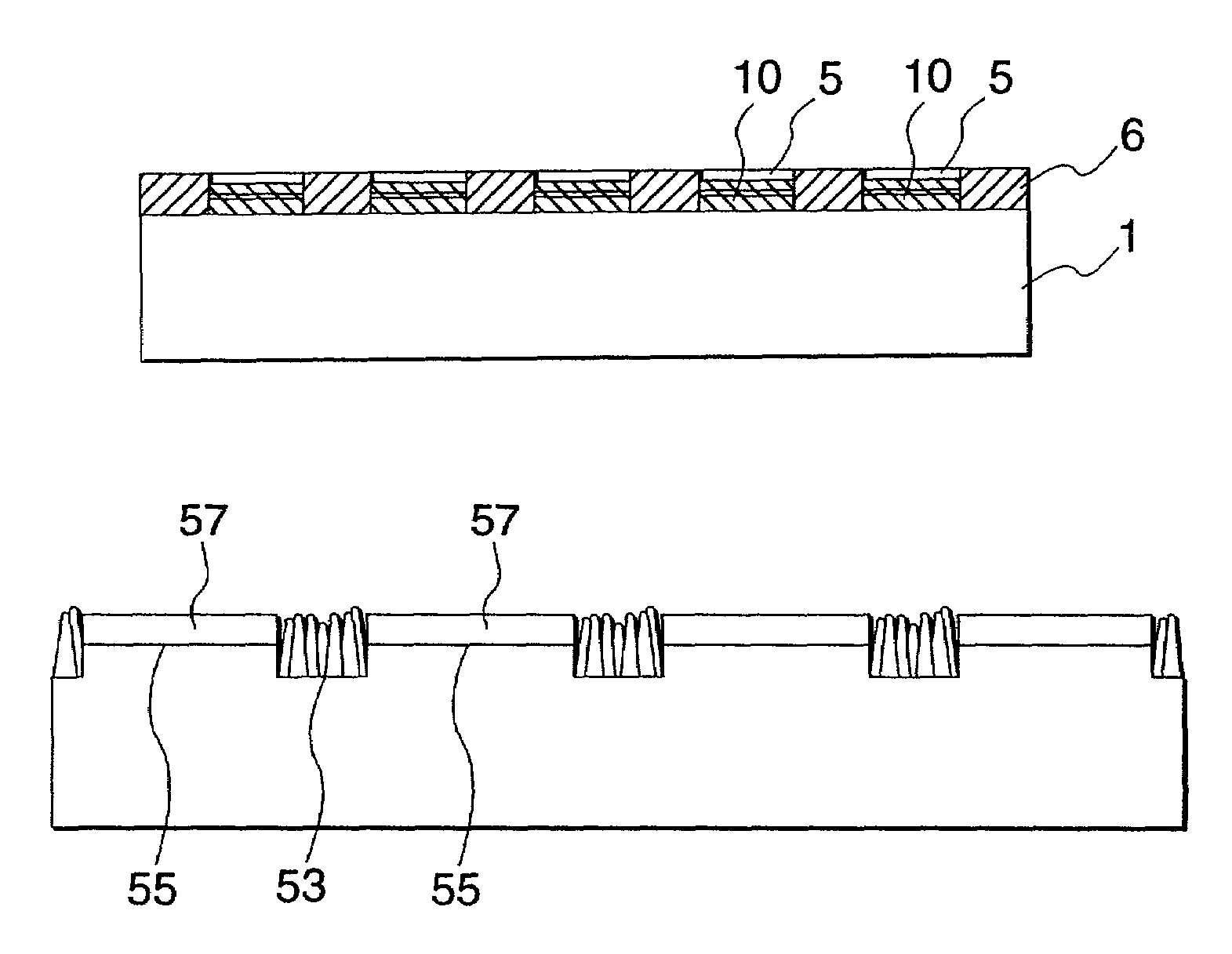

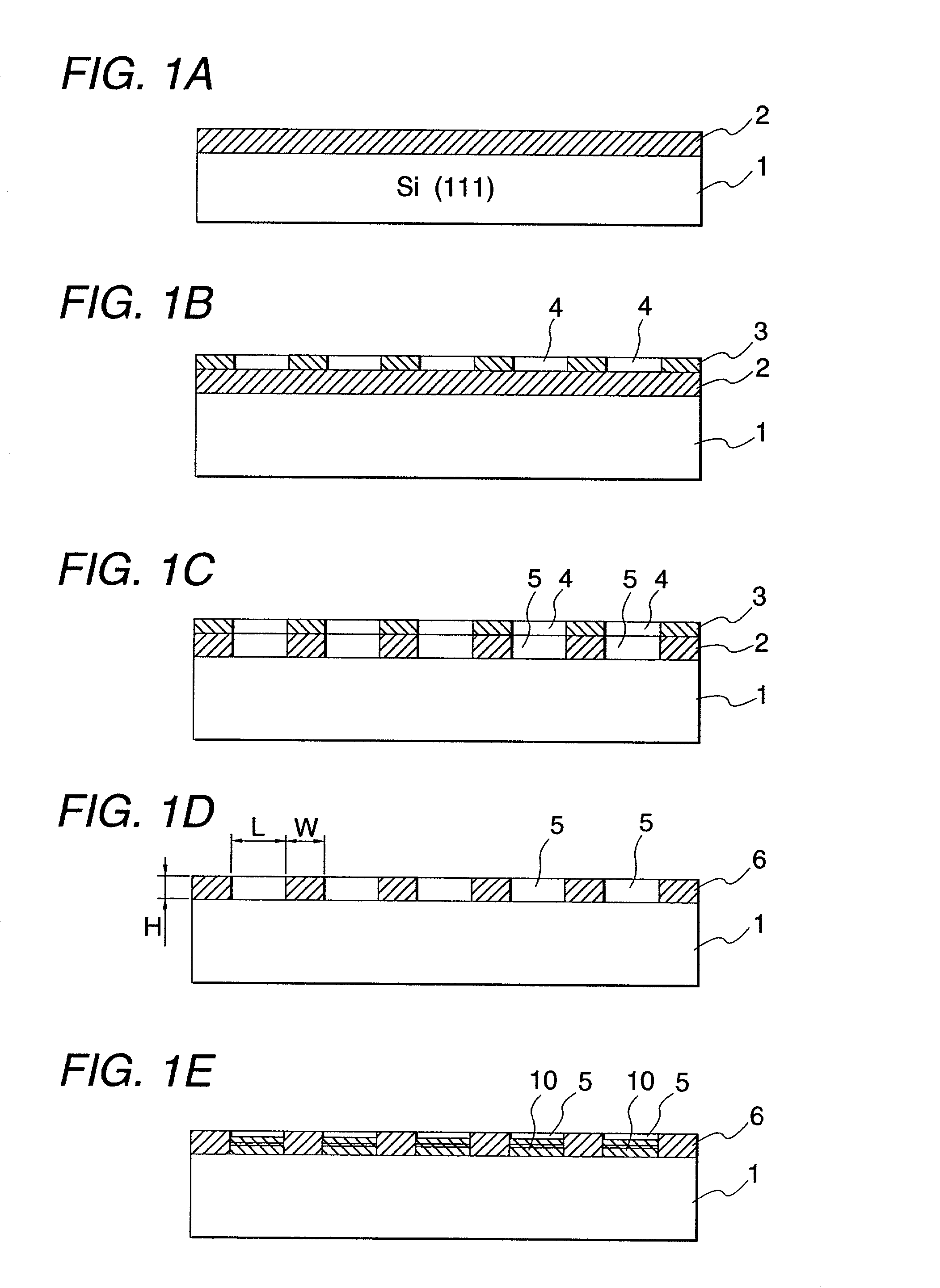

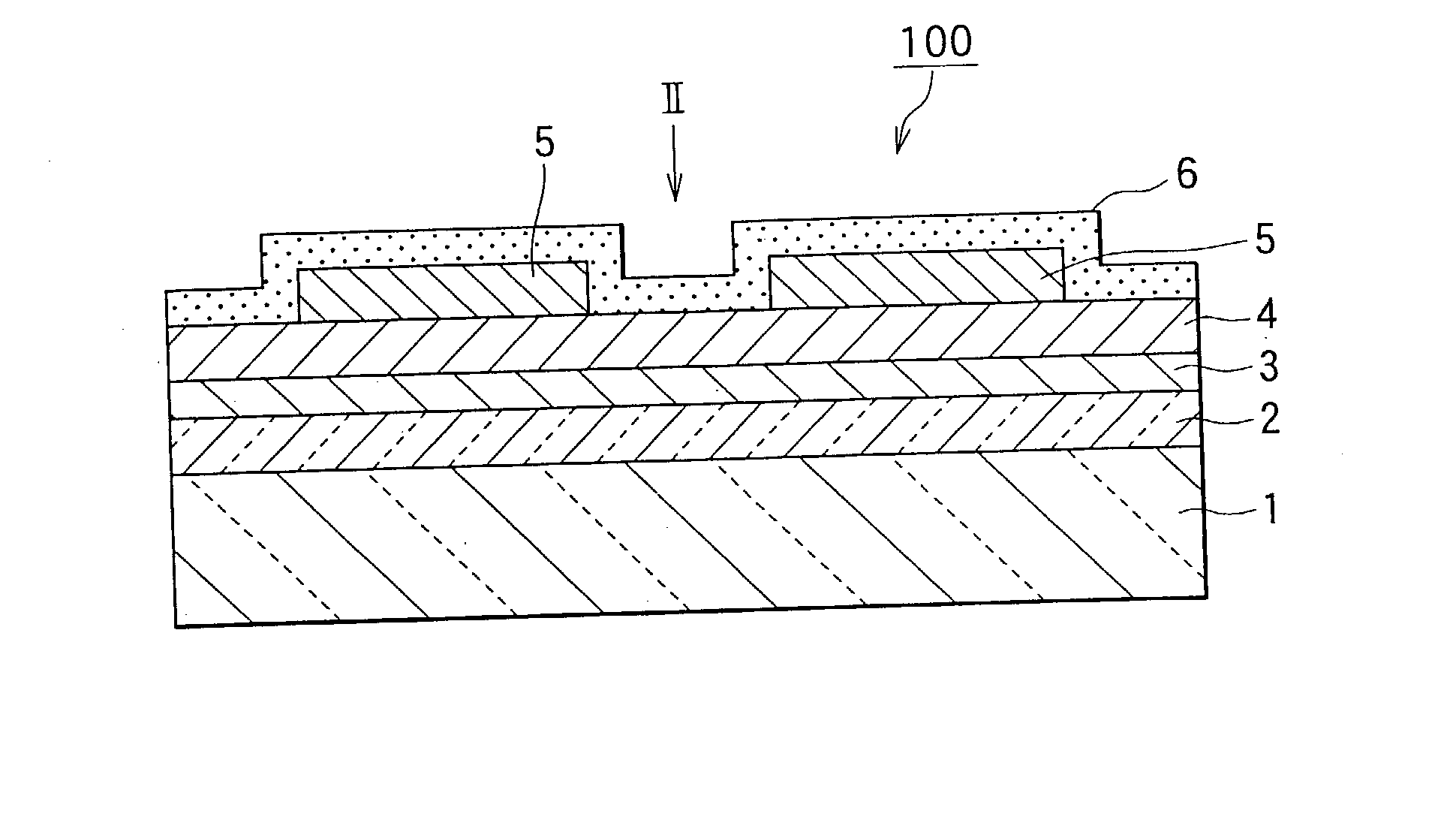

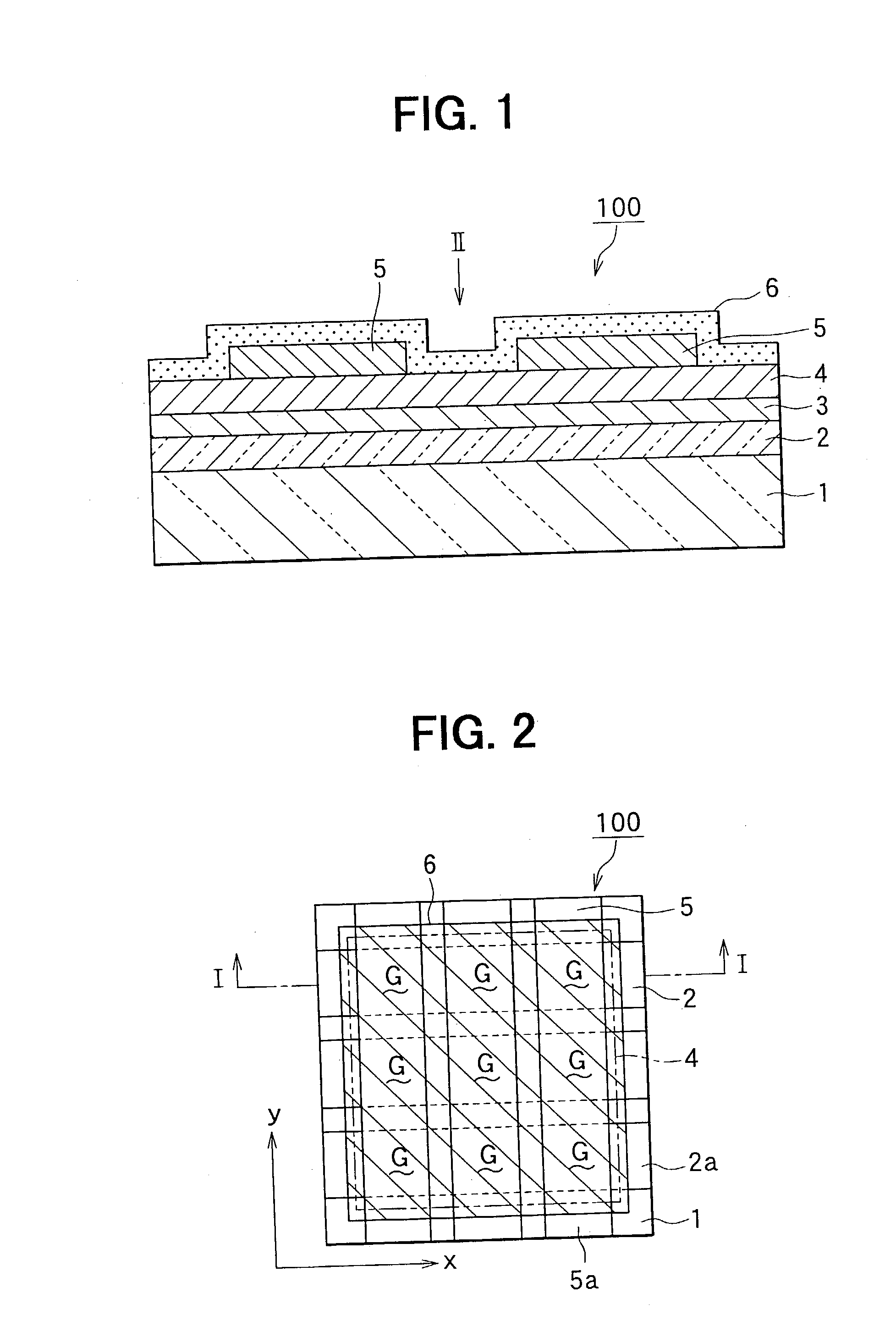

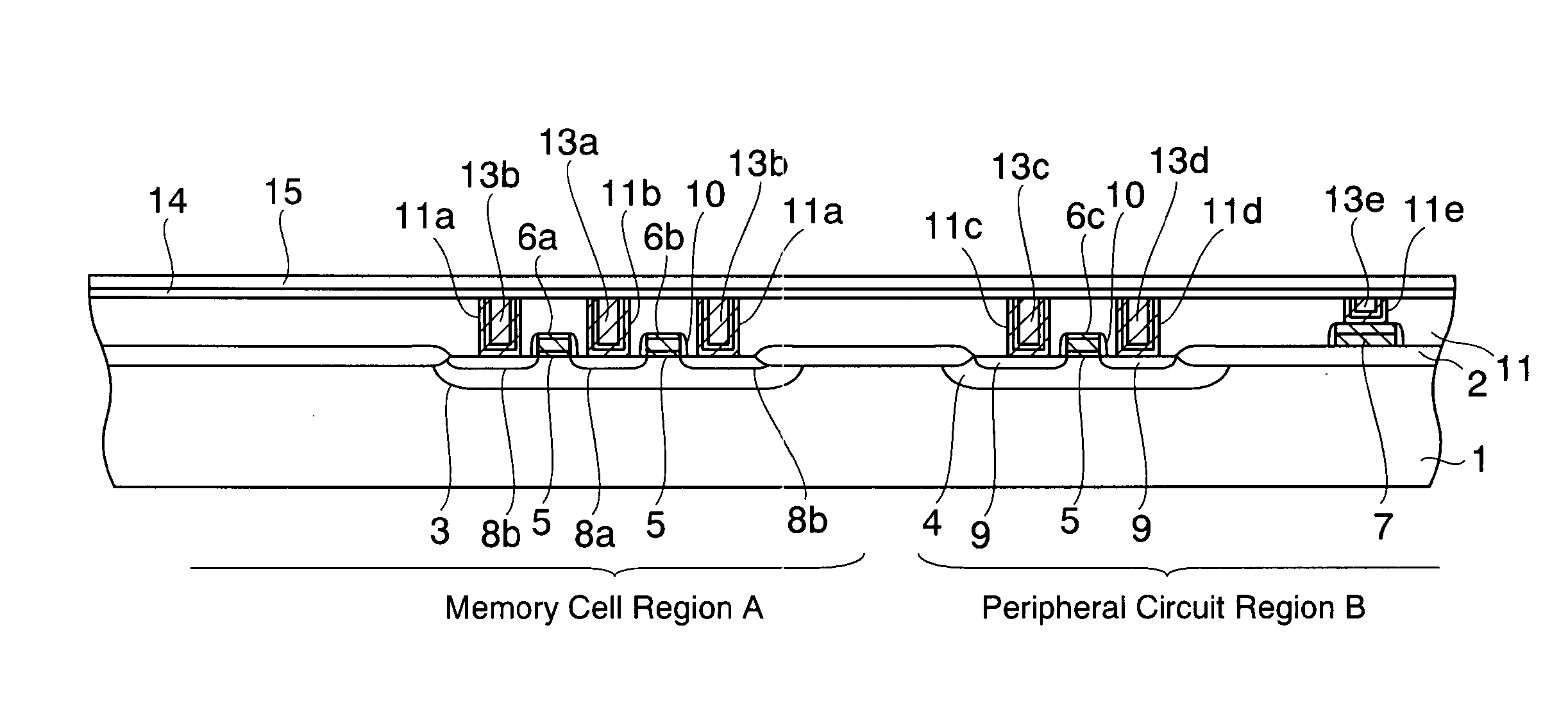

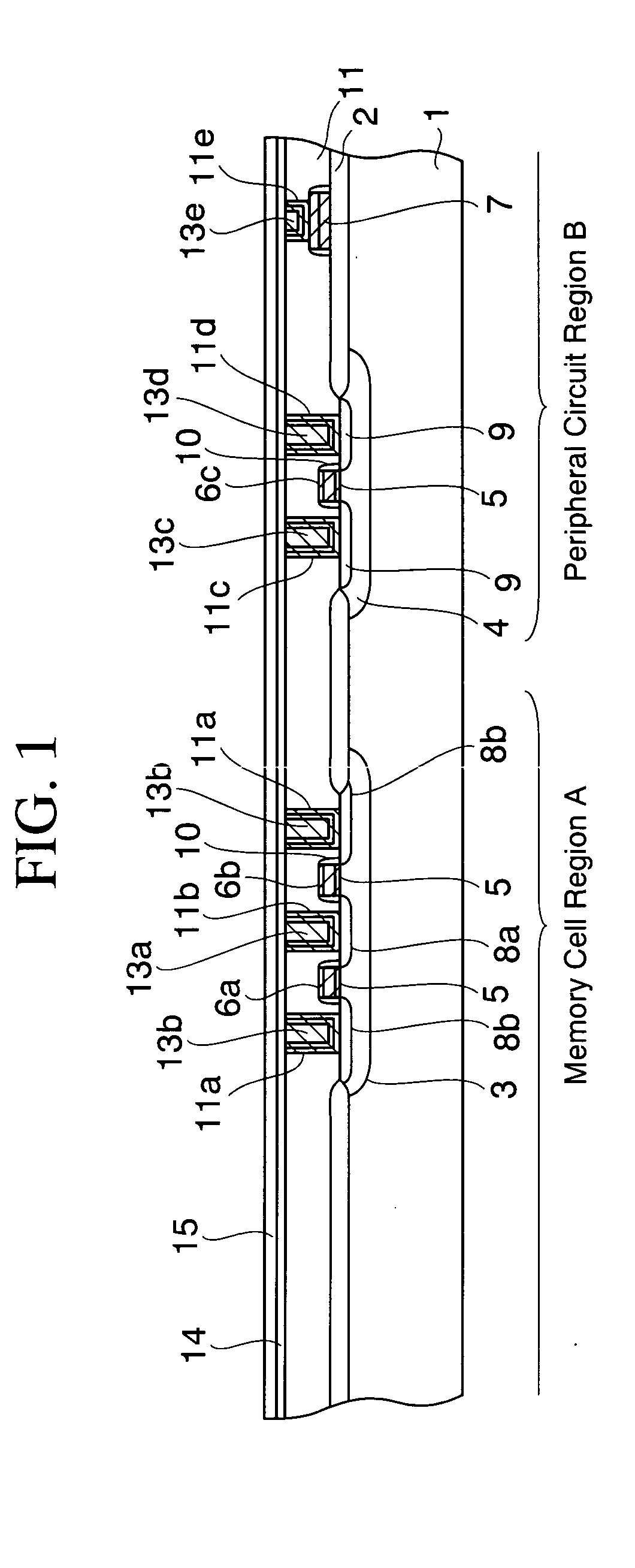

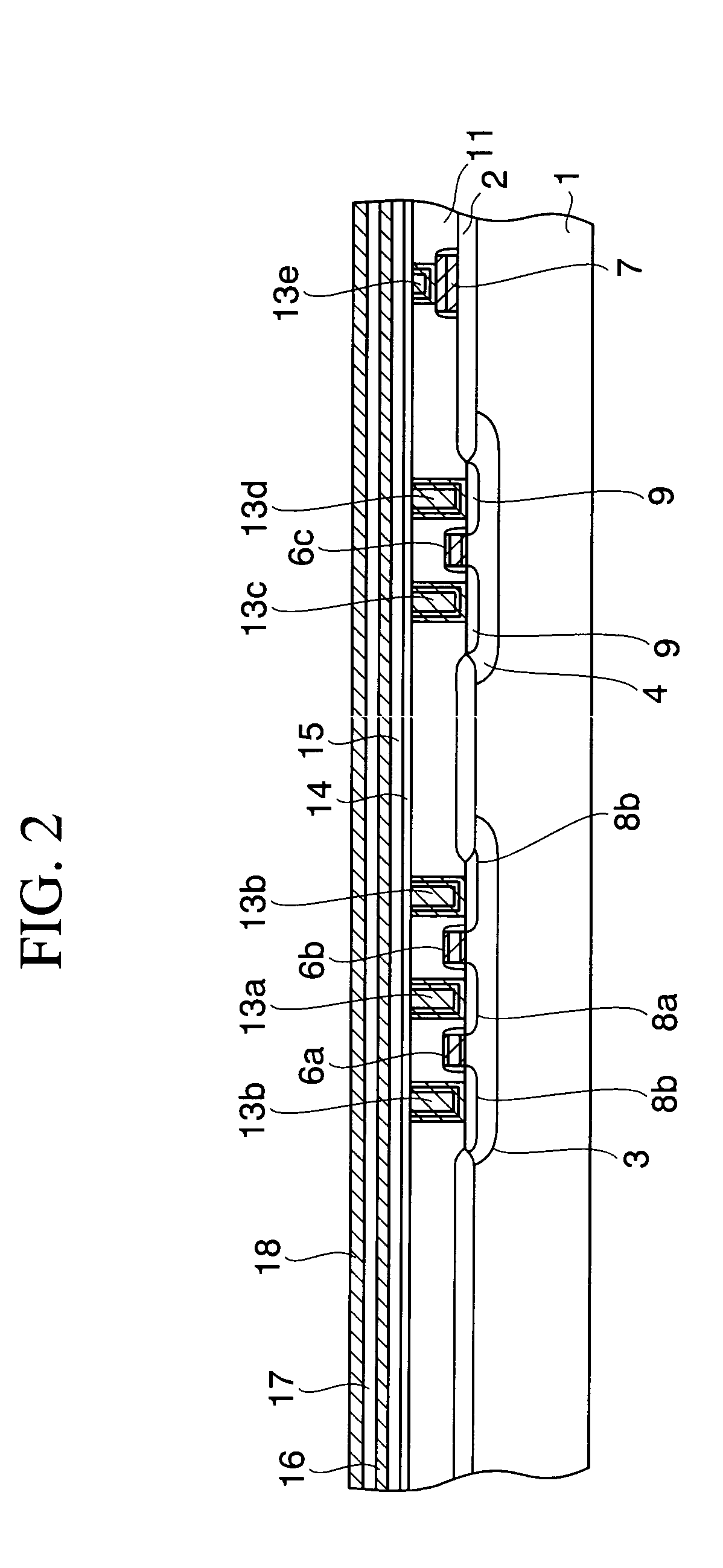

Method of manufacturing a semiconductor device

InactiveUS7199024B2Relaxation stressGuaranteed uptimeTransistorSolid-state devicesSmart CutSemiconductor

There is provided a method of removing trap levels and defects, which are caused by stress, from a single crystal silicon thin film formed by an SOI technique. First, a single crystal silicon film is formed by using a typical bonding SOI technique such as Smart-Cut or ELTRAN. Next, the single crystal silicon thin film is patterned to form an island-like silicon layer, and then, a thermal oxidation treatment is carried out in an oxidizing atmosphere containing a halogen element, so that an island-like silicon layer in which the trap levels and the defects are removed is obtained.

Owner:SEMICON ENERGY LAB CO LTD

Method of manufacturing a semiconductor device

InactiveUS20070173000A1Improve business performanceImprove performanceTransistorSolid-state devicesDevice materialSmart Cut

There is provided a method of removing trap levels and defects, which are caused by stress, from a single crystal silicon thin film formed by an SOI technique. First, a single crystal silicon film is formed by using a typical bonding SOI technique such as Smart-Cut or ELTRAN. Next, the single crystal silicon thin film is patterned to form an island-like silicon layer, and then, a thermal oxidation treatment is carried out in an oxidizing atmosphere containing a halogen element, so that an island-like silicon layer in which the trap levels and the defects are removed is obtained.

Owner:SEMICON ENERGY LAB CO LTD

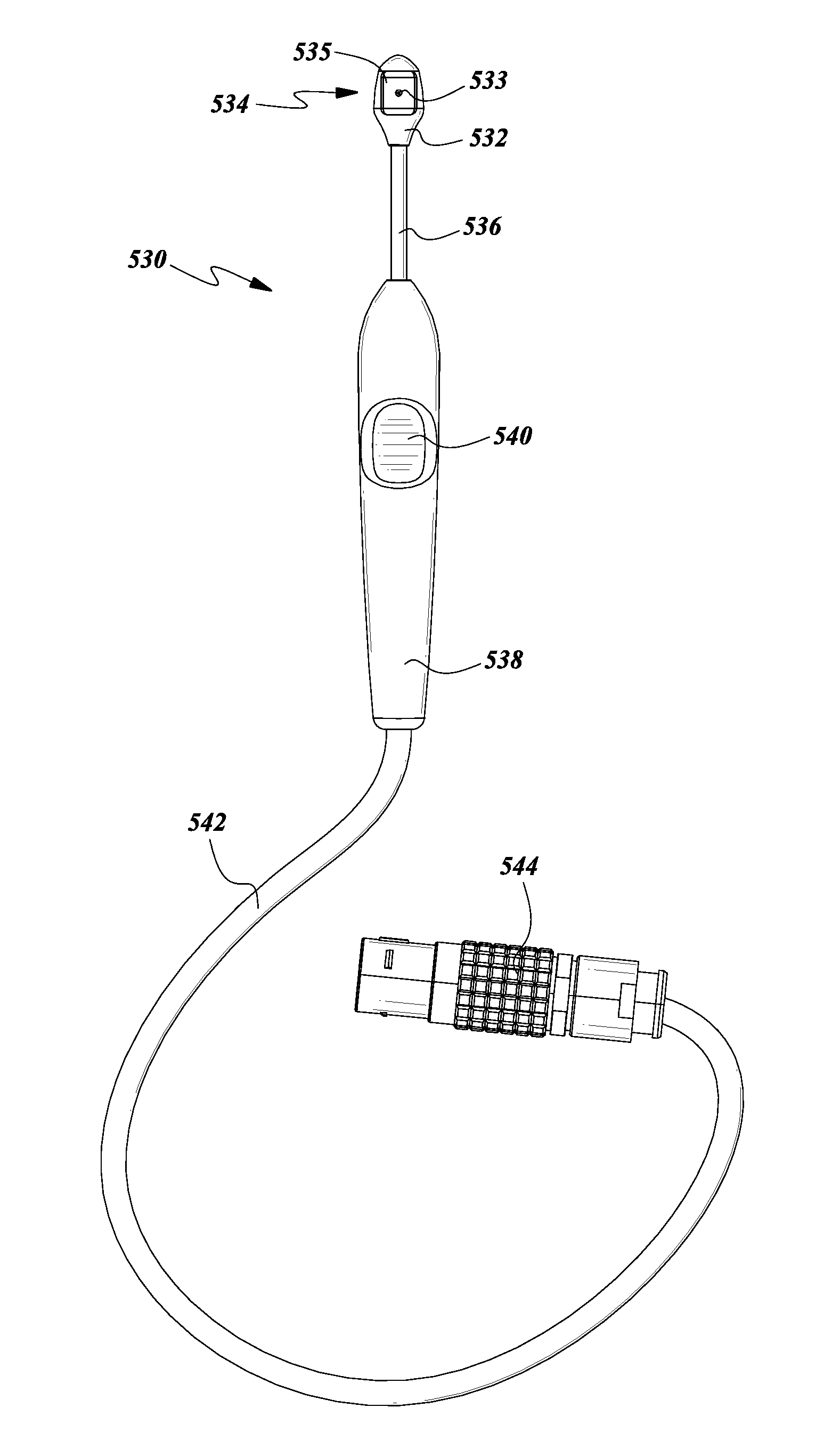

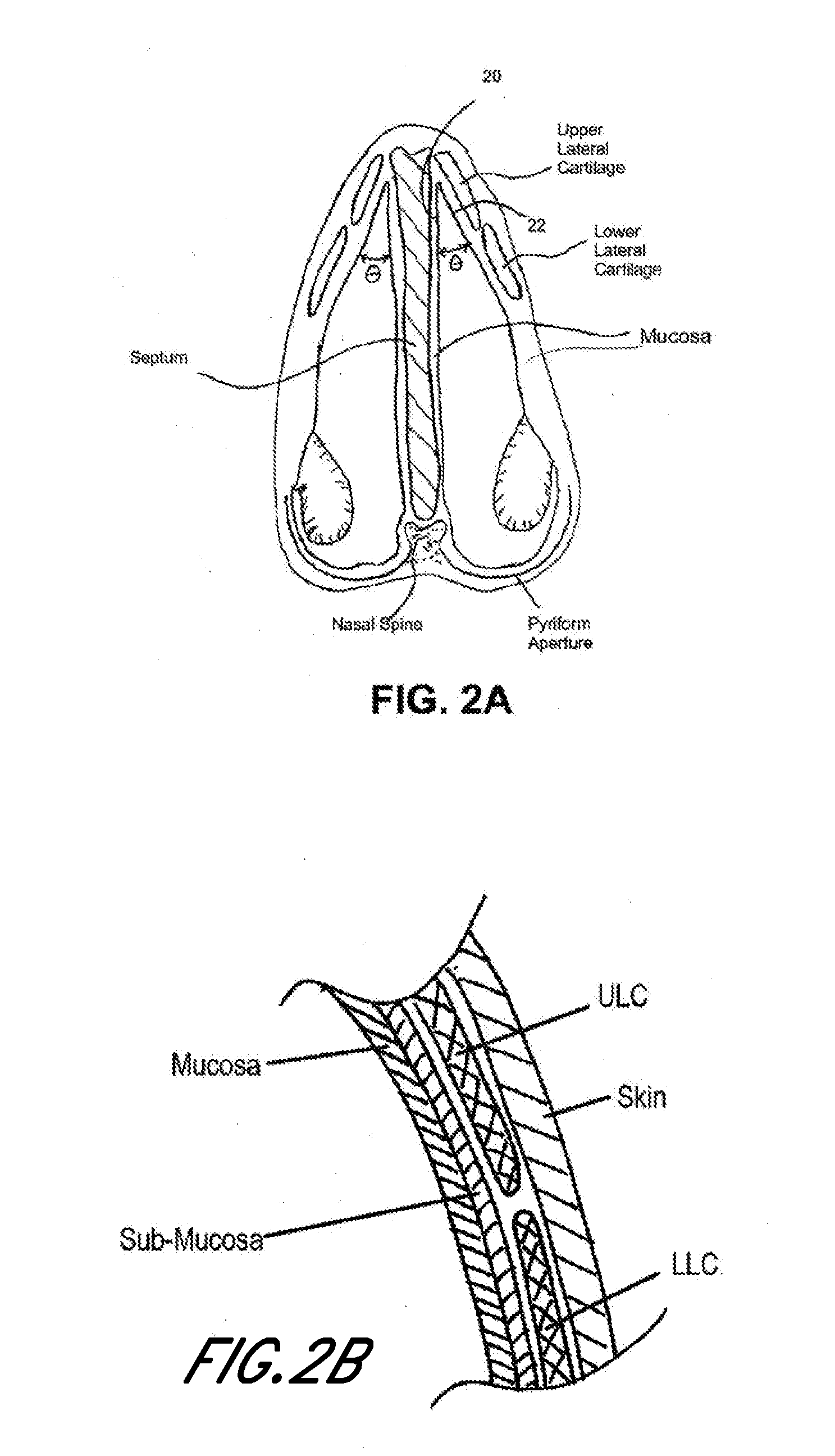

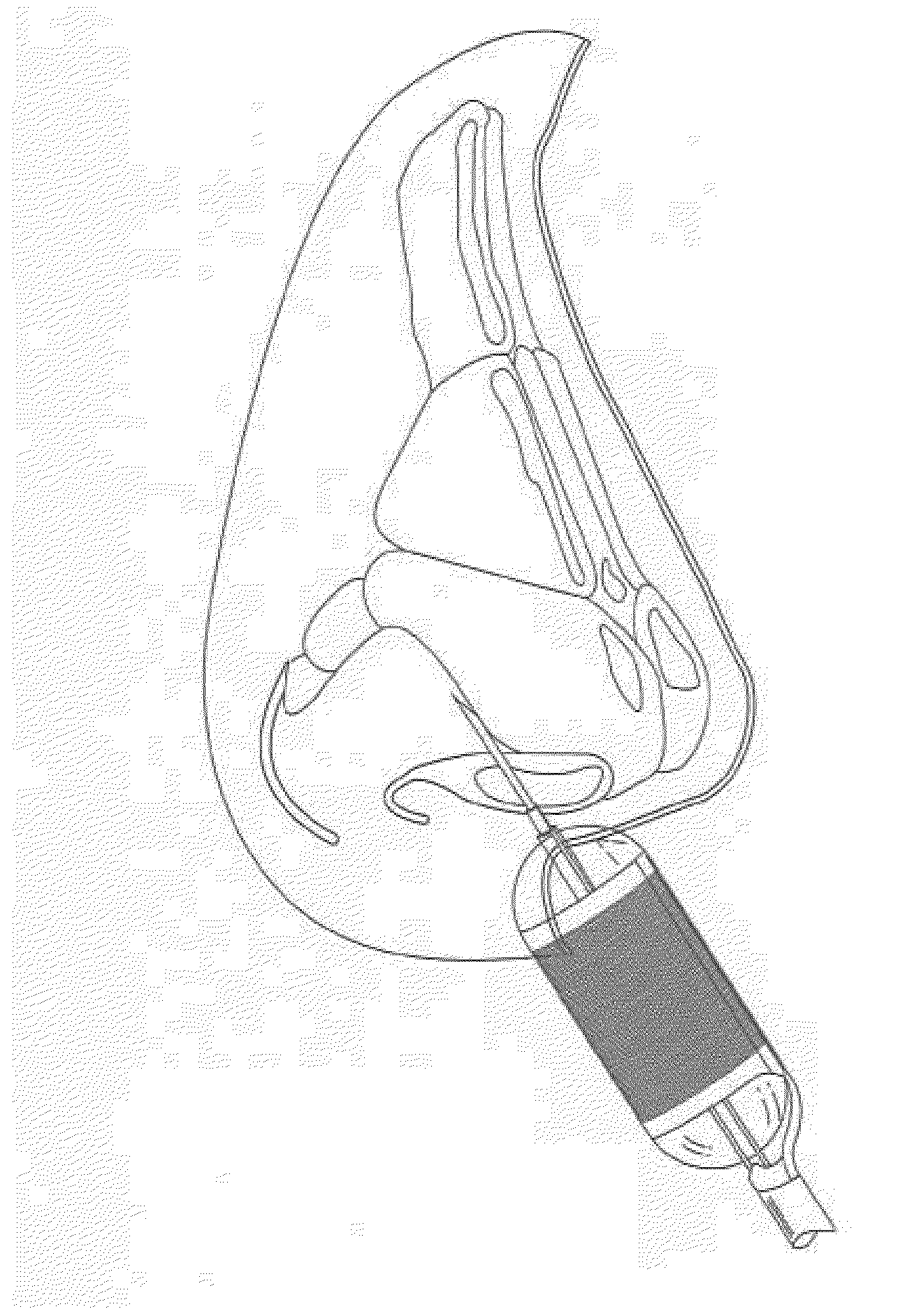

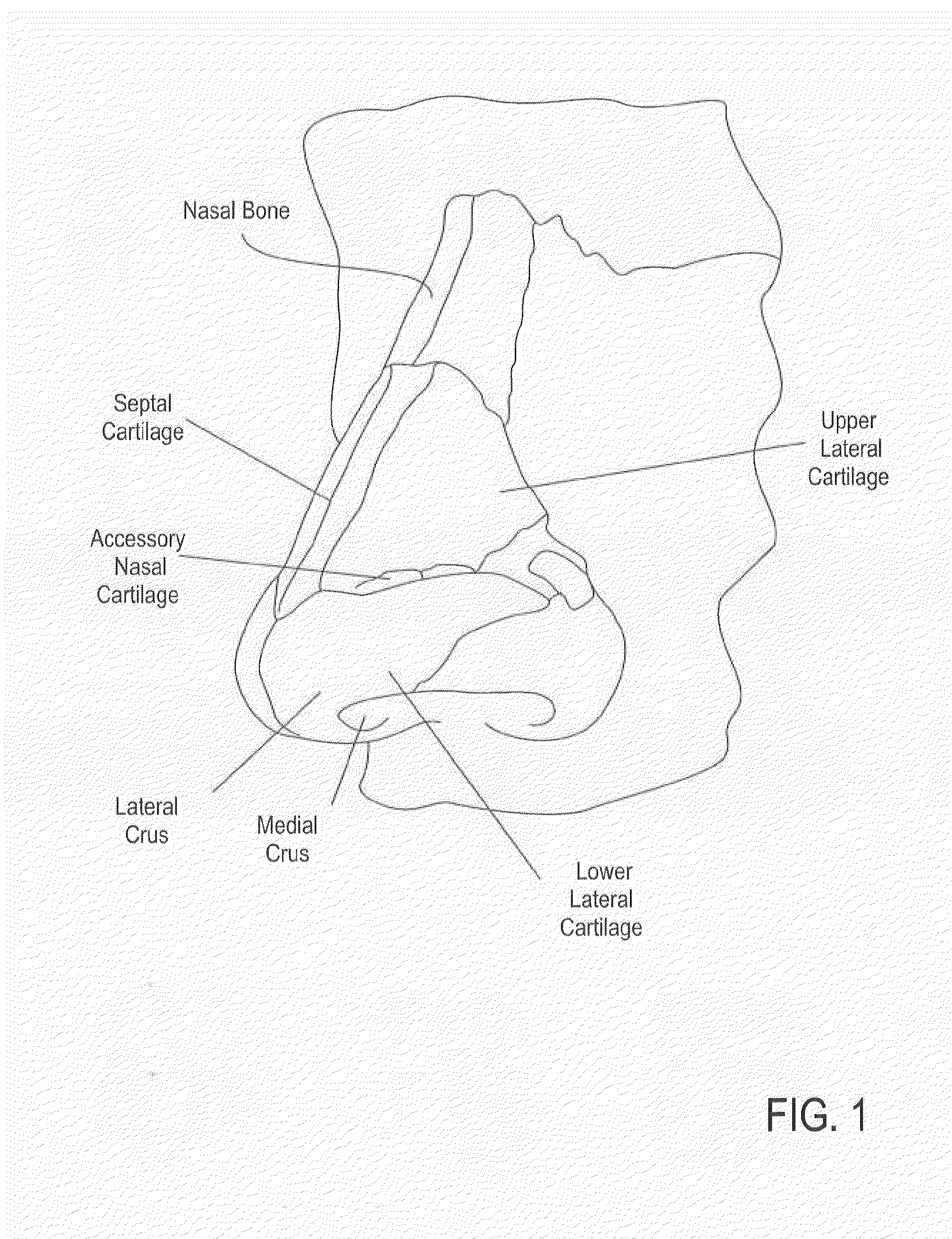

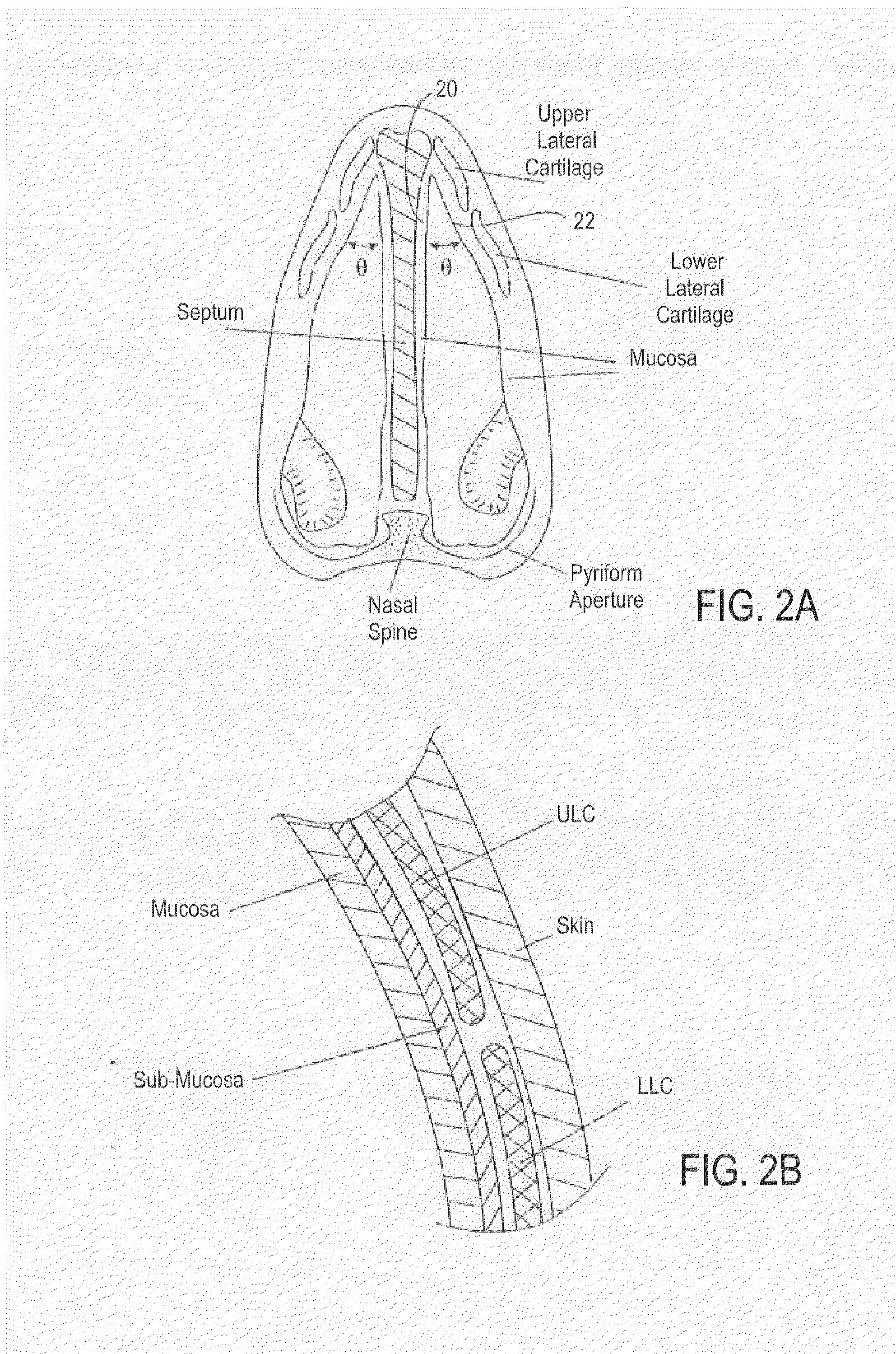

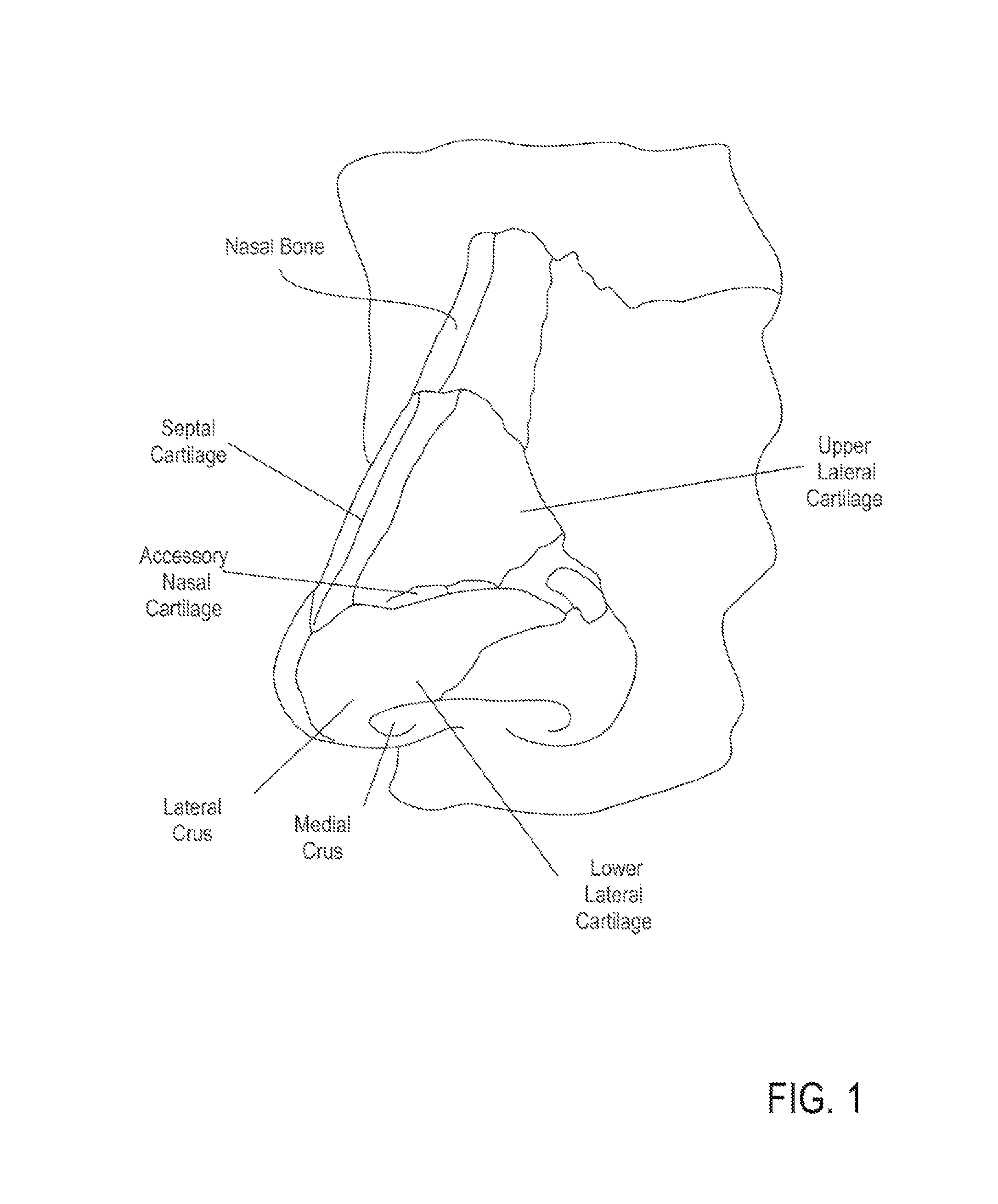

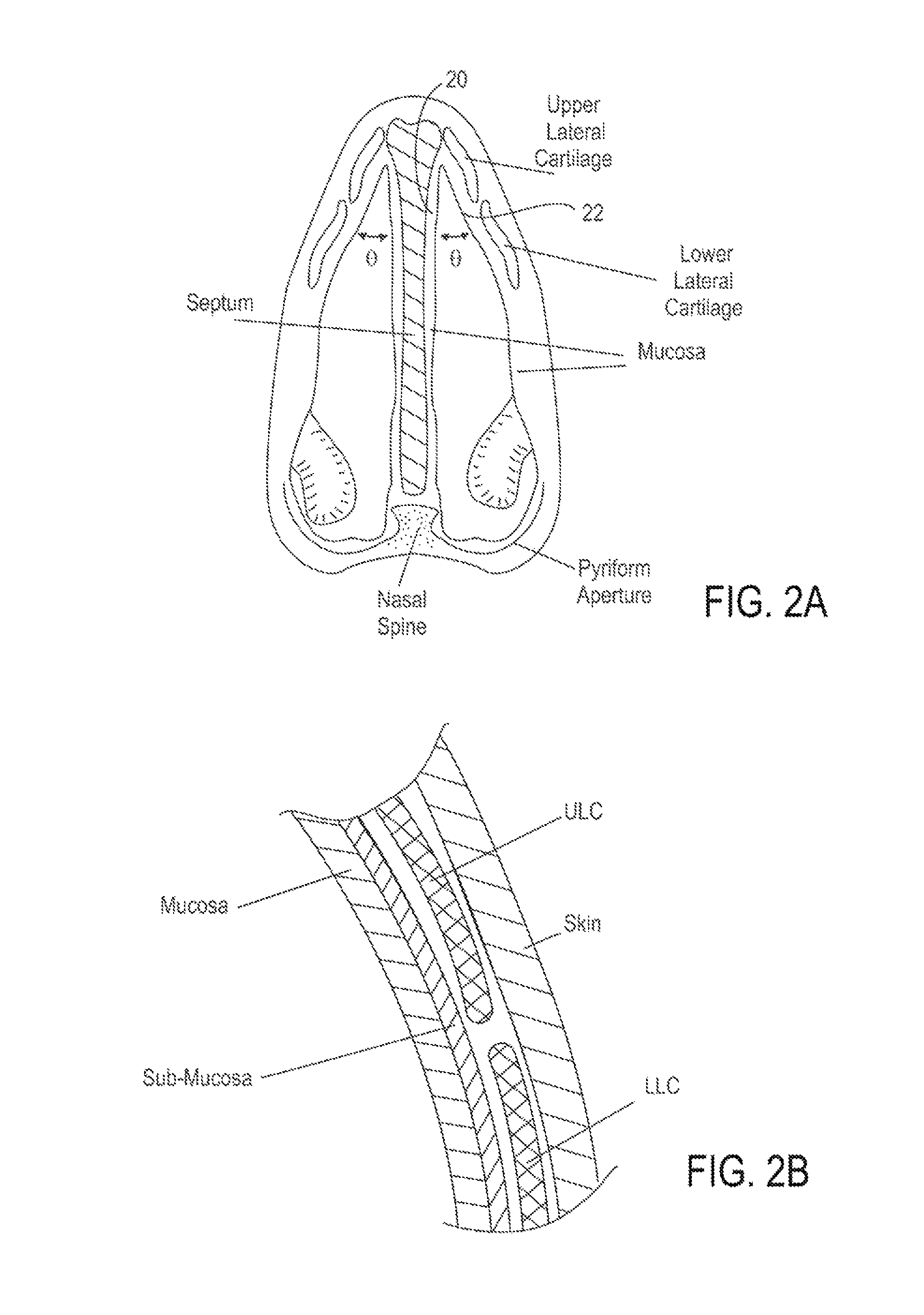

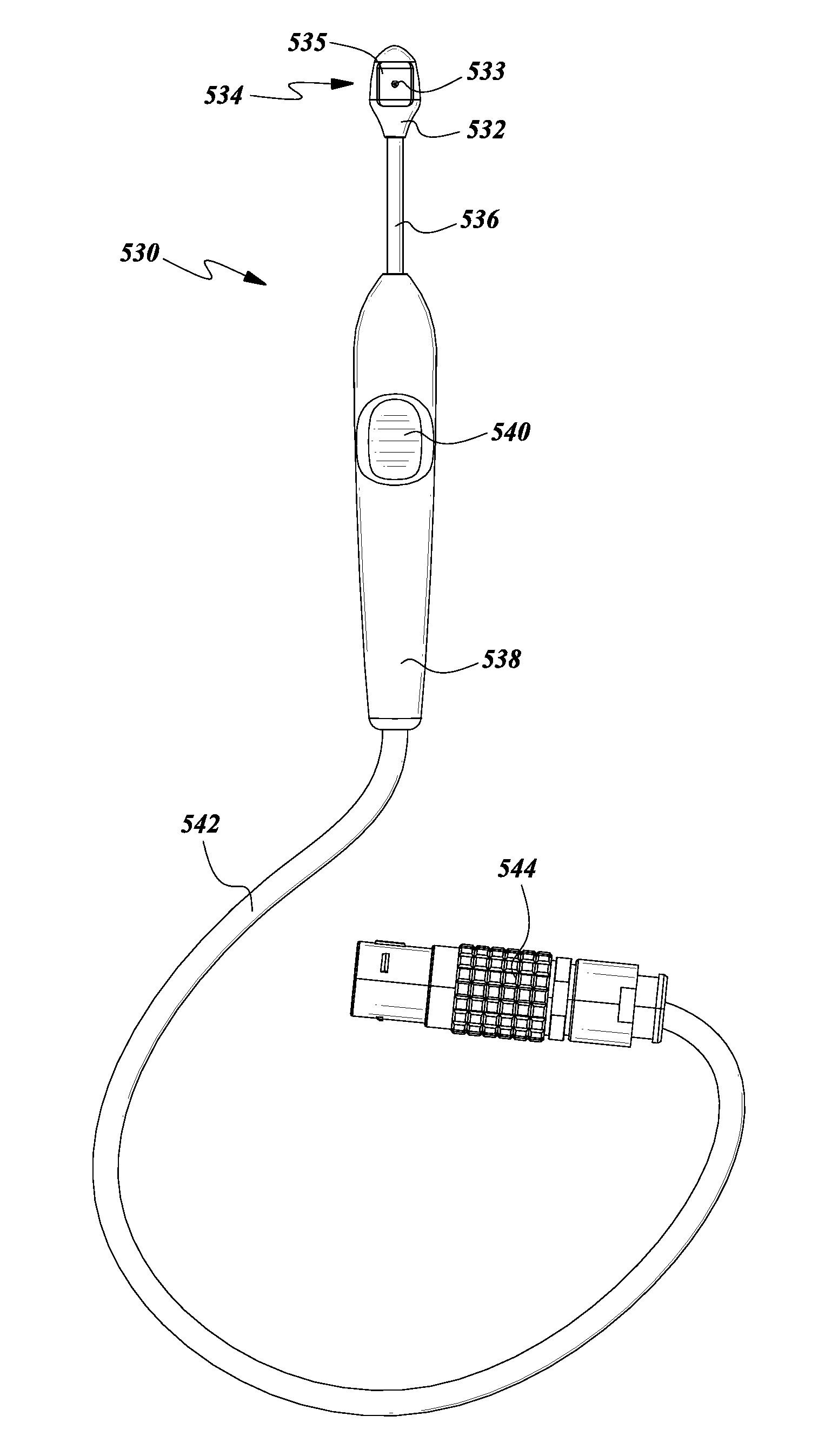

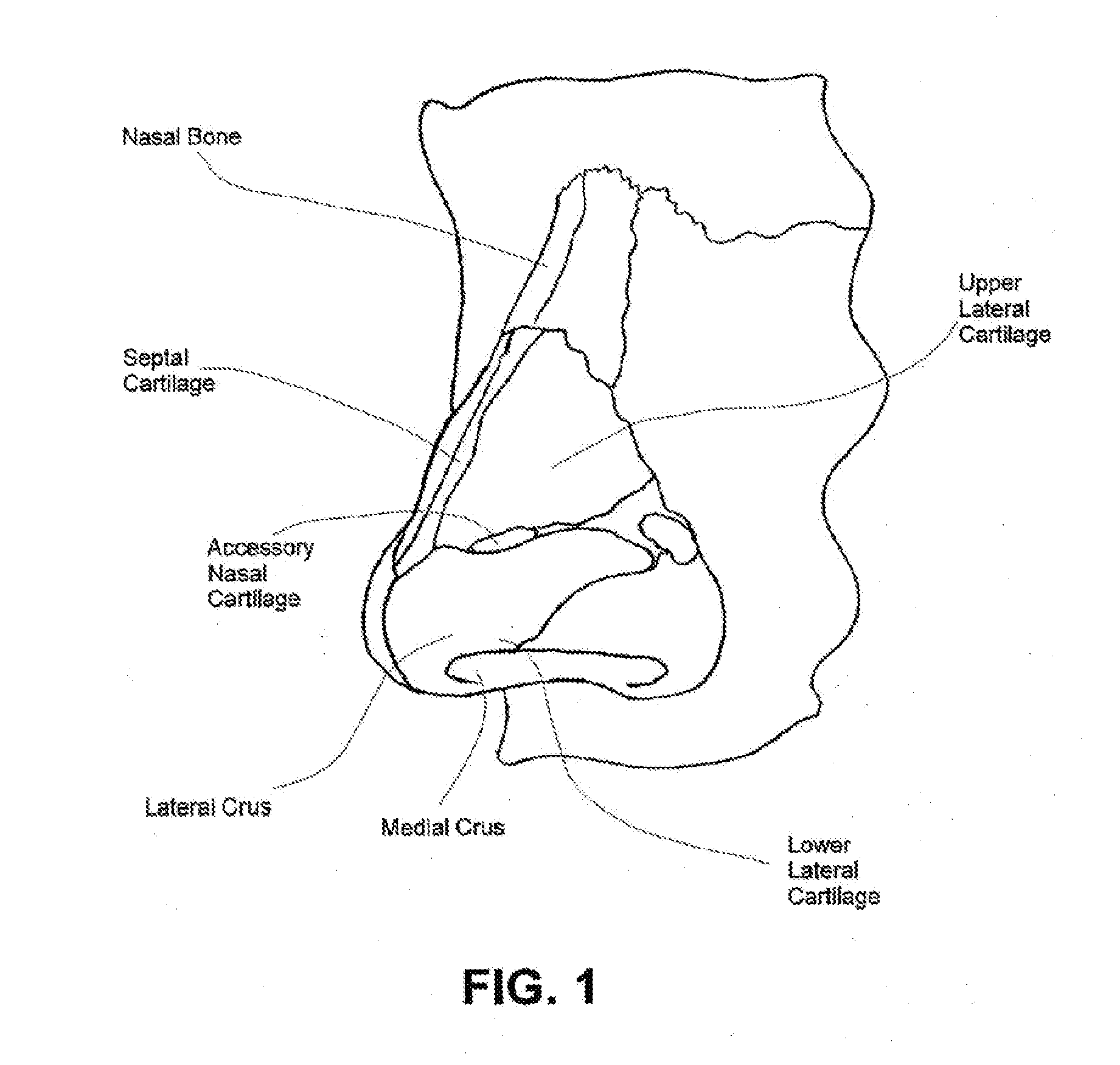

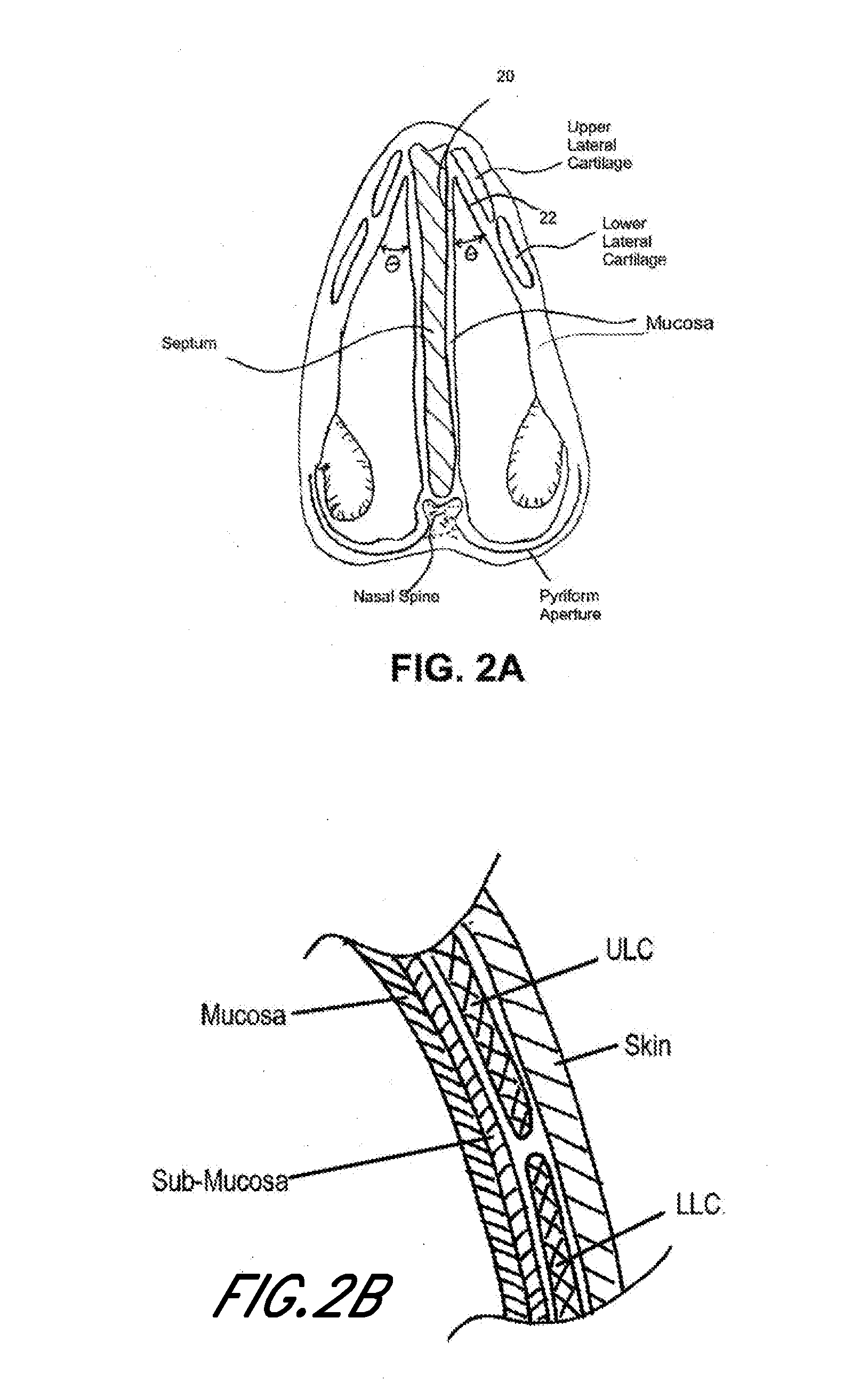

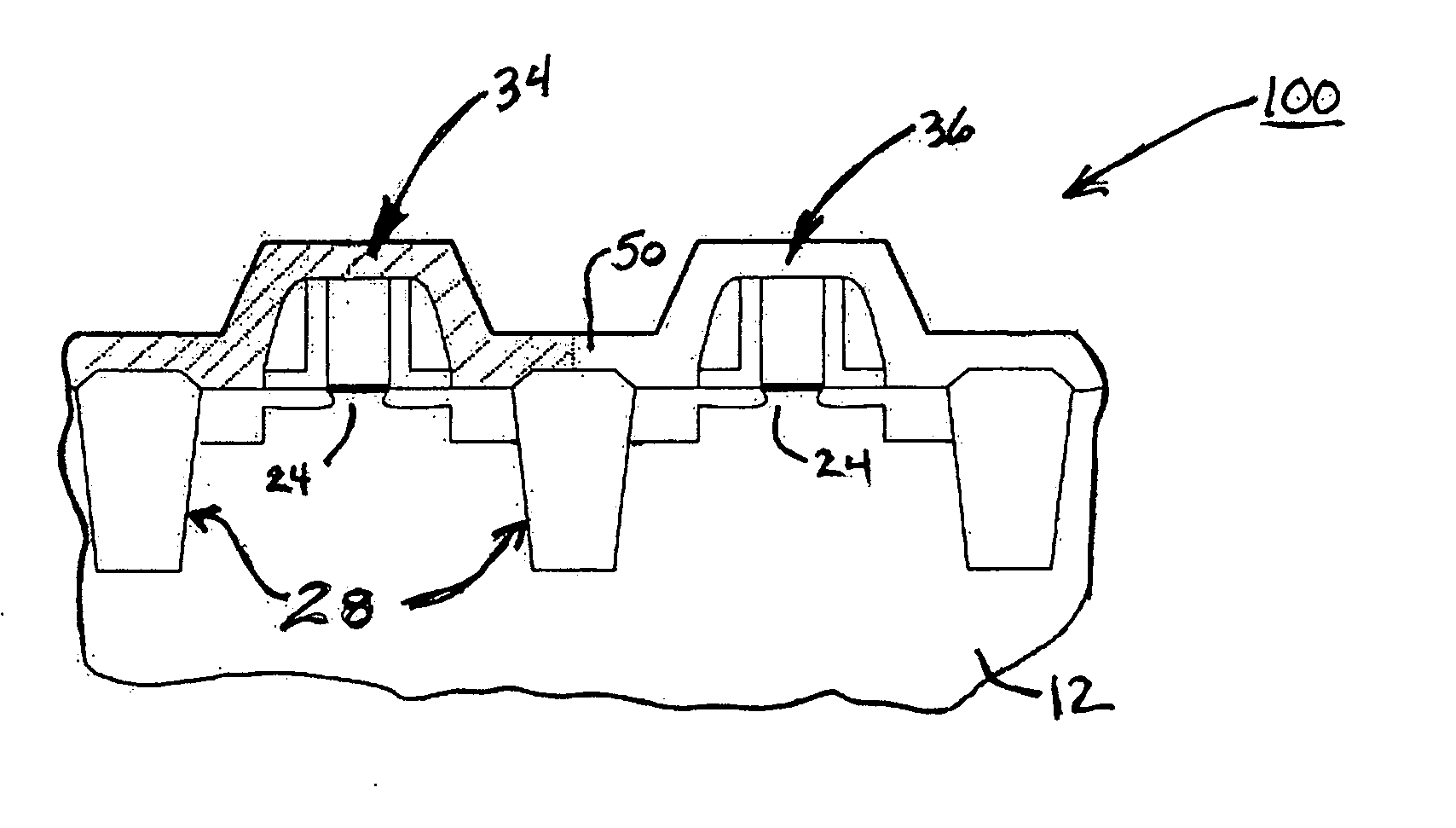

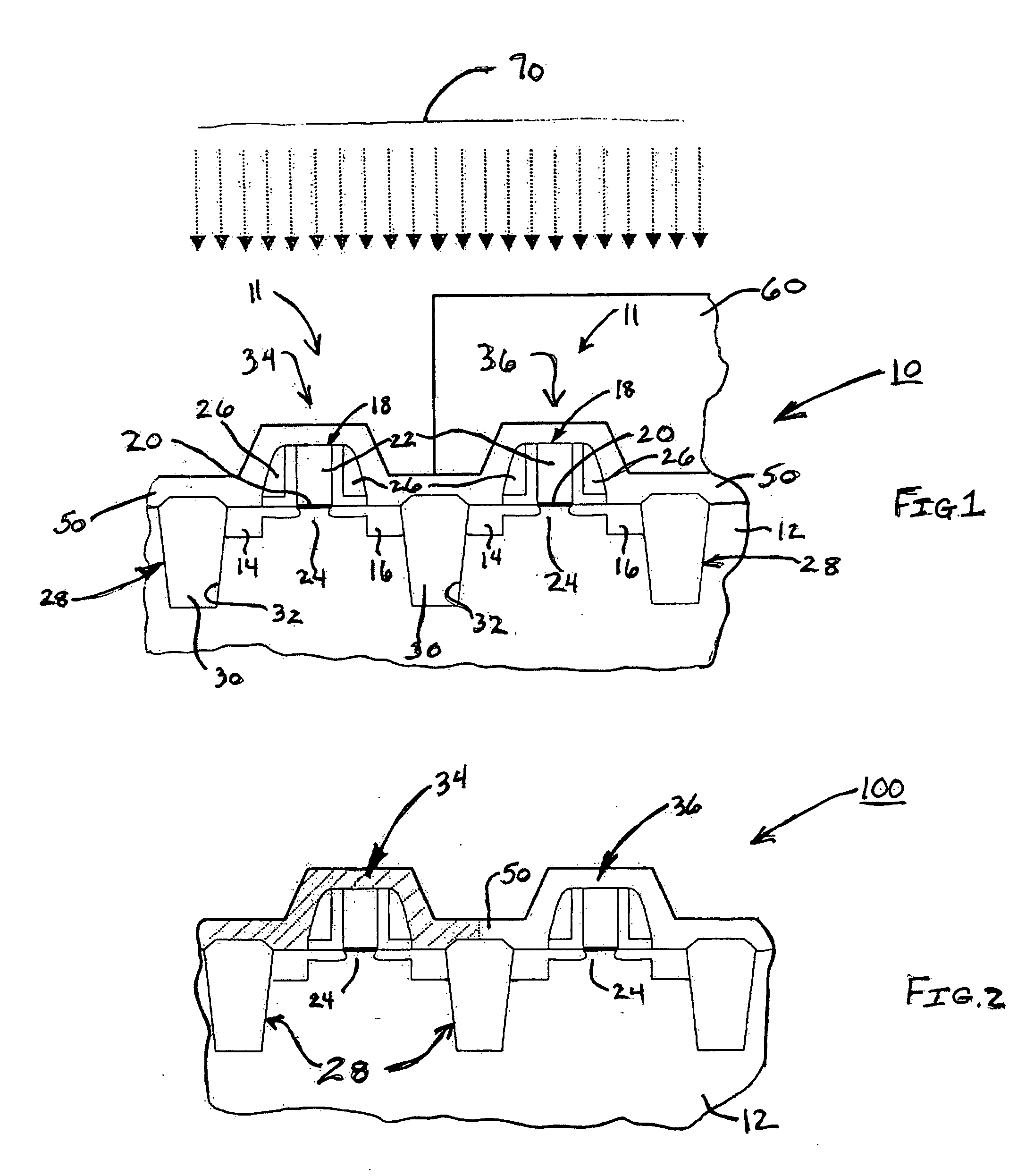

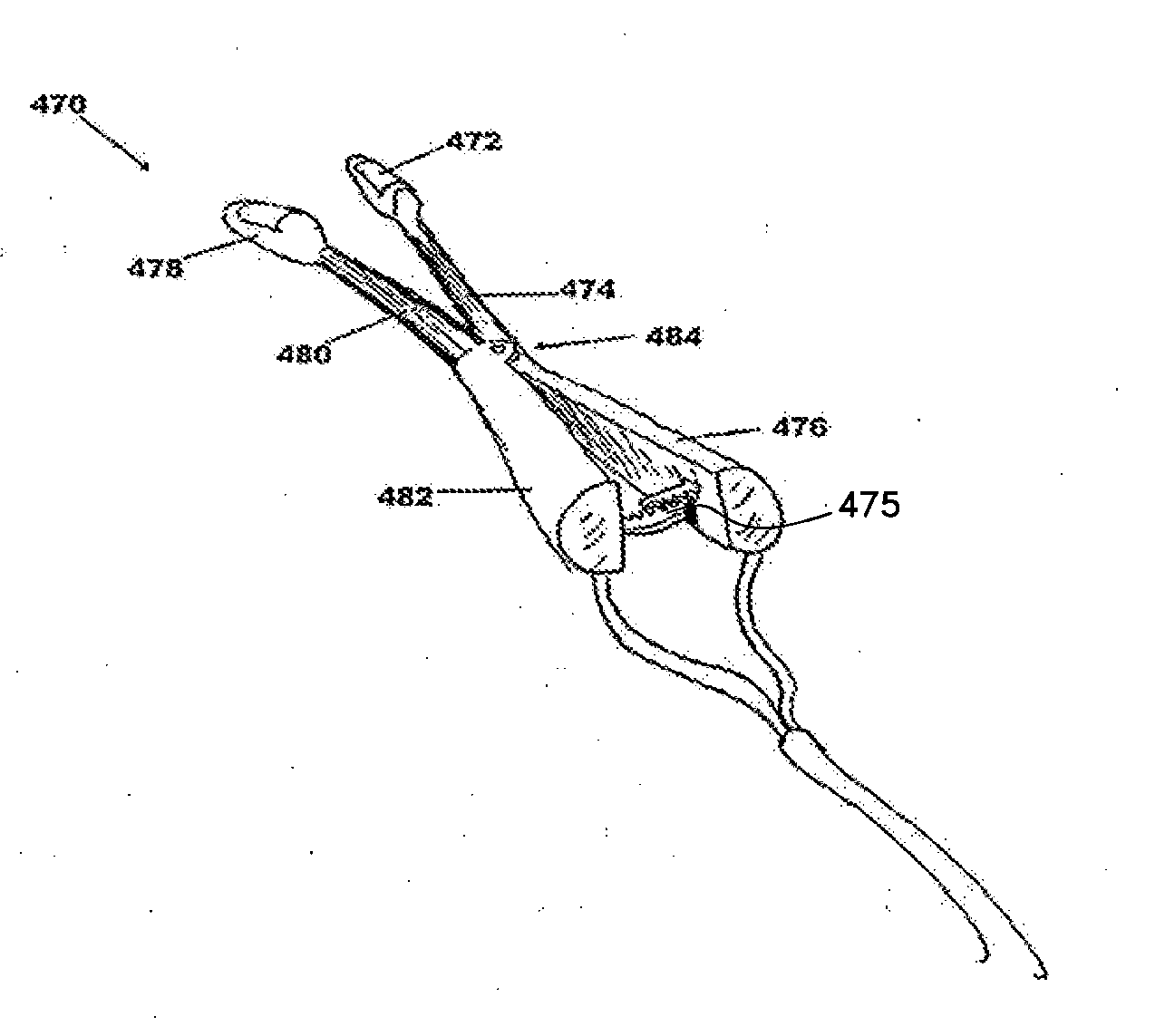

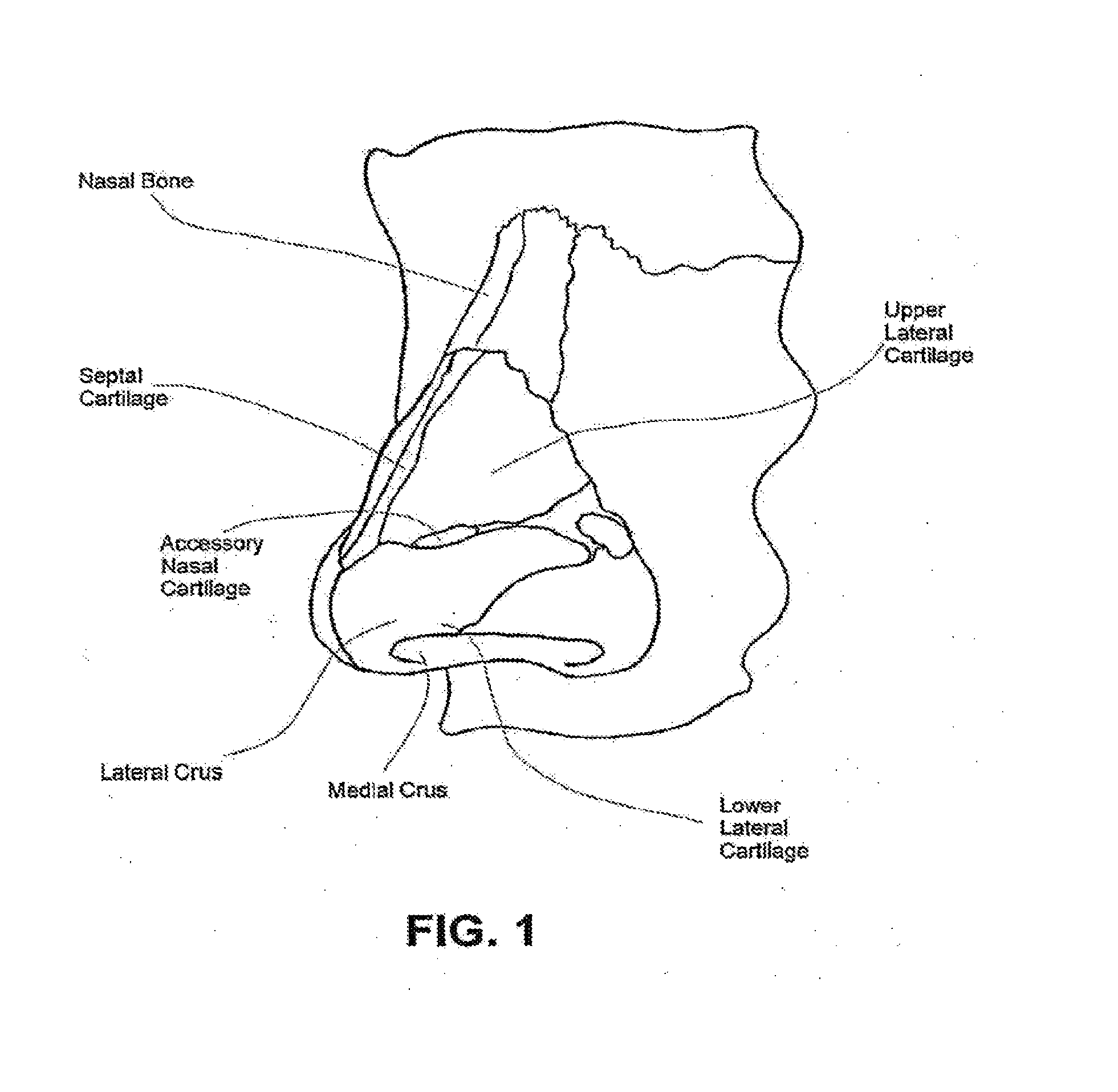

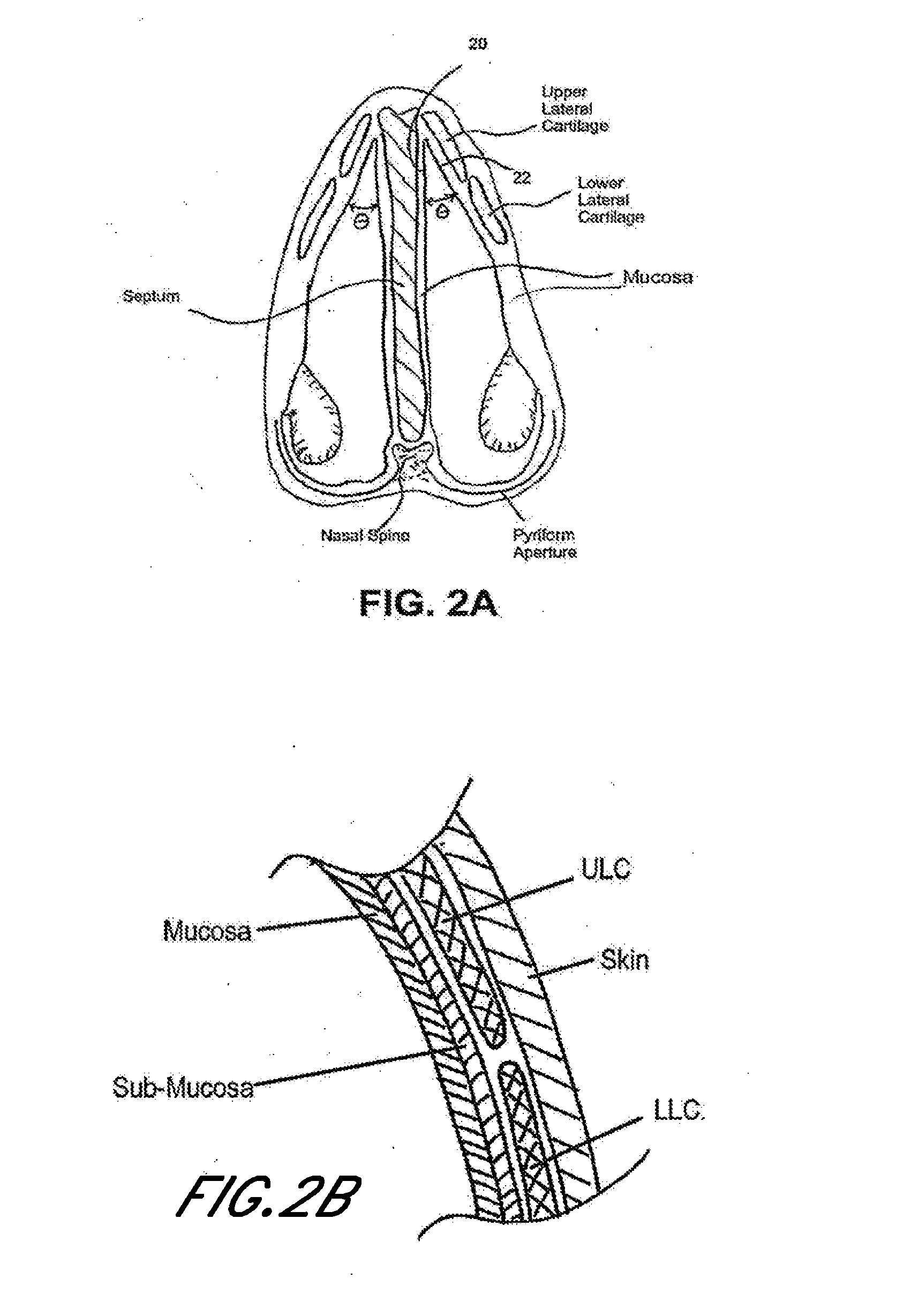

Methods and devices to treat nasal airways

ActiveUS20120323227A1Increase ratingsWithout weakeningElectrotherapySurgical needlesNasal cavityNose

Methods and devices for treating nasal airways are provided. Such devices and methods may improve airflow through an internal and / or external nasal valve, and comprise the use of mechanical re-shaping, energy application and other treatments to modify the shape, structure, and / or air flow characteristics of an internal nasal valve, an external nasal valve or other nasal airways.

Owner:AERIN MEDICAL

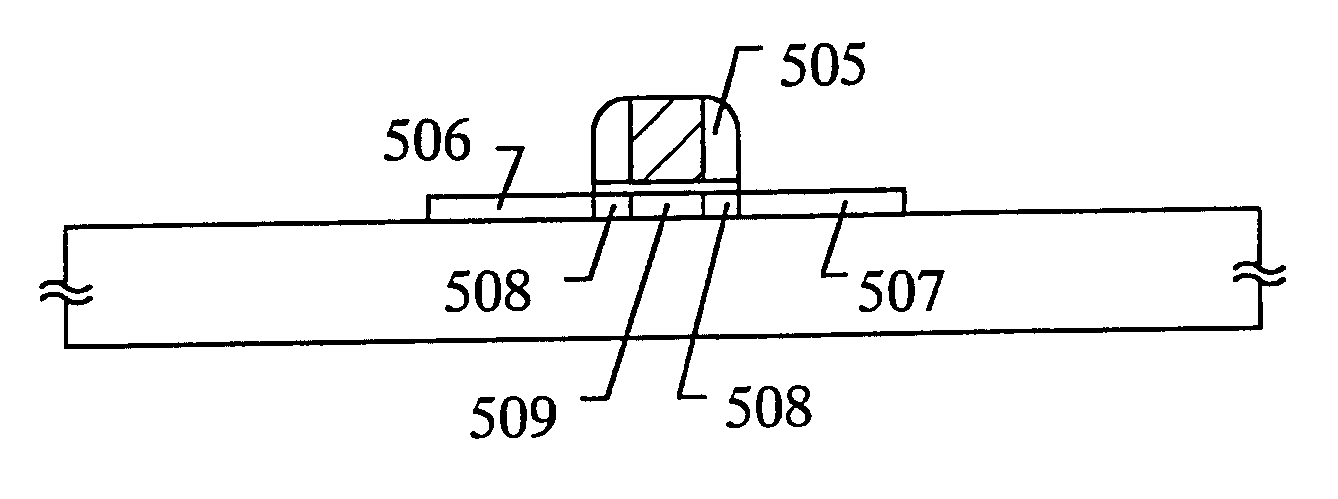

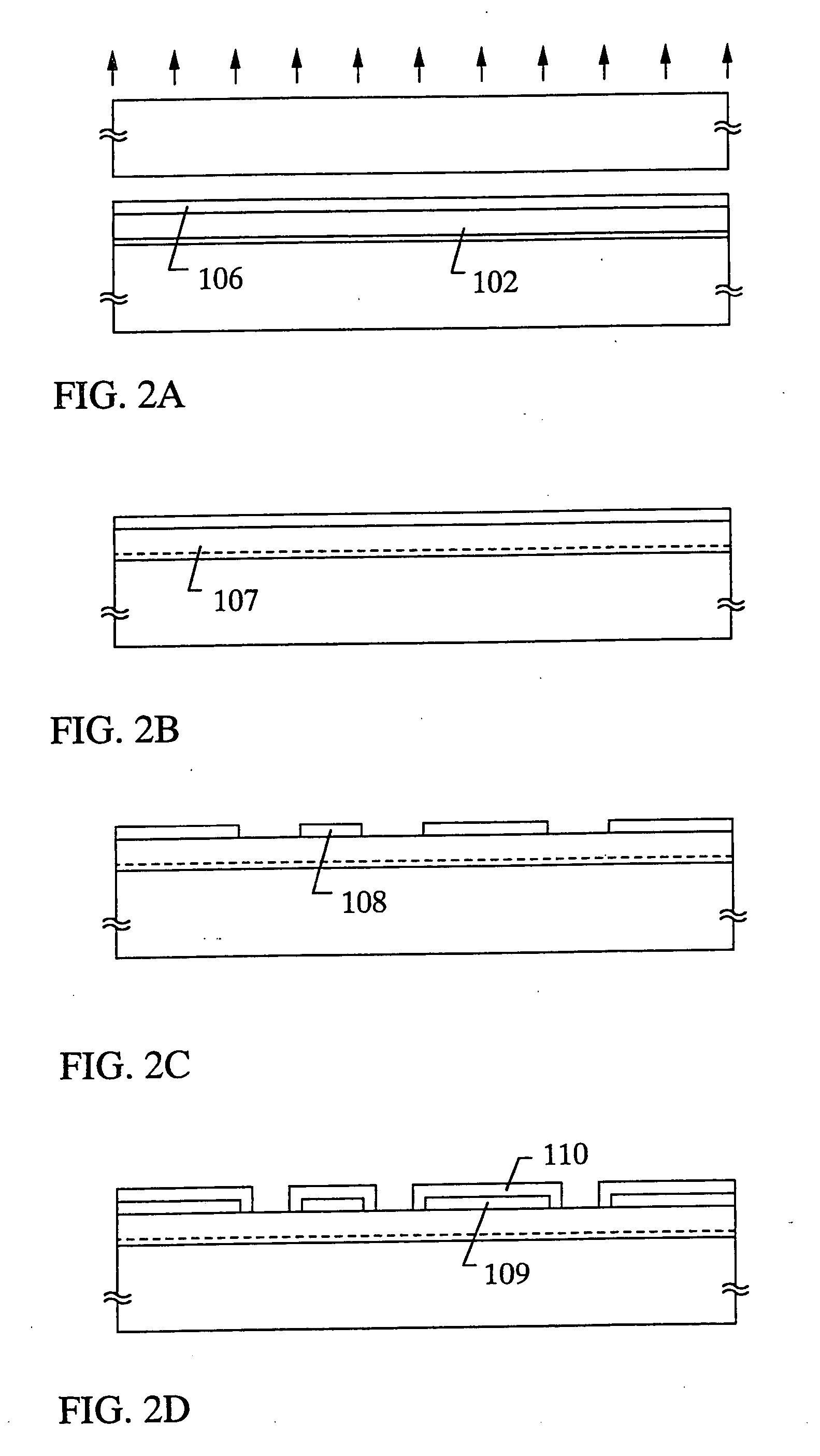

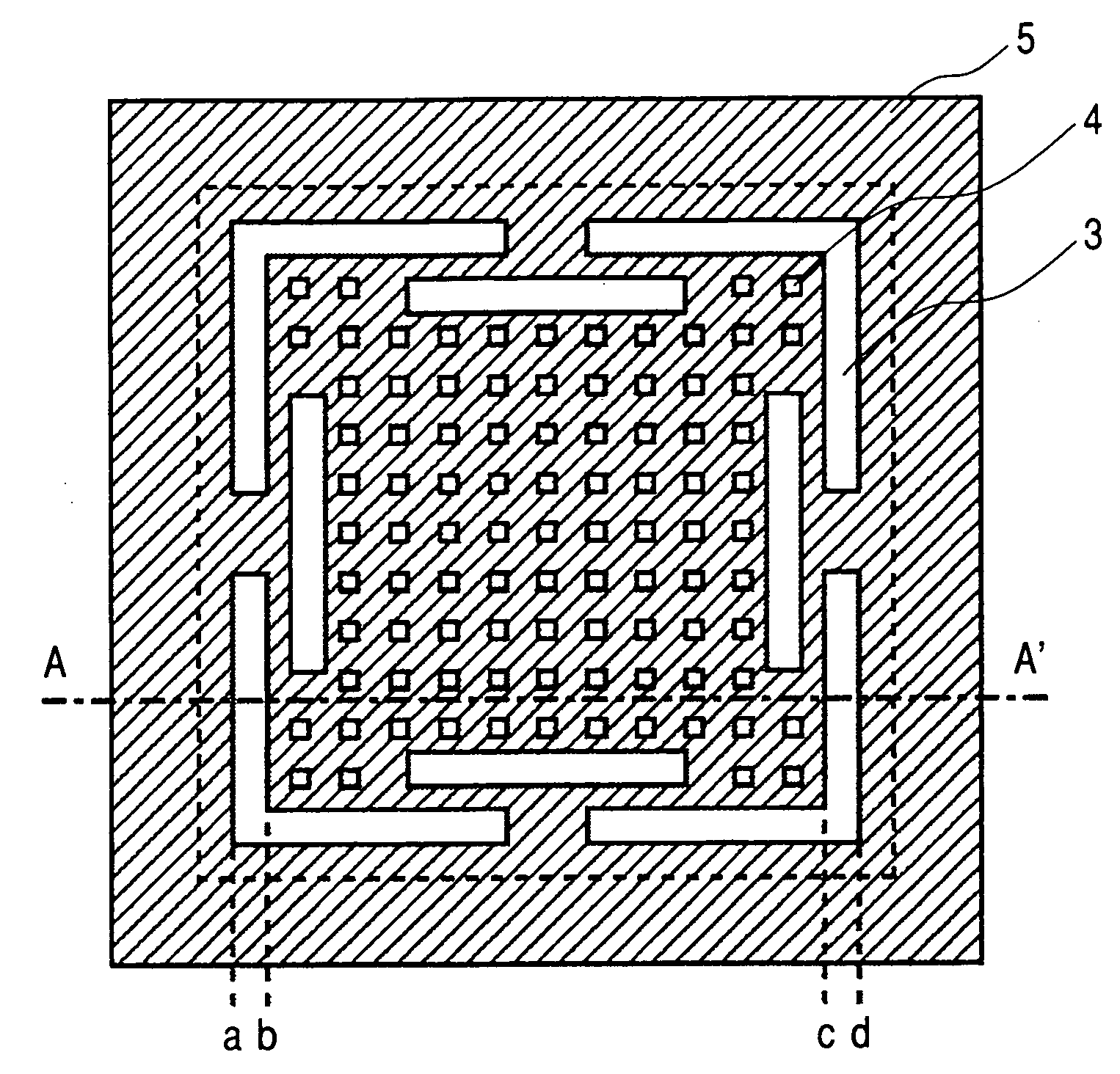

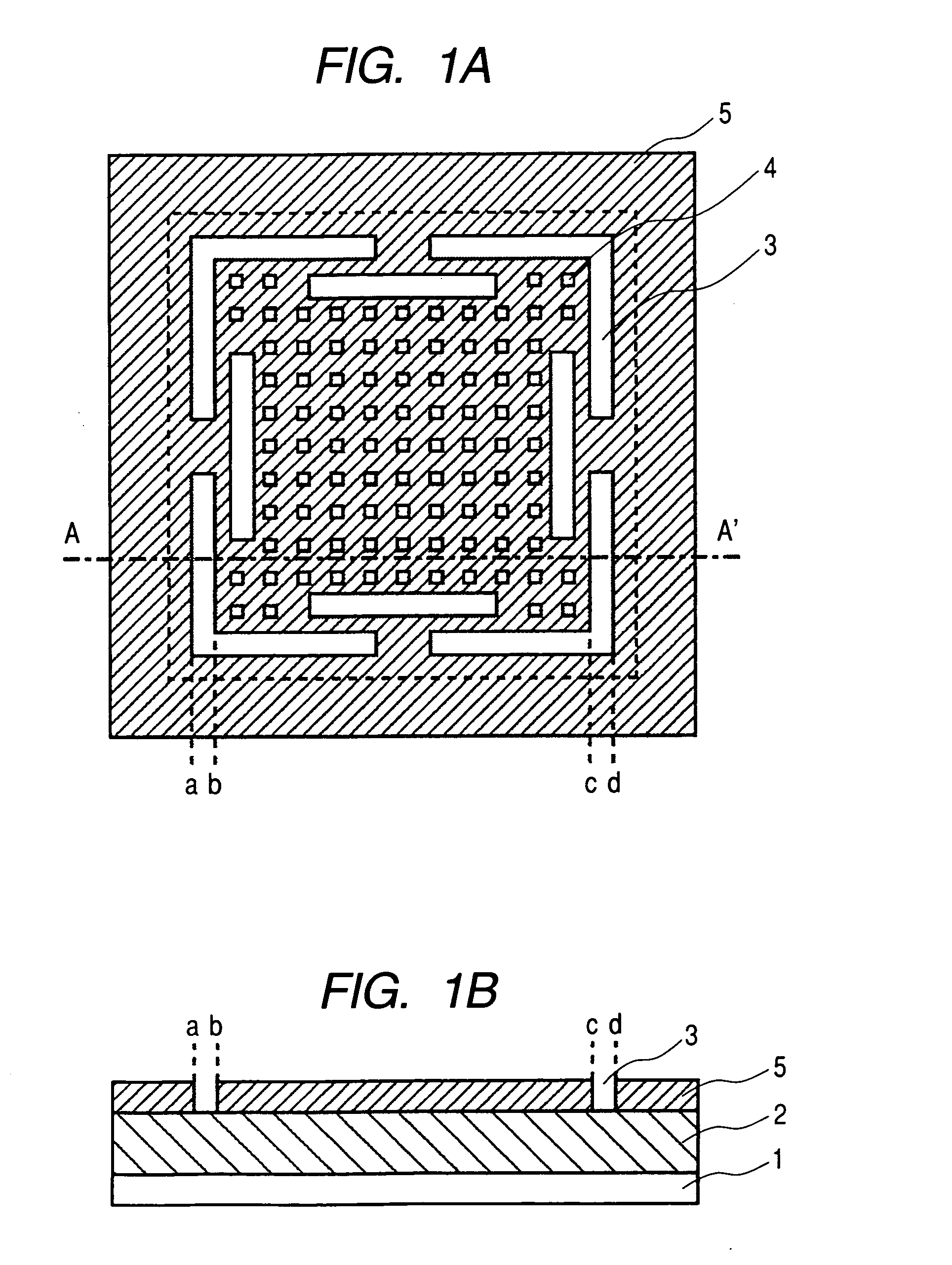

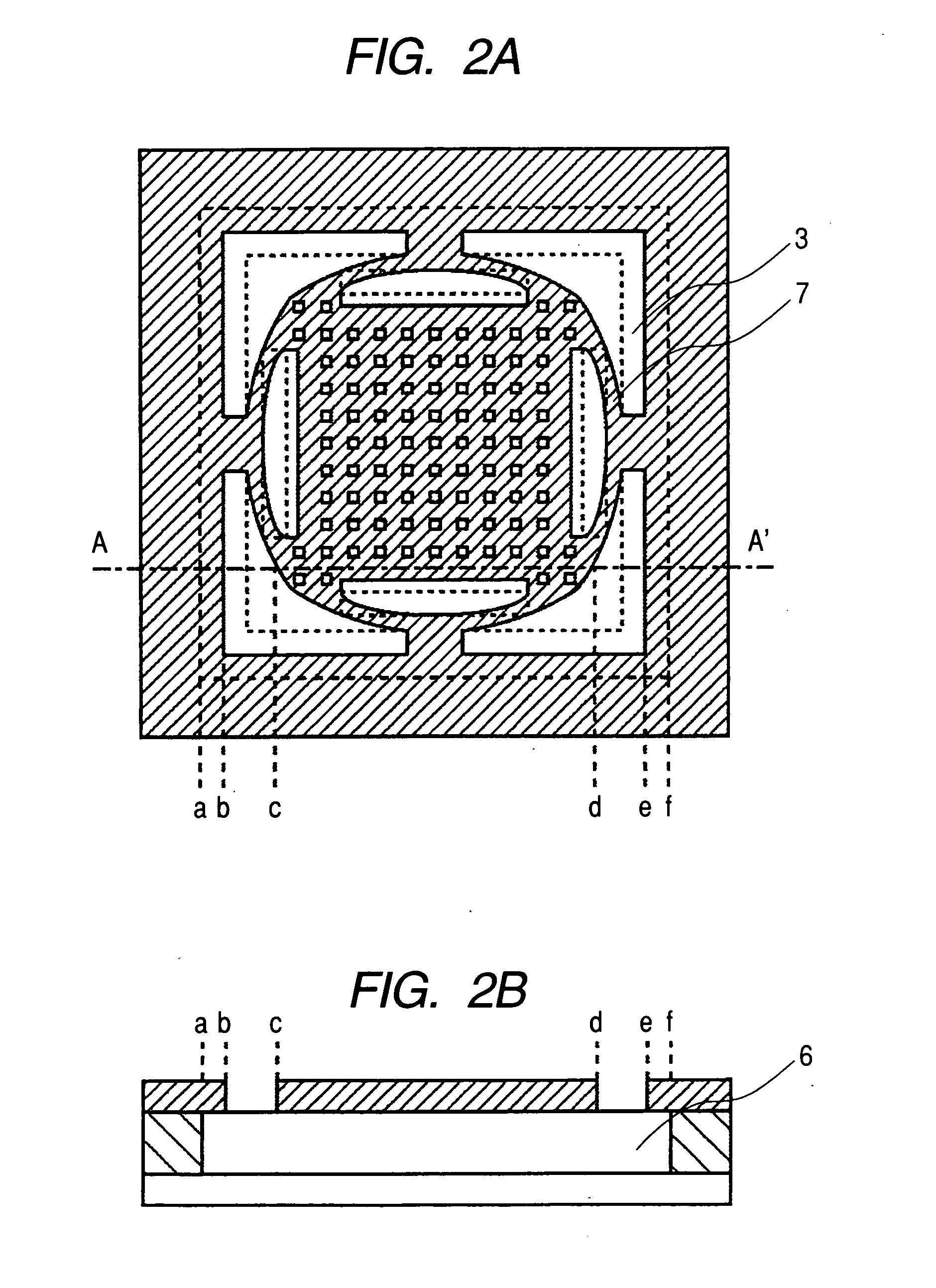

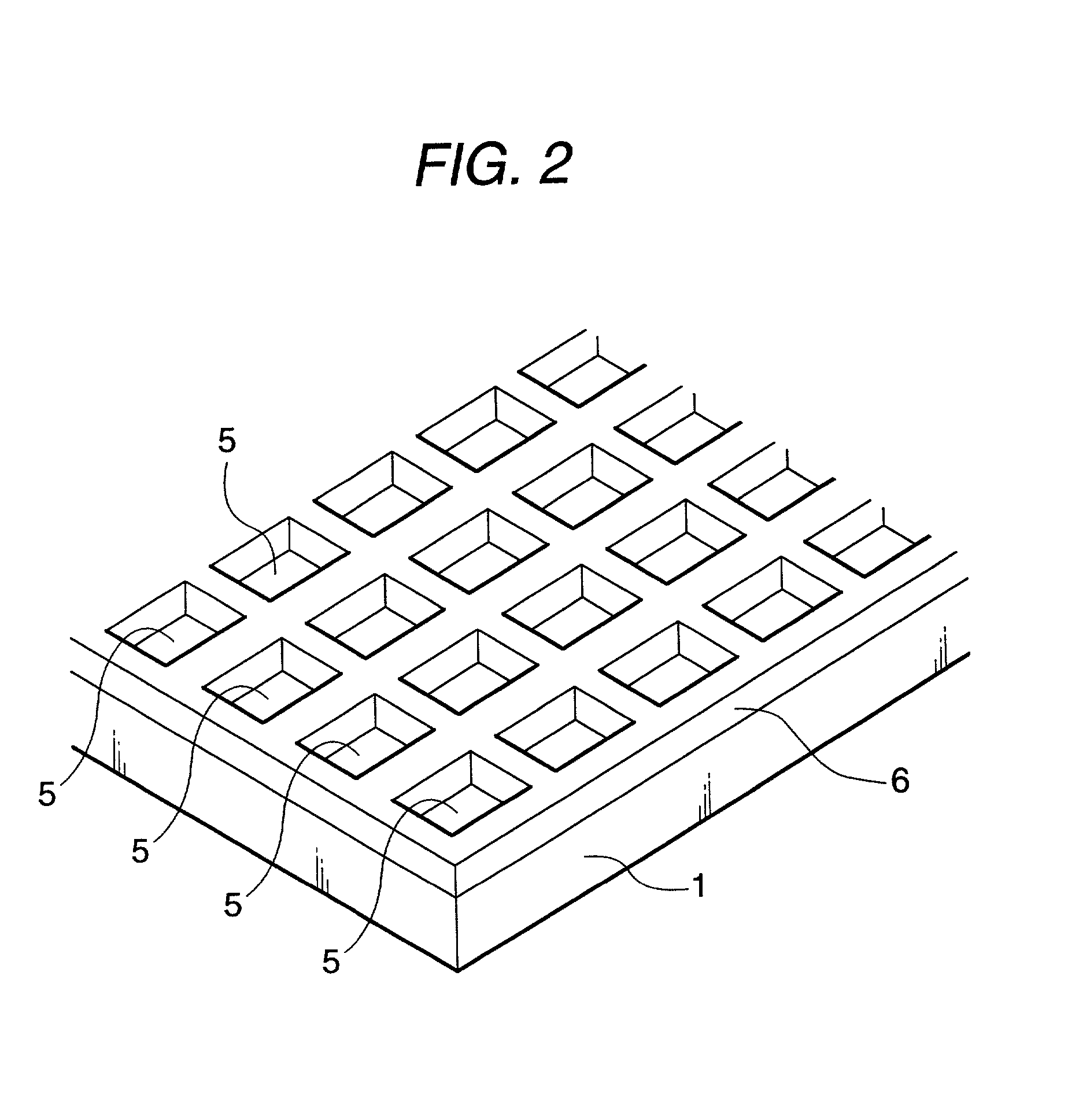

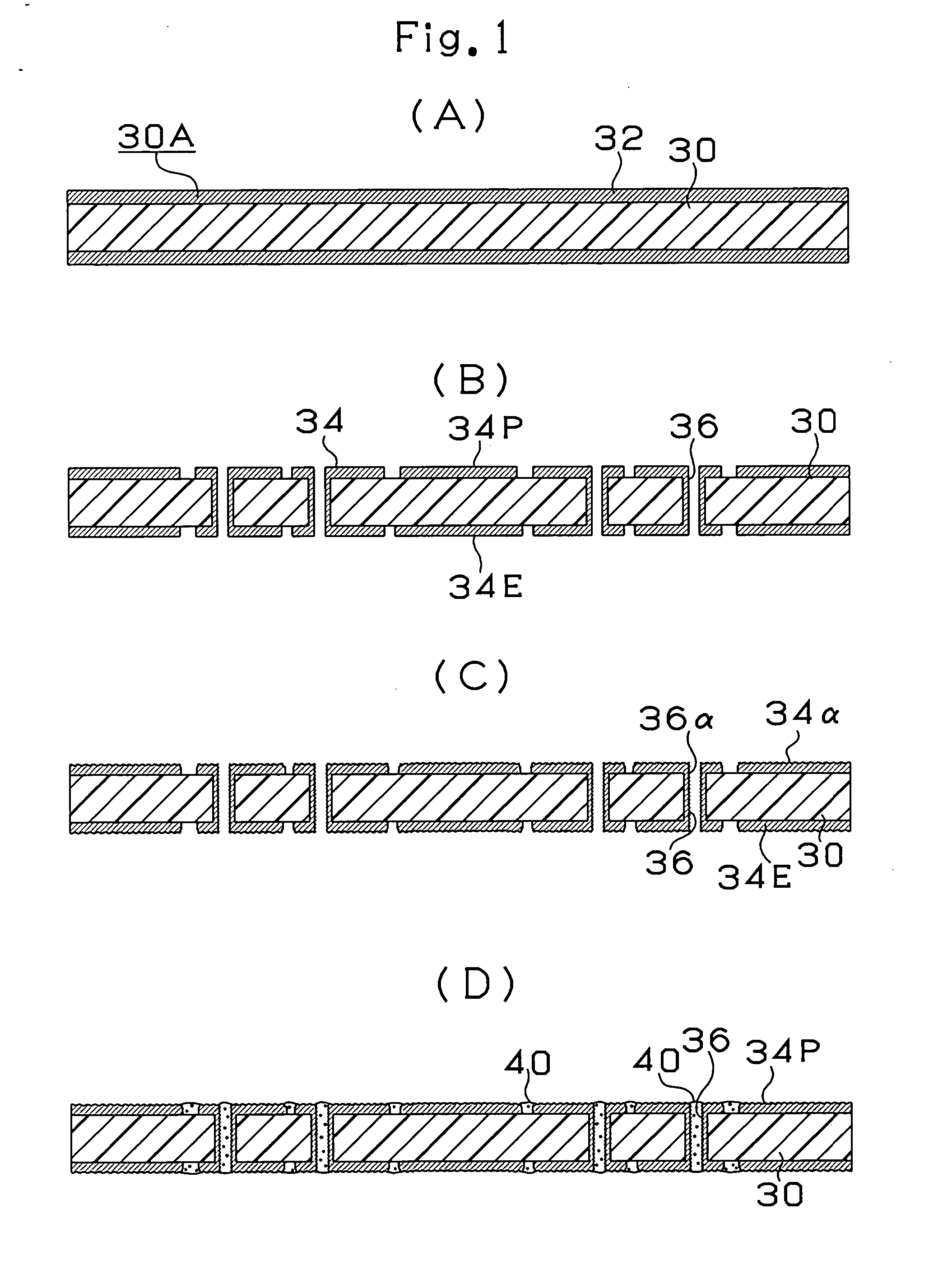

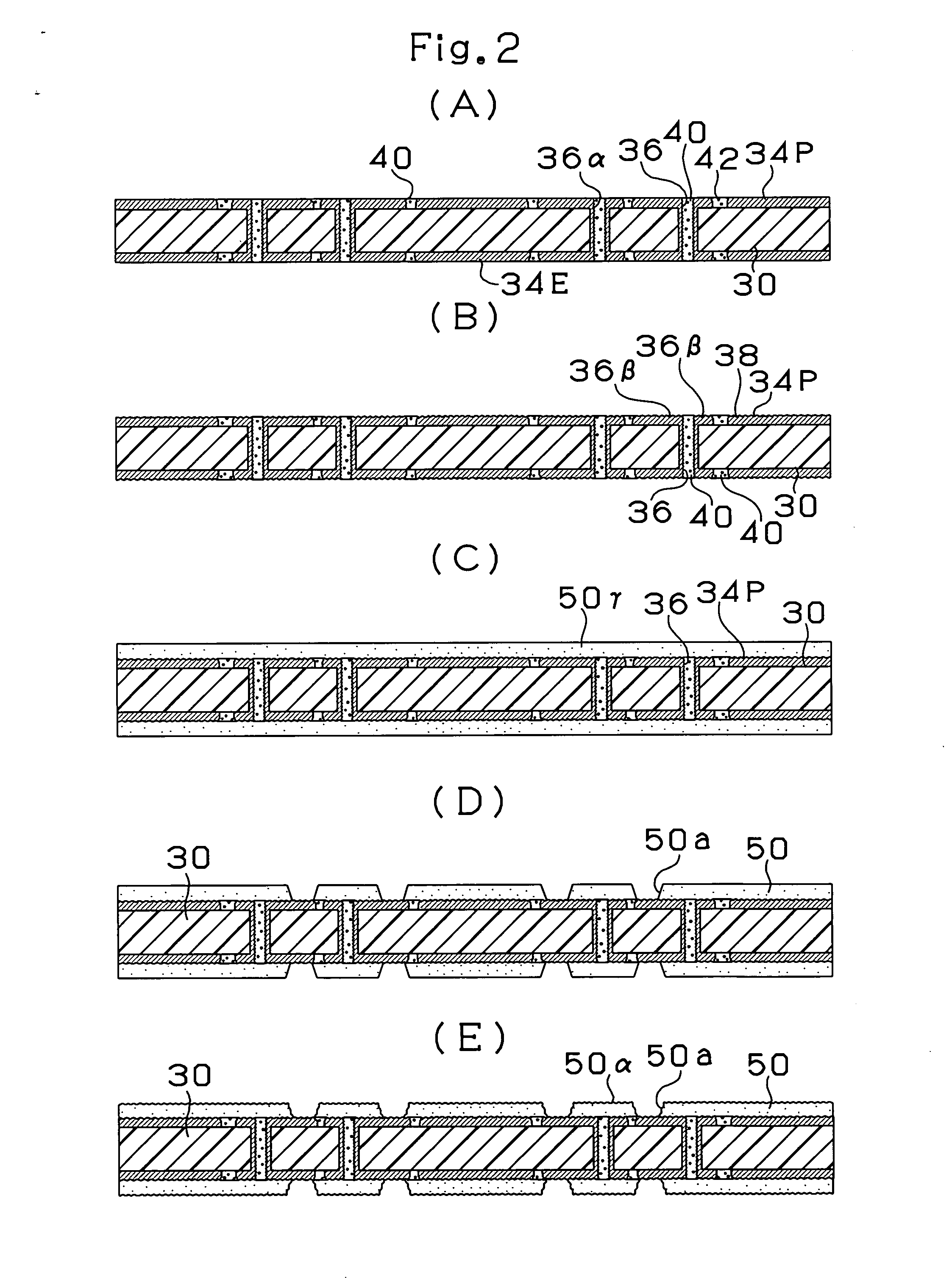

MEMS device and manufacturing process thereof

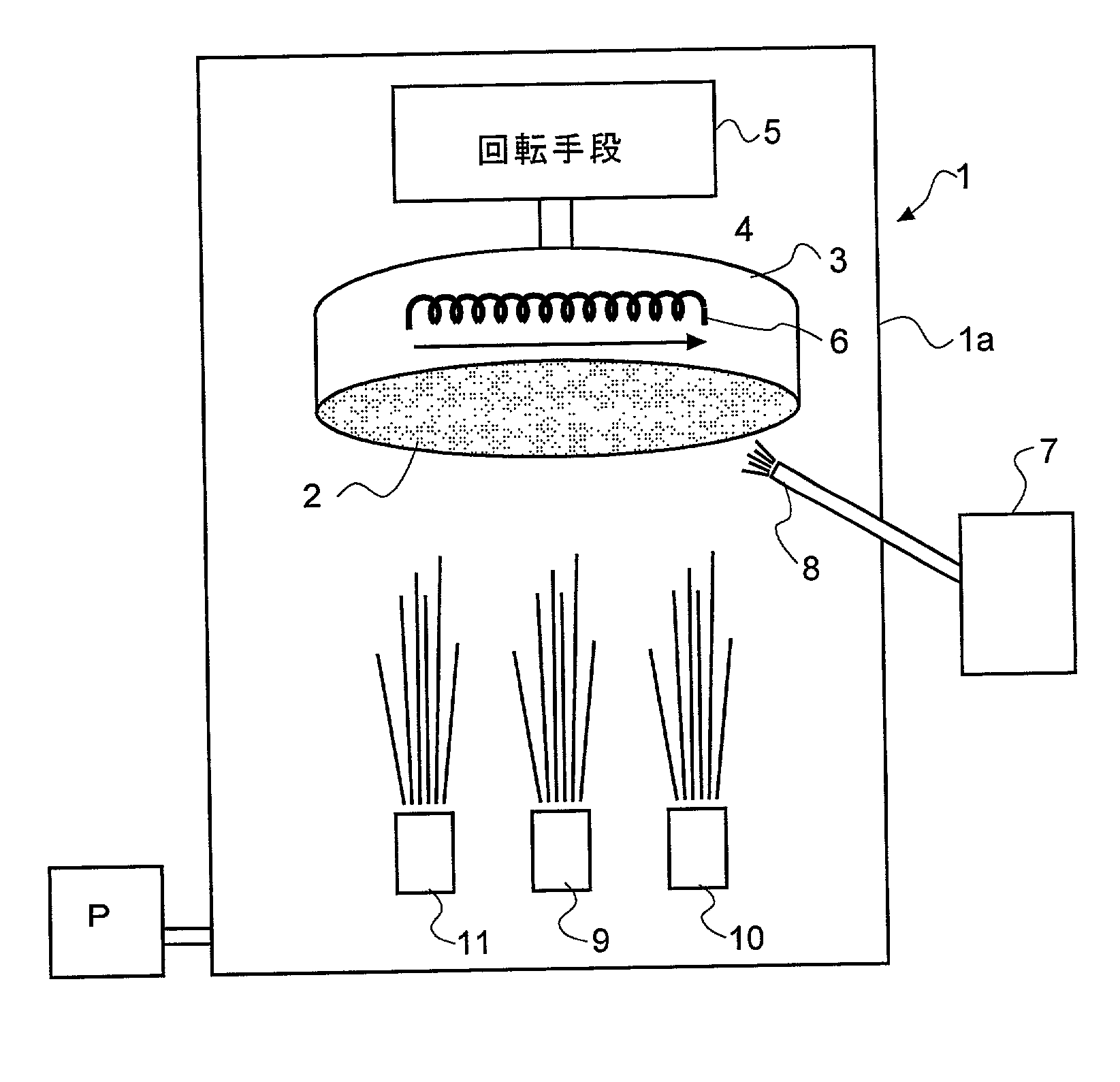

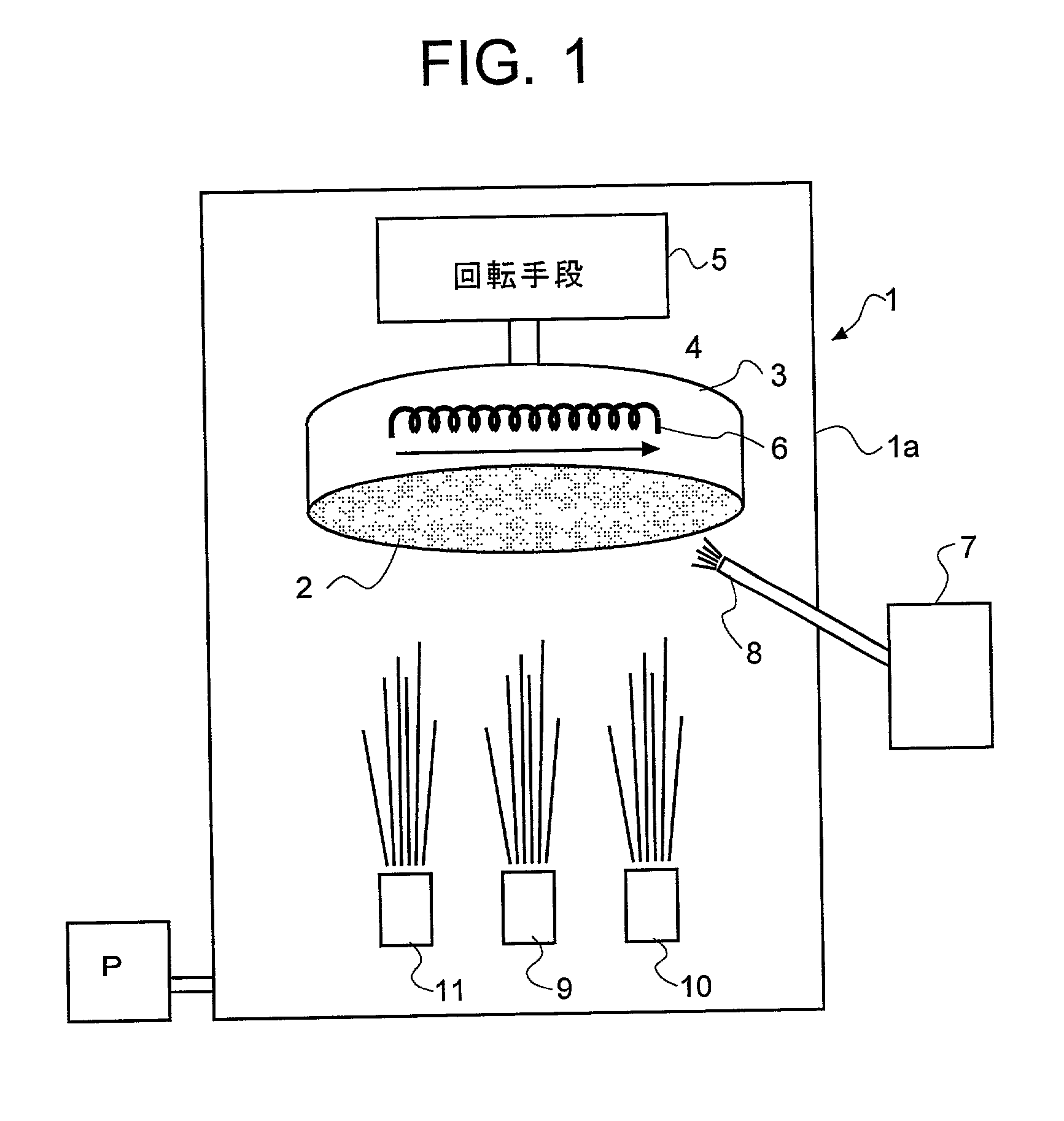

InactiveUS20070190680A1Relaxation stressSemiconductor/solid-state device manufacturingForming microstructural systemsEngineeringWafer bonding

MEMS devices require special cavity formation and sealing steps such as wafer bonding which reduce the yield and increase the cost. In addition, it is difficult to form a cavity of a large area by the LSI process owing to a residual stress of a sealing film which will be a lid. This leads to a difficulty of realizing an integrated MEMS having a MEMS and a high-performance LSI mounted on one substrate. The lid (or diaphragm) covering therewith a cavity is equipped with slits or beams. During the formation of the cavity, the slits are deformed to absorb and relax the internal stress of the thin sealing film. Then, the cavity is sealed by filling the open portions of the film overlying the cavity between the inside and outside of the cavity. The cavity is formed by removing a portion of the interlayer film of LSI multilevel interconnects and the lid is made of a LSI-process thin film.

Owner:HITACHI LTD

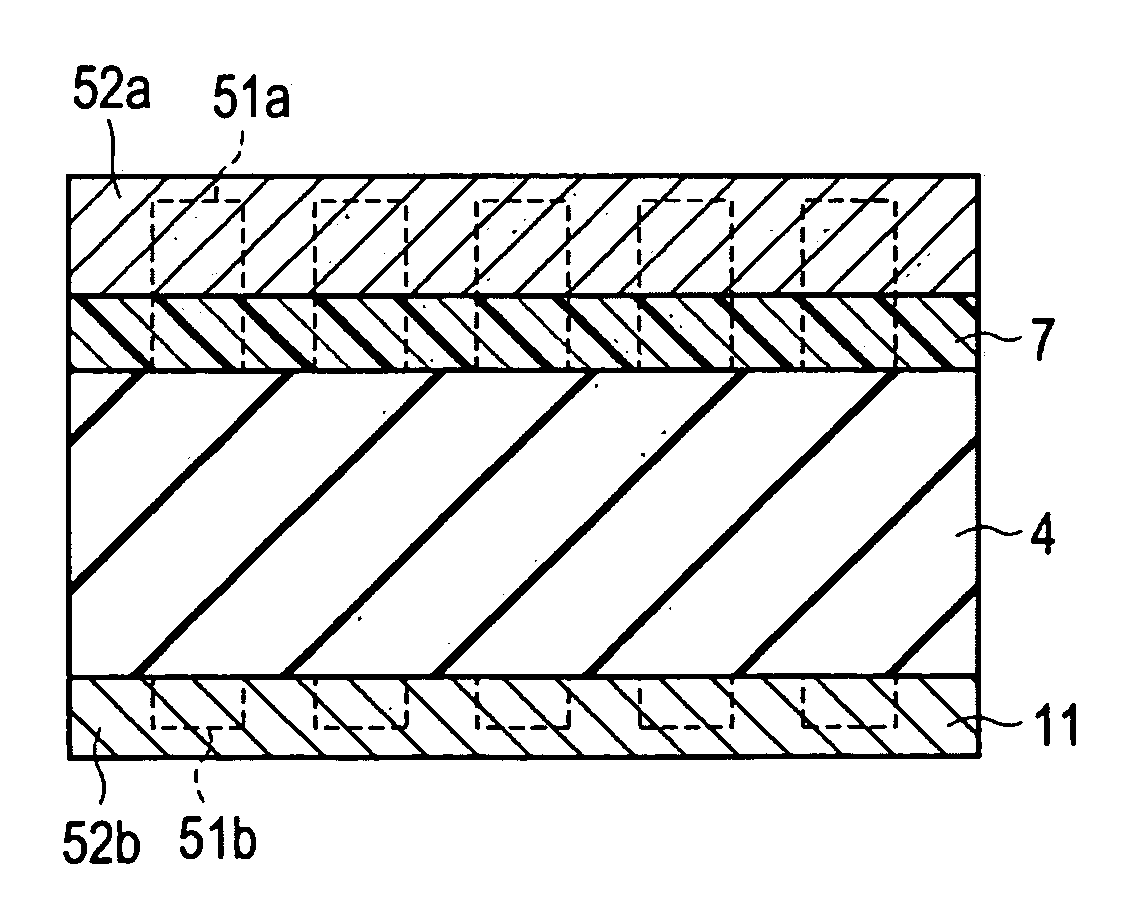

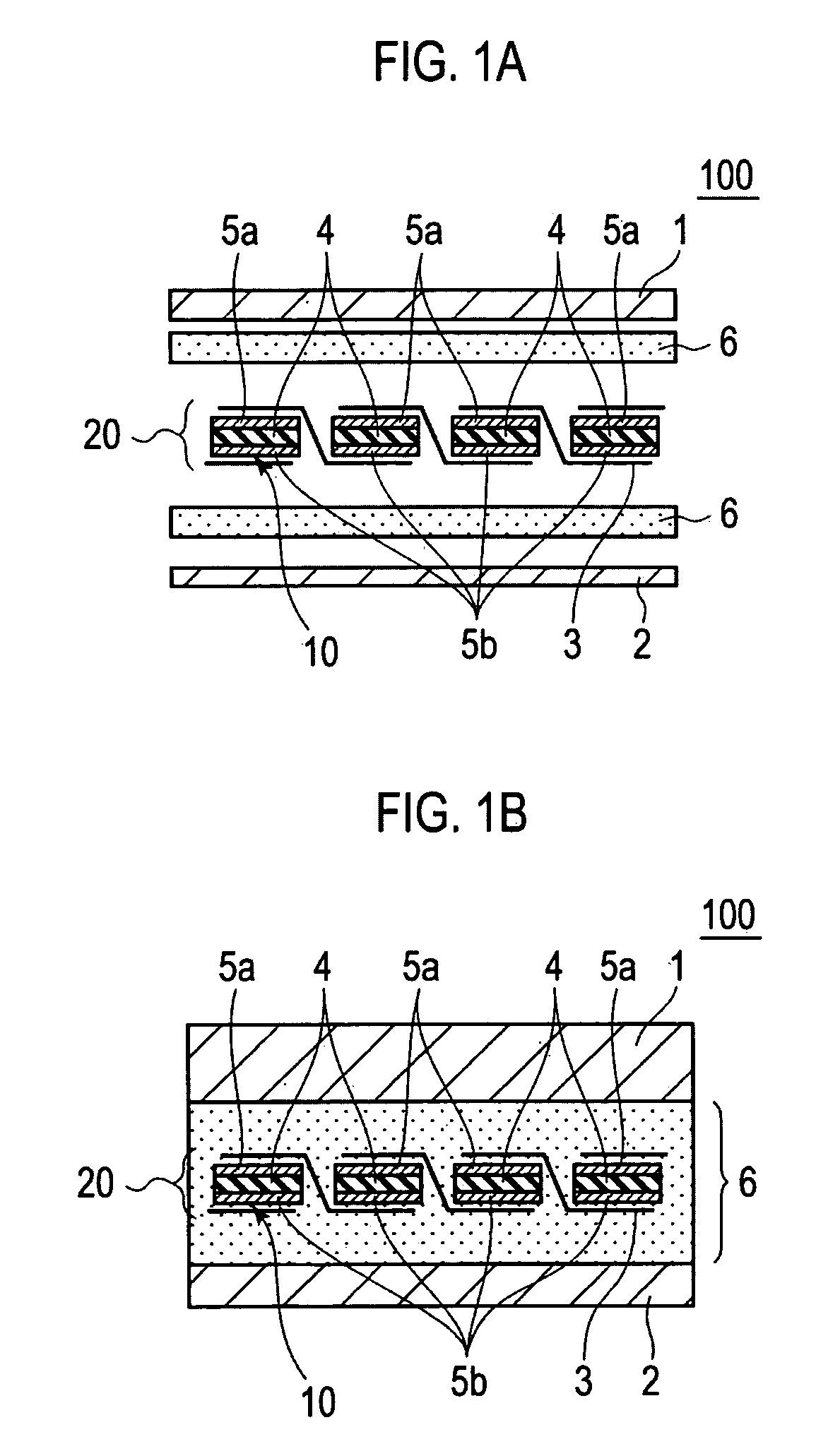

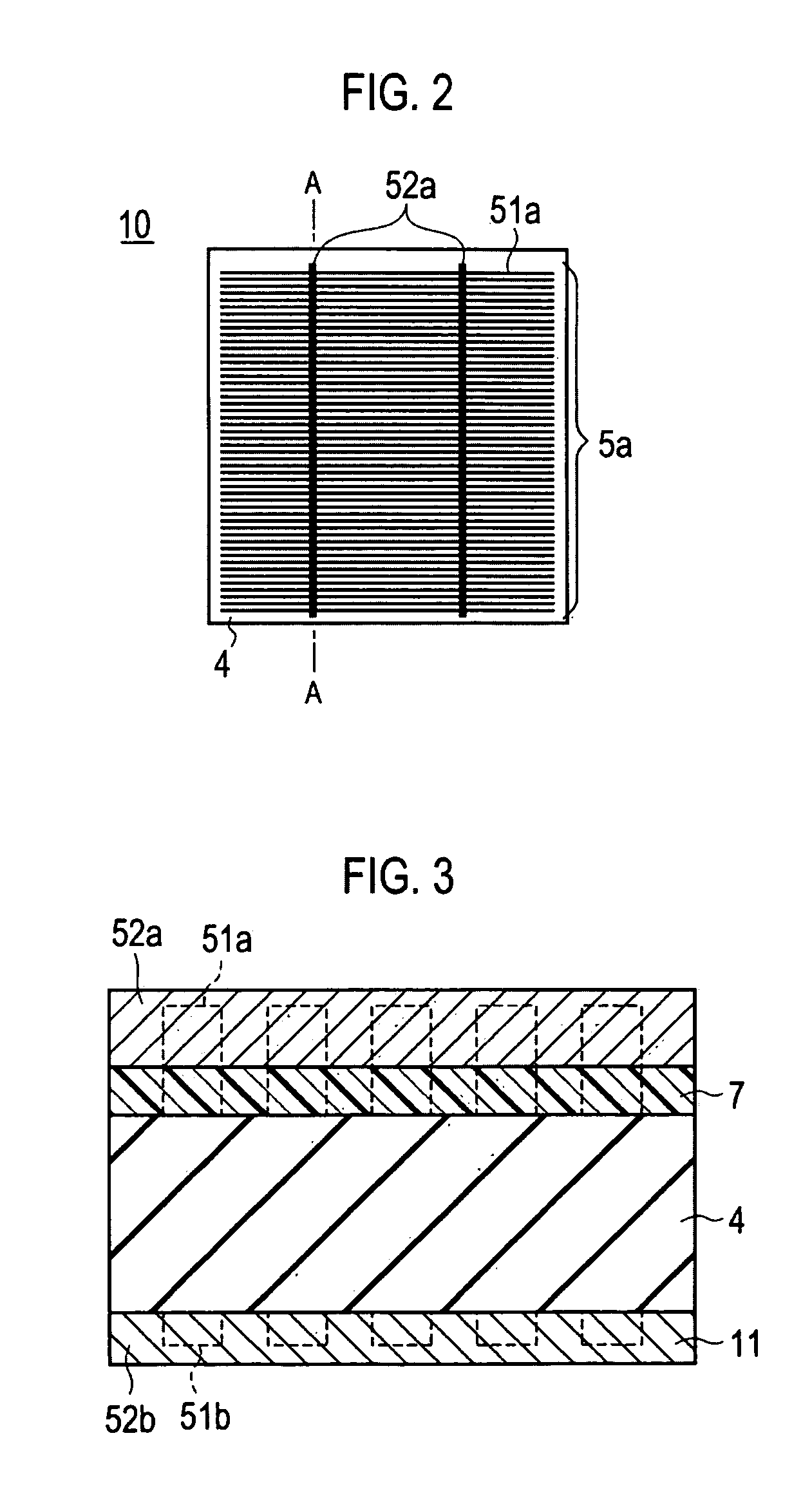

Solar cell and solar cell module

InactiveUS20080196757A1Improve reliabilityEasily deformable propertyPV power plantsPhotovoltaic energy generationPhotoelectric conversionEngineering

A photoelectric converter generates carriers by photoelectric conversion. A multiple finger electrodes are electrically coupled to the photoelectric converter. The finger electrodes collect carriers generated in the photoelectric converter. The finger electrodes contain a sintering conductive material as an essential ingredient. A bus-bar electrode is electrically coupled to the multiple finger electrodes. The bus-bar electrode collects the carriers from the finger electrodes. The bus-bar electrode contains a thermosetting conductive material as an essential ingredient.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

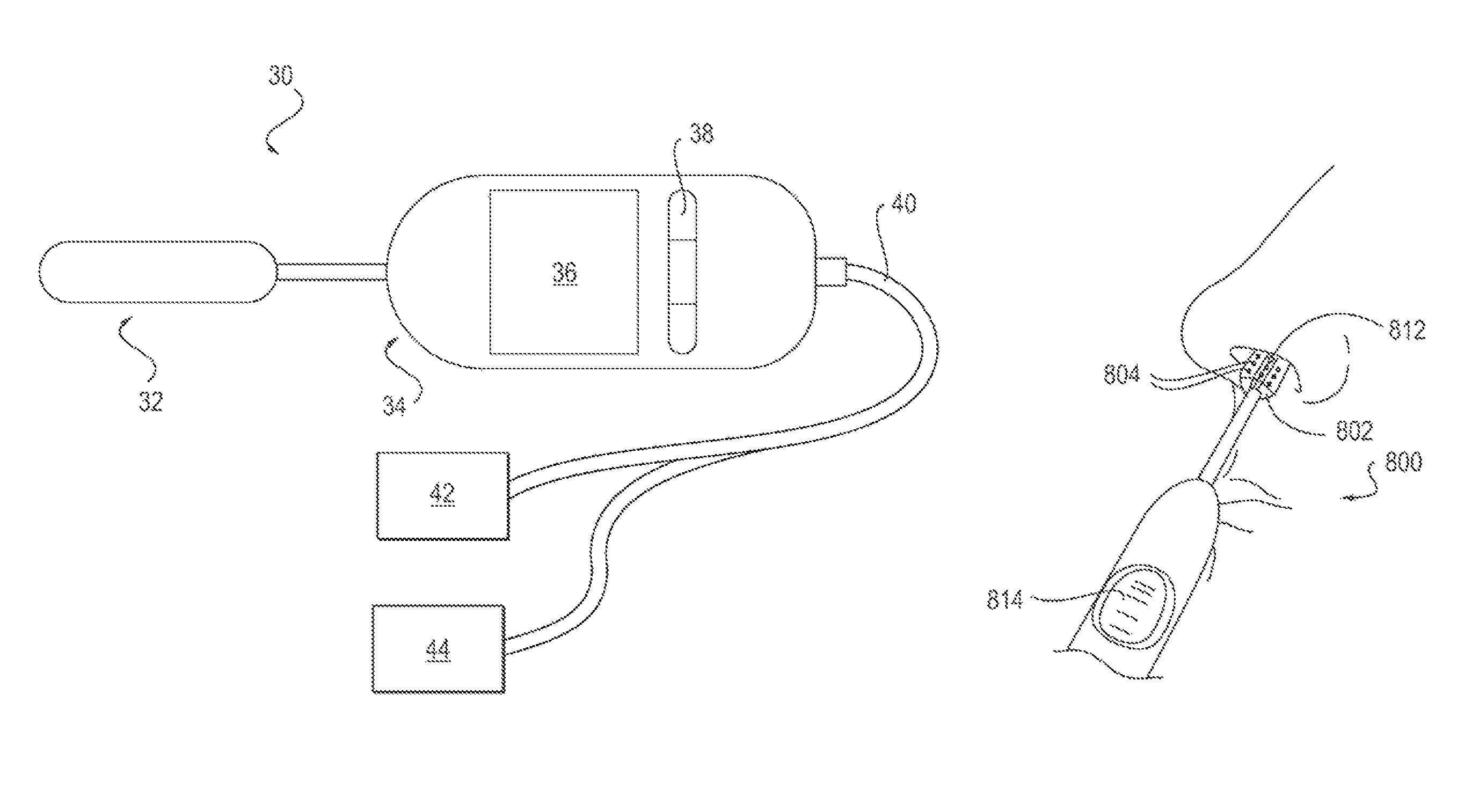

Methods and devices to treat nasal airways

ActiveUS20140088463A1Decrease airflow resistance perceived airflowIncrease ratingsElectrotherapySurgical needlesSmall airwaysNostril

A method is described for modifying at least one property of a tissue of or near a nasal valve of a nose, without using a surgical incision or an implant, to decrease airflow resistance or perceived airflow resistance in a nasal airway. The method may involve contacting a treatment element of a treatment device with the at least one tissue inside the nasal airway, with sufficient force to at least temporarily deform the at least one tissue, applying energy to, or removing energy from, the at least one tissue, using the treatment element, and removing the treatment element from the nostril.

Owner:AERIN MEDICAL

Methods and devices to treat nasal airways

ActiveUS8986301B2Increase ratingsWithout weakeningUltrasound therapyElectrotherapyNostrilSurgical incision

Owner:AERIN MEDICAL INC

Group III nitride compound semiconductor device and method for producing the same

InactiveUS6982435B2Substrate surface efficientlyEfficiently formedLaser detailsSolid-state devicesNitrideSubstrate surface

A group III nitride compound semiconductor device is produced according to the following manner. A separation layer made of a material which prevents group III nitride compound semiconductors from being grown thereon is formed on a substrate. Group III nitride compound semiconductors is grown on a surface of the substrate uncovered with the separation layer while keeping the uncovered substrate surface separated by the separation layer.

Owner:TOYODA GOSEI CO LTD

Methods and devices to treat nasal airways

ActiveUS20120323232A1Increase ratingsWithout weakeningElectrotherapySurgical needlesSmall airwaysNose

Methods and devices for treating nasal airways are provided. Such devices and methods may improve airflow through an internal and / or external nasal valve, and comprise the use of mechanical re-shaping, energy application and other treatments to modify the shape, structure, and / or air flow characteristics of an internal nasal valve, an external nasal valve or other nasal airways.

Owner:AERIN MEDICAL

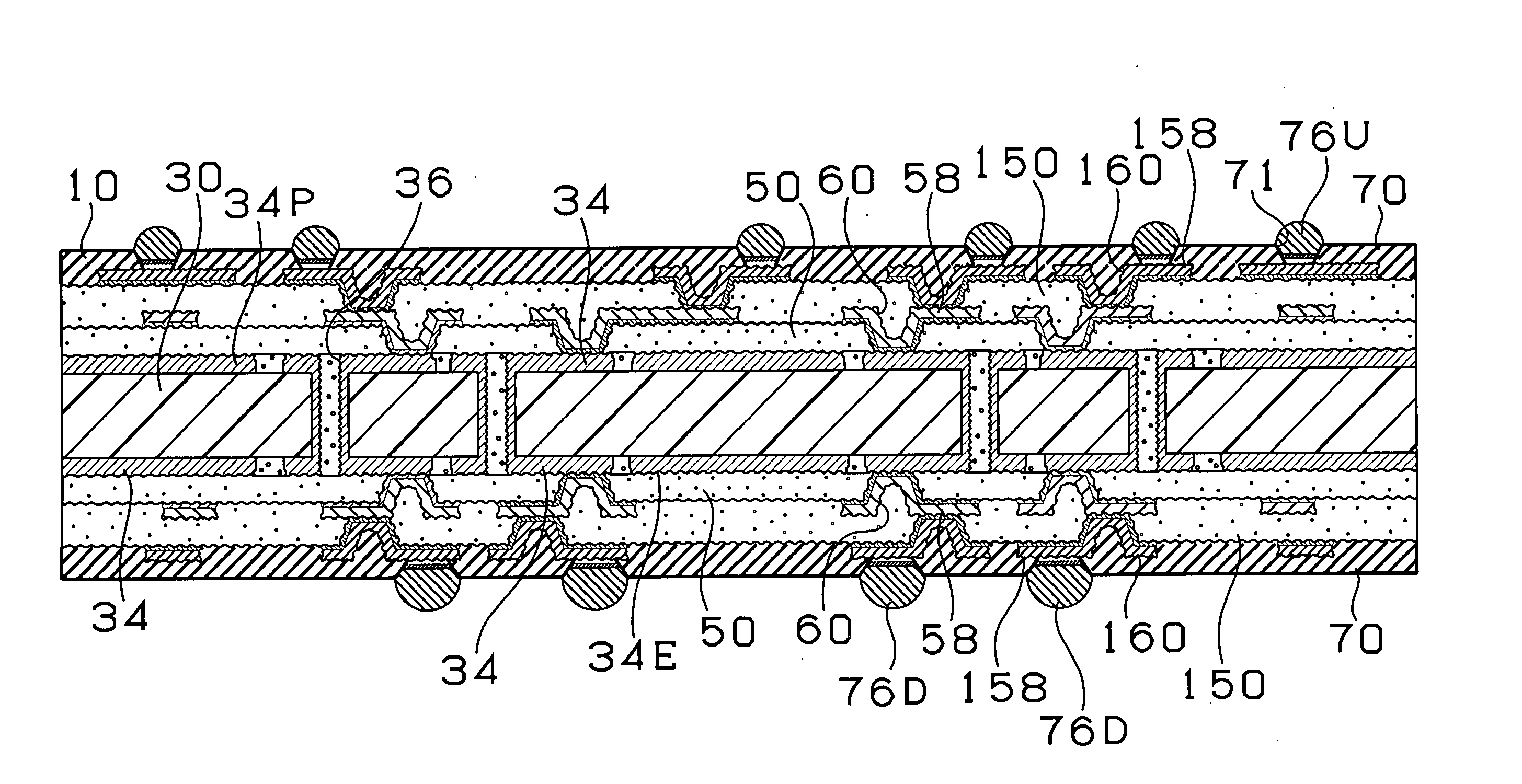

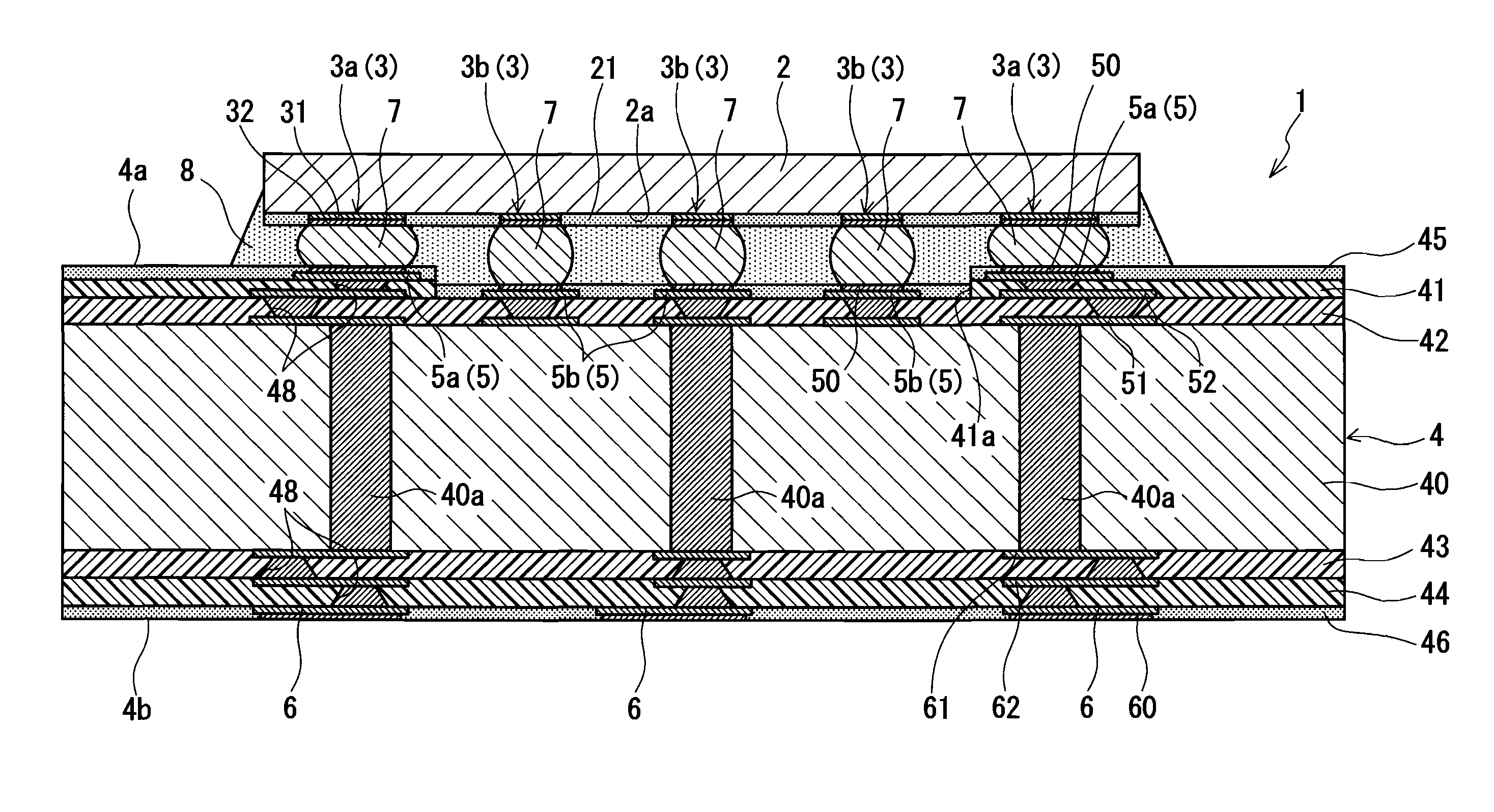

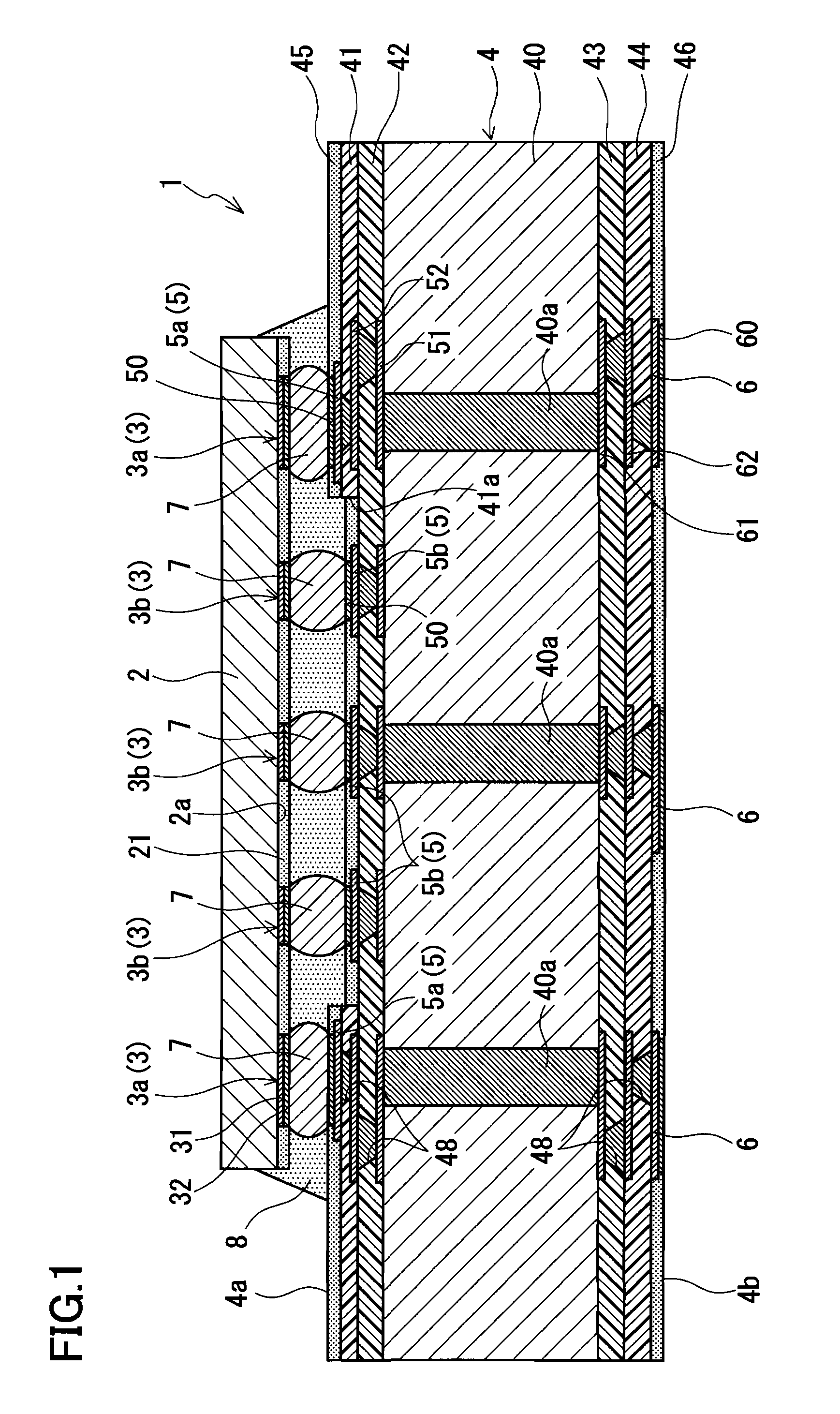

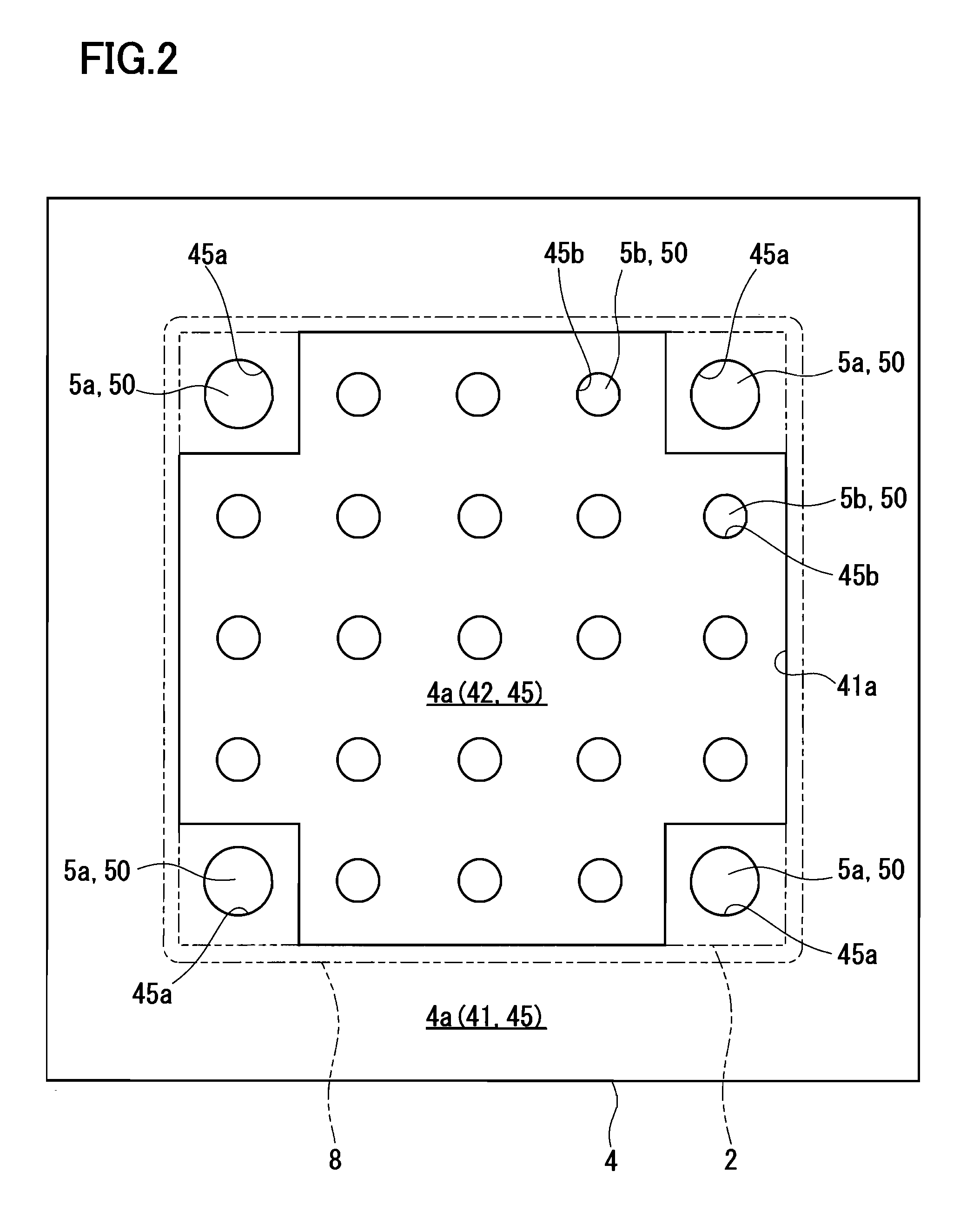

Multilayer printed wiring board

ActiveUS20060243478A1Intensify strengthStress be relaxPrinted electric component incorporationSemiconductor/solid-state device detailsEngineeringElectrical conductor

An IC chip for a high frequency region, particularly a packaged substrate in which no malfunction or error occurs even if 3 GHz is exceeded. A conductive layer on a core substrate is formed at a thickness of 30 μm and a conductor circuit on an interlayer resin insulation layer is formed at a thickness of 15 μm. By thickening the conductive layer, the volume of the conductor can be increased and resistance can be reduced. Further, by using the conductive layer as a power source layer, the capacity of supply of power to an IC chip can be improved.

Owner:IBIDEN CO LTD

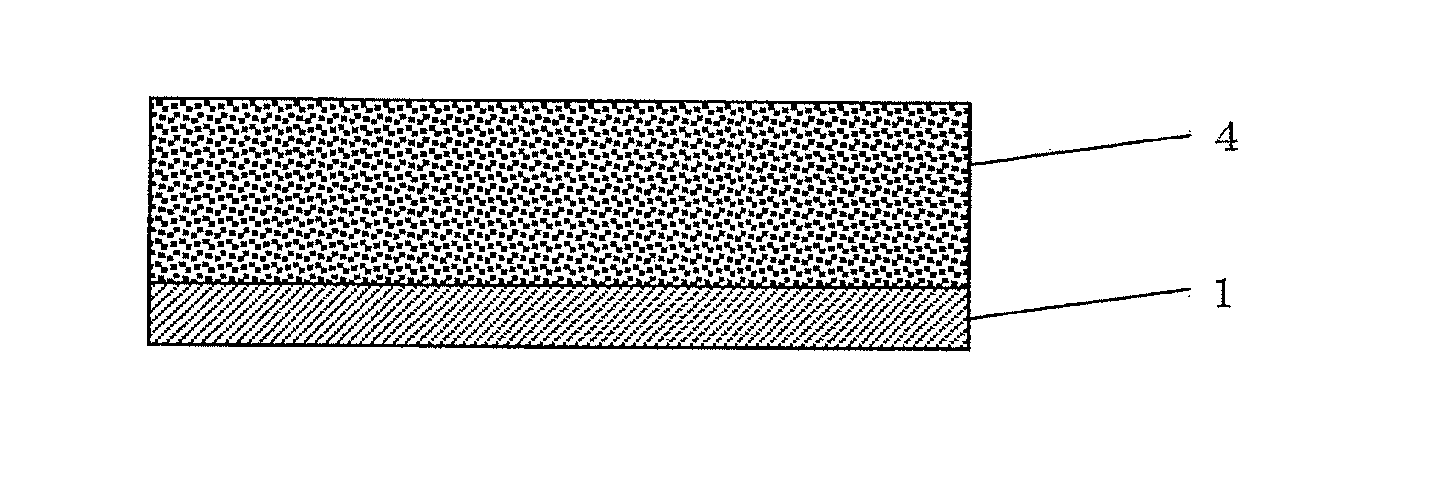

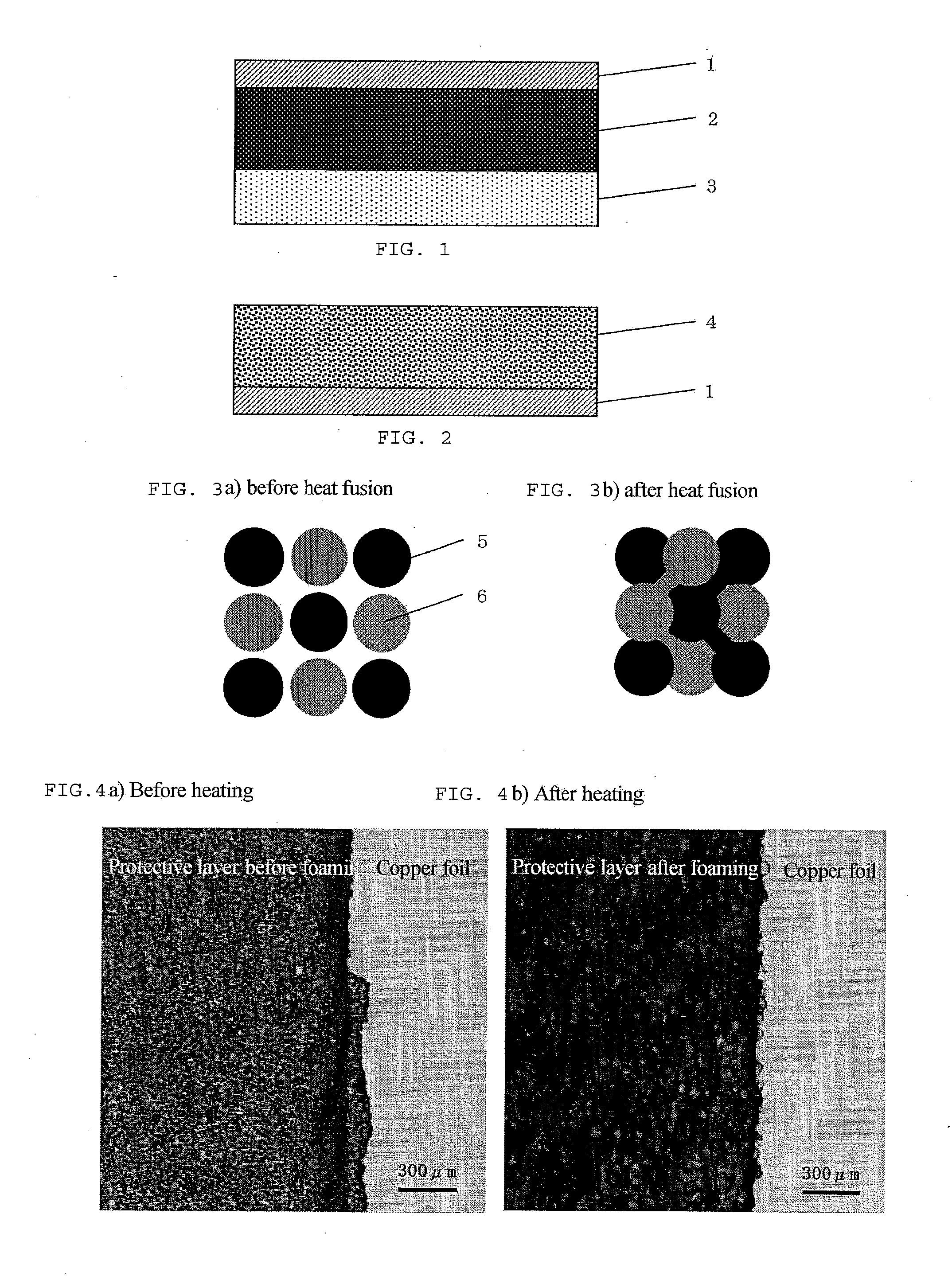

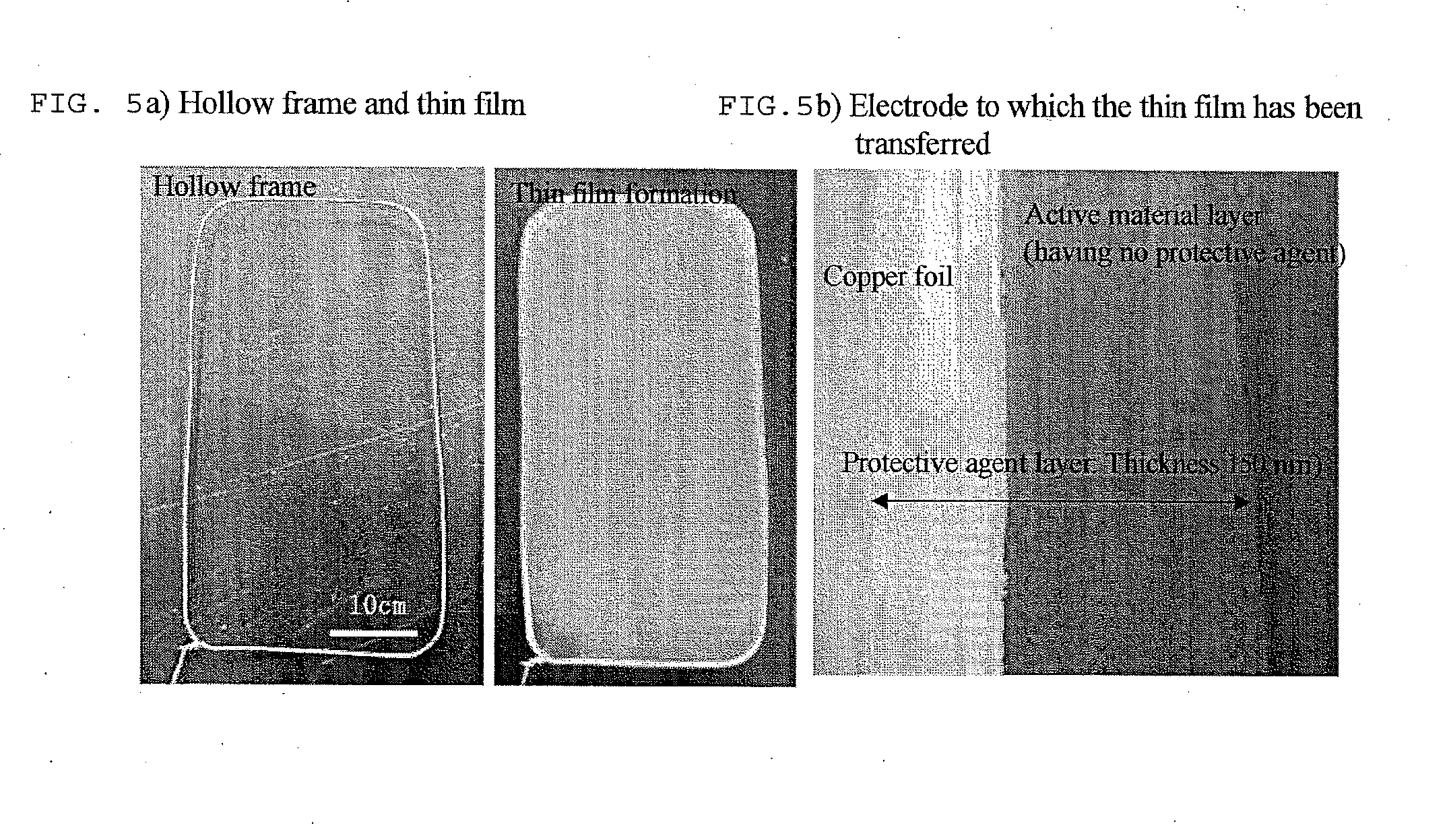

Battery electrode or separator surface protective agent composition, battery electrode or separator protected by the composition, and battery having the battery electrode or separator

ActiveUS20130260207A1Excellent electrolytic solution impregnation propertyImprove heat resistanceCosmetic preparationsNon-fibrous pulp additionHot meltEngineering

A battery electrode or separator surface protective agent composition having fluidity and being capable of being solidified by hot melt, and comprising at least two types of organic particles comprising organic materials, wherein the organic particles of types different from each other are substantially incompatible with each other, wherein when the composition is solidified by hot melt, the organic particles of the same type thermally fuse with one another to form a continuous phase.

Owner:KYORITSU KAGAKU SANGYO KK

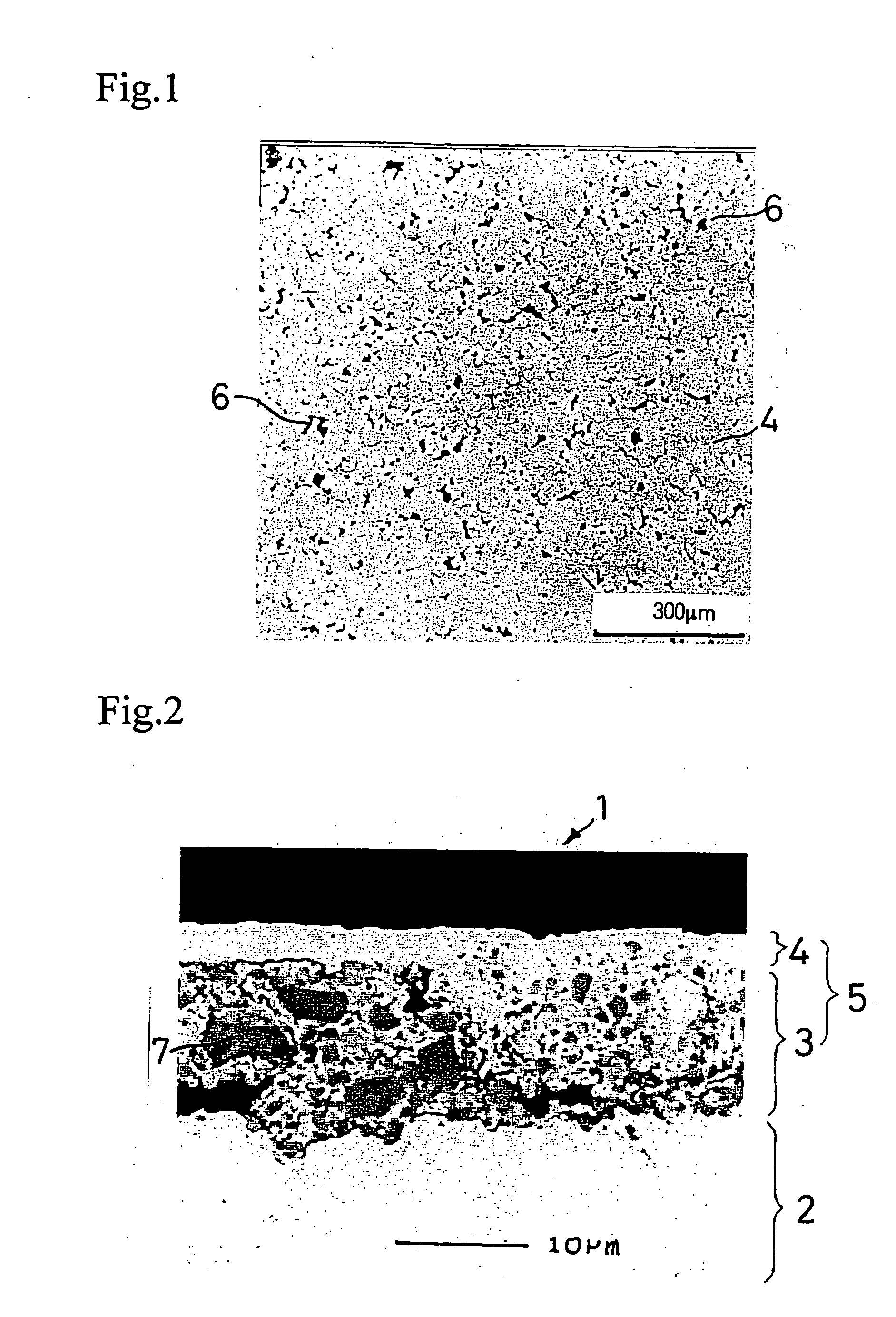

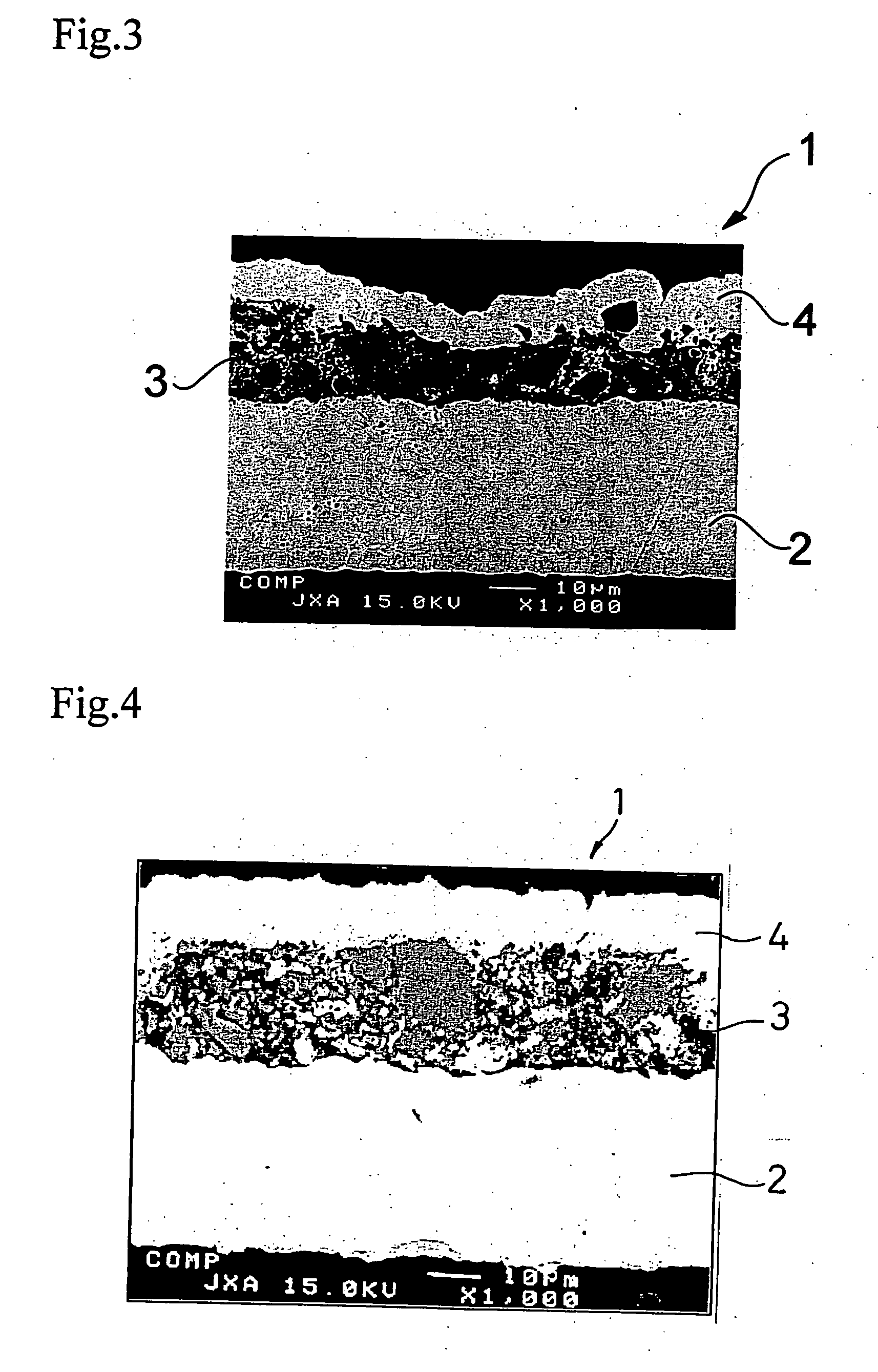

Negative electrode for nonaqueous secondary battery, process of producing the negative electrode, and nonaqueous secondary battery

InactiveUS20050208379A1Relaxation stressImprove electronic conductivityElectrolytic coatingsVacuum evaporation coatingLithium compoundCurrent collector

Disclosed is a negative electrode for a nonaqueous secondary battery comprised of a current collector and an active material structure containing an electro-conductive material having low capability of forming a lithium compound on at least one side of the current collector, the active material structure containing 5 to 80% by weight of active material particles containing a material having high capability of forming a lithium compound. The active material structure preferably has an active material layer containing the active material particles and a surface coating layer formed on the active material layer.

Owner:MITSUI MINING & SMELTING CO LTD

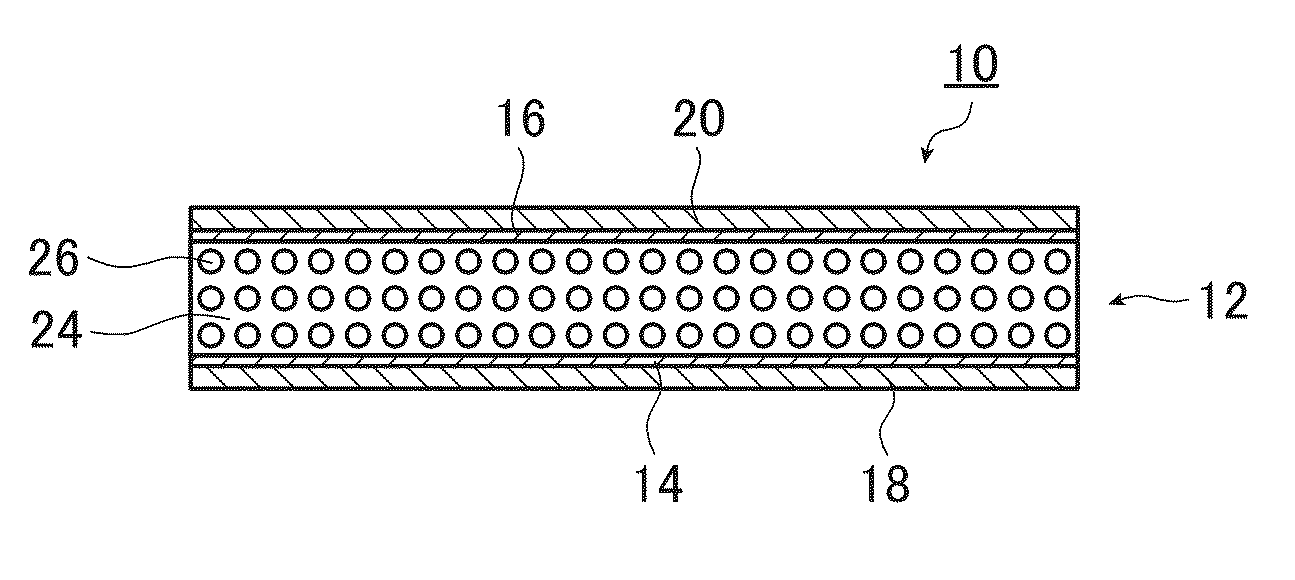

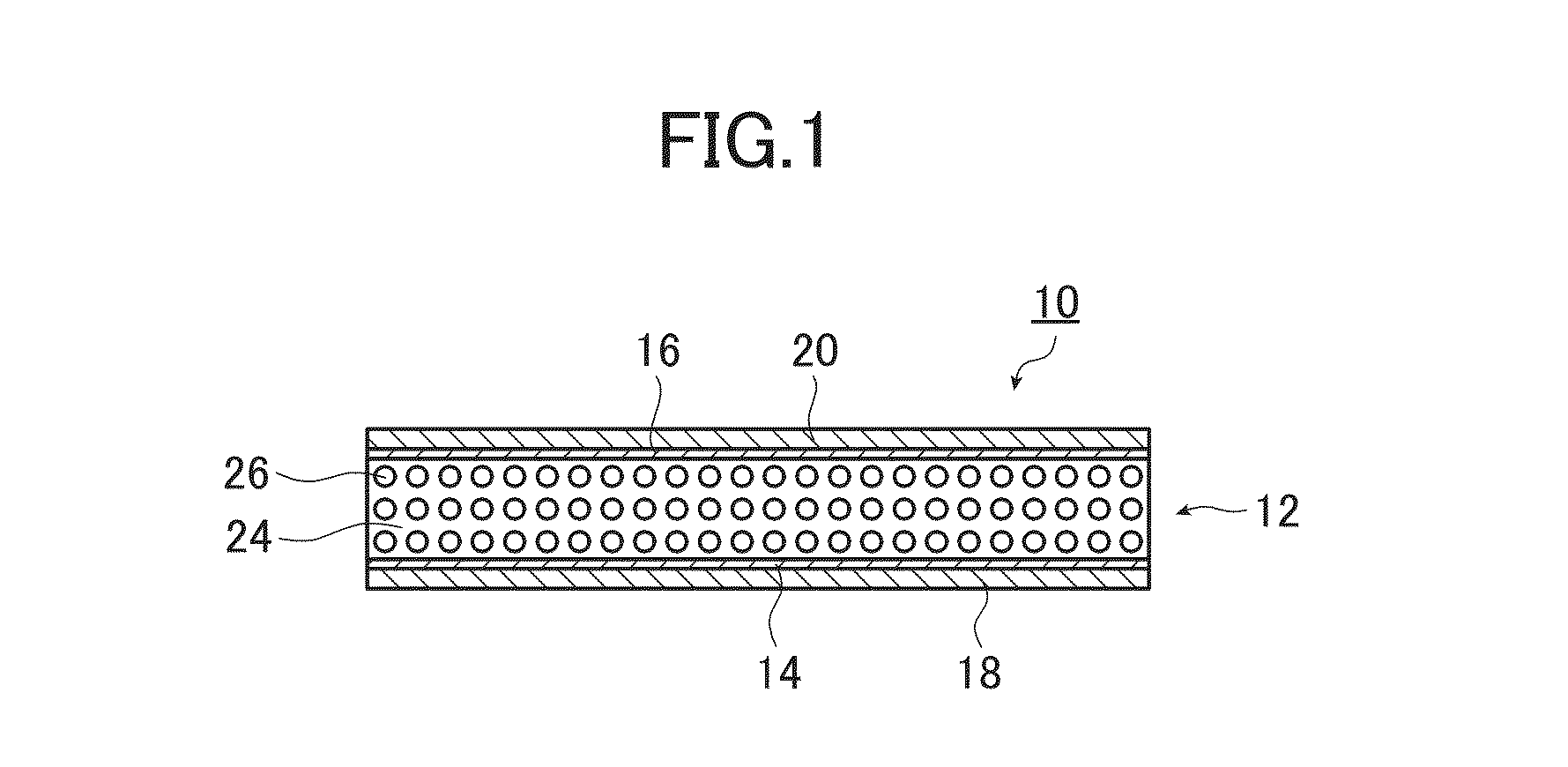

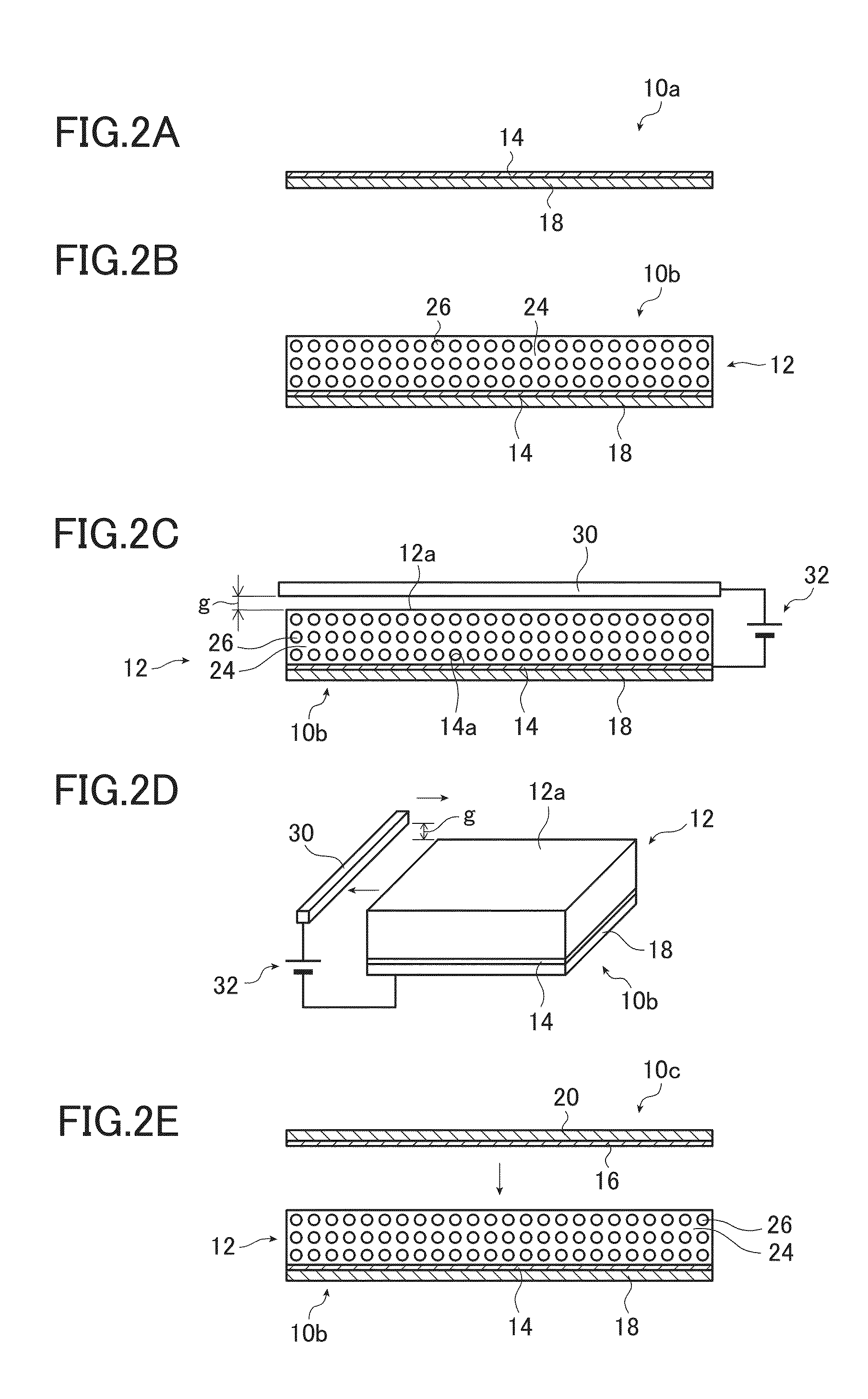

Electroacoustic converter film, flexible display, vocal cord microphone, and musical instrument sensor

ActiveUS20140210309A1Increase flexibilityExcellent acoustic characteristicsElectrophonic musical instrumentsPiezoelectric/electrostriction/magnetostriction machinesThin film electrodeDisplay device

Provided is an electroacoustic converter film including: a polymeric composite piezoelectric body having piezoelectric particles dispersed in a viscoelastic matrix which is formed of a polymer material exhibiting viscoelasticity at ordinary temperatures; thin film electrodes formed on both sides of the polymeric composite piezoelectric body; and protective layers formed on surfaces of the thin film electrodes. The electroacoustic converter film serves as a speaker capable of being integrated with a flexible display without impairing lightweightness or flexibility, and has considerable frequency dispersion in the storage modulus and also has a local maximum of the loss tangent around ordinary temperatures. A flexible display, a vocal cord microphone and a musical instrument sensor, in each of which the electroacoustic converter film is used, are also provided.

Owner:FUJIFILM CORP

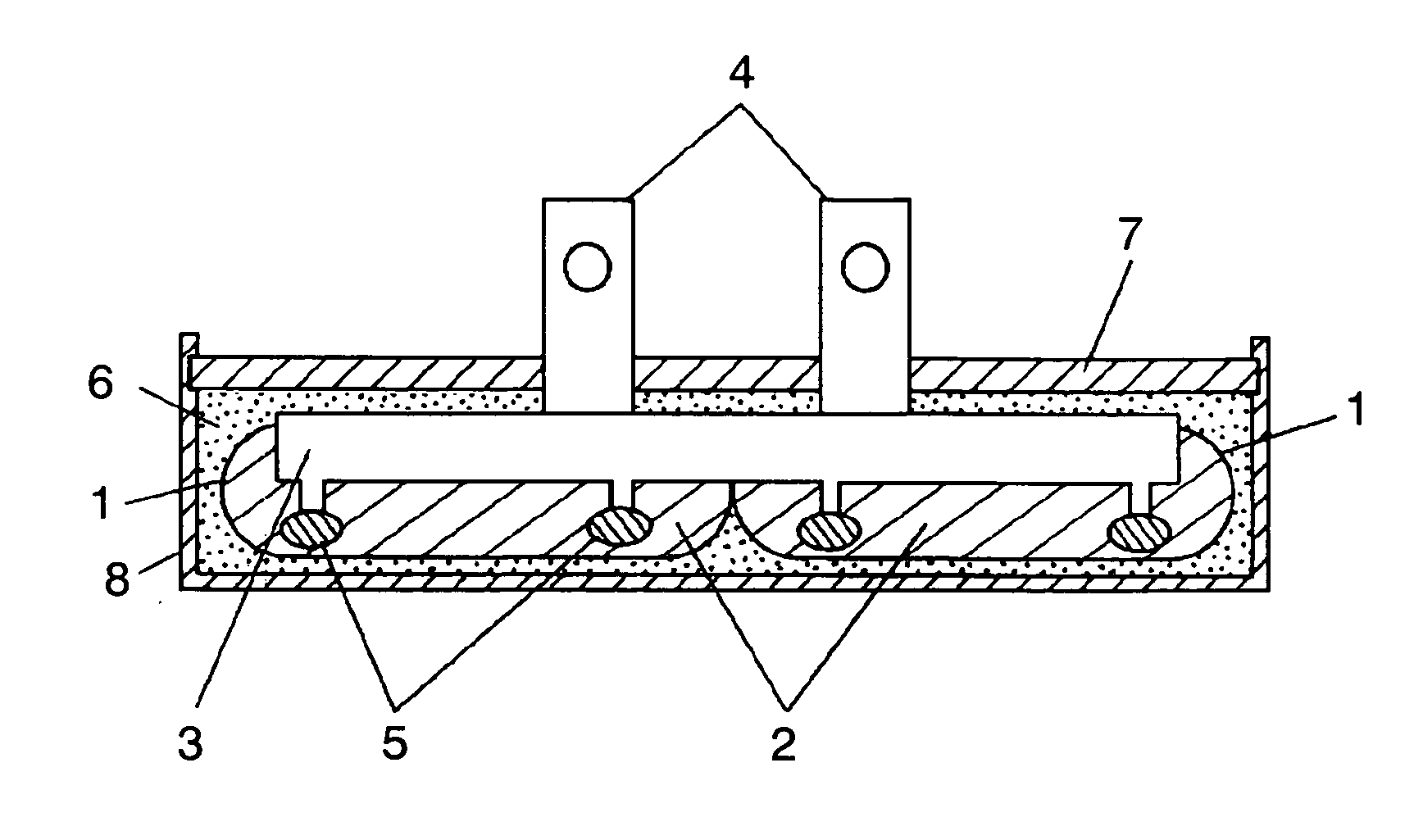

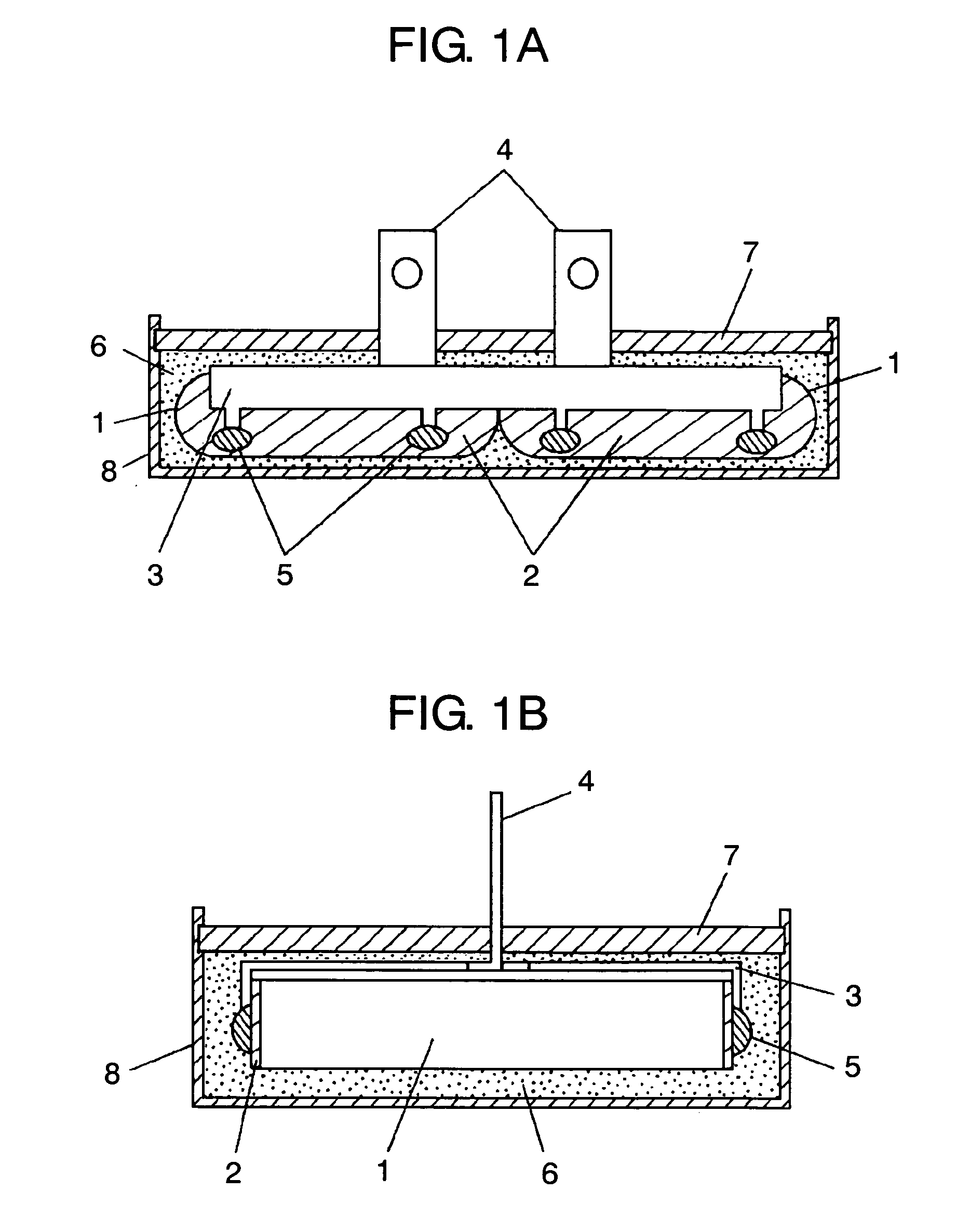

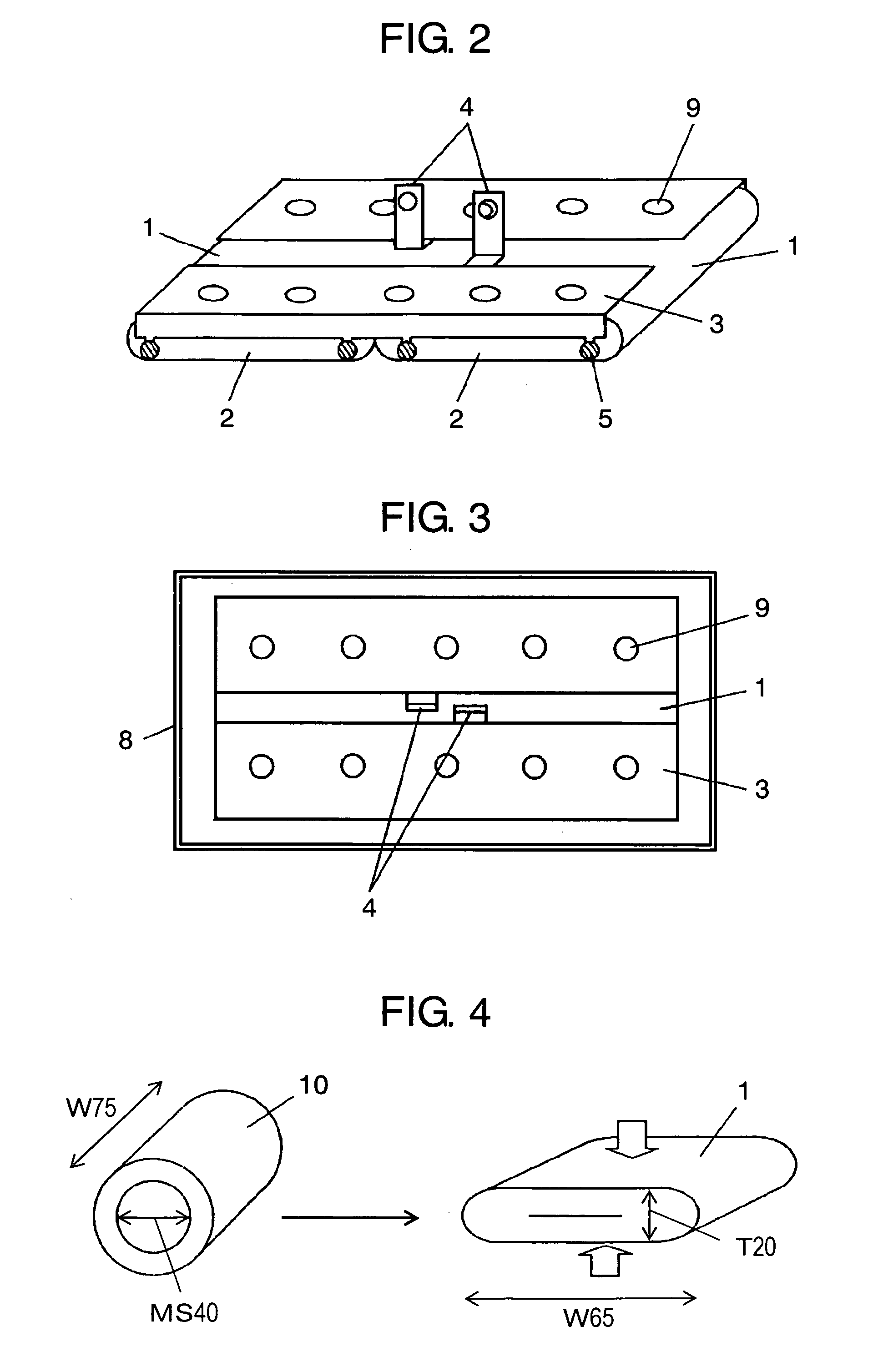

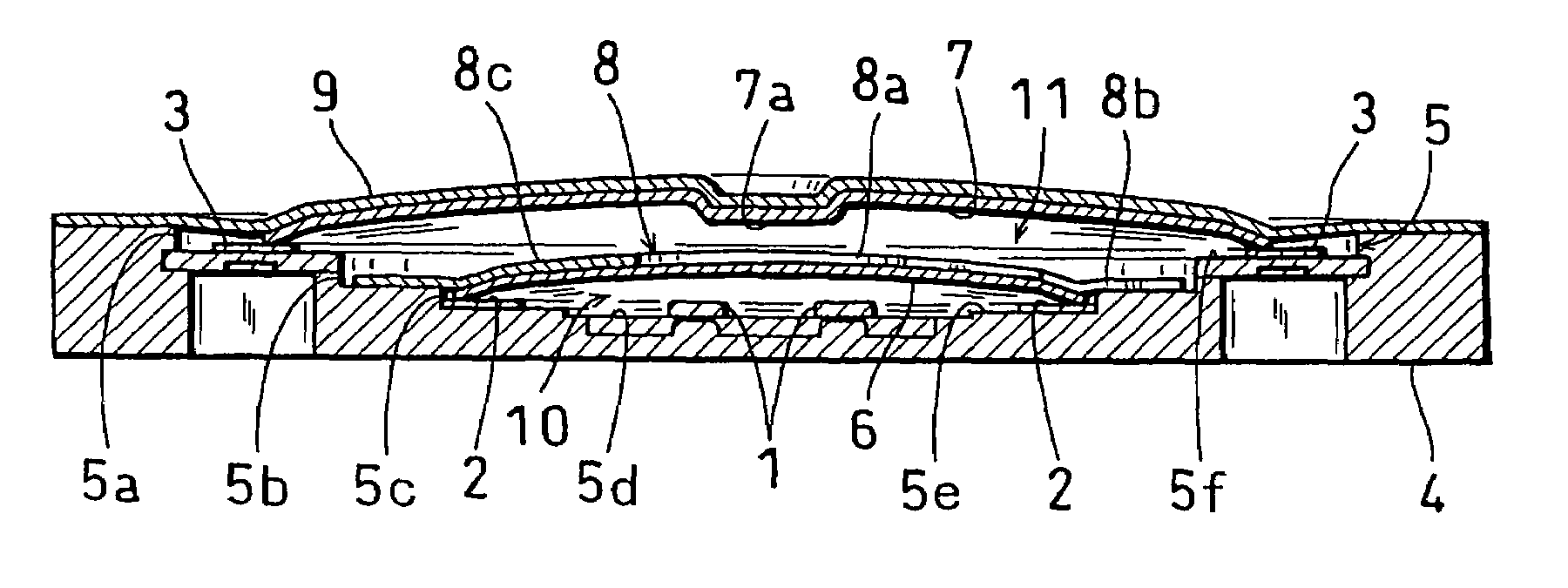

Film capacitor and method of manufacturing the same

ActiveUS20060104006A1Improve moisture resistanceLow exothermic characteristicMultiple fixed capacitorsFixed capacitor dielectricEpoxyProduction rate

The invention provides a film capacitor and its manufacturing method suited to car-mount application, excellent in heat cycle tolerance and humidity resistance, and high in productivity, while maintaining low heat generation and low inductance characteristic. A film capacitor comprises a film capacitor element 1, a bus bar 3 as metal terminal connected to electrode 2 of this film capacitor element 1, and a case 8 for containing them, in which the film capacitor element 1 and bus bar 3 are packed within the case 8 by plural layers of epoxy resin compositions 6, 7, and the plural layers of epoxy resin compositions 6, 7 are formed in layers, and are composed so that the coefficient of linear expansion may be smallest in the epoxy resin composition 7 disposed in the uppermost layer, and therefore resin cracks can be prevented at the time of heat cycle, and a film capacitor of high reliability excellent inhumidity resistance is obtained.

Owner:PANASONIC CORP

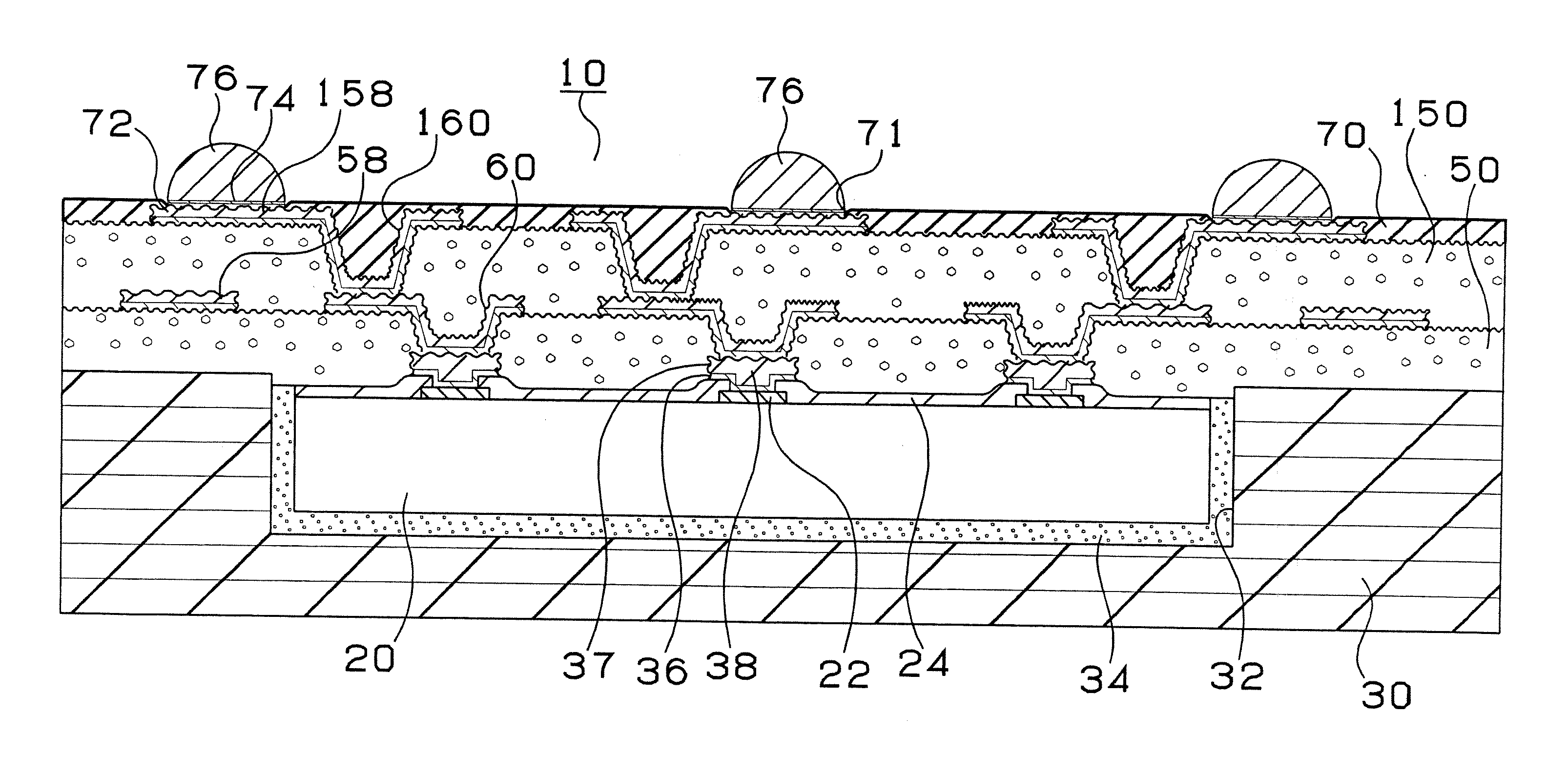

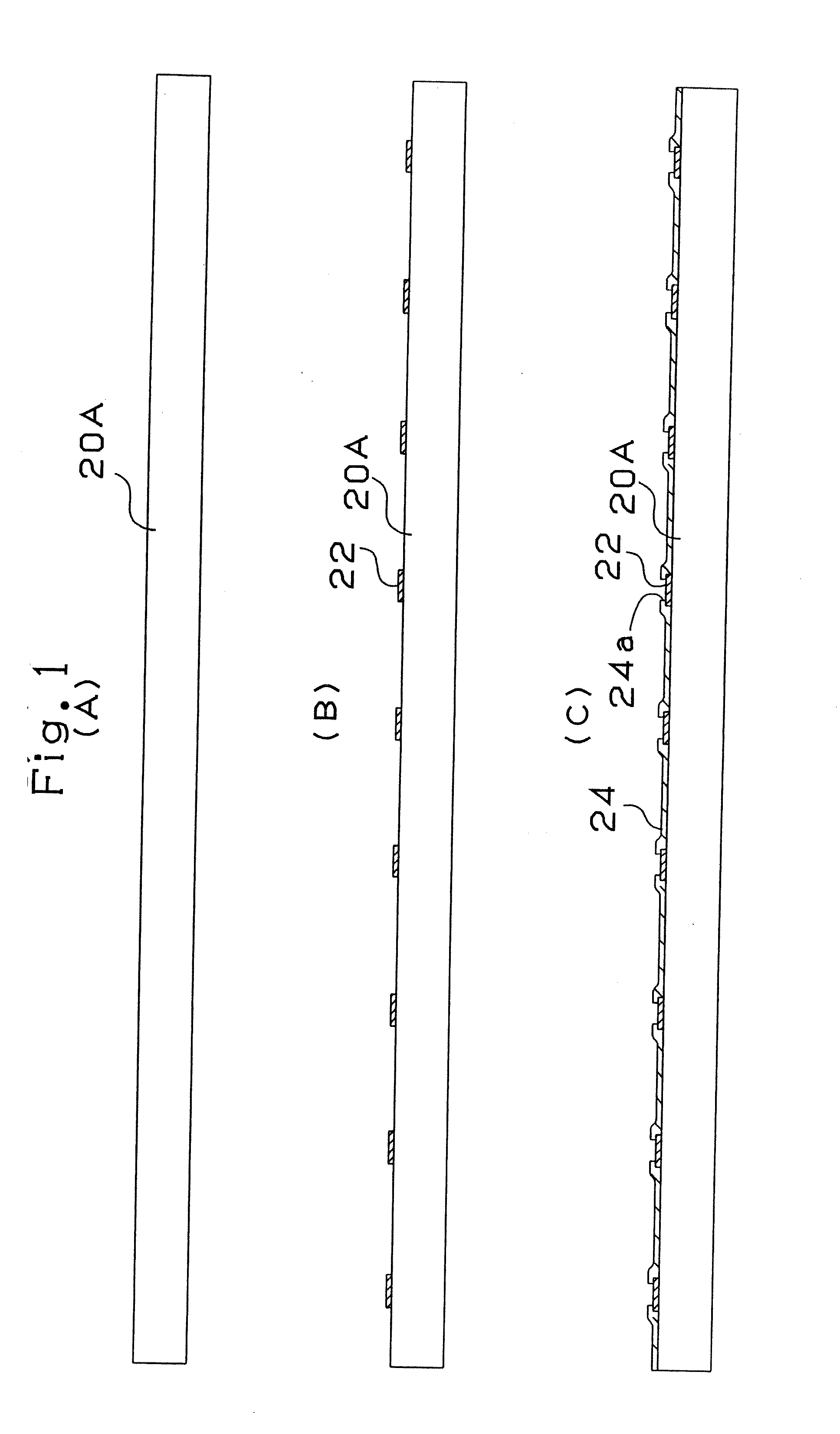

Semiconductor element, method of manufacturing semiconductor element, multi-layer printed circuit board, and method of manufacturing multi-layer printed circuit board

InactiveUS20070209831A1Improve adhesionAvoid crackingPrinted electric component incorporationSemiconductor/solid-state device detailsEngineeringCopper

A transition layer 38 is provided on a die pad 22 of an IC chip 20 and integrated into a multilayer printed circuit board 10. Due to this, it is possible to electrically connect the IC chip 20 to the multilayer printed circuit board 10 without using lead members and a sealing resin. Also, by providing the transition layer 38 made of copper on an aluminum pad 24, it is possible to prevent a resin residue on the pad 24 and to improve connection characteristics between the die pad 24 and a via hole 60 and reliability.

Owner:IBIDEN CO LTD

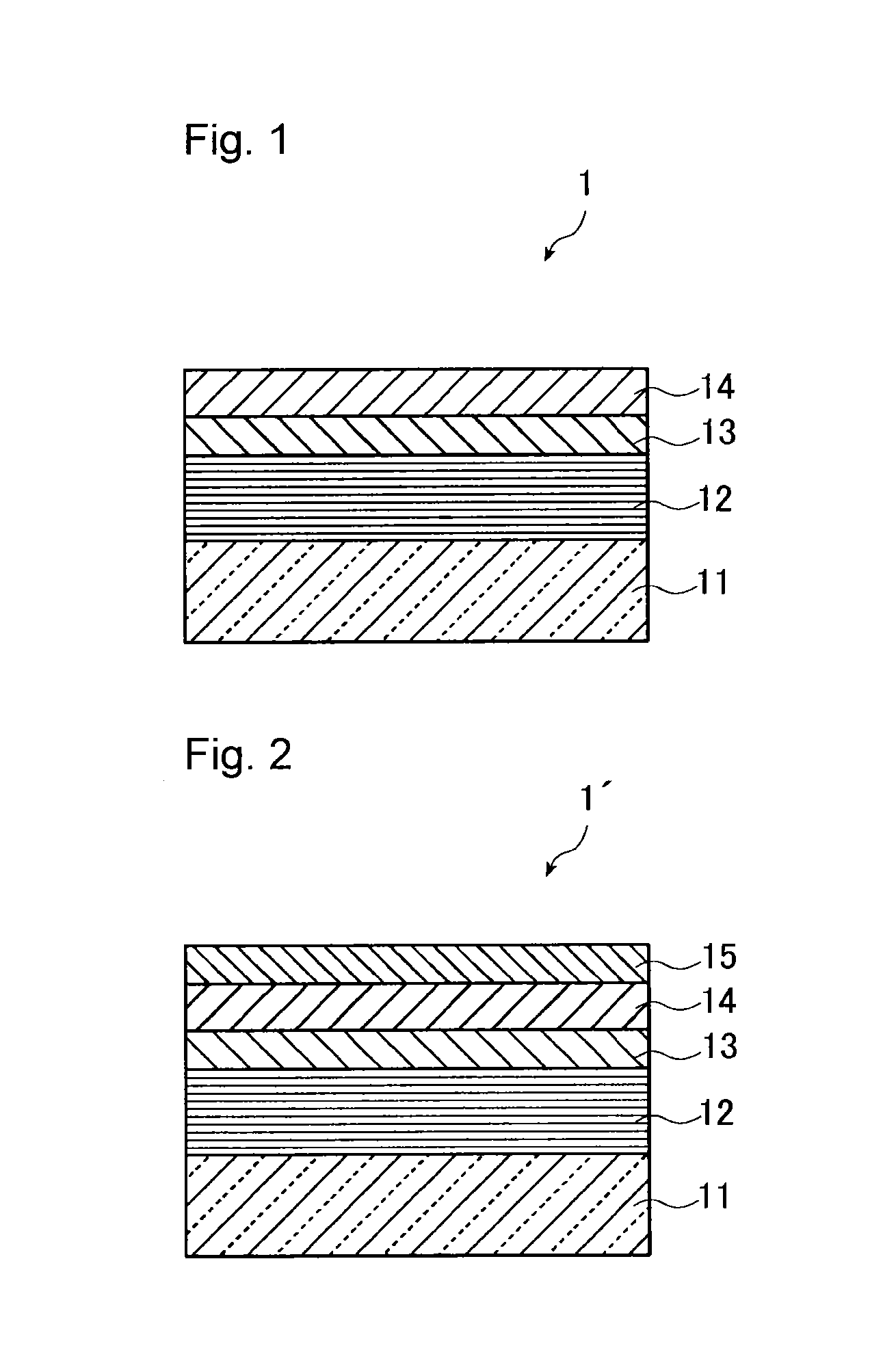

Reflective mask blank for EUV lithography and process for its production

ActiveUS20140212794A1Film stress can be relaxedRelaxation of film stressNanoinformaticsSemiconductor/solid-state device manufacturingLithographic artistLithography

To provide a process for producing an EUV mask blank, whereby the deformation of a substrate due to film stress in a Mo / Si multilayer reflective film can be reduced, and the change with time of the film stress in the Mo / Si multilayer reflective film can be reduced.A process for producing a reflective mask blank for EUVL, which comprises forming a multilayer reflective film for reflecting EUV light on a film-forming surface of a substrate, then forming an absorber layer for absorbing EUV light, on the multilayer reflective film, to produce a reflective mask blank for EUV lithography, wherein the multilayer reflective film is a Mo / Si multilayer reflective film, the uppermost layer of the multilayer reflective film is a Si film, and after forming the absorber layer, the substrate on which the absorber layer is formed is subjected to heating treatment at a temperature of from 110 to 170° C.

Owner:ASAHI GLASS CO LTD

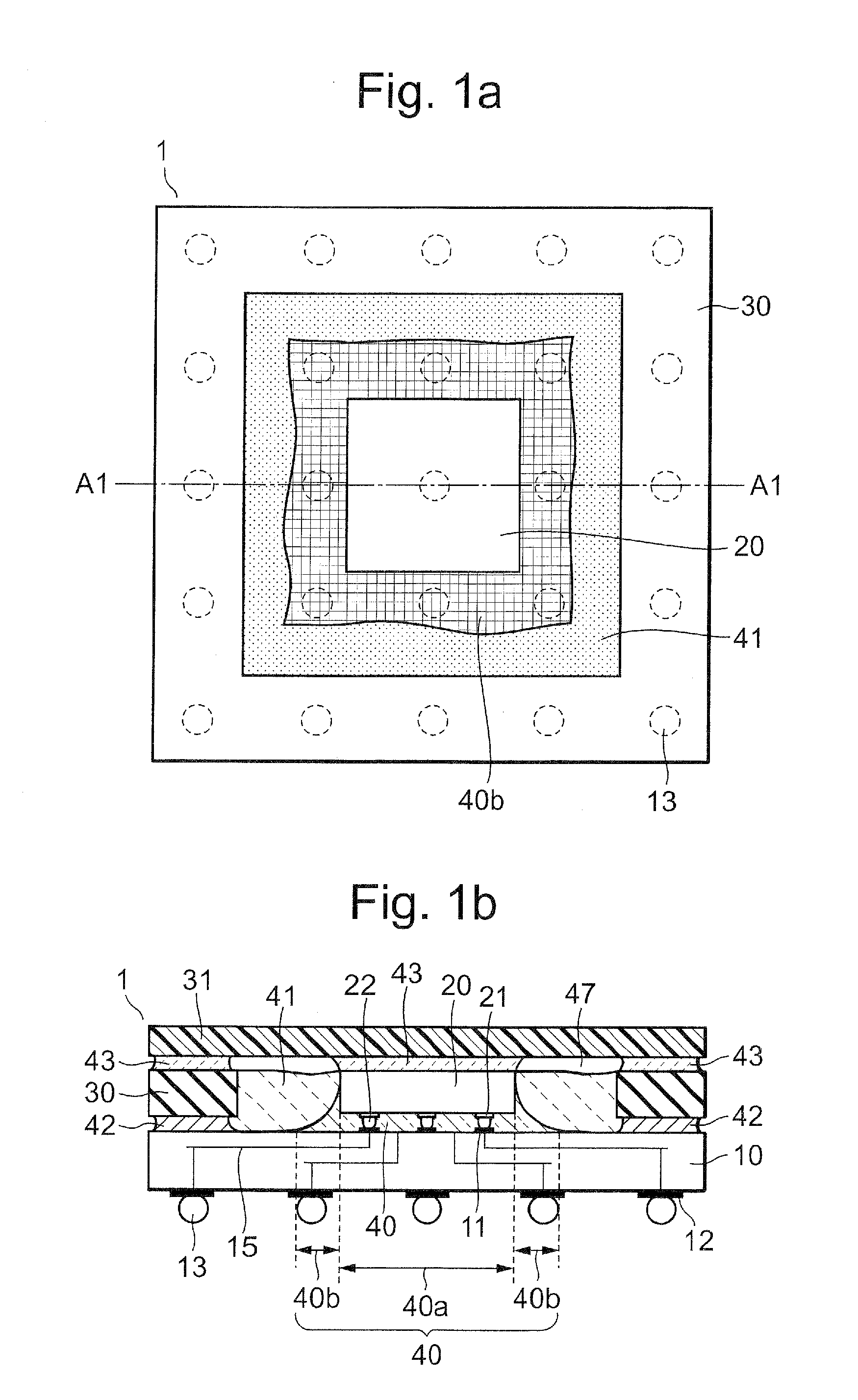

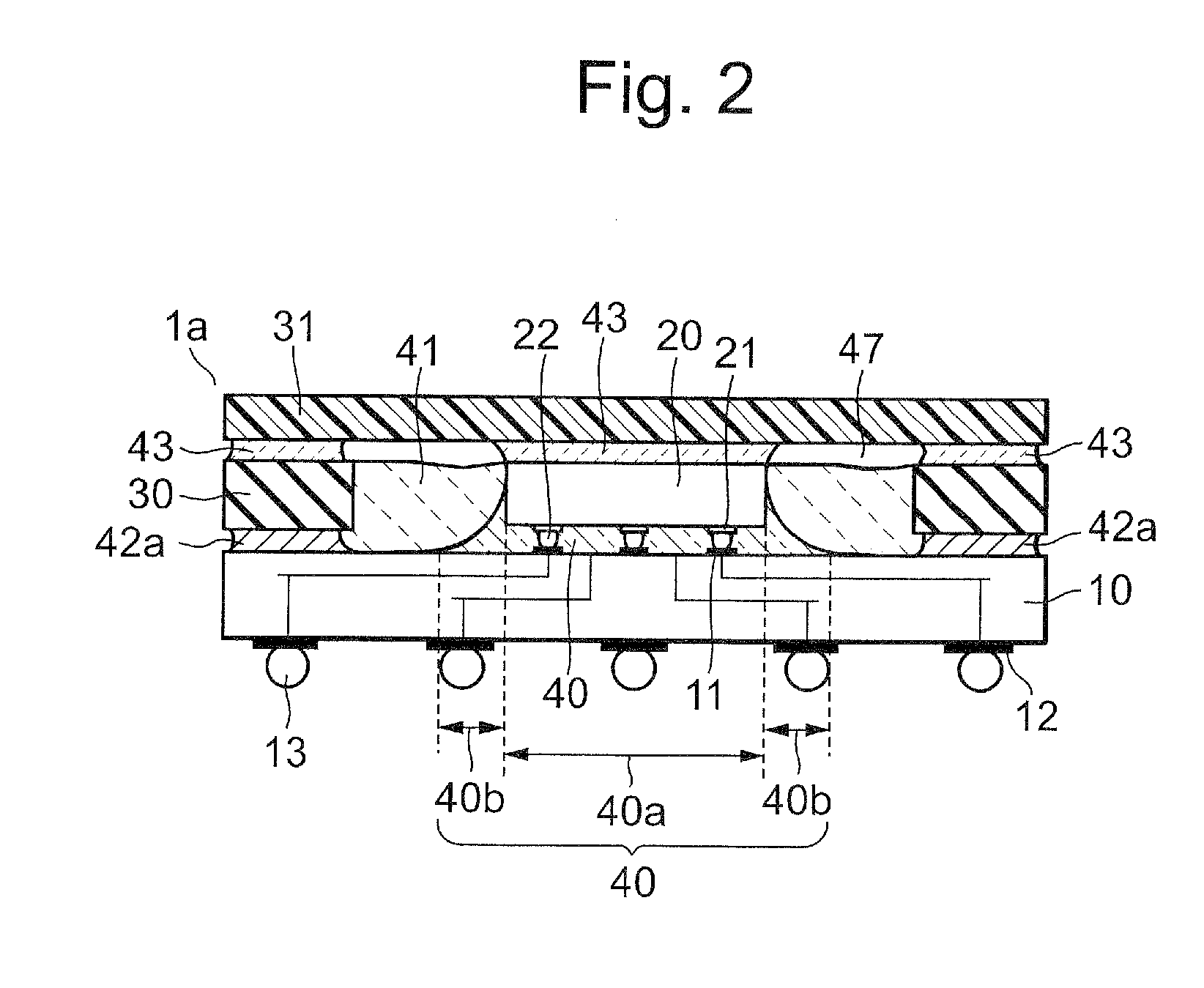

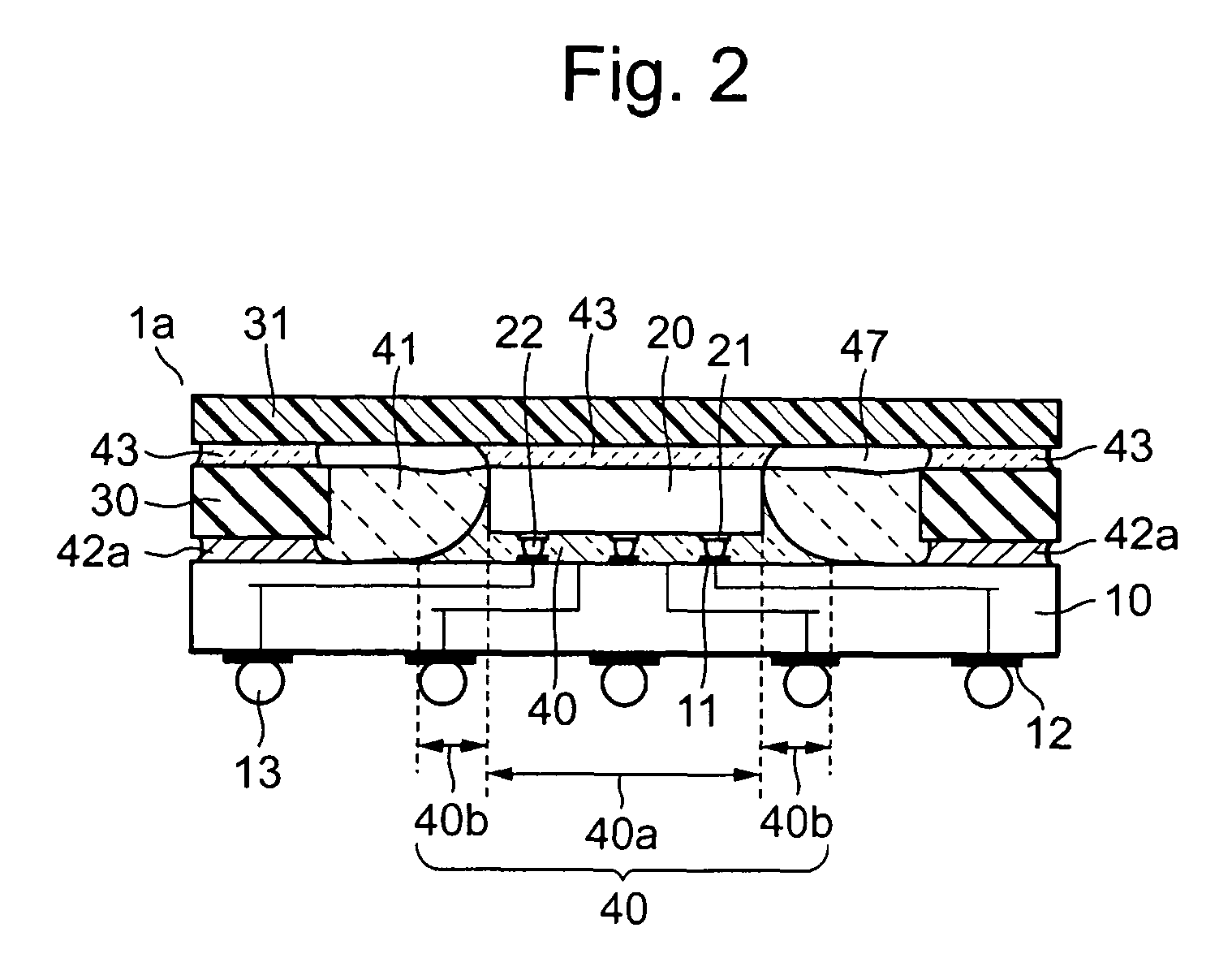

Warp-suppressed semiconductor device

InactiveUS20100230797A1Warpage suppressionLow viscositySemiconductor/solid-state device detailsSolid-state devicesAdhesiveSemiconductor chip

A semiconductor device includes: a semiconductor chip mounted on a mounting substrate; a first resin filling a gap between the chip and the substrate; a frame-shaped stiffener surrounding the chip; a first adhesive for bonding the stiffener to the substrate; a lid for covering the stiffener and an area surrounded by the stiffener; and a second resin filling a space between the stiffener and the chip. A thermal expansion coefficient of the second resin is smaller than that of the first resin. The first resin includes an underfill part filling a gap between the chip and the substrate and a fillet part extended from the chip region.

Owner:RENESAS ELECTRONICS CORP

Method and structure for CMOS device with stress relaxed by ion implantation of carbon or oxygen containing ions

InactiveUS20050186722A1Prevent implantationRelaxation stressSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSCarbon ion

Stress in a silicon nitride contact etch stop layer on a CMOS structure having NMOS and PMOS devices is selectively relieved by selective implantation of oxygen-containing or carbon-containing ions resulting in there being no tensile stress in areas of the layer above the PMOS devices and no compressive stress in areas of the layer above the NMOS devices.

Owner:TAIWAN SEMICON MFG CO LTD

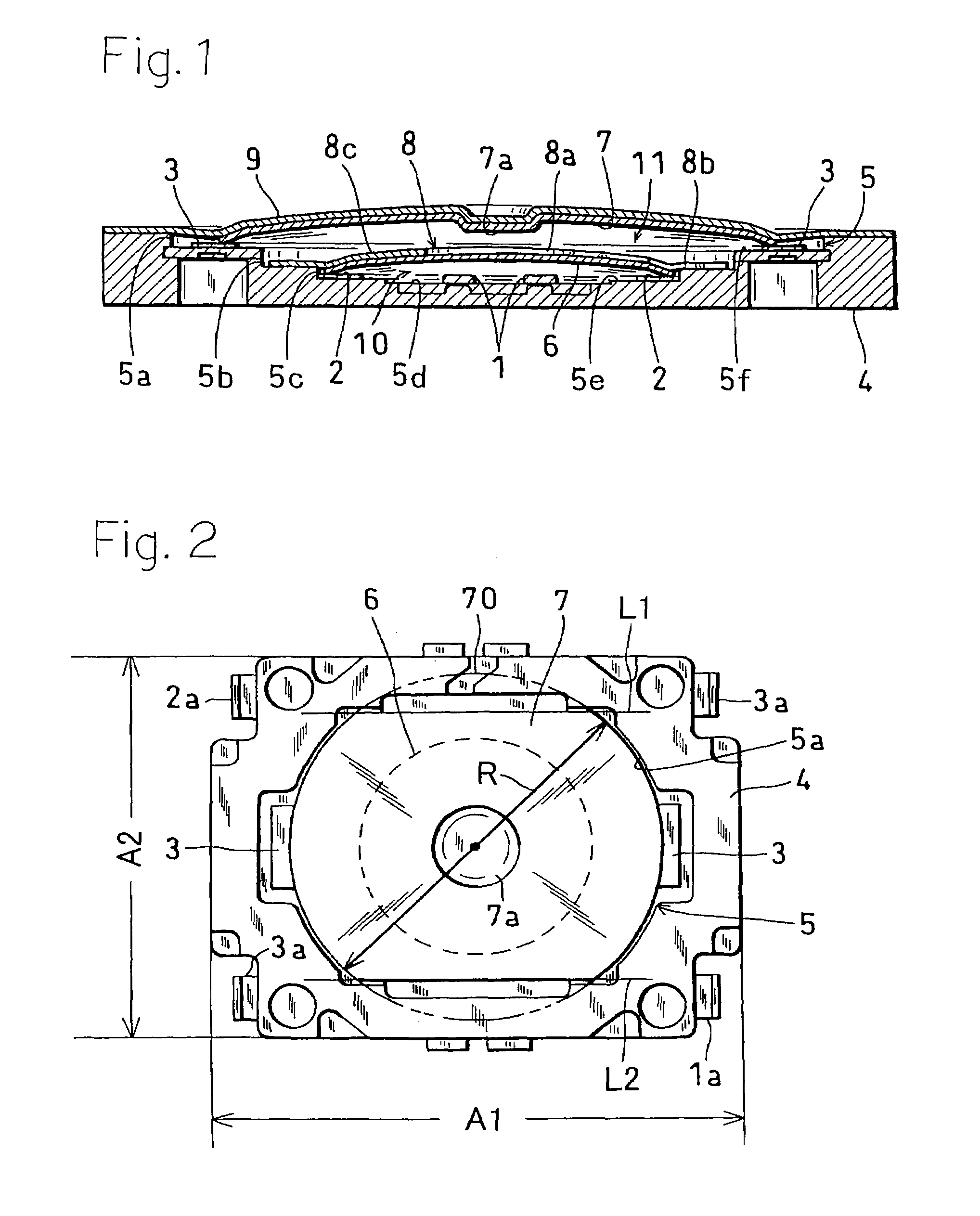

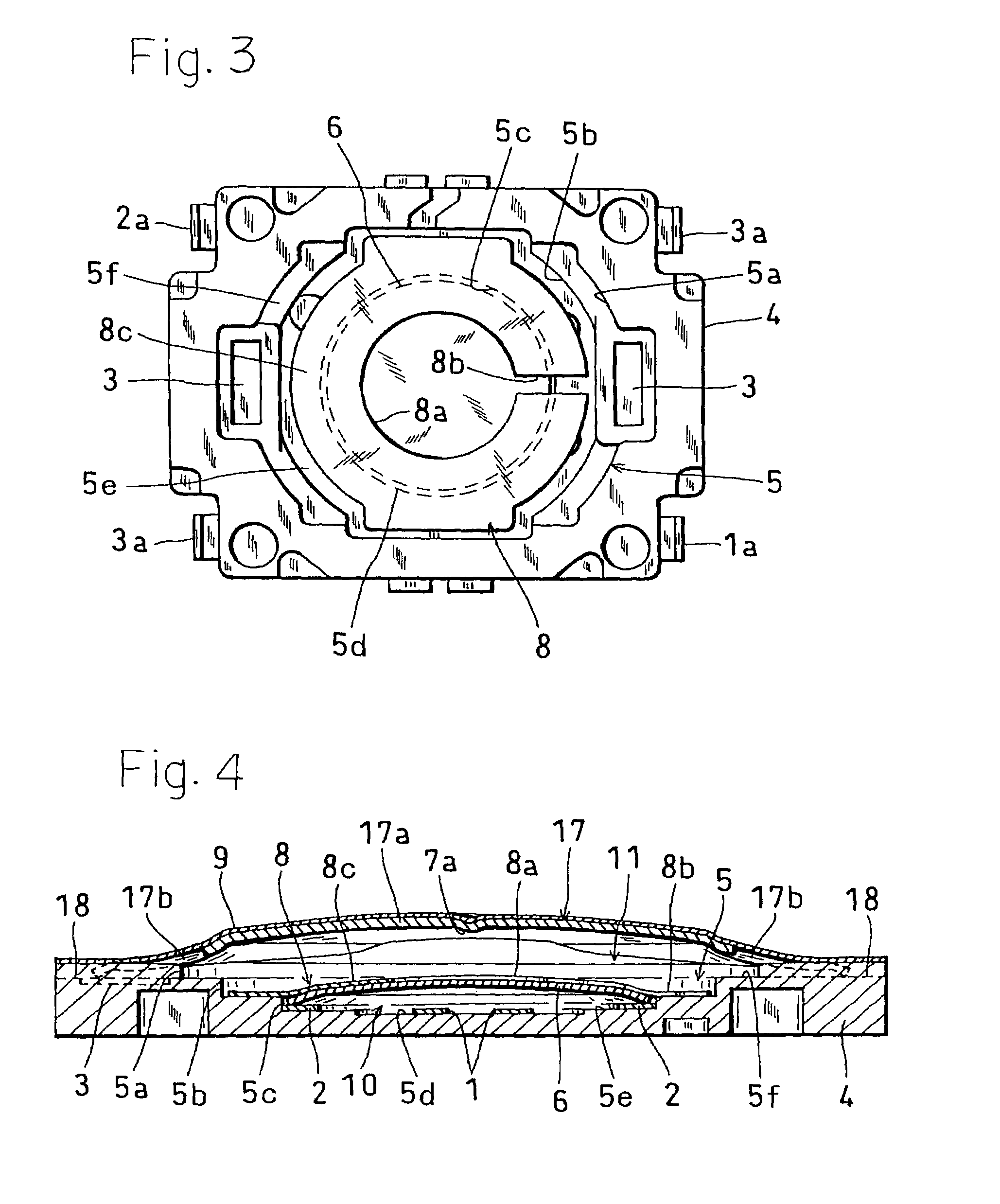

Push-on switch

ActiveUS6995324B2Reduced dimensionReduce widthContact surface shape/structureSnap-action arrangementsTwo stepElectrical and Electronics engineering

A two-step push-on switch in which the operating stroke of an upper movable contact is ensured, and particularly the width of the switch is reduced while the durability of the upper movable contact is improved, the number of parts is reduced, an the operation is improved. Dome-like movable contacts are placed in two or upper and lower stages in an invertible manner in a recess of an insulative body having a plurality of stationary contacts, and the upper movable contact is formed into an oval shape.

Owner:HOSIDEN CORP

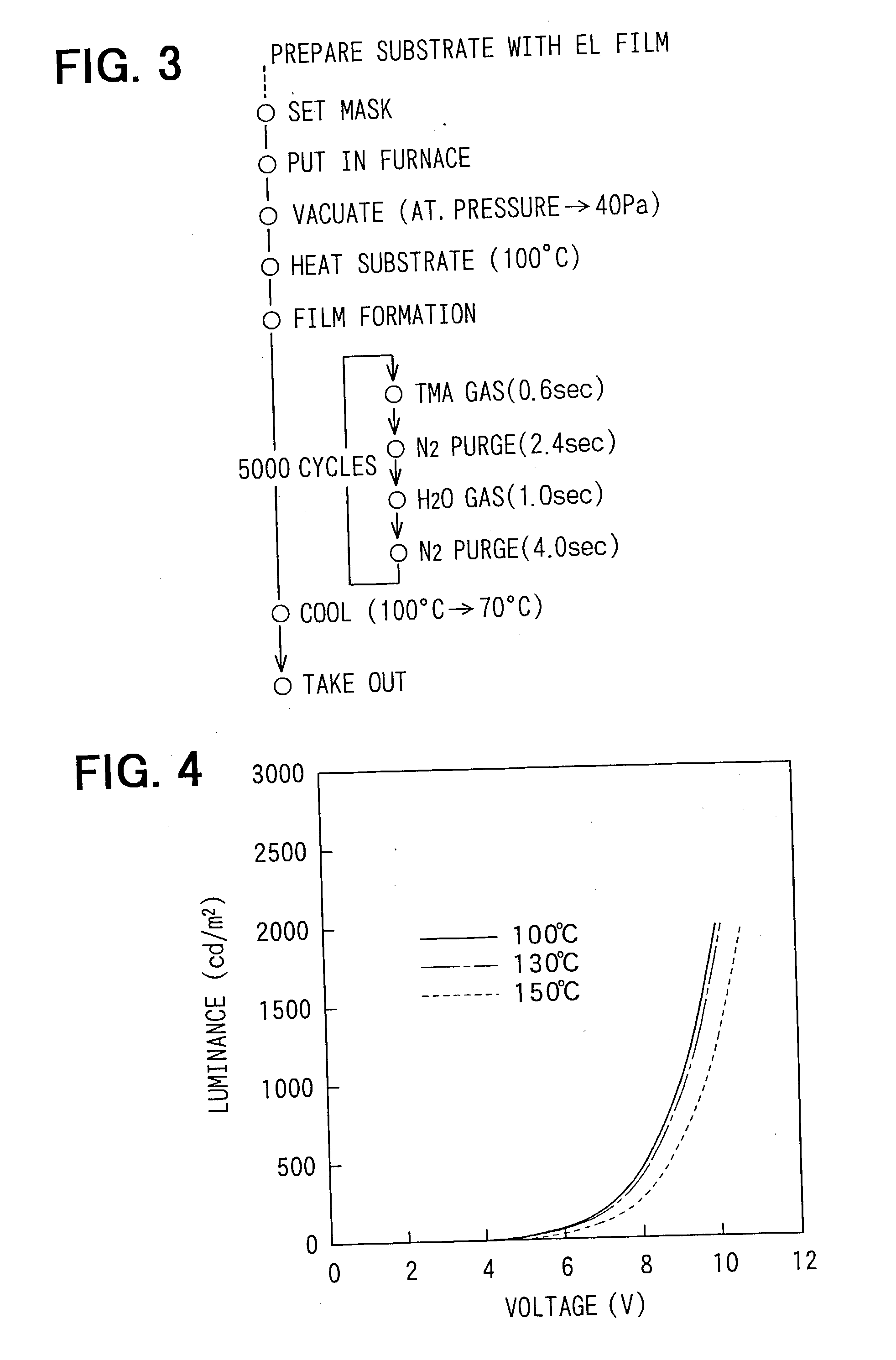

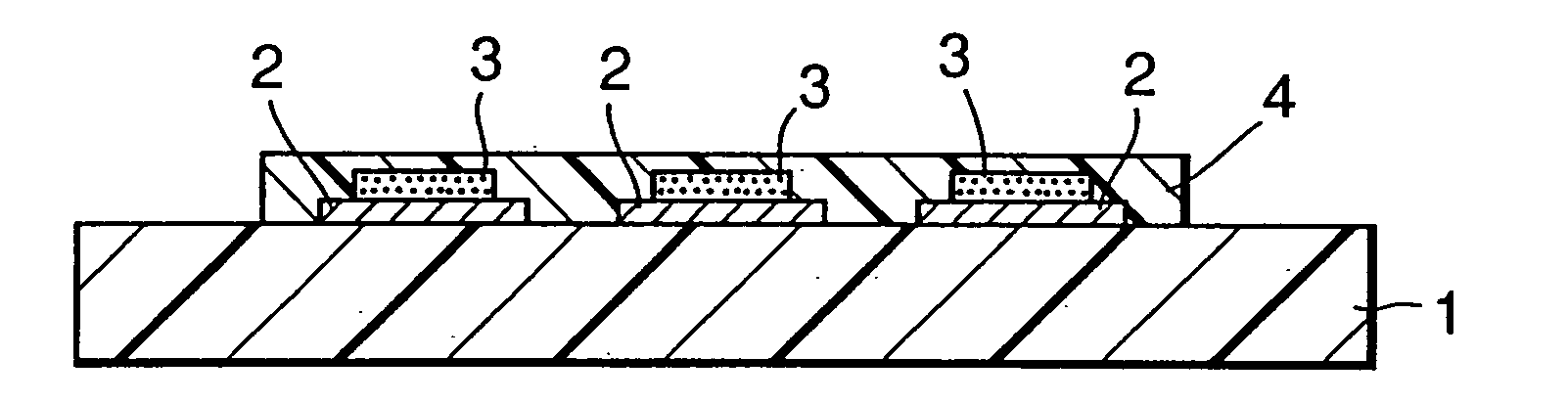

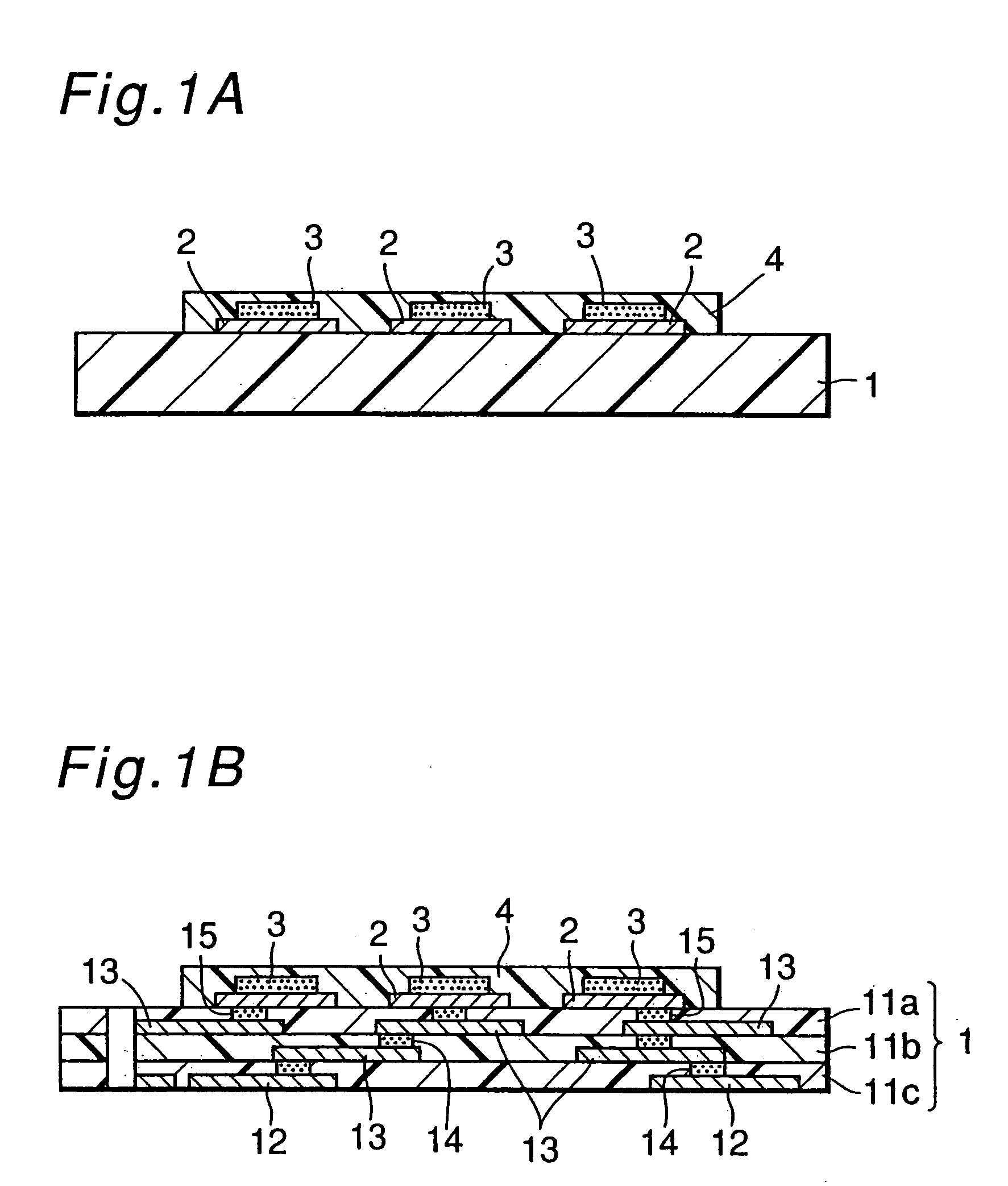

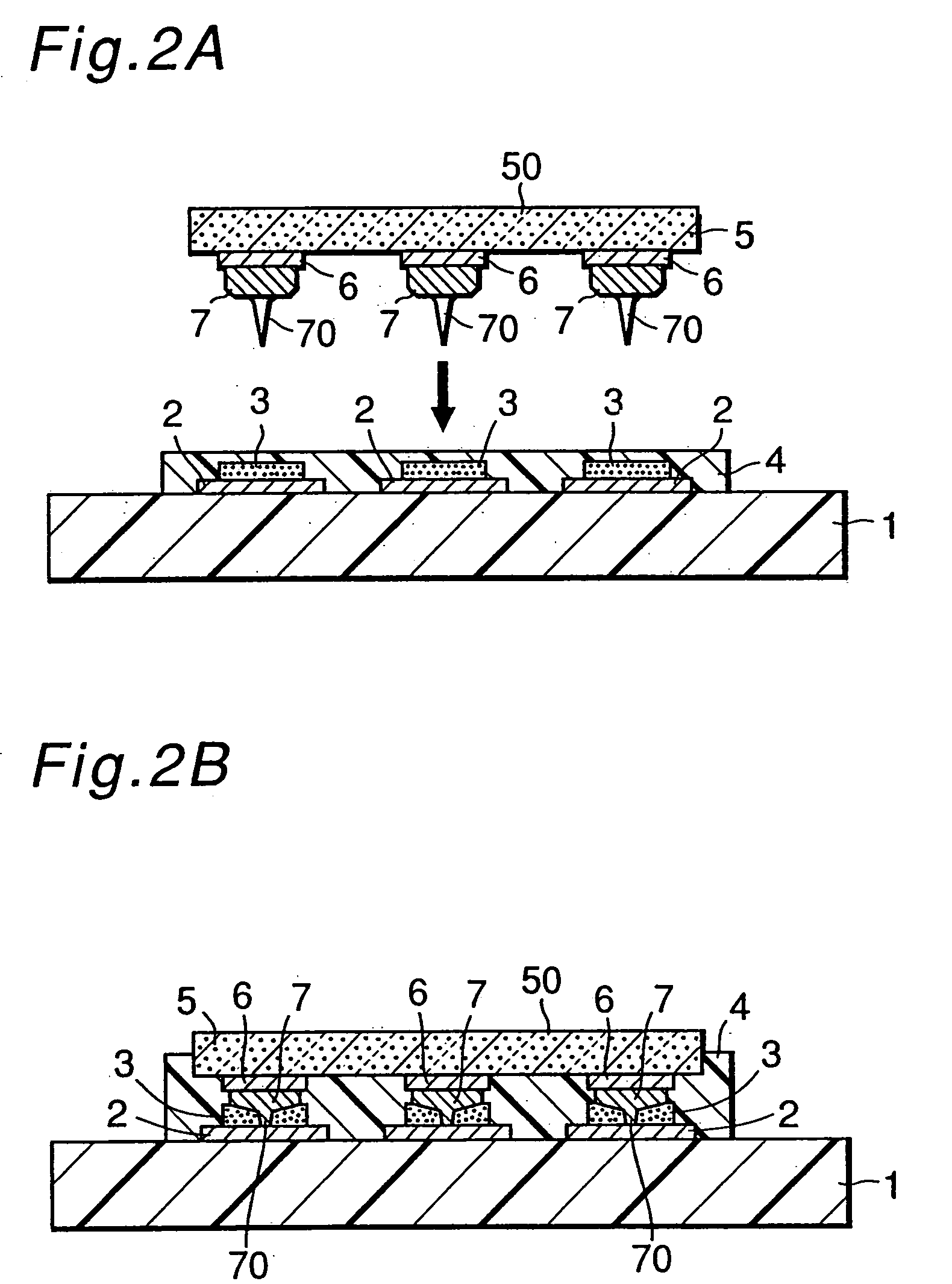

Method for manufacturing organic EL device with protective layer

InactiveUS20030129298A1Expand coverageImprove moisture resistanceDischarge tube luminescnet screensElectroluminescent light sourcesEngineeringGlass transition

An organic EL device has a structure in which an anode, a hole transporting layer, an organic luminescent layer, and a cathode are disposed on a glass substrate in this order. The organic EL device further has a protective layer covering an outer surface of the structure to protect it from an external environment. The protective layer is formed by an ALE method at a temperature lower than glass transition temperatures materials constituting the hole transporting layer and the organic luminescent layer.

Owner:DENSO CORP

Circuit substrate for packaging semiconductor device, method for producing the same, and method for producing semiconductor device package structure using the same

InactiveUS20050163982A1Reduced characteristicsAvoid damagePrinted circuit assemblingSemiconductor/solid-state device detailsAnisotropic conductive filmDevice material

The invention is intended for providing a semiconductor package structure which prevents degradation in characteristics of a semiconductor device, and breakage of interconnections, when the semiconductor device is packaged on a circuit substrate. In the package structure having the semiconductor device mounted on the circuit substrate, bump electrodes of the semiconductor device are placed on input / output terminal electrodes of the circuit substrate and are electrically and mechanically connected thereto by bonding with a conductive adhesive, and the semiconductor device is bonded and fixed to the circuit substrate by a resin film formed previously on a surface of a main body of the circuit substrate. The structure does no damage to a semiconductor functional part and to interconnections, and allows mounting with a lower load as compared to structures using conventional anisotropic conductive films and the like.

Owner:ONO MASAHIRO +1

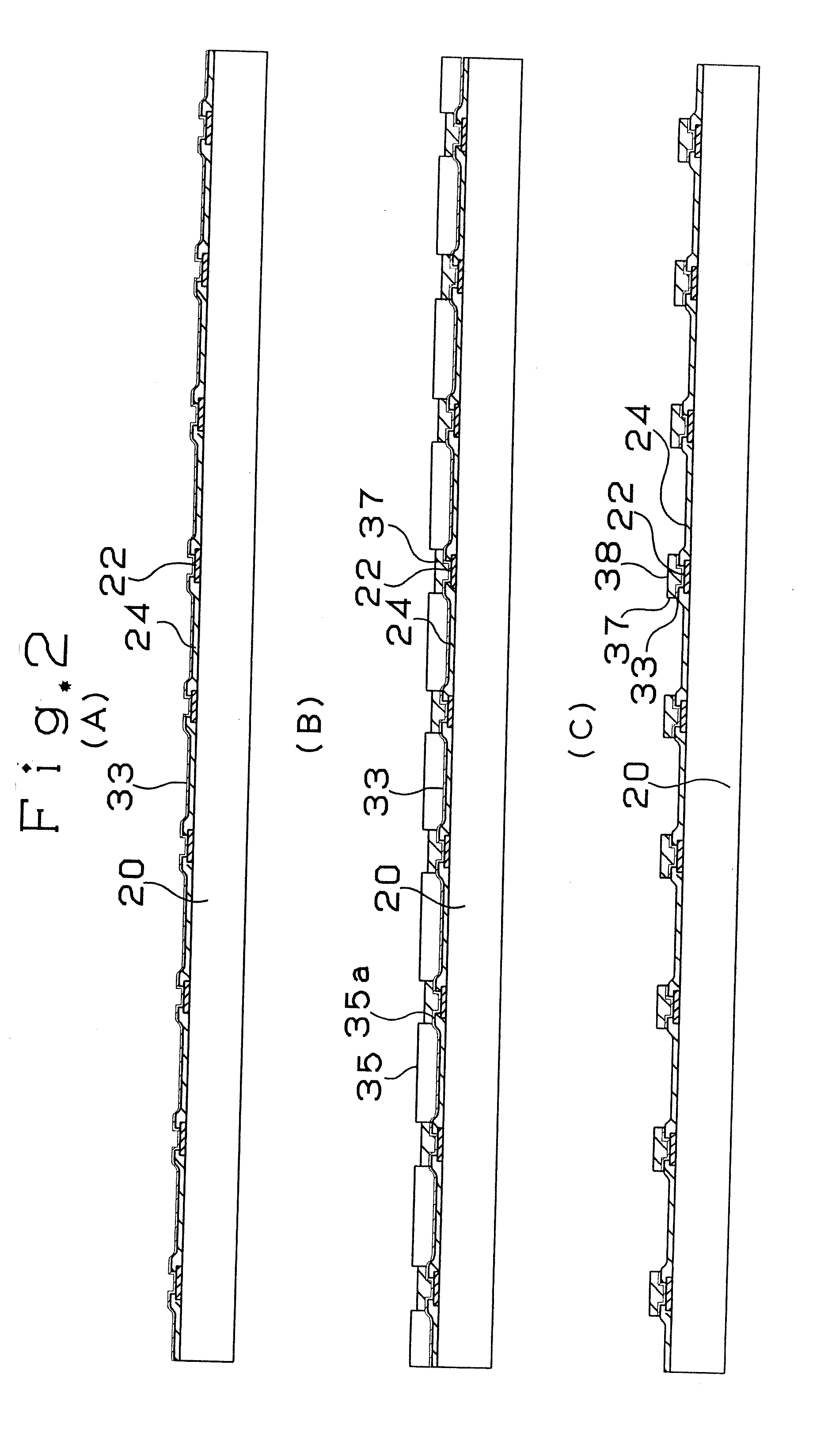

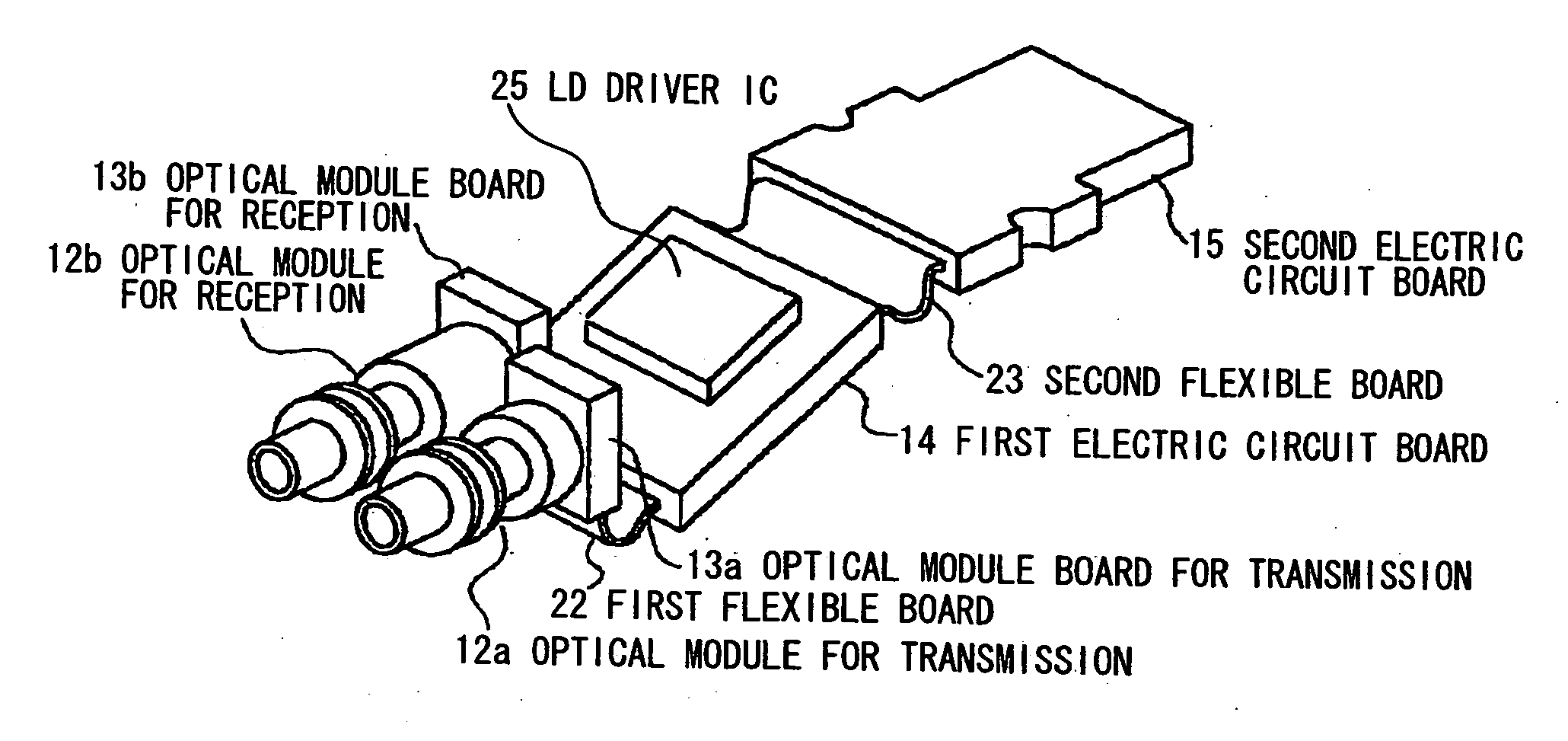

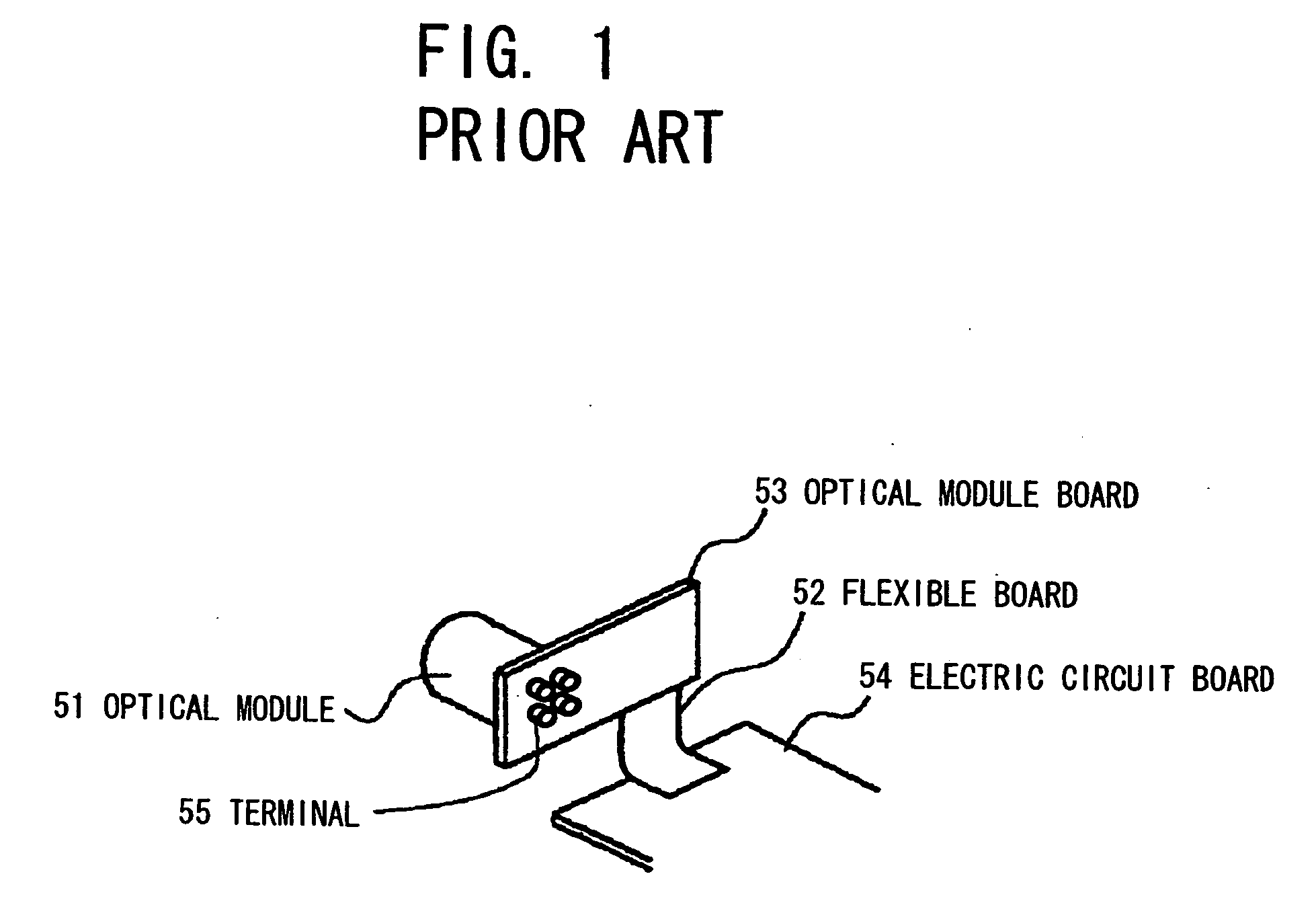

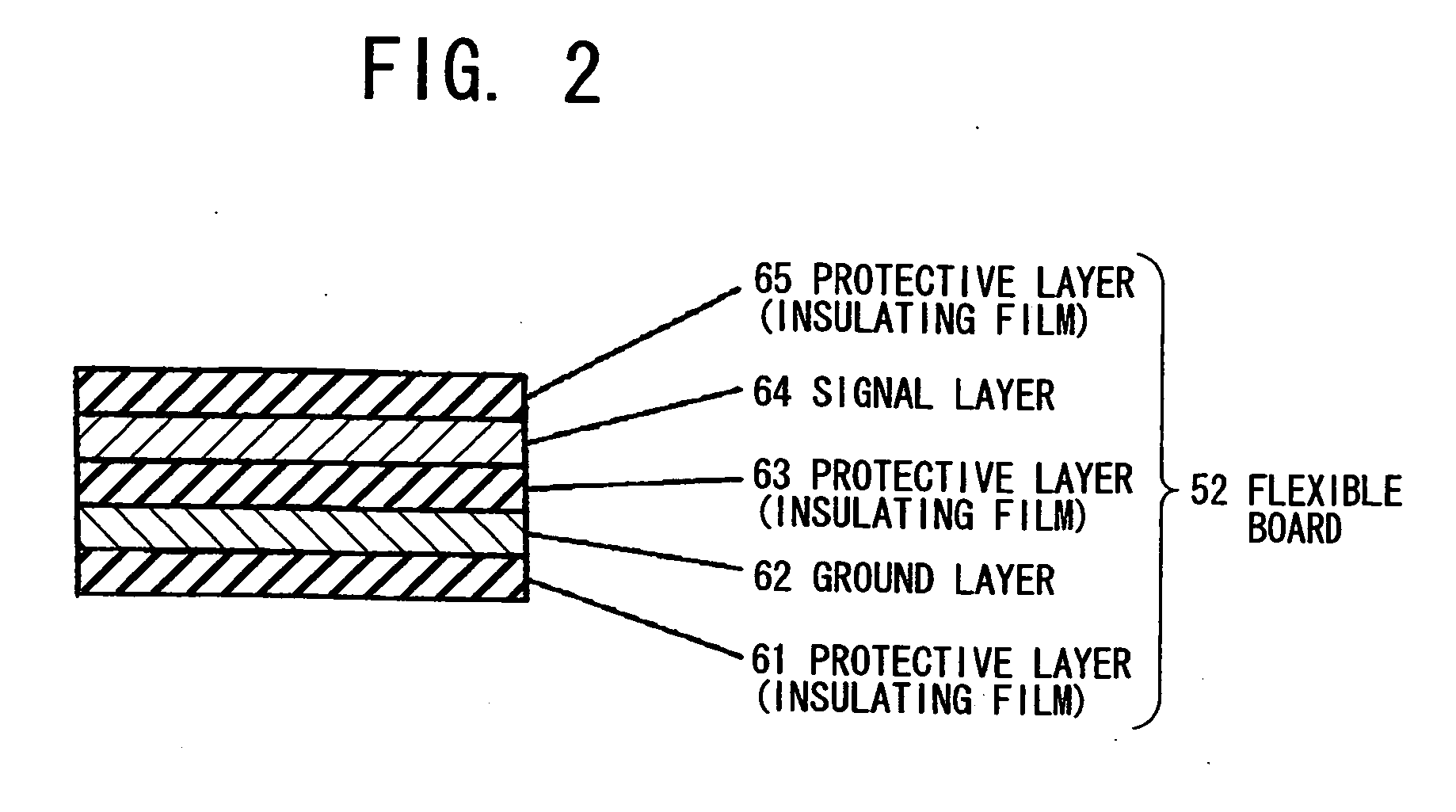

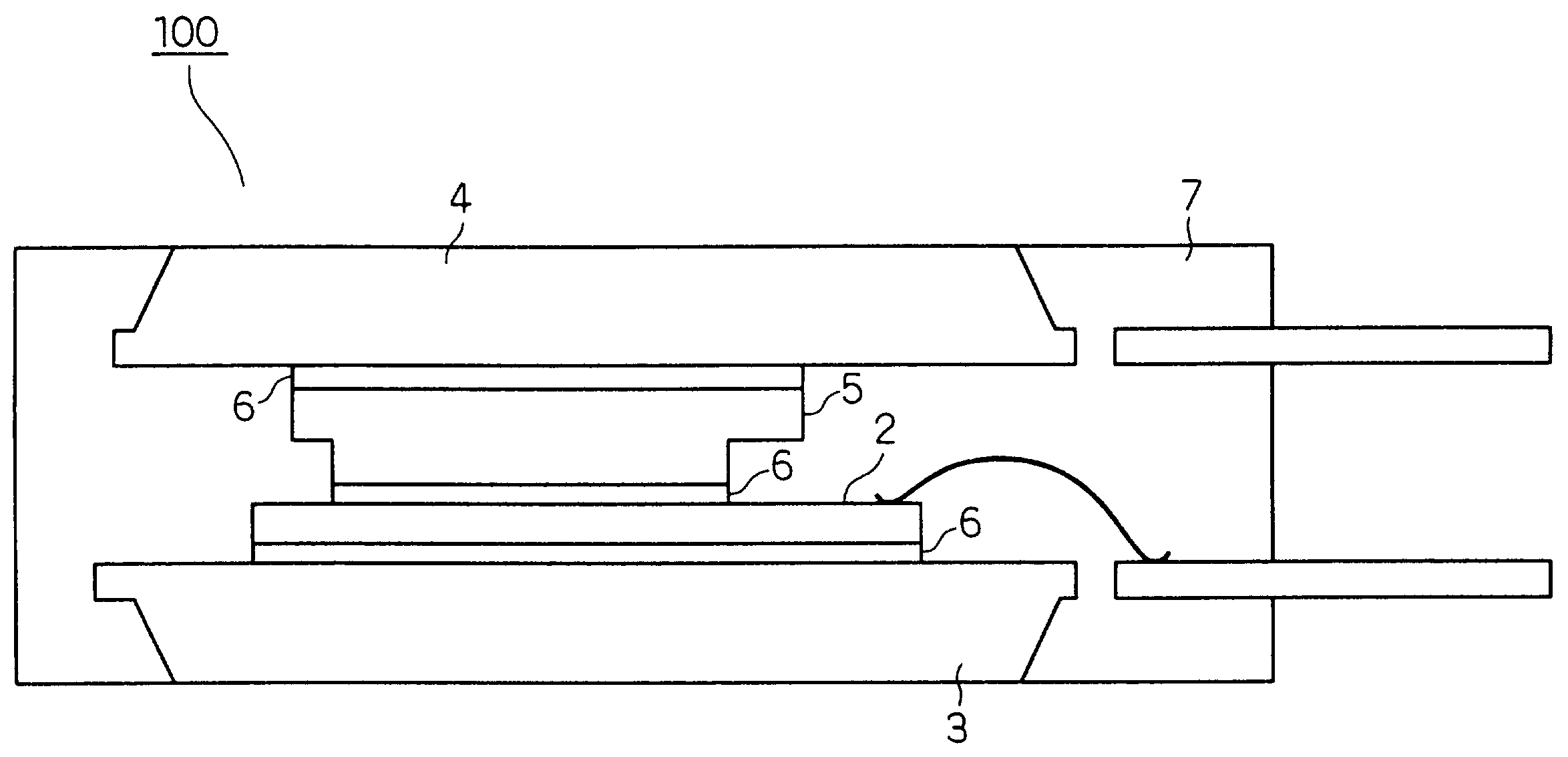

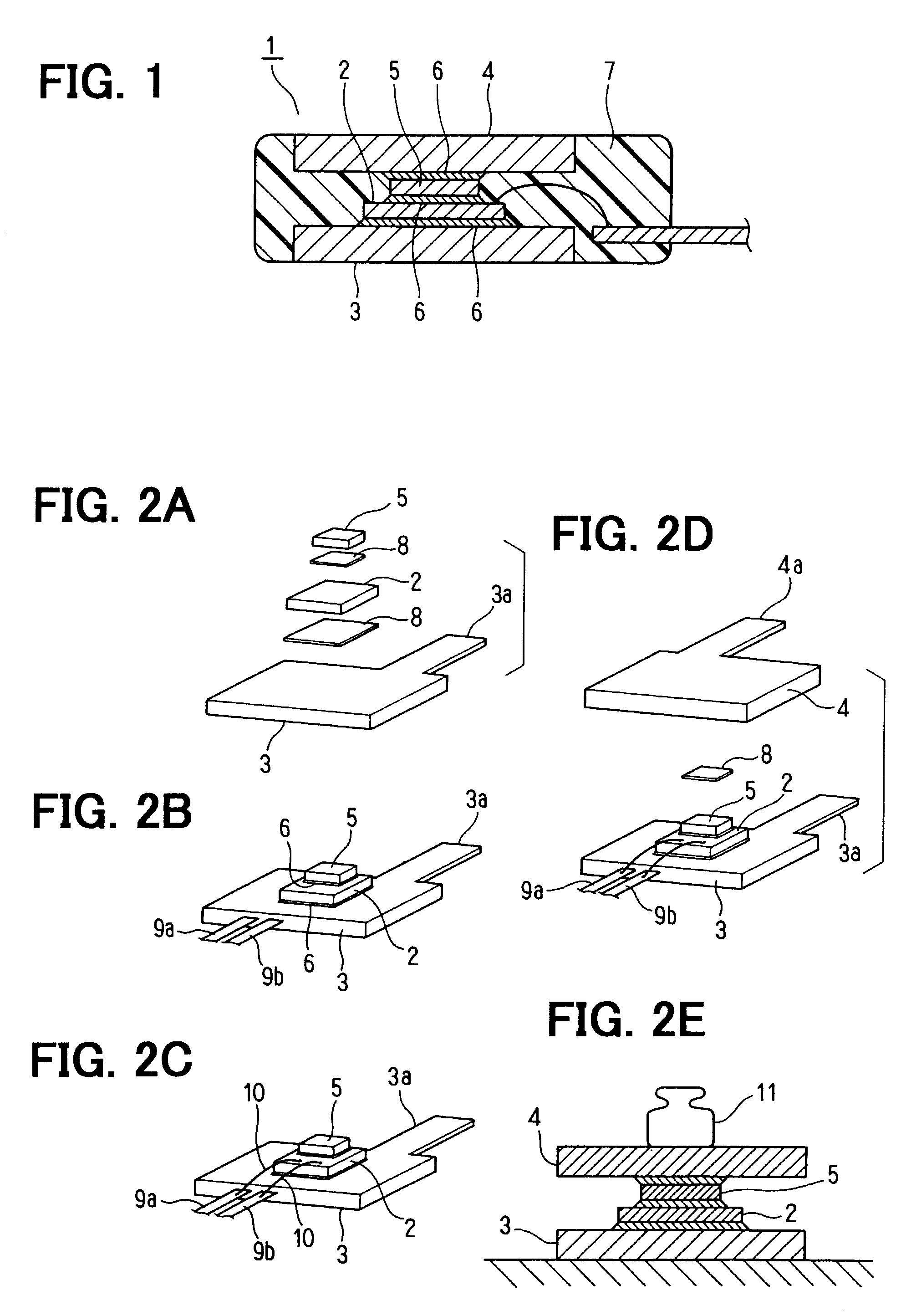

Board assembly, optical transceiver using same and method for mounting same on object

InactiveUS20060257081A1Relaxation stressPrinted circuit aspectsCoupling light guidesTransceiverEngineering

A board assembly, an optical transceiver using same, and a method for mounting a board assembly that can relax a stress occurred at a flexible board. A board assembly 1 comprises a flexible board 2, a first rigid board 3, and a second rigid board 4. The first rigid board 3 and the second rigid board 4 are connected with each other by means of the flexible board 2. Since the flexible board 2 is preformed before the attachment, the stress occurred at the flexible board 2 can be relaxed.

Owner:HITACHI CABLE

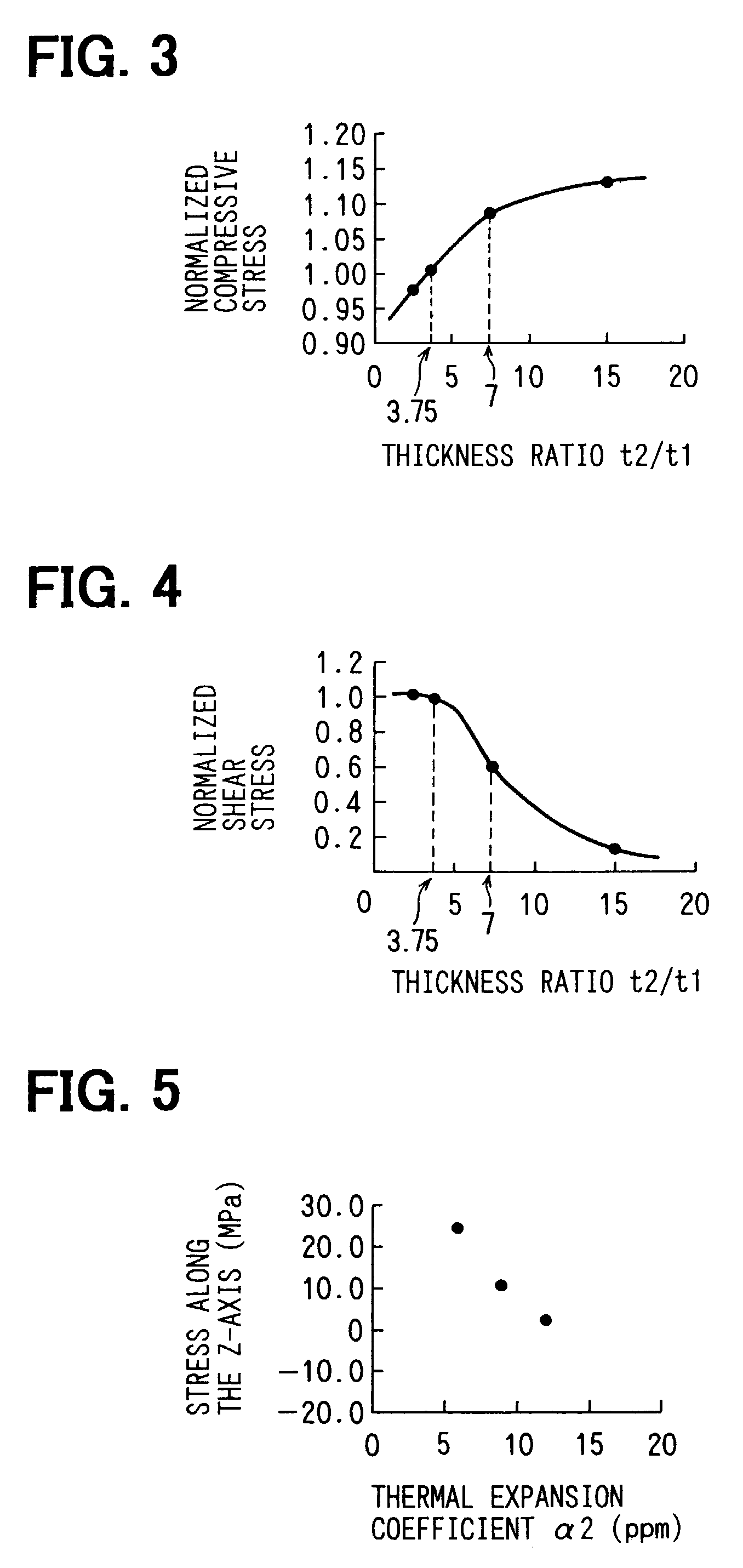

Transfer-molded power device and method for manufacturing transfer-molded power device

InactiveUS7145254B2Improve vulnerabilityPreventing a solder from breakingSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipTransfer molding

A semiconductor device includes a semiconductor chip that generates heat in operation, a pair of heat sinks for cooling the chip, and a mold resin, in which the chip and the heat sinks are embedded. The thickness t1 of the chip and the thickness t2 of one of heat sinks that is joined to the chip using a solder satisfy the equation of t2 / t1≧5. Furthermore, the thermal expansion coefficient α1 of the heat sinks and the thermal expansion coefficient α2 of the mold resin satisfy the equation of 0.5≦α2 / α1≦1.5. In addition, the surface of the chip that faces the solder has a roughness Ra that satisfies the equation of Ra≦500 nm. Moreover, the solder is a Sn-based solder to suppress relaxation of a compressive stress in the chip, which is caused by the creeping of the solder.

Owner:DENSO CORP

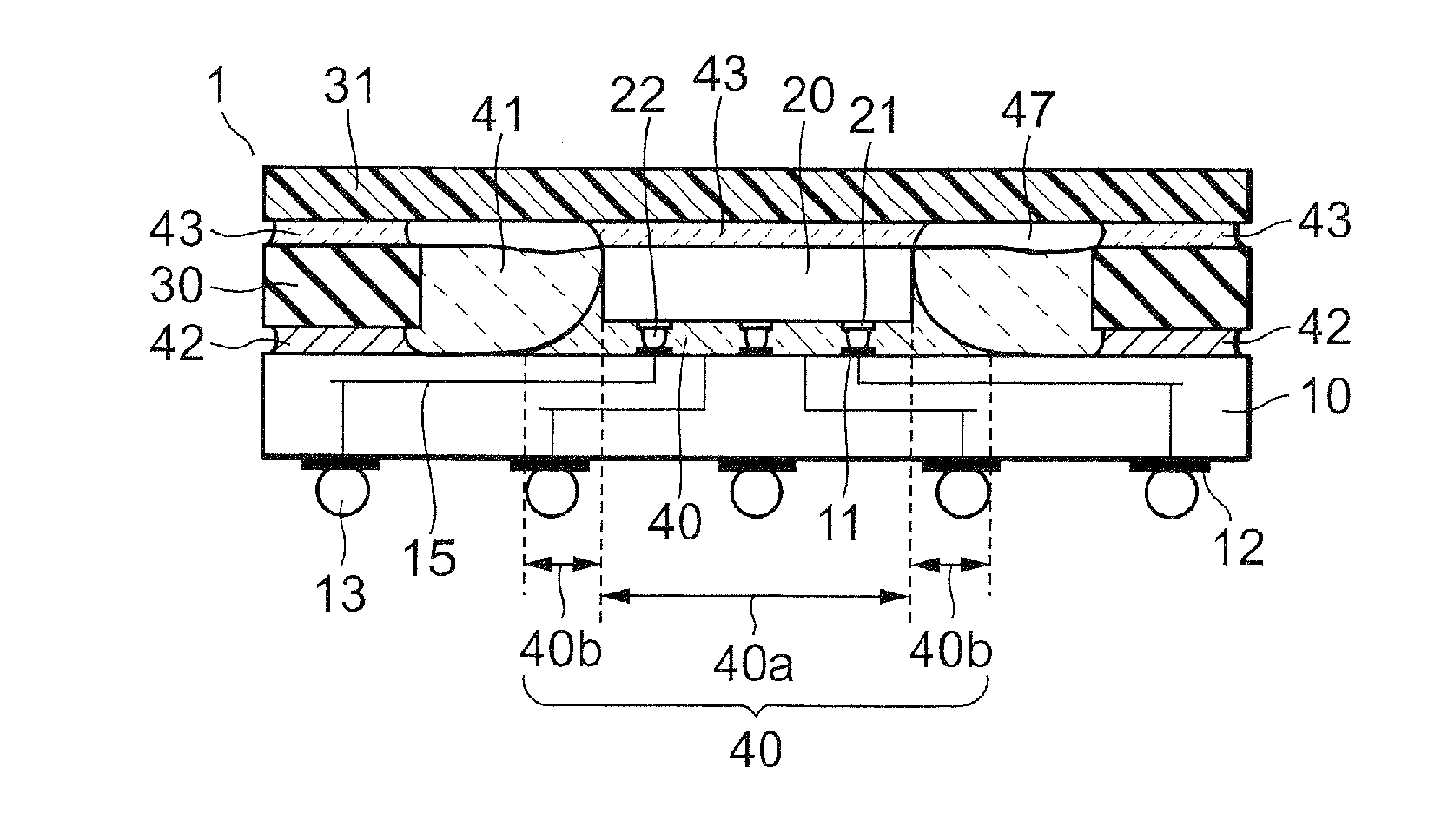

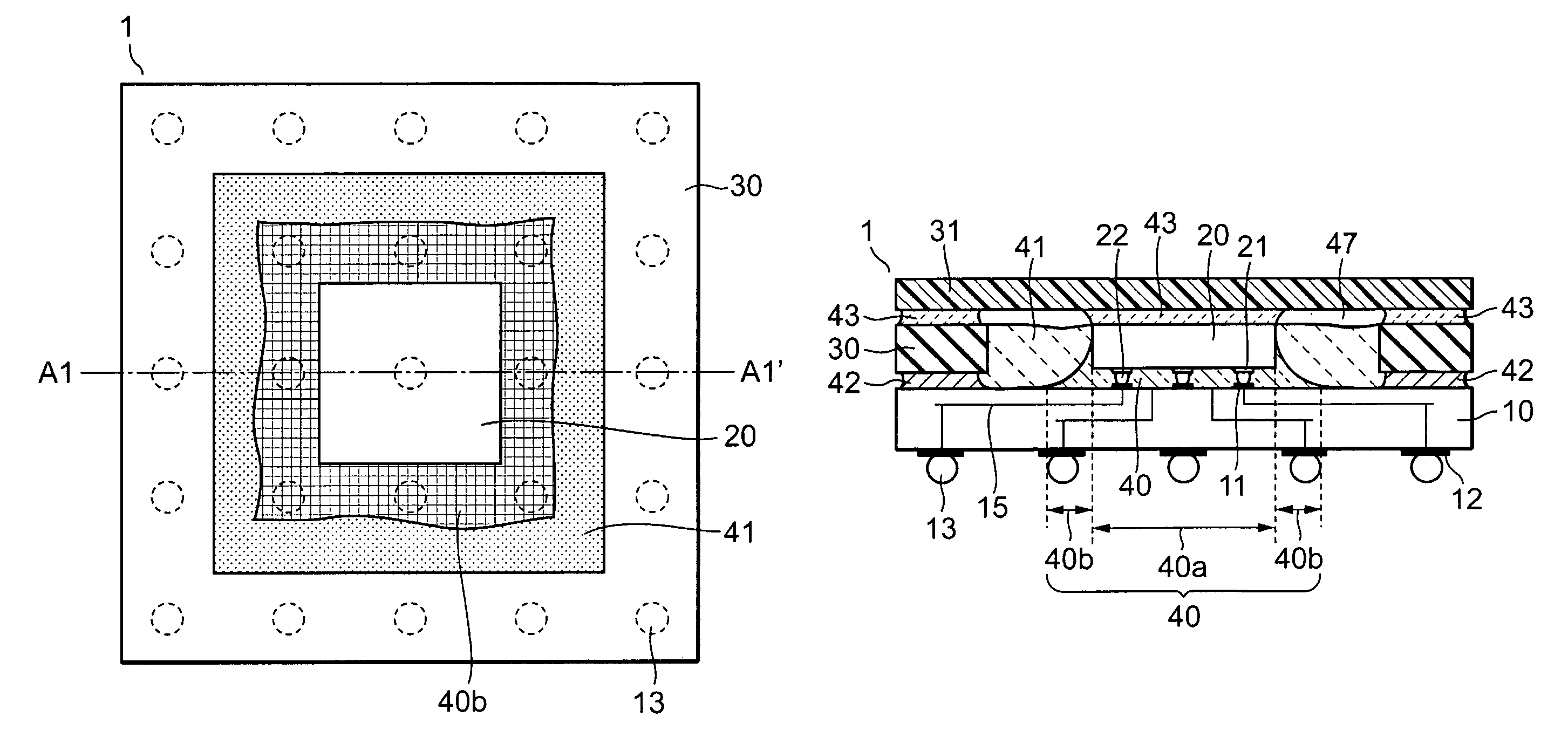

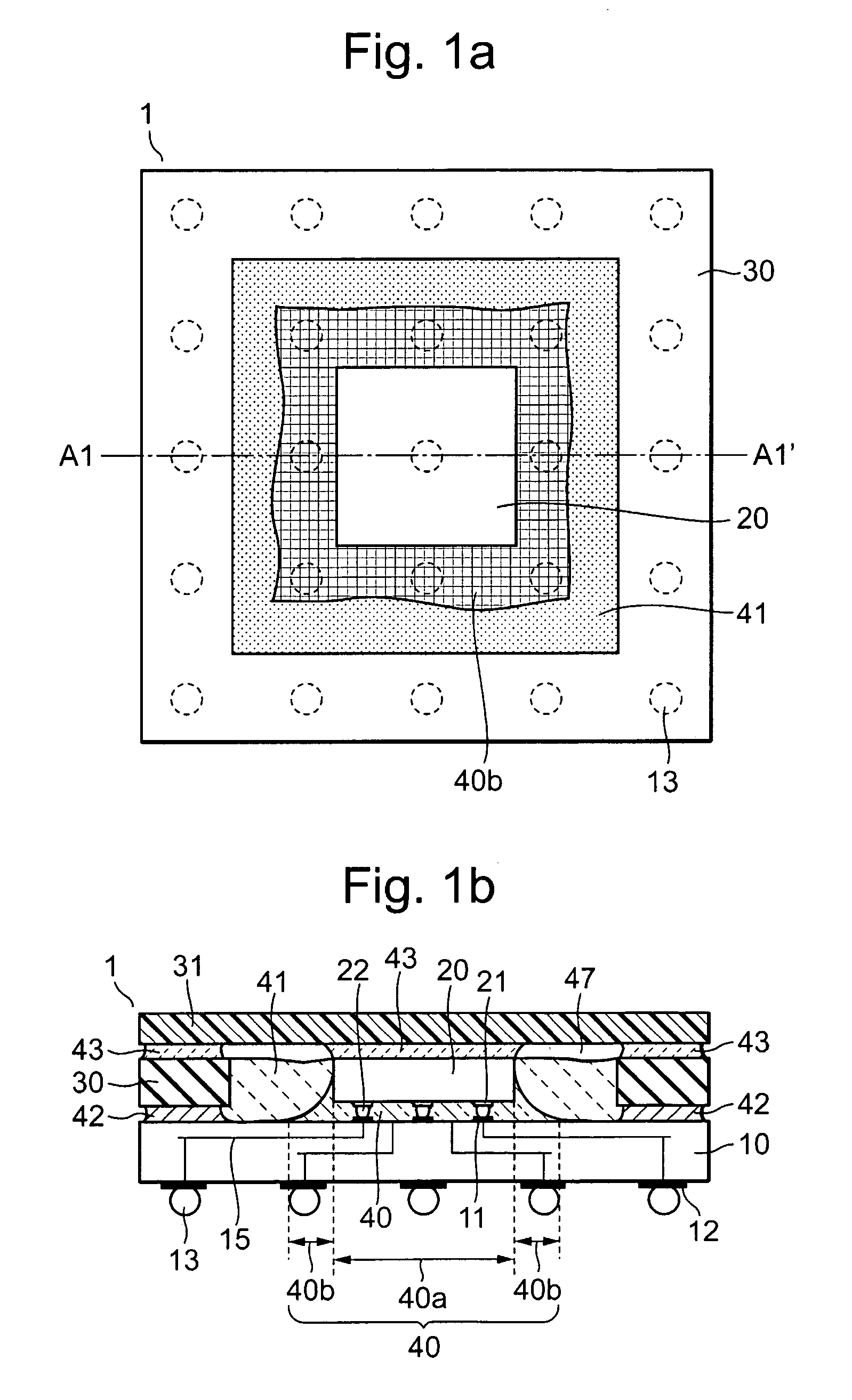

Warp-suppressed semiconductor device

InactiveUS7728440B2Suppression of deformationWarpage suppressionSemiconductor/solid-state device detailsSolid-state devicesAdhesiveSemiconductor chip

A semiconductor device includes: a semiconductor chip mounted on a mounting substrate; a first resin filling a gap between the chip and the substrate; a frame-shaped stiffener surrounding the chip; a first adhesive for bonding the stiffener to the substrate; a lid for covering the stiffener and an area surrounded by the stiffener; and a second resin filling a space between the stiffener and the chip. A thermal expansion coefficient of the second resin is smaller than that of the first resin. The first resin includes an underfill part filling a gap between the chip and the substrate and a fillet part extended from the chip region.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device, and method of manufacturing multilayer wiring board and semiconductor device

ActiveUS20100140800A1Avoid crackingReducing stress appliedSemiconductor/solid-state device detailsPrinted circuits stress/warp reductionSemiconductor chipEngineering

A semiconductor device includes a multilayer wiring board and a semiconductor chip mounted on the multilayer wiring board. Electrode pads of the semiconductor chip include: first electrode pads including electrode pads respectively disposed in the vicinity of corners of the back surface of the semiconductor chip; and second electrode pads other than the first electrode pads. Connection pads of the multilayer wiring board include: first connection pads connected to the first electrode pads via bumps; and second connection pads connected to the second electrode pads via bumps. The first connection pads are supported by a first insulating region made of a thermoplastic resin, and the second connection pads are supported by a second insulating region made of a thermosetting resin.

Owner:PANASONIC CORP

Methods and devices to treat nasal airways

ActiveUS20140316396A1Easy to breatheReduce airflow resistanceElectrotherapySurgical needlesNasal valveSurgery

Methods and devices for treating nasal airways are provided. Such devices and methods may improve airflow through an internal and / or external nasal valve, and comprise the use of mechanical re-shaping, energy application and other treatments to modify the shape, structure, and / or air flow characteristics of an internal nasal valve, an external nasal valve or other nasal airways.

Owner:AERIN MEDICAL INC

Semiconductor device and method of manufacturing the same

ActiveUS20040046185A1Improve featuresRelaxation stressSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorSilicon

There is provided a semiconductor device which comprises a first interlayer insulating film (first insulating film) formed over a silicon (semiconductor) substrate, a capacitor formed on the first interlayer insulating film and having a lower electrode, a dielectric film, and an upper electrode, a fourth interlayer insulating film (second insulating film) formed over the capacitor and the first interlayer insulating film, and a metal pattern formed on the fourth interlayer insulating film over the capacitor and its periphery to have a stress in an opposite direction to the fourth interlayer insulating film. As a result, characteristics of the capacitor covered with the interlayer insulating film can be improved.

Owner:FUJITSU SEMICON LTD

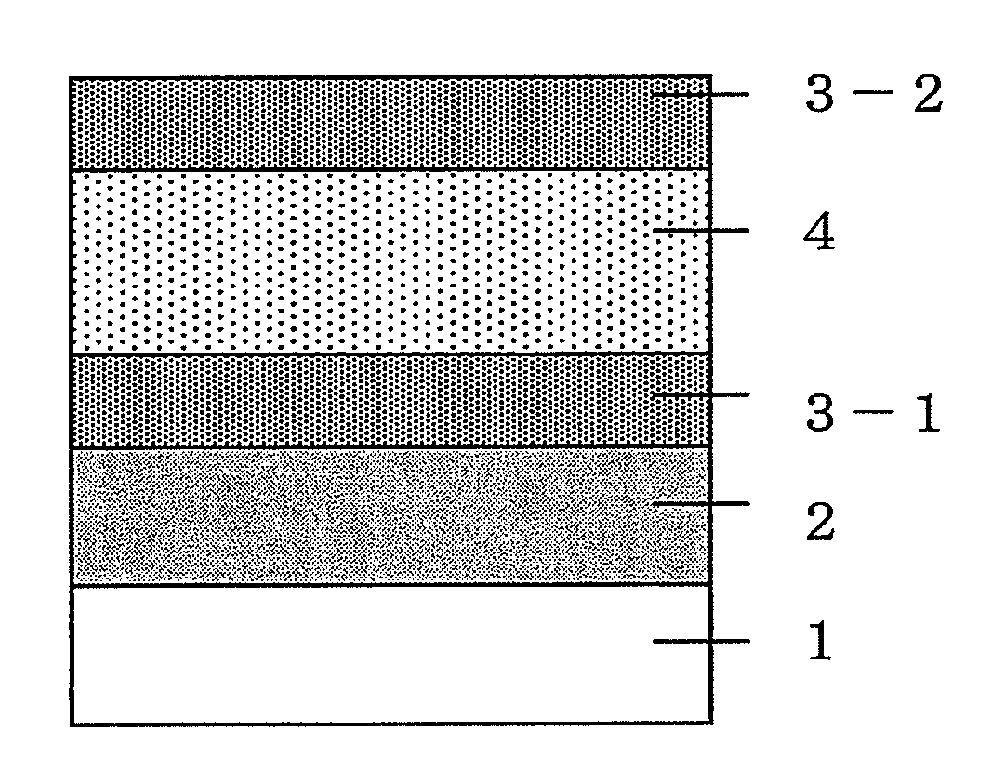

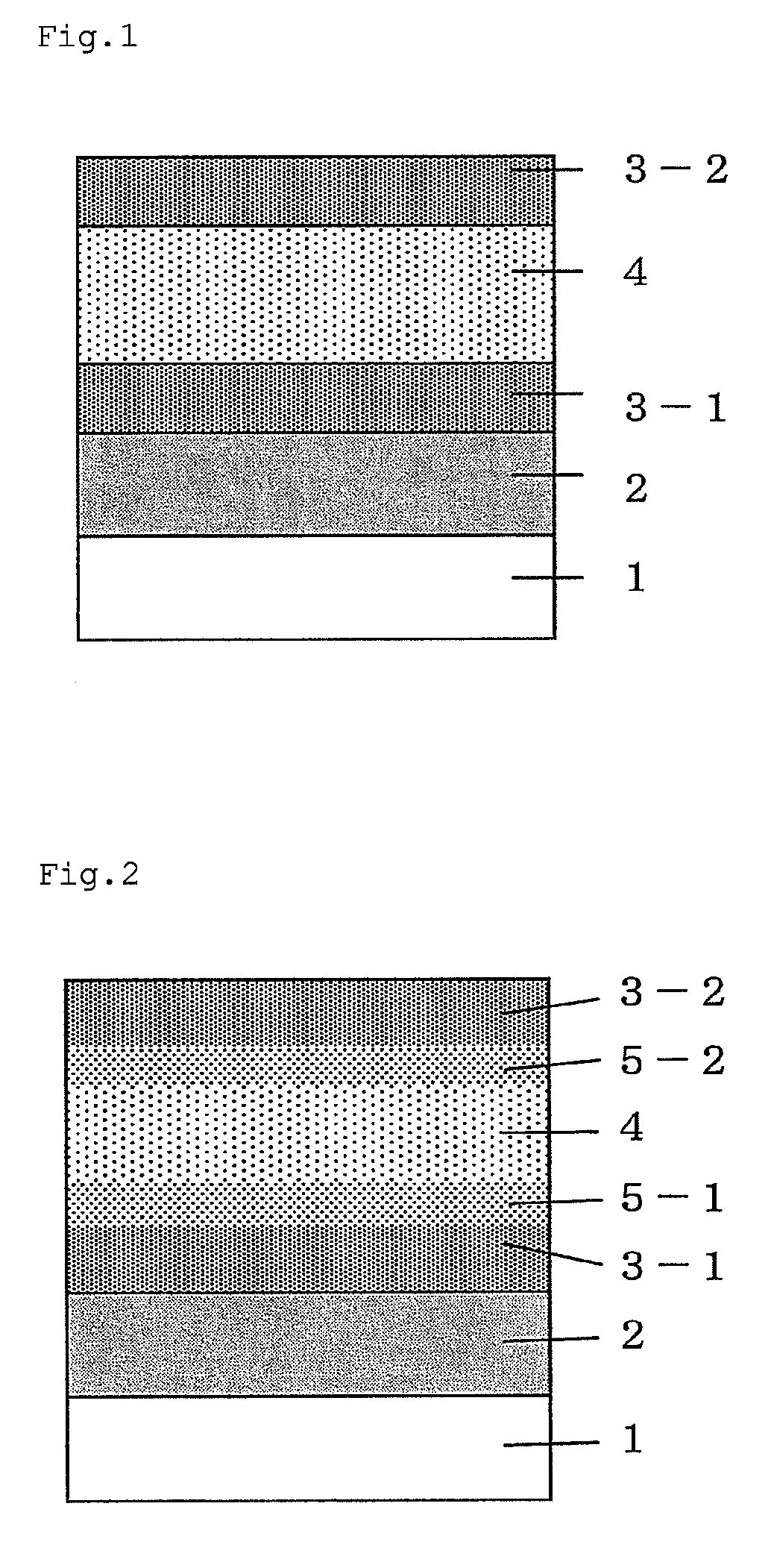

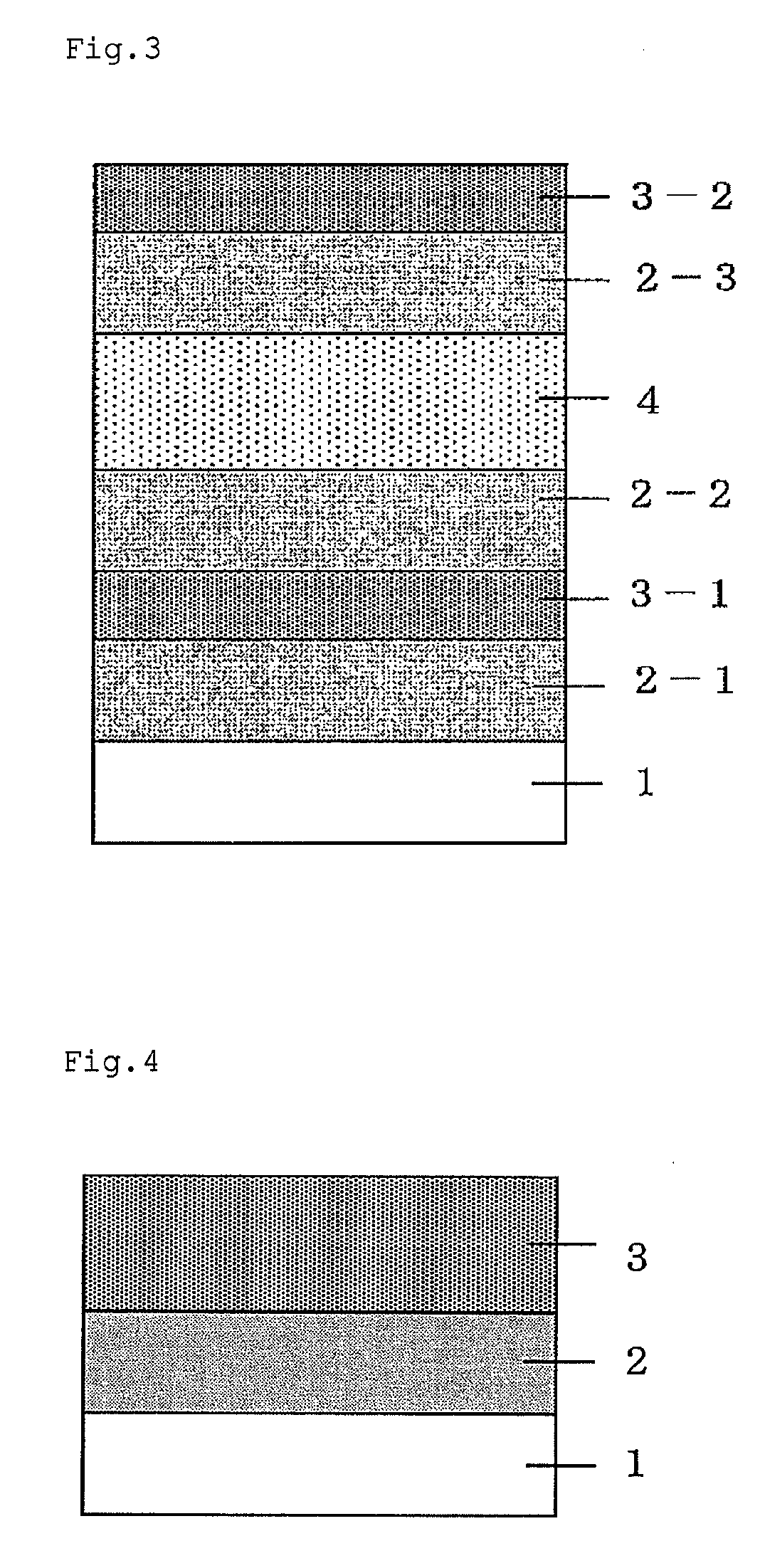

Multilayer thin film and its fabrication process as well as electron device

InactiveUS20020015852A1Preferential (001) orientationRelaxation stressPolycrystalline material growthFrom chemically reactive gasesFerroelectric thin filmsOptoelectronics

Owner:SNAPTRACK

Gas-barrier film and organic device comprising same

InactiveUS20090072230A1Improve water vapor barrier performanceImprove the immunityLiquid crystal compositionsLayered productsMaterials scienceGas barrier

Owner:FUJIFILM CORP

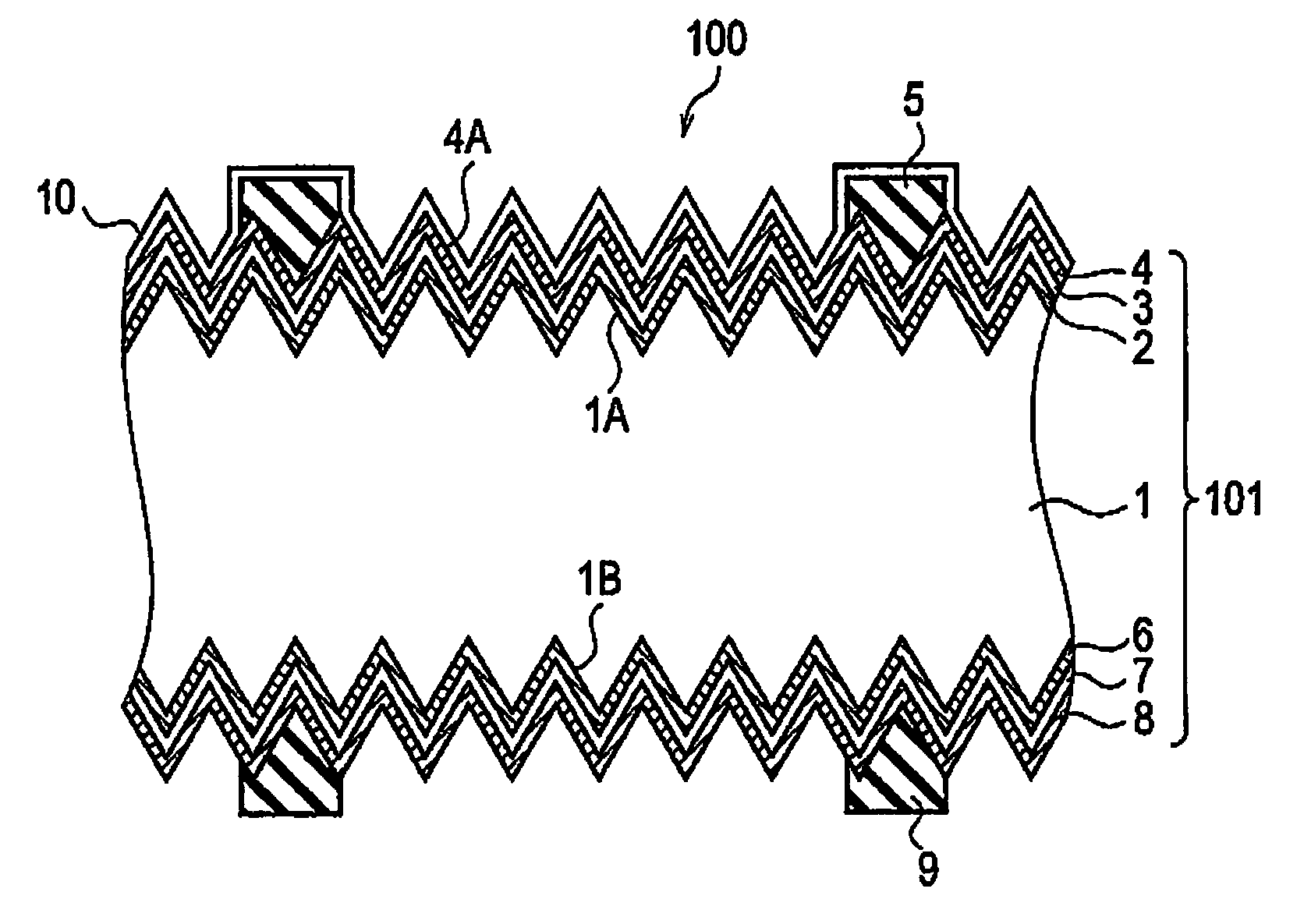

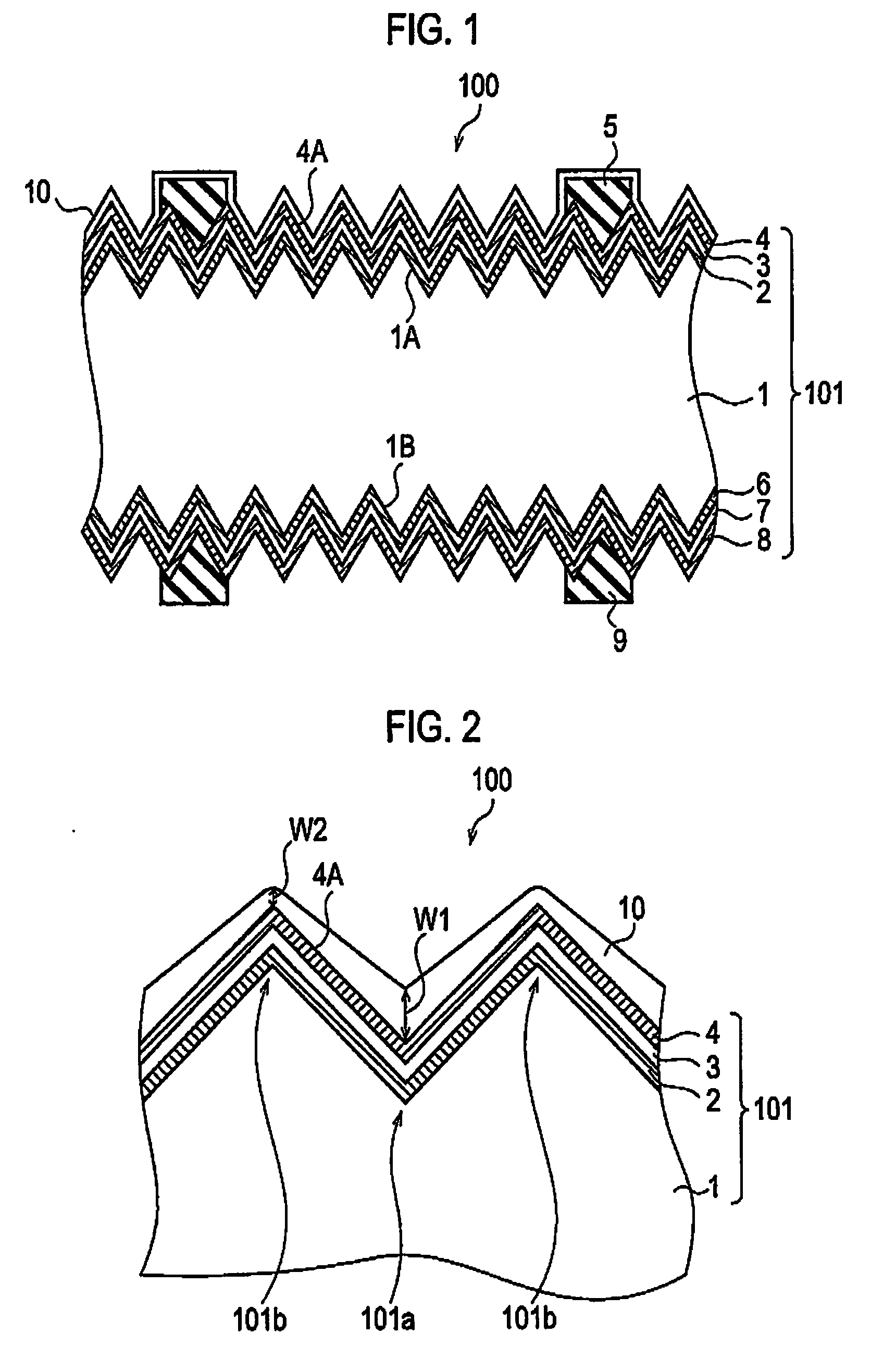

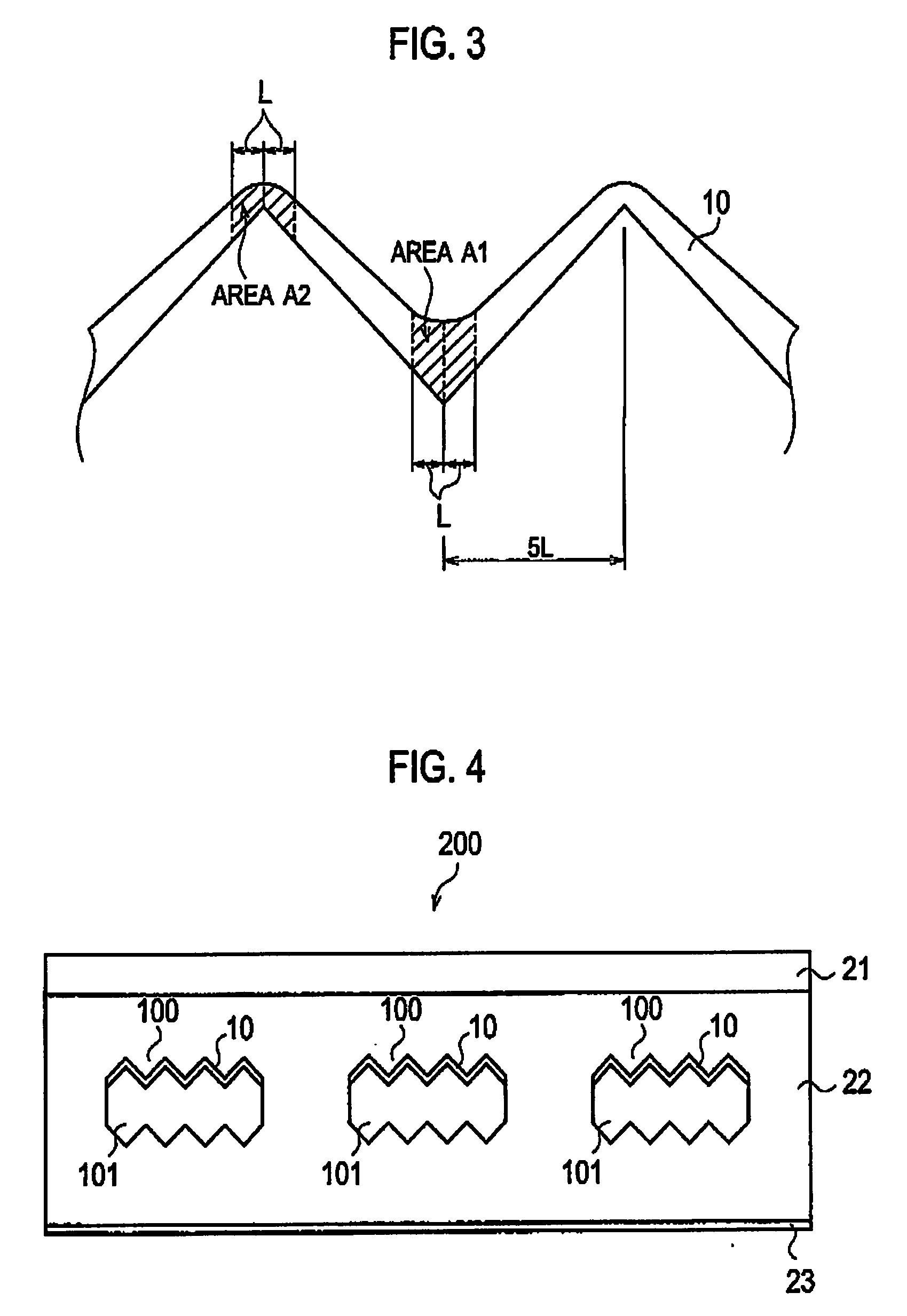

Solar cell module

InactiveUS20100006147A1Relieve pressureReduce warpagePhotovoltaic energy generationSemiconductor devicesPhotoelectric conversionEngineering

A solar cell module includes: a photoelectric conversion body 101 having an uneven surface on a light-entering surface; and a protection layer 10 made of a resin and provided to cover the uneven surface. In a cross section of the protection layer 10 taken in parallel to a light-entering direction, a thickness W2 of a projected portion on the uneven surface is smaller than a thickness W1 of a recessed portion on the uneven surface.

Owner:SANYO ELECTRIC CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com