Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

36 results about "Smart Cut" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Smart cut is a technological process that enables the transfer of very fine layers of crystalline silicon material onto a mechanical support. It was invented by Michel Bruel of CEA-Leti, and is protected by US patent 5374564. The application of this technological procedure is mainly in the production of silicon-on-insulator (SOI) wafer substrates.

Method of manufacturing a semiconductor device

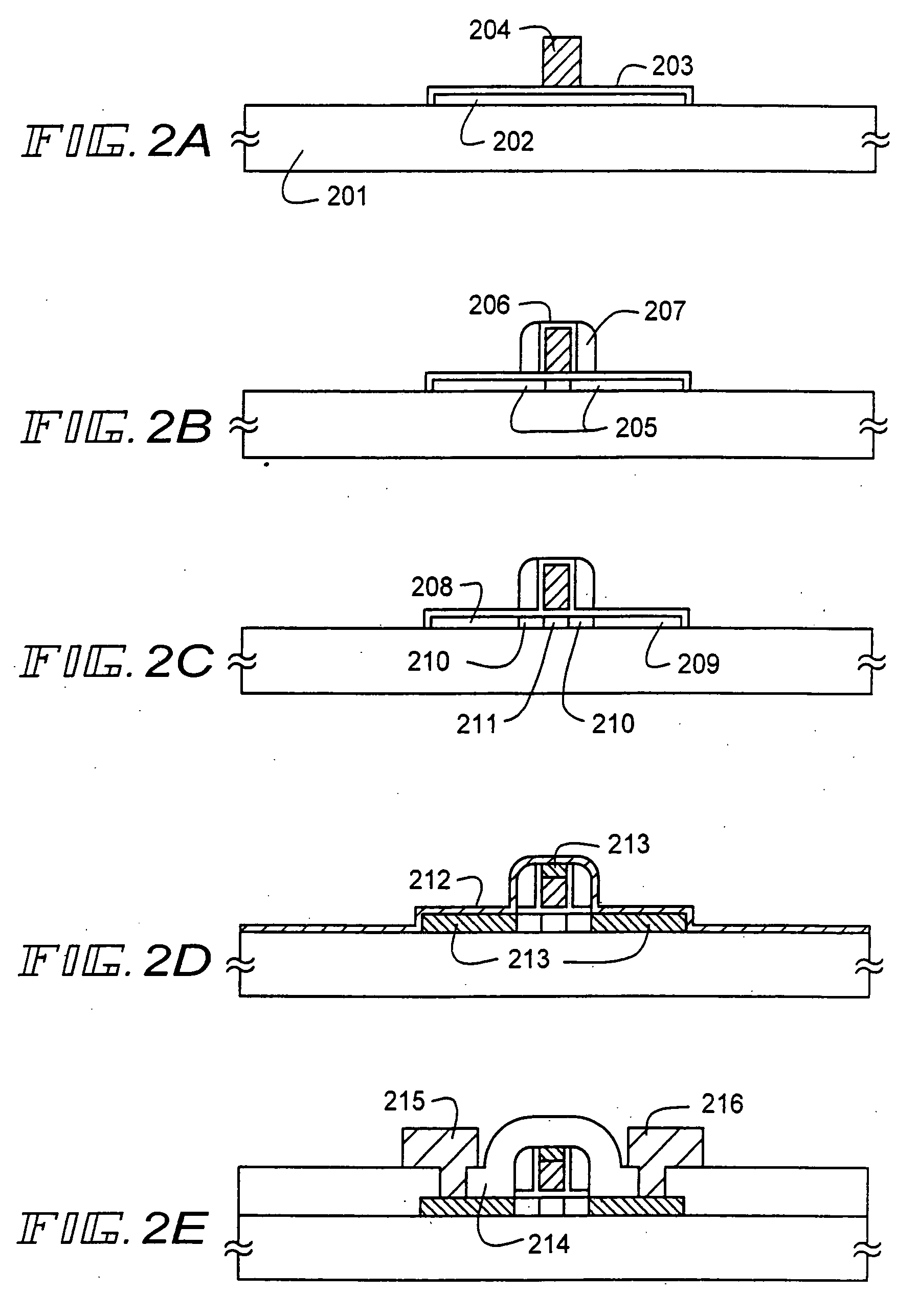

InactiveUS7199024B2Relaxation stressGuaranteed uptimeTransistorSolid-state devicesSmart CutSemiconductor

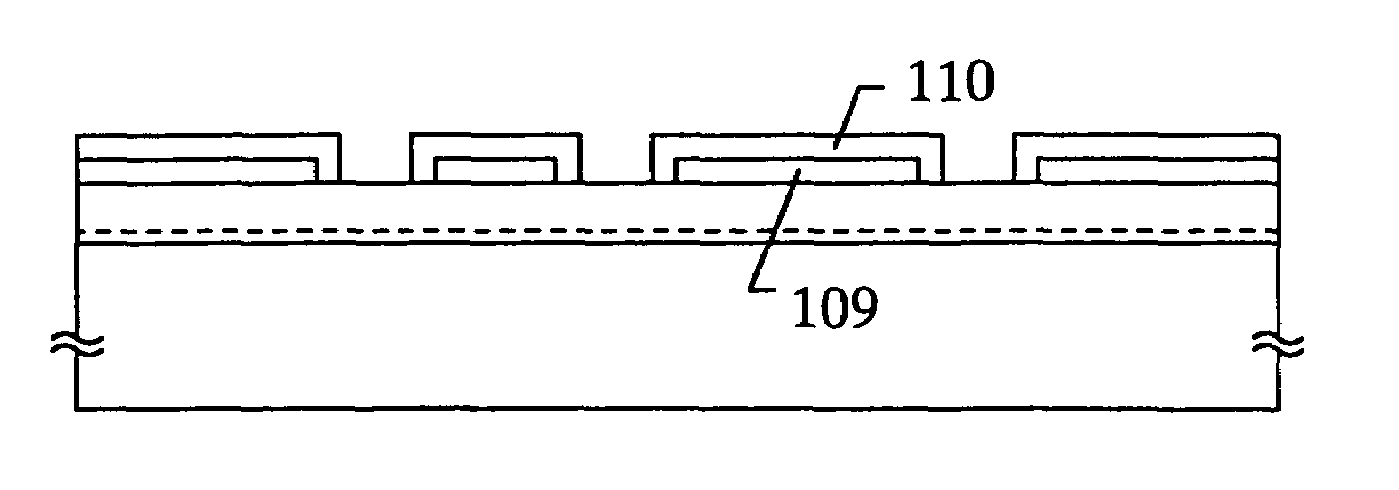

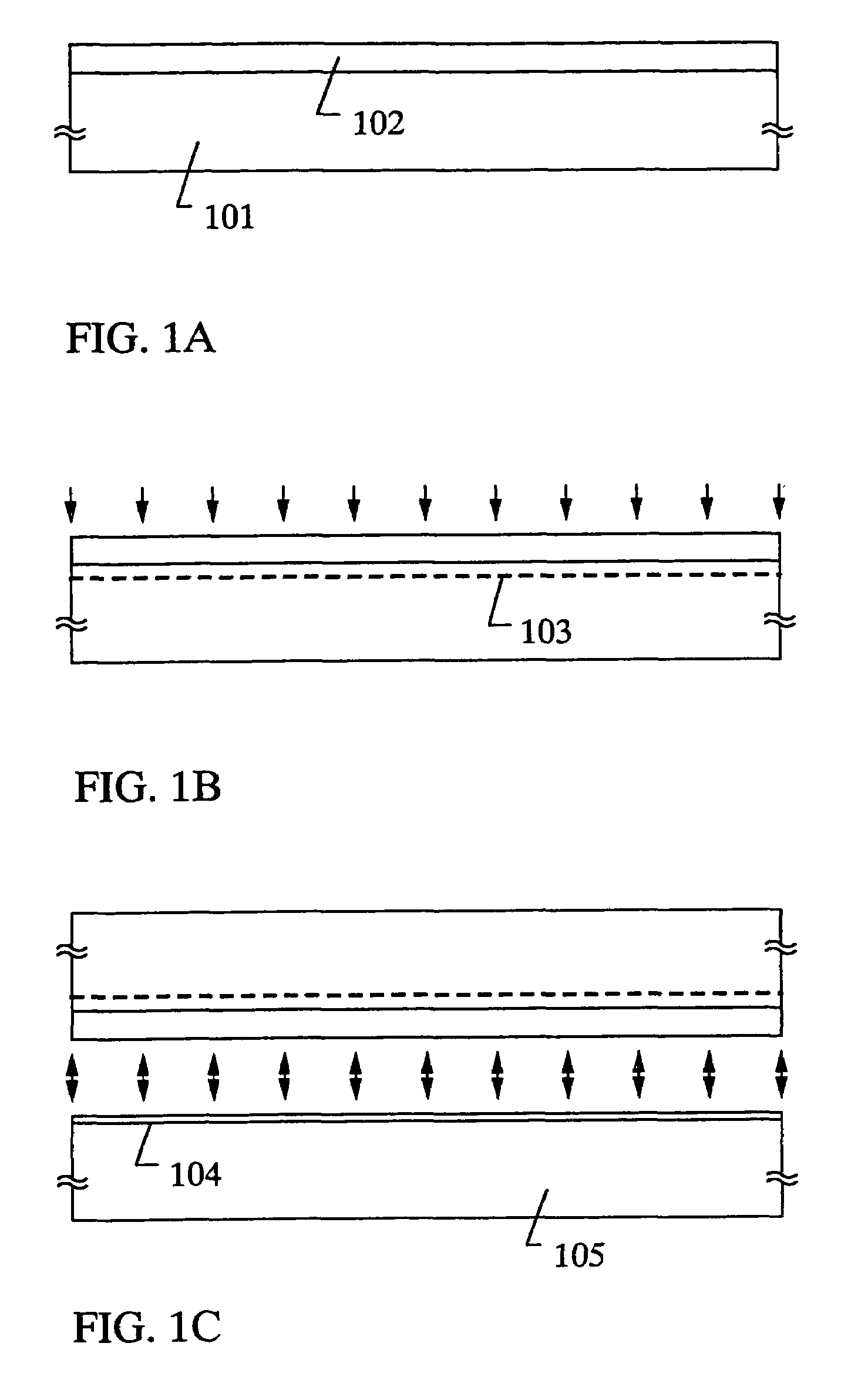

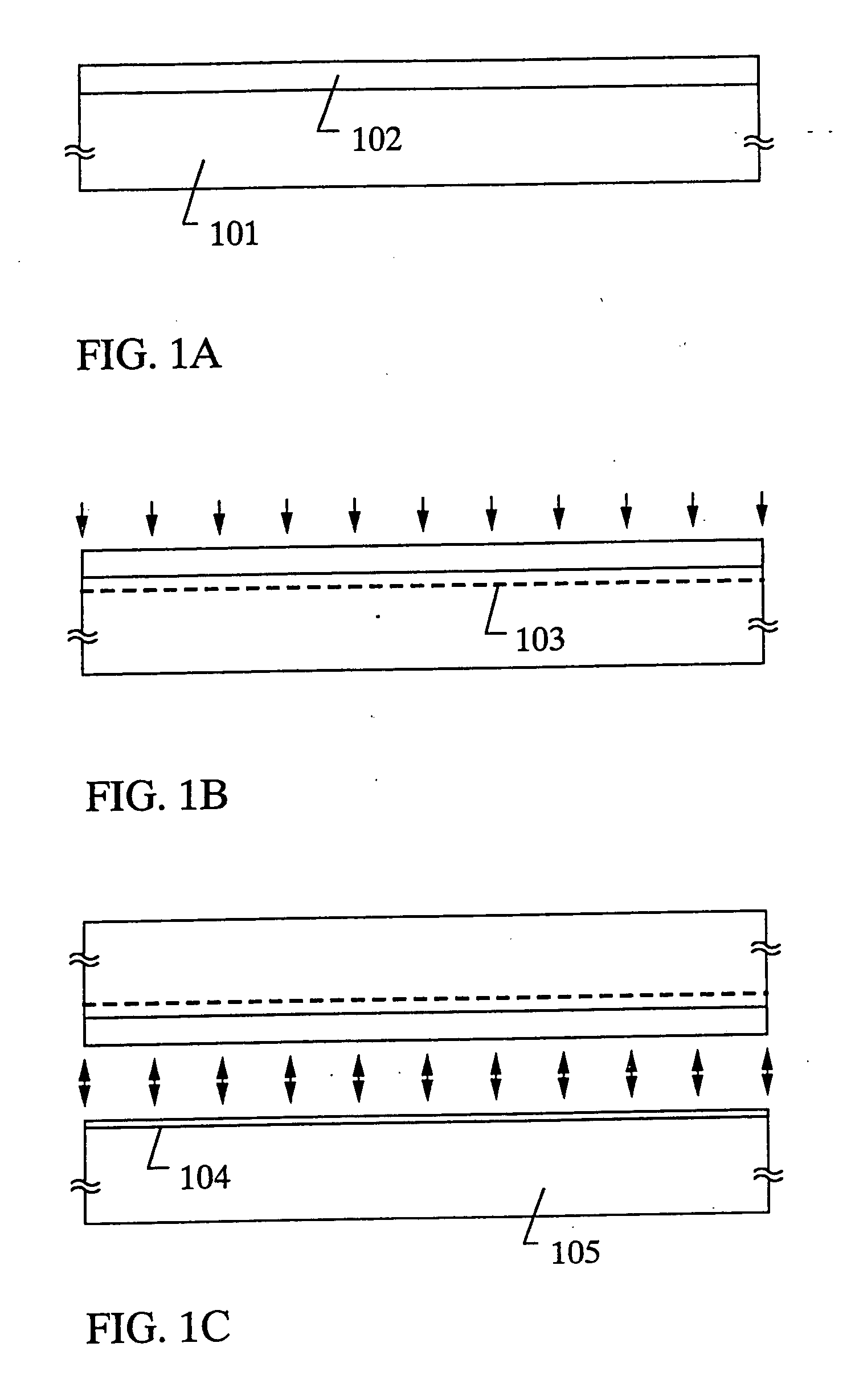

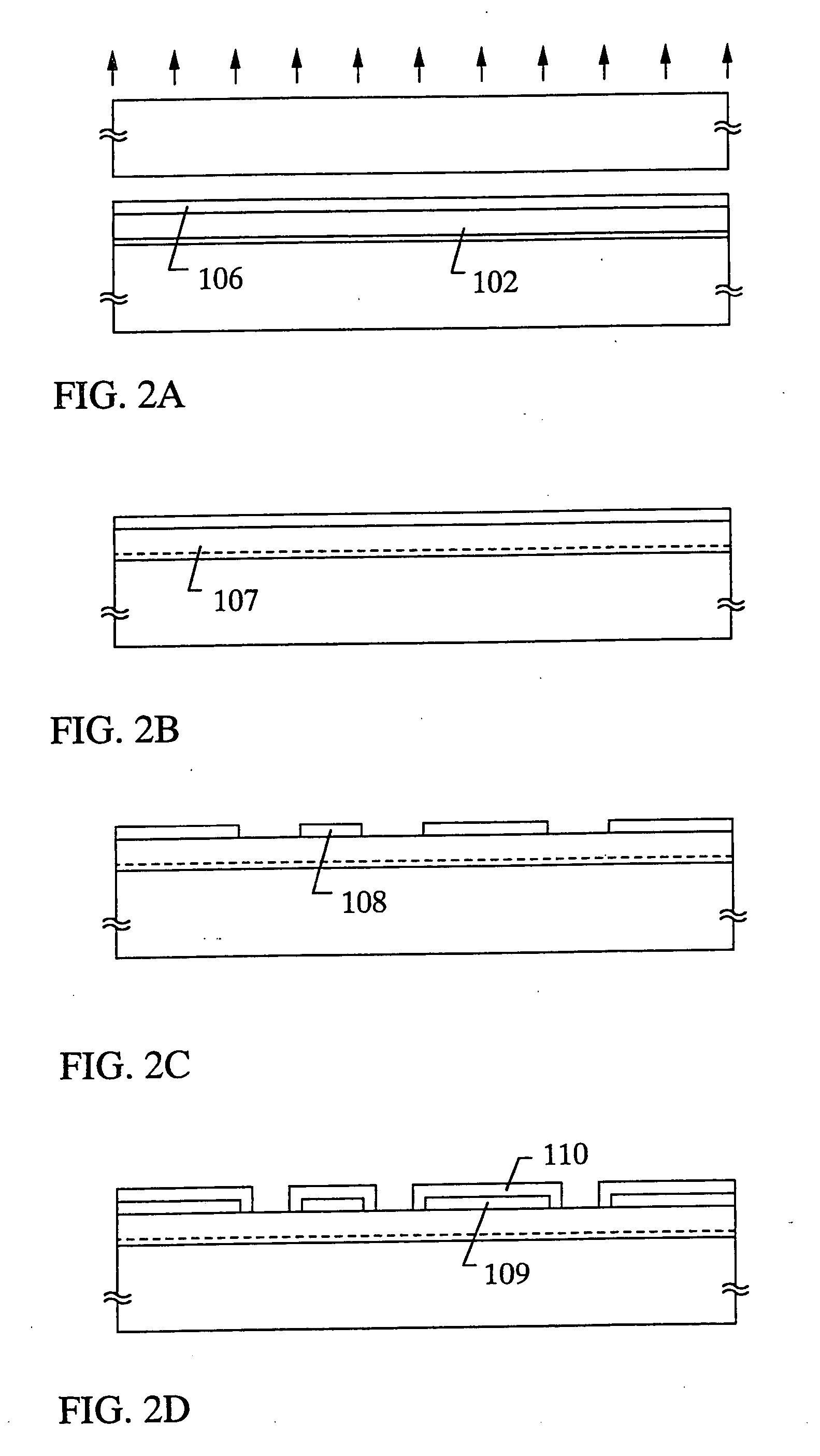

There is provided a method of removing trap levels and defects, which are caused by stress, from a single crystal silicon thin film formed by an SOI technique. First, a single crystal silicon film is formed by using a typical bonding SOI technique such as Smart-Cut or ELTRAN. Next, the single crystal silicon thin film is patterned to form an island-like silicon layer, and then, a thermal oxidation treatment is carried out in an oxidizing atmosphere containing a halogen element, so that an island-like silicon layer in which the trap levels and the defects are removed is obtained.

Owner:SEMICON ENERGY LAB CO LTD

Method of manufacturing a semiconductor device

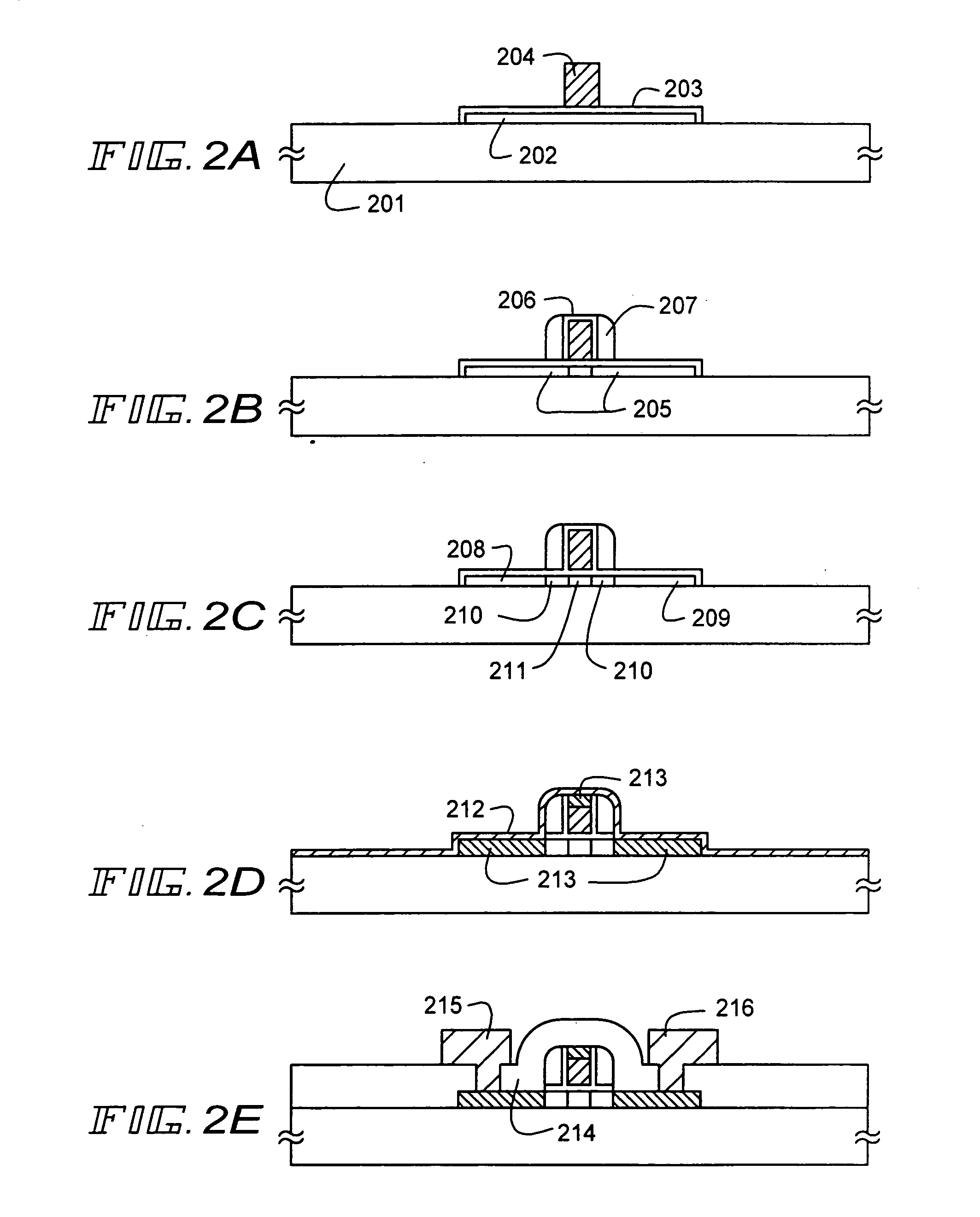

InactiveUS20070173000A1Improve business performanceImprove performanceTransistorSolid-state devicesDevice materialSmart Cut

There is provided a method of removing trap levels and defects, which are caused by stress, from a single crystal silicon thin film formed by an SOI technique. First, a single crystal silicon film is formed by using a typical bonding SOI technique such as Smart-Cut or ELTRAN. Next, the single crystal silicon thin film is patterned to form an island-like silicon layer, and then, a thermal oxidation treatment is carried out in an oxidizing atmosphere containing a halogen element, so that an island-like silicon layer in which the trap levels and the defects are removed is obtained.

Owner:SEMICON ENERGY LAB CO LTD

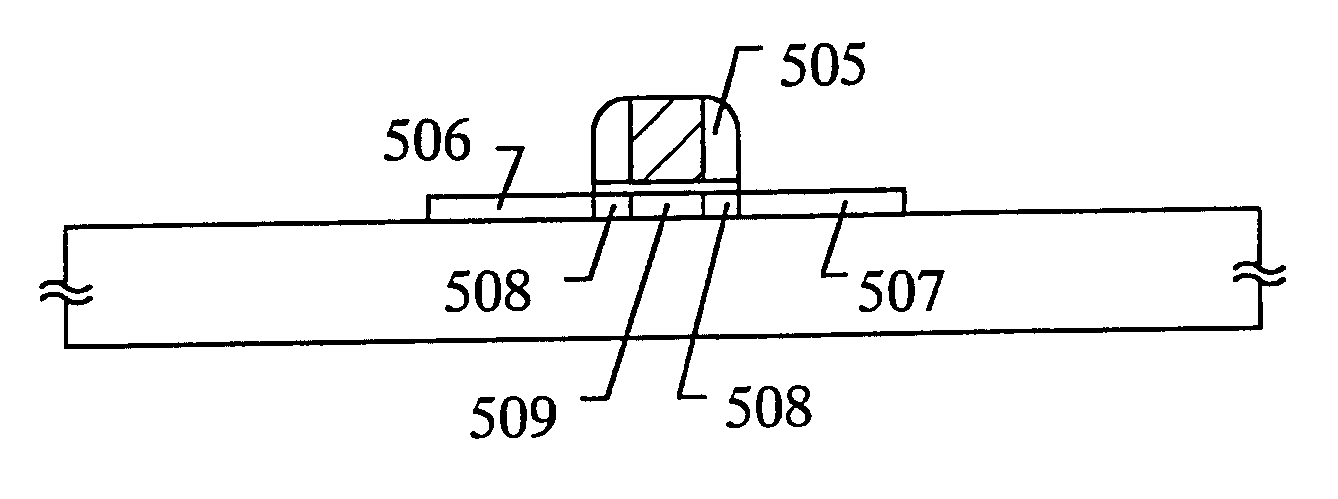

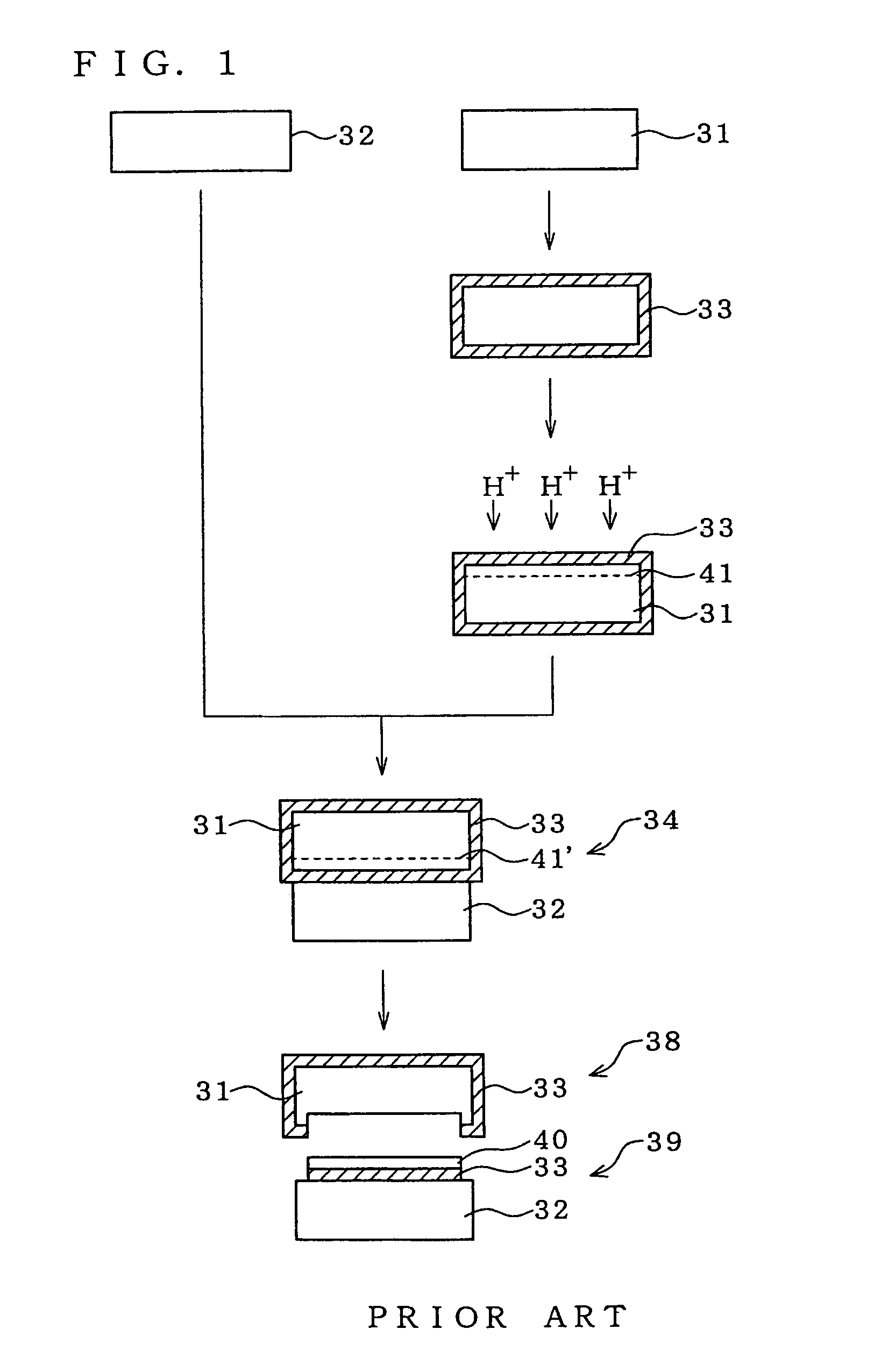

Method of fabricating a semiconductor device

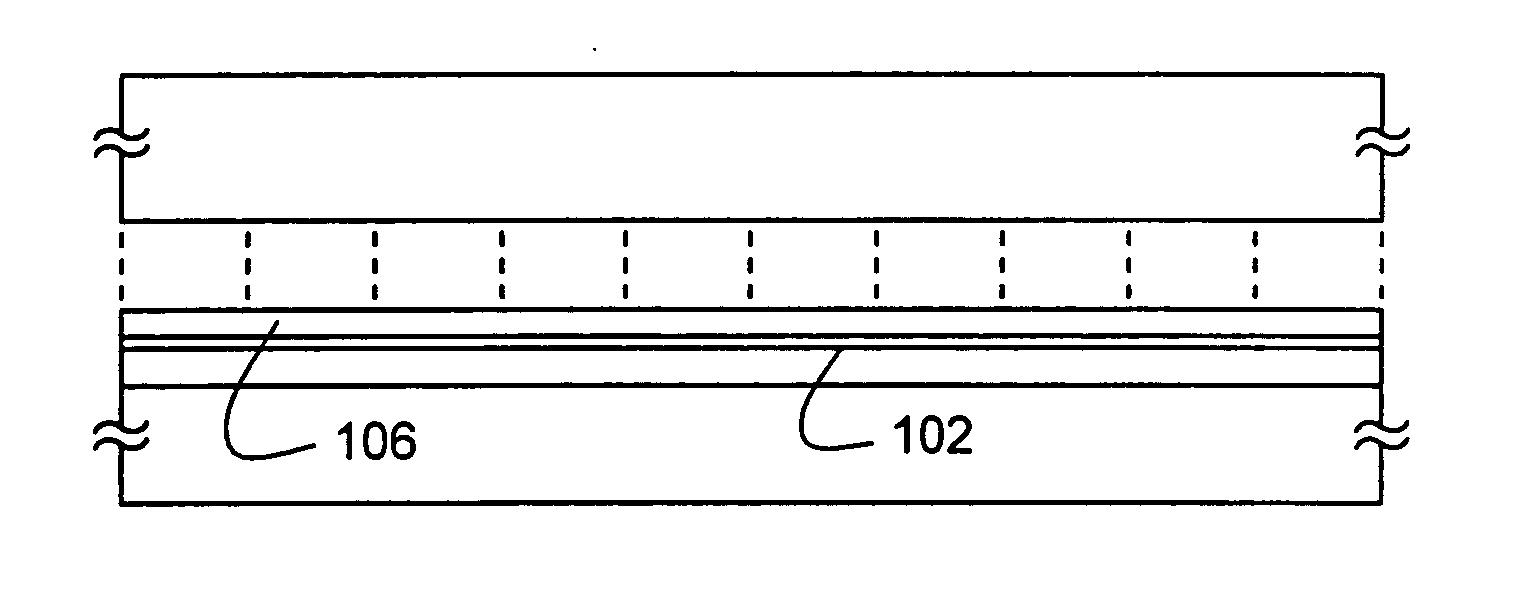

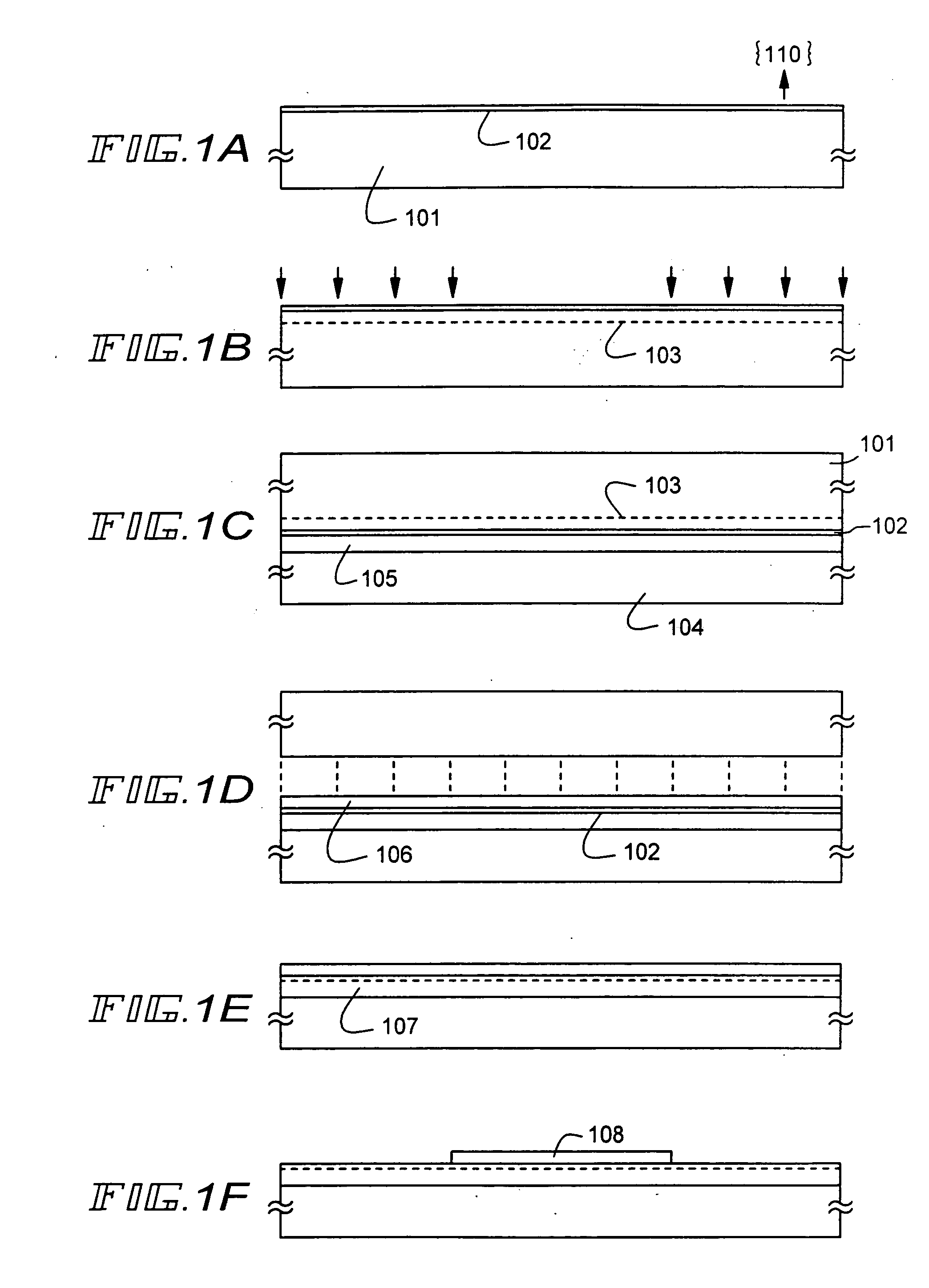

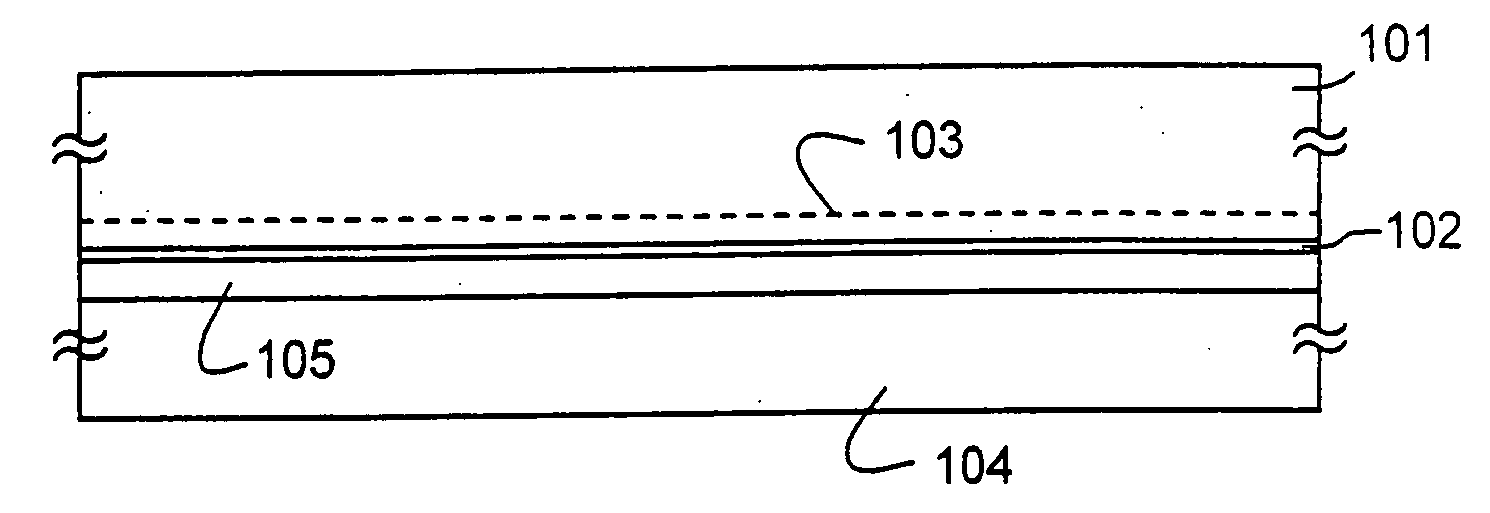

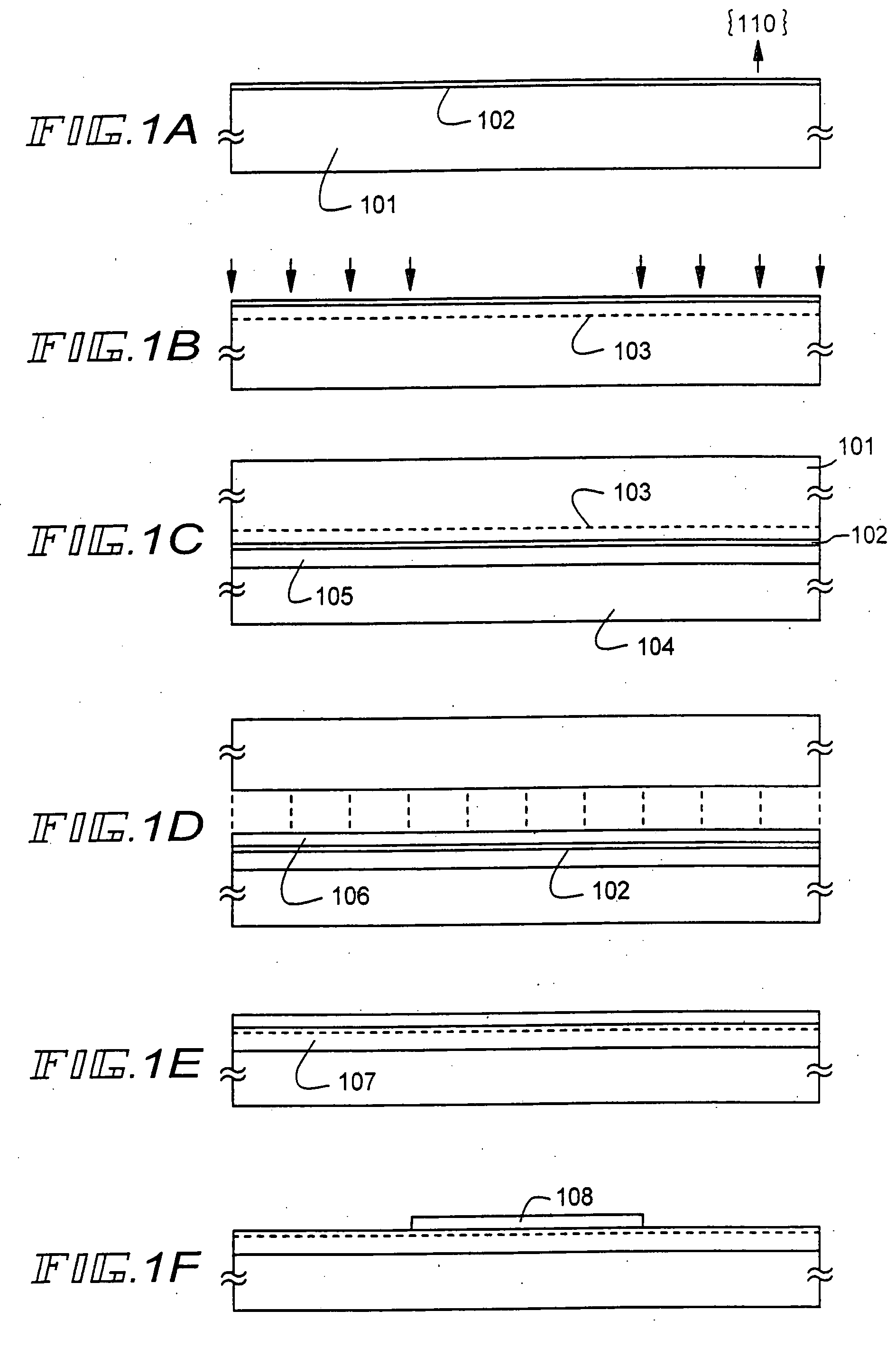

A semiconductor device with high reliability is provided using an SOI substrate. When the SOI substrate is fabricated by using a technique typified by SIMOX, ELTRAN, or Smart-Cut, a single crystal semiconductor substrate having a main surface (crystal face) of a {110} plane is used. In such an SOI substrate, adhesion between a buried insulating layer as an under layer and a single crystal silicon layer is high, and it becomes possible to realize a semiconductor device with high reliability.

Owner:SEMICON ENERGY LAB CO LTD

Method of fabricating a semiconductor device

A semiconductor device with high reliability is provided using an SOI substrate. When the SOI substrate is fabricated by using a technique typified by SIMOX, ELTRAN, or Smart-Cut, a single crystal semiconductor substrate having a main surface (crystal face) of a {110} plane is used. In such an SOI substrate, adhesion between a buried insulating layer as an under layer and a single crystal silicon layer is high, and it becomes possible to realize a semiconductor device with high reliability.

Owner:SEMICON ENERGY LAB CO LTD

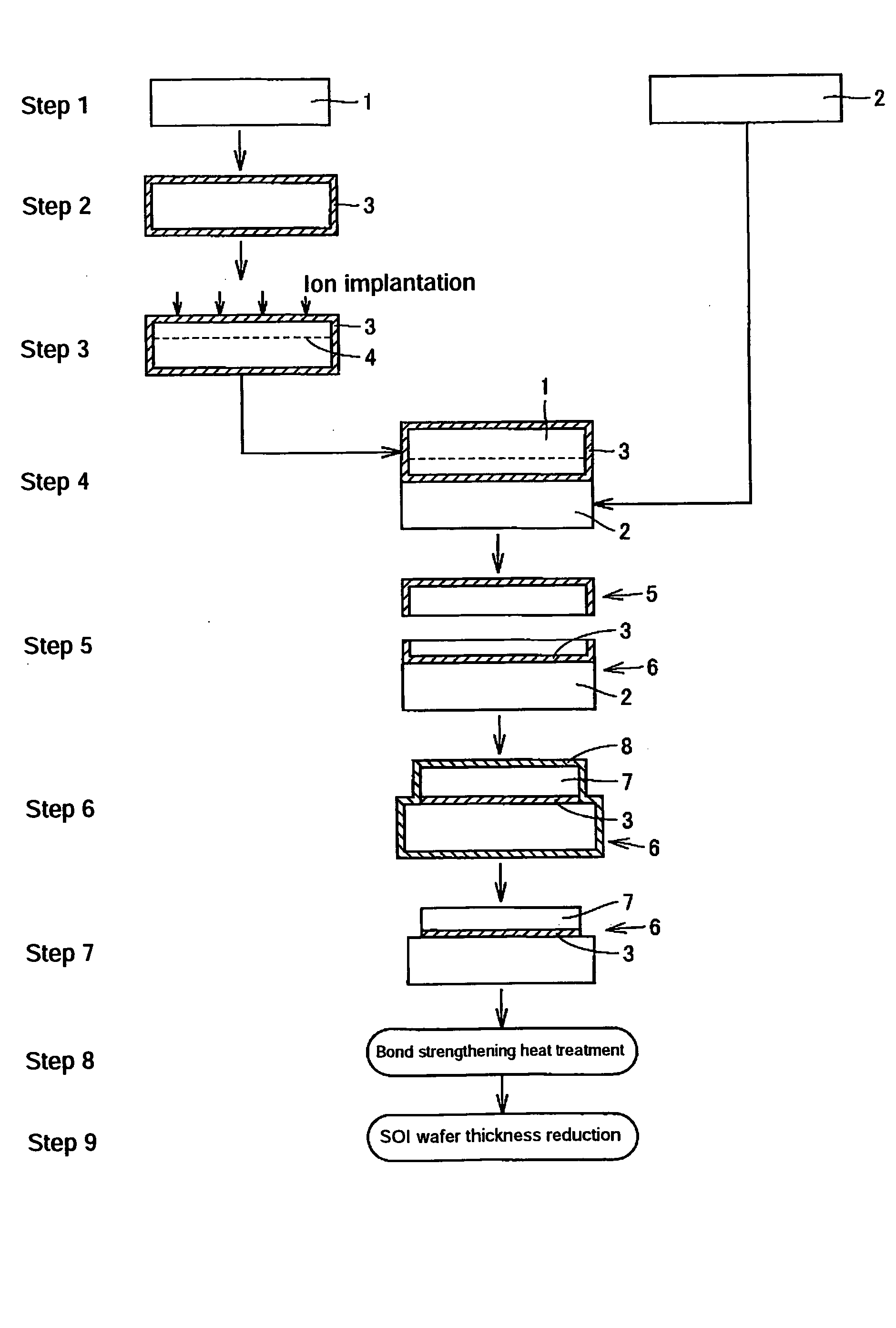

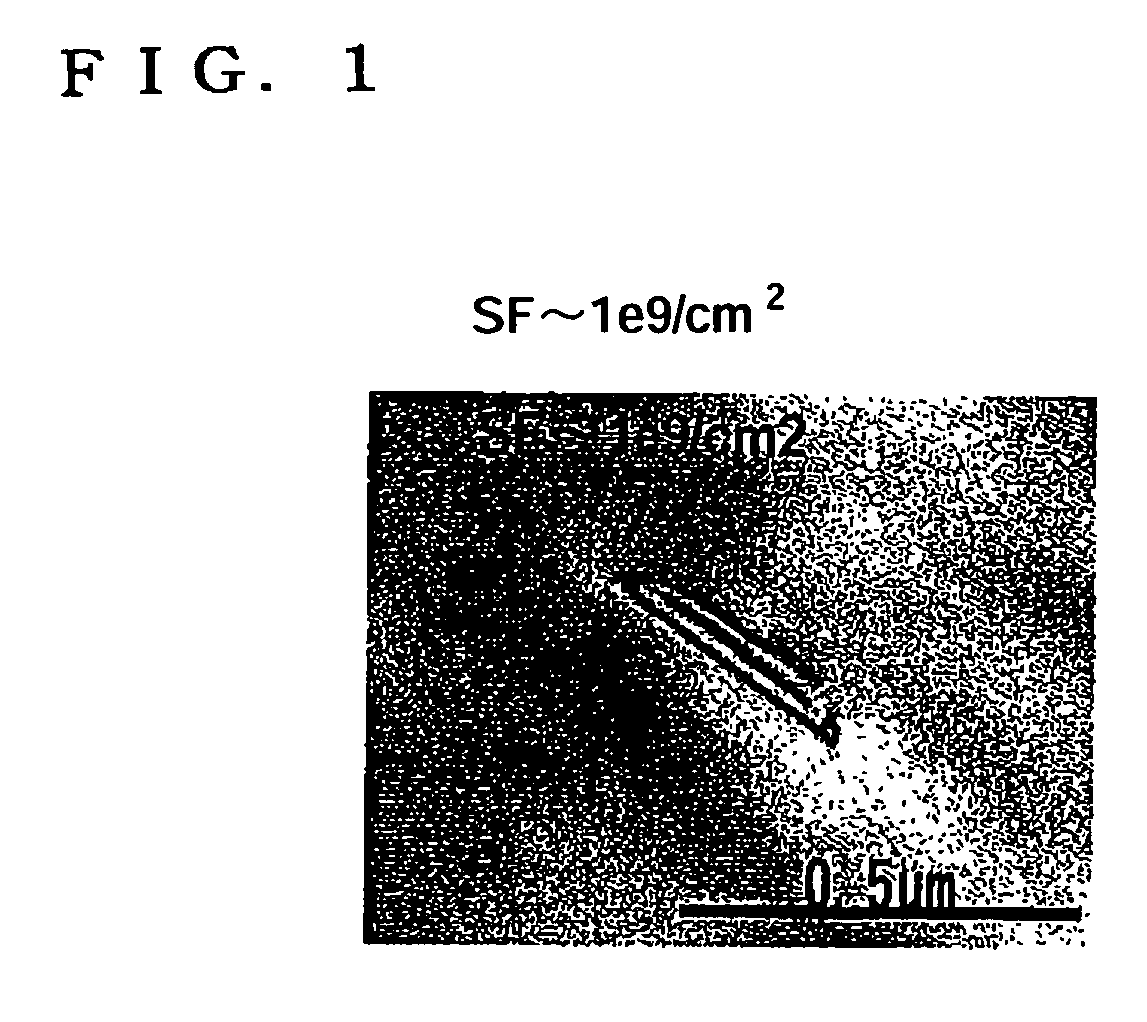

SOI wafer production method

InactiveUS20060177991A1Without deteriorating uniformity in SOI layer thicknessPromote lowerSemiconductor/solid-state device manufacturingWaferingStacking fault

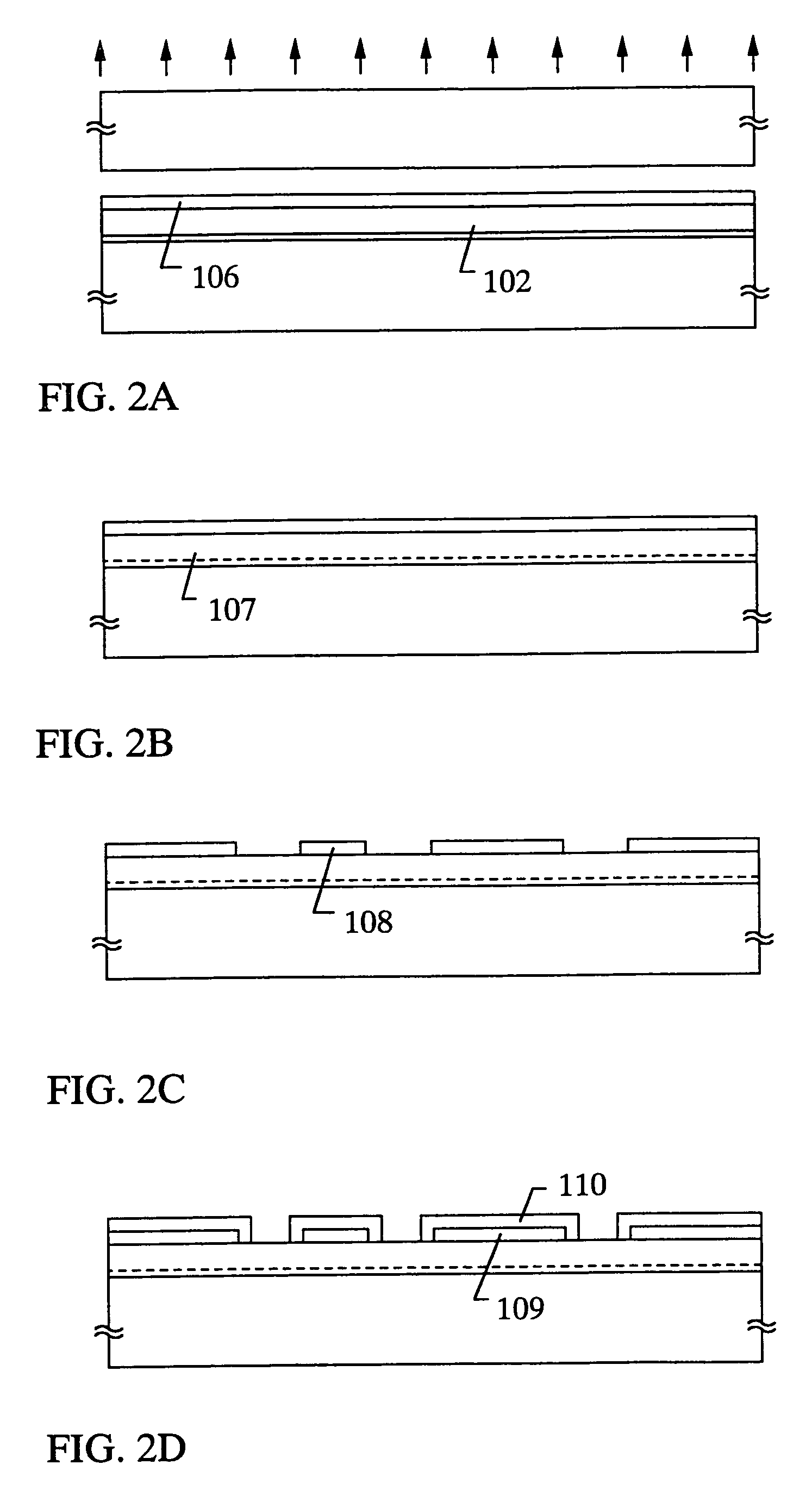

By using, in the so-called Smart Cut process comprising the steps of bonding an ion-implanted active layer wafer to a base wafer and later splitting off the base wafer to produce a SOI wafer, a wafer doped with C in a single crystal ingot growing process (desirably to a carbon concentration of not lower than 1×1016 atoms / cm3) as the active layer wafer, it becomes possible to exhibit the effect of inhibiting agglomeration of interstitial Si atoms and prevent development of stacking faults even when the SOI wafer is subjected to thermal oxidation treatment. Furthermore, the technique of sacrificial oxidation can be applied to production of SOI wafers and, thus, a damaged layer formed on the SOI layer surface can be removed and surface roughness can be improved without impairing crystalline integrity and, further, SOI layer thickness can be efficiently reduced.

Owner:SUMCO CORP

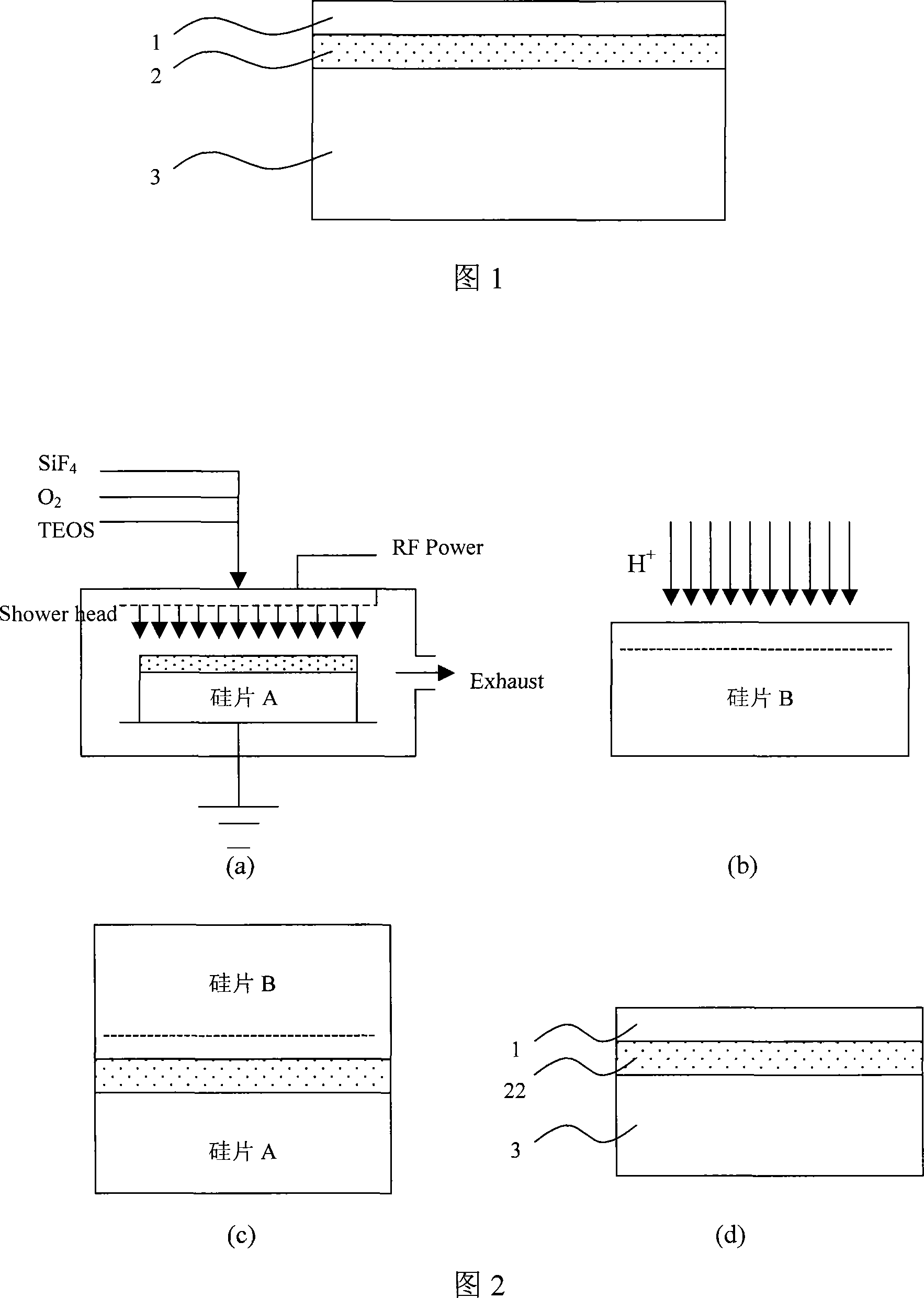

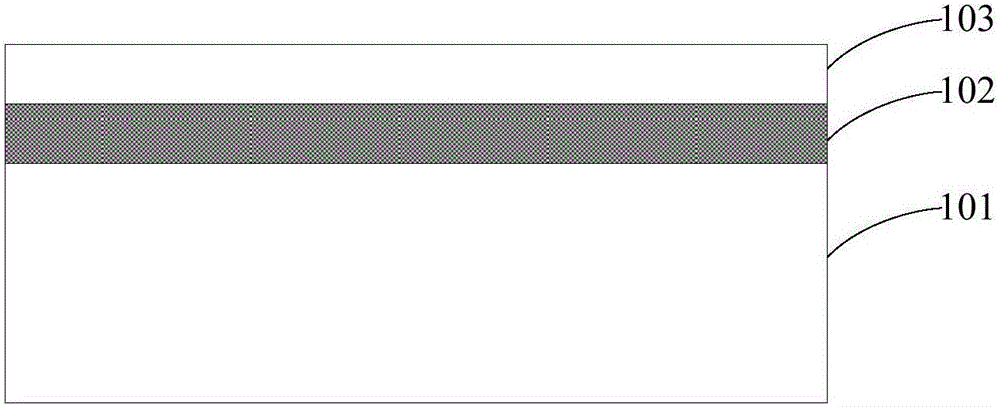

Insulating layer upper semiconductor structure with low dielectric constant as insulation buried layer and its method

InactiveCN101174640AReduce capacitanceIncrease the equivalent impedanceTransistorSolid-state devicesCapacitanceLow noise

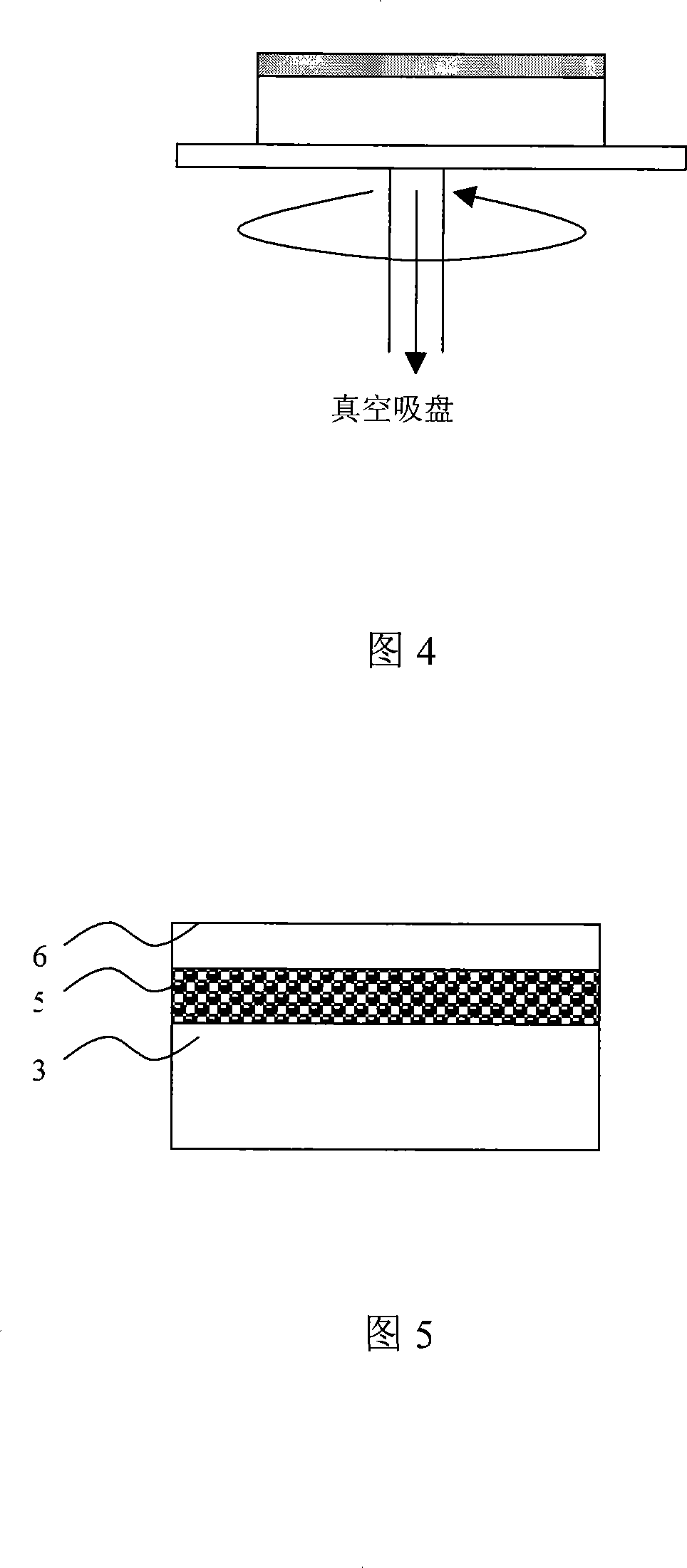

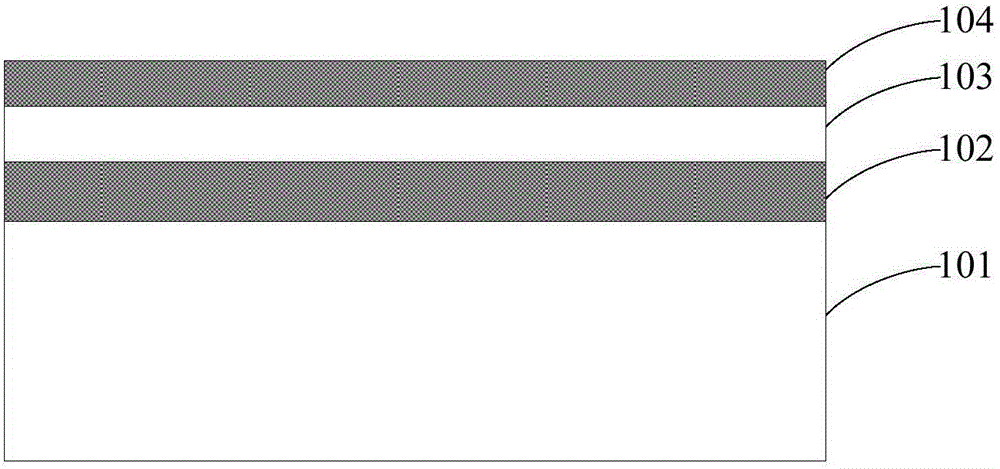

The invention provides a semiconductor structure on an insulation layer with low dielectric constant material as the insulation buried layer and the preparation method thereof, which belongs to the microelectronic semiconductor material and the preparation craft thereof. The invention is characterized in that the structure comprises three layers: a semiconductor layer at the top, an insulation buried layer with the relative dielectric constant being smaller than 4.2 in the middle and a silicon substrate on the lower layer. The preparation is characterized in that low dielectric constant film is prepared on a silicon wafer by utilizing methods such as a chemical vapor deposition method or a sol gel method, then linked with the silicon wafer containing the semiconductor layer, and the transfer of the semiconductor layer at the top is realized by adopting a smart-cut technology or a back grinding technology. The low dielectric constant material is adopted to replace the prior SiO2 buried layer in the silicon (SOI) on the insulation layer, in order to reduce the capacitance of the insulation buried layer, thus increasing the equivalent impedance (1 / 2 Pi fC) of the buried layer under high frequency, therefore, compared with the prior SOI substrate material, the invention can reduce the signal crosstalk via the substrate under high frequency, thereby being more suitable for the requirement of a low-noise SOI circuit.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI +1

Device for polishing the edge of a semiconductor substrate

InactiveUS20100190416A1Less materialImprove product qualityEdge grinding machinesRevolution surface grinding machinesSmart CutEngineering

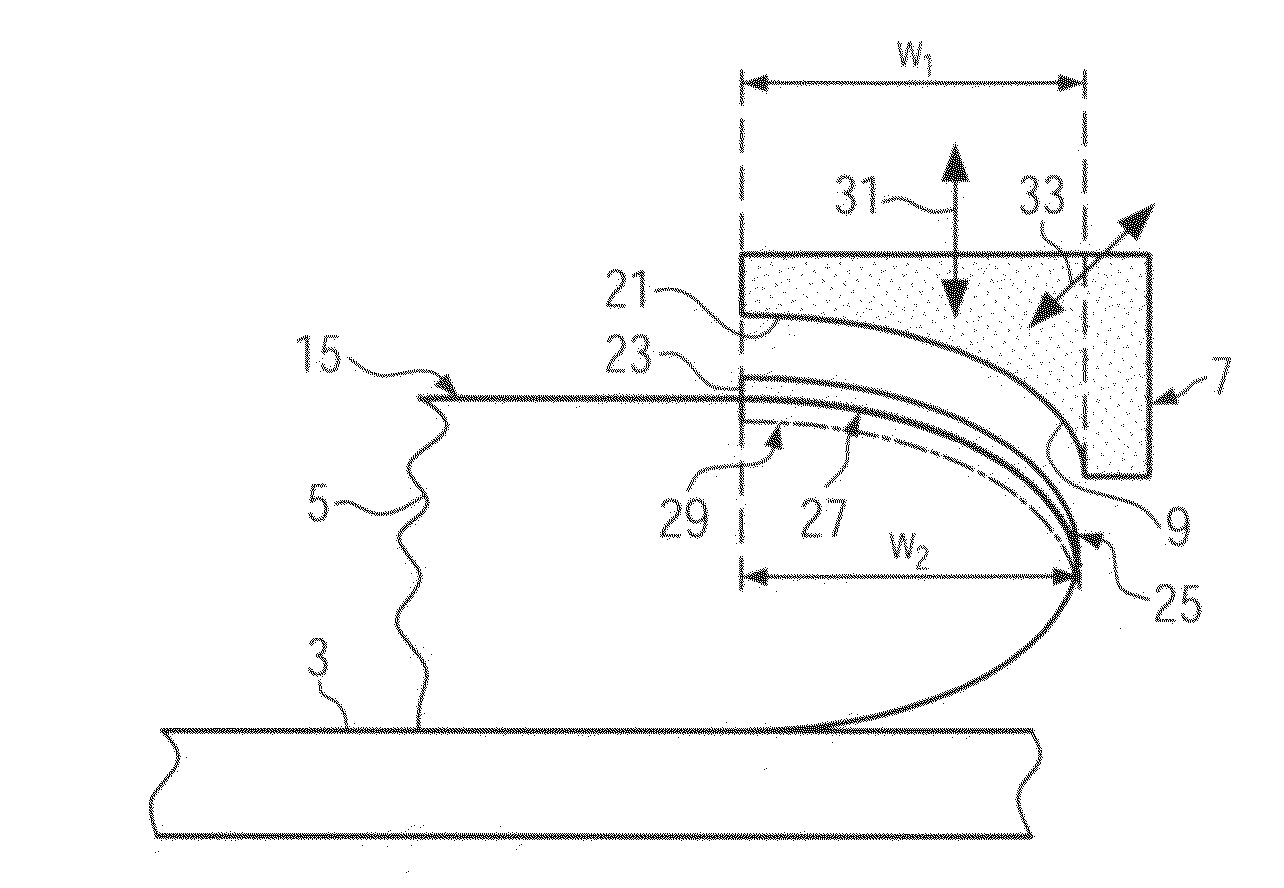

Disclosed are devices and methods for chemical and mechanical polishing of the edge of a semiconductor substrate that includes a protruding residual topography in a peripheral region of the substrate resulting from a layer transfer process based on an ion implantation step, a bonding step and a detachment step, such as Smart-Cut™. To be able to remove this step-like region, exemplary devices include a polishing pad, wherein the polishing pad is arranged and configured such that its cross section in a plane perpendicular to the surface of a substrate holder is curved. The disclosure furthermore relates to a pad holder used certain exemplary devices and methods for polishing a semiconductor substrate that has a protruding residual topography.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

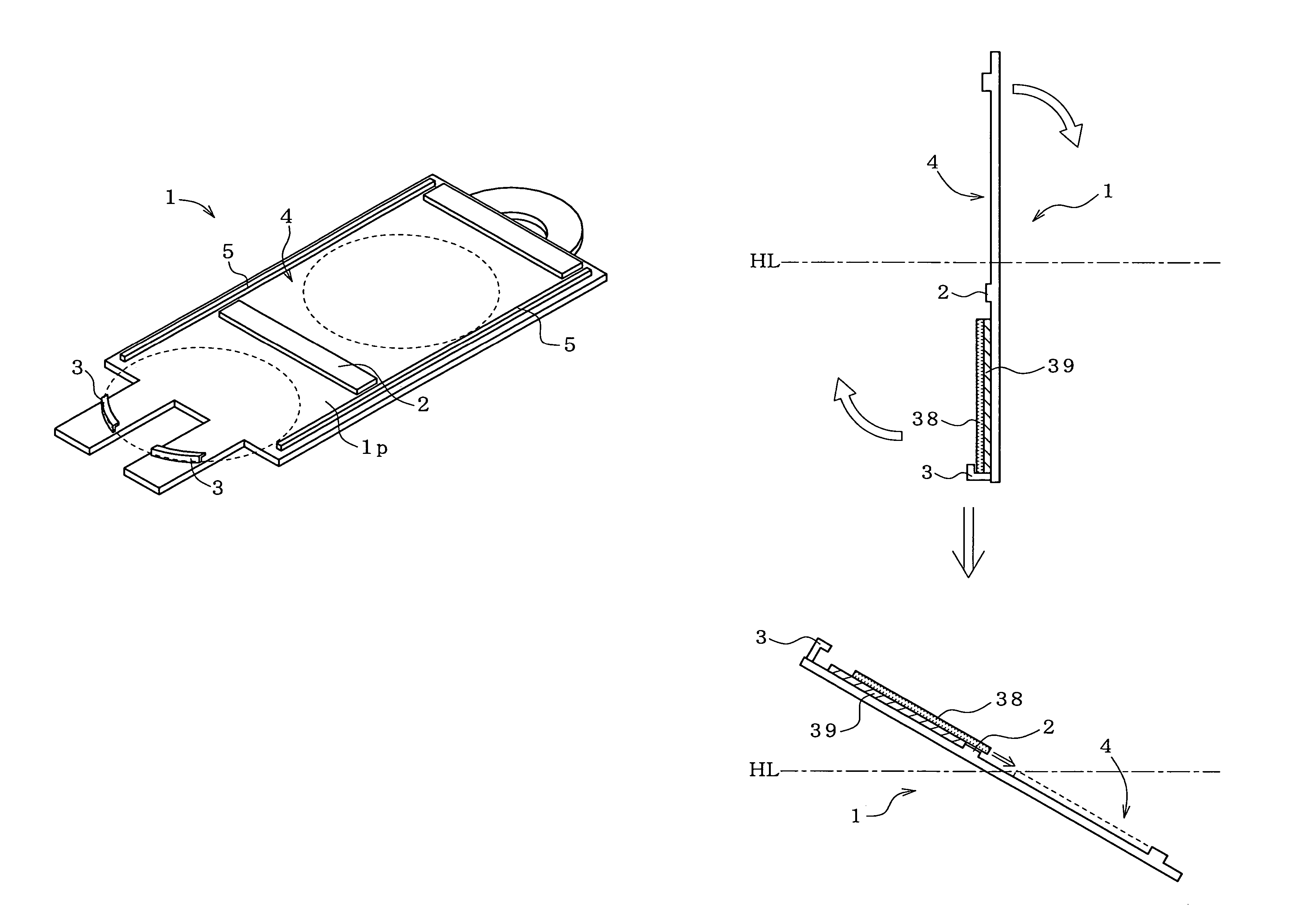

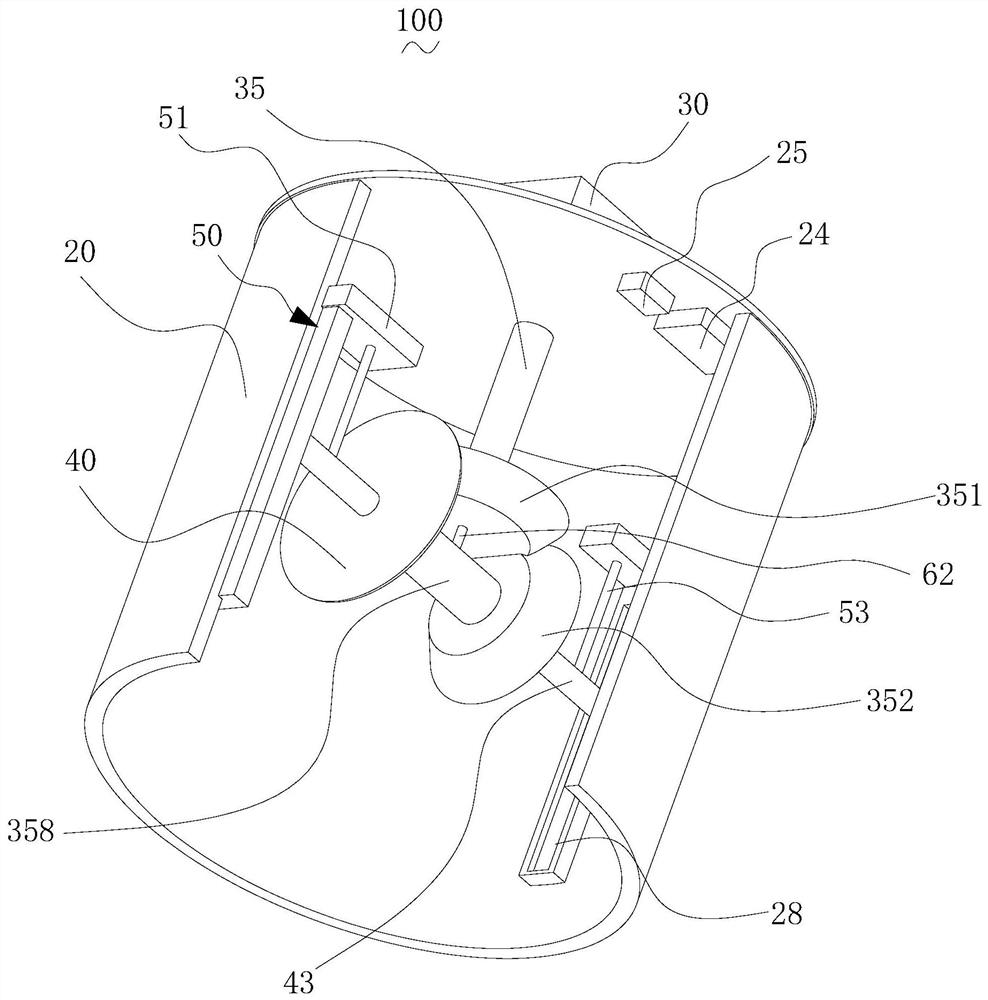

SOI wafer producing method, and wafer separating jig

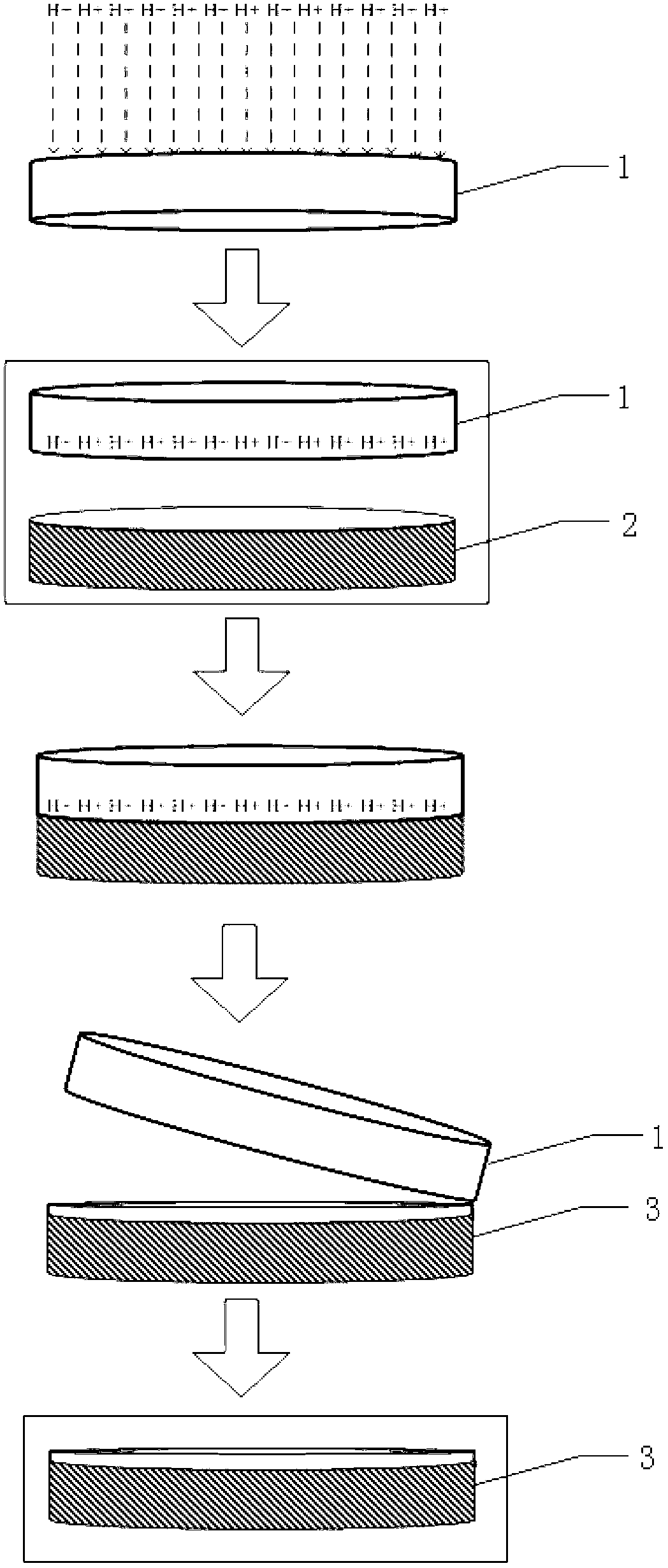

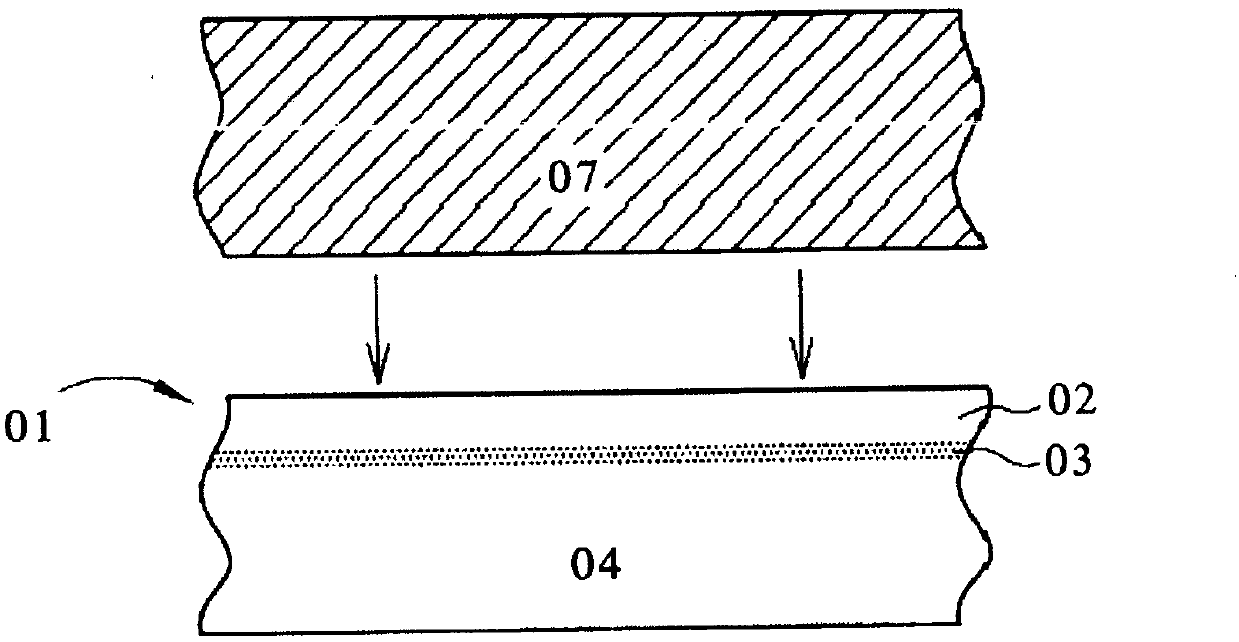

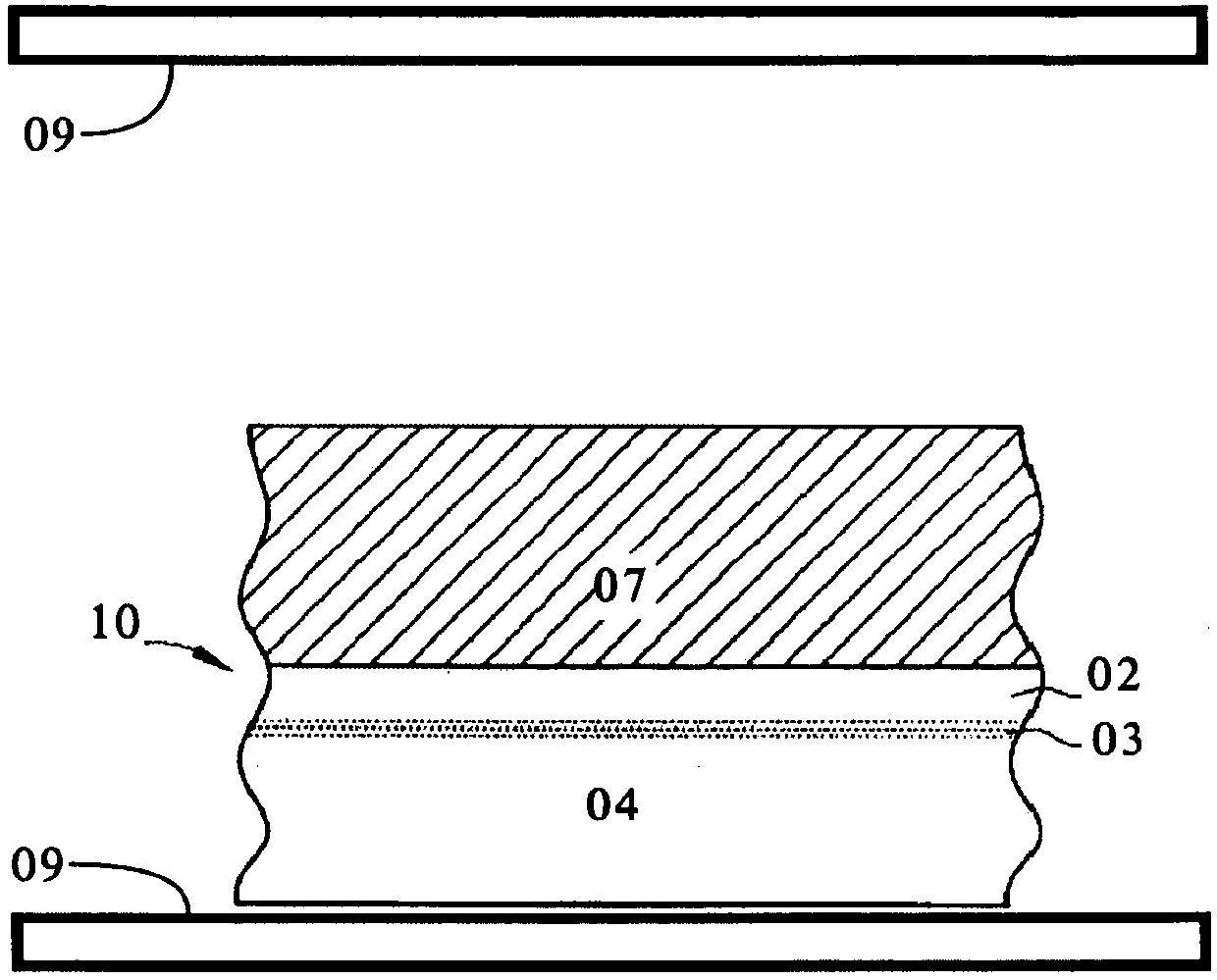

InactiveUS6998329B2Yield ratio can be improvedEasy to separateSolid-state devicesSemiconductor/solid-state device manufacturingIn planeWafering

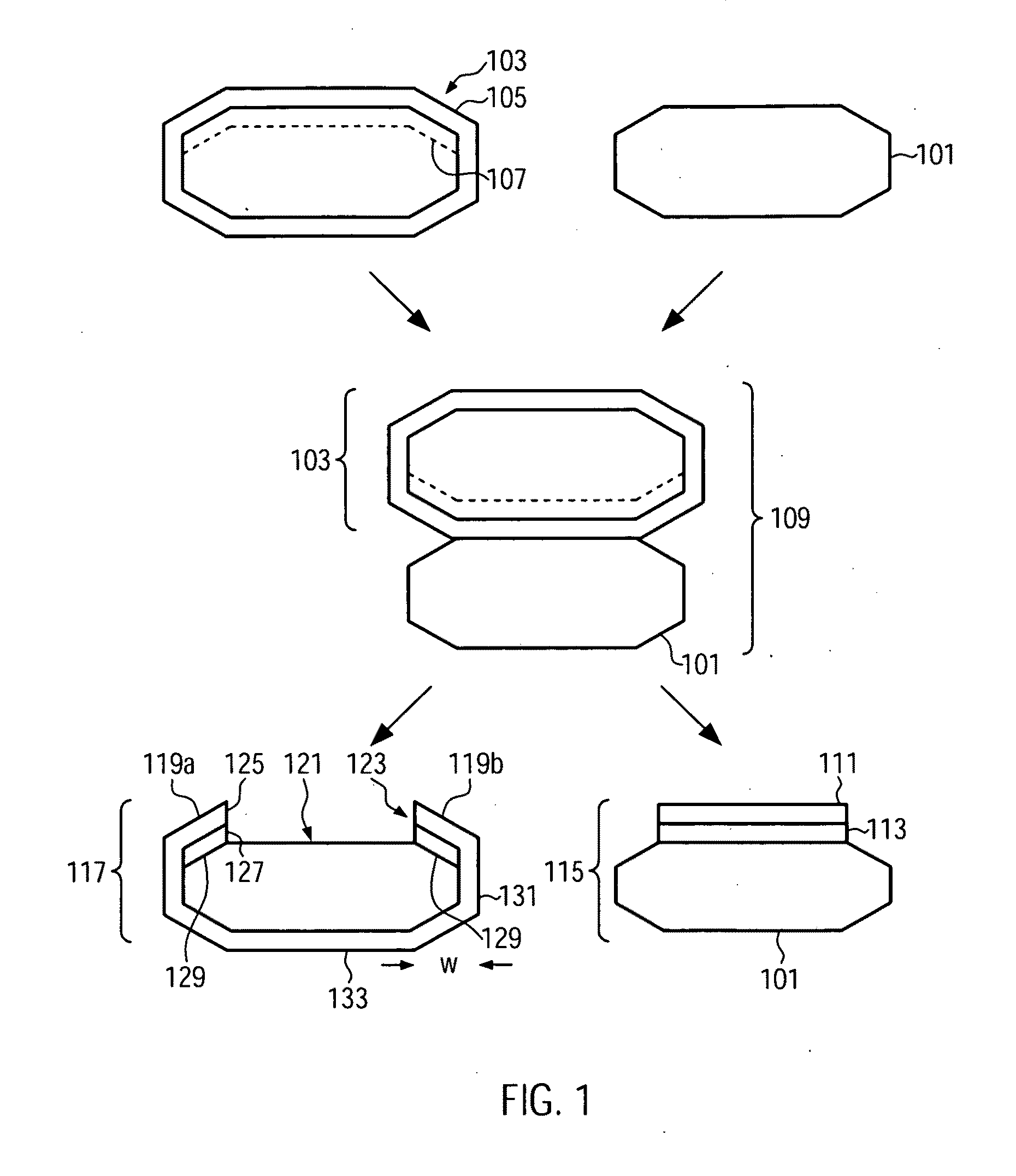

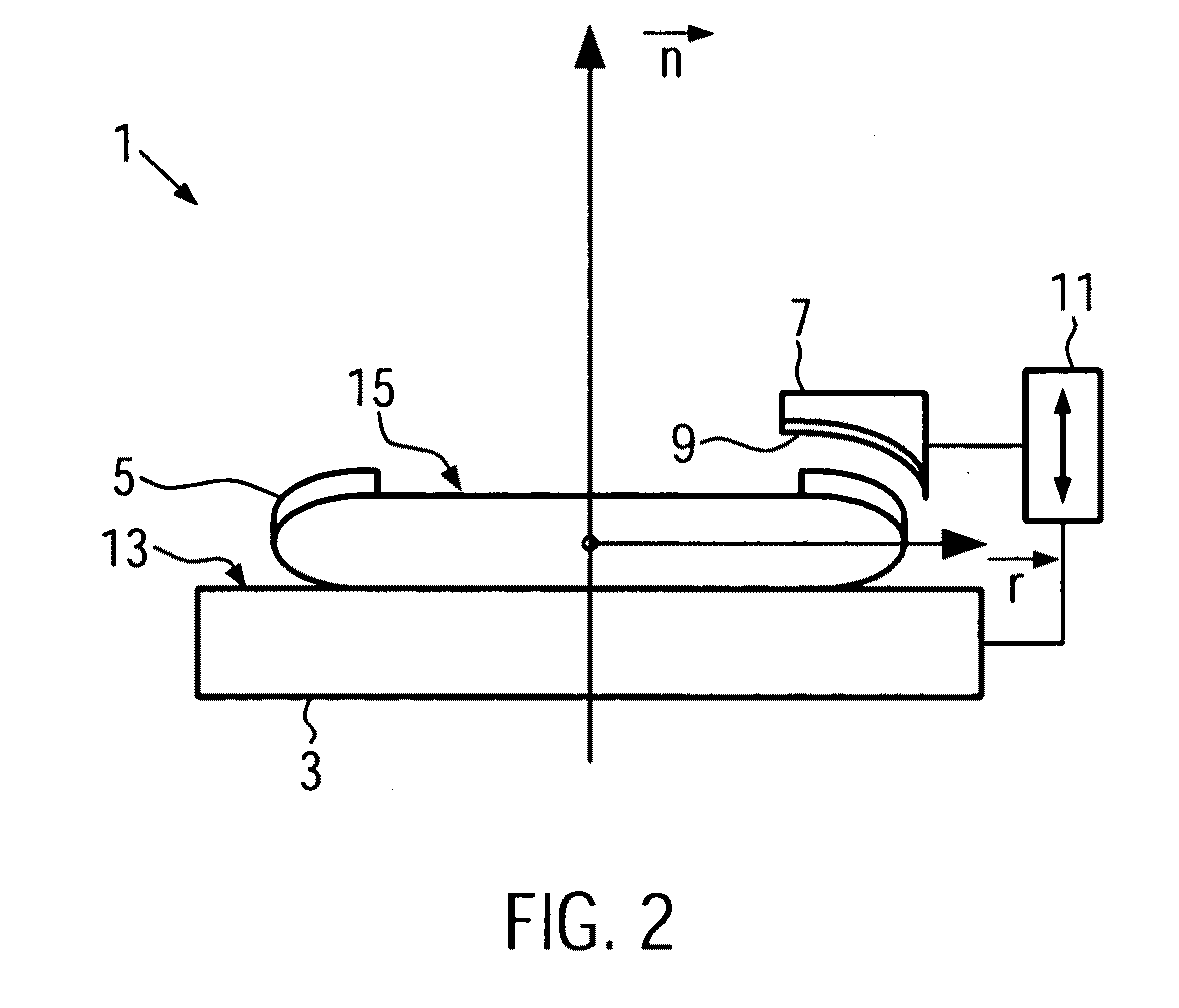

In the process of fabricating an SOI wafer based on the Smart Cut® Process, a stack 34 of an SOI wafer 39 and a residual wafer 38 are separated into the individual wafers using a wafer separation jig 1 of this invention. The wafer separation jig 1 comprises a supporting plane 1p on which the stack 34 is supported in the thickness-wise direction, and a stepped portion 2 disposed on the supporting plane 1p, and having a height adjusted so as to stop movement-by-sliding of the lower wafer of the stack, but so as to allow movement-by-sliding of the upper wafer relative to the lower wafer. Both wafers are separated from each other by inclining the supporting plane 1p with the stack 34 placed thereon, so as to allow the upper wafer to move by sliding as being driven by its own weight in the in-plane direction relative to the lower wafer. This method is successful in effectively suppressing friction between the wafers, and thus in preventing the wafer surface from being scratched.

Owner:SHIN-ETSU HANDOTAI CO LTD

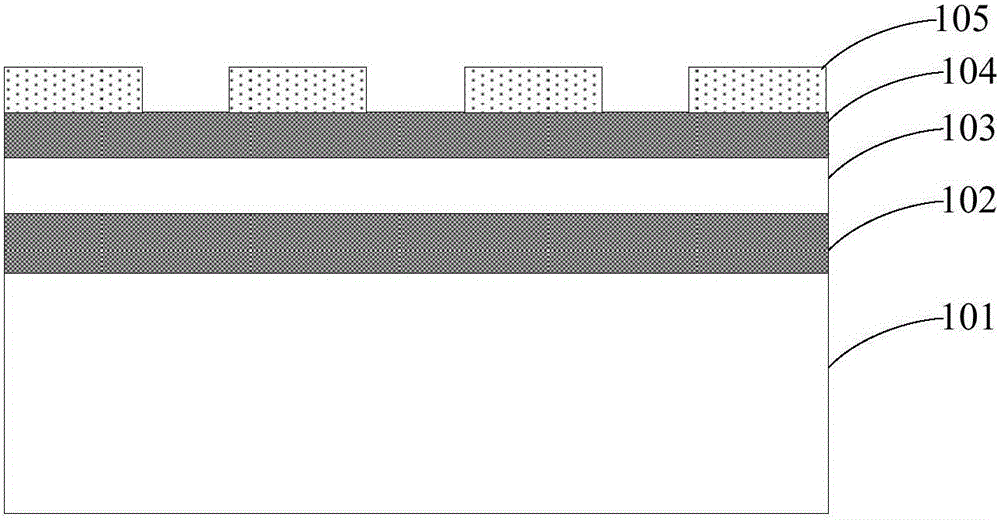

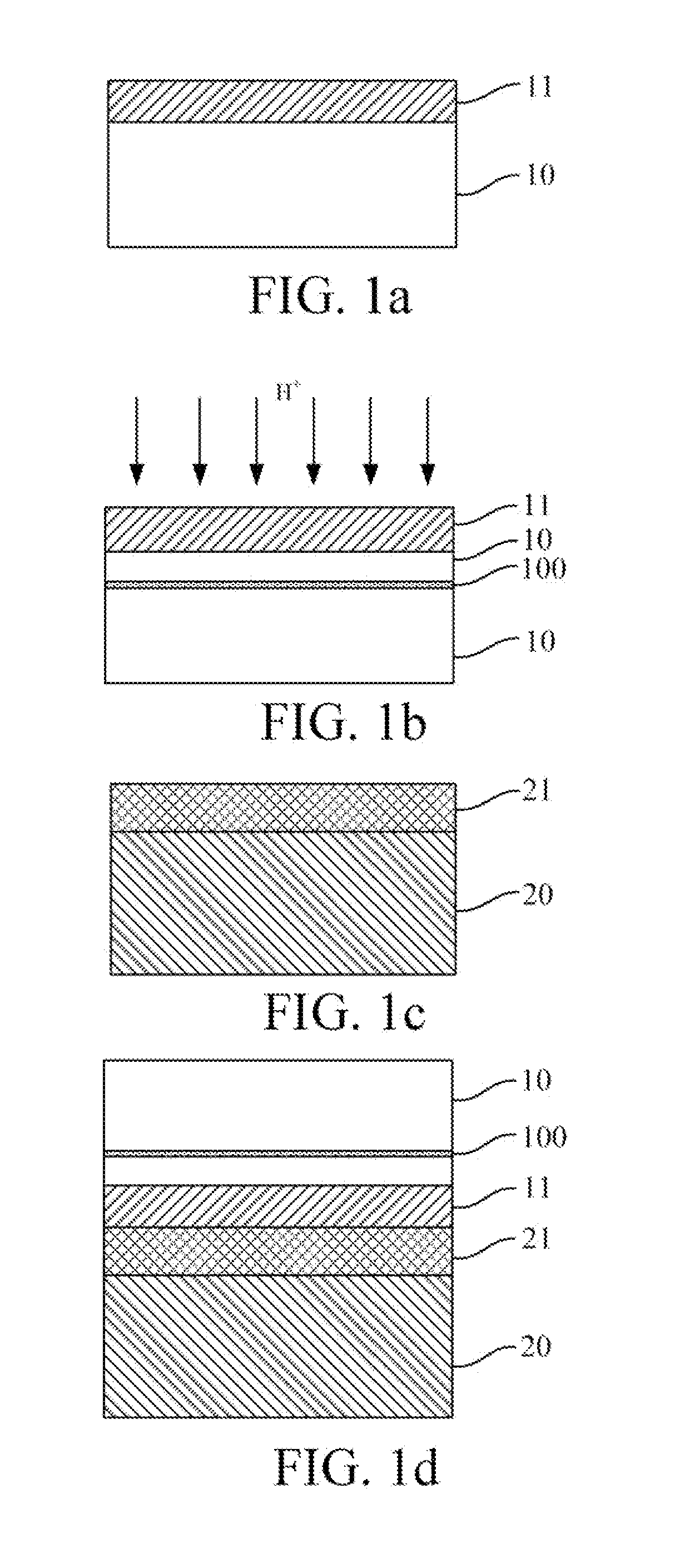

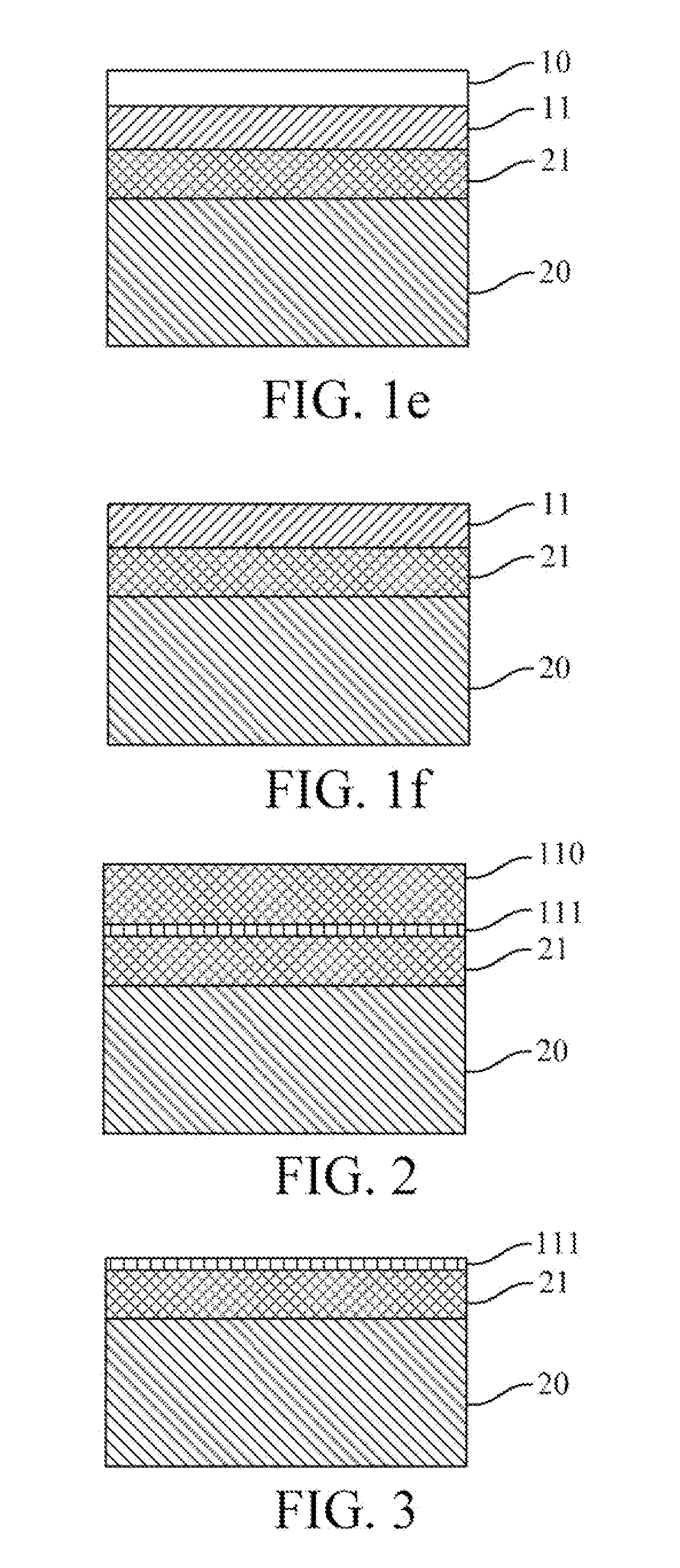

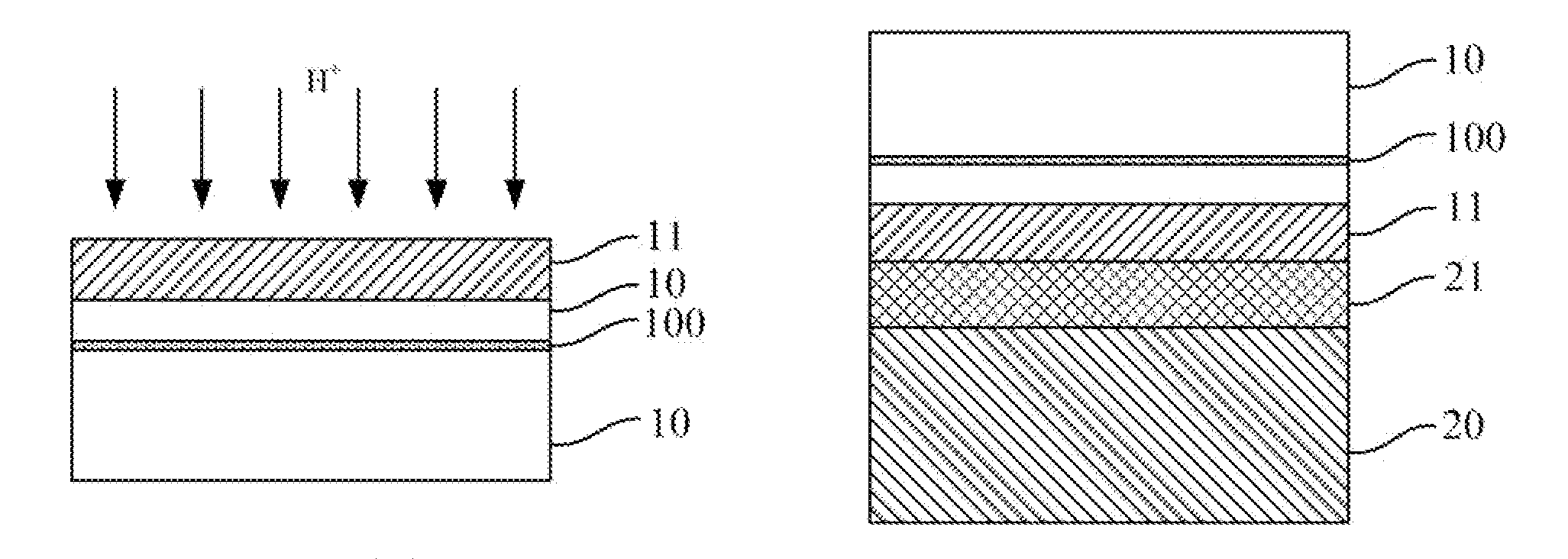

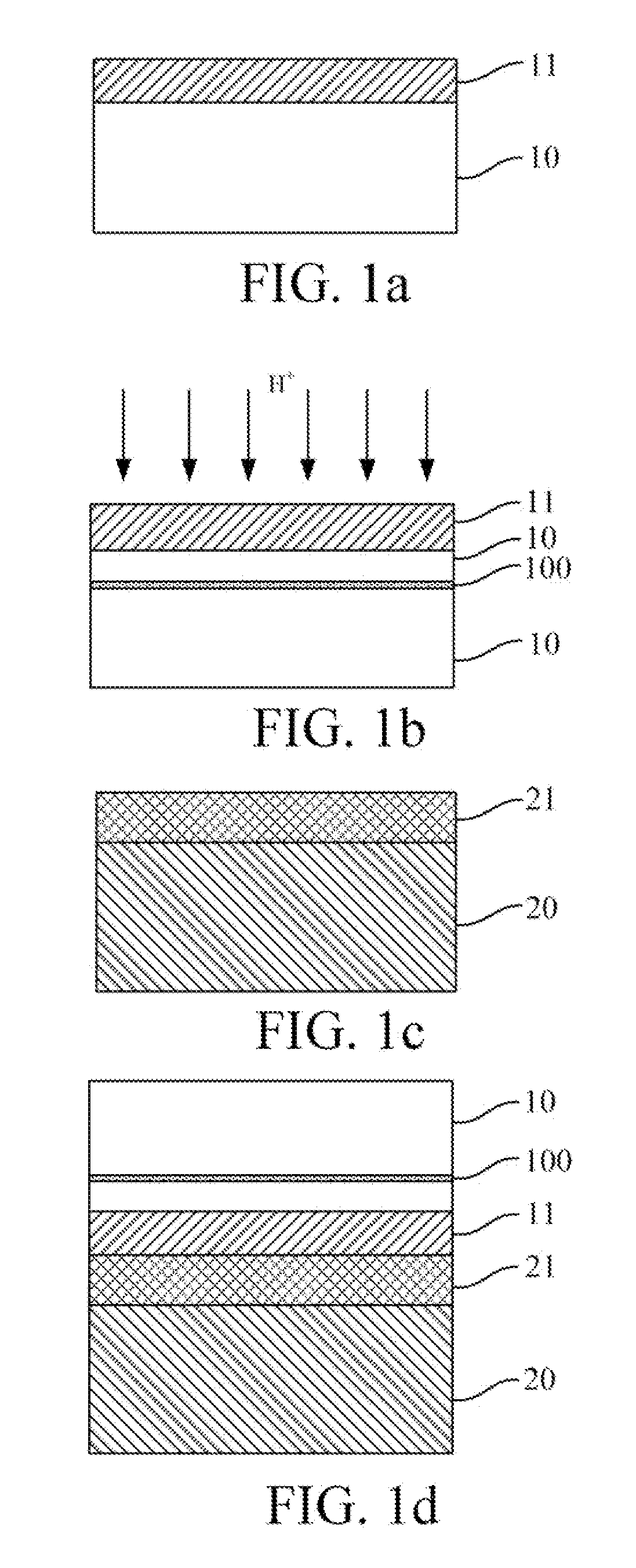

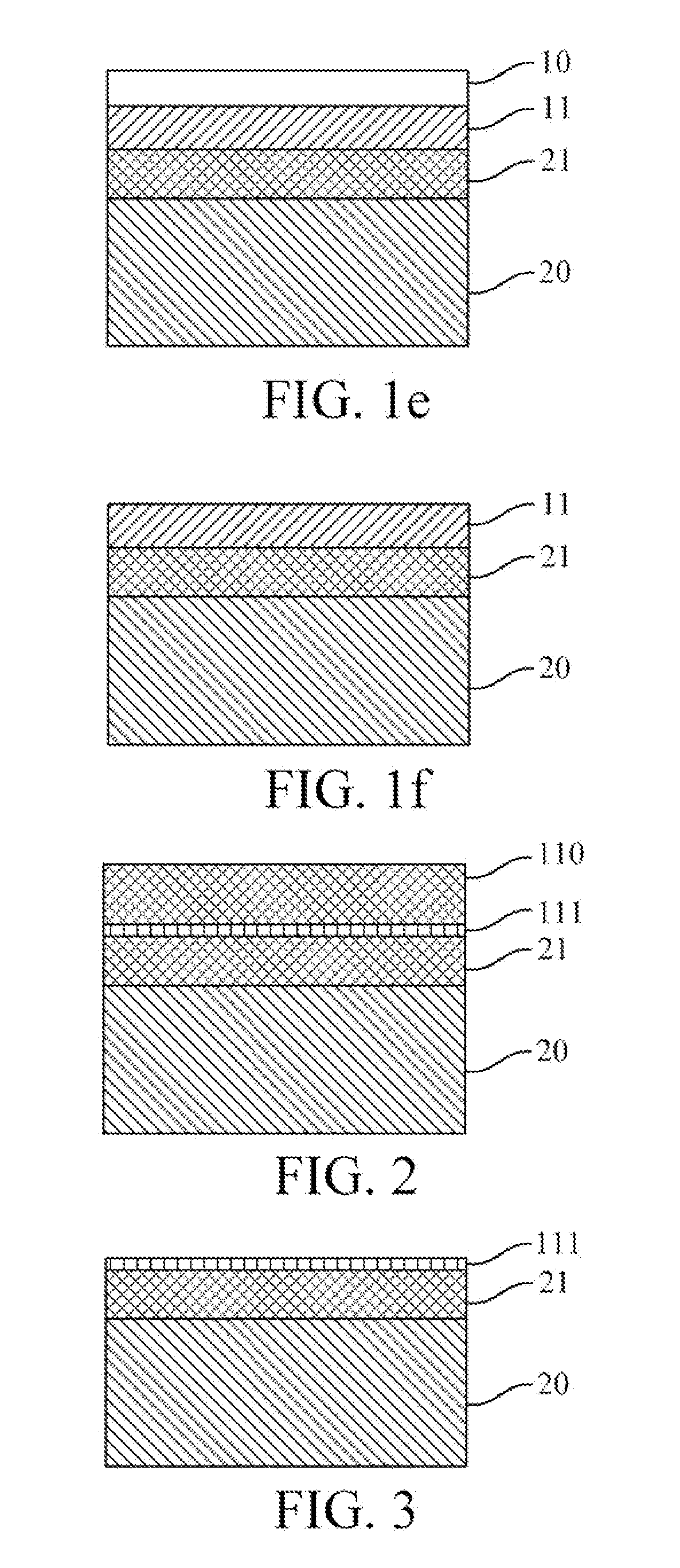

Graphical silicon-on-insulator substrate material and preparation method thereof

ActiveCN105895575AQuality assuranceAvoid breakingSolid-state devicesSemiconductor/solid-state device manufacturingSmart CutSoi substrate

The invention provides a graphical silicon-on-insulator (SOI) substrate material and a preparation method thereof. The preparation method comprises the steps of 1) providing an SOI substrate comprising bottom silicon, a buried oxide layer and top silicon, and forming an insulating layer on the surface of the top silicon; 2) forming an etching window corresponding to a position for preparing a transistor channel; 3) etching the insulating layer to form a groove penetrating through the top silicon; 4) providing a silicon substrate, and bonding the silicon substrate and the insulating layer; 5) removing the bottom silicon; and 6) removing the buried oxide layer. The groove is formed in the insulating layer corresponding to the position for preparing the transistor channel, and the groove completely penetrates through the space between the top silicon and the bottom silicon, so that a hollowed area is formed below the transistor channel prepared later. In the substrate preparation process, annealing and peeling steps in a Smart-cut method are avoided while the quality of the material is guaranteed, so that the problem of breakage of the top silicon in the graphical area due to high stress is solved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

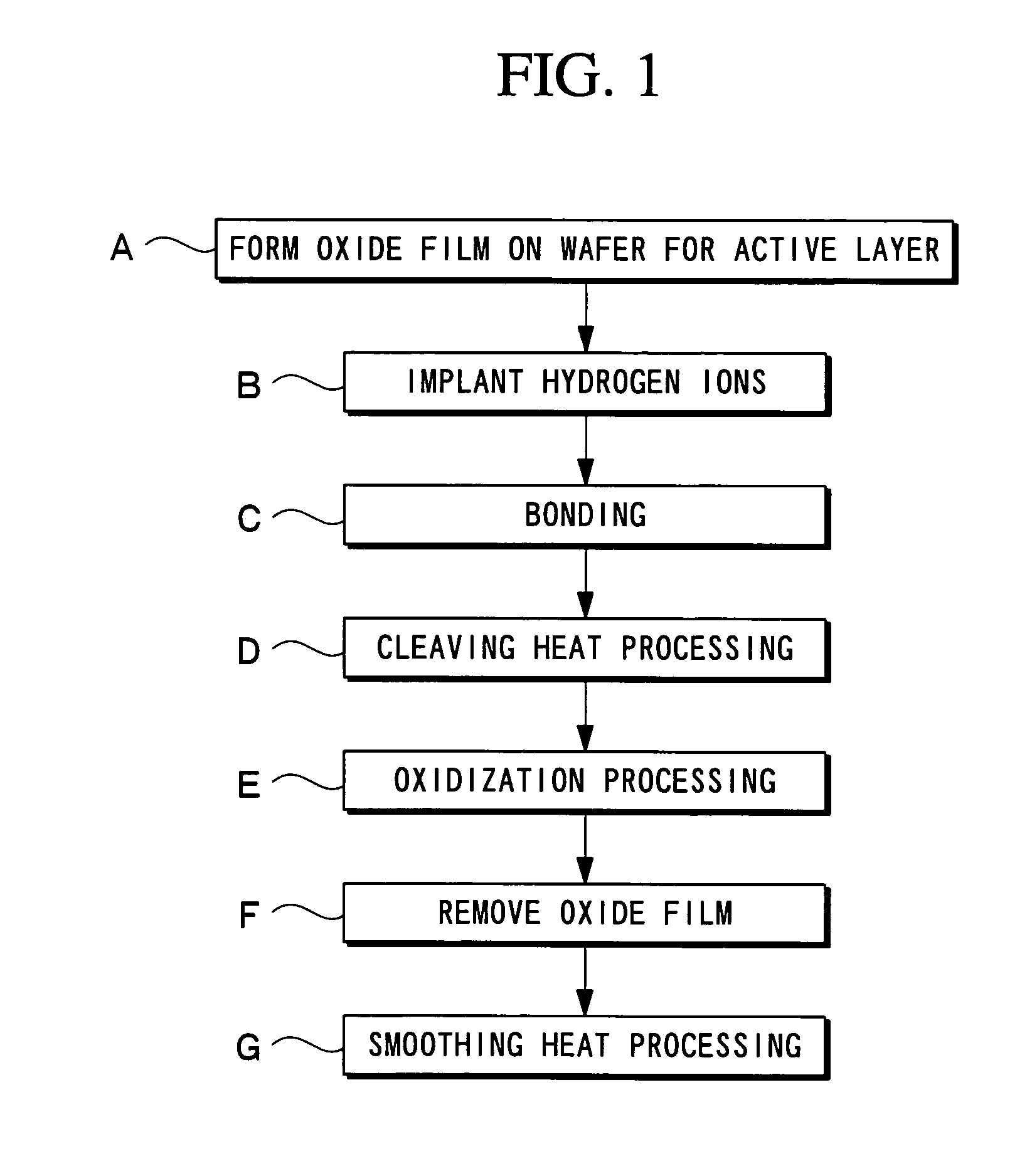

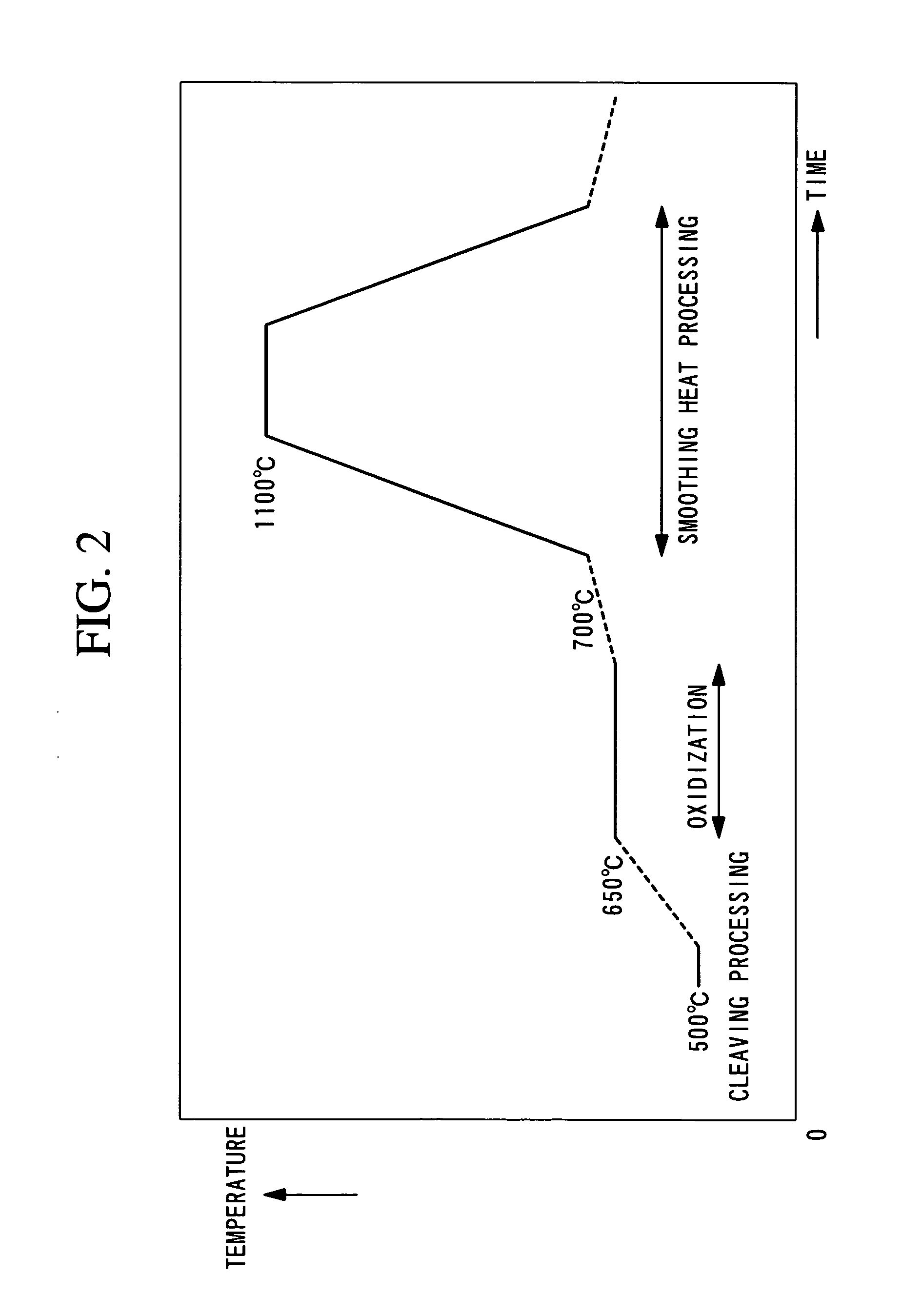

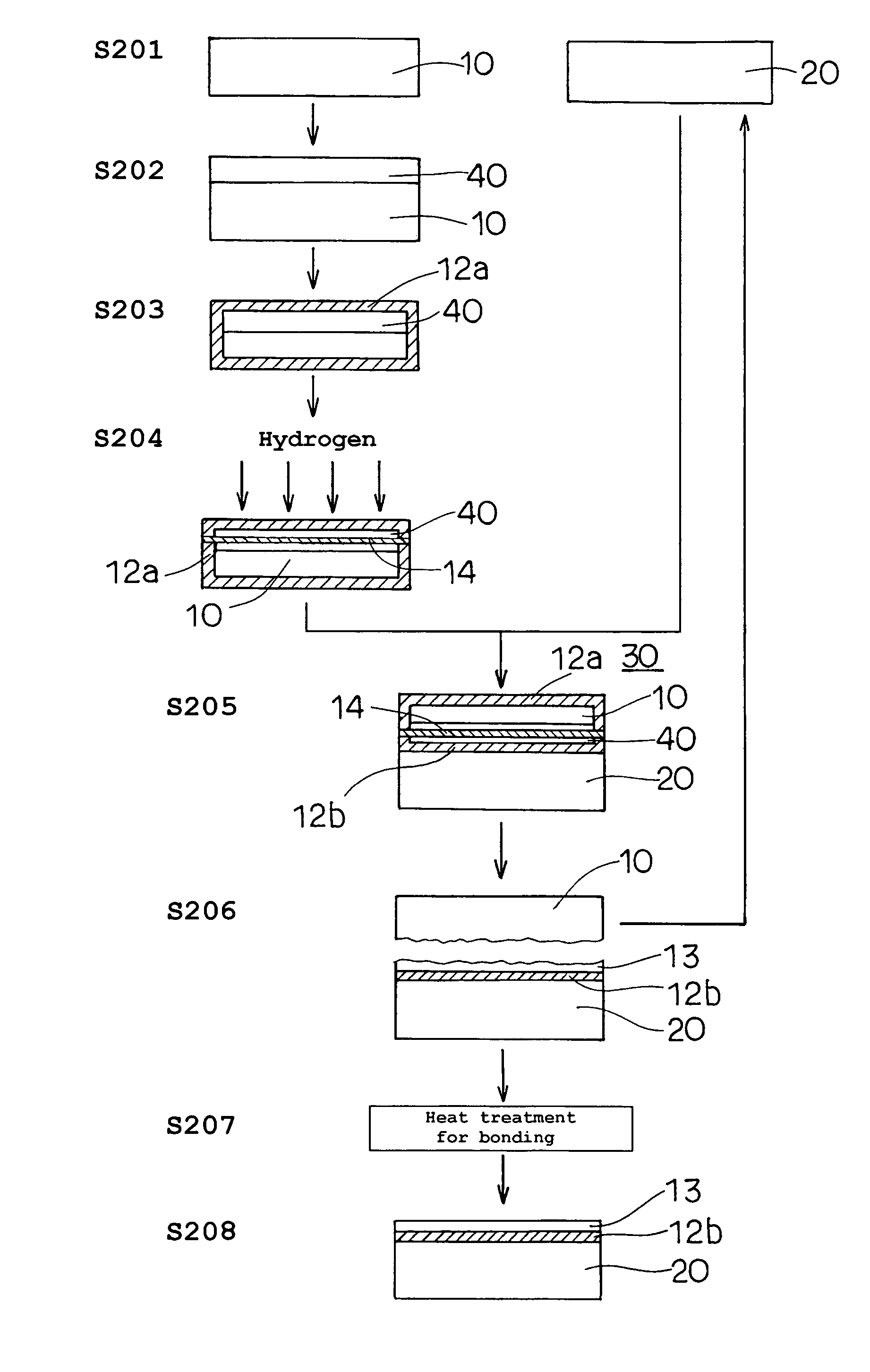

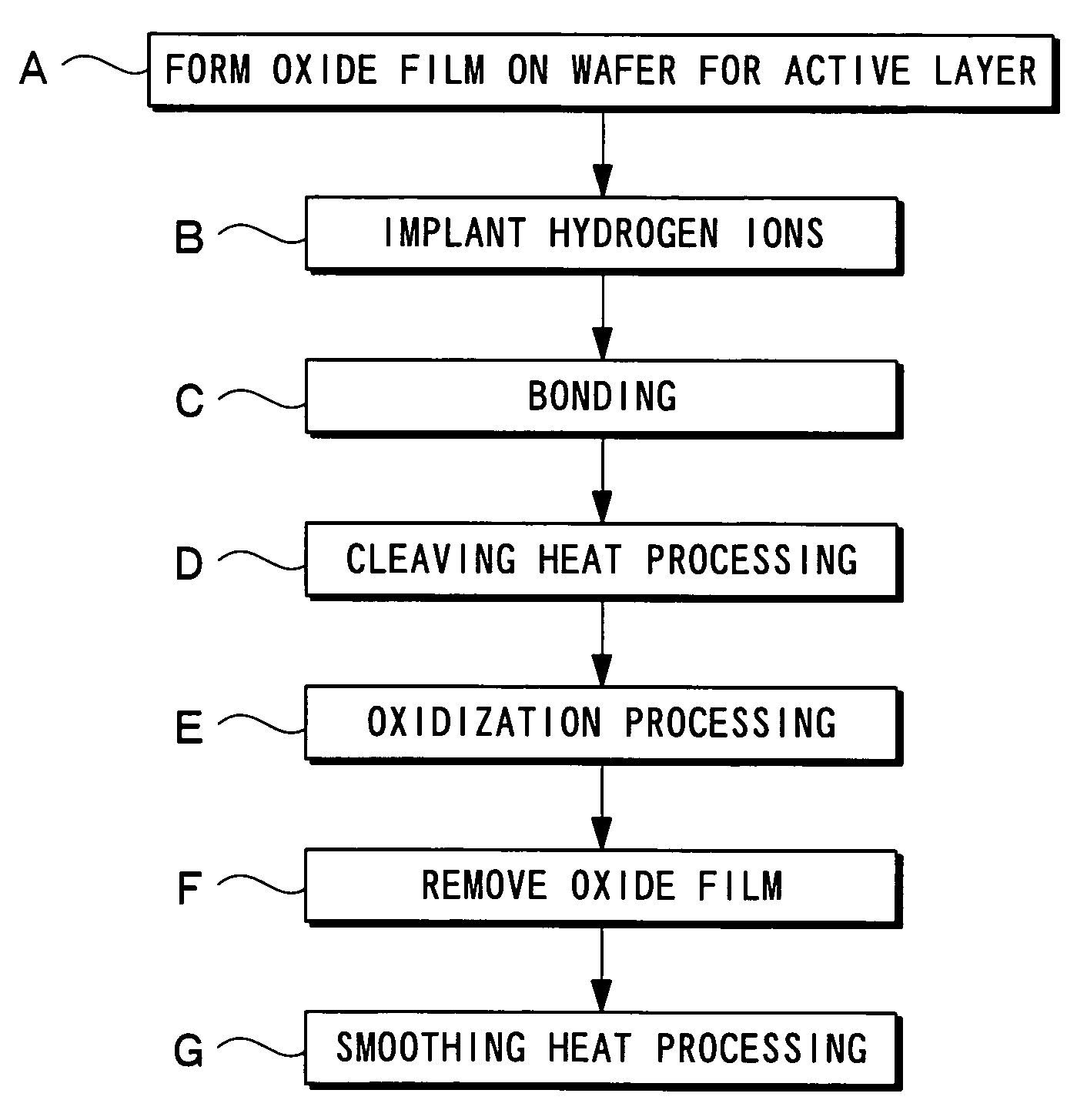

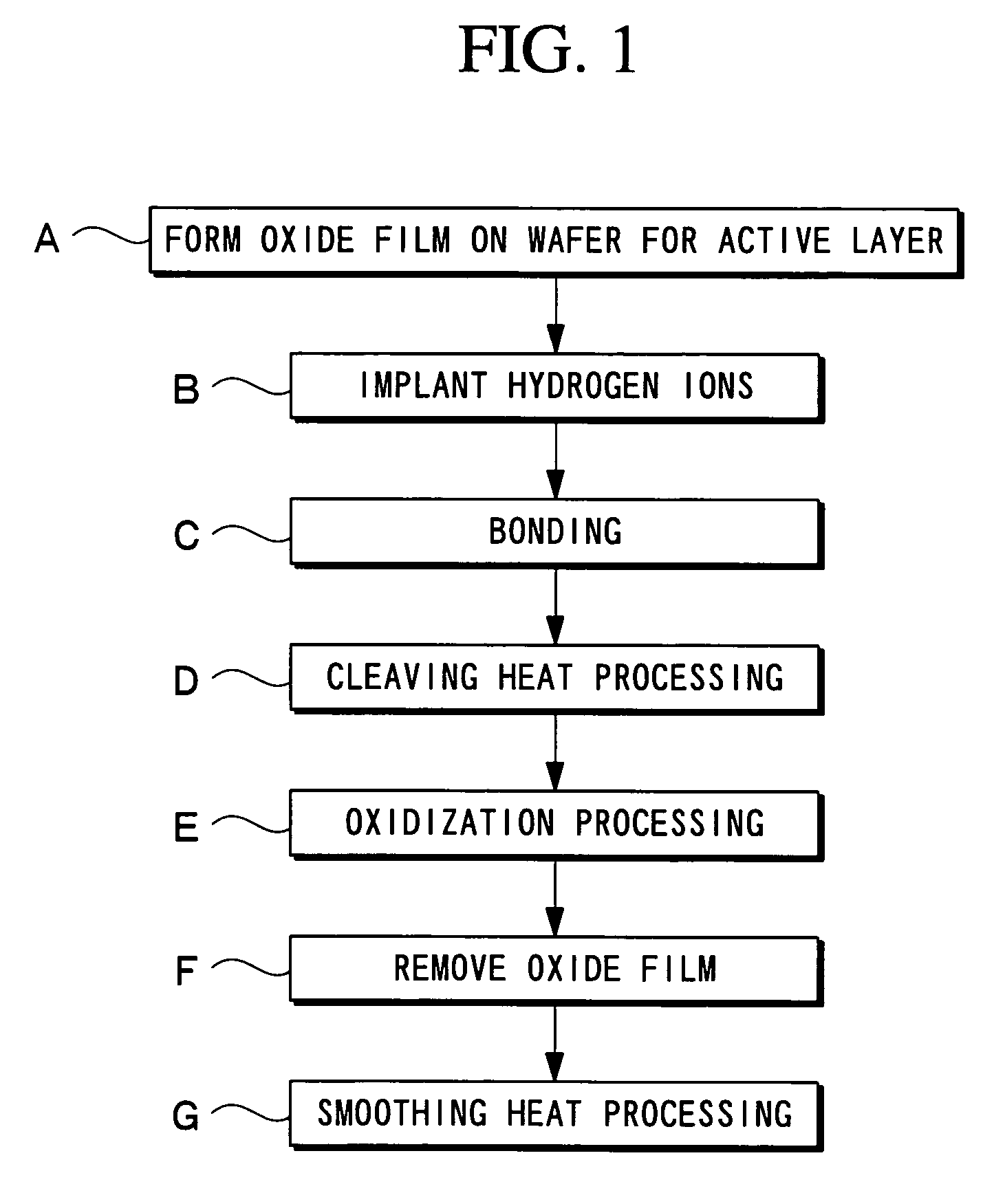

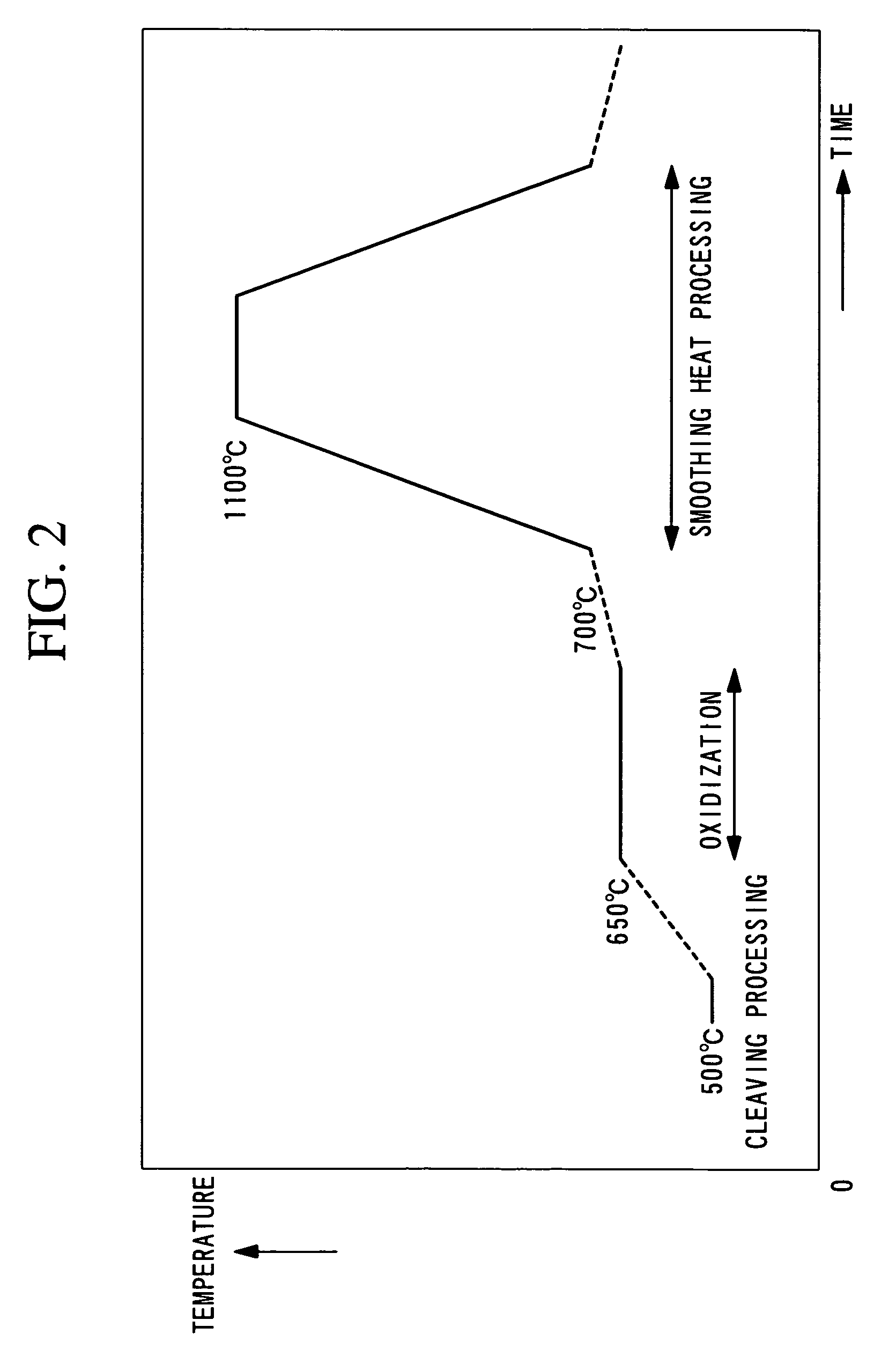

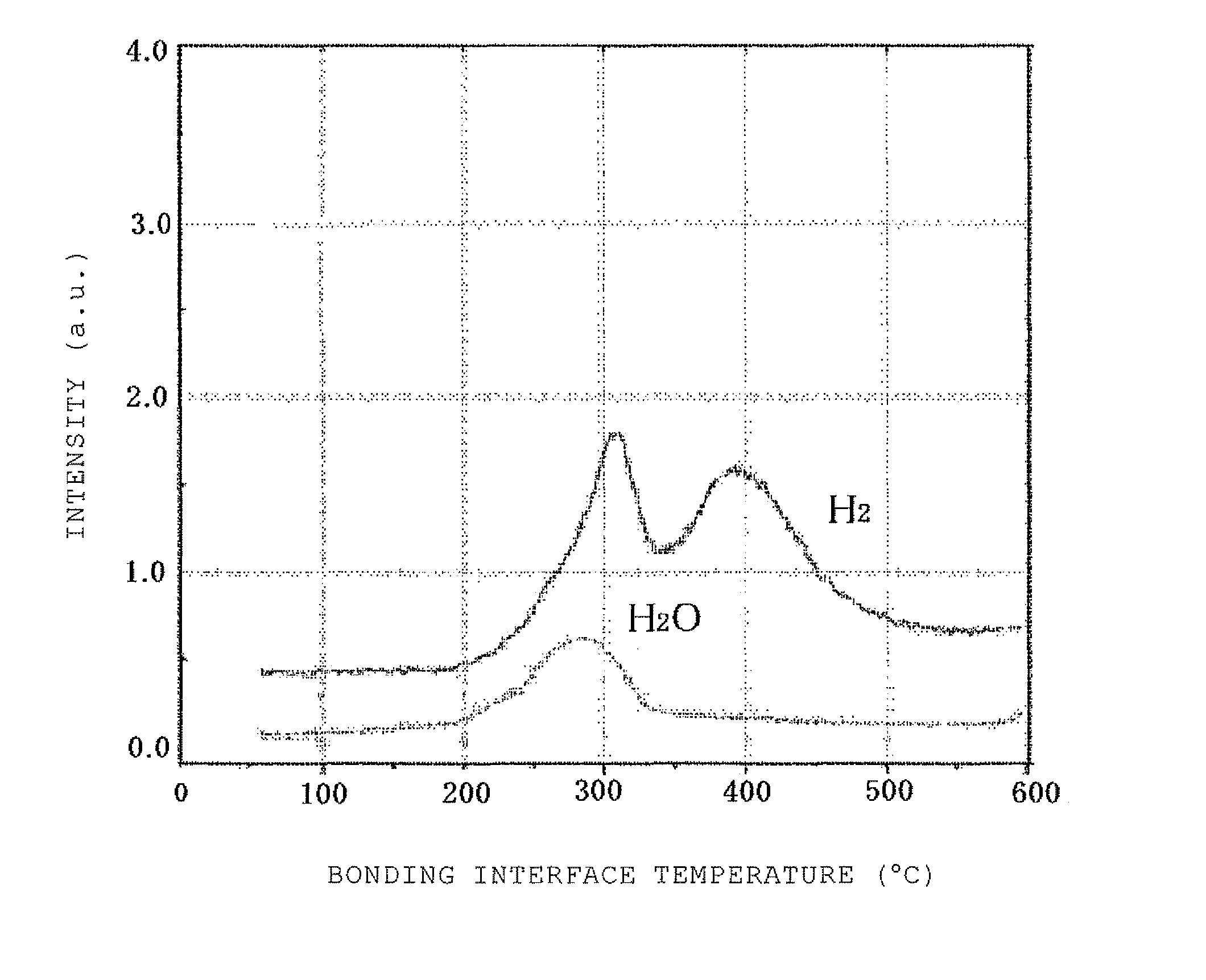

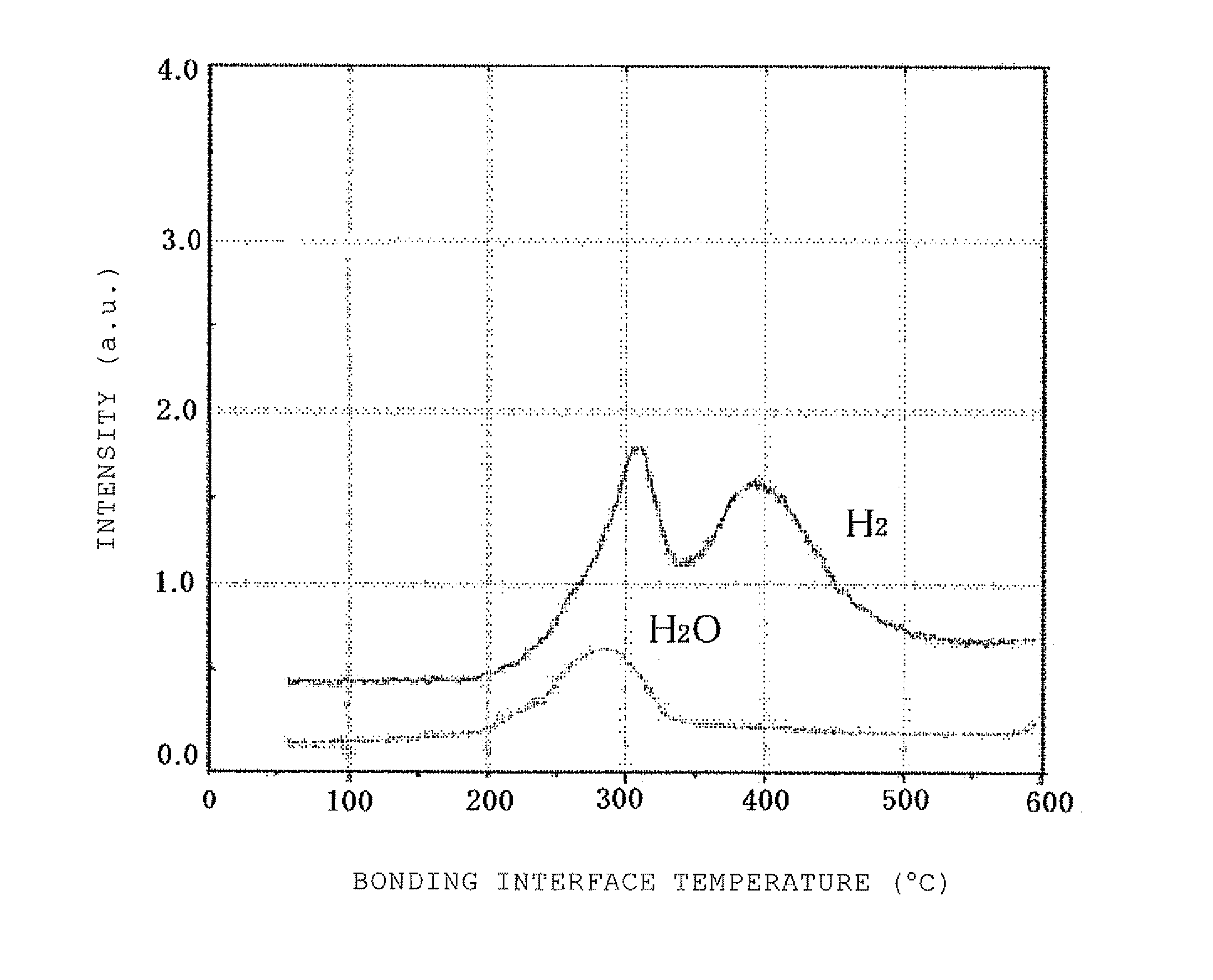

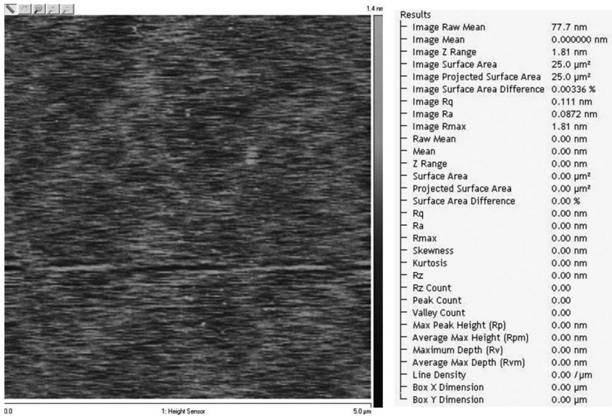

Process for producing soi wafer

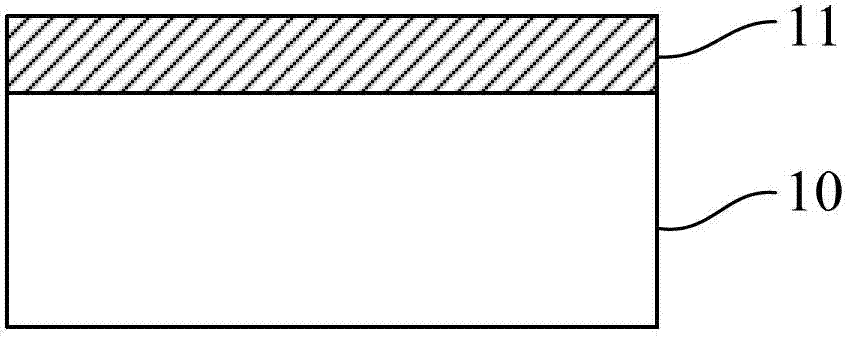

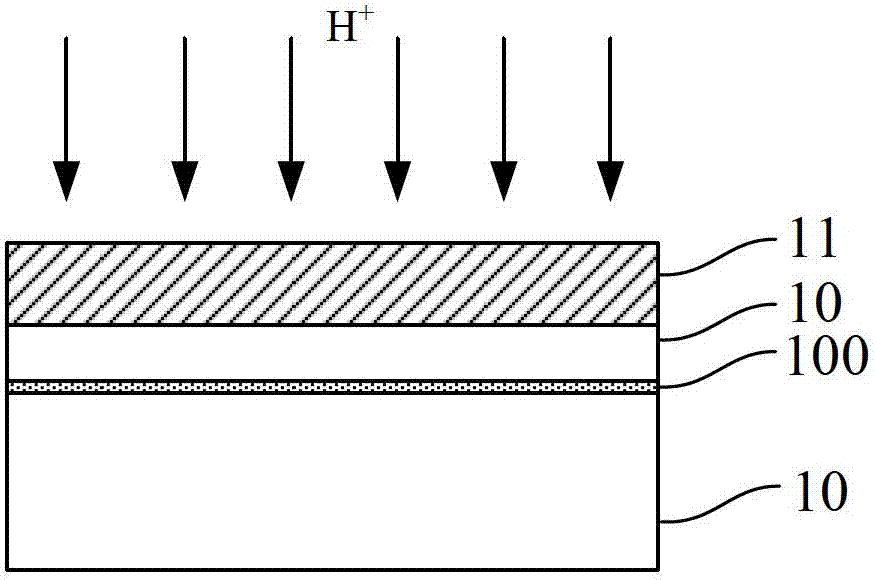

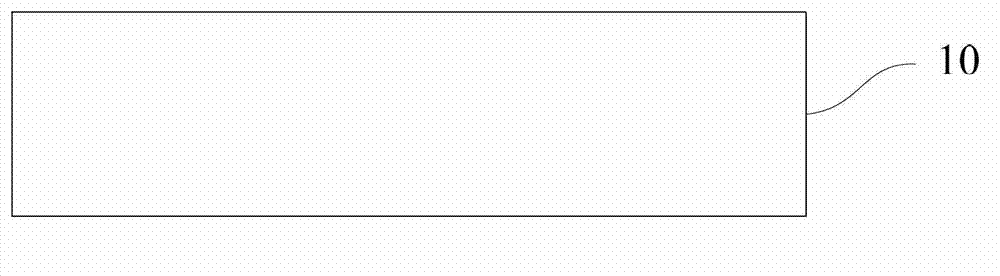

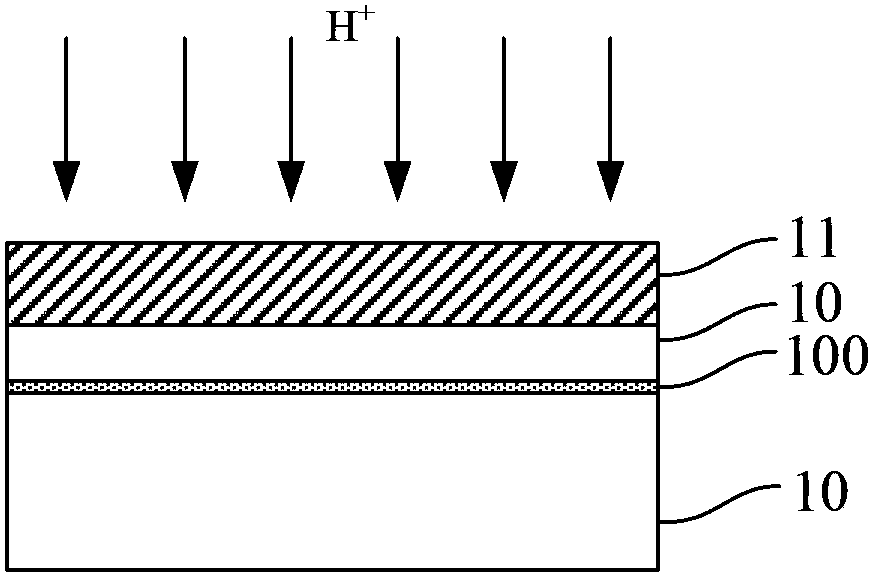

ActiveUS20070190737A1Reduce roughnessUniform film thicknessSolid-state devicesSemiconductor/solid-state device manufacturingManufacturing technologyHydrogen

There is provided a process for producing an SOI wafer in which, when producing an SOI wafer using Smart Cut technology, the surface can be smoothed after cleaving, the thickness of the SOI layer can be reduced, and the film thickness of the SOI wafer can be made uniform. In this process for producing an SOI wafer, hydrogen gas ions are implanted via an oxide film in a silicon wafer that is to be used for an active layer, so that an ion implanted layer is formed in the silicon bulk. Next, this active layer silicon wafer is bonded via an insulating film to a base wafer. By heating this base wafer, a portion thereof can be cleaved using the ion implanted layer as a boundary, thereby forming an SOI wafer. After the cleaving has been performed using the ion implanted layer as a boundary, the SOI wafer undergoes oxidization processing in an oxidizing atmosphere. This oxide film is then removed by, for example, HF solution. Thereafter, the SOI wafer undergoes heat processing for approximately three hours in an argon gas atmosphere at 1100° C. or more. As a result, the root mean square roughness of the SOI wafer surface is improved to 0.1 nm or less.

Owner:SUMCO CORP

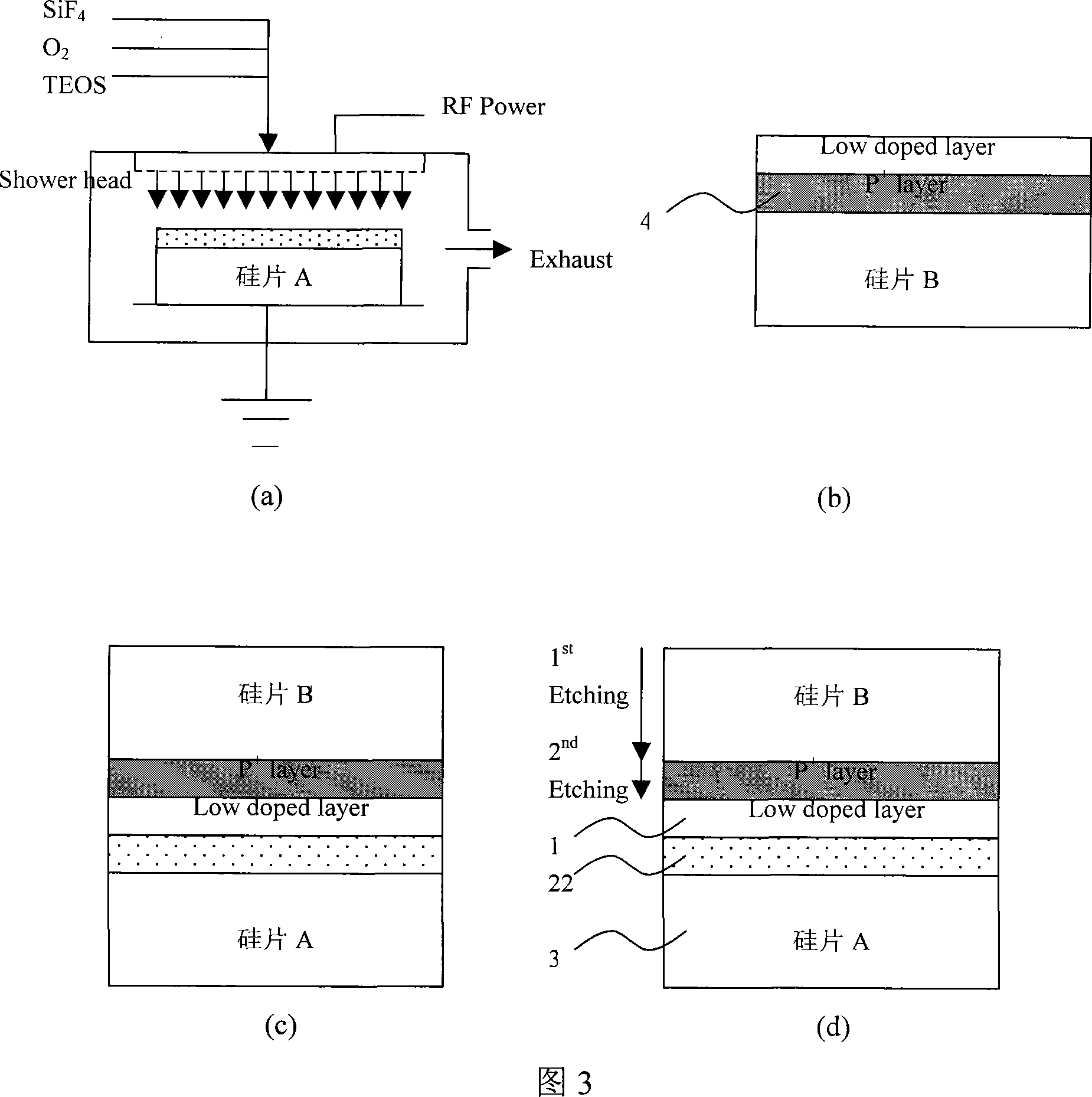

Preparation method of gate oxide integrity (GOI) wafer structure

ActiveCN102738060AReduce threading dislocationsQuality improvementSemiconductor/solid-state device manufacturingSmart CutOptoelectronics

The invention provides a preparation method of a gate oxide integrity (GOI) wafer structure, which comprises the following steps that firstly, a SiGe-on-insulator (SGOI) wafer structure is prepared through a Smart-Cut technology, then germanium concentration is carried out on the SGOI wafer structure, and the GOI wafer structure is obtained. Because the SGOI which is prepared through the Smart-Cut technology basically is not mismatched or dislocated on an SGOI / BOX interface, the penetrated dislocation of the GOI is finally reduced. According to the preparation method of the GOI wafer structure, the process is simple, the high-quality GOI wafer structure can be realized, a germanium concentration technology is greatly improved, an ion injection technology and an annealing technology are very mature processes in the current semi-conductor industry, and the preparation method greatly improves the wide application possibility of germanium concentration in the semi-conductor industry.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Method for preparing semiconductor material through ion injection and fixed-point adsorption technologies

ActiveCN102737963AReduce defect densityHigh relaxivitySemiconductor/solid-state device manufacturingSemiconductor materialsSmart Cut

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Method for preparing epitaxial composite substrate of gallium nitride based semiconducting material

InactiveCN103021814AHigh thermal conductivityEfficient reuseSemiconductor/solid-state device manufacturingSemiconductor materialsSurface cleaning

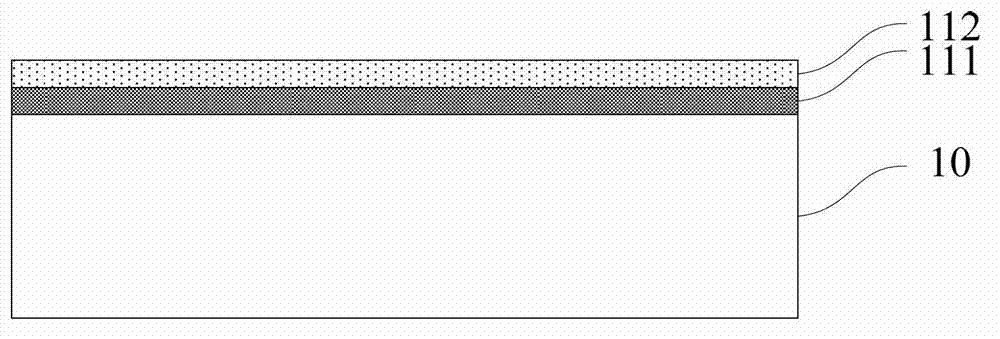

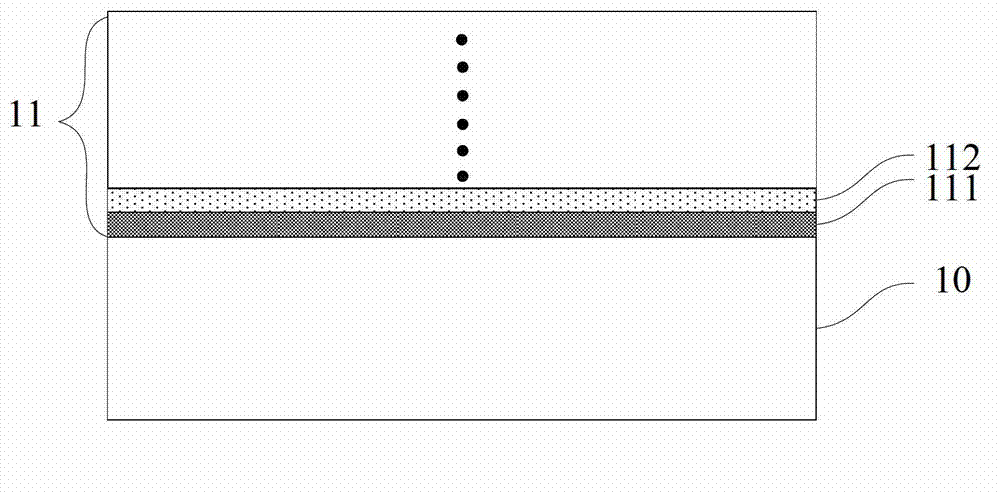

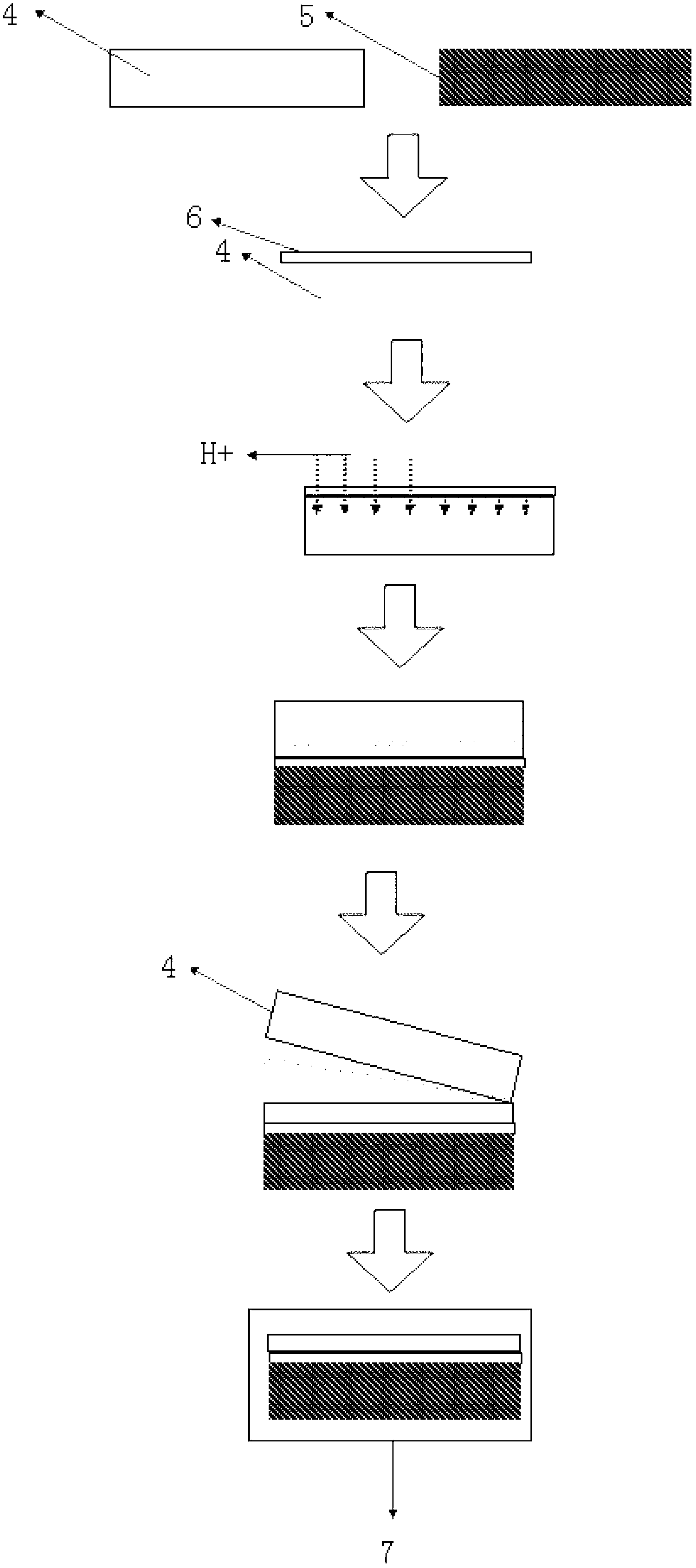

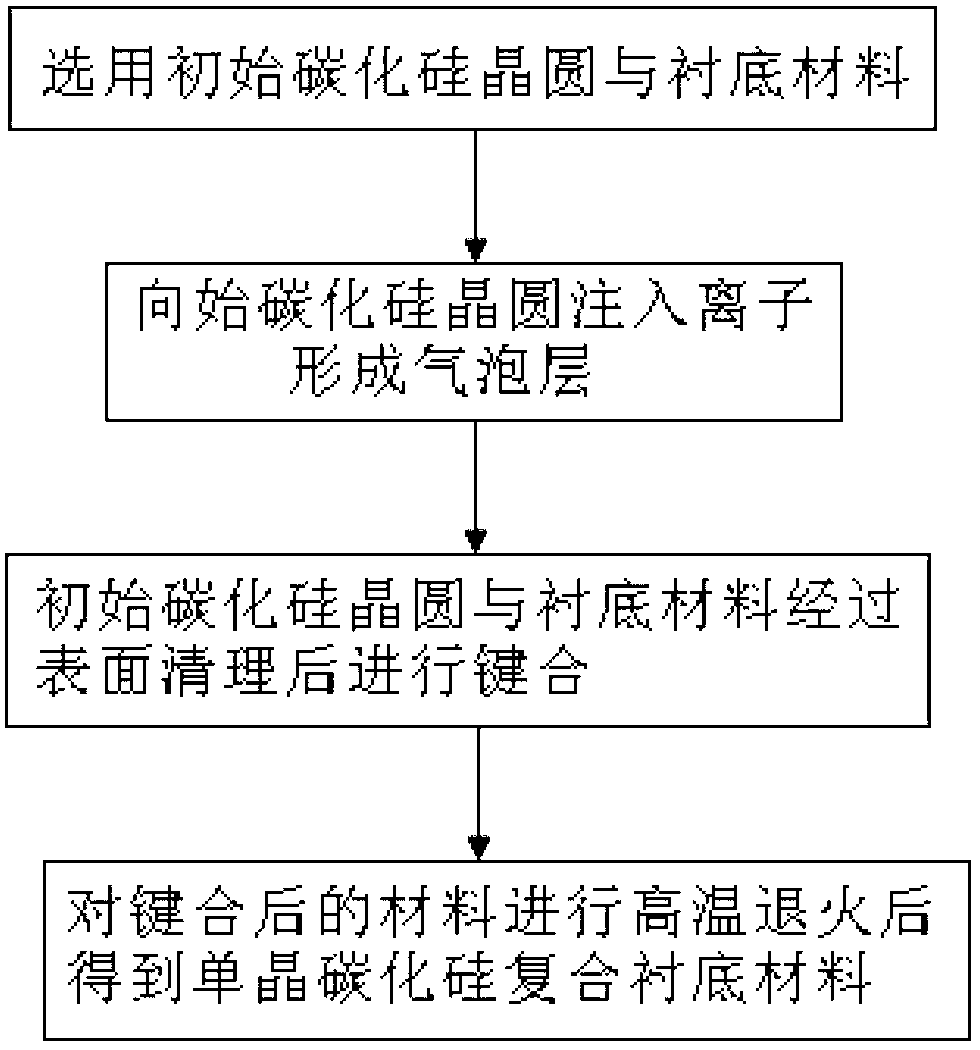

The invention discloses a method for preparing an epitaxial composite substrate of a gallium nitride based semiconducting material. The method includes the steps of selecting an initial single crystal silicon carbide wafer and a substrate material; injecting ion in the initial single crystal silicon carbide wafer to form an air bubble layer via a hydrogen-injecting smart-cut method; subjecting the initial single crystal silicon carbide wafer and the substrate material to auxiliary plasma bonding after surface processing including surface cleaning and spin-drying; subjecting the material obtained in the auxiliary plasma bonding to high temperature annealing to enable the air bubble layer of the initial single crystal silicon carbide wafer to converge so as to enable the initial single crystal silicon carbide wafer to jump off, and obtaining a composite single crystal silicon carbide substrate material. By the aid of the method for preparing the epitaxial composite substrate of the gallium nitride based semiconducting material, an epitaxy of the gallium nitride based material is enabled to obtain the high-quality single crystal silicon carbide substrate, and cost for the substrate material can be effectively reduced.

Owner:SHANGHAI XINCHU INTEGRATED CIRCUIT

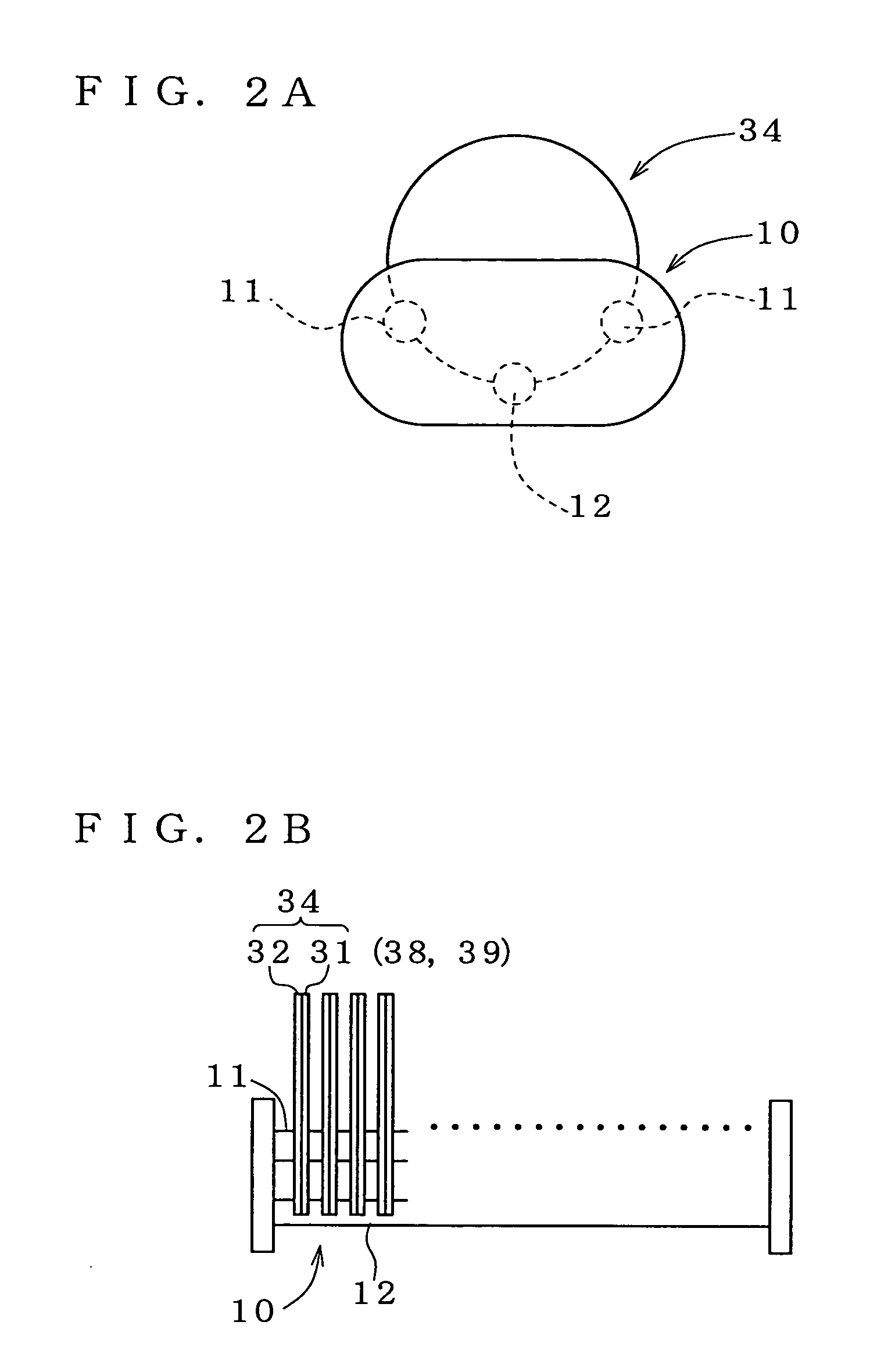

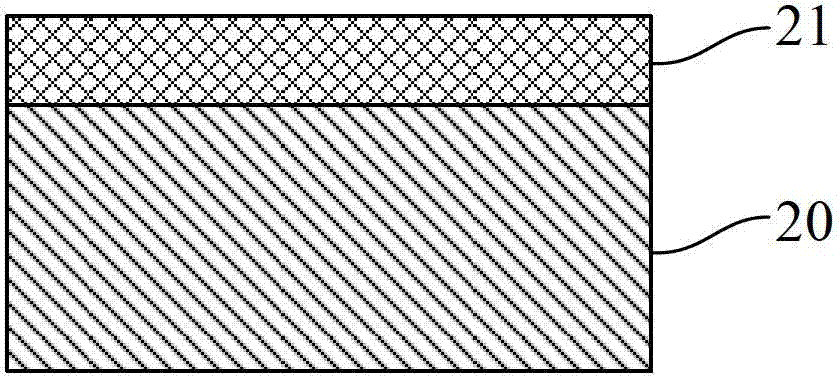

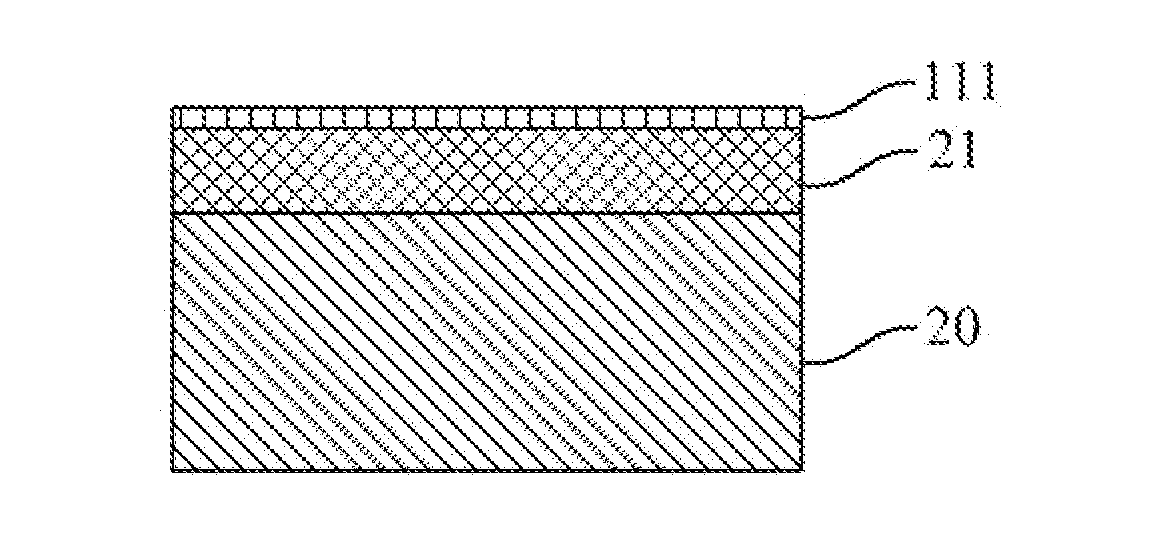

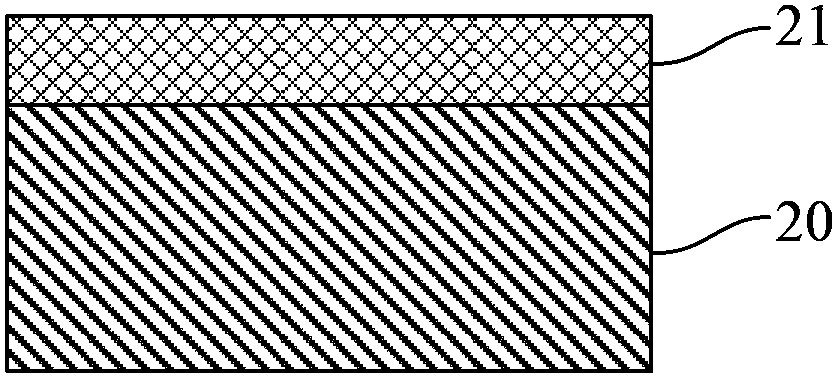

Method for producing bonded wafer

InactiveUS7446016B2Quality improvementImprove throughputSemiconductor/solid-state device manufacturingHigh rateSmart Cut

A bonded SOI substrate having an active layer which is free from crystal defects is obtained by adding more than 9×1018 atoms / cm3 of boron to a wafer for active layer (10). Since the boron concentration in the wafer for active layer is high, a silicon oxide film is formed at a high rate. Consequently, there can be obtained a Smart-Cut wafer with high throughput. Furthermore, damages to the active layer due to the ion implantation can be reduced, thereby improving the quality of the active layer.

Owner:SUMCO CORP

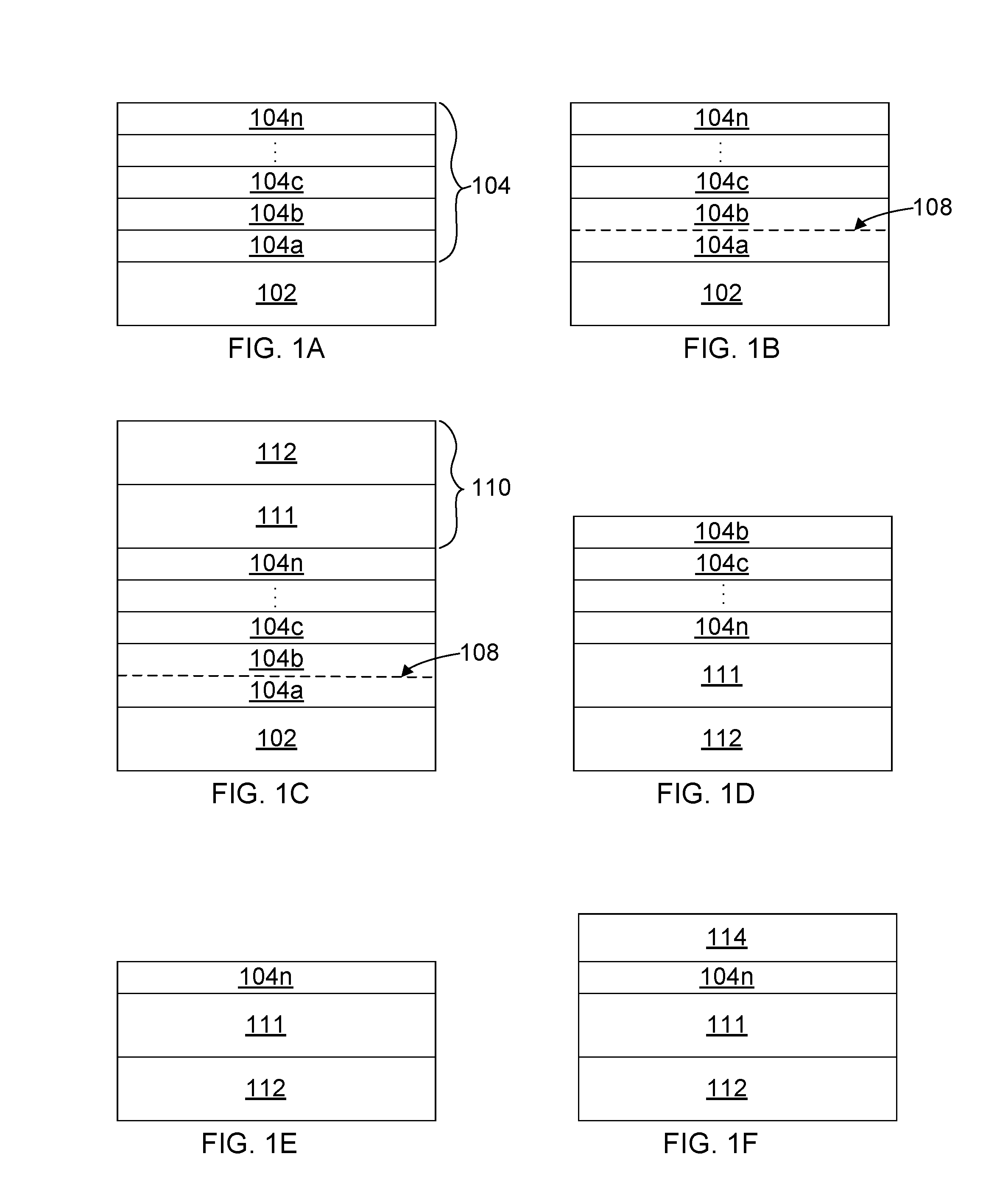

Manufacturing method of multilayer nanowire structure

ActiveCN103295878AInconsistent crystal orientationSemiconductor/solid-state device manufacturingSemiconductor devicesSilicon matrixNanowire

The invention provides a manufacturing method of a multilayer nanowire structure. The manufacturing method comprises the following steps: a. providing a first silicon matrix and forming a first oxide layer on the first silicon matrix, b. providing a second silicon matrix, injecting hydrogen ions into the second silicon matrix, forming a position mark on the second silicon matrix, c. cutting the first silicon matrix intelligently and forming an insulator upper silicon structure on the first silicon matrix, d. forming a second oxide layer on the insulator upper silicon structure, e. repeating step b and step d, forming a multilayer insulator upper silicon structure on the first silicon matrix, f. defining the graph of the multilayer nanowire structure, g. etching the multilayer isolator upper silicon structure to form a multilayer nanowire structure on the first silicon matrix, and h. removing the second oxide layer under the nanowires in the multilayer nanowire structure. By means of the manufacturing method of the multilayer nanowire structure, the crystal orientations of the nanowires are different.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method for Preparing GOI Chip Structure

ActiveUS20140004684A1Lower reaction temperatureHigh-quality GOI chip structureSemiconductor/solid-state device manufacturingSmart CutEngineering

The present invention provides a method for preparing a GOI chip structure, where, in the method, first, a SiGe on insulator (SGOI) chip structure is made by using a Smart-Cut technology, and then, germanium condensation technology is performed on the SGOI chip structure, so as to obtain a GOI chip structure. Because the SGOI made by the Smart-Cut technology basically has no misfit dislocation in an SGOI / BOX interface, the threading dislocation density of the GOI is finally reduced. A technique of the present invention is simple, the high-quality GOI chip structure can be implemented, and the germanium condensation technology is greatly improved. An ion implantation technology and an annealing technology are quite mature techniques in the current semiconductor industry, so that such a preparation method greatly improves the possibility of wide use of the germanium concentration technology in the semiconductor industry.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Method for preparing GOI chip structure

ActiveUS8877608B2Reduce the temperatureReduce dislocation densitySemiconductor/solid-state device manufacturingSmart CutEngineering

The present invention provides a method for preparing a GOI chip structure, where, in the method, first, a SiGe on insulator (SGOI) chip structure is made by using a SMART CUT technology, and then, germanium condensation technology is performed on the SGOI chip structure, so as to obtain a GOI chip structure. Because the SGOI made by the Smart-Cut technology basically has no misfit dislocation in an SGOI / BOX interface, the threading dislocation density of the GOI is finally reduced. A technique of the present invention is simple, the high-quality GOI chip structure can be implemented, and the germanium condensation technology is greatly improved. An ion implantation technology and an annealing technology are quite mature techniques in the current semiconductor industry, so that such a preparation method greatly improves the possibility of wide use of the germanium concentration technology in the semiconductor industry.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

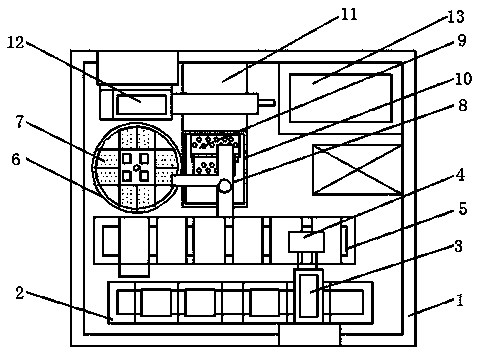

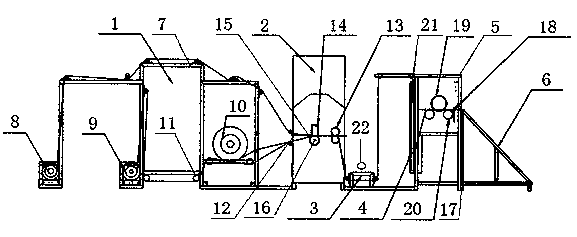

Intelligent equipment for photovoltaic cell piece cutting

InactiveCN107671437AProtection against collision damageSimple structureMetal working apparatusLaser beam welding apparatusSmart CutEngineering

The invention discloses an intelligent device for cutting photovoltaic cells in the technical field of cutting intelligence. The placement plate is movably connected to the fixed block through a rotating shaft. The front end of the hydraulic device is provided with a lifting rod. The inner cavity of the collection bin is uniformly provided with three sets of partitions from left to right. The inner wall is provided with a protective layer, and the left and right sides of the rear end surface of the collection bin are provided with connecting blocks, and the end of the connecting block away from the collection bin is provided with a fixed plate, and the fixed plate is rollingly connected to the wheel through a fixed bearing. , Add a telescopic rod and a placement tray on the conveyor belt, and the placement tray reaches a certain angle through the lifting of the telescopic rod and then falls to the workbench, and a collection bin is set up to effectively collect the cut batteries.

Owner:苏州目天光电设备有限公司

Process for producing SOI wafer

ActiveUS7358147B2Uniform film thicknessReduce roughnessSolid-state devicesSemiconductor/solid-state device manufacturingHydrogenWafering

There is provided a process for producing an SOI wafer in which, when producing an SOI wafer using Smart Cut technology, the surface can be smoothed after cleaving, the thickness of the SOI layer can be reduced, and the film thickness of the SOI wafer can be made uniform. In this process for producing an SOI wafer, hydrogen gas ions are implanted via an oxide film in a silicon wafer that is to be used for an active layer, so that an ion implanted layer is formed in the silicon bulk. Next, this active layer silicon wafer is bonded via an insulating film to a base wafer. By heating this base wafer, a portion thereof can be cleaved using the ion implanted layer as a boundary, thereby forming an SOI wafer. After the cleaving has been performed using the ion implanted layer as a boundary, the SOI wafer undergoes oxidization processing in an oxidizing atmosphere. This oxide film is then removed by, for example, HF solution. Thereafter, the SOI wafer undergoes heat processing for approximately three hours in an argon gas atmosphere at 1100° C. or more. As a result, the root mean square roughness of the SOI wafer surface is improved to 0.1 nm or less.

Owner:SUMCO CORP

Method for manufacturing thin film on substrate

InactiveCN107785235AHigh dielectric constantIncrease lossSemiconductor/solid-state device manufacturingSmart CutRoom temperature

The present invention provides a method for manufacturing a thin film on a substrate. The method comprises the following steps that: an original substrate is provided; an ion separation layer is formed in the original substrate by using an ion implantation method, so that a thin film layer and a remaining medium layer can be formed on the original substrate through the ion separation layer, wherein the thin film layer is a region for bearing ion implantation in the original substrate, and the remaining medium layer is a region where no ions are implanted; a target substrate is bonded to the original substrate through a wafer bonding method, so that the target substrate and the original substrate can be bonded to a bonded structural body; and the bonded structural body is heated, and laseris adopted to irradiate the bonded structural body, so that the thin film layer and the remaining medium layer can be separated from each other, and the thin film layer can be transferred from the original substrate to the target substrate, and the heating temperature of the bonded structural body is higher than room temperature and conversion temperature that enables the dielectric constant and loss factor of the bonded structural body to be converted, and is lower than temperature that activates a smart cut method.

Owner:SHENYANG SILICON TECH

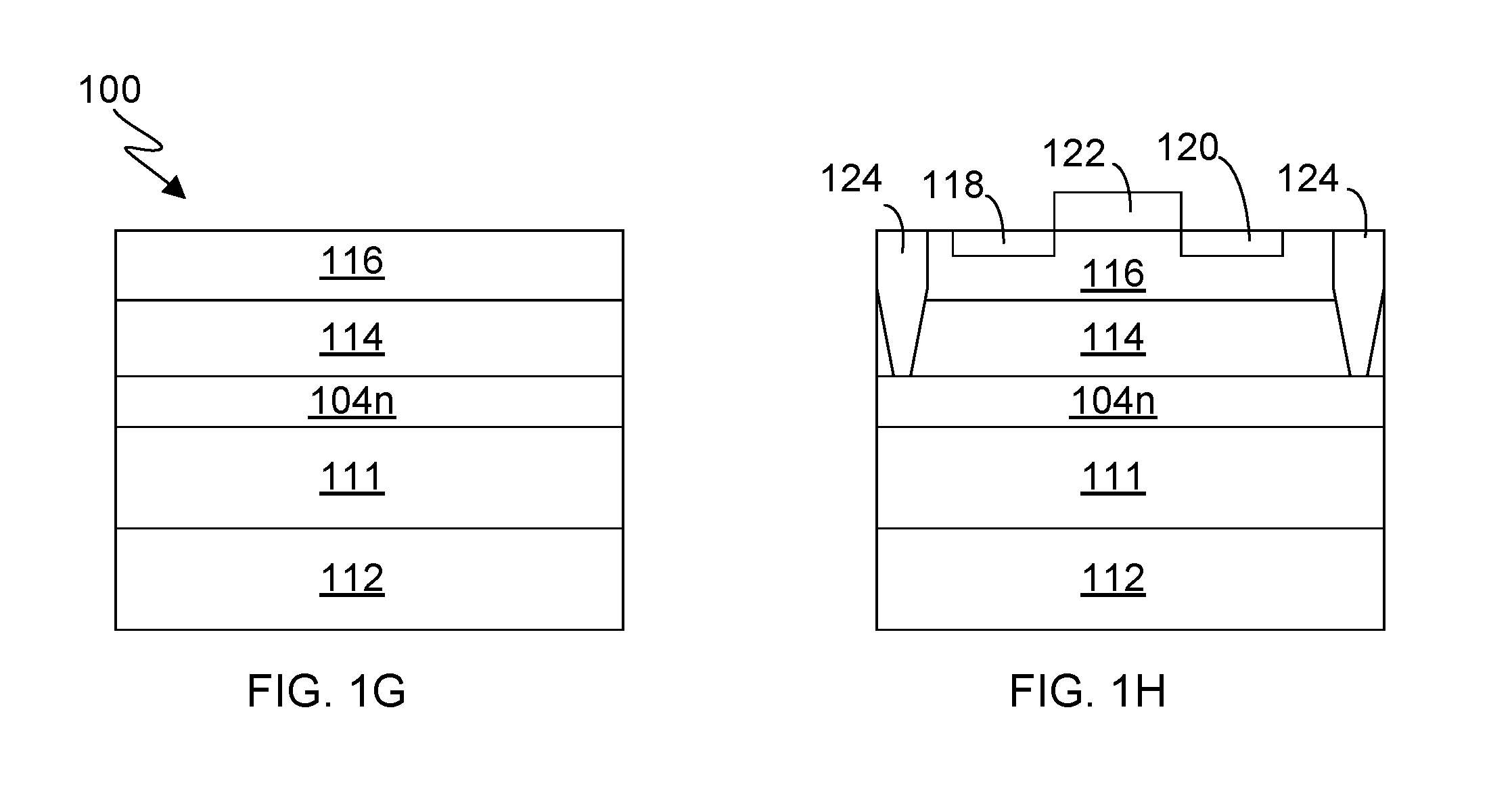

A patterned silicon-on-insulator substrate material and preparation method thereof

ActiveCN105895575BQuality assuranceAvoid breakingSolid-state devicesSemiconductor/solid-state device manufacturingSmart CutSoi substrate

The invention provides a graphical silicon-on-insulator (SOI) substrate material and a preparation method thereof. The preparation method comprises the steps of 1) providing an SOI substrate comprising bottom silicon, a buried oxide layer and top silicon, and forming an insulating layer on the surface of the top silicon; 2) forming an etching window corresponding to a position for preparing a transistor channel; 3) etching the insulating layer to form a groove penetrating through the top silicon; 4) providing a silicon substrate, and bonding the silicon substrate and the insulating layer; 5) removing the bottom silicon; and 6) removing the buried oxide layer. The groove is formed in the insulating layer corresponding to the position for preparing the transistor channel, and the groove completely penetrates through the space between the top silicon and the bottom silicon, so that a hollowed area is formed below the transistor channel prepared later. In the substrate preparation process, annealing and peeling steps in a Smart-cut method are avoided while the quality of the material is guaranteed, so that the problem of breakage of the top silicon in the graphical area due to high stress is solved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

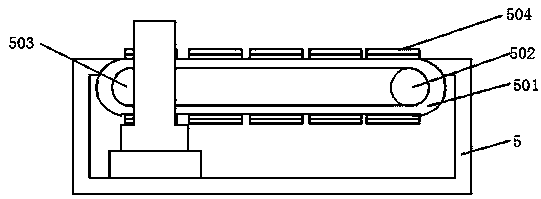

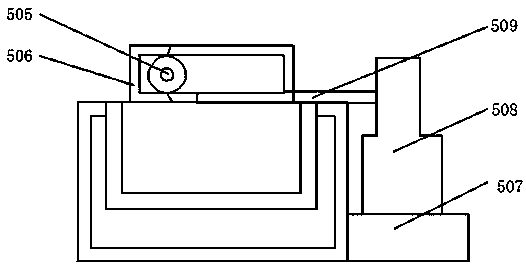

Ultrasonic composite Jian cotton intelligent slitting integrated machine and subsequent slitting mechanism

PendingCN107791659ANovel structureEasy to useLamination ancillary operationsLaminationSmart CutTest platform

The invention discloses an ultrasonic composite Jian cotton intelligent slitting integrated machine and subsequent slitting mechanism. Materials are fed by a feeding mechanism and embossed by an ultrasonic composite structure, pass a checking platform, a storage mechanism and a cutting mechanism and finally are discharged from a discharging platform. The ultrasonic composite Jian cotton intelligent slitting integrated machine and subsequent slitting mechanism is novel in structure, convenient to use, short in embossing time, strong in cementation force, clear in embossed lines, low in processing loss and high in working efficiency, surfaces have stereoscopic embossment effects, finished products are free from needle holes and water seepage and have waterproof and warm-keeping effects, an embossing roller is simply and conveniently adjusted and easily replaced, ever-changing, complicated, non-continuous and symmetric patterns can be sewn according to customer requirements, and the slitting process is non-stop.

Owner:盐城精通源机械有限公司

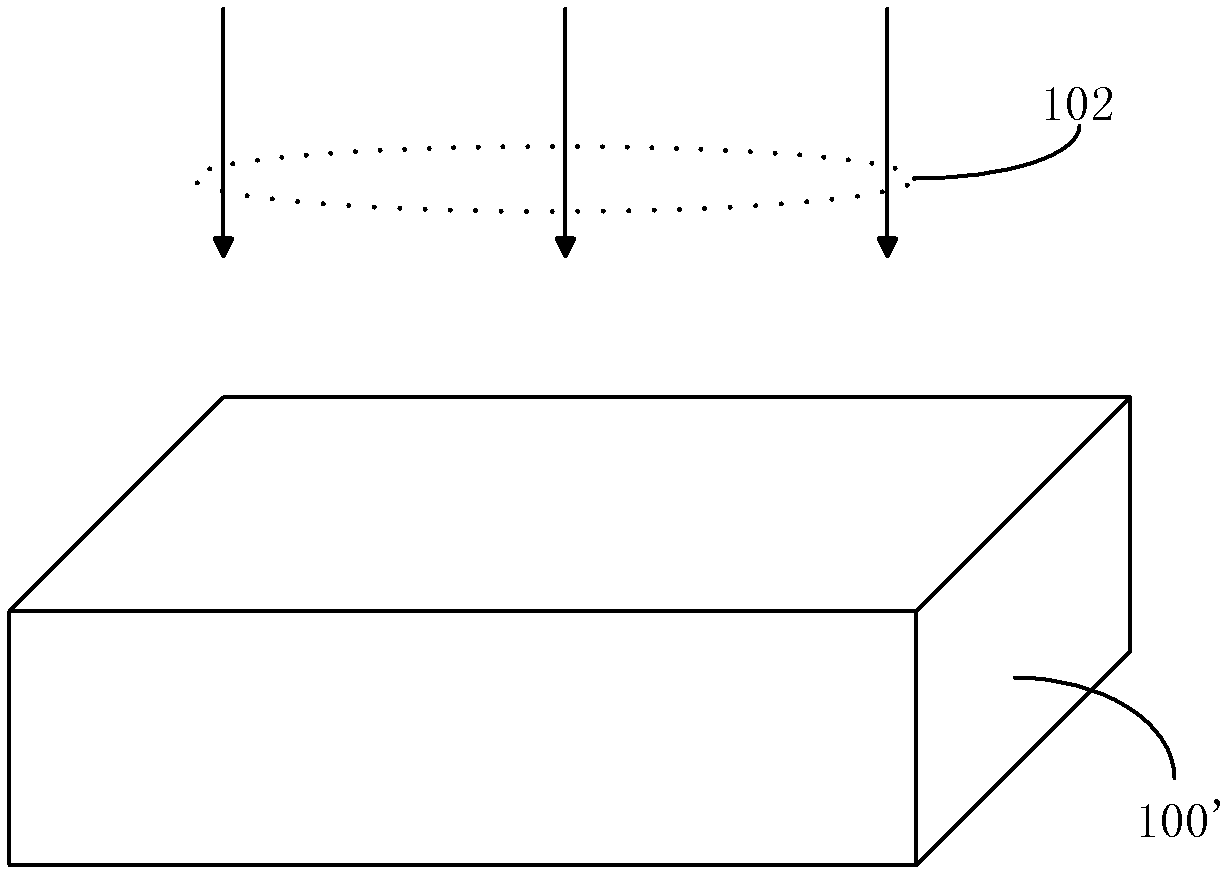

Method for manufacturing bonded wafer

ActiveUS8697544B2Reduce generationQuality improvementSolid-state devicesSemiconductor/solid-state device manufacturingSmart CutSilicon oxide

The present invention is a method for manufacturing a bonded wafer including at least the steps of: forming an ion-implanted layer inside a bond wafer; bringing the ion-implanted surface of the bond wafer into close contact with a surface of a base wafer directly or through a silicon oxide film; and performing heat treatment for delaminating the bond wafer at the ion-implanted layer, wherein the heat treatment step for delaminating includes performing a pre-annealing at a temperature of less than 500° C. and thereafter performing a delamination heat treatment at a temperature of 500° C. or more, and the pre-annealing is performed at least by a heat treatment at a first temperature and a subsequent heat treatment at a second temperature higher than the first temperature. As a result, there is provided a method for manufacturing a bonded wafer having high quality, for example, mainly the reduction of defects, by forming a high bonding strength state at a lower temperature than the temperature at which the delamination is caused, in the manufacture of the bonded wafer by the Smart Cut method (registered trademark).

Owner:SHIN-ETSU HANDOTAI CO LTD

Method for preparing semiconductor material through ion injection and fixed-point adsorption technologies

ActiveCN102737963BReduce defect densityHigh relaxivitySemiconductor/solid-state device manufacturingSemiconductor materialsSmart Cut

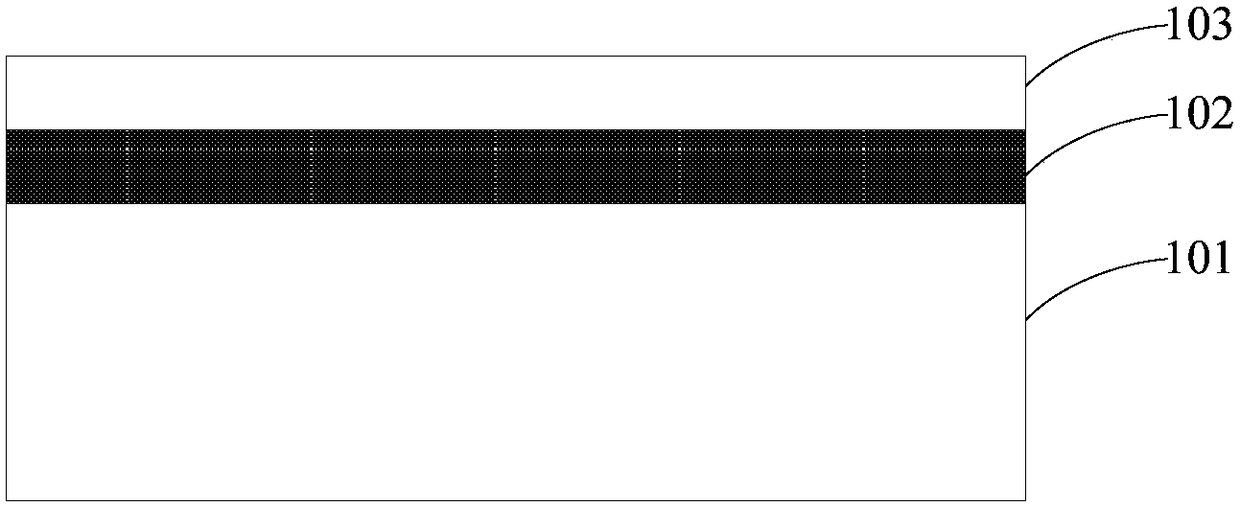

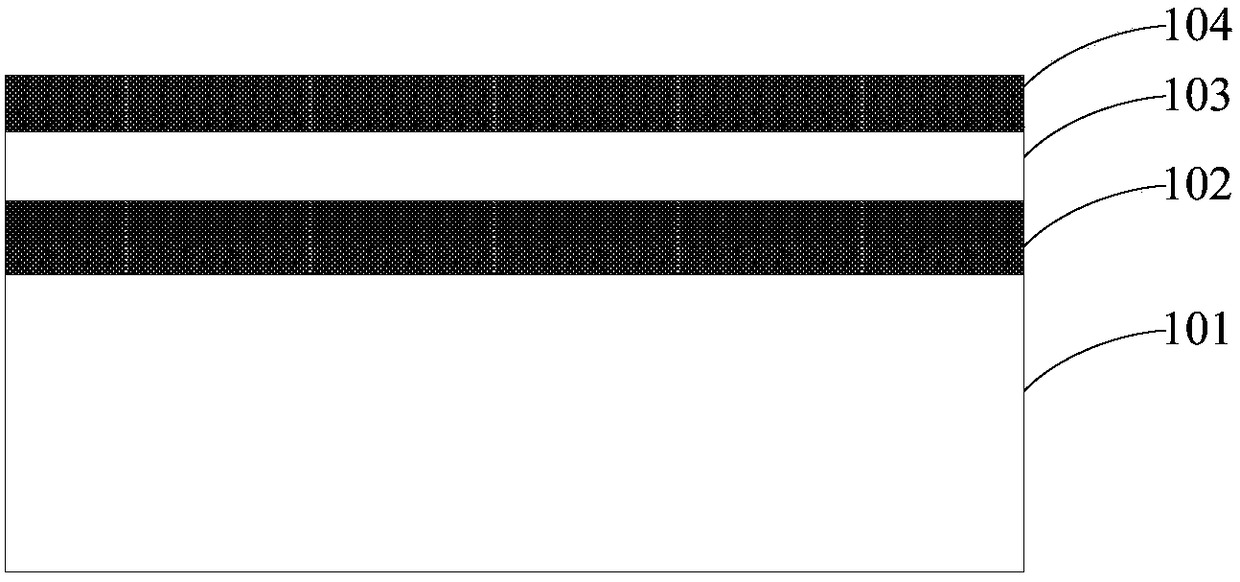

The invention provides a method for preparing a semiconductor material through ion injection and fixed-point adsorption technologies. The method comprises the steps of firstly extending at least one period of an SixGe1-x / Si superlattice structure (x is greater than or equal to 0 and smaller than 1) on an Si substrate, sequentially growing an Si buffer layer and an SizGe1-z layer on the superlattice structure, then injecting H or He ions into the Si substrate and performing rapid annealing treatment, so as to ensure that the superlattice structure is adsorbed to the ions, and finally obtaining an SizGe1-z layer with low defect concentration and high relaxation. By bonding with the Si substrate with an oxidation layer, SGOI with low defect concentration and high relaxation can be prepared through smart cut, strained silicon with the thickness being smaller than the critical thickness is expanded on the obtained relaxation SizGe1-z layer, and strained silicon (sSOI) with high relaxation and low defect concentration on insulators can be prepared through smart cut. The method improves the stability of relaxation SiGe material prepared through ion injection through superlattice adion, obtains SiGe material with low defect concentration and high relaxation, reduces the technology difficulty, and is applicable to industrial production.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

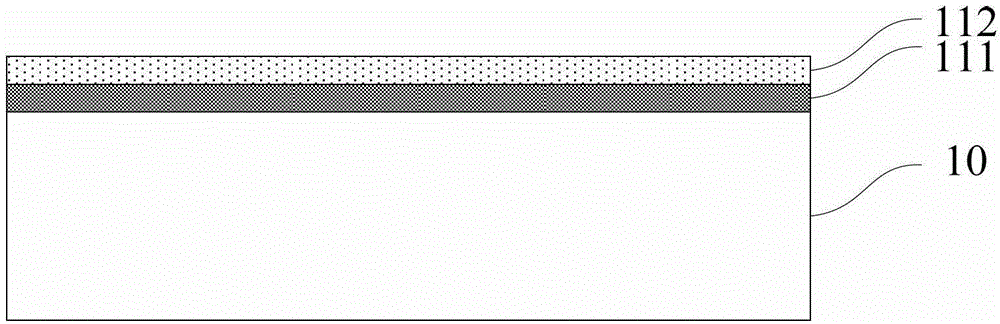

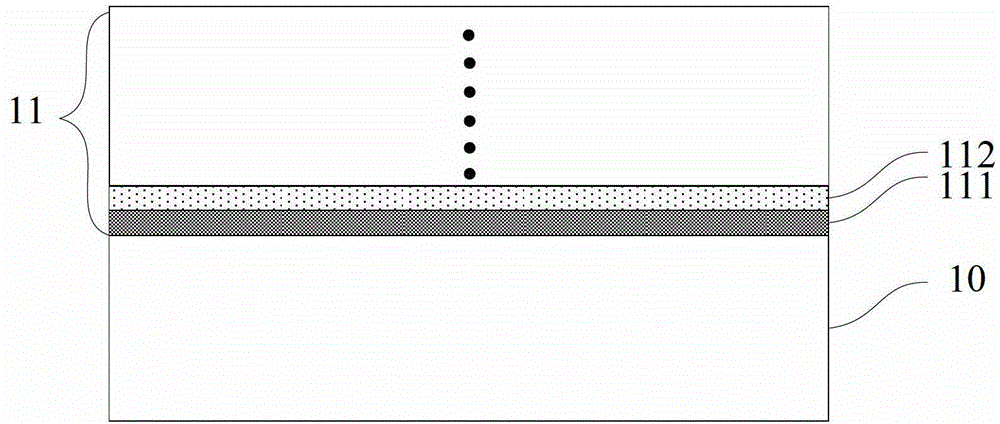

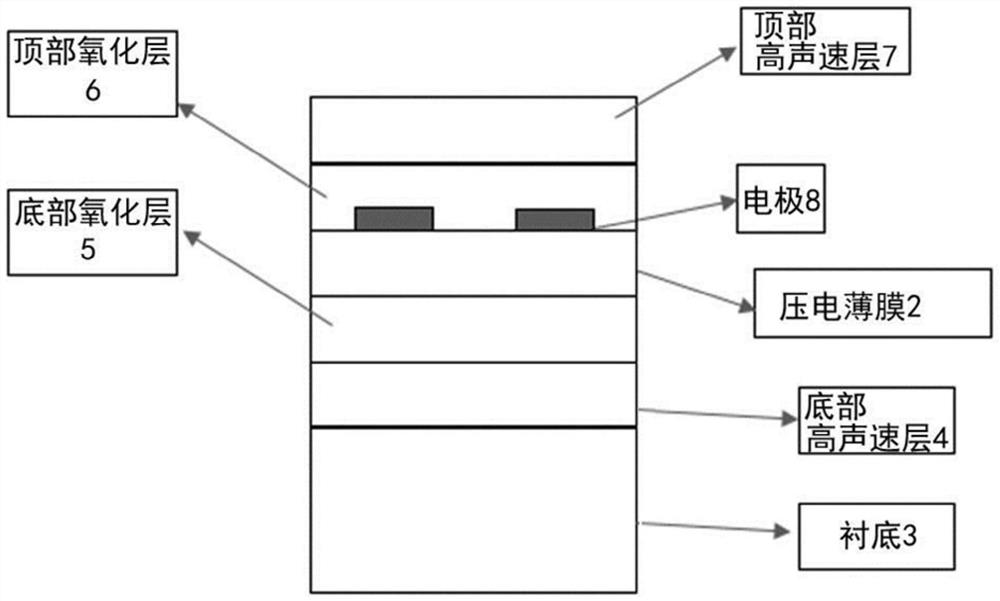

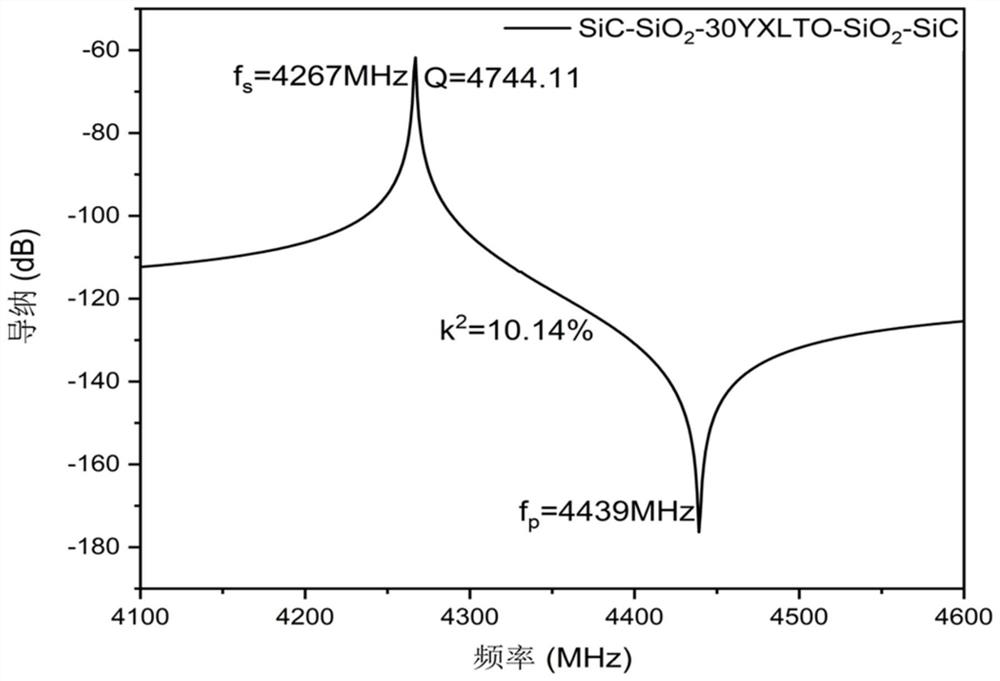

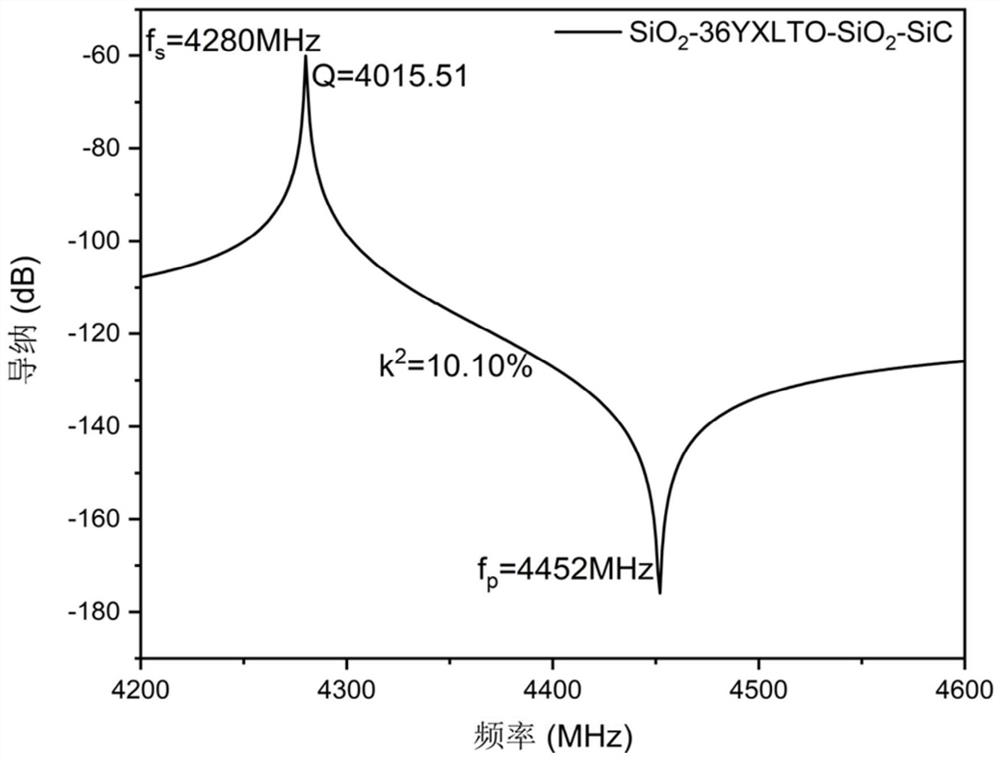

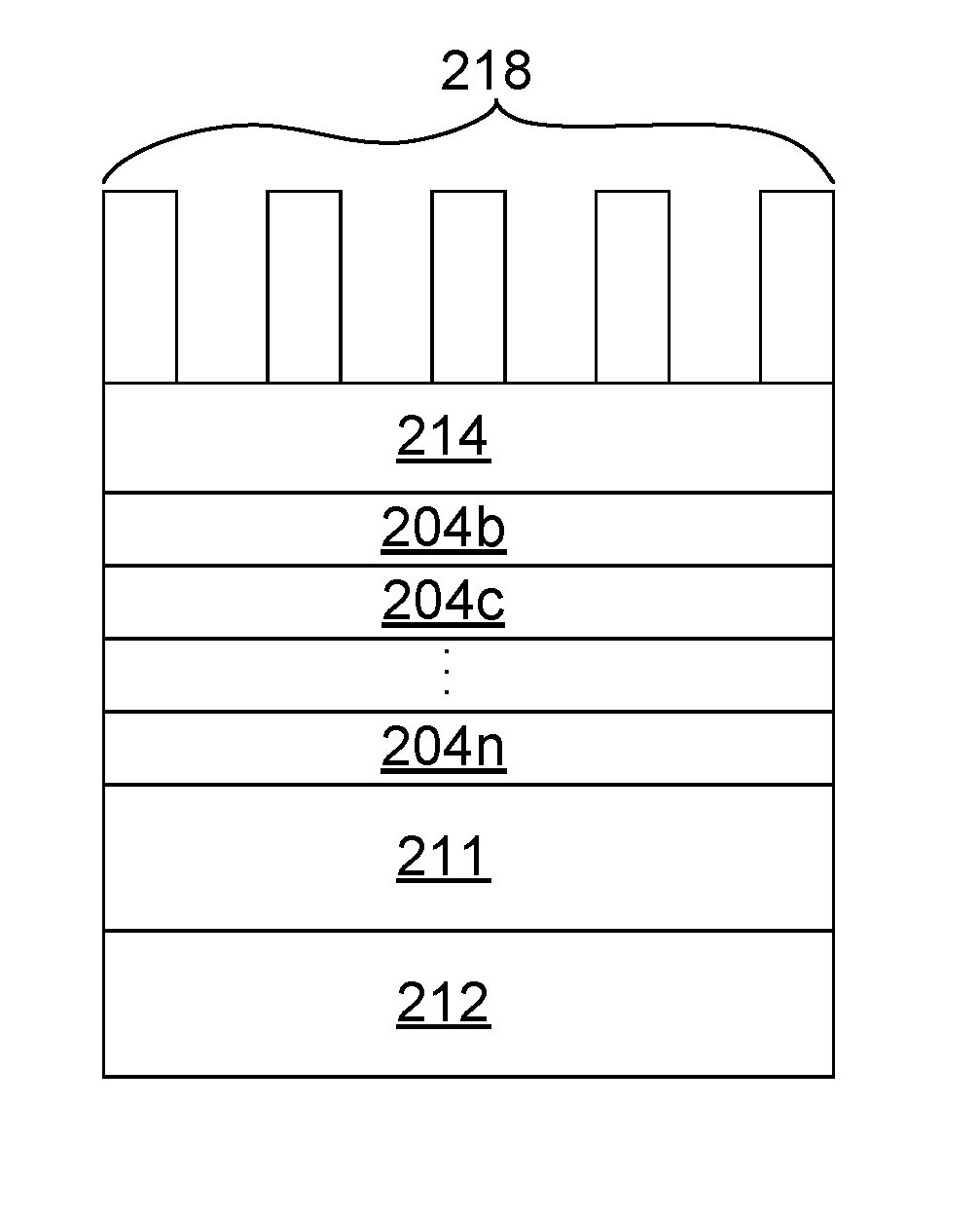

Surface acoustic wave resonator with double-layer POI structure and manufacturing method

The invention discloses a surface acoustic wave resonator with a double-layer POI structure and a manufacturing method. The resonator includes a substrate, a bottom POI structure over the substrate, an electrode over the bottom POI structure, and a top POI structure over the electrode. The bottom POI structure comprises a bottom high sound velocity layer, a bottom oxide layer and a piezoelectric film; the top POI structure comprises a top oxide layer and a top high-sound-velocity layer. The resonator manufacturing method comprises the following steps: sequentially depositing a bottom high-sound-velocity layer and a bottom oxide layer on a substrate, performing low-temperature bonding with one surface of a LiTaO3 piezoelectric film obtained by a smart cut method, depositing an electrode on the other surface of the piezoelectric film, and sequentially depositing a top oxide layer and a top high-sound-velocity layer on the electrode. The comprehensive performance of the surface acoustic wave resonator is greatly improved.

Owner:GUANGDONG CANCHIP TECH CO LTD

A kind of intelligent cutting method and cutting system of solar cells

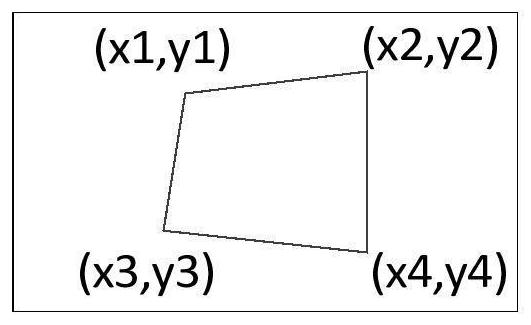

ActiveCN110600587BEnsure consistencyAvoid errorsSemiconductor/solid-state device testing/measurementFinal product manufactureElectrical batterySmart Cut

The invention relates to an intelligent cutting method and system for a solar battery piece, and the system is carried out according to the following steps: after the system is installed, coordinate correction needs to be carried out once. The correction method comprises the following steps: shooting a correction plate by using a camera to obtain coordinates of correction points on an image, calculating a coordinate correction comparison table by combining actual coordinates of the correction points, and storing the coordinate correction comparison table into a computer in a file form; when the system carries out cutting work, photographing a to-be-cut solar battery piece, obtaining the correction coordinates corresponding to the coordinates of the battery piece from the coordinate correction comparison table, reconstructing the corrected image, obtaining a cutting path according to the corrected image, and cutting the solar battery piece according to the cutting path. According to thesystem, the image of the solar battery piece captured by the camera is reconstructed, and the cutting path is obtained through the reconstructed image, so that errors caused by distortion of the shotimage are avoided, and the cutting precision is effectively improved.

Owner:安徽图算智能科技有限公司

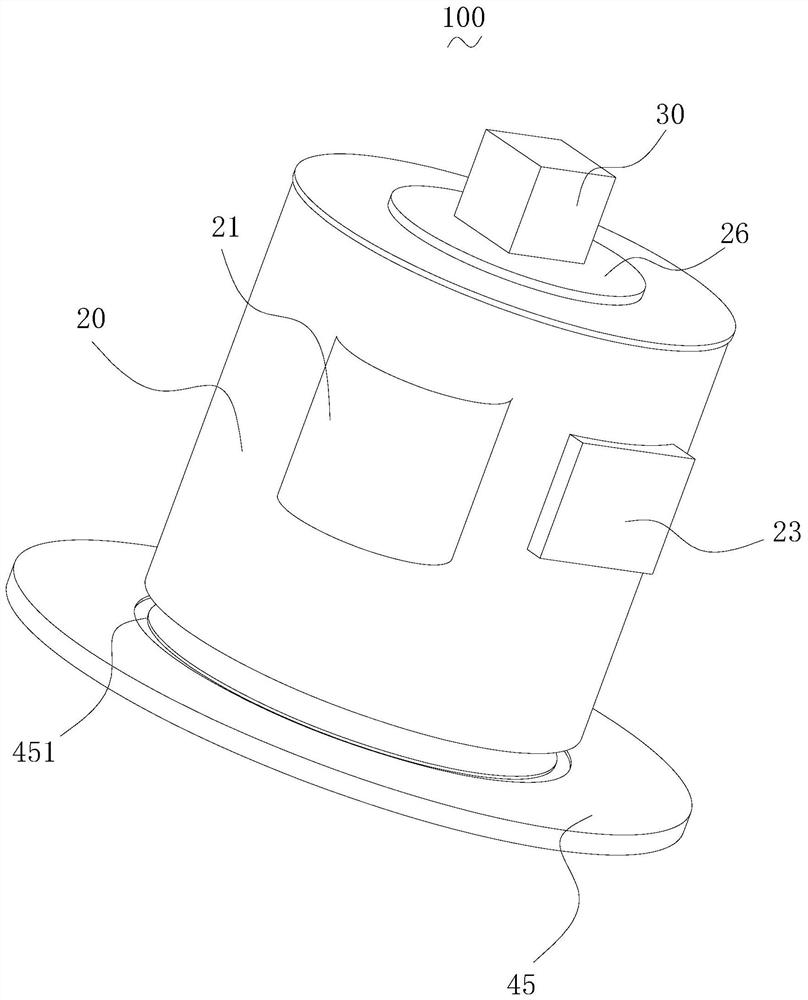

Intelligent cutting mechanism

The invention relates to an intelligent cutting mechanism. The intelligent cutting mechanism includes a casing, a motor and a cutting wheel, the casing is cylindrical, a transparent observation window and an intelligent display screen are arranged on the side wall of the casing, and the inner side of the casing is arranged There is a temperature sensor and a camera, the smart display screen is used to display the temperature and image in the casing, the top of the casing is provided with a buffer block, and the motor is arranged on the top of the casing and located at the top of the casing. On the buffer block, the cutting wheel is arranged in the casing and connected with the electric motor, and the inner side of the casing is provided with an insulating and refractory coating. The intelligent cutting mechanism has high safety performance.

Owner:常州市武进东风汽车部件有限公司

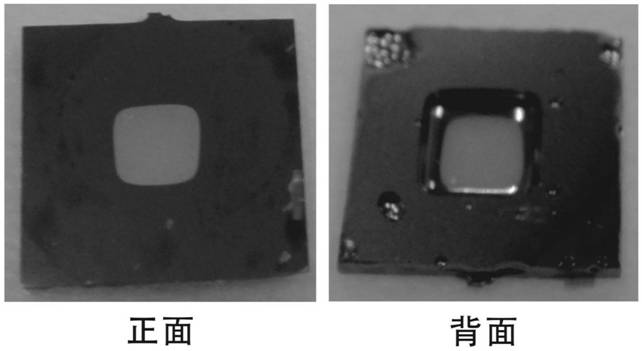

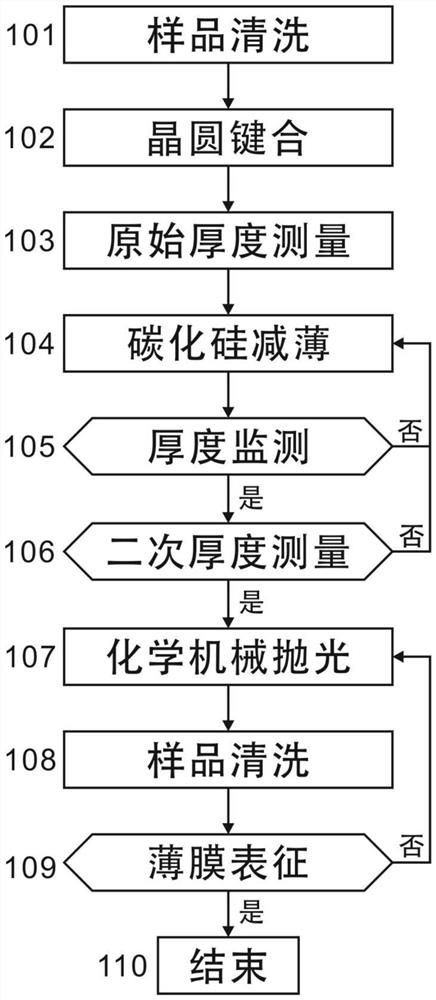

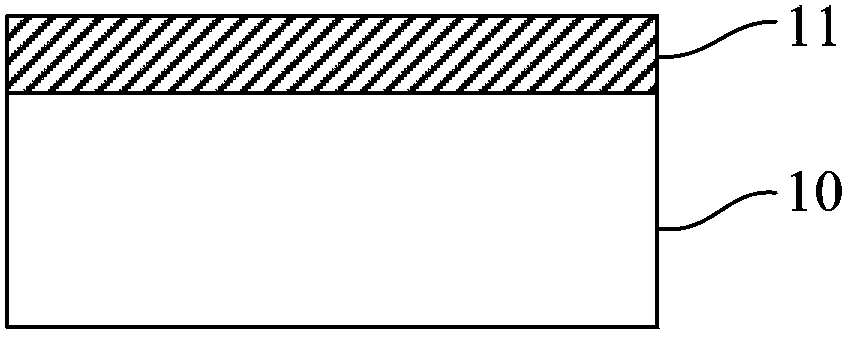

A kind of preparation method of silicon carbide single crystal thin film

ActiveCN109659221BEasy to separateEasy to useSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingCarbide siliconSmart Cut

The invention discloses a method for preparing a silicon carbide single crystal thin film. The technological process mainly includes: sample cleaning, wafer bonding, original thickness measurement, silicon carbide thinning, thickness monitoring, secondary thickness measurement, chemical mechanical polishing, sample Cleaning, thin film characterization and other processes. This method can obtain a silicon carbide single crystal film with a flat surface and a micron-scale thickness, and at the same time avoid the impact of defects that need to be implanted with high doses of hydrogen ions during the smart cut process, another common film preparation method. The prepared silicon carbide single crystal thin film is a heterogeneous material on a silicon substrate. Users can easily separate it from the substrate, or selectively retain part of the thin film substrate for subsequent use. In principle, silicon carbide thin film materials and other thin film materials that are difficult to grow heteroepitaxially or along a specific crystal direction can also be obtained from bulk samples by this method.

Owner:UNIV OF SCI & TECH OF CHINA

Fabrication of iii-v-on-insulator platforms for semiconductor devices

InactiveUS20160211170A1Semiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSmart Cut

Owner:ELPIS TECH INC

Preparation method of gate oxide integrity (GOI) wafer structure

ActiveCN102738060BReduce threading dislocationsQuality improvementSemiconductor/solid-state device manufacturingSmart CutEngineering

Provided is a method for fabricating a GOI wafer structure, the method comprising: firstly utilizing Smart-Cut technology to fabricate an SGOI wafer structure, and then conducting germanium concentration on the SGOI wafer structure to obtain the GOI wafer structure. The SGOI fabricated by the Smart-Cut technology basically has no mismatching or dislocation on an SGOI / BOX interface, thus ultimately reducing the penetrating dislocation of the GOI. The present invention has a simple process, and can fabricate high quality GOI wafer structure, thus greatly improving germanium concentration technology. With ion injection technology and annealing technology both being highly mature processes in the current semi-conductor industry, the fabrication method greatly improves the possibility of widely applying germanium concentration in the semi-conductor industry.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com