Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

44results about How to "Improve the conduction voltage drop" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

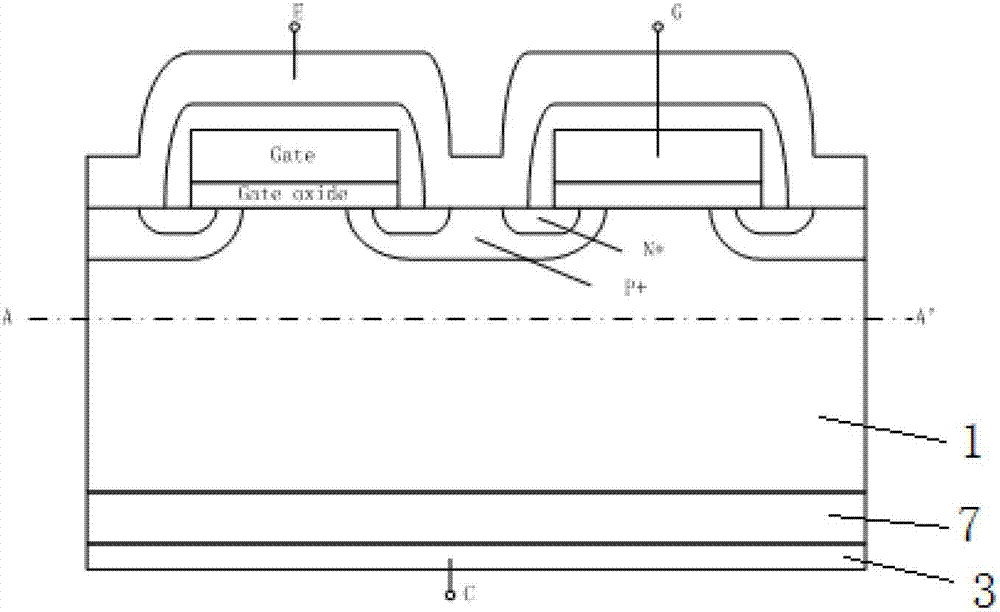

Accumulation layer controlled insulation gate type bipolar transistor

InactiveCN101393927AIncreased saturation current densityElimination of parasitic thyristor effectsSemiconductor devicesElectron flowParasitic bipolar transistor

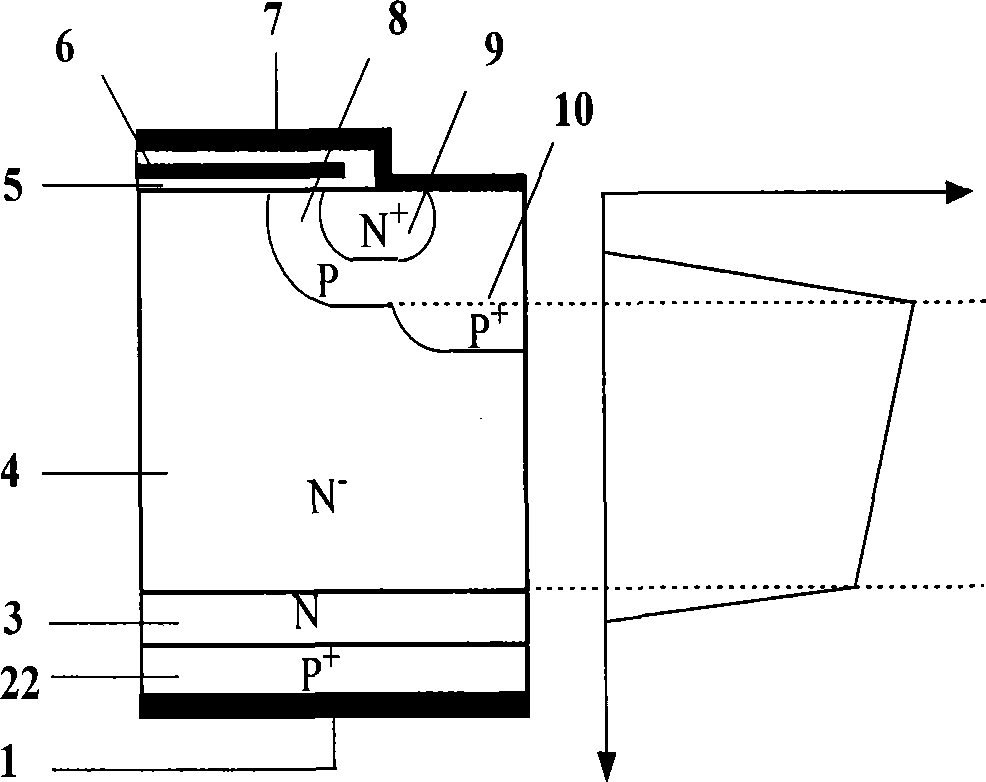

Insulated gate bipolar transistors controlled by an accumulation layer belong to the technical field of semiconductor power devices. The transistors include a channel insulated gate bipolar transistor, a plane insulated gate bipolar transistor and a transverse insulated gate bipolar transistor. According to the invention, when a device is in the blocking state, a built-in electric field formed by a P body region (10) and an N base region (4) forms part of an electron barrier which stops electrons flowing from an N source region (9) into the N base region(4) with the voltage-resistance of the device improved; when the device is in the conductive state, the accumulation layer is formed between the N source region (4) and a gate oxide layer (5), and the electrons can flow from the N source region (9) to the N base region (4) through the accumulation layer so as to control the normal operation of the device. With the accumulation layer rather than a P-type base region and an MOS inversion channel of a traditional insulated gate bipolar transistor, the invention can achieve lower conductive voltage drop and greater saturation current density, thereby avoiding parasitic thyristor effect, and ensuring that the safe operating area, the reliability and the high-temperature working characteristics of the device can be greatly promoted.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

SiC power device

ActiveCN110767753ASmall pressure dropEliminate minority carrier injection effectDiodeHeterojunction diodeMinority carrier injection

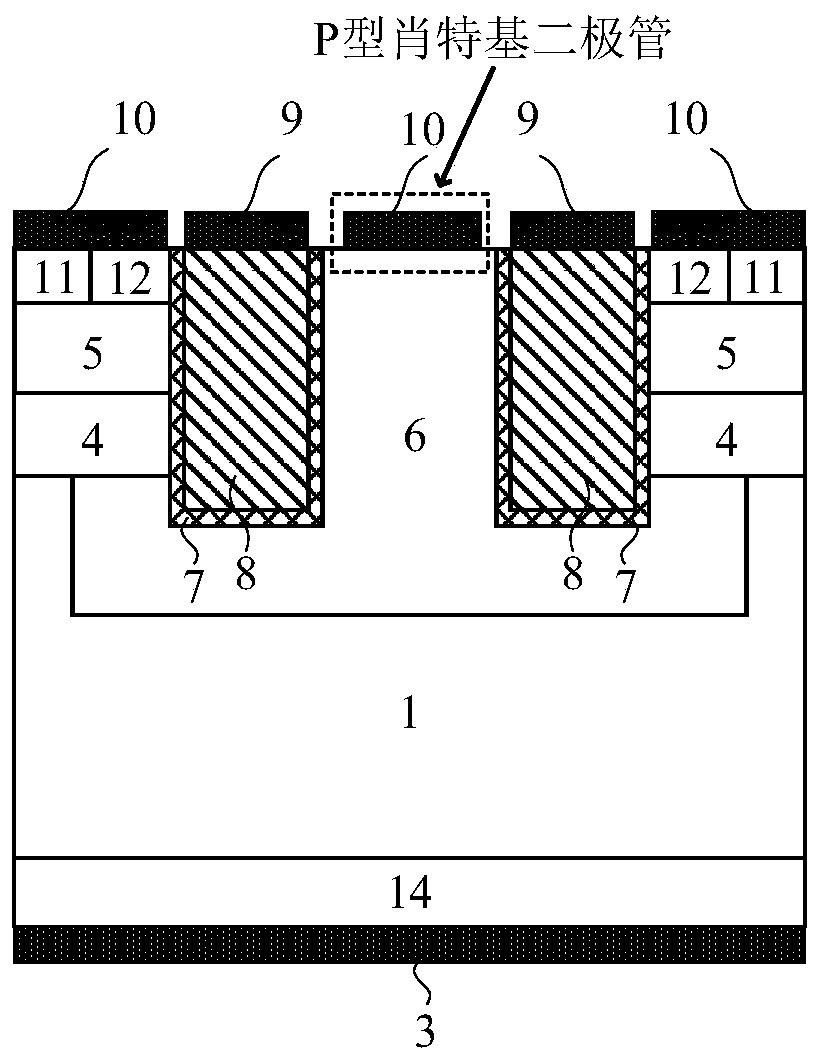

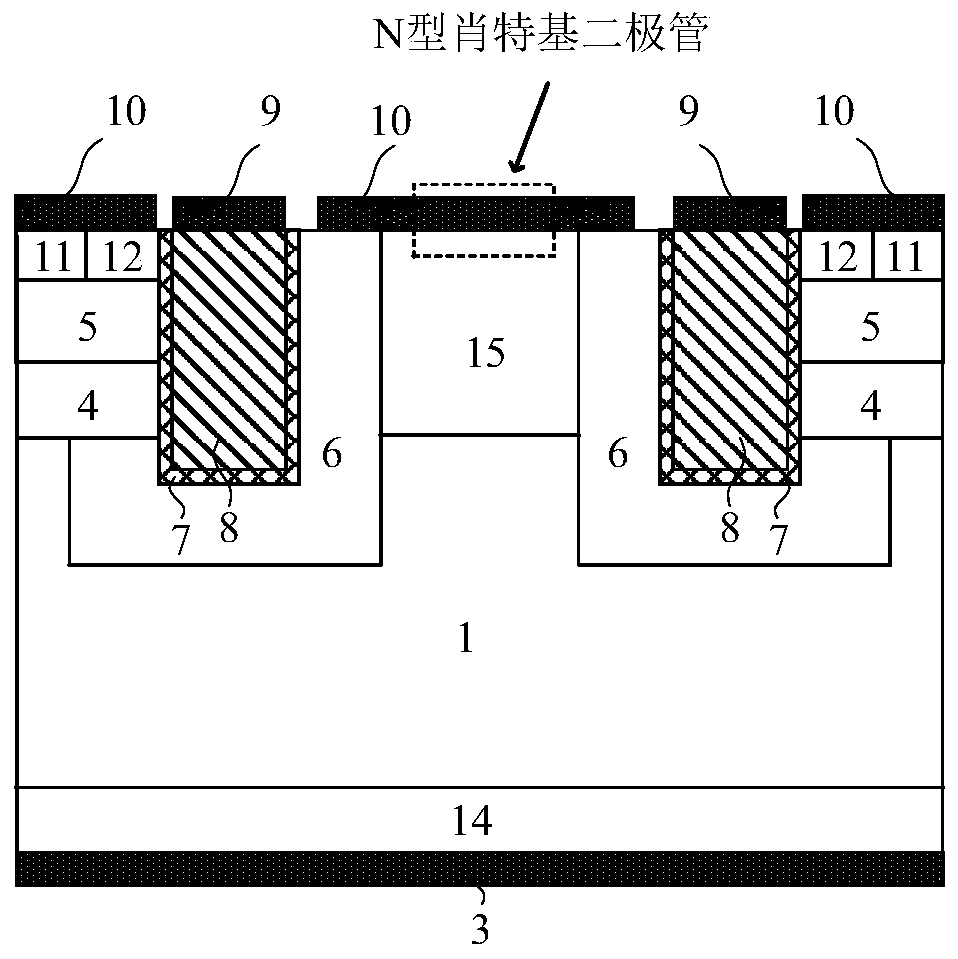

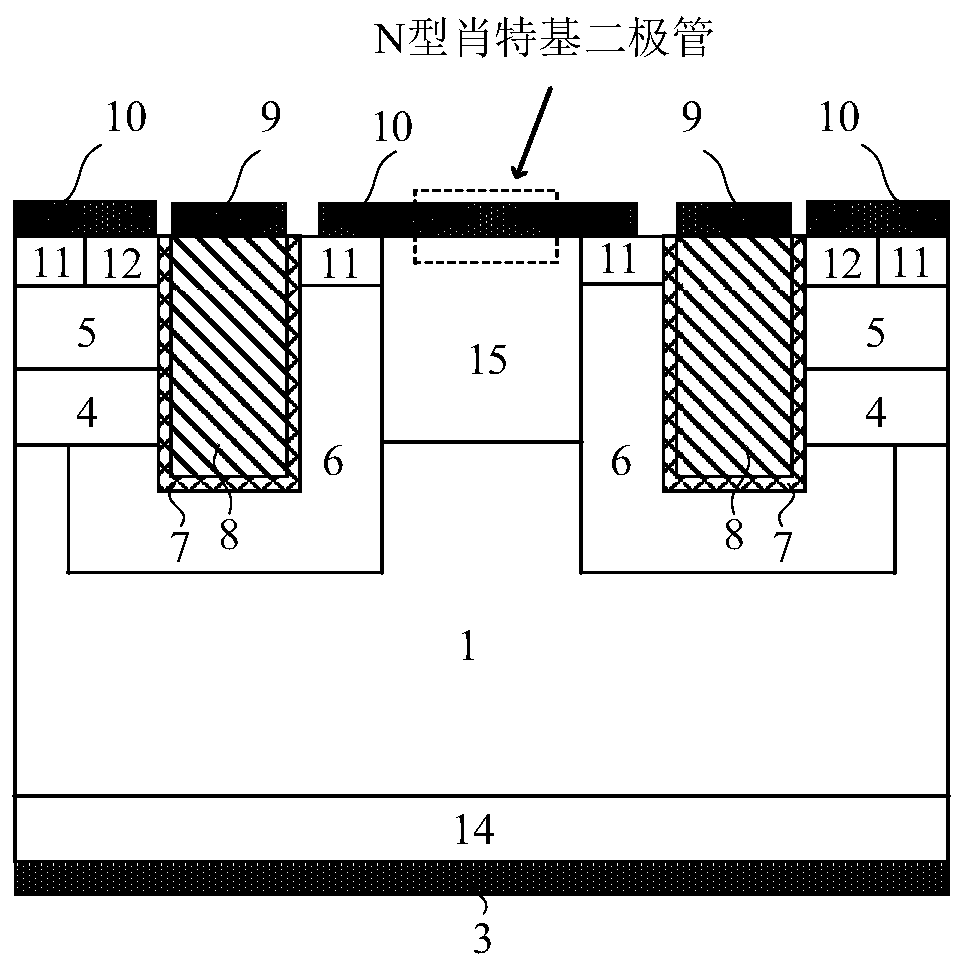

The invention belongs to the field of power semiconductors, and particularly provides a SiC power device. The SiC power device comprises a SiC MOSFET and a SiC IGBT. For the SiC MOSFET device integrated with a PN junction body diode, the reverse recovery charge and related loss of the body diode can be greatly reduced, the reverse recovery peak current is reduced, and the EMI noise is reduced; forthe SiC MOSFET device integrated with an N-type Schottky diode or an integrated heterojunction diode, the voltage drop during reverse conduction of the MOSFET can be reduced, and the minority carrierinjection effect is eliminated, so that the conduction loss and reverse recovery loss of the diode are reduced; for the reverse conduction type SiC IGBT device integrated with the PN junction body diode, the reverse recovery charge and related loss of the body diode can be greatly reduced, the reverse recovery peak current is reduced, and the EMI noise is reduced; and moreover, for the reverse conduction type SiC IGBT device integrated with the N-type Schottky diode or the heterojunction diode, the voltage drop during reverse conduction of the reverse conduction IGBT can be reduced, the minority carrier injection effect is eliminated, and the conduction loss and reverse recovery loss of the diode are reduced.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

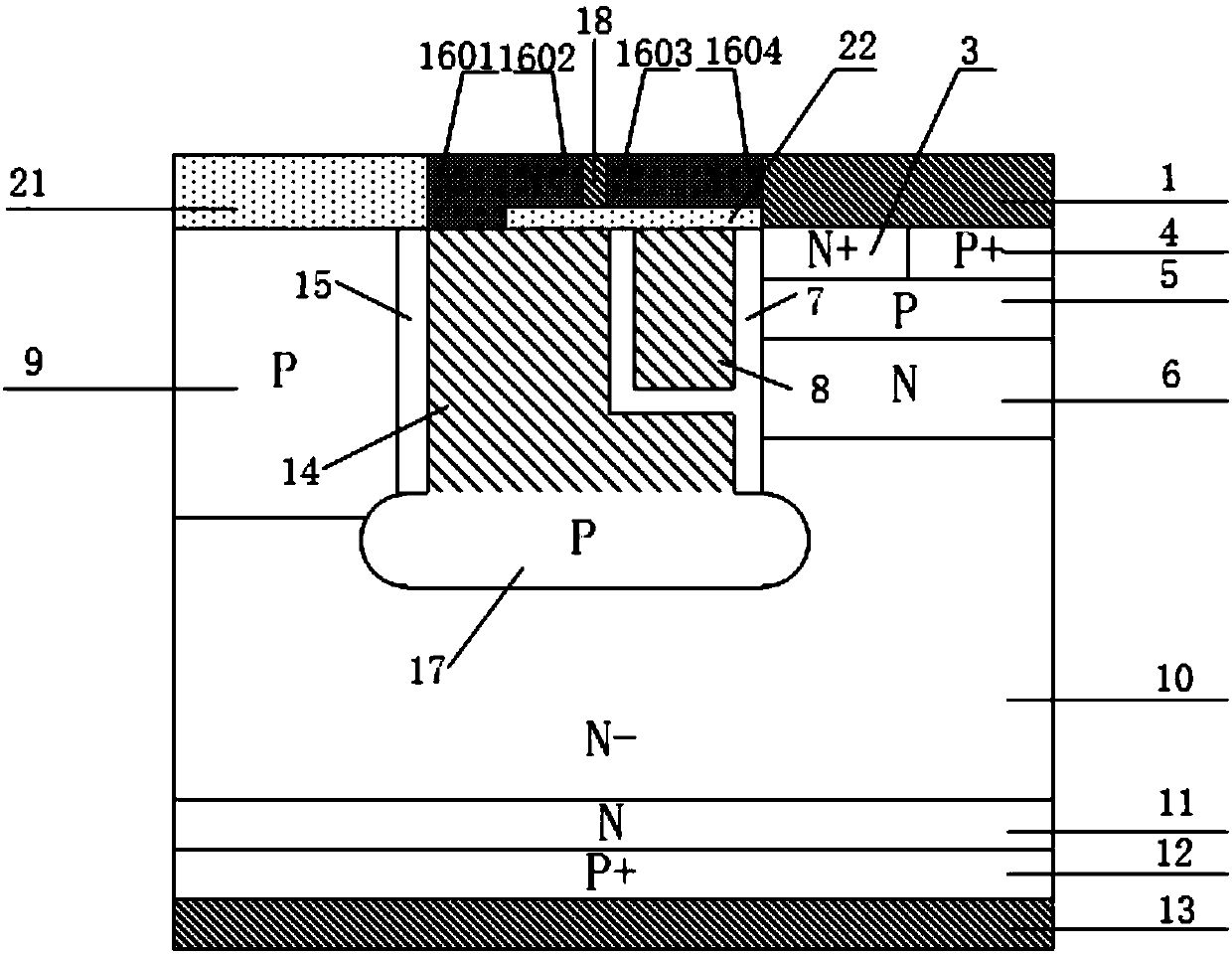

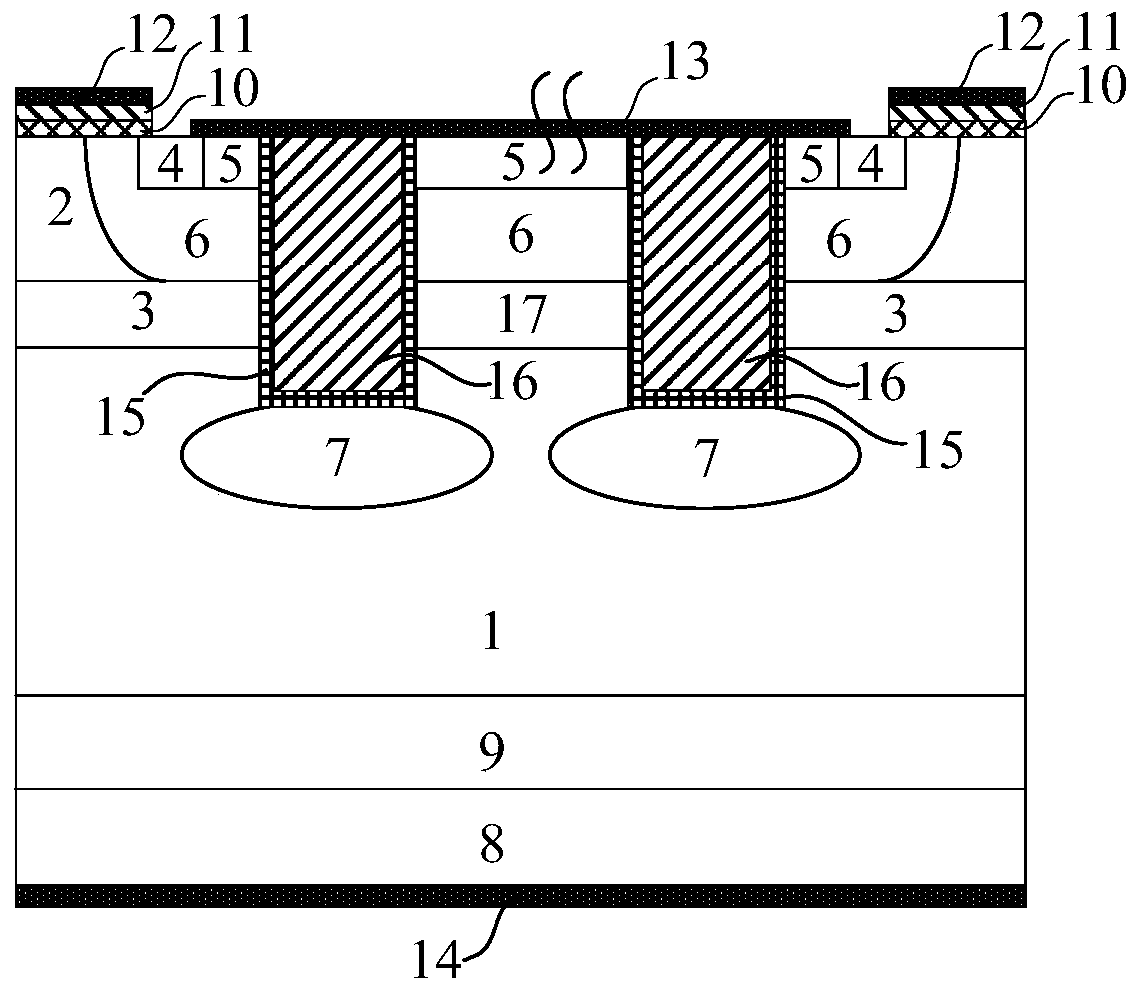

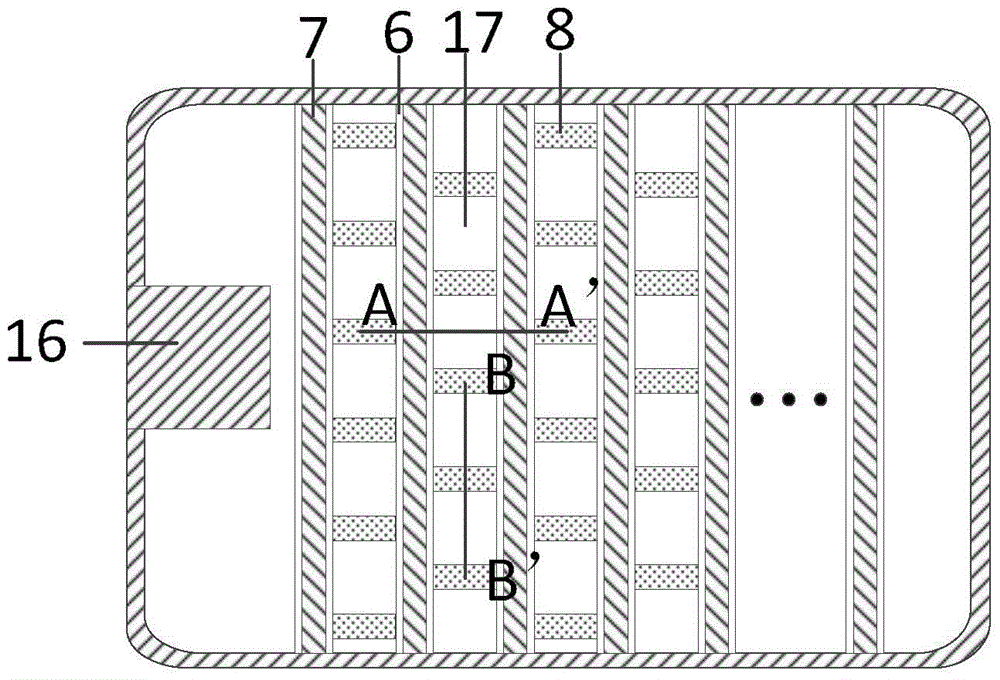

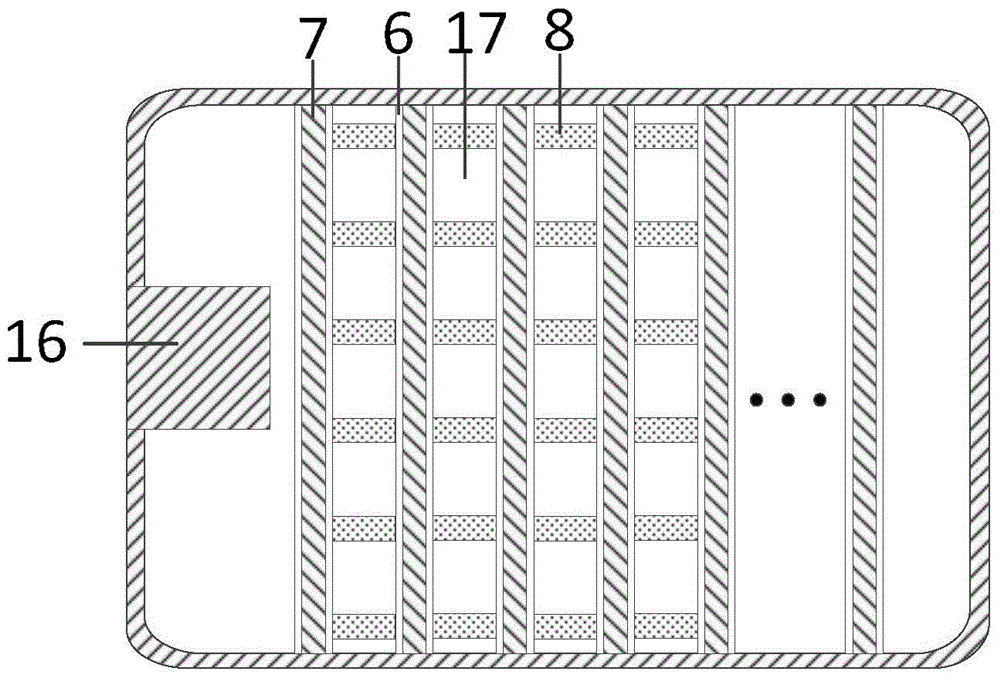

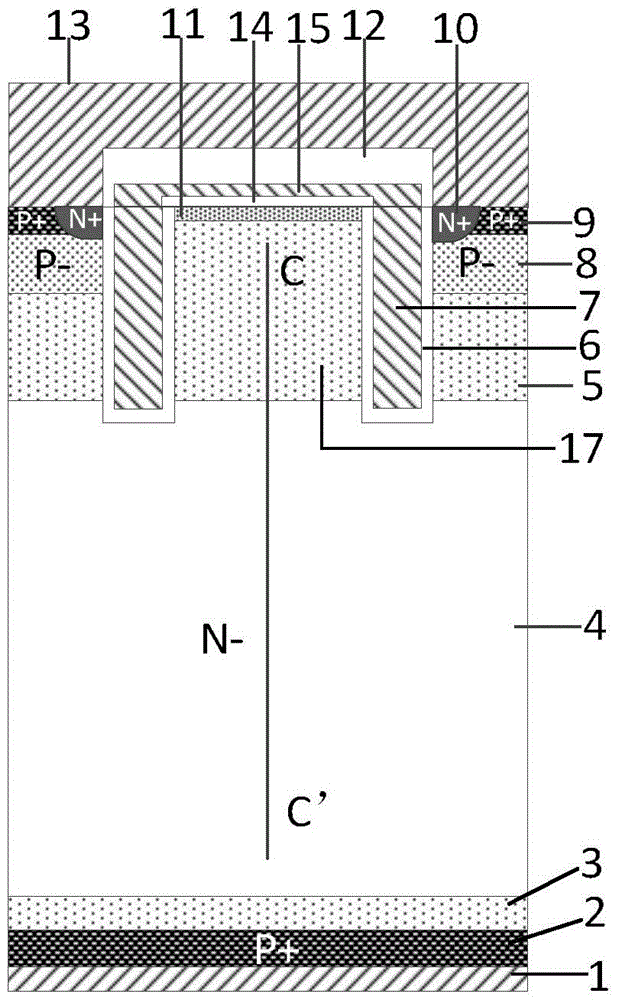

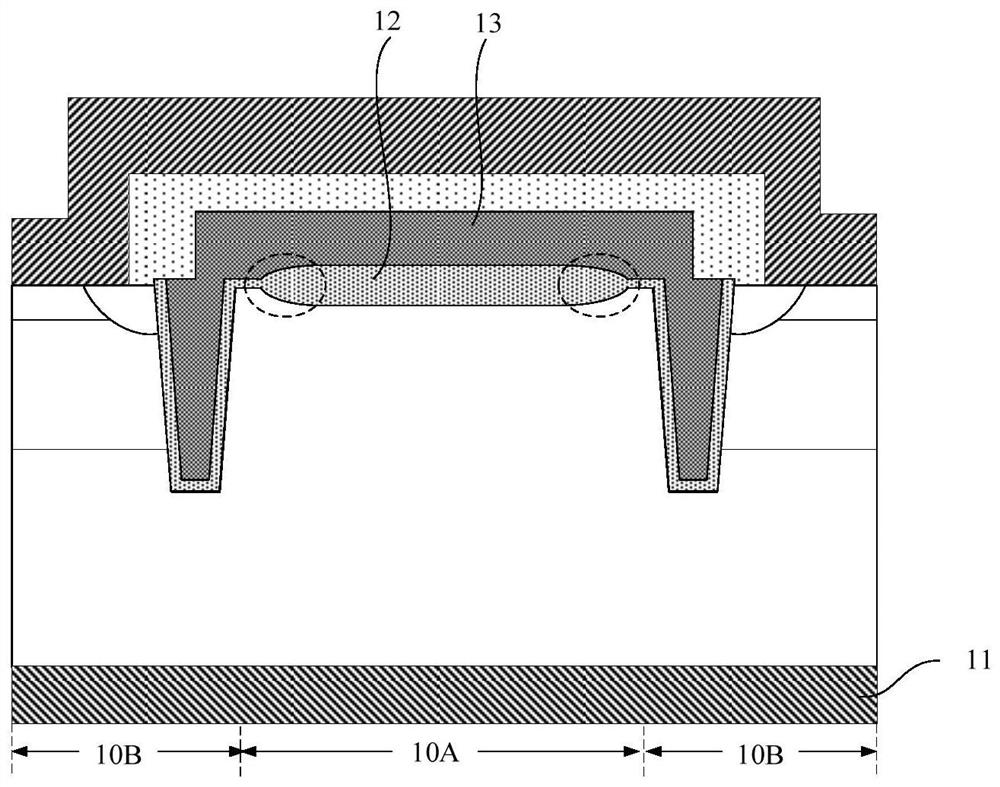

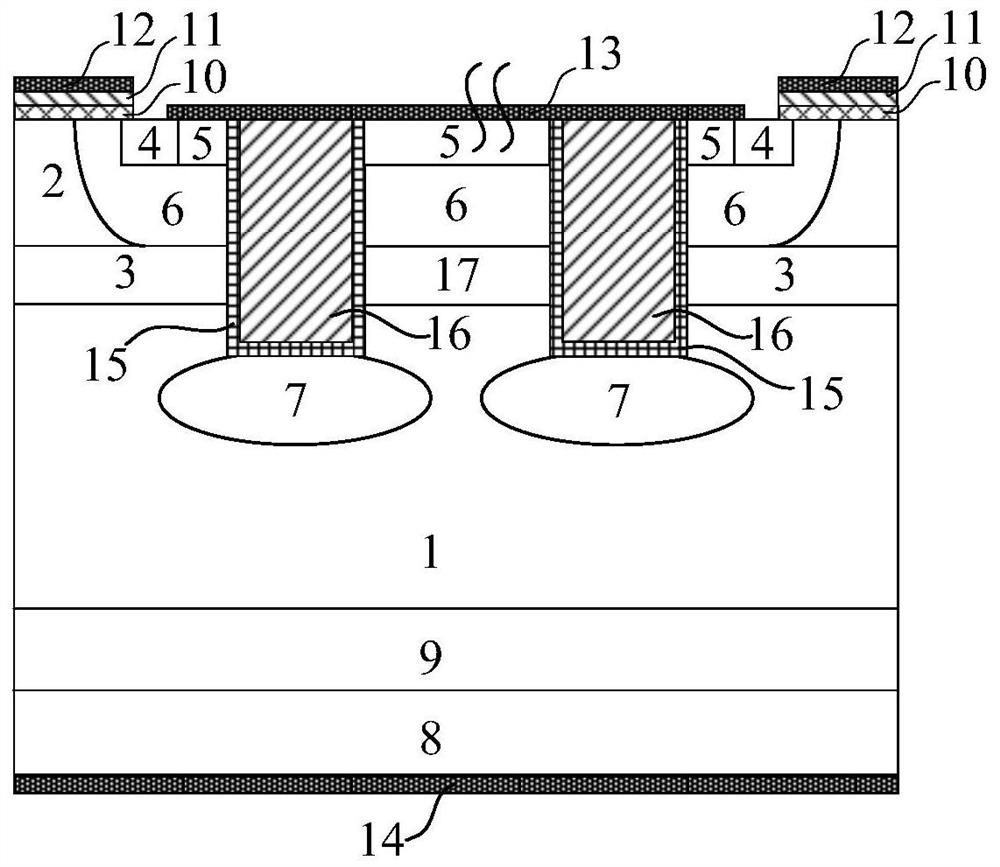

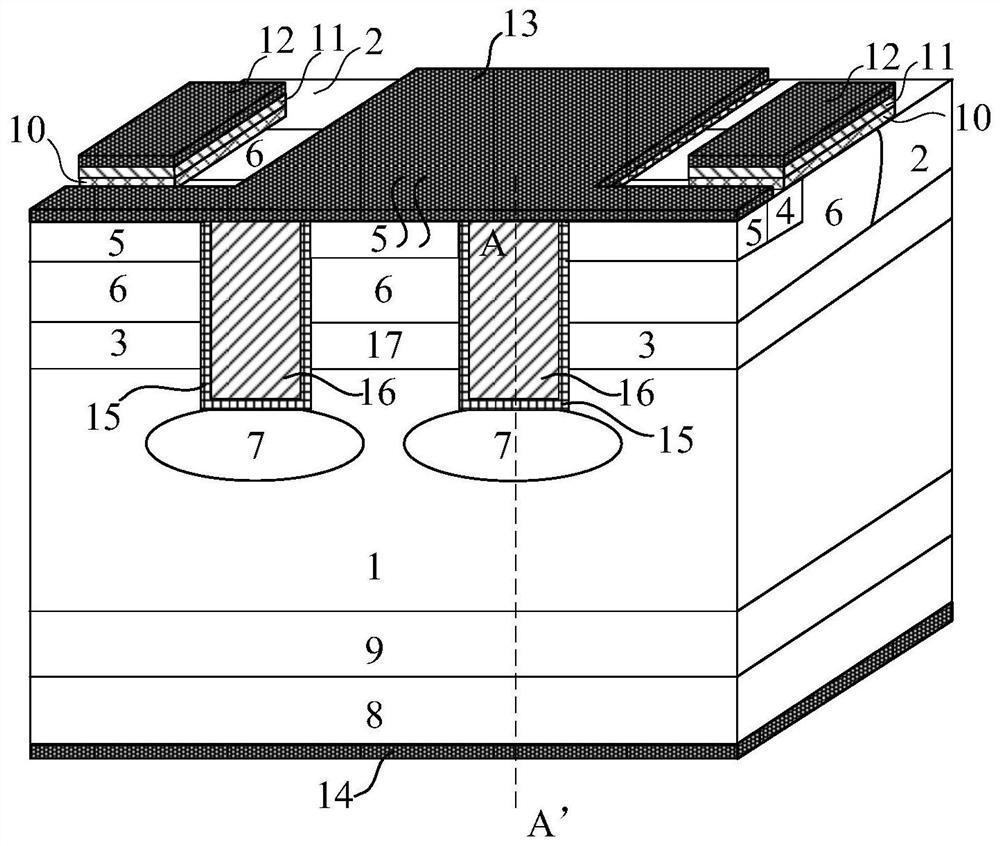

CSTBT device and manufacturing method thereof

ActiveCN107731898AImprove performanceLower saturation current densitySolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceEngineering

The invention discloses a CSTBT device and a manufacturing method thereof, which belong to the field of semiconductor power devices. A groove gate structure is together formed through introducing a groove split electrode below a gate electrode, a P-type layer is introduced below the groove split electrode, a series diode structure is arranged above the groove split electrode, and the problem of acontradictory relationship existing between the forward conduction performance of the device and the voltage-withstanding performance caused through improving the doping concentration of an N-type charge storage layer in the traditional CSTBT device is solved. The saturation current density is reduced and the short circuit safety working area of the device is improved. The gate capacitance of thedevice is reduced, the switching speed is improved, the switching loss is reduced, and the switching performance of the device is improved. The electric field concentration effects at the bottom of the groove are improved to further improve the breakdown voltage of the device. The carrier enhancement effects at the emitter end of the device are improved, the carrier concentration distribution in the whole N-drift region is improved, and the compromise characteristics between forward conduction voltage drop and turning-off losses are further optimized. Besides, the device manufacturing method is compatible with the manufacturing process of the existing CSTBT device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

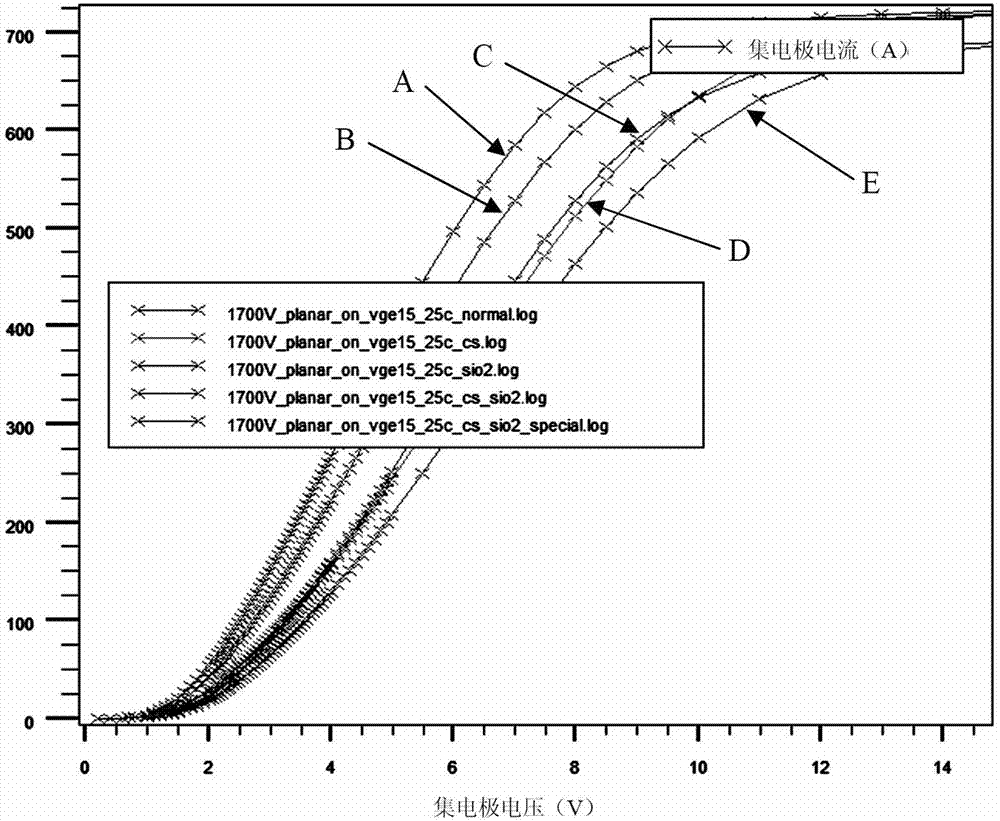

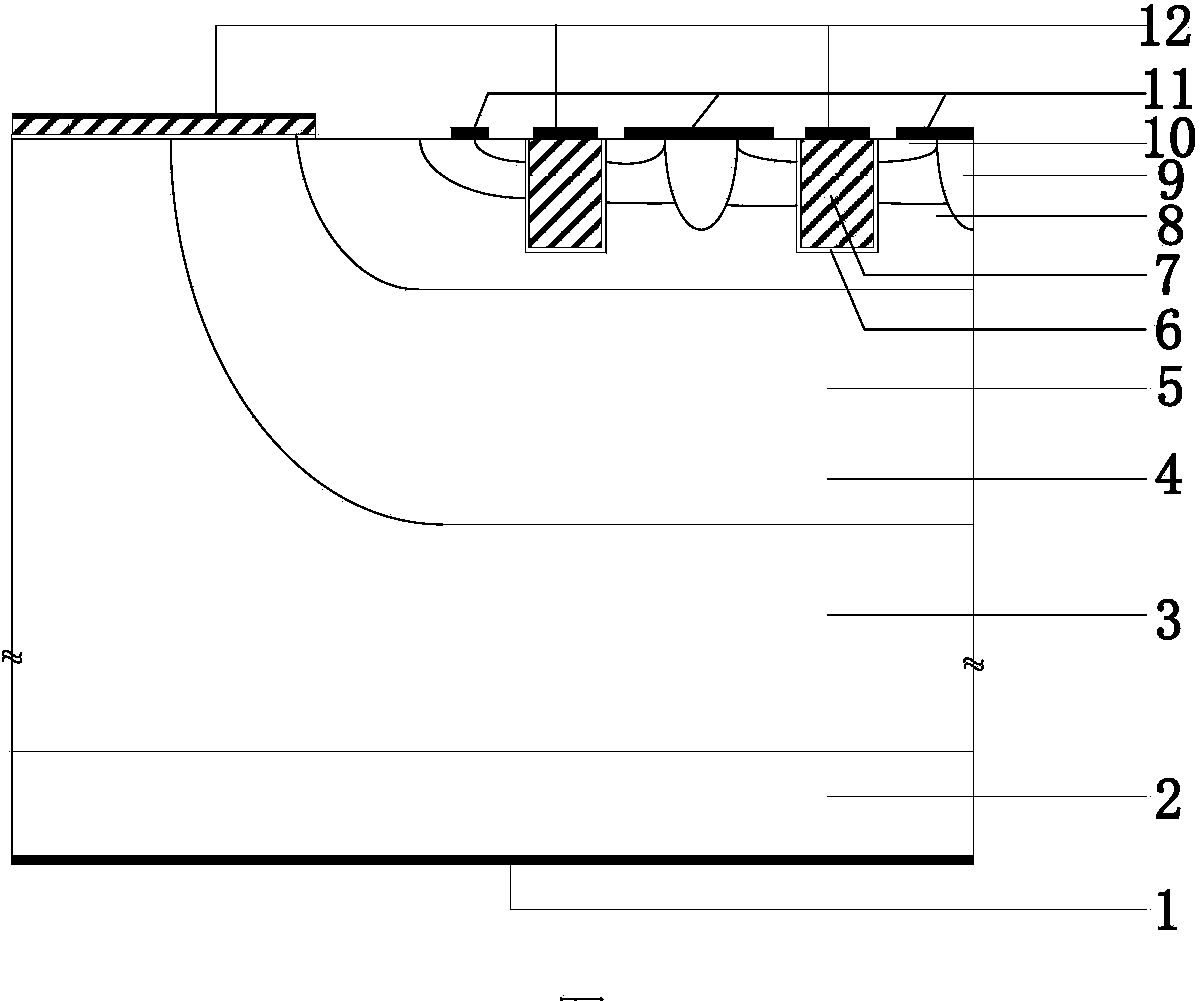

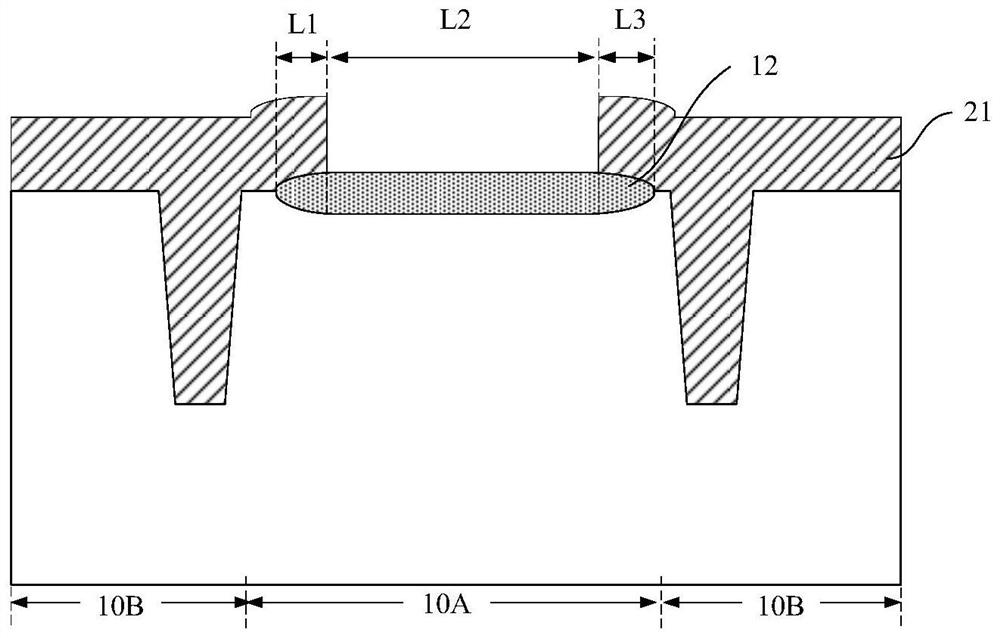

Planar gate IGBT (Insulated Gate Bipolar Transistor) chip

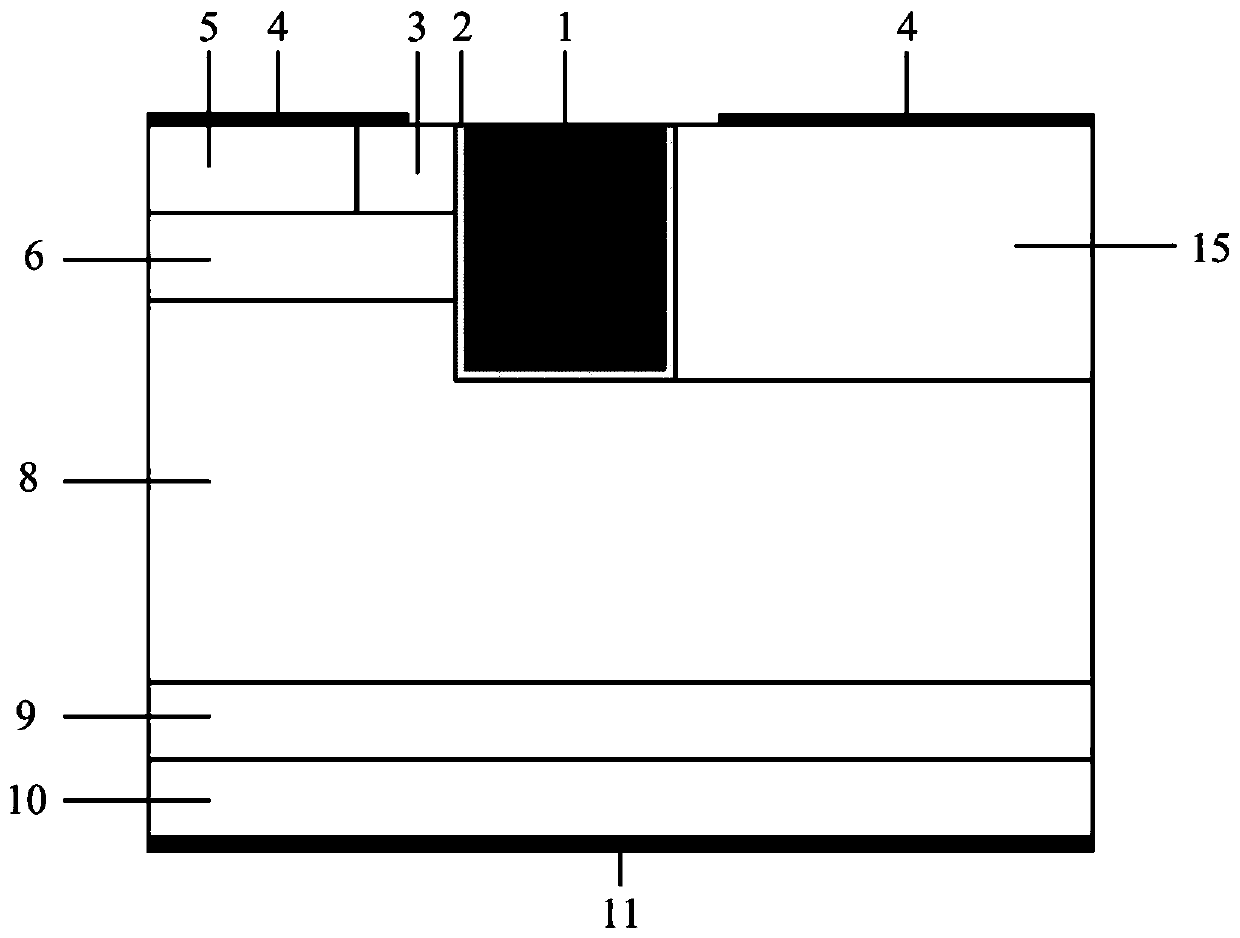

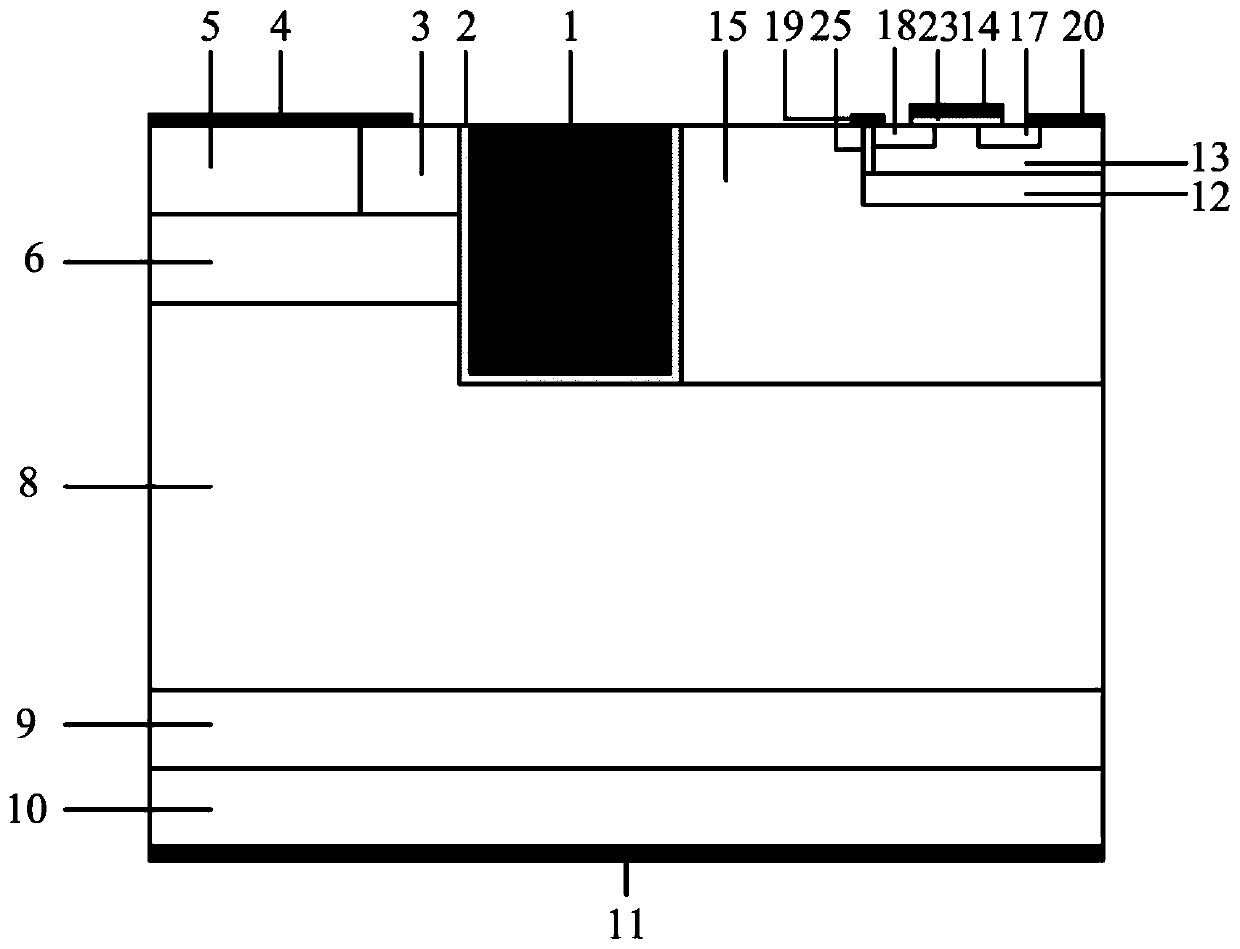

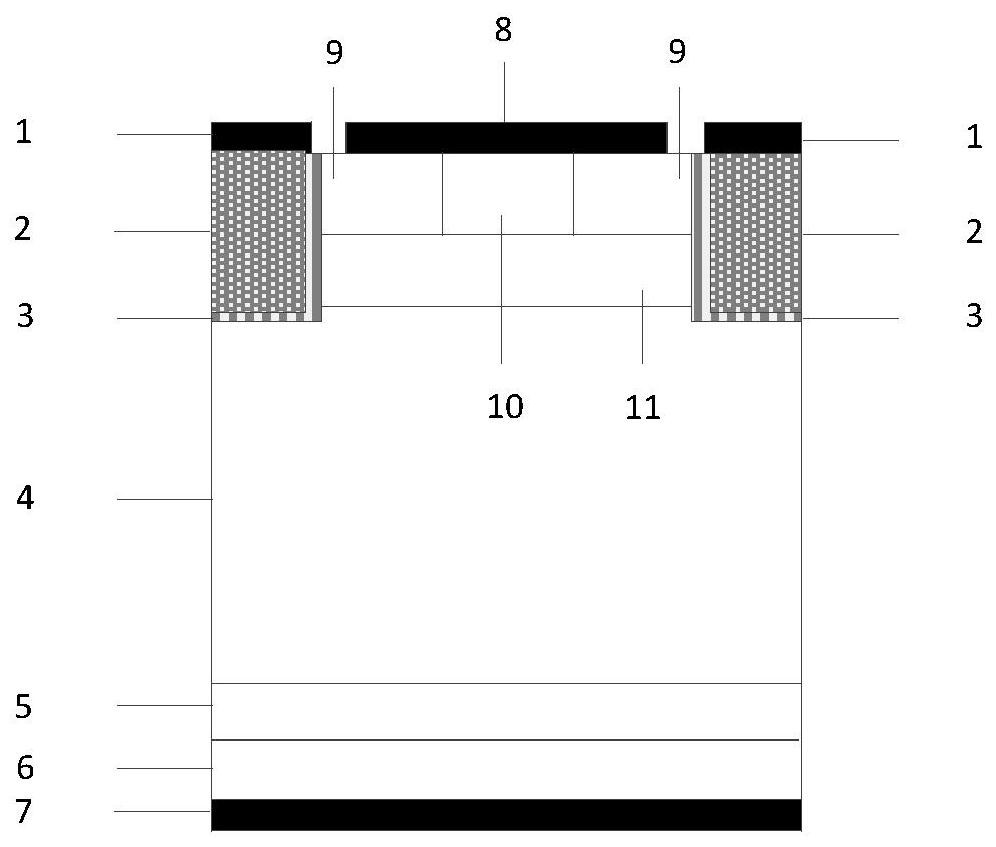

ActiveCN102969351AReduce conduction voltage dropImprove the conduction voltage dropSemiconductor devicesOhmic contactCharge carrier

The invention discloses a planar gate IGBT (Insulated Gate Bipolar Transistor) chip, which comprises a collector metal electrode, a P+ collector region, an N- drift region, a P- base region, a P+ ohmic contact region, an N+ source region, a gate oxide layer, a polysilicon gate and a gate metal electrode which are arranged successively, and an emitter metal electrode arranged above the P+ ohmic contact region, wherein the polysilicon gate of the planar gate IGBT chip adopts a planar gate structure. The planar gate IGBT chip also comprises a first N-type carrier buried layer and / or a second N-type carrier buried layer. The first N-type carrier buried layer is located below the P- base region. The second N-type carrier buried layer is located below the gate oxide layer and at both sides of the P- base region. The planar gate IGBT chip has the beneficial effects that the compromise relation between conduction pressure drop and turn-off loss of the IGBT is reduced, lower power consumption is realized, and thus the power density, the operating junction temperature and the long-term reliability of the IGBT chip are increased.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

MOS grid-control thyristor

InactiveCN103956381AImprove short-circuit safe working abilityShorten off timeThyristorAnode voltageElectron flow

The invention relates to the semiconductor technology, in particular to an MOS grid-control thyristor. A P+ cathode contact area 10 is modified, the width of the P+ cathode contact area 10 is increased, the metallurgical junction form is changed, and the conveying passage of electrons flowing from cathode metal 11 is shortened. The forward direction work characteristic of a device is controlled by a JFET composed of the P+ cathode contact area 10 and an N-trap 9, a channel pinch-off effect can occur under a relatively small anode voltage, the intensity of saturation current of the device can be controlled, and optimization valuing can be carried on the junction depth and width of the P+ cathode contact area 10 according to the design requirements of the device. The MOS grid-control thyristor is particularly suitable for the MOS grid-control thyristor.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

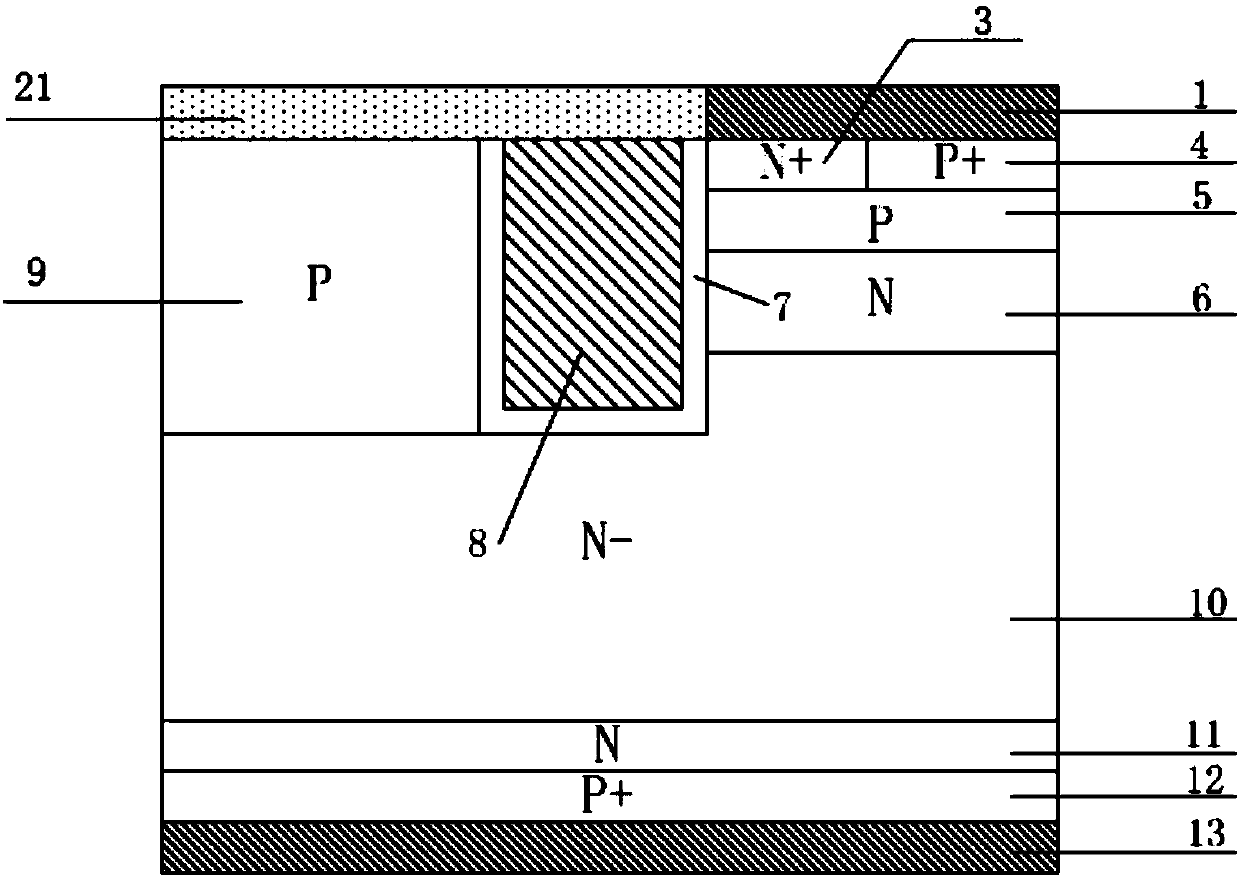

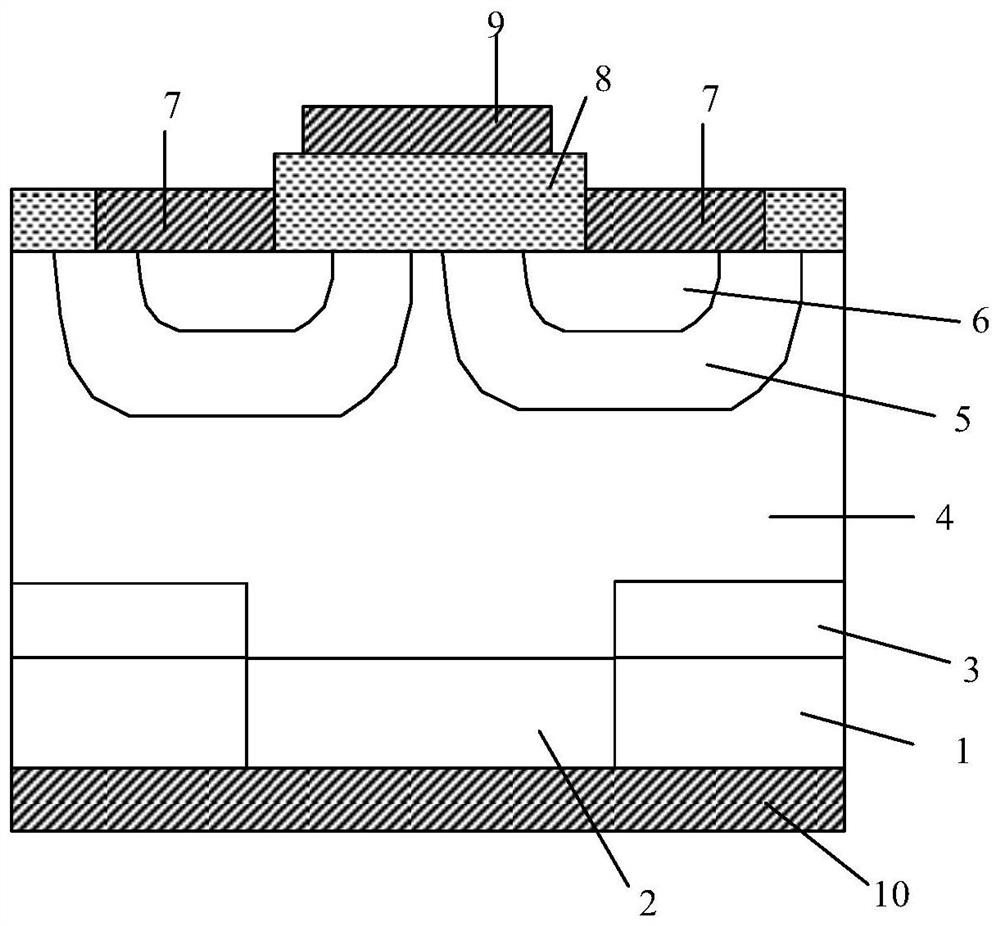

Planar gate IGBT device with deep trench electric field shielding structure

ActiveCN109728084AImprove safe work areaIncrease concentrationSemiconductor devicesCharge carrierEngineering

The invention relates to the field of power semiconductors, and provides a planar gate IGBT device with a deep trench electric field shielding structure, which is used for overcoming the problems thata current groove-gate IGBT gate with a carrier storage layer is too large in drive charges and small in short-circuit safety working region and is limited in the concentration of the CSL layer. The deep groove used for manufacturing the groove-gate IGBT channel traditionally and a P-type buried layer at the bottom portion of the groove are combined to form an electric field shielding structure toachieve clamping of the potential of the carrier storage layer; one IGBT cell is internally provided with a plurality of deep grooves to improve the concentration of the carrier storage layer of theIGBT compared to a traditional IGBT, have the higher cathode injection efficiency, and obtain the better trade-off relation of the on-state voltage and the turn-off loss. A planar gate and an electricfield shielding structure are employed, the IGBT has lower gate drive power consumption and lower saturation current density so as to improve the safety working region of the IGBT.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

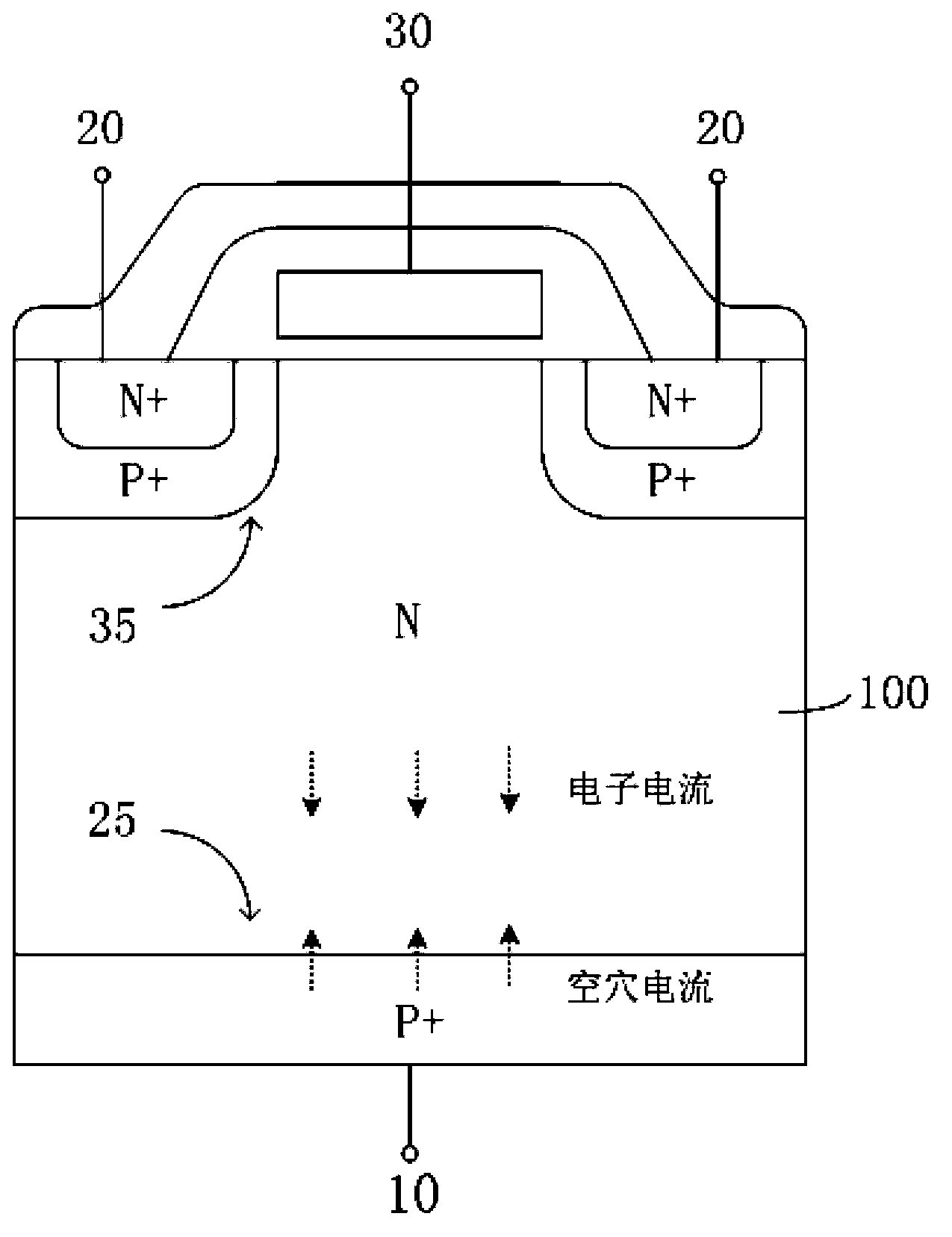

IGBT (Insulated Gate Bipolar Transistor) and manufacture method thereof

InactiveCN104299990AFlow distribution regulationDistribution regulationSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowWork function

Provided is an IGBT and a manufacture method thereof. The IGBT is formed on a semiconductor substrate, and comprises an MOS structure placed at the surface of the semiconductor substrate and a PN junction placed at the bottom of the semiconductor substrate. Multiple grooved structures are placed at the bottom of the semiconductor substrate, penetrate P and N zones of the PN junction, and divide the PN junction into multiple areas. Each grooved structure comprises a metal block at the bottom of the semiconductor substrate and an oxidation layer between the metal block and the semiconductor substrate, and the work function of metal of the metal block is lower than that of a material of the semiconductor substrate. The grooved structures enable that the direction and distribution of electronic current and hole current in the PN junction of the semiconductor substrate are changed, distribution of carriers in the semiconductor substrate can be adjusted by adjusting the grooved structures, and thus, the relation between the connecting voltage drop and turnoff time of the IGBT can be optimized.

Owner:CSMC TECH FAB2 CO LTD

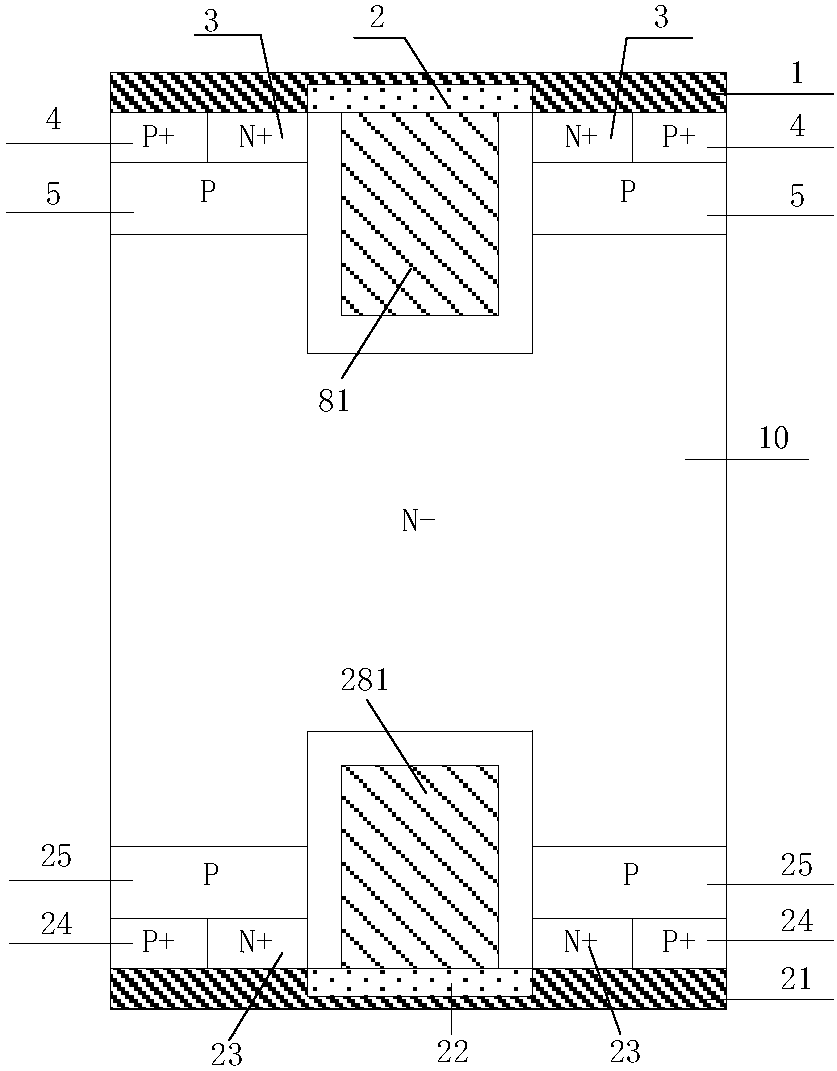

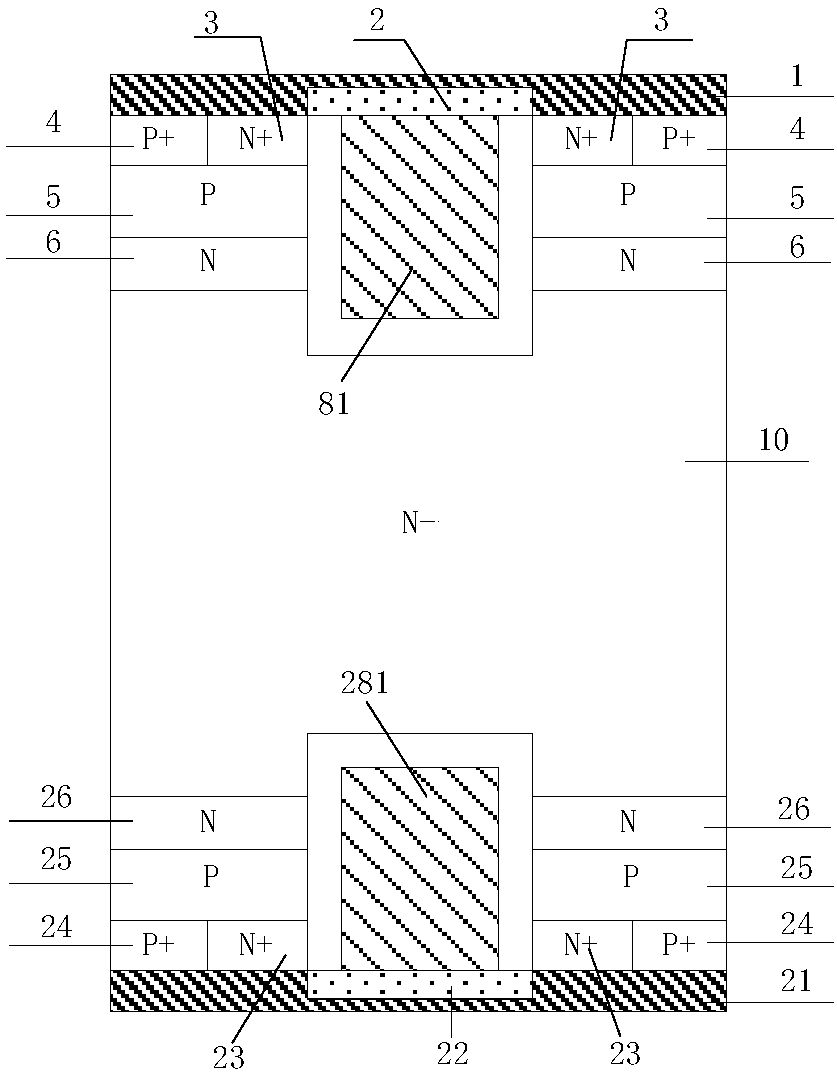

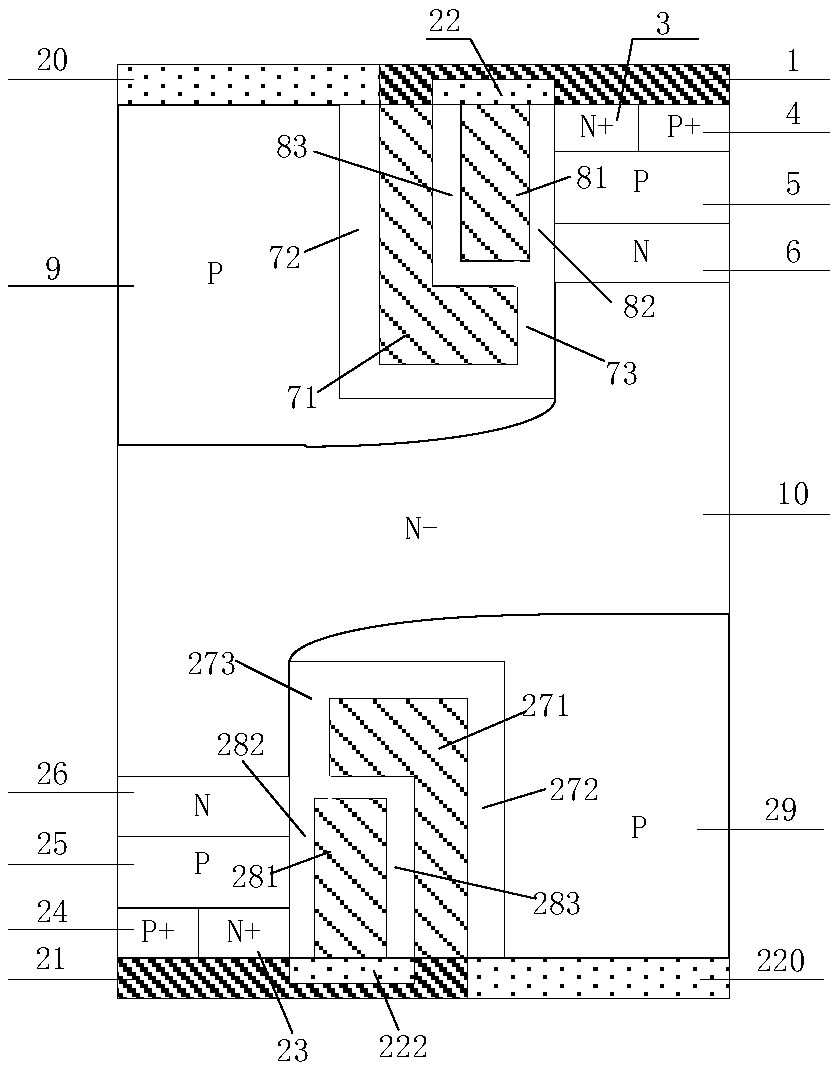

Bidirectional IGBT and manufacturing method therefor

InactiveCN107768435AImprove adverse effectsReduced Miller CapacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEquipotential

The invention discloses a bidirectional IGBT and a manufacturing method therefor, and belongs to the technical field of power semiconductor devices. According to the invention, a split electrode whichis equipotential with a surface metal and a thick dielectric layer located at a peripheral side of the split electrode are introduced to a conventional trench gate structure, and a floating P-type body region is introduced to one side of a split trench gate structure, thereby achieving the symmetric forwarding and reverse on / off characteristics of an IGBT structure under the condition that a threshold voltage and connection of an IGBT device are not affected. The adverse effect caused by the Miller effect is improved, and the drive power consumption is reduced. The current and voltage oscillation and EMI problems are avoided in a start dynamic process of the device. The short-circuit safety working area of the device is improved. The gate capacitance is reduced, the switching speed of thedevice is improved, and the switching loss of the device is reduced. The concentration of an electric field at the bottom of a trench is improved, and the breakdown voltage of the device is improved.The carrier enhancement effect of an emitter electrode is improved, the carrier concentration distribution of the whole N-type drift region is improved, and the compromise between the forwarding conduction voltage drop and switching-off loss is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Planar gate IGBT (Insulated Gate Bipolar Transistor) chip

ActiveCN102969351BReduce conduction voltage dropImprove the conduction voltage dropSemiconductor devicesOhmic contactCharge carrier

The invention discloses a planar gate IGBT (Insulated Gate Bipolar Transistor) chip, which comprises a collector metal electrode, a P+ collector region, an N- drift region, a P- base region, a P+ ohmic contact region, an N+ source region, a gate oxide layer, a polysilicon gate and a gate metal electrode which are arranged successively, and an emitter metal electrode arranged above the P+ ohmic contact region, wherein the polysilicon gate of the planar gate IGBT chip adopts a planar gate structure. The planar gate IGBT chip also comprises a first N-type carrier buried layer and / or a second N-type carrier buried layer. The first N-type carrier buried layer is located below the P- base region. The second N-type carrier buried layer is located below the gate oxide layer and at both sides of the P- base region. The planar gate IGBT chip has the beneficial effects that the compromise relation between conduction pressure drop and turn-off loss of the IGBT is reduced, lower power consumption is realized, and thus the power density, the operating junction temperature and the long-term reliability of the IGBT chip are increased.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

Insulated gate bipolar transistor and manufacturing method thereof, IPM module, and air conditioner

InactiveCN107910367AReduce conduction voltage dropShorten off timeSemiconductor/solid-state device manufacturingSemiconductor devicesOff timeInsulated-gate bipolar transistor

The invention discloses an insulated gate bipolar transistor, an IPM module, an air conditioner and a manufacturing method of the insulated gate bipolar transistor. The insulated gate bipolar transistor comprises a semiconductor substrate, wherein the semiconductor substrate has a first surface and a second surface which are arranged relatively; and the insulated gate bipolar transistor also comprises a drift region and an active region formed on the first surface of the semiconductor substrate, and a collector region formed on the second surface of the semiconductor substrate; wherein the collector region comprises a first collector layer, a second collector layer, a third collector layer and a collector metal layer, which are sequentially connected to the drift region along the thicknessdirection of the semiconductor substrate; and the dosage concentration of the third collector layer is greater than the dosage concentration of the second collector layer, and is less than the dosageconcentration of the first collector layer. According to the invention, the conduction voltage drop and the off time of the insulated gate bipolar transistor are reduced at the same time under the circumstances that the dosage concentration is not increased and the lower conduction voltage drop of the insulated gate bipolar transistor is ensured through setting the dosage concentrations of the collector region uneven.

Owner:GD MIDEA AIR-CONDITIONING EQUIP CO LTD +1

Trench type insulated gate bipolar transistor and preparation method thereof

ActiveCN110416295AReduce capacitanceFast switching speedSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsTrade offs

The invention provides a trench type insulated gate bipolar transistor and a preparation method thereof, which belong to the technical field of power semiconductors. According to the invention, a narrow bandgap semiconductor material is used to form a conductive channel and form ohmic contact with emitter metal due to the characteristics of high channel mobility of a narrow bandgap material such as silicon and small ohmic contact resistance with the emitter metal; channel resistance and ohmic resistance are reduced; the forward conduction voltage drop of a device is reduced; in addition, due to the characteristic of high critical breakdown field strength of a wide bandgap material such as silicon carbide, the device is not limited by a gate oxide layer and prevented from avalanche breakdown; the position of a breakdown point is changed; the breakdown voltage of the device is improved to a certain extent, so that the thickness of a drift region can be appropriately reduced at a certainvoltage level; the forward conduction voltage drop and the turn-off loss are further reduced; and the trade-off relationship between the turn-on voltage drop and the turn-off loss is optimized. In addition, the invention further provides a preparation method of the trench type insulated gate bipolar transistor.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

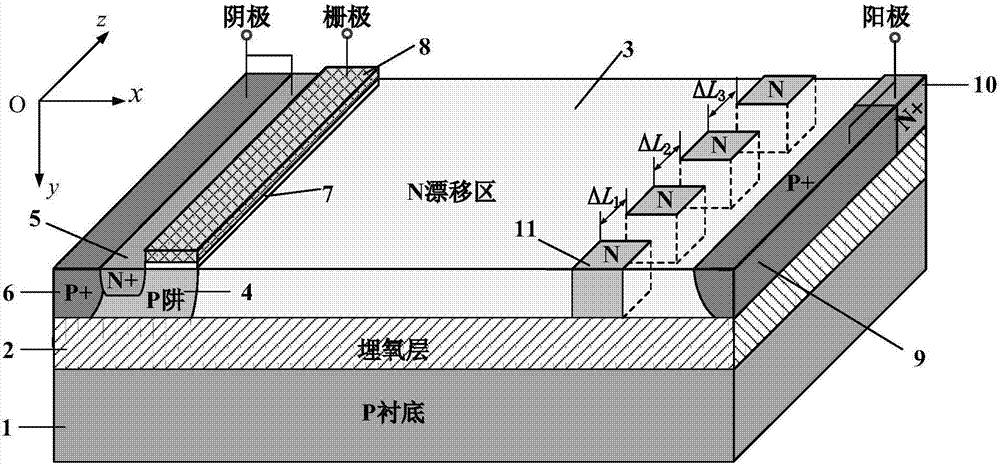

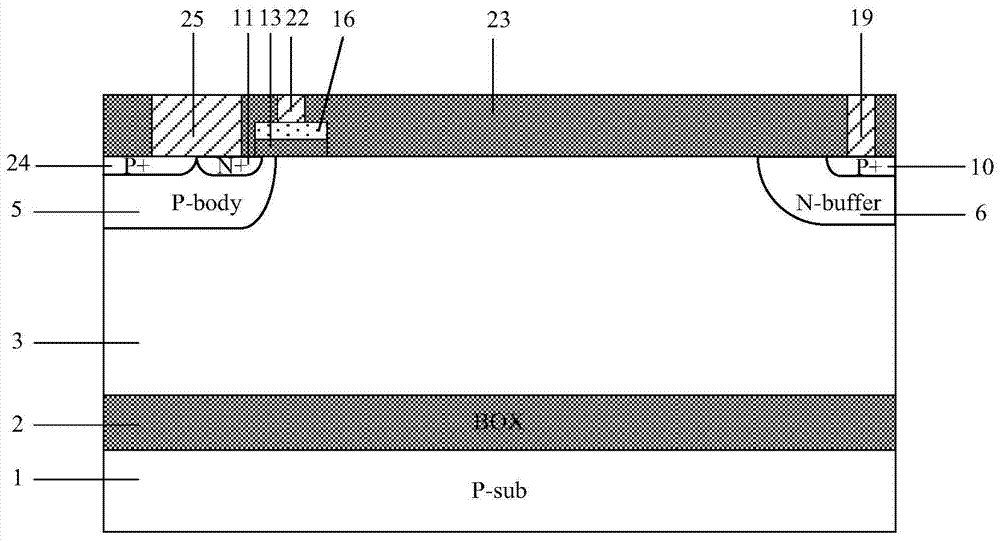

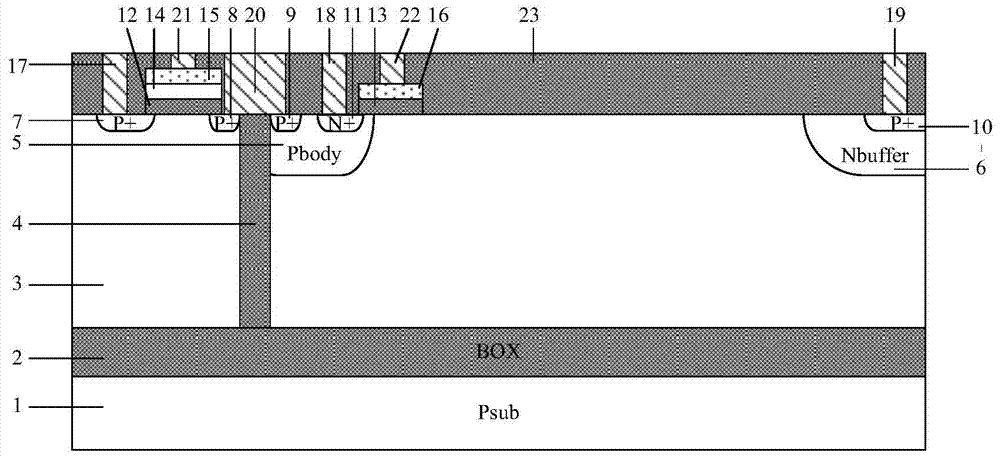

Thin SOI short circuit anode LIGBT

InactiveCN107240603AEasy Process CompatibilityInhibit the snapback effectSemiconductor devicesHigh resistanceSmall cell

The invention belongs to the technical field of power semiconductor, and specifically relates to a thin SOI short circuit anode LIGBT (Lateral Insulated Gate Bipolar Transistor). Compared with a traditional SOI base LIGBT, the thin SOI short circuit anode LIGBT is characterized in that an N+ anode region which is in parallel with a P+ anode region in the vertical direction, and introducing disjunctively distributed N type islands at one side, approaching a cathode structure, in the P+ anode region (9) and the N+ anode region (10); when a new device in the blockout state, the N type islands are not completely depleted, thus effectively preventing further expansion of a depletion region and preventing break-through and breakdown of the N type islands; when the initial stage is started, an electro current flows by the N type islands and the high resistance drift regions among the adjacent N type islands; and compared with traditional continuous N buffer layers, the disjunctively distributed N type islands can increase the distribution resistance at one side of the anode side to enable the device to enter the bipolar mode under a smaller current. Compared with a traditional LIGBT, the thin SOI short circuit anode LIGBT has the advantages of high speed and low on-off loss. Compared with a traditional short circuit anode LIGBT, the thin SOI short circuit anode LIGBT can eliminate the snapback effect even under a small cell size.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

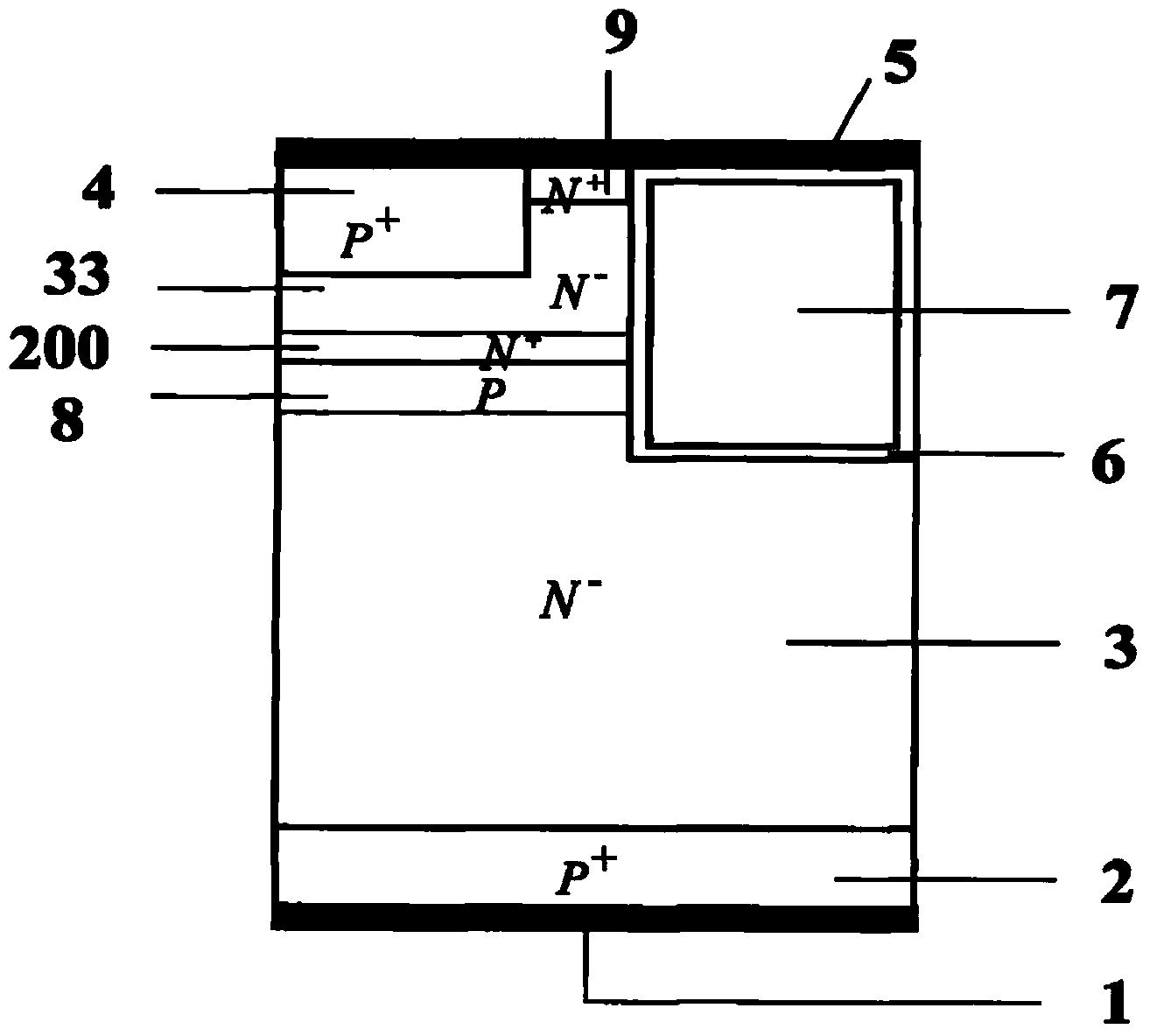

A turn-off performance improving method for an insulated gate bipolar transistor

ActiveCN105702720AImprove the conduction voltage dropIncrease lossSemiconductor devicesCharge carrierPolysilicon gate

An insulated gate bipolar transistor structure comprises collector metal, a P-type collector region and an N-type base region. The surface of the N-type base region is provided with an N-type carrier storage layer and a groove gates. The groove gates divide the N-type carrier storage layer into strips. The surface of the strip-shaped N-type carrier storage layer is uniformly provided with block-shaped P-type body regions. The block-shaped carrier storage layer is provided with a second-type gate oxide layer connected to a first-type gate oxide layer. The second-type gate oxide layer is provided with a second polysilicon gate connected to a first polysilicon gate. The surfaces of the block-shaped P-type body regions are provided with P-type source regions and N-type source regions and are connected to emitter metal. The structure is characterized in that the surface of the block-shaped carrier storage layer is provided with light-doped shallow P-wells connected to the block-shaped P-type body regions. When the device in conduction, a grid electrode applies a positive grid voltage which is completely exhausted by the light-doped shallow P-wells to realize an injection efficiency enhance effect and enable the device to have a relatively small conduction pressure drop. When the device is turned off, the light-doped shallow P-wells are not completely exhausted, and conductive channels form to accelerate the device turn-off speed.

Owner:SOUTHEAST UNIV

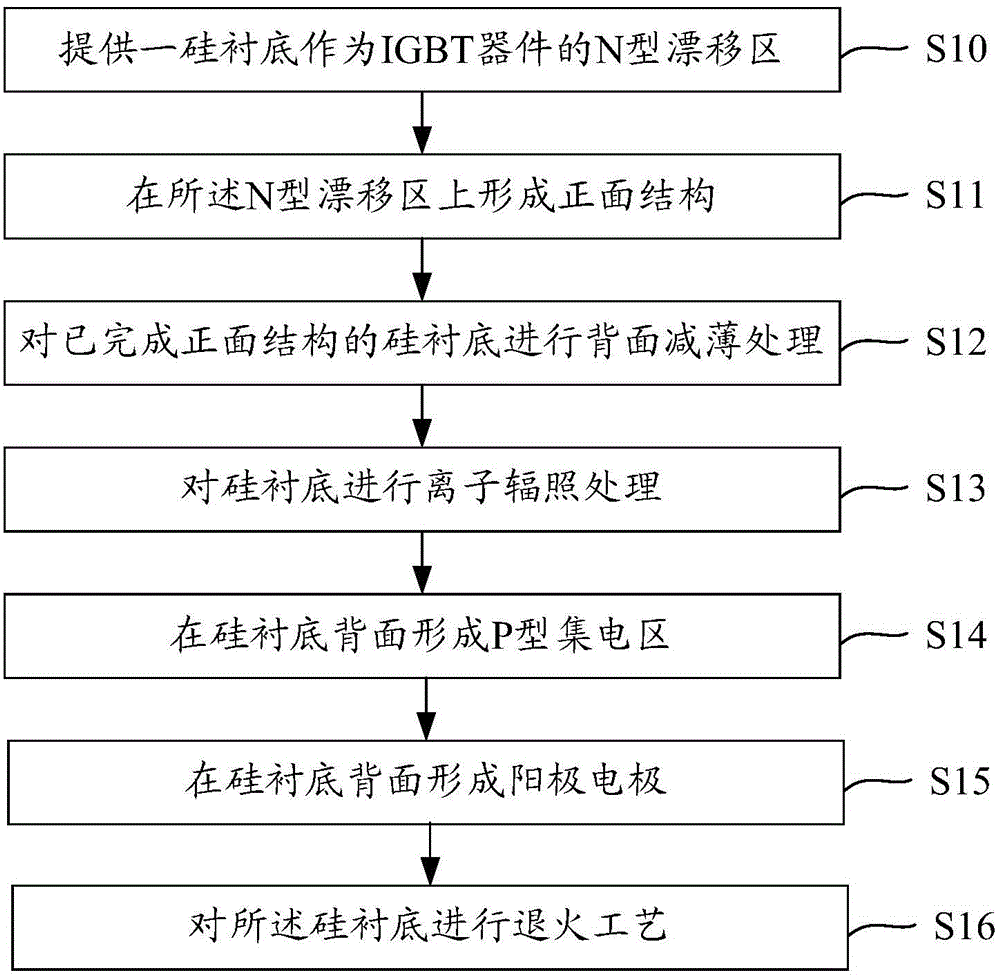

Manufacturing method of semiconductor device

InactiveCN106548938AImprove the conduction voltage dropReduce conduction lossTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceMetal alloy

The invention provides a manufacturing method of a semiconductor device. The method comprises the following steps: performing ion irradiation treatment on a back of a silicon substrate to promote an activation rate of anodic impurities of the semiconductor device, improve the breakover voltage drop of the semiconductor device and lower the breakover loss; and forming an extra compound center in the silicon substrate after annealing the silicon substrate through the ion irradiation treatment, thereby reducing the minority carrier lifetime of the semiconductor device and achieving an aim of lowering the switch loss of the semiconductor device. Furthermore, a metal layer is directly deposited on the back of the silicon substrate after injecting the impurity ions into the back of the silicon substrate; and then the annealing process is performed on the silicon substrate, namely, the impurity activation of the semiconductor device and the metal alloy process are integrated, the aims of impurity activation and metal alloying are realized at the same time through the annealing process after the deposition of the metal layer without additionally performing the annealing process after the impurity ion injection; the process step is reduced, and the treatment cost is saved.

Owner:HANGZHOU SILAN INTEGRATED CIRCUIT

Trench type insulated gate bipolar transistor and preparation method thereof

ActiveCN110504314AImprove the conduction voltage dropIncrease lossSemiconductor/solid-state device manufacturingSemiconductor devicesElectron flowParasitic bipolar transistor

The invention relates to a trench type insulated gate bipolar transistor and a preparation method thereof, belonging to the technical field of power semiconductors. A first conductive trench MOSFET isintroduced in a second conductive floating zone of a trench type insulated gate bipolar transistor, a gate electrode of the MOSFET is in short circuit with current conversion metal, so that when thedevice is conducted forwardly, the MOSFET turns off due to low electric potential of the floating zone, electronic current converted by the conversion metal cannot flow out of a leakage electrode through MOSFET, so as not to increase voltage drop of forward conducting; when the device is turned off, MOSFET surface trench electron inverses so as to form an electron flow path due to very high electric potential of the floating zone, so that electron current converted from hole current by the conversion metal can flow out of the leakage electrode through MOSFET, surplus carriers are extracted atfaster speed, off time is shortened and off loss is reduced, and forward conducting and off loss are further balanced. The invention further relates to a preparation method for the trench type insulated gate bipolar transistor.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

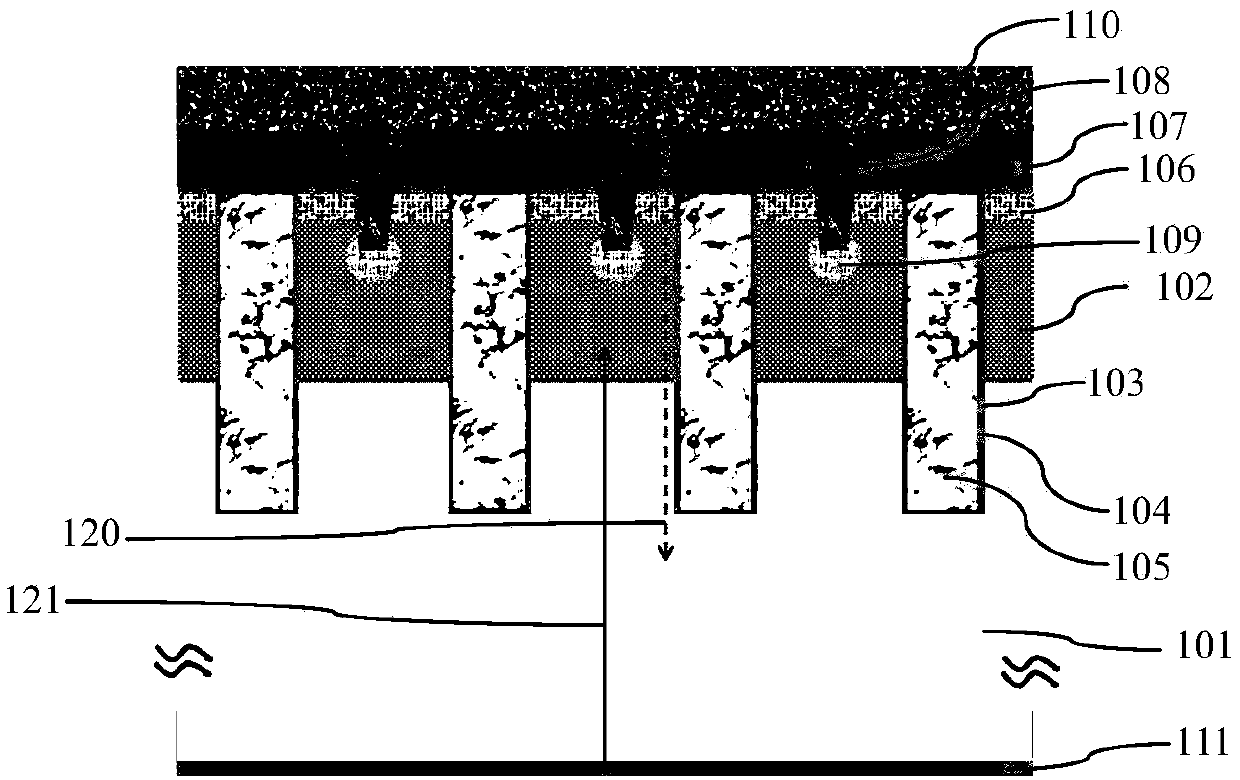

Formation method of IGBT device, and structure of IGBT device

ActiveCN108962748AImprove the conduction voltage dropIncreased process windowSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceVoltage drop

The invention provides a formation method of an IGBT (Insulated Gate Bipolar Transistor) device, and a structure of an IGBT device. The IGBT device is provided with a plurality of functional cells andredundant cells located between the plurality of functional cells. The formation method of the IGBT device includes the steps: performing an ion implantation process on a semiconductor substrate, ofa first region, for formation of the redundant cells; and performing an oxidation process to form a dielectric layer on the semiconductor substrate of the first region. Therefore, after executing theion implantation process, the oxidation rate of the semiconductor substrate of the first region can be effectively improved, and then the dielectric layer having a higher and more uniform thickness can be formed, and then the capacitance Cgc between a gate and a collector in the IGBT device can be effectively improved. Moreover, the dielectric layer formed by the combination of the ion implantation process and the first oxidation process also has a smaller size, thus reducing the area occupied by the redundant cells, and greatly improving the conduction voltage drop of the IGBT device.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Insulated gate bipolar transistor and manufacturing method thereof

ActiveCN112310205AReduce conduction voltage dropImprove the conduction voltage dropTransistorSemiconductor/solid-state device manufacturingPhysical chemistryEngineering

The embodiment of the invention discloses an insulated gate bipolar transistor and a manufacturing method thereof. The insulated gate bipolar transistor comprises a drift region and a body region, wherein the drift region comprises a first doped region and a second doped region, the first doped region and the second doped region are the same in doping type, and the doping concentration of the first doped region is greater than that of the second doped region; the body region different from the drift region in doping type comprises a first part and a second part; the first part is located between the first doped region and an emitter region and is in contact with the first doped region; and the second part is located between the second doped region and the gate region and is in contact withthe second doped region.

Owner:GUANGDONG MIDEA WHITE HOME APPLIANCE TECH INNOVATION CENT CO LTD +1

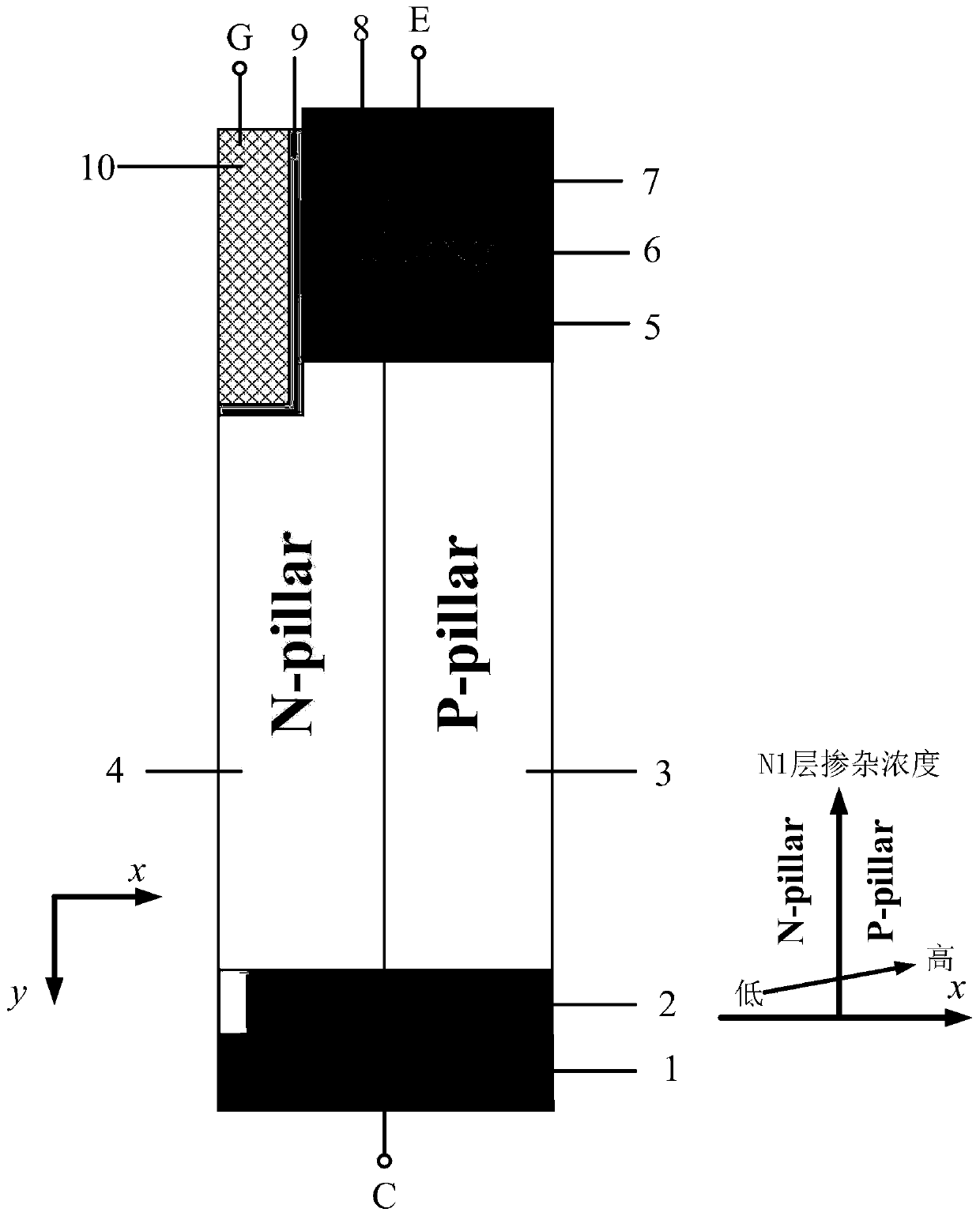

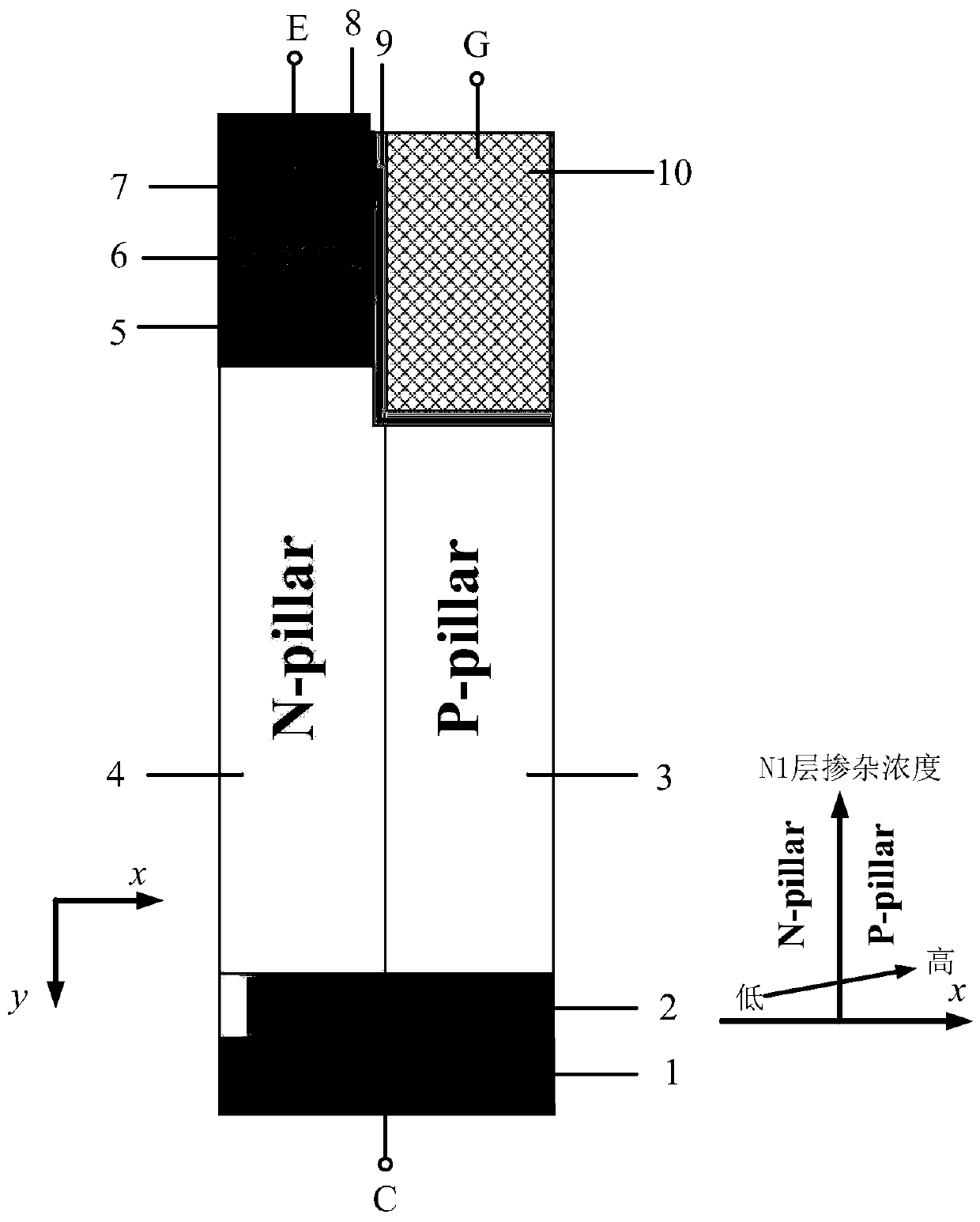

A superjunction reverse resistance type igbt with variable doping field stop layer

ActiveCN110391290BImprove the conduction voltage dropIncrease lossSemiconductor devicesVoltage dropCondensed matter physics

The invention relates to a power semiconductor technology, and particularly relates to a superjunction reverse-resistance IGBT with a variable doped field stop layer. Compared with a conventional superjunction reverse-resistance IGBT, the IGBT provided by the invention has the advantages that a superjunction structure is arranged in a drift region, and the concentration distribution of a first N-type layer is optimized: the concentration thereof gradually increases from left to right. The introduction of the superjunction structure makes an electric field in the drift region of the device in approximate rectangular distribution. Compared with the longitudinal electric field distribution of a conventional NPT reverse-resistance IGBT triangle, the same withstand voltage can be acquired in the shorter drift region length, thereby improving the compromise between the turn-on voltage drop of the device and the turn-off loss. According to the invention, the concentration distribution of thefirst N-type layer is optimized; punch-through of the first N-type layer is prevented when the device is at forward withstand voltage; and the first N-type layer can be completely depleted at the reverse withstand voltage and the peak electric field thereat is more uniform. The IGBT provided by the invention has the advantages that the bidirectional withstand voltage is realized, and the compromise between the turn-on voltage drop and the turn-off loss is optimized.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

A trench isolated lateral insulated gate bipolar transistor

ActiveCN104701362BImprove injection effectIncreased current capabilitySemiconductor devicesIsolation layerBody region

A trench-isolated lateral insulated gate bipolar transistor, comprising: a P-type substrate, on which a buried oxide layer is arranged, an N-type drift region is arranged on the buried oxide layer, and an N-type drift region is arranged below the upper surface of the N-type drift region. There is a P-type body region and an N-type buffer layer, and a P-type collector region is arranged in the N-type buffer layer. It is characterized in that a trench isolation layer is arranged in the N-type drift region, and the upper surface of the N-type drift region is connected to the The two corners formed by the trench isolation layer are respectively provided with a first P-type emitter region and a second P-type emitter region, and a metal electrode is connected to the first P-type emitter region and the second P-type emitter region , a third P-type emitter region is also provided below the upper surface of the N-type drift region, and a second emitter aluminum electrode is connected to the third P-type emitter region, and the second P-type emitter region and the third A second gate oxide layer is provided on the upper surface of the N-type drift region between the P-type emitter regions, a silicon nitride layer is provided on the second gate oxide layer, and a second polysilicon layer is provided above the silicon nitride layer. grid.

Owner:SOUTHEAST UNIV

Formation method and structure of igbt device

ActiveCN108962748BImprove the conduction voltage dropIncreased process windowSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceVoltage drop

The invention provides a method for forming an IGBT device and its structure. The IGBT device has multiple functional cells and redundant cells between the multiple functional cells. The forming method includes: performing an ion implantation process on the semiconductor substrate in the first region of the redundant cells; and performing a first oxidation process to form a dielectric layer on the semiconductor substrate in the first region. That is, after performing the ion implantation process, the oxidation rate of the semiconductor substrate in the first region can be effectively increased, and a dielectric layer with a thicker and more uniform thickness can be formed, thereby effectively improving the gate and collector in the IGBT device. The capacitance Cgc between the electrodes. Moreover, the dielectric layer formed by combining the ion implantation and the first oxidation process has a smaller size, which reduces the area occupied by the redundant cells and greatly improves the conduction voltage drop of the IGBT device.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

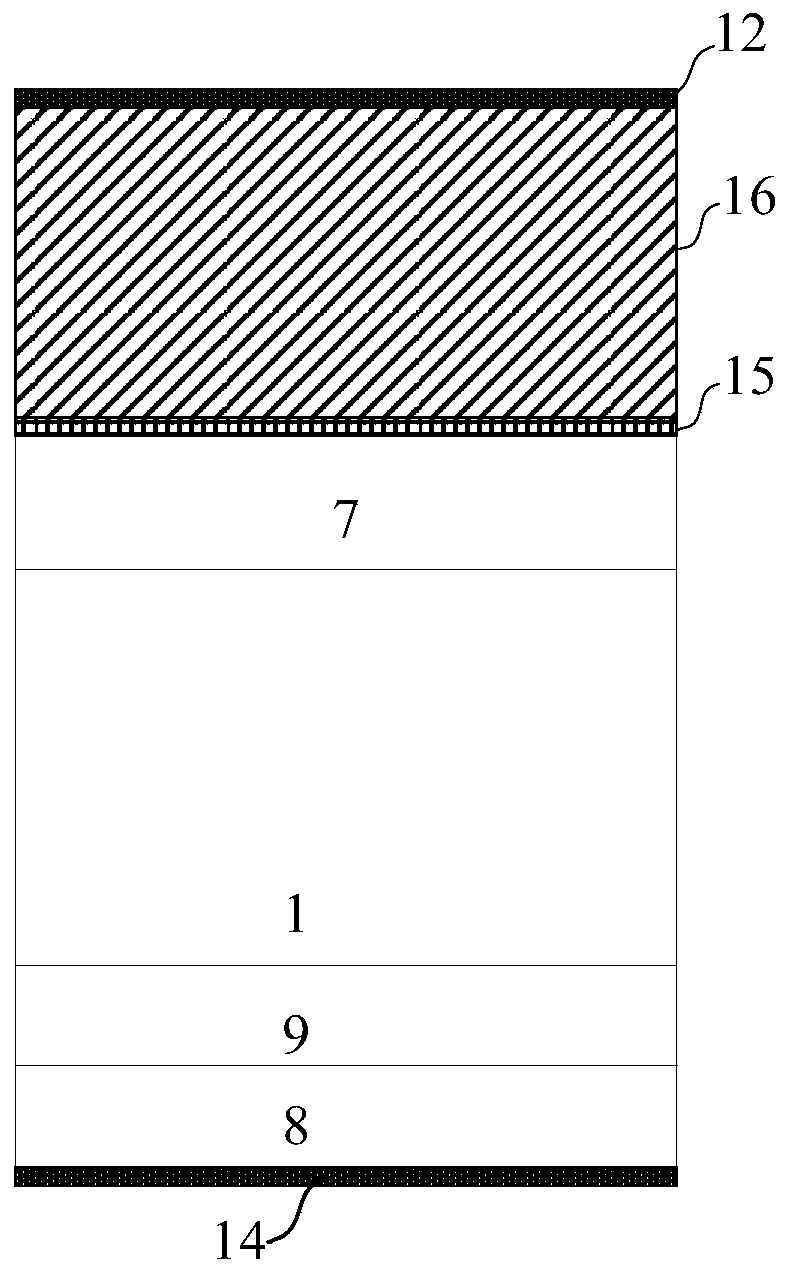

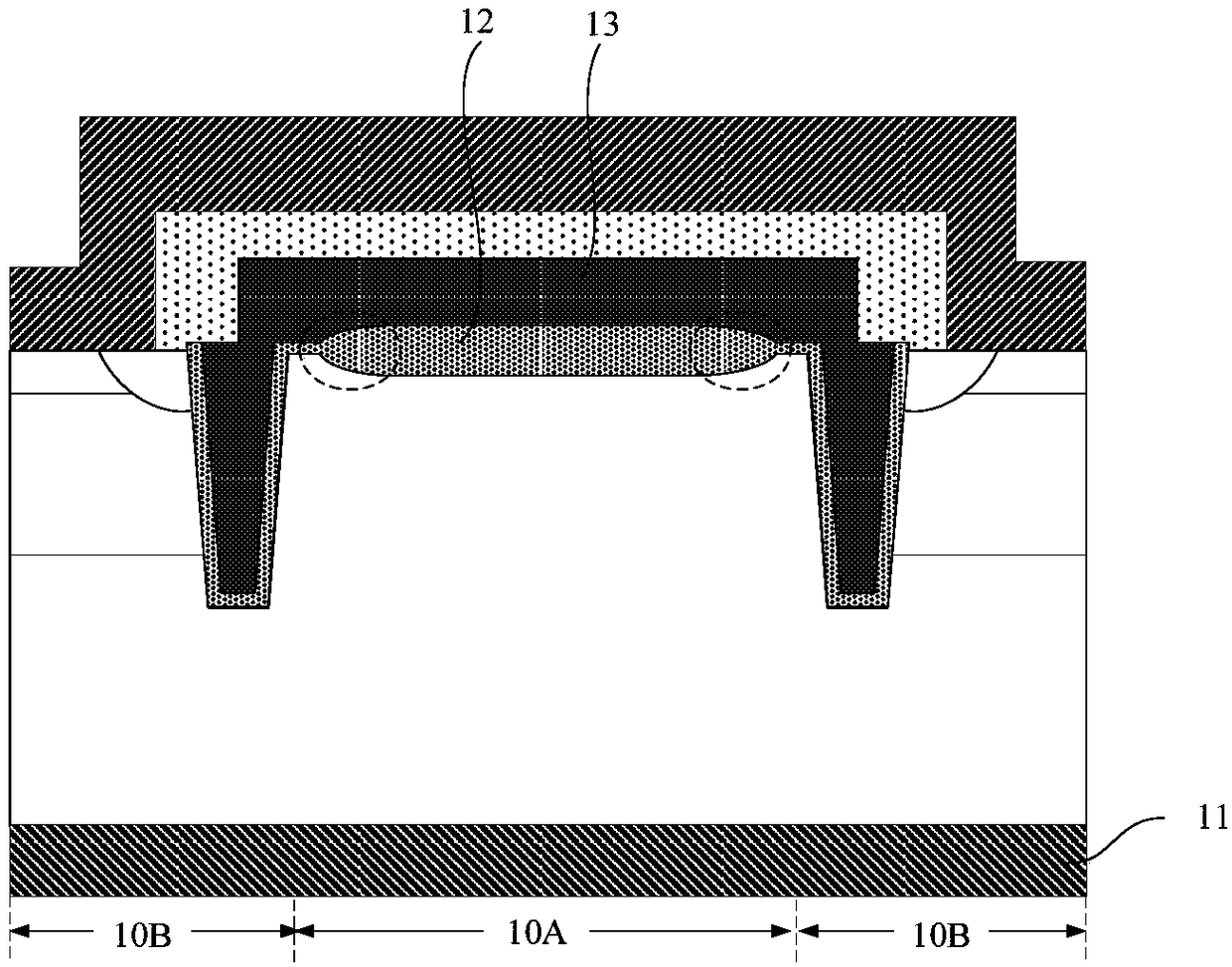

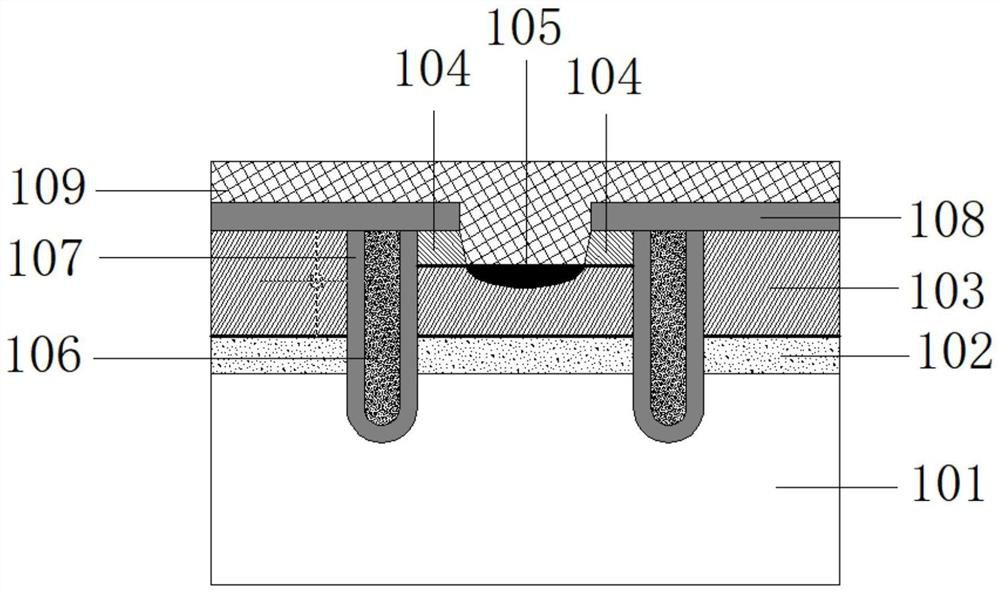

Carrier storage type igbt and manufacturing method thereof

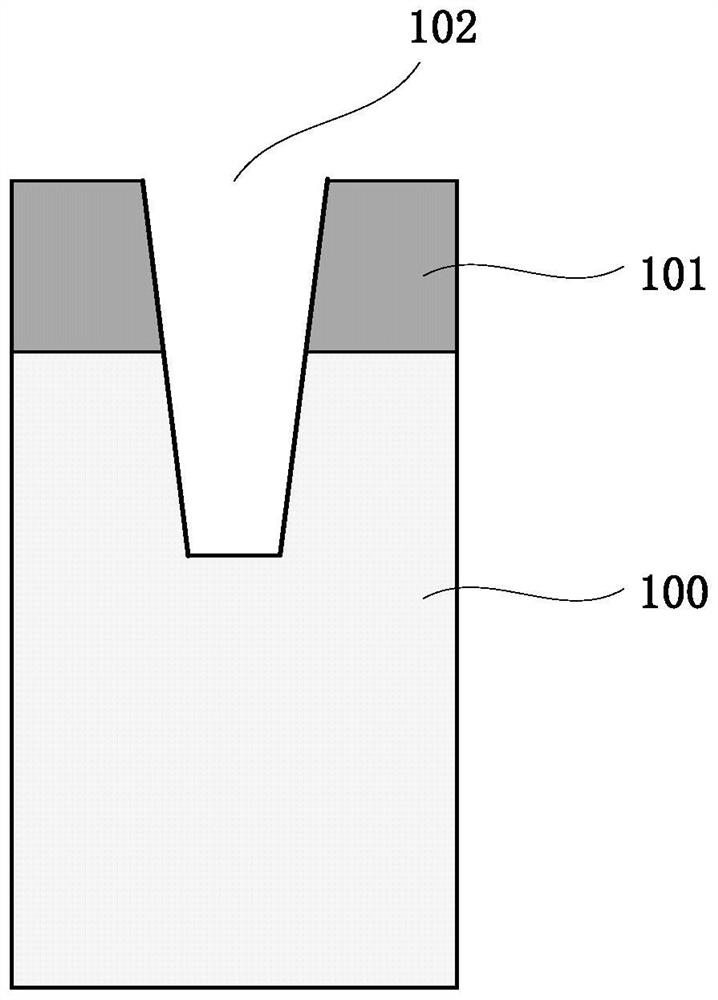

ActiveCN106057877BEnhanced memory effectImprove the conduction voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricHole injection layer

The invention discloses a carrier storage type IGBT which comprises a drift area, a P type body area, and a hole injection layer. Multiple first and second grooves are arranged alternately. Each of the second trenches is formed by the longitudinal superposition of a bottom trench and a top trench, and a gate dielectric layer and a polysilicon gate are formed in each of the first and two trenches. The bottom trench of the second trench is formed by using isotropic etching after forming the top trench. The bottom trench allows the coverage areas of the side face of the bottom area and the bottom surface of the second trench to be increased. When a device is conducted, a hole storage layer is formed by an N type accumulation layer formed by a drift area surface covered by the side face and bottom surface of the bottom trench. The invention also discloses a manufacturing method of the carrier storage type IGBT. According to the carrier storage type IGBT and the manufacturing method thereof, the storage effect of a hole at the drift area can be enhanced, the pressure drop and anti-latch performance of the IGBT are improved, and breakdown voltage is not sacrificed.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Insulated gate bipolar transistor and manufacturing method thereof

PendingCN112331715AImprove compound efficiencyReduce time lossSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringBody region

The embodiment of the invention discloses an insulated gate bipolar transistor and a manufacturing method thereof. The insulated gate bipolar transistor comprises an emitter region, a body region, a drift region and a collector region which are located in the same predetermined plane, wherein the body region is positioned between the emitter region and the drift region and is in contact with the emitter region and the drift region; the drift region is located between the body region and the collector region and is in contact with the collector region; at least one suppression unit is located in the drift region, comprises a concave surface with an opening facing the emitter region, and is used for suppressing at least part of carriers injected into the drift region to move towards the collector region; wherein the carriers are injected into the drift region from the emitter region, and the suppressed carriers are gathered on the surface of the suppression unit.

Owner:GUANGDONG MIDEA WHITE GOODS TECH INNOVATION CENT CO LTD +1

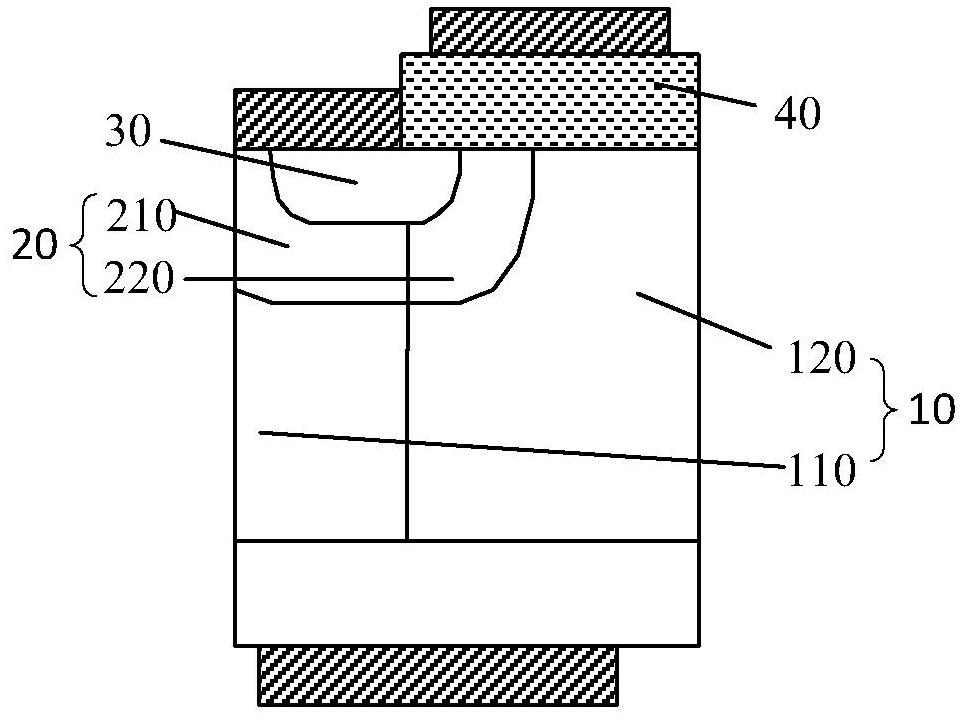

A kind of rc-igbt device and preparation method thereof

ActiveCN108122971BEliminate voltage foldbackImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionSemiconductor materials

The invention discloses an RC-IGBT device and a preparation method thereof, belonging to the technical field of semiconductor power devices. The present invention uses semiconductor materials with different bandgap widths in traditional RC-IGBT devices to form collector short-circuit regions. The characteristic heterojunction structure, so that a single cell structure can eliminate the voltage snapback phenomenon (Voltage Snapback) in the forward conduction process of the traditional RC-IGBT, and optimize the current distribution and heat distribution in the drift region, avoiding current concentration and Reliability issues caused by heat concentration, and improve the reverse recovery capability of the device. Further, semiconductor materials with different forbidden band widths are used to form the emission region, and the forbidden band width of the emission region is larger than that of the semiconductor material in contact with it, thereby improving the anti-latch capability of the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

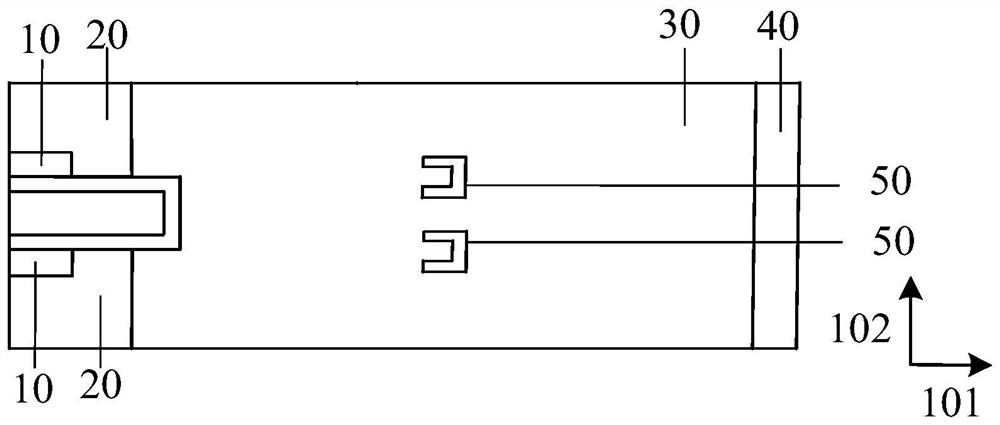

Split gate trench power semiconductor device

ActiveCN112786695AReduce parasitic effectsReduce lossSemiconductor devicesPower semiconductor deviceHemt circuits

The present invention discloses a split-gate trench power semiconductor device which comprises: an active region arranged on a semiconductor substrate, wherein the active region comprises a first well region and a second well region which are longitudinally stacked in the direction from the surface of the semiconductor substrate to the bottom of the semiconductor substrate; and one or more than one true gate grooves which are formed by etching and penetrate through the first well region and the second well region, wherein split type polycrystalline silicon true gates are arranged in the true gate grooves and comprise polycrystalline silicon main true gates and polycrystalline silicon auxiliary true gates, and the polycrystalline silicon main true gates and the polycrystalline silicon auxiliary true gates are arranged close to the tops and the bottoms of the grooves in a separated mode respectively. The polycrystalline silicon main true gates are control gates used for being connected with an external gate drive circuit, and the polycrystalline silicon main true gates and the polycrystalline silicon auxiliary true gates, the polycrystalline silicon true gates and the side wall of the true gate grooves and the polycrystalline silicon true gates and the bottom of the true gate grooves are isolated through interlayer media. According to the invention, the polysilicon gate in the strip-shaped groove is split to form the split gate, so that the stray capacitance is reduced, different electric connections are adopted, and the thickness of the oxide layer is set, so that the overall optimization of the chip performance is realized.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

Insulated gate bipolar transistor and manufacturing method thereof

PendingCN112310206AReduce conduction voltage dropImprove the conduction voltage dropTransistorSemiconductor/solid-state device manufacturingPhysical chemistryEngineering

The embodiment of the invention discloses an insulated gate bipolar transistor and a manufacturing method thereof. The insulated gate bipolar transistor comprises a collector region, a buffer region and a drift region; the collector region comprises a first type doped region and a second type doped region; the doping concentration of the first type doped region is greater than that of the second type doped region; the buffer region is located above the first type doped region; the doping type of the buffer region is different from the doping type of the first type doped region; the drift region is located above the buffer region and the second type doped region; the doping concentration of the drift region is smaller than that of the buffer region.

Owner:GUANGDONG MIDEA WHITE HOME APPLIANCE TECH INNOVATION CENT CO LTD +1

Process optimization method of carrier storage trench gate bipolar transistor structure

PendingCN114171386AImprove injection efficiencyIncrease concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryVoltage drop

The invention discloses a process optimization method of a carrier storage trench gate bipolar transistor structure. By adjusting the injection sequence and the injection energy of the carrier storage layer, the injection efficiency of the carrier storage layer is remarkably improved, the concentration of the carrier storage layer is increased, and the conduction voltage drop and the saturation current of the carrier storage trench gate bipolar transistor are reduced.

Owner:FUDAN UNIV

A kind of cstbt device and manufacturing method thereof

ActiveCN107731898BImprove performanceLower saturation current densitySolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceManufacturing technology

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Back collector structure of power semiconductor devices

ActiveCN103077962BImprove the conduction voltage dropImprove injection efficiencySemiconductor devicesPower semiconductor deviceHeterojunction

Owner:JIANGSU R & D CENTER FOR INTERNET OF THINGS +2

A planar gate igbt device with deep trench electric field shielding structure

ActiveCN109728084BImprove safe work areaIncrease concentrationSemiconductor devicesEngineeringCondensed matter physics

The invention relates to the field of power semiconductors, and provides a planar gate IGBT device with a deep groove electric field shielding structure, which is used to overcome the excessive gate drive charge and small short-circuit safe working area of the existing groove gate IGBT with a carrier storage layer And the problem of the limited concentration of the CSL layer; the present invention combines the deep groove traditionally used to make the trench gate IGBT channel with the P-type buried layer at the bottom of the groove to form an electric field shielding structure, and realizes the clamping of the potential of the carrier storage layer; Moreover, multiple deep grooves are set in one IGBT cell; thus, the concentration of the carrier storage layer of the IGBT of the present invention can be much higher than that of the traditional IGBT, which can have higher cathode injection efficiency and obtain better turn-on voltage The trade-off relationship between drop and turn-off loss. At the same time, the IGBT of the present invention has lower gate drive power consumption and lower saturation current density due to the adoption of a planar grid and an electric field shielding structure, thereby improving the safe working area of the IGBT.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

A sic power device

The invention belongs to the field of power semiconductors, and specifically provides a SiC power device, including a SiC MOSFET and a SiC IGBT; wherein: for a SiC MOSFET device integrated with a PN junction body diode, the reverse recovery charge of the body diode and related losses can be greatly reduced , Reduce the reverse recovery peak current, reduce EMI noise; for SiC MOSFET devices with integrated N-type Schottky diodes or integrated heterojunction diodes, it can reduce the voltage drop when the MOSFET is reversed, eliminate the minority carrier injection effect, thereby reducing the diode Conduction loss and reverse recovery loss; for reverse-conducting SiC IGBT devices with integrated PN junction body diodes, it can greatly reduce the reverse recovery charge of the body diode and related losses, reduce the reverse recovery peak current, and reduce EMI noise; For the reverse conduction SiC IGBT device integrated with N-type Schottky diode or heterojunction diode, it can reduce the voltage drop when the reverse conduction IGBT conducts in reverse, eliminate the minority carrier injection effect, and reduce the diode conduction loss and reverse recovery loss.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com