Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

37results about How to "Easy Process Compatibility" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

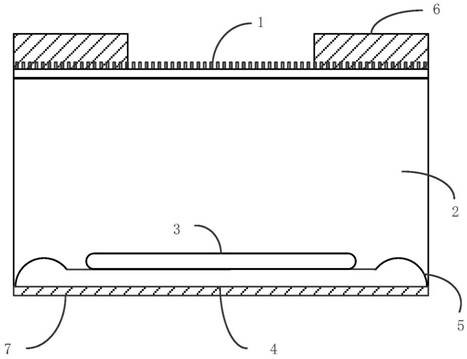

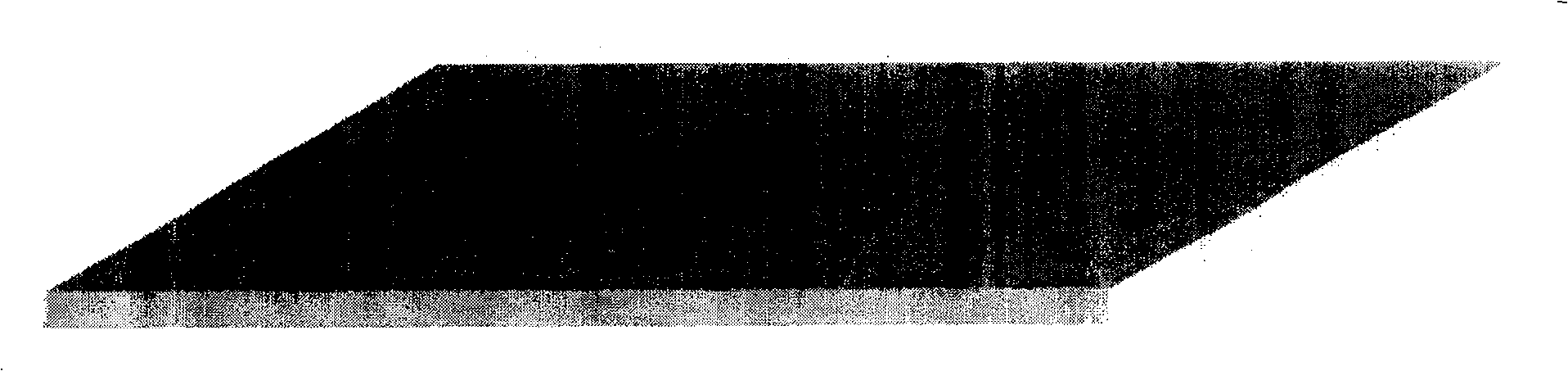

Backside illuminated Si-PIN photoelectric detector and preparation method thereof

InactiveCN103400887AImprove responsivenessImprove uniformityFinal product manufactureSemiconductor devicesNano structuringPhotovoltaic detectors

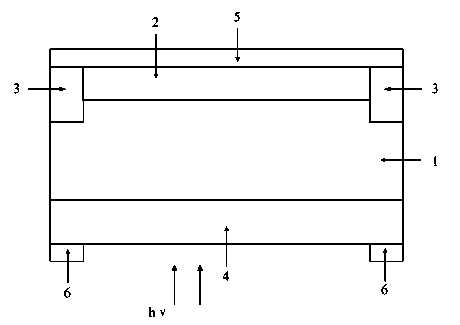

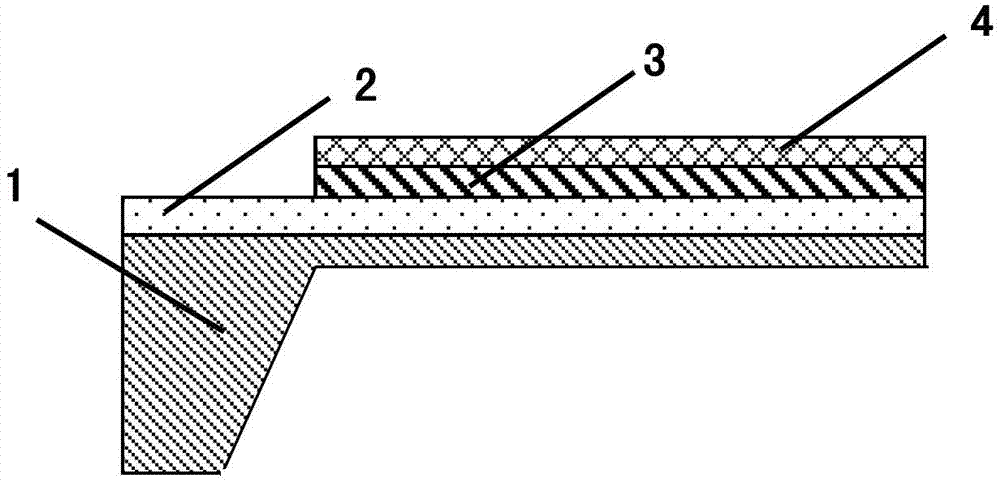

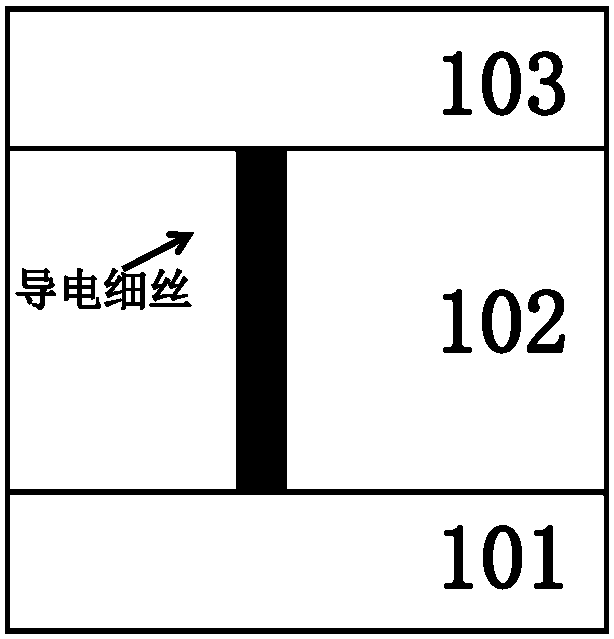

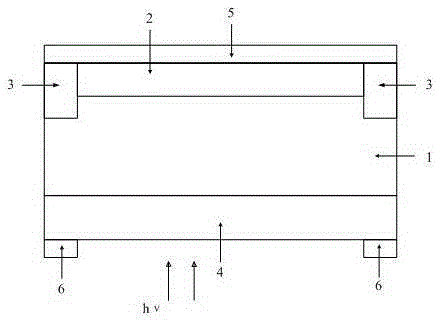

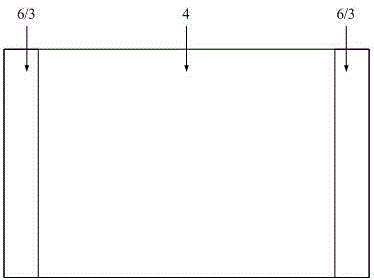

The invention discloses a backside illuminated Si-PIN photoelectric detector and a preparation method thereof and relates to a photoelectric detector structure in the technical field of photoelectric detection. The photoelectric detector comprises an I-type substrate 1, an area P 2, areas P+ 3, a nano structure silicon layer area N 4 and an upper end and lower end electrodes; the electrode comprises the upper end electrode 5 positioned on the area P 2 and the areas P+3, and the lower end electrodes 6 positioned on the nano structure silicon layer area N 4, wherein the upper end electrode 5 is used for being connected with the negative electrode of an external circuit, and the lower end electrodes 6 are used for being connected with the positive electrode of the external circuit. The novel Si photoelectric detector solves the problem that a traditional Si photoelectric detector is relatively low in responsitivity and cannot respond to the near infrared wave band, improves the absorption rate to visible light and near infrared light, has the responding wave band expanded to the near infrared wave band, and is higher in responsitivity.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Microsilicon microphone and its preparing method

InactiveCN1684546AHigh strengthPrevent Waveform DistortionElectrets selectrostatic transducerCapacitanceCapacitor

This invention provides a micro-silicon microphone and its preparation method, in which, said microphone includes a monocrystal silicon film and polysilicon film as the capacitor pole plates, the polysilicon film is a movable pole plate, several release holes are set on the monosilicon film and rib reinforcement structures are formed on the polysilicon film, the rib reinforcement structure is corresponding to the release hole on the monocrystal silicon film and inlayed in the release holes. The preparation method utilizes ICP technology to carry out deep bar etching to either get the release holes or realize polysilicon films with the rib reinforcement structure.

Owner:PEKING UNIV

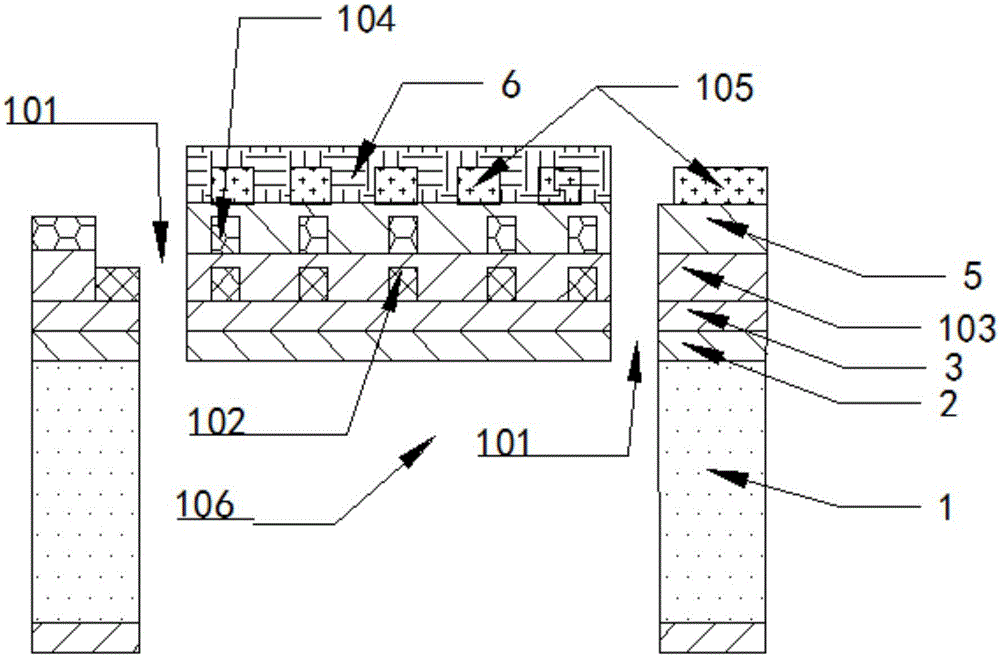

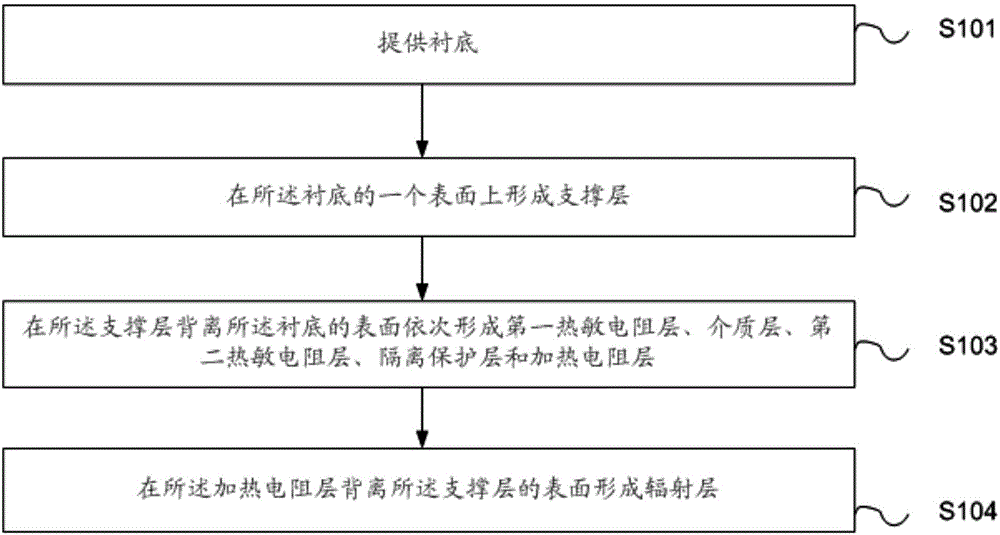

MEMS infrared light source and manufacturing method thereof

ActiveCN106629574AImprove measurement linearityAvoid influenceTelevision system detailsImpedence networksElectrical resistance and conductanceHeat sensitive

The invention discloses an MEMS infrared light source and a manufacturing method thereof. The MEMS infrared light source comprises a substrate, a supporting layer, a first thermistor layer, a dielectric layer, a second thermistor layer, an isolation and protection layer, a heating resistance layer and a radiation layer. In the MEMS infrared light source disclosed by the invention, one thermistor layer in the first thermistor layer and the second thermistor layer is used as a temperature sensor to directly measure the temperature change of a radiation area of the MEMS infrared light source through the resistance change of the thermistor layer at the outside; the other thermistor layer is used as temperature compensation performance to counteract the error generated by temperature excursion in a peripheral compensation circuit within a certain temperature range, namely the MEMS infrared light source provided by the invention can perform real-time temperature compensation while monitoring the temperature offset in real time, thereby improving the measurement linearity of the MEMS infrared light source and avoiding the influence by the external environment. The manufacturing method is convenient to be compatible with an internal chip process of the infrared light source, and the process difficulty is reduced.

Owner:锐立平芯微电子(广州)有限责任公司

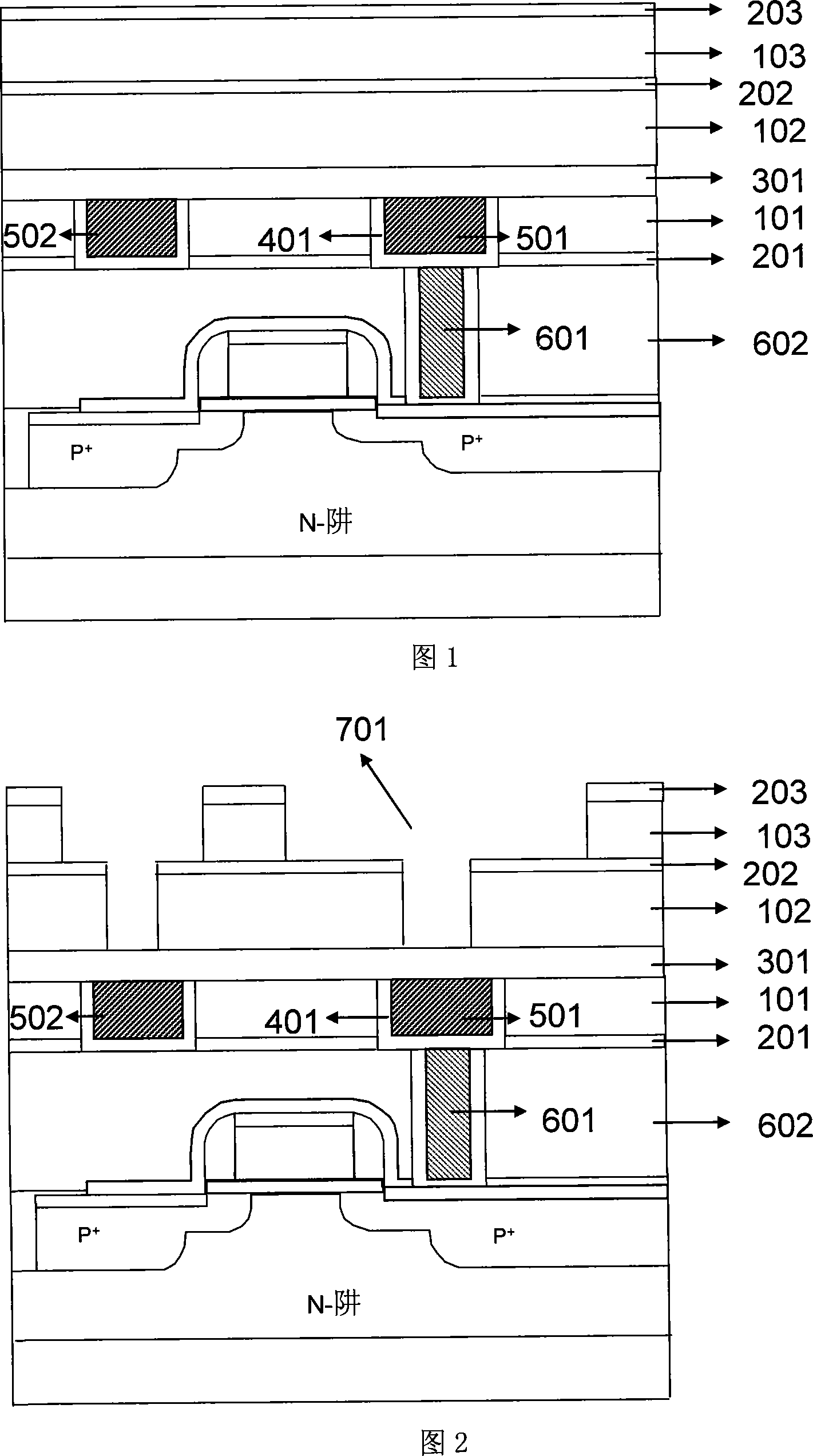

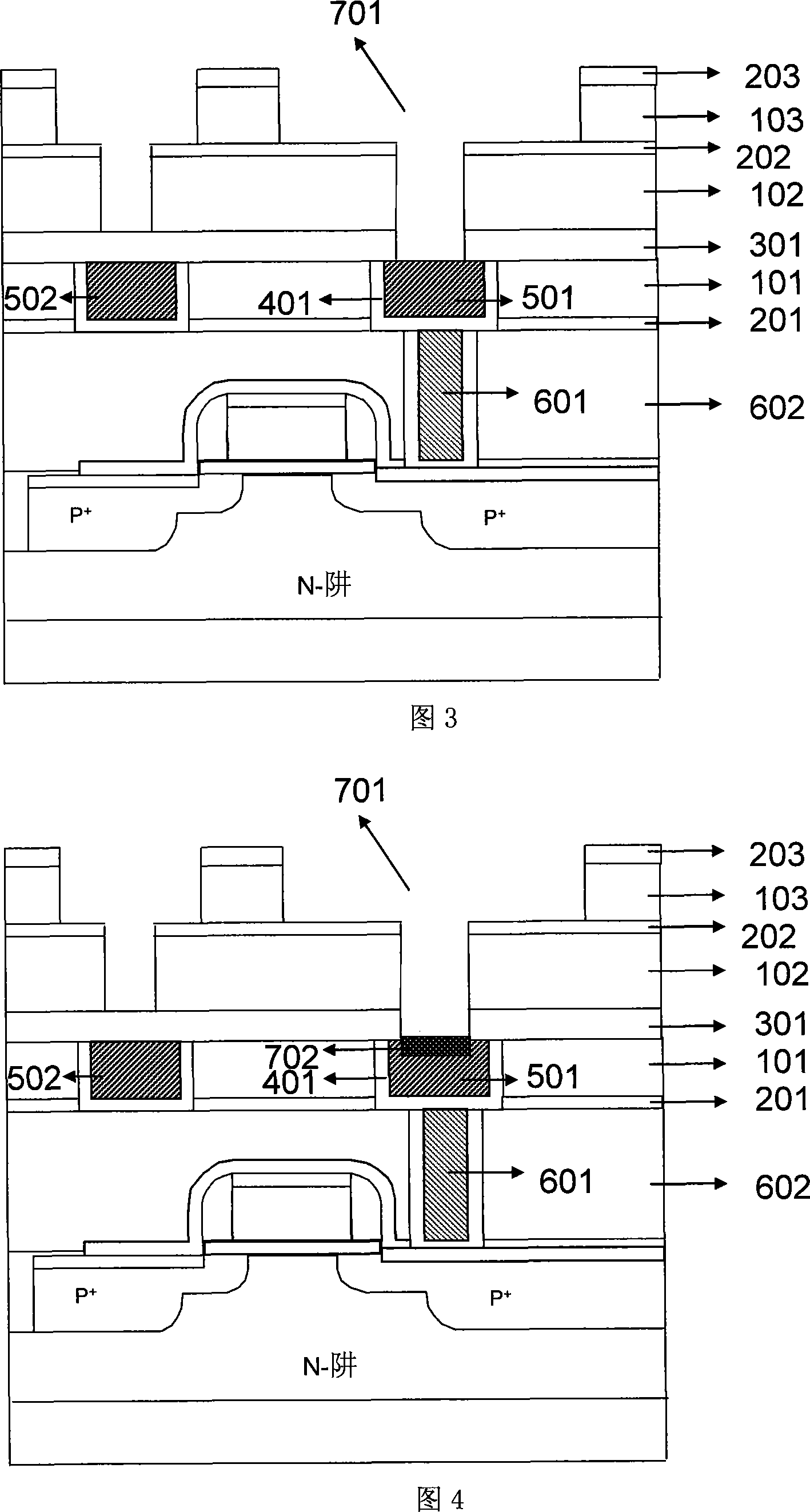

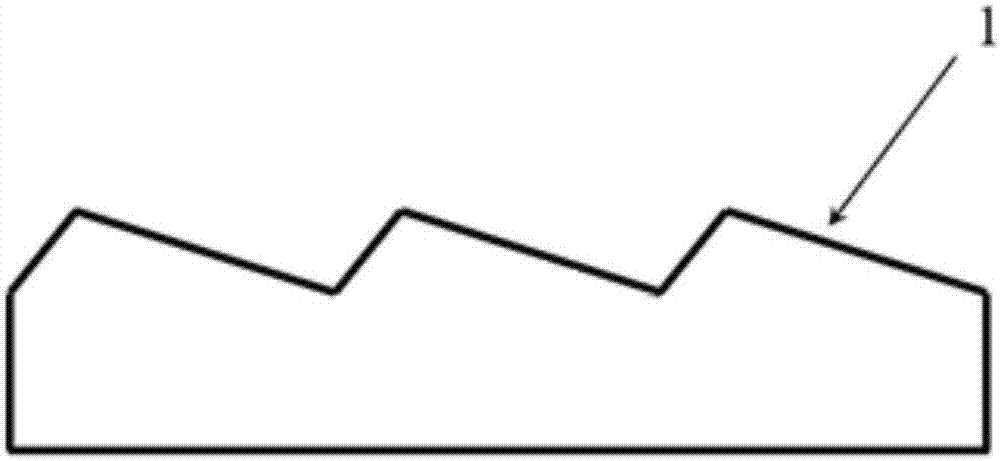

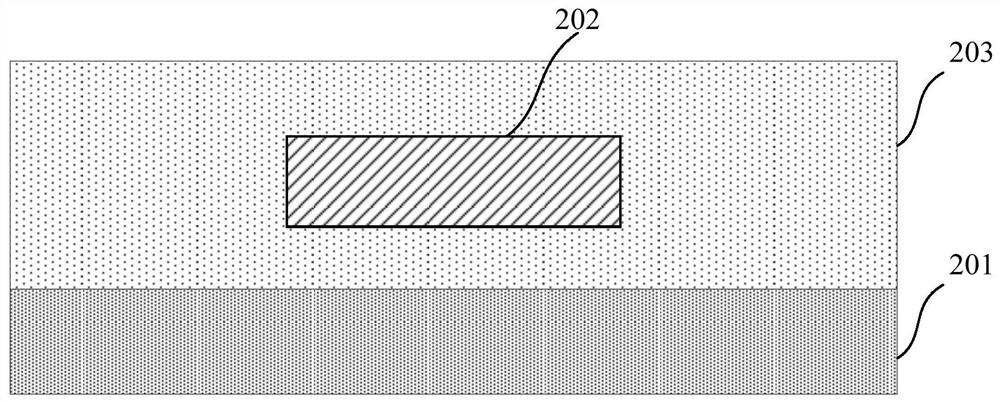

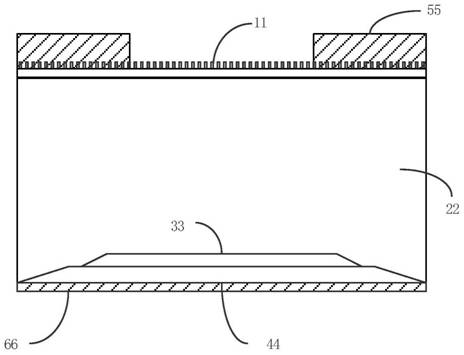

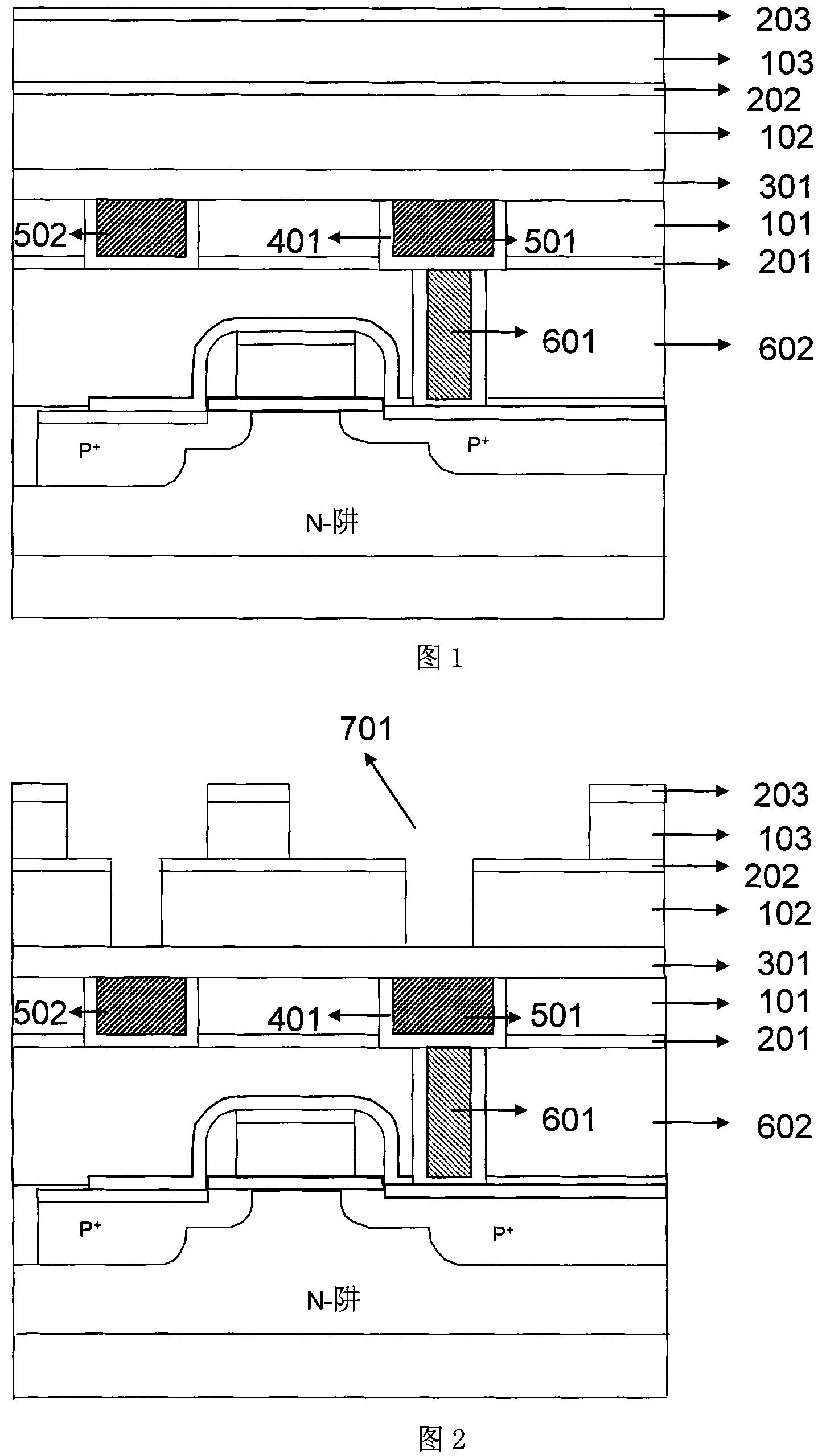

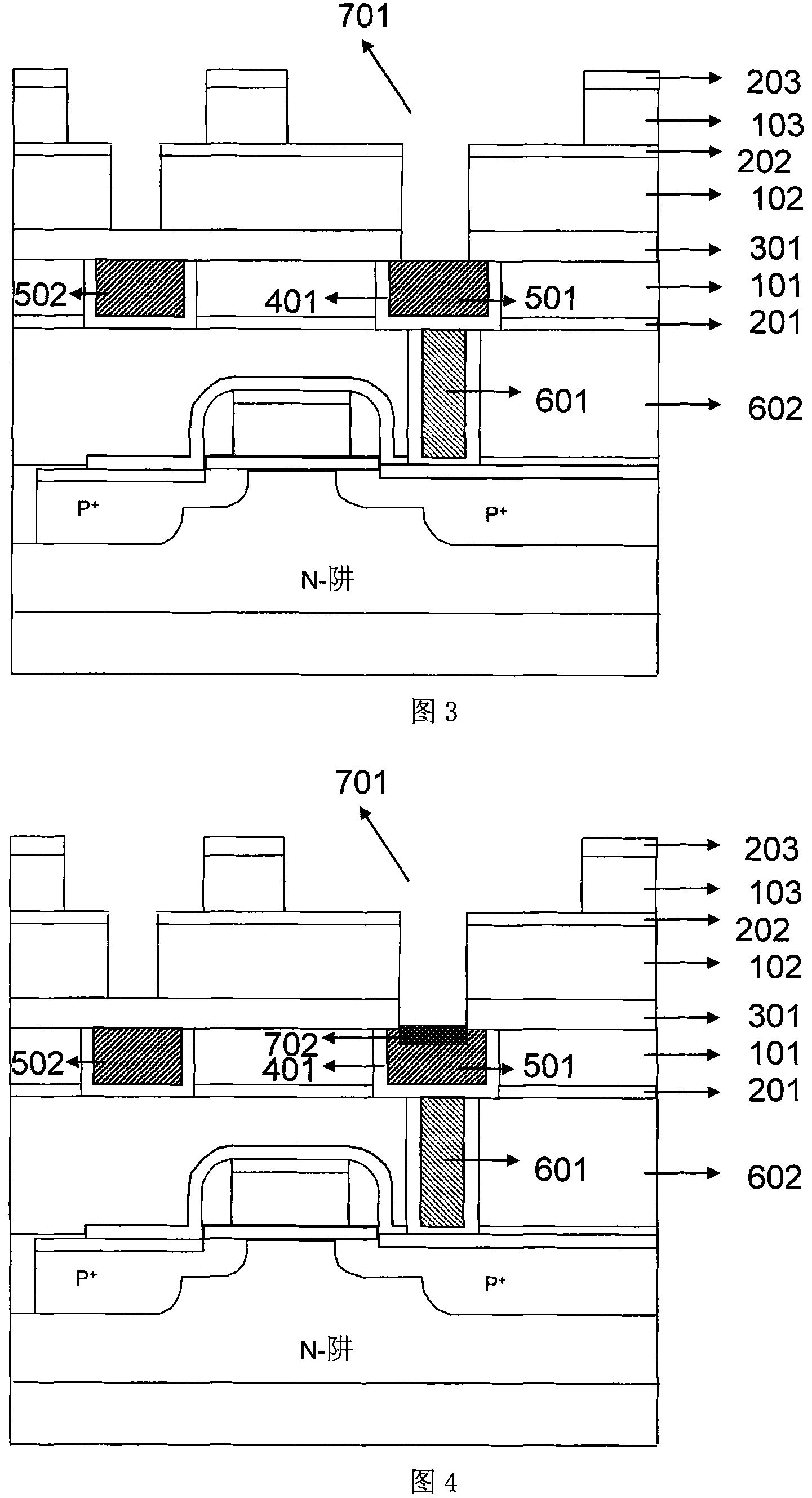

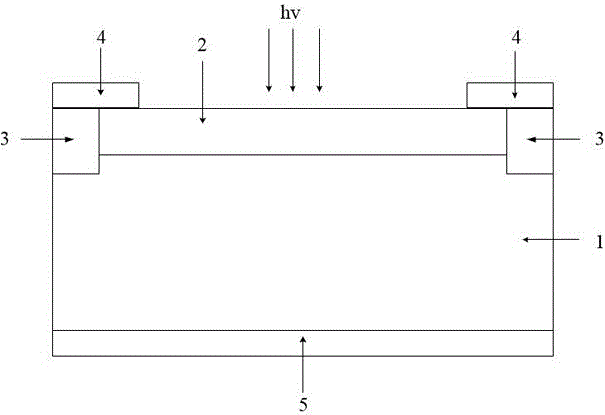

Right side illuminated Si-PIN photoelectric detector taking micro-nano structural silicone as light-sensitive layer and preparation method thereof

InactiveCN104064610ABroad absorption spectrumReduce reflectivityFinal product manufactureSemiconductor devicesMicro nanoEngineering

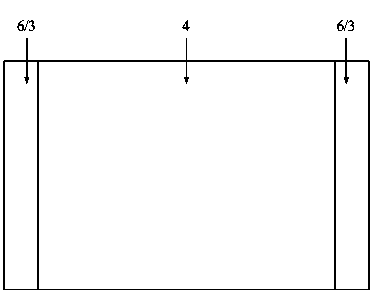

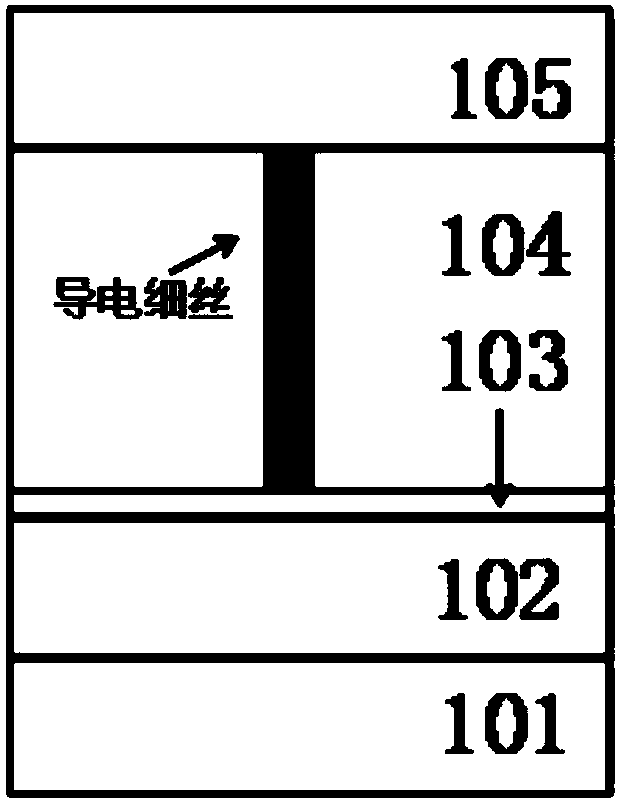

The present invention discloses a right side illuminated Si-PIN photoelectric detector taking the micro-nano structural silicone as a light-sensitive layer and a preparation method thereof. The right side illuminated Si-PIN photoelectric detector taking the micro-nano structural silicone as the light-sensitive layer comprises an I-type substrate, an N area located under the I-type substrate, a micro-nano structural layer P area located in the center of the upper part of the I-type substrate, P+ areas located at the two sides of the upper part of the I-type substrate, upper-end electrodes located on the upper surface of the I-type substrate and a lower-end electrode located on the lower surface of an N area. Compared with the conventional Si photoelectric detector, the right side illuminated Si-PIN photoelectric detector taking the micro-nano structural silicone as the light-sensitive layer of the present invention has a higher responsivity, also can detect the near infrared light, is simple in preparation technology, and is compatible with a conventional silicon semiconductor technology.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Method for preparing multi-grade antimonytelluride nano wire harness array by adopting physical vapour deposition

ActiveCN102330058AEfficient thermoelectric performanceEasy Process CompatibilityPolycrystalline material growthVacuum evaporation coatingPower flowGas phase

The invention discloses a method for preparing a multi-grade antimonytelluride nano wire harness array by adopting physical vapour deposition. The method comprises the step of depositing multi-grade nano wire harness array antimonytelluride on a glass substrate in vacuum low temperature environment by regulating distance between a glass substrate and a tungsten boat, magnitude of output current of an alternating current power supply and deposition speed of an evaporation source antimonytelluride. Because of low temperature environment, the multi-grade nano wire harness array antimonytelluridecan be deposited on a processor such as a CPU (central processing unit). By applying the method disclosed by the invention, the antimonytelluride nano wire harness array prepared by physical vapour deposition has uniform structure, and uniform distribution of a nano phase is effectively guaranteed.

Owner:HANGZHOU INNOVATION RES INST OF BEIJING UNIV OF AERONAUTICS & ASTRONAUTICS

Wet oxidation preparation method of Cu2O resistor memory

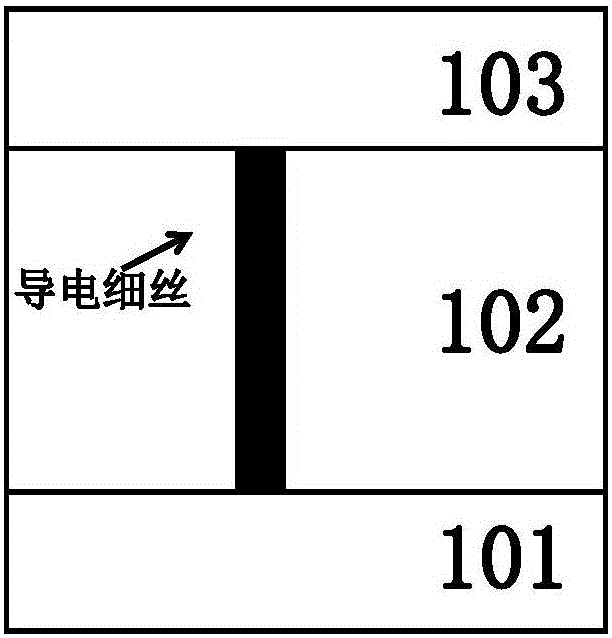

InactiveCN101159310ASimple processLow costSemiconductor/solid-state device manufacturingElectrical resistance and conductanceInterconnection

The invention pertains to the field of microelectronic technology, in particular to a wet oxidation fabrication method of a CuxO resistance memory and an integration method of copper interconnection technique. In the memory, CuxO acting as the memory medium is fabricated by a wet oxidation method. The detailed steps are that hydrogen peroxide aqueous with a certain concentration (10 percent to 50 percent) has a contact with the surface of the exposed Cu leads under a certain temperature (40 to 80 degree) to obtain the memory medium CuxO. The method in the invention has easy technique, low cost and no pollution, the memory medium formed is uniform, and no new impurity is introduced, with the ease to integrate with the copper interconnection technique of integrated circuit.

Owner:FUDAN UNIV

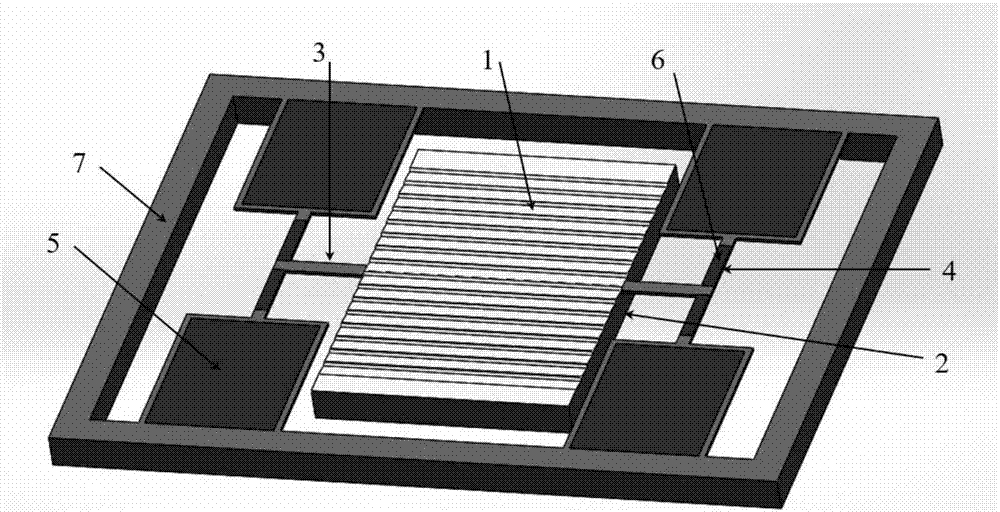

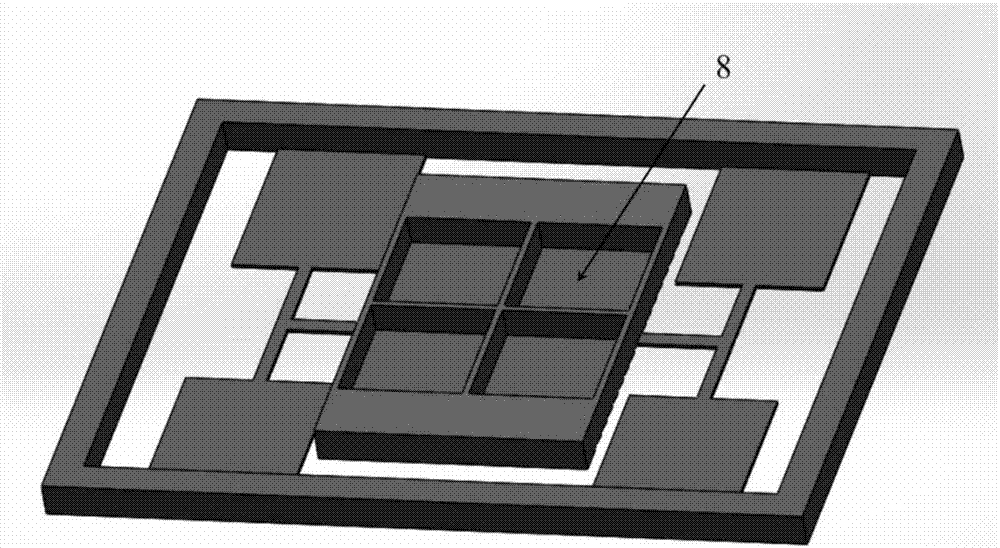

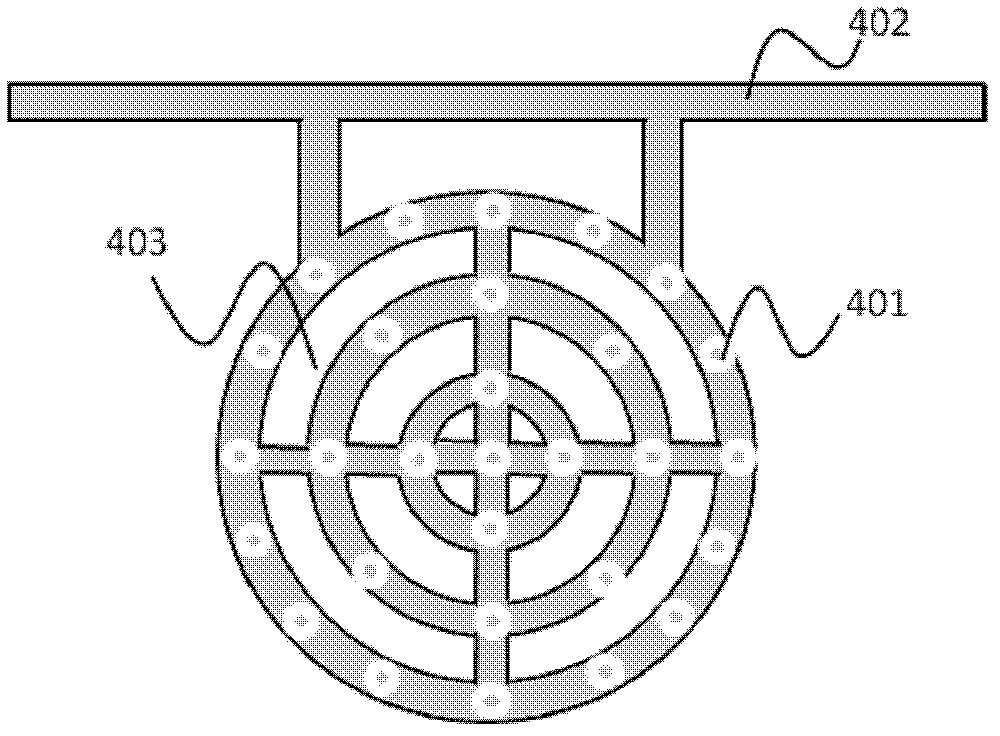

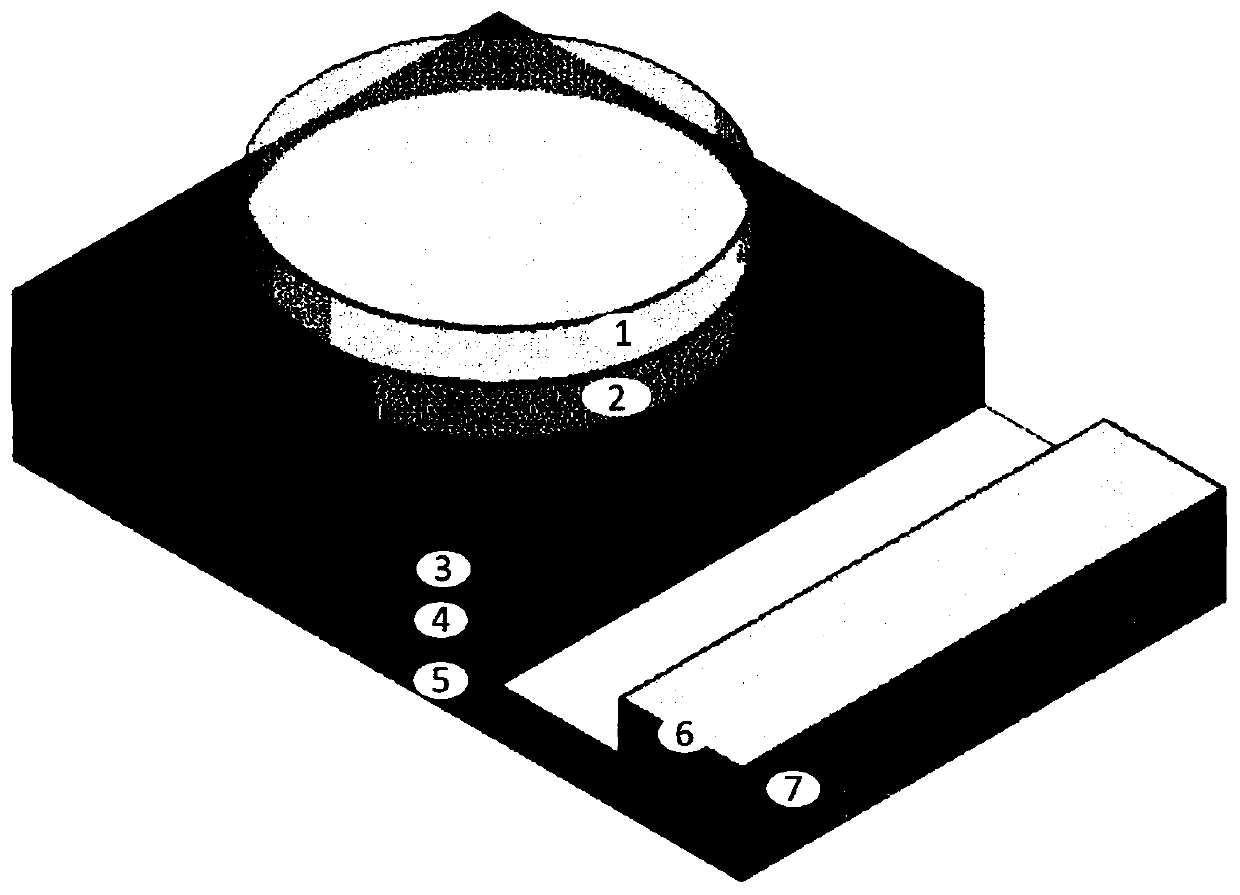

Piezoelectric integrated MOEMS scanning raster micromirror

InactiveCN107247330AEasy Process CompatibilityReduce volumeOptical elementsBlazed gratingFixed frame

The invention discloses a piezoelectric integrated MOEMS scanning raster micromirror and relates to the field of spectrum analysis and micro optical electro mechanical systems. The piezoelectric integrated MOEMS scanning raster micromirror consists of an integrated scanning raster micromirror, a torsion beam, a connecting beam, an angle sensor, a piezoelectric micro driver and a fixing frame. The integrated scanning raster micromirror is based on monotectic orientation (111) silicon substrate, a blazed grating is integrated on the front side, a groove is sapped in the back side, and the diffraction efficiency and device robustness are improved. For achieving large-angle scanning under low-drive voltage, the piezoelectric micro driver and the connecting beam are adopted to amplify drive displacement. For monitoring the motion state of the integrated scanning raster micromirror in real time, the piezoelectric angle sensor is integrally integrated on the connecting beam. The piezoelectric integrated MOEMS scanning raster micromirror is novel and simple in structure and compatible with an integration process, the diffraction efficiency, resolution ratio, robustness and integration level of the scanning raster micromirror can be remarkably improved, and the driving and angle sensing properties of the scanning raster micromirror are improved.

Owner:CHONGQING UNIV

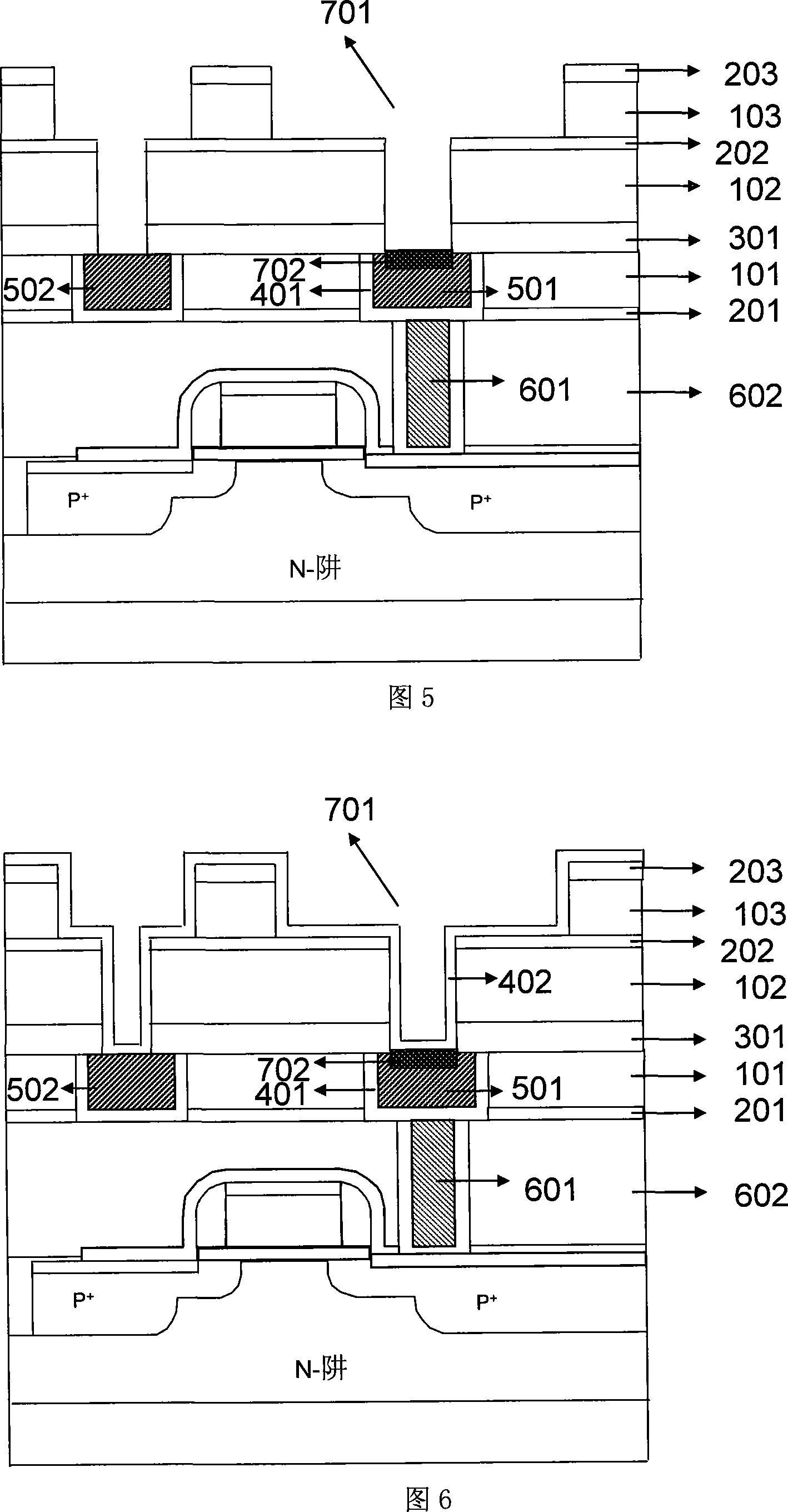

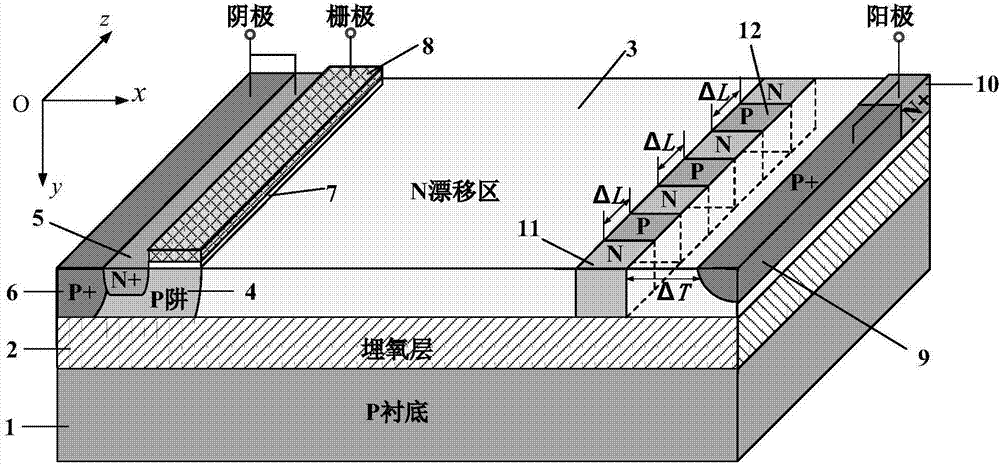

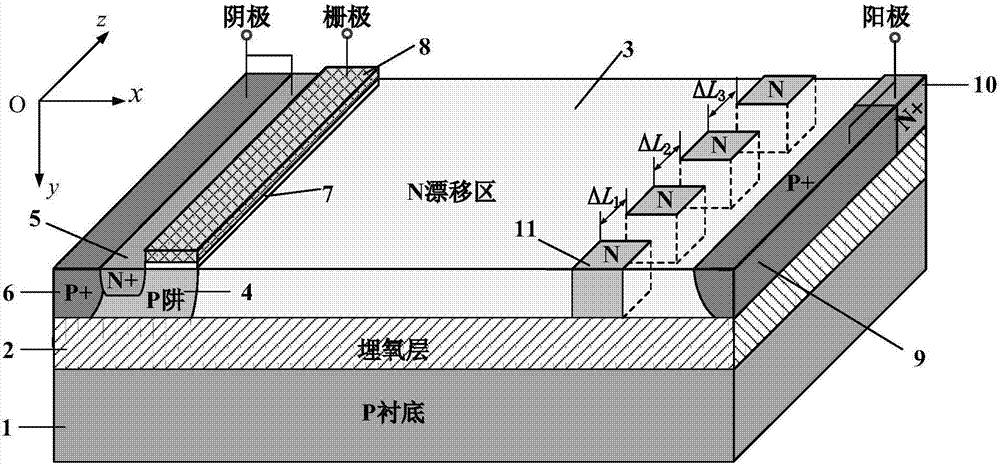

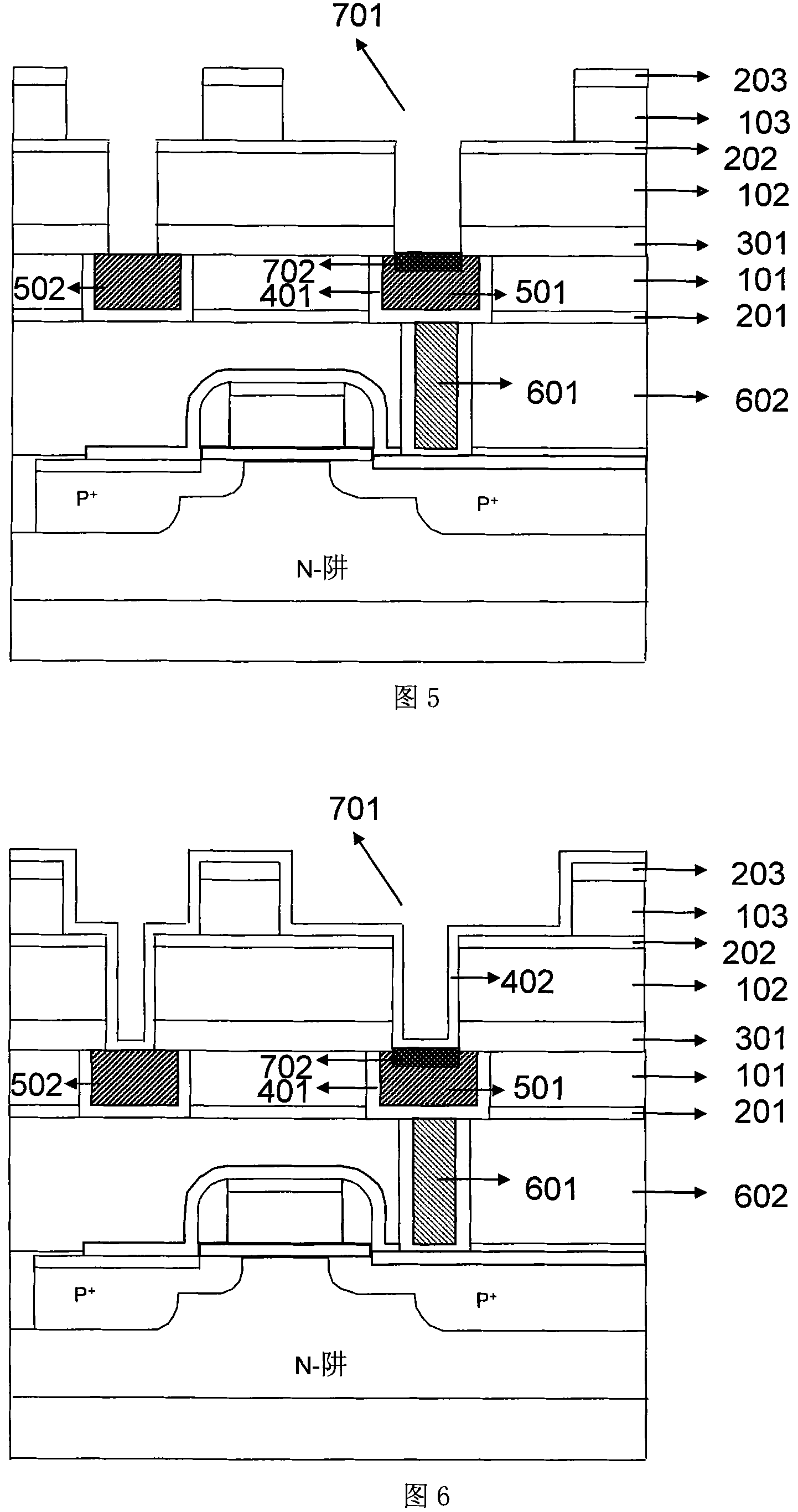

Short circuit anode SOI LIGBT

ActiveCN107170802AFast turn-off and lossSmall longitudinal cell sizeSemiconductor devicesPhysicsContinuous field

The invention belongs to the technical field of power semiconductors, and relates to a short circuit anode SOI LIGBT having alternate NP voltage withstand buffer layer structures. Compared with the conventional short circuit anode LIGBT, alternately distributed N-type island regions and P-type island regions are introduced to an anode region without high concentration field stop layer. The P-type island regions are completely exhausted in forward blocking, and the incompletely exhausted N-type island regions have the field stop effect. The device is affected by electron barrier blocking of the P-type island regions under unipolar mode conduction, and electron current in a drift region flows through the N-type island regions and a high resistance drift region between the island regions and the anode structure and is finally collected by the N+ anode. The beneficial effects of the short circuit anode SOI LIGBT are that the short circuit anode SOI LIGBT has faster disconnection speed and lower loss in comparison with the conventional LIGBT and eliminates the voltage return phenomenon under the smaller size of longitudinal cells in comparison with the conventional short circuit anode LIGBT having the continuous field stop layer.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

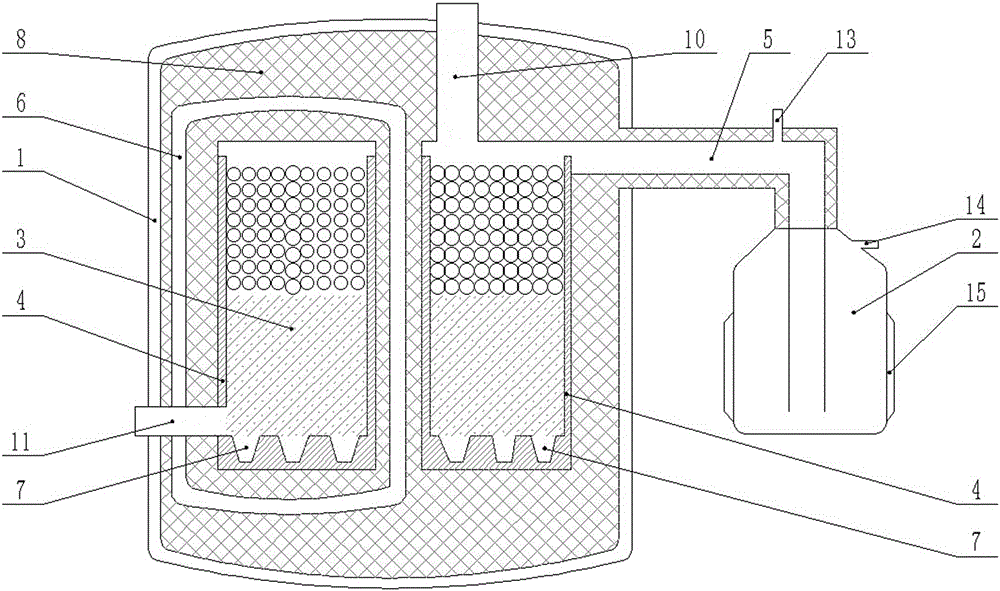

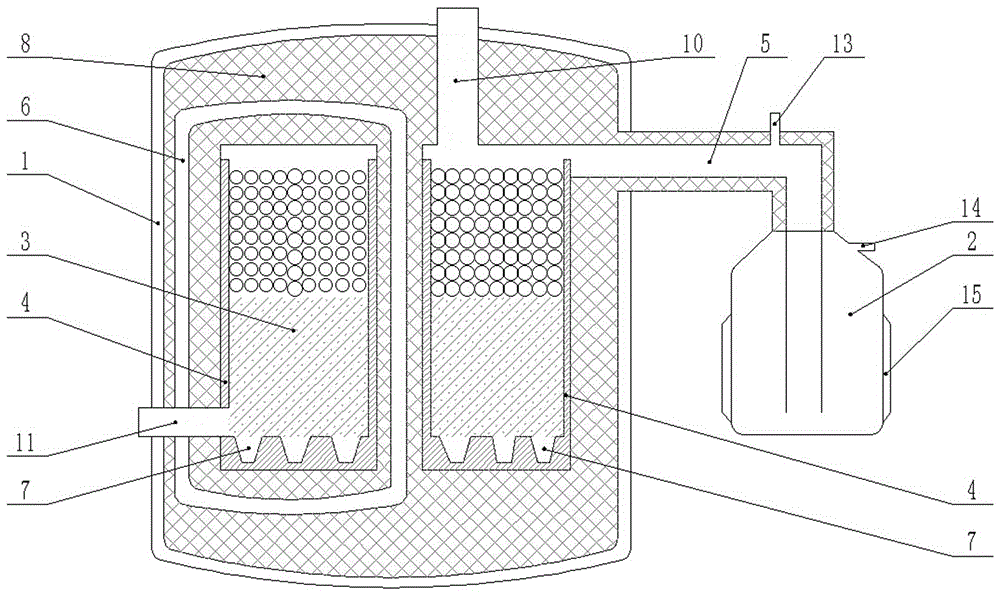

Vacuum reduction furnace for electromagnetic induction heating melting reduction of magnesium metal

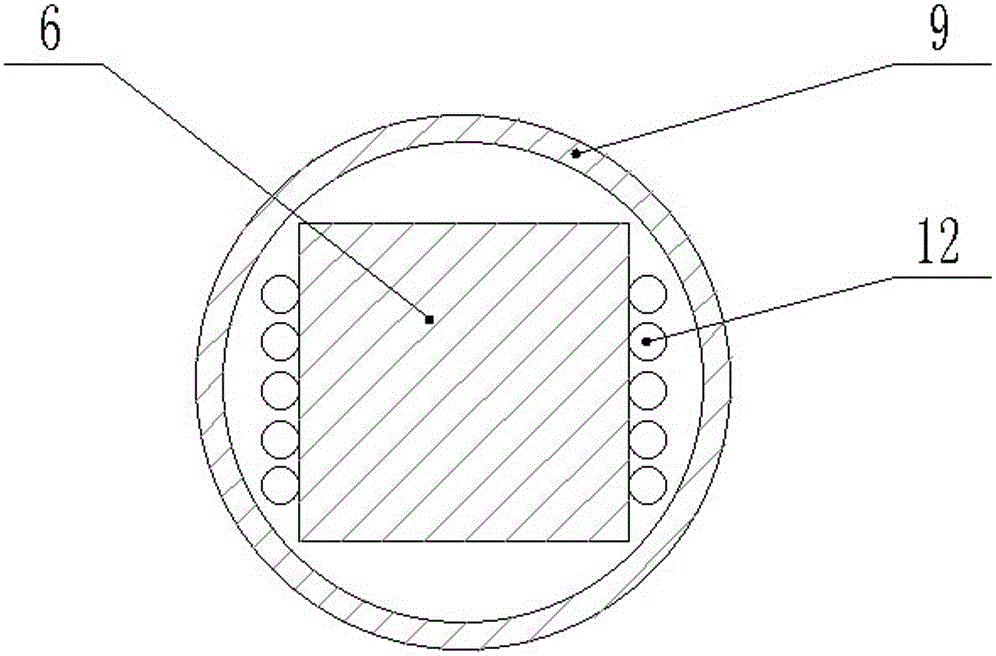

InactiveCN105018740ALow costLow operating and maintenance costsIncreasing energy efficiencyMolten stateConductor Coil

The invention relates to the technical field of vacuum metallurgy equipment, in particular to a vacuum reduction furnace for electromagnetic induction heating melting reduction of magnesium metal. The vacuum reduction furnace comprises a furnace body (1), a hopper (4) made of a hard insulating material is arranged in the furnace body (1), and a center channel penetrating the bottom face of the hopper (4) is arranged in the center position of the hopper (4); one or more annular grooves (7) are concentrically arranged in the bottom face of the hopper (4), and iron in the solid state or the molten state is arranged in the grooves (7); a rectangular iron core (6) is arranged in the furnace body (1), one side of the rectangular iron core (6) penetrates the center channel of the hopper (4), and the other side of the rectangular iron core (6) is wound with a primary side coil (9); and the leading-out end of a copper winding of the primary side coil (9) is led out of the furnace through an insulation sealing device on the furnace body (1) so as to be connected with a power device. The vacuum reduction furnace is reasonable in design, distribution of a temperature field of the reduction furnace can be adjusted, and the heat transferring efficiency is high; and the vacuum reduction furnace is used for thermal reduction production of high-vapor-pressure metal such as magnesium, lithium, strontium and calcium and the like.

Owner:SHANXI UNIV

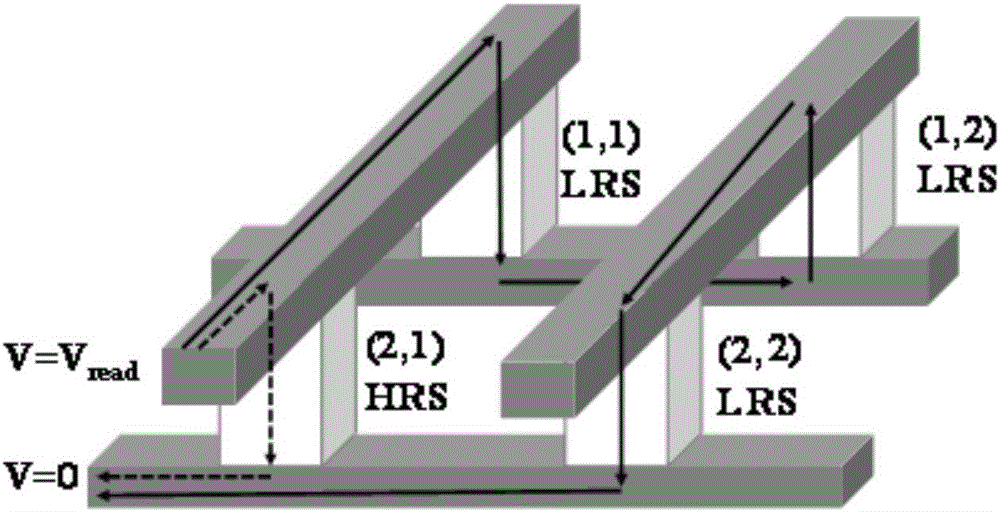

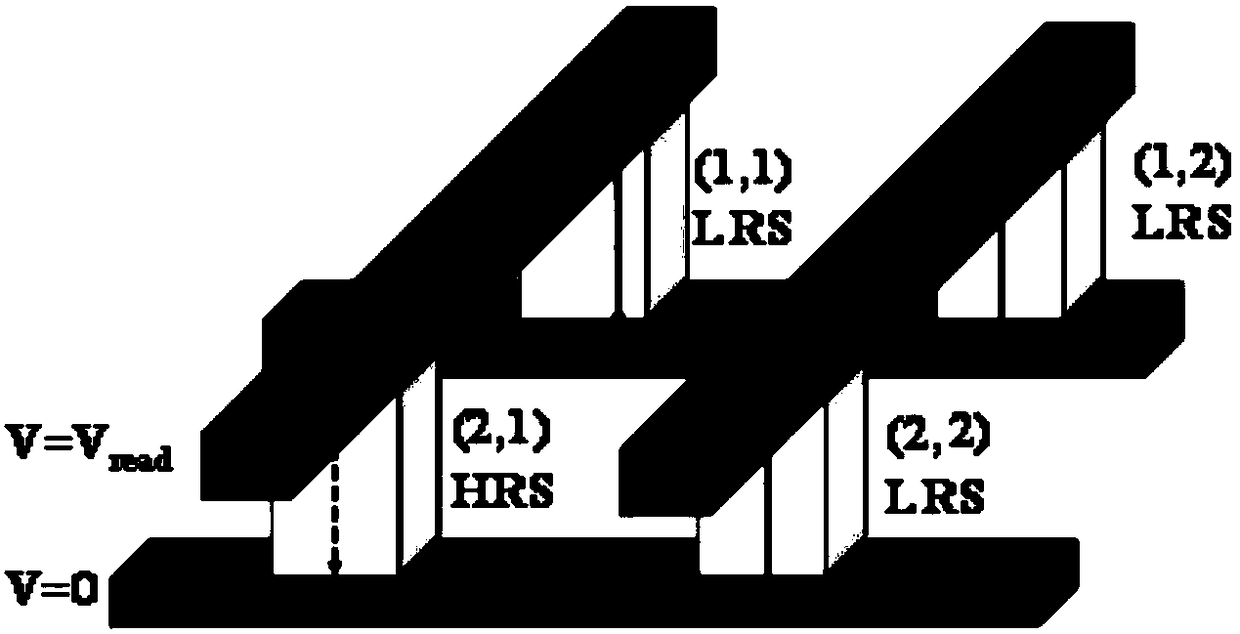

Bipolar resistive random access memory and preparation method thereof

ActiveCN105895800AWell formedSolving High-Density Integration ProblemsElectrical apparatusState of artReaction speed

The invention provides a bipolar resistive random access memory and a preparation method thereof. The bipolar resistive random access memory includes a substrate, a lower electrode which is composited with the upper surface of the substrate, a rectification function layer which is composited with the lower electrode, a graphene layer which is composited with the rectification function layer, a resistive dielectric layer which is composited with the graphene layer, and an upper electrode which is composited with the resistive dielectric layer, wherein the rectification function layer is formed by one or more of Al203, TiO2 and MgO. Compared with the prior art, the rectification function layer in the bipolar resistive random access memory can play a role in tunneling rectification and realize bidirectional rectification, and can also effectively restrain the crosstalk misreading phenomenon between adjacent units in a resistive random access memory array; and at the same time, because of existence of the graphene layer, the device performance is improved; the reset current is reduced; the response speed is improved; and the power consumption is reduced.

Owner:合肥中科微电子创新中心有限公司

Capacitive humidity sensor

InactiveCN103018289BImprove linearityReduce lossMaterial capacitancePiezoelectric/electrostrictive devicesCMOSMetallic electrode

The invention discloses a capacitive humidity sensor. The capacitive humidity sensor comprises a detection capacitor which consists of a substrate, a dielectric layer and a metallic electrode layer, wherein the detection capacitor is of a cantilever beam structure shape, the dielectric layer is arranged on the substrate, and the metallic electrode layer is located on the dielectric layer; and a humidity-sensitive strain layer is further arranged on the metallic electrode layer. The capacitive humidity sensor disclosed by the invention is simple in structure and convenient in manufacturing and has the advantages of good linearity, little temperature drift, high response speed, low sensitive capacitive loss, low parasitic capacitance, easiness in process compatibility with a CMOS (Complementary Metal Oxide Semiconductor), and the like.

Owner:SOUTHEAST UNIV

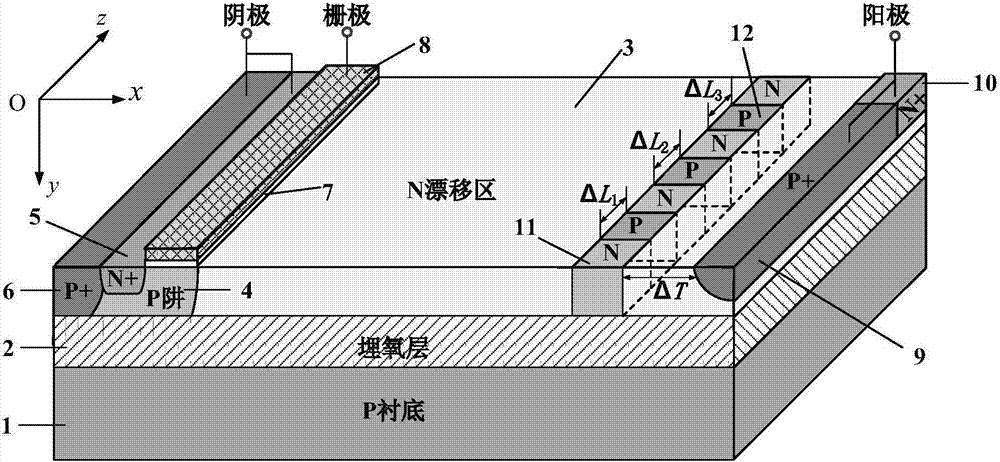

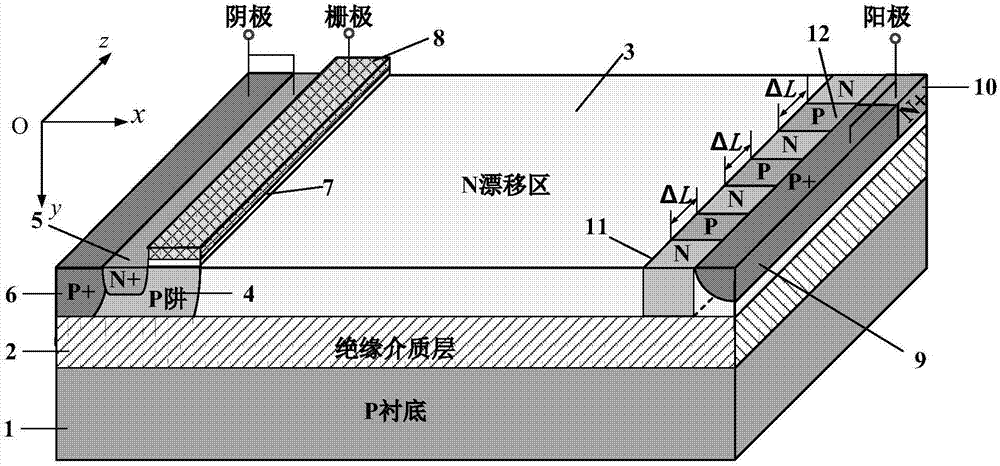

Thin SOI short circuit anode LIGBT

InactiveCN107240603AEasy Process CompatibilityInhibit the snapback effectSemiconductor devicesHigh resistanceSmall cell

The invention belongs to the technical field of power semiconductor, and specifically relates to a thin SOI short circuit anode LIGBT (Lateral Insulated Gate Bipolar Transistor). Compared with a traditional SOI base LIGBT, the thin SOI short circuit anode LIGBT is characterized in that an N+ anode region which is in parallel with a P+ anode region in the vertical direction, and introducing disjunctively distributed N type islands at one side, approaching a cathode structure, in the P+ anode region (9) and the N+ anode region (10); when a new device in the blockout state, the N type islands are not completely depleted, thus effectively preventing further expansion of a depletion region and preventing break-through and breakdown of the N type islands; when the initial stage is started, an electro current flows by the N type islands and the high resistance drift regions among the adjacent N type islands; and compared with traditional continuous N buffer layers, the disjunctively distributed N type islands can increase the distribution resistance at one side of the anode side to enable the device to enter the bipolar mode under a smaller current. Compared with a traditional LIGBT, the thin SOI short circuit anode LIGBT has the advantages of high speed and low on-off loss. Compared with a traditional short circuit anode LIGBT, the thin SOI short circuit anode LIGBT can eliminate the snapback effect even under a small cell size.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

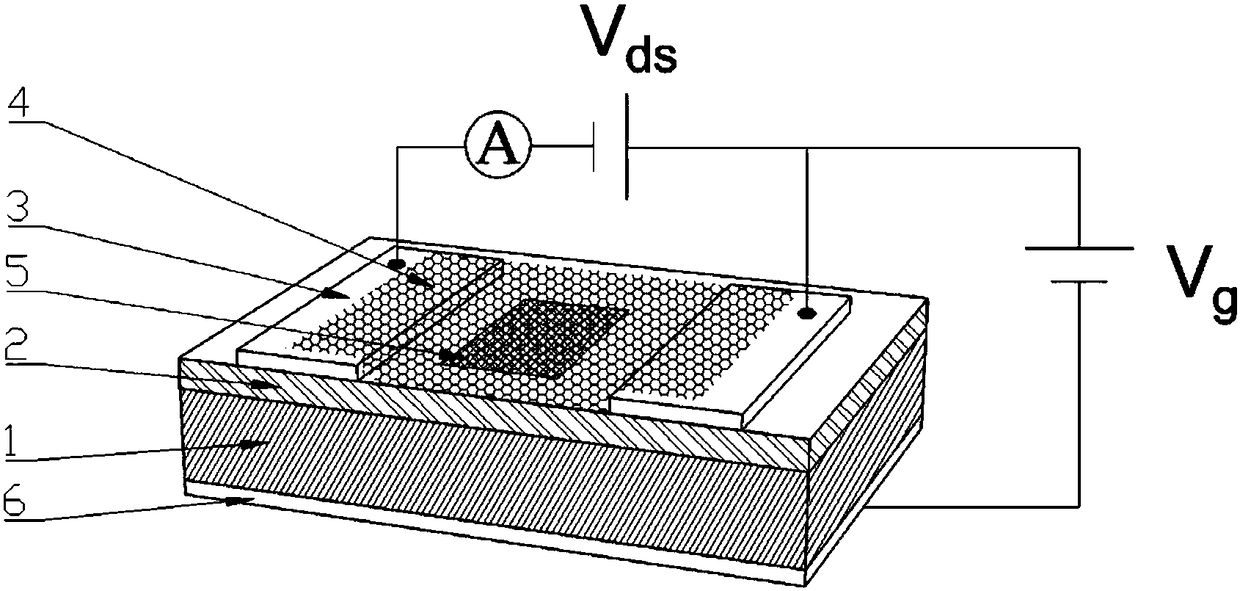

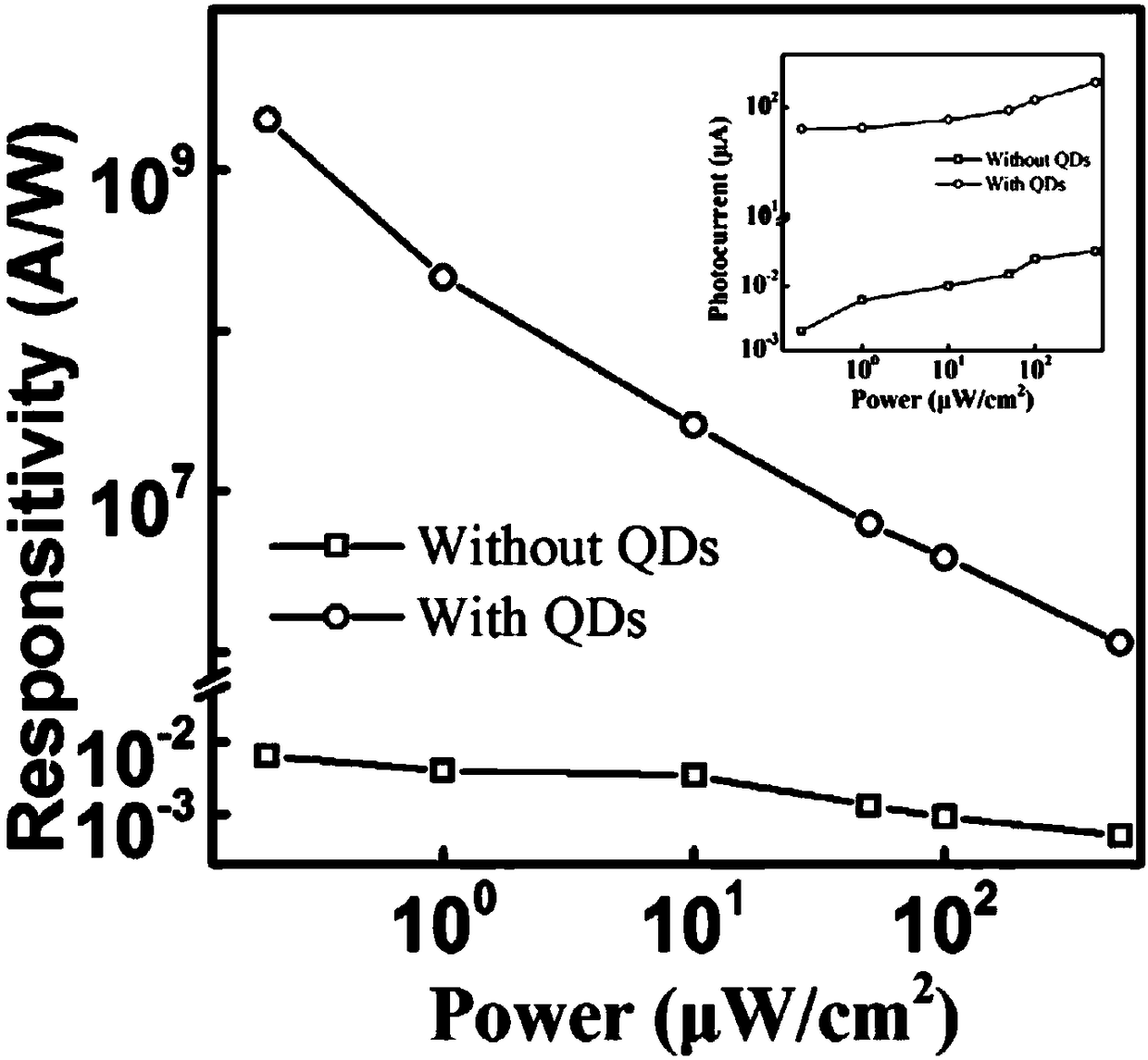

Photodetector and preparation method based on graphene/boron-doped silicon quantum dots/silicon

ActiveCN106784122BPromote absorptionReduce surface recombination rateFinal product manufactureSemiconductor devicesDead layerPhoton

The invention discloses a photoelectric detector based on graphene / boron-doped silicon quantum dots / silicon and a preparation method thereof. The photoelectric detector comprises an n type silicon substrate, a top electrode, a graphene film, a boron-doped silicon quantum dot film, and a bottom electrode. The photoelectric detector can carry out wide spectral detection, and a problem of low infrared detection response of a traditional silicon-based PIN junction is solved. According to the detector, graphene is used as an active layer and a transparent electrode, a dead layer is eliminated, and the absorption of incident light is enhanced. The boron-doped silicon quantum dot film is in the middle, the influence of a silicon surface state is reduced, and the reverse saturation current is suppressed at the same time. Under a certain reverse bias voltage effect, collision ionization is generated by photon-generated carriers and silicon lattice, and a high photoelectric response is obtained. The photoelectric detector and the preparation method have the advantages of a simple preparation process, low cost, a high response degree, fast response speed, a large internal gain, a small switching ratio, and easy integration.

Owner:ZHEJIANG UNIV

Photoconductive detector and preparation method based on boron-doped silicon quantum dot/graphene/silicon dioxide

ActiveCN106601857BLarge light signal currentHigh gainFinal product manufactureSemiconductor devicesPhotoconductive detectorP type silicon

The invention discloses a photoconductive detector based on boron-doped silicon quantum dot / graphene / silicon dioxide and a preparation method thereof. The photoconductive detector includes a p-type silicon substrate, a silicon dioxide isolation layer, a top electrode, a graphene film, a boron-doped silicon quantum dot film and a bottom electrode. The photoconductive detector is capable of carrying out wide-spectrum detection, so that a problem of low response to infrared detection by the traditional silicon-based PIN structure can be solved. Because the graphene is used to form an active layer and a transparent electrode, a dead layer is eliminated and incident light absorption is enhanced. With the silicon dioxide isolation layer, the silicon surface state can be reduced. The detector can work normally at a low bias voltage; the absorbed light of the boron-doped silicon quantum dot layer is converted into photon-generated carriers and the generated photon-generated carriers being hole electron pairs are separated under the effect of the built-in electric field, so that the high gain can be obtained. In addition, the preparation method is simple; the cost is low; the response degree is high; the response speed is fast; the internal gain is high; the switch ratio is low; and integration is easy to realize.

Owner:ZHEJIANG UNIV

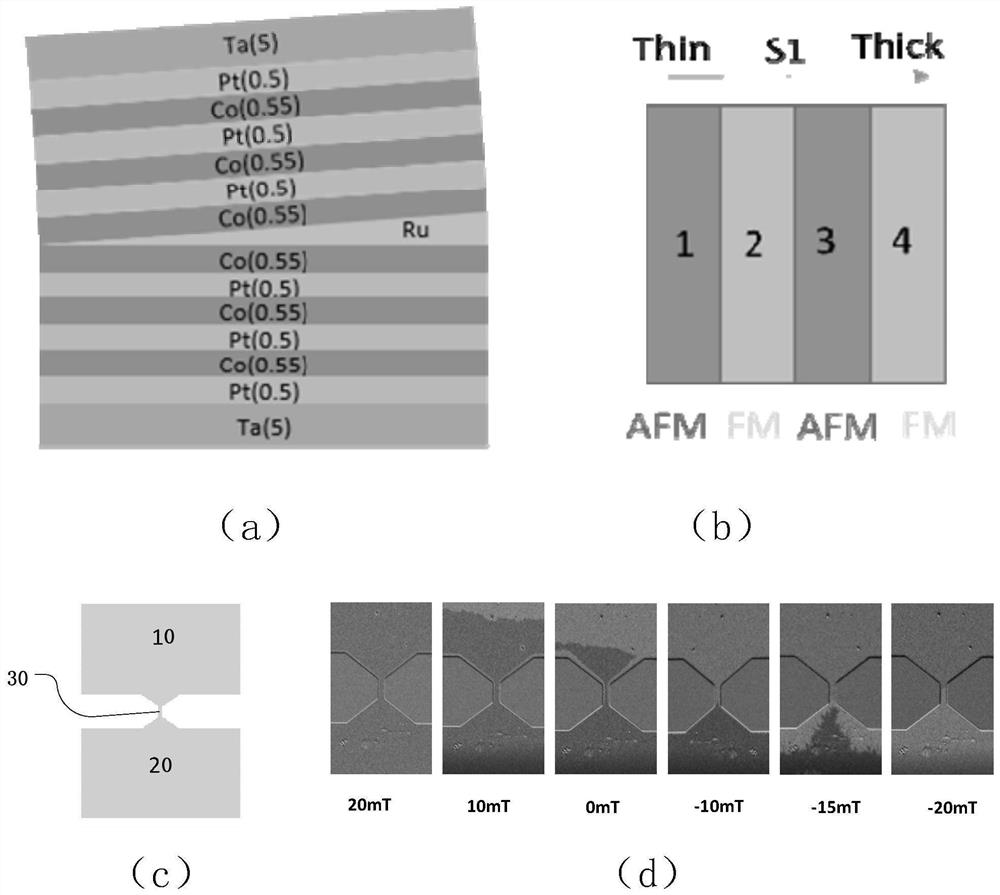

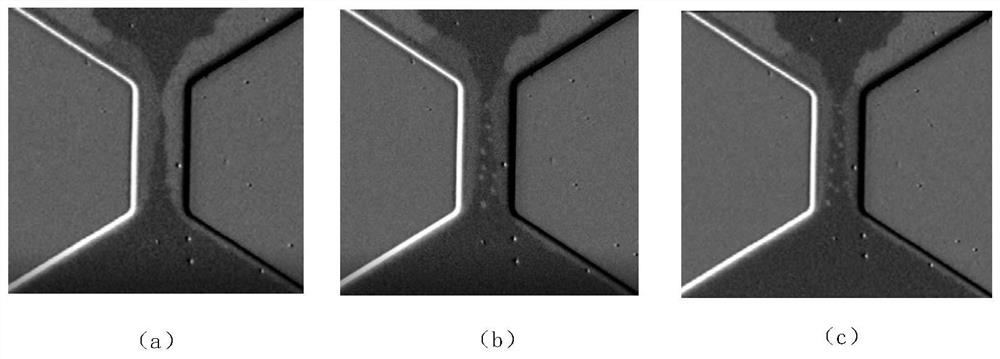

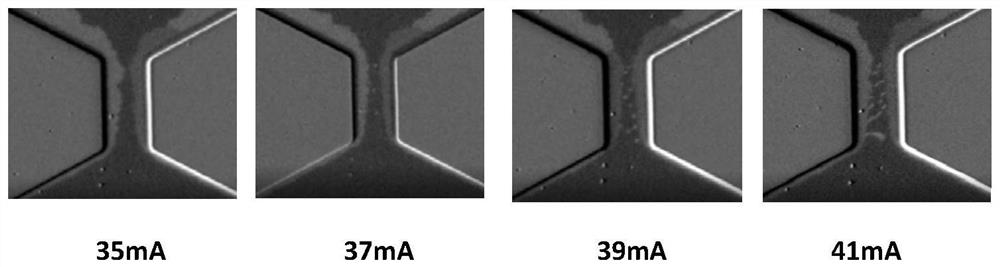

Method for generating skyrmion in magnetic multilayer film through current induction, magnetic storage unit and memory

PendingCN112510146AEasy Process CompatibilityGalvano-magnetic material selectionGalvano-magnetic device detailsAntiferromagnetic couplingMagnetic storage

The invention provides a method for generating skyrmion in a magnetic multilayer film through current induction, and the method comprises the following steps: S1, providing a magnetic multilayer filmwhich comprises a first magnetic layer, a non-magnetic metal layer and a second magnetic layer which are sequentially stacked, wherein more than one antiferromagnetic coupled first strip and more thanone ferromagnetic coupled second strip are formed in the magnetic multilayer film, and the first strips and the second strips are alternately formed; the first strip and the second strip are parallelto each other along a first direction; S2, connecting the magnetic multilayer film into a circuit, and introducing alternating current to generate the skyrmion at the junction of the first strip andthe second strip, wherein the frequency of the alternating current is 47 kHz and 52 kHz, and the peak value of the alternating current is 37 mA-39mA. The method can be used for preparing a device withhigh integration level, and is also convenient to be compatible with the existing semiconductor process.

Owner:THE CHINESE UNIV OF HONG KONG SHENZHEN

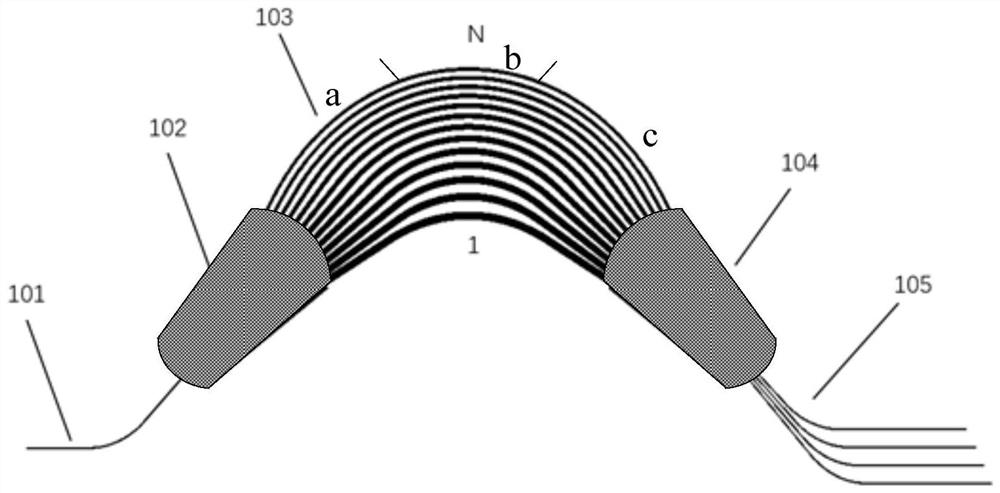

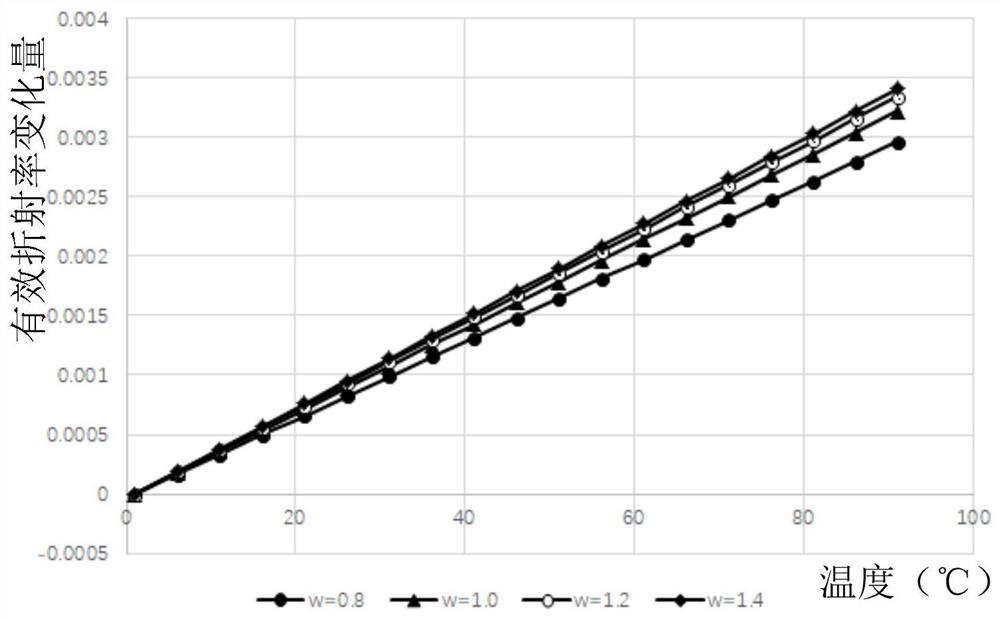

Athermal arrayed waveguide grating

ActiveCN112068244AReduced waveguide lengthAchieve athermalizationOptical waveguide light guideCMOSExternal energy

The invention provides an athermal arrayed waveguide grating. In arrayed waveguides, the adjacent arrayed waveguides have different waveguide lengths, the corresponding adjacent arrayed waveguides have different waveguide widths, and the waveguide widths of the arrayed waveguides are reduced along with the increase of the waveguide lengths of the arrayed waveguides. By changing the waveguide widths of the arrayed waveguides, athermalization of the arrayed waveguide grating is achieved. Good temperature stability can be maintained without external energy supply. The arrayed waveguide grating isa passive device, and the maintenance cost of the system can be greatly reduced. The design and the process are simple, a post-treatment process is not needed, the grating can adapt to large-scale mass production and commercialization, and the performance is stable; good process compatibility is achieved, and standard CMOS processing can be adopted; and multi-channel wavelength division multiplexing can be realized. According to the athermal arrayed waveguide grating, on the premise that the optical path difference of the adjacent arrayed waveguides is fixed on the whole, insensitivity of thecentral wavelength to temperature can be achieved.

Owner:UNITED MICROELECTRONICS CENT CO LTD

Electromagnetic Induction Heating Melting Reduction Metal Magnesium Vacuum Reduction Furnace

InactiveCN105018740BLow costLow operating and maintenance costsIncreasing energy efficiencyMolten stateLithium

Owner:SHANXI UNIV

A kind of bipolar resistive variable memory and preparation method thereof

ActiveCN105895800BWell formedSolving High-Density Integration ProblemsElectrical apparatusEngineeringGraphite

The invention provides a bipolar resistive memory and a preparation method thereof. The bipolar resistive memory comprises a substrate; a lower electrode compounded on the upper surface of the substrate; a rectification function compounded on the lower electrode layer; a graphene layer compounded on the rectifying functional layer; a resistive dielectric layer compounded on the graphene layer; an upper electrode compounded on the resistive dielectric layer; the rectifying functional layer is composed of Al 2 o 3 、TiO 2 Formed with one or more of MgO. Compared with the prior art, the rectification functional layer in the bipolar resistive memory provided by the present invention can play the role of tunnel rectification, realize bidirectional rectification, and can also effectively suppress the gap between adjacent cells in the resistive memory array. The phenomenon of crosstalk misreading; at the same time, due to the existence of the graphene layer, the performance of the device is improved, the reset current is reduced, the response speed is improved, and the power consumption is reduced.

Owner:合肥中科微电子创新中心有限公司

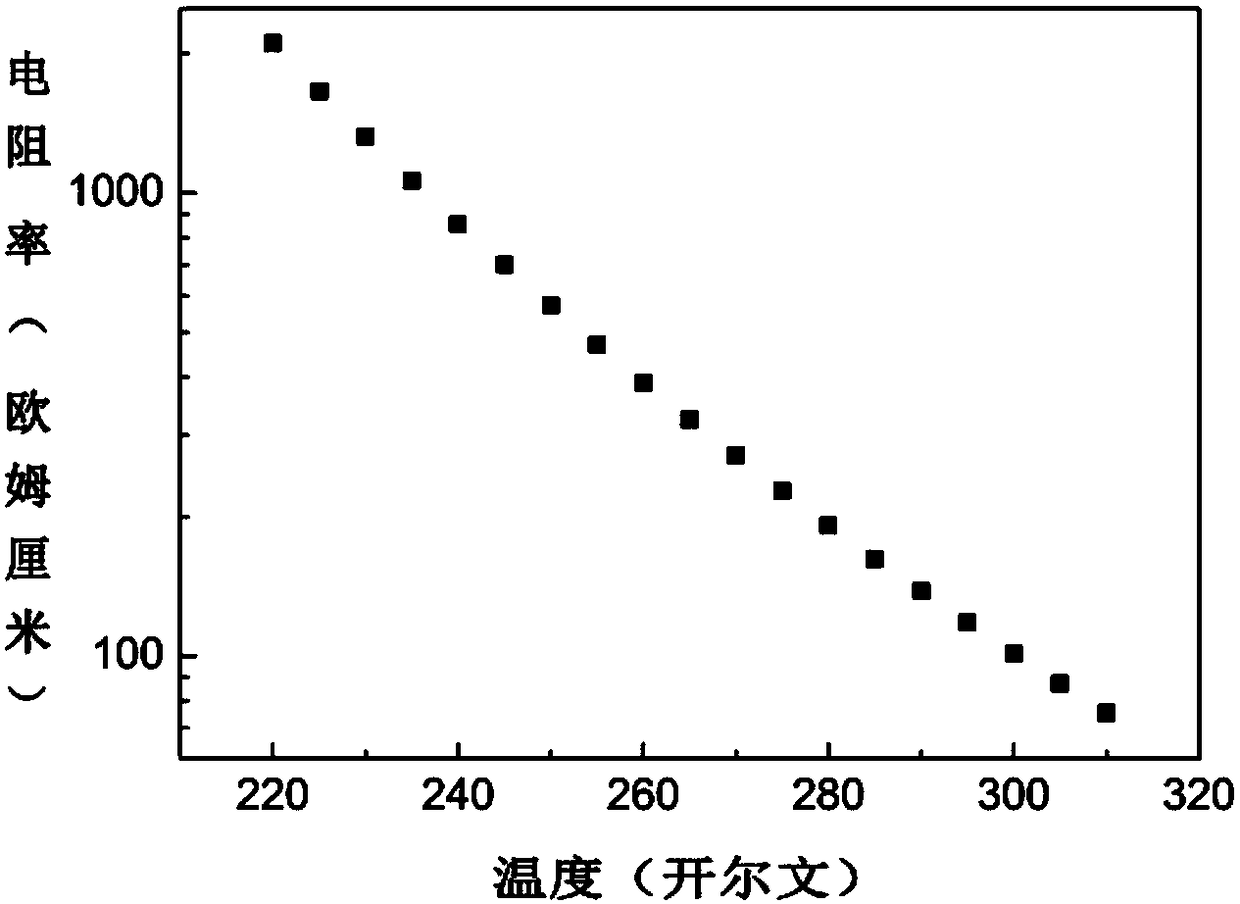

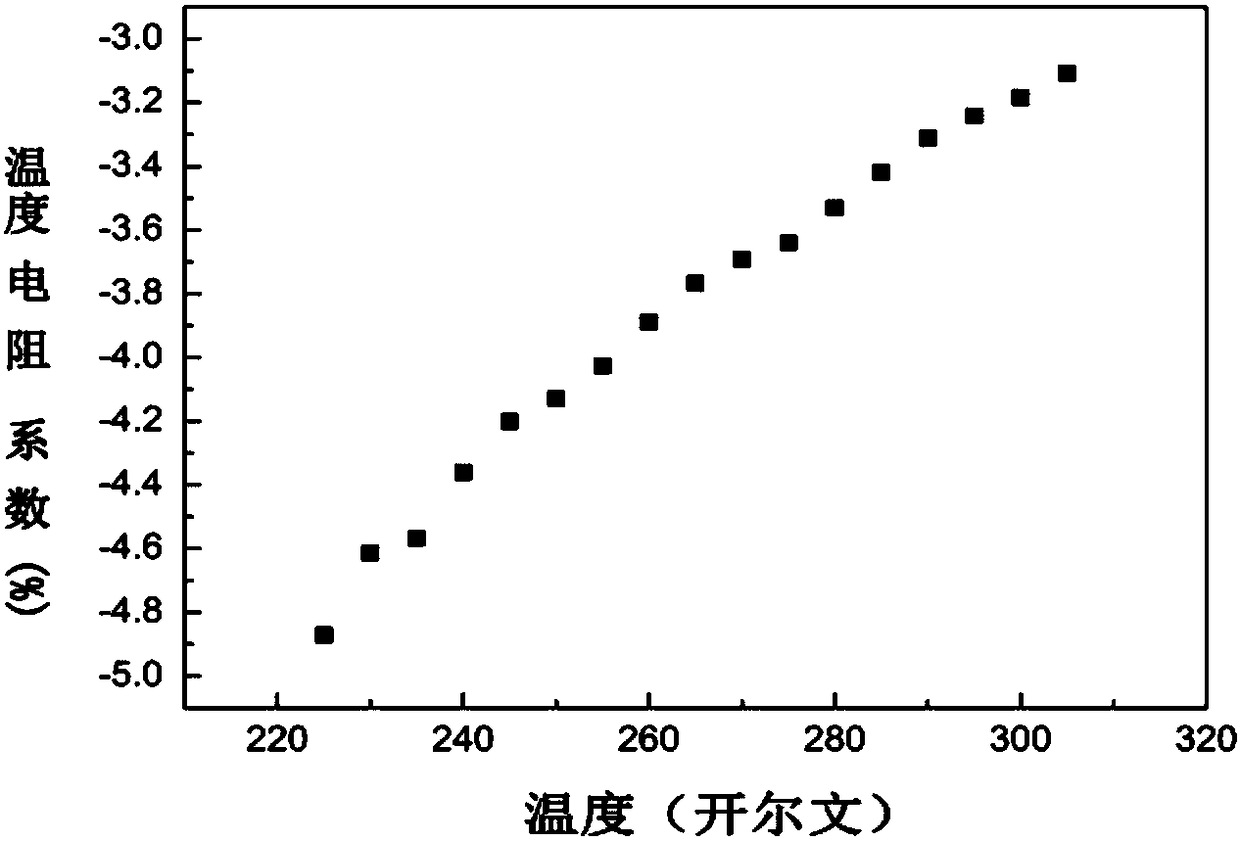

A kind of method for preparing flexible thermal film material

ActiveCN106048527BAchieve depositionLow resistivityVacuum evaporation coatingSputtering coatingRadio frequency magnetron sputteringPolyethylene glycol

The invention discloses a method for preparing a flexible thermosensitive film material. According to the method, MnCO3 powder, Co2O3 powder, Ni2O3 powder are used as raw materials and subjected to grinding, screening, synthesizing, fine grinding, pre-molding forming and sintering under the oxygen-enriched atmosphere to be made into a ceramic target, a polyethylene glycol terephthalate sheet and a polyimide sheet are used as substrates, and an MCNO film is deposited at the room temperature in a sputtered mode through a radio frequency magnetron sputtering method. The method has the advantages that firstly, sputter deposition is completed at the room temperature, and the purpose of depositing the MCNO thermosensitive film on the polyethylene glycol terephthalate substrate, the polyimide substrate and other organic flexible substrates is achieved; secondly, the MCNO film prepared through the method is low in specific resistance, and the negative temperature resistance coefficient is high, so that responsivity of elements is better increased, and noise of the elements is better lowered; thirdly, preparation is conducted at the normal temperature, high-temperature heat treatment is not needed, energy consumption is low, energy is saved, and the environment is protected; and fourthly, the sputter deposition temperature is low, the method is easily compatible with a Si-based semiconductor process, and the thermosensitive elements can be directly prepared on Si-based reading circuit chips, so that the cost for preparing thermosensitive type uncooled infrared focal plane arrays is greatly lowered.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

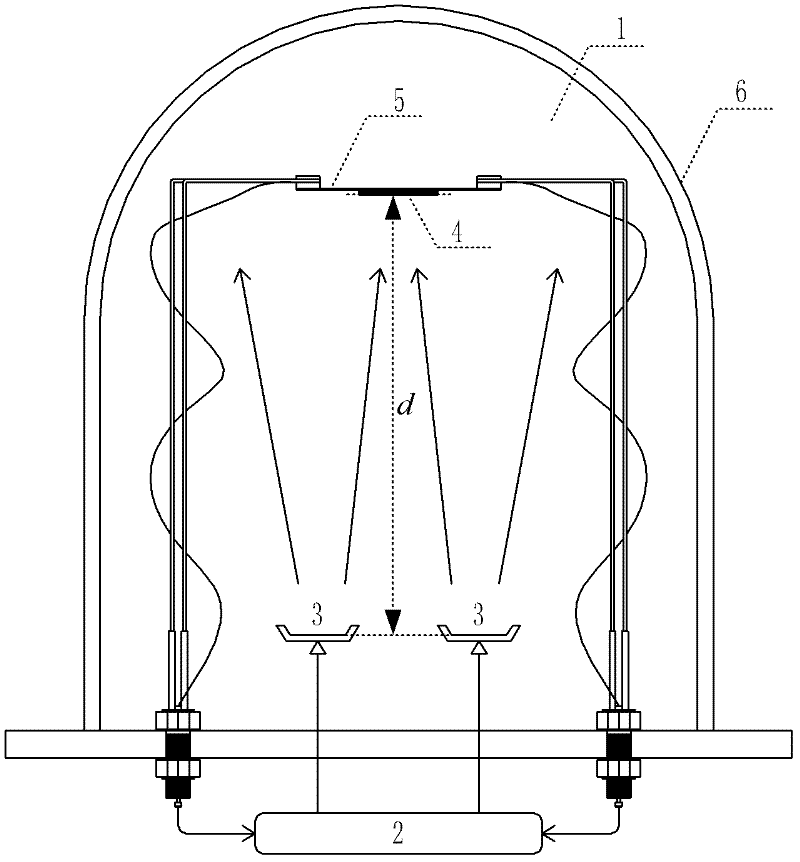

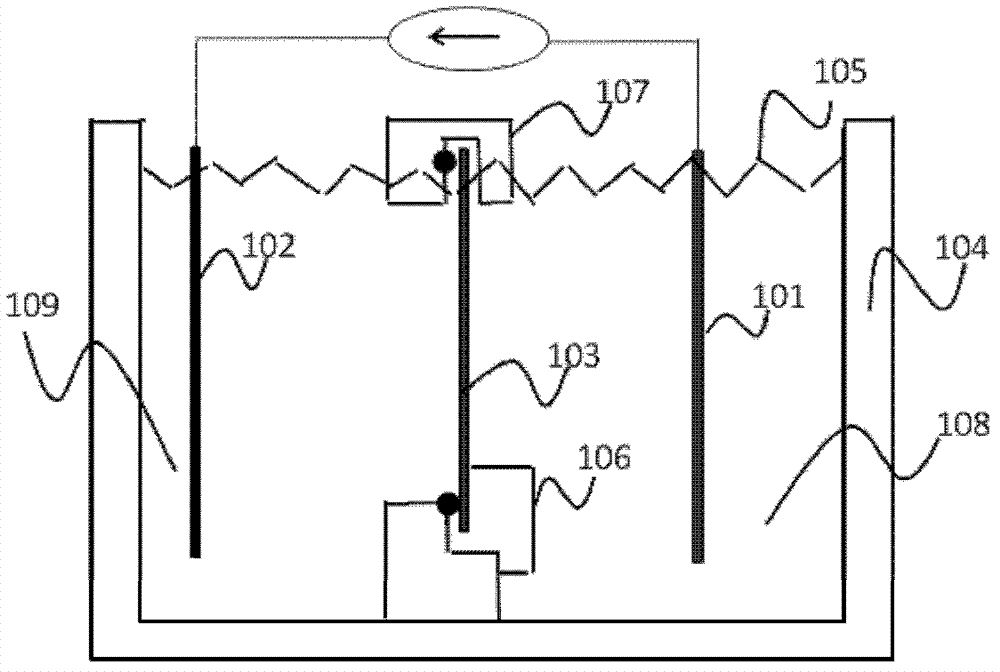

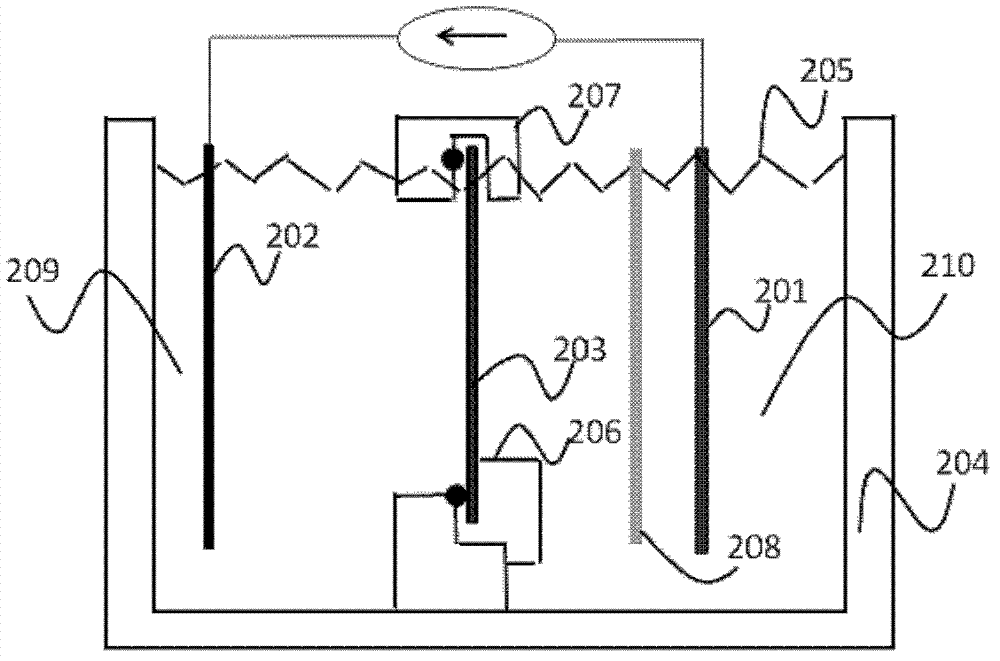

Photon-assisted porous silicon electrochemical etching tank

InactiveCN102618914BQuality assuranceGuaranteed efficiencyElectrolysis componentsEngineeringElectrochemistry

The invention provides a photon-assisted porous silicon electrochemical etching tank which comprises a tank body, a fixing support, electrodes and a photon-assisted mechanism. The fixing support, the electrodes and the photon-assisted mechanism are arranged in the tank body; the fixing support is used for fixing a silicon chip to be etched; the electrodes comprises a cathode and an anode, and the cathode and the anode are fixed on two sides of the fixing support respectively; and the photon-assisted mechanism is arranged between the fixing support and the cathode, used for providing illumination for the silicon chip to be etched, and light source of the photon-assisted mechanism is sealed in transparent polycarbonate (PC) plastic which has a grooved gate structure to facilitate flow of etching solution. During a double groove electrochemical etching process, the photon-assisted mechanism between the cathode and the silicon chip to be etched in the tank body is used for irradiating the silicon chip to be etched directly at close range, therefore holes with a certain concentration are formed in the silicon chip to be etched, and quality and efficiency of the double groove electrochemical etching process are guaranteed.

Owner:HANGZHOU SILAN INTEGRATED CIRCUIT

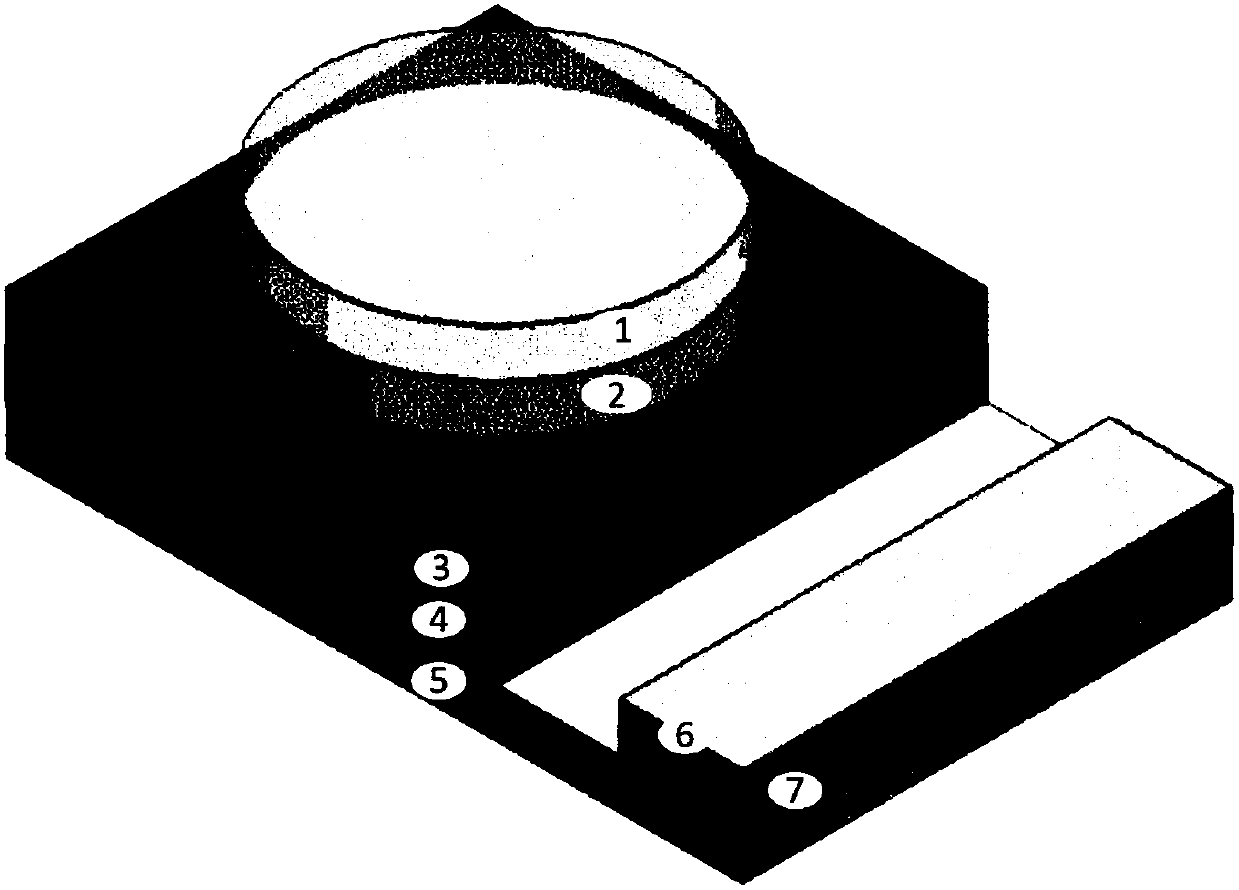

A si-apd photodetector based on fractal nanowire surface structure and its preparation method

ActiveCN110429156BEasy Process CompatibilityEasy to makeFinal product manufactureSemiconductor devicesElectrode ContactMaterials science

Owner:重庆连芯智能科技研究院有限公司

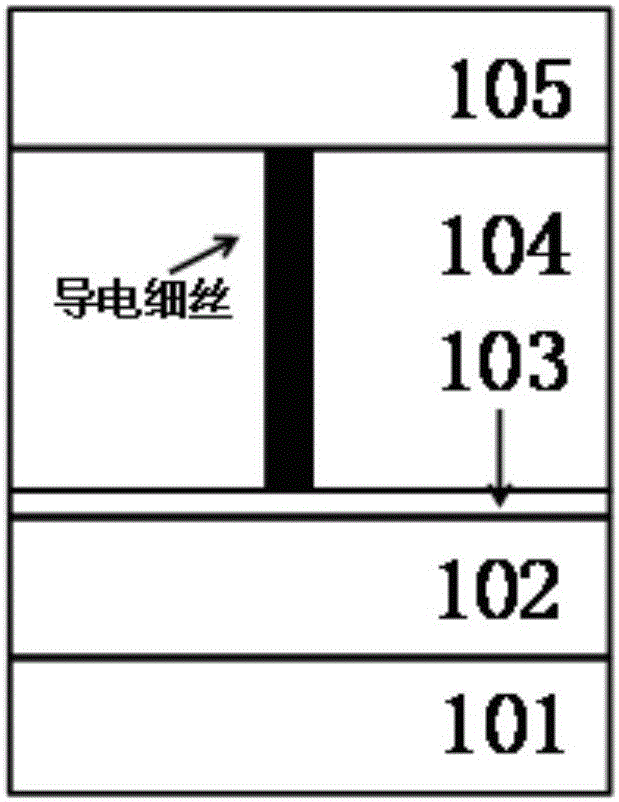

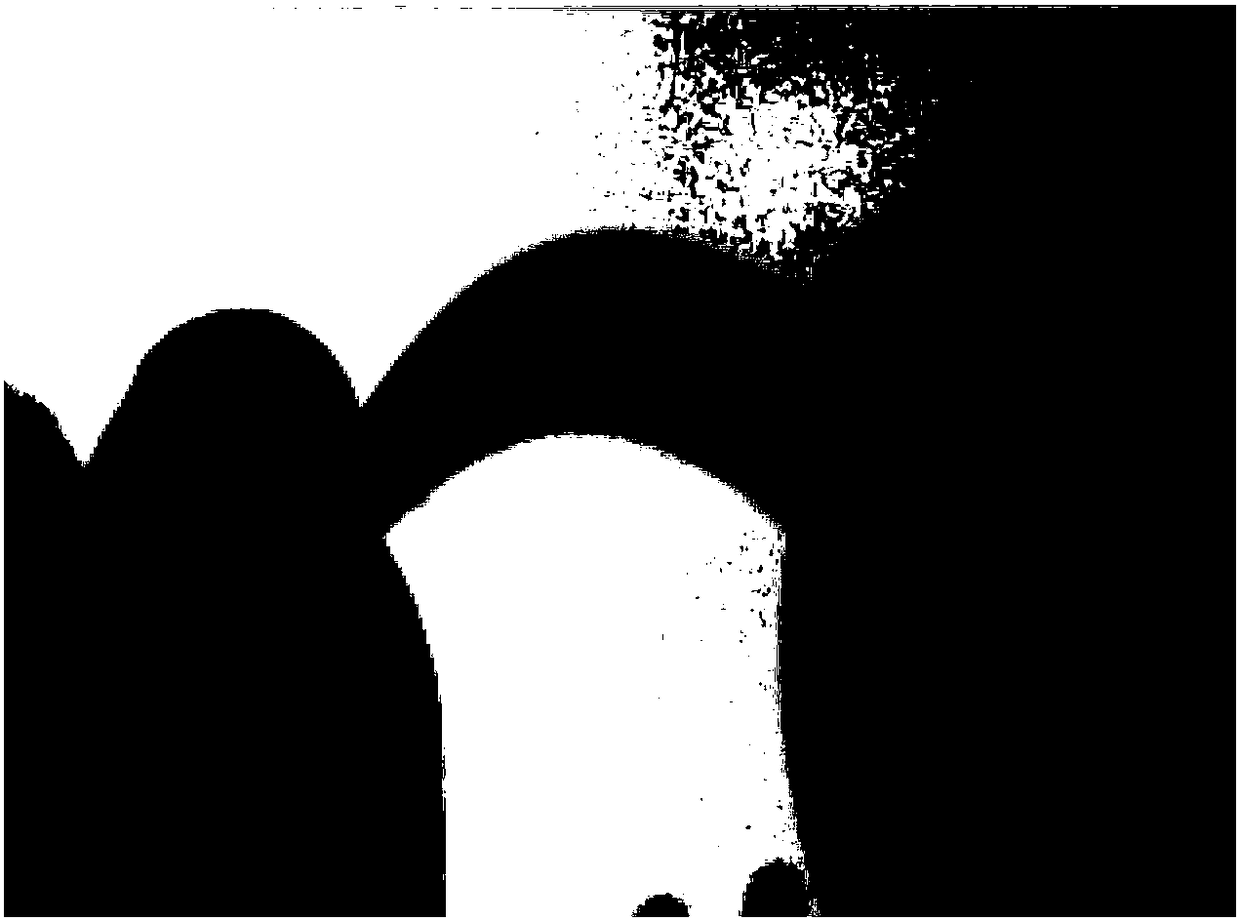

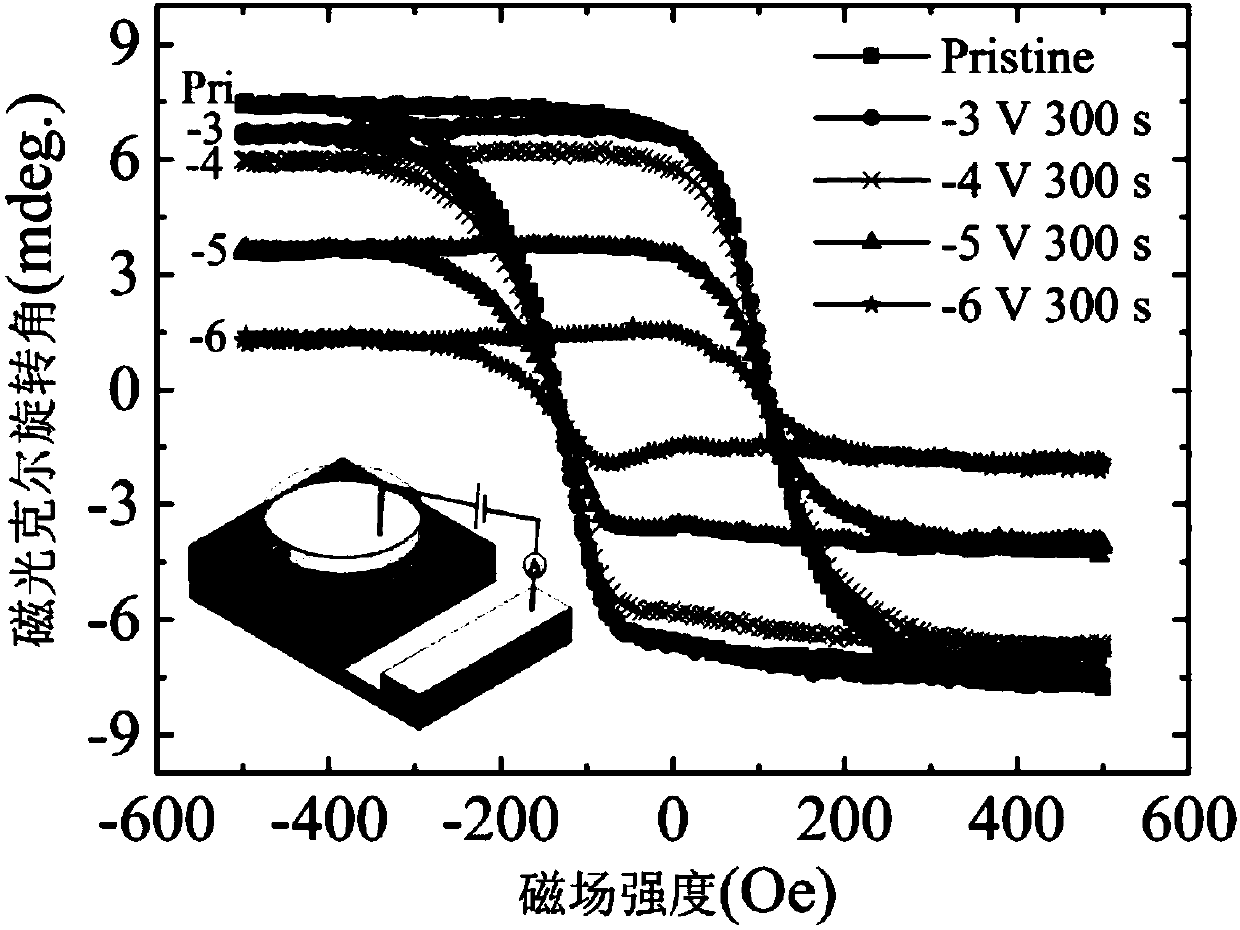

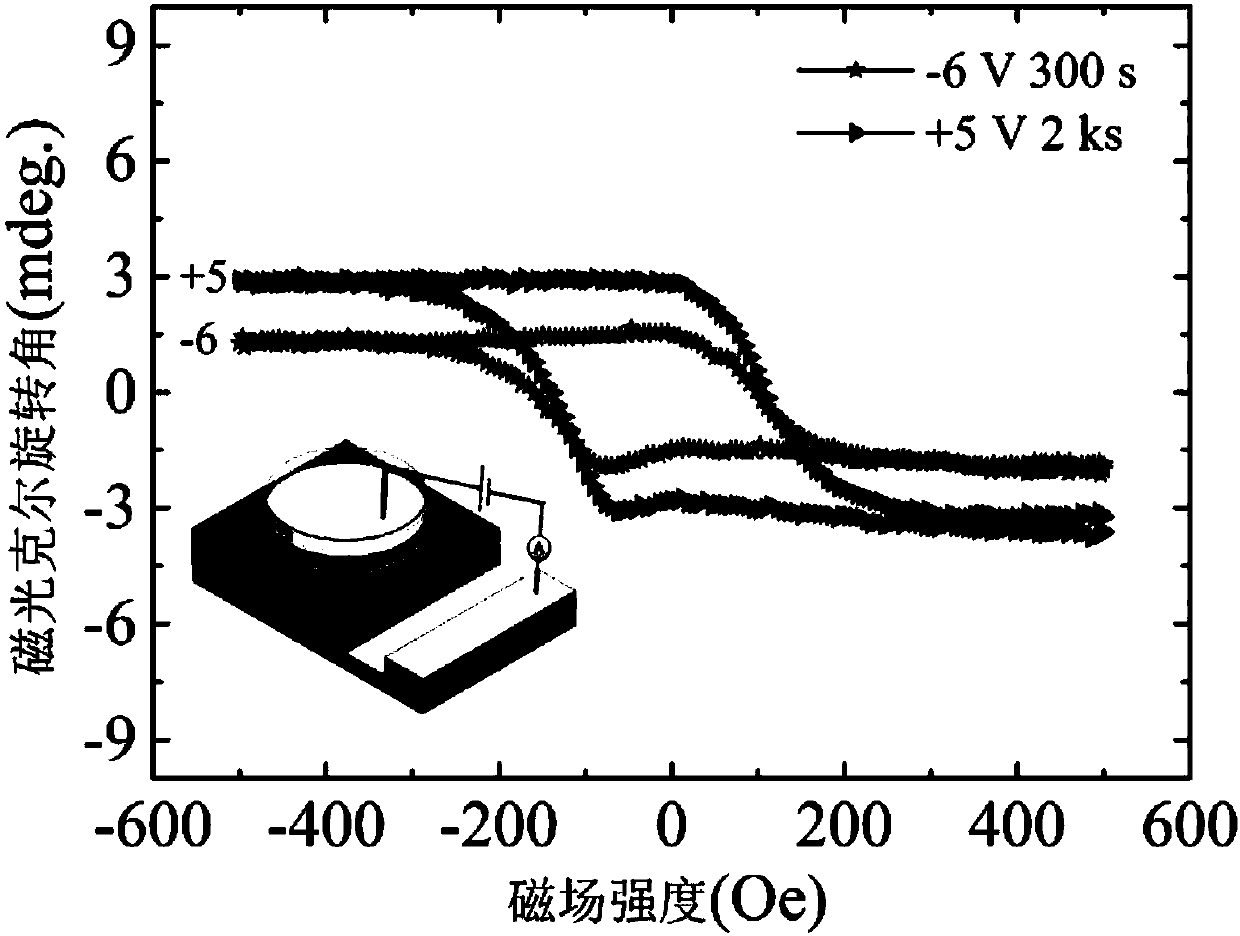

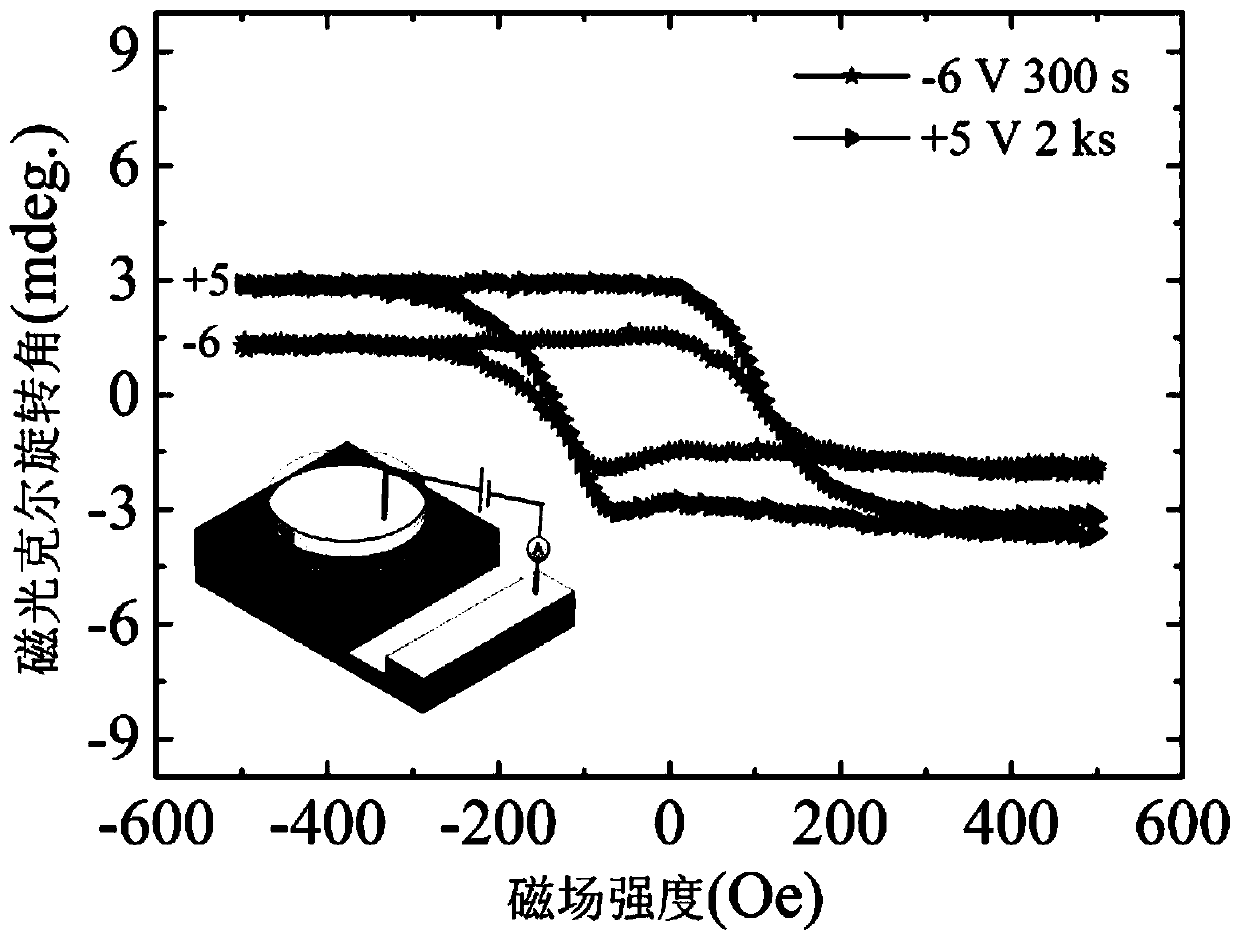

All-solid-state electric field reconfigurable magneto-optic device

ActiveCN107678190ASolve poor process compatibilityEasy Process CompatibilityNon-linear opticsIonSemiconductor

The invention belongs to the technical field of magneto-optic devices, in particular to an all-solid-state electric field reconfigurable magneto-optic device. An all-solid-state structure is adopted,so that the structure is compatible with a semiconductor technology more easily; an electric field is utilized to manipulate the magneto-optic effect of magnetic film in a nonvolatile mode, and staticpower dissipation of the device is lowered; through the uniformity of ionic migration of an adjustable material layer, consistent manipulation of the magneto-optic effect within the range of severalhundred micron scales is achieved, and the problem that it is hard to scale down filament machine-made devices based on ionic conduction in equal proportion is solved; the adjustable material layer and a magnetic dielectric layer which are separated are adopted, and the purpose that the electric field manipulates the magneto-optic effect of a wide class of magnetic insulators or semiconductors isachieved. According to the all-solid-state electric field reconfigurable magneto-optic device, regarding one device, it is achieved that the structure is in an all solid state, the electric field manipulates the magneto-optic effect in a nonvolatile mode, the magneto-optic effect of the magnetic film is manipulated on a large scale and the magneto-optic effect of multiple magnetic insulators or semiconductors is manipulated in a generalization mode.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Wet oxidation preparation method of Cu2O resistor memory

InactiveCN101159310BSimple processLow costSemiconductor/solid-state device manufacturingCopper interconnectEngineering

The invention pertains to the field of microelectronic technology, in particular to a wet oxidation fabrication method of a CuxO resistance memory and an integration method of copper interconnection technique. In the memory, CuxO acting as the memory medium is fabricated by a wet oxidation method. The detailed steps are that hydrogen peroxide aqueous with a certain concentration (10 percent to 50percent) has a contact with the surface of the exposed Cu leads under a certain temperature (40 to 80 degree) to obtain the memory medium CuxO. The method in the invention has easy technique, low cost and no pollution, the memory medium formed is uniform, and no new impurity is introduced, with the ease to integrate with the copper interconnection technique of integrated circuit.

Owner:FUDAN UNIV

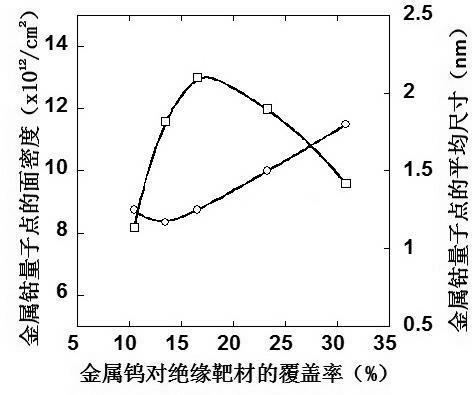

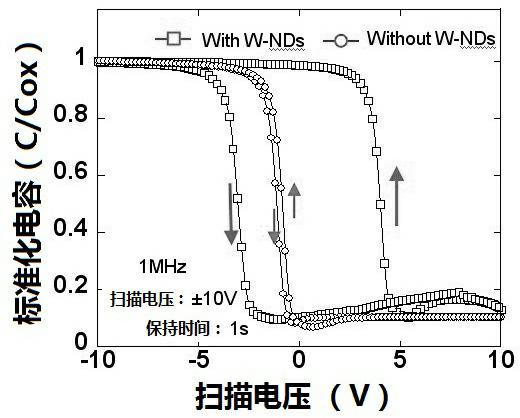

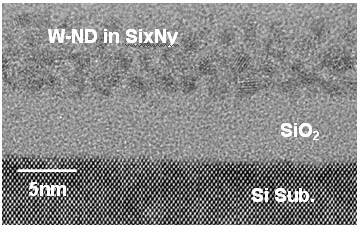

Self-assembly preparation method for floating gate layer of silicon nitride dielectric film with embedded metal tungsten quantum dots

InactiveCN102592981ASmall sizeHigh densitySemiconductor/solid-state device manufacturingPhysicsOxide semiconductor

The invention discloses a self-assembly preparation method for a floating gate layer of a silicon nitride dielectric film with embedded metal tungsten quantum dots. According to the invention, at a room temperature, a magnetron sputtering method is adopted to prepare the silicon nitride dielectric film with the embedded metal tungsten quantum dots, and the film serves as a floating gate structure of a non-volatile memory; a sputtering target material is formed by small metal tungsten blocks on a silicon nitride target material, and the nano-scale metal tungsten quantum dots, which are uniformly distributed on the silicon nitride dielectric film, can be obtained through cosputtering at the room temperature; and the size and density of the metal tungsten quantum dots can be adjusted through adjusting the amount of the small metal blocks, namely by adjusting the coverage rate of the small metal blocks to the silicon nitride target material. The high-density metal tungsten quantum dots prepared by the invention have favorable thermal stability at the high temperature of 800 DEG C and are easy to compatible with a CMOS (Complementary Metal Oxide Semiconductor) technology. The silicon nitride dielectric film with embedded high-density metal tungsten quantum dots serves as the floating gate layer of the non-volatile memory and has good charge storage characteristics.

Owner:SUN YAT SEN UNIV

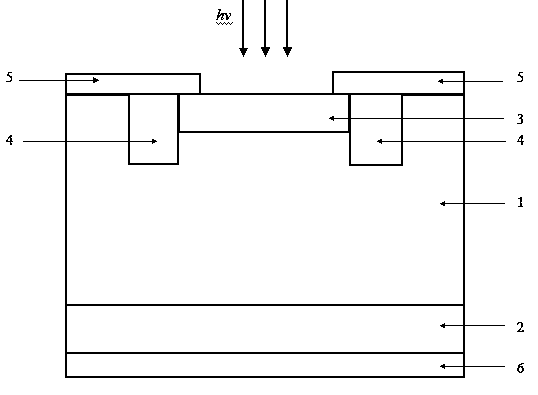

A kind of preparation method of back-illuminated si-pin photodetector

InactiveCN103400887BImprove responsivenessImprove uniformityFinal product manufactureSemiconductor devicesNano structuringPhotovoltaic detectors

The invention discloses a back-illuminated Si-PIN photodetector and a preparation method thereof, which relates to a photodetection device structure in the field of photodetection technology, and the photodetector includes an I-type substrate 1, a P region 2, and a P+ region 3. The N region 4 of the nanostructured silicon layer and the upper and lower electrodes, the electrodes include the upper electrode 5 located on the P region 2 and the P+ region 3 and the lower electrode 6 located on the N region 4 of the nanostructured silicon layer. The upper electrode 5 is used for connecting with the cathode of the external circuit; the lower electrode 6 is used for connecting with the anode of the external circuit. This new type of Si photodetector solves the problems of low responsivity and inability to respond to near-infrared bands of traditional Si photodetectors, improves the absorption rate of visible light and near-infrared light, extends the response band to the near-infrared band, and has a higher responsivity. high.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Front-illuminated si-pin photodetector using micro-nano structured silicon as photosensitive layer and preparation method thereof

InactiveCN104064610BBroad absorption spectrumReduce reflectivityFinal product manufactureSemiconductor devicesMicro nanoResponsivity

The invention discloses a front-illuminated Si-PIN photodetector with micro-nanostructure silicon as the photosensitive layer and a preparation method thereof. The front-illumination Si-PIN photodetector with micro-nanostructure silicon as the photosensitive layer includes an I-type substrate , the N region located below the I-type substrate, the micro-nano structure layer P region located above the center of the I-type substrate, the P+ region located above both sides of the I-type substrate, the upper electrode located on the upper surface of the I-type substrate, and the The lower end electrode on the lower surface of the N region. The front-illuminated Si-PIN photodetector with micro-nanostructure silicon as the photosensitive layer of the present invention has higher responsivity than traditional Si photodetectors, and can also realize the detection of near-infrared light at the same time. The preparation process is simple and can be Compatible with conventional silicon semiconductor processes.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Microsilicon microphone and its preparing method

InactiveCN100536608CHigh strengthPrevent Waveform DistortionElectrets selectrostatic transducerCapacitanceEngineering

This invention provides a micro-silicon microphone and its preparation method, in which, said microphone includes a monocrystal silicon film and polysilicon film as the capacitor pole plates, the polysilicon film is a movable pole plate, several release holes are set on the monosilicon film and rib reinforcement structures are formed on the polysilicon film, the rib reinforcement structure is corresponding to the release hole on the monocrystal silicon film and inlayed in the release holes. The preparation method utilizes ICP technology to carry out deep bar etching to either get the release holes or realize polysilicon films with the rib reinforcement structure.

Owner:PEKING UNIV

An all-solid-state electric field reconfigurable magneto-optical device

ActiveCN107678190BRealize full solid stateSolve the problem of poor process compatibilityNon-linear opticsMagnetic mediaMagneto

The invention belongs to the technical field of magneto-optical devices, in particular to an all-solid-state electric field reconfigurable magneto-optic device. The invention adopts an all-solid-state structure to make it more compatible with the semiconductor process; utilizes the electric field to control the magneto-optic effect of the magnetic thin film in a non-volatile way, and reduces the static power consumption of the device; utilizes the uniformity of the ion migration of the adjustable material layer to realize The consistent control of the magneto-optical effect in the range of hundreds of microns has been achieved, and the problem that the device based on the ion-conducting filament mechanism is difficult to scale down has been solved; the separated adjustable material layer and magnetic medium layer have been used to realize the electric field control. Magneto-optical effect of a large class of magnetic insulators or semiconductors. Finally, the present invention realizes in one device at the same time: an all-solid-state structure; non-volatile manipulation of the magneto-optical effect by an electric field; large-area manipulation of the magneto-optic effect of magnetic thin films; universal manipulation of the magneto-optic effect of various magnetic insulators or semiconductors .

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

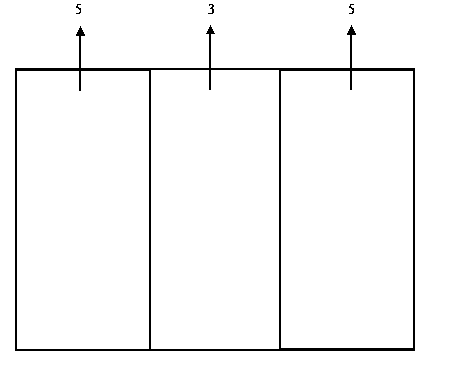

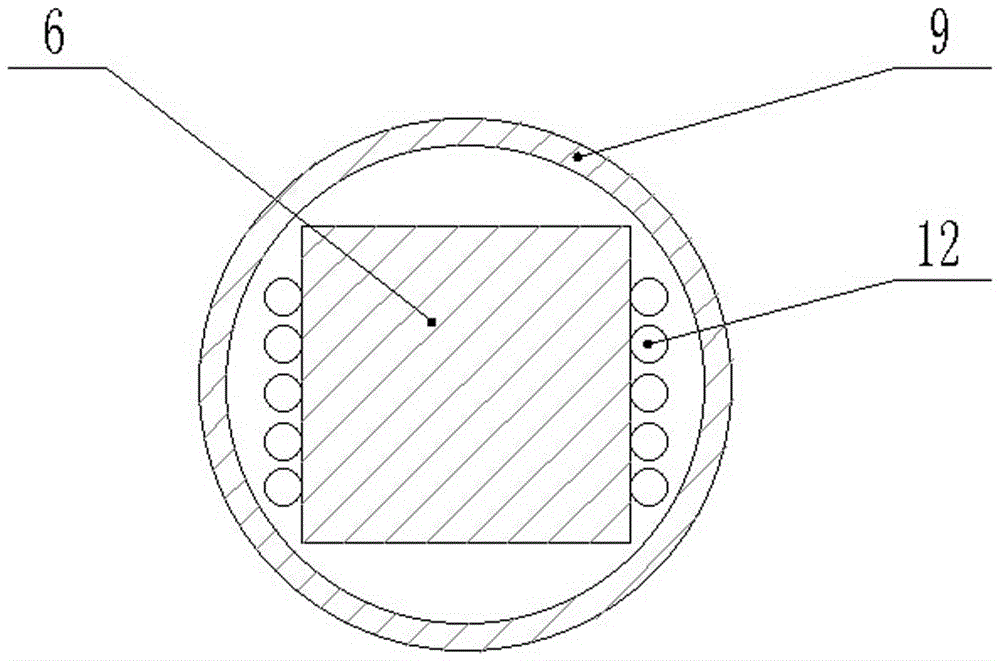

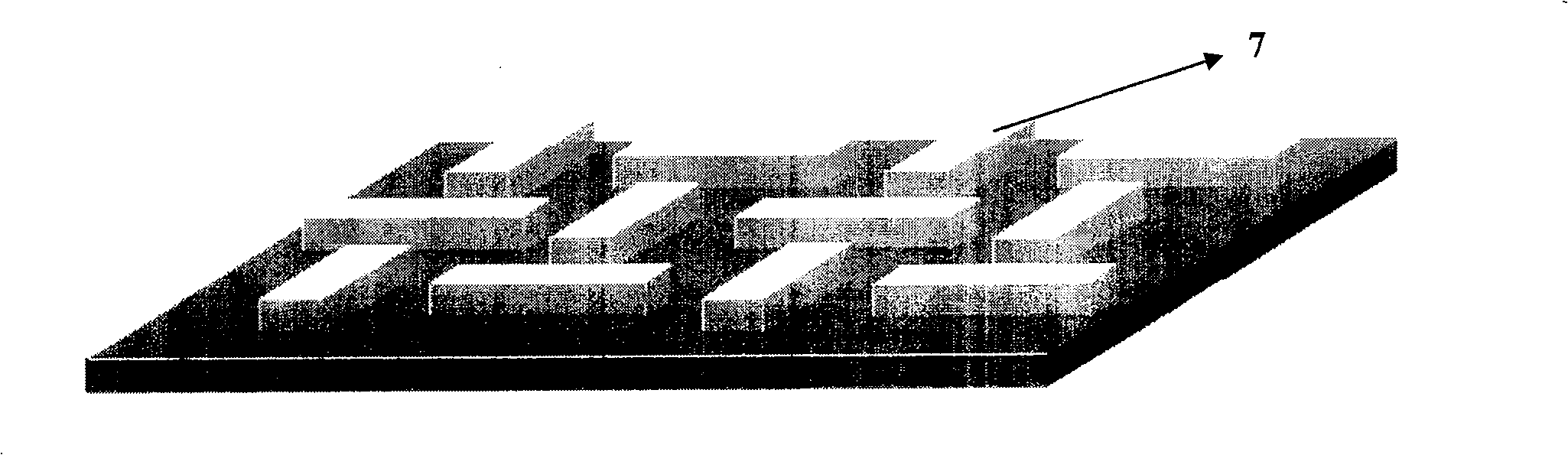

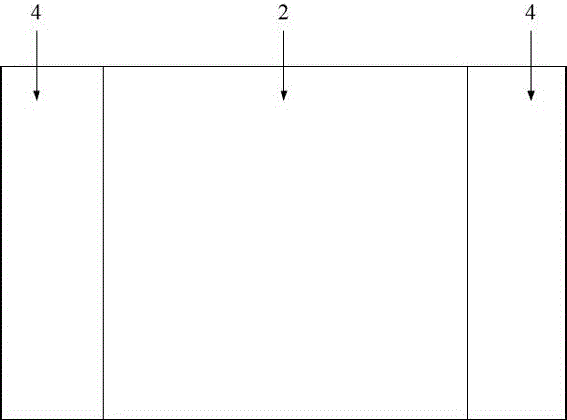

Si-apd photodetector based on micro-nano structure and its preparation method

InactiveCN104064611BGood process repeatabilityImprove responsivenessFinal product manufactureSemiconductor devicesMicro nanoResponsivity

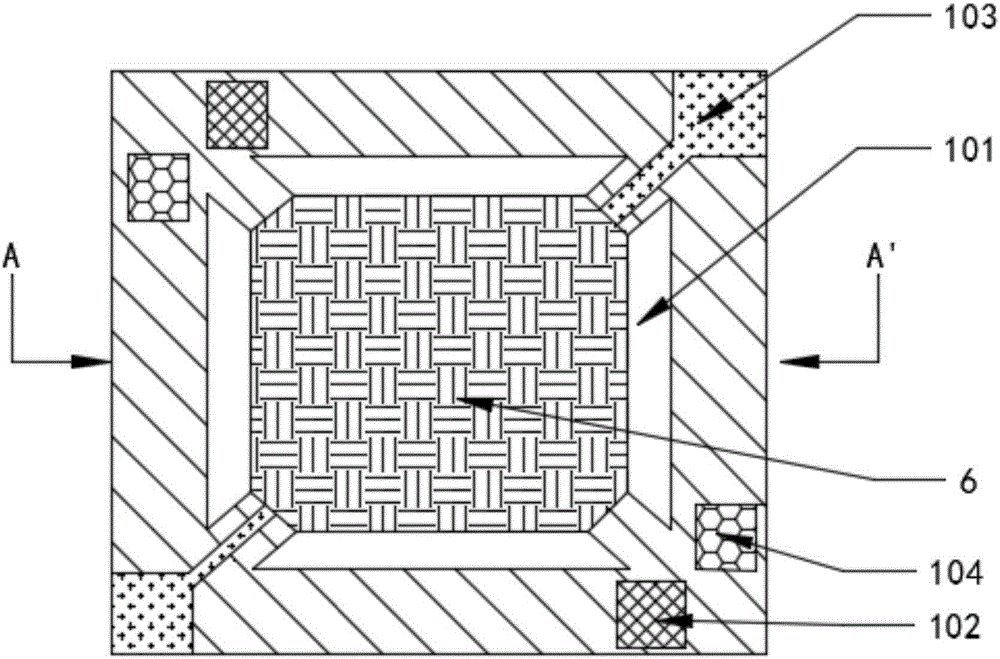

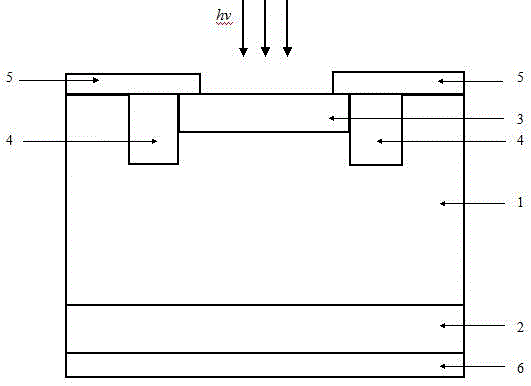

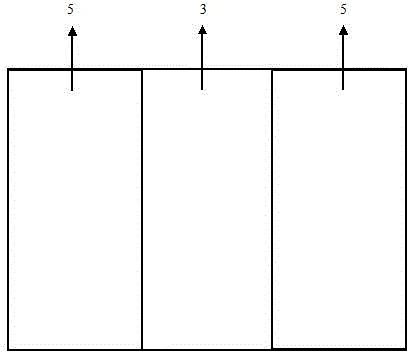

The present invention discloses a Si-APD photoelectric detector based on a micro-nano structure and a preparation method thereof, belonging to the photoelectric detection technology field. The Si-APD photoelectric detector based on the micro-nano structure comprises a P-type Si substrate (1), a micro-nano structure silicon layer N+ area (2) located above the center of the P-type Si substrate (1), protection annular areas, namely N areas (3) located above the two sides of the P-type Si substrate (1), upper-end electrodes (4) arranged on the upper surfaces of the micro-nano structure silicon layer N+ area (2) and the N areas, and a lower-end electrode (5) located on the lower surface of the P-type Si substrate (1), wherein the depth of the micro-nano structure silicon layer N+ area (2) is less than the depths of the protection annular areas, namely the N areas (3). The Si-APD photoelectric detector based on the micro-nano structure and the preparation method thereof of the present invention solve the problems that the conventional Si-APD photoelectric detector is lower in responsivity, can not respond a near-infrared band, etc., enables the response wave band to be expanded to the near-infrared band, and is higher in responsivity.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

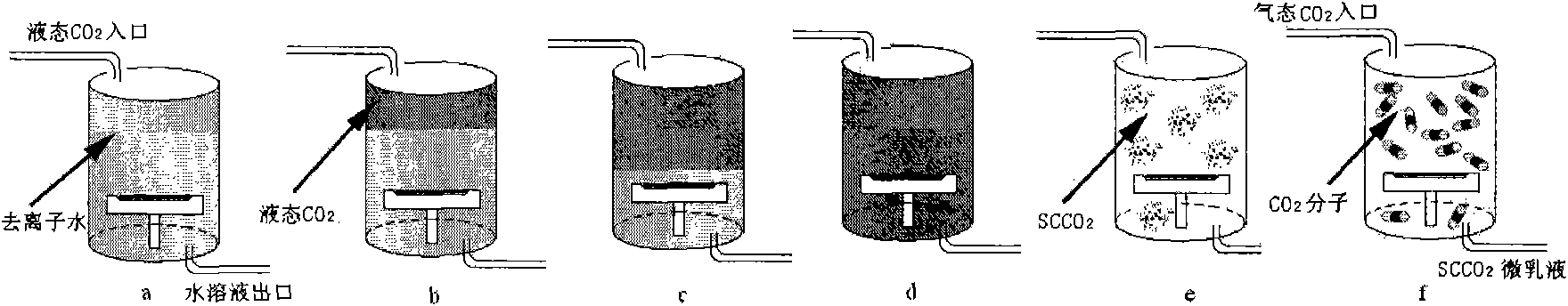

Device and method for drying supercritical carbon dioxide microemulsion

ActiveCN102345968BLow viscosity coefficientImprove diffusion abilityDrying solid materials without heatWater basedDrying time

Owner:新疆中科丝路物联科技有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com