Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

93results about How to "Reduced Miller Capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

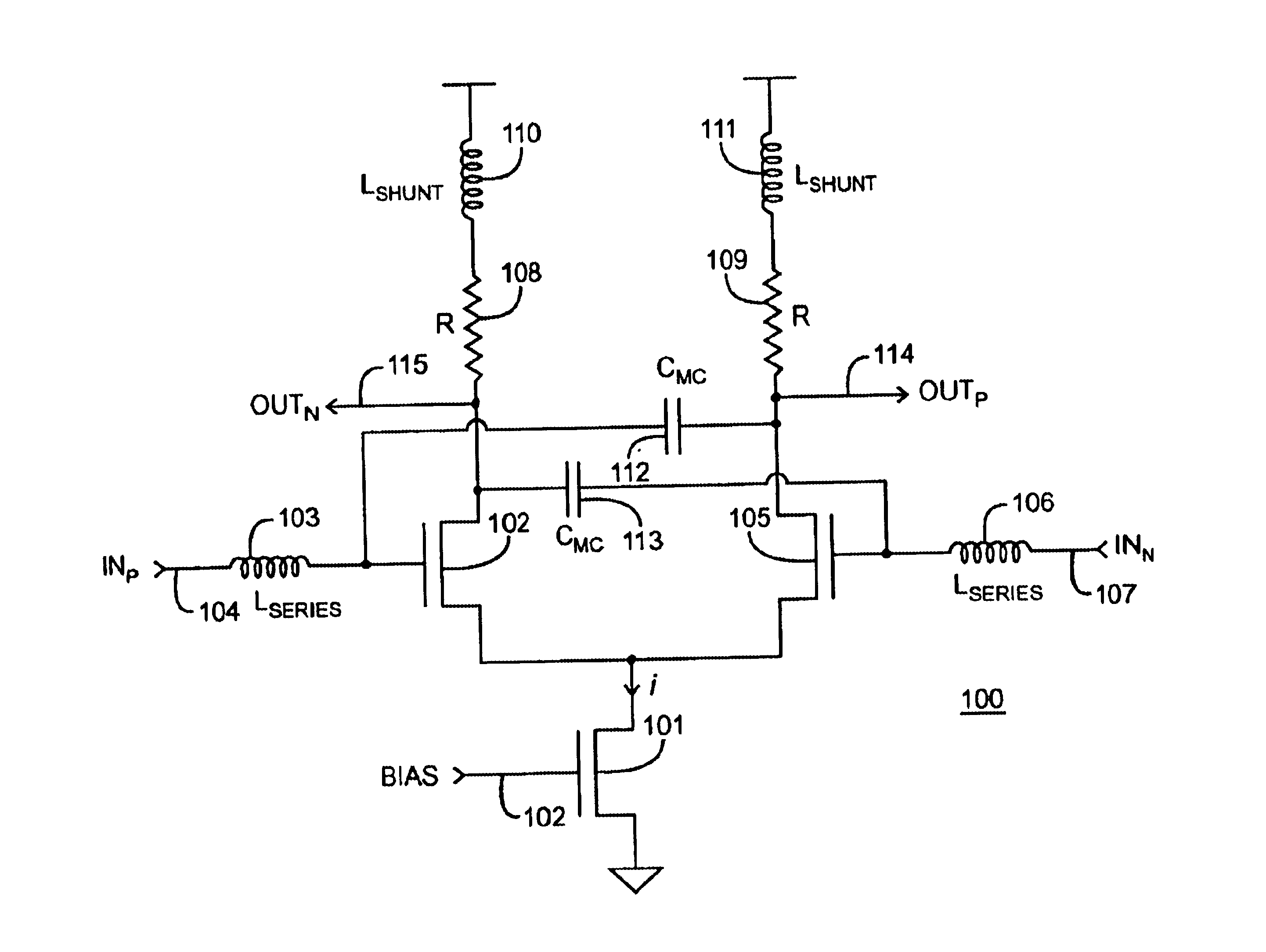

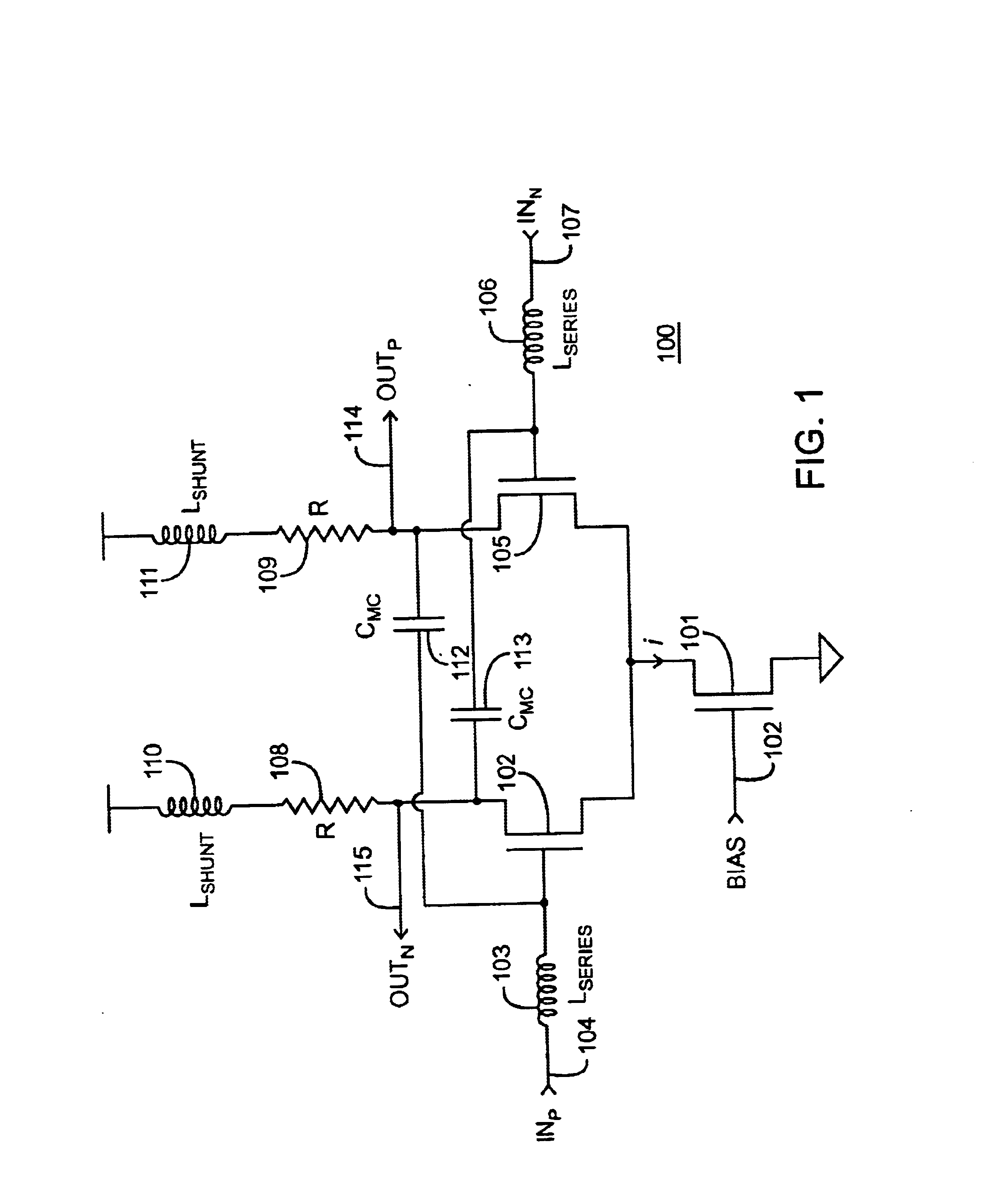

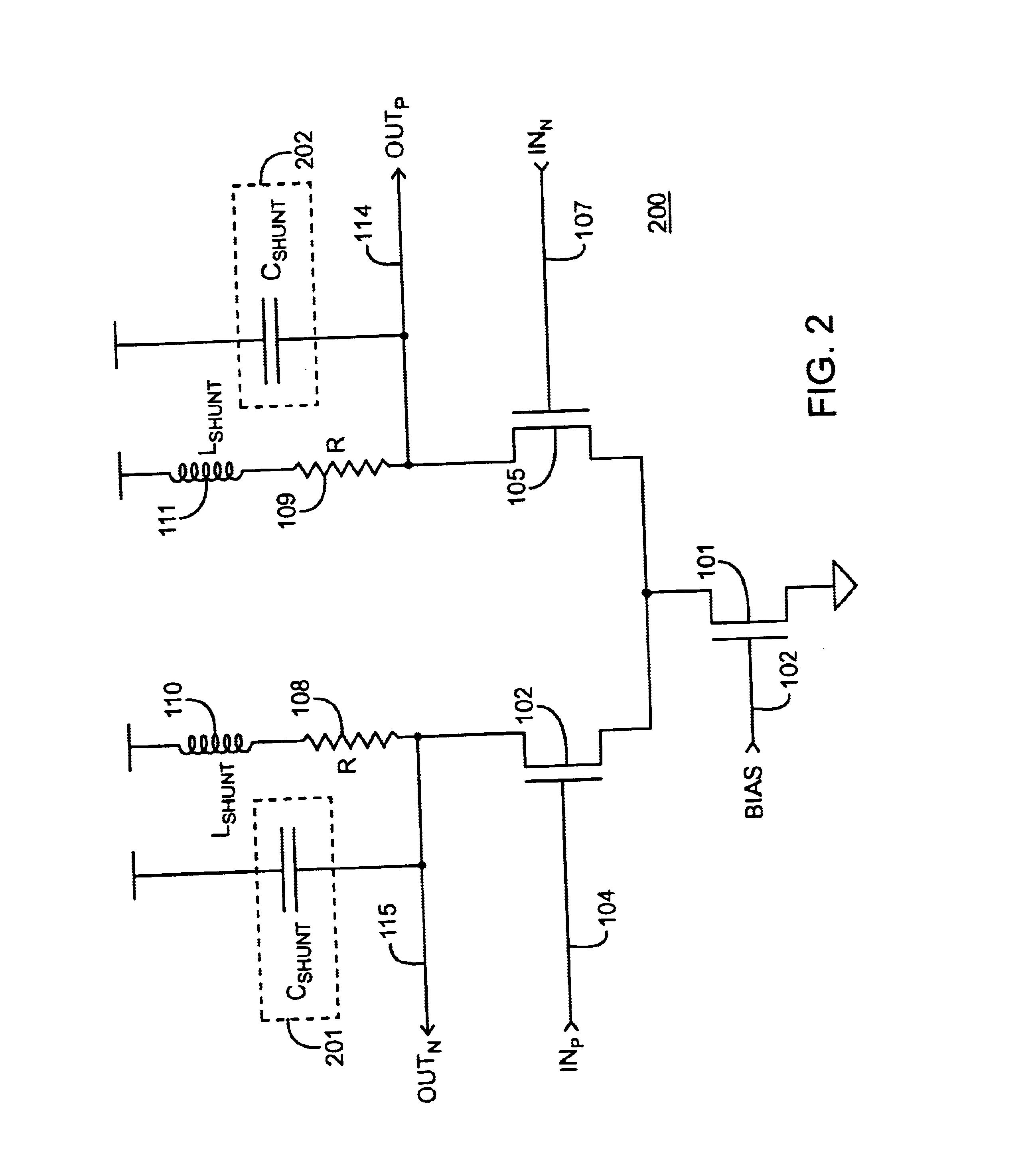

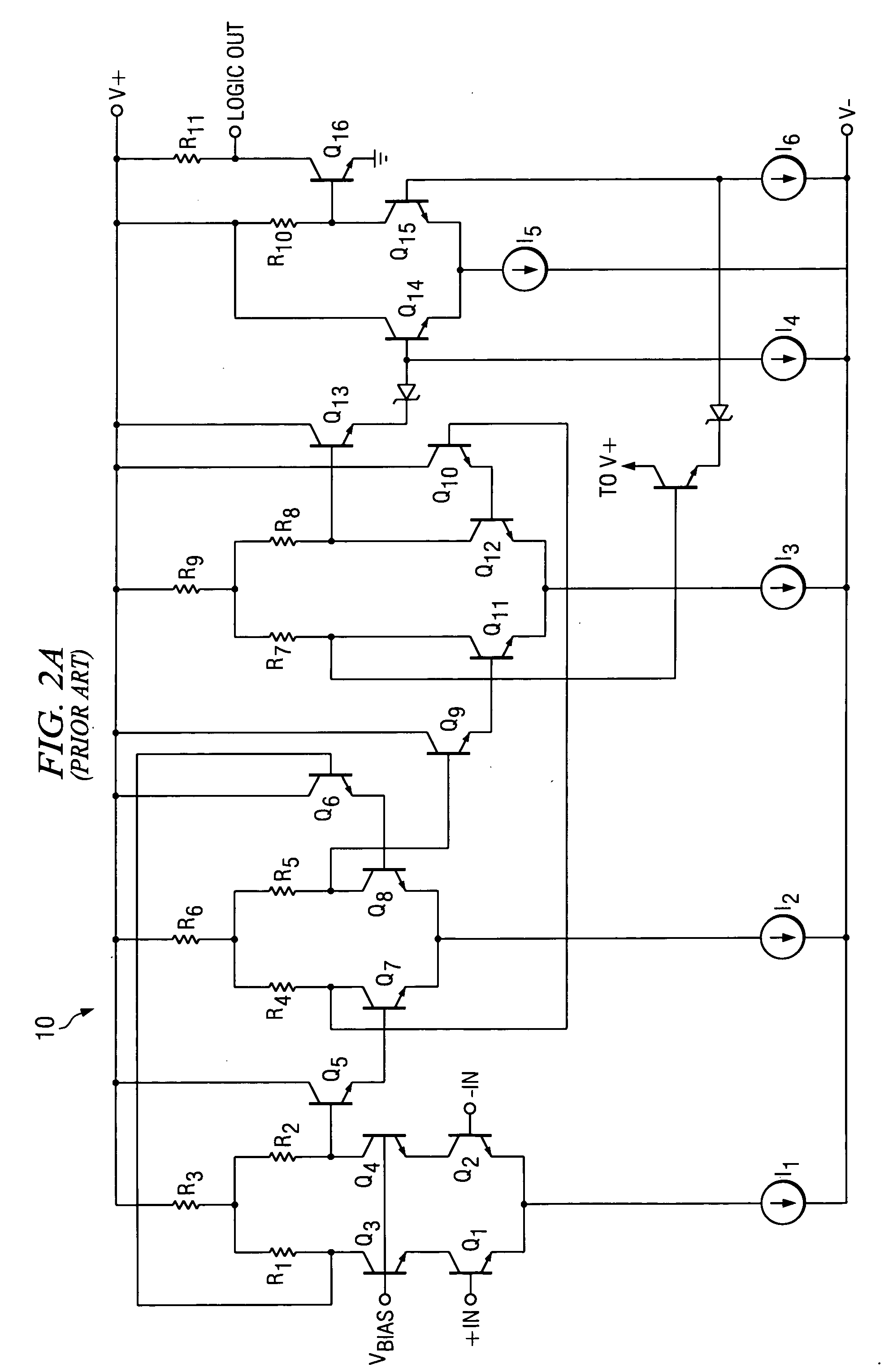

Current-controlled CMOS wideband data amplifier circuits

InactiveUS6624699B2Maximum bandwidth expansionReduced Miller CapacitanceAmplifier combinationsAmplifier modifications to reduce detrimental impedenceCapacitanceCMOS

Expansion of the bandwidth of a wideband CMOS data amplifier is accomplished using various combinations of shunt peaking, series peaking, and miller capacitance cancellation. These various combinations are employed in any of the amplifier input stage, in intermediate stages, or in the last stage.

Owner:AVAGO TECH INT SALES PTE LTD

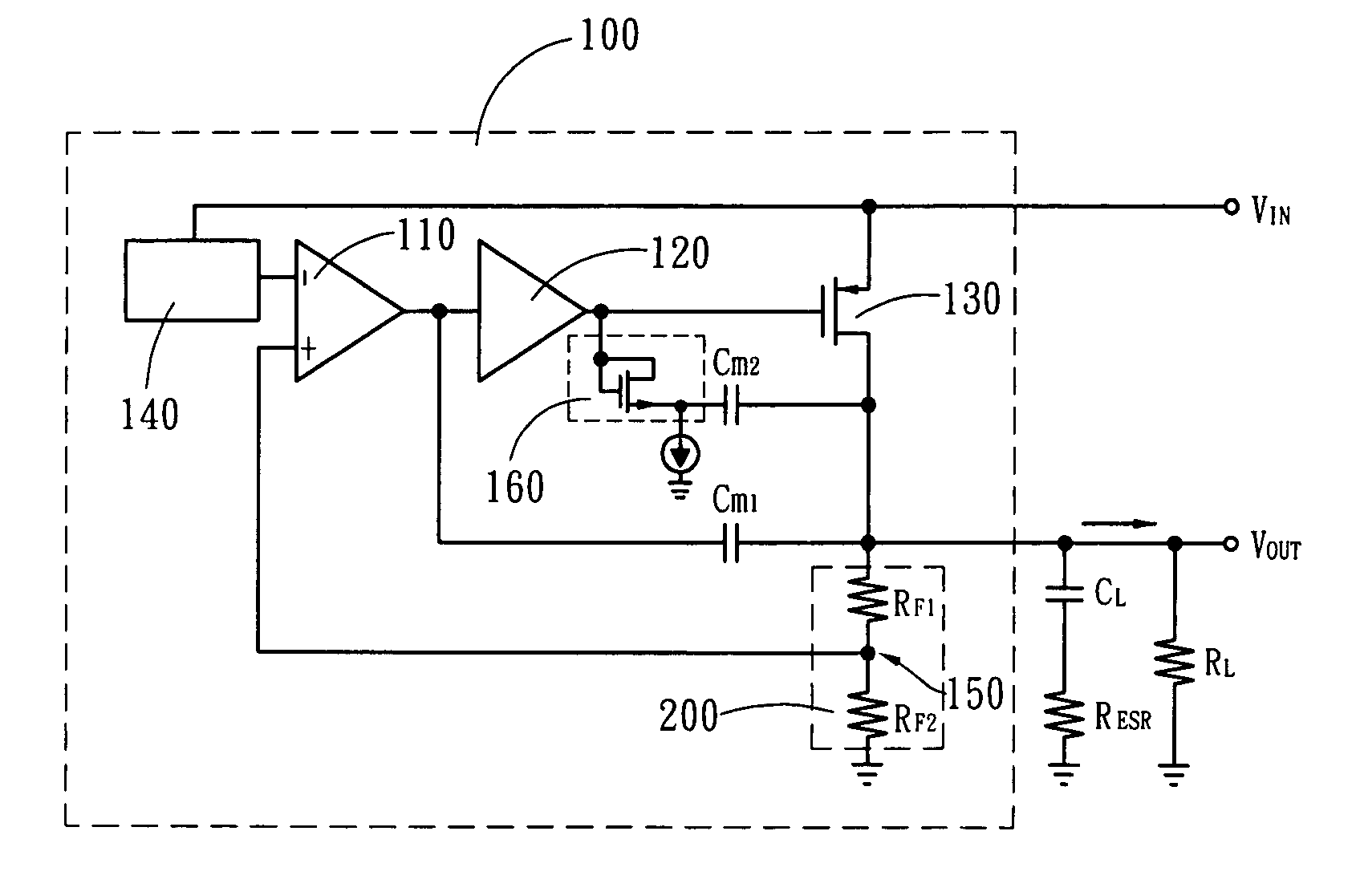

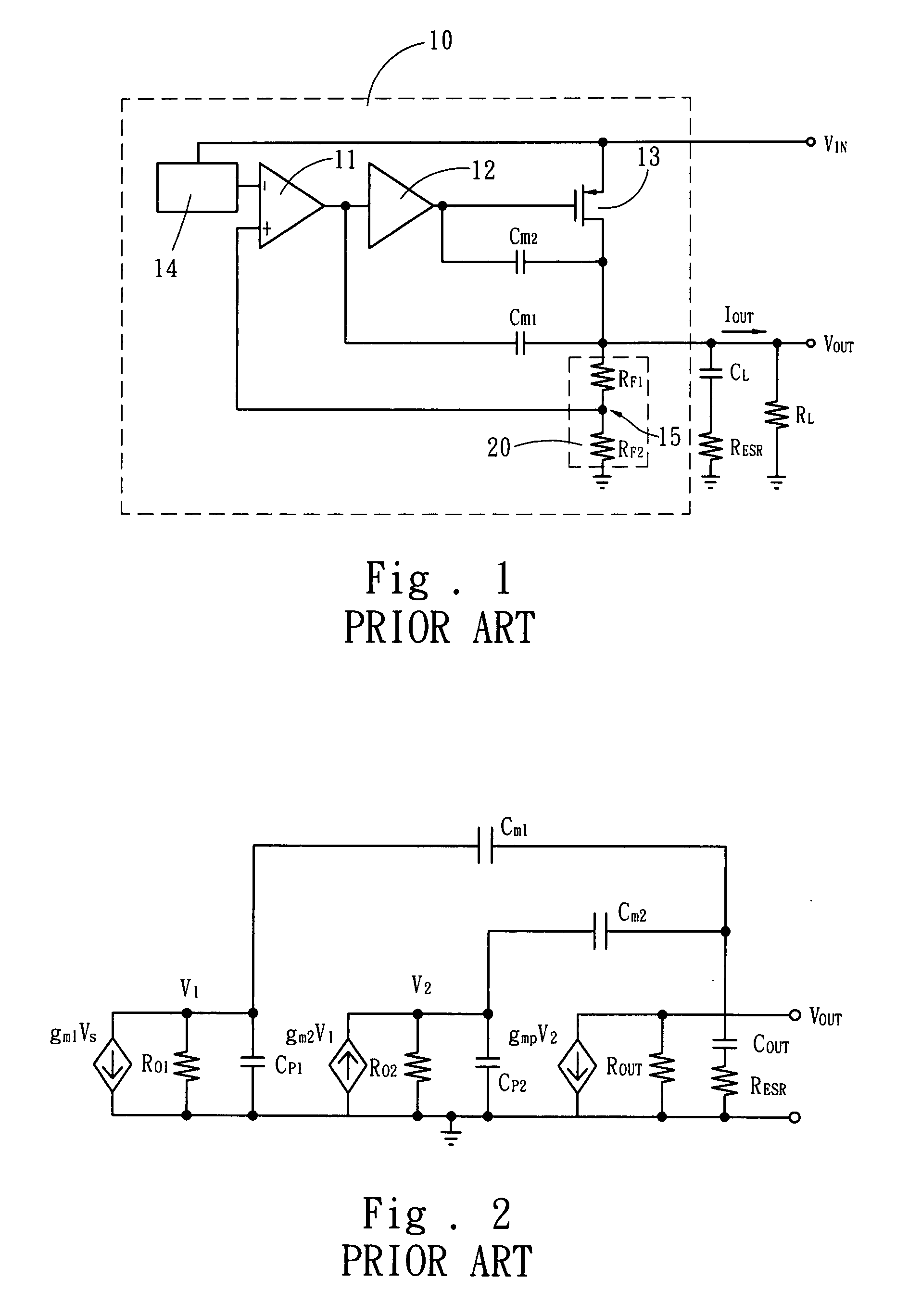

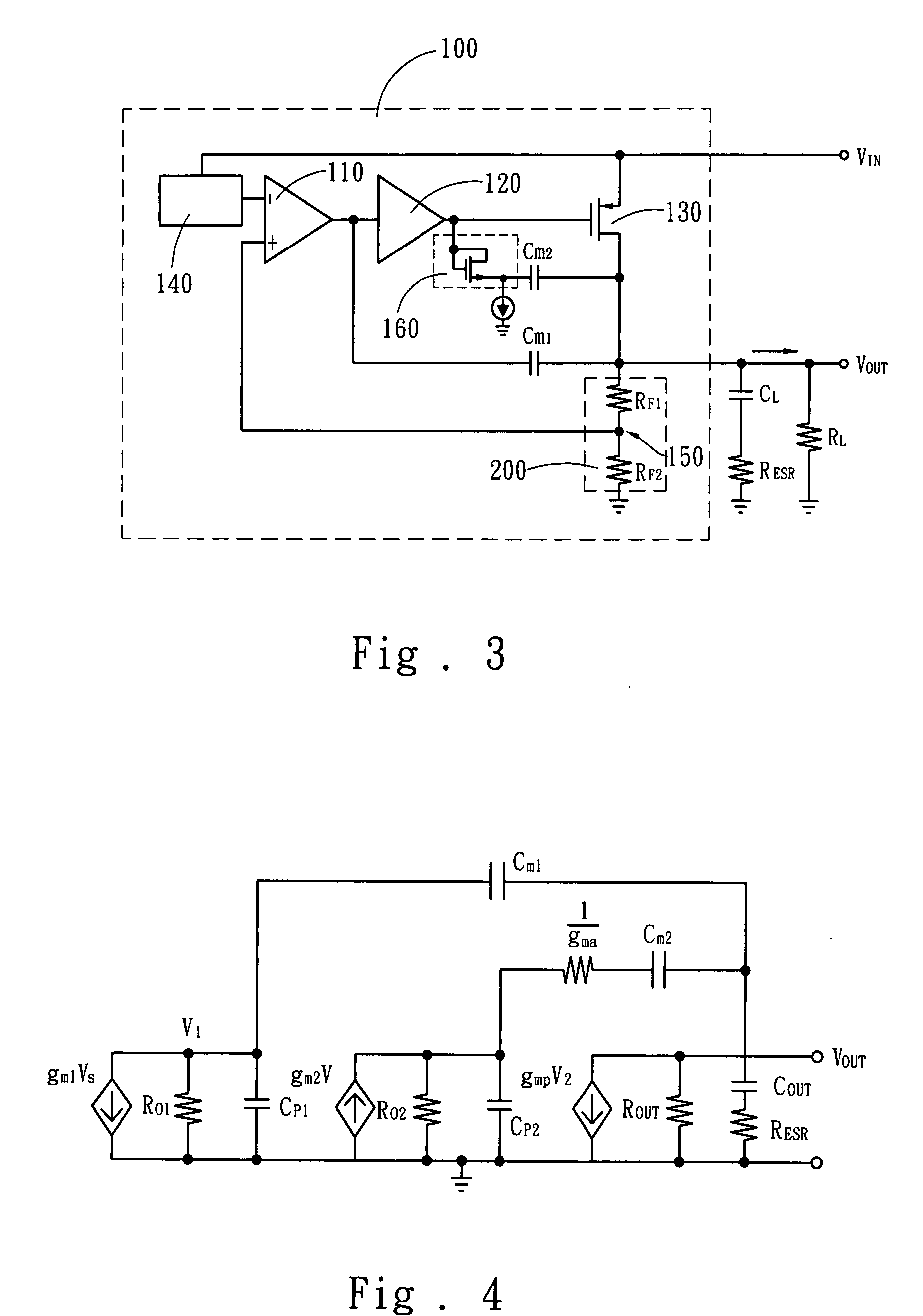

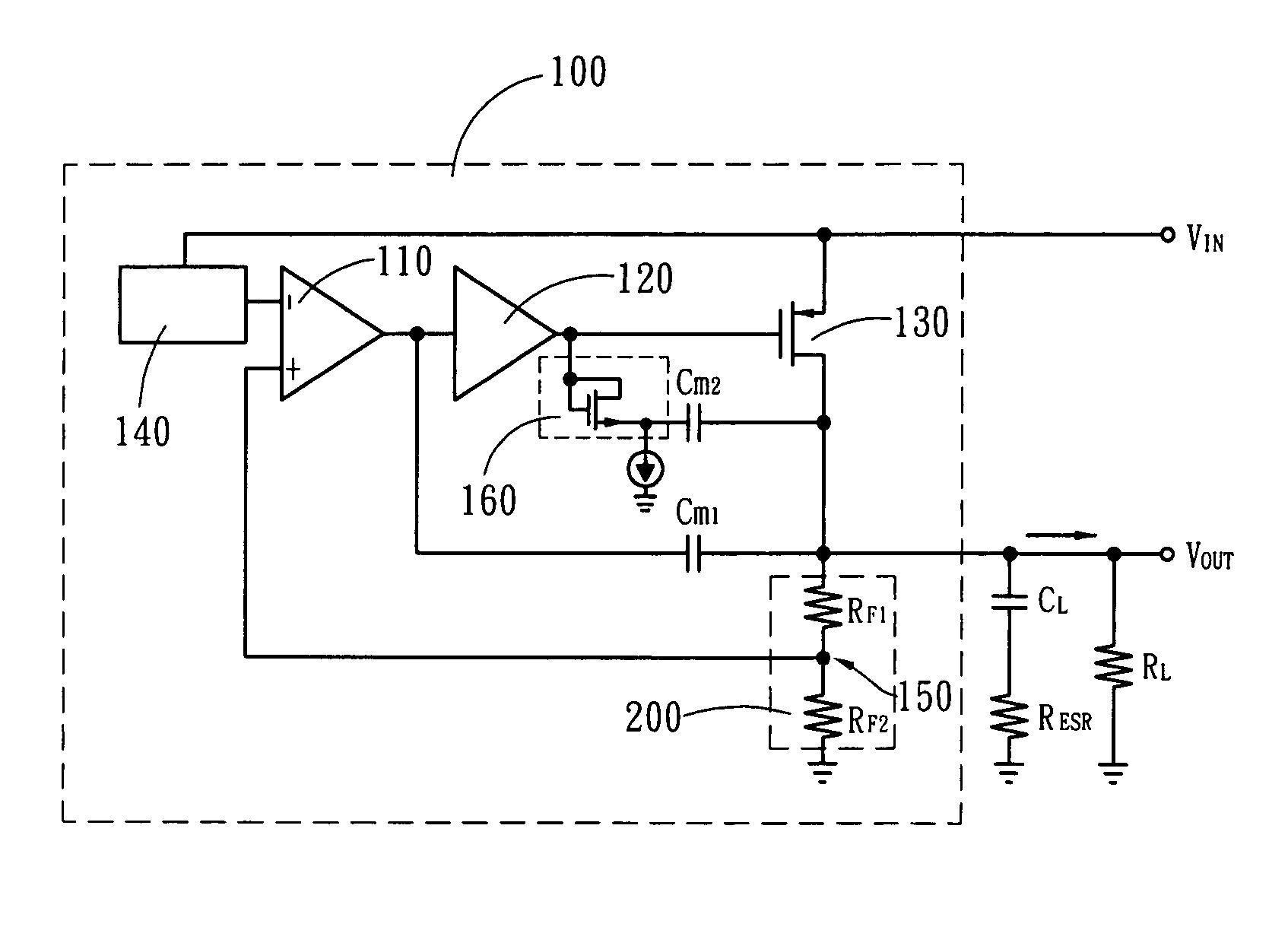

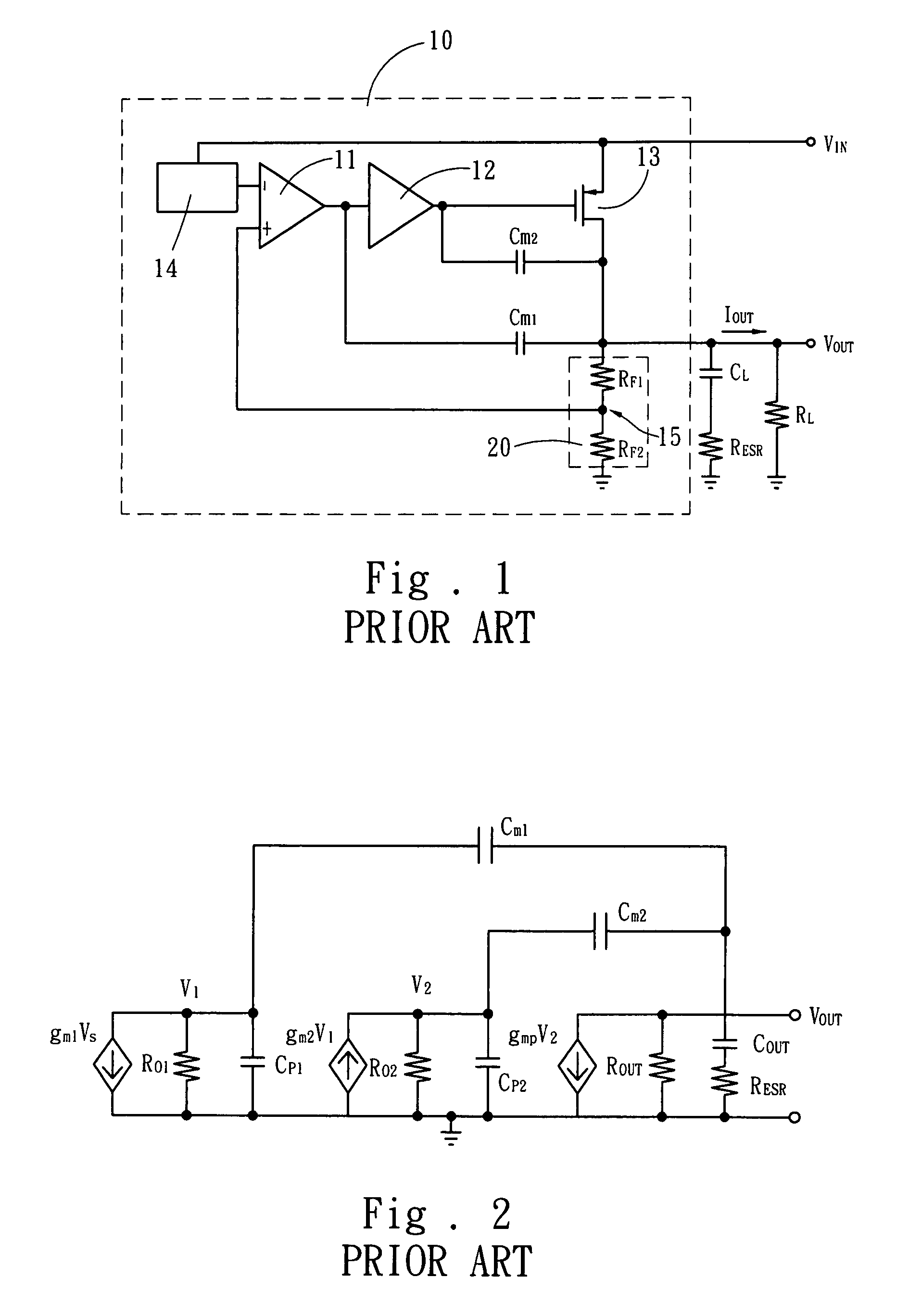

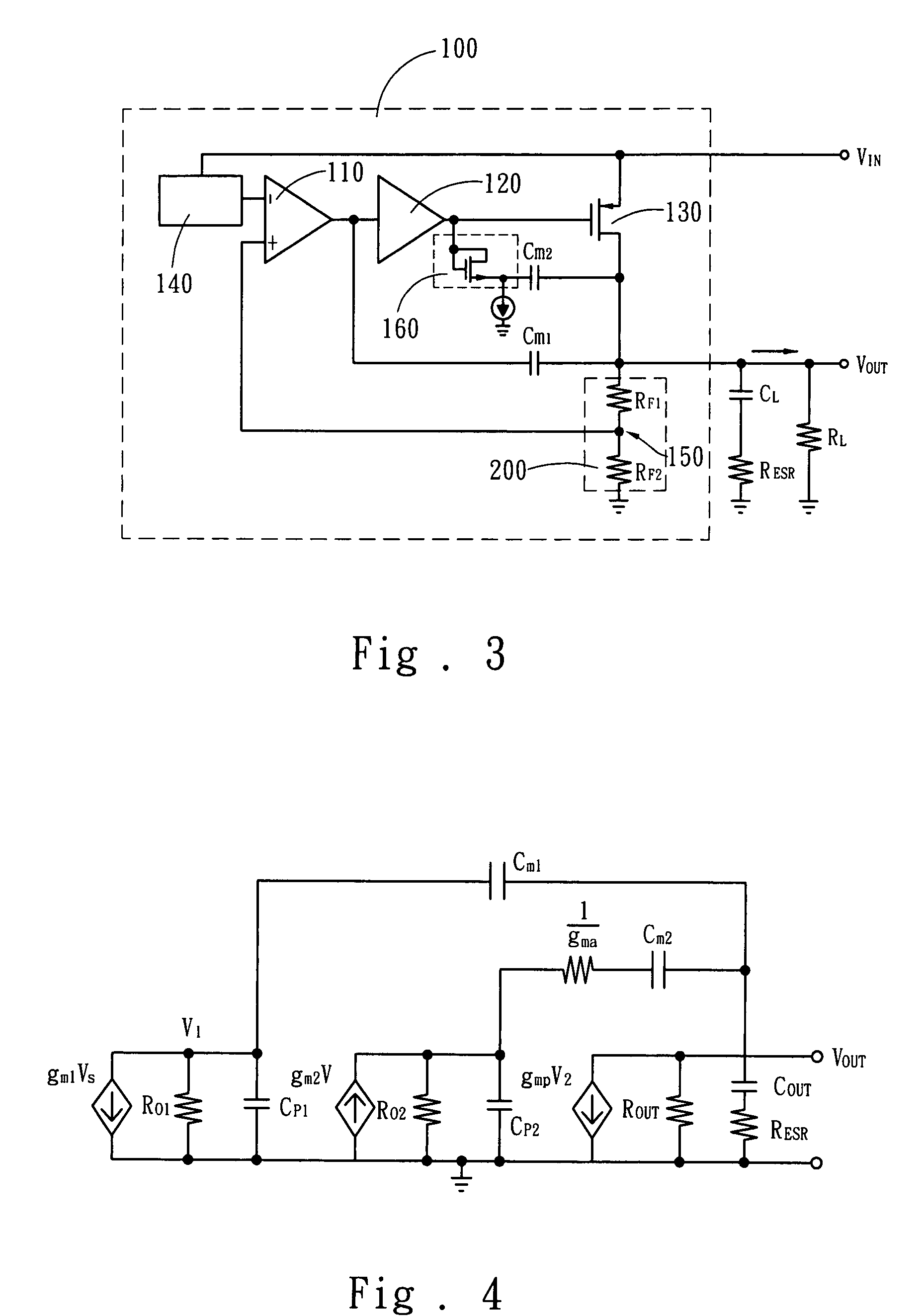

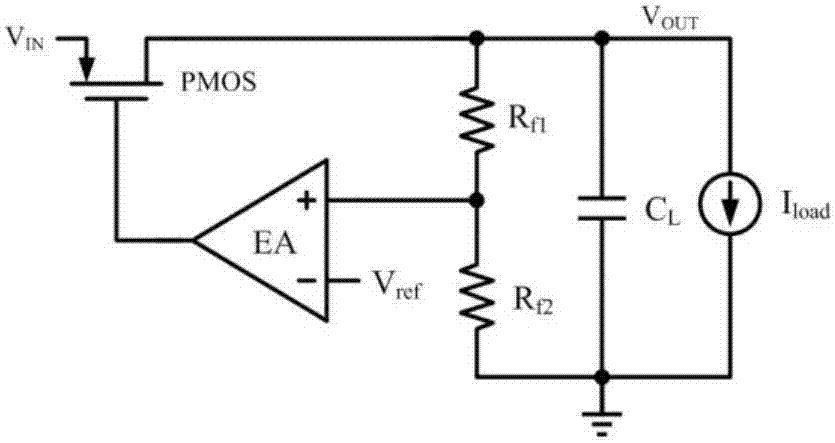

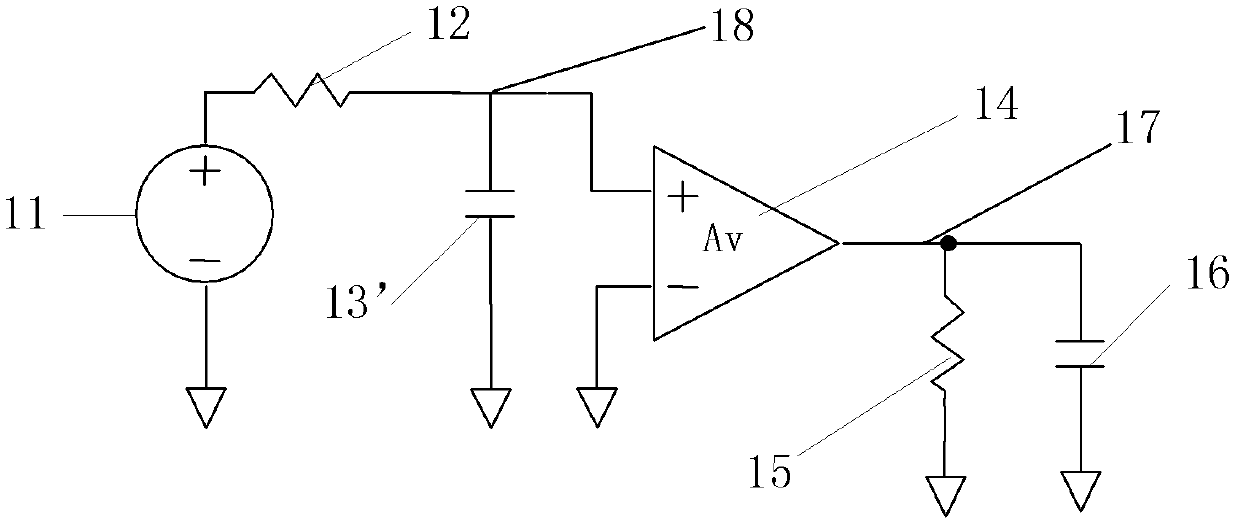

Low dropout linear voltage regulator

InactiveUS20090001953A1Sufficient phase-angle marginIncrease capacitanceNegative-feedback-circuit arrangementsAmplifiers with impedence circuitsLinear regulatorCapacitance

The present invention discloses an LDO (Low DropOut) linear voltage regulator, which is based on an NMC (Nested Miller Compensation) architecture and can be capacitor-free, wherein an active resistor is added to the feedback path of the Miller compensation capacitor to increase the controllability of the damping factor, solve the problem of extensively using the output capacitor with a parasitic resistance, and solve the problem that a compromise must be made between the damping factor control and the system loop gain. Further, the present invention utilizes a capacitor-sharing technique to reduce the Miller capacitance required by the entire system and accelerate the stabilization of output voltage without influencing stability.

Owner:SITRONIX TECH CORP

Low dropout linear voltage regulator with an active resistance for frequency compensation to improve stability

InactiveUS7710091B2Improve controllabilityImprove stabilityNegative-feedback-circuit arrangementsAmplifiers with impedence circuitsDamping factorCapacitance

The present invention discloses an LDO (Low DropOut) linear voltage regulator, which is based on an NMC (Nested Miller Compensation) architecture and can be capacitor-free, wherein an active resistor is added to the feedback path of the Miller compensation capacitor to increase the controllability of the damping factor, solve the problem of extensively using the output capacitor with a parasitic resistance, and solve the problem that a compromise must be made between the damping factor control and the system loop gain. Further, the present invention utilizes a capacitor-sharing technique to reduce the Miller capacitance required by the entire system and accelerate the stabilization of output voltage without influencing stability.

Owner:SITRONIX TECH CORP

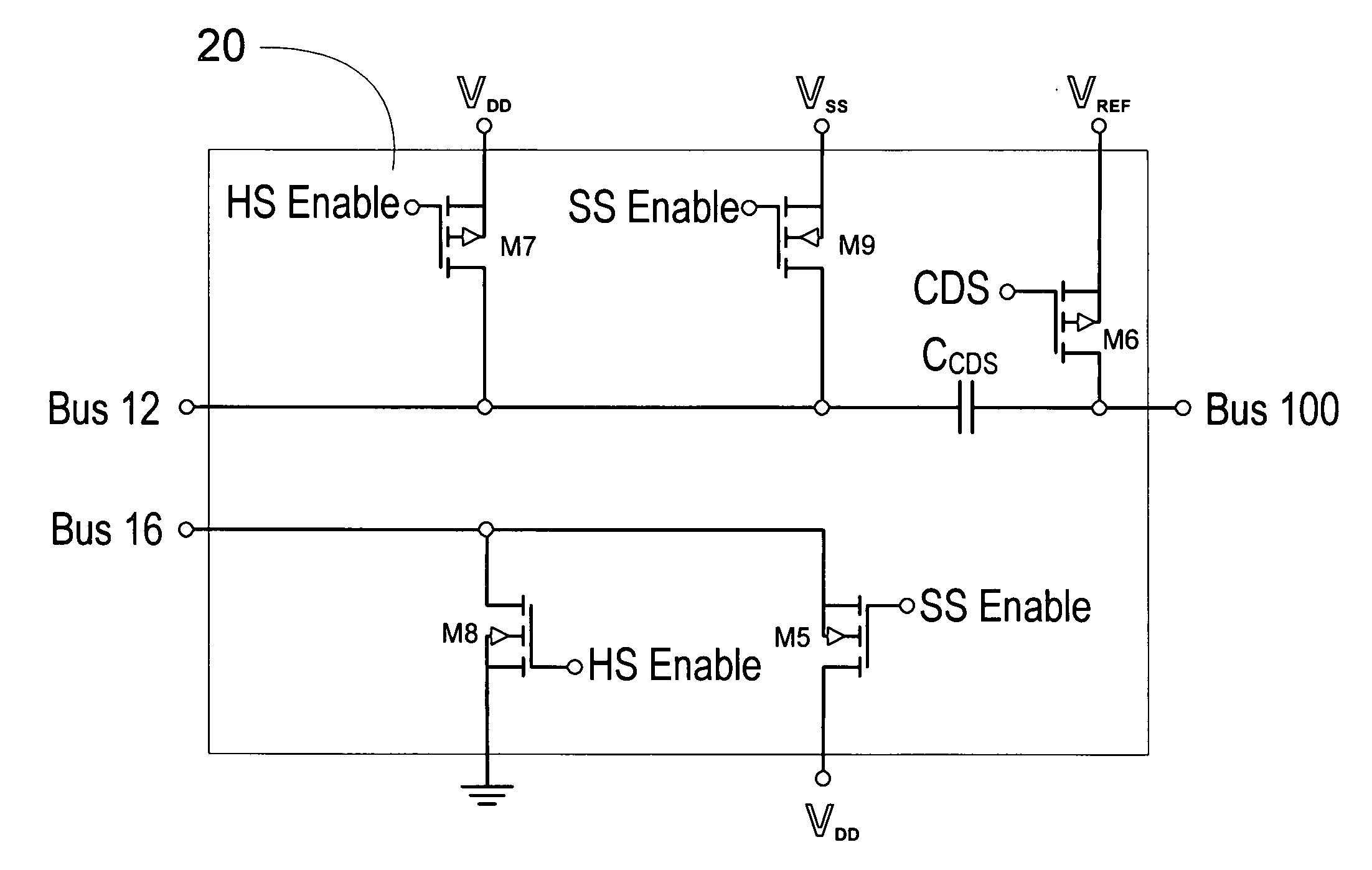

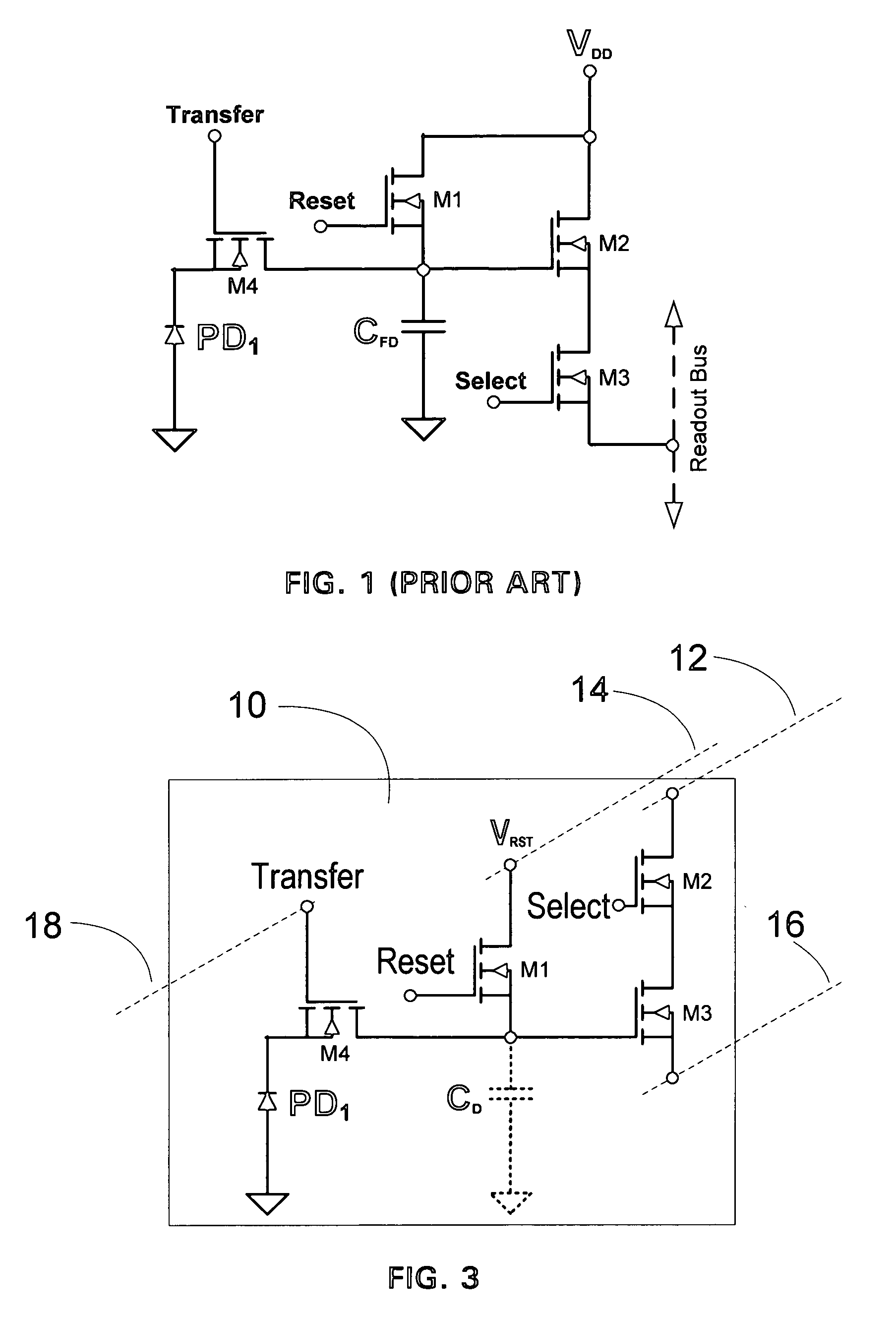

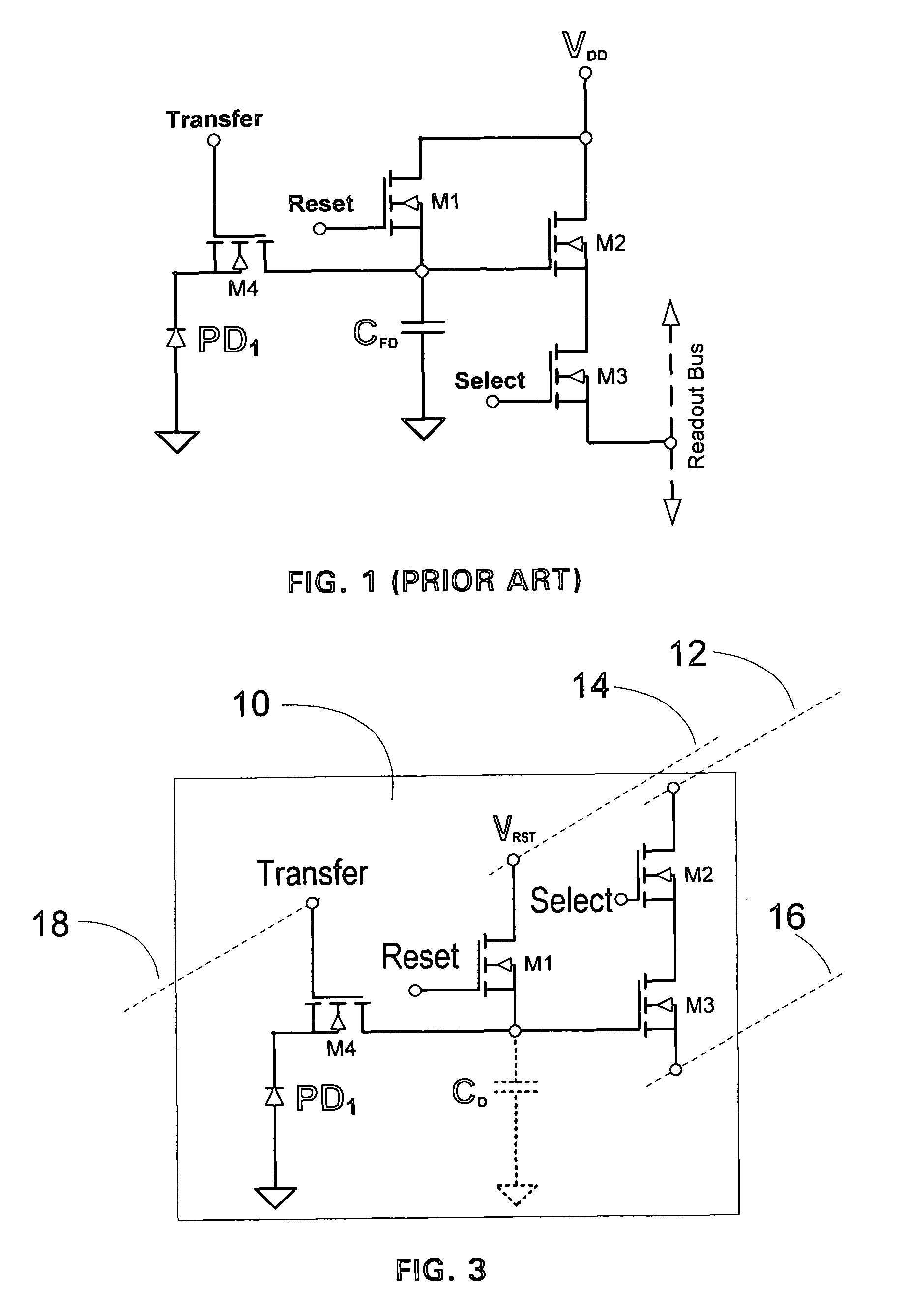

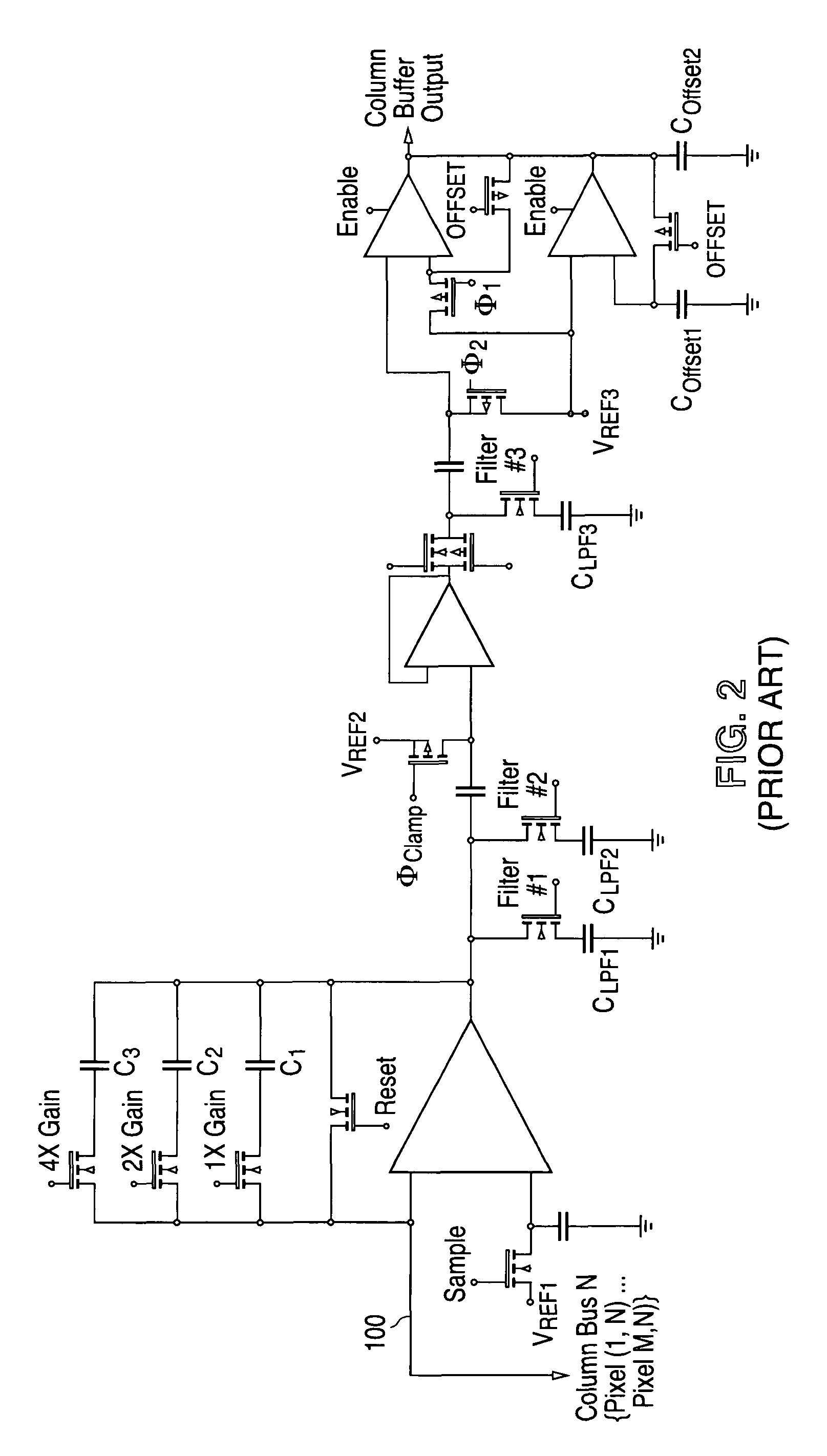

Dual sensitivity image sensor

ActiveUS20090128677A1Increase in pixel complexityHigh sensitivityTelevision system detailsTelevision system scanning detailsSignal-to-noise ratio (imaging)Operation mode

A dual sensitivity image sensor provides a standard mode and a high-sensitivity mode of operation via iSoC integration. In addition to boosting sensitivity, the high sensitivity mode also reduces temporal noise thereby optimally boosting the Signal-to-Noise Ratio (SNR) of the image sensor. The circuit does not significantly increase pixel complexity and requires minimal changes to the support circuits in the iSoC including the addition of support and control circuitry to facilitate seamless mode change.

Owner:SAMSUNG ELECTRONICS CO LTD

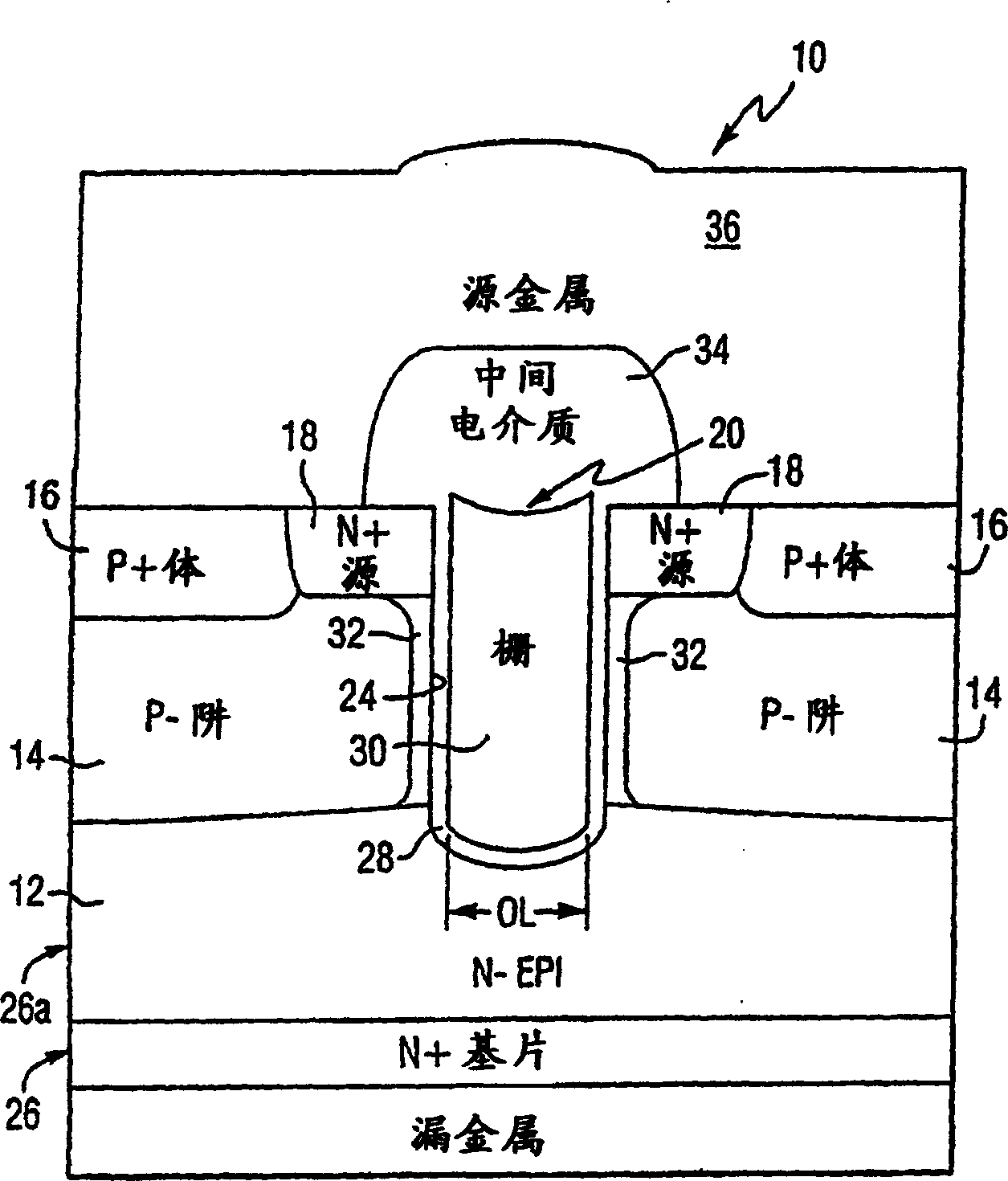

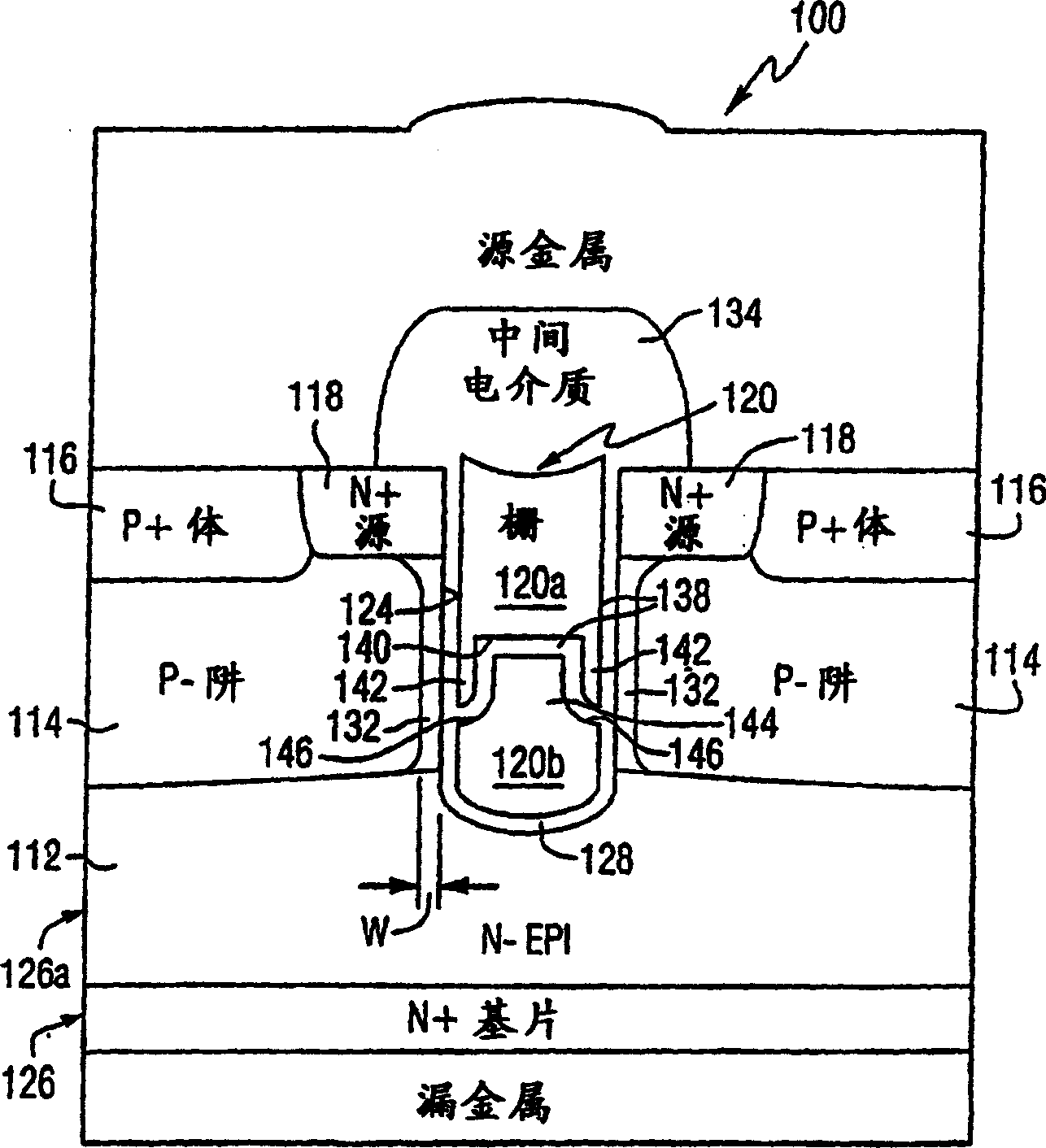

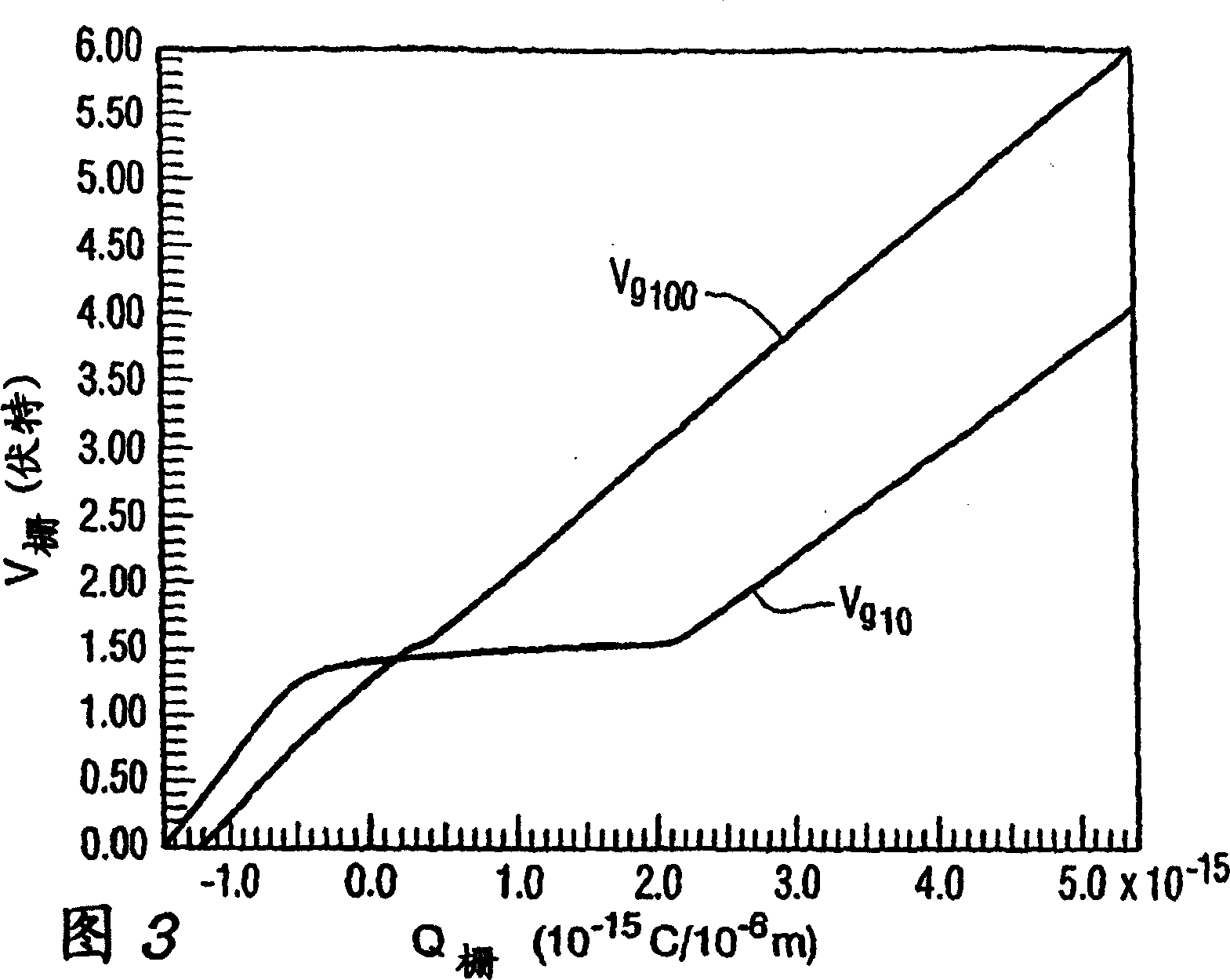

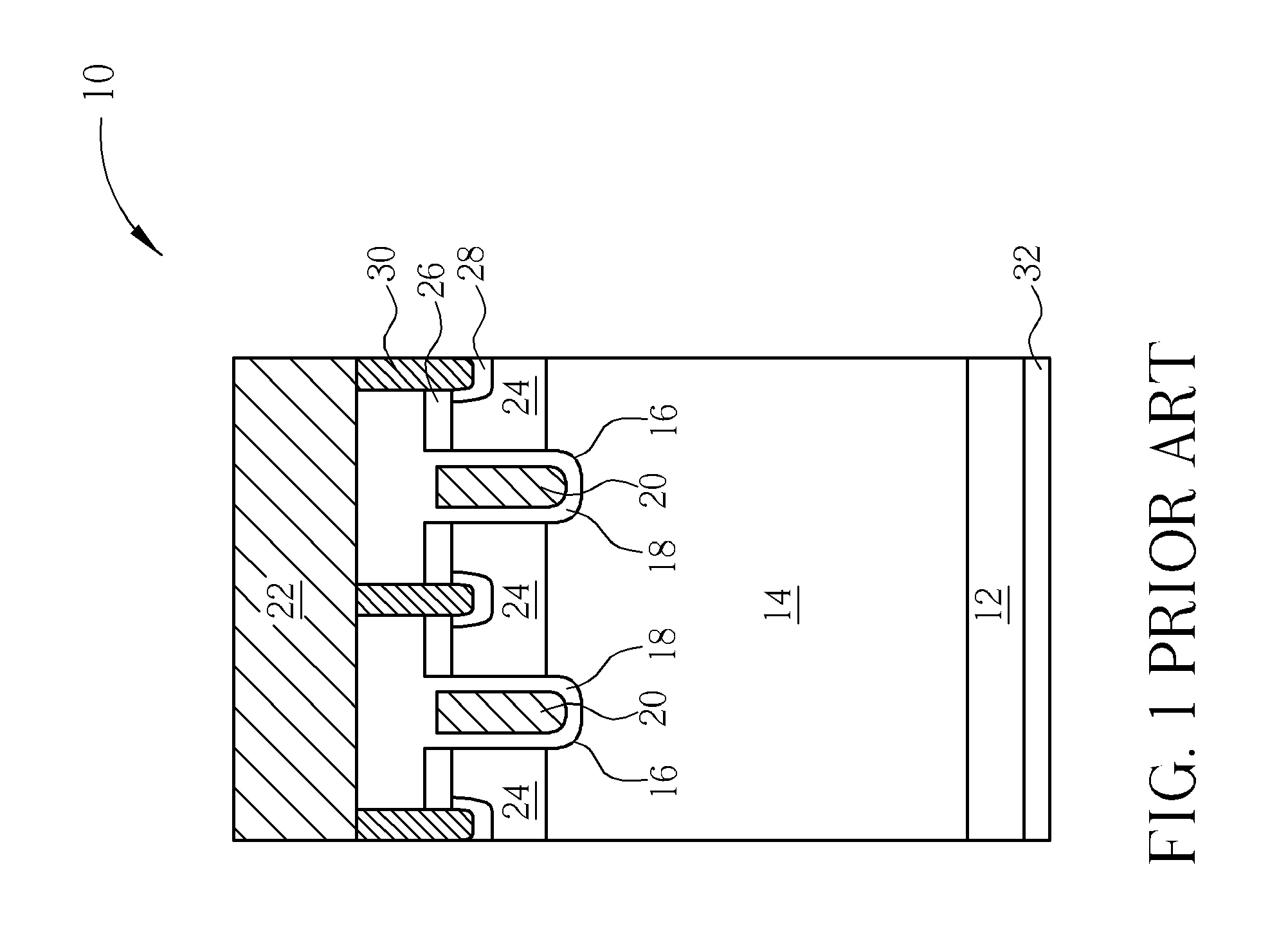

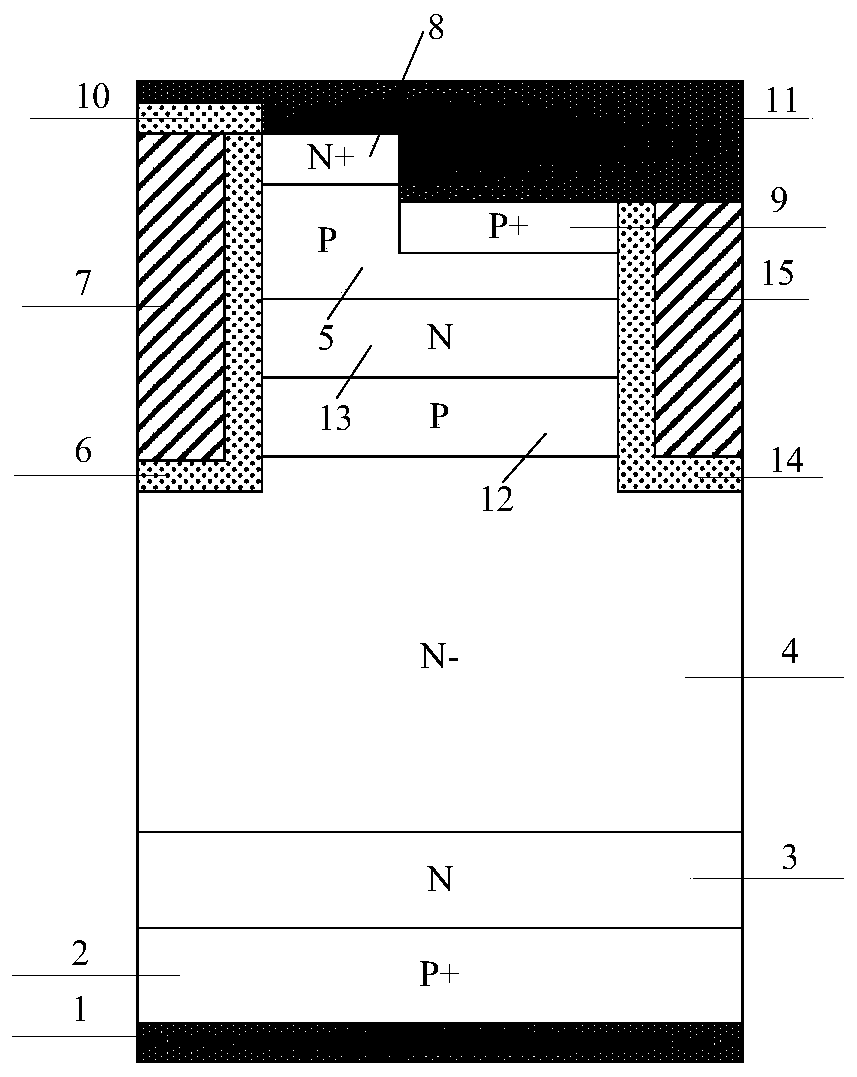

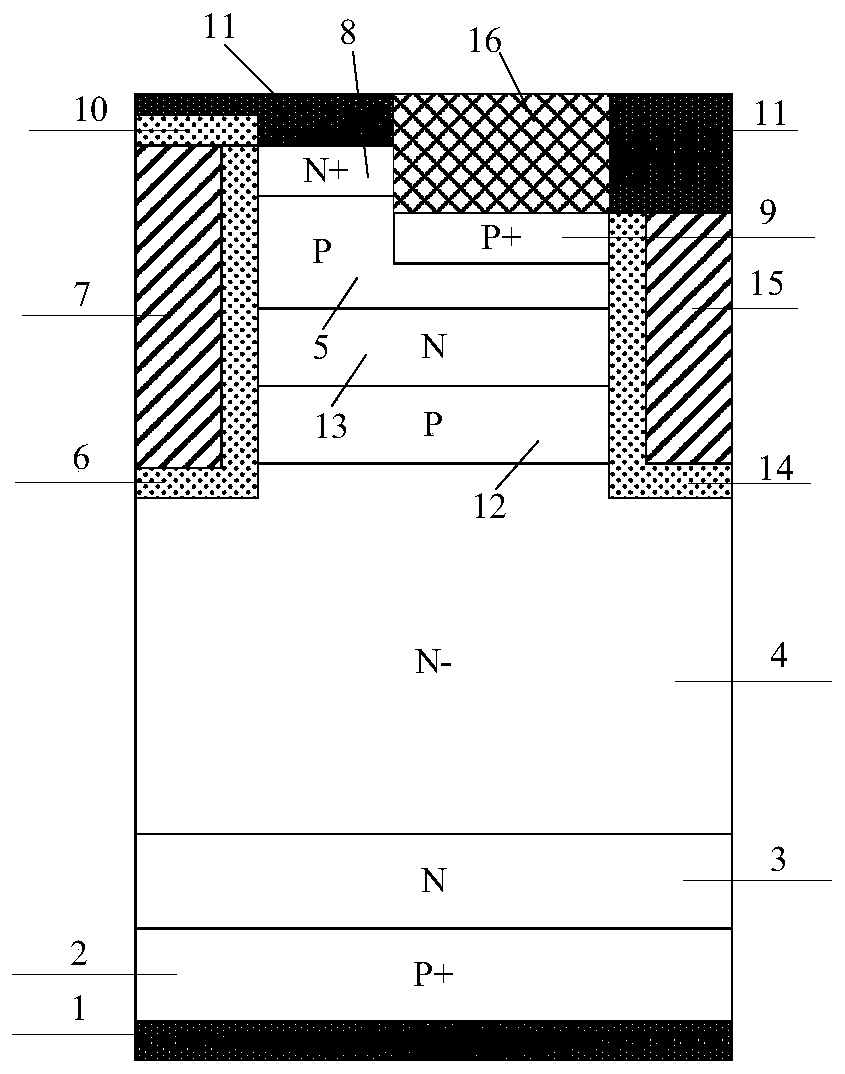

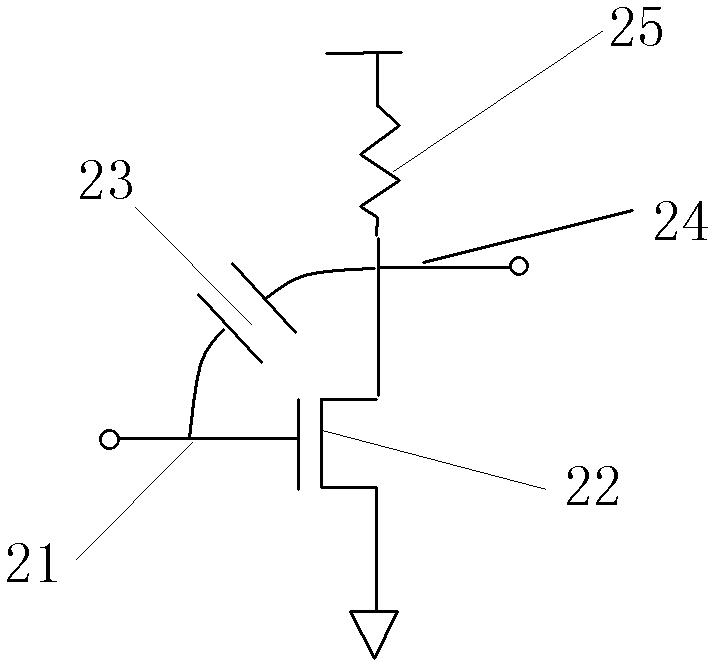

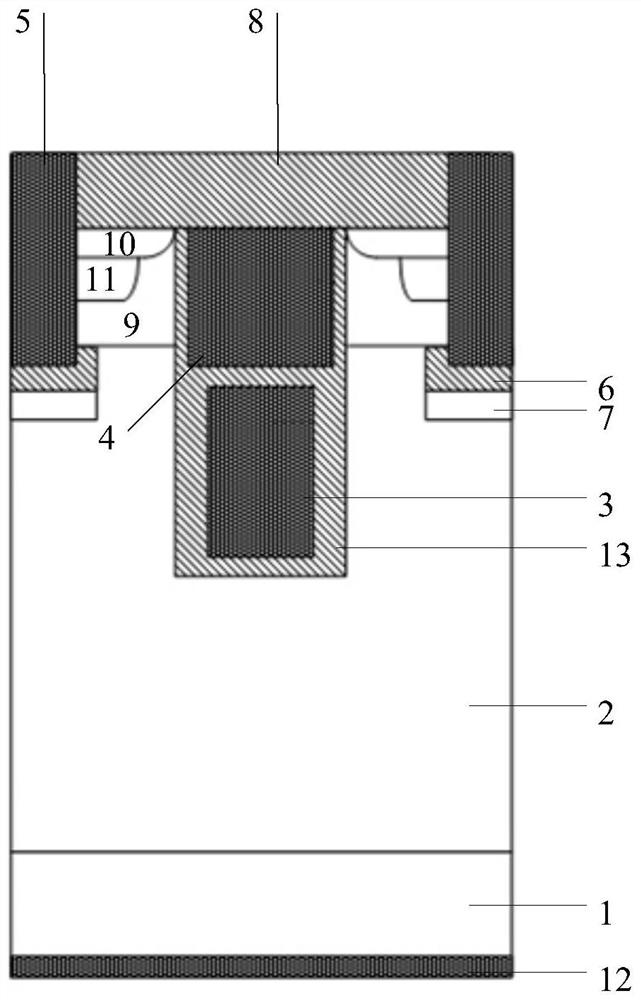

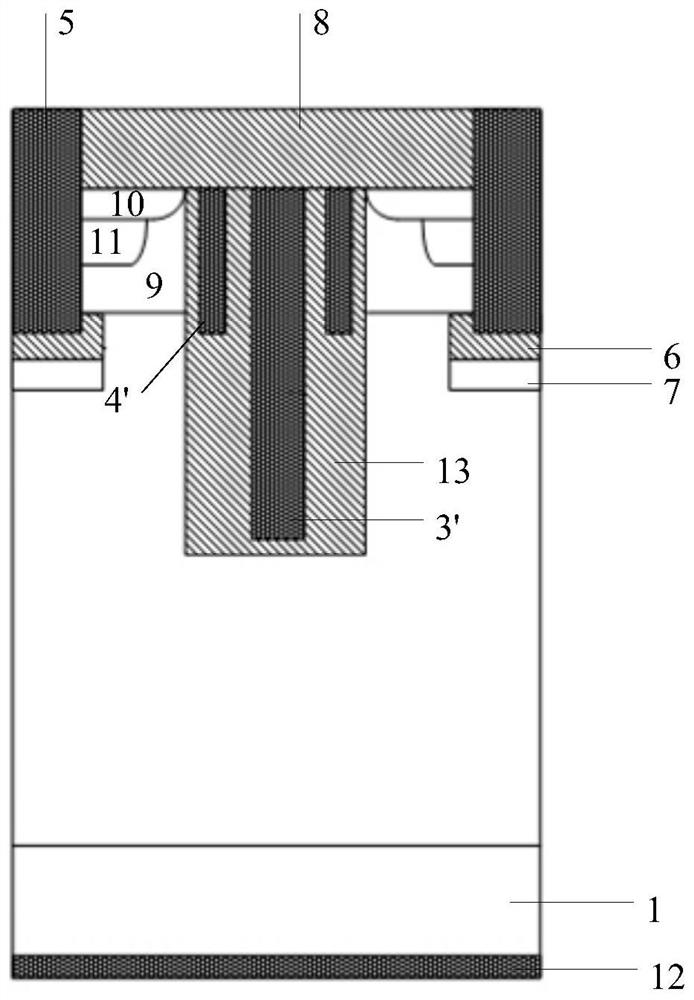

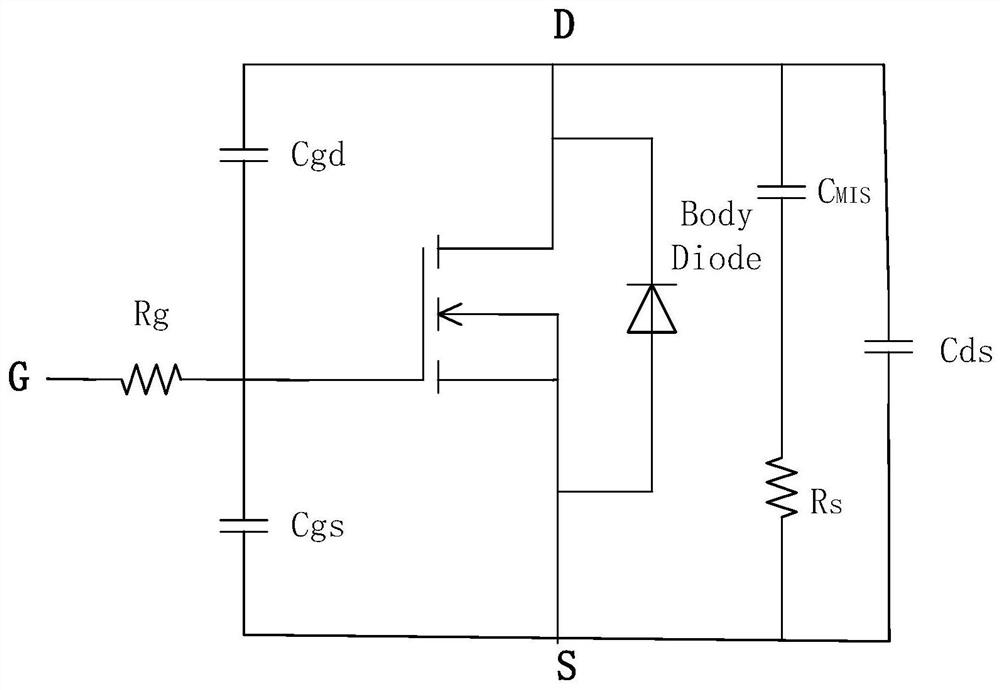

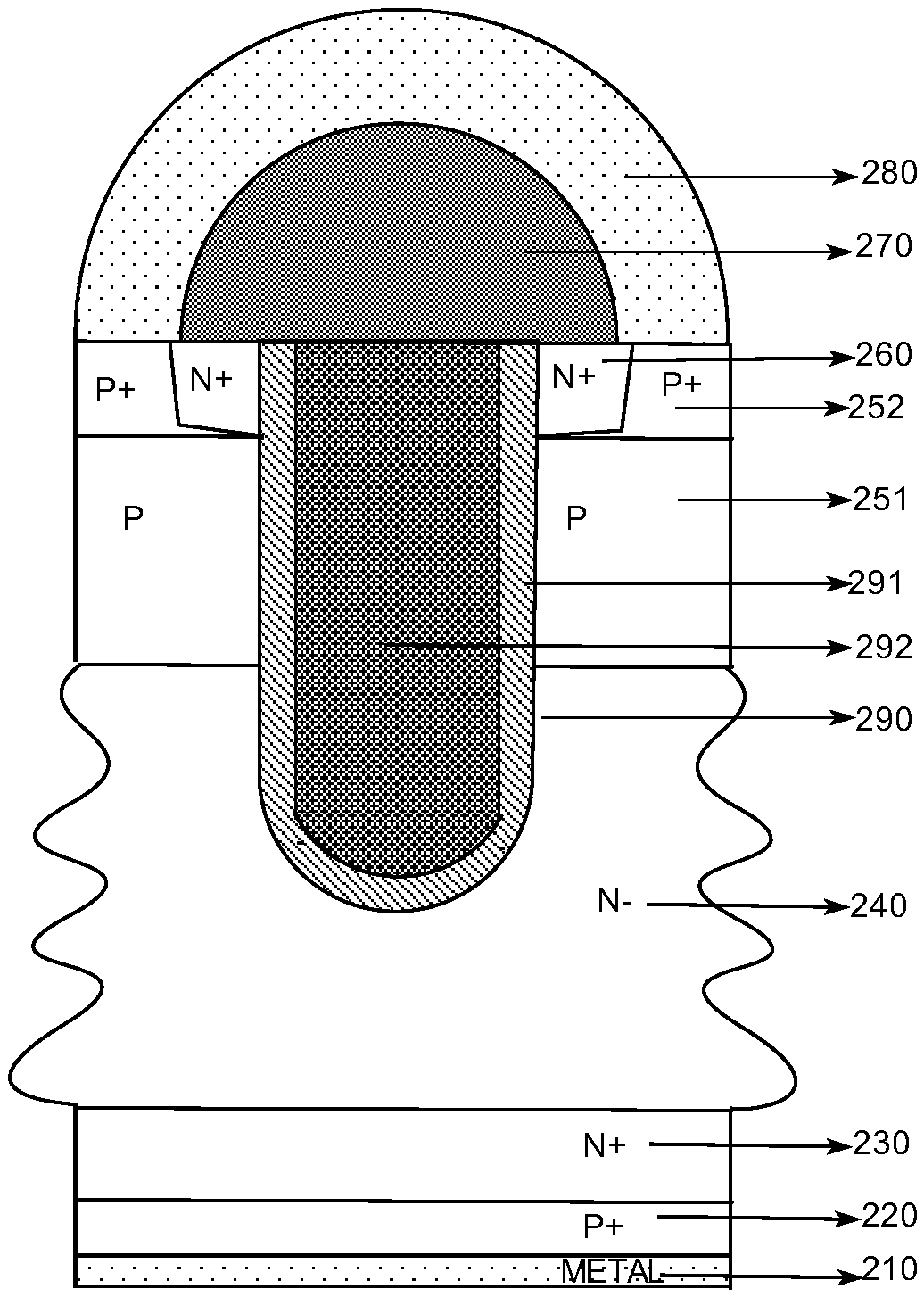

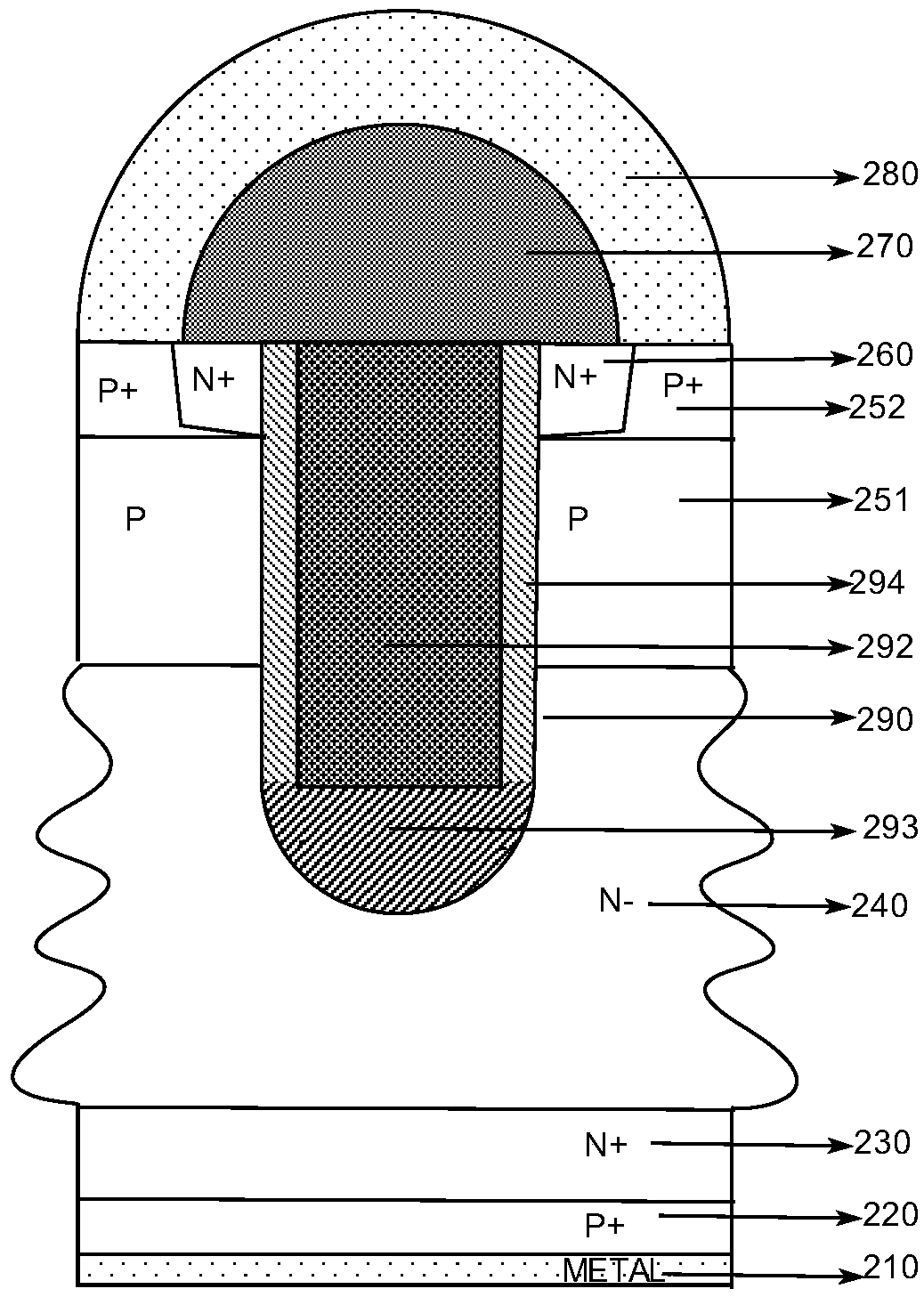

Method and apparatus for improved MOS gating to reduce miller capacitance and switching losses

A semiconductor gate structure includes a shielding electrode and a switching electrode. Portions of a shield electrode are located over the drain region and the well region. The first dielectric layer is located between the shielding electrode and the drain and well regions. Portions of switch electrodes are located over the well region and the source region. A second dielectric layer is located between the switch electrode and the well and source regions. A third dielectric layer is located between the shield electrode and the switch electrode.

Owner:FAIRCHILD SEMICON CORP

Dual sensitivity image sensor

ActiveUS8063964B2Increase in pixel complexityHigh sensitivityTelevision system detailsTelevision system scanning detailsSignal-to-noise ratio (imaging)Mode change

A dual sensitivity image sensor provides a standard mode and a high-sensitivity mode of operation via iSoC integration. In addition to boosting sensitivity, the high sensitivity mode also reduces temporal noise thereby optimally boosting the Signal-to-Noise Ratio (SNR) of the image sensor. The circuit does not significantly increase pixel complexity and requires minimal changes to the support circuits in the iSoC including the addition of support and control circuitry to facilitate seamless mode change.

Owner:SAMSUNG ELECTRONICS CO LTD

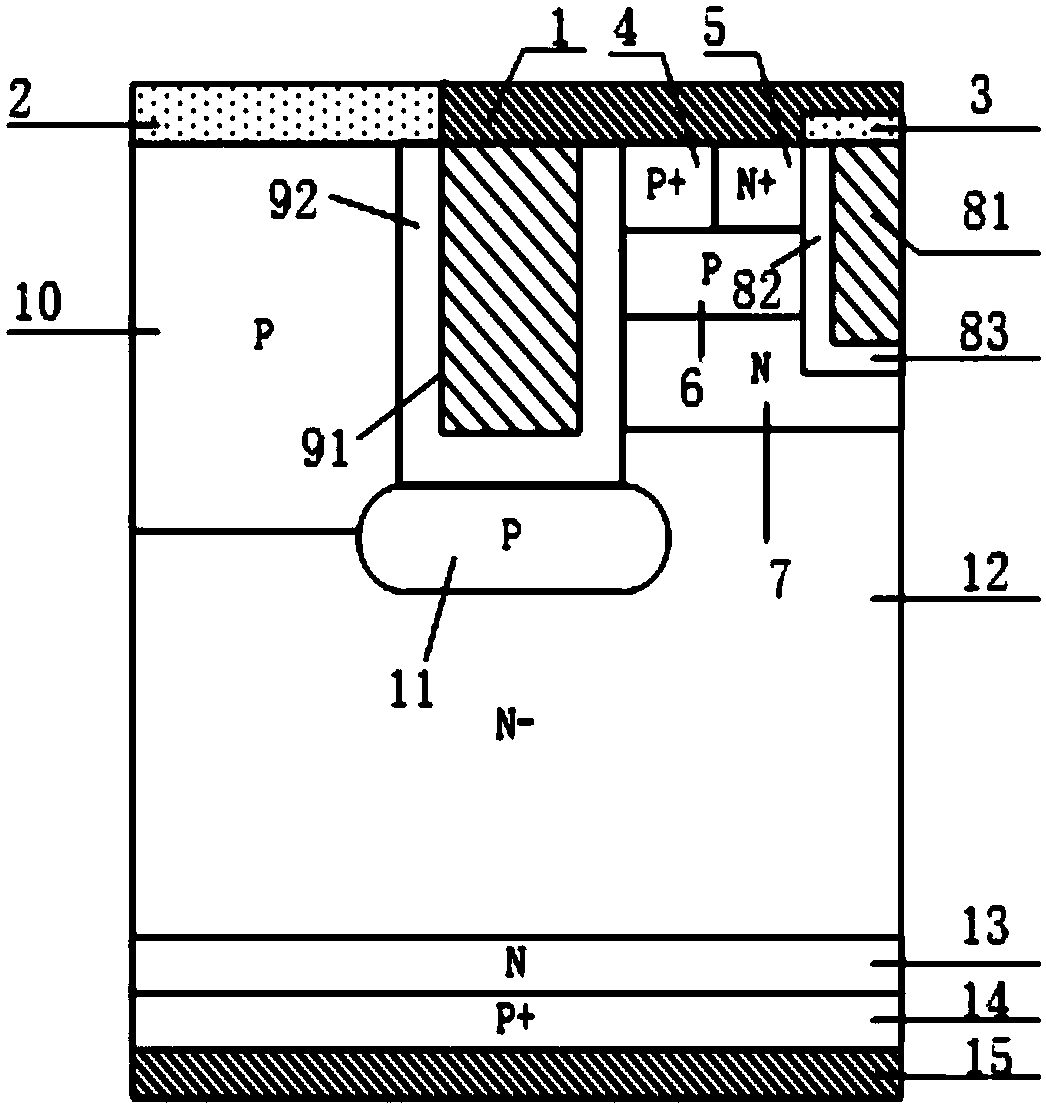

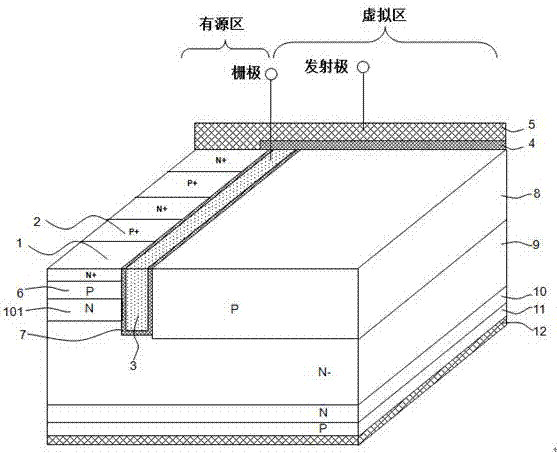

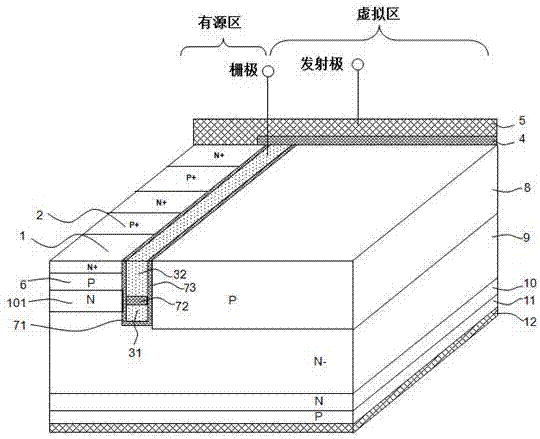

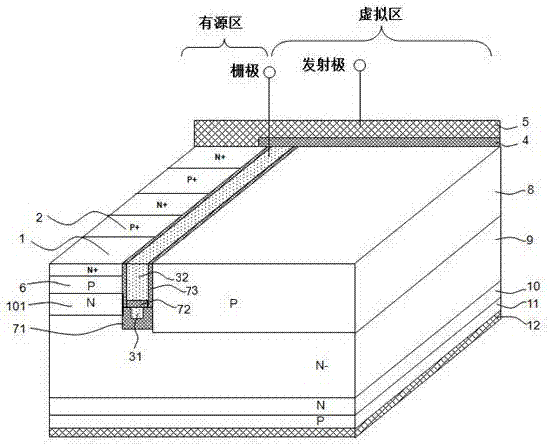

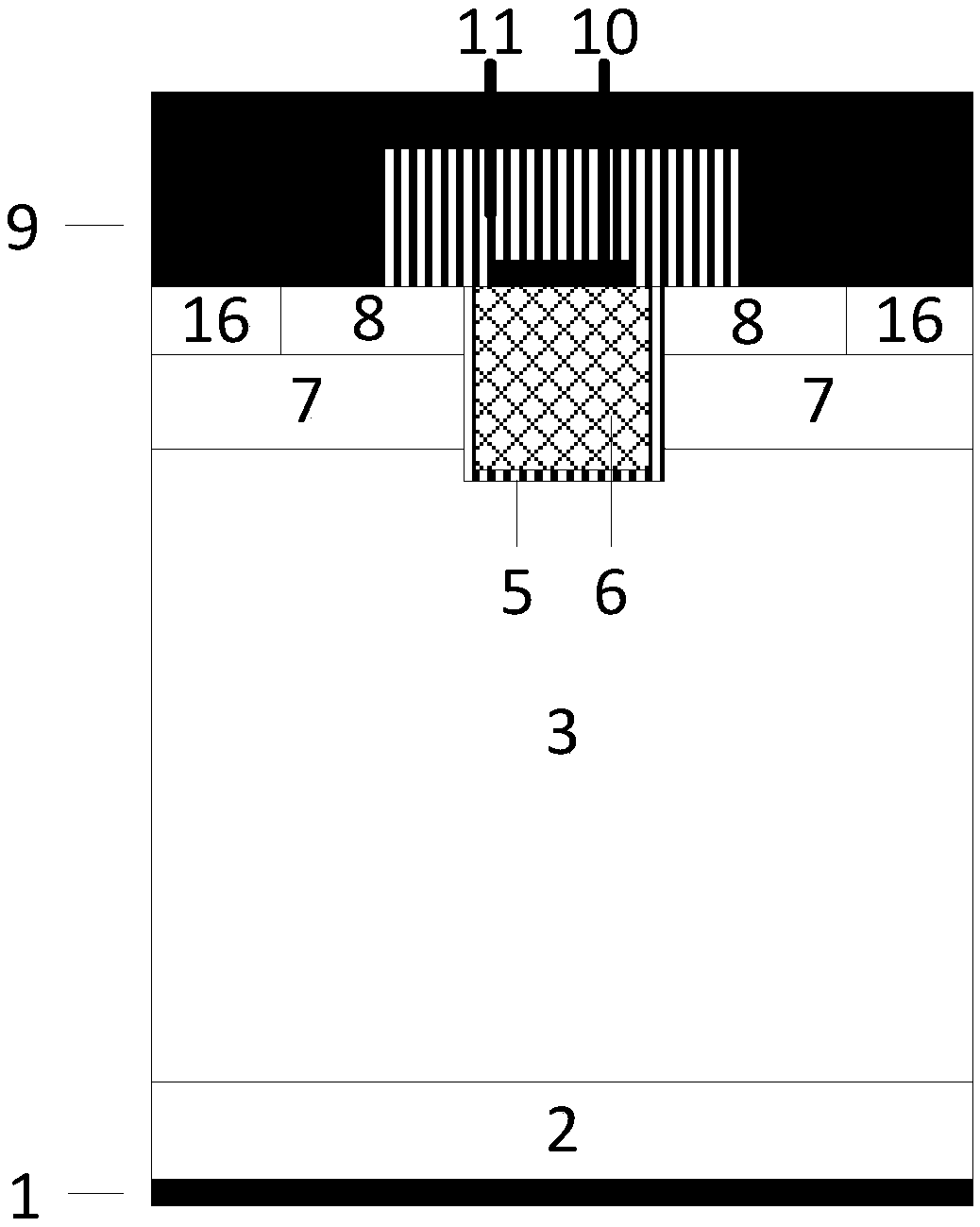

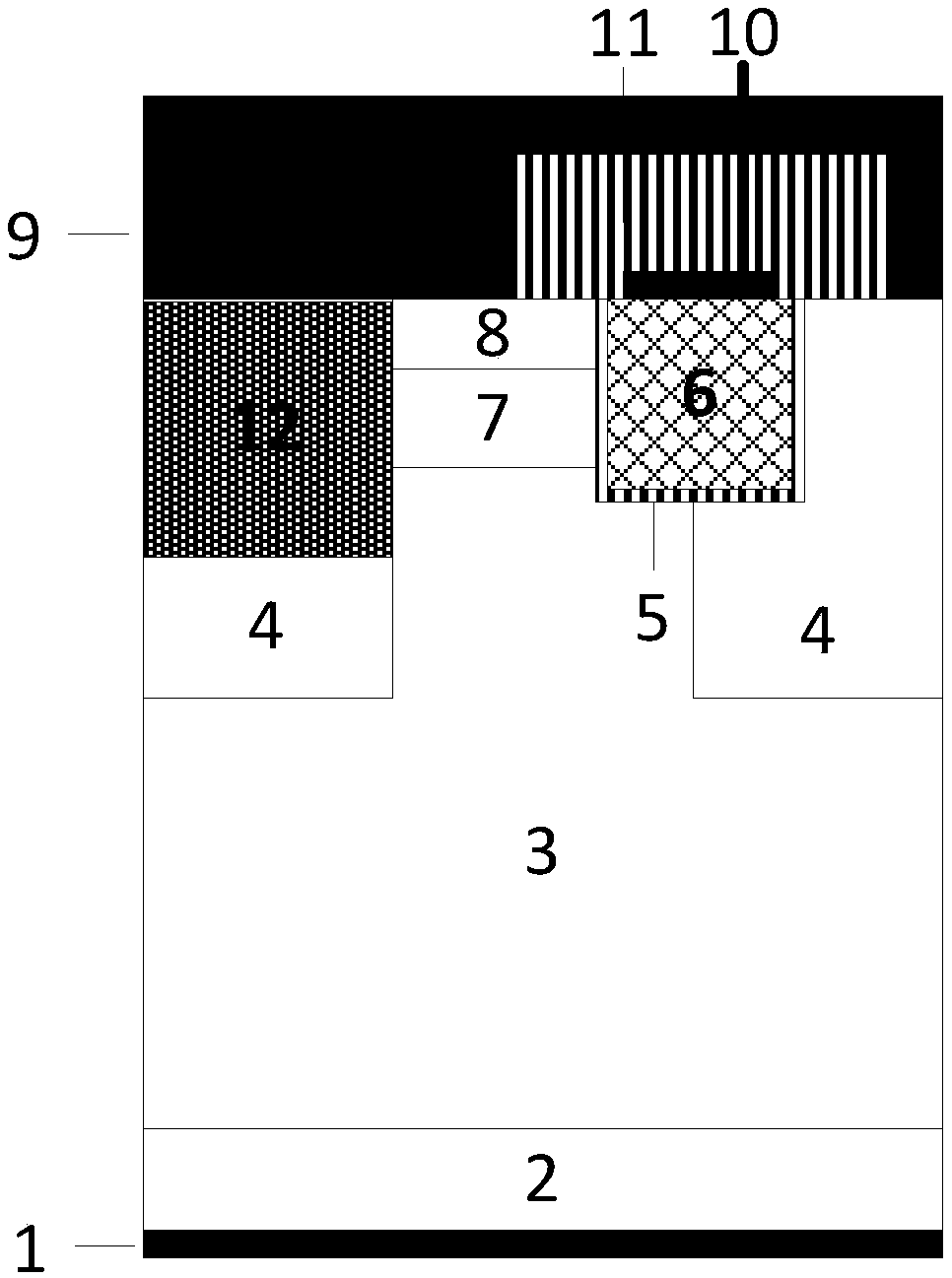

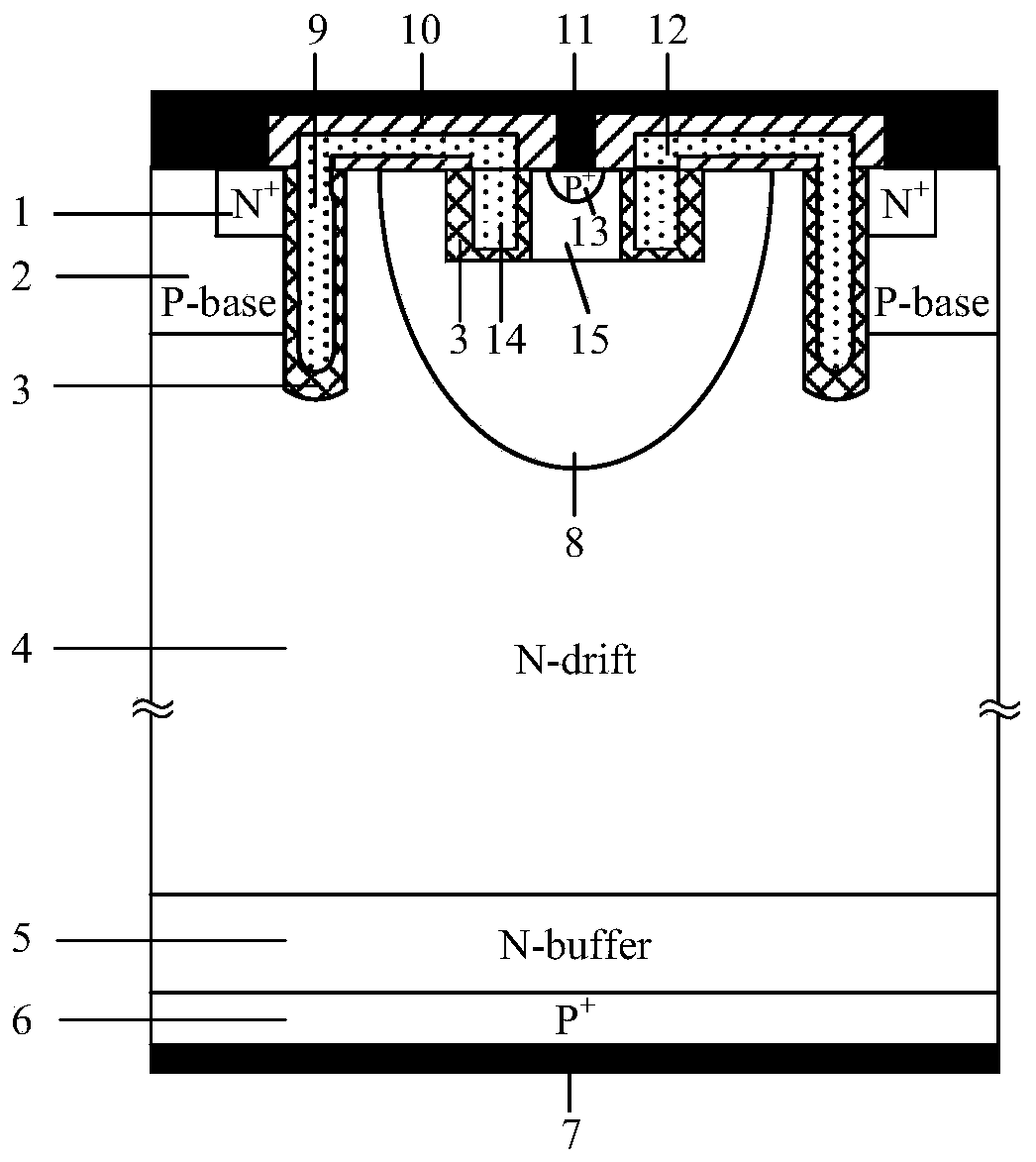

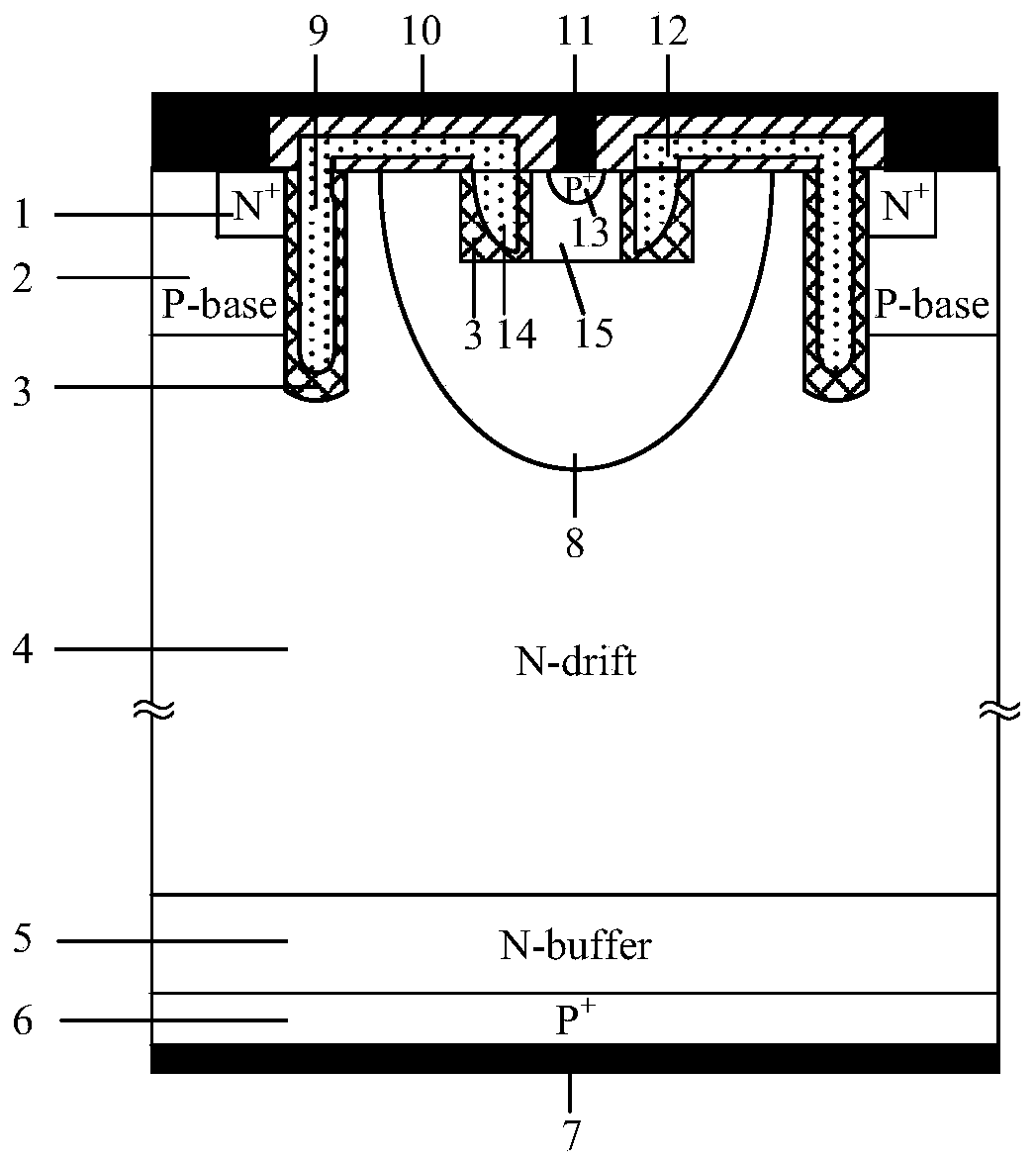

Trench-gate charge storage type IGBT and manufacturing method therefor

InactiveCN107768436ANo negative differential capacitance effectImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceDielectric layer

The invention discloses a trench-gate charge storage type IGBT and a manufacturing method therefor, and belongs to the technical field of semiconductor power devices. A trench-gate emitter structure connected with a P-type volume region is introduced to an N-type drift region at one side of a trench gate in a conventional CSTBT device, thereby enabling the gate-collector capacitance into gate-emitter capacitance, and improving the adverse effect of Miller capacitance. A thick dielectric layer of the trench-gate emitter structure avoids an electric field concentration effect at the bottom of atrench, and improves the breakdown voltage of a device. The depth of a gate electrode is enabled to be less than the junction depth of an N-type charge storage layer, thereby reducing the overall gatecapacitance under the condition that the connection of an IGBT is not affected, improving the switching speed of the device, reducing the switching loss of the device, and improving the compromise characteristics between a positive conduction voltage and the switching-off loss. According to the invention, the existing of the P-type volume region can reduce the extraction area of a hole, and improves the carrier concentration distribution of the whole N-type drift region. Moreover, the noise impact is reduced, and the EMI effect is avoided.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

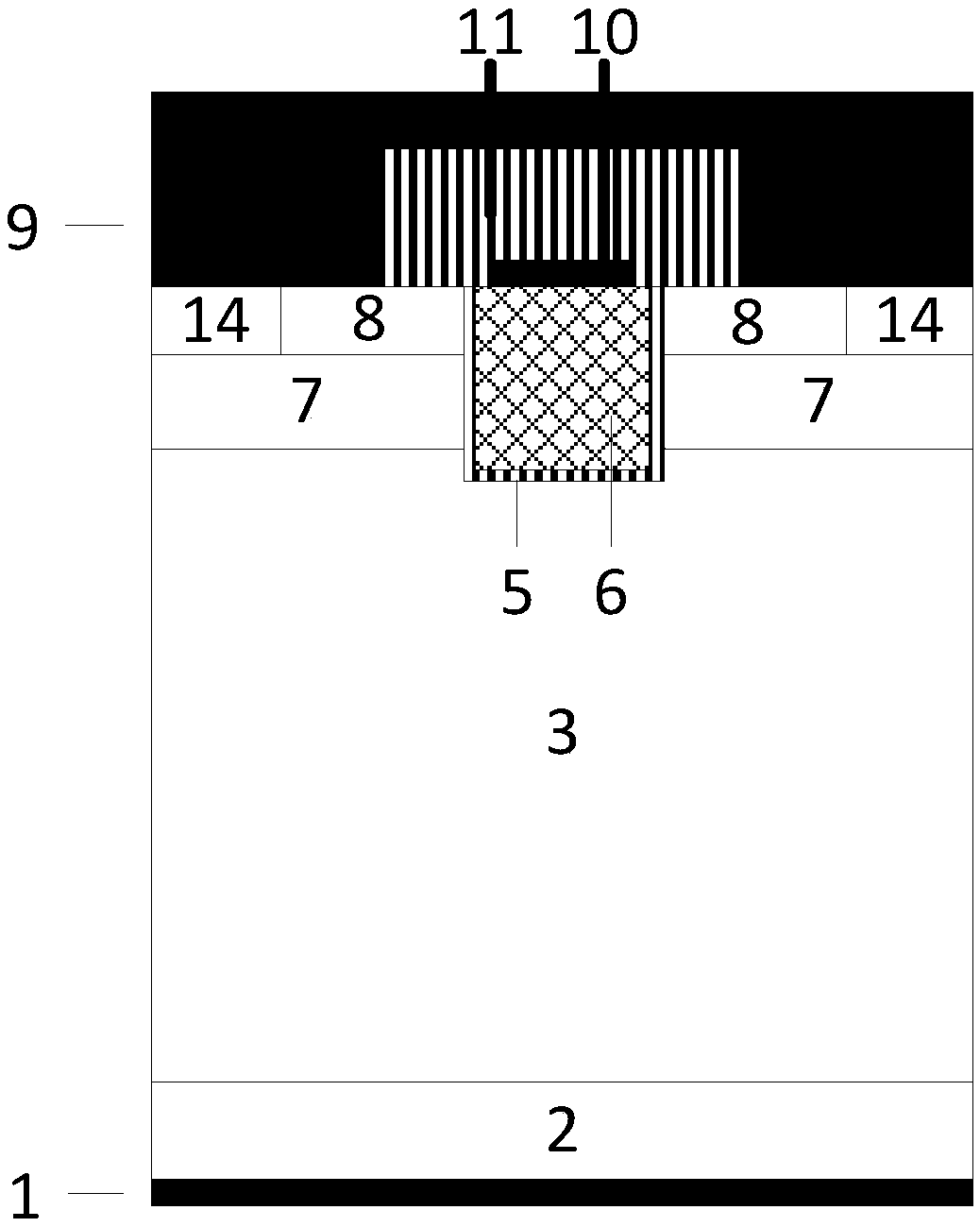

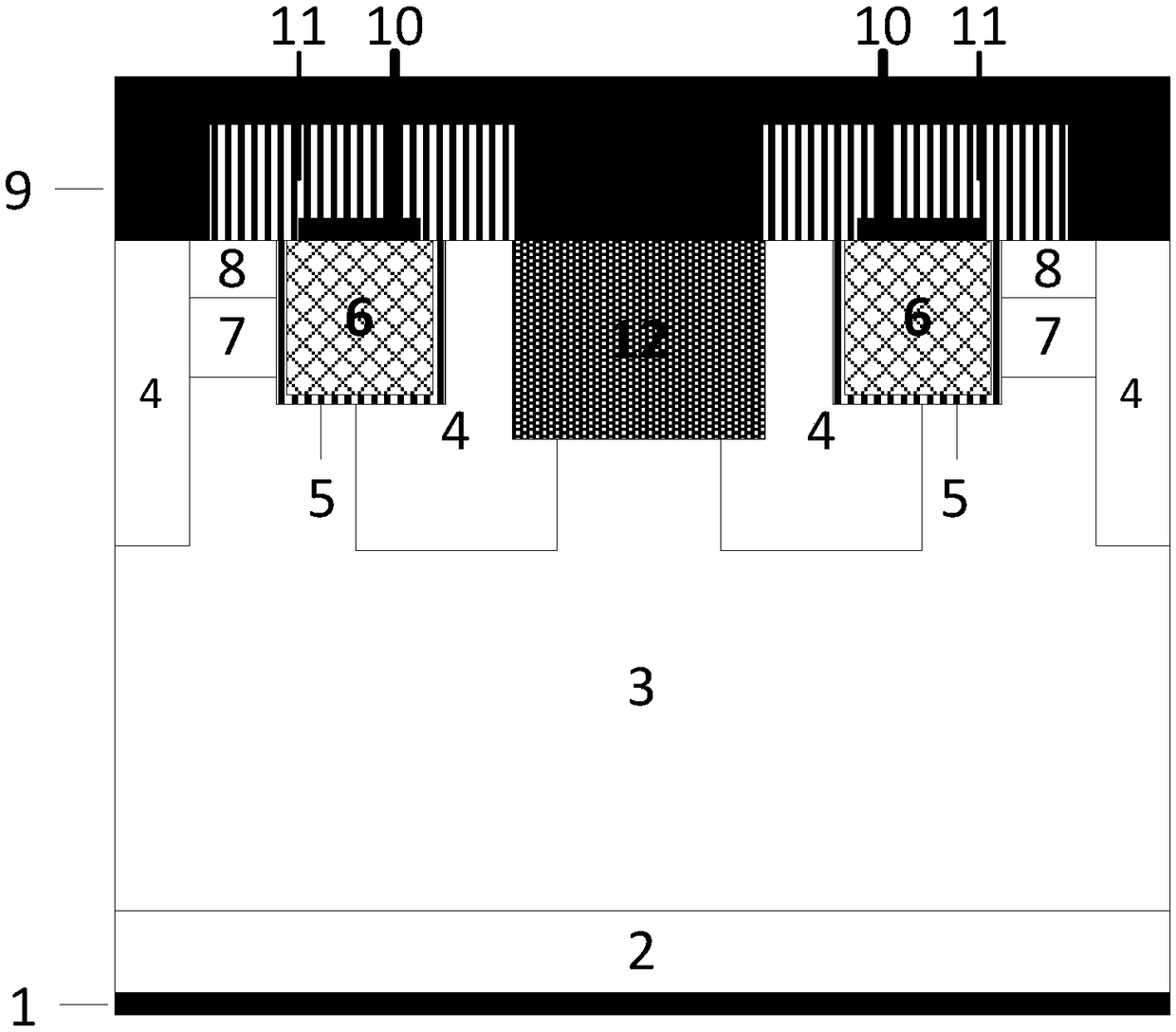

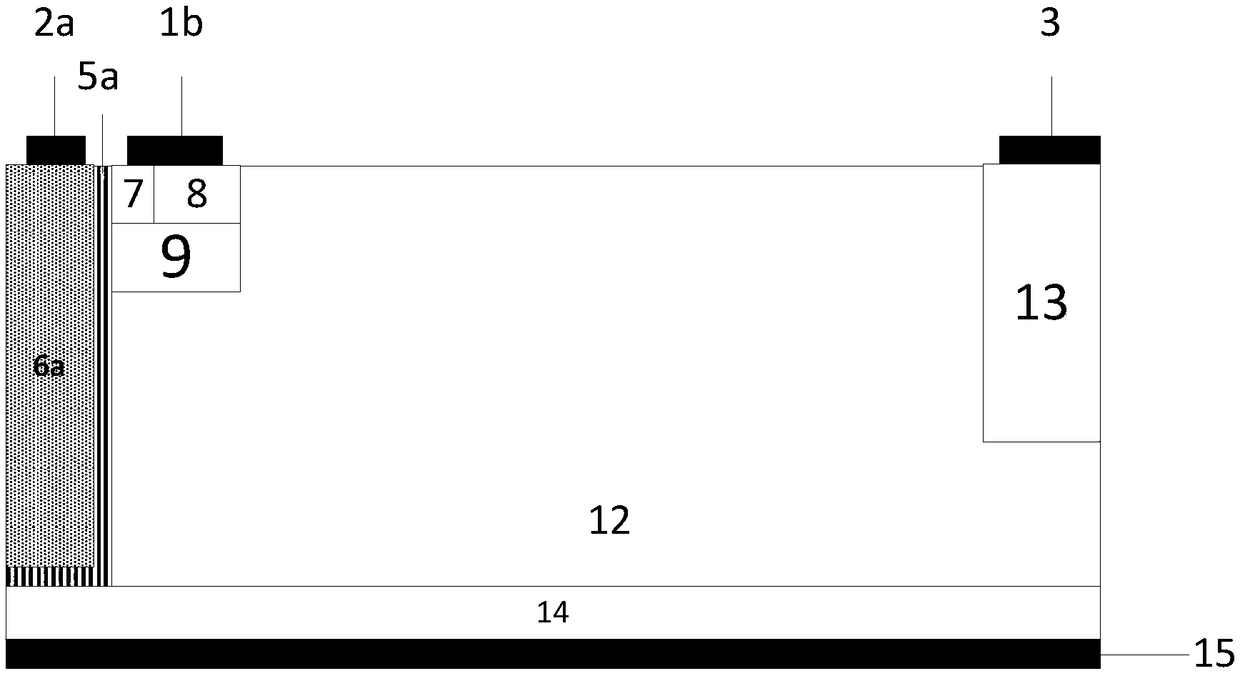

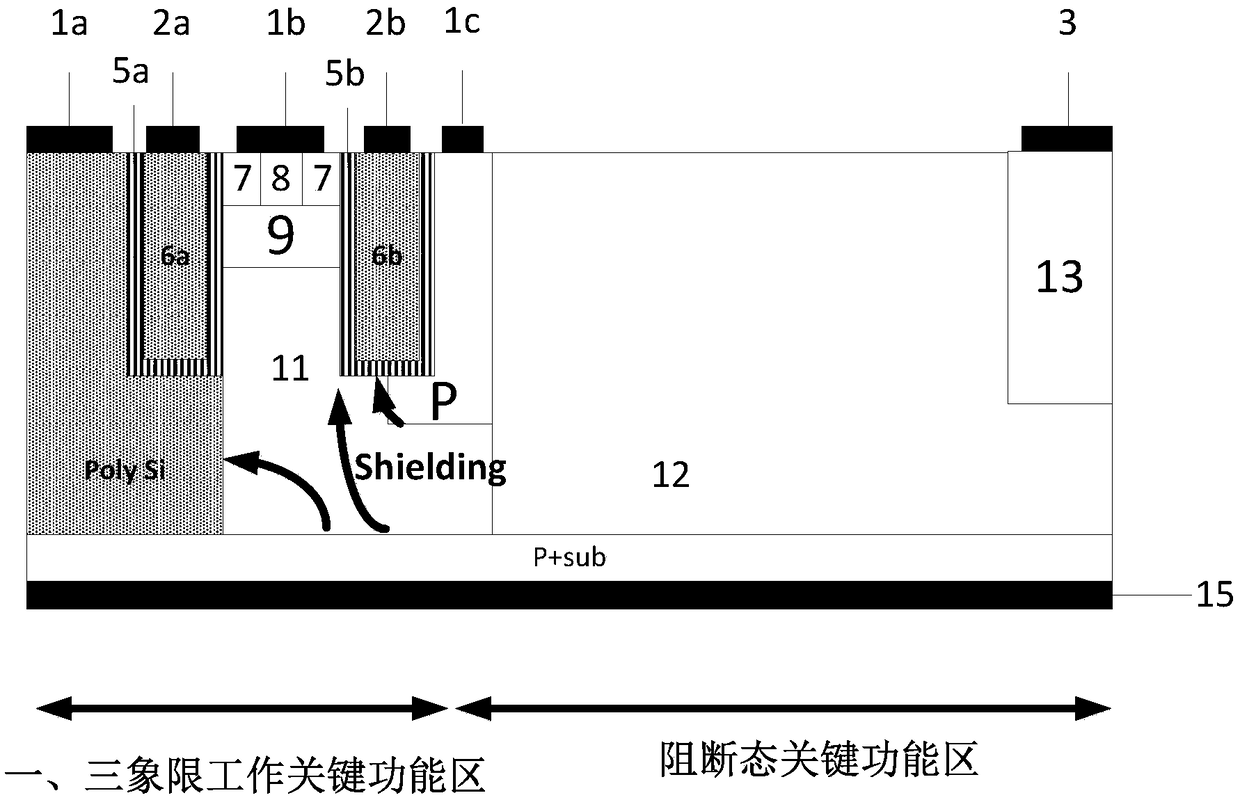

Silicon carbide MOSFET device and manufacturing method thereof

The invention provides a silicon carbide MOSFET device and a manufacturing method thereof. Discontinuous gate structures are formed on the basis of the common silicon carbide MOSFET structure, two silicon carbide deep P injection regions are introduced between the two gate structure and metal or polycrystalline silicon is introduced between the two silicon carbide deep P injection regions. The metal or the polycrystalline silicon directly contacts the silicon carbide N-epitaxy so as to form the Schottky contact or the heterojunction contact having the rectification characteristic. The improvement greatly optimizes the conventional silicon carbide UMOSFET basic characteristics, realizes integration of multiple sub-rectifiers and greatly optimizes the third quadrant performance of the device. Meanwhile, the silicon carbide MOSFET device has the characteristics of low Miller capacitance, simple process and easy implementation.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

A superjunction IGBT with a shielded gate and a manufacturing method thereof

PendingCN109037312AReduce lossLow resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceCell region

The invention discloses a superjunction IGBT with a shield gate and a manufacturing method thereof. The superjunction IGBT comprises a semiconductor substrate, a cell region and a terminal protectionarea. The semiconductor substrate comprises a second conductivity type collector region, a first conductivity type field termination layer and at least one first conductivity type epitaxial layer. Thecell region comprises a plurality of cells connected in parallel with each other, which includes a plurality of cell trenches and a gate conductive polysilicon and a shield gate filled in the cell trenches, A seventh oxide layer is arranged on both sides and sidewalls of the notch of the cell trench opposite to the gate conductive polysilicon, a fifth oxide layer is arranged between the gate conductive polysilicon and the shield gate, and a fourth oxide layer is arranged on the bottom and sidewalls of the cell trench opposite to the shield gate. A P-pillar is also provided in the first conductivity type epitaxial layer, one end of the P-pillar is connected to the second conductivity type well layer, and the other end extends toward the first conductivity type field termination layer. Theinvention adopts the shielding gate structure, reduces the Miller capacitance, thereby reducing the switching loss.

Owner:无锡市乾野微纳科技有限公司

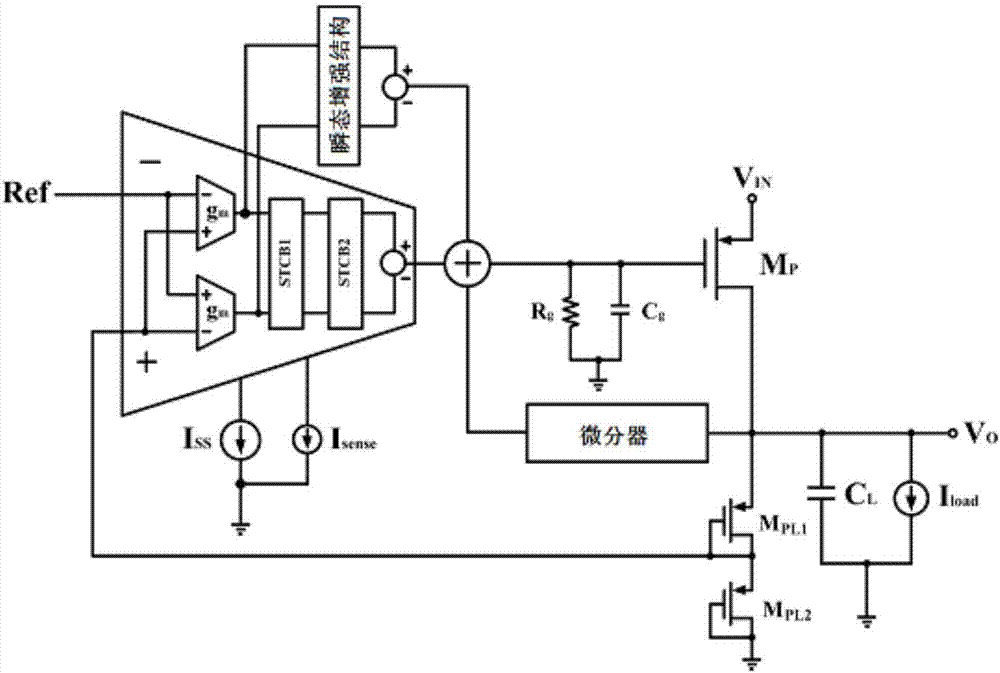

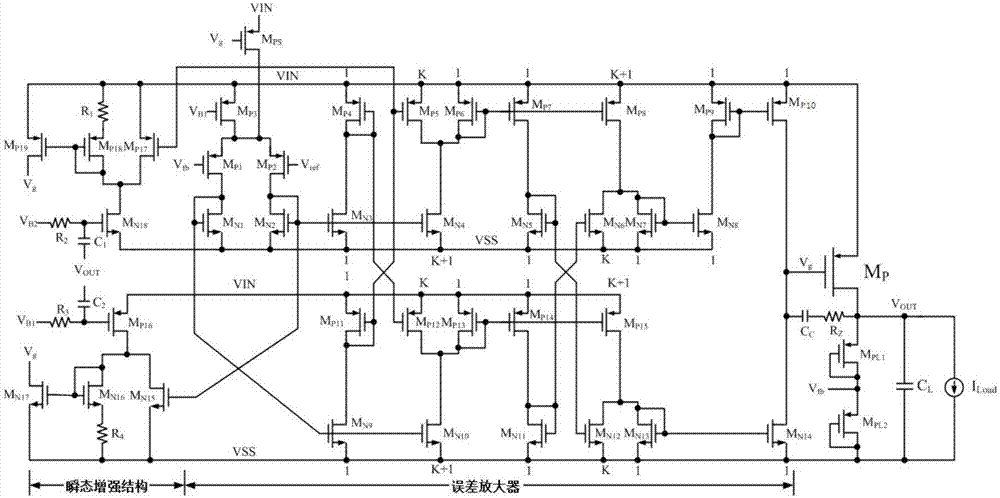

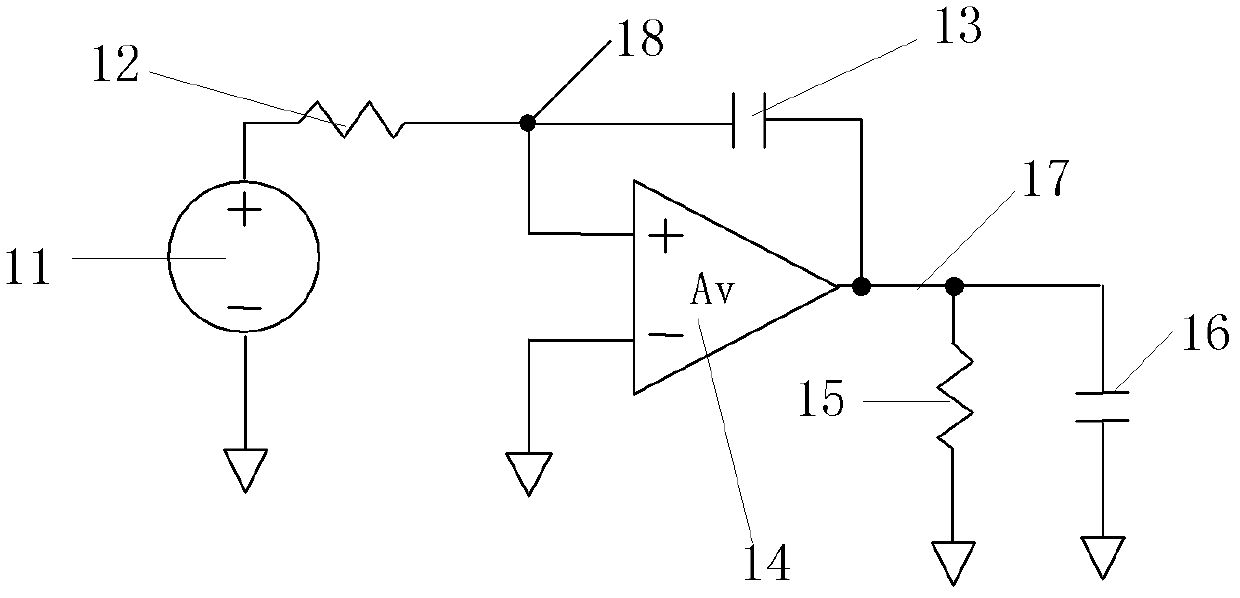

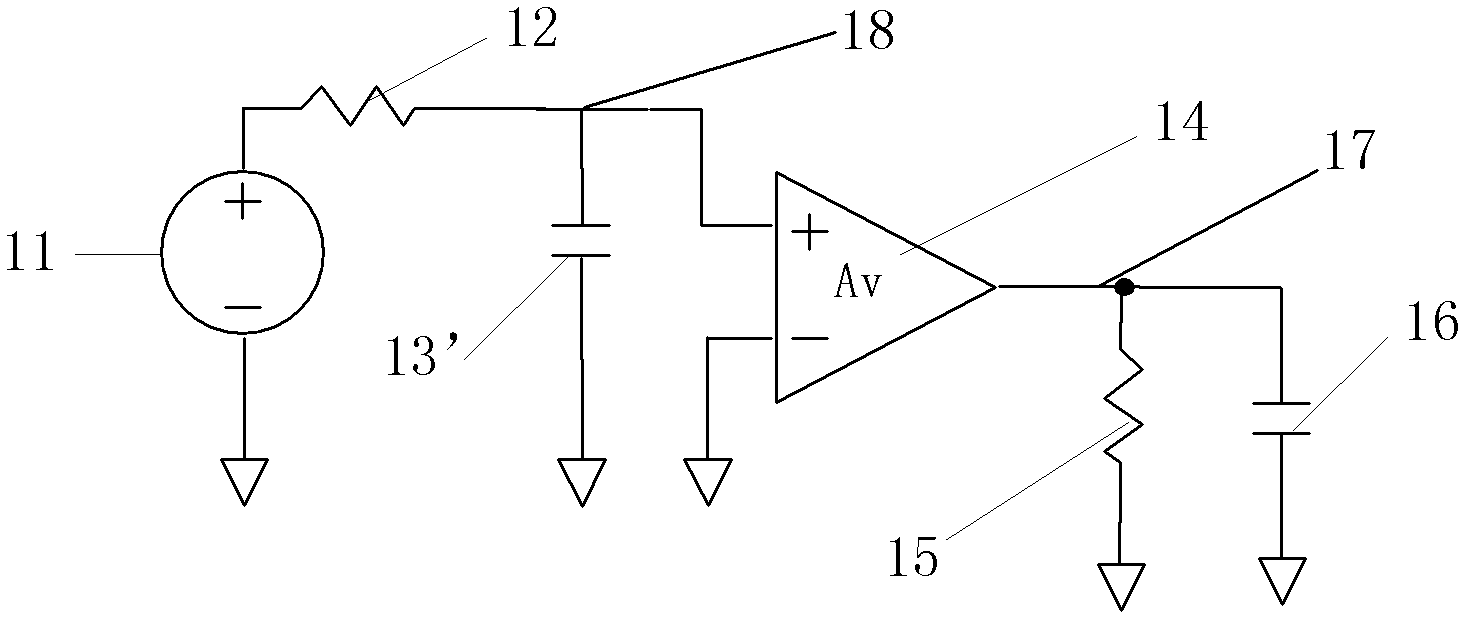

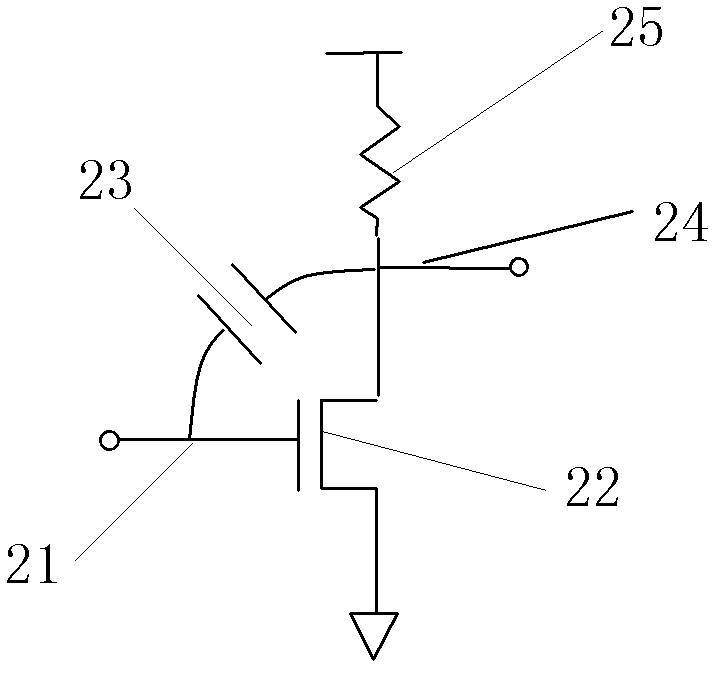

On-chip low dropout regulator with fast transient response function

InactiveCN107315441AReduced Miller CapacitanceGood compensationElectric variable regulationCapacitanceDifferentiator

The invention belongs to the technical field of power source management, and relates to an on-chip low dropout regulator with the fast transient response function. The on-chip low dropout regulator comprises an error amplifier, a power tube MP, a Miller capacitor CL, a first divider resistor and a second divider resistor, wherein the source electrode of the power tube MP is connected with input voltage VIN, and the drain electrode of the power tube MP is grounded after passing through a series structure of the first divider resistor and the second divider resistor; the negative input end of the error amplifier is connected with the reference voltage Vref, the positive input end of the error amplifier is connected with the series point of the first divider resistor and the second divider resistor, the output end is connected with the grid electrode of the power tube MP, and the Miller capacitor CL is connected between the drain electrode of the power tube MP and the ground; an error amplifier of an STCB structure is adopted, and a transient enhancing structure is inserted into the input stage of the error amplifier; a differentiator is connected between the grid electrode and the drain electrode of the power tube MP, and meanwhile a self-biasing structure is introduced into the LDO. Miller capacitance needed by loop compensation is substantially reduced while transient response speed is increased.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

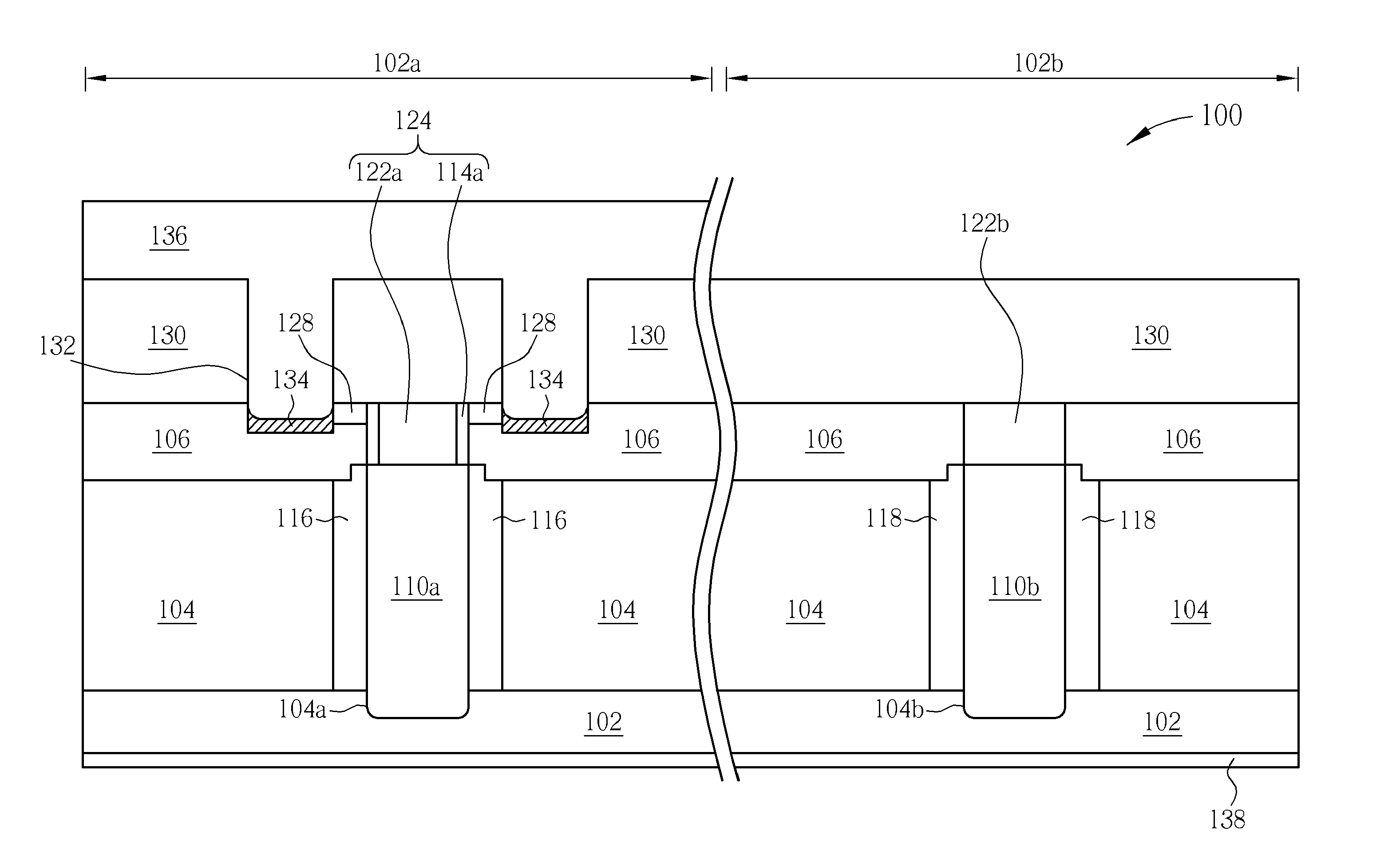

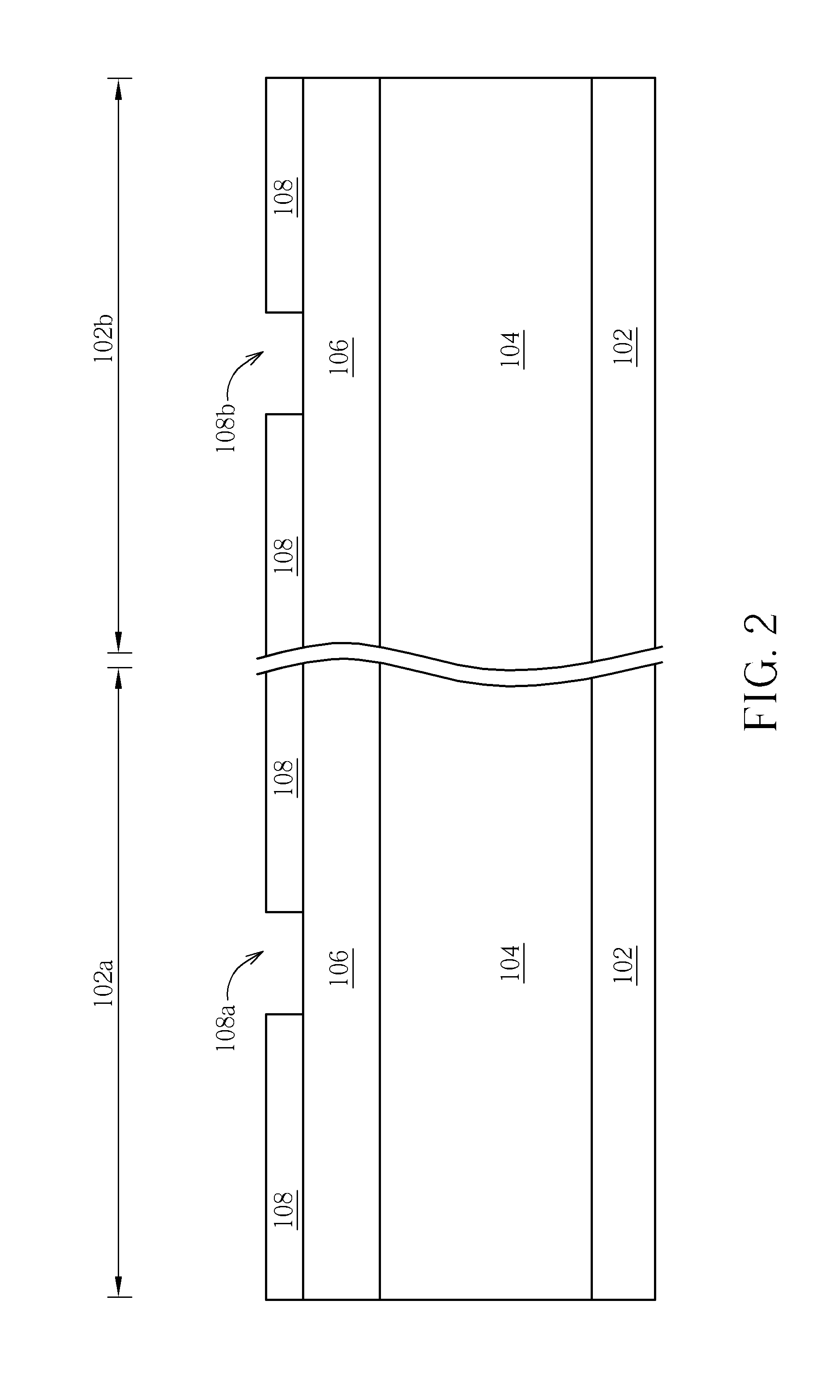

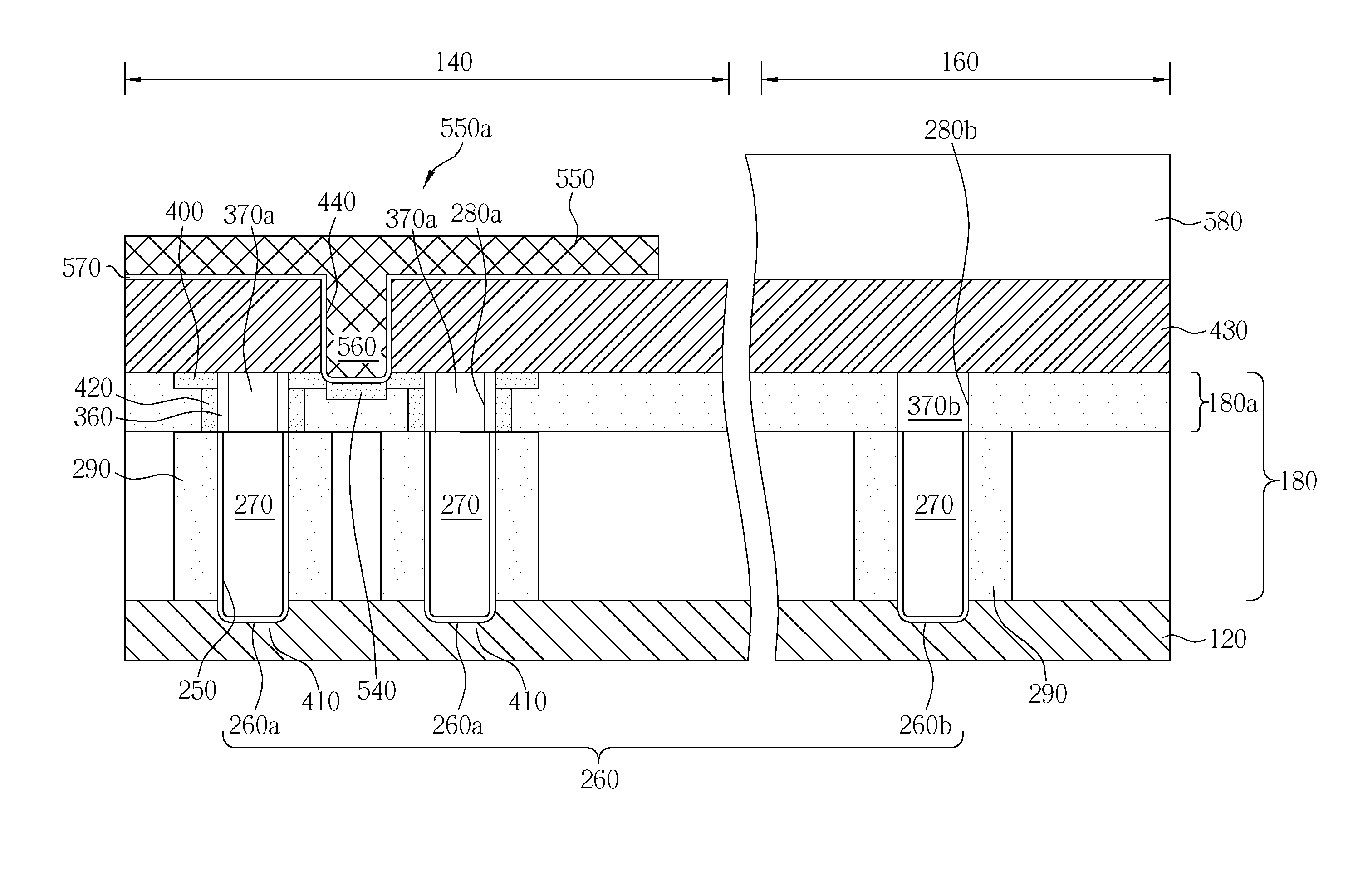

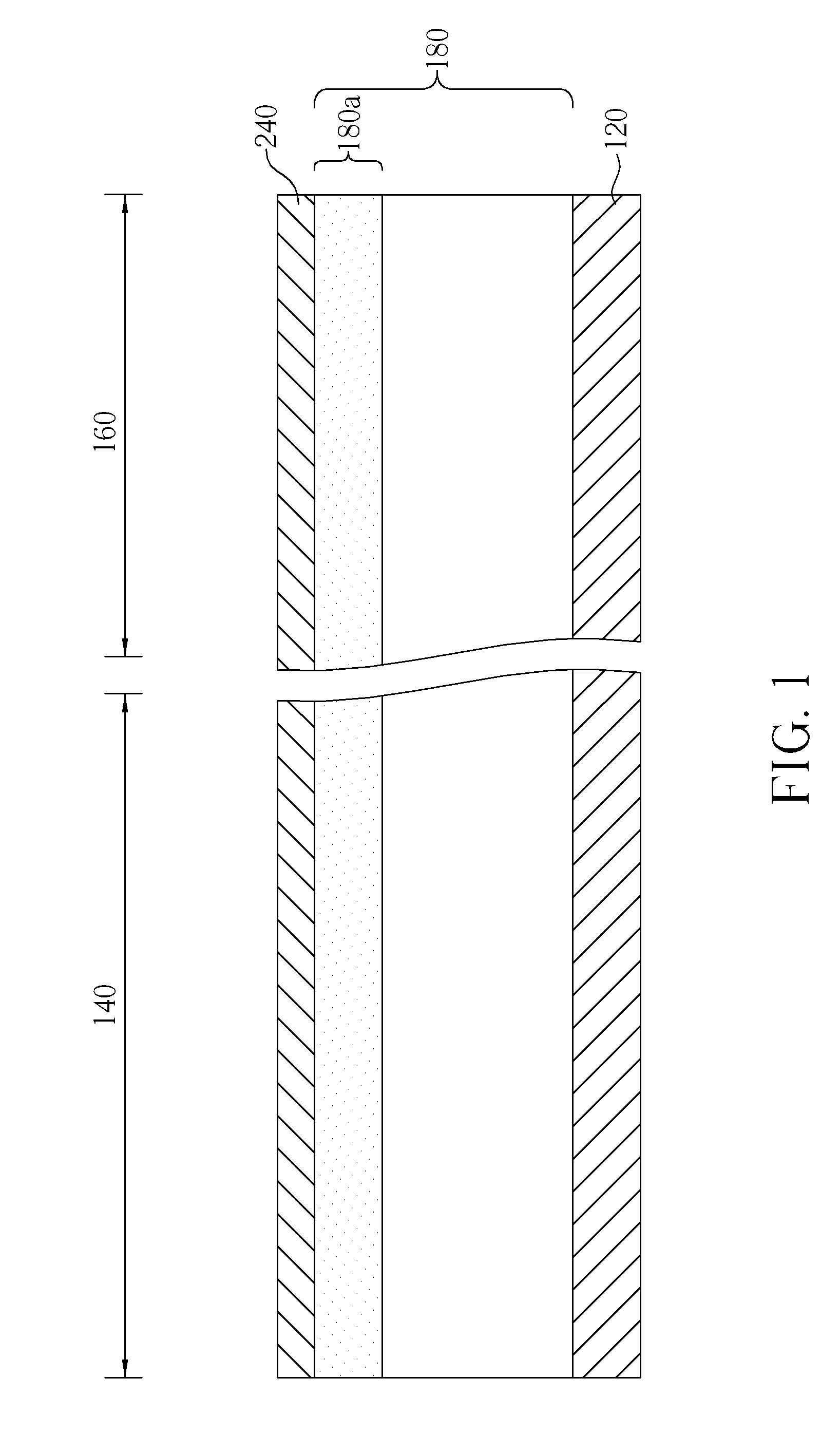

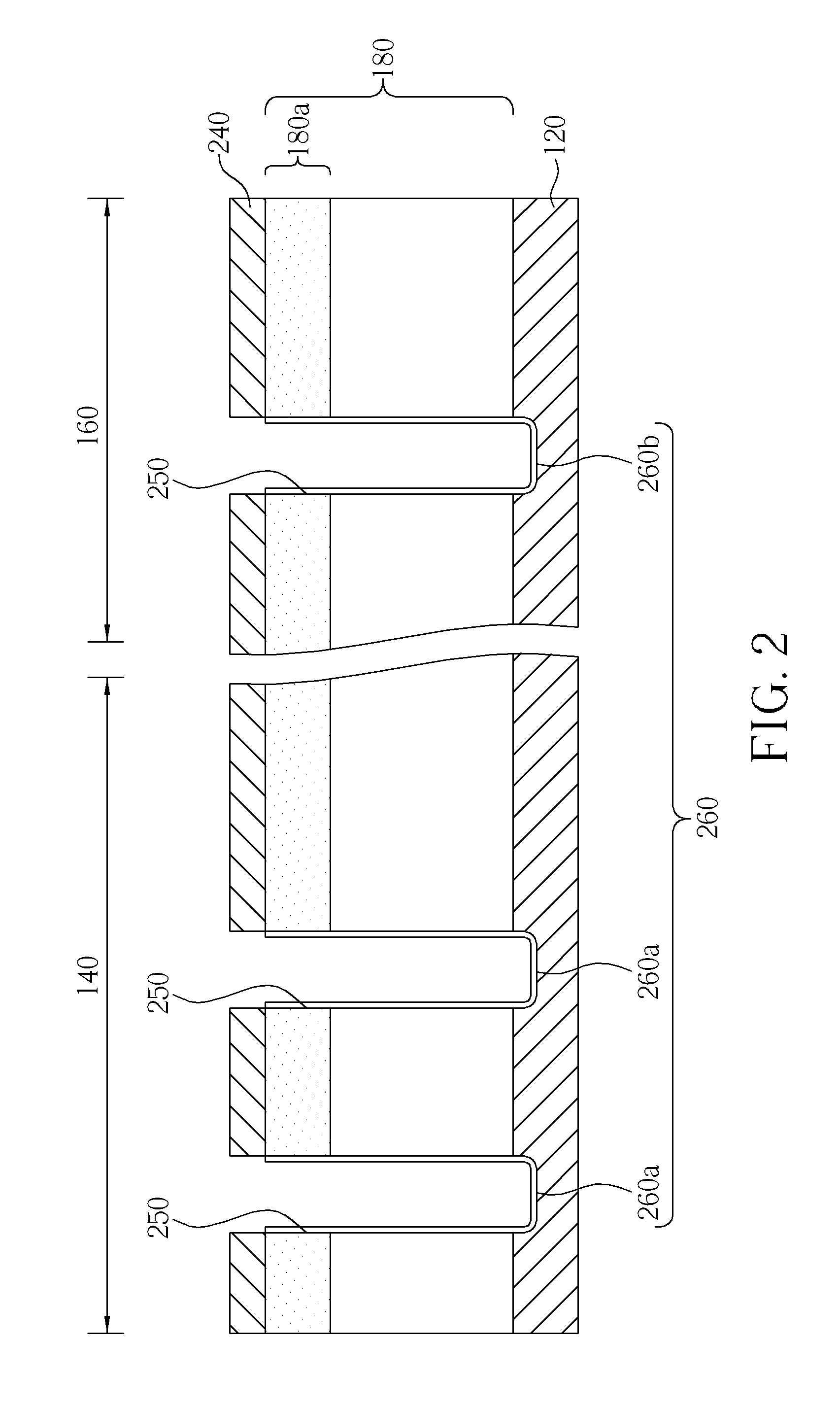

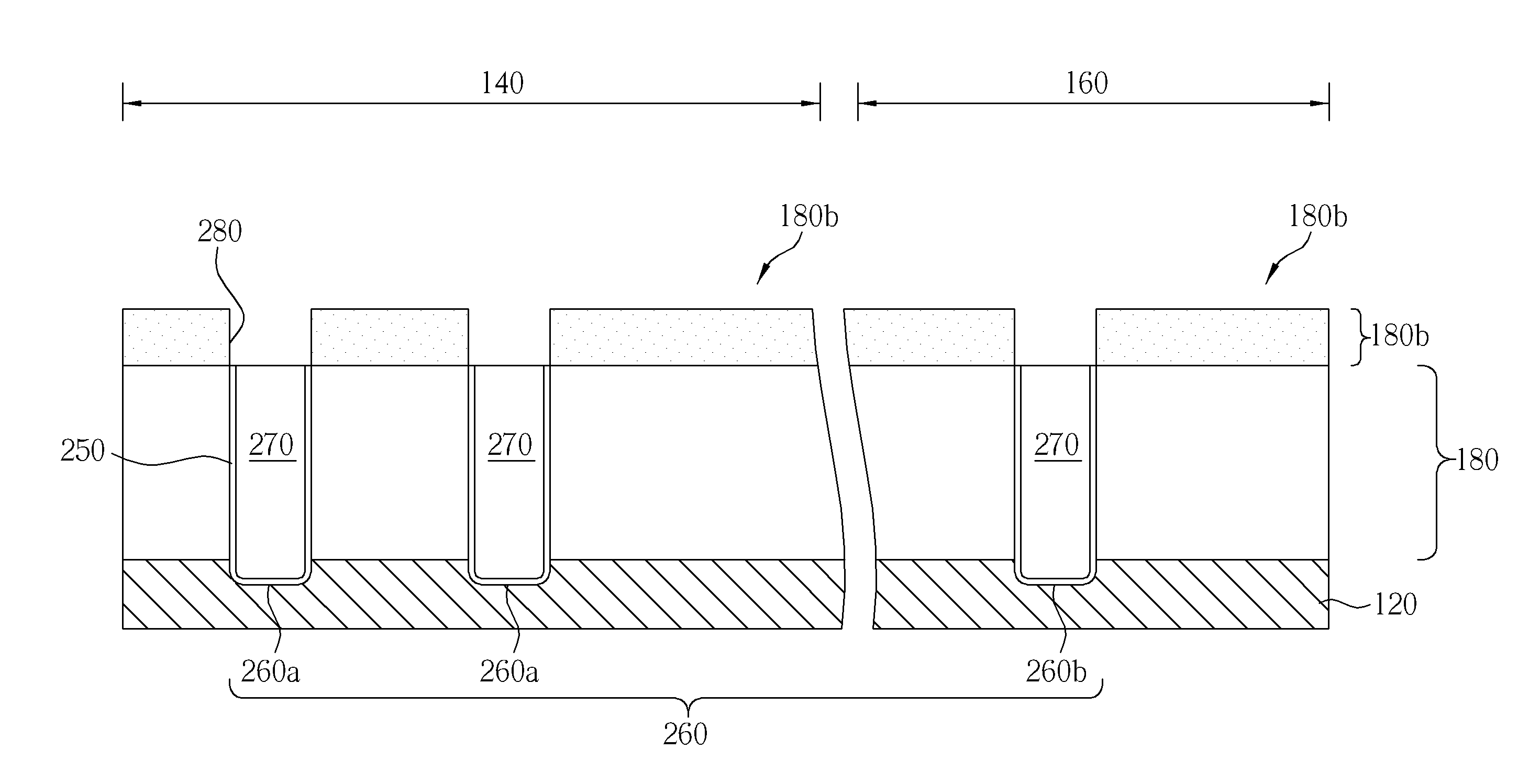

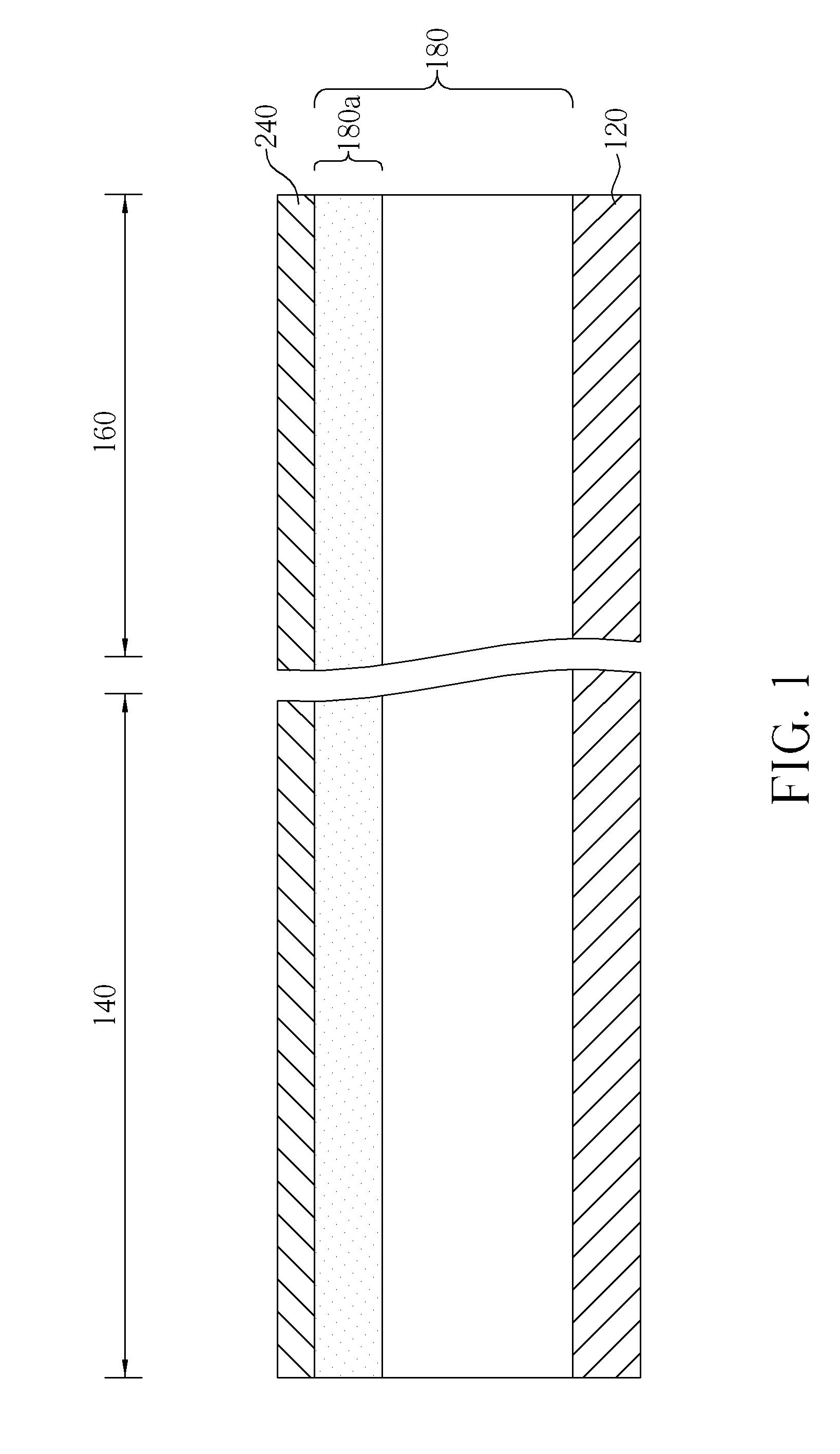

Trench type power transistor device

InactiveUS20140327039A1Reduced Miller CapacitanceImprove abilitiesSemiconductor/solid-state device manufacturingSemiconductor devicesTransistorPhysics

The present invention provides a trench type power transistor device including a substrate, an epitaxial layer, a doped diffusion region, a doped source region, and a gate structure. The substrate, the doped diffusion region, and the doped source region have a first conductivity type, and the substrate has an active region and a termination region. The epitaxial layer is disposed on the substrate, and has a second conductivity type. The epitaxial layer has a through hole disposed in the active region. The doped diffusion region is disposed in the epitaxial layer at a side of the through hole, and is in contact with the substrate. The doped source region is disposed in the epitaxial layer disposed right on the doped diffusion region, and the gate structure is disposed in the through hole between the doped diffusion region and the doped source region.

Owner:ANPEC ELECTRONICS CORPORATION

Insulated gate bipolar transistor

InactiveCN107425056AReduced Miller CapacitanceReduce energy consumptionSemiconductor devicesCapacitanceDielectric layer

The invention discloses an insulated gate bipolar transistor. Compared with the prior art, polycrystalline silicon filled in a trench is separated by a dielectric layer into an upper polycrystalline silicon layer and a lower polycrystalline silicon layer, the upper polycrystalline silicon layer and the lower polycrystalline silicon layer are mutually contacted with an oxide layer at the upper part of the trench and an oxide layer at the lower part of the trench respectively, the upper polycrystalline silicon layer is connected with a gate electrode, and the lower polycrystalline silicon layer is connected with an emitting electrode; and bottom part of the upper polycrystalline silicon layer in the trench is deeper than a P-type well region of an active primitive cell. The structure disclosed by the invention reduces the Miller capacitance and the turn-on power consumption of the device.

Owner:CHANGZHOU ZHONGMING SEMICON TECH

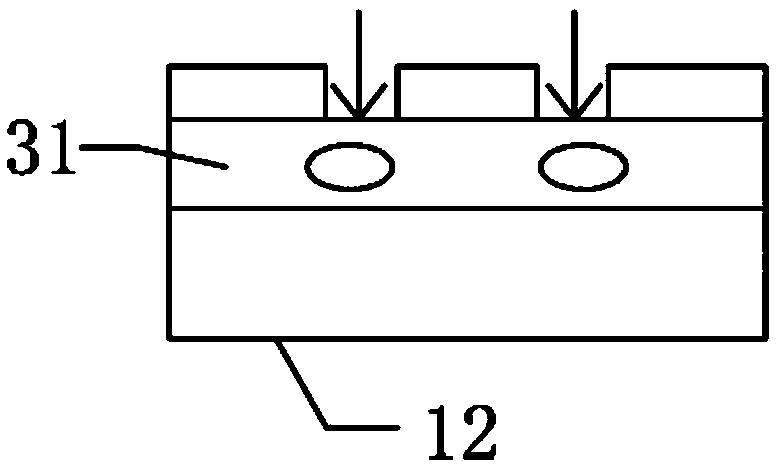

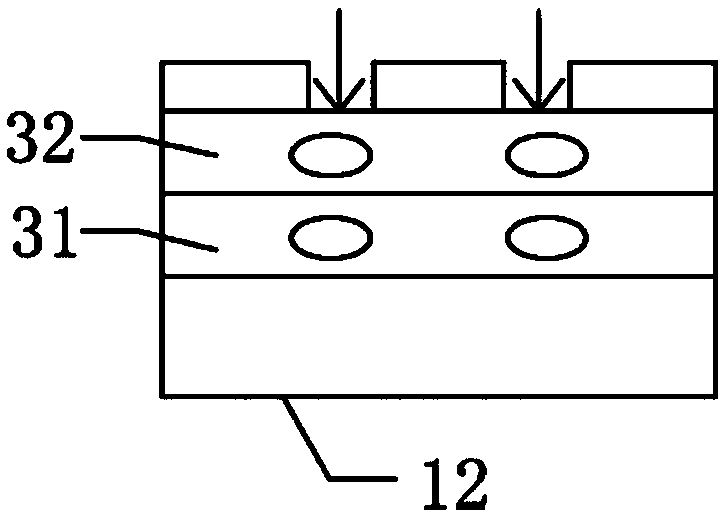

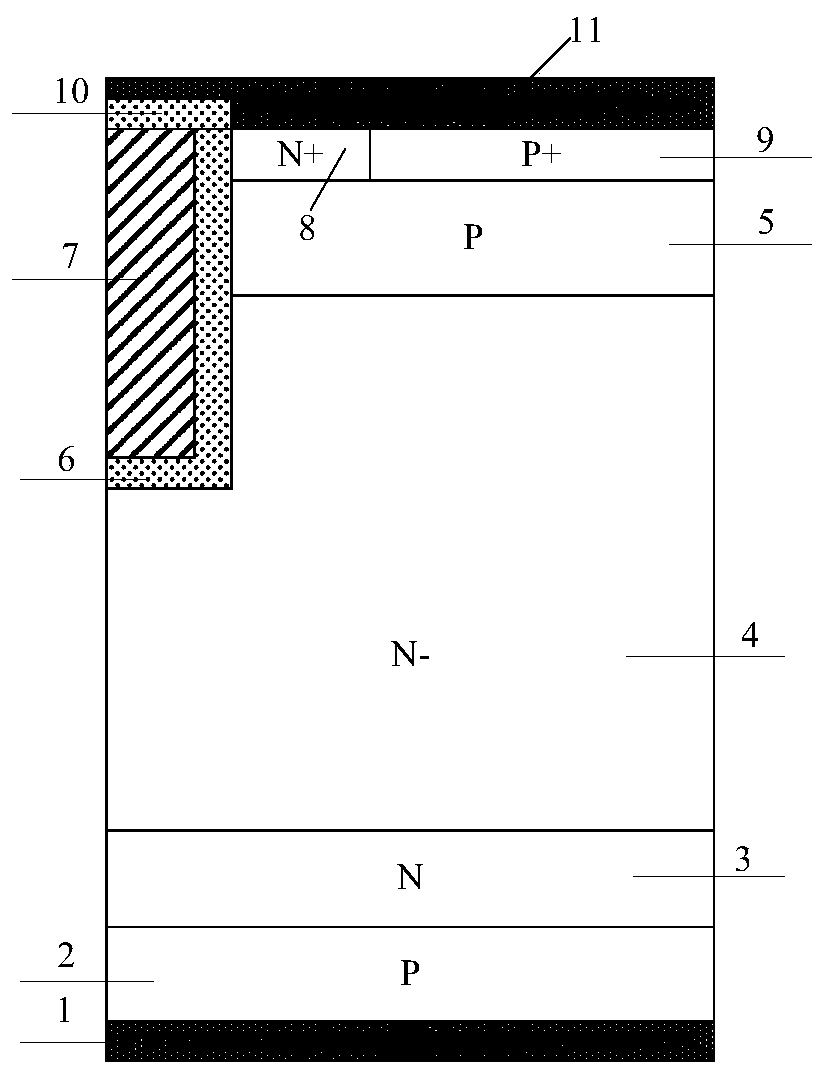

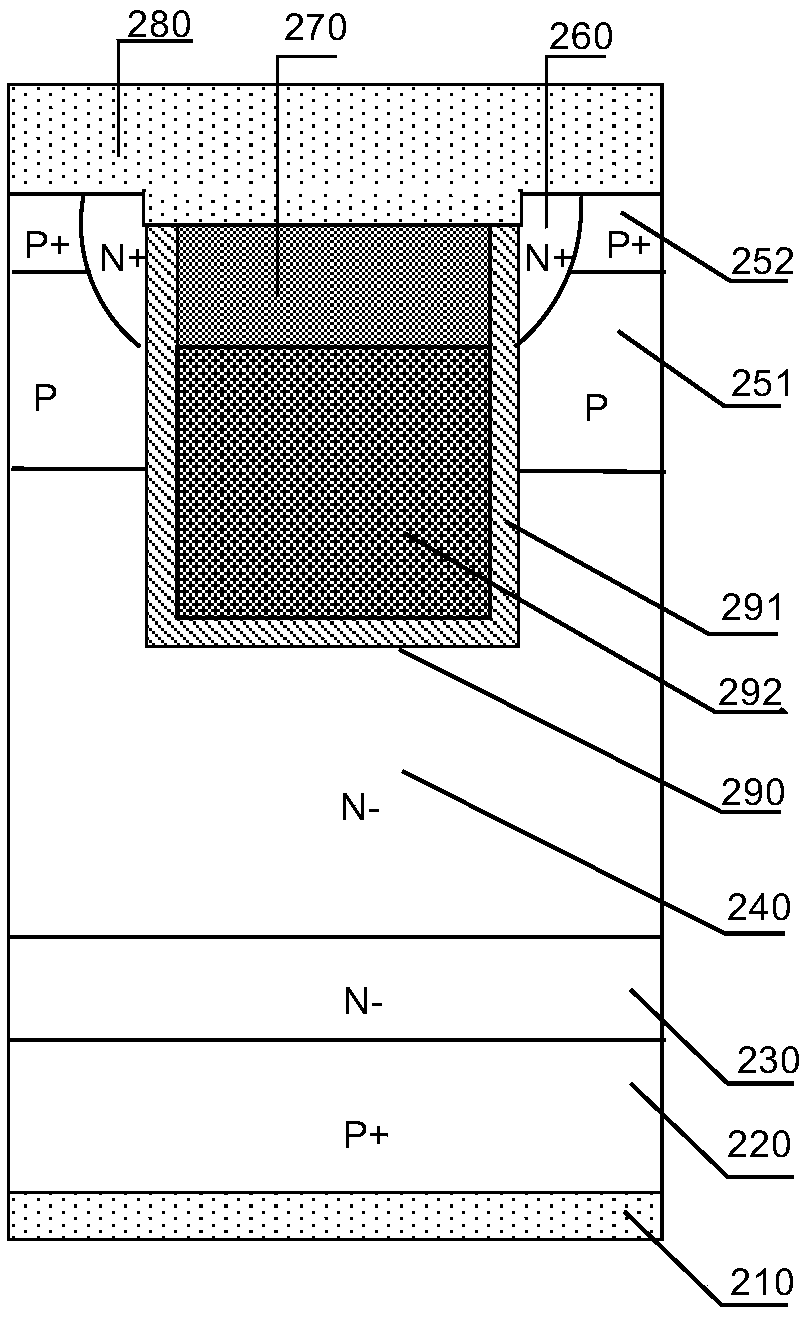

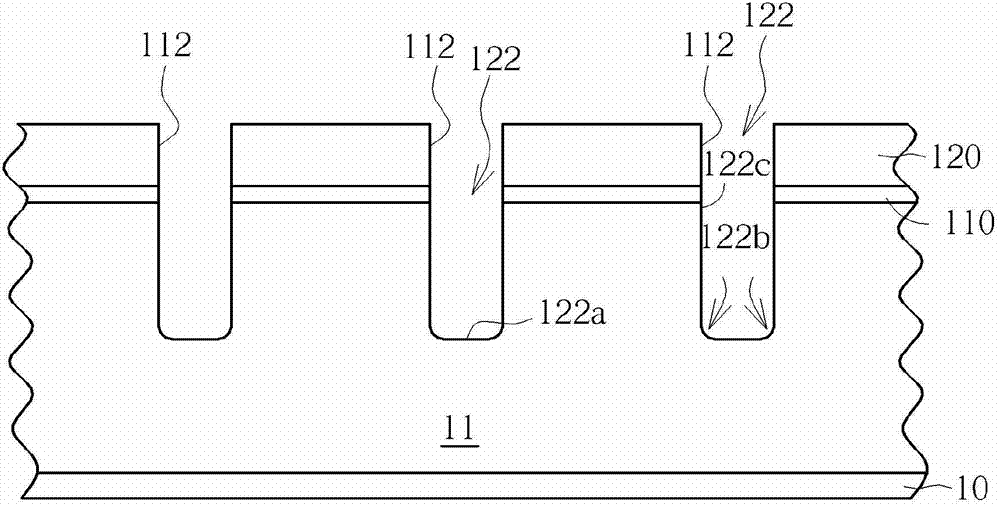

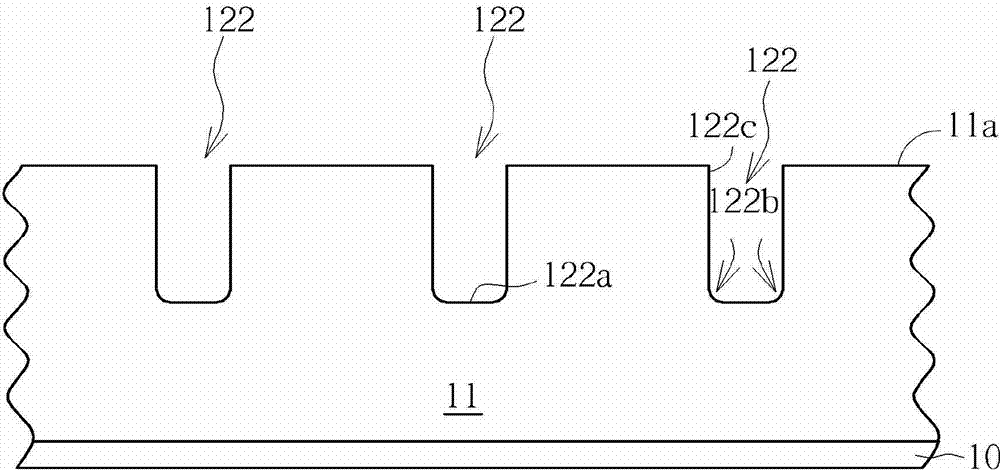

Method for fabricating super-junction power device with reduced miller capacitance

InactiveUS8541278B2Reduced Miller CapacitanceThe process steps are simpleSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceDopant

A method for fabricating a super-junction semiconductor power device with reduced Miller capacitance includes the following steps. An N-type substrate is provided and a P-type epitaxial layer is formed on the N-type substrate. At least a trench is formed in the P-type epitaxial layer followed by forming a buffer layer on interior surface in the trench. An N-type dopant layer is filled into the trench and then the N-type dopant layer is etched to form a recessed structure at an upper portion of the trench. A gate oxide layer is formed, and simultaneously, dopants in the N-type dopant layer diffuse into the P-type epitaxial layer, forming an N-type diffusion layer. Finally, a gate conductor is filled into the recessed structure and an N-type source doped region is formed around the gate conductor in the P-type epitaxial layer.

Owner:ANPEC ELECTRONICS CORPORATION

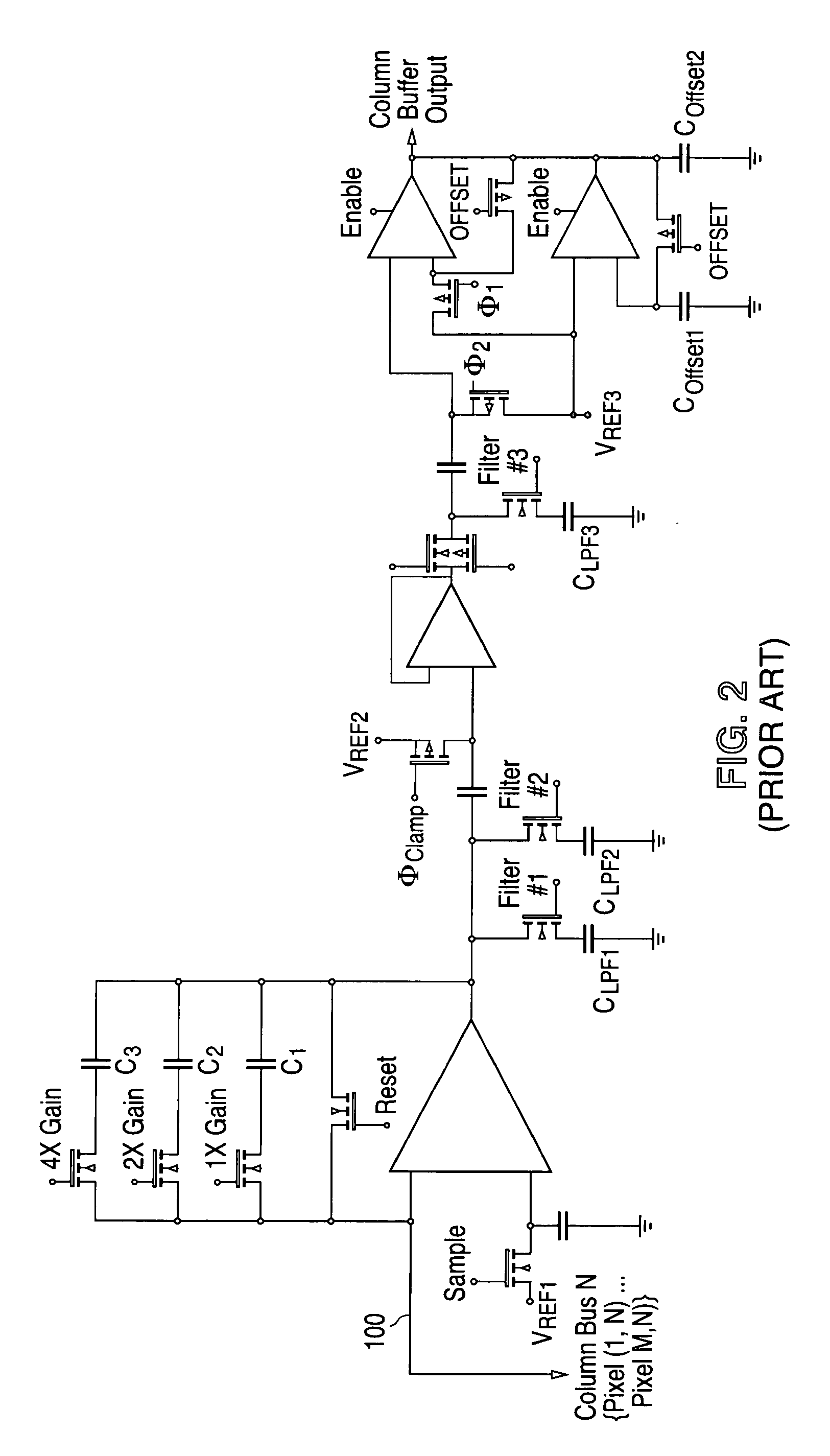

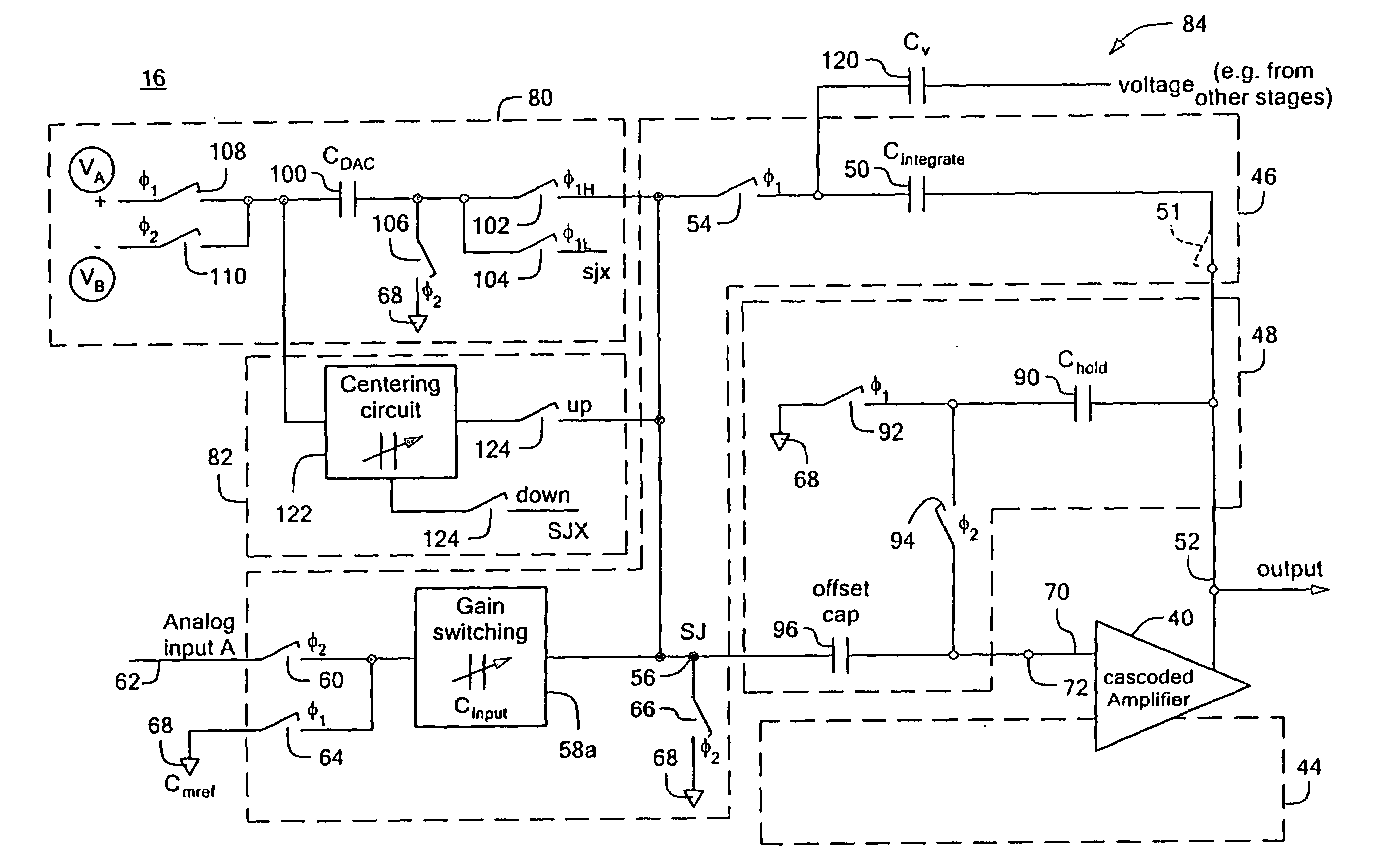

Switched capacitor integrator system

ActiveUS7138848B2Improve errorGain fluctuationsComputing operations for integral formationElectric signal transmission systemsCascode amplifierSwitched capacitor integrator

A switched capacitor integrator system includes an input cascoded amplifier circuit; a summing junction; an integrating switched capacitor circuit connected to the output of the input cascoded amplifier circuit and to the summing junction; the integrating switched capacitor circuit including an input switched capacitor circuit responsive to an input and connected to the summing junction; and a correlated double sampling capacitor circuit including an offset capacitor interconnected between the summing junction and the input of the input cascoded amplifier circuit.

Owner:ANALOG DEVICES INC

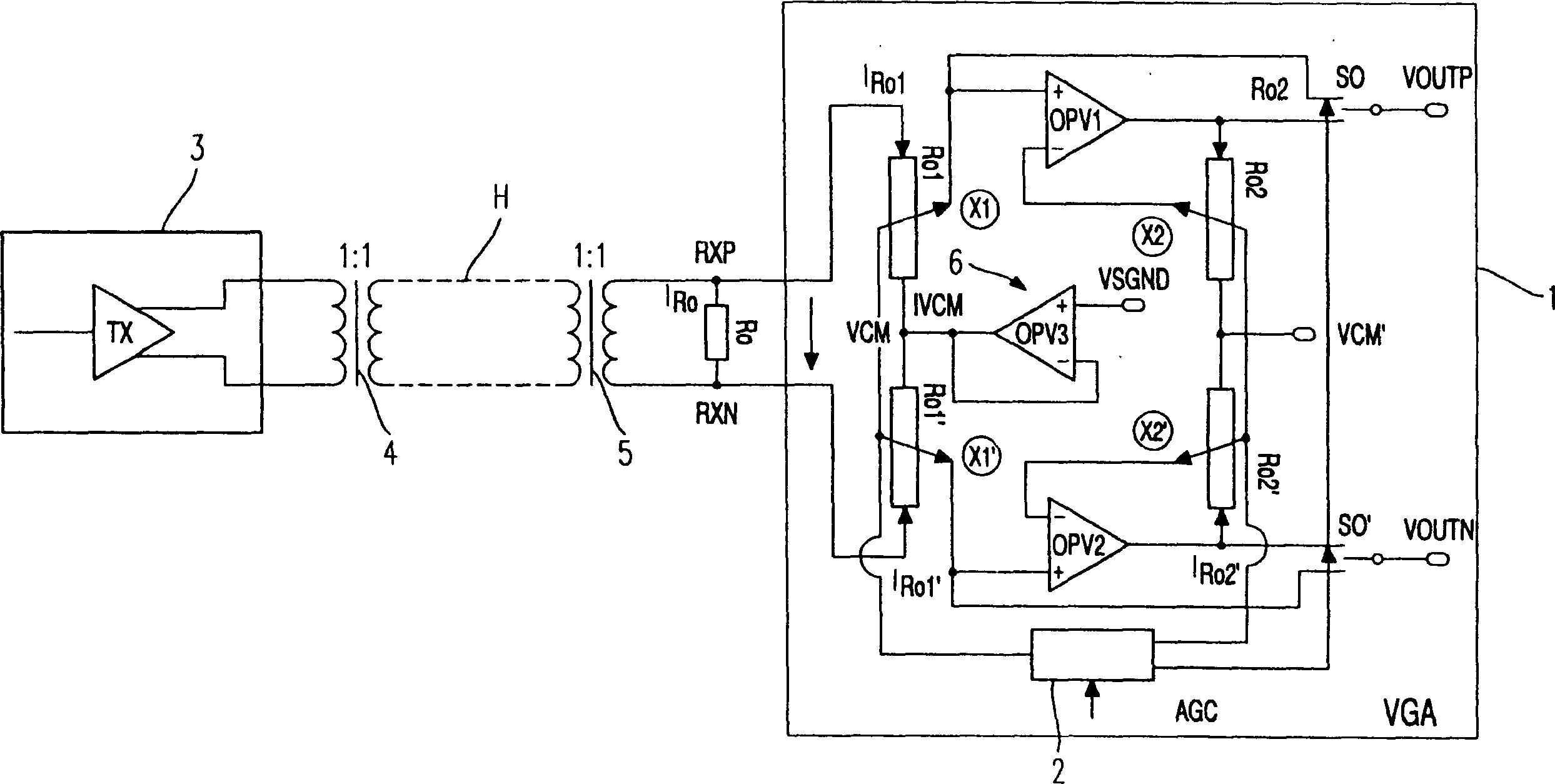

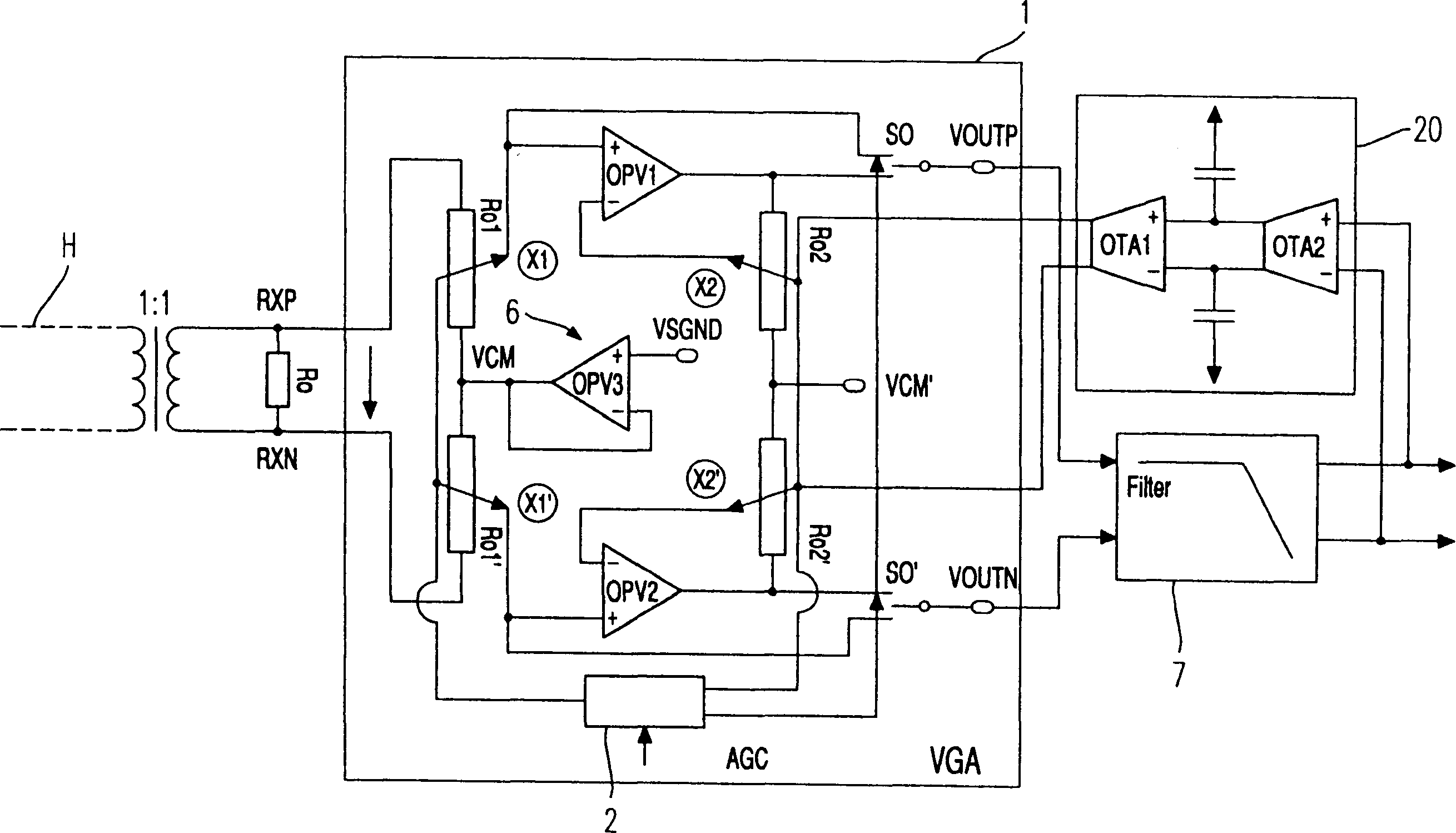

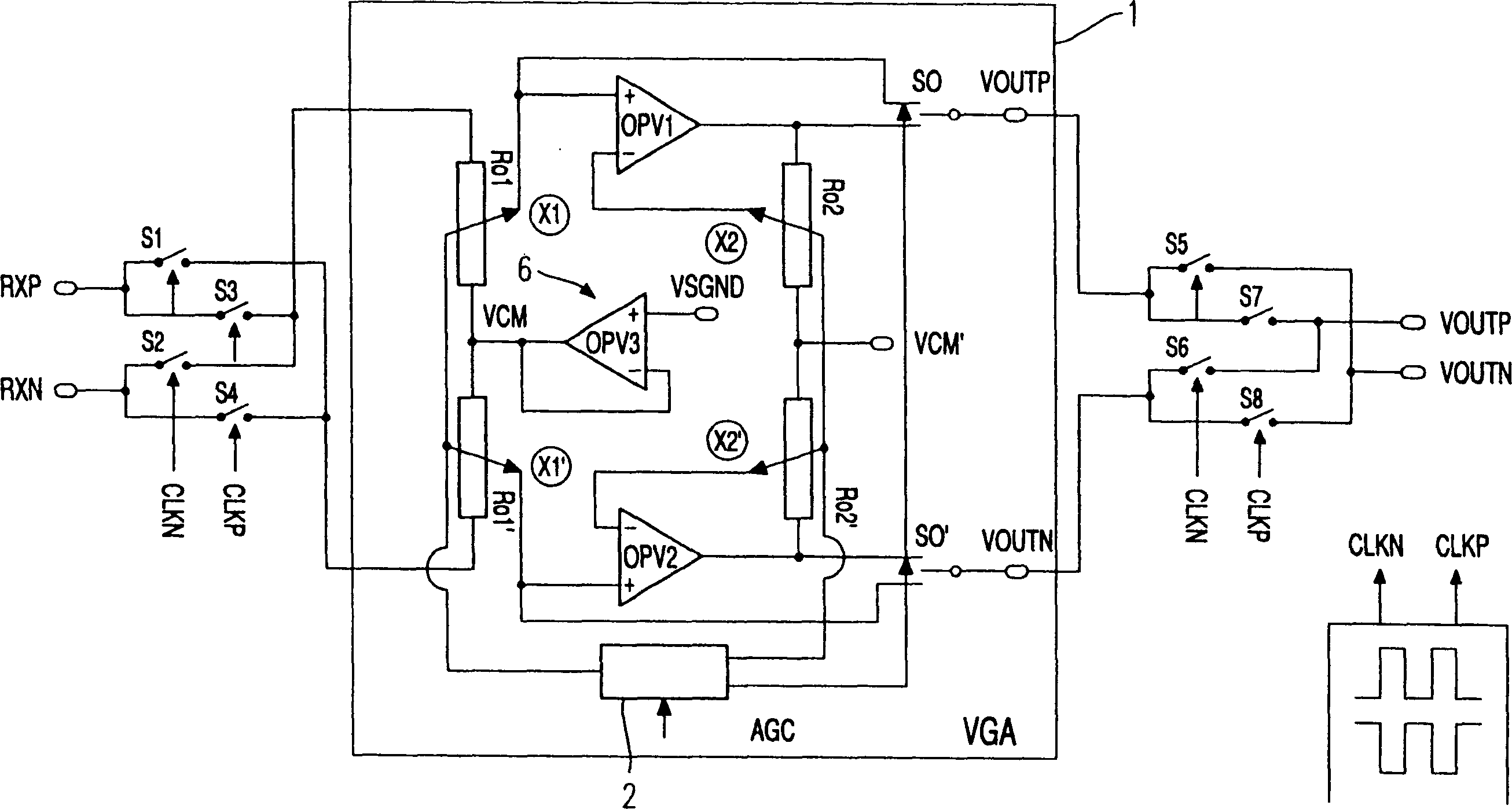

Db-linear variable gain amplifier (vga) stage with a high broad band

InactiveCN1555601AHigh bandwidthReduce stabilityAnalog signal digital controlAmplification control detailsAudio power amplifierVariable-gain amplifier

The invention relates to a VGA stage having a novel circuit configuration for amplifying / attenuating a differential input signal which is transmitted via a transmission line (H). The VGA stage comprises an operational amplifier (OPV1, OPV2), which is connected as shunt feedback, for amplifying the input signal; a string of resistors (R01, R01') for attenuating the signal; and a control device (2) for switching the string of resistors (R01, R01').

Owner:LANTIQ BET GMBH & CO KG

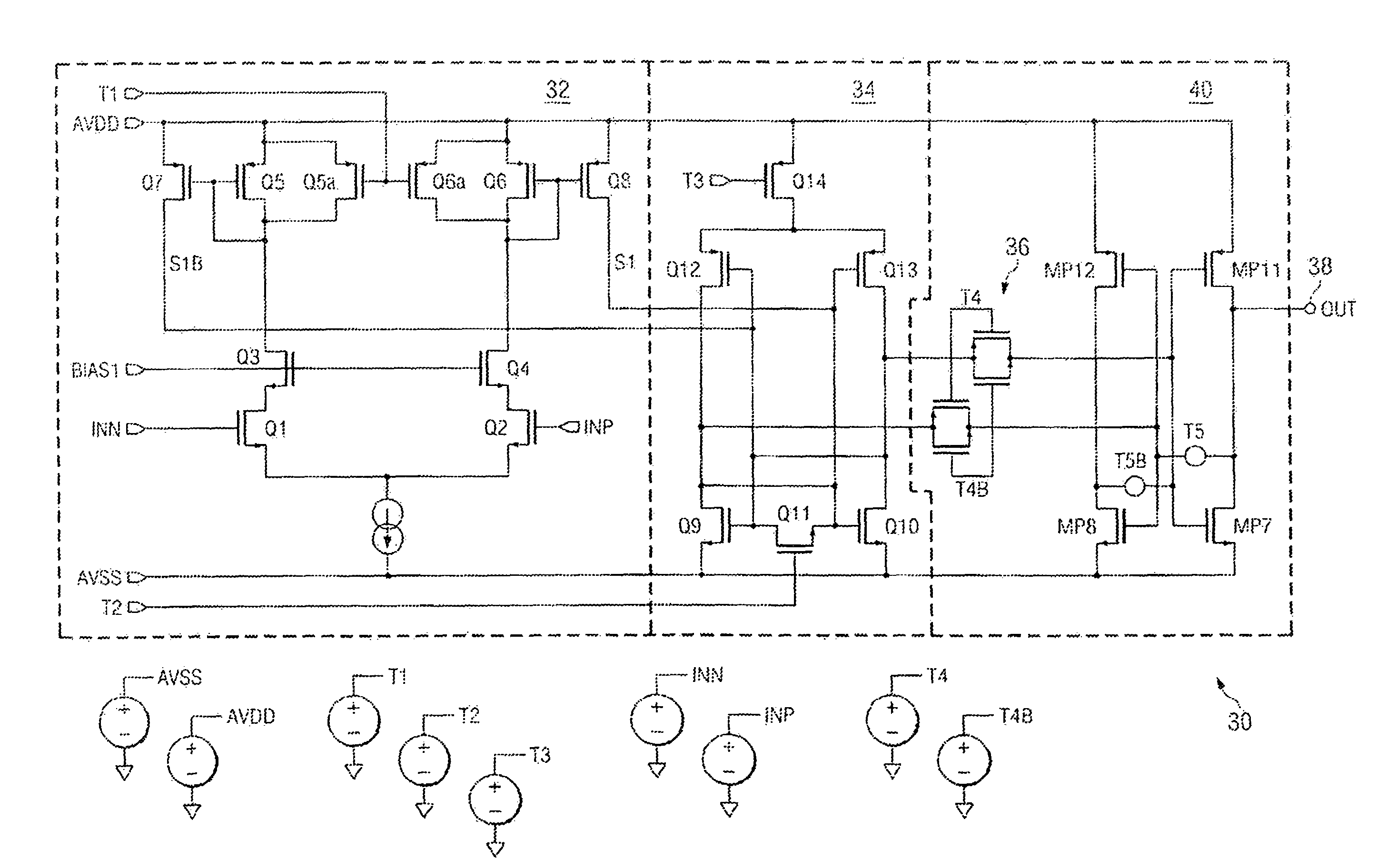

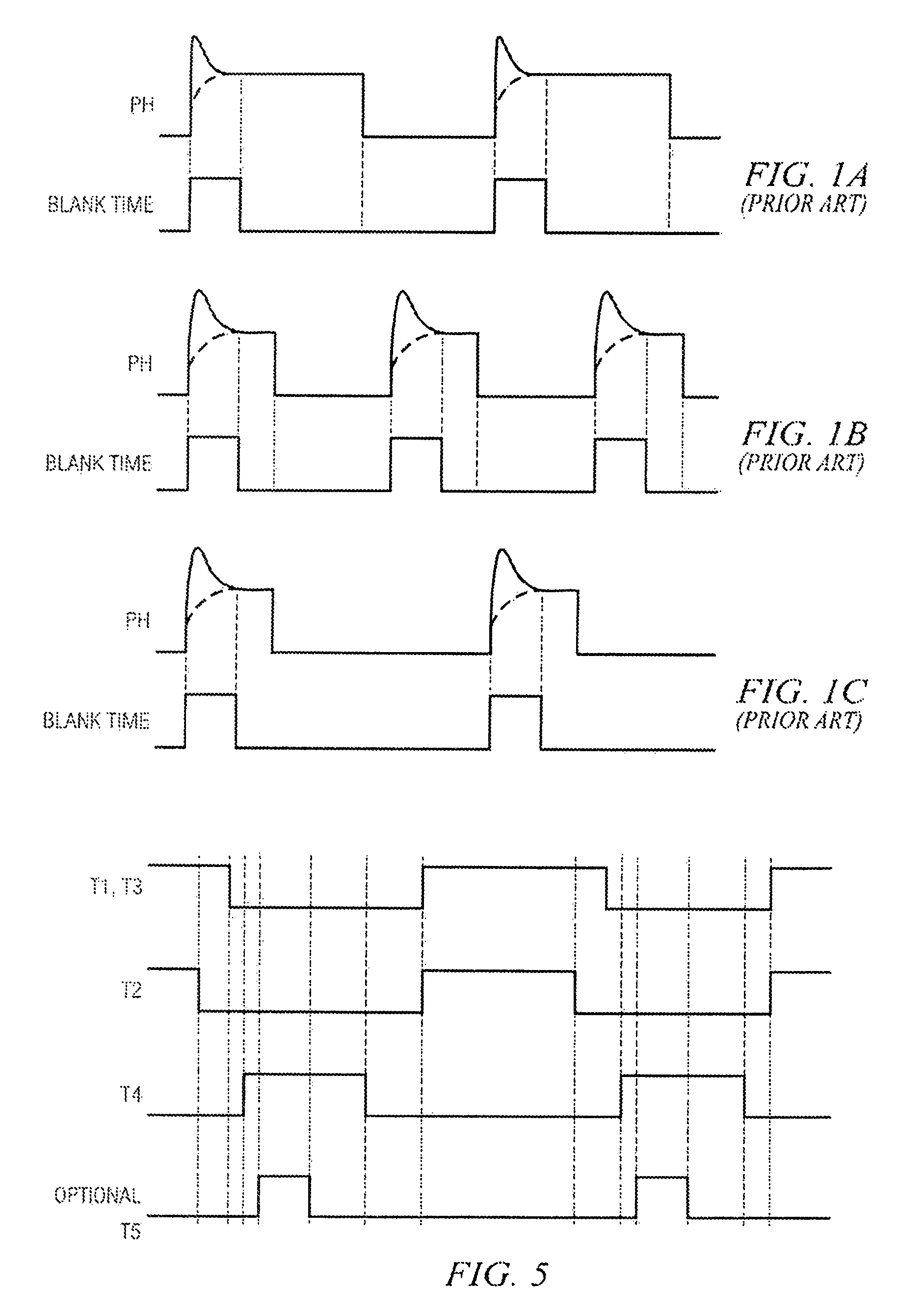

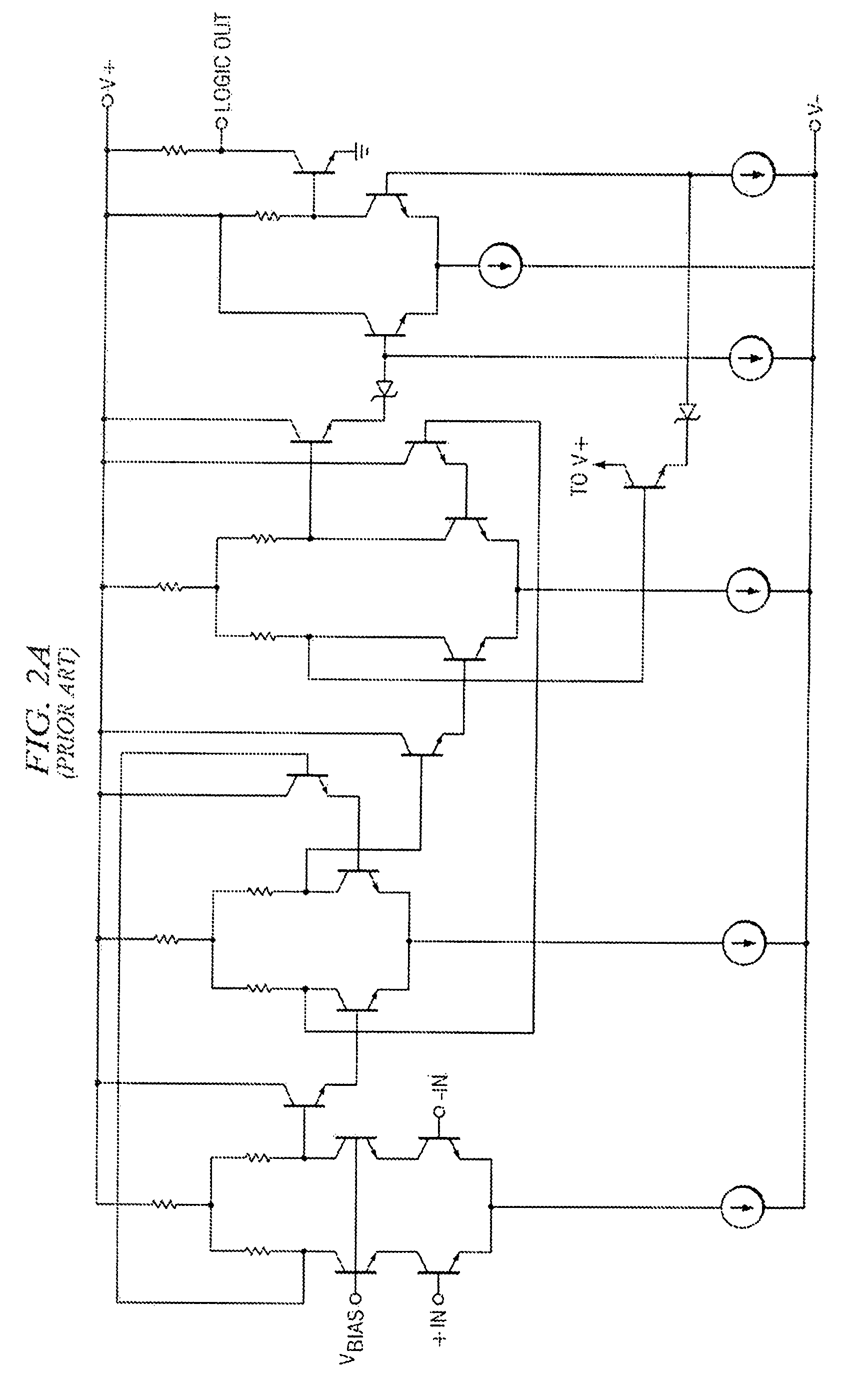

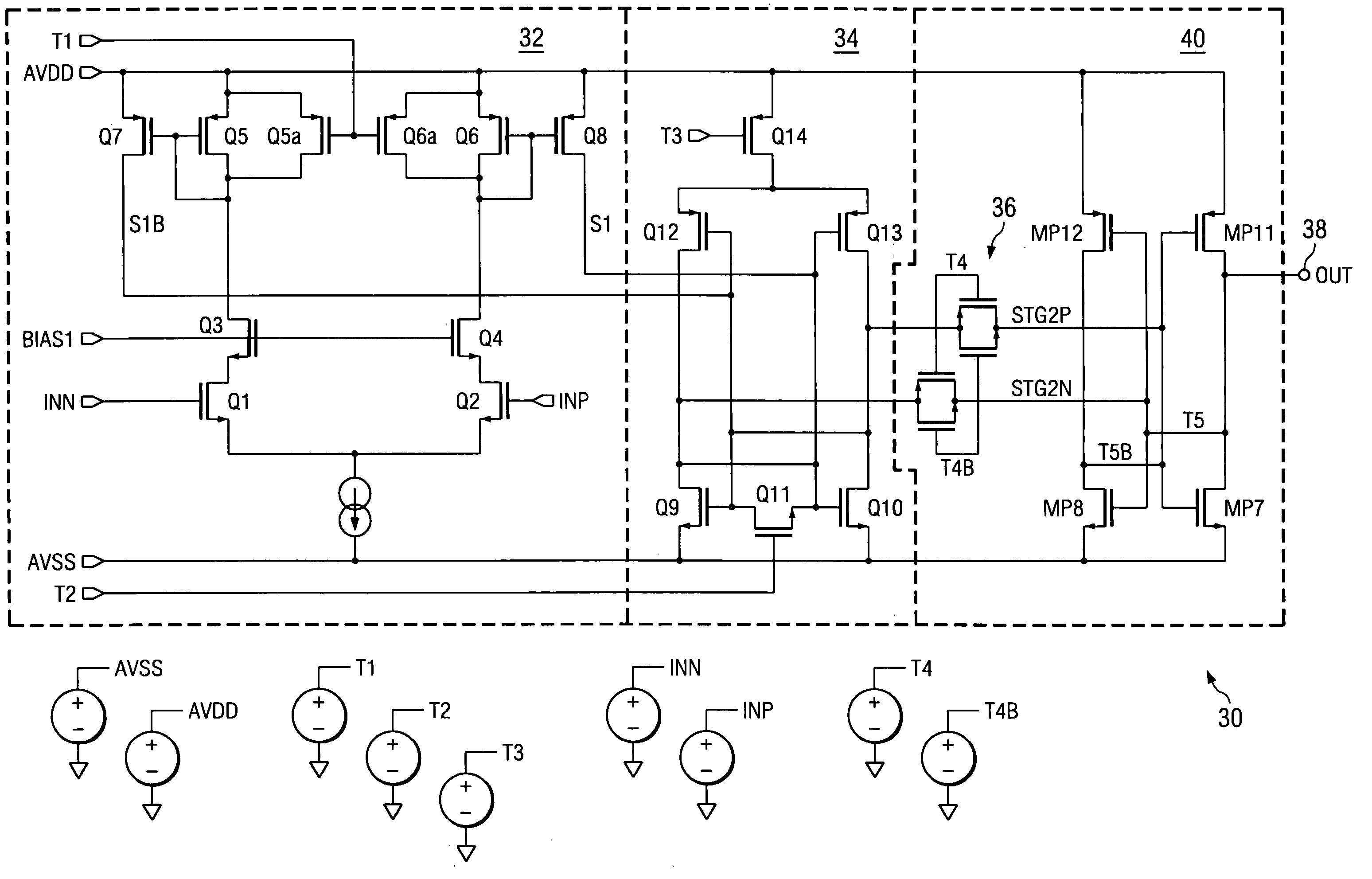

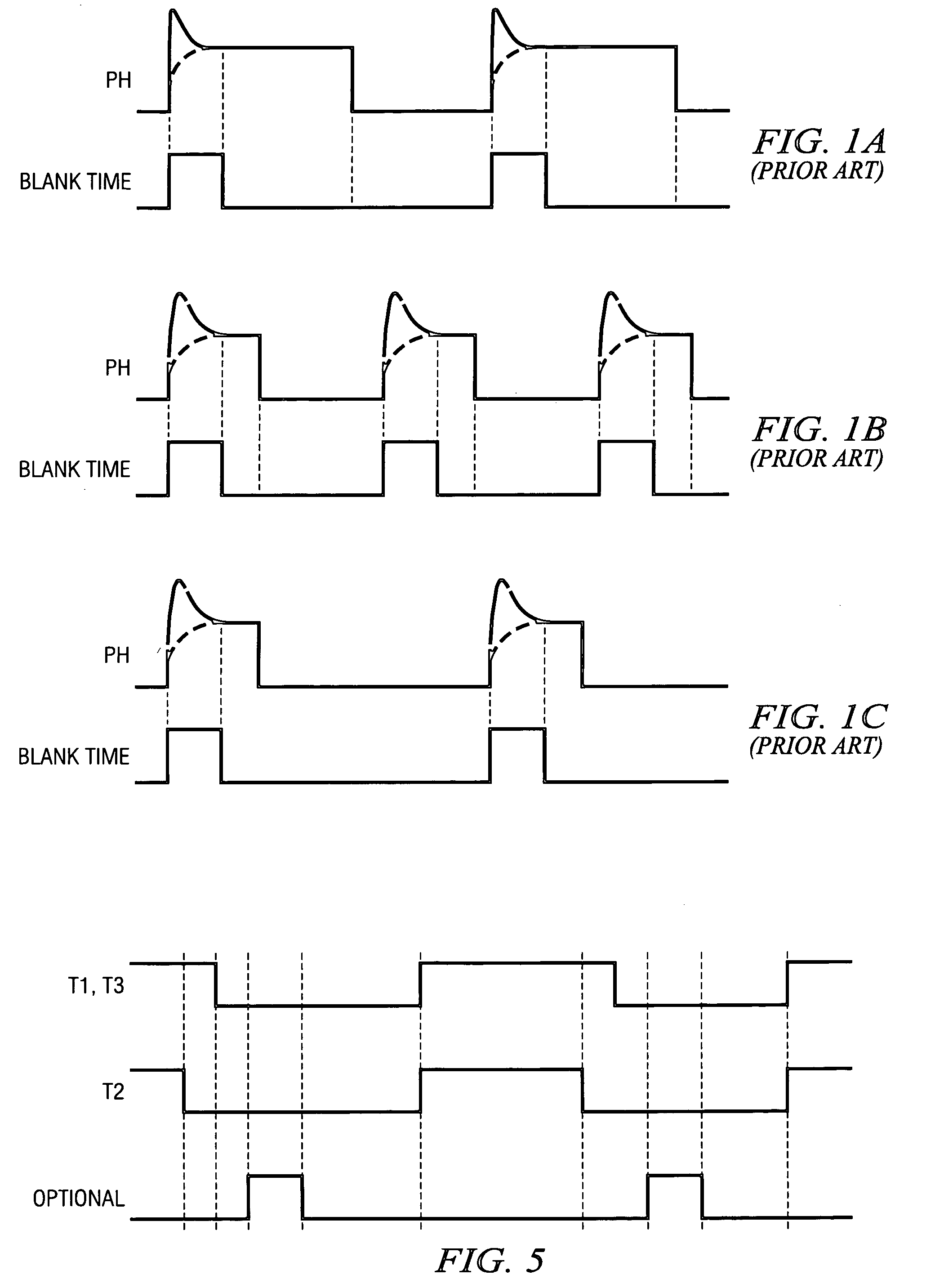

Efficient current monitoring for DC-DC converters

ActiveUS7372307B1Speed up signal processingInhibit inputAnalogue/digital conversionMultiple input and output pulse circuitsAudio power amplifierComparators circuits

A current monitoring circuit for DC-DC switching converters includes a track and latch comparator circuit (30) having a preamplifier (32) that is controlled independently of a latch circuit (34). The comparator is small and operates very fast and with improved sensitivity. For example, the preamplifier circuit is disabled when the latch stage is making its decision to avoid noise and input disturbances from affecting the latch stage. This selective disabling feature speeds up the signal processing of the comparator and allows it to work in parallel with other circuits. The latch stage can make its decision later, regardless of any further activity at the inputs of the comparator.

Owner:TERIDIAN SEMICONDUCTOR

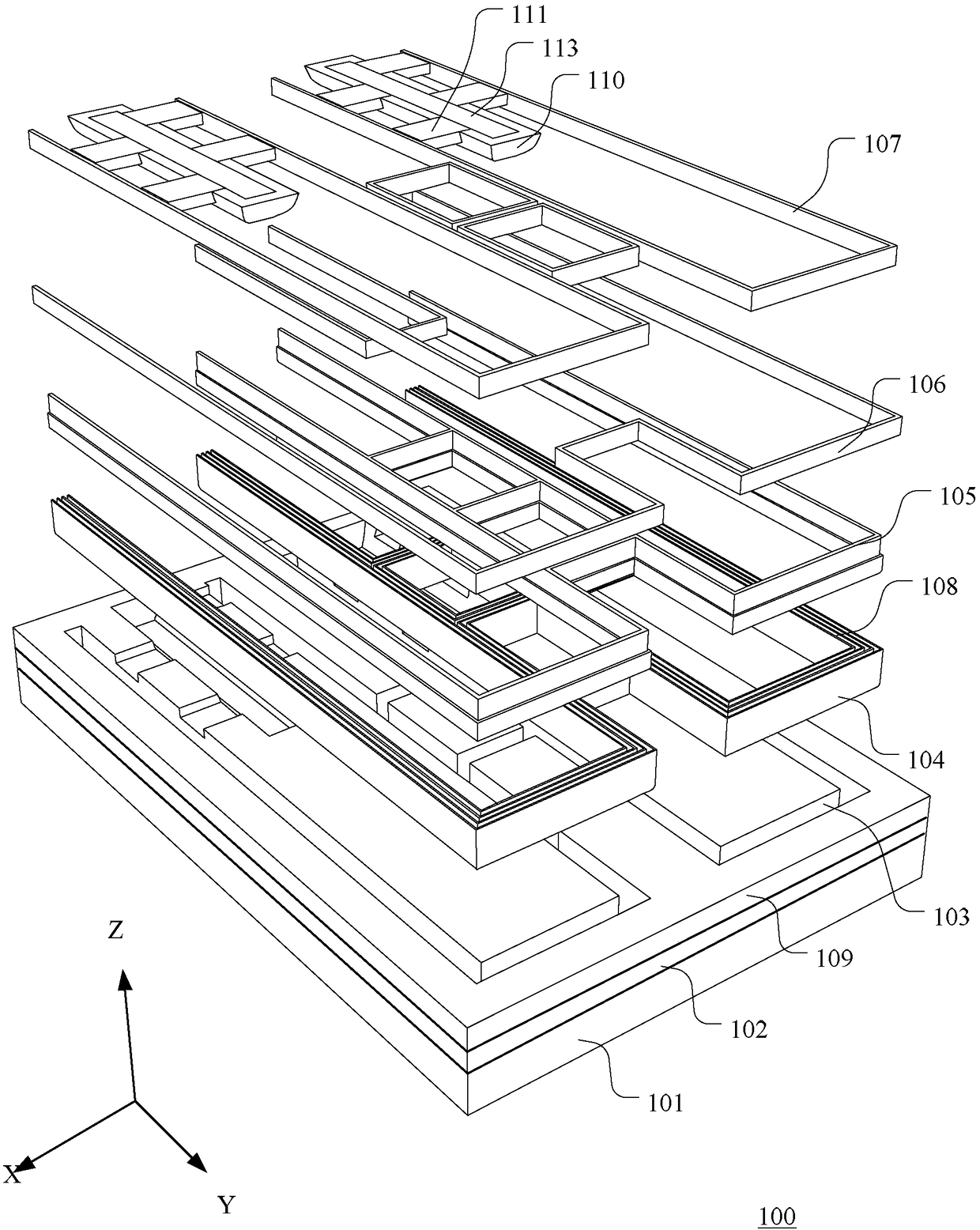

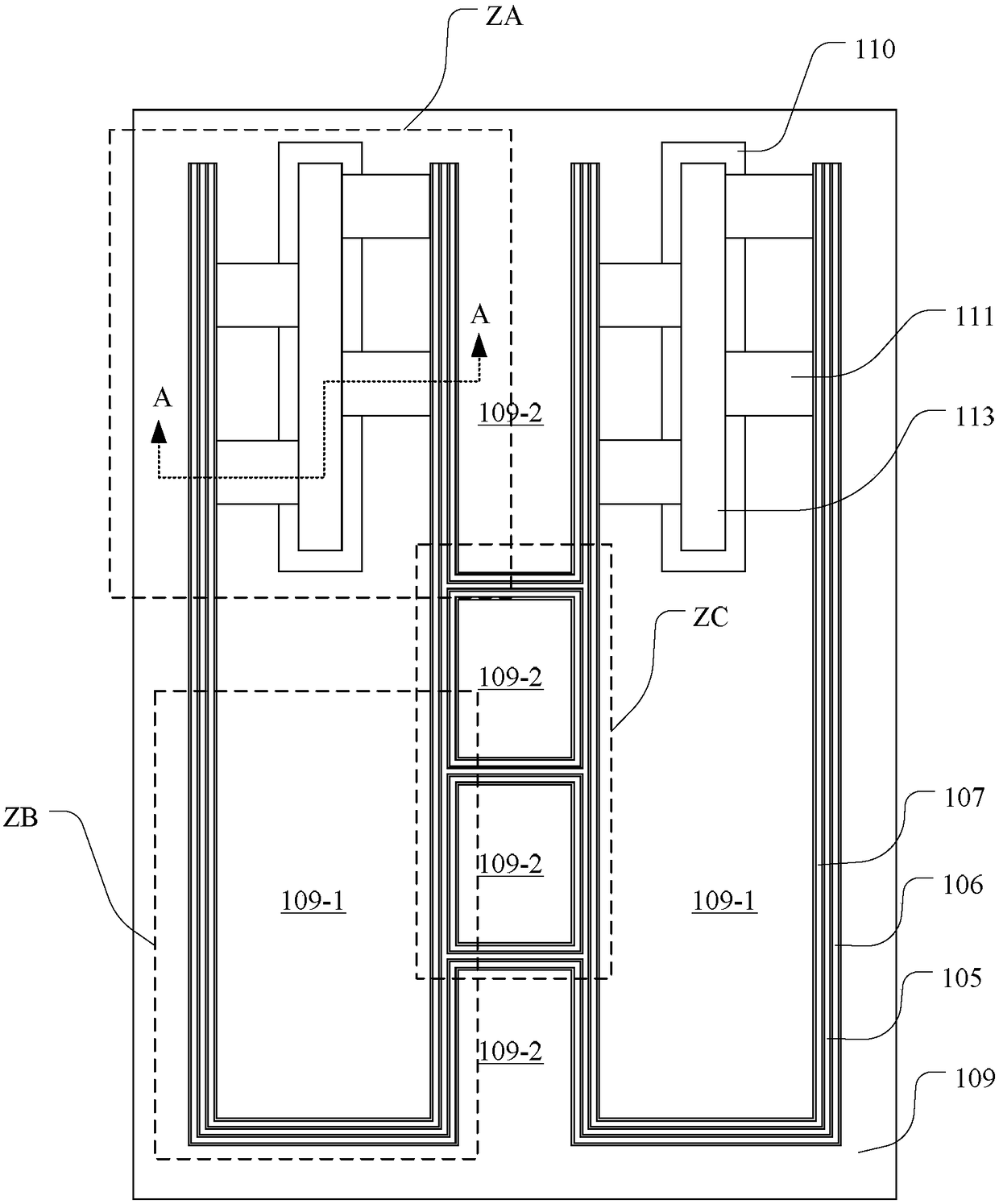

RET IGBT with self-bias PMOS and manufacturing method thereof

ActiveCN110504310AImprove forward conduction characteristicsEffect of shield breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceCapacitance

The invention belongs to the technical field of power semiconductor devices, and relates to a RET IGBT with a self-biased PMOS and a manufacturing method thereof. According to the RET IGBT with the self-biased PMOS and the manufacturing method thereof, a N-type charge storage layer is arranged between a P-type base region and a P-type buried layer, so that the influence of the N-type charge storage layer on the breakdown voltage of the device can be shielded while the forward conduction characteristic of the device is improved; by introducing a PMOS structure, an extra path is provided for theextraction of holes, the extraction speed of current carriers is accelerated, the switching speed of the device is improved, and the turn-off loss of the device is reduced; and meanwhile, an emitterembedded type separation gate structure can meet the requirement that a table top of the device is further narrowed to improve the forward conduction characteristic of the device, metal and contact holes of the emitter of the device can be easily and irregularly made, and meanwhile, the Miller capacitance of the device can be reduced further.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Efficient current monitoring for DC-DC converters

InactiveUS20050242845A1Prevent degradationFast decision circuitMultiple input and output pulse circuitsCurrent/voltage measurementAudio power amplifierComparators circuits

The present invention achieves technical advantages as a current monitoring circuit for DC-DC switching converters, including a track and latch comparator circuit (30) having a preamplifier (32) that is controlled independently of a latch circuit (34). Advantageously, the comparator is small and operates very fast and with improved sensitivity. For example, the preamplifier circuit is disabled when the latch stage is making its decision to avoid noise and input disturbances from affecting the latch stage. This selective disabling feature speeds up the signal processing of the comparator and allows it to work in parallel with other circuits. The latch stage can make its decision later, regardless of any further activity at the inputs of the comparator.

Owner:TEXAS INSTR INC

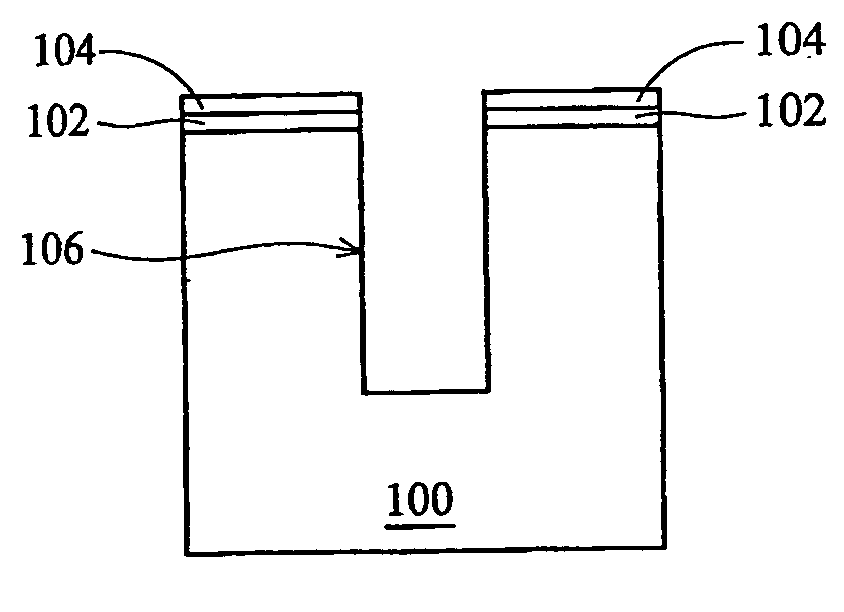

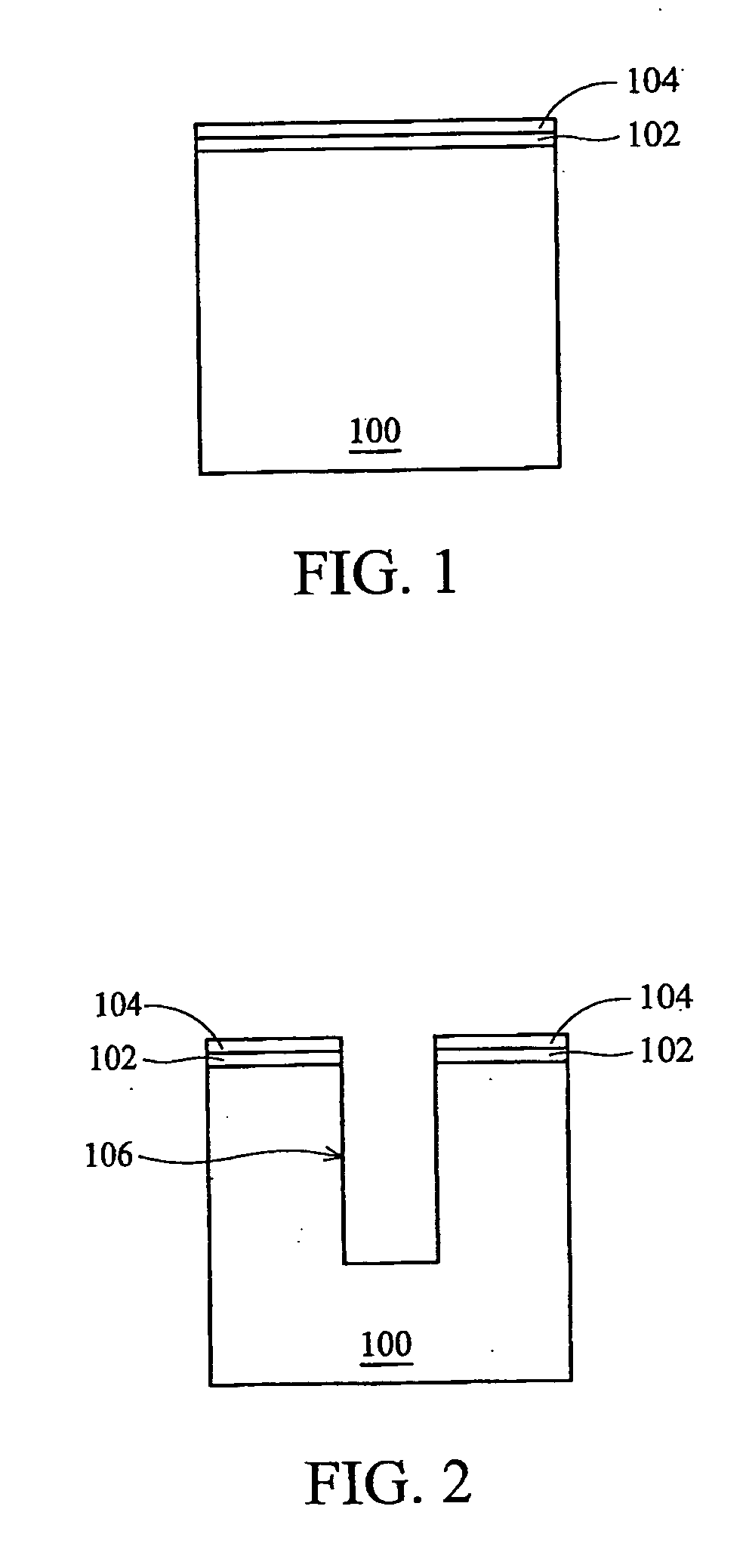

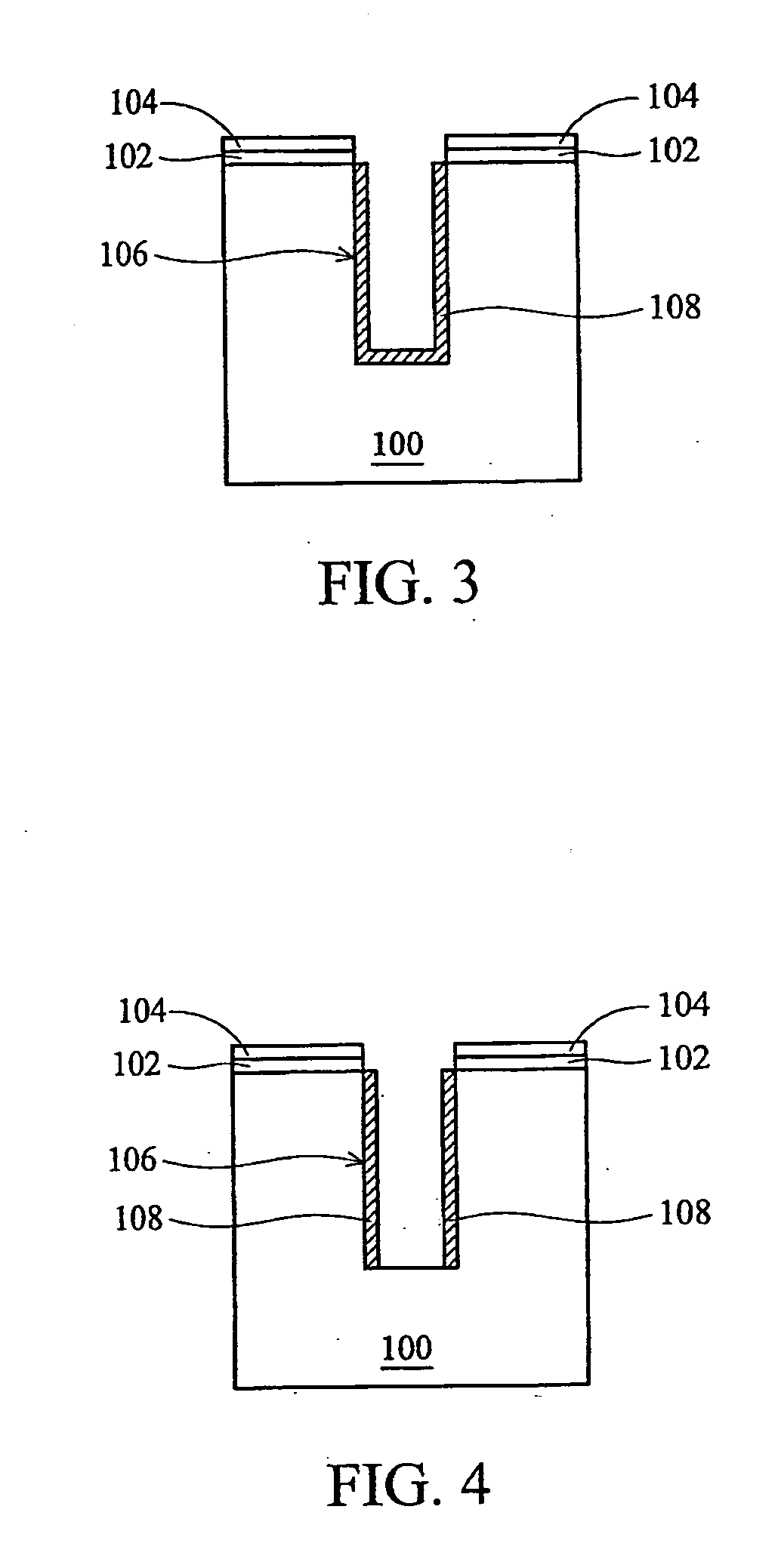

Method for fabricating super-junction power device with reduced miller capacitance

InactiveUS20120295410A1Reduced Miller CapacitanceThe process steps are simpleSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsCapacitance

A method for fabricating a super-junction semiconductor power device with reduced Miller capacitance includes the following steps. An N-type substrate is provided and a P-type epitaxial layer is formed on the N-type substrate. At least a trench is formed in the P-type epitaxial layer followed by forming a buffer layer on interior surface in the trench. An N-type dopant layer is filled into the trench and then the N-type dopant layer is etched to form a recessed structure at an upper portion of the trench. A gate oxide layer is formed, and simultaneously, dopants in the N-type dopant layer diffuse into the P-type epitaxial layer, forming an N-type diffusion layer. Finally, a gate conductor is filled into the recessed structure and an N-type source doped region is formed around the gate conductor in the P-type epitaxial layer.

Owner:ANPEC ELECTRONICS CORPORATION

A silicon carbide MOSFET device and a manufacturing method thereof

ActiveCN109148566AImprove the withstand voltage levelImprove long-term application reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionMOSFET

The invention provides a silicon carbide MOSFET device and a manufacturing method thereof. The invention aims at a conventional silicon carbide UMOSFET structure, and proposes a multi-sub rectifier device integration mode, and includes implementation methods of Schottky contact and Si / SiC heterojunction contact. While effectively improving the basic characteristics of the traditional carbonize UMOSFET and optimizing the long-term application reliability of the device, the invention realizes the integration of the multi-sub rectifier devices, thereby greatly optimizing the work performance of the device in the third quadrant. The implementation process of the structure is compatible with the traditional silicon carbide UMOSFET process, and has the characteristic of easy fabrication.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

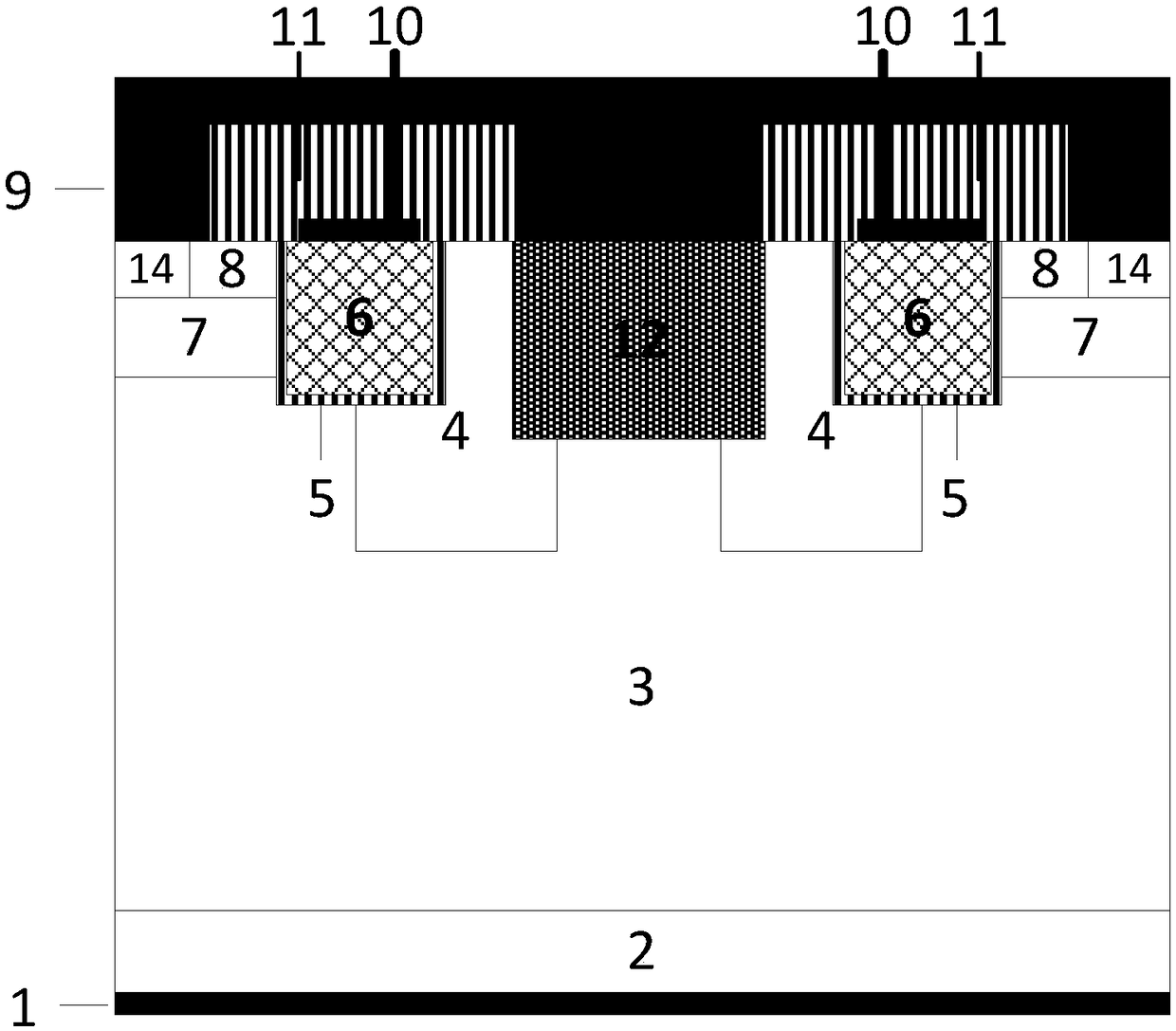

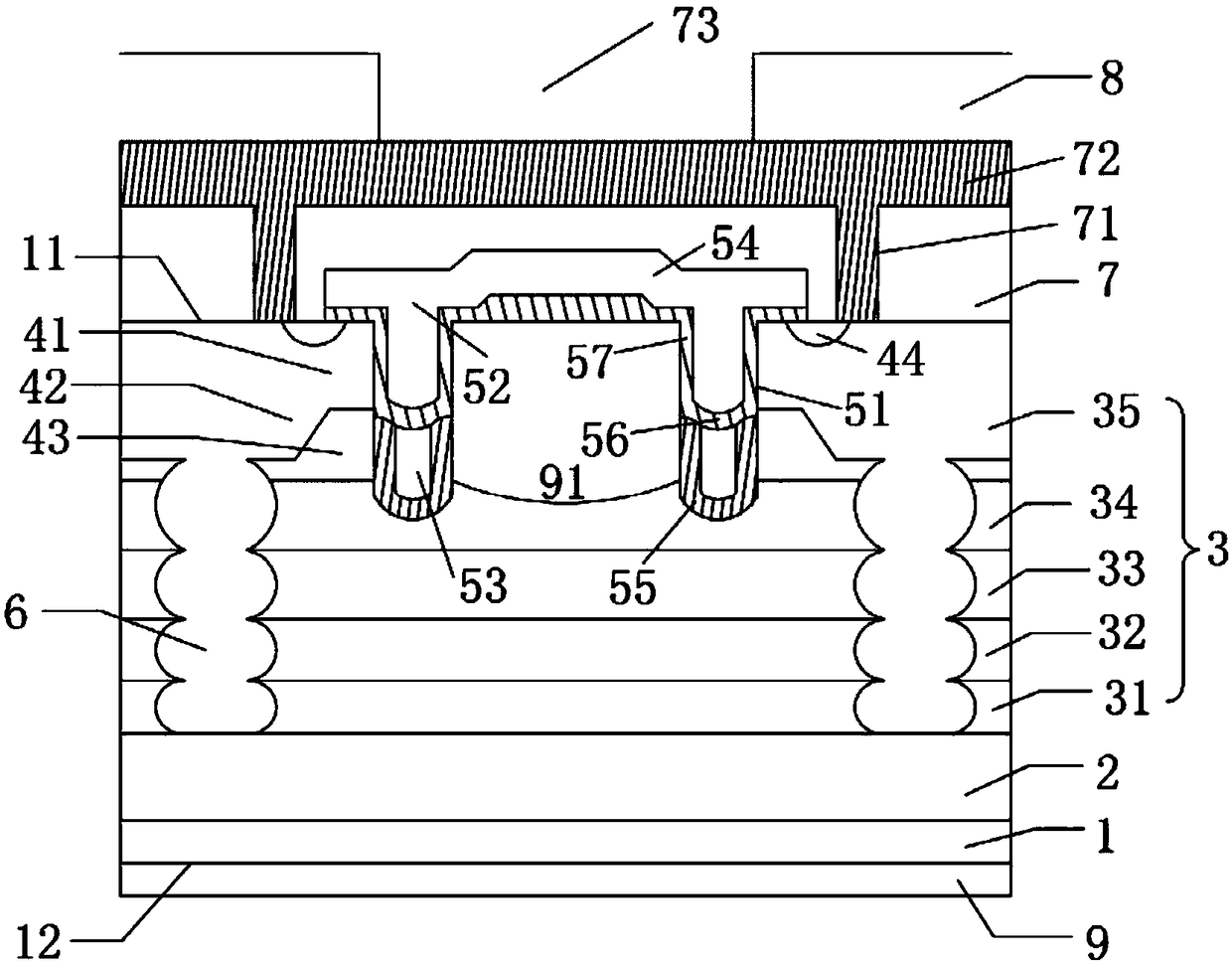

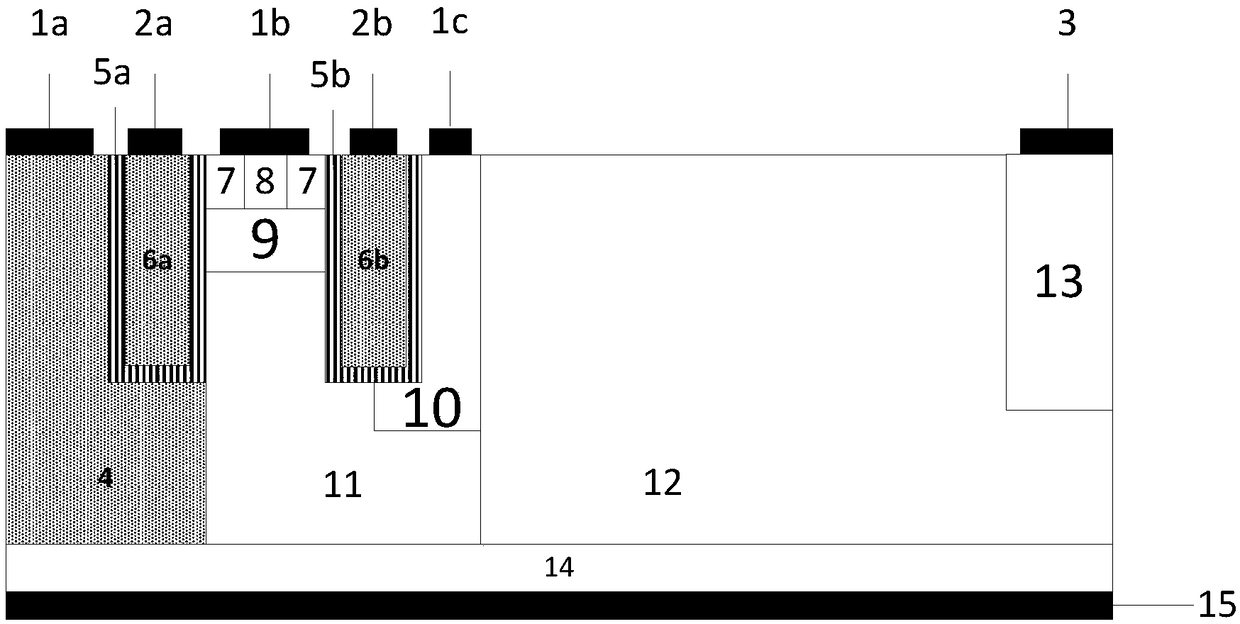

Transverse groove-type MOSFET device and preparation method thereof

ActiveCN109119463AAchieve integrationImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionMOSFET

The present invention provides a transverse groove-type MOSFET device, belonging to the technical field of semiconductor power devices. A polycrystalline silicon region or a Schottky contact metal region is formed at the circumference side of the gate structure to allow polycrystalline silicon region or the Schottky contact metal region and the drift region to form heterojunction or Schottky contact with rectification characteristics. Because the heterojunction or Schottky contact is multiple sub devices and is lower in conduction pressure drop compared to a traditional parasitic diode, the reverse recovery characteristic of the device can be optimized, and an excellent three-quadrant on-state performance is achieved; and compared to an external antiparallel diode mode, the size of the electrical power system can be significantly reduced, the package cost is reduced, interconnection lines are reduced, and the parasitic effect of the interconnection lines is reduced so as to improve thereliability of the system. Aiming at the problem that the device gate medium electric field is too high, the optimization is design to improve the long application reliability performance of the device. Besides, the preparation method of the device is simple and controllable and easy to achieve, and promotes the popularization of the semiconductor power device in the many actual applications.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Heavy doping method of source electrode and drain electrode, semiconductor device and manufacturing method thereof

InactiveCN102610505AReduce parasitic overlap capacitanceReduced Miller CapacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceIon implantation

The invention discloses a heavy doping method of a source electrode and a drain electrode. According to the heavy doping method of the source electrode and the drain electrode, the ion implantation direction inclines to the direction of the source electrode and is vertical to the direction of a substrate so as to form an included angle, the heavy doping area of the source electrode and a heavy doping area of the drain electrode are of asymmetrical structures as the ion implantation direction is not vertical to the surface of the substrate, the distance between the heavy doping area of the drain electrode is far from a groove by pulling, and the area of the overlapping region between the heavy doping area of the drain electrode and a gate electrode structure is reduced, so that the parasitic overlapping capacitance between the drain electrode and the gate electrode can be reduced, further the Miller capacitance of a common-source amplifier can be reduced, and the frequency response characteristics of the common-source amplifier are improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Anti-EMI SGT device

PendingCN112002686AReduce Switching ShockLower on-resistanceSemiconductor/solid-state device detailsSolid-state devicesCapacitancePolysilicon gate

The invention discloses an anti-EMI SGT device. The device comprises a substrate of a first conductive type, an epitaxial layer of the first conductive type which is positioned on the upper surface ofthe substrate of the first conductive type, a trench gate structure located in the epitaxial layer of the first conductive type, a trench source structure located above the side surface of the epitaxial layer of the first conductive type, a first dielectric layer and a heavily doped body region of the first conductive type located between the trench source structure and the epitaxial layer of thefirst conductive type, and a second dielectric layer located above the trench gate structure, wherein the trench gate structure comprises a gate trench, and a shielding gate and a polycrystalline silicon gate which are positioned in the gate trench; the trench source structure includes a source trench and a source metal located within the source trench. According to the device disclosed in the invention, the SGT source-drain capacitance Cds is increased, the switching oscillation is reduced, and therefore the voltage oscillation dv / dt failure possibility and EMI noise of the device are reduced.

Owner:VANGUARD SEMICON CORP

Trench insulated gate bipolar transistor device and generating method thereof

InactiveCN109473474AImprove consistencyEnsure consistencySemiconductor/solid-state device manufacturingSemiconductor devicesEtchingDelayed time

The invention provides a trench insulated gate bipolar transistor device and a generating method thereof. A relatively thick gate oxide film is formed at the bottom of a trench region through a plasmafilm forming process. Due to the fact that the thickness of the gate oxide film at the bottom of a trench is increased, the consistency of the gate oxide thickness is guaranteed, the defect that a gate oxide layer at the bottom of the trench is easy to break down is eliminated, and the robustness of a gate oxide breakdown voltage is improved. Meanwhile, the area of a gate-drain capacitor is reduced, so that the Miller capacitance is reduced, the switch delay time is shortened, the switch dynamic loss of a device is reduced, and the switch characteristic of the device is improved. Meanwhile, the relatively thick gate oxide film is formed at the bottom of the trench, so that the upper surface of polycrystalline silicon subjected to back etching can be leveled and is slightly higher than thesurface of a silicon wafer of a N-type base region; and higher N+ emitter junction depth can be formed without increasing the injection energy of an N+ emitter and carrying out longer-time high-temperature trap pushing, so that the vertical overlapping area of the gate and the source is reduced, the gate-source capacitance is reduced, and the switch loss of an IGBT is reduced.

Owner:上海擎茂微电子科技有限公司

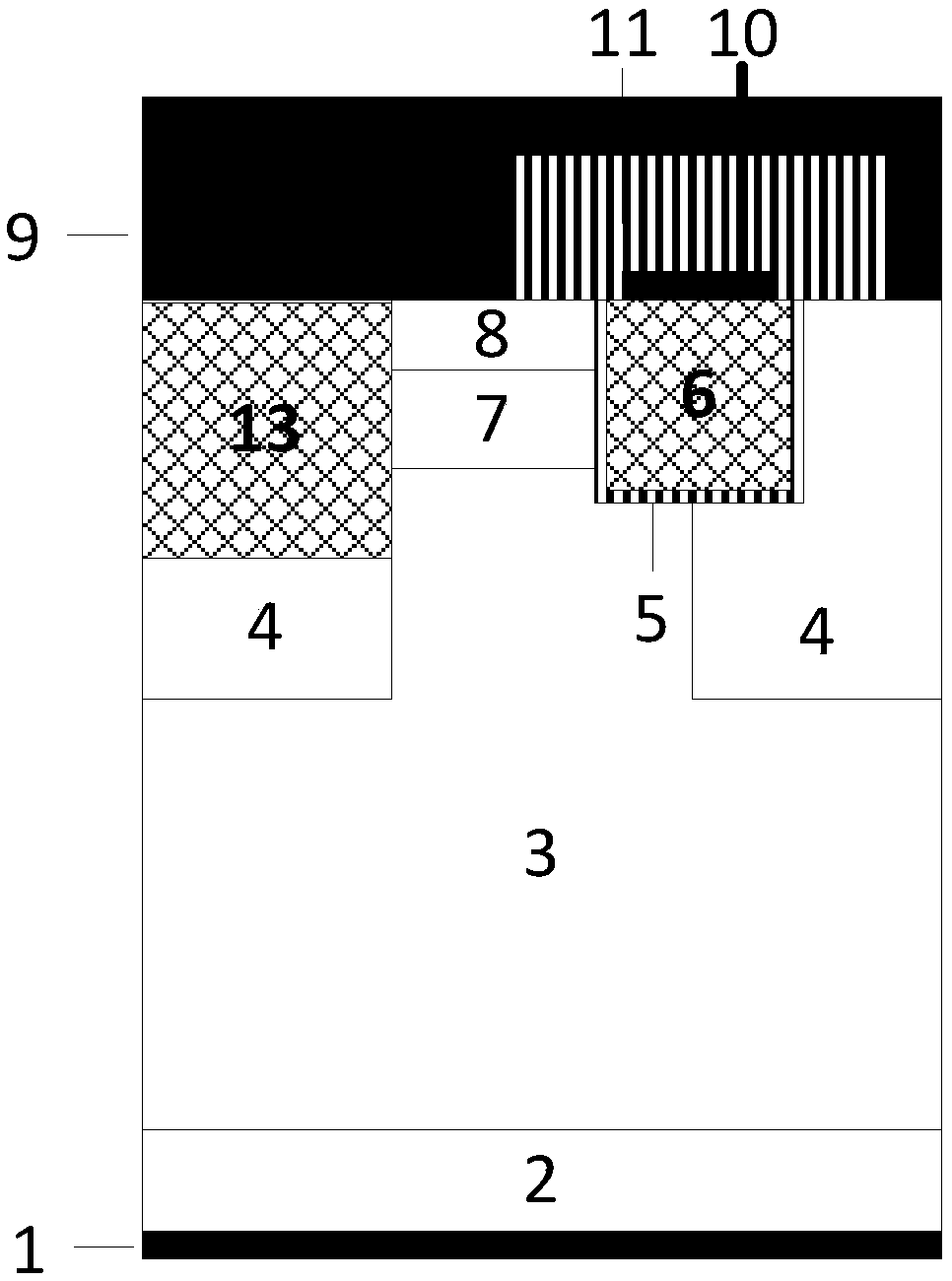

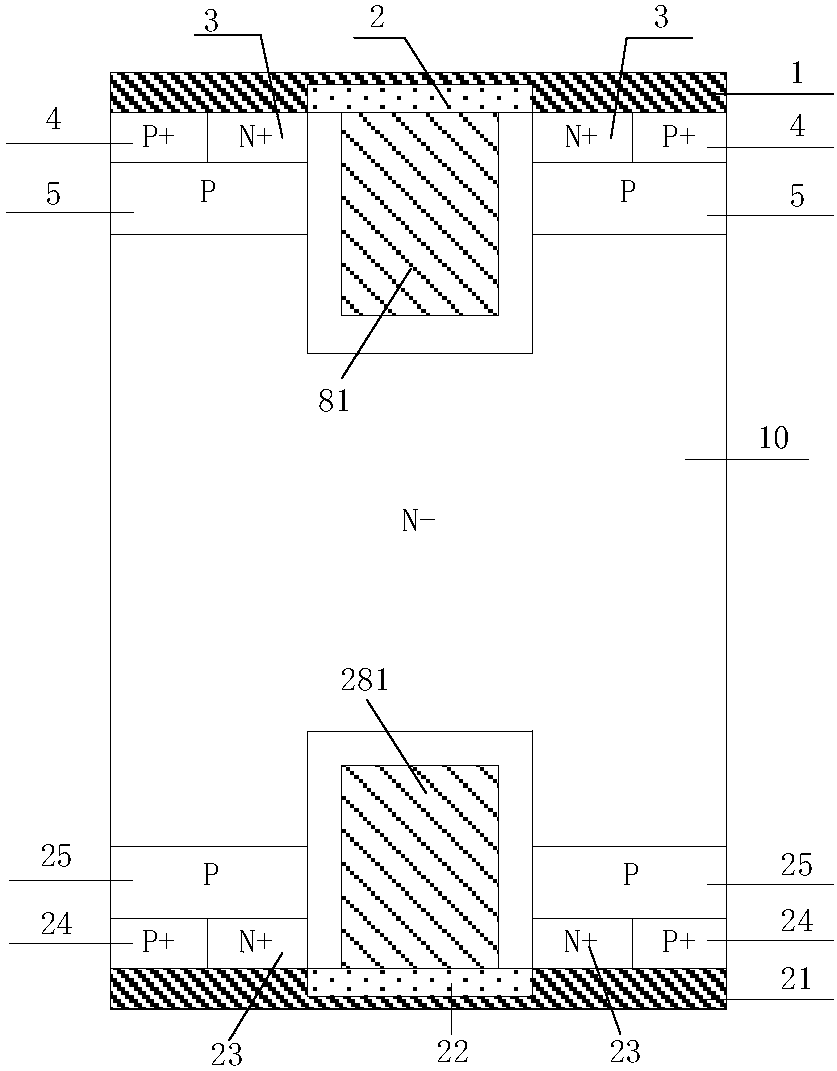

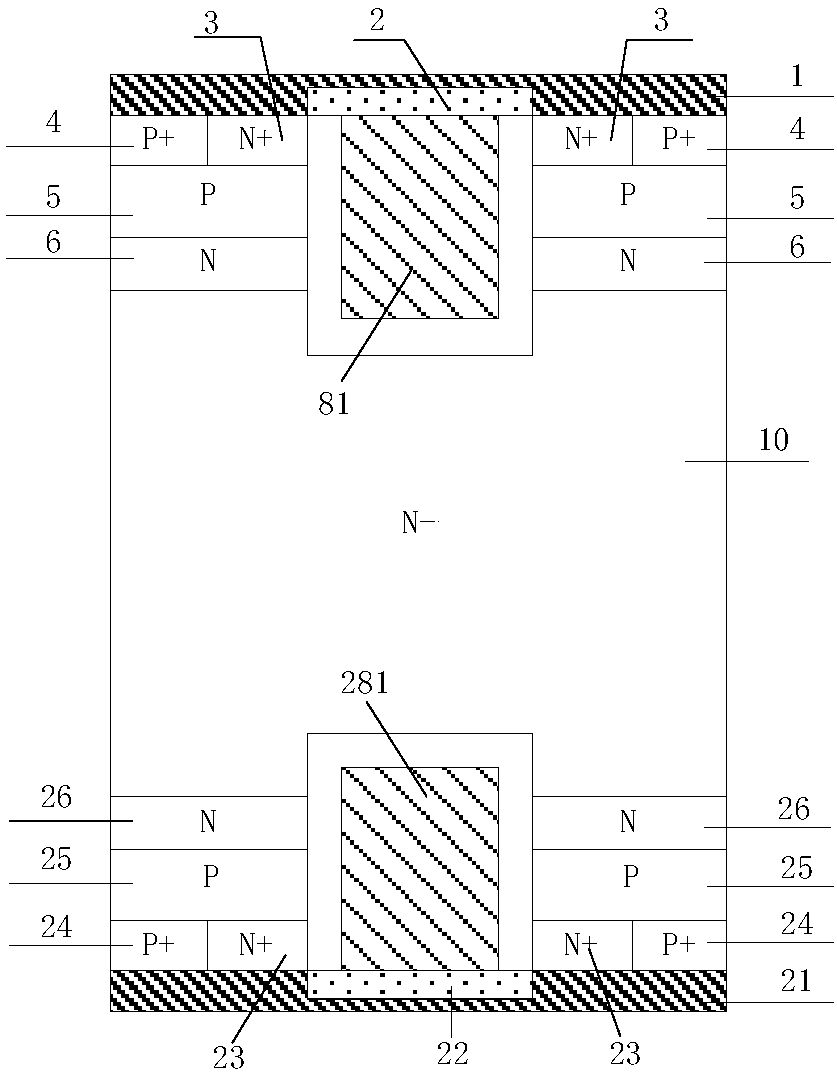

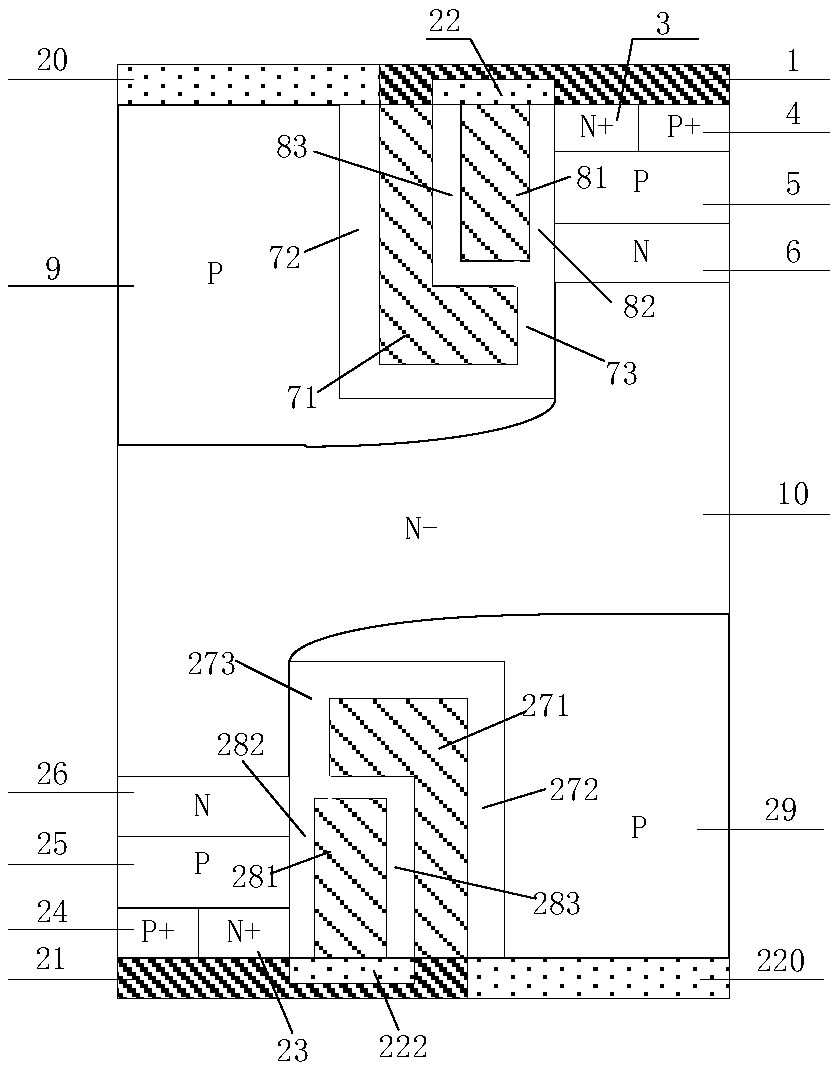

Bidirectional IGBT and manufacturing method therefor

InactiveCN107768435AImprove adverse effectsReduced Miller CapacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEquipotential

The invention discloses a bidirectional IGBT and a manufacturing method therefor, and belongs to the technical field of power semiconductor devices. According to the invention, a split electrode whichis equipotential with a surface metal and a thick dielectric layer located at a peripheral side of the split electrode are introduced to a conventional trench gate structure, and a floating P-type body region is introduced to one side of a split trench gate structure, thereby achieving the symmetric forwarding and reverse on / off characteristics of an IGBT structure under the condition that a threshold voltage and connection of an IGBT device are not affected. The adverse effect caused by the Miller effect is improved, and the drive power consumption is reduced. The current and voltage oscillation and EMI problems are avoided in a start dynamic process of the device. The short-circuit safety working area of the device is improved. The gate capacitance is reduced, the switching speed of thedevice is improved, and the switching loss of the device is reduced. The concentration of an electric field at the bottom of a trench is improved, and the breakdown voltage of the device is improved.The carrier enhancement effect of an emitter electrode is improved, the carrier concentration distribution of the whole N-type drift region is improved, and the compromise between the forwarding conduction voltage drop and switching-off loss is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Semiconductor device with reduced miller capacitance and fabrication method thereof

InactiveCN103840000AReduced Miller CapacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceCapacitance

A semiconductor power device includes an epitaxial layer grown on a semiconductor substrate; an ion well with a junction depth in the epitaxial layer; a gate trench with a depth deeper than the junction depth in the ion well; a gate oxide layer in the gate trench; a gate embedded the gate trench; and a pocket doping region in the epitaxial layer. The pocket doping region is adjacent to and covers at least a corner of the gate trench.

Owner:ANPEC ELECTRONICS CORPORATION

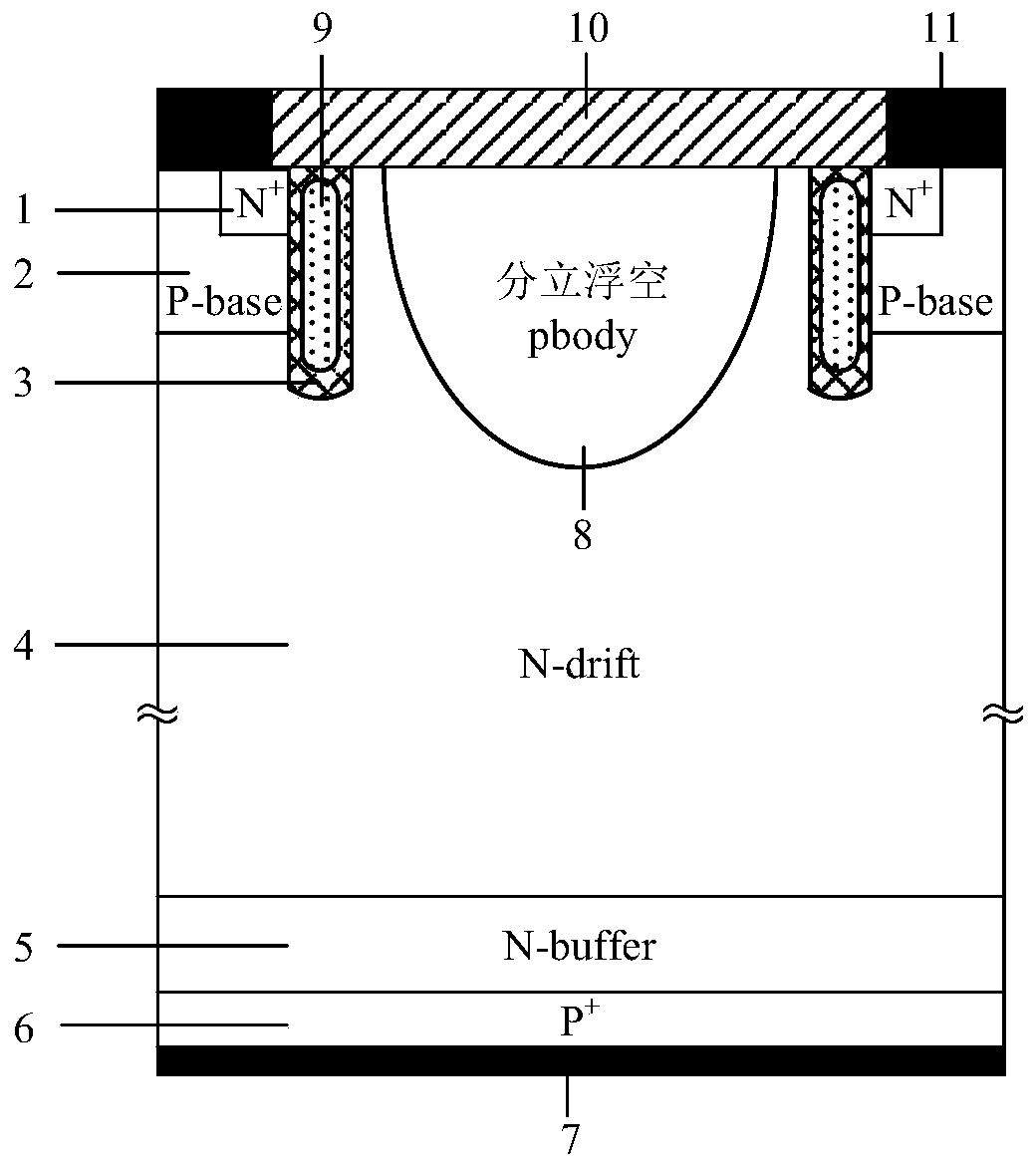

IGBT (Insulated Gate Bipolar Translator) device with MOS (Metal Oxide Semiconductor) control hole path

ActiveCN109768080AReduce the saturation conduction voltage dropReduced turn-off time and turn-off lossesThyristorSemiconductor/solid-state device manufacturingOxide semiconductorCapacitance

The invention provides an IGBT (Insulated Gate Bipolar Translator) device with a MOS (Metal Oxide Semiconductor) control hole path, and belongs to the technical field of power semiconductor devices. AMOS control gate structure formed by a gate dielectric layer, a MOS control gate electrode and a P-type MOS channel area is introduced into a P+ floating pbody area of a traditional IGBT device, anda MOS region is equivalent to a switch under gate voltage control. When the device is conducted forwardly, the potential of the pbody area floats, so that hole storage is realized, and the saturated on-off voltage drop of the device is reduced. When the device is off and short-circuited, a hole discharge path is provided; the Miller capacitance is reduced; and the low on-off loss and more stable short circuit capability are realized.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Power semiconductor device and manufacturing method thereof

PendingCN108346692AFast response timeReduce switching lossesSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceGrating

The invention discloses a power semiconductor device and a manufacturing method thereof. The power semiconductor device comprises a separation grating structure located in a groove; the separation grating structure comprises a first gate conductor, a second gate conductor and a third gate conductor which are separated mutually; the first part of the first gate conductor is located at the upper part of the groove and is clamped between the second gate conductor and the third gate conductor; and the second part of the first gate conductor extends to the lower part of the groove. The power semiconductor device adopts the separation grating structure to improve the response speed and reduce the switch loss.

Owner:HANGZHOU SILAN INTEGRATED CIRCUIT

Method for fabricating trench power device

ActiveUS20050287734A1Reduce RC delayReduced Miller CapacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceEngineering

Embodiments of the invention relate to a fabrication method of an electronic device, more particularly to a fabrication method of a power device in which an oxide layer at the bottom of the trench is provided to reduce Miller capacitance and further reduce RC delay. In one embodiment, a method for forming an oxide layer at the bottom of a trench comprises providing a first substrate with at least one trench therein; forming a first oxide layer on the bottom and sidewalls of the trench; removing the first oxide layer at the bottom of the trench; and forming a second oxide layer at the bottom of the trench.

Owner:MOSEL VITELIC INC

Ring ion injection method, semiconductor device and manufacture method thereof

InactiveCN102623313AReduced Miller CapacitanceThe effective channel length does not changeSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceAmplifier

The invention provides a ring ion injection method which comprises the steps of: respectively carrying out ion injection on a source electrode and a drain electrode on a substrate, wherein an included angle of a drain electrode ion injection direction and a direction vertical to the surface of the substrate is more than that of a source electrode ion injection direction and the direction vertical to the surface of the substrate; and enabling a charge region of a drain electrode space to be compressed from a trench direction so that an overlapping area of the drain electrode and a grid electrode is compressed, thus a parasitic overlap capacitance between the drain electrode and the grid electrode of a semiconductor device is decreased, a Miller capacitance of a common-source amplifier is reduced, and the frequency response characteristic of the common-source amplifier is improved. In addition, though the charge region of the drain electrode space is compressed, a charge region of a source electrode space extends into a trench, the effective trench length of the semiconductor device is basically kept unchangeable, and other properties of the semiconductor device can be maintained.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com