Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

86 results about "Switched capacitor integrator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

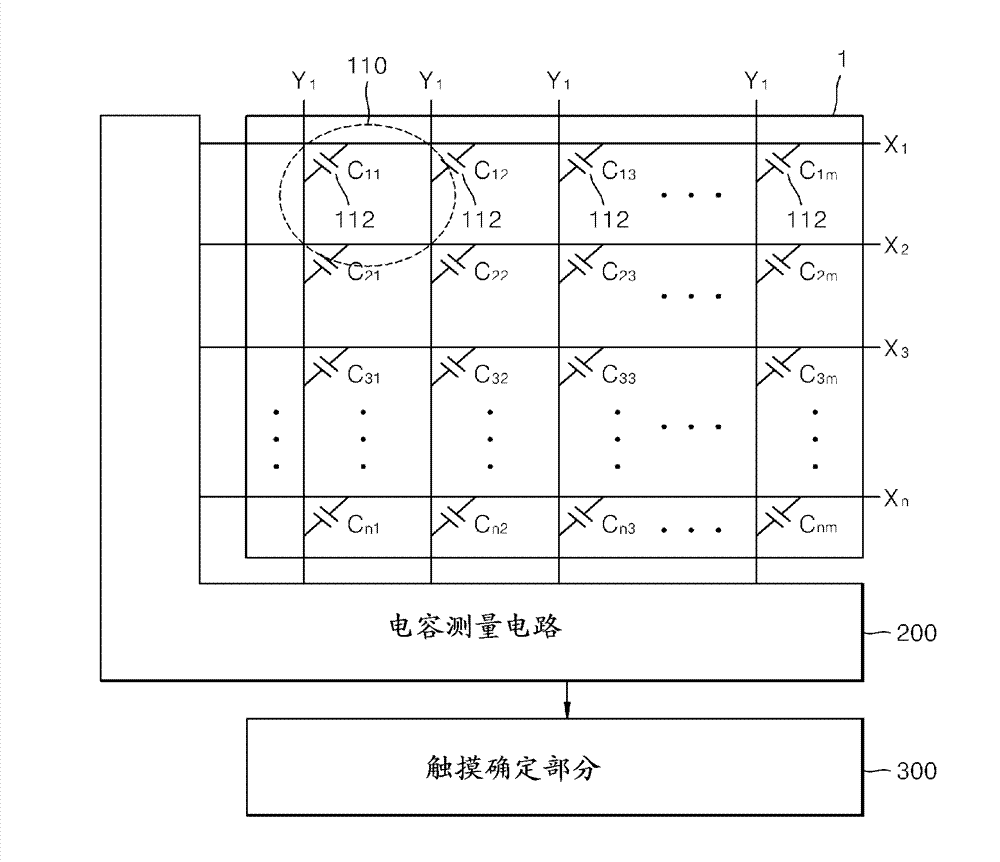

Capacitive touch sensing system with interference rejection

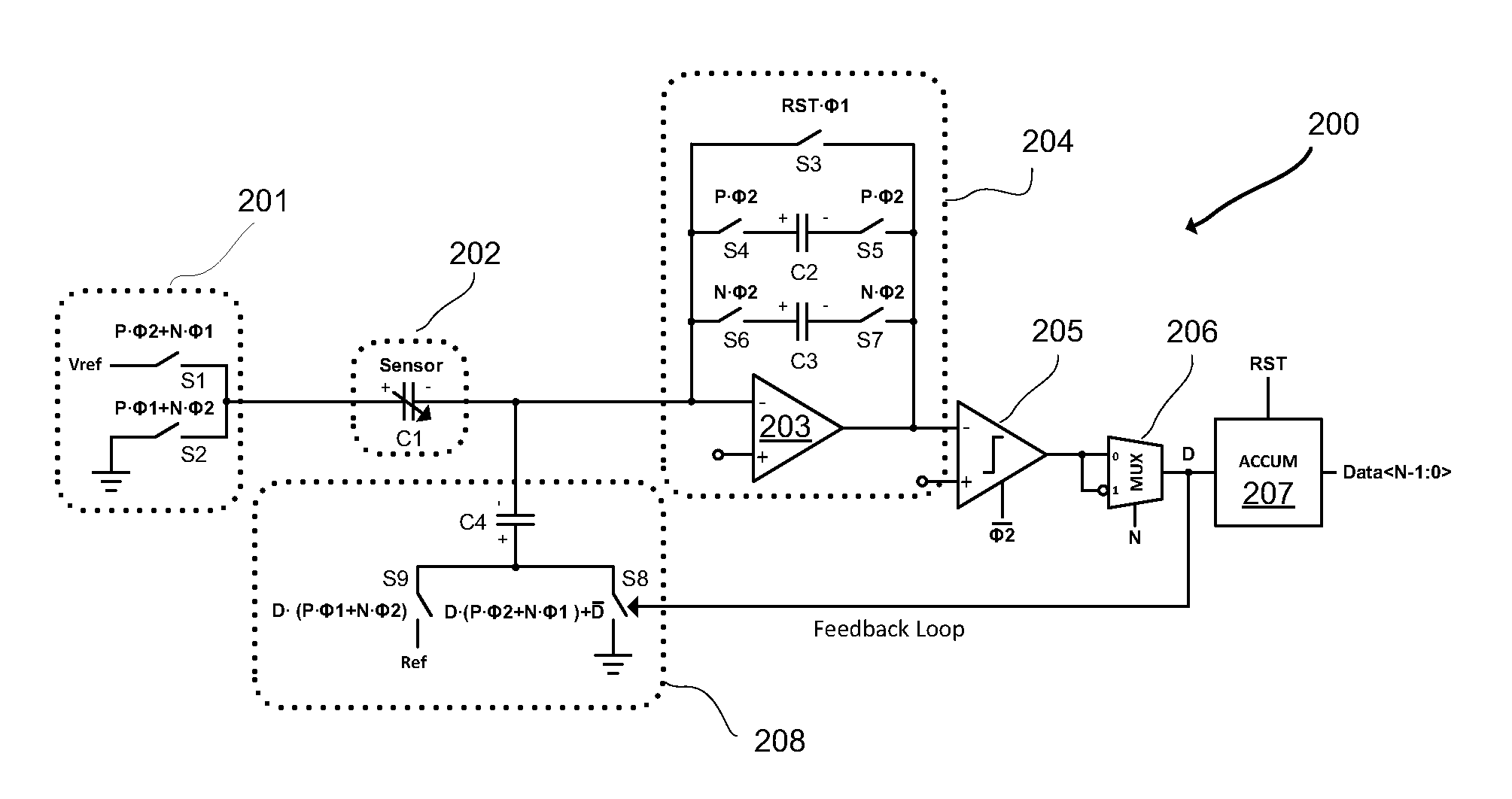

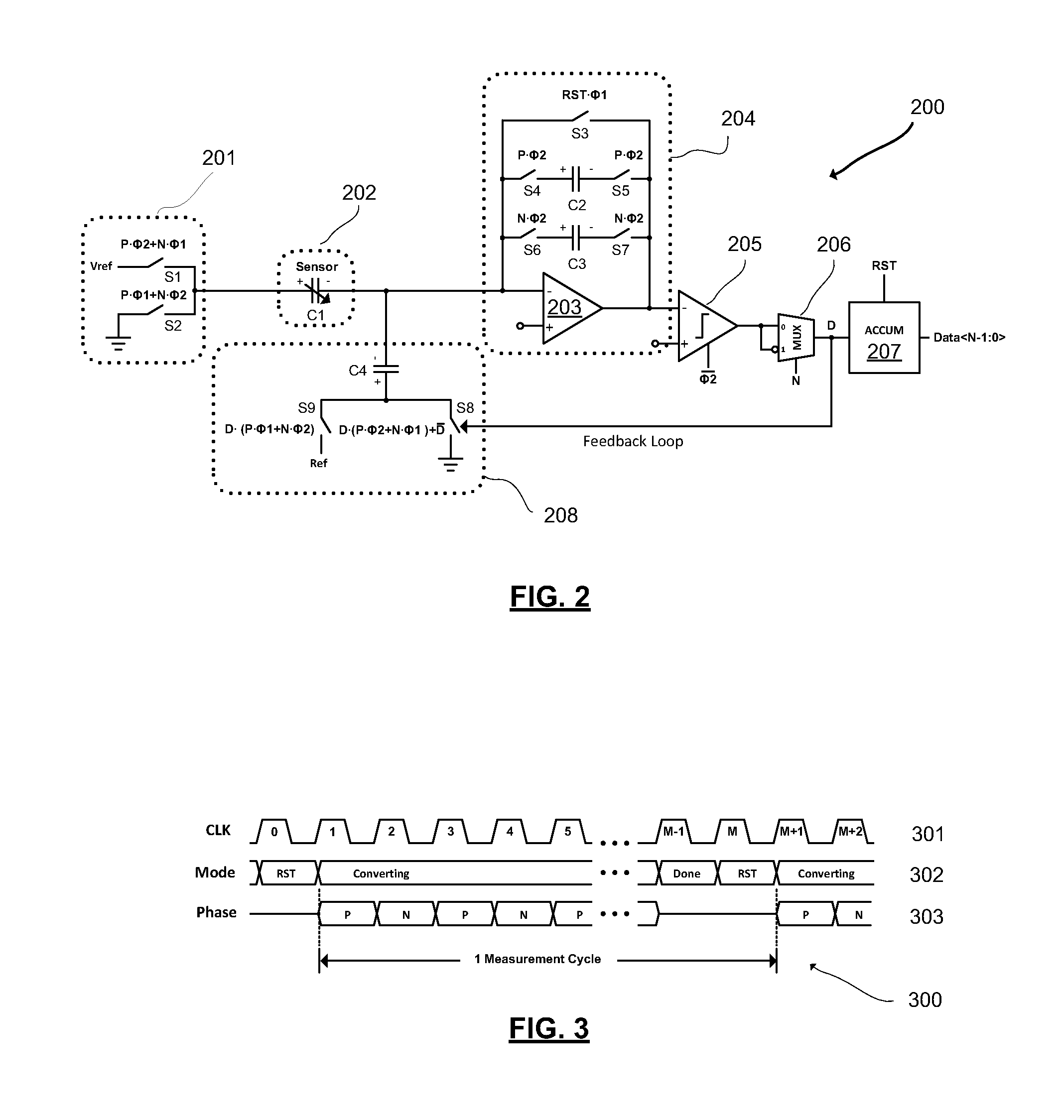

An interference tolerant capacitive touch sensor readout circuit having improved power and area efficiency is disclosed. Interference rejection for the capacitive touch sensing system is realized by transferring charge between a capacitive touch sensor and the readout circuit at frequencies outside bands where a level of interference is unacceptable. Improved power and area efficient come from the simplicity of the readout circuit which comprises a switched-capacitor integrator, a comparator, a digital accumulator and number of switches for driving a touch sensor and a capacitive feedback loop. The readout circuit is capable of interfacing with both self and mutual capacitance sensor to achieve compatibility with a larger collection of sensors and provides additional sensing and diagnostic functionalities.

Owner:AVAGO TECH INT SALES PTE LTD

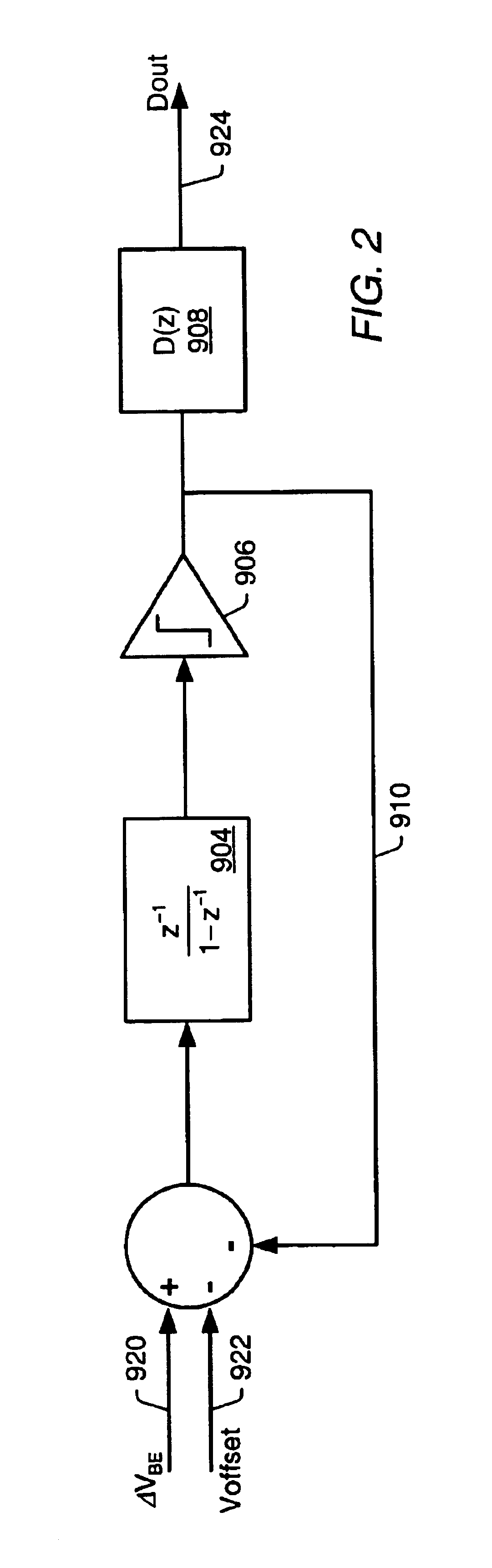

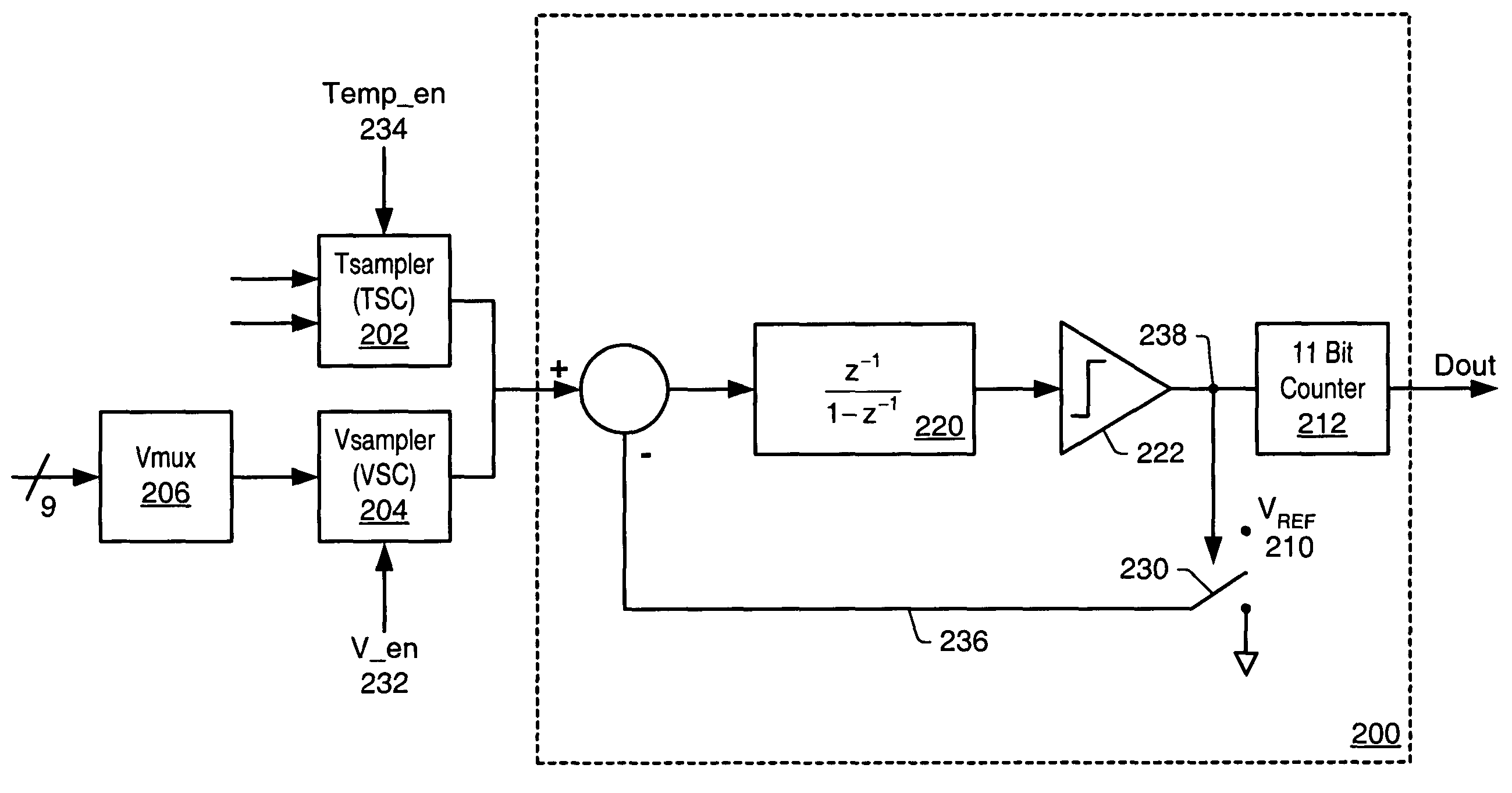

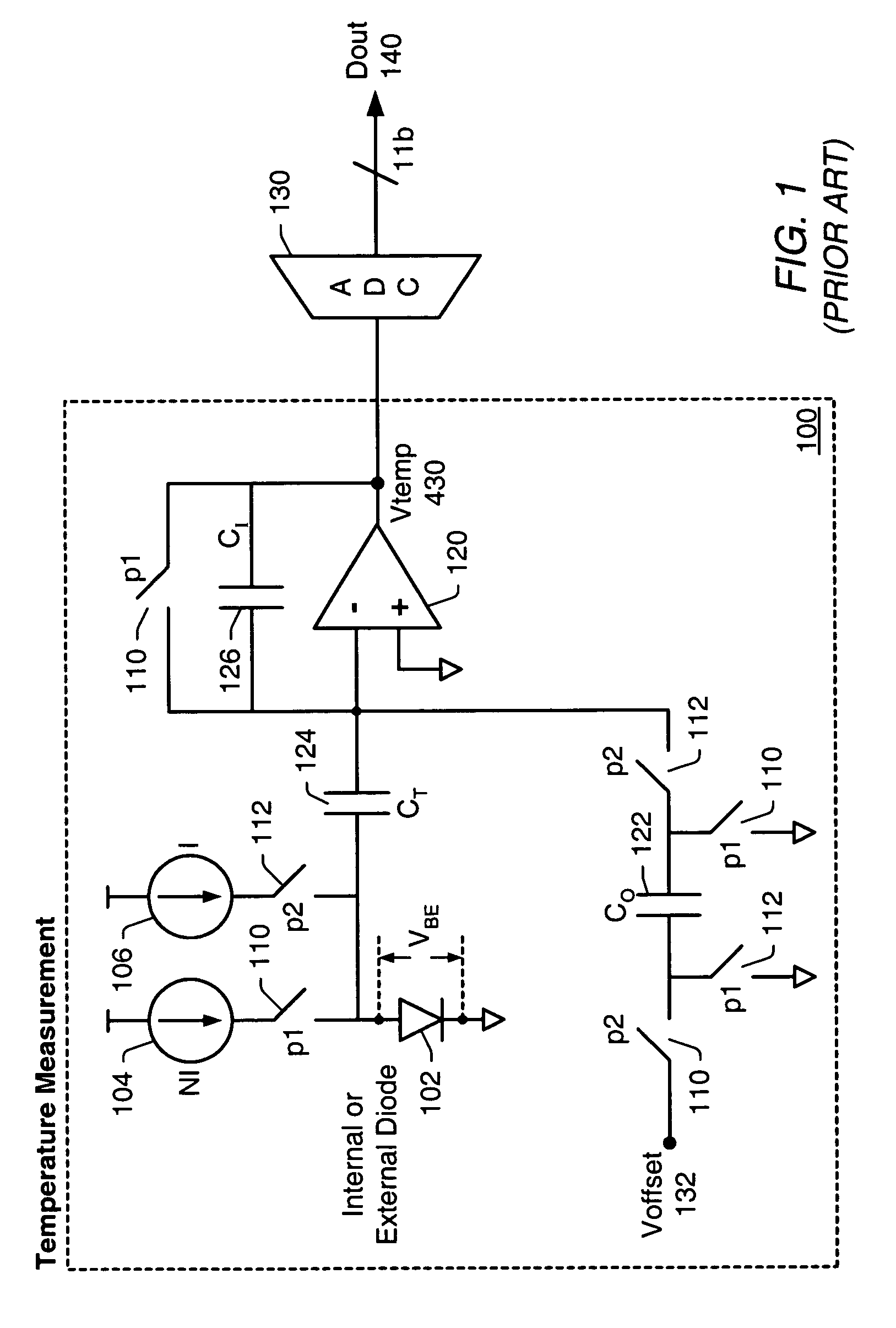

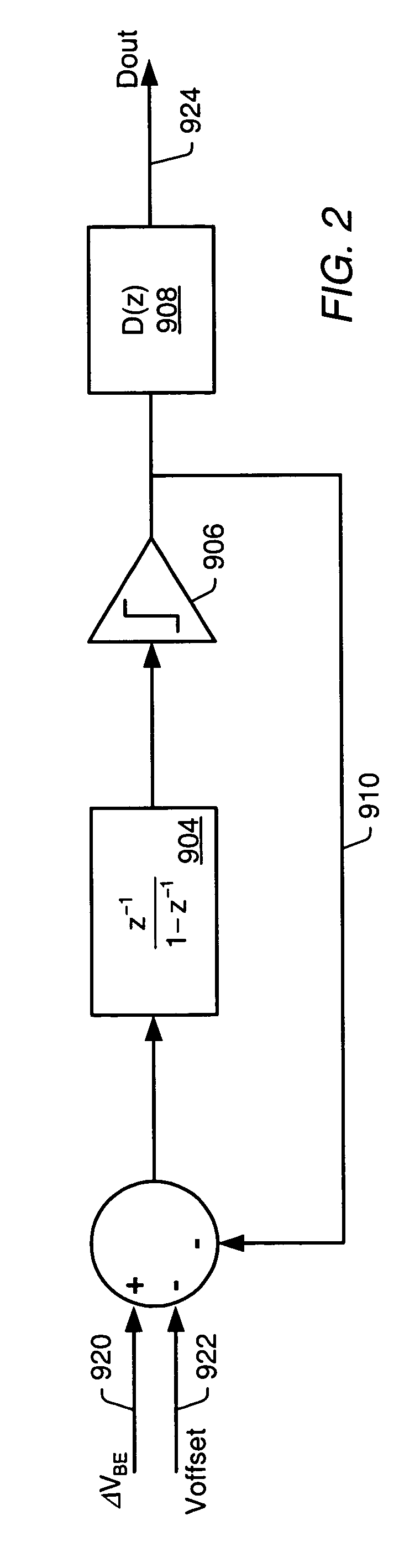

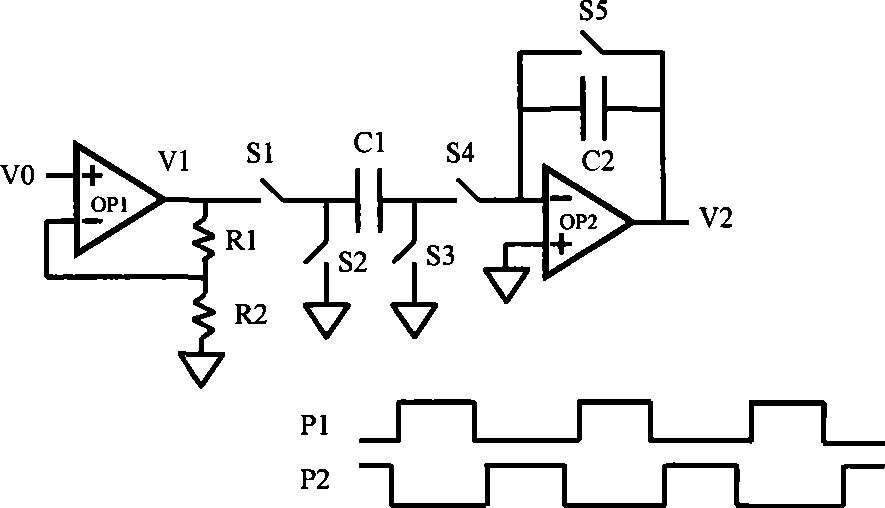

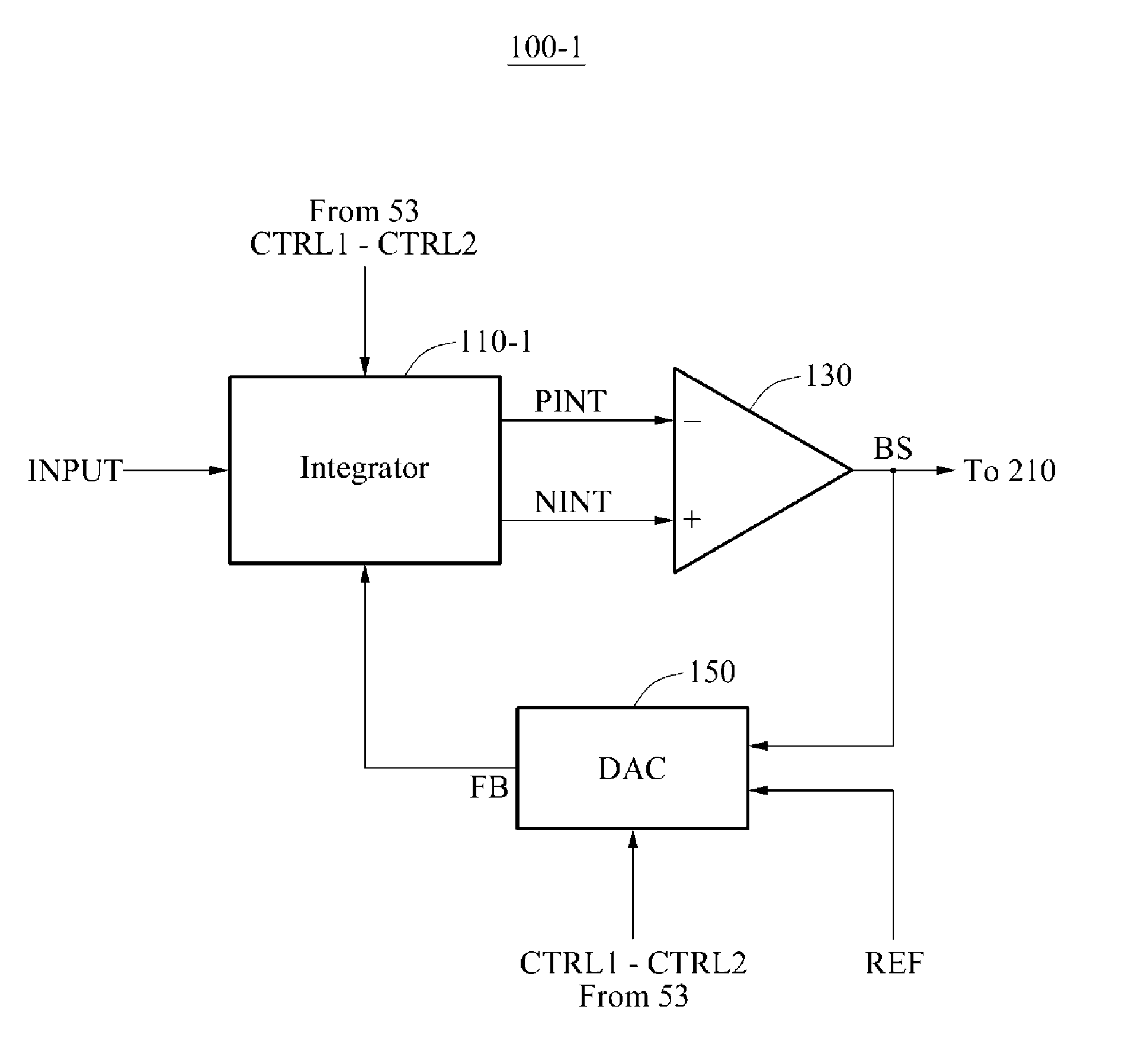

Temperature-to-digital converter

ActiveUS6847319B1Eliminate needElectric signal transmission systemsThermometers using electric/magnetic elementsDigital down converterIntegrator

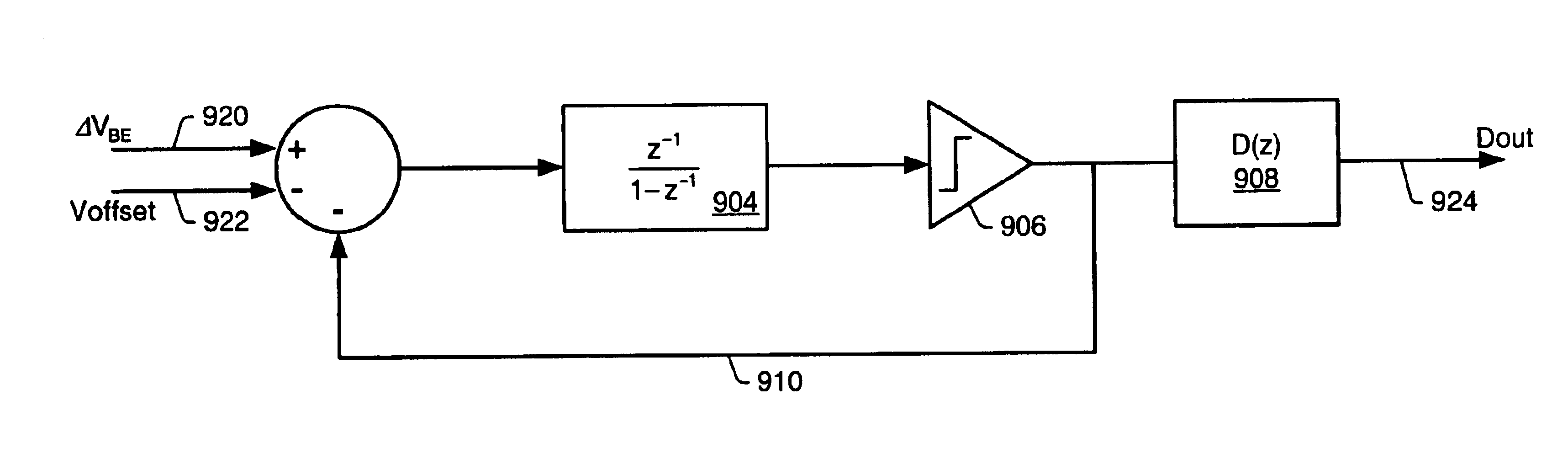

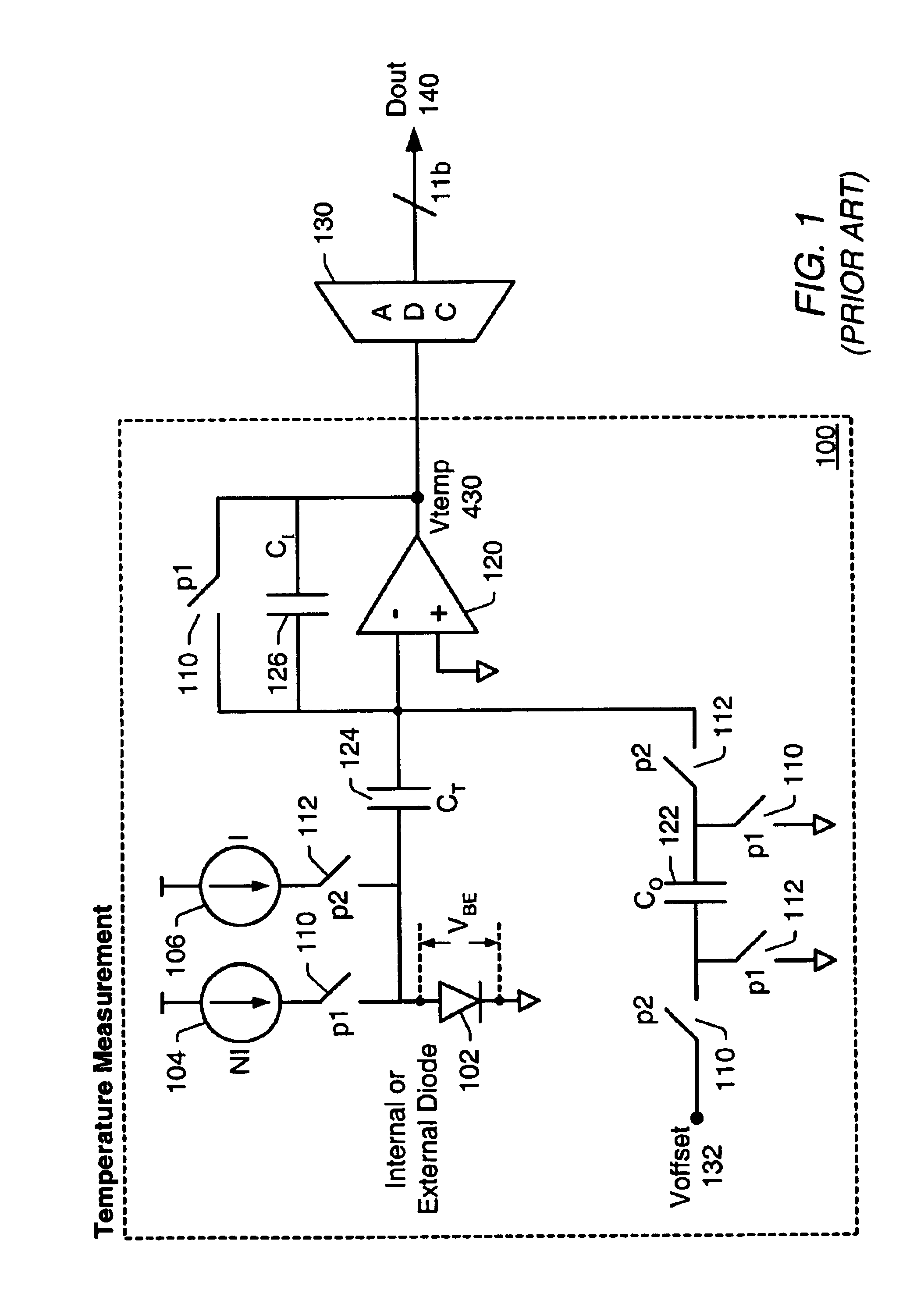

A temperature to digital converter device is implemented by integrating a temperature sensor circuit into an analog-to-digital converter (ADC). Temperature-to-digital conversion is accomplished by first measuring a change in voltage (ΔVBE) across the junction of a diode when different current densities are forced through the junction. The thus obtained ΔVBE is proportional to temperature. As part of the conversion processing, ΔVBE is multiplied by a fixed gain, and an offset voltage value is subtracted from ΔVBE. The multiplication and subtraction functions are performed by a switched-capacitor integrator in a delta-sigma ADC and the ADC itself operates as the temperature-to-digital converter device, eliminating the extra amplifier and / or capacitors required when the multiplication and / or subtraction function are performed outside the ADC. Alternately, other ADC topologies that include an integrator or gain amplifier, such as pipeline ADCs and cyclic ADCs may be used in place of the delta-sigma ADC.

Owner:MICROCHIP TECH INC

Temperature-to-digital converter

InactiveUS20050017889A1Eliminate needElectric signal transmission systemsThermometers using electric/magnetic elementsDigital down converterIntegrator

A temperature to digital converter device is implemented by integrating a temperature sensor circuit into an analog-to-digital converter (ADC). Temperature-to-digital conversion is accomplished by first measuring a change in voltage (ΔVBE) across the junction of a diode when different current densities are forced through the junction. The thus obtained ΔVBE is proportional to temperature. As part of the conversion processing, ΔVBE is multiplied by a fixed gain, and an offset voltage value is subtracted from ΔVBE. The multiplication and subtraction functions are performed by a switched-capacitor integrator in a delta-sigma ADC and the ADC itself operates as the temperature-to-digital converter device, eliminating the extra amplifier and / or capacitors required when the multiplication and / or subtraction function are performed outside the ADC. Alternately, other ADC topologies that include an integrator or gain amplifier, such as pipeline ADCs and cyclic ADCs may be used in place of the delta-sigma ADC.

Owner:MICROCHIP TECH INC

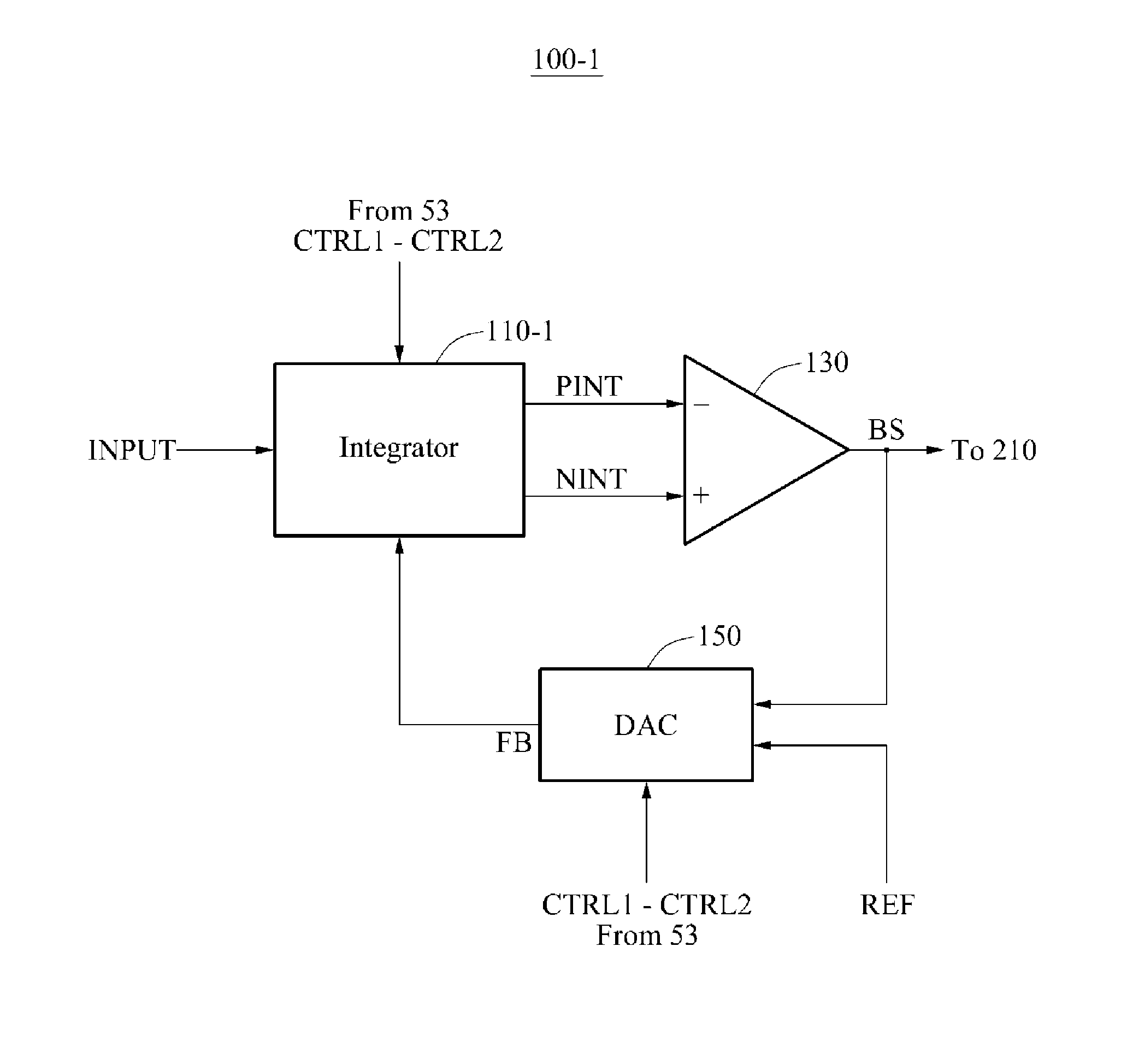

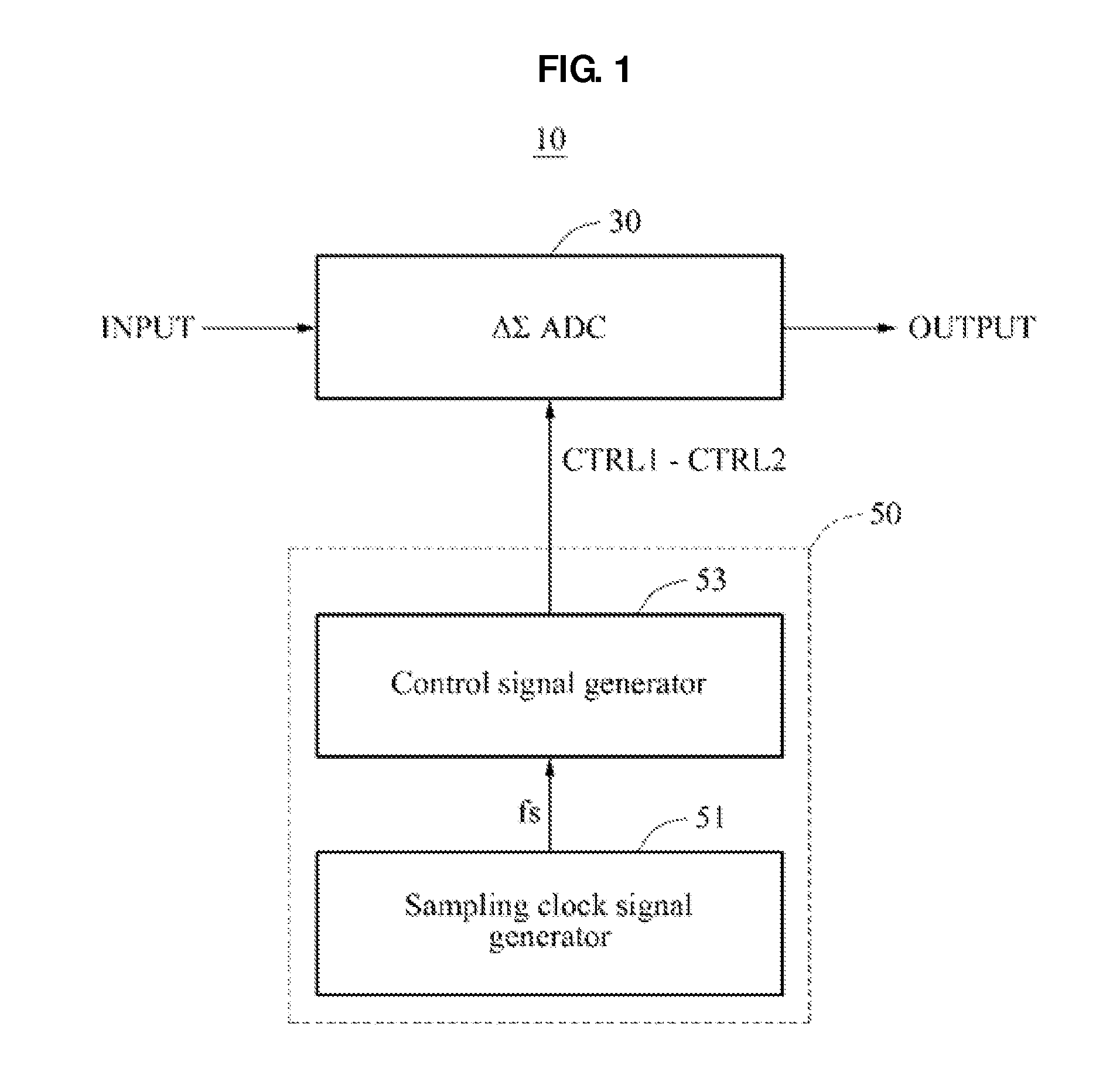

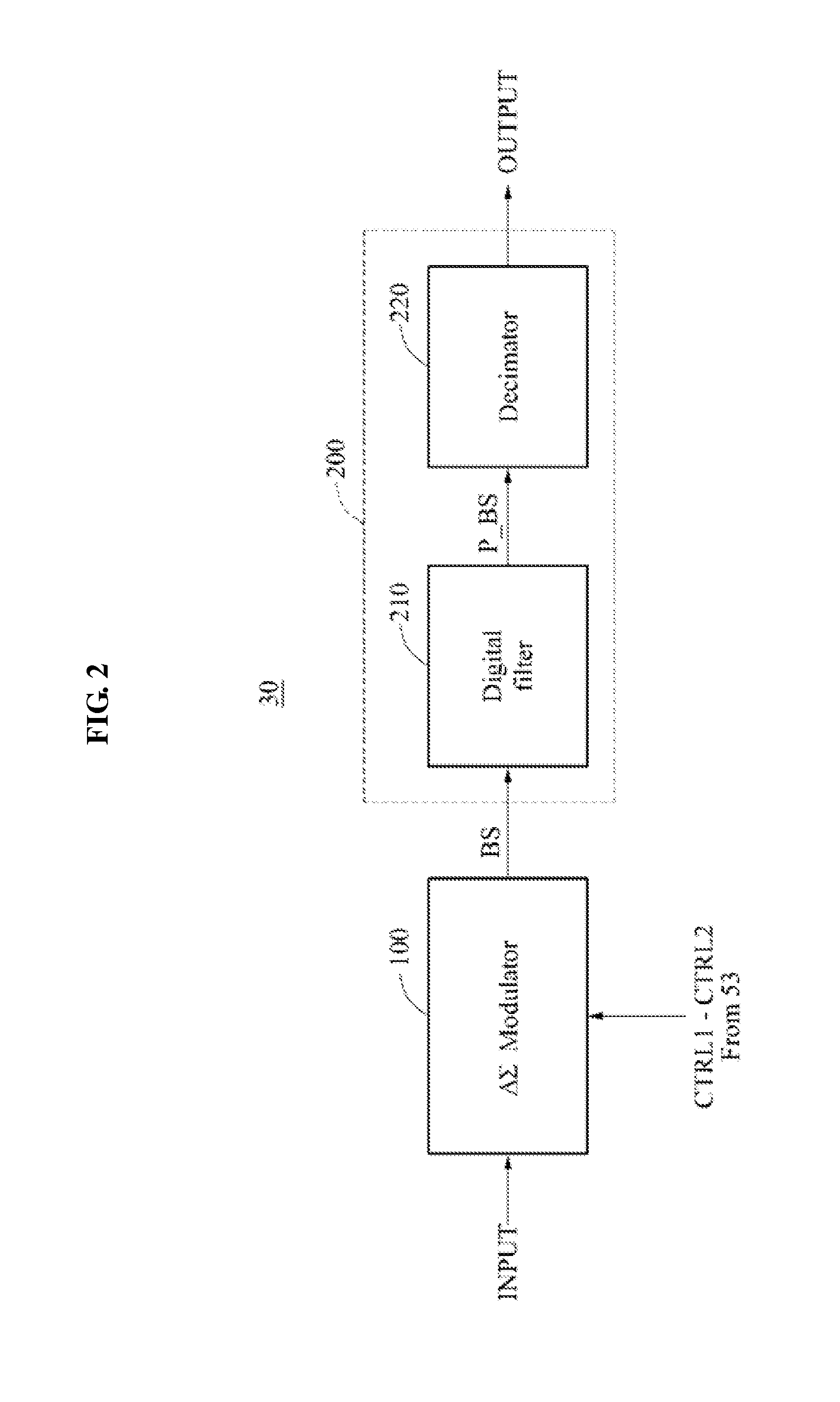

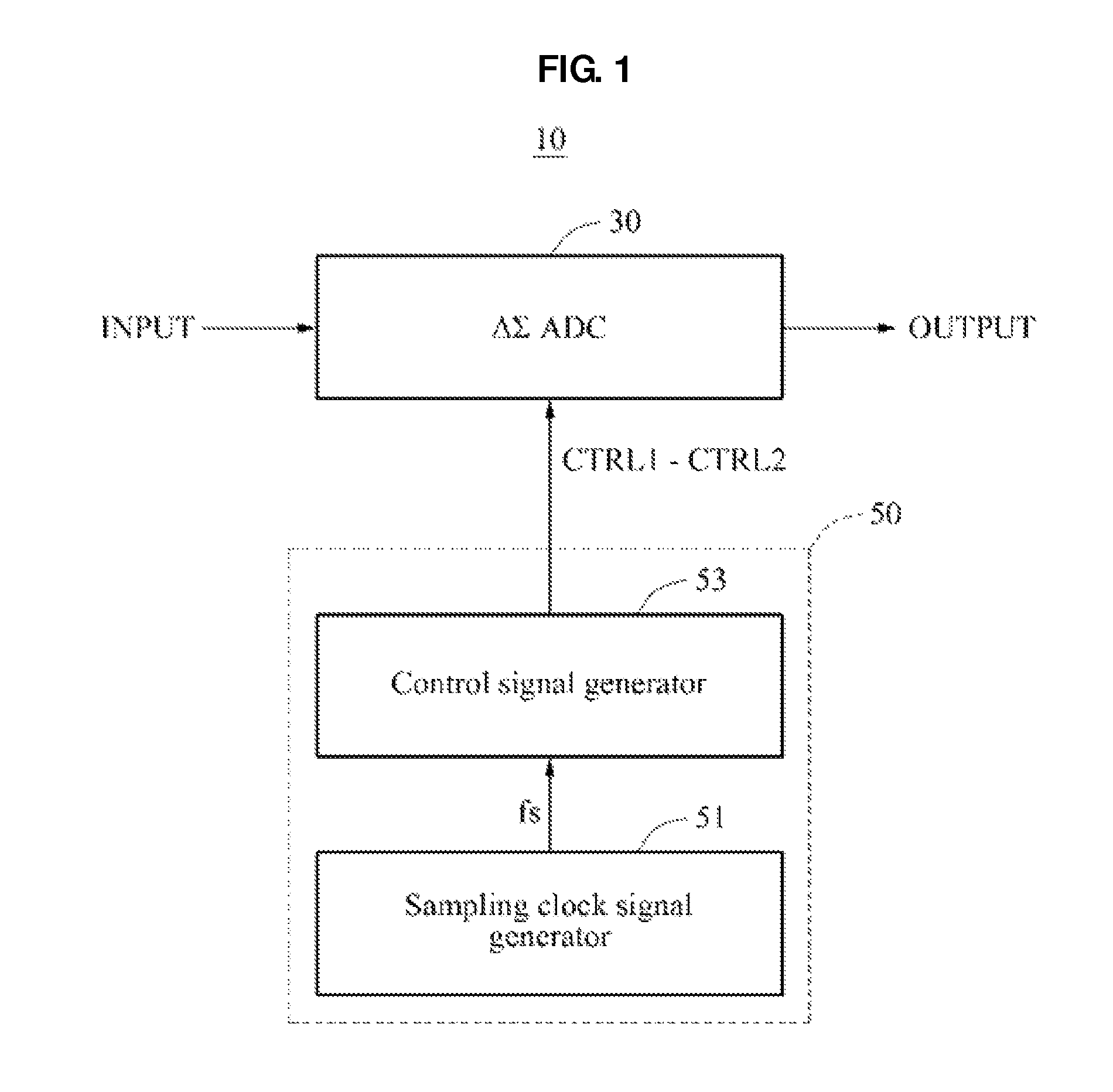

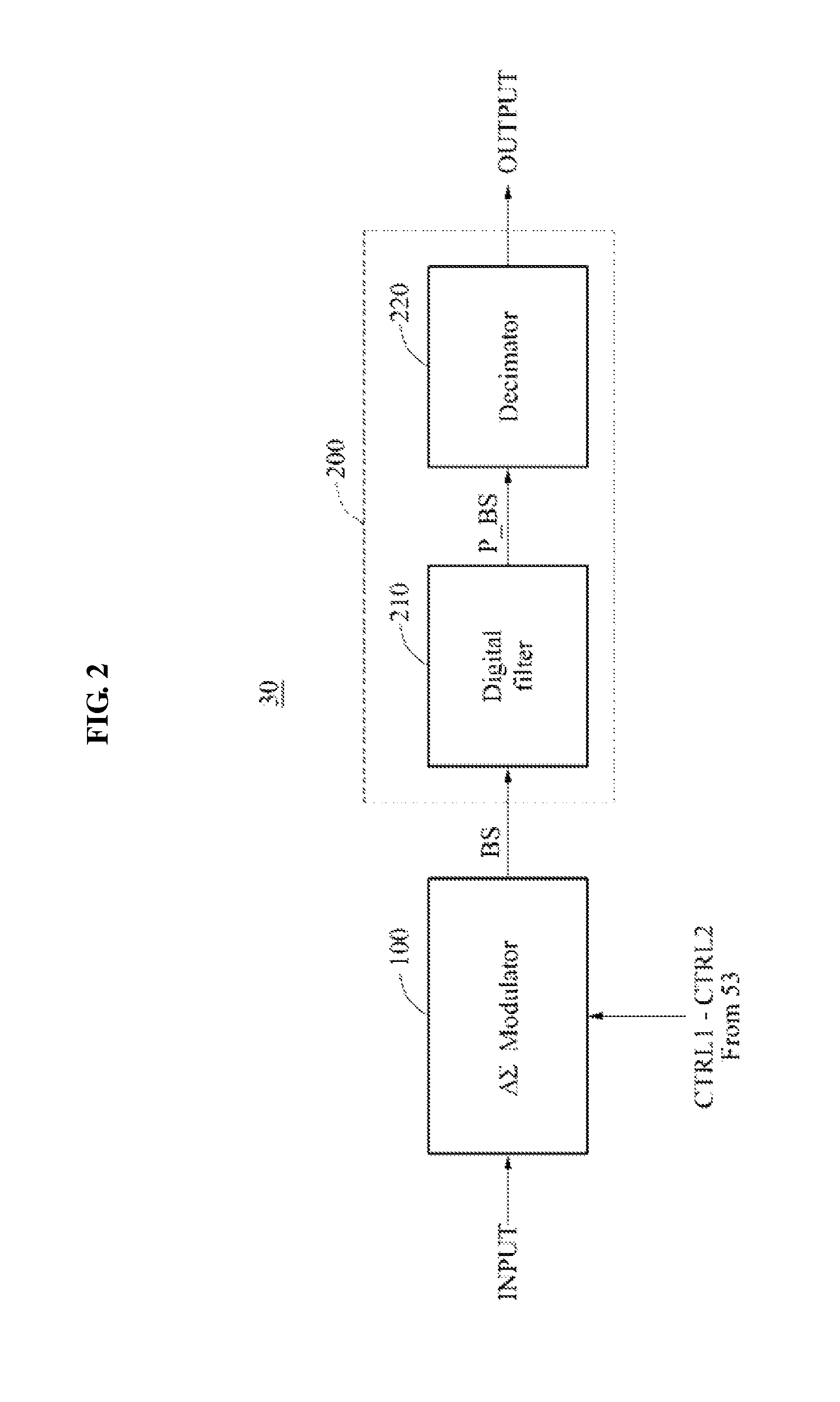

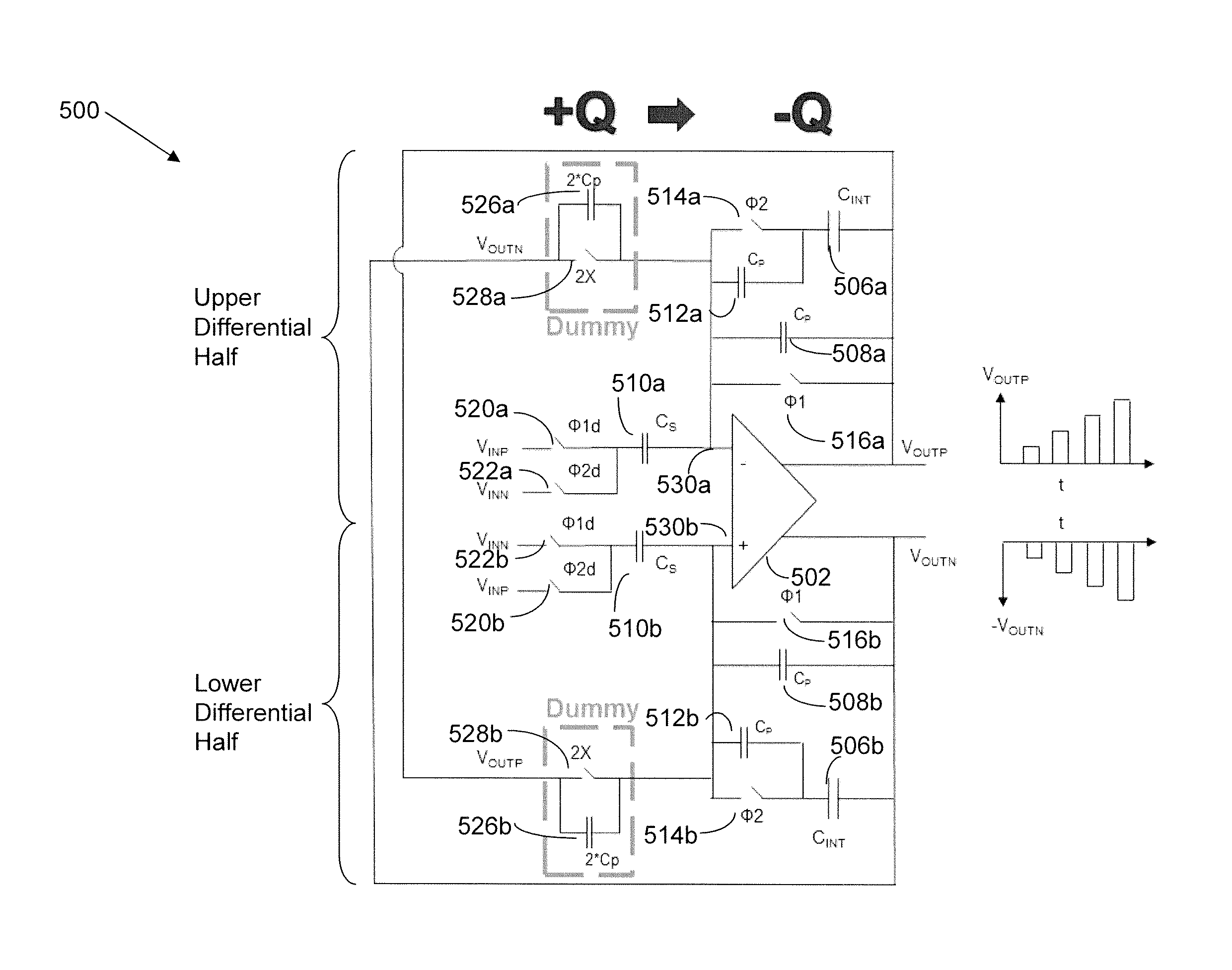

Delta-sigma modulator having differential output

ActiveUS20160149586A1Well formedComputing operations for integral formationComputing operations for integration/differentiationControl signalFeedback circuits

Provided is a delta-sigma modulator having a differential output, the modulator including a switched-capacitor integrator configured to generate a non-inverted integral signal and an inverted integral signal and also including a switched-capacitor circuit configured to sample an input signal based on a control signal and to integrate the feedback signal and the input signal based on the control signal and also a feedback circuit configured to generate the feedback signal.

Owner:SAMSUNG ELECTRONICS CO LTD +1

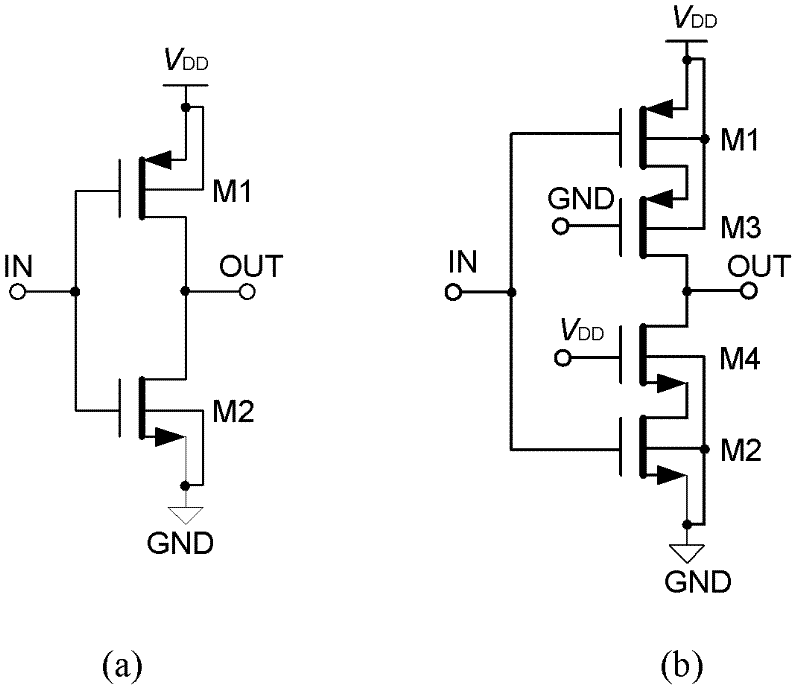

Switch-capacitor integrator

InactiveCN101621292ARelax requirementsOptimize topologyElectric pulse generator detailsLogic circuitsCapacitanceIntegrator

The invention discloses a switch-capacitor integrator adopting novel C-class inverters and a switch-capacitor integrator realizing form of a pseudodifferential structure. The switch-capacitor integrator in a pseudodifferential structure comprises two novel C-class inverters (60) and capacitors such as a sampling capacitor CS, a compensation capacitor CC, an integrating capacitor CI, and the like, switches such as an NMOS switch S2, an NMOS switch S4, an NMOS switch S7, an NMOS switch S8, a CMOS switch S3, a CMOS switch S5, a bootstrap NMOS switch S1, a bootstrap NMOS switch S6, a bootstrap NMOS switch S9, and the like and a common mode feedback circuit (61) in the prior art, wherein the two novel C-class inverters (60) are respectively positioned in a positive branch and a negative branch of the integrator and differentially symmetrized to be in the pseudodifferential structure. The invention overcomes the effects of indexes of working efficiency, establishing time, integrating accuracy, power consumption, and the like on the switch-capacitor integrator by technical deviation through the bulk potential modulation effect of a bulk potential modulator in the novel C-class inverters and greatly improves the stability and the robustness of the integrator without obviously increasing the power consumption.

Owner:ZHEJIANG UNIV

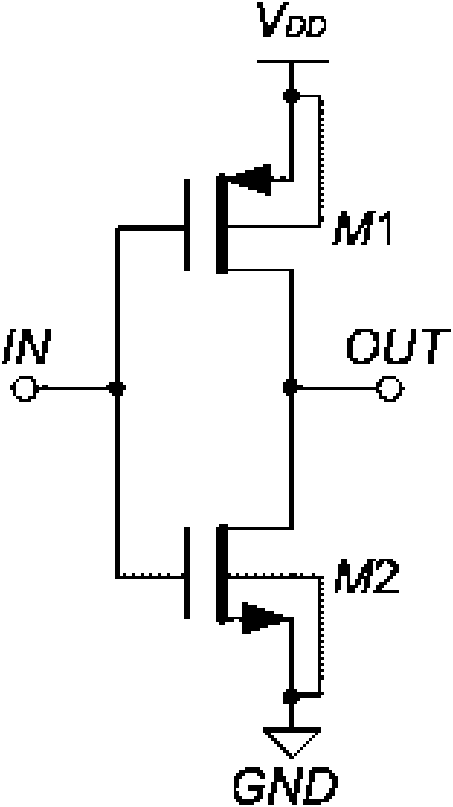

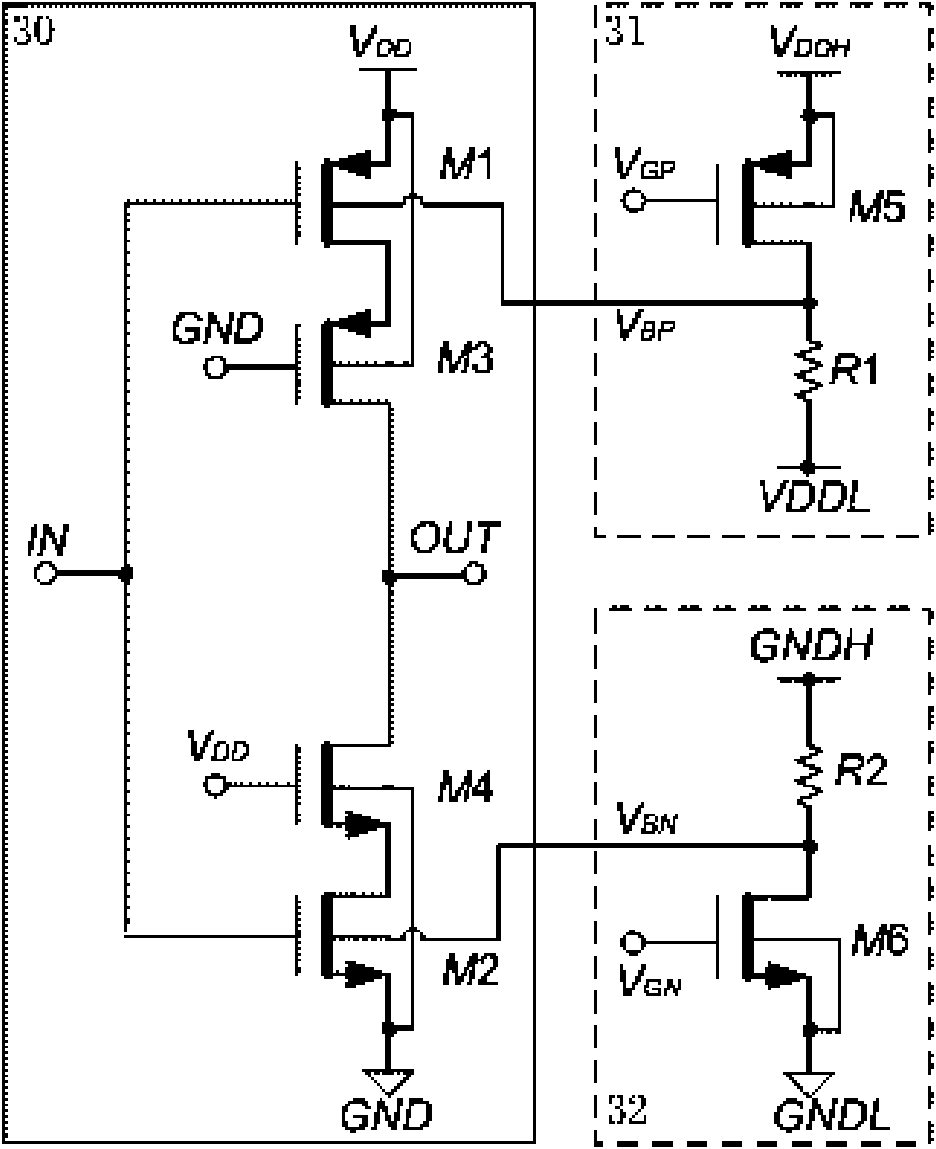

Dynamic Body Bias Type C Inverter and Its Application

ActiveCN102291103AReduce static power consumptionElectric pulse generator detailsCapacitanceIntegrator

The invention discloses a dynamic body biasing class-C inverter and application thereof. The dynamic body biasing class-C inverter provided by the invention comprises a switch body biasing class-C inverter, a first gain boosting module, a second gain boosting module, a P-channel metal oxide semiconductor (PMOS) body potential modulation module and an N-channel metal oxide semiconductor (NMOS) body potential modulation module, wherein the body ends of two input tubes of the switch body biasing class-C inverter are independently led out to be connected with a switch and perform dynamic body biasing by the switching of the switch, so that the two input tubes have different parameters such as threshold value voltages, transconductances and the like at different switch phases. The inverter hasthe advantages of high DC gain, relatively higher process fluctuation resistance, relatively higher power voltage disturbance resistance, relatively higher temperature deviation resistance and the like, simultaneously greatly reduces the static power consumption of the class-C inverter in a sub-threshold value state, can form a switching capacitance integrator having a pseudo-differential structure, and is applied to application occasions such as 2-1 cascaded Sigma-Delta analogue-to-digital converters and the like with extremely low power consumption and high accuracy.

Owner:ZHEJIANG UNIV

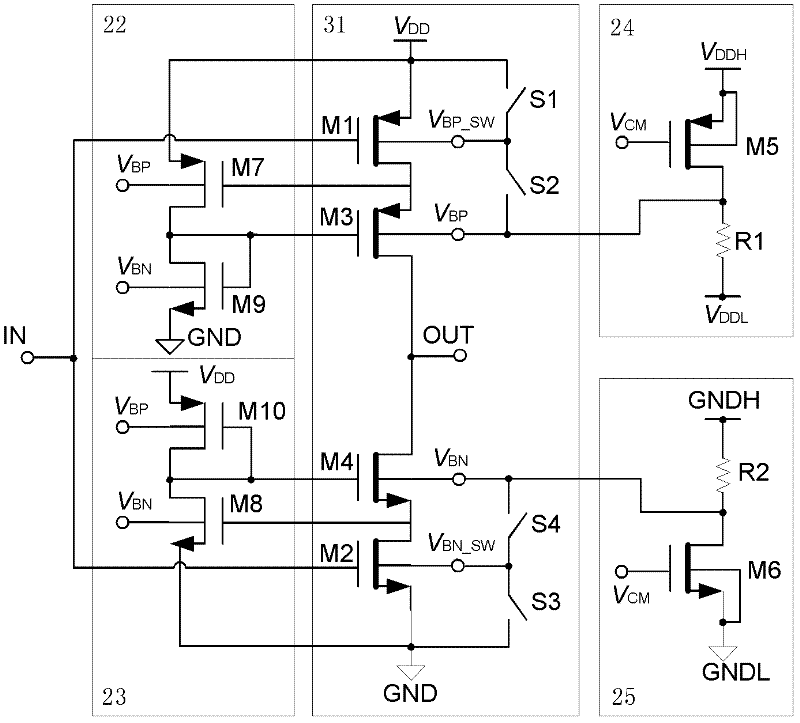

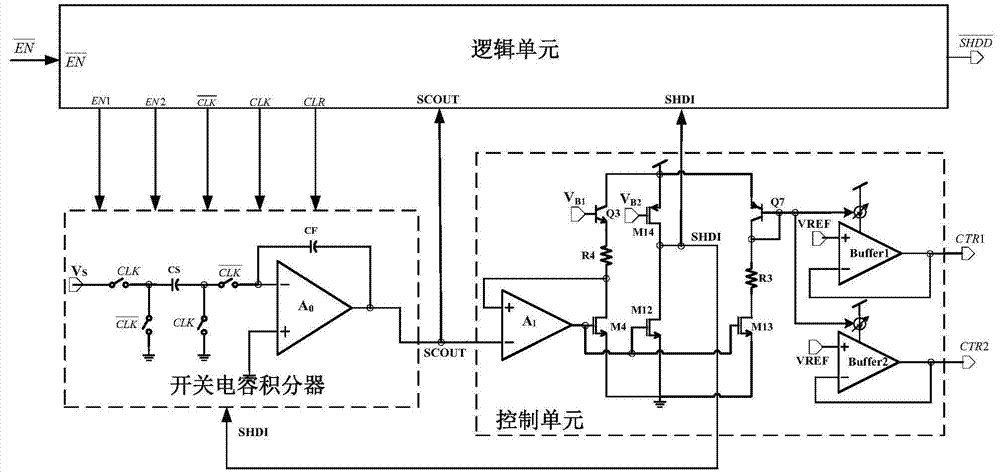

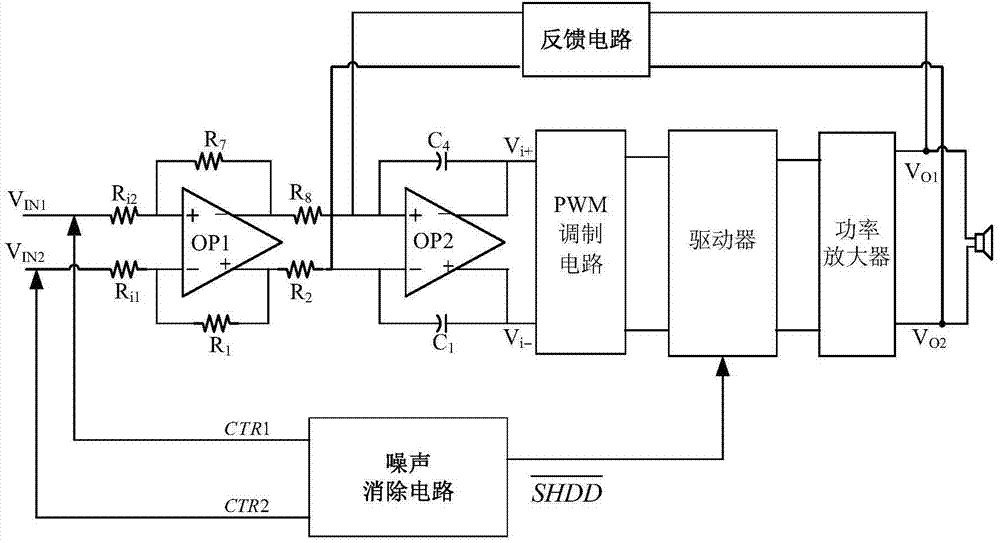

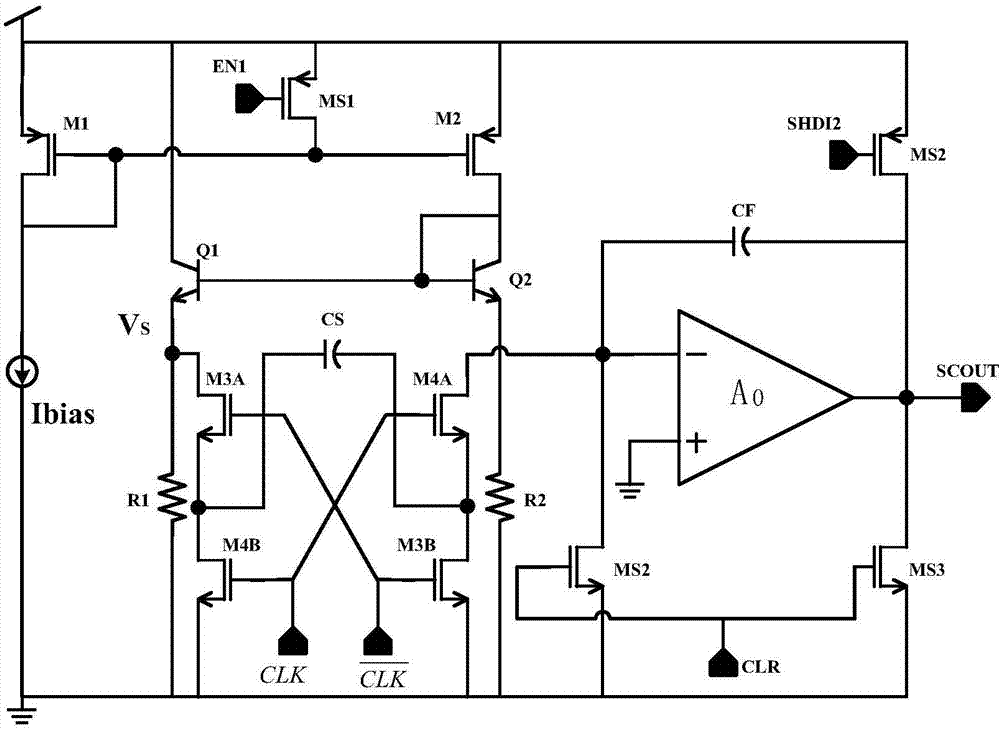

High-fidelity D-type audio frequency amplifier chip with noise canceller circuit

InactiveCN103501162AGuaranteed rigidityGuarantor power downAmplifier modifications to reduce noise influenceAmplifier with semiconductor-devices/discharge-tubesIntegratorAudio power amplifier

The invention relates to a high-fidelity D-type audio frequency amplifier, in particular to a high-fidelity D-type audio frequency amplifier chip with a noise canceller circuit. The high-fidelity D-type audio frequency amplifier chip comprises a pre-amplifier, a second-level amplifier, a PWM circuit, a driver, a power amplifier and a feedback circuit. The high-fidelity D-type audio frequency amplifier chip is characterized in that the noise canceller circuit is included, the noise canceller circuit is connected with the driver and the pre-amplifier, the noise canceller circuit turns on and off the power amplifier through the driver during electrifying and power failure of the chip, an audio input end is subjected to clamping during a recovery process of the chip, so that the chip is in a soft-starting working mode, the noise canceller circuit comprises a logic unit, a switch capacitance integrator and a control unit, the logic unit, the switch capacitance integrator and the control unit are connected, the switch capacitance integrator and the control unit are connected, the control unit is connected with the input end of the pre-amplifier, and the logic unit is connected with the driver. The high-fidelity D-type audio frequency amplifier chip is mainly used for the audio frequency amplifier.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

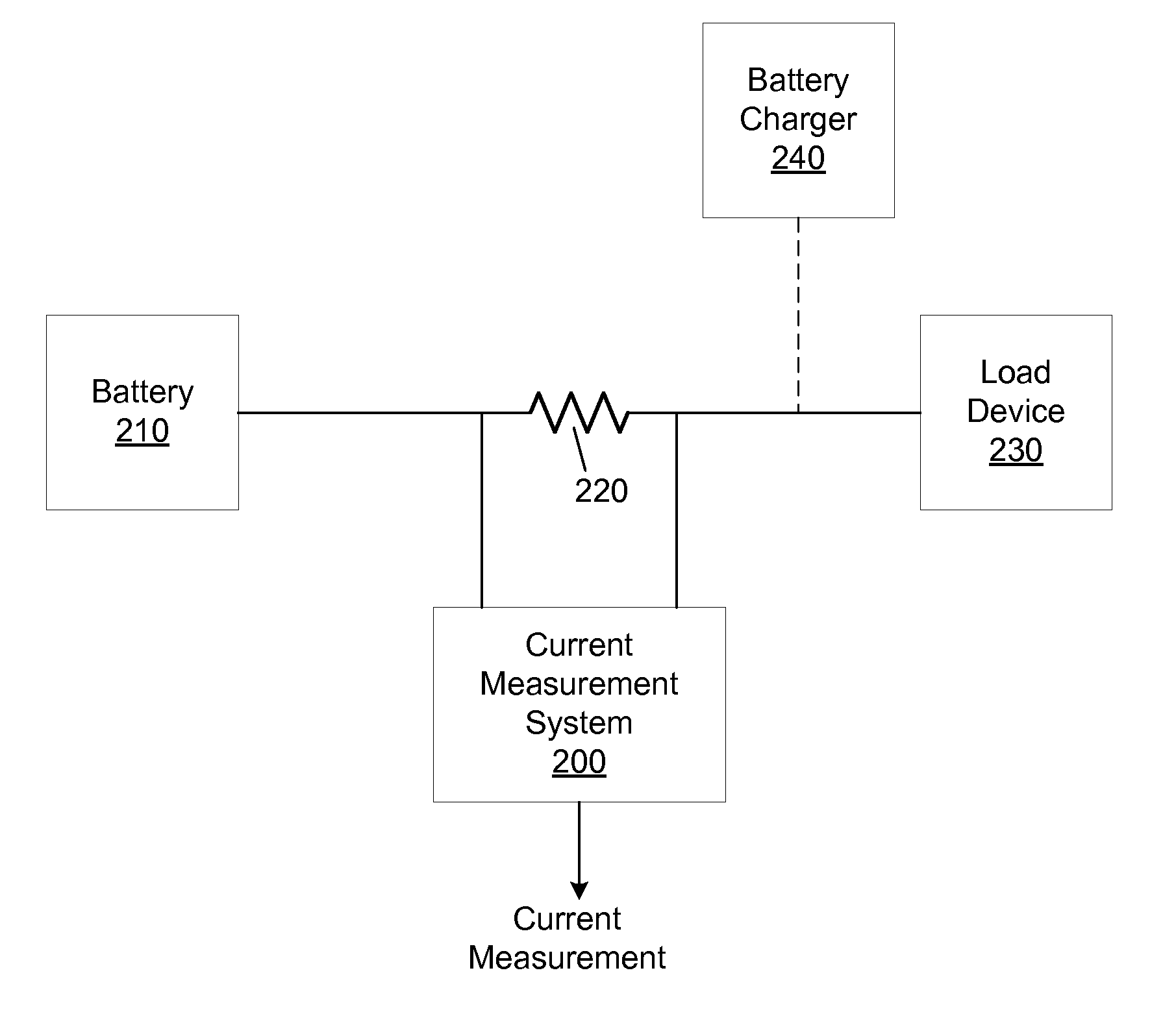

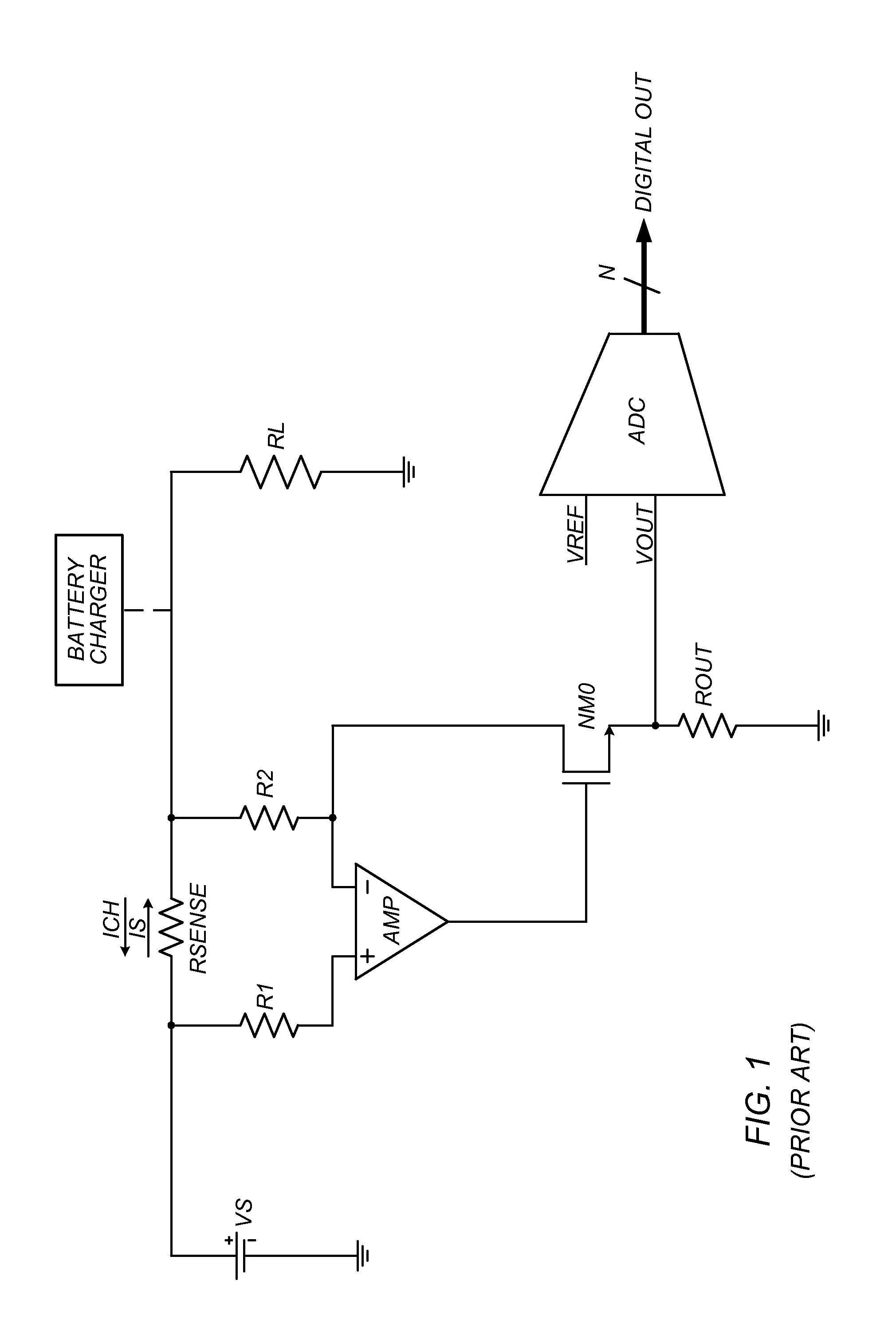

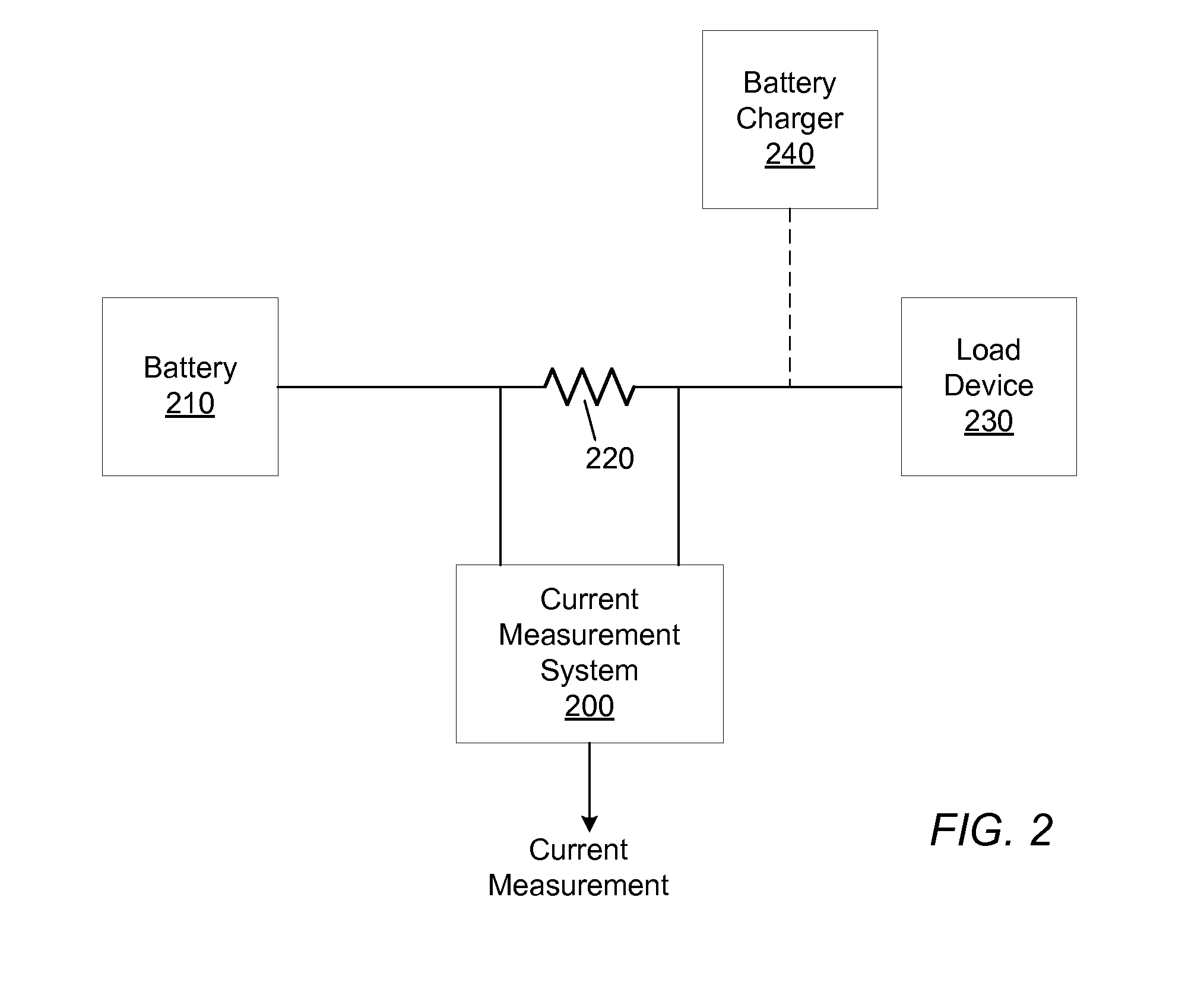

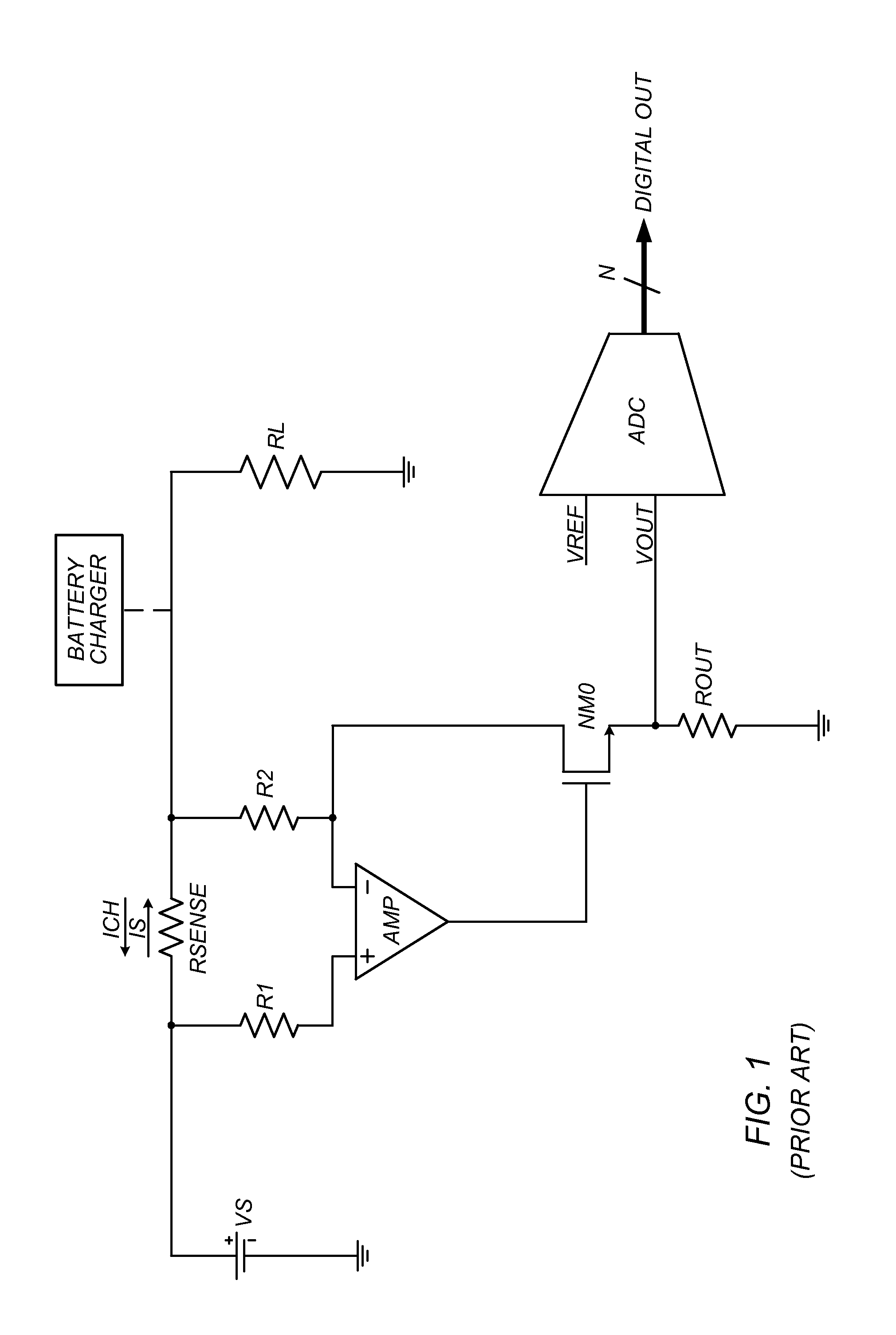

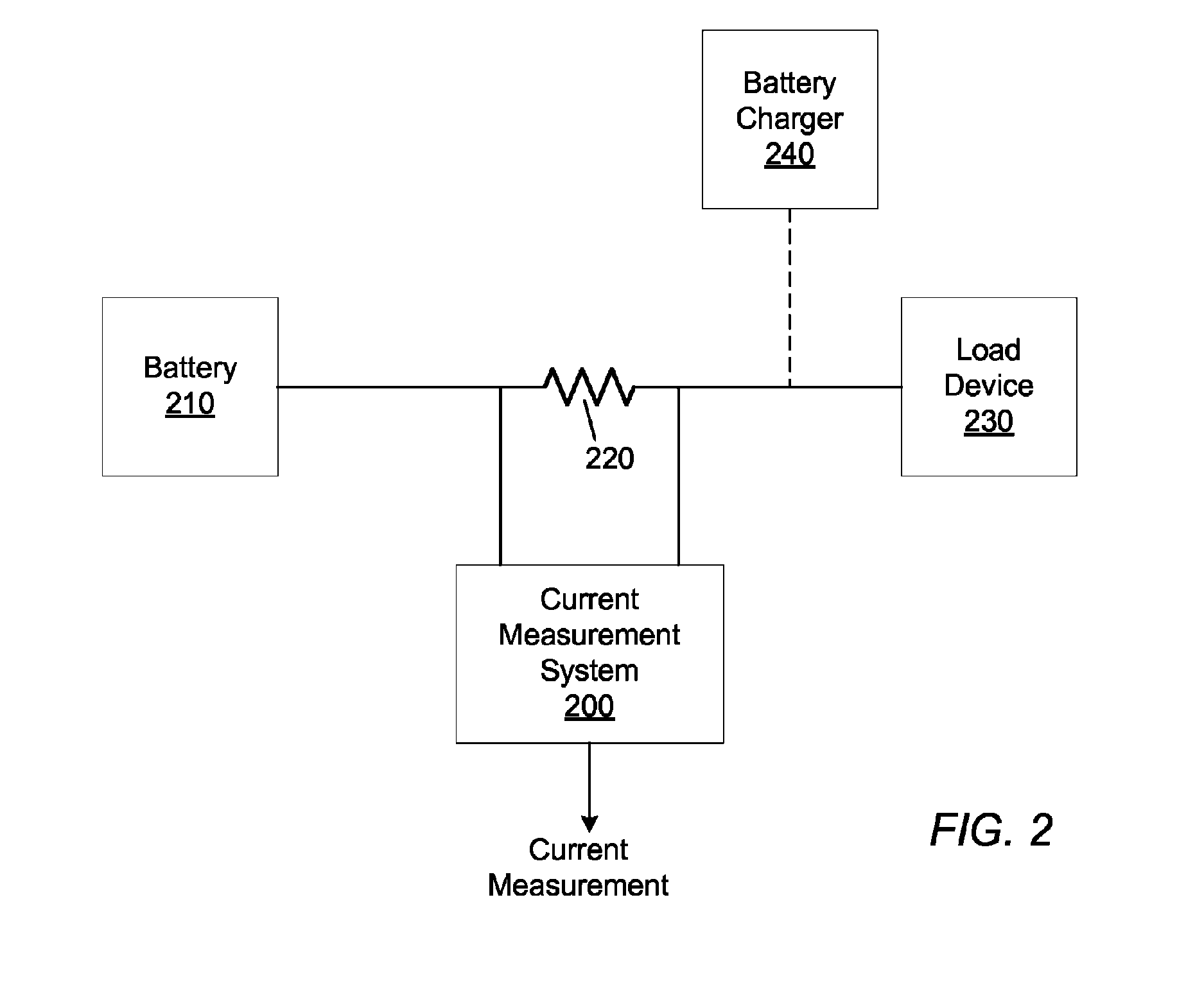

Bi-Directional High Side Current Sense Measurement

ActiveUS20110291675A1Digital variable displayResistance/reactance/impedenceElectrical resistance and conductanceVoltage drop

A system for measuring a voltage drop between two nodes in an electrical circuit, comprising a switched capacitor integrator (SCI), a comparator and a counter. The SCI alternately (a) captures charge onto a set of sampling capacitors and (b) selectively accumulates / transfers the charge onto a pair of integration capacitors, where the charge includes a first portion that is based on the voltage drop and a second portion that depends on a digital indicator signal. The comparator generates the digital indicator signal based on whether an analog output of the SCI is positive or negative. The counter counts a number of ones occurring in the digital indicator signal during a measurement interval. At the end of the measurement interval, the count value represents a measure of the voltage drop. Knowing the resistance between the two nodes, the voltage drop may be converted into a current measurement.

Owner:MICROCHIP TECH INC

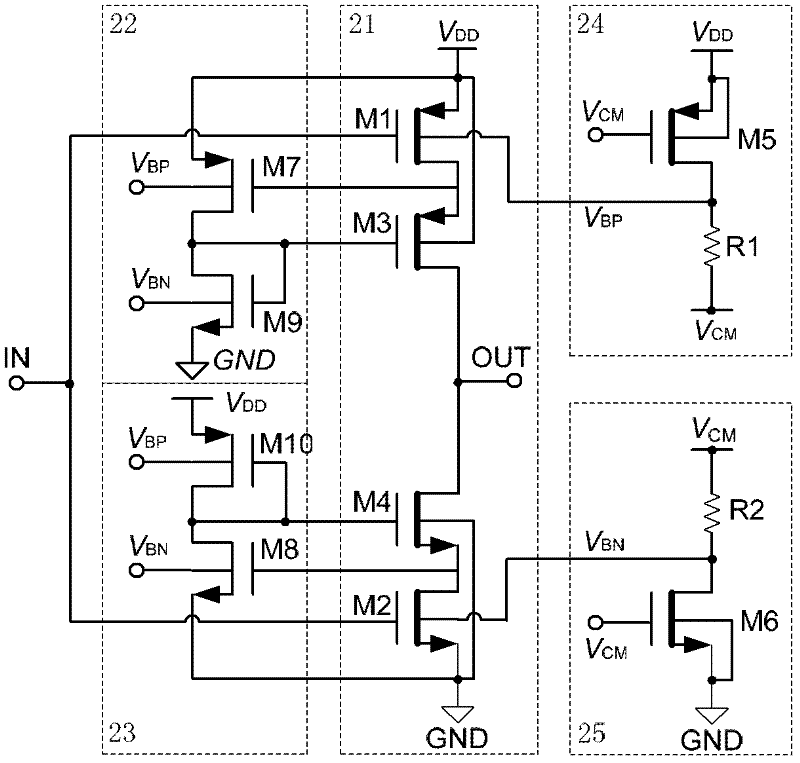

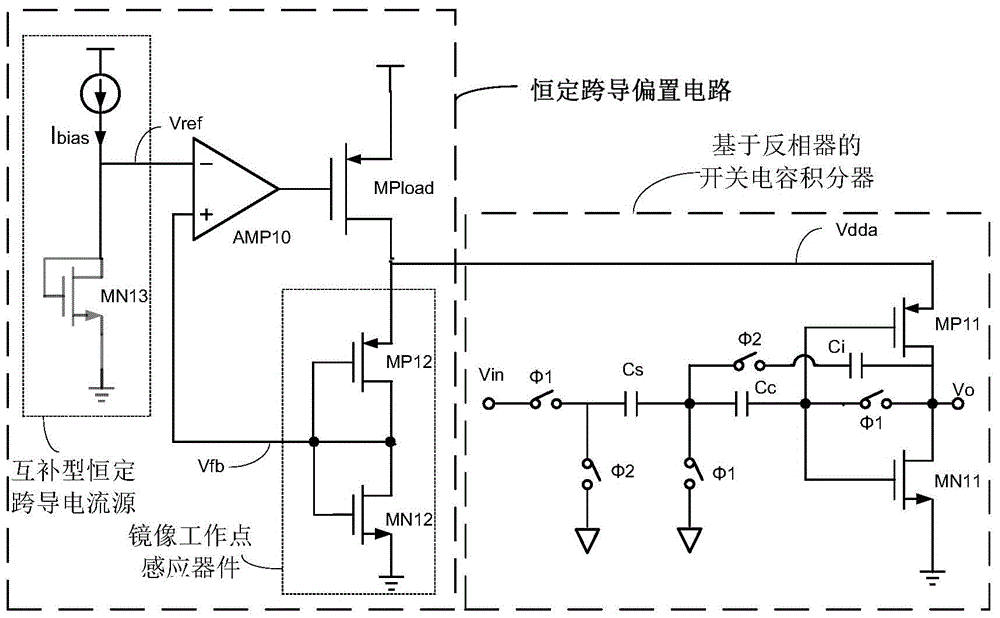

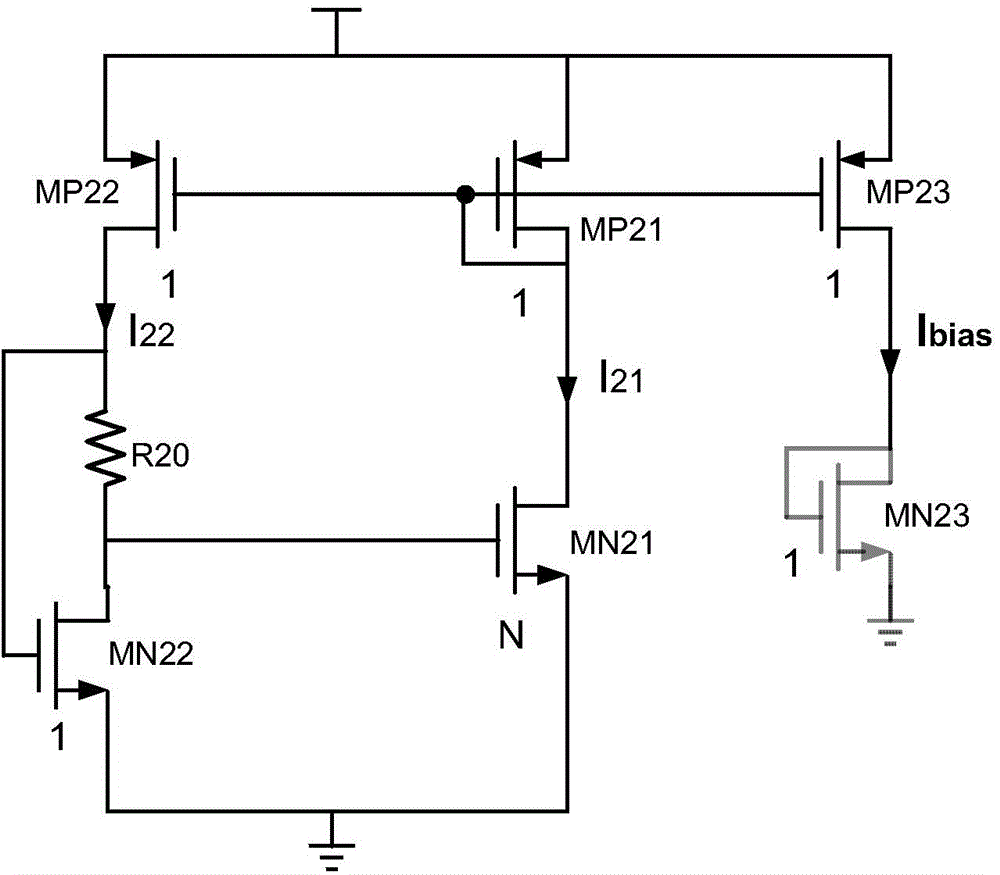

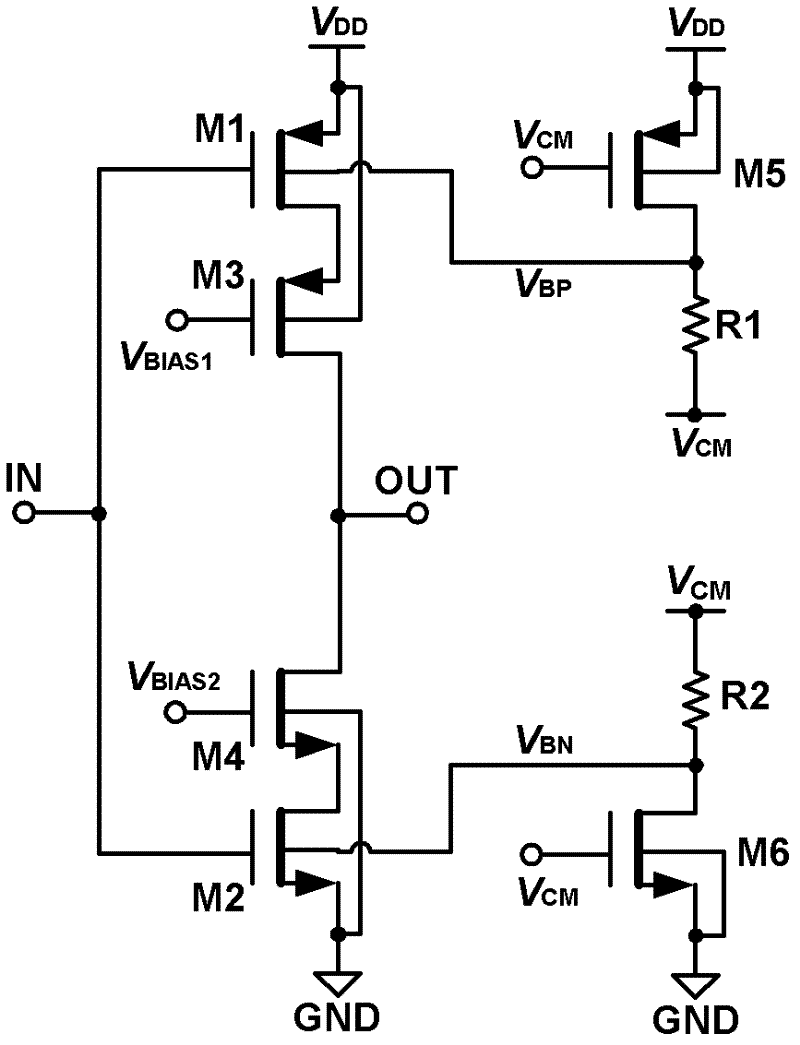

Constant trans-conductance bias circuit for C-type inverter

ActiveCN104699159AImprove stabilityElectric variable regulationTransconductanceOperational amplifier

The invention discloses a constant trans-conductance bias circuit for a C-type inverter. The constant trans-conductance bias circuit comprises an inverter-based switched capacitor integrator and a constant trans-conductance bias circuit body, wherein an OTA in the inverter-based switched capacitor integrator is communicated with the constant trans-conductance bias circuit body through a modulating signal Vdda; the inverter-based switched capacitor integrator comprises an inverter composed of a first NMOS transistor and a first PMOS transistor; the constant trans-conductance bias circuit body comprises a mirror working point sensing device, a complementary type constant trans-conductance bias current source, an operational amplifier and an output load transistor; through the complementary constant trans-conductance bias current source, the total trans-conductance of a bias inverter can be constant, and prevented from changing along with the process bias and the temperature of the NMOS transistor and the PMOS transistor. Therefore, the unity-gain bandwidth and built-up time of the inverter can also keep constant when the process bias and the temperature change, and the stability of a circuit can be improved.

Owner:SOI MICRO CO LTD

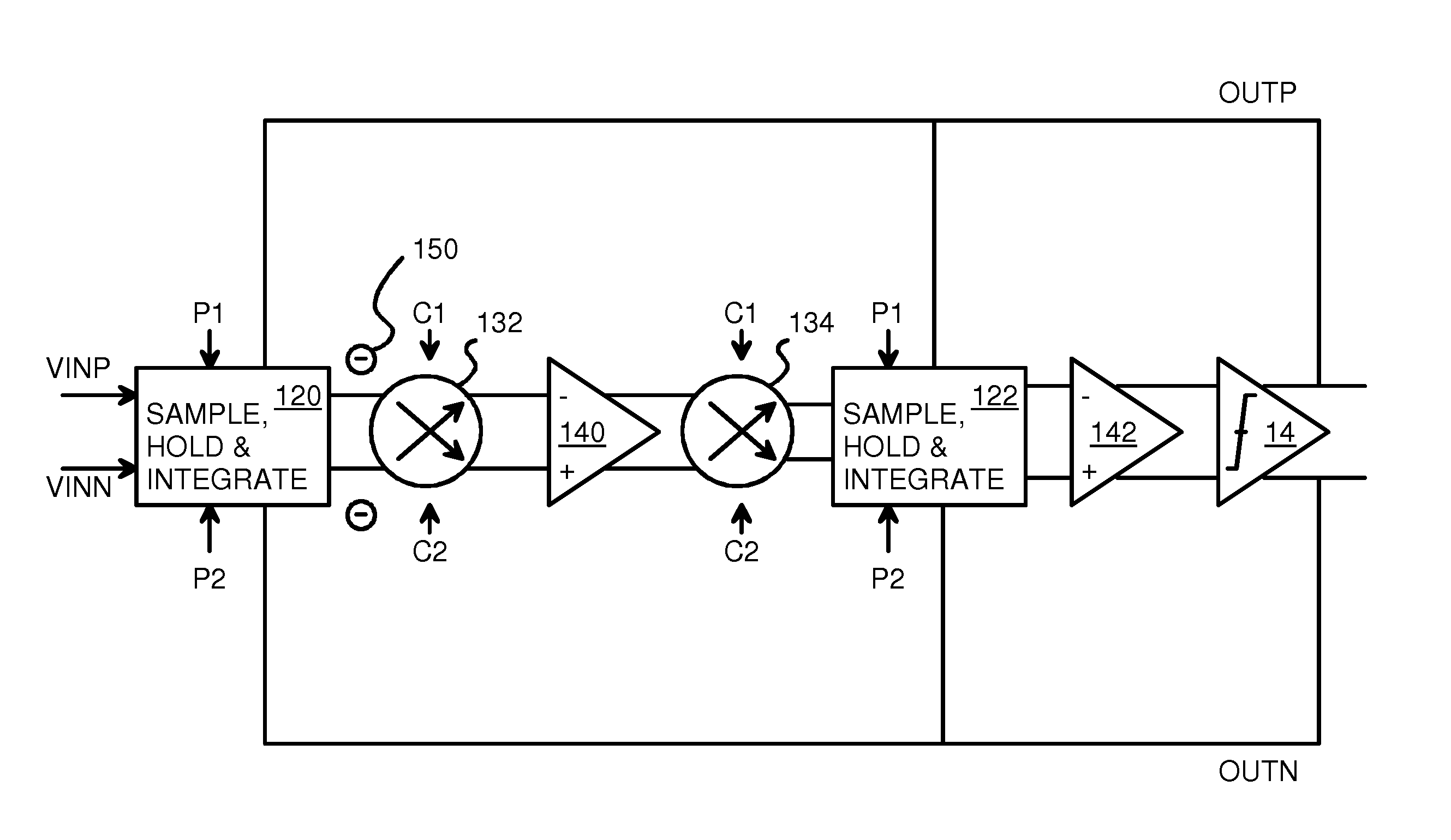

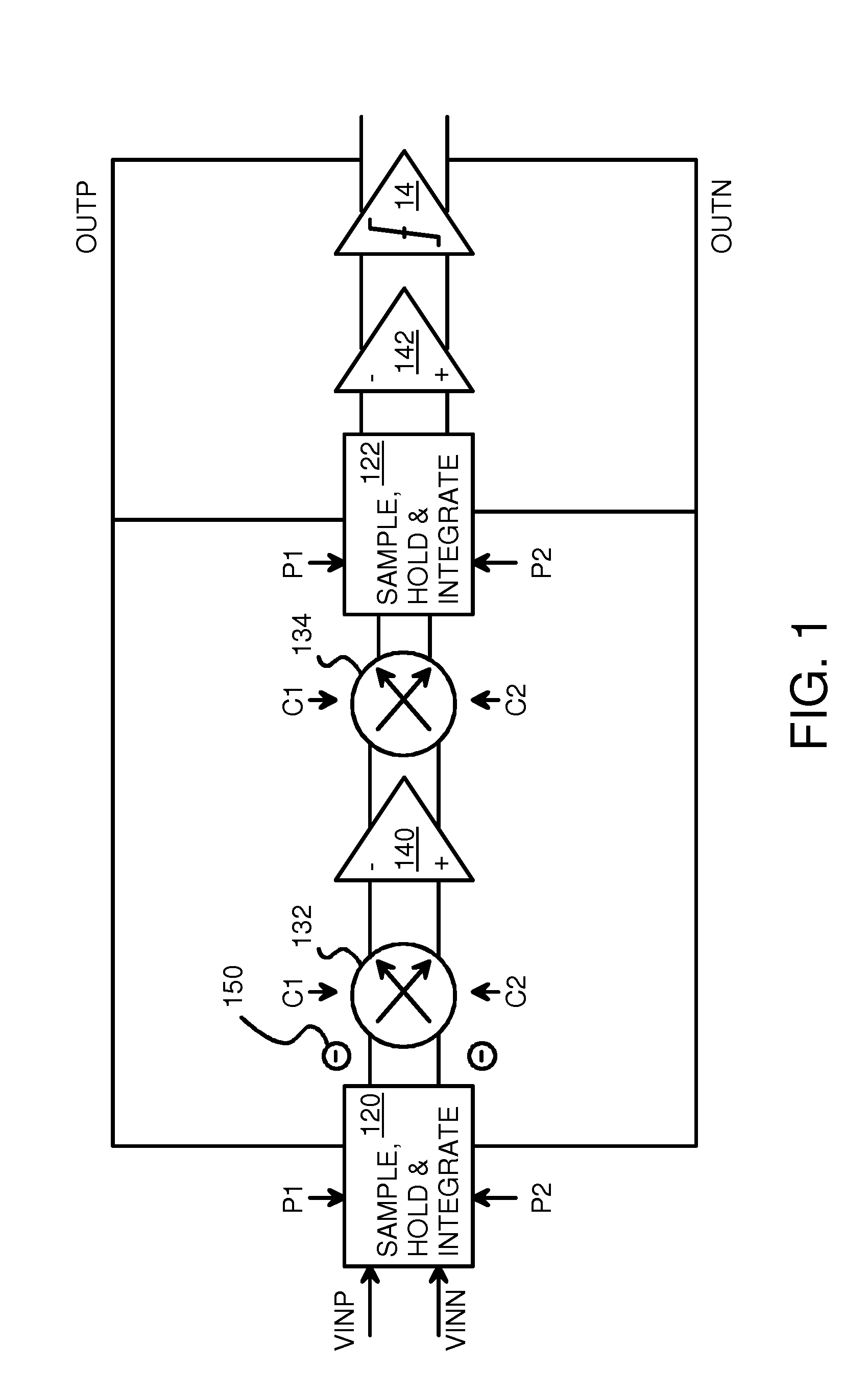

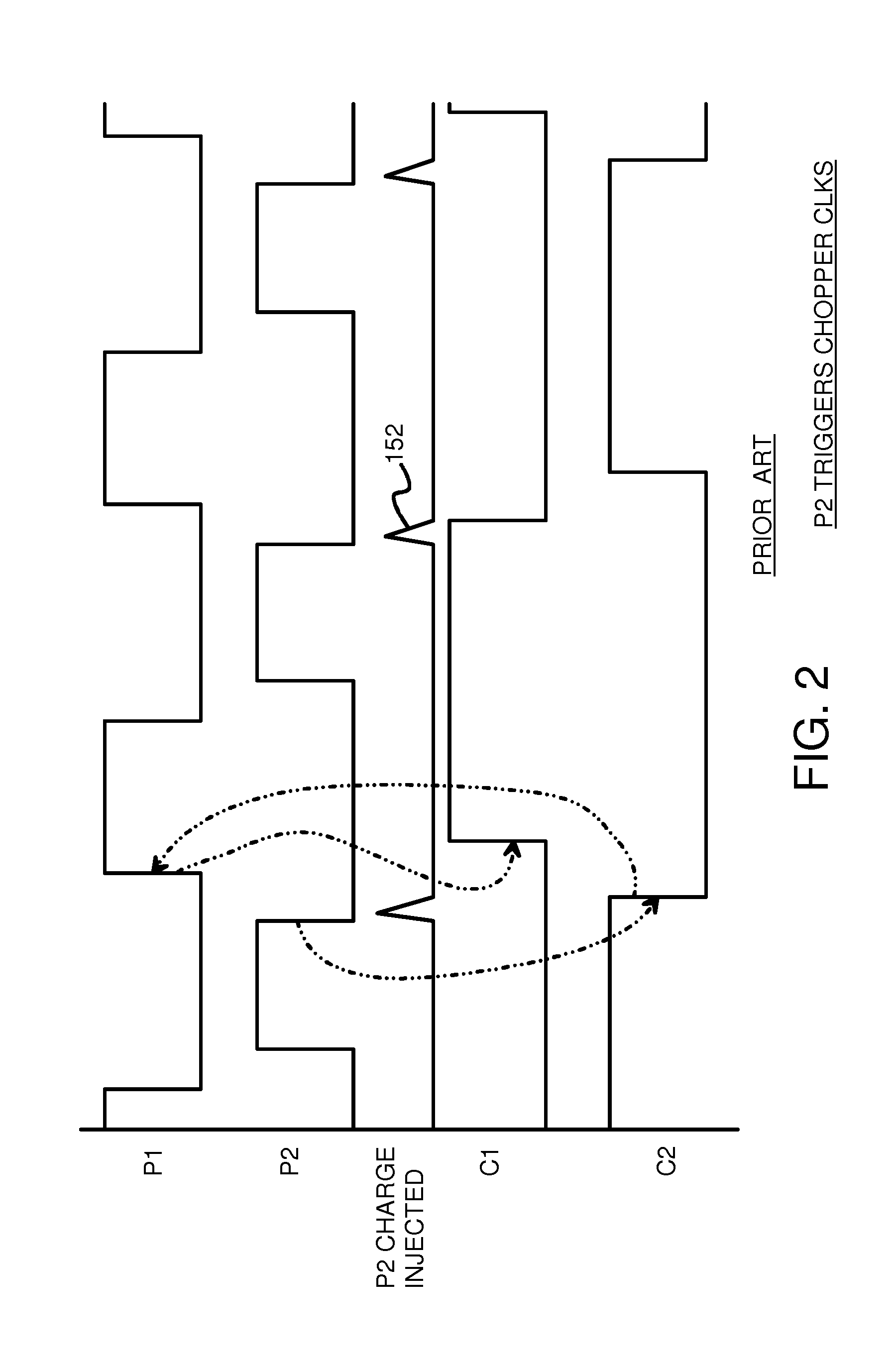

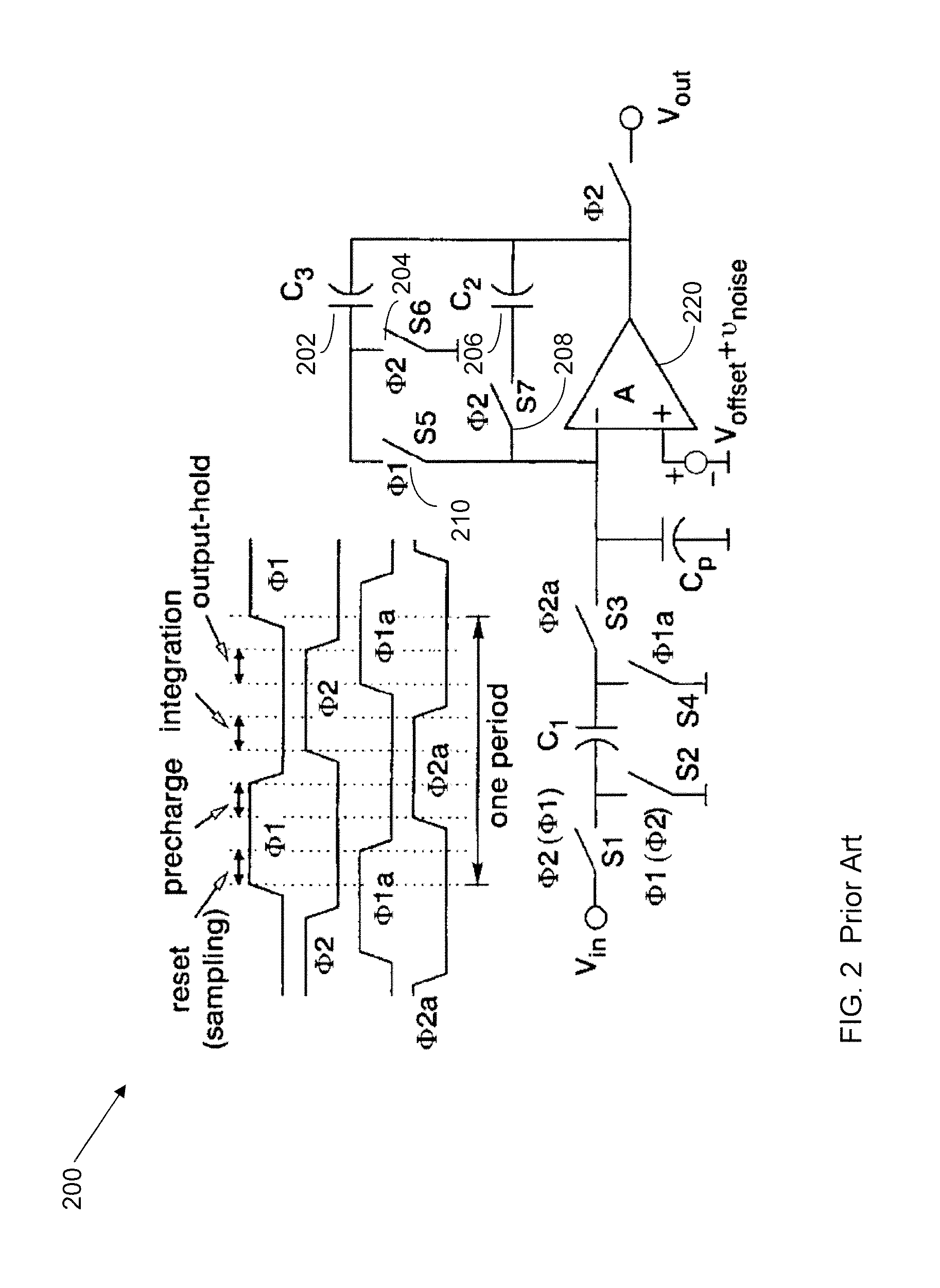

Reduced residual offset sigma delta analog-to-digital converter (ADC) with chopper timing at end of integrating phase before trailing edge

ActiveUS20130141264A1Electric signal transmission systemsDelta modulationDigital down converterIntegrator

An analog-to-digital converter (ADC) has a chopper-stabilized sigma-delta modulator (SDM). The SDM uses switched-capacitor integrators to sample, hold, and integrate an analog input in response to non-overlapping multi-phase clocks. Chopper multipliers are inserted on the inputs and outputs of an op amp in a first stage integrator. The chopper multipliers swap or pass through differential inputs in response to non-overlapping chopper clocks. A master clock operating at a frequency of the multi-phase clocks is divided down to trigger generation of the chopper clocks. Delay lines ensure that the edges of the chopper clocks occur before the edges of the multi-phase clocks. The chopper multipliers have already switched and are thus stable when multi-phase clocks change so charge injection at switches controlled by the multi-phase clocks is not immediately modulated by chopper multipliers. This clock timing increases the time available to respond to charge injection at switches improving linearity.

Owner:HONG KONG APPLIED SCI & TECH RES INST

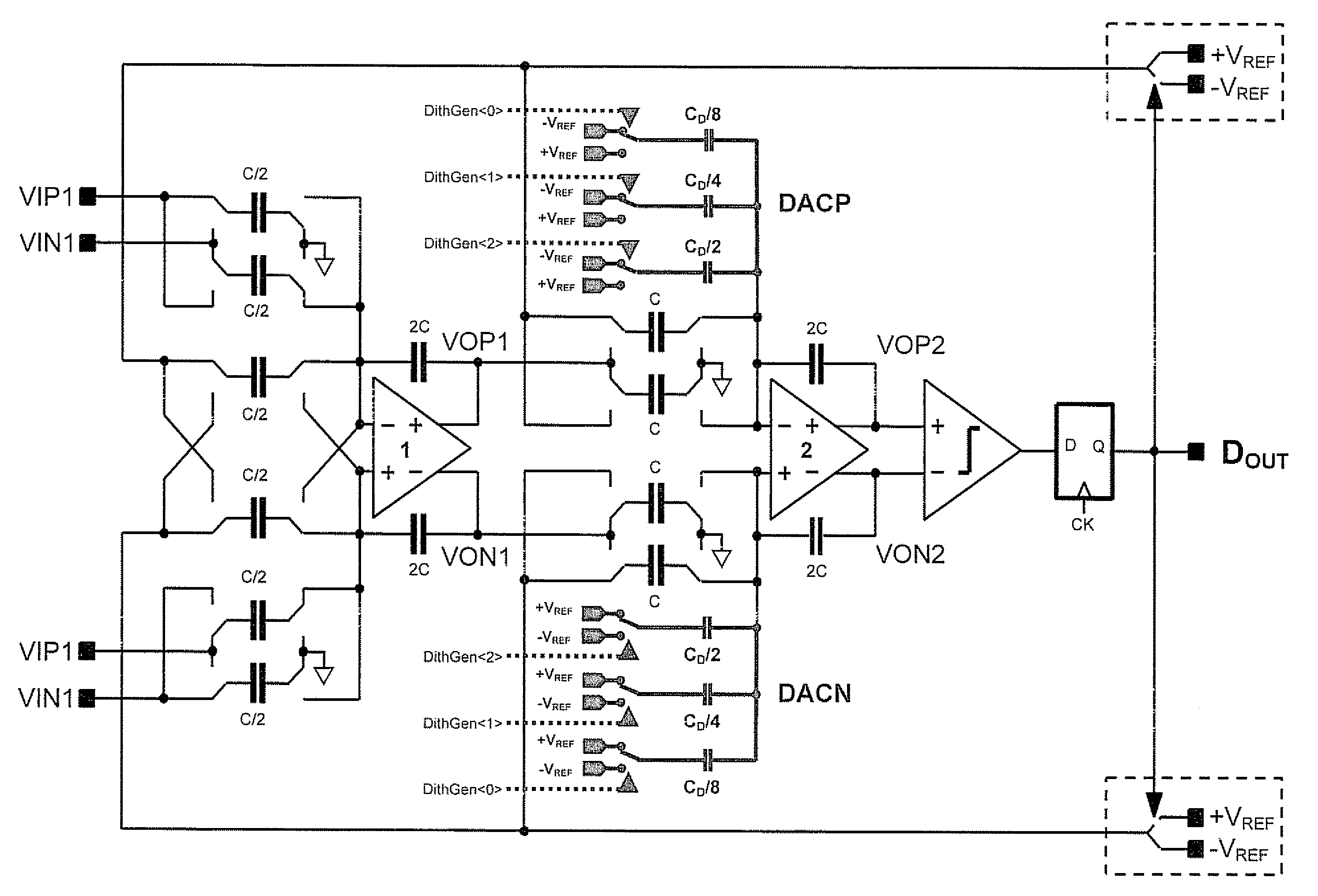

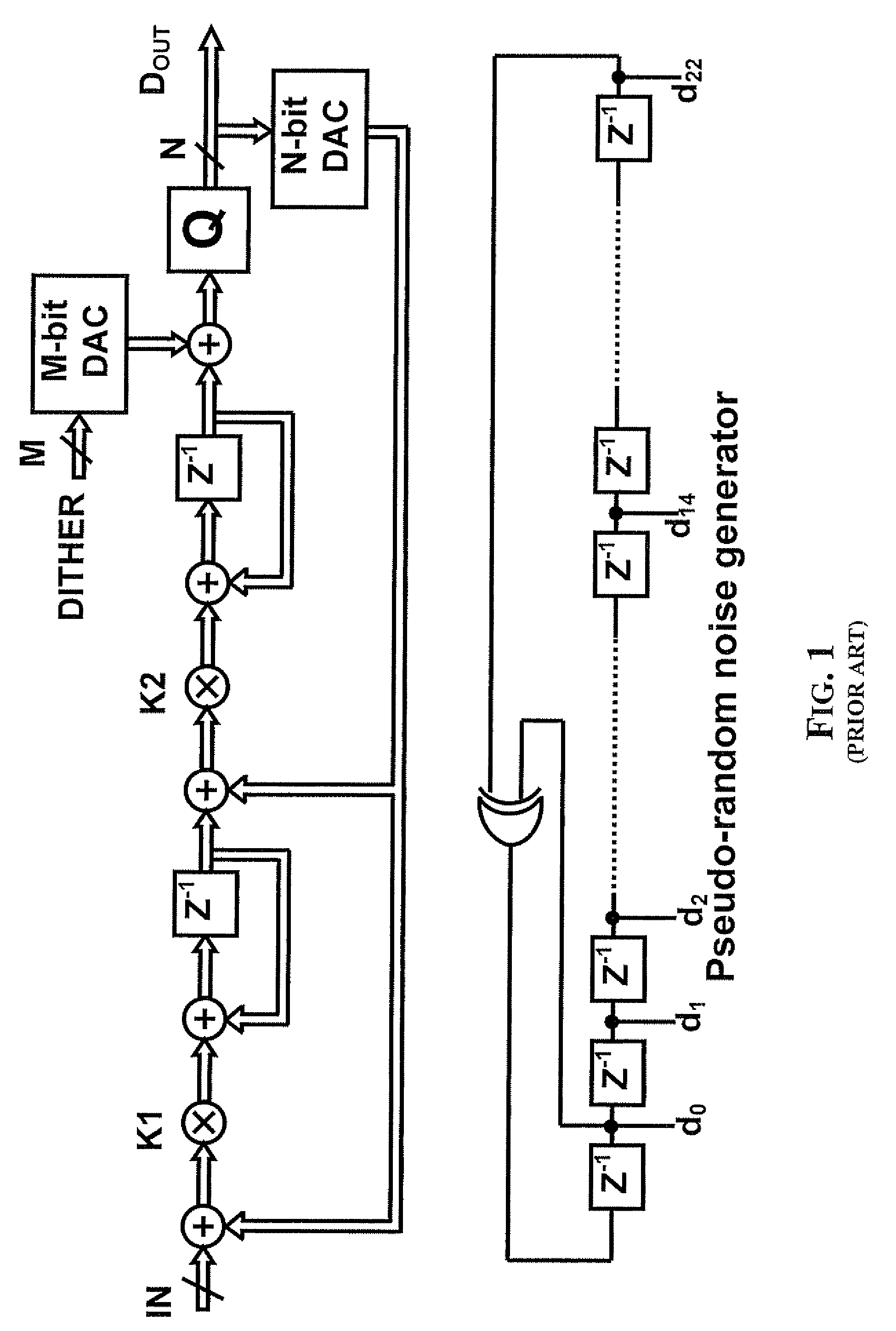

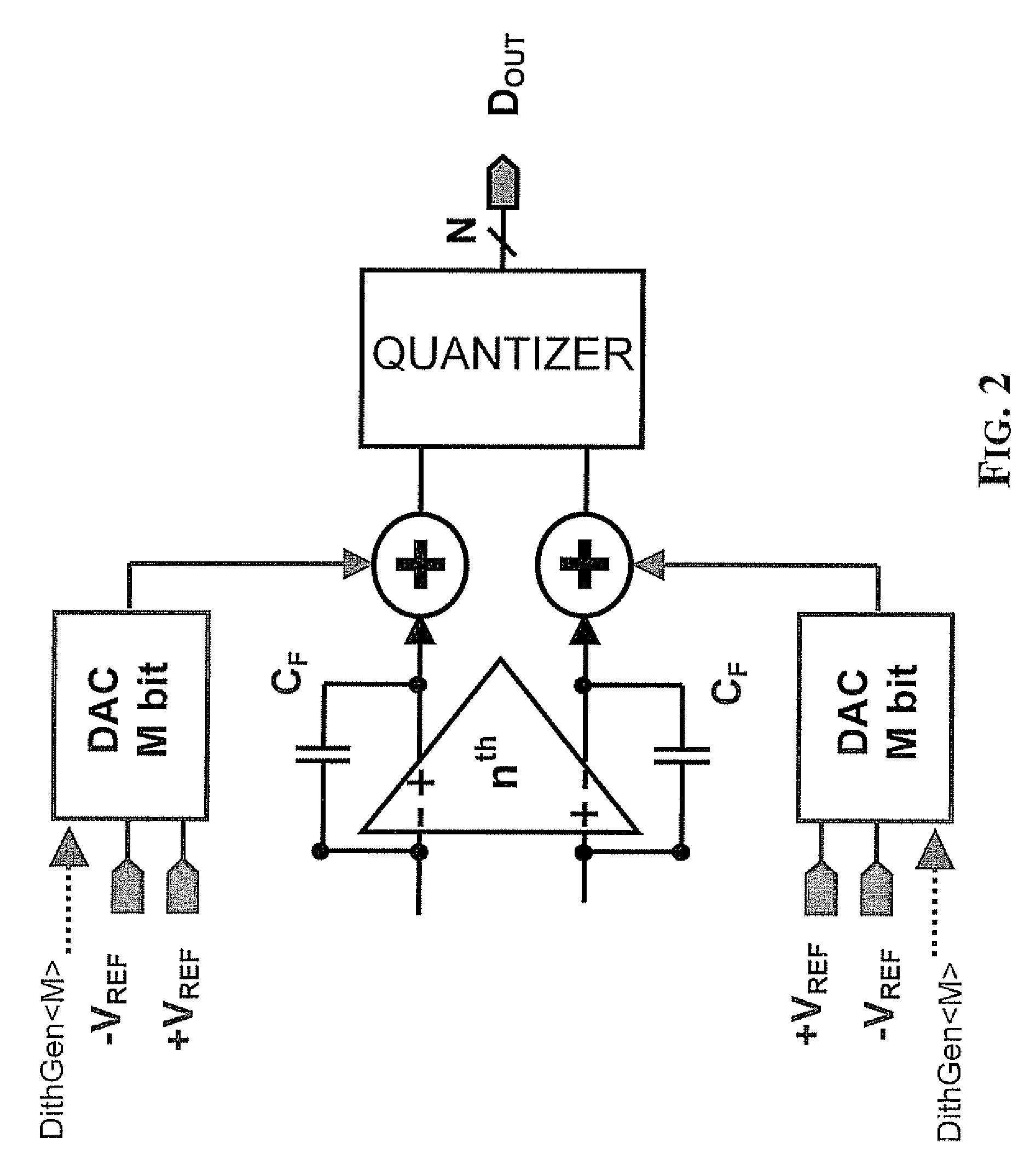

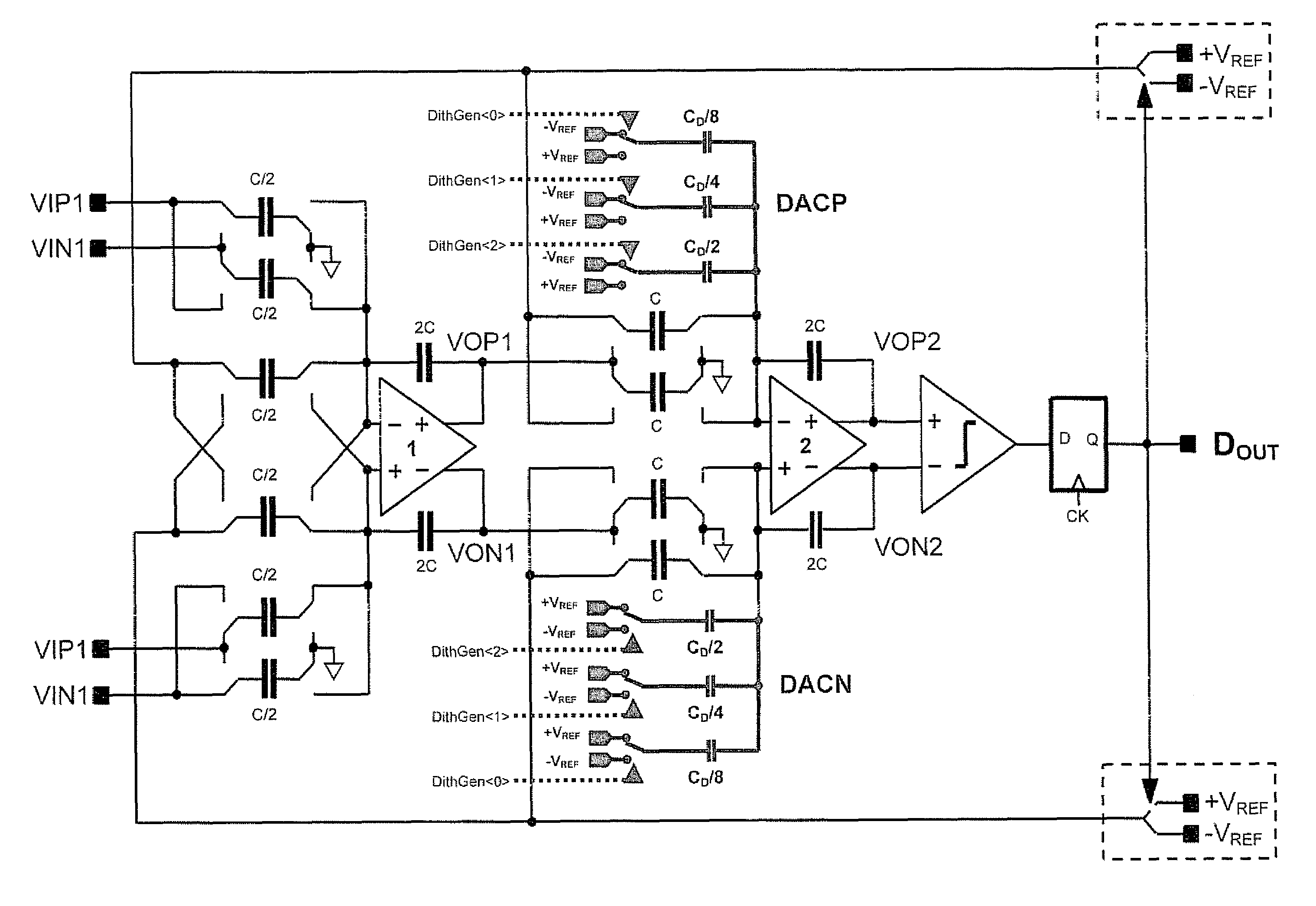

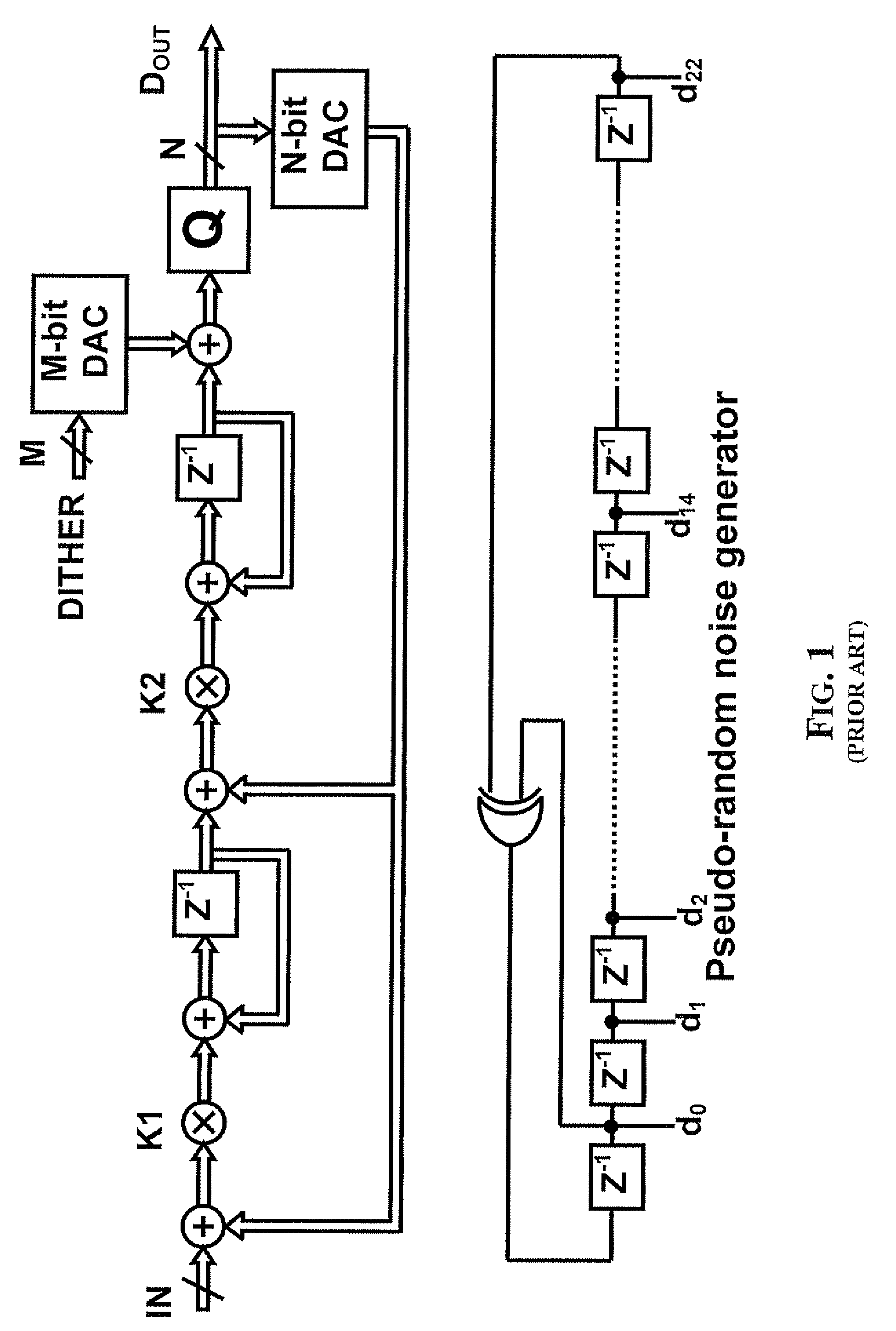

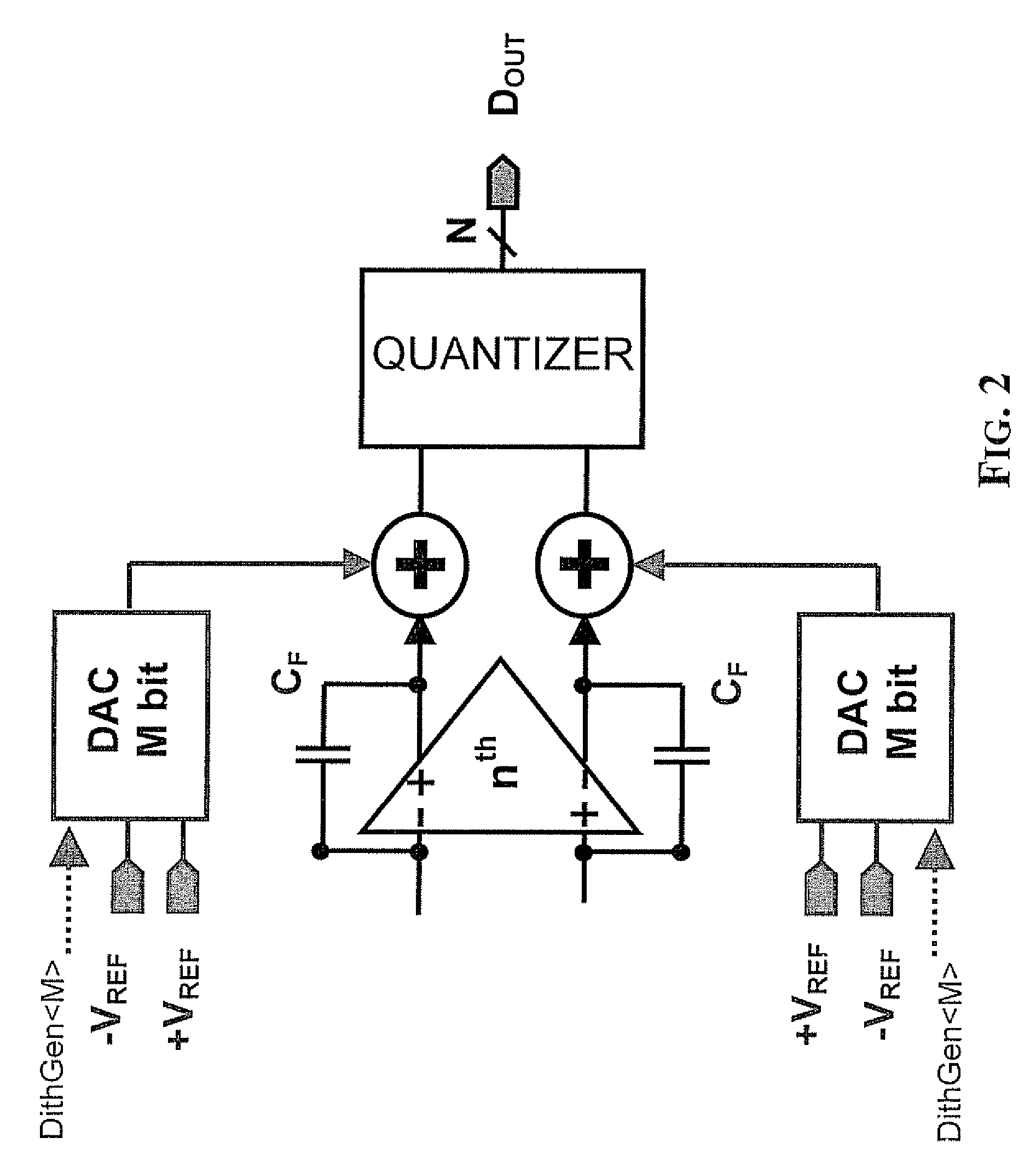

Method of adding a dither signal in output to the last integrator of a sigma-delta converter and relative sigma-delta converter

A single-ended or differential single-stage, or multi-stage sigma-delta analog-to-digital converter includes at least one switched-capacitor integrator comprising a switched-capacitor network receiving as input a signal to be sampled, and an amplifier coupled in cascade to the switched-capacitor network. A circuit is coupled to the amplifier for feeding an analog dither signal to a virtual ground of the amplifier.

Owner:TELEFON AB LM ERICSSON (PUBL)

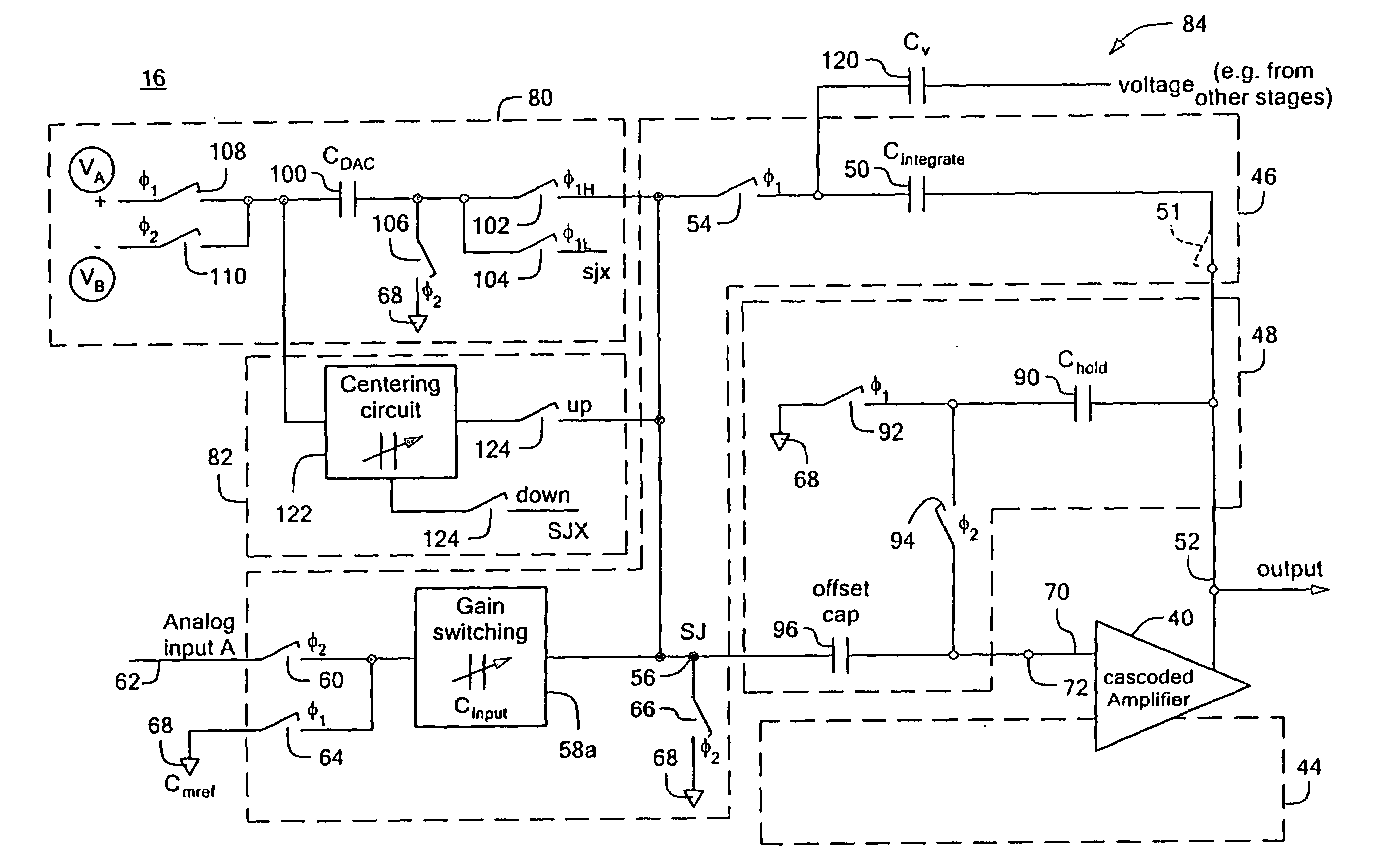

Switched capacitor integrator system

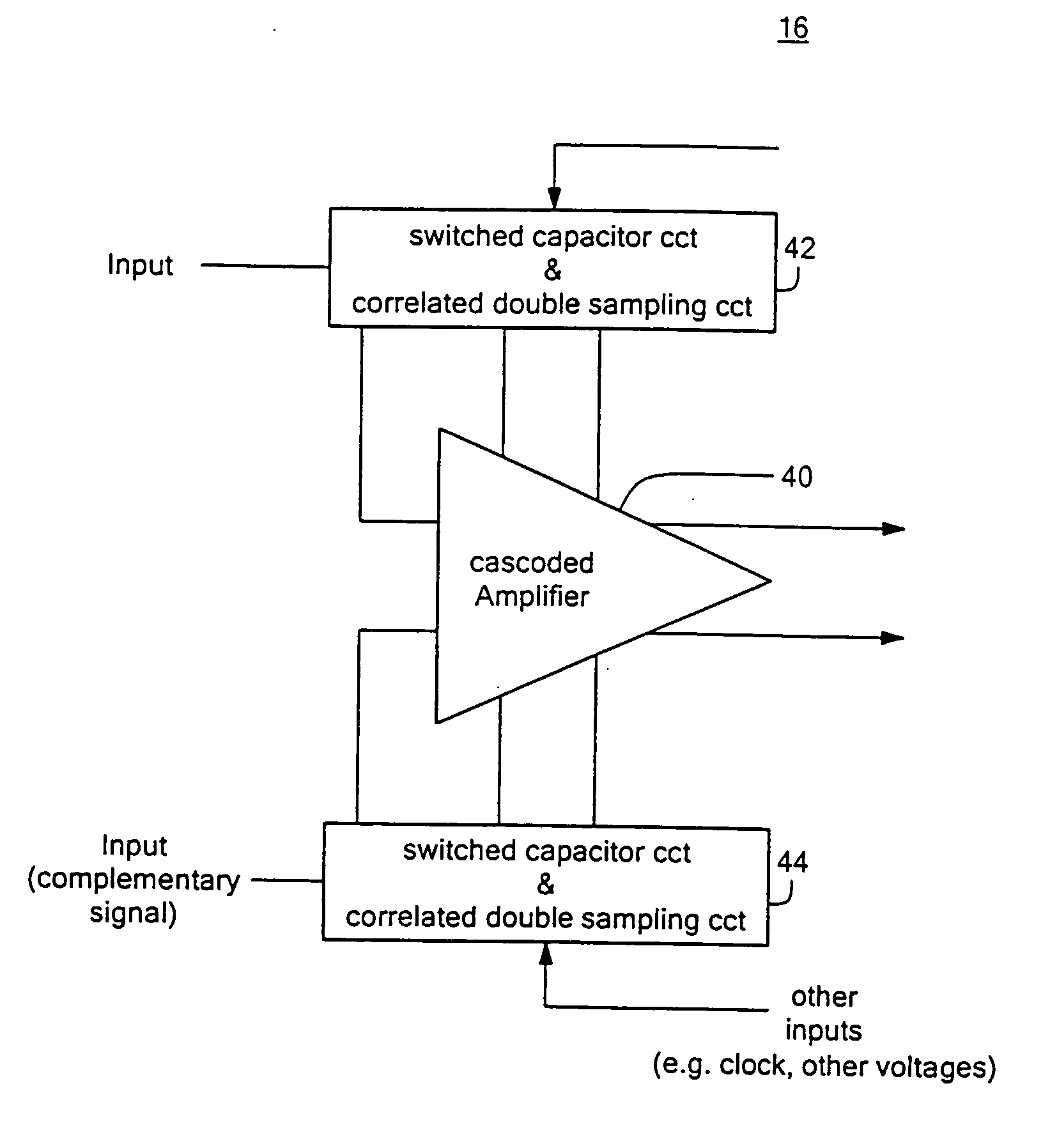

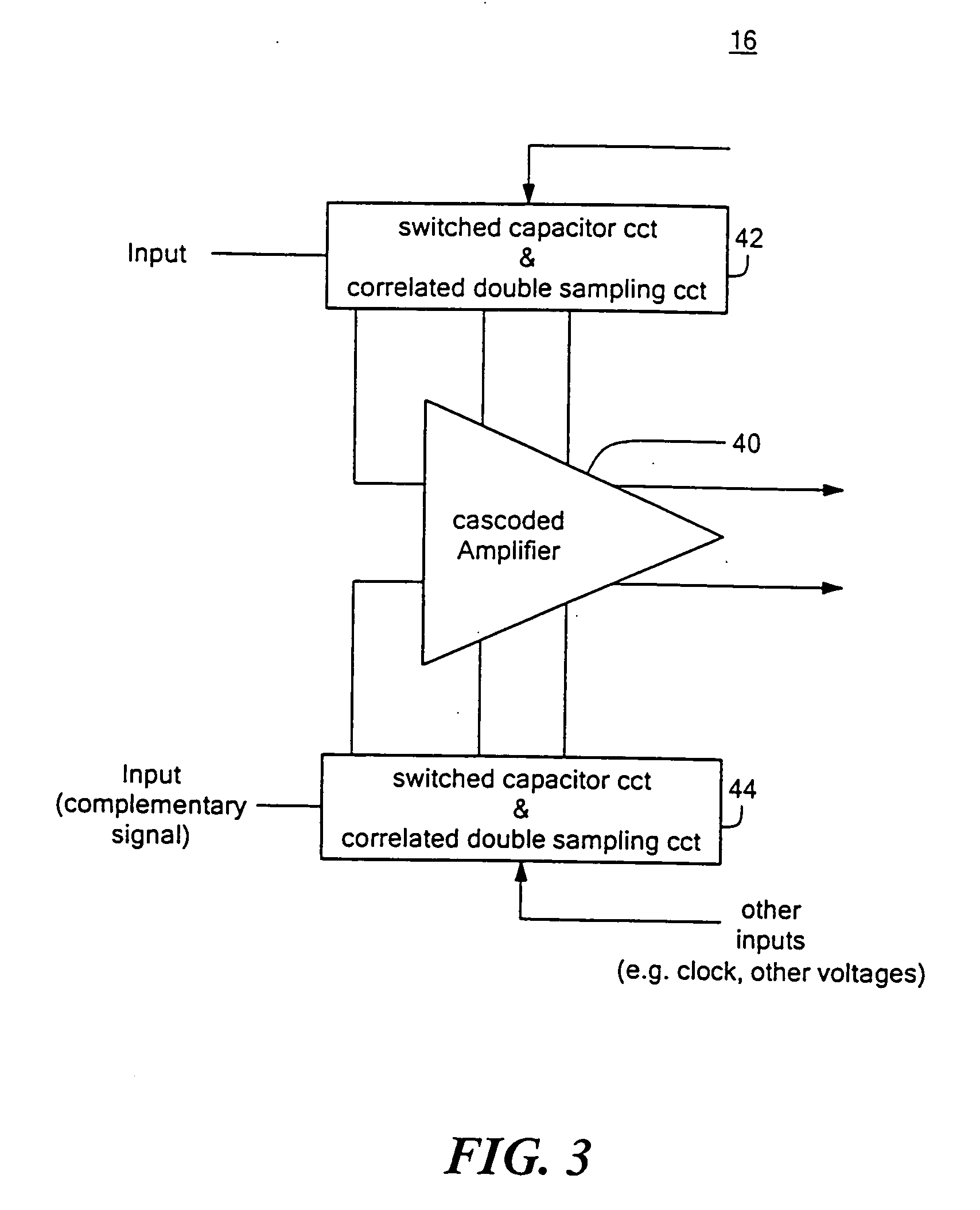

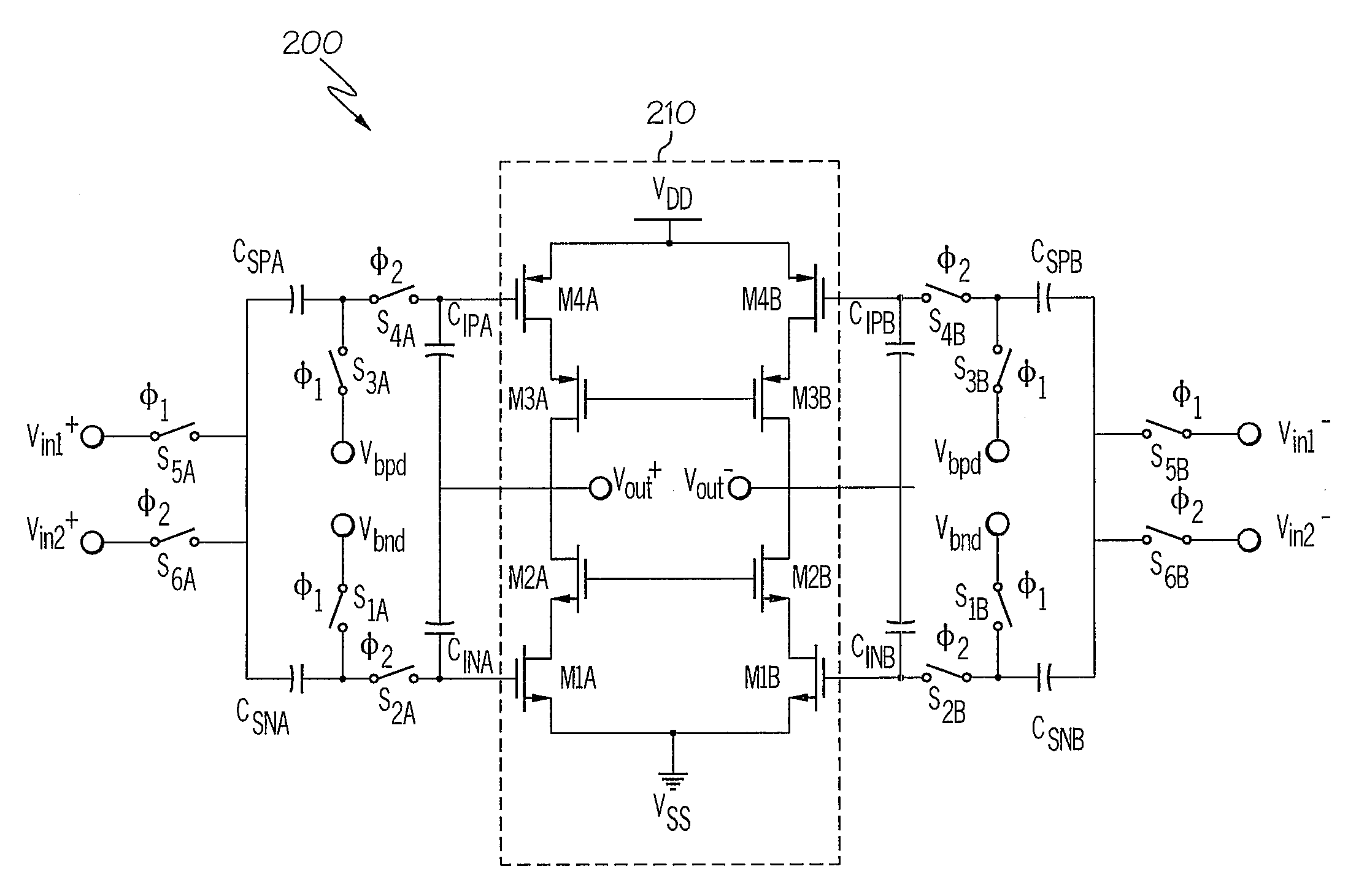

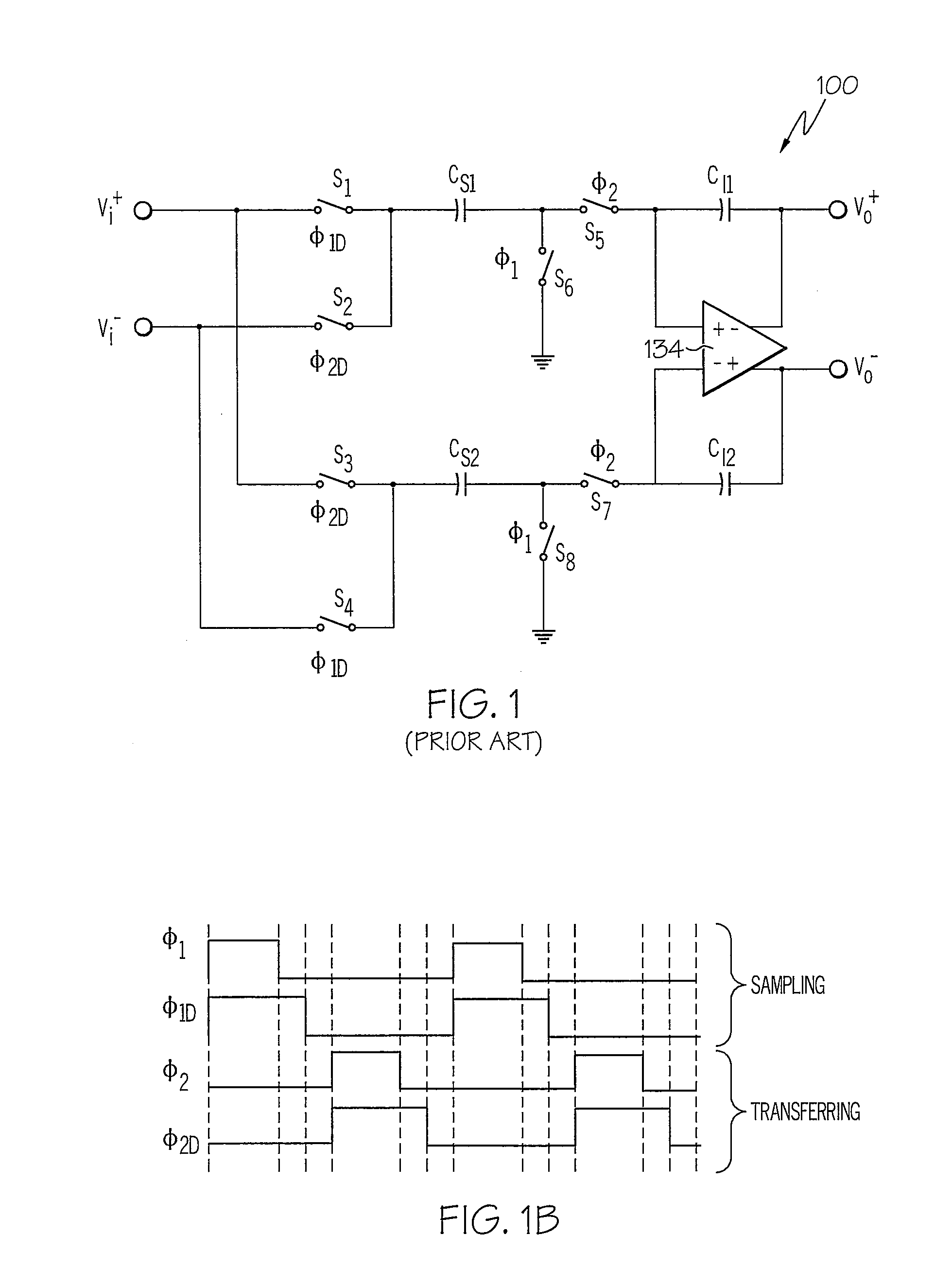

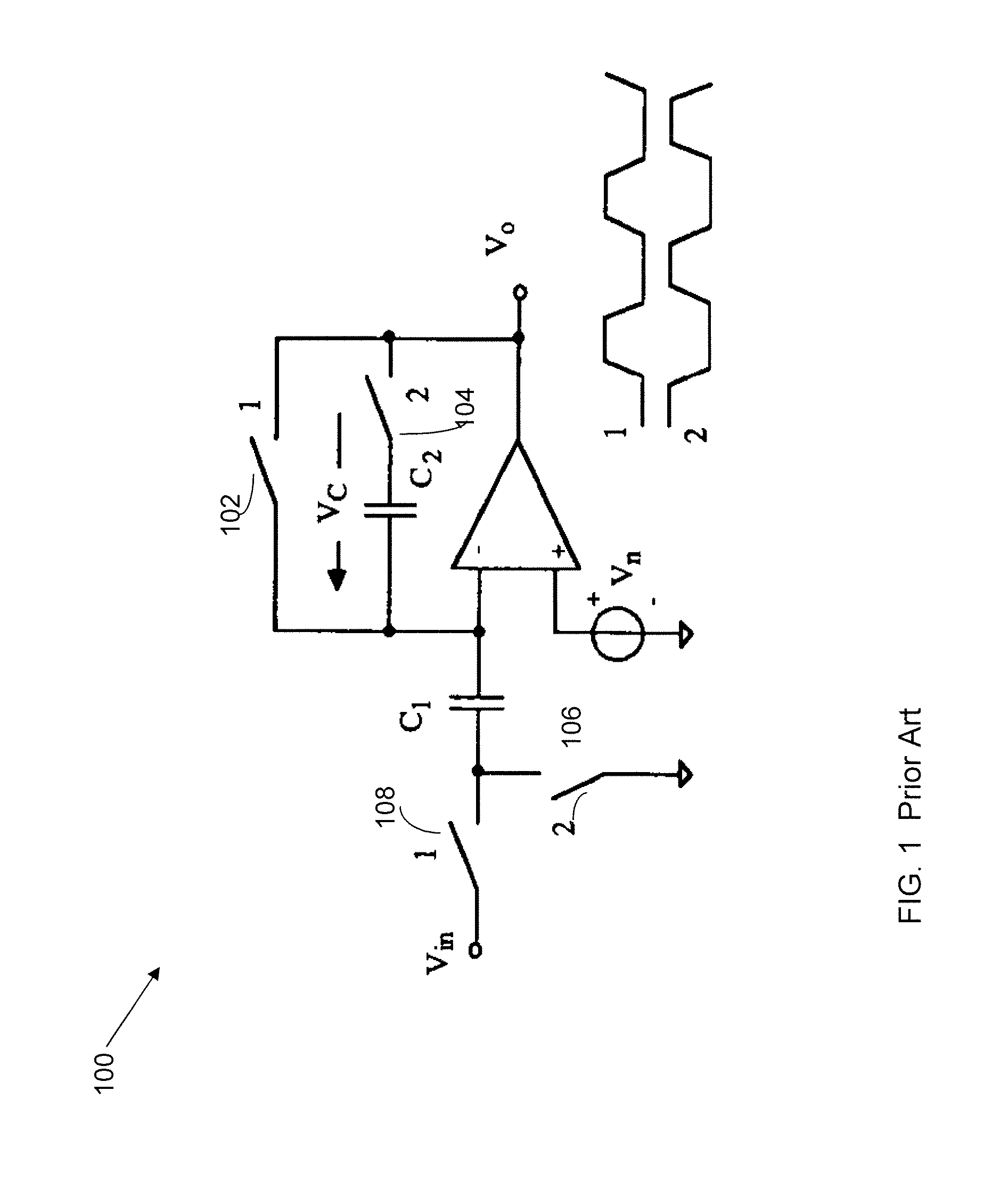

ActiveUS20050231411A1Improve the problemImprove linearityComputing operations for integral formationMultiple input and output pulse circuitsEngineeringCascode amplifier

A switched capacitor integrator system includes an input cascoded amplifier circuit; a summing junction; an integrating switched capacitor circuit connected to the output of the input cascoded amplifier circuit and to the summing junction; the integrating switched capacitor circuit including an input switched capacitor circuit responsive to an input and connected to the summing junction; and a correlated double sampling capacitor circuit including an offset capacitor interconnected between the summing junction and the input of the input cascoded amplifier circuit.

Owner:ANALOG DEVICES INC

Switched-Capacitor Circuit

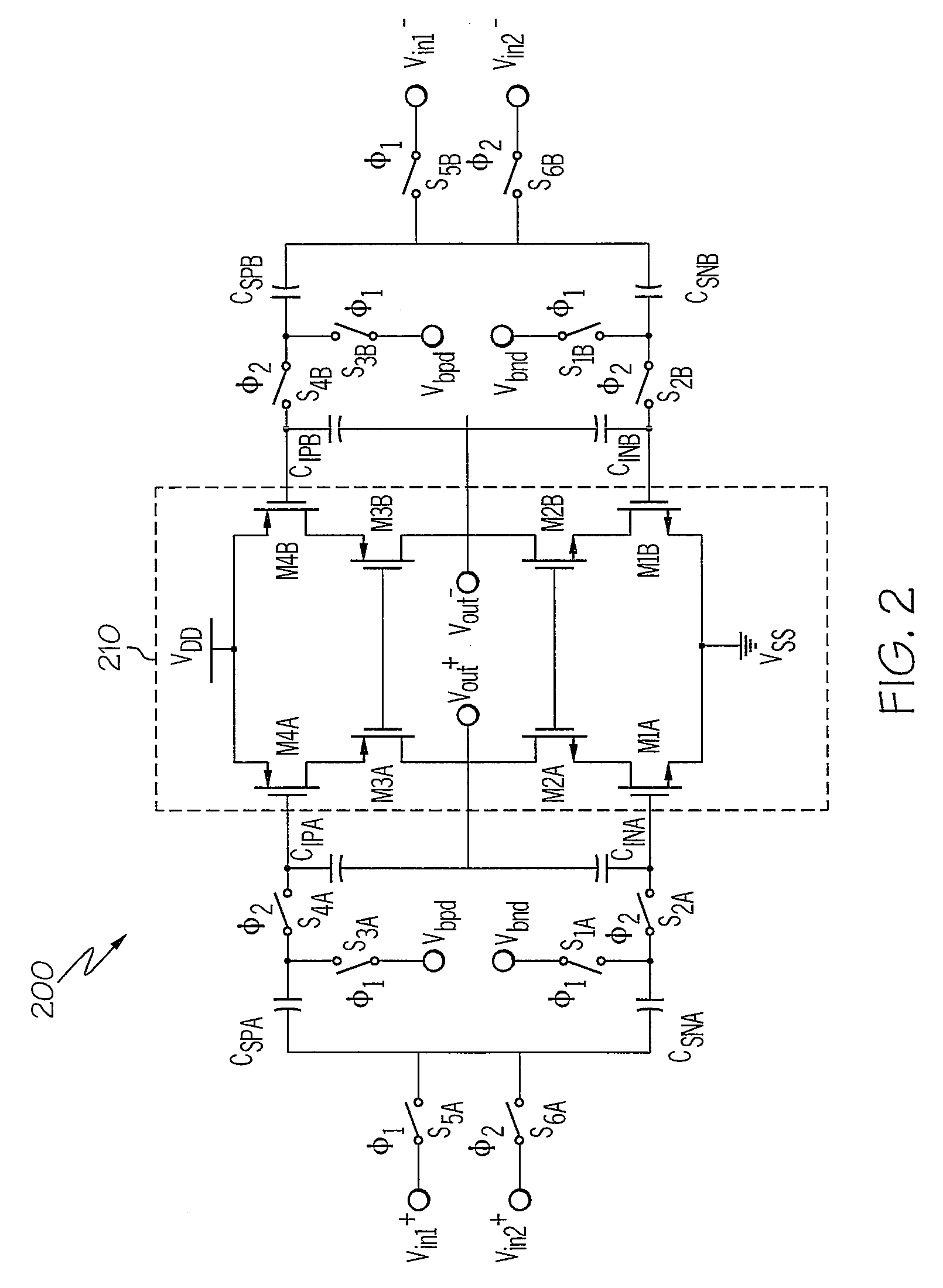

InactiveUS20080061858A1Computing operations for integral formationComputing operations for integration/differentiationCapacitancePush pull

A low-power switched-capacitor circuit is disclosed. The low-power switched-capacitor circuit includes a p-channel switched-capacitor integrator and an n-channel switched-capacitor integrator. The p-channel switched-capacitor integrator includes a first set of input transistors controlled by a first set of capacitors and switches. The n-channel switched-capacitor integrator includes a second set of input transistors controlled by a second set of capacitors and switches. The p-channel switched-capacitor integrator and the n-channel switched-capacitor integrator function together in a push-pull fashion such that a required transconductance as well as width and drain current of the first and second sets of input transistors are reduced by half of those in a conventional switch-capacitor circuit.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

Low noise switch capacitor circuit having embedded amplifier

ActiveCN101364800AReduce areaReduce power consumptionTime-varying networkDifferential amplifiersCapacitanceLow noise

A low-noise switched-capacitor circuit with a built-in amplifier relates to a switched-capacitor circuit. The low-noise switched-capacitor circuit comprises a switched-capacitor circuit and an active amplifier, wherein the switched-capacitor circuit includes a switch, a capacitor and an amplifier; the input terminal of the active amplifier is connected with the switch; the output terminal of the active amplifier is connected with the capacitor; and the capacitor is connected with the negative input terminal of an operational amplifier. The low-noise switched-capacitor circuit can be used for a switched-capacitor amplifier, a switched-capacitor integrator and other switched-capacitor circuits of other types to meet the requirement for low noise of the system and simultaneously reduce the occupied chip areas and the power consumptions of the capacitor and the operational amplifier. The low-noise switched-capacitor circuit can maximally reduce the desired chip area and the power consumption for the switched-capacitor circuit during low-noise operation, so that the noise index of the switched-capacitor circuit is not restricted by sampling noise, i.e. KT / C noise, of the capacitor.

Owner:海芯科技(厦门)有限公司

Method of adding a dither signal in output to the last integrator of a sigma-delta converter and relative sigma-delta converter

A single-ended or differential single-stage, or multi-stage sigma-delta analog-to-digital converter includes at least one switched-capacitor integrator comprising a switched-capacitor network receiving as input a signal to be sampled, and an amplifier coupled in cascade to the switched-capacitor network. A circuit is coupled to the amplifier for feeding an analog dither signal to a virtual ground of the amplifier.

Owner:TELEFON AB LM ERICSSON (PUBL)

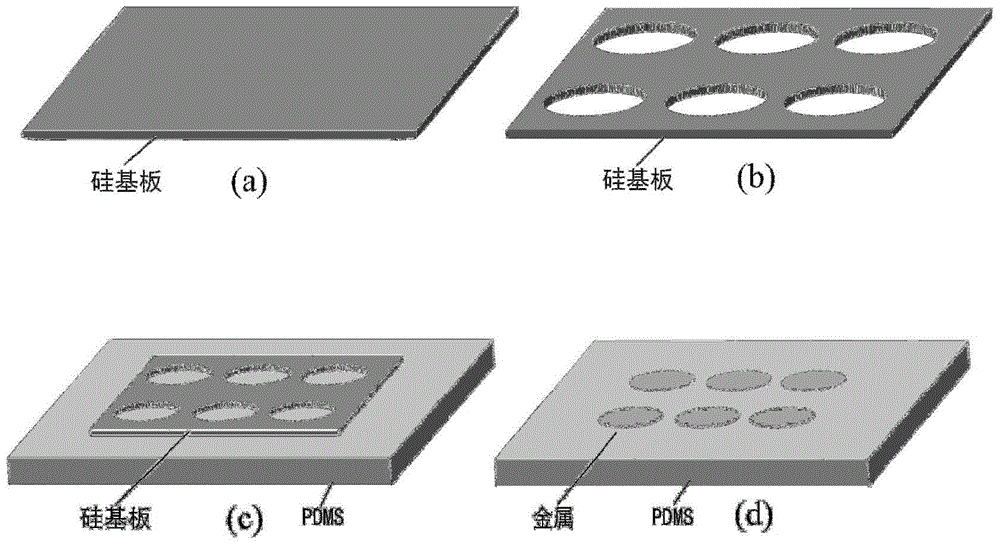

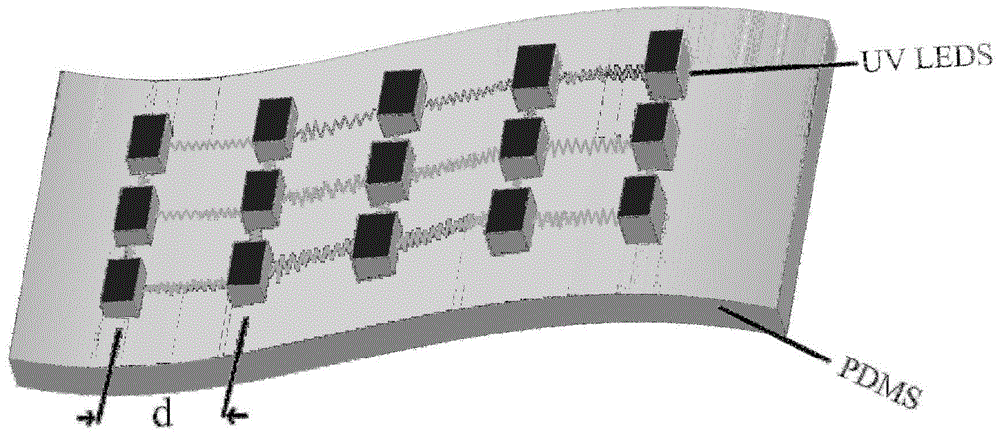

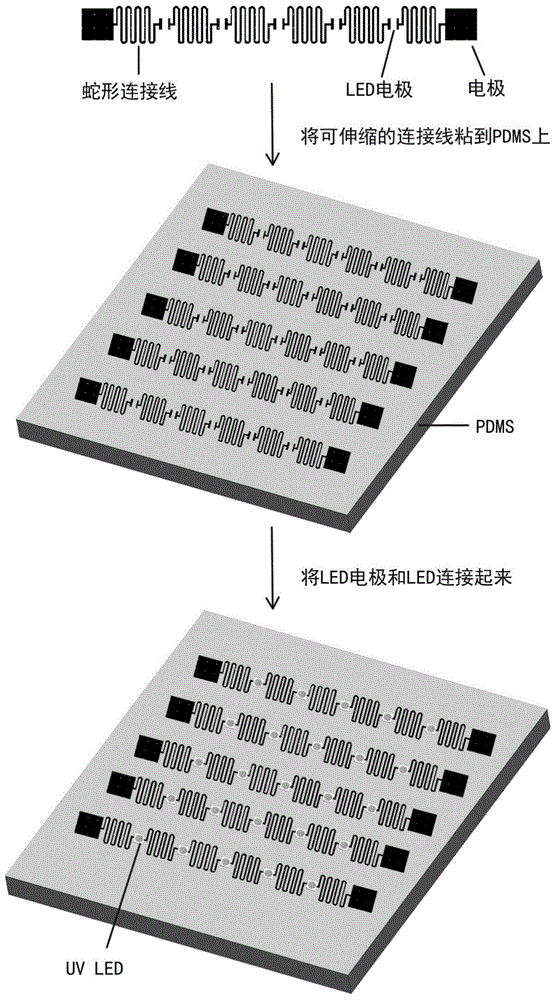

Flexible, stretchable and deformable curved surface optical lithography template as well as optical lithography method and device

ActiveCN104614947ARealize multiplexingReduce manufacturing costPhotomechanical exposure apparatusMicrolithography exposure apparatusIntegratorLithographic artist

The invention relates to the field of nano processing. In order to realize that (1) a system can realize optical lithography on a substrate of a complicated curved surface, and (2) the system can realize optical lithography of similar figures, which are different from one another in period or interval, by using one template, the invention provides a flexible, stretchable and deformable curved surface optical lithography template and an optical lithography method. The method comprises the following steps: manufacturing a stretchable flexible optical lithography mask plate; manufacturing a flexible ultraviolet light-emitting diode LED panel used as a light source for exposure; tightly adhering the stretchable flexible optical lithography mask plate to a substrate coated with photoresist under the effect of controllable stress; tightly adhering the flexible LED panel to the flexible template; turning on the LED for exposure of the photoresist according to a proper amount of dosage and corresponding exposure time; taking down the flexible LED panel; taking down the mask plate; completing the exposure; performing developing and subsequent machining processes. The flexible, stretchable and deformable curved optical lithography template and the optical lithography method are mainly used for design and manufacture of switch capacitance integrators.

Owner:TIANJIN UNIV

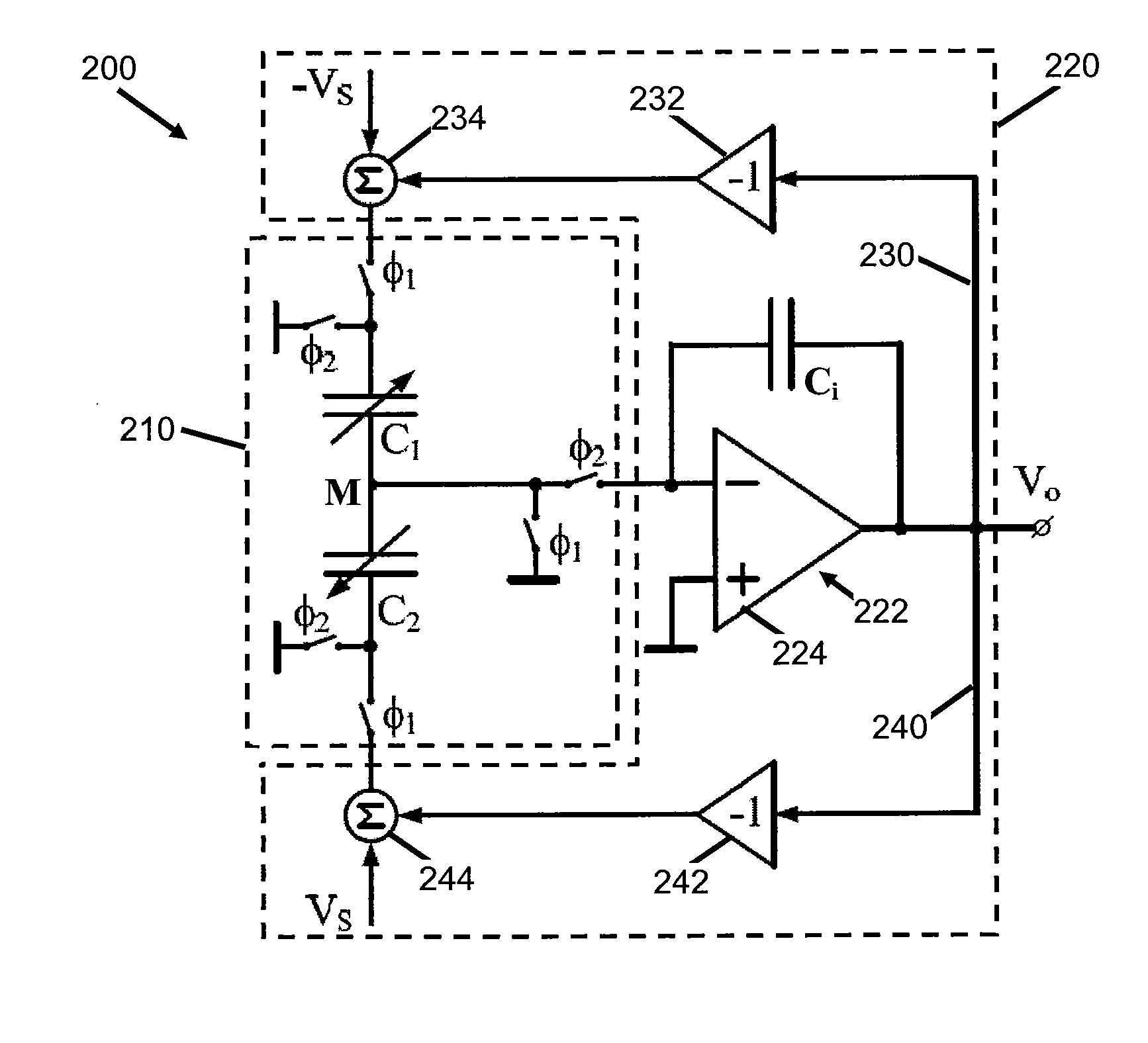

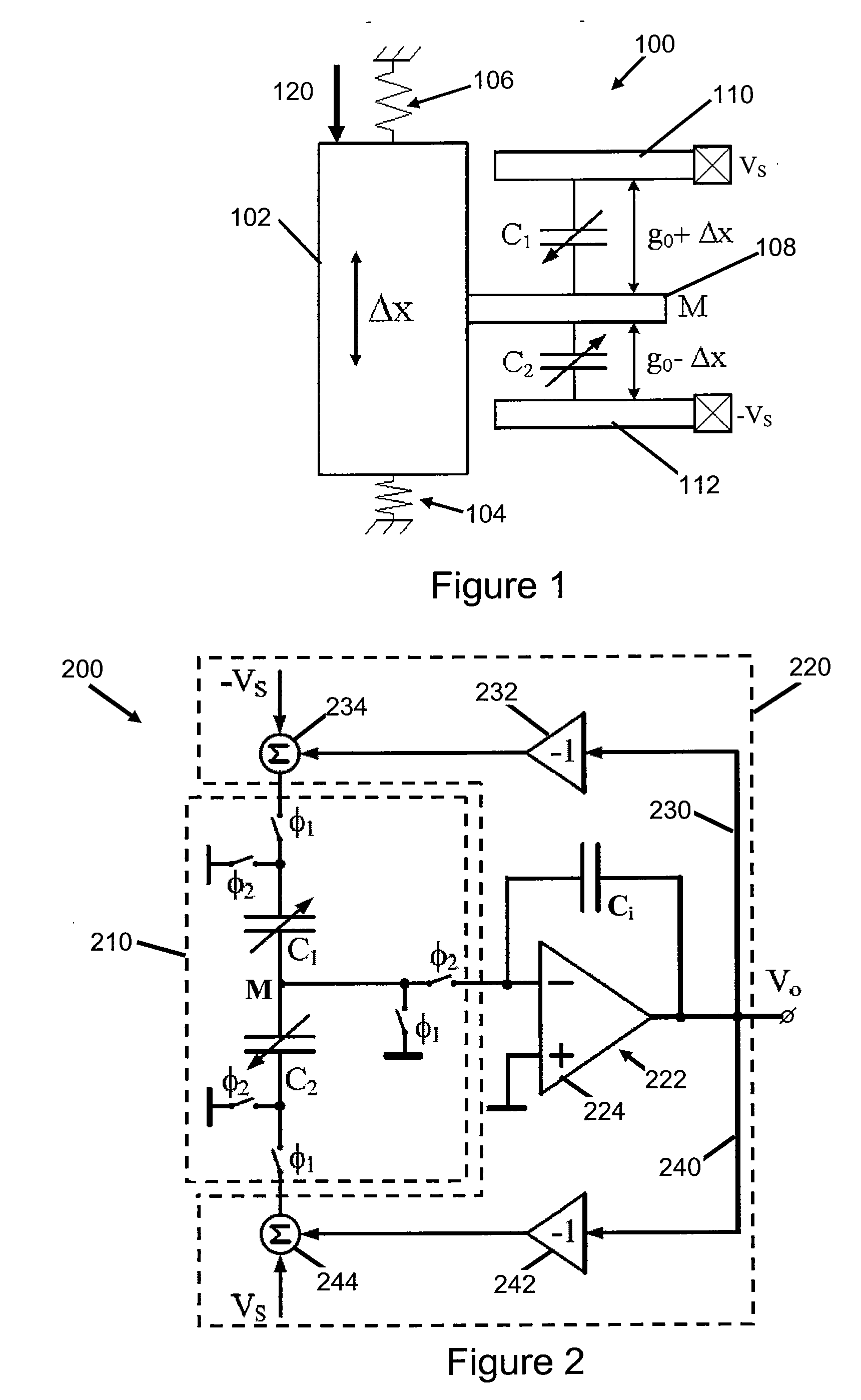

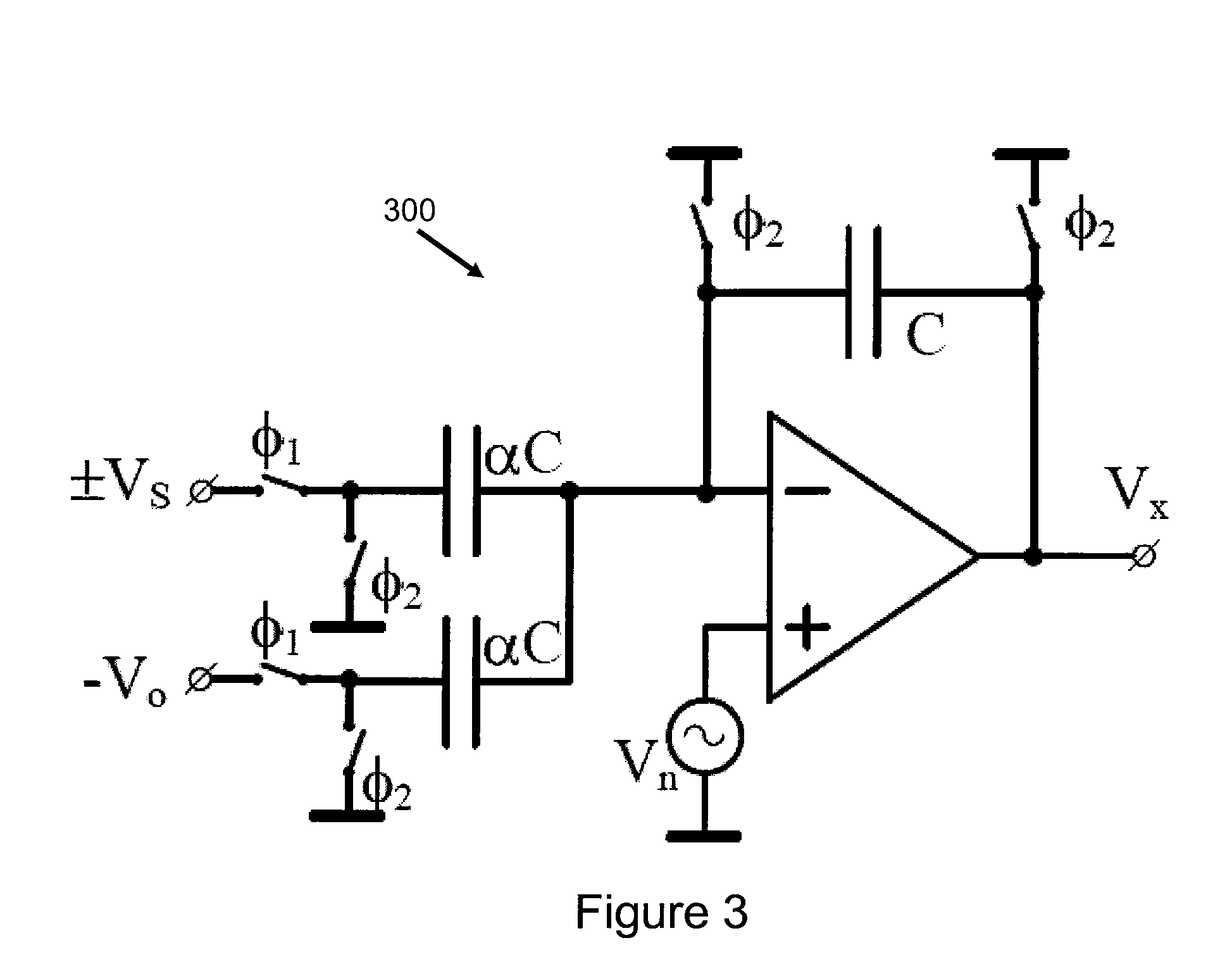

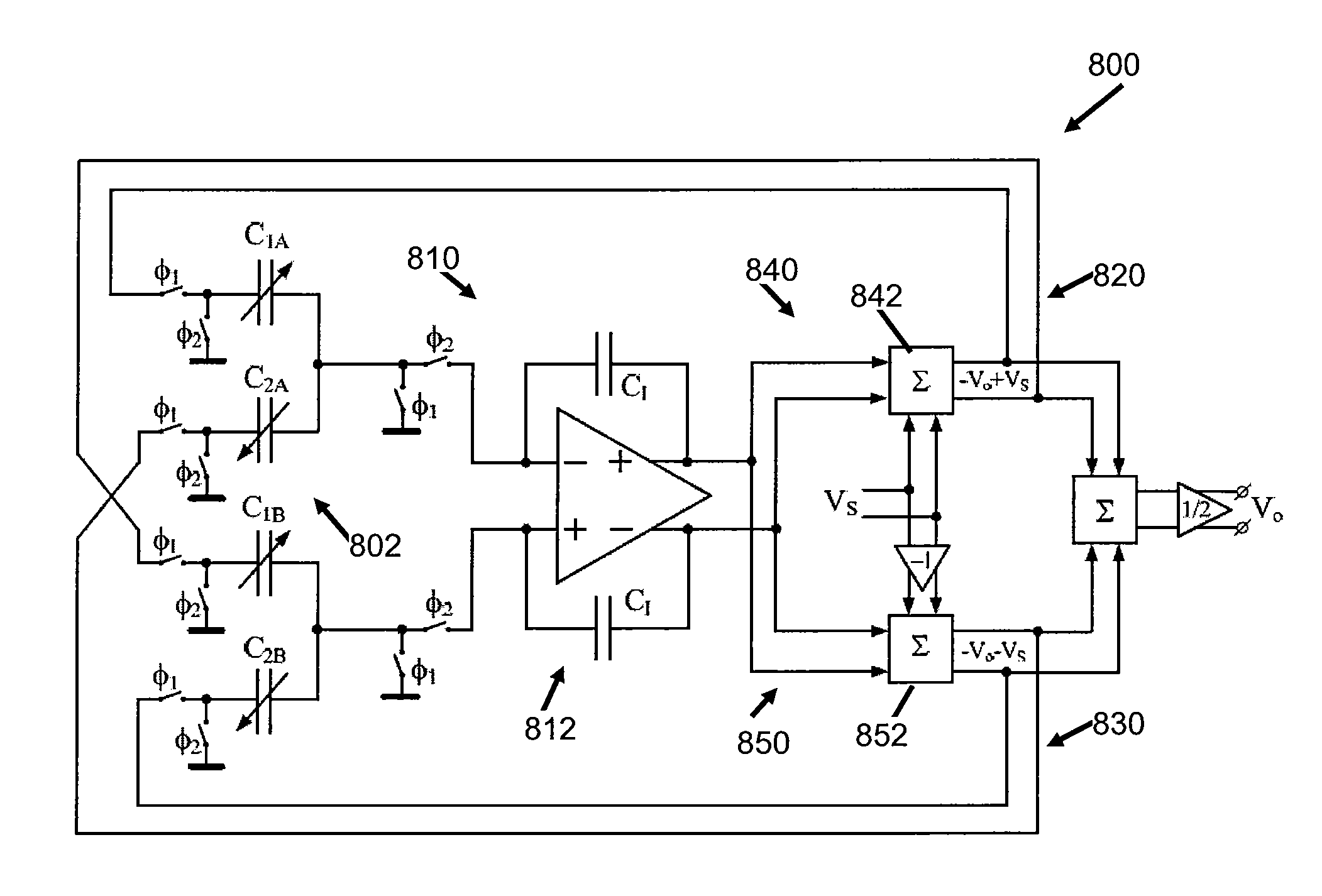

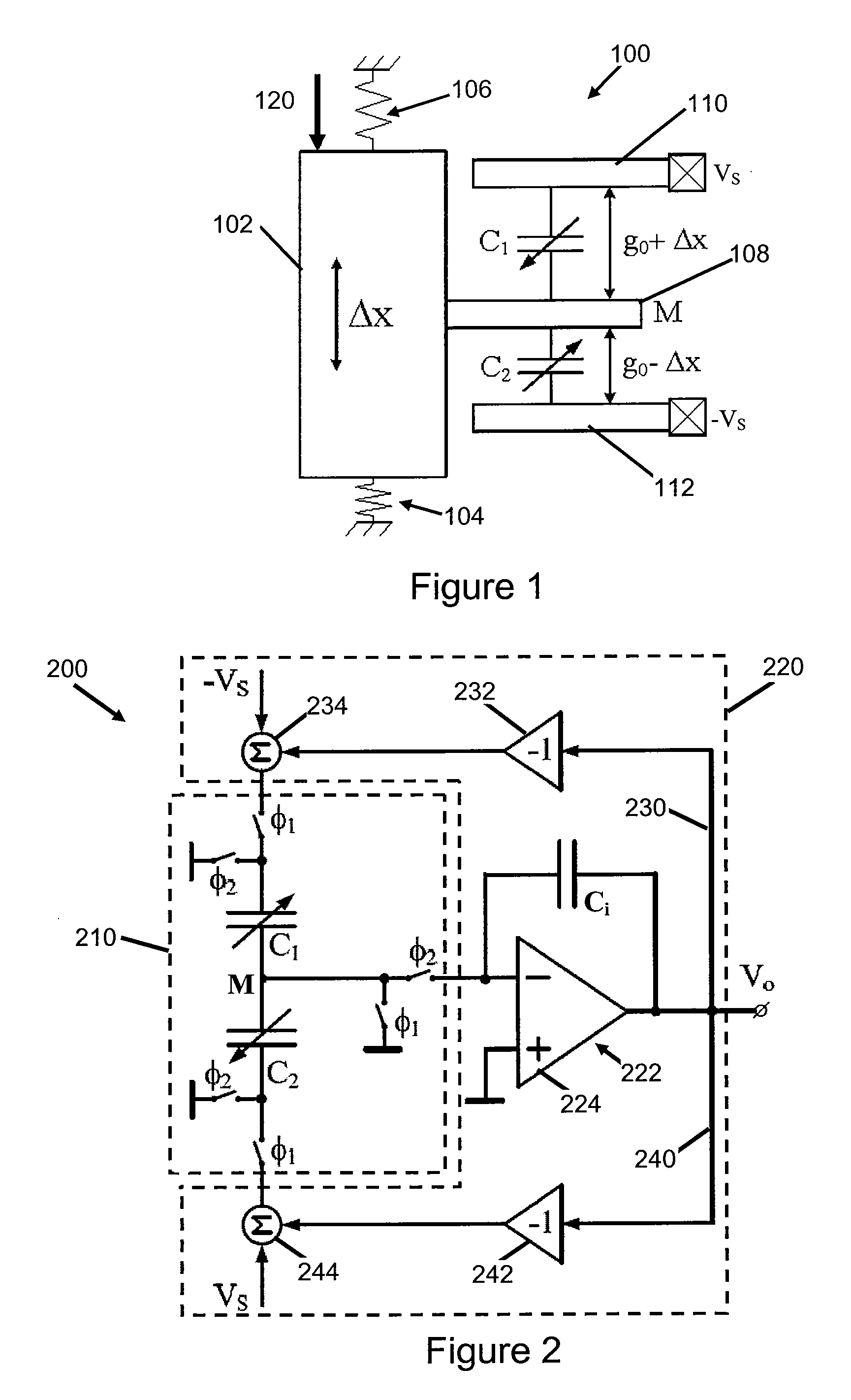

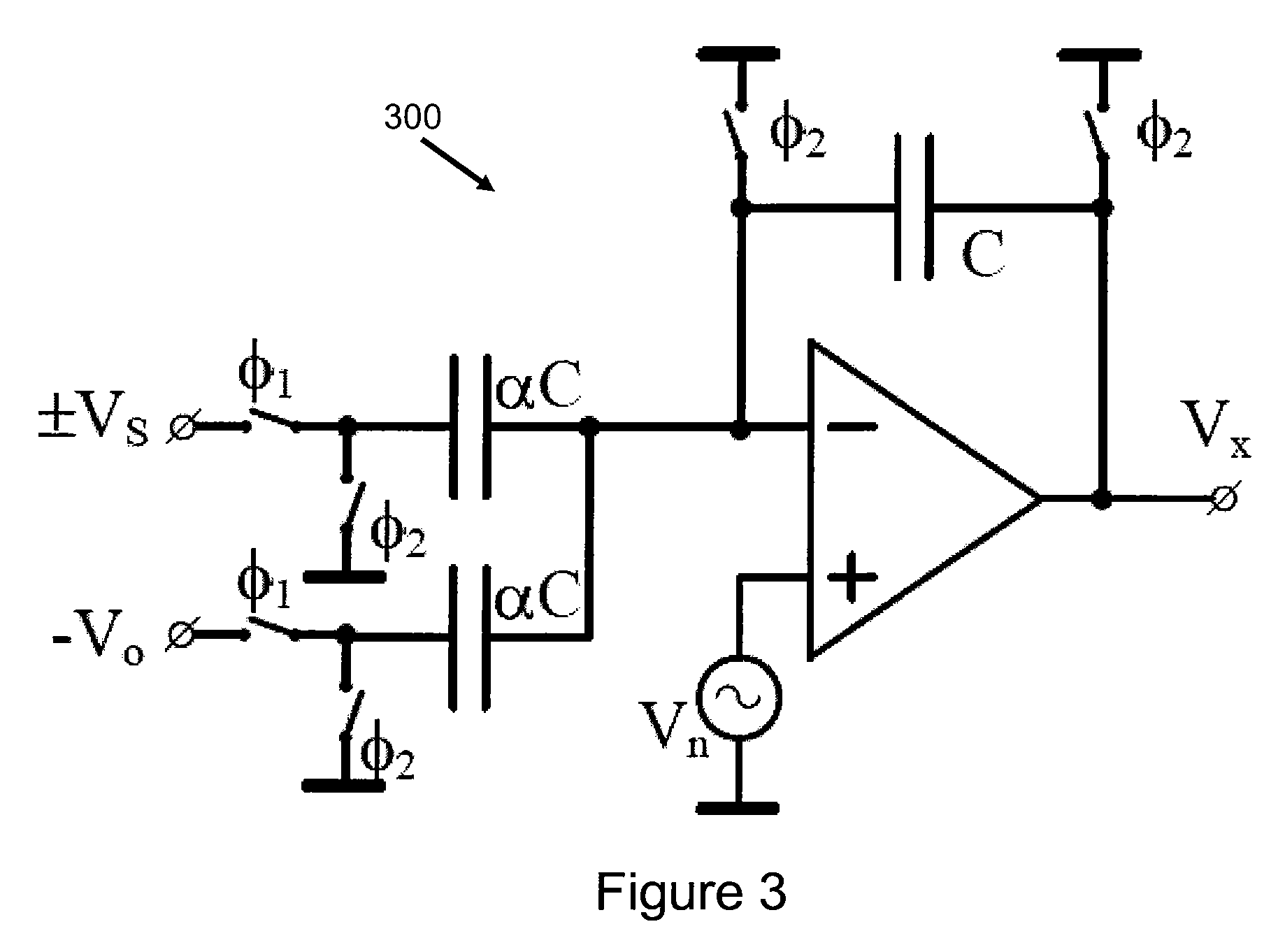

Readout circuit for self-balancing capacitor bridge

A capacitive transducer and a readout circuit for processing a signal from a capacitive transducer. The readout circuit includes a high gain circuit element, two summing amplifiers and two feedback path. The high gain circuit element generates an amplified transducer signal, and the summing amplifiers sum the amplified transducer signal with a positive reference voltage and the negative reference voltage, respectively, to generate a first summation signal and a second summation signal. The feedback paths feed back the summation signals to the transducer. Output circuitry generates an output signal based on the summation signals. The high gain circuit element can be a a switched capacitor integrator. The output circuitry can generates the output signal based on the first and second summation signals.

Owner:ROBERT BOSCH GMBH

Readout circuit for self-balancing capacitor bridge

ActiveUS20130049776A1Printed circuit assemblingResistance/reactance/impedenceAudio power amplifierIntegrator

A capacitive transducer and a readout circuit for processing a signal from a capacitive transducer. The readout circuit includes a high gain circuit element, two summing amplifiers and two feedback path. The high gain circuit element generates an amplified transducer signal, and the summing amplifiers sum the amplified transducer signal with a positive reference voltage and the negative reference voltage, respectively, to generate a first summation signal and a second summation signal. The feedback paths feed back the summation signals to the transducer. Output circuitry generates an output signal based on the summation signals. The high gain circuit element can be a switched capacitor integrator. The output circuitry can generates the output signal based on the first and second summation signals.

Owner:ROBERT BOSCH GMBH

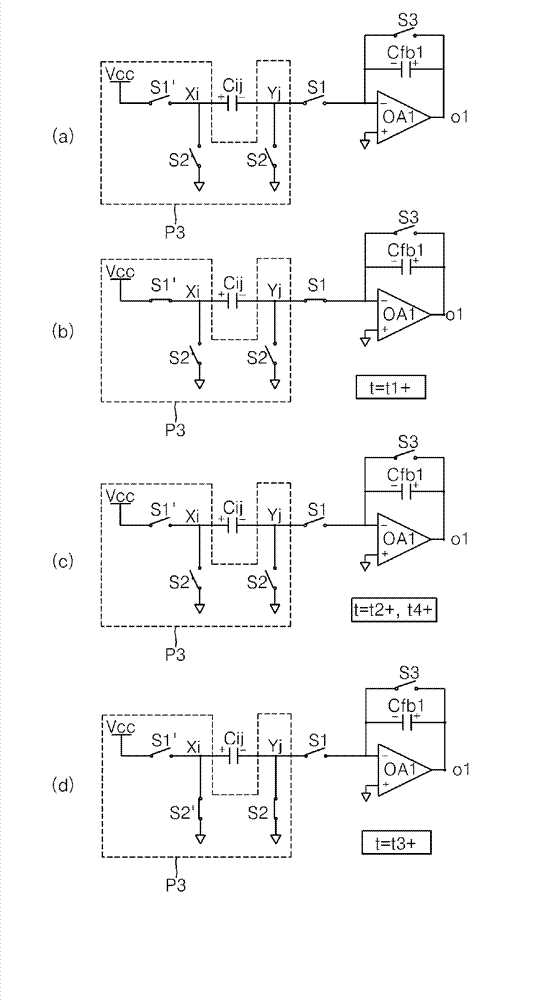

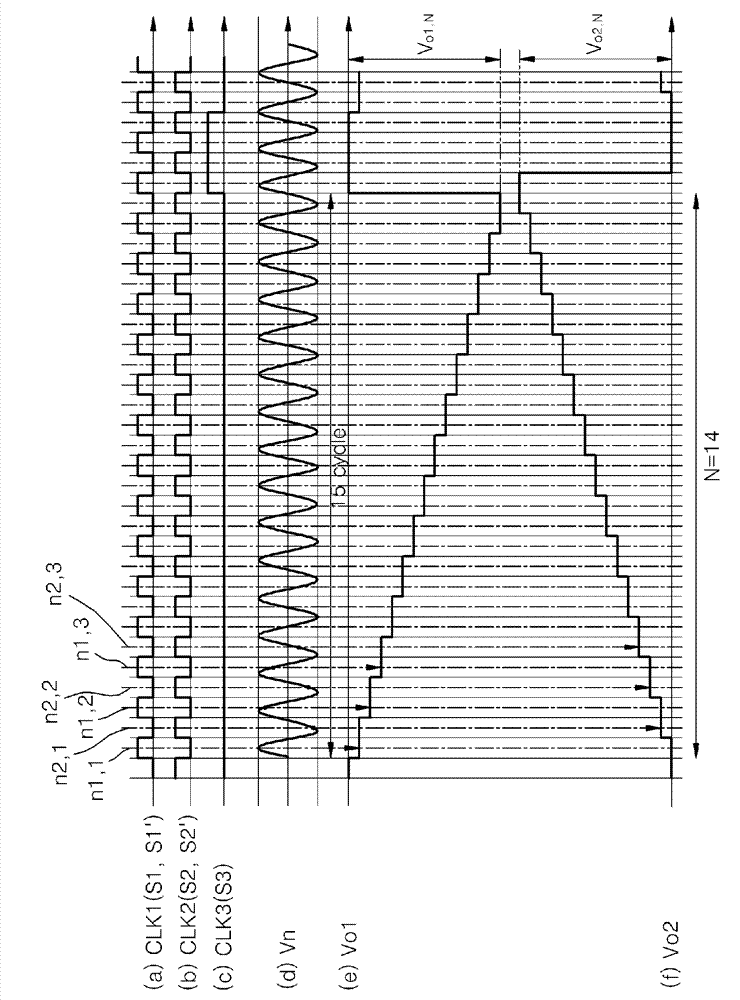

Integrator circuit with inverting integrator and non-inverting integrator

ActiveCN103097994AReduced influence of noise integrationStatic indicating devicesInput/output processes for data processingIntegratorEngineering

A switched capacitor integrator circuit is disclosed. The switched capacitor integrator circuit comprises an inverting switched capacitor integrator circuit, and a non-inverting switched capacitor integrator circuit connected to the inverting switched capacitor integrator circuit. A sampling capacitor of the inverting switched capacitor integrator circuit is shared by the non-inverting switched capacitor integrator circuit.

Owner:ZINITIX

Delta-sigma modulator having differential output

Provided is a delta-sigma modulator having a differential output, the modulator including a switched-capacitor integrator configured to generate a non-inverted integral signal and an inverted integral signal and also including a switched-capacitor circuit configured to sample an input signal based on a control signal and to integrate the feedback signal and the input signal based on the control signal and also a feedback circuit configured to generate the feedback signal.

Owner:SAMSUNG ELECTRONICS CO LTD +1

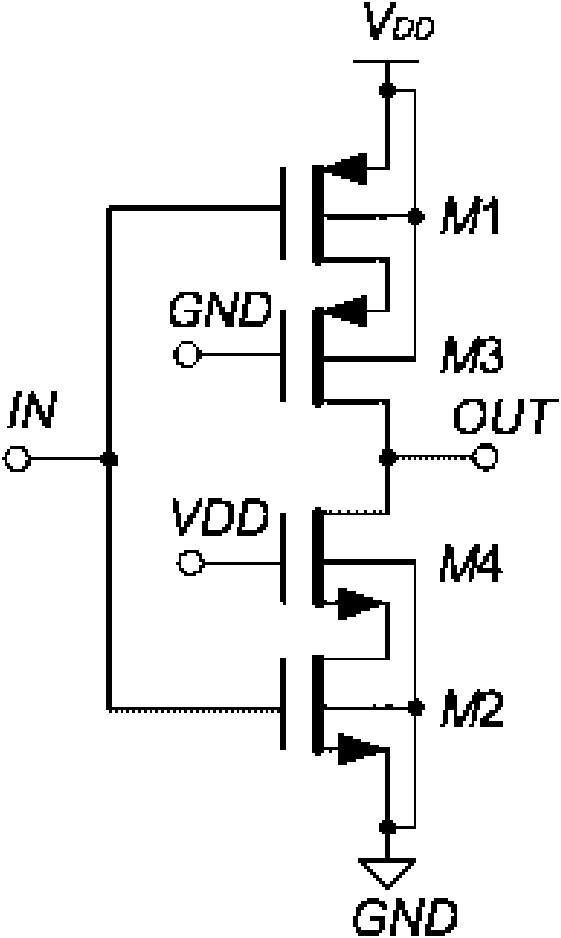

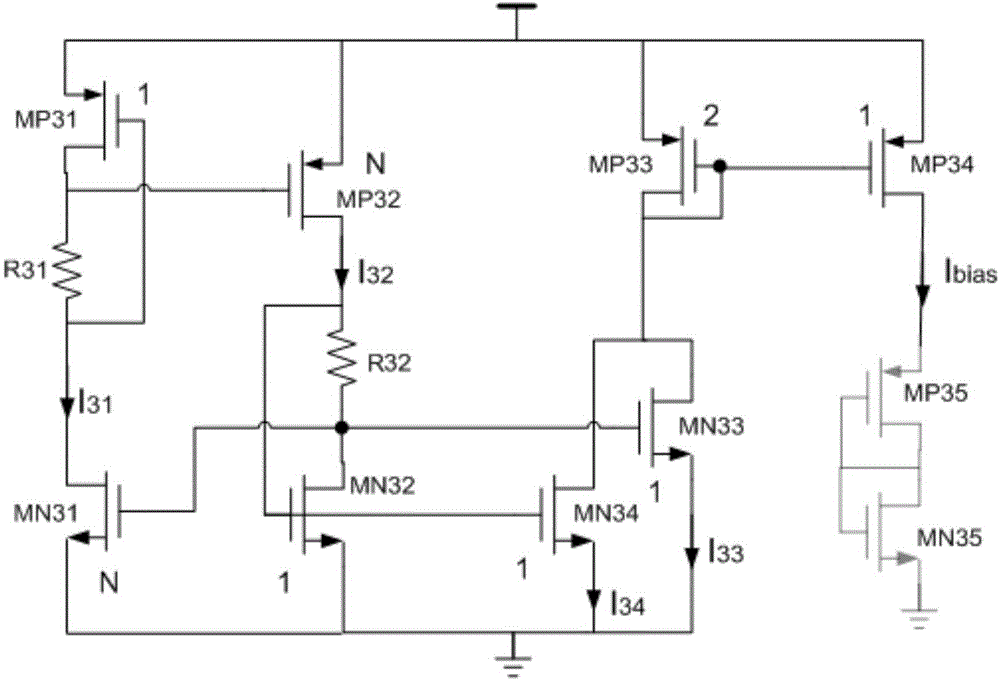

Digital-analog combined control body-bias class-C inverter

InactiveCN102394634AReduce adverse effectsSmall process deviationLogic circuits characterised by logic functionProcess deviationsEngineering

The invention discloses a digital-analog combined control body-bias class-C inverter, which comprises a main body class-C inverter module, a P-channel metal-oxide semiconductor (PMOS) body modulation module and an N-channel metal-oxide semiconductor (NMOS) body modulation module, wherein the PMOS body modulation module and the NMOS body modulation module can more precisely control parameters suchas a threshold voltage, a drain-source current, transconductance and the like of a first PMOS tube and a first NMOS tube in the main body class-C inverter module through links such as parameter sensing - current comparison - numeric counting - analog conversion - substrate bias voltage production and feedback and the like, so unfavorable influence of process deviation, power supply voltage disturbance and temperature variation on the main body class-C inverter module can be greatly reduced. The digital-analog combined control body-bias class-C inverter is applicable to the application fields requiring ultra-low power consumption and high precision such as switch capacitance integrating device, a sigma-delta analog-digital converter and the like.

Owner:ZHEJIANG UNIV

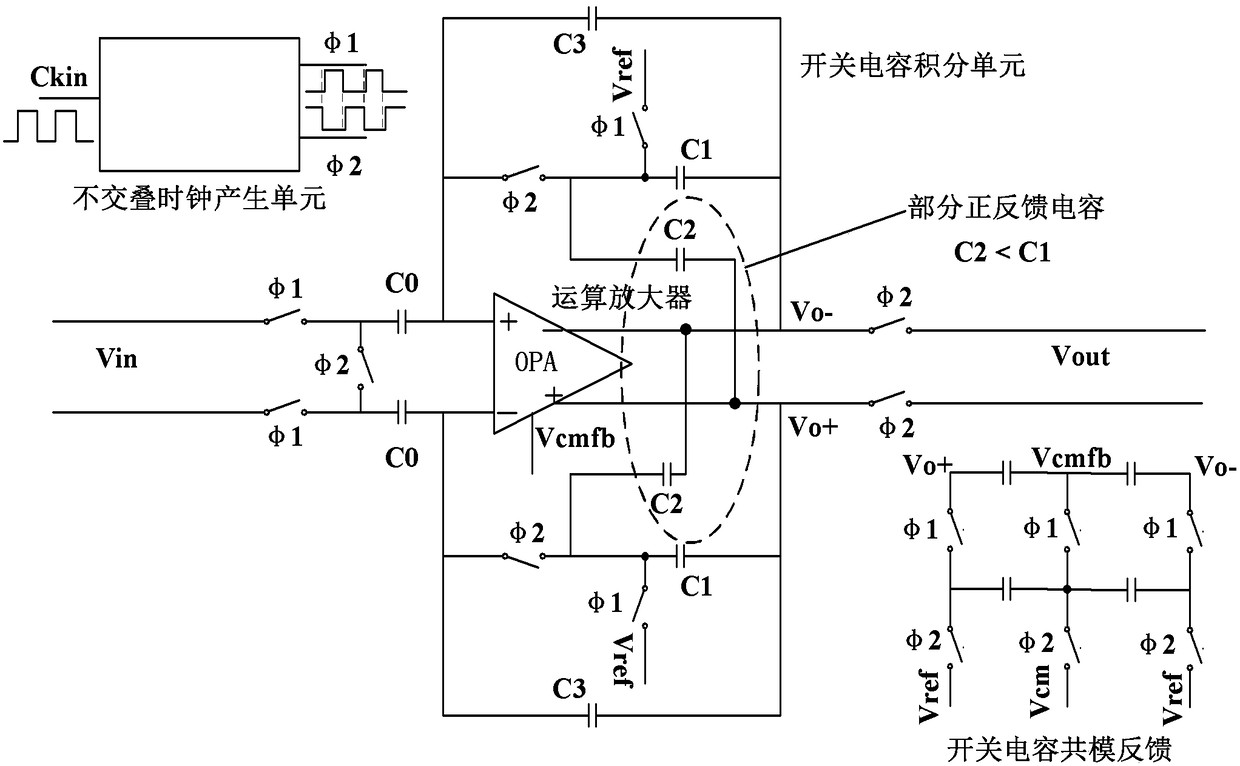

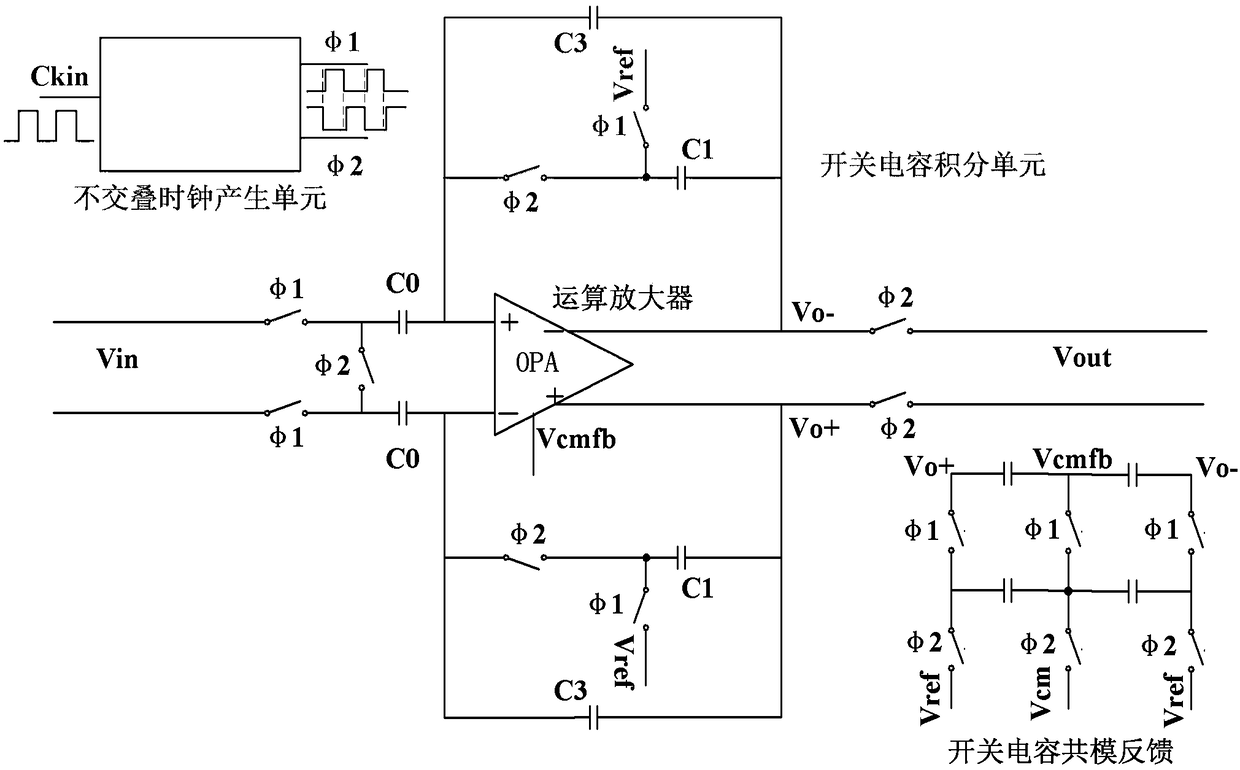

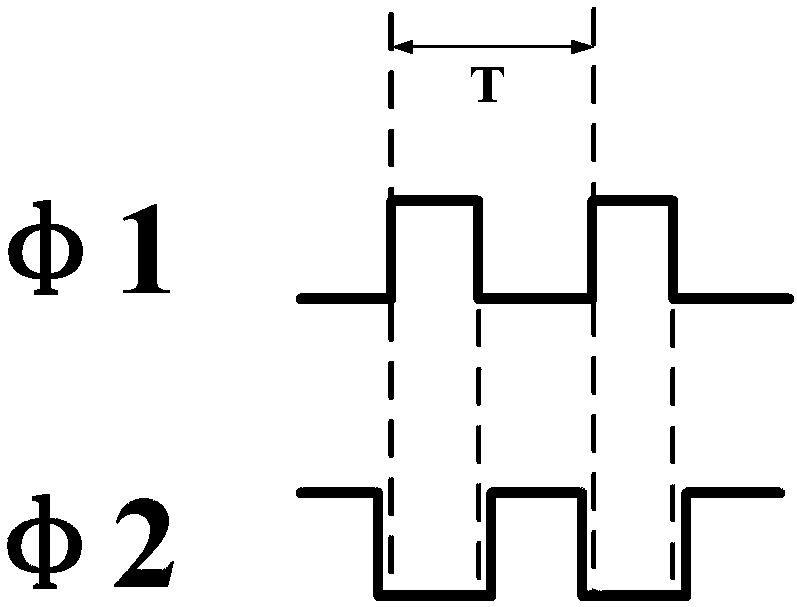

Fully differential switch capacitor integrator

ActiveCN108233933AIncrease time constantReduce chip areaElectric signal transmission systemsAnalogue-digital convertersCapacitanceAudio power amplifier

The invention provides a fully differential switch capacitor integrator. The fully differential switch capacitor integrator comprises an operational amplifier unit, a switch capacitor unit, a switch capacitor common-mode feedback unit, and a non-overlapping clock production unit, wherein the operational amplifier unit comprises an operational amplifier for providing predetermined gain and bandwidth; the switch capacitor unit comprises a switch capacitor integral unit bridged between the input end and output end of the operational amplifier, a serial branch comprising a MOS switch phi2 and a capacitor C1, wherein the capacitor C3 is connected with the above branch in parallel, and a MOS switch phi1 is further arranged between the MOS tube phi2 and the capacitor C1 to connect to a referencevoltage Vref, and partial positive feedback capacitor C2 connected to the output end of the opposite polarity of the operational amplifier; the switch capacitor common-mode feedback unit is arranged between the positive output end and the negative output end of the operational amplifier, and is a six-switch four-capacitor structure; the non-overlapping clock production unit produces a clock signalof the MOS switch. The fully differential switch capacitor integrator provided by the invention is insensitive to parasitic, and has efficient area utilization rate and greater time constant.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

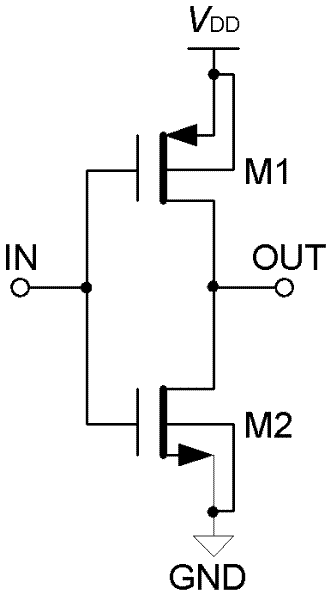

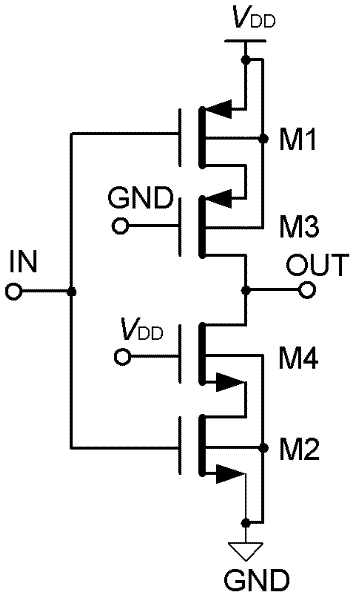

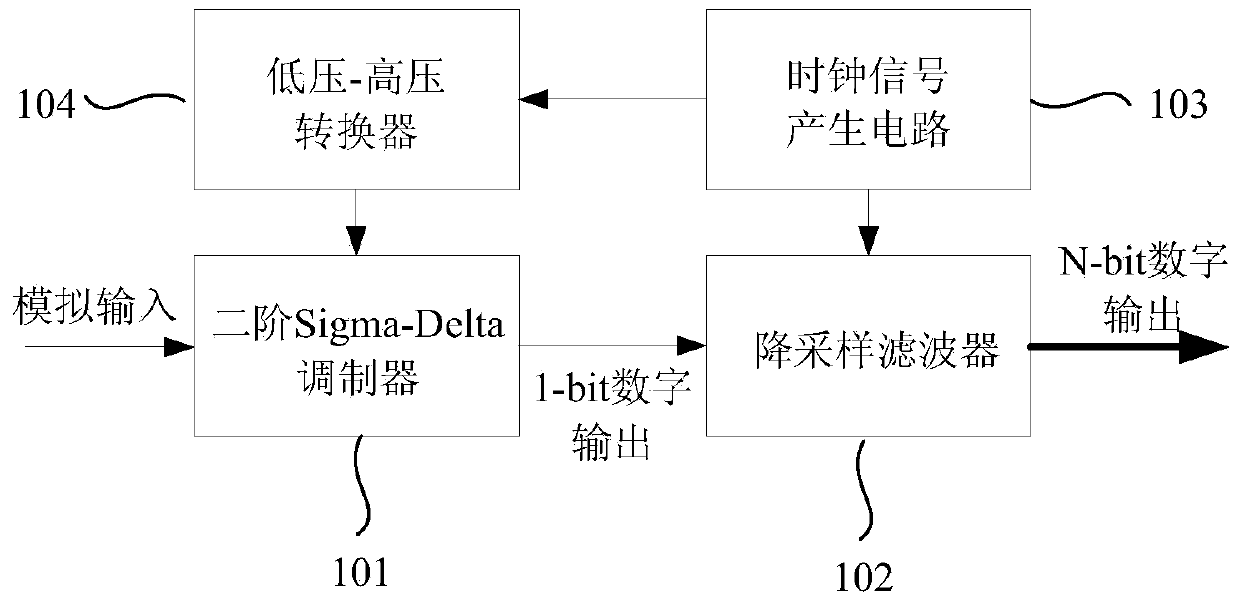

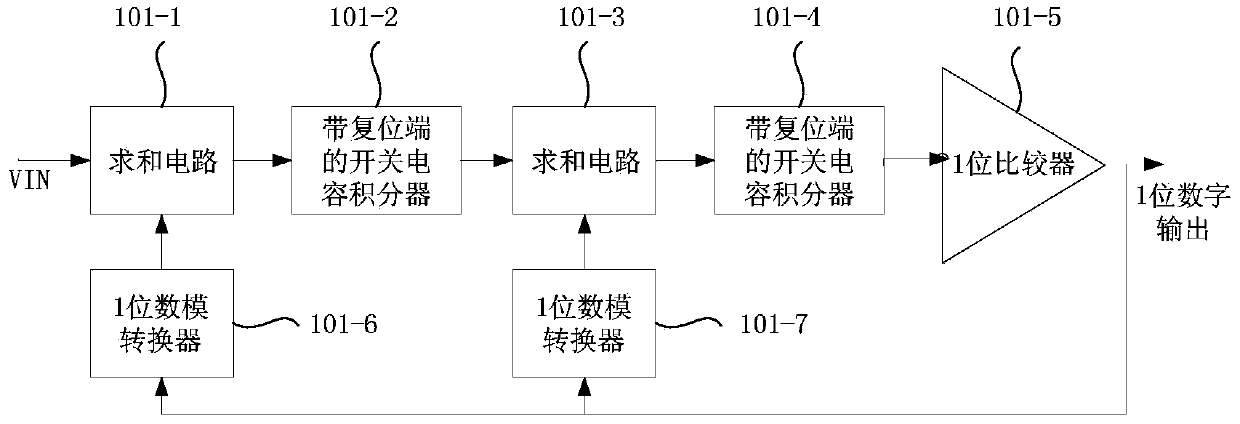

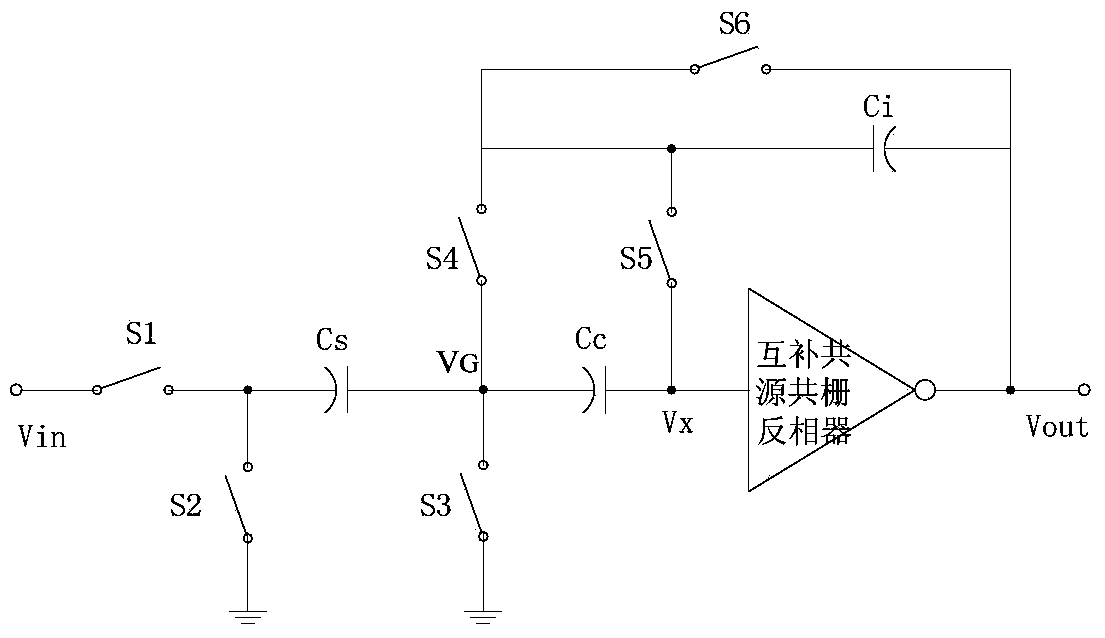

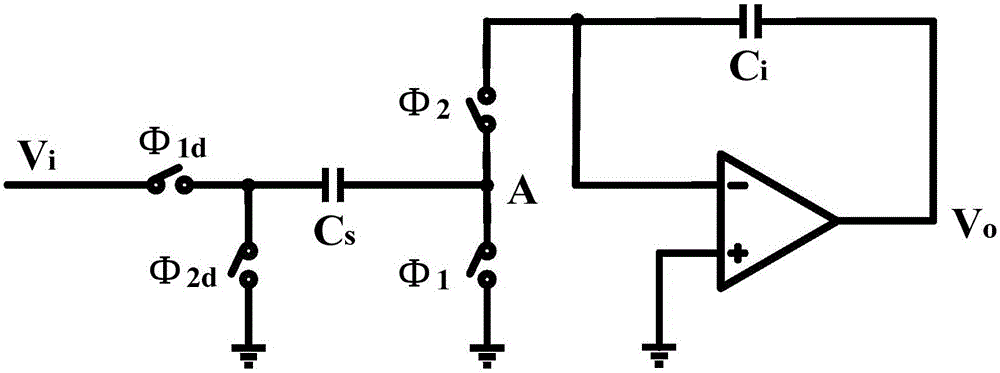

Complementation common-source common-grid inverter and increment Sigma-Delta analog-to-digital conversion circuit

The invention provides a complementation common-source common-grid inverter and an increment Sigma-Delta analog-to-digital conversion circuit. The increment Sigma-Delta analog-to-digital conversion circuit is composed of a second-order sigma delta modulator (101), a reduction sampling filter (102), a clock signal generation circuit (103) and a low-to-high voltage converter (104). A switch capacitance integrator at the band reset end of the second-order sigma delta modulator (101) comprises the complementation common-source common-grid inverter. The complementation common-source common-grid inverter comprises a first PMOS1 tube and a first NMOS1 tube. A second NMOS2 tube and a second PMOS2 tube are connected in series between the first PMOS1 tube and the first NMOS1, the second NMOS2 tube is arranged at an upper position, the grid end of the second NMOS2 tube is connected with a power supply voltage VDD, the second PMOS2 tube is disposed at a lower position, and the grid end of the second PMOS2 tube is grounded GND. The ADC provided by the invention has quite low power consumption and can work under the condition of low power supply voltage, thereby being applied to such fields of a portable instrument, measuring, and the like.

Owner:HARBIN ENG UNIV

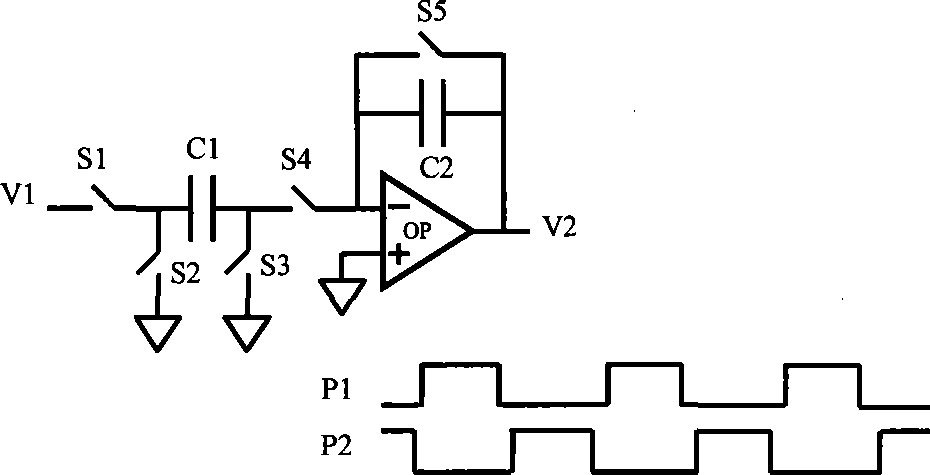

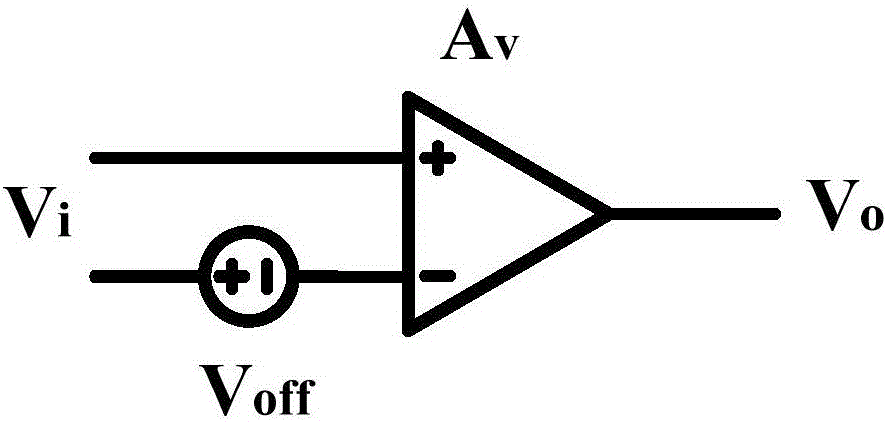

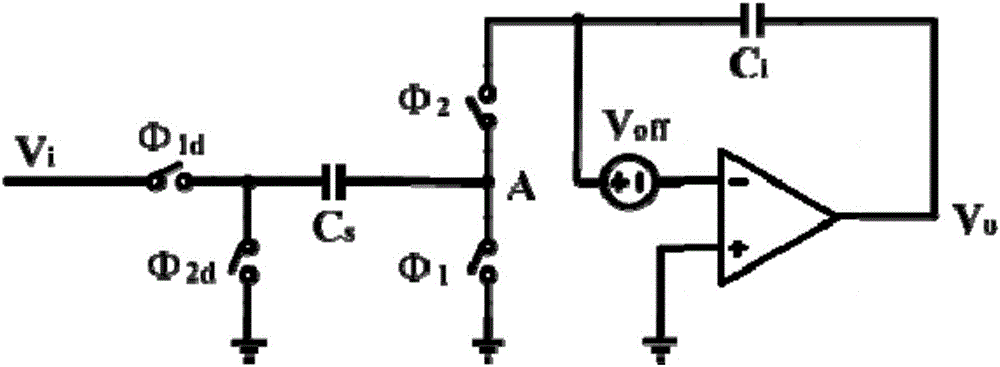

Switch capacitor integrator circuit for eliminating offset voltage

ActiveCN106027025AHigh precisionCompensation for integral deviationVoltage/temperature variation compensationCapacitanceIntegrator

The invention provides a switch capacitor integrator circuit for eliminating offset voltage. The switch capacitor integrator circuit for eliminating the offset voltage comprises a first capacitor, a second capacitor, a third capacitor, a fourth capacitor, a first switch, a second switch, a third switch, a fourth switch, a fifth switch, an offset voltage source and an amplifier or a phase inverter. The size of integral output voltage of an amplifier offset voltage eliminating circuit of a switch capacitor integrator is unrelated to threshold voltage of the amplifier, and the precision of the integrator is improved; additionally, the offset voltage eliminating structure can be used for compensating integral offset caused by offset voltage inputted by the phase inverter when the phase inverter is taken as the amplifier. The switch capacitor integrator circuit for eliminating the offset voltage has a simple structure, and has the wide application prospect in the switch capacitor integrator circuit.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

Leakage compensation for switched capacitor integrators

ActiveUS8841962B1Computing operations for integral formationNegative-feedback-circuit arrangementsParasitic capacitanceEngineering

Methods and systems for a differential correlated double sampling (CDS) switched capacitor integrator circuit. The circuit includes a differential amplifier that has a differential input and a differential output. There is a first feedback path between the negative output node and the positive input node, and a second feedback path between the positive output node and the negative input node. Each feedback path includes an integration capacitor and at least one switch that has a parasitic capacitance. A first capacitive element is coupled between the negative input node and the negative output node, and a second capacitive element is coupled between the positive input node and the positive output node. Each capacitive element is configured to cancel the parasitic capacitance of its corresponding feedback path.

Owner:ANALOG DEVICES INT UNLTD

Switched capacitor integrator system

ActiveUS7138848B2Improve errorGain fluctuationsComputing operations for integral formationElectric signal transmission systemsCascode amplifierSwitched capacitor integrator

A switched capacitor integrator system includes an input cascoded amplifier circuit; a summing junction; an integrating switched capacitor circuit connected to the output of the input cascoded amplifier circuit and to the summing junction; the integrating switched capacitor circuit including an input switched capacitor circuit responsive to an input and connected to the summing junction; and a correlated double sampling capacitor circuit including an offset capacitor interconnected between the summing junction and the input of the input cascoded amplifier circuit.

Owner:ANALOG DEVICES INC

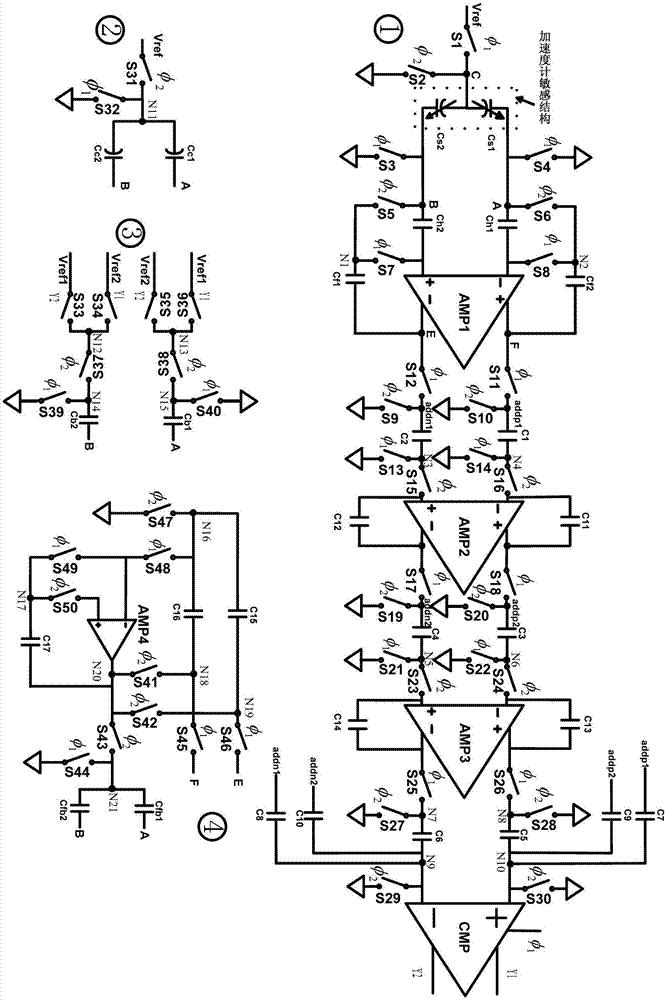

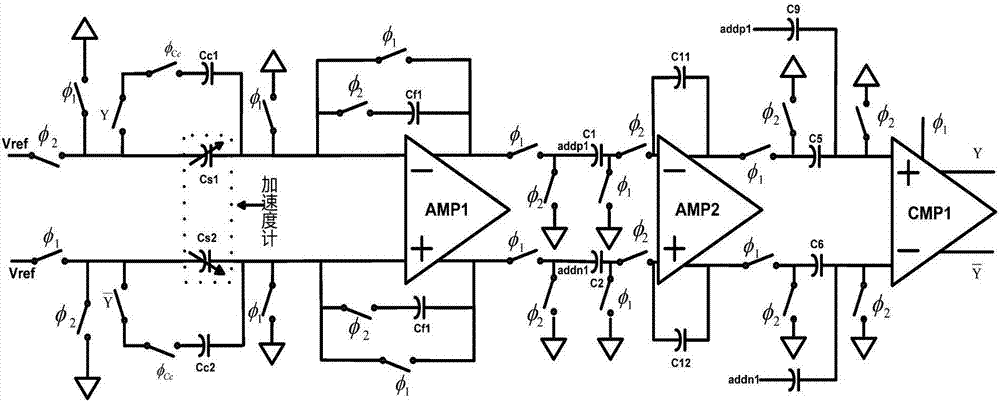

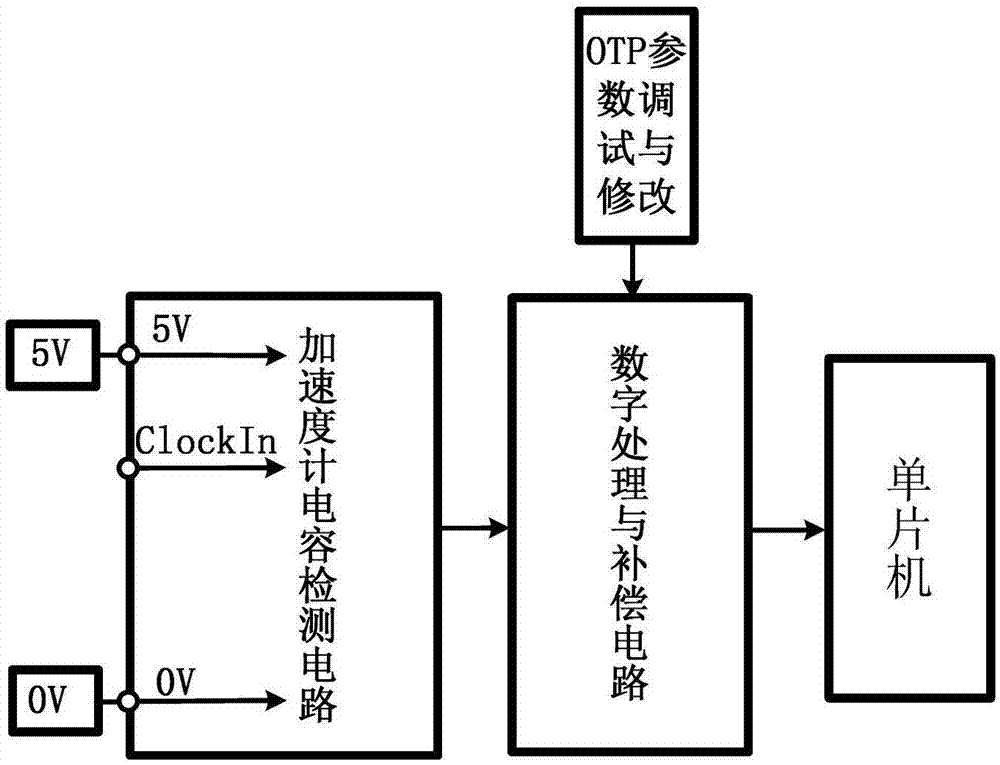

Accelerometer capacitance detection circuit

ActiveCN107192850AReasonable designSolve environmental problemsAcceleration measurementCapacitanceIntegrator

The invention discloses an accelerometer capacitance detection circuit. The accelerometer capacitance detection circuit comprises a modulator structure module, a capacitance compensation array module, a digital-to-analog conversion circuit module, and an input common mode compensation circuit module. The capacitance compensation array is connected with the front end of the first stage switch capacitance integrator of the modulator module, and the digital-to-analog conversion circuit is connected with the first stage switch capacitance integrator under control of one-bit digital output. The input common mode compensation circuit is used to sample the output of the first stage switch capacitance integrator, and is used to acquire a common mode voltage, and is used to feed the common mode voltage back to the input of the first stage switch capacitance integrator to eliminate an input common mode voltage deviation. Problems that the conventional accelerometer capacitance detection circuits are easily affected by environmental and own factors, power consumption is high, and processing is inconvenient are solved, and therefore the accelerometer capacitance detection circuit is advantageous in that circuit design is reasonable, the accelerometer capacitance detection circuit is not easily affected by the environmental and own factors, detection results are accurate, and the power consumption is low.

Owner:四川知微传感技术有限公司

Bi-directional high side current sense measurement

A system for measuring a voltage drop between two nodes in an electrical circuit, comprising a switched capacitor integrator (SCI), a comparator and a counter. The SCI alternately (a) captures charge onto a set of sampling capacitors and (b) selectively accumulates / transfers the charge onto a pair of integration capacitors, where the charge includes a first portion that is based on the voltage drop and a second portion that depends on a digital indicator signal. The comparator generates the digital indicator signal based on whether an analog output of the SCI is positive or negative. The counter counts a number of ones occurring in the digital indicator signal during a measurement interval. At the end of the measurement interval, the count value represents a measure of the voltage drop. Knowing the resistance between the two nodes, the voltage drop may be converted into a current measurement.

Owner:MICROCHIP TECH INC

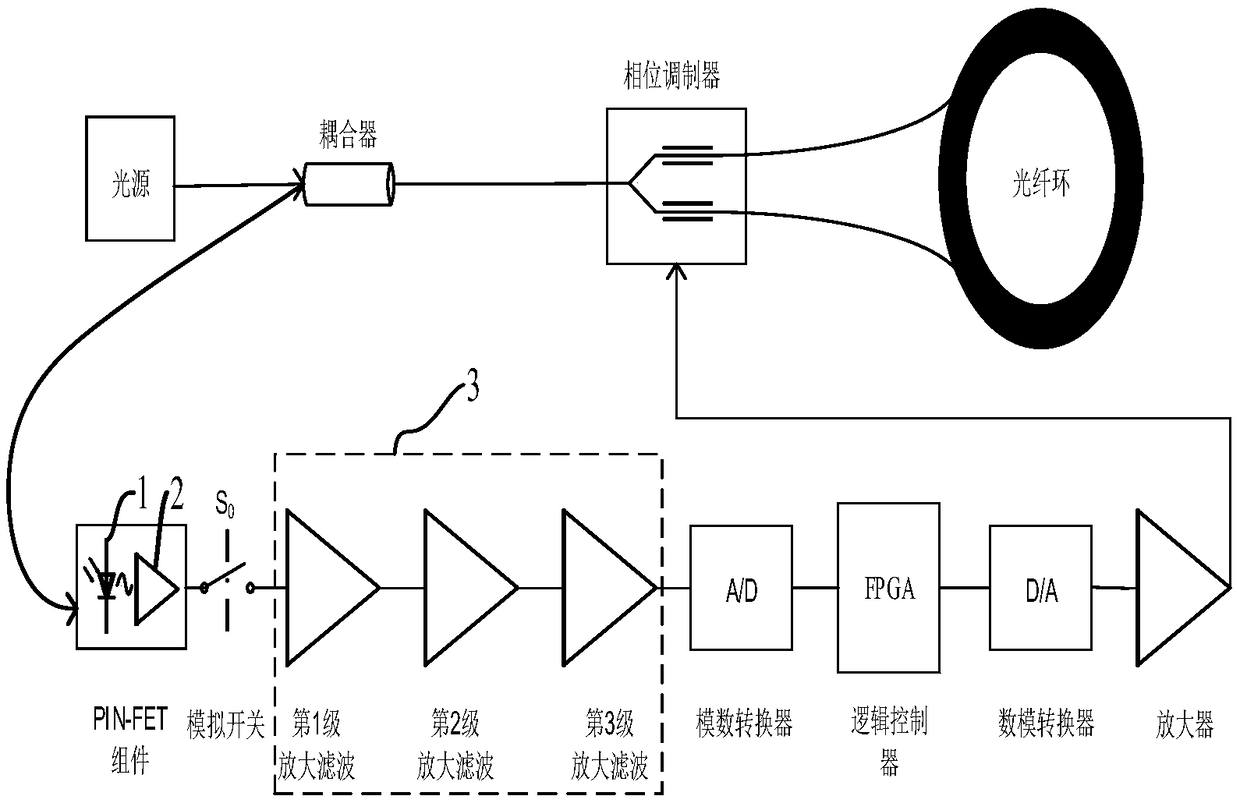

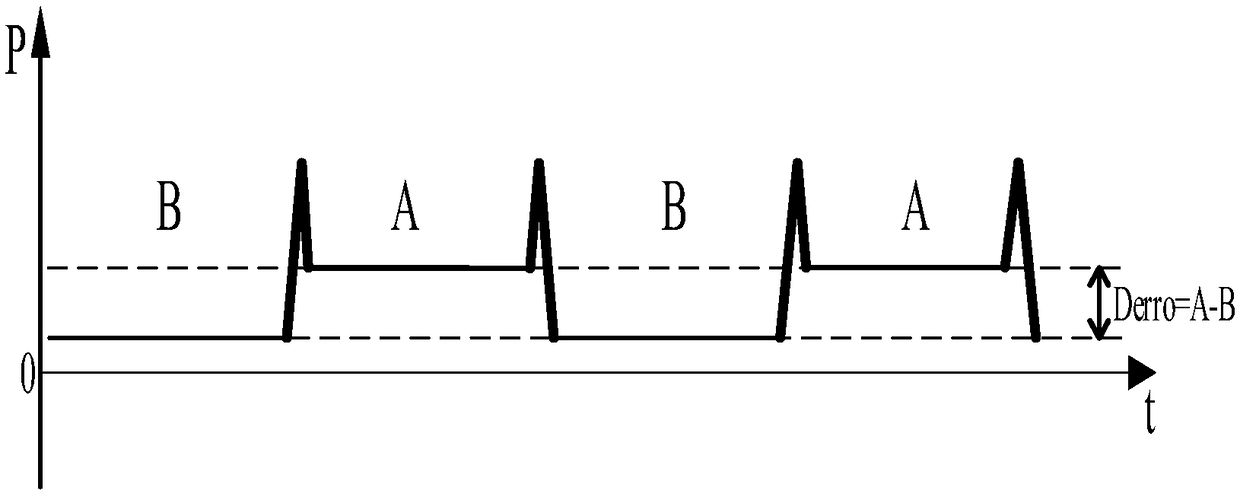

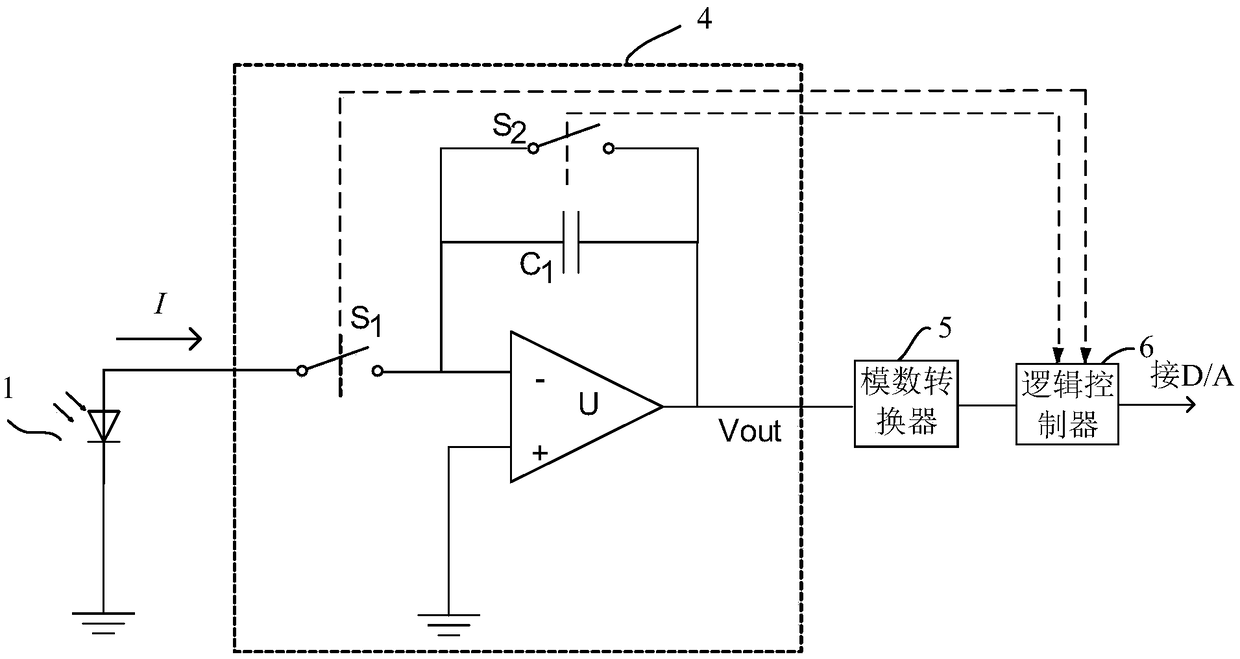

Optical-fiber gyroscope pre-amplification circuit based on switch capacitance integrator

The invention discloses an optical-fiber gyroscope front-mounted amplification circuit based on a switch capacitance integrator, which belongs to the technical field of weak signal detection and optical-fiber gyroscope inertia measurement. The switch capacitance integrator comprises an operation amplifier, a first high-speed analog switch, a second high-speed analog switch and a precision capacitor; and the switch capacitance integrator is used for substituting for an FET amplification circuit and a subsequent cascade amplification circuit in an original optical-fiber gyroscope photoelectric conversion element, so that the complexity of the circuit is reduced, the circuit dimension is reduced, no heat noise is produced, and the signal-to-noise ratio of the circuit is increased; and meanwhile, by virtue of the way for dynamically adjusting the circuit gain by virtue of the integral time, the sampling data of an analog-to-digital converter does not need to be accumulated by a logic controller, so that the clock frequency of the analog-to-digital converter can be effectively reduced, the reduction of noise and interference can be facilitated, and the circuit power consumption can be further reduced.

Owner:BEIHANG UNIV

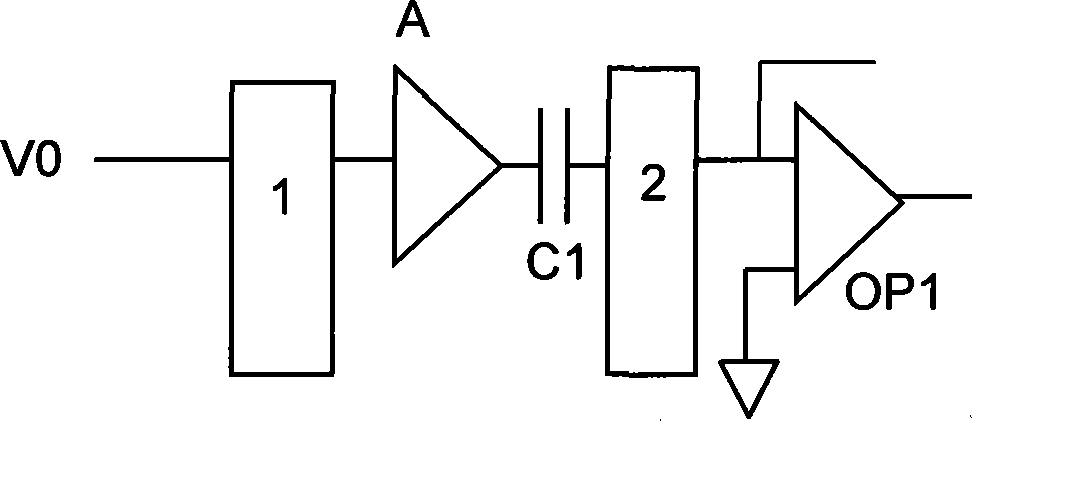

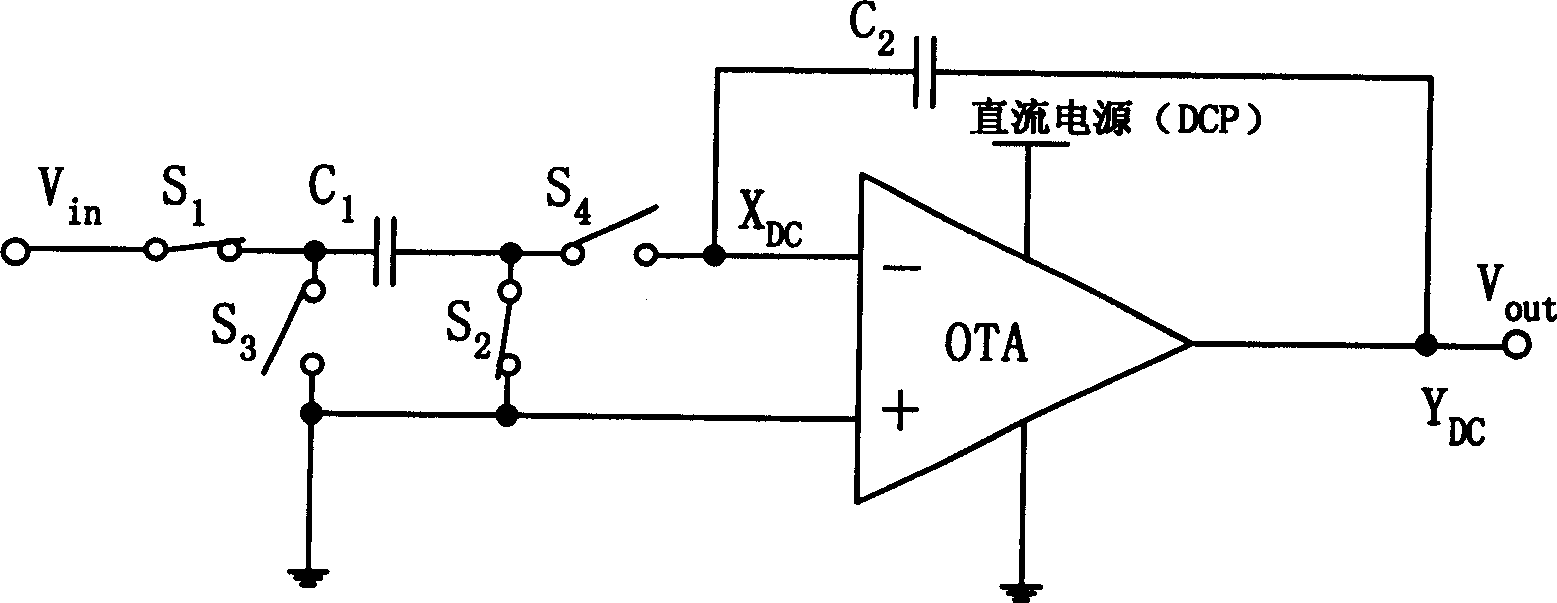

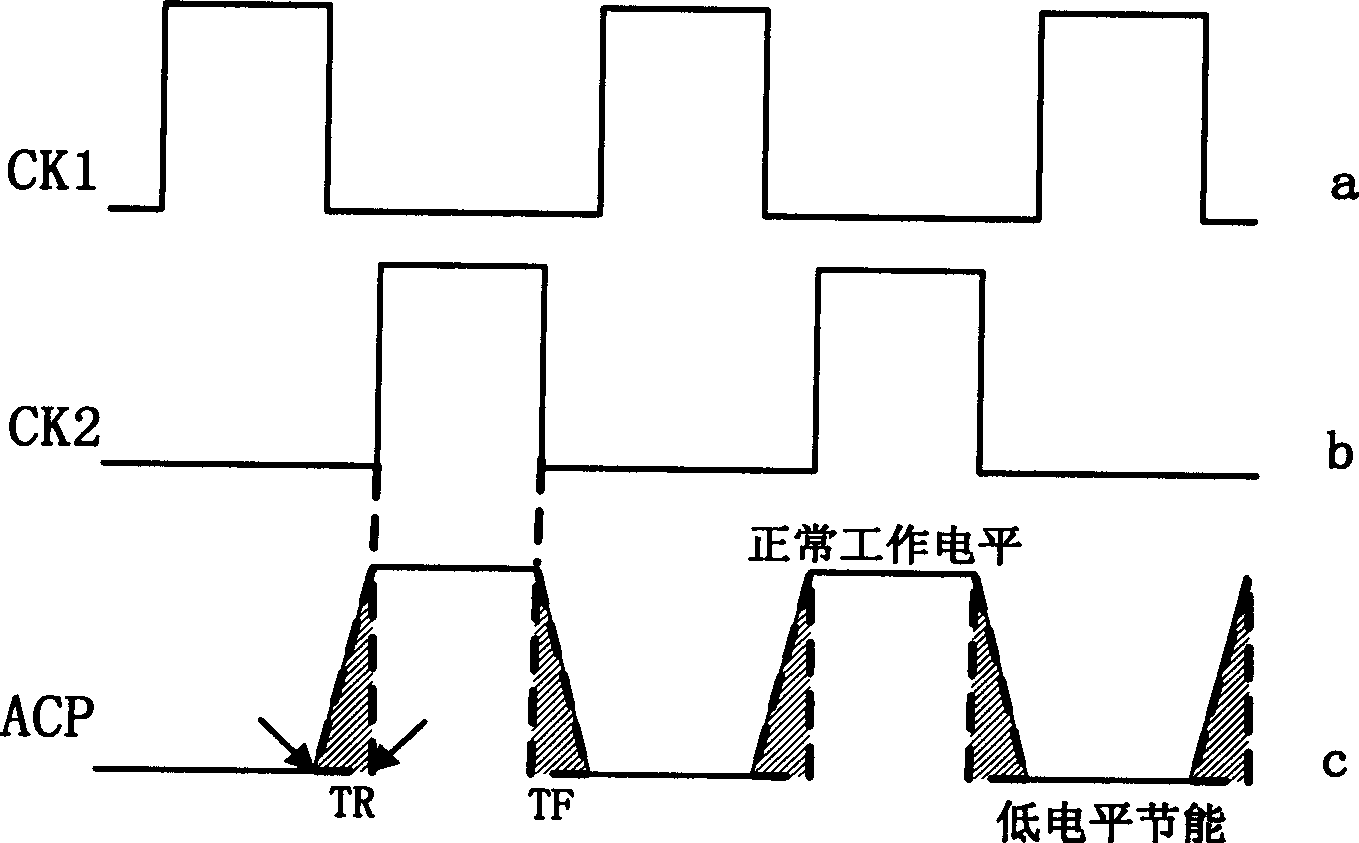

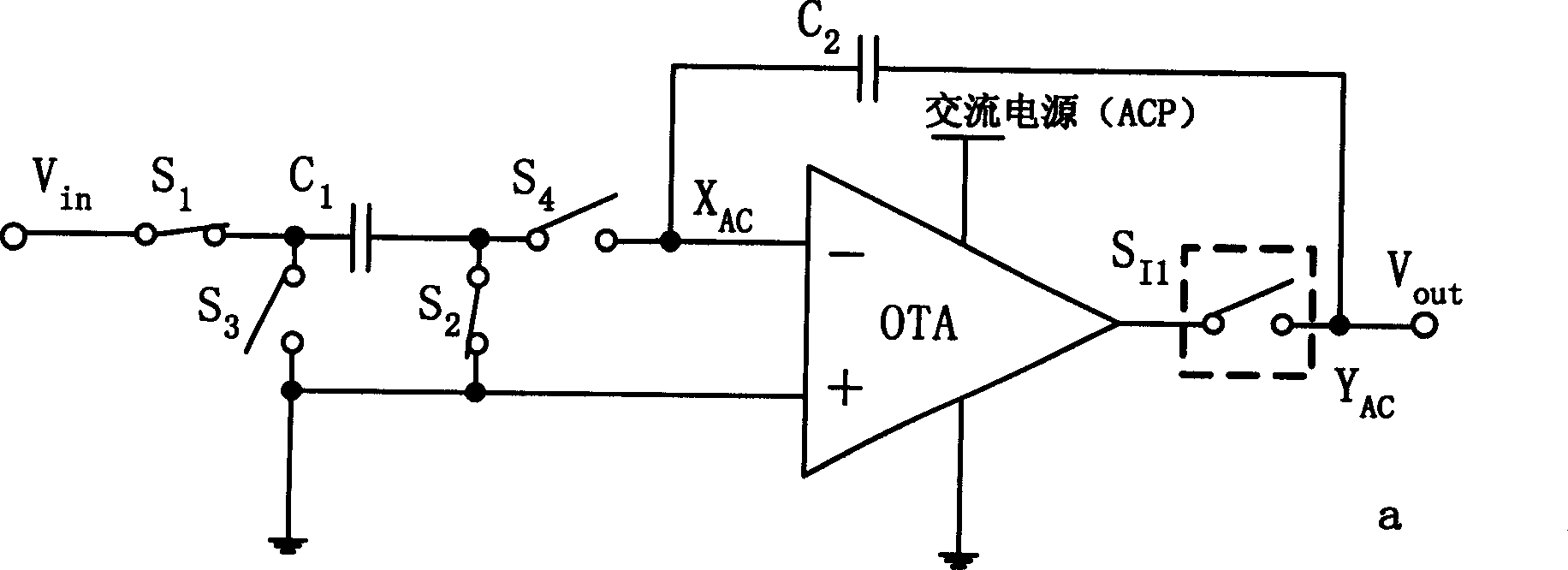

Integrator of power supply by AC power supply in switch condenser circuit

InactiveCN1658494AReduce power consumptionEasy to implementAnalogue-digital convertersDifferential amplifiersCapacitanceAudio power amplifier

This invention is the integrating device supplied by AC power in the condenser network. The characteristics are: it series connects a switch that opens as the sampling phase and closes as the integrating phase at the output end of the amplifier in the traditional integrating device of AC power supply switch; and meanwhile synchronize the integrating clock signals when the sampling and integrating phases of the amplifier and make the same width of the pulses of the AC power supply signal as the power input, and maintain the same state switching time and minimize the time when the low energy saving state in the sampling phase and when the normal working state in the integrating phase. Because it closes the amplifier in the sampling phase, so compared with the switch condenser network supplied by DC power it has the superiority of low power consumption.

Owner:TSINGHUA UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com