Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

229results about How to "Reduce RC delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Low-carbon-doped silicon oxide film and damascene structure using same

ActiveUS20050260850A1Reduce electrical circuit lifetimeEnhance moisture intakeSemiconductor/solid-state device detailsSolid-state devicesMetal interconnectDevice material

A method of forming an interconnect for a semiconductor device using triple hard layers, comprises: forming a first hard layer serving as an etch stop layer on a metal interconnect-formed dielectric layer; forming a second hard layer on the first hard layer; forming a dielectric layer on the second hard layer; forming a third hard layer on the dielectric layer; forming a hole through the third and second hard layers, the dielectric layer, and the first hard layer; and filling the hole with metal to establish an interconnect. The second and third hard layers are each made of carbon-doped silicon oxide formed from a source gas and a redox gas, while controlling the carbon content in the second hard layer as a function of a flow rate of the redox gas.

Owner:ASM JAPAN

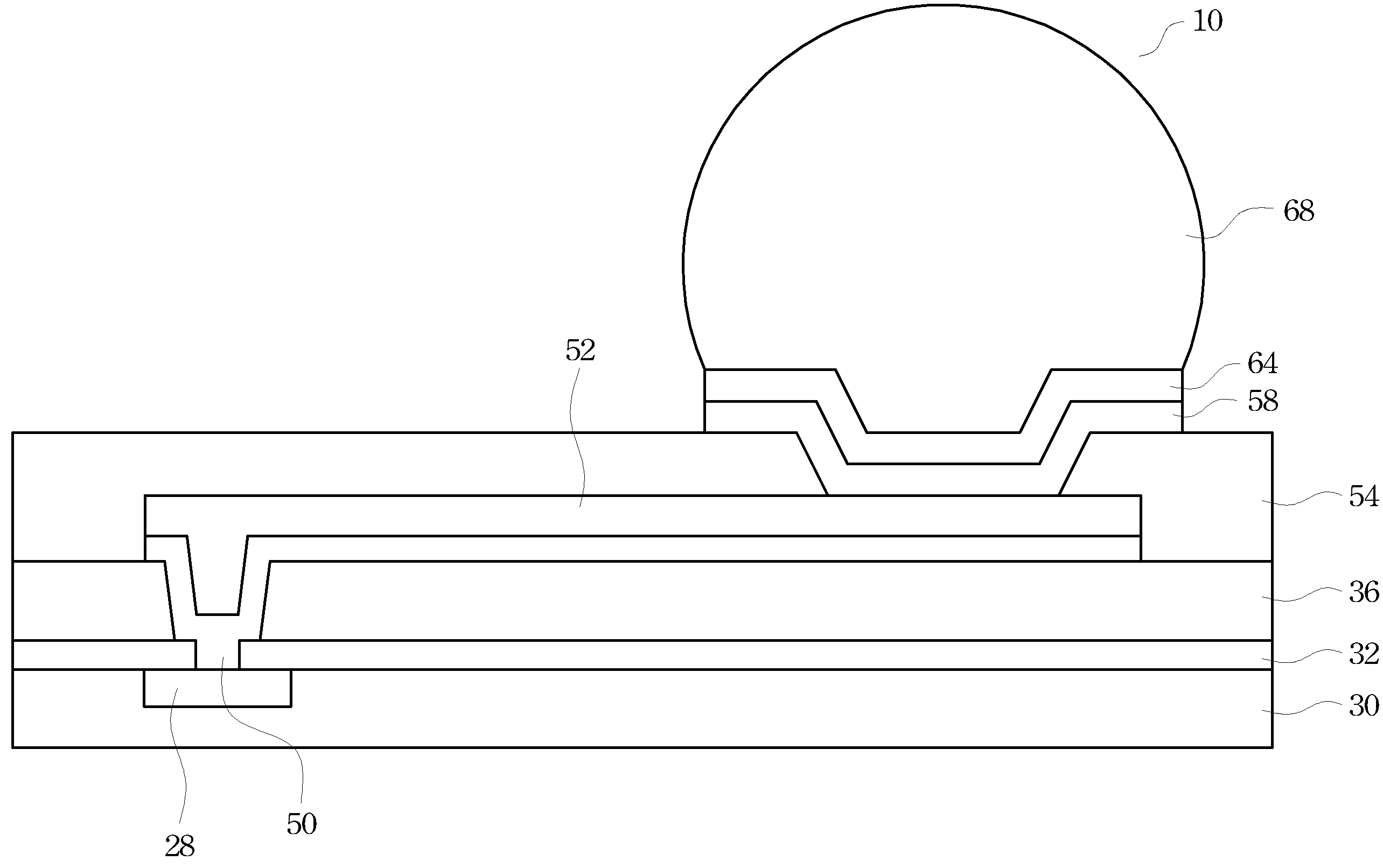

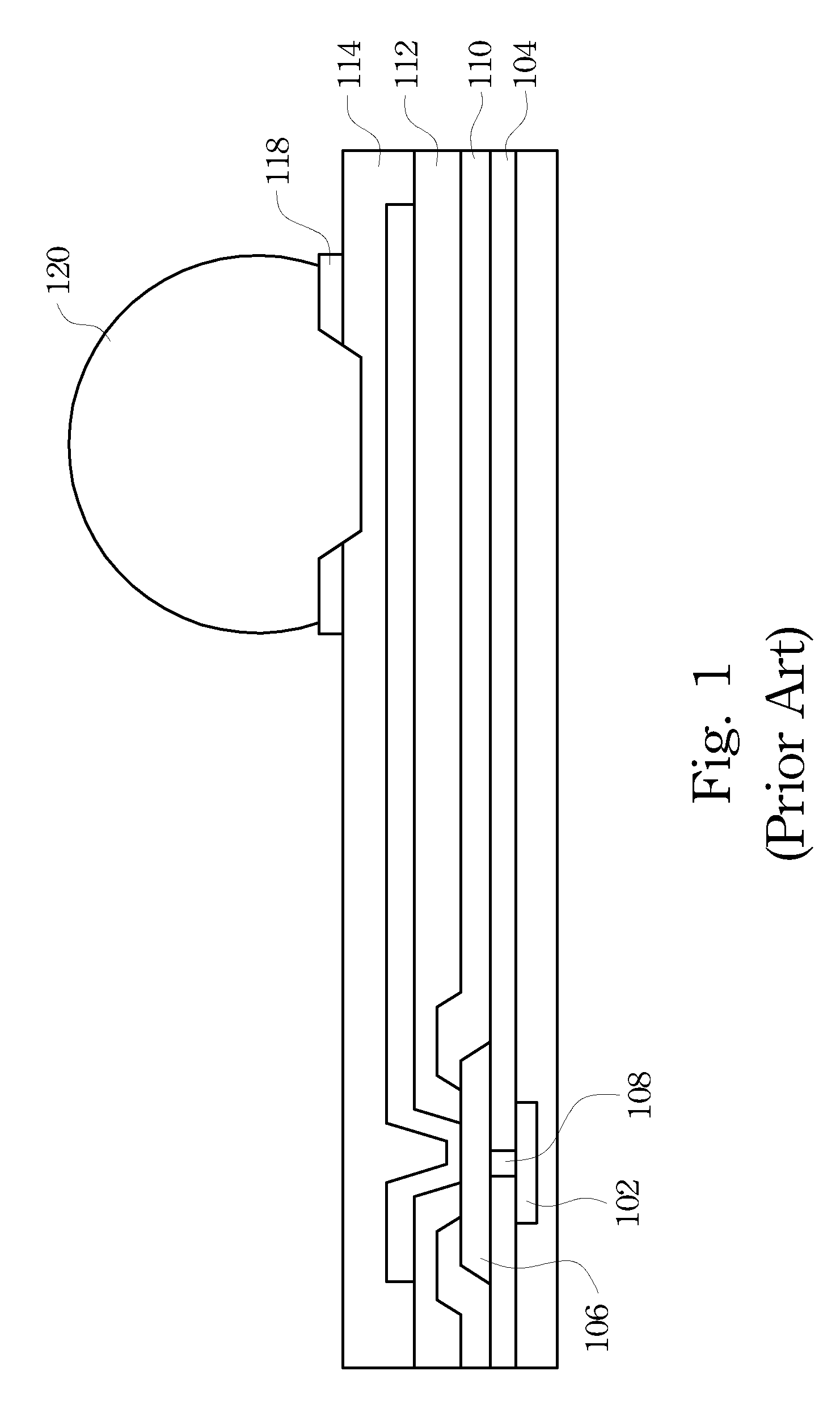

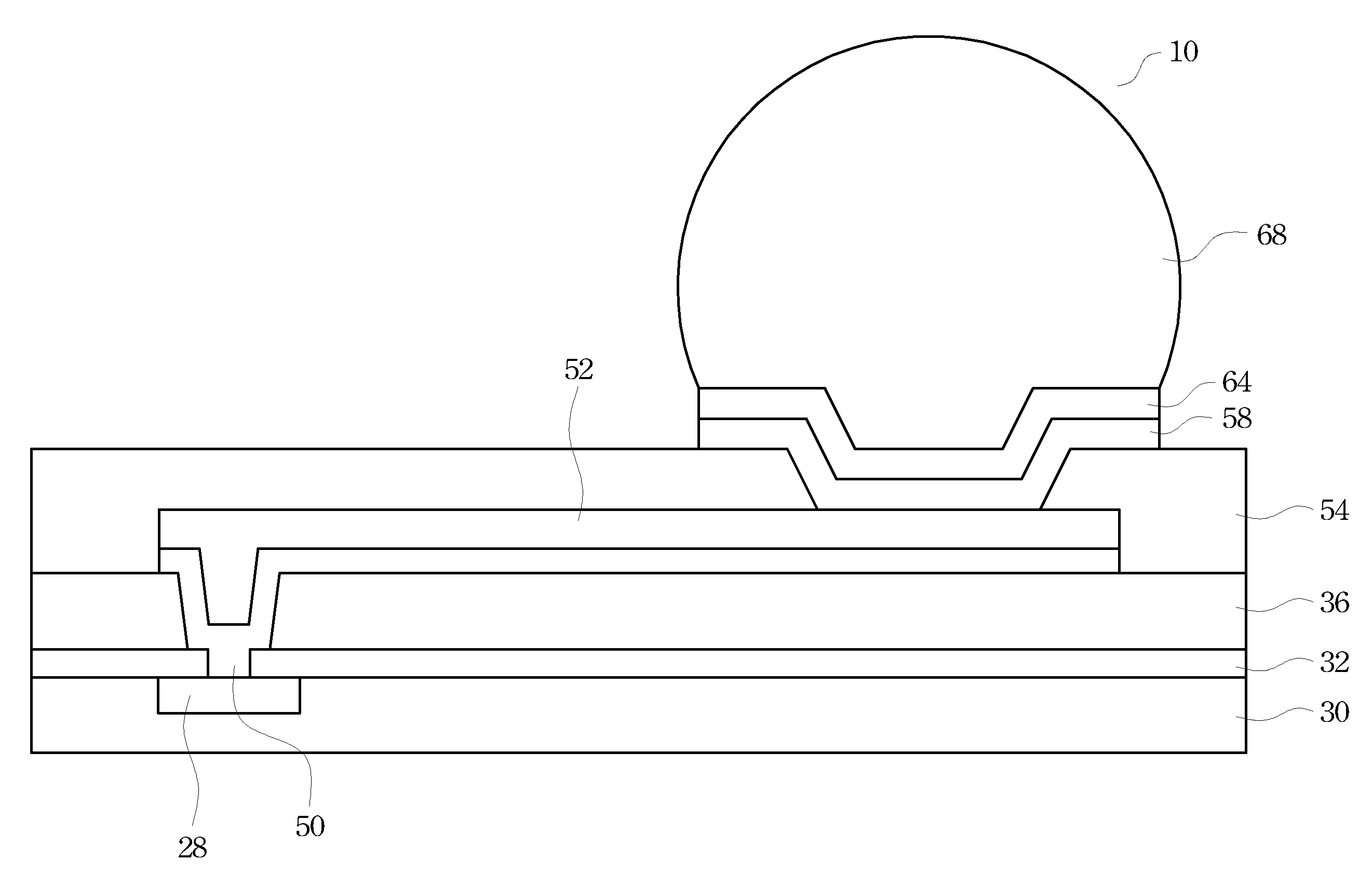

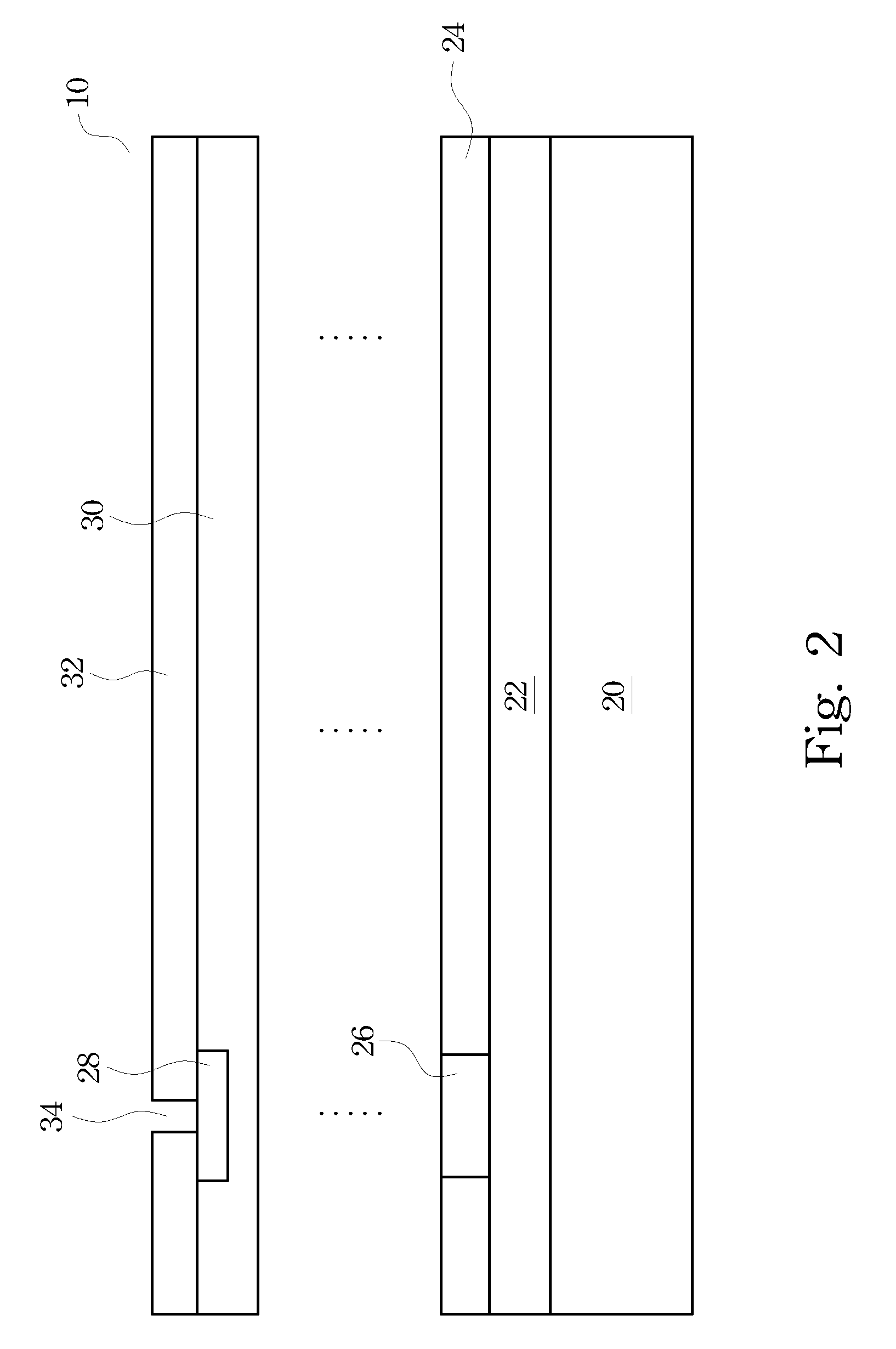

Back end integrated WLCSP structure without aluminum pads

ActiveUS7863742B2Reduce RC delayReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesCopperUnder bump metallurgy

Owner:TAIWAN SEMICON MFG CO LTD

High selectivity Si-rich SiON etch-stop layer

InactiveUS6245669B1Superior light absorption qualityReduce RC delaySemiconductor/solid-state device manufacturingResistSilicon oxide

The present invention provides an anti-reflective Si-Rich Silicon oxynitride (SiON) etch barrier layer and two compatible oxide etch processes. The Si-Rich Silicon oxynitride (SiON) etch barrier layer can be used as a hard mask in a dual damascene structure and as a hard mask for over a polysilicon gate. The invention has the following key elements: 1) Si rich Silicon oxynitride (SiON) ARC layer, 2) Special Silicon oxide Etch process that has a high selectivity of Si-Rich SiON to silicon oxide or SiN; 3) Special Si Rich SiON spacer process for a self aligned contact (SAC).A dual damascene structure is formed by depositing a first dielectric layer. A novel anti-reflective Si-Rich Silicon oxynitride (SiON) etch barrier layer is deposited on top of the first dielectric layer. A first opening is etched in the first insulating layer. A second dielectric layer is deposited on the anti-reflective Si-Rich Silicon oxynitride (SiON) etch barrier layer. A second dual damascene opening is etched into the dielectric layers. The anti-reflective Si-Rich Silicon oxynitride (SiON) etch barrier layer can also serve as an ARC layer during these operations to reduce the amount of reflectance from conductive region to reduce distortion of the photoresist pattern.

Owner:TAIWAN SEMICON MFG CO LTD

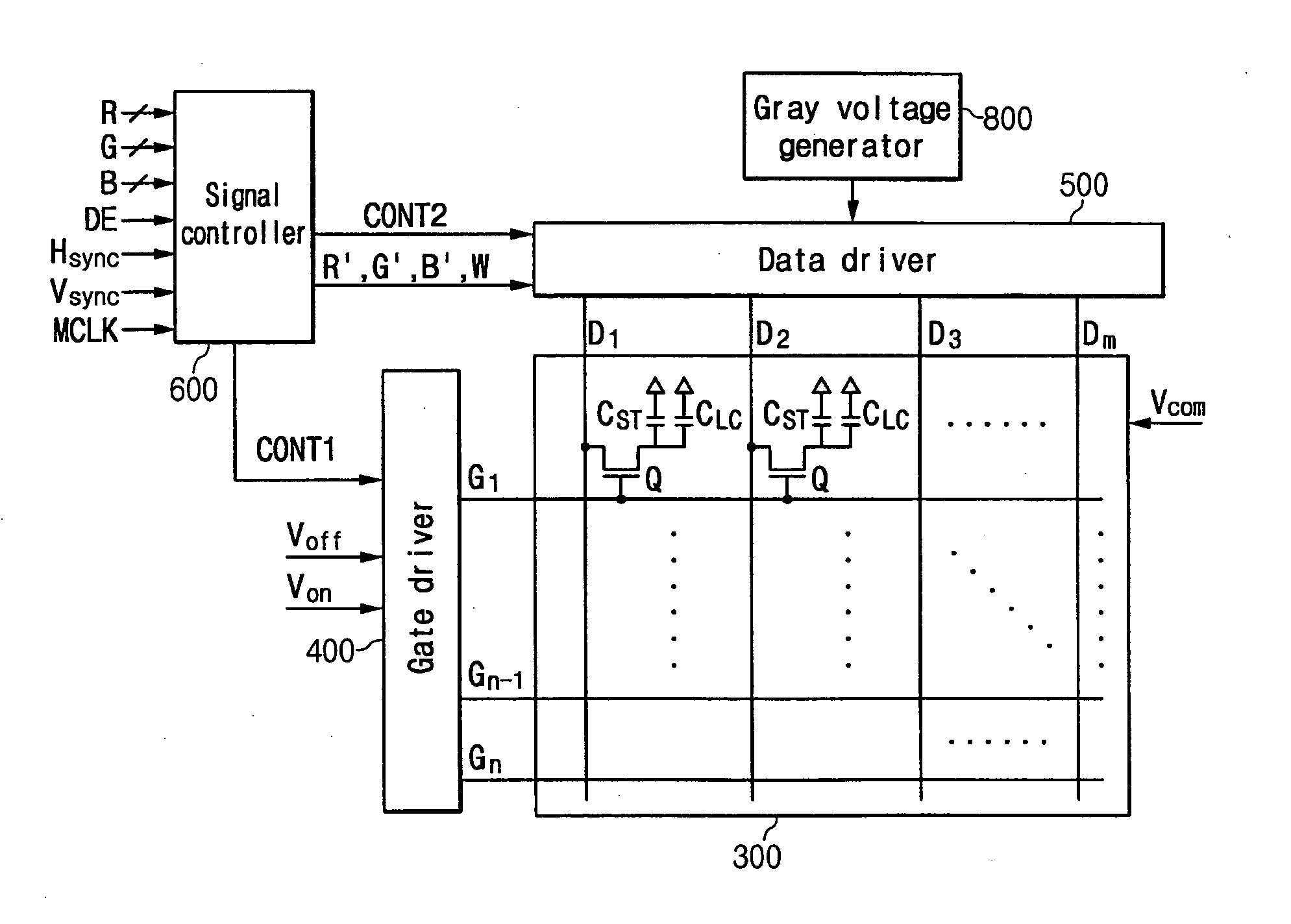

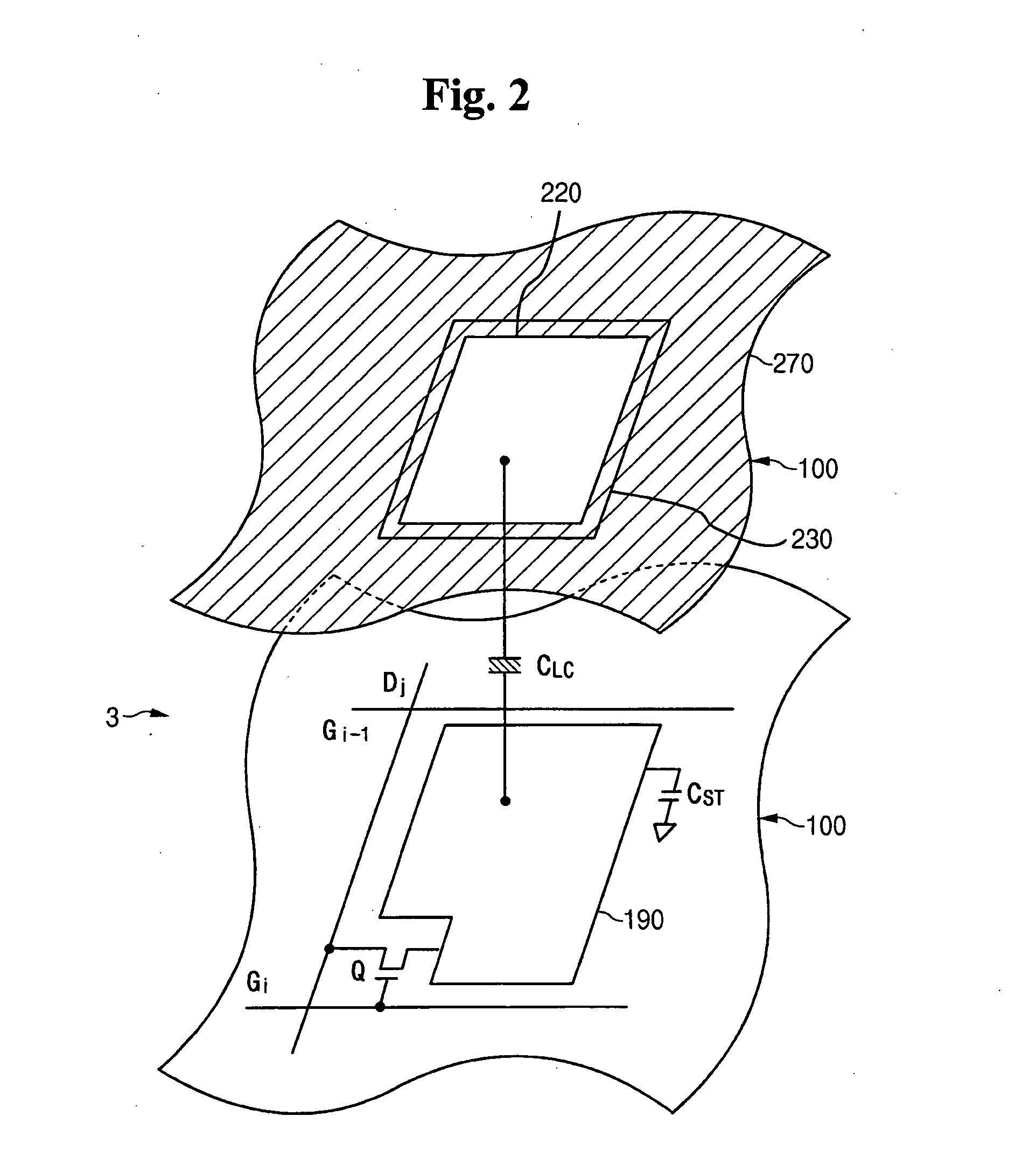

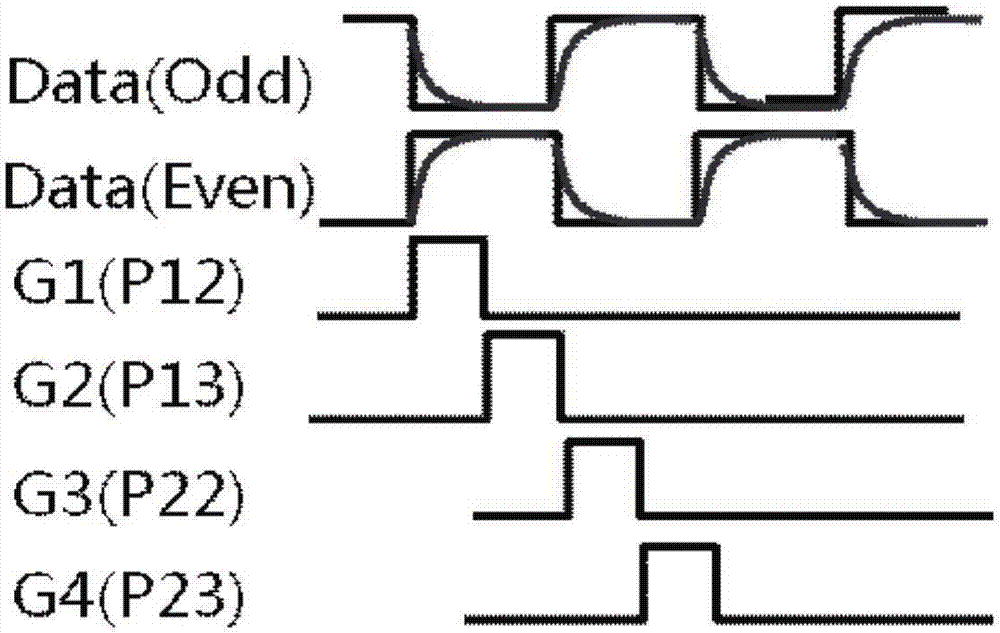

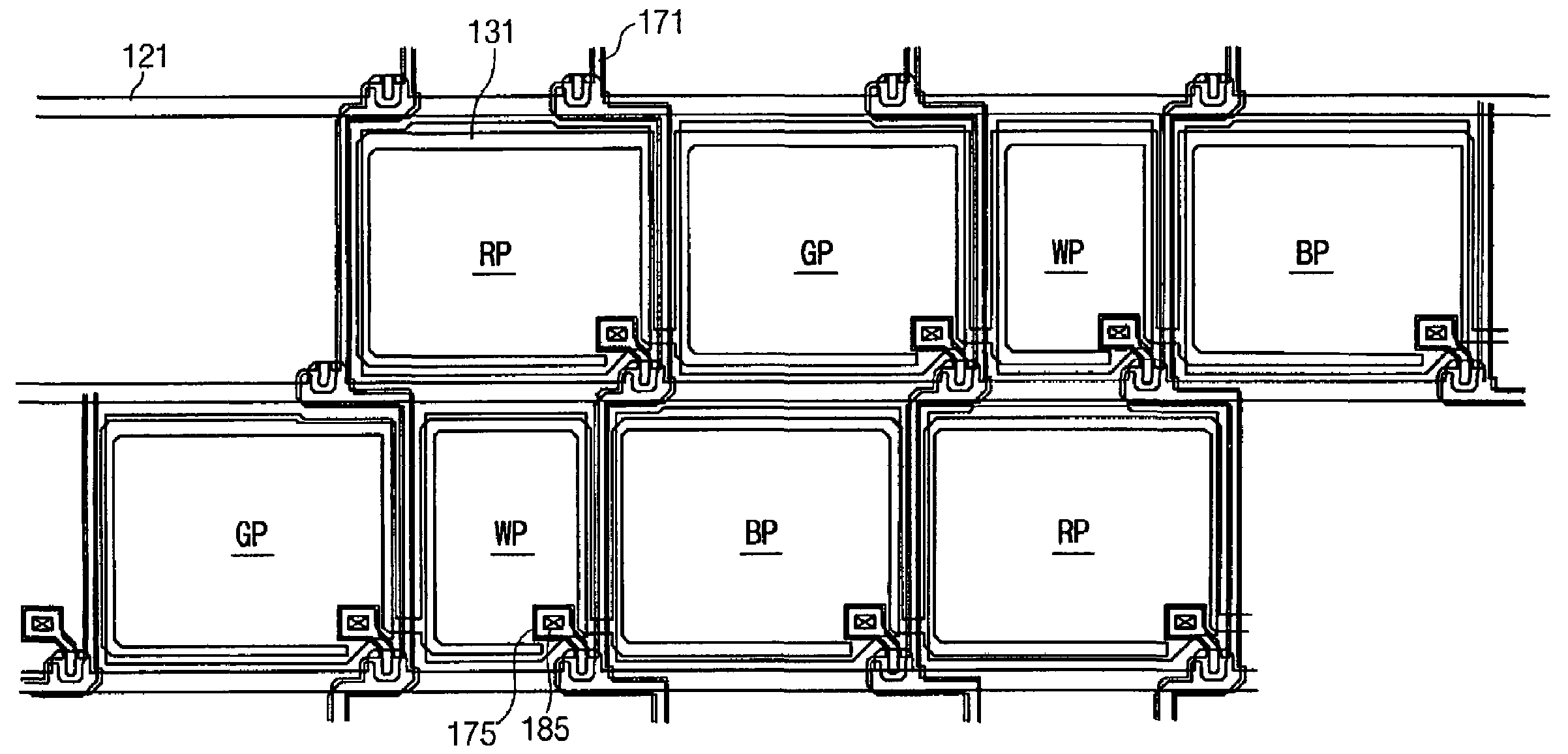

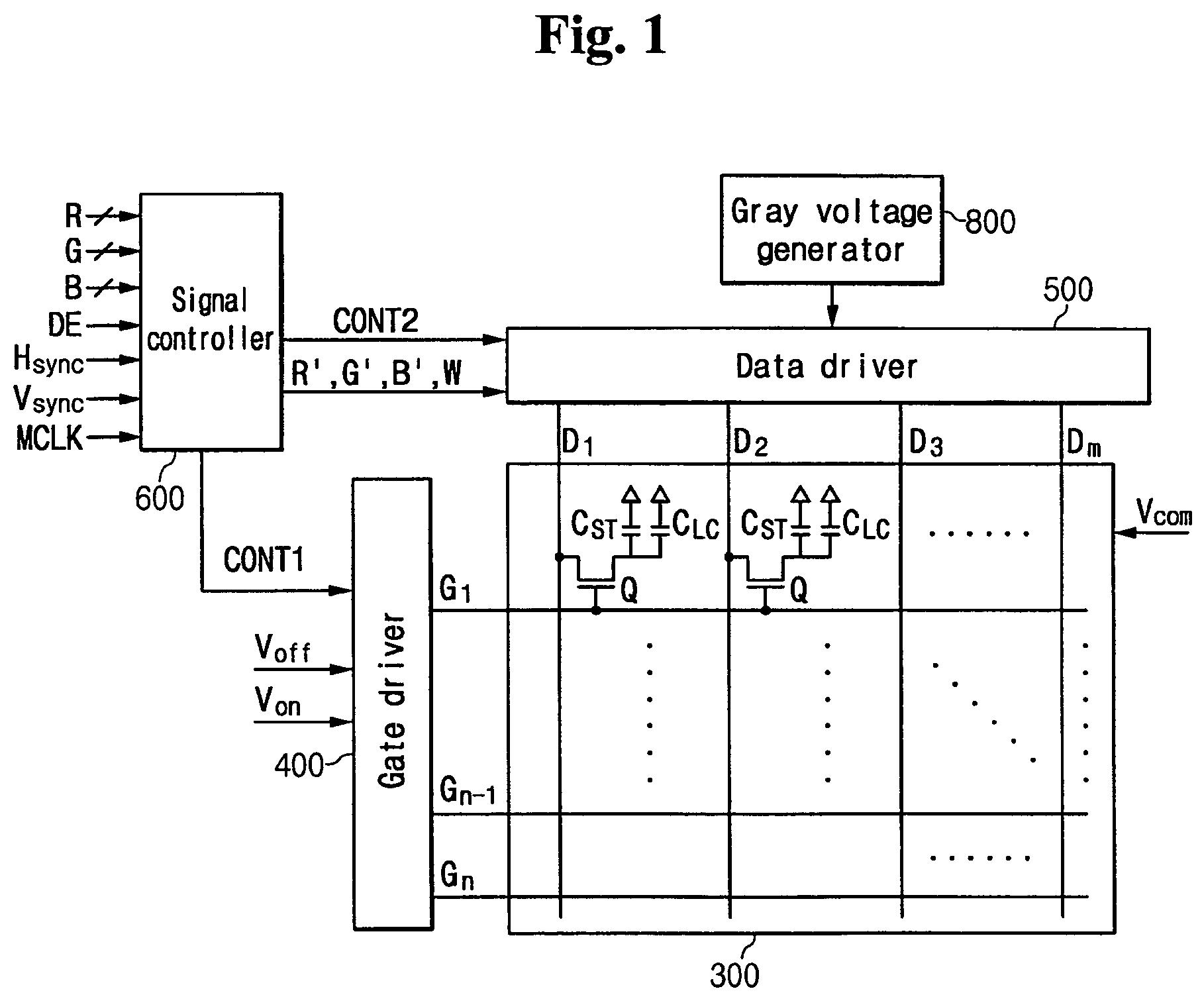

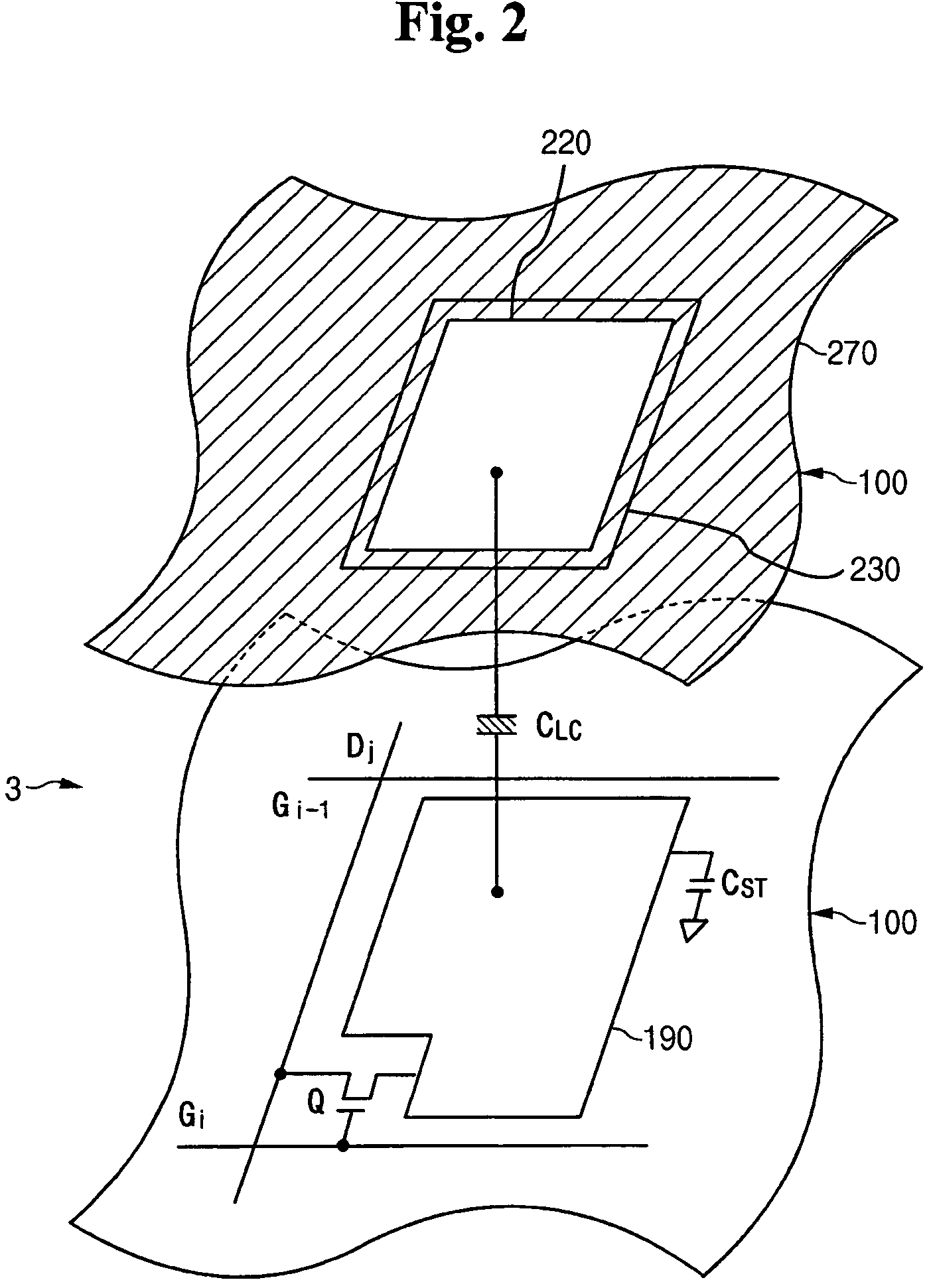

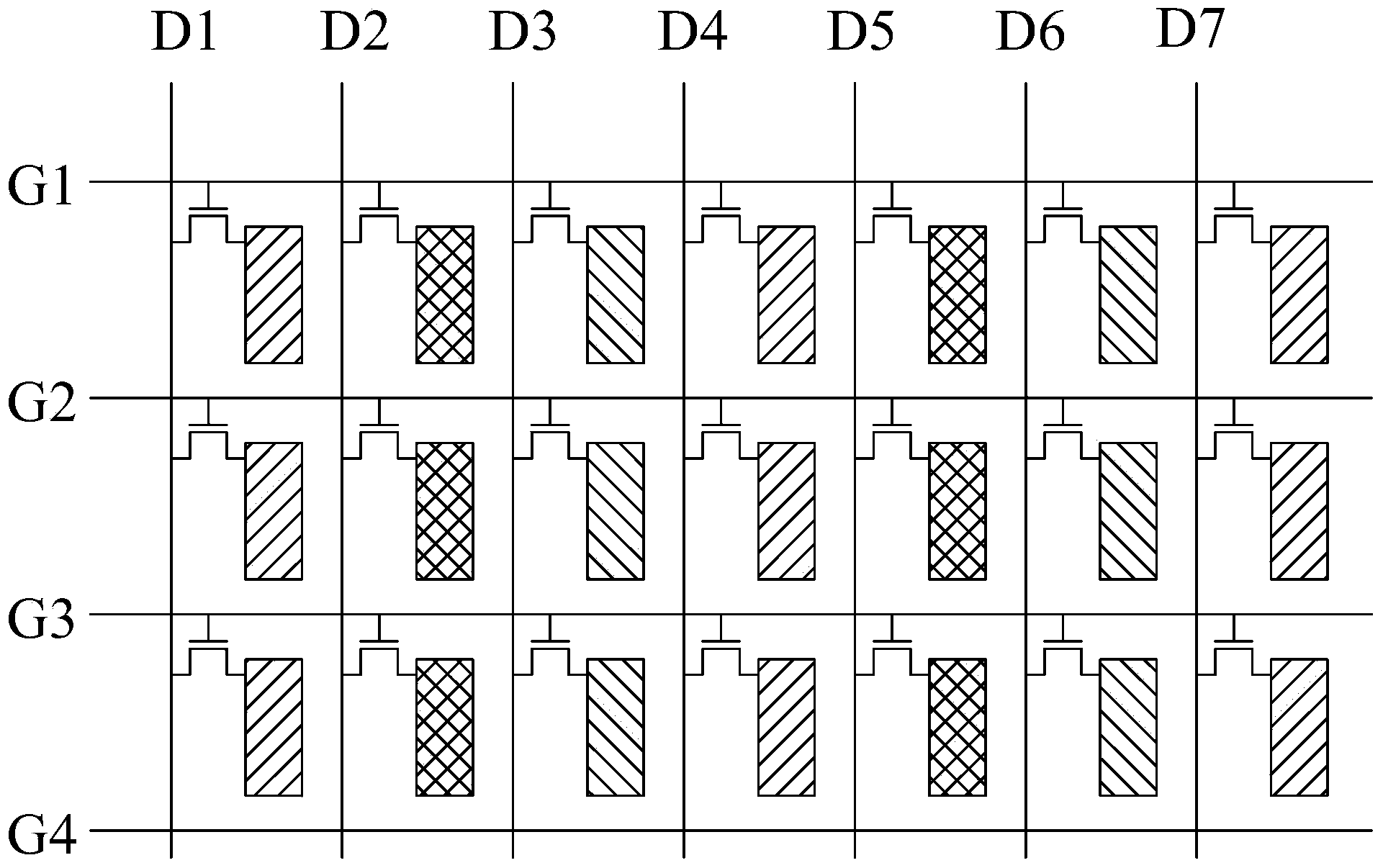

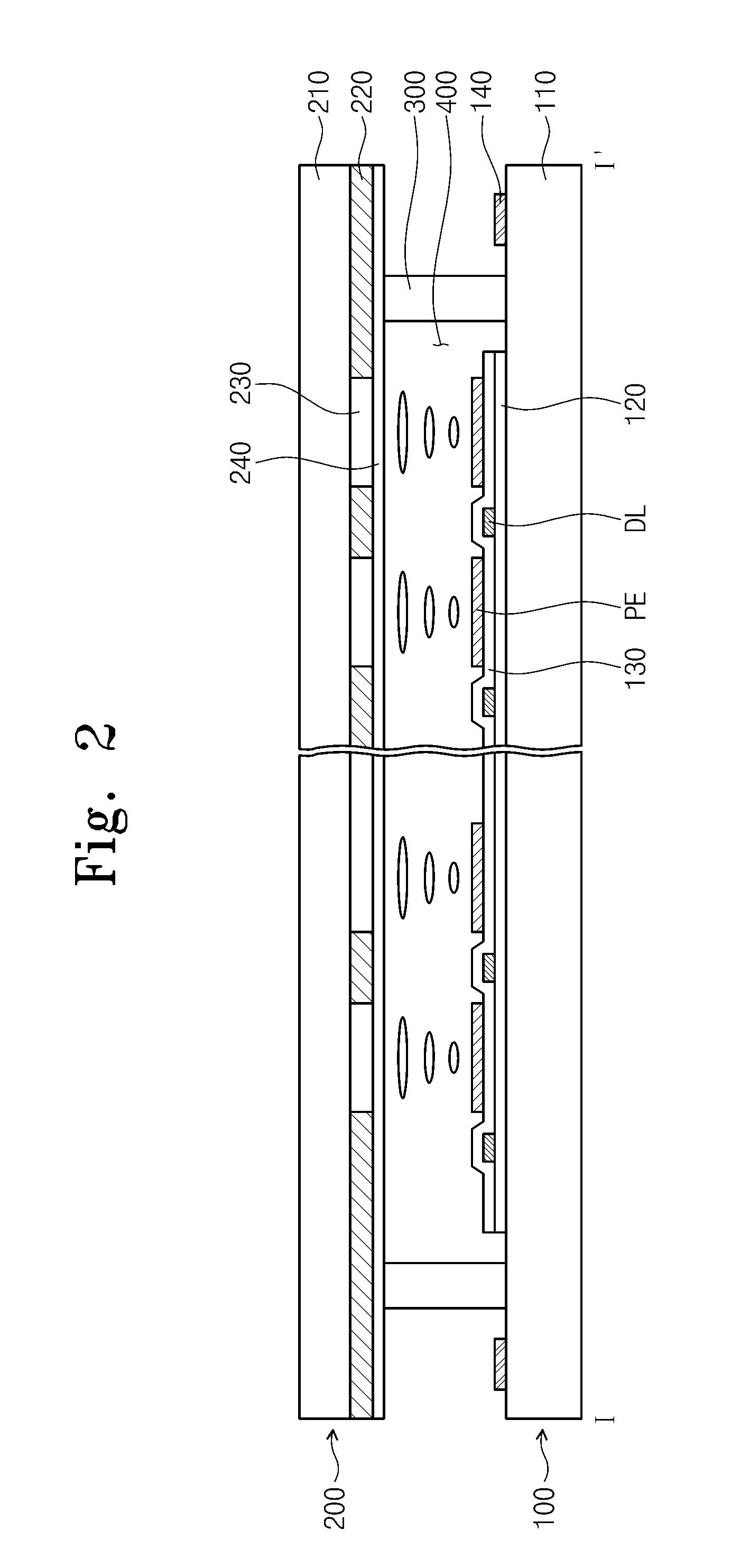

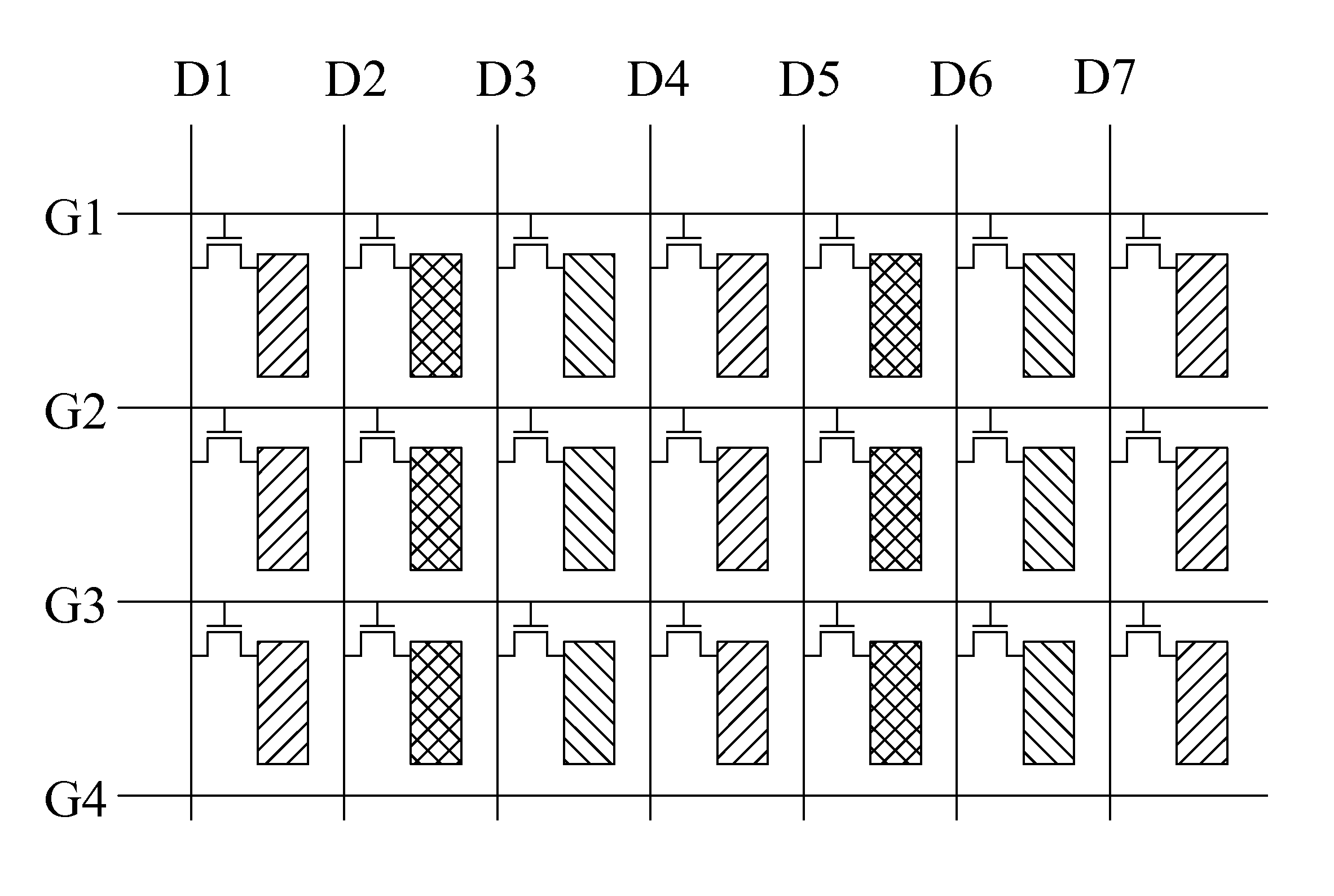

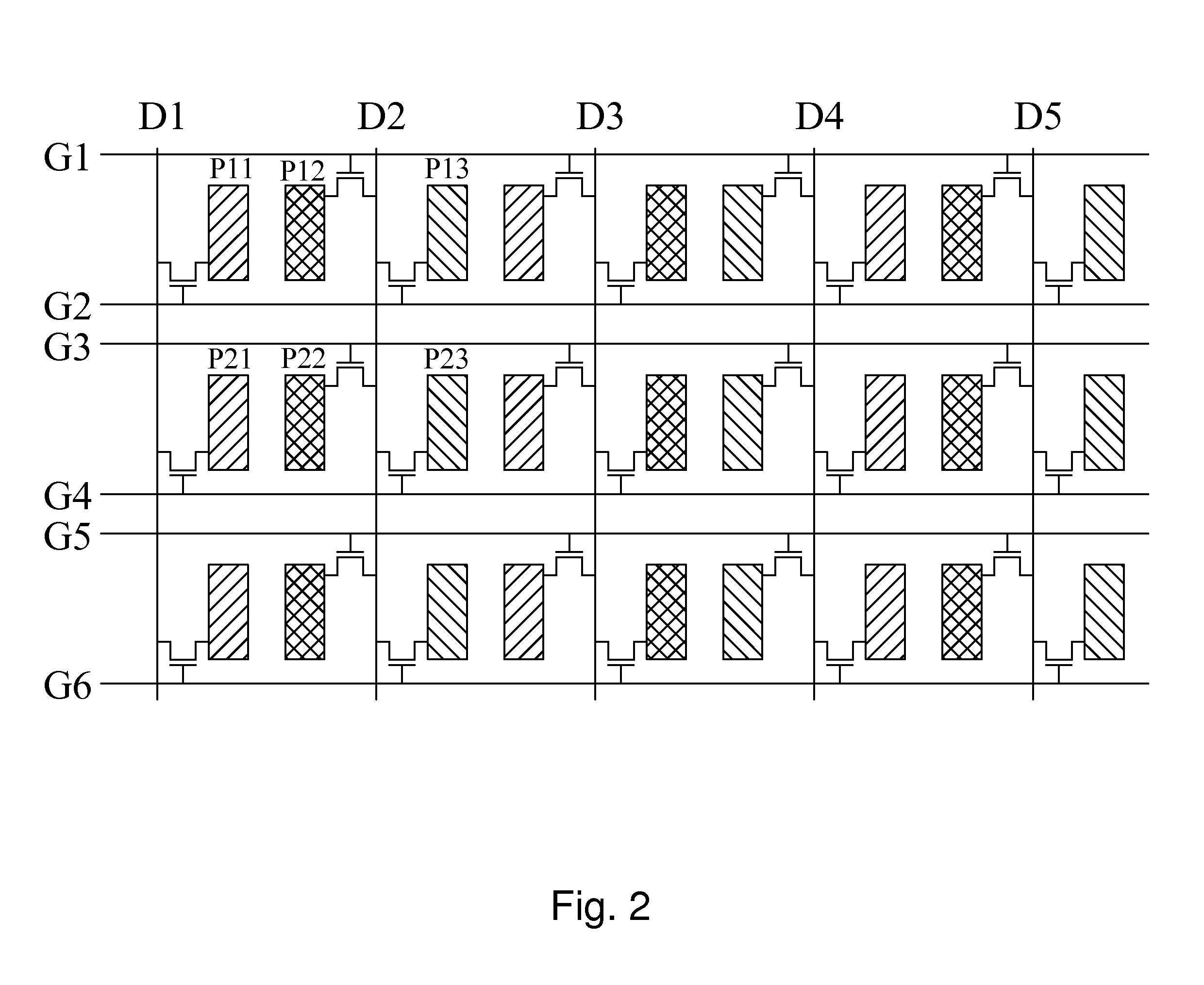

Liquid crystal display

ActiveUS20050068281A1Solve the real problemIncrease brightnessColor signal processing circuitsStatic indicating devicesLiquid-crystal displayData signal

A four color liquid crystal display (LCD) including red, green, blue, and white sub-pixels are provided. The LCD also includes a plurality of gate lines for transmitting gate signals to the sub-pixels and a plurality of data lines for transmitting data signals to the sub-pixels. The white sub-pixel is smaller than the other sub-pixels, and each of the data lines passes between adjacent two sub-pixels and includes at least one curved portion. Furthermore, the lengths of the data lines are substantially uniform.

Owner:SAMSUNG DISPLAY CO LTD

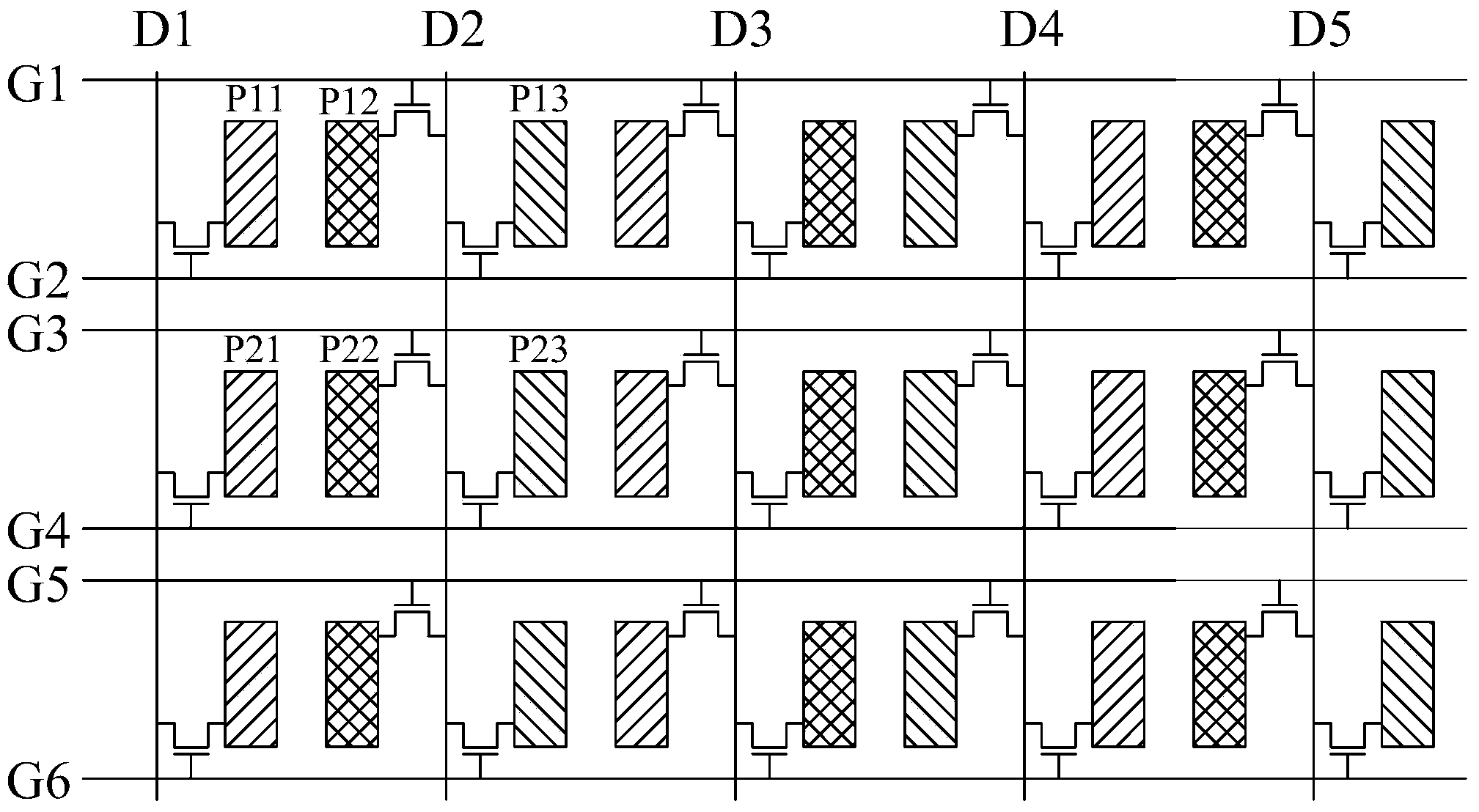

TFT (Thin Film Transistor) array substrate

ActiveCN104267519AImprove display defectsLower resistanceStatic indicating devicesSolid-state devicesElectrical resistance and conductanceEngineering

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

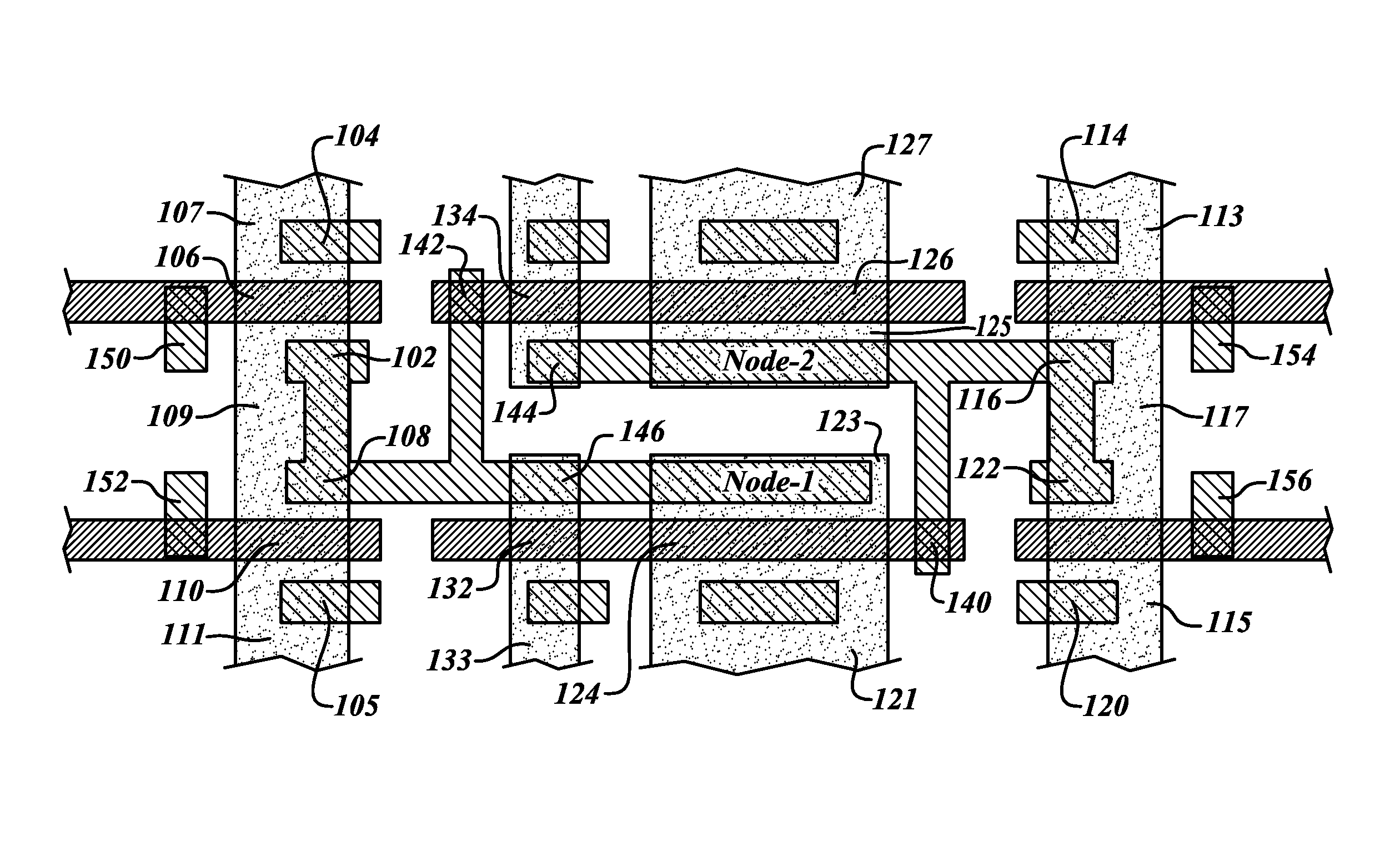

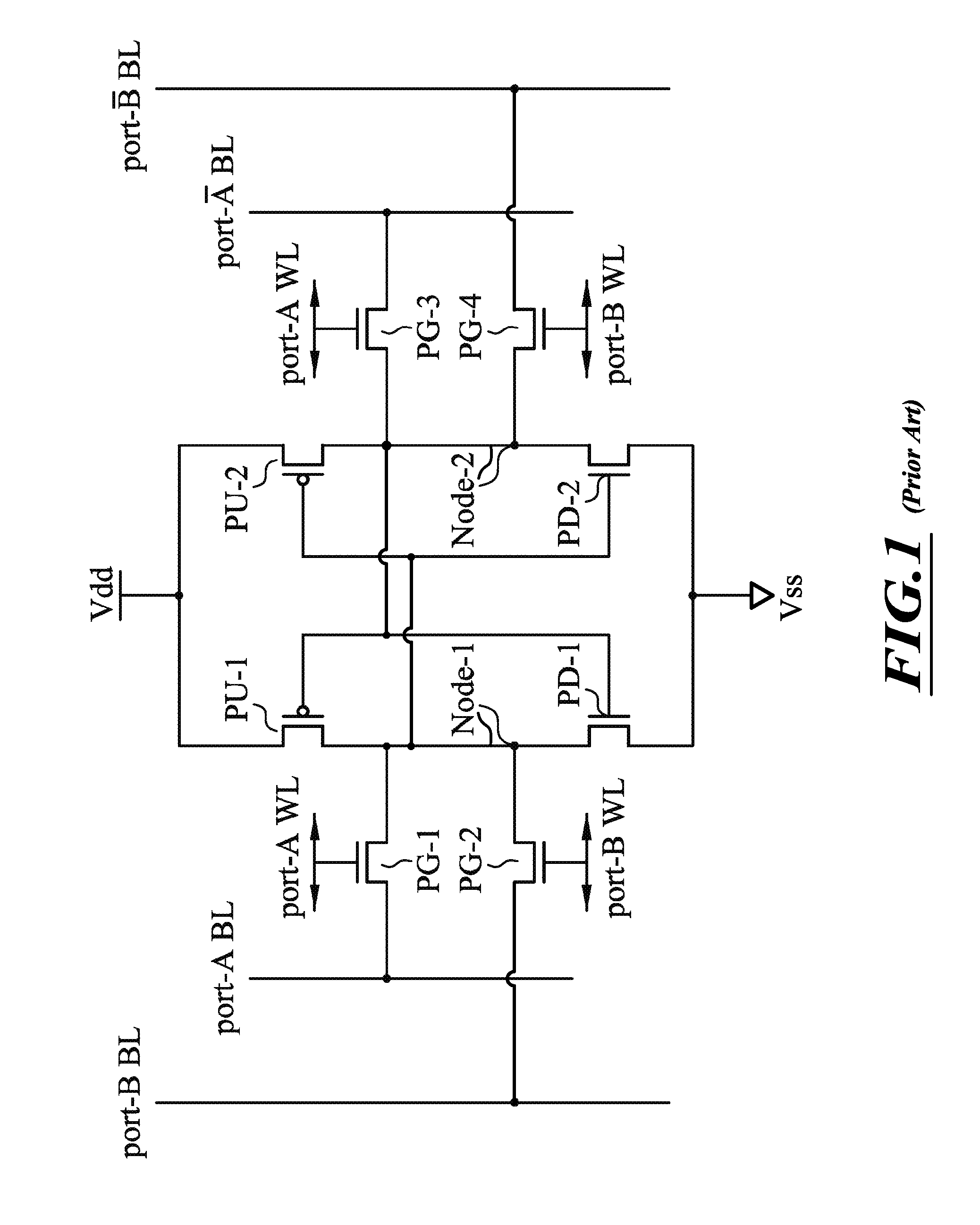

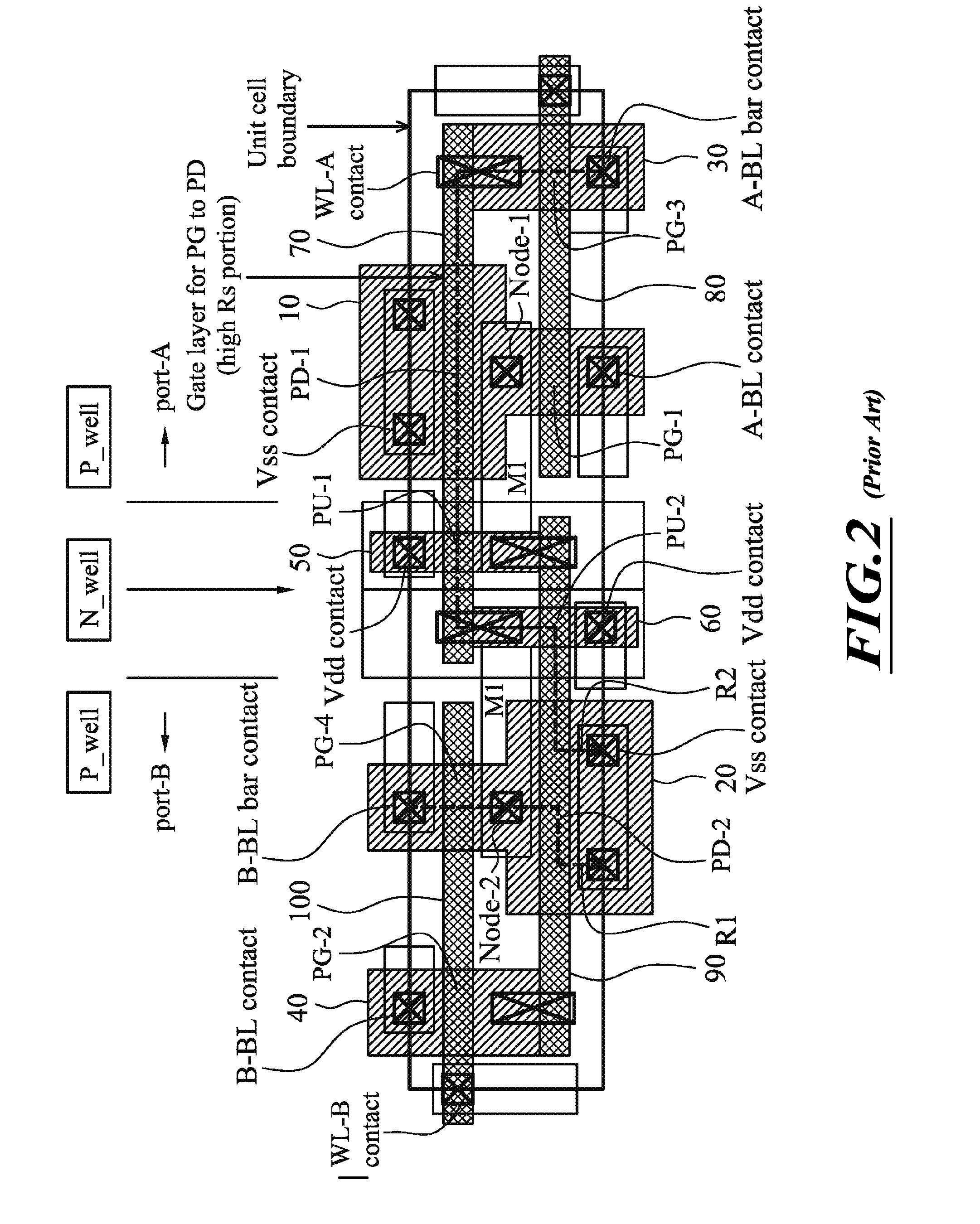

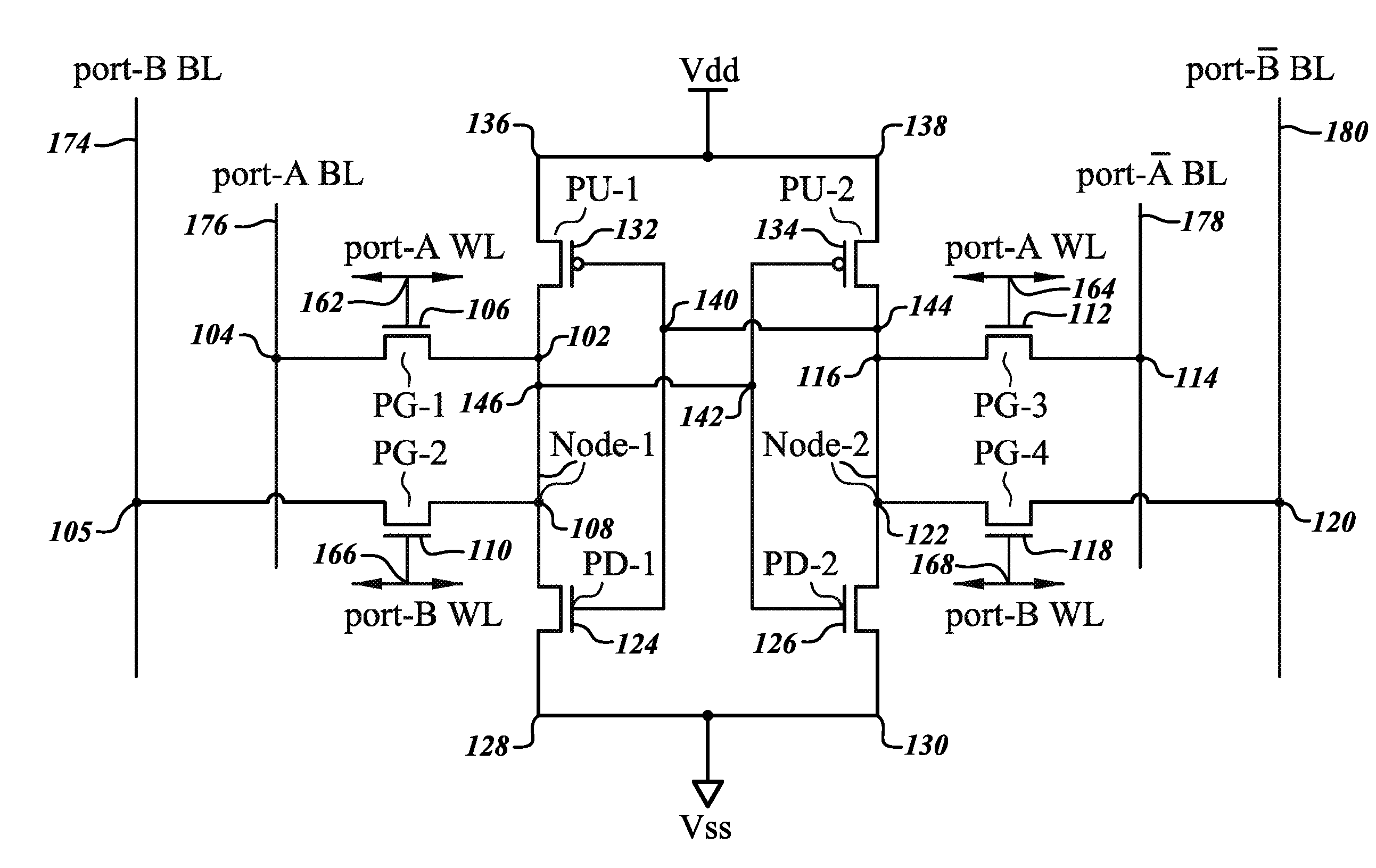

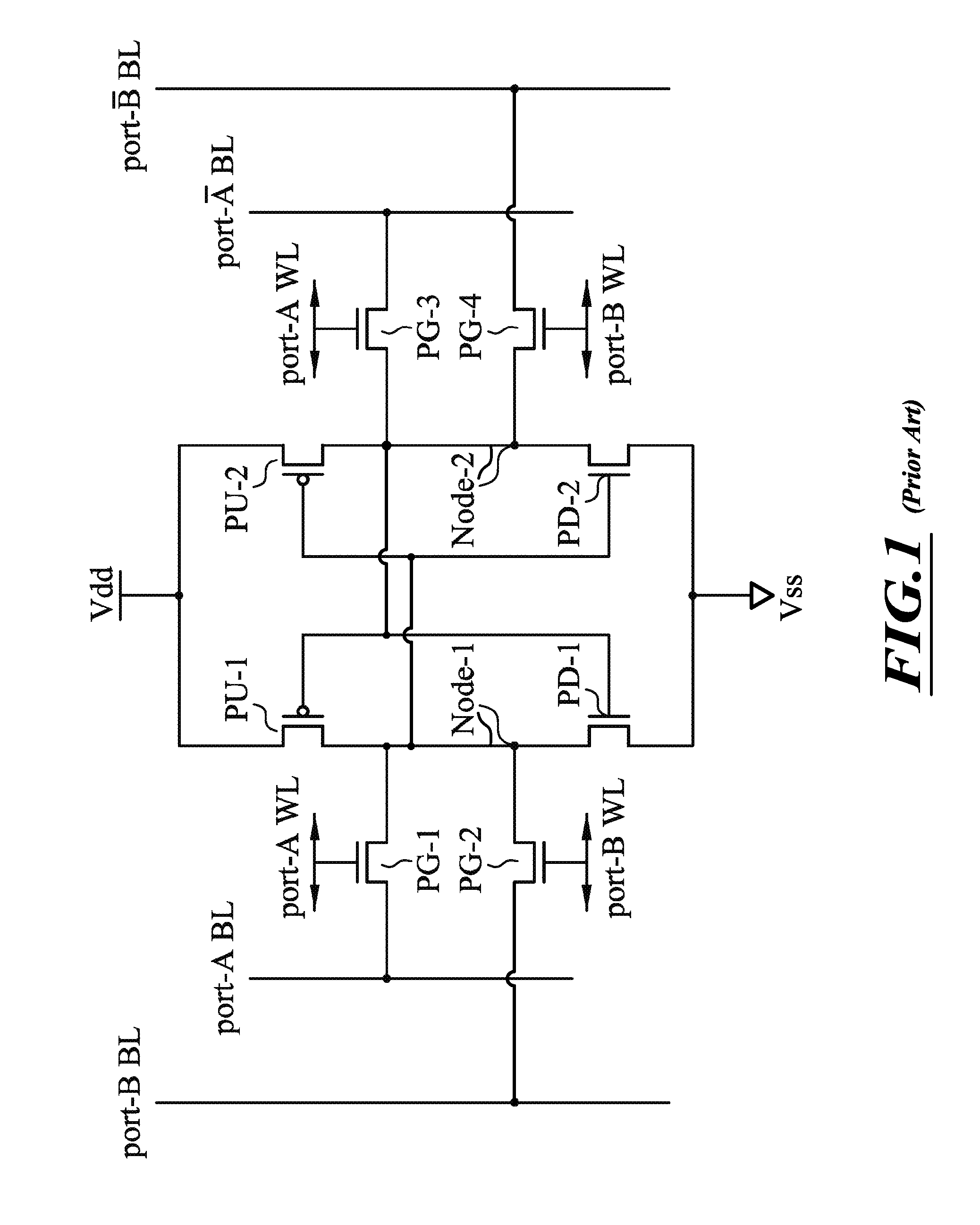

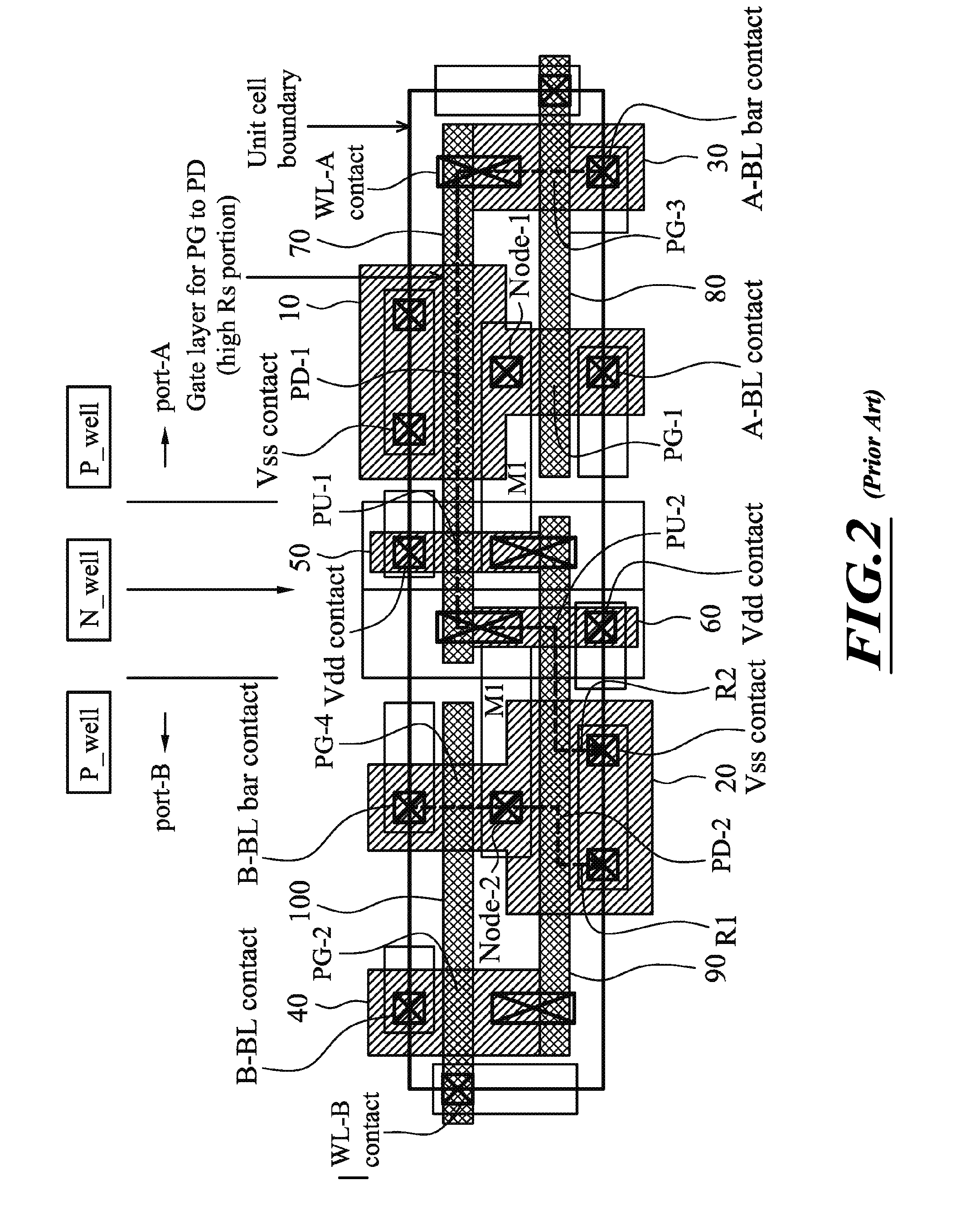

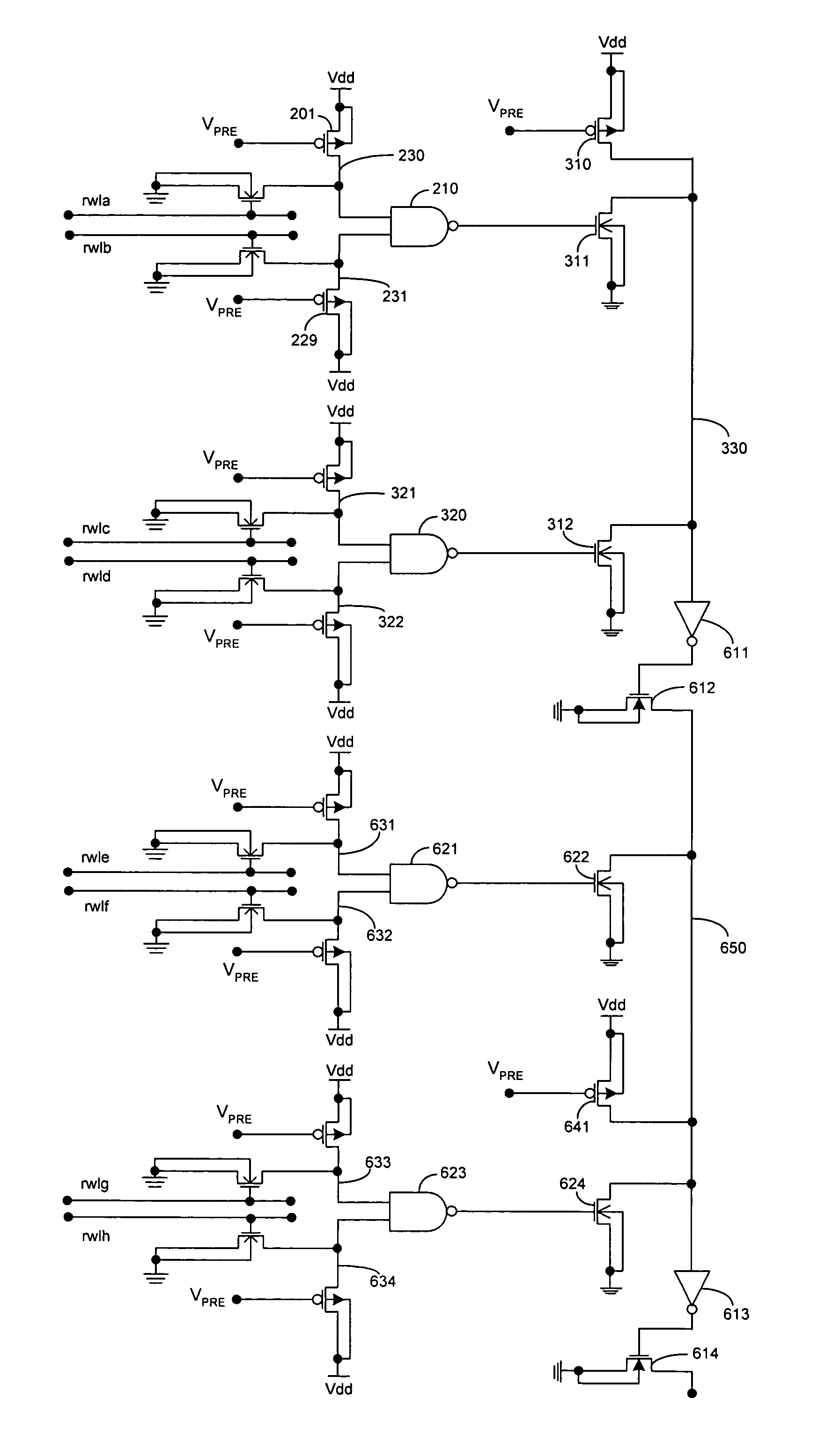

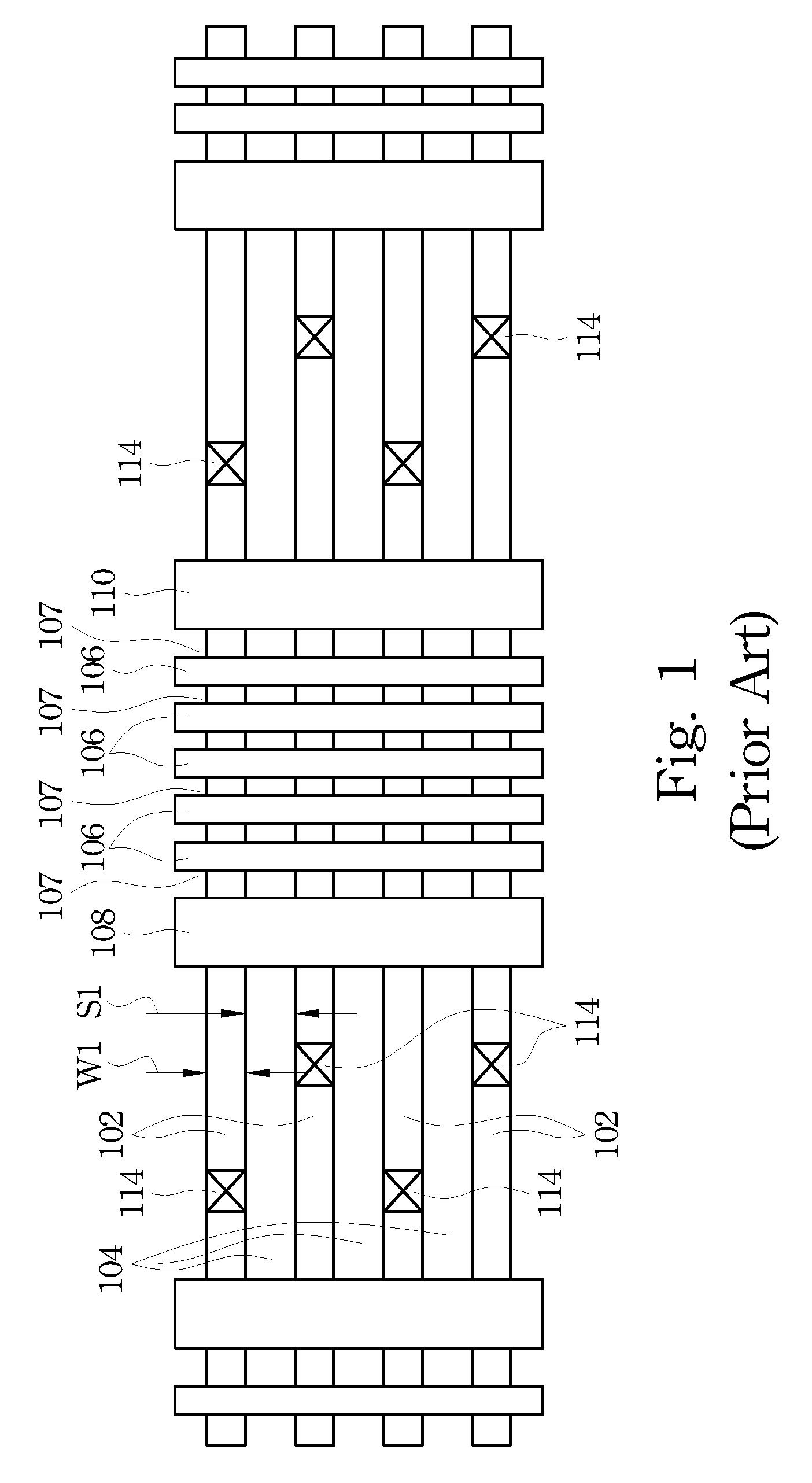

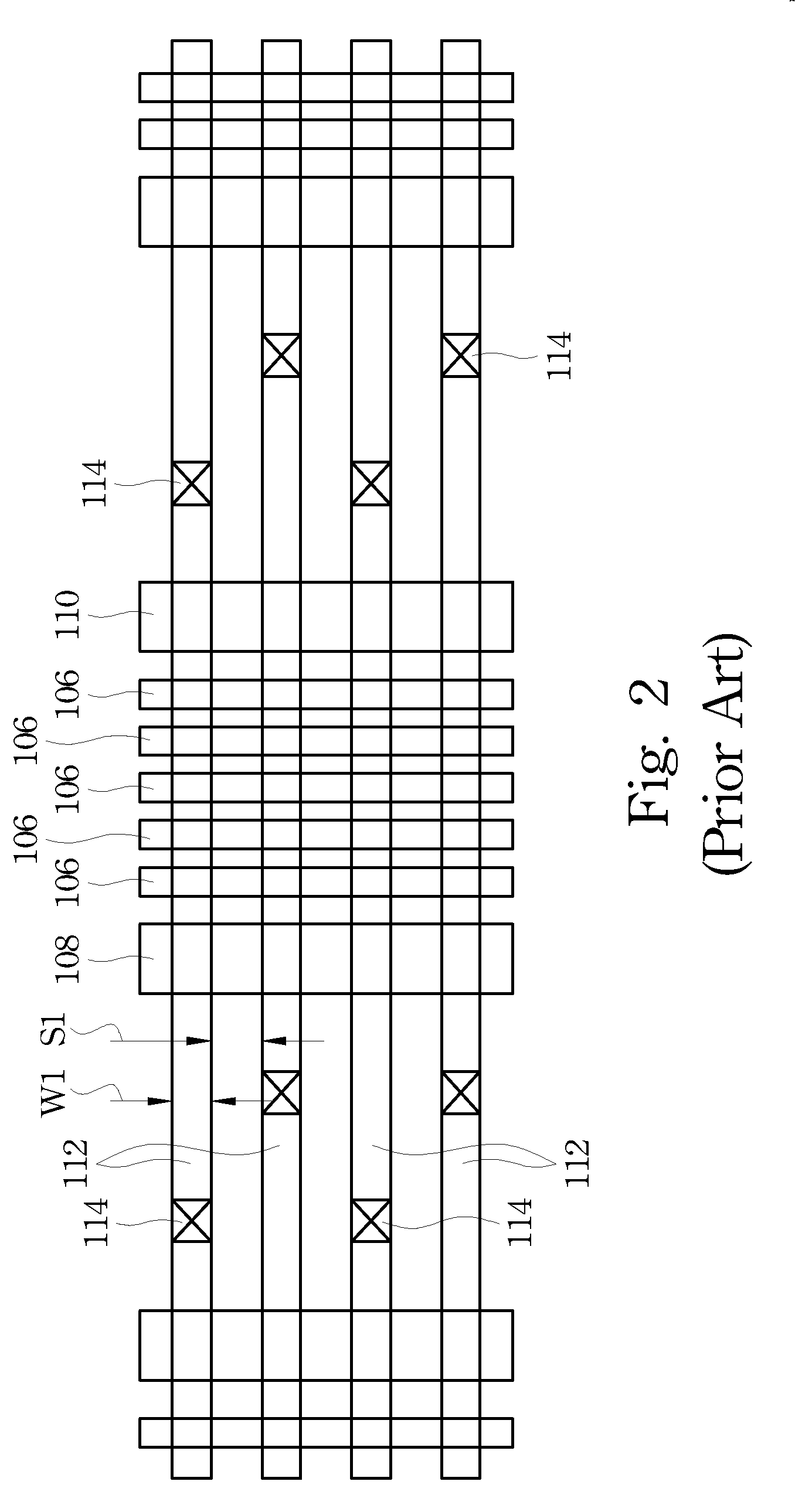

Dual port SRAM having reduced cell size and rectangular shape

ActiveUS9006841B2Improve performanceFunction increaseTransistorSolid-state devicesCell sizeTransistor

A dual port SRAM has two data storage nodes, a true data and complementary data. A first pull down transistor has an active area that forms the drain region of the first transistor and the true data storage node that is physically isolated from all other transistor active areas of the memory cell. A second pull down transistor has an active area that forms the drain region of a second transistor that is the complementary data node that is physically isolated from all other transistor active areas of the memory cell.

Owner:STMICROELECTRONICS INT NV

Back End Integrated WLCSP Structure without Aluminum Pads

ActiveUS20090115058A1Reduce RC delayReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesCopperUnder bump metallurgy

An integrated circuit structure includes a passivation layer; a via opening in the passivation layer; a copper-containing via in the via opening; a polymer layer over the passivation layer, wherein the polymer layer comprises an aperture, and wherein the copper-containing via is exposed through the aperture; a post-passivation interconnect (PPI) line over the polymer layer, wherein the PPI line extends into the aperture and physically contacts the copper-via opening; and an under-bump metallurgy (UBM) over and electrically connected to the PPI line.

Owner:TAIWAN SEMICON MFG CO LTD

Liquid crystal display having particular sub-pixels

ActiveUS7388630B2Increase brightnessAvoid attenuationColor signal processing circuitsStatic indicating devicesLiquid-crystal displayComputer science

A four color liquid crystal display (LCD) including red, green, blue, and white sub-pixels are provided. The LCD also includes a plurality of gate lines for transmitting gate signals to the sub-pixels and a plurality of data lines for transmitting data signals to the sub-pixels. The white sub-pixel is smaller than the other sub-pixels, and each of the data lines passes between adjacent two sub-pixels and includes at least one curved portion. Furthermore, the lengths of the data lines are substantially uniform.

Owner:SAMSUNG DISPLAY CO LTD

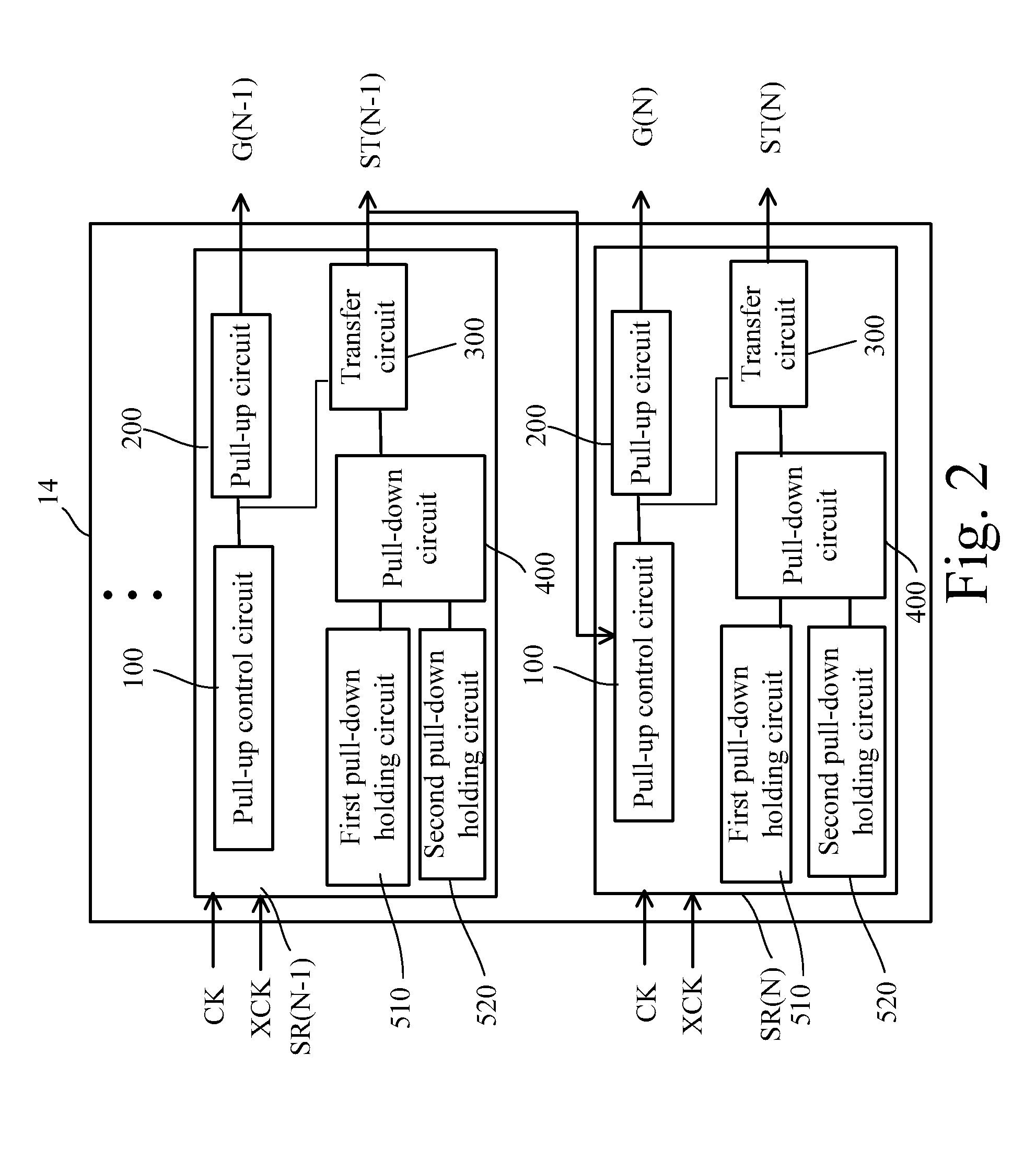

Gate Driver for Narrow Bezel LCD

ActiveUS20150310819A1Simple circuit structureReduce voltage offsetCathode-ray tube indicatorsDigital storageLiquid-crystal displayEnergy consumption

The present invention proposes a gate driver which simplifies a circuit structure by effectively compounding the pull-down holding circuit and signals to achieve a design for ultra-narrow bezel gate driver. In addition, It effectively lessens voltage offset at the second node and prolongs GOA circuit operating time to prolongs lifetime of the LCD when the seventh transistor of the first pull-down holding circuit adopts equivalent diode connection. At last, it reduces RC delay to efficiently lower power-consumption to more effectively decrease LCD energy-consumption when amount of transistors and signals of the first and the second pull-down holding circuits decreases.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Dual port SRAM having reduced cell size and rectangular shape

ActiveUS20130170275A1Improve performanceOptimally perform its functionTransistorSolid-state devicesData nodeCell size

A dual port SRAM has two data storage nodes, a true data and complementary data. A first pull down transistor has an active are that forms the drain region of the first transistor and the true data storage node that is physically isolated from all other transistor active areas of the memory cell. A second pull down transistor has an active area that form the drain region of a second transistor that is the complementary data node that is physically isolated from all other transistor active areas of the memory cell.

Owner:STMICROELECTRONICS INT NV

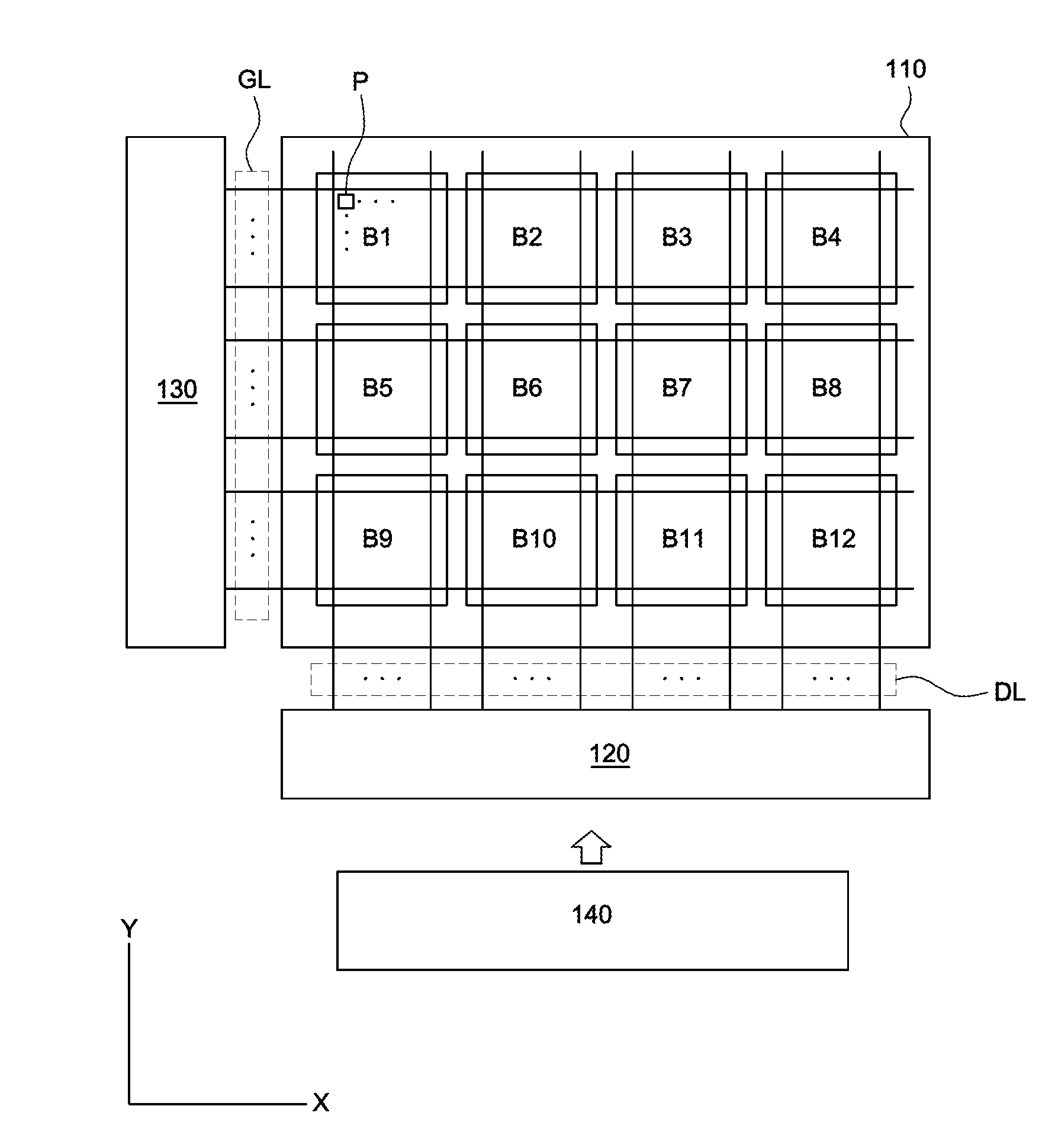

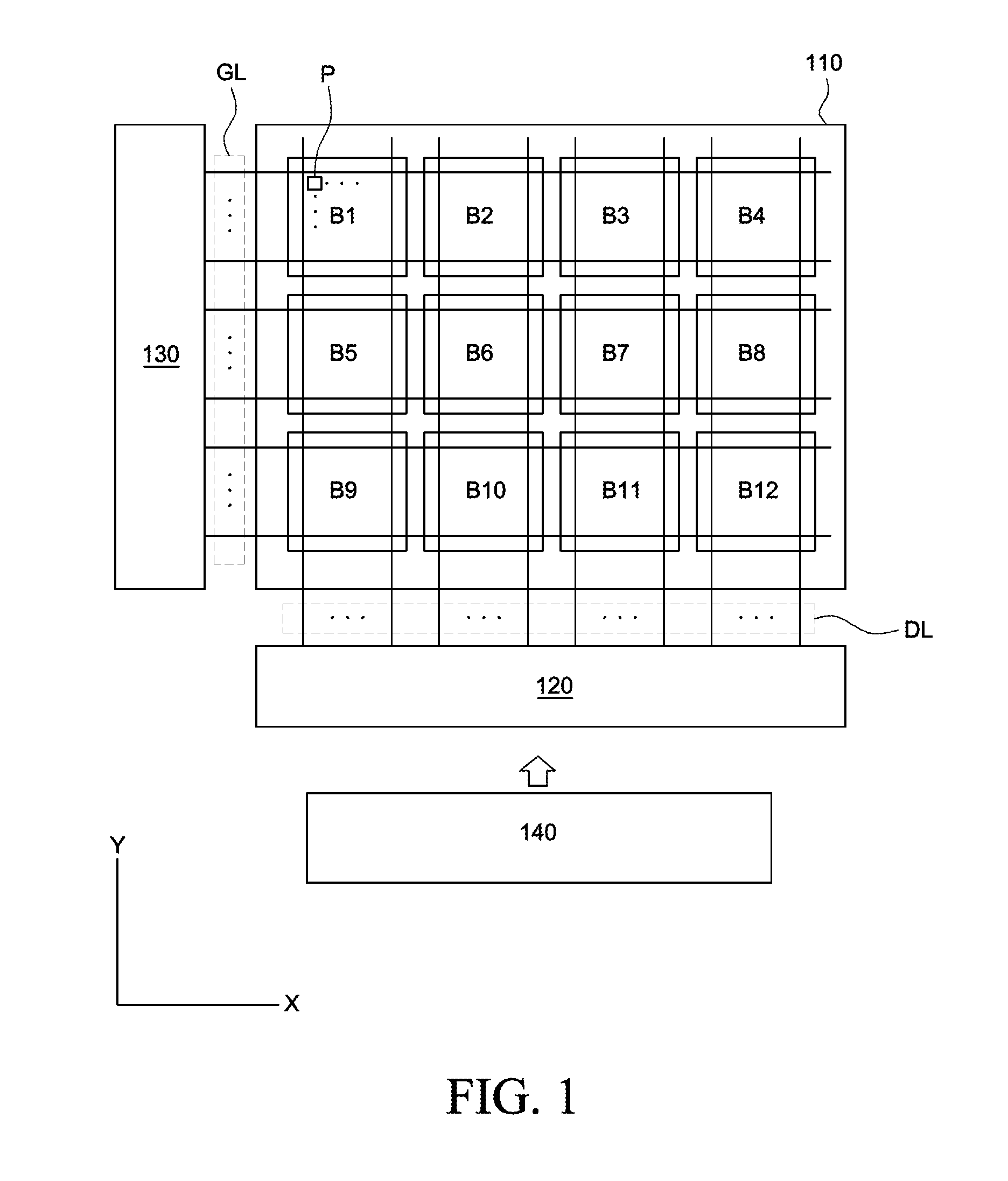

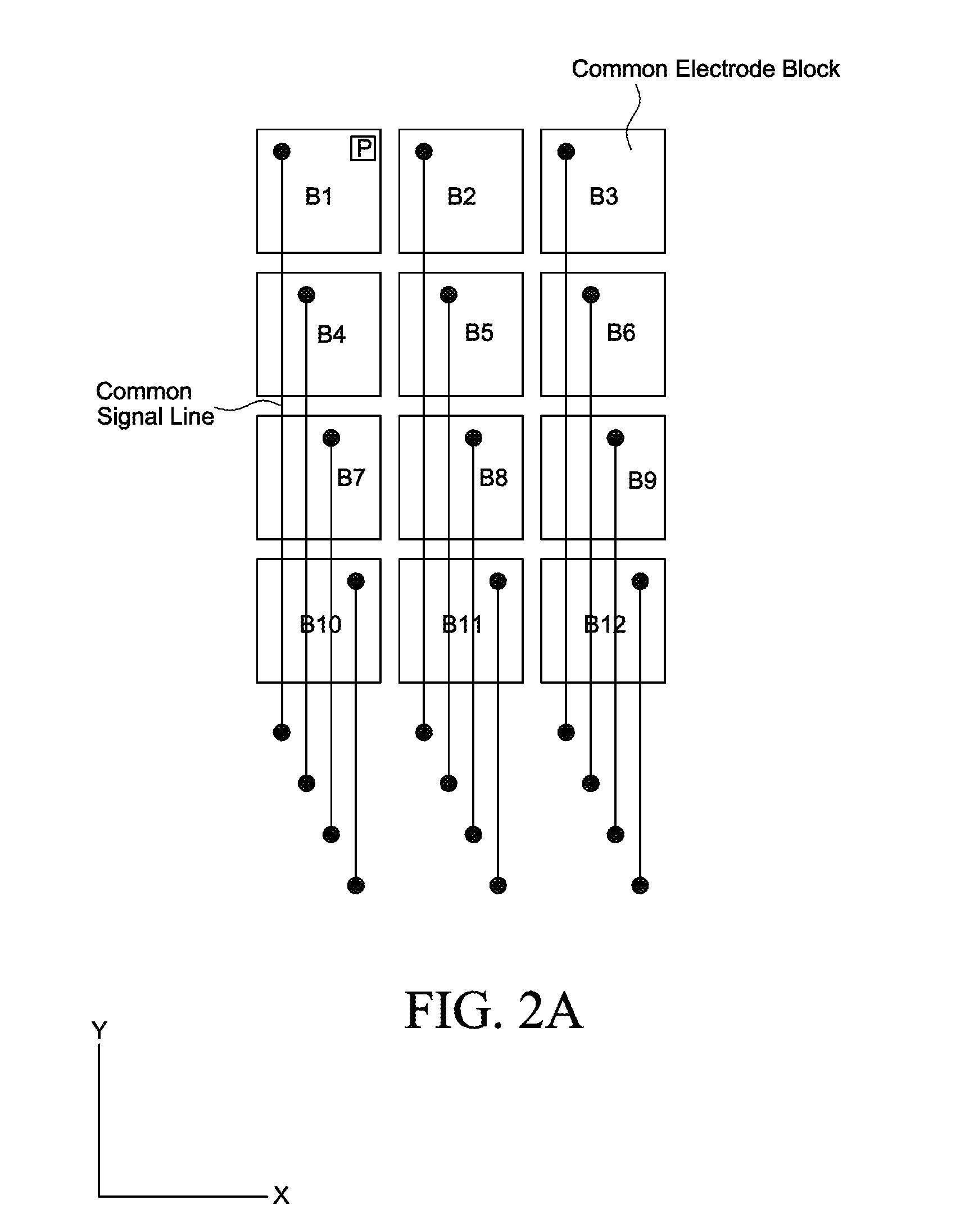

Touch recognition enabled display device with asymmetric black matrix pattern

ActiveUS20160320882A1Reduce distanceSmall sizeCathode-ray tube indicatorsNon-linear opticsTouch SensesDisplay device

A touch recognition enabled display device includes a plurality of common electrode blocks serving as touch-sensing regions and / or touch-driving regions. Conductive lines connected to the common electrode blocks are placed under the common electrode blocks and the pixel electrodes of the pixels, and they are routed across the active area, directly toward an inactive area where drive-integrated circuits are located. The conductive lines are positioned under one or more planarization layers, and are connected to the corresponding common electrode blocks via one or more contact holes.

Owner:LG DISPLAY CO LTD

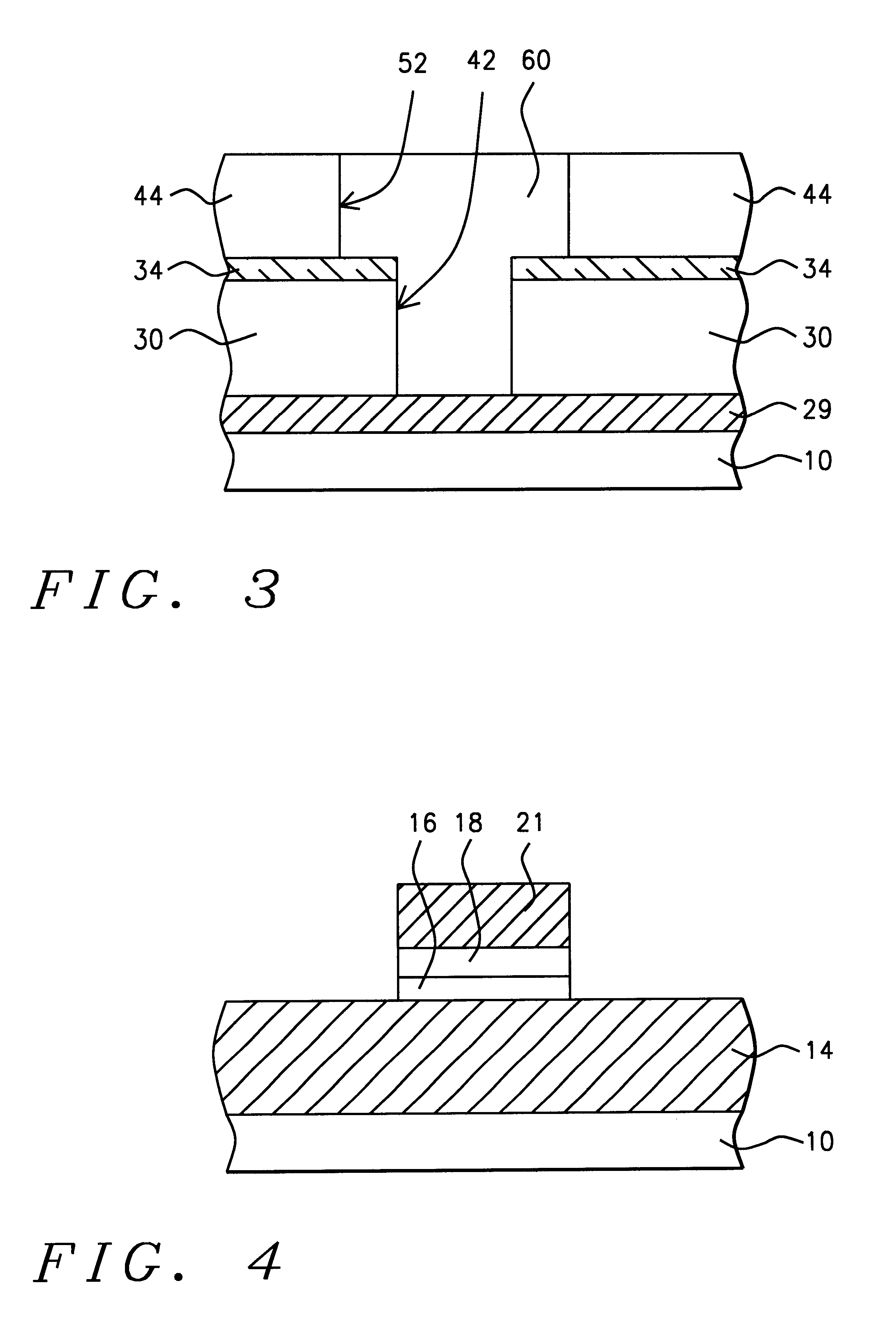

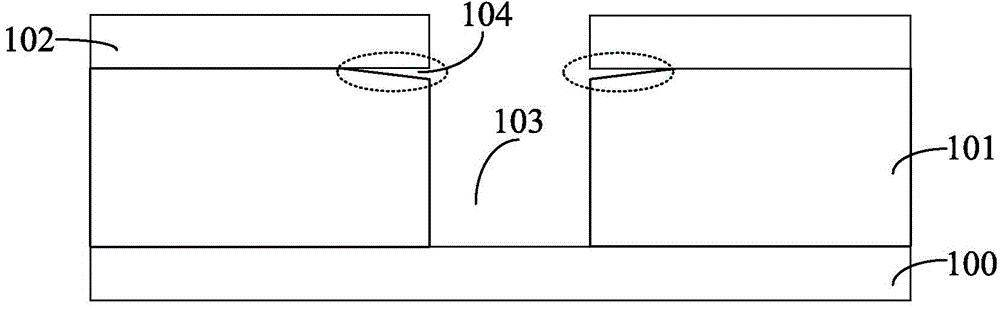

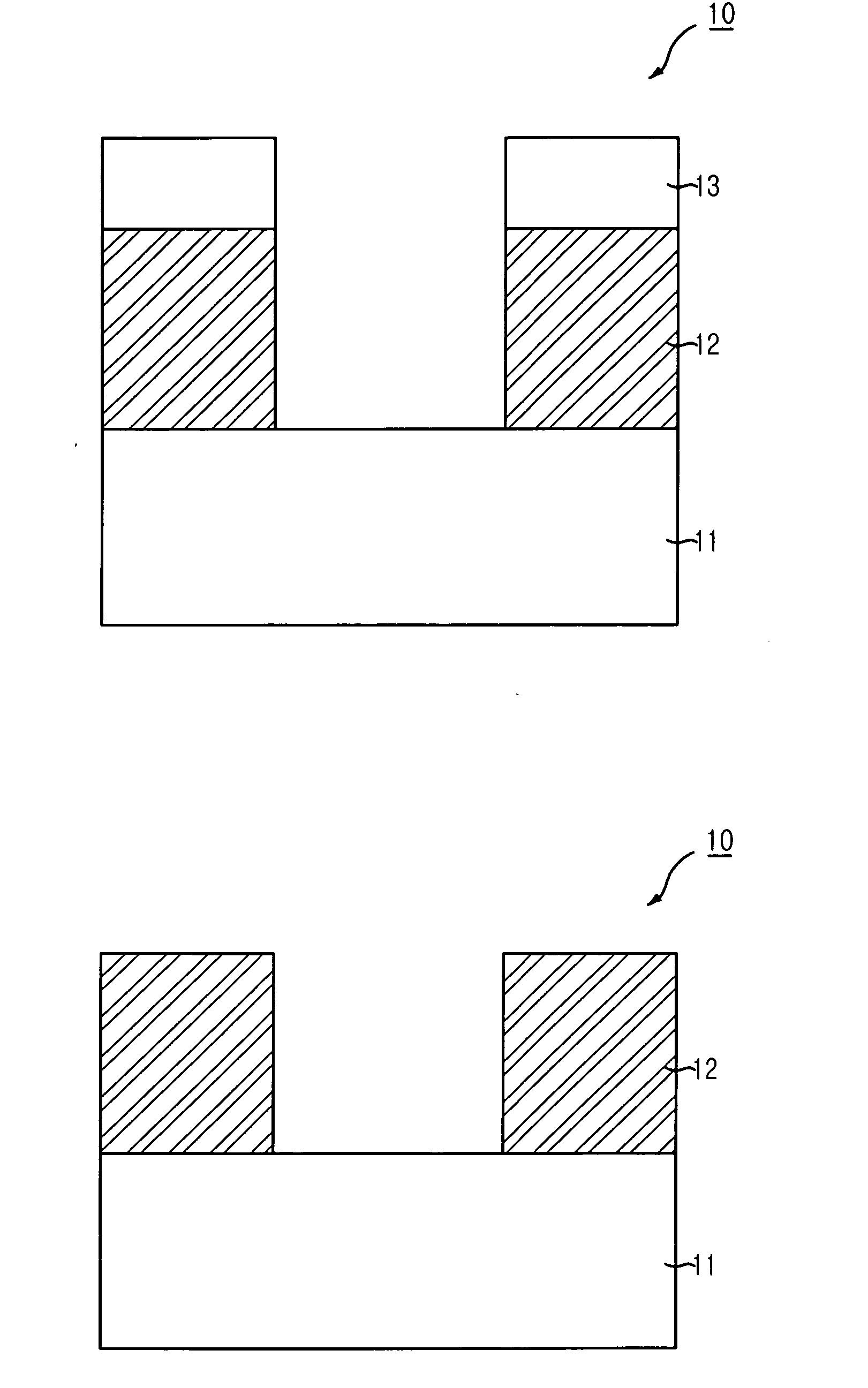

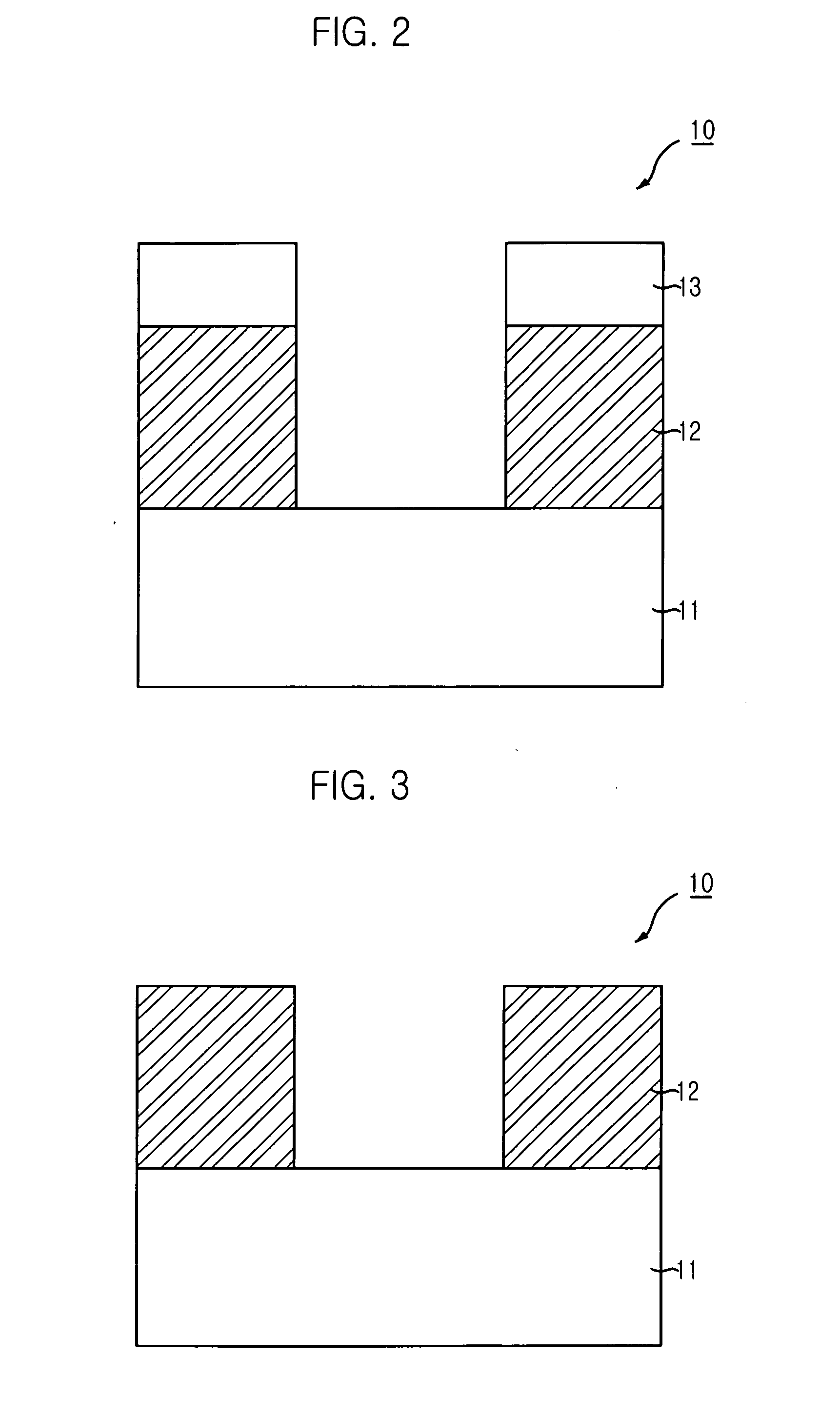

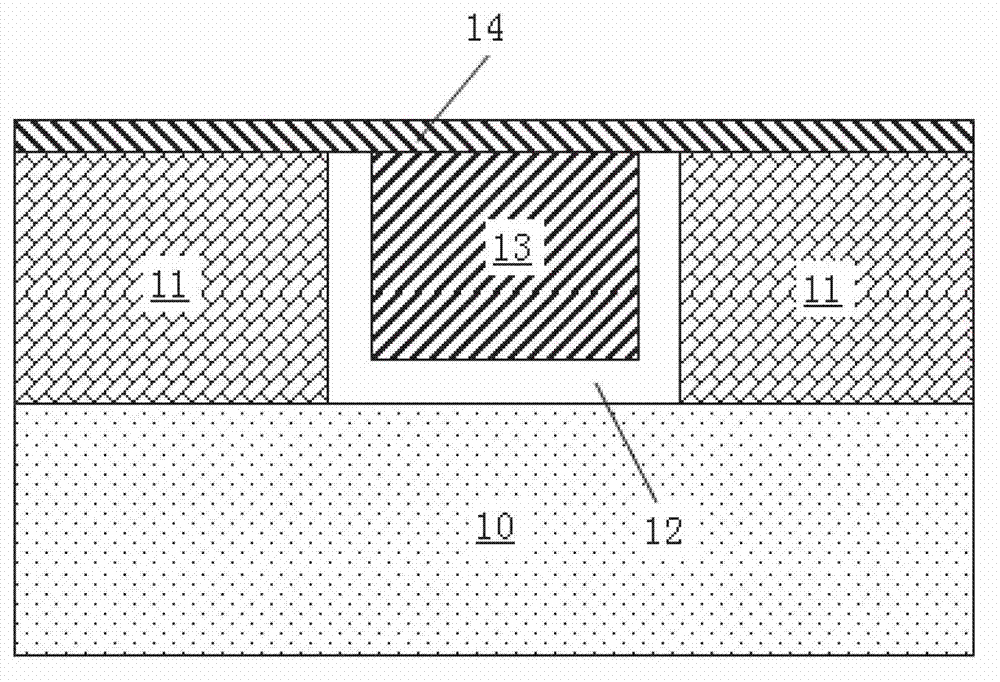

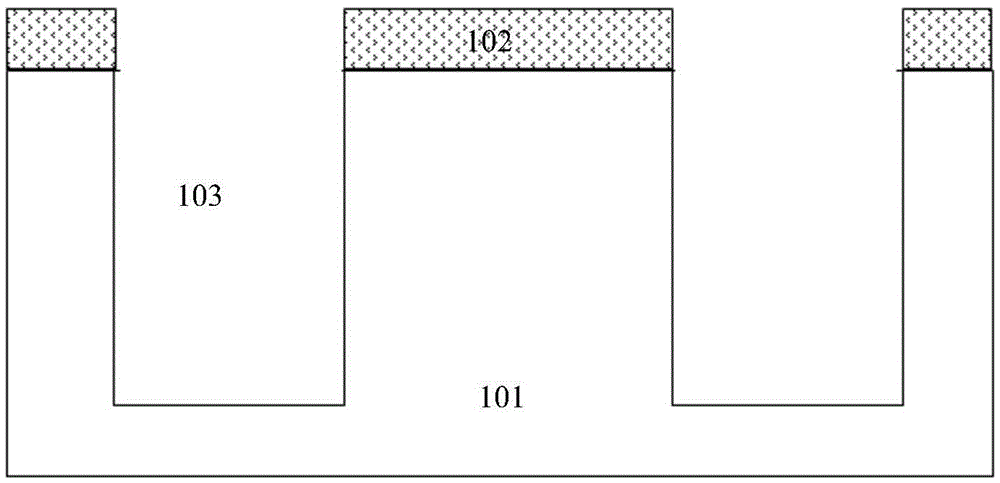

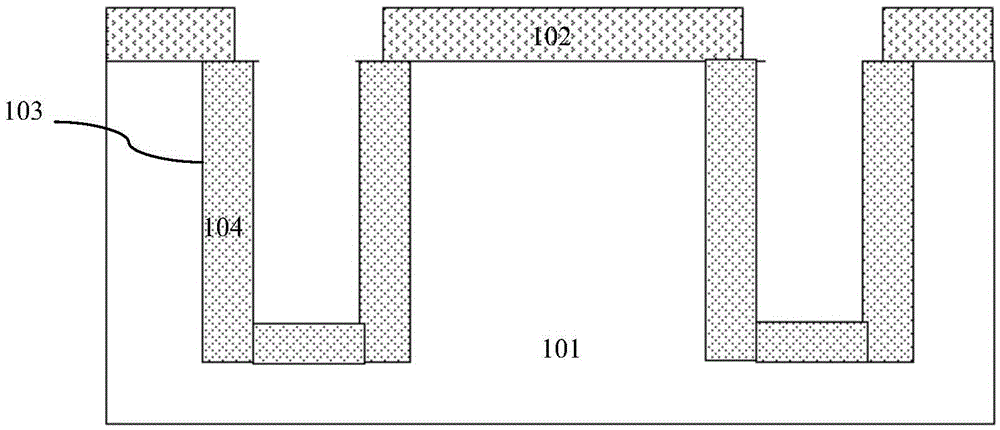

Semiconductor structure forming method

ActiveCN105097657AAvoid undercutInhibit sheddingSemiconductor/solid-state device manufacturingSemiconductor structureDielectric layer

The invention relates to a semiconductor structure. A semiconductor structure forming method comprises the following steps of providing a substrate; forming a carbon-containing dielectric layer on the surface of the substrate; forming a carbon-rich protecting layer on the surface of the carbon-containing dielectric layer, wherein the carbon atom concentration in the carbon-rich protecting layer material is greater than that in the carbon-containing dielectric layer material; forming a graphical hard mask layer on the surface of the carbon-rich protecting layer; and with the graphical hard mask layer as a mask, etching the carbon-rich protecting layer and the carbon-containing dielectric layer to form an opening, wherein the opening bottom makes the substrate surface exposed; and forming a metal layer filling the opening. An undercut phenomenon is prevented. The quality of the formed metal layer is improved. The performance of the semiconductor structure is further optimized.

Owner:SEMICON MFG INT (SHANGHAI) CORP

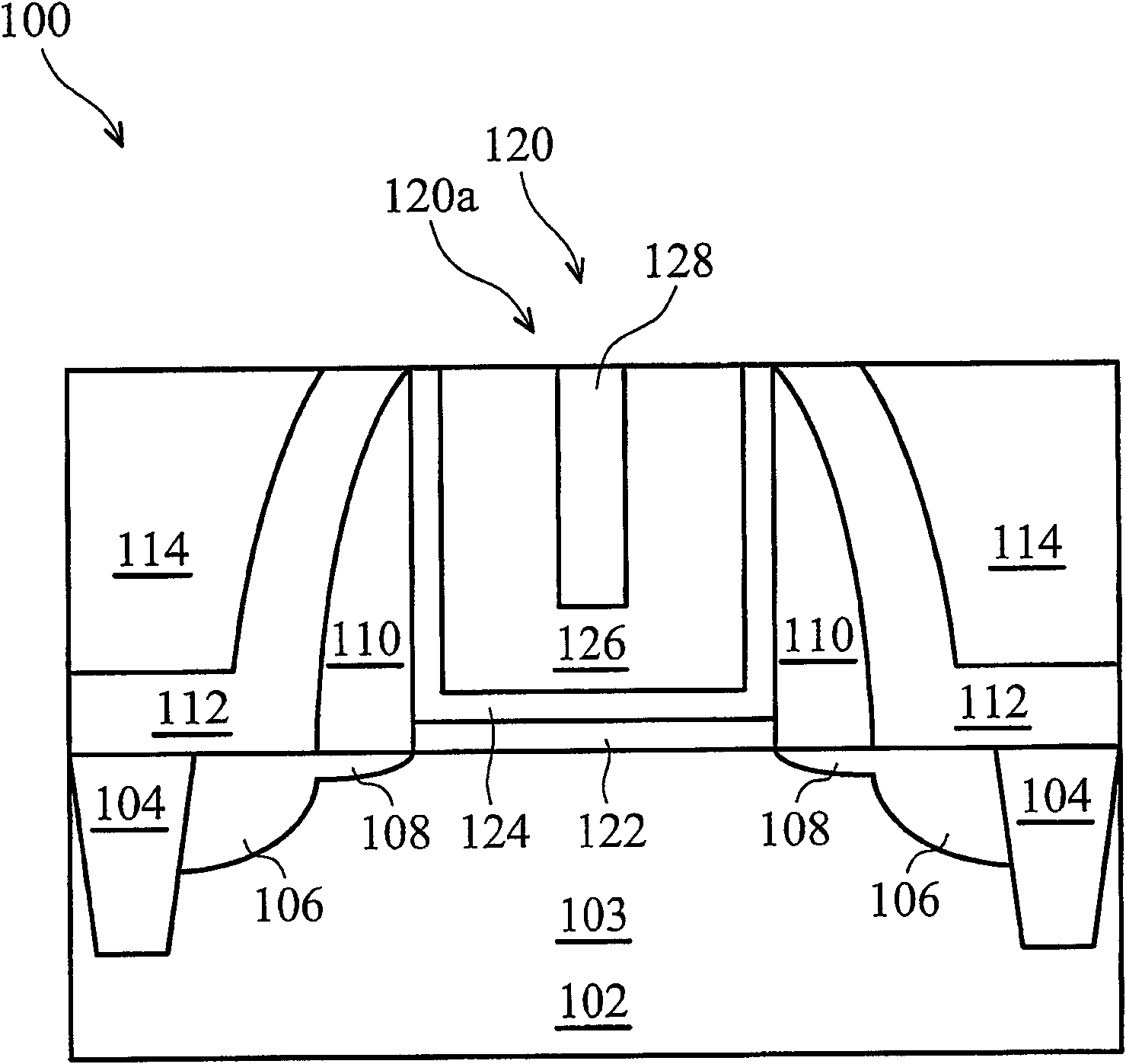

Metal gate structure of a field effect transistor and field effect transistor

InactiveCN102104061ALow Gate ResistanceReduce RC delaySemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceMetallic materials

The invention relates to integrated circuit fabrication, and more particularly to a Field Effect Transistor with a low resistance metal gate electrode. An exemplary structure for a gate electrode for a Field Effect Transistor comprises a lower portion formed of a first metal material having a recess and a first resistance; and an upper portion formed of a second metal material having a protrusion and a second resistance, wherein the protrusion extends into the recess, wherein the second resistance is lower than the first resistance. The metal gate electrode provided in the invention has a low gate resistance value, so can reduce the capacitance-resistance delay of circuit and improve the performance an apparatus.

Owner:TAIWAN SEMICON MFG CO LTD

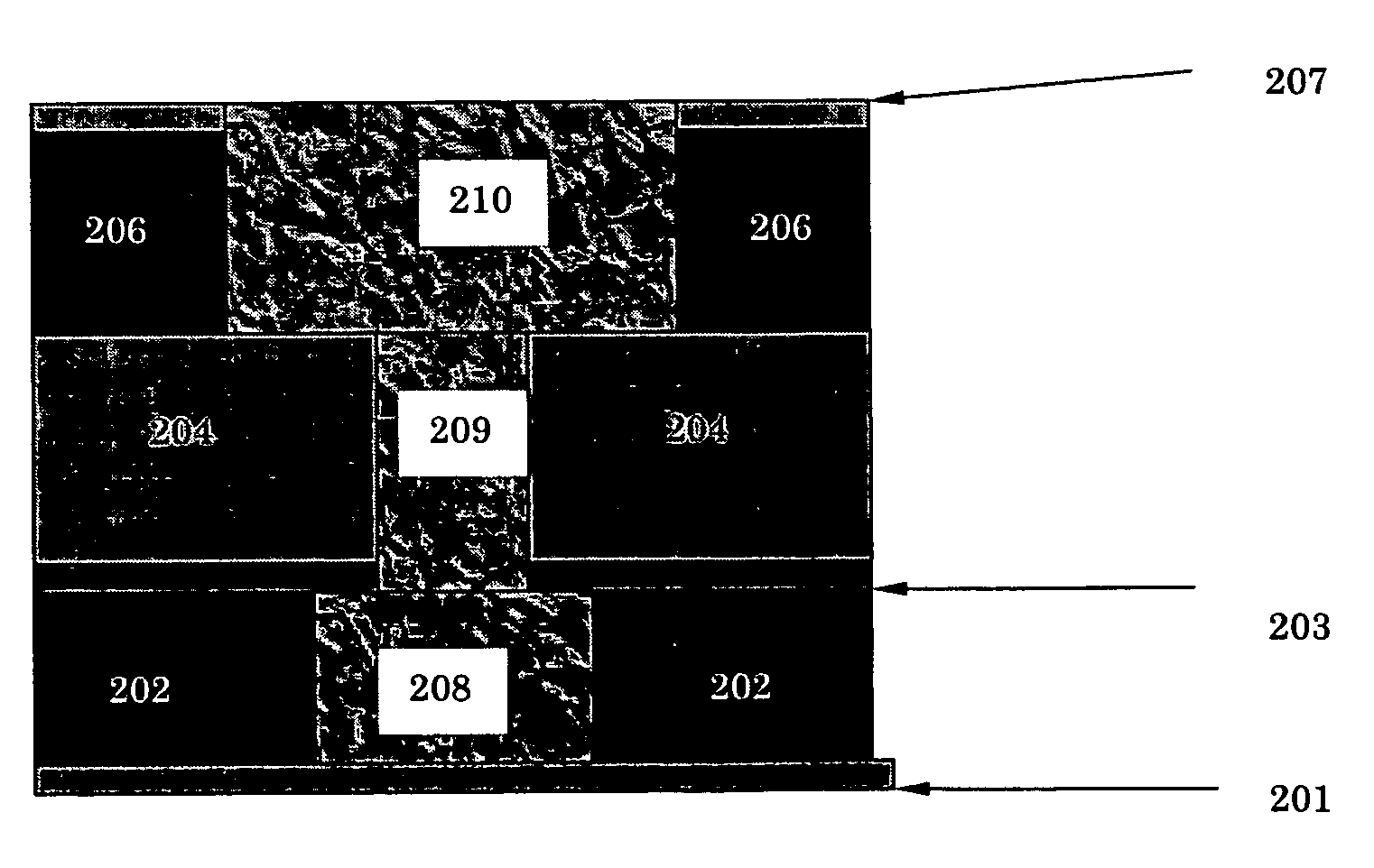

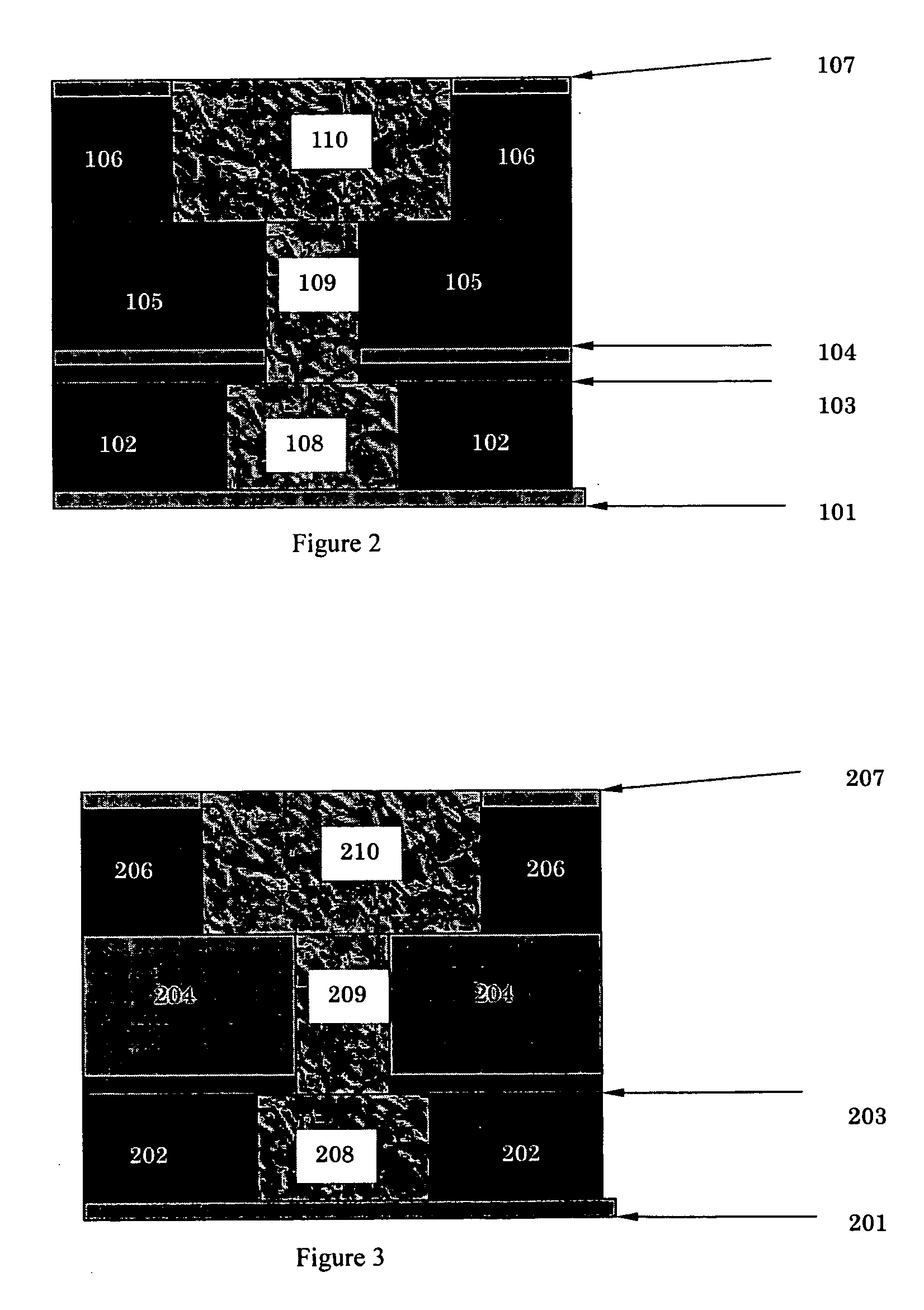

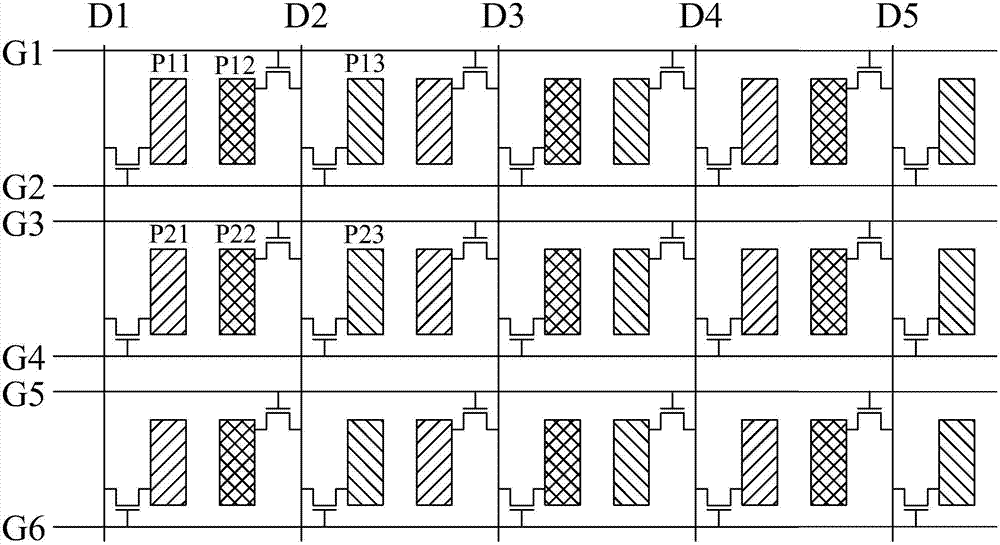

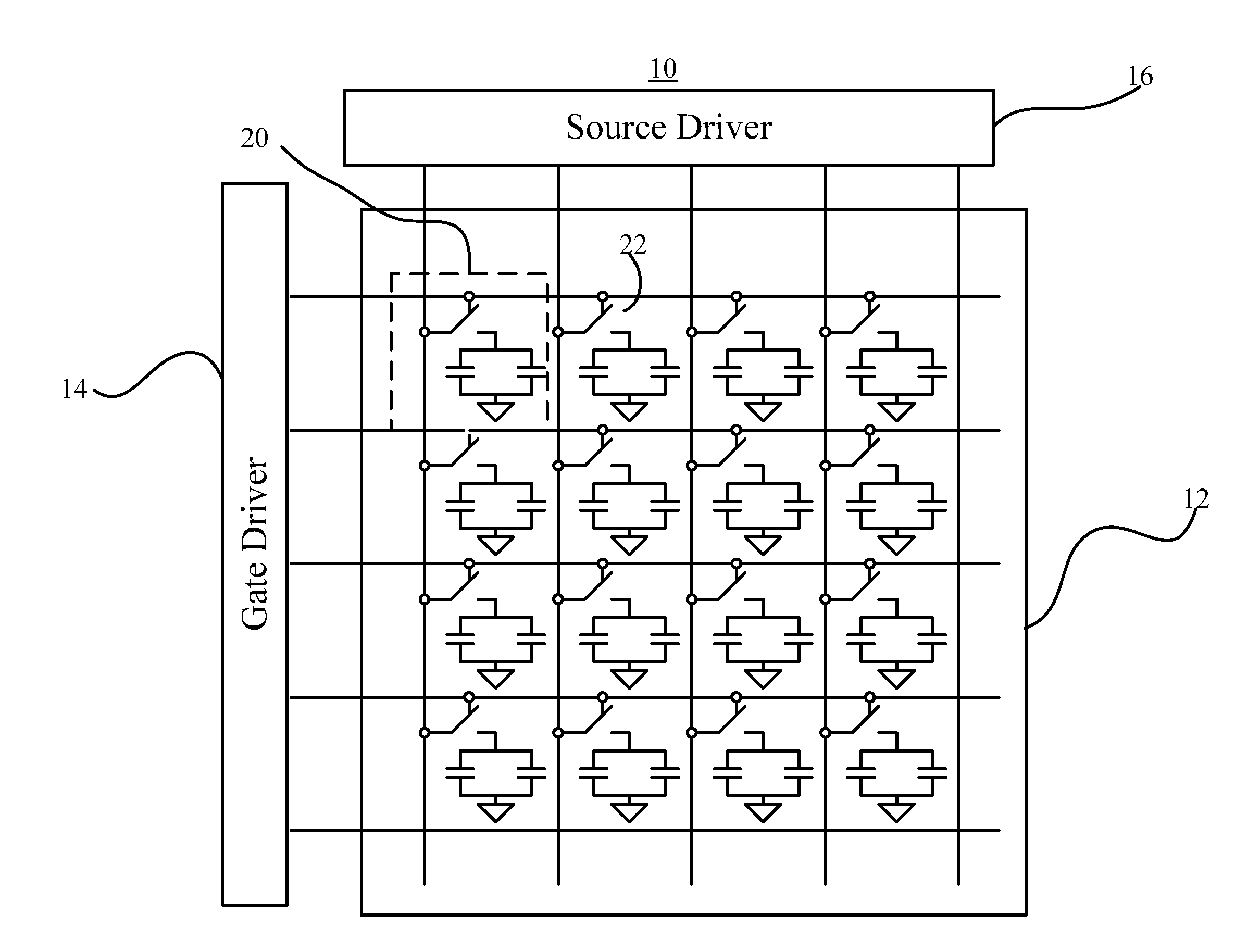

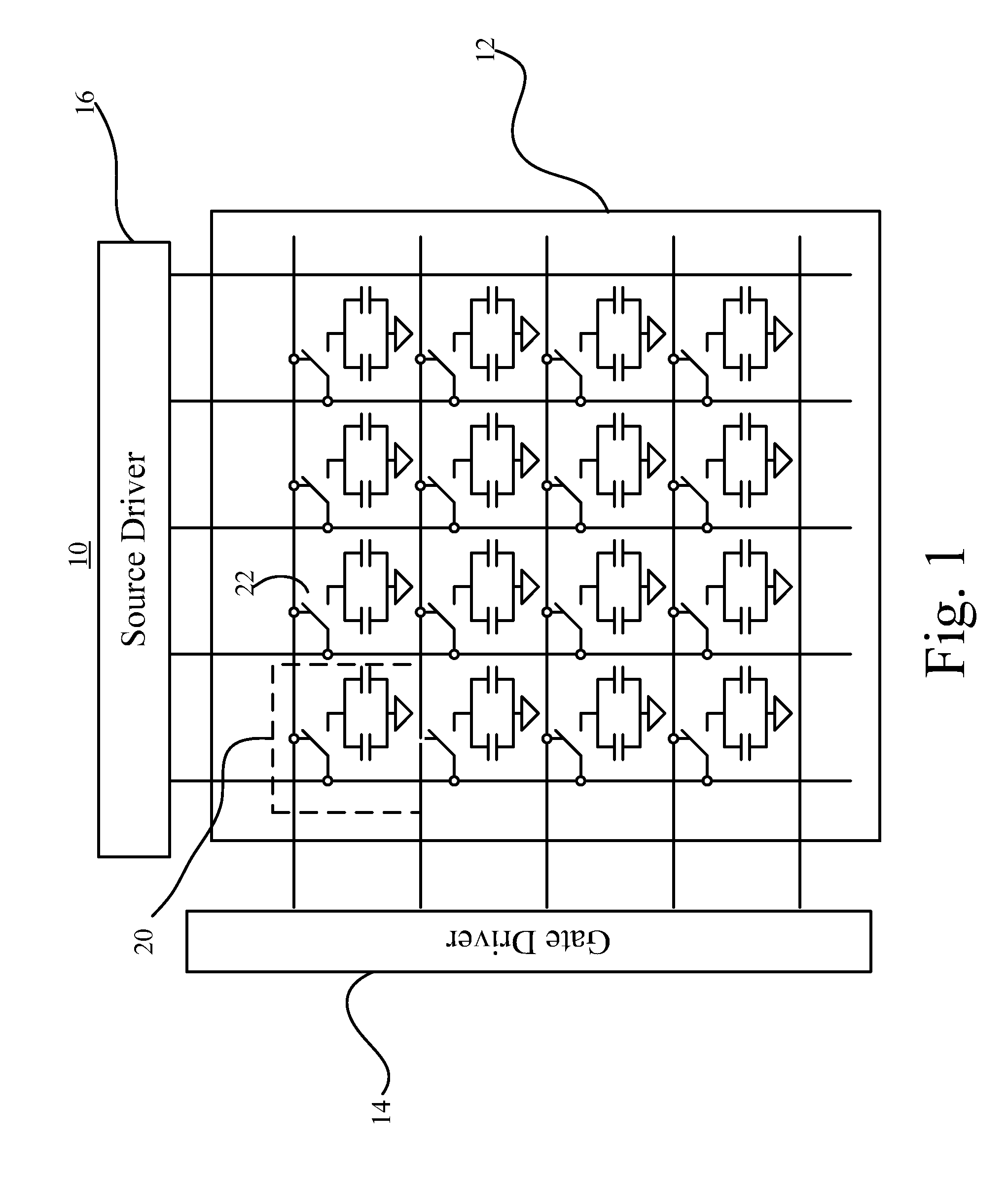

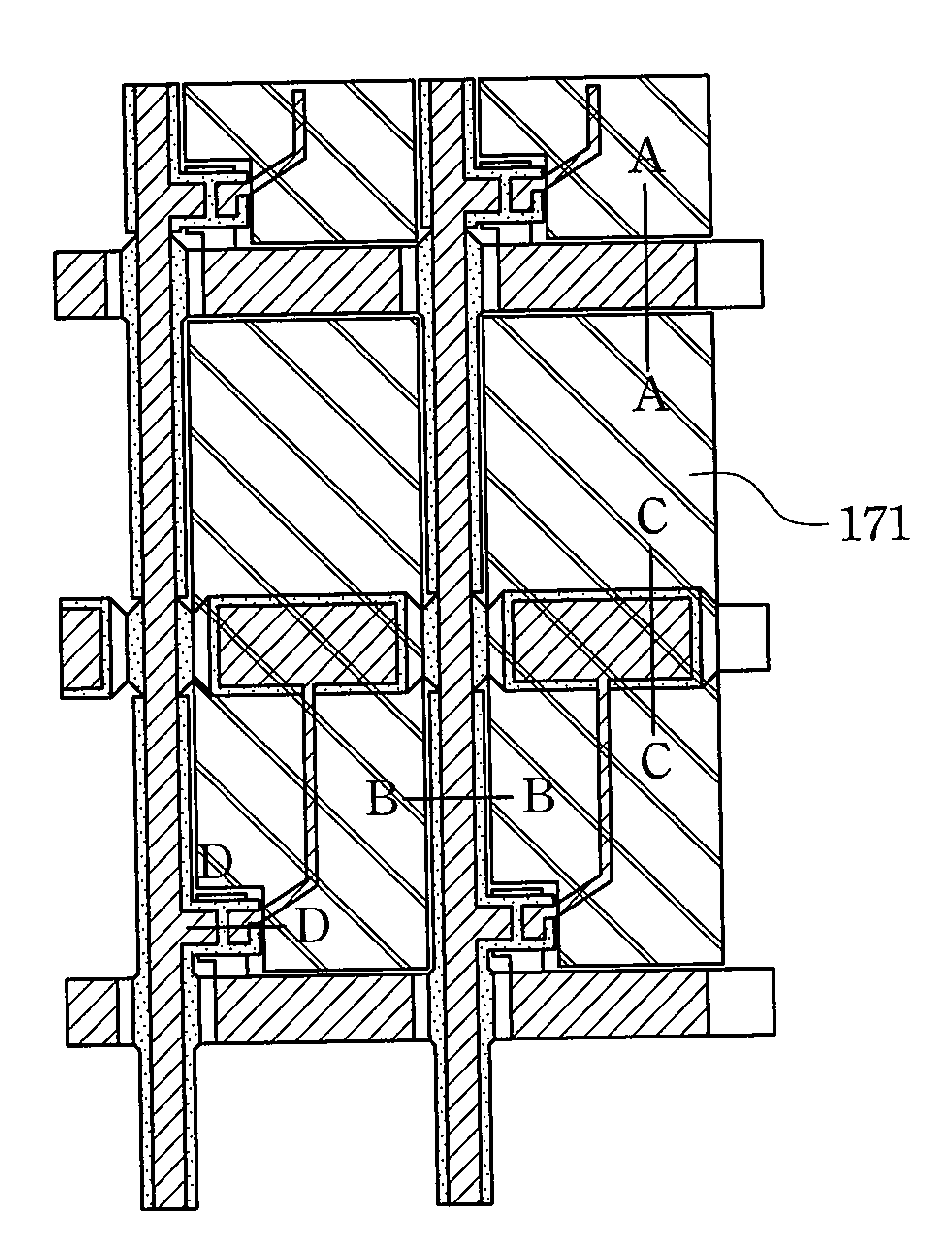

TFT array substrate

InactiveCN104280962AImprove display defectsLower resistanceStatic indicating devicesSolid-state devicesResistance capacitanceDark line

The invention provides a TFT array substrate. The sub pixel arraying manner is changed, the sub pixels, with uneven brightness, of the space are arrayed in a staggered manner in the same frame image display period, and the display defects of vertical bright and dark lines are optimized; the entire resistance of a data line can be reduced, resistance-capacitance delay can be reduced, and wrong charge of the tail end of a scanning line or data line is avoided.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

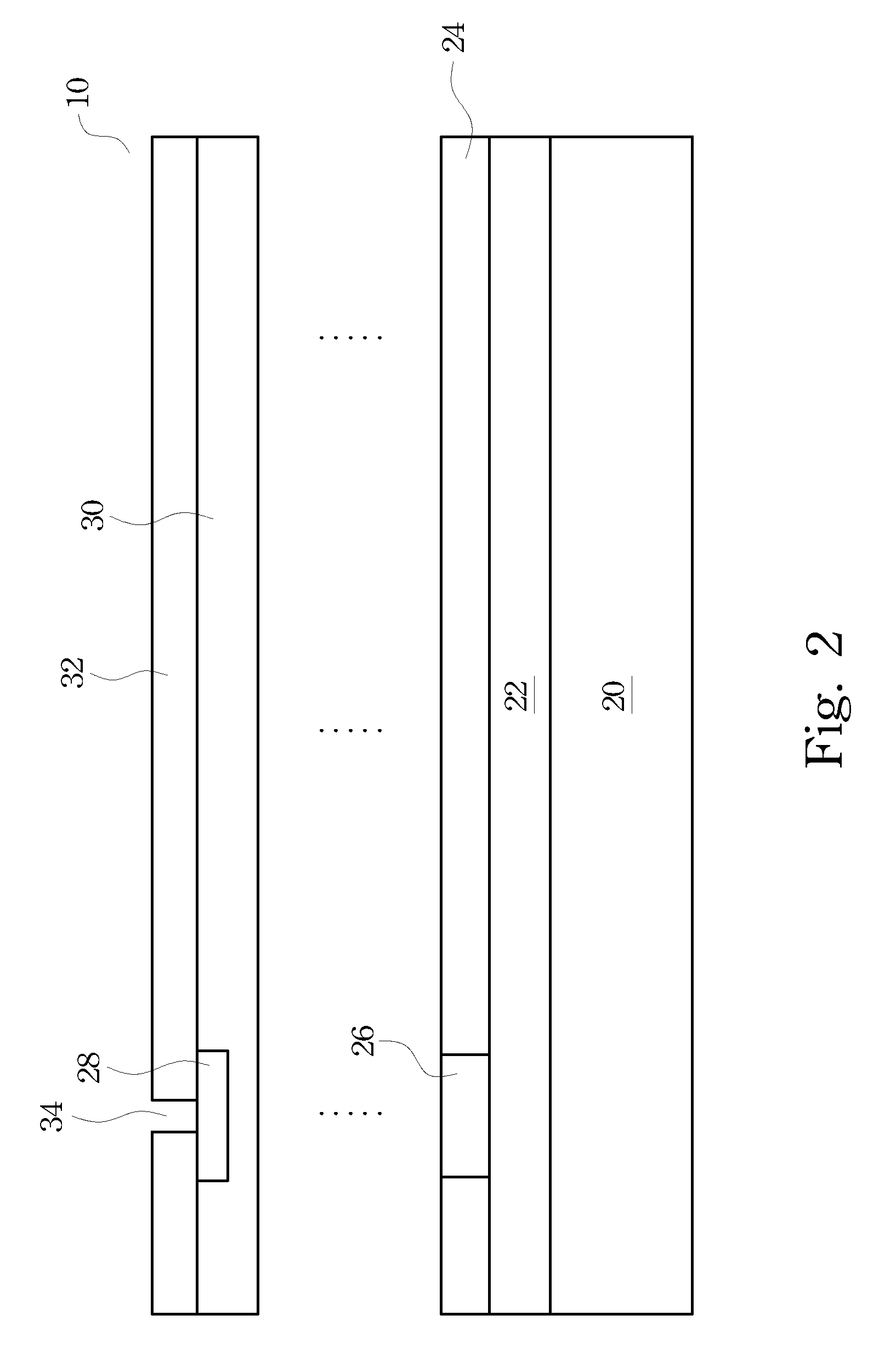

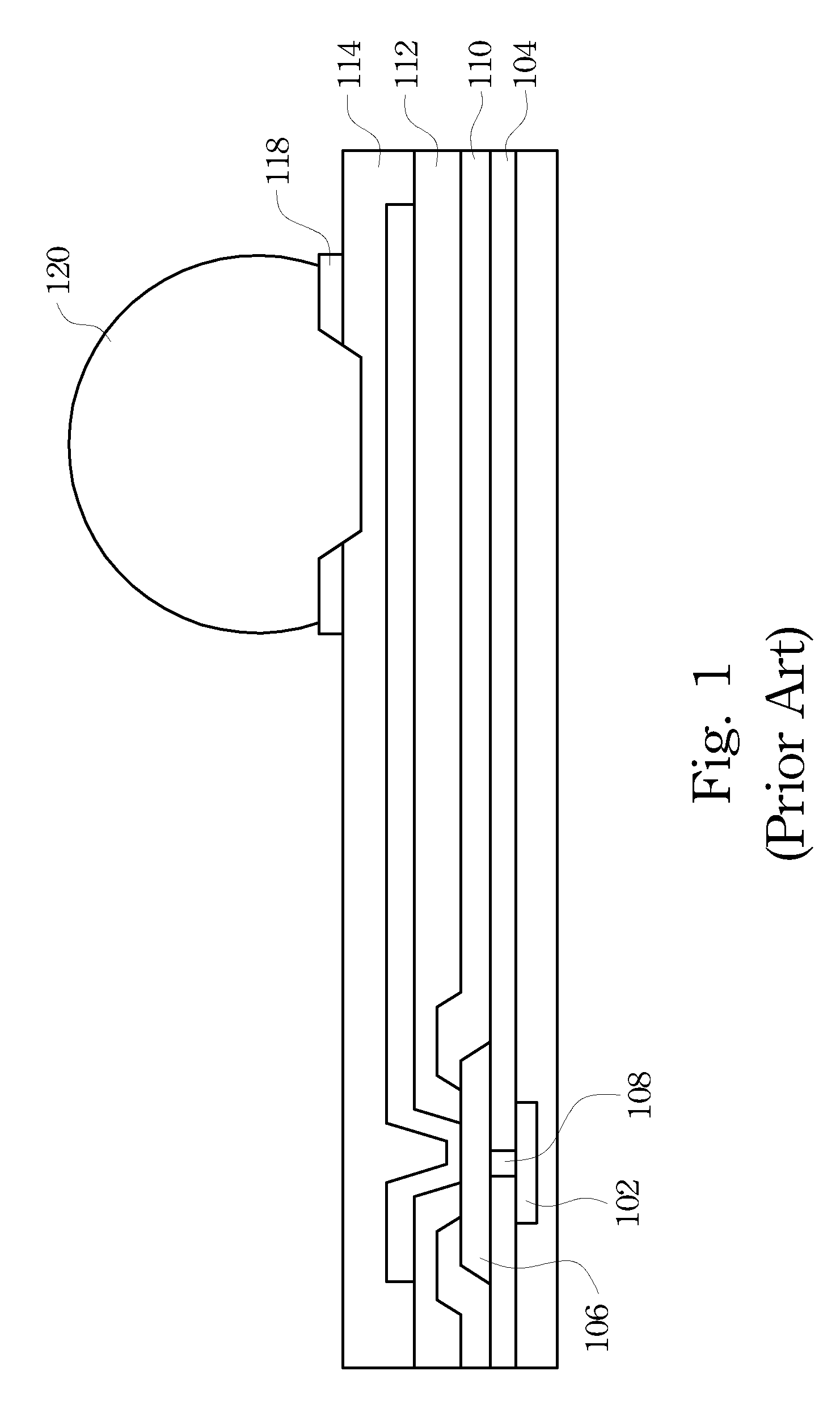

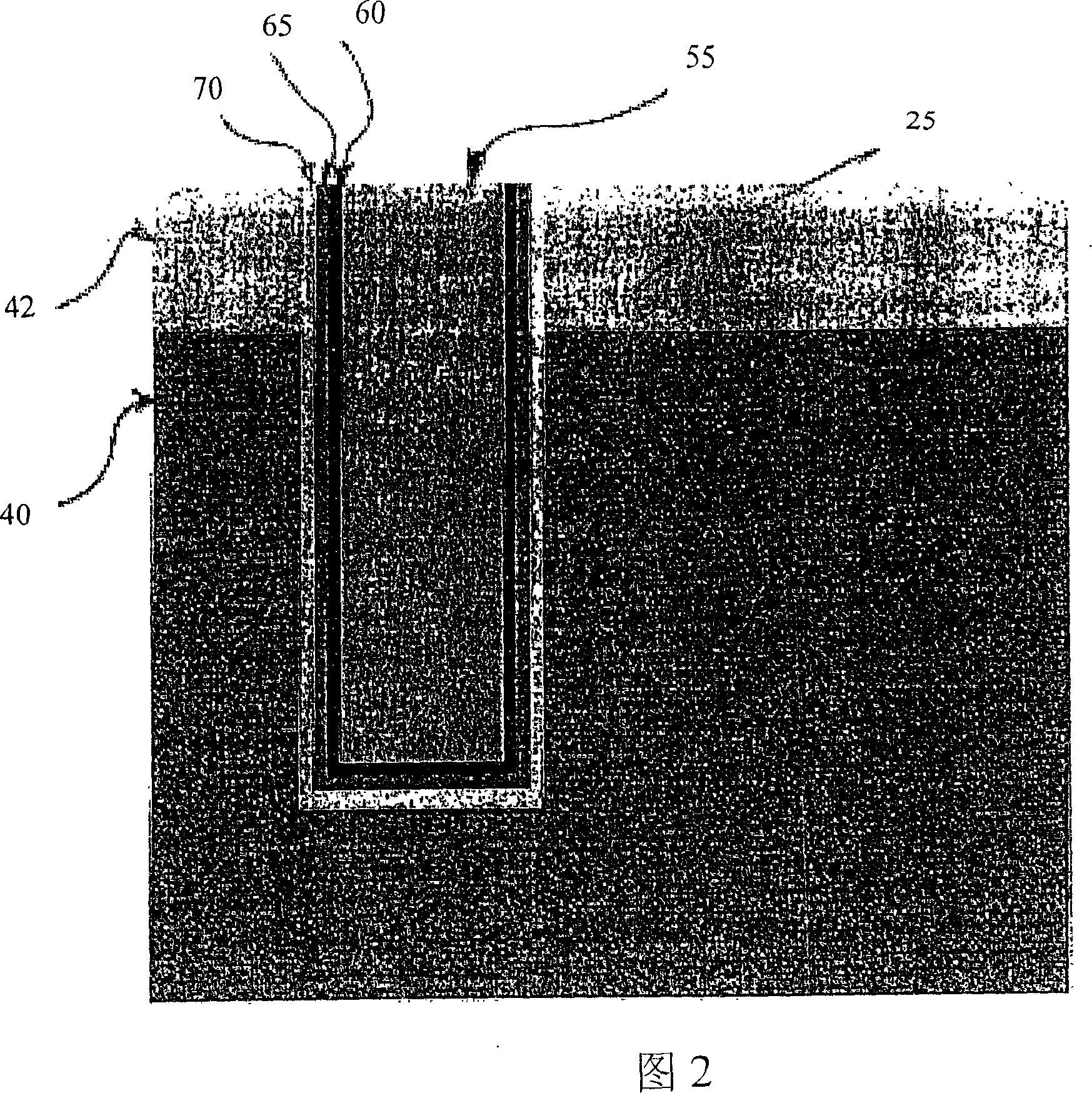

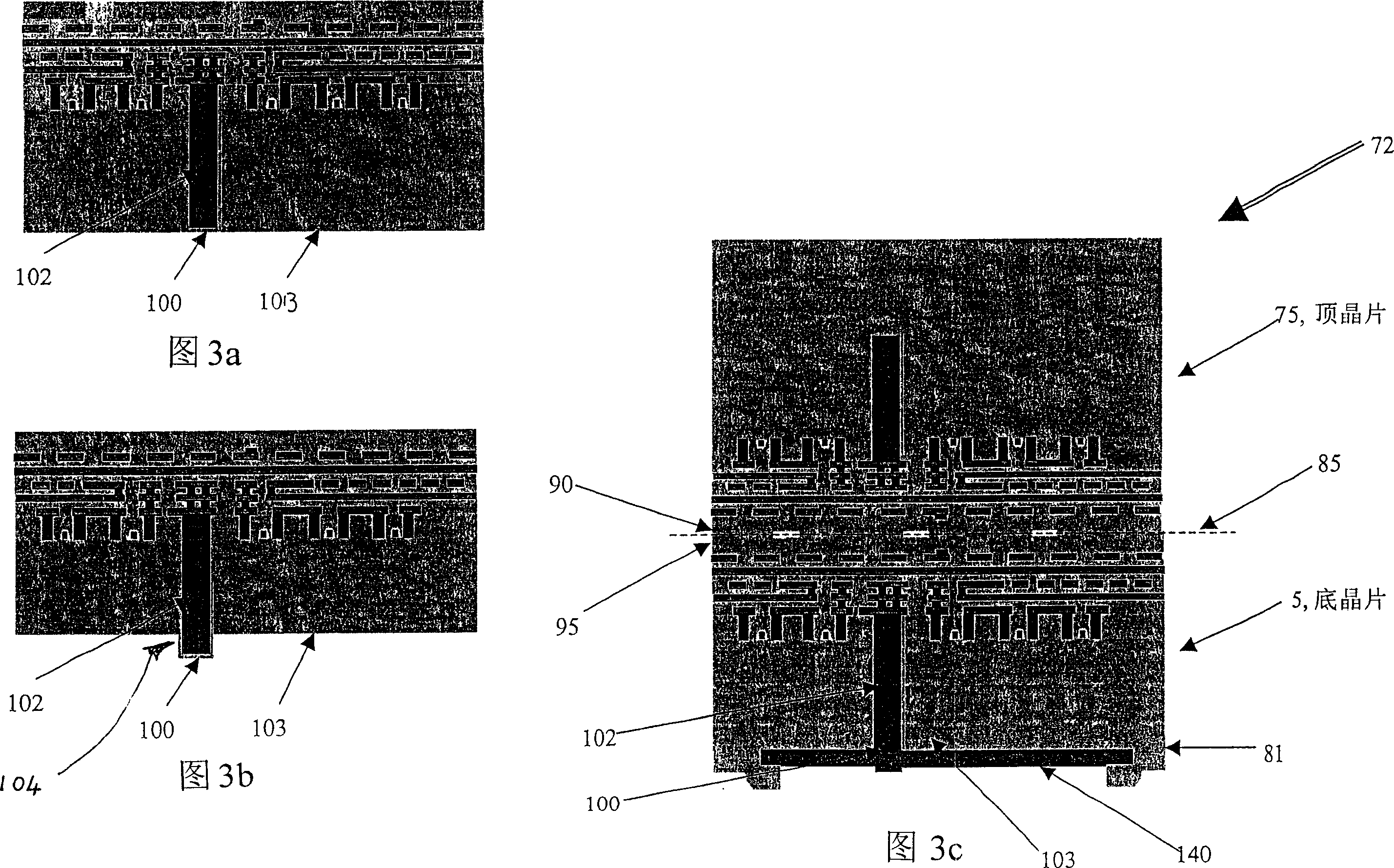

Stacked wafer for 3-D integration

InactiveCN101000880AHigh speedHigh densitySolid-state devicesSemiconductor/solid-state device manufacturingCopperMaterials science

The invention discloses a method for producing a stack wafer device, including the steps: providing a first wafer; forming a plurality of brazing trays on the first surface of the first wafer; forming at least an embedded vertical linker separated from the brazing trays of the first wafer in the first wafer; providing a second wafer; forming a plurality of brazing trays on the first surface of the second wafer, the posithion of which is coincident to the position of the the brazing trays of the first wafer; forming at least an embedded vertical linker separated from the brazing trays of the second wafer in the second wafer; contacting with the first surface of the wafers in order to contact with the brazing trays; supplying the power to the wafer in the predeterminded pressure and at the predetermined temperature until the brazing trays can be bonded, and the first wafer and the second safer are bonded to produce a stack wafer device.

Owner:TEZZARON SEMICON S PTE

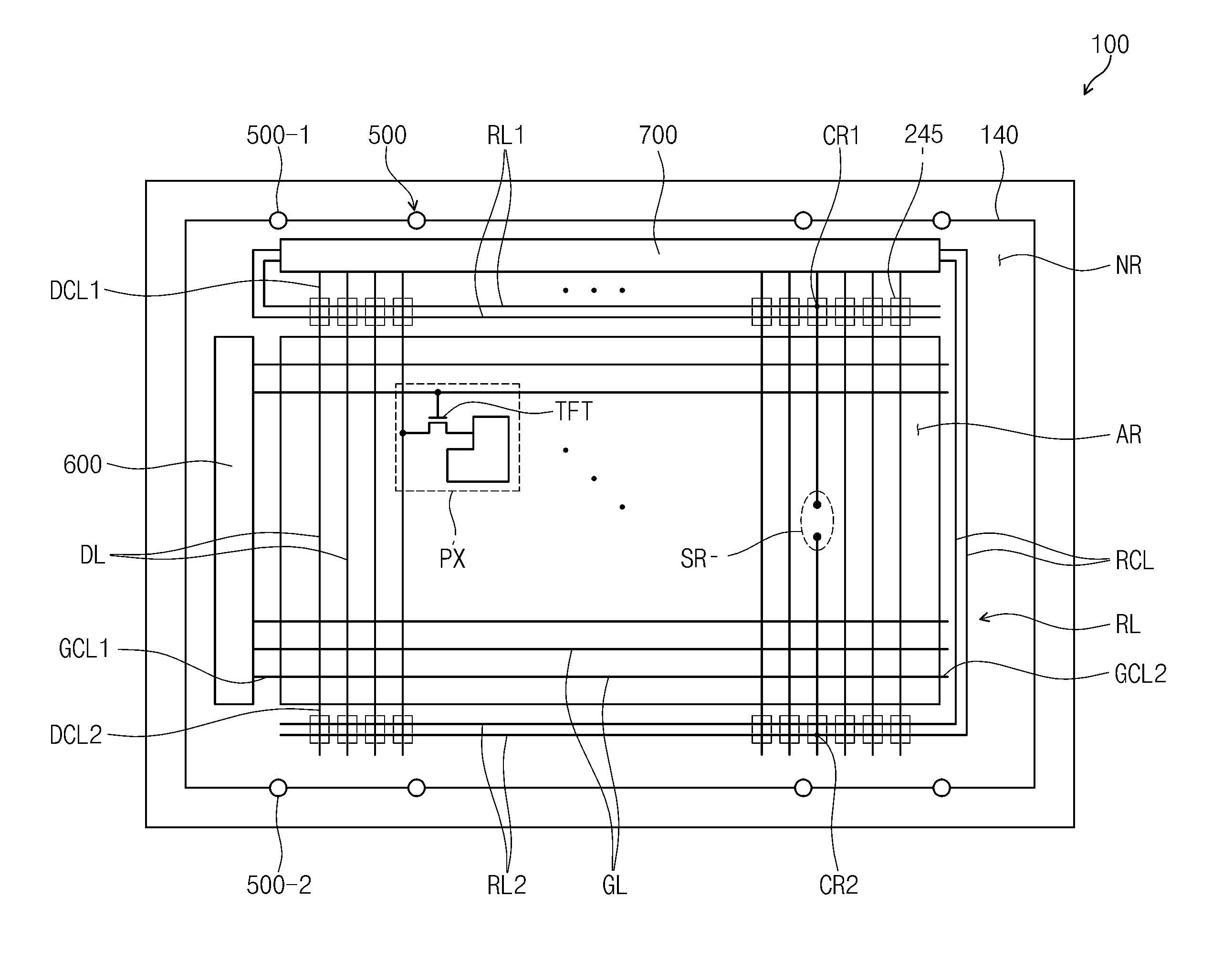

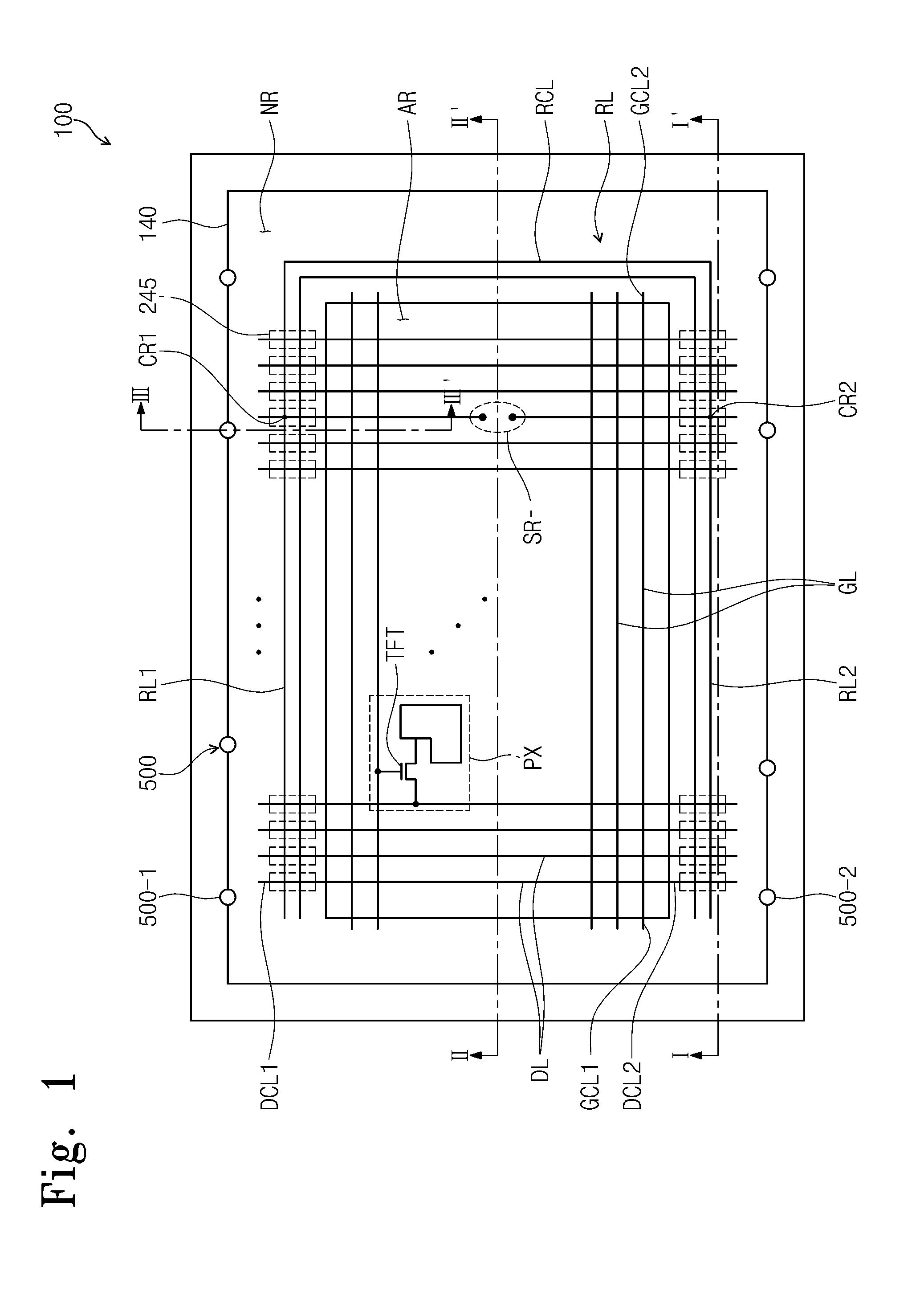

Liquid crystal display panel

A display panel includes an array substrate including a plurality of connection lines extending from a plurality of signal lines and at least one repair line crossing the connection lines. An opposite substrate including a common electrode formed on a surface of the second substrate that is closest to the array substrate is coupled to the array substrate. The common electrode includes a plurality of openings that are positioned to align with a plurality of intersections between the connection lines and the repair line, thereby preventing an electrical coupling between the signal line and the common electrode.

Owner:SAMSUNG DISPLAY CO LTD

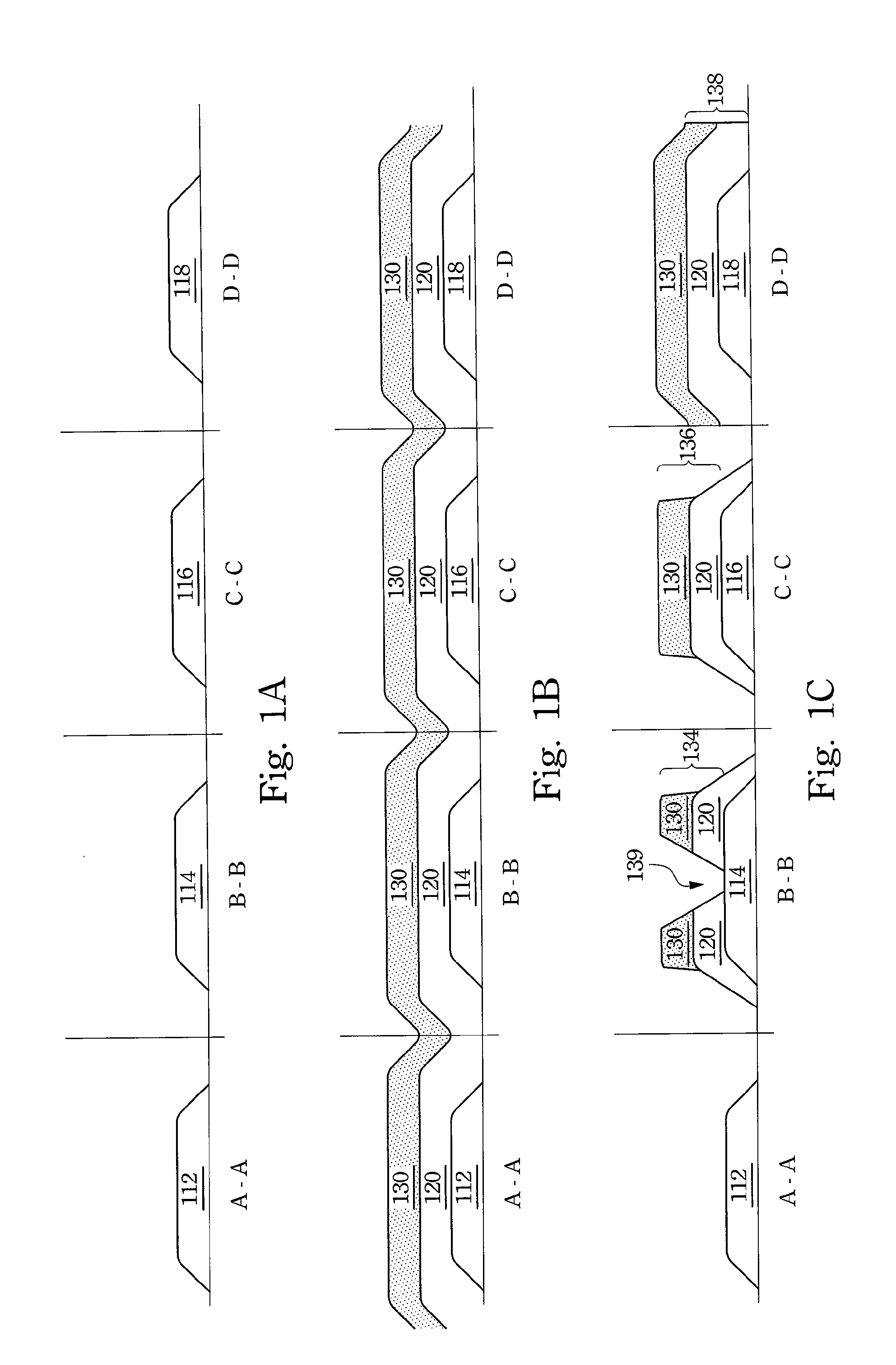

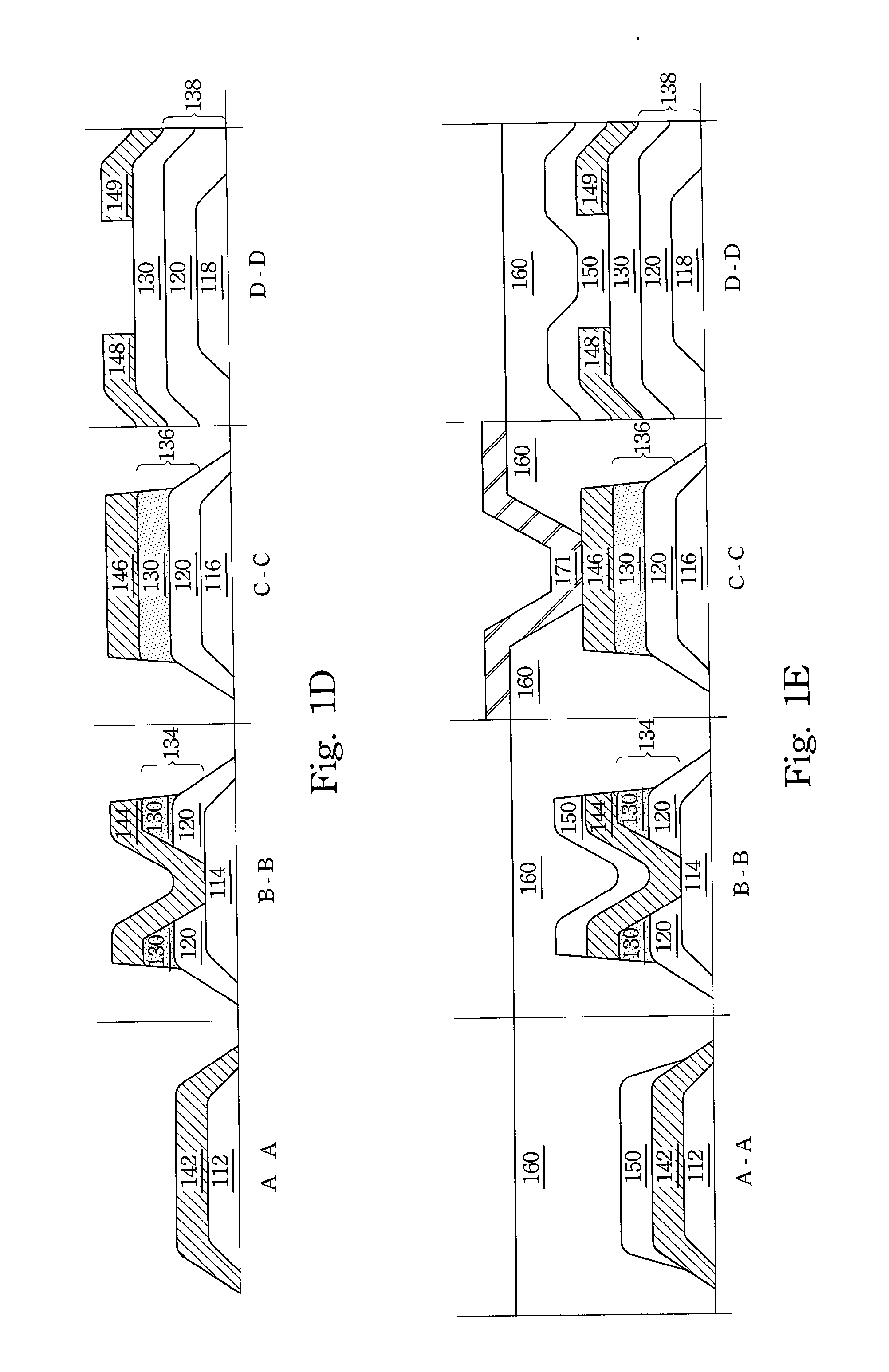

Liquid Crystal Display Array Substrate and its Manufacturing Method

ActiveUS20070258035A1Lower on-resistanceIncrease the cross-sectional areaNon-linear opticsLiquid-crystal displayScan line

A liquid crystal display (LCD) array substrate and its manufacturing method are provided. Scan lines and data lines of the LCD array substrate are composed of two conductive layers to decrease their RC delay. Moreover, the dielectric layer and even the planarization layer are removed from pixel areas defined by the scan lines and the data lines to increase the light penetration percentage.

Owner:AU OPTRONICS CORP

Touch sensor integrated display device with multiple planarization layers

ActiveUS20160291746A1Increase capacitanceReduce RC delayInput/output processes for data processingTouch SensesDisplay device

A touch sensor integrated display device includes a plurality of common electrode blocks serving as touch-sensing regions and / or touch-driving regions. Conductive lines connected to the common electrode blocks are placed under the common electrode blocks and the pixel electrodes of the pixels, and they are routed across the active area, directly toward an inactive area where drive-integrated circuits are located. The conductive lines are positioned under one or more planarization layers, and are connected to the corresponding common electrode blocks via one or more contact holes.

Owner:LG DISPLAY CO LTD

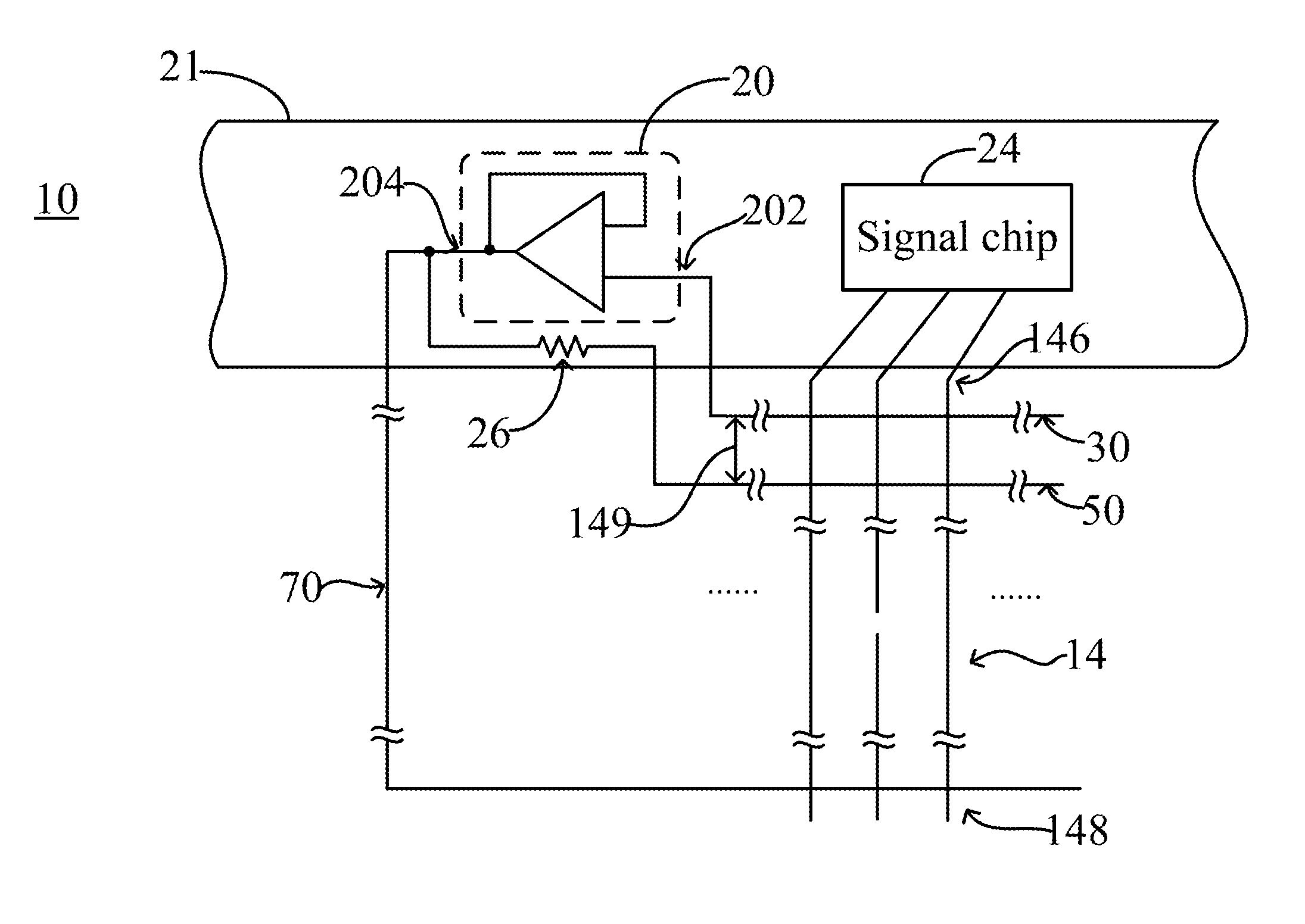

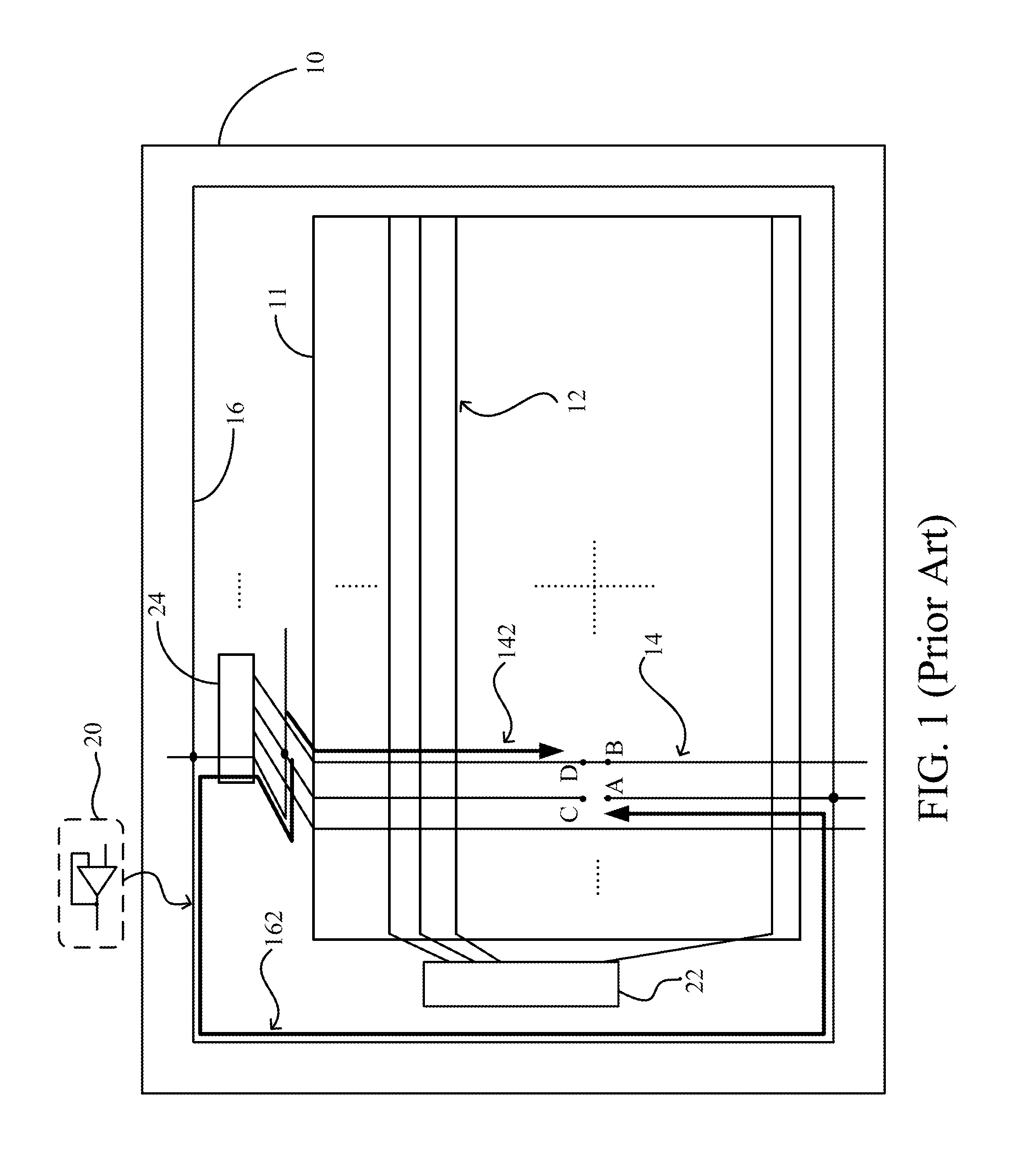

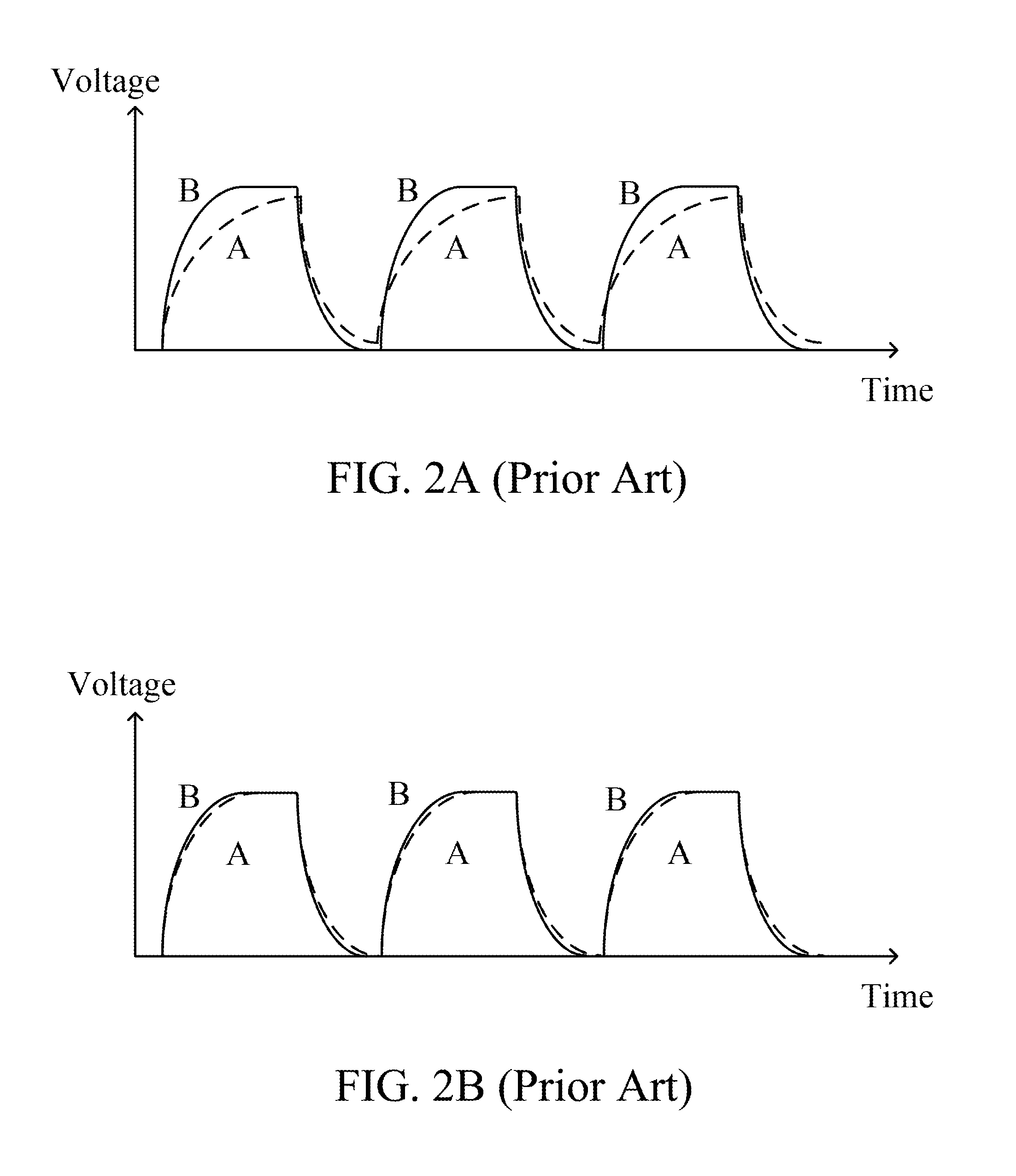

Rescue circuit of display panel and rescue method thereof

ActiveUS20120147311A1Reduce RC delayStatic indicating devicesNon-linear opticsElectrical resistance and conductanceAudio power amplifier

The present invention discloses a rescue circuit of display panel and a rescue method thereof. The rescue circuit includes an amplifier, a first conductive line, a second conductive line, and a third conductive line. The amplifier has an input end and an output end. The first conductive line and the second conductive line intersect and are isolated from signal input terminals of the plurality of signal lines. The first conductive line is electrically connected to the input end and the second conductive line is electrically connected through an electrical resistor to the output end. The third conductive line intersects and is isolated from signal distal ends of the signal lines and is electrically connected to the output end. The rescue method includes performing a welding operation and performing a cutting operation. With such a rescue, a broken signal line may effectively overcome the problem of weak line with the electrical resistor connected to the second conductive line.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

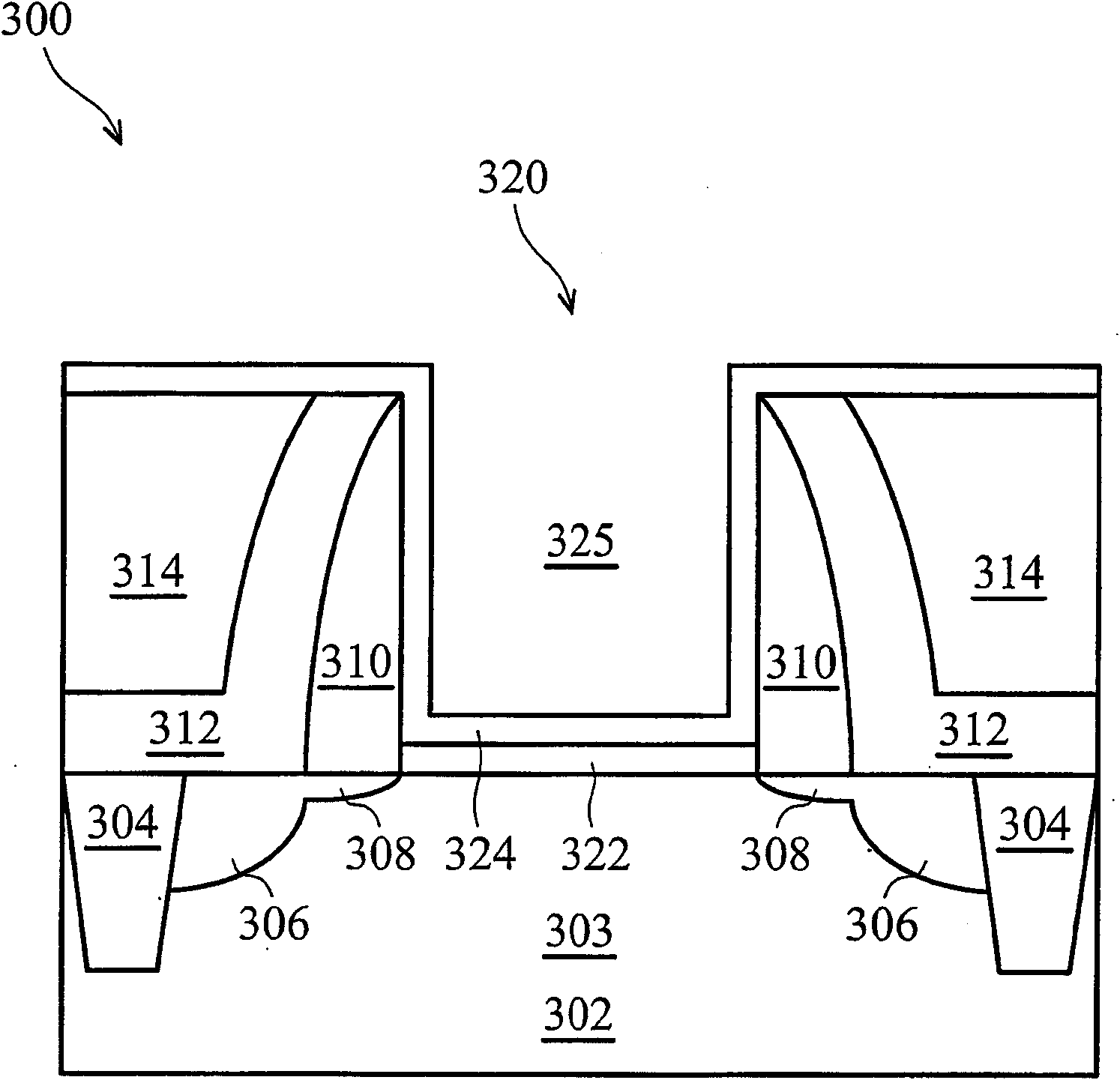

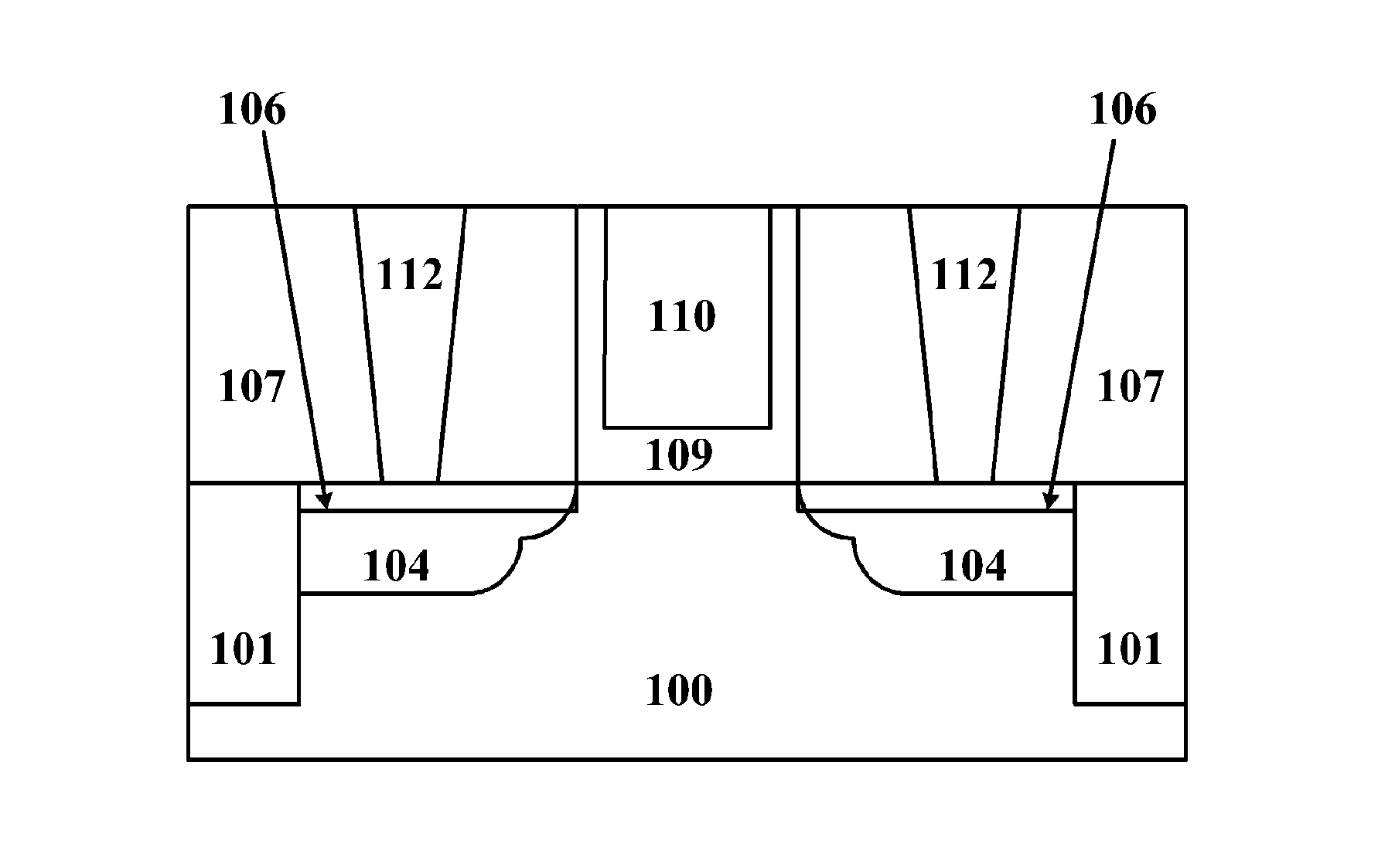

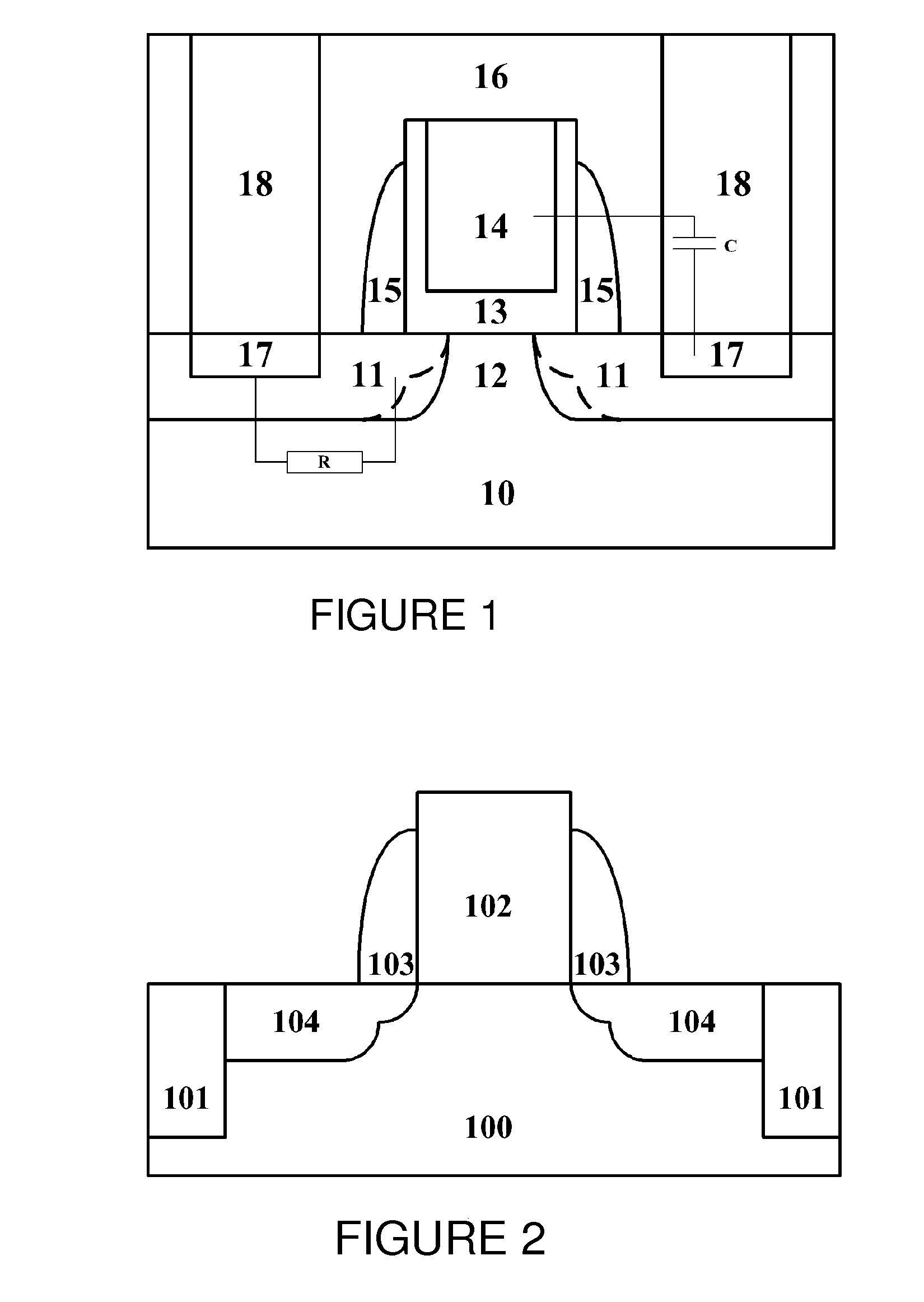

Semiconductor device and manufacturing method thereof

InactiveUS20120267706A1Reduced series resistanceReduce RC delaySolid-state devicesSemiconductor/solid-state device manufacturingMOSFETCapacitance

The invention discloses a novel MOSFET device and its implementation method, the device comprising: a substrate; a gate stack structure, on either side of which is eliminated a conventional isolation spacer; source / drain regions located in the substrate on opposite sides of the gate stack structure; epitaxially grown metal silicide located on the source / drain regions; characterized in that, the epitaxially grown metal silicide is in direct contact with a channel region controlled by the gate stack structure, thereby eliminating the high resistance region below the conventional isolation spacer. At the same time, the epitaxially grown metal silicide can withstand a second high-temperature annealing used for improving the performance of a high-k gate dielectric material, which further improves the performance of the device. The MOSFET according to the invention reduces the parasitic resistance and capacitance greatly and thereby decreases the RC delay, thus improving the switching performance of the MOSFET device significantly.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

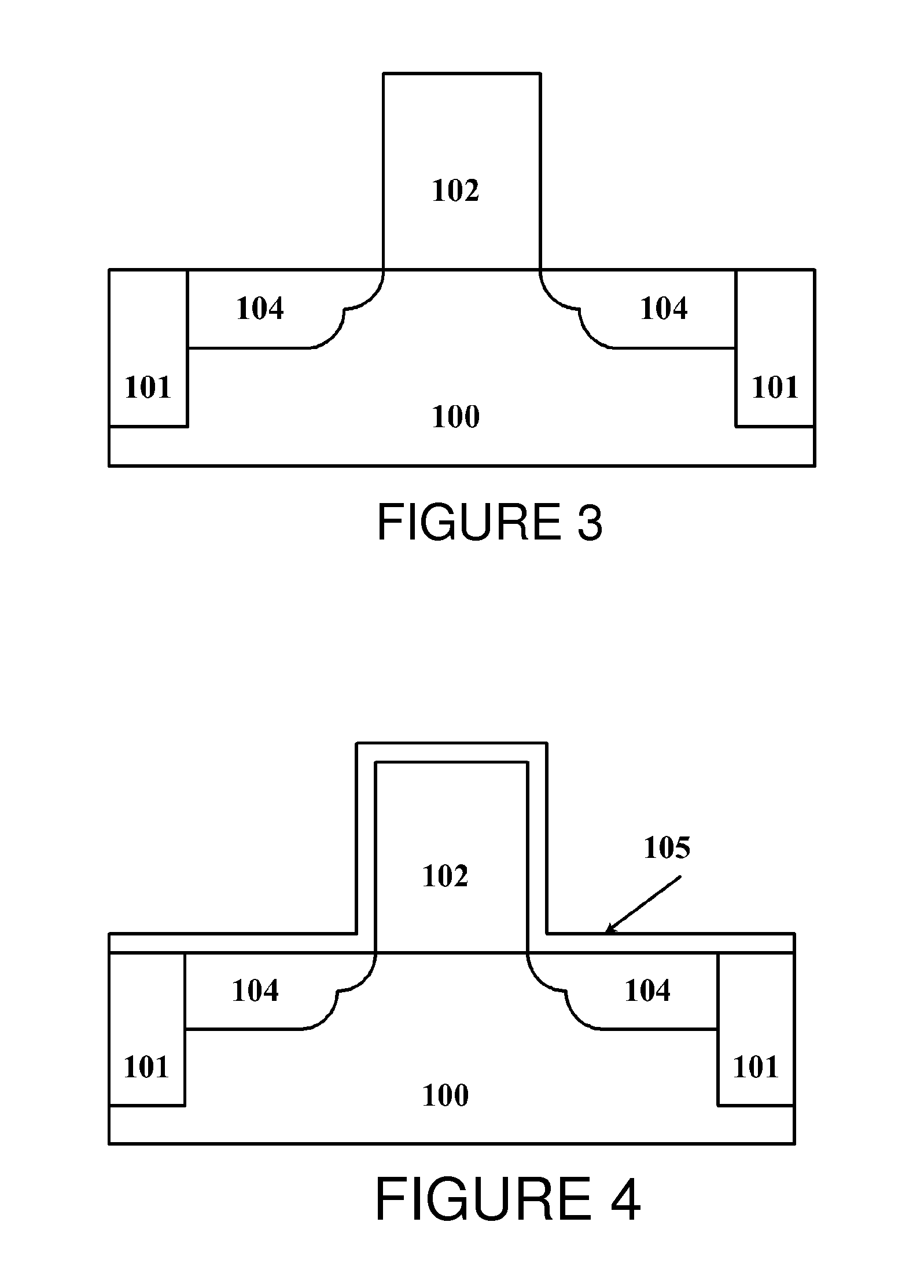

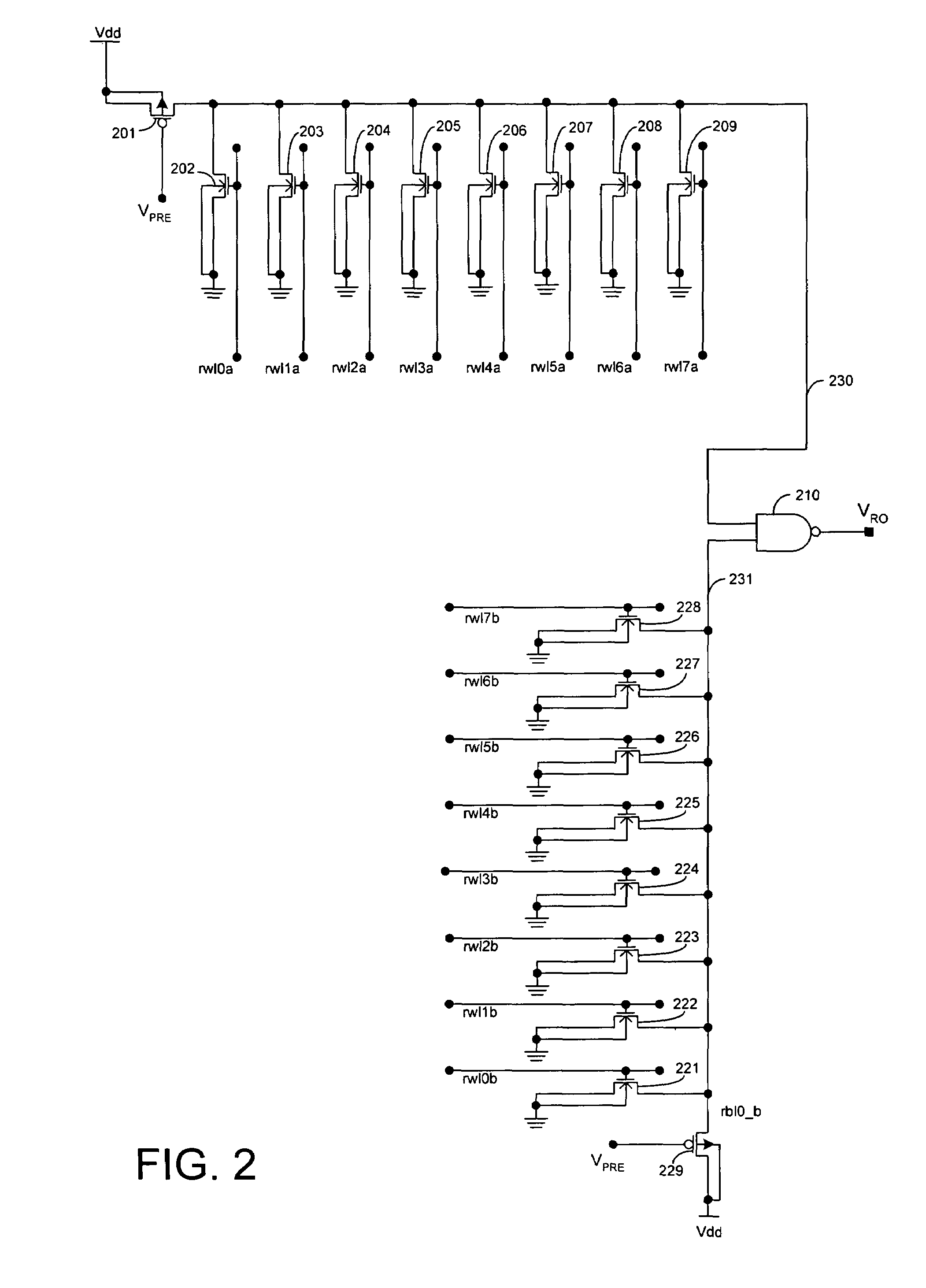

High speed data access memory arrays

Techniques for reading data from memory cells in memory arrays are provided. Local read bit lines are coupled to logic gates such as NAND gates. The input terminals of each logic gate are coupled to receive signals from two of the local read bit lines. The output of the logic gate changes state when a signal on one of the local read bit lines changes state. The signal from the logic gates are transmitted to global bit lines. Memory arrays can have multiple global bit lines to reduce delays caused by resistance and capacitance on the wire. Repeater circuits can propagate a signal from one global bit line to another global bit line.

Owner:MEADLOCK JAMES W MEAD

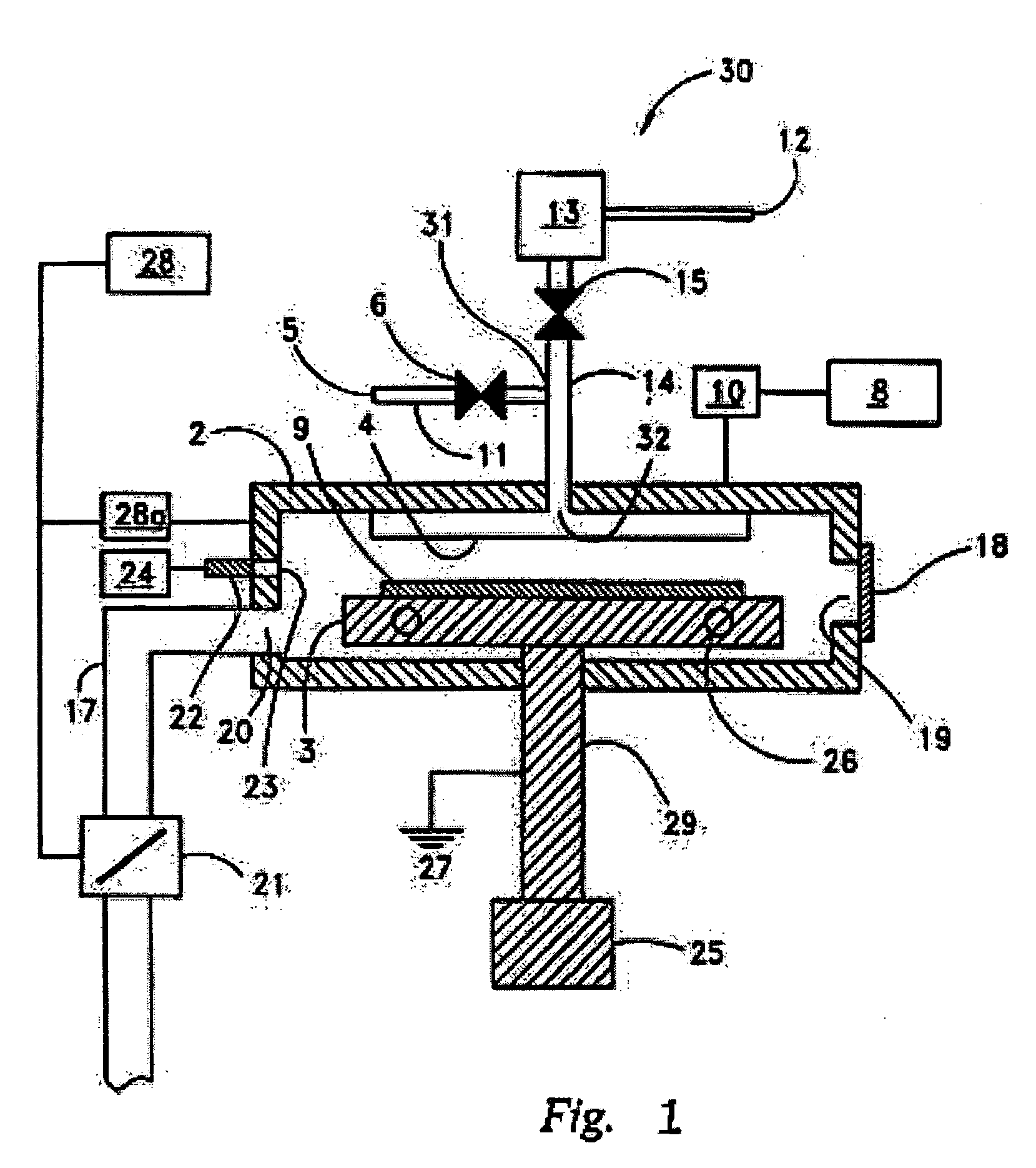

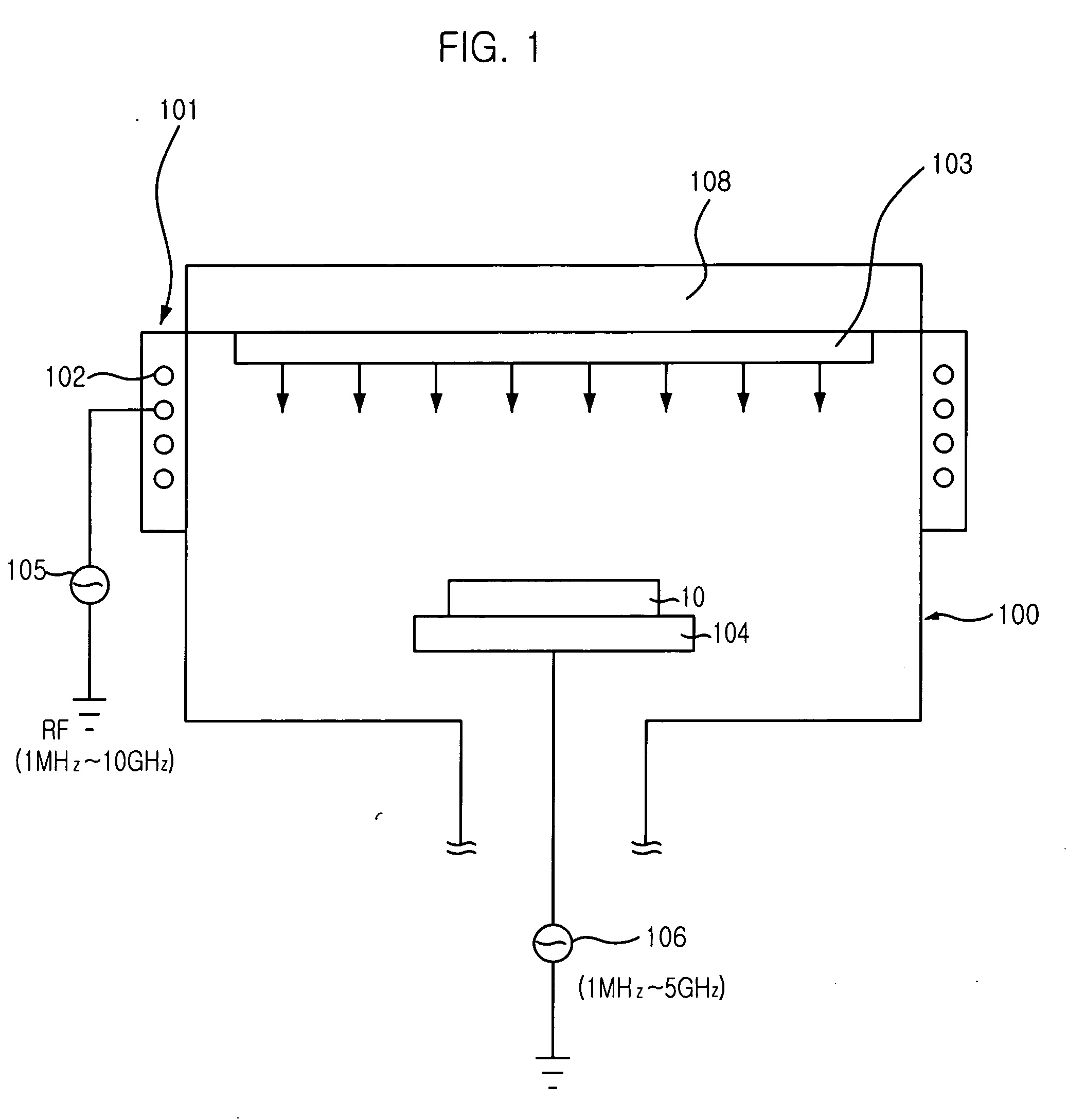

Method for removing photoresist layer and method for forming metal line in semiconductor device using the same

ActiveUS20060128151A1Improve device characteristicsReduce oxidation rateDecorative surface effectsPhotomechanical apparatusInsulation layerInter layer

Disclosed are a method for removing a photoresist layer and a method for forming a metal line using the same. The method for removing a photoresist pattern, including the steps of: forming a bottom layer on a substrate by using the photoresist pattern as a mask; and removing the photoresist pattern with use of a high density plasma (HDP) apparatus. The method for forming a metal line, including the steps of: preparing a semi-finished substrate including an inter-layer insulation layer; forming a photoresist pattern on the inter-layer insulation layer; forming an opening by etching the inter-layer insulation layer with use of the photoresist pattern as an etch mask; removing the photoresist pattern by using a high density plasma (HDP) apparatus; and forming the metal line by filling the opening with a predetermined material.

Owner:KEY FOUNDRY CO LTD

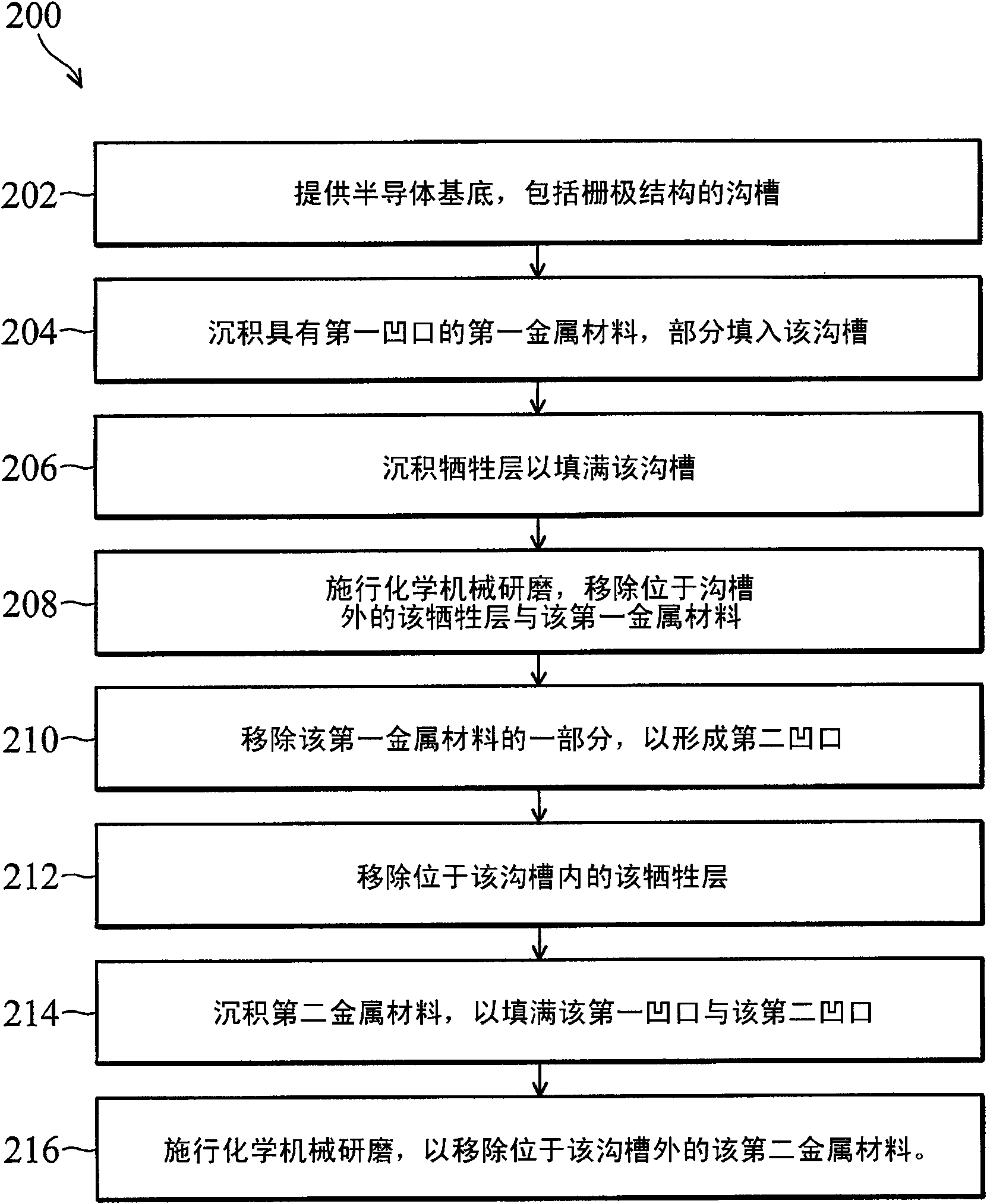

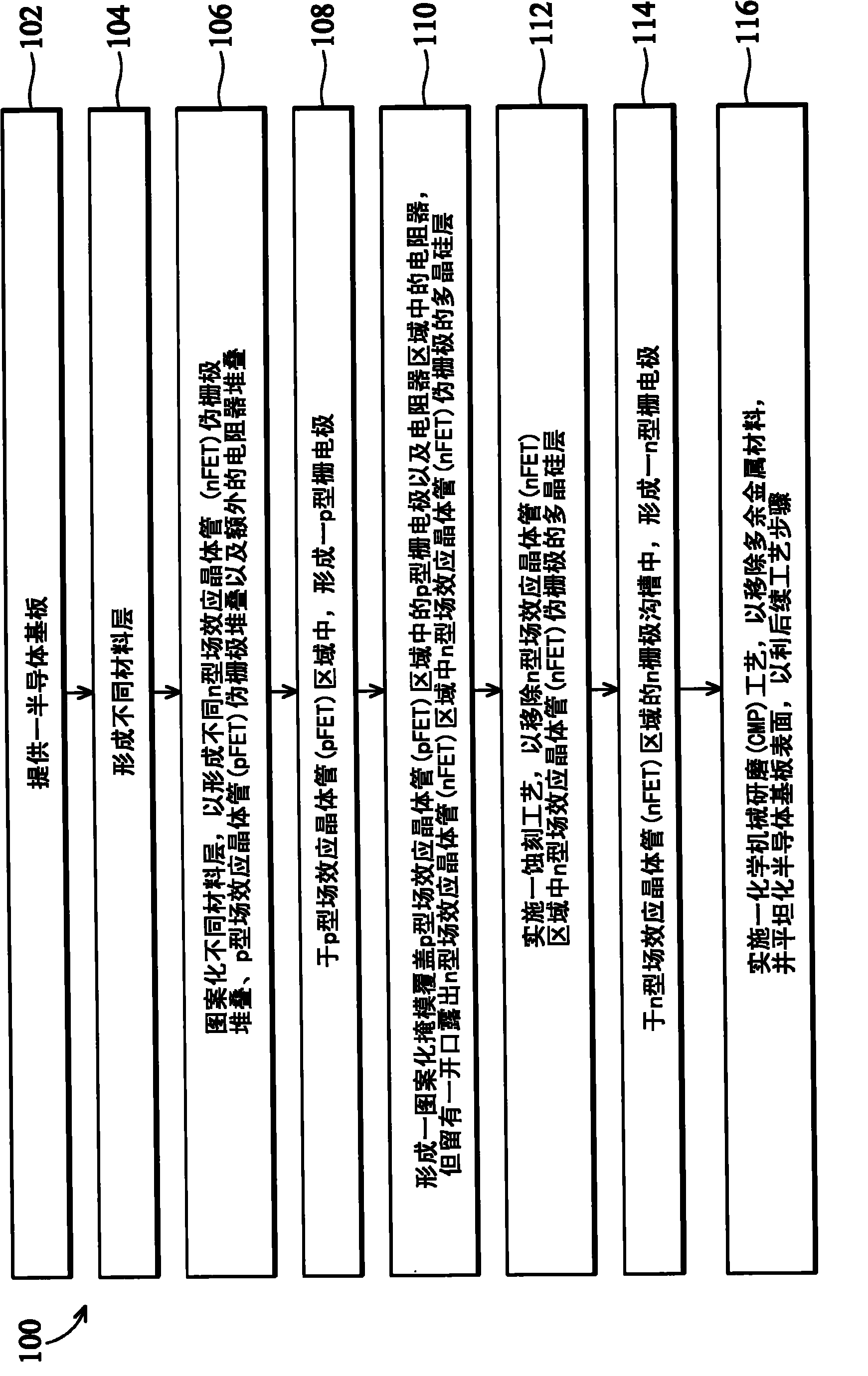

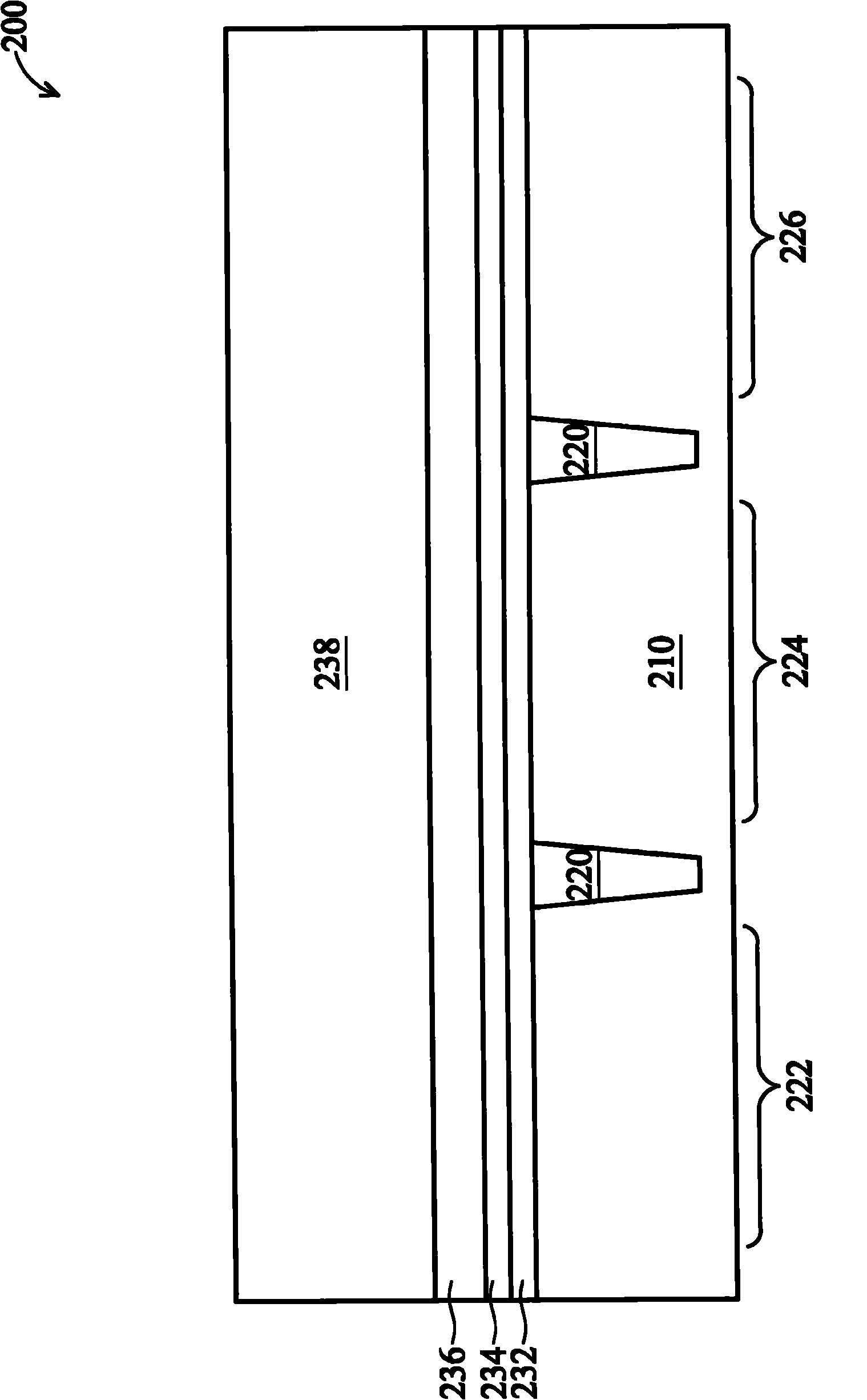

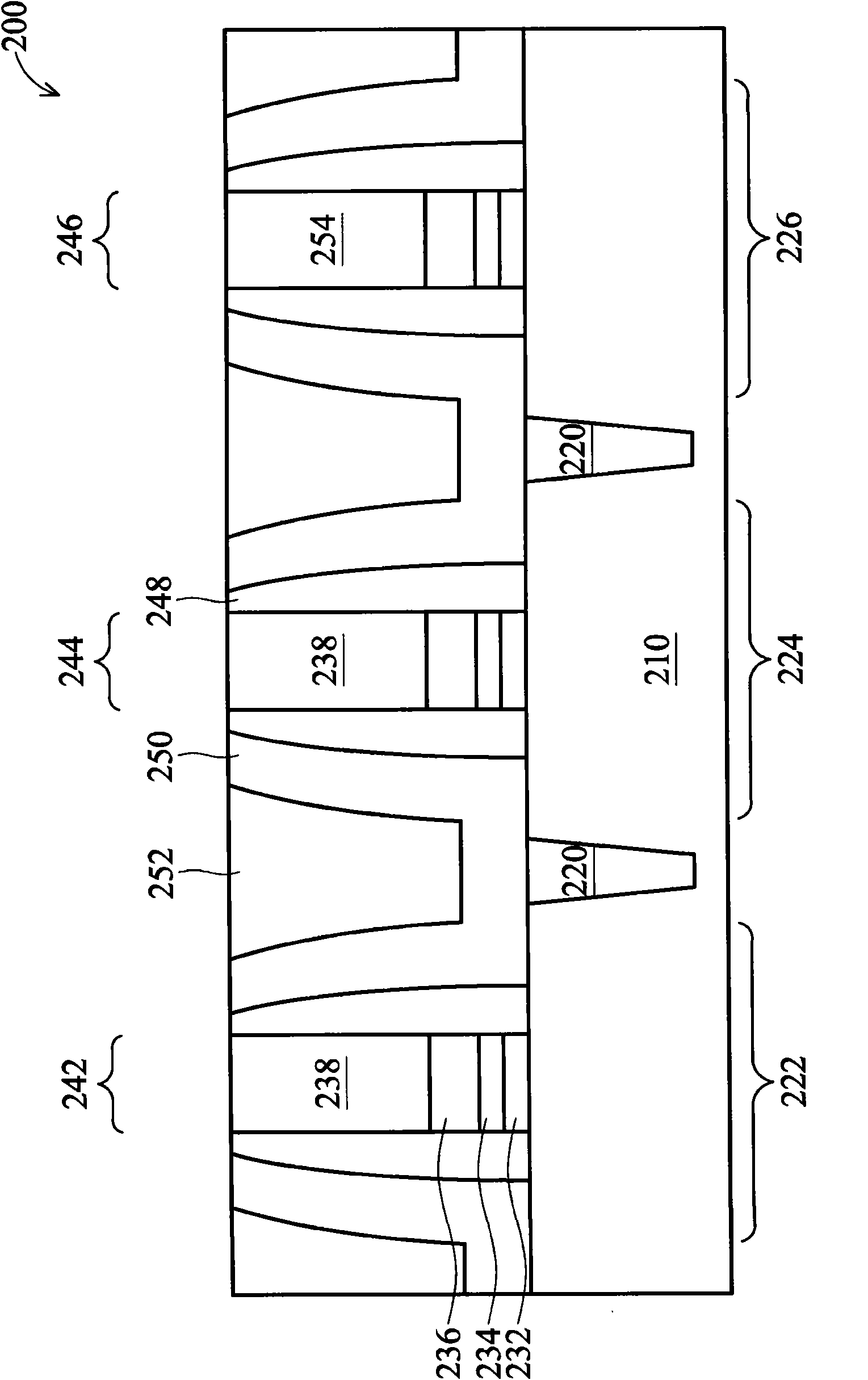

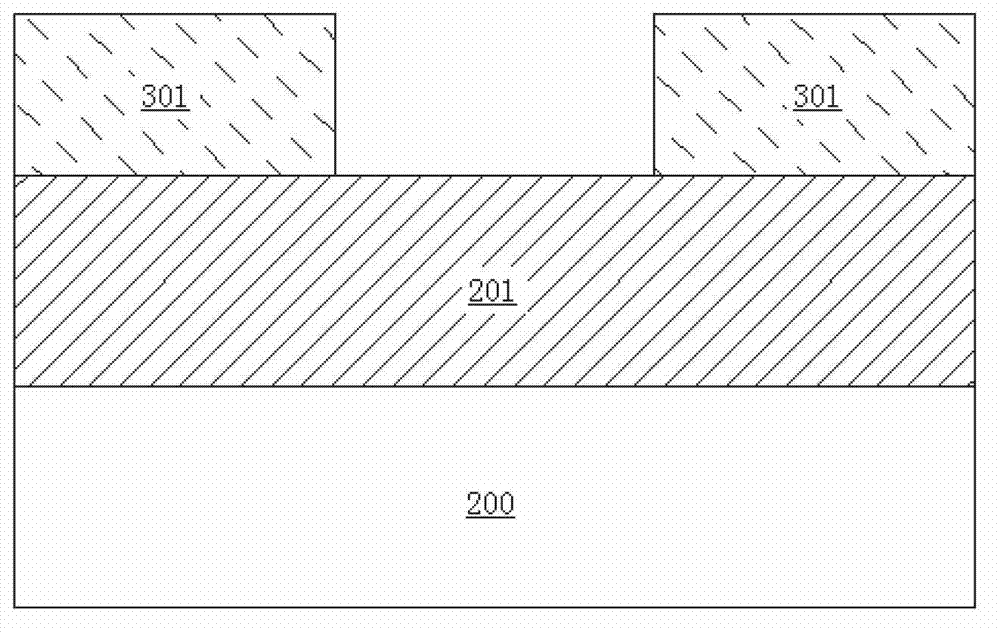

Method of manufacturing semiconductor element metal gate stack

InactiveCN102148147AIncreased negativityReduce RC delayTransistorSemiconductor/solid-state device manufacturingWork functionSemiconductor components

The invention provides a method of manufacturing a semiconductor element metal gate stack. The present disclosure provides a method that includes forming a high k dielectric layer on a semiconductor substrate; forming a polysilicon layer on the high k dielectric layer; patterning the high k dielectric layer and polysilicon layer to form first and second dummy gates in first and second field effect transistor (FET) regions, respectively; forming an inter-level dielectric (ILD); applying a first CMP process to the semiconductor substrate, exposing the first and second dummy gates; removing the polysilicon from the first dummy gate, resulting in a first gate trench; forming a first metal electrode in the first gate trench; applying a second CMP process; forming a mask covering the first FET region and exposing the second dummy gate; thereafter removing the polysilicon from the second dummy gate, resulting in a second gate trench; forming a second metal electrode in the second gate trench; and applying a third CMP process. The invention maintains the integration of metal gate electrode and the expected working function and improves the circuit effect.

Owner:TAIWAN SEMICON MFG CO LTD

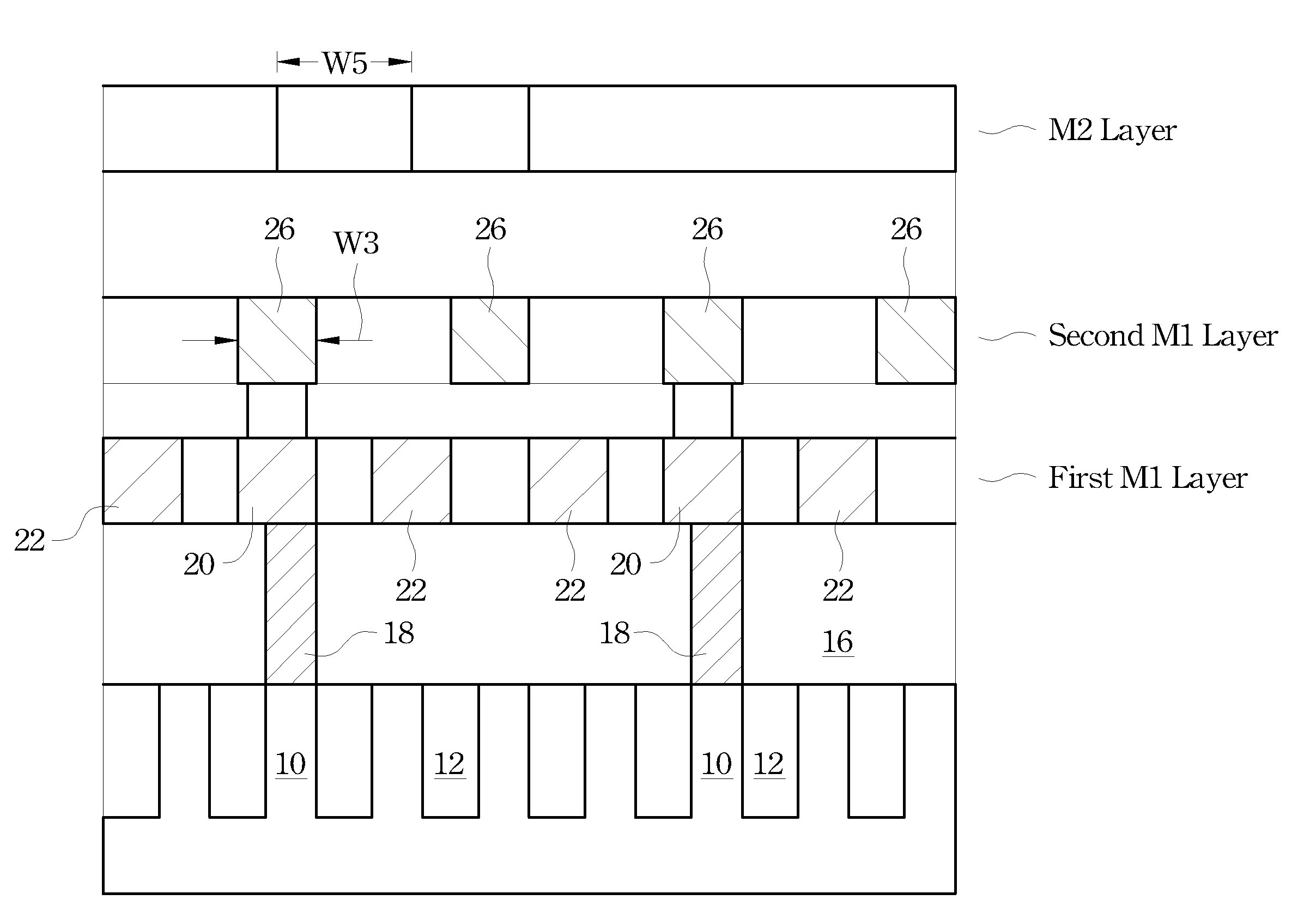

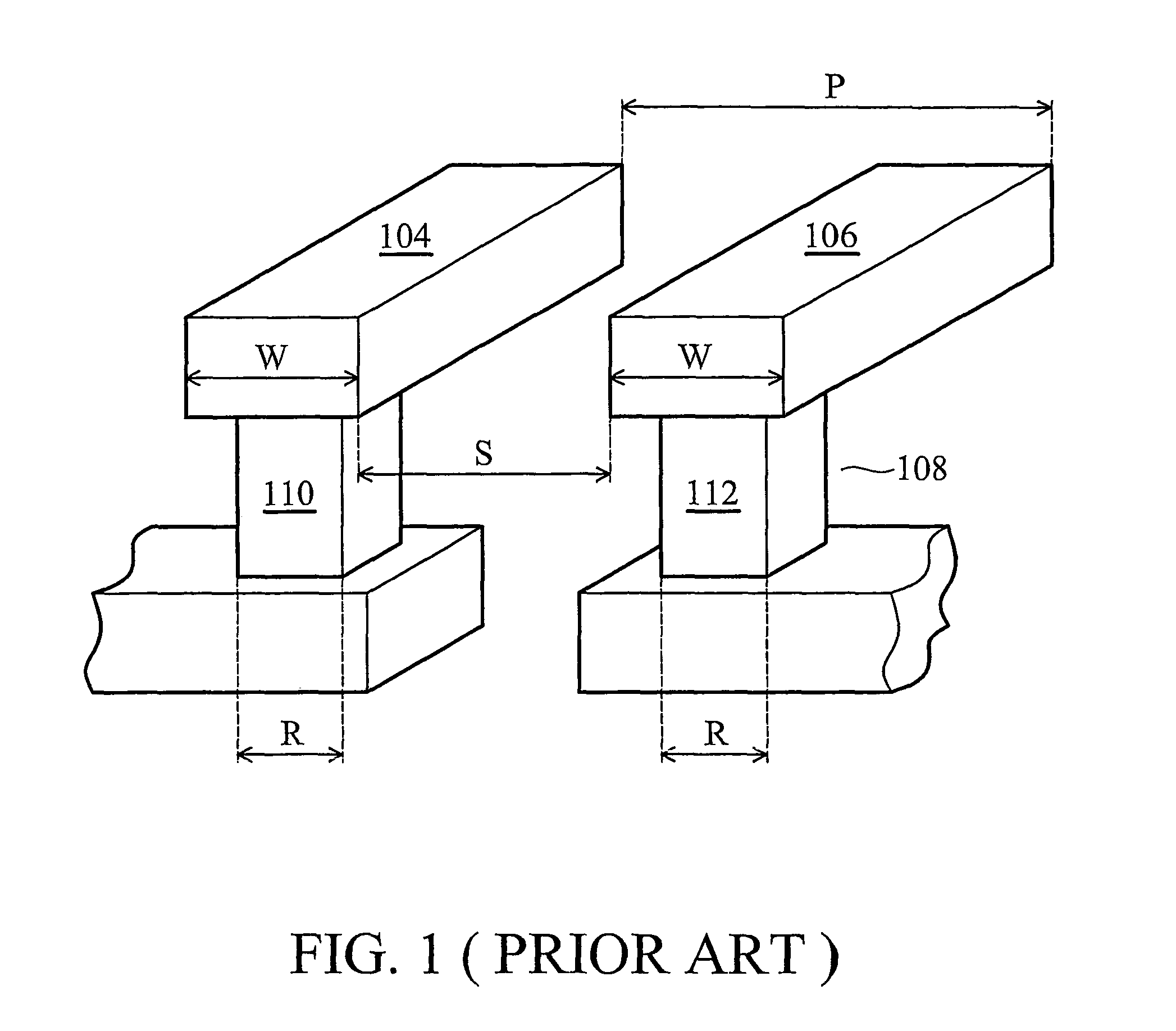

Pitch by Splitting Bottom Metallization Layer

ActiveUS20080315348A1Resistivity of metal is reducedReduce RC delaySemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

An integrated circuit structure includes a semiconductor substrate; a first bottom metallization (M1) layer over the semiconductor substrate; a second M1 layer over the first M1 layer, wherein metal lines in the first and the second M1 layer have widths of greater than about a minimum feature size; and vias connecting the first and the second M1 layers.

Owner:TAIWAN SEMICON MFG CO LTD

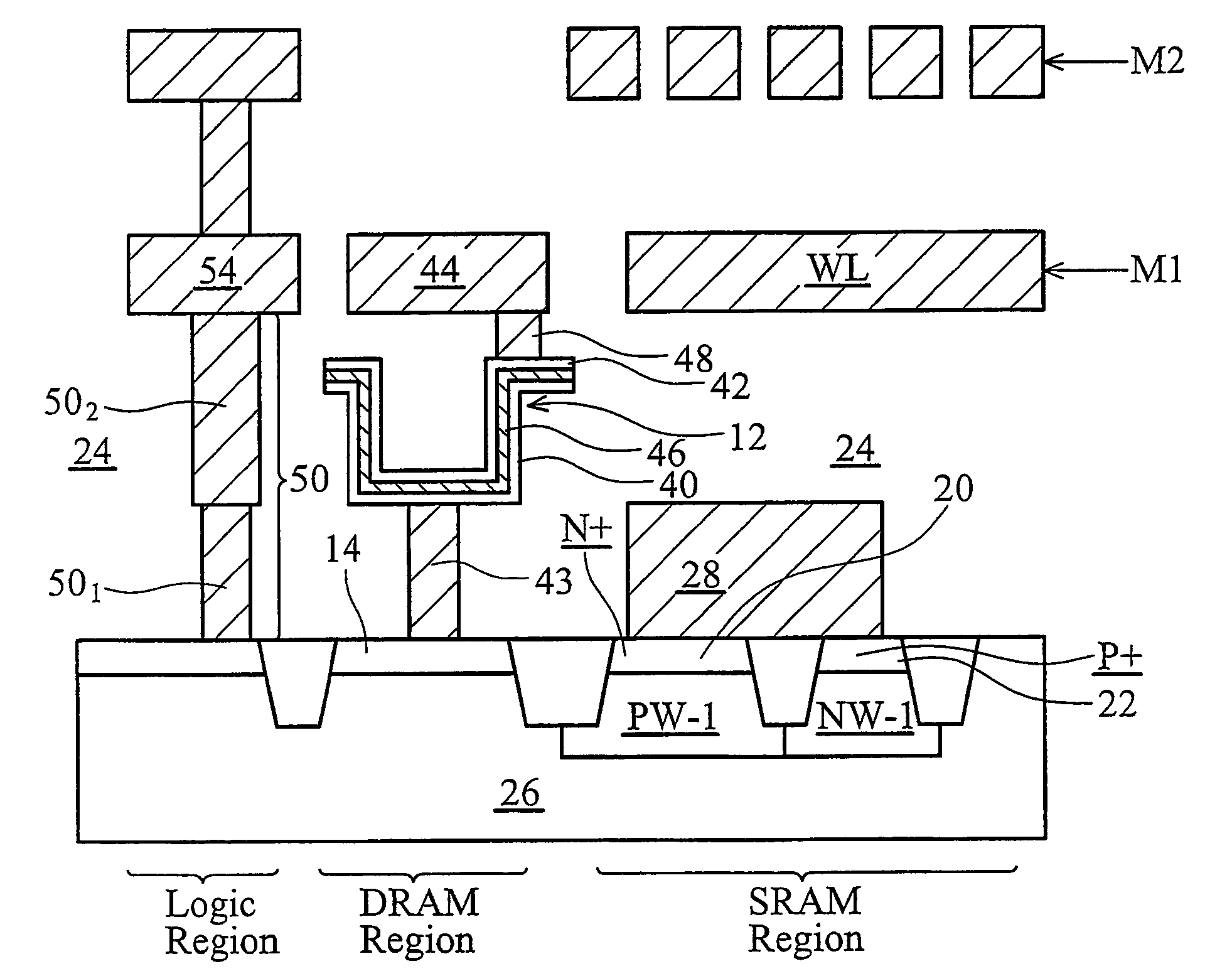

Memory formation with reduced metallization layers

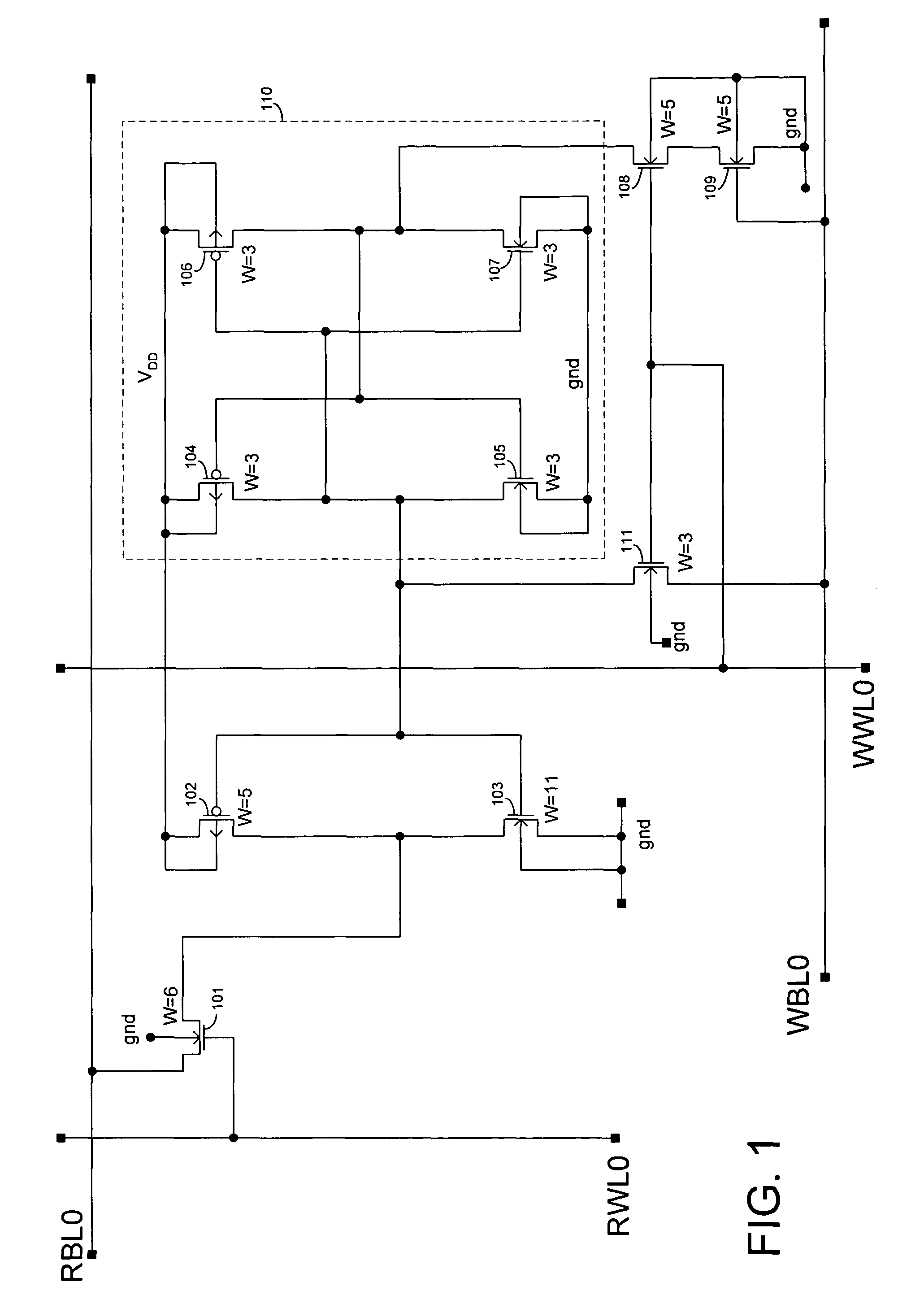

ActiveUS7514757B2Reduce layeringReduce RC delayTransistorSolid-state devicesDielectricStatic random-access memory

A semiconductor structure includes a static random access memory (SRAM) cell comprising a first pull-up MOS device, a first pull-down MOS device and a first pass-gate MOS device, a first metallization layer, and an inter-layer dielectric (ILD) underlying the first metallization layer, wherein the ILD comprises an upper portion and a lower portion, a first first-layer contact in the lower portion of the ILD and connecting at least two of the first pull-up MOS device, the first pull-down MOS device and the first pass-gate MOS device. The first first-layer contact is physically isolated from second layer contacts in the upper portion of the ILD. The semiconductor structure further includes a second first-layer contact in the lower portion of the ILD, and a second-layer contact having at least a portion on the second first-layer contact, wherein the second layer contact electrically connects the second first-layer contact.

Owner:MOSAID TECH

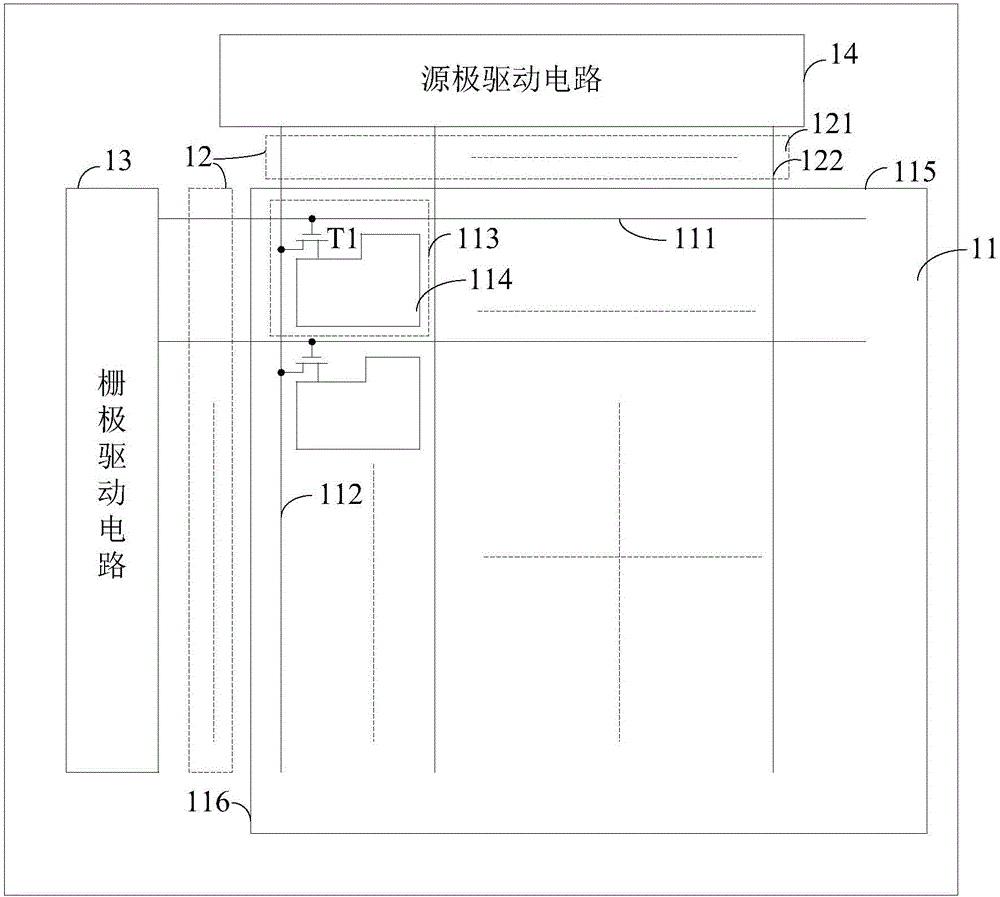

TFT array substrate

ActiveUS20160247822A1Overall resistance of a data line is reducedReduce RC delayStatic indicating devicesSolid-state devicesTransistor arrayResistance capacitance

The present invention provides a thin-film transistor (TFT) array substrate. The TFT array substrate is structured to change the way that sub-pixels are arranged so that during a displaying period of a frame of image, the sub-pixels that have inconsistent brightness / darkness become alternate with each other spatially so that a displaying defect of vertical bright / dark lines can be improved and the overall resistance of the data line can be reduced to thereby reduce resistance-capacitance delay and prevent incorrect charging at a tail end of a scan line or a data line.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Mixed-media copper-diffusion-resistant blocking layer for copper interconnection and fabrication method of blocking layer

InactiveCN102832199AImprove diffusion resistanceAvoid failureSemiconductor/solid-state device detailsSolid-state devicesCopper interconnectHemt circuits

The invention belongs to the field of fabrication and interconnection of integrated circuits, and particularly relates to a mixed-media copper-diffusion-resistant blocking layer for copper interconnection and a manufacturing method of the blocking layer. The mixed-media copper-diffusion-resistant blocking layer has the advantages that the mixed media (oxidation layer / metal) is used as the copper-diffusion-resistant blocking layer, so that (1) the diffusion resistance of metal on copper can be effectively enhanced, the blocking layer is effectively prevented from being oxidized and falling, and the service life of the diffusion blocking layer is prolonged; (2) the effective dielectric constant value of interconnected circuits can be reduced, and further the whole RC delay of the interconnected circuits is reduced; and (3) since the metal and copper have good adhesion and contact, copper can be directly electroplated on the surface of the metal without depositing a layer of copper seed crystal firstly, so that the process is simple and feasible, and is expected to be applied to fabrication of the diffusion blocking layer of copper interconnection in future.

Owner:FUDAN UNIV

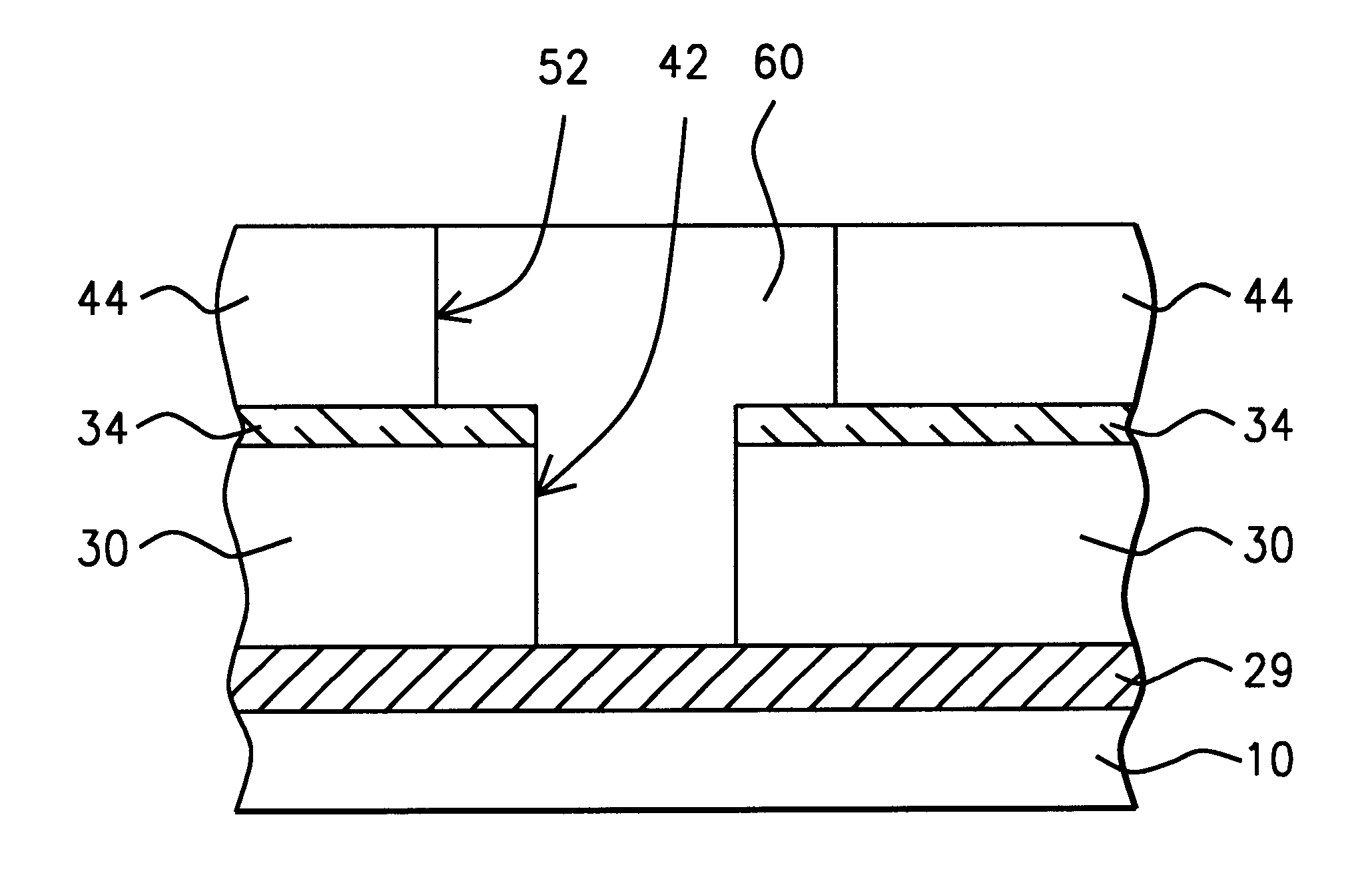

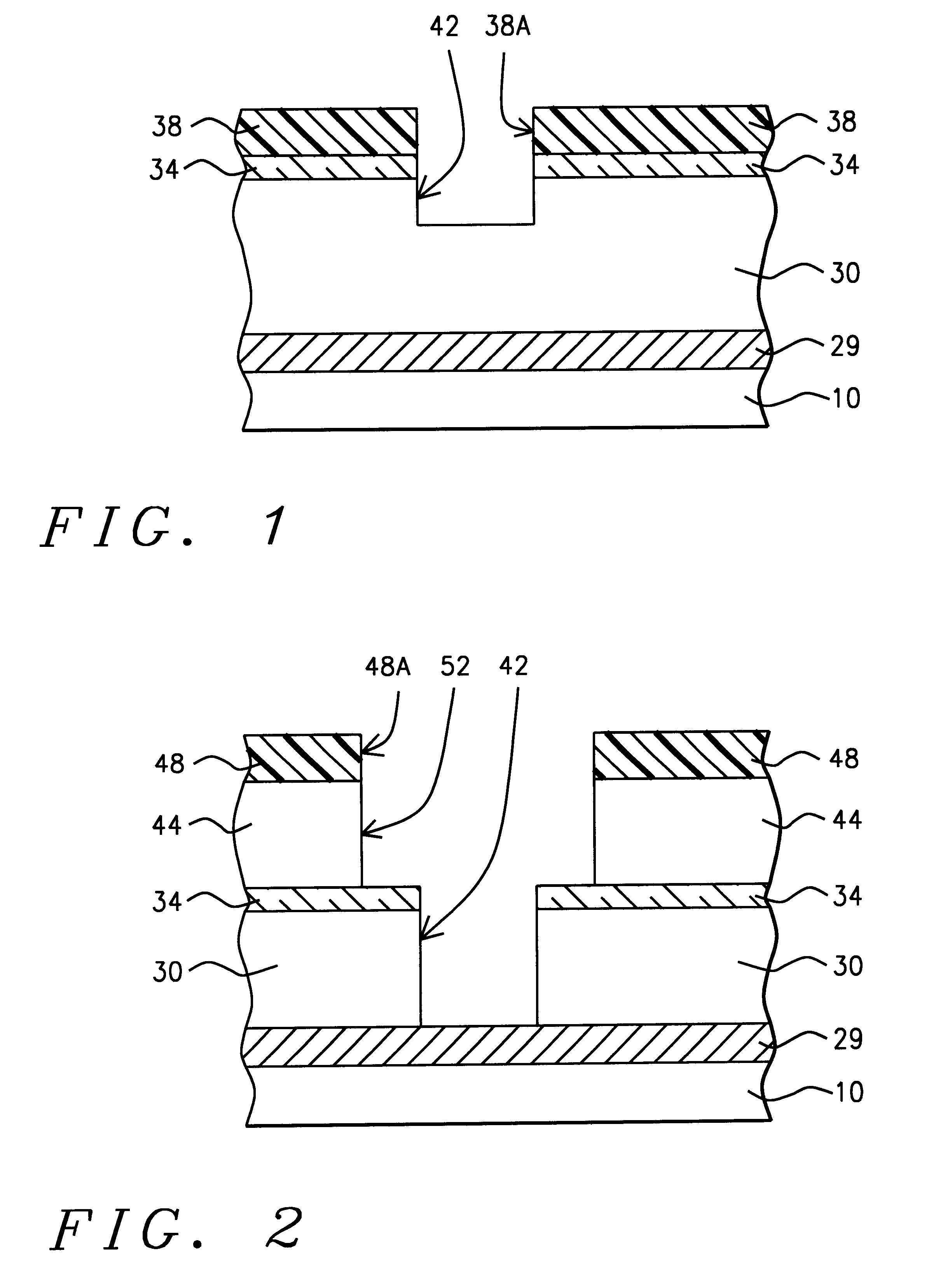

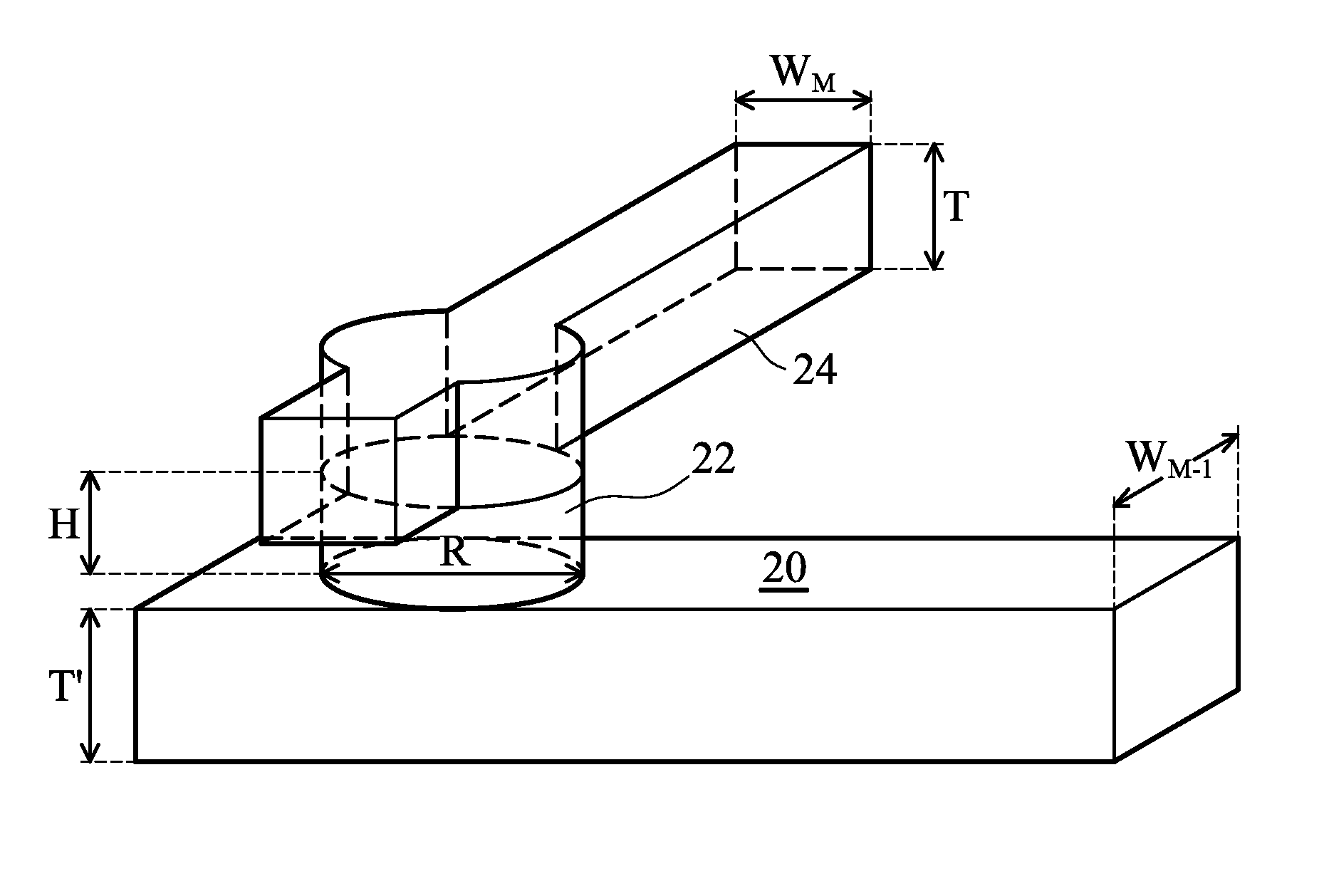

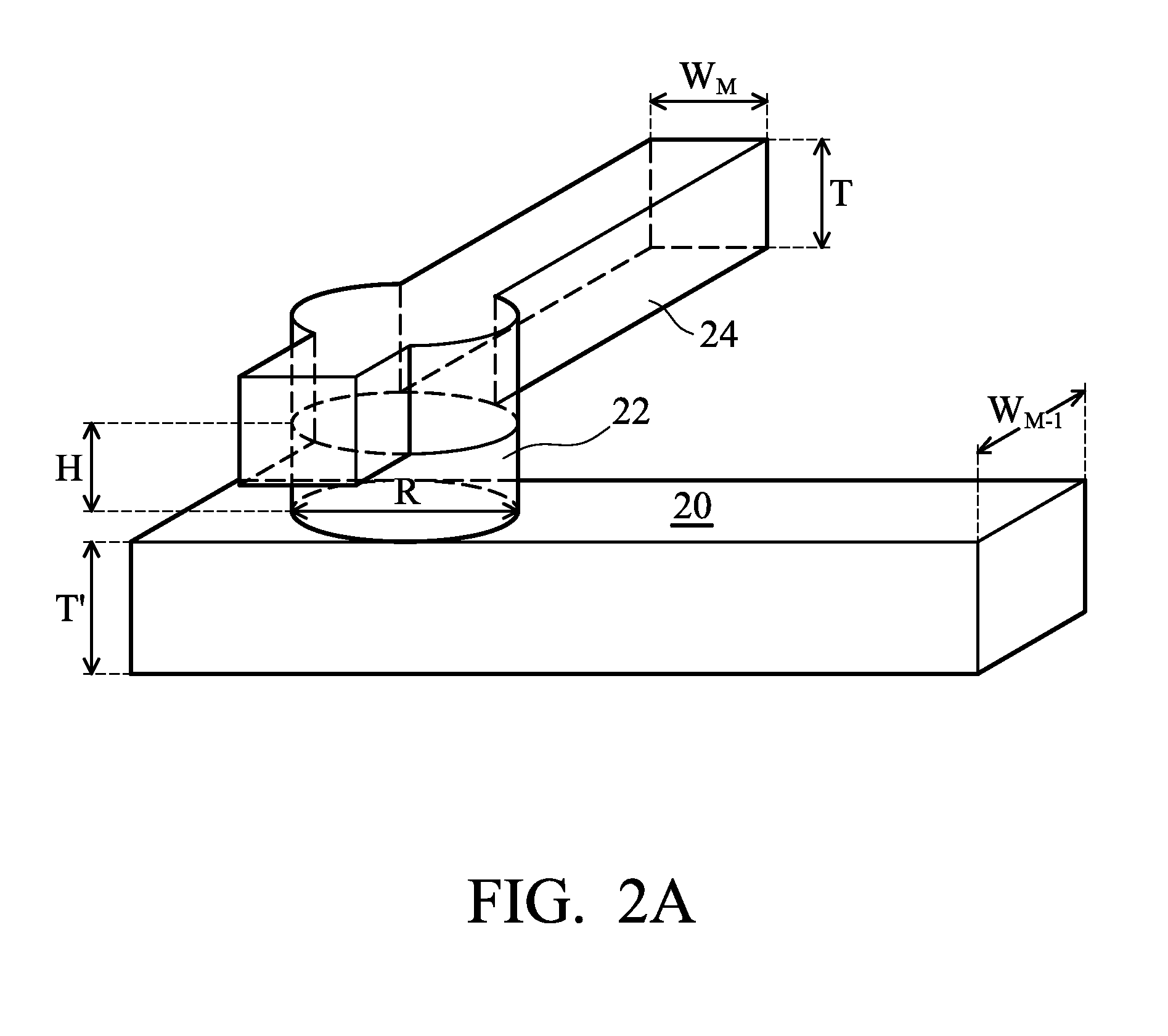

Interconnection structure design for low RC delay and leakage

ActiveUS8432040B2Reduce RC delayReduce leakage currentSemiconductor/solid-state device detailsSolid-state devicesInterconnectionEngineering

An interconnection structure for integrated circuits having reduced RC delay and leakage is provided. The interconnection structure includes a first conductive line in a first dielectric layer, a second dielectric layer over the first dielectric layer and the first conductive line, and a dual damascene structure in the second dielectric layer. The dual damascene structure includes a second conductive line and a via between and adjoining the first and the second conductive lines, wherein the second conductive line comprises a first portion directly over and adjoining the via, and a second portion having no underlying and adjoining vias. The second portion has a second width less than a first width of the first portion.

Owner:ADVANCED MFG INNOVATIONS INC

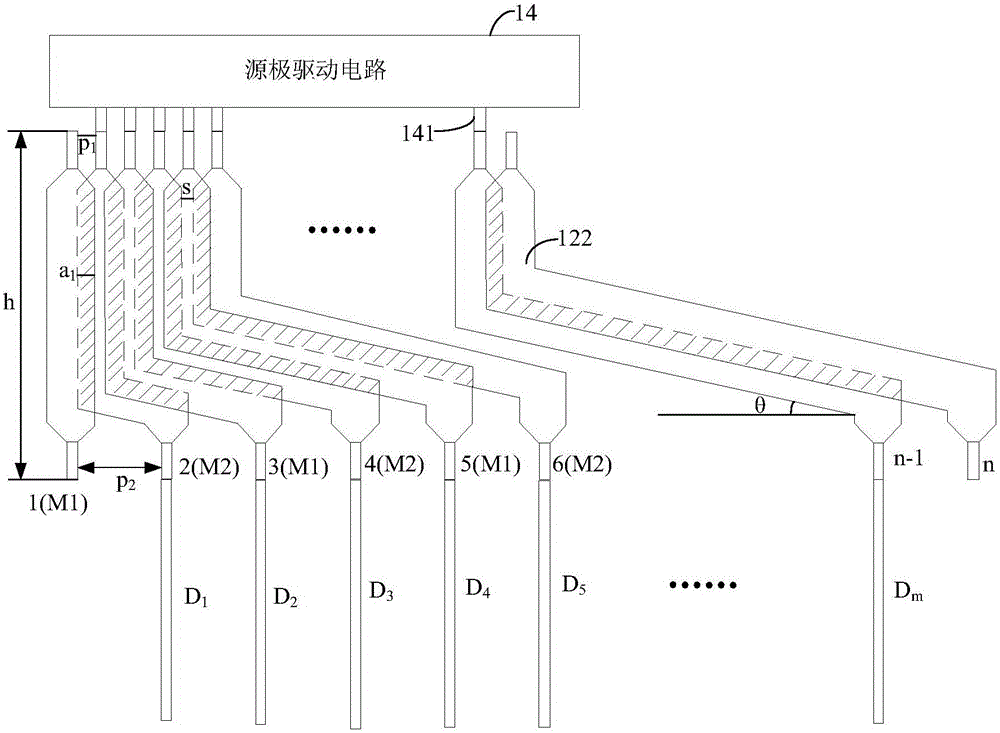

Liquid crystal display device and display panel thereof

ActiveCN105158998AReduce RC delayImprove display qualityStatic indicating devicesNon-linear opticsLiquid-crystal displayTime delays

The invention discloses a liquid crystal display device and a display panel thereof. The display panel comprises a display region, and a fan-out region connected with at least one side of the display region, wherein the fan-out region comprises at least one group of fan-out routings; each group of fan-out routings comprise a plurality of routings; the multiple routings comprise first layers of metal routings and second layers of metal routings which are arranged alternately; the adjacent first layer and second layer of metal routings are partially superposed. Due to the mode, the liquid crystal display device has the advantages that the RC time delay among all the routings of each group of fan-out routings can be reduced, and the display quality is improved.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

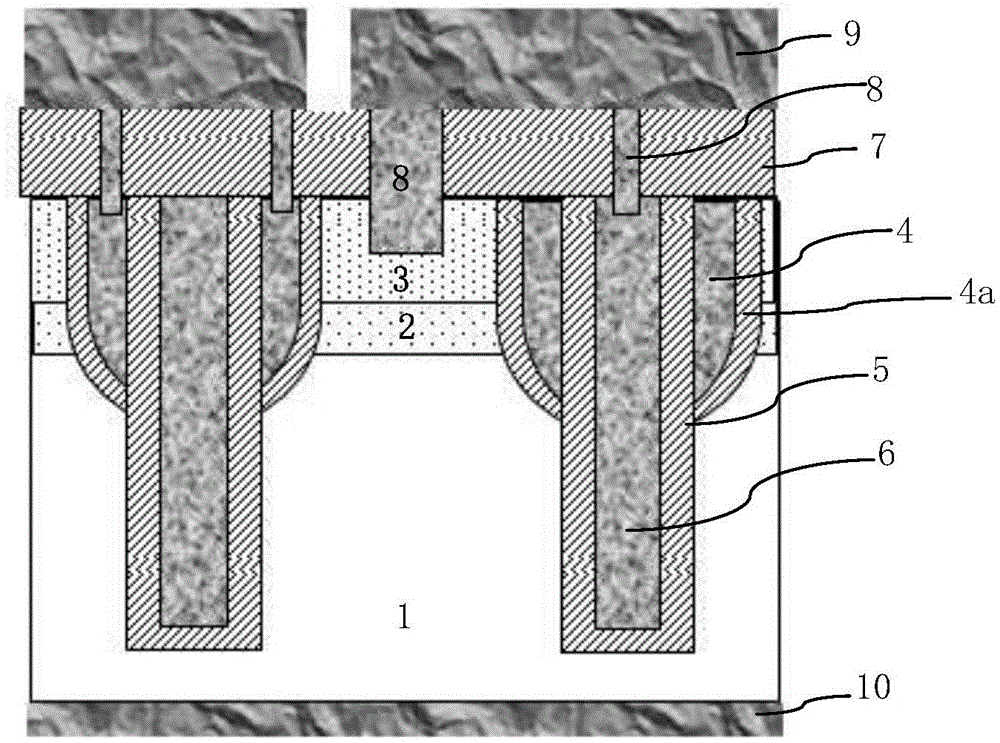

Manufacturing method for MOSFET adopting separated trench side gate structure with shield gate

ActiveCN105551964AImprove frequency characteristicsLower gate resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETCapacitance

The invention discloses a manufacturing method for a MOSFET adopting a separated trench side gate structure with a shield gate. The manufacturing method comprises the steps of performing injection for a well region and a source region in a semiconductor substrate and performing an annealing-boosting process; forming a hard mask layer, and performing a photoetching process to define a gate formation region; performing anisotropic etching for the first time to form a trench; performing anisotropic etching for the second time to increase the width and the depth of the trench; forming a gate dielectric layer and a gate metal layer; performing back etching on the gate metal layer; performing anisotropic etching for the semiconductor substrate at the bottom of the trench; forming oxide layers on the internal surface of the deep trench and the side face of the gate metal layer at the same time; and performing source shield metal layer growth. According to the manufacturing method, the gate resistance can be lowered, the application of the device in a high-frequency circuit is expanded by reducing RC delay, technological steps in a thermal process are reduced, the product manufacturing period is shortened, gate drain capacitance can be lowered, the thickness of the gate source isolating oxide layer can be improved, and the gate source electric leakage can be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com