Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

673 results about "Negative bias" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A negative bias is a lamprey of the mind, a deadly parasite, and this parasite uses your lifeblood, your energy, your mind, to breed and spread to other minds, using and destroying life force wherever it goes.

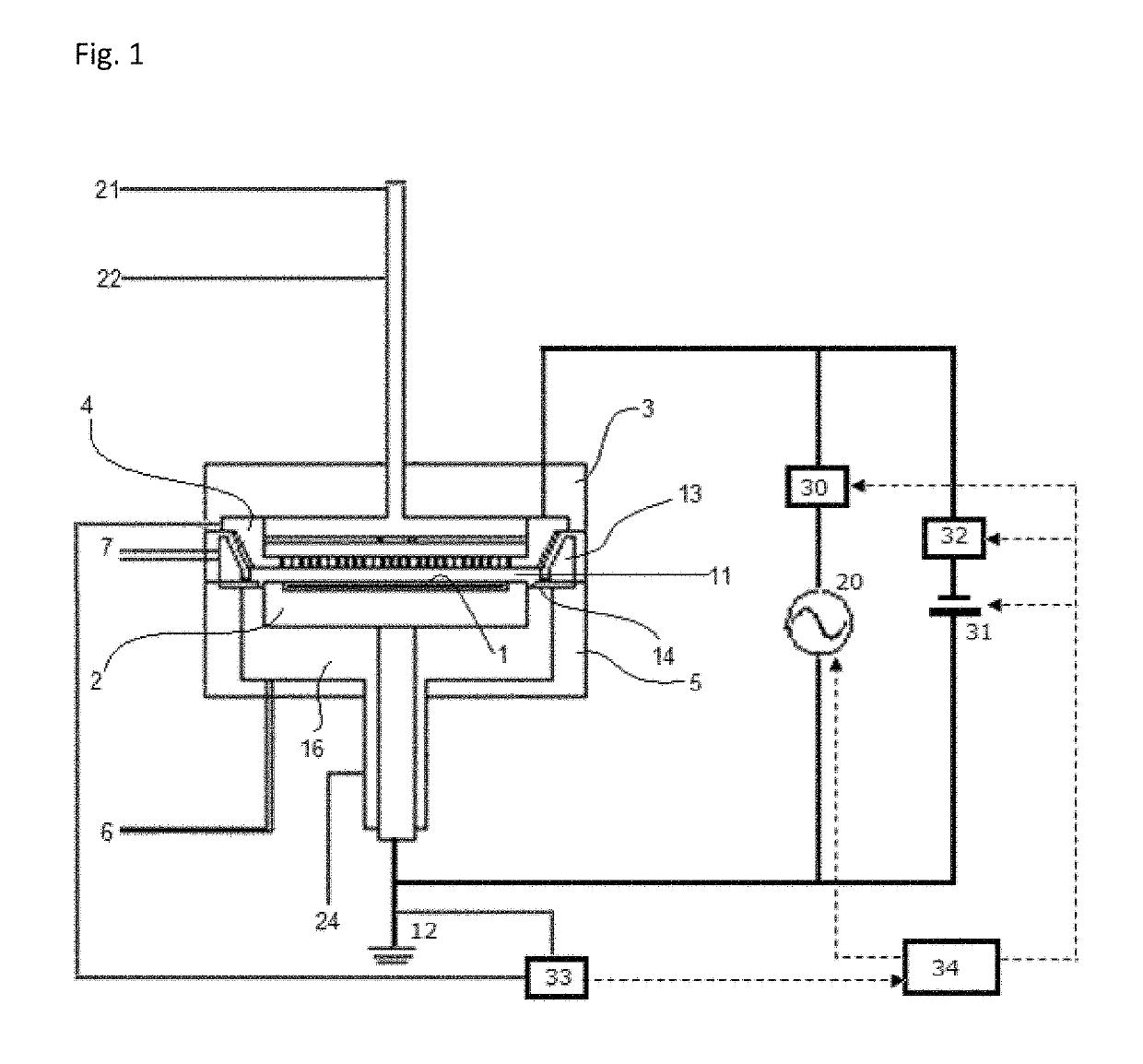

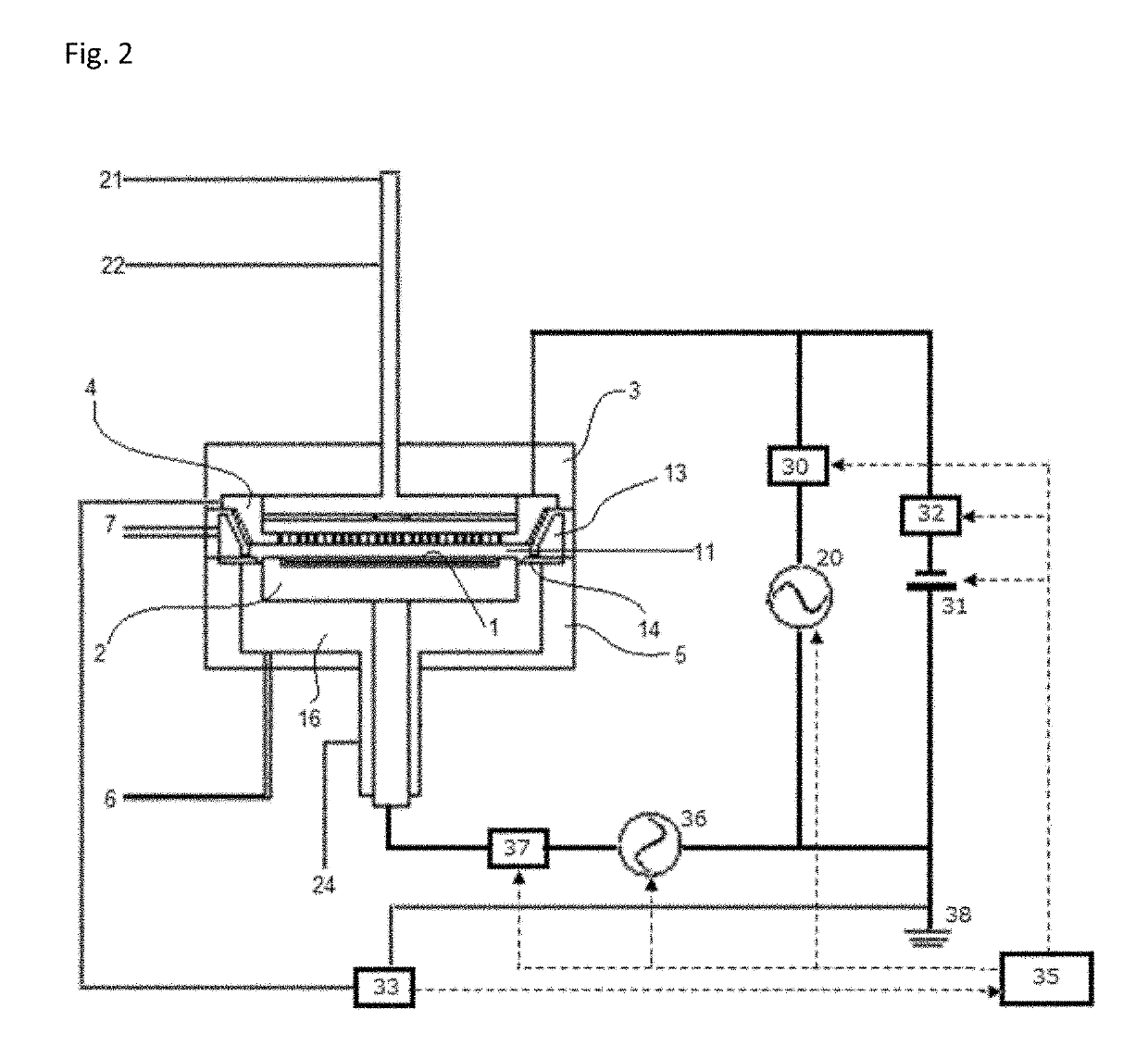

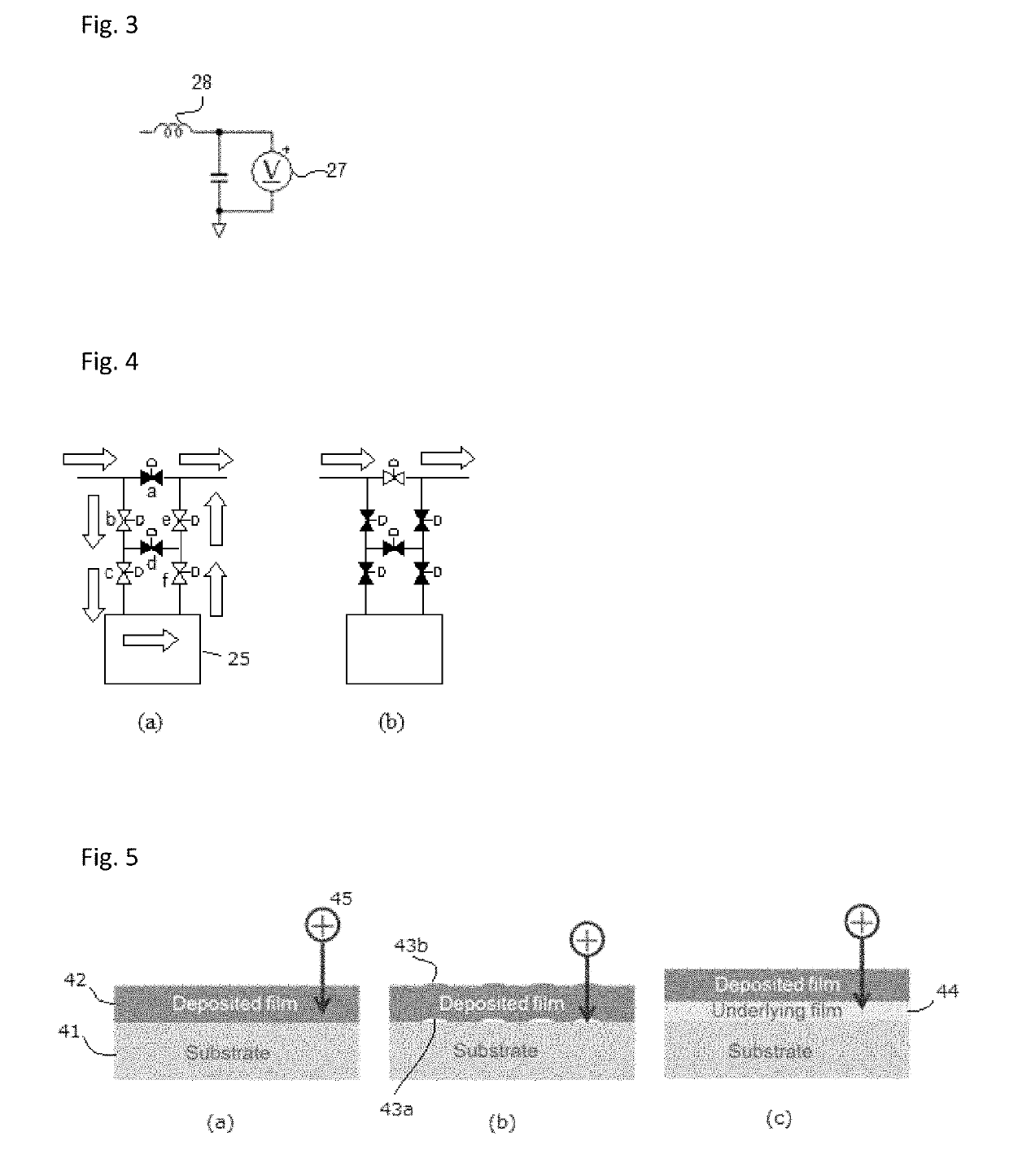

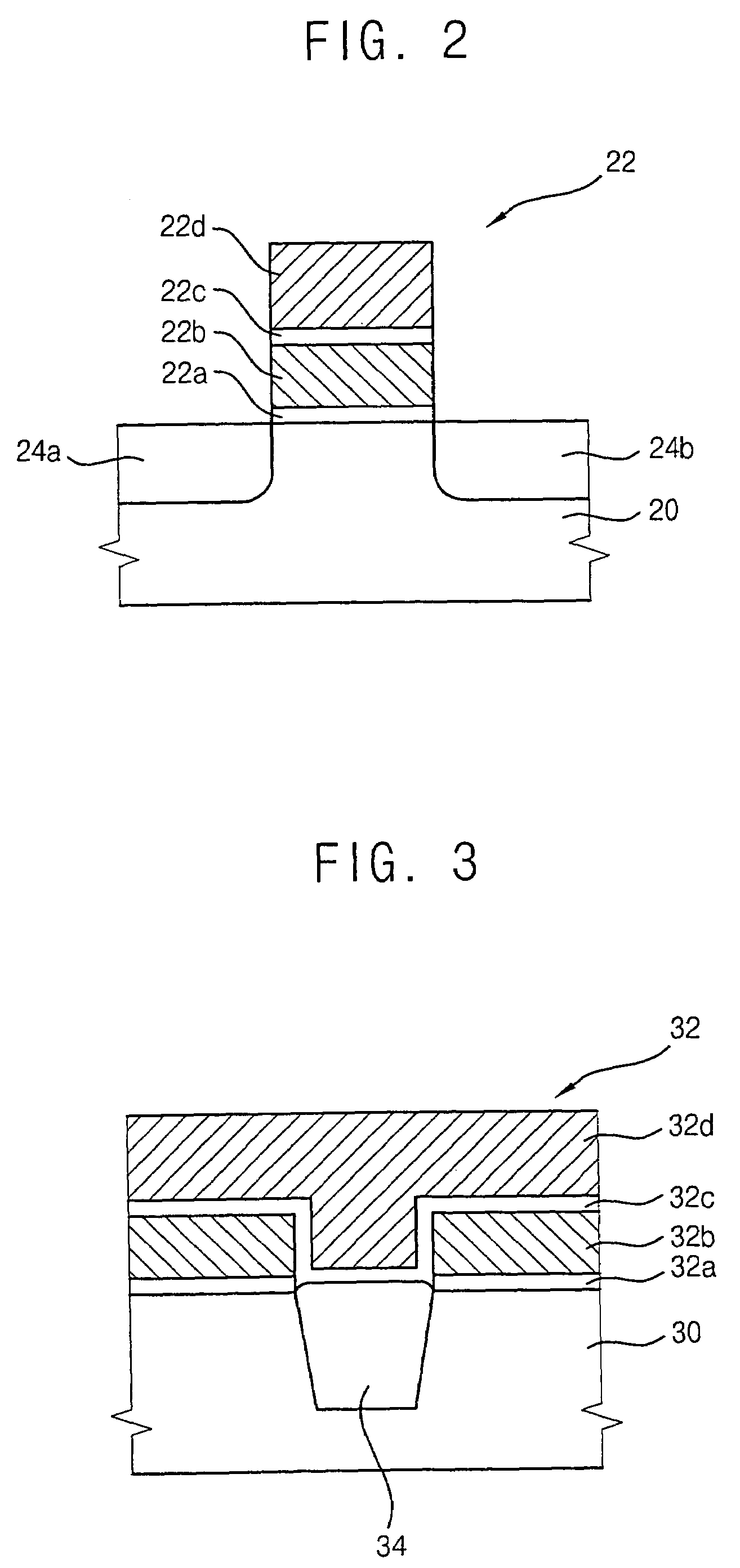

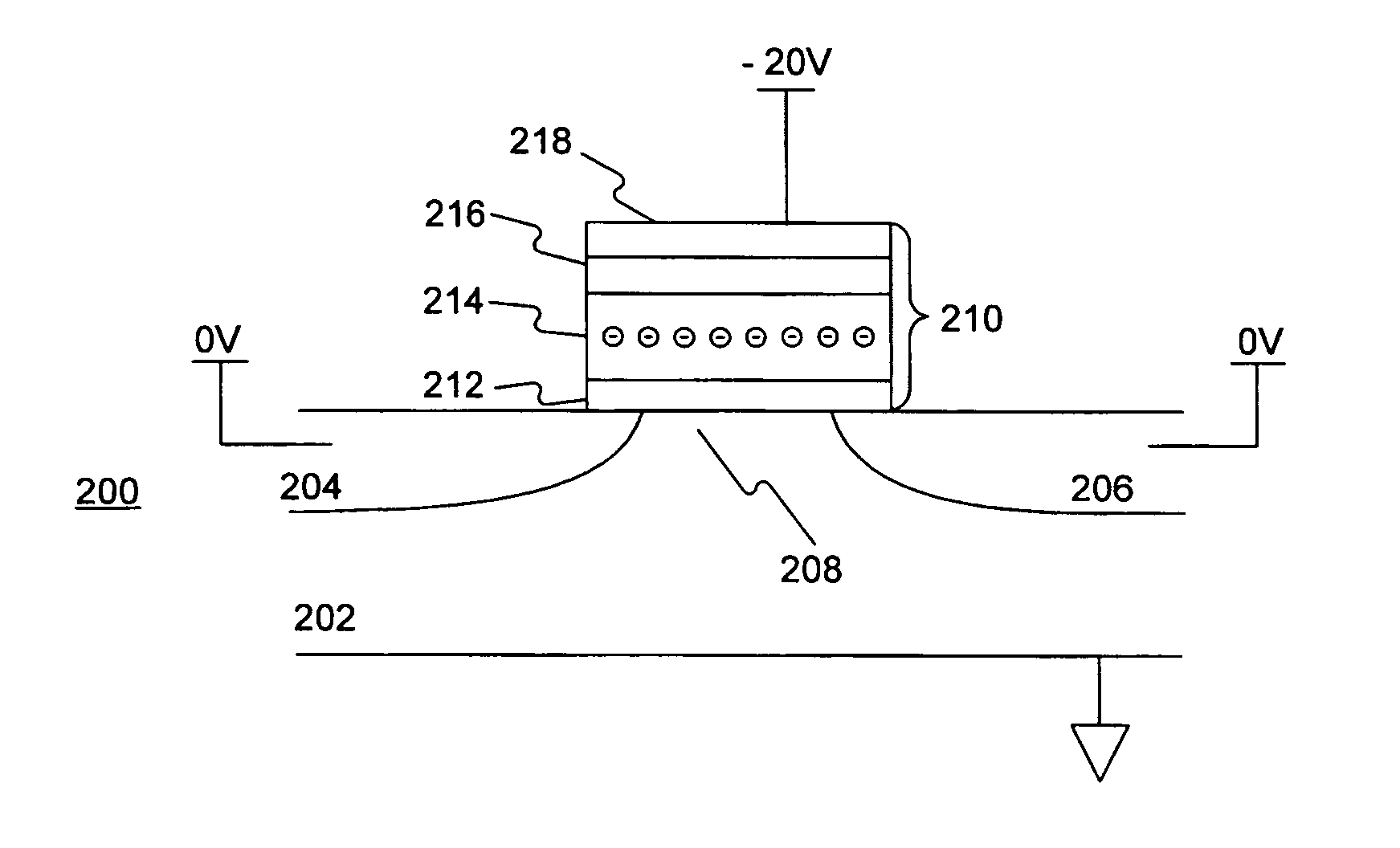

Method of depositing film by PEALD using negative bias

ActiveUS10312055B2Less particle generationLower average energyElectric discharge tubesSemiconductor/solid-state device manufacturingPhysical chemistryThin membrane

A method of forming a film on a substrate by PEALD includes deposition cycles, each including (i) feeding a precursor in a pulse to a reaction space to adsorb a precursor on a surface of a substrate; (ii) after step (i), applying RF power to a second electrode to generate in the reaction space a plasma to which the precursor-adsorbed surface is exposed, thereby forming a sublayer on the surface; and (iii) applying a bias voltage to the second electrode while applying RF power in step (ii), which bias voltage is negative with reference to a potential on a surface of the first electrode, wherein the cycle is repeated to deposit multiple sublayers until a film constituted by the sublayers has a desired thickness.

Owner:ASM IP HLDG BV

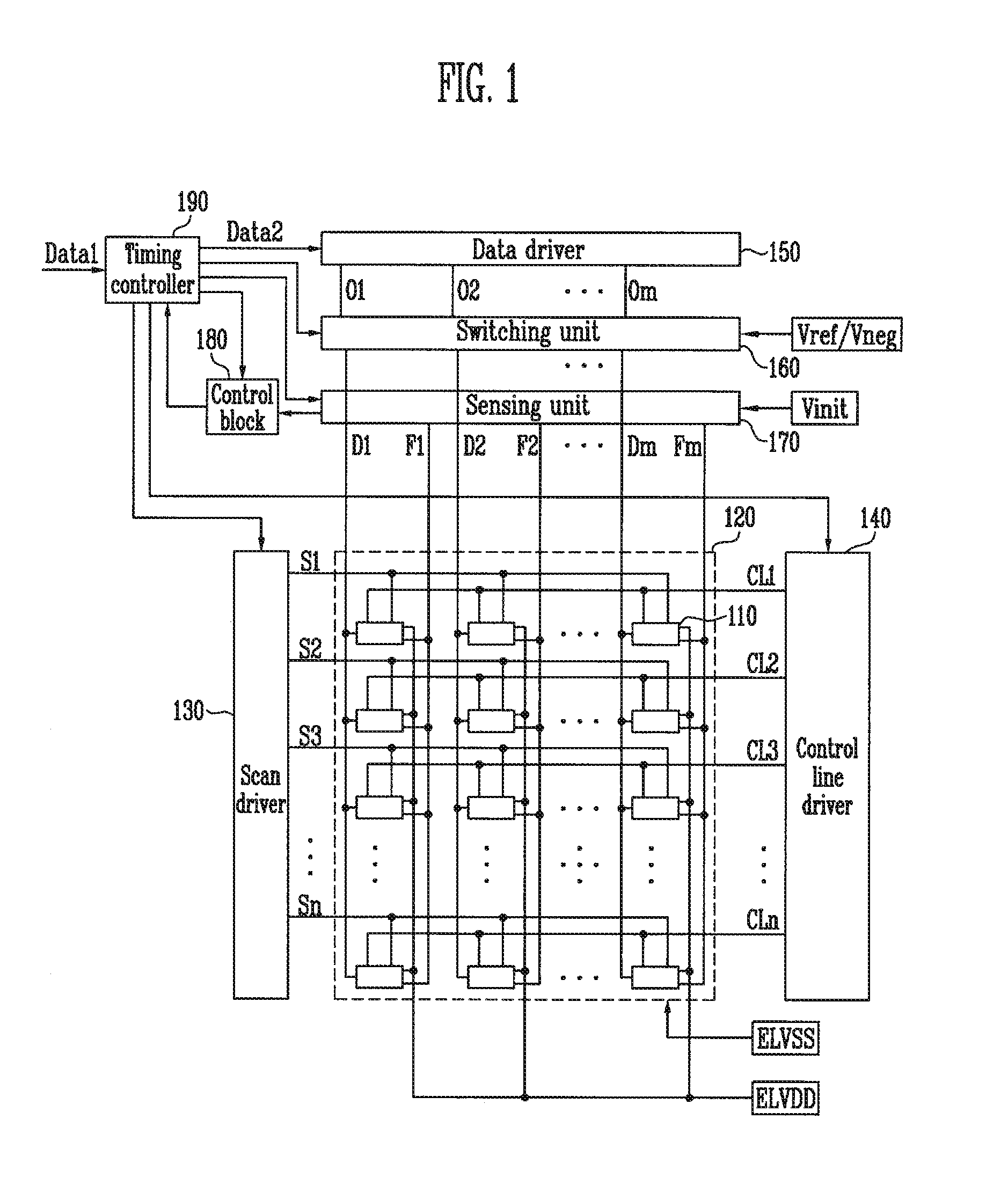

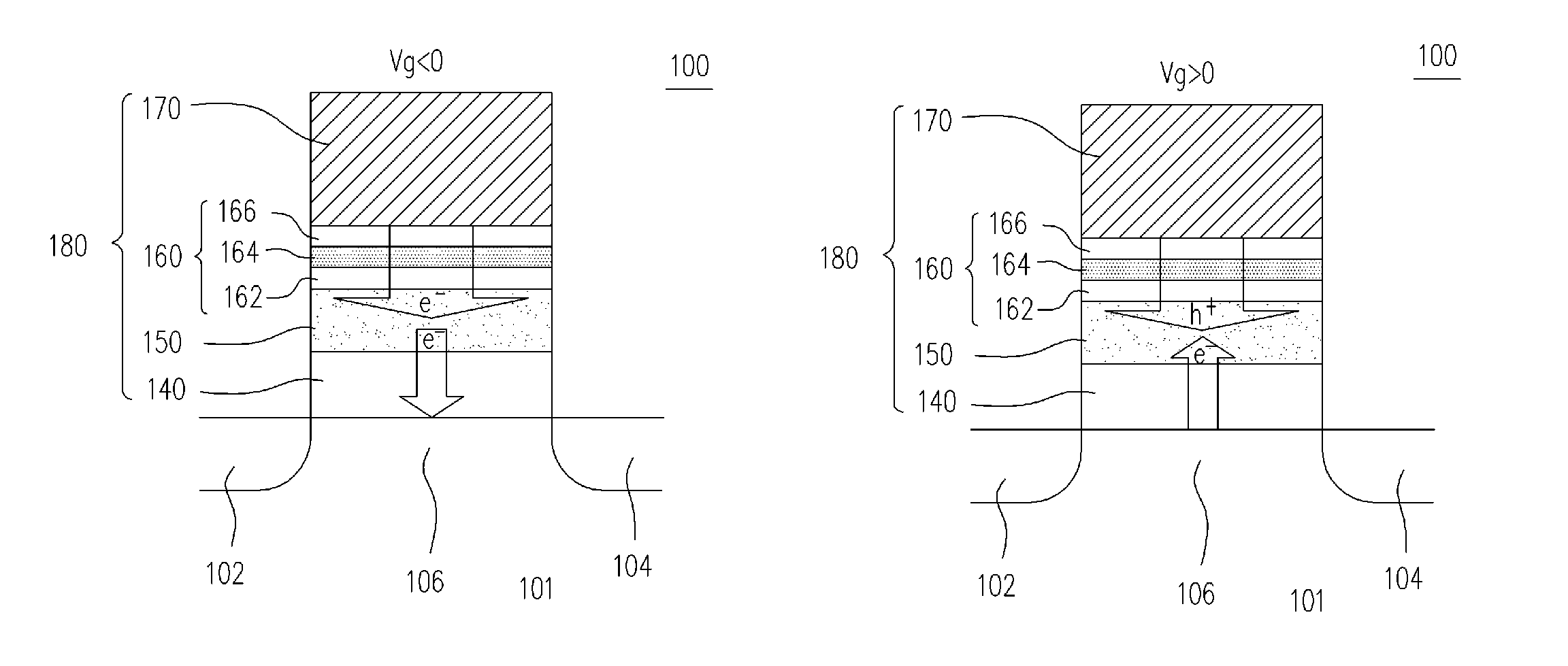

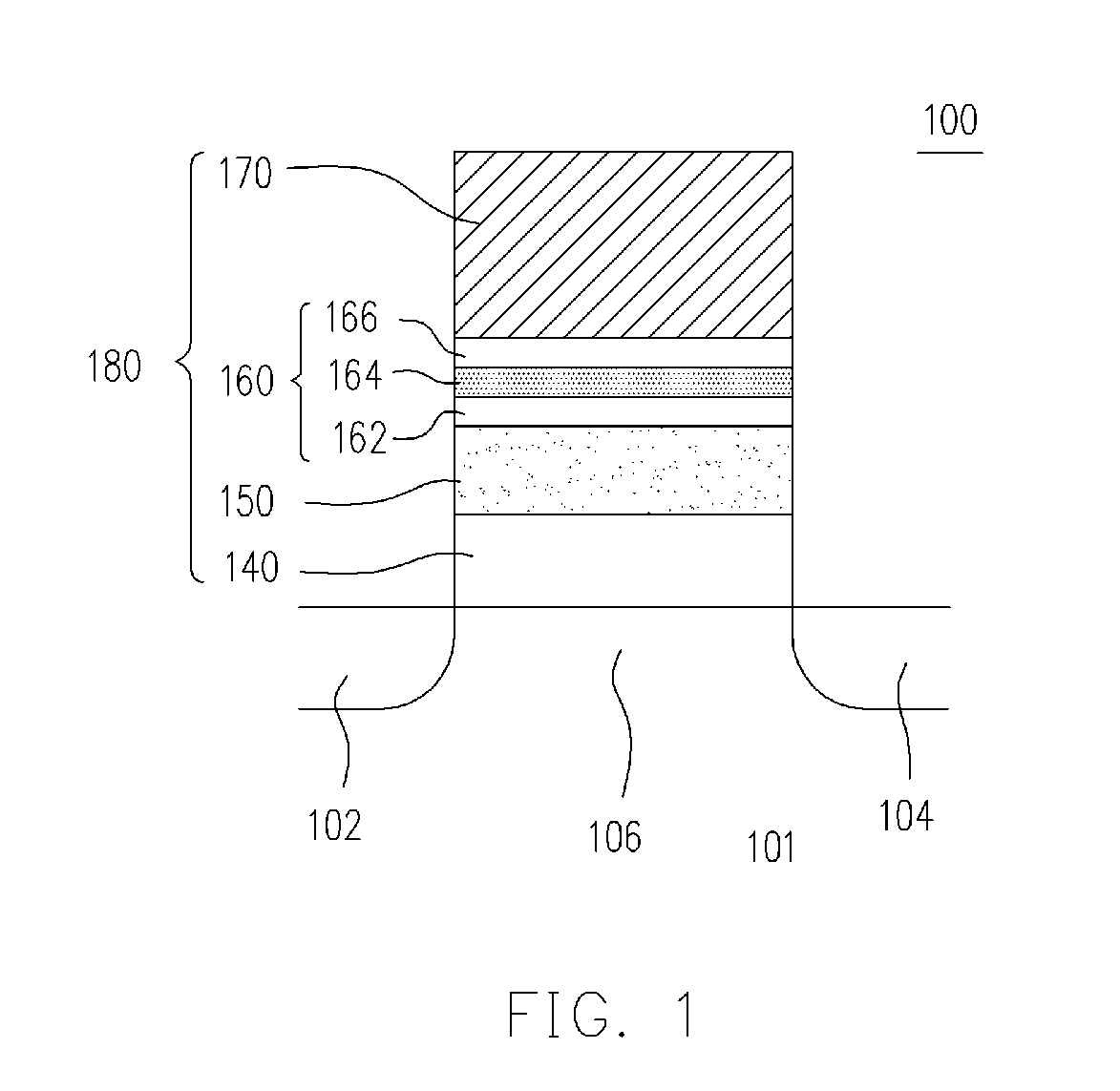

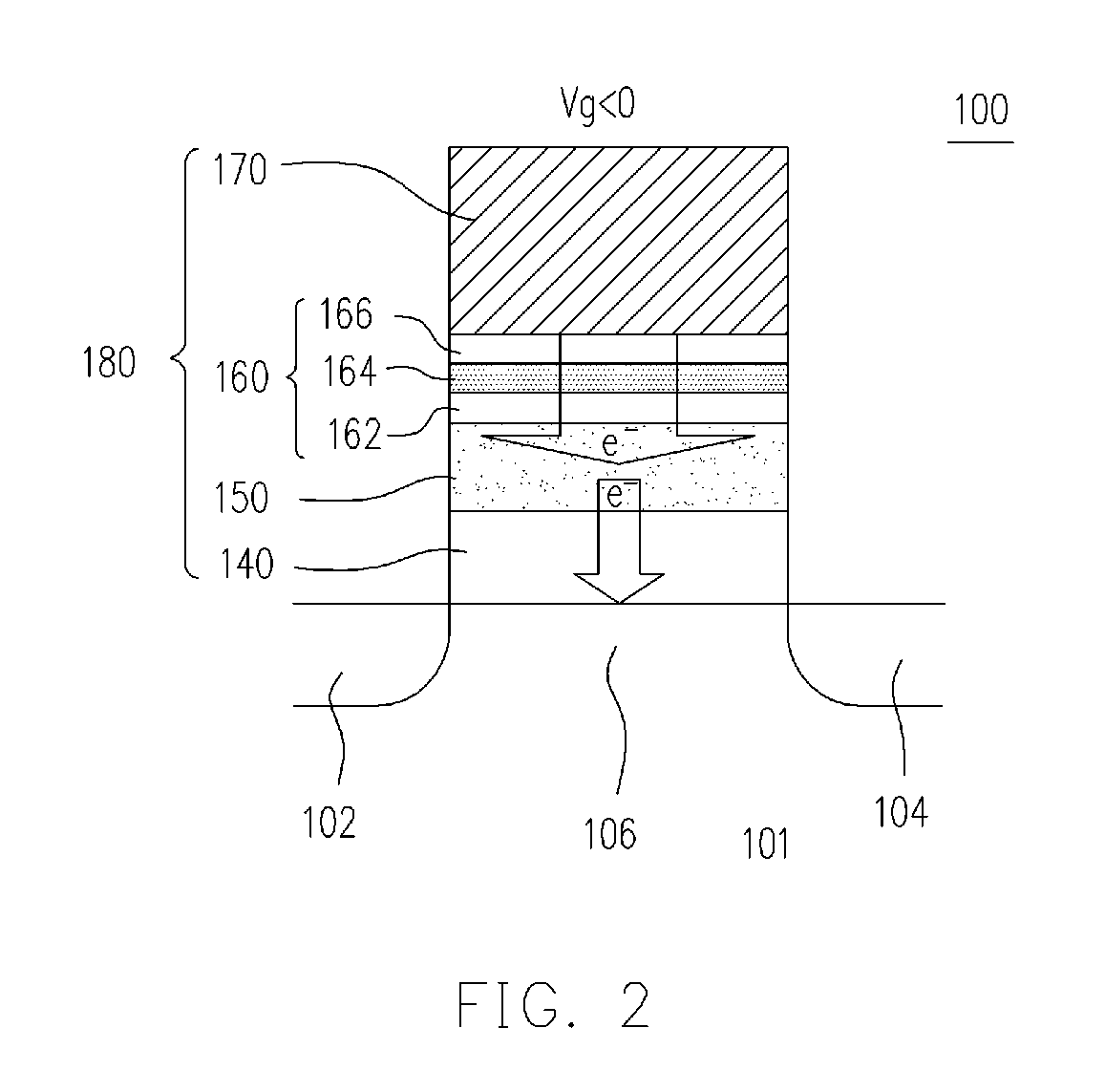

Organic light emitting display device

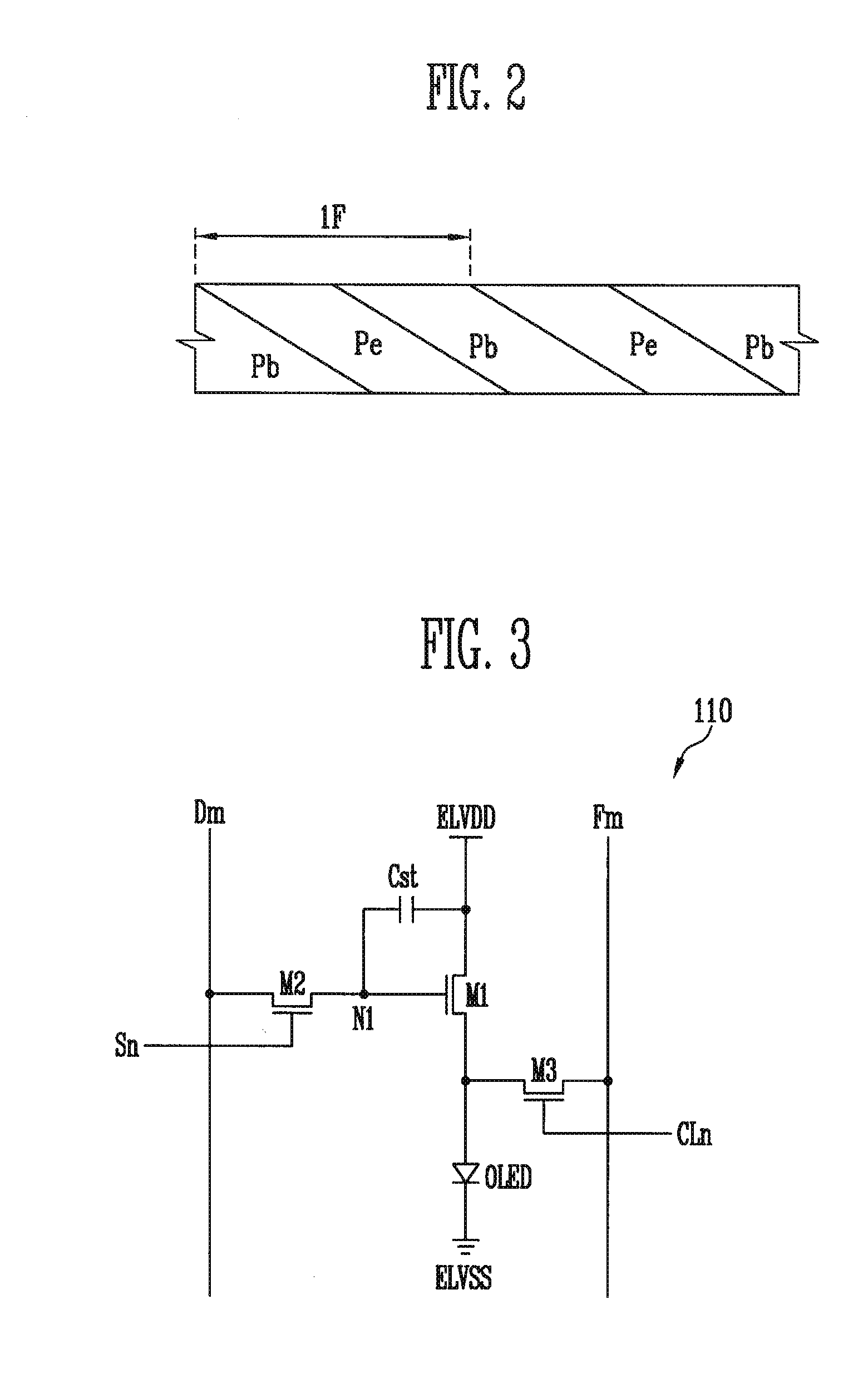

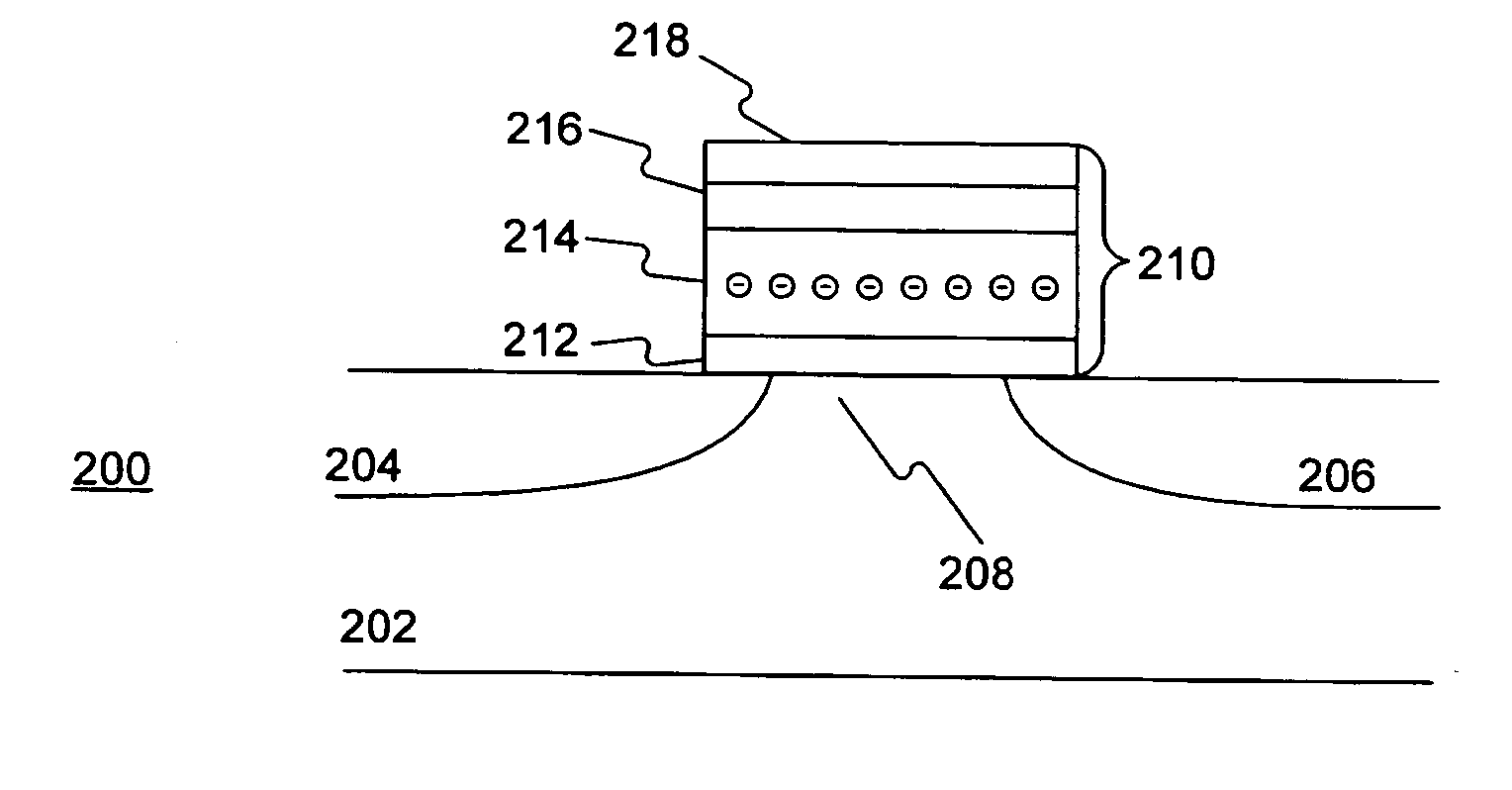

InactiveUS20110227505A1Uniform brightnessThreshold Voltage StabilityElectrical apparatusStatic indicating devicesDisplay deviceControl line

An organic light emitting display device includes a display unit having pixels located at crossing regions of scan, control, data and sensing lines. Scan, control line, and data drivers respectively supply scan, control, and data signals to the scan, control, and data lines. A switching unit selectively couples the data lines to output lines of the data driver, a reference voltage source, or a negative bias voltage source. A sensing unit senses degradation information of an organic light emitting diode in the pixels and threshold voltage of a driving transistor in the pixels through the sensing lines. A control block stores the sensed degradation information and threshold voltage information. A timing controller is configured to generate a second data by converting an externally inputted first data using the degradation information and the threshold voltage information, and supply the second data to the data driver.

Owner:SAMSUNG DISPLAY CO LTD

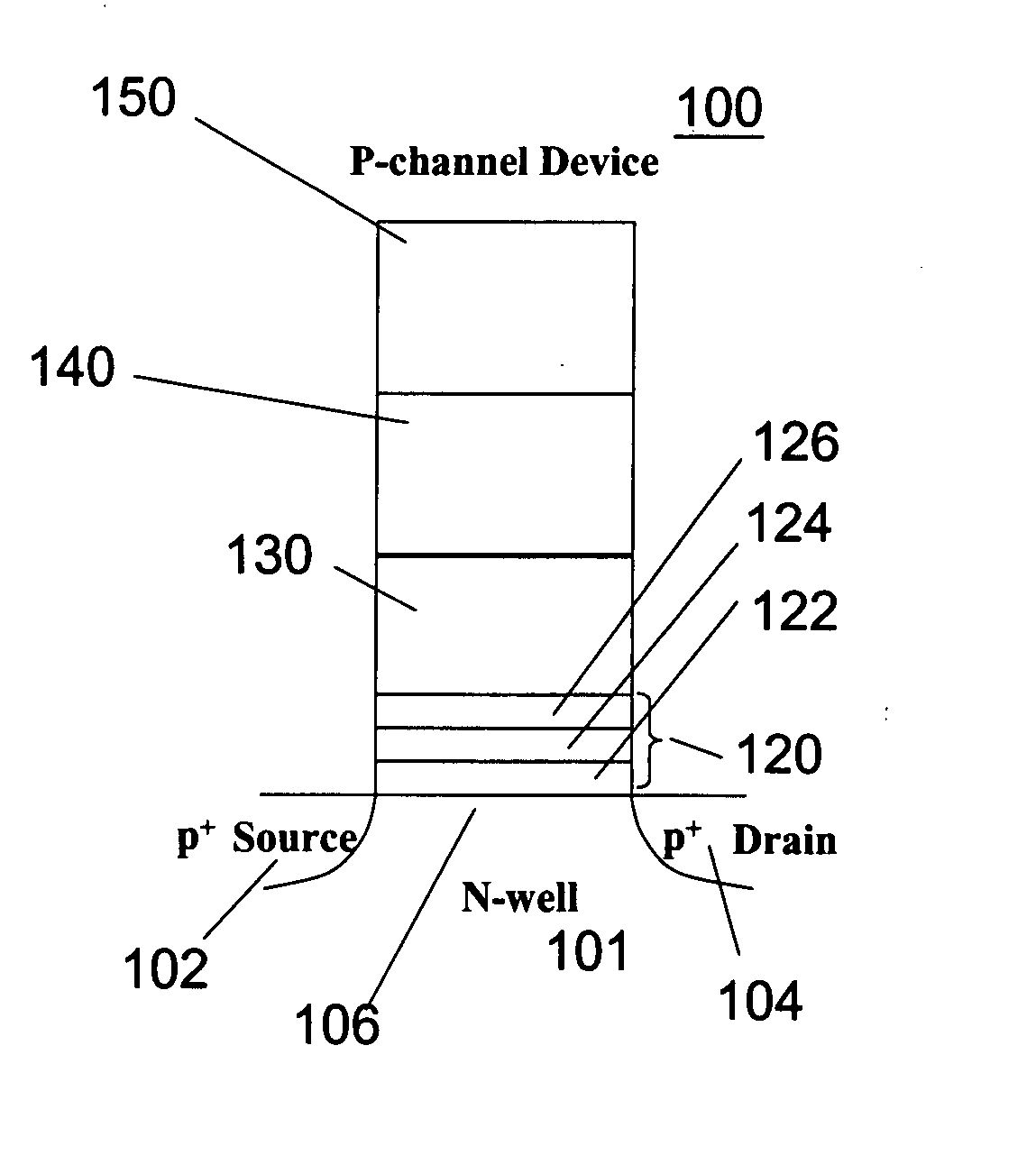

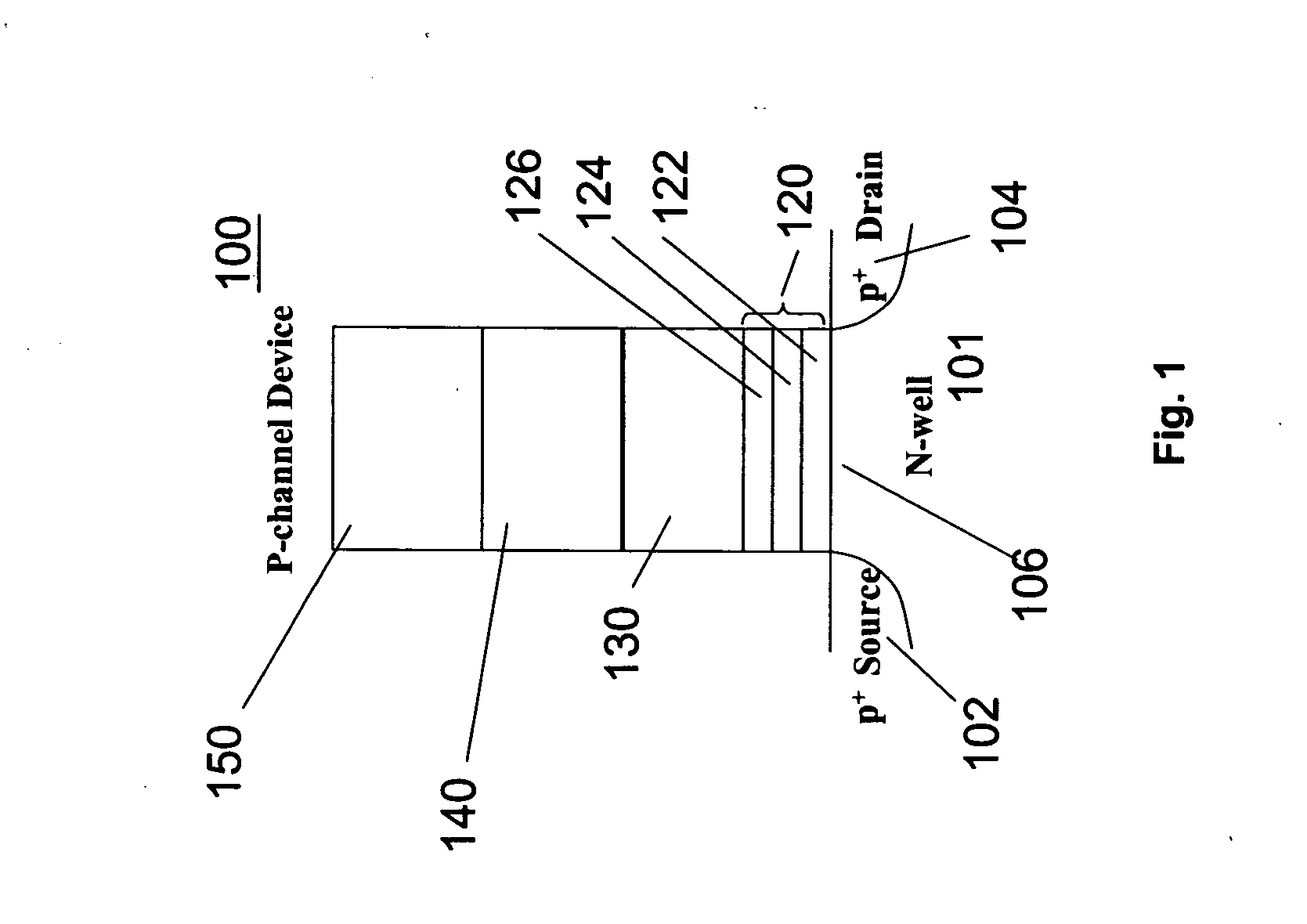

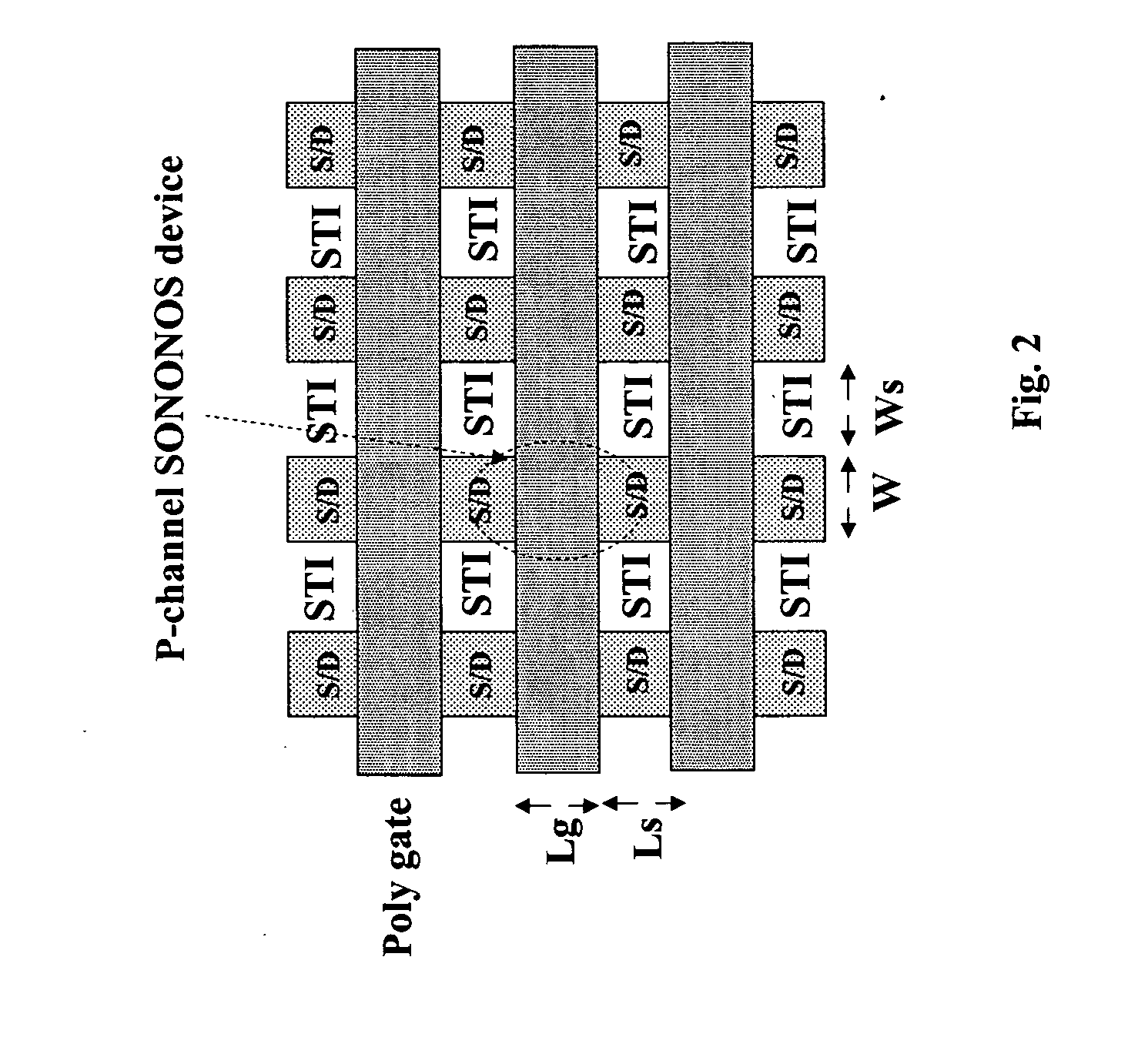

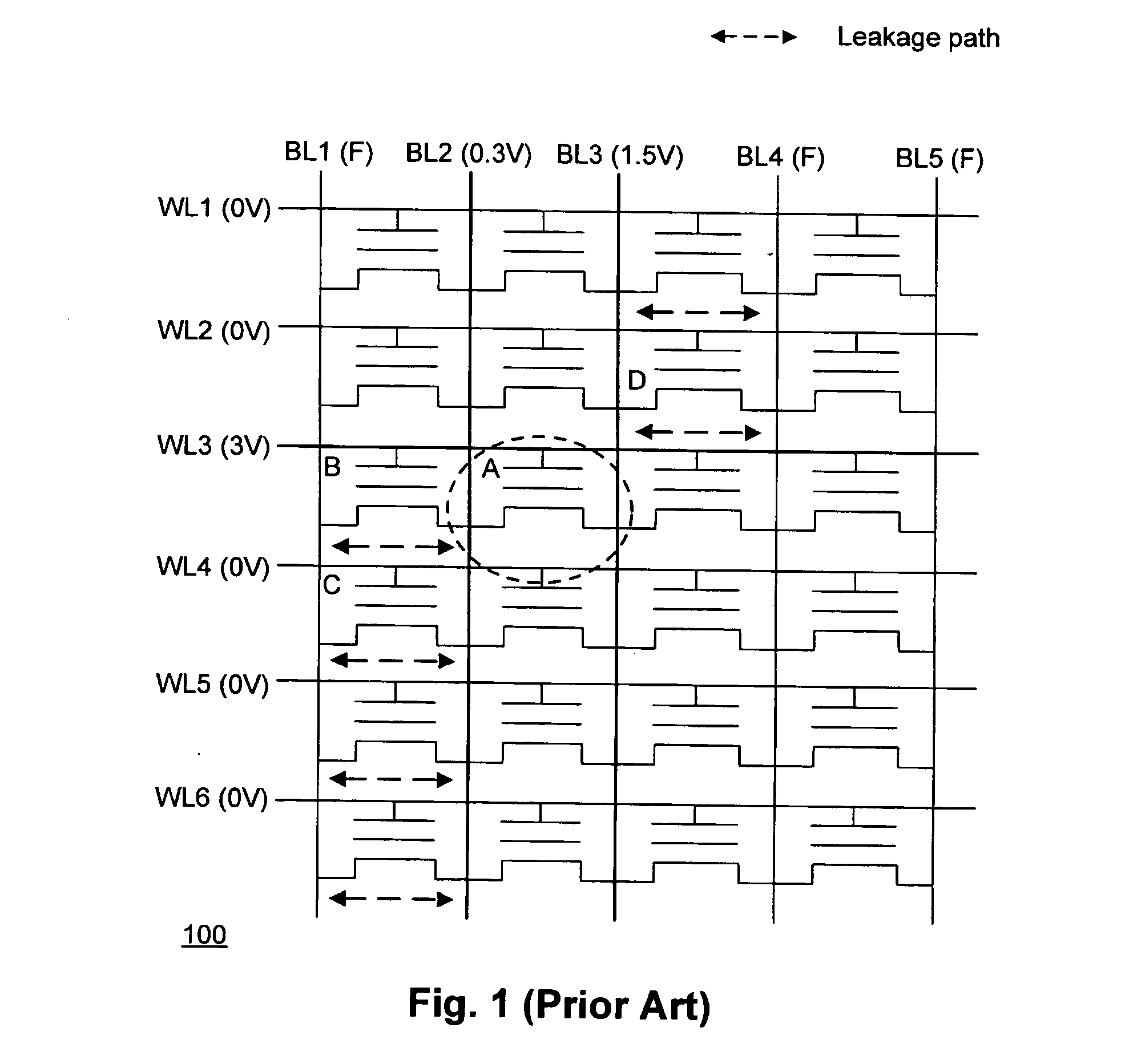

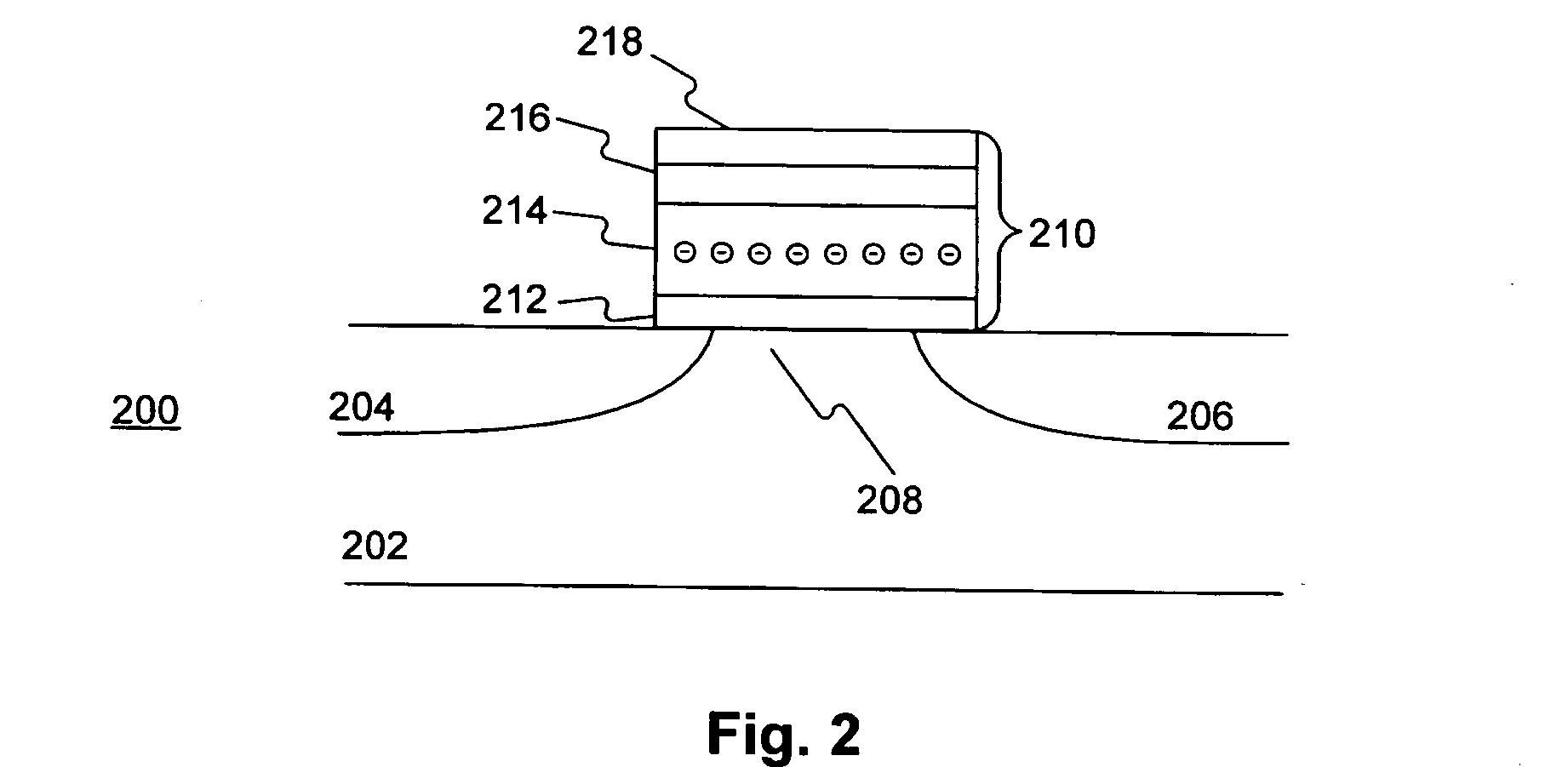

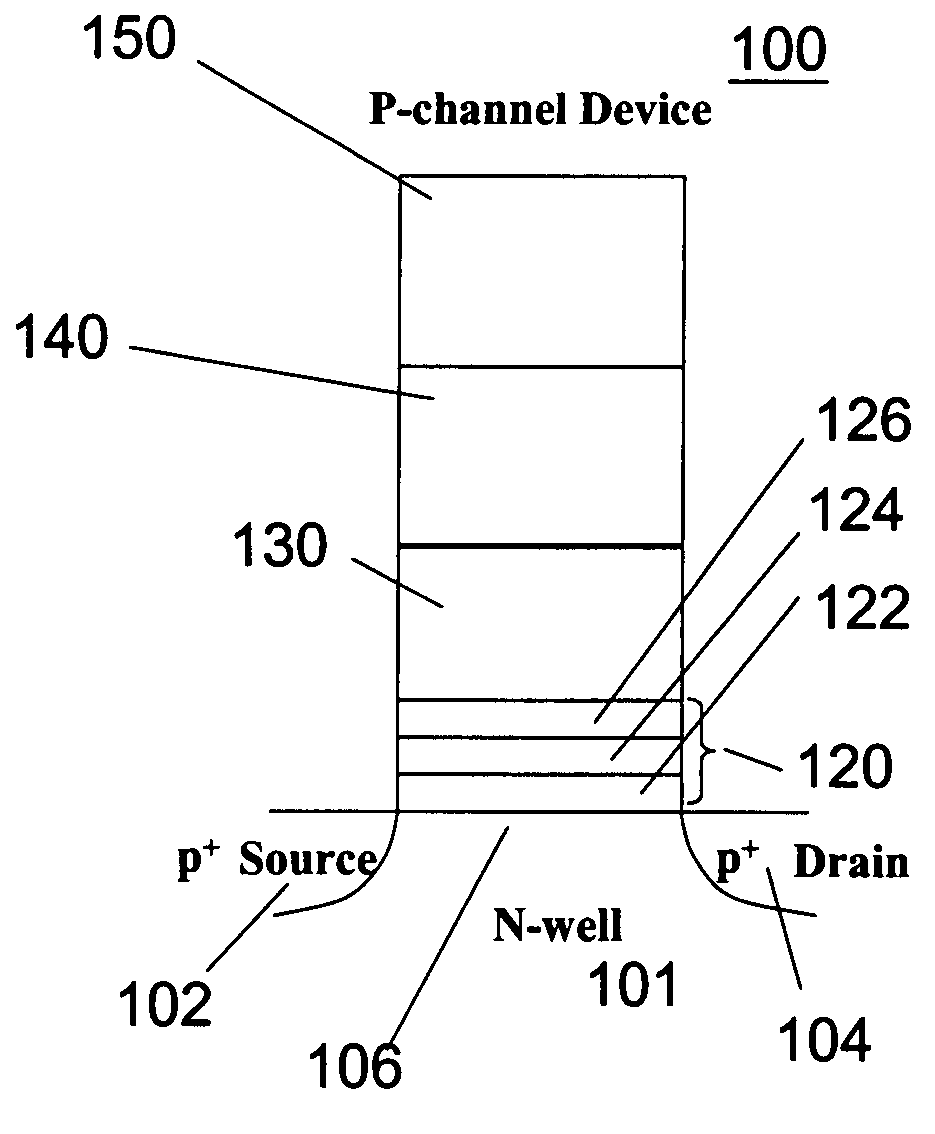

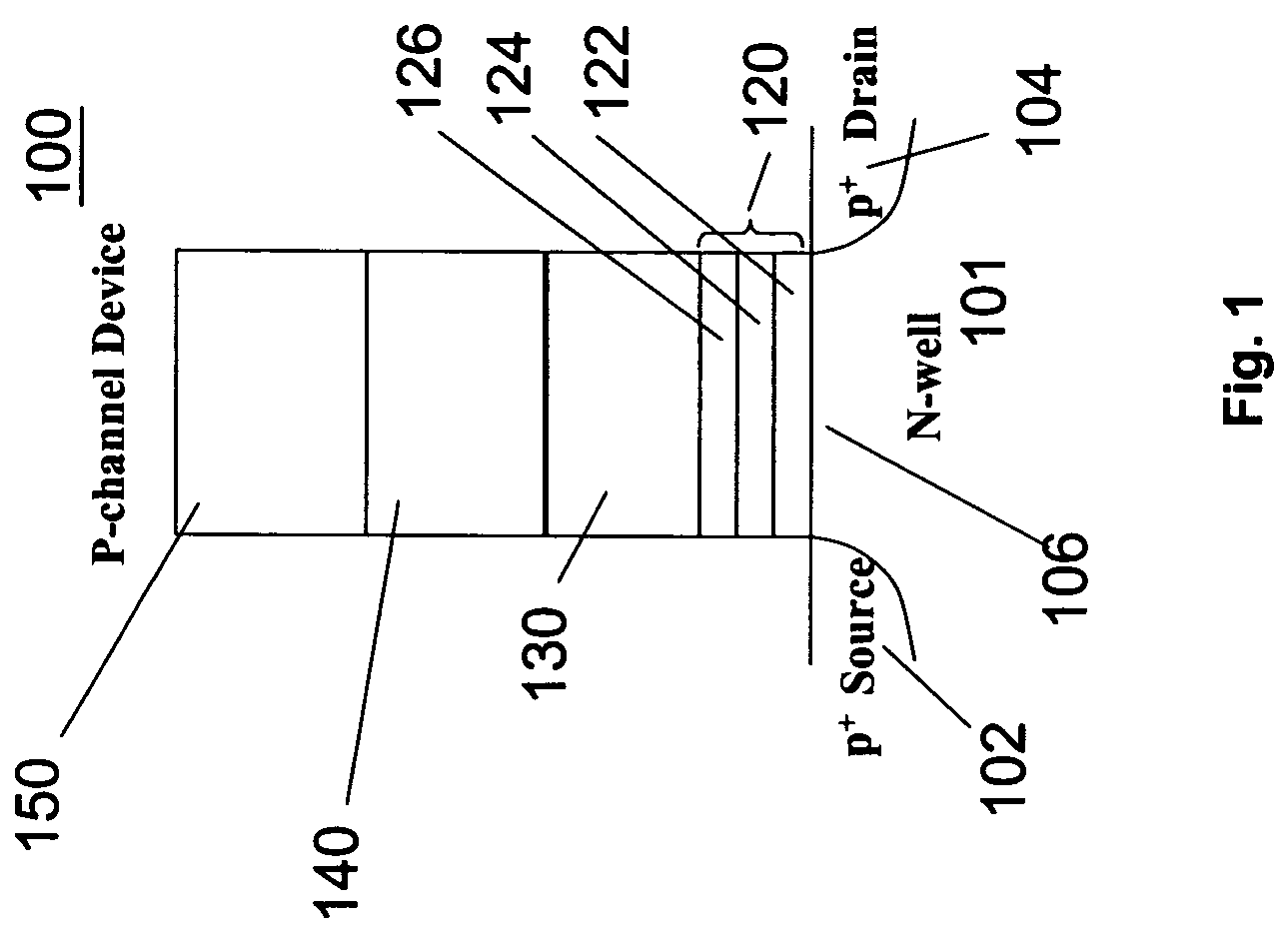

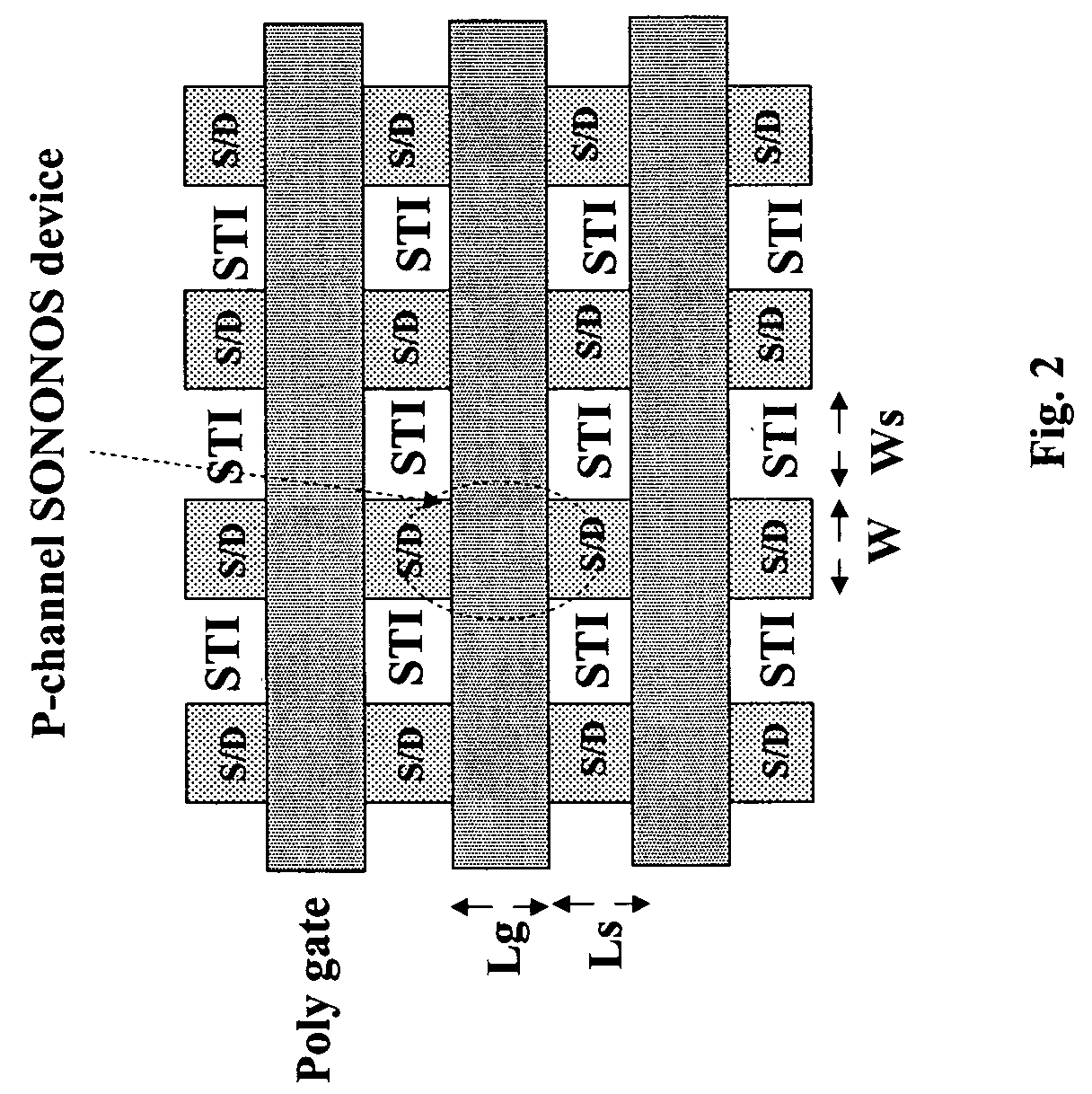

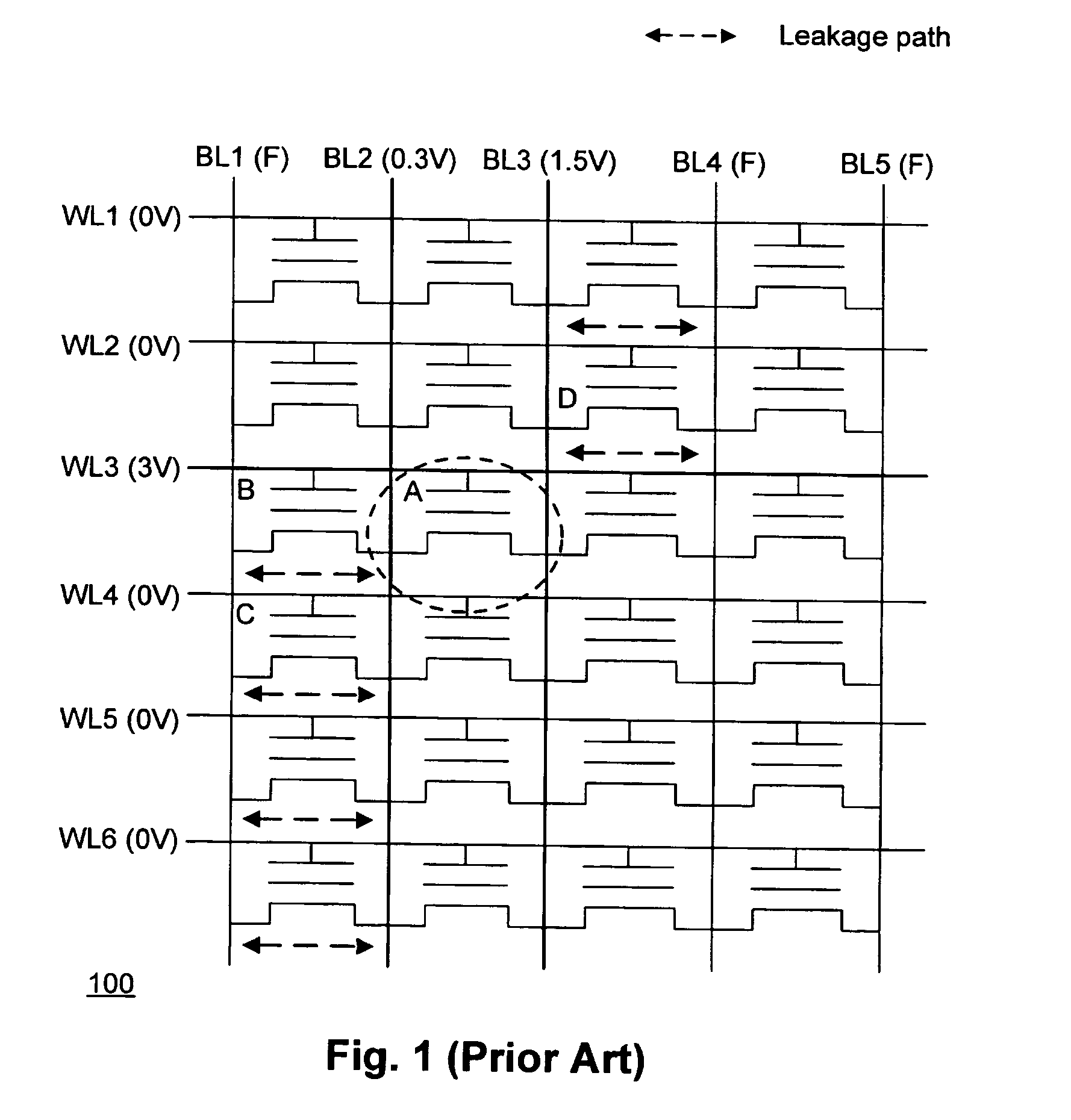

Methods of operating p-channel non-volatile memory devices

ActiveUS20060281260A1Disturbing effectNegative biasSolid-state devicesRead-only memoriesBit lineEngineering

Methods of operating non-volatile memory devices are described. The memory devices comprise memory cells having an n-type semiconductor substrate and p-type source and drain regions disposed below a surface of the substrate and separated by a channel region. A tunneling dielectric layer is disposed above the channel region. A charge storage layer is disposed above the tunneling dielectric layer. An upper insulating layer is disposed above the charge storage layer, and a gate is disposed above the upper insulating multi-layer structure. A positive bias is applied to a word lines of the memory device in a selected memory cell and a negative bias is applied to a bit line in the selected cell.

Owner:MACRONIX INT CO LTD

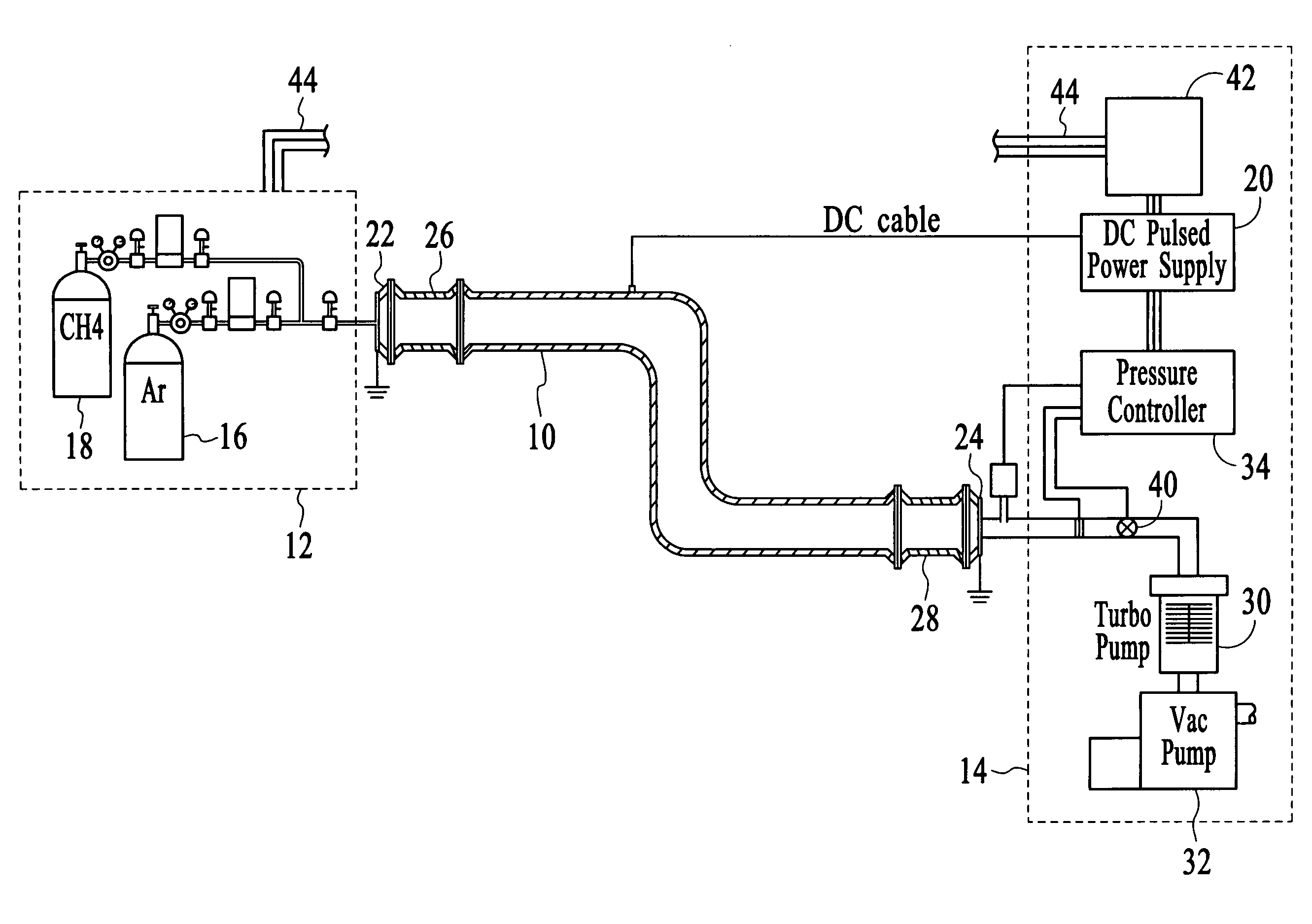

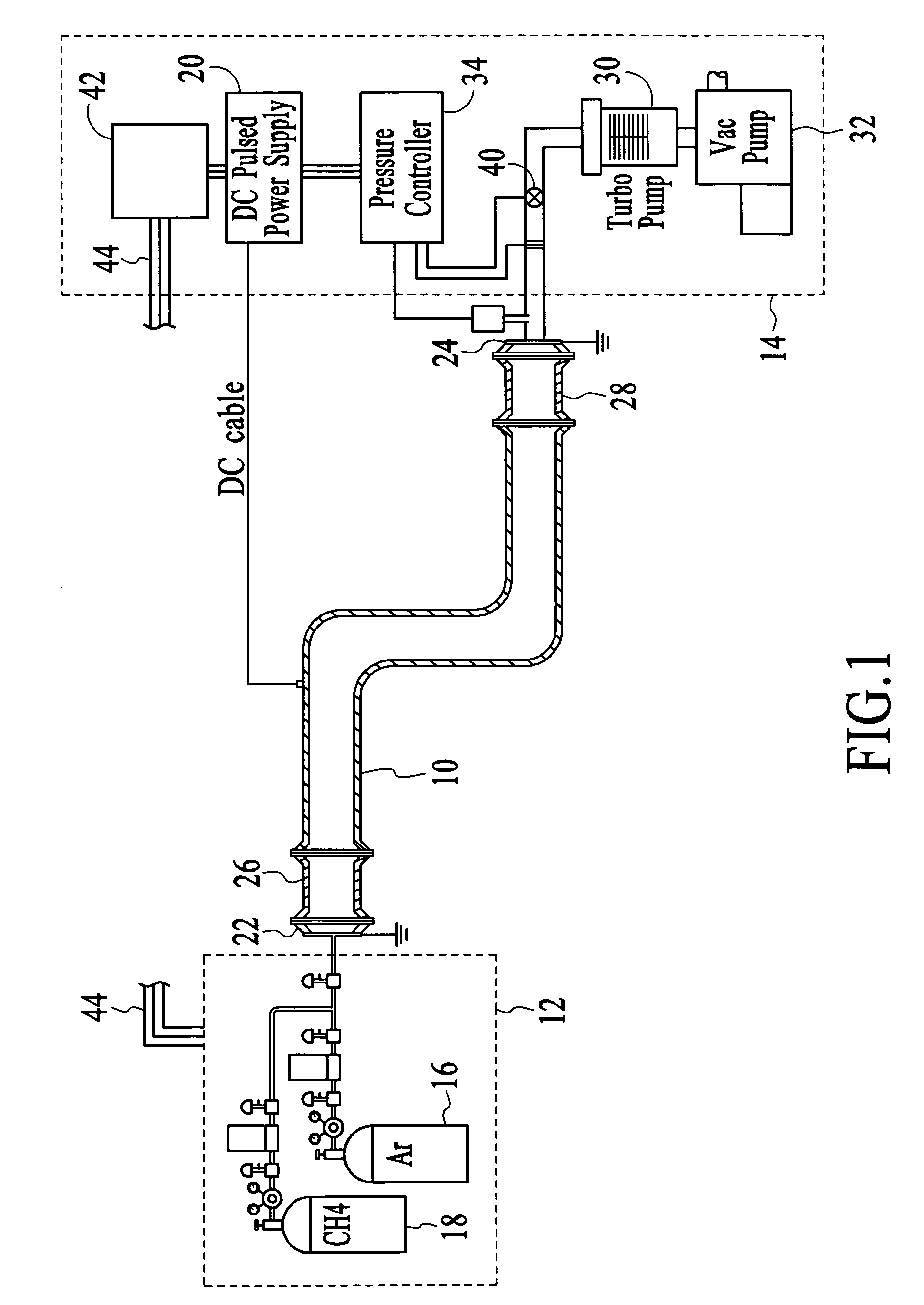

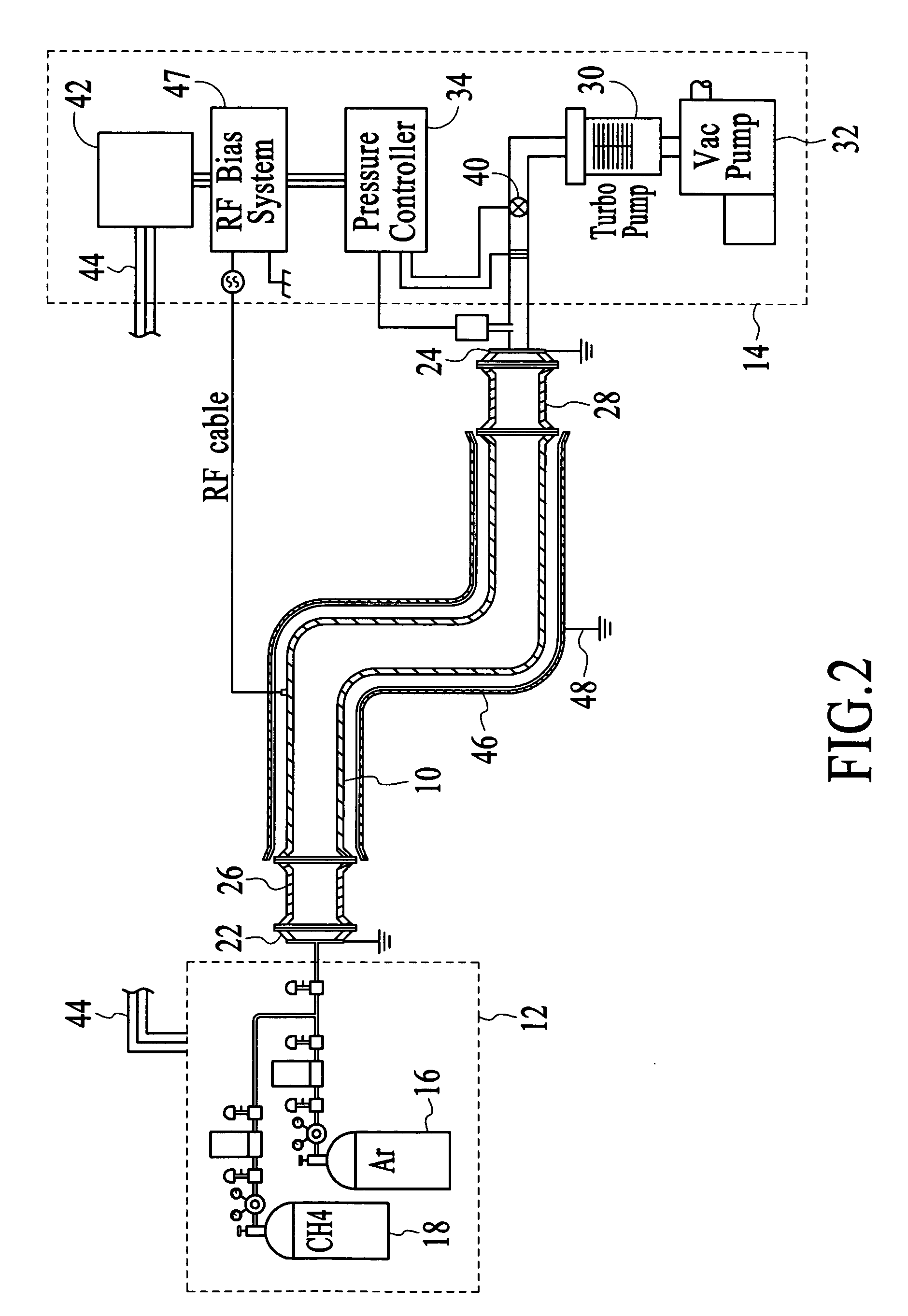

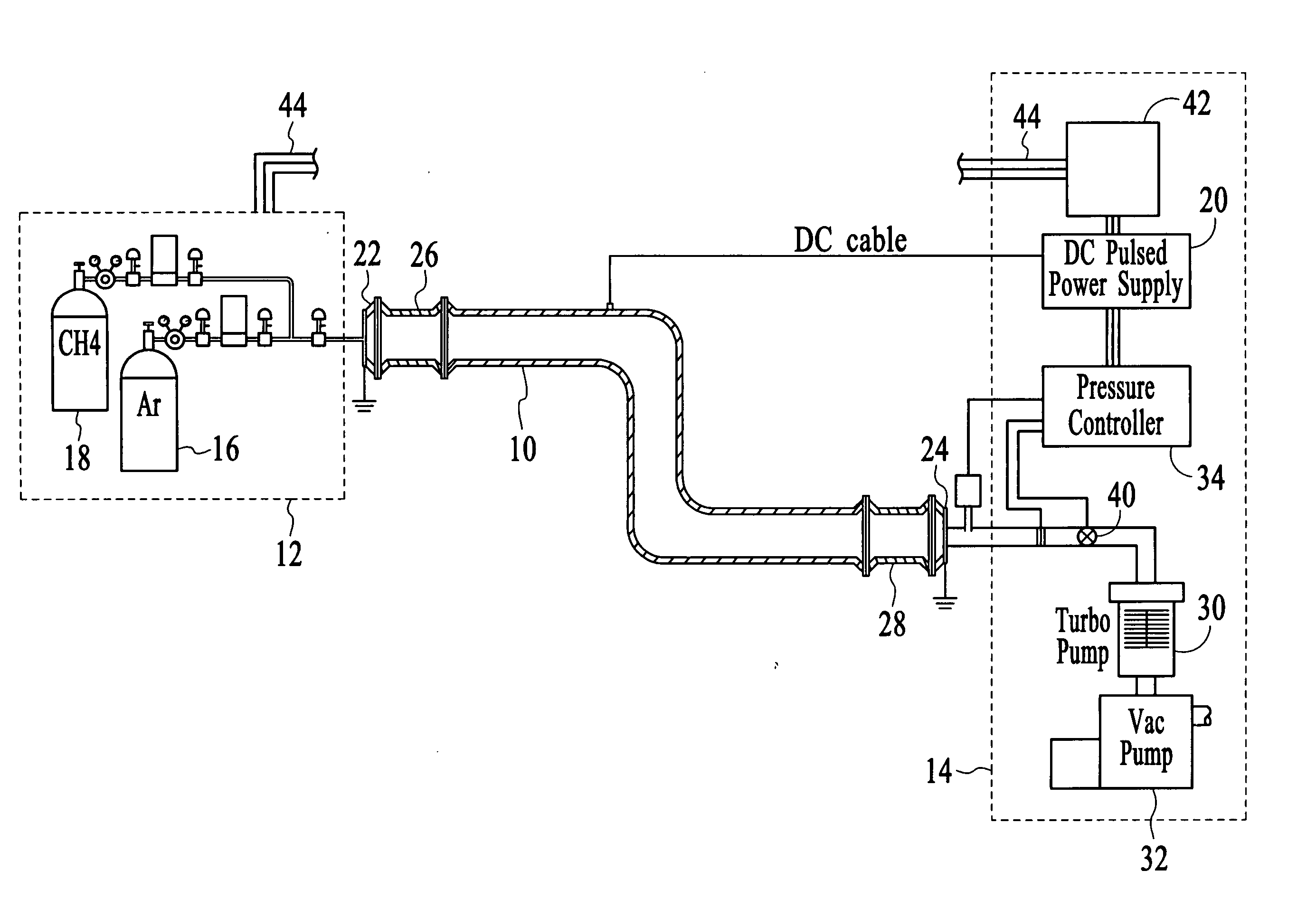

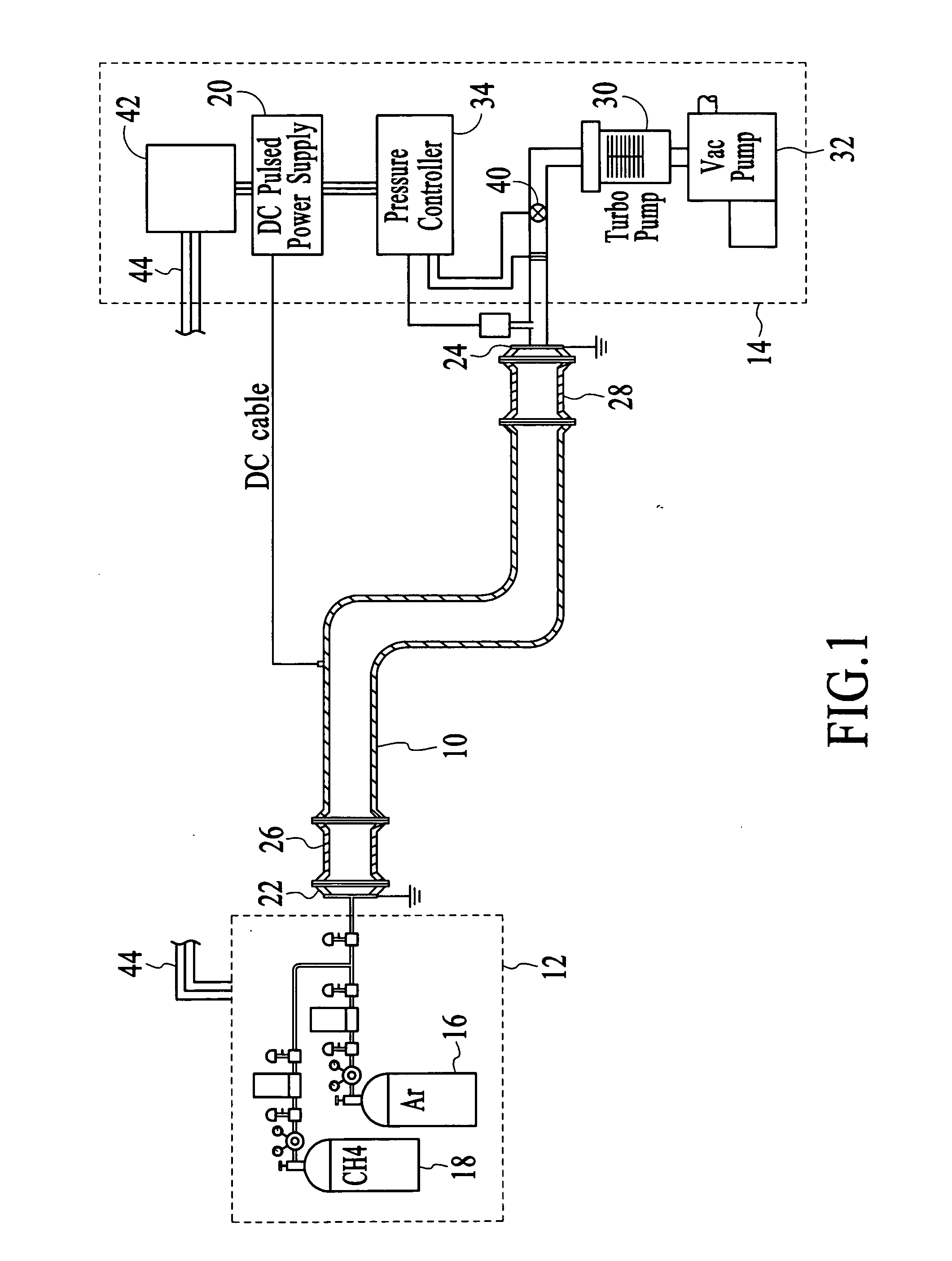

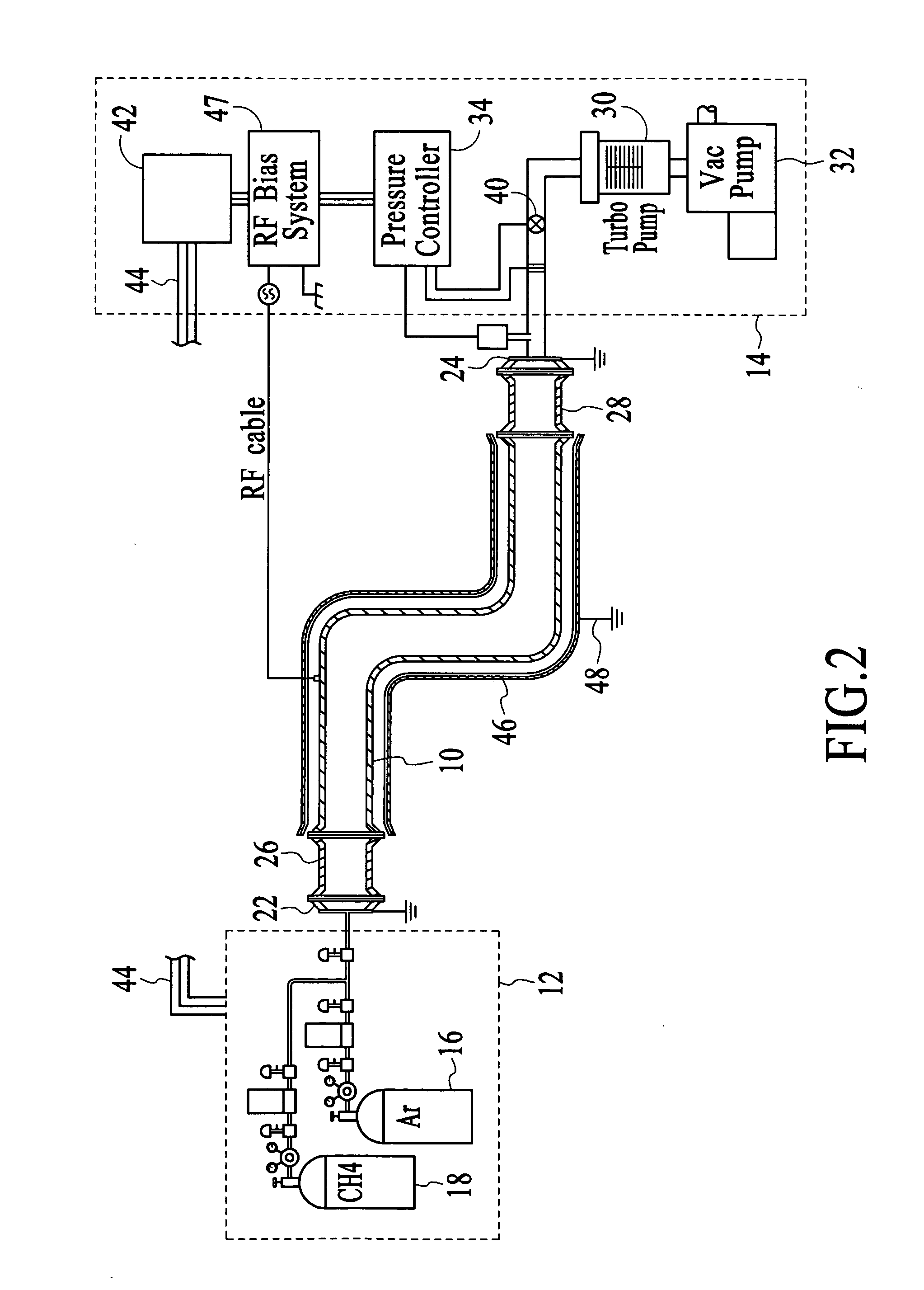

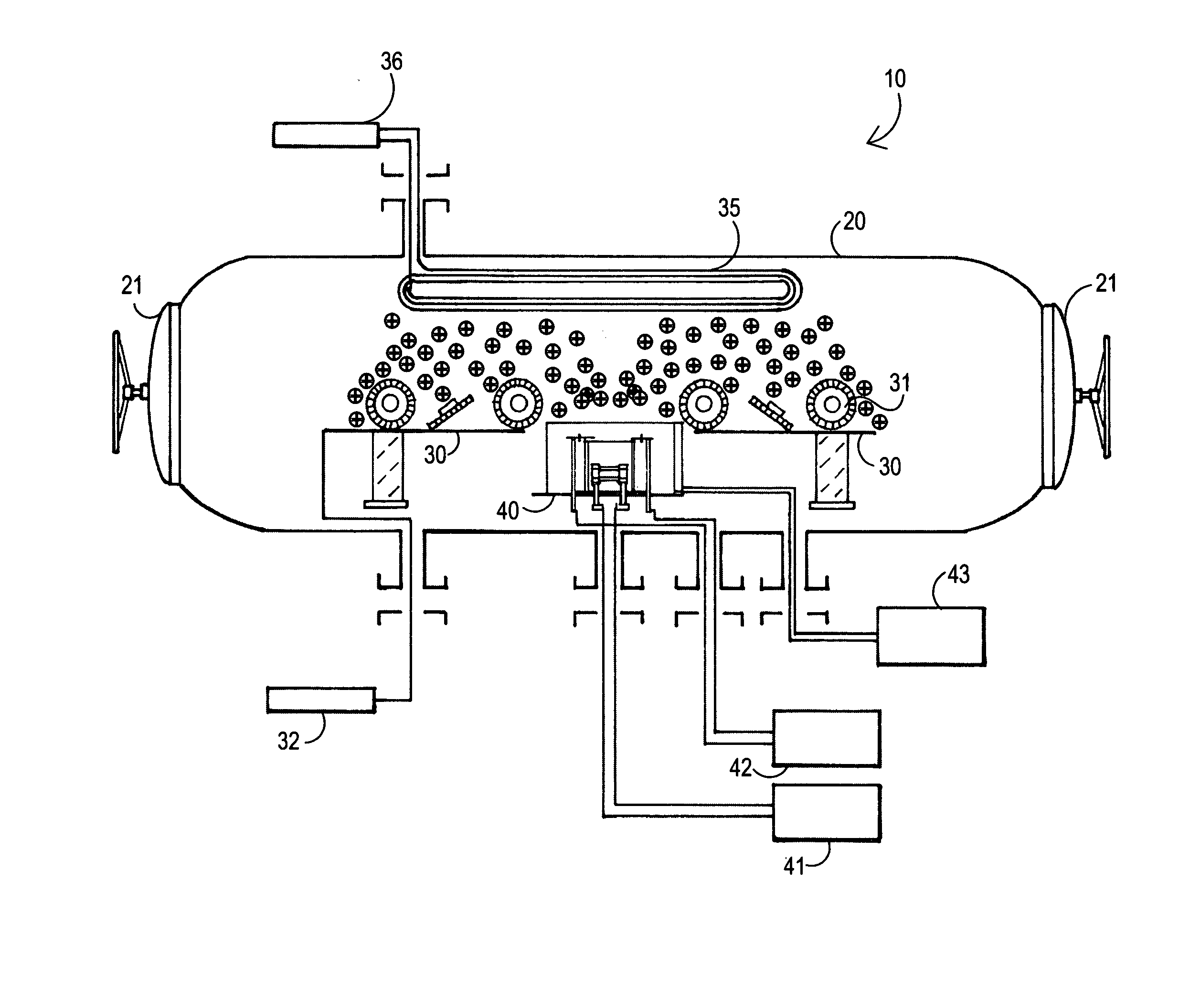

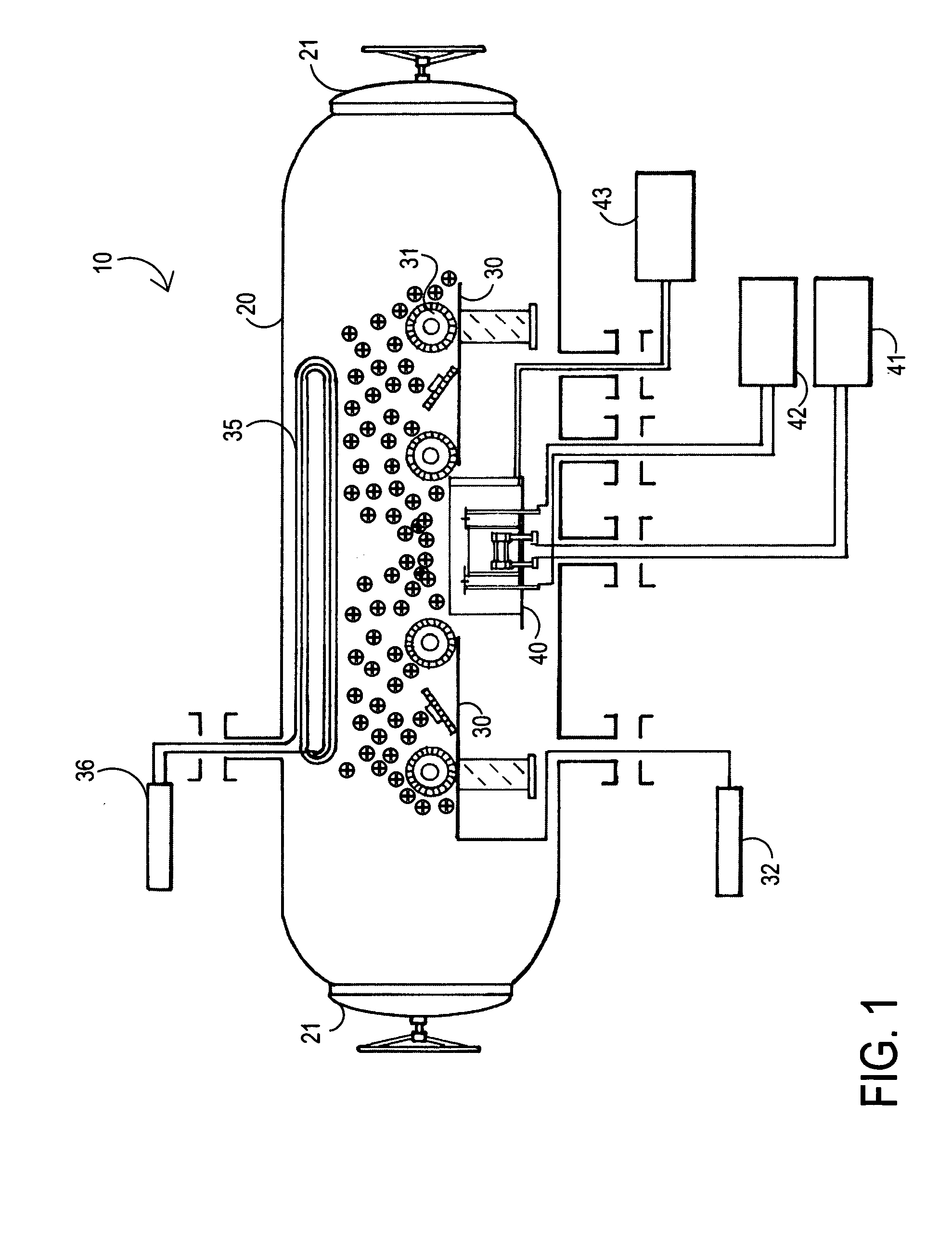

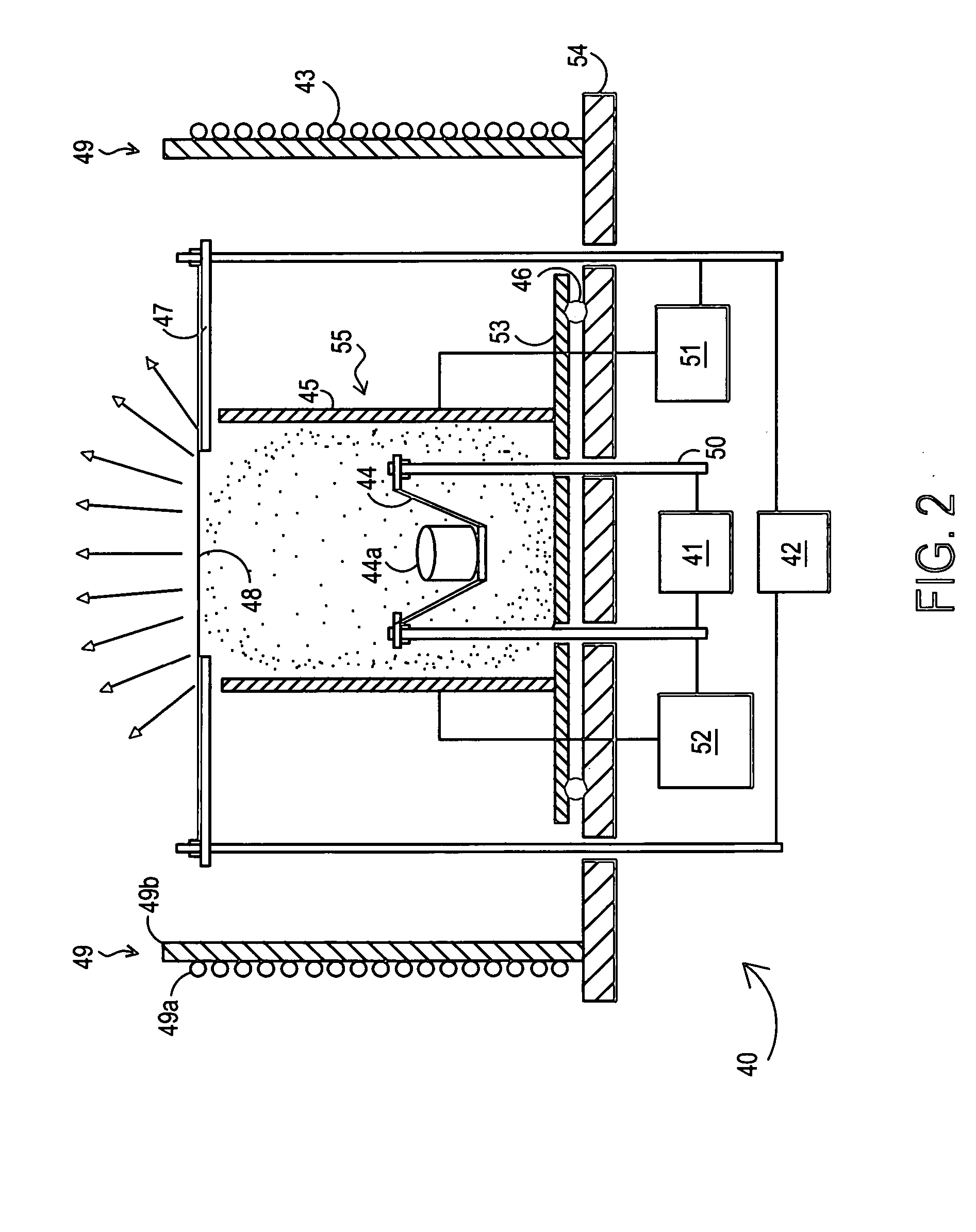

Method and system for coating internal surfaces of prefabricated process piping in the field

ActiveUS7300684B2Improve adhesionIncreases magnitudeLiquid surface applicatorsVacuum evaporation coatingHydrocarbon mixturesDiamond-like carbon

The coating of internal surfaces of a workpiece is achieved by connecting a bias voltage such that the workpiece functions as a cathode and by connecting an anode at each opening of the workpiece. A source gas is introduced at an entrance opening, while a vacuum source is connected at an exit opening. Pressure within the workpiece is monitored and the resulting pressure information is used for maintaining a condition that exhibits the hollow cathode effect. Optionally, a pre-cleaning may be provided by introducing a hydrocarbon mixture and applying a negative bias to the workpiece, so as to sputter contaminants from the workpiece using argon gas. Argon gas may also be introduced during the coating processing to re-sputter the coating, thereby improving uniformity along the length of the workpiece. The coating may be a diamond-like carbon material having properties which are determined by controlling ion bombardment energy.

Owner:AGM CONTAINER CONTROLS

Program/erase method for p-channel charge trapping memory device

ActiveUS20050270849A1Improve efficiencyIncrease speedTransistorSolid-state devicesBit lineComputer science

A method of operating a memory device is disclosed, wherein the memory device includes an n-type substrate and a plurality of memory cells formed thereon, each memory cell corresponding to a word line, a first bit line, and second bit line, and including a first bit portion and a second bit portion each for storing one bit of information. The method includes resetting a selected memory cell by applying a first negative bias to the word line of the selected memory cell and applying a ground bias to the first and second bit lines, and programming the first bit portion of the selected memory cell by applying a first positive bias to the word line of the selected memory cell, applying a second negative bias to the first bit line of the selected memory cell, and applying a ground bias to the second bit line of the selected memory cell.

Owner:MACRONIX INT CO LTD

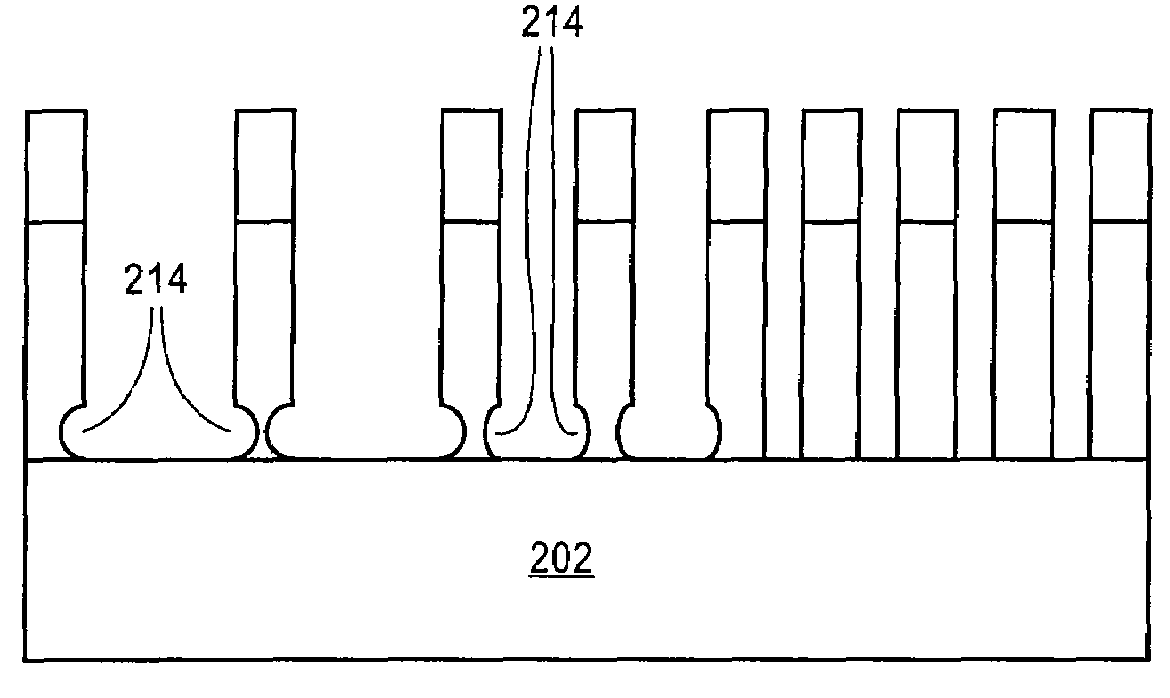

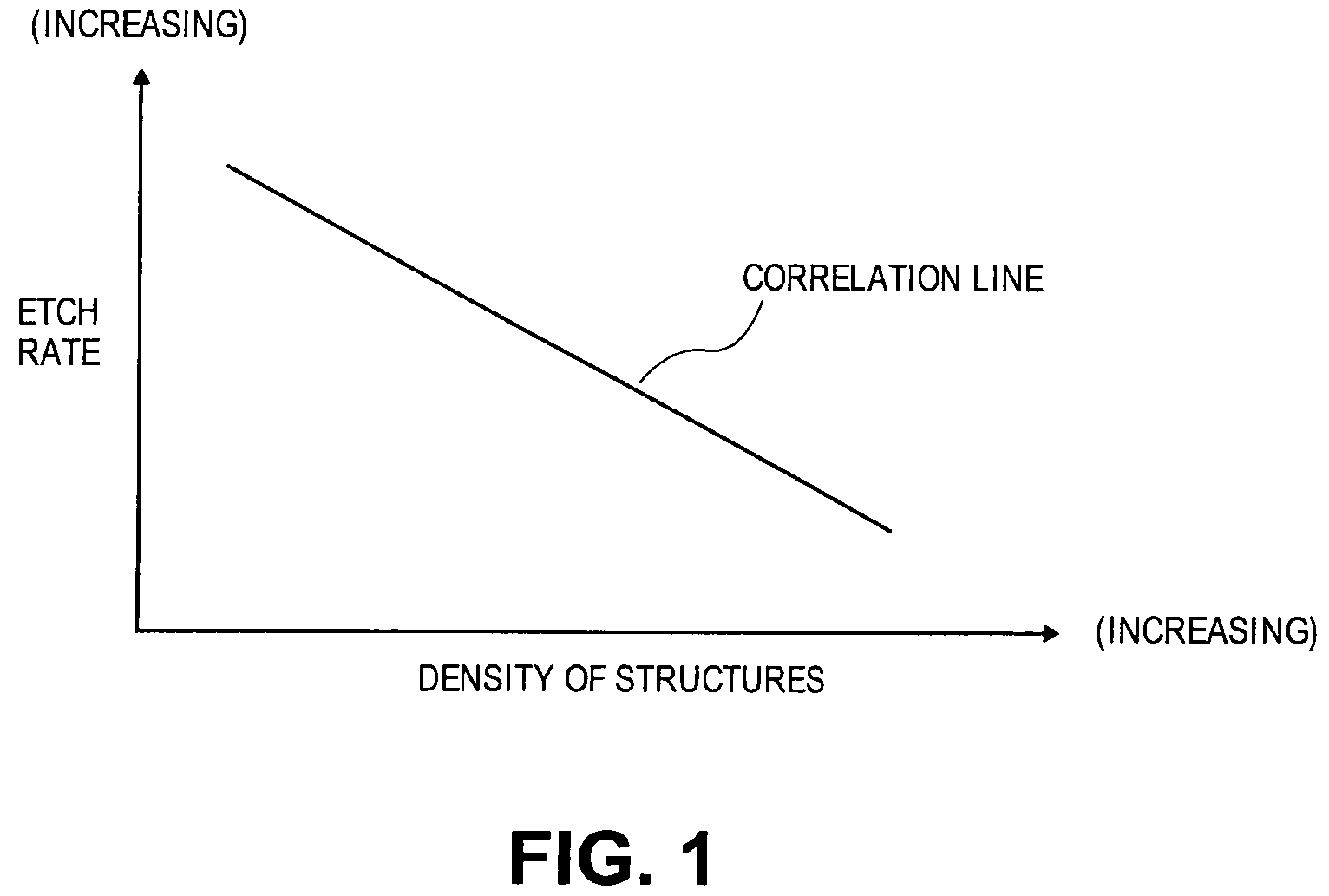

Pulsed-plasma system with pulsed sample bias for etching semiconductor substrates

ActiveUS7718538B2Electric discharge tubesDecorative surface effectsSemiconductor structureNegative bias

A pulsed plasma system with pulsed sample bias for etching semiconductor structures is described. In one embodiment, a portion of a sample is removed by applying a pulsed plasma process, wherein the pulsed plasma process comprises a plurality of duty cycles. A negative bias is applied to the sample during the ON state of each duty cycle, while a zero bias is applied to the sample during the OFF state of each duty cycle. In another embodiment, a first portion of a sample is removed by applying a continuous plasma process. The continuous plasma process is then terminated and a second portion of the sample is removed by applying a pulsed plasma process.

Owner:APPLIED MATERIALS INC

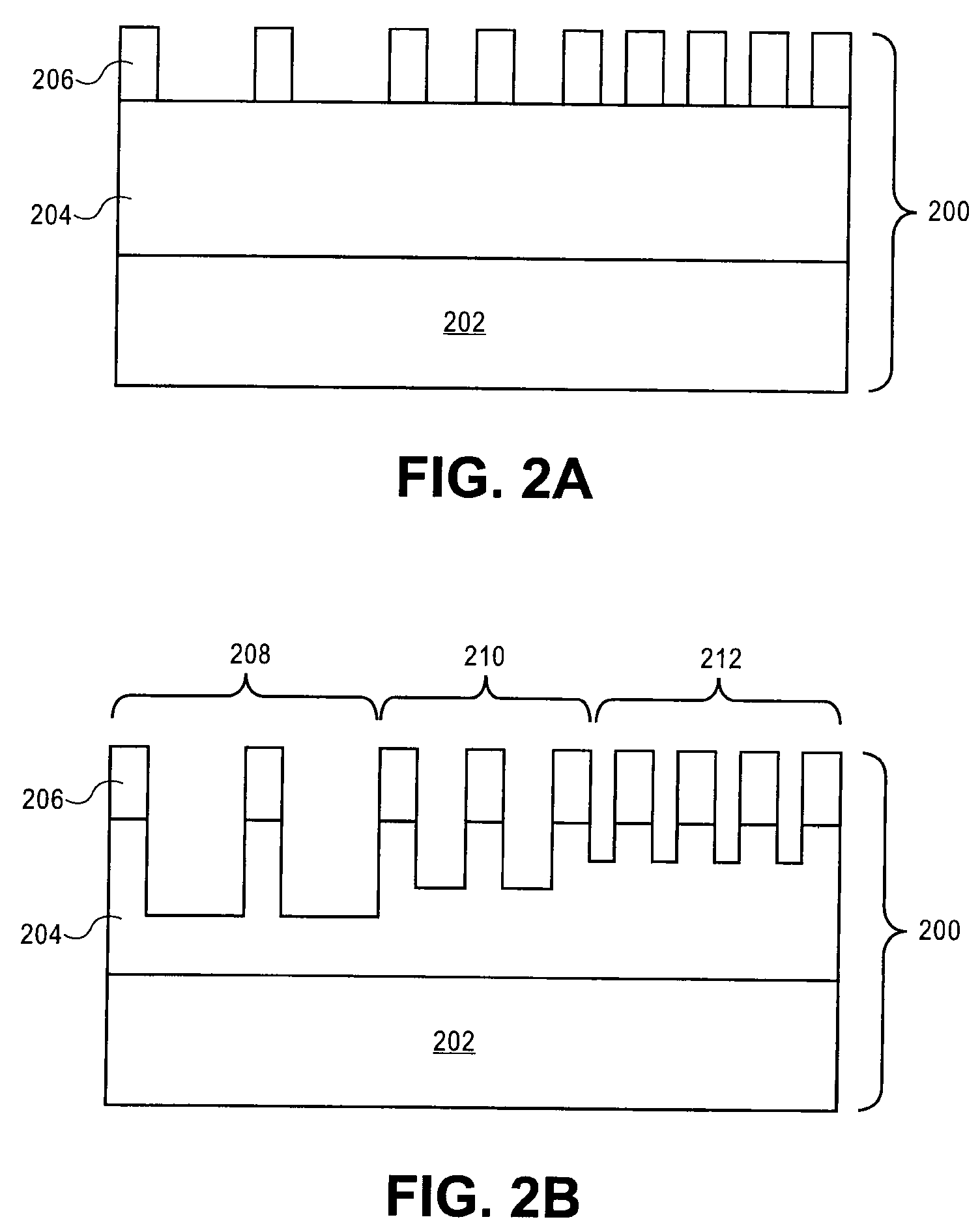

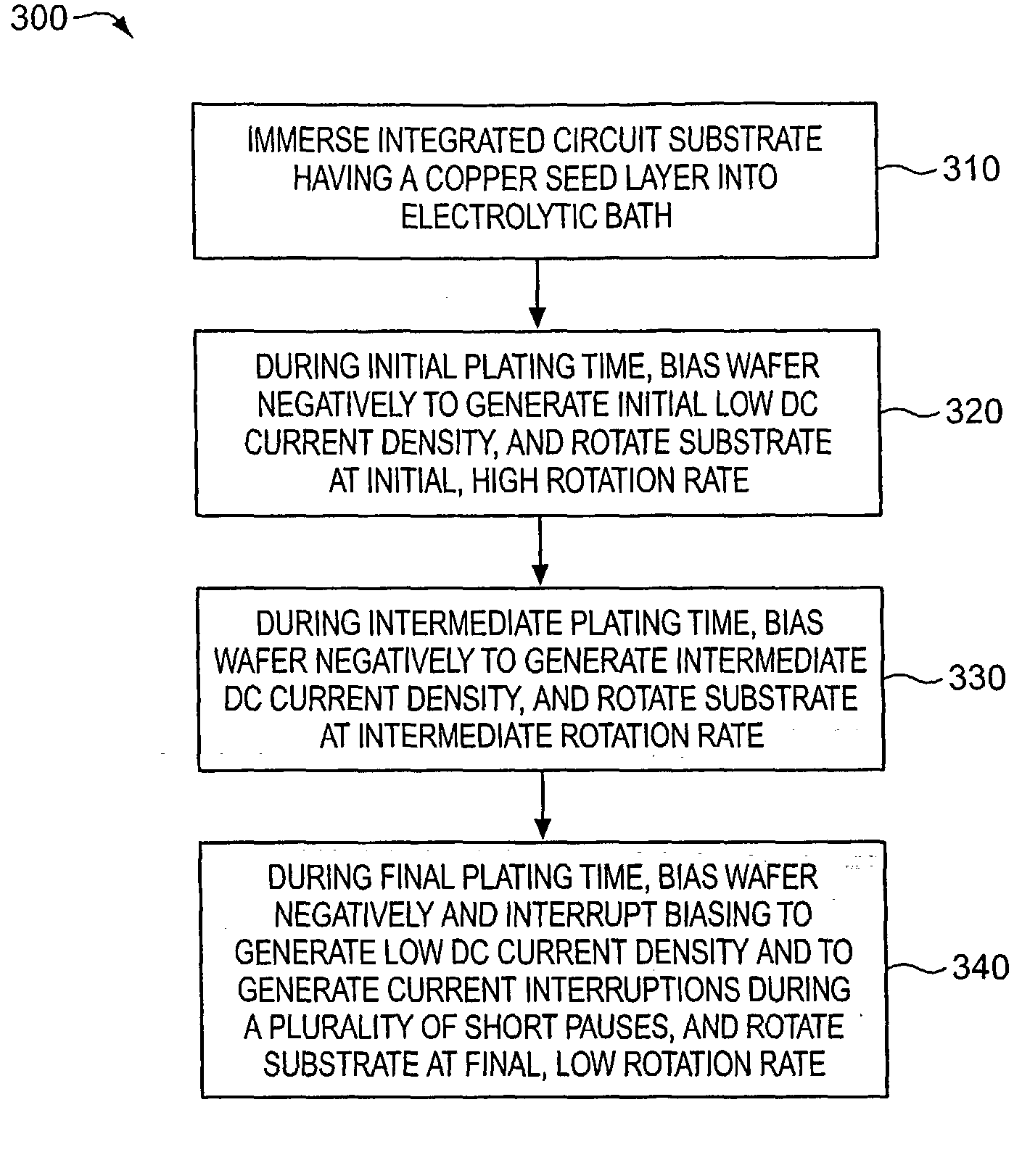

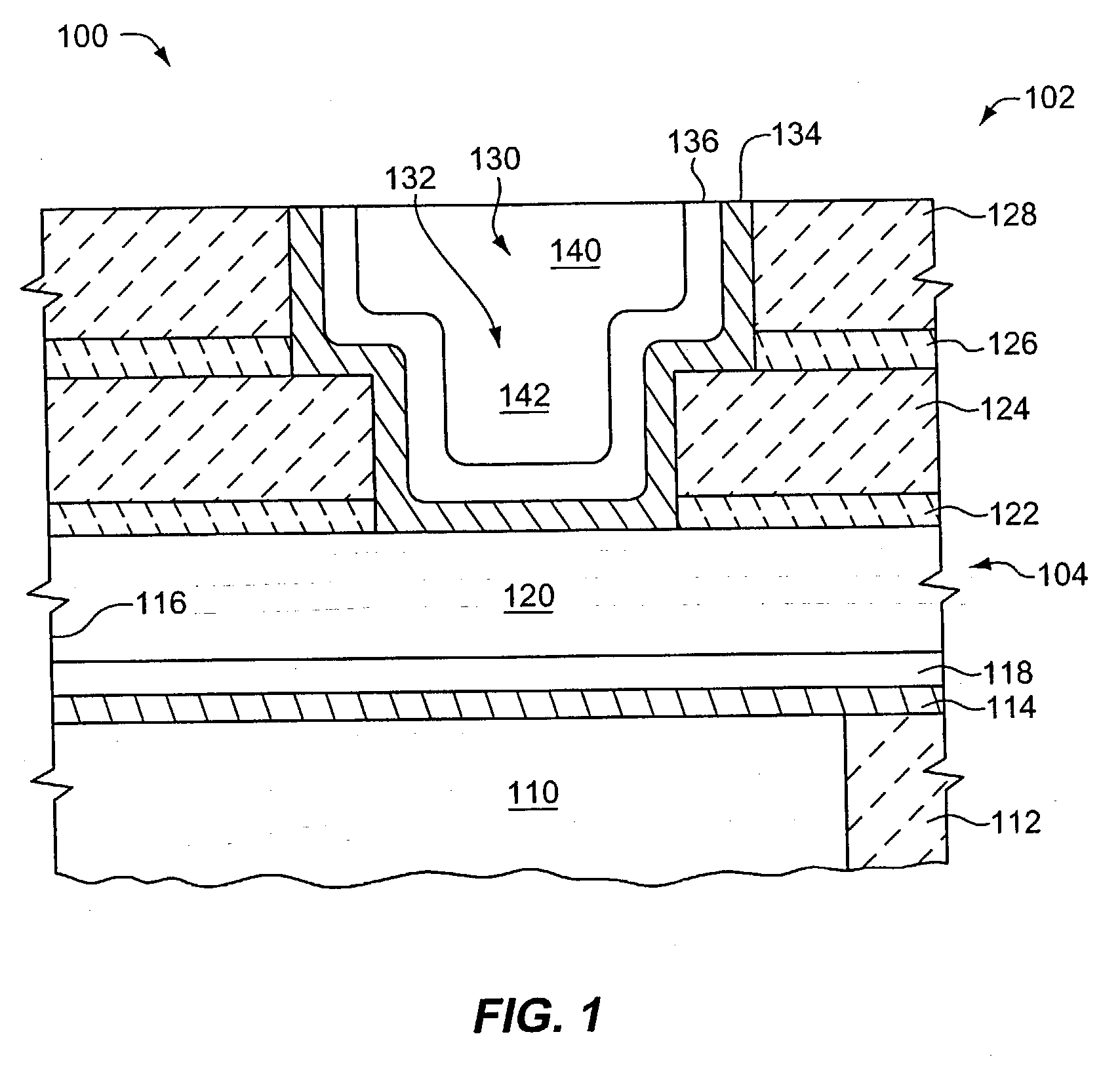

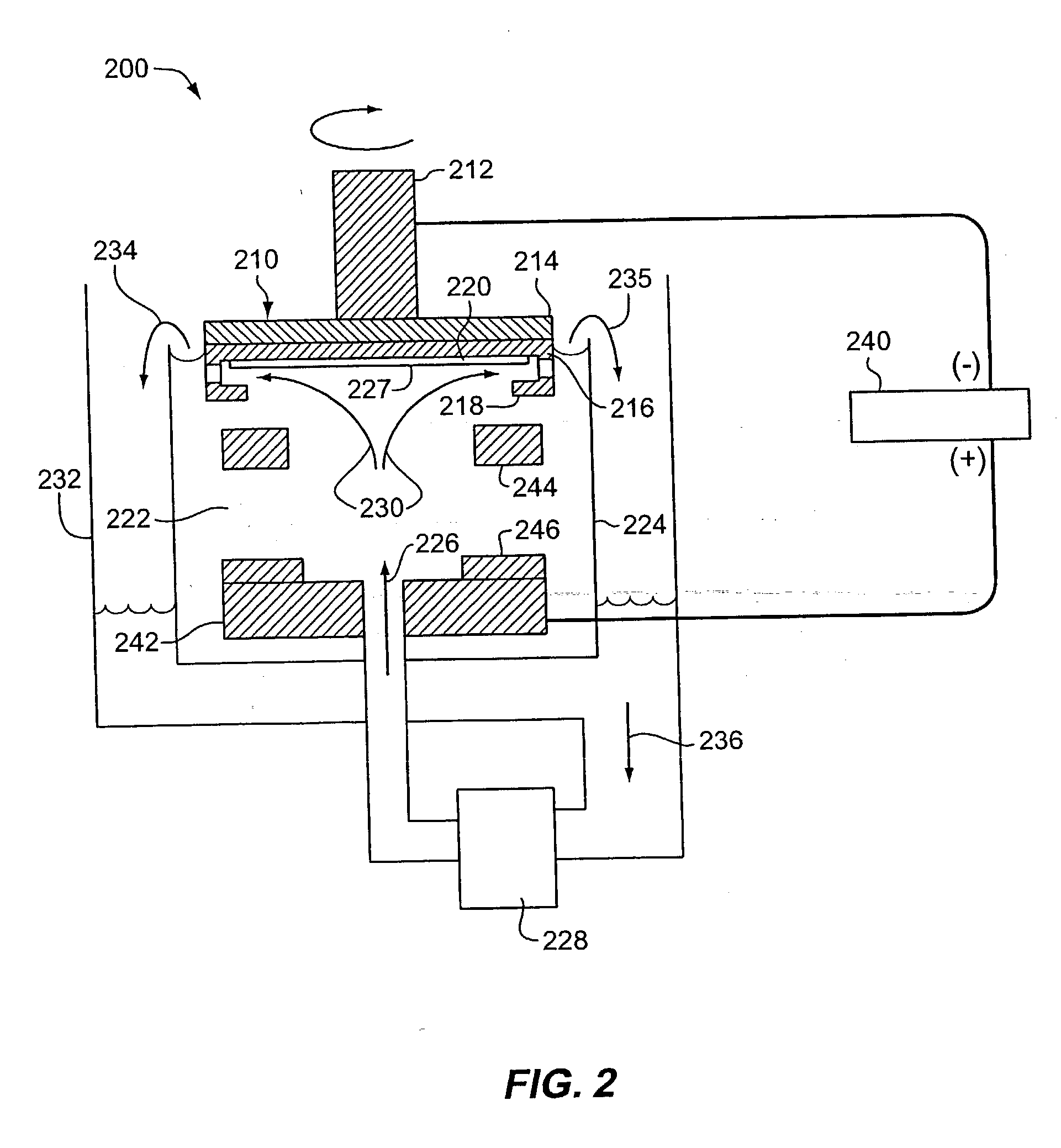

Electroplating using DC current interruption and variable rotation rate

A negative bias is applied to an integrated circuit wafer immersed in an electrolytic plating solution to generate a DC current. After about ten percent to sixty percent of the final layer thickness has formed in a first plating time, biasing is interrupted during short pauses during a second plating time to generate substantially zero DC current. The pauses are from about 2 milliseconds to 5 seconds long, and typically about 10 milliseconds to 500 milliseconds. Generally, about 2 pauses to 100 pauses are used, and typically about 3 pauses to 15 pauses. Generally, the DC current density during the second plating time is greater than the DC current density during the initial plating time. Typically, the integrated circuit wafer is rotated during electroplating. Preferably, the wafer is rotated at a slower rotation rate during the second plating time than during the first plating time.

Owner:NOVELLUS SYSTEMS

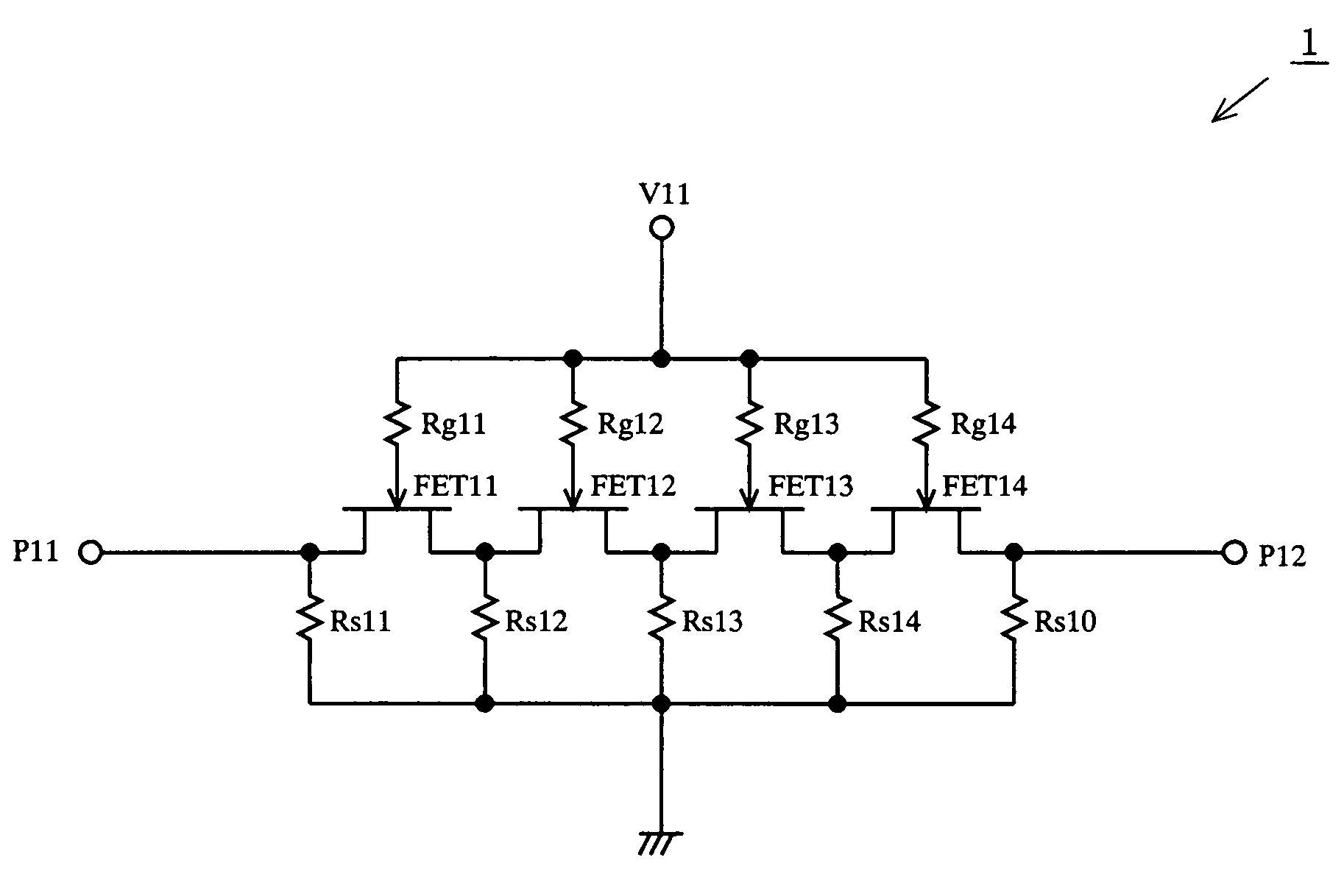

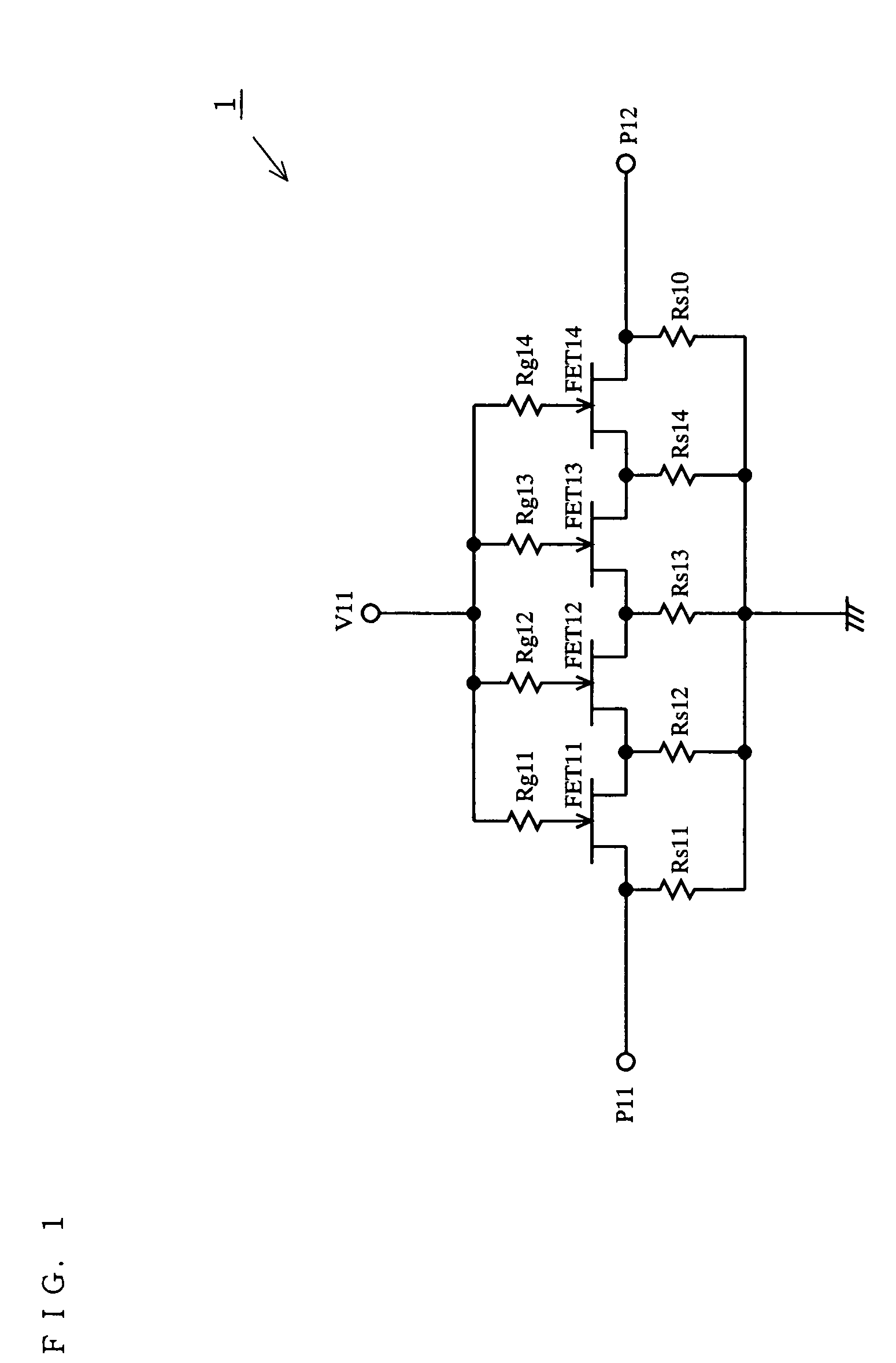

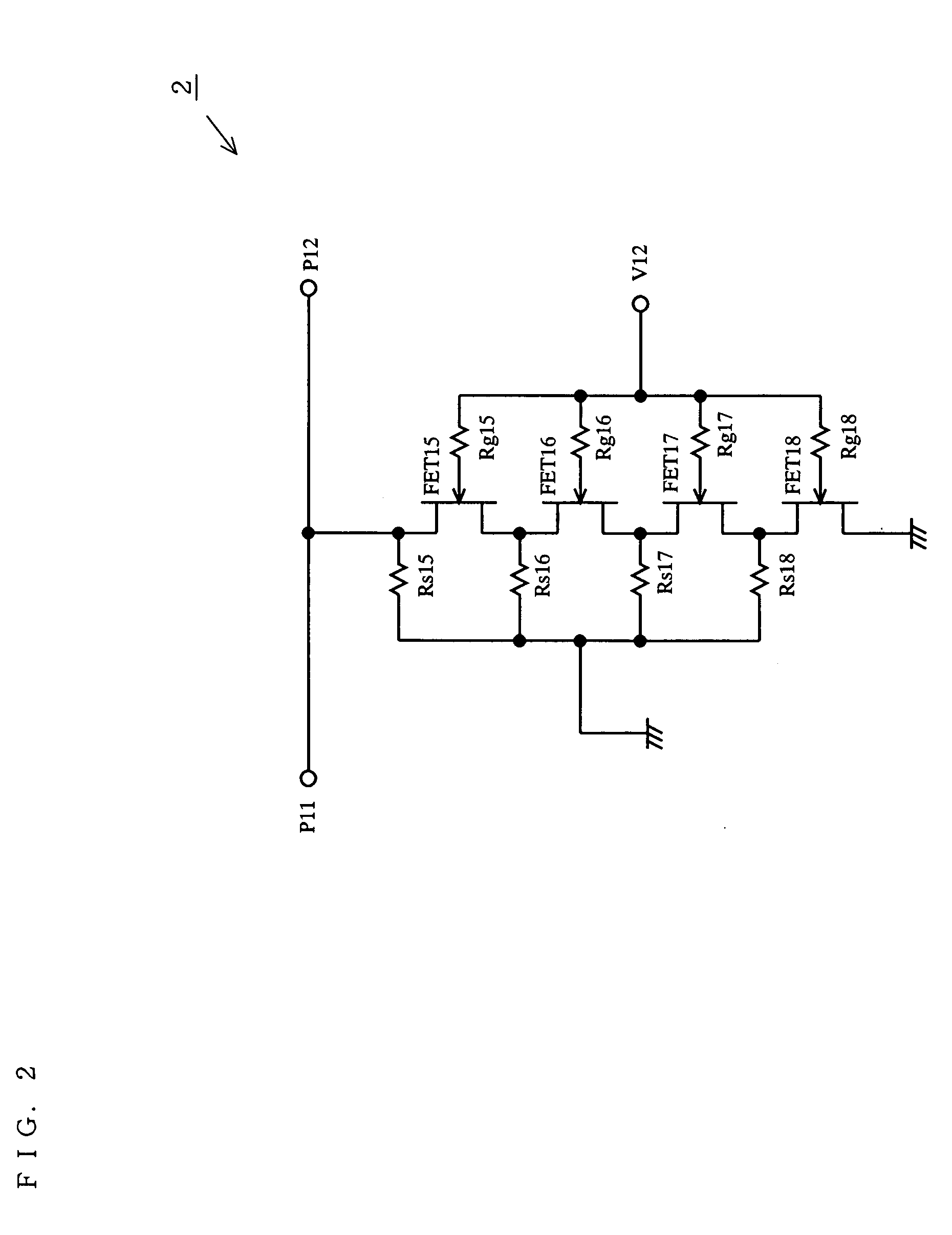

Radio frequency switching circuit, radio frequency switching device, and transmitter module device

InactiveUS20070290744A1Desirable radio frequency characteristicDesirable endurancePower amplifiersSolid-state devicesHigh pressureWide band

The present invention provides an inexpensive radio frequency switching circuit having desirable radio frequency characteristics over a wide band and desirable endurance against the inflow of a high voltage signal such as an electrostatic surge. Either a negative bias voltage or a positive bias voltage being greater than or equal to 0V and less than or equal to a Schottky forward voltage is used for the control terminals V11 and V12 for controlling FETs 11 to 18 and FETs 21 to 28 so as to turn ON / OFF the path extending from the first input / output terminal P11 to the second input / output terminal P12 and the path extending from the first input / output terminal P11 to the third input / output terminal P13. Thus, it is possible to eliminate the need for DC cut capacitors.

Owner:PANASONIC CORP

Method for preparing multi-metal element doped diamond film

InactiveCN101787512AImprove performanceVacuum evaporation coatingSputtering coatingCathodic arc depositionIon bombardment

The invention discloses a method for preparing a multi-metal element doped diamond film, which is characterized by comprising the following steps: removing a pollution layer on matrix surface by using the ultrasonic cleaning technology, carrying out ion beam bombardment cleaning on the matrix surface by using inert gas ion beam produced by an ion source, carrying out metal ion bombardment cleaning on the matrix surface by using metal ions produced by a cathodic arc source under a condition of high workpiece negative bias, preparing a gradient transition layer by using a cathodic arc deposition or ion beam assisted magnetron sputtering (IBAMS), and synthesizing a multi-metal element doped DLC film on the transition layer by using ion beam deposition and mosaic composite target magnetron sputtering, wherein the ion beam deposition is realized by introducing carbon gas in the ion source; and the mosaic composite target doped multiple metal are used, and the main body material of the mosaic composite target can be any one of Ti, Cr, W, Zr, Nb and Ta, and the mosaic block material is one or more of other metals except the above main body materials.

Owner:CHINA UNIV OF GEOSCIENCES (BEIJING)

Method and system for coating internal surfaces of prefabricated process piping in the field

ActiveUS20060011468A1Improve adhesionIncreases magnitudeCellsLiquid surface applicatorsDiamond-like carbonHydrocarbon mixtures

The coating of internal surfaces of a workpiece is achieved by connecting a bias voltage such that the workpiece functions as a cathode and by connecting an anode at each opening of the workpiece. A source gas is introduced at an entrance opening, while a vacuum source is connected at an exit opening. Pressure within the workpiece is monitored and the resulting pressure information is used for maintaining a condition that exhibits the hollow cathode effect. Optionally, a pre-cleaning may be provided by introducing a hydrocarbon mixture and applying a negative bias to the workpiece, so as to sputter contaminants from the workpiece using argon gas. Argon gas may also be introduced during the coating processing to re-sputter the coating, thereby improving uniformity along the length of the workpiece. The coating may be a diamond-like carbon material having properties which are determined by controlling ion bombardment energy.

Owner:AGM CONTAINER CONTROLS

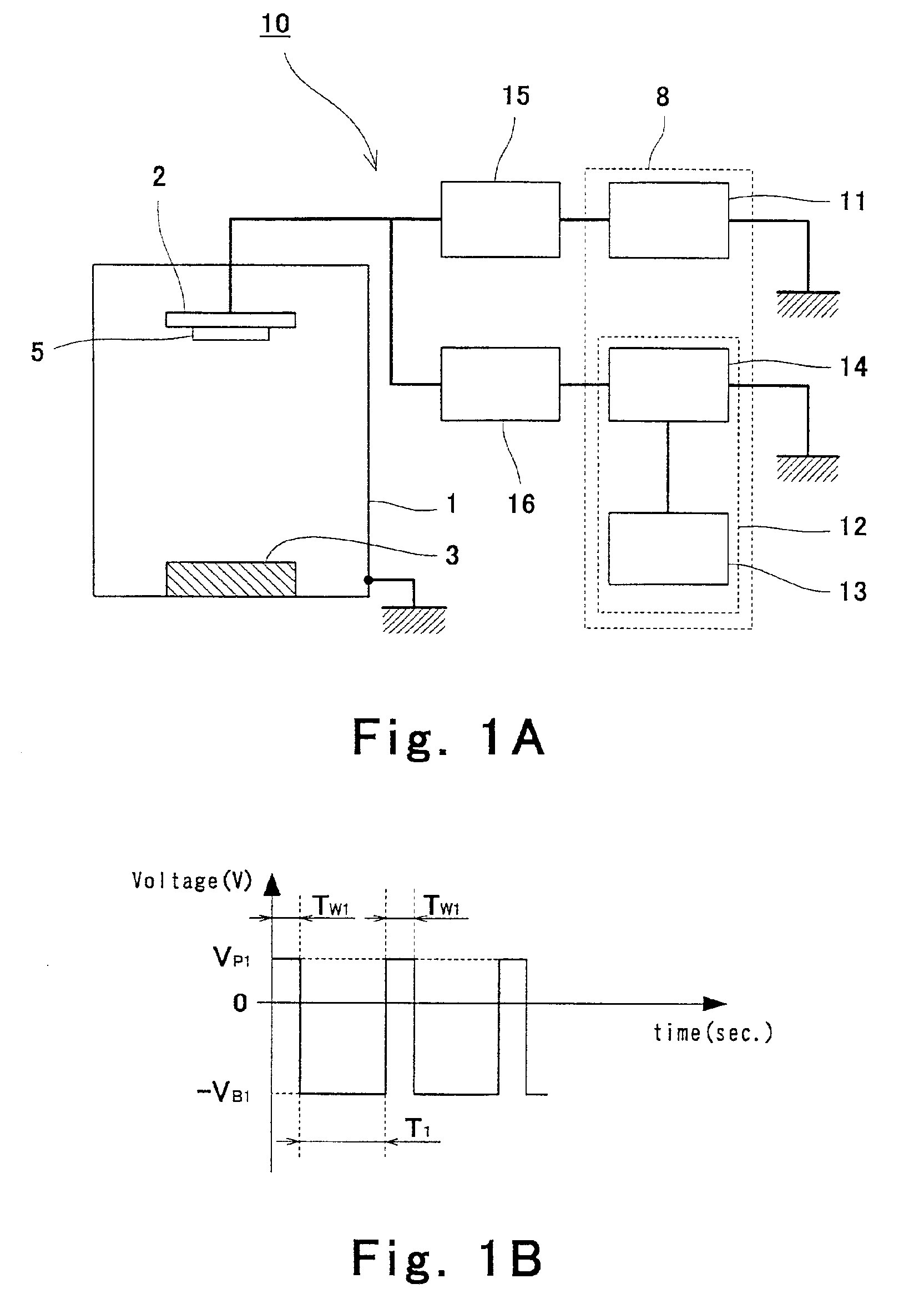

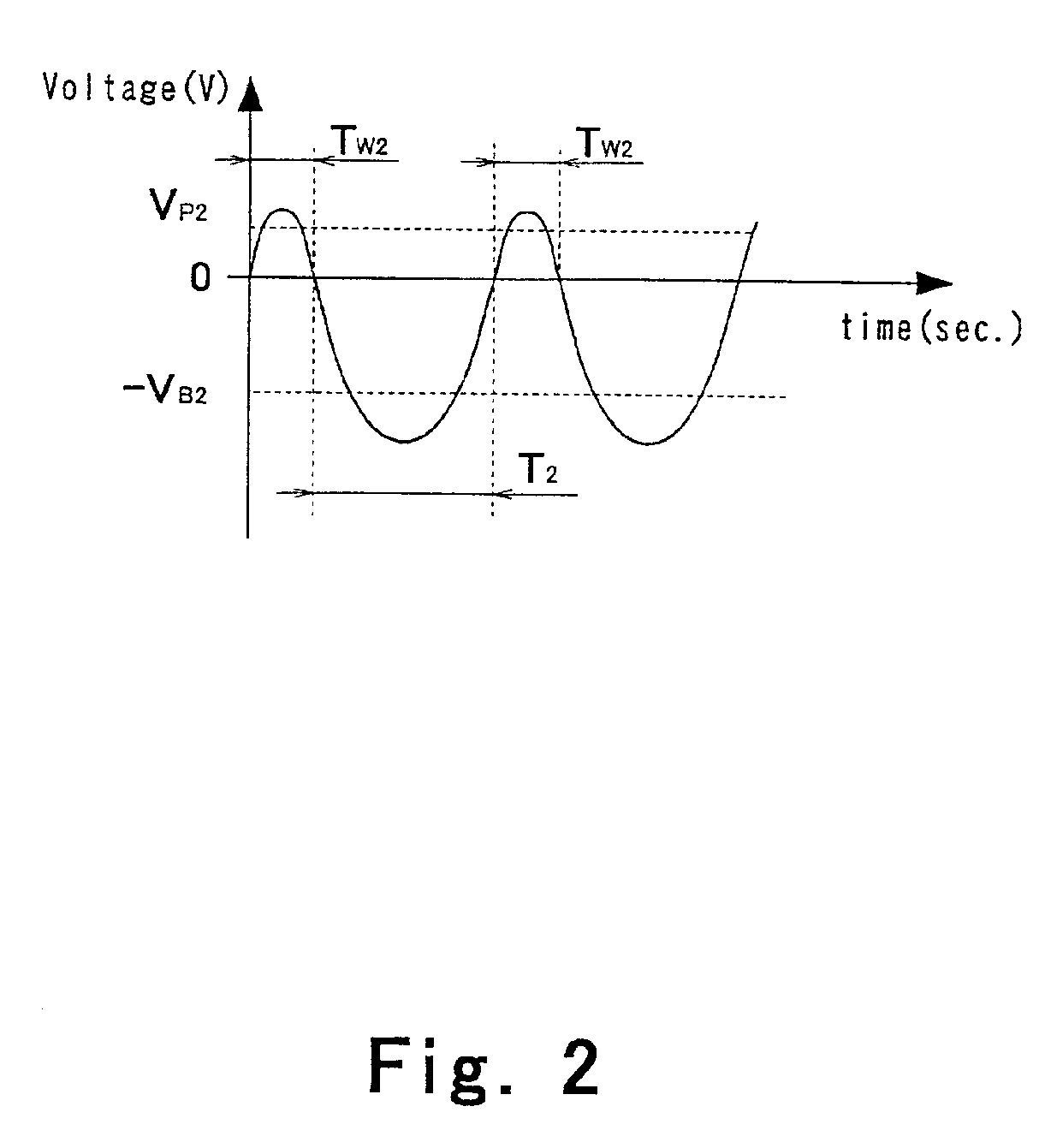

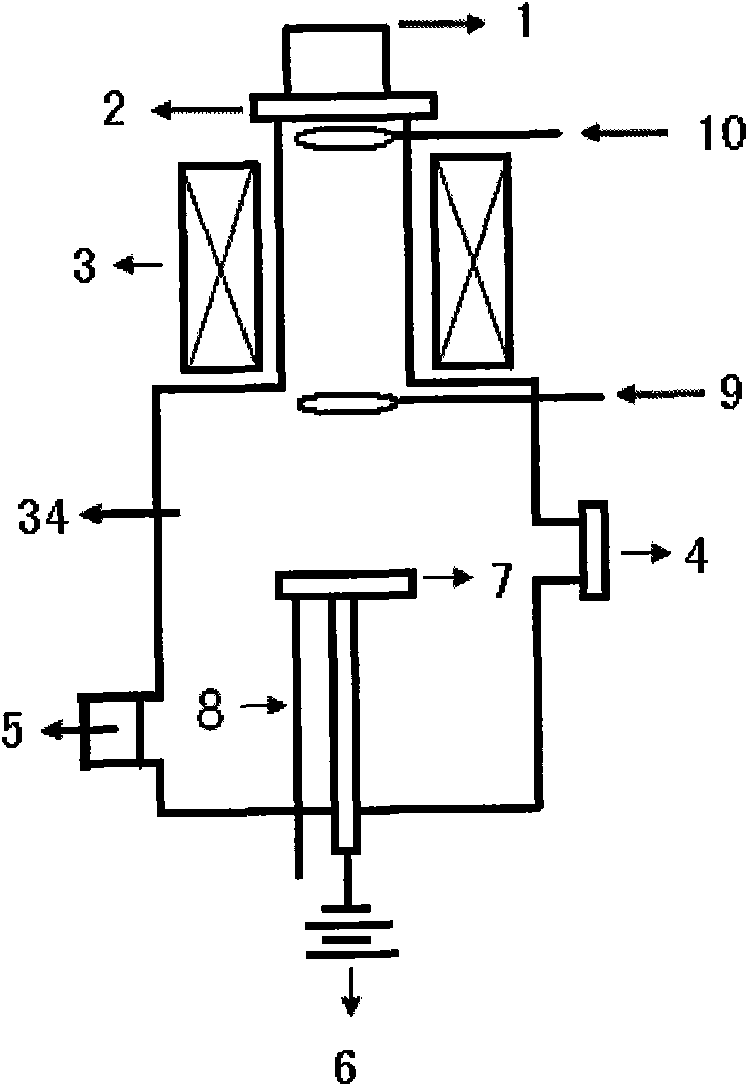

Ion plating device and ion plating method

InactiveUS6863018B2Avoid it happening againHigh densityElectric discharge tubesVacuum evaporation coatingEngineeringVacuum chamber

In ion plating in which a substrate is held on a substrate holder placed in an evacuated vacuum chamber and plasma is generated in the vacuum chamber to be formed into a film, a bias voltage composed of a negative bias component having a predetermined negative voltage value for a predetermined output time and a pulse bias component corresponding to a pulse output having a constant positive value for a predetermined time and output with a cycle set in the rage of 1 kHz-1 GHz is supplied to the inside of the vacuum chamber through the substrate holder by a power supply unit.

Owner:SHIN MEIWA IND CO LTD

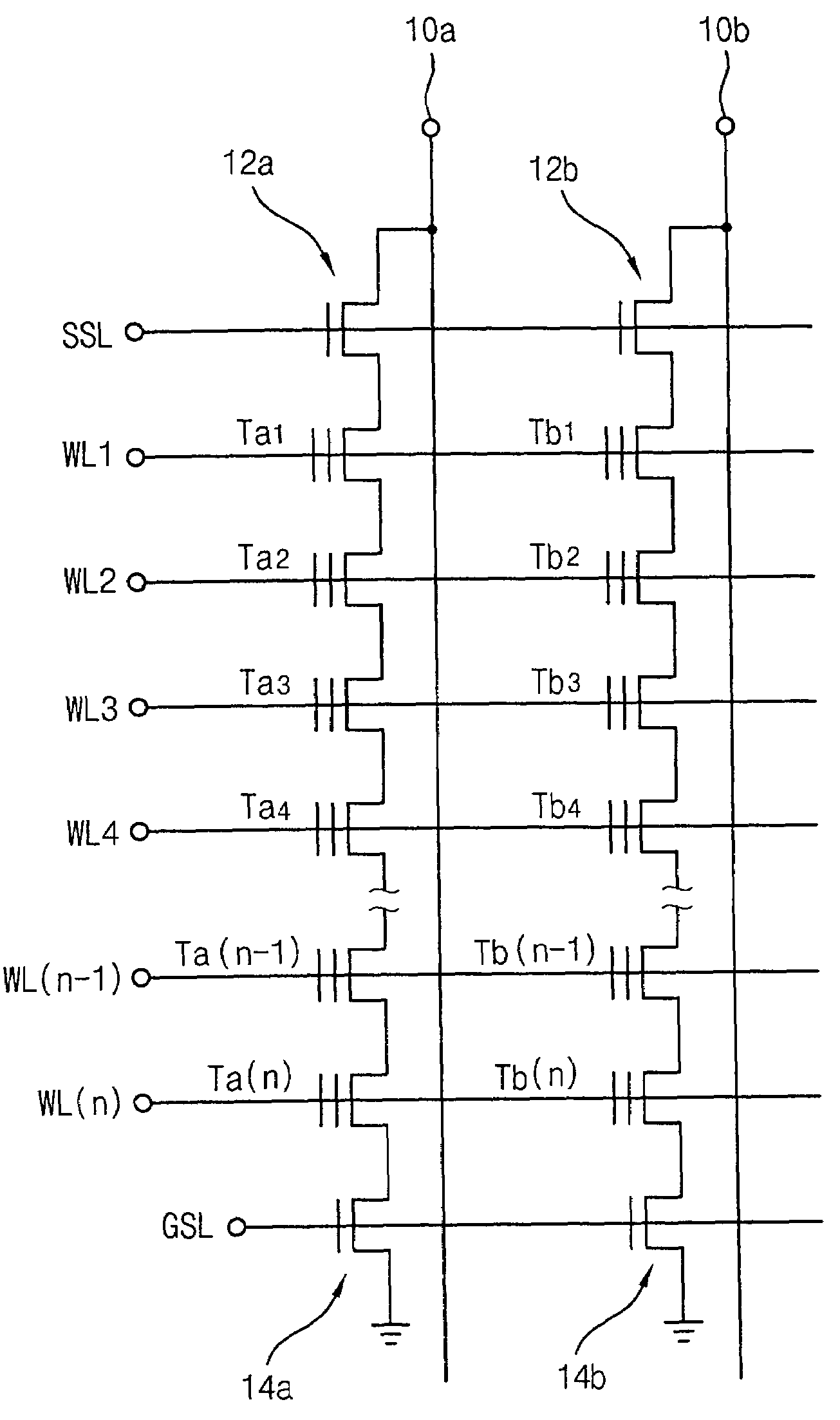

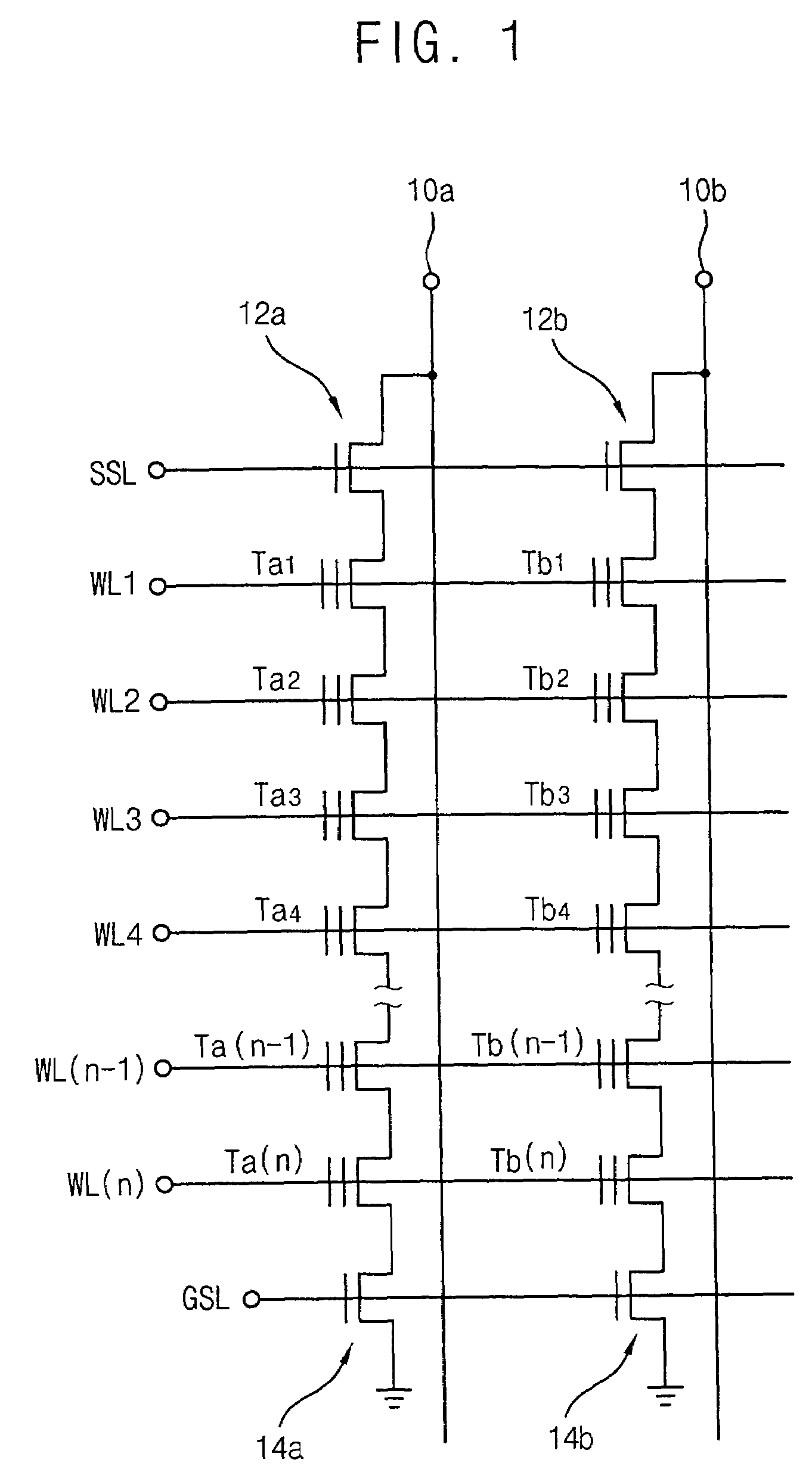

Operating method of non-volatile memory device

An operating method of non-volatile memory device is provided. The device includes memory cells having a semiconductor substrate, a stack layer, and source and drain regions disposed below a surface of the substrate and separated by a channel region. The stack layer includes an insulating layer disposed on the channel region, a charge storage layer disposed on the insulating layer, a multi-layer tunneling dielectric structure on the charge storage layer, and a gate disposed on the multi-layer tunneling dielectric structure. A negative bias is supplied to the gate to inject electrons into the charge storage layer through the multi-layer tunneling dielectric structure by −FN tunneling so that the threshold voltage of the device is increased. A positive bias is supplied to the gate to inject holes into the charge storage layer through the multi-layer tunneling dielectric structure by +FN tunneling so that the threshold voltage of the device is decreased.

Owner:MACRONIX INT CO LTD

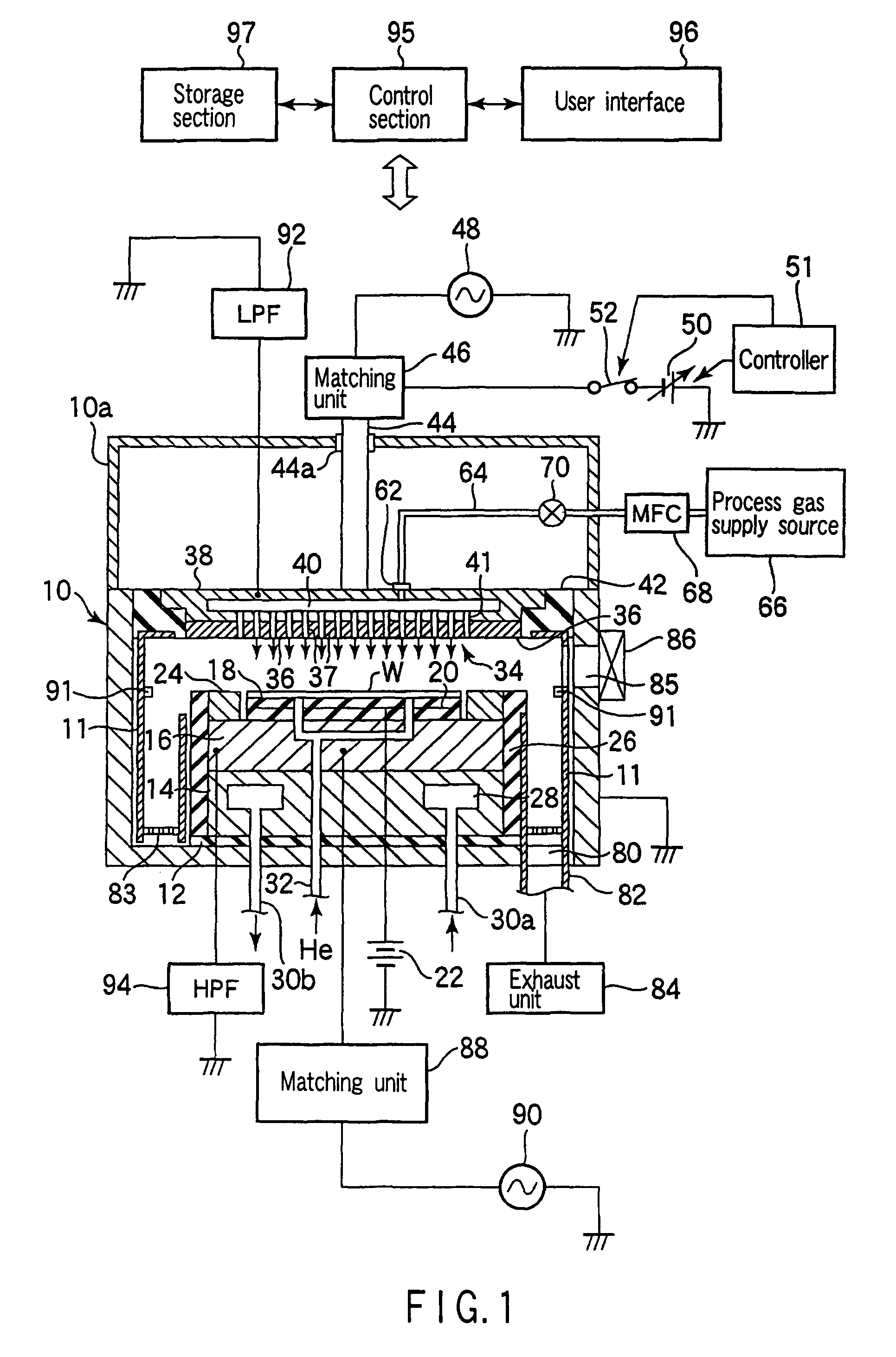

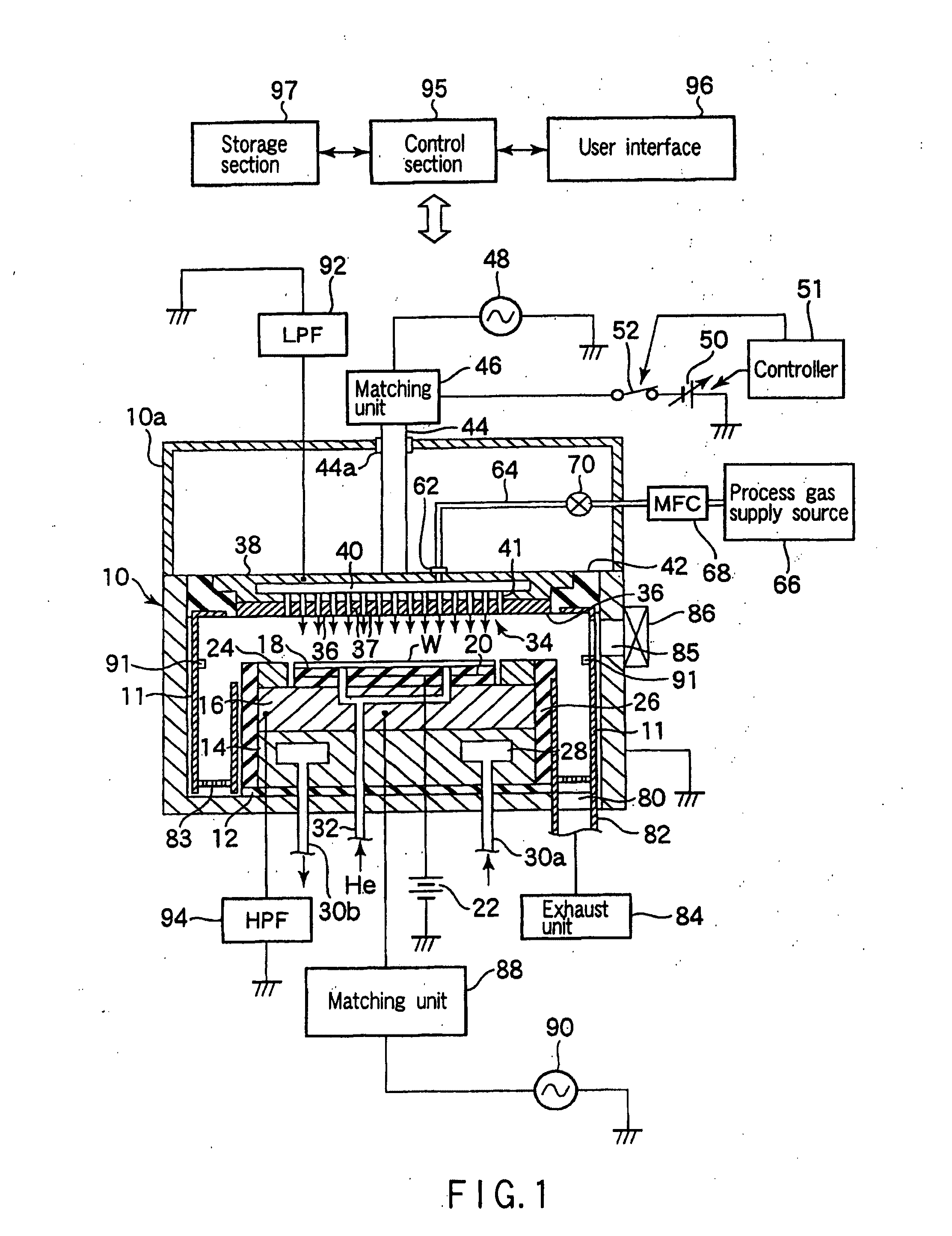

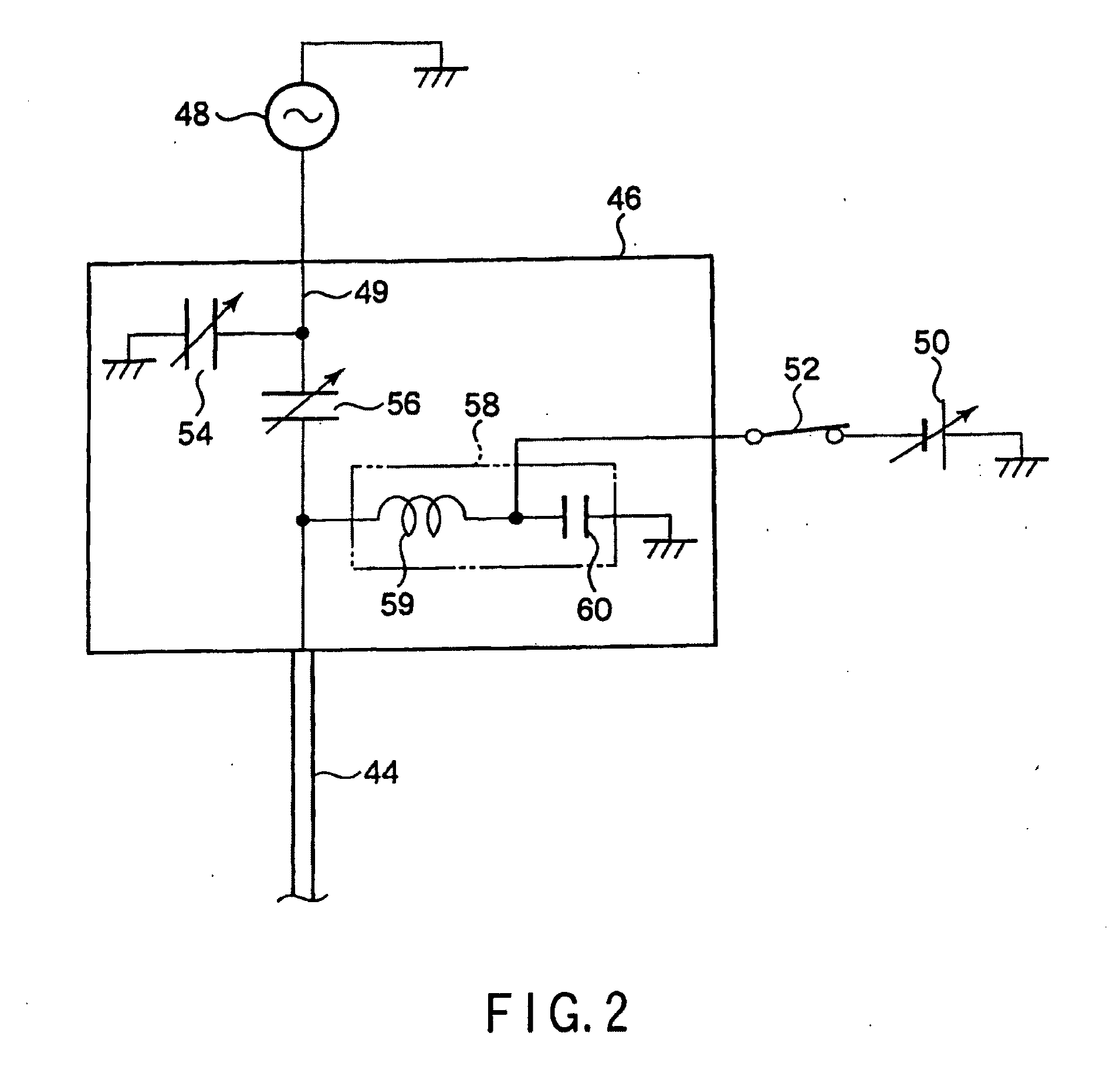

Plasma processing apparatus and method

ActiveUS7988816B2Improved resistance characteristicsIncrease chanceElectric discharge tubesElectric arc lampsNegative biasDc voltage

A plasma etching apparatus includes an upper electrode and a lower electrode, between which plasma of a process gas is generated to perform plasma etching on a wafer W. The apparatus further comprises a cooling ring disposed around the wafer, a correction ring disposed around the cooling ring, and a variable DC power supply directly connected to the correction ring, the DC voltage being preset to provide the correction ring with a negative bias, relative to ground potential, for attracting ions in the plasma and to increase temperature of the correction ring to compensate for a decrease in temperature of a space near the edge of the target substrate due to the cooling ring.

Owner:TOKYO ELECTRON LTD

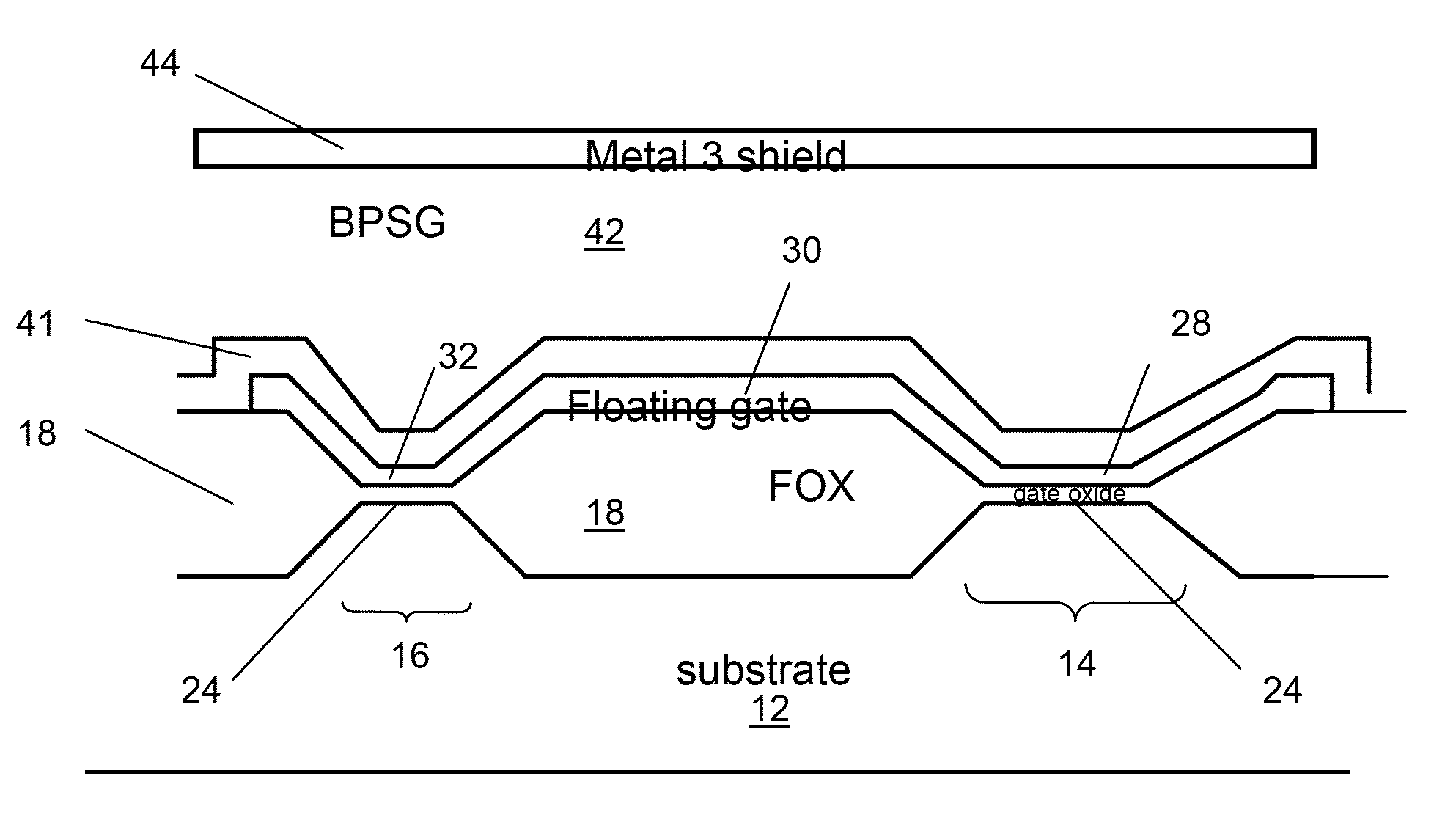

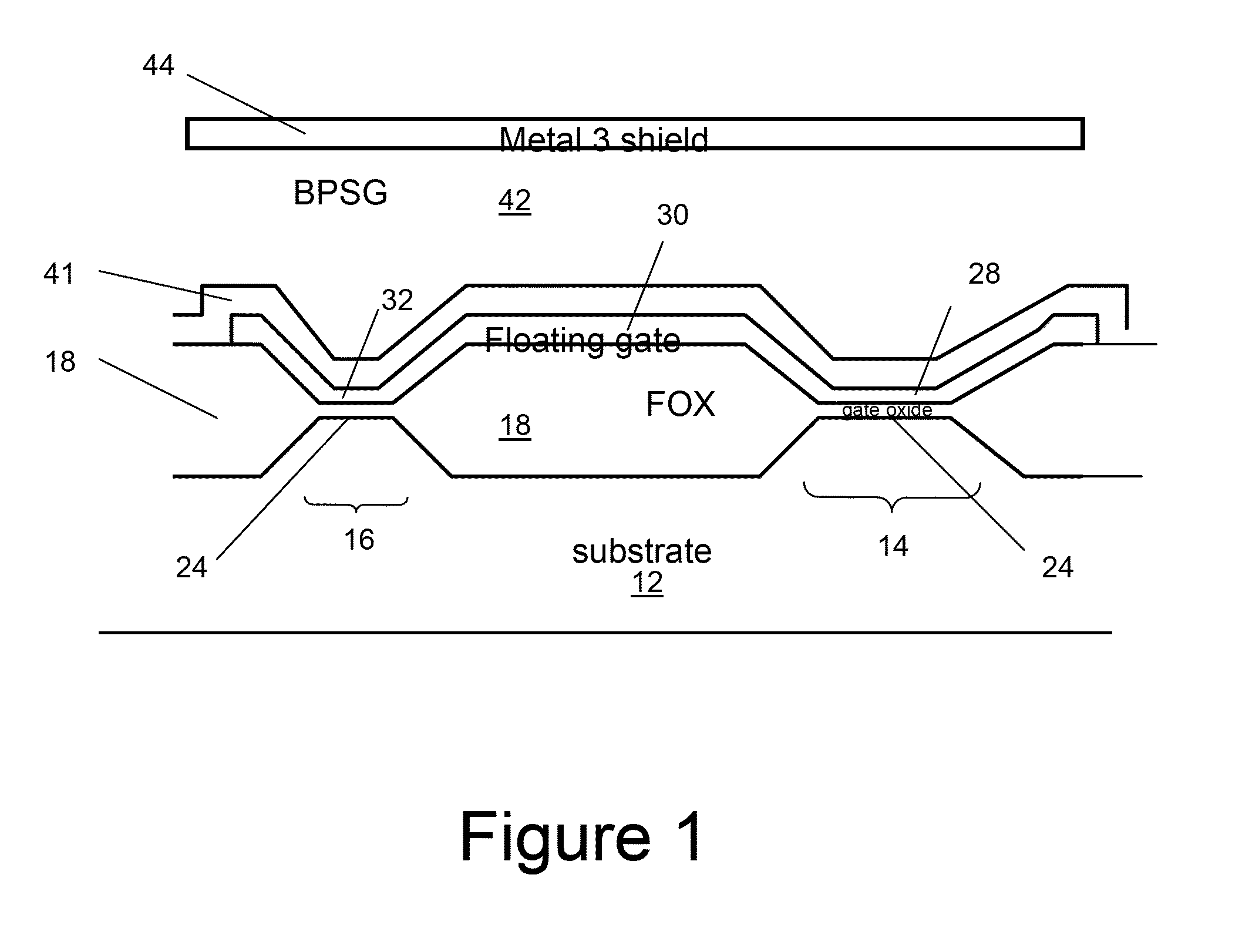

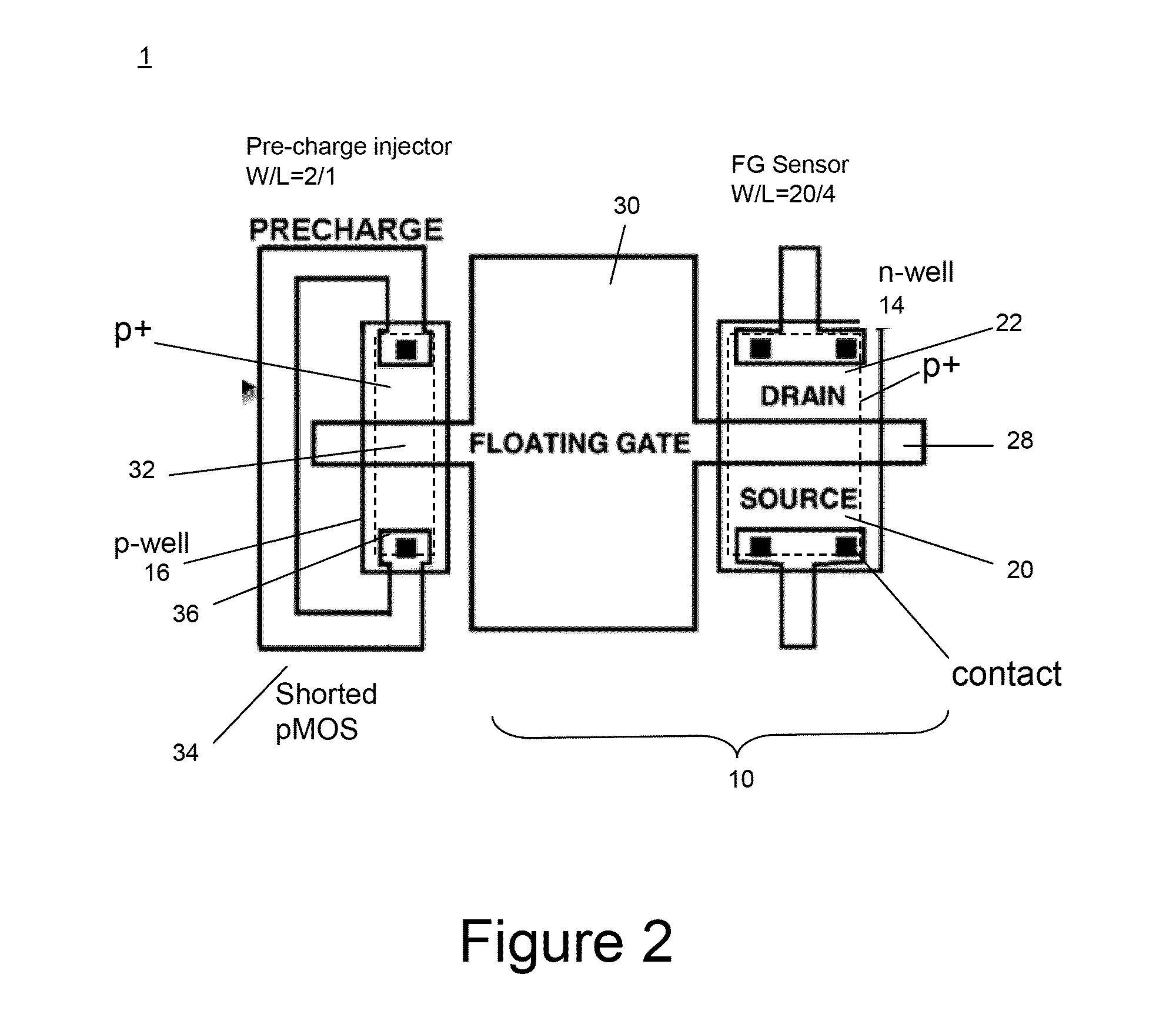

Miniaturized, low power fgmosfet radiation sensor and wireless dosimeter system

ActiveUS20100096556A1Reduce capacitanceHigh sensitivityDosimetersSolid-state devicesCapacitanceMOSFET

A miniaturized floating gate (FG) MOSFET radiation sensor system is disclosed, The sensor preferably comprises a matched pair of sensor and reference FGMOSFETs wherein the sensor FGMOSFET has a larger area floating gate with an extension over a field oxide layer, for accumulation of charge and increased sensitivity. Elimination of a conventional control gate and injector gate reduces capacitance, and increases sensitivity, and allows for fabrication using standard low cost CMOS technology. A sensor system may be provided with integrated signal processing electronics, for monitoring a change in differential channel current ID, indicative of radiation dose, and an integrated negative bias generator for automatic pre-charging from a low voltage power source. Optionally, the system may be coupled to a wireless transmitter. A compact wireless sensor System on Package solution is presented, suitable for dosimetry for radiotherapy or other biomedical applications.

Owner:KING ABDULLAH UNIV OF SCI & TECH

Methods of operating p-channel non-volatile memory devices

ActiveUS7636257B2Negative biasDisturbing effectSolid-state devicesRead-only memoriesBit lineElectricity

Owner:MACRONIX INT CO LTD

Method of operating a flash memory device

A method of operating a NAND flash memory device that comprising a unit string comprising a string selection transistor connected to a bit line, a cell transistor connected to the string selection transistor, and a ground selection transistor connected to the cell transistor is provided. The method comprises applying a negative bias voltage to the string selection transistor and the ground selection transistor in a stand-by mode of the NAND flash memory device.

Owner:SAMSUNG ELECTRONICS CO LTD

Conducting fiber and preparation method thereof

InactiveCN101349007AImprove bindingImprove conductivityPlastic/resin/waxes insulatorsPhysical treatmentFiberMetal coating

The invention provides conductive fibers and a preparation method thereof. The preparation method comprises the following steps that: firstly, the fibers are subjected to warping; secondly, the warped row of fibers is subjected to plasma processing; thirdly, the processed fibers are plated by vacuum physically to generate a physically plated metal coating, the order of magnitude of the specific resistance is between 10<7> and 10<0>Omega.cm; the metal coating is mainly used for being anti-static and sterilizing clothes; a metal layer is plated outside the physically plated metal coating, the order of magnitude of the specific resistance is less than or equal to 10<0>Omega.cm; the metal layer is mainly used for shielding electromagnetic wave and absorbing materials; and the plasma processing comprises the ion beam processing or the negative bias addition. The preparation method has simple technique, low cost, and strong feasibility of the industrial production on a large scale. The manufactured conductive fibers have the characteristics that the product is combined firmly, the dyeing property and the conductivity are good, the chemical resistance and the wash resistance are good and the tactility is soft.

Owner:TIANNUO PHOTOELECTRIC MATERIAL

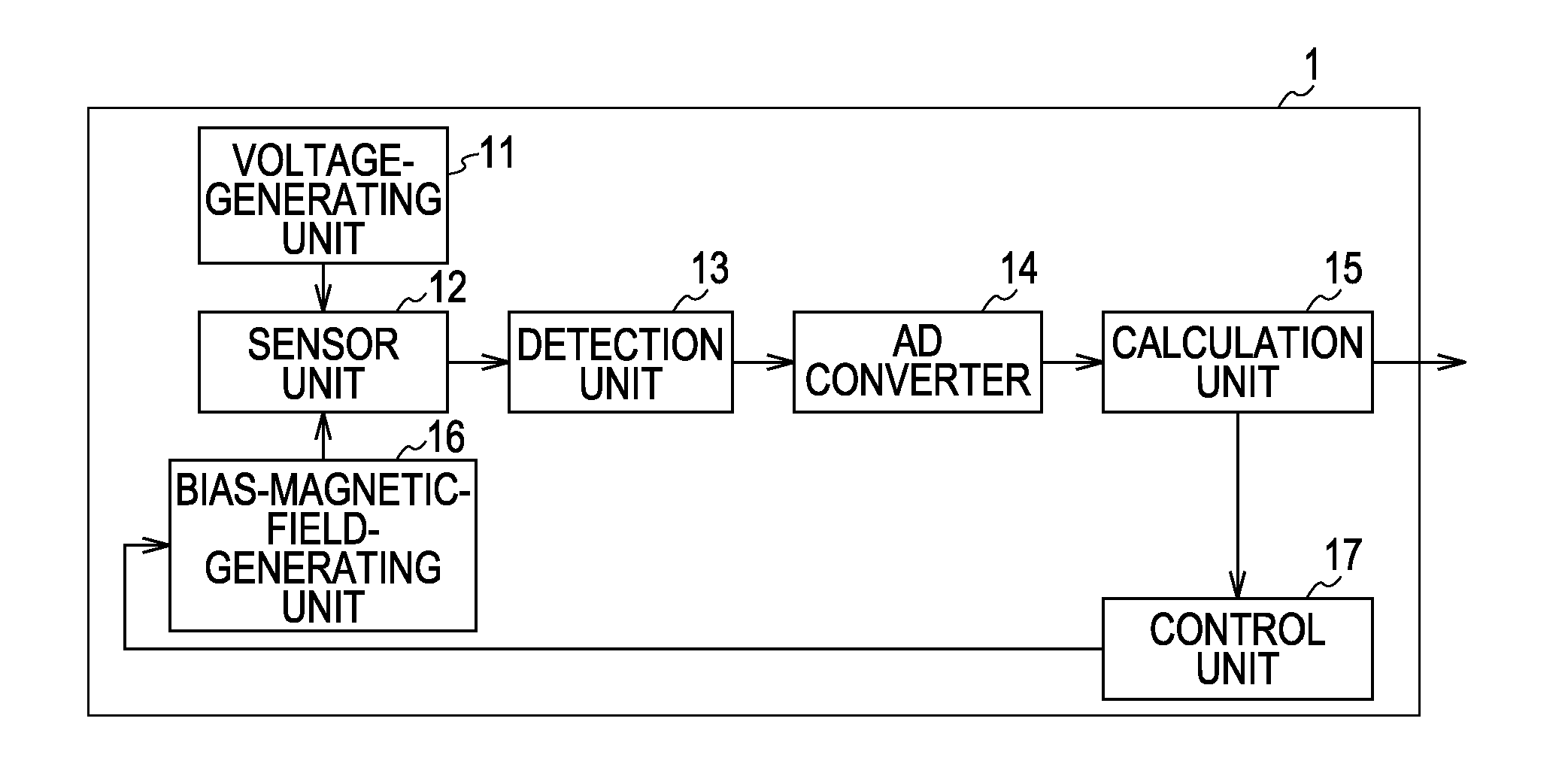

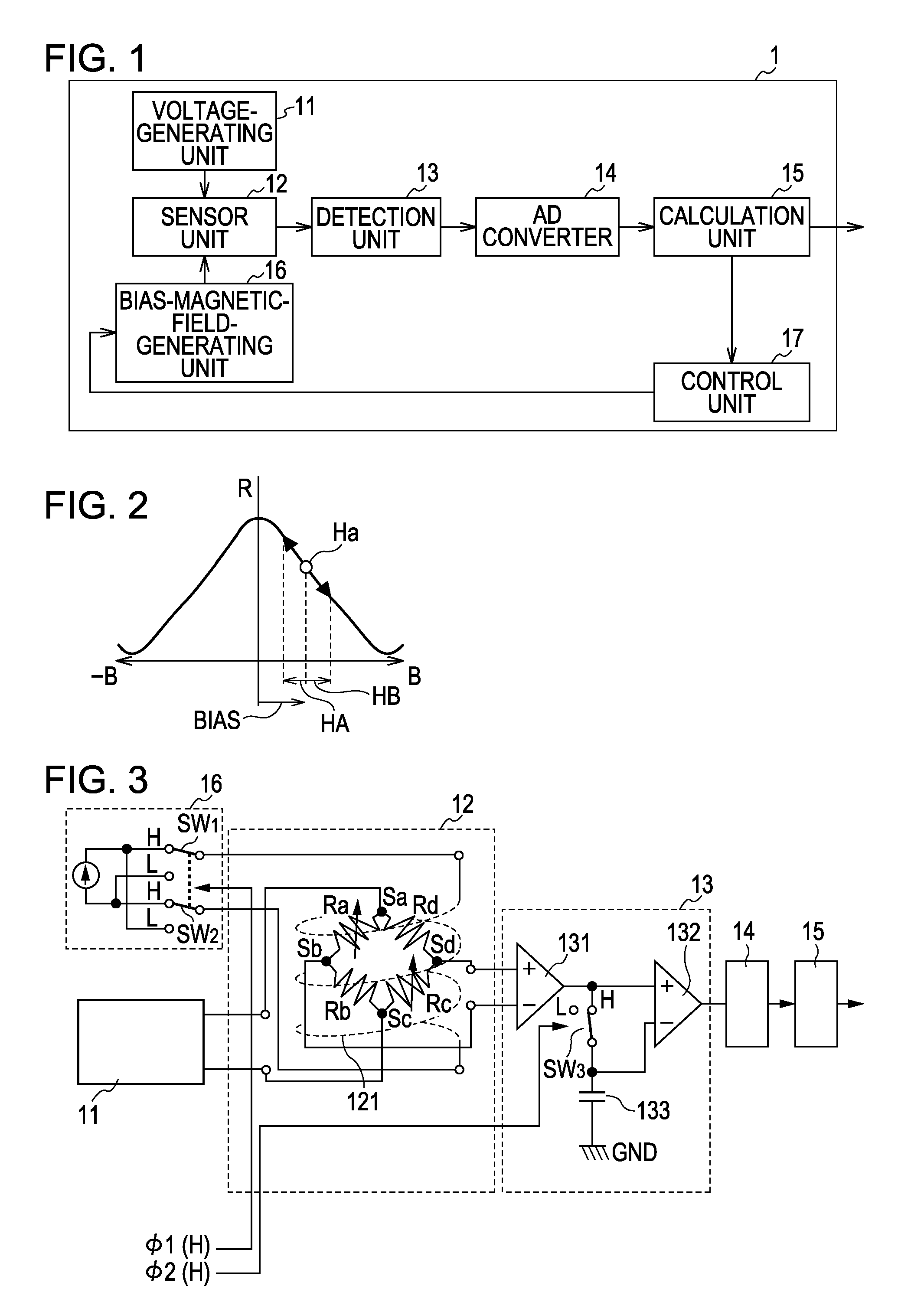

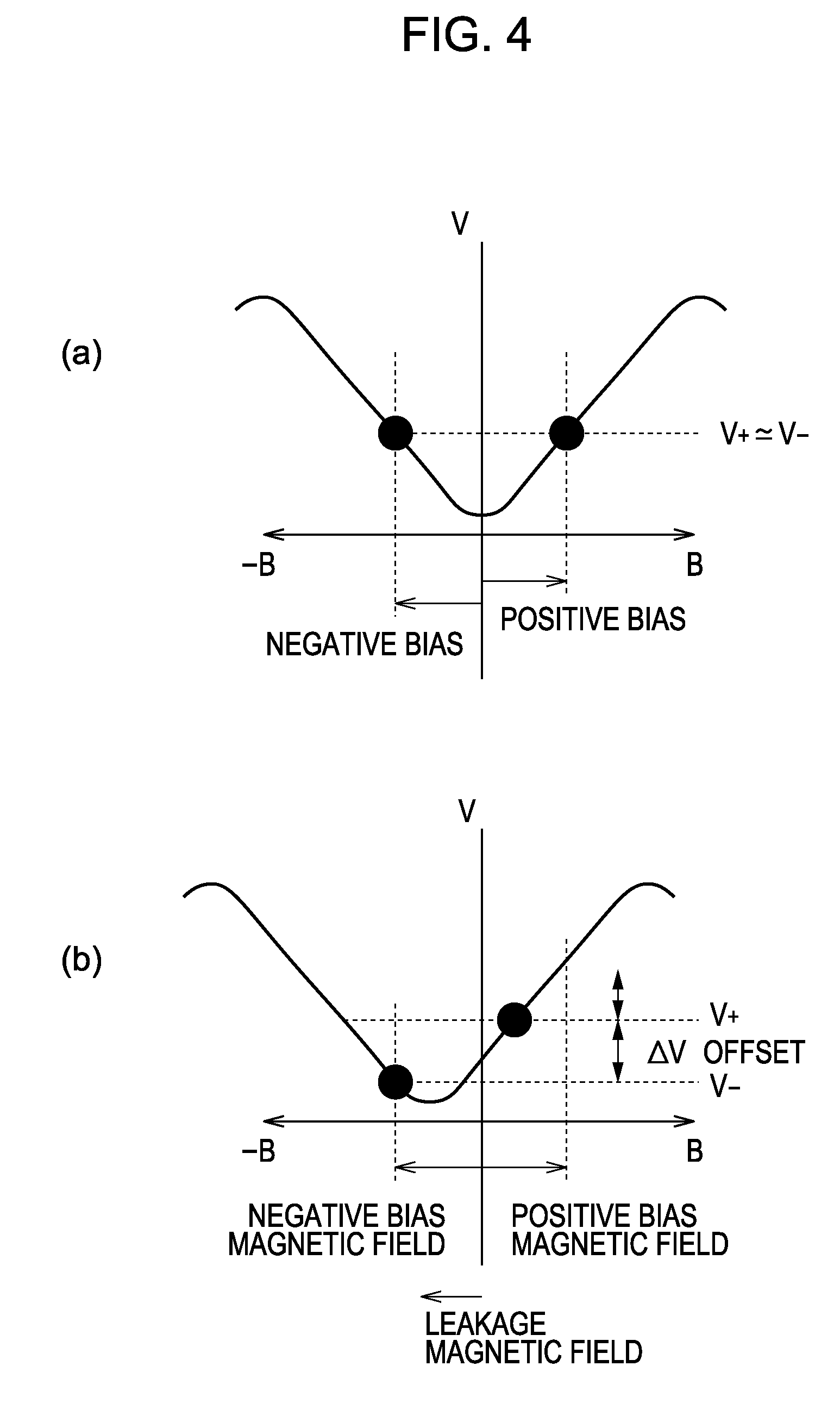

Magnetic sensing device and electronic compass using the same

InactiveUS20090009163A1Accurate detectionAccurately determineMagnitude/direction of magnetic fieldsNegative biasCondensed matter physics

Positive and negative bias magnetic fields are applied to a sensor unit 12 to determine first and second output voltages. A first difference between the first and second output voltages is calculated. Next, correction bias magnetic fields, each of which is obtained by adding an additional bias magnetic field to a corresponding one of the positive and negative bias magnetic fields, are applied to the sensor unit 12 to determine first and second output voltages. A second difference between the first and second output voltages is calculated. Then, the first difference is compared with the second difference. When the first difference is larger than the second difference, the magnitude of the additional bias magnetic field is increased to minimize the difference, i.e., to made the difference substantially zero.

Owner:ALPS ALPINE CO LTD

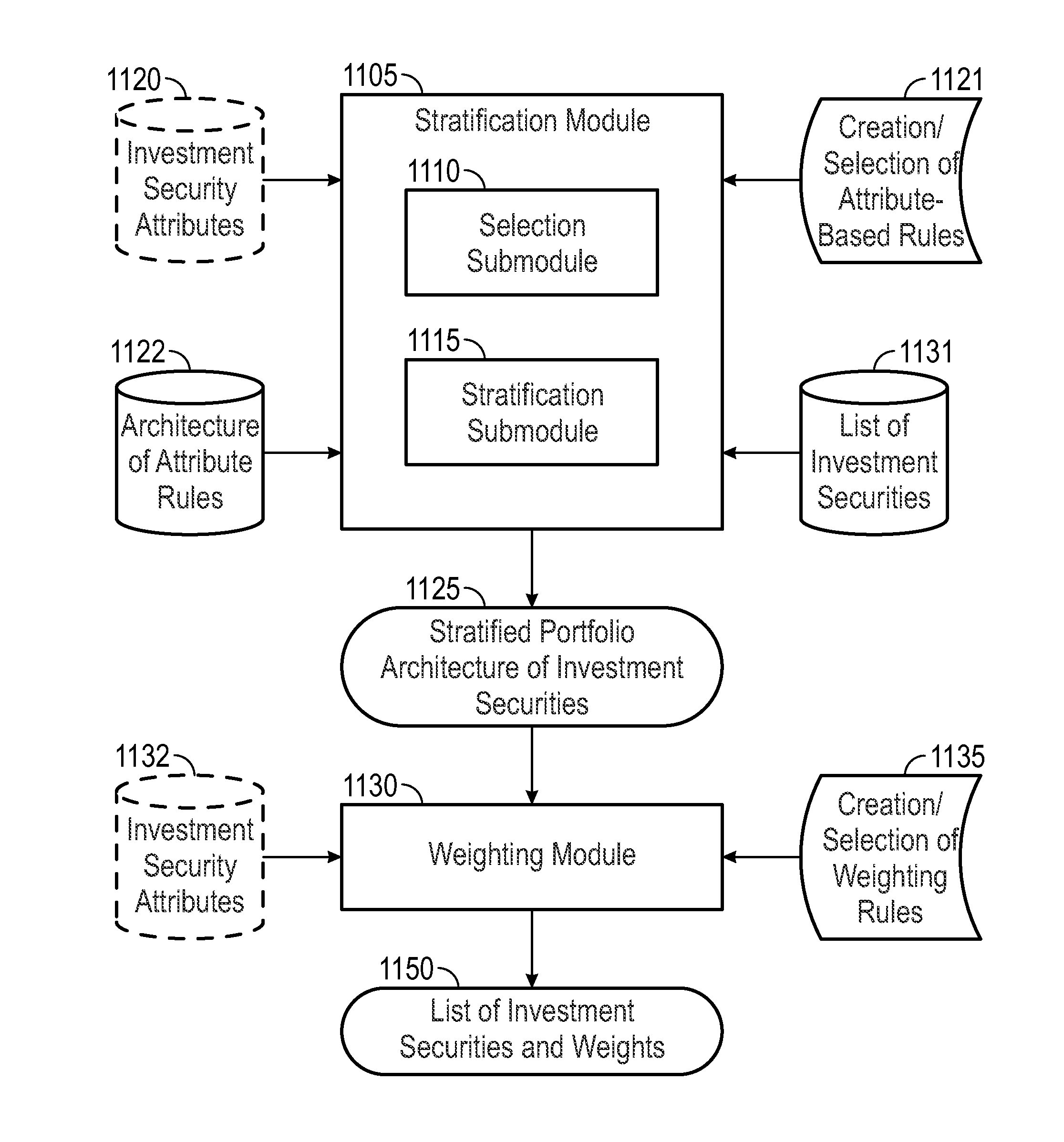

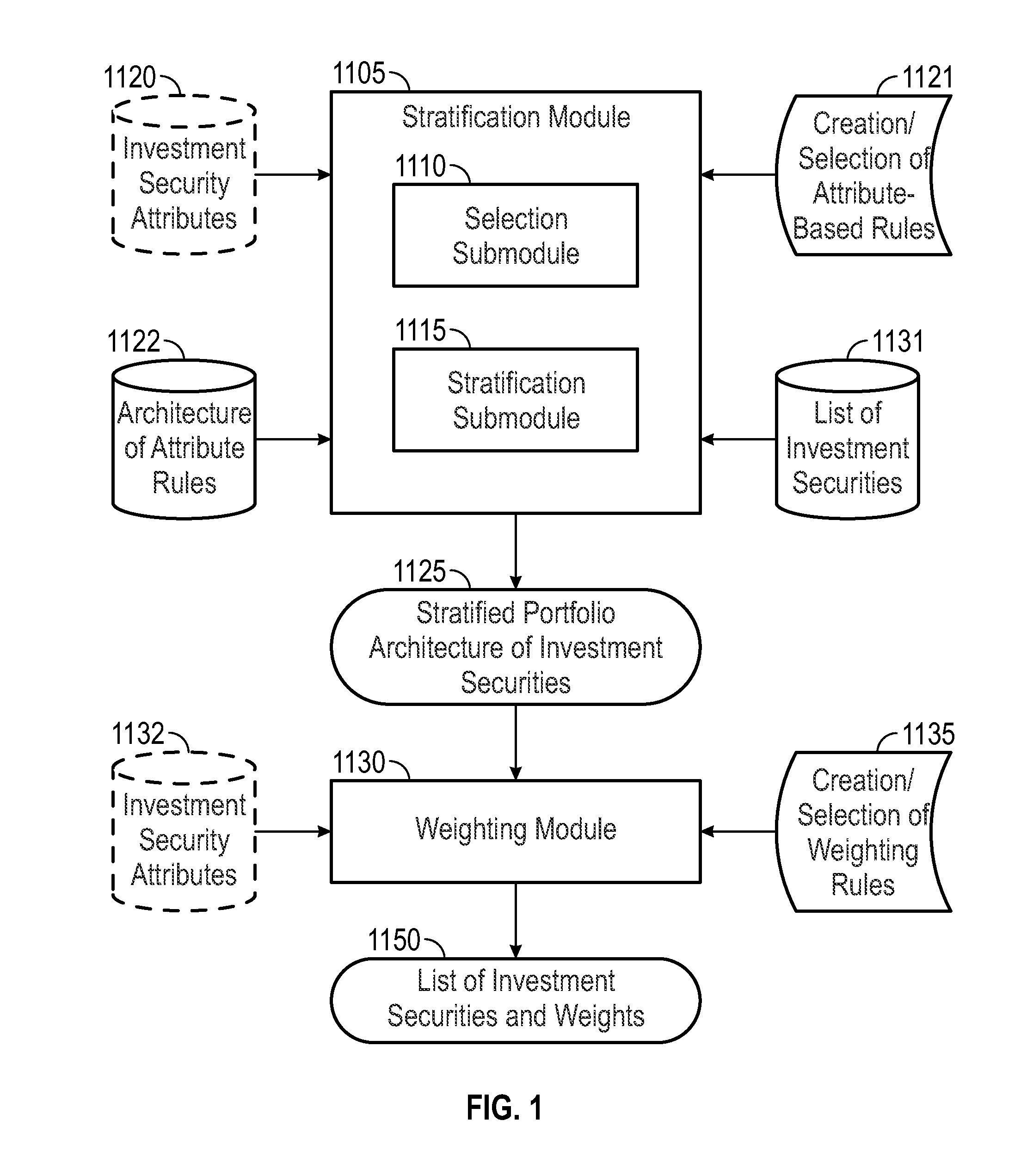

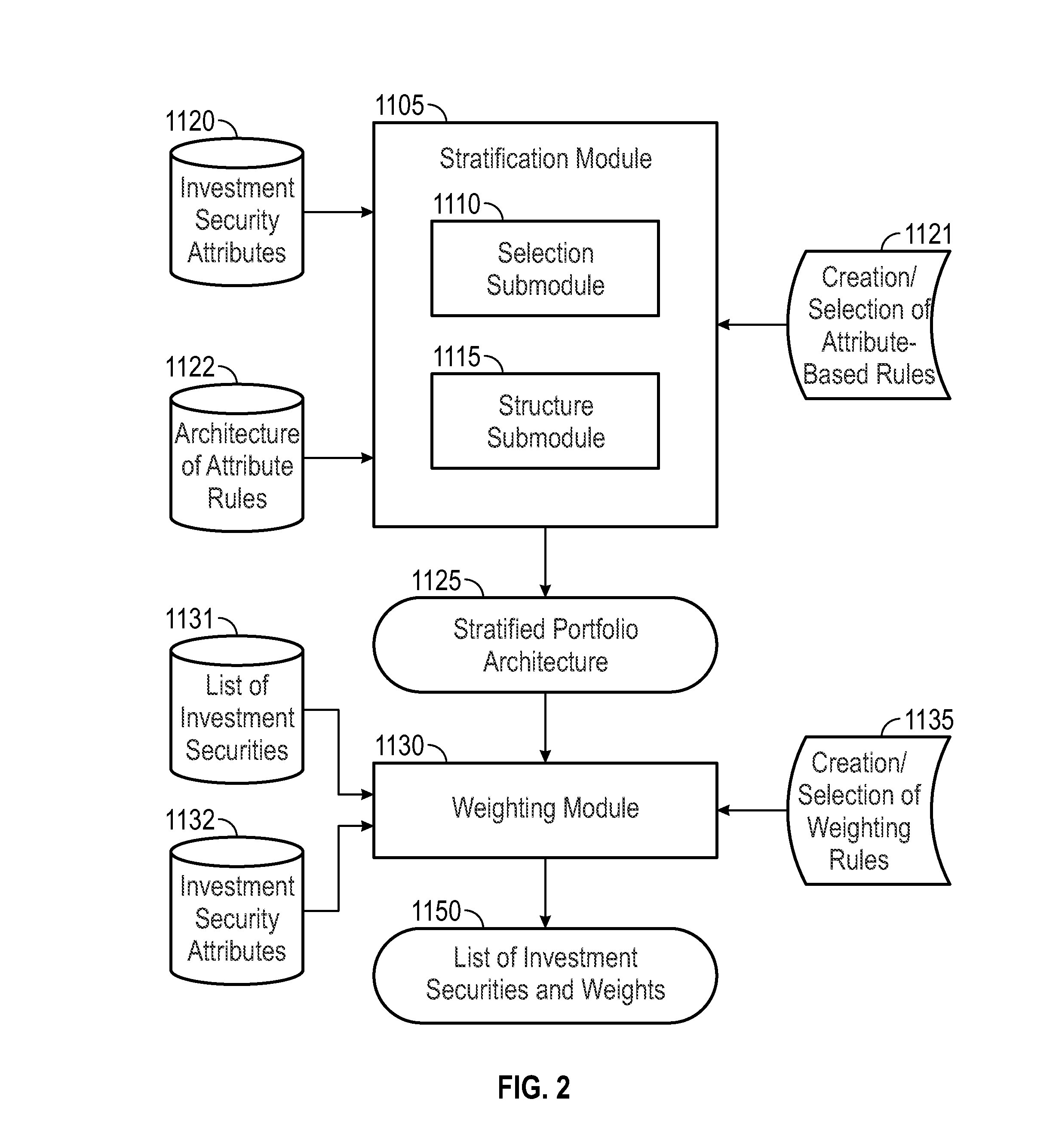

Segmentation and stratification of composite portfolios of investment securities

ActiveUS20150324919A1Reduce the impactReducing and minimizing potential riskFinanceRelational databasesAlgorithmData mining

A stratified or segmented composite portfolio can be formed by selecting a group of investment securities, stratifying or segmenting them according to attributes that correlate to a specific asset risk, and assigning relative portfolio weights to the components based on their stratified or segmented positions. The attributes are selected from a universe of possible values. Further positive and negative biases can be applied at any arbitrary point or position, including to individual assets, groups of arbitrarily selected assets, or arbitrary positions.

Owner:LOCUS

Apparatus and method for metal plasma immersion ion implantation and metal plasma immersion ion deposition

InactiveUS20050061251A1Large-scale processingReduce pressureElectric discharge tubesVacuum evaporation coatingIon depositionPlasma deposition

This invention is a method for metal plasma ion implantation and metal plasma ion deposition, comprising: providing a vacuum chamber with at least one workpiece having a surface positioned on a worktable within the vacuum chamber; reducing the pressure in the vacuum chamber; generating a plasma of metal ions within the vacuum chamber, applying a negative bias to the worktable to thereby accelerate metal ions from the plasma toward at least one workpiece to thereby either implant metal ions into or deposit metal ions onto the workpiece or both. This invention includes an apparatus for metal ion implantation and metal ion plasma deposition, comprising: a vacuum chamber, a metal plasma generator within the vacuum chamber, and at least one worktable within the vacuum chamber.

Owner:SOUTHWEST RES INST

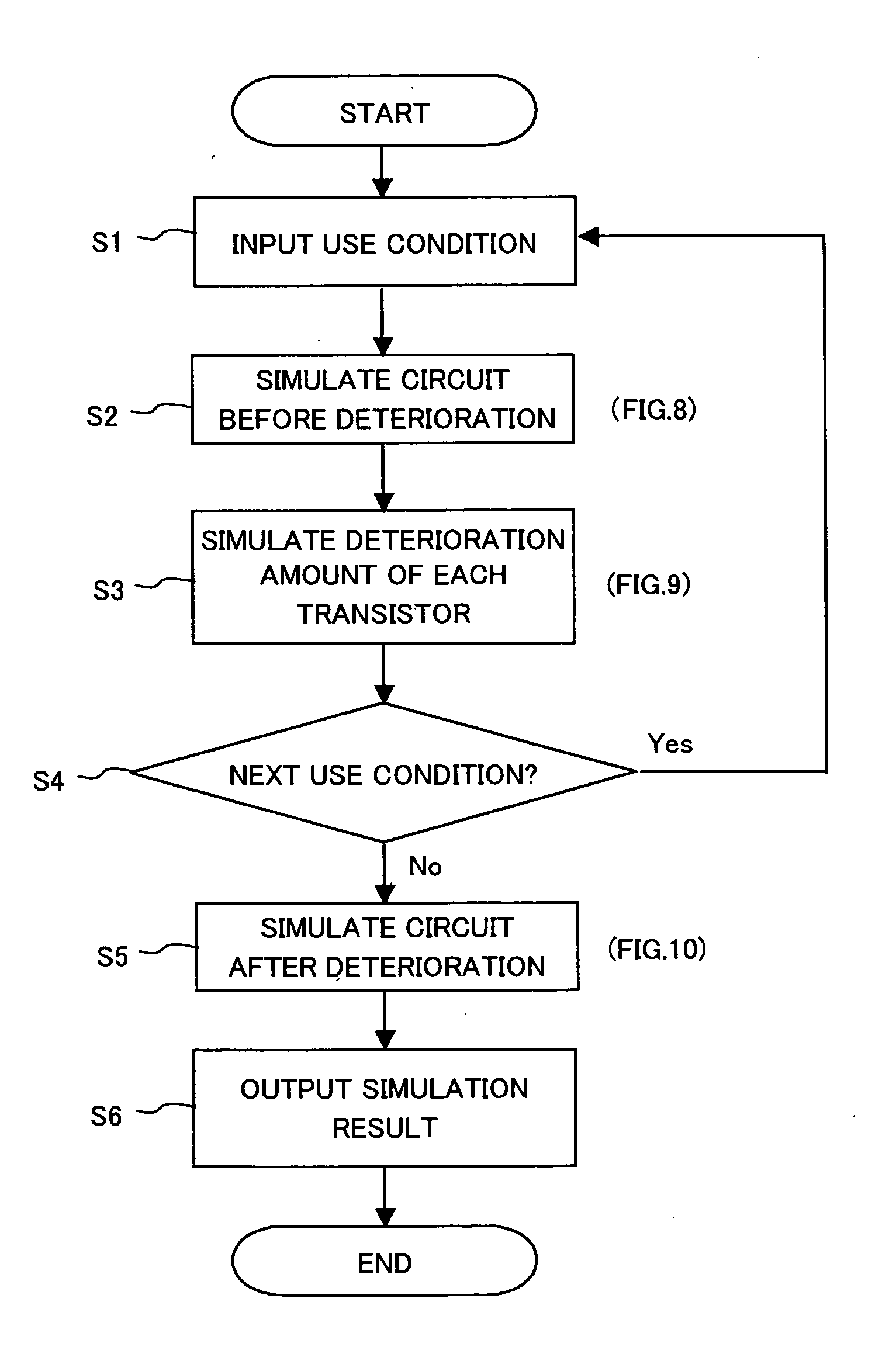

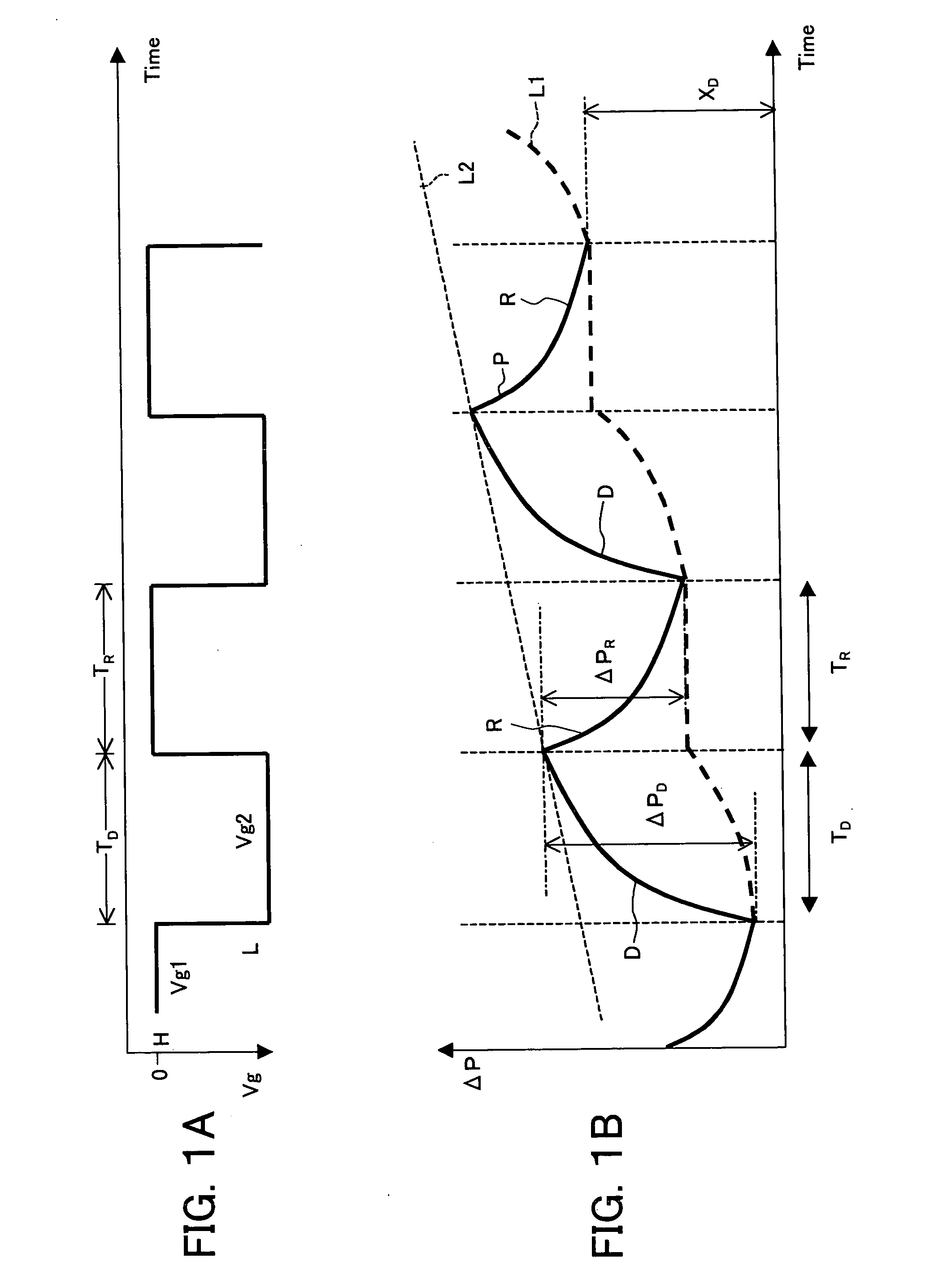

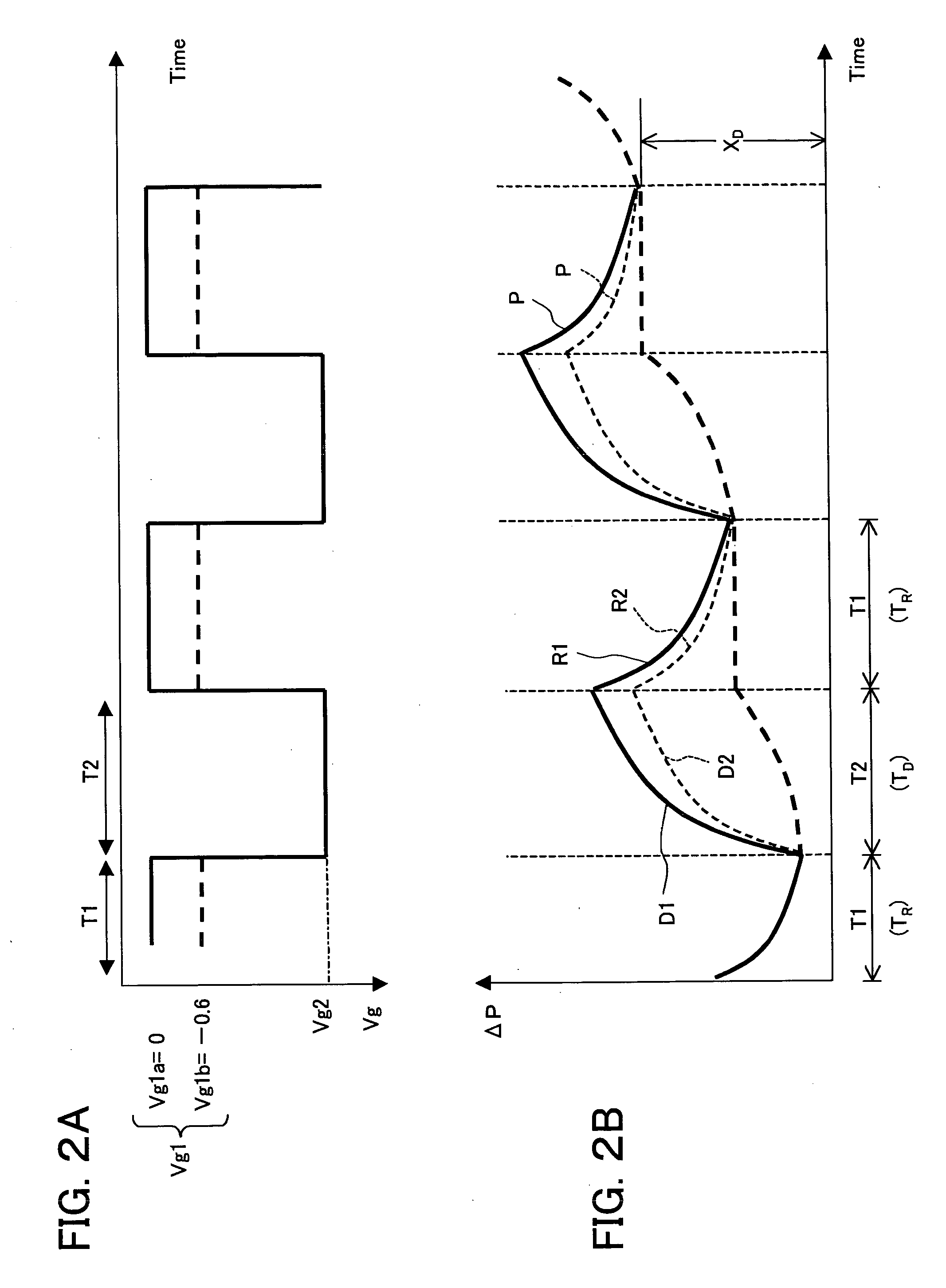

Semiconductor circuit device simulation method and semiconductor circuit device simulator

InactiveUS20050138581A1Accurate estimateSimulation is accurateTransistorAnalogue computers for electric apparatusDevice materialRecovery period

A simulator for accurately simulating a deterioration amount and a recovery amount of transistor characteristics, by which a semiconductor device can be designed with high reliability, and the method are provided. When a gate voltage of a negative level (a negative bias voltage) “Vg” is applied to a gate of the transistor, characteristics of the transistor are deteriorated. When application of the negative level gate voltage “Vg” is terminated (when applying a bias free voltage), the deteriorated transistor characteristics are recovered. In a deterioration period and a recovery period, a logarithm “log(t)” is obtained for an application time “t” of the gate voltage, a deterioration amount ΔPD(t)=CD+BD·log(t) is calculated by using constants CD and BD depending on the negative bias voltage, a recovery amount ΔPR(t)=CR+BR·log(t) is calculated by using constants CR and BR depending on the bias free voltage, and the deterioration amount (ΔPD), the recovery amount (ΔPR) and a basic deterioration amount (XD) are summed up. Preferably, passage of time is divided, and a deterioration amount and a recovery amount are obtained for each time zone by using different deterioration and recovery functions for each time zone.

Owner:SONY CORP

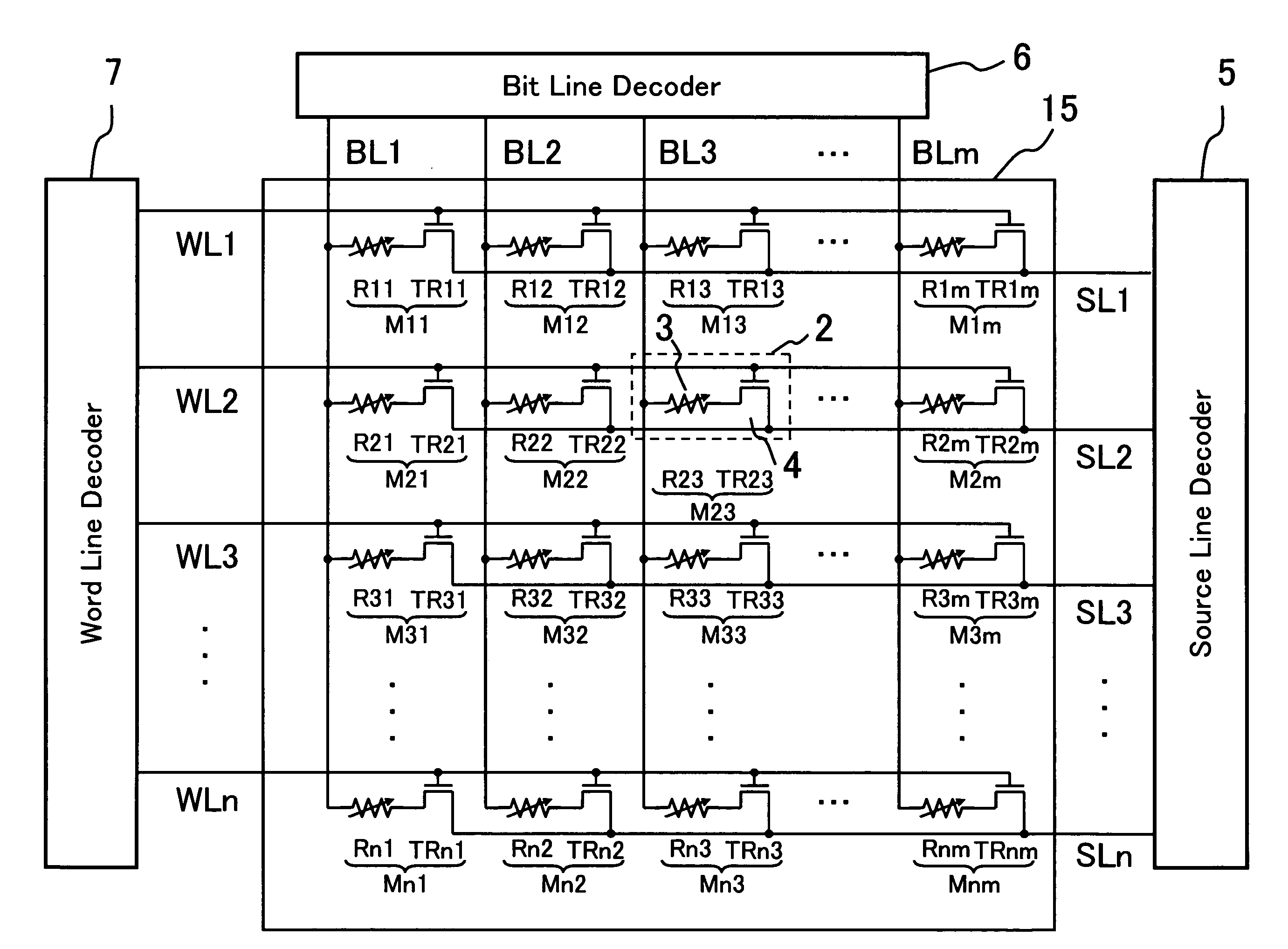

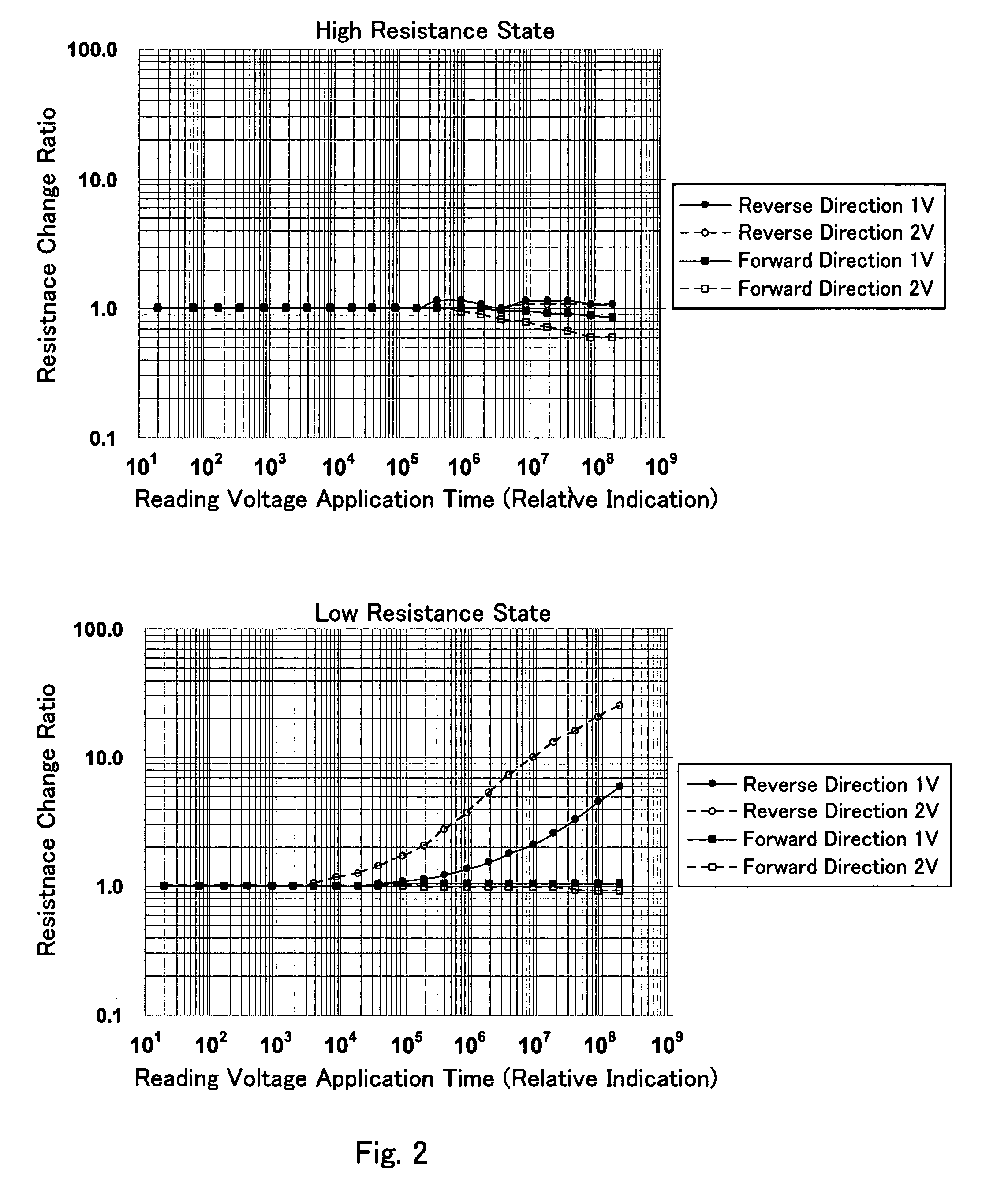

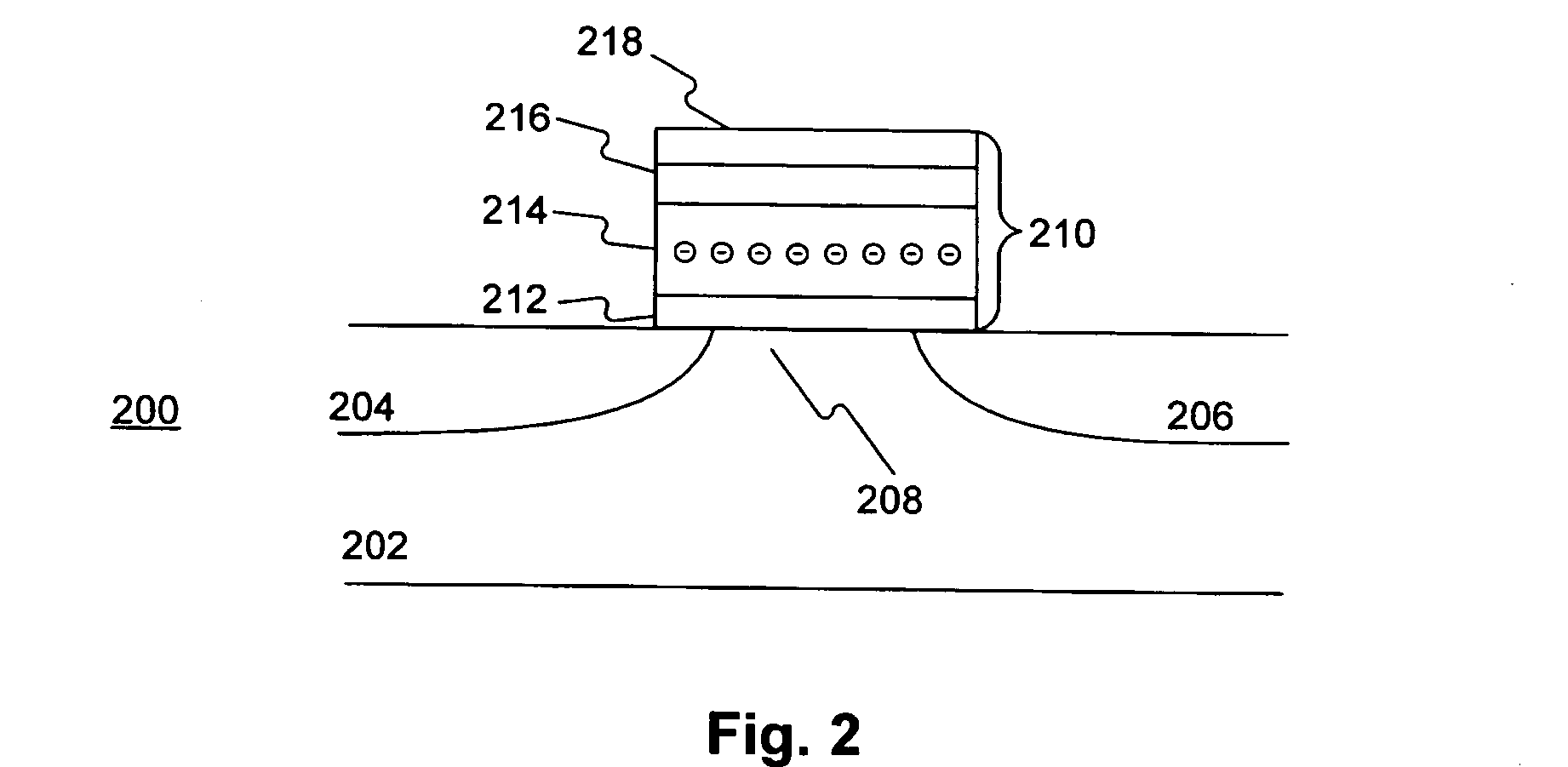

Nonvolatile semiconductor memory device

InactiveUS20080025072A1Keep reading marginAvoid changeRead-only memoriesDigital storageHemt circuitsEngineering

A nonvolatile semiconductor memory device comprises a memory cell including a variable resistance element changing its electric resistance by voltage application and having current-voltage characteristics in which a positive bias current flowing when a positive voltage is applied from one electrode as a reference electrode to the other electrode through an incorporated rectifier junction is larger than a negative bias current, a memory cell selection circuit for selecting the memory cell from the memory cell array, a voltage supply circuit for supplying a voltage to the memory cell so that a predetermined positive voltage corresponding to the reading operation is applied to the other electrode of the variable resistance element, in the reading operation, and a readout circuit for detecting the amount of the positive bias current and reading the information stored in the selected memory cell, in order to suppress the reading disturbance of the memory cell.

Owner:SHARP KK +1

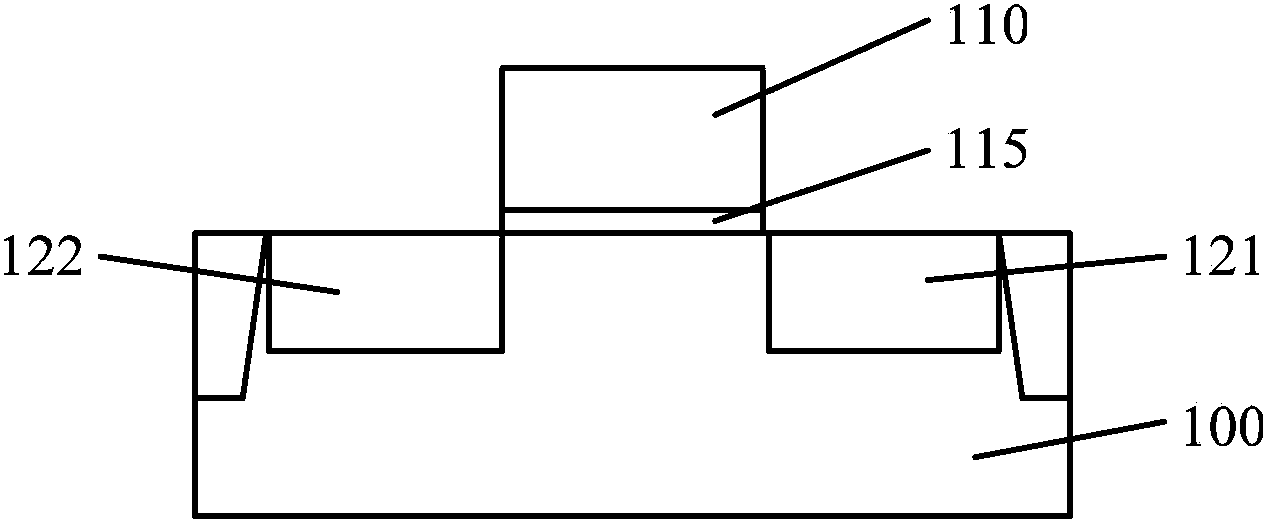

Forming method of metal gate, forming method of MOS transistor and forming method of CMOS structure

ActiveCN103681276AStrong oxidation abilityReduced negative bias temperature instabilitySemiconductor/solid-state device manufacturingSemiconductor devicesBond energyOxygen vacancy

Owner:SEMICON MFG INT (SHANGHAI) CORP

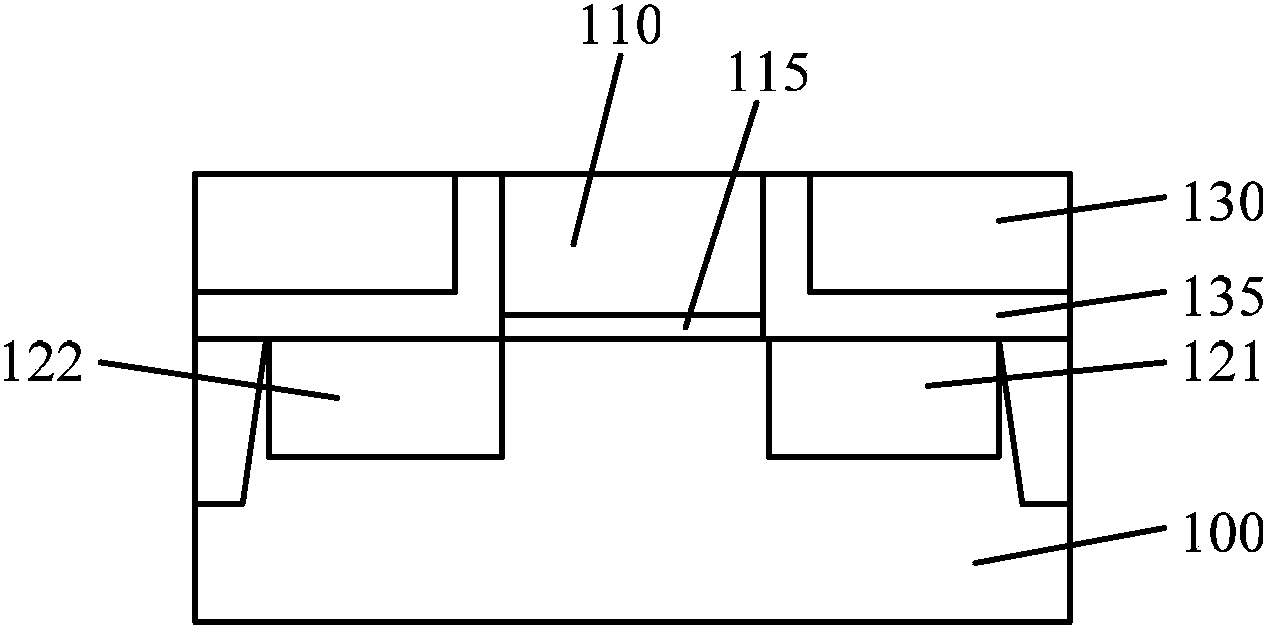

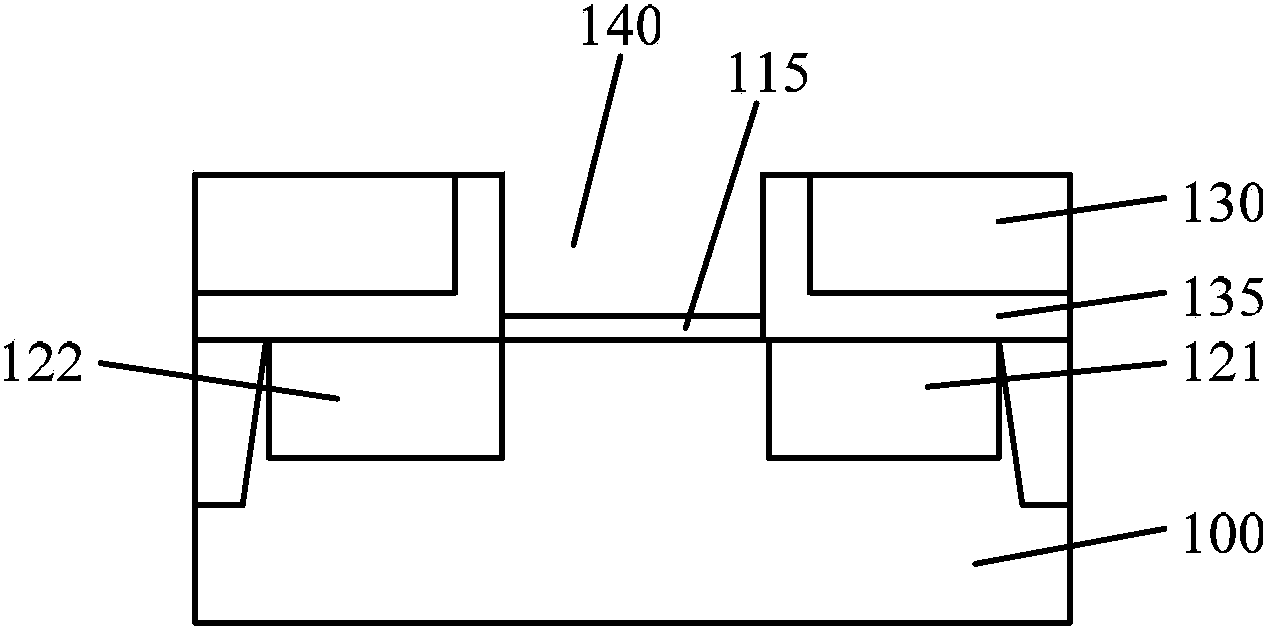

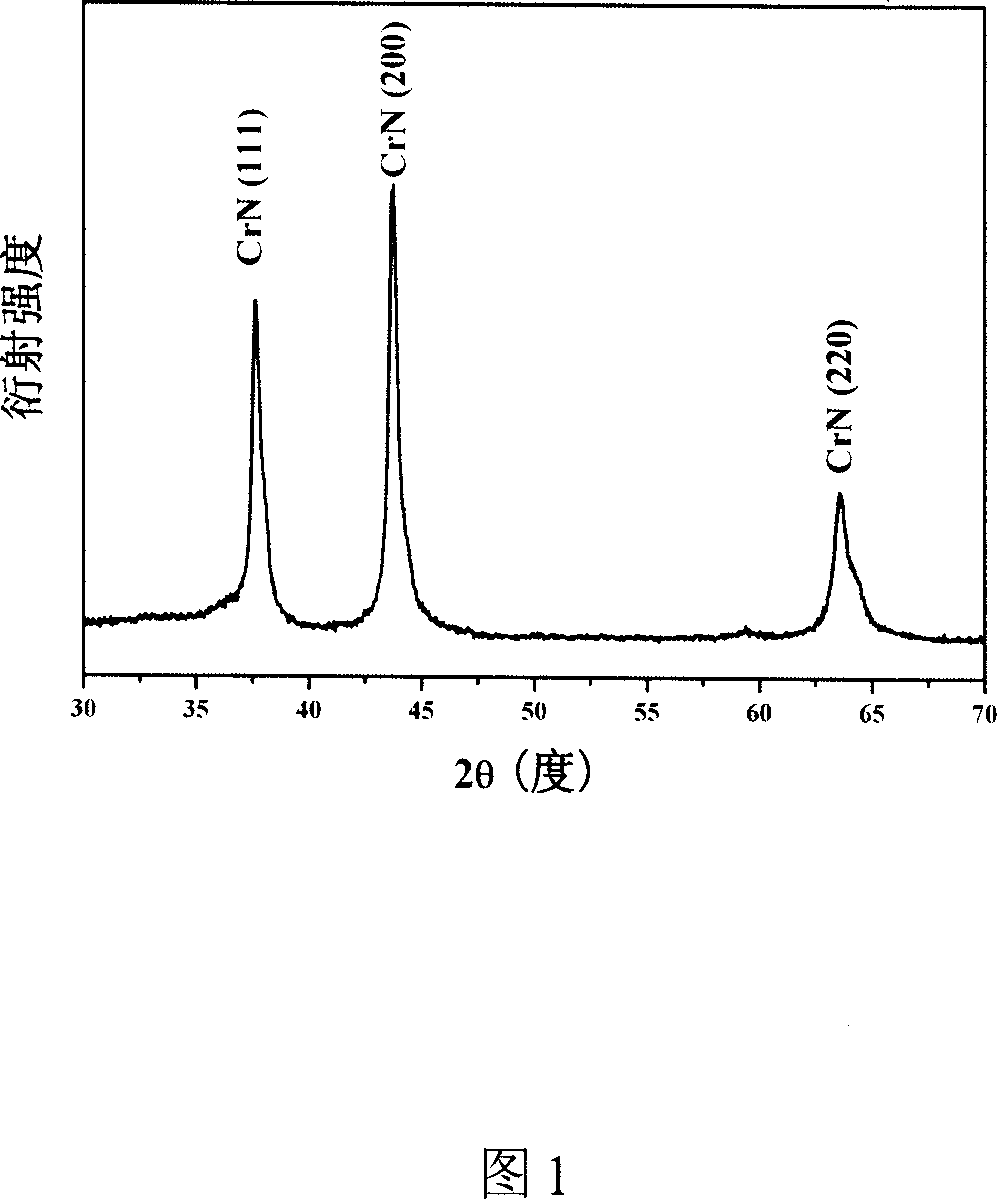

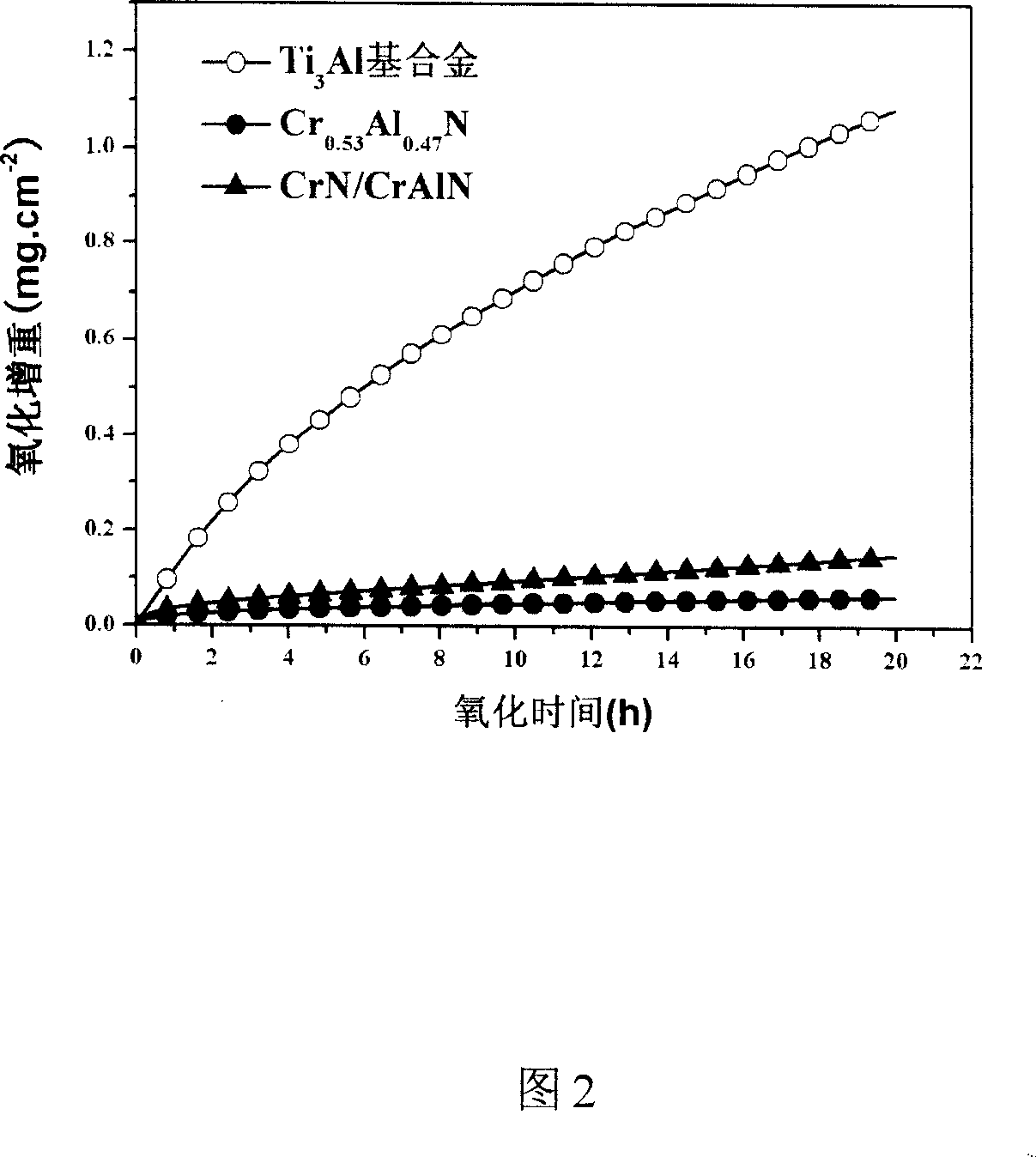

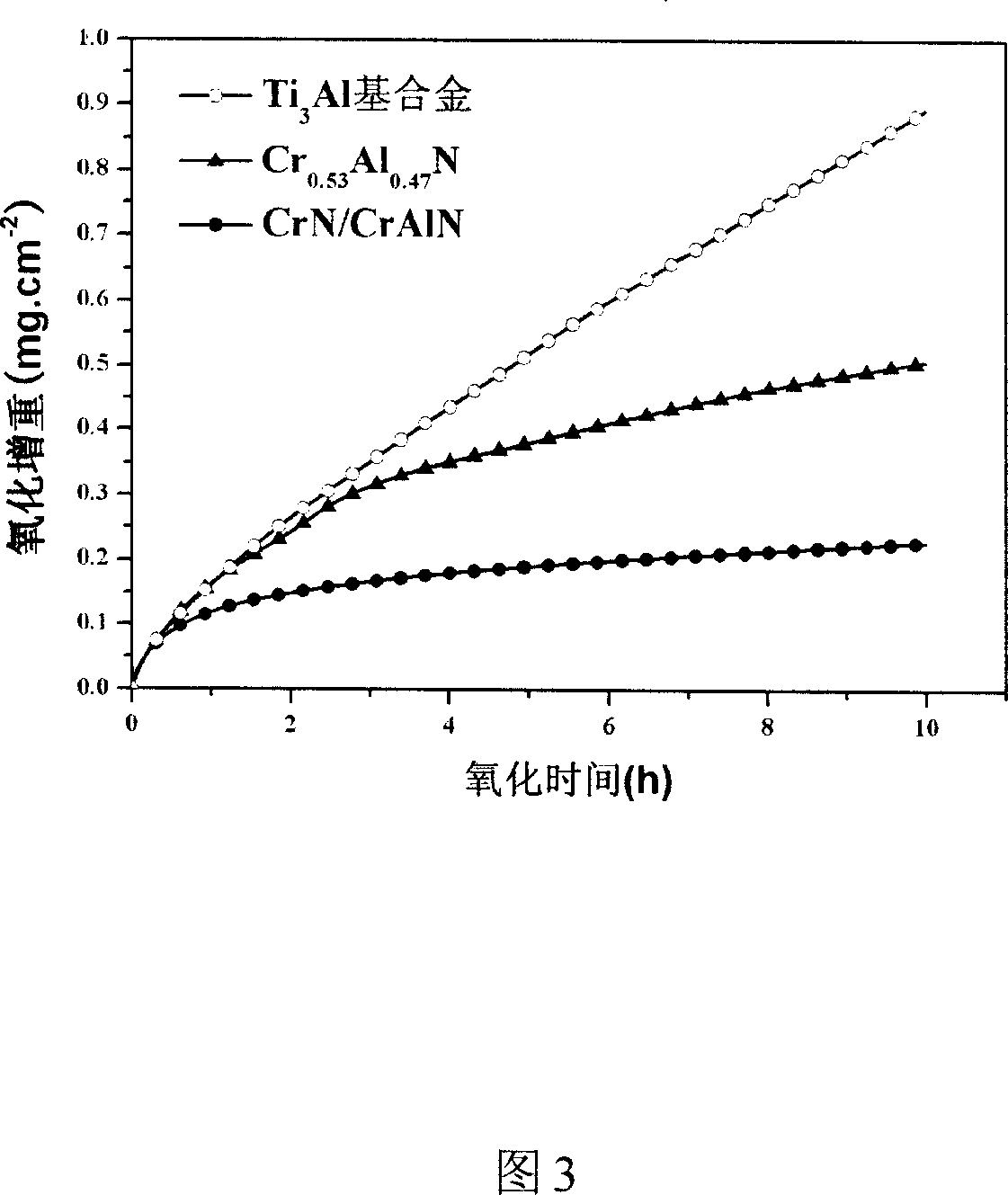

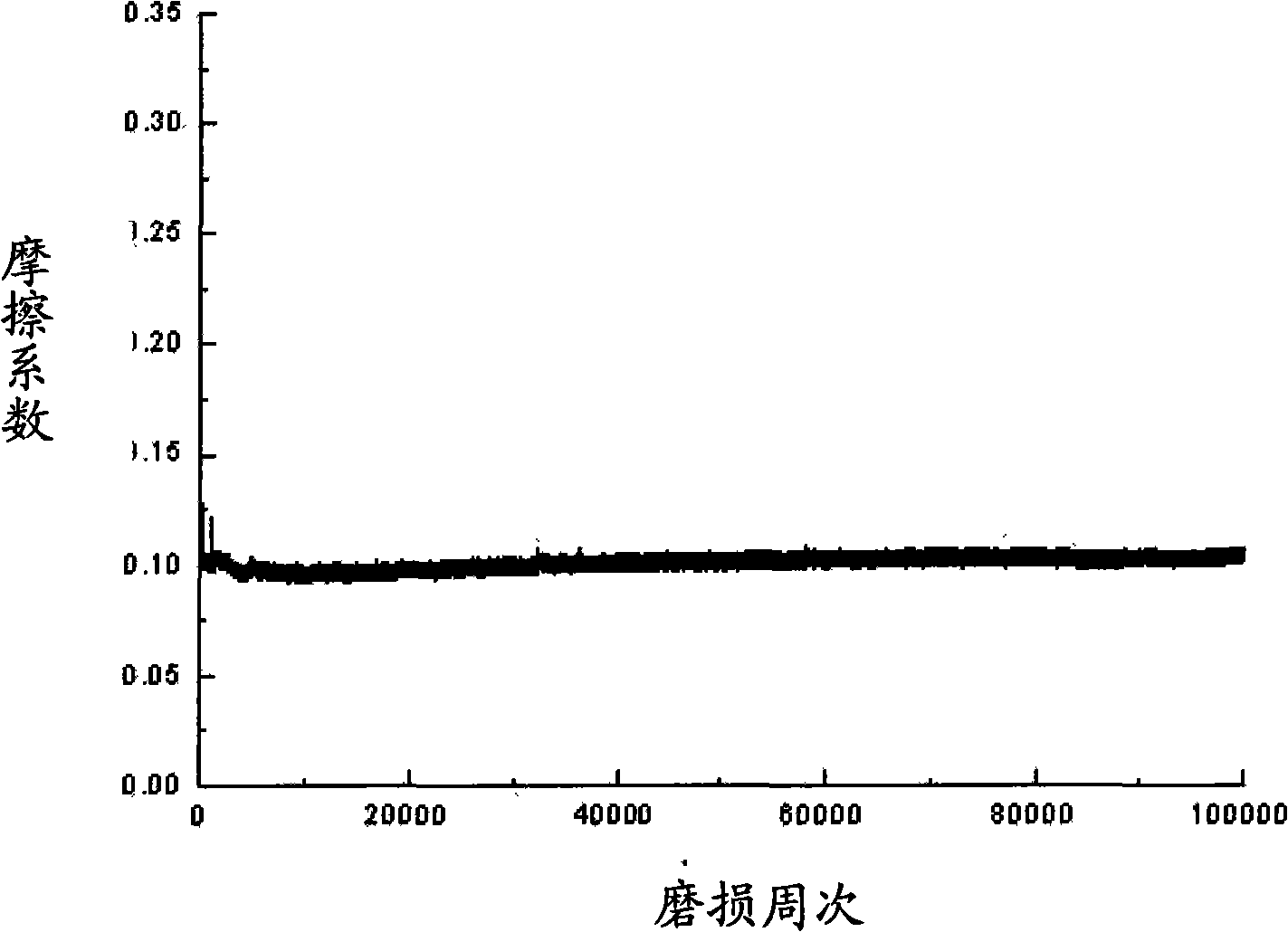

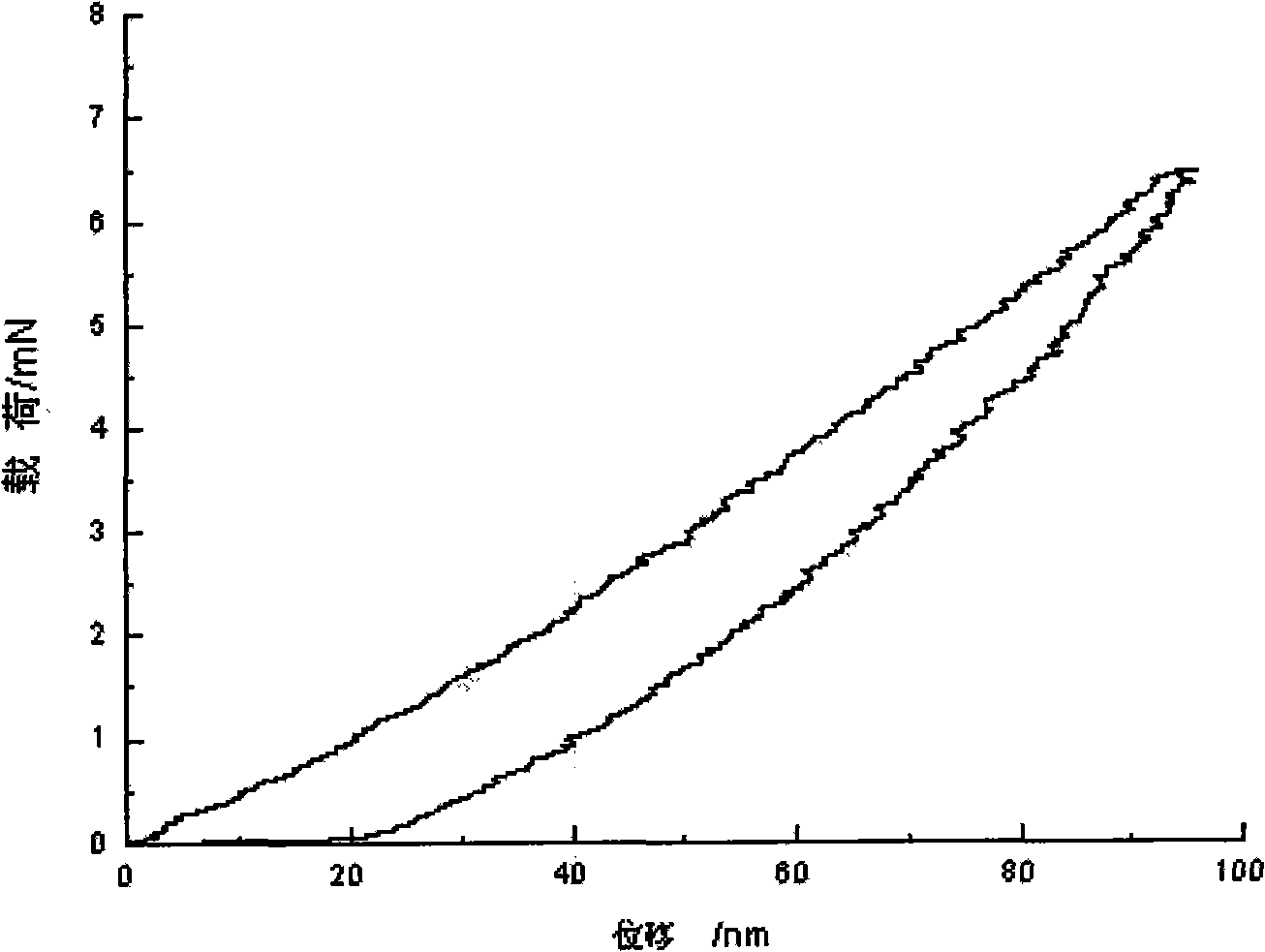

CrN/CrAlN protective coating capable of resisting high temperature corrosion in wide temperature range and preparing method

InactiveCN101033539AExcellent high temperature protection performanceEffective protectionVacuum evaporation coatingSputtering coatingRoom temperatureOxidation resistant

This invention relates to a CrN / CrAlN anti-hot corrosion protection coating in a wide temperature sphere and its preparation method, which applies a mode of DC reaction cosputter to Cr and Al targets to get a CrN / CrAlN coating, in which, the chip temperature is room temperature-300deg.C, Ar and N2 are controlled by mass flowmeter, the flow is 6-20SCCM and 6-20SCCM, the working air pressure is 0.1-0.8Pa, Al content in the coating is controlled by adjusting the power ratio of Cr and Al targets, and 0-150V base negative bias voltage is applied on the base to increase the binding force between the coating and the base, the inner layer of the coating is CrN, the outer is Cr-Al-N with grads distributed Al, and the coating forms a Cr2O3 film with solid solution Al after being oxidized in 800-900deg.C and forms Al oxidation film with rich Al over 1000deg.C and the CrN / CrAlN coating is very good at anti-hot corrosion from hot corrosion experiment.

Owner:INST OF METAL RESEARCH - CHINESE ACAD OF SCI

Preparation of high-hardness diamond-like multi-layer film

InactiveCN101298656AIncreasing the thicknessReduce hardnessVacuum evaporation coatingSputtering coatingVacuum chamberVacuum arc

The invention discloses a preparation method of a multilayer diamond-like film with high hardness, which comprises the following steps: a substrate is sputter cleaned, the diamond-like film is deposited by a depositing method with magnetic filtering and cathode vacuum arc, and the depositing method comprises steps of closing a vacuum chamber, vacuumizing the vacuum chamber to the pressure of 10<-3> Pa, turning on a pot lead cathode arc source, exerting negative bias voltage from minus 50 V to minus 200 V on the substrate and simultaneously and periodically letting in argon of 99.99 percent; furthermore, a control period lasts for 120 to 600 seconds, the time for letting in the argon is 10 to 50 percent of the control period, and the argon pressure in the vacuum chamber during argon inletting is 0.01 to 0.1 Pa; time for shutting off the argon is 90 to 50 percent of the control period, and the vacuum degree of the vacuum chamber at the time is 10<-4> to 10<-3> Pa; the number of the control periods is 3 to 50. The preparation method of the multilayer diamond-like film with high hardness has simple technique, low cost, produced films with strong bonding force, high hardness, large thickness, small stress and excellent mechanical and tribology performance; as well as wide application space in the industrial application field.

Owner:SOUTHWEST JIAOTONG UNIV

Program/erase method for P-channel charge trapping memory device

ActiveUS7133316B2Improve efficiencyIncrease speedTransistorSolid-state devicesBit lineComputer science

A method of operating a memory device is disclosed, wherein the memory device includes an n-type substrate and a plurality of memory cells formed thereon, each memory cell corresponding to a word line, a first bit line, and second bit line, and including a first bit portion and a second bit portion each for storing one bit of information. The method includes resetting a selected memory cell by applying a first negative bias to the word line of the selected memory cell and applying a ground bias to the first and second bit lines, and programming the first bit portion of the selected memory cell by applying a first positive bias to the word line of the selected memory cell, applying a second negative bias to the first bit line of the selected memory cell, and applying a ground bias to the second bit line of the selected memory cell.

Owner:MACRONIX INT CO LTD

Manufacturing method for CVD (Chemical Vapor Deposition) diamond/diamond-like composite coating tool with complex shape

ActiveCN102650053AExcellent film-substrate adhesion strengthSmooth surface qualityVacuum evaporation coatingSputtering coatingDiamond-like carbonAlloy

The invention discloses a manufacturing method for a CVD (Chemical Vapor Deposition) diamond / diamond-like composite coating tool with a complex shape. The manufacturing method comprises the steps as follows: depositing a layer of MCD (Micro Crystalline Diamond) film on the surface of the tool by a hot wire CVD method, and generating ion bombardment by negative bias in the depositing process so as to ensure that the surface of the MCD film is smooth; and continuously depositing a layer of DLC (Diamond-like Carbon) film, carrying out ion bombardment on the tool surface coated with the MCD film by positive and negative pulse ion power so as to remove impurities on the tool surface in the initial period, and removing the sharp crystalline grain edge of the coating surface to enhance the flatness of the coating and improve the surface activity of the coating so as to achieve the effect of enhancing the interlayer adhesion strength. Due to the manufacturing method, the surface of the integrated hard alloy tool with the complex shape can be deposited to obtain the CVD diamond / diamond-like composite coating with excellent film-based adhesion strength, surface wear and friction resistance and self lubricating property, and the composite coating also has the characteristics of low internal stress, smooth and flat surface, uniform thickness and the like.

Owner:SHANGHAI JIAO TONG UNIV +1

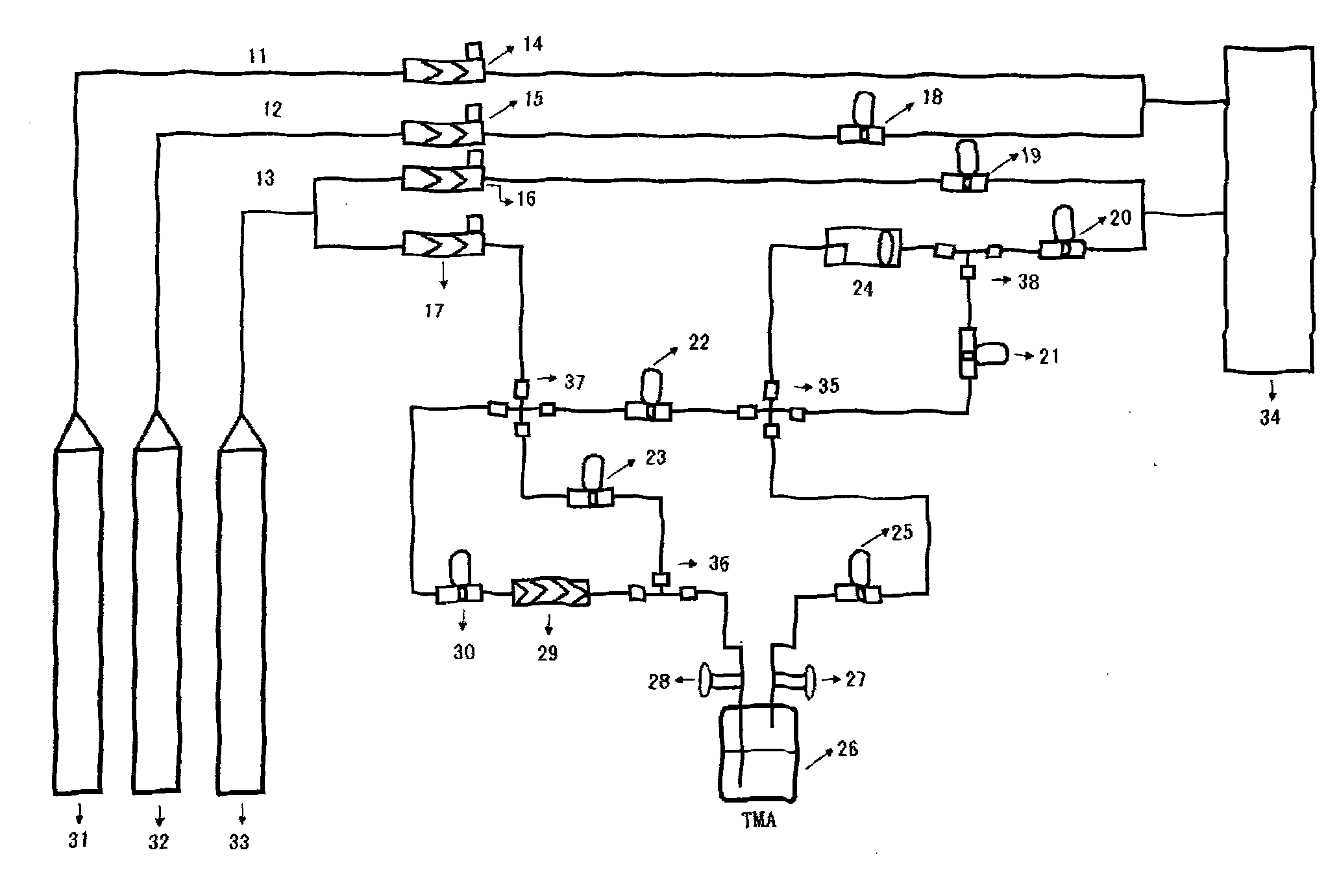

Device and method for depositing ultrathin alumina film by atomic layer

InactiveCN101921994ASolve the disadvantage of needing high temperature heatingChemical vapor deposition coatingPlasma depositionRadio frequency

The invention relates to device and method for depositing an ultrathin alumina film by an atomic layer. Plasma is generated by combining double frequency which is microwave ECR with radio frequency negative bias voltage equipment and used for depositing the alumina film. By using the microwave ECR and the radio frequency negative bias voltage system, the work gas generates the plasma; and by using trimethyl aluminum (TMA) as a monomer and the mode of TMA-Ar-O2-Ar alternate pulse, the alumina film is deposited by using the atomic layer, wherein the deposition temperature is room temperature. By adopting the generating mode of using the plasma as an active group, the deposition can be carried out in a lower ambient temperature, the growth speed is higher compared with the deposition by a hot atomic layer and is about 0.12nm / period and the quality of the prepared film is higher compared with the deposition by the hot atomic layer. The prepared Al2O3 film can be widely applied to the fields of microelectronic devices, electroluminescent devices, wave optical devices, corrosion-resistant coatings and the like.

Owner:BEIJING INSTITUTE OF GRAPHIC COMMUNICATION

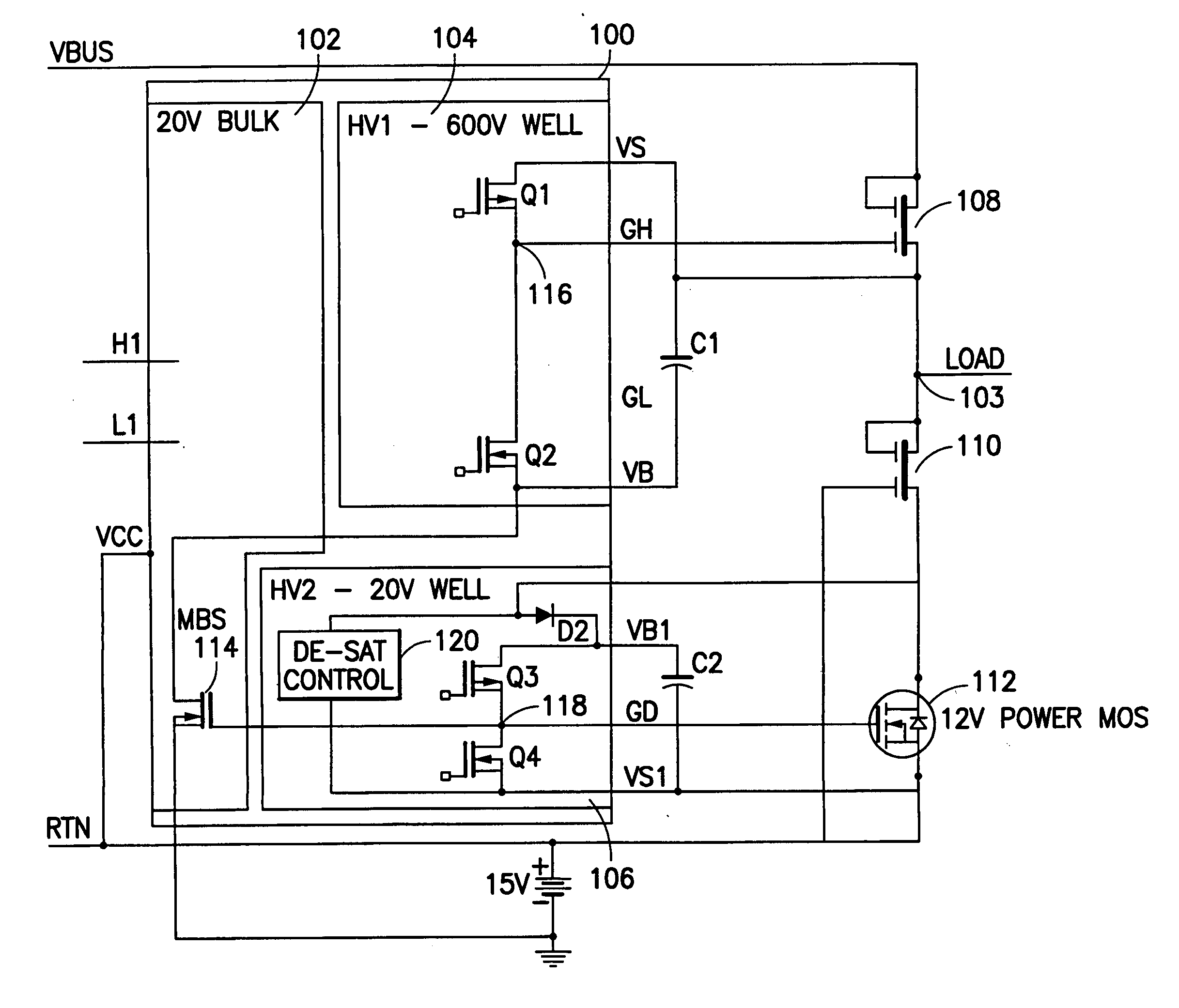

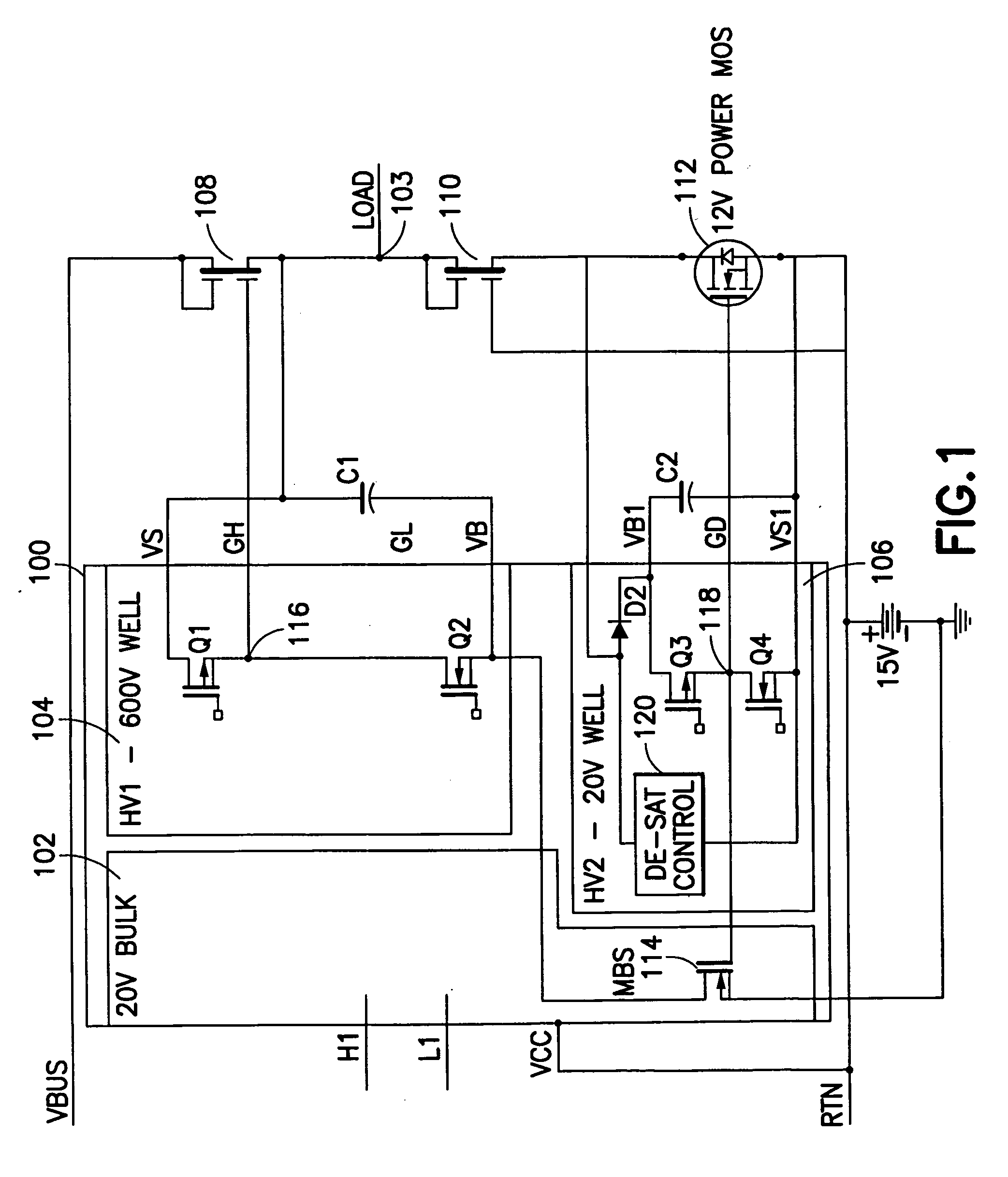

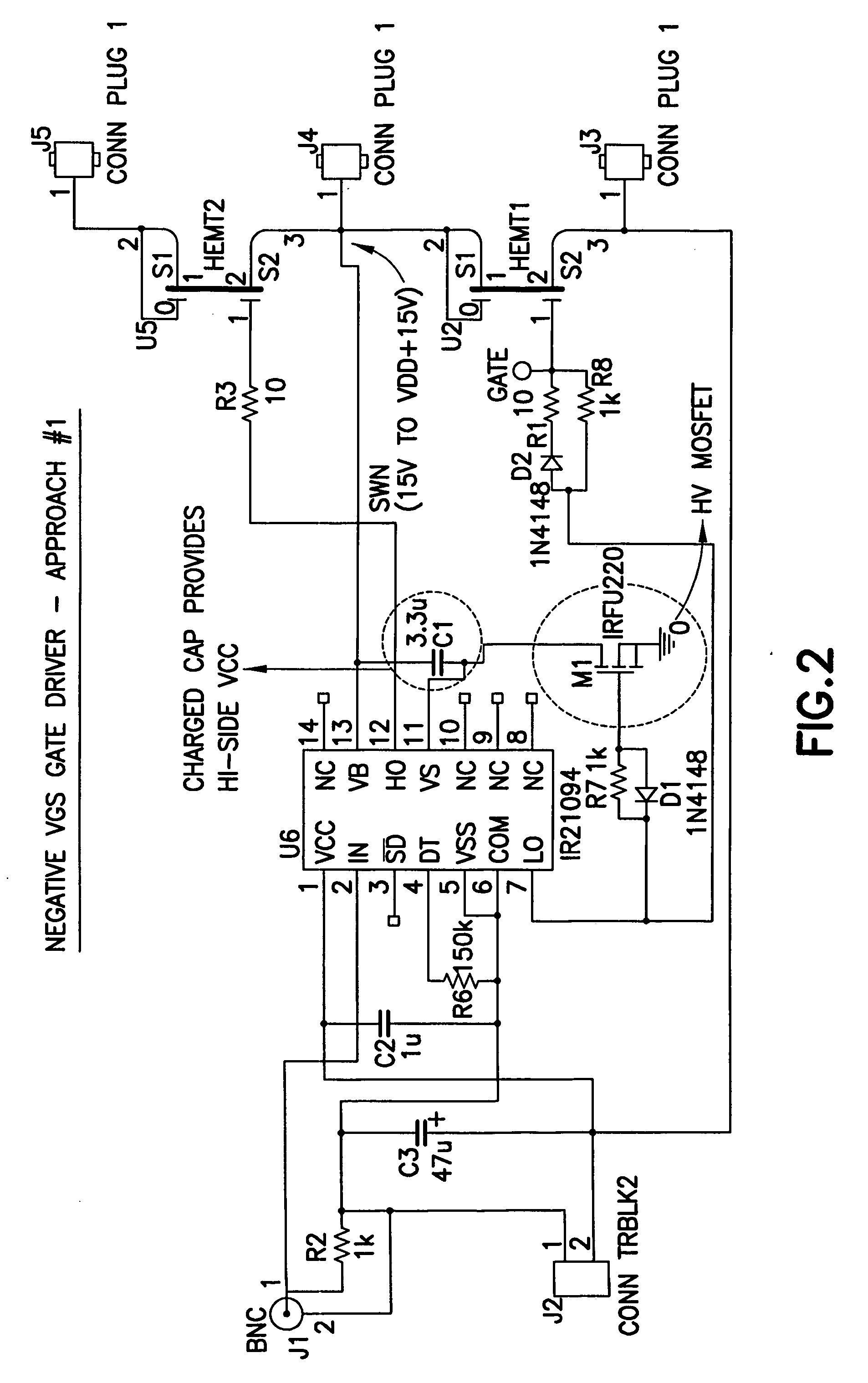

Driving circuit for use with high voltage bidirectional semiconductor switches

A driving circuit for a half bridge utilizing bidirectional semiconductor switches in accordance with an embodiment of the present application includes a high side driver operable to control a high side bidirectional semiconductor switch, wherein the high side driver provides a negative bias voltage to the bidirectional semiconductor switch to turn the high side bidirectional semiconductor switch OFF. A low side driver may be operable to control a low side bidirectional semiconductor switch. An external voltage source with a negative terminal of the voltage source connected to the high side driver may be provided. A high side driving switch may be positioned between the negative terminal of the voltage source and the high side driver and operable to connect the high side driver to the negative terminal of the voltage source when the low side driver turns the low side bidirectional semiconductor switch ON.

Owner:INFINEON TECH AMERICAS CORP

Plasma processing apparatus and method

ActiveUS20110272097A1Improved resistance characteristicsIncrease chanceElectric discharge tubesSemiconductor/solid-state device manufacturingNegative biasDc voltage

A plasma etching apparatus includes an upper electrode and a lower electrode, between which plasma of a process gas is generated to perform plasma etching on a wafer W. The apparatus further comprises a cooling ring disposed around the wafer, a correction ring disposed around the cooling ring, and a variable DC power supply directly connected to the correction ring, the DC voltage being preset to provide the correction ring with a negative bias, relative to ground potential, for attracting ions in the plasma and to increase temperature of the correction ring to compensate for a decrease in temperature of a space near the edge of the target substrate due to the cooling ring.

Owner:TOKYO ELECTRON LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com