Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

85results about How to "Threshold Voltage Stability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

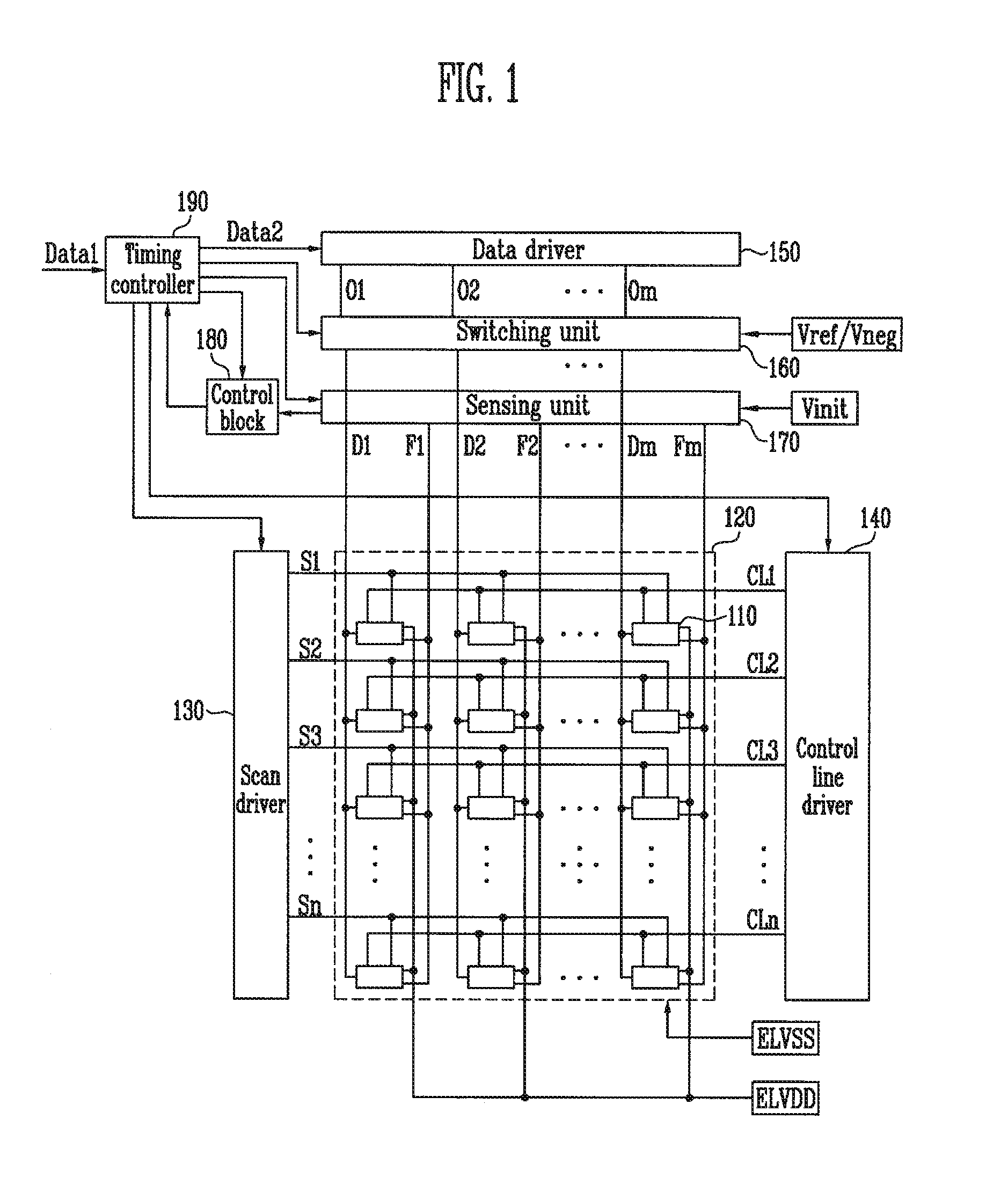

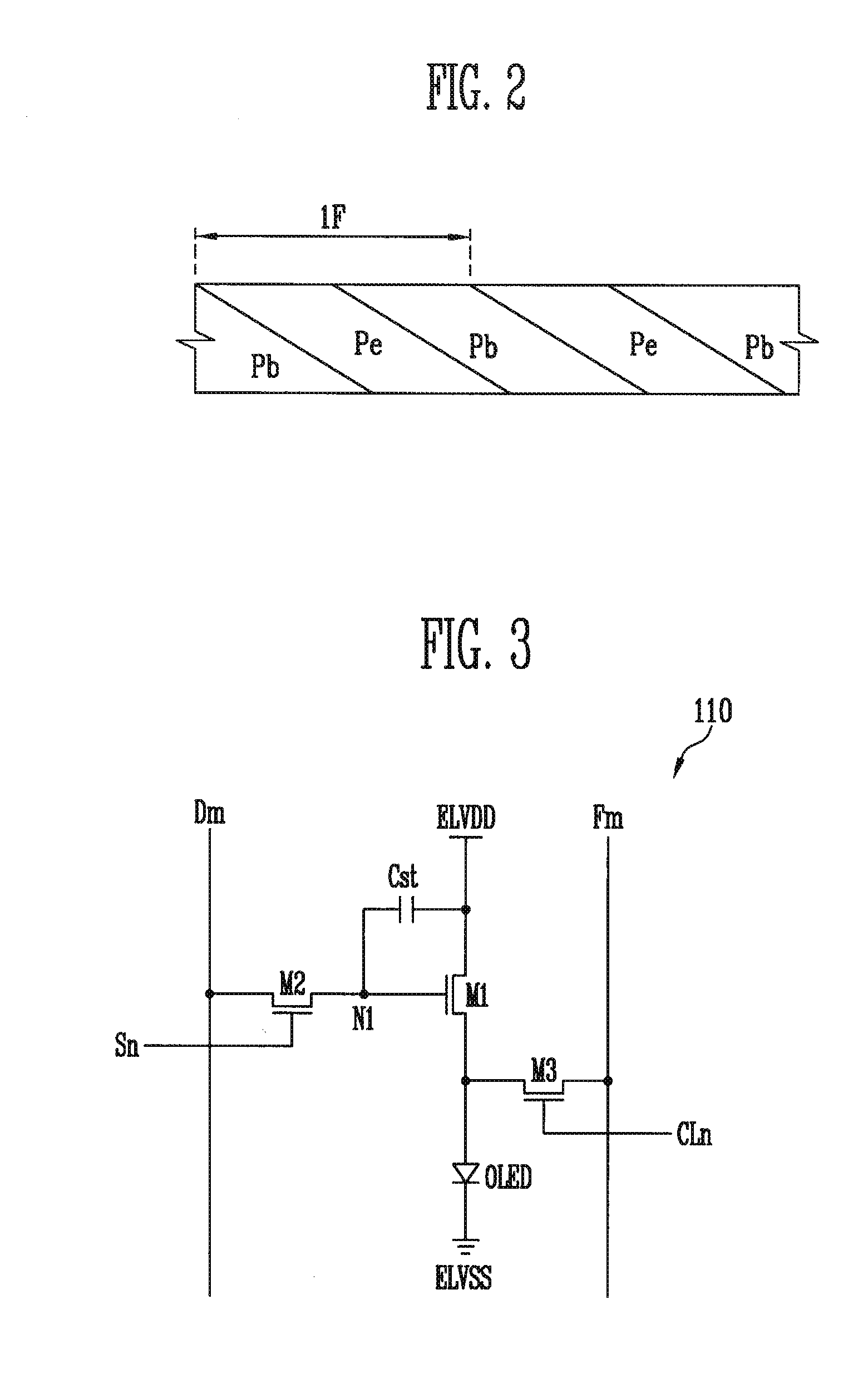

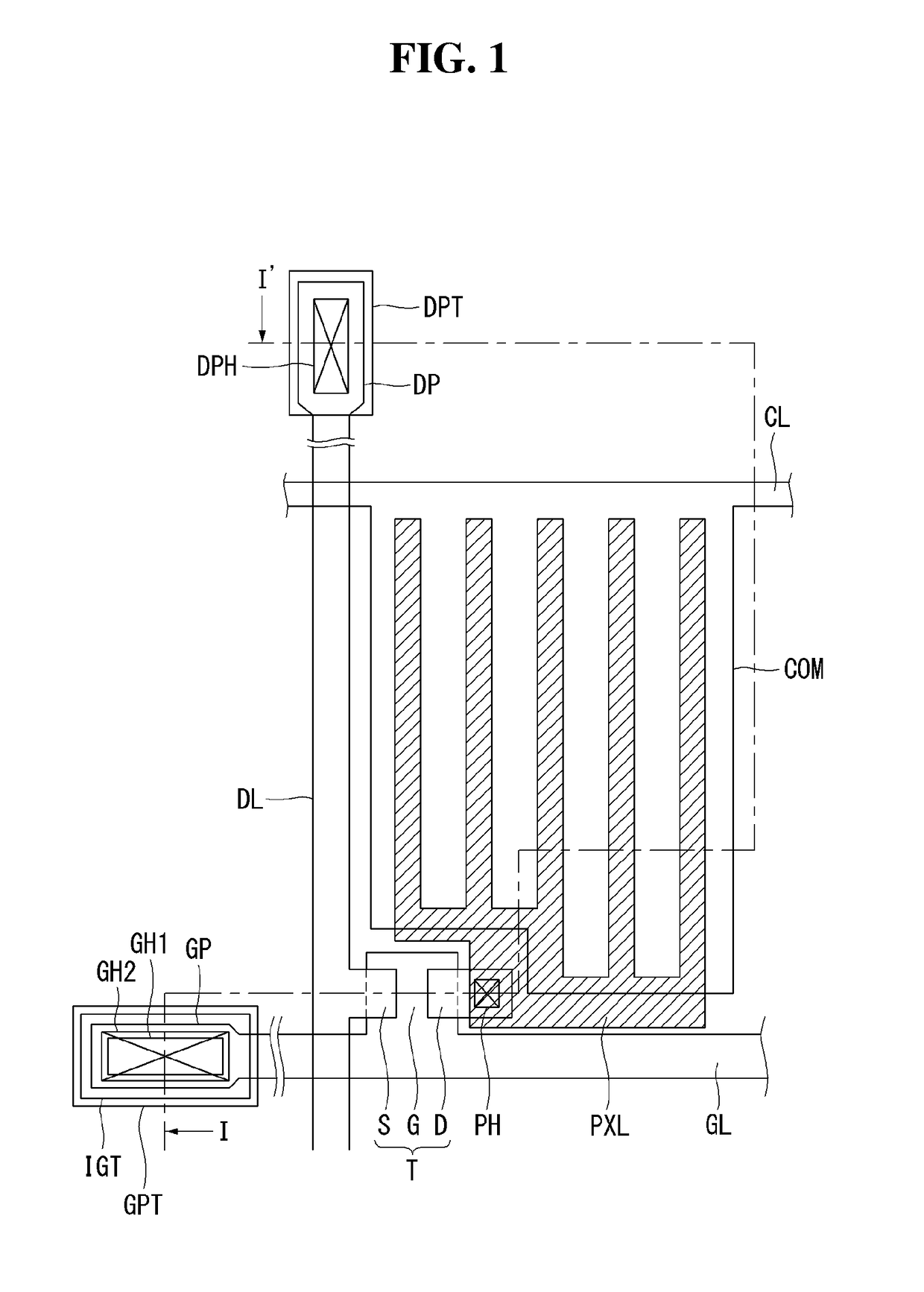

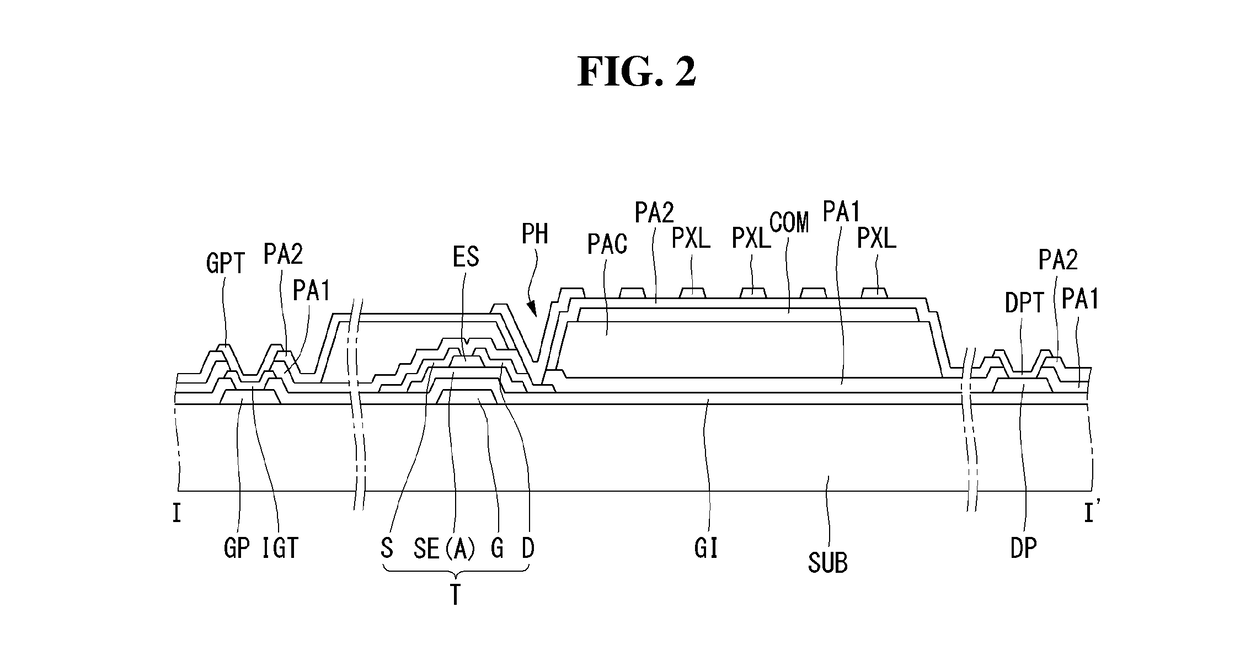

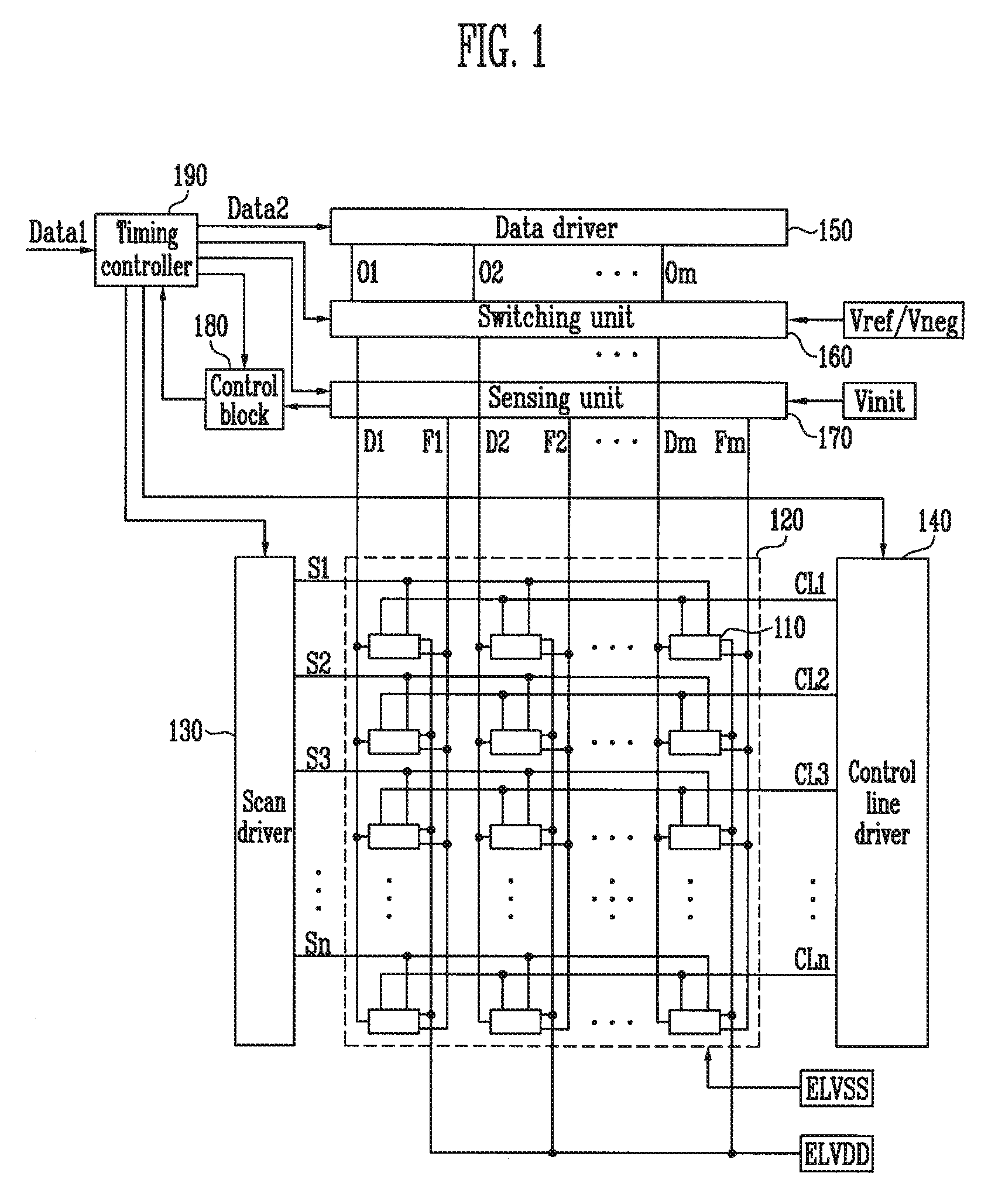

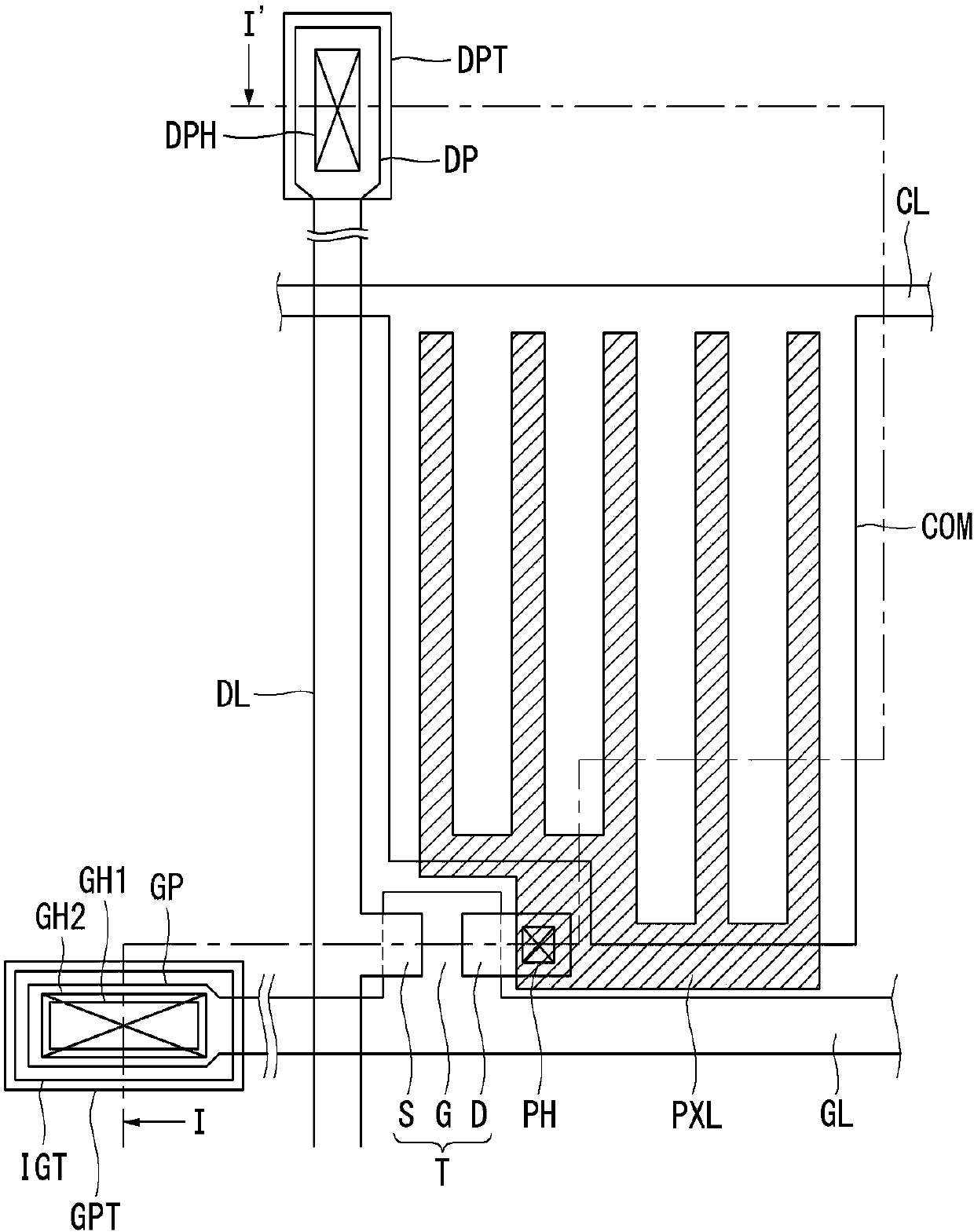

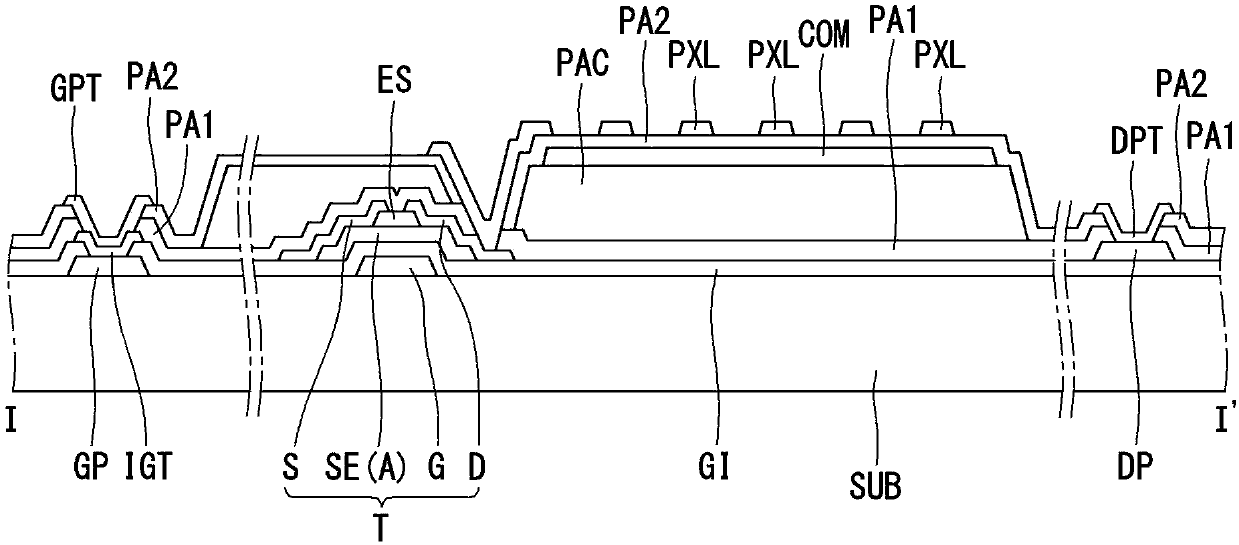

Organic light emitting display device

InactiveUS20110227505A1Uniform brightnessThreshold Voltage StabilityElectrical apparatusStatic indicating devicesDisplay deviceControl line

An organic light emitting display device includes a display unit having pixels located at crossing regions of scan, control, data and sensing lines. Scan, control line, and data drivers respectively supply scan, control, and data signals to the scan, control, and data lines. A switching unit selectively couples the data lines to output lines of the data driver, a reference voltage source, or a negative bias voltage source. A sensing unit senses degradation information of an organic light emitting diode in the pixels and threshold voltage of a driving transistor in the pixels through the sensing lines. A control block stores the sensed degradation information and threshold voltage information. A timing controller is configured to generate a second data by converting an externally inputted first data using the degradation information and the threshold voltage information, and supply the second data to the data driver.

Owner:SAMSUNG DISPLAY CO LTD

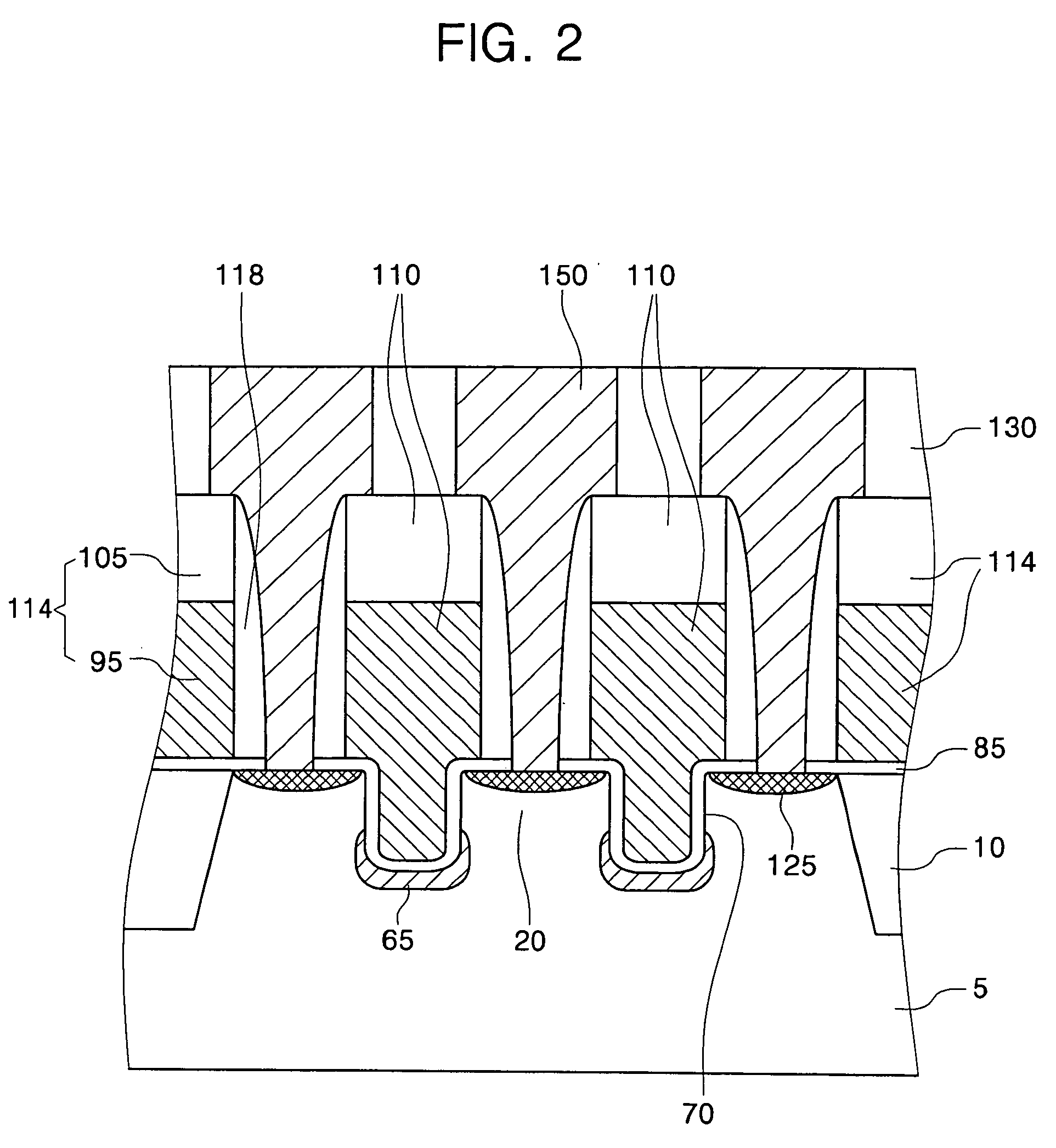

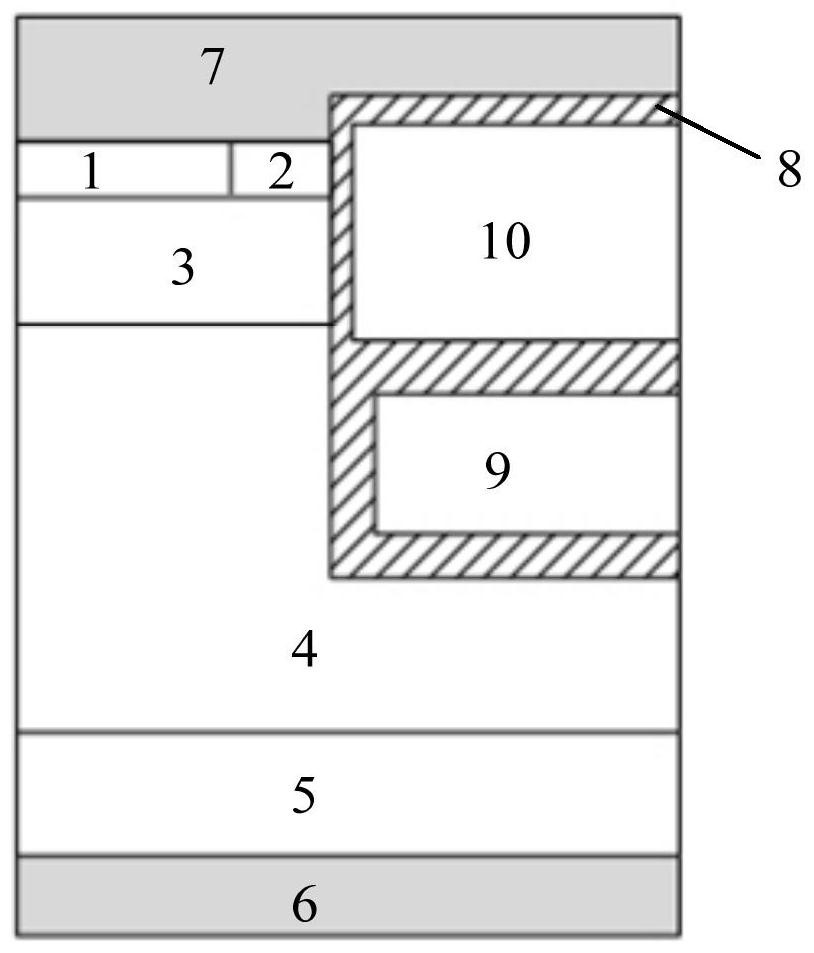

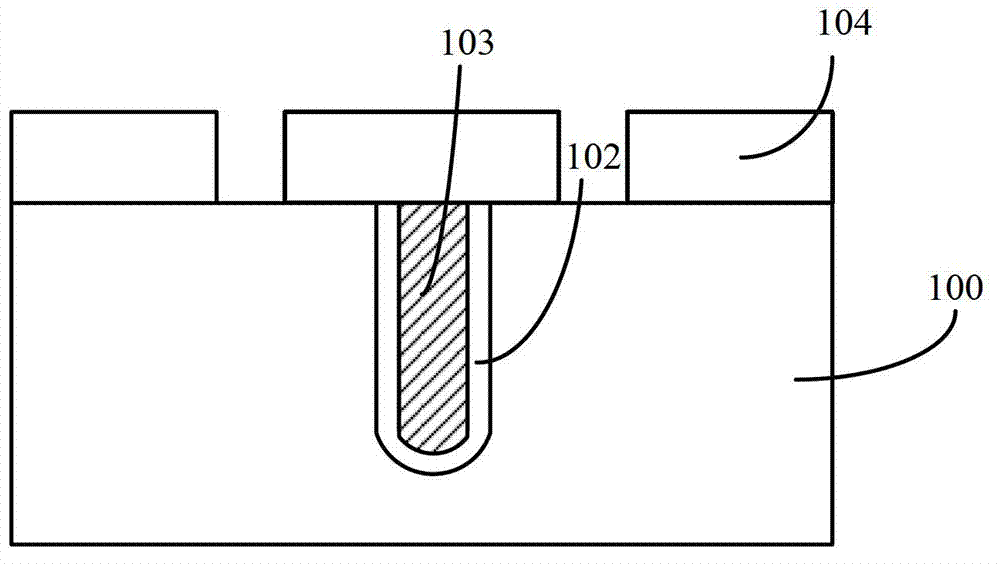

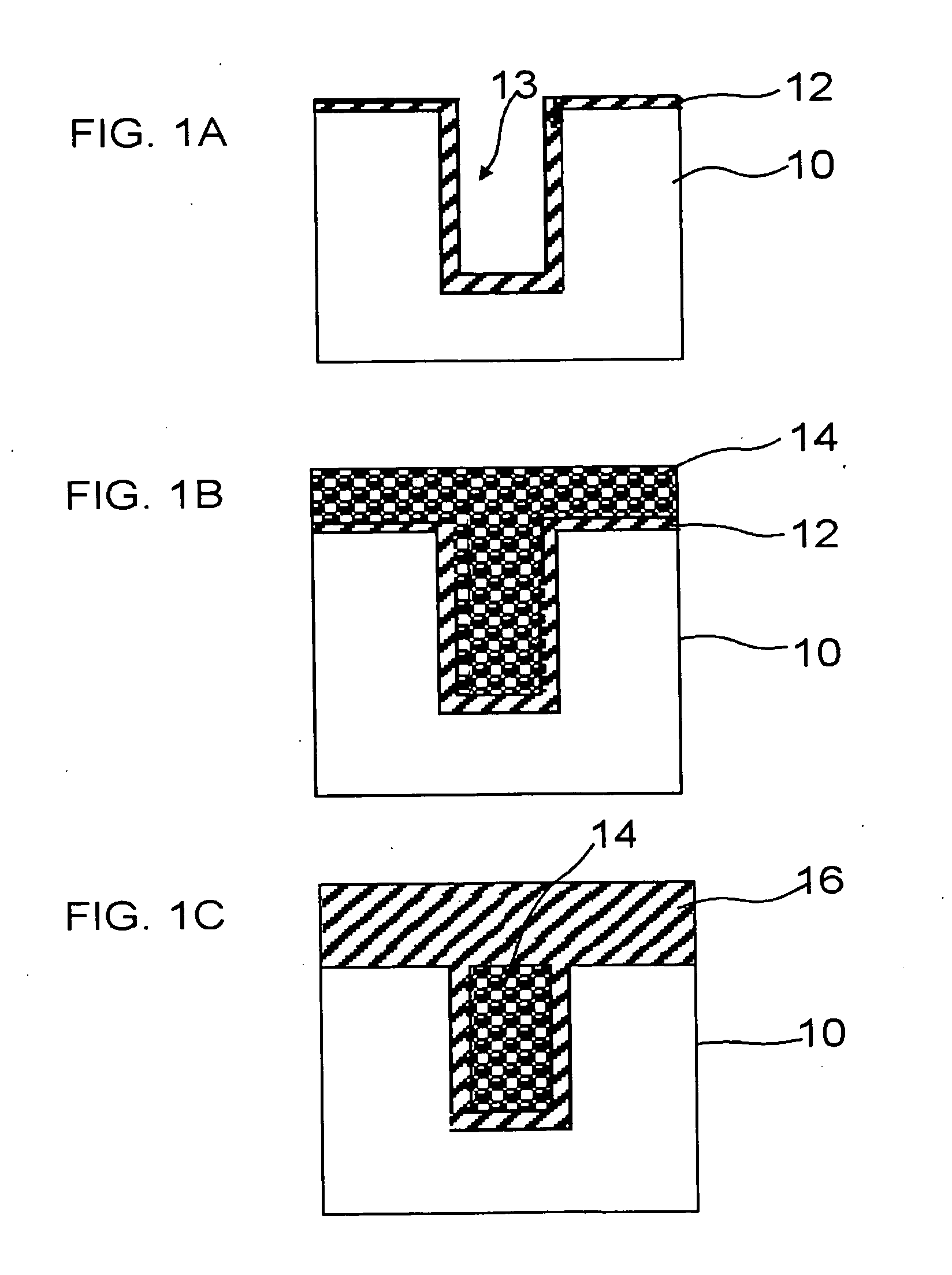

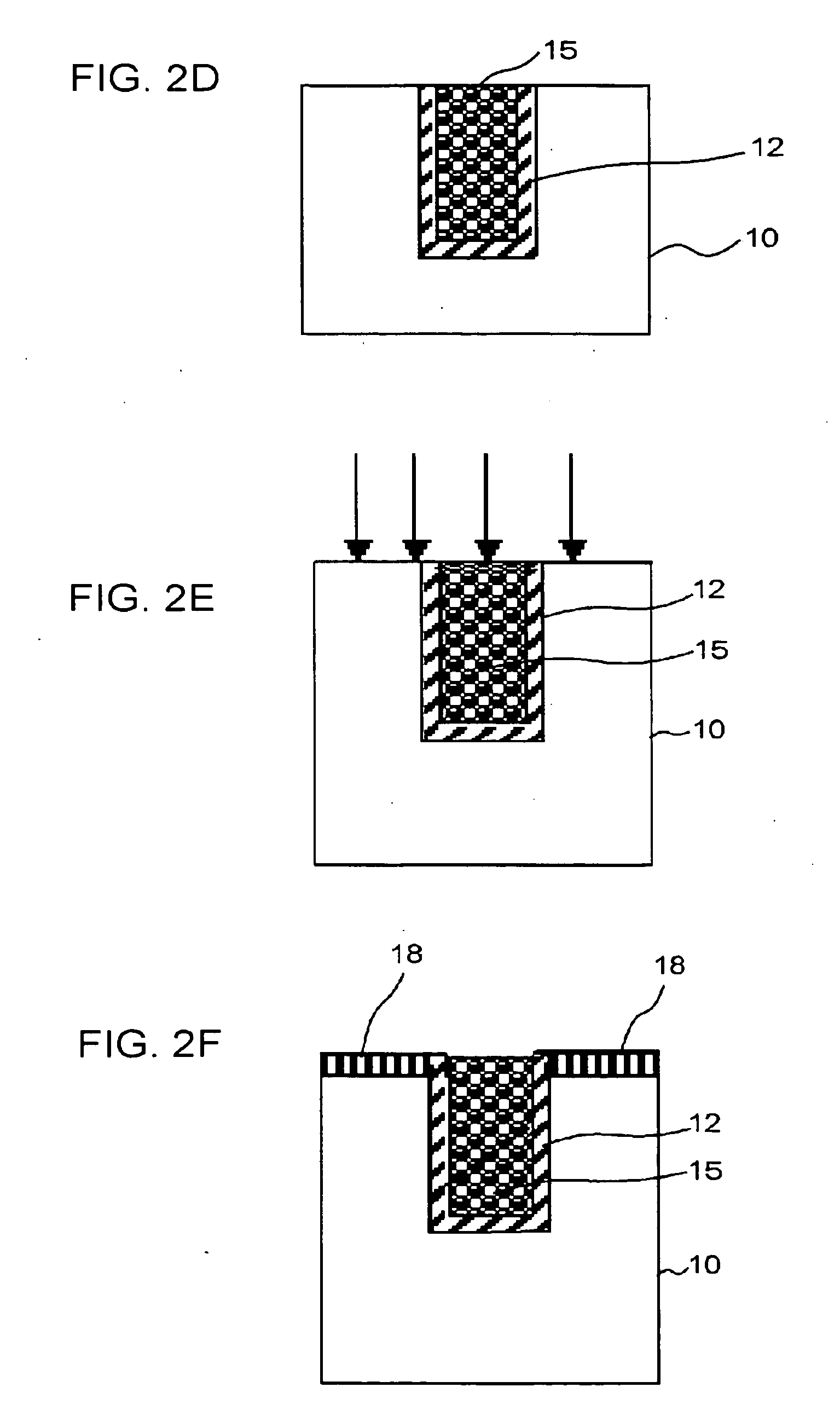

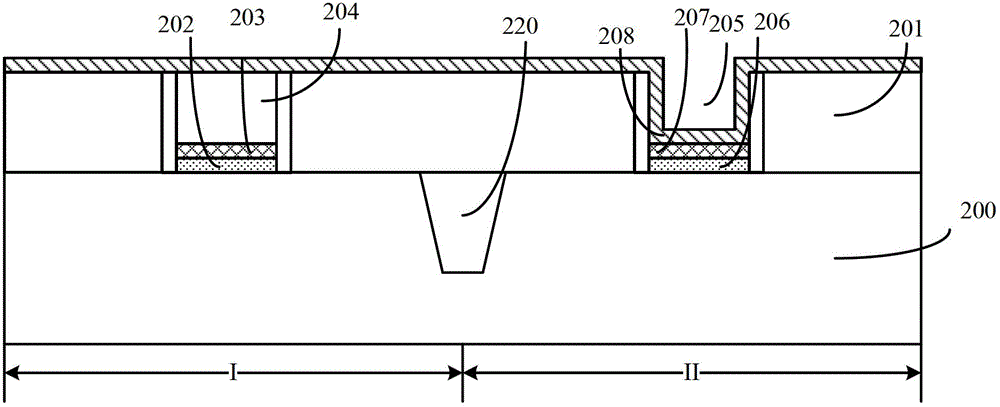

Recessed-type field effect transistor with reduced body effect

InactiveUS20050173744A1Threshold Voltage StabilityBody effect is preventedTransistorSolid-state devicesGate insulatorEngineering

For fabricating a field effect transistor, an extra-doped channel region is formed below a surface of a semiconductor substrate. An opening is formed in the semiconductor substrate into the extra-doped channel region. A gate insulator is formed at walls of the opening such that the extra-doped channel region abuts the gate insulator at a bottom portion of the opening. The opening is filled with a gate electrode. Such an extra-doped channel region prevents undesired body effect in the field effect transistor.

Owner:SAMSUNG ELECTRONICS CO LTD

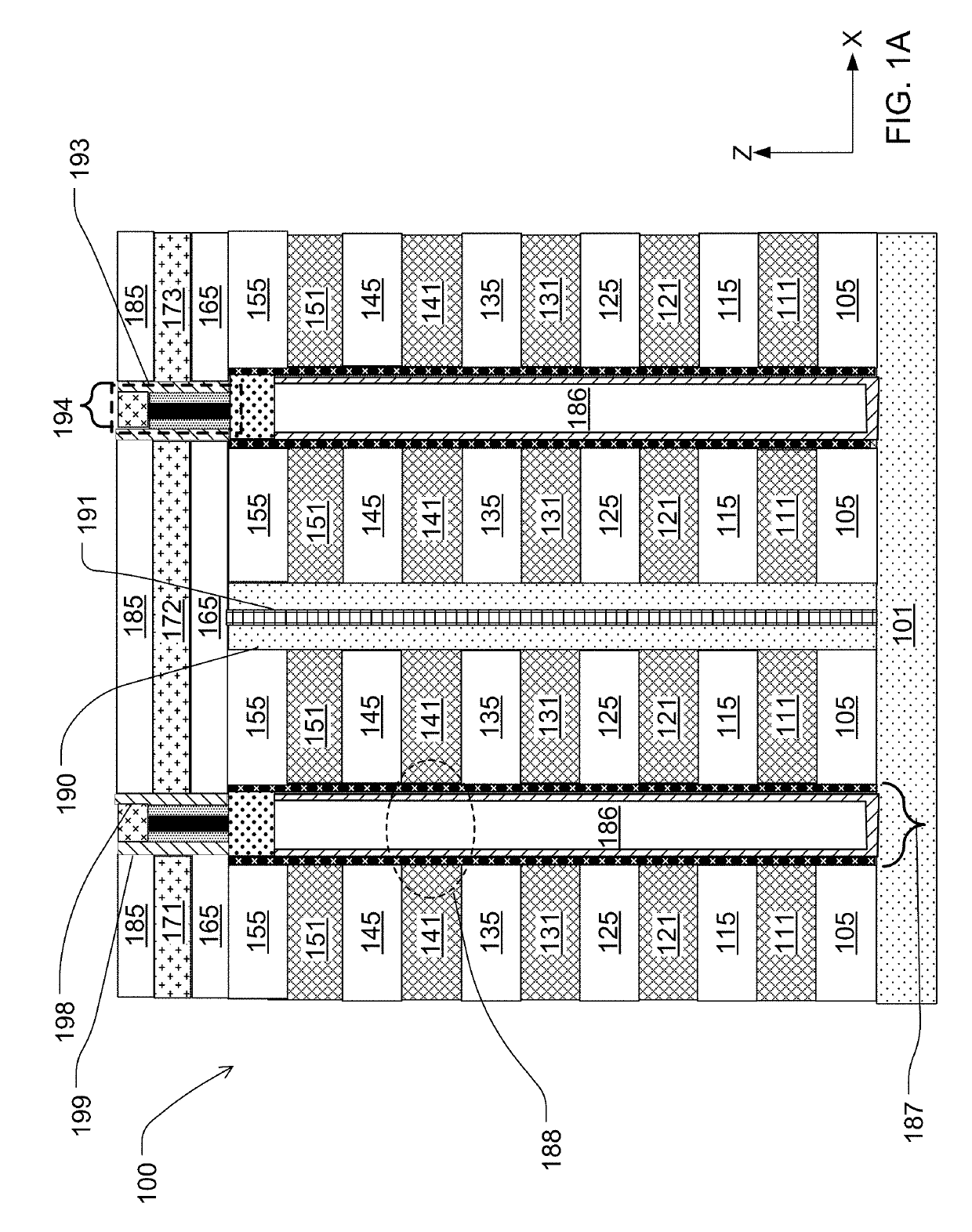

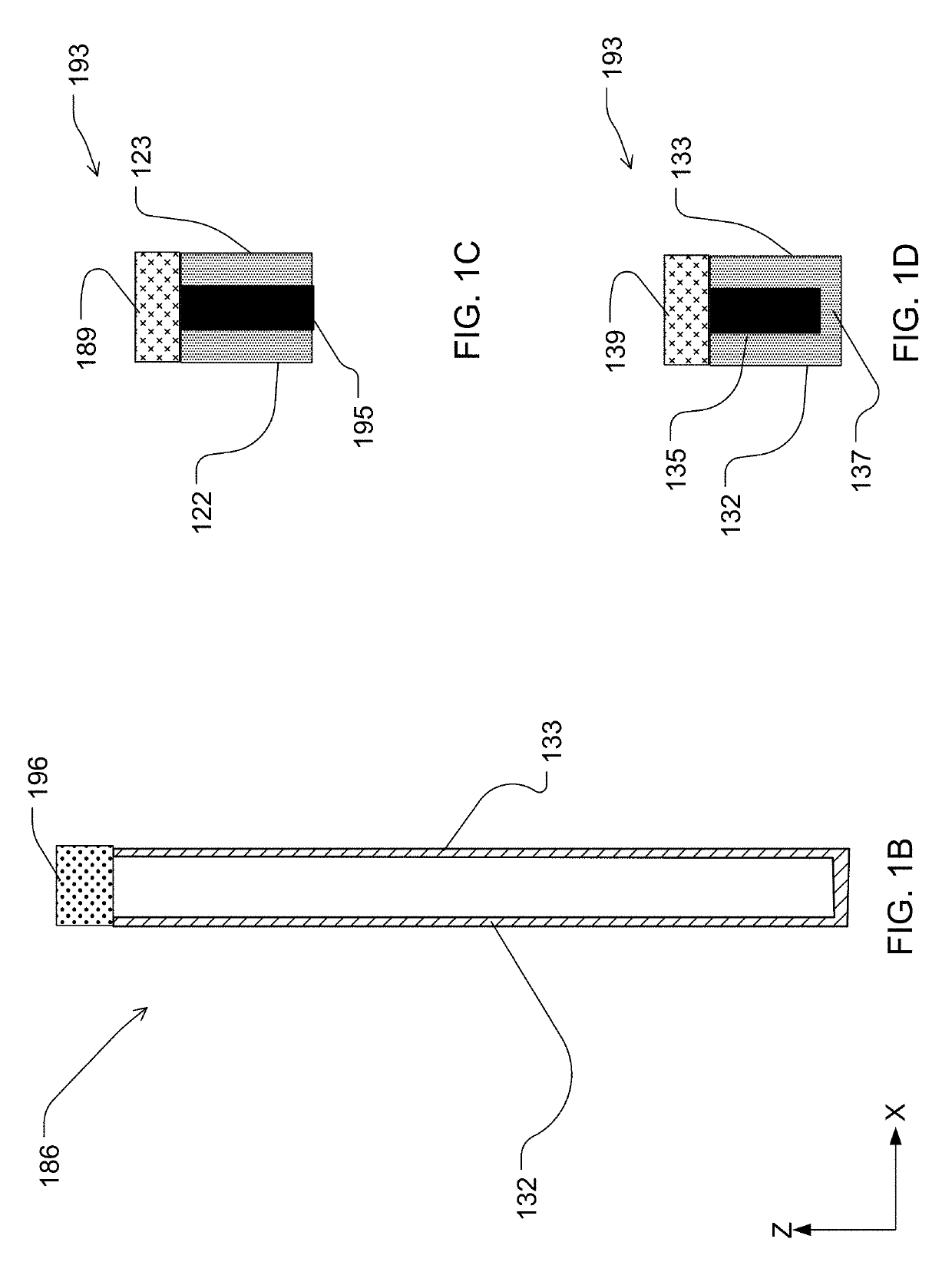

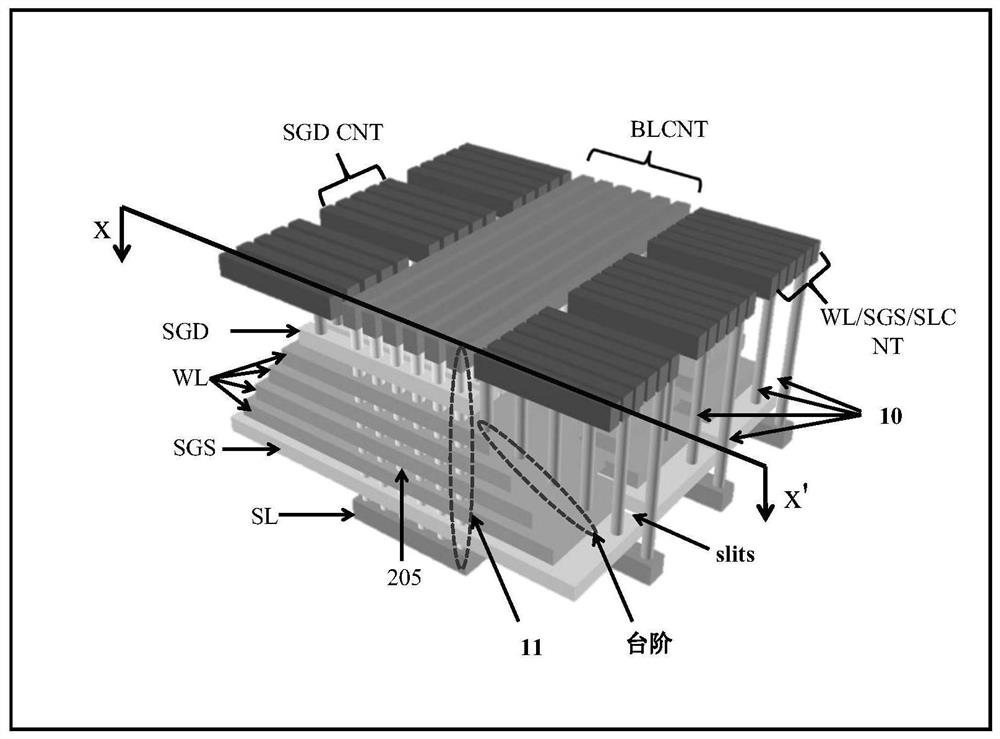

String select line gate oxide method for 3D vertical channel NAND memory

InactiveUS20190312050A1Well control of their channelStable threshold voltageSemiconductor/solid-state device detailsSolid-state devicesSecondary layerEngineering

A memory device includes a stack of conductive strips in a plurality of first levels with a first opening and a conductive strip in the second level with a second opening, both openings exposing sidewalls. Data storage structures are formed on the sidewalls of the conductive strips in the plurality of first levels. A first vertical channel structure including vertical channel films is disposed in the first opening, the vertical channel films in contact with the data storage structures. The second opening is aligned with the first vertical channel structure. A gate dielectric layer is disposed on the sidewall of the conductive strip in the second level. A second vertical channel structure including vertical channel films is disposed in the second opening in contact with the gate dielectric layer on the sidewall of the conductive strip in the second level.

Owner:MACRONIX INT CO LTD

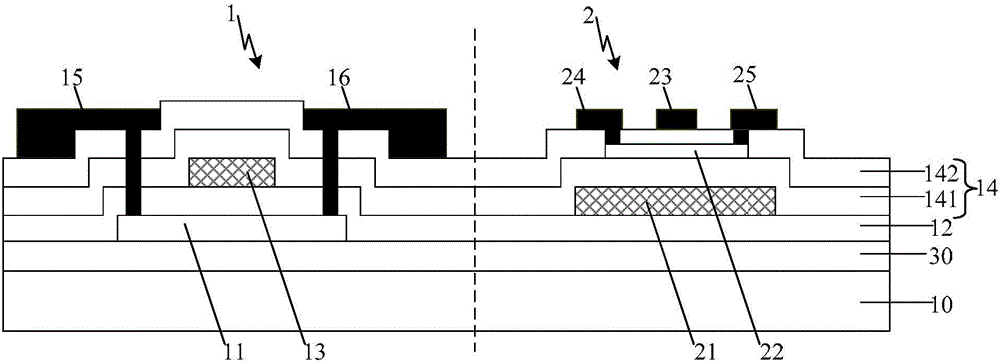

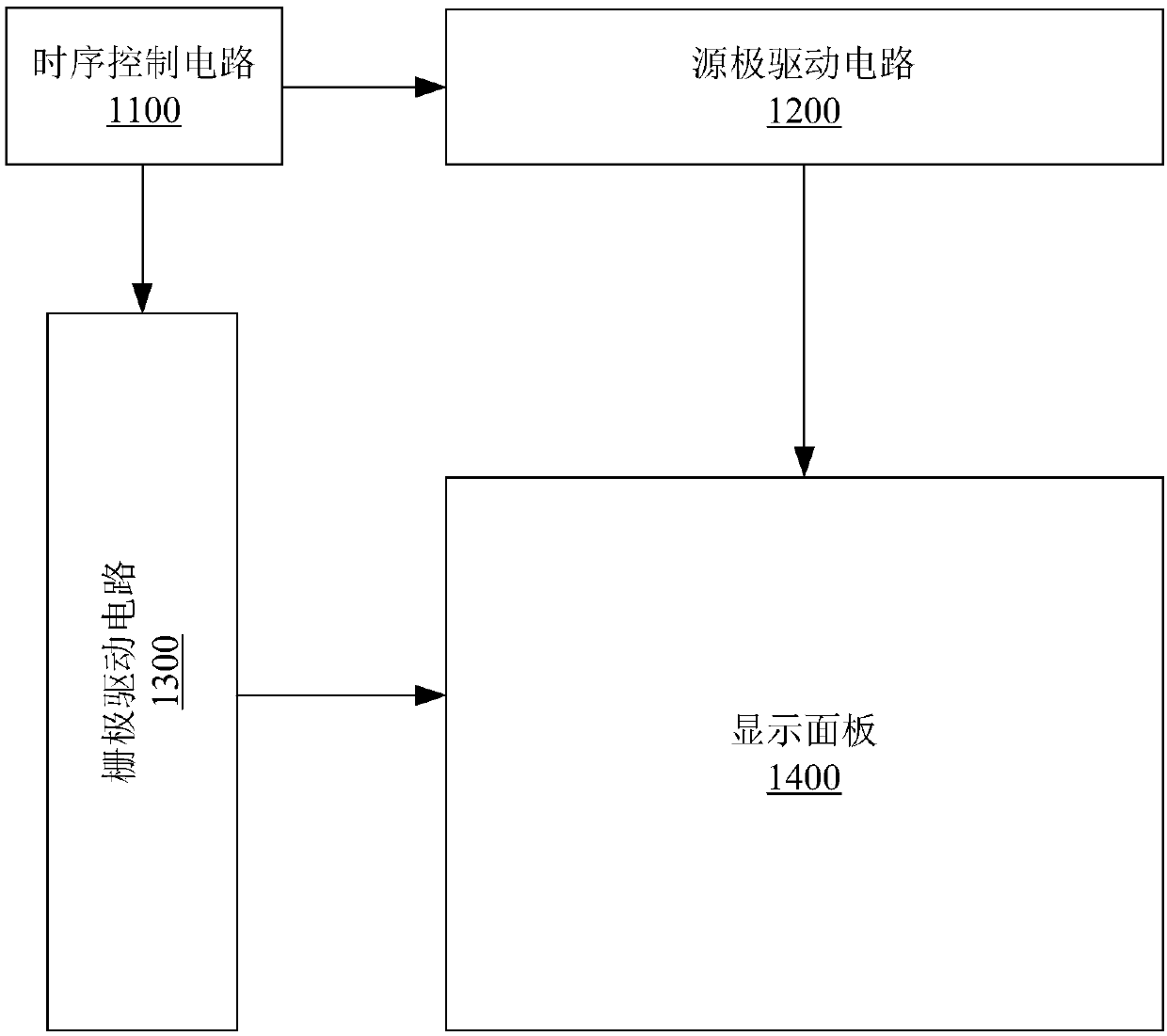

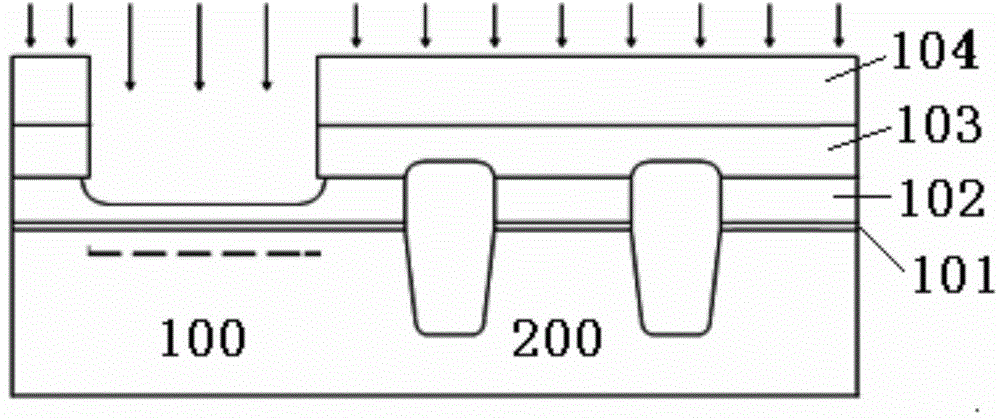

Array substrate and preparation method thereof and display panel

ActiveCN106847834AFast switching speedFast on state currentSolid-state devicesNon-linear opticsEngineeringDouble gate

The embodiment of the invention provides an array substrate and a preparation method thereof and a display panel and relates to the technical field of display. The display panel has good display performance by adopting two types of TFTs on the array substrate. The array substrate comprises a substrate, double-gate oxide TFTs, a display electrode and a polysilicon TFT arranged on the substrate, wherein one double-gate oxide TFT is arranged in each sub-pixel on the substrate; and a drain of each double-gate oxide TFT is electrically connected with the display electrode.

Owner:BOE TECH GRP CO LTD +1

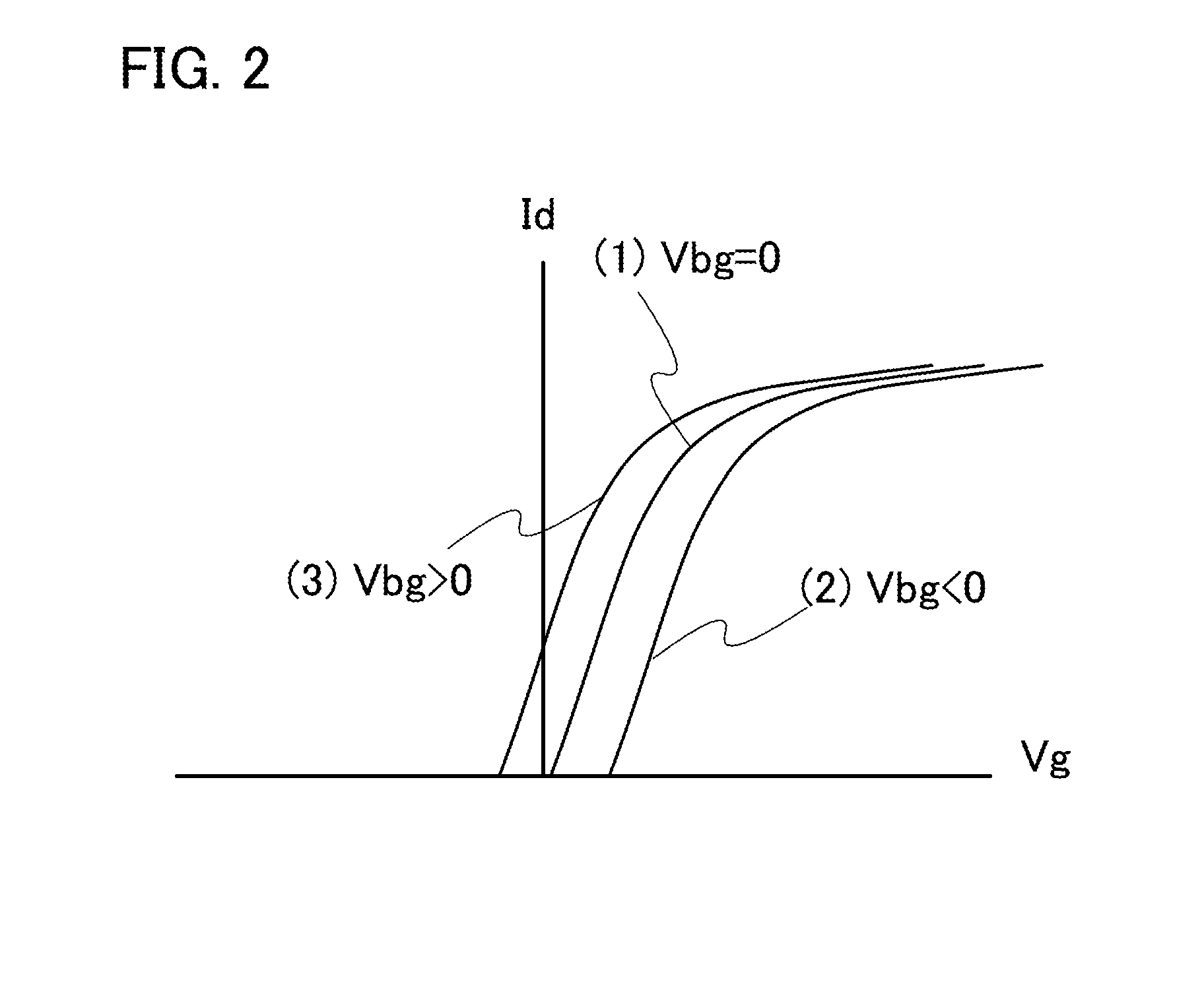

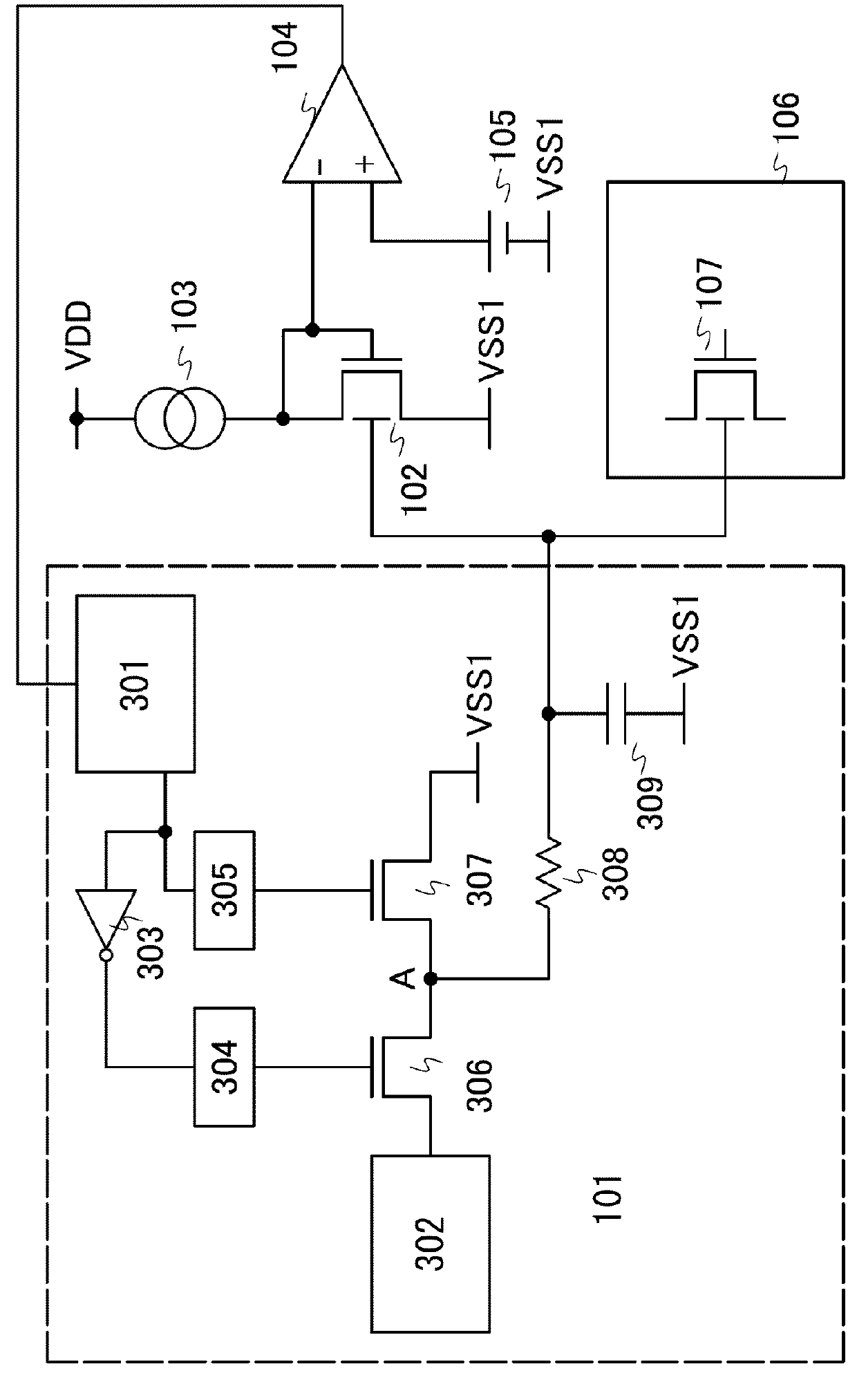

Semiconductor device

ActiveUS20150263175A1Stable controlLess power consumptionTransistorSolid-state devicesPower semiconductor devicePower flow

To stably control a threshold voltage of a functional circuit using an oxide semiconductor. A variable bias circuit, a monitoring oxide semiconductor transistor including a back gate, a current source, a differential amplifier, a reference voltage source, and a functional circuit which includes an oxide semiconductor transistor including a back gate are provided. The current source supplies current between a source and a drain of the monitoring oxide semiconductor transistor to generate a gate-source voltage in accordance with the current. The differential amplifier compares the voltage with a voltage of the reference voltage source, amplifies a difference, and outputs a resulting voltage to the variable bias circuit. The variable bias circuit is controlled by an output of the differential amplifier and supplies voltage to the back gate of the monitoring oxide semiconductor transistor and the back gate of the oxide semiconductor transistor included in the functional circuit.

Owner:SEMICON ENERGY LAB CO LTD

Recessed-type field effect transistor with reduced body effect

ActiveUS20060234437A1Preventing undesired body effectThreshold Voltage StabilitySolid-state devicesSemiconductor/solid-state device manufacturingGate insulatorEngineering

For fabricating a field effect transistor, an extra-doped channel region is formed below a surface of a semiconductor substrate. An opening is formed in the semiconductor substrate into the extra-doped channel region. A gate insulator is formed at walls of the opening such that the extra-doped channel region abuts the gate insulator at a bottom portion of the opening. The opening is filled with a gate electrode. Such an extra-doped channel region prevents undesired body effect in the field effect transistor.

Owner:SAMSUNG ELECTRONICS CO LTD

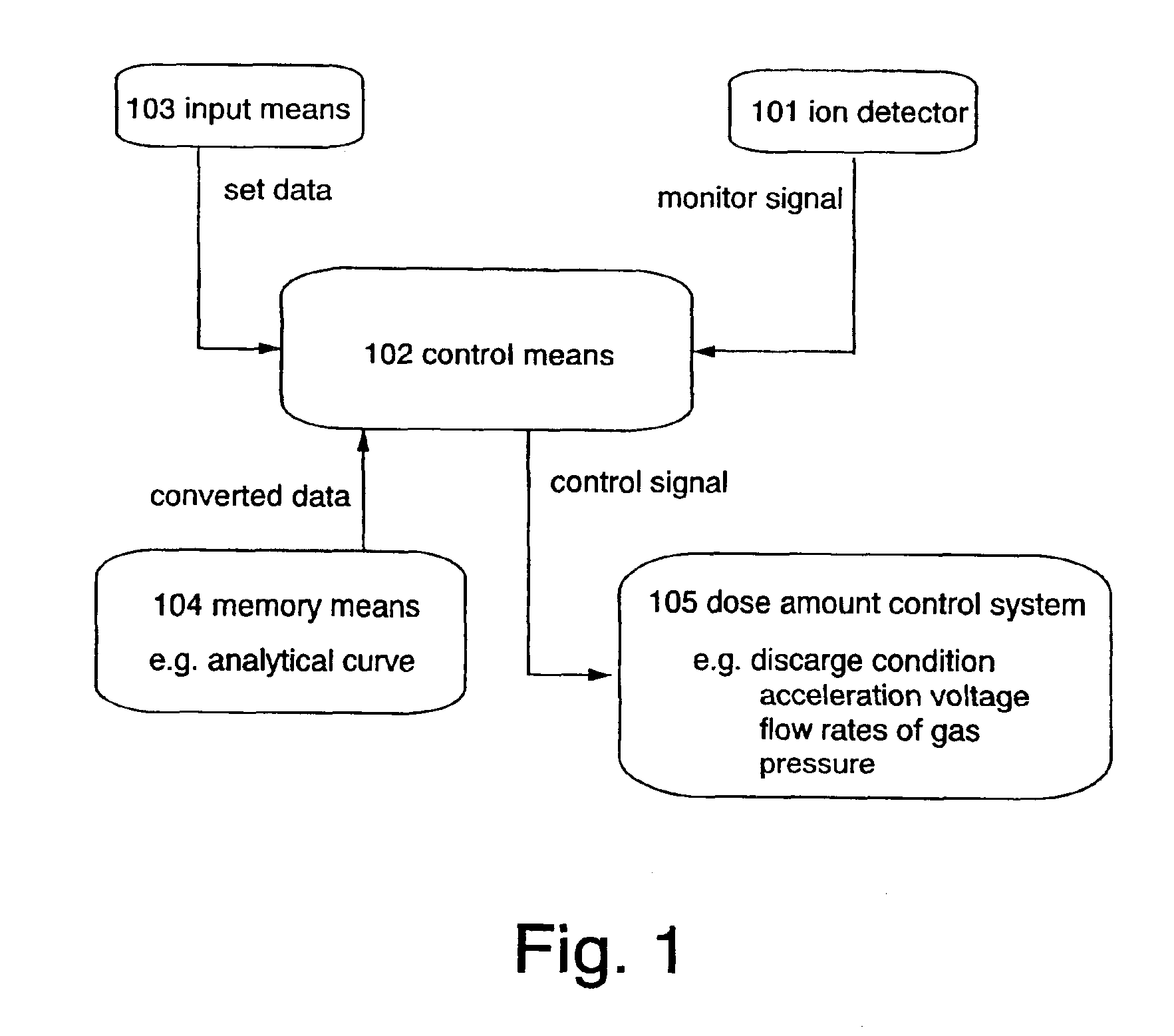

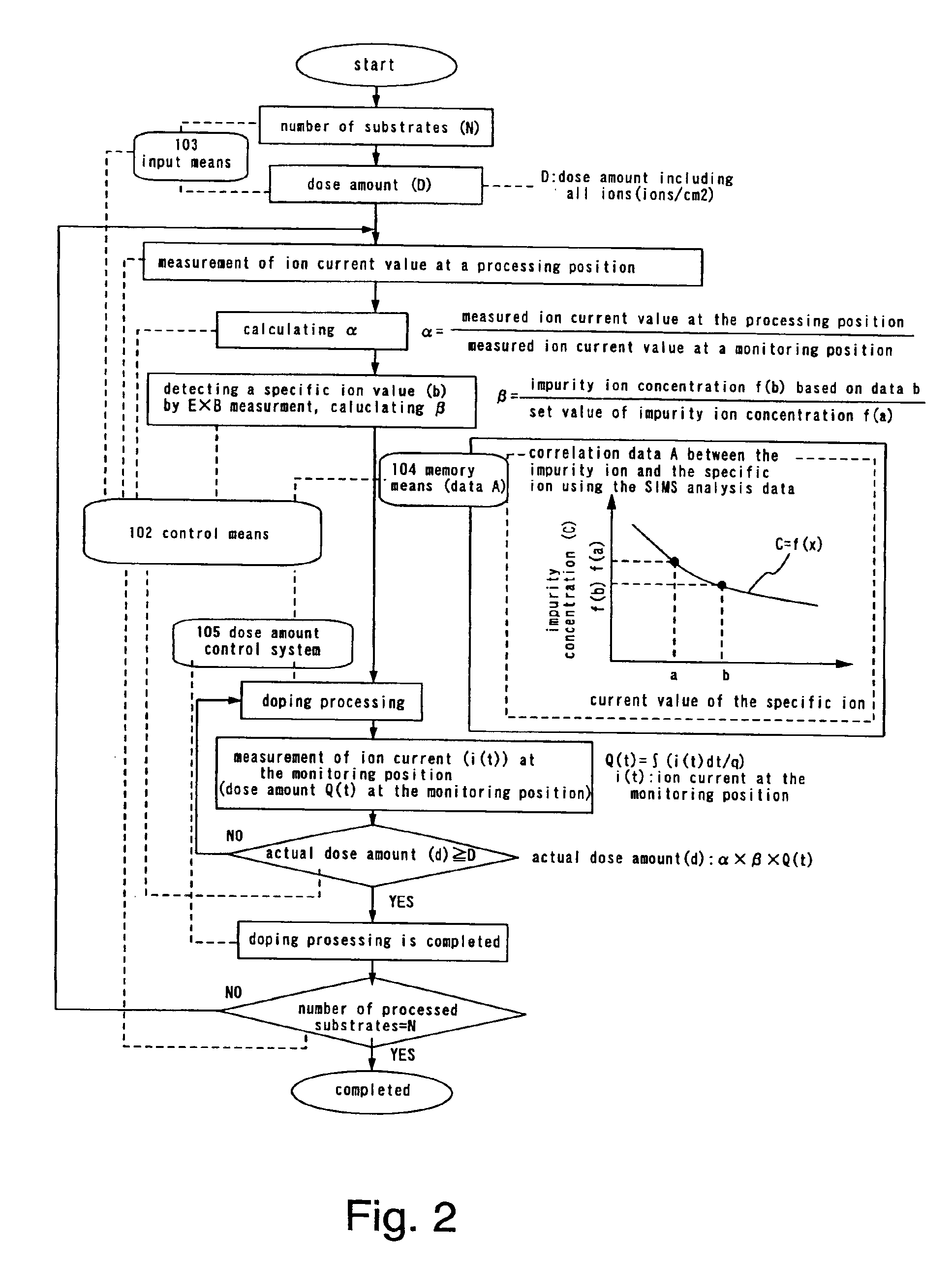

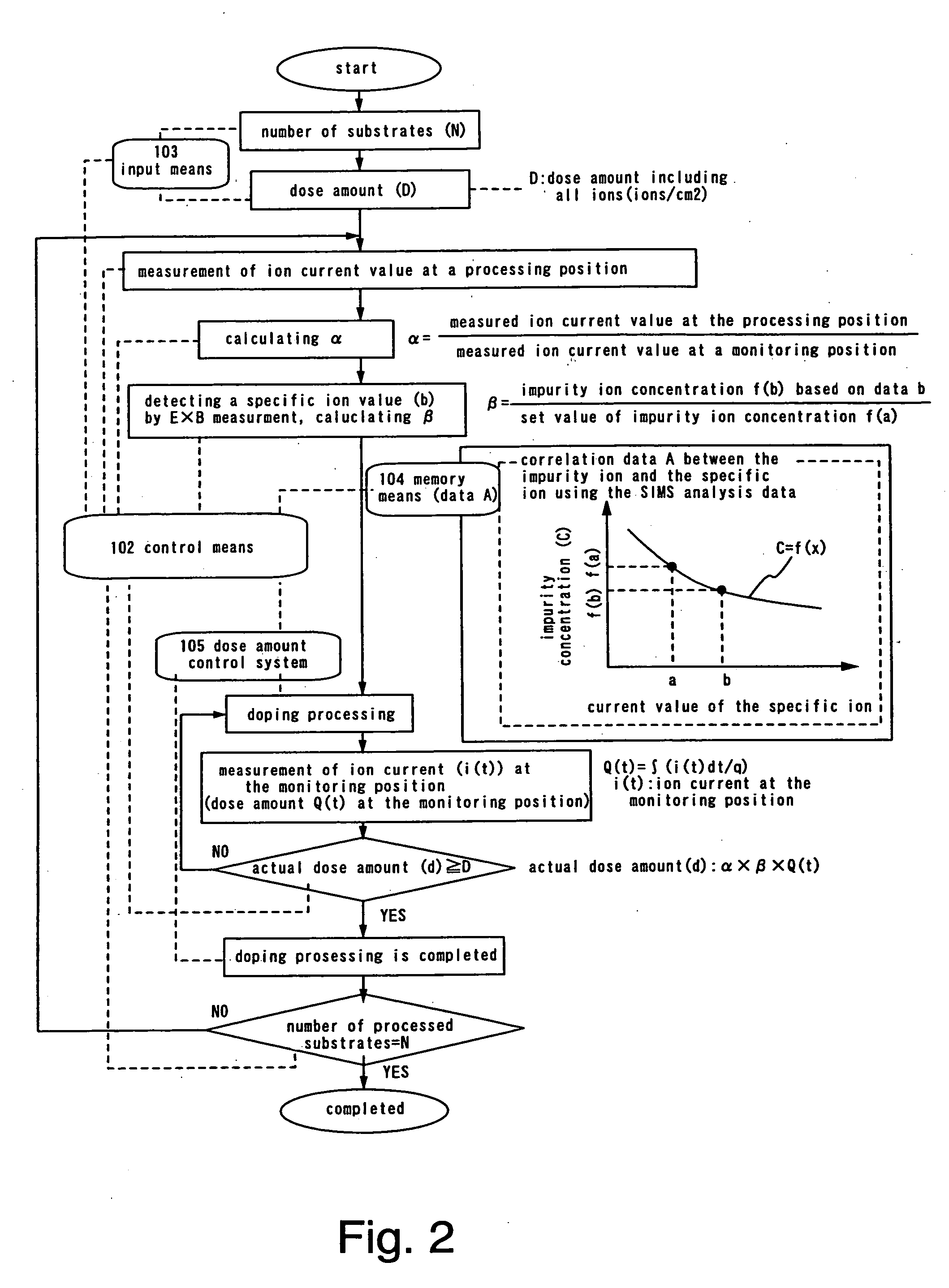

Doping method, doping apparatus, and control system for doping apparatus

InactiveUS6960498B2High precisionAccurate measurementElectric discharge tubesSemiconductor/solid-state device manufacturingIon currentControl system

A doping method capable of controlling a dose amount in response to a change the ratio in ion species during a doping process, a control system for controlling a doping amount, and a doping apparatus having a control system are provided. An ion current value of a specific ion in an ion beam is measured. There is an ion detector that measures an ion current value of a specific ion in an ion beam and enters the obtained monitor signal into a control means. Set data for setting a predetermined dose amount is entered into the control means, convert data for obtaining an actual dose amount from the monitor signal is entered into the control means by a memory means. The control means performs data processing on the basis of the input monitor signal and the convert data, a control signal for obtaining the predetermined dose amount is entered from the control means to the dose amount control system to dope the controlled ion beam into the target material.

Owner:SEMICON ENERGY LAB CO LTD

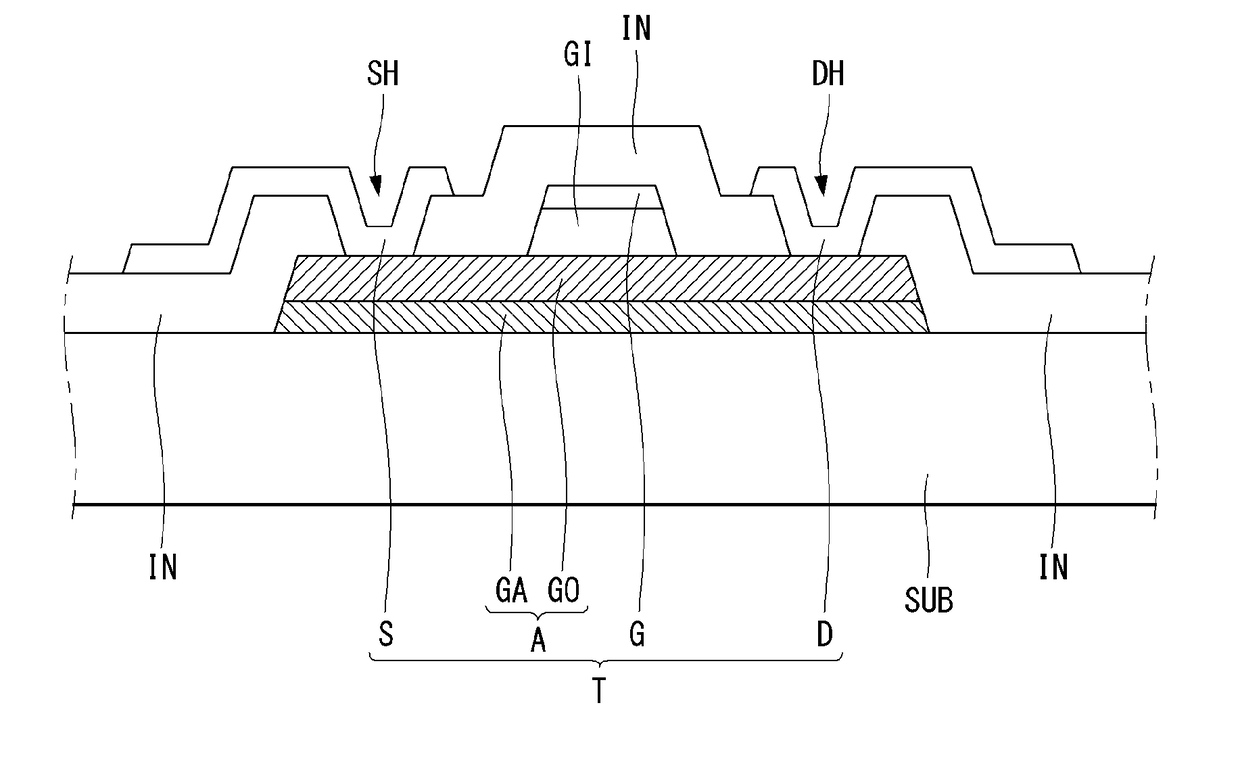

Thin film transistor substrate having bi-layer oxide semiconductor

InactiveUS20180122833A1Short channel lengthThreshold Voltage StabilityTransistorSolid-state devicesIndiumZinc

The present disclosure relates to a thin film transistor substrate having a bi-layer oxide semiconductor. The present disclosure provides a thin film transistor substrate comprising: a substrate; and an oxide semiconductor layer on the substrate, wherein the oxide semiconductor layer includes: a first oxide semiconductor layer having indium, gallium and zinc; and a second oxide semiconductor layer stacked on the first oxide semiconductor layer having the indium, gallium and zinc, wherein any one layer of the first and the second oxide semiconductor layers has a first composition ratio of the indium, gallium and zinc of 1:1:1; and wherein other layer has a second composition ratio of the indium, gallium and zinc in which the indium ratio is higher than the zinc ratio.

Owner:LG DISPLAY CO LTD

Organic light emitting display device

InactiveUS9041633B2Uniform brightnessThreshold Voltage StabilityElectrical apparatusStatic indicating devicesDisplay deviceControl line

An organic light emitting display device includes a display unit having pixels located at crossing regions of scan, control, data and sensing lines. Scan, control line, and data drivers respectively supply scan, control, and data signals to the scan, control, and data lines. A switching unit selectively couples the data lines to output lines of the data driver, a reference voltage source, or a negative bias voltage source. A sensing unit senses degradation information of an organic light emitting diode in the pixels and threshold voltage of a driving transistor in the pixels through the sensing lines. A control block stores the sensed degradation information and threshold voltage information. A timing controller is configured to generate a second data by converting an externally inputted first data using the degradation information and the threshold voltage information, and supply the second data to the data driver.

Owner:SAMSUNG DISPLAY CO LTD

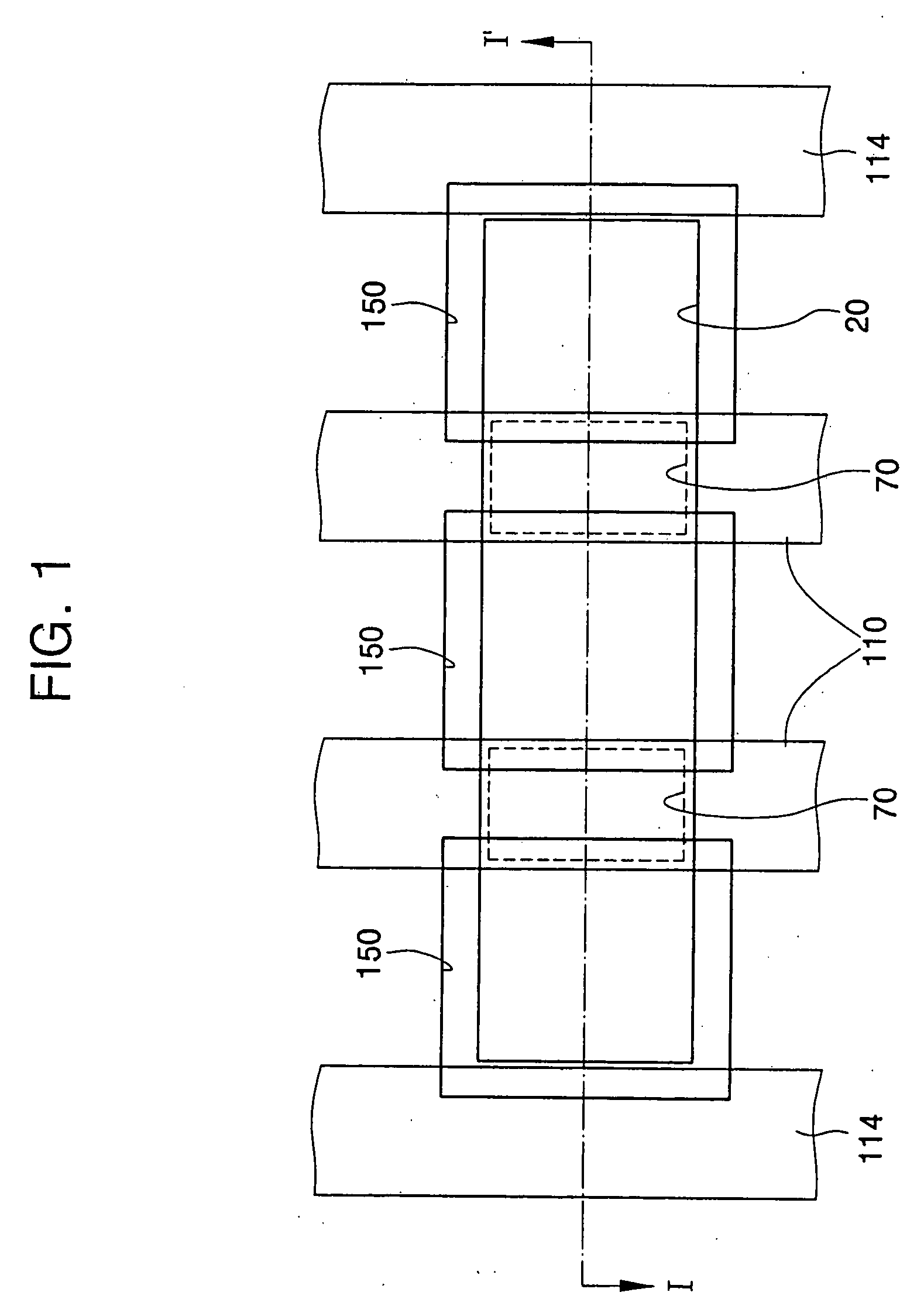

Array substrate, driving method thereof and display device

InactiveCN106502015AAvoid unidirectional biasThreshold Voltage StabilityStatic indicating devicesNon-linear opticsDisplay deviceComputer module

The embodiment of the invention provides an array substrate, a driving method thereof and a display device, relates to the technical field of display and is used for avoiding that a TFT (thin film transistor) is in a one-way bias state for a long time. The array substrate comprises multiple pixel groups in matrix arrangement, each pixel group comprises a first pixel unit and a second pixel unit. The first pixel unit comprises a first switch module connected with the pixel electrode of the first pixel unit. In a closed phase of the first switch module, the signals output by a first grid line and a common grid line are different, and the signals output, in a first subphase and a second subphase, by the first grid line and the common grid line are opposite. The second pixel unit comprises a second switch module connected with the pixel electrode of the second pixel unit. In a closed phase of the second switch module, the signals output by a second grid line and the common grid line are different, and the signals output, in a third subphase and a fourth subphase, by the second grid line and the common grid line are opposite.

Owner:BOE TECH GRP CO LTD

Doping method, doping apparatus, and control system for doping apparatus

ActiveUS20060005768A1High precisionAccurate measurementElectric discharge tubesSemiconductor/solid-state device manufacturingIon currentControl signal

A doping method capable of controlling a dose amount in response to a change the ratio in ion species during a doping process, a control system for controlling a doping amount, and a doping apparatus having a control system are provided. An ion current value of a specific ion in an ion beam is measured. There is an ion detector that measures an ion current value of a specific ion in an ion beam and enters the obtained monitor signal into a control means. Set data for setting a predetermined dose amount is entered into the control means, convert data for obtaining an actual dose amount from the monitor signal is entered into the control means by a memory means. The control means performs data processing on the basis of the input monitor signal and the convert data, a control signal for obtaining the predetermined dose amount is entered from the control means to the dose amount control system to dope the controlled ion beam into the target material.

Owner:SEMICON ENERGY LAB CO LTD

Transistor and formation method thereof

InactiveCN104064464APromote formationThreshold Voltage StabilitySemiconductor/solid-state device manufacturingSemiconductor devicesVoltage regulationSemiconductor

The invention discloses a transistor and a formation method thereof. The formation method of the transistor comprises: providing a semiconductor substrate, wherein the surface of the semiconductor substrate is provided with a threshold voltage adjusting film, the surface of the threshold voltage adjusting film is provided with a barrier film, the surface of the barrier film is provided with a channel film, the threshold voltage adjusting film is internally provided with doped irons, the channel film is at an intrinsic state, and the barrier film is used for preventing penetration by the doped irons in the threshold voltage adjusting film; forming a grid structure on the surface of the channel film; forming a first side wall on the surface of the channel film at the two sides of the grid structure; by taking the grid structure and the first side wall as masks, etching the channel film, the barrier film, the threshold voltage adjusting film and a part of the semiconductor substrate to form a channel layer, a barrier layer and a threshold voltage adjusting layer; and forming a doping layer on the surface of the semiconductor substrate at the two sides of the threshold voltage adjusting layer, the barrier layer, the channel layer and the grid structure, wherein the surface of the doping layer is not lower than the surface of the channel layer. The performance of the formed transistor is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Pixel circuit structure of silicon-based organic light-emitting diode (OLED) display chip and drive method thereof

InactiveCN102074195AHigh carrier mobilityThreshold Voltage StabilityStatic indicating devicesSolid-state devicesElectricityNegative phase

The invention discloses a pixel circuit structure of a silicon-based OLED display chip and a drive method thereof. The pixel circuit structure at least has a reading-in p-channel metal oxide semiconductor (PMOS) pipe, a polysilicon-isolator-polysilicon (PIP) capacitor, a drive PMOS pipe, a writing-out PMOS pipe, a ground wire protection PMOS pipe, a video data serial bit line, a power wire which is connected with a PIP upper electrode connecting wire and a source connecting wire of the drive PMOS pipe at the same time, a 0V ground wire connected with a drain of the ground wire protection PMOS pipe through a drain connecting wire of the ground wire protection PMOS pipe, a positive phase row selection wire connected with a grid of the writing-in PMOS pipe through a grid connecting wire of the writing-in PMOS pipe, a negative phase row selection wire connected with the gird of the writing-out PMOS pipe through the grid connecting wire of the writing-out PMOS pipe, and an OLED luminescent layer drive electrode connected with a drive electrode connecting wire. The drive method comprises 9 steps which are carried out circularly after energization. The pixel circuit structure and the drive method thereof reduce production cost, the weight and space volume of the control drive circuit, and the power consumption of the whole machine.

Owner:GUANGDONG SINODISPLAY TECH

Shield gate MOSFET device with uniformly doped channel and processing technology

PendingCN112164722AIncrease stretch widthReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETEngineering

The invention discloses a shield gate MOSFET device with a uniformly doped channel and a processing technology, which are characterized in that on the basis of the existing shield gate MOSFET device,a heavily doped first conductive type polycrystalline silicon column region is formed in a groove etching heavily doped polycrystalline silicon filling mode, and then a first conductive type body region is formed in a rapid thermal annealing mode; by optimizing the doping concentration of the first conductive type body region, a mutation junction is formed between the first conductive type body region and the drift region, so that the threshold consistency of the device is improved, meanwhile, the problem that the first conductive type body region is excessively compensated by the drift regionis solved, the doping concentration of the body region is improved, and the possibility that a parasitic triode of the device is turned on is reduced; reliability of the device is improved.

Owner:VANGUARD SEMICON CORP

Gate drive circuit and display device

ActiveCN107564450AReduce power consumptionThreshold Voltage StabilityStatic indicating devicesControl signalDisplay device

The invention discloses a gate drive circuit. The gate drive circuit comprises multiple gate drive units which are controlled by a first mode signal and a second mode signal. Each gate drive unit comprises an input module which is used for controlling the voltage of a first node according to a former gate transmission signal and a latter gate transmission signal; a control module which is used forgenerating a first control signal when the first mode signal is effective and generating a second control signal when the second mode signal is effective, wherein the first mode signal and the secondmode signal are alternately effective; a pull-down module which is used for pulling down the voltage of the first node when the first control signal or the second control signal is effective; a resetmodule which is used for resetting the second control signal to the low level when the first control signal is effective and resetting the first control signal to the low level when the second control signal is effective; and an output module which is used for generating the present gate drive signal according to the first control signal, the second control signal and the voltage of the first node.

Owner:KUSN INFOVISION OPTOELECTRONICS

Back gate bias voltage control of oxide semiconductor transistor

ActiveUS9378777B2Threshold Voltage StabilityStable controlTransistorSolid-state devicesPower flowVoltage reference

To stably control a threshold voltage of a functional circuit using an oxide semiconductor. A variable bias circuit, a monitoring oxide semiconductor transistor including a back gate, a current source, a differential amplifier, a reference voltage source, and a functional circuit which includes an oxide semiconductor transistor including a back gate are provided. The current source supplies current between a source and a drain of the monitoring oxide semiconductor transistor to generate a gate-source voltage in accordance with the current. The differential amplifier compares the voltage with a voltage of the reference voltage source, amplifies a difference, and outputs a resulting voltage to the variable bias circuit. The variable bias circuit is controlled by an output of the differential amplifier and supplies voltage to the back gate of the monitoring oxide semiconductor transistor and the back gate of the oxide semiconductor transistor included in the functional circuit.

Owner:SEMICON ENERGY LAB CO LTD

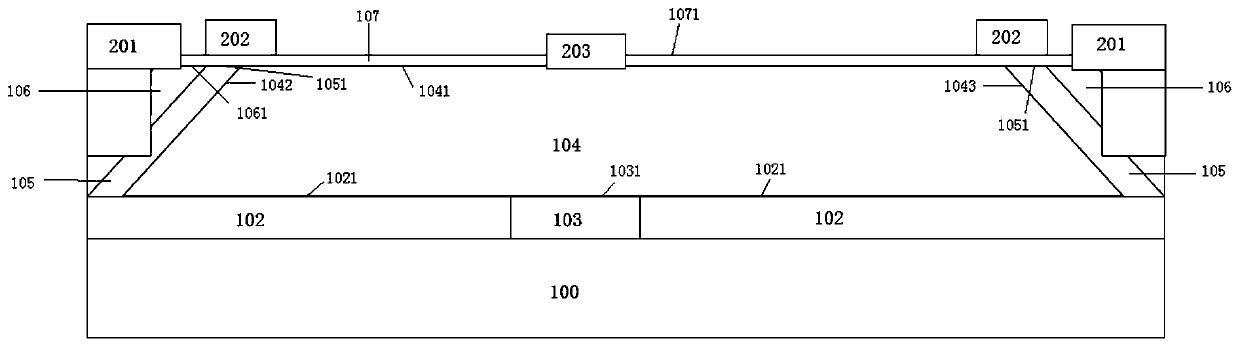

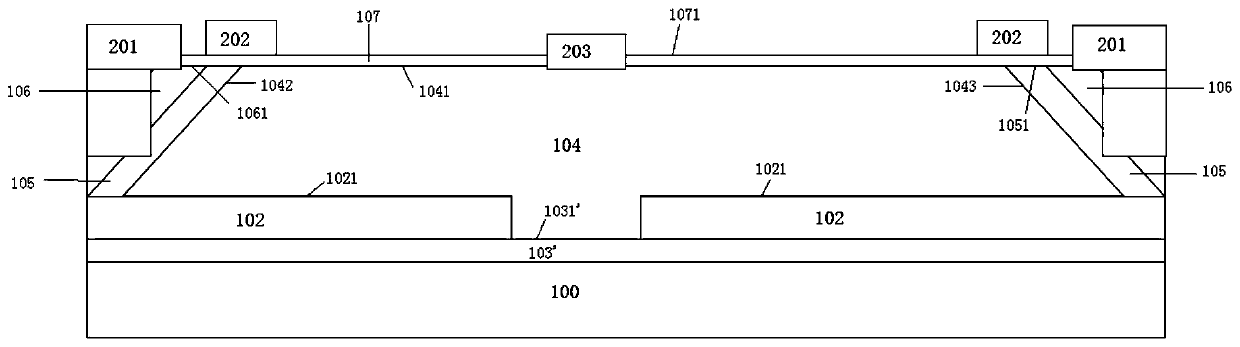

Transistor and forming method thereof

ActiveCN102779843AReduce contact resistanceThreshold Voltage StabilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor

Provided are a transistor and a forming method thereof. The transistor comprises a semiconductor substrate, a groove located in the semiconductor substrate, a gate dielectric layer located on the lateral wall and the bottom surface of the groove, a gate electrode layer located on the surface of the gate dielectric layer, a source region and a drain region. The groove is formed by a first sub groove and a second sub groove located below the first sub groove, wherein the second sub groove is communicated with the first sub groove, an opening of the first sub groove is larger than that of the second sub groove, the lateral wall of the first sub groove is inclined relative to the surface of the semiconductor substrate, and the lateral wall of the second sub groove is perpendicular to the surface of the semiconductor substrate. The gate electrode layer fully fills the groove and the surface of the gate electrode layer is level to that of the semiconductor substrate. The source region is located in the semiconductor substrate on two sides of the groove. The drain region is located in the semiconductor substrate on one side opposite to the groove and is opposite to the second sub groove. The transistor is stable in threshold voltage and good in performance.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

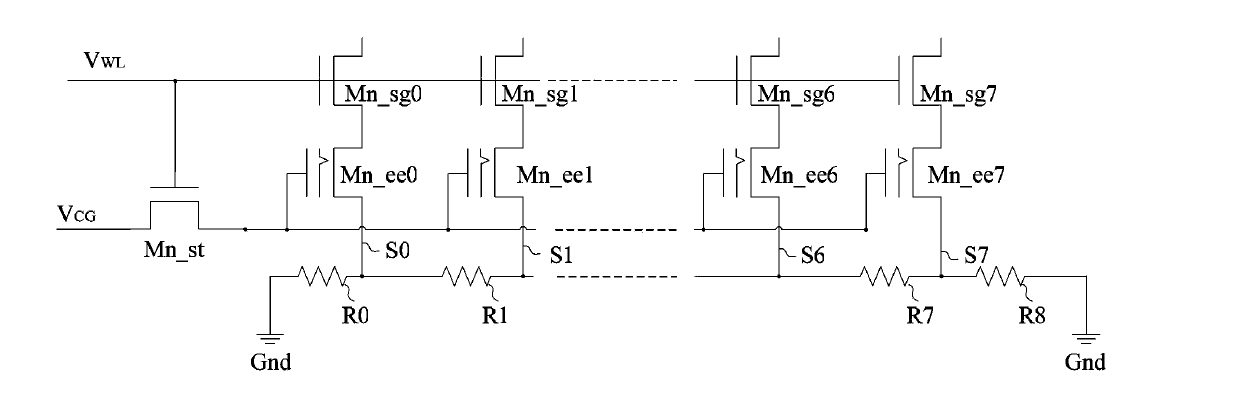

Read amplification circuit for nonvolatile memory and memory

ActiveCN103377708AThreshold Voltage StabilityEliminate errorsRead-only memoriesDigital storageAudio power amplifierComputer science

The invention relates to a read amplification circuit for a nonvolatile memory and a memory. The read circuit comprises a basic physical unit composed of a plurality of storage units, a reference unit set and a read amplifier, wherein the storage units are correspondingly connected to respective read bit lines; the basic physical unit is gated via a first gate tube; the reference unit set has the same configuration as the basic physical unit and is composed of a plurality of reference units; the reference units and the storage units are one-to-one correspondence; the reference units are correspondingly connected with respective reference voltage lines, and respectively have the same structure as the corresponding storage units; the reference unit set is gated via a second gate tube; the second gate tube has the same structure as the first gate tube; the read amplifier is connected with the read bit lines and the reference voltage lines, and outputs corresponding read data according to the comparative result between the read bit lines and the voltages on the corresponding reference voltage lines. The read amplification circuit can enhance the data read speed when reading the memory, and prolong the service life of the memory.

Owner:SHANGHAI FUDAN MICROELECTRONICS GROUP

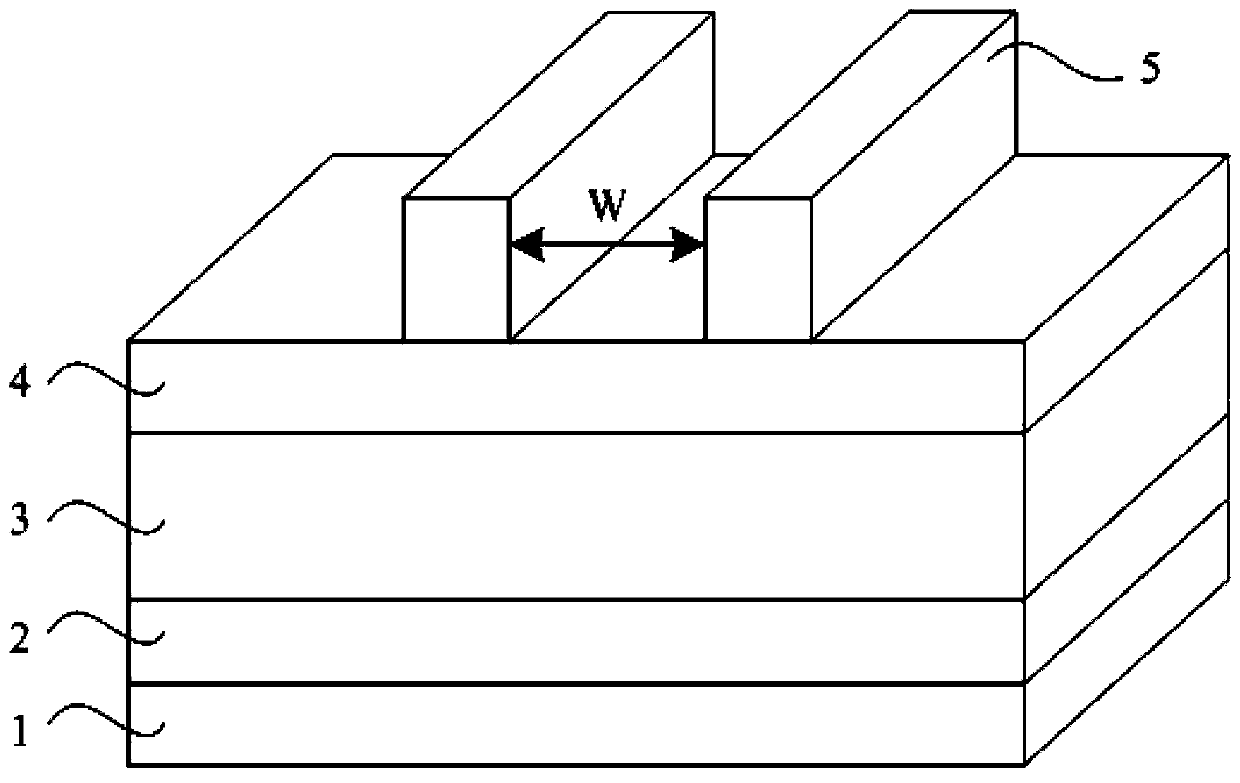

Iii-nitride field-effect transistor with dual gates

A field effect transistor (FET) includes a III-nitride channel layer, a III-nitride barrier layer on the channel layer, a first dielectric on the barrier layer, a first gate trench extending through the first dielectric, and partially or entirely through the barrier layer, a second dielectric on a bottom and walls of the first gate trench, a source electrode on a first side of the first gate trench, a drain electrode on a second side of the first gate trench opposite the first side, a first gate electrode on the second dielectric and filling the first gate trench, a third dielectric between the first gate trench and the drain electrode, a second gate trench extending through the third dielectric and laterally located between the first gate trench and the drain electrode, and a second gateelectrode filling the second gate trench.

Owner:HRL LAB

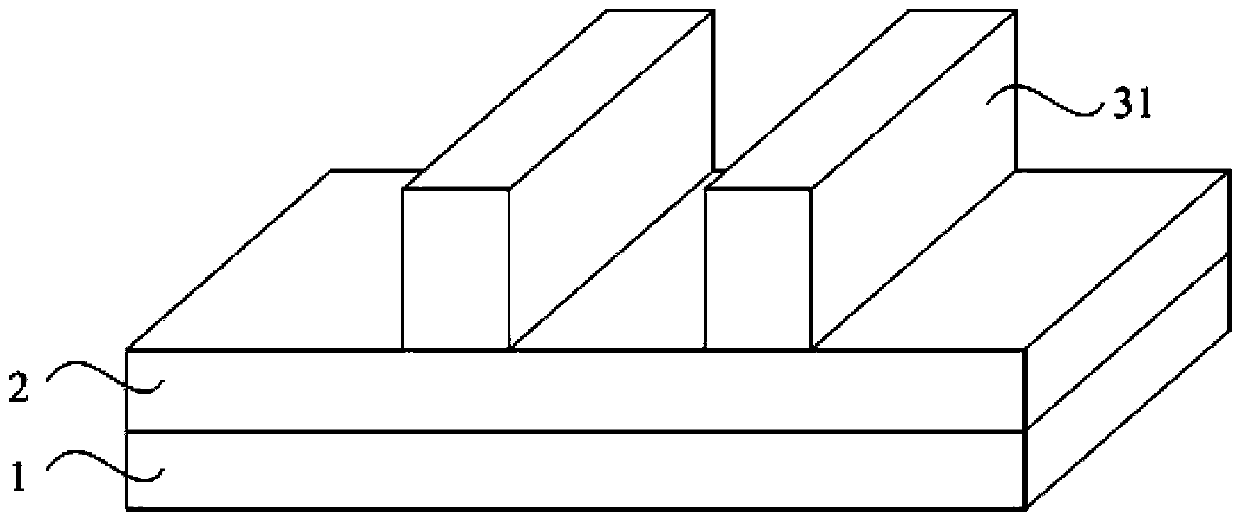

Semiconductor structure and fin field-effect tube forming method and etching device

ActiveCN103578964AHigh precisionIncreasing the thicknessLiquid surface applicatorsSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

The invention discloses a semiconductor structure and fin field-effect tube forming method and an etching device. The fin field-effect tube forming method comprises the step of providing a semiconductor substrate; the step of etching the semiconductor substrate to form a plurality of fin parts, wherein first grooves are formed between every two adjacent fin parts; the step of filling the first grooves with isolation materials to form an isolation structure; the step of spraying liquid, spraying a layer of liquid on the surface of the isolation structure and the surfaces of the fin parts, wherein the semiconductor substrate is rotated in the process of spraying; the step of supplying reaction gas, wherein the reaction gas is blended with the layer of liquid spraying the surface of the isolation structure and the surfaces of the fin parts to form an etching solution used for etching the isolation structure; the step of executing the liquid spraying process and the reaction gas supplying process repeatedly until the isolation structure is removed by certain thickness to form a second groove and to expose the fin parts by certain height; the step of forming a gate structure striding the surfaces and the side walls of the fin parts which are exposed by the certain height. The precision of removing the isolation structure by the certain thickness is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

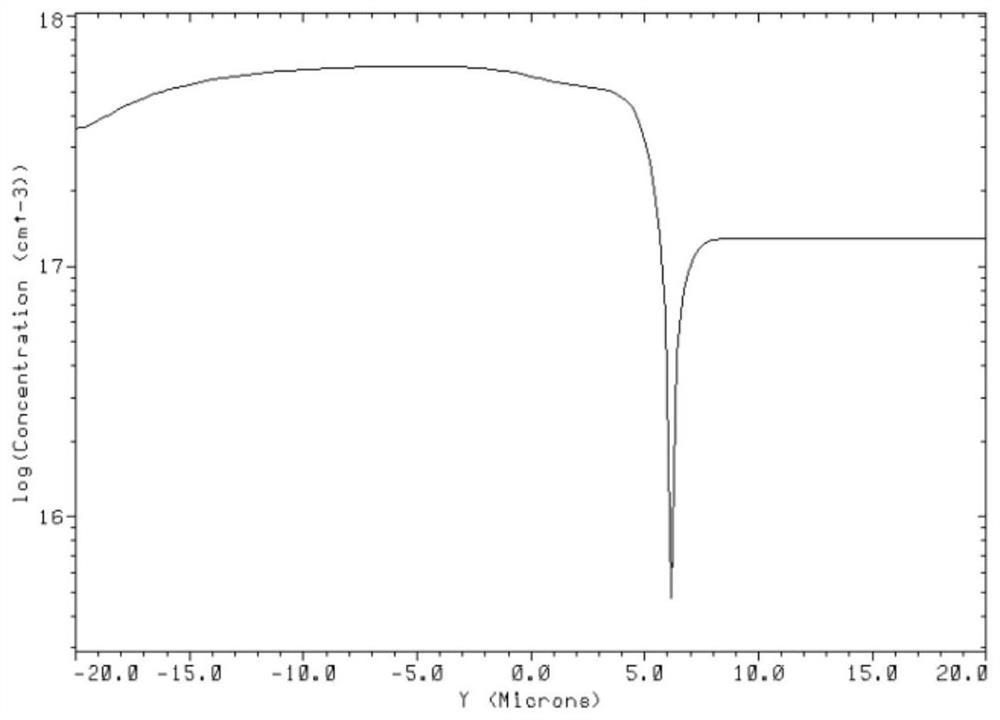

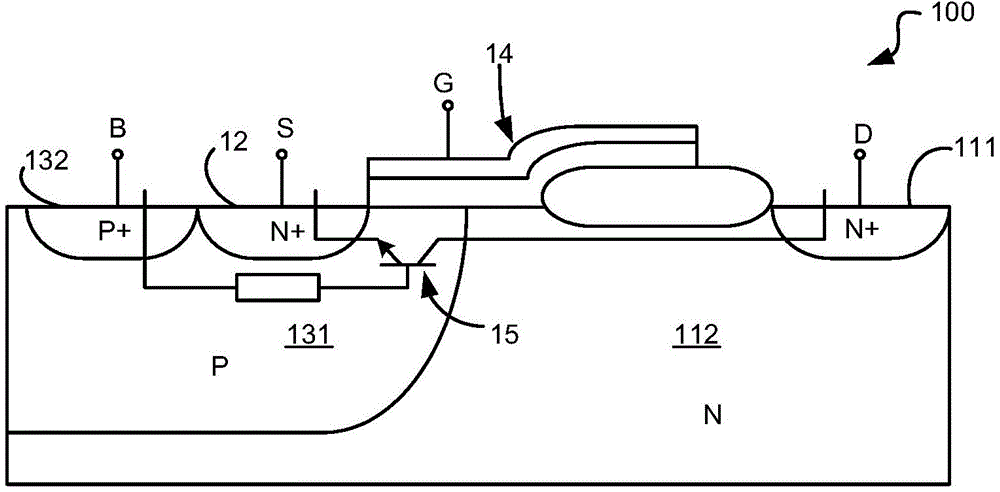

Semiconductor device and method for production of high avalanche energy LDMOS device

ActiveCN104091828AIncreased avalanche energyLower resistanceTransistorThyristorPower semiconductor deviceLDMOS

The invention discloses a semiconductor device, an LDMOS device and a method for the production of a high avalanche energy LDMOS device. The semiconductor device includes a gate region, an N-type drain region, a P-type body region and an N-type source region, wherein the body region comprises a first body region, a second body region and a body contact region, wherein the first body region is doped with boron atoms, the second body region is doped with indium atoms and boron atoms, and the second body region is located beneath and adjacent to the source region. The semiconductor device, the LDMOS device and the method for the production of the high avalanche energy LDMOS device have the advantages of lower resistance, higher avalanche energy and stable threshold voltage and so on.

Owner:CHENGDU MONOLITHIC POWER SYST

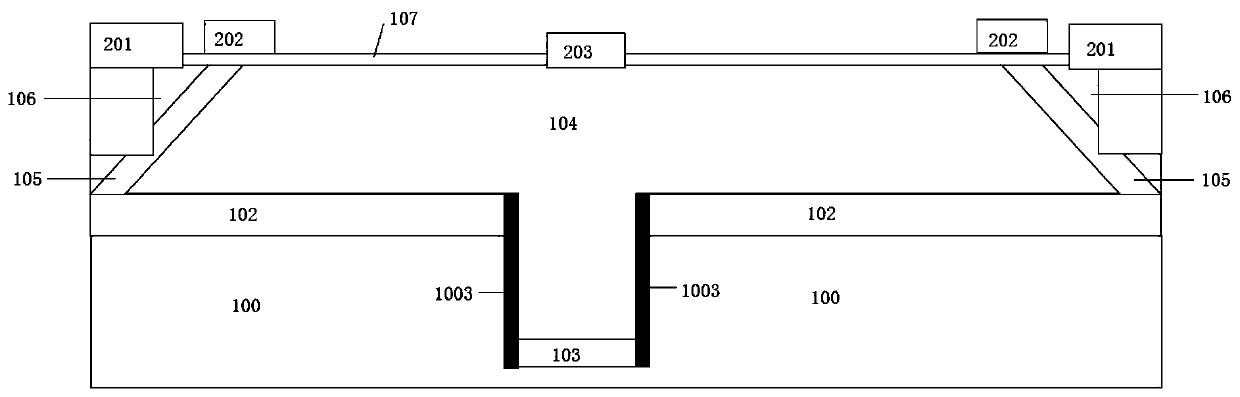

Groove type power device and manufacturing method thereof

PendingCN113035714AStable Threshold Voltage and Breakdown VoltageThreshold Voltage StabilitySolid-state devicesSemiconductor/solid-state device manufacturingBody regionElectrically conductive

The invention provides a groove type power device and a manufacturing method thereof. The method comprises the following steps: providing a substrate sequentially comprising a first conductive type heavily doped layer and a first conductive type lightly doped epitaxial layer from bottom to top; forming a cellular region groove and a terminal region groove in the lightly doped epitaxial layer; forming a gate dielectric layer on the side wall and the bottom surface of the groove and the top surface of the lightly doped epitaxial layer; forming a polycrystalline silicon layer so as to fill the cellular region groove and the terminal region groove, and carrying out second conduction type doping on the polycrystalline silicon layer; etching the polycrystalline silicon layer until the polycrystalline silicon layer is flush with the top surface of the lightly doped epitaxial layer to obtain a cellular region groove gate and terminal region groove polycrystalline silicon; performing first conduction type doping on the cellular region groove gate and the terminal region groove polycrystalline silicon; forming a body region in the lightly doped epitaxial layer; and forming a source region in the body region. According to the invention, the groove type terminal is adopted, and body region injection can be carried out by adopting relatively high energy, so that the device has more stable threshold voltage and breakdown voltage.

Owner:CHINA RESOURCES MICROELECTRONICS (CHONGQING) CO LTD

Thin film transistor substrate having bi-layer oxide semiconductor

The present disclosure relates to a thin film transistor substrate having a bi-layer oxide semiconductor. The present disclosure provides a thin film transistor substrate comprising: a substrate; andan oxide semiconductor layer on the substrate, wherein the oxide semiconductor layer includes: a first oxide semiconductor layer having indium, gallium and zinc; and a second oxide semiconductor layerstacked on the first oxide semiconductor layer having the indium, gallium and zinc, wherein any one layer of the first and the second oxide semiconductor layers has a first composition ratio of the indium, gallium and zinc of 1:1:1; and wherein other layer has a second composition ratio of the indium, gallium and zinc in which the indium ratio is higher than the zinc ratio.

Owner:LG DISPLAY CO LTD

Method for manufacturing semiconductor device

InactiveUS20060234471A1Simple and easy processImprove connection reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesPolycrystalline siliconEngineering

A semiconductor device having an improved connecting reliability of an interconnect is presented via a simple and easy process, and further, a semiconductor device having a stable threshold voltage of a transistor that provide a stable electrical characteristic is also presented. A method for manufacturing a semiconductor device according to the present invention comprises: forming a trench in a silicon substrate; forming a first insulating film on a surface of said silicon substrate, said surface including an interior wall of said trench; forming a polysilicon film which plugged in said trench and covered on an entire surface of said silicon substrate; forming a second insulating film with oxidizing a portion of said polysilicon film disposed outside of said trench, and oxidizing a surface region of said silicon substrate located right under said first insulating film disposed outside of said trench and a surface region of said polysilicon film in said trench; and forming an embedded polysilicon layer with removing said second insulating film so that the surface of said silicon substrate is partially exposed and said polysilicon film is partially remained in said trench.

Owner:RENESAS ELECTRONICS CORP

Method for stabilizing flash memory unit word line threshold voltage

ActiveCN104538364AThreshold Voltage StabilityAffect thicknessSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringPhotoresist

The invention provides a method for stabilizing flash memory unit word line threshold voltage. The method includes the steps that photoresist is distributed on a silicon wafer, the photoresist on an active area of the silicon wafer is removed, and the photoresist on the peripheral portion of the silicon wafer is left; first injection treatment is executed on a flash memory unit forming area of the active area of the silicon wafer, and an injection condition of the first injection treatment is selected so that an expected floating gate lower threshold can be formed on a final flash memory unit; the flash memory unit forming process is executed on the silicon wafer so that the flash memory unit can be formed on the flash memory unit forming area of the active area; second injection treatment is executed on the active area of the silicon wafer so that doping can be formed on the positions, corresponding to the silicon wafer area, of word lines on the two sides of the flash memory unit, and an injection condition of the second injection treatment is selected so that an expected word line lower threshold can be formed on the final flash memory unit, wherein ion injection is not carried out on the flash memory unit forming area in the flash memory unit forming process.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Grid electrode forming method

ActiveCN104217934AReduce roughnessSmall sizeSemiconductor/solid-state device manufacturingSemiconductor devicesSize increaseEtching

A grid electrode forming method includes: providing a substrate; forming a polycrystalline silicon layer on the substrate; subjecting the polycrystalline silicon layer to primary etching in a grid width direction, subjecting the polycrystalline silicon layer to secondary etching in a grid length direction, and forming a grid electrode after primary etching and second etching are finished. The secondary etching includes: forming a photoresist with a window on the polycrystalline silicon layer, wherein the window exposes an area between two adjacent grid electrodes in the grid width direction, and residues are attached in the window; removing the residues; forming a side wall on the side wall of the window after the residues are removed; after the side wall is formed, etching the polycrystalline silicon layer to the upper surface of the substrate through the window. The grid electrode forming method has the advantages that roughness of the window is reduced by removing the residues; the problem of size increase caused by excessive etching of the photoresist in removing of the residues is solved by forming the side wall on the side wall of the window after the residues are removed.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method for forming complementary metal oxide semiconductor tube

ActiveCN103531538BPrevent backflowHigh melting pointSemiconductor/solid-state device manufacturingSemiconductor devicesWork functionCopper

A forming method of a complementary type metal-oxide semiconductor tube comprises the following steps: providing a semiconductor substrate which comprises a first area and a second area, wherein the surface of the semiconductor substrate is provided with an insulating layer, the surface of the first area is provided with a first opening, the bottom of the first opening is provided with a first high-K dielectric layer, the surface of the first high-K dielectric layer is provided with a dummy gate layer, the surface of the second area is provided with a second opening, and the bottom of the second opening is provided with a second high-K dielectric layer; forming a second work function layer on the side wall of the second opening and the surface of the second high-K dielectric layer; forming a second gate electrode layer on the surface of the second work function layer, wherein the second gate electrode layer is made of copper; afterwards eliminating the dummy gate layer in the first opening; successively forming the first work function layer on the side wall of the first opening and the surface of the first high-K dielectric layer; and successively forming a first barrier layer and a first gate electrode layer on the surface of the first work function layer, wherein the first gate electrode layer is made of aluminum. The formed complementary type metal-oxide semiconductor tube has stable performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP

3d NAND memory and its manufacturing method

ActiveCN108447870BHigh electron mobilityGood electrical propertiesSolid-state devicesSemiconductor devicesCharge carrier mobilityThin membrane

The application discloses a 3D NAND memory and a manufacturing method thereof. The channel layer in the memory is formed of a two-dimensional material that can grow stably. Because two-dimensional materials have higher electron mobility, 3D NAND memories made of two-dimensional materials as channel layer materials can achieve better electrical performance of 3D NAND memories. In addition, due to the higher carrier mobility and velocity of 2D materials, 3D NAND memory can have better read and write efficiency. Moreover, because the film thickness of the two-dimensional material can reach the thickness of the atomic film, it is very beneficial to the reduction of the diameter of the channel hole and the distance between the channel holes of the 3D NAND memory, thereby helping to improve the storage density of the 3D NAND memory.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

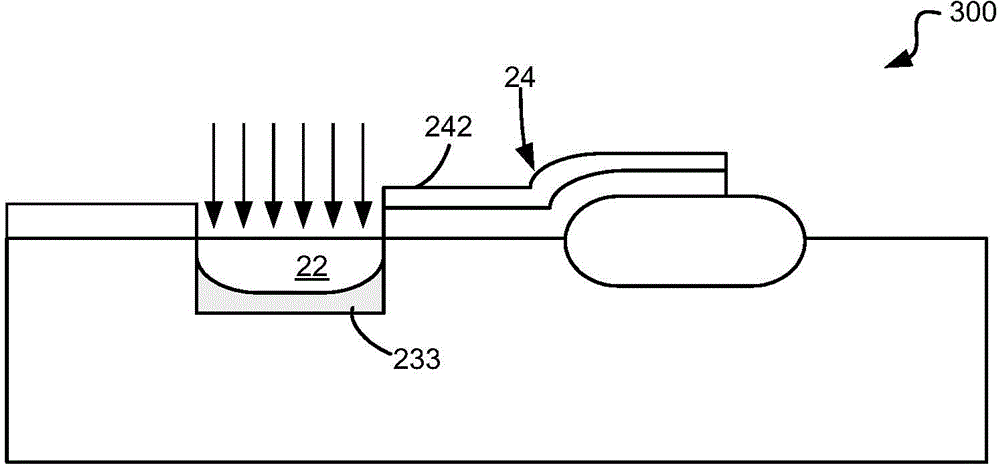

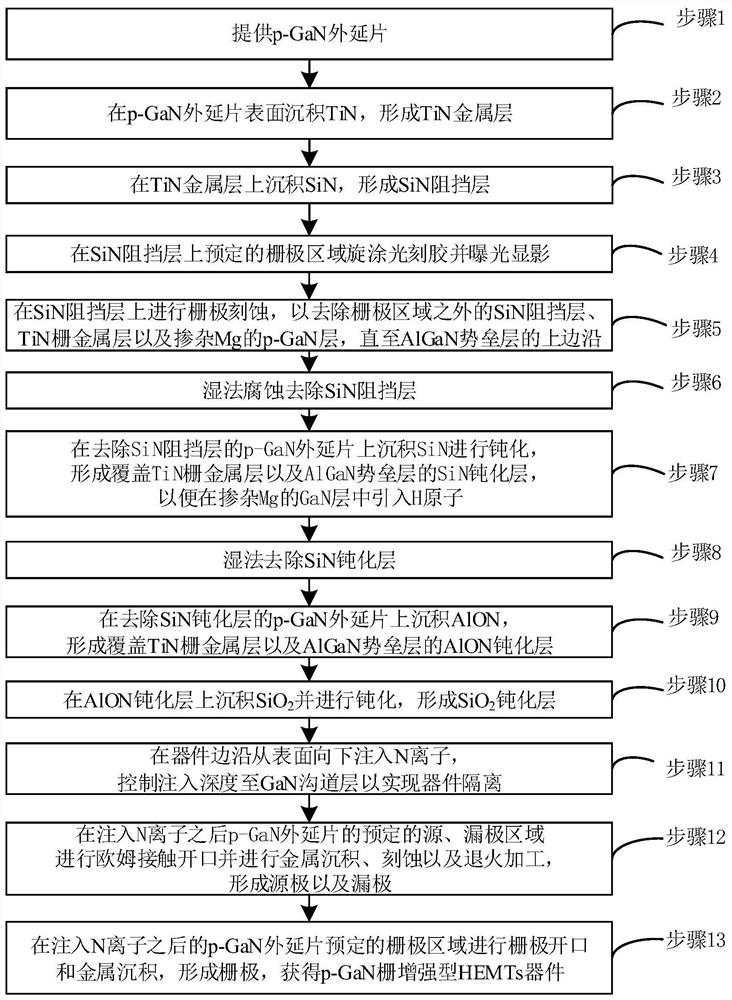

Preparation method of p-GaN gate enhanced HEMTs device with stable threshold voltage

PendingCN113658862AThreshold Voltage StabilitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringMaterials science

The invention provides a preparation method of a p-GaN gate enhanced HEMTs device with a stable threshold voltage. Improvement is carried out on the basis of a p-type gate enhanced HEMTs manufacturing method, the SiN passivation layer is arranged on the p-GaN cap layer in an epitaxial mode to introduce hydrogen elements to passivate a defect state in p-GaN, the p-GaN gate enhanced HEMTs with the high threshold voltage stability are obtained, and the threshold voltage of the p-GaN gate enhanced GaN HEMTs does not drift when the p-GaN gate enhanced GaN HEMTs works at high voltage and high frequency.

Owner:XIDIAN UNIV +1

Semiconductor device and manufacturing method thereof

PendingCN110676318AImprove switching characteristicsReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialCharge carrier

The disclosure provides a semiconductor device and a manufacturing method thereof. The device comprises a substrate, a first insulating layer formed on the substrate, a first semiconductor layer formed on the first insulating layer, a second semiconductor layer formed on the side surface of the first semiconductor layer, a third semiconductor layer formed on the side surface of the second semiconductor layer, and a fourth semiconductor layer formed on the first, second and third semiconductor layers. The side surface of the first semiconductor layer is obliquely intersected with the upper surface of the first insulating layer. Two-dimensional charge carrier gas is formed at interfaces between the fourth semiconductor layer and the first to third semiconductor layers. Therefore, the semiconductor device has the following beneficial effects: the device structure is simple; the process is simple; cost is low; and the electrical performance is excellent.

Owner:GUANGDONG ZHINENG TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com