Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

30results about How to "Solve the large leakage current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

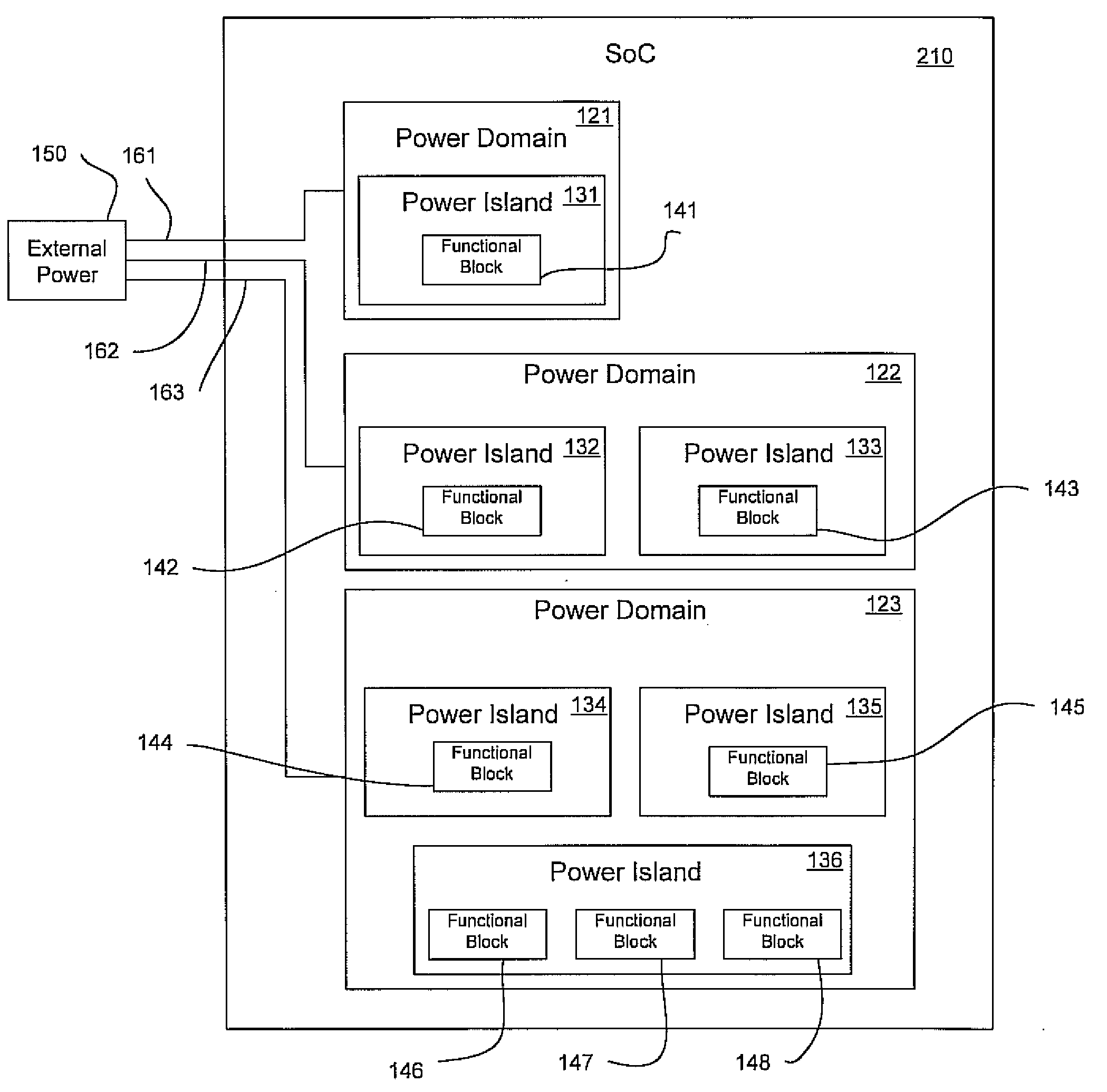

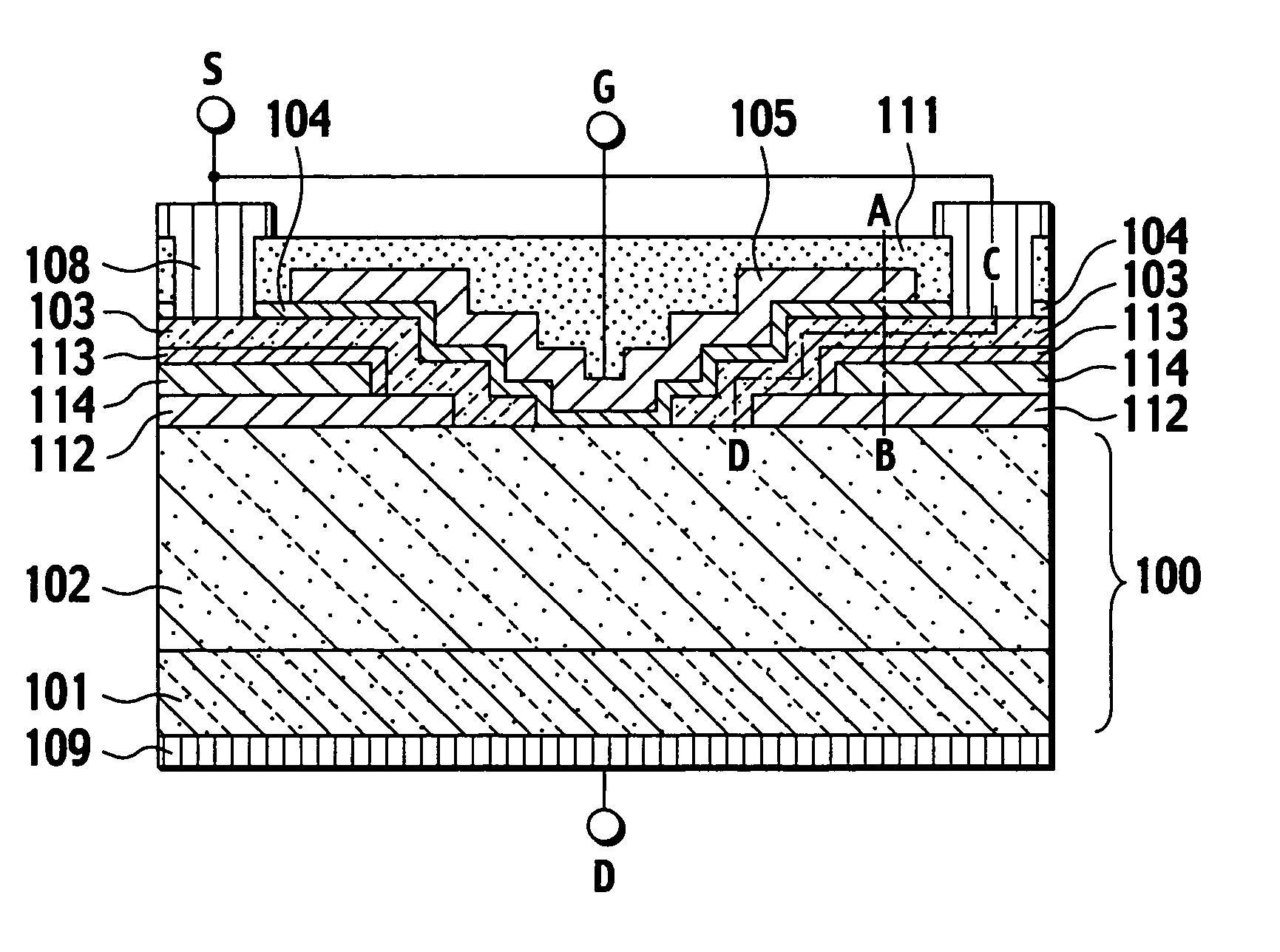

Integrated circuit device having power domains and partitions based on use case power optimization

ActiveUS20090201082A1Minimize leakage currentSolve the large leakage currentEnergy efficient ICTDigital data processing detailsEngineeringPower domains

A programmable SoC (system on a chip) having optimized power domains and power islands. The SoC is an integrated circuit device including a plurality of power domains, each of the power domains having a respective voltage rail to supply power to the power domain. A plurality of power islands are included within the integrated circuit device, wherein each power domain includes at least one power island. A plurality of functional blocks are included within the integrated circuit device, wherein each power island includes at least one functional block. Each functional block is configured to provide a specific device functionality. The integrated circuit device adjusts power consumption in relation to a requested device functionality by individually turning on or turning off power to a selected one or more power domains, and for each turned on power domain, individually power gating one or more power islands.

Owner:NVIDIA CORP

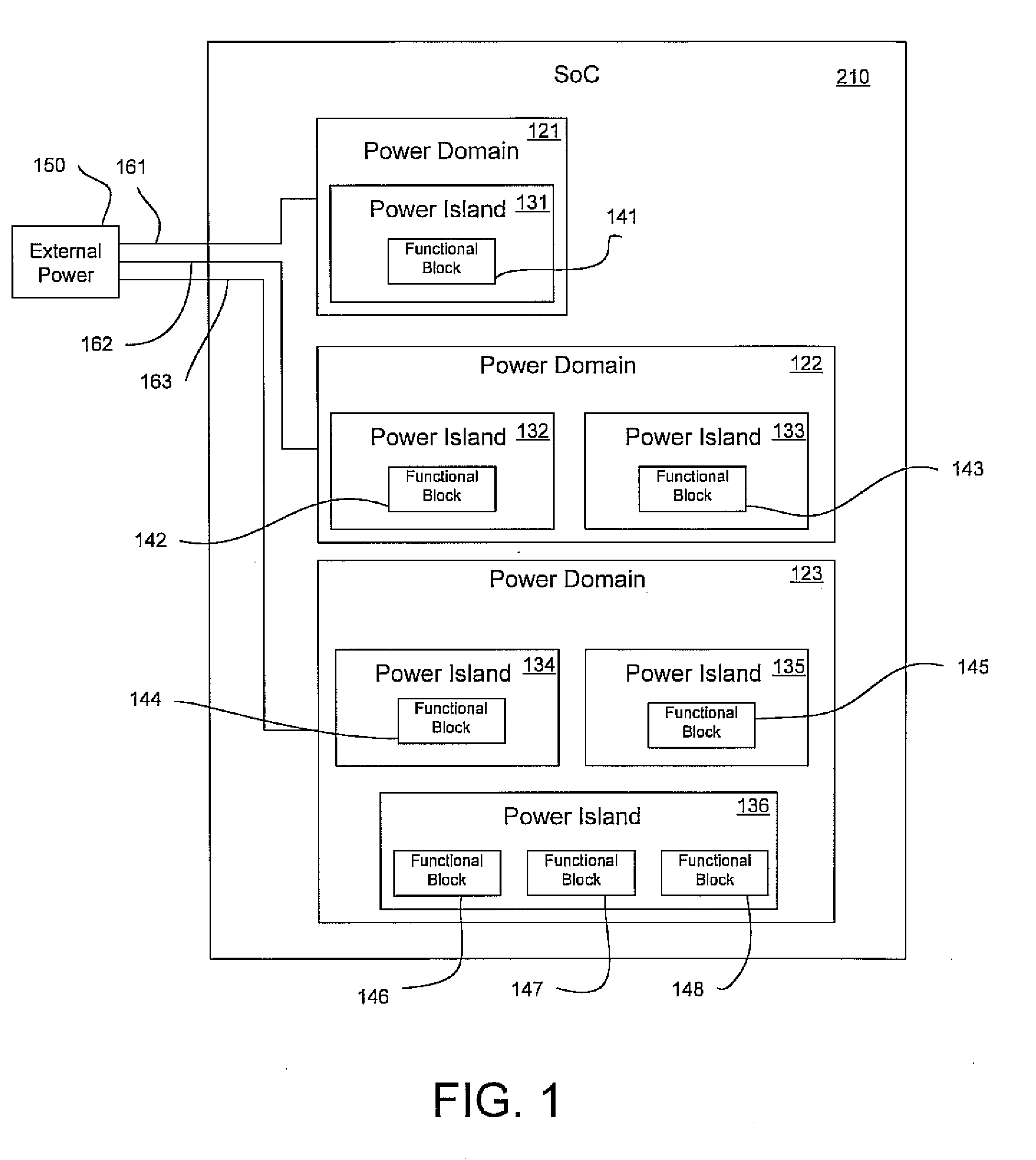

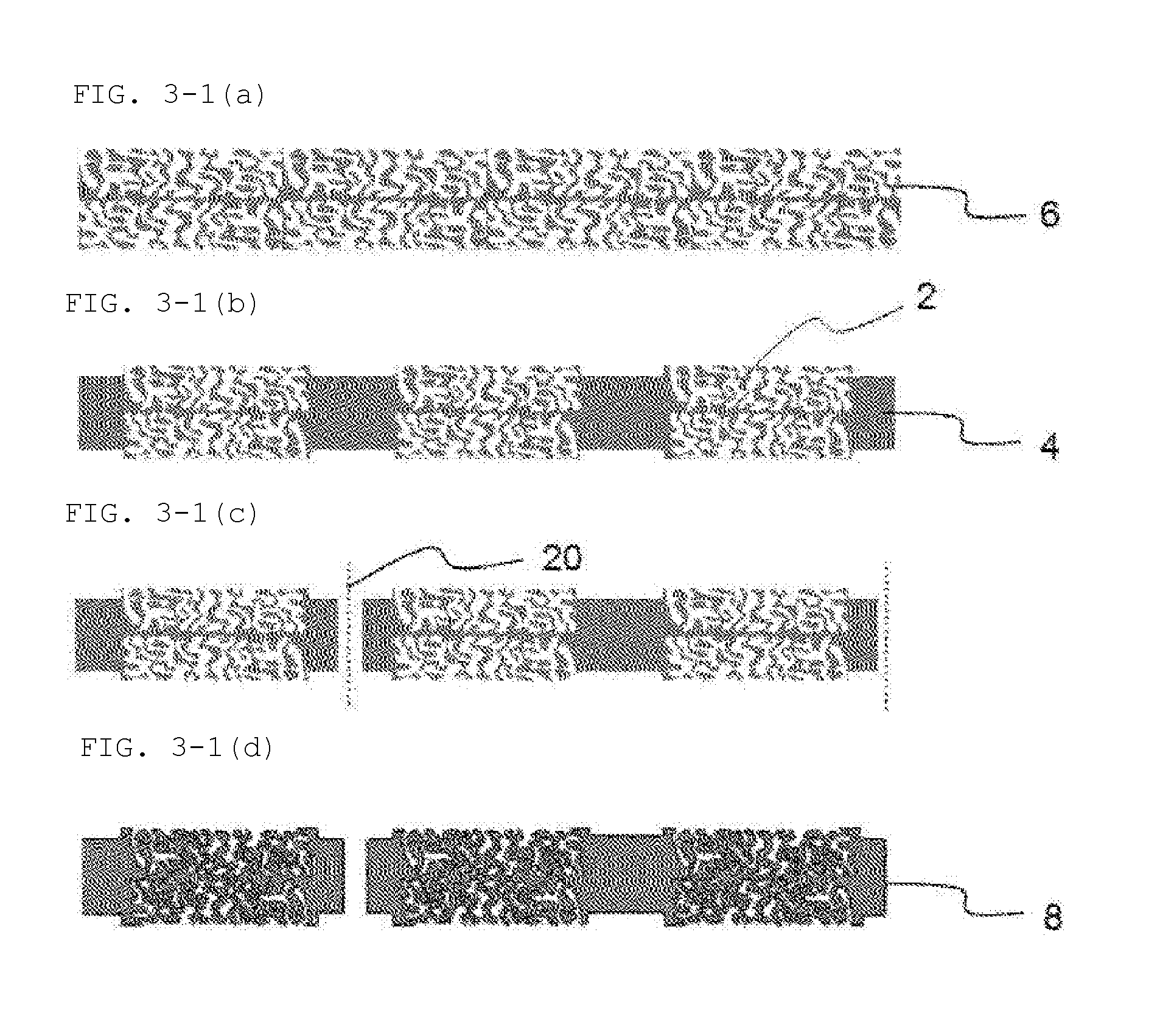

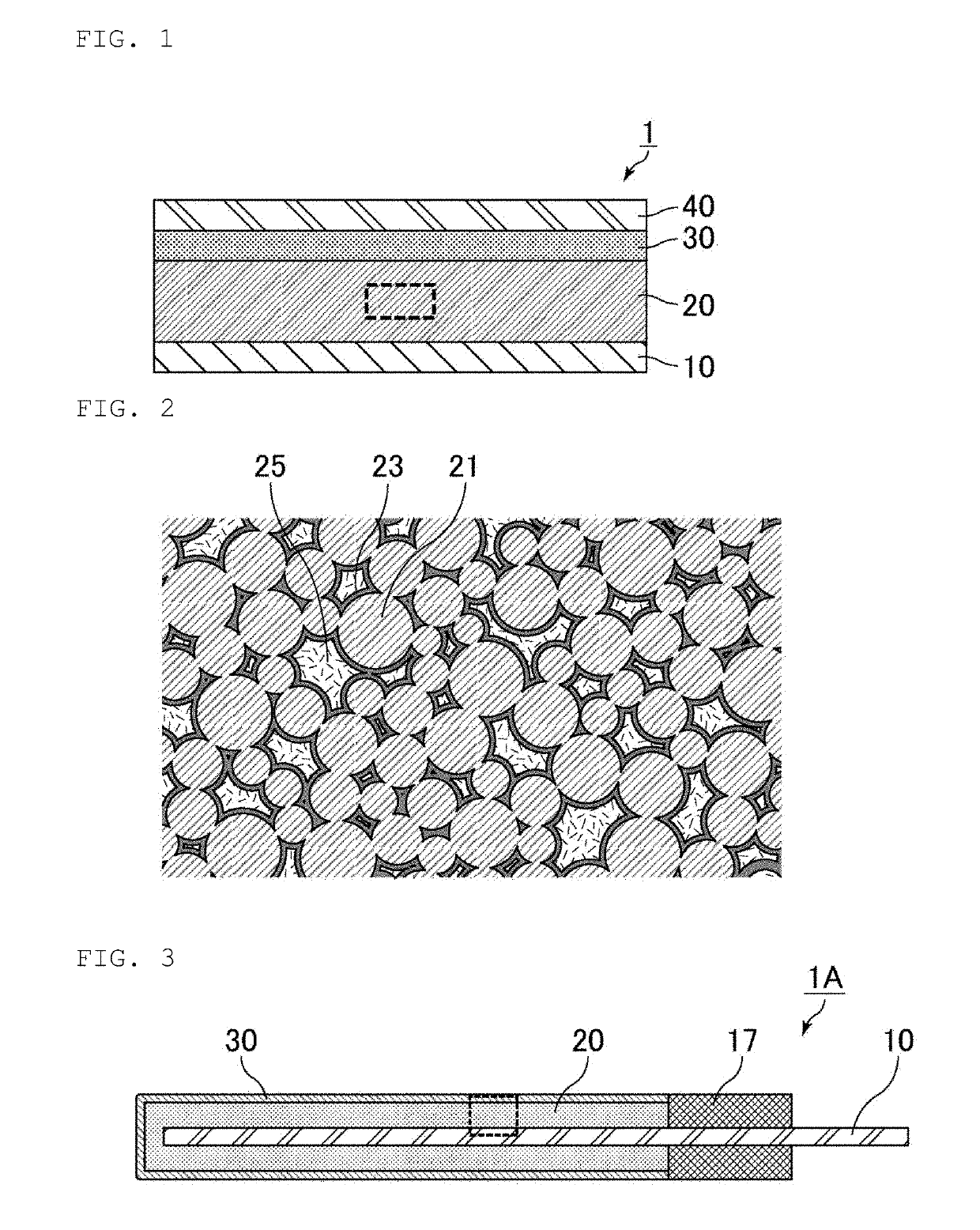

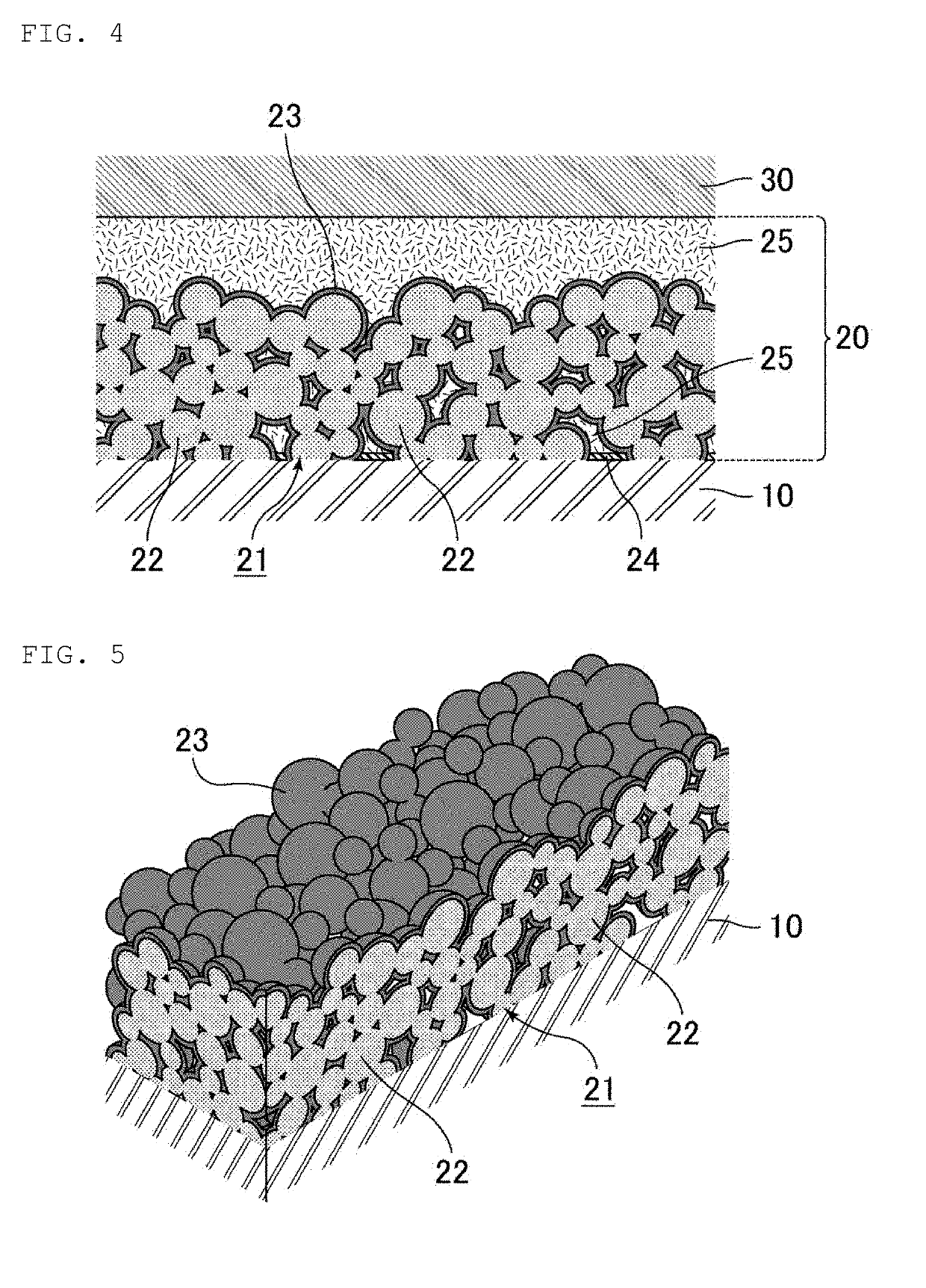

Method of manufacturing electrolytic capacitor and electrolytic capacitor

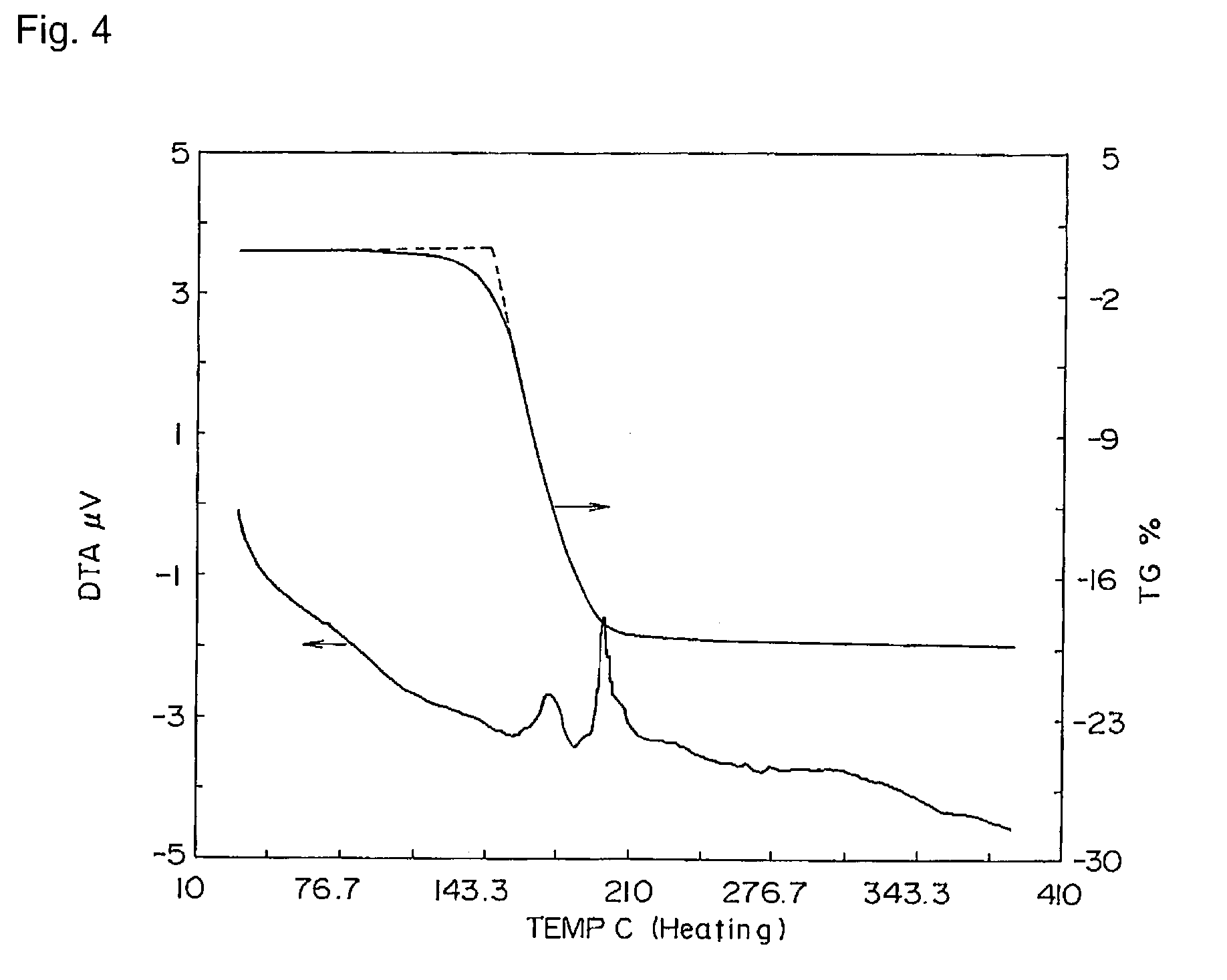

ActiveUS20080002334A1Improve pressure resistanceSolve the large leakage currentHybrid capacitor electrolytesSolid electrolytic capacitorsDielectricElectrolysis

A method of manufacturing an electrolytic capacitor including the following steps as well as an electrolytic capacitor manufactured by the method are provided. The method includes: a dispersion impregnation step of impregnating, with a dispersion containing electrically conductive solid particles or powder and a solvent, a capacitor element having an anode foil with a dielectric coating film formed thereon and an opposite cathode foil that are wound with a separator interposed therebetween; a dry step of evaporating the solvent after the dispersion impregnation step to form an electrically conductive solid layer on a surface of the dielectric coating film; and an electrolytic solution impregnation step of impregnating a gap in the electrically conductive solid layer with an electrolytic solution. Accordingly, an electrolytic capacitor that can be manufactured more easily that is excellent in voltage proofing property and that has a lower ESR and a lower leakage current is provided.

Owner:SANYO ELECTRIC CO LTD +1

Method for preparing high-purity ruthenium sputtering target and high-purity ruthenium sputtering target

InactiveUS6284013B1Minimize formation of particleSolve the large leakage currentTransportation and packagingRuthenium/rhodium/palladium/osmium/iridium/platinum compoundsHydrogen atmosphereImpurity

There is provided a high-purity ruthenium sputtering target with a low impurity content, in particular producing extremely few particles, which is suitable for applications such as the formation of semiconductor thin films. The high-purity ruthenium sputtering target is manufactured by feeding crude ruthenium powder into a sodium hydroxide solution; blowing an ozone-containing gas while or after blowing chlorine gas into the solution to form ruthenium tetroxide; absorbing the ruthenium tetroxide in a hydrochloric acid solution or a mixed solution of hydrochloric acid and ammonium chloride, and evaporating the solution to dryness; sintering the resultant ruthenium salt in a hydrogen atmosphere to form high-purity ruthenium powder; and hot-pressing the ruthenium powder into a sputtering target.

Owner:NIKKO MATERIALS CO LTD

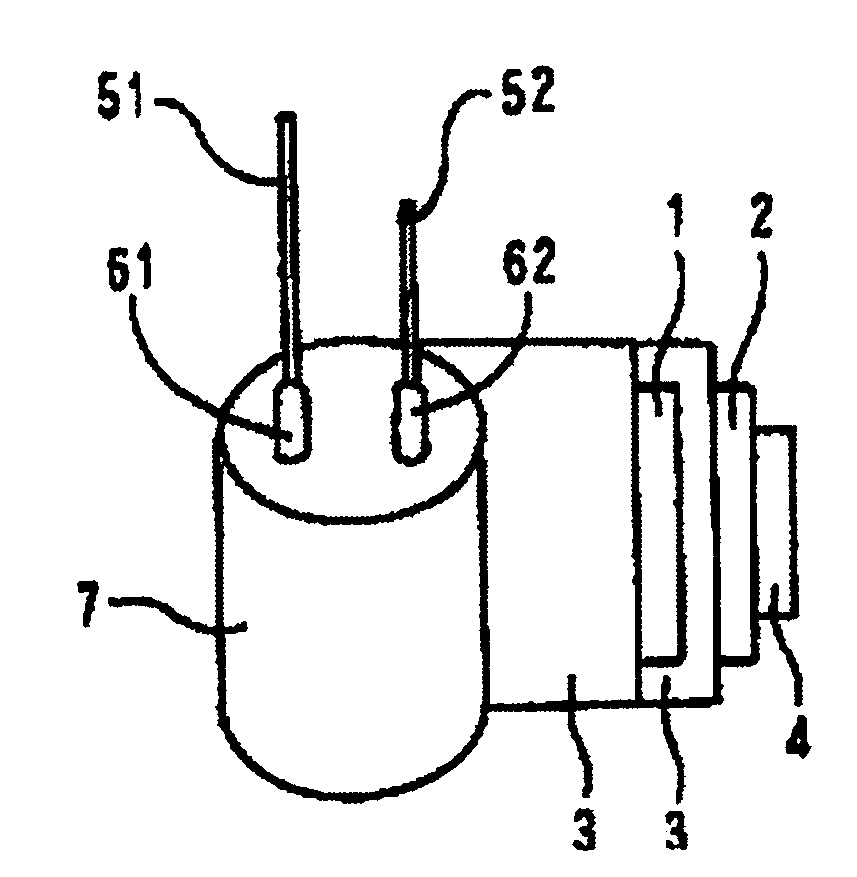

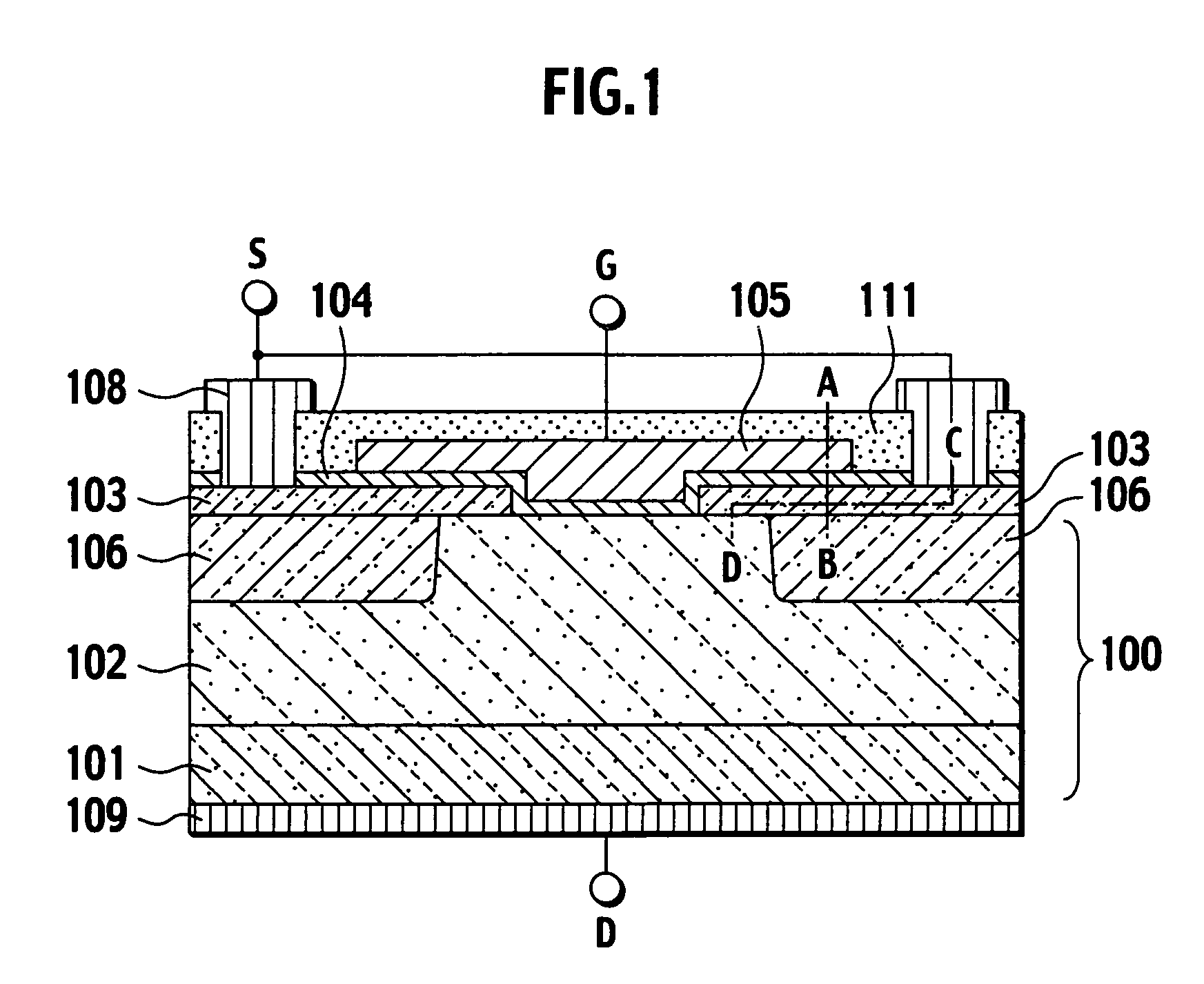

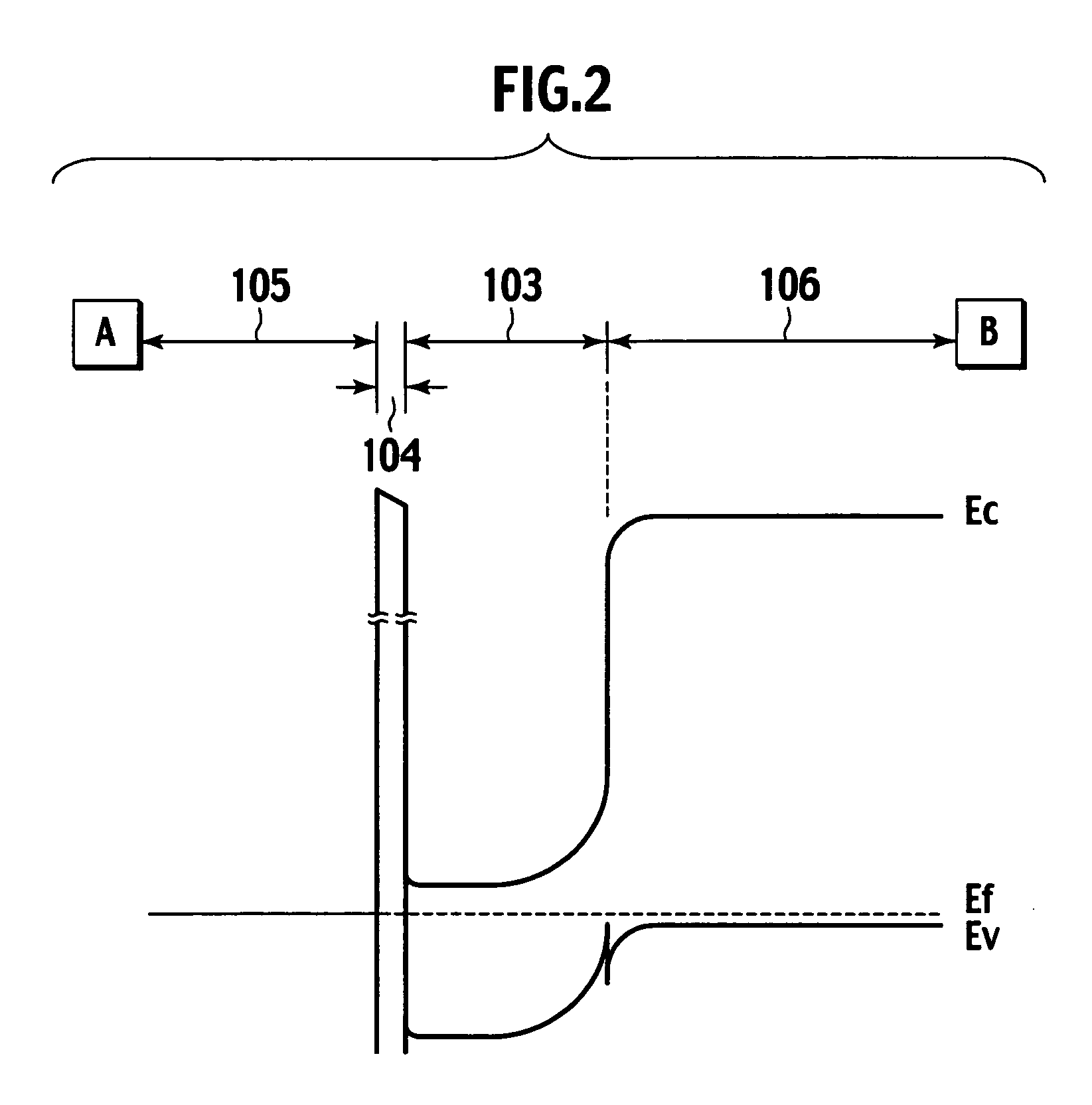

Semiconductor device with heterojunction

ActiveUS20050199873A1Lower barrier heightImprove transistor driving forceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionContact formation

An aspect of the present invention provides a semiconductor device that includes a semiconductor base made of a first semiconductor material of a first conductivity type, a hetero-semiconductor region forming a heterojunction with the semiconductor base and made of a second semiconductor material having a different band gap from the first semiconductor material, a first gate electrode arranged in the vicinity of the heterojunction, a first gate insulating film configured to insulate the first gate electrode from the semiconductor base, a source electrode formed in contact with the hetero-semiconductor region, a dram electrode formed in contact with the semiconductor base, and an electric field extending region partly facing the first gate electrode, the first gate insulating film and hetero-semiconductor region interposed between the electric field extending region and the first gate electrode, the electric field extending region extending a built-in electric field into the hetero-semiconductor region.

Owner:NISSAN MOTOR CO LTD

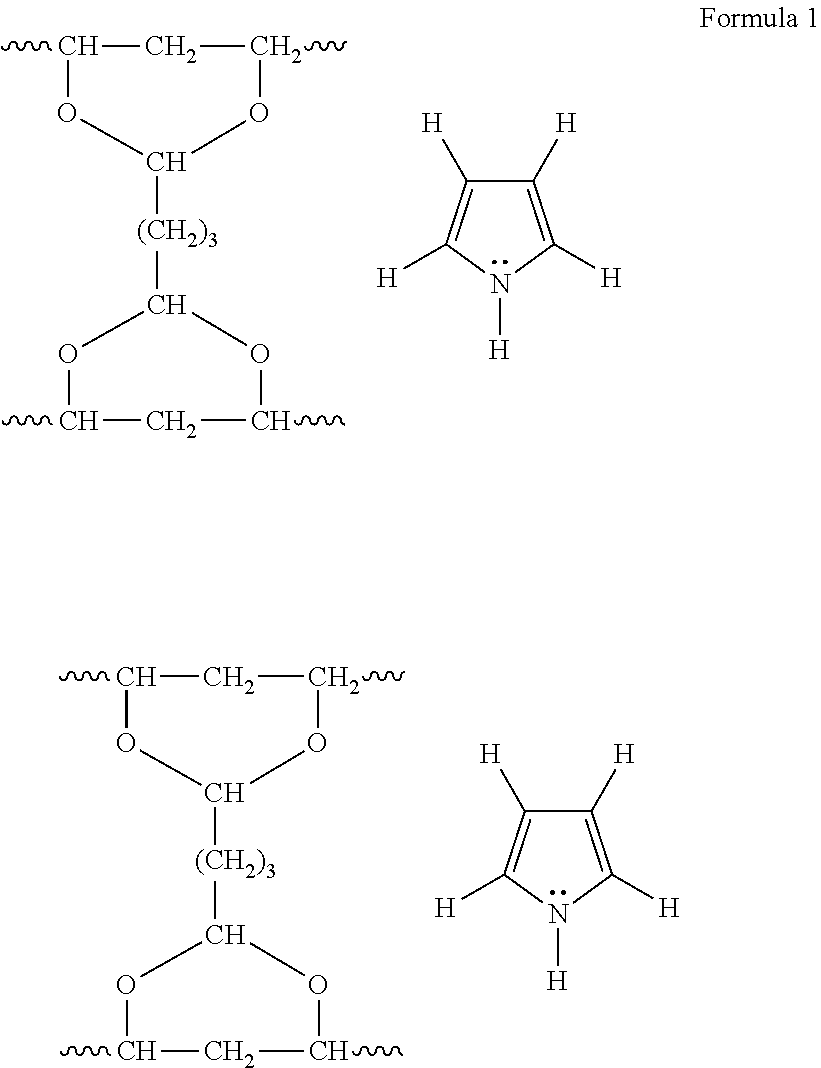

Organic semiconductor material and organic electronic device

InactiveUS7193237B2Light weightGood flexibilityOrganic chemistrySolid-state devicesPorphyrinOrganic semiconductor

An organic semiconductor material comprising a compound which has a generalized porphyrin skeleton and which has a molecular structure such that the distance from the generalized porphyrin ring plane to the center of each atom forming the generalized porphyrin skeleton, is not more than 1 Å.

Owner:MITSUBISHI CHEM CORP

Porcelain composition for varistor and varistor

InactiveUS20050143262A1Solve the large leakage currentHigh surge resistanceCurrent responsive resistorsConductive materialIndiumLow voltage

A varistor is provided which can be driven at a low voltage, has a small leak current, and can realize a high ESD resistance and a high surge resistance. The varistor is formed using a ceramic composition for a varistor which contains zinc oxide as a primary component and sub-components including praseodymium at a content of 0.05 to 3.0 atomic percent of the total, cobalt at a content of 0.5 to 10 atom percent of the total, at least one of potassium, sodium, and lithium at a total content of 0.005 to 0.5 atom percent of the total, at least one of aluminum, gallium, and indium at a total content of 2×10−5 to 0.5 atom percent of the total, and zirconium at a content of 0.005 to 5.0 atom percent of the total.

Owner:MURATA MFG CO LTD

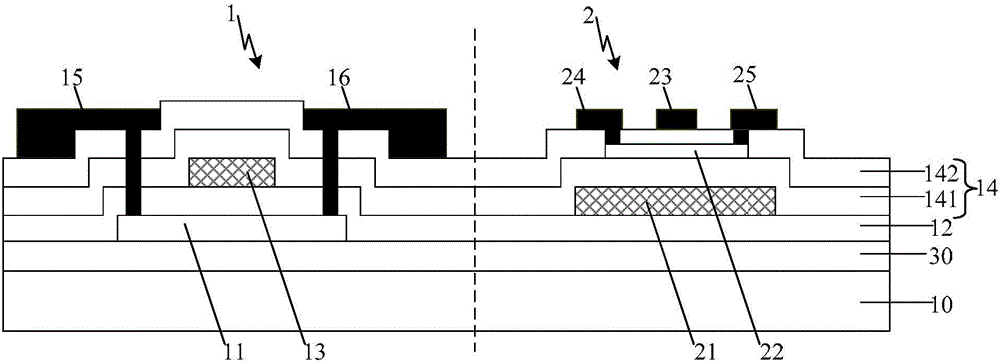

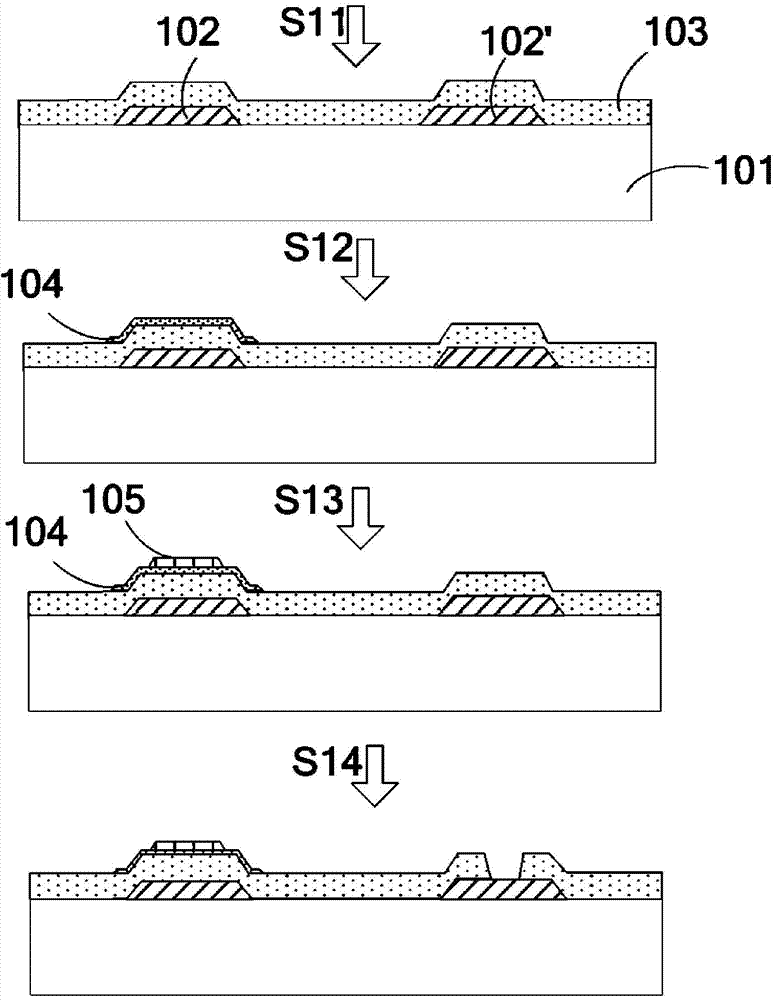

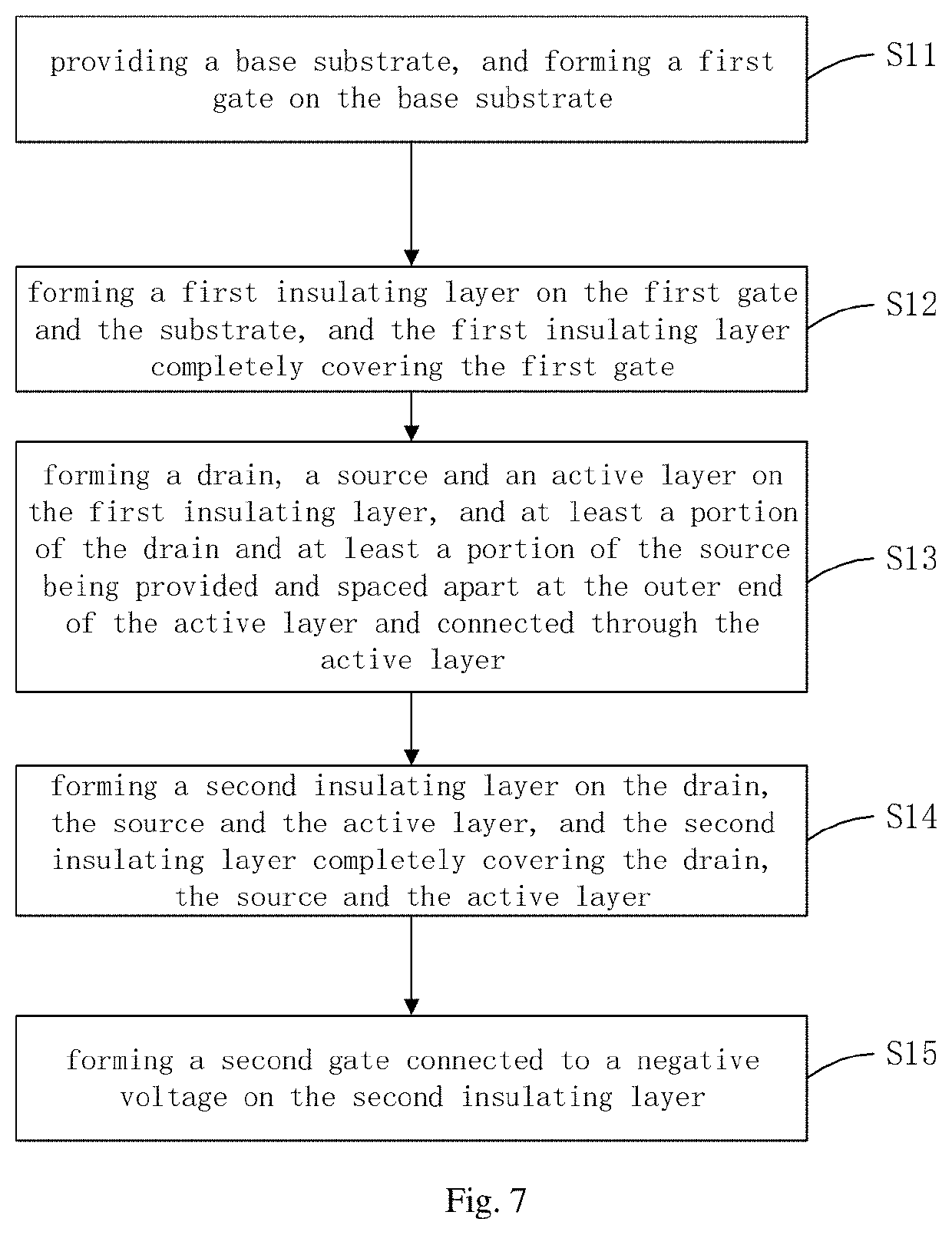

Array substrate and preparation method thereof and display panel

ActiveCN106847834AFast switching speedFast on state currentSolid-state devicesNon-linear opticsEngineeringDouble gate

The embodiment of the invention provides an array substrate and a preparation method thereof and a display panel and relates to the technical field of display. The display panel has good display performance by adopting two types of TFTs on the array substrate. The array substrate comprises a substrate, double-gate oxide TFTs, a display electrode and a polysilicon TFT arranged on the substrate, wherein one double-gate oxide TFT is arranged in each sub-pixel on the substrate; and a drain of each double-gate oxide TFT is electrically connected with the display electrode.

Owner:BOE TECH GRP CO LTD +1

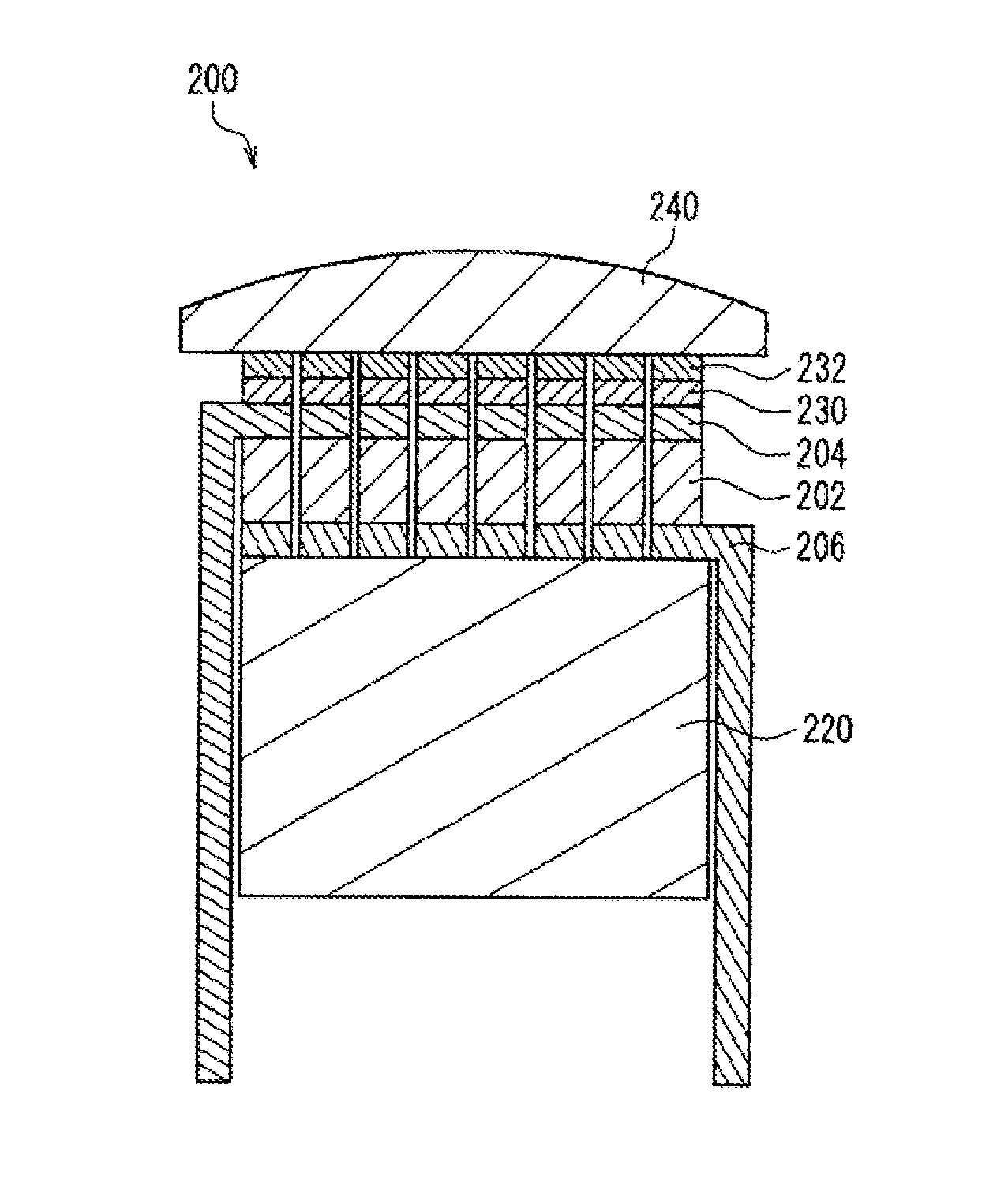

Solid electrolytic capacitor

InactiveUS20090296318A1Solve the large leakage currentClosuresSolid electrolytic capacitorsElectrolytic capacitorElectrical and Electronics engineering

A solid electrolytic capacitor includes a negative terminal, first to fourth capacitor elements coupled to the negative terminal, first and second positive terminals connected to the first to fourth capacitor elements, and a package resin covering the first to fourth capacitor elements. Each of the first to fourth capacitor elements has a first end and a second end opposite to the first end, and each of the first to fourth capacitor elements includes a negative electrode provided at the first end and a positive electrode provided at the second end. The first to fourth capacitor elements are stacked in this order. The positive electrodes of the first and fourth capacitor elements extend in a first direction from the respective negative electrodes of the first and fourth capacitor elements. The positive electrodes of the second and third capacitor elements extend in a second direction, opposite to the first direction, from the respective negative electrodes of the second and third capacitor elements. This solid electrolytic capacitor has a small leakage current.

Owner:PANASONIC CORP

MIM capacitor structure and method of manufacturing the same

InactiveUS20070145525A1Solve the large leakage currentSmall currentSemiconductor/solid-state device manufacturingCapacitorsMetal insulatorNitrogen

A metal-insulator-insulator (MIM) capacitor structure is provided. The MIM capacitor includes a top electrode, a bottom electrode and a dielectric layer. The dielectric layer is disposed between the top electrode and the bottom electrode. The main feature for this kind of MIM capacitor is that the bottom electrode includes a conductive layer and a metal nitride with multi-layered structure. The metal nitride with multi-layered structure is disposed between the conductive layer and the dielectric layer. The nitrogen content in the metal nitride with multi-layered structure gradually increases toward the dielectric layer and the metal nitride belongs to the amorphous type. Due to the presence of the metal nitride, the dielectric layer is prevented from crystallization, thereby reducing the current leakage of the MIM capacitor.

Owner:IND TECH RES INST

capacitor

ActiveUS20160329158A1High capacitanceSolve the large leakage currentSolid electrolytic capacitorsCapacitor electrodesDielectric layerCapacitor

A capacitor that includes a porous metal base material, a dielectric layer formed on the porous metal base material, an upper electrode formed on the dielectric layer, a first terminal electrode electrically connected to the porous metal base material, and a second terminal electrode electrically connected to the upper electrode. The porous metal base material includes a high-porosity part and low-porosity parts, and the low-porosity parts are present at a pair of opposed side surfaces of the porous metal base material.

Owner:MURATA MFG CO LTD

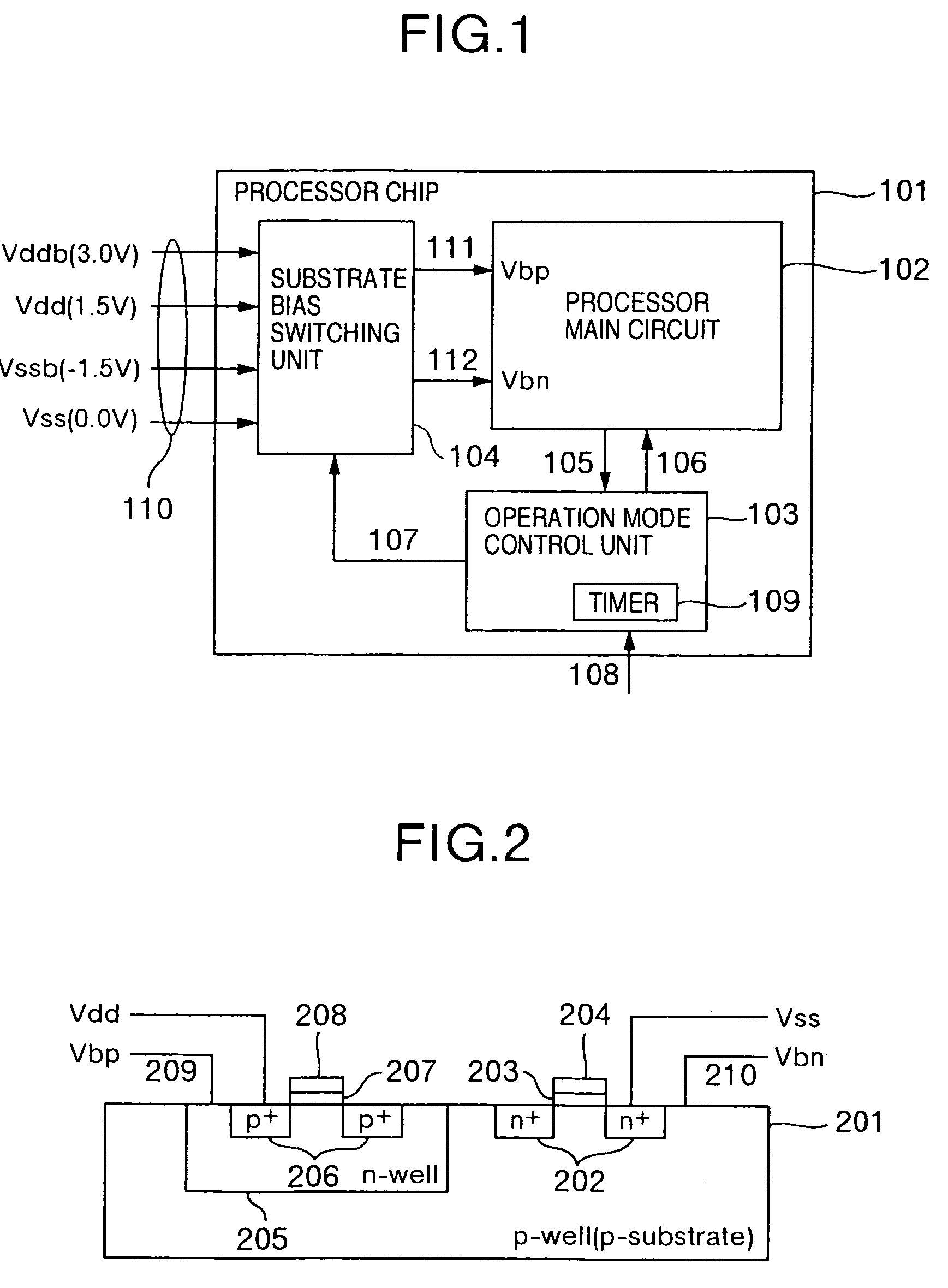

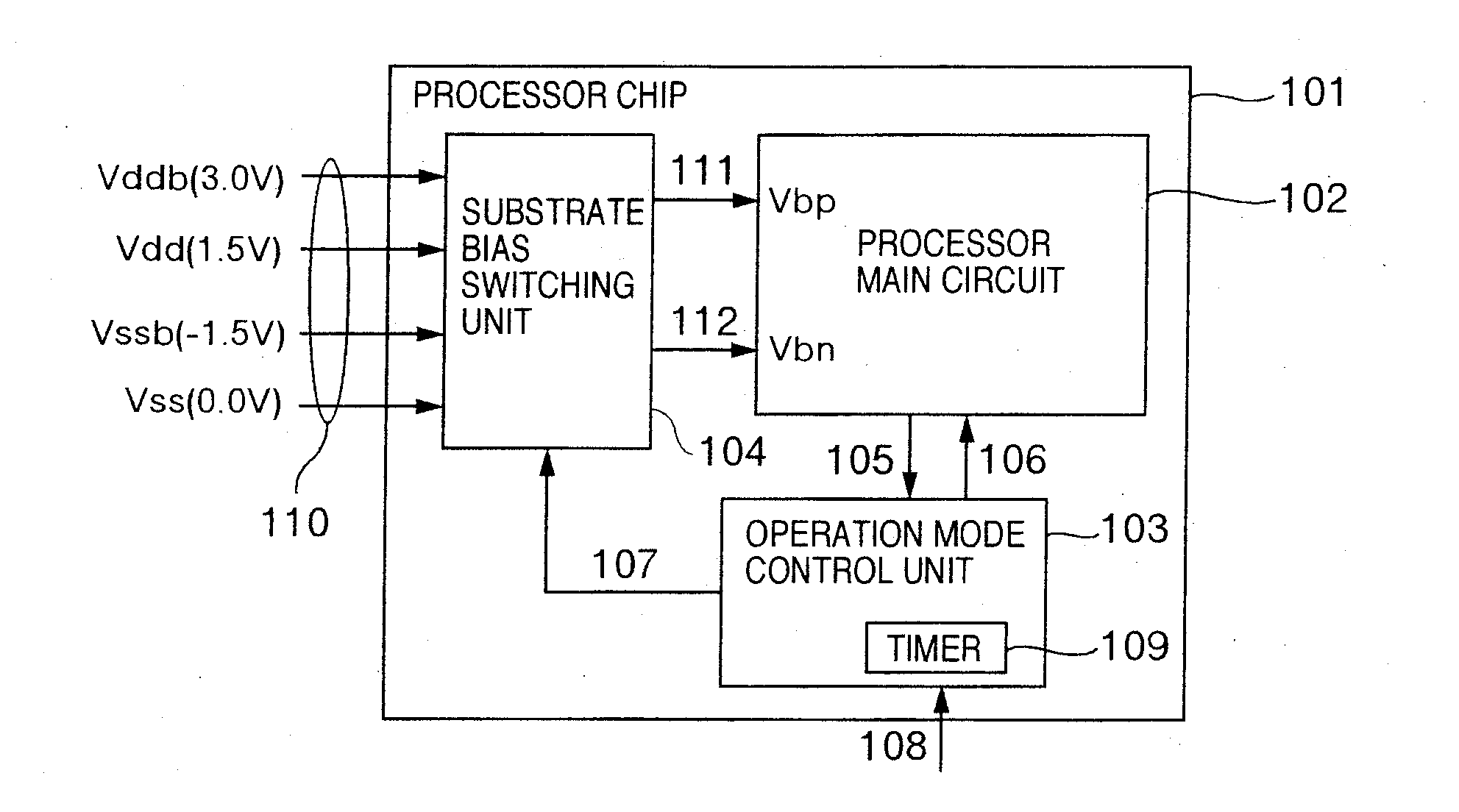

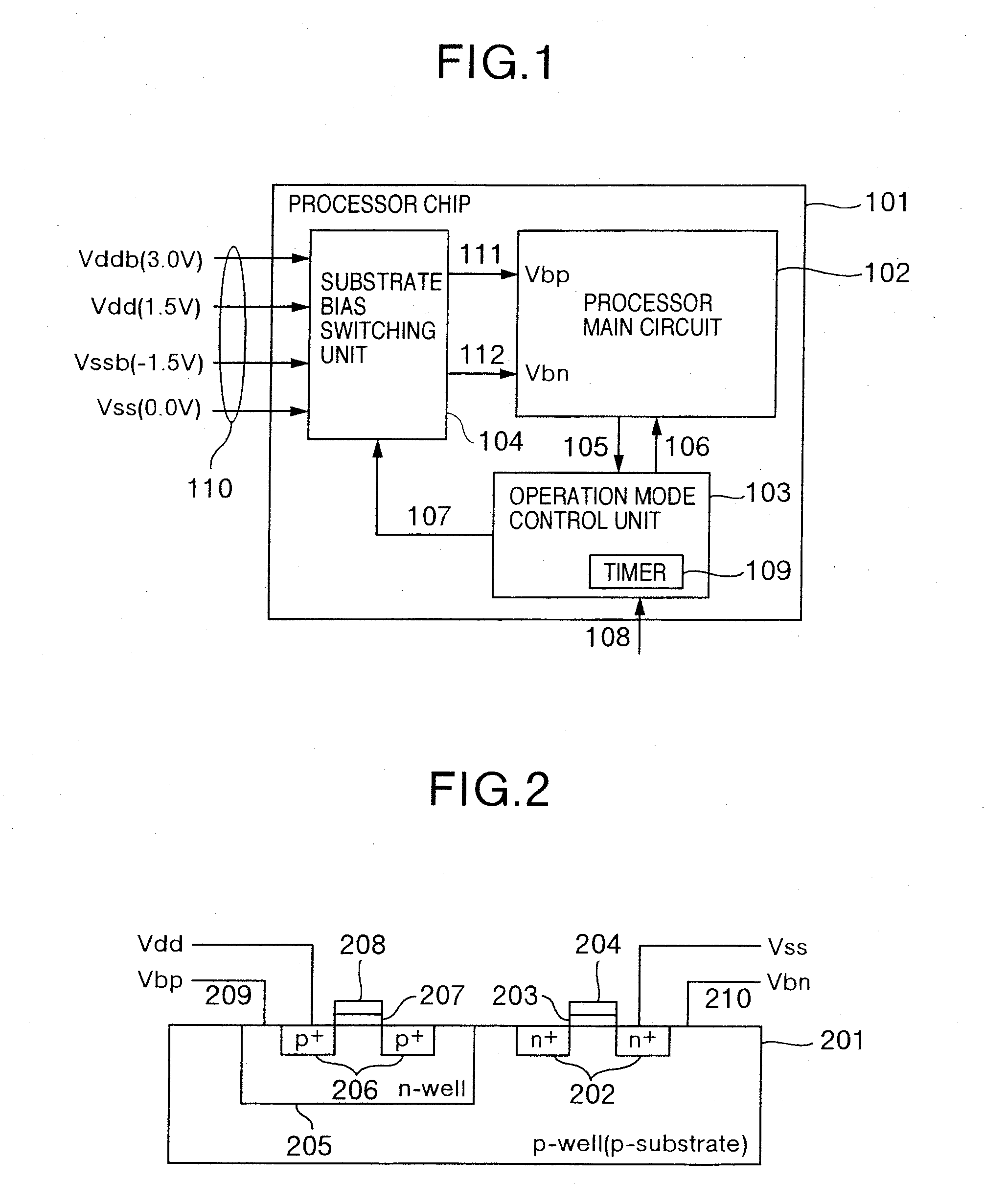

Substrate bias switching unit for a low power processor

InactiveUS7475261B2High speedReduce leakage currentEnergy efficient ICTVolume/mass flow measurementProgram instructionNormal mode

The feature of the present invention consists in: a processor main circuit for executing program instruction strings on a processor chip; a substrate bias switching unit for switching voltages of substrate biases applied to a substrate of the processor main circuit; and an operation mode control unit for controlling, in response to the execution of an instruction to proceed to a stand-by mode in the processor main circuit, the substrate bias switching unit in such a way that the biases are switched over to voltages for the stand-by mode, and for controlling, in response to an interruption of the stand-by release from the outside, the substrate bias switching unit in such a way that the biases are switched over to voltages for a normal mode, and also for releasing, after the bias voltages switched thereto have been stabilized, the stand-by of the processor main circuit to restart the operation.

Owner:RENESAS ELECTRONICS CORP

Separator for an Electric Double Layer Capacitor

InactiveUS20090280308A1Solve the large leakage currentLower internal resistanceElectrolytic capacitorsRecord information storageCellulosePolyester

The present invention provides a separator for an electric double layer capacitor comprising a porous sheet containing fibrillated heat-resistant fibers, polyester fibers having a fineness of 0.01 dtex to less than 0.10 dtex, and fibrillated cellulose, which is suitable for use as a separator for an electric double layer capacitor operating at high voltages of 3 V or more.

Owner:MITSUBISHI PAPER MILLS LTD

Piezoelectric composition and method for producing same, piezoelectric element/non-lead piezoelectric element and method for producing same, ultrasonic probe and diagnostic imaging device

InactiveUS20150141834A1Produce compositionConveniently producedUltrasonic/sonic/infrasonic diagnosticsPiezoelectric/electrostrictive device manufacture/assemblyPerovskite (structure)Nuclear physics

The present invention is a piezoelectric composition and a piezoelectric element using the piezoelectric composition, the composition being characterized by: having a Perovskite structure represented by general formula ABO3; being represented by composition formula x(Bi0.5K0.5)TiO3-yBi(Mg0.5Ti0.5)O3-zBiFeO3, x+y+z=1 in the composition formula above; and in a triangular coordinate using x, y and z in the composition formula above, having a composition represented by a region which is surrounded by a pentagon ABCDE with apexes of point A (1, 0, 0), point B (0.7, 0.3, 0), point C (0.1, 0.3, 0.6), point D (0.1, 0.1, 0.8) and point E (0.2, 0, 0.8) and which does not include the line segment AE that connects point A (1, 0, 0) and point E (0.2, 0, 0.8).

Owner:KONICA MINOLTA INC

Triode field emission device having mesh gate and field emission display using the same

ActiveUS6958499B2Low working voltageIncrease concentrationControl electrodesNanoinformaticsField emission deviceHigh concentration

Provided is a field emission device having a mesh gate. The object of this research is to provide a field emission display (FED) using a triode field emission device for preventing increase of operation voltage, and securing high concentration of electron beams. The operation properties of the FED is different based on a structure of an extraction electrode. In this research, the extraction electrode is formed on the electron emitting source and it has a plurality of openings corresponding to the locations of carbon nanotube mixture. The concentration of the electron beams is raised and leakage current is suppressed by using an insulating mesh gate plate. The upper part of the openings has a smaller diagram than the lower part. The high concentration of electron beams and little leakage current can be generated by adding auxiliary electrodes or optimizing the shape of electrodes.

Owner:ELECTRONICS & TELECOMM RES INST

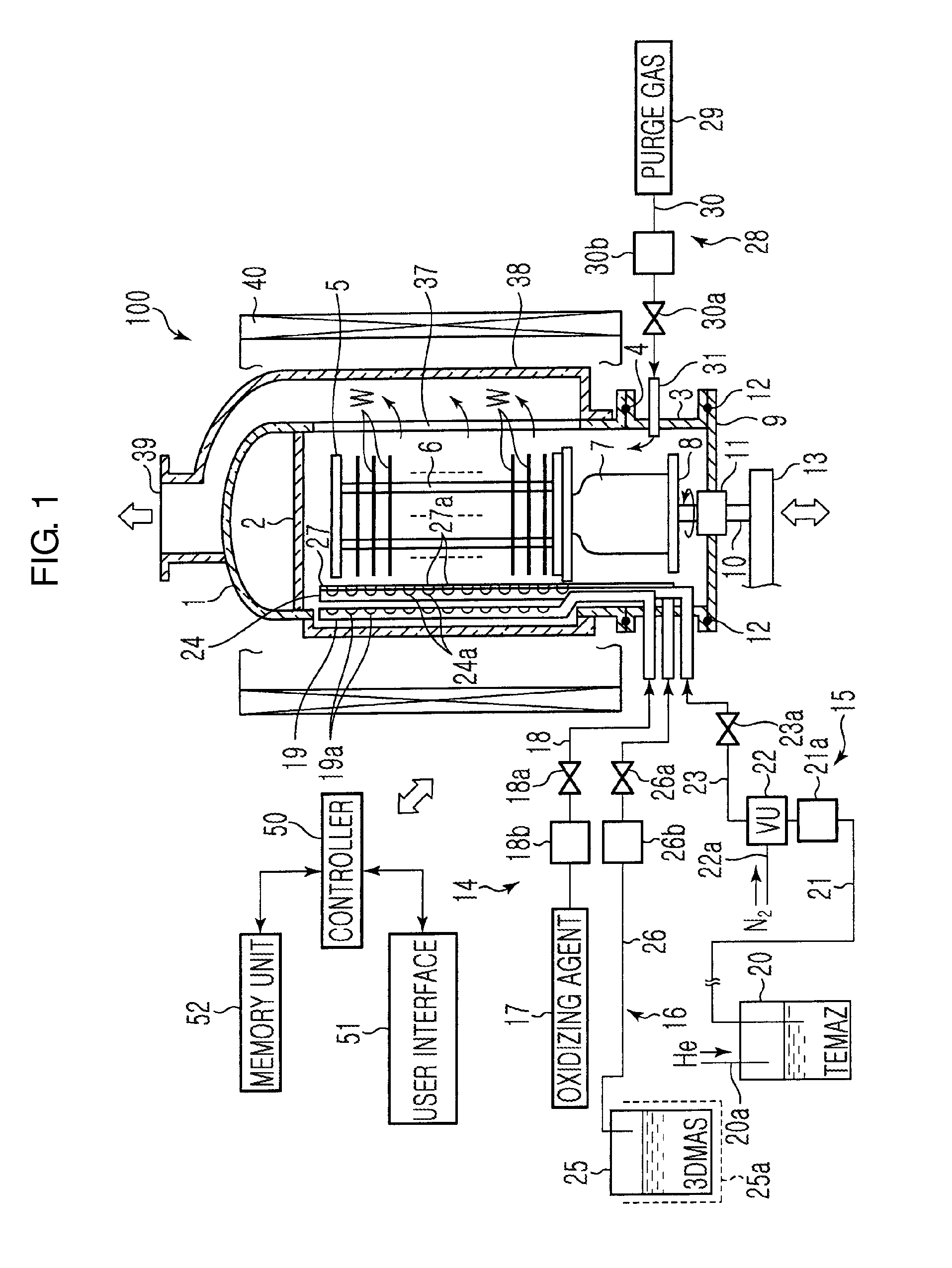

Film formation method and film formation apparatus

ActiveUS20110300719A1High dielectric constantSolve the large leakage currentLiquid surface applicatorsSemiconductor/solid-state device manufacturingEngineeringOxidizing agent

When an object to be processed is transferred into a process chamber capable of keeping a vacuum and an interior of the process chamber is kept in a vacuum state, the film formation method includes performing forming a first ZrO film on the object to be processed by supplying a zirconium material and an oxidizing agent in the order listed above into the process chamber and forming a second ZrO film doped with Si on the object to be processed by supplying the zirconium material, a silicon material, and the oxidizing agent in the order listed above into the process chamber, in such a way that a number of times the forming the first ZrO film is performed and a number of times the forming the second ZrO film is performed are adjusted, respectively, to form a zirconia-based film having a predetermined film thickness while controlling a Si concentration in the film.

Owner:TOKYO ELECTRON LTD

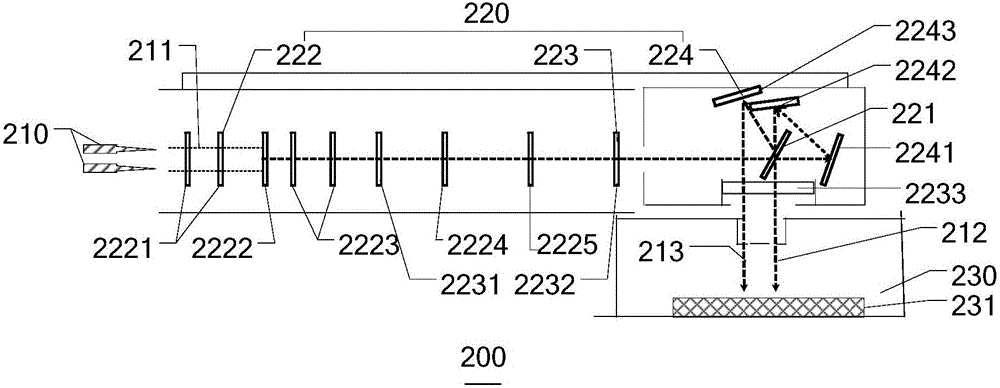

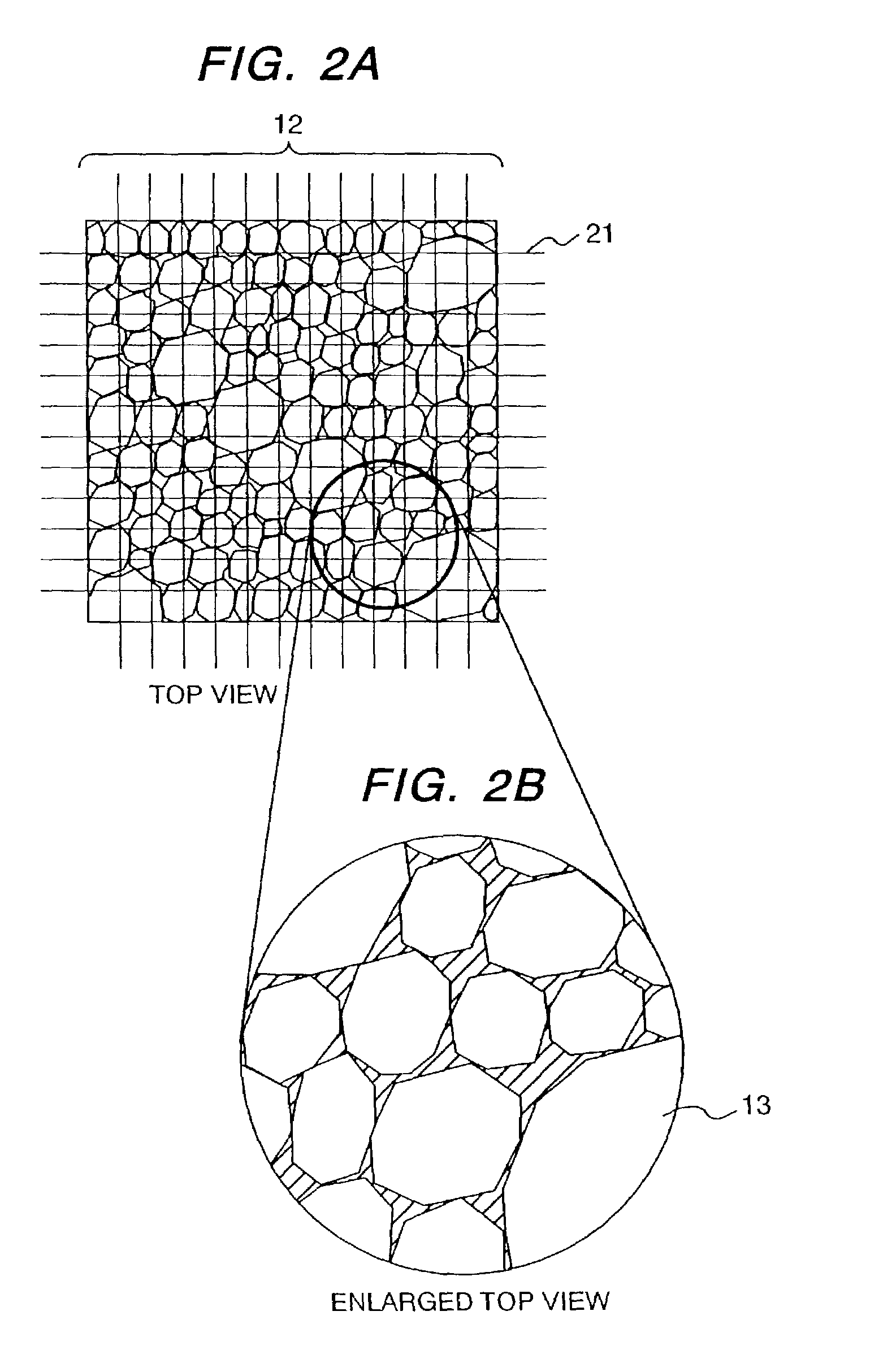

Laser annealing apparatus, preparation method of polycrystalline silicon thin film and preparation method of thin film transistor

ActiveCN106783536ASolve the large leakage currentSolve the mobilityTransistorLaser detailsBeam splitterOptoelectronics

The present invention provides a laser annealing apparatus, a preparation method of a polycrystalline silicon thin film and a preparation method of a thin film transistor. The laser annealing apparatus comprises a laser generator, optical path elements and an annealing chamber; the laser generator is configured to emit a laser beam; the laser beam is guided to the annealing chamber through the optical path elements; the optical path elements comprise a beam splitter; the beam splitter divides the laser beam into a first light beam and a second light beam, and the energy density of the first light beam is greater than the energy density of the second light beam; and the first light beam and the second light beam are guided to the annealing chamber for laser annealing. When the laser annealing apparatus is adopted to perform annealing processing on the polycrystalline silicon thin film, the non-uniformity of the surface of the polycrystalline silicon thin film can be decreased, so that the mobility of electrons and holes can be improved, and therefore, the problems of large leakage current, non-uniform mobility and non-uniform threshold voltage of the thin film transistor can be solved.

Owner:BOE TECH GRP CO LTD +1

Solid electrolytic capacitor and manufacturing method thereof

InactiveUS20120218682A1Reduce leakage currentImprove pressure resistanceSolid electrolytic capacitorsCapacitor electrolytes/absorbentsCross-linkConductive polymer

A solid electrolytic capacitor including an anode, a dielectric layer formed on the anode, a polyvinyl alcohol film formed on the dielectric layer, and a conductive polymer layer formed on the polyvinyl alcohol film, wherein the polyvinyl alcohol film has a cross-linked structure.

Owner:SANYO ELECTRIC CO LTD

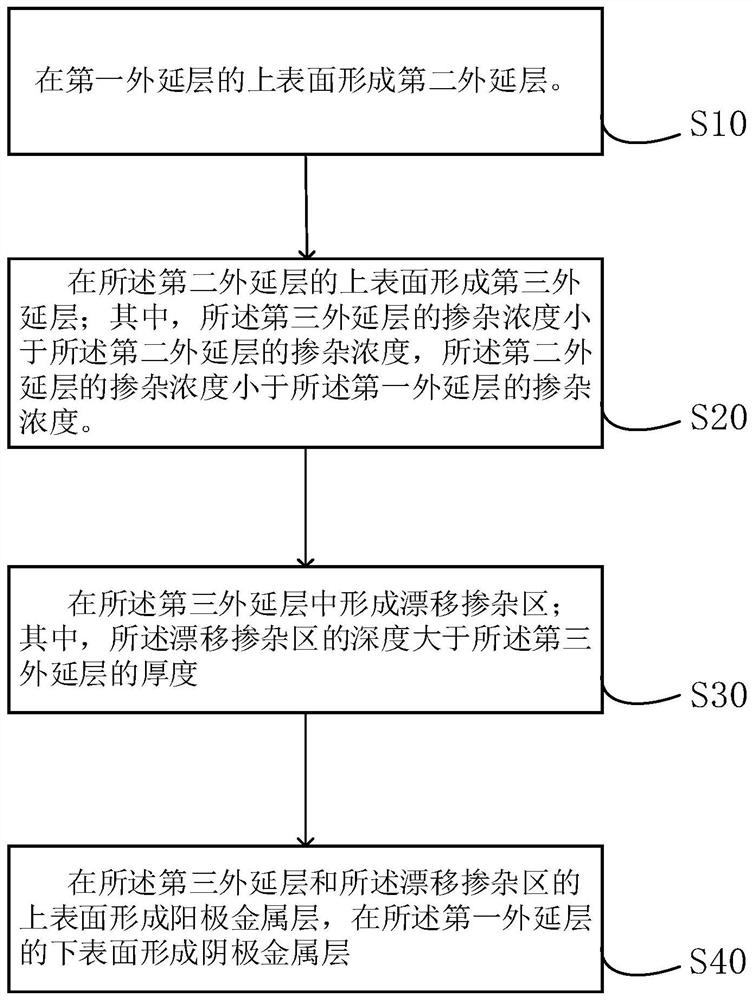

Preparation method of MPS diode and MPS diode

PendingCN114242767ASolve the large leakage currentLow resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceElectrical field strength

The invention belongs to the field of semiconductors, and provides a preparation method of an MPS diode and the MPS diode, and the method comprises the following steps: forming a second epitaxial layer on the upper surface of a first epitaxial layer; a third epitaxial layer is formed on the upper surface of the second epitaxial layer, the doping concentration of the third epitaxial layer is smaller than that of the second epitaxial layer, and the doping concentration of the second epitaxial layer is larger than that of the first epitaxial layer; a drift doping region is formed in the third epitaxial layer, and the depth of the drift doping region is larger than the thickness of the third epitaxial layer; and forming an anode metal layer on the upper surfaces of the third epitaxial layer and the drift doping region, and forming a cathode metal layer on the lower surface of the first epitaxial layer. When the MPS diode is turned on in the forward direction, the resistivity of the MPS diode is low, when the MPS diode is turned on in the reverse direction, the second epitaxial layer and the third epitaxial layer are in a high-resistance state, the surface electric field intensity distribution below the anode metal layer can be reduced, and the problem that the leakage current of the MPS is large is solved.

Owner:SHENZHEN XINER SEMICON TECH CO LTD

Solid electrolytic capacitor and manufacturing method thereof

ActiveUS20120218681A1Reduce leakage currentImprove reliabilitySolid electrolytic capacitorsCapacitor electrolytes/absorbentsElectrolysisConductive polymer

Provided are a solid electrolytic capacitor including an anode, a dielectric layer provided on a surface of the anode, a coupling agent layer provided on the dielectric layer, a conductive polymer layer provided on the coupling agent layer, and a cathode layer provided on the conductive polymer layer, wherein the coupling agent layer contains a first coupling agent having a phosphonic acid group and a second coupling agent which is a silane coupling agent, and a method for manufacturing the solid electrolytic capacitor.

Owner:SANYO ELECTRIC CO LTD

Substrate bias switching unit for a low power processor

InactiveUS20100005324A1Increase speedReduce leakage currentEnergy efficient ICTDc network circuit arrangementsProgram instructionMode control

The feature of the present invention consists in: a processor main circuit for executing program instruction strings on a processor chip; a substrate bias switching unit for switching voltages of substrate biases applied to a substrate of the processor main circuit; and an operation mode control unit for controlling, in response to the execution of an instruction to proceed to a stand-by mode in the processor main circuit, the substrate bias switching unit in such a way that the biases are switched over to voltages for the stand-by mode, and for controlling, in response to an interruption of the stand-by release from the outside, the substrate bias switching unit in such a way that the biases are switched over to voltages for a normal mode, and also for releasing, after the bias voltages switched thereto have been stabilized, the stand-by of the processor main circuit to restart the operation.

Owner:RENESAS ELECTRONICS CORP

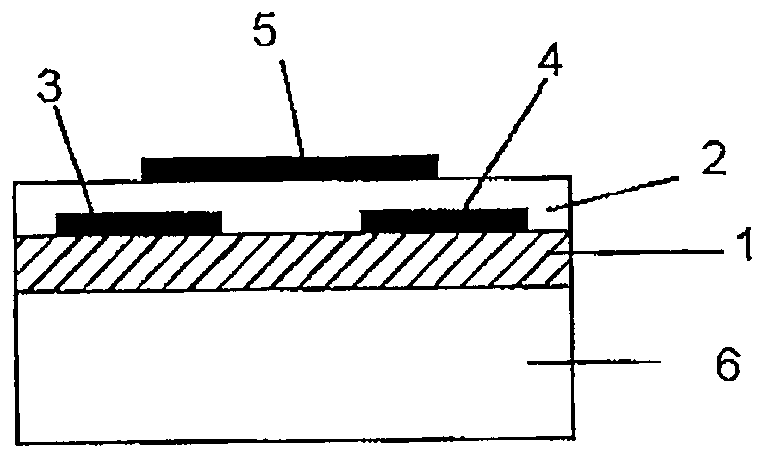

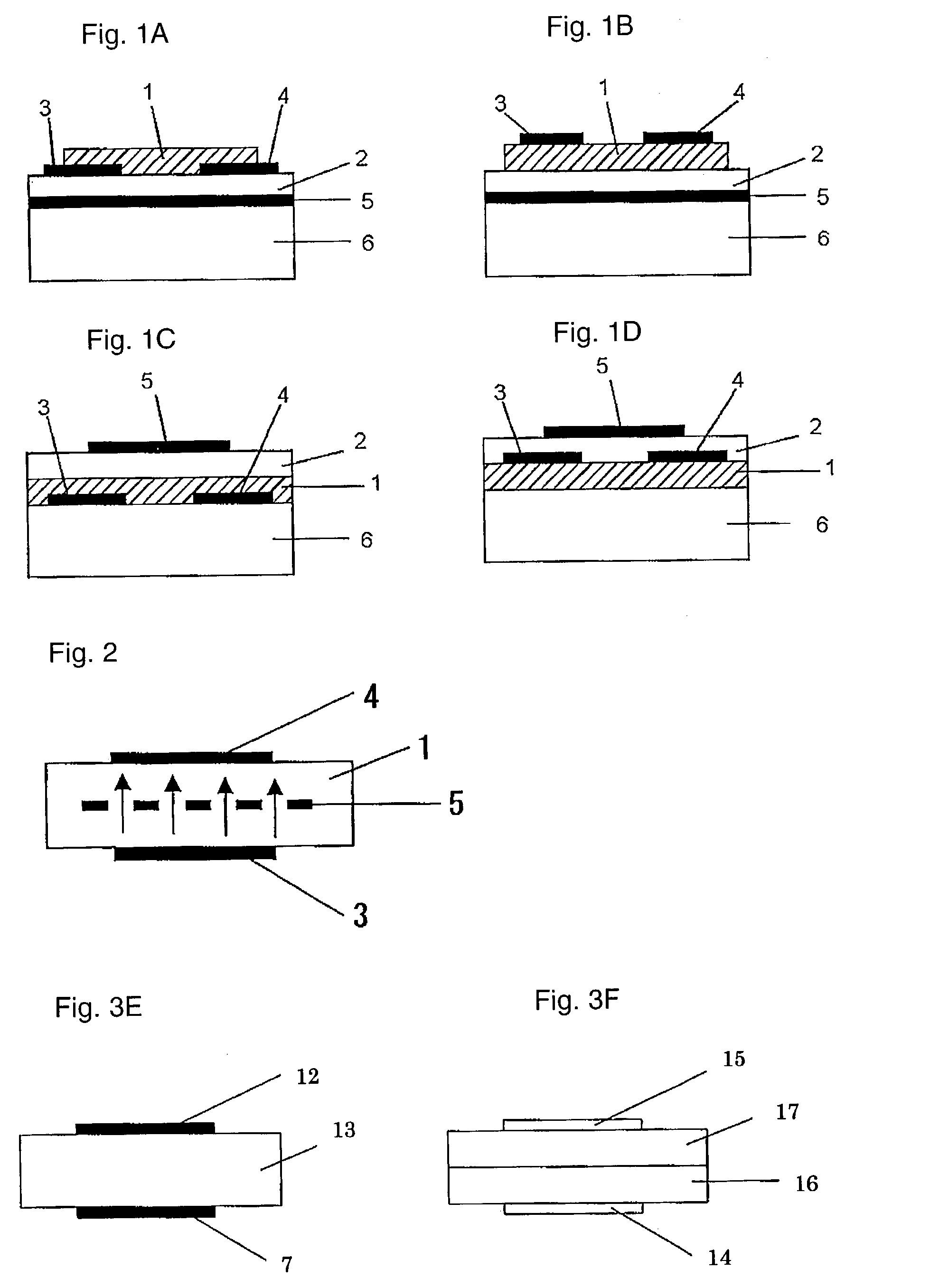

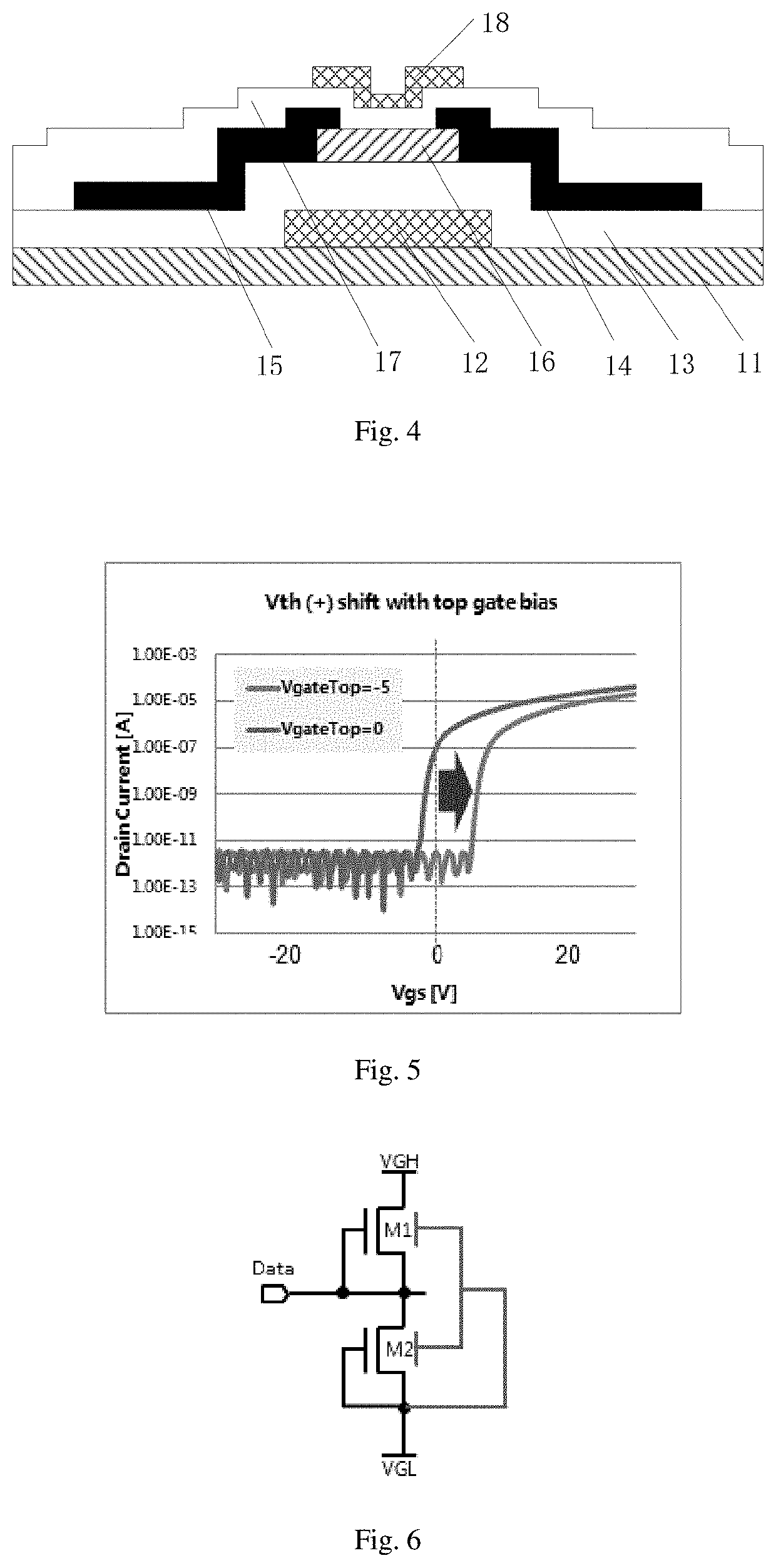

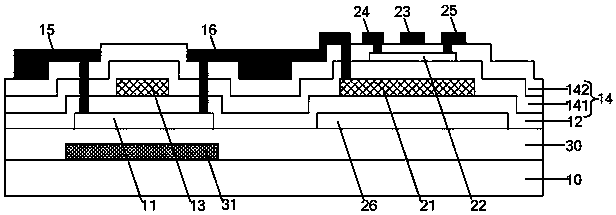

Unit pixel, array substrate, display apparatus, and manufacture methods thereof

ActiveCN104332476ASolving Diffusion ProblemsSolve the large leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringActive layer

The invention discloses a unit pixel, an array substrate, a display apparatus, and manufacture methods thereof. In one embodiment of the invention, the unit pixel comprises a grid wire, a source-drain electrode wire and a TFT, wherein the grid wire is of a lamination structure and comprises a first MoW layer, a Cu layer and a second MoW layer, and the grid of the TFT is formed by the first MoW layer. In another embodiment of the invention, the source-drain electrode wire is of the same lamination structure, and the source-drain electrode of the TFT employs the first MoW layer. According to the invention, the previous mode can be realized by use of a semi-exposure technology, and the second mode can be realized by use of a peeling technology. The influence exerted by diffusion of Cu in the grid or a source-drain layer on an oxide active layer can be prevented.

Owner:BOE TECH GRP CO LTD

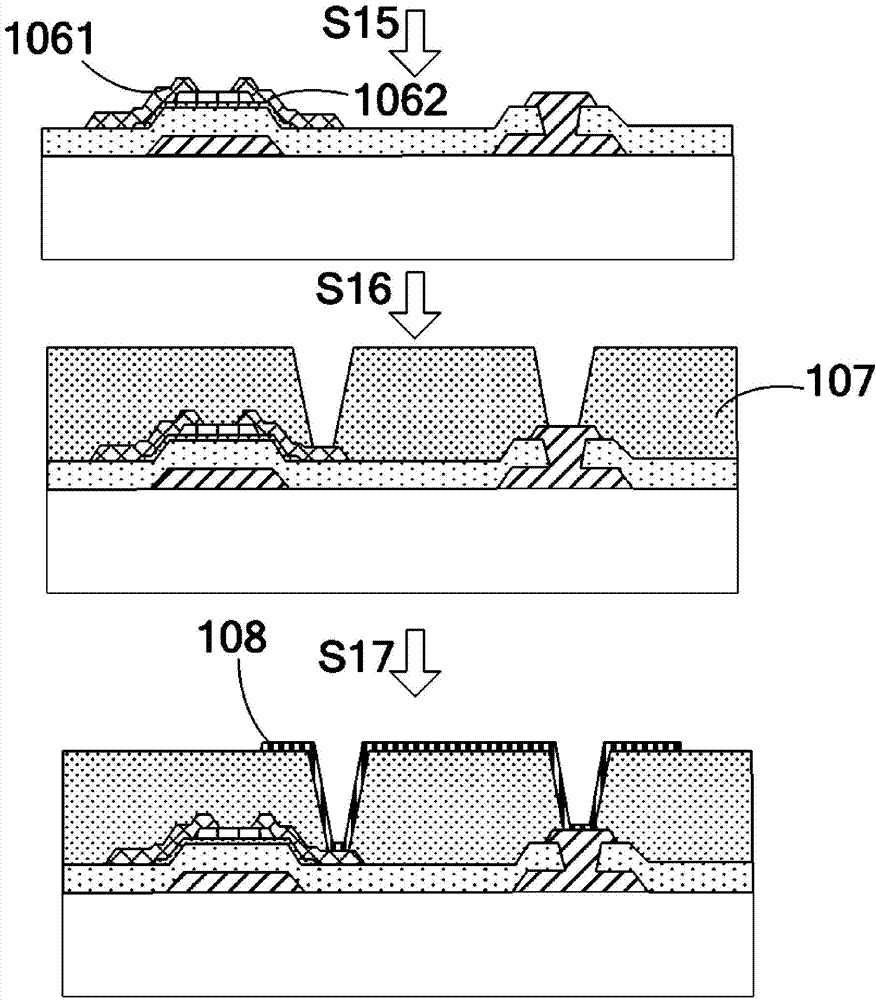

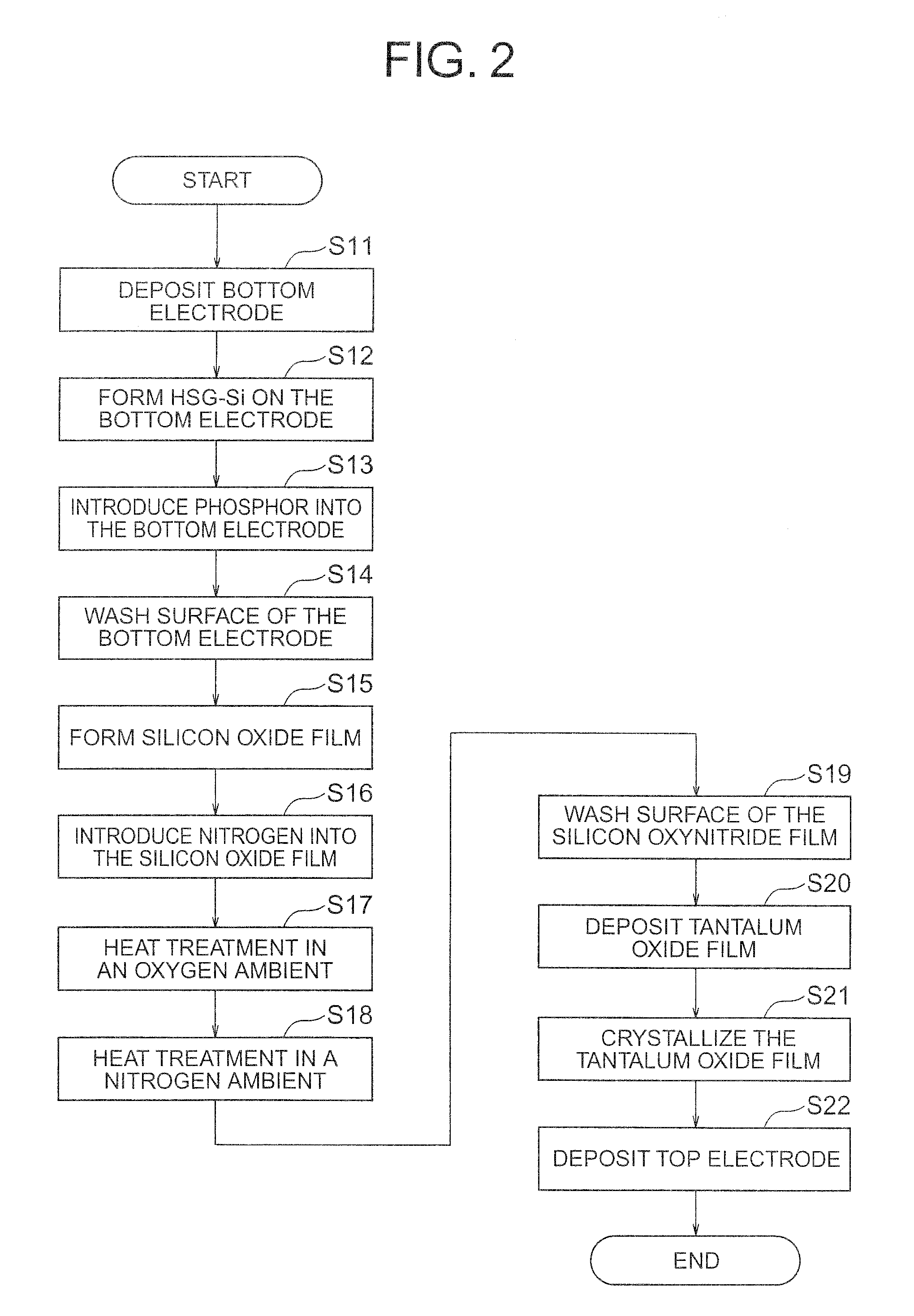

Method for manufacturing a semiconductor device including a stacked capacitor

InactiveUS20080090375A1Good thickness controllabilityIncrease capacitance per unit areaSemiconductor/solid-state device manufacturingCapacitorsCapacitanceDevice material

A process for forming a capacitor in a semiconductor device includes the step of forming a two-layer capacitor insulation film including a silicon oxynitride film and a tantalum oxide film. The step for forming the silicon oxynitride film is performed at a first substrate temperature, and the step of forming the tantalum oxide film uses a heat treatment performed at a second substrate temperature. The second substrate temperature is lower than the maximum of the first substrate temperature, to provide a higher capacitance per unit area and a lower leakage current in the capacitor.

Owner:ELPIDA MEMORY INC

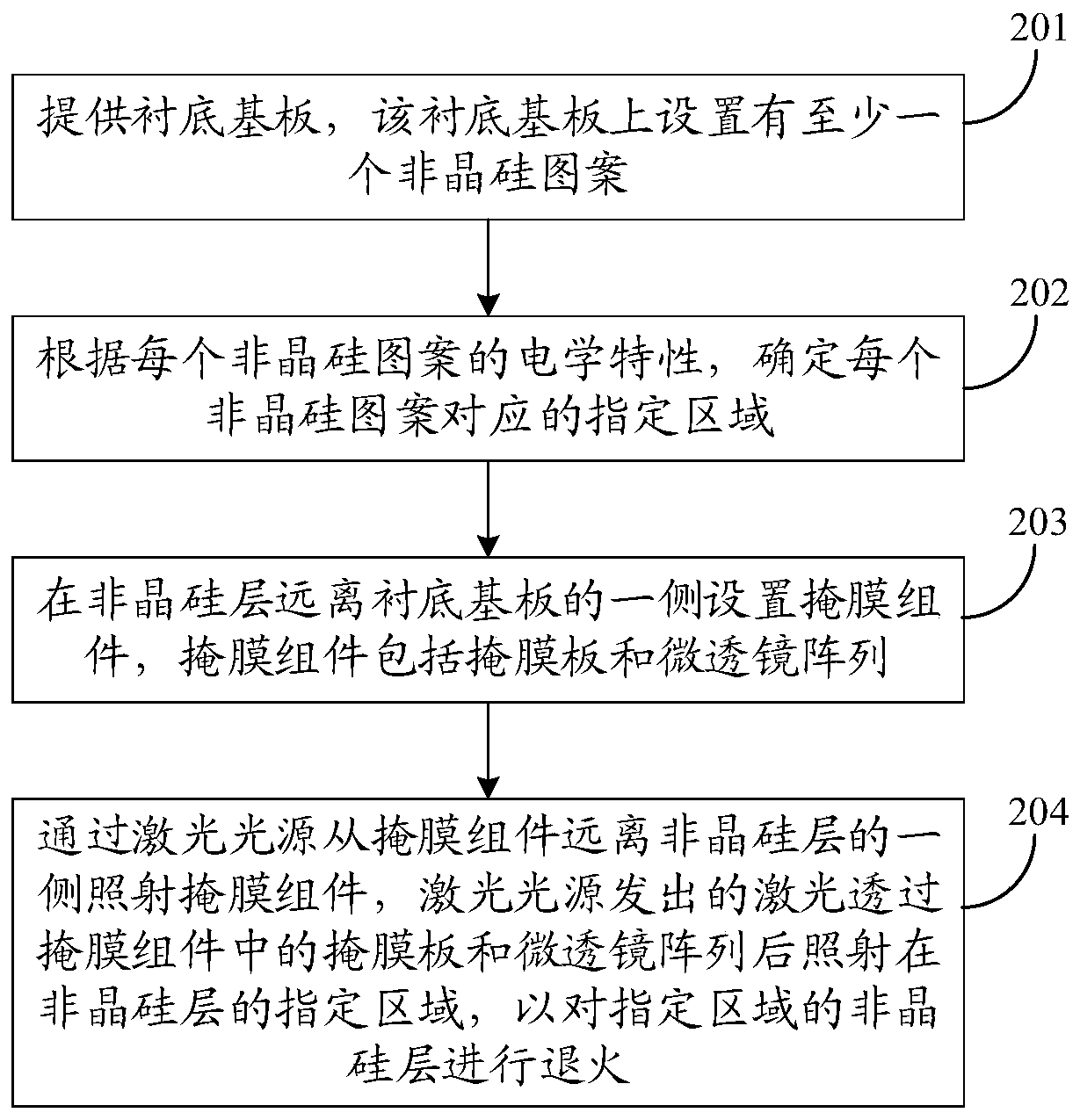

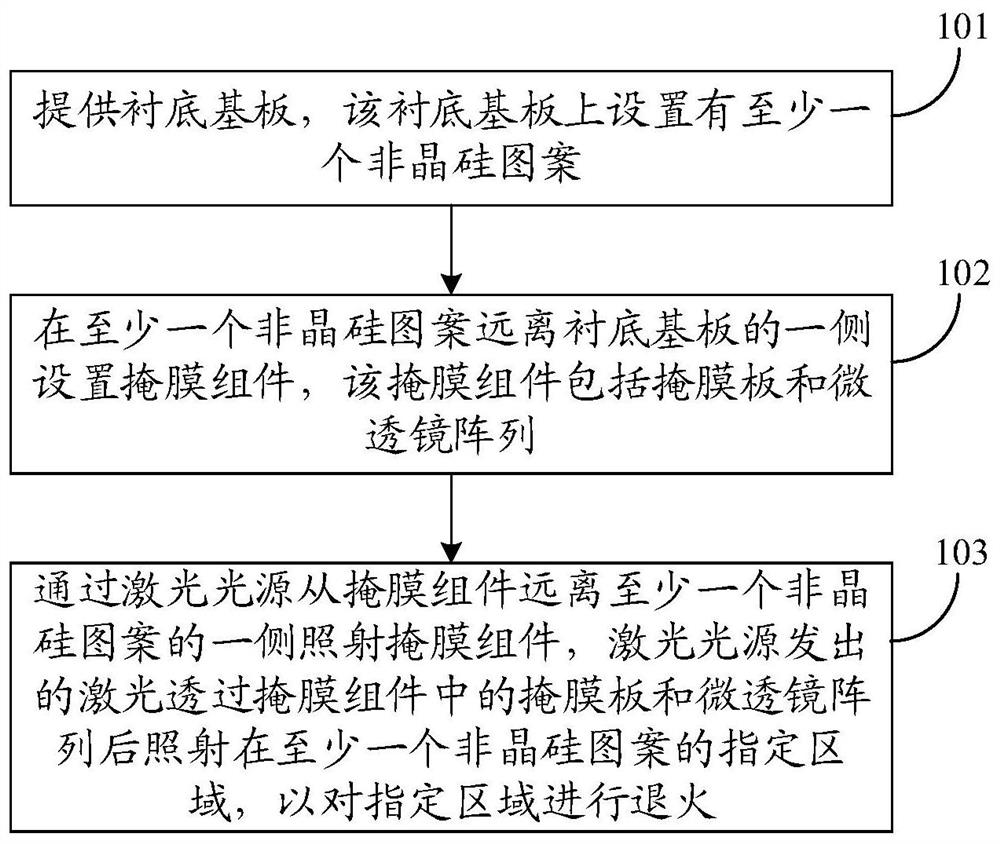

Laser annealing method and array substrate

ActiveCN109742024AReduce areaSolve the large leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingAmorphous siliconActive layer

The invention discloses a laser annealing method and an array substrate, belonging to the technical field of display. The method comprises steps of: providing a substrate; arranging a mask component at one side, far from the substrate, of at least one amorphous silicon pattern, wherein the mask component comprises a mask plate and a microlens array; irradiating the mask component from one side, far from the amorphous silicon pattern, of the mask component by a laser source, wherein laser emitted by the laser source penetrates the mask plate and the microlens array in the mask component and then irradiates a designated area of the at least one amorphous silicon pattern. In the method, the mask component consisting the mask plate and the microlens array controls laser emitted by the laser source to irradiate the designated area of an amorphous silicon layer. A laser annealing area is limited, so that area of the amorphous silicon layer converted into polysilicon layer is reduced. The method solves a problem of greater leakage current of TFT consisting of an active layer in related technology, and reduces leakage current of the TFT consisting of the active layer.

Owner:BOE TECH GRP CO LTD

Operating method of the memory

InactiveCN1670943BNo penetration effectSolve the large leakage currentTransistorSolid-state devicesTrappingElectrical current

A method of programming the storage comprises setting the storage to an initial state of a first grid threshold voltage, performing a processing sequence including: applying a voltage bias between the grid and the first junction region to cause electric hole to migrate towards and be retained in the trapping layer, and evaluating a read current generated in response to the voltage bias to determine whether a second grid threshold voltage is reached, wherein the second grid threshold voltage is lower than the first grid threshold voltage. The processing sequence is repeated a number of times by varying one or more time the voltage bias between the grid and the first junction region until the second grid threshold voltage is reached and the storage is in a program state.

Owner:MACRONIX INT CO LTD

TFT substrate, ESD protection circuit and manufacturing method of TFT substrate

InactiveUS20200365576A1Avoid exceptionSolve the large leakage currentTransistorStatic indicating devicesHemt circuitsActive layer

A TFT substrate, an ESD protection circuit, and a method for manufacturing the TFT substrate. The TFT substrate comprises: a base substrate; a first gate provided on the base substrate; a first insulating layer provided on the first gate; a drain, a source, and an active layer provided on the first insulating layer; a second insulating layer provided on the drain, the source, and the active layer; and a second gate provided on the second insulating layer. In this way, display abnormality of a liquid crystal panel screen can be avoided.

Owner:SHENZHEN ROYOLE TECH CO LTD

Semiconductor memory device and manufacturing method thereof

InactiveUS6995058B2Improve performanceImprove manufacturing yieldSemiconductor/solid-state device manufacturingDigital storageRelative standard deviationFerroelectric thin films

The present invention is a high quality semiconductor memory device using a ferroelectric thin film capacitor as a memory capacitor at a high manufacturing yield, the ferroelectric thin film of the capacitor is specified such that the relative standard deviation of crystal grain sizes is 13% or less, to thereby ensure a high remanent polarization value and a small film fatigue (large rewritable number).

Owner:RENESAS TECH CORP

Solid electrolytic capacitor element, solid electrolytic capacitor, and manufacturing method of solid electrolytic capacitor element

ActiveUS20190267195A1Solve the large leakage currentReduce the valueSolid electrolytic capacitorsCapacitor terminalsMetalDielectric layer

A solid electrolytic capacitor element that includes a porous body, a dielectric layer on a surface of the porous body, and a solid electrolyte layer on a surface of the dielectric layer. The porous body is made from a sintered body of a Ti-alloy-containing grain having a Ti—Zr—X multicomponent alloy on a surface thereof, where X is at least one valve metal element selected from Si, Hf, Y, Al, Mo, W, Ta, Nb, and V, and a composition of the Ti—Zr—X multicomponent alloy is Ti: 50 atm % to 80 atm %, Zr: 8 atm % to 32 atm %, and X: 1 atm % to 20 atm %.

Owner:MURATA MFG CO LTD

A kind of array substrate and its preparation method, display panel

ActiveCN106847834BFast switching speedFast on state currentSolid-state devicesNon-linear opticsEngineeringDouble gate

Embodiments of the present invention provide an array substrate, a preparation method thereof, and a display panel, which relate to the field of display technology. By using two types of TFTs on the array substrate, the display panel can have good display performance. The array substrate includes a substrate, a double-gate oxide TFT disposed in each sub-pixel on the substrate, and a display electrode; the drain of the double-gate oxide TFT is electrically connected to the display electrode; It also includes a polysilicon TFT arranged on the substrate.

Owner:BOE TECH GRP CO LTD +1

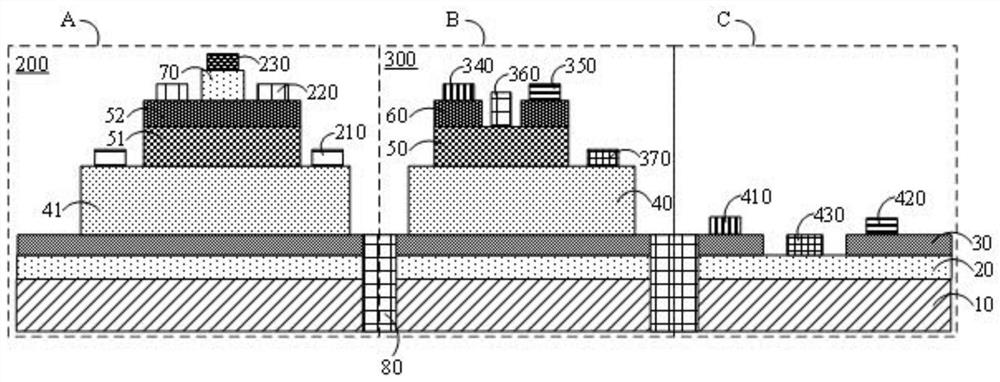

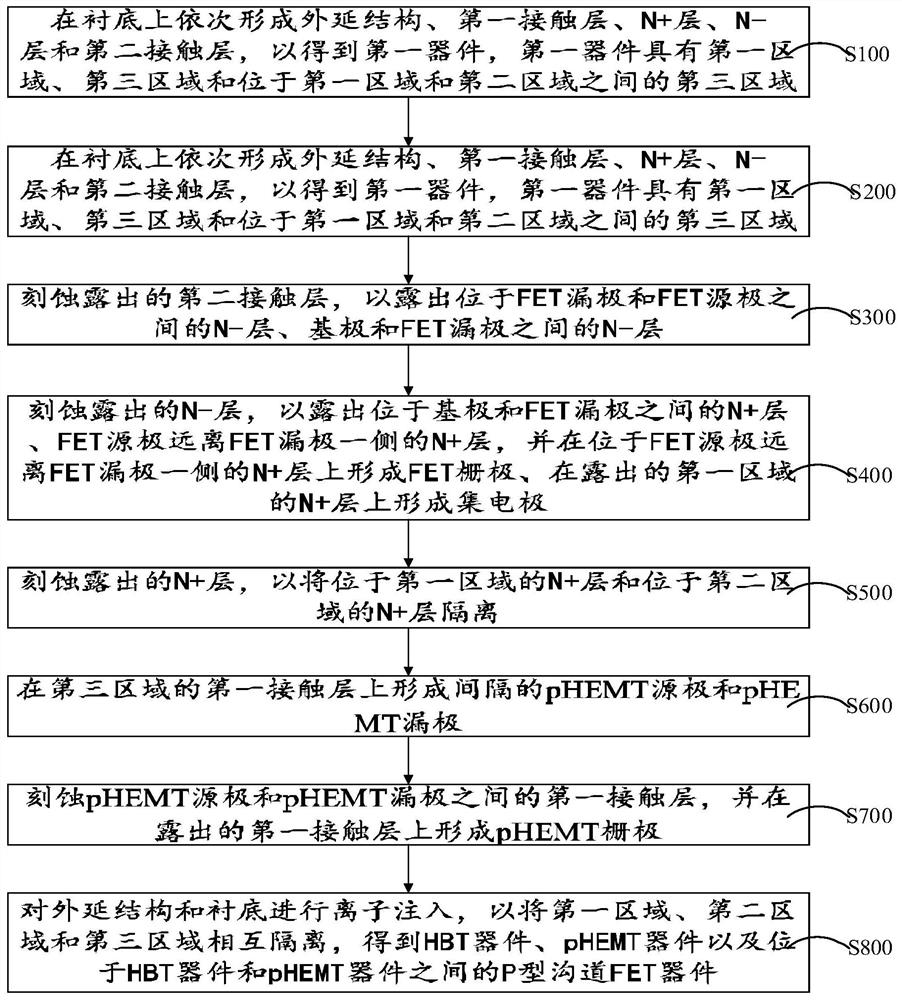

Bi-HEMT device and preparation method thereof

PendingCN113838848ASolve the large leakage currentReduce leakage currentTransistorSolid-state devicesDrain currentEngineering

Owner:泉州市三安集成电路有限公司

Laser annealing method and array substrate

ActiveCN109742024BReduce areaSolve the large leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringLaser light

The invention discloses a laser annealing method and an array substrate, which belong to the technical field of display. The method includes: providing a base substrate; setting a mask assembly on a side of at least one amorphous silicon pattern away from the base substrate, the mask assembly including a mask plate and a microlens array; One side of the crystalline silicon pattern irradiates the mask assembly, and the laser light emitted by the laser light source passes through the mask plate and the microlens array in the mask assembly and then irradiates on at least one designated area of the amorphous silicon pattern. The invention controls the laser light emitted by the laser light source through a mask assembly including a mask plate and a microlens array, so that the laser light is irradiated on a designated area on the amorphous silicon layer. The area for laser annealing is limited, thereby reducing the area of the amorphous silicon layer converted into a polysilicon layer. The problem of relatively large leakage current of the TFT formed by the active layer in the related art is solved. The effect of reducing the leakage current of the TFT formed by the active layer is achieved.

Owner:BOE TECH GRP CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com