Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2125 results about "Electrical field strength" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Electric field strength is a quantitative expression of the intensity of an electric field at a particular location. The standard unit is the volt per meter (v/m or v · m -1). A field strength of 1 v/m represents a potential difference of one volt between points separated by one meter. Any electrically charged object produces an electric field.

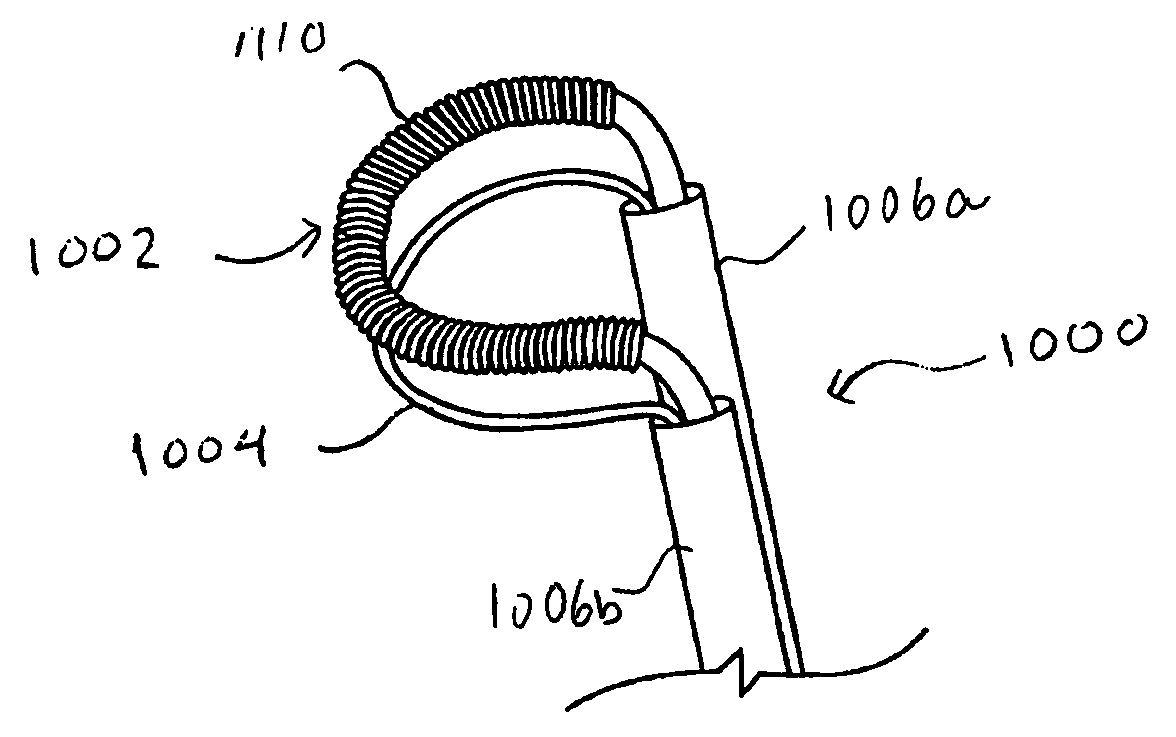

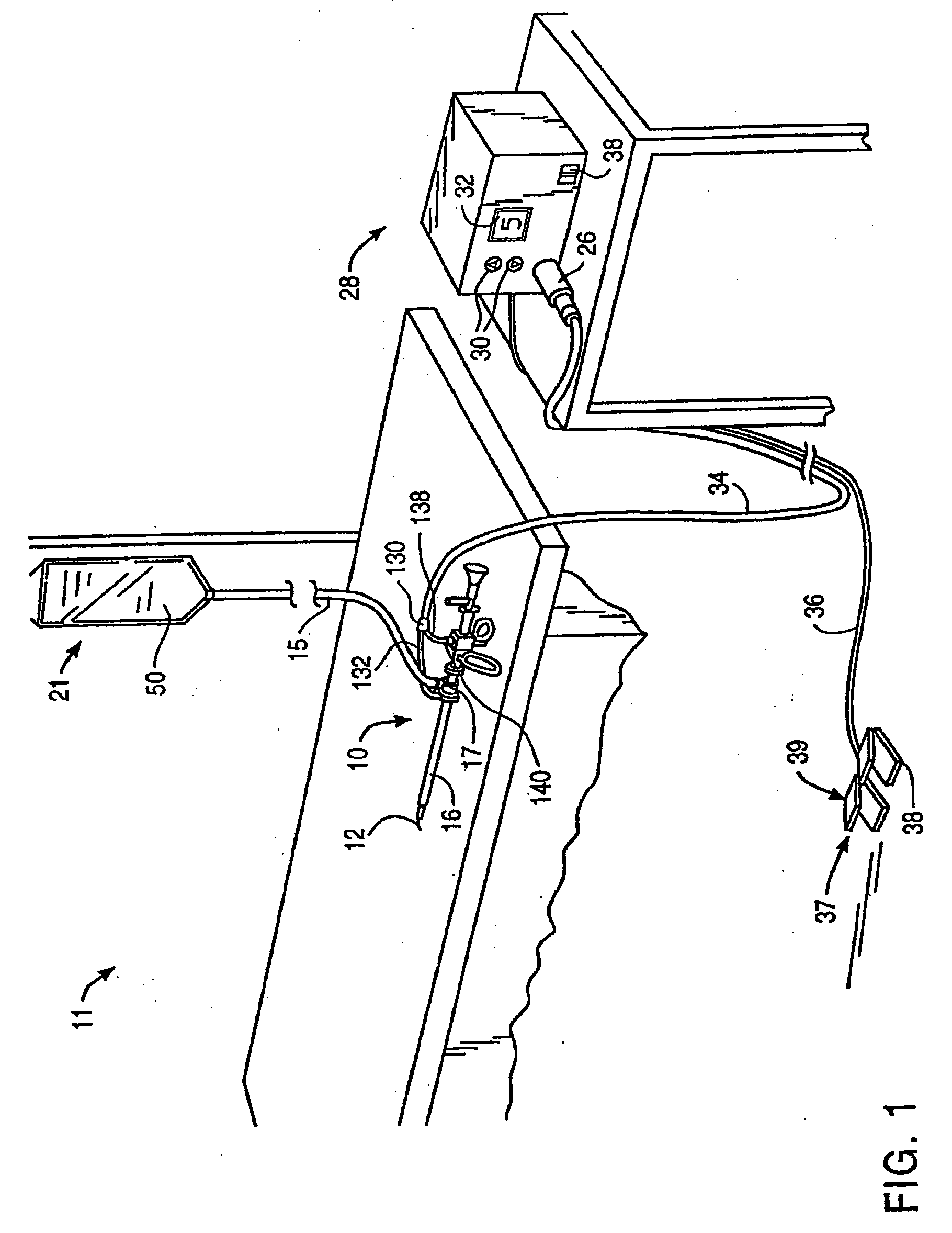

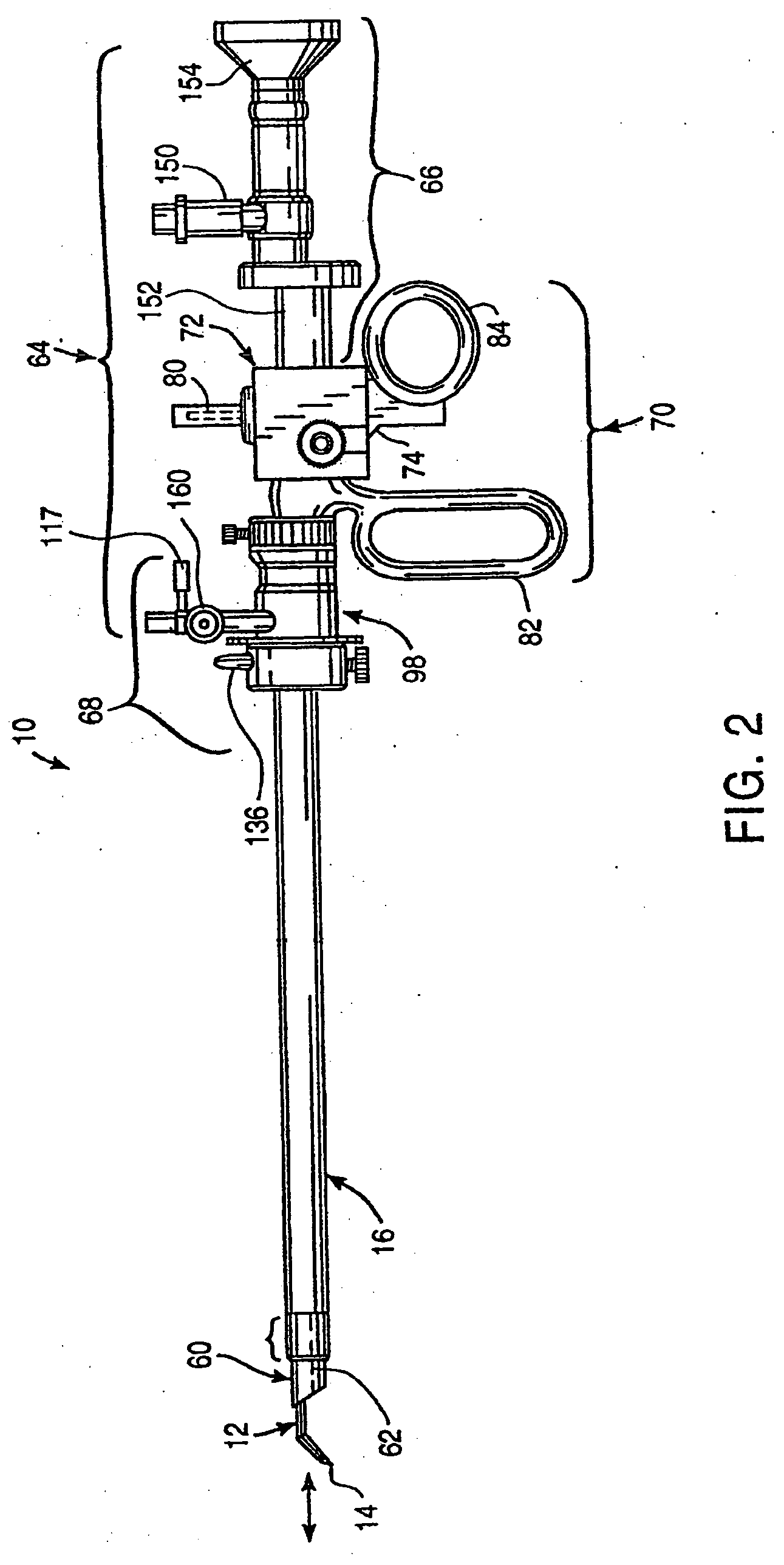

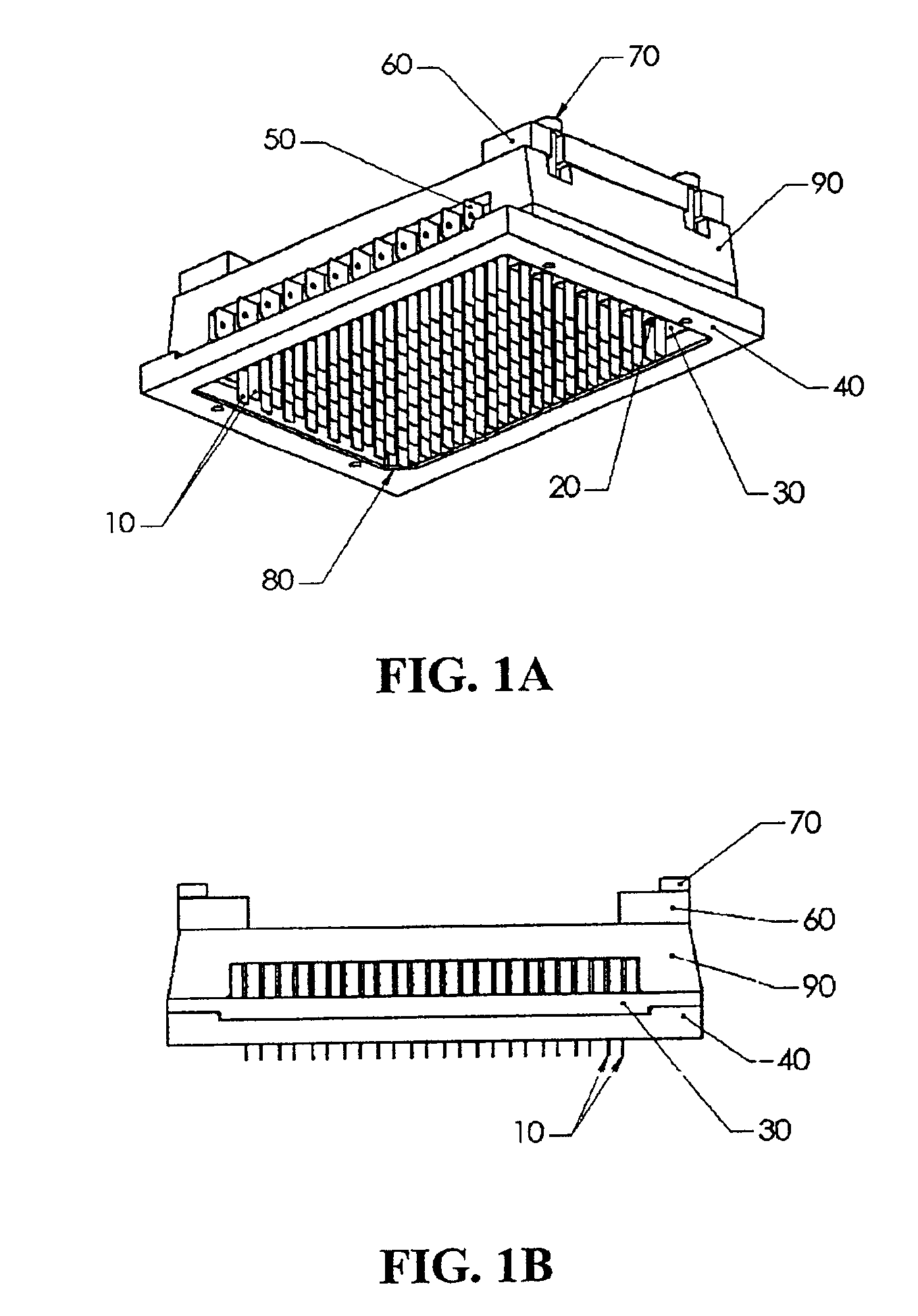

Apparatus and methods for electrosurgical ablation and resection of target tissue

InactiveUS20050251134A1Little and no damageSurgical instruments for heatingHigh current densityElectrical field strength

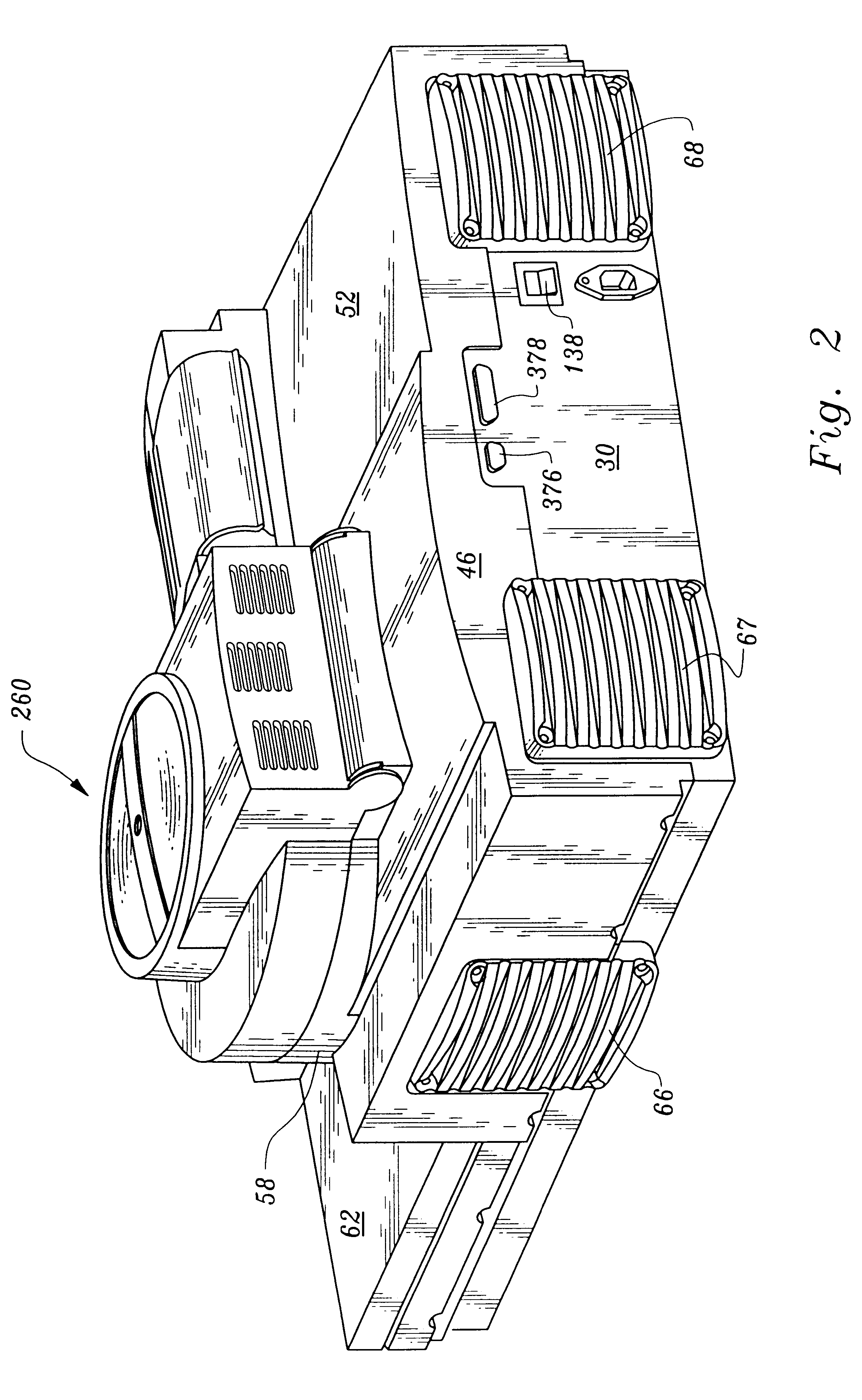

An electrosurgical system and method for ablating, resecting, or cutting body structures, with minimal or no damage to tissue adjacent to the treatment site. The system includes an electrosurgical probe having a shaft with a shaft distal end bifurcated to provide first and second arms. First and second electrode supports are disposed on the first and second arms, respectively. At least one active electrode, in the form of a loop or partial loop, is arranged between the first and second electrode supports. A return electrode, also in the form of a loop or partial loop, is arranged between the first and second electrode supports distal to the active electrode. The active and return electrodes are configured to promote substantially high electric field intensities and associated high current densities between the active portion and the target site when a high frequency voltage is applied to the electrodes. These high current densities are sufficient to break down the tissue by processes including molecular dissociation of tissue components. In one embodiment, the high frequency voltage imparts energy to the target site to effect the vaporization and volumetric removal of a layer of tissue without causing substantial tissue damage beyond the layer of tissue ablated. In another embodiment, a fragment of target tissue is removed, with minimal or no damage to surrounding tissue, by a process including the molecular dissociation of tissue components, and the tissue fragment is retrieved for biopsy.

Owner:ARTHROCARE

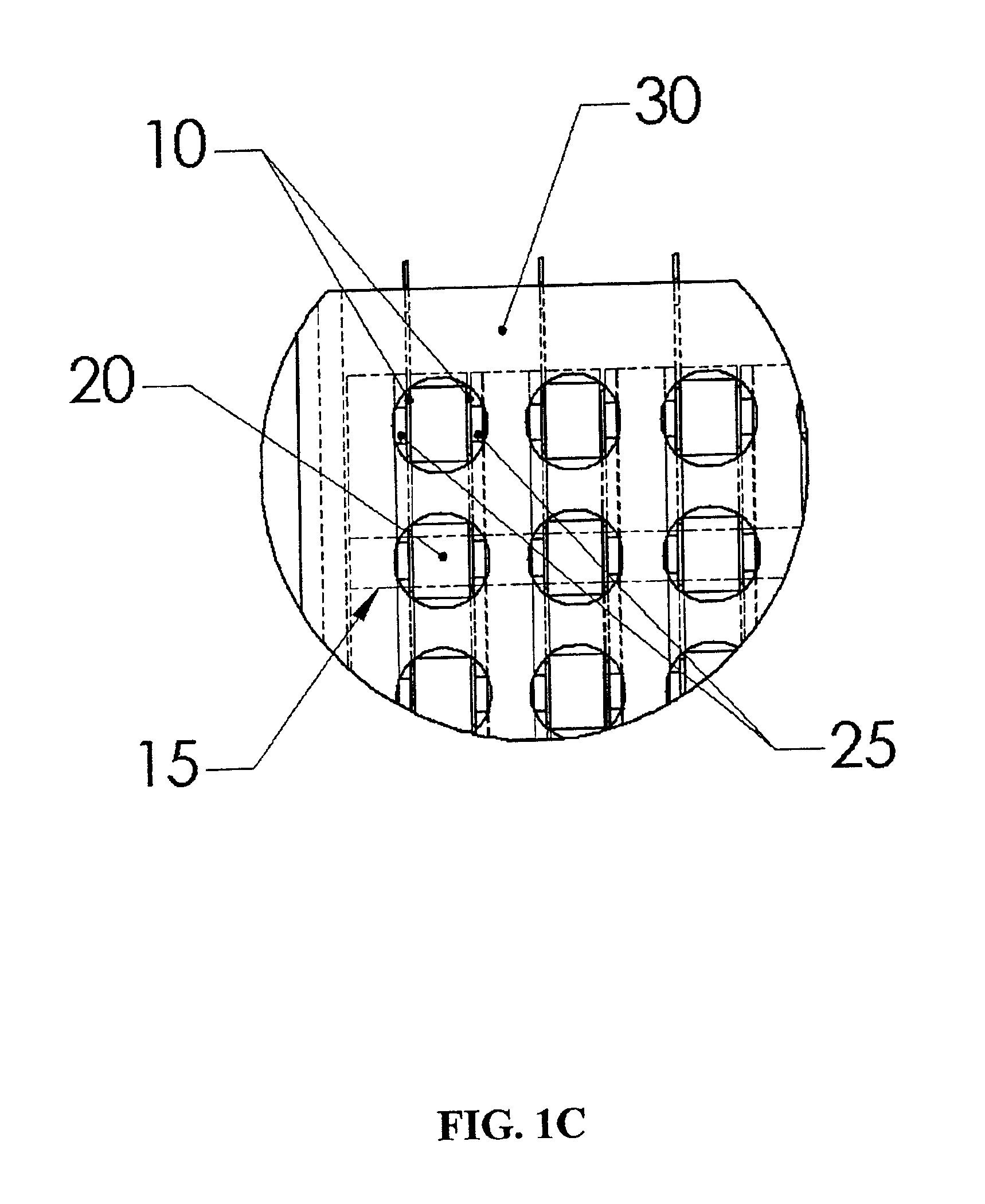

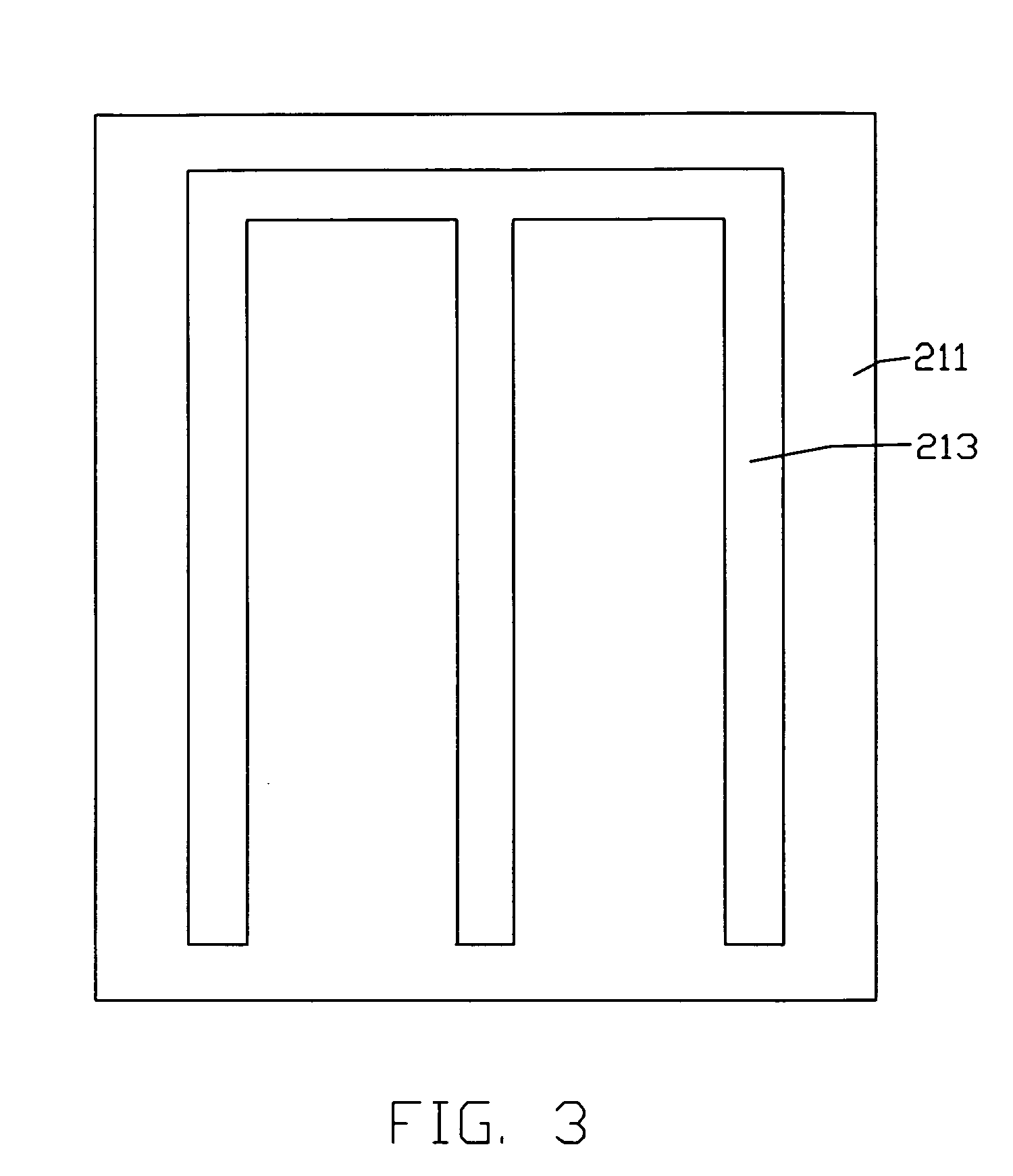

Multi-well plate and electrode assemblies for ion channel assays

InactiveUS6969449B2Immobilised enzymesBioreactor/fermenter combinationsElectrical field strengthEngineering

Plate and electrode assemblies include configurations allowing for relatively uniform electric field production. The electrodes may comprise strips of conductive material plated onto the bottom surface of sample wells or they may comprise plate electrodes extending down into the well. In some embodiments, the electric field strength varies by less than about 10% from a mean field intensity over at least about 20% of the surface area of the bottom surface of a sample well.

Owner:VERTEX PHARMA SAN DIEGO LLC

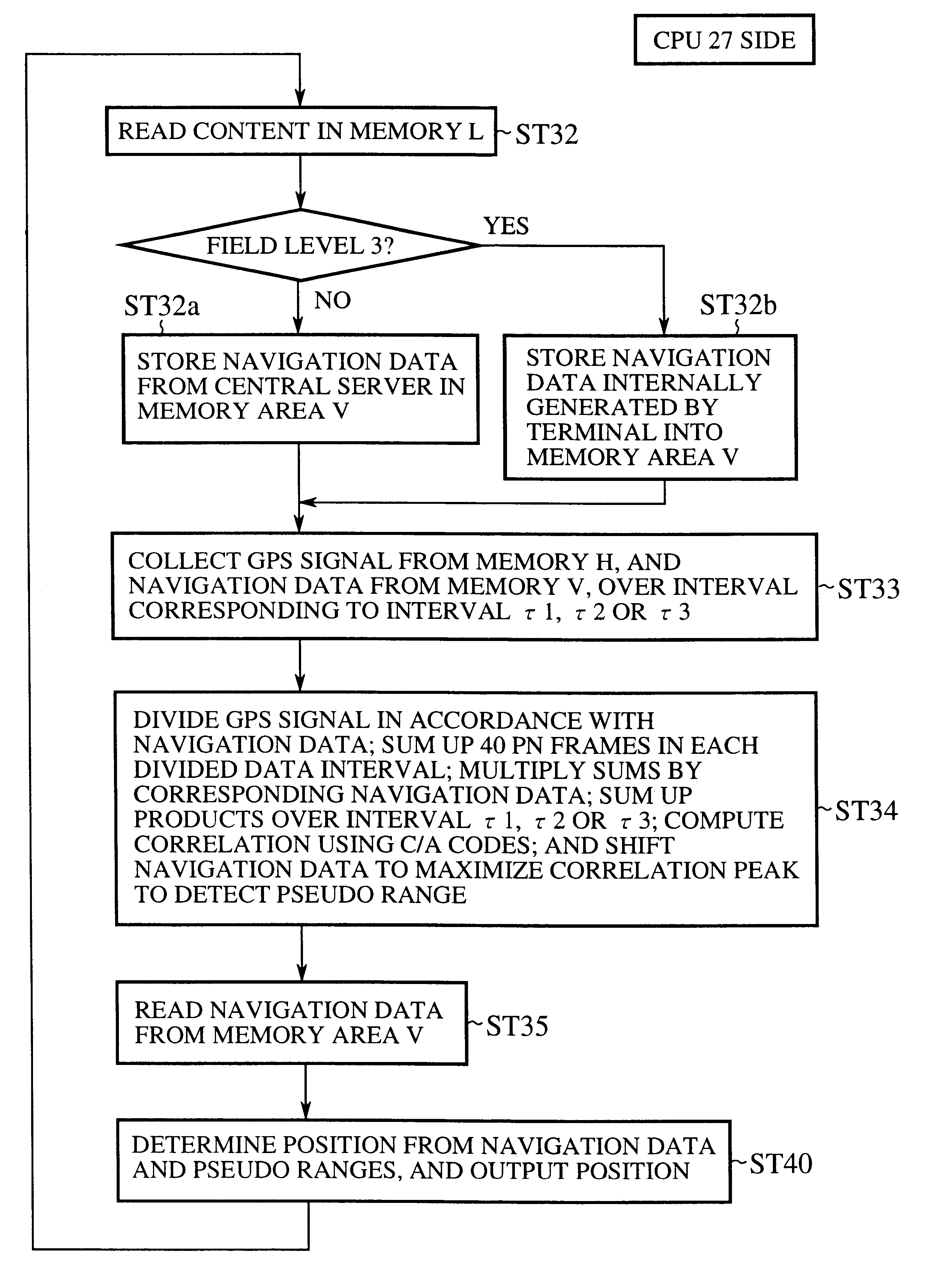

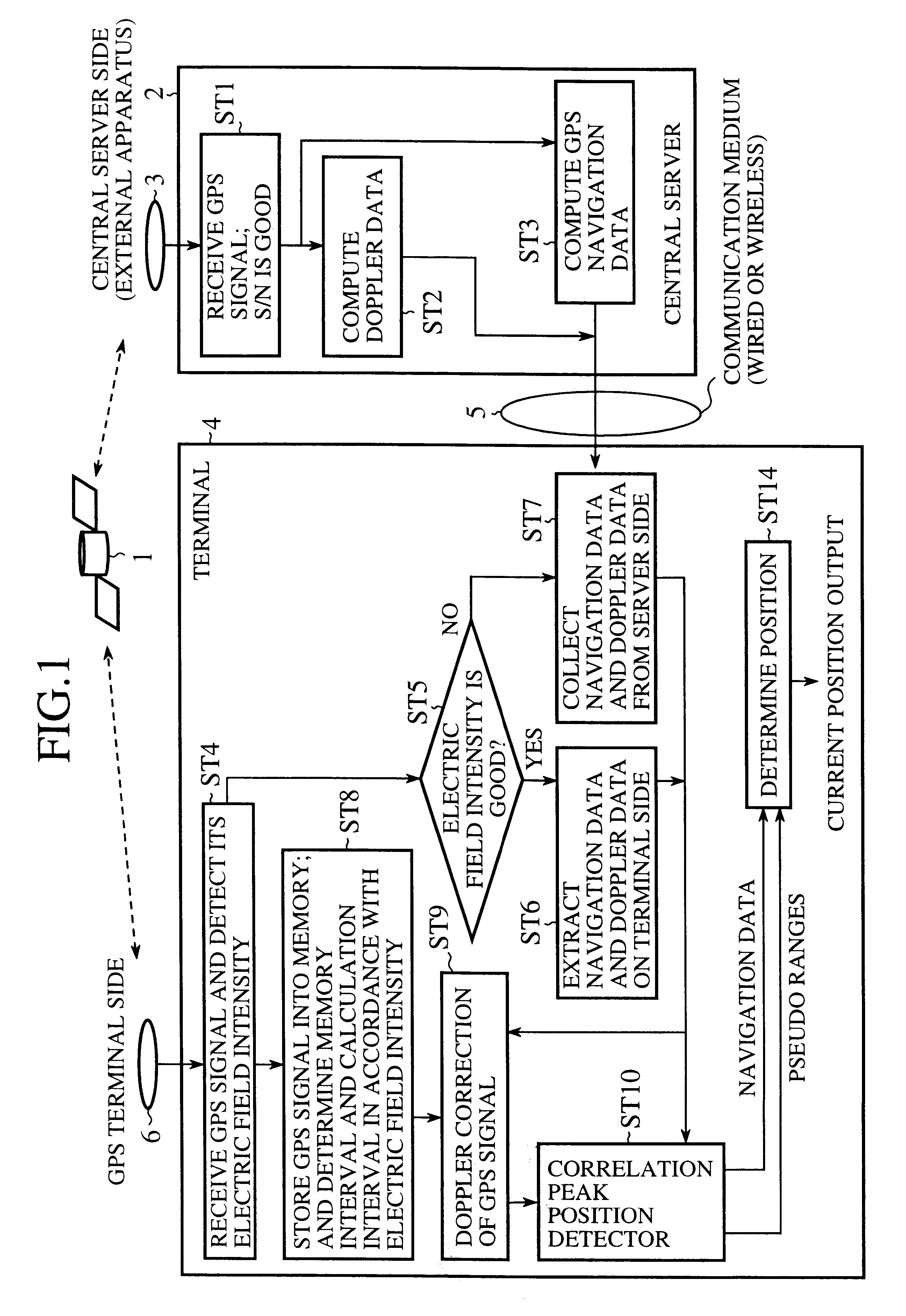

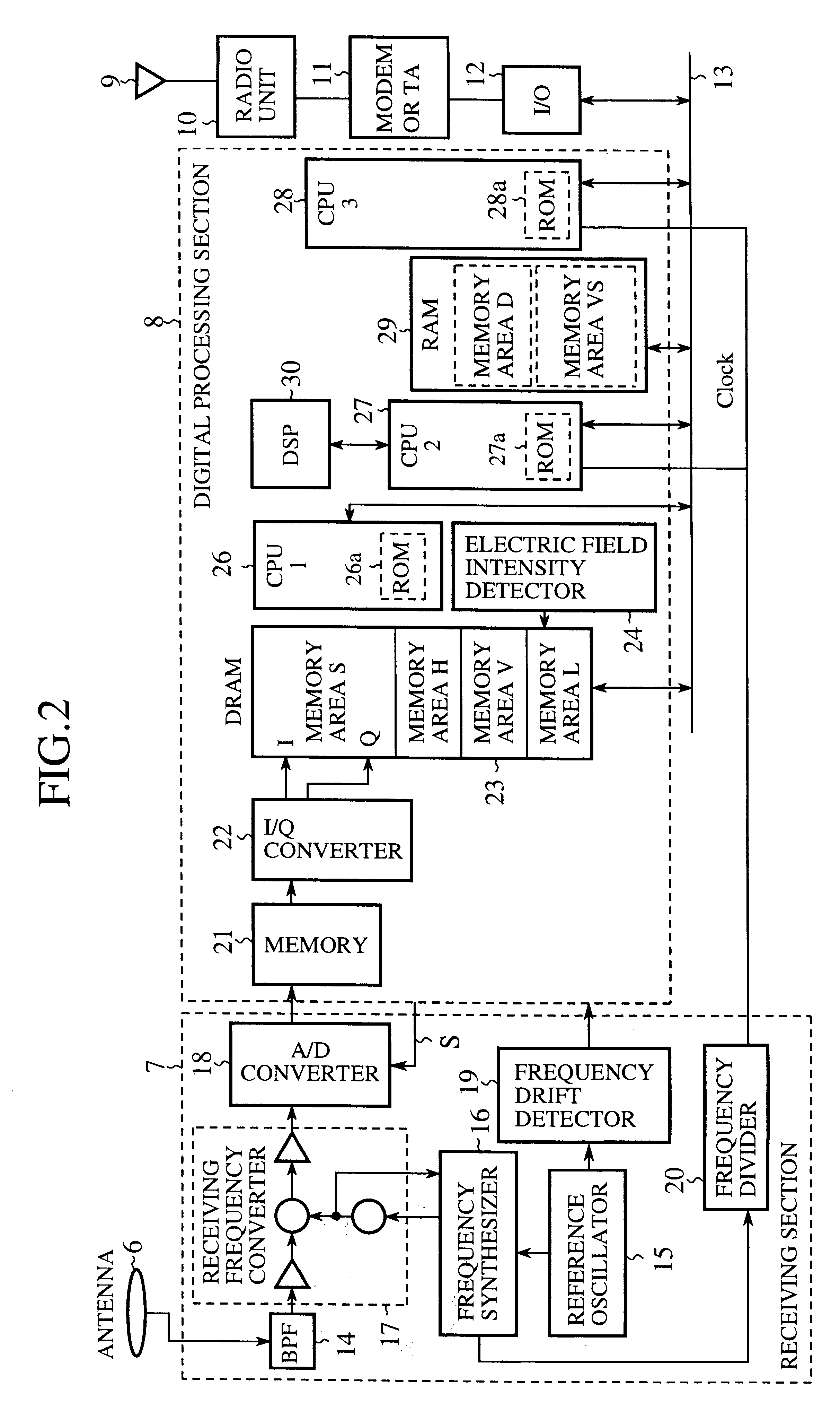

GPS position measuring system and GPS position measuring apparatus

InactiveUS6329946B1Increase the number ofPosition fixationBeacon systemsMeasurement deviceElectrical field strength

A Global Positioning System carries out Doppler correction of a C / A code sequence after a frequency conversion, and calculates a pseudo range by performing correlation calculation between the C / A code, which is obtained by summing up the C / A code sequence beginning from a polarity inversion boundary determined at a correlation peak detecting step ST10, and a C / A code generated in a GPS terminal. When a received electric field detected by a received electric field intensity detector 11 is good, the current position is determined from the pseudo range and the navigation data extracted by the GPS terminal itself, whereas when the received electric field is poor, the current position is determined from the pseudo range and the navigation data sent from an external apparatus.

Owner:MITAC INT CORP +1

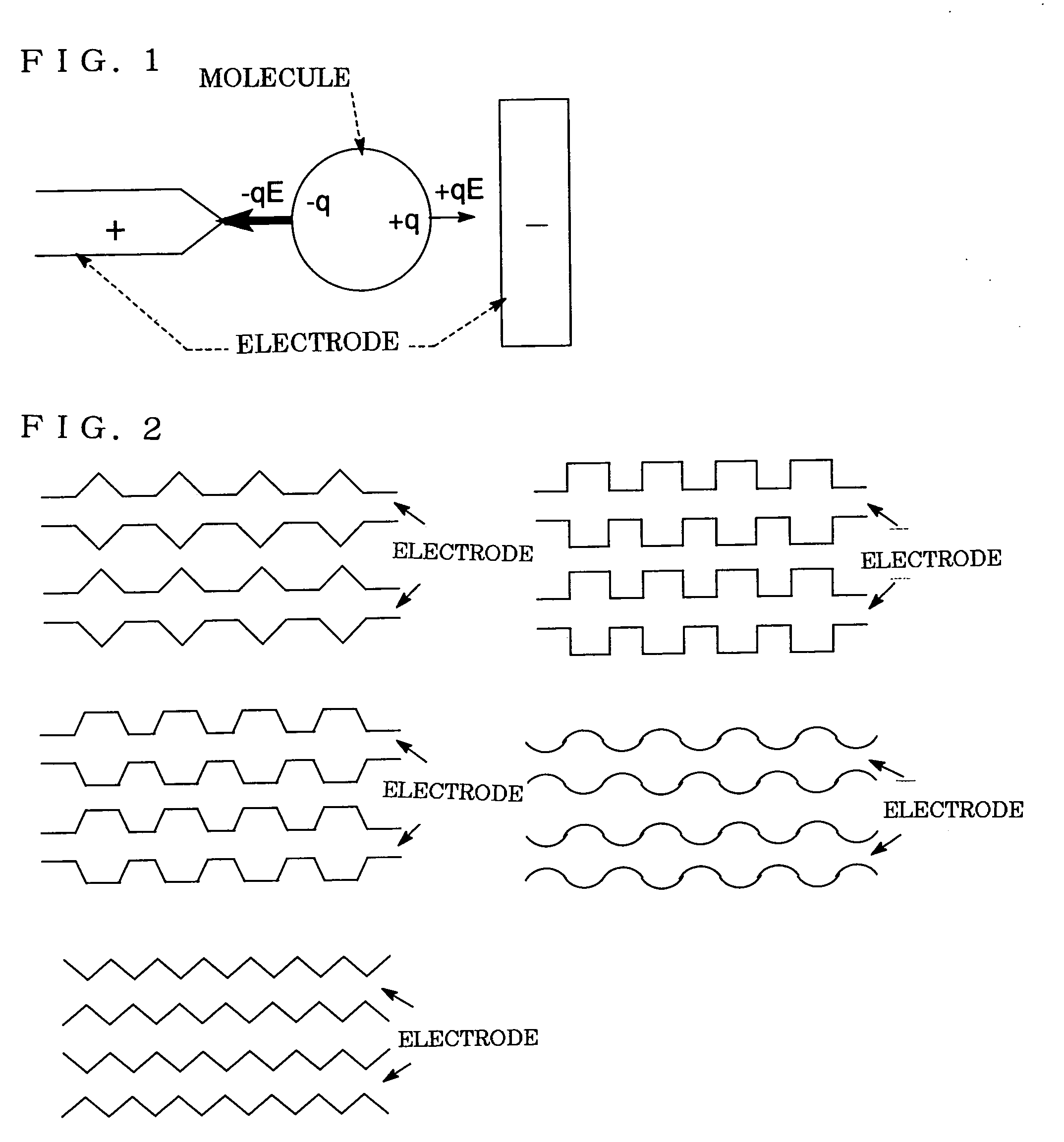

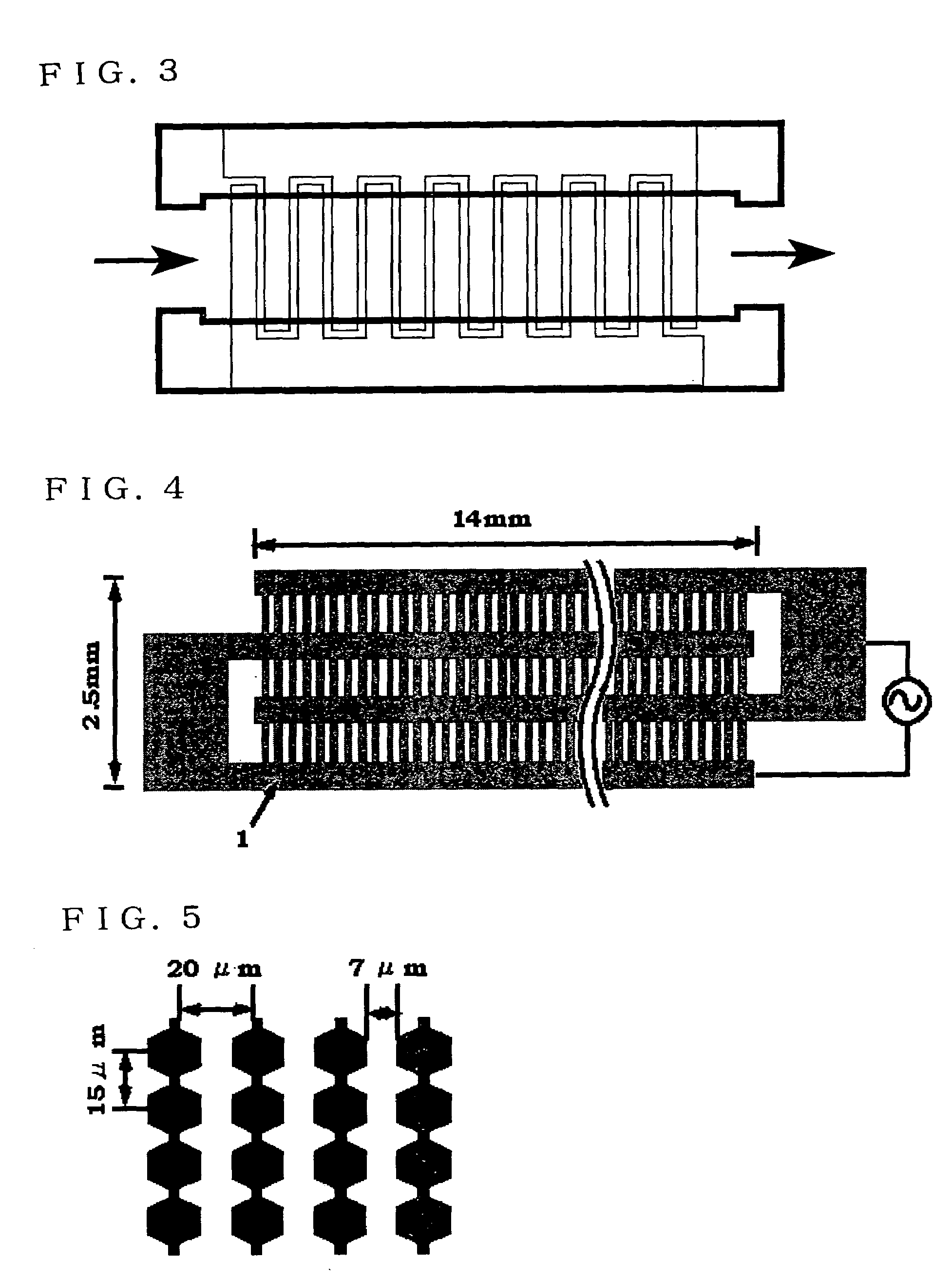

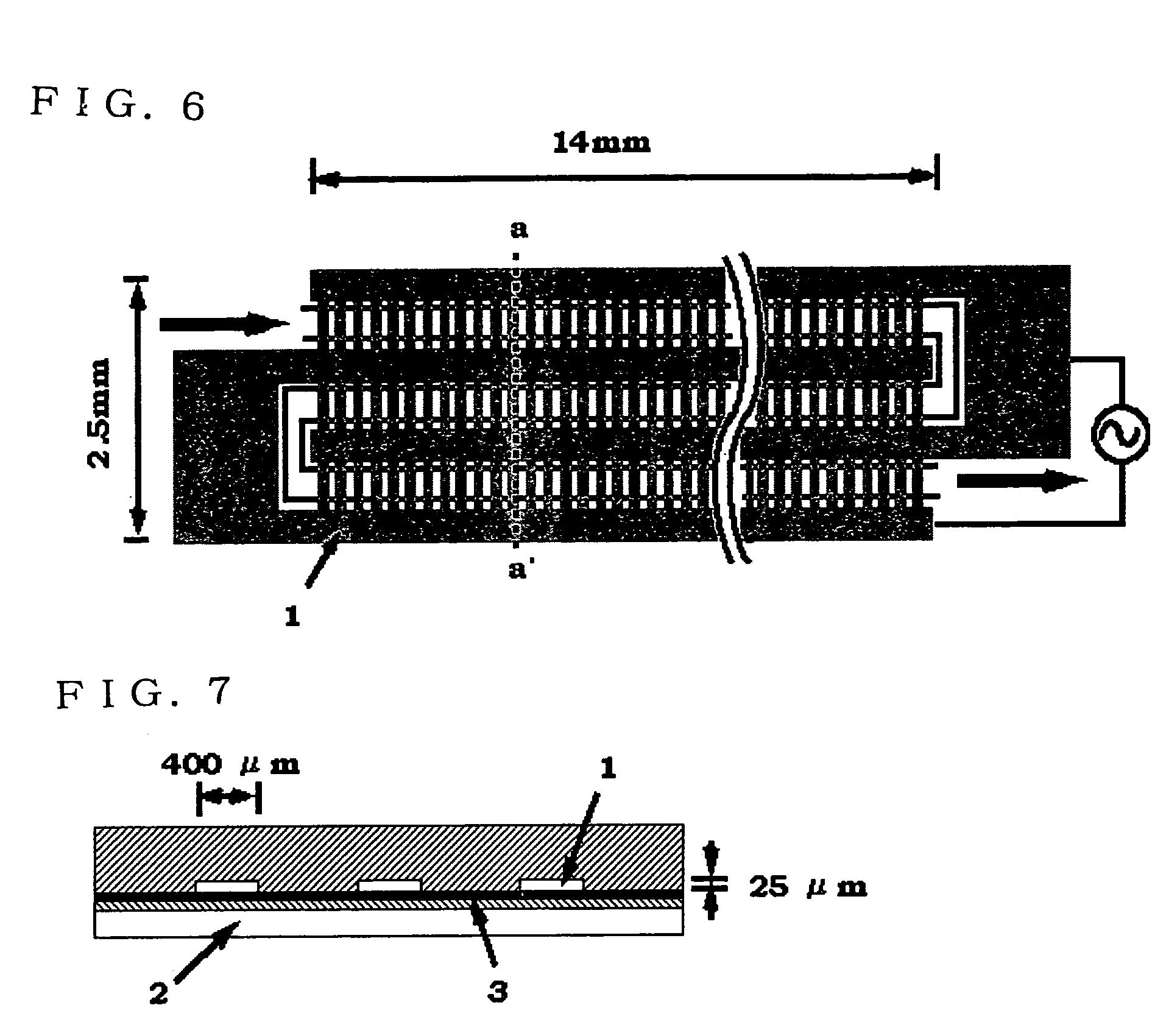

Method for separating substances using dielectrophoretic forces

InactiveUS7198702B1Rapidly and readily separatingDielectrophoresisSludge treatmentElectrical field strengthDielectrophoretic force

The present invention has an object of providing a method by which two kinds or more of molecules can be separated each other by using dielectrophoretic forces. The present invention comprises two methods. The first method is a method comprising forming a complex substance of a “specific molecule” containing in a sample, and a “substance capable of changing dielectrophoretic properties of the specific molecule”, which binds to the “specific molecule” contained therein, and thereby separating the complex substance and the molecules other than the specific molecule in the sample from each other. The second method is a method comprising placing a solution in which two kinds or more of molecules are dissolved under a strong electric field strength, that is, under a nonuniform electric field having an electric field strength of 500 KV / m or higher, by using dielectrophoretic forces.

Owner:WAKO PURE CHEMICAL INDUSTRIES

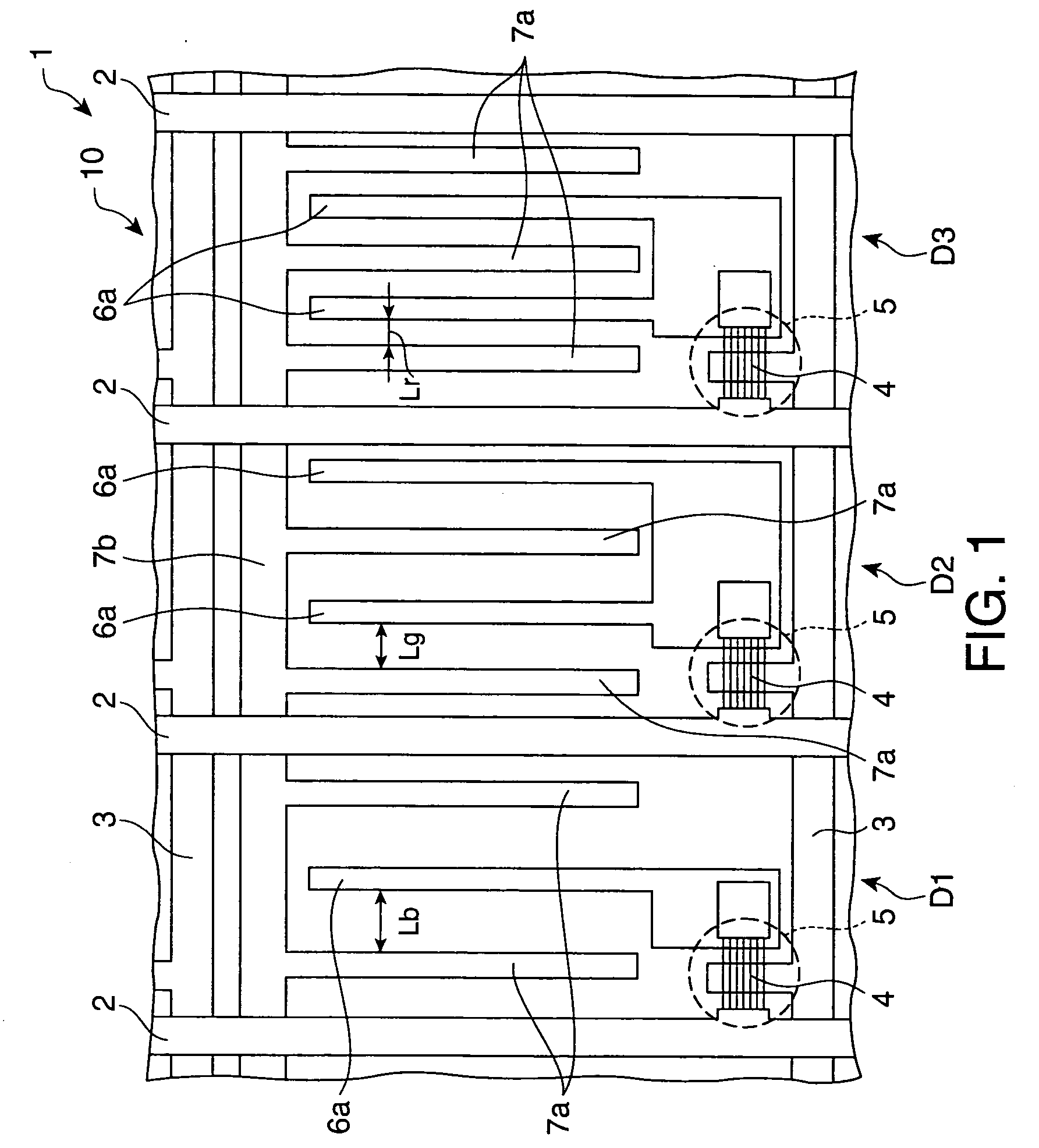

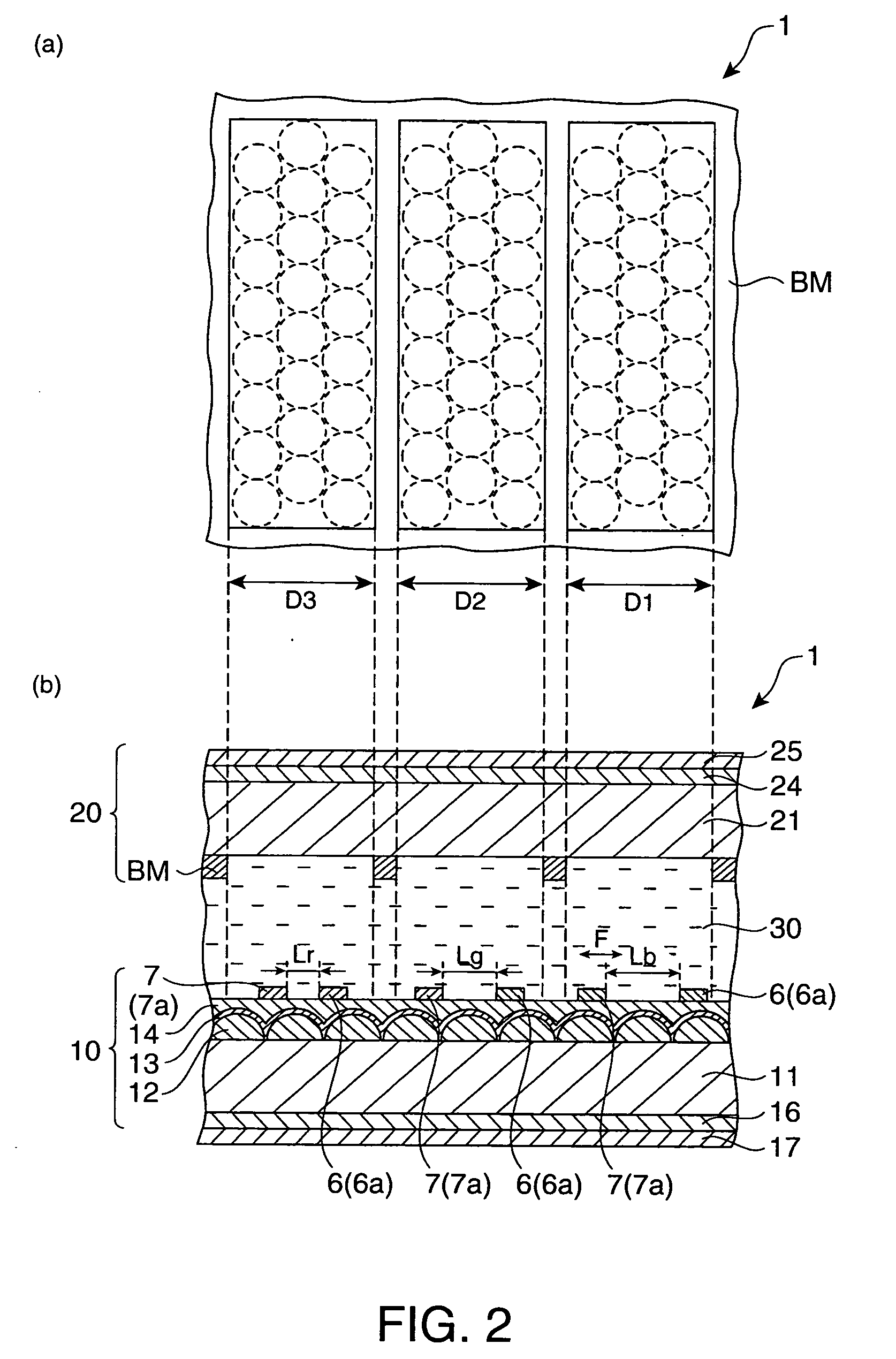

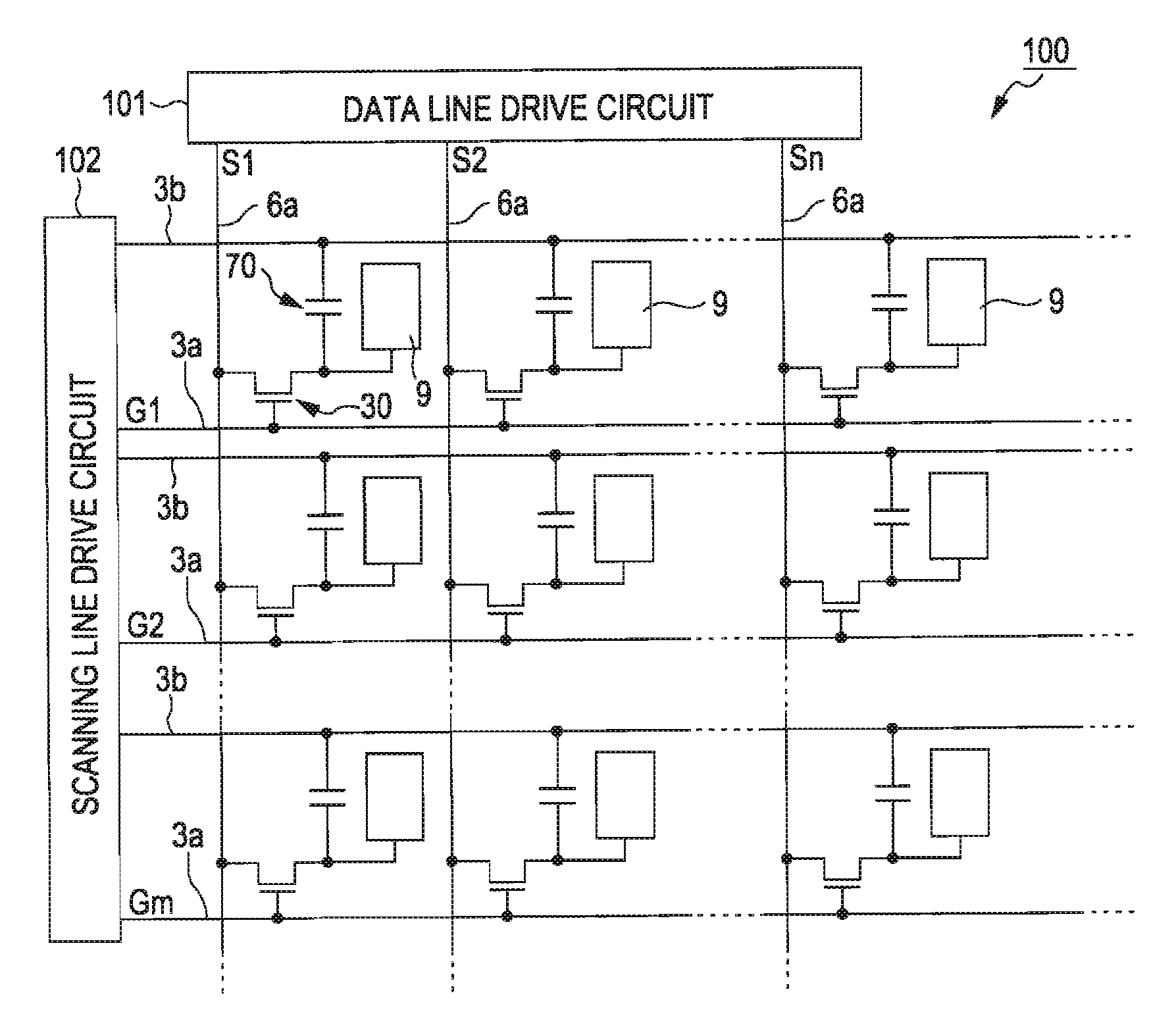

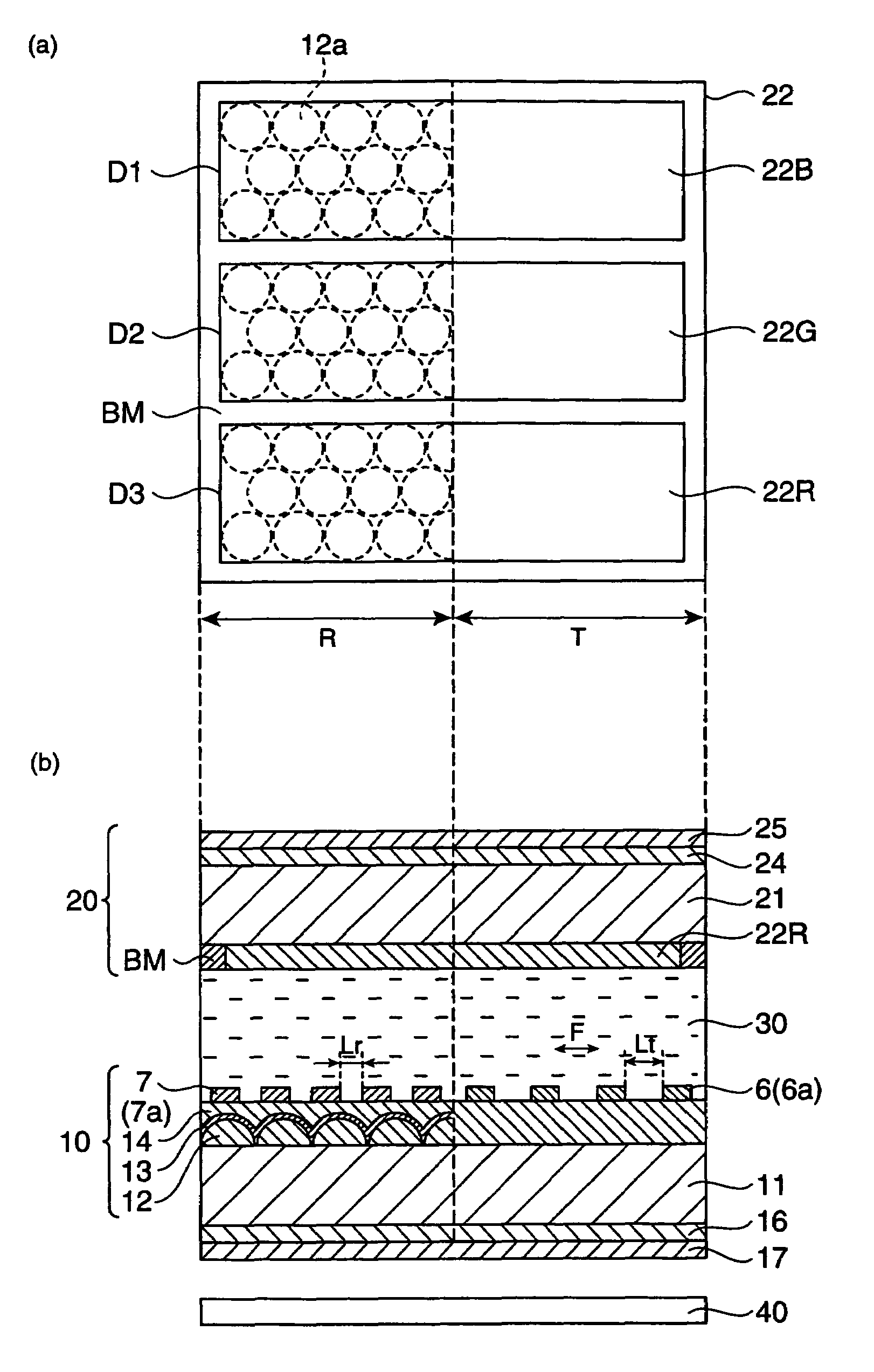

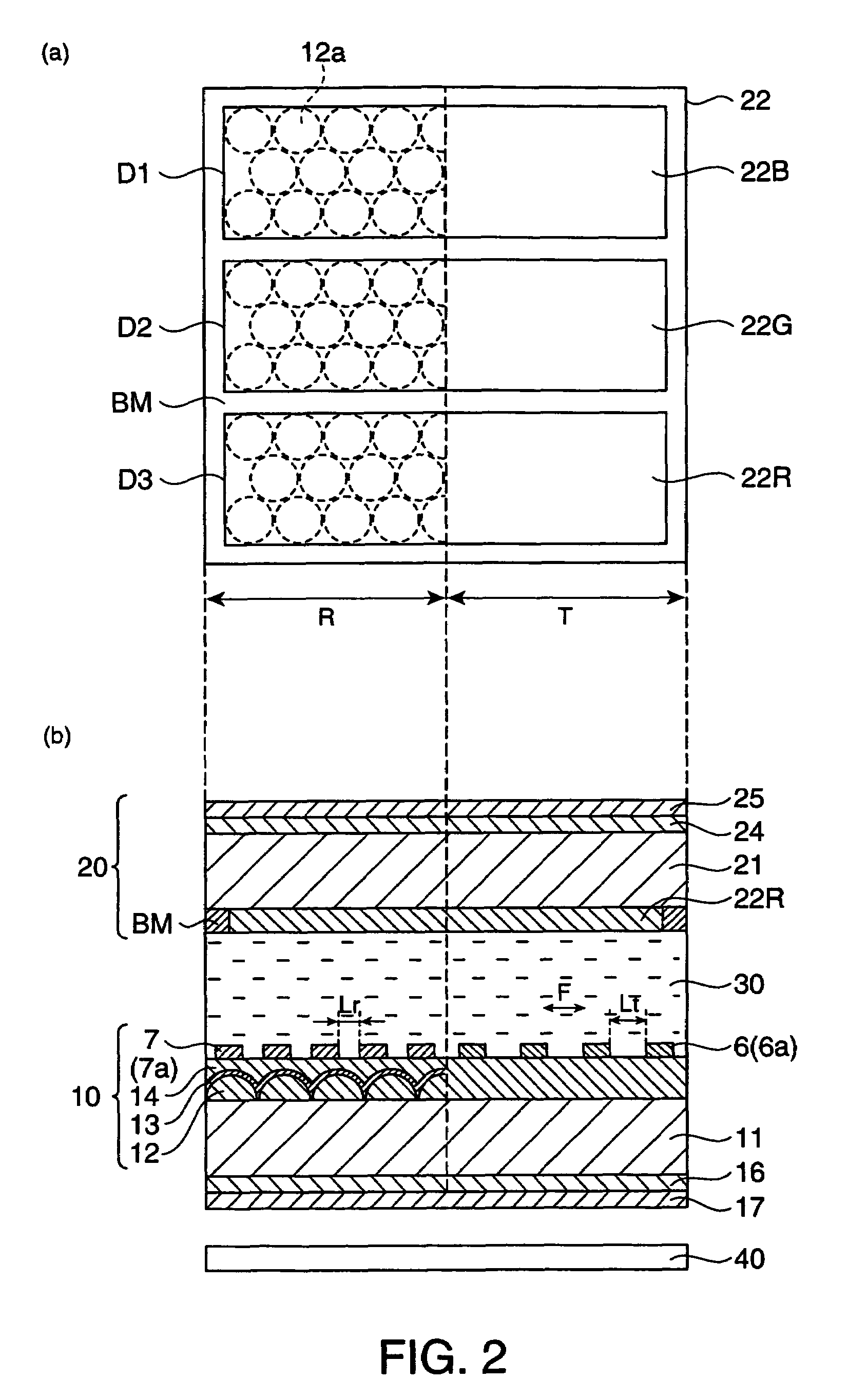

Liquid crystal display device and electronic apparatus

InactiveUS20060203169A1Improve reliabilityLight utilization efficiency can be improvedNon-linear opticsElectrical field strengthLiquid-crystal display

A liquid crystal display device of the present invention is a liquid crystal display device having a first substrate, a second substrate, a liquid crystal layer disposed between the first and second substrates, and a plurality of pixels each having a display region, in that: the liquid crystal layer is optically isotropic when an selective electric field is not applied and optically aisotropic when an electric field is applied and includes a material whose refractive index changes depending on the strength of the electric field; and the plurality of pixels include first and second pixels different in the electric field strength.

Owner:SEIKO EPSON CORP

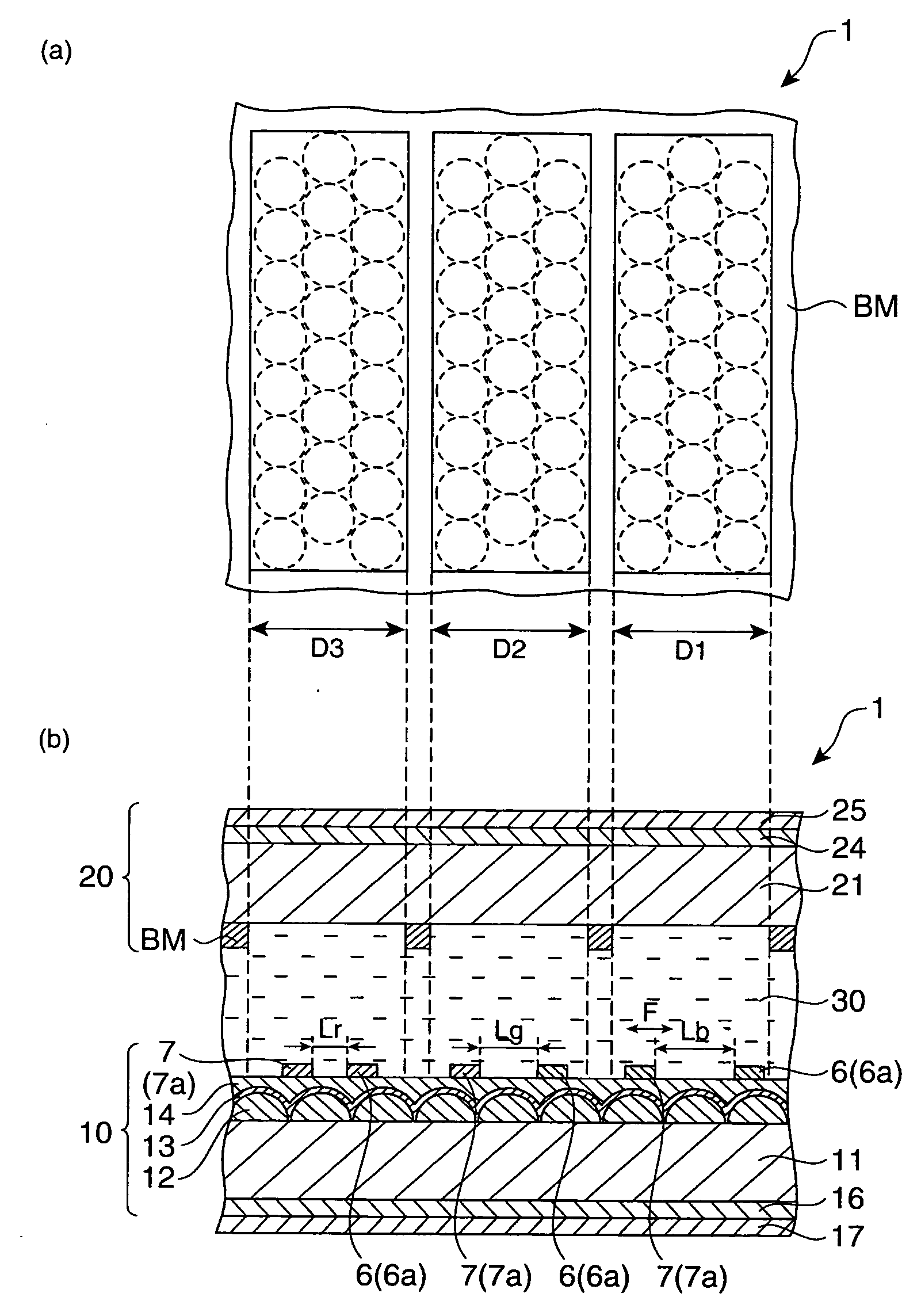

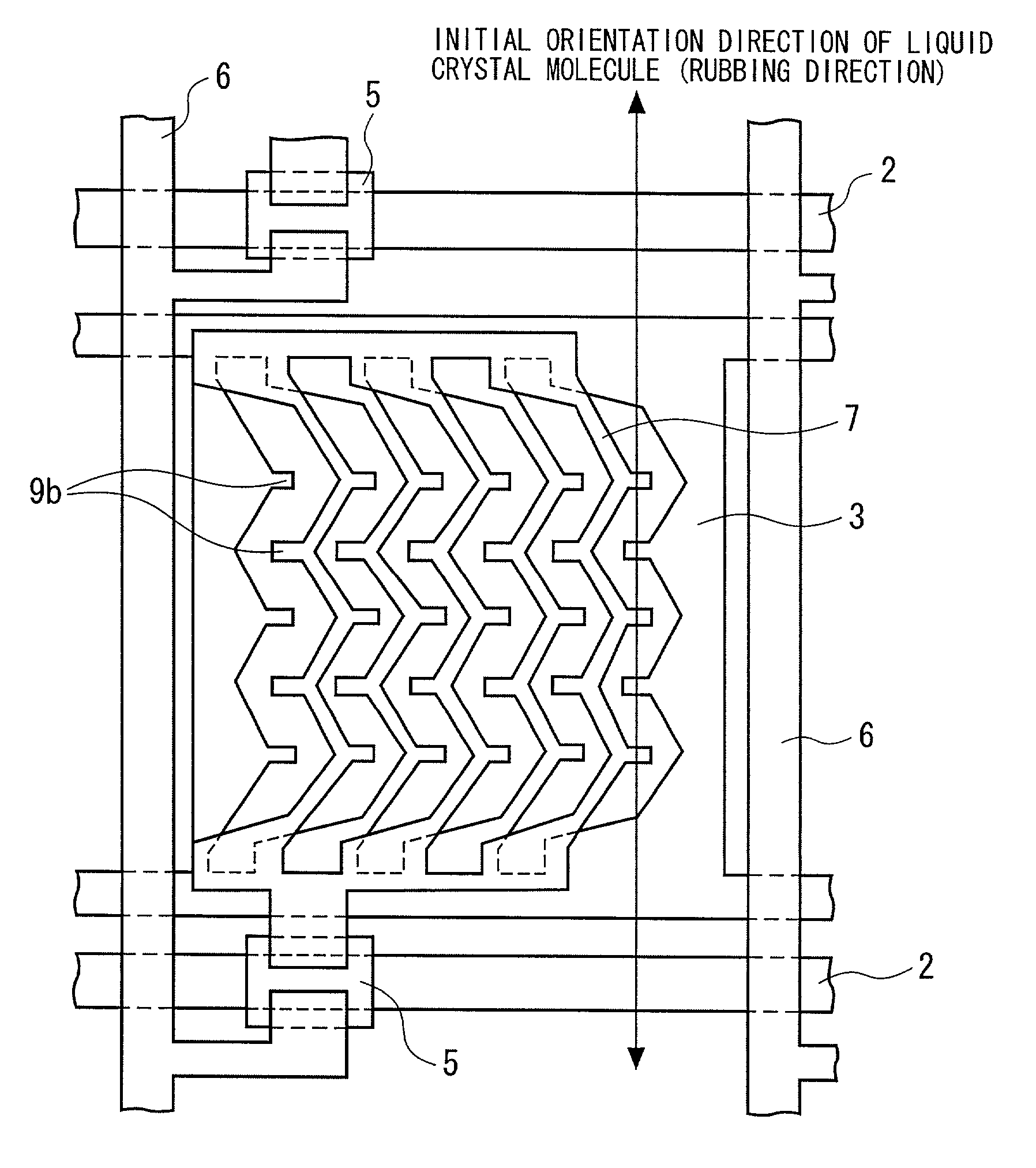

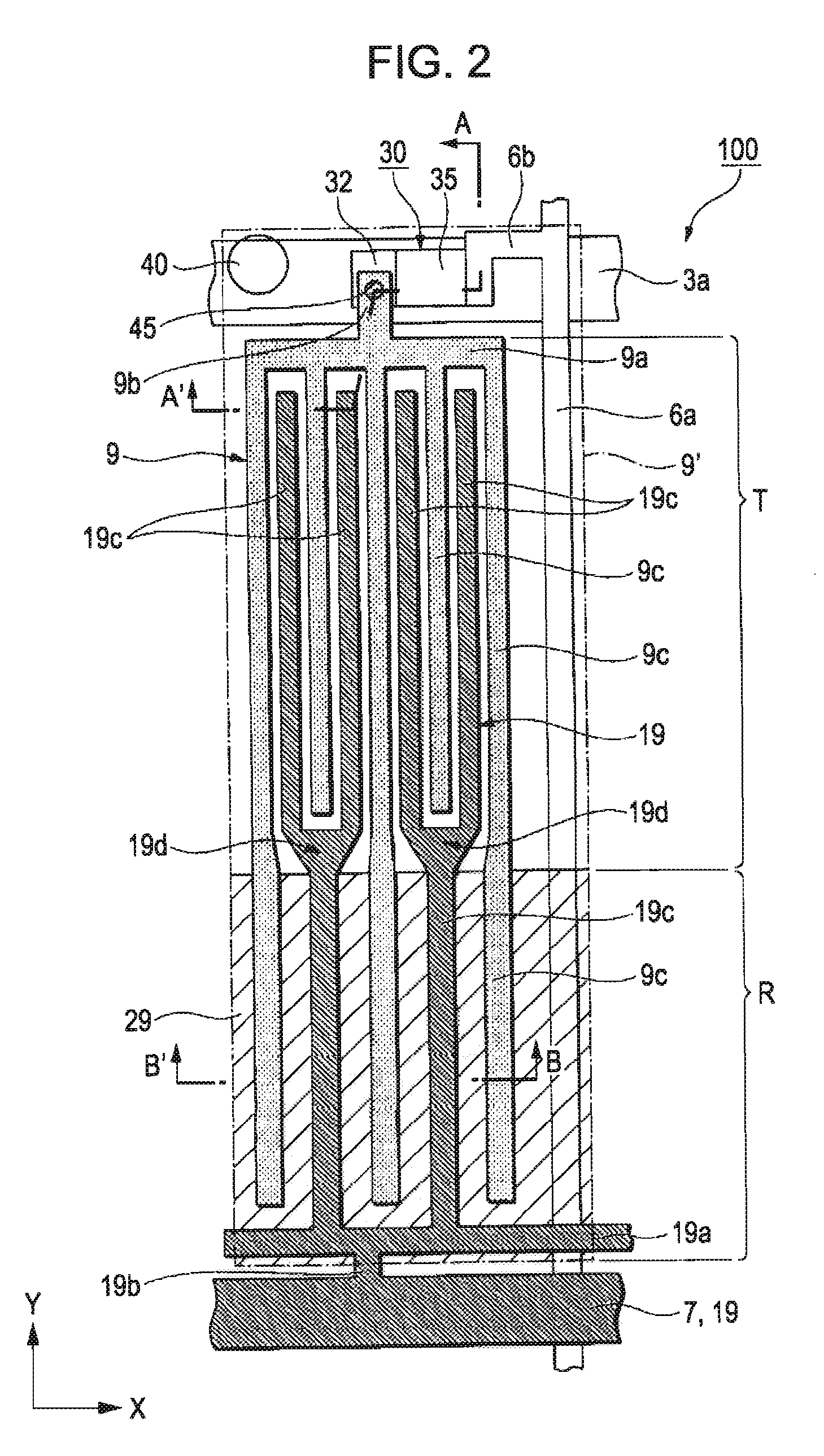

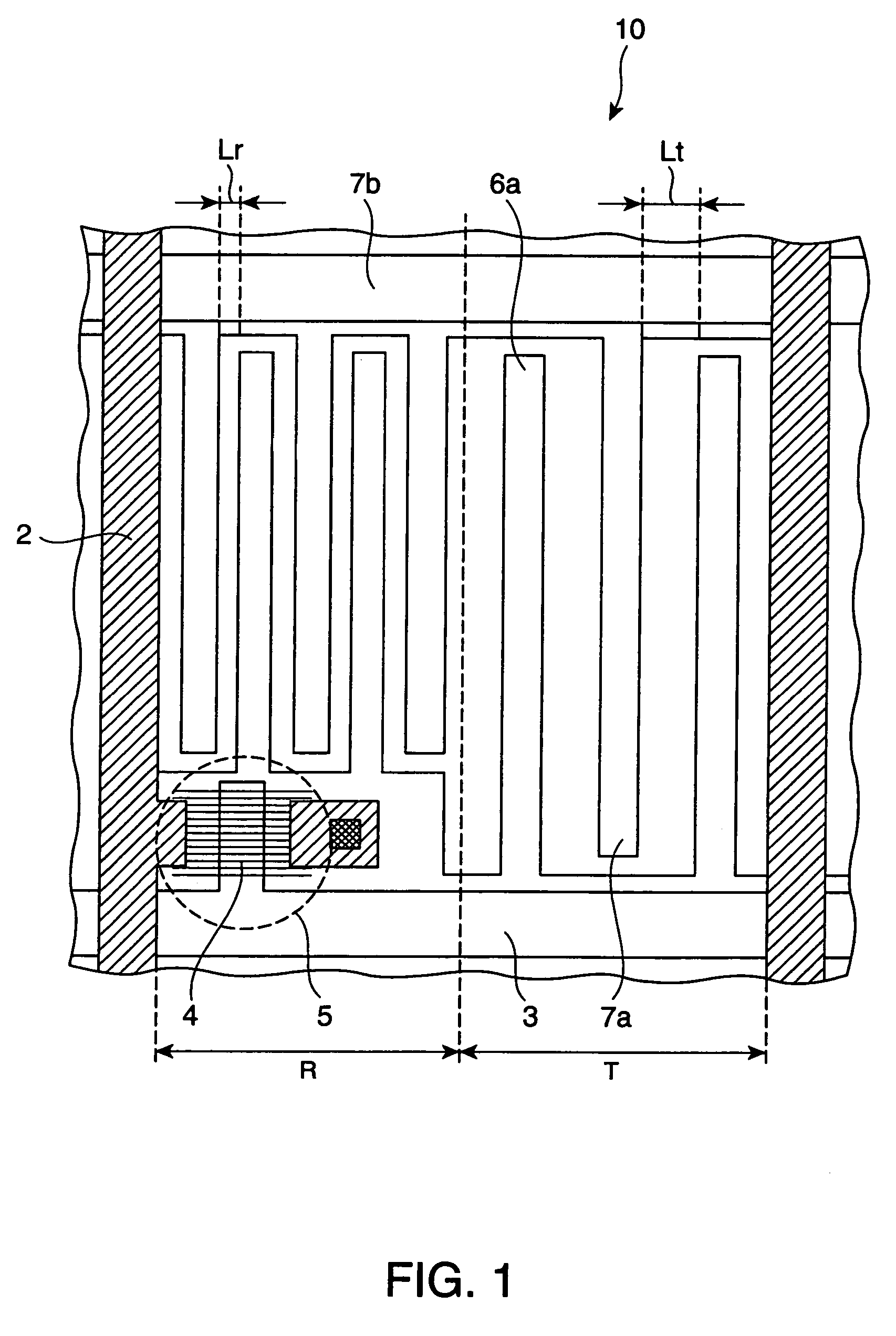

Liquid crystal display apparatus

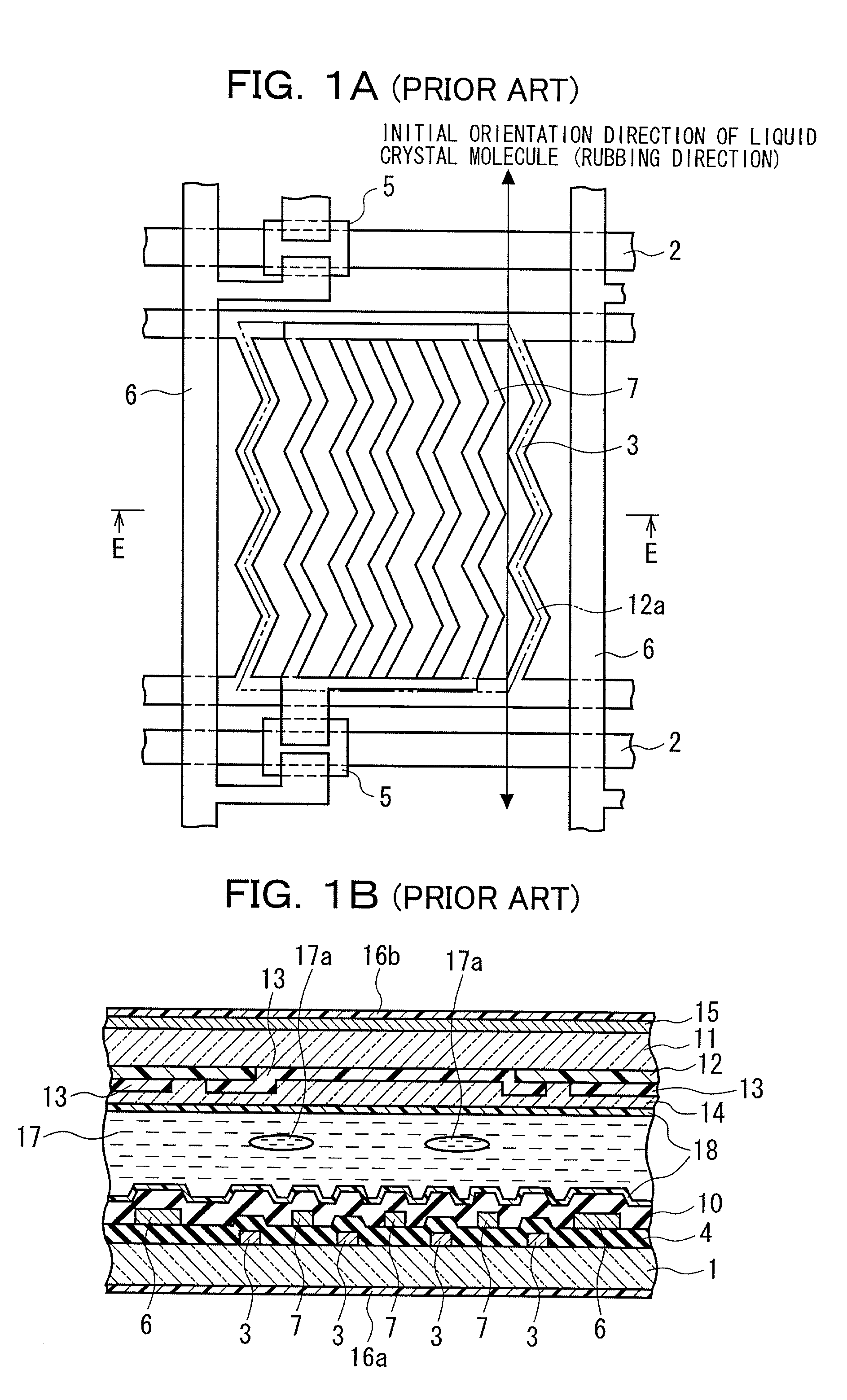

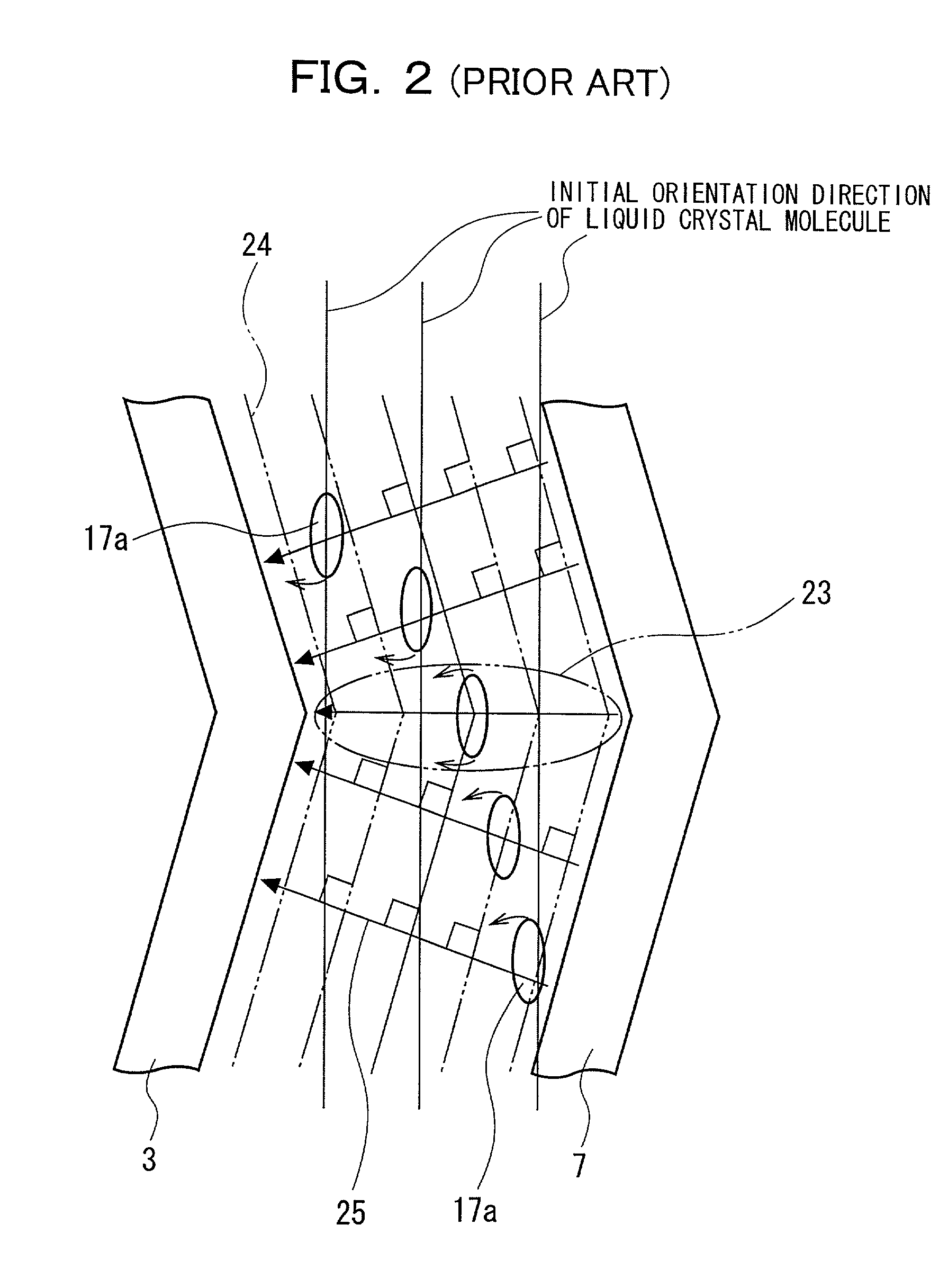

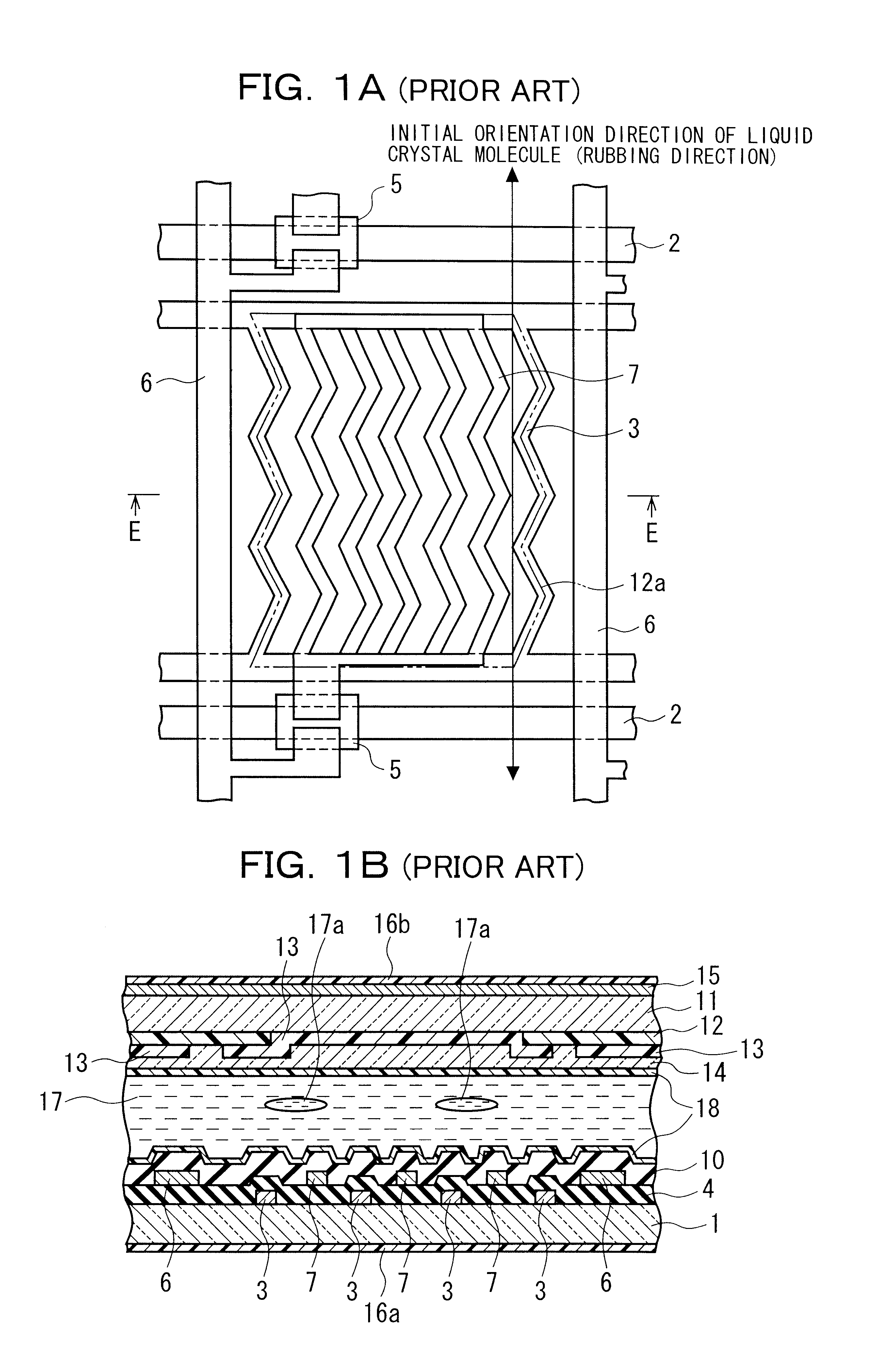

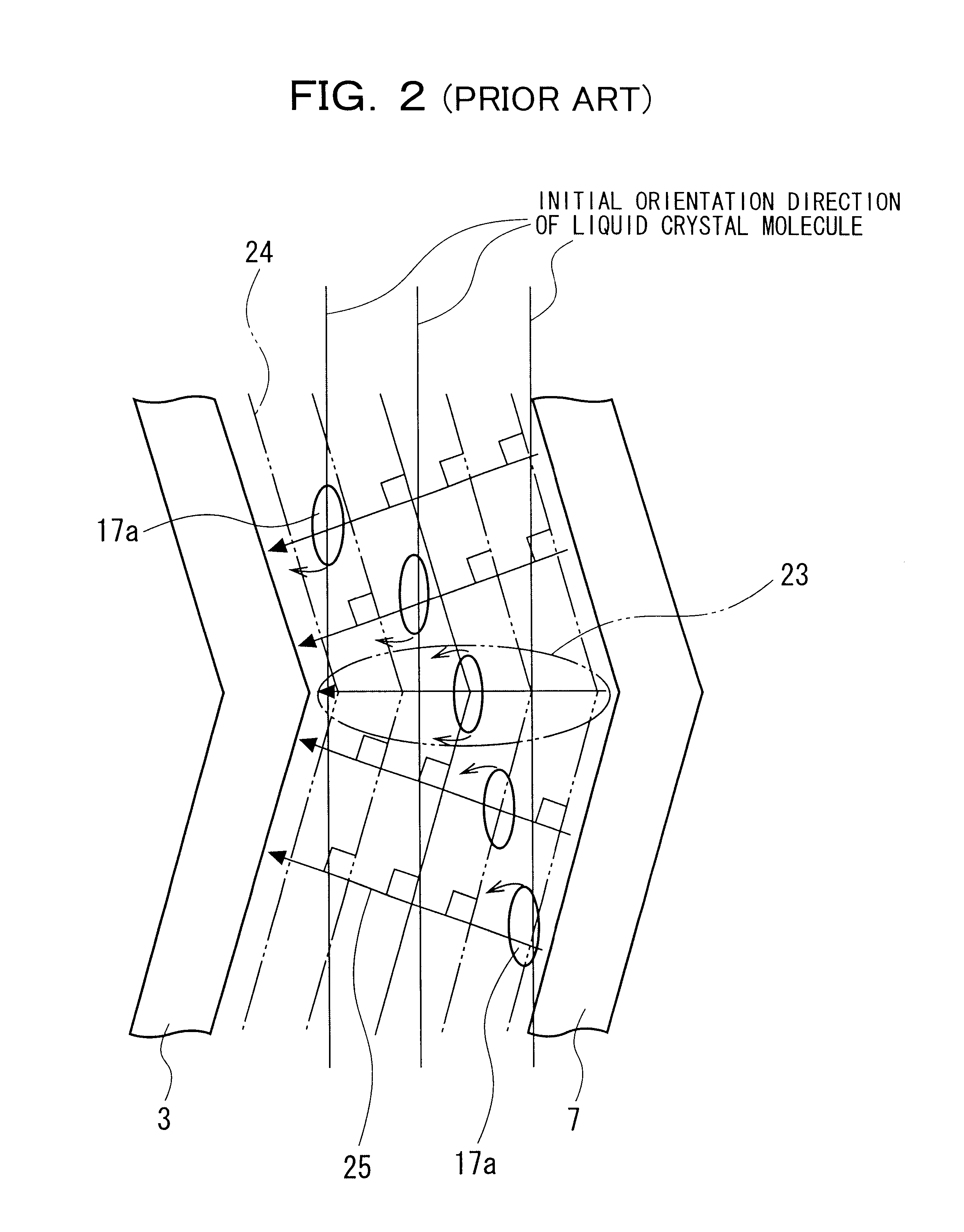

InactiveUS20020033922A1Non-linear opticsIdentification meansElectrical field strengthLiquid-crystal display

A liquid crystal display apparatus has a pair of substrates opposing to each other and a liquid crystals sandwiched between the pair of substrates. One side of substrate is provided with gate lines and signal lines which approximately cross each other. TFTs are provided close to intersection portion of the gate line and the signal line. Pixel electrodes and common electrodes are provided at each pixel enclosed by the gate line and the signal line. Each of pixel electrodes and common electrodes has bent points more than one and is alternately formed in parallel with each other. Both the pixel electrode and the common electrode are made up of bent sections and projected sections projecting toward concave sections of opposite electrodes from convex side top sections of the bent sections. In the liquid crystal display apparatus, improvement of visual angle characteristics and response characteristics is planned in such a way that the projected section allows electric field close to the bent section to be stabilized, and allows electric field strength to be enhanced.

Owner:GOLD CHARM LTD

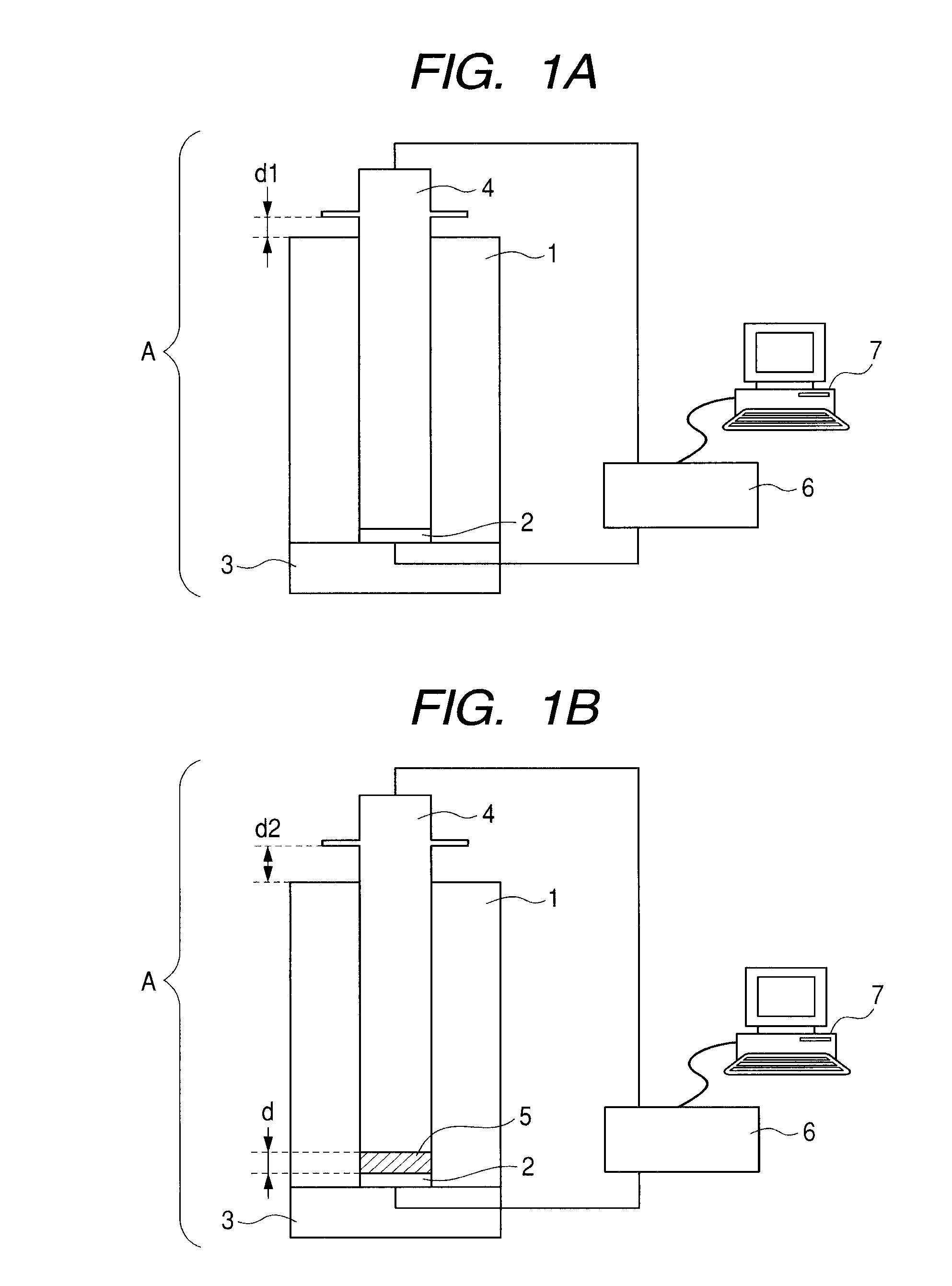

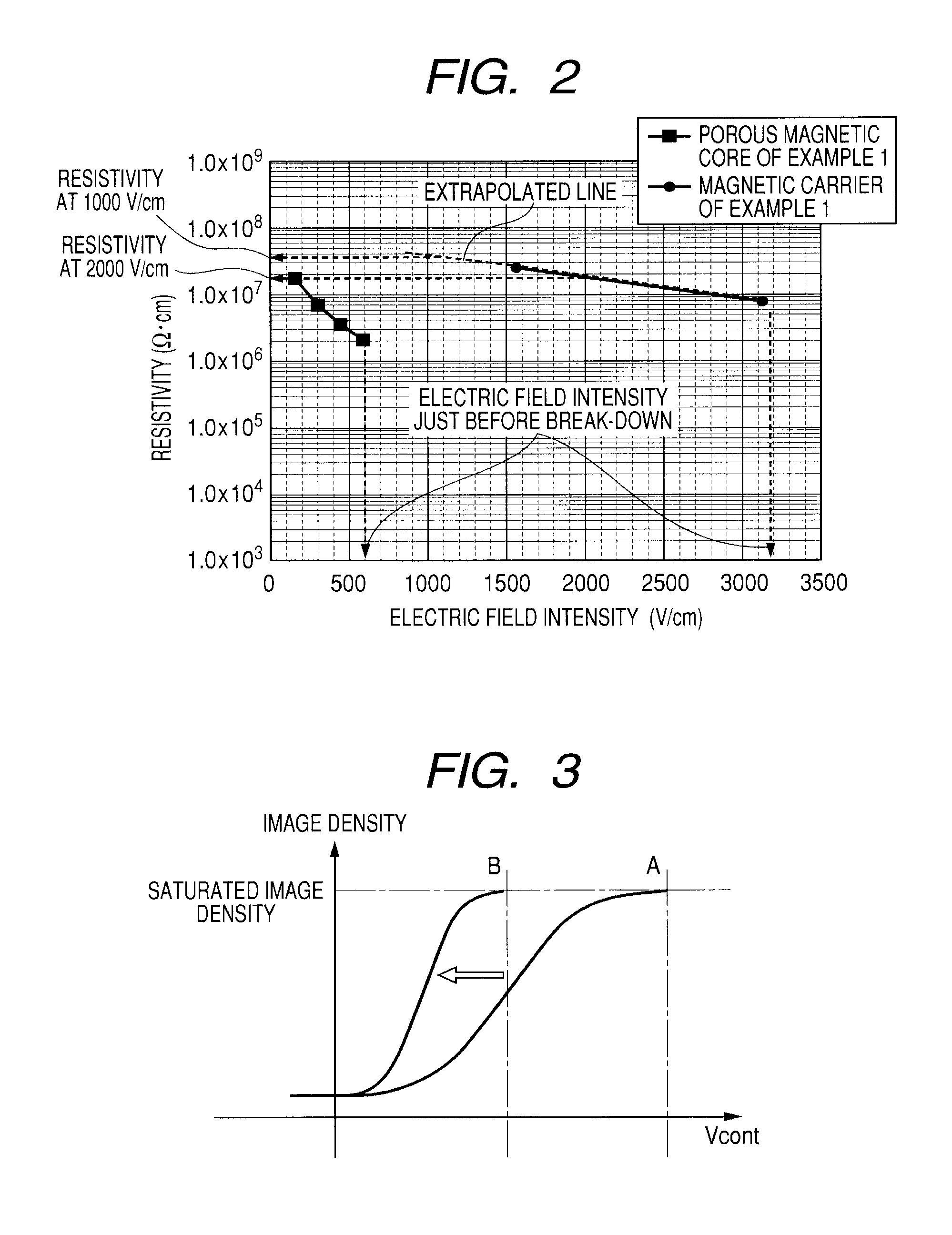

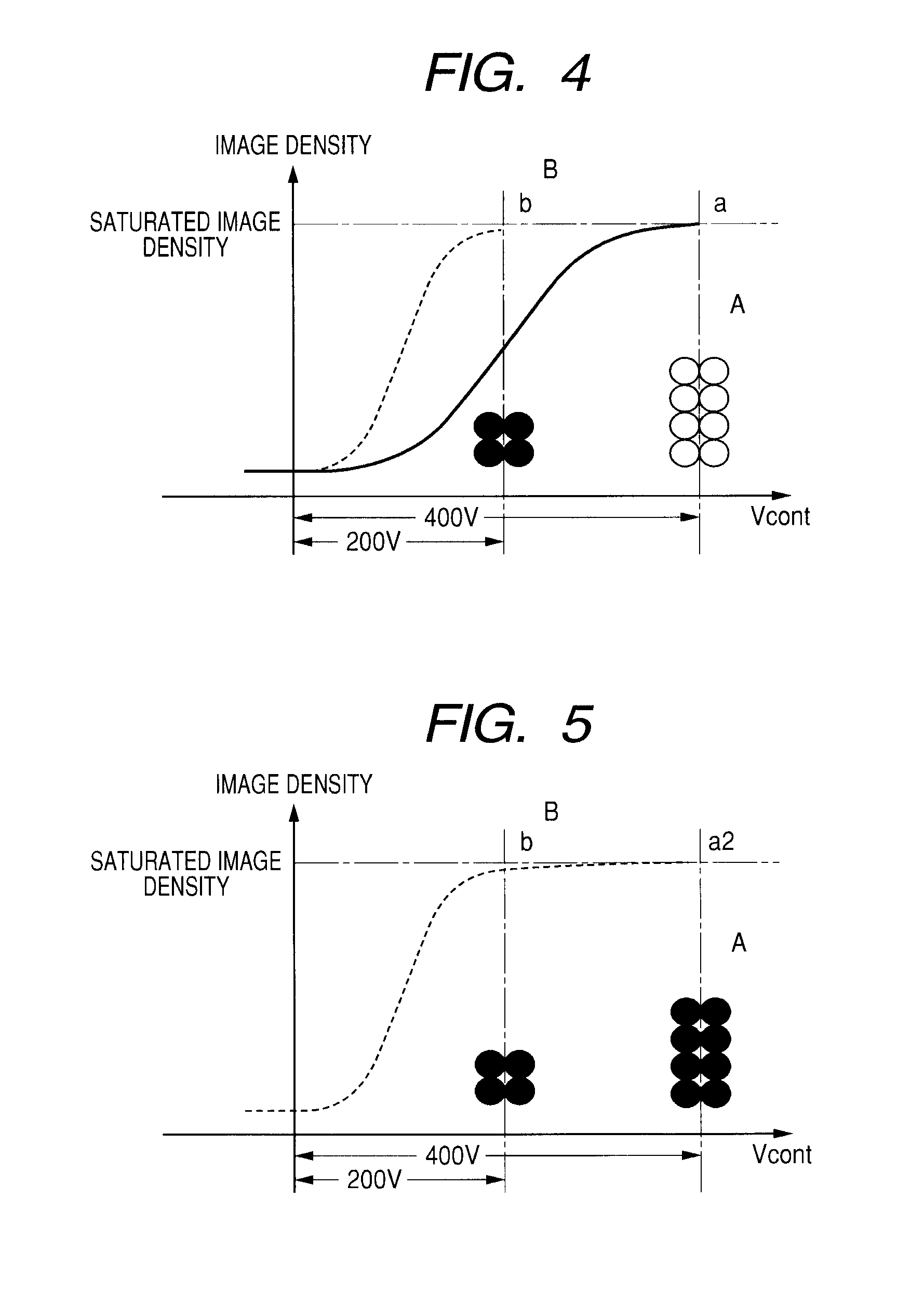

Magnetic carrier, two-component developer and image forming method

InactiveUS8137886B2High-quality image formationSolve the lack of densityDevelopersElectrographic processes using charge patternElectrical field strengthUltimate tensile strength

A magnetic carrier is provided which uses a toner having high coloring power and enables development to be performed at low electric field intensity and can form high quality images while keeping gradation characteristics. The magnetic carrier includes magnetic carrier particles including at least porous magnetic core particles and a resin. The electric field intensity just before the break-down of the magnetic carrier is 1,300 V / cm or more and 5,000 V / cm or less.

Owner:CANON KK

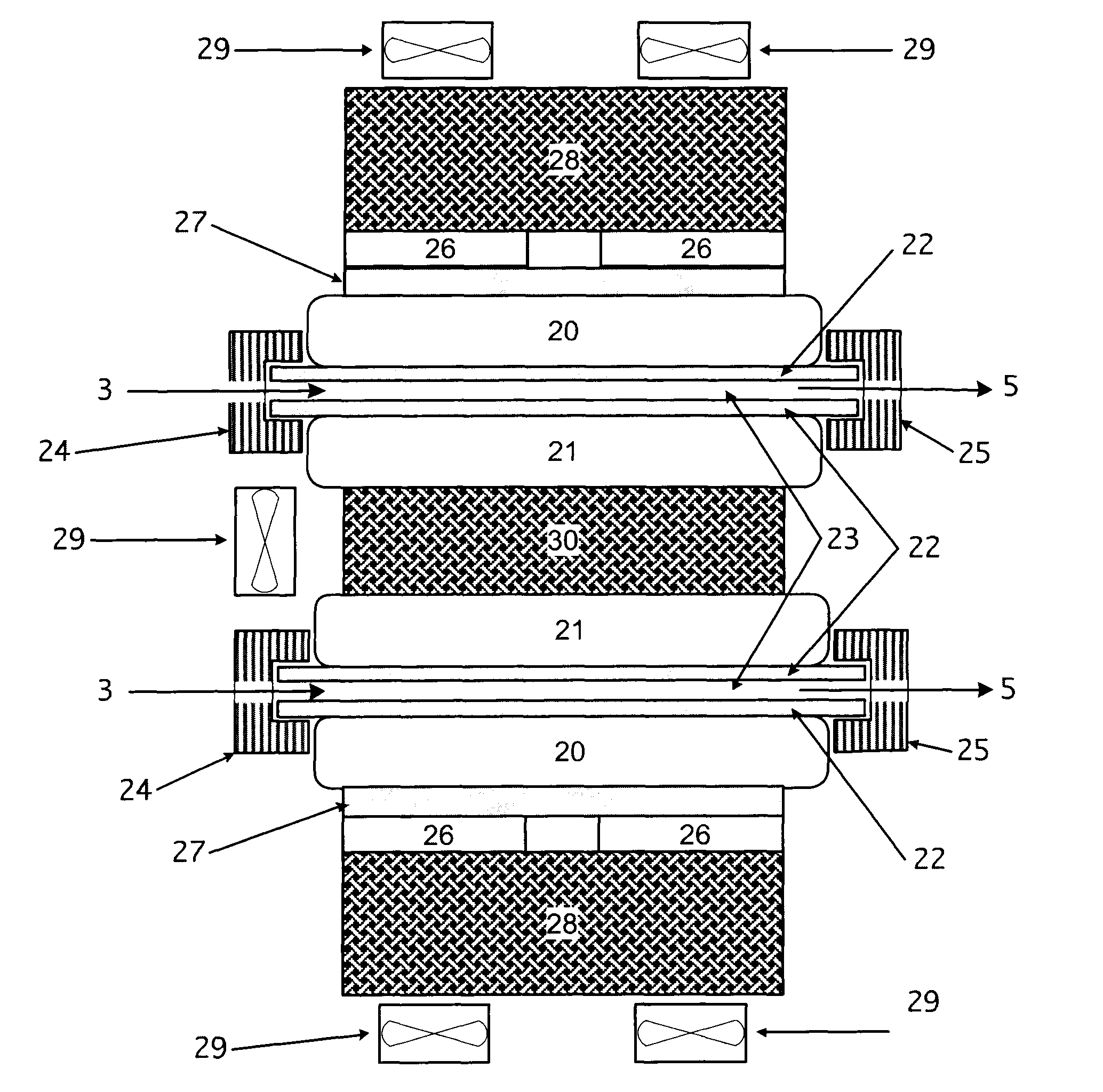

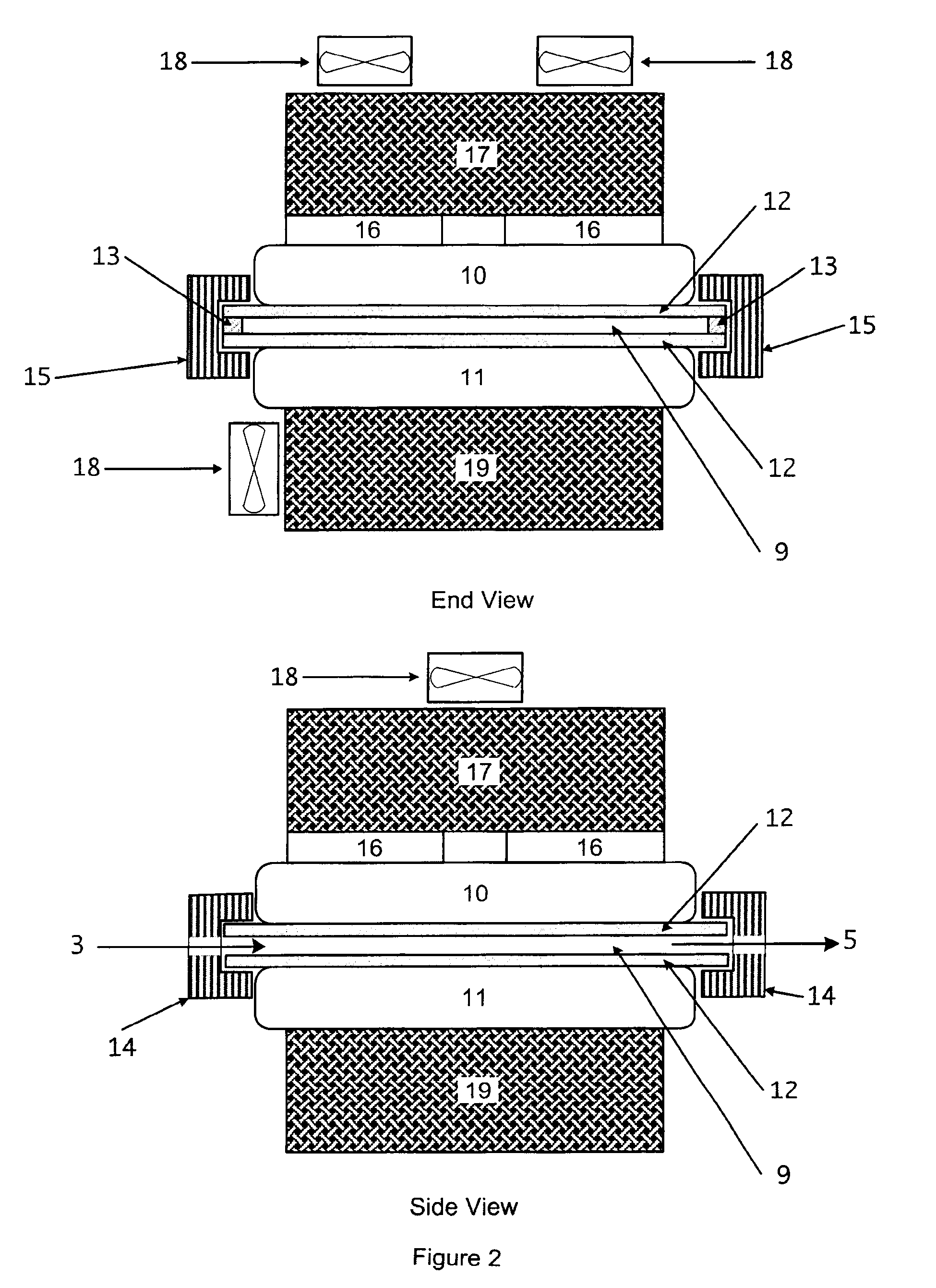

Apparatus for highly efficient cold-plasma ozone production

An apparatus for efficiently generating ozone in dry air or in oxygen at about 1 bar pressure. The apparatus generates a uniform cold plasma having no arcs or localized discharges that fills the entire generator volume. Electrical pulses having a peak voltage of approximately 20 kV, pulse width of approximately 20-ns FWHM, and repetition rate of approximately 10 kHz drive the generator. Short pulses apply voltage to the generator on a short time scale compared to the time required to form an arc-like discharge, and at an electric field strength many times over DC breakdown, which is not achievable with long electrical pulse widths. The generator is optimized for cool, UV-free operation. Dimensions of the generator are adjusted to optimize production of ozone by tailoring the distribution function of the electrons in the cold plasma. Overall efficiency of the generator approaches 50% of the theoretical quantum efficiency of generating ozone.

Owner:SPIELMAN RICK B

Detection device and image forming device

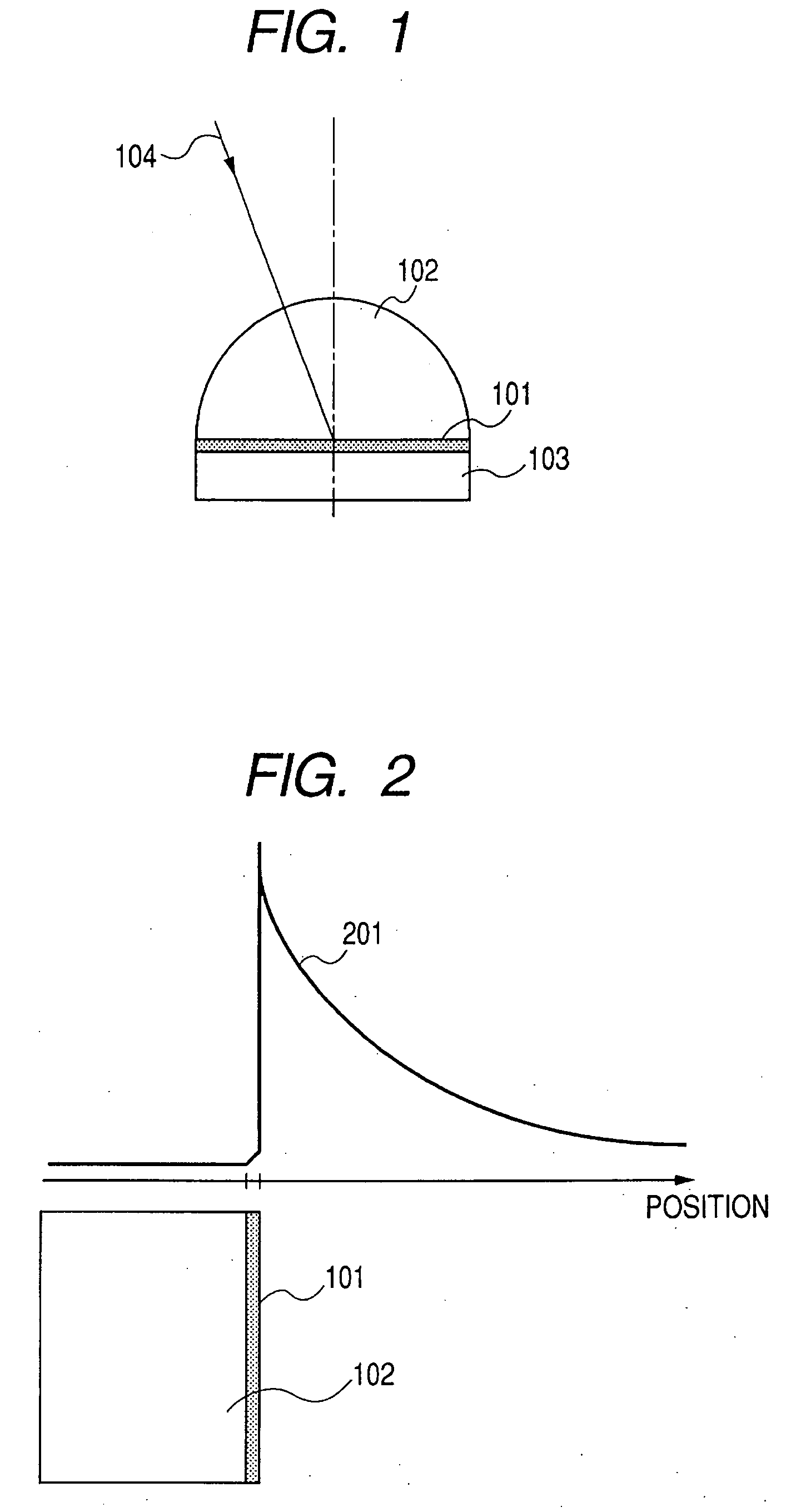

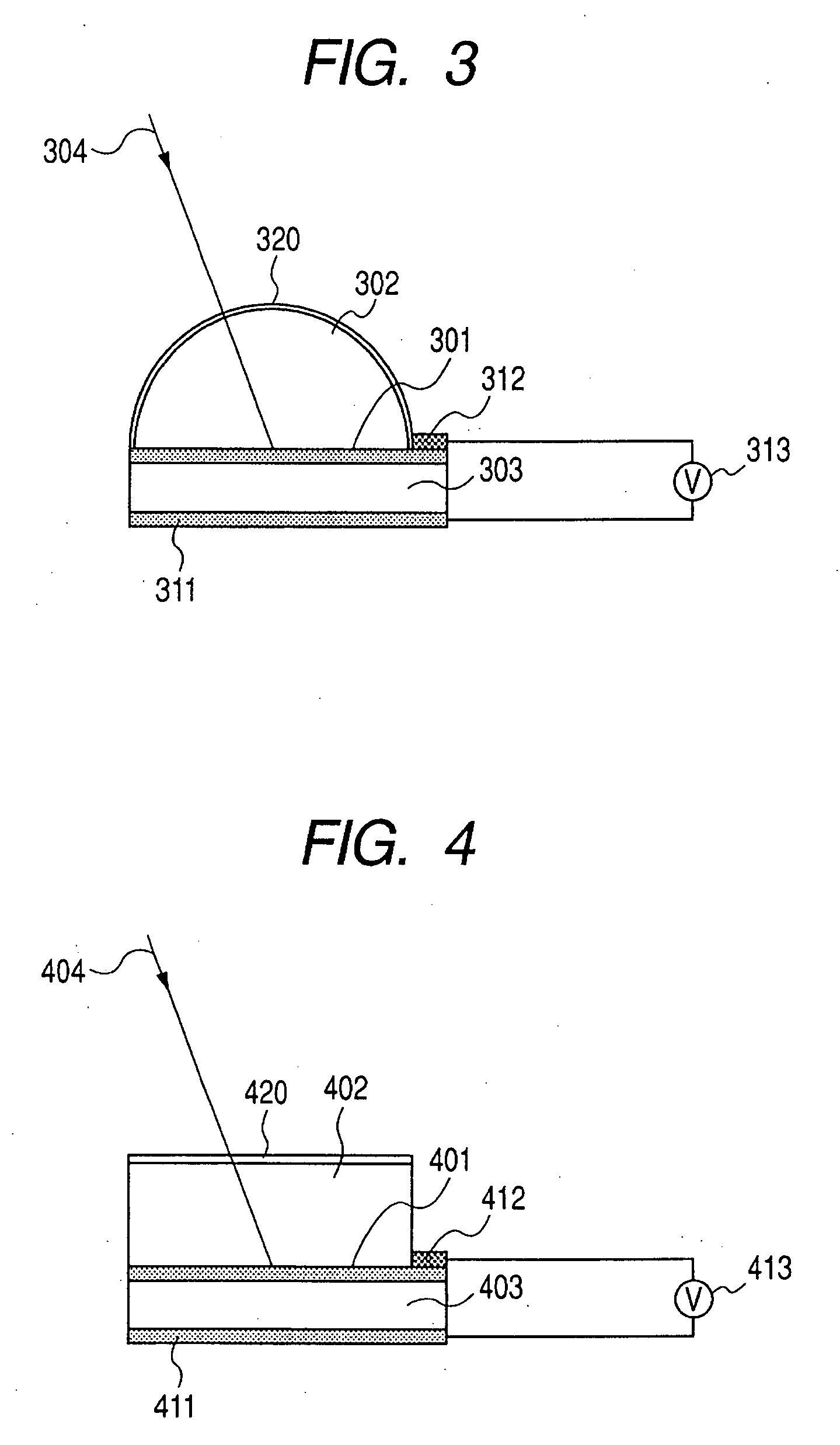

InactiveUS20070215808A1Large detection areaHigh sensitivityRadiation pyrometrySpectrum investigationElectrical field strengthWave detection

There is a need for a detection device which has high photoreceptive sensitivity in a generally wide frequency region including the infrared region. Therefore, in the present invention, by utilizing a phenomenon in which electric field strength is enhanced by surface plasmon resonance in a negative dielectric constant medium, a detection device is provided which has an electromagnetic wave detection portion disposed at a position where the electric field strength is large.

Owner:CANON KK

Liquid crystal display apparatus

InactiveUS6618109B2Non-linear opticsIdentification meansElectrical field strengthLiquid-crystal display

A liquid crystal display apparatus has a pair of substrates opposing to each other and a liquid crystals sandwiched between the pair of substrates. One side of substrate is provided with gate lines and signal lines which approximately cross each other. TFTs are provided close to intersection portion of the gate line and the signal line. Pixel electrodes and common electrodes are provided at each pixel enclosed by the gate line and the signal line. Each of pixel electrodes and common electrodes has bent points more than one and is alternately formed in parallel with each other. Both the pixel electrode and the common electrode are made up of bent sections and projected sections projecting toward concave sections of opposite electrodes from convex side top sections of the bent sections. In the liquid crystal display apparatus, improvement of visual angle characteristics and response characteristics is planned in such a way that the projected section allows electric field close to the bent section to be stabilized, and allows electric field strength to be enhanced.

Owner:GOLD CHARM LTD

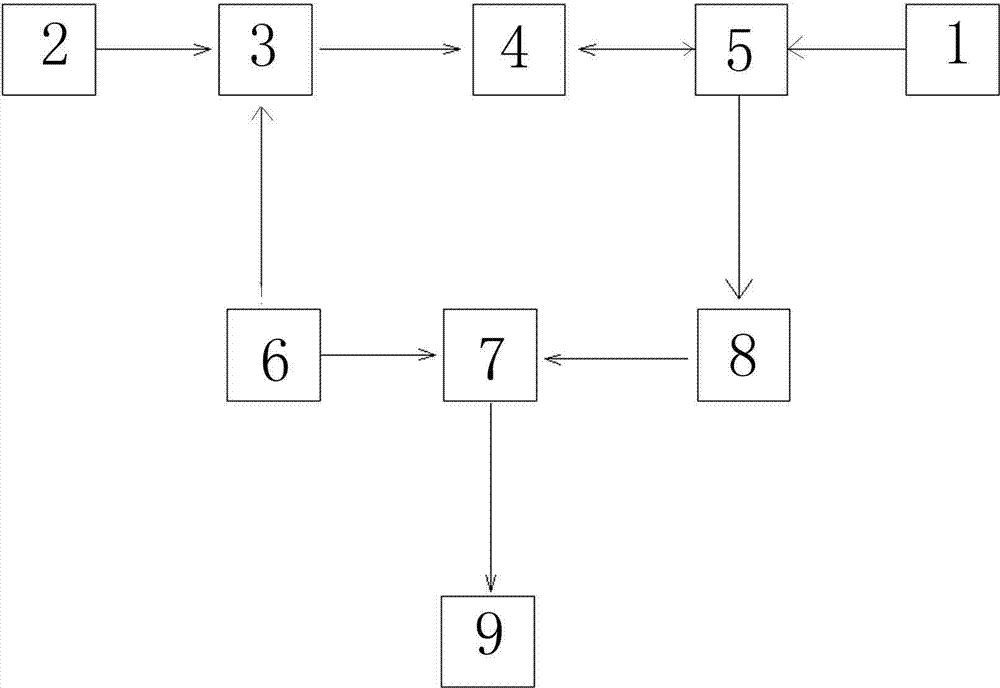

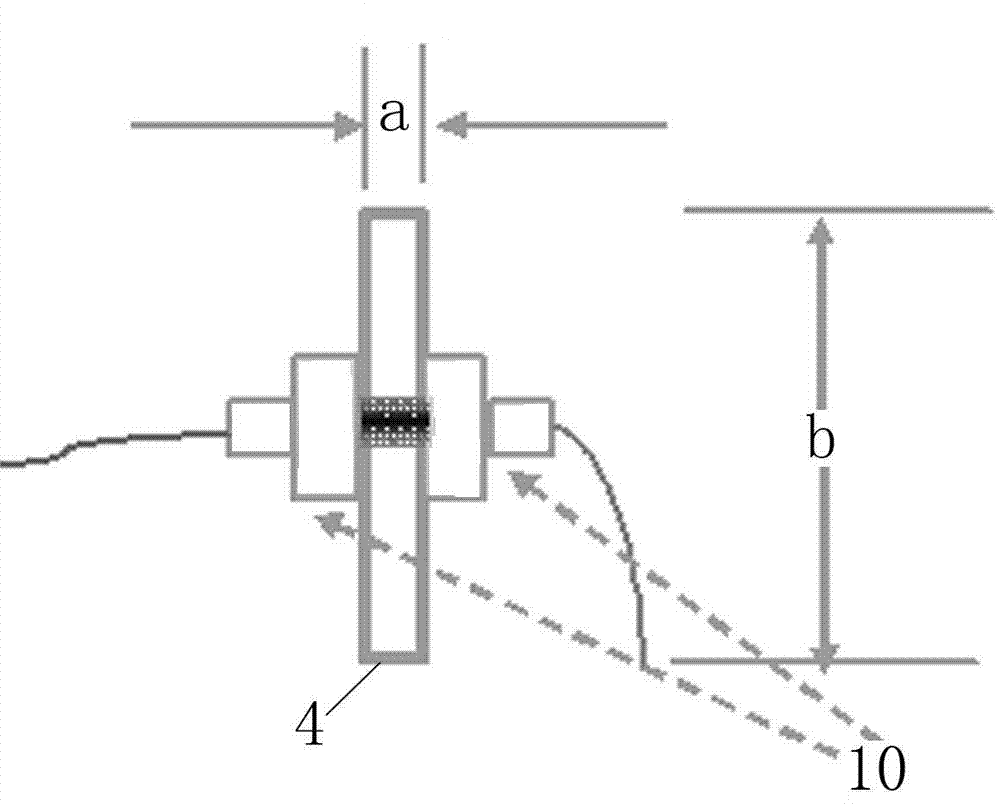

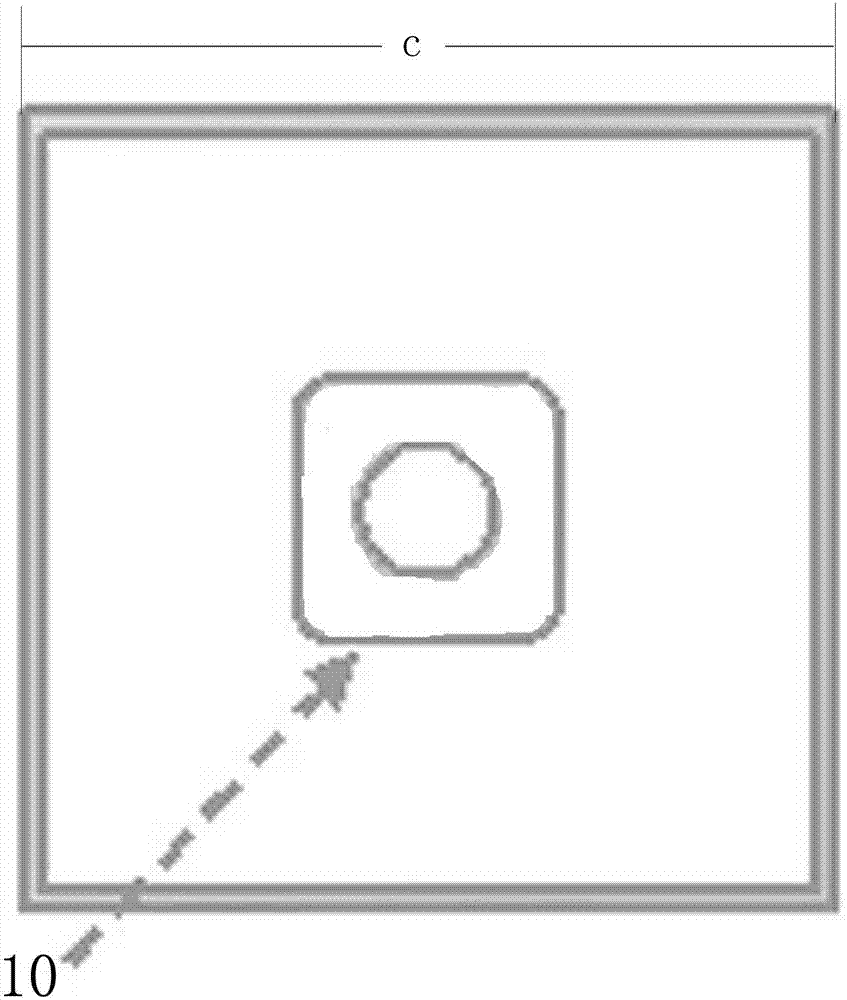

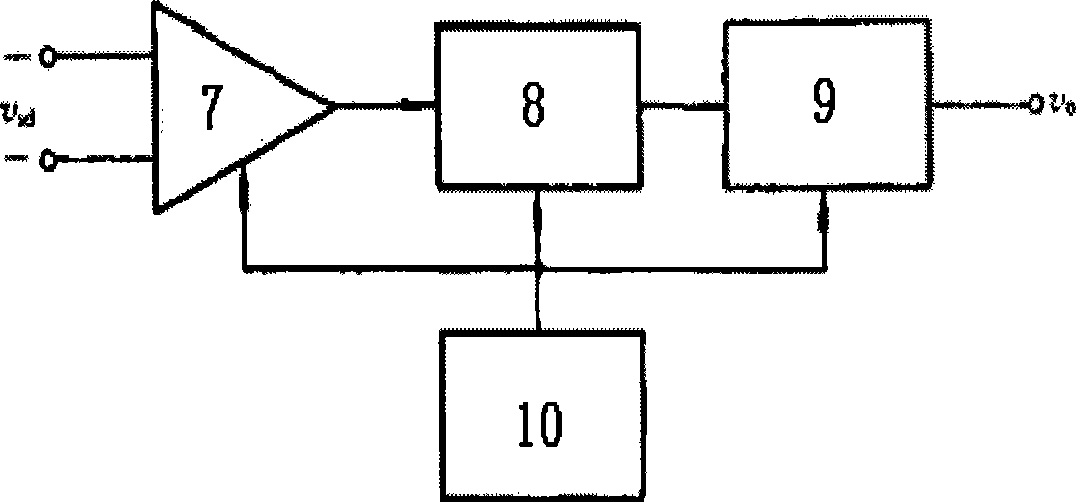

Electric field detection method and device based on stark effects of Rydberg atoms

ActiveCN103616571AUnique structureHigh measurement accuracyElectrostatic field measurementsRydberg atomElectrical field strength

The invention relates to a weak electric field detection technology, particularly relates to an electric field detection method and device based on stark effects of Rydberg atoms, and solves the technical problems that the measurement on an electric field, particularly a weak electric field, is not accurate enough at present, and the sensitivity is not high enough. The electric field detection method based on the stark effects of the Rydberg atoms comprises the following steps: (a) oppositely arranging two beams of laser and collinearly emitting the laser into a sample tank which is internally filled with alkaline metal atom steam; (b) acquiring a signal of the second beam of the laser emitted out by the sample tank and converting the signal into a corresponding electric signal; and (c) analyzing the acquired electric signal, and if the electric field exists, observing an absorption spectrum with a stark cracking phenomenon from the signal, so as to further solve the intensity of the electric field E. According to the electric field detection method and device based on the stark effects of the Rydberg atoms, the electric field can be measured by the stark effects with an alkaline metal atom Rydberg energy level; the measurement precision is high and the electric field strength which is weakened to an mV / cm grade can be measured.

Owner:SHANXI UNIV

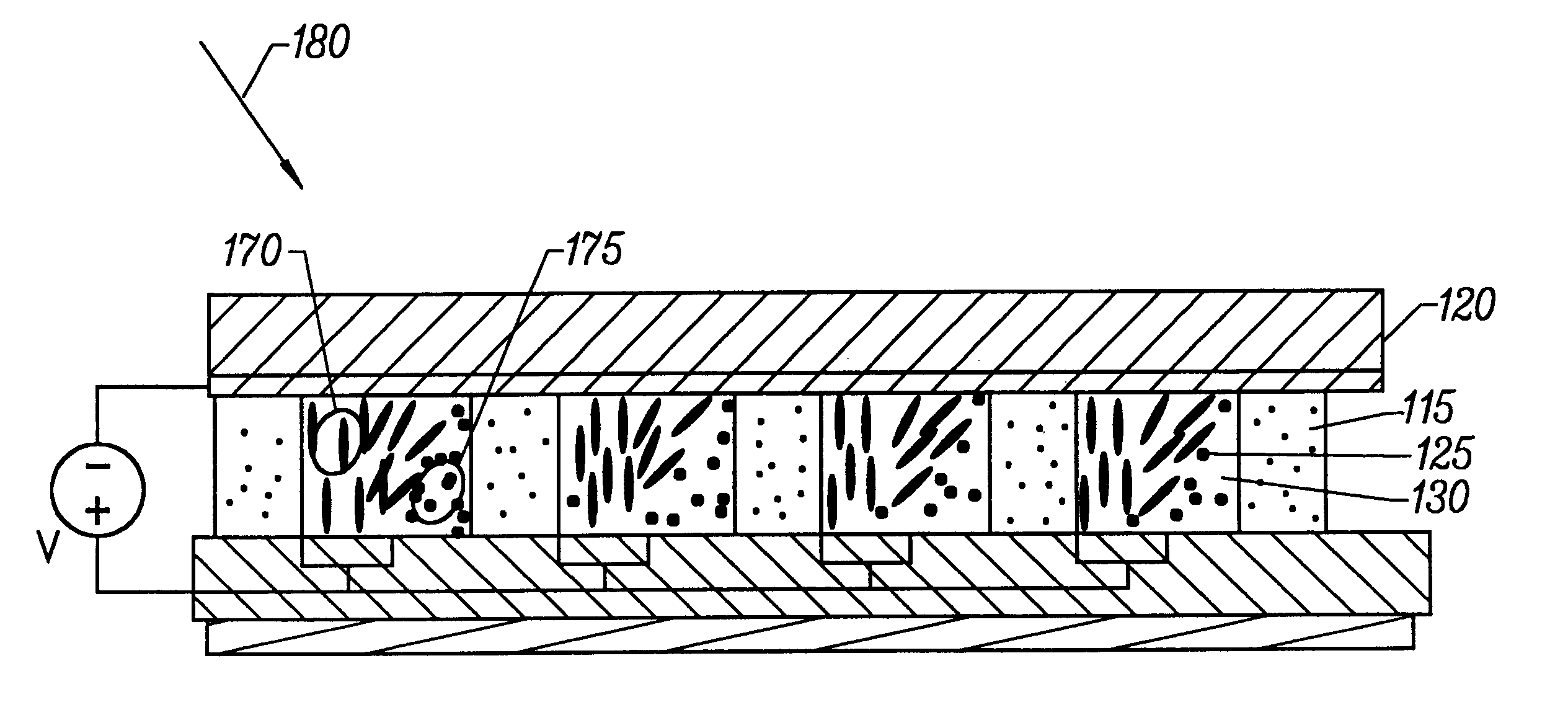

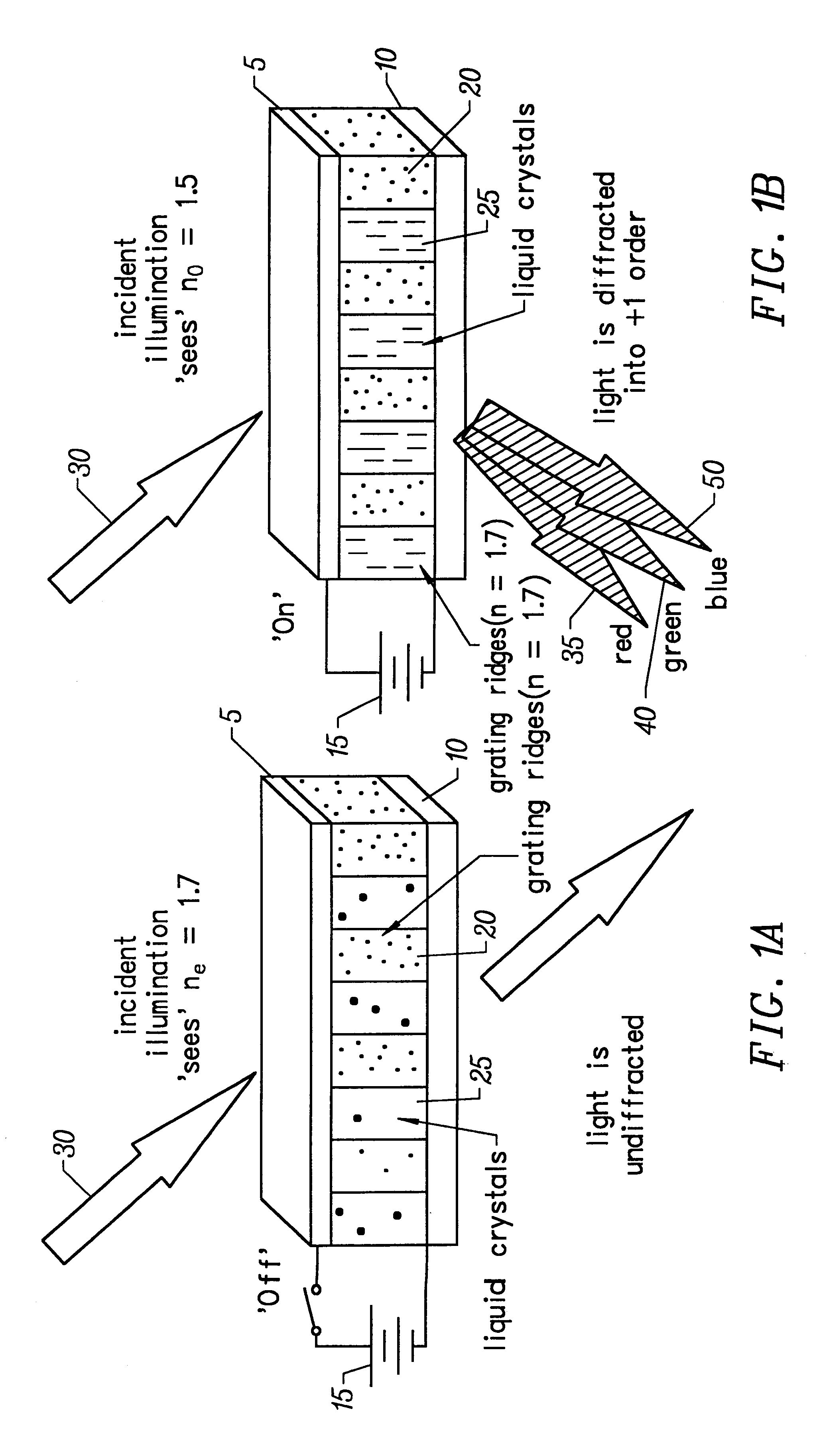

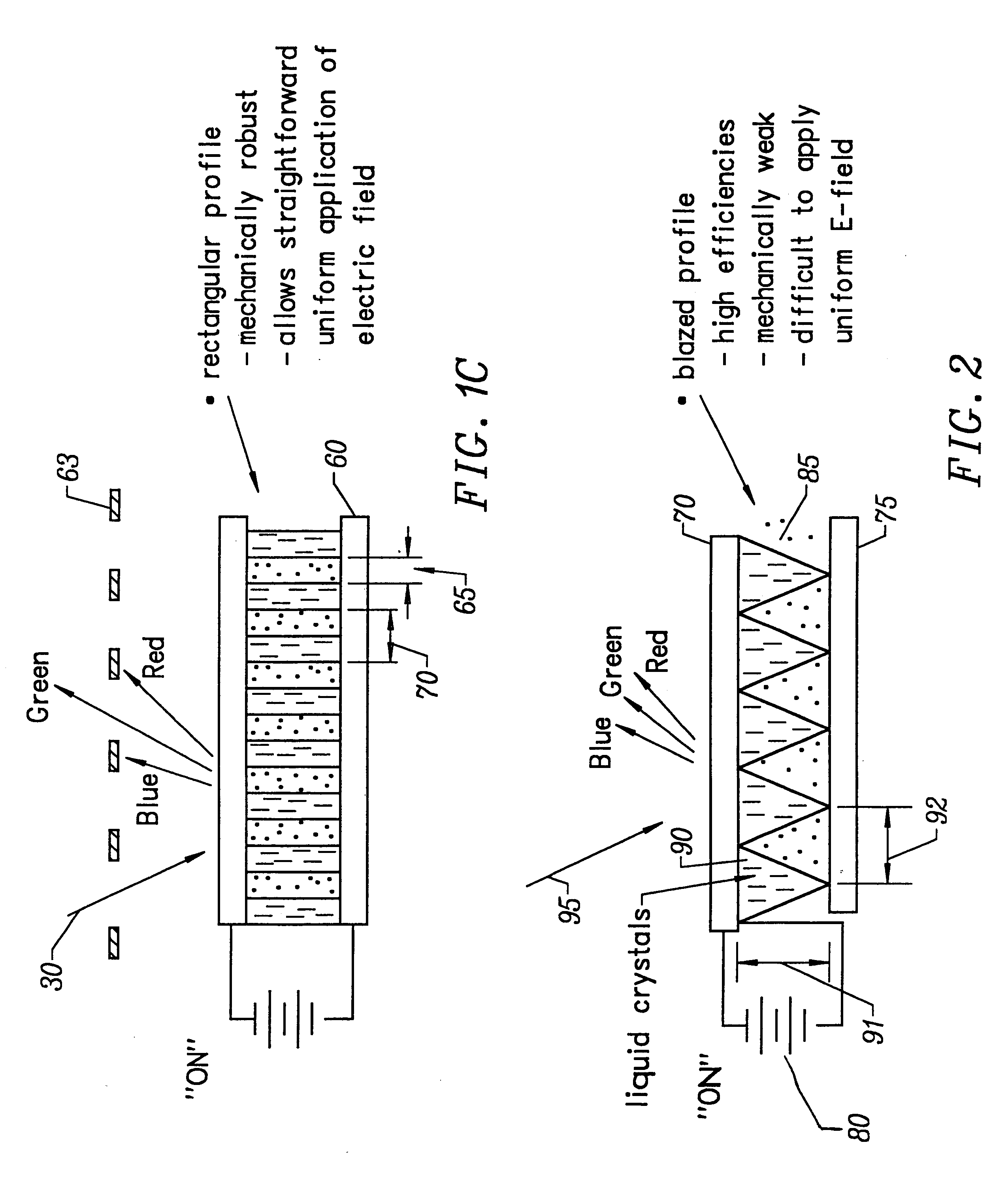

Method and apparatus for forming optical gratings

InactiveUS6172792B1Increase contrastFast response timeDiffraction gratingsNon-linear opticsGratingElectrical field strength

An apparatus for redirecting physical energy includes a substrate defining a first boundary of a region, a first electrode defining a second boundary of the region, the second boundary disposed opposite to the first boundary, a second electrode adjacent to the first boundary for cooperating with the first electrode to apply a non-uniform electric field to the region, the non-uniform electric field having electrical field intensities simultaneously including a first electric field intensity and a second electric field intensity, and a layer of material disposed in the region, the layer having a variable index of refraction responsive to the electric field intensities of the non-uniform electric field, the variable index of refraction including a first index of refraction in response to the first electric field intensity and a second index of refraction in response to the second electric field intensity.

Owner:ROSSELLA

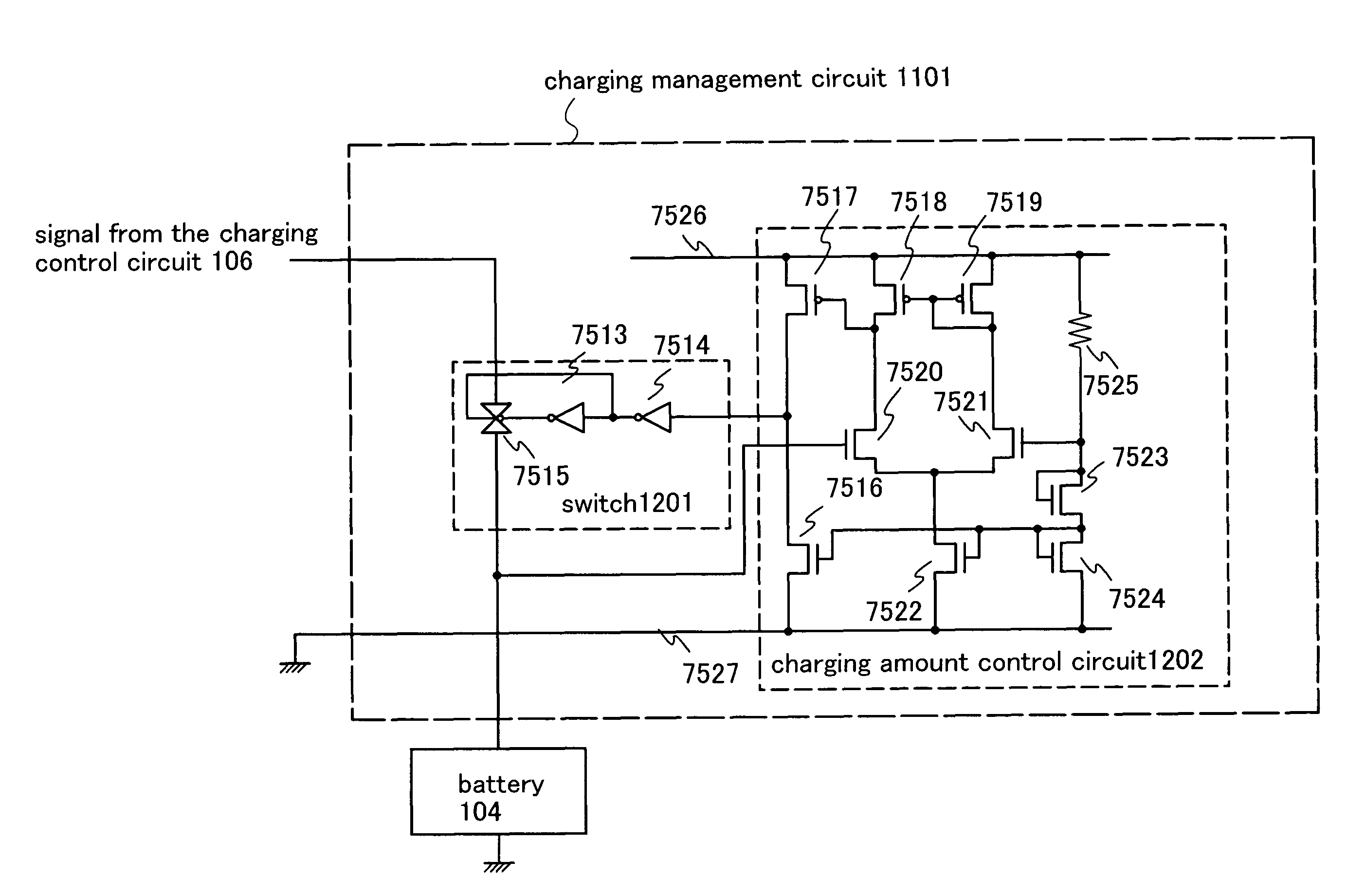

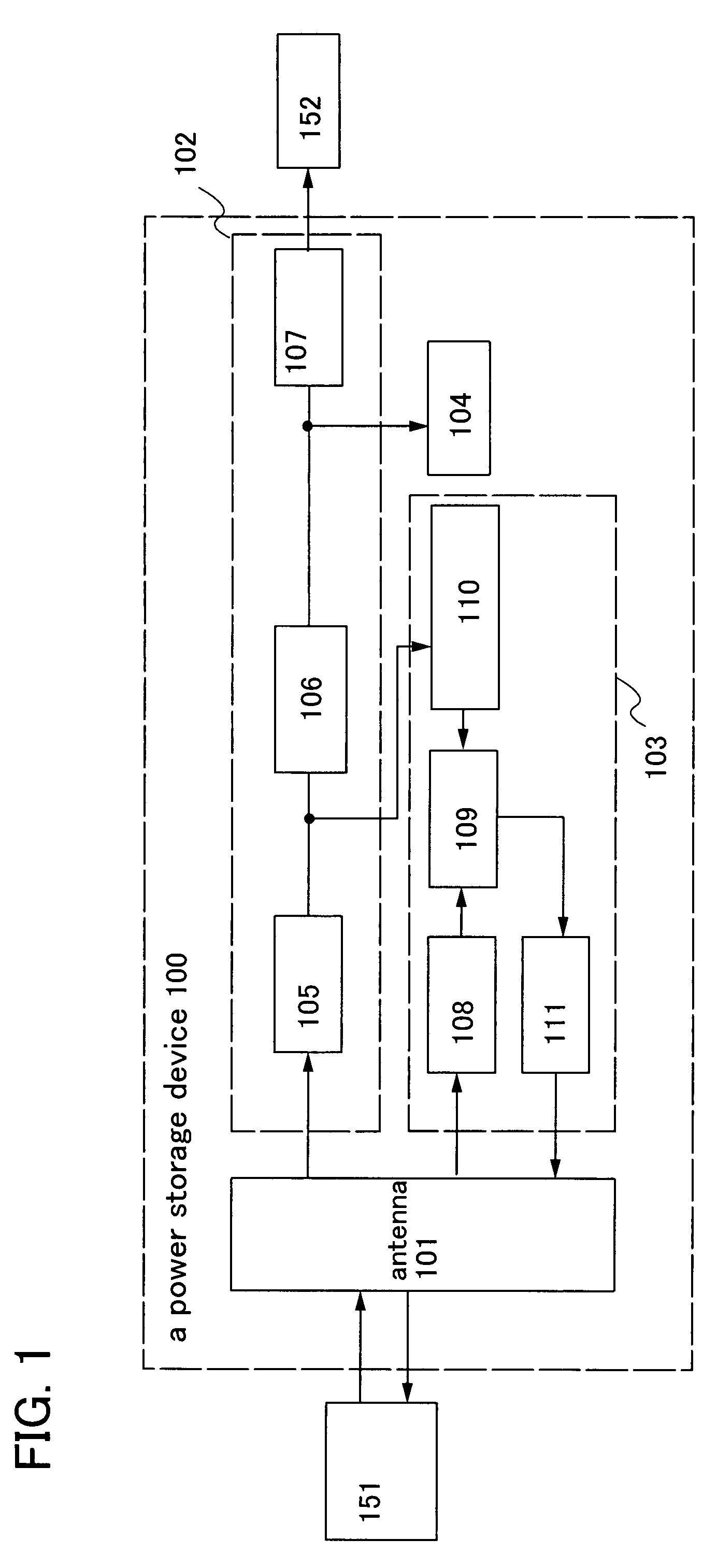

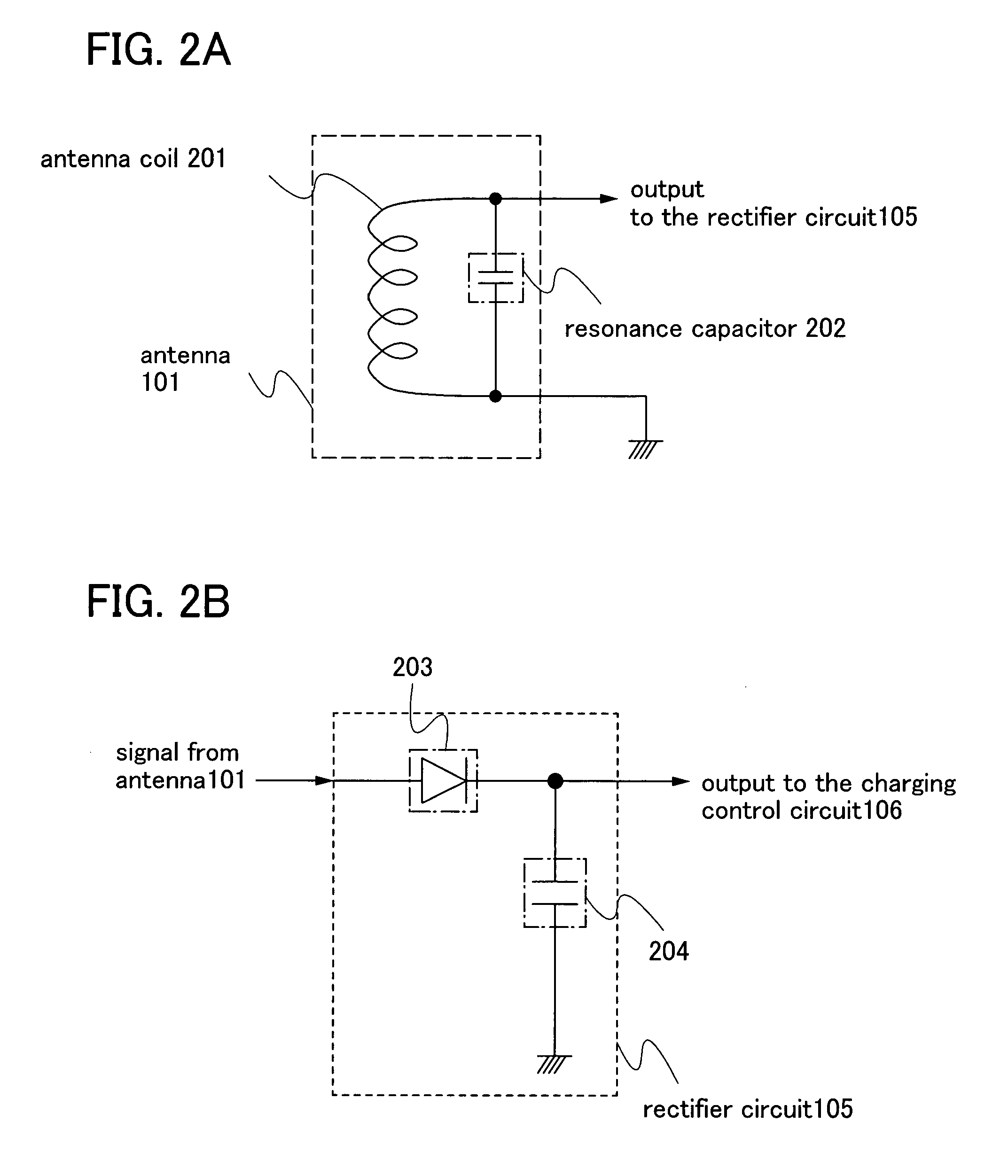

Power storage device and semiconductor device provided with the power storage device

InactiveUS7764046B2Increase powerShort timeNear-field transmissionElectromagnetic wave systemElectrical field strengthElectrical battery

An object is to provide a power storage device provided with a battery that is a power storage means, for safe and accurate supply of electric power in a short period of time for drive power supply voltage without checking remaining capacity of the battery or changing batteries with deterioration over time of the battery for drive power supply voltage. The power storage device is provided with a battery that is a power storage means as a power supply for supplying electric power and a counter circuit for counting charging time of the power storage means. An electromagnetic wave with electric field intensity, magnetic field intensity, and power flux density per unit time which are transmitted from a power feeder are controlled, and the power storage means is efficiently charged using the electromagnetic wave in a short period of time.

Owner:SEMICON ENERGY LAB CO LTD

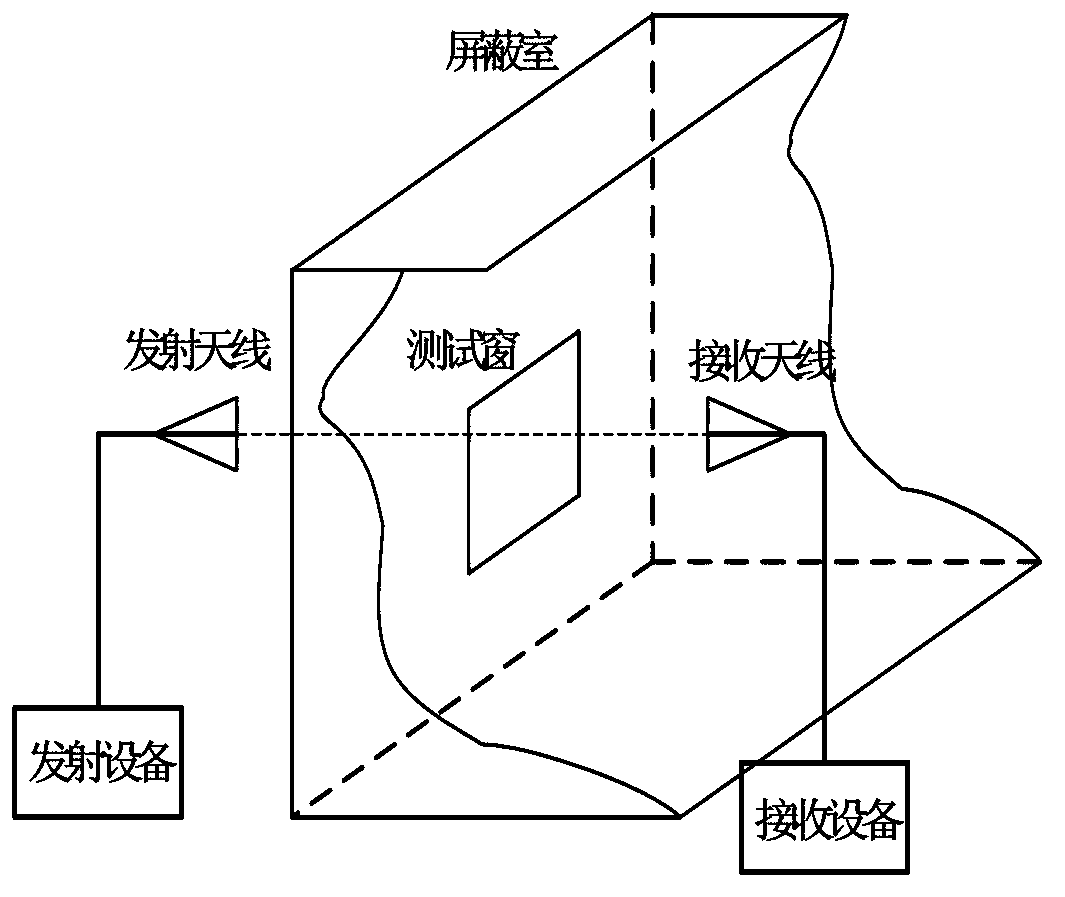

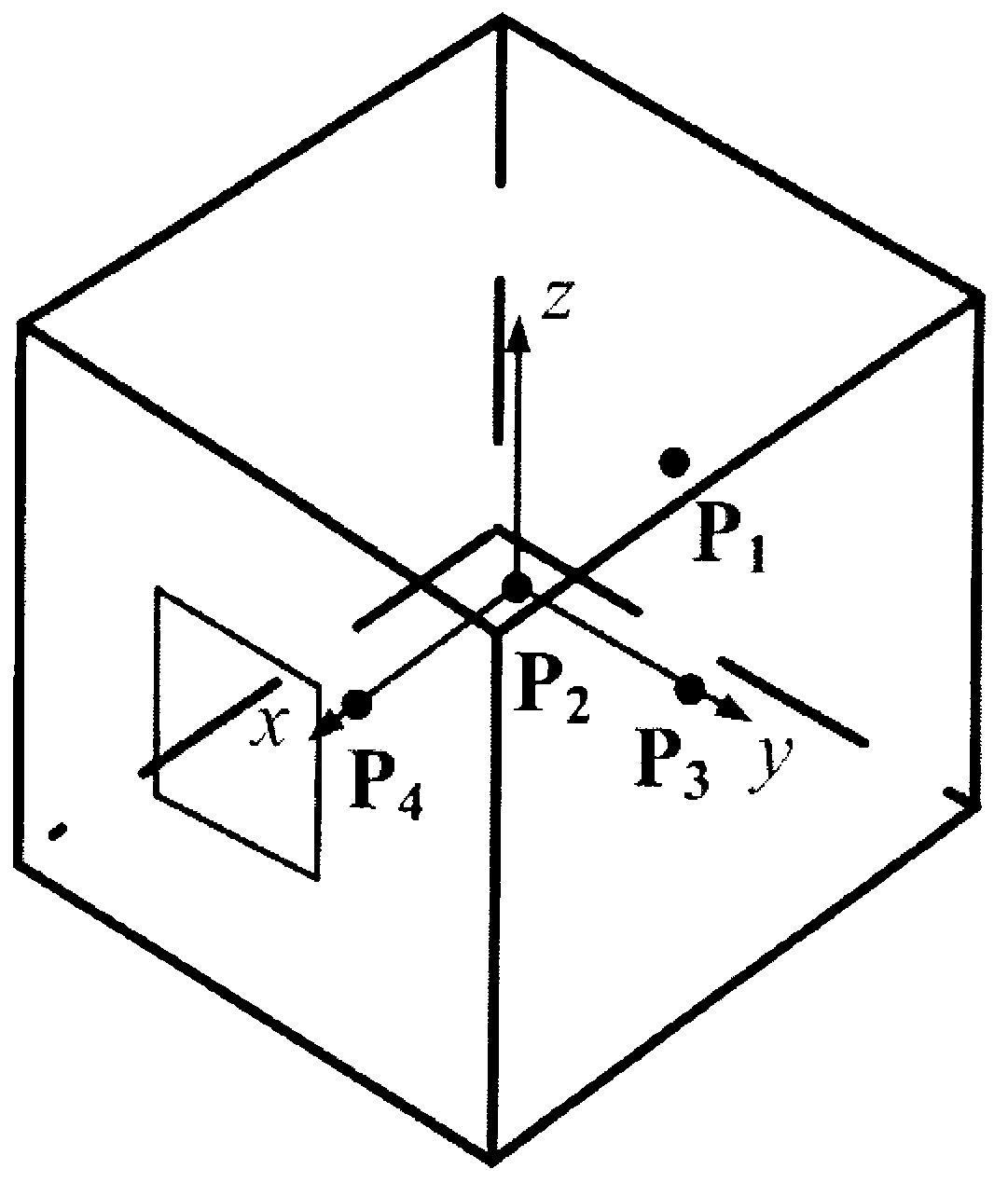

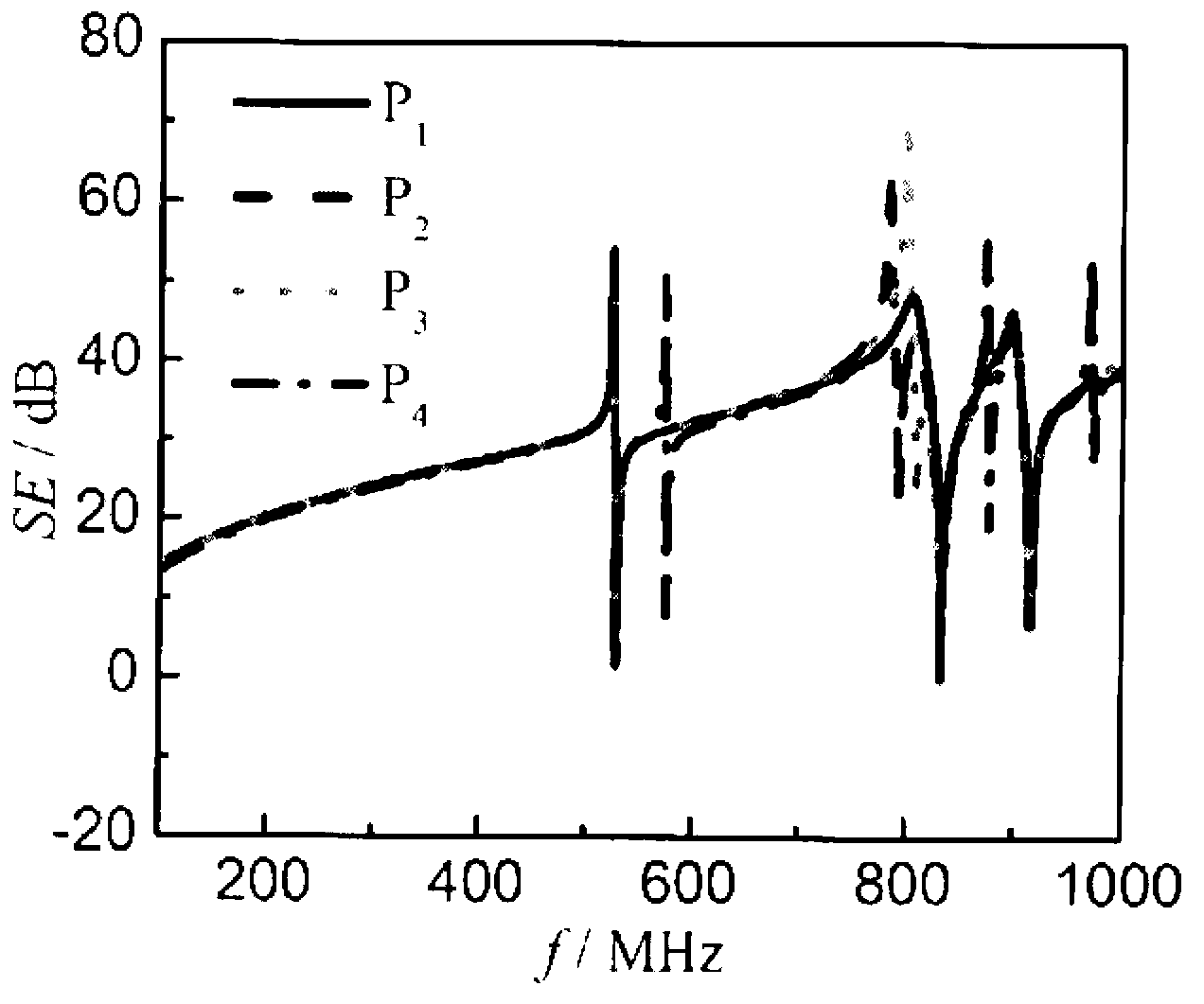

Method for testing shielding effectiveness of electromagnetic shielding material

InactiveCN103308798AOvercome the disadvantage of not being portableElectrical testingReference sampleElectrical field strength

The invention discloses a method for testing the shielding effectiveness of an electromagnetic shielding material in the technical field of electromagnetic shielding. The method comprises the following steps that a reference sample with known electromagnetic parameters and different electromagnetic frequencies are selected, and the electromagnetic transmission intensity of an electromagnetic transmitter is set; a testing window is sealed by the reference sample, and the electric field intensity received by electromagnetic receivers which correspond to different electromagnetic frequencies is measured; the testing window is tested by a material to be tested, and the electric field intensity received by the electromagnetic receivers which correspond to different electromagnetic frequencies is measured; and the shielding effectiveness of materials to be tested corresponding to different frequencies relative to the reference sample is calculated and the conductivity of the materials to be tested is estimated. The testing method is not affected by the size of a shielding room (box), the size of the window, the resonance of the shielding room and other factors, and overcomes the defect that the testing results of a traditional shielding room method are not portable among different configuration.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING) +1

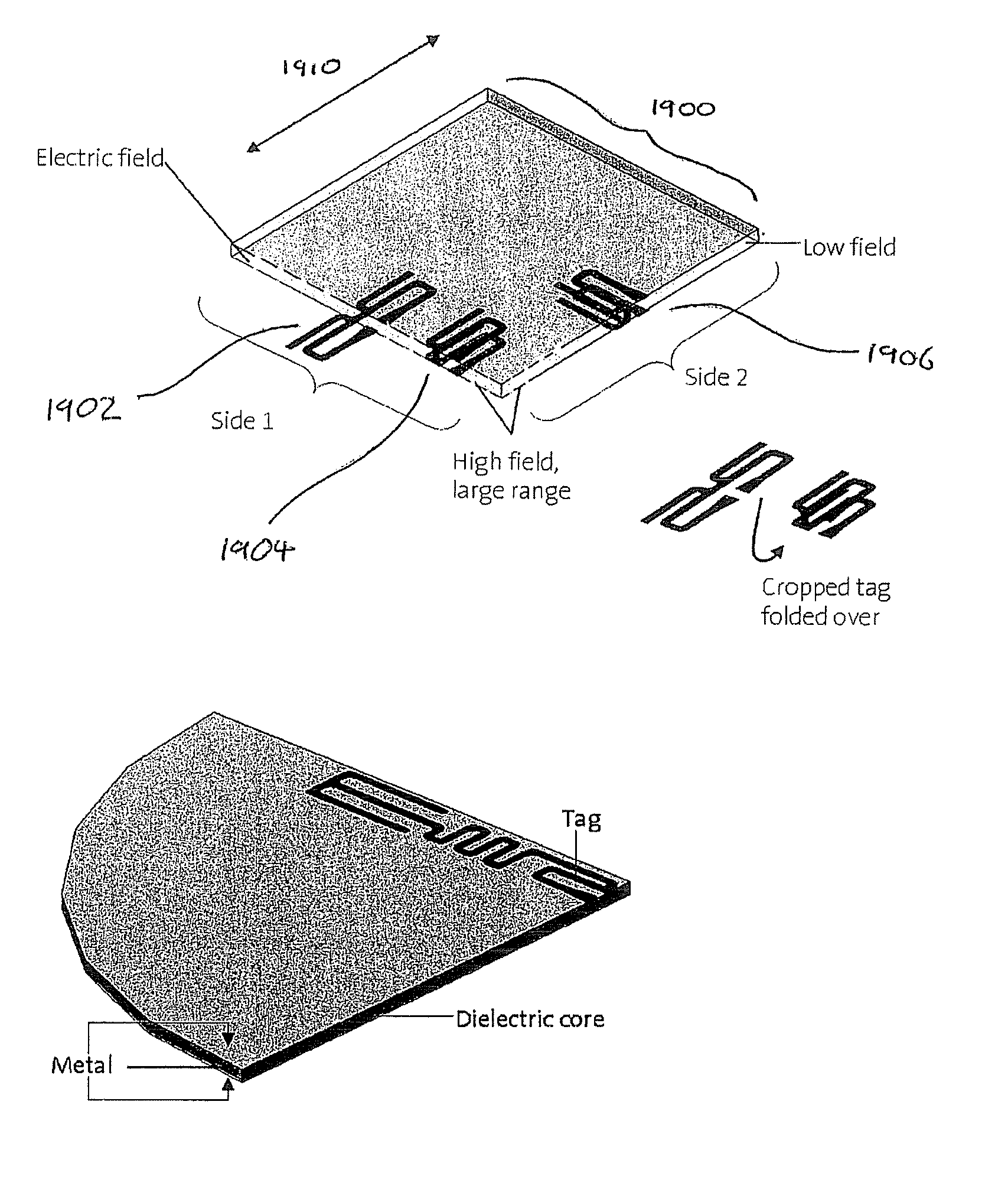

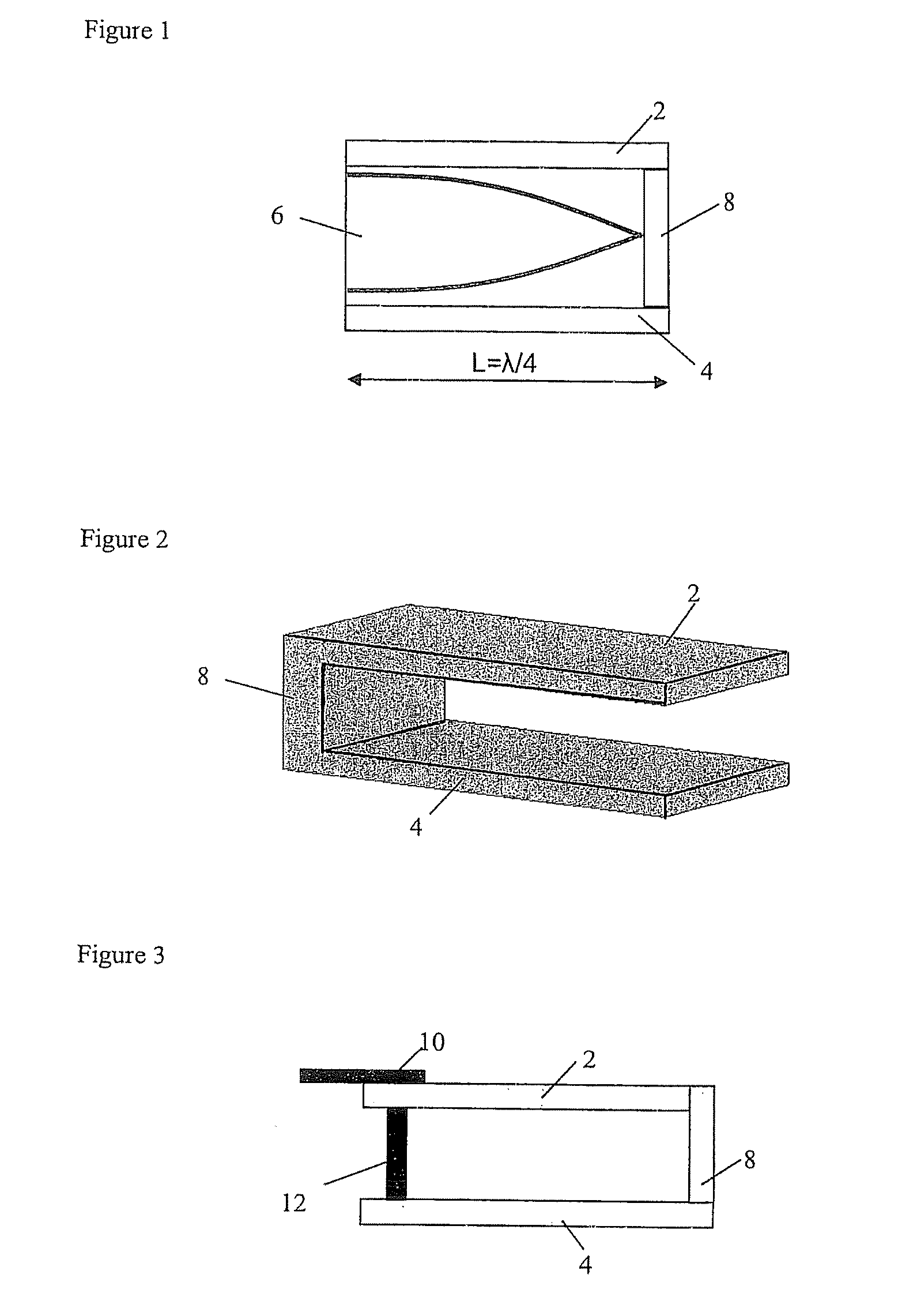

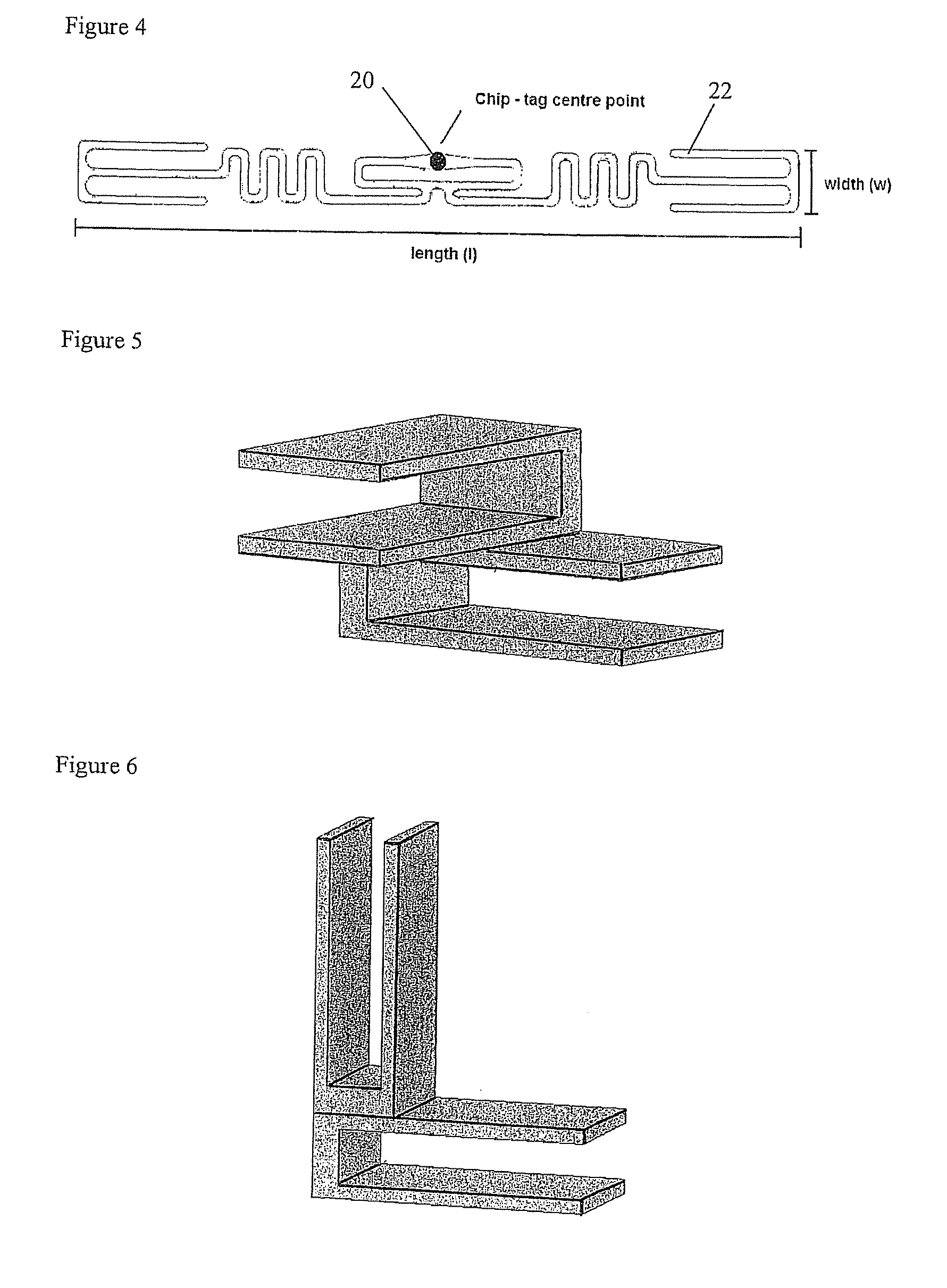

Electromagnetic Enhancement and Decoupling

ActiveUS20070290941A1Reduce decreaseMagnetic/electric field screeningAntenna supports/mountingsElectrical field strengthElectron

Apparatus and methods for providing a substantially surface independent tagging system are disclosed. A resonant dielectric cavity is defined between upper and lower conducting layers, and closed at one end by a conducting base portion. Incident radiation couples into the cavity and is resonantly enhanced. An electronic device or tag paced at the edge of the cavity experiences a high electric field strength on account of this enhancement and is driven into operation.

Owner:HID GLOBAL CORP

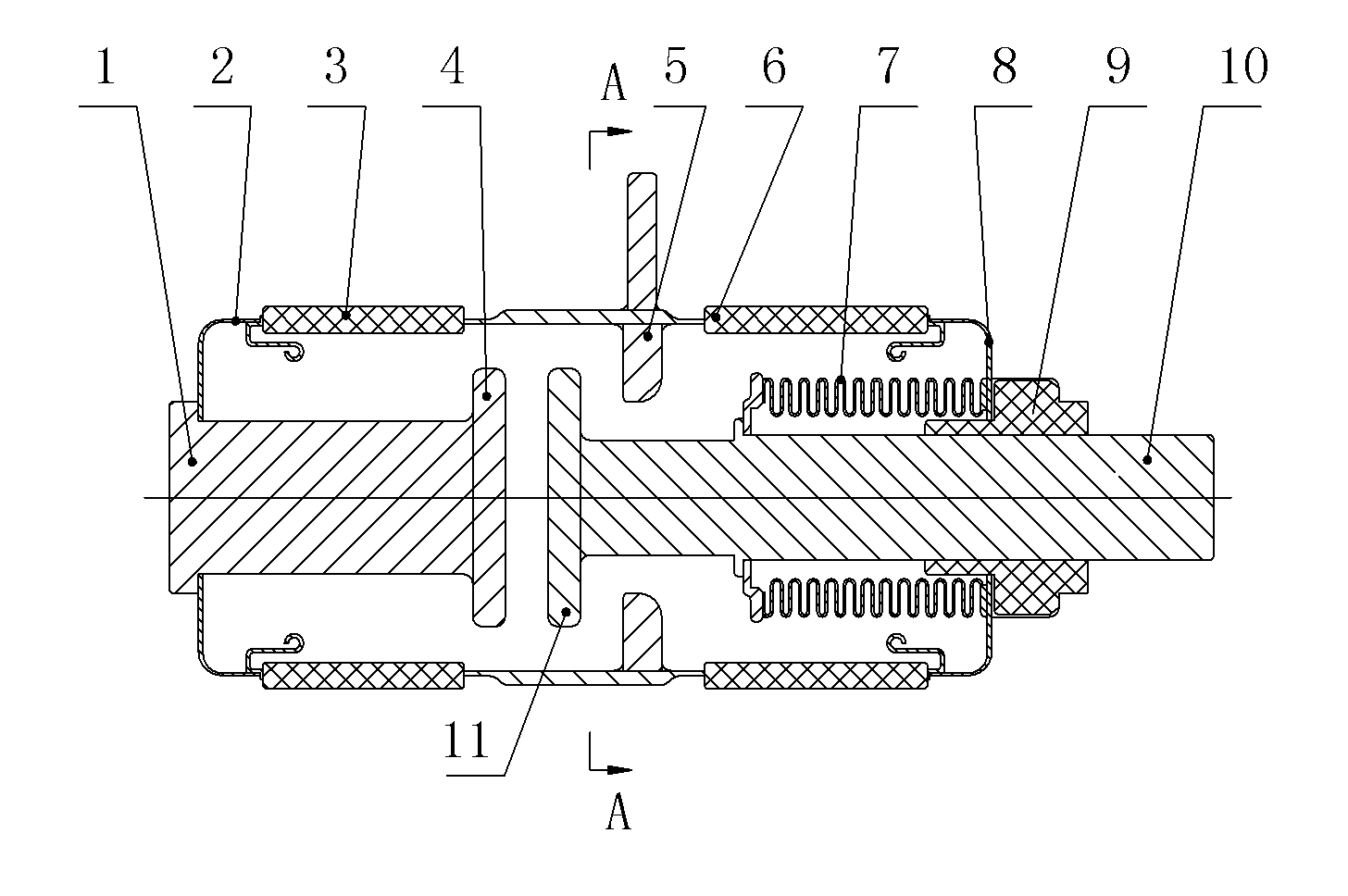

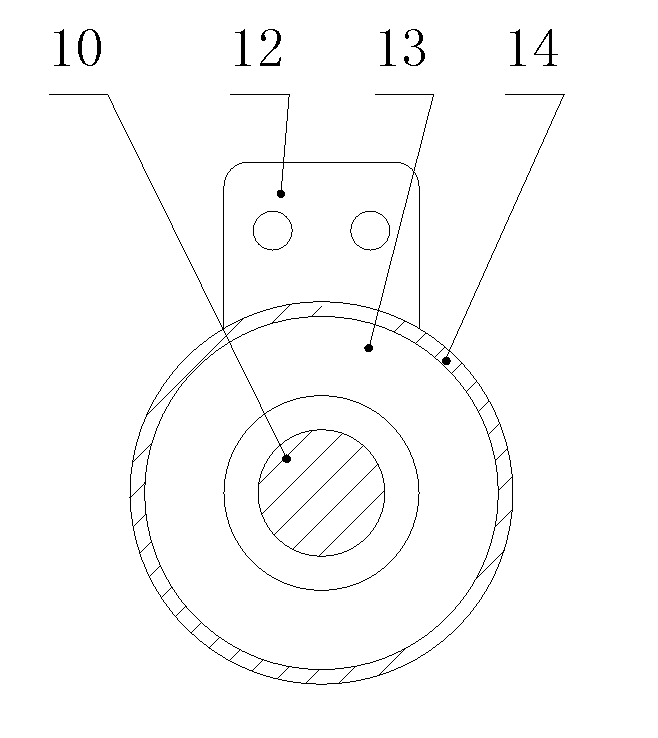

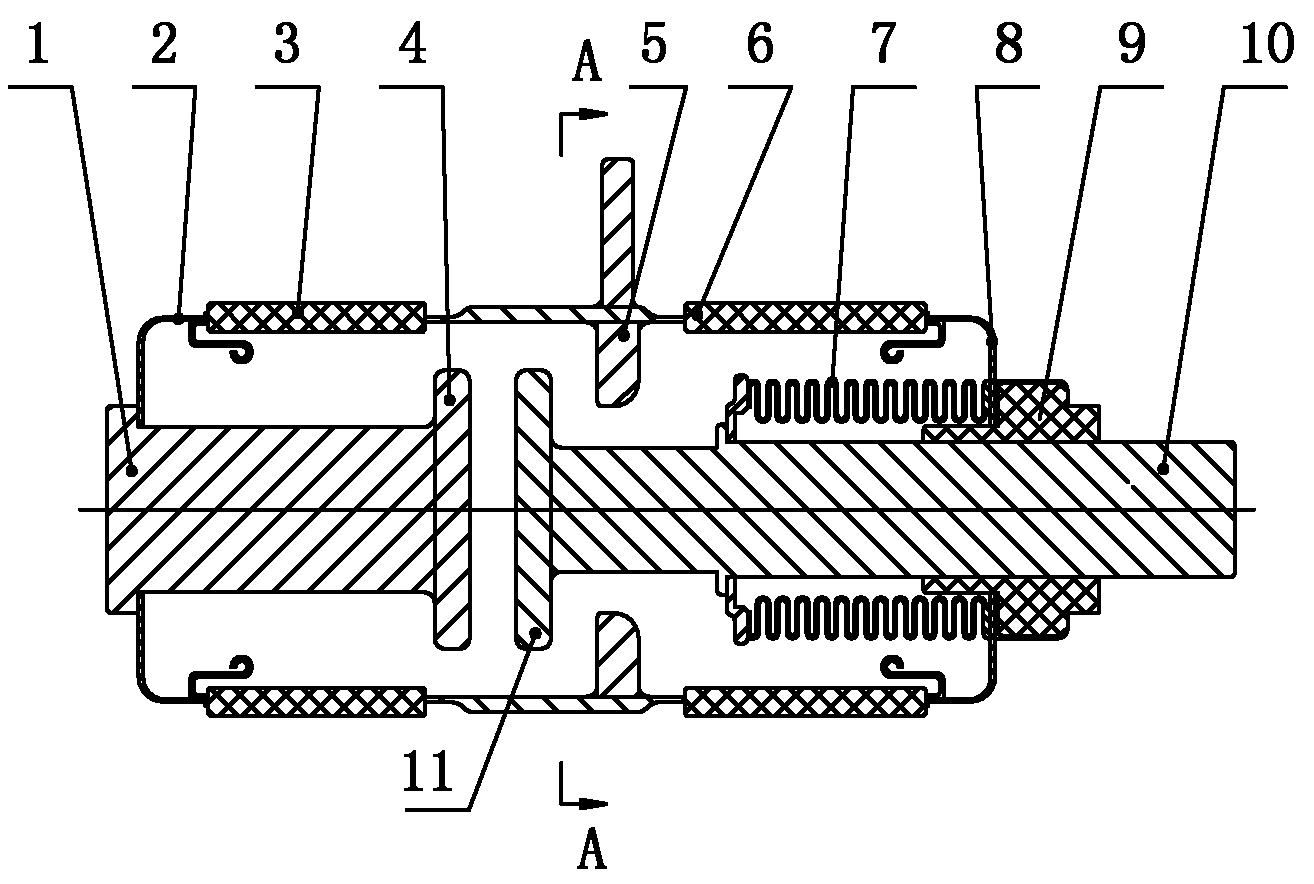

Three-station vacuum switch tube

ActiveCN102157297AAdvanced technologyReasonable designHigh-tension/heavy-dress switchesAir-break switchesElectricityGround contact

The invention discloses a three-station vacuum switch tube comprising a vacuum chamber, a fixed contact assembly, a moving contact assembly and a grounding contact, wherein the grounding contact comprises a grounding contact ring and a grounding terminal, wherein the grounding terminal is electrically connected with the grounding contact ring, and a moving contact is driven by an operating mechanism to take linear back-and-forth movement between a fixed contact and the grounding contact ring; and when the moving contact, the fixed contact and the grounding contact ring are all in off states, the tolerance electric field intensity between the moving contact and the fixed contact is higher than that between the moving contact or the fixed contact and the grounding contact ring. The invention realizes the switch-on, isolation and grounding three-station functions, also not only has the advantages of compact structure, reasonable design, advanced technology, current relative standard accordance, long electrical life and mechanical life, wide application range, high safety and reliability, and the like, but also realizes that electric breakdown firstly generates between a loading terminal and a grounding terminal once vacuum degree is reduced, enables the leakage currents and the short-circuit currents to flow into earth and ensures the safety of maintenance personnel who possibly mistakenly contact the loading terminal.

Owner:西安森源开关技术研究所有限公司

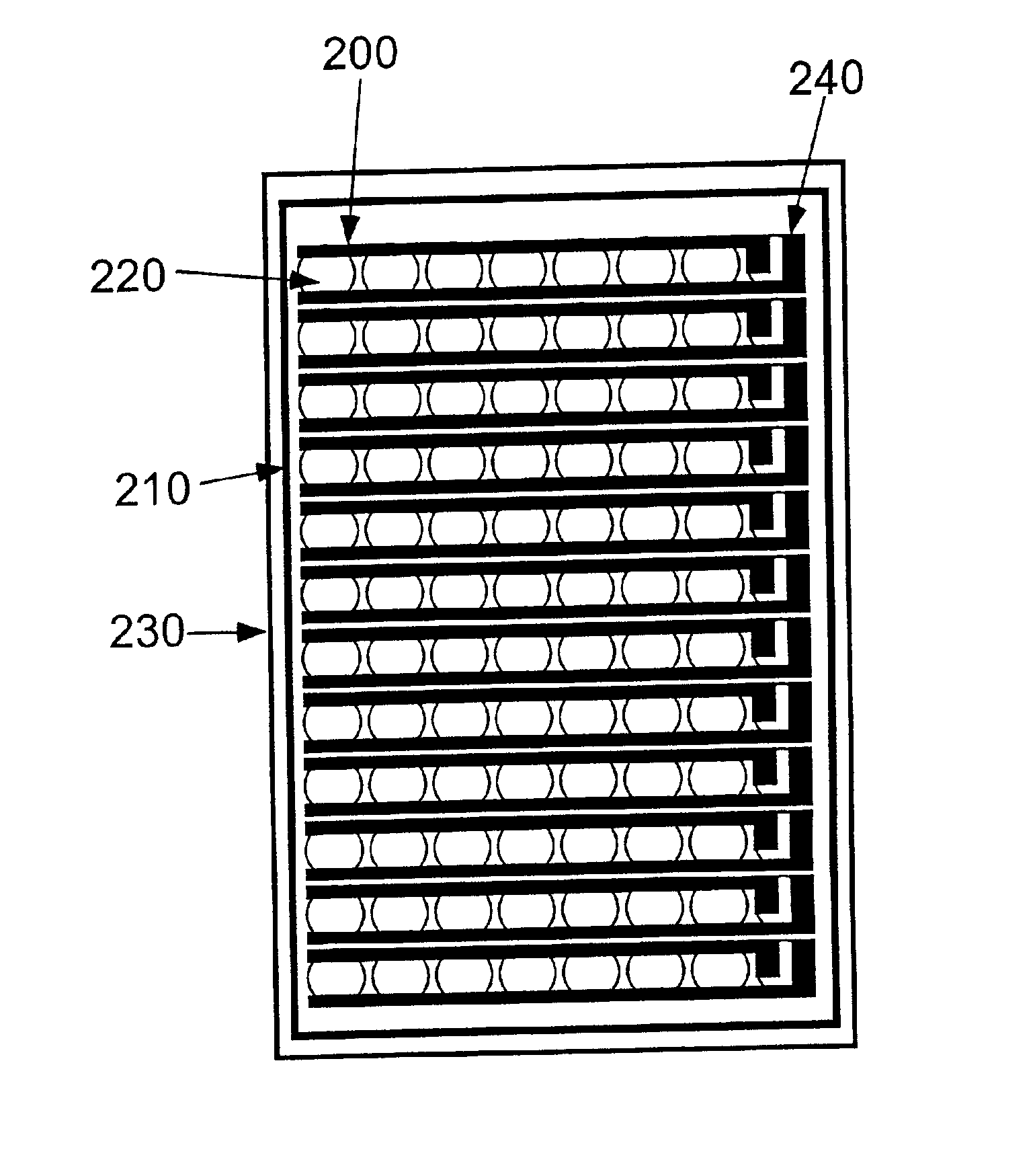

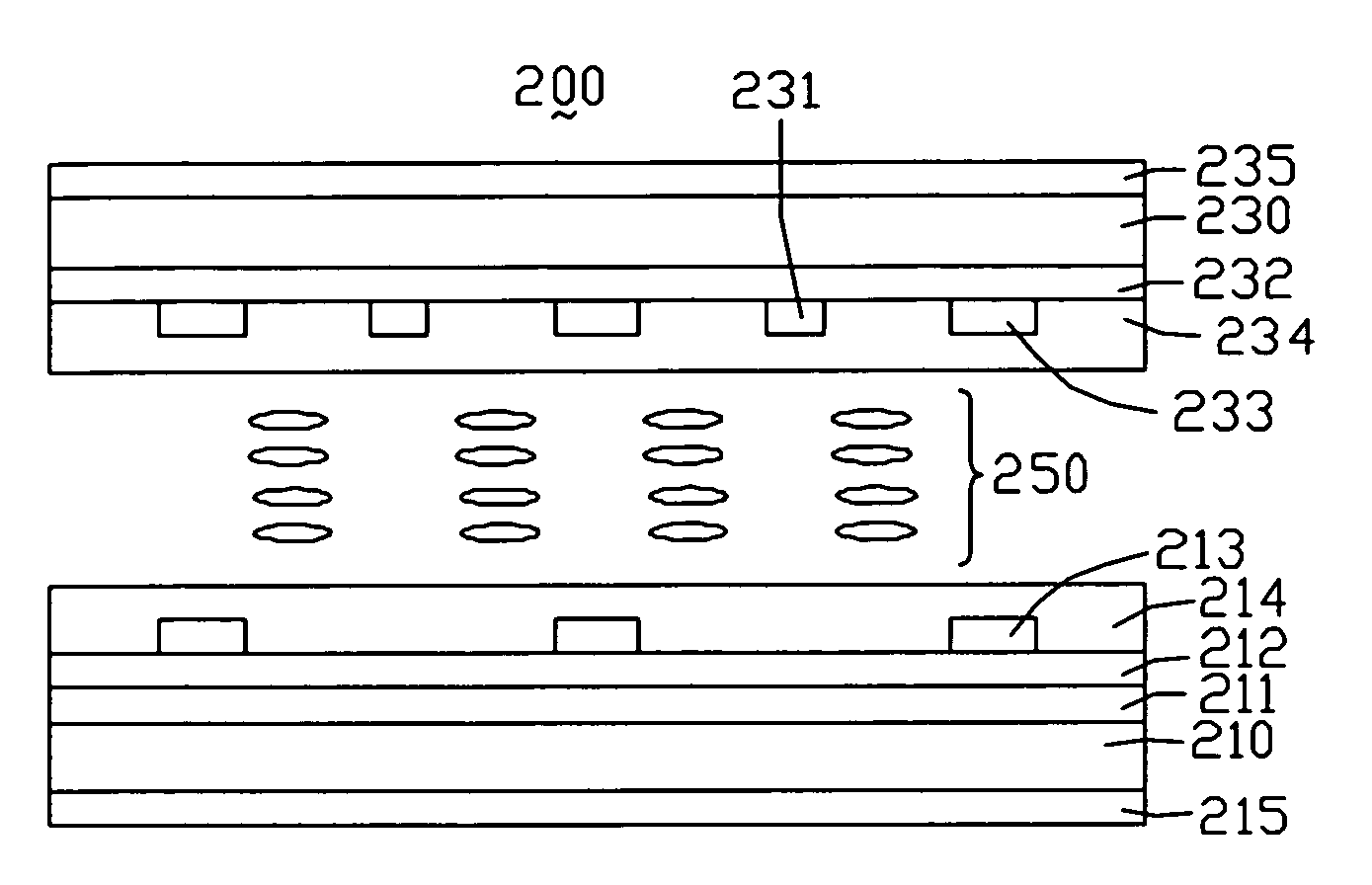

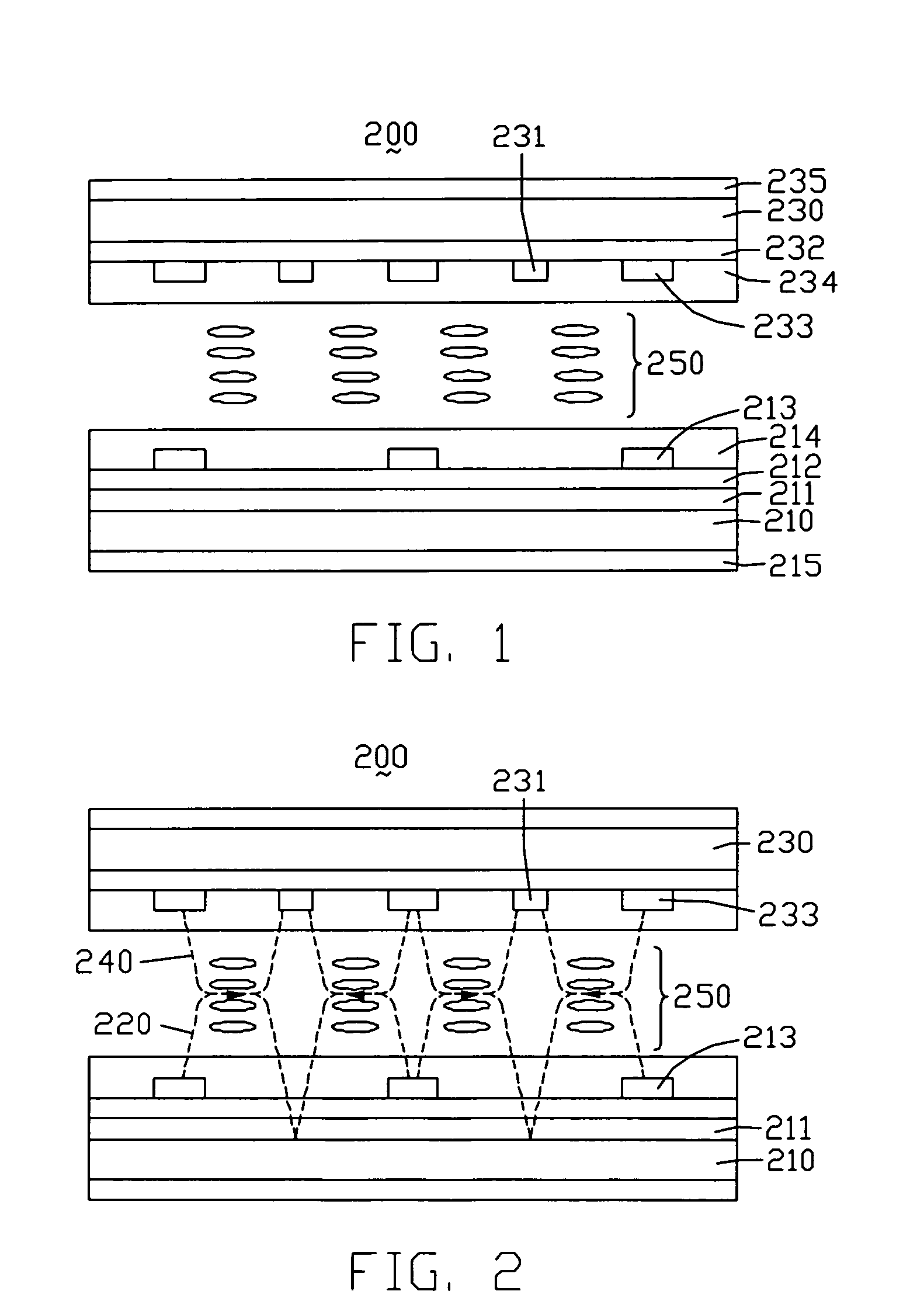

Liquid crystal display having common and floating electrodes on one of substrates thereof

An exemplary liquid crystal display (LCD) (200) includes a first substrate (210); a second substrate (230) opposite to the first substrate; a liquid crystal layer (250) sandwiched between the first substrate and the second substrate; a first common electrode (211), a first insulating layer (212), and pixel electrodes provided at an inner surface of the first substrate in that order; and second common electrodes (231) and floating electrodes (233) provided at the second substrate. The first common electrode and the pixel electrodes, and the second common electrodes and the floating electrodes, respectively produce two electric fields in the liquid crystal layer corresponding to each other. A combined electric field strength is uniformly distributed in the liquid crystal layer, so that all the liquid crystal molecules can be sufficiently twisted. Thus a viewing angle, a degree of chroma, and a transmission ratio of the LCD are improved.

Owner:INNOLUX CORP

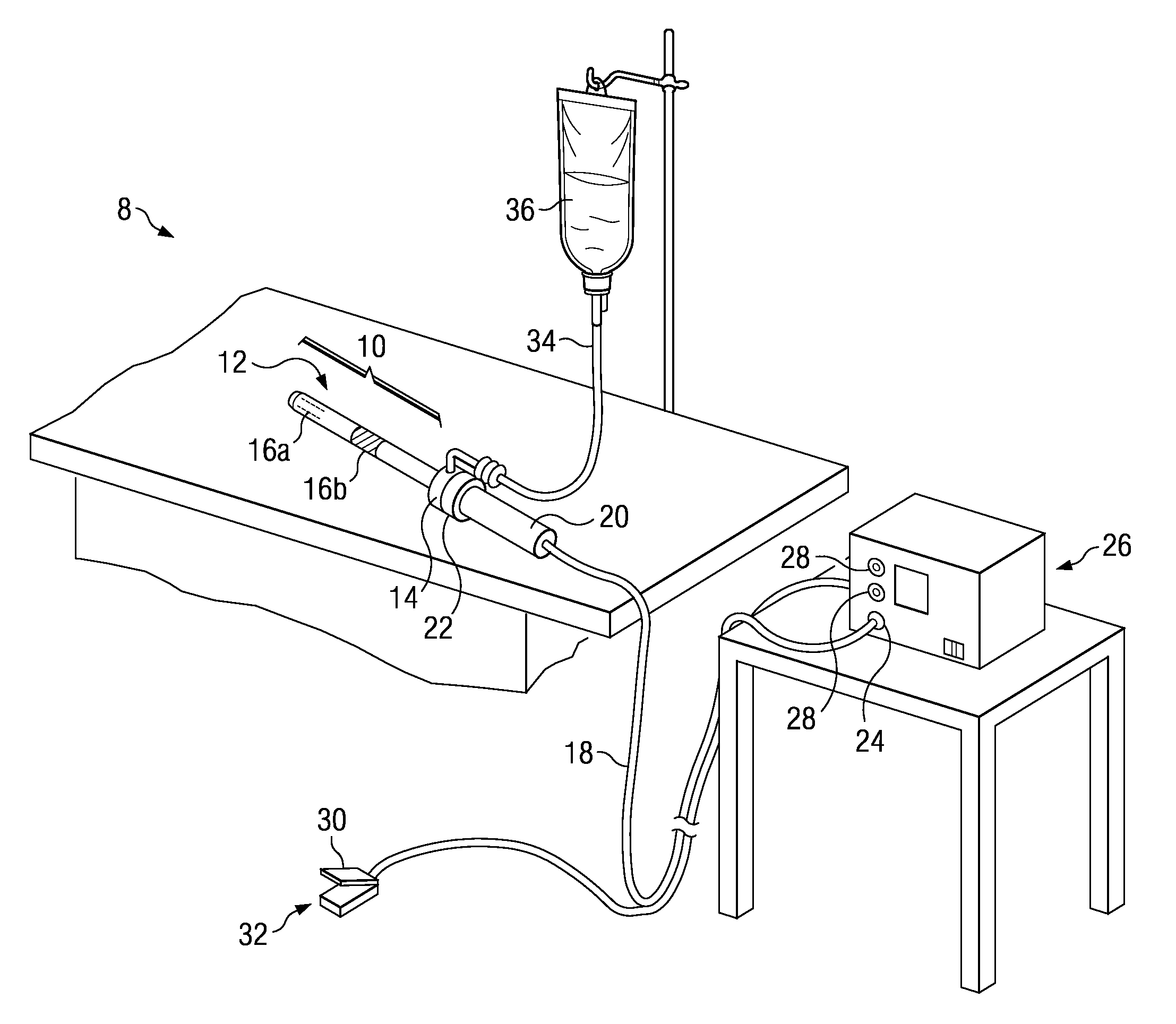

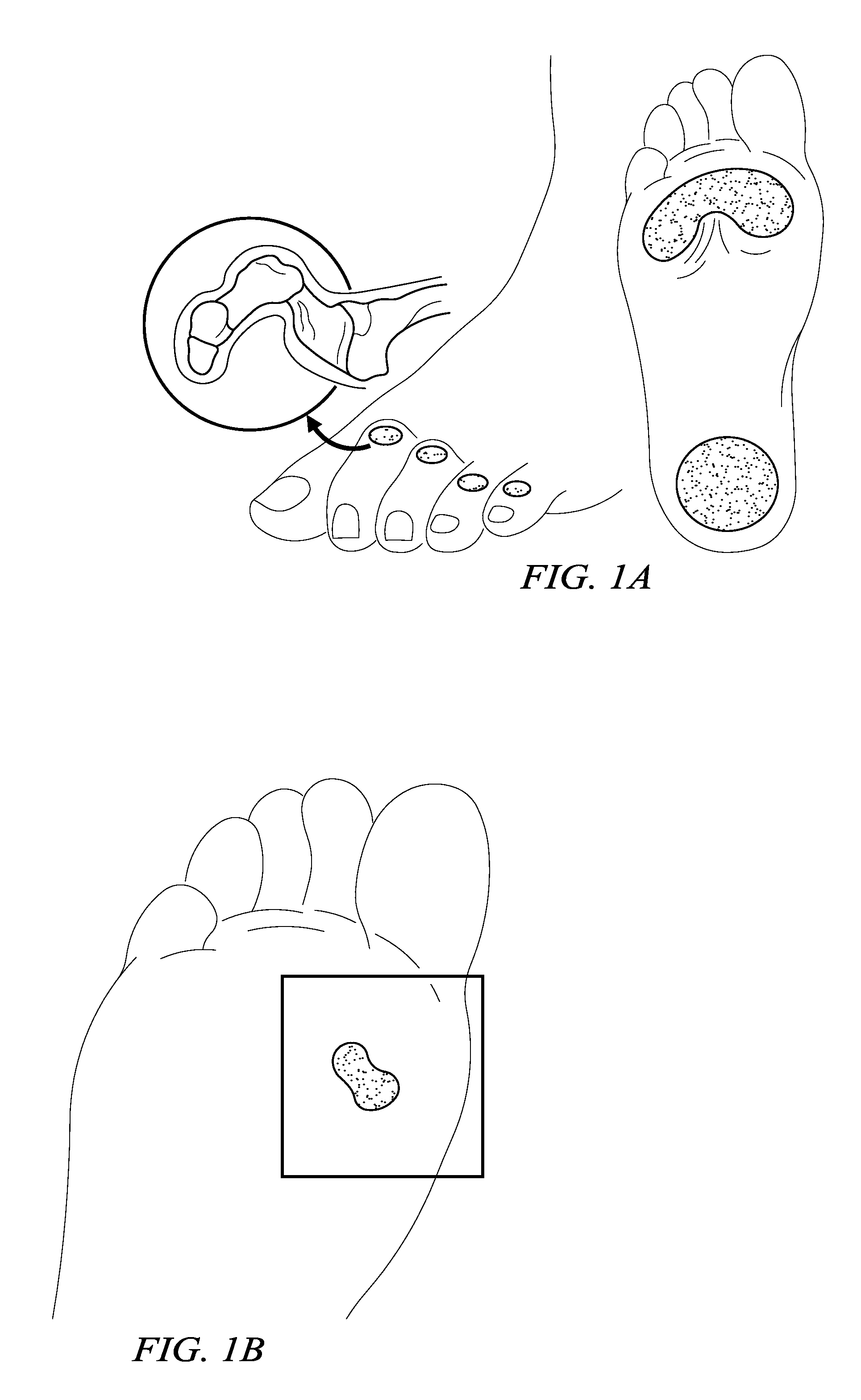

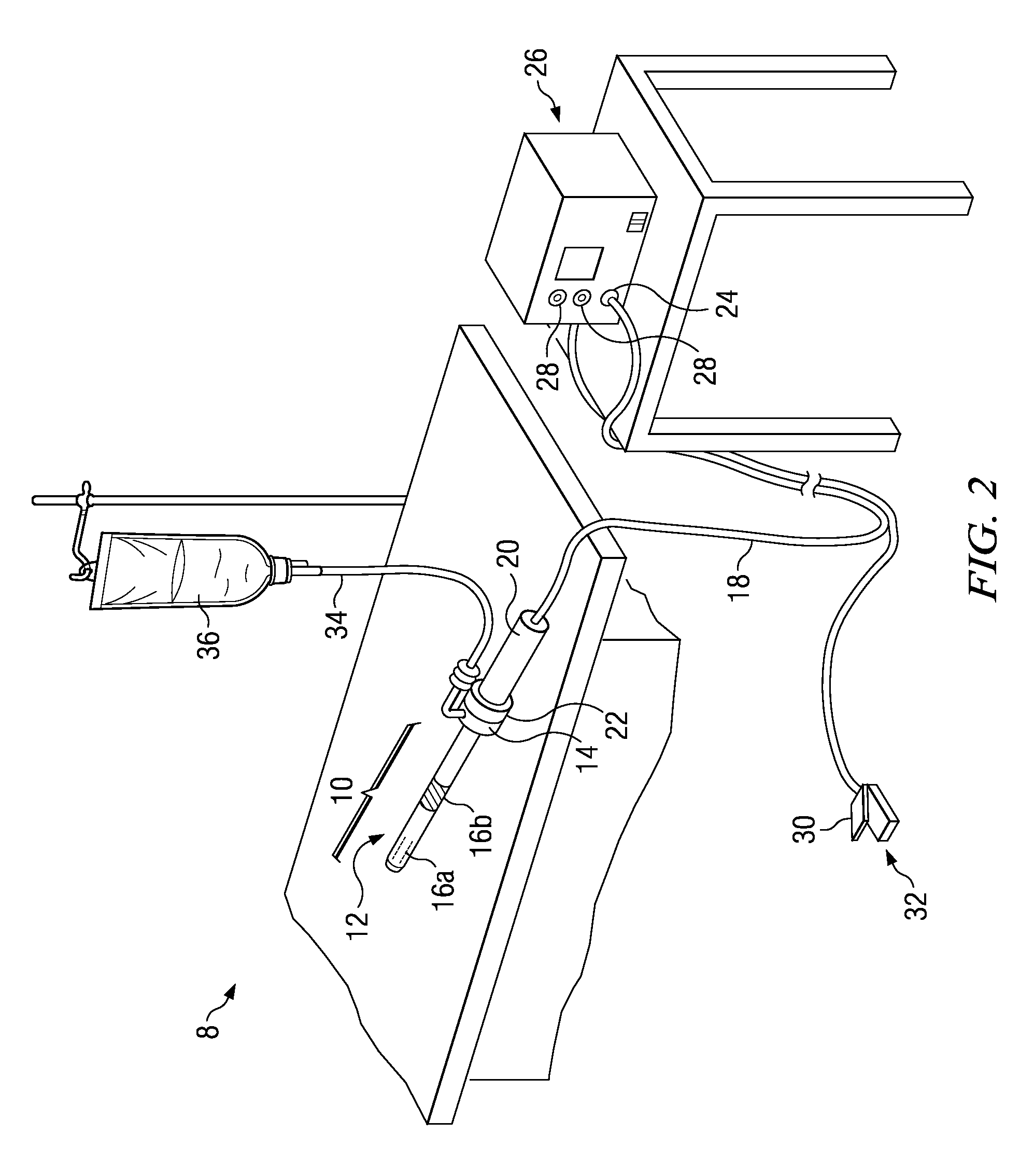

Electrosurgical system and method for treating chronic wound tissue

InactiveUS20090209958A1Promote healingIncrease the electric field strengthSurgical instruments for heatingSurgical instruments for aspiration of substancesElectrical field strengthMedicine

An electrosurgical method for treating chronic wound tissue, comprising: positioning an active electrode in close proximity to the chronic wound, the active electrode being disposed on a distal end of an electrosurgical shaft; applying a high-frequency voltage potential difference across the active electrode and a return electrode sufficient to develop a high electric field intensity associated with a vapor layer proximate the active electrode and in close proximity to the wound tissue; and stimulating an expression of at least one healing mediator.

Owner:ARTHROCARE

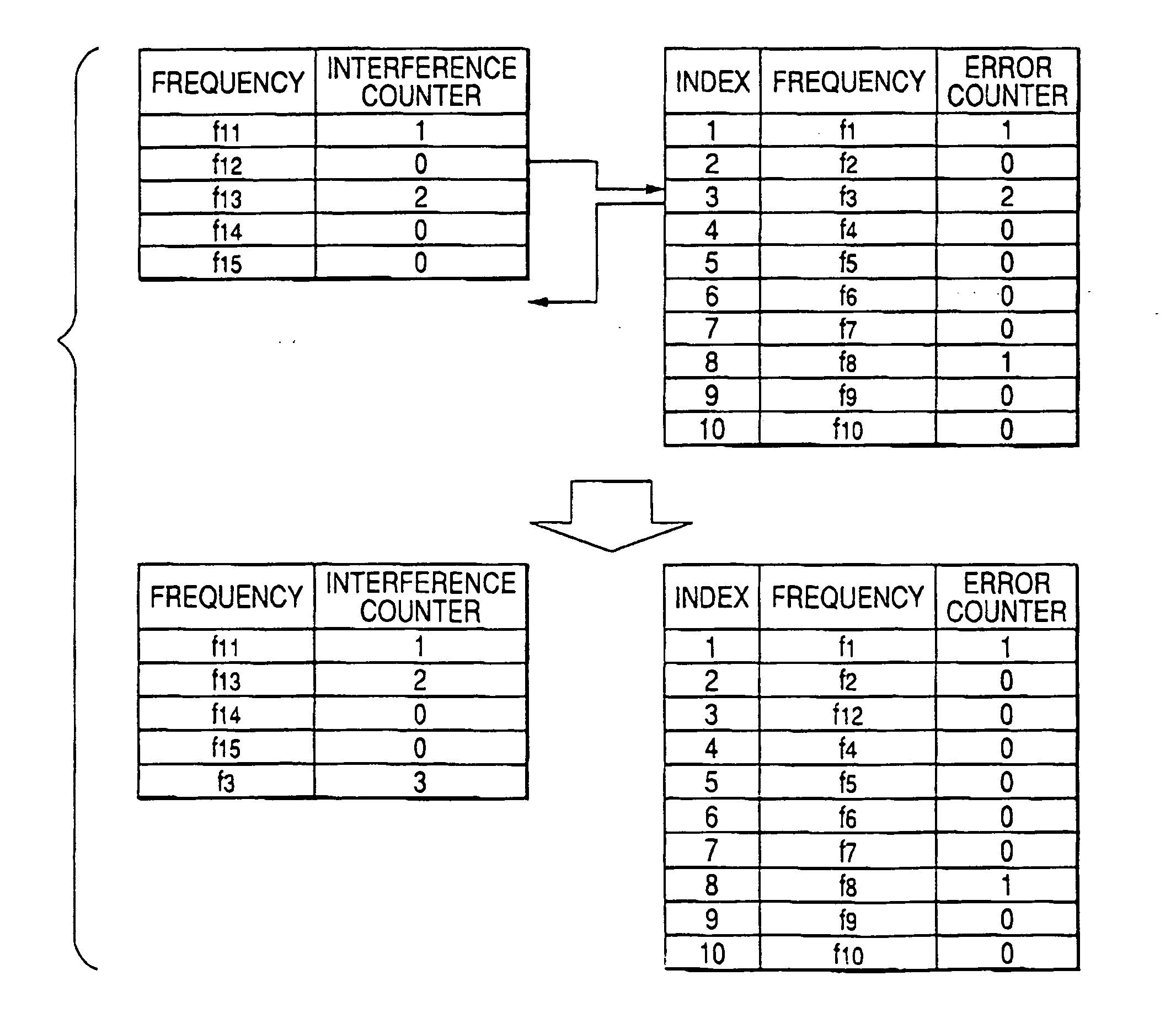

Radio communication apparatus and interference avoiding method

ActiveUS20050020271A1Avoid interferenceError preventionLine-faulsts/interference reductionCarrier signalEngineering

The invention provides a frequency hopping method for switching a hopping carrier frequency in a predetermined hopping pattern based on a hopping carrier table, in which there is provided intermittent receiving means for starting carrier frequency designating means every constant cycle to give a command for receiving the control channels of opposed radio base stations. In the case in which a hopping order in a hopping carrier table is skipped by n to carry out switching every intermittent receiving cycle in an intermittent receiving operation, an intermittent receiving cycle is set in such a manner that the n and a total number m of hopping carrier frequencies in the hopping carrier table have a prime relationship with each other. Moreover, the electric field strength of a carrier frequency in a spare carrier list is measured by the intermittent receiving operation and an interference counter of a spare carrier is increased or decreased corresponding to a frequency at which the electric field strength exceeds a predetermined threshold, and a carrier frequency deleted from a hopping pattern is set to have the worst value as the initialized value of the interference counter. A standby is maintained in a state of a non-exchange until the frequency at which an electric field strength measured for the frequency exceeds a threshold is sufficiently reduced, and the same frequency is recycled as an exchangeable carrier frequency after sufficiently confirming that a communication can be carried out.

Owner:PANASONIC CORP

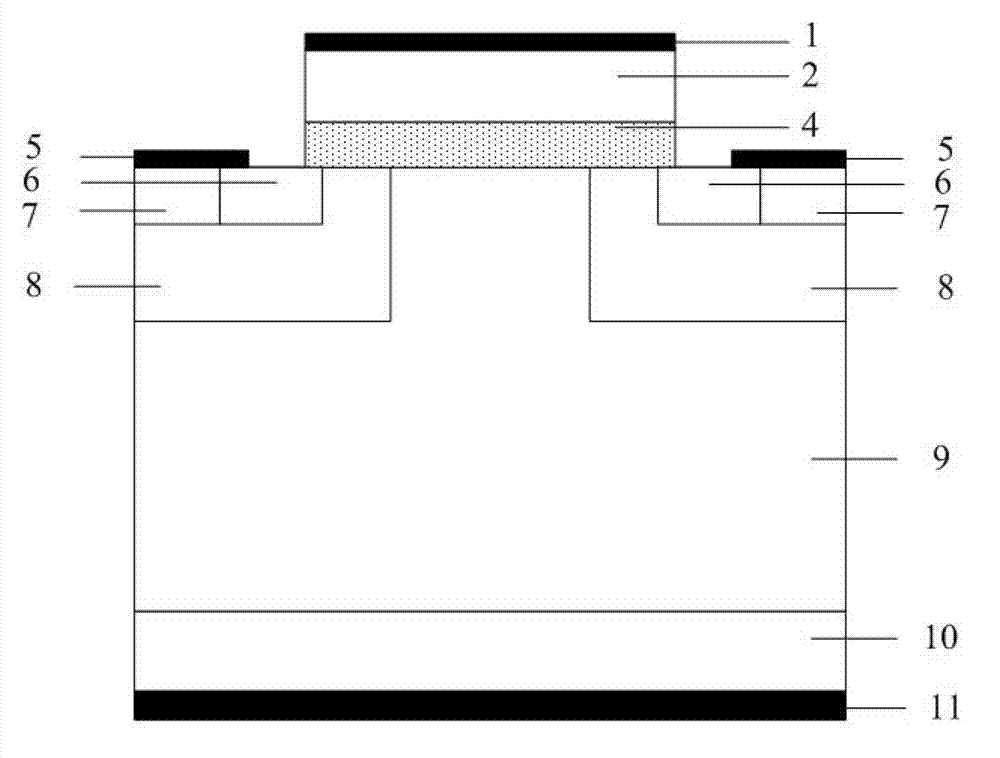

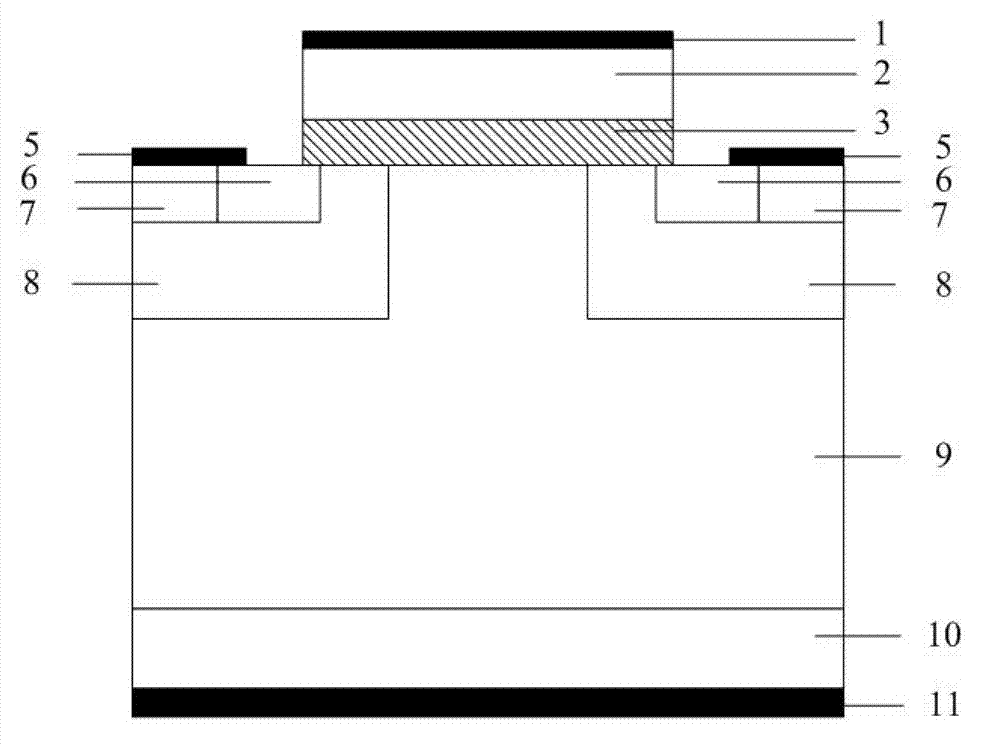

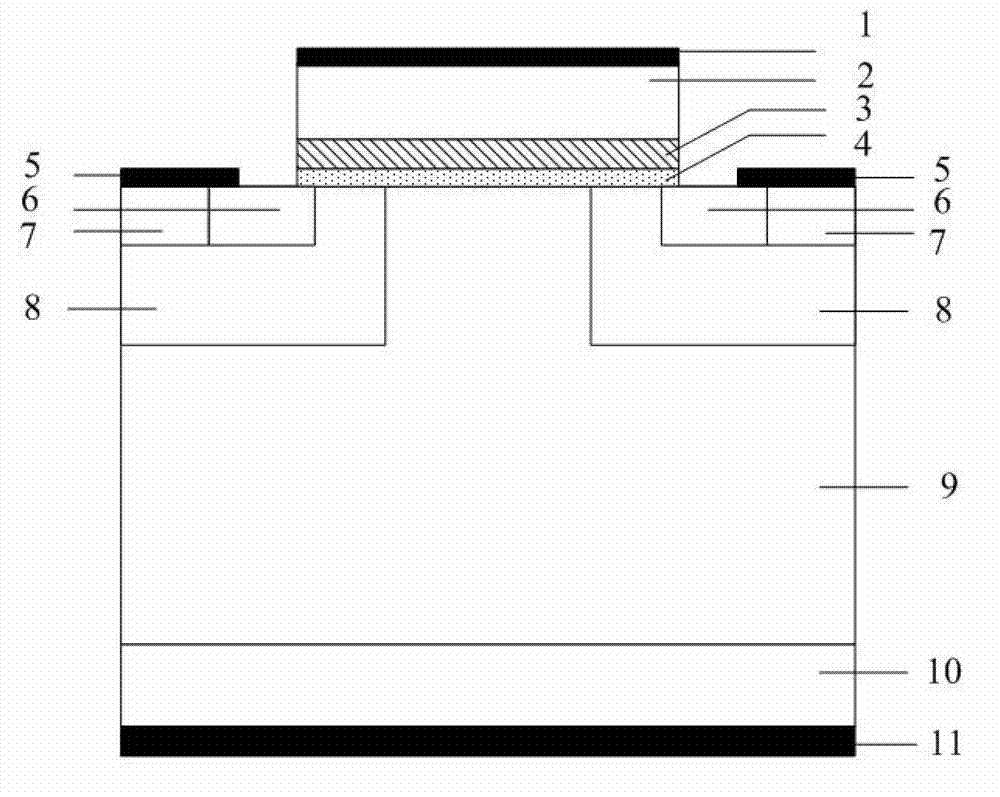

SiC vertical double diffusion metal oxide semiconductor structure (VDMOS) device with composite gate dielectric structure

InactiveCN102779852ALower breakdown voltageAvoid premature breakdownSemiconductor devicesDielectricGate dielectric

The invention discloses a SiC vertical double diffusion metal oxide semiconductor structure (VDMOS) device with a composite gate dielectric structure, and belongs to the technical field of power semiconductor devices. A thought of differentiating modulation of electric fields is adopted according to difference of intensities of electric fields and difference of defect concentrations of gate dielectrics in different areas, namely, high-k gate dielectrics are adopted in channel regions with high-defect concentration and a low electric field, so that a large quantity of trap states caused by using a SiO2 / SiC interface is avoided; the influence on Fowler-Nordheim (FN) tunneling current is obviously reduced; and meanwhile, because the electric field intensity in a channel injection area is small, the reduction on gate dielectric breakdown voltage caused by small offset of conduction band / valence band is weakened; and moreover, a SiO2 gate dielectric (a junction field-effect transistor (JFET) area is formed in a way of extension and is not subjected to ion injection, the surface quality of the JFET area is good, and the SiO2 / SiC interface state is low) is adopted by the JFET area with low defect concentration and a high electric field, and enough high conduction band offset is supplied by the SiO2 dielectric, so that the ahead breakdown of the gate dielectric is avoided.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

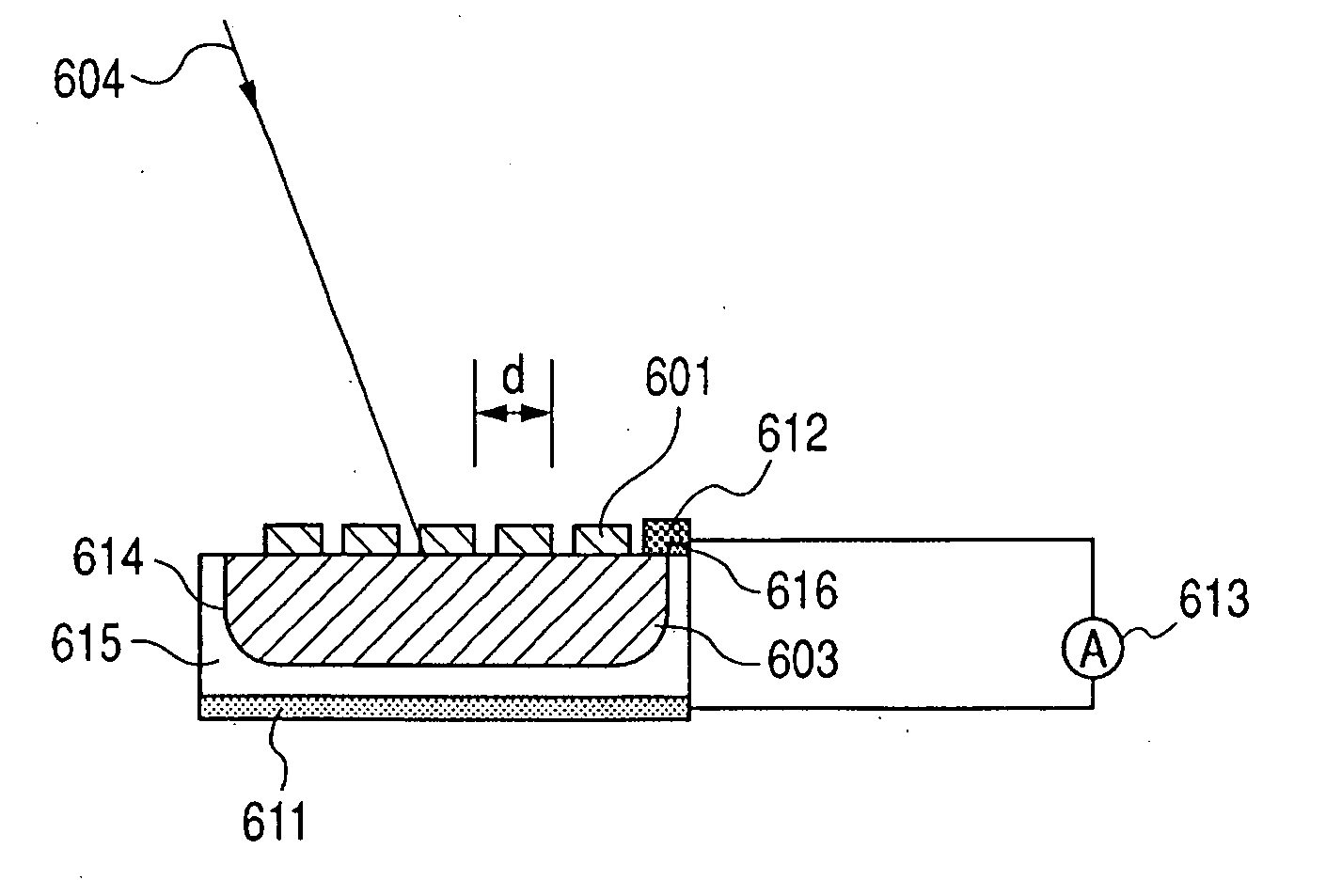

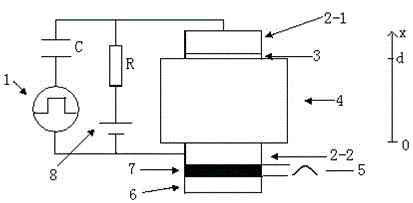

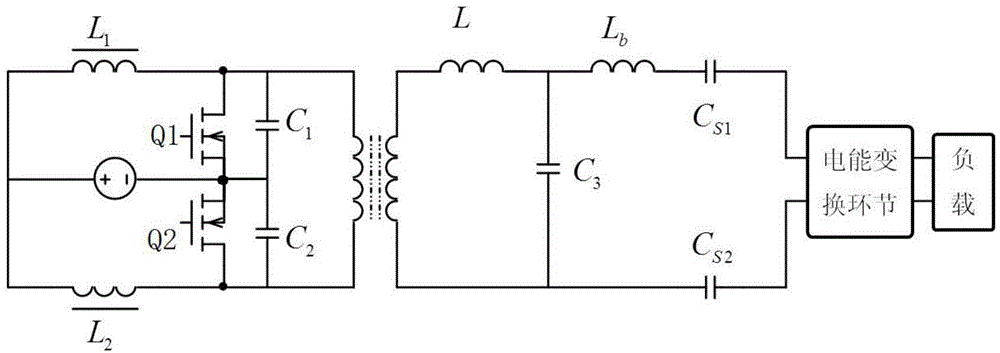

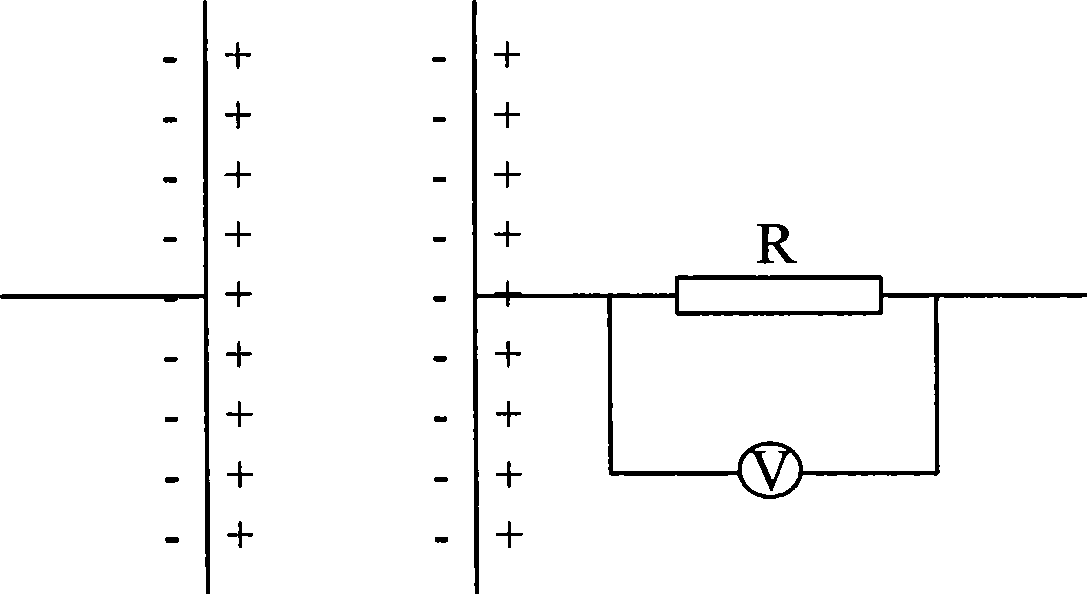

Method for measuring and judging insulation aging based on PEA space charges

ActiveCN103558531AAchieve statisticsImplement aging assessmentTesting dielectric strengthElectrical field strengthHigh pressure

The invention relates to a method for measuring and judging insulation aging based on PEA space charges. The method includes the steps that a pulsed electro-acoustic space charge measurement system is built, a space charge test is conducted on an insulating layer of a power cable, statistics is conducted on the absolute charge quantity of the space charges, the currently measured quantity and a threshold value are compared with historical data, and insulation is evaluated by utilizing the total quantity and the charge increased speed to analyze parameters; according to an externally applied high voltage power supply electric field and an insulation internal space charge distribution curve, an electric field intensity method is utilized to analyze insulation of the power cable, when calculated field intensity is higher than a design value, the insulation can be damaged, and the aging degree of insulation can be judged according to the increased speed of the electric field intensity. According to the method, the insulation internal space charges of the power cable are online monitored, and insulation aging of the power cable is evaluated according to data.

Owner:FOSHAN POWER SUPPLY BUREAU GUANGDONG POWER GRID

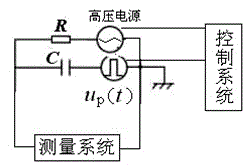

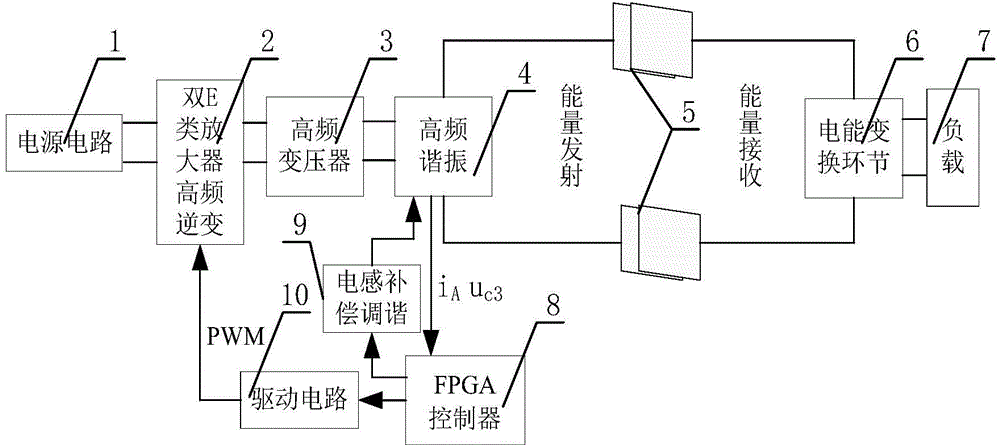

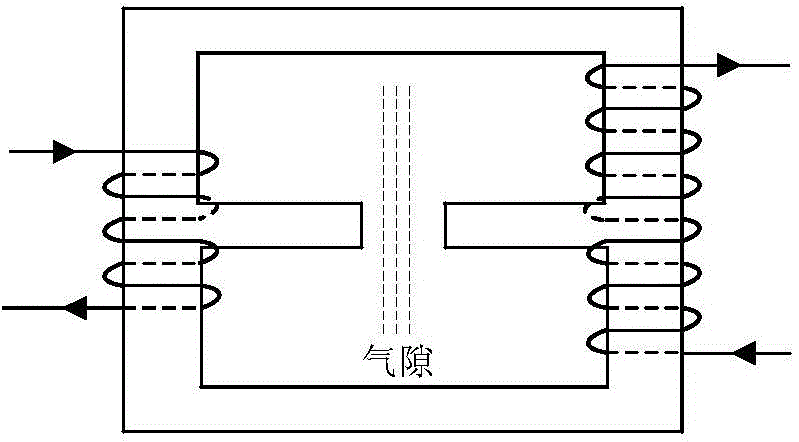

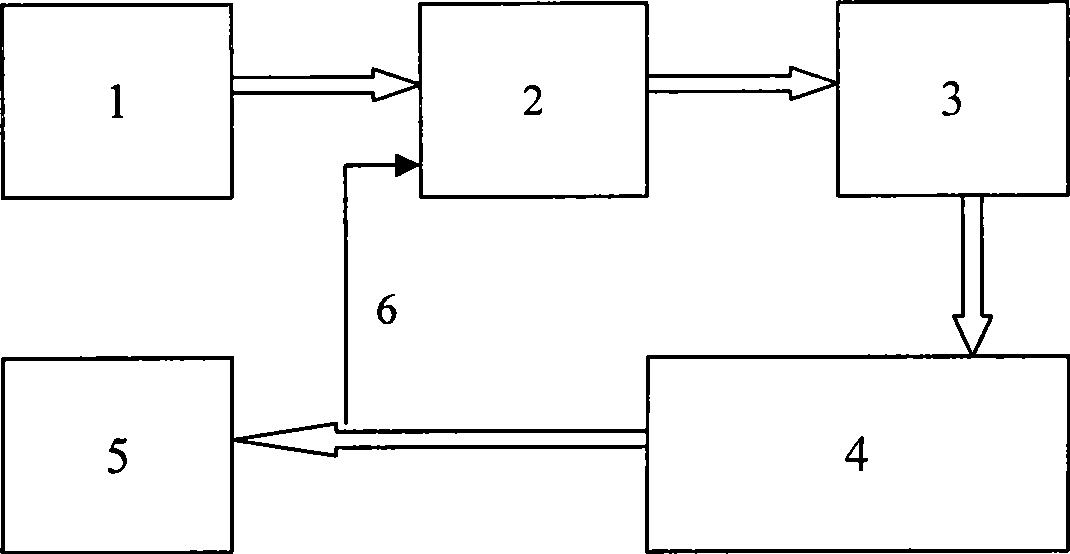

Electric field coupled power transfer system and control method based on novel topology

ActiveCN103560593AReduce voltageTransmission Density EnhancementElectromagnetic wave systemCircuit arrangementsElectrical field strengthPower capability

The invention discloses an electric field coupled power transfer system and a control method based on the novel topology. The system comprises a high-frequency inverter, a high-frequency resonator, an electric field coupling mechanism and an electric energy conversion link, and is characterized in that the high-frequency inverter is a double-E type amplifying high-frequency inverter, a high-frequency transformer is arranged between the high-frequency inverter and the high-frequency resonator, the high-frequency resonator is further connected with a controller, and the output end of the controller is connected with an inductance compensation tuning module and a drive circuit. The electric field coupled power transfer system has the obvious effects that the high-frequency voltage at the two ends of a coupling mechanism is increased, the strength of an electric field is enhanced, the transmission distance is lengthened, the voltage at the two ends of a high-frequency switch tube is increased to meet the requirement of high-frequency power electronic devices at the present stage, the power capacity of the system is improved, the voltage of the switch tube is reduced, the switch loss is reduced, and the adaptive ability of the system is improved.

Owner:重庆华创智能科技研究院有限公司

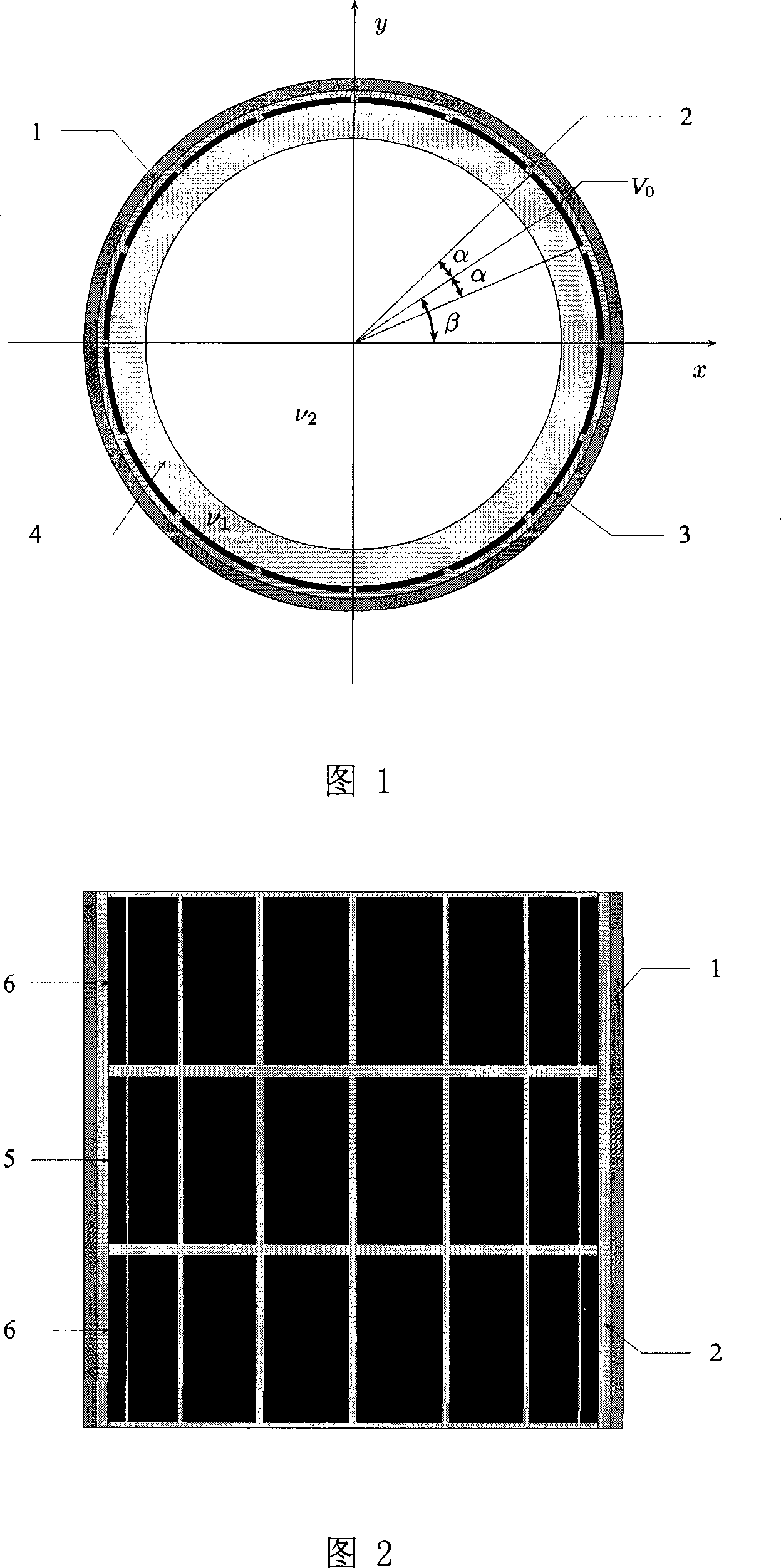

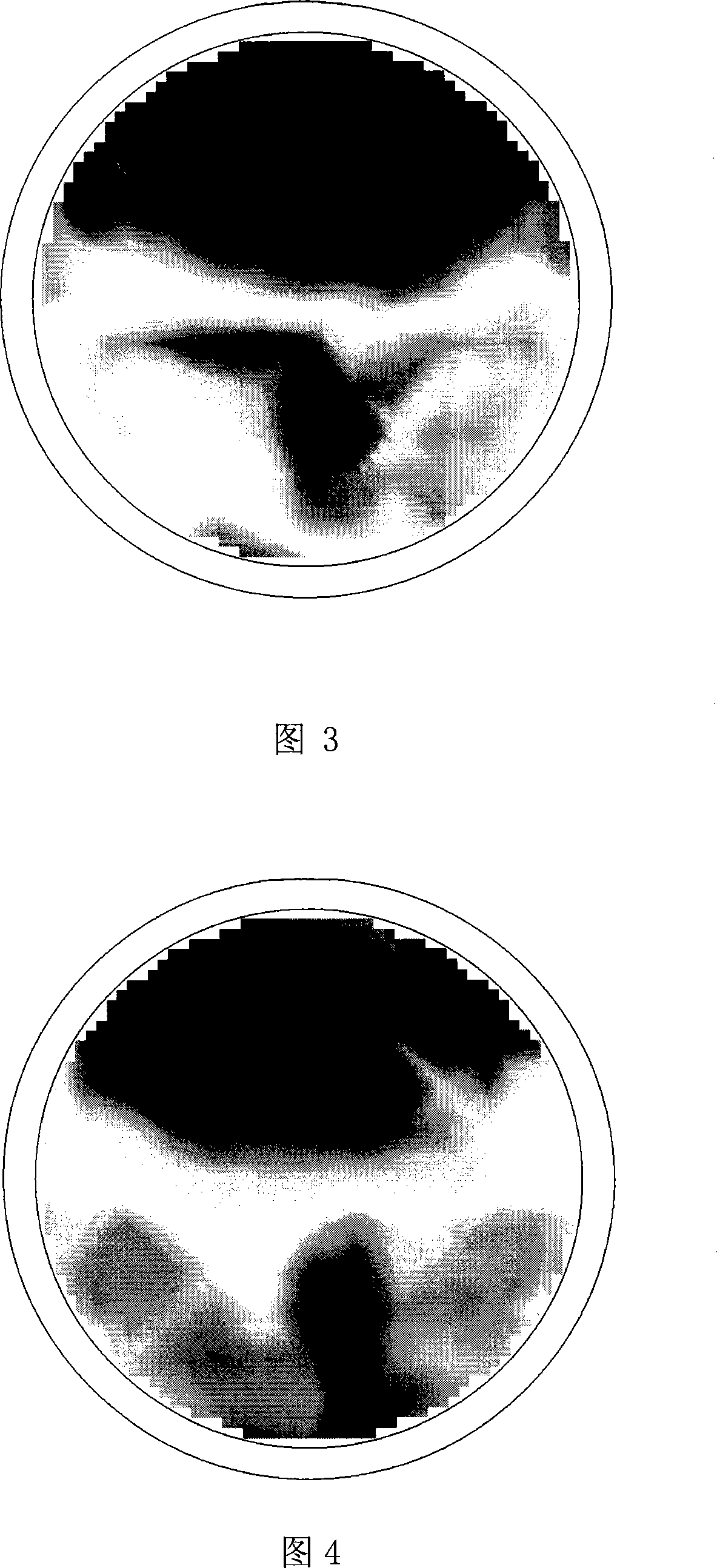

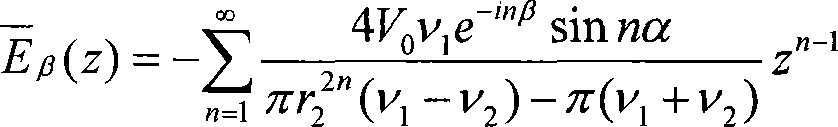

Non-contact type electric impedance sensor and image rebuilding method based on the sensor

InactiveCN101241094AQuick responseLow costDiagnostic recording/measuringSensorsRapid imagingBreakdown strength

The present invention provides a non-contact impedance sensor which is mounted on measuring region, the radial section structure of the sensor comprises of four layers, metal tube layer, insulation material layer, electrode array layer and insulation ring layer from outside to inside in turn. At least two electrodes are distributed in one circle on the insulation ring layer whose thickness is less than 1% of external diameter, and electric field intensity between electrode array and metal tube layer is less than breakdown strength of insulation layer. The electrode array is separated with measuring region by insulation ring layer. Two image reconstruction algorithms to realize electrical impedance tomography based on the said sensor are also provided. The present invention provides analytical medel, corresponding sensitivity distribution expression and two rapid imaging methods, the sensor can measuring synchronous same-positional dual-mode impedance, advance mutual fusion of real parts and imaginary part information of impedance distribution, predigest the design and implement of software and hardware of dual-mode measuring system.

Owner:TIANJIN UNIV

Liquid crystal device and electronic equipment

InactiveUS20080100764A1Reduce displayReduce widthNon-linear opticsElectrical field strengthLiquid-crystal display

A liquid crystal device including a liquid crystal layer having liquid crystal which demonstrates an optically isotropic property when no electric field is applied and demonstrates an optically anisotropic property which is proportional to the square of the electric field strength when electric field is applied, and a pair of substrates which sandwich the liquid crystal layer, including sub-pixel areas each including a reflective display area for reflective display and a transmissive display area for transmissive display; and first and second electrodes provided in both of the reflective display area and the transmissive display area, wherein the liquid crystal layer is driven by an electric field generated between the first electrode and the second electrode, and wherein the distance between the first electrode and the second electrode in the transmissive display area is smaller than the distance between the first electrode and the second electrode in the reflective display area.

Owner:JAPAN DISPLAY WEST

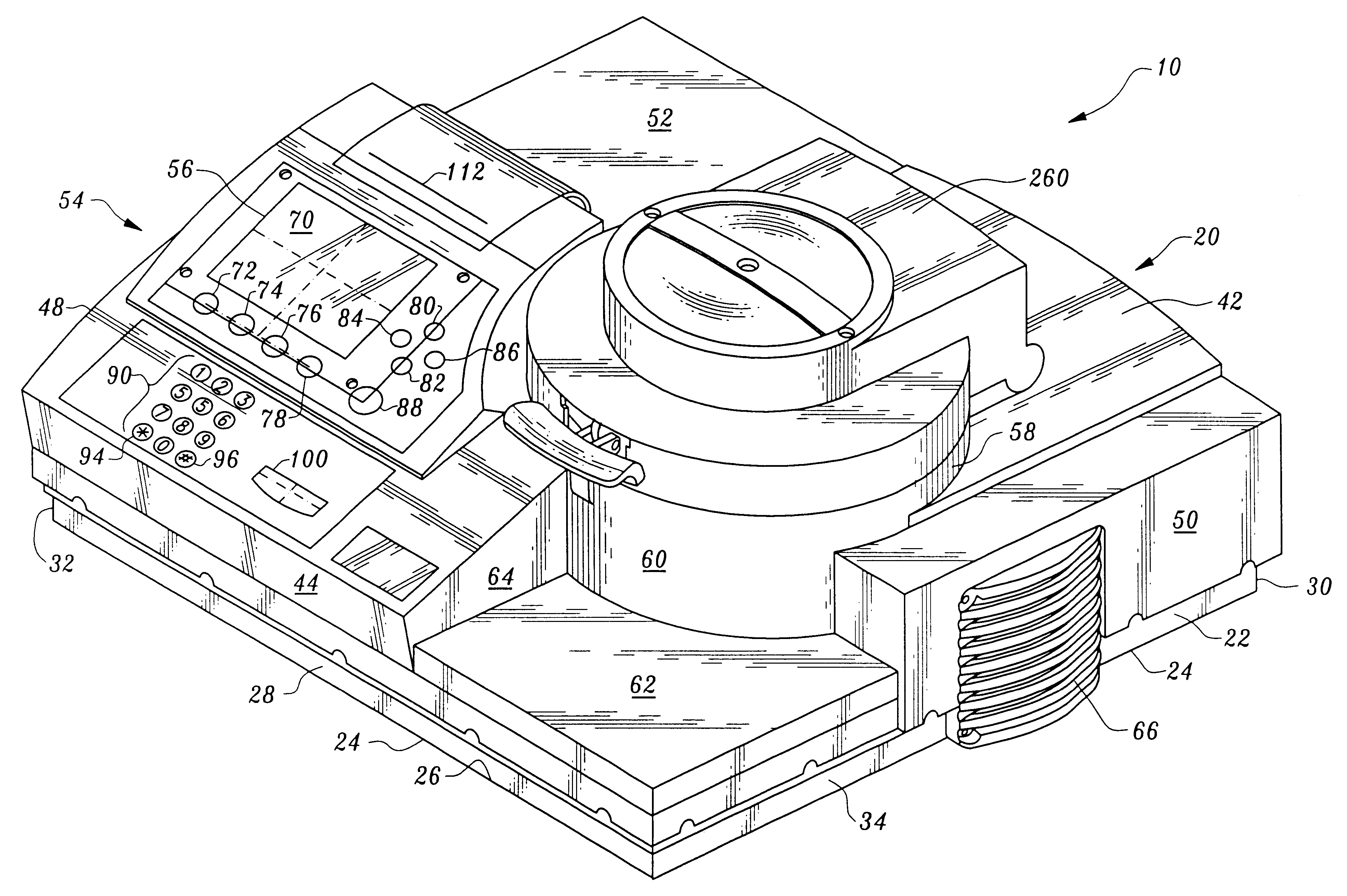

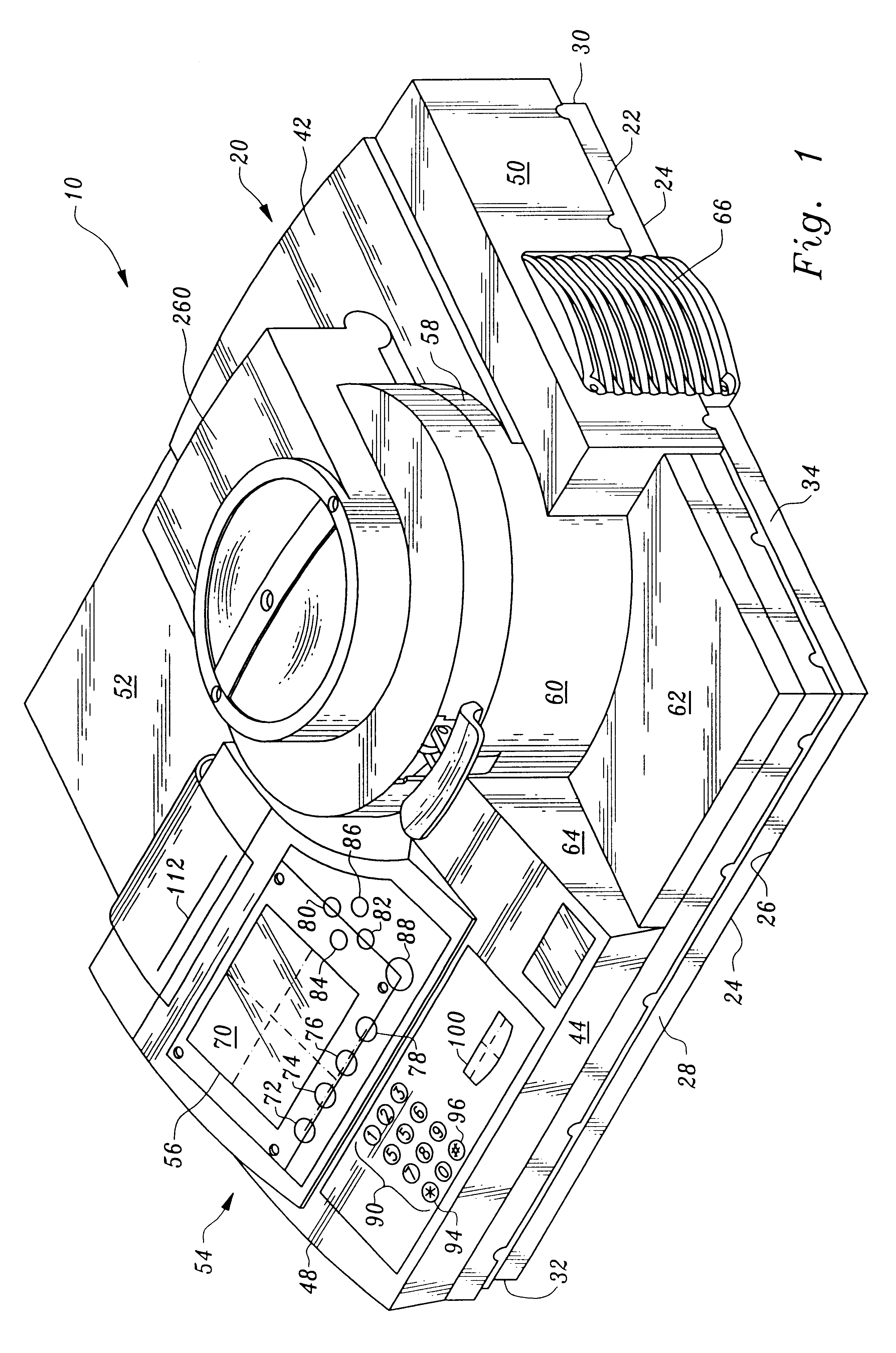

Microwave moisture analyzer: apparatus and method

InactiveUS6247246B1Reduce power consumptionWeighing by removing componentDrying solid materials with heatMicrowaveElectrical field strength

A toploading weighing instrumentality which determines loss on drying by a cylindrical microwave. The cylindrical cavity of the microwave includes a power supply, a magnetron, a power module operatively coupled between said power supply and said magnetron for driving said magnetron, a wave guide communicating with the magnetron and with a microwave containment chamber for delivering energy thereto, at least one microwave energy sensor for sensing microwave energy or magnetic and / or electric field strength within the chamber for controlling, inter alia, the loss on drying process of the sample being assayed and determining when the drying process is complete. A precision electronic balance is operatively disposed within the microwave chamber for allowing a specimen being assayed to be weighed. In addition, a ventilation chamber is provided for venting moisture from the microwave chamber. A processing unit and associated memory allows means for data acquisition, processing and storage of data from the power module driving the magnetron, the microwave energy sensor(s) for sensing magnetic and / or electric fields and the electronic balance for weighing the initial and final weights of the specimen for loss on drying moisture analysis. Both signaling the removal of microwave energy in the chamber.

Owner:DENVER INSTR

Electromobility focusing controlled channel electrophoresis system

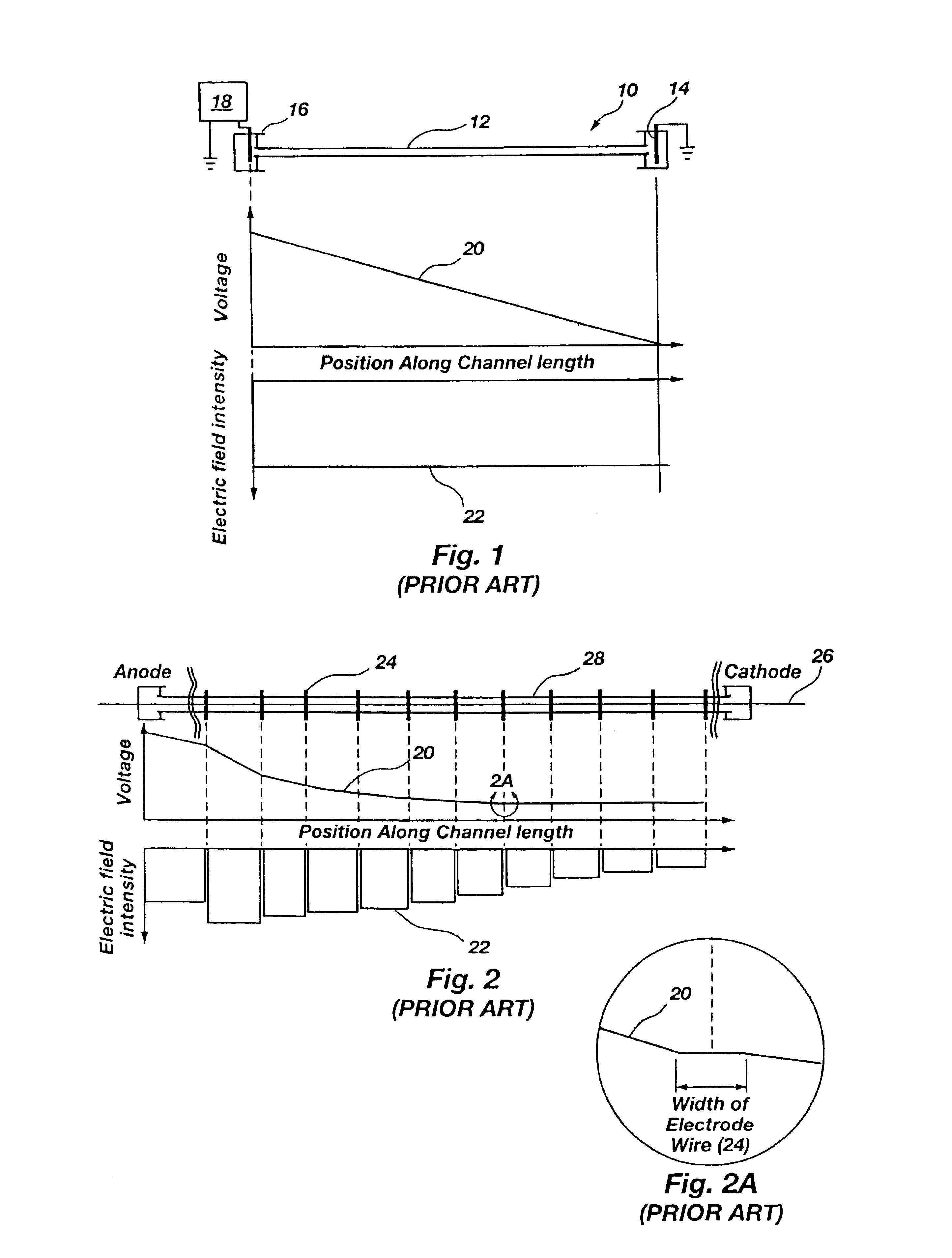

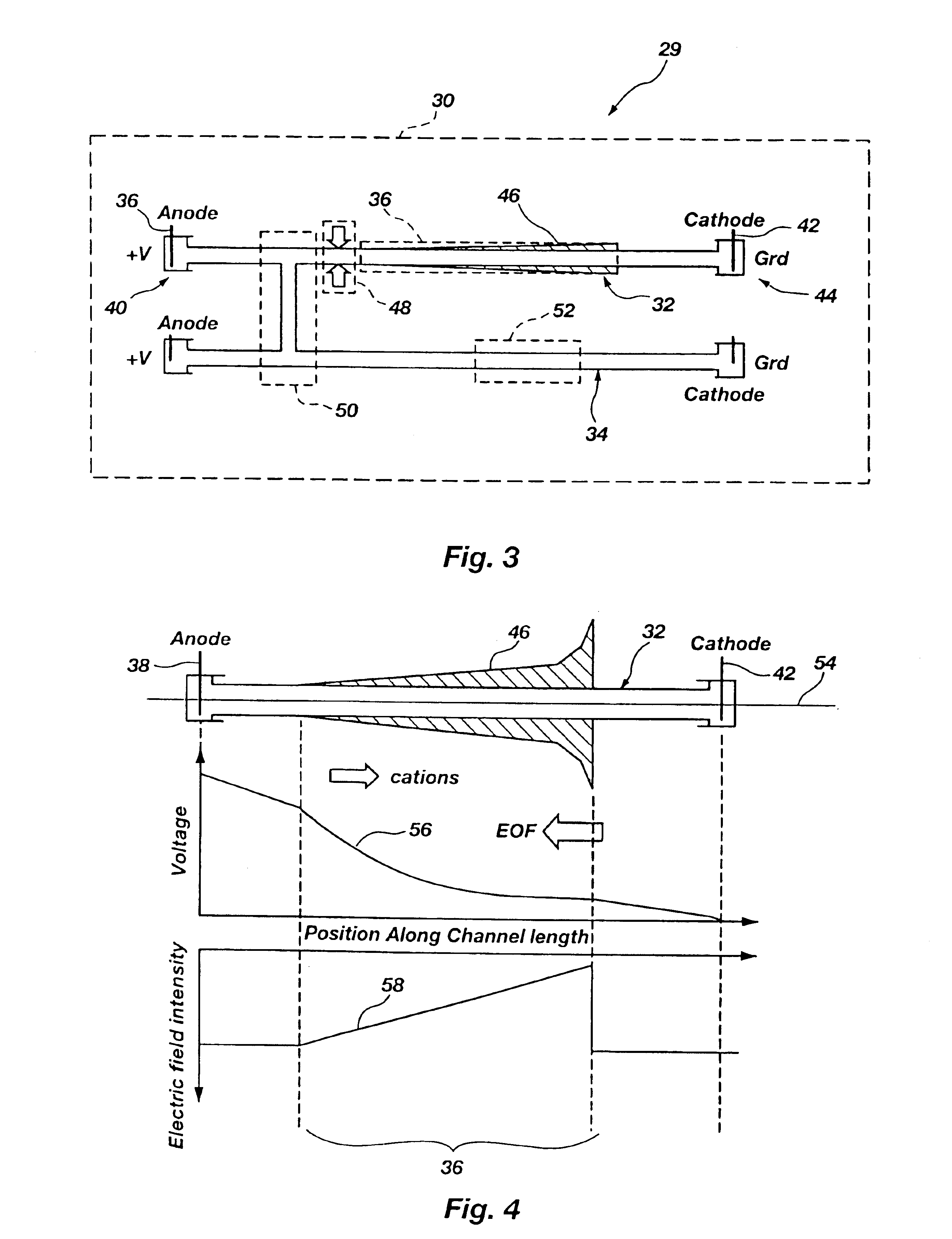

An electromobility focusing controlled channel electrophoresis system includes a first separation channel including an electric field intensity gradient profile in which the intensity is a continuous function of position within the channel over at least a portion of the channel, and the electrophoretic migration facilitated by the electric field is countered by an opposing force, which can be an electroosmotic flow force, to focus analyte species in the separation channel. A second channel including an analyte concentrator and a collection or transfer port is fluidly connected to the first channel by a steering valve facilitating manipulation of separated analyte species. Means for altering and controlling the electroosmotic force for moving analytes within the system and detectors configured for detecting analyte species are also included.

Owner:LE FEBRE DAVID

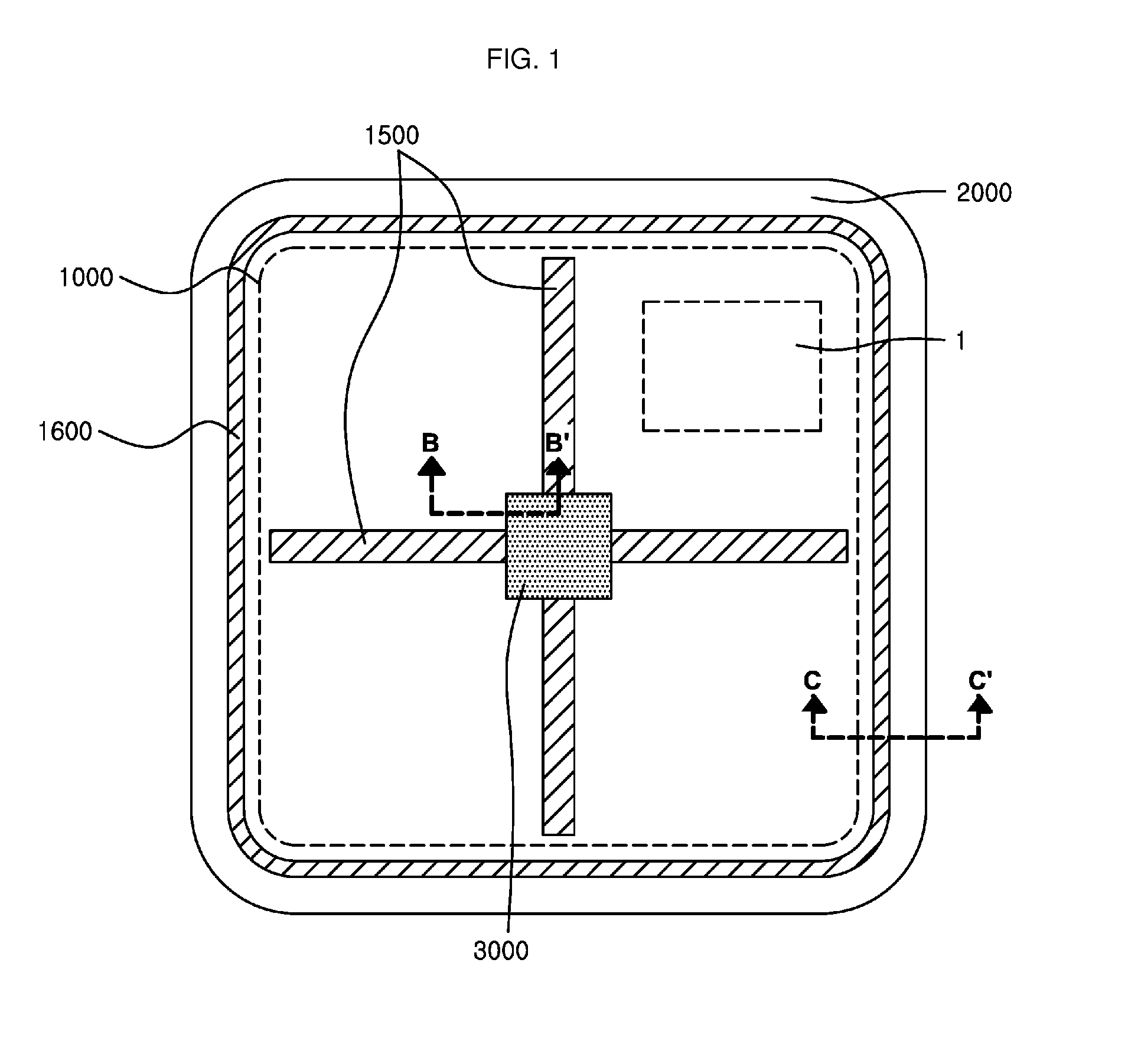

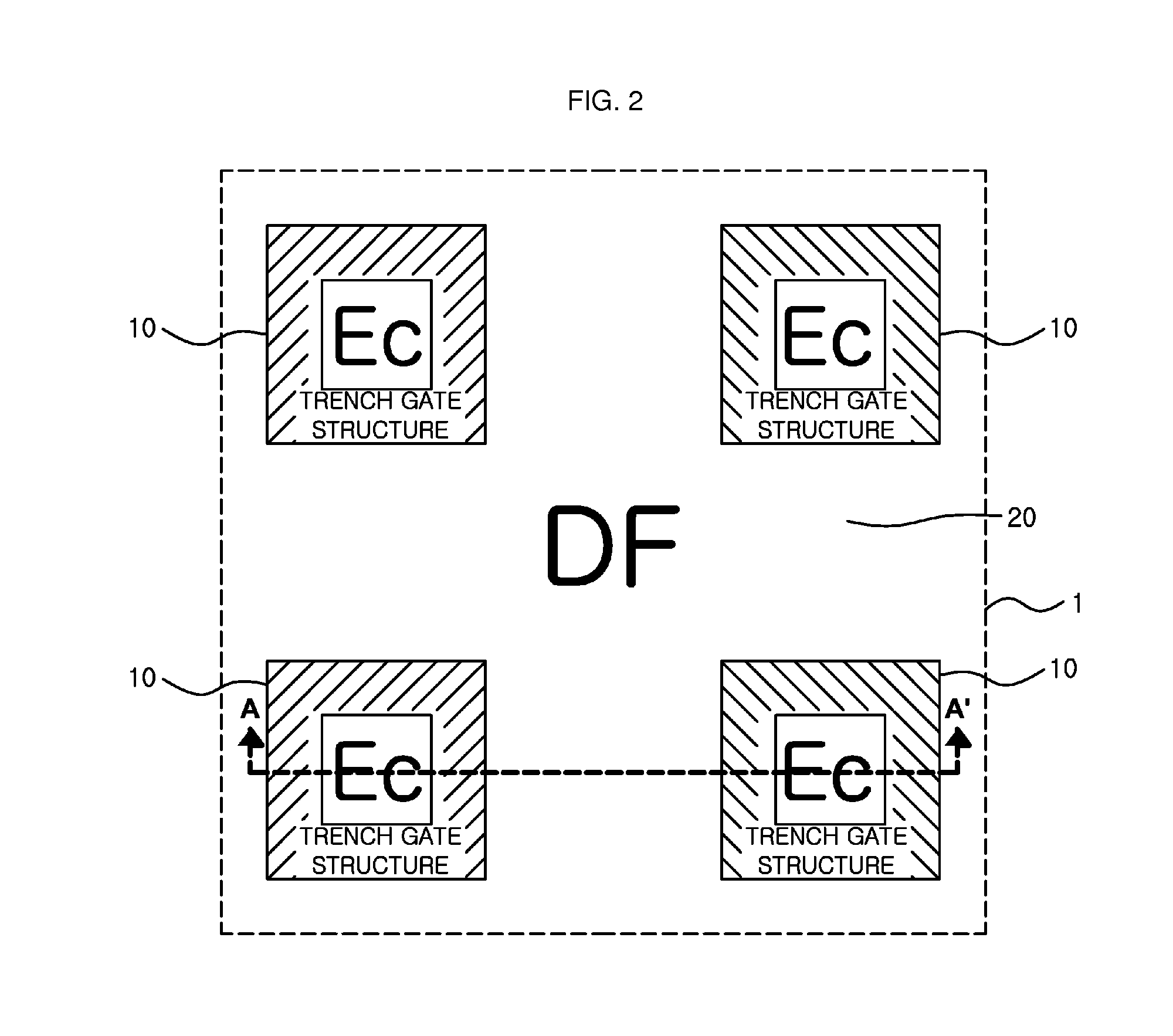

Power semiconductor device

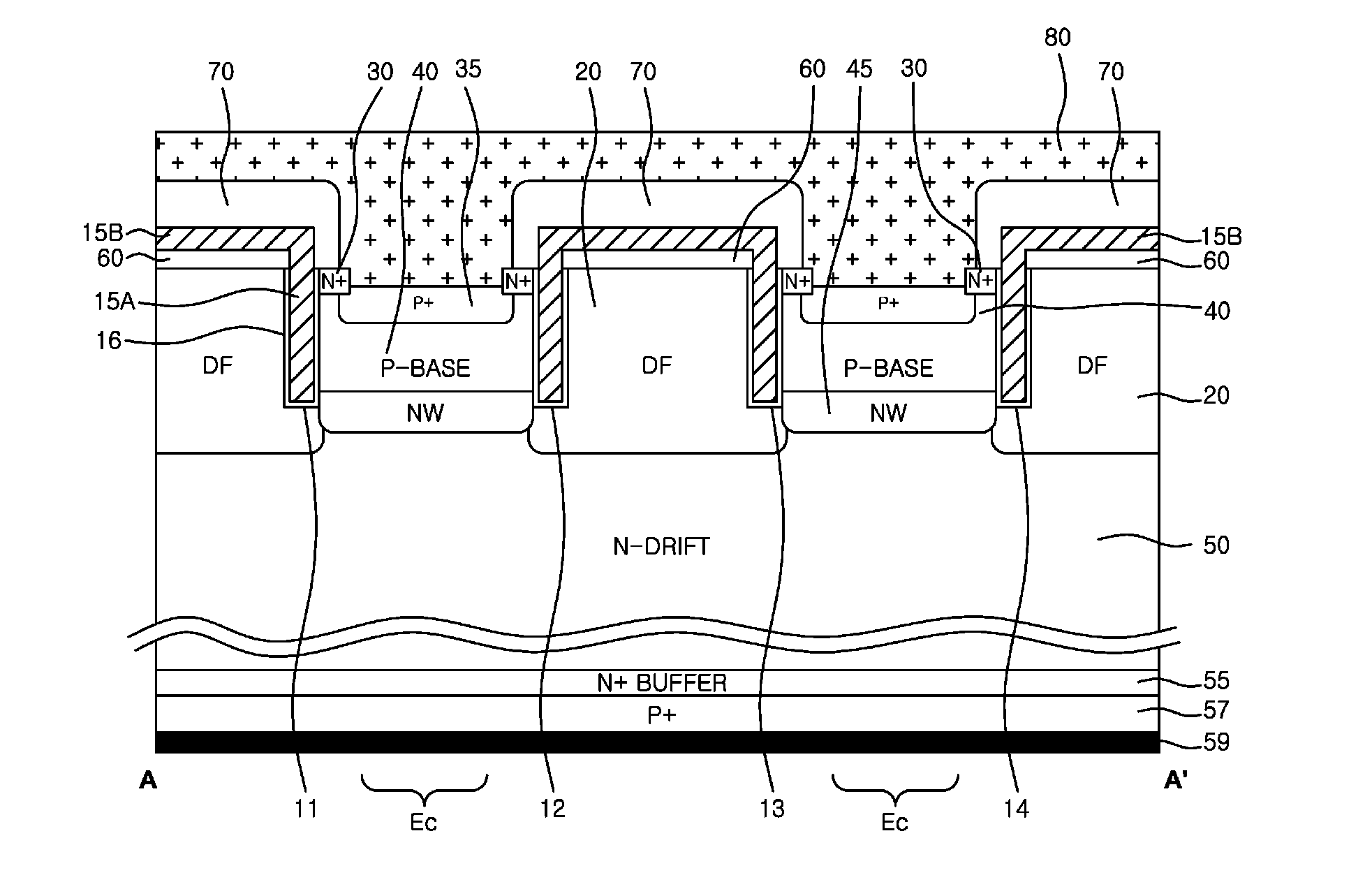

ActiveUS20160336393A1Reduce gate capacitanceSolve the large consumptionSemiconductor/solid-state device detailsSolid-state devicesCapacitancePower semiconductor device

The present examples relate to a power semiconductor device. The present examples also relate to a power semiconductor device that maintains a breakdown voltage and reduces a gate capacitance through improving the structure of an Injection Enhanced Gate Transistor (IEGT), and thereby reduces strength of an electric field compared to alternative technologies. Accordingly, the present examples provide a power semiconductor device with a small energy consumption and with an improved switching functionality.

Owner:MAGNACHIP SEMICONDUCTOR LTD

Liquid crystal display and electronic apparatus having a quasi-isotropic liquid crystal material

ActiveUS7420635B2Improve reliabilityImprove visibilityNon-linear opticsElectrical field strengthLiquid-crystal display

A transflective liquid crystal display that includes a liquid crystal layer interposed between a pair of substrates facing each other and a transparent display area for transparent display and a reflecting display area for reflecting display within a single pixel area, wherein the liquid crystal layer is composed of a quasi-isotropic liquid crystal material that is optically isotropic when non-selected electric field is applied and is optically anisotropic when selected electric field is applied, the flexibility of which changing according to the electric field intensity, and the electric field intensity is supposed to be set smaller in the reflecting display area than in the transparent display area.

Owner:BOE TECH GRP CO LTD

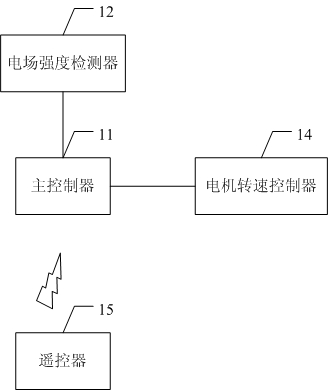

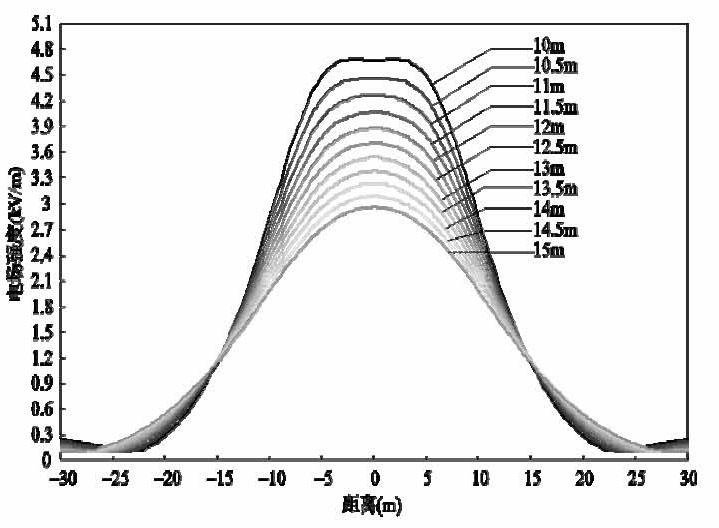

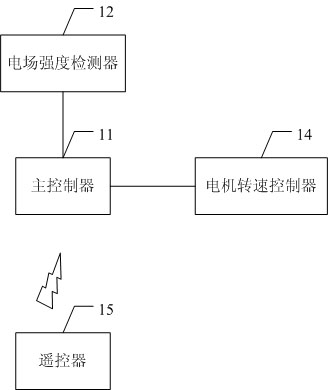

Auxiliary control system for power line inspection unmanned aerial vehicle, and control method thereof

InactiveCN102591357AReduce R&D costsShorten the development cyclePosition/course control in three dimensionsApparatus for overhead lines/cablesElectricityFlight direction

The invention provides an auxiliary control system for a power line inspection unmanned aerial vehicle, which comprises a camera. The auxiliary control system for the power line inspection unmanned aerial vehicle further comprises an electric field intensity detector, a flying sensor, a motor rotational speed controller, a remote controller and a main controller; the electric field intensity detector is installed on the camera and used for detecting the electric field intensity around a power line; the flying sensor is used for controlling the flight direction of the unmanned aerial vehicle under the control of the main controller; the motor rotational speed controller is used for controlling the rotational speed of a motor in the unmanned aerial vehicle under the control of the main controller; the remote controller is communicated with the main controller and sends a control command to the main controller; the main controller is used for calculating the distance value between the unmanned aerial vehicle and the power line according to the electric field intensity detected by the electric field intensity detector, and also used for controlling the work of the flying sensor and the motor rotational speed controller according to the control command sent by the remote controller and the distance value; and the electric field intensity detector, the flying sensor and the motor rotational speed controller are electrically connected with the main controller respectively. By adopting the scheme, the problem that the unmanned aerial vehicle collides with the power line during the process of power line inspection can be effectively solved.

Owner:AEROSPACE SCI & IND SHENZHEN GROUP

1000kv extra-high voltage ac non-contact type electricity checking method and apparatus

ActiveCN101487858AEliminate distractionsSolve the repeatabilityCurrent/voltage measurementElectrostatic field measurementsElectrical field strengthData acquisition

The invention provides a 1000kV ultrahigh voltage alternating current non-contact-type electroscopy and an electroscope thereof, the hardware part of the electroscope consists of a signal acquisition module, a signal amplification module, a signal processing module, an analog-to-digital conversion and data processing module and an alarm module, the software part thereof is divided into five stages comprising self-check, pre-check, checkup, comparison and alarm; after the self-check is passed and time delay of 3 seconds elapses, a value, which is obtained by performing a data acquisition in 10KHz frequency on the electric field intensity of the working location, is regarded as a reference value for the electroscopy, the inventive reference value is an electric field value of the on-site working location, which effectively enhances the use range and accuracy of the electroscope; the invention implements the electroscopy in terms of field intensity curves of space electric fields and gives a reflection of the size of the electric field via the frequency velocity of acoustic, optical signals for the alarm, which effectually eradicates the interferences from adjacent charged equipment and settles the difficult problem of inferior repetitiveness and low accuracy of the electroscopy result which is resulted from the interference with the space field intensity by charged bodies of the adjacent measured equipment.

Owner:STATE GRID ELECTRIC POWER RES INST

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com