Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

234 results about "Metal insulator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Insulators typically become metallic by a reduction in the spacing between atoms in the material. Hemley and Naumov demonstrated that for a metal to become an insulator, these reduced-spacing overlaps must be organized in a specific kind of asymmetry that was not previously recognized.

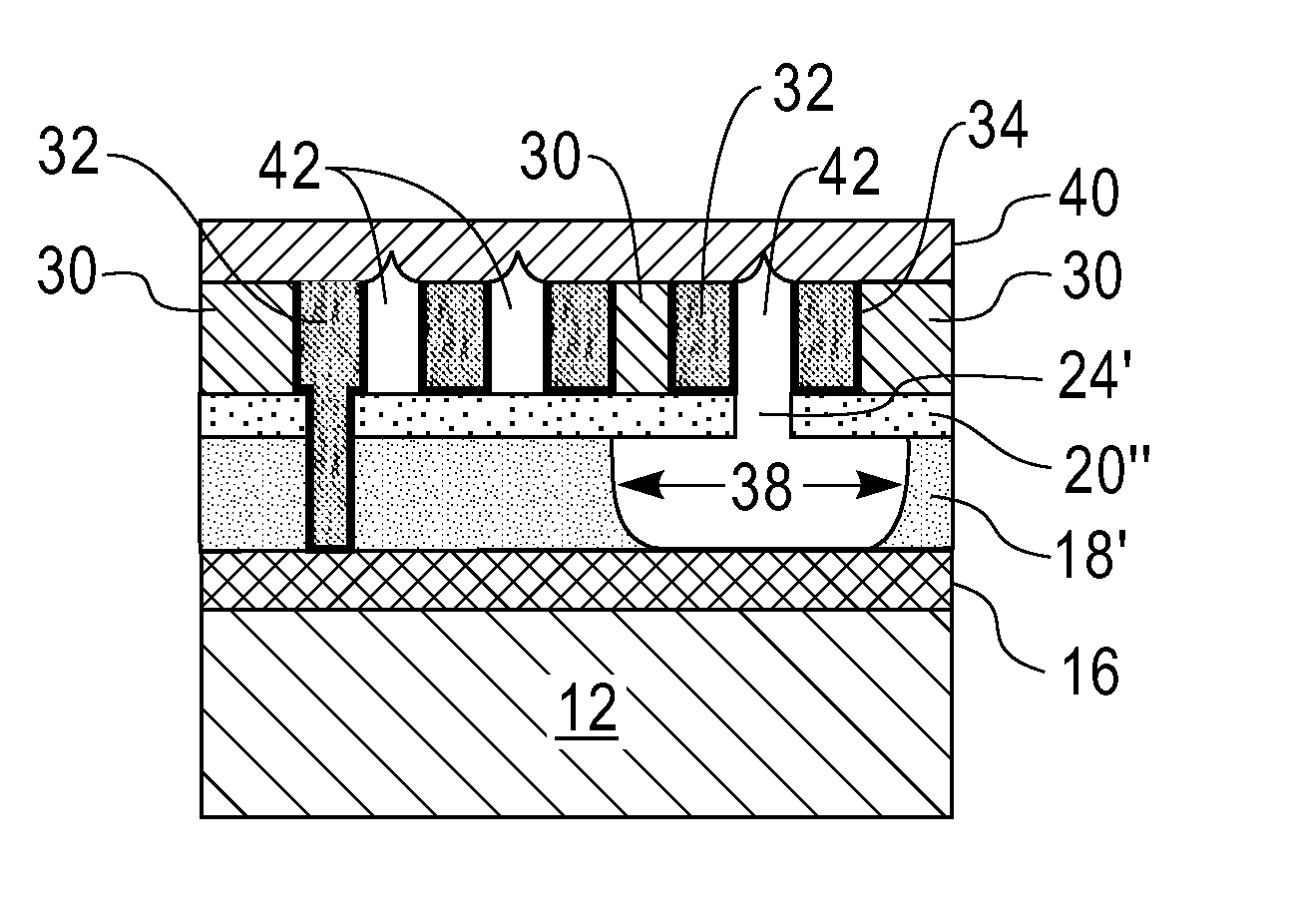

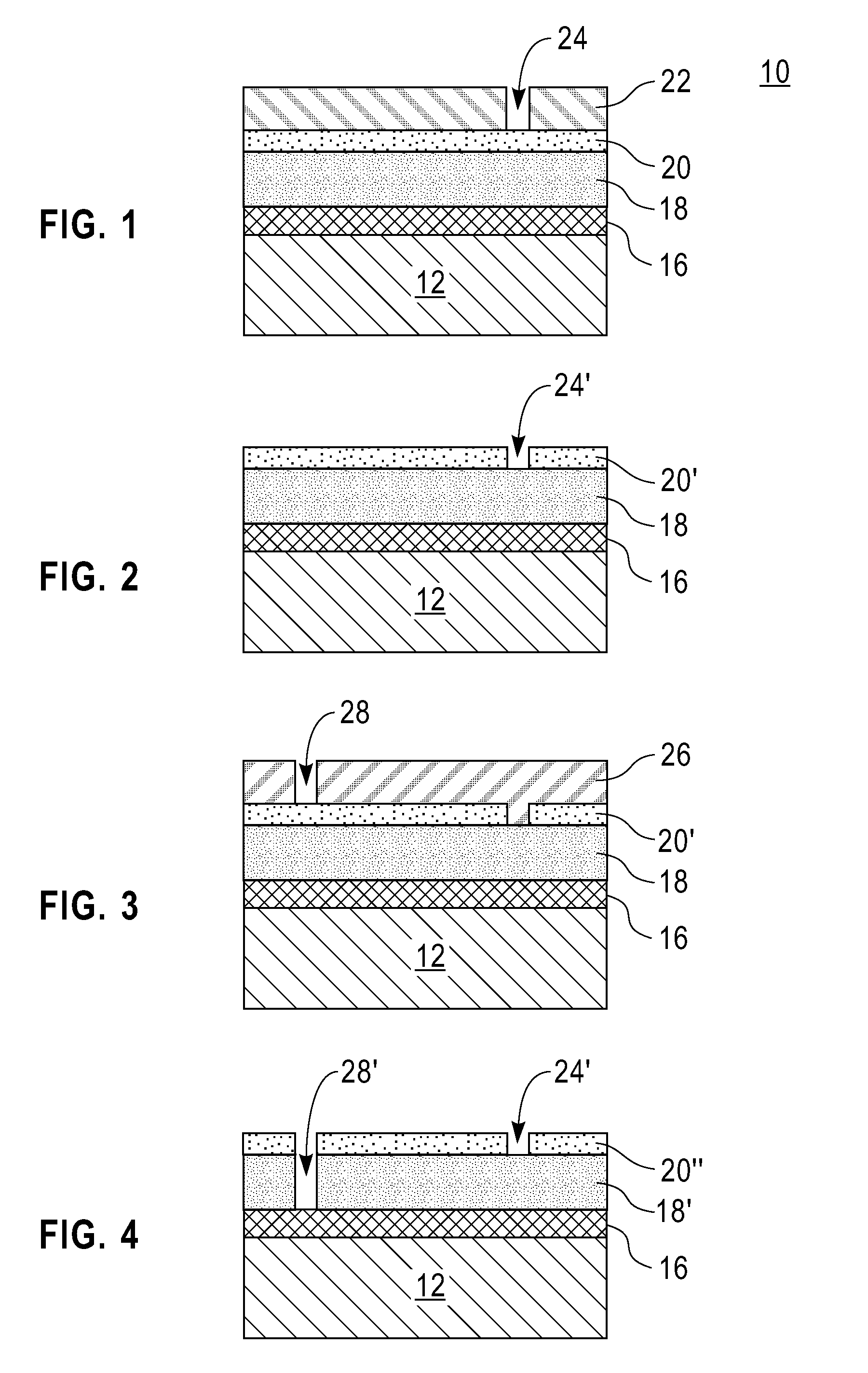

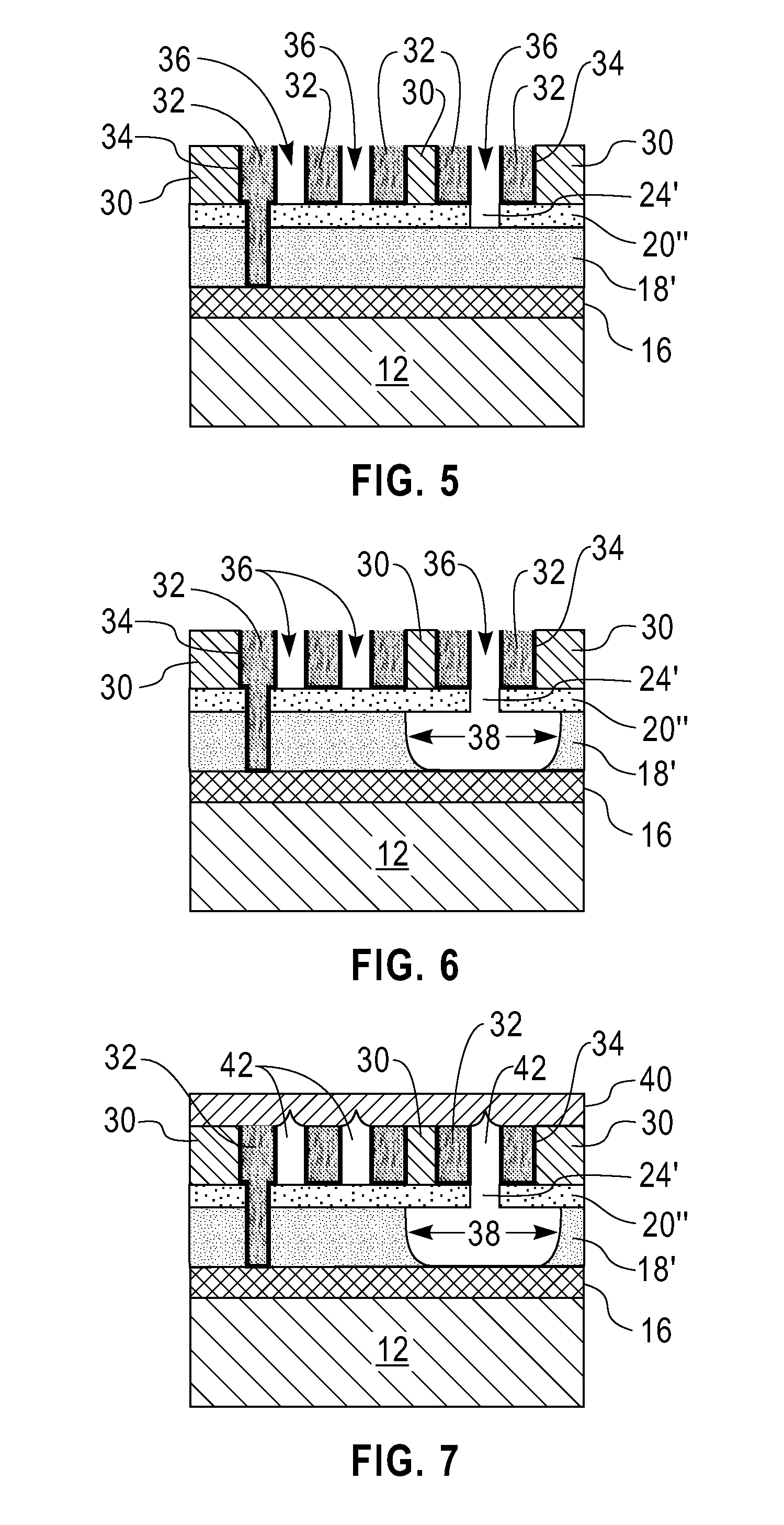

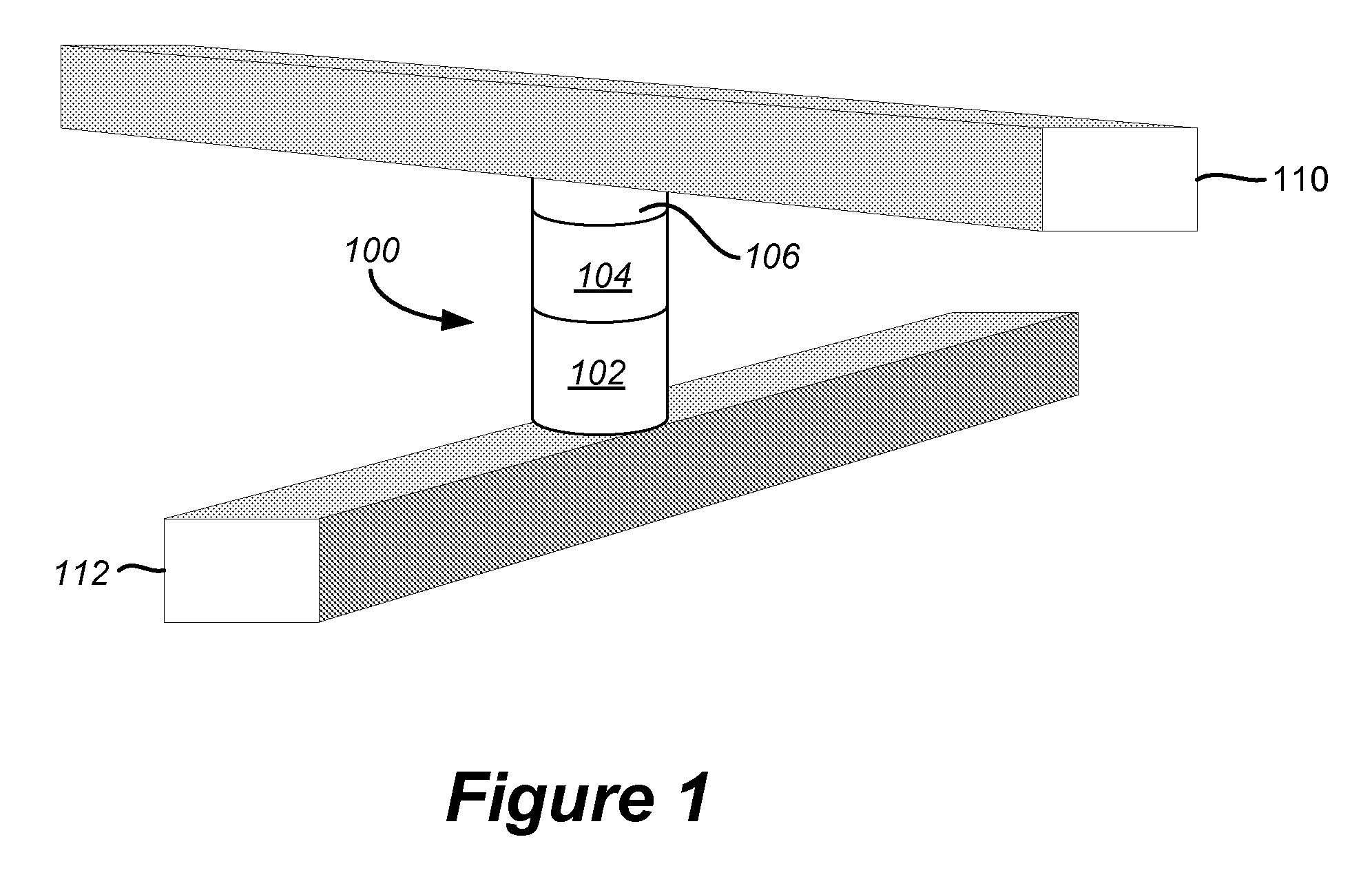

Method for air gap interconnect integration using photo-patternable low k material

ActiveUS8241992B2Stable structureSemiconductor/solid-state device detailsSolid-state devicesMetal insulatorPhotolithography

Methods for producing air gap-containing metal-insulator interconnect structures for VLSI and ULSI devices using a photo-patternable low k material as well as the air gap-containing interconnect structure that is formed are disclosed. More particularly, the methods described herein provide interconnect structures built in a photo-patternable low k material in which air gaps are defined by photolithography in the photo-patternable low k material. In the methods of the present invention, no etch step is required to form the air gaps. Since no etch step is required in forming the air gaps within the photo-patternable low k material, the methods disclosed in this invention provide highly reliable interconnect structures.

Owner:ALSEPHINA INNOVATIONS INC

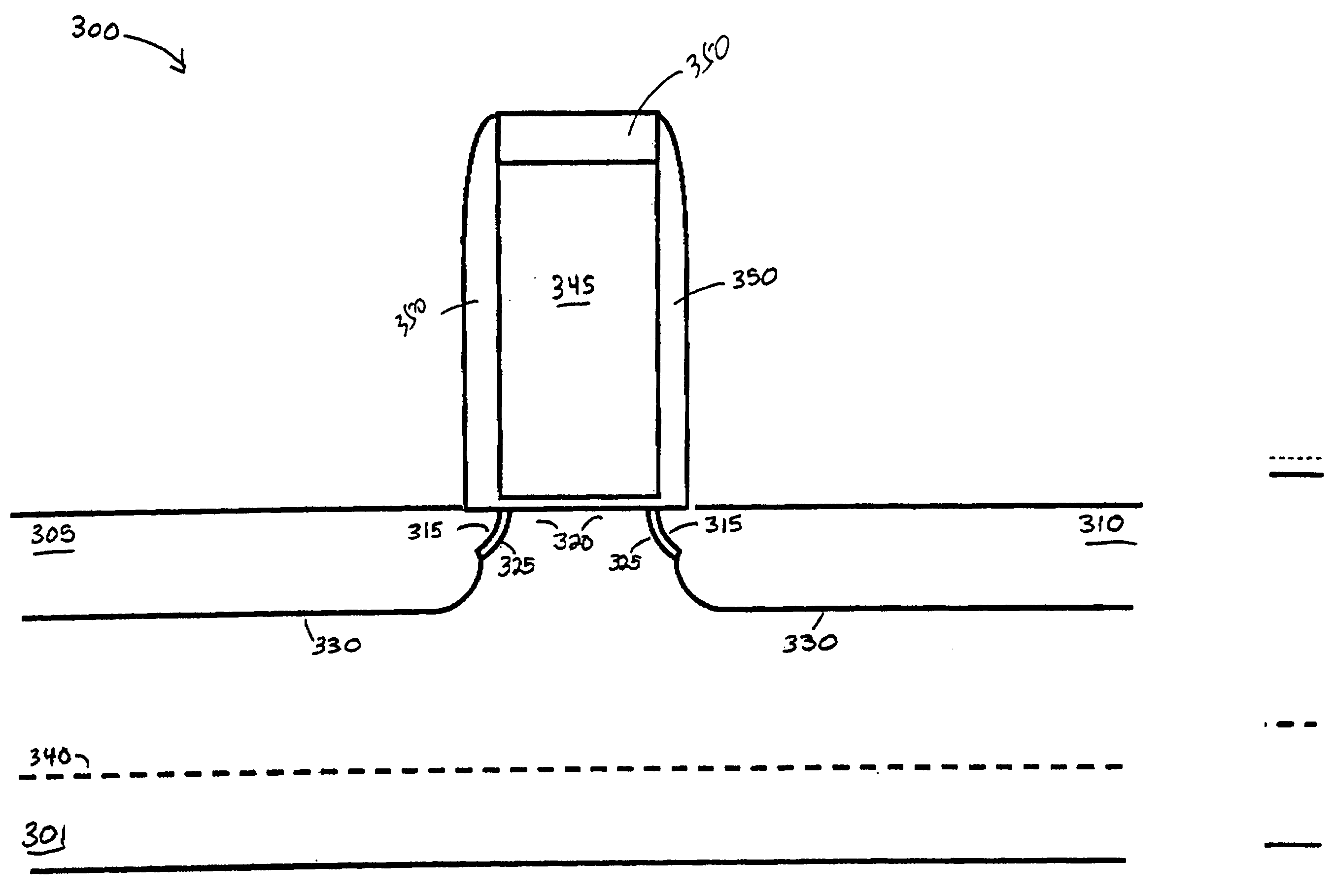

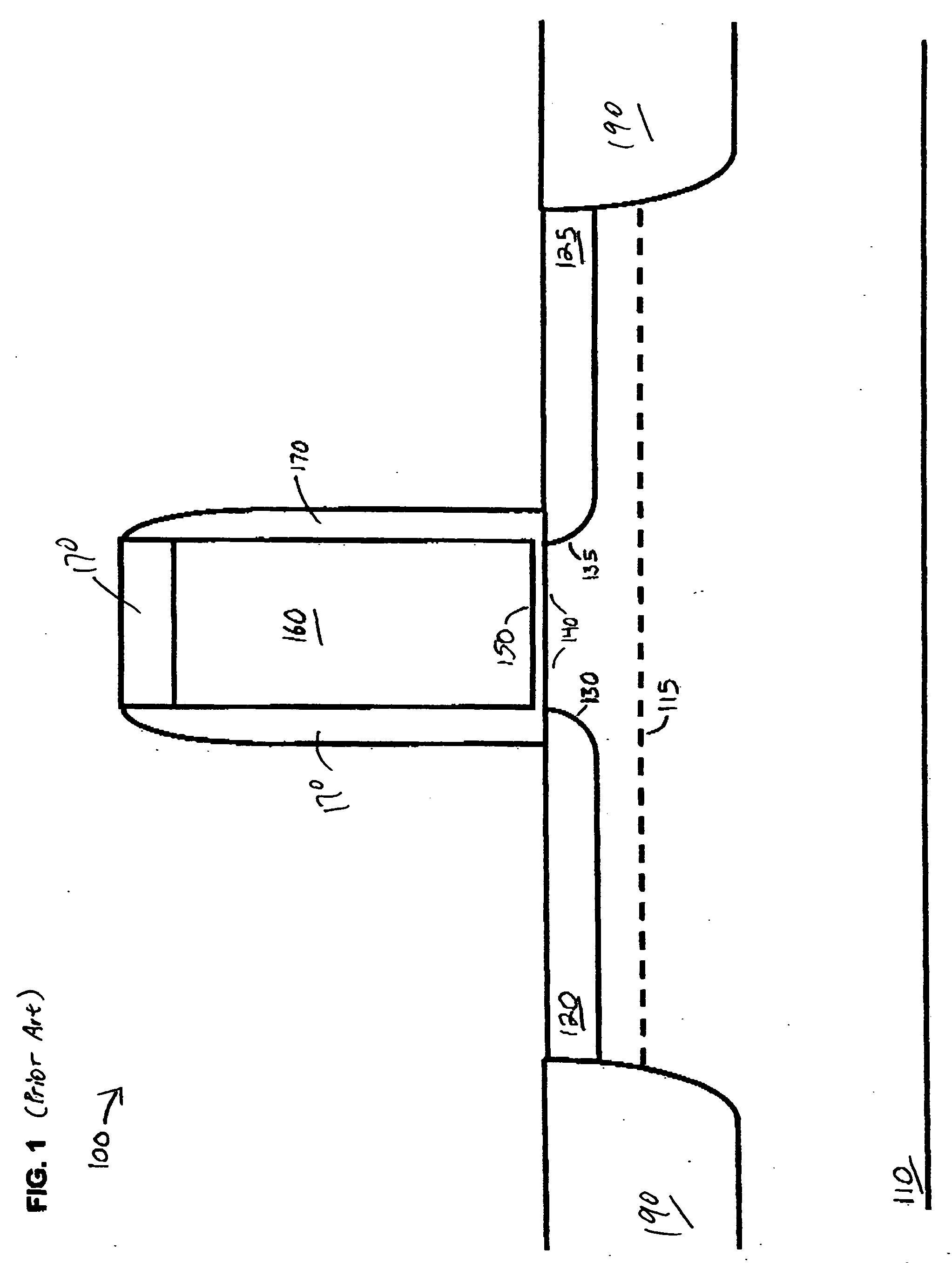

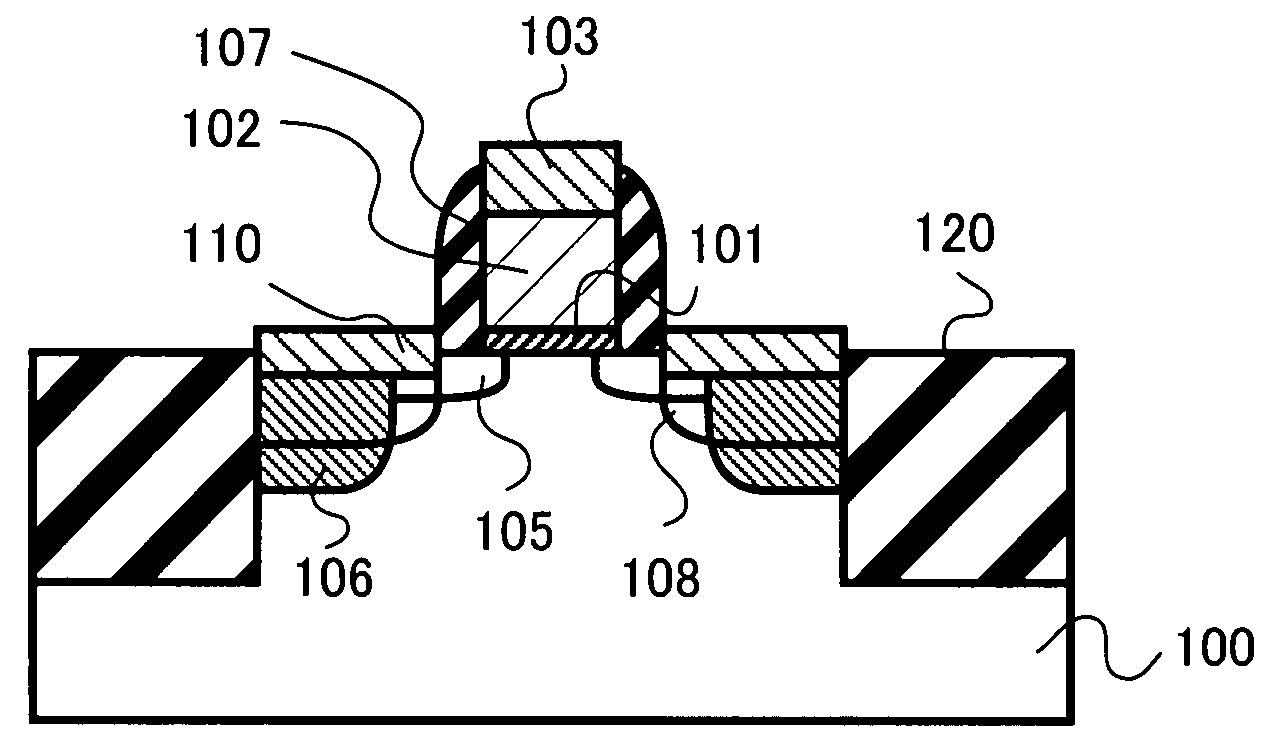

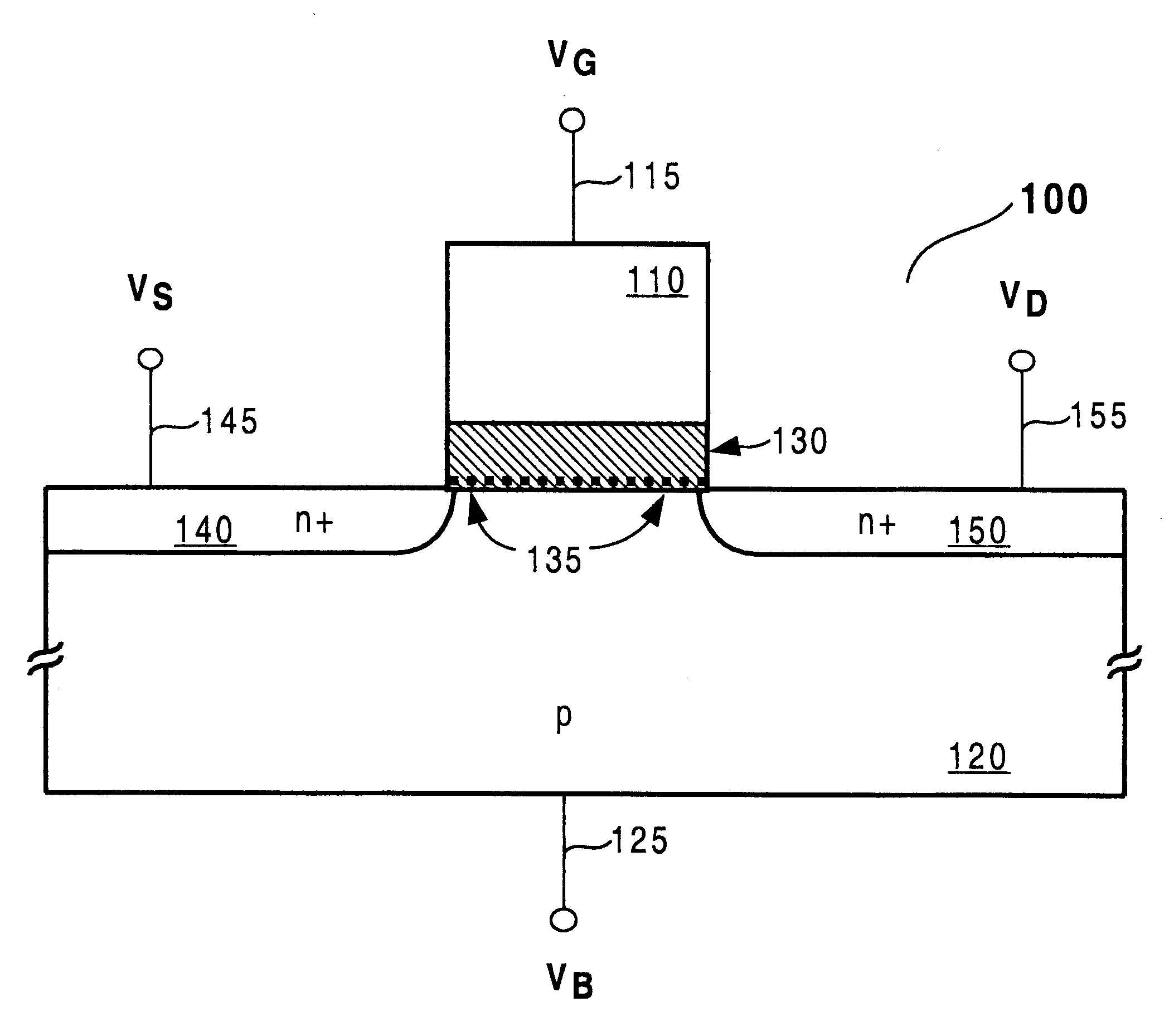

Dynamic schottky barrier MOSFET device and method of manufacture

InactiveUS20050139860A1ThyristorSemiconductor/solid-state device manufacturingMOSFETSchottky barrier

A device for regulating a flow of electric current and its manufacturing method are provided. The device includes metal-insulator-semiconductor source-drain contacts forming Schottky barrier or Schottky-like junctions to the semiconductor substrate. The device includes an interfacial layer between the semiconductor substrate and a metal source and / or drain electrode, thereby dynamically adjusting a Schottky barrier height by applying different bias conditions. The dynamic Schottky barrier modulation provides increased electric current for low drain bias conditions, reducing the sub-linear turn-on characteristic of Schottky barrier MOSFET devices and improving device performance.

Owner:SPINNAKER SEMICON

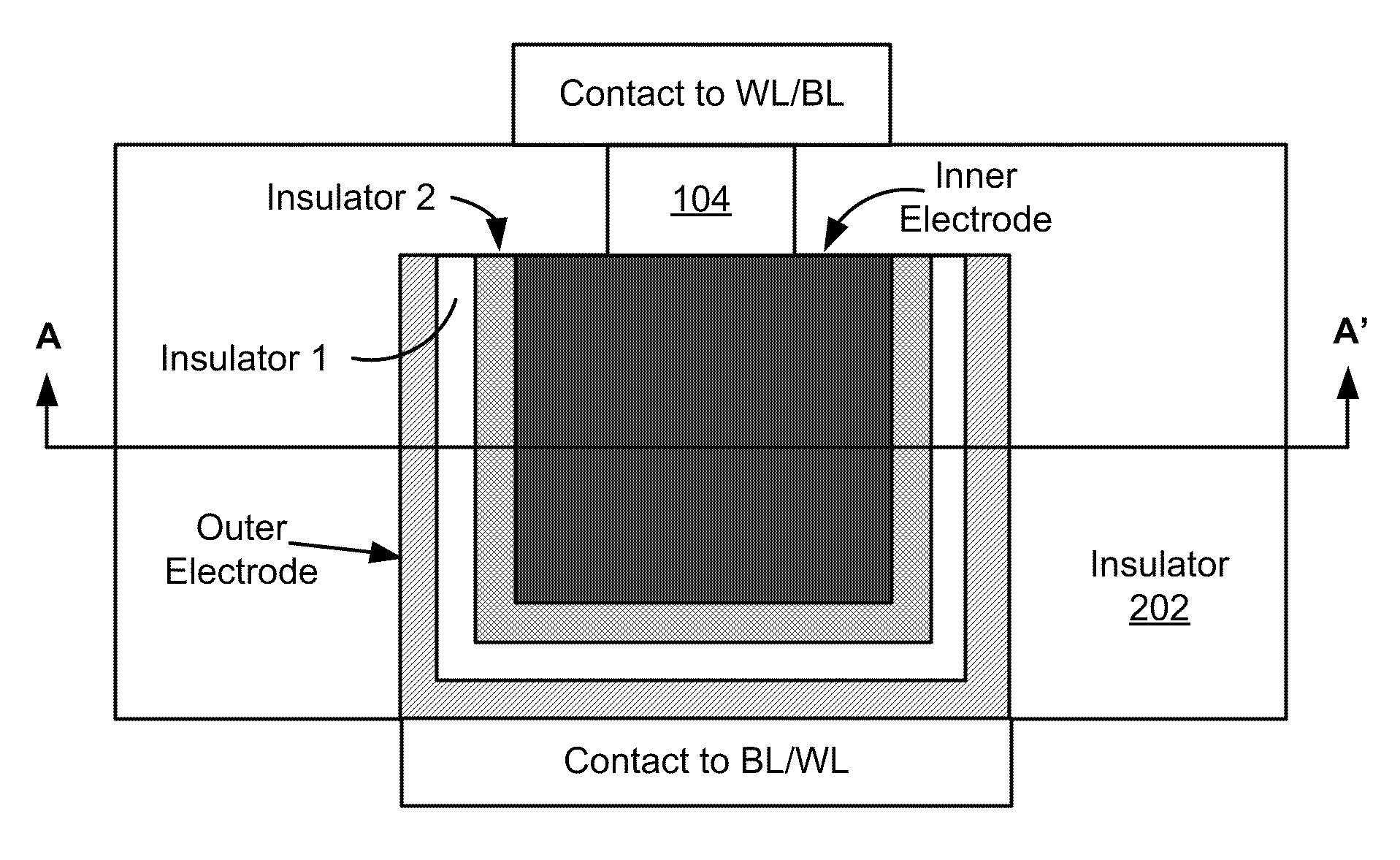

Damascene process for carbon memory element with MIIM diode

InactiveUS7615439B1Small aspect ratioSolid-state devicesSemiconductor/solid-state device manufacturingMetal insulatorEngineering

Forming a metal-insulator diode and carbon memory element in a single damascene process is disclosed. A trench having a bottom and a sidewall is formed in an insulator. A first diode electrode is formed in the trench during a single damascene process. A first insulating region comprising a first insulating material is formed in the trench during the single damascene process. A second insulating region comprising a second insulating material is formed in the trench during the single damascene process. A second diode electrode is formed in the trench during the single damascene process. The first insulating region and the second insulating region reside between the first diode electrode and the second diode electrode to form a metal-insulator-insulator-metal (MIIM) diode. A region of carbon is formed in the trench during the single damascene process. At least a portion of the carbon is electrically in series with the MIIM diode.

Owner:SANDISK TECH LLC

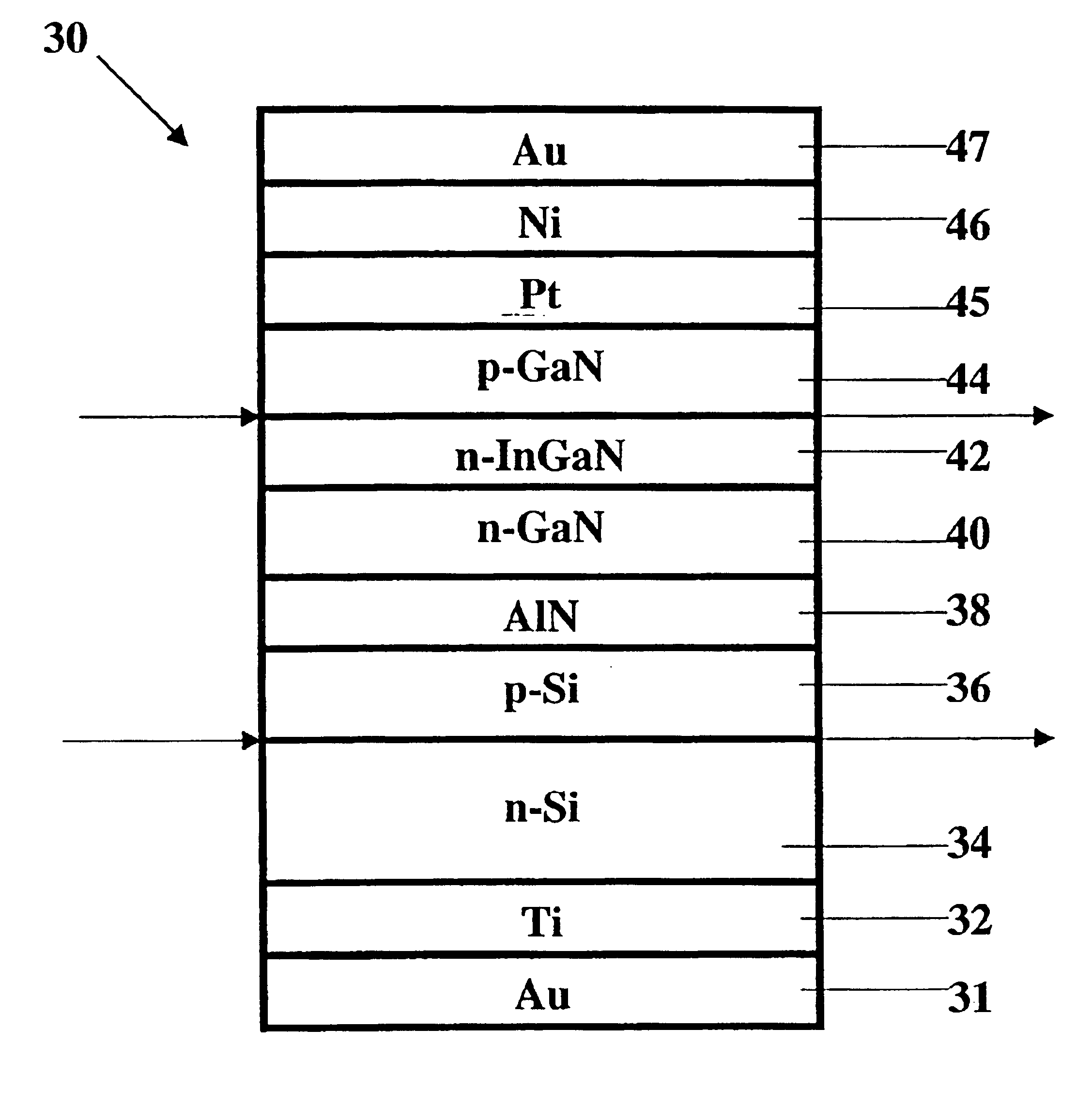

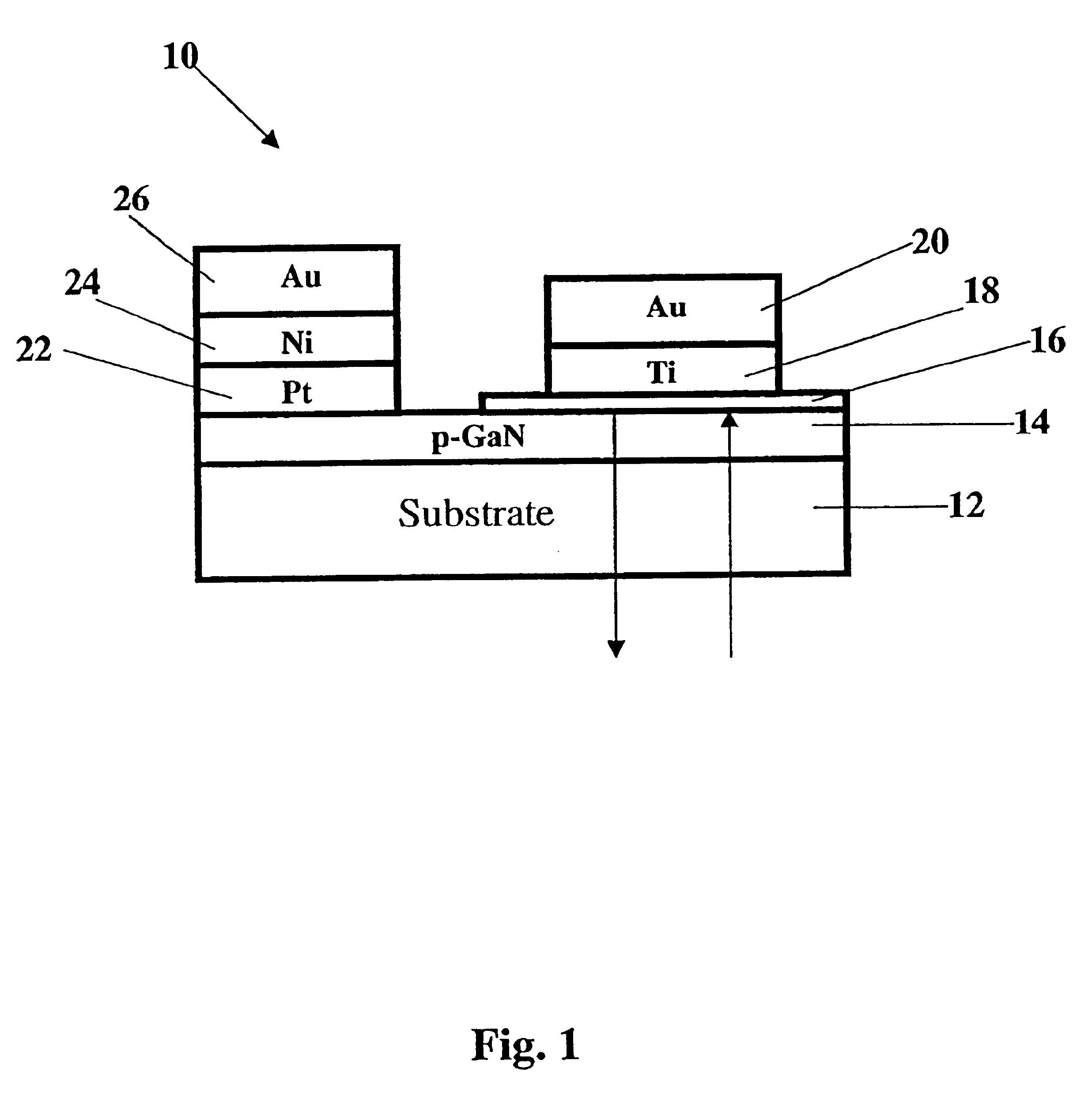

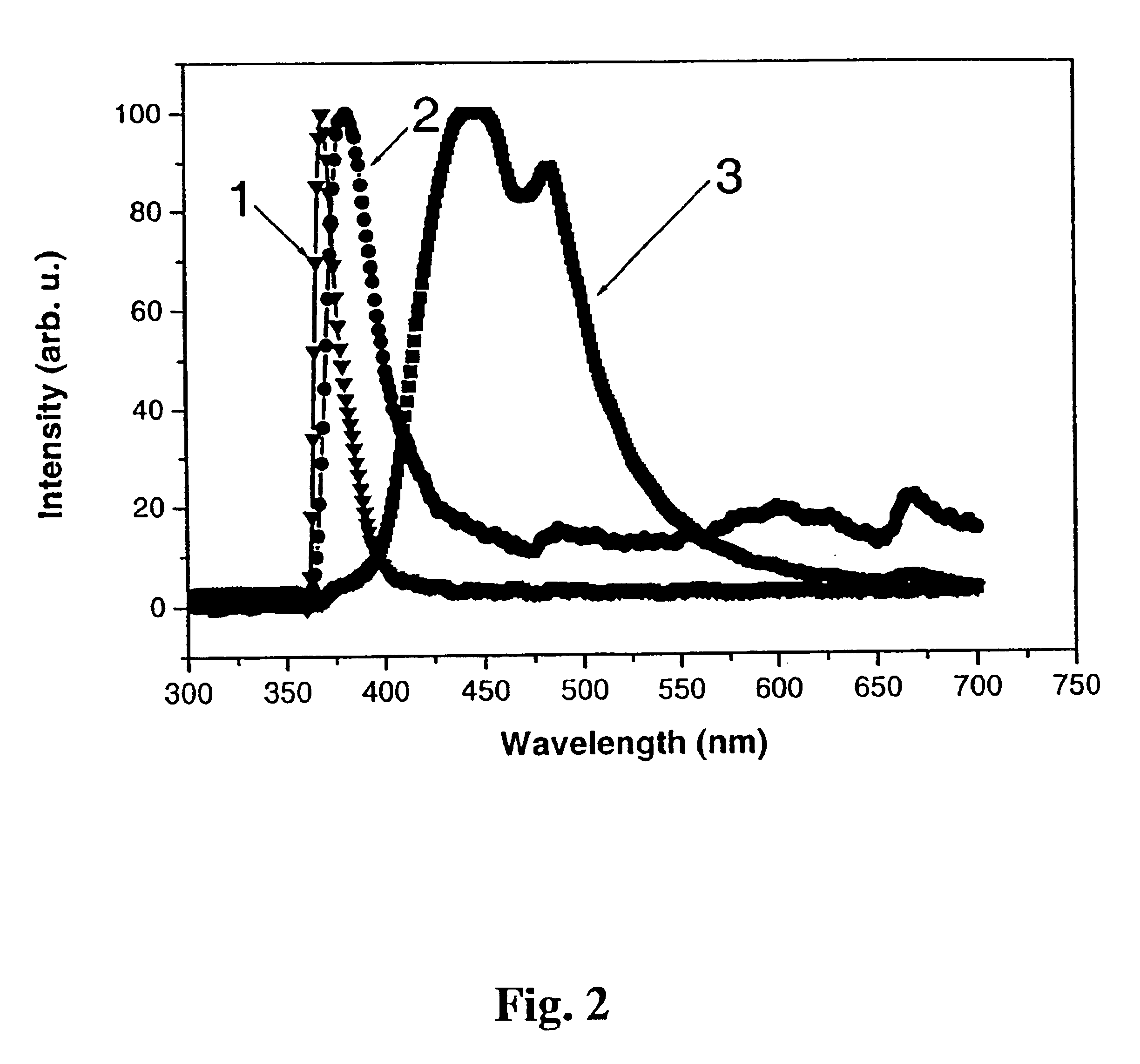

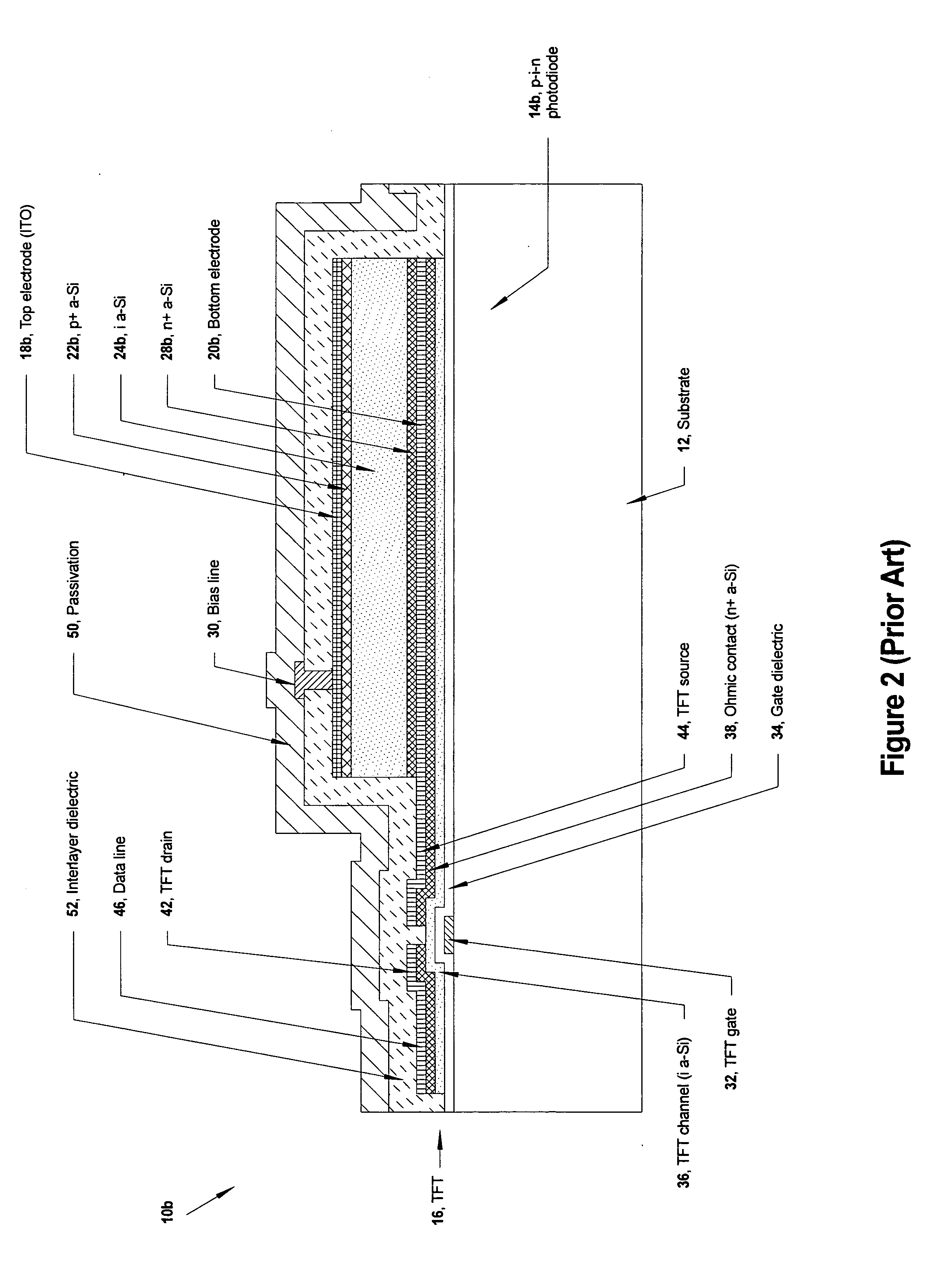

One-chip micro-integrated optoelectronic sensor

InactiveUS6881979B2High sensitivityLaser detailsFinal product manufactureOptical reflectionPhotovoltaic detectors

This disclosure describes one-chip micro-integrated optoelectronic sensors and methods for fabricating and using the same. The sensors may include an optical emission source, optical filter and a photodetector fabricated on the same transparent substrate using the same technological processes. Optical emission may occur when a bias voltage is applied across a metal-insulator-semiconductor Schottky contact or a p-n junction. The photodetector may be a Schottky contact or a p-n junction in a semiconductor. Some sensors can be fabricated on optically transparent substrate and employ back-side illumination. In the other sensors provided, the substrate is not transparent and emission occurs from the edge of a p-n junction or through a transparent electrode. The sensors may be used to measure optical absorption, optical reflection, scattering or fluorescence. The sensors may be fabricated and operated to provide a selected spectrum of light emitted and a multi-quantum well heterostructure may be fabricated to filter light reaching the photodetector.

Owner:HOUSTON UNIV OF

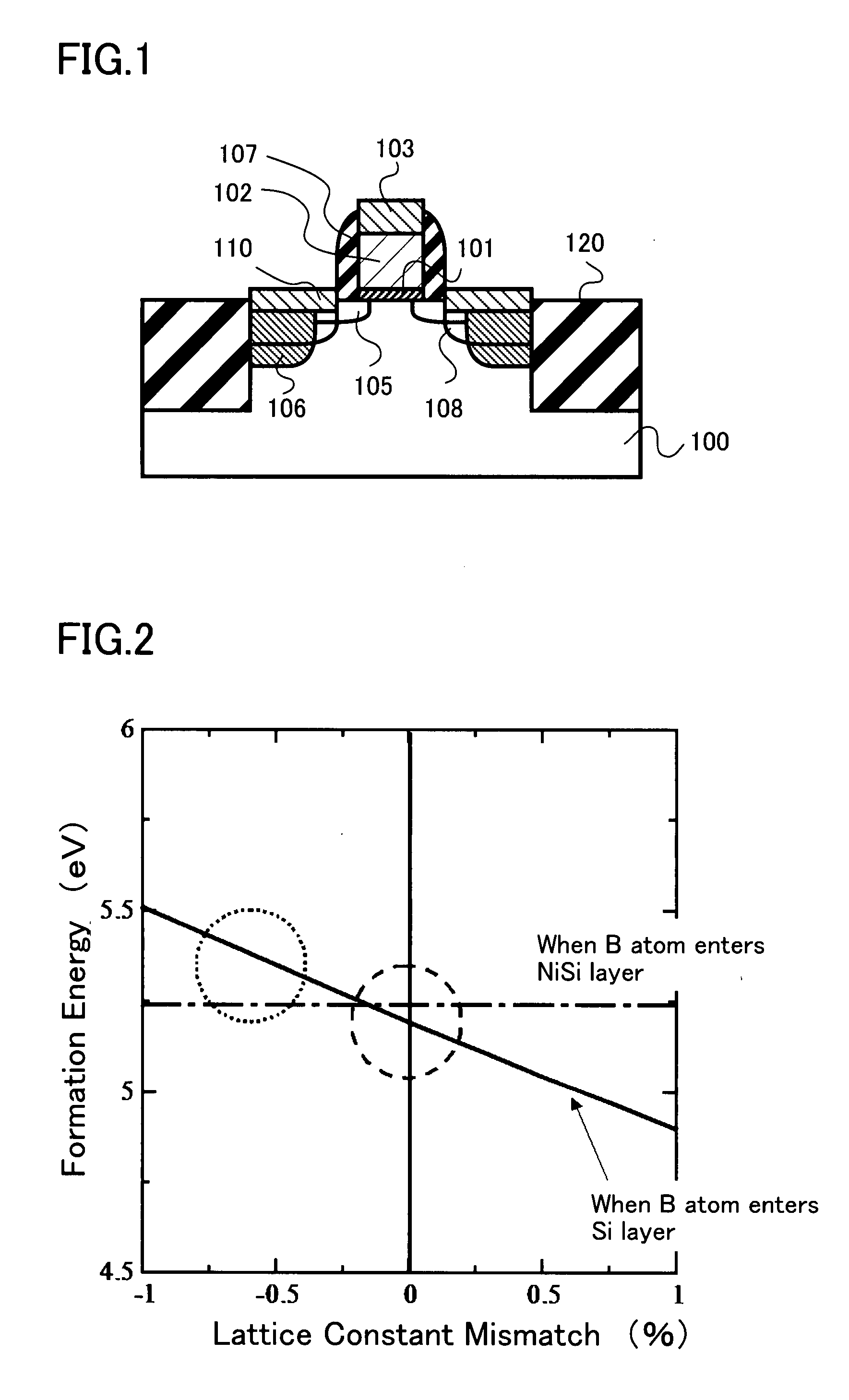

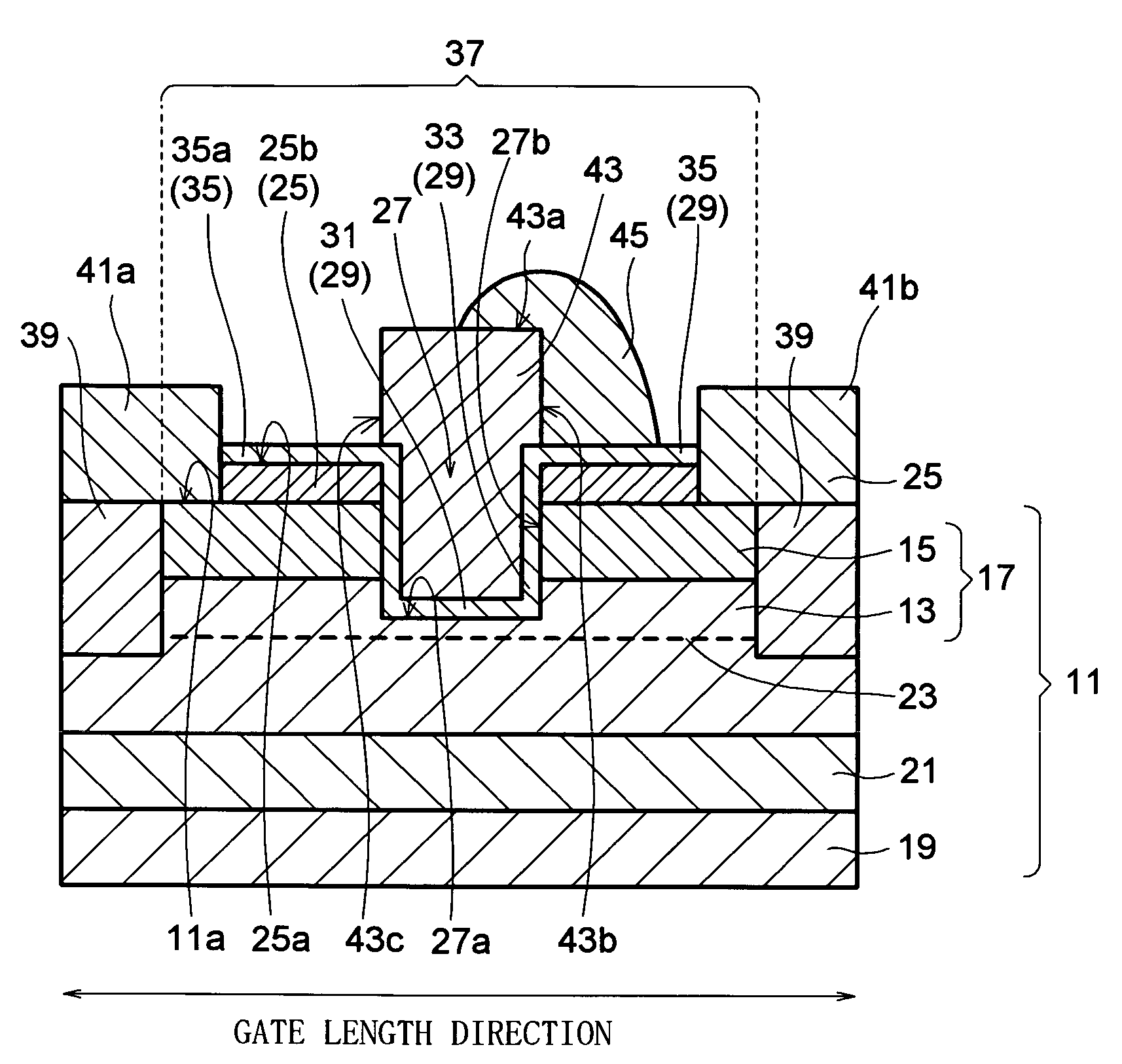

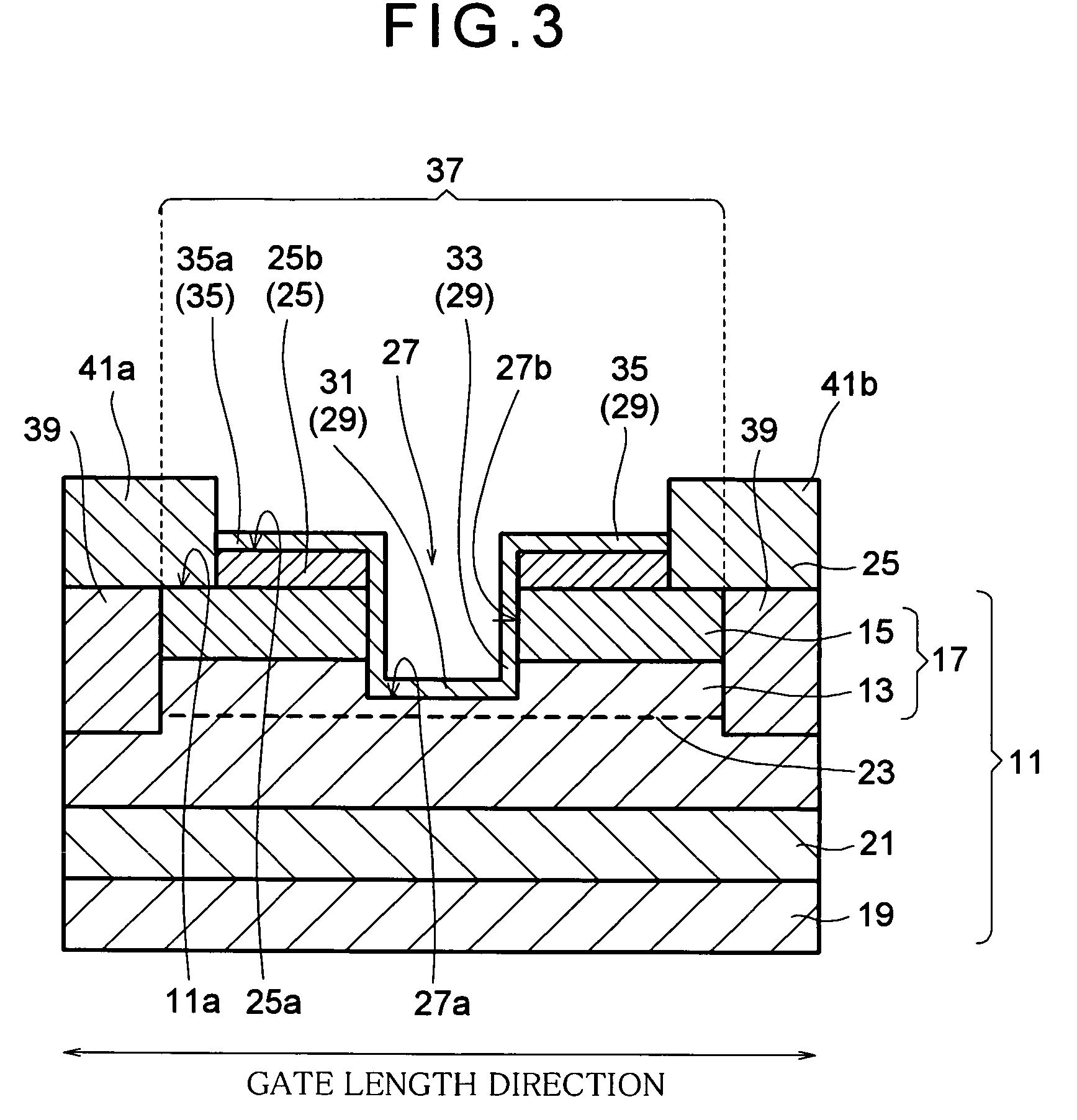

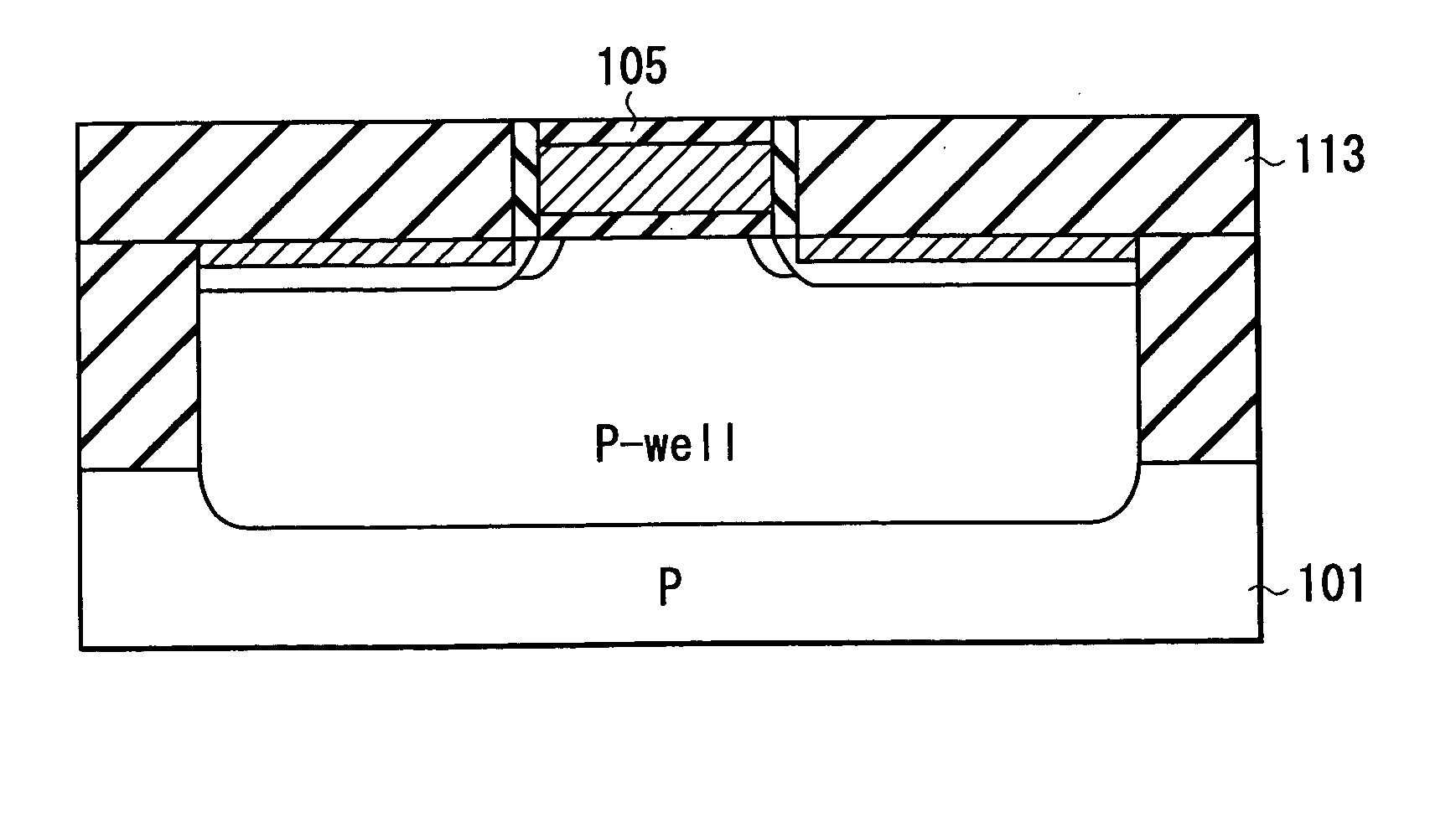

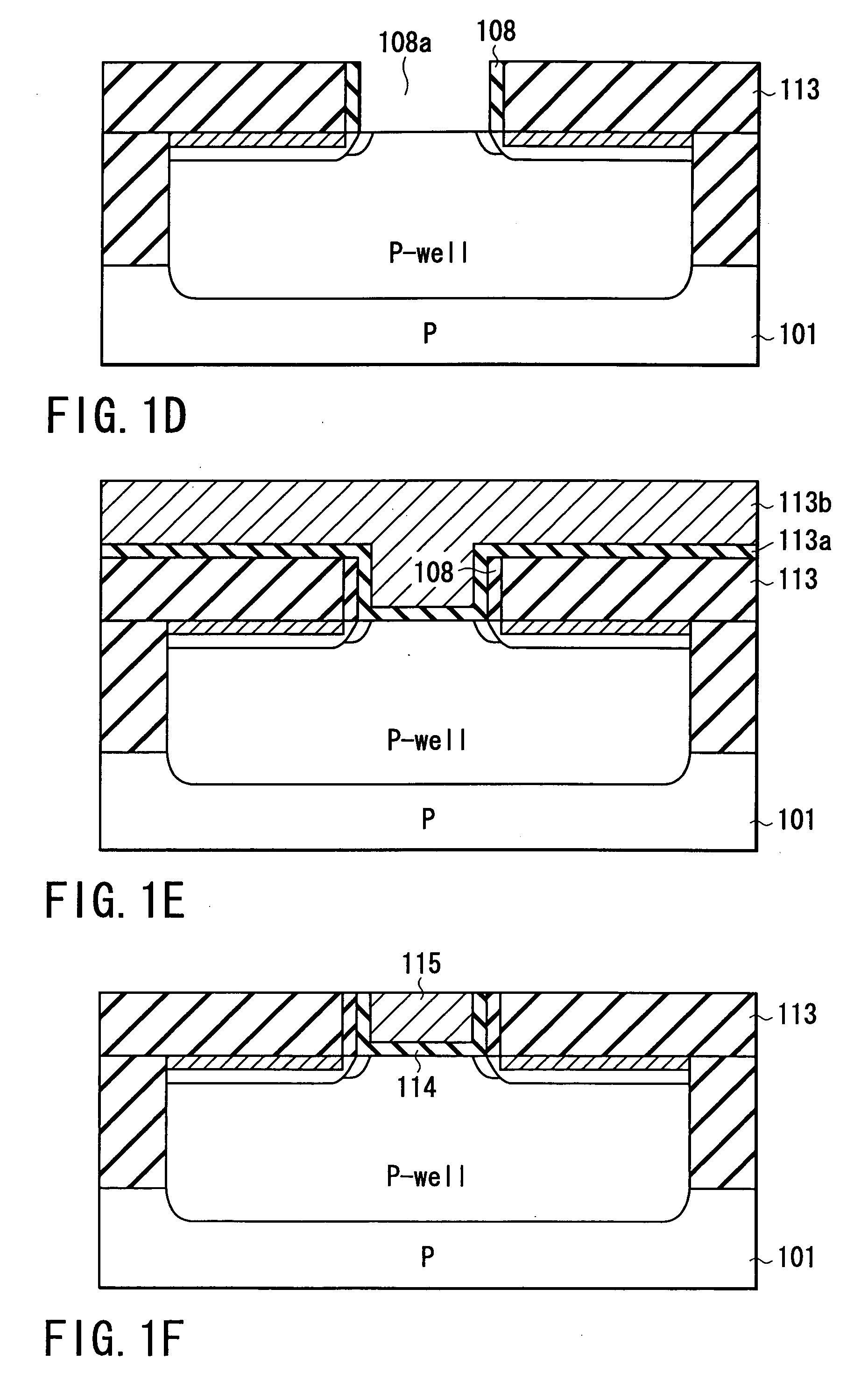

Method of making semiconductor device and semiconductor device

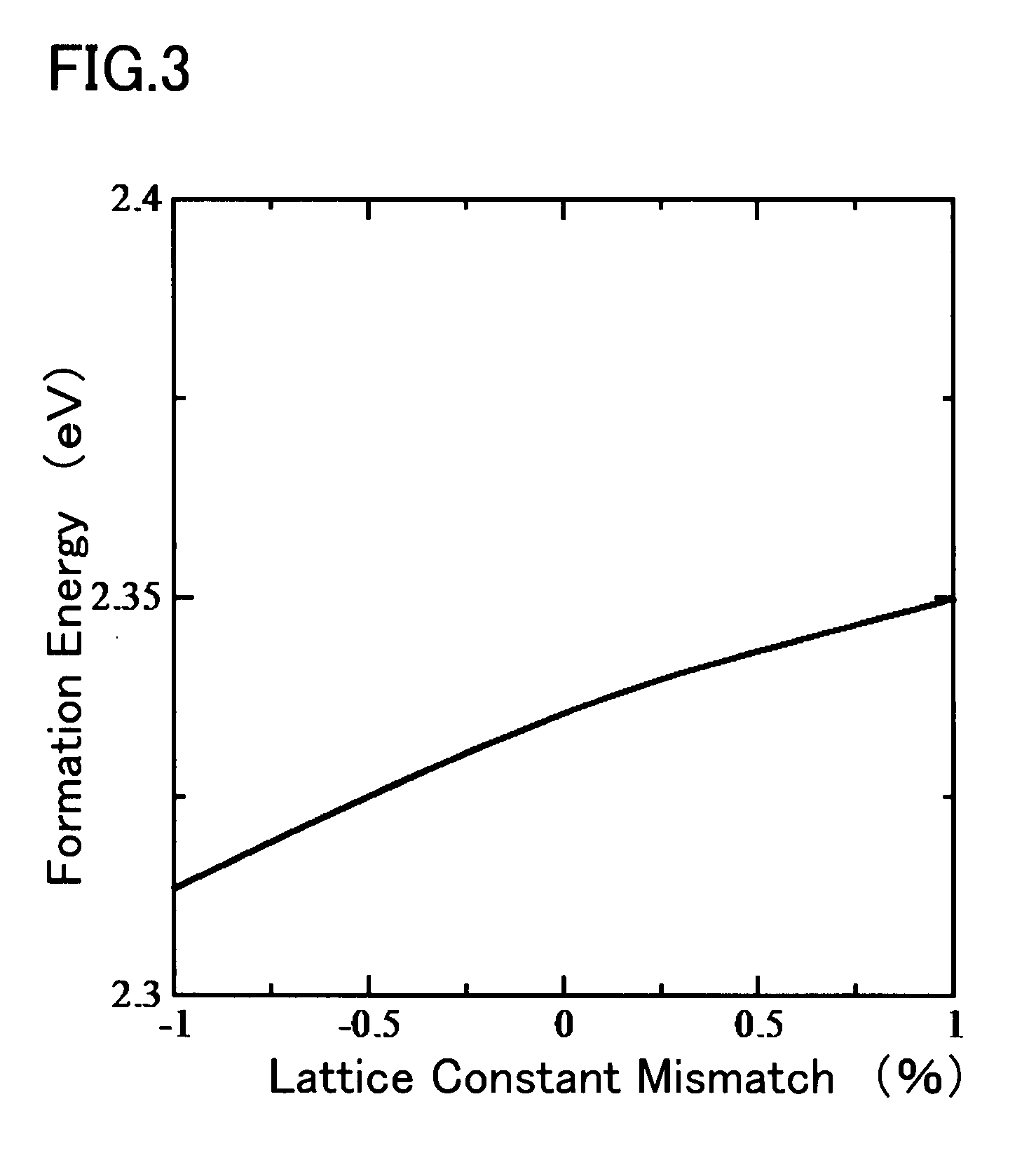

InactiveUS20080179752A1Lower junction resistanceTransistorSemiconductor/solid-state device detailsDevice materialGate insulator

A metal insulator semiconductor field effect transistor (MISFET) having a strained channel region is disclosed. Also disclosed is a method of fabricating a semiconductor device having a low-resistance junction interface. This fabrication method includes the step of forming a gate electrode above a silicon substrate with a gate insulator film being sandwiched therebetween. Then, form a pair of heavily-doped p (p+) type diffusion layers in or on the substrate surface at both sides of the gate electrode to a concentration of 5×1019 atoms / cm3 or more and yet less than or equal to 1×1021 atoms / cm3. Next, silicidize the p+-type layers by reaction with a metal in the state that each layer is applied a compressive strain.

Owner:KK TOSHIBA

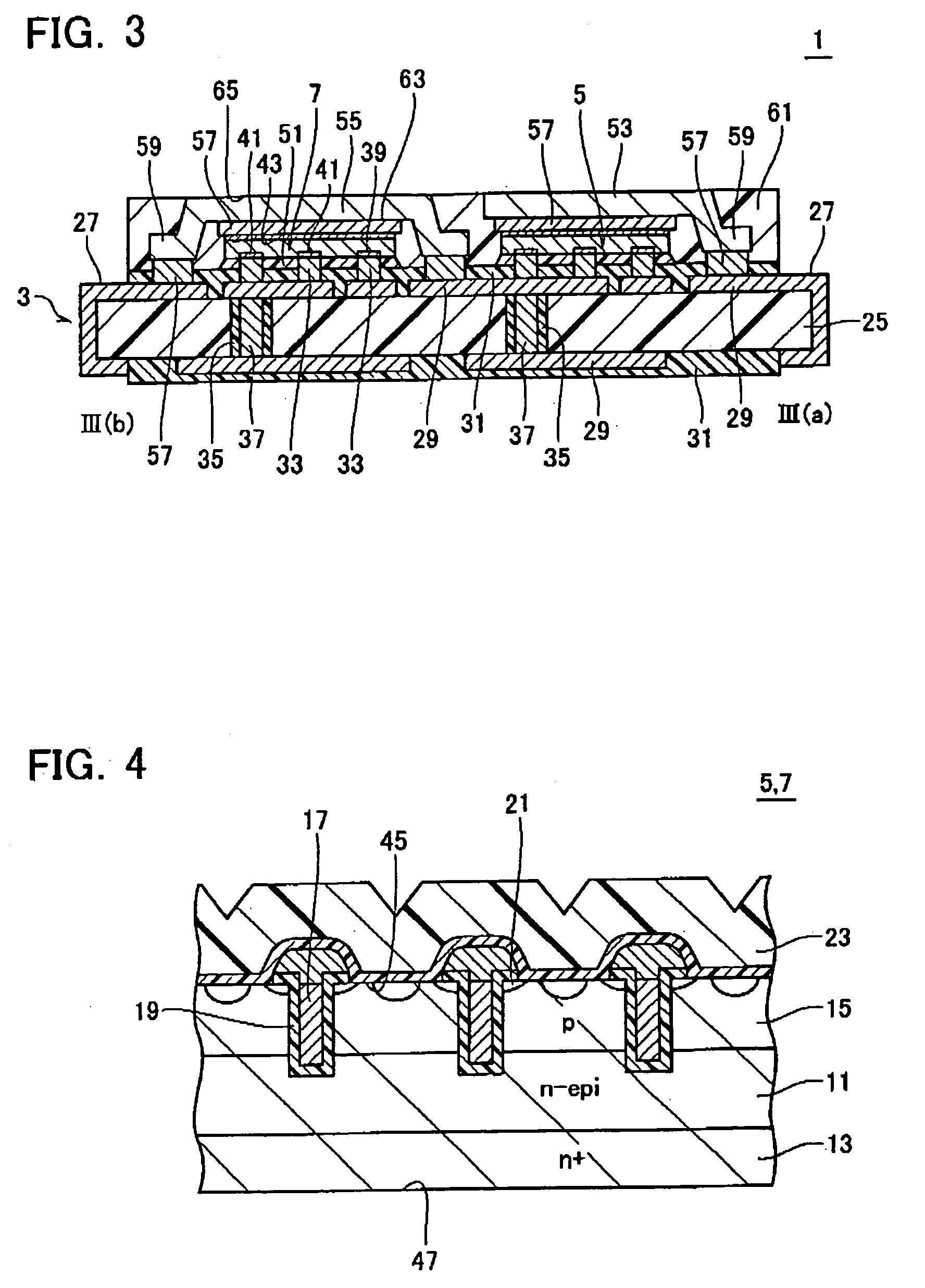

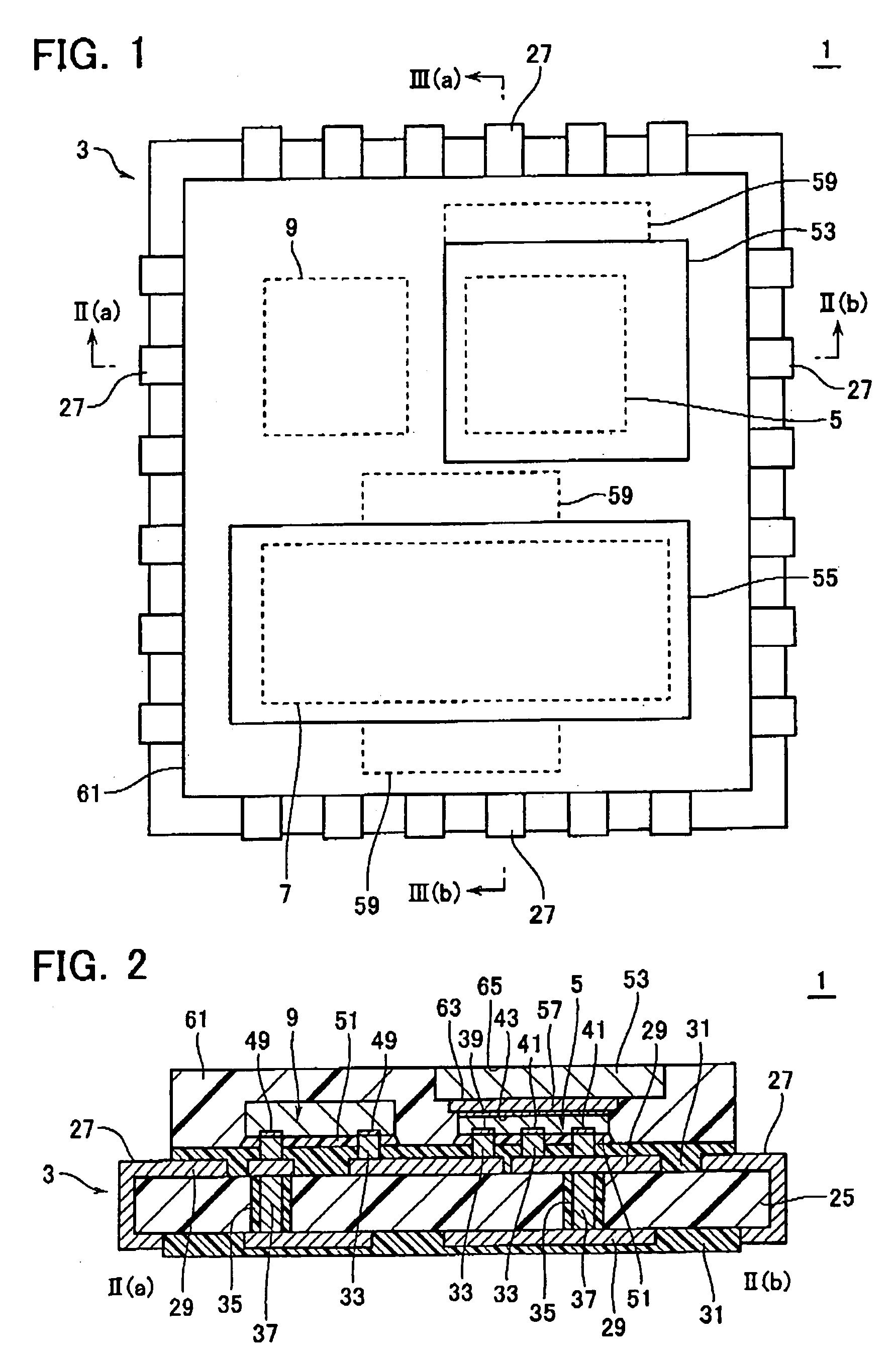

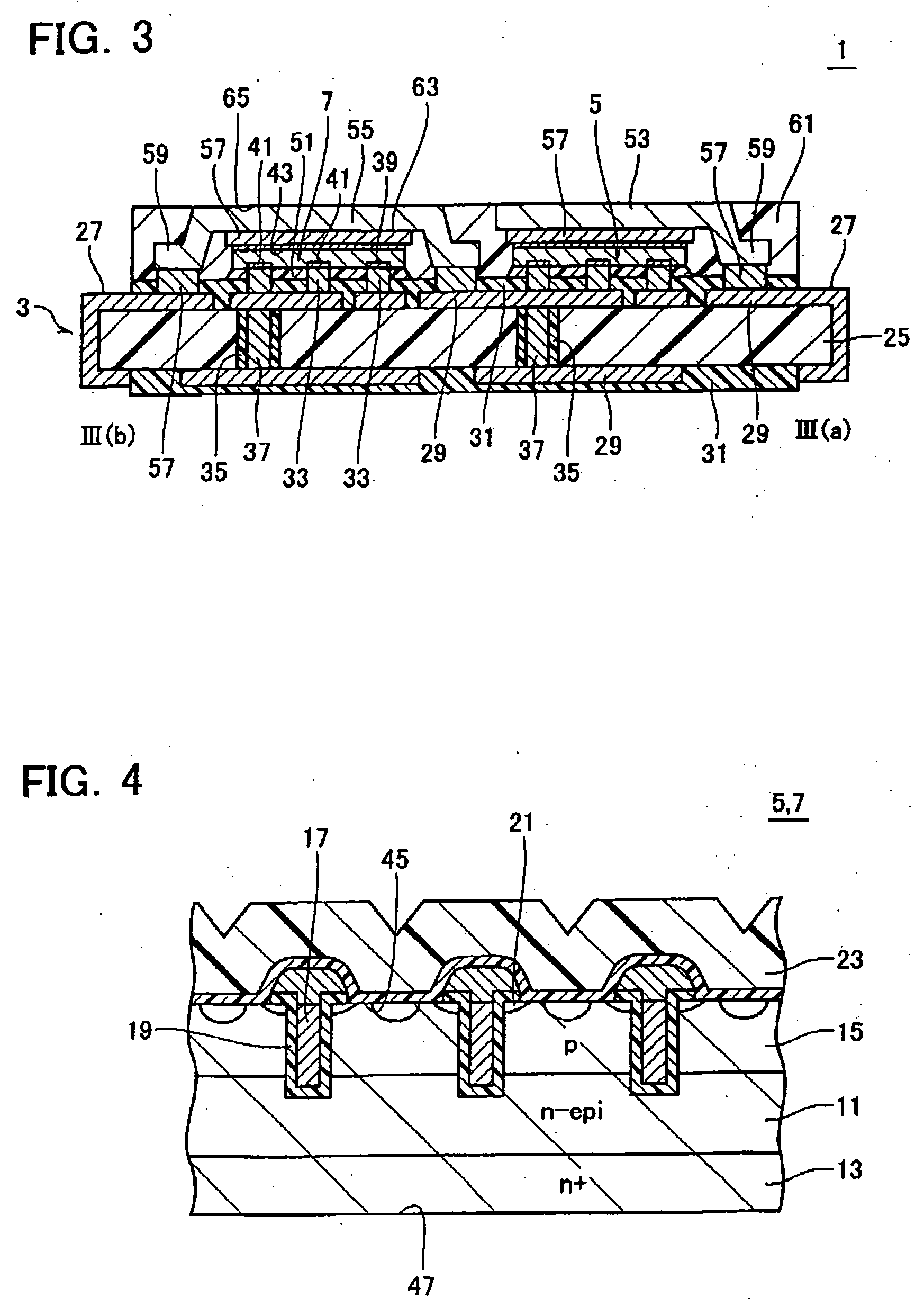

Semiconductor module

InactiveUS20050167849A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipMetal insulator

A semiconductor module includes a parts-mounting or packaging substrate, a plurality of power metal insulator semiconductor (MIS) chips which have top surfaces and back surfaces and are mounted by flip chip bonding on or above the package substrate while letting the top-surfaces face the package substrate, a drive-use integrated circuit (IC) chip which is mounted by flip chip bonding above the package substrate for driving the gates of metal insulator semiconductor field effect transistors (MISFETs) that are formed on the power MIS chips a plurality of heat sinks disposed on or above the back surfaces of the power MXS chips, and a resin member for sealing the power MIS chips and the driver IC chip together in a single package.

Owner:KK TOSHIBA

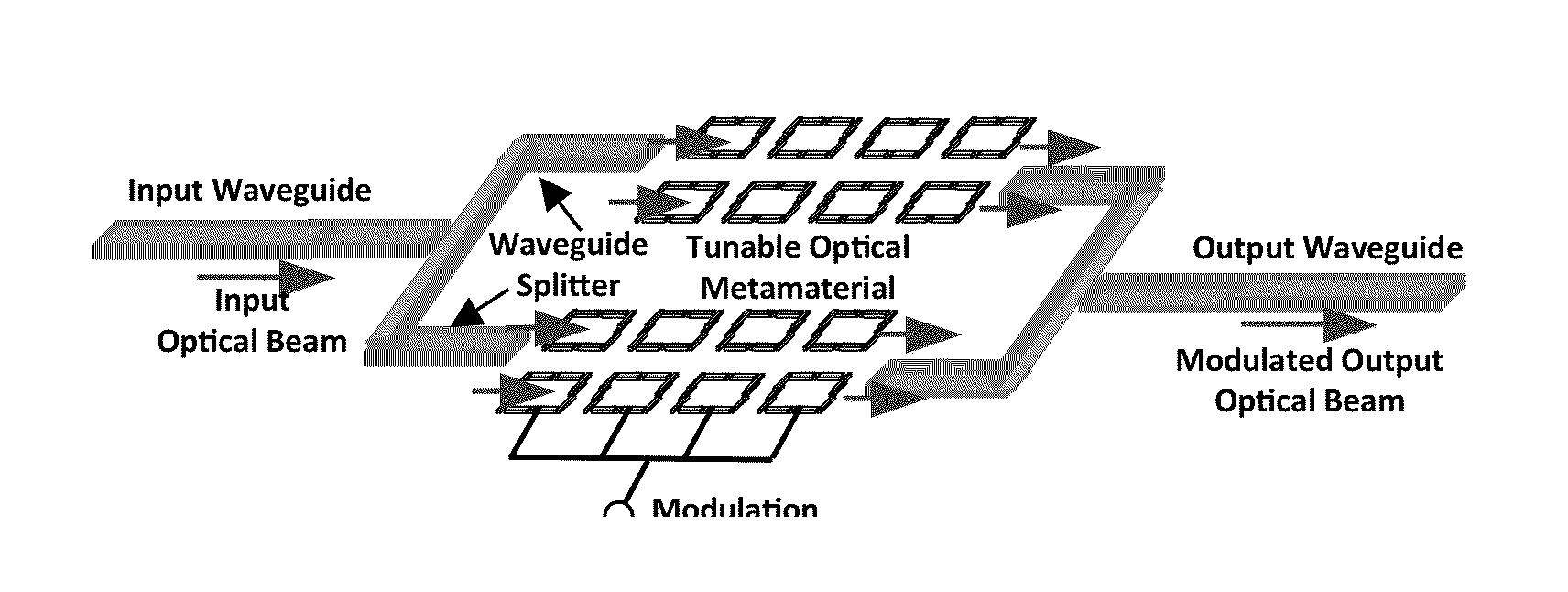

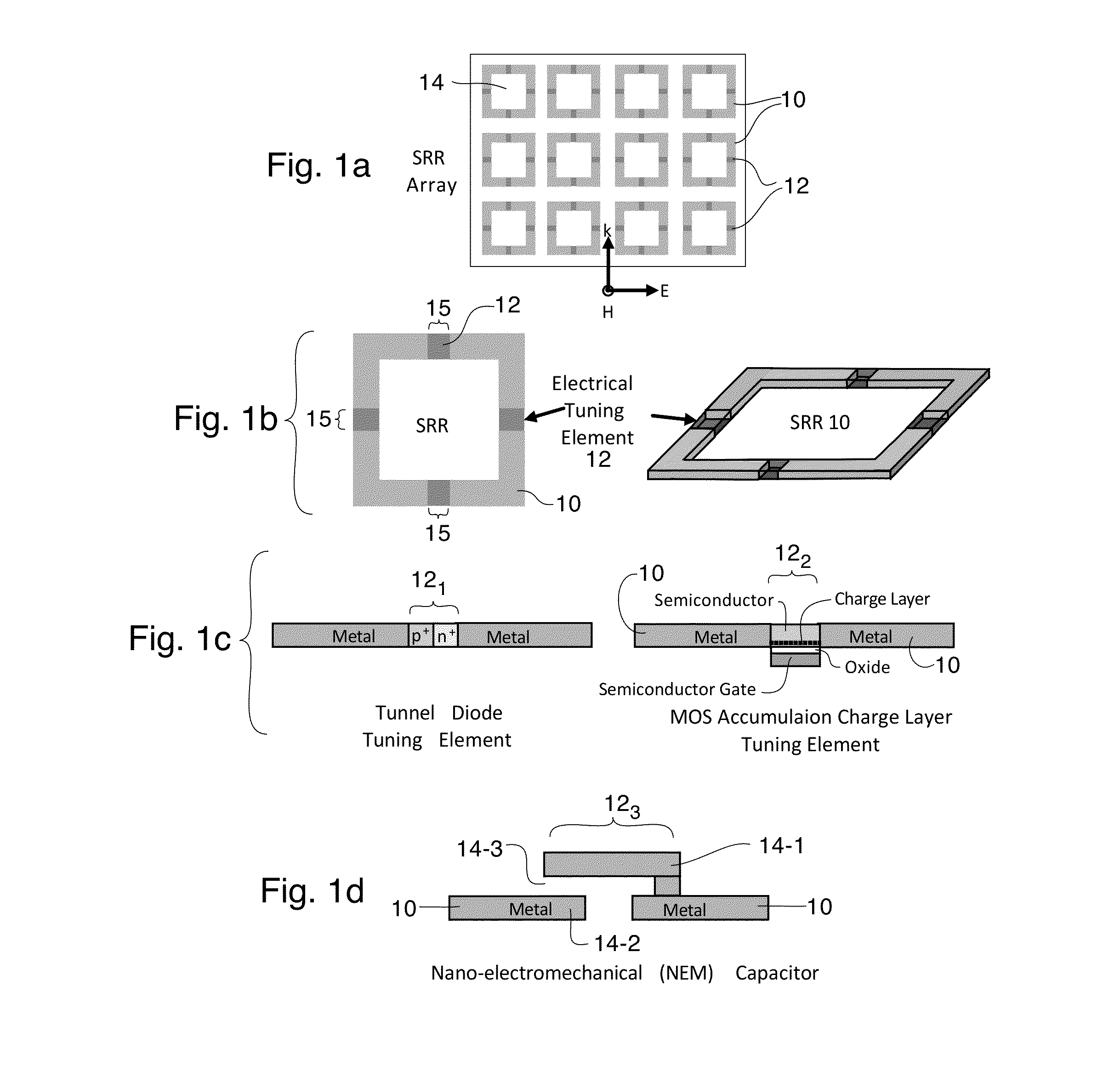

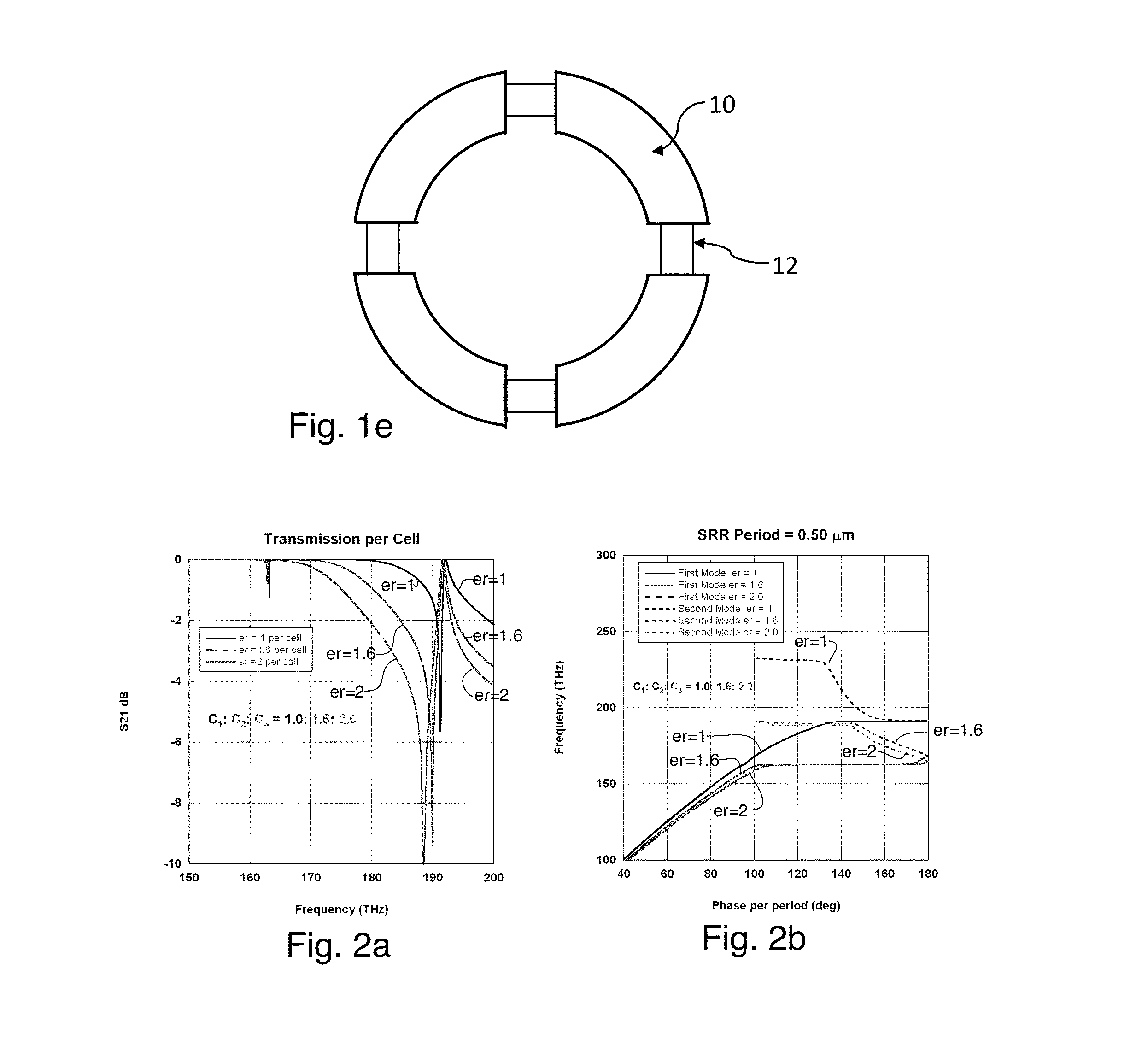

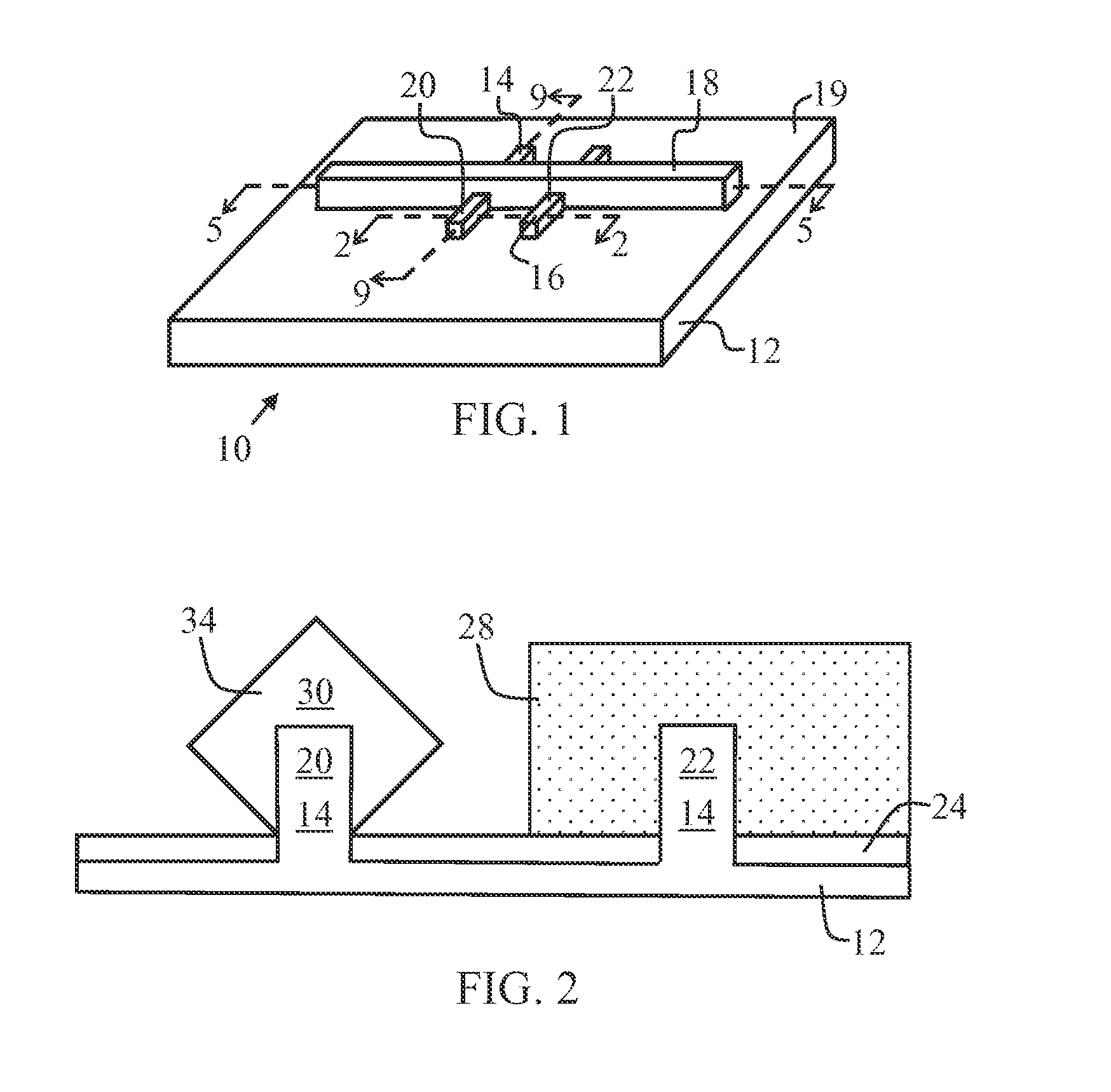

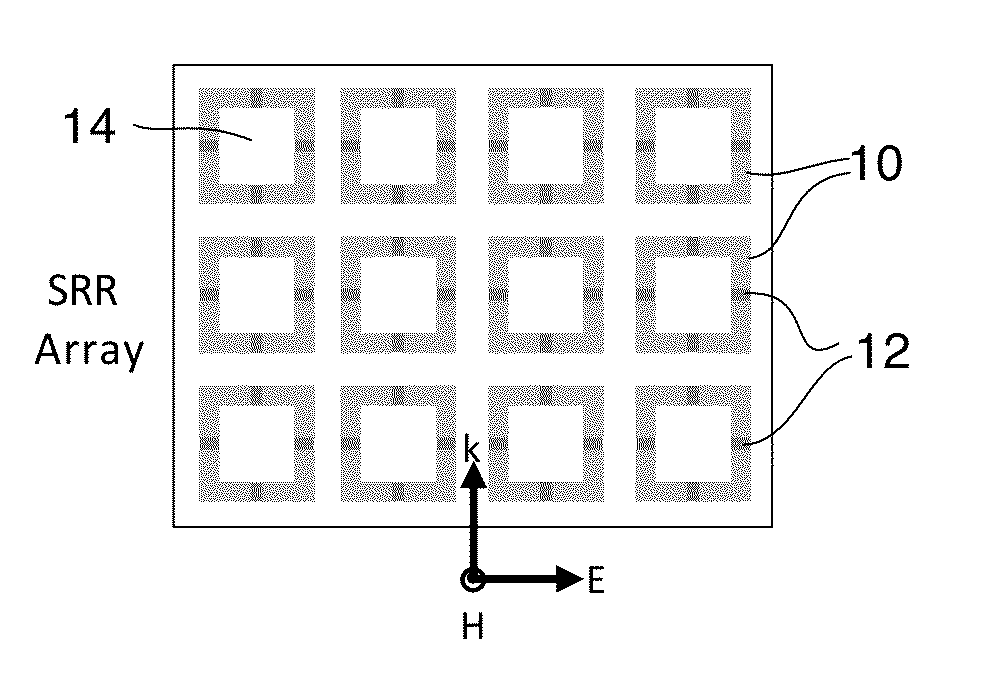

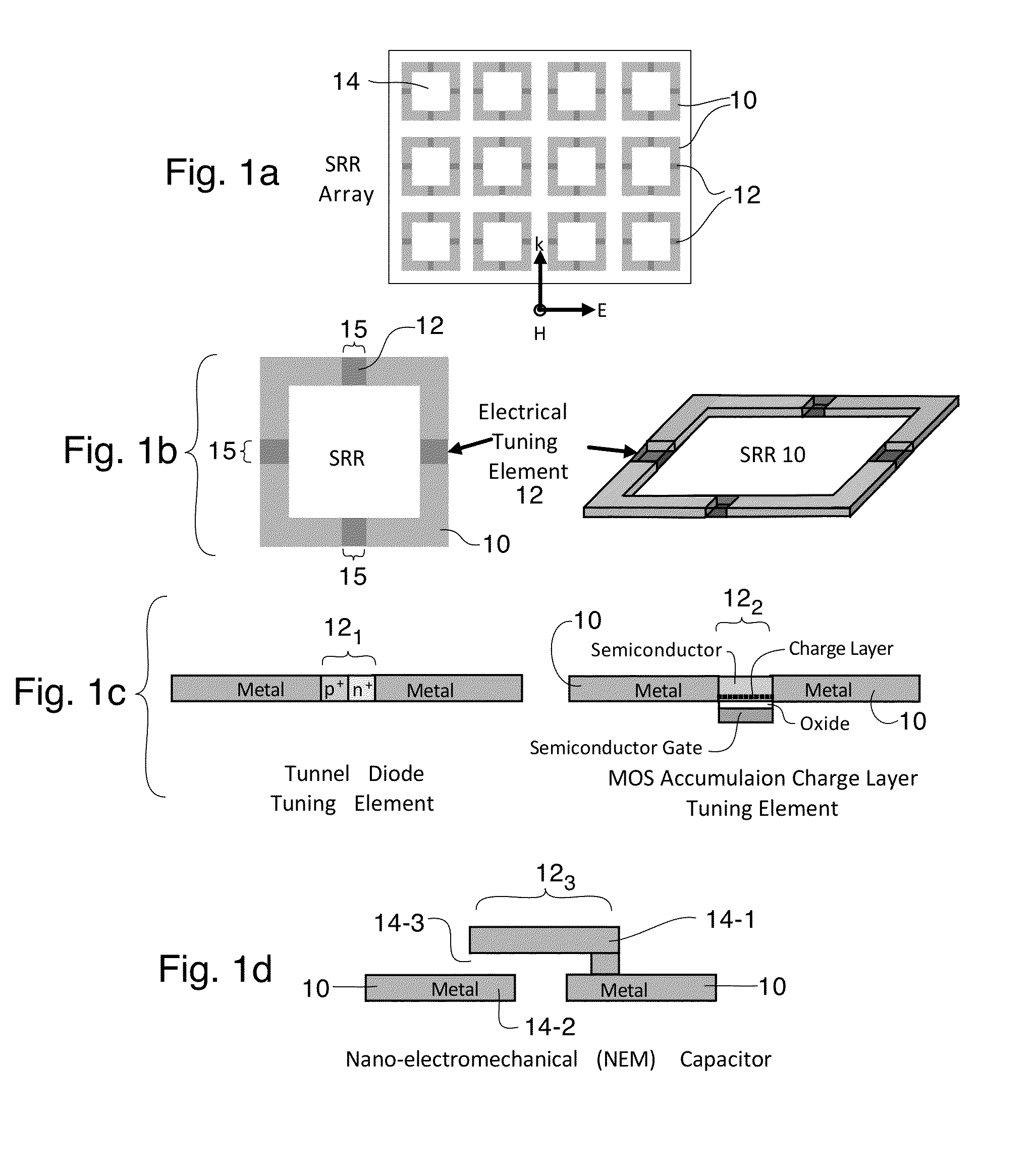

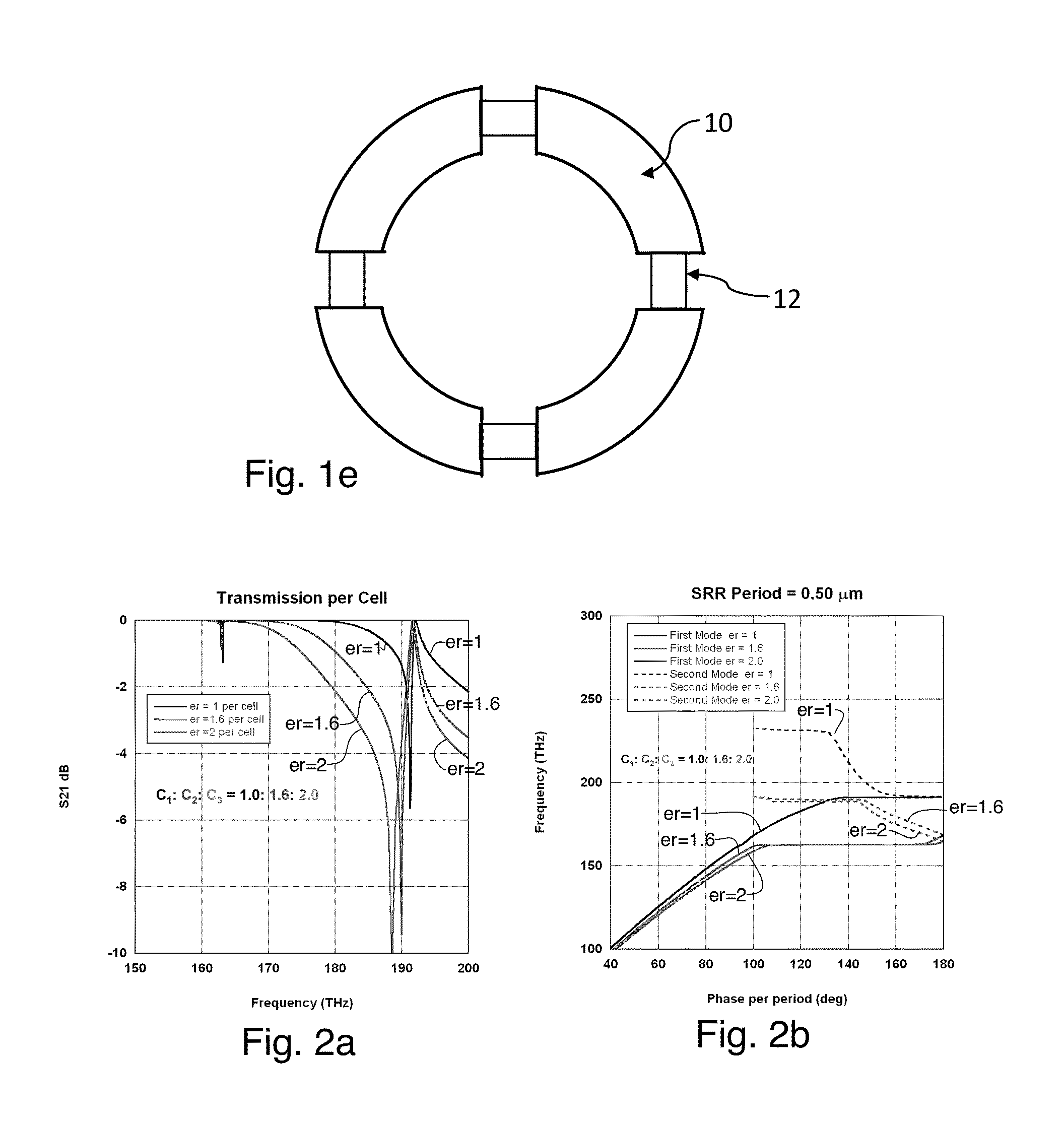

Tunable optical metamaterial

ActiveUS20140211298A1Semiconductor/solid-state device manufacturingNanoopticsTunnel diodeSemiconductor structure

A tunable metamaterial has a two dimensional array of resonant annular ring elements; and a plurality of voltage controllable electrical tuning elements disposed in or adjacent openings in each of said ring elements, each of said voltage controllable electrical tuning element ohmically contacting portions of only one of said ring elements. The voltage controllable electrical tuning elements may comprise highly doped semiconductor tunnel diodes, or the charge accumulation layer at the semiconductor / insulator interface of a metal-insulator-semiconductor structure, or nanoelectromechanical (NEMs) capacitors. The tunable metamaterial may be used, for example, in an optical beam steering device using the aforementioned tunable optical metamaterial in which a free-space optical beam is coupled into a receiving portion of a plane of the optical metamaterial and is steered out of a transmitter portion of the plane of the optical metamaterial in controllable azimuthal and elevational directions. The tunable metamaterial additionally has other applications.

Owner:HRL LAB

Miim diodes having stacked structure

ActiveUS20100078759A1Semiconductor/solid-state device detailsSolid-state devicesMetal insulatorDiode

A metal-insulator diode is disclosed. In one aspect, the metal-insulator diode comprises first and second electrode and first and second insulators arraigned as follows. An insulating region has a trench formed therein. The trench has a bottom and side walls. The first electrode, which comprises a first metal, is on the side walls and over the bottom of the trench. A first insulator has a first interface with the first electrode. At least a portion of the first insulator is within the trench. A second insulator has a second interface with the first insulator. At least a portion of the second insulator is within the trench. The second electrode, which comprises a second metal, is in contact with the second insulator. The second electrode at least partially fills the trench.

Owner:SANDISK TECH LLC

Light emitting nanowires for macroelectronics

Systems and methods to fabricate macroelectronic light emitting devices using densely oriented nanowires are disclosed. In one embodiment, core nanowires are synthesized and an insulating shell is fabricated around the nanowires. The nanowire core-shell structures are then deposited on a substrate to create a densely oriented nanowire thin film. Once the densely oriented nanowire thin film is created, a metal-insulator nanowire structure is fabricated by layering a metal on the nanowire thin film. Ohmic contacts are then created on the metal-insulator nanowire structure for operation. Application of electrical signals to the ohmic contacts causes light emission from the metal-insulator nanowire structure. Light emitting devices having densely oriented nanowire thin films are also disclosed. In an embodiment the light emitting device is, for example, a LED. The nanowires can include, for example, GaN, InP, CdS nanowires or a combination of these and other nanowires. Different colors of light can be produced based on the type of nanowire, the combination of nanowire types and the physical characteristics of the nanowires.

Owner:NANOSYS INC

Miim diodes

InactiveUS20100078758A1Improve propertiesIncrease currentSemiconductor/solid-state device detailsSolid-state devicesMetal insulatorNitrogen

A metal-insulator diode is disclosed. In one aspect, the metal-insulator diode comprises a first electrode comprising a first metal, a first region comprising a first insulating material, a second region comprising a second insulating material, and a second electrode comprising a second metal. The first region and the second region reside between the first electrode and the second electrode. The second insulating material is doped with nitrogen. Note that the second insulating material may have an interface with either the first electrode or the second electrode.

Owner:SANDISK TECH LLC

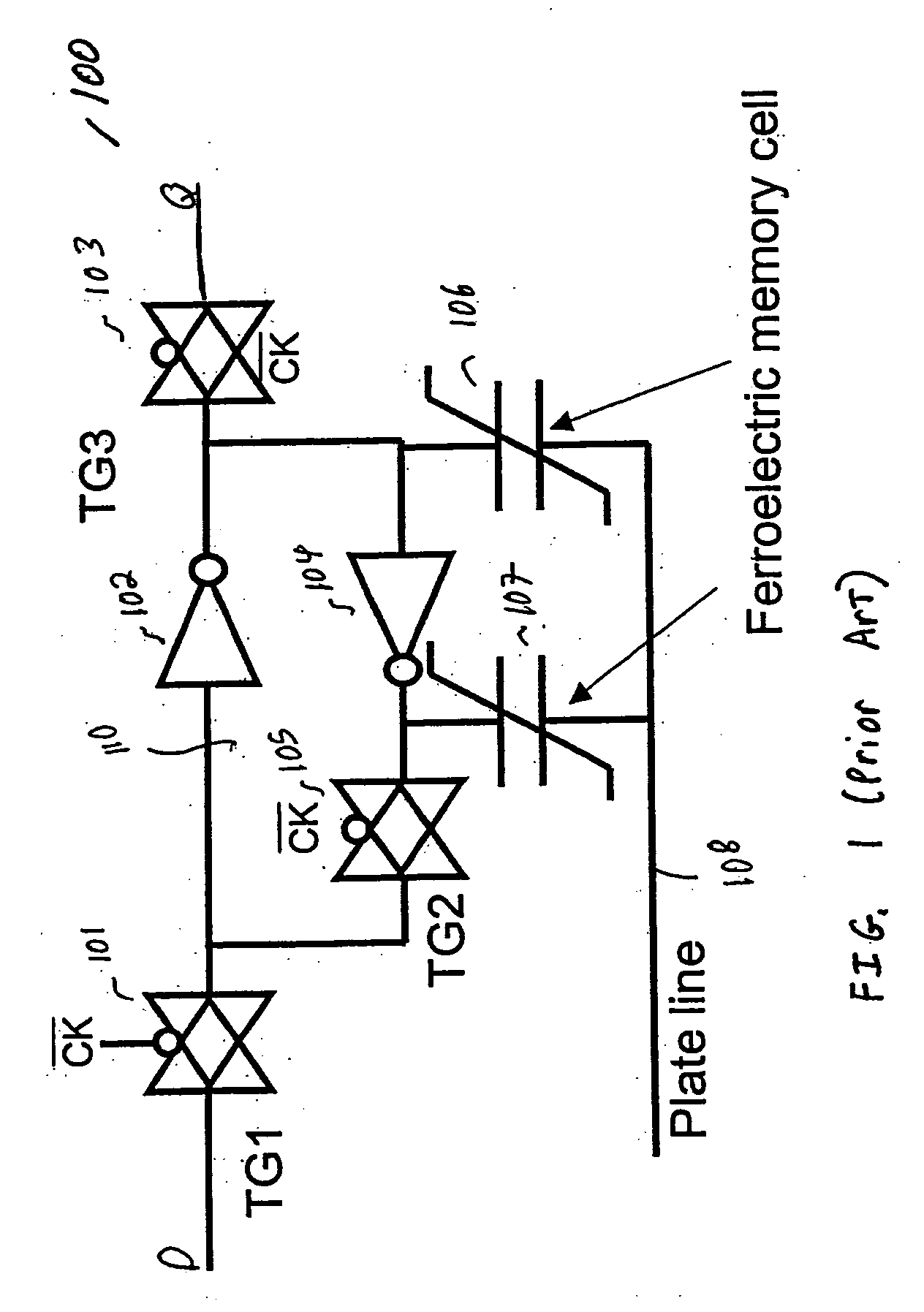

Nonvolatile memory for logic circuits

ActiveUS20060083047A1High resistance stateDigital storagePhase-change memoryMetal insulator phase transition

A memory circuit that retains stored data upon power down includes a volatile data storage circuit; and at least one nonvolatile memory coupled within the volatile data storage circuit, wherein the at least one nonvolatile memory includes a high resistive state and a low resistive state. The volatile data storage circuit can include cross-coupled inverters, cross- coupled NAND gates, or another volatile data storage circuit. The nonvolatile memories can include a spin-injection magnetic tunnel junction memory, a magnetic tunnel junction memory, a metal insulator phase change memory, an organic memory, or some other memory with two resistive states.

Owner:KK TOSHIBA +1

Semiconductor device and manufacturing method

InactiveUS20100044752A1Mitigates reduction in threshold voltageReduce voltageSemiconductor/solid-state device manufacturingSemiconductor devicesMetal insulatorElectron mobility

A metal-insulator-semiconductor high electron mobility transistor (MIS-HEMT) has a substrate in which an electron supply layer is interposed between an electron channel layer and the surface of the substrate. A pair of main electrodes are formed on the surface of the substrate. A recess is formed in the surface of the substrate between the main electrodes. A gate insulation film is formed on the surface of the substrate, at least between the first and second main electrodes, covering the inside walls and floor of the recess. A gate electrode is formed on the gate insulation film, filling in the recess. The gate insulation film has a crystal density of at least 2.9 g / cm3, which mitigates the reduction in threshold voltage caused by the recess.

Owner:OKI ELECTRIC IND CO LTD

Photovoltaic devices using semiconducting nanotube layers

InactiveUS20110203632A1Improve light absorptionPV power plantsNanoinformaticsSchottky barrierMetal insulator

Photovoltaic (PV) devices employing layers of semiconducting carbon nanotubes as light absorption elements are disclosed. In one aspect a layer of p-type carbon nanotubes and a layer of n-type carbon nanotubes are used to form a p-n junction PV device. In another aspect a mixed layer of p-type and n-type carbon nanotubes are used to form a bulk hetero-junction PV device. In another aspect a metal such as a low work function metal electrode is formed adjacent to a layer of semiconducting nanotubes to form a Schottky barrier PV device. In another aspect various material deposition techniques well suited to working with nanotube layers are employed to realize a practical metal-insulator-semiconductor (MIS) PV device. In another aspect layers of metallic nanotubes are used to provide flexible electrode elements for PV devices. In another aspect layers of metallic nanotubes are used to provide transparent electrode elements for PV devices.

Owner:NANTERO

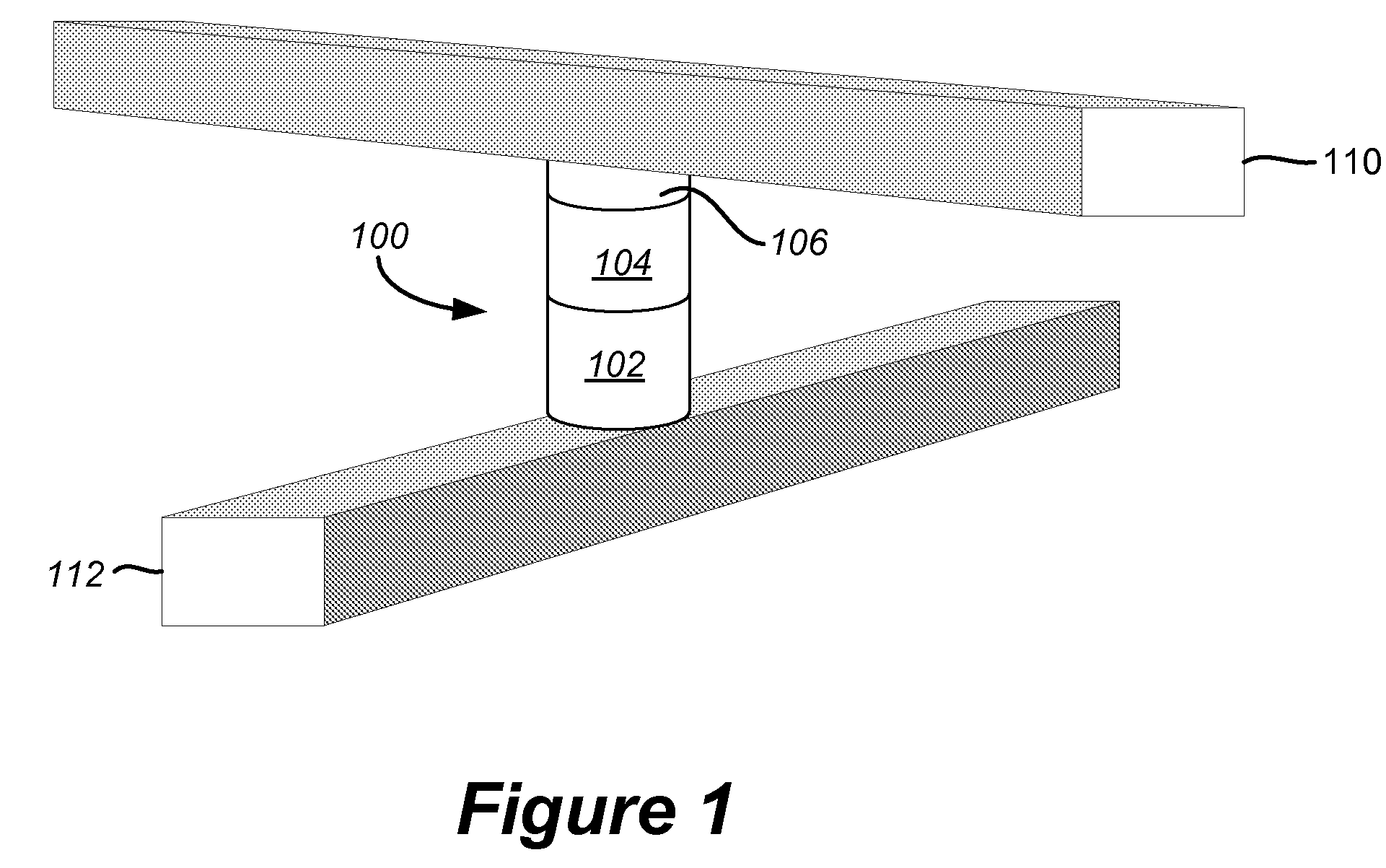

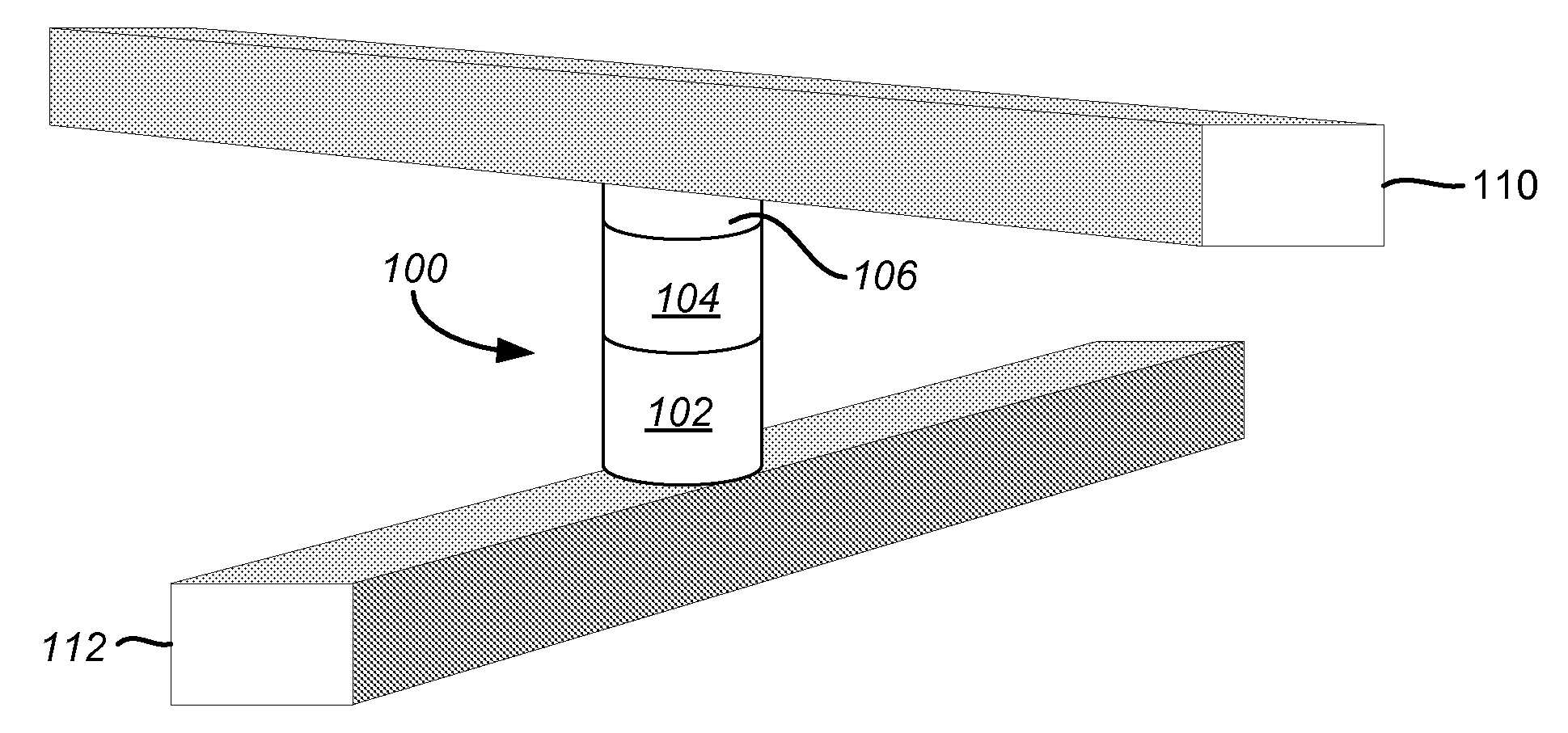

Methods of forming nanowire devices with metal-insulator-semiconductor source/drain contacts and the resulting devices

InactiveUS20150333162A1NanoinformaticsSemiconductor/solid-state device manufacturingNanowireMetal insulator

A device includes a gate structure and a nanowire channel structure positioned under the gate structure. The nanowire channel structure includes first and second end surfaces. The device further includes a first insulating liner positioned on the first end surface and a second insulating liner positioned on the second end surface. The device further includes a metal-containing source contact positioned on the first insulating liner and a metal-containing drain contact positioned on the second insulating liner.

Owner:GLOBALFOUNDRIES INC

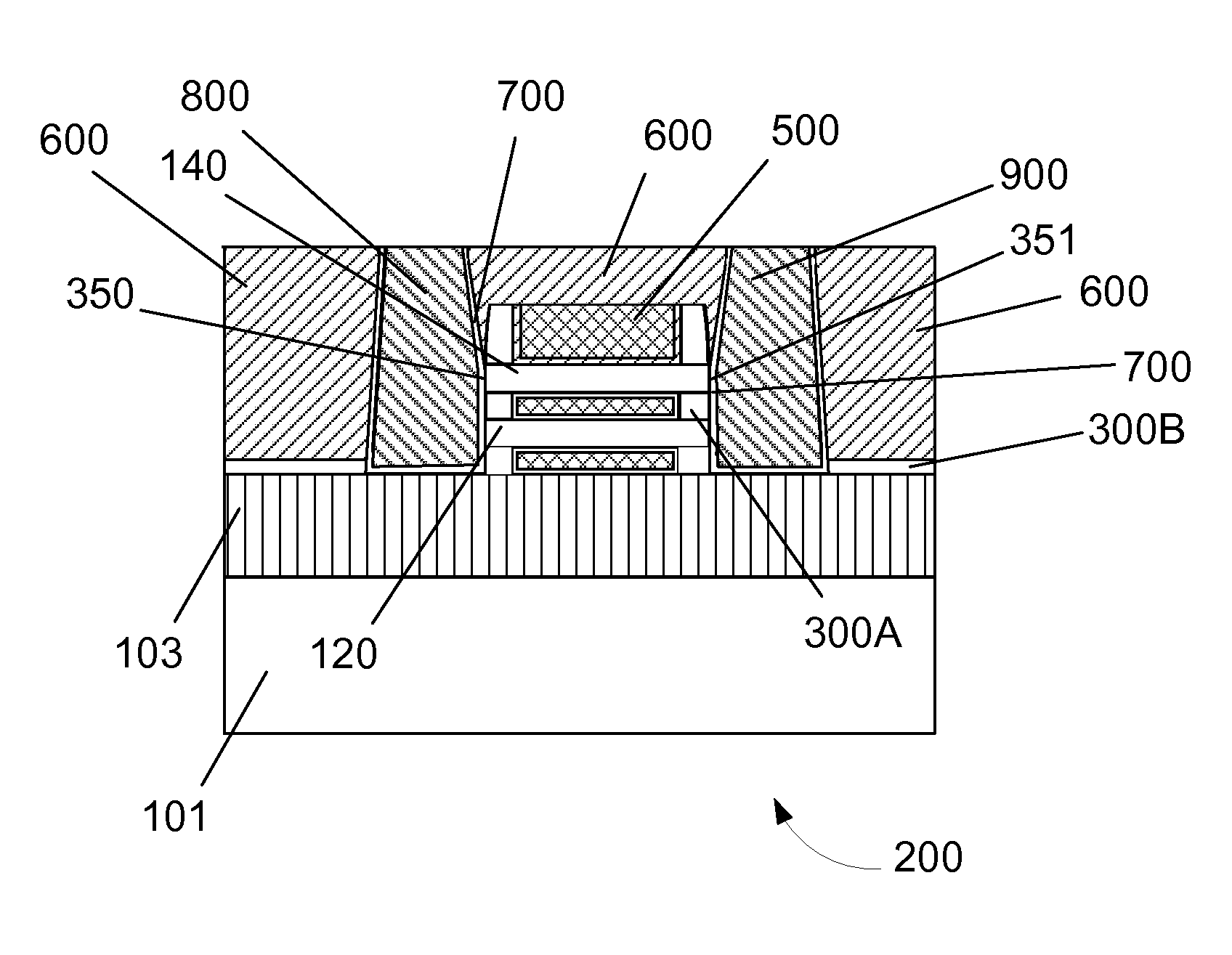

Integrated circuits with metal-insulator-semiconductor (MIS) contact structures and methods for fabricating same

Integrated circuits having metal-insulator-semiconductor (MIS) contact structures and methods for fabricating integrated circuits having metal-insulator-semiconductor (MIS) contact structures are provided. In an embodiment, a method for fabricating an integrated circuit includes providing a fin structure formed from semiconductor material overlying a semiconductor substrate. The method includes depositing a layer of high-k dielectric material over the fin structure. Further, the method includes forming a metal layer or layers over the layer of high-k dielectric material to provide the fin structure with a metal-insulator-semiconductor (MIS) contact structure.

Owner:GLOBALFOUNDRIES US INC

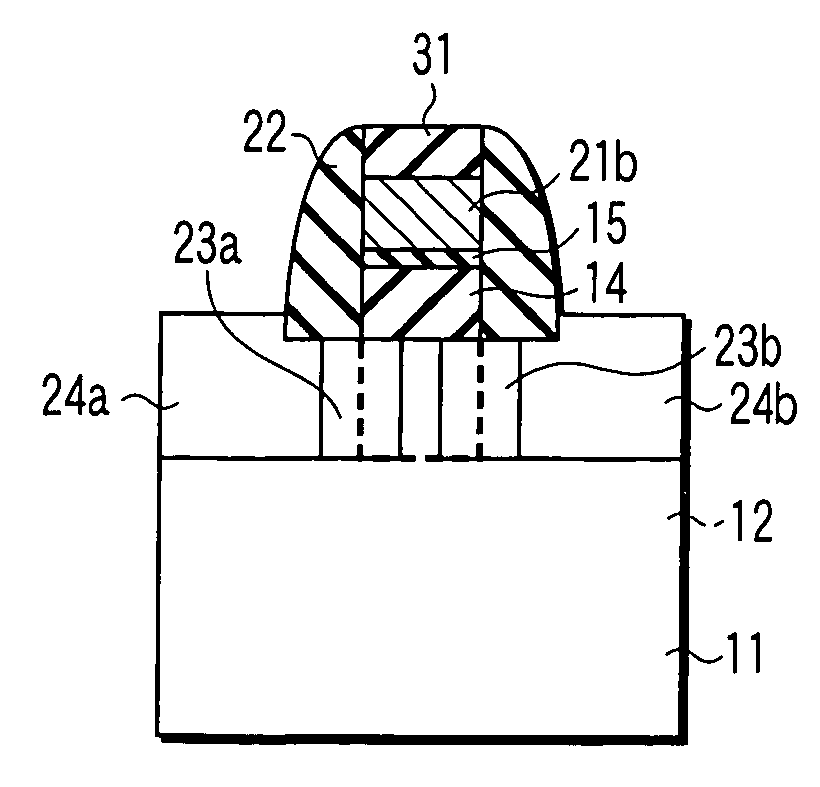

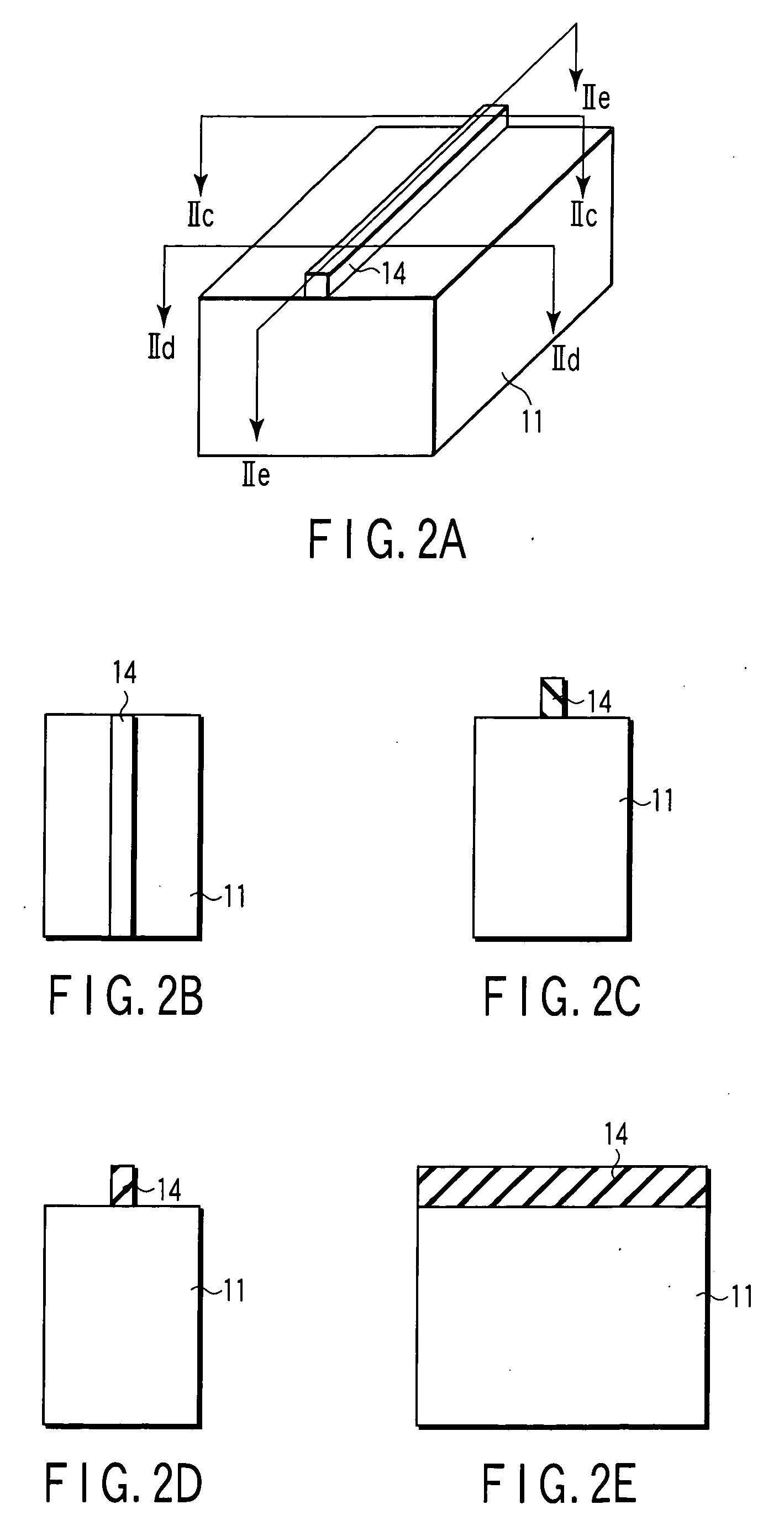

Semiconductor device including multi-gate metal-insulator-semiconductor (MIS) transistor

ActiveUS7622773B2Solid-state devicesSemiconductor/solid-state device manufacturingDevice materialMetal insulator

In a semiconductor device including a multi-gate MIS transistor having a channel on a plurality of surfaces, a gate electrode is formed on a gate insulating film on side surfaces of an island-like semiconductor layer formed along a given direction on an insulating film, and source / drain electrodes are formed in contact with the semiconductor layer. The semiconductor layer has a plurality of side surfaces along the given direction. All angles formed by adjacent side surfaces are larger than 90°. A section perpendicular to the given direction is vertically and horizontally symmetrical.

Owner:KK TOSHIBA

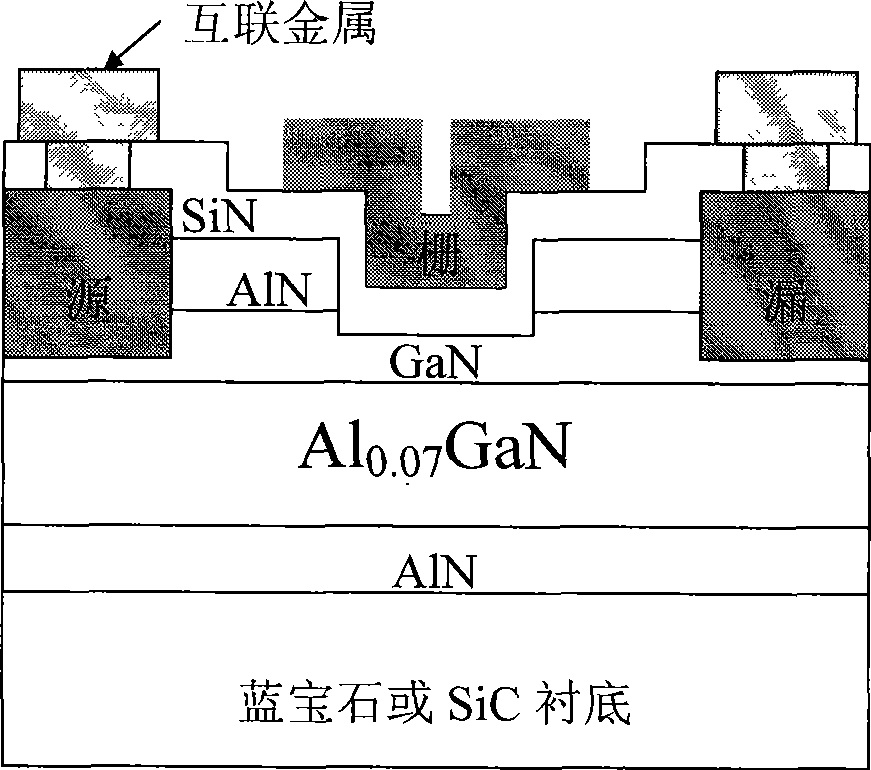

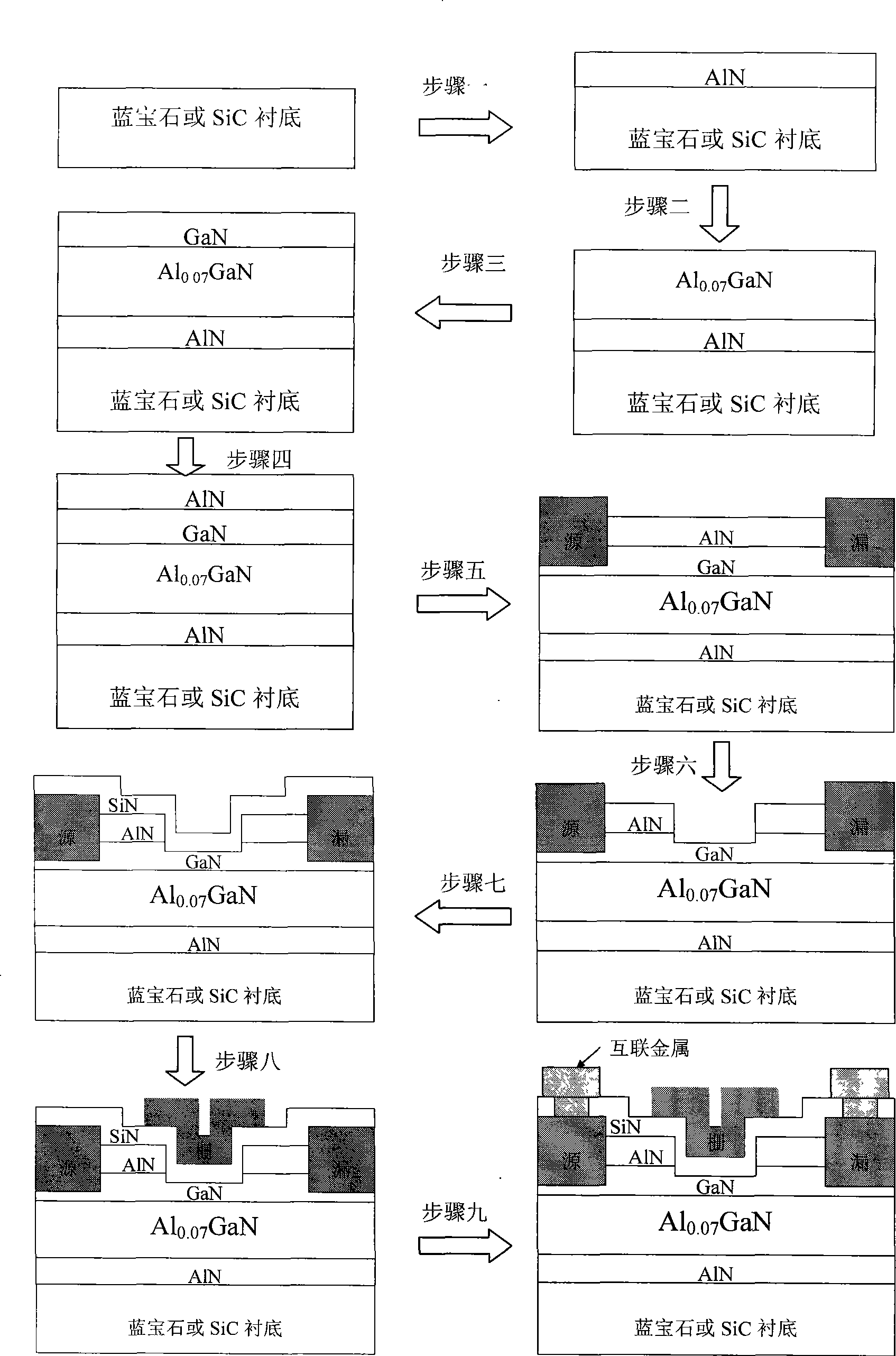

AlN/GaN enhancement type metal-insulator-semiconductor field effect transistor and method of producing the same

InactiveCN101465372AQuality improvementReduce random scatteringSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricMetal insulator

The invention discloses an AIN / GaN reinforced metal-insulator-semiconductor field effect transistor, mainly solving the problem that high-threshold voltage and large output current can not be realized at the same time in the existing device. The AIN / GaN reinforced metal-insulator-semiconductor field effect transistor is mainly characterized in that an AIN barrier layer is adopted to increase the concentration of channel two-dimensional electron gas and increase the output current at the time of high-threshold voltage. The manufacturing process comprises the following steps: growing an AIN nucleating layer on a substrate; growing an AI0.07GaN epitaxial layer on the AIN nucleating layer; growing a GaN layer on the AI0.07GaN epitaxial layer; growing an AIN barrier layer with a thickness of 3-6nm on the GaN layer; after the completion of material growing, photo-etching and vaporizing source-drain metals on the AIN barrier layer; photo-etching and etching a grooved gate between the source and the drain; after the grooved gate is etched, depositing SiN gate dielectric layers on the surfaces of the grooved gate and the AIN barrier layer; and photo-etching and vaporizing gate metals on the SiN gate dielectric layers and interconnecting the metals. The invention is applicable to the production of switch devices with high-threshold voltage and small transmission resistance.

Owner:XIDIAN UNIV

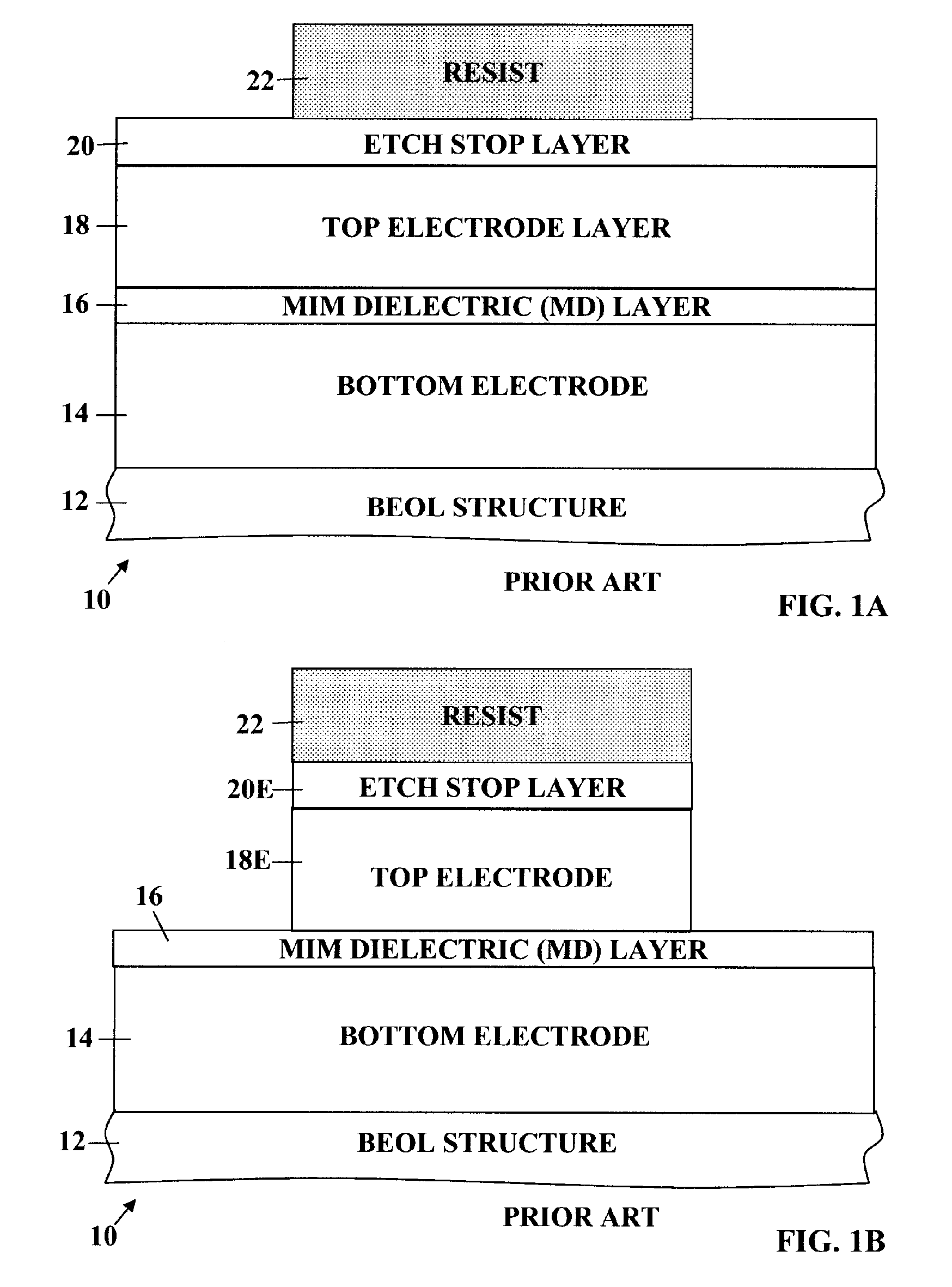

Integration of a MIM capacitor over a metal gate or silicide with high-k dielectric materials

InactiveUS20070057343A1Eliminate needImprove linearityTransistorSolid-state devicesCapacitanceMetal-insulator-metal

A Metal Insulator-Metal (MIM) capacitor is formed on a semiconductor substrate with a base comprising a semiconductor substrate having a top surface and including regions formed in the surface selected from a Shallow Trench Isolation (STI) region and a doped well having exterior surfaces coplanar with the semiconductor substrate. An ancillary MIM capacitor plate is selected either a lower electrode formed on the STI region in the semiconductor substrate or a doped well formed in the top surface of the semiconductor substrate. A capacitor HiK dielectric layer is formed on or above the MIM capacitor lower plate. A second MIM capacitor plate is formed on the HiK dielectric layer above the MIM capacitor lower plate.

Owner:GLOBALFOUNDRIES INC

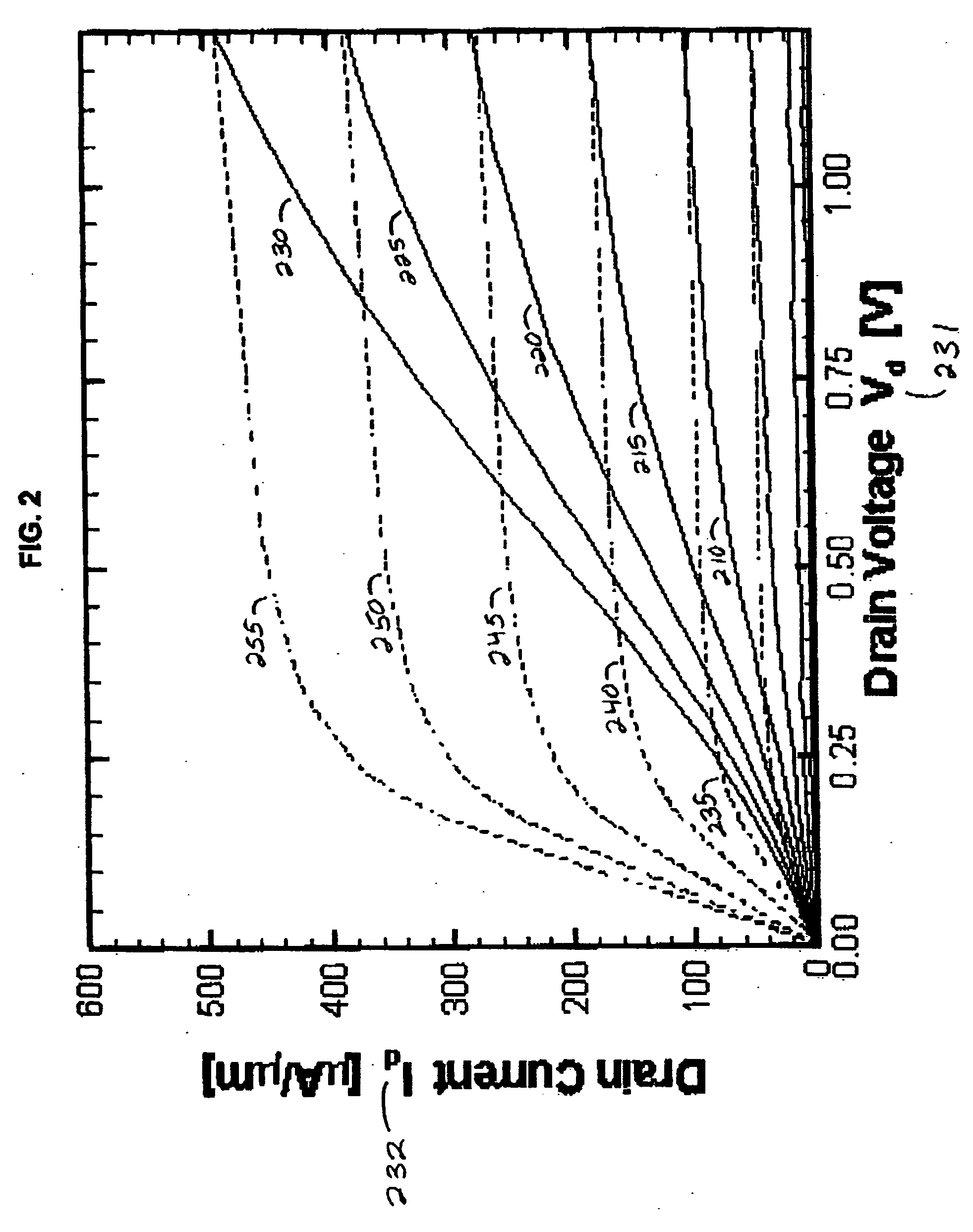

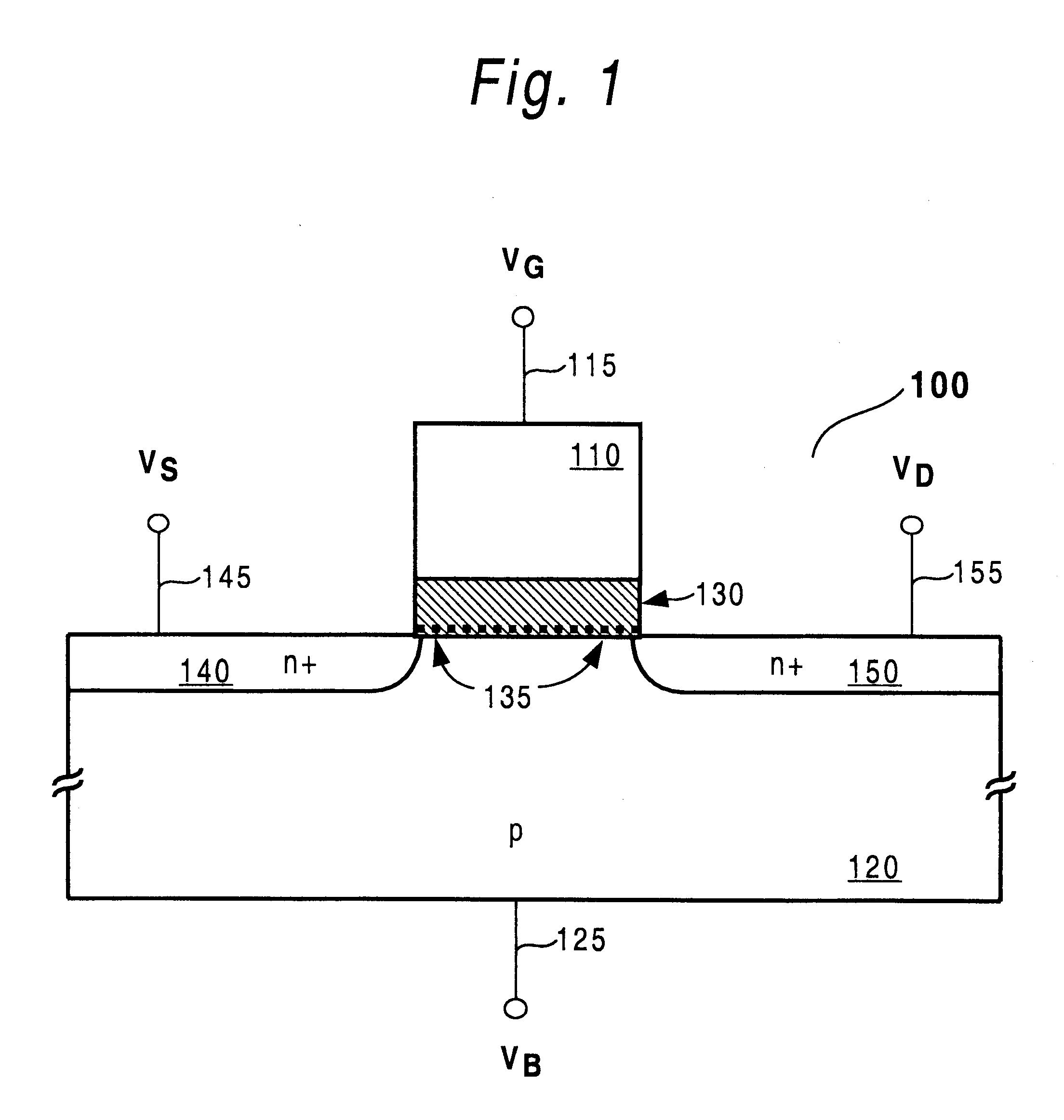

CMOS compatible process for making a tunable negative differential resistance (NDR) device

InactiveUS6596617B1Improve performance and functionalityNegative differential resistance (NDR) characteristicTransistorSemiconductor/solid-state device manufacturingCMOSMetal insulator

A method of making an n-channel metal-insulator-semiconductor field-effect transistor (MISFET) that exhibits negative differential resistance in its output characteristic (drain current as a function of drain voltage) is disclosed. By implanting ions into a substrate that is later thermally oxidized, a number of temporary charge trapping sites can be established above a channel region of a transistor. The channel is also heavily doped, so that a strong electrical field can be generated to accelerate hot carriers into the temporary charge trapping sites. The insulating layer formed during the oxidation step is made sufficiently thick to prevent quantum tunnelingo of the hot carriers into a gate electrode. Other suitable and conventional processing steps are used to finalize completion of the fabrication of the NDR device so that the entire process is compatible and achieved with CMOS processing techniques.

Owner:SYNOPSYS INC

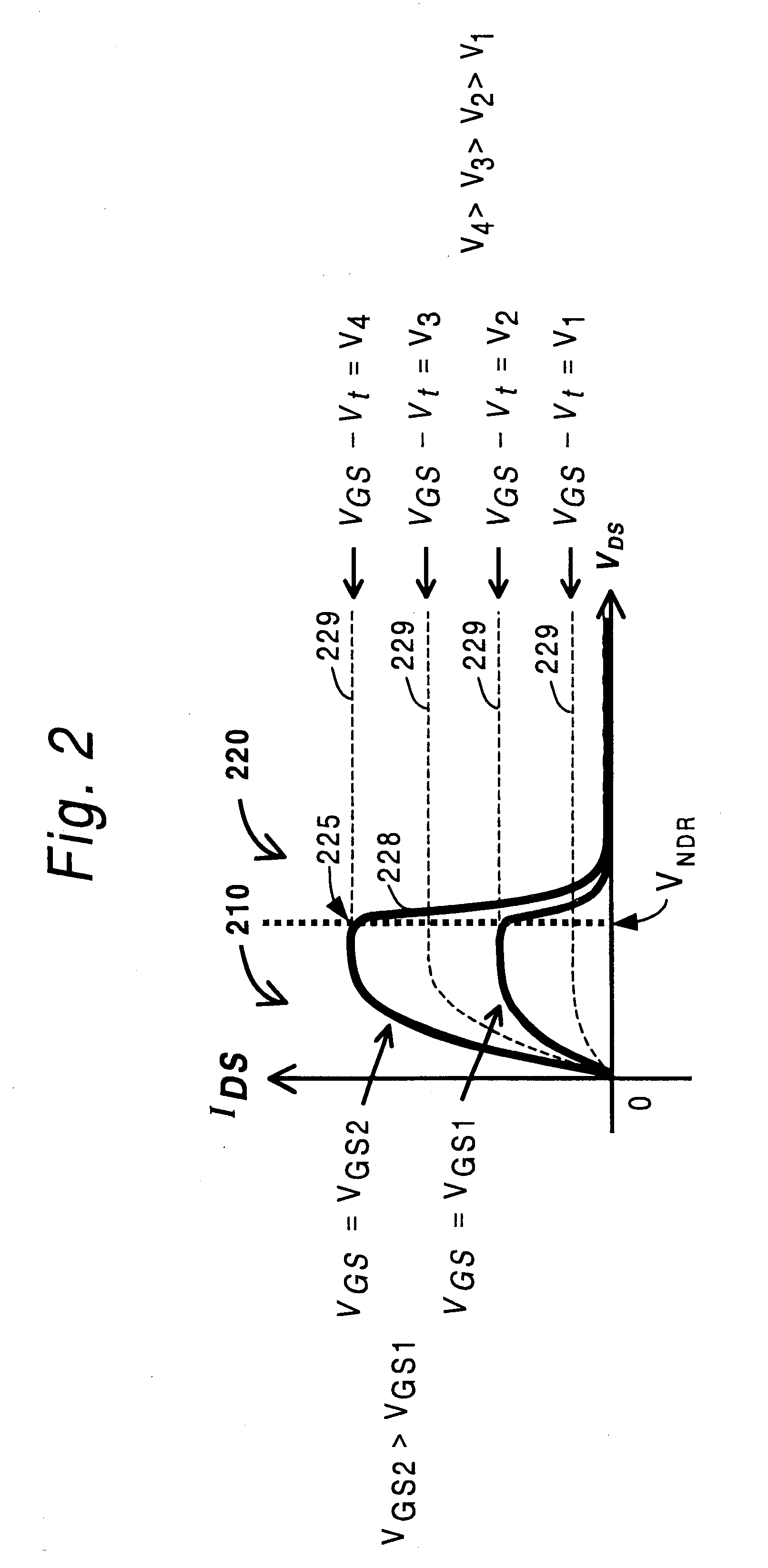

Dual layer gate dielectrics for non-silicon semiconductor devices

InactiveUS20110147710A1Semiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceGate dielectric

Non-silicon metal-insulator-semiconductor (MIS) devices and methods of forming the same. The non-silicon MIS device includes a gate dielectric stack which comprises at least two layers of non-native oxide or nitride material. The first material layer of the gate dielectric forms an interface with the non-silicon semiconductor surface and has a lower dielectric constant than a second material layer of the gate dielectric. In an embodiment, a dual layer including a first metal silicate layer and a second oxide layer provides both a good quality oxide-semiconductor interface and a high effective gate dielectric constant.

Owner:INTEL CORP

Semiconductor device including metal insulator semiconductor field effect transistor and method of manufacturing the same

A semiconductor device comprises a semiconductor substrate, an N-channel MISFET and a P-channel MISFET provided on the semiconductor substrate, each of the N- and P-channel MISFETs being isolated by an isolation region and having a gate insulating film, a first gate electrode film provided on the gate insulating film of the N-channel MISFET and composed of a first metal silicide, a second gate electrode film provided on the gate insulating film of the P-channel MISFET and composed of a second metal silicide made of a second metal material different from a first metal material composing the first metal silicide, and a work function of the first gate electrode film being lower than that of the second gate electrode film.

Owner:KIOXIA CORP

Semiconductor module having heat sink serving as wiring line

InactiveUS7071550B2Semiconductor/solid-state device detailsSolid-state devicesMetal insulatorField-effect transistor

A semiconductor module includes a parts-mounting or packaging substrate, a plurality of power metal insulator semiconductor (MIS) chips which have top surfaces and back surfaces and are mounted by flip chip bonding on or above the package substrate while letting the top-surfaces face the package substrate, a drive-use integrated circuit (IC) chip which is mounted by flip chip bonding above the package substrate for driving the gates of metal insulator semiconductor field effect transistors (MISFETs) that are formed on the power MIS chips, a plurality of heat sinks disposed on or above the back surfaces of the power MXS chips, and a resin member for sealing the power MIS chips and the driver IC chip together in a single package.

Owner:KK TOSHIBA

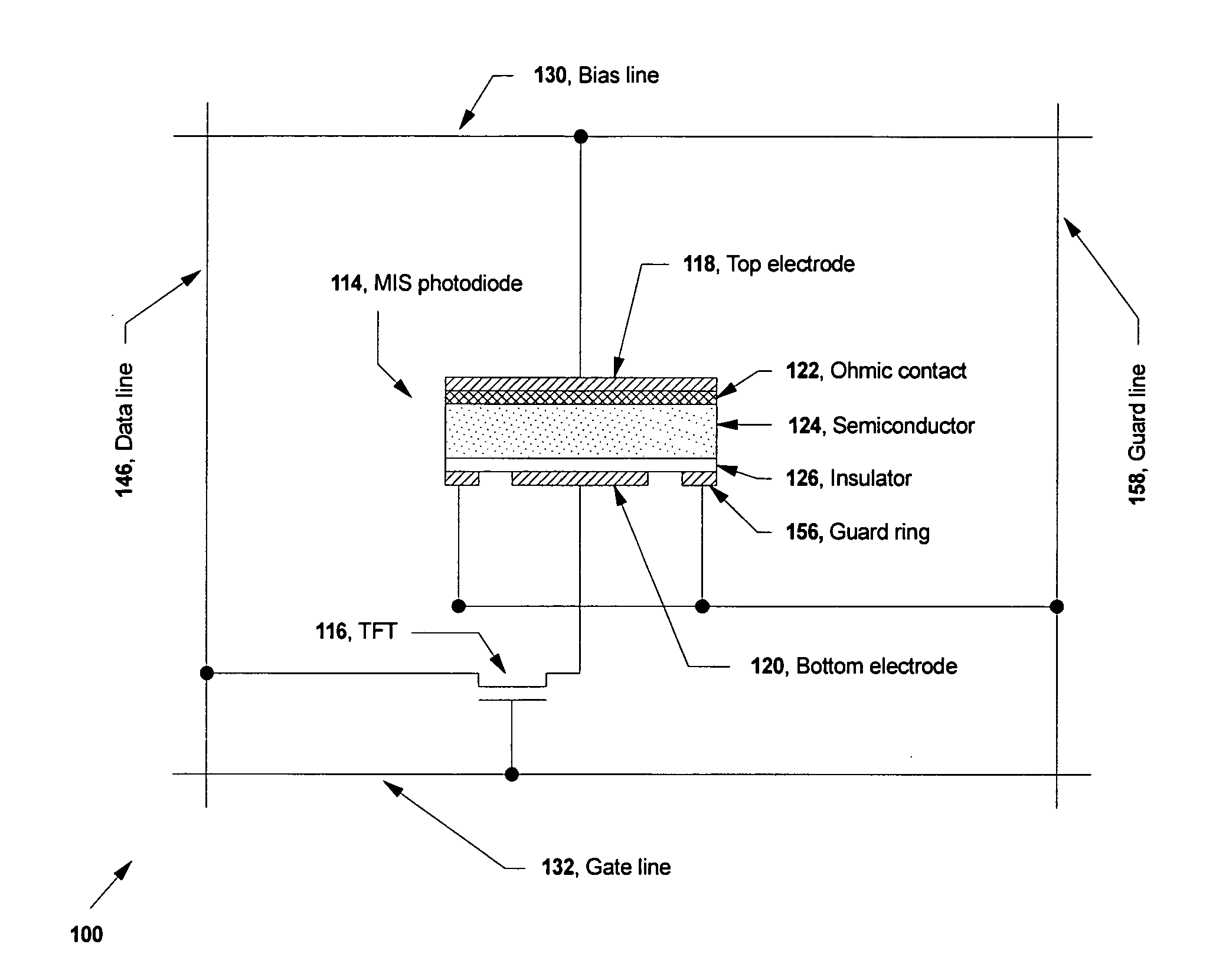

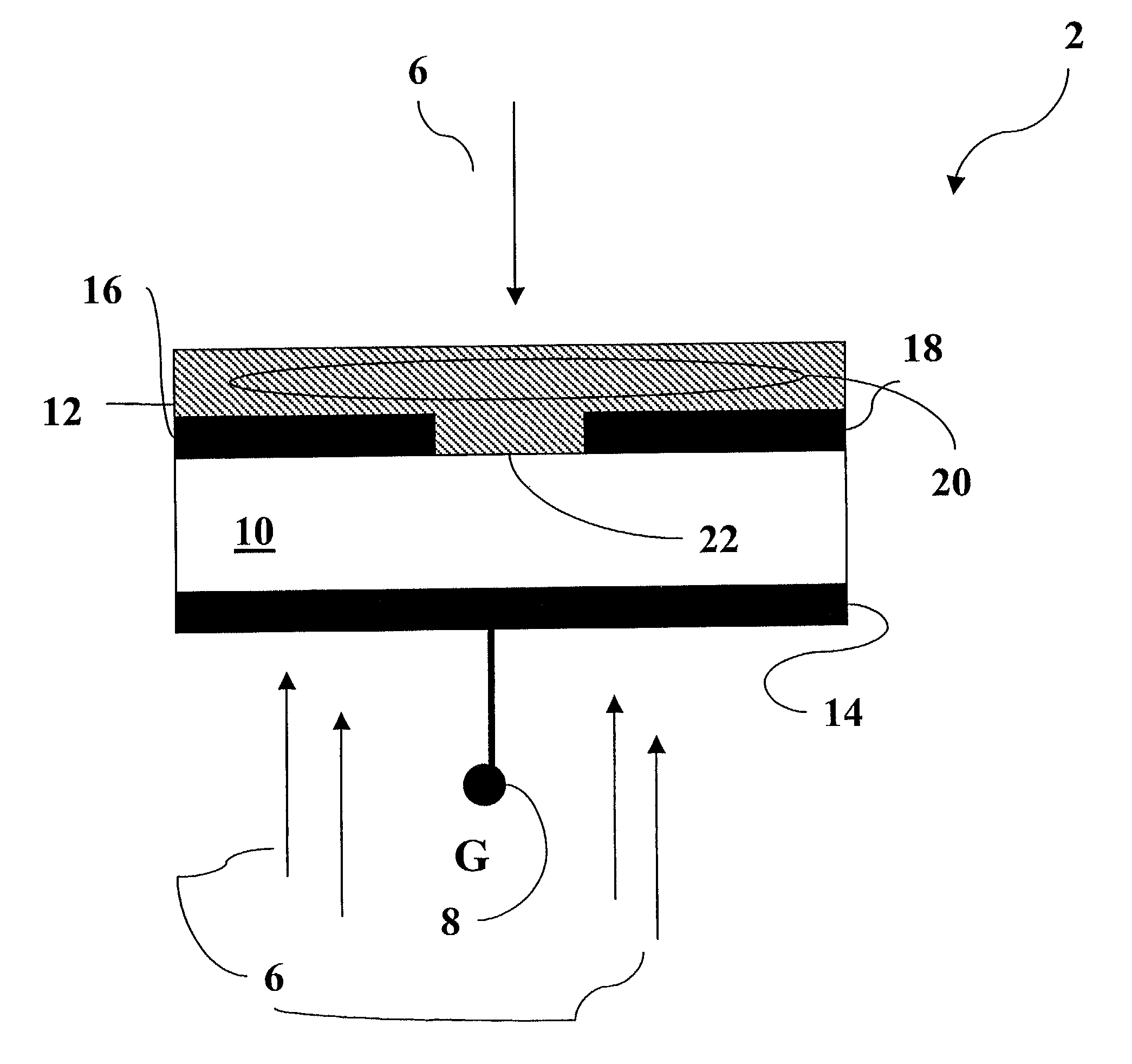

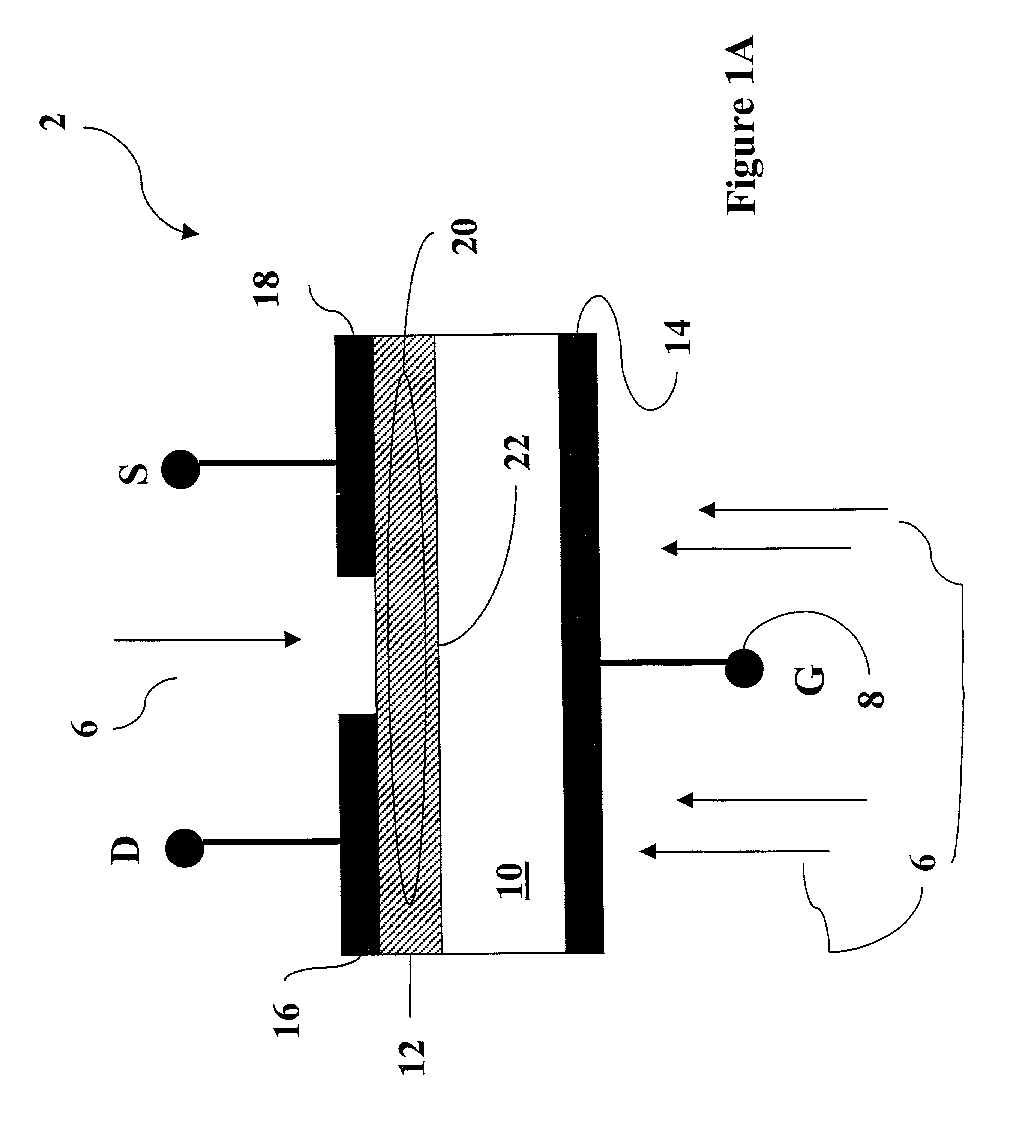

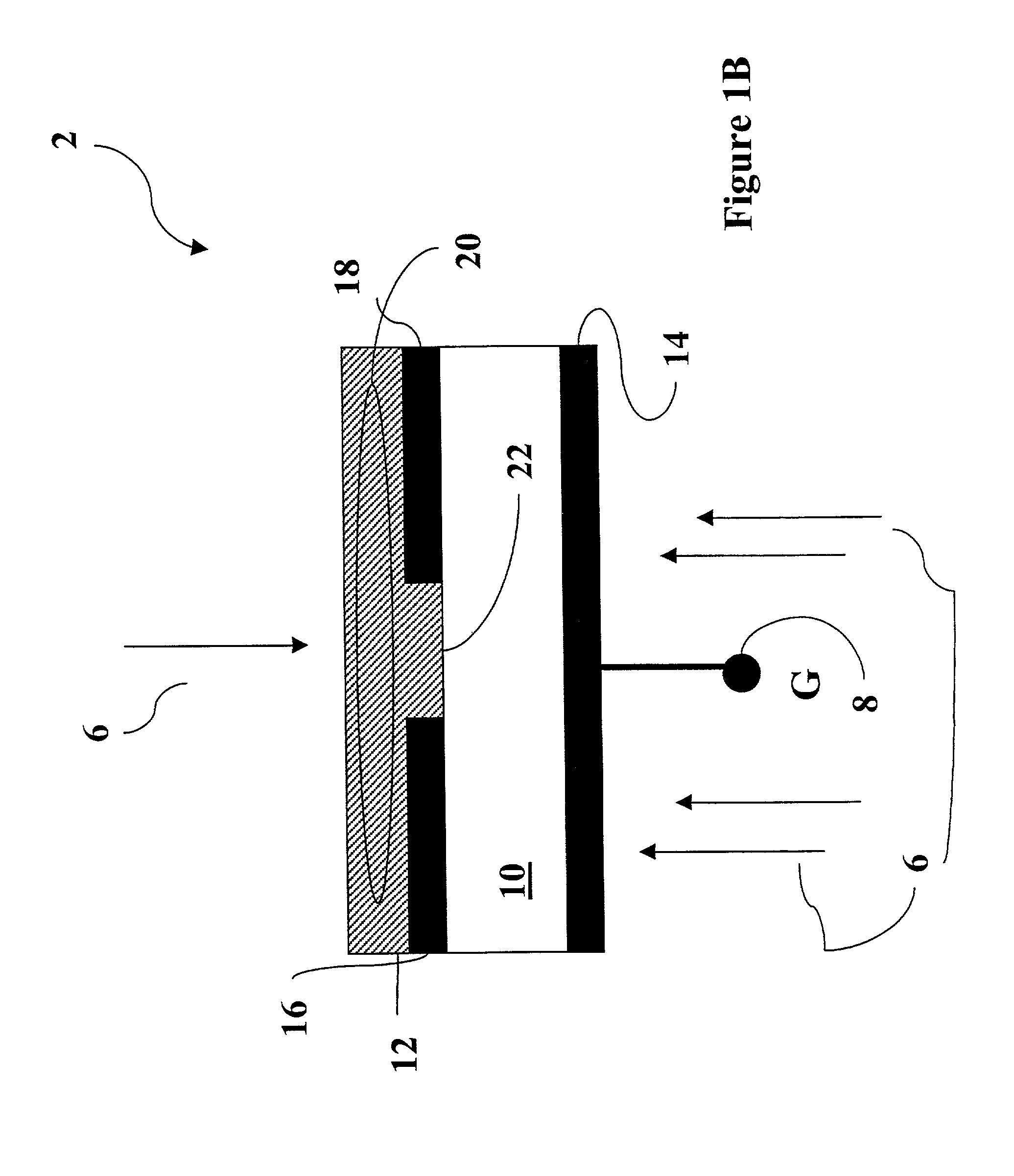

Integrated MIS photosensitive device using continuous films

InactiveUS20060001120A1Sufficient thickness and structural integritySolid-state devicesRadiation controlled devicesSemiconductor materialsMetal insulator

An integrated photosensitive device with a metal-insulator-semiconductor (MIS) photodiode constructed with one or more substantially continuous layers of semiconductor material and with a substantially continuous layer of dielectric material.

Owner:VAREX IMAGING CORP

Tunable optical metamaterial

InactiveUS20150062691A1Semiconductor/solid-state device manufacturingNanoopticsElectricityTunnel diode

A tunable metamaterial has a two dimensional array of resonant annular ring elements; and a plurality of voltage controllable electrical tuning elements disposed in or adjacent openings in each of said ring elements, each of said voltage controllable electrical tuning element ohmically contacting portions of only one of said ring elements. The voltage controllable electrical tuning elements may comprise highly doped semiconductor tunnel diodes, or the charge accumulation layer at the semiconductor / insulator interface of a metal-insulator-semiconductor structure, or nanoelectromechanical (NEMs) capacitors. The tunable metamaterial may be used, for example, in an optical beam steering device using the aforementioned tunable optical metamaterial in which a free-space optical beam is coupled into a receiving portion of a plane of the optical metamaterial and is steered out of a transmitter portion of the plane of the optical metamaterial in controllable azimuthal and elevational directions. The tunable metamaterial additionally has other applications.

Owner:HRL LAB

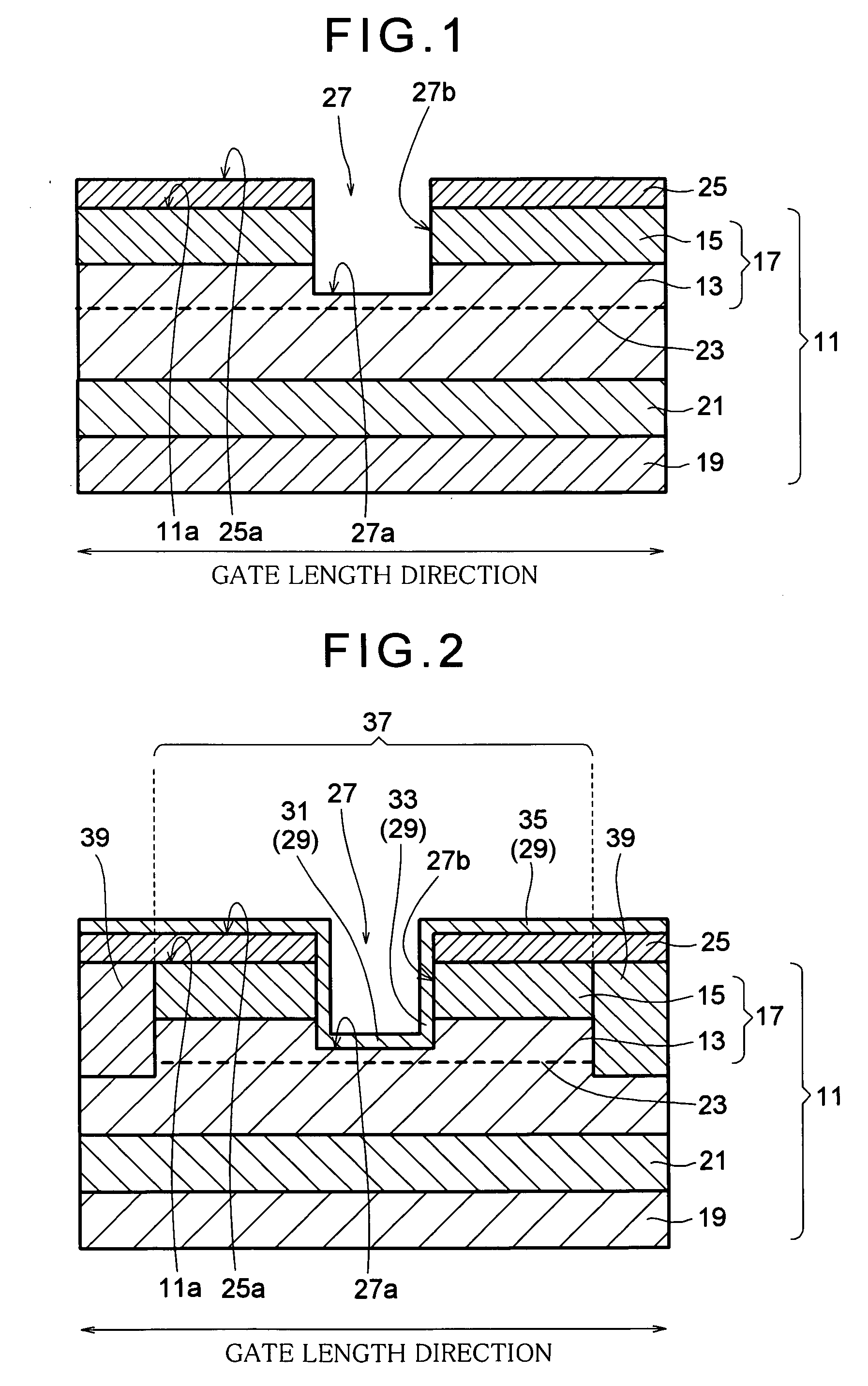

Metal insulator semiconductor field effect transistor having fin structure

A semiconductor device includes a fin-shaped semiconductor layer, a gate electrode section formed in a widthwise direction of the semiconductor layer with a gate insulation film interposed therebetween, the gate electrode section including a plurality of electrode materials having different work functions and stacked one another, and a channel section formed adjacent to the gate insulation film in the semiconductor layer. The semiconductor device further includes source and drain regions formed adjacent to the channel section.

Owner:MICROSOFT TECH LICENSING LLC

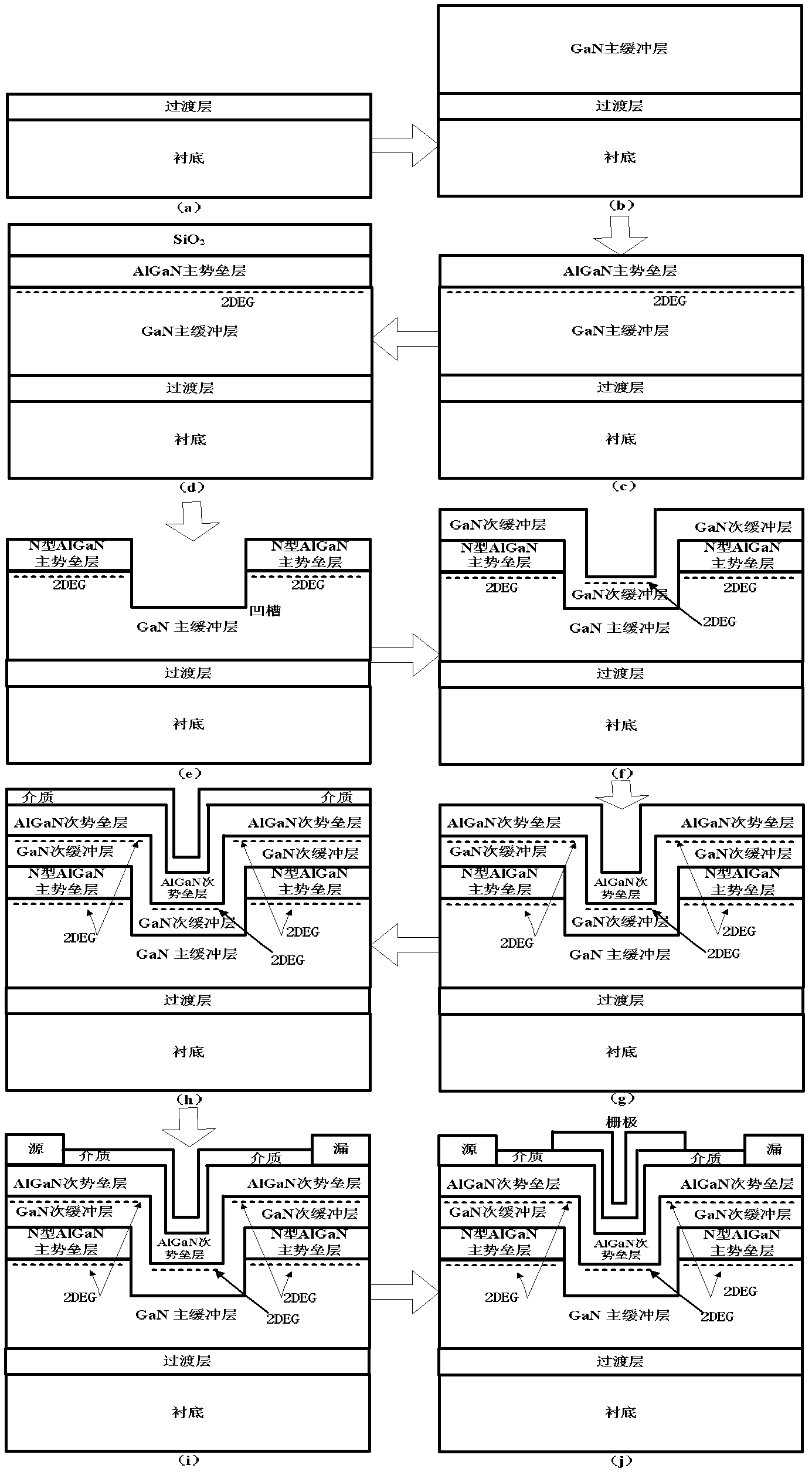

Metal-insulator-semiconductor (MIS) grid enhanced high electron mobility transistor (HEMT) device based on gallium nitride (GaN) and manufacture method of MIS grid enhanced HEMT device

ActiveCN102629624AReduce concentrationReduce or even eliminate polarization effectsSemiconductor/solid-state device manufacturingSemiconductor devicesMetal insulatorGallium nitride

The invention discloses a metal-insulator-semiconductor (MIS) grid enhanced high electron mobility transistor (HEMT) device based on gallium nitride (GaN) and a manufacture method of the MIS grid enhanced HEMT device and mainly solves the problems that the current density and the reliability of the existing GaN base enhanced device are low. The device is structurally characterized in that a transition layer (2) and a GaN main buffer layer (3) are sequentially arranged on a substrate (1), the middle of the GaN main buffer layer (3) is provided with a groove (11), an AlGaN main barrier layer (4) is arranged above the GaN main buffer layer arranged at two sides of the groove, a GaN sub buffer layer (5) and an AlGaN sub barrier layer (6) are sequentially arranged on the surface of the AlGaN main barrier layer (4) arranged above the groove inner wall and the two sides of the groove, the two sides of the top end of the AlGaN sub barrier layer (6) are respectively a source electrode (8) and a drain electrode (9), a medium layer (7) is arranged outside the source electrode and the drain electrode, a grid electrode (10) is arranged on the medium layer (7) and covers the whole groove region, and the mature flow process is adopted for the whole device manufacture. The MIS grid enhanced HEMT device has the advantages that the enhanced type characteristics are good, the current density is high, the breakdown voltage is high, and the device reliability is high. The MIS grid enhanced HEMT device can be used in high-temperature high-frequency high-power devices, high-power switches and digital circuits.

Owner:云南凝慧电子科技有限公司

Semiconductor module

InactiveUS20060097380A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipMetal insulator

Owner:KK TOSHIBA

misfet

InactiveUS20050072988A1Simple preparation processTransistorSemiconductor/solid-state device detailsMetal insulatorContact layer

A metal insulator semiconductor field effect transistor (MISFET) is disclosed comprising a source layer being made with a material having a source band-gap (EG2) and a source mid-gap value (EGM2), the source layer having a source Fermi-Level (EF2). A drain layer has a drain Fermi-Level (EF4). A channel layer is provided between the source layer and the drain layer, the channel layer being made with a material having a channel band-gap (EG3) and a channel mid-gap value (EGM3), the channel layer having a channel Fermi-Level (EF3). A source contact layer is connected to the source layer opposite the channel layer, the source contact layer having a source contact Fermi-Level (EF1). A gate electrode has a gate electrode Fermi-Level (EF6). The source band-gap is substantially narrower (EG2) than the channel band-gap (EG3). The source contact Fermi-Level (EF1), the source Fermi-Level (EF2), the channel Fermi-Level (EF3), the drain Fermi-Level (EF4) and the gate electrode Fermi-Level (EF6) are equal to the source mid-gap value (EGM2) and the channel mid-gap value (EGM3), within a predetermined tolerance value, when no voltage is applied to the device.

Owner:QUANTUM SEMICON

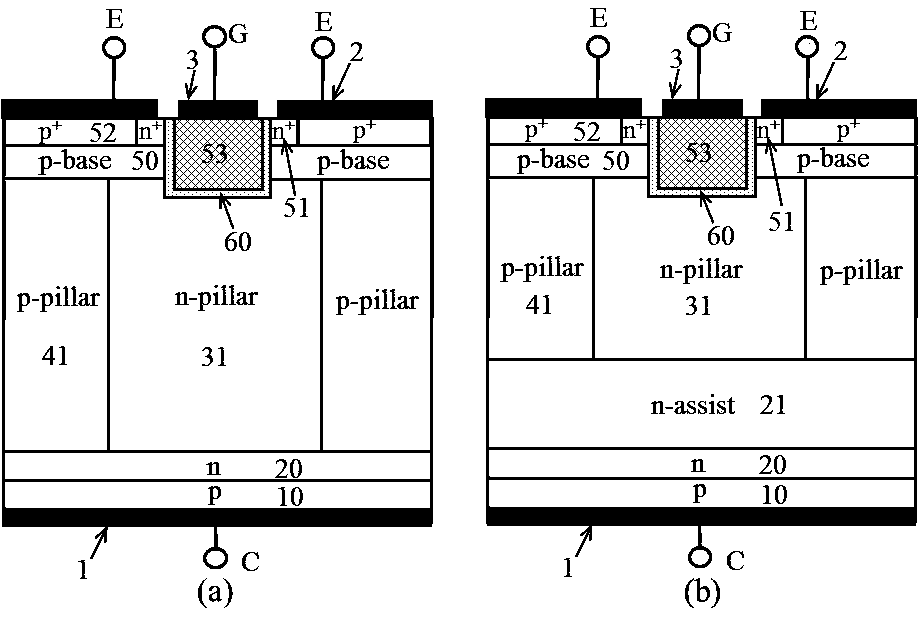

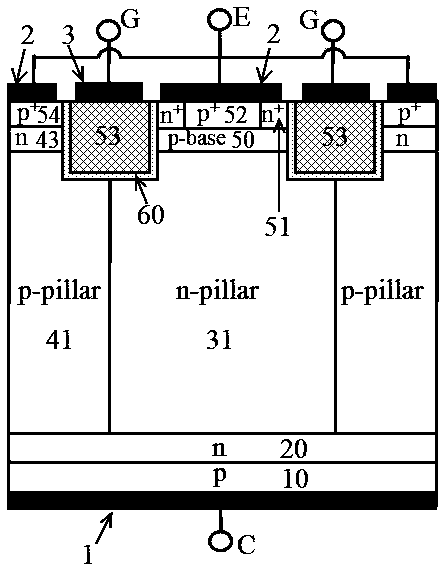

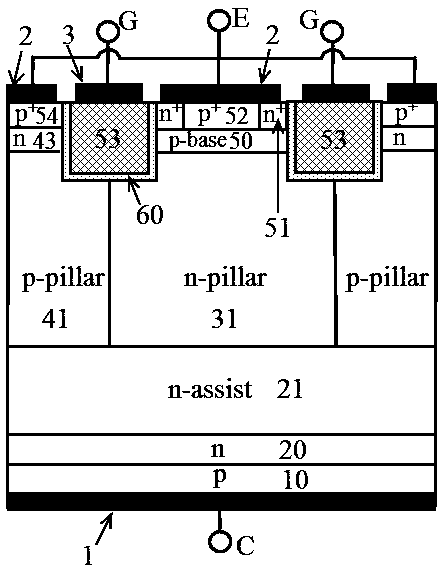

Superjunction IGBT with enhanced carrier storage effect

The invention provides a sperjunction IGBT (Insulated Gate Bipolar Transistor) device. A semiconductor region of the second conductivity type in a voltage resistance layer is connected with an emitterthrough a bipolar transistor of a base open circuit; the bipolar transistor of the base open circuit and the semiconductor region of the second conductivity type in the voltage resistance layer are isolated from a base region through a slot gate structure; the bipolar transistor of the base open circuit and the slot gate structure form an MISFET (metal-Insulator-Semiconductor Field Effect Transistor) with a floating substrate; and an electrode of the slot gate structure can be connected with a gate or the emitter. The bipolar transistor of the base open circuit can help to enhance the carrierstorage effect in a voltage resistance region during forward conduction, thereby reducing a conduction voltage drop.

Owner:SICHUAN UNIV

Photo-responsive organic field effect transistor

InactiveUS6992322B2NanoinformaticsSolid-state devicesOrganic field-effect transistorSemiconductor structure

A polymer-based field effect transistor photosensitive to incident light, which may enhance the transistor's characteristics and controlling parameters of the transistor state. The transistor is comprised of a metal-insulator-semiconductor structure with the insulating and semiconducting layers made of a polymeric media. The semiconducting polymer which also is photoconducting, forms the charge transport layer between the source and drain. The transistor exhibits large photosensitivity indicated by the sizable changes in the drain-source current, by a factor of 100–1000 even at low levels of light with illumination of approximately 1 mlux. The photosensitivity of the transistor is further enhanced with introduction of dilute quantity electron acceptor moieties in the semiconducting polymer matrix. Several applications of the light-responsive polymer-transistor are disclosed, such as use as a logic element and as a backbone of an image sensor.

Owner:JAWAHARLAL NEHRU CENT FOR ADVANCED SCI RES

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com