Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

42results about How to "Lower junction resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

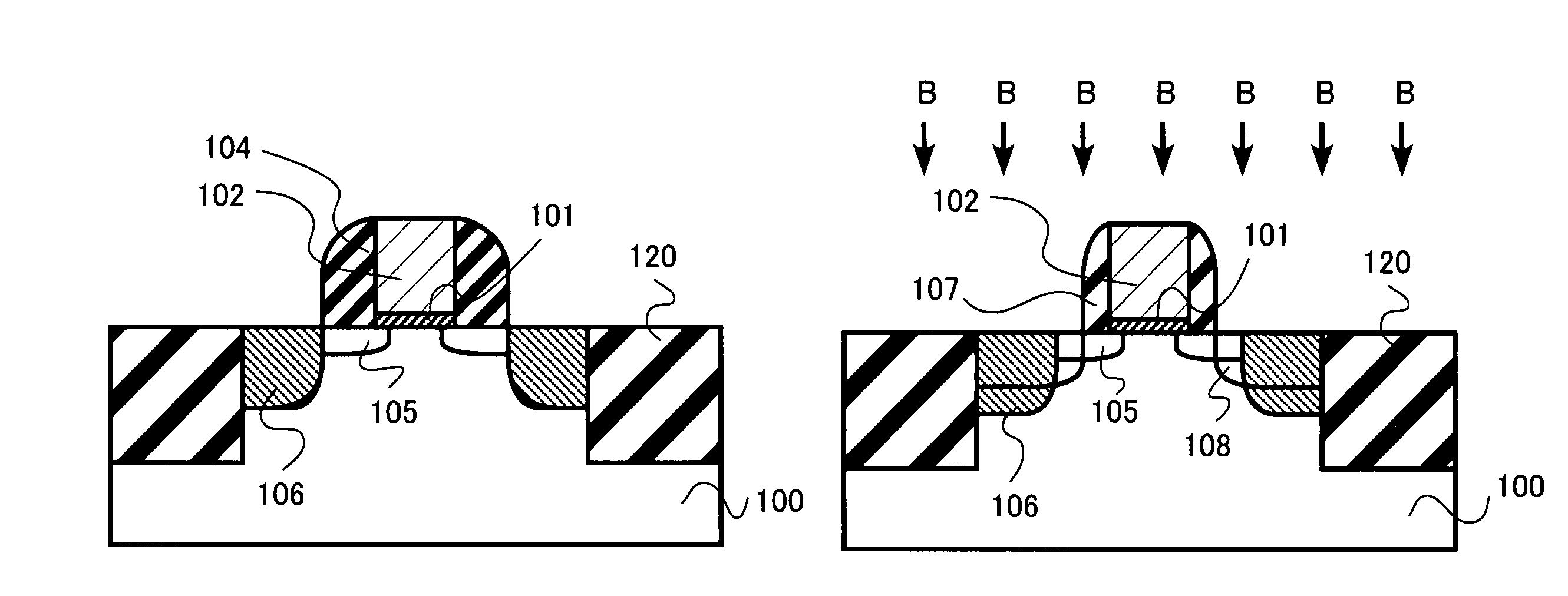

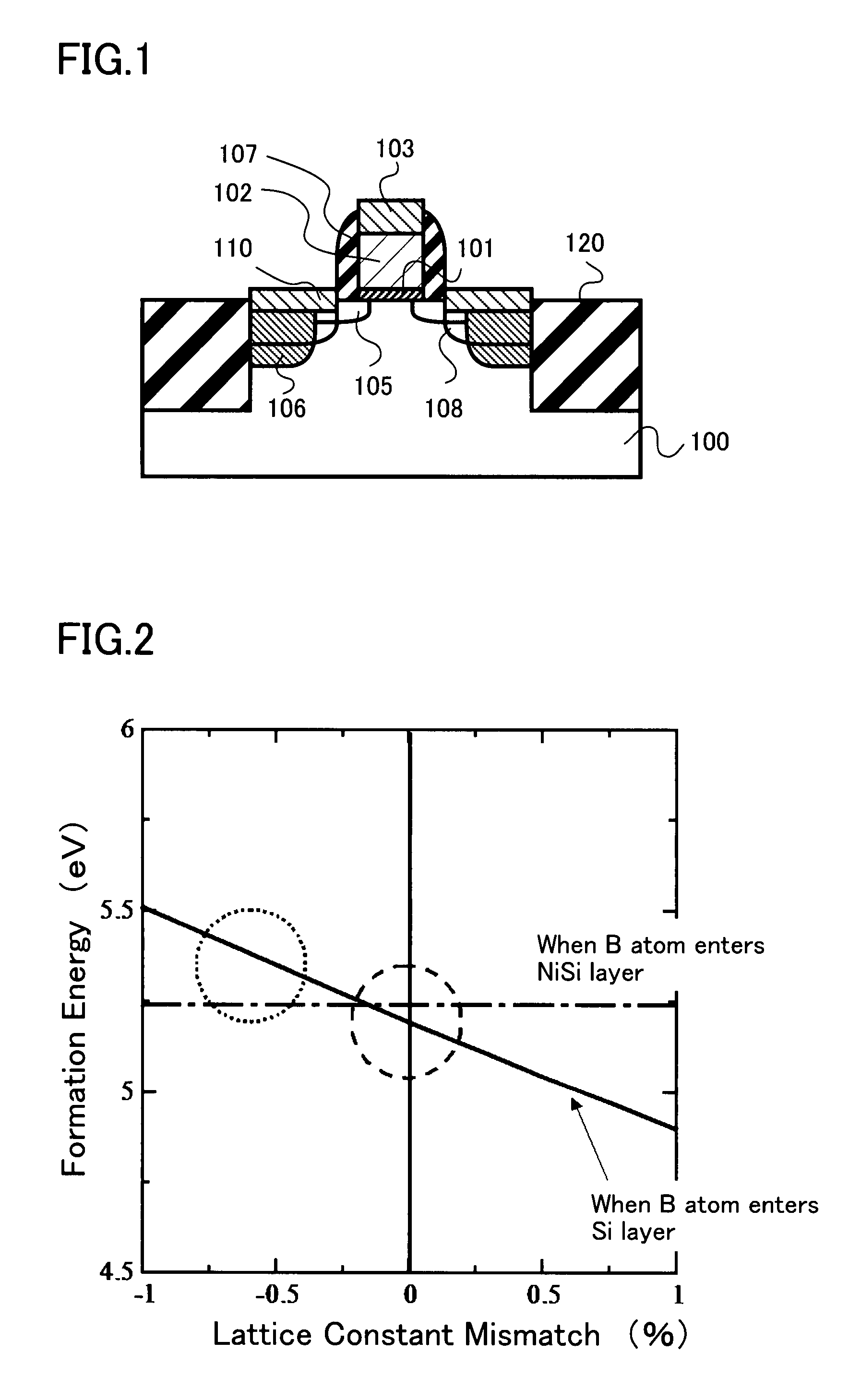

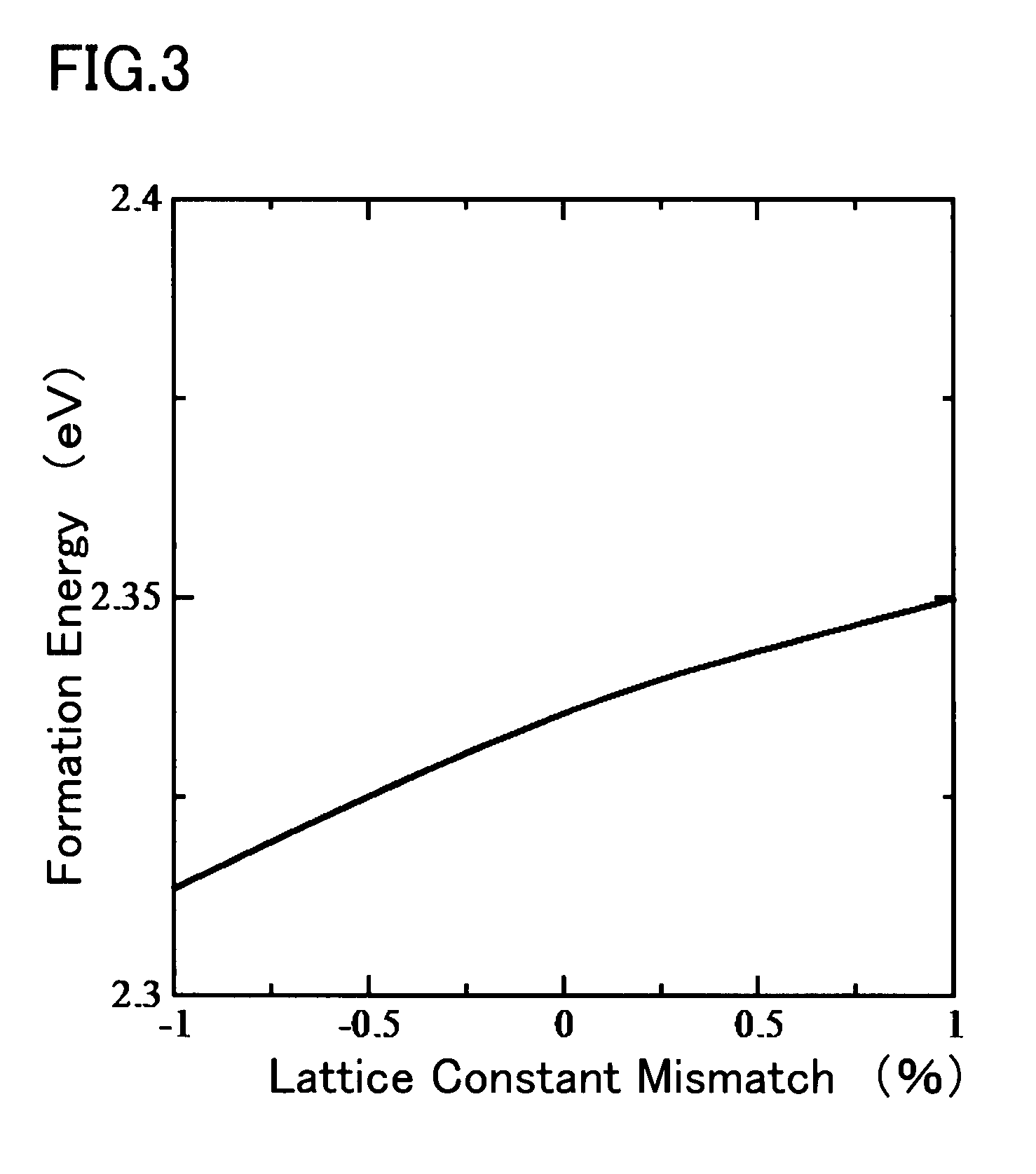

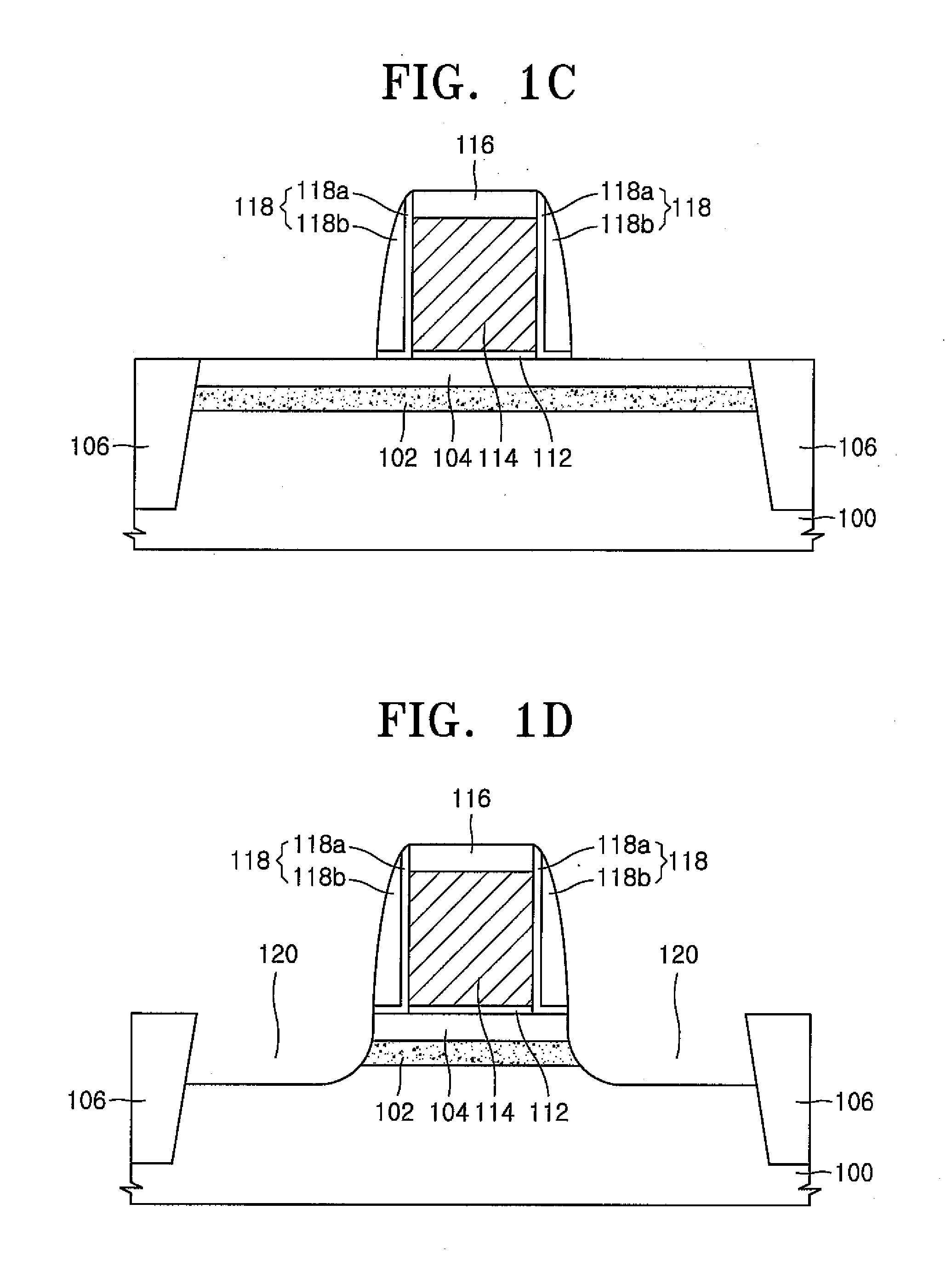

Method of making semiconductor device and semiconductor device

InactiveUS20080179752A1Lower junction resistanceTransistorSemiconductor/solid-state device detailsDevice materialGate insulator

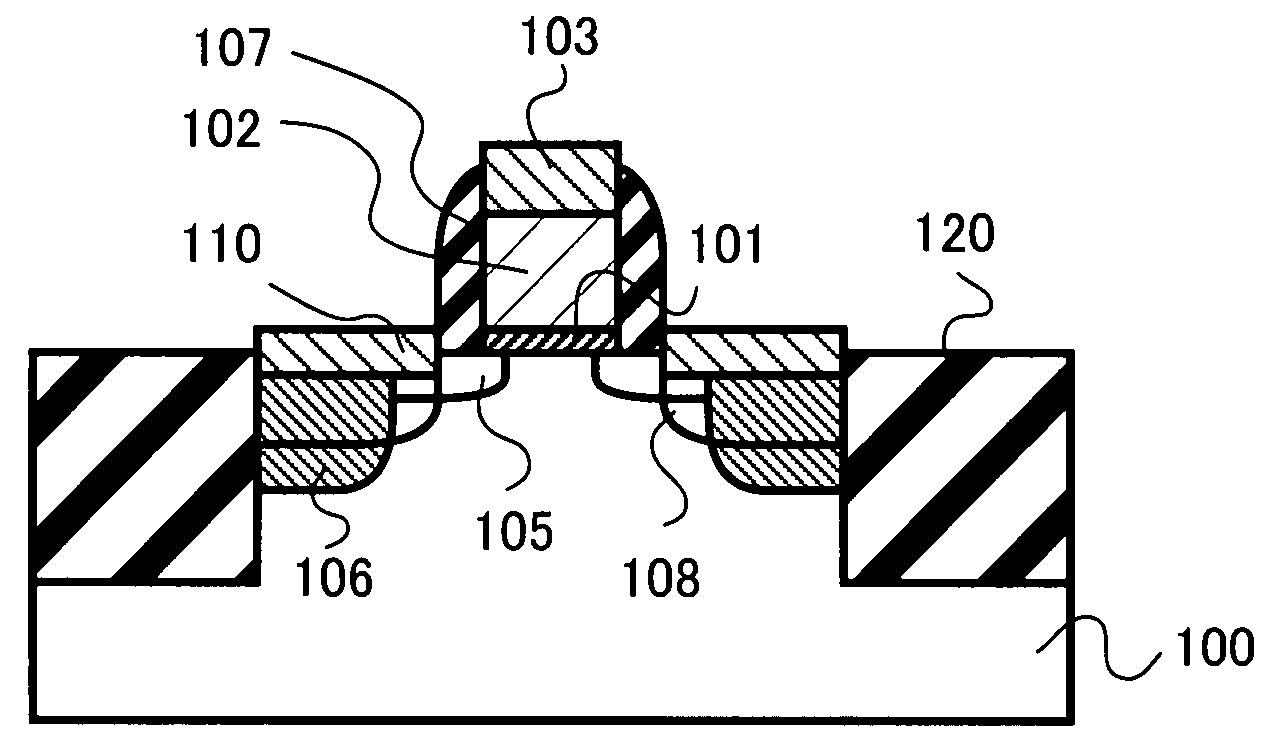

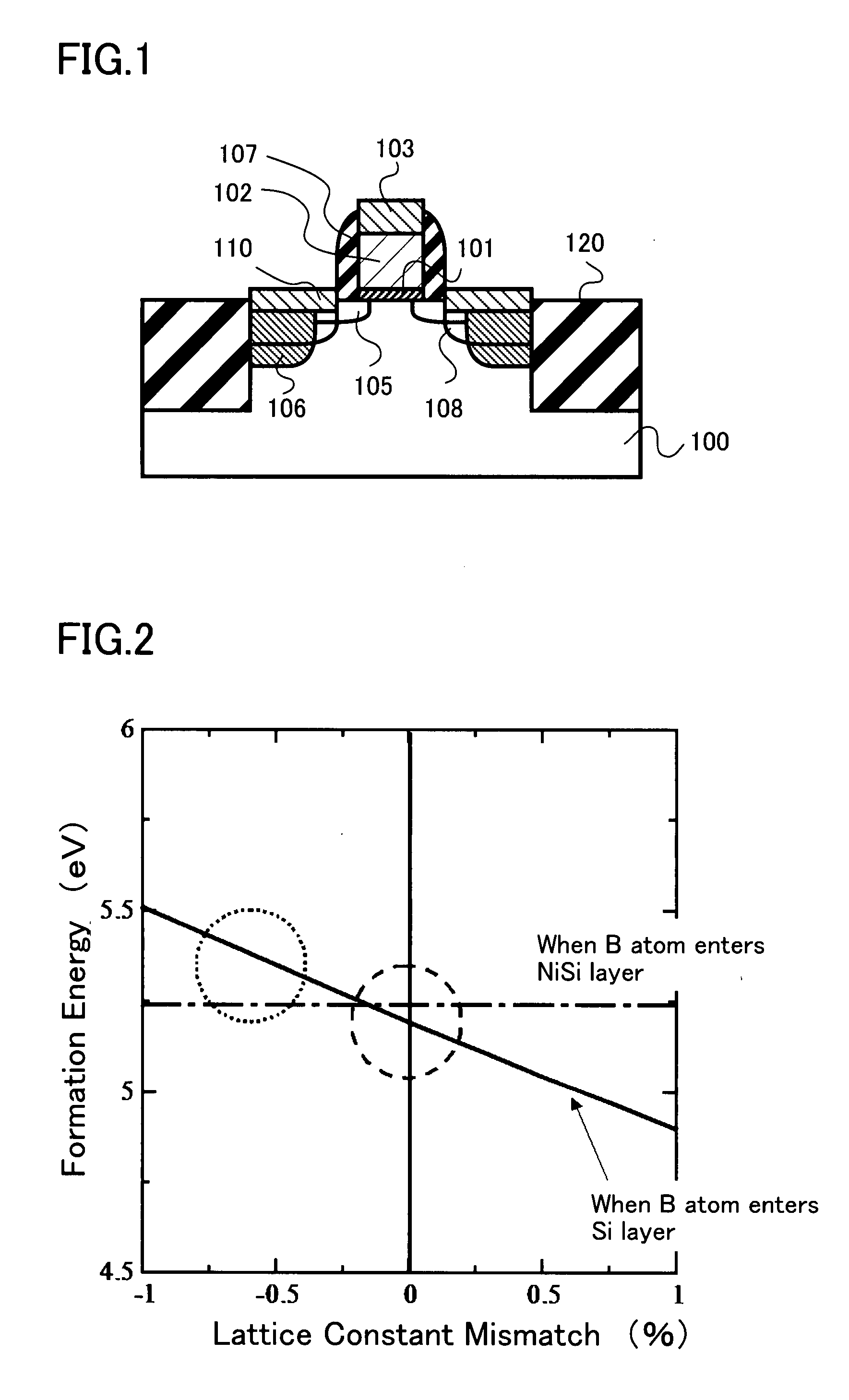

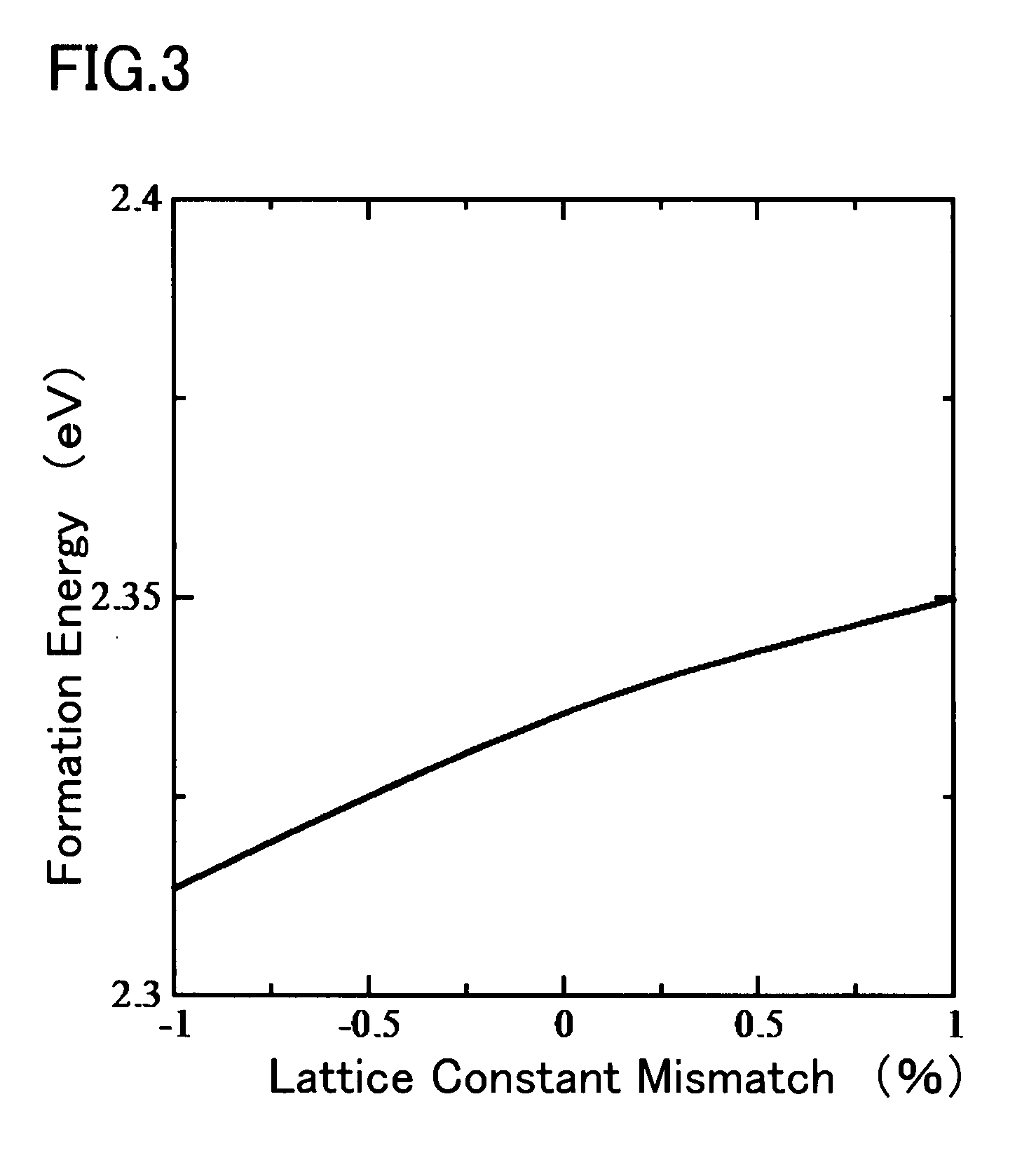

A metal insulator semiconductor field effect transistor (MISFET) having a strained channel region is disclosed. Also disclosed is a method of fabricating a semiconductor device having a low-resistance junction interface. This fabrication method includes the step of forming a gate electrode above a silicon substrate with a gate insulator film being sandwiched therebetween. Then, form a pair of heavily-doped p (p+) type diffusion layers in or on the substrate surface at both sides of the gate electrode to a concentration of 5×1019 atoms / cm3 or more and yet less than or equal to 1×1021 atoms / cm3. Next, silicidize the p+-type layers by reaction with a metal in the state that each layer is applied a compressive strain.

Owner:KK TOSHIBA

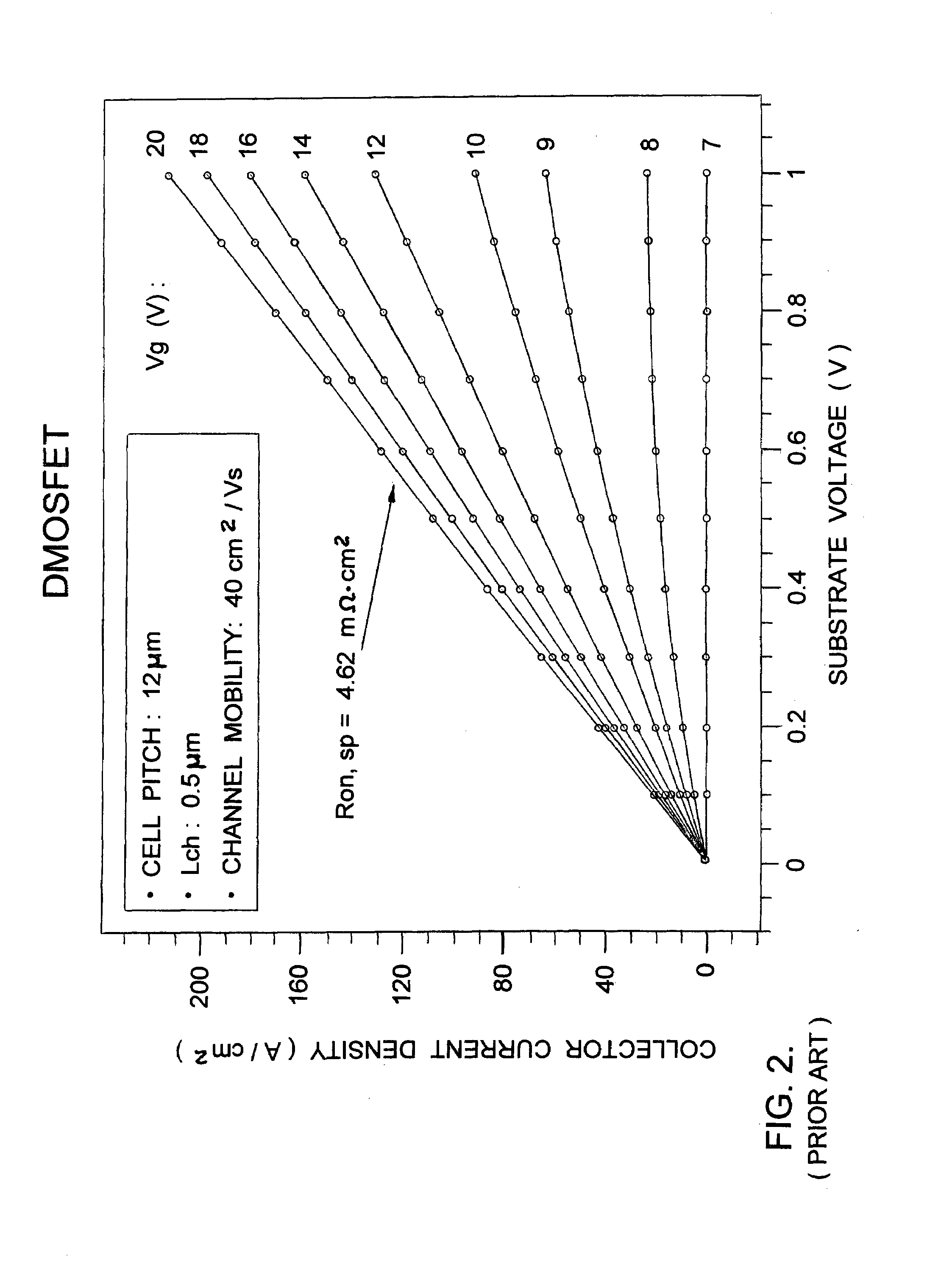

Transistor with A-Face Conductive Channel and Trench Protecting Well Region

ActiveUS20090146154A1High voltage blocking abilityMinimize JFET effectThyristorSemiconductor/solid-state device manufacturingTrench gateSemiconductor

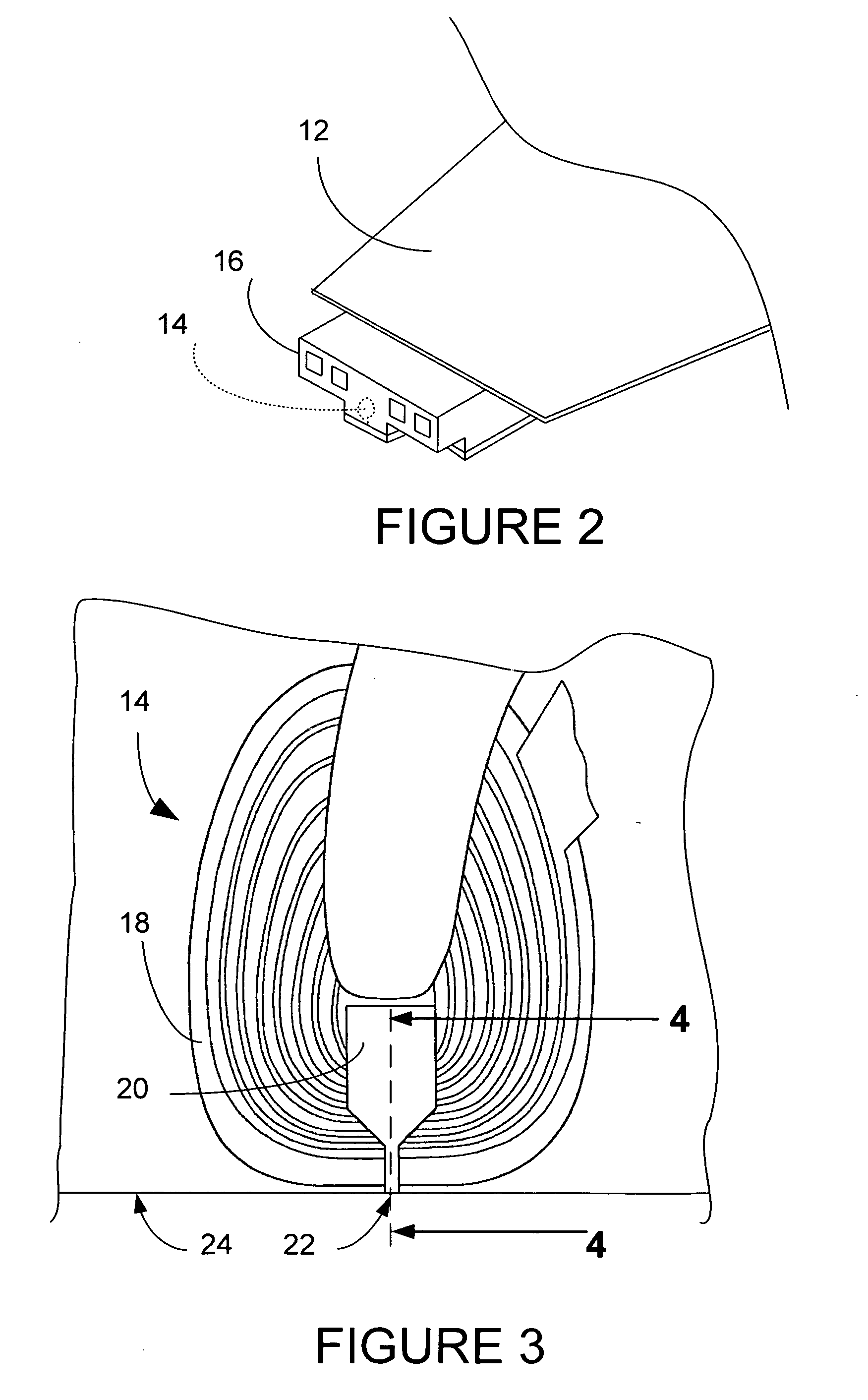

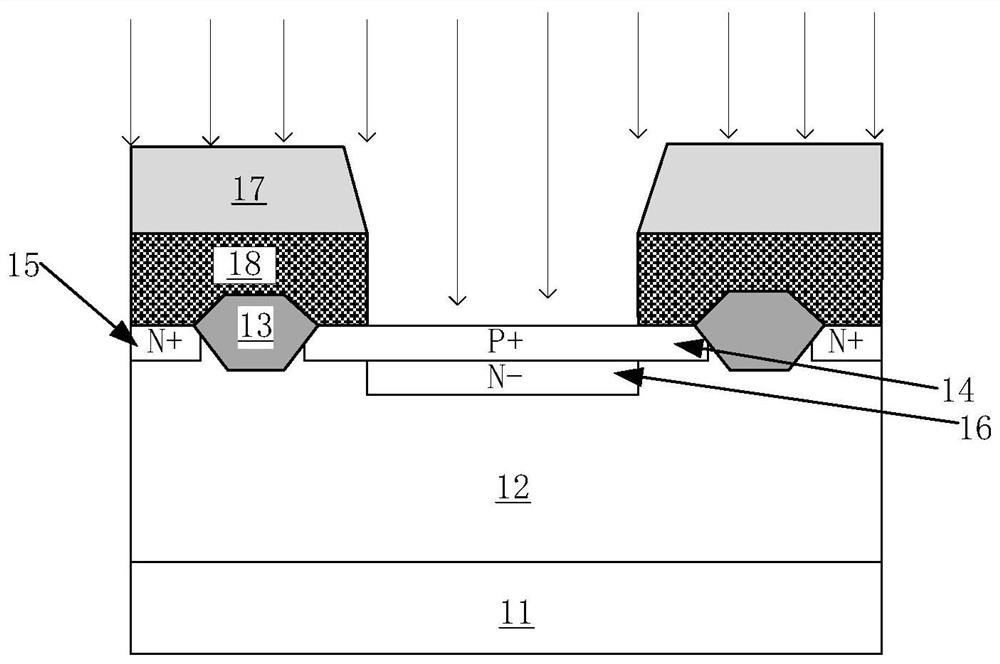

A transistor structure optimizes current along the A-face of a silicon carbide body to form an AMOSFET that minimizes the JFET effect in the drift region during forward conduction in the on-state. The AMOSFET further shows high voltage blocking ability due to the addition of a highly doped well region that protects the gate corner region in a trench-gated device. The AMOSFET uses the A-face conduction along a trench sidewall in addition to a buried channel layer extending across portions of the semiconductor mesas defining the trench. A doped well extends from at least one of the mesas to a depth within the current spreading layer that is greater than the depth of the trench. A current spreading layer extends between the semiconductor mesas beneath the bottom of the trench to reduce junction resistance in the on-state. A buffer layer between the trench and the deep well further provides protection from field crowding at the trench corner.

Owner:WOLFSPEED INC

Transistor with A-face conductive channel and trench protecting well region

ActiveUS7989882B2Improve abilitiesMinimize JFET effectSemiconductor/solid-state device manufacturingSemiconductor devicesTrench gateSemiconductor

A transistor structure optimizes current along the A-face of a silicon carbide body to form an AMOSFET that minimizes the JFET effect in the drift region during forward conduction in the on-state. The AMOSFET further shows high voltage blocking ability due to the addition of a highly doped well region that protects the gate corner region in a trench-gated device. The AMOSFET uses the A-face conduction along a trench sidewall in addition to a buried channel layer extending across portions of the semiconductor mesas defining the trench. A doped well extends from at least one of the mesas to a depth within the current spreading layer that is greater than the depth of the trench. A current spreading layer extends between the semiconductor mesas beneath the bottom of the trench to reduce junction resistance in the on-state. A buffer layer between the trench and the deep well further provides protection from field crowding at the trench corner.

Owner:WOLFSPEED INC

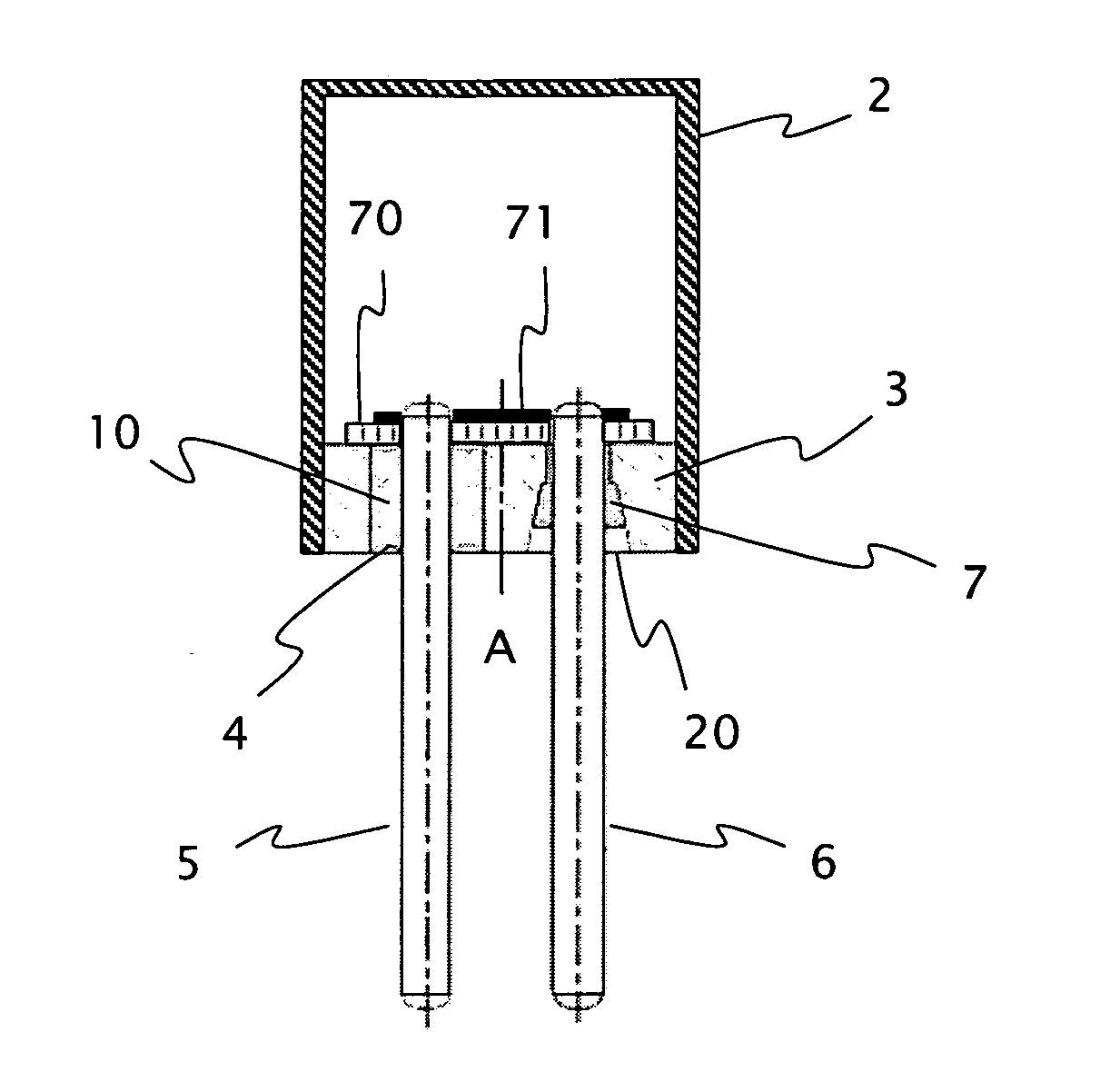

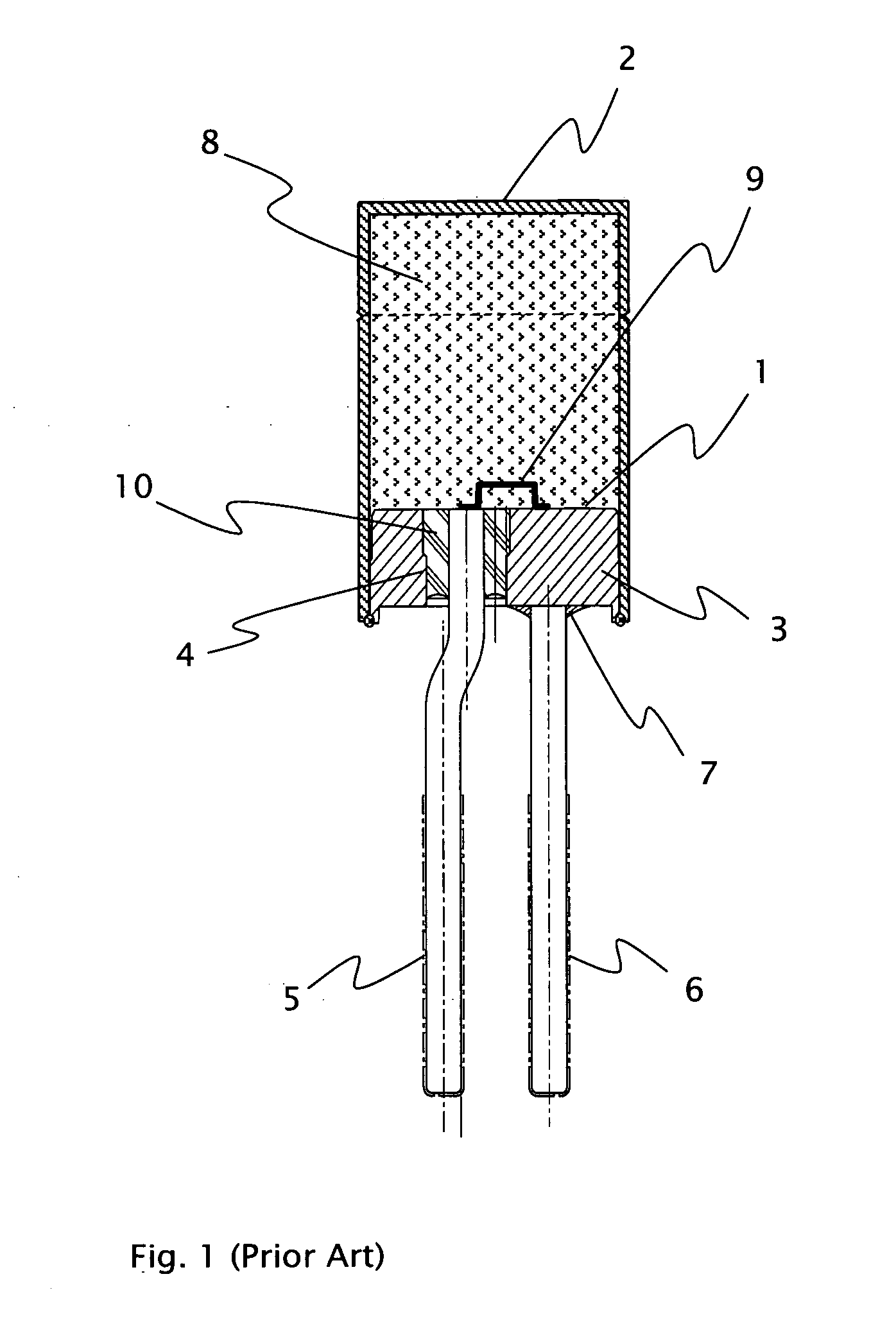

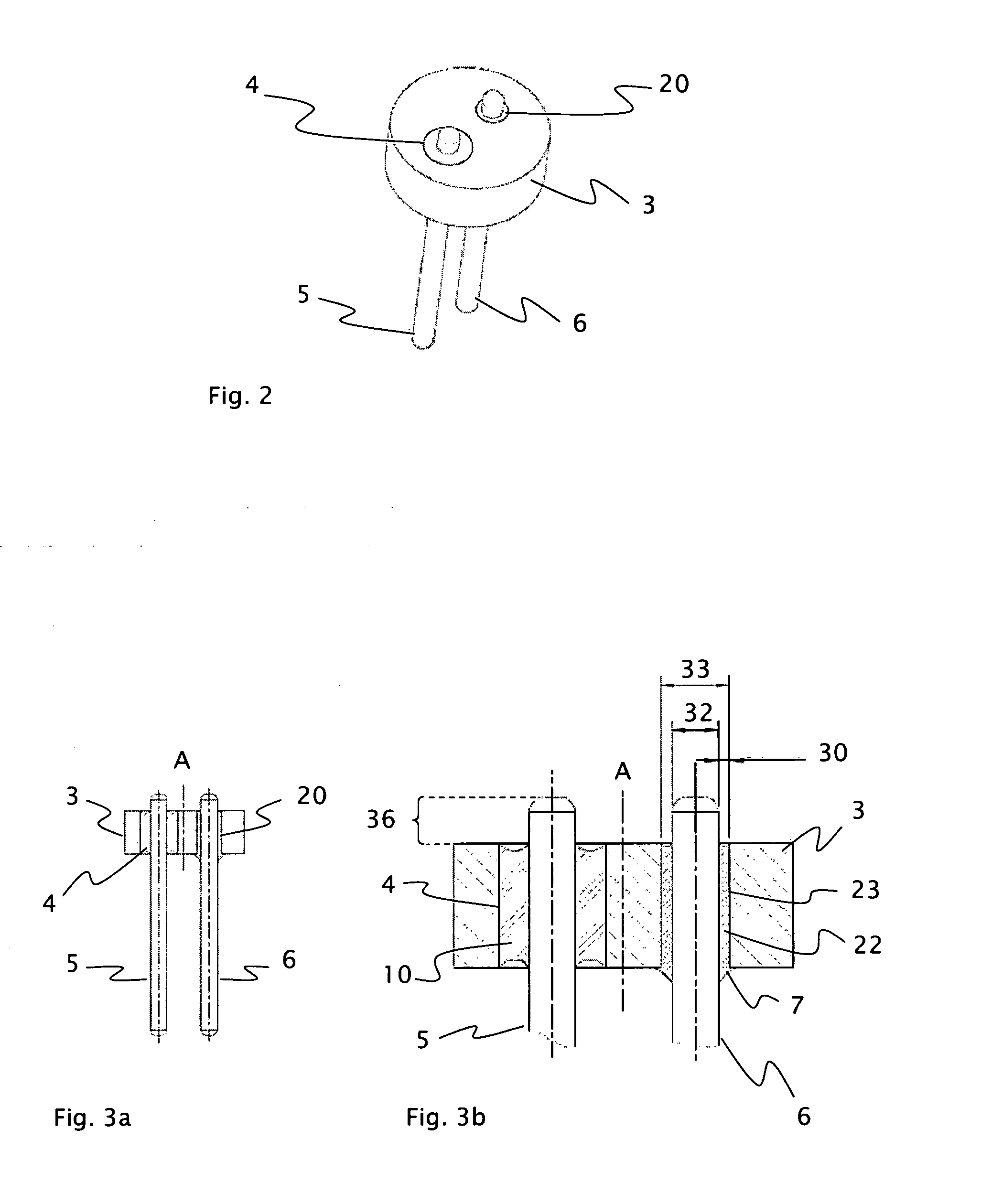

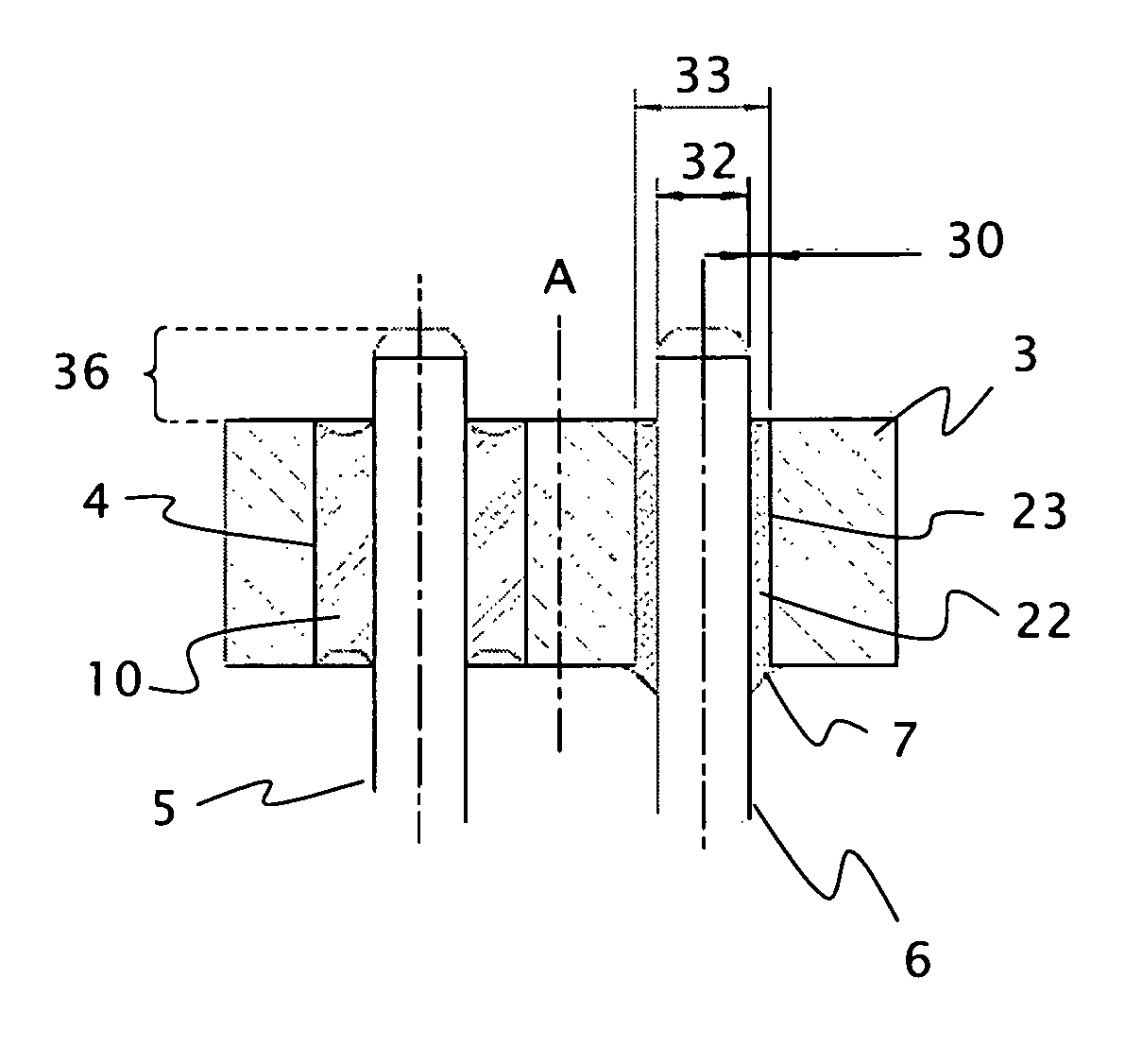

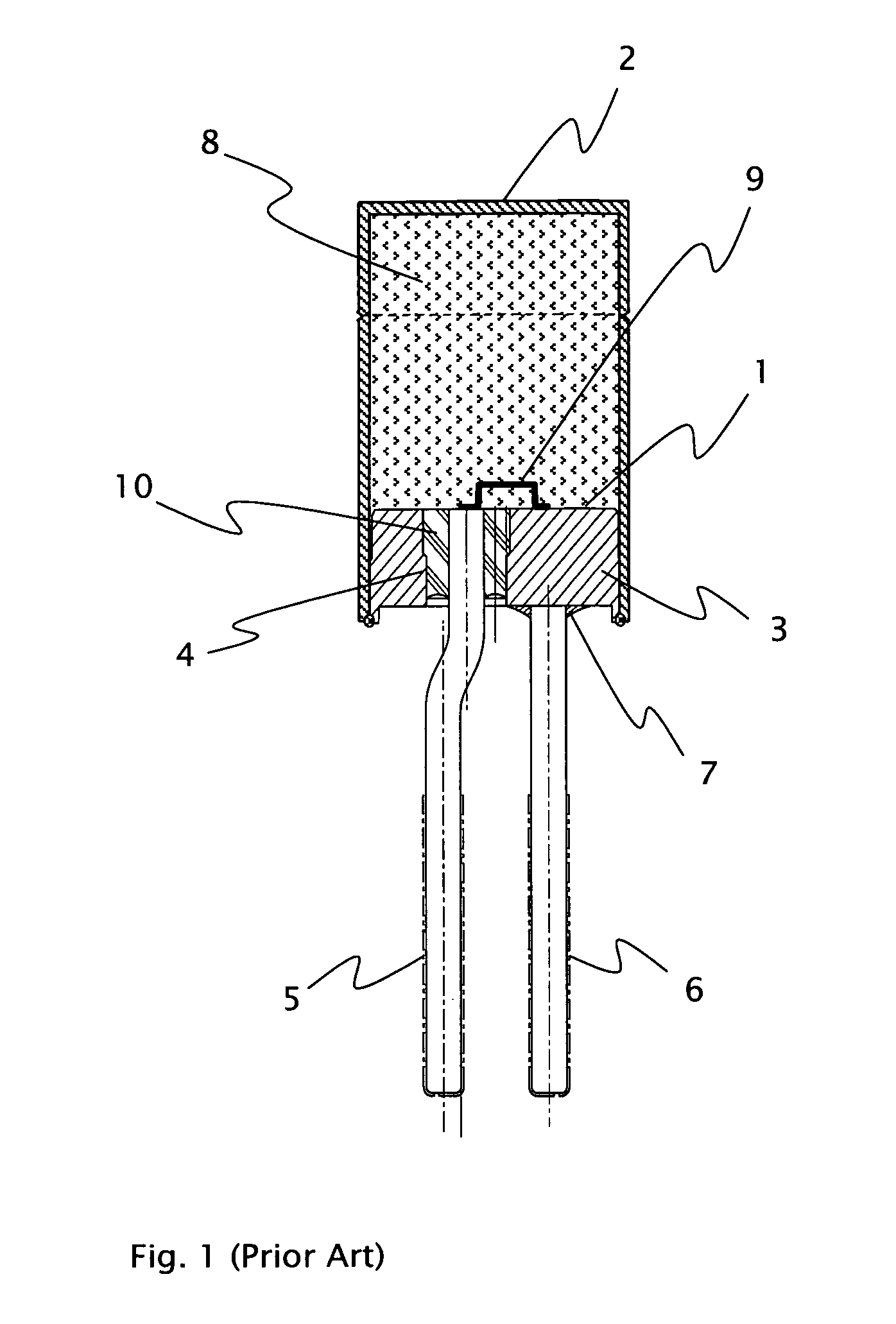

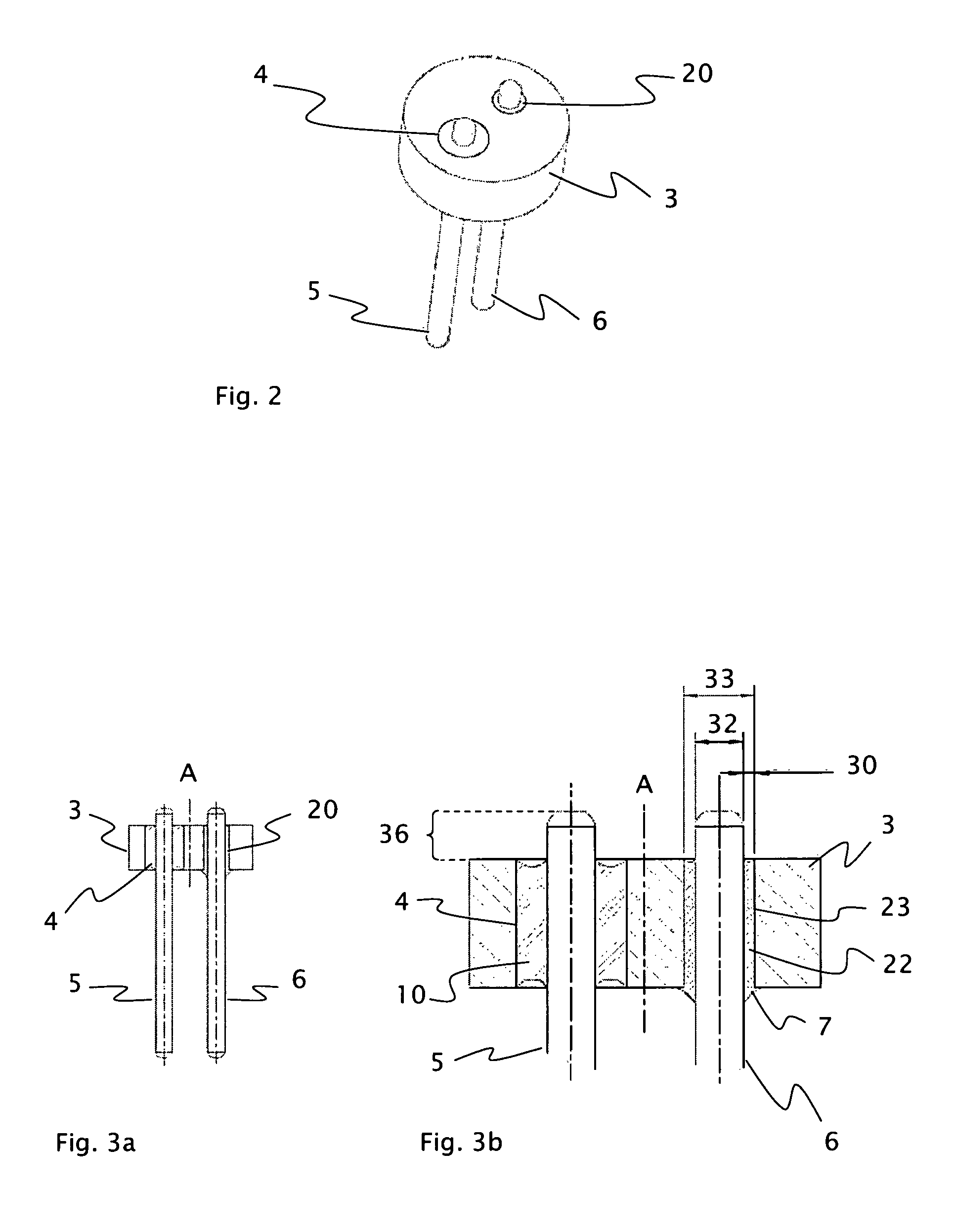

Shaped feed-through element with contact rod soldered in

ActiveUS20100199872A1Reduce system costProduction costBlasting cartridgesElectric fuzesEngineeringAirbag

A feed-through element of an ignition device for igniters of airbags or seatbelt tighteners is provided. The feed-through element has a metal support body, at least one first access opening in which a metal rod is arranged in an electrically insulating fixing material, and at least one second access opening in which a further metal rod is electrically conductively fixed to the support body by a soldered connection in this access opening. The support body and the access openings are configured as a shaped part. The feed-through element further includes a solder gap between the metal rod and the wall of the second access opening, where the solder gap has a small width.

Owner:SCHOTT AG

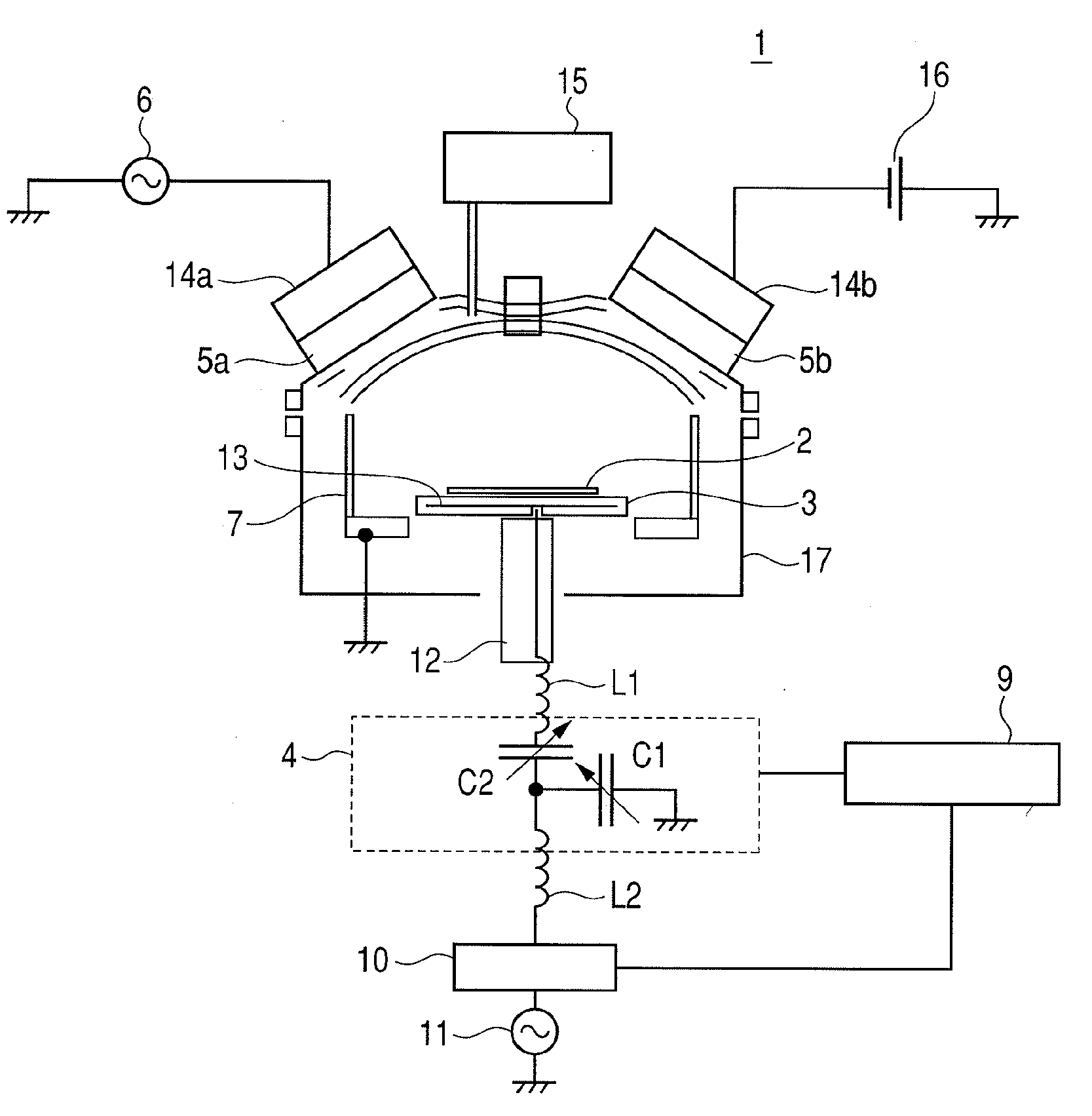

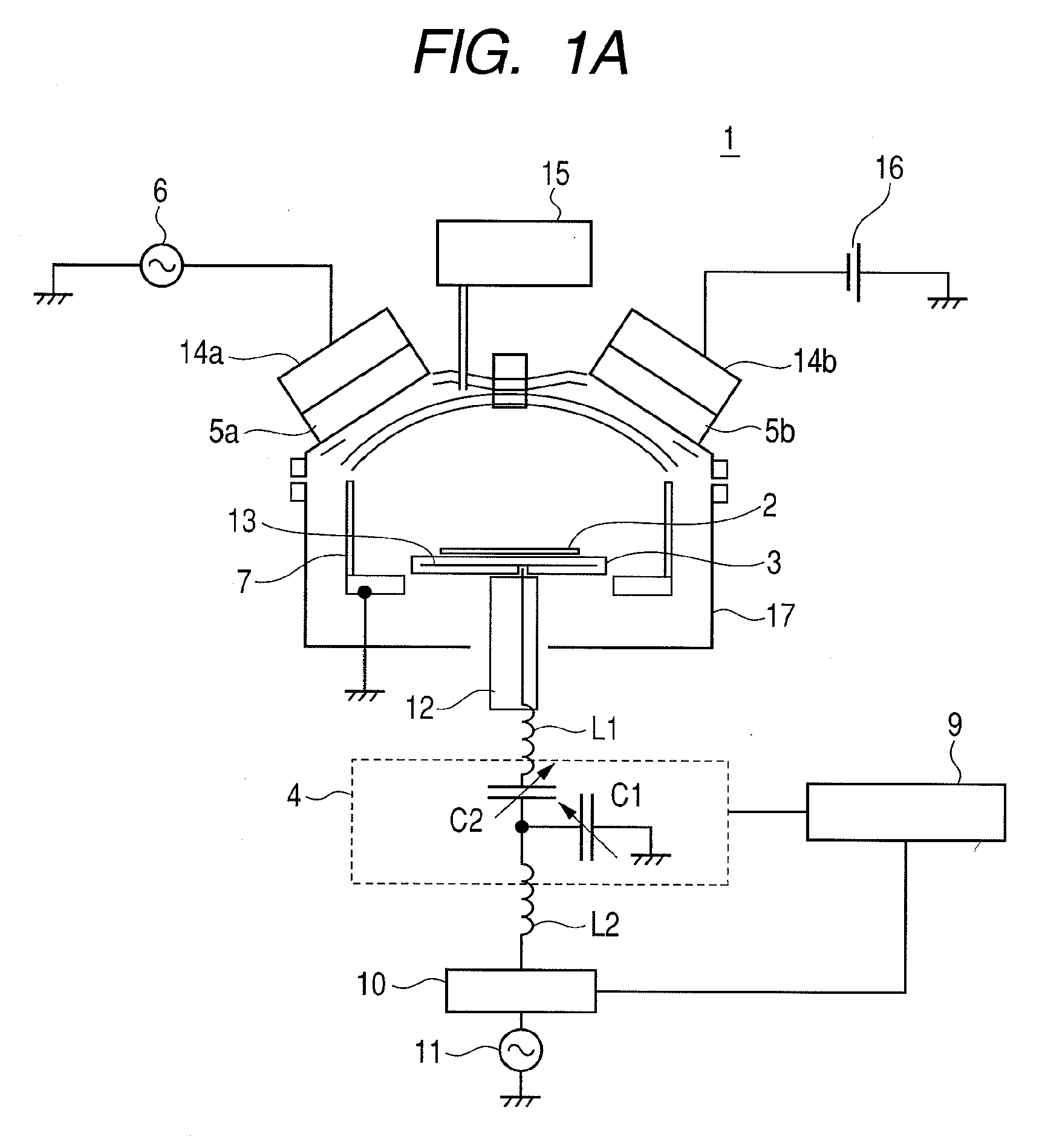

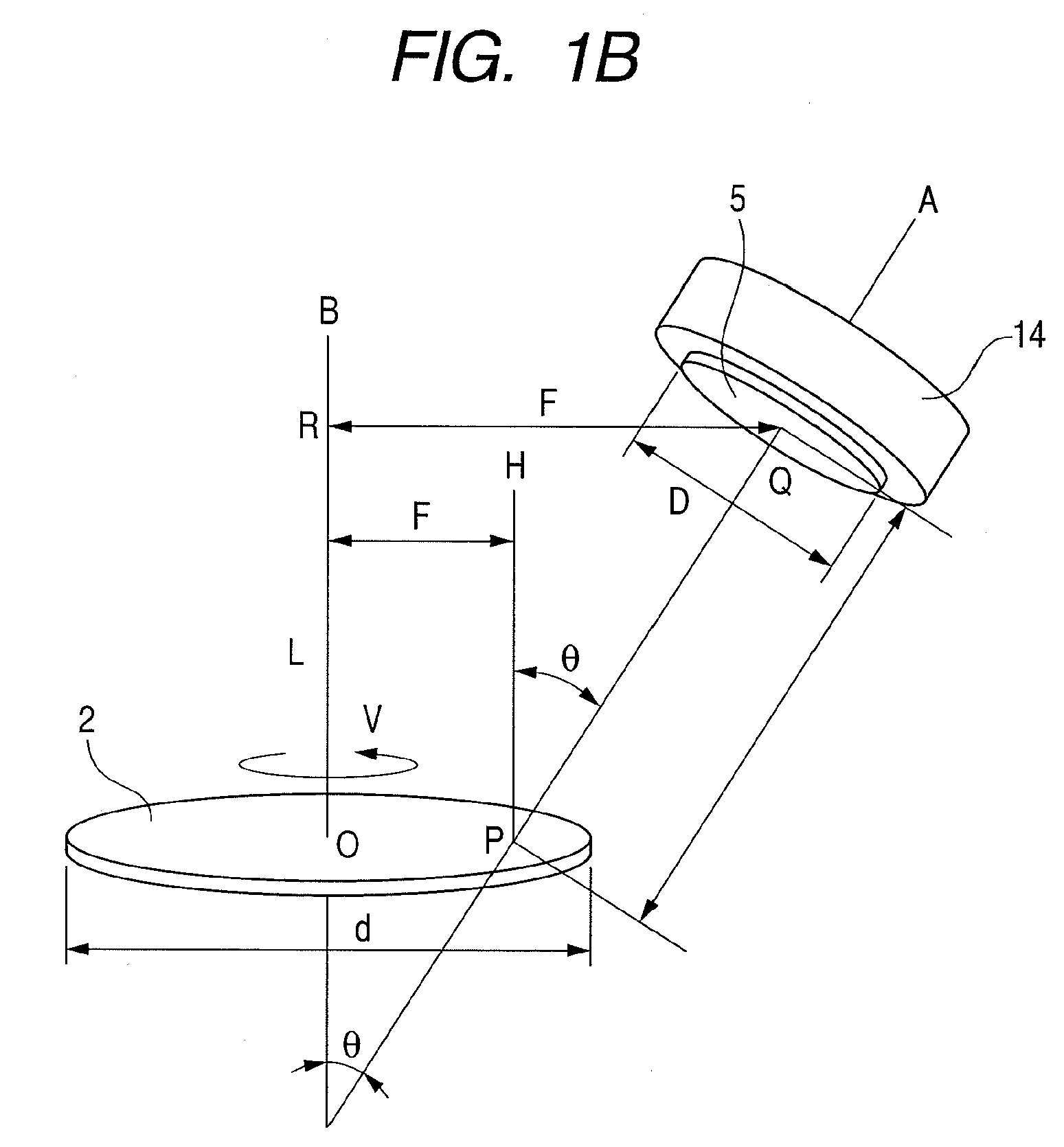

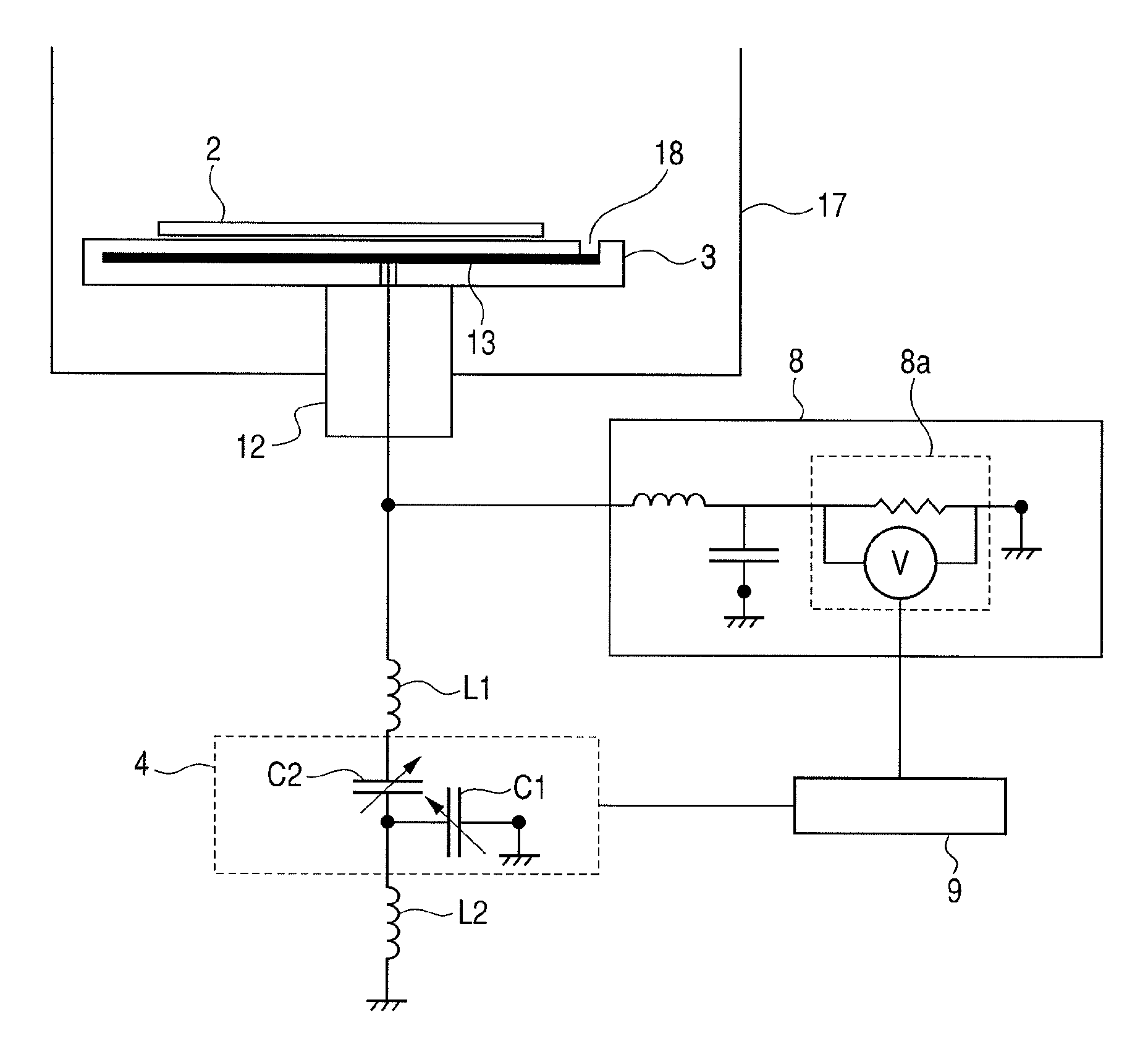

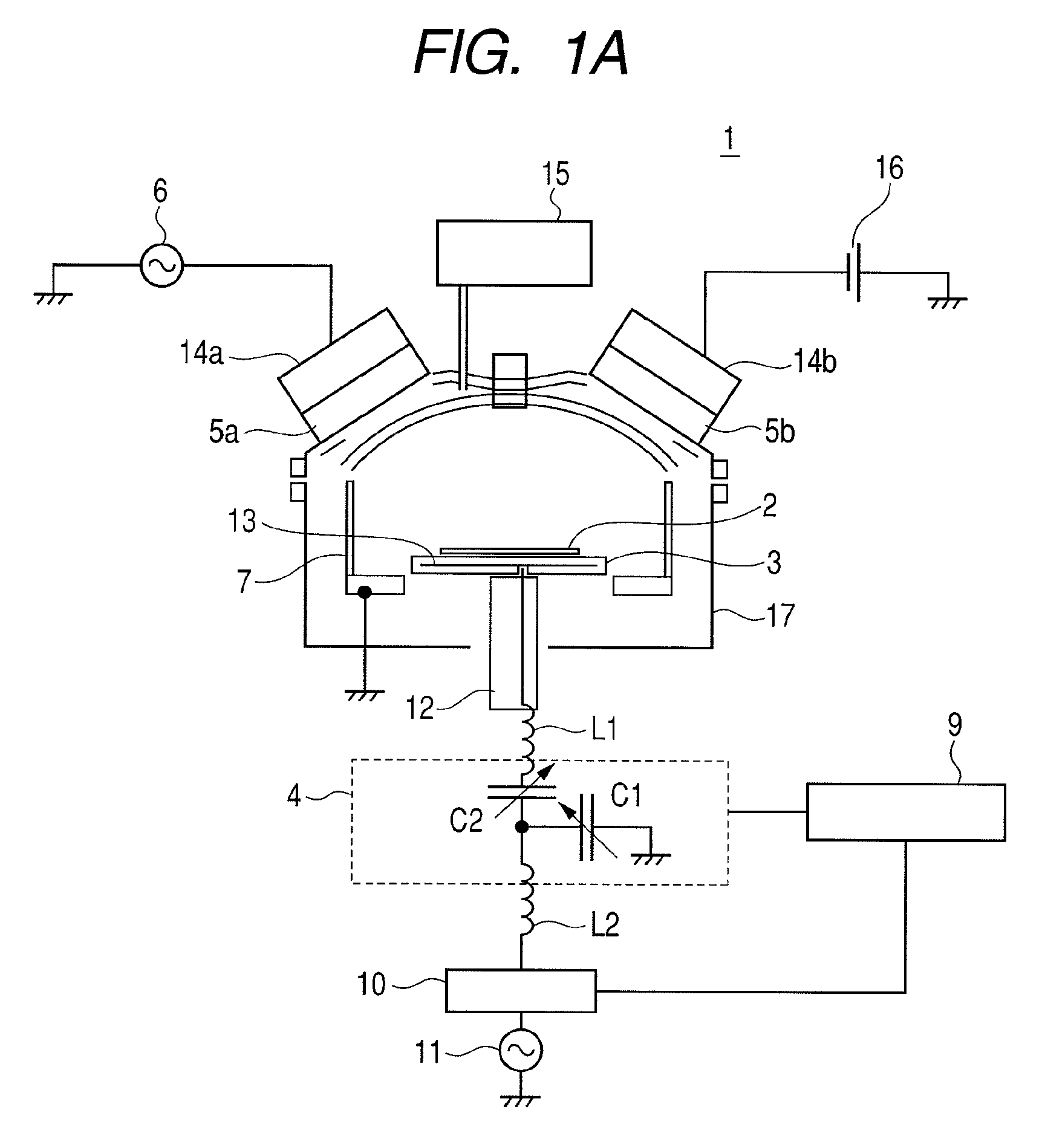

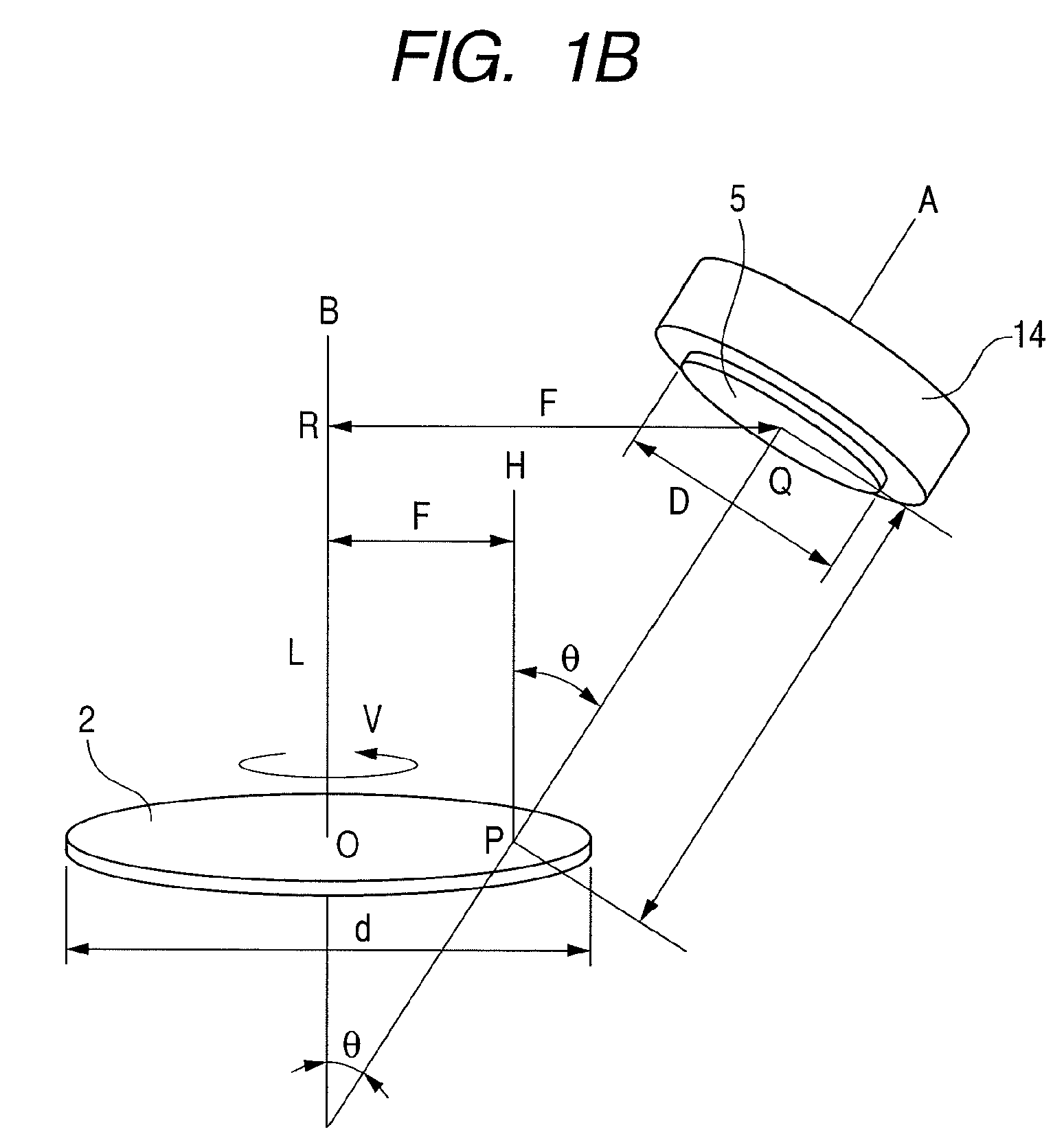

High-frequency sputtering device

ActiveUS20100213047A1Facilitated DiffusionLower junction resistanceCellsElectric discharge tubesSputteringEngineering

Provided is a high-quality magnetoresistive thin film by using a method of controlling self bias of a high-frequency sputtering device. In order to control the self bias for the substrate by adjusting a substrate potential, the high-frequency sputtering device according to the present invention includes: a chamber; evacuation means for evacuating the inside of the chamber; gas introduction means for supplying a gas into the chamber; a substrate holder provided with a substrate mounting table; rotation drive means capable of rotating the substrate holder; a sputtering cathode provided with a target mounting table and arranged such that the surface of the target mounting table is non-parallel to the surface of the substrate mounting table; an electrode disposed inside the substrate holder; and a variable impedance mechanism electrically connected to the electrode, for adjusting the substrate potential on the substrate holder.

Owner:CANON ANELVA CORP

Shaped feed-through element with contact rod soldered in

ActiveUS8397638B2Resistance againstLower junction resistanceBlasting cartridgesElectric fuzesEngineeringAirbag

A feed-through element of an ignition device for igniters of airbags or seatbelt tighteners is provided. The feed-through element has a metal support body, at least one first access opening in which a metal rod is arranged in an electrically insulating fixing material, and at least one second access opening in which a further metal rod is electrically conductively fixed to the support body by a soldered connection in this access opening. The support body and the access openings are configured as a shaped part. The feed-through element further includes a solder gap between the metal rod and the wall of the second access opening, where the solder gap has a small width.

Owner:SCHOTT AG

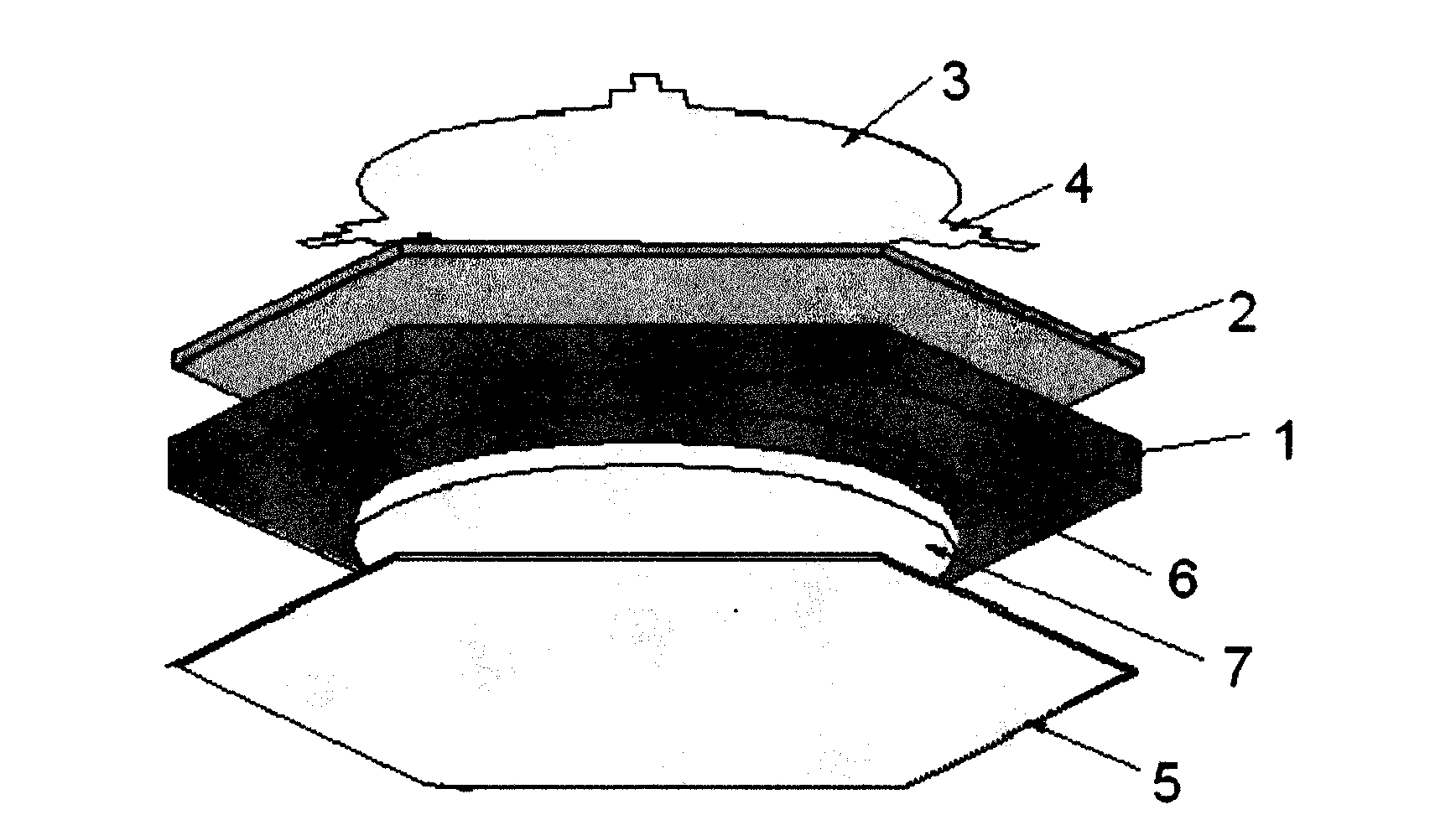

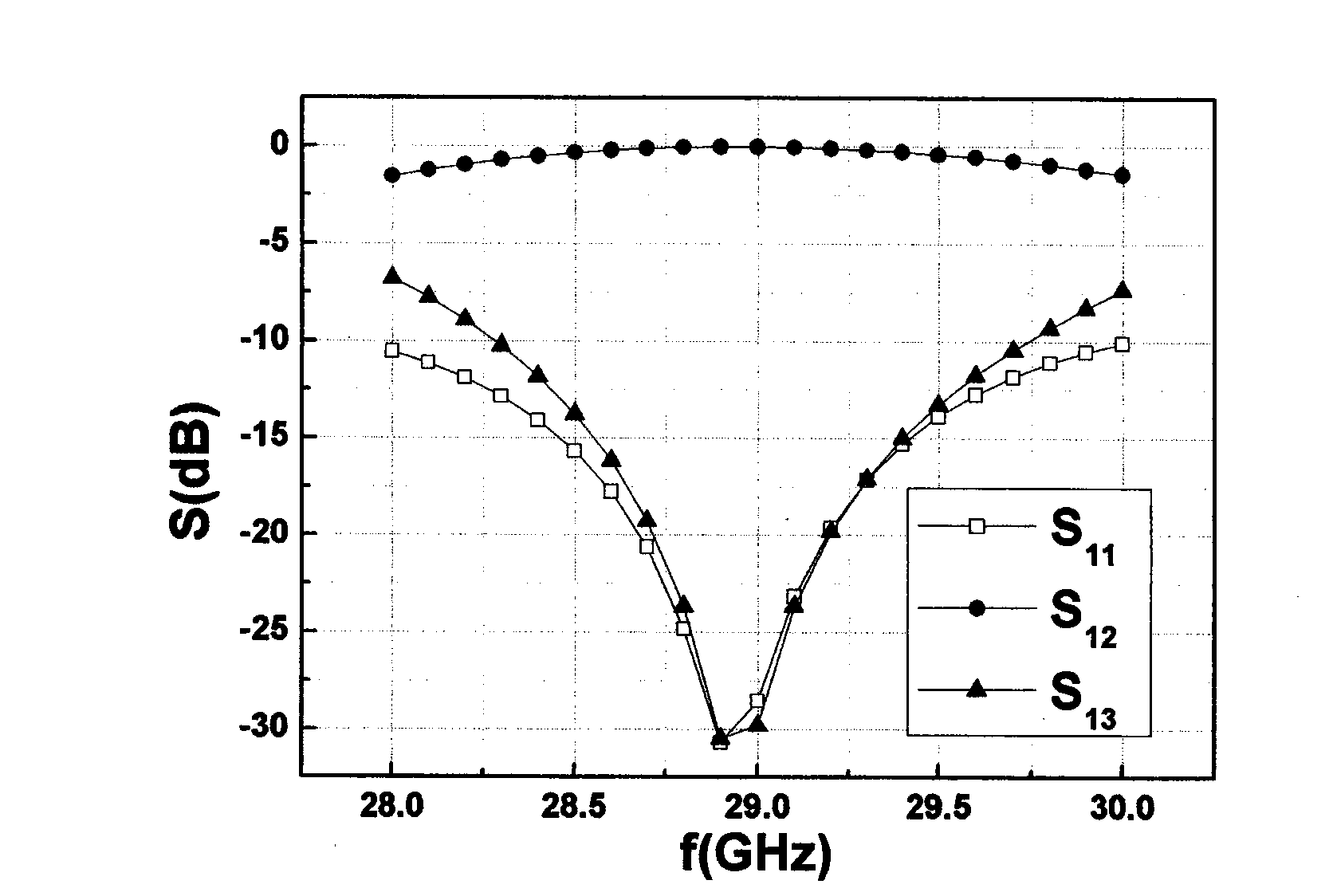

Membrane integrated microtrip ferrite circulator

InactiveCN101667673AReduce the proportionReduce the ratioWaveguide type devicesDielectricMiniaturization

The invention belongs to an integrated microtrip ferrite circulator in solid electronic devices, comprising a dielectric or a semiconductor substrate, a high-conductivity metal block or an earthing membrane, a ferrite membrane, a high-conductivity centre junction, a matching section of the high-conductivity centre junction and a high-conductivity earthing membrane, wherein, the dielectric is provided with a groove at the bottom; the high-conductivity metal block is arranged in the groove; the ferrite membrane is adhered above the substrate; the high-conductivity centre junction tightly clingsto the ferrite membrane; the high-conductivity earthing membrane is positioned on the bottom surface of the substrate. The circulator is additionally provided with a groove at the bottom surface of the substrate, a metal block is arranged in the groove, wherein, the volume of the metal block is the same as that of the groove, or an earthing membrane is covered on the internal surface of the groove, so that the effective permeability tensor k / mu is greatly improved, while the impedance is greatly reduced; on the premise of the same performance and compared with the background technology, the volume and thickness of the circulator can be effectively reduced; on the premise that the performance and the reliability of the ferrite circulator are ensured, the volume and thickness of the circulator can be effectively reduced; miniaturization, planarity and the convenient integration of microwave circuits are realized, thus the development of monolithic microwave integrated circuit is promoted.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

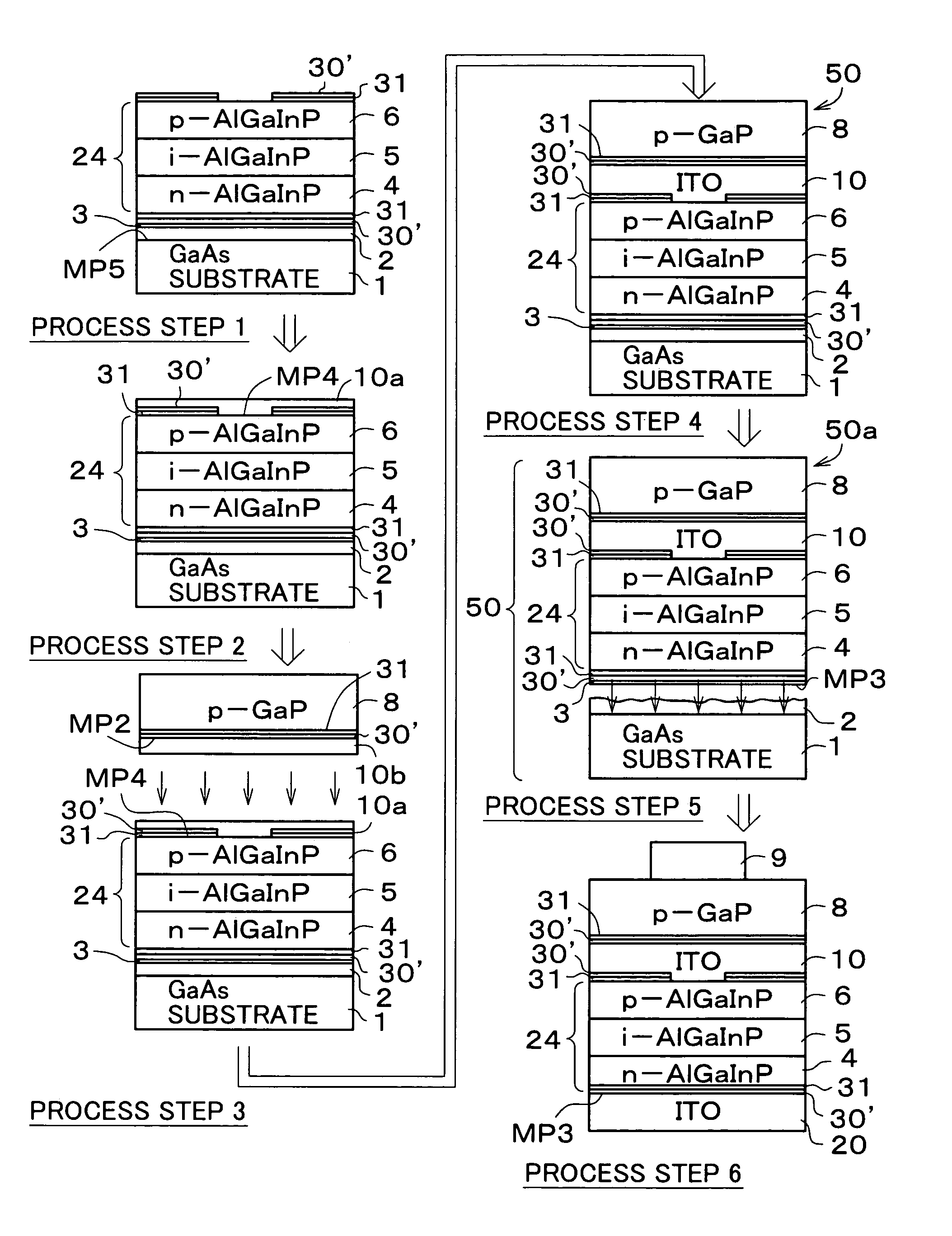

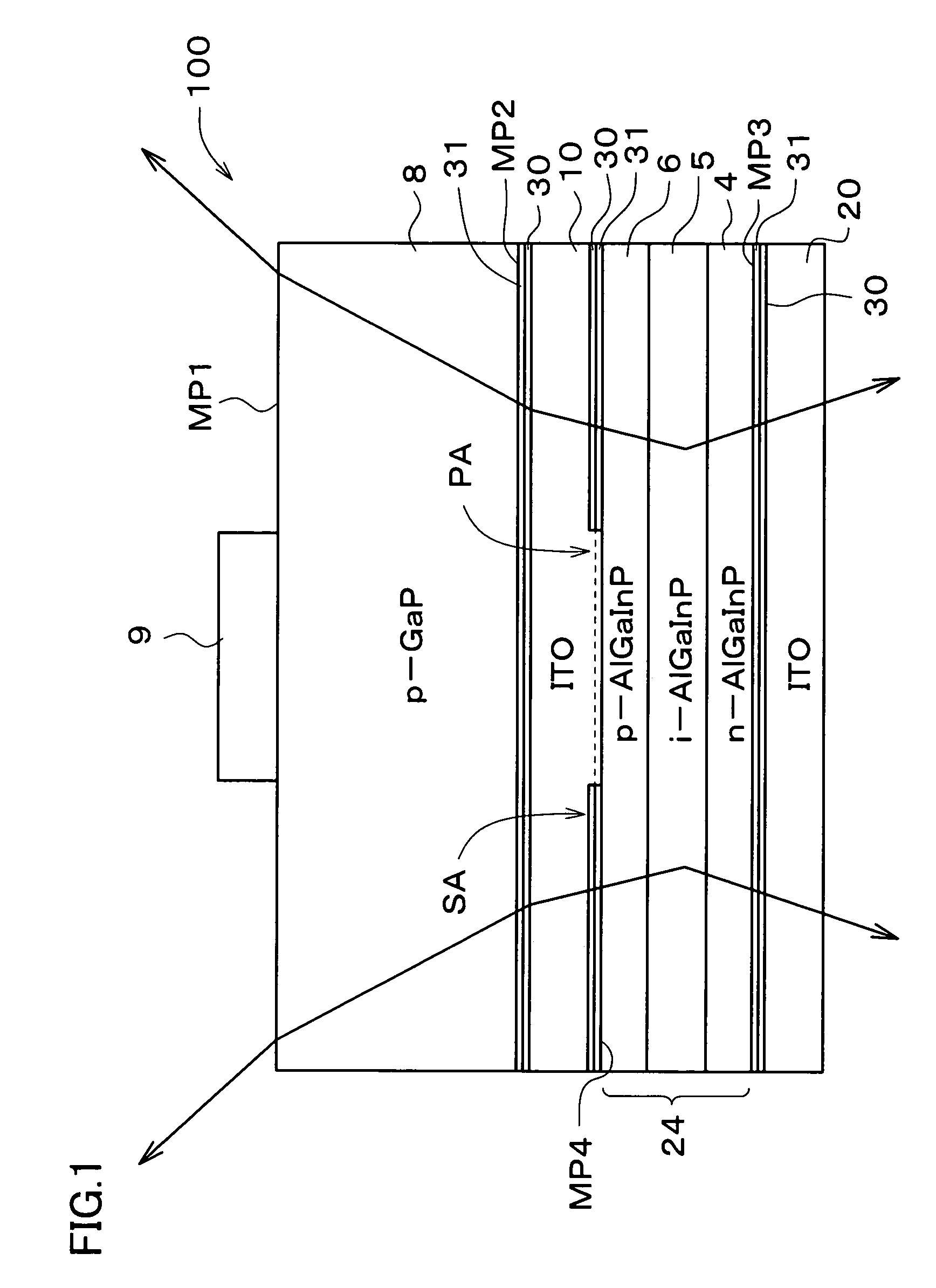

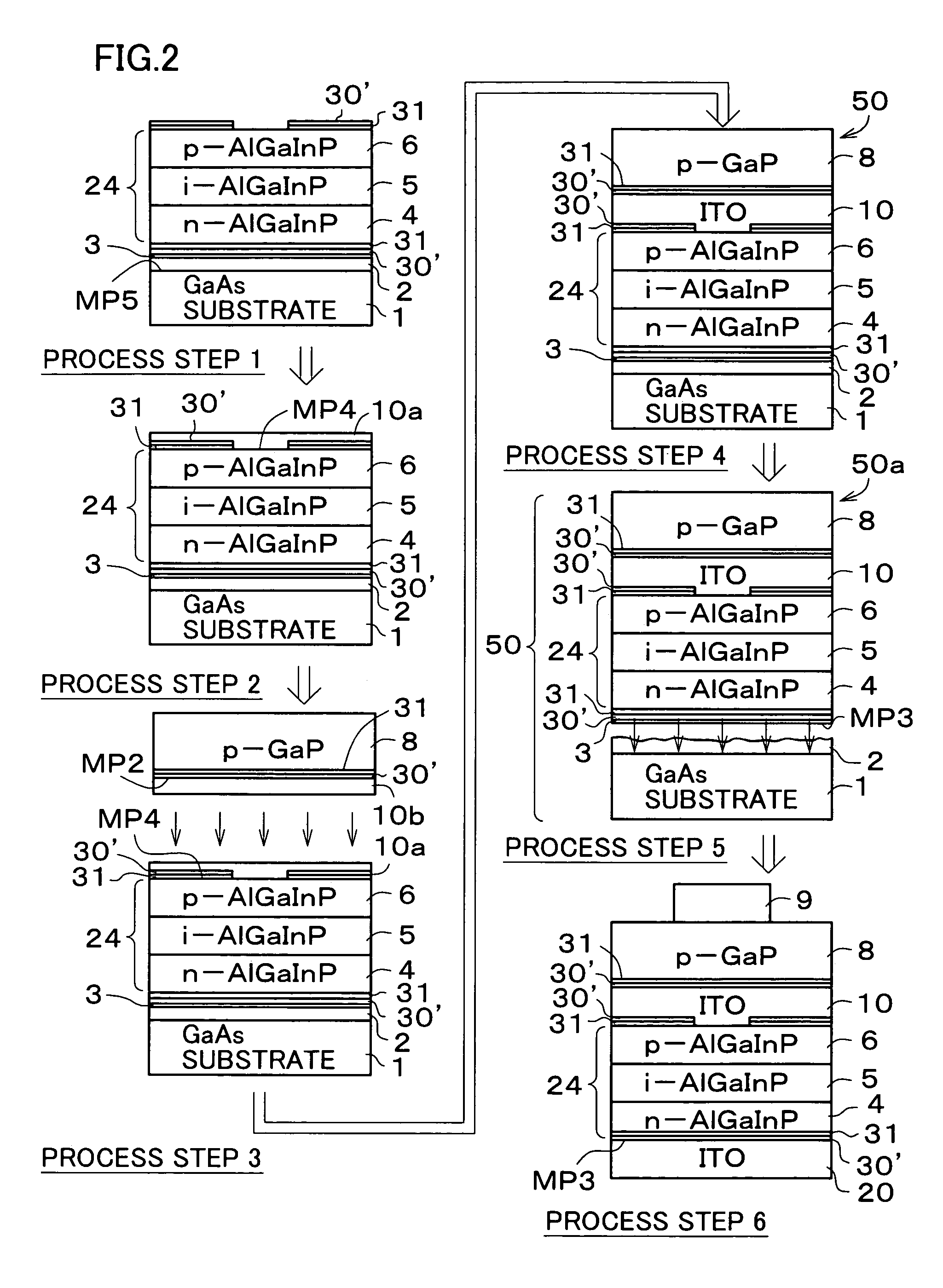

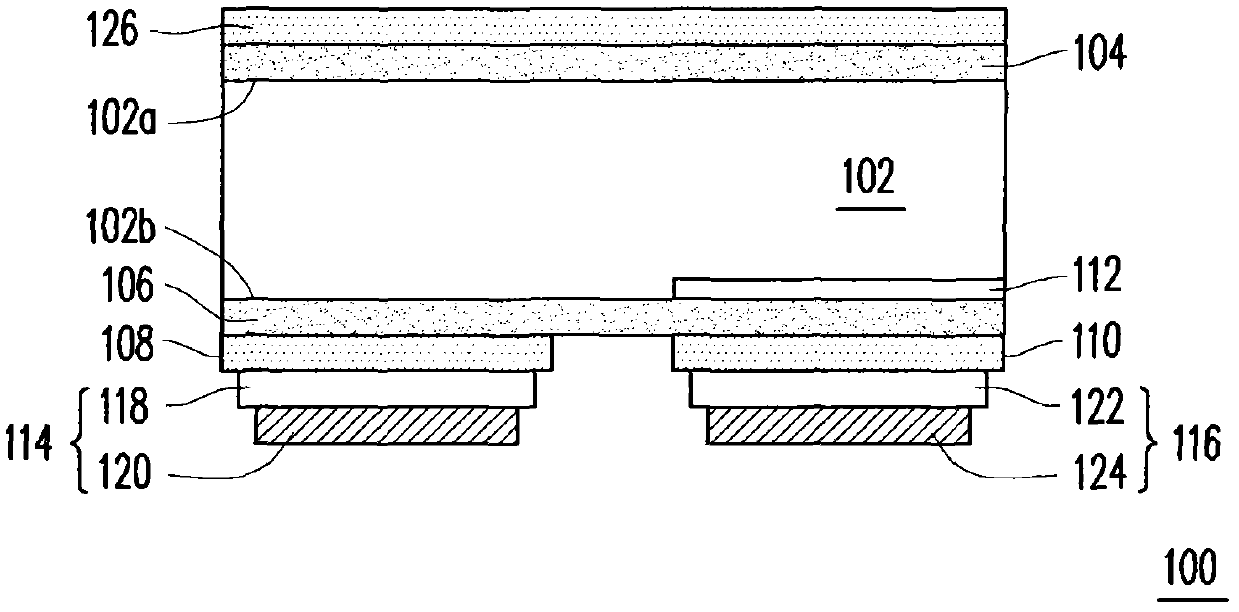

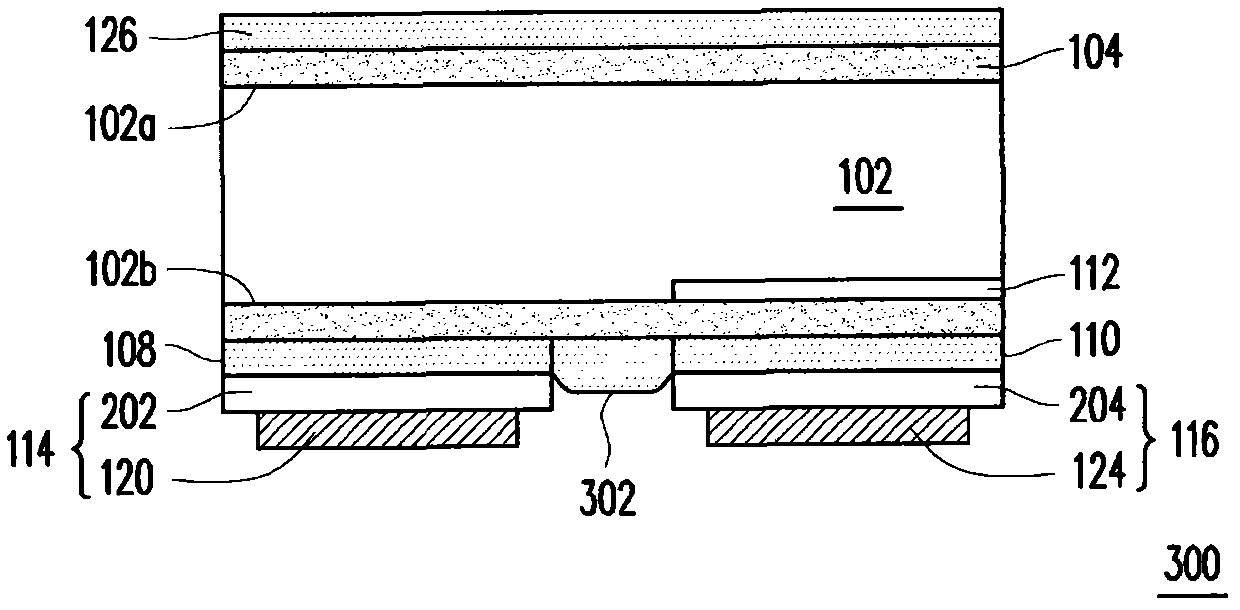

Light-emitting device and method of fabricating the same

ActiveUS7041529B2Lower junction resistanceReduce contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesContact layerEmission efficiency

In a light-emitting device, a light-emitting layer portion composed of a compound semiconductor is bonded on one main surface of a transparent conductive semiconductor substrate while placing a substrate-bonding conductive oxide layer composed of a conductive oxide in between. Between the light-emitting layer portion and the substrate-bonding conductive oxide layer, a contact layer for reducing junction resistance with the substrate-bonding conductive oxide layer so as to contact with the substrate-bonding conductive oxide layer. This is successful in providing the light-emitting device which is producible at low costs, has a low series resistance, and can attain a sufficient emission efficiency despite it has a thick current-spreading layer.

Owner:SHIN-ETSU HANDOTAI CO LTD +1

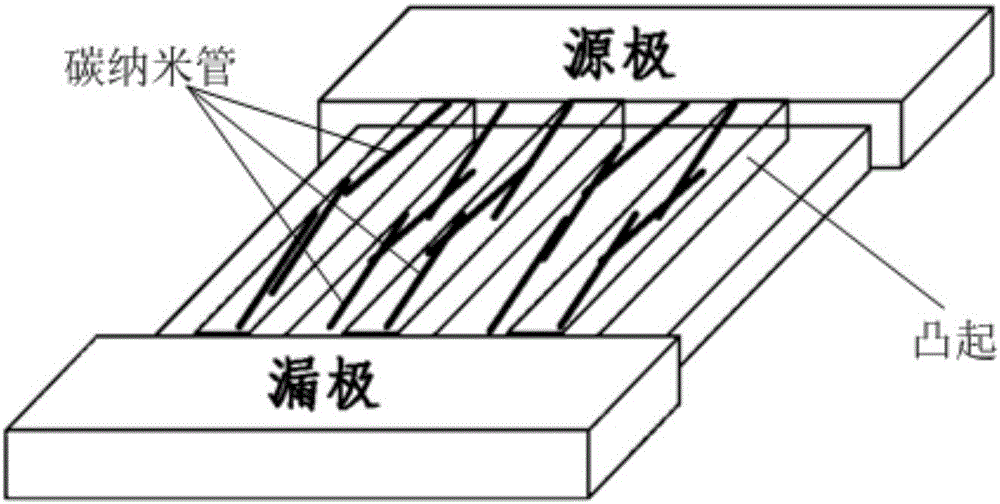

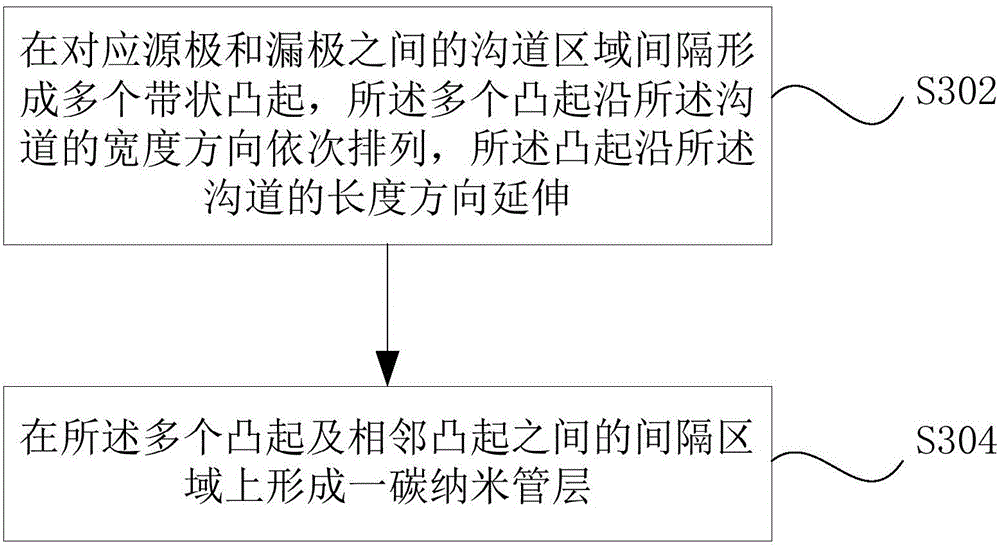

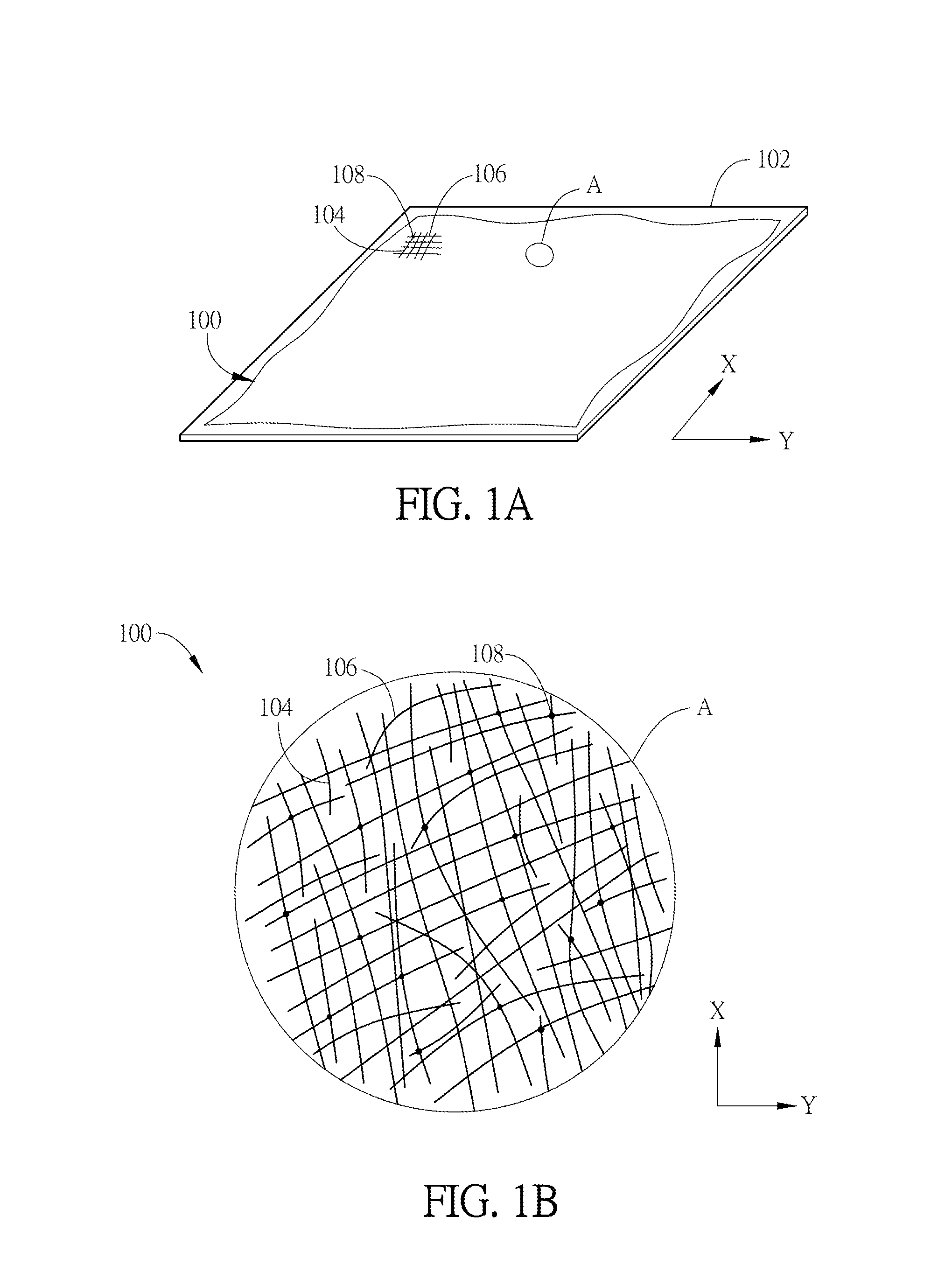

Carbon nano tube thin film transistor and manufacturing method thereof

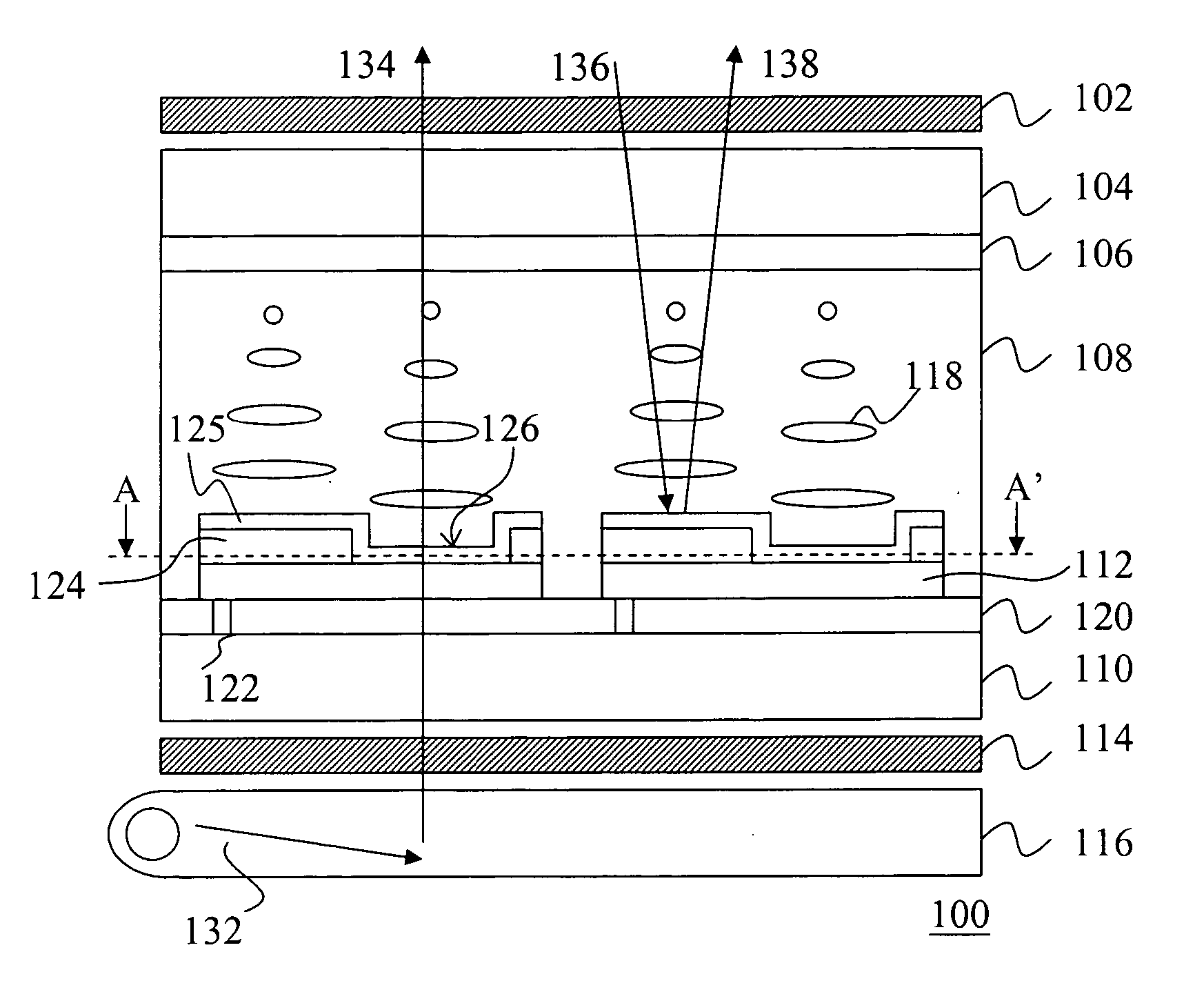

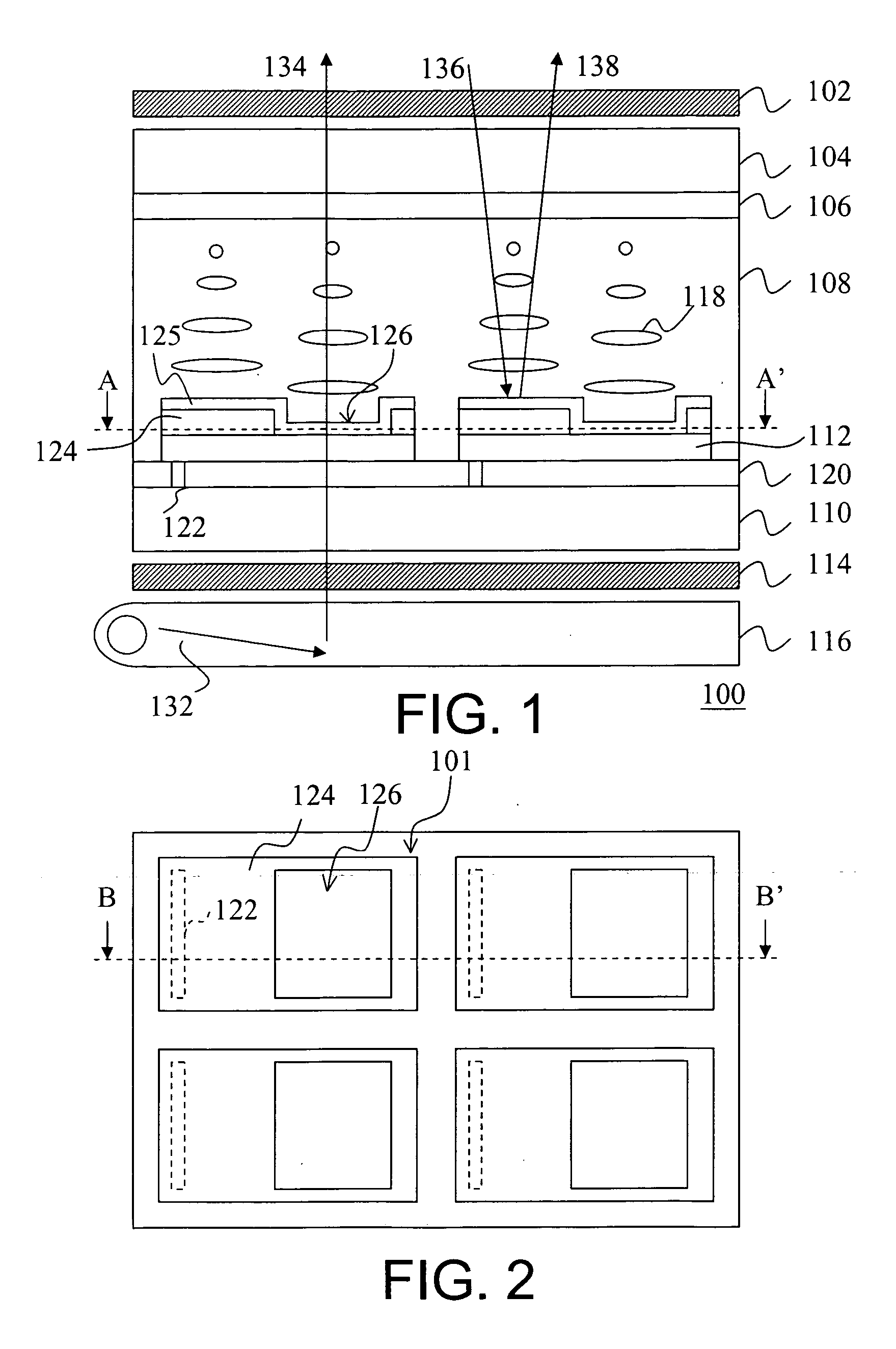

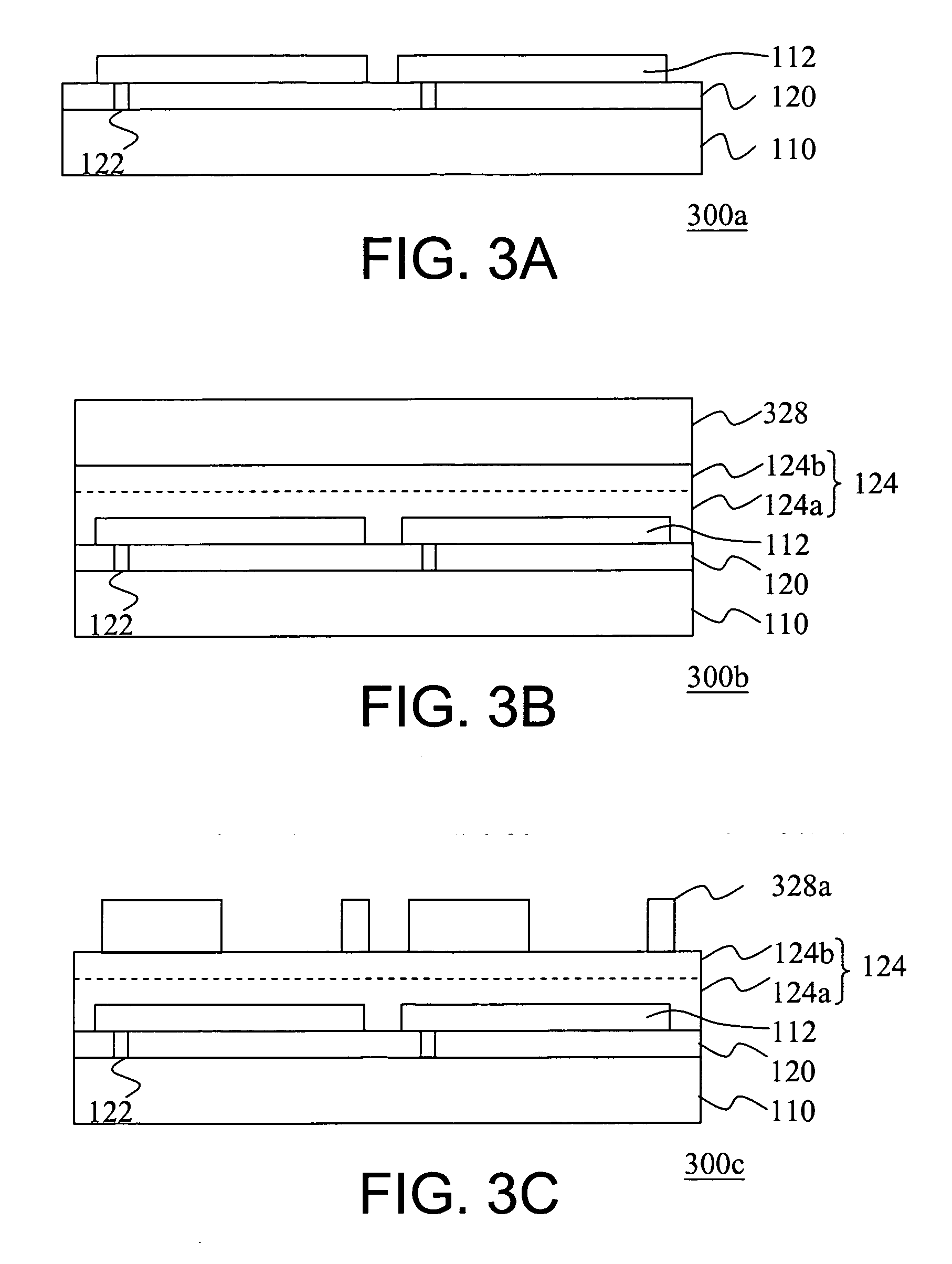

InactiveCN105655406AArranged in an orderly mannerReduce the number of nodesTransistorSemiconductor/solid-state device manufacturingCarbon nanotubeTransistor

The invention discloses a carbon nano tube thin film transistor and a manufacturing method thereof. The carbon nano tube thin film transistor comprises a source electrode, a drain electrode, multiple strap-shaped protrusions arranged in the channel area between the source electrode and the drain electrode at intervals and a carbon nano tube layer arranged in the interval area between the multiple protrusions and adjacent protrusions, wherein the multiple protrusions are sequentially arranged in the width direction of a channel and extend in the length direction of the channel. By the adoption of the carbon nano tube thin film transistor and the manufacturing method, network-shaped carbon nano tubes can be more orderly arranged in the thin film transistor, and the effect of improving the performance of the thin film transistor with the network-shaped carbon nano tubes is achieved.

Owner:BOE TECH GRP CO LTD +1

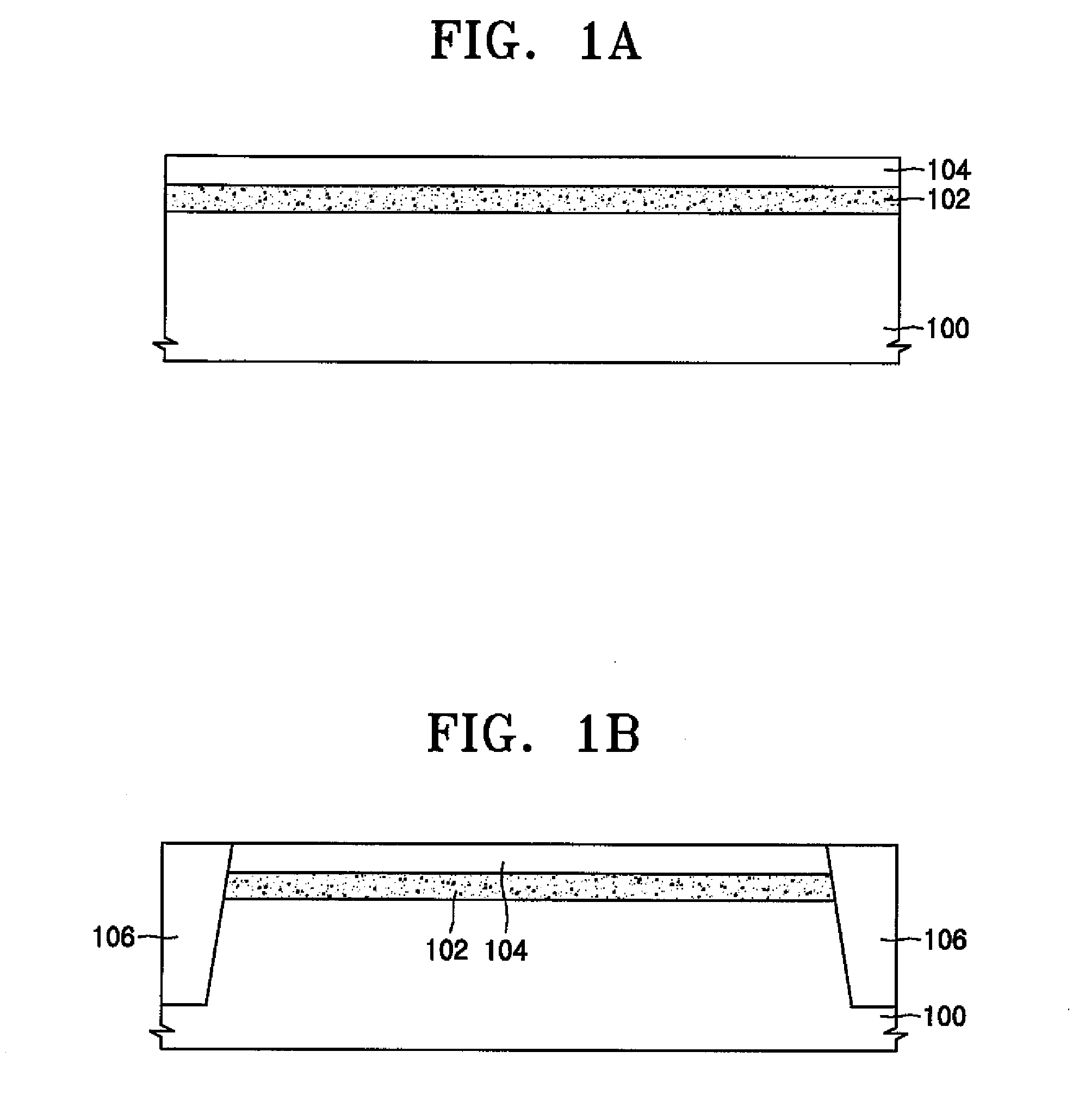

Method of forming a silicide layer while applying a compressive or tensile strain to impurity layers

InactiveUS7807538B2Lower junction resistanceTransistorSemiconductor/solid-state device detailsDevice materialField-effect transistor

A metal insulator semiconductor field effect transistor (MISFET) having a strained channel region is disclosed. Also disclosed is a method of fabricating a semiconductor device having a low-resistance junction interface. This fabrication method includes the step of forming a gate electrode above a silicon substrate with a gate insulator film being sandwiched therebetween. Then, form a pair of heavily-doped p (p+) type diffusion layers in or on the substrate surface at both sides of the gate electrode to a concentration of 5×1019 atoms / cm3 or more and yet less than or equal to 1×1021 atoms / cm3. Next, silicidize the p+-type layers by reaction with a metal in the state that each layer is applied a compressive strain.

Owner:KK TOSHIBA

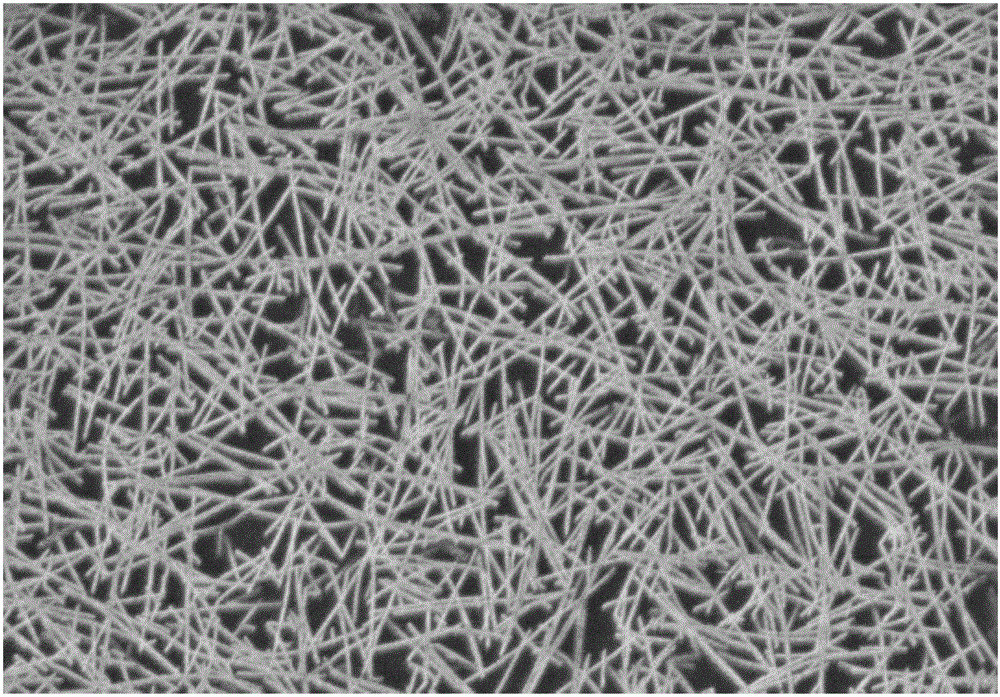

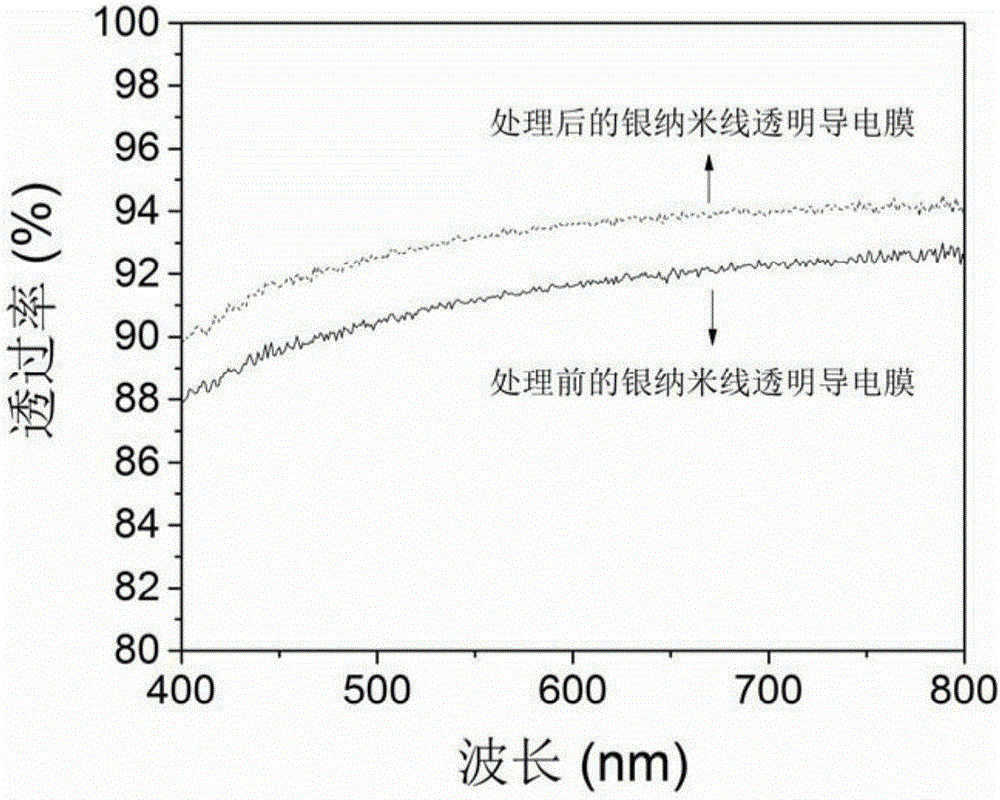

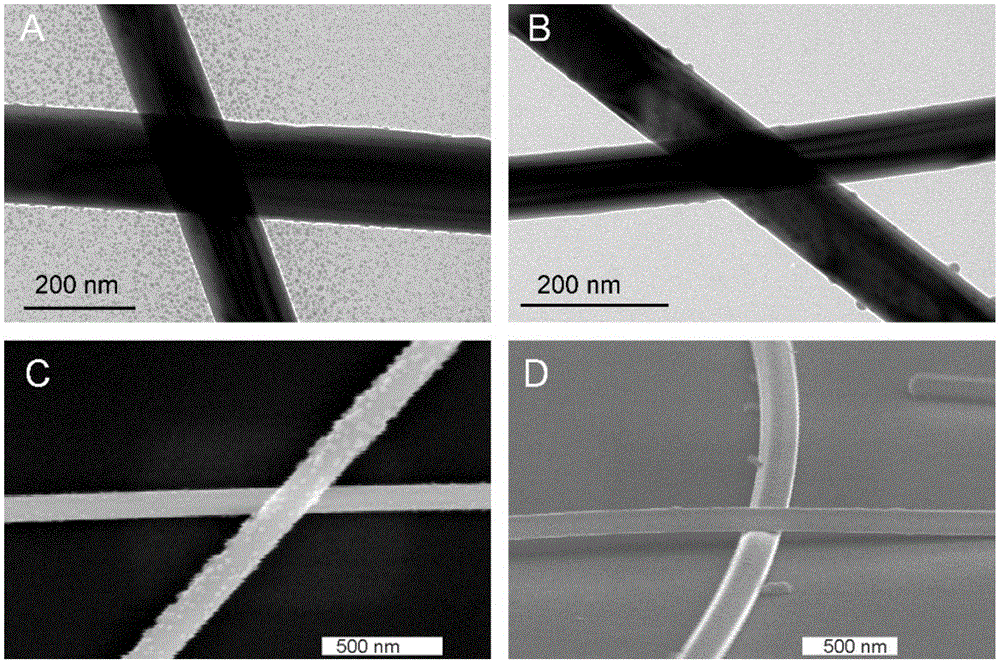

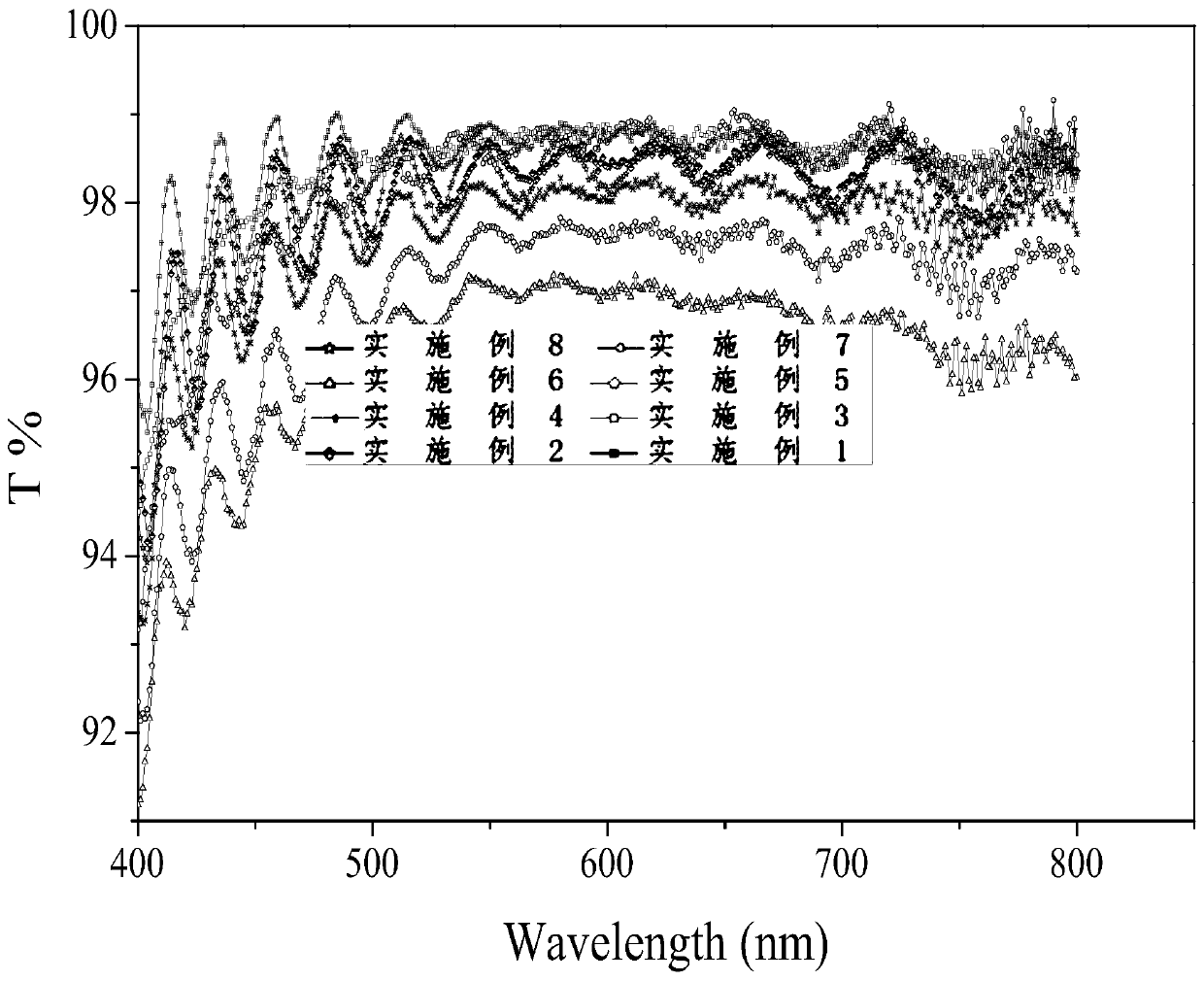

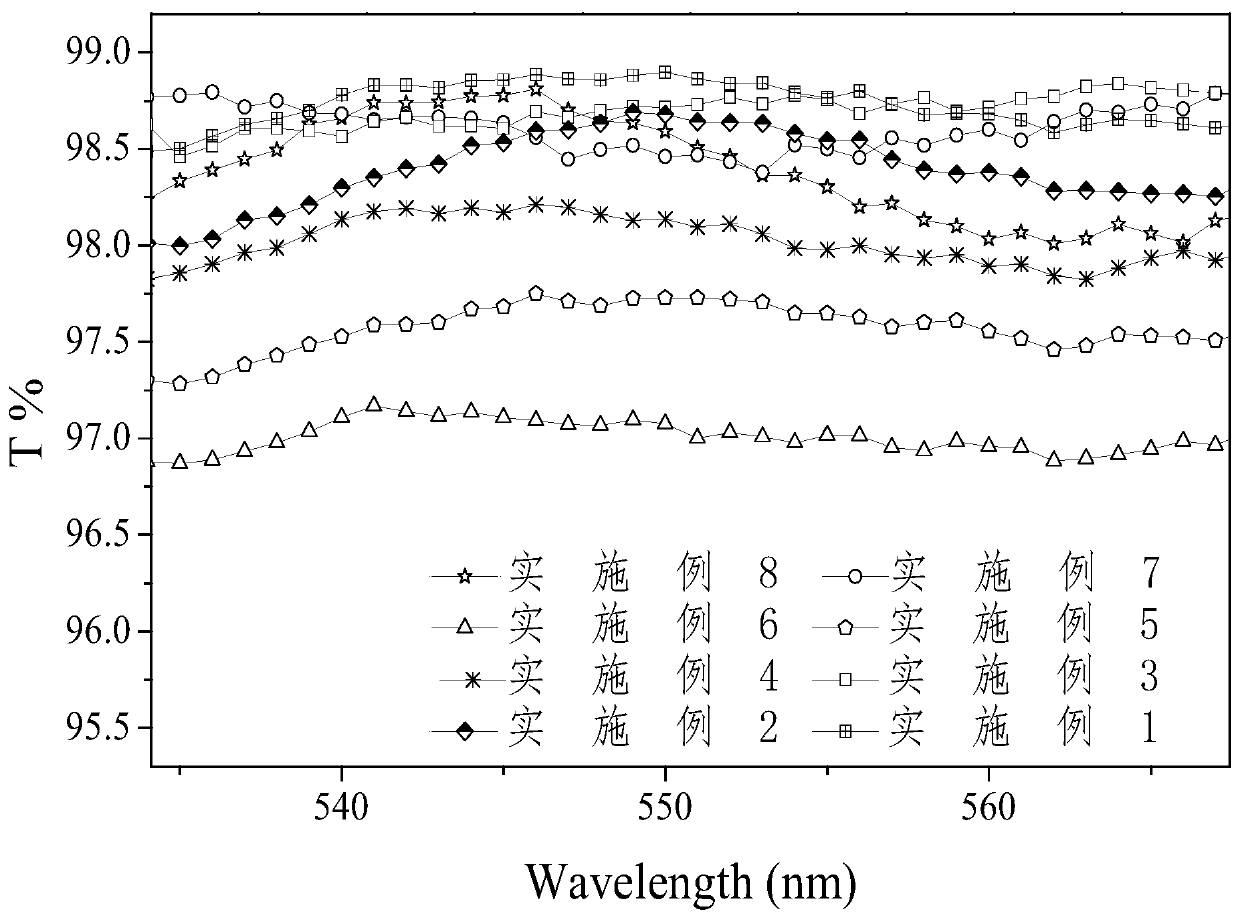

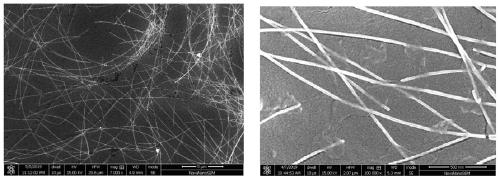

Method for improving conductivity and transmittance of silver nanowire transparent conductive film

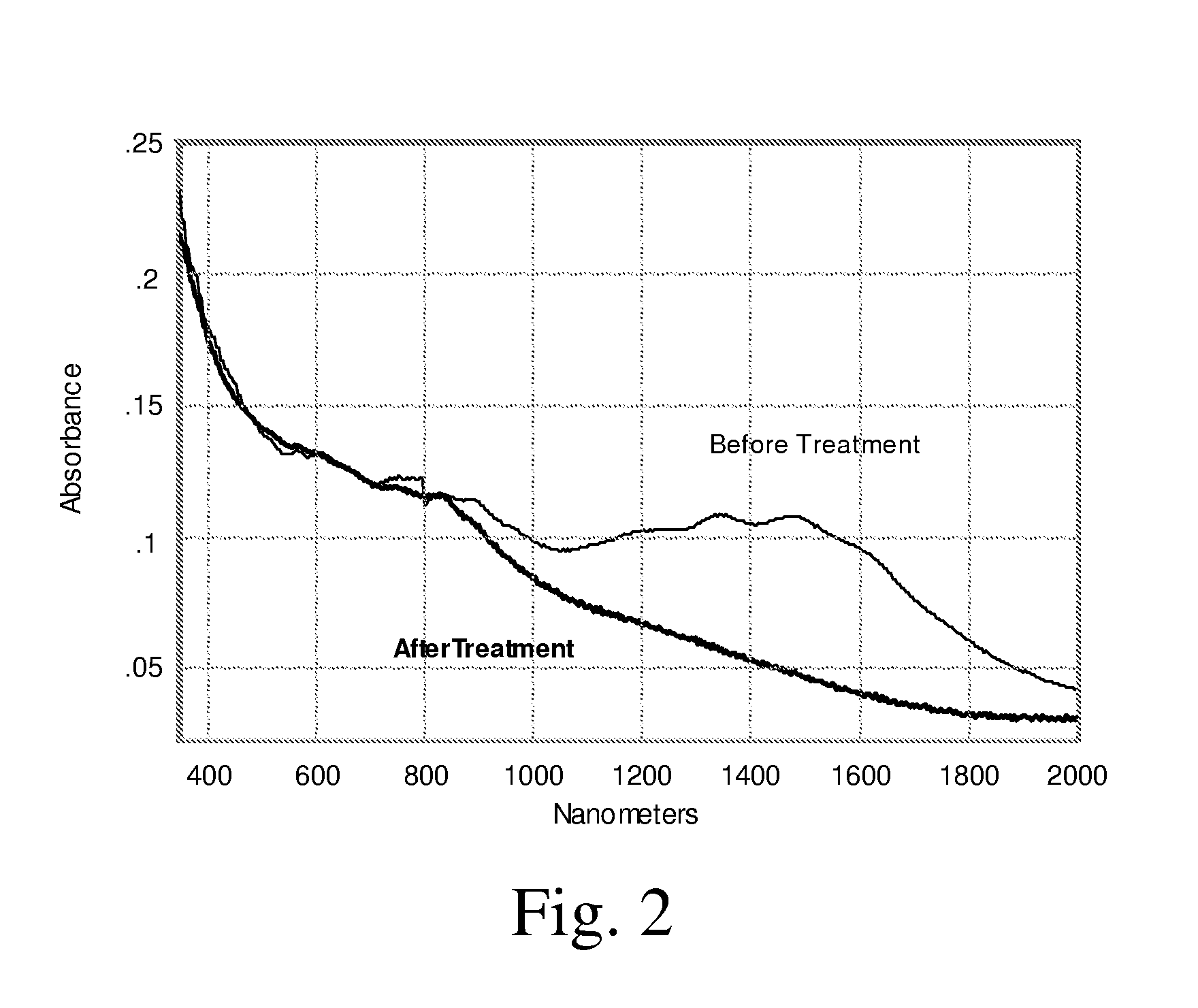

ActiveCN106548828AImprove conductivityImprove transmittanceMetal/alloy conductorsCable/conductor manufactureTransmittanceRoom temperature

The invention discloses a method for improving conductivity and transmittance of a silver nanowire transparent conductive film. Under the room temperature and normal pressure, the silver nanowire transparent conductive film is soaked in a quaternary ammonium salt surfactant solution in specific concentration to remove polyvinylpyrrolidone (PVP) coated on the surface of each silver nanowire; and after the PVP is removed, due to high surface energy of the silver nanowire, junction points between the silver nanowires make contact and realize automatic fusion and welding to enable junction resistance between the silver nanowires to be reduced greatly, so that transmittance of the silver nanowire transparent conductive film is improved while improving the conductivity thereof, and a silver nanowire conductive network and a substrate can be prevented from being damaged due to conventional high-temperature and high-pressure welding. The method is simple to operate, low in cost and suitable for large-scale industrial production.

Owner:CHANGZHOU HUAWEI ADVANCED MATERIAL

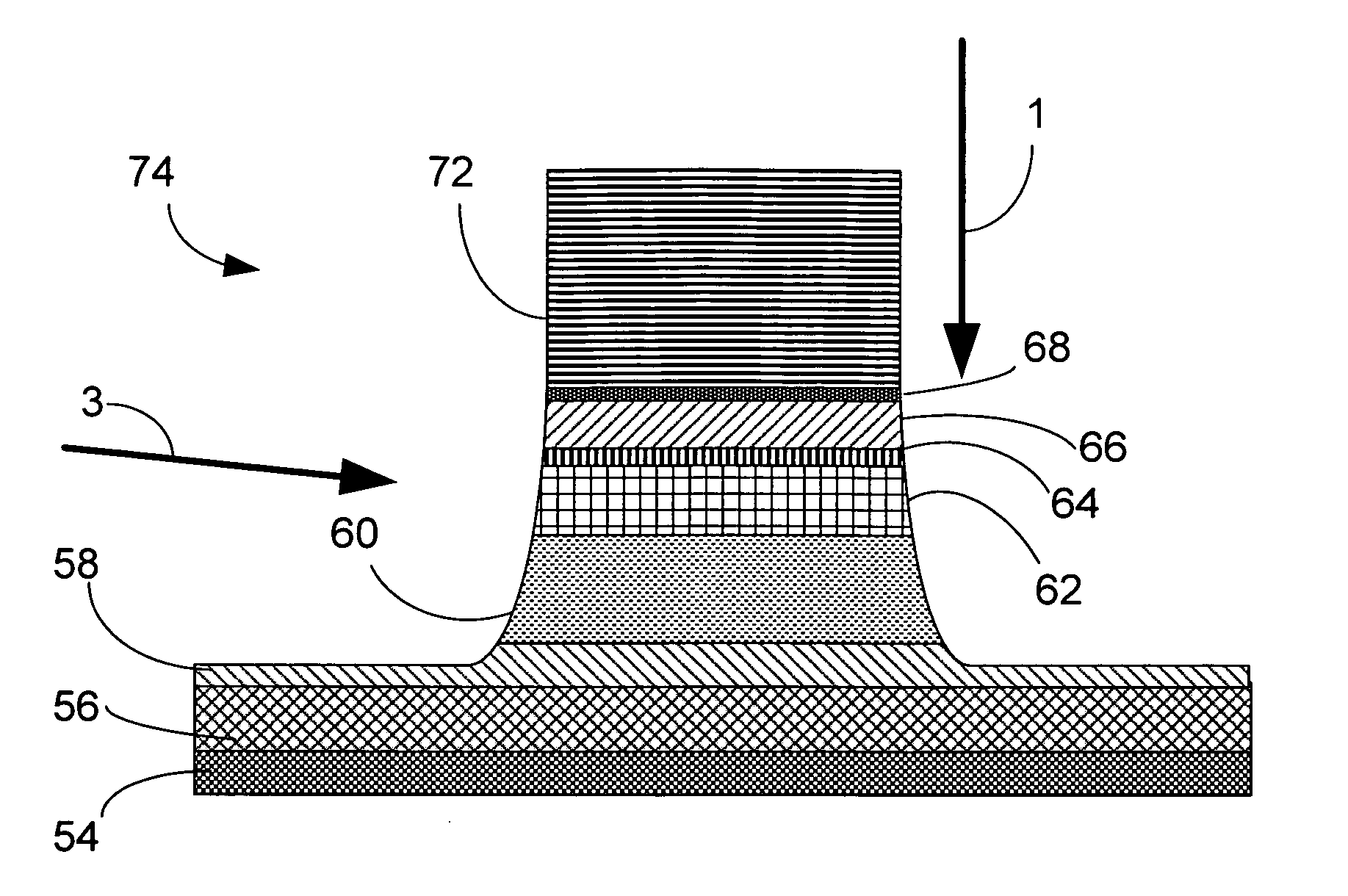

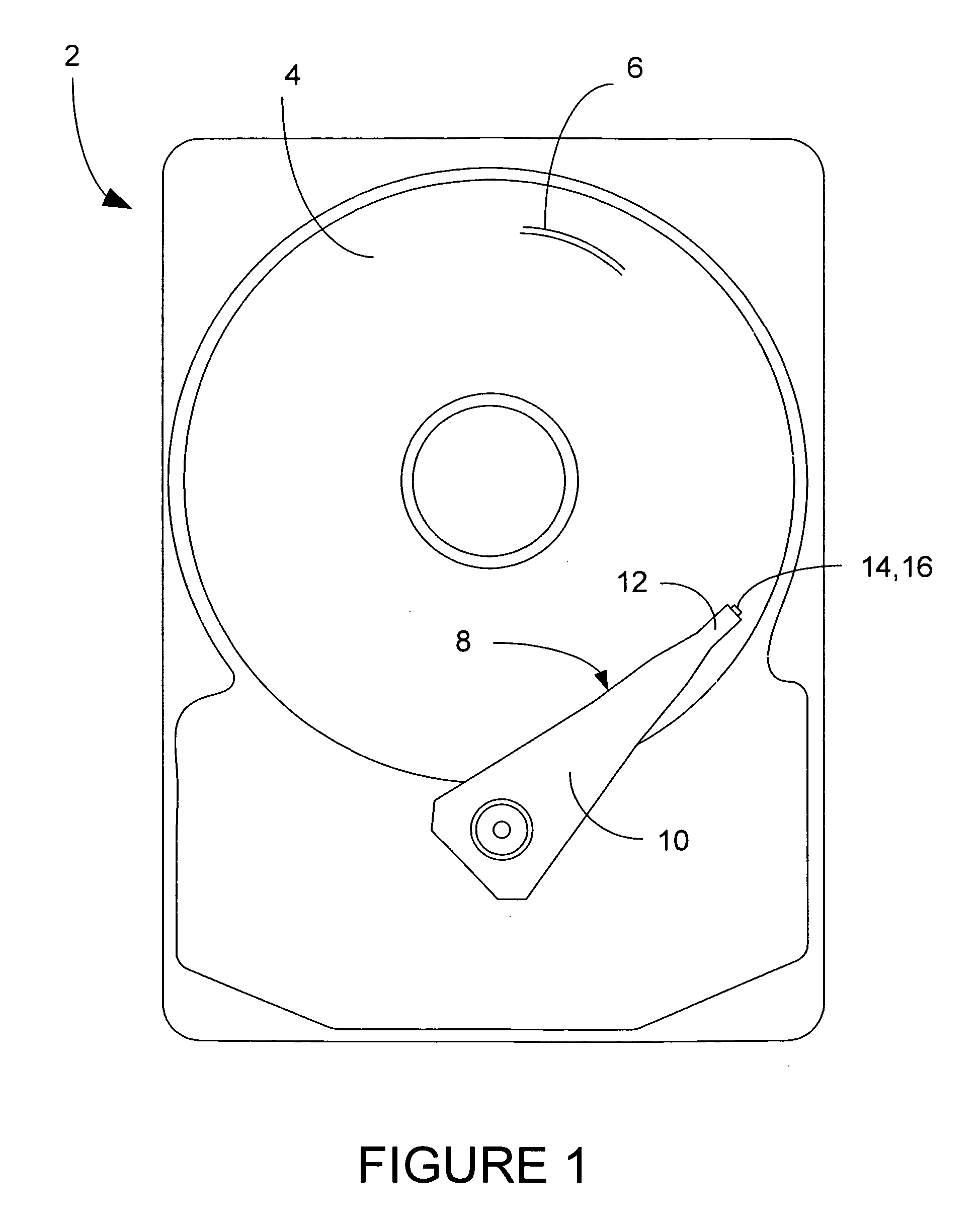

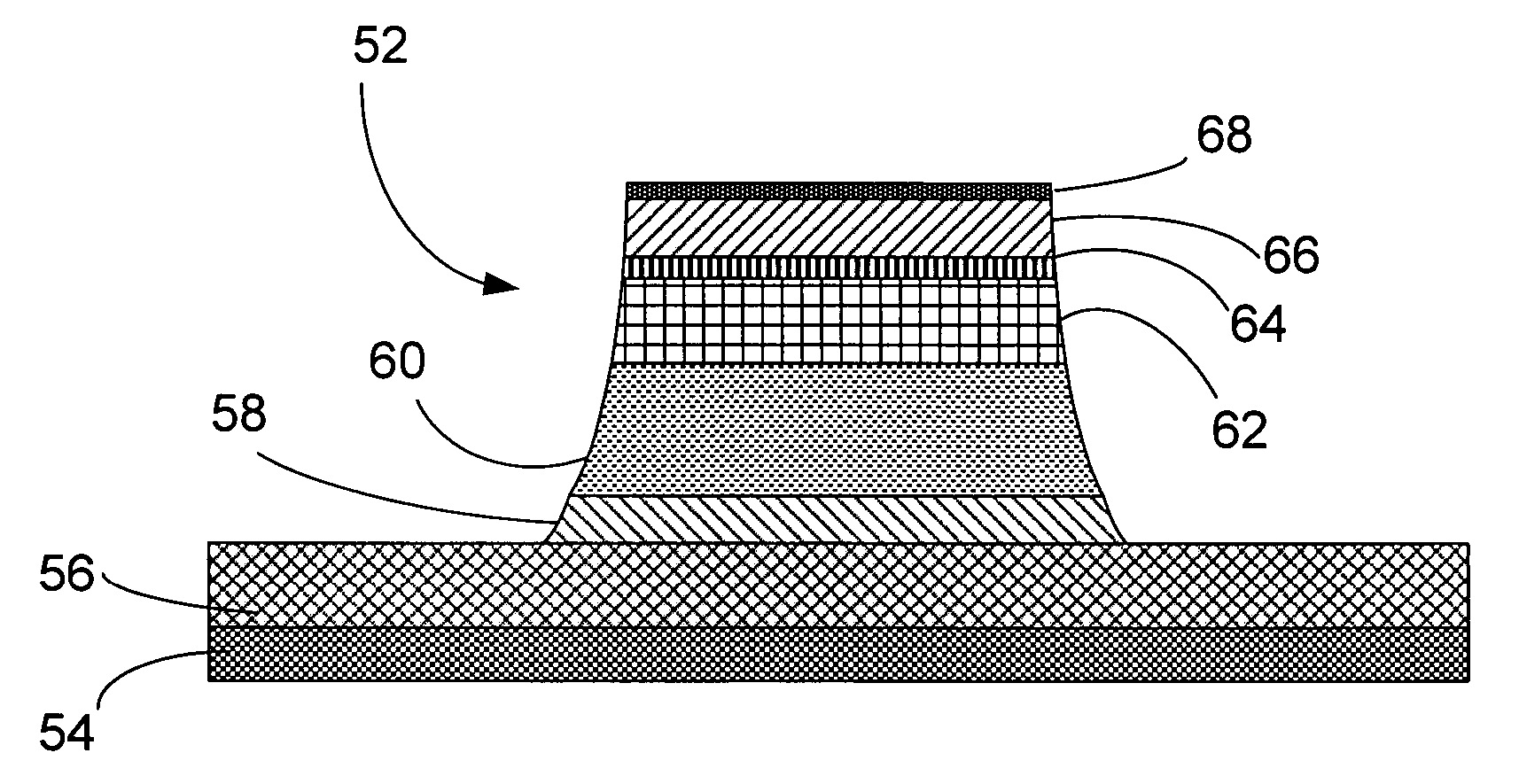

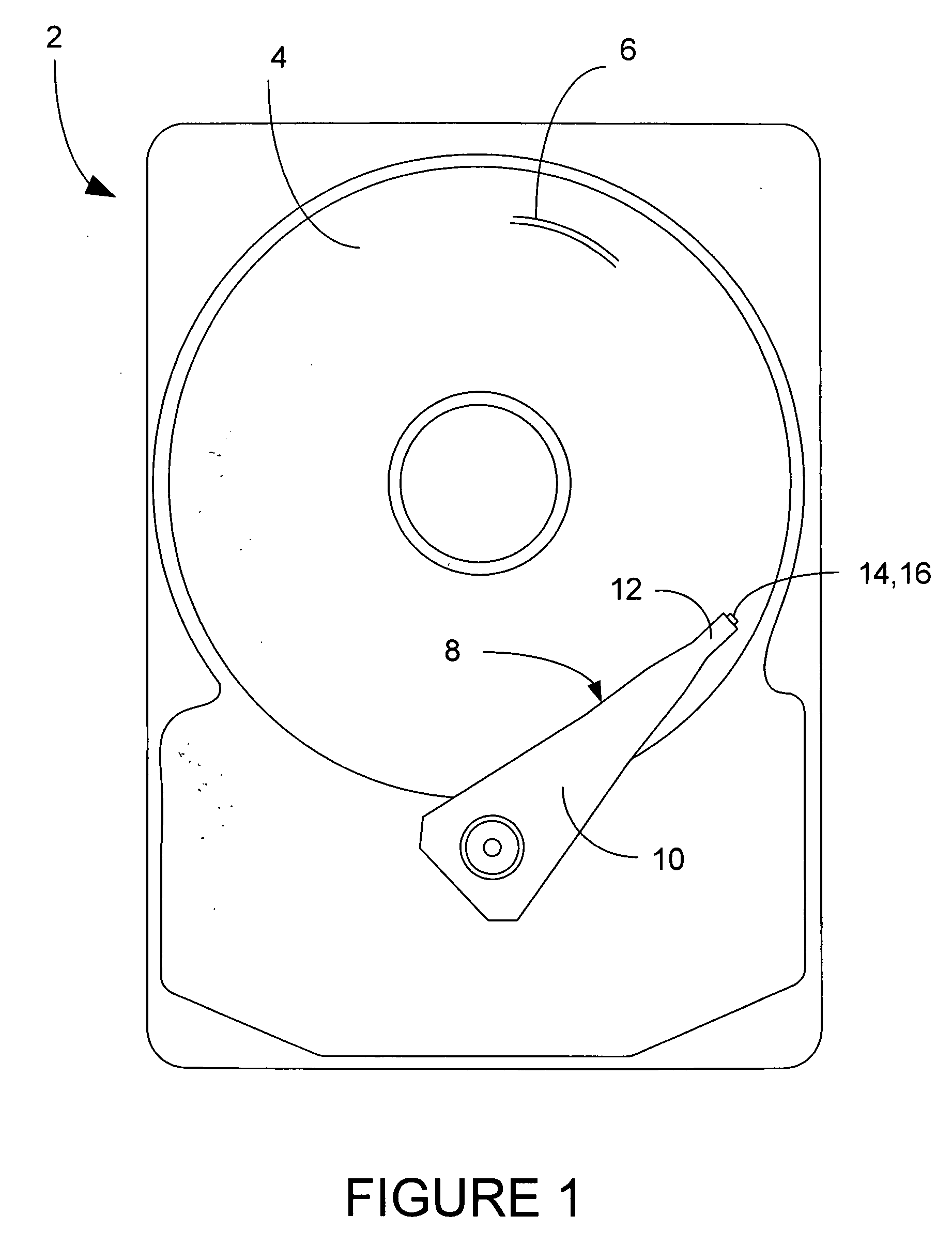

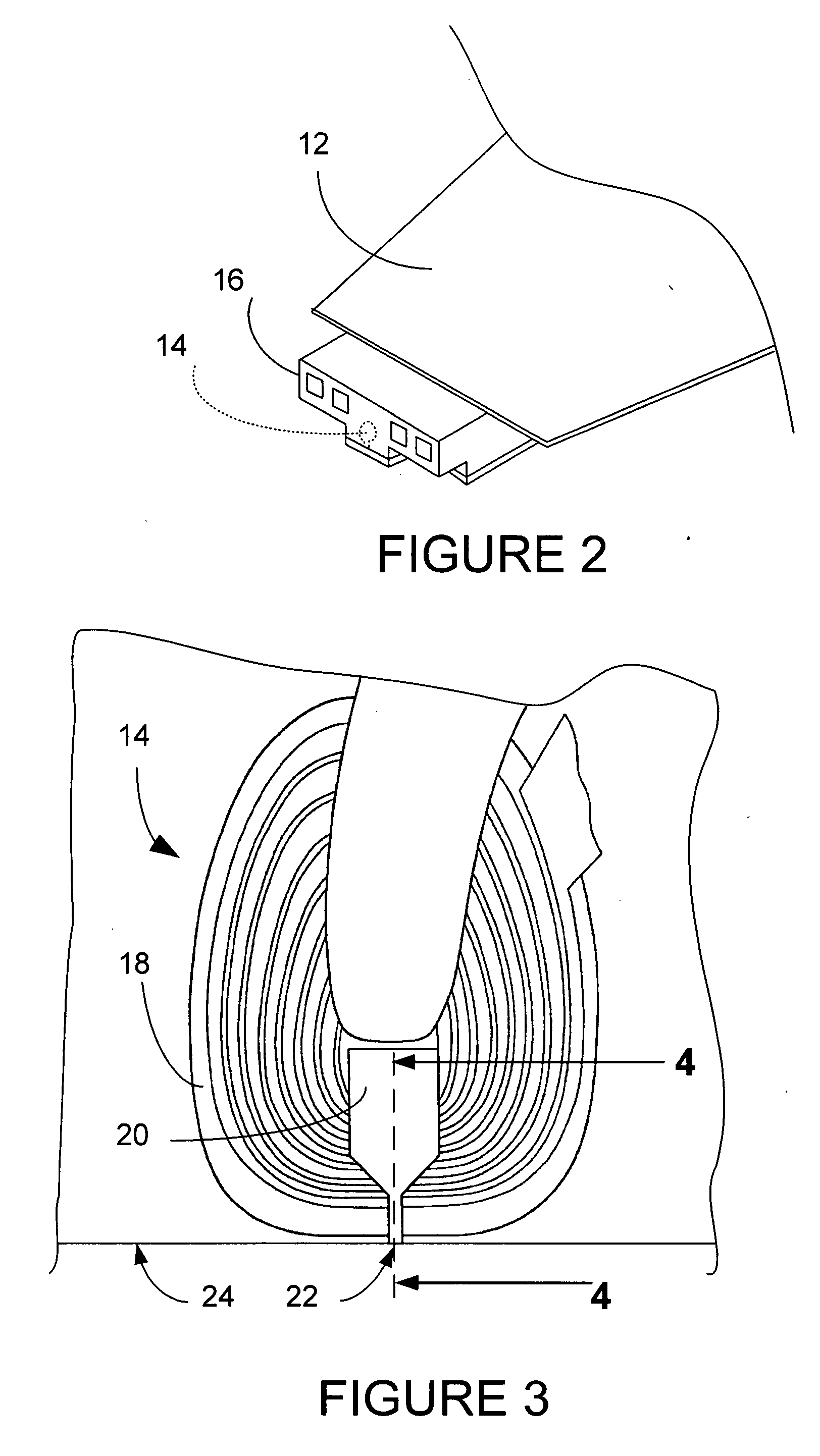

Read head having shaped read sensor-biasing layer junctions using partial milling and method of fabrication

InactiveUS20060067009A1Improve manufacturing yieldLess yield lossElectrical transducersRecord information storageMagnetic disksPhotoresist

A method is disclosed for fabricating a read head for a magnetic disk drive having a read head sensor and a hard bias layer, where the read head has a shaped junction between the read head sensor and the hard bias layer. The method includes providing a layered wafer stack to be shaped. A single- or multi-layered photoresist mask having no undercut is deposited upon the layered wafer stack to be shaped. The layered wafer stack is shaped by the output of a milling source, where the shaping includes partial milling to within a partial milling range to form a shaped junction. A hard bias layer is then deposited which is in contact with the shaped junction of the wafer stack. A read head and a magnetic hard disk drive having a read head layer stack which has been partially milled are also disclosed.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

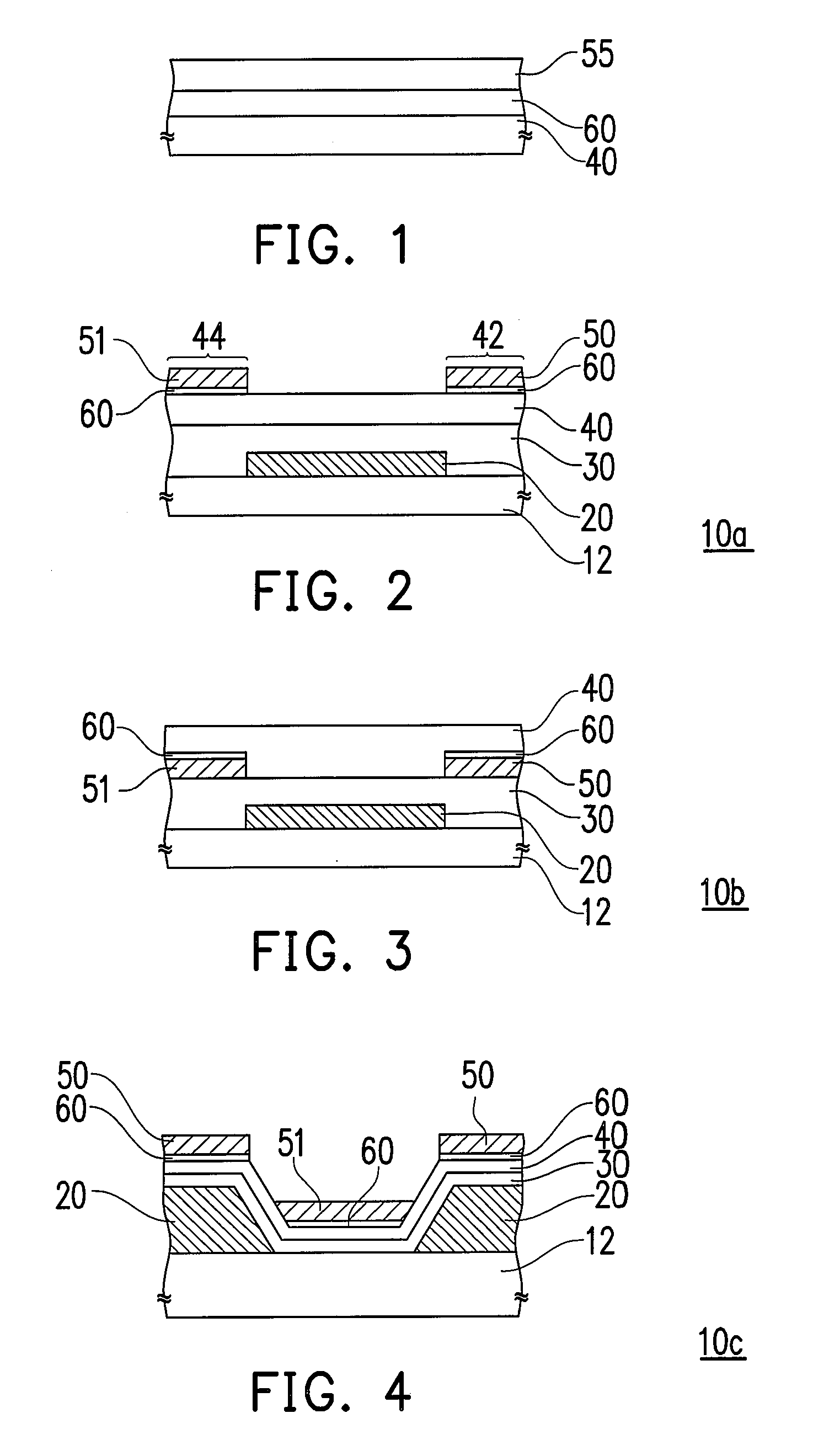

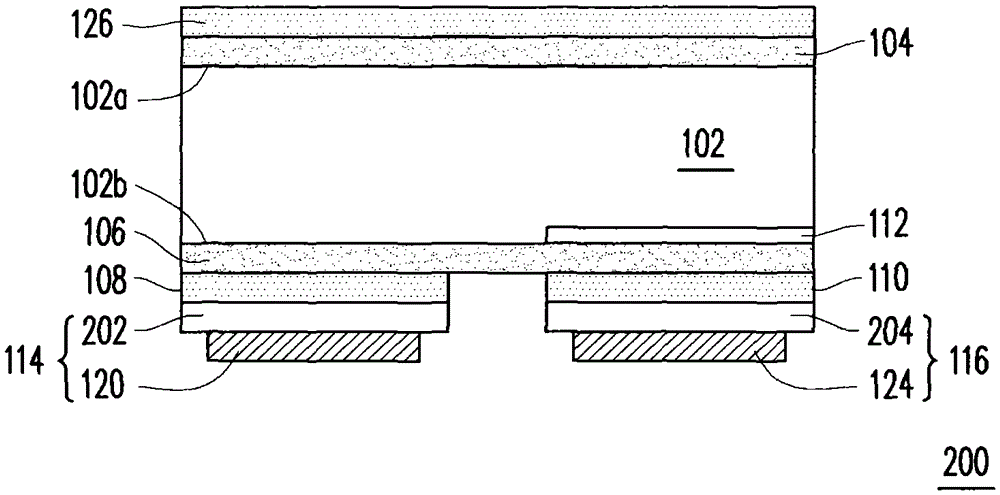

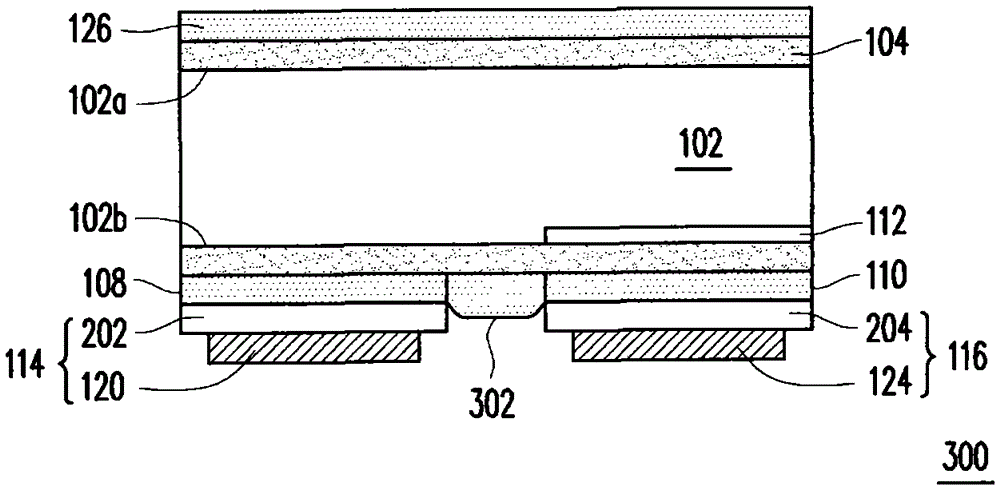

Junction structure of organic semiconductor device, organic thin film transistor and fabricating method thereof

InactiveUS20070158647A1Lower junction resistanceSolid-state devicesSemiconductor/solid-state device manufacturingOrganic semiconductorSemiconductor

A junction structure of an organic semiconductor device including an organic semiconductor layer, a conductive layer and a modifying layer is provided. The modifying layer is formed between the organic semiconductor layer and the conductive layer, wherein the modifying layer includes an inorganic compound or an organic complex compound. An organic thin film transistor including a gate, a source / drain, a dielectric layer, an organic semiconductor layer and at least a modifying layer is also provided. The gate is electrically isolated from the source / drain. The dielectric layer is disposed between the gate and the source / drain. The organic semiconductor layer is disposed between the source and the drain. The modifying layer is disposed between the organic semiconductor layer and the source / drain, wherein the modifying layer includes an inorganic compound or an organic complex compound.

Owner:CHUNGHWA PICTURE TUBES LTD

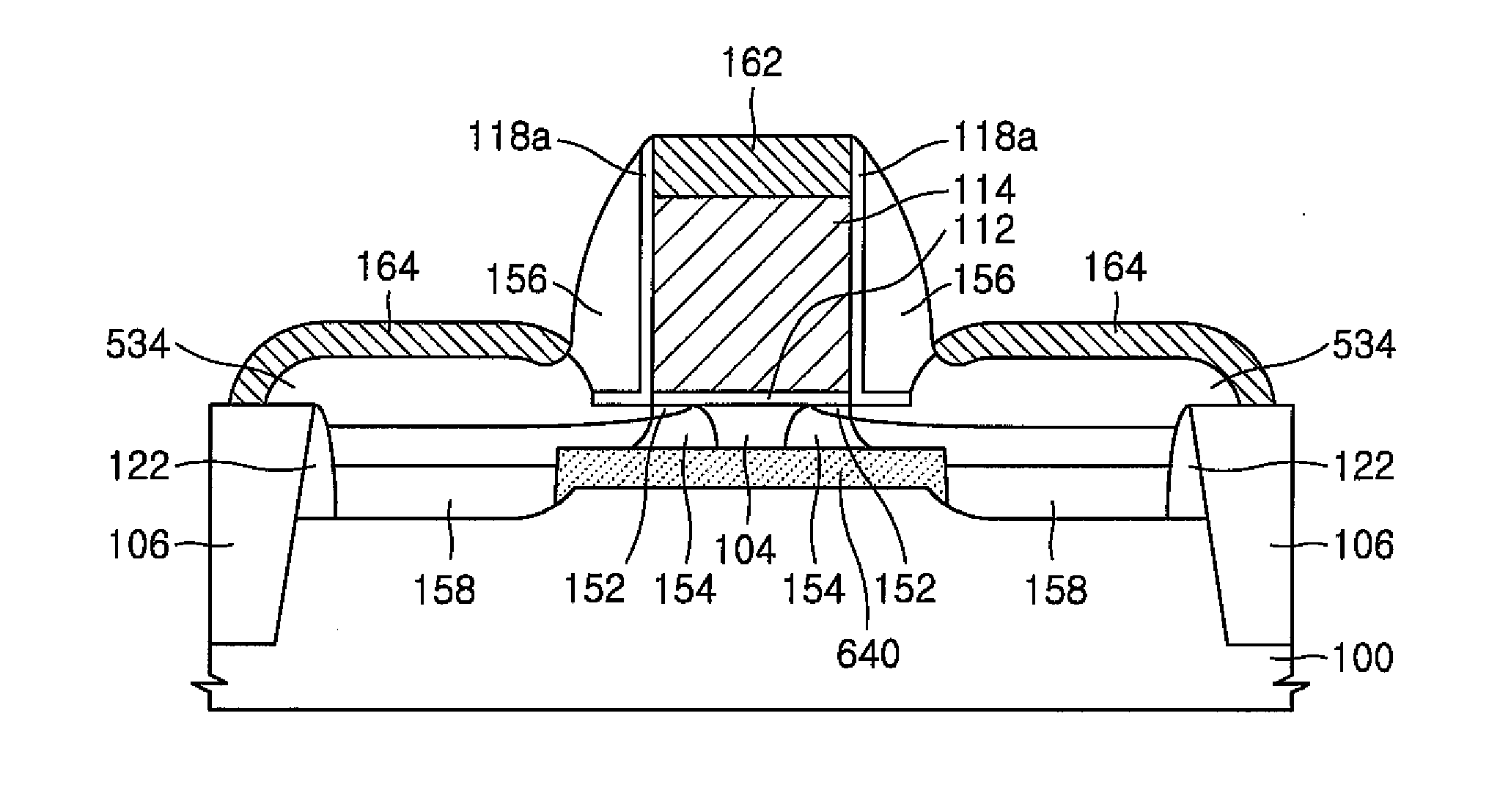

Semiconductor device and method of manufacturing same

InactiveUS20080132011A1High carrier mobilitySuppression of short channel effectsTransistorSolid-state devicesDevice materialEngineering

A semiconductor device and related method of manufacture are disclosed. The semiconductor device comprises a gate electrode formed on a semiconductor substrate, an active region containing spaces formed below the gate electrode, a channel region formed between the gate electrode and the spaces, and source and drain regions formed on opposite sides of the gate electrode within the active region. The spaces are formed by etching a semiconductor layer formed below the gate electrode in the active region.

Owner:SAMSUNG ELECTRONICS CO LTD

High-frequency sputtering device

ActiveUS9017535B2Facilitated DiffusionLower junction resistanceCellsElectric discharge tubesSputteringElectricity

Provided is a high-quality magnetoresistive thin film by using a method of controlling self bias of a high-frequency sputtering device. In order to control the self bias for the substrate by adjusting a substrate potential, the high-frequency sputtering device according to the present invention includes: a chamber; evacuation means for evacuating the inside of the chamber; gas introduction means for supplying a gas into the chamber; a substrate holder provided with a substrate mounting table; rotation drive means capable of rotating the substrate holder; a sputtering cathode provided with a target mounting table and arranged such that the surface of the target mounting table is non-parallel to the surface of the substrate mounting table; an electrode disposed inside the substrate holder; and a variable impedance mechanism electrically connected to the electrode, for adjusting the substrate potential on the substrate holder.

Owner:CANON ANELVA CORP

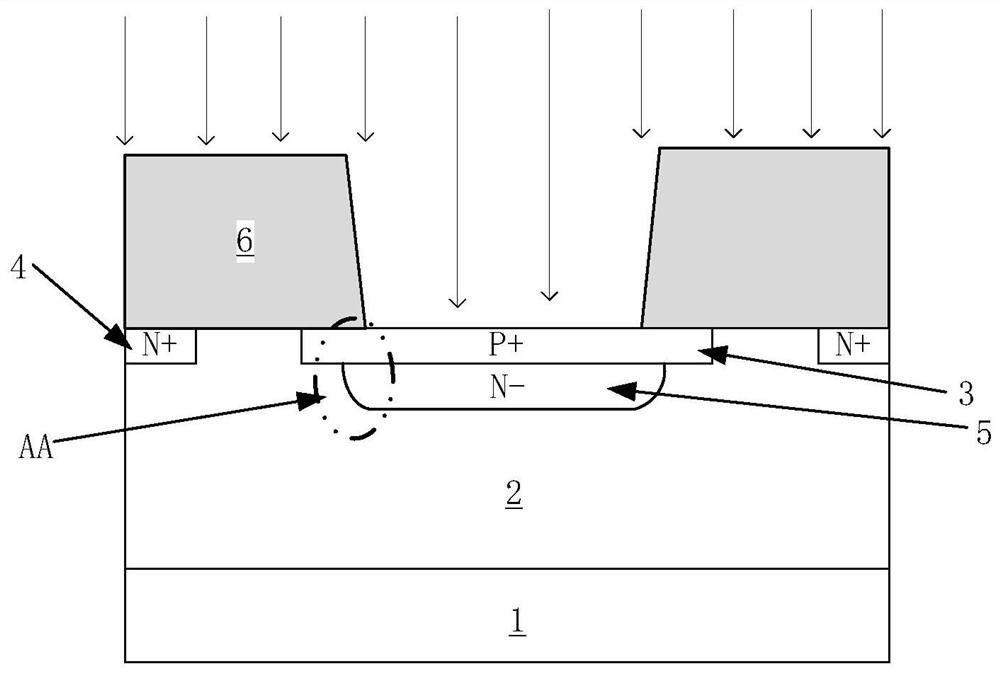

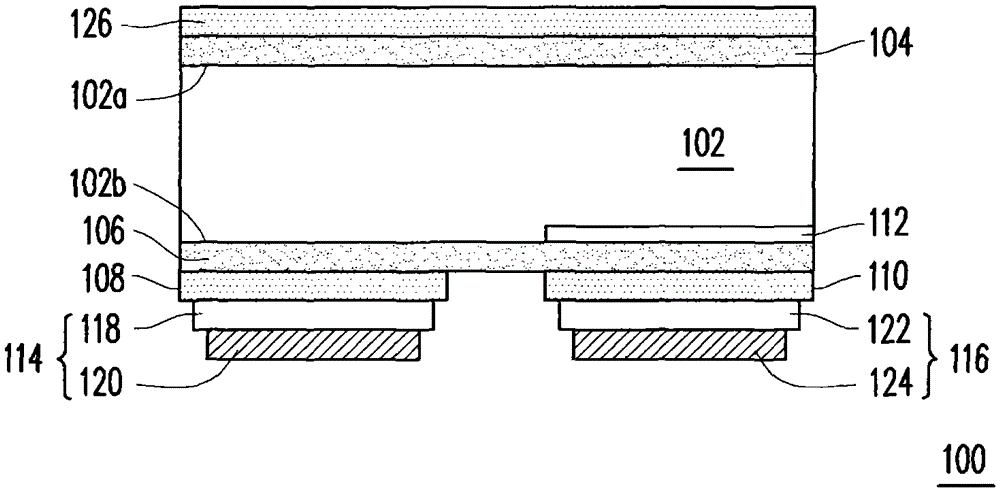

Back-contact heterojunction solar cell

ActiveCN103137767AConversion efficiency jumpsReduce output lossPhotovoltaic energy generationSemiconductor devicesHeterojunctionSolar cell

A back-contact heterojunction solar cell, having a first conductive type silicon substrate, a first amorphous semiconductor layer, a second amorphous semiconductor layer, a first conductive type semiconductor layer, a second conductive type semiconductor layer and a second conductive type doped region is introduced. The first amorphous semiconductor layer disposed on the illuminated surface of the silicon substrate is an intrinsic semiconductor layer or is of the first conductive type. The second amorphous semiconductor layer disposed on the non-illuminated surface of the silicon substrate is an intrinsic semiconductor layer. The first and the second conductive type semiconductor layers are disposed on the second amorphous semiconductor layer. The second conductive type doped region is located in the silicon substrate under the second conductive type semiconductor layer and is in contact with the second amorphous semiconductor layer.

Owner:IND TECH RES INST

Crosslinkable and chemically sinterable high-cohesiveness silver nanowire conductive ink and conductive film prepared from same

ActiveCN111057414AImprove adhesionSolve the adhesionConductive layers on insulating-supportsApparatus for manufacturing conducting/semi-conducting layersPolymer sciencePolyvinyl alcohol

The invention discloses crosslinkable and chemically sinterable high-cohesiveness silver nanowire conductive ink and a conductive film prepared from the same. The formula of the conductive ink comprises the following components in percentage by mass: 0.1 to 2.0 percent of silver nanowires; 0.01 to 0.5 percent of a bonding agent; 0.001 to 0.008 percent of a dispersing agent; 0.001 to 0.016 percentof a leveling agent, 0.001 to 0.005 percent of a surfactant, 0.1 to 1 percent of a thickening agent, 0.001 to 0.1 percent of a defoaming agent, 0.001 to 0.01 percent of a cross-linking agent and chemical sintering agent, and 96.361 to 99.785 percent of a solvent, and the binding agent is one or a mixture of more of sodium alginate, polyvinyl alcohol, polyurethane, chitosan and the like; and the cross-linking agent and chemical sintering agent is one or a mixture of more of calcium chloride, magnesium chloride, zinc chloride, nickel chloride and the like. According to the invention, the problem of poor adhesiveness of the silver nanowire transparent conductive film on the substrate is solved, and the film has structural stability, high conductivity and high visible light transmittance.

Owner:ZHEJIANG UNIV OF TECH

Method of fabrication for read head having shaped read sensor-biasing layer junctions using partial milling

InactiveUS20080002310A1Not to damageImprove manufacturing yieldElectrical transducersDecorative surface effectsWafer stackingEngineering

A method is disclosed for fabricating a read head for a magnetic disk drive having a read head sensor and a hard bias layer, where the read head has a shaped junction between the read head sensor and the hard bias layer. The method includes providing a layered wafer stack to be shaped. A single- or multi-layered photoresist mask having no undercut is deposited upon the layered wafer stack to be shaped. The layered wafer stack is shaped by the output of a milling source, where the shaping includes partial milling to within a partial milling range to form a shaped junction. A hard bias layer is then deposited which is in contact with the shaped junction of the wafer stack.

Owner:WESTERN DIGITAL TECH INC

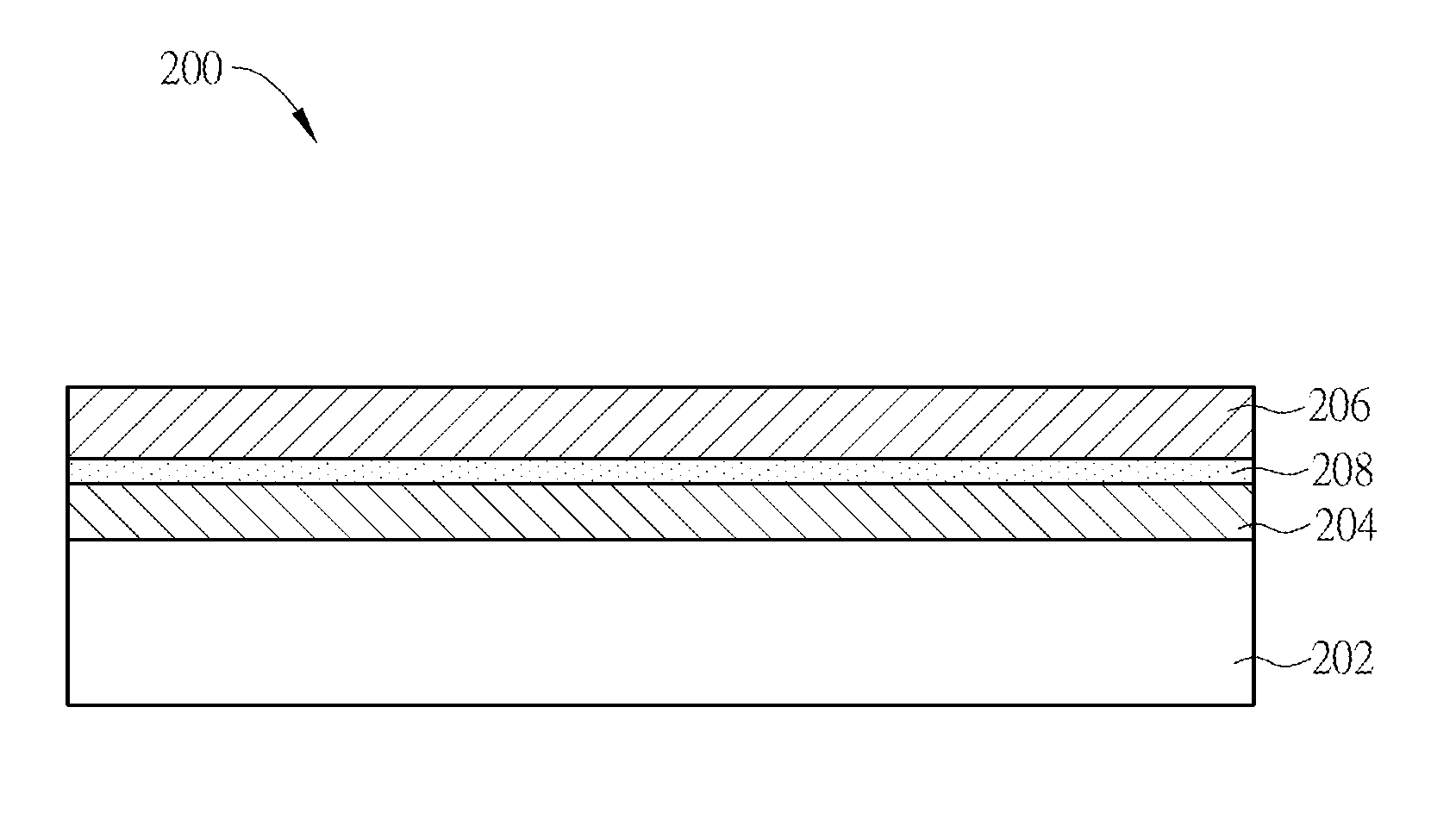

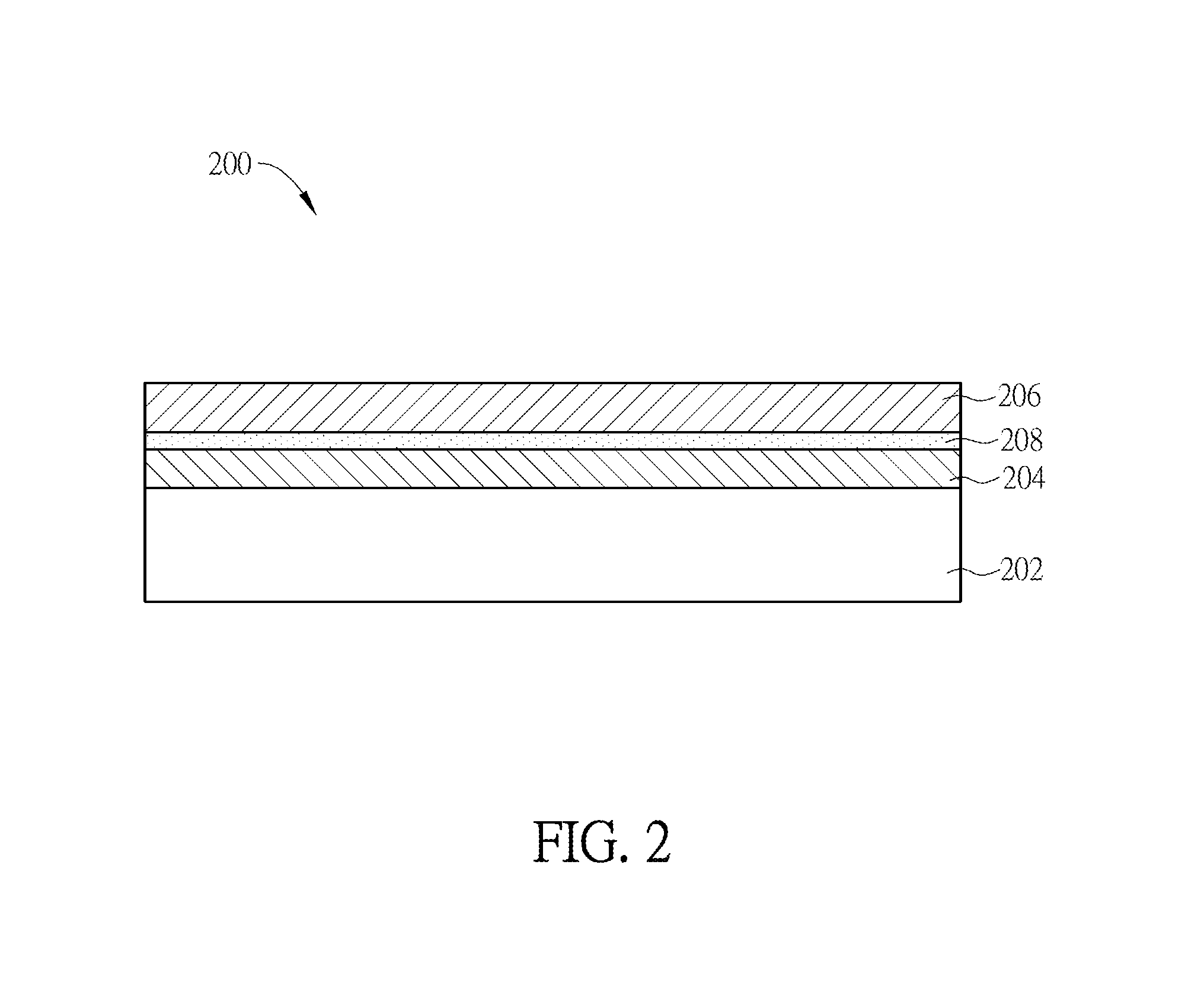

Display panel having a reflective layer therein

InactiveUS20070076145A1Displayed image be eliminatedEliminate flickeringNon-linear opticsLiquid-crystal displayOptoelectronics

A liquid crystal display panel having a plurality of pixels is provided. Each pixel may include a first substrate, a second substrate, a liquid crystal layer, a reflective layer and a cover layer. A surface of the second substrate includes a second transparent electrode. The liquid crystal layer is disposed between the first substrate and the second substrate. The reflective layer is disposed over at least a portion of the second transparent electrode. The cover layer is disposed over the reflective layer.

Owner:INNOLUX CORP

Zener diode and manufacturing method thereof

ActiveCN112002767AImprove stabilityAccurate control of junction areaSemiconductor/solid-state device manufacturingSemiconductor devicesZener diodeEngineering

The invention discloses a Zener diode and a manufacturing method thereof. The Zener diode comprises: a substrate; a well region of a first doping type, which is formed in the substrate; a first dopedregion of a second doped type, which is formed in the well region, wherein the first doped type is opposite to the second doped type; and a second doped region formed below the first doped region, wherein the first part of the lower surface of the first doped region is adjacent to the well region to form a first PN junction, the second part of the lower surface of the first doped region is adjacent to the second doped region to form a second PN junction, and the second doped region adopts a hard mask to limit a boundary extending transversely in order to make the boundary of the second doped region form a plane and an included angle between the plane and the vertical direction smaller than or equal to a first angle. Uniform doping of the second doped region can be realized, so that stability of breakdown voltage of the Zener diode can be enhanced, and reverse electric leakage before breakdown can be reduced.

Owner:JOULWATT TECH INC LTD

Magnetic tunnel junction structure and tunneling magneto resistance element

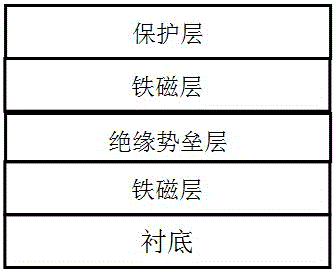

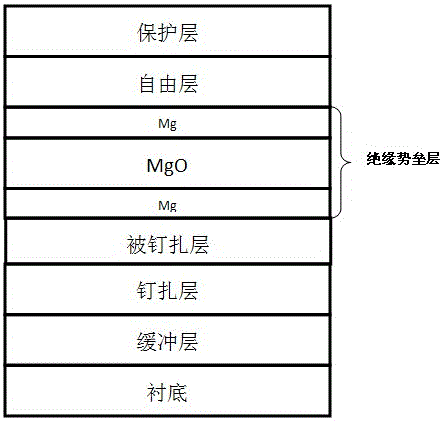

InactiveCN105938872AStop the spreadLower junction resistanceMagnetic-field-controlled resistorsGalvano-magnetic material selectionMagnetic storageMagnetic reluctance

The invention discloses a magnetic tunnel junction structure, and belongs to the technical field of magnetic electronics. The magnetic tunnel junction structure comprises the improvements as follows: an ultra-thin metal Mg layer is imported to form an insulating barrier layer with an Mg / MgO / Mg sandwich superlattice structure; the superlattice structure formed by two kinds of ferromagnetic materials with opposite magnetostriction characteristics is used as the free layer of a pinning type TMR (tunneling magneto resistance) structure; and an additional pinning layer capable of realizing the pinning effect on the micro magnetic domain on the edge of the free layer can be imported to the side wall of the free layer. The invention also discloses a tunneling magneto resistance element, and a tunneling magneto resistance magnetic head, a tunneling magneto resistance sensor and a magnetic storage unit which applies the tunneling magneto resistance element. Compared with the prior art, electromagnetic noise in the MTJ (magnetic tunnel junction) element can be effectively lowered, and the sensitivity of the TMR sensor can be greatly improved.

Owner:NANJING UNIV OF TECH +1

Conductive structure and manufacturing method thereof

InactiveUS20150060119A1High transparencyLower junction resistanceCircuit optical detailsPrinted circuit aspectsNanowireEngineering

Owner:NATIONAL TSING HUA UNIVERSITY

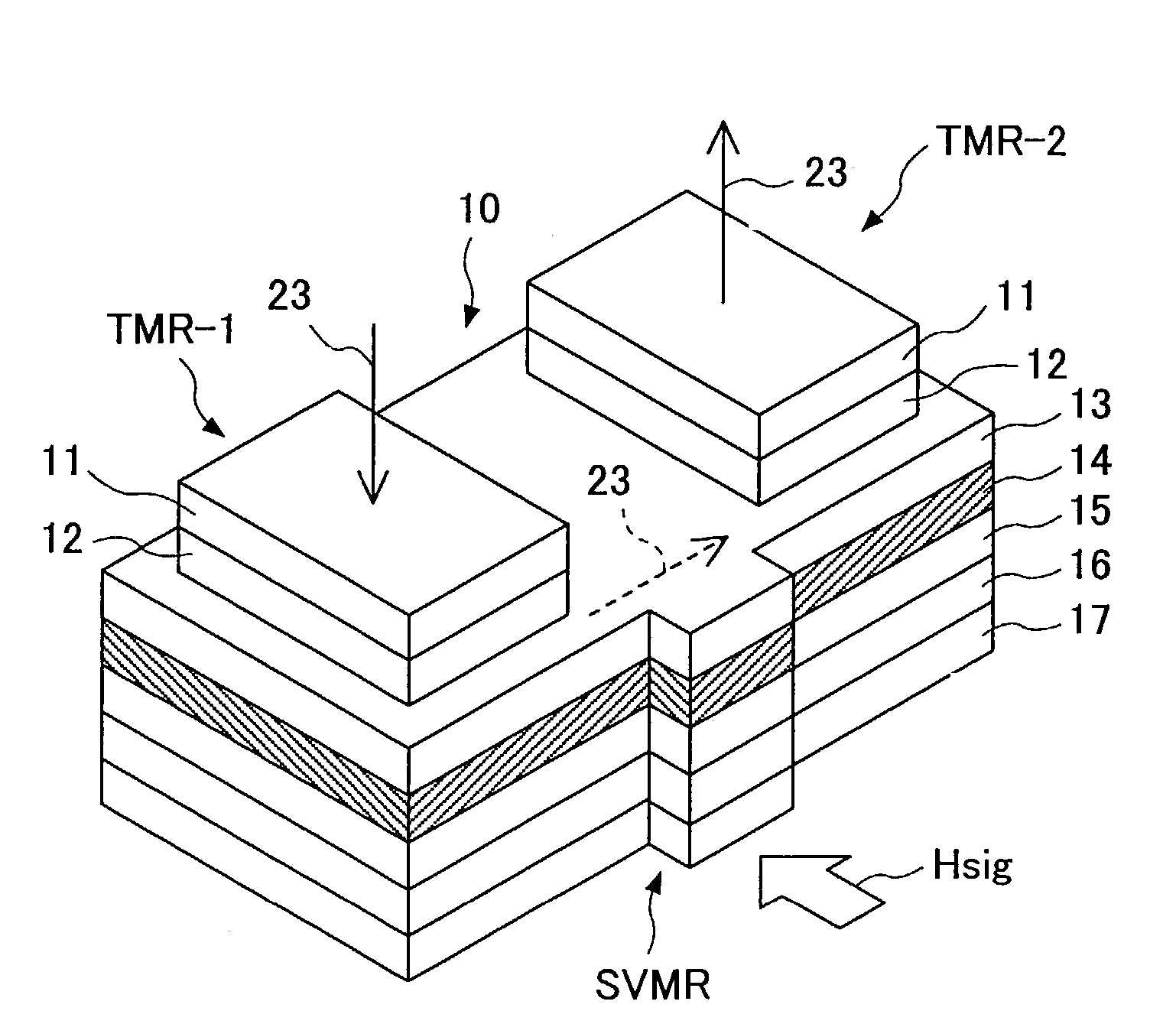

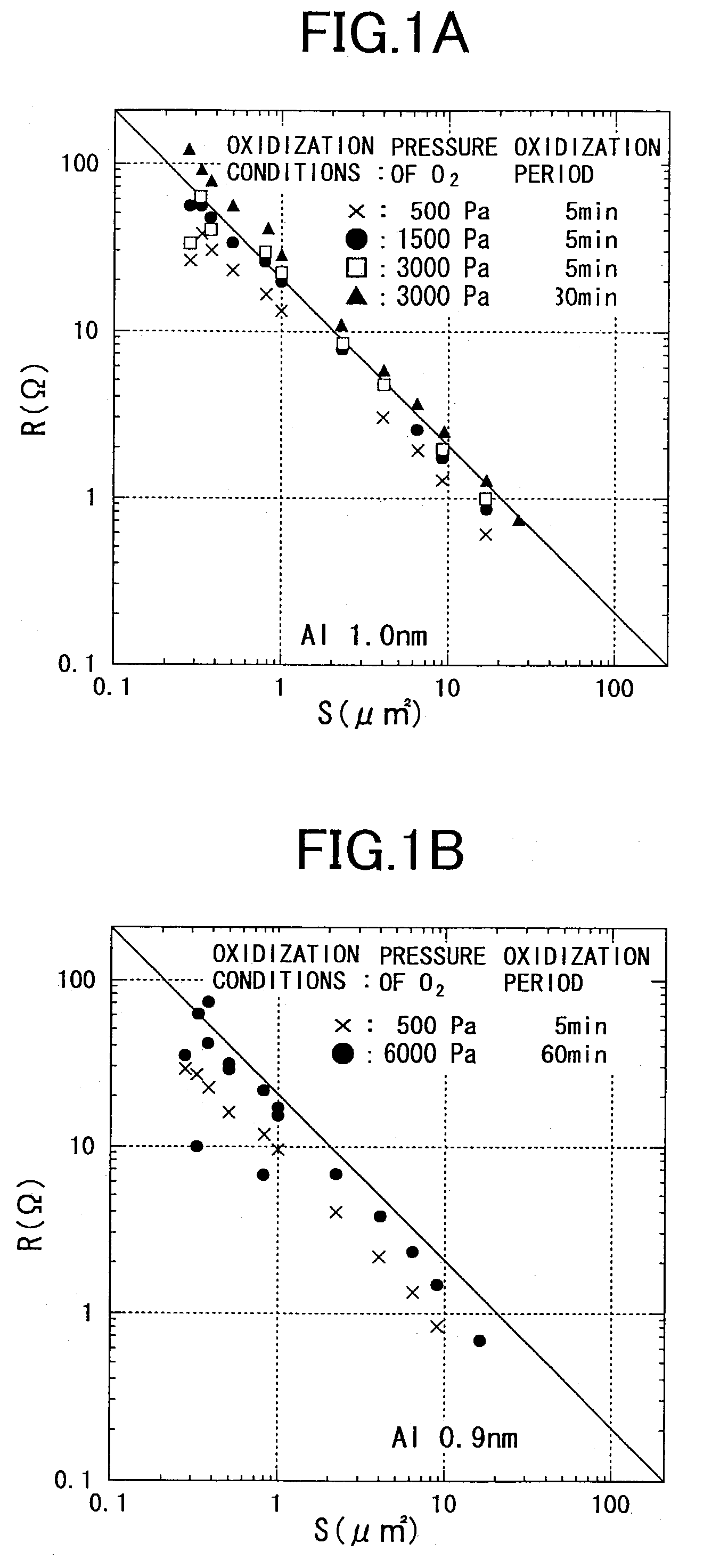

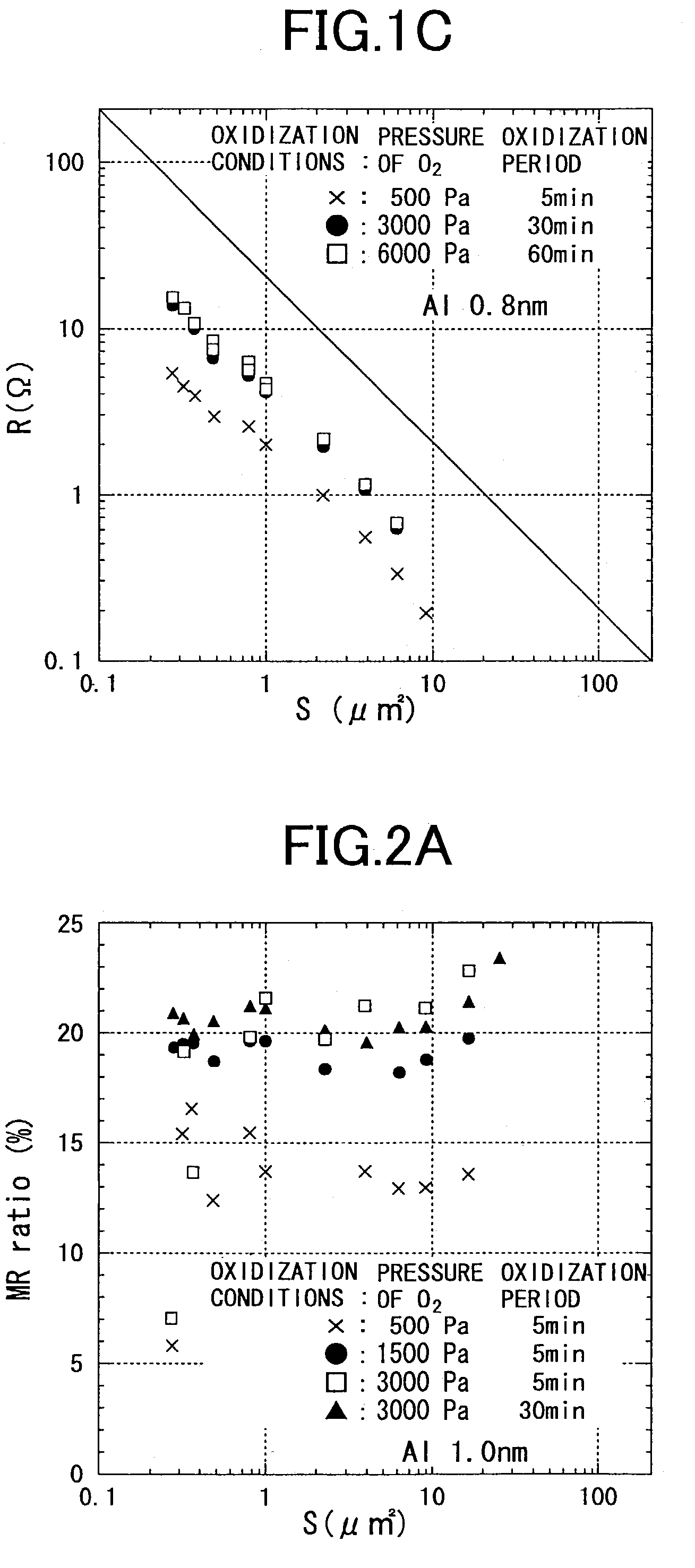

Magnetoresistive effect element, a magnetic head, and a magnetic reproducing apparatus therewith

InactiveUS7221547B2High sensitivityImprove recording densityNanomagnetismMagnetic measurementsInsulation layerNon magnetic

A magnetoresistive effect element is a compound lamination including a first anti-ferromagnetic layer, a first fixed magnetic layer, a tunnel insulation layer, a free magnetic layer, a non-magnetic metal layer, a second fixed magnetic layer, and a second anti-ferromagnetic layer such that a TMR element and a SVMR element are formed, sharing the free magnetic layer.

Owner:FUJITSU LTD

Preparation method of carbon nanotube composite transparent conductive film

PendingCN112652424AImprove conductivityLower junction resistanceConductive layers on insulating-supportsCable/conductor manufactureThioureaElectroless deposition

Owner:邵峥业

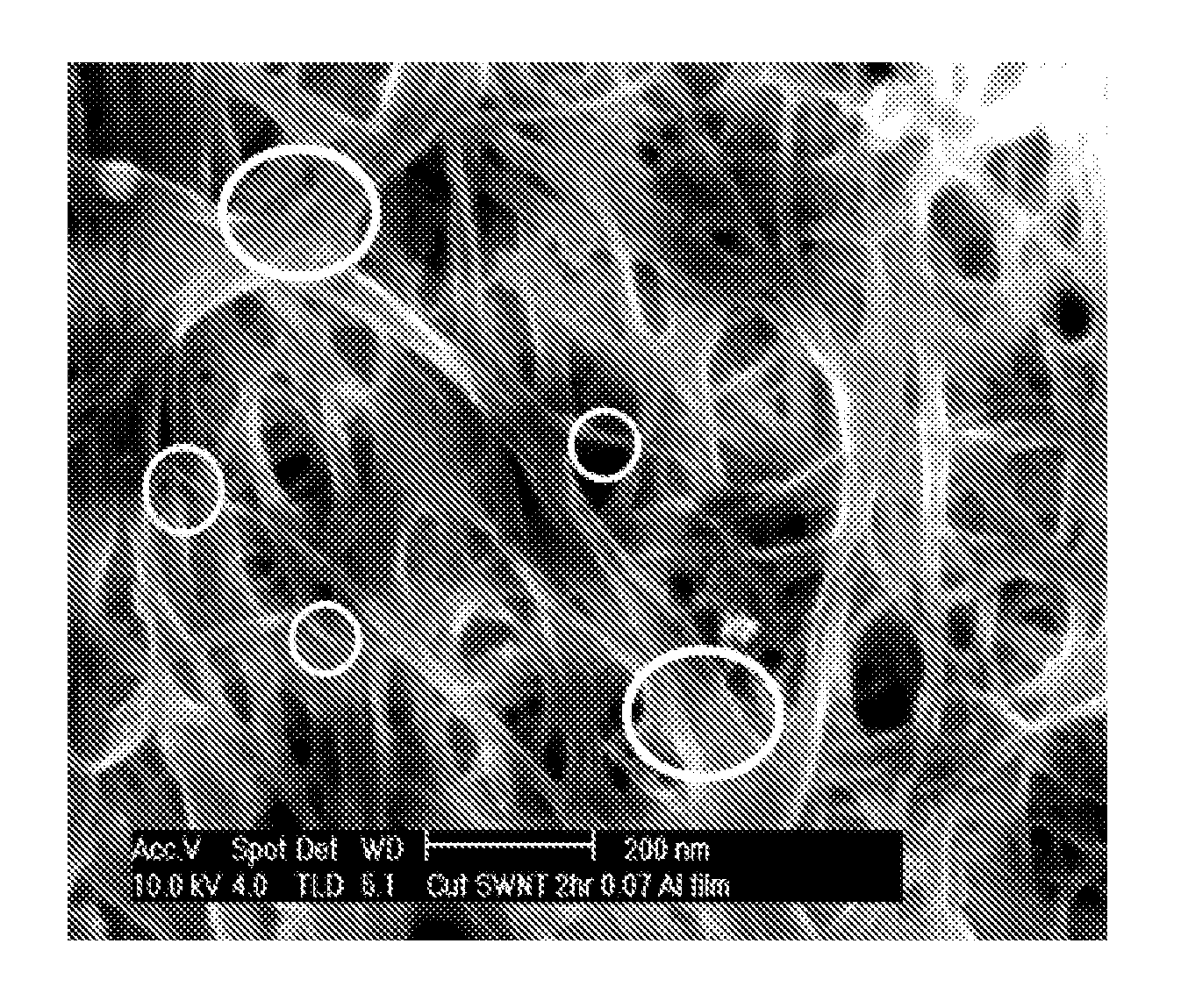

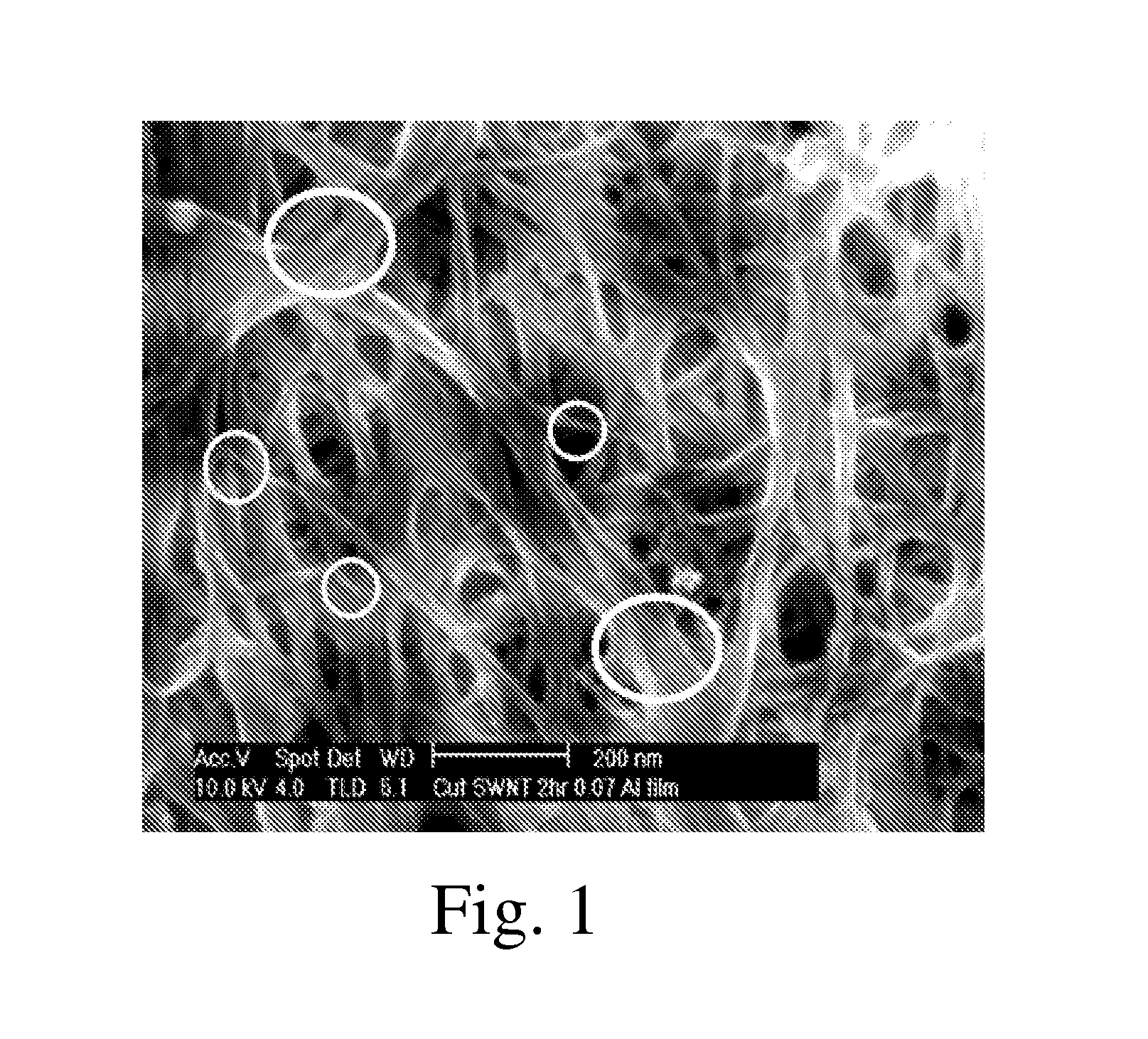

Modified carbon nanotubes and methods of forming carbon nanotubes

ActiveUS9365728B2Improve transmittanceImprove work functionMaterial nanotechnologyLayered productsDopantModified carbon

In this invention, processes which can be used to achieve stable doped carbon nanotubes are disclosed. Preferred CNT structures and morphologies for achieving maximum doping effects are also described. Dopant formulations and methods for achieving doping of a broad distribution of tube types are also described.

Owner:BATTELLE MEMORIAL INST

Uniform-performance silver nanowire transparent conductive thin-film preparation method by means of dynamic infrared heating

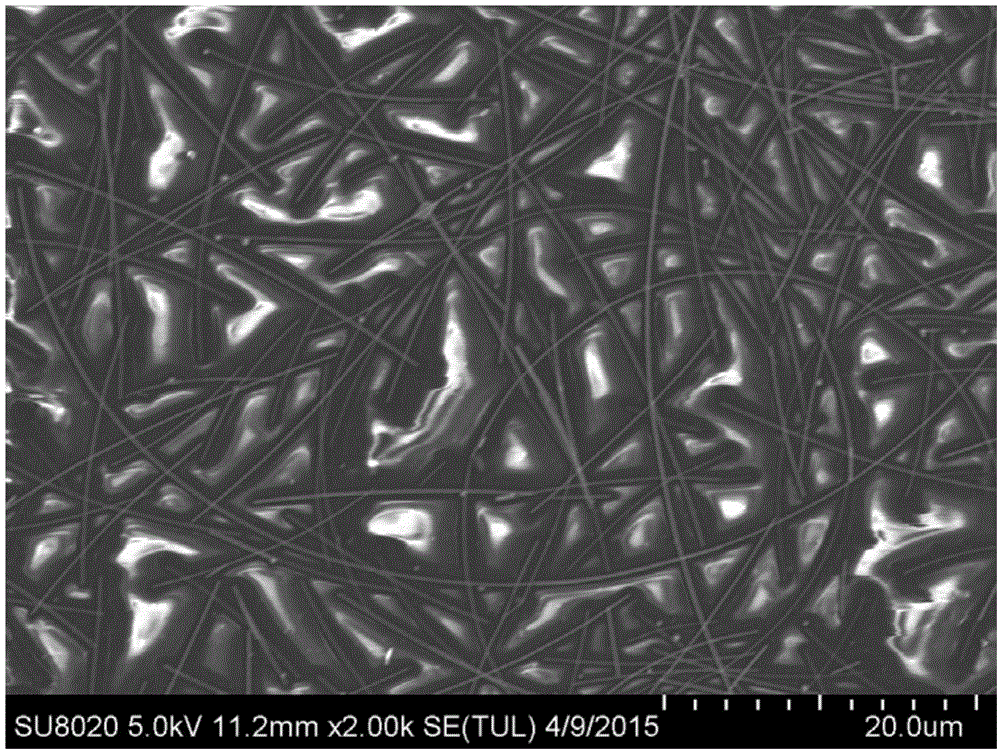

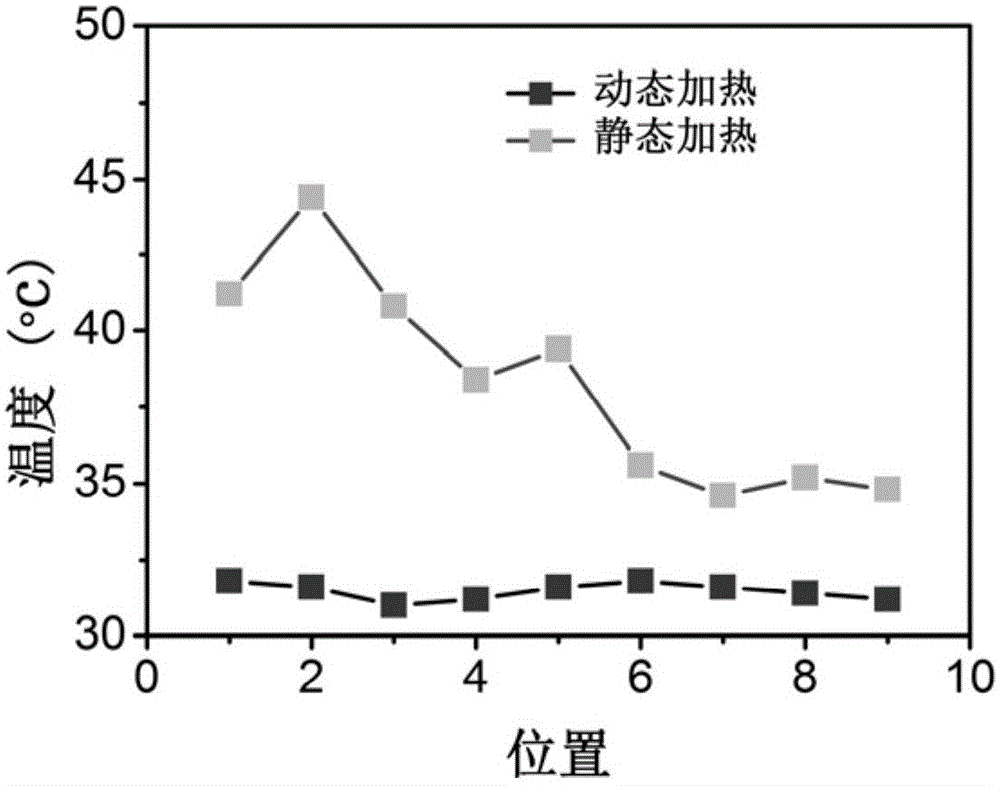

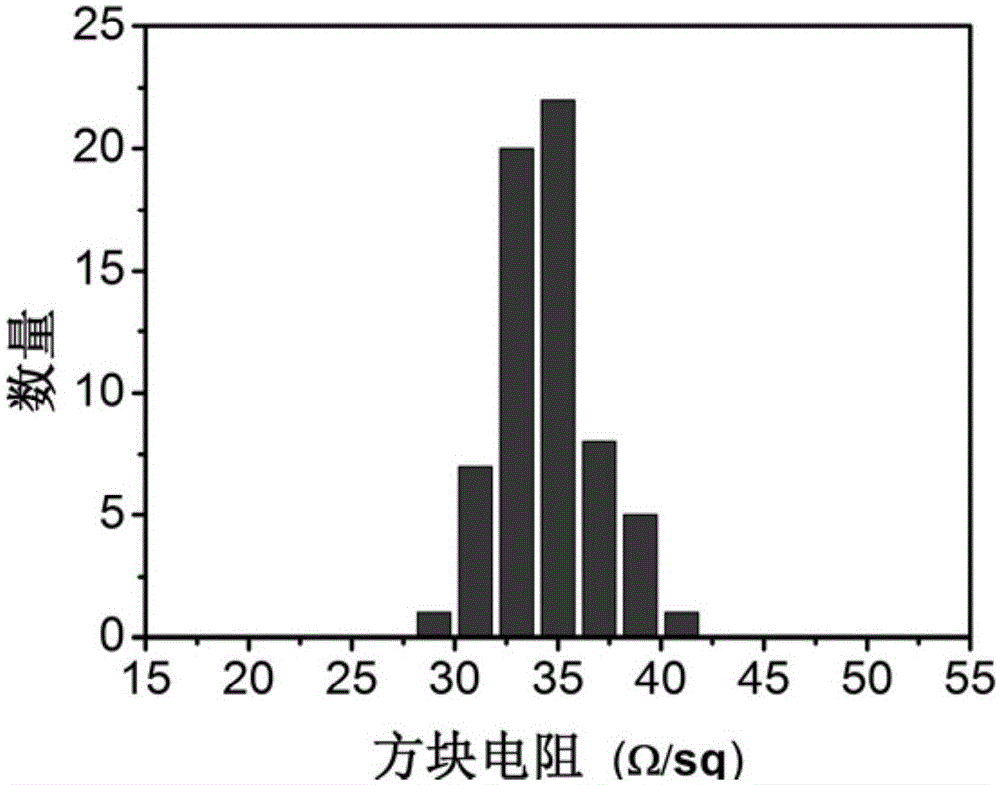

InactiveCN105139964AUniform temperature controlGood dispersionMaterial nanotechnologyCable/conductor manufactureElectrical resistance and conductancePhysical chemistry

The invention provides a uniform-performance silver nanowire transparent conductive thin-film preparation method by means of dynamic infrared heating so that uniformity of the optical and electrical properties of the thin-film is ensured to be better than that of ITO and other similar products. A wet film on which silver nanowire dispersion liquid is coated is uniformly heated and dried by adopting a dynamic infrared heating method so that the silver nanowire transparent conductive thin-film with uniform electrical performance and optical performance is obtained. The silver nanowire transparent conductive thin-film of which average square resistance is lower than 35ohm / square, resistance non-uniformity is less than 7% in two-dimensional space and transmittance can be more than 95% can be obtained by utilizing the method.

Owner:HEFEI INSTITUTES OF PHYSICAL SCIENCE - CHINESE ACAD OF SCI

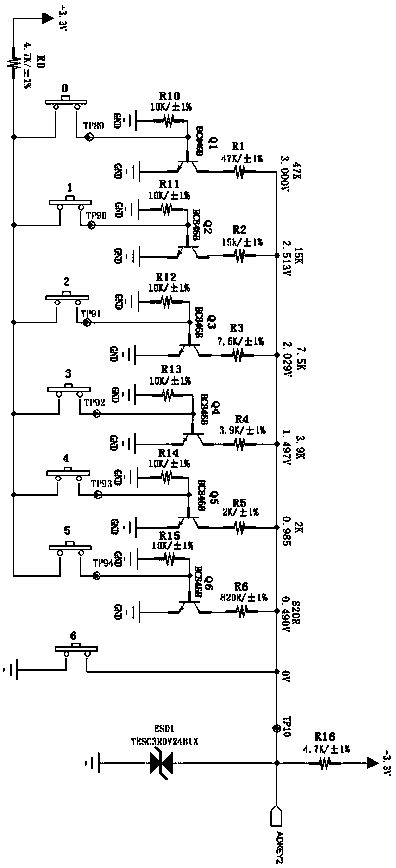

Improved circuit of vehicle-mounted navigation key switch

PendingCN110635806AWork reliablyPartial pressure effectDynamic codingKey pressingElectrical resistance and conductance

The invention aims to provide an improved circuit of a vehicle-mounted navigation key switch. On the basis of a circuit of an AD voltage identification key, a triode and a resistor are additionally arranged on each switch; the small voltage drop difference of the C electrode and the E electrode of the triode in a saturated conduction state is skillfully utilized; the key switch has the advantagesthat the key switch is simple in structure, low in junction resistance and free of change of external factors and self factors, the key switch is only used for switching on a base loop of the triode to enable the triode to be in saturated conduction, the internal resistance of the key switch can be greatly changed, the circuit is reliable in operation as long as the triode is in saturated conduction, and the internal resistance of the switch has no influence on voltage division of the circuit.

Owner:WUHU HONGJING ELECTRONICS

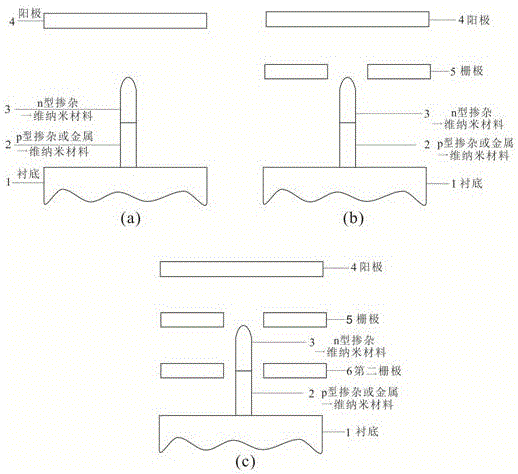

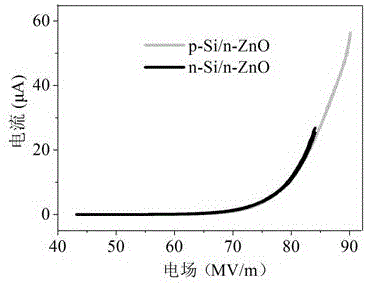

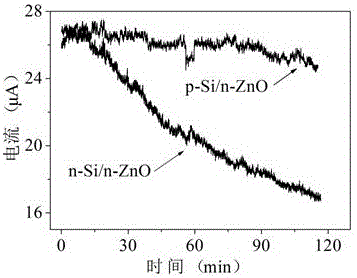

Field electron emission device structure with reverse bias nano junction

ActiveCN105679628AImproving chances of tunneling through nanojunctionsImprove the withstand voltage (current resistance) capabilityElectrode and associated part arrangementsCold cathode manufactureParticle physicsMaterials science

The invention discloses a field electron emission device structure with a reverse bias nano junction. The device structure comprises an emitter and an electrode, wherein the electrode comprises two segments of one-dimensional nano materials; one segment is an N-type doped semiconductor for emitting electrons; the other segment is a P-type doped semiconductor or a metal capable of forming a schottky contact with the N-type doped semiconductor; the two segments of one-dimensional nano materials are in contact to form a PN junction or a schottky junction; and the PN junction or the schottky junction protrudes on the surface of a substrate. The reverse bias nano junction of the device structure has a current limiting effect and can inhibit field emission current fluctuation; meanwhile, due to the punch-through effect of an electric field, exerted by the electrode, in a nanojunction region, the resistance of a nanojunction is reduced along with an increase of the electric field; the voltage (current) endurance capability of an emitter is improved; the reliability of the device is improved; the problems of over-high drive voltage and over-high power consumption caused by a voltage drop of a junction resistor are reduced; and improvement of the uniformity of the field emission characteristics of the emitter in an array is facilitated.

Owner:SUN YAT SEN UNIV

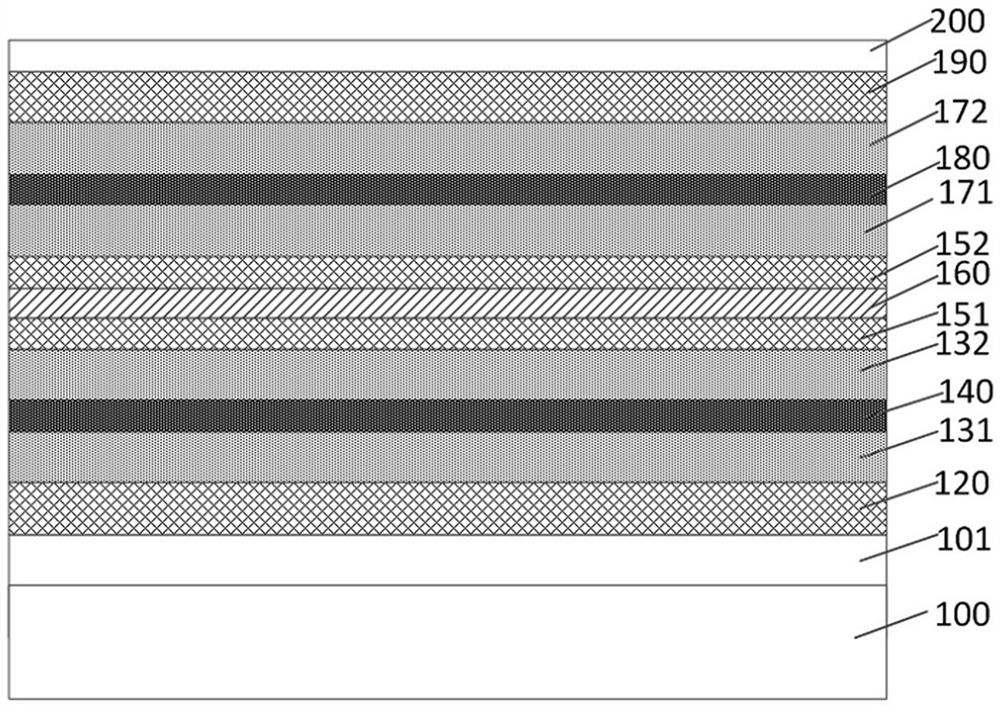

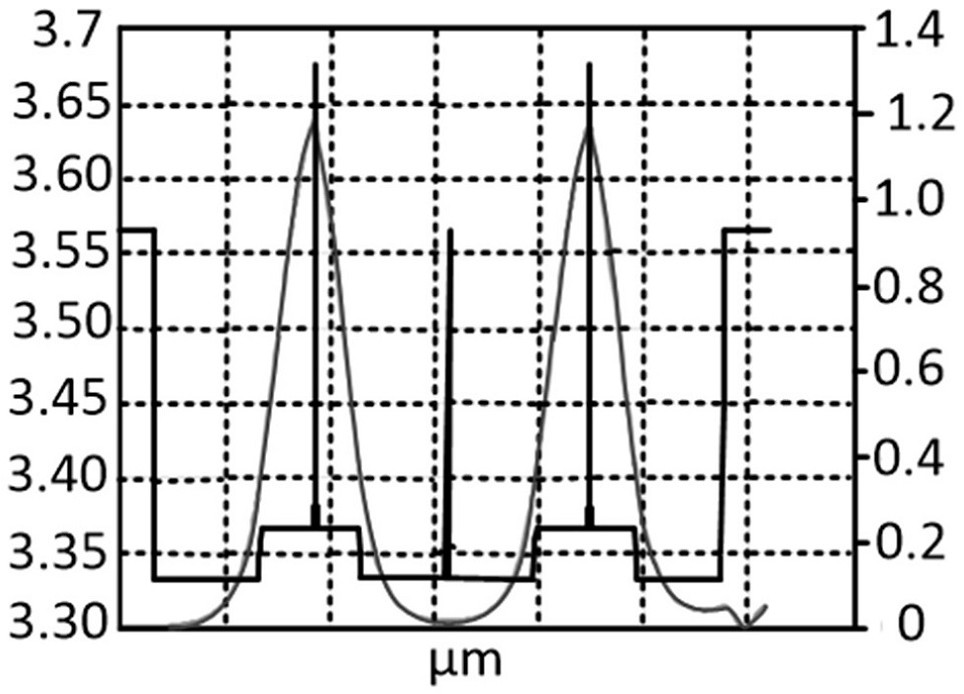

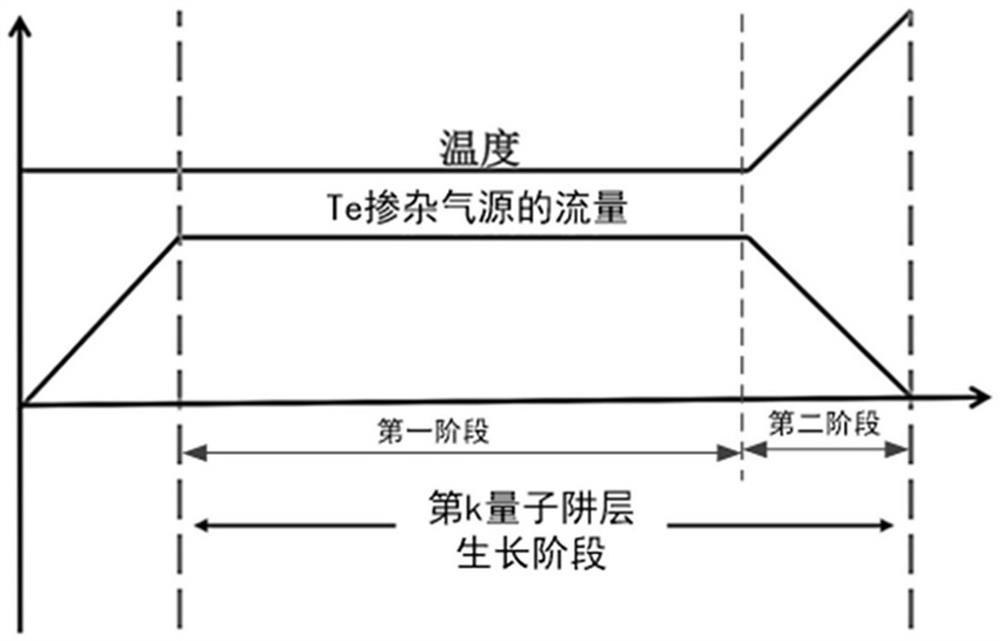

A semiconductor structure with multiple active regions and its preparation method

ActiveCN114006268BReduce thicknessThickness greater than the critical field coupling thickness decreasesLaser detailsLaser active region structureSemiconductor structureQuantum well

Owner:SUZHOU EVERBRIGHT PHOTONICS CO LTD +1

Full Back Electrode Heterojunction Solar Cell

ActiveCN103137767BConversion efficiency jumpsReduce output lossPhotovoltaic energy generationSemiconductor devicesHeterojunctionSolar cell

A full back electrode heterojunction solar cell, comprising a first conductivity type silicon substrate, a first amorphous semiconductor layer, a second amorphous semiconductor layer, a first conductivity type semiconductor layer, and a second conductivity type semiconductor layer and a second conductivity type doped region. The first amorphous semiconductor layer is located on the light-receiving surface of the silicon substrate, and is an intrinsic semiconductor layer or a first conductivity type layer. The second amorphous semiconductor layer is located on the non-light-receiving surface of the silicon substrate, wherein the second amorphous semiconductor layer is an intrinsic semiconductor layer. The first and second conductive type semiconductor layers are located on the second amorphous semiconductor layer respectively. As for the second conductive type doped region, it is located in the silicon substrate under the second conductive type semiconductor layer and contacts with the second amorphous semiconductor layer.

Owner:IND TECH RES INST

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com