Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

7083 results about "Electrical performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

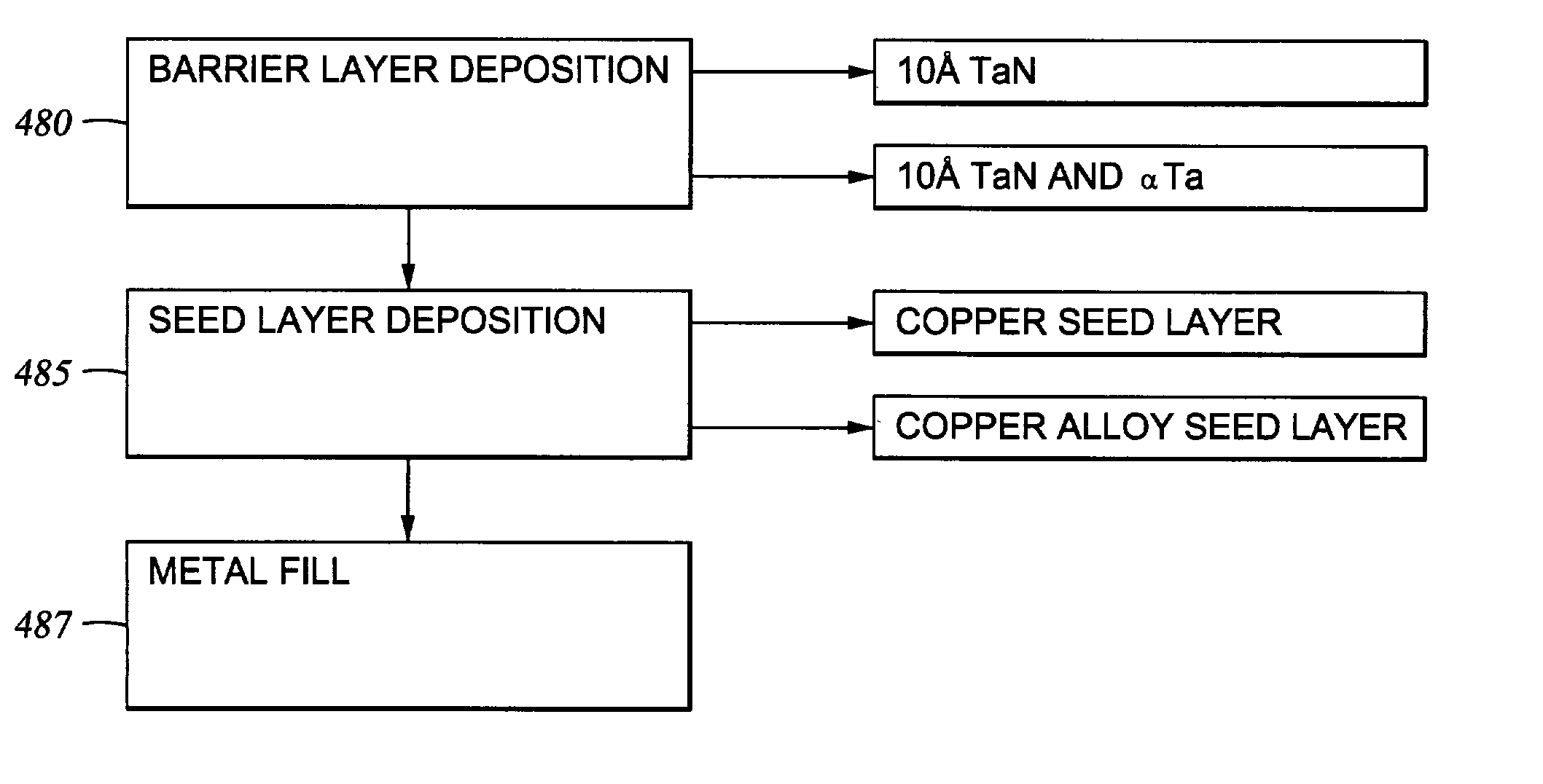

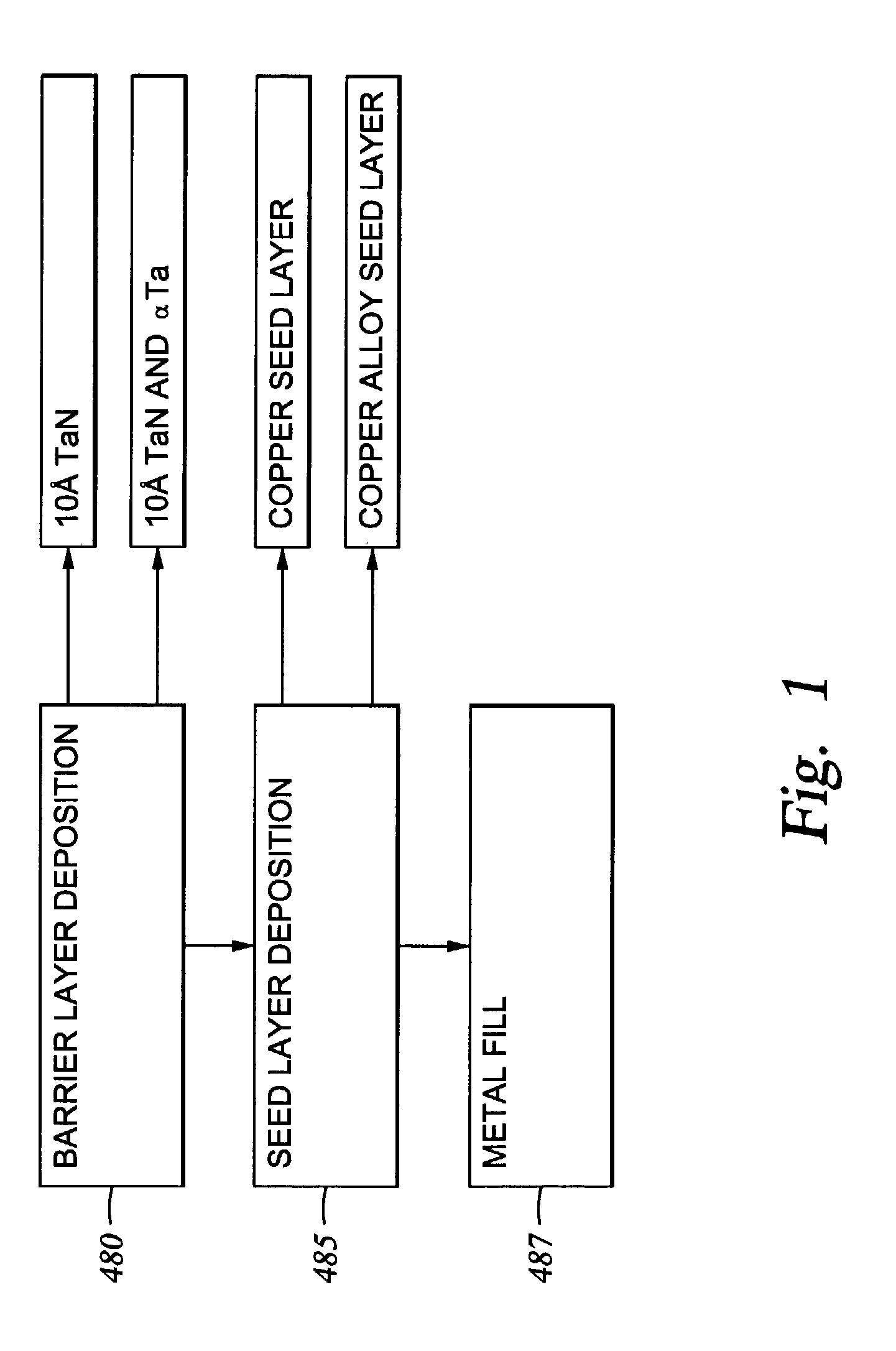

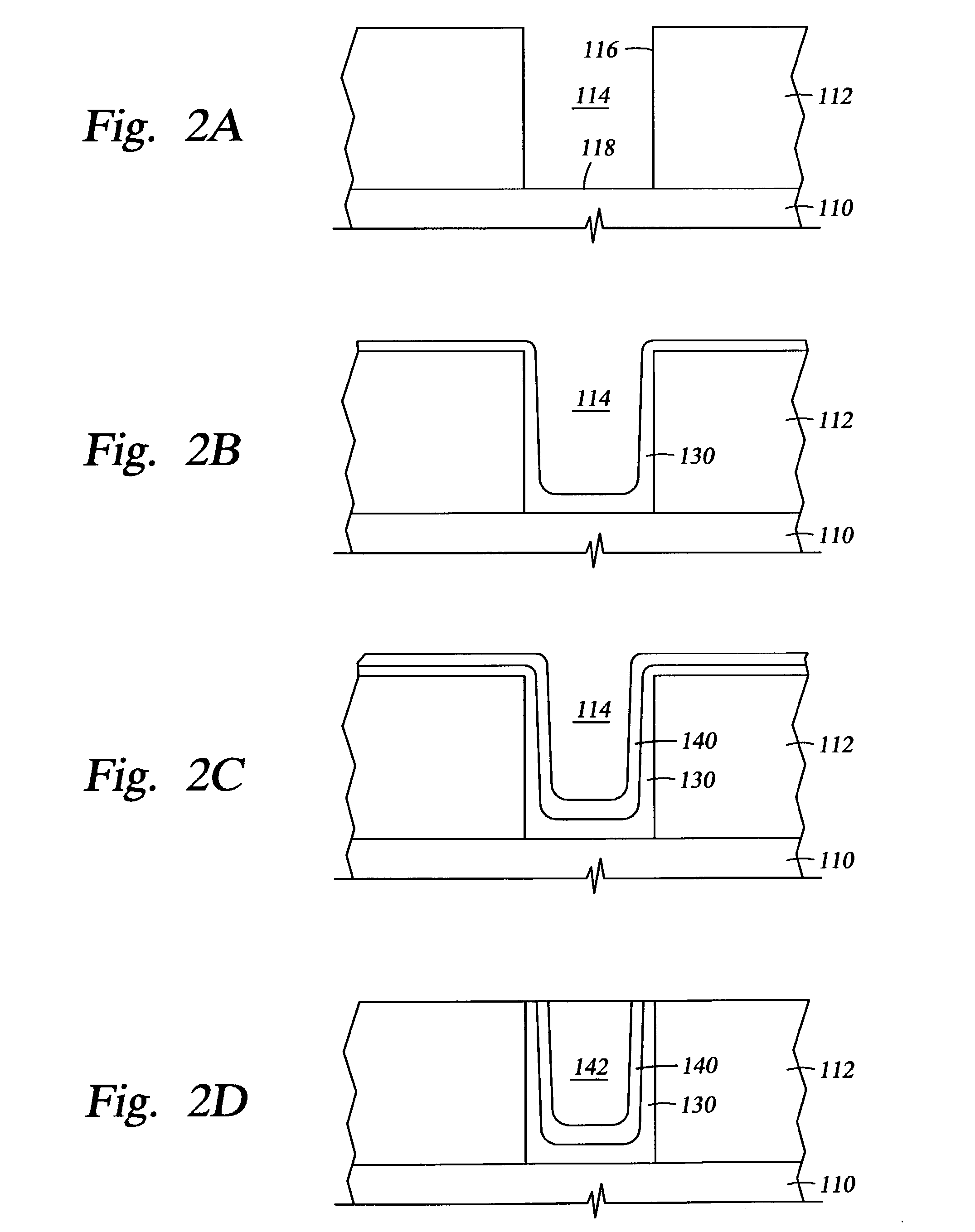

Integration of ALD tantalum nitride and alpha-phase tantalum for copper metallization application

InactiveUS20030082307A1Pretreated surfacesSemiconductor/solid-state device manufacturingMetal interconnectTantalum nitride

A method for forming a metal interconnect on a substrate is provided. The method includes depositing a refractory metal-containing barrier layer having a thickness less than about 20 angstroms on at least a portion of a metal layer by alternately introducing one or more pulses of a metal-containing compound and one or more pulses of a nitrogen-containing compound. The method also includes depositing a seed layer on at least a portion of the barrier layer, and depositing a second metal layer on at least a portion of the seed layer. The barrier layer provides adequate barrier properties and allows the grain growth of the metal layer to continue across the barrier layer into the second metal layer thereby enhancing the electrical performance of the interconnect.

Owner:APPLIED MATERIALS INC

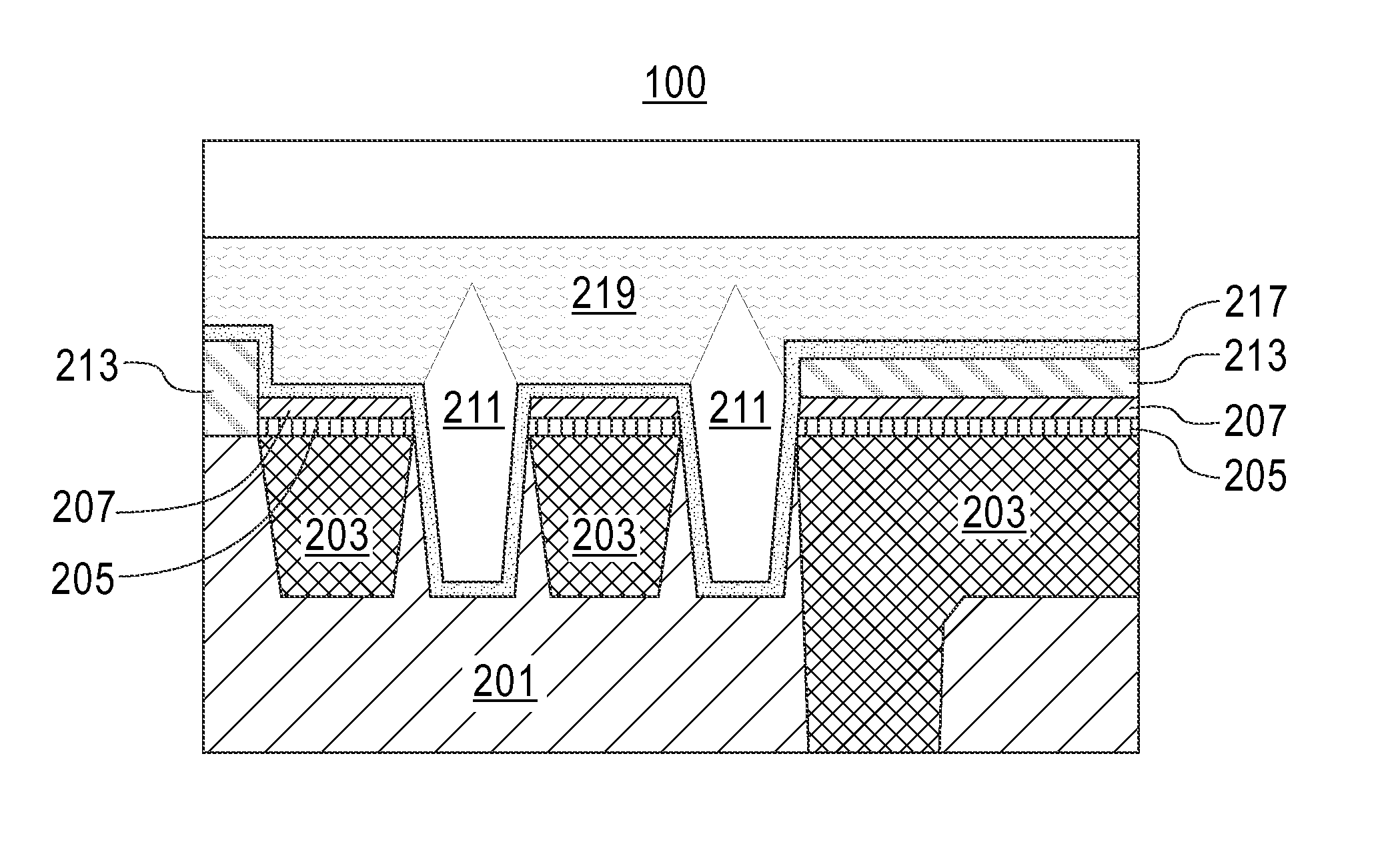

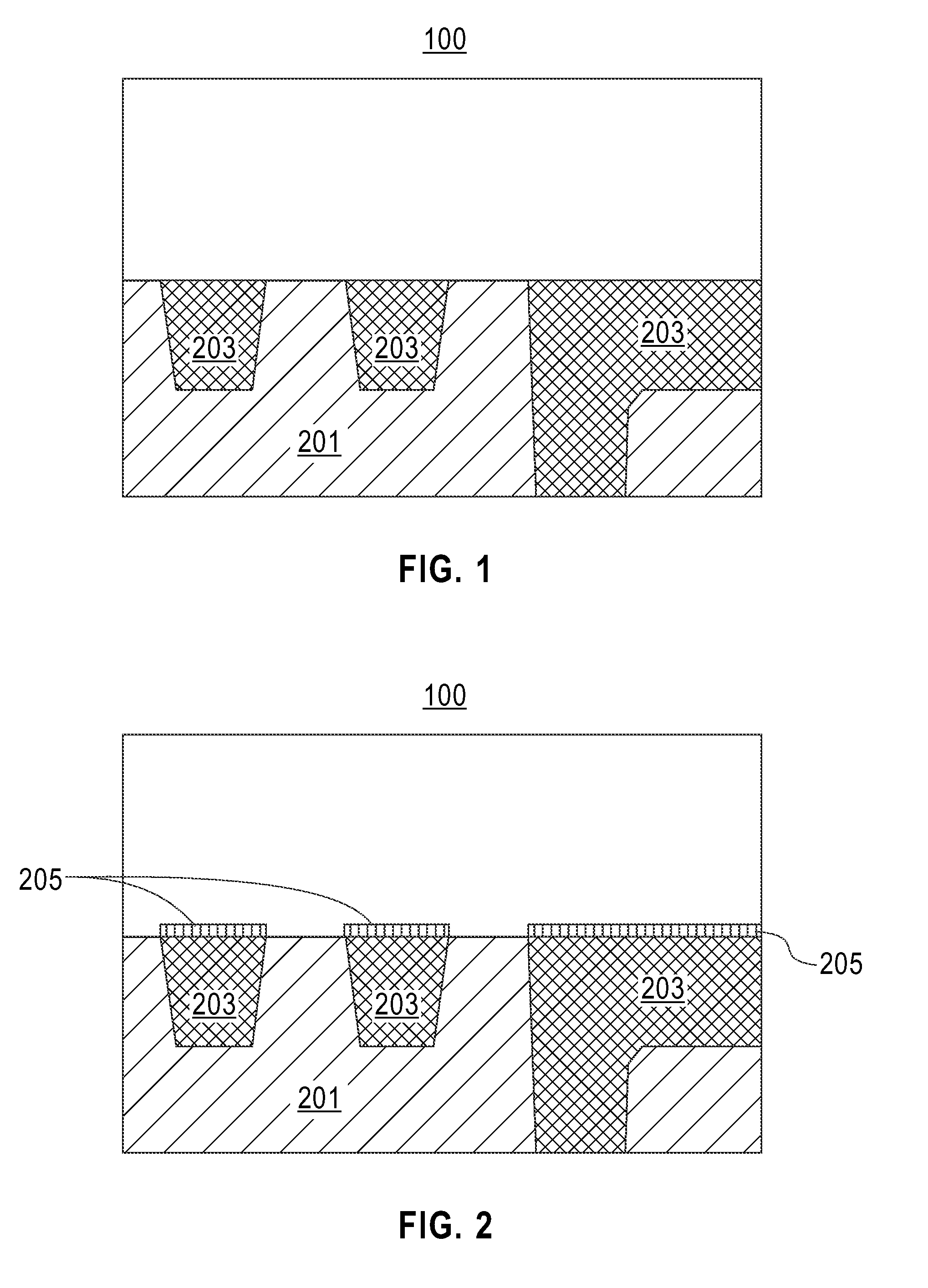

Air gap semiconductor structure with selective cap bilayer

ActiveUS9305836B1Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor structure

A semiconductor substrate including one or more conductors is provided. A first layer and a second layer are deposited on the top surface of the conductors. A dielectric cap layer is formed over the semiconductor substrate and air gaps are etched into the dielectric layer. The result is a bilayer cap air gap structure with effective electrical performance.

Owner:TESSERA INC

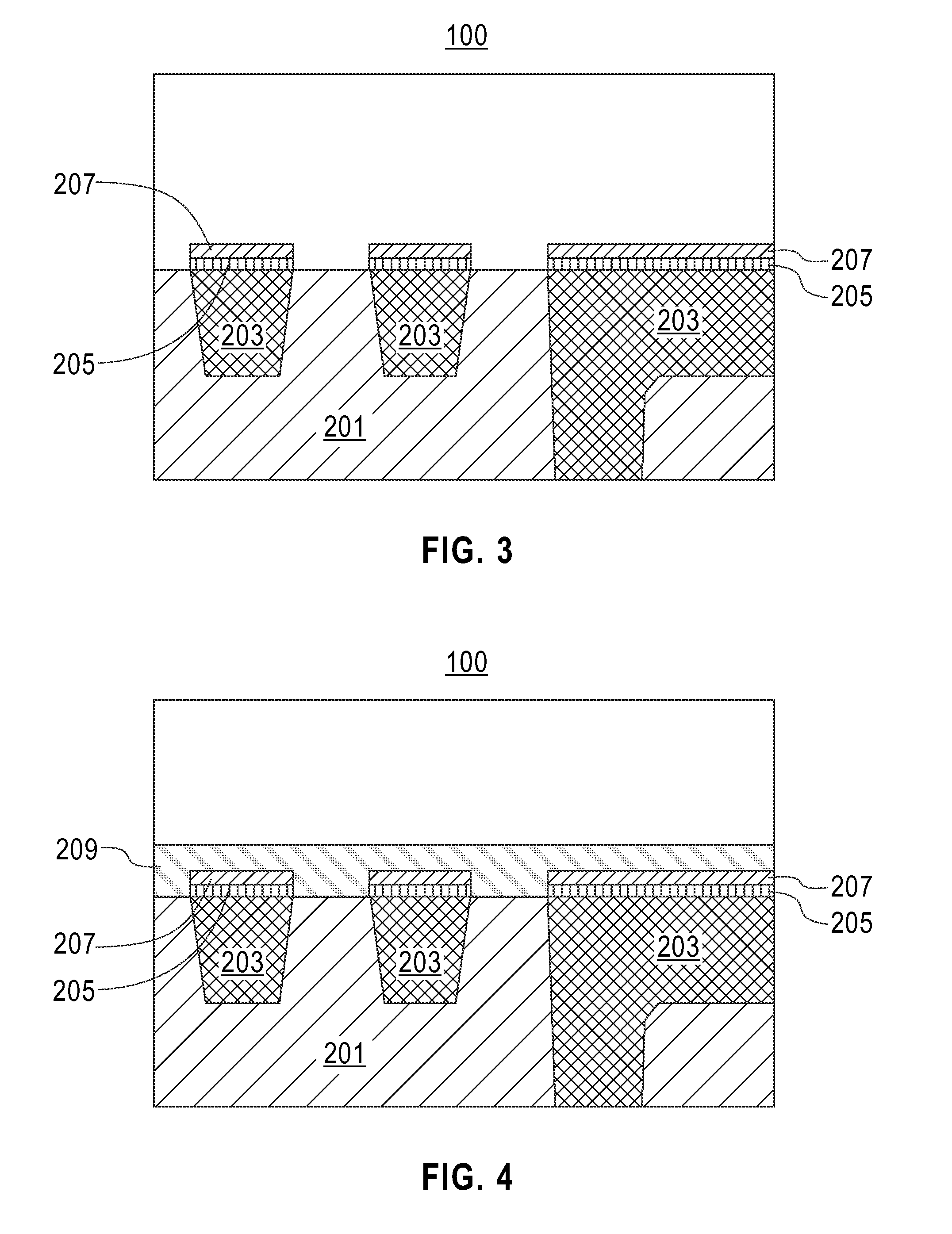

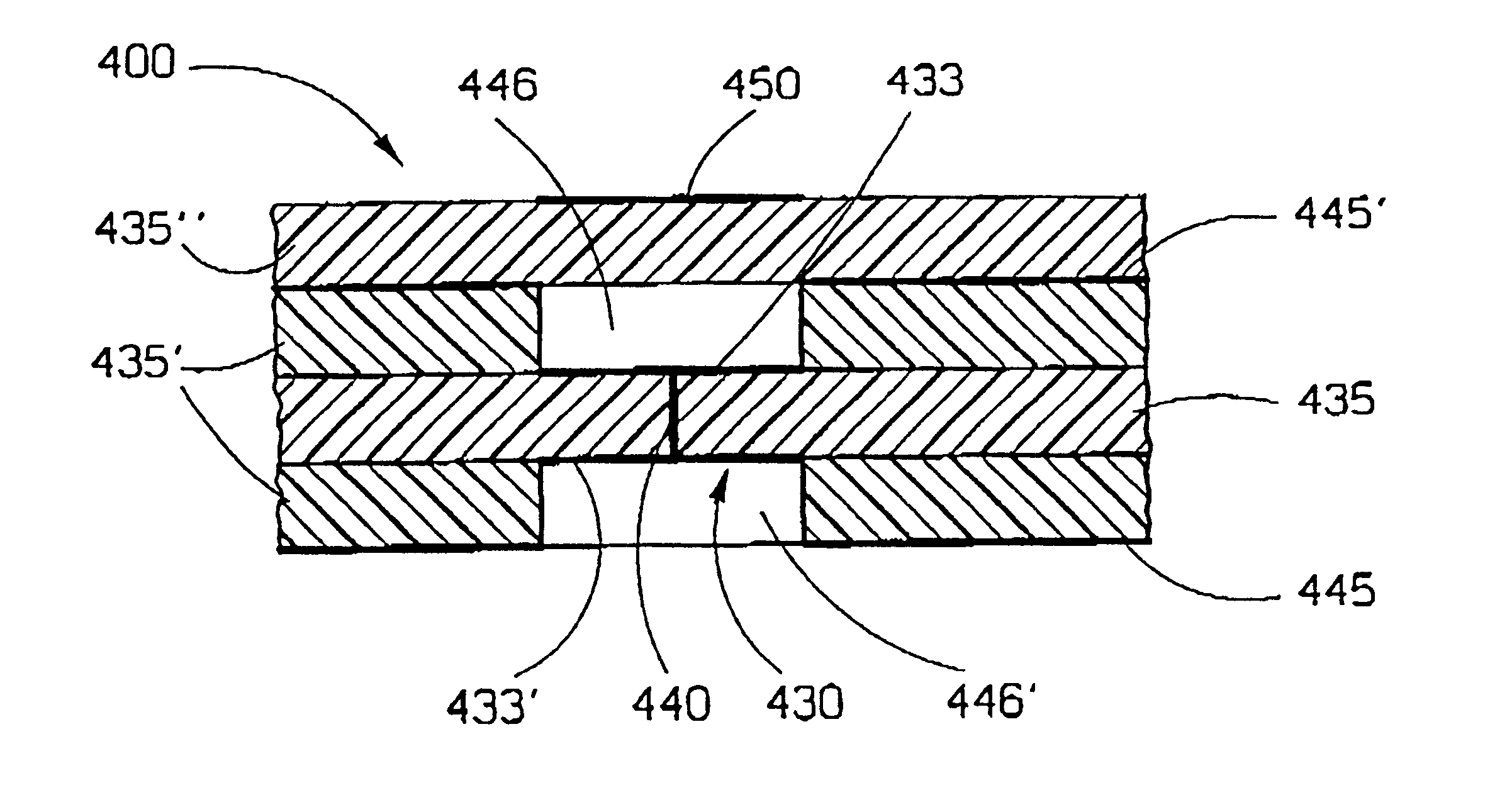

Microstrip arrangement

InactiveUS6266016B1Simultaneous aerial operationsPrinted circuit aspectsElectrical conductorEngineering

The invention relates to a microstrip arrangement comprising a first and a second microstrip conductor. The two microstrip conductors have essentially the same dimensions in their longitudinal direction and transverse direction, and are galvanically interconnected by means of at least one connection. The two microstrip conductors also extend essentially parallel to one another on either side of a dielectric material. As a result of this design of the microstrip arrangement, the field losses and also other influences caused by the dielectric material will be very considerably reduced, and in practice a resultant microstrip arrangement is obtained, which, with regard to its electrical performance, appears to be suspended in the air. Preferred embodiments comprise a microstrip antenna, a circuit board and a conductor application.

Owner:HIGHBRIDGE PRINCIPAL STRATEGIES LLC AS COLLATERAL AGENT

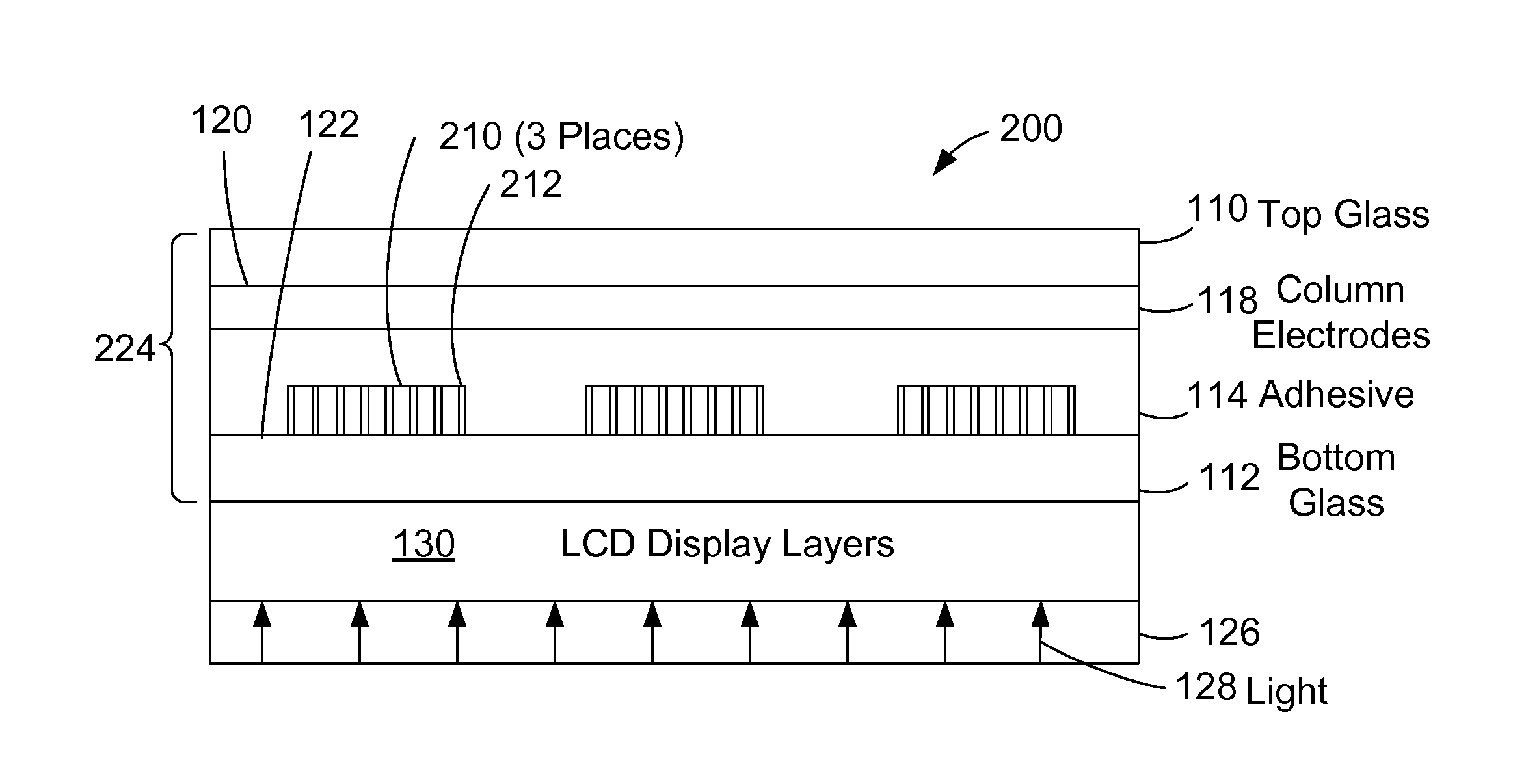

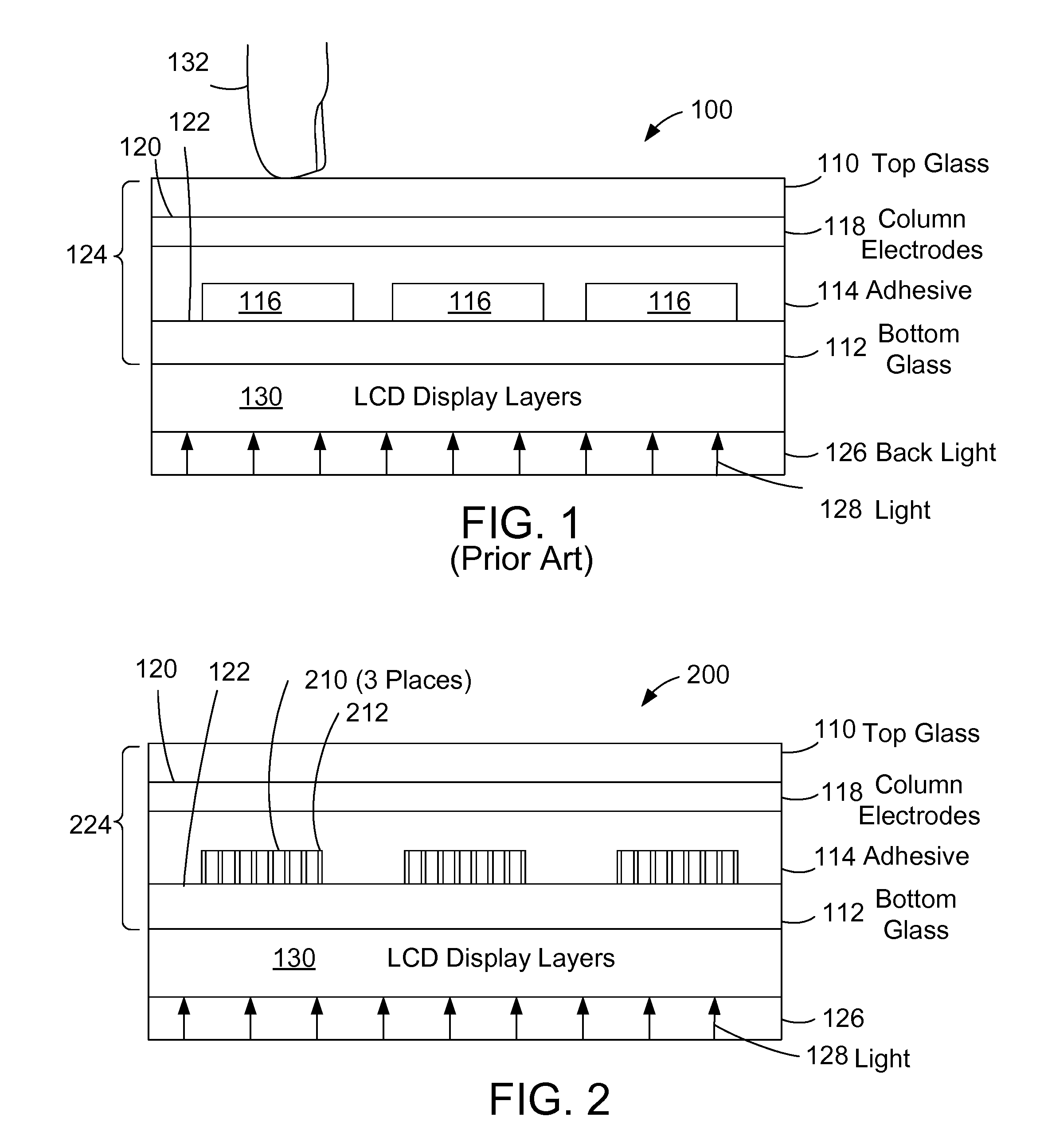

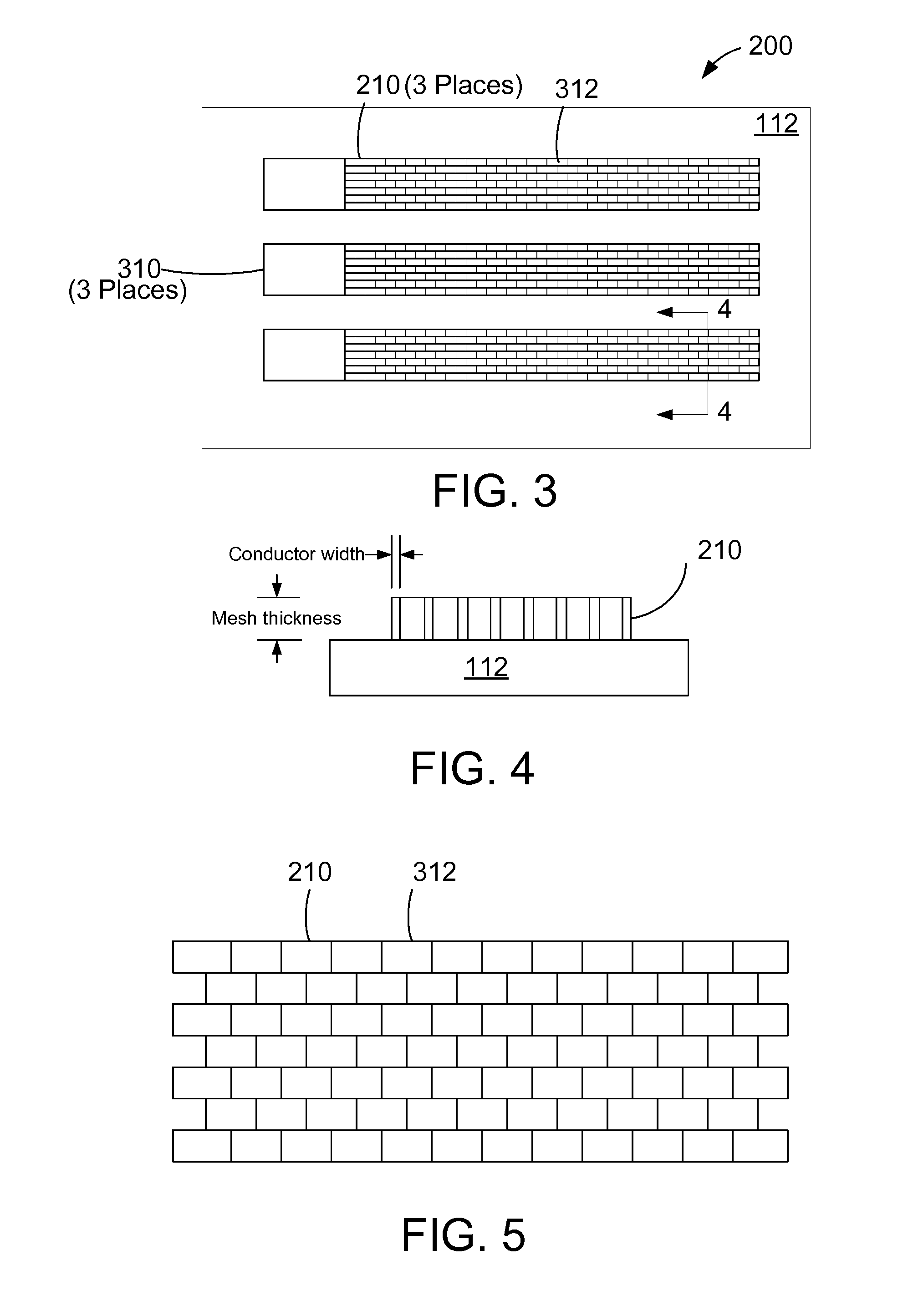

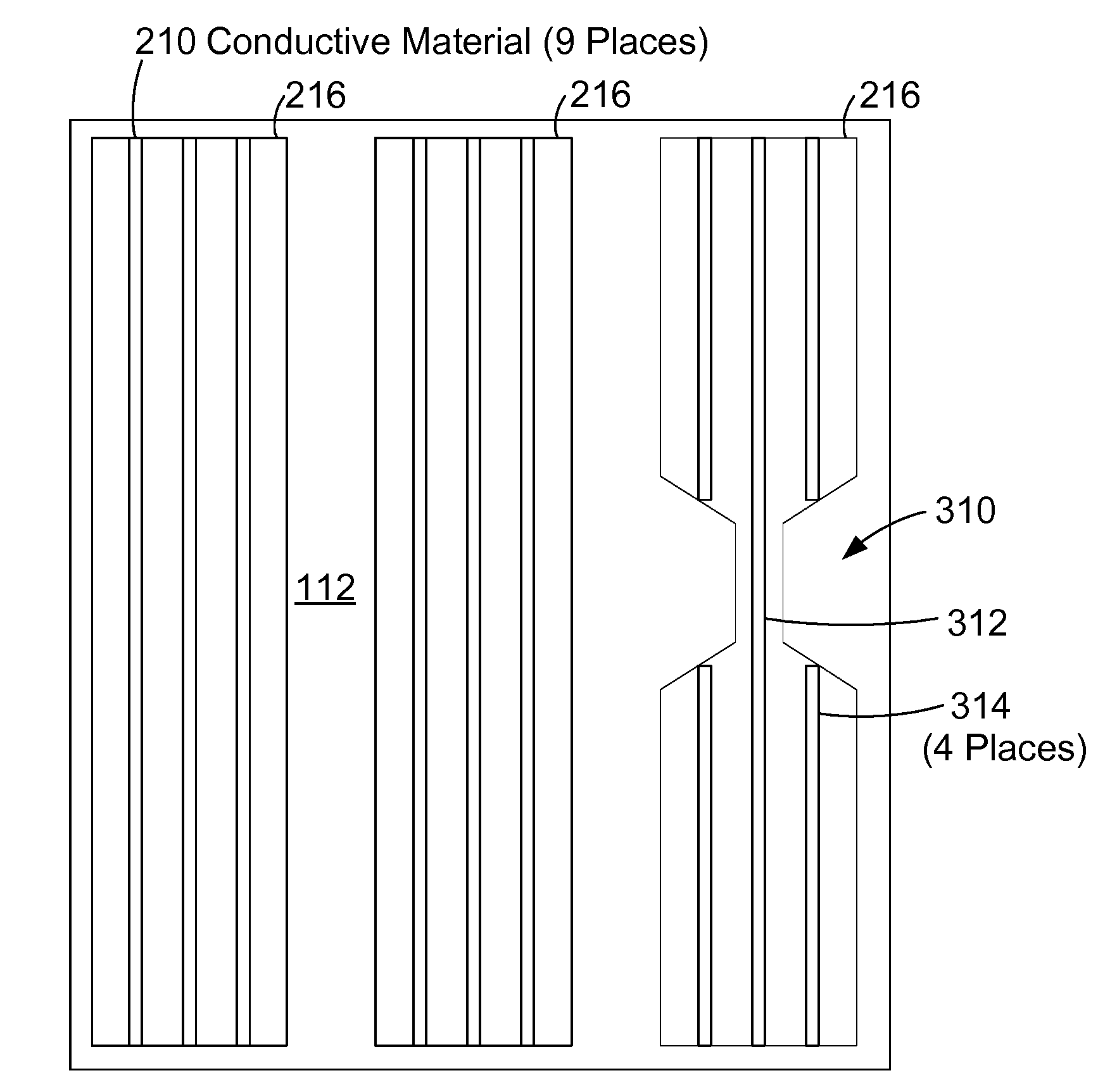

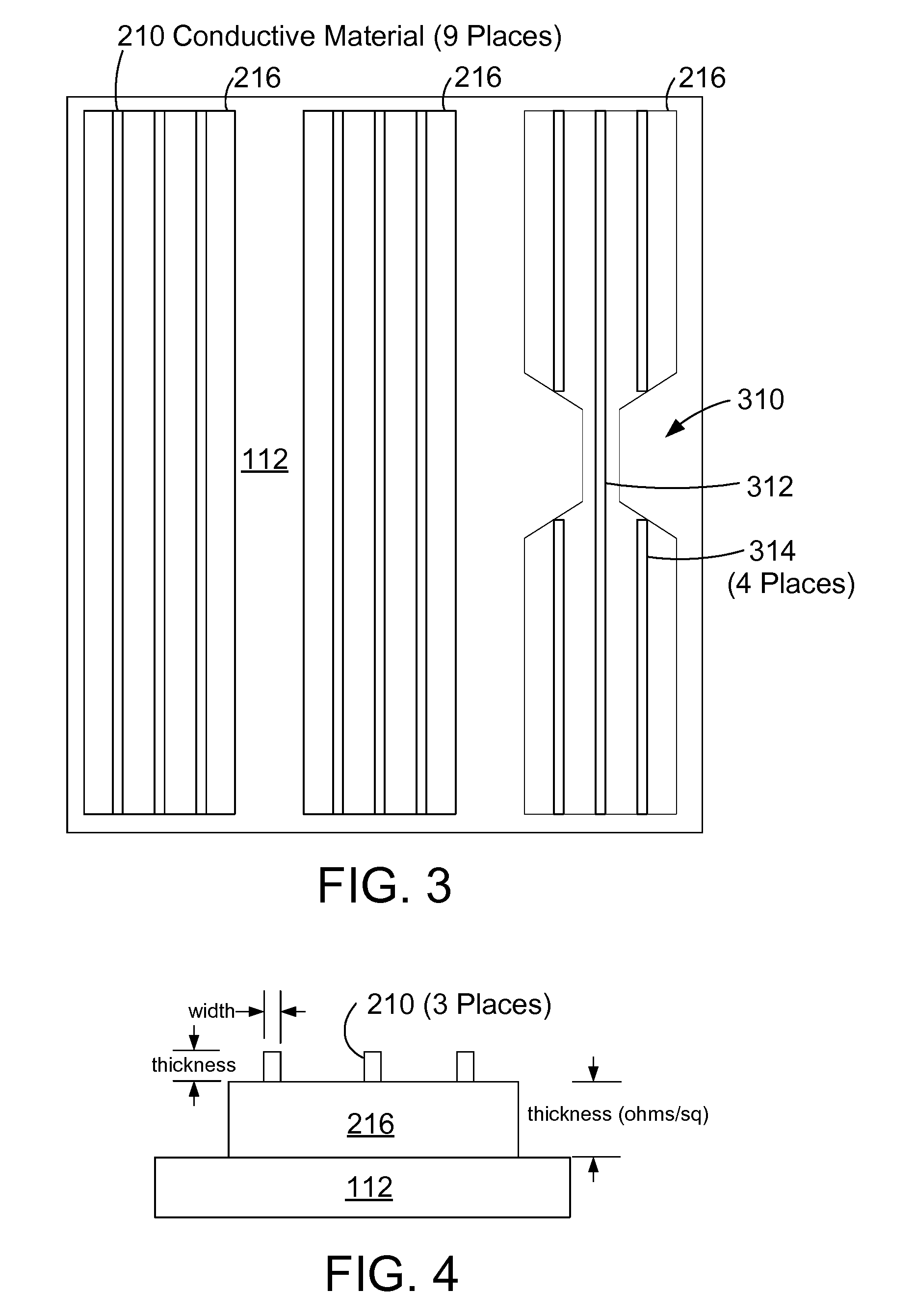

Capacitive touch screen with a mesh electrode

InactiveUS20110007011A1Improve electrical performanceImprove optical qualityInput/output processes for data processingElectrical resistance and conductanceConductive materials

An improved touch screen provides enhanced electrical performance and optical quality. The electrodes on the touch screen are made of a mesh of conductors to reduce the overall electrode resistance thereby increasing the electrical performance without sacrificing optical quality. The mesh electrodes comprise a mesh pattern of conductive material with each conductor comprising the mesh having a very small width such that the conductors are essentially invisible to the user of the touch screen.

Owner:OCULAR LCD

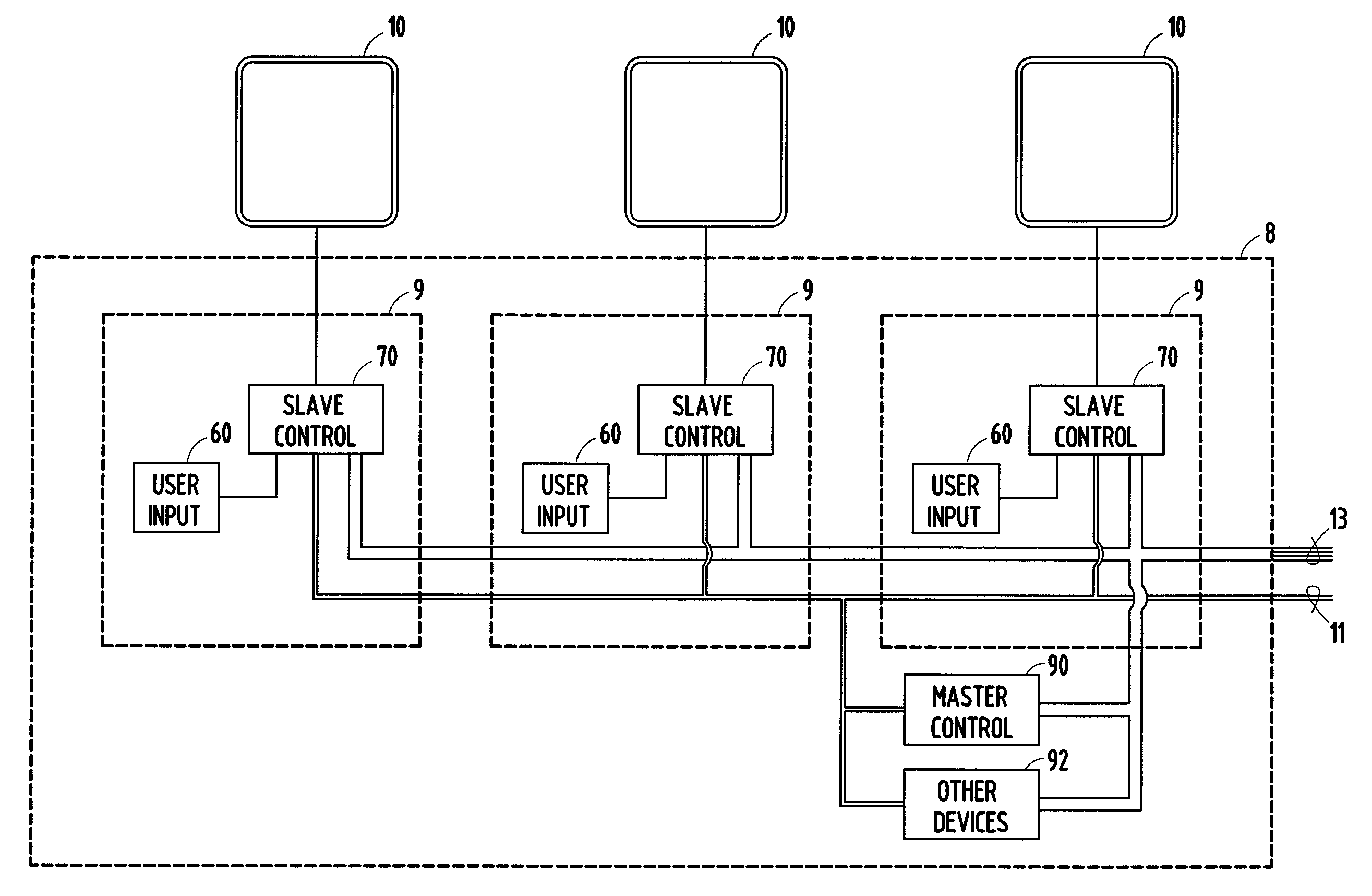

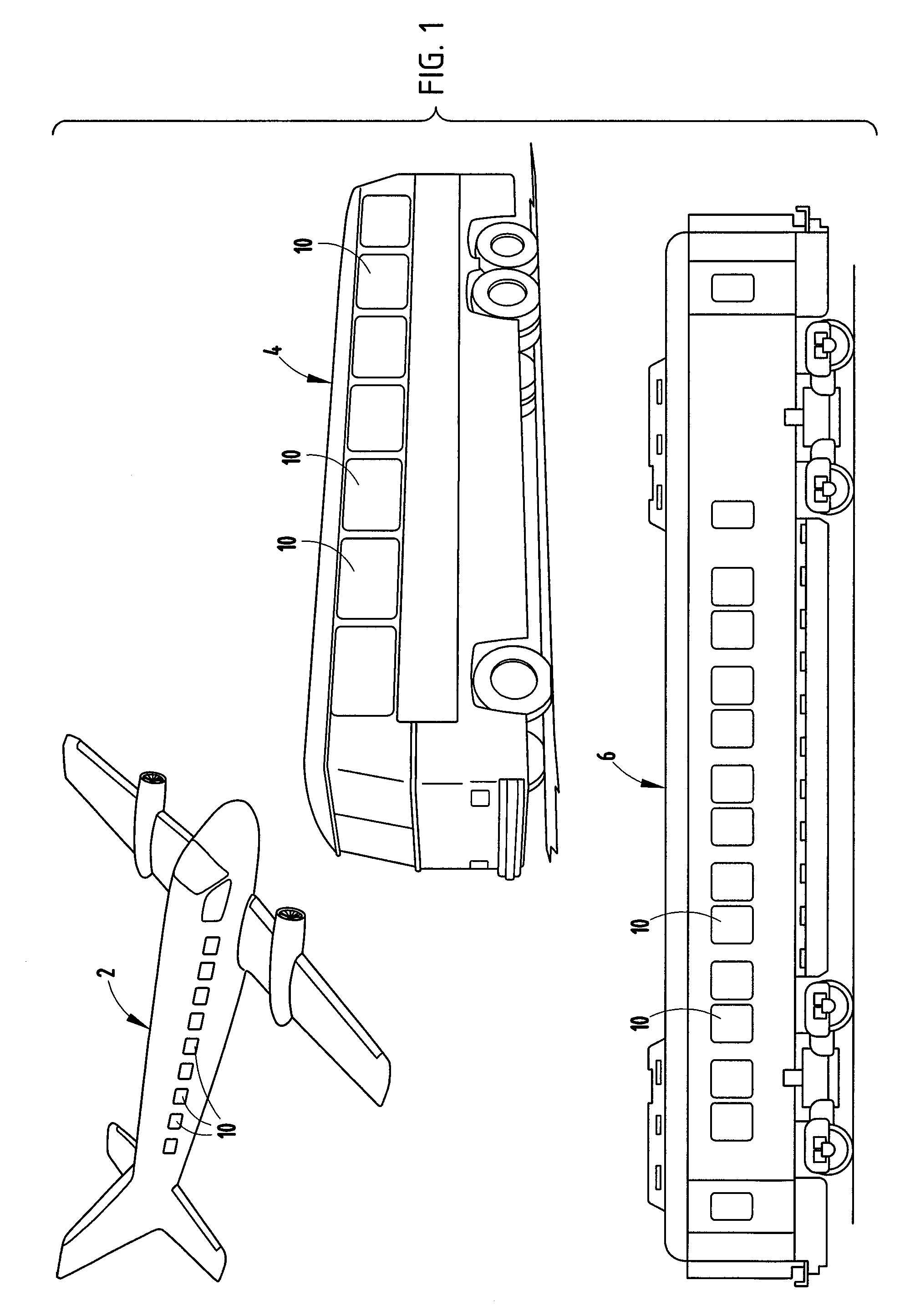

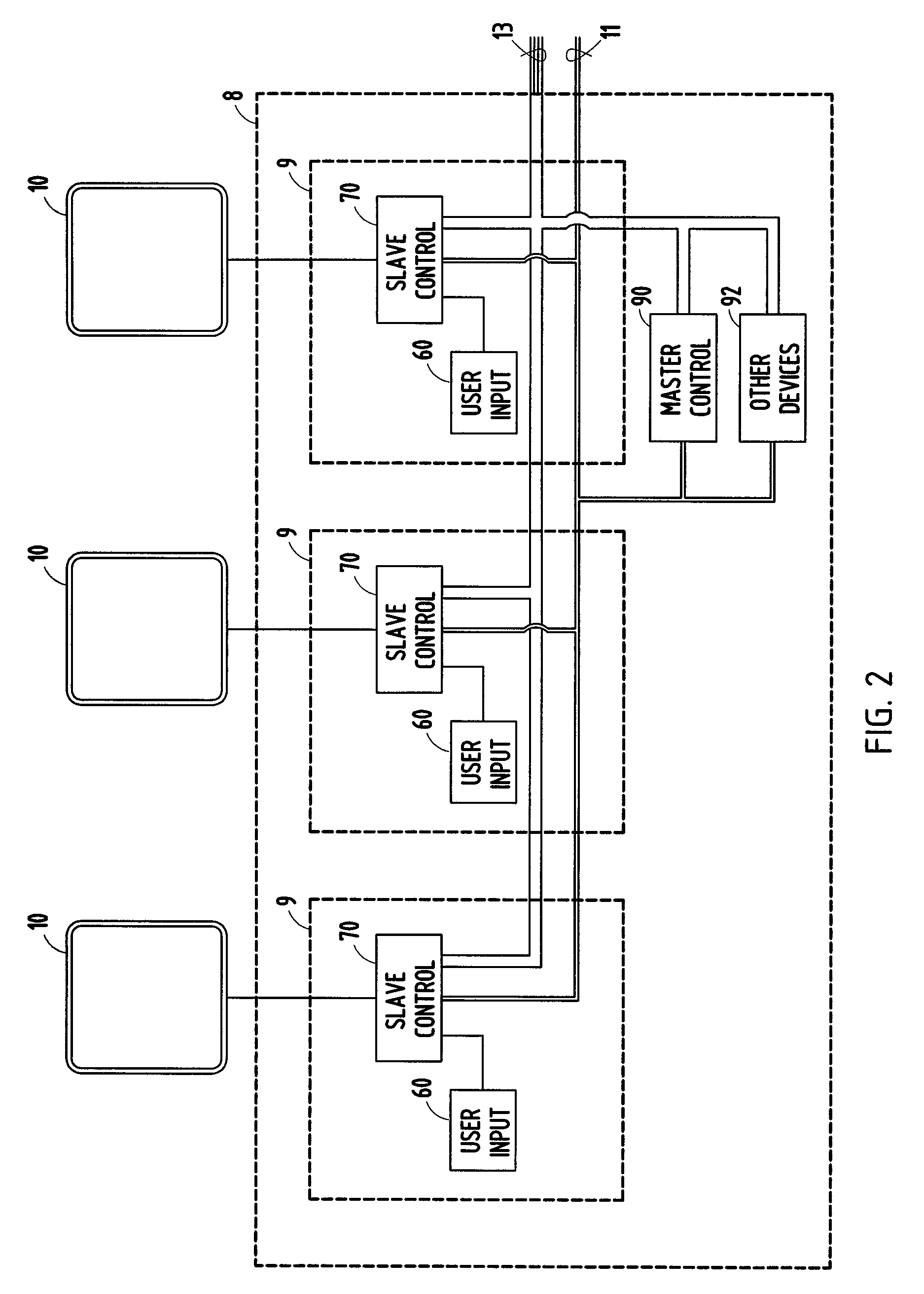

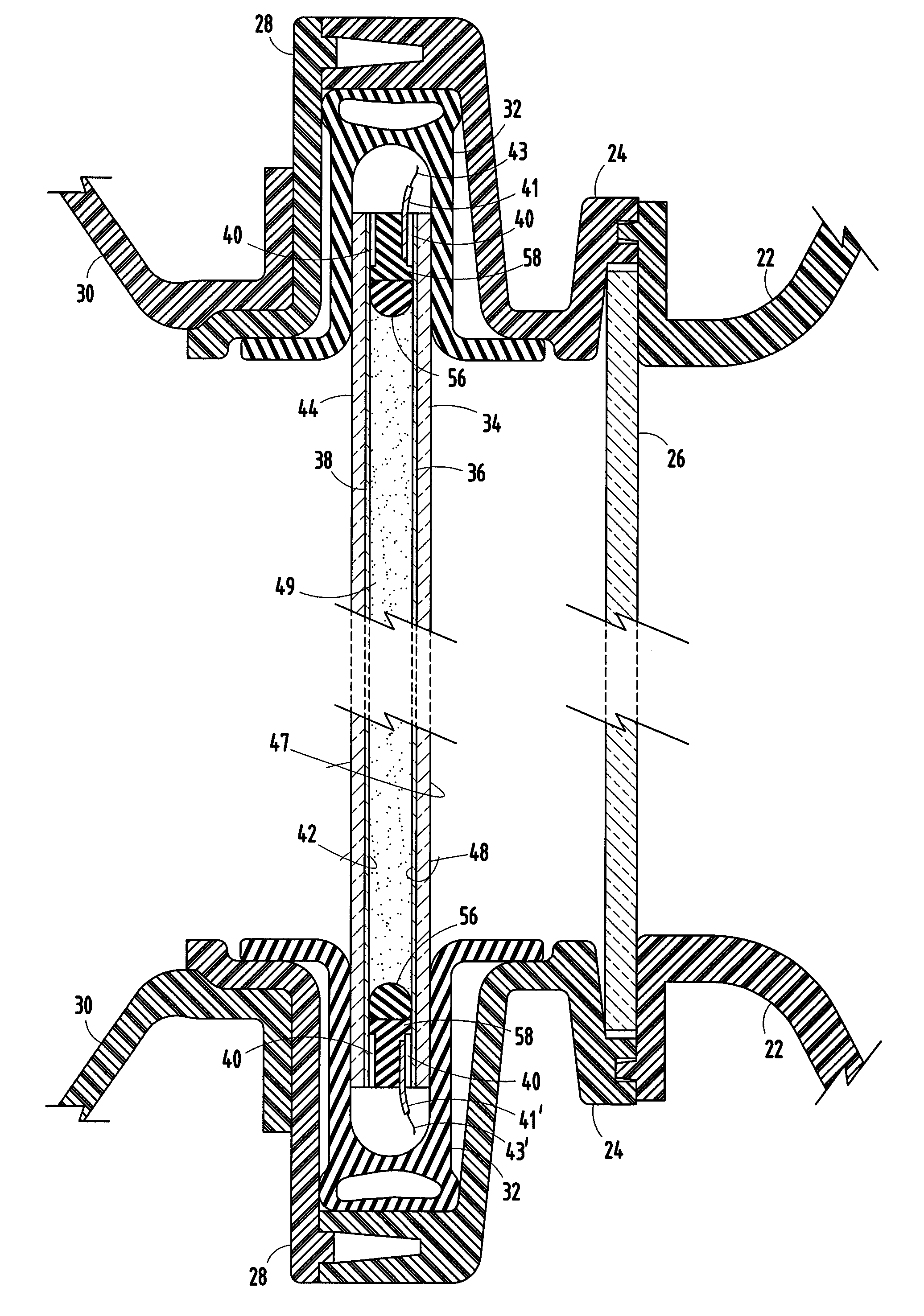

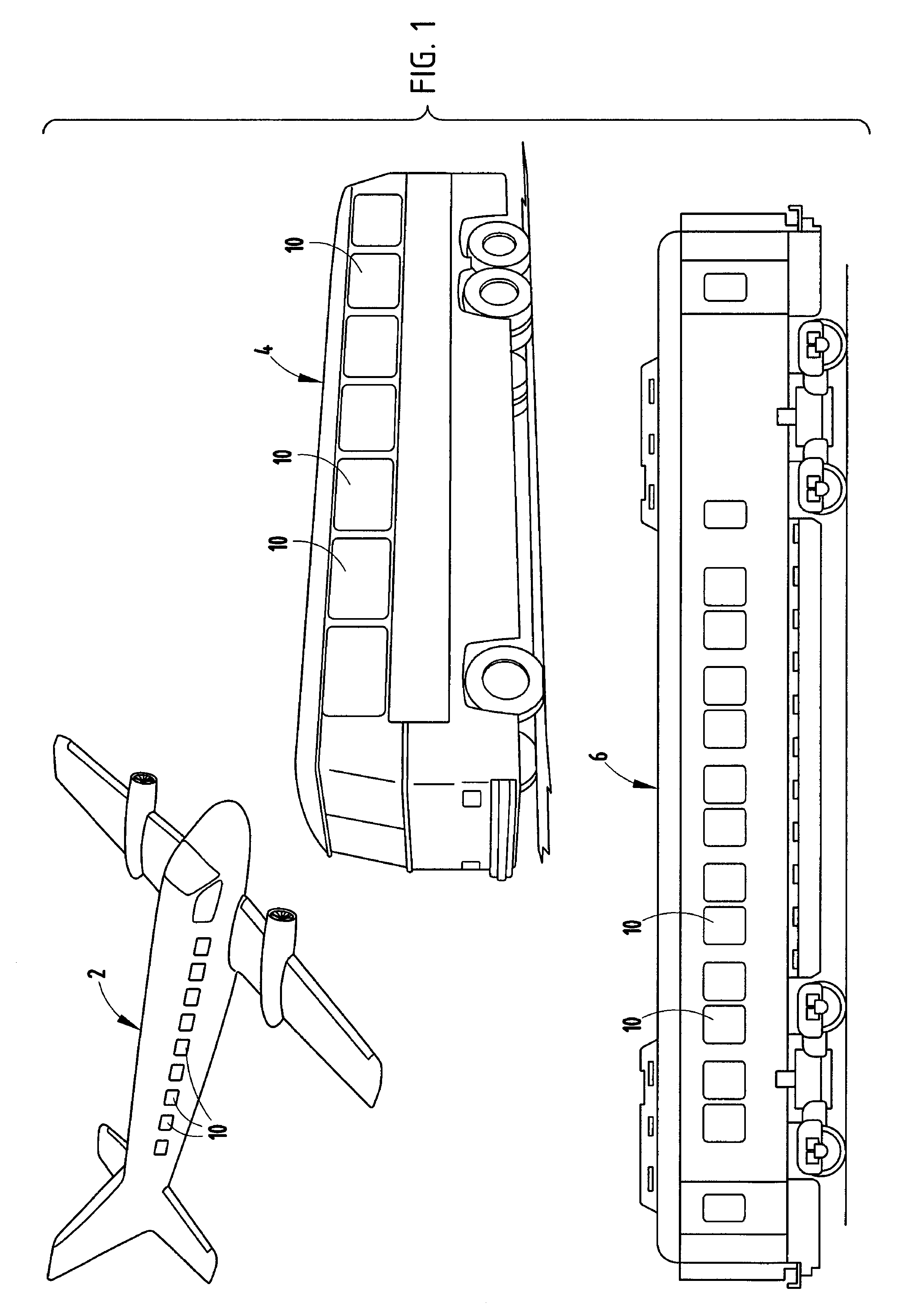

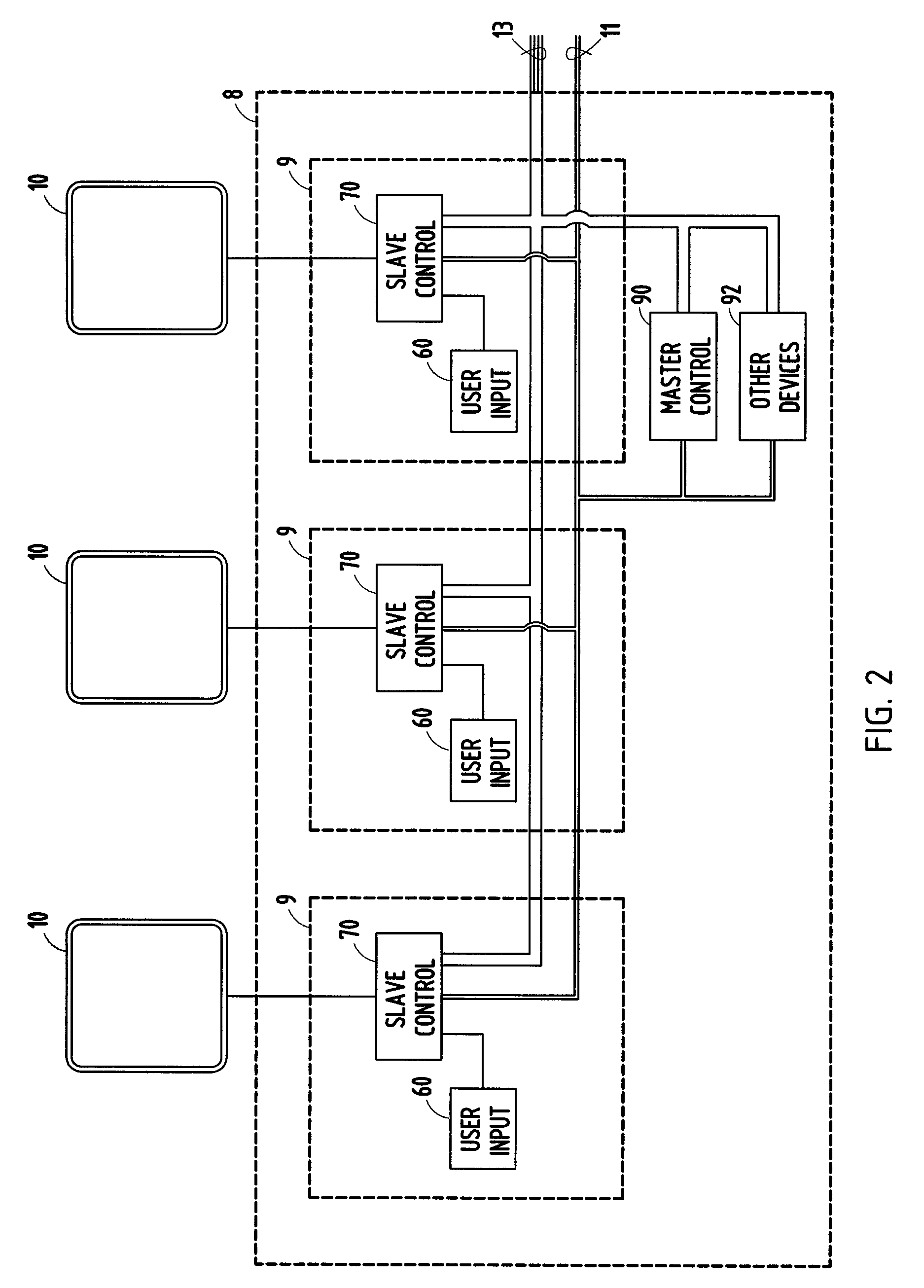

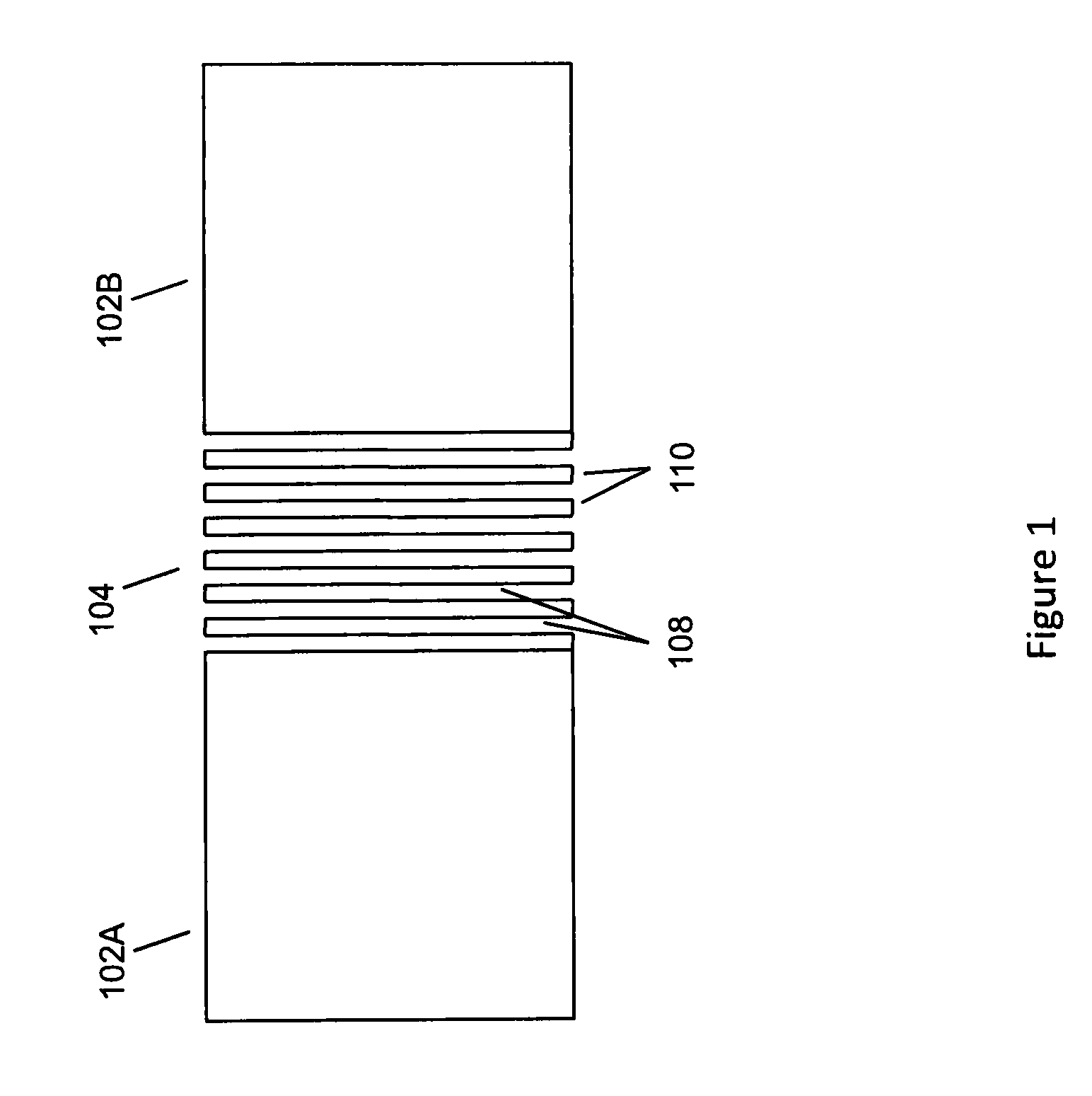

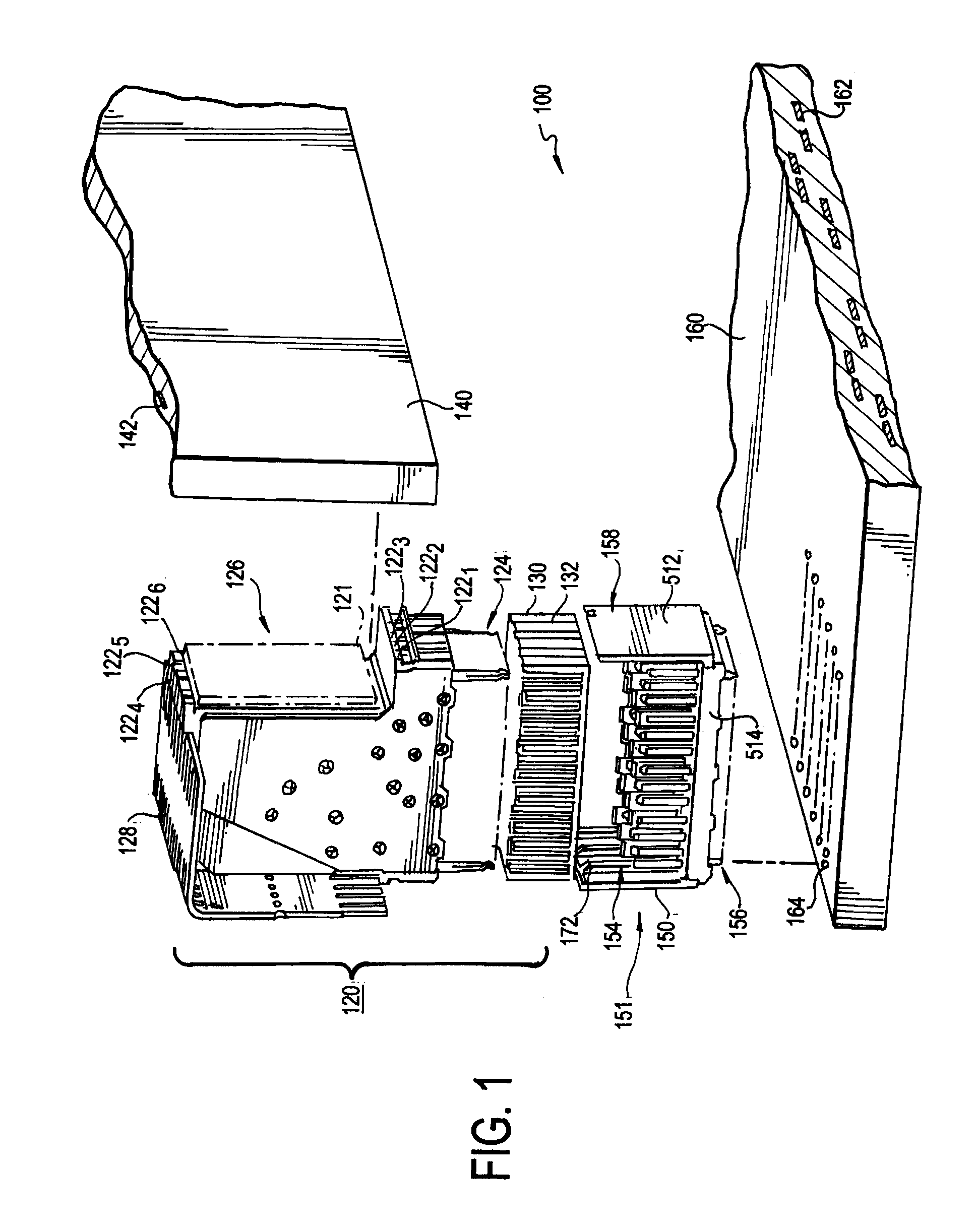

Variable Transmission Window System

An electrical control system is disclosed for controlling a plurality of variable transmittance windows. The electrical control system comprises a master control circuit and user input circuits for supplying control signals representing transmittance levels for the variable transmission windows, and a plurality of slave window control circuits coupled to the master control circuit, user input circuits and the variable transmittance windows. Each slave window control circuit controls the transmittance of at least one of the variable transmission windows in response to control signals received from the master control circuit and / or user input circuits. Also disclosed are novel methods for the manufacture of an electrochromic device used in variable transmittance windows. Novel structural features for improving heat transfer away from the windows, shielding the window from external loads, and improving the electrical performance of the windows are also disclosed.

Owner:GENTEX CORP

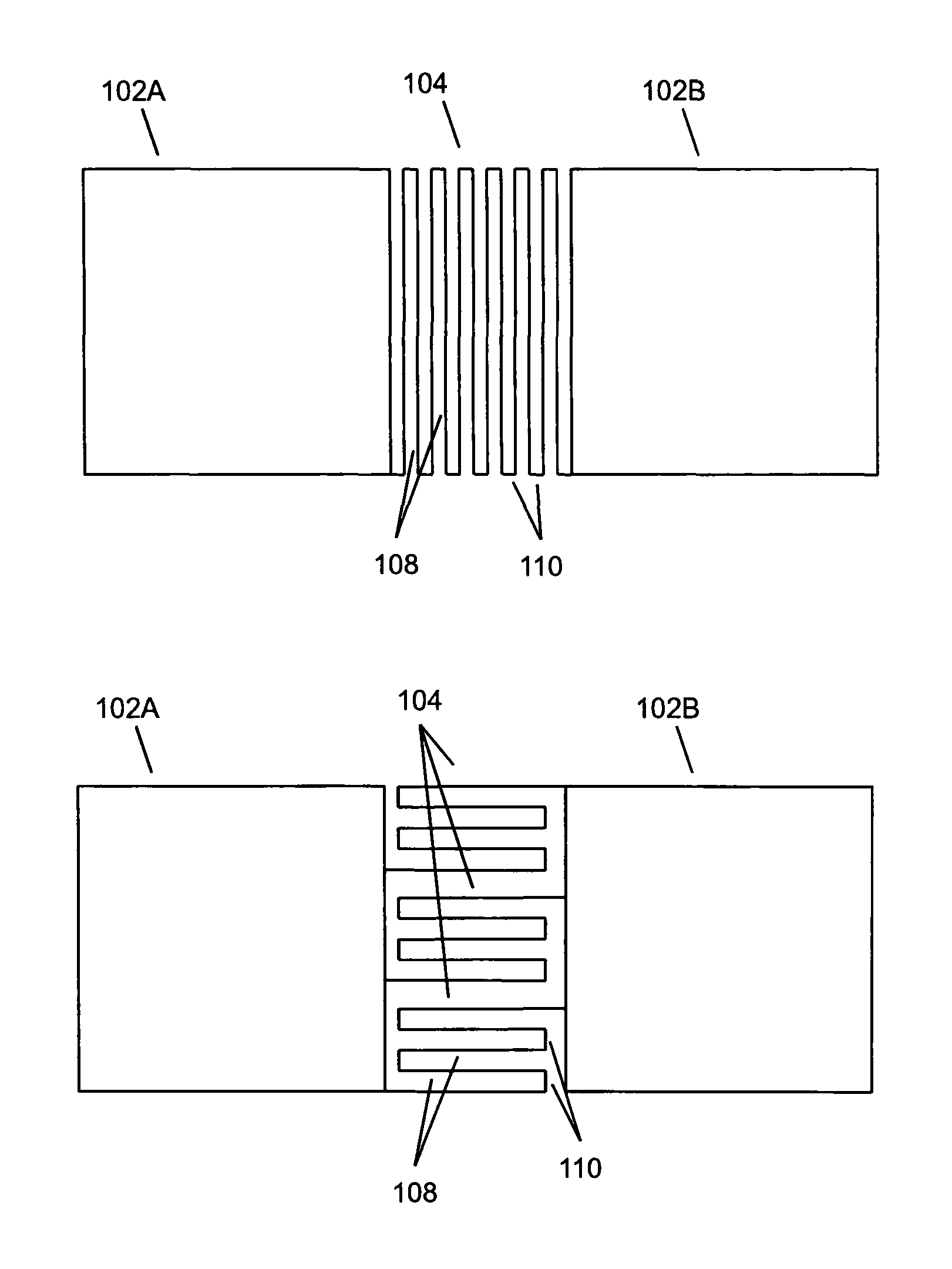

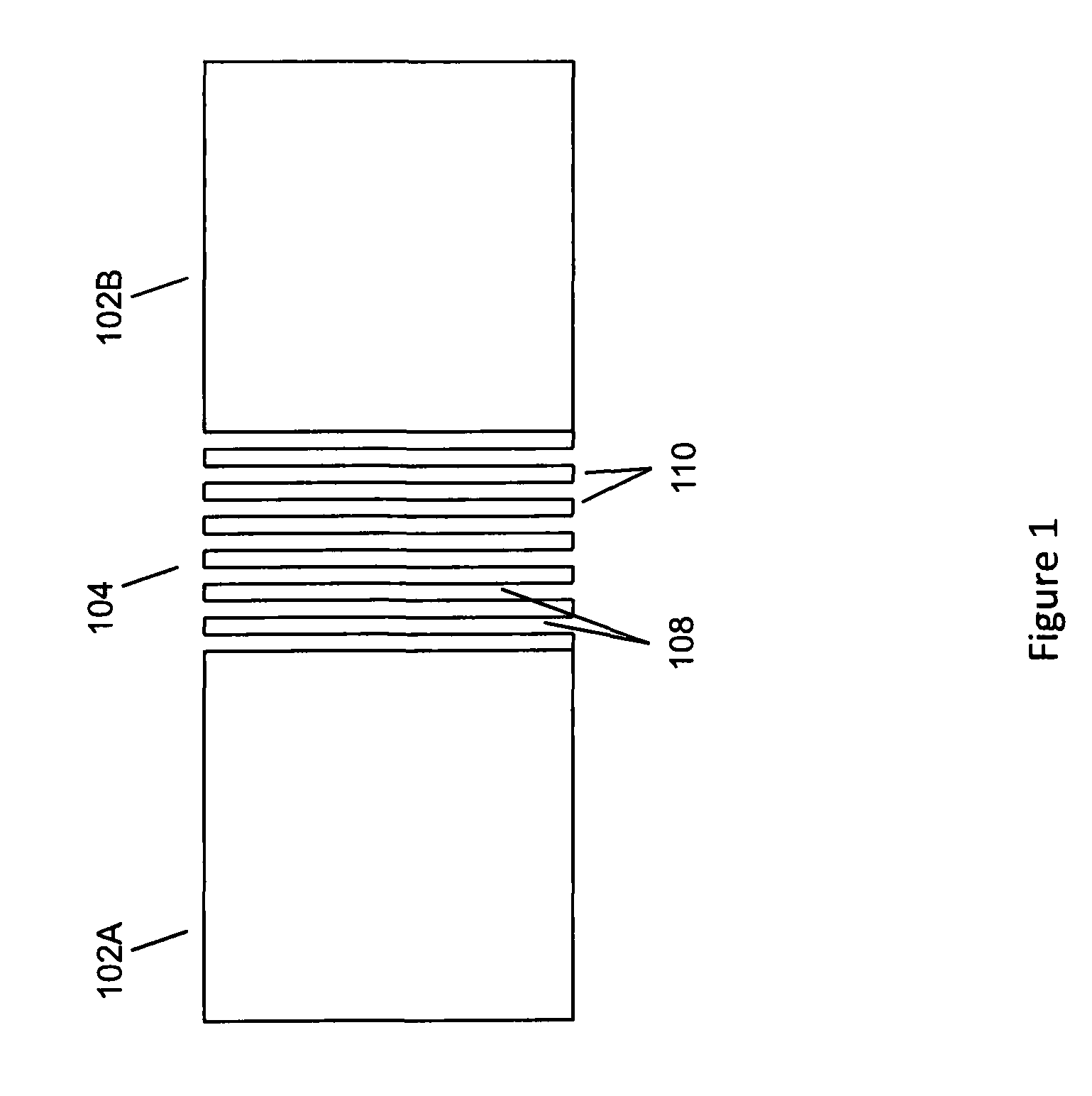

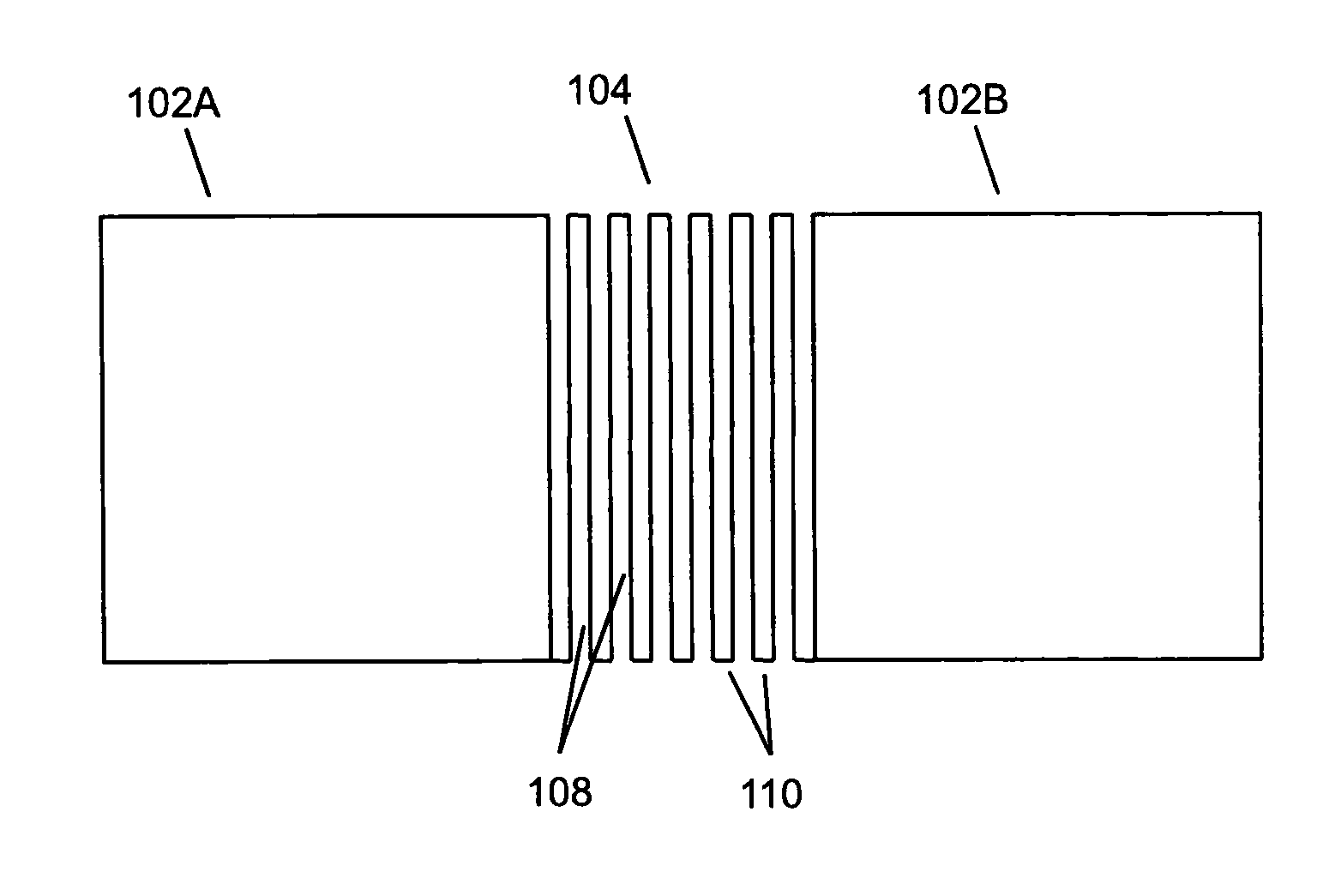

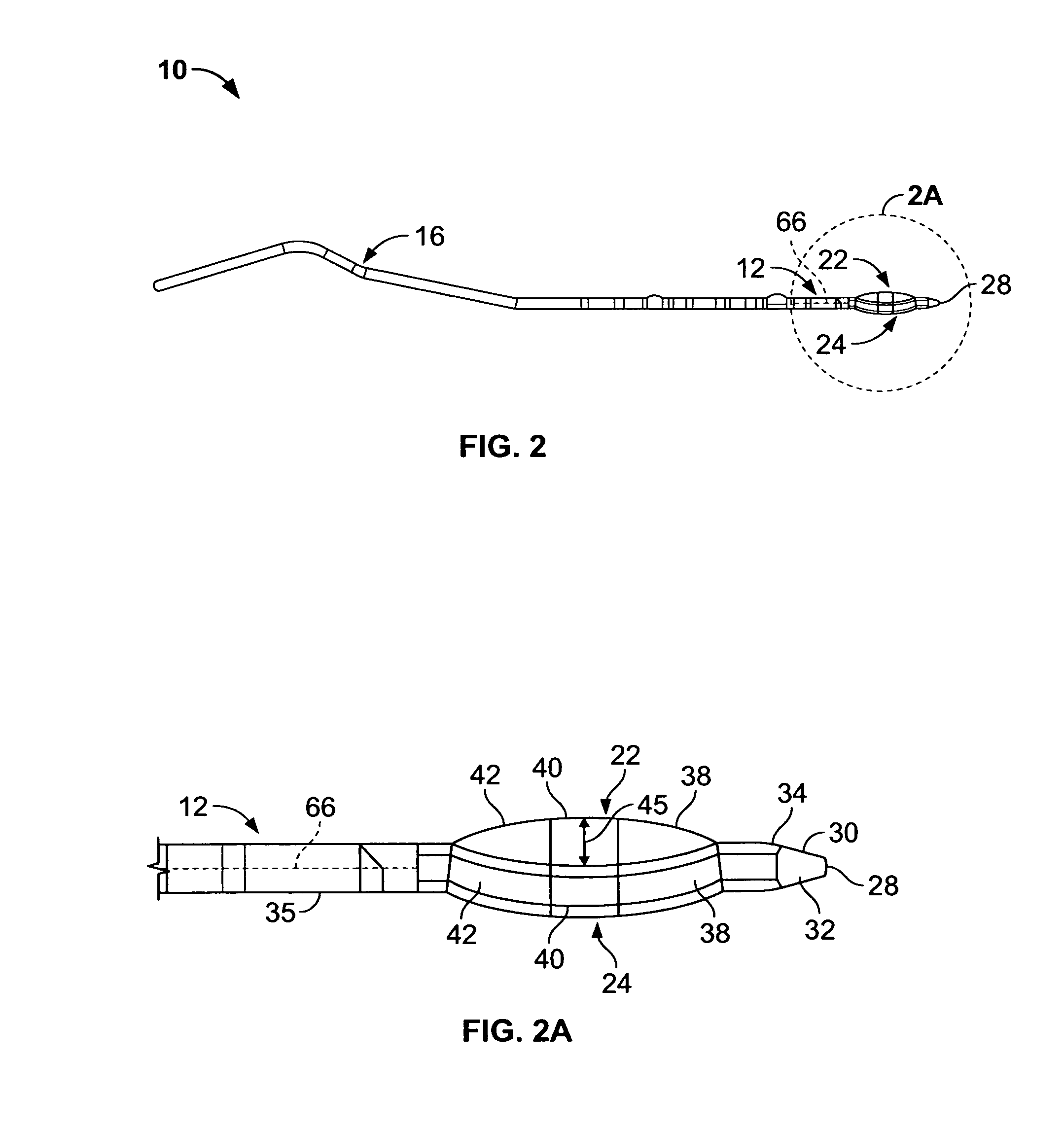

Extremely stretchable electronics

ActiveUS8389862B2Non-insulated conductorsContact member manufacturingStretchable electronicsElastomer

In embodiments, the present invention may attach at least two isolated electronic components to an elastomeric substrate, and arrange an electrical interconnection between the components in a boustrophedonic pattern interconnecting the two isolated electronic components with the electrical interconnection. The elastomeric substrate may then be stretched such that the components separate relative to one another, where the electrical interconnection maintains substantially identical electrical performance characteristics during stretching, and where the stretching may extend the separation distance between the electrical components to many times that of the unstretched distance.

Owner:MEDIDATA SOLUTIONS

Radome attachment band clamp

ActiveUS9083083B2RF leakageClamp firmlyPretreated surfacesRadiating element housingsInterference fitElectrical performance

Owner:COMMSCOPE TECH LLC

Variable transmission window system

An electrical control system is disclosed for controlling a plurality of variable transmittance windows. The electrical control system comprises a master control circuit and user input circuits for supplying control signals representing transmittance levels for the variable transmission windows, and a plurality of slave window control circuits coupled to the master control circuit, user input circuits and the variable transmittance windows. Each slave window control circuit controls the transmittance of at least one of the variable transmission windows in response to control signals received from the master control circuit and / or user input circuits. Also disclosed are novel methods for the manufacture of an electrochromic device used in variable transmittance windows. Novel structural features for improving heat transfer away from the windows, shielding the window from external loads, and improving the electrical performance of the windows are also disclosed.

Owner:GENTEX CORP

Extremely stretchable electronics

ActiveUS20100116526A1Minimal strainNon-insulated conductorsContact member manufacturingStretchable electronicsElastomer

In embodiments, the present invention may attach at least two isolated electronic components to an elastomeric substrate, and arrange an electrical interconnection between the components in a boustrophedonic pattern interconnecting the two isolated electronic components with the electrical interconnection. The elastomeric substrate may then be stretched such that the components separate relative to one another, where the electrical interconnection maintains substantially identical electrical performance characteristics during stretching, and where the stretching may extend the separation distance between the electrical components to many times that of the unstretched distance.

Owner:MEDIDATA SOLUTIONS

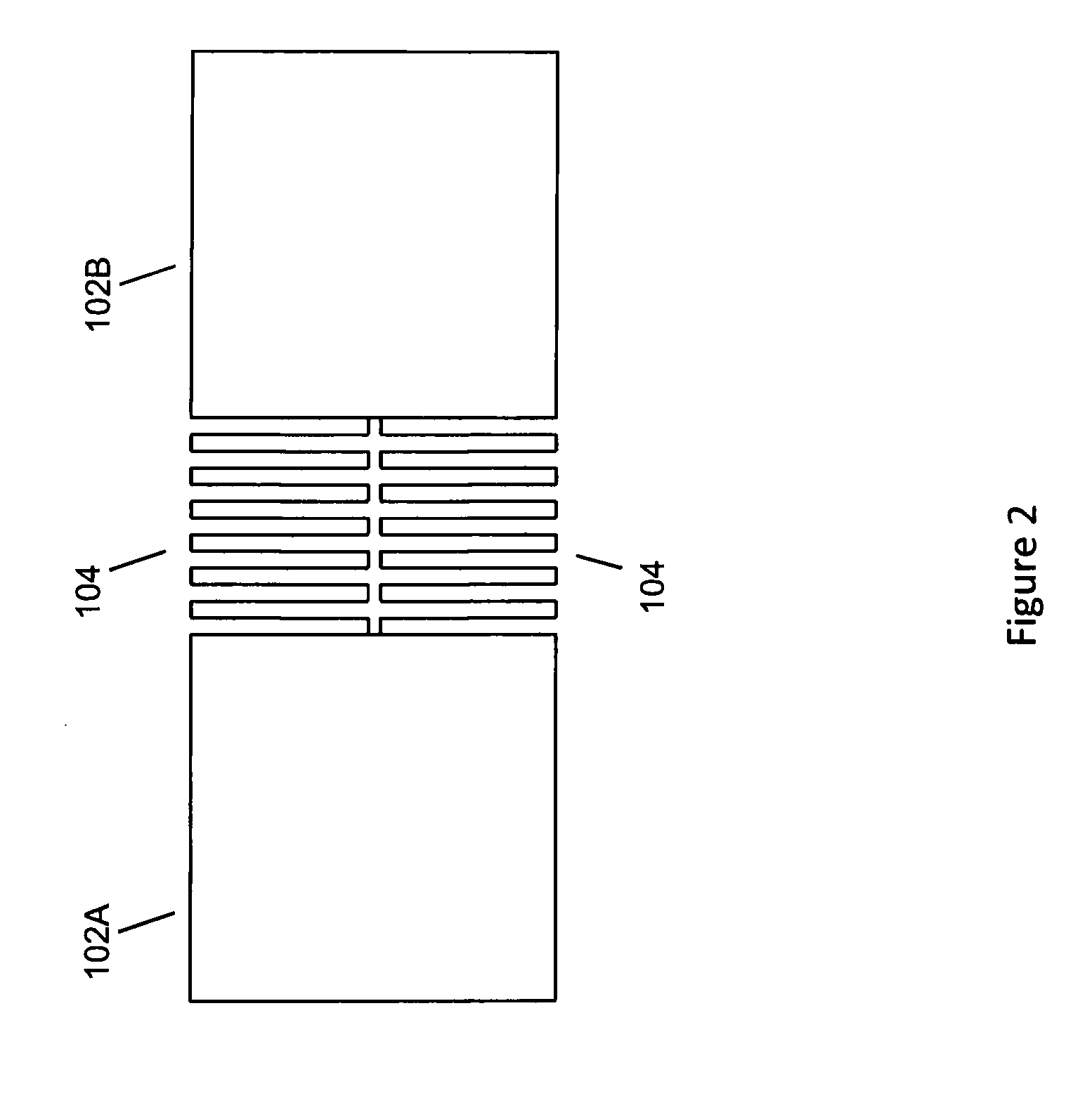

Capacitive touch screen with reduced electrode trace resistance

InactiveUS20100328248A1Improve electrical performanceImprove optical qualityInput/output processes for data processingVisibilityElectricity

An improved touch screen has enhanced optical performance and aesthetic quality. The electrodes on the touch screen employ additional fine traces of conductive material to reduce the overall electrode trace resistance to increase electrical performance without sacrificing optical quality. The additional fine traces of conductive material may be placed on the top of the ITO traces or in channels inside the boundaries of the ITO traces. The additional traces preferably run the length of the ITO traces to reduce the resistance in the longer dimension. Further, the additional traces are very small in width such that in the aggregate they cover only a small portion of the ITO electrode trace in lateral dimension to reduce the visibility of the additional traces. The conductive material may also be formed as a plurality of geometric shapes substantially forming a line in the longer dimension of the transparent conductive traces to reduce the visibility of the conductive material.

Owner:OCULAR LCD

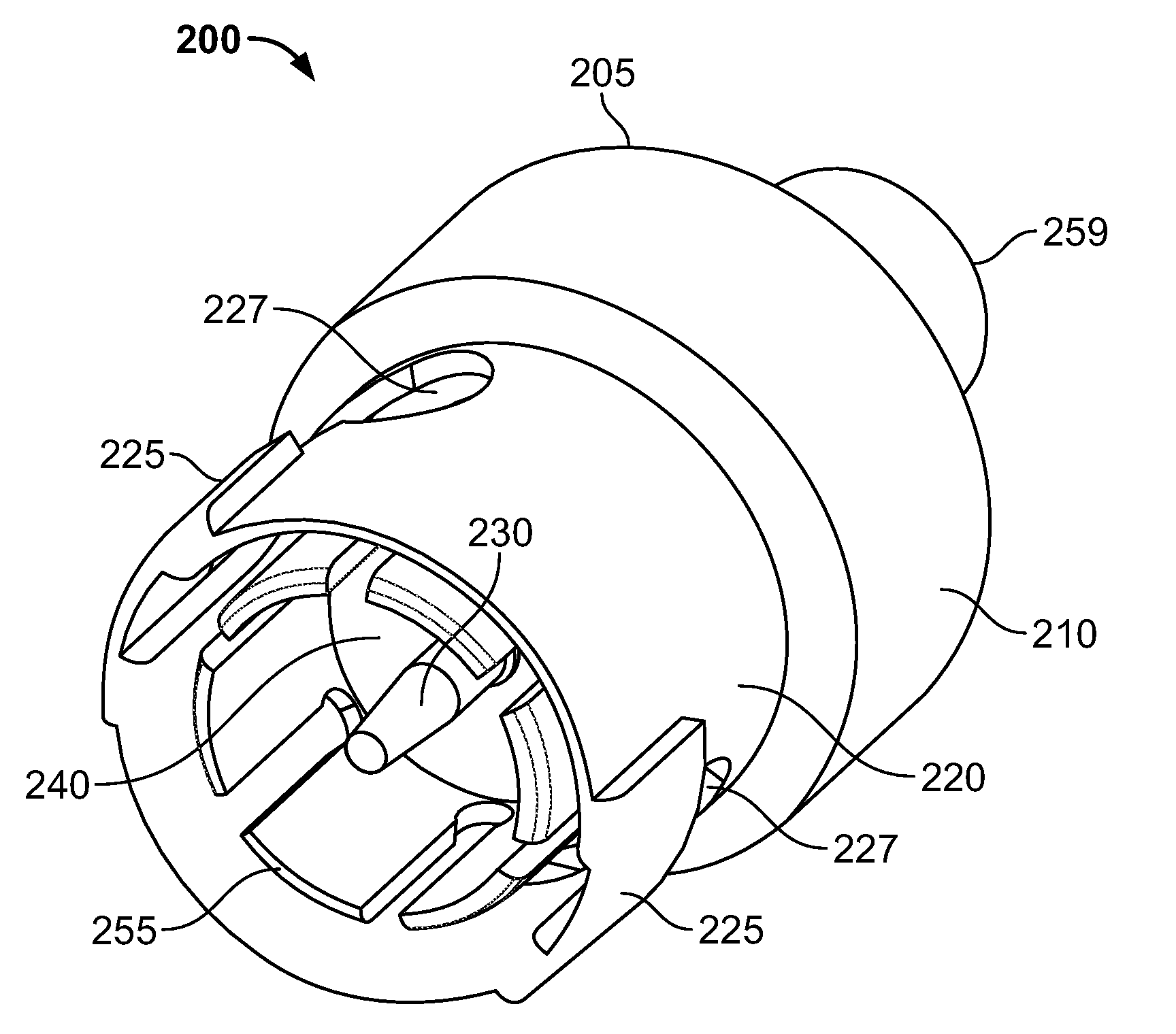

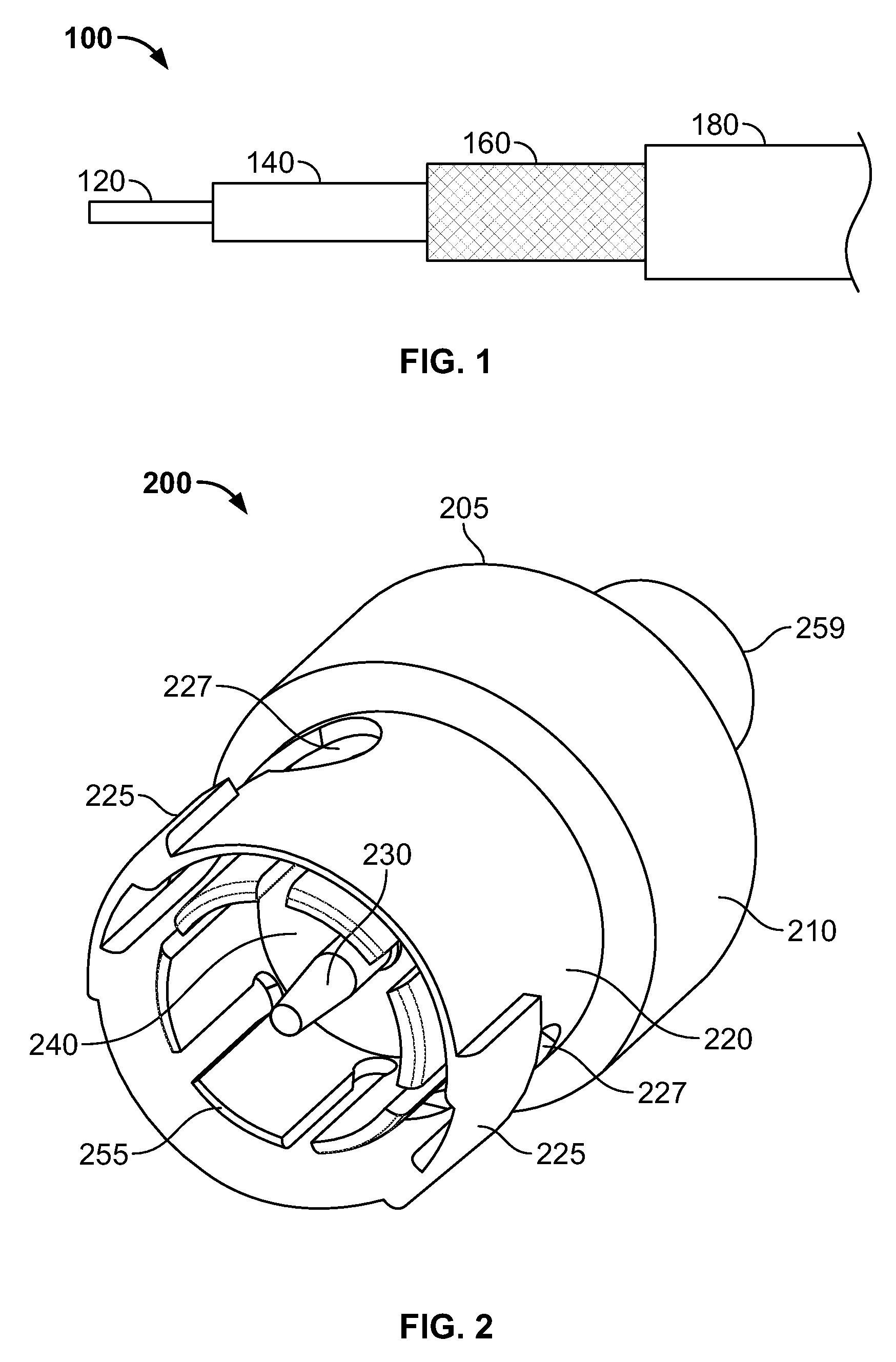

High performance coaxial connector

InactiveUS20090029590A1Improve electrical performanceElectrically conductive connectionsTwo pole connectionsCoaxial cableElectrical connection

A high performance coaxial connector used to terminate a coaxial cable and provide an electrical connection to a mating coaxial connector is disclosed. The coaxial connector is formed with few individual parts and may be configured to provide enhanced electrical performance greater than or equal to 4 GHz.

Owner:TE CONNECTIVITY CORP

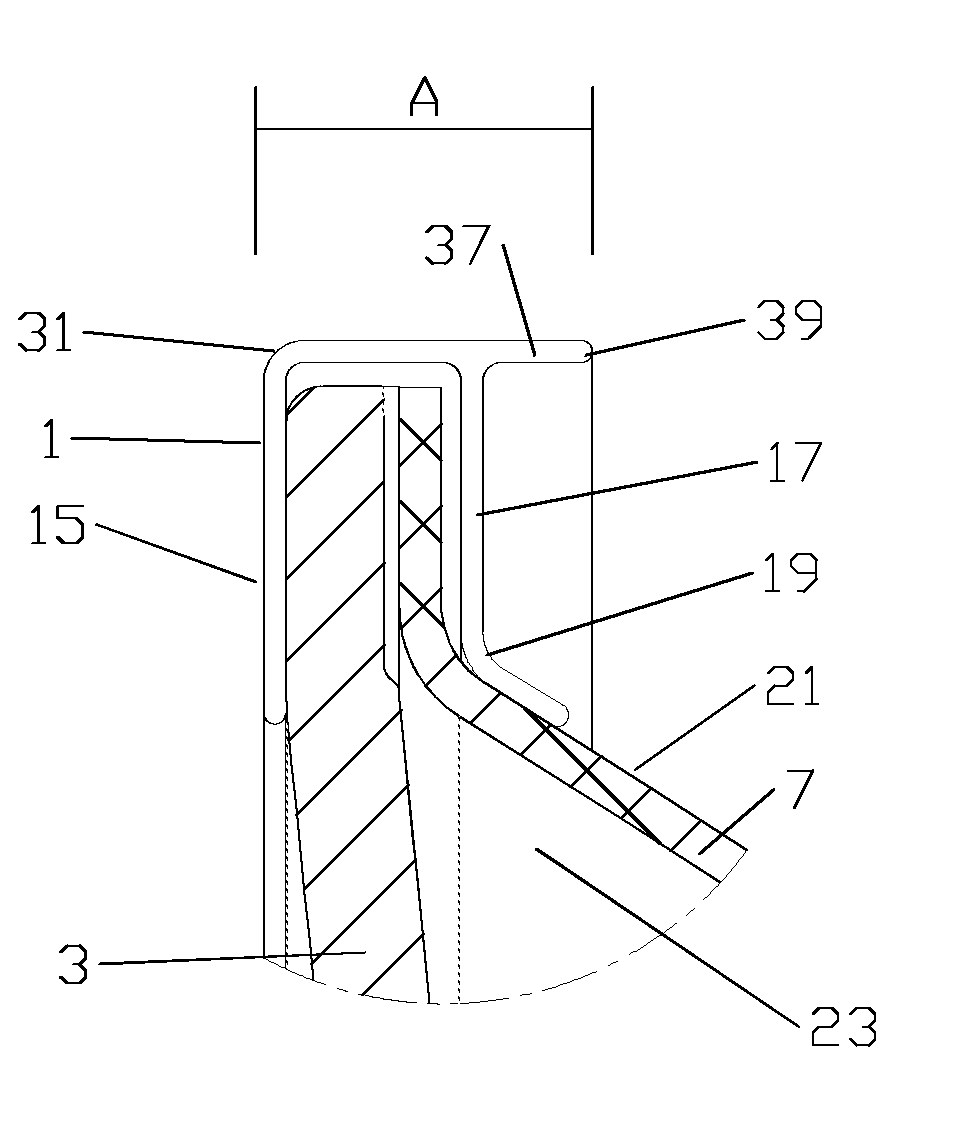

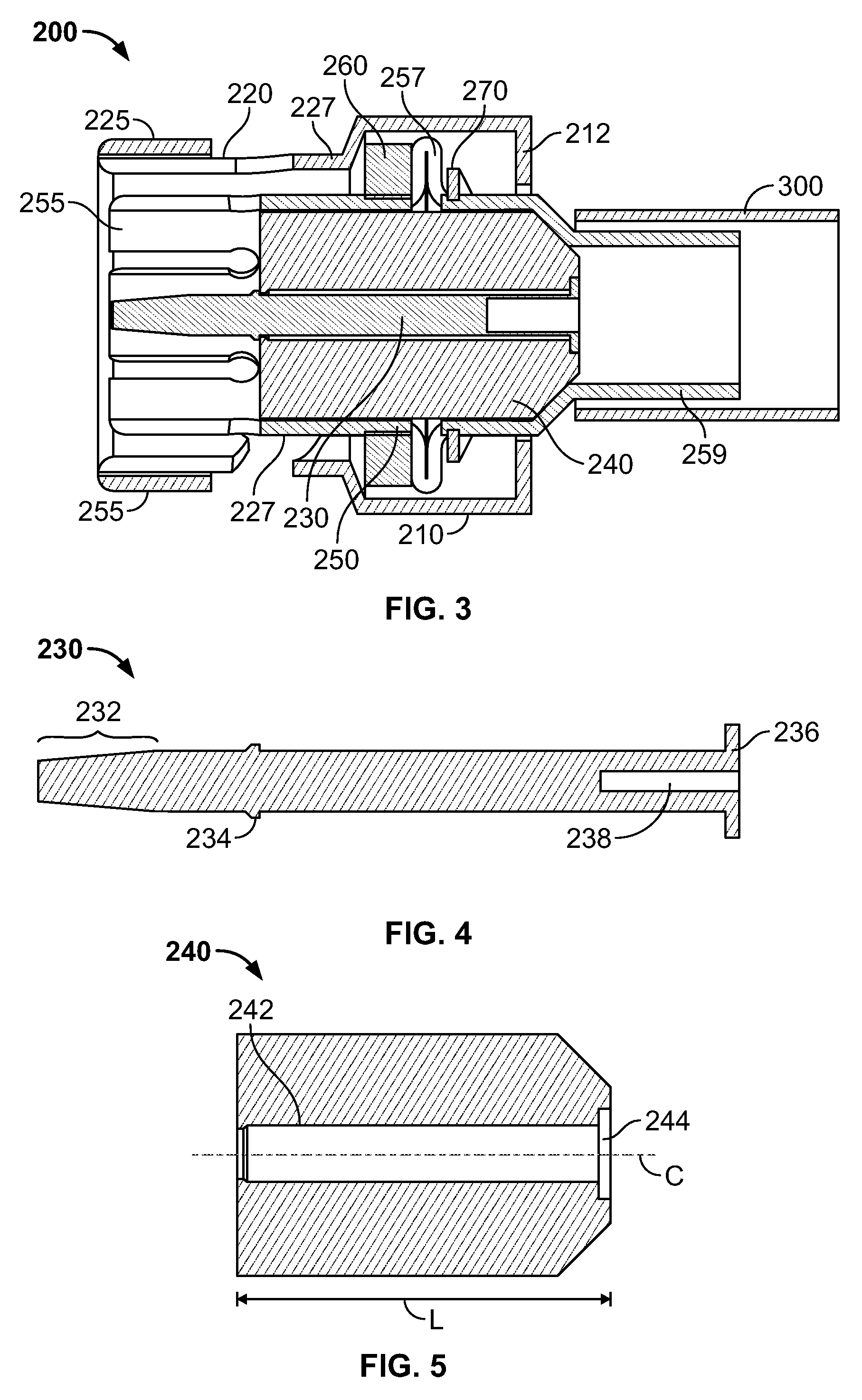

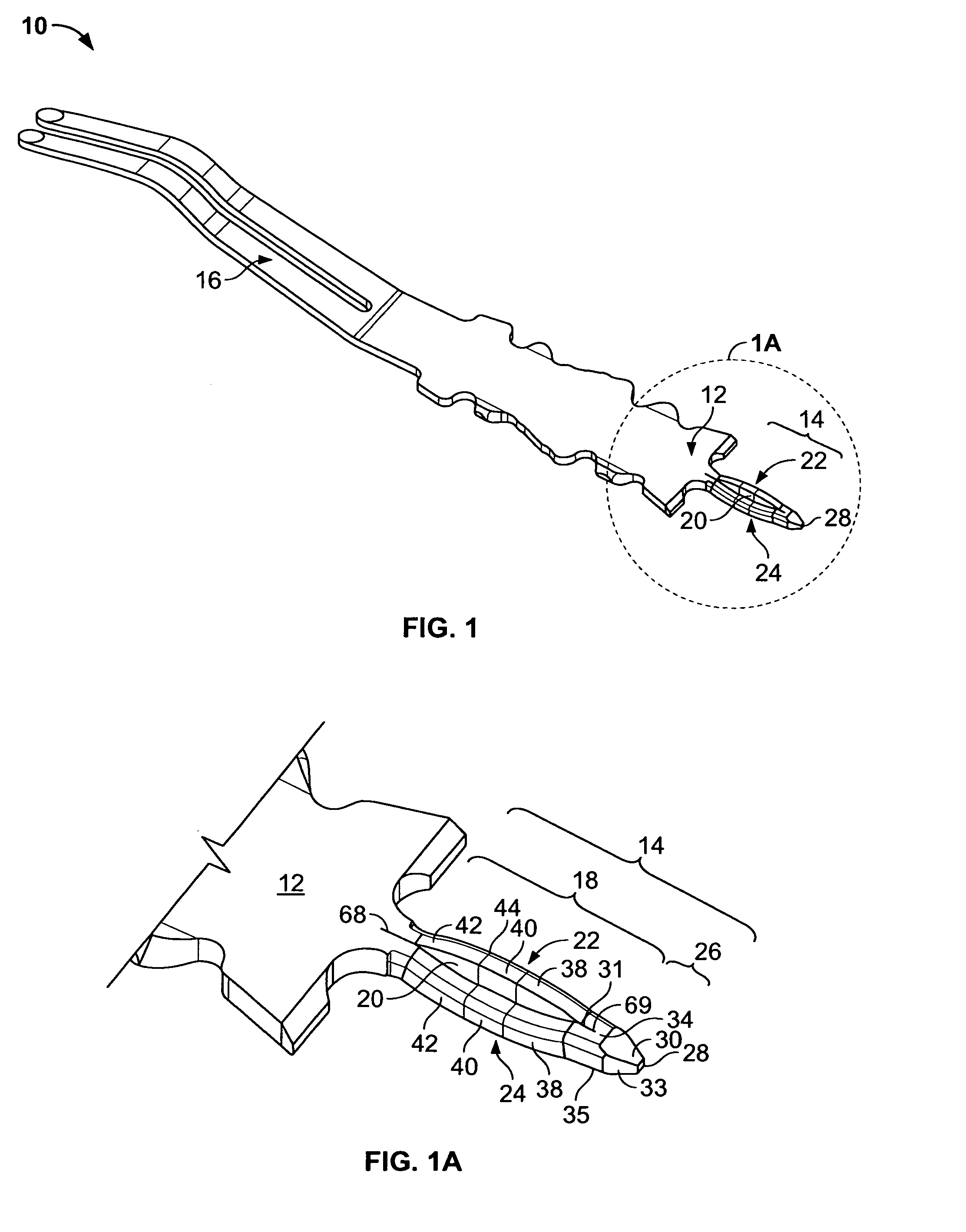

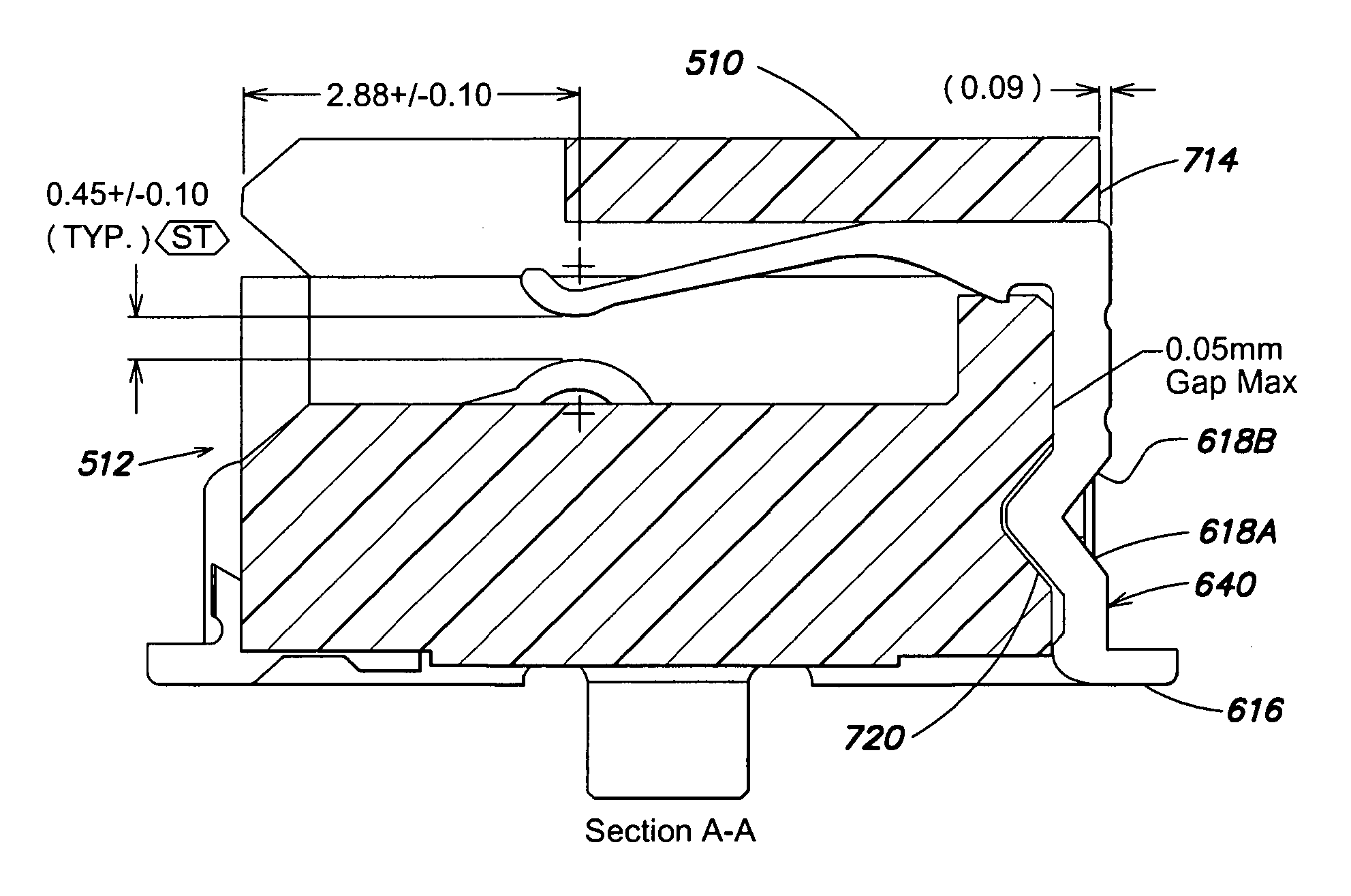

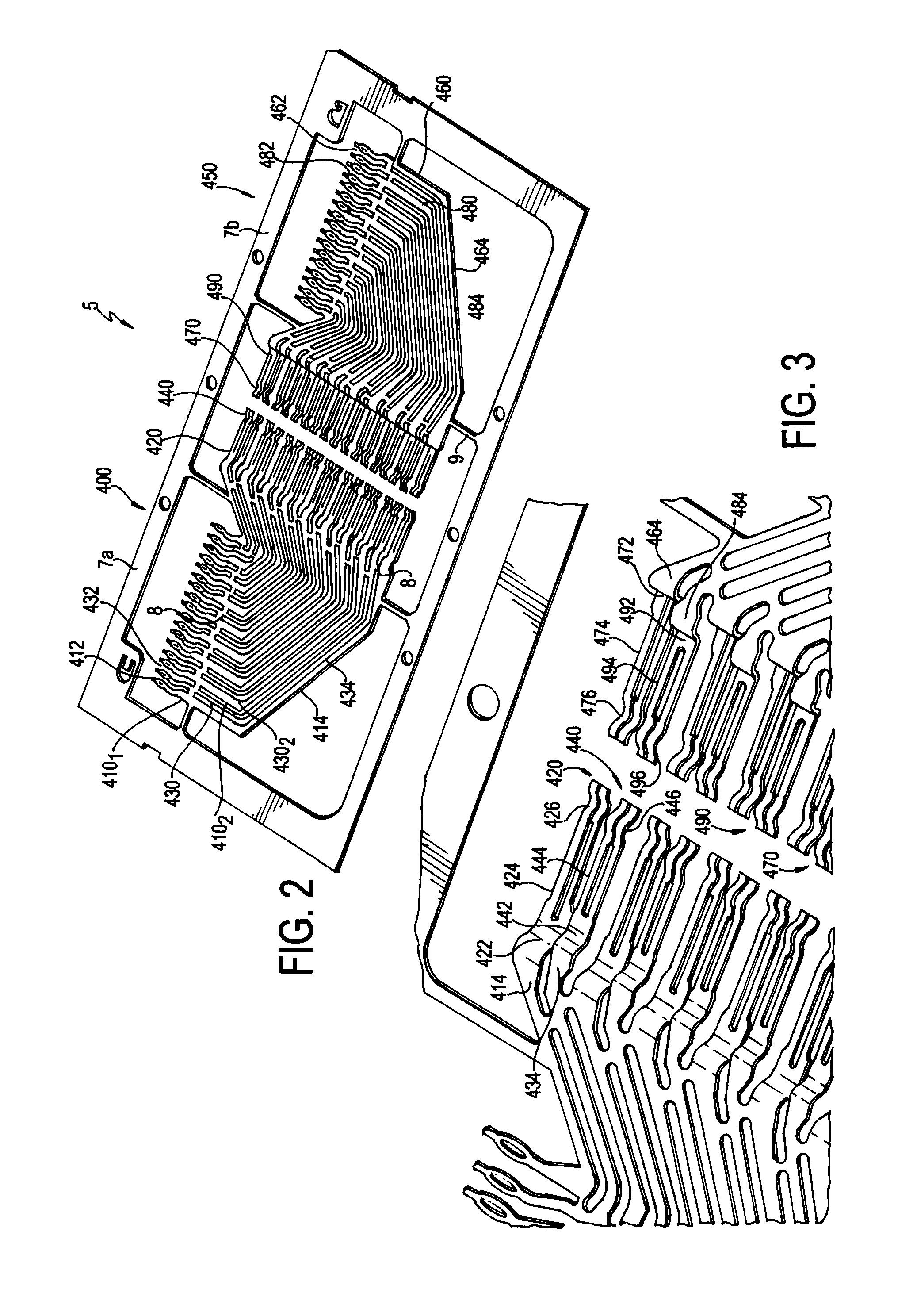

Electrical connector having improved terminal configuration

ActiveUS7549897B2Small sizeImproving impedanceElectric discharge tubesSecuring/insulating coupling contact membersElectrical performanceEngineering

An electrical terminal of the type to be inserted into an aperture of an electrical panel member is provided. The electrical terminal may include a base, an insertion portion extending from the base to a first end, a slit formed through the insertion portion and defining a compliant portion having a first leg and a second leg. Midpoints of each or both legs may be offset from the midpoint of the slit to achieve improved mechanical and electrical performance within a connector. Also provided is an electrical terminal having a tip that facilitates alignment with a panel member aperture and provides tactile feedback to a user, as well as an electrical terminal having a mounting end that is substantially smaller than its mating end, and connectors containing such terminals. Methods of routing electrical traces between adjacent electrical terminals are also provided.

Owner:TYCO ELECTRONICS LOGISTICS AG (CH)

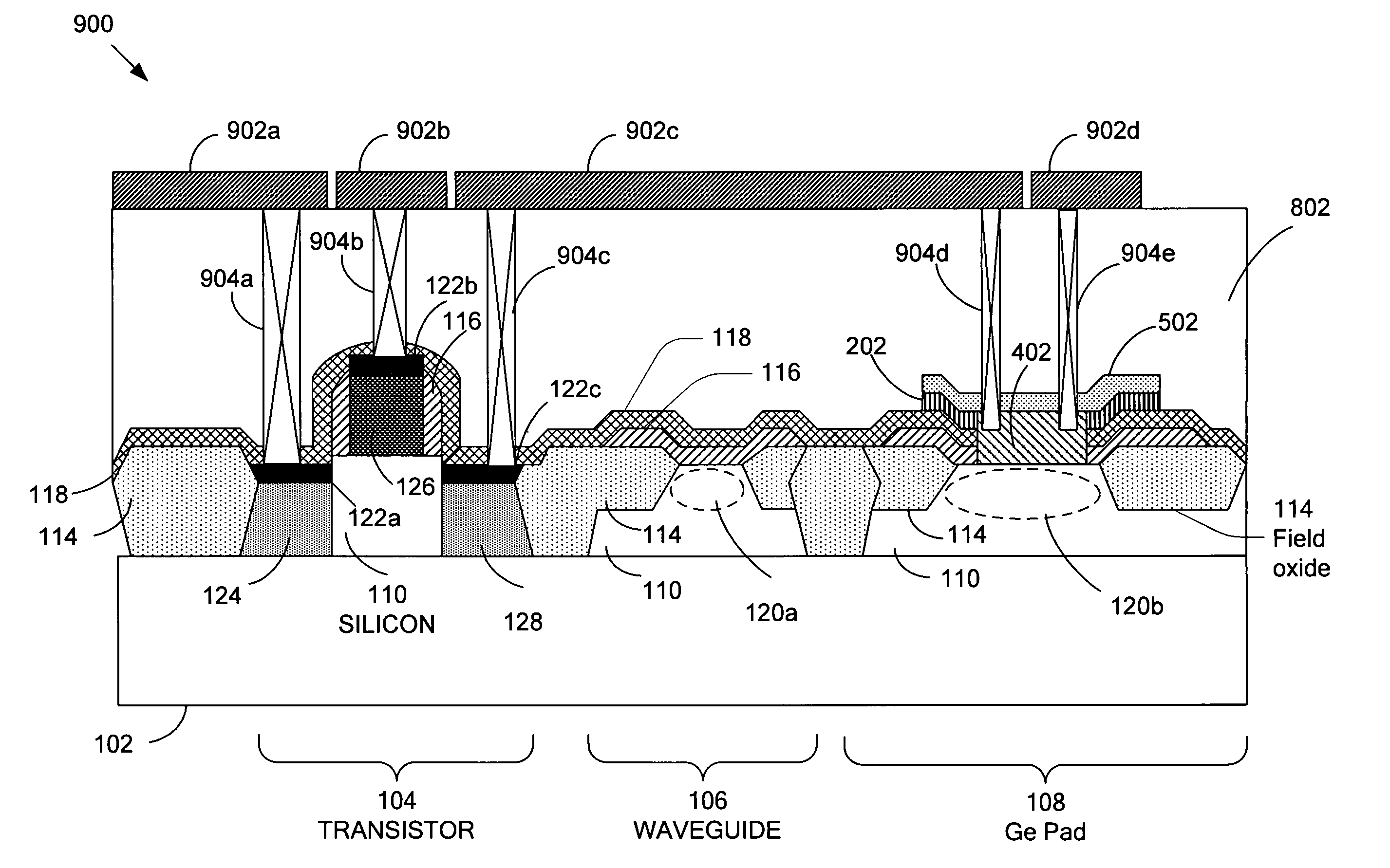

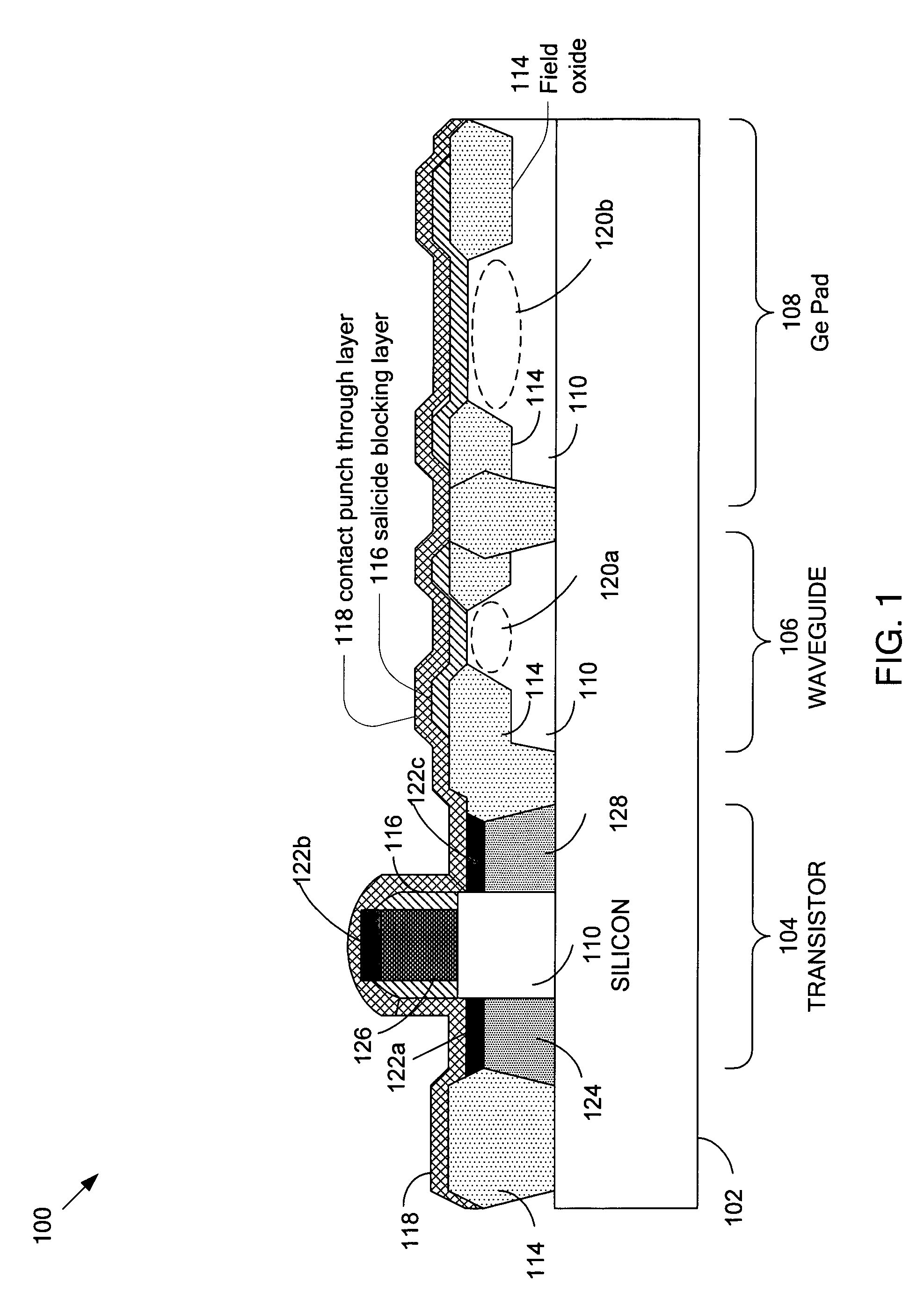

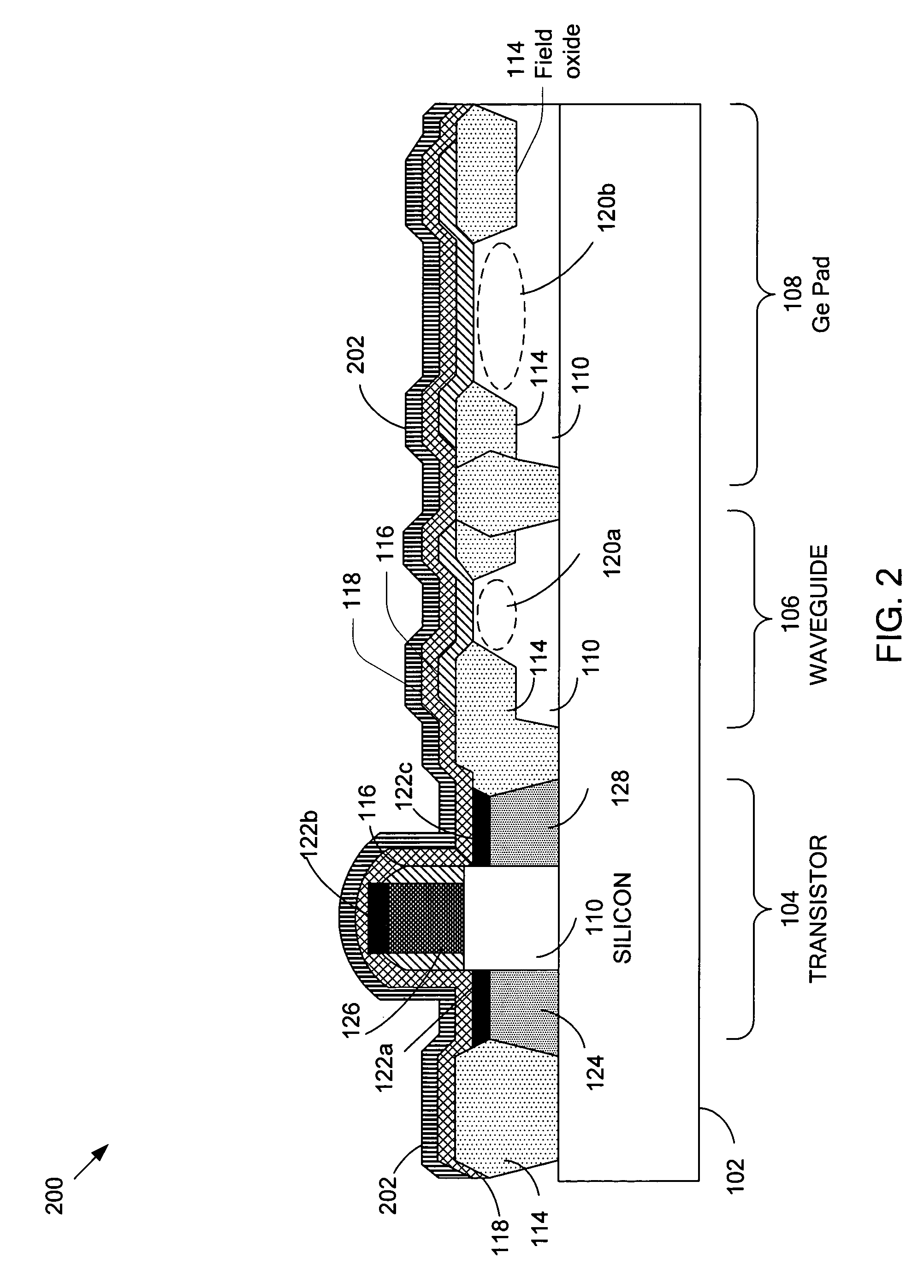

Germanium integrated CMOS wafer and method for manufacturing the same

ActiveUS7262117B1Solid-state devicesSemiconductor/solid-state device manufacturingPhotovoltaic detectorsPhotodetector

The present invention discloses an integration flow of germanium into a conventional CMOS process, with improvements in performing selective area growth, and implementing electrical contacts to the germanium, in a way that has minimal impact on the preexisting transistor devices. The present invention also provides methods to integrate the germanium without impacting the optical or electrical performance of these devices, except where intended, such as in a germanium photodetector, or germanium waveguide photodetector.

Owner:CISCO TECH INC

Preparation of multi-position doped lithium iron phosphate positive electrode material and application thereof

ActiveCN101339994AWide range of materialsIncrease base capacityElectrode manufacturing processesPhosphorus compoundsElectricityLithium iron phosphate

The invention discloses a preparation method of a multi-place doped lithium iron phosphate anode material and an application thereof, which belong to the technical field of the preparation of electrochemical power materials. The multi-place doped lithium iron phosphate anode material is expressed by the following formula: Li1-xAxFe1-yByP1-zCzO4Ddelta, wherein, at least two of x, y, x and delta can not be expressed zero at the same time. Multi-place doped anode material lithium iron phosphate powder which is used in a secondary lithium-ion battery and has good crystallization performance and even composition is prepared by adopting a solid phase method and a simple mixing and drying process; compared with the method doping in a certain crystal lattice place, the multi-place doped anode material lithium iron phosphate powder has wide doping material source, which can greatly improve the basic capacity and cycling electrical performance of matrix and is applied to a stable industrialized production and non-high-purity materials. The multi-place lithium iron phosphate of the invention is taken as the anode material and is usually used in the secondary lithium-ion battery and the secondary lithium-ion battery is taken as a power source.

Owner:甘肃大象能源科技有限公司

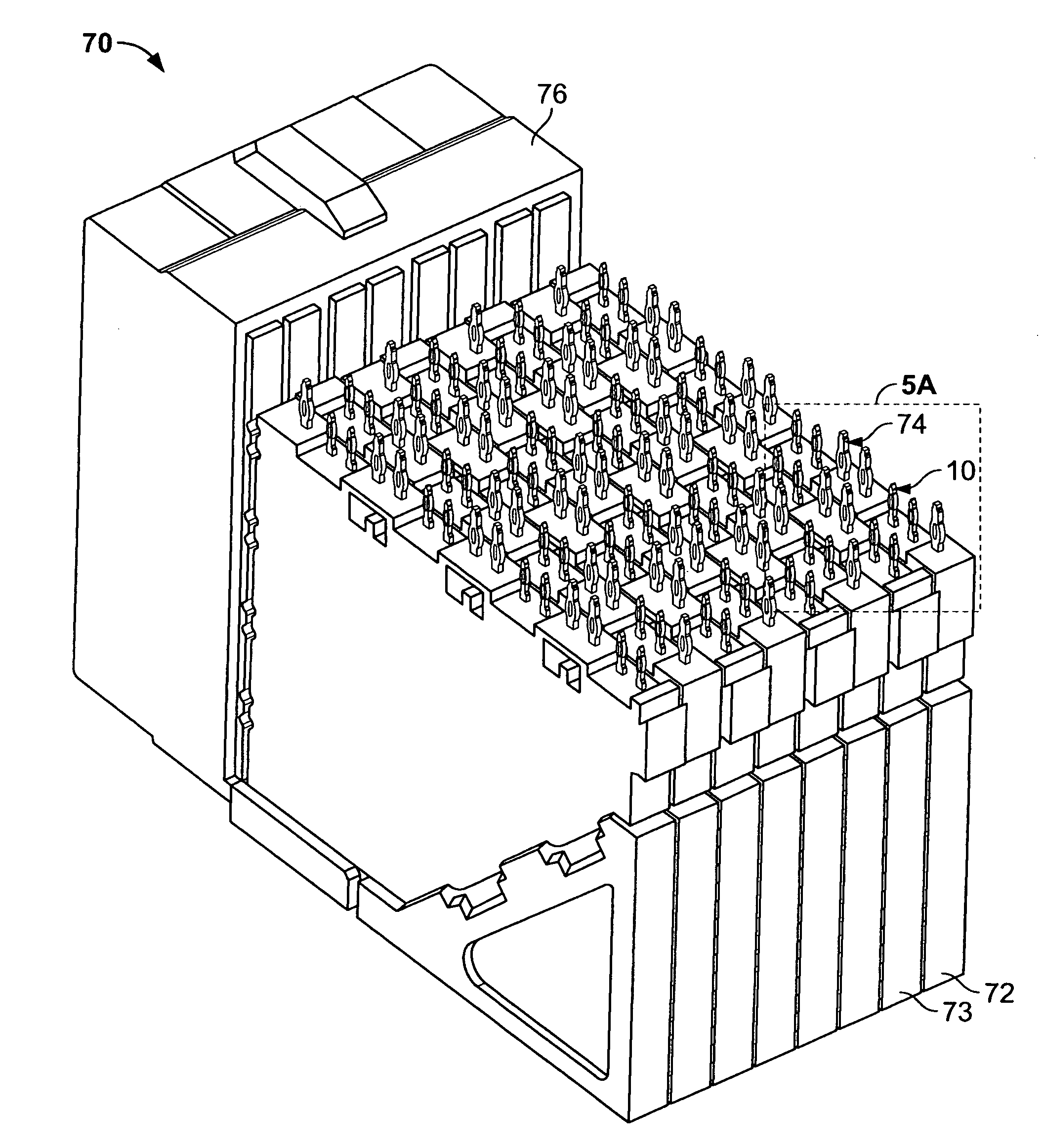

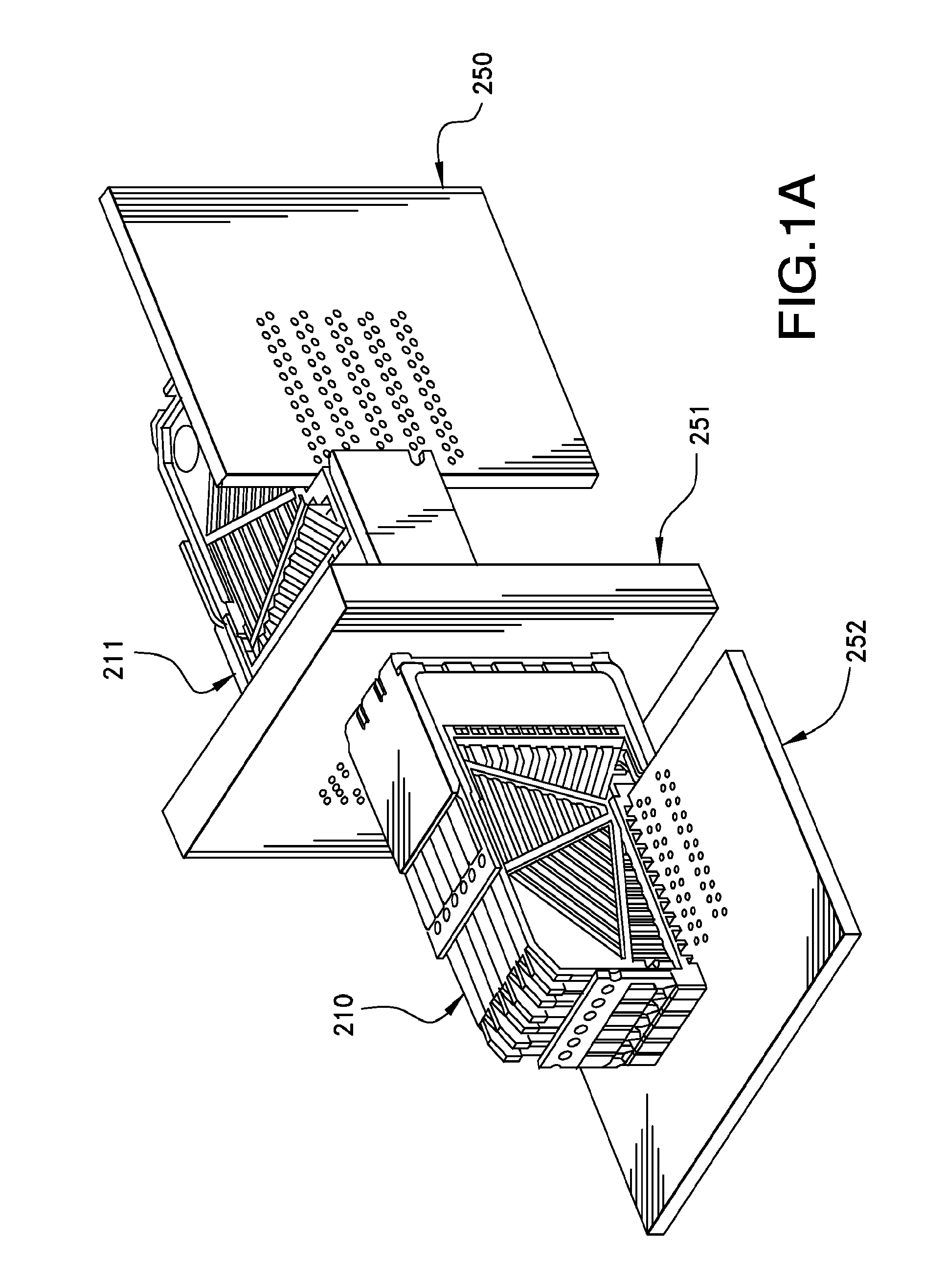

High bandwidth connector

ActiveUS8771016B2Improved open pin field connectorReduce resonanceCoupling protective earth/shielding arrangementsCapacitanceHigh bandwidth

An improved open pin field connector is provided for enhanced performance when carrying high speed signals by selective application of one or more techniques for controlling electrical performance parameters. Lossy material may be positioned adjacent to conductive elements of the connector so as to reduce resonance in pairs of conductive elements and / or to provide a desired characteristic impedance for pairs of differential signal conductors. The lossy material may be shaped and positioned to avoid capacitive coupling that might otherwise increase cross talk. In a right angle connector, the lossy material may have a step-wise increase in thickness to provide comparable loss along longer and shorter conductive elements. Conductive elements may be shaped to balance performance characteristics of pairs selected to carry differential signals regardless of orientation along a row or column. Alternatively, conductive elements may have narrowed regions, covered with lossy portions, for reducing resonance while supporting DC signal propagation.

Owner:AMPHENOL CORP

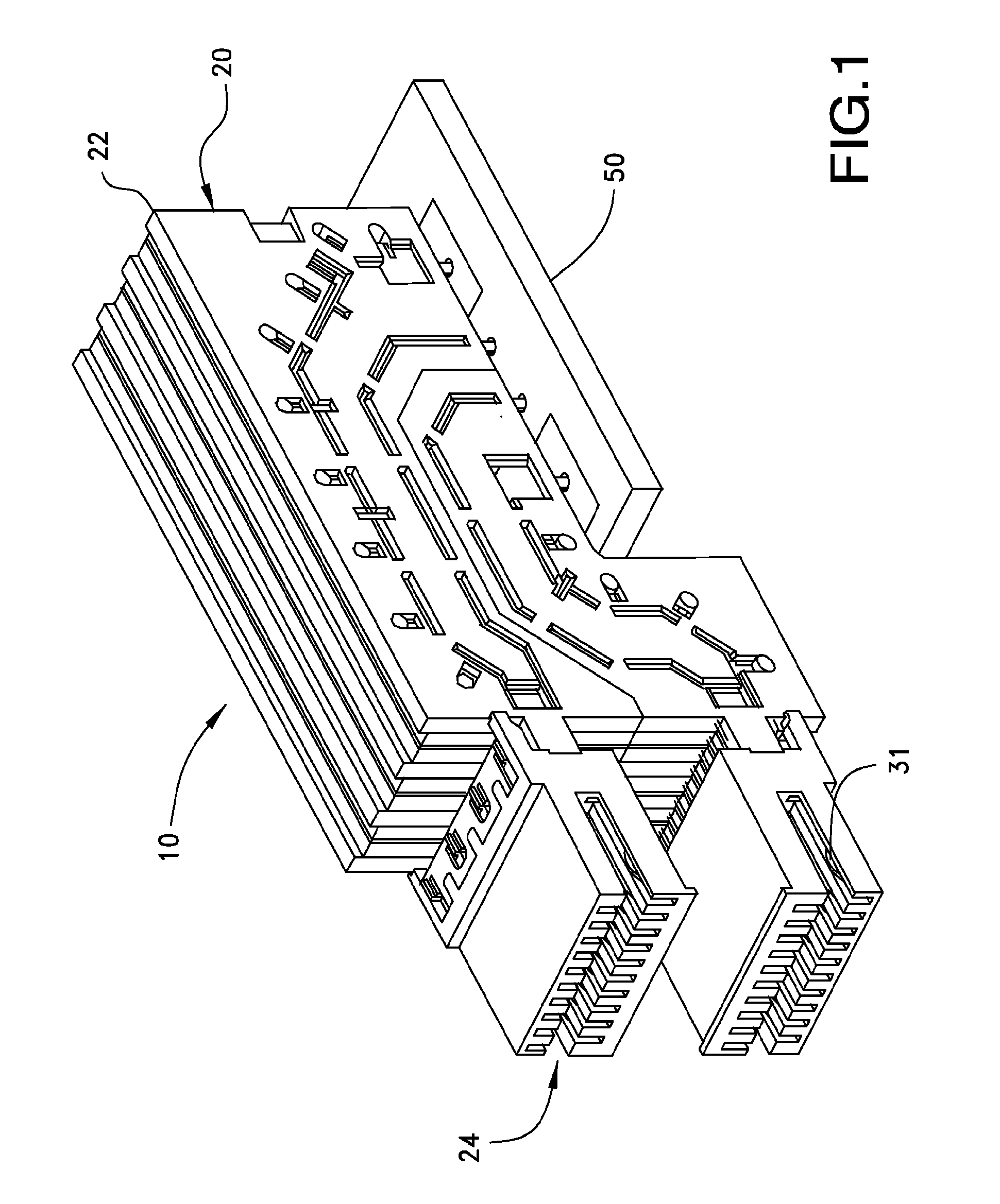

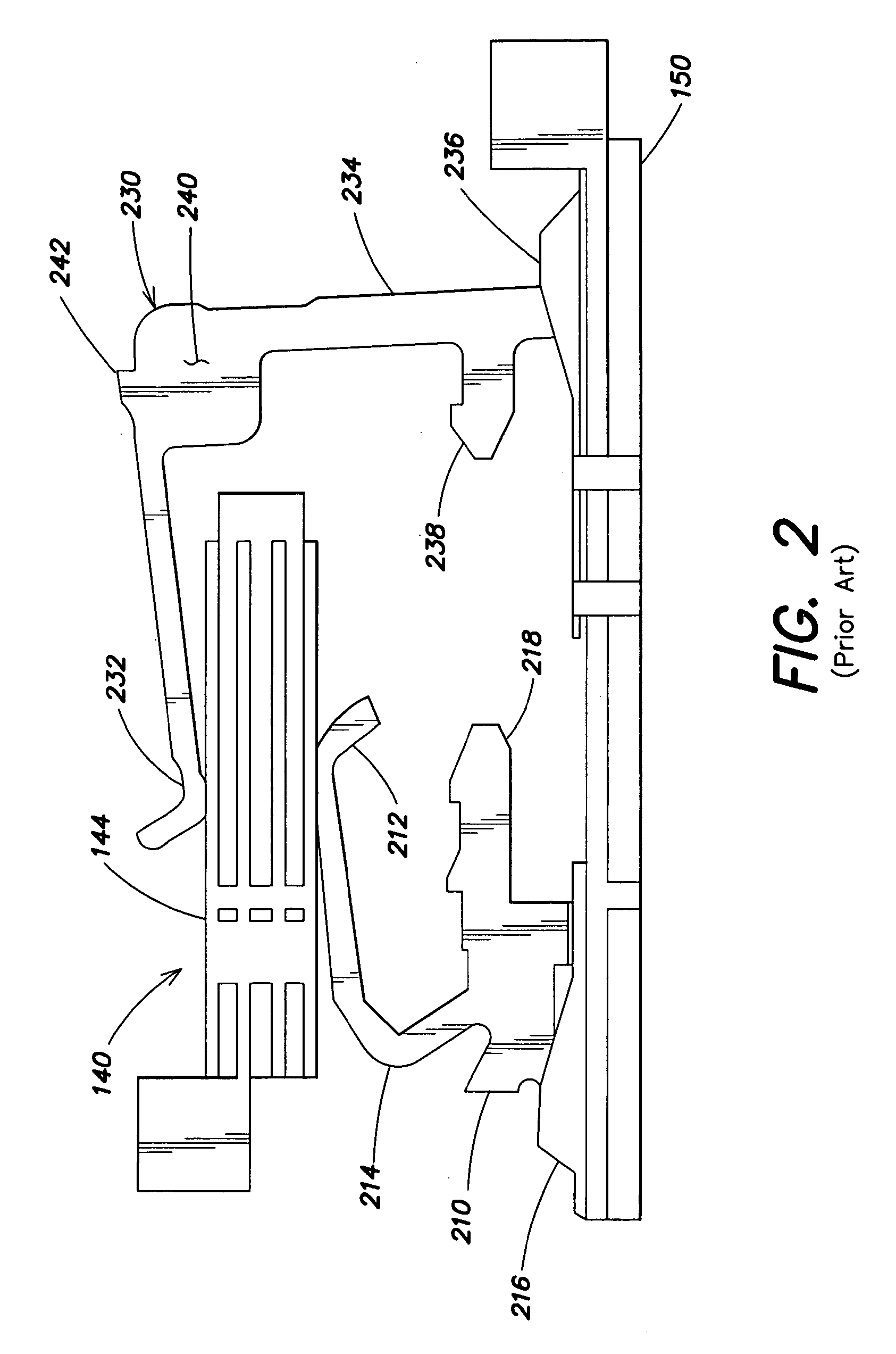

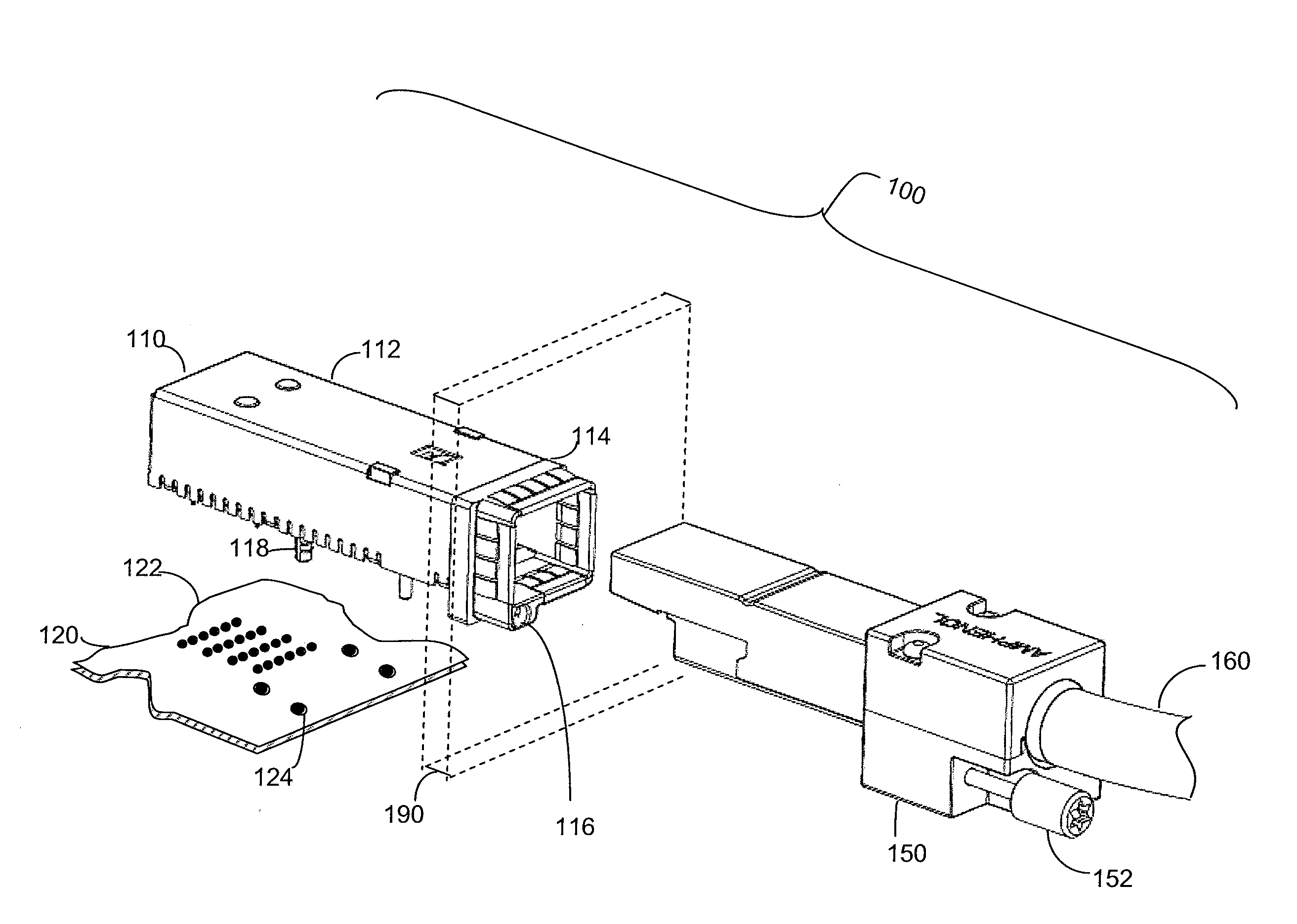

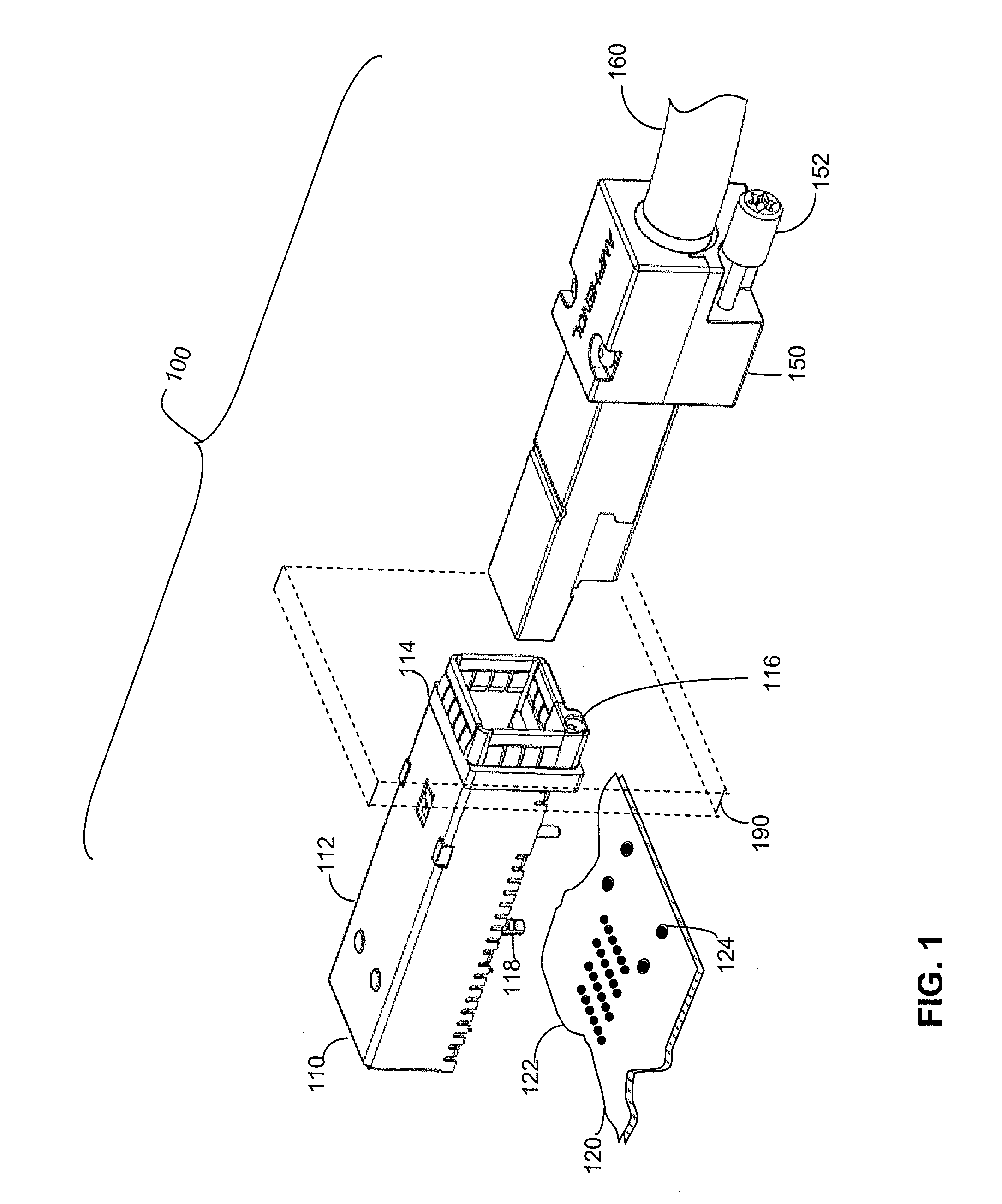

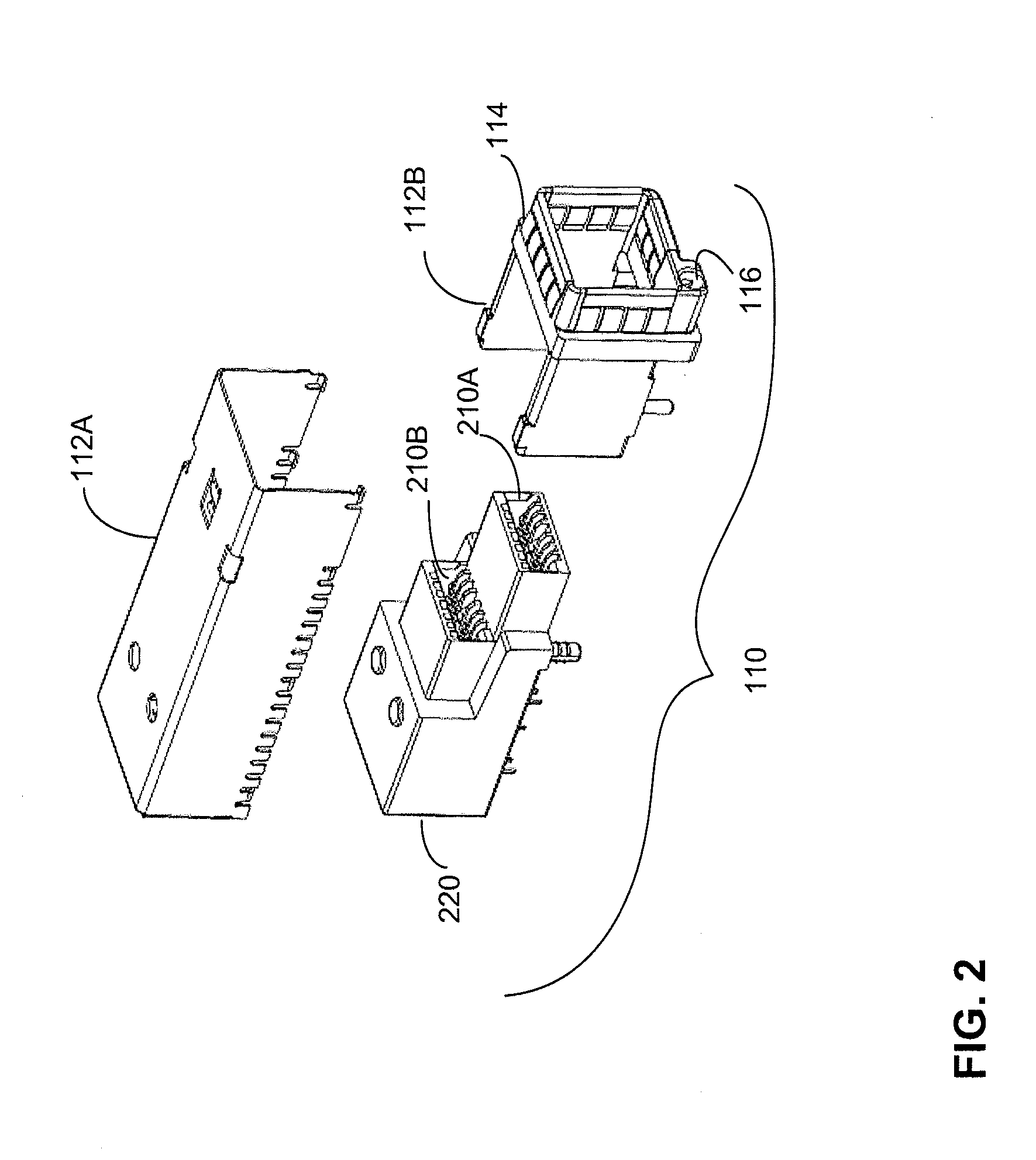

High performance, small form factor connector with common mode impedance control

Techniques for improving electrical performance of a connector. The techniques are compatible with the form factor of a standardized connector, such as an SFP connector or stacked SFP. The resulting connector has reduced insertion loss for high speed signals. Such techniques, which can be used separately or together, include shaping of conductive elements within the connector while still retaining the same mating contact arrangement. Changes may be made at the contact tail portions or in the intermediate portions where engagement to a connector housing occurs. The techniques also include the incorporation of lossy bridging members between conductive elements designated to be ground conductors. For connectors according to the stacked SFP configuration, multiple bridging members may be incorporated at multiple locations within the connector.

Owner:AMPHENOL CORP

High performance, small form factor connector

ActiveUS20130012038A1Improve electrical performanceImprove performanceElectric discharge tubesCoupling contact membersElectricitySmall form factor

Techniques for improving electrical performance of a connector. The techniques are compatible with the form factor of a standardized connector, such as an SFP connector or stacked SFP. The resulting connector has reduced insertion loss for high speed signals. Such techniques, which can be used separately or together, include shaping of conductive elements within the connector while still retaining the same mating contact arrangement. Changes may be made at the contact tail portions or in the intermediate portions where engagement to a connector housing occurs. The techniques also include the incorporation of lossy bridging members between conductive elements designated to be ground conductors. For connectors according to the stacked SFP configuration, multiple bridging members may be incorporated at multiple locations within the connector.

Owner:AMPHENOL CORP

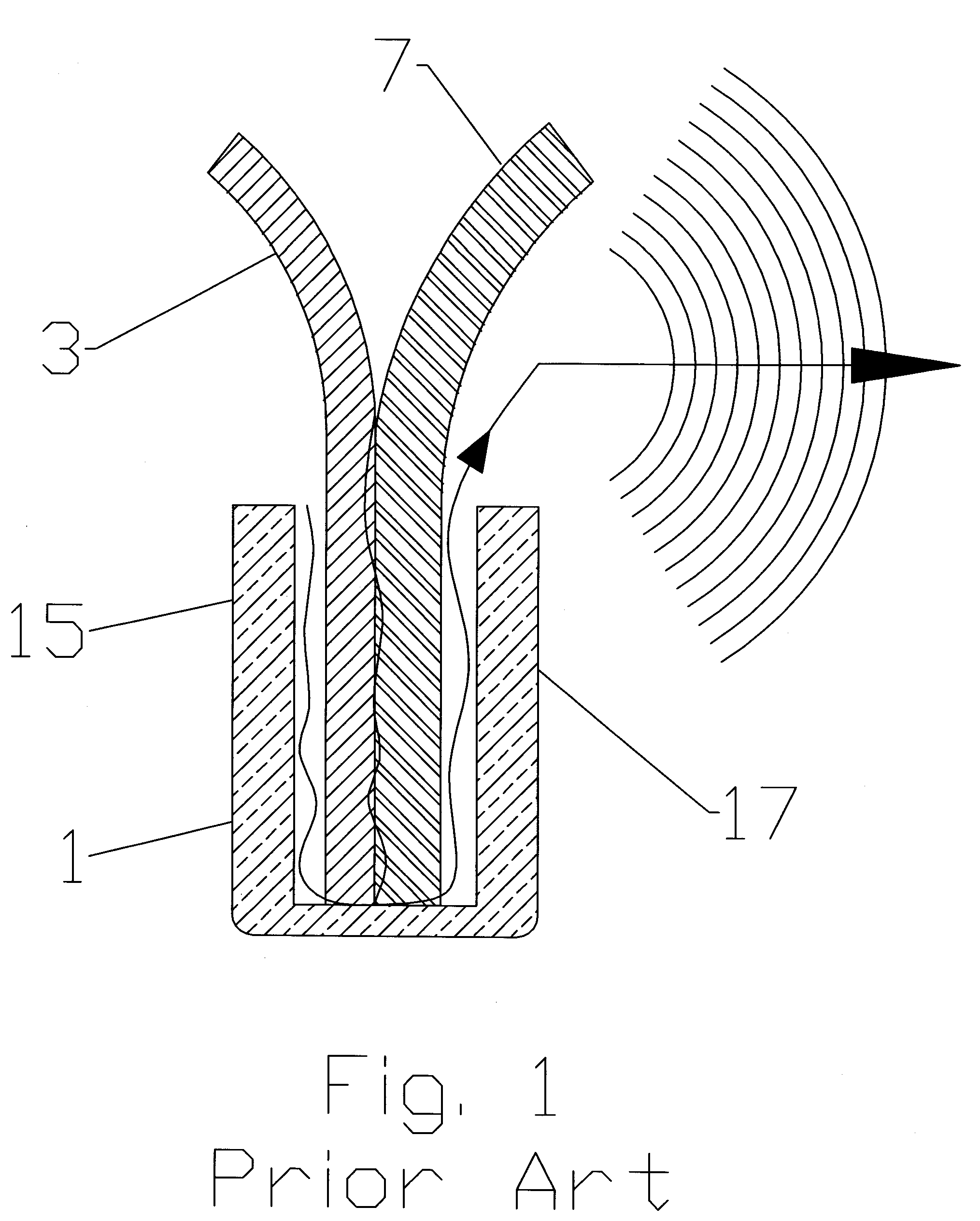

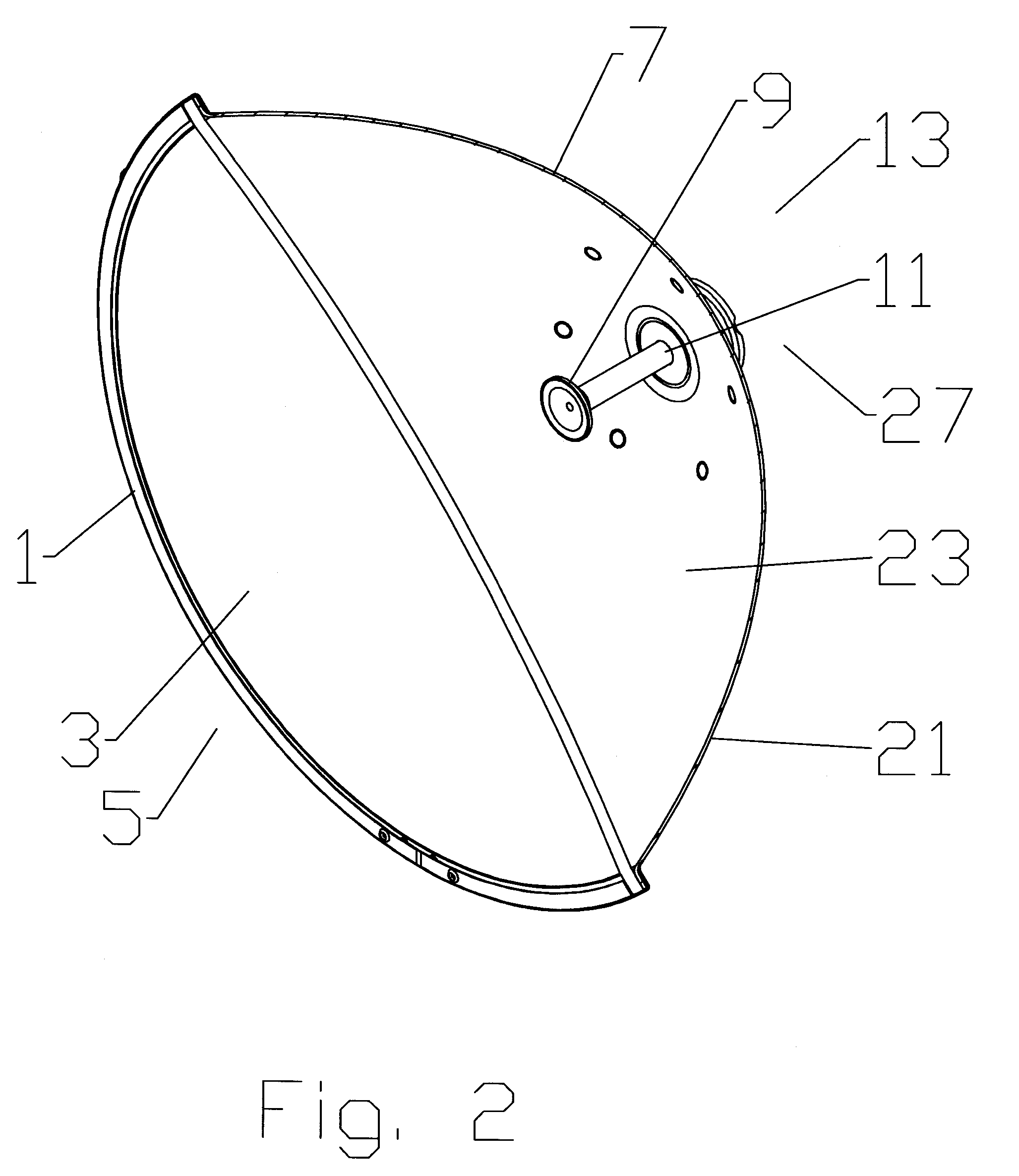

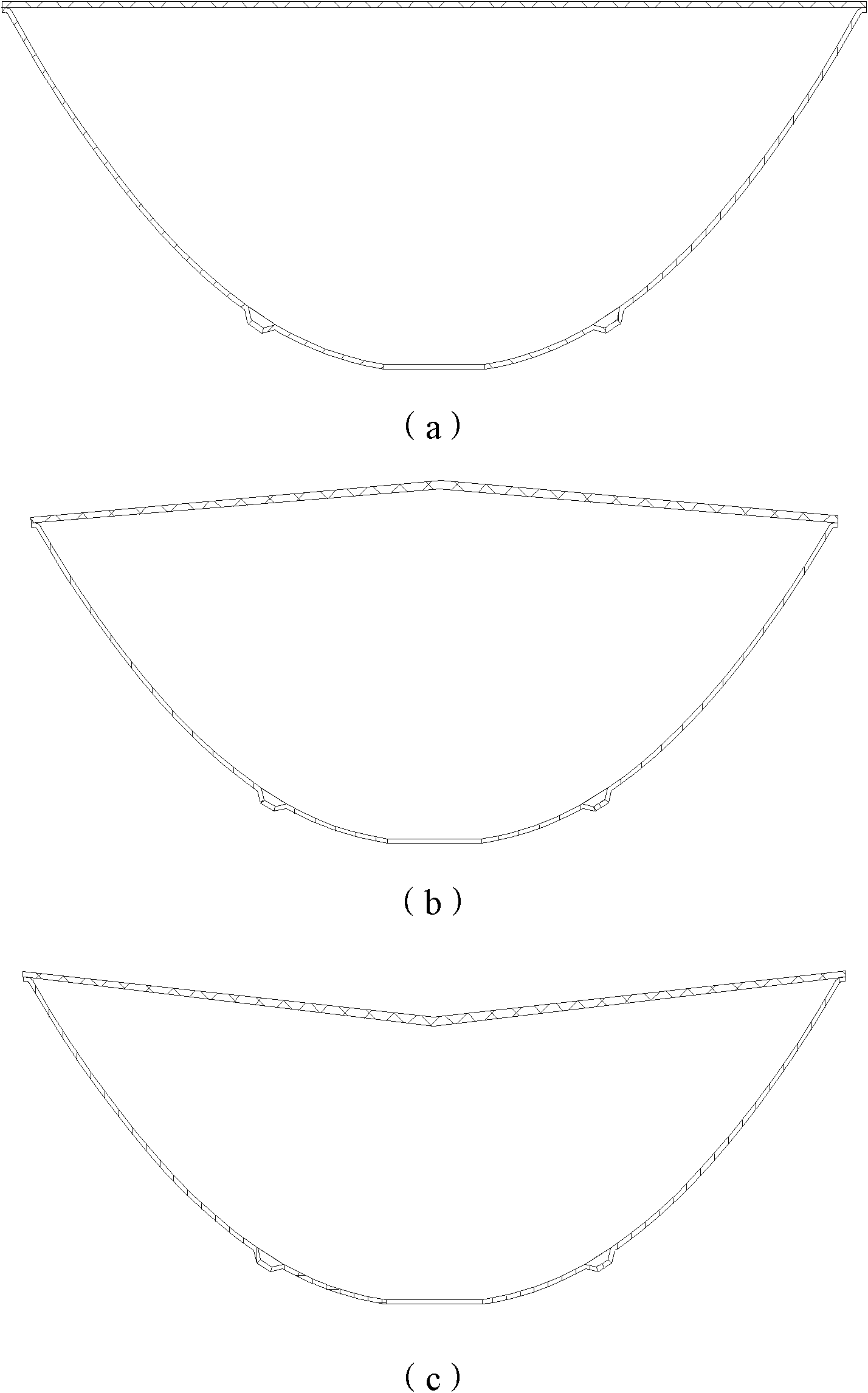

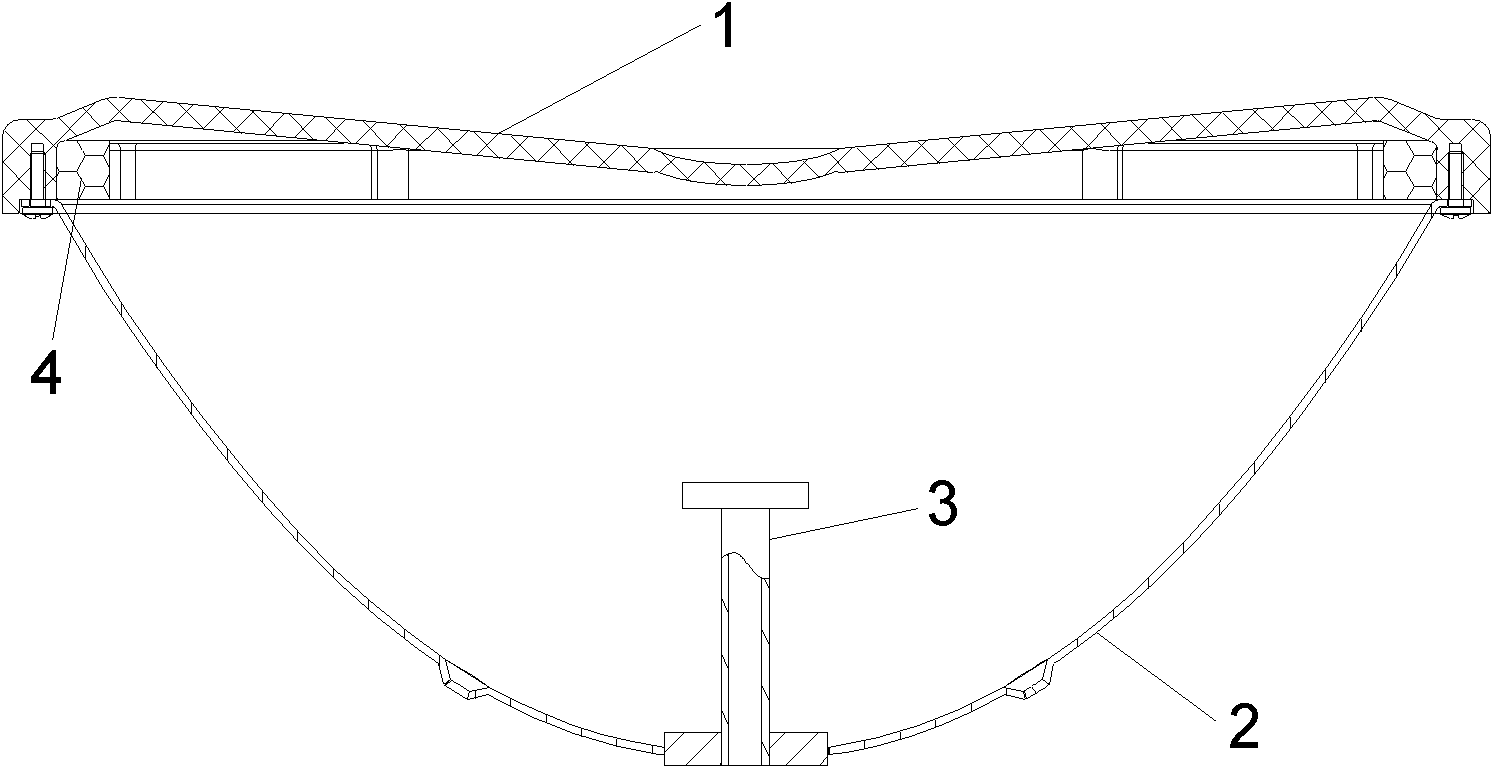

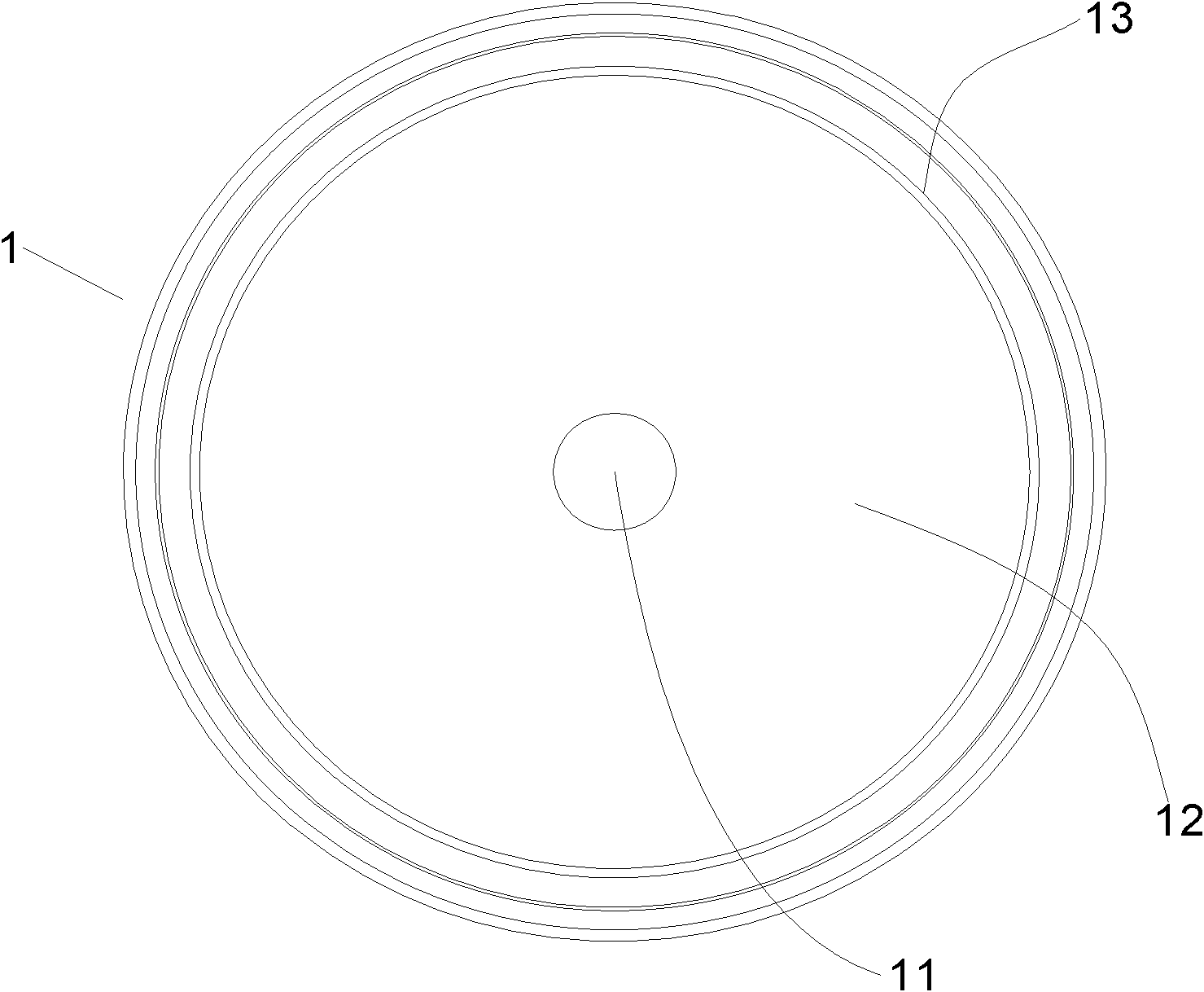

Microwave antenna and outer cover thereof

ActiveCN101958461BImproved radiation F/B performanceHigh gainRadiating element housingsMicrowavePhase retardation

A microwave antenna radome used for covering a microwave antenna and of rotatablely symmetrical includes the following components all of which are arranged concentrically; a compensation portion located at a central portion of the radome and used for compensating phase delay of electrical field at the central portion of an antenna aperture plane caused by blocking of a feed; a main reflective portion located on a periphery of the compensation portion and used for reflecting electromagnetic wave originating from the feed of the microwave antenna at a specific direction biased from the feed; and an auxiliary reflective portion located on a periphery of the main reflective portion and used for bunching and reflecting diffraction electromagnetic wave at edge of the microwave antenna. All components of the radome are specifically shaped. The microwave antenna thus formed has good electrical performance, stable structure and low cost.

Owner:COMBA TELECOM SYST (GUANGZHOU) LTD

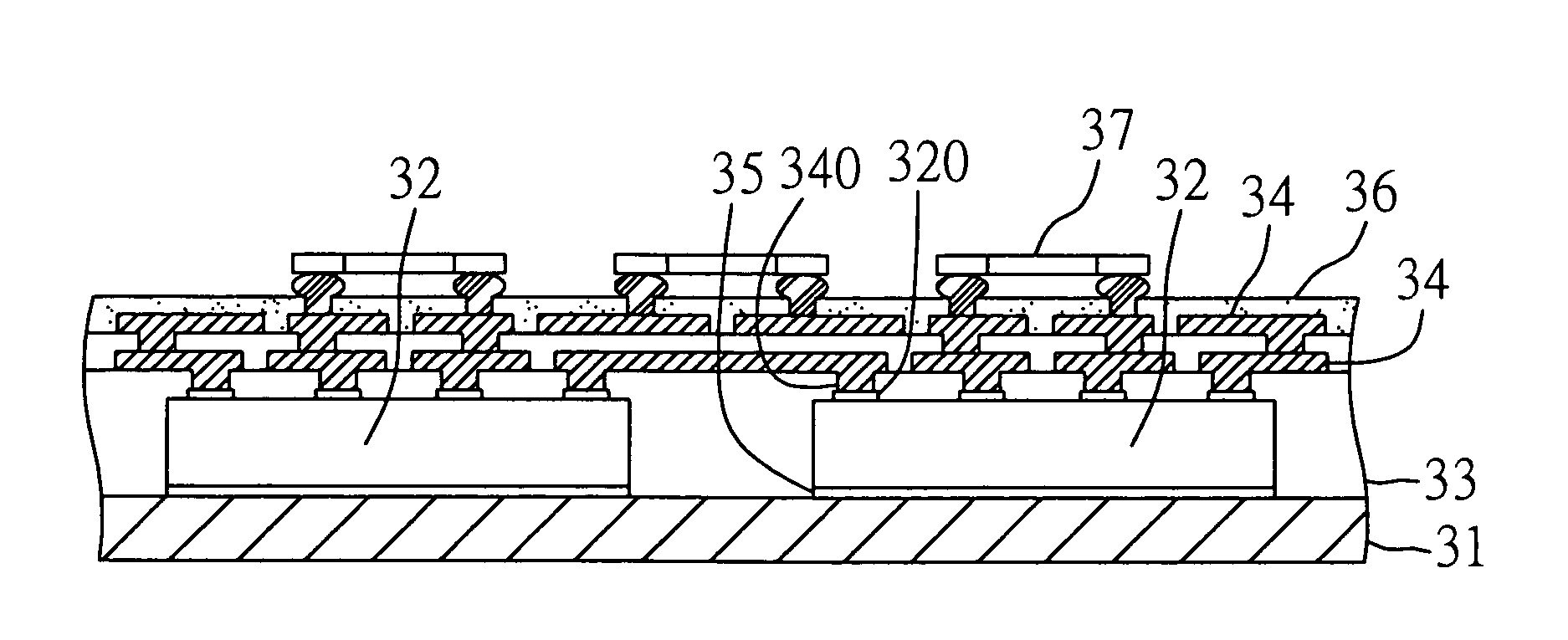

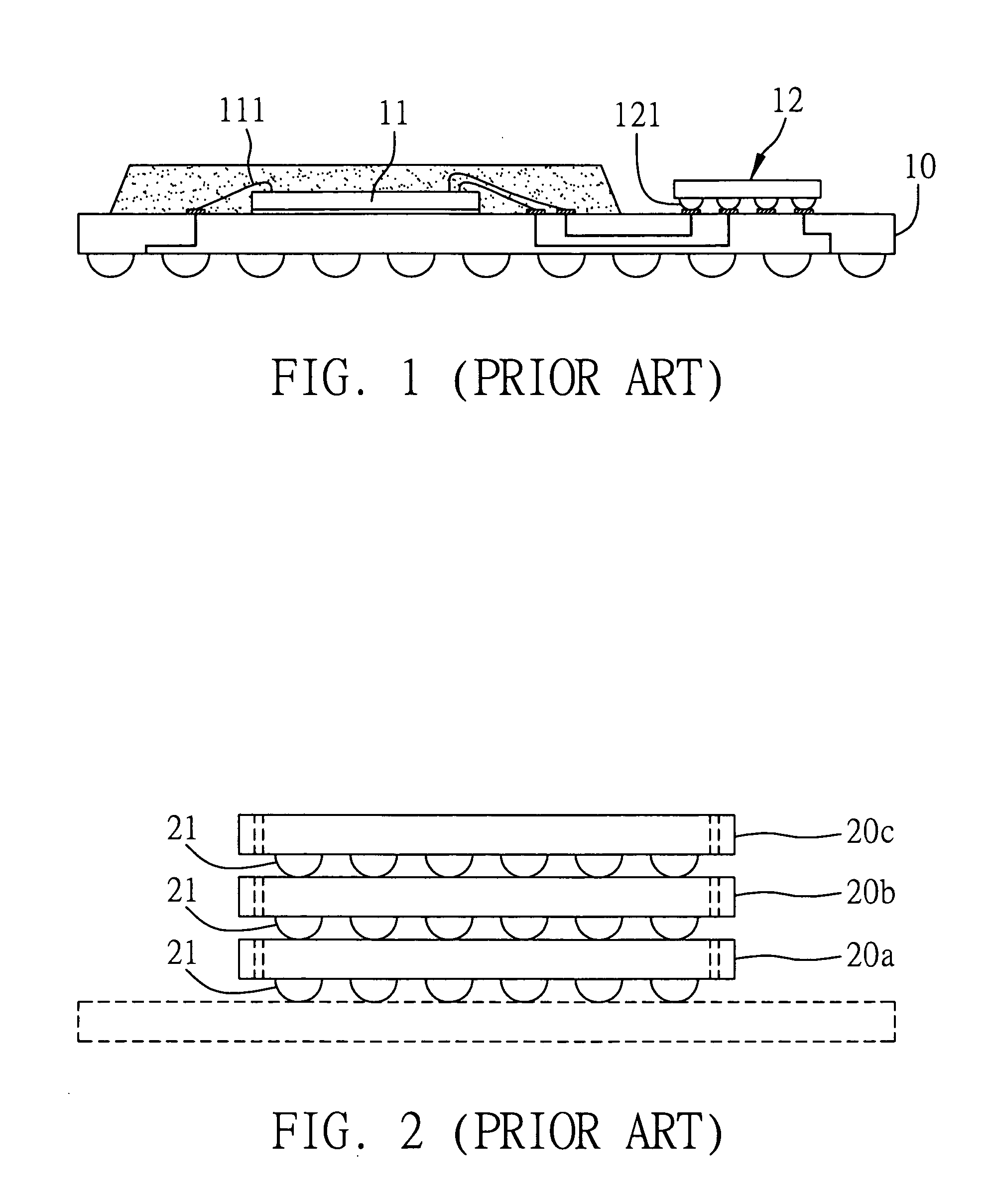

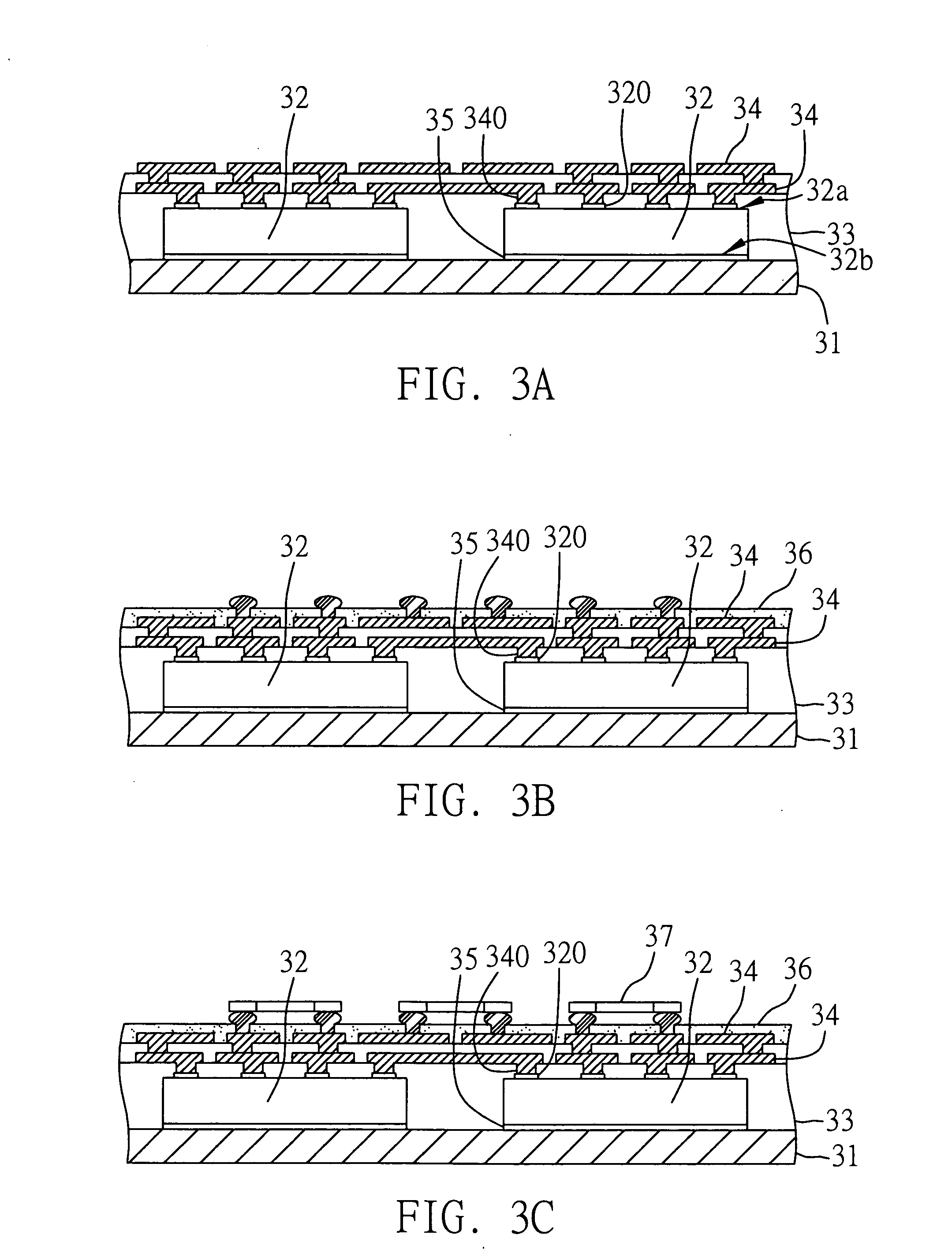

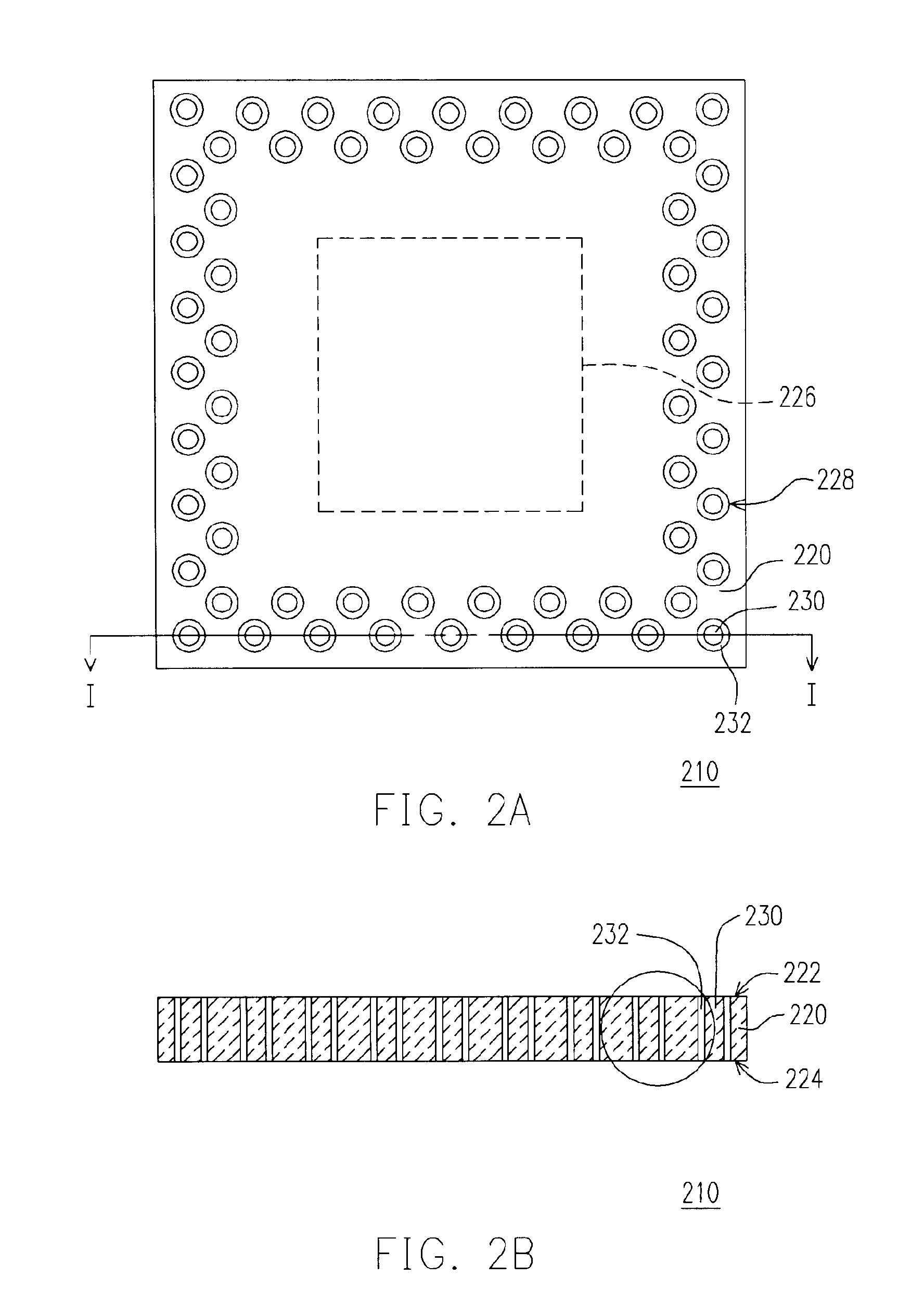

Direct connection multi-chip semiconductor element structure

ActiveUS20060001152A1Reduce thicknessImprove electrical performanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipElectrical connection

A direct connection multi-chip semiconductor element structure is proposed. A plurality of semiconductor chips are mounted and supported on a metal heat sink, such that heat generated by the chips during operation can be dissipated via the heat sink. A circuit structure is extended from the chips to provide direct electrical extension for the chips and improve the electrical performances. And exposed electrical connection terminals can be formed in the circuit structure extended from the chips to be directly electrically connected to an external electronic device.

Owner:PHOENIX PRECISION TECH CORP

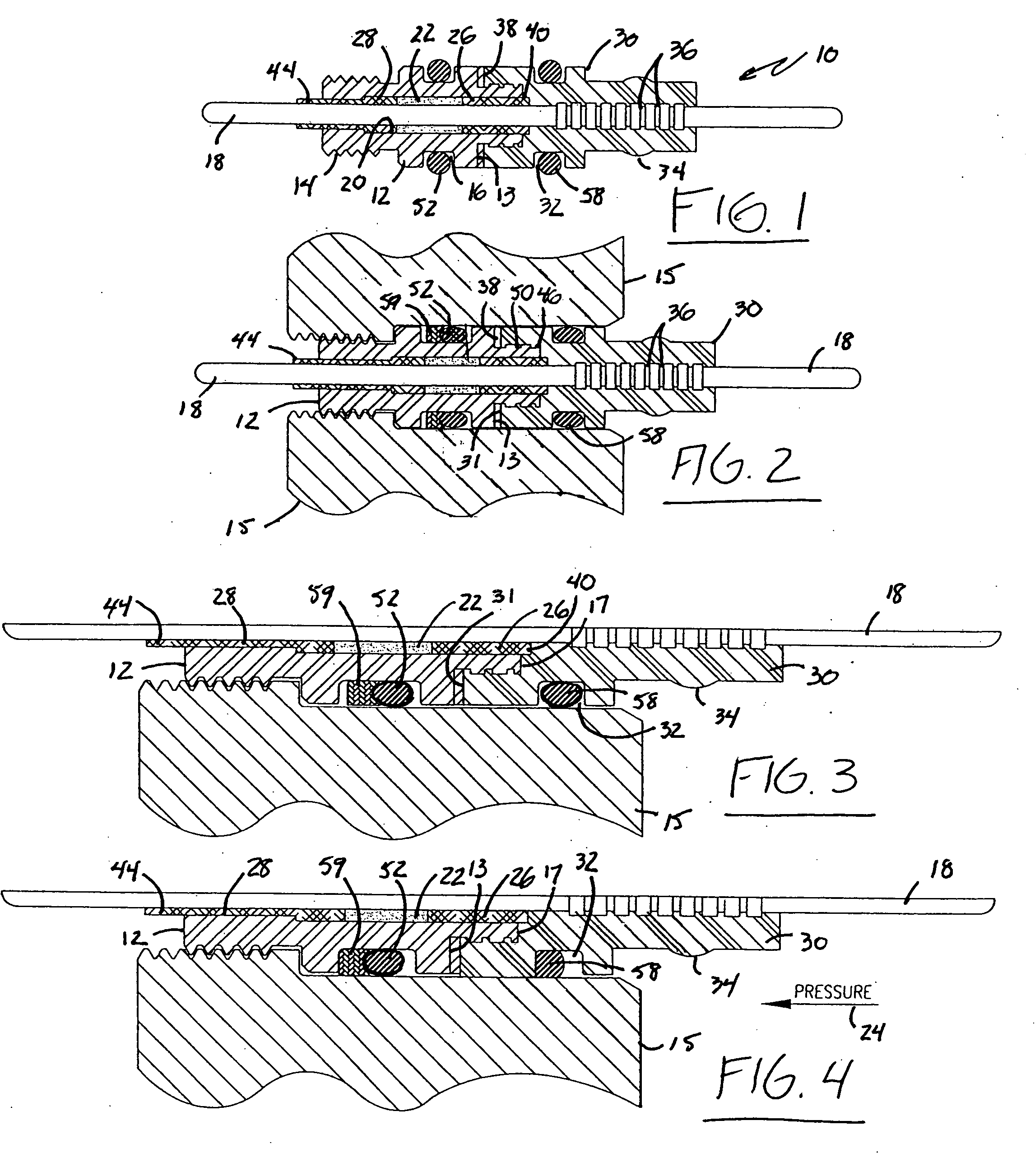

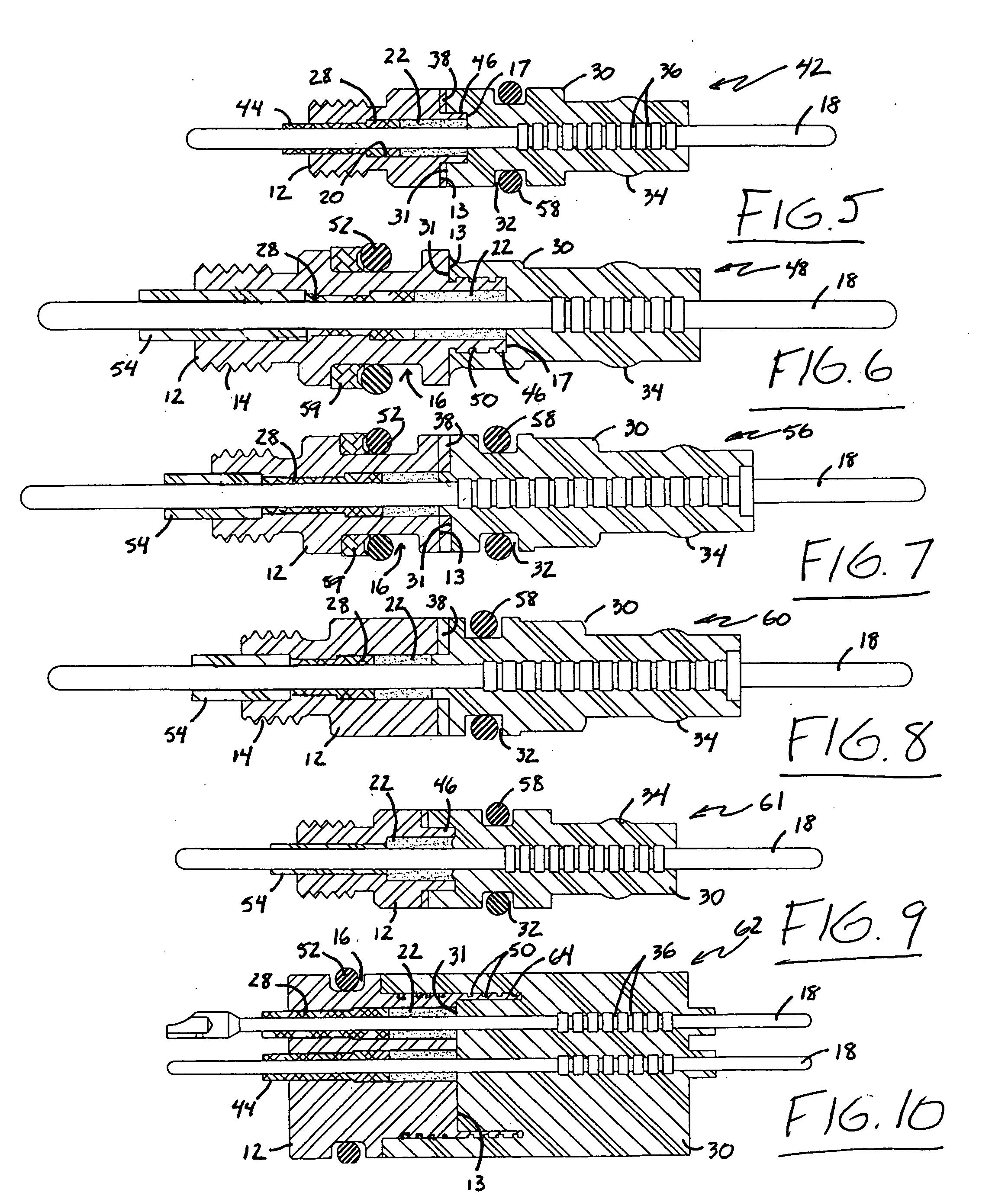

Hybrid glass-sealed electrical connectors

An electrical connector adapted for mounting to an electrical apparatus used in either high pressure or high temperature, or both high temperature and high pressure, applications. A metal body is provided for mounting to the electrical apparatus with at least one conductor for carrying electricity to or from the electrical apparatus extending therethrough and a thermoplastic jacket is applied over the conductors to the end of the metal body that is subjected to either high pressure or high temperature, or both high temperature and high pressure, for sealing around the conductor. An insulative material is interposed between the metal body and the conductor for sealing around the conductor. In addition to providing two independent internal and two independent external seals, the glass-to-metal seal limits cold-flow (creep) of thermoplastic along the pin and through the metal body. This feature effectively eliminates the catastrophic hydraulic failures possible with prior connectors utilizing a pin, metal body, and high temperature thermoplastic. Because of the redundant internal and external seals, the connector provides undistorted electrical performance in the most hostile environments of temperature and pressure.

Owner:RING JOHN H +1

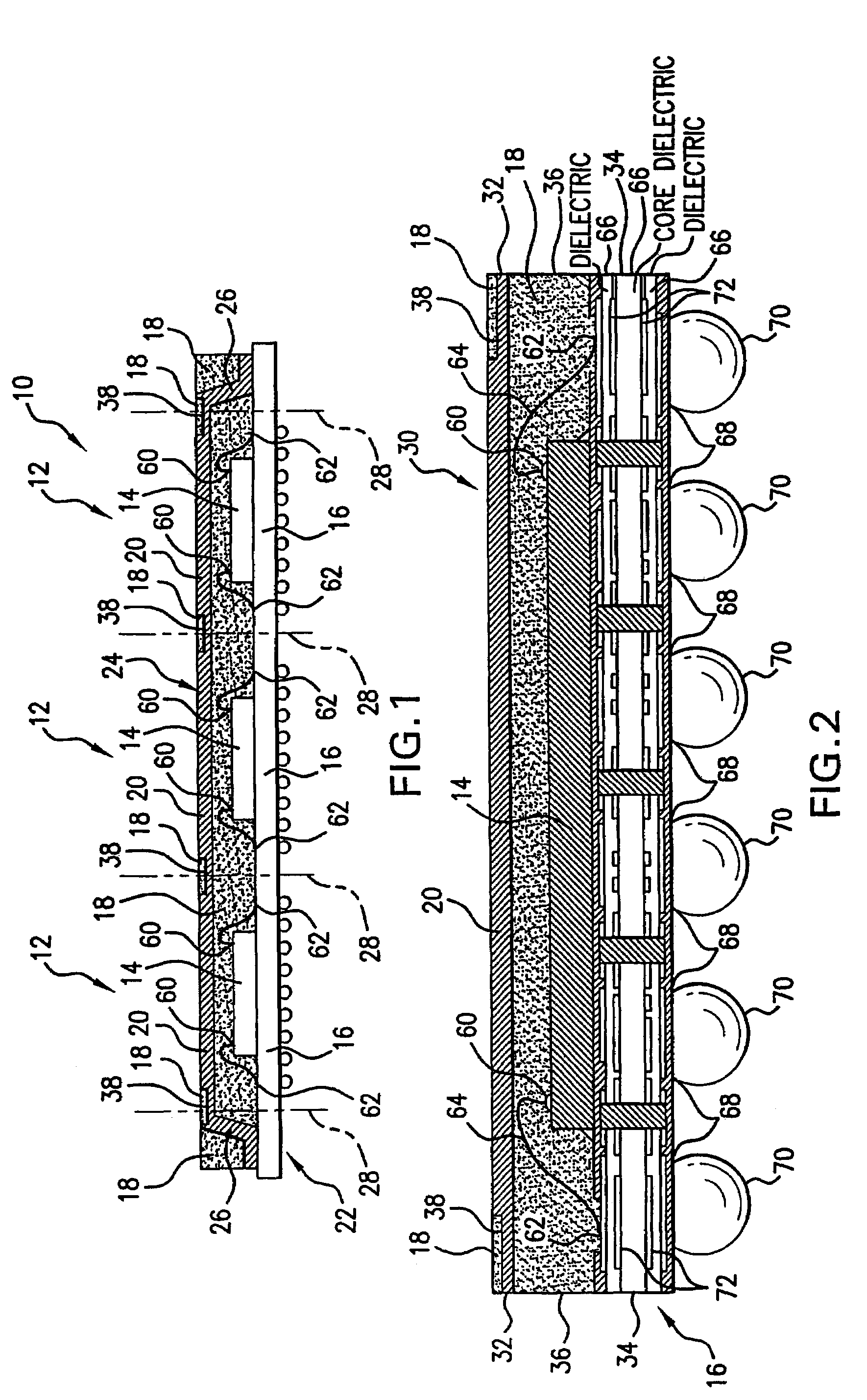

Very low effective dielectric constant interconnect Structures and methods for fabricating the same

InactiveUS7023093B2Low structural requirementsHigh mechanical strengthSemiconductor/solid-state device detailsSolid-state devicesCopper-wiringElectrical performance

A structure incorporates very low dielectric constant (k) insulators with copper wiring to achieve high performance interconnects. The wiring is supported by a relatively durable low k dielectric such as SiLk or SiO2 and a very low k and less robust gap fill dielectric is disposed in the remainder of the structure, so that the structure combines a durable layer for strength with a very low k dielectric for interconnect electrical performance.

Owner:GLOBALFOUNDRIES US INC

High bandwidth connector

ActiveUS20110230096A1Improved open pin field connectorReduce resonanceCoupling protective earth/shielding arrangementsCapacitanceElectricity

An improved open pin field connector is provided for enhanced performance when carrying high speed signals by selective application of one or more techniques for controlling electrical performance parameters. Lossy material may be positioned adjacent to conductive elements of the connector so as to reduce resonance in pairs of conductive elements and / or to provide a desired characteristic impedance for pairs of differential signal conductors. The lossy material may be shaped and positioned to avoid capacitive coupling that might otherwise increase cross talk. In a right angle connector, the lossy material may have a step-wise increase in thickness to provide comparable loss along longer and shorter conductive elements. Conductive elements may be shaped to balance performance characteristics of pairs selected to carry differential signals regardless of orientation along a row or column. Alternatively, conductive elements may have narrowed regions, covered with lossy portions, for reducing resonance while supporting DC signal propagation.

Owner:AMPHENOL CORP

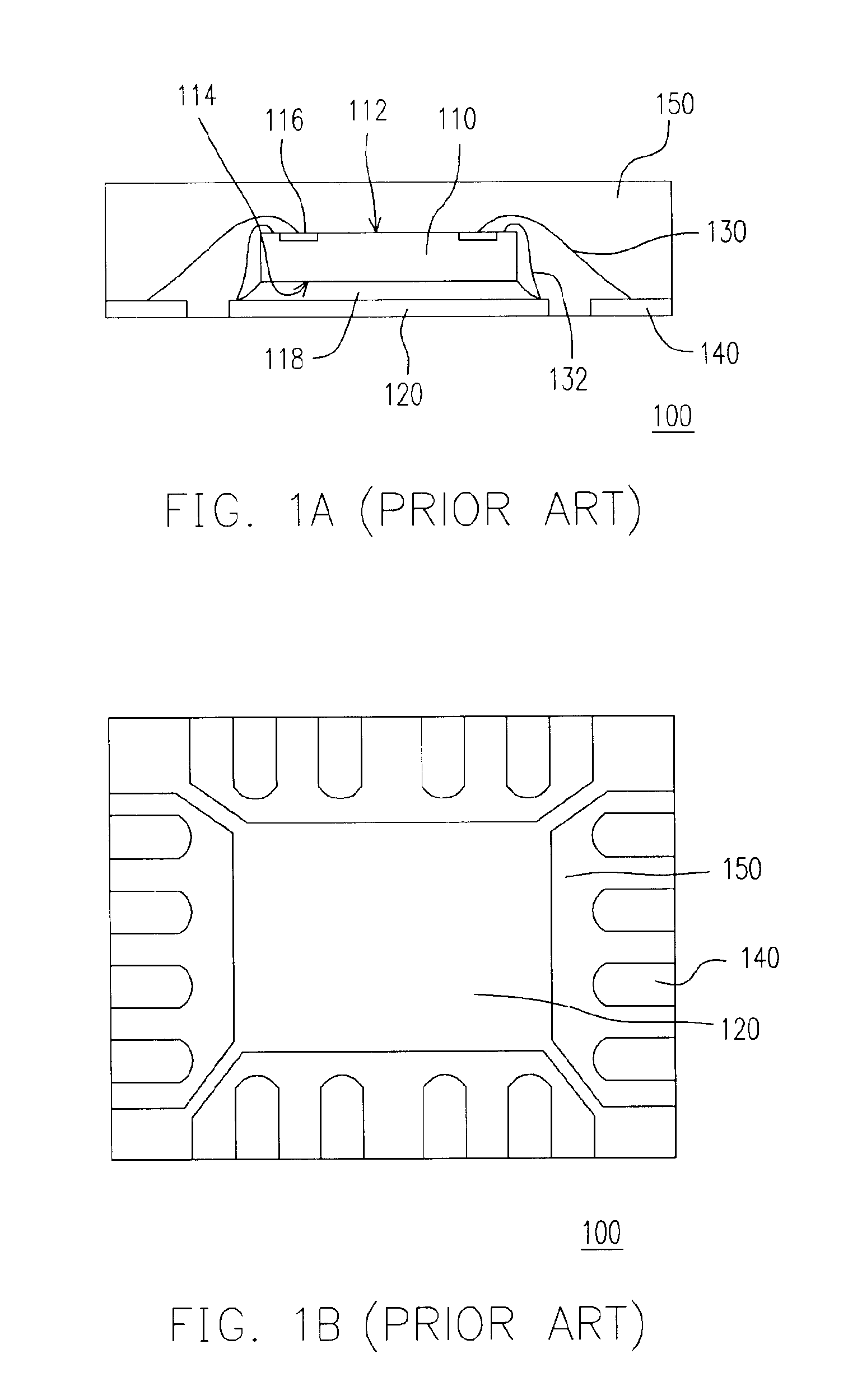

Quad flat no-lead chip carrier

ActiveUS6882057B2High I/O densityImprove chip qualitySemiconductor/solid-state device detailsSolid-state devicesLead bondingEngineering

A quad flat no-lead chip carrier for a wire-bonded chip package is provided. The chip carrier comprises a conductive plate, a plurality of conductive columns and a plurality of dielectric walls. A chip is attached to the conductive plate. The conductive plate furthermore has a plurality of columnar through holes distributed around a chip-bonding region. The conductive columns are set up within the columnar through holes. The dielectric walls are set up between the sidewall of the conductive columns and the inner surface of the columnar through holes. The chip is electrically connected to the conductive columns via conductive wires. The bottom end of the conductive columns serves as input / output contacts for connecting with external contacts. The chip carrier is able to increase overall density of the input / output contacts and improve the electrical performance of the chip package.

Owner:VIA TECH INC

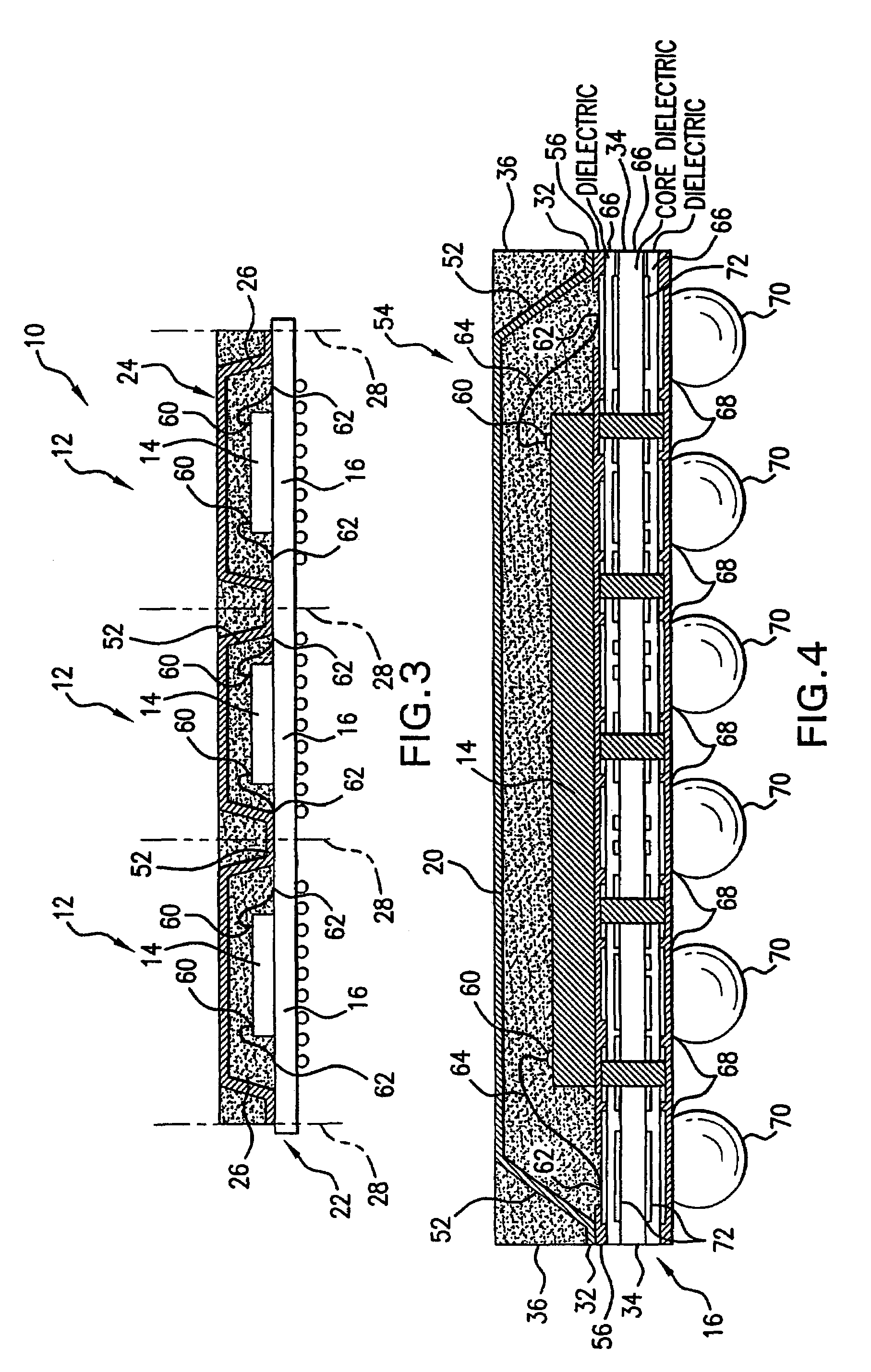

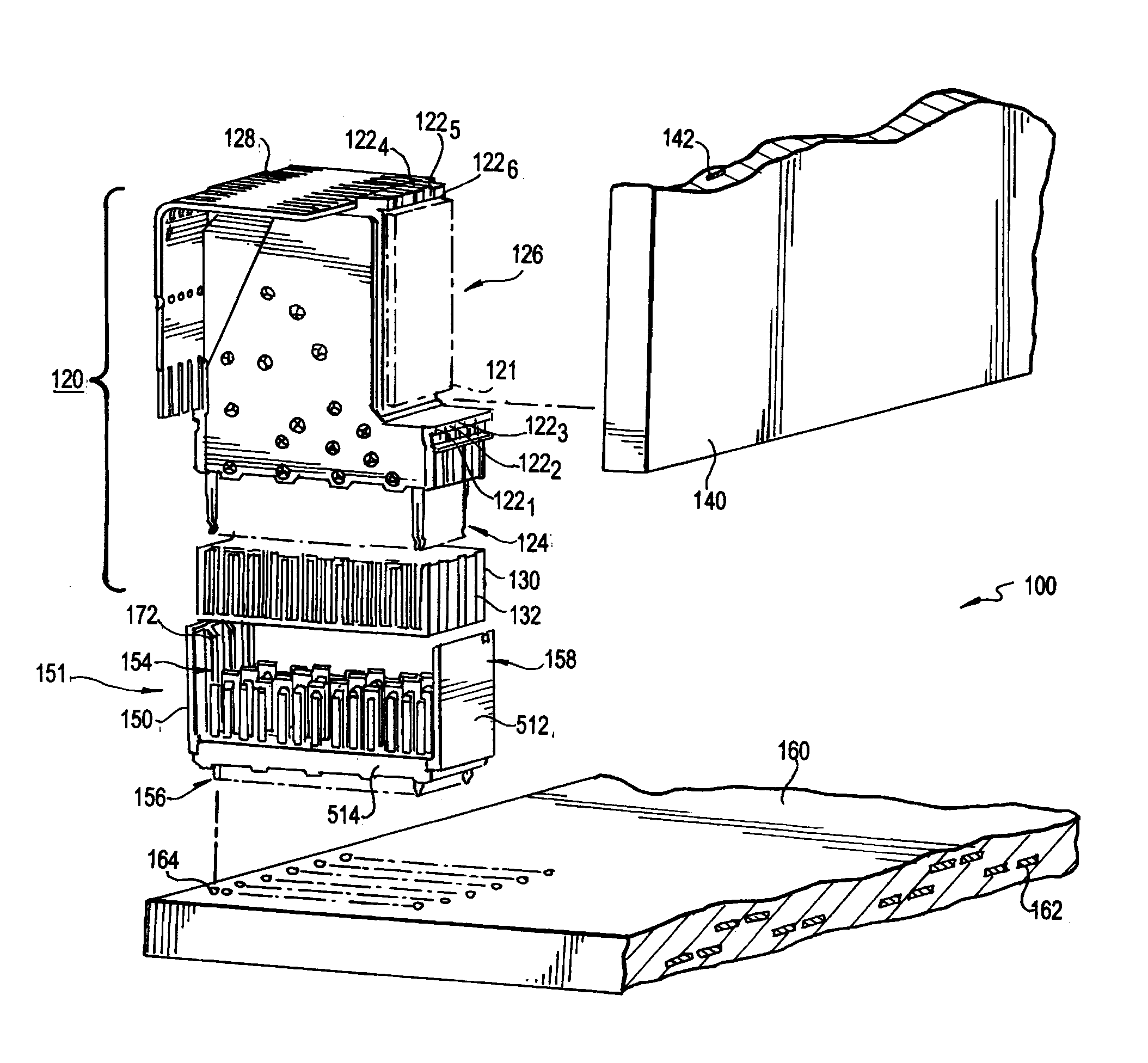

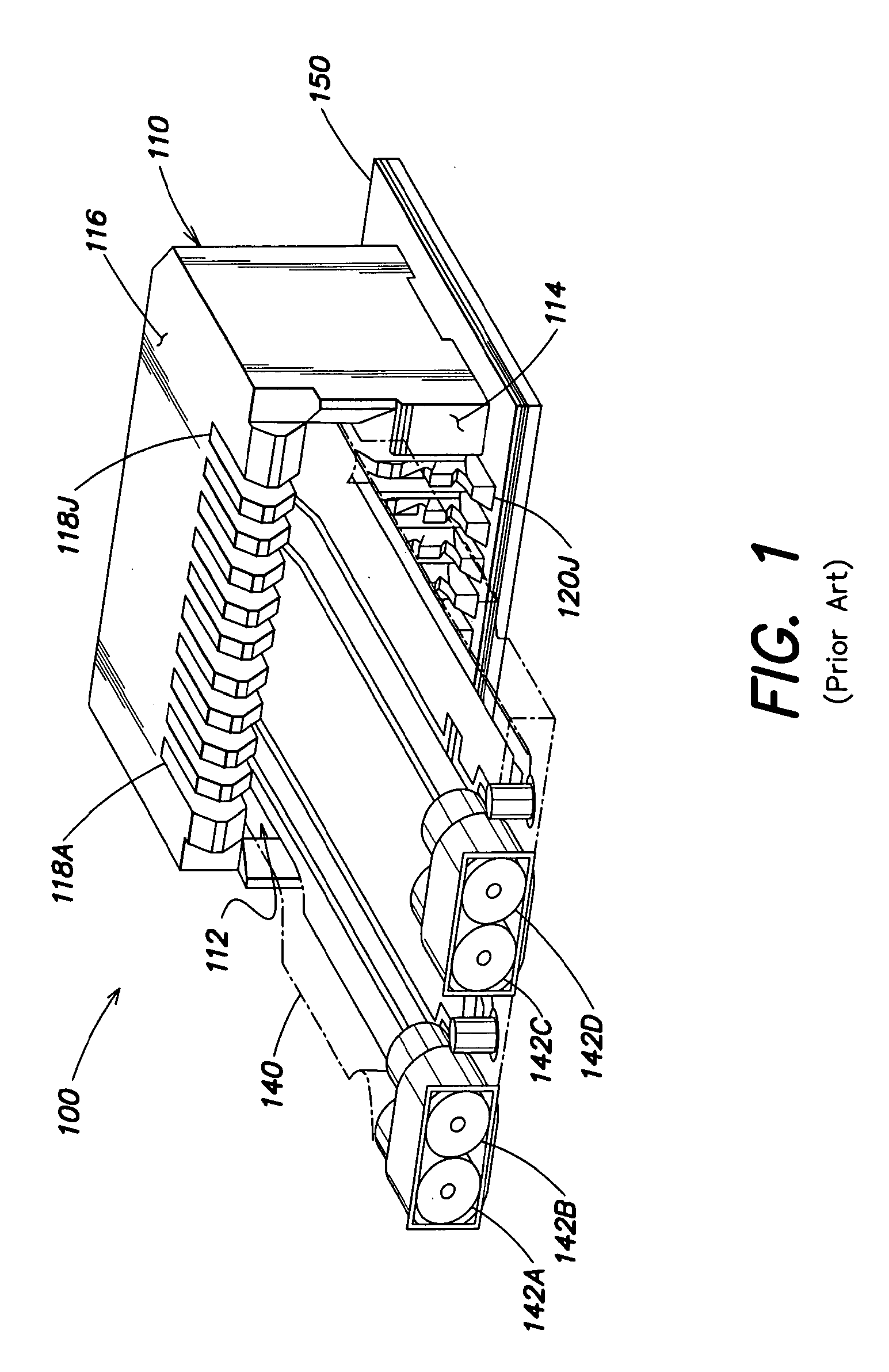

Thermal enhanced package for block mold assembly

InactiveUS7259445B2Semiconductor/solid-state device detailsSolid-state devicesElectrical performanceEngineering

A heat spreader (20) is added to a package to enhance thermal and advantageously electrical performance. In manufacture, a heat spreader precursor (24) is advantageously placed over a group of dies and secured after bonding (e.g., wire or tape bonding or flip-chip bonding) and before matrix / block mold. For example, a package strip (10) may consist of a row (linear array) of groups of die attach areas (e.g. in a rectangular array of four). The heat spreader precursor (20) may accommodate one such group or multiple groups along the package strip (10). The package strip (10) may then be singulated to form the individual packages. Each singulated package includes a die (14), its associated substrate 16 (e.g., either a lead frame or interposer type substrate) and a portion of the heat spreader precursor (24) as a heat spreader (20).

Owner:ADVANCED INTERCONNECT TECH LTD

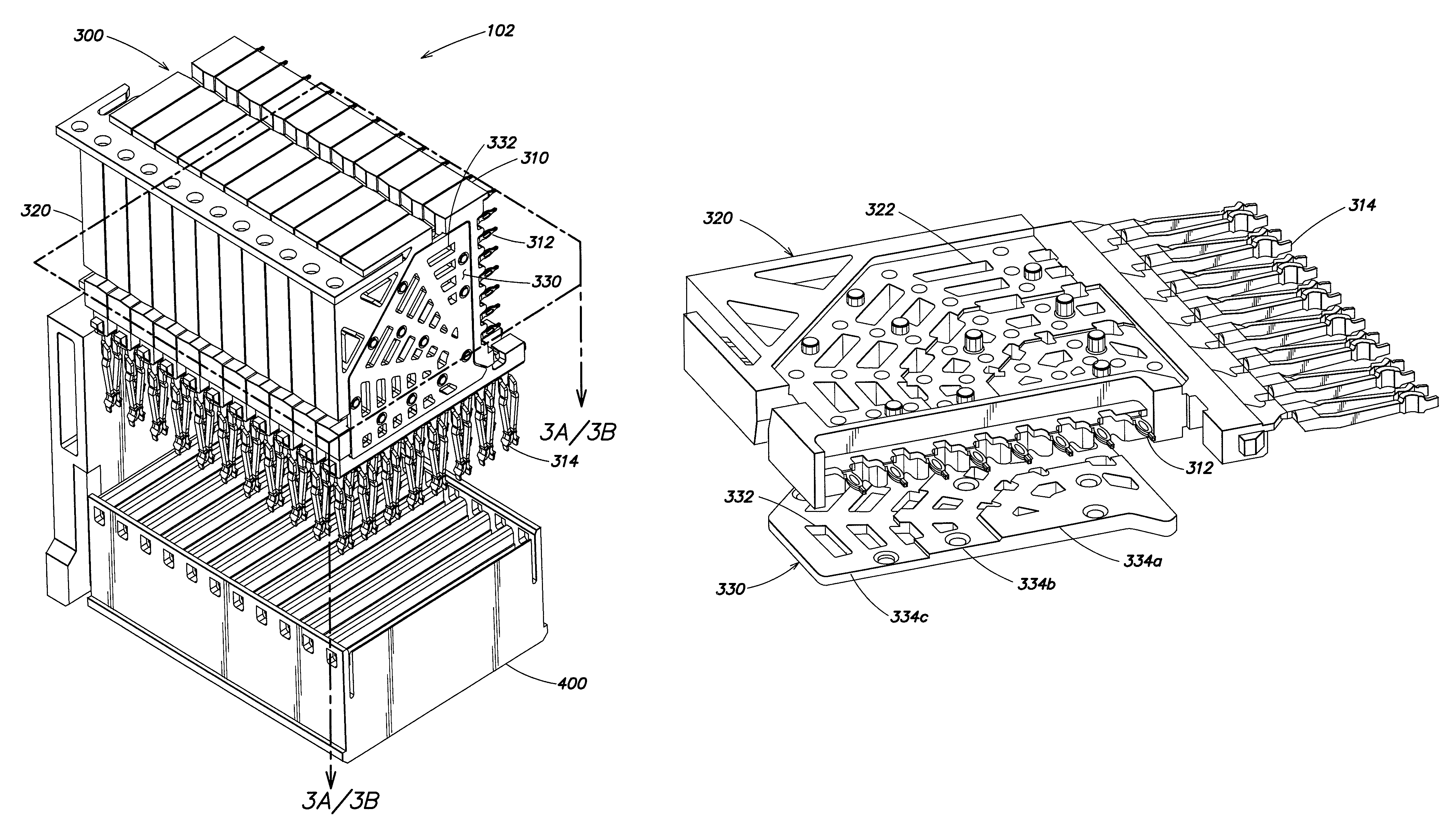

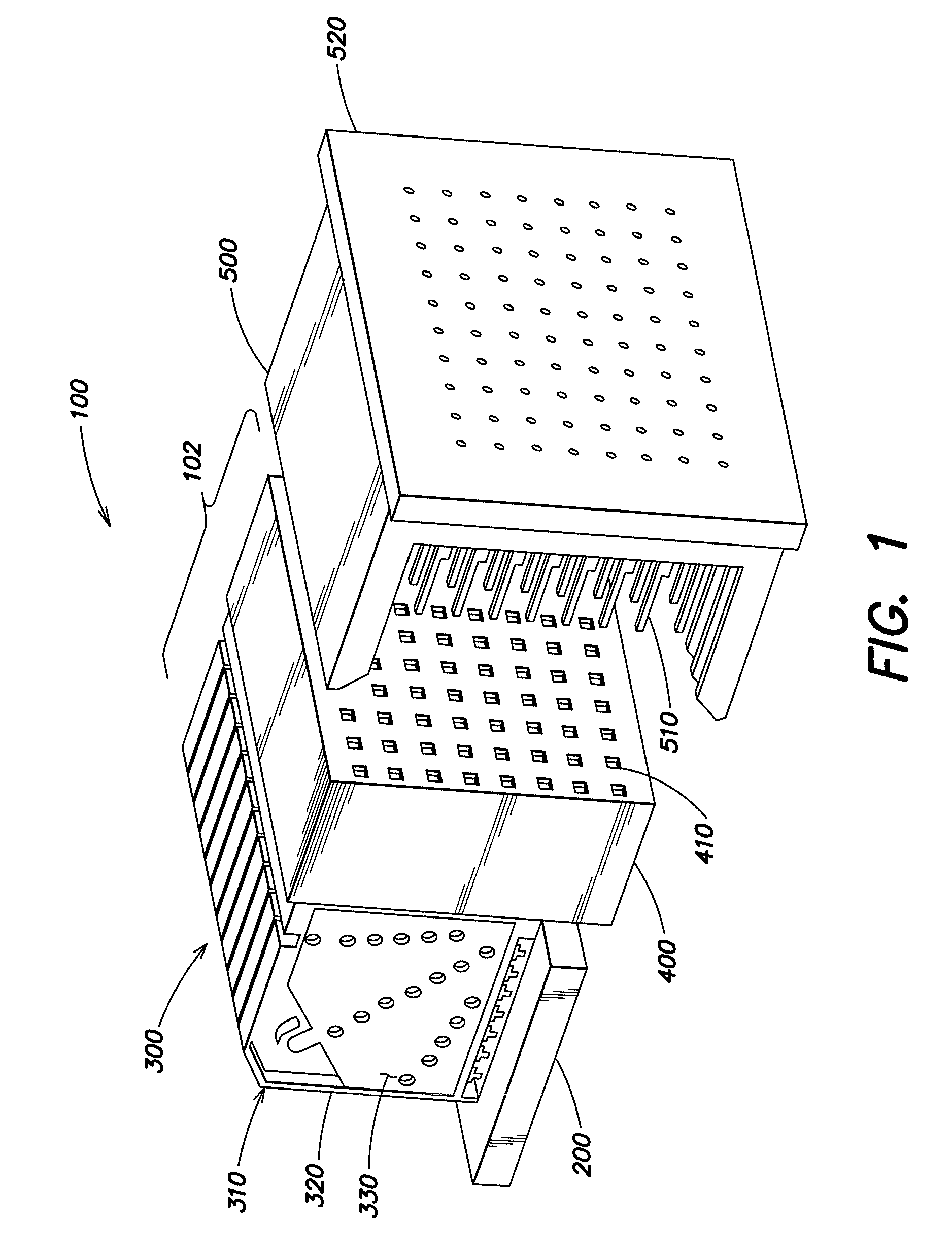

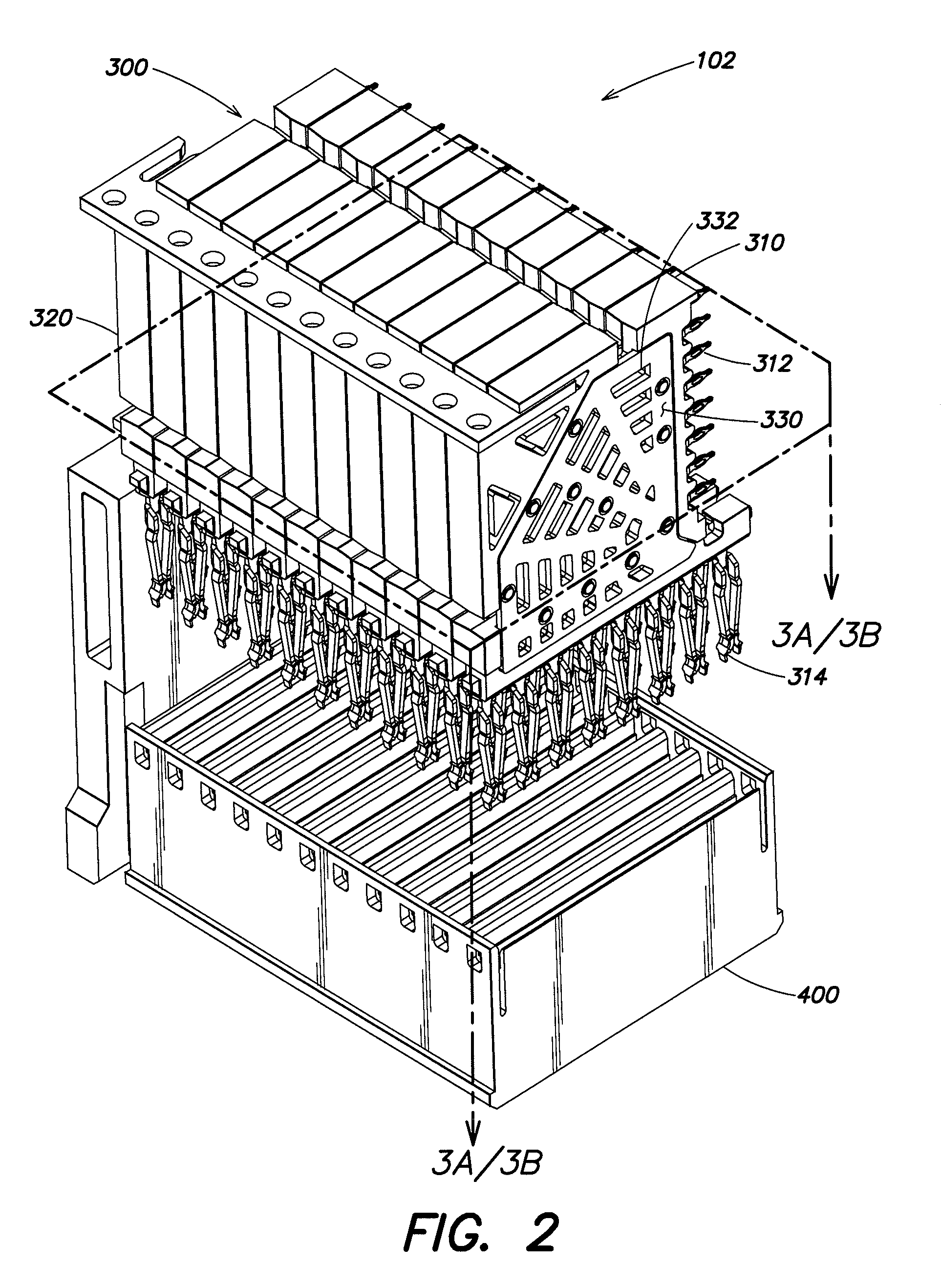

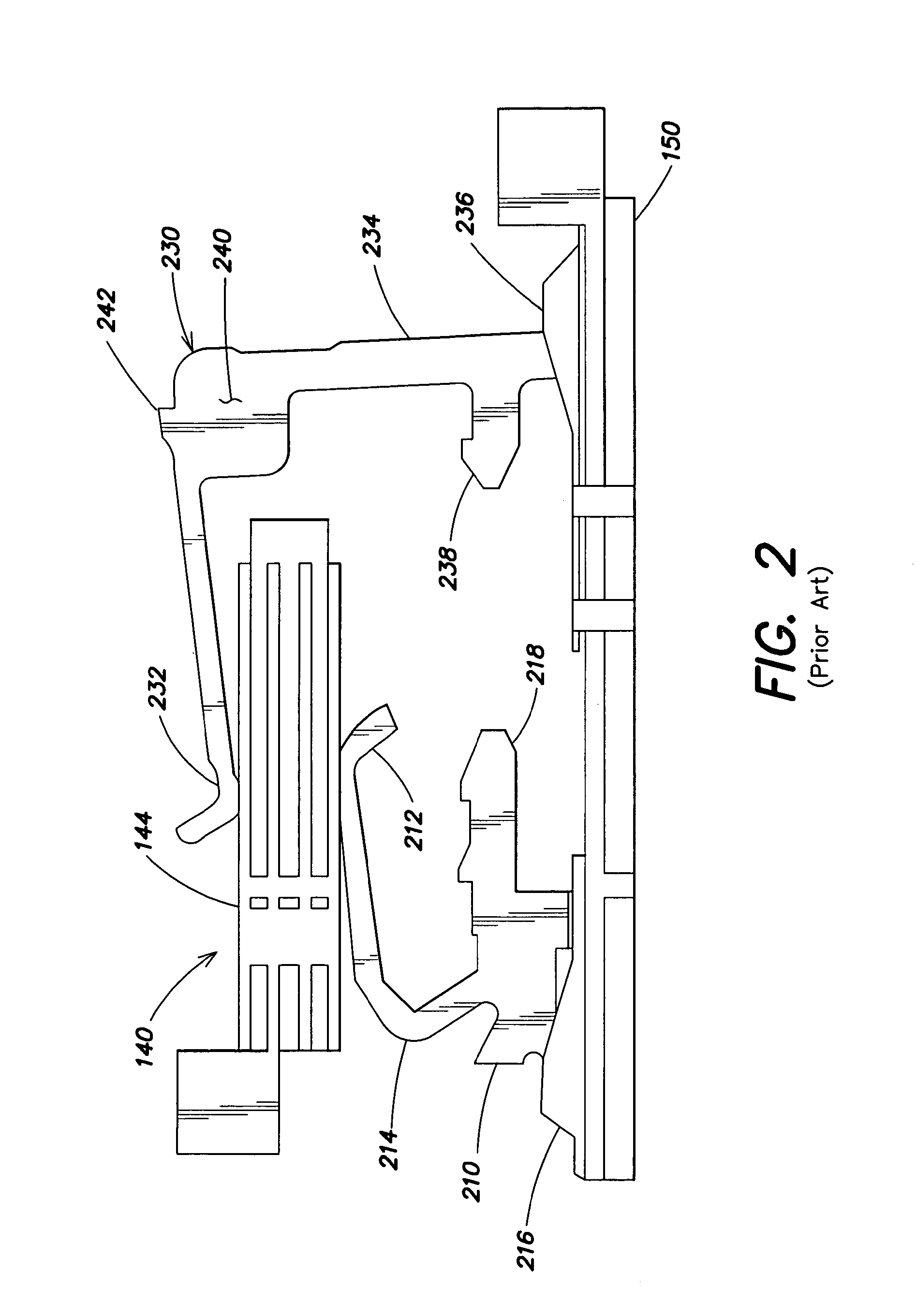

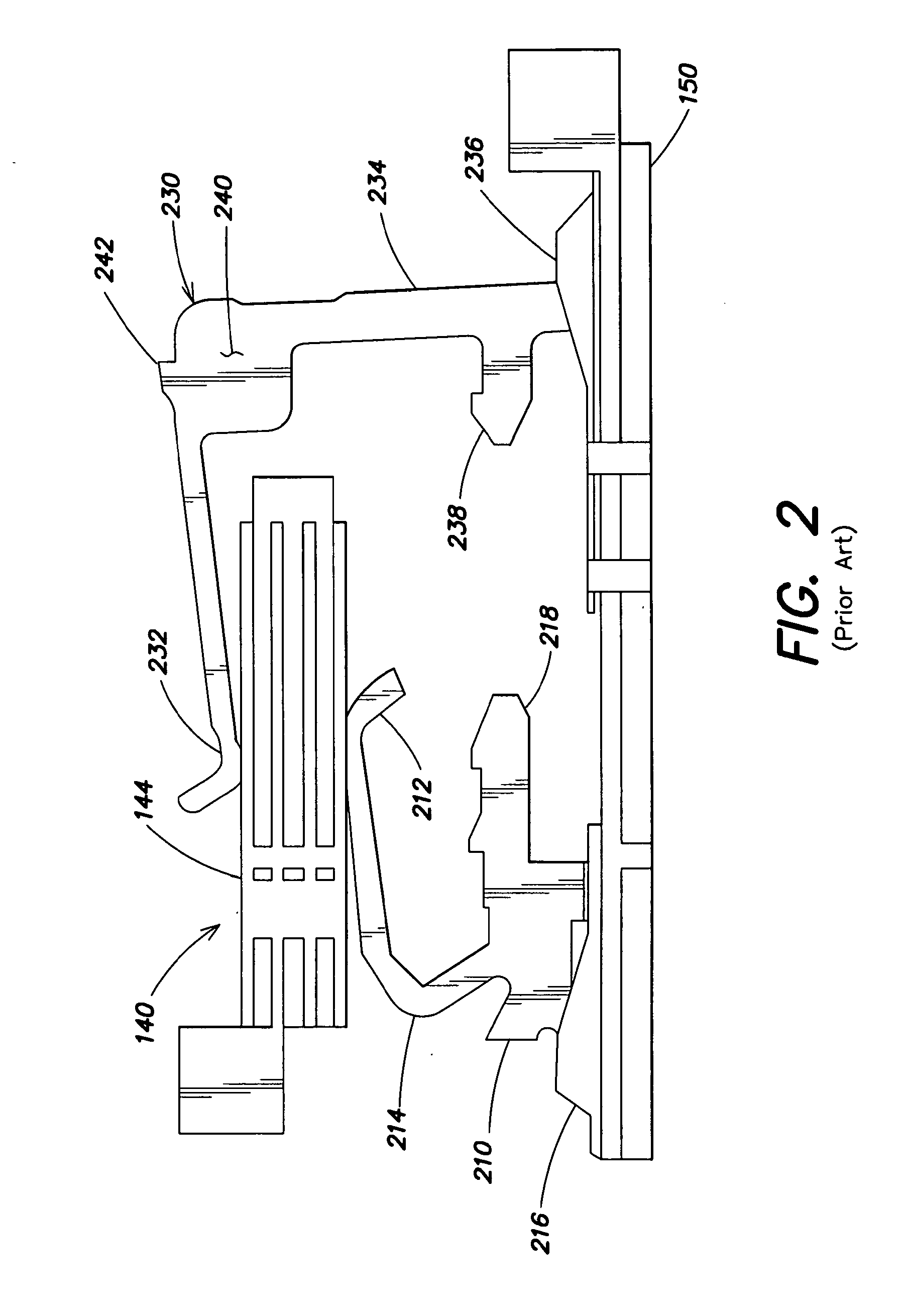

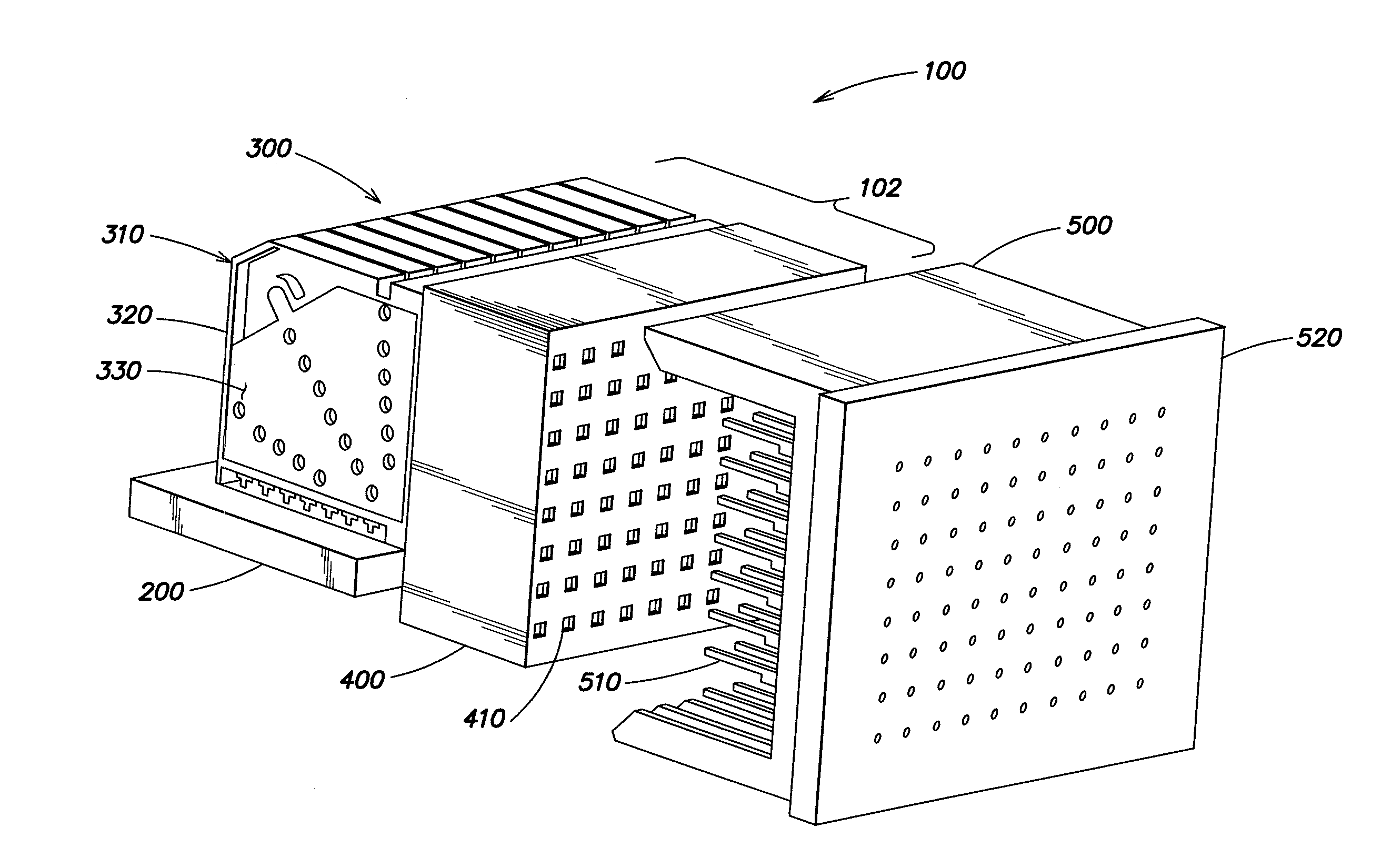

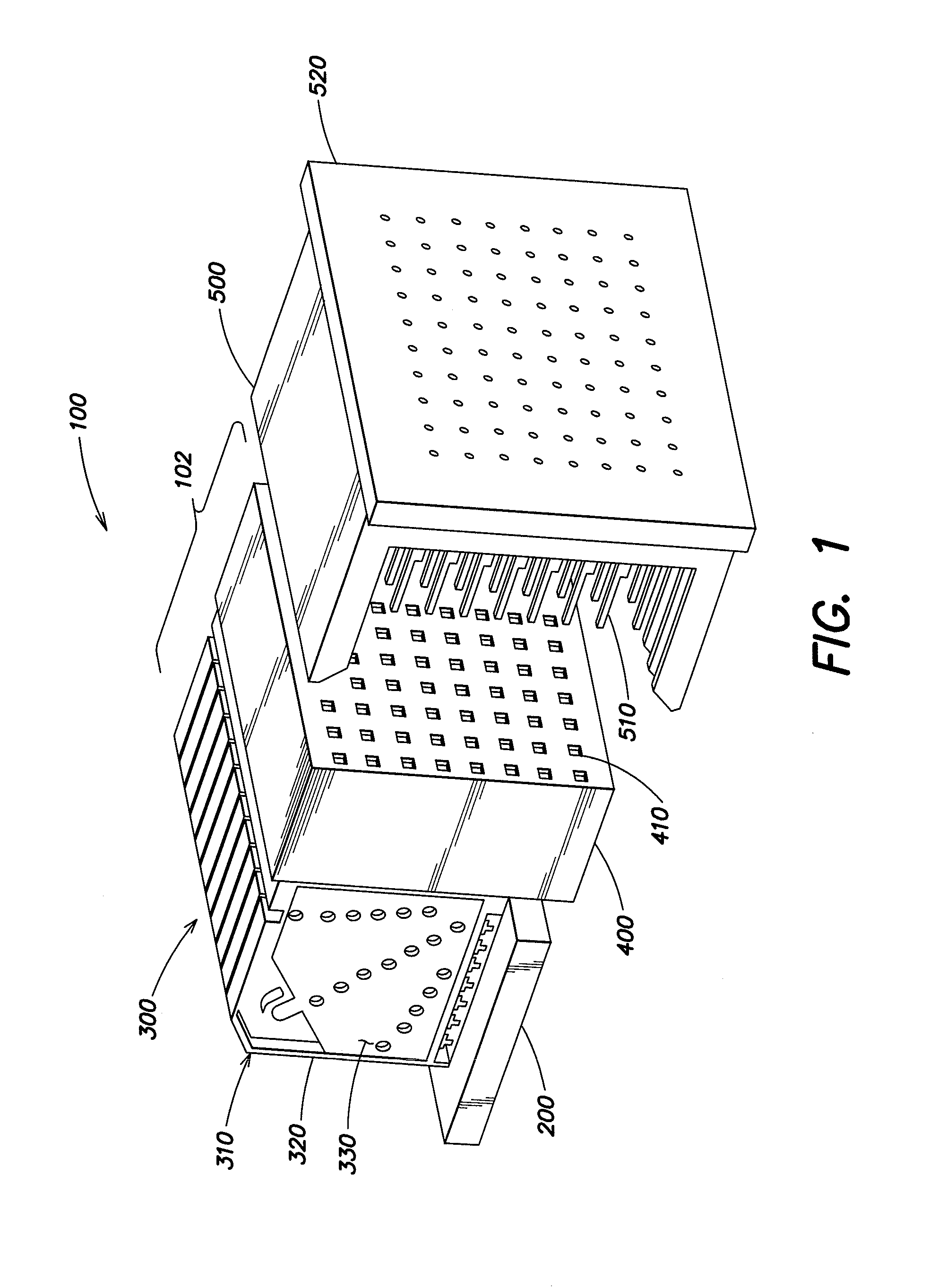

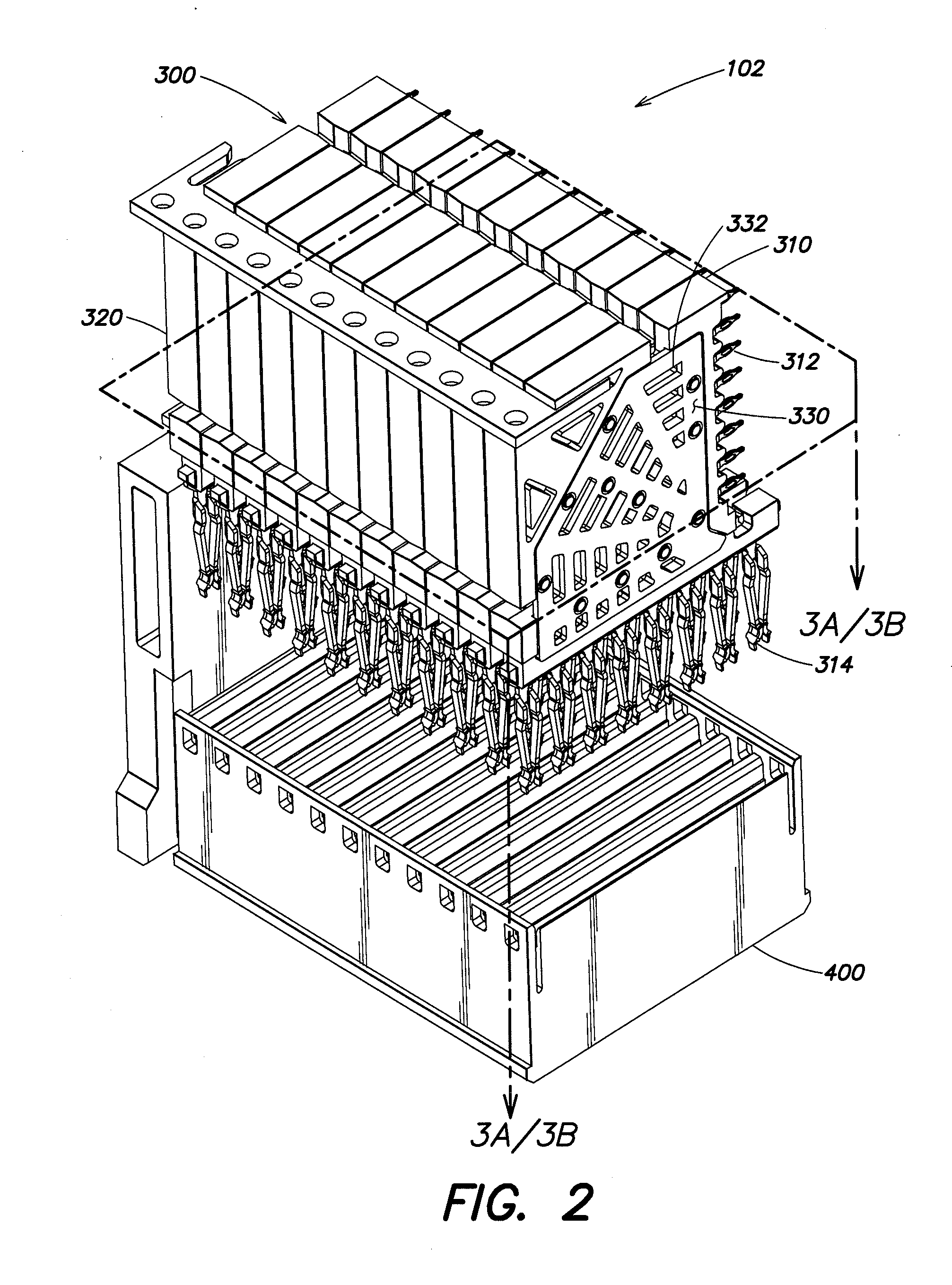

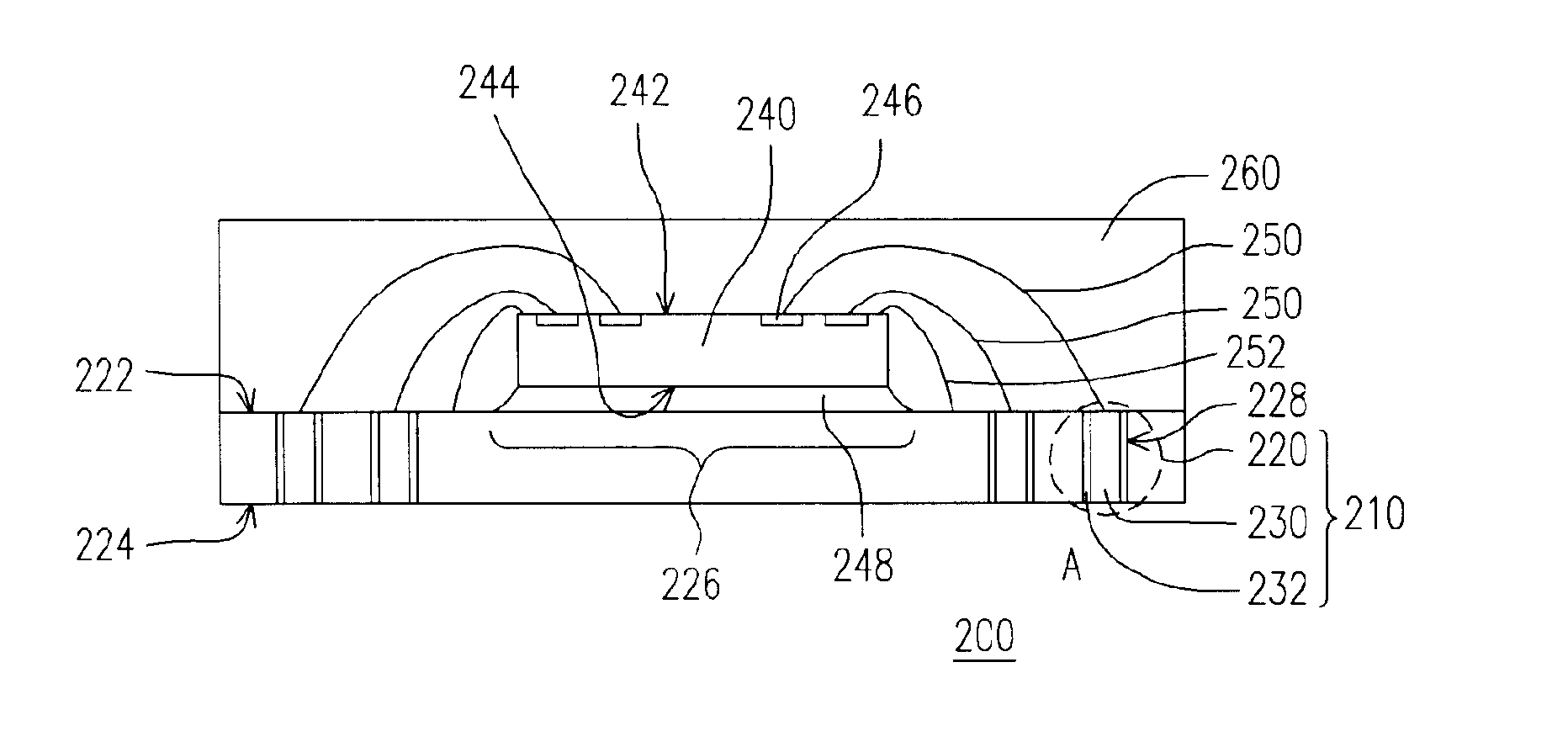

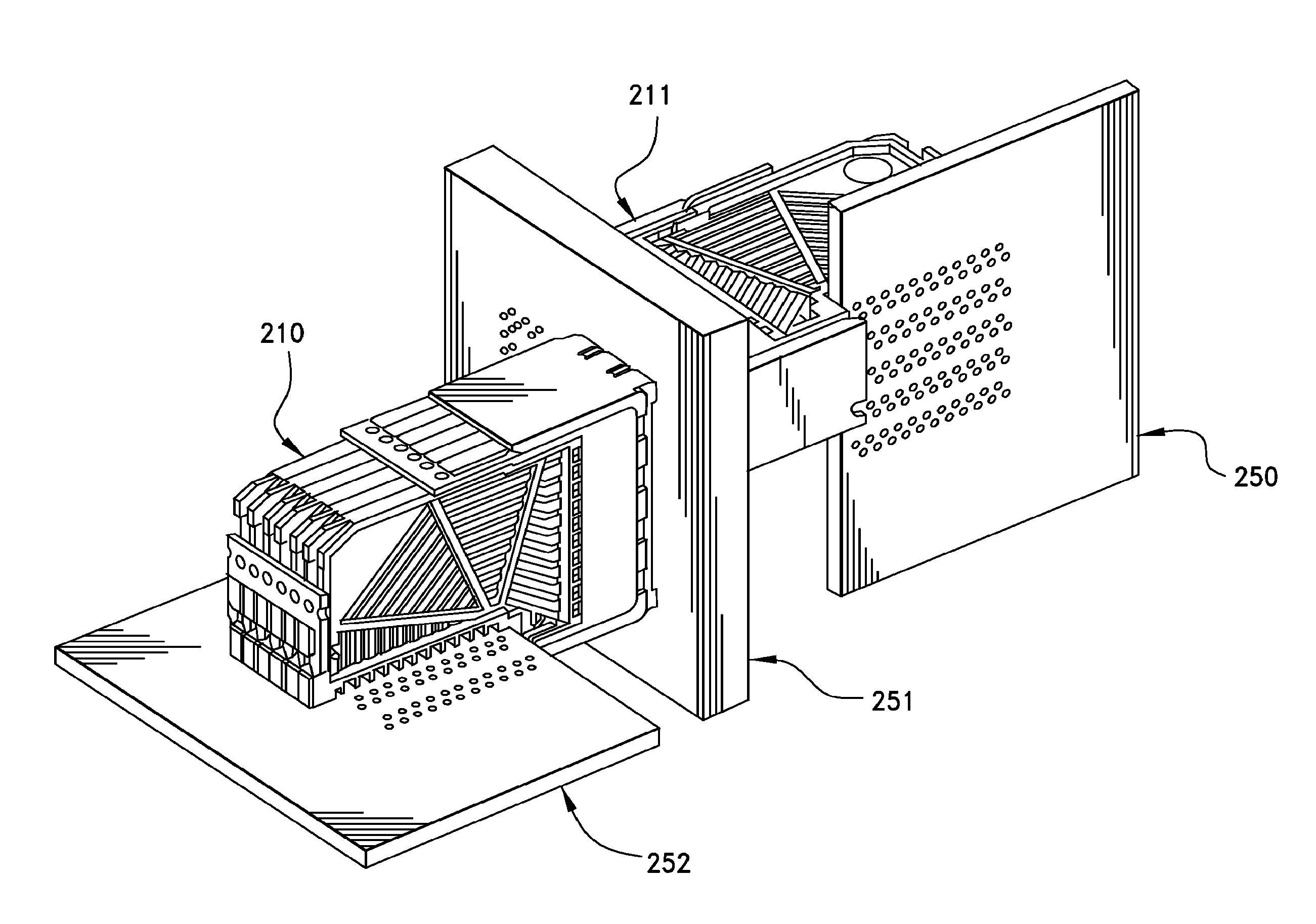

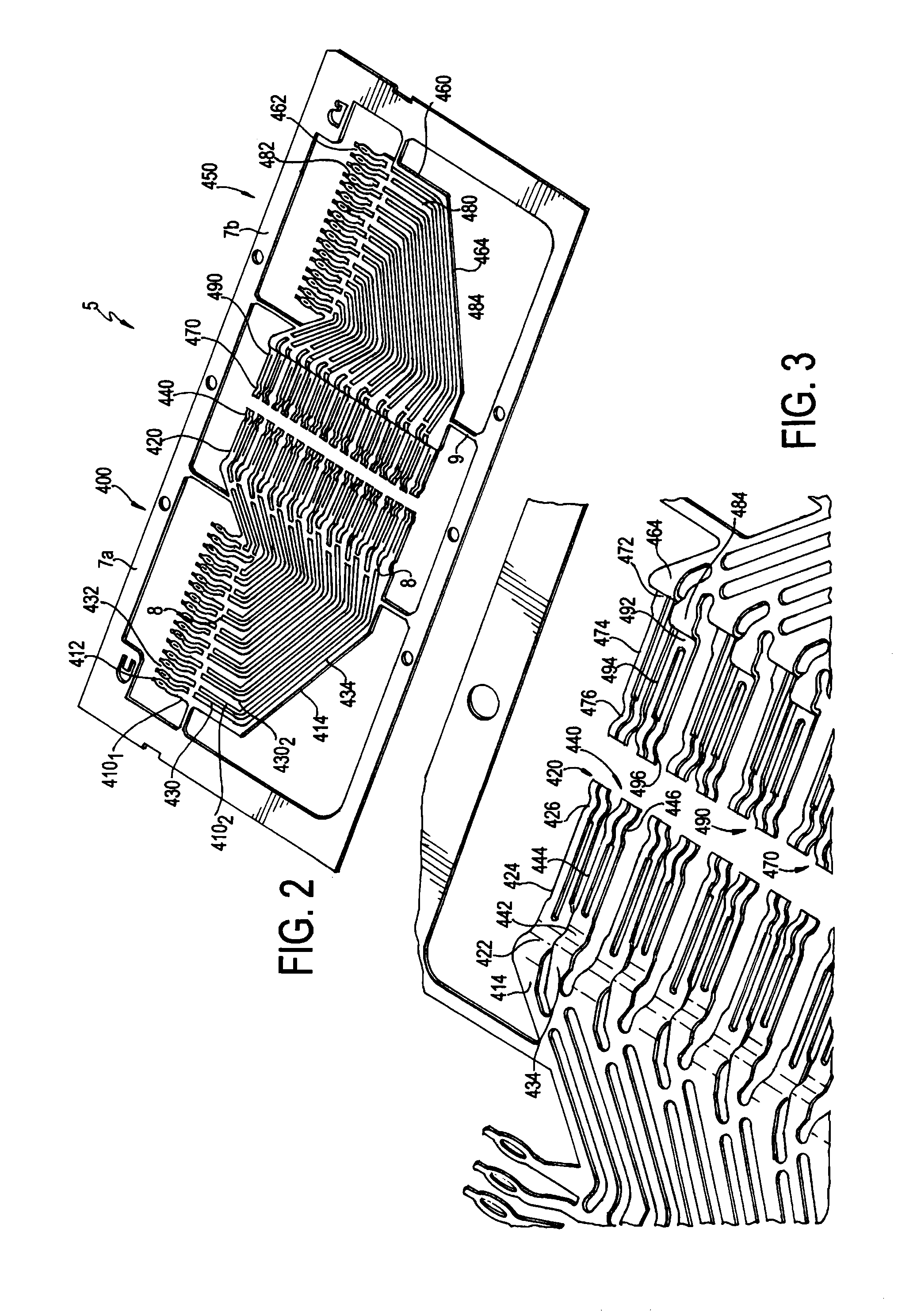

High data rate connector system

InactiveUS20120003848A1Avoid crosstalkMinimizes separationCoupling device detailsPrinted circuit aspectsElectricityCoupling

A connector and circuit board assembly includes terminals in a connector that are mounted to vias in a circuit board. Signal and ground terminals are thus coupled to signal traces and ground planes in the circuit board. Additional pinning vias that are aligned with the ground vias may be provided in a circuit board to help improve electrical performance at the interface between the terminals in the connector and the signal traces in the circuit board. A signal collar may allow pairs of signal traces to be split and routed around two difference sides of a via before rejoining while maintaining close electrical proximity that provides for relatively consistent electrical coupling between the traces in the pair of signal traces.

Owner:MOLEX INC

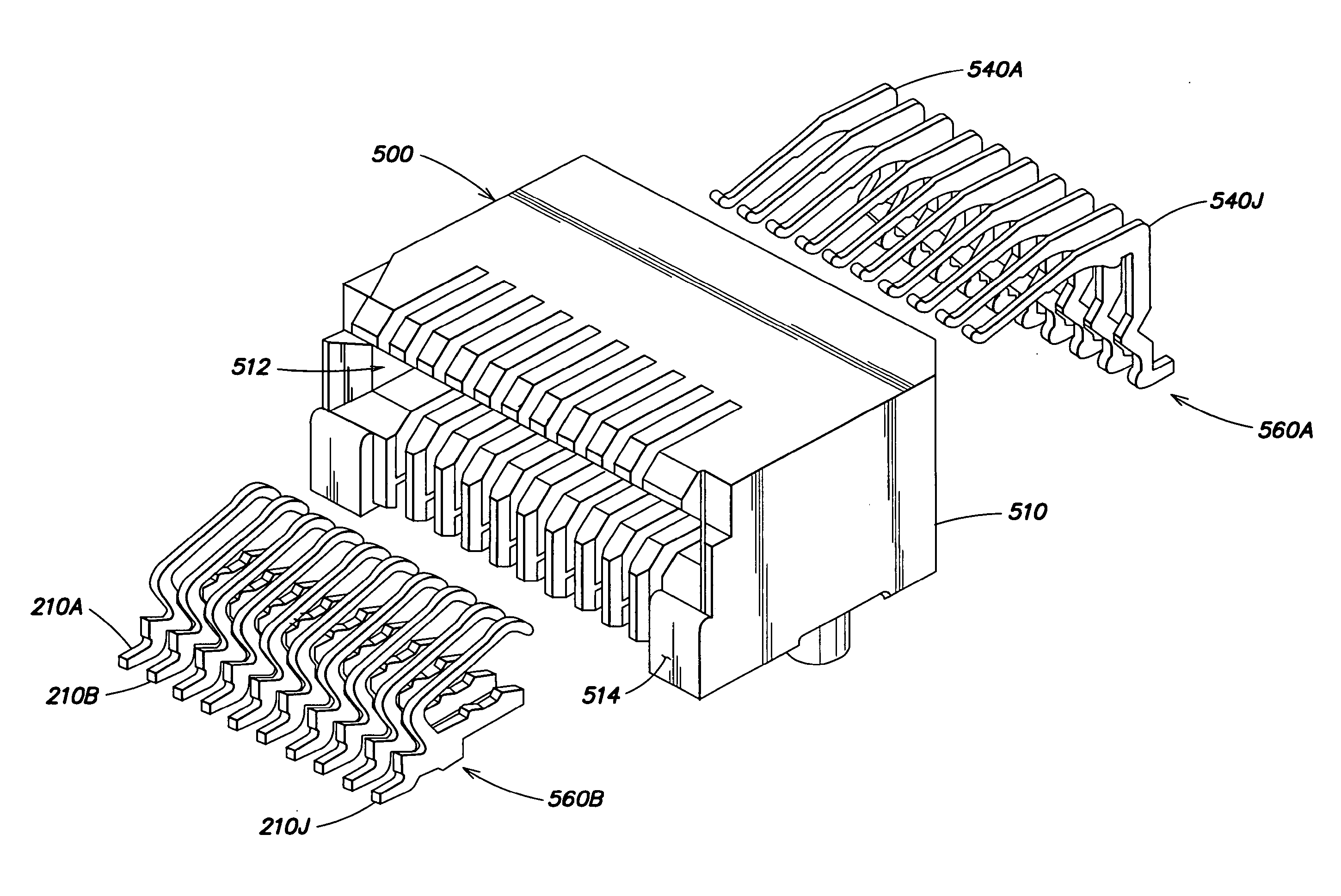

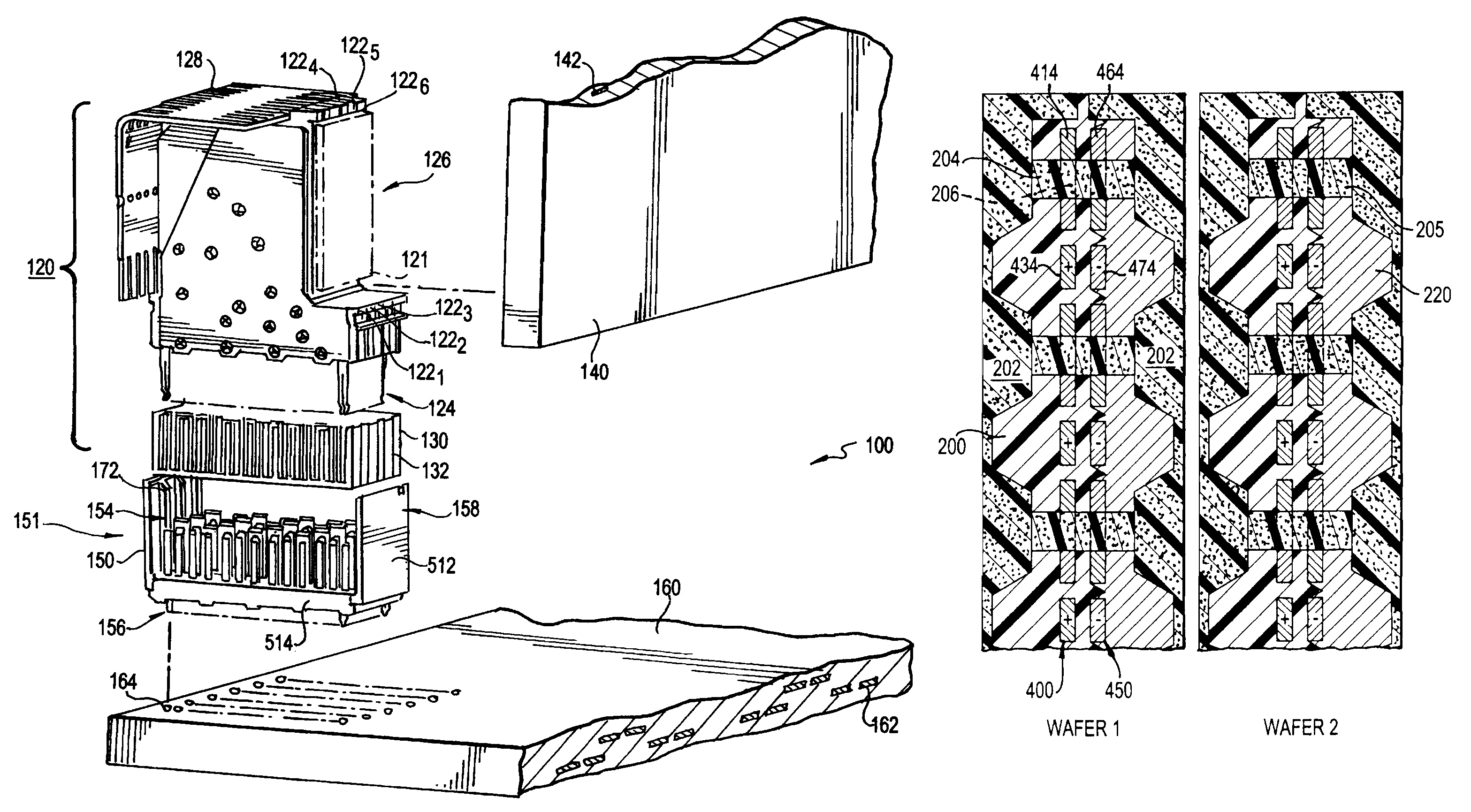

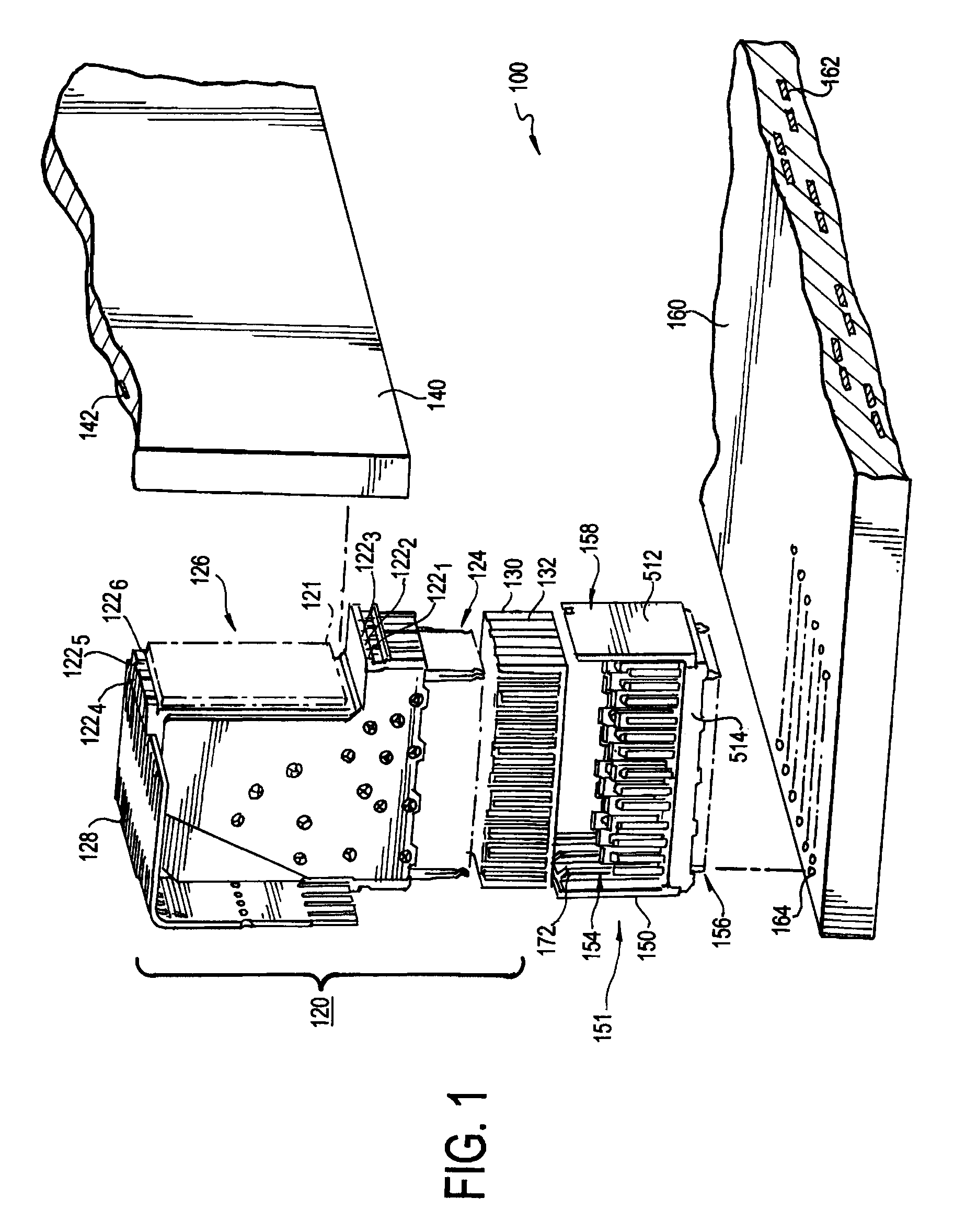

High speed, high density electrical connector

ActiveUS20120214344A1Smooth connectionLower insertion forceElectric discharge tubesCoupling contact membersPath lengthHigh density

A broadside coupled connector assembly has two sets of conductors, each separate planes. By providing the same path lengths, there is no skew between the conductors of the differential pair and the impedance of those conductors is identical. The conductor sets are formed by embedding the first set of conductors in an insulated housing having a top surface with channels. The second set of conductors is placed within the channels so that no air gaps form between the two sets of conductors. A second insulated housing is filled over the second set of conductors and into the channels to form a completed wafer. The ends of the first and second sets of conductors and the blades are jogged in both an x- and y-coordinate to reduce crosstalk and improve electrical performance.

Owner:AMPHENOL CORP

High performance, small form factor connector with common mode impedance control

Techniques for improving electrical performance of a connector. The techniques are compatible with the form factor of a standardized connector, such as an SFP connector or stacked SFP. The resulting connector has reduced insertion loss for high speed signals. Such techniques, which can be used separately or together, include shaping of conductive elements within the connector while still retaining the same mating contact arrangement. Changes may be made at the contact tail portions or in the intermediate portions where engagement to a connector housing occurs. The techniques also include the incorporation of lossy bridging members between conductive elements designated to be ground conductors. For connectors according to the stacked SFP configuration, multiple bridging members may be incorporated at multiple locations within the connector.

Owner:AMPHENOL CORP

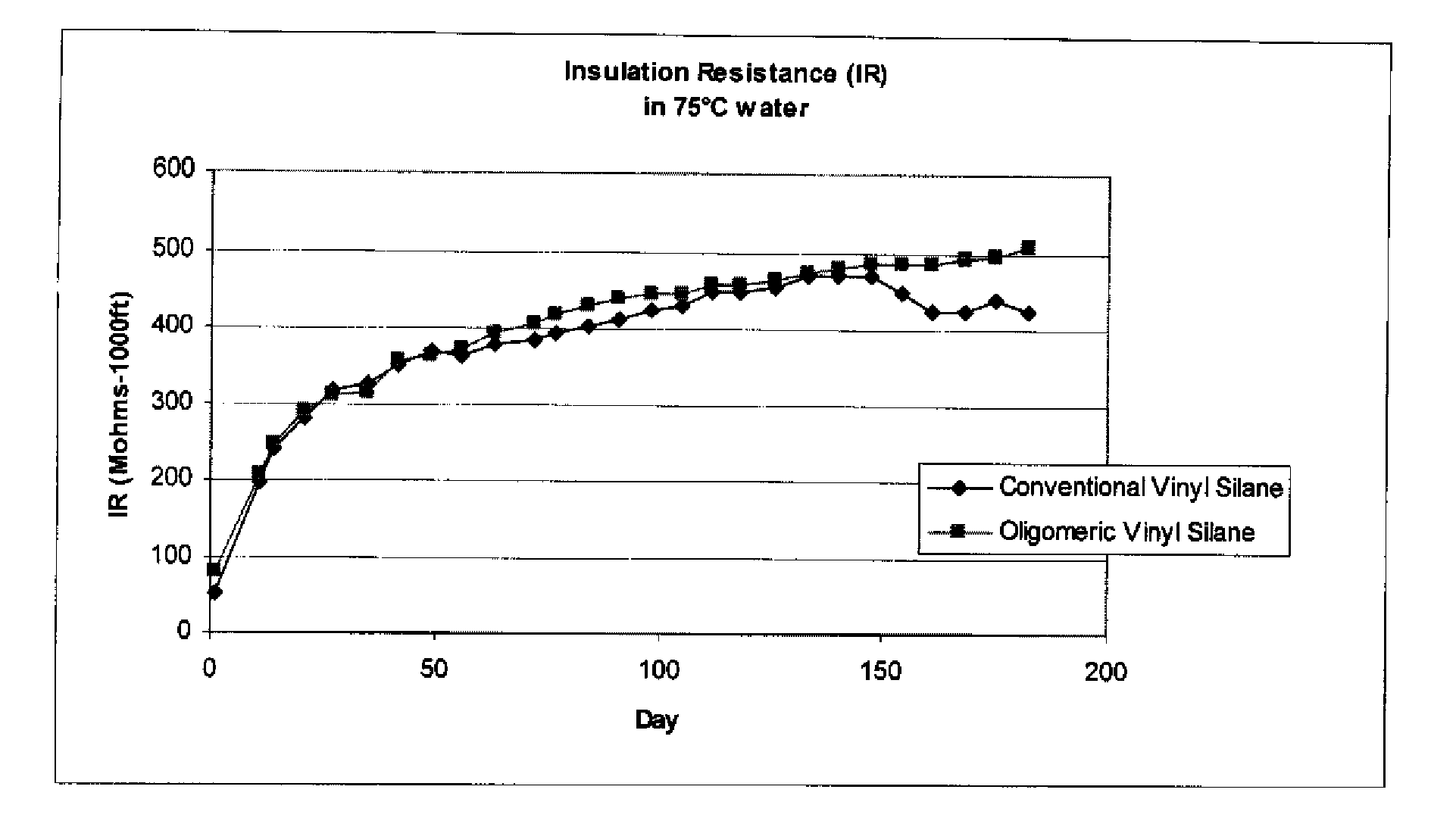

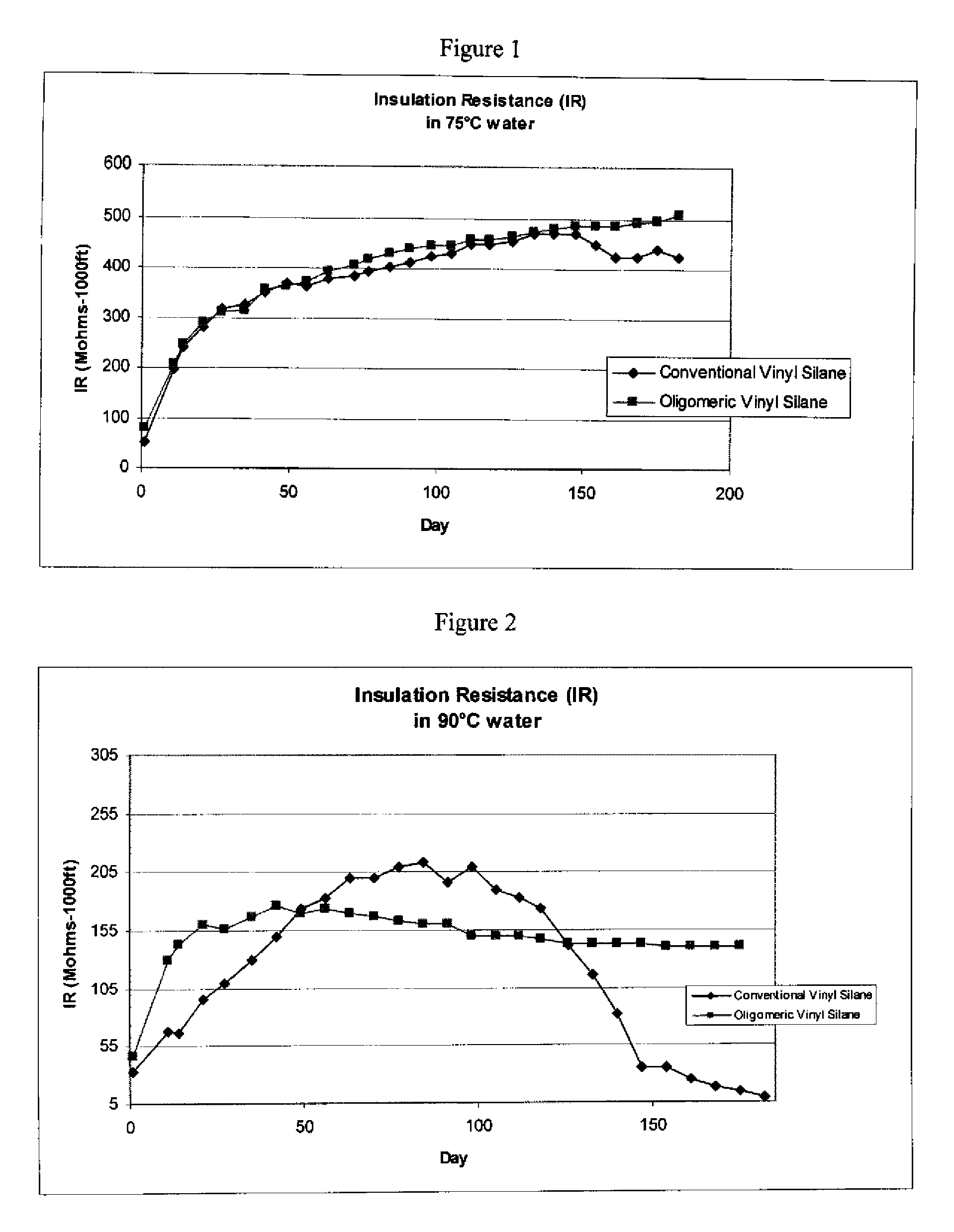

Low smoke, fire and water resistant cable coating

ActiveUS20090238957A1Limited smoke characteristicWet electrical performanceFireproof paintsRubber insulatorsMoisture resistanceOxygen

Cable coatings having effective low-smoke emission, fire resistance and moisture resistance provided by a single layer are described. The cable coatings contain an base polymer, a oxygen containing ethylene copolymer, a fire retardant and a synergistic blend of magnesium hydroxide and aluminum hydroxide. Cables coated with the described coatings have improved wet electrical performance, and satisfactory fire performance and smoke characteristics.

Owner:GENERAL CABLE TECH CORP

High performance cable connector

ActiveUS20130078870A1Contact member manufacturingContact member assembly/disassemblyElectricityElectrical conductor

A cable connector with improved performance and ease of use. The connector has staggered ports to reduce crosstalk and to prevent incorrect insertion of a plug into a receptacle. The plug may be constructed with subassemblies, each of which has a lossy central portion. Conductive members embedded within an insulative housing of the subassemblies may be used to electrically connect ground conductors within the subassemblies. Further, the connector may have a quick connect locking screw that can be engaged by pressing on the screw, but requires rotation of the screw to remove. Additionally, a ferrule may be used in making a mechanical connection between a cable bundle and a plug and making an electrical connection between a braid of the cable bundle and a conductive shell of the plug. The ferrule may be in multiple pieces for easy attachment while precluding deformation of the cable, which disrupts electrical performance.

Owner:AMPHENOL CORP

High speed, high density electrical connector

ActiveUS8814595B2Smooth connectionEnhanced couplingElectric discharge tubesCoupling contact membersElectricityPath length

A broadside coupled connector assembly has two sets of conductors, each separate planes. By providing the same path lengths, there is no skew between the conductors of the differential pair and the impedance of those conductors is identical. The conductor sets are formed by embedding the first set of conductors in an insulated housing having a top surface with channels. The second set of conductors is placed within the channels so that no air gaps form between the two sets of conductors. A second insulated housing is filled over the second set of conductors and into the channels to form a completed wafer. The ends of the first and second sets of conductors and the blades are jogged in both an x- and y-coordinate to reduce crosstalk and improve electrical performance.

Owner:AMPHENOL CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com