Patents

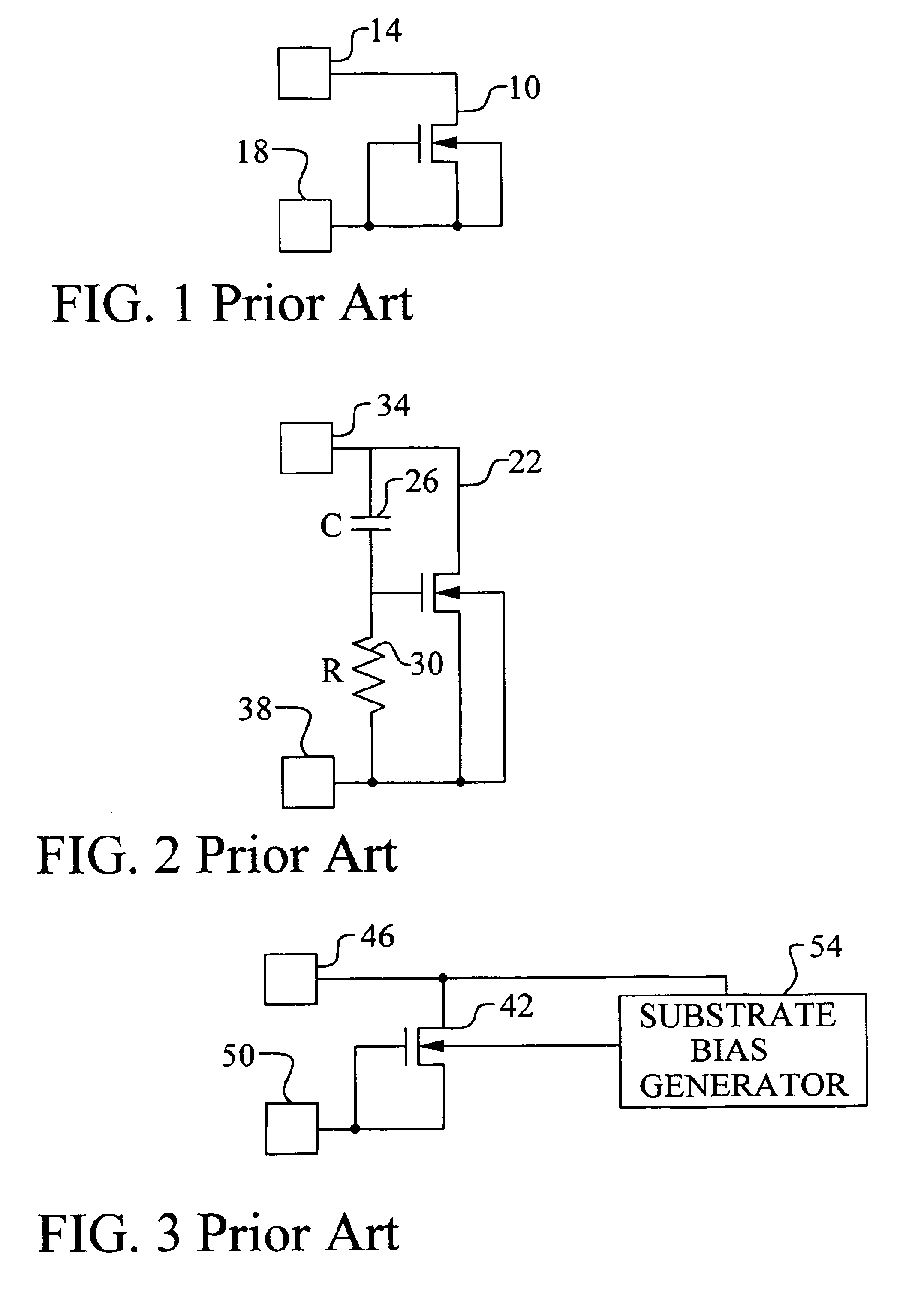

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

467 results about "Intrinsic semiconductor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An intrinsic(pure) semiconductor, also called an undoped semiconductor or i-type semiconductor, is a pure semiconductor without any significant dopant species present. The number of charge carriers is therefore determined by the properties of the material itself instead of the amount of impurities. In intrinsic semiconductors the number of excited electrons and the number of holes are equal: n = p. This may even be the case after doping the semiconductor, though only if it is doped with both donors and acceptors equally. In this case, n = p still holds, and the semiconductor remains intrinsic, though doped.

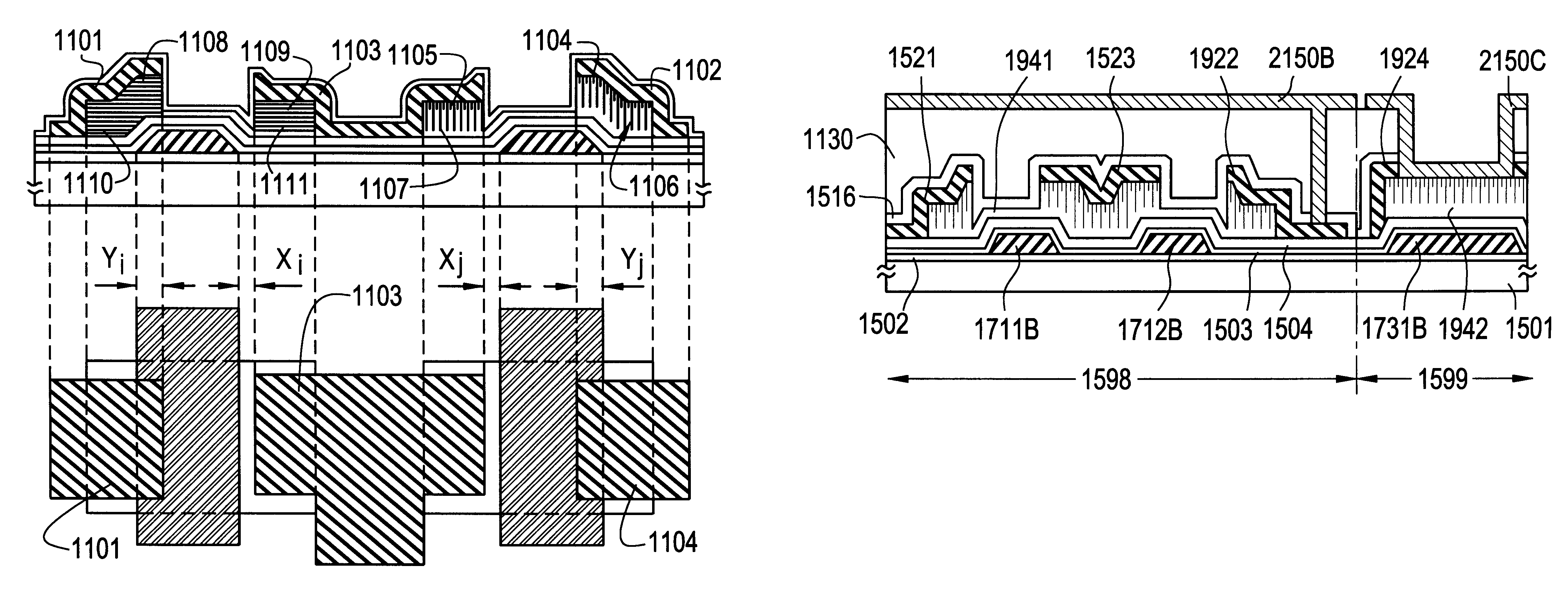

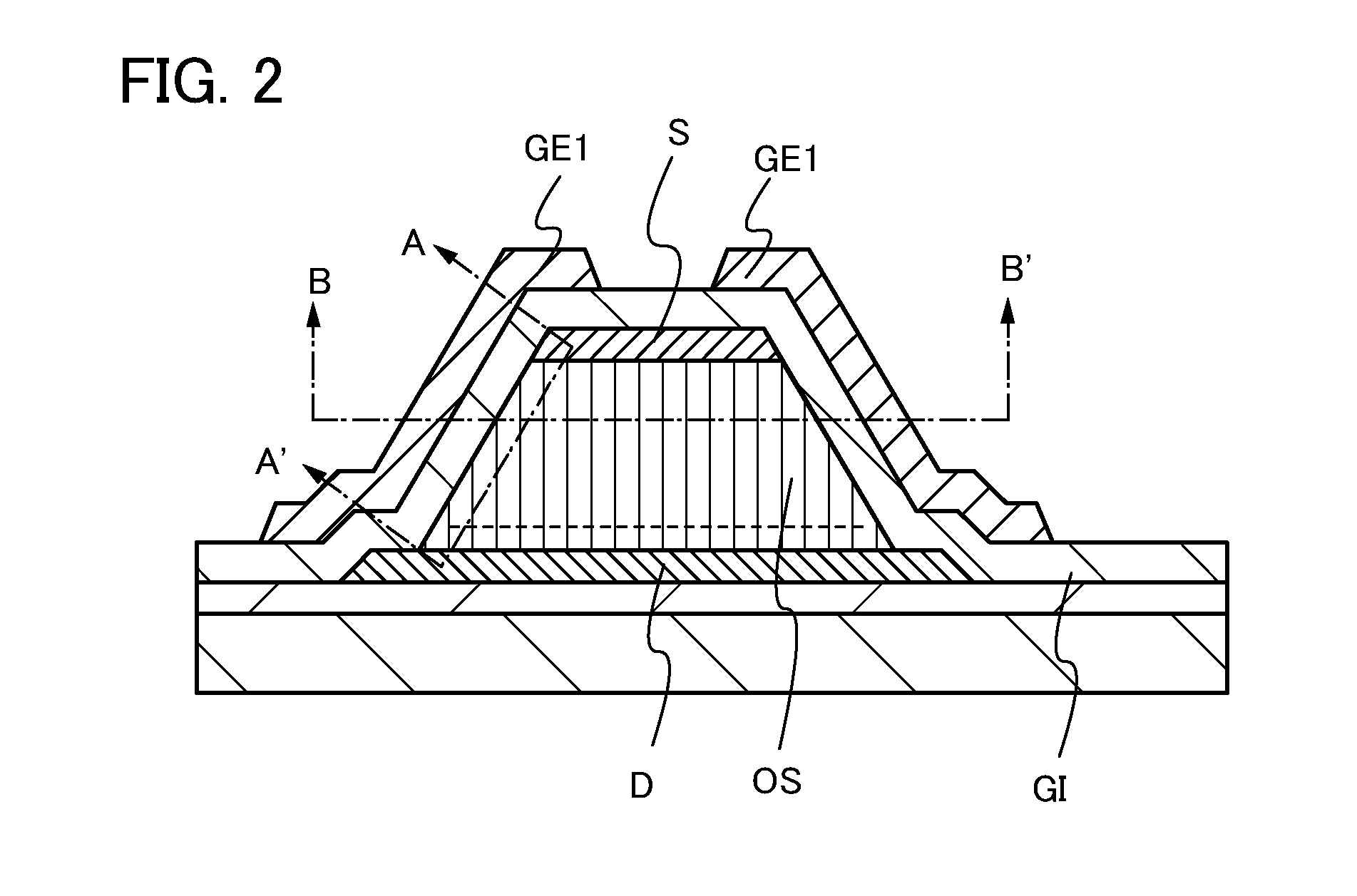

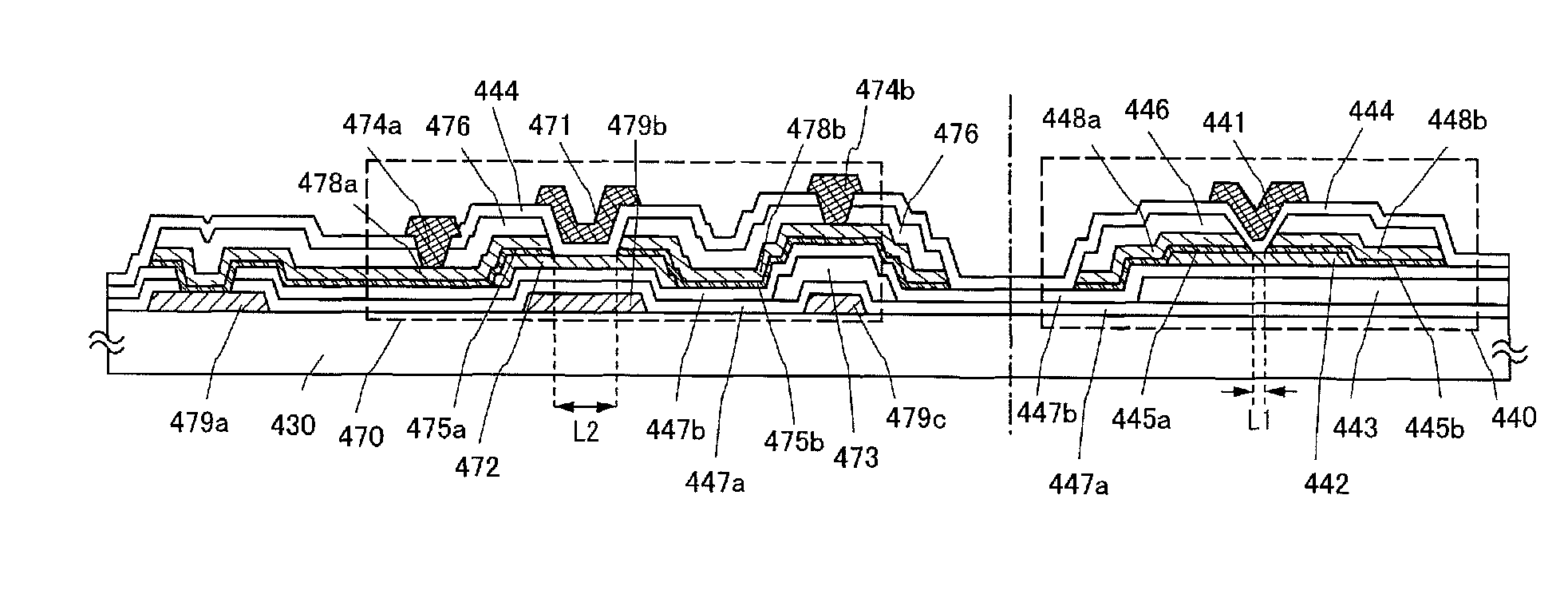

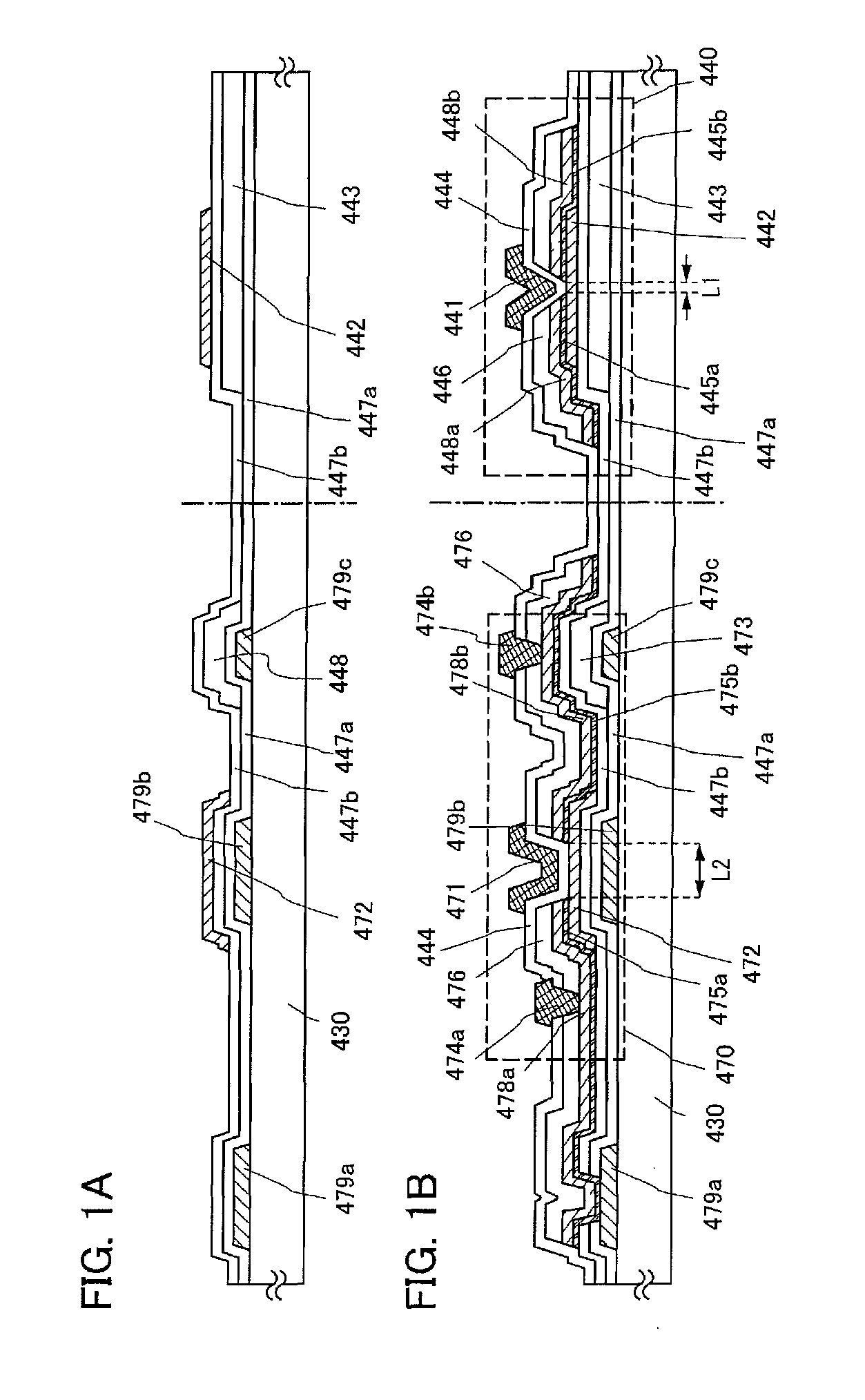

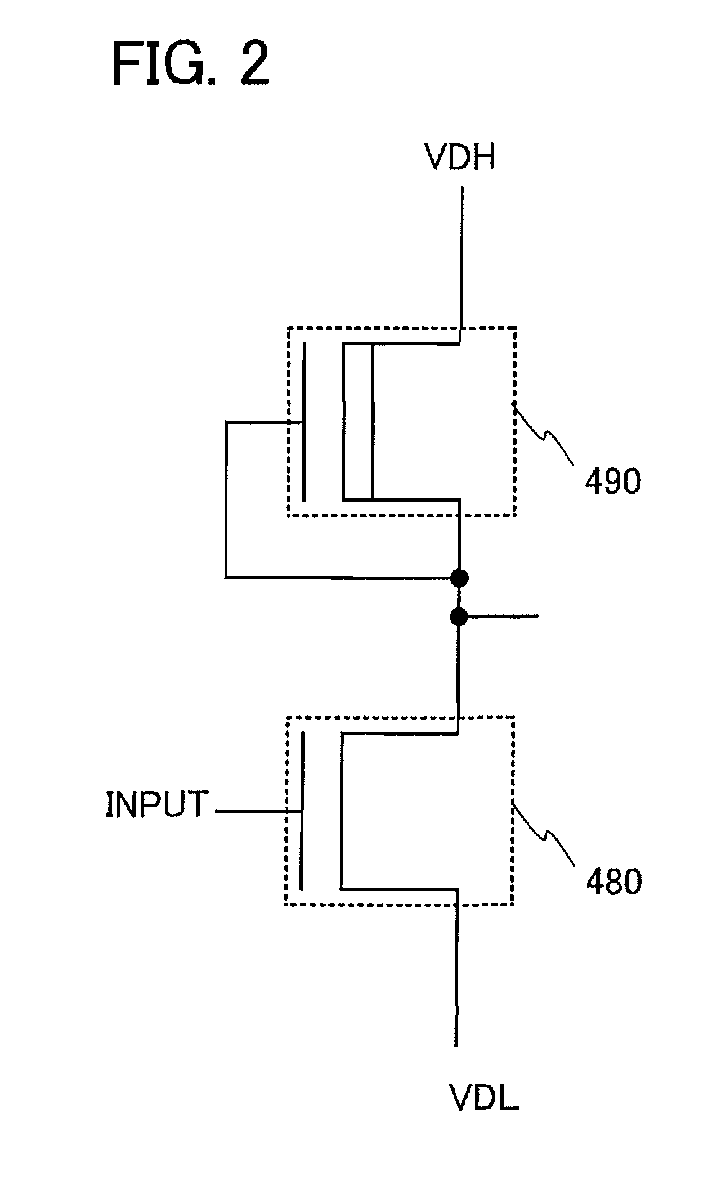

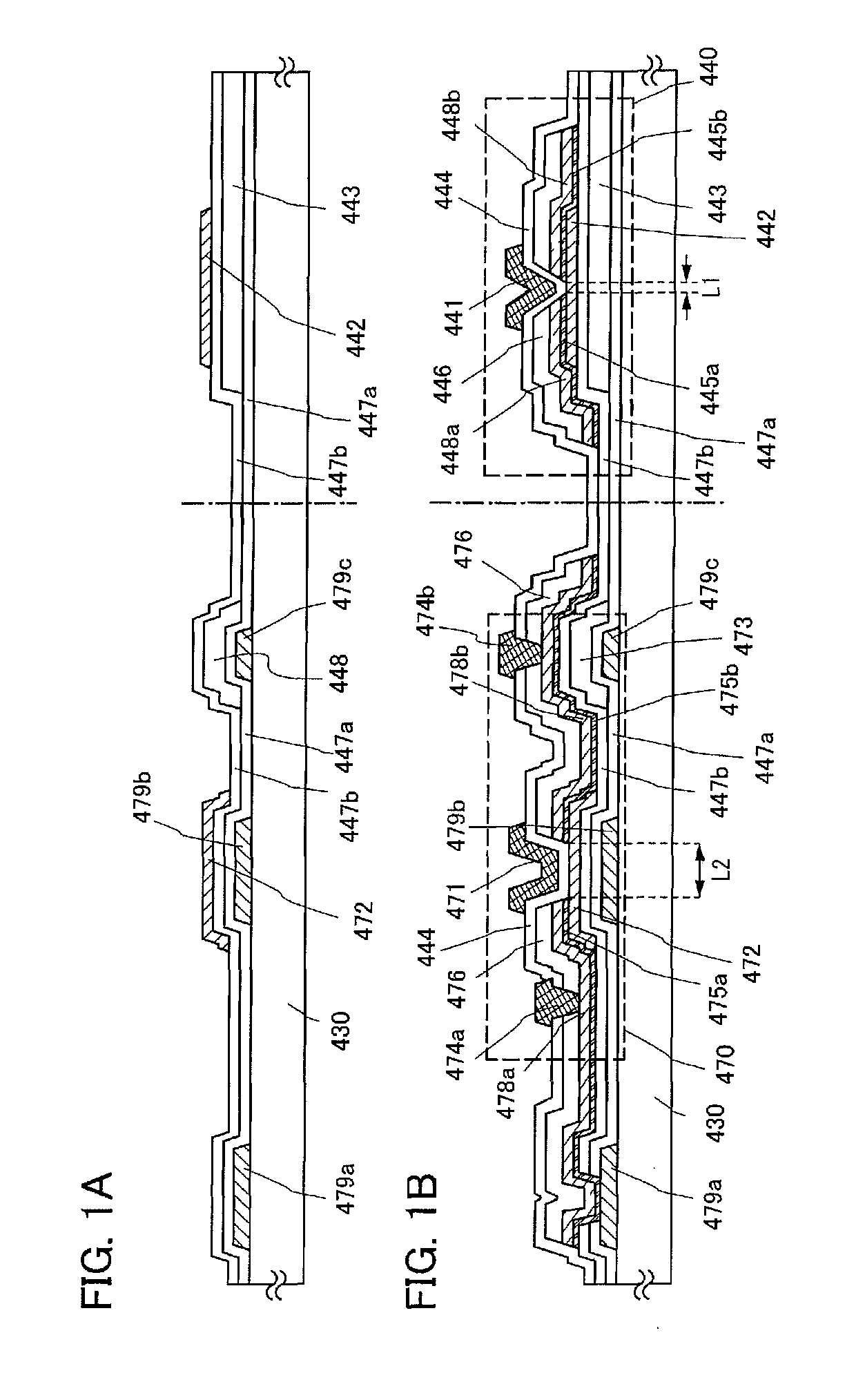

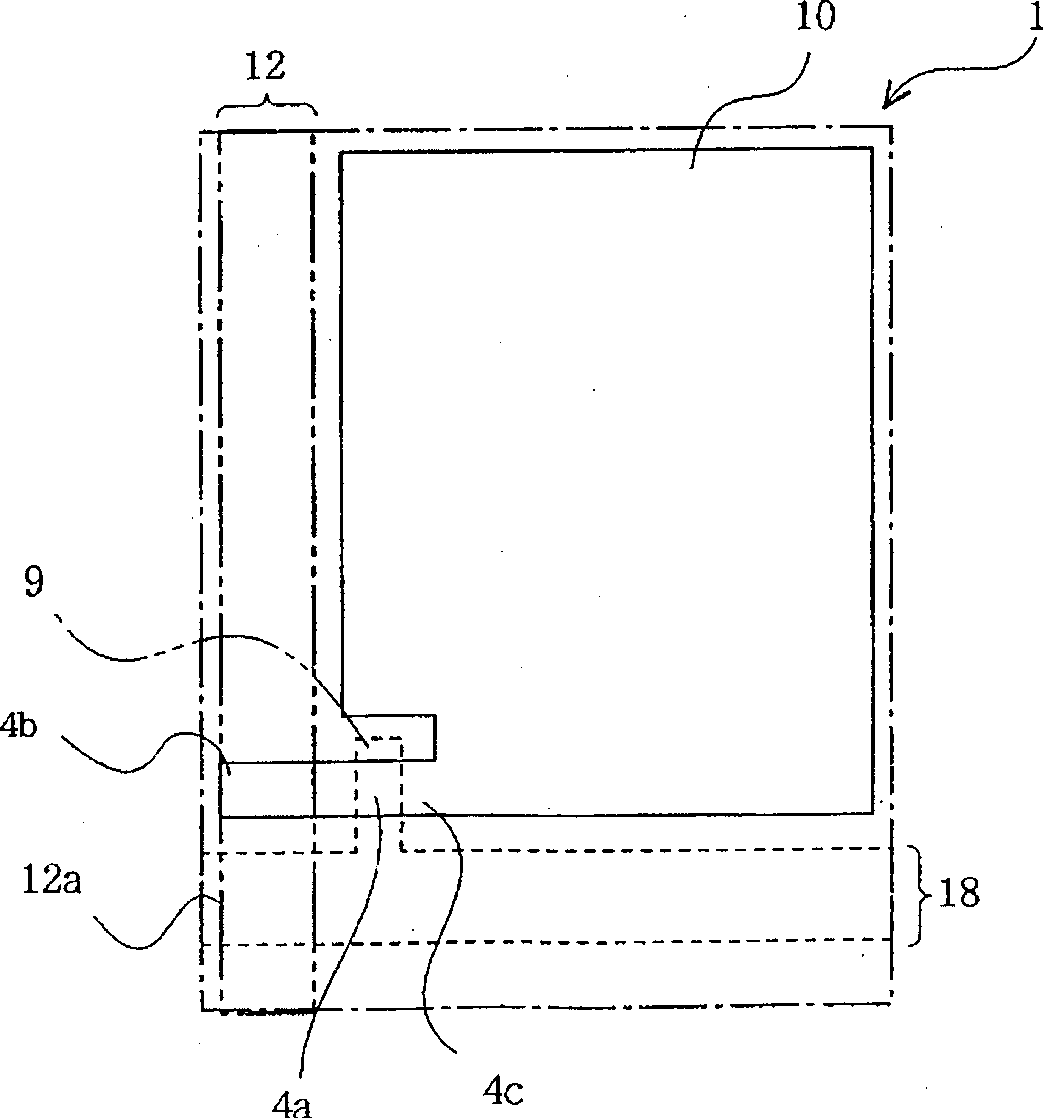

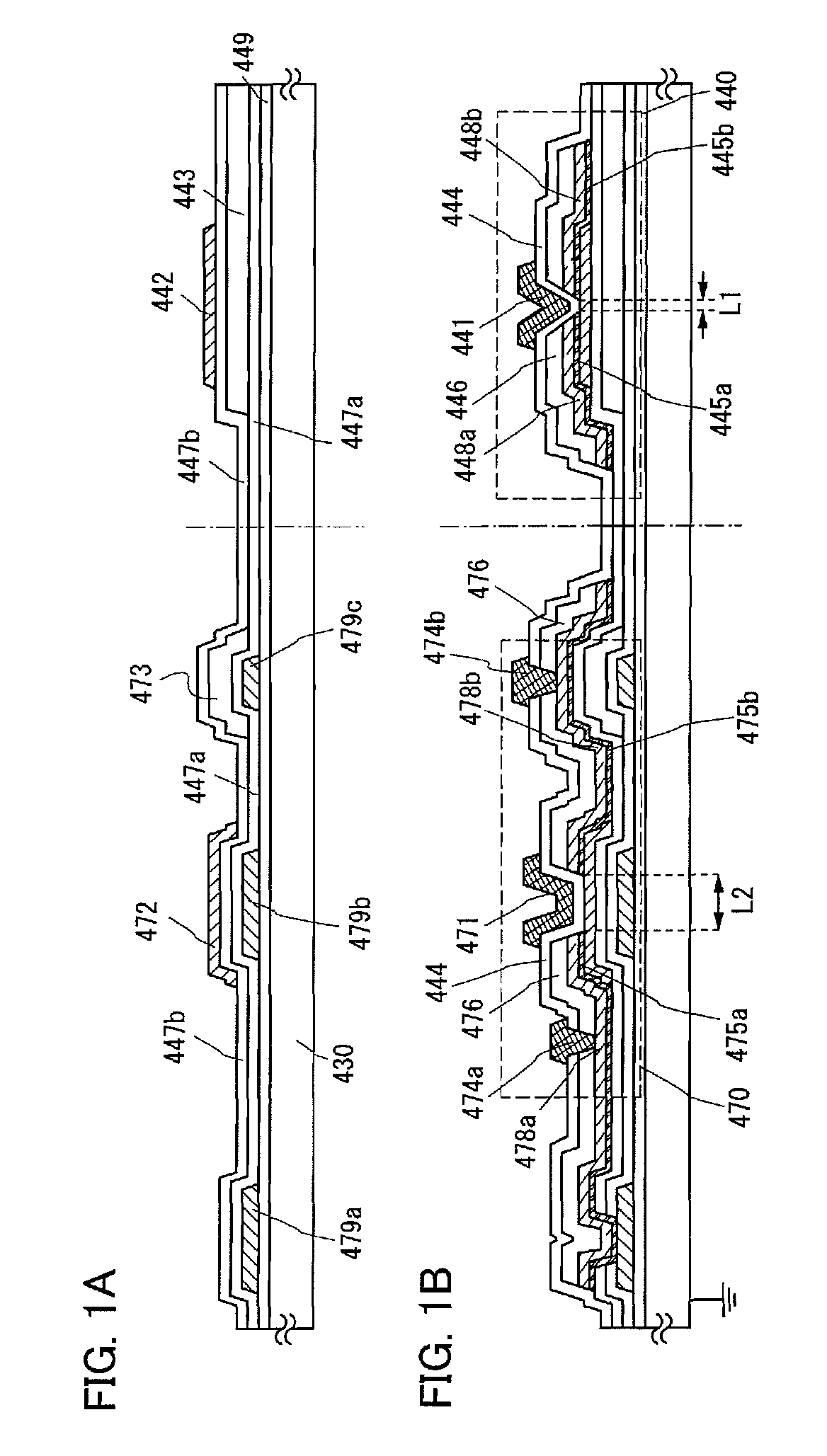

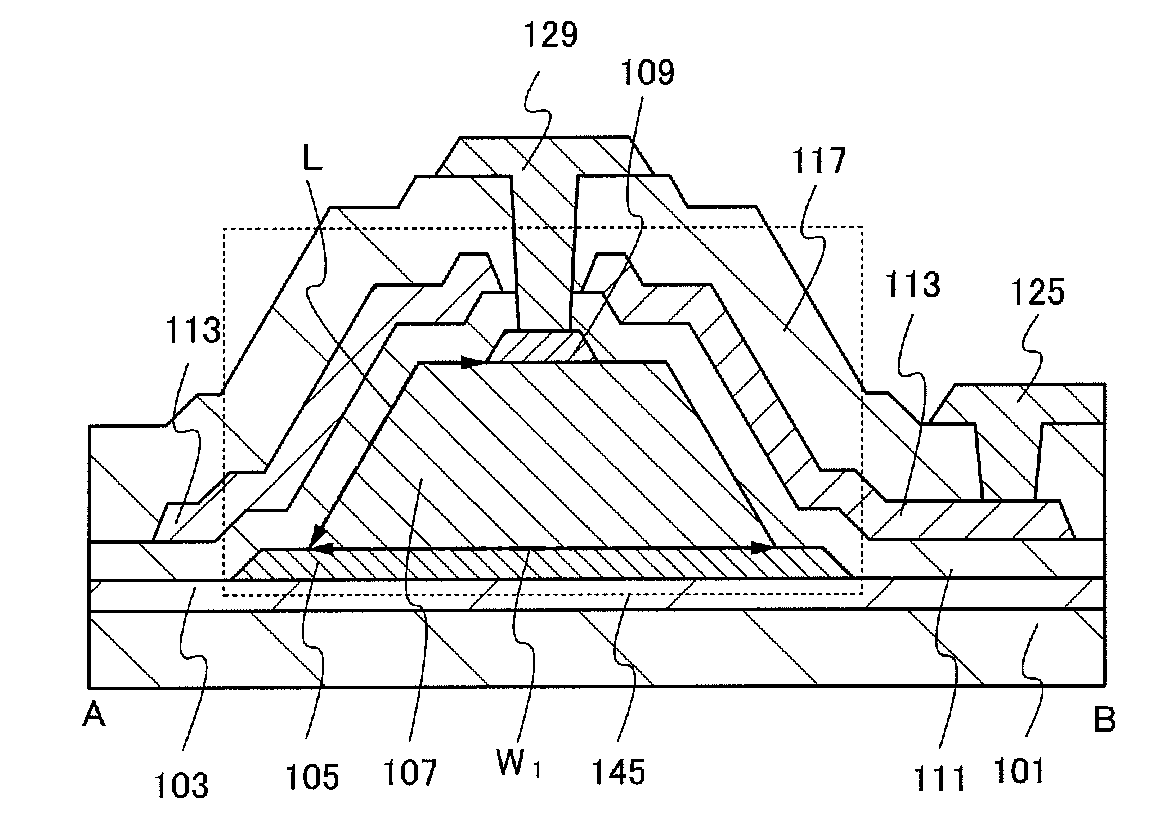

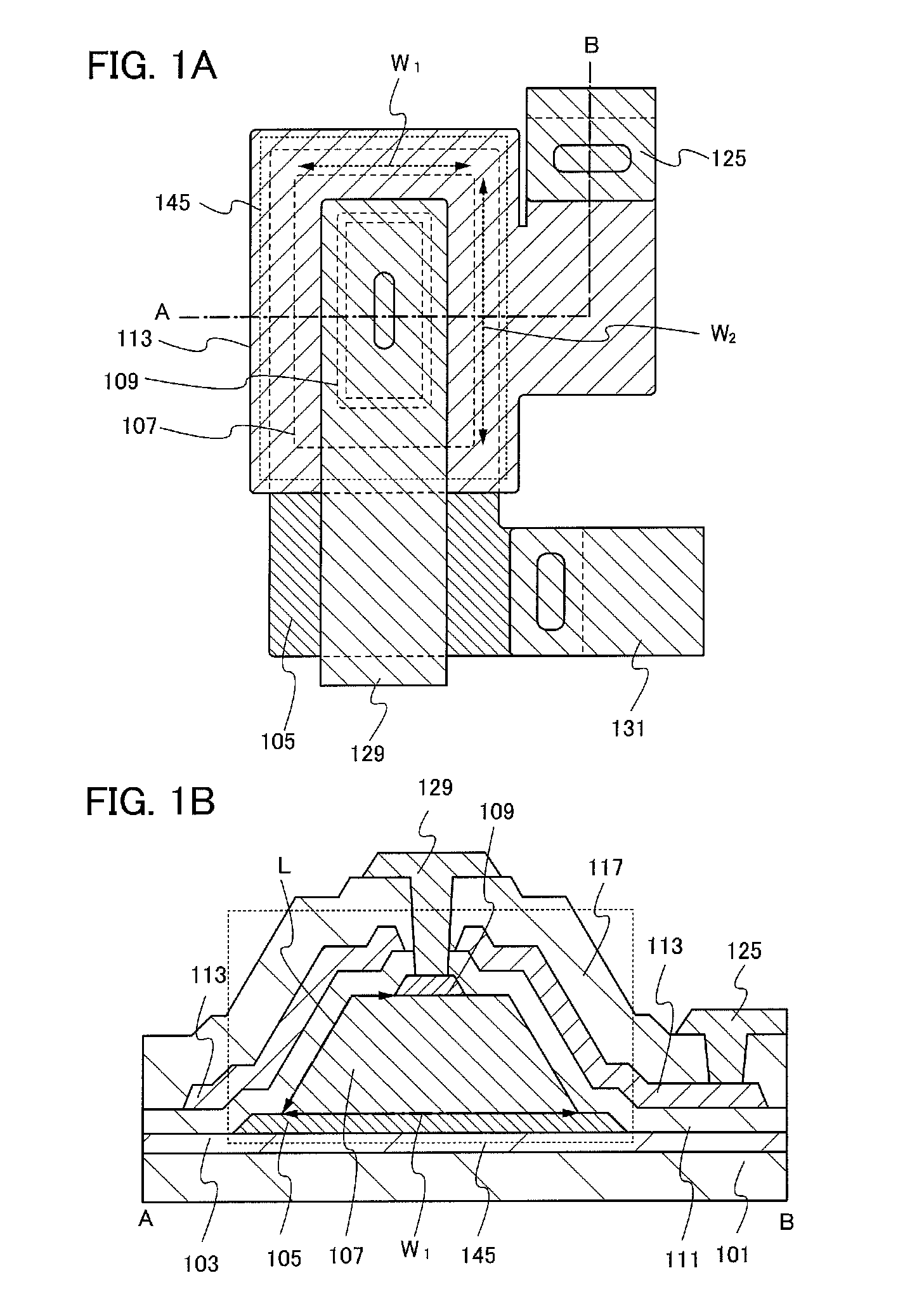

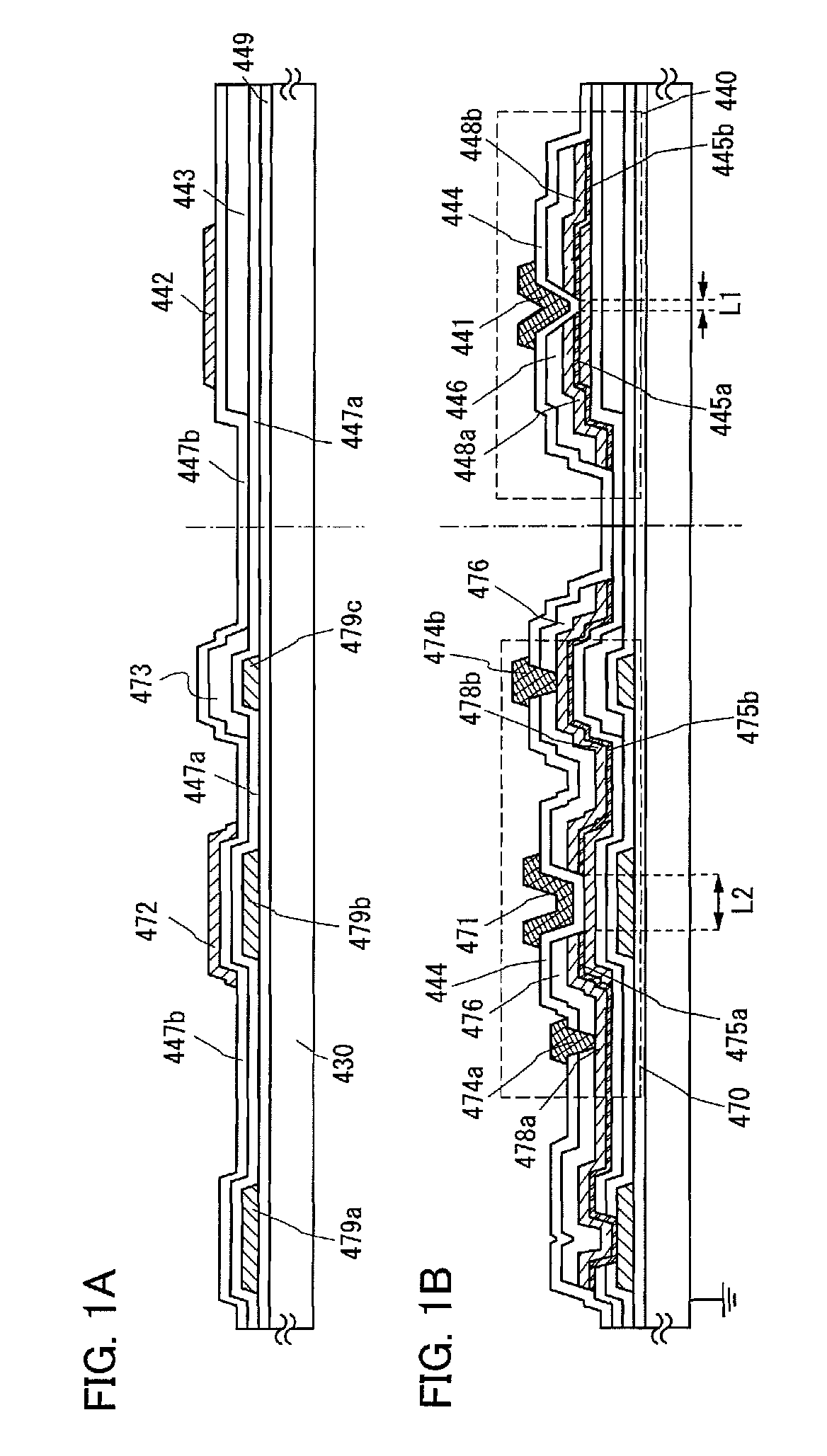

Semiconductor device and fabrication method thereof

To provide a semiconductor device having high mass production performance and high reliability and reproducibility by simple fabrication steps, in a constitution of a semiconductor device of a bottom gate type formed by a semiconductor layer having a crystal structure, source and drain regions are constituted by a laminated layer structure comprising a first conductive layer (n+ layer), a second conductive layer (n- layer) having resistance higher than the first conductive layer and an intrinsic or a substantially intrinsic semiconductor layer (i layer) in which the n- layer functions as an LDD region and the i layer functions as an offset region in a film thickness direction.

Owner:SEMICON ENERGY LAB CO LTD

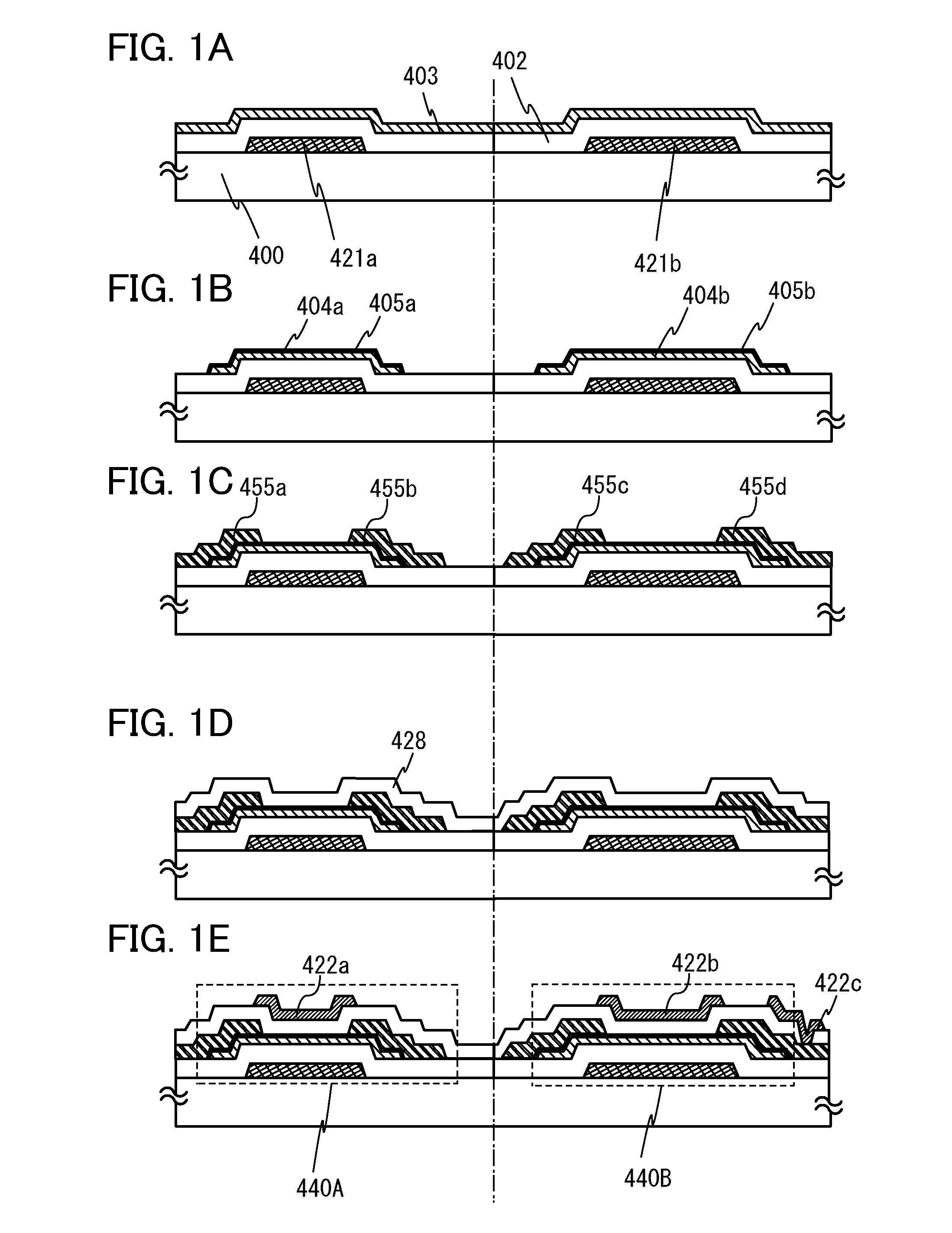

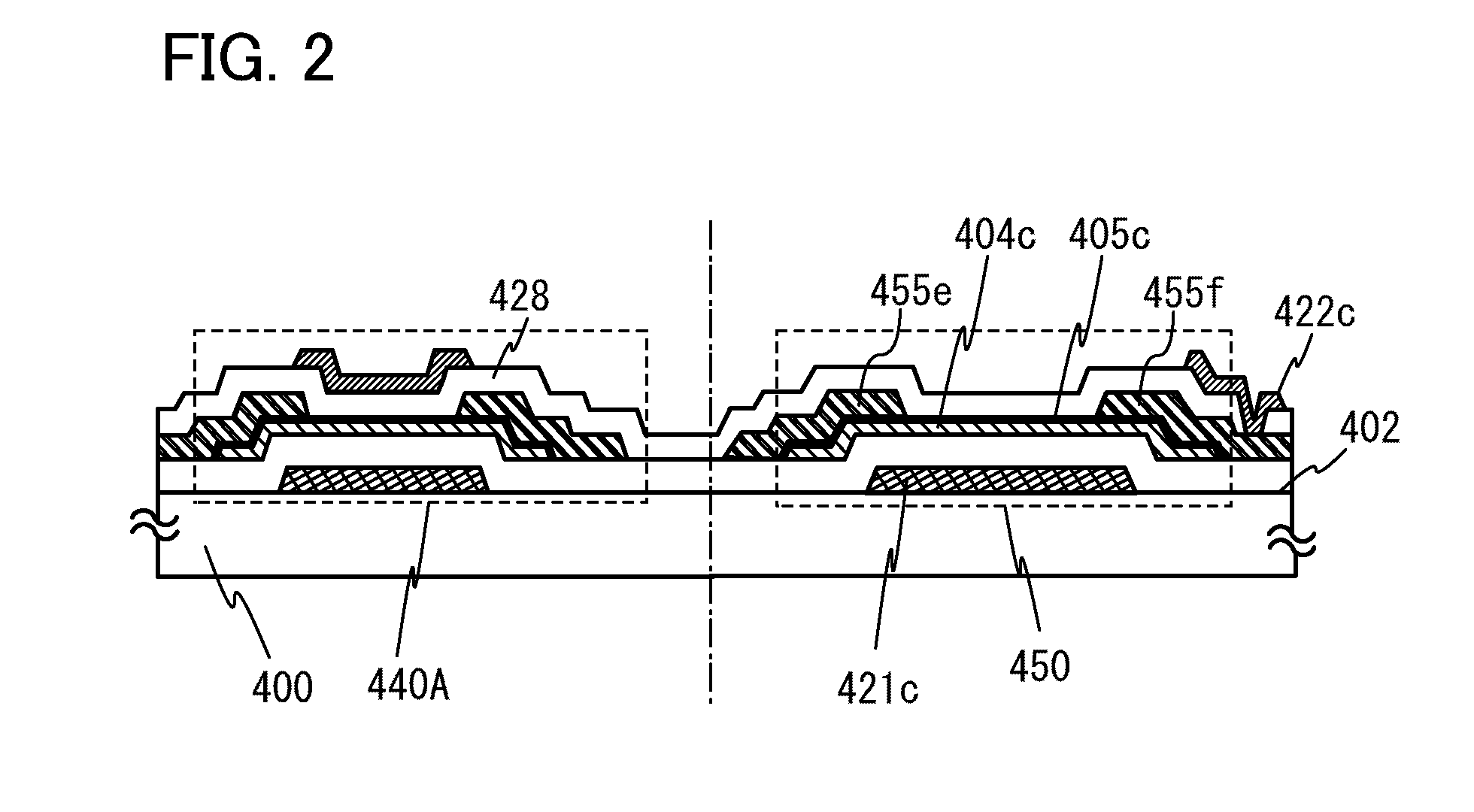

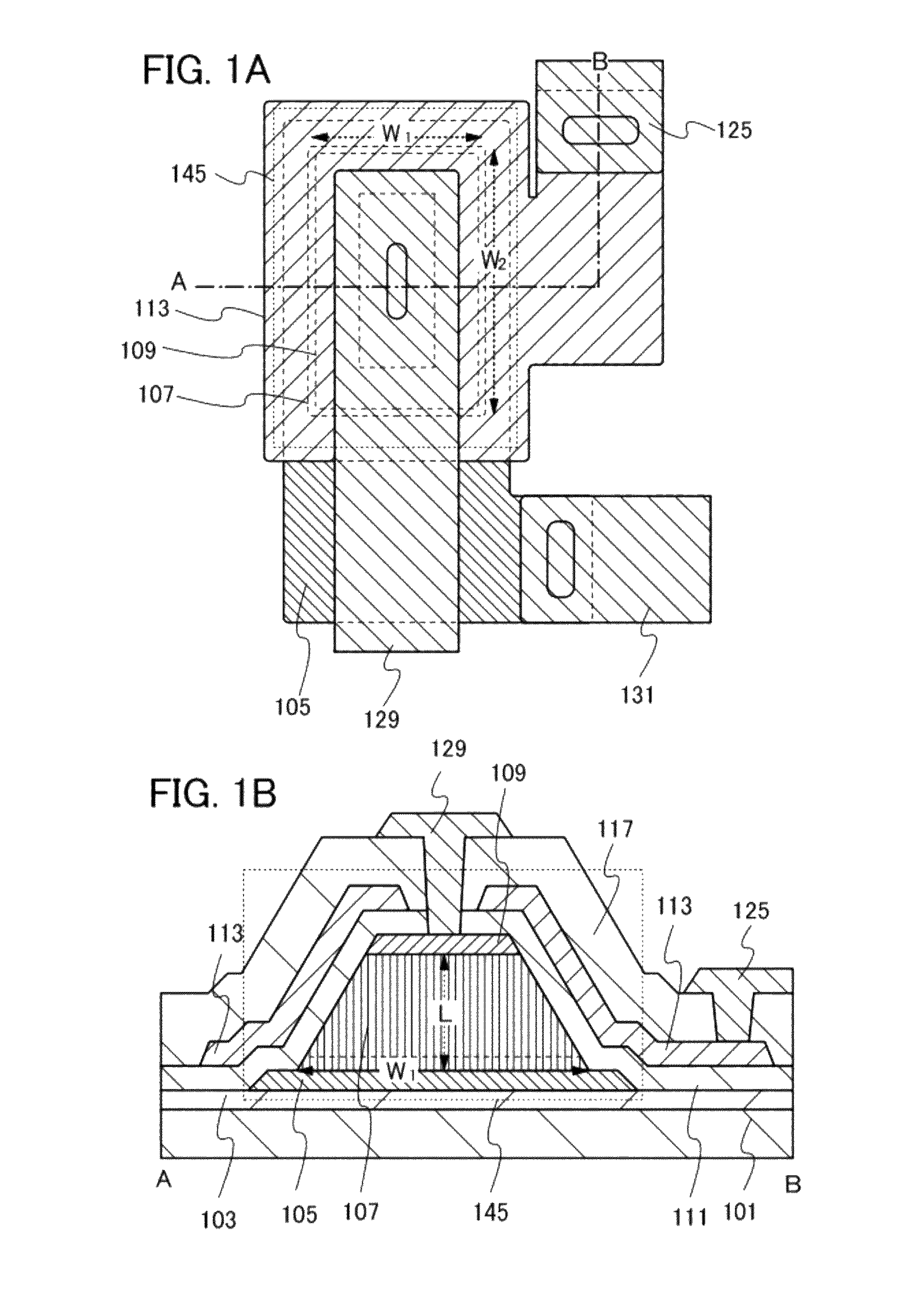

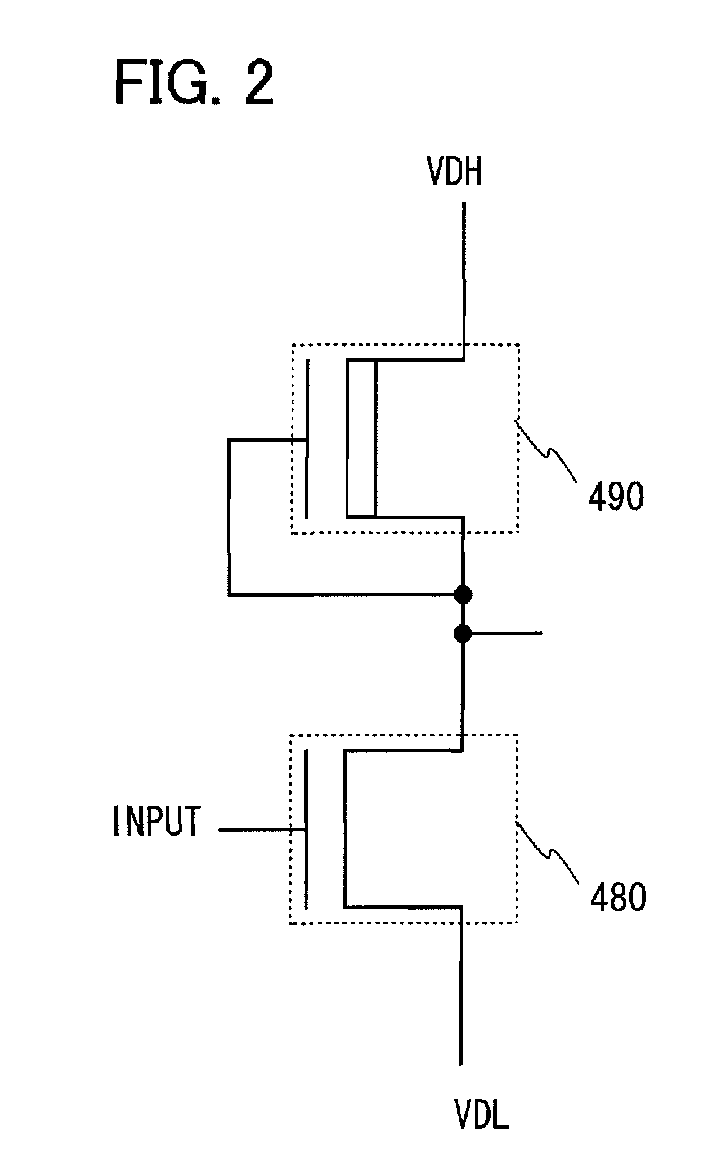

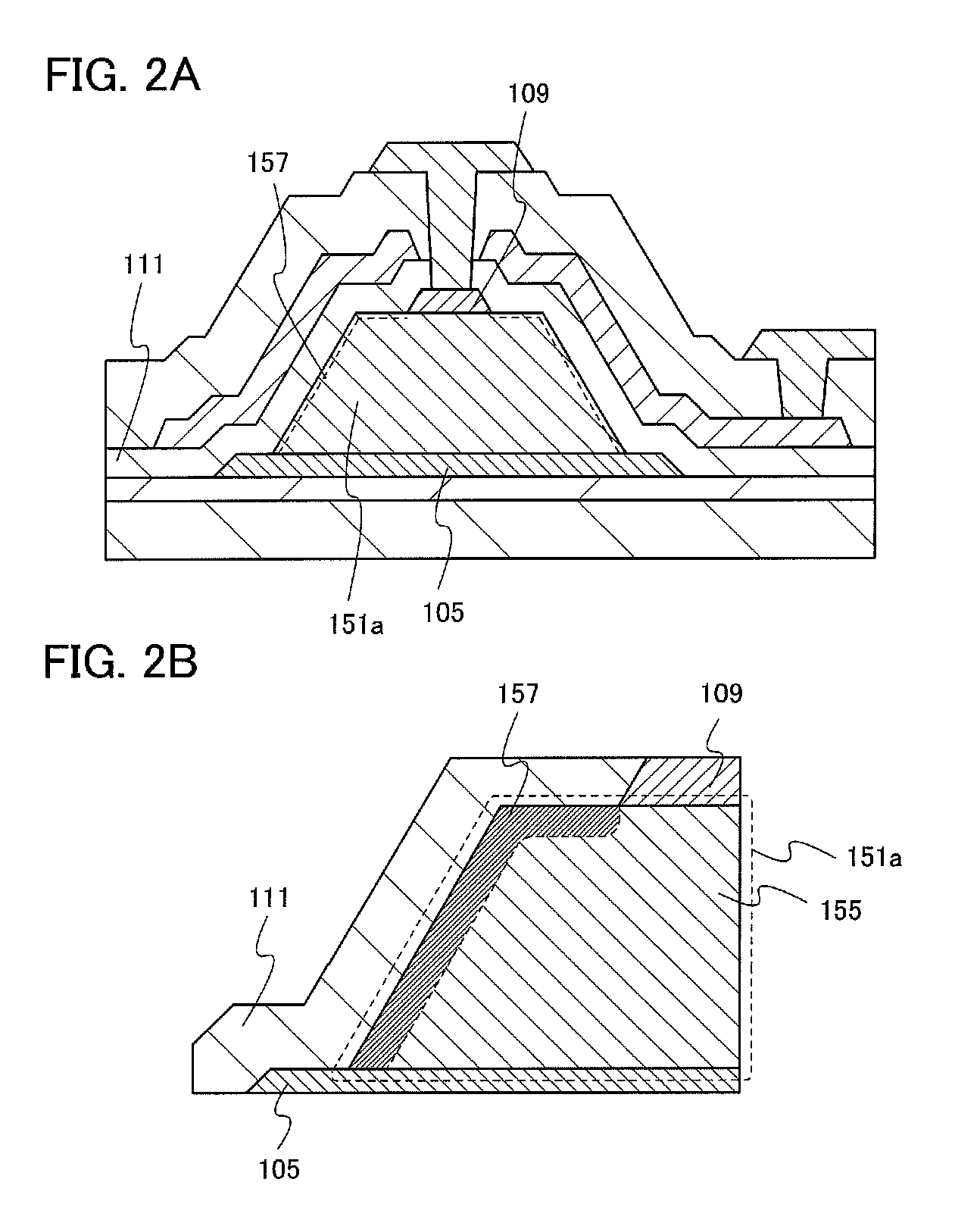

Semiconductor device and manufacturing method thereof

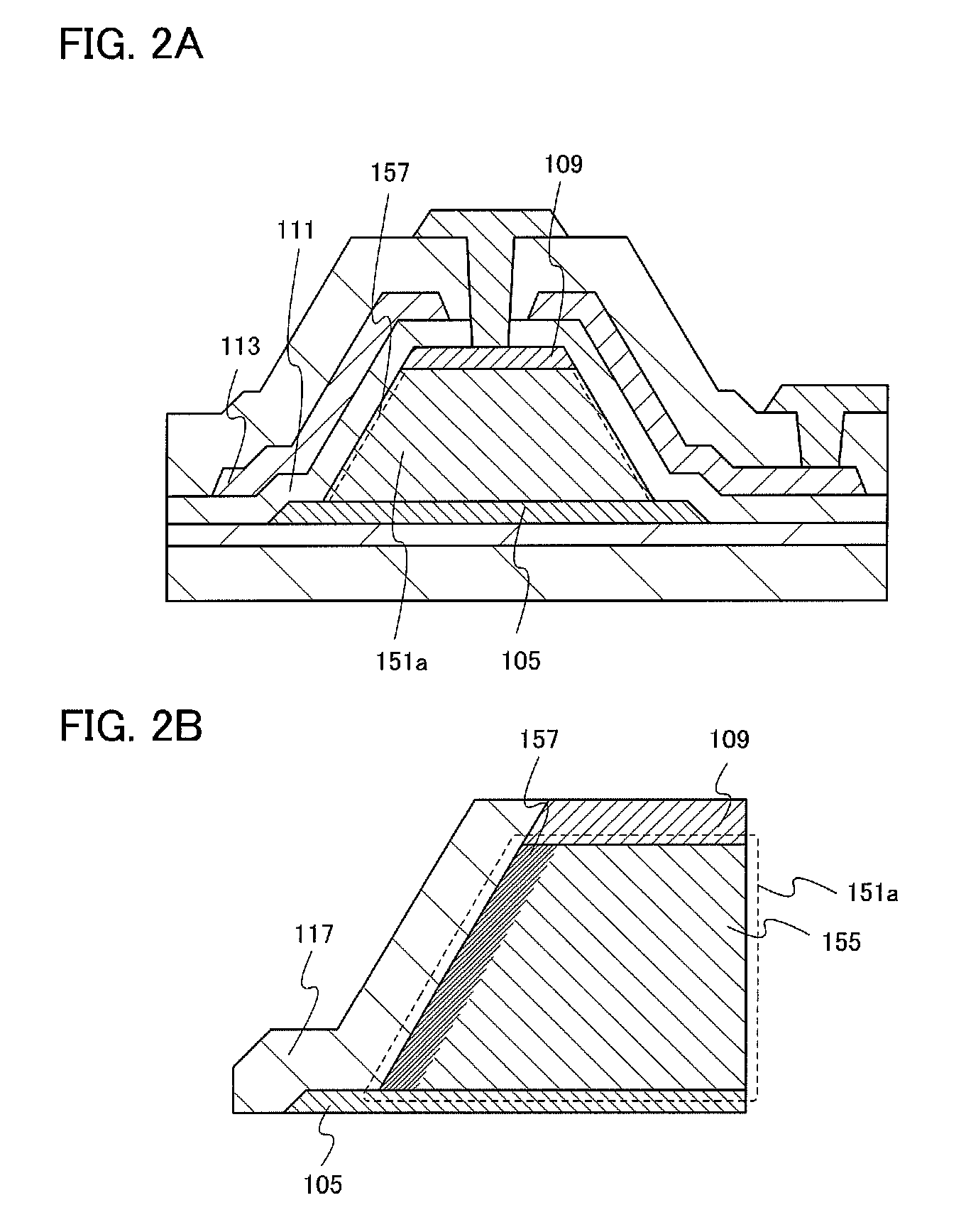

An oxide semiconductor layer which is intrinsic or substantially intrinsic and includes a crystalline region in a surface portion of the oxide semiconductor layer is used for the transistors. An intrinsic or substantially intrinsic semiconductor from which an impurity which is to be an electron donor (donor) is removed from an oxide semiconductor and which has a larger energy gap than a silicon semiconductor is used. Electrical characteristics of the transistors can be controlled by controlling the potential of a pair of conductive films which are provided on opposite sides from each other with respect to the oxide semiconductor layer, each with an insulating film arranged therebetween, so that the position of a channel formed in the oxide semiconductor layer is determined.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and method for manufacturing the same

ActiveUS20110127522A1High on-off ratioHigh puritySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsElectron donor

Objects are to provide a semiconductor device for high power application in which a novel semiconductor material having high productivity is used and to provide a semiconductor device having a novel structure in which a novel semiconductor material is used. The present invention is a vertical transistor and a vertical diode each of which has a stacked body of an oxide semiconductor in which a first oxide semiconductor film having crystallinity and a second oxide semiconductor film having crystallinity are stacked. An impurity serving as an electron donor (donor) which is contained in the stacked body of an oxide semiconductor is removed in a step of crystal growth; therefore, the stacked body of an oxide semiconductor is highly purified and is an intrinsic semiconductor or a substantially intrinsic semiconductor whose carrier density is low. The stacked body of an oxide semiconductor has a wider band gap than a silicon semiconductor.

Owner:SEMICON ENERGY LAB CO LTD

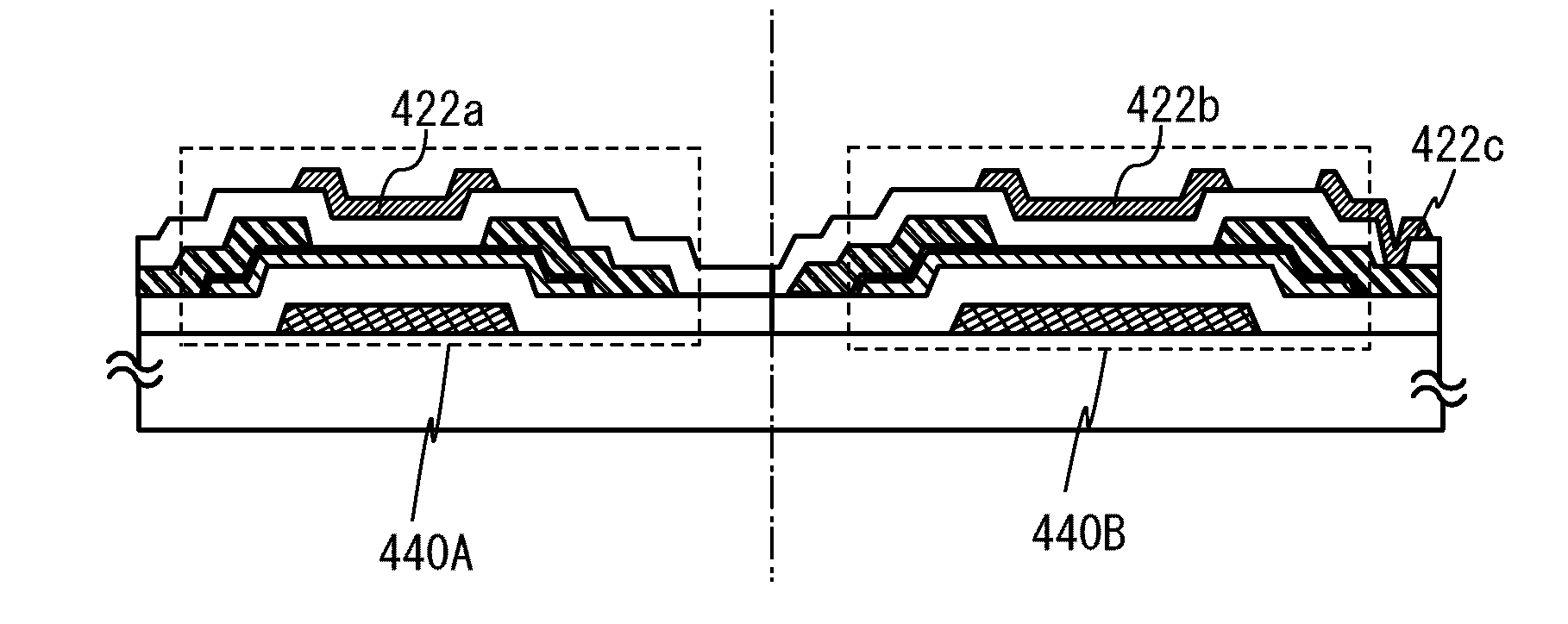

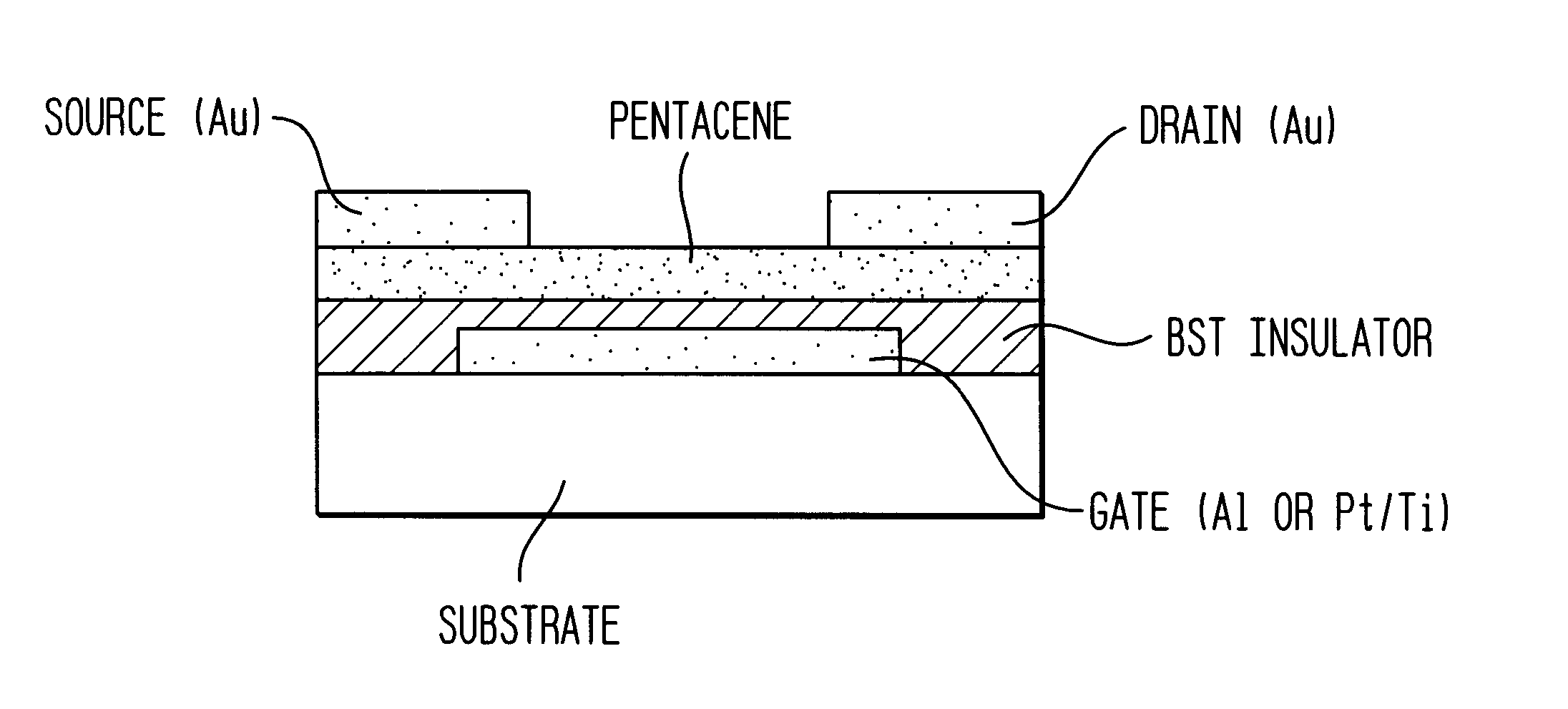

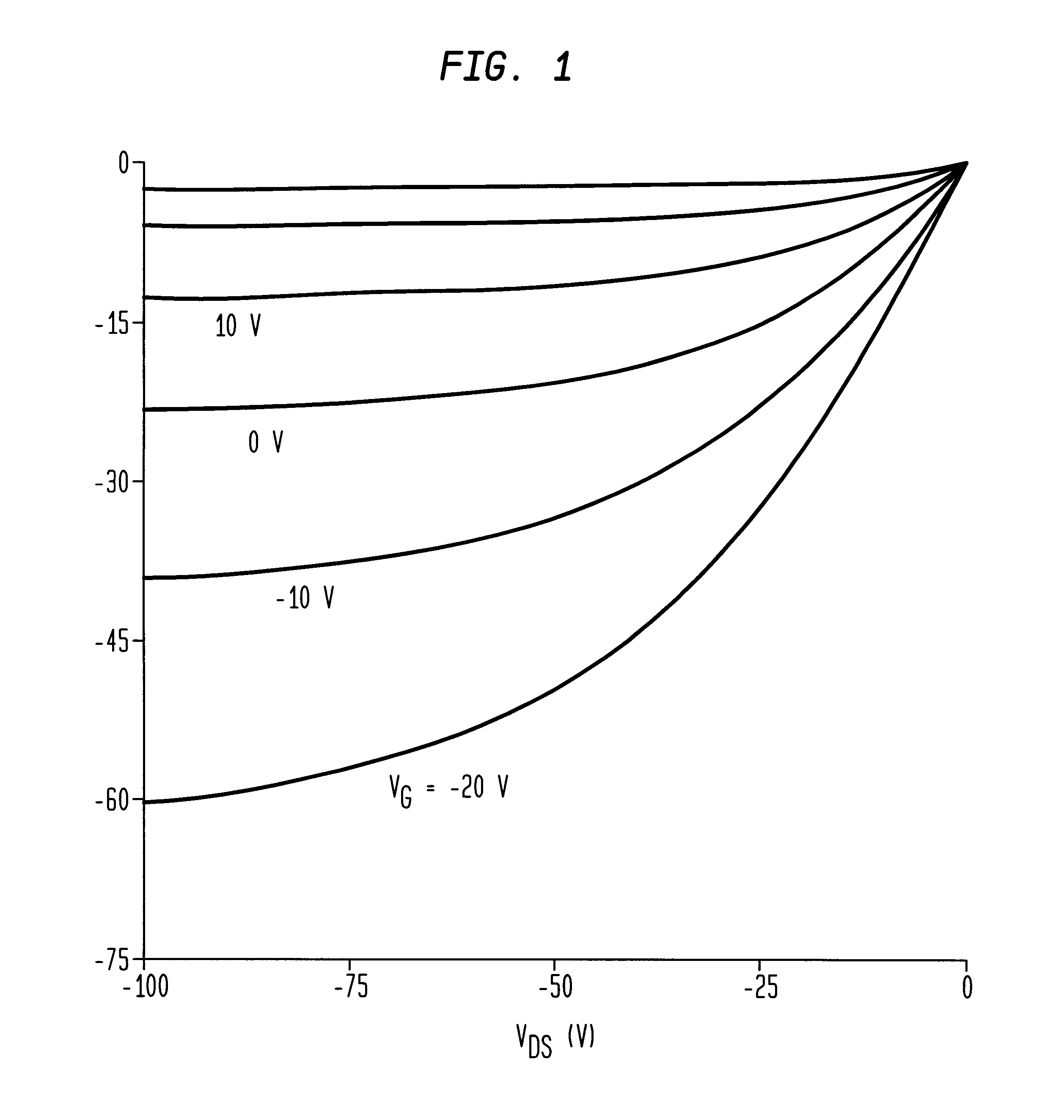

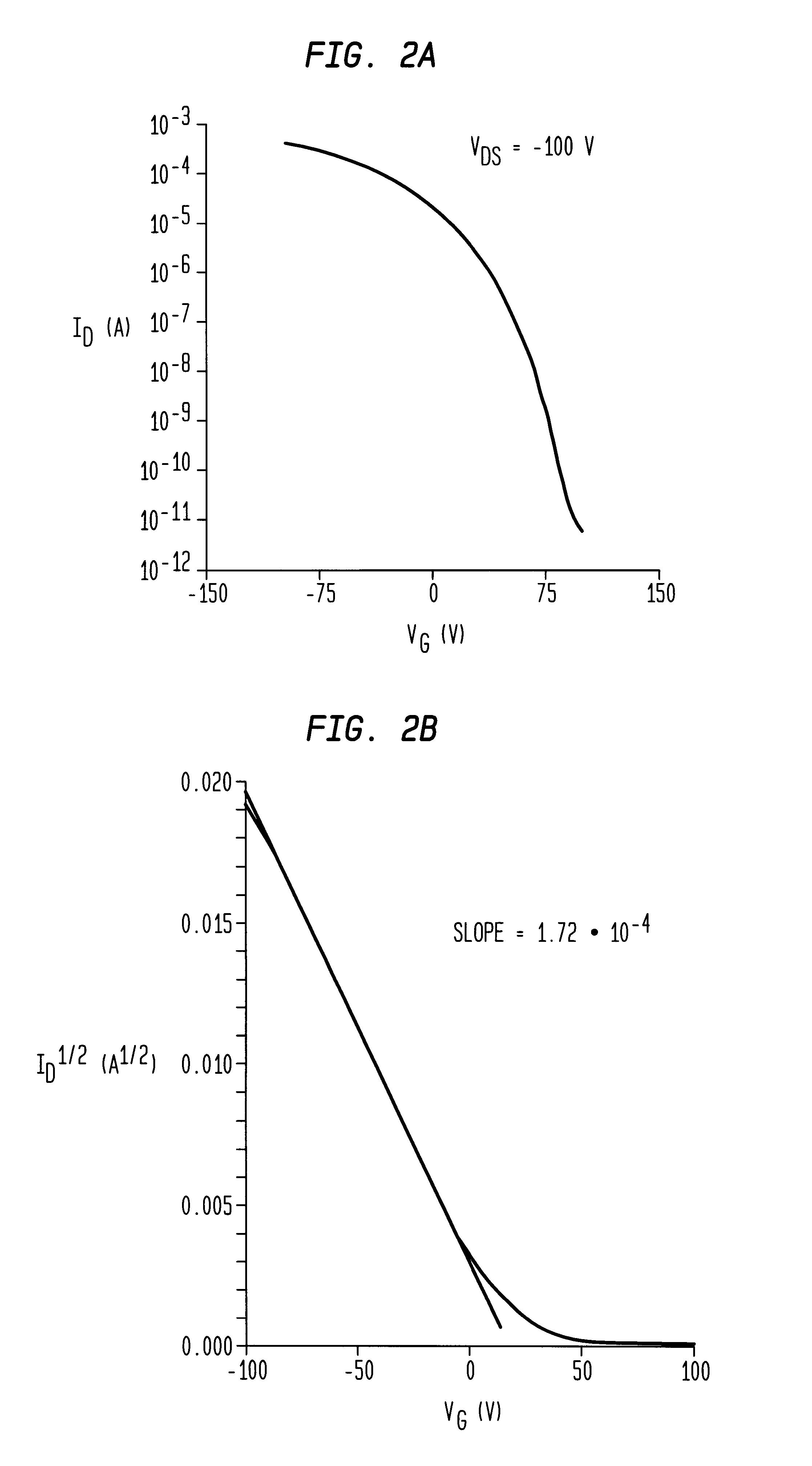

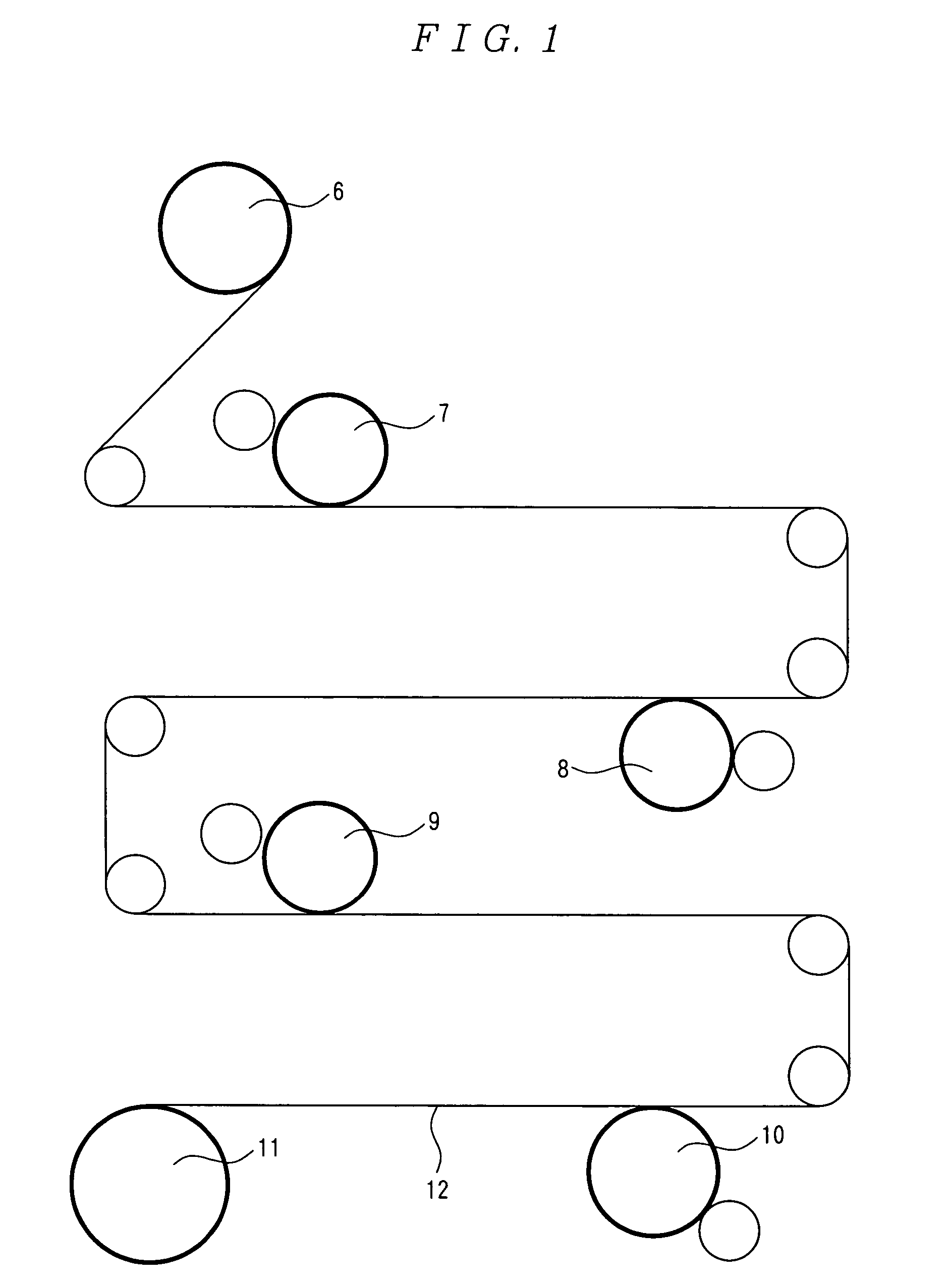

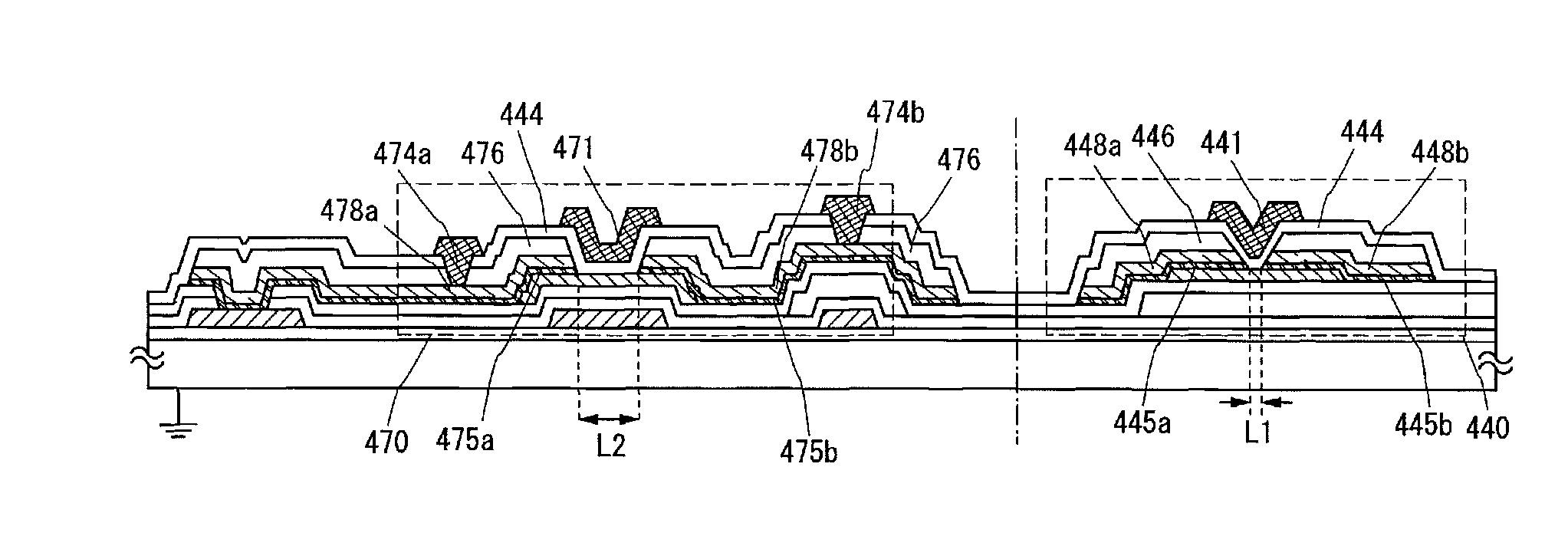

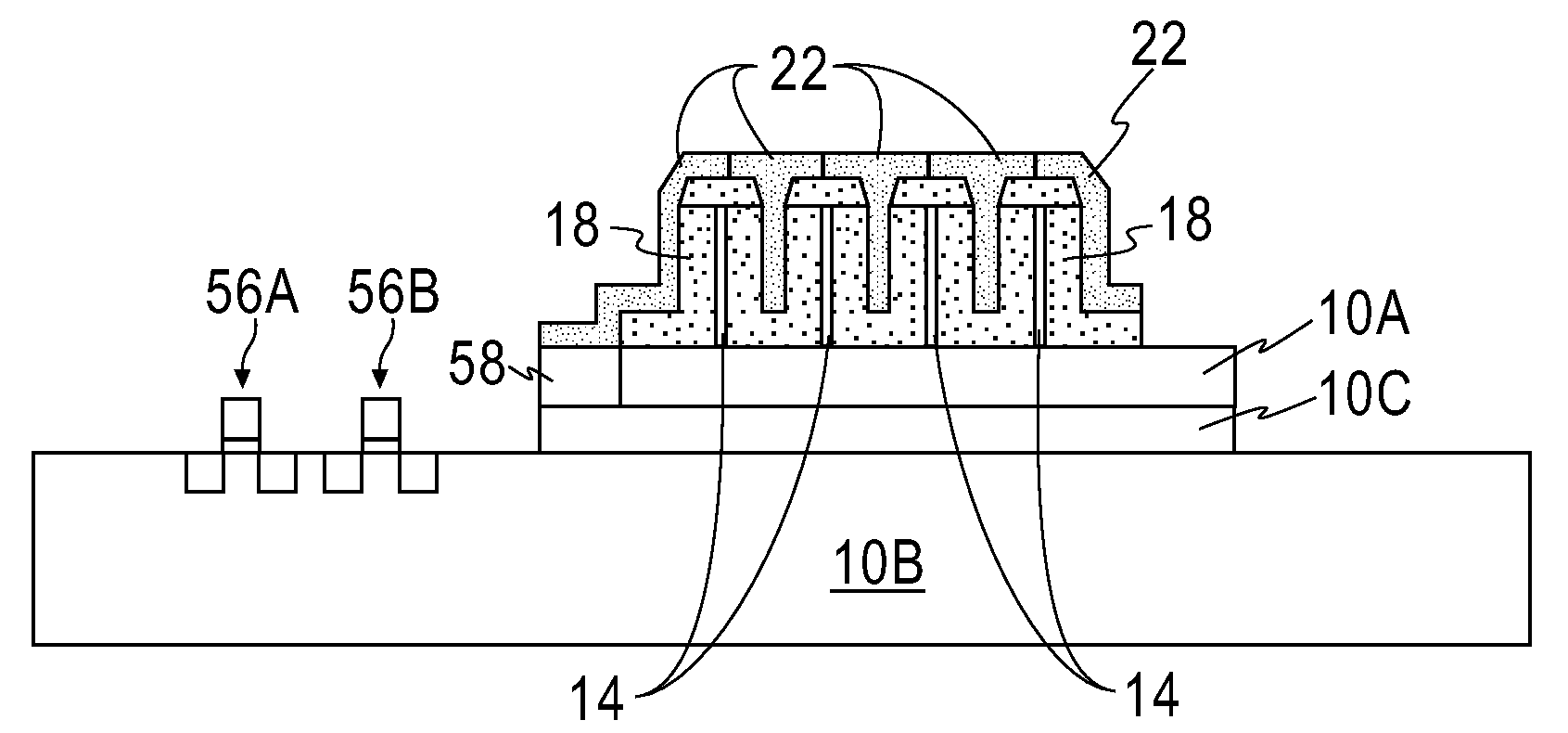

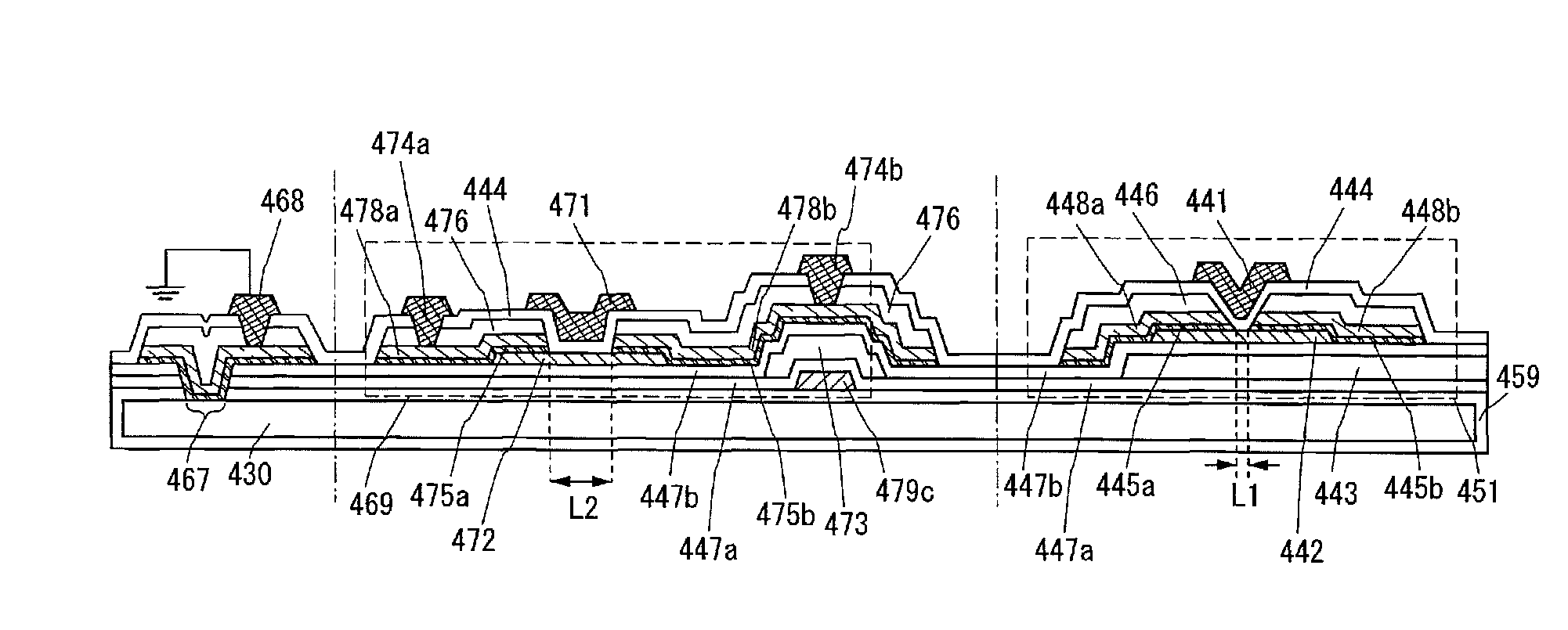

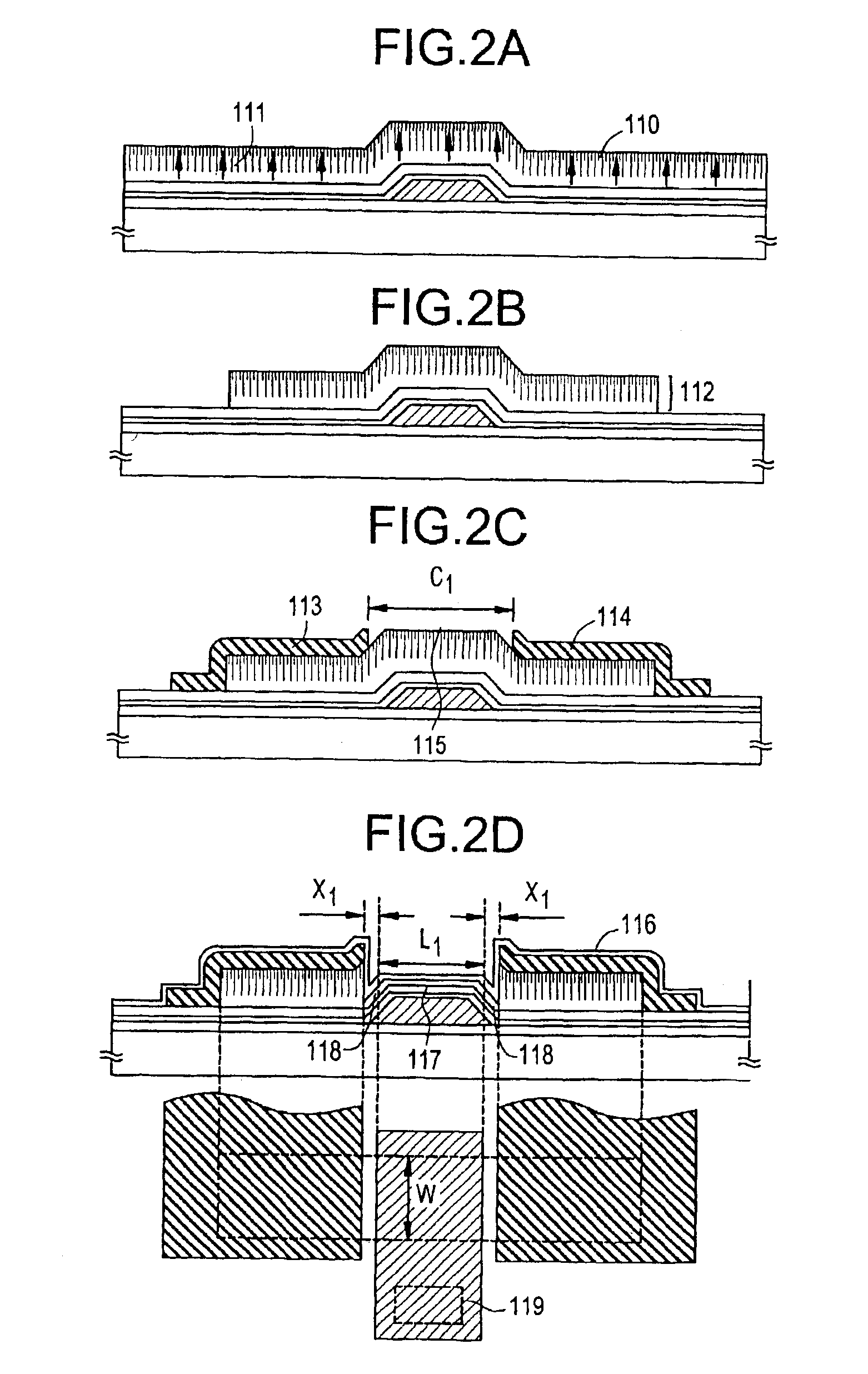

Thin-film field-effect transistor with organic semiconductor requiring low operating voltages

InactiveUS6344660B1Reduce thicknessImprove mobilityTransistorSolid-state devicesDisplay deviceFlat panel display

A thin film transistor (TFT) device structure based on an organic semiconductor material, that exhibits a high field effect mobility, high current modulation and a low sub-threshold slope at lower operating voltages than the current state of the art organic TFT devices. The structure comprises a suitable substrate disposed with he following sequence of features: a set of conducting gate electrodes covered with a high dielectric constant insulator, a layer of the organic semiconductor, sets of electrically conducting source and drain electrodes corresponding to each of the gate lines, and an optional passivation layer that can overcoat and protect the device structure. Use of high dielectric constant gate insulators exploits the unexpected gate voltage dependence of the organic semiconductor to achieve high field effect mobility levels at very low operating voltages. Judicious combinations of the choice of this insulator material and the means to integrate it into the TFT structure are taught that would enable easy fabrication on glass or plastic substrates and the use of such devices in flat panel display applications.

Owner:GLOBALFOUNDRIES INC

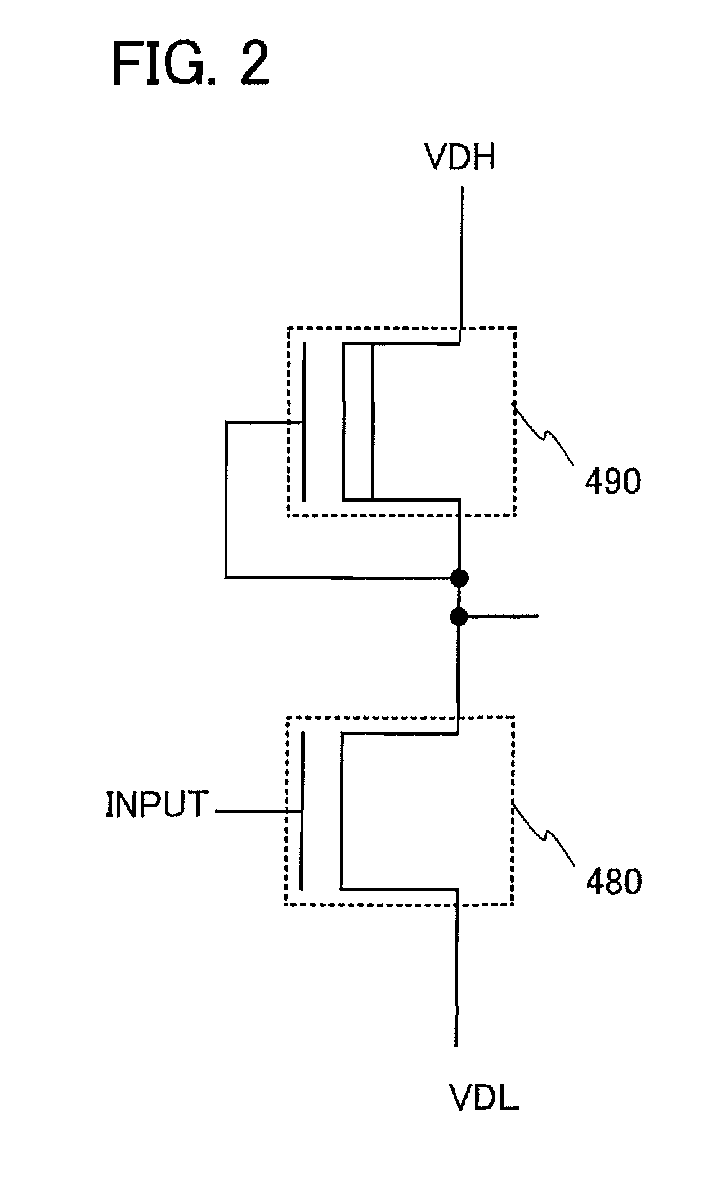

Semiconductor device and manufacturing method thereof

ActiveUS8421068B2Shorten driving distanceTimely controlSemiconductor/solid-state device detailsSolid-state devicesElectron donorElectron

An object is to reduce leakage current and parasitic capacitance of a transistor used for an LSI, a CPU, or a memory. A semiconductor integrated circuit such as an LSI, a CPU, or a memory is manufactured using a thin film transistor in which a channel formation region is formed using an oxide semiconductor which becomes an intrinsic or substantially intrinsic semiconductor by removing impurities which serve as electron donors (donors) from the oxide semiconductor and has larger energy gap than that of a silicon semiconductor. With use of a thin film transistor using a highly purified oxide semiconductor layer with sufficiently reduced hydrogen concentration, a semiconductor device with low power consumption due to leakage current can be realized.

Owner:SEMICON ENERGY LAB CO LTD

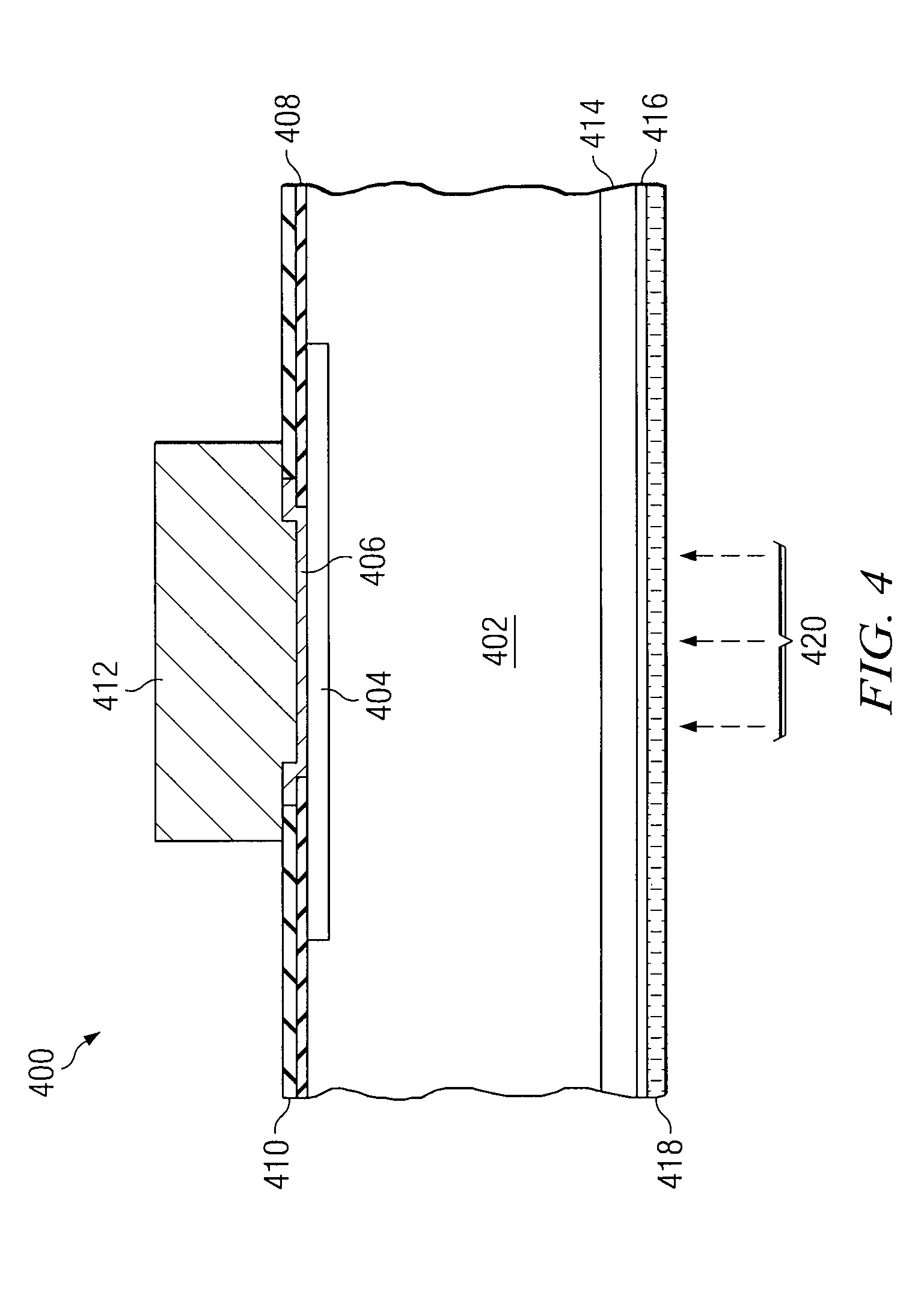

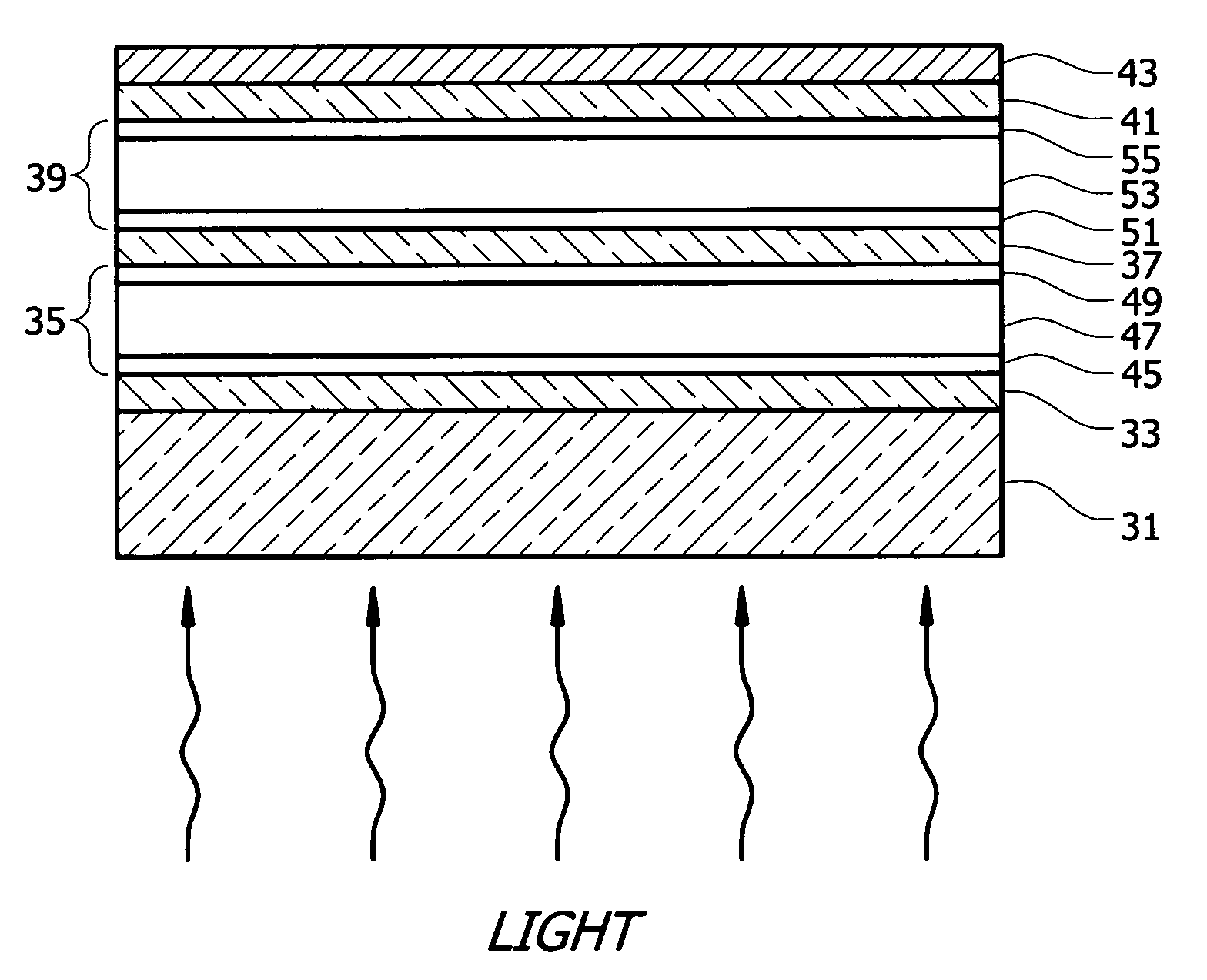

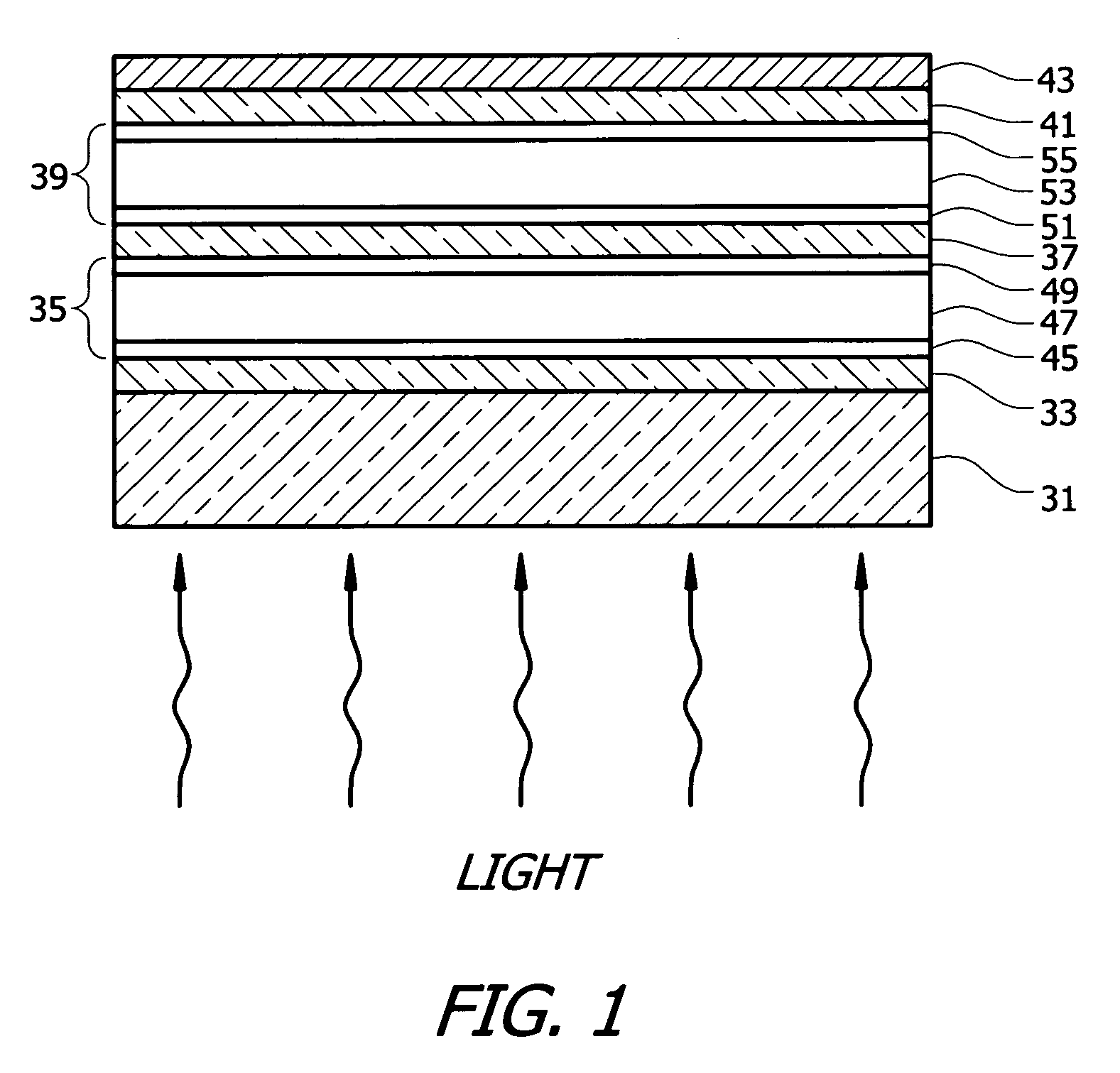

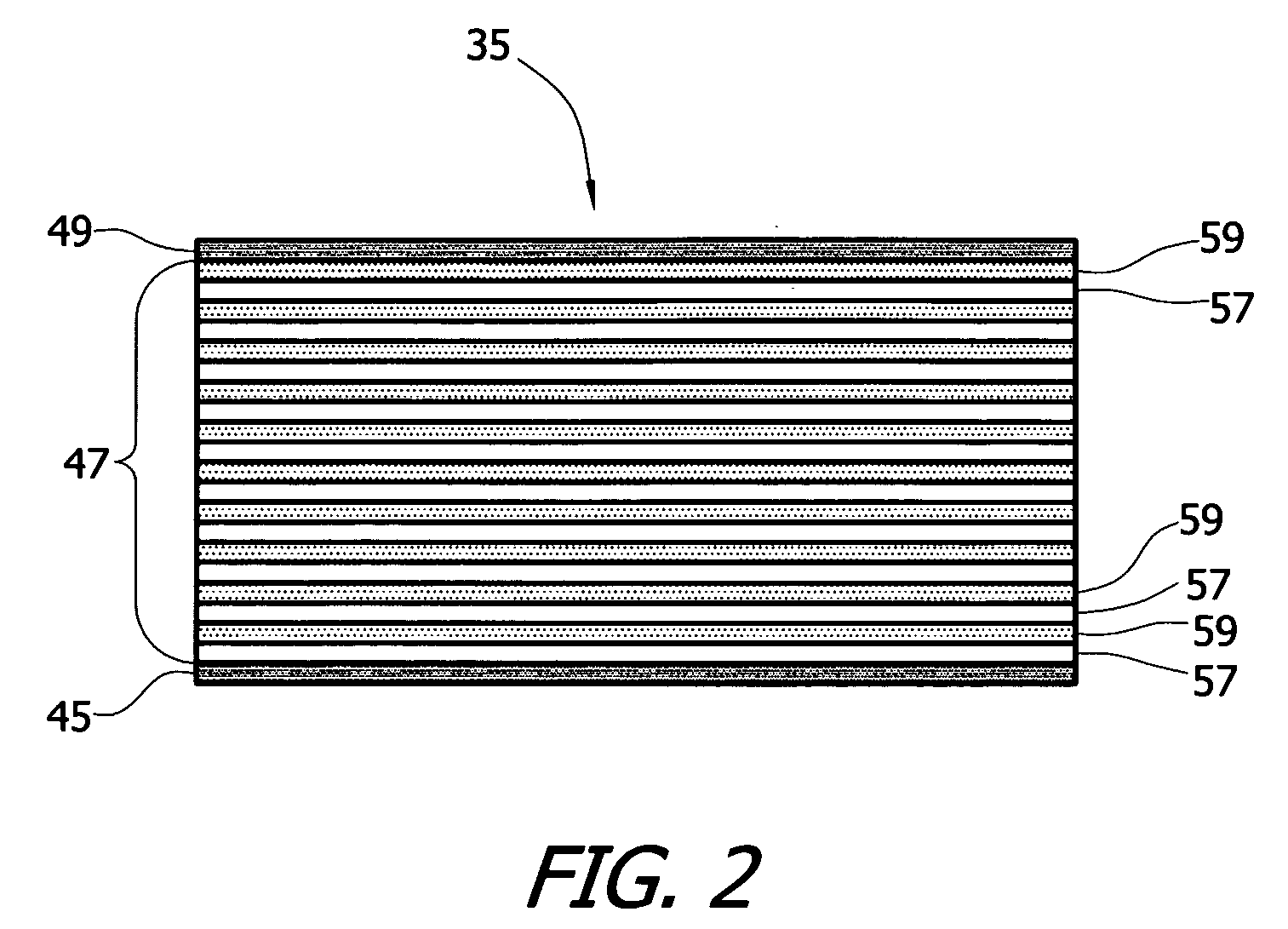

Stacked photoelectric converter

ActiveUS20060043517A1Increase currentLow production costPV power plantsPhotovoltaic energy generationEngineeringPhotoelectric conversion

In a stacked-layer type photoelectric conversion device, a plurality of photoelectric conversion units are stacked on a substrate, each of which includes a one conductivity-type layer, a photoelectric conversion layer of substantially intrinsic semiconductor and an opposite conductivity-type layer in this order from a light-incident side. At least one of the opposite conductivity-type layer in a front photoelectric conversion unit arranged relatively closer to the light-incident side and the one conductivity-type layer in a back photoelectric conversion unit arranged adjacent to the front photoelectric conversion unit includes a silicon composite layer at least in a part thereof. The silicon composite layer has a thickness of more than 20 nm and less than 130 nm and an oxygen concentration of more than 25 atomic % and less than 60 atomic %, and includes silicon-rich phase parts in an amorphous alloy phase of silicon and oxygen.

Owner:KANEKA CORP

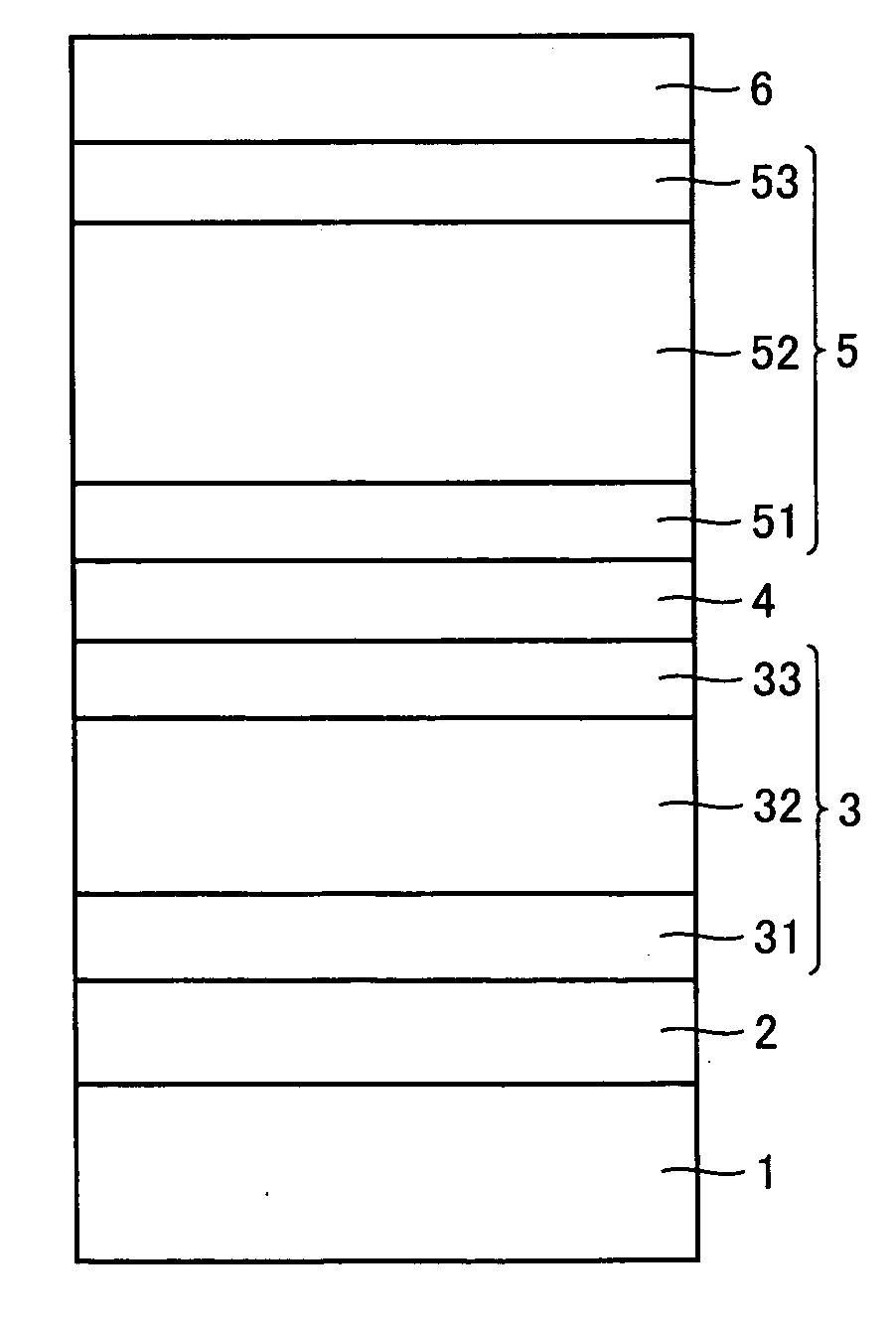

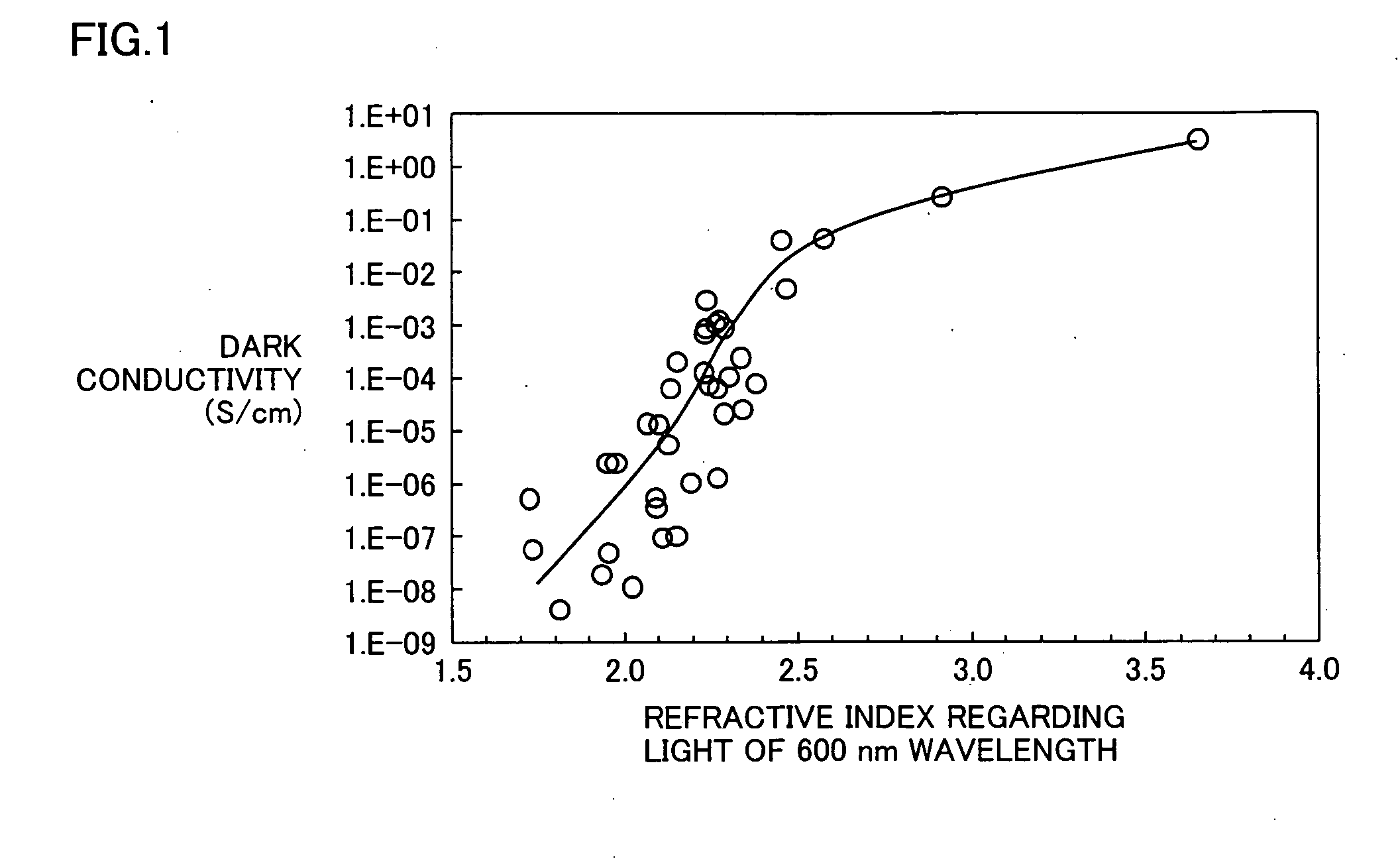

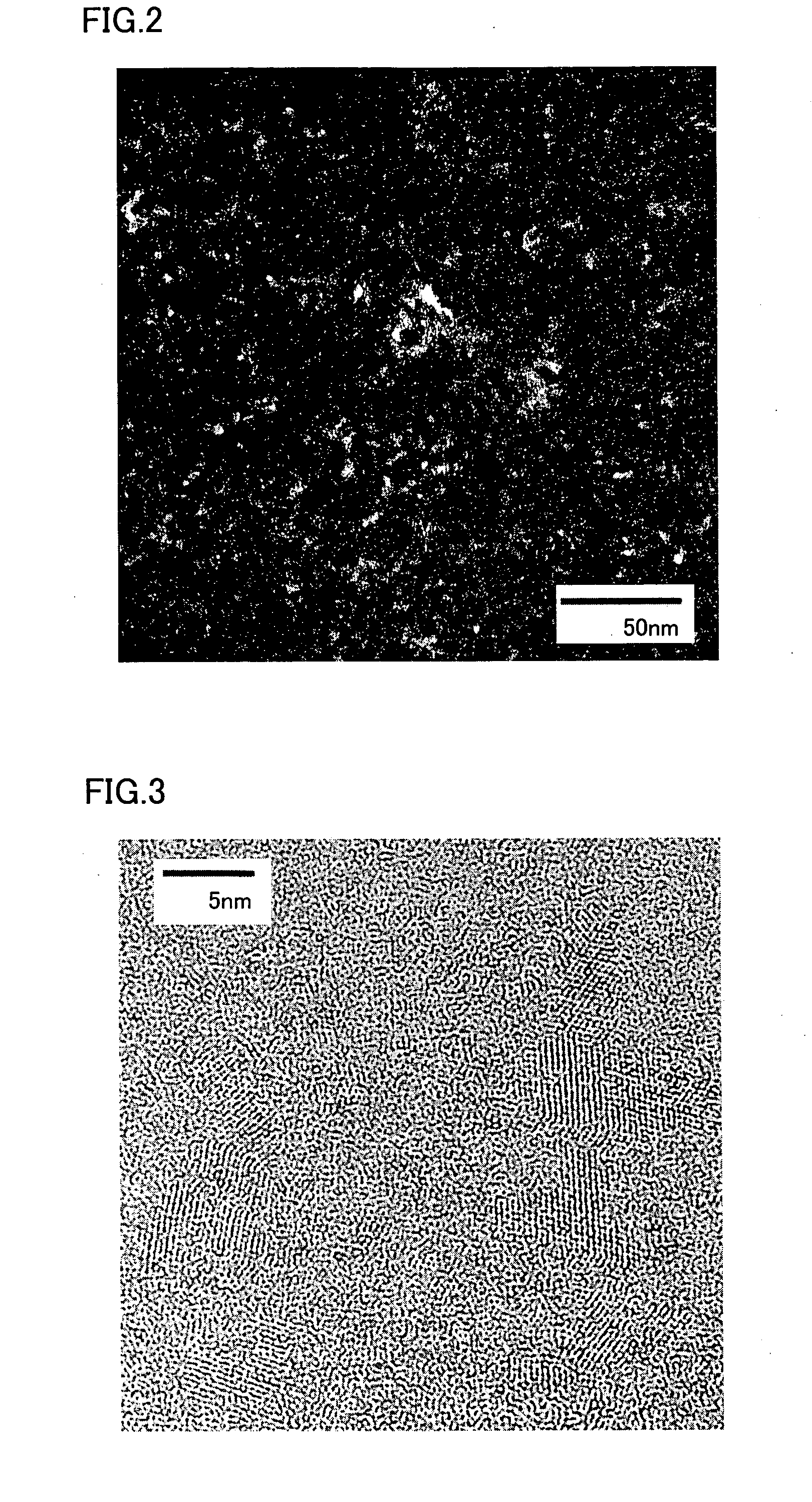

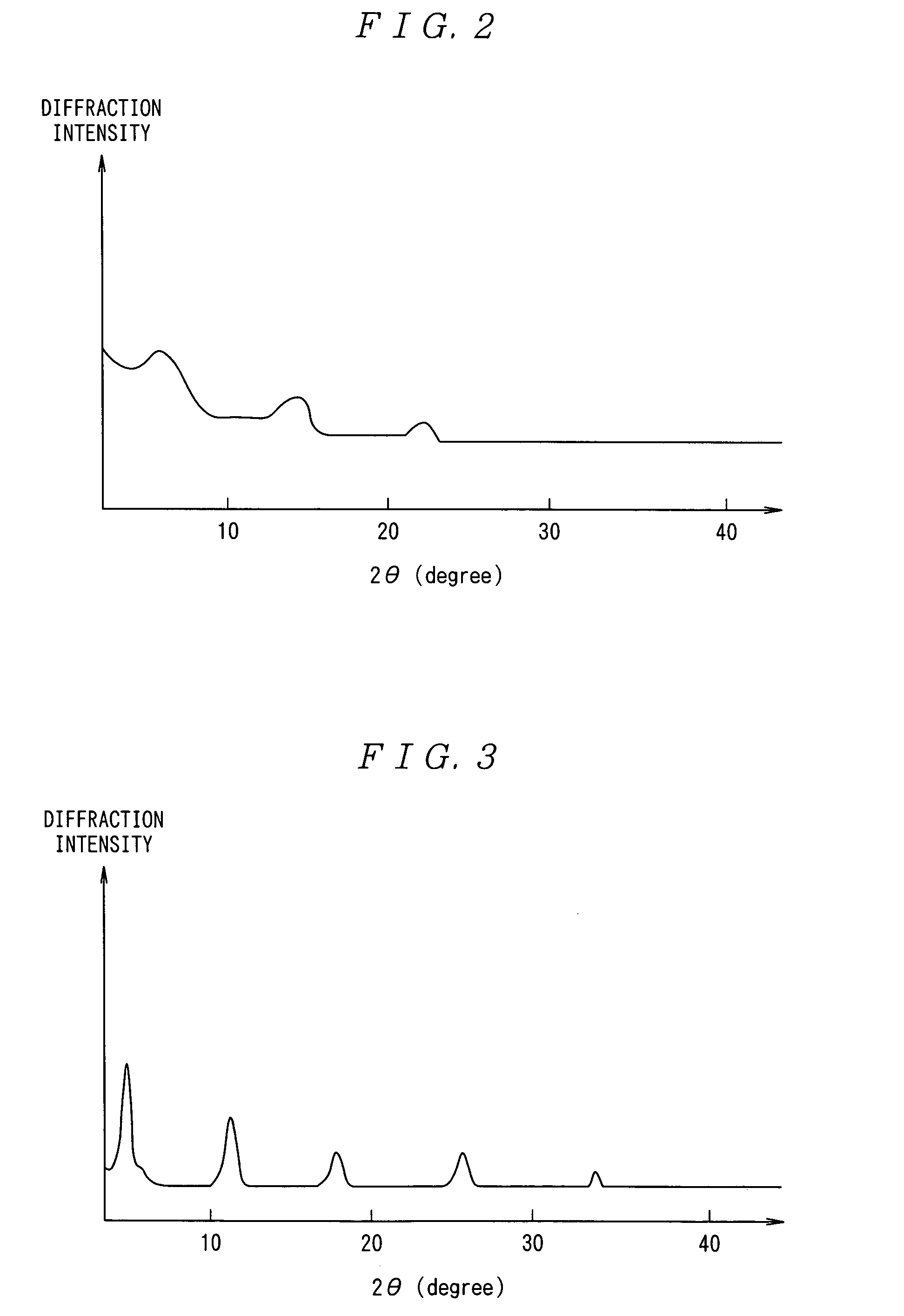

Organic semiconductor element

InactiveUS7061010B2Easy to produceLow costPolycrystalline material growthFrom normal temperature solutionsPhotonicsElectronic properties

The present invention relates to an organic semiconductor thin film suitably employed in electronics, photonics, bioelectronics, or the like, and a method for forming the same. The present invention further relates to a solution for an organic semiconductor used to form the organic semiconductor thin film and an organic semiconductor device using the organic semiconductor thin film.The transistor of the present invention is manufactured by forming sequentially a gate electrode (2), an insulator layer (3), a source electrode and drain electrode (4, 4) on a glass substrate (5), applying thereto a 0.05% (by mass) solution of pentacene in o-dichlorobenzene and drying the solution to form an organic semiconductor thin film (1).The present invention provides a transistor with superior electronic characteristics because the organic semiconductor thin film (1), which can be formed easily at low cost, is almost free of defects.

Owner:ASAHI KASEI KK

Method of fabricating a stacked oxide material for thin film transistor

ActiveUS8367489B2Improve conversion efficiencyImprove featuresSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsElectron donor

Objects are to provide a semiconductor device for high power application in which a novel semiconductor material having high productivity is used and to provide a semiconductor device having a novel structure in which a novel semiconductor material is used. The present invention is a vertical transistor and a vertical diode each of which has a stacked body of an oxide semiconductor in which a first oxide semiconductor film having crystallinity and a second oxide semiconductor film having crystallinity are stacked. An impurity serving as an electron donor (donor) which is contained in the stacked body of an oxide semiconductor is removed in a step of crystal growth; therefore, the stacked body of an oxide semiconductor is highly purified and is an intrinsic semiconductor or a substantially intrinsic semiconductor whose carrier density is low. The stacked body of an oxide semiconductor has a wider band gap than a silicon semiconductor.

Owner:SEMICON ENERGY LAB CO LTD

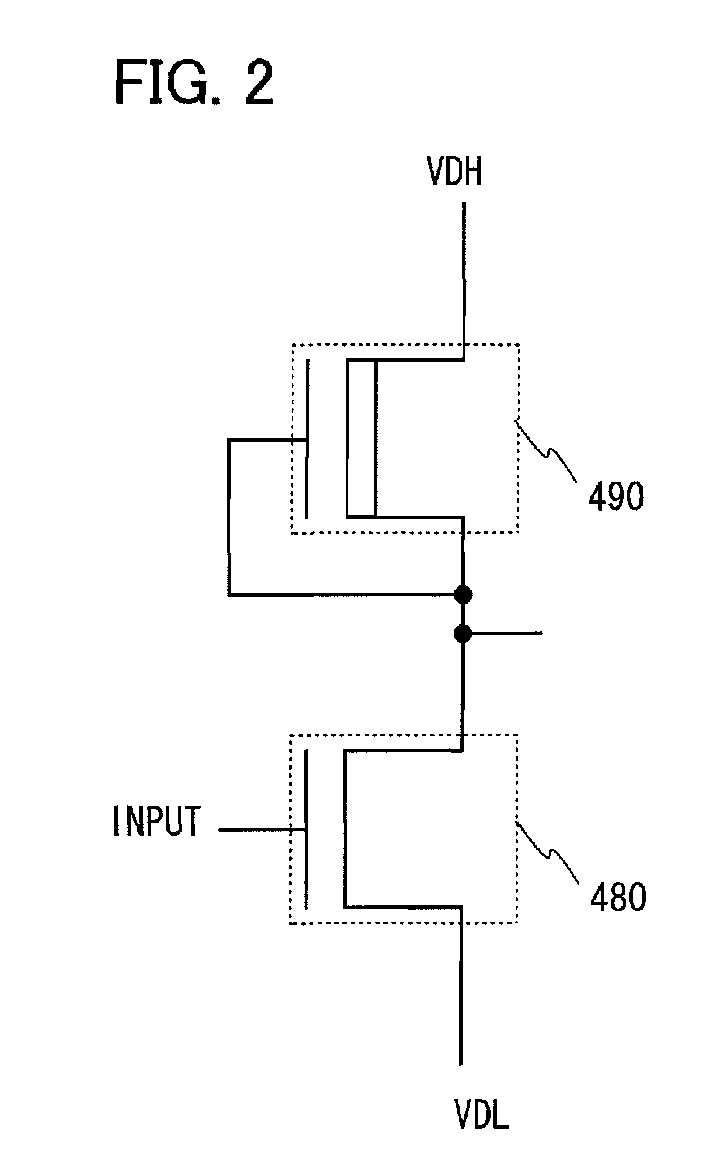

Semiconductor device and manufacturing method thereof

ActiveUS20110089414A1Reduce leakage currentReduce power consumptionSemiconductor/solid-state device detailsSolid-state devicesElectron donorElectron

An object is to reduce leakage current and parasitic capacitance of a transistor used for an LSI, a CPU, or a memory. A semiconductor integrated circuit such as an LSI, a CPU, or a memory is manufactured using a thin film transistor in which a channel formation region is formed using an oxide semiconductor which becomes an intrinsic or substantially intrinsic semiconductor by removing impurities which serve as electron donors (donors) from the oxide semiconductor and has larger energy gap than that of a silicon semiconductor. With use of a thin film transistor using a highly purified oxide semiconductor layer with sufficiently reduced hydrogen concentration, a semiconductor device with low power consumption due to leakage current can be realized.

Owner:SEMICON ENERGY LAB CO LTD

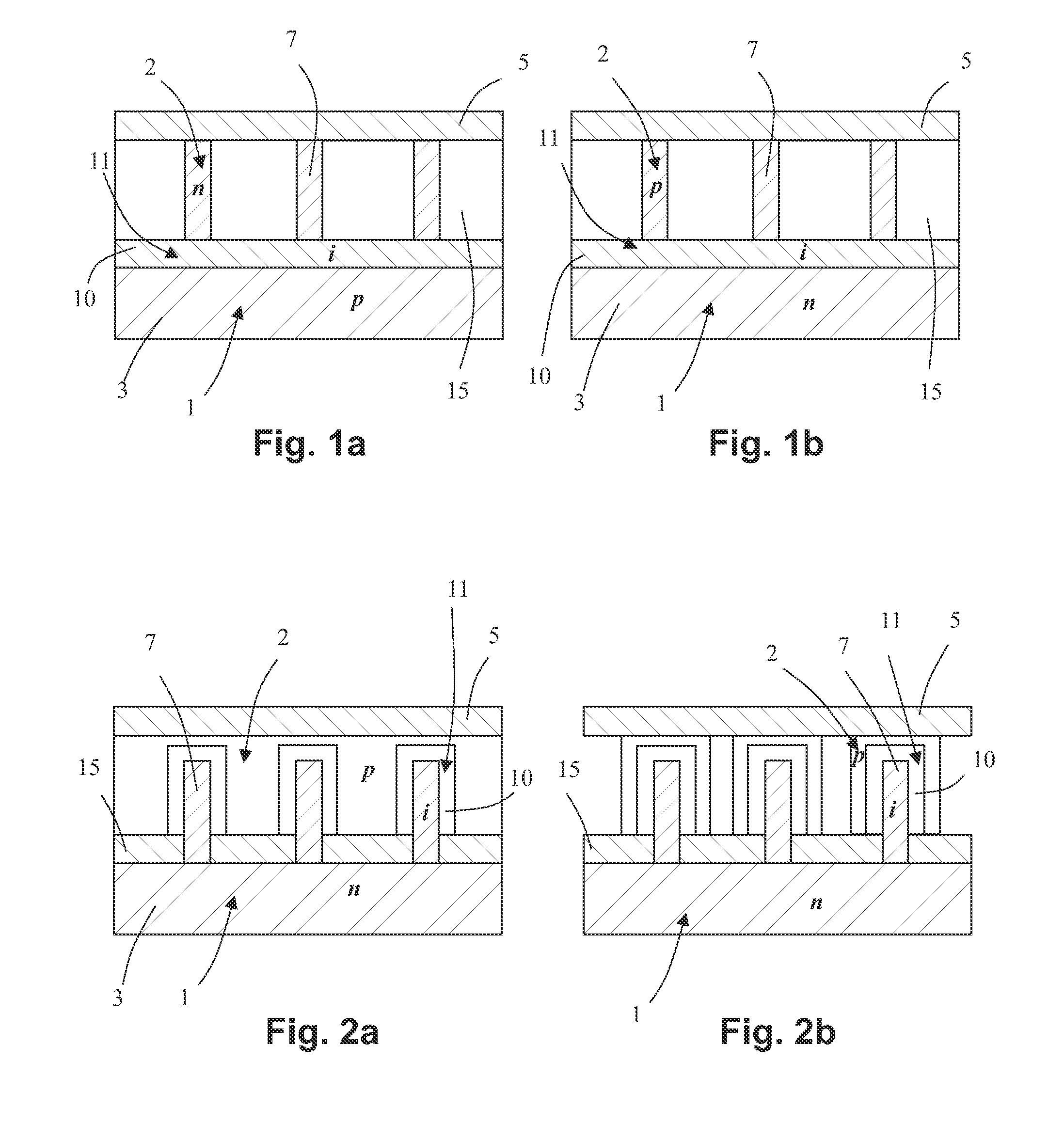

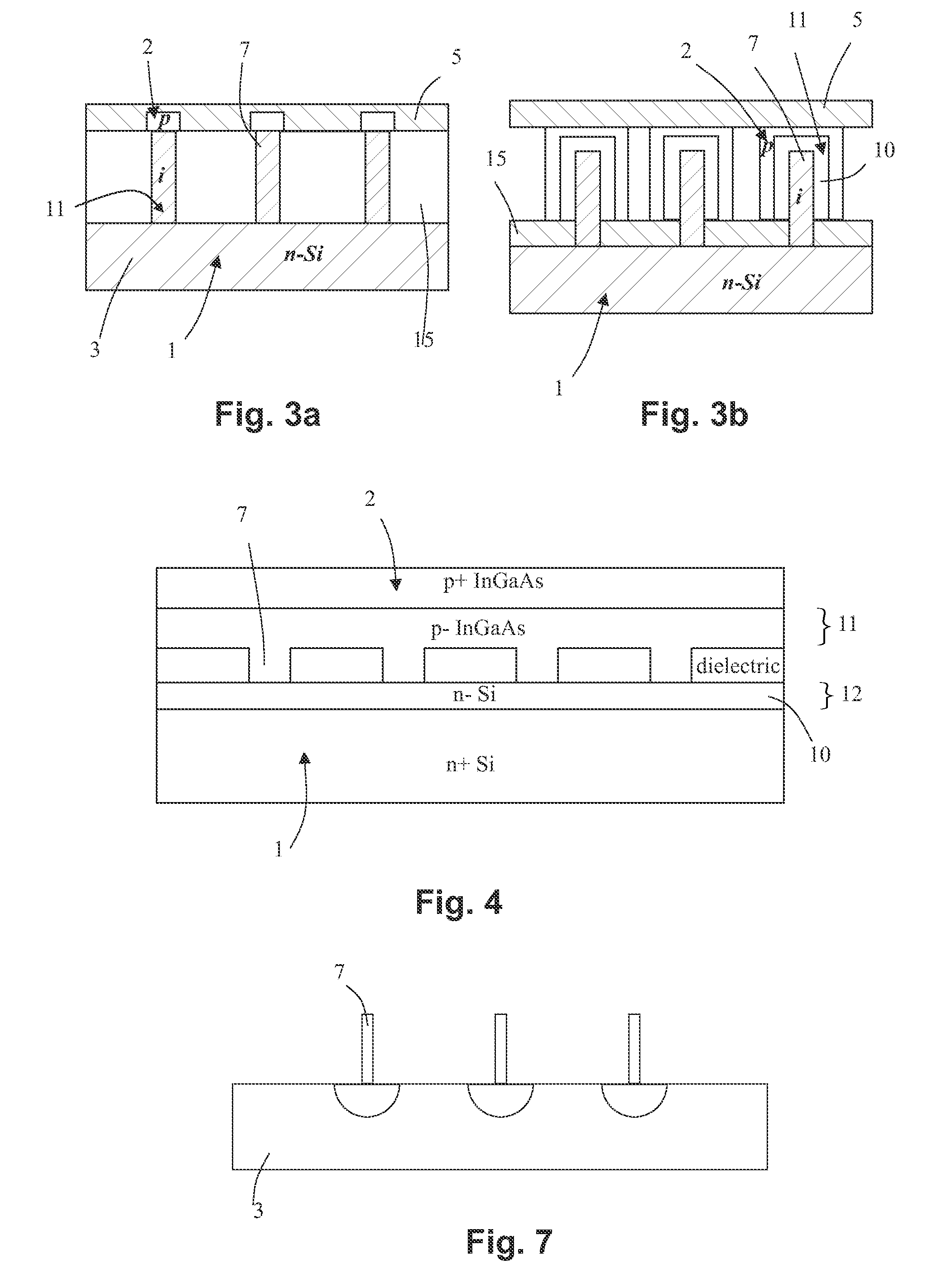

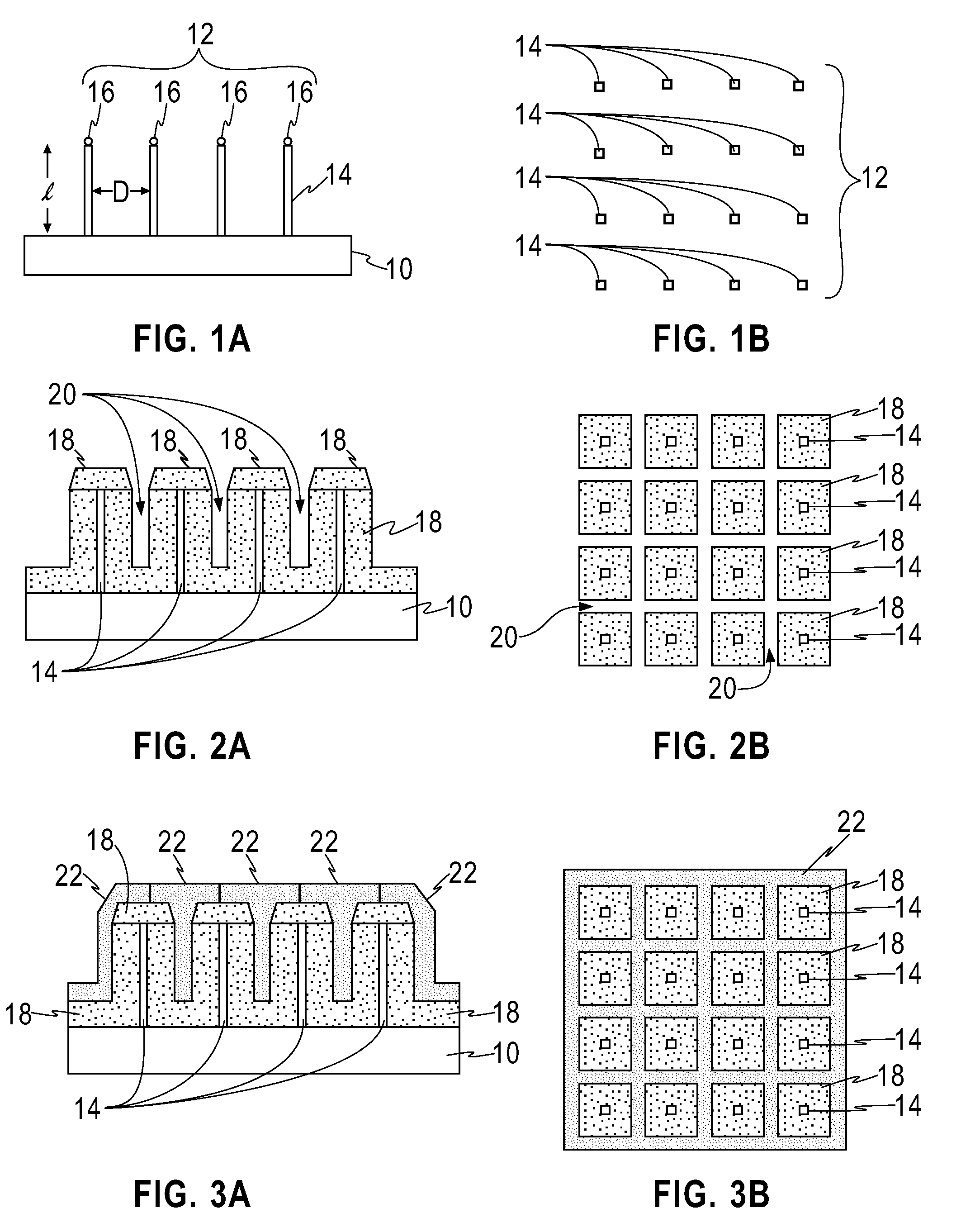

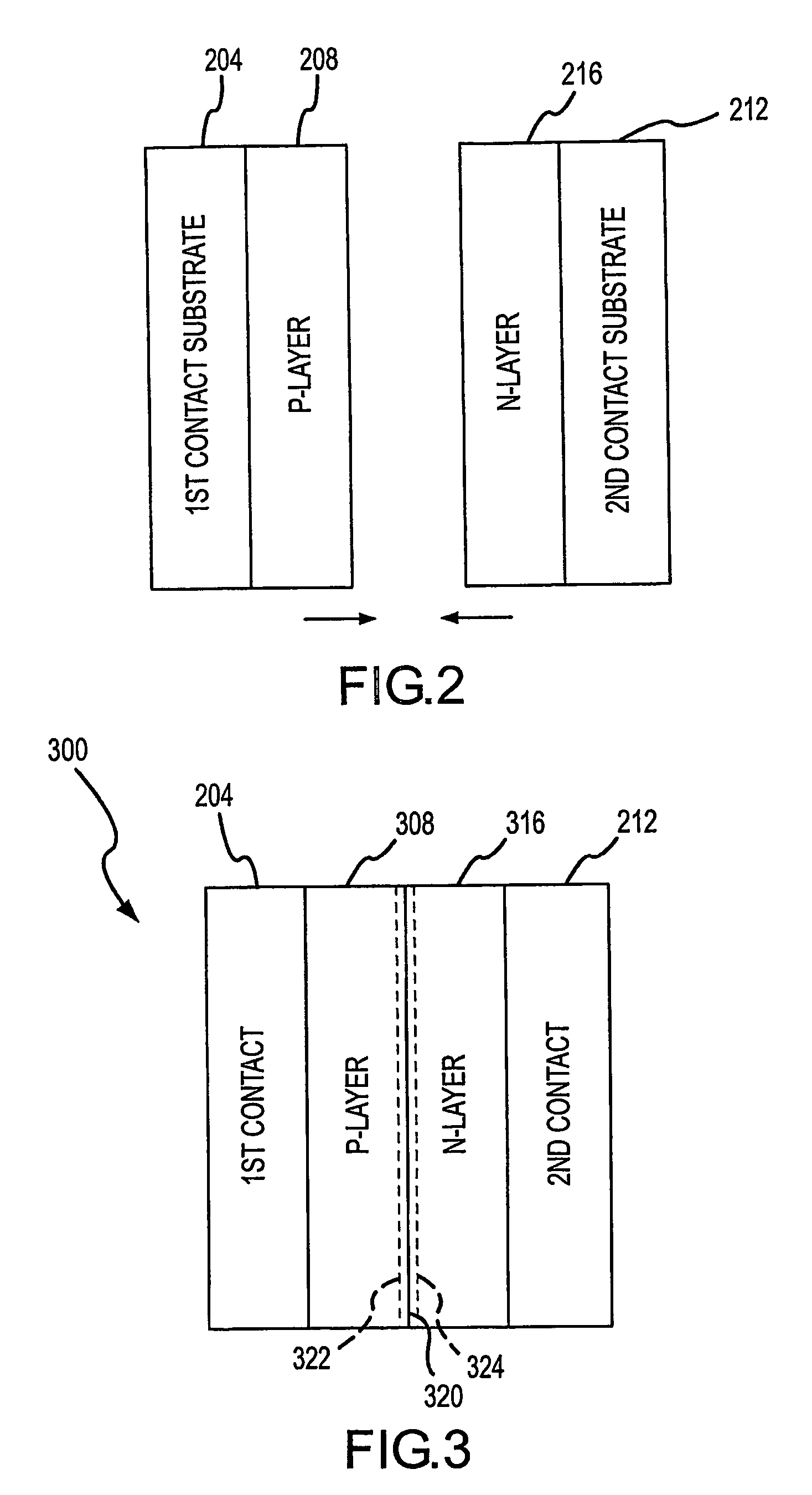

Nanostructured photodiode

InactiveUS20110180894A1Prevent excessive current leakageAvoid device failureNanosensorsPhotovoltaic energy generationNanowireSemiconductor materials

The present invention provides a photodiode comprising a p-i-n or pn junction at least partly formed by first and second regions (2) made of semiconductor materials having opposite conductivity type, wherein the p-i-n or pn junction comprises a light absorption region (11) for generation of charge carriers from absorbed light. One section of the p-i-n or pn junction is comprises by one or more nanowires (7) that are spaced apart and arranged to collect charge carriers generated in the light absorption region (11). At least one low doped region (10) made of a low doped or intrinsic semiconductor material provided between the nanowires (7) and one of said first region (1) and said second region (2) enables custom made light absorption region and / or avalanche multiplication region of the active region (9).

Owner:QUNANO

Avalanche Photodiode

InactiveUS20100327387A1Improve signal-to-noise ratioSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsPhotodiode

Owner:RAYTHEON CO

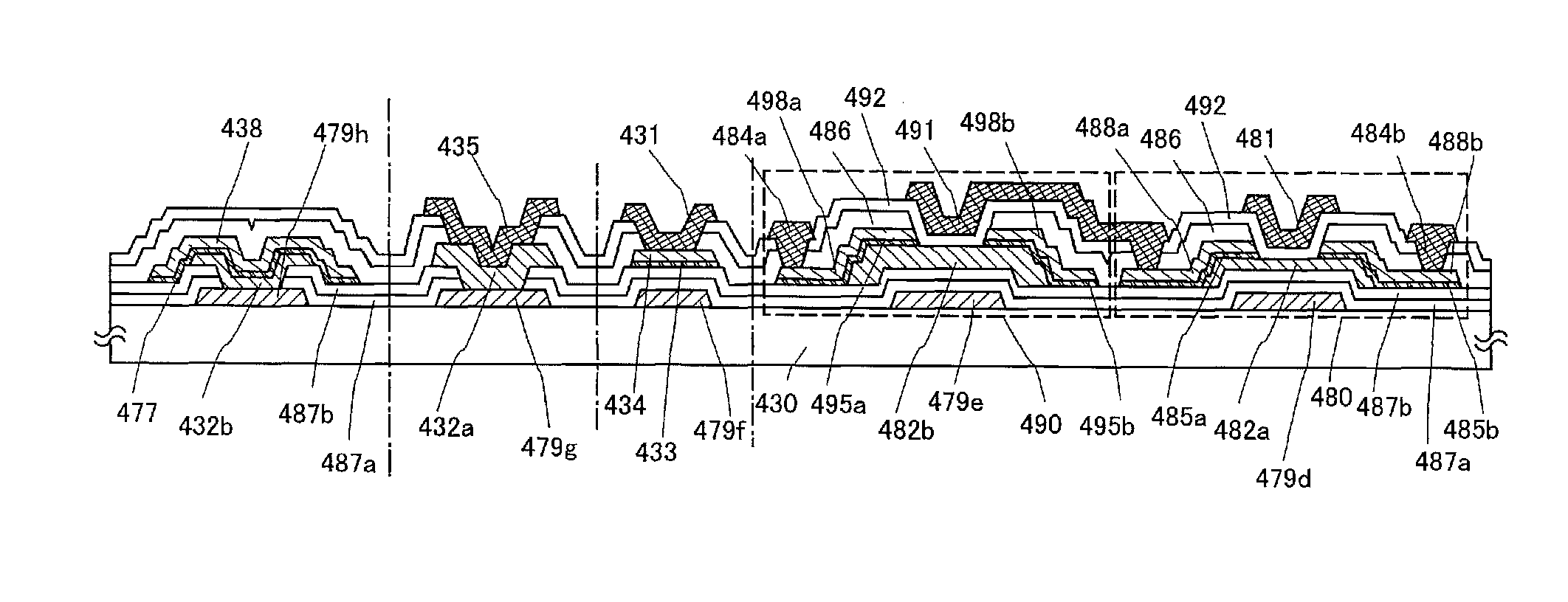

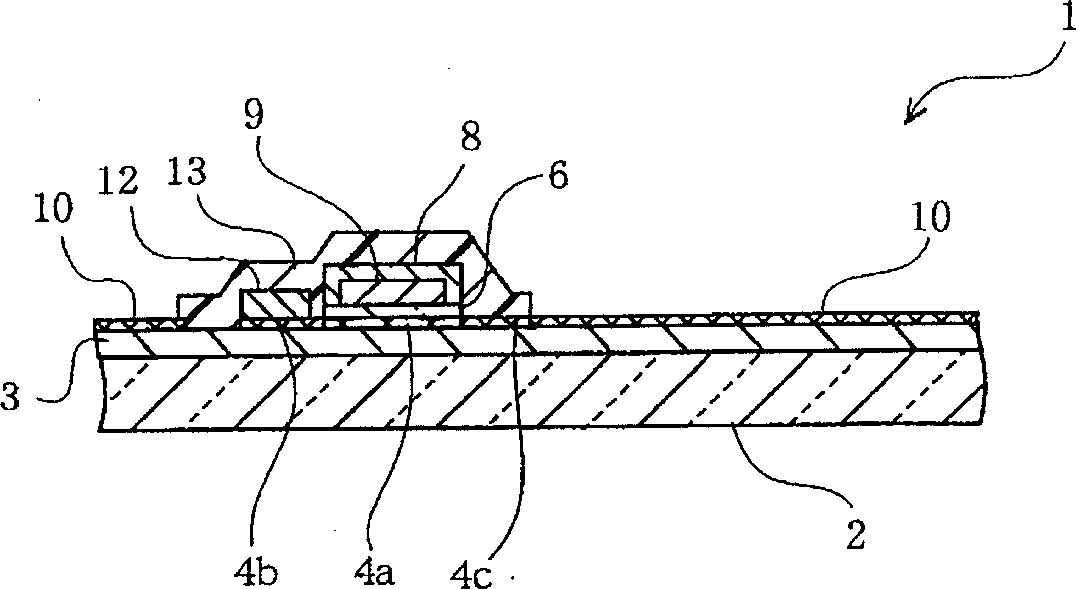

Thin film transistor array and its manufacturing method and display board using same

InactiveCN1353329AEasy to manufactureTransistorSolid-state devicesDisplay boardSemiconductor materials

By imparting conductivity to specified regions of a semiconductor material film formed over a substrate, the semiconductor material film, in addition to being processed into channel portions, source portions, and drain portions of TFTs, is processed into conductive elements containing pixel electrodes connected to the drain portions. Regions composed of an intrinsic semiconductor to which impurities have not been added serve as the active layers (channel regions) of the TFTs and regions to which impurities have been added serve as conductive elements. When transparent electrodes are formed, an oxide semiconductor is used.

Owner:PANASONIC CORP

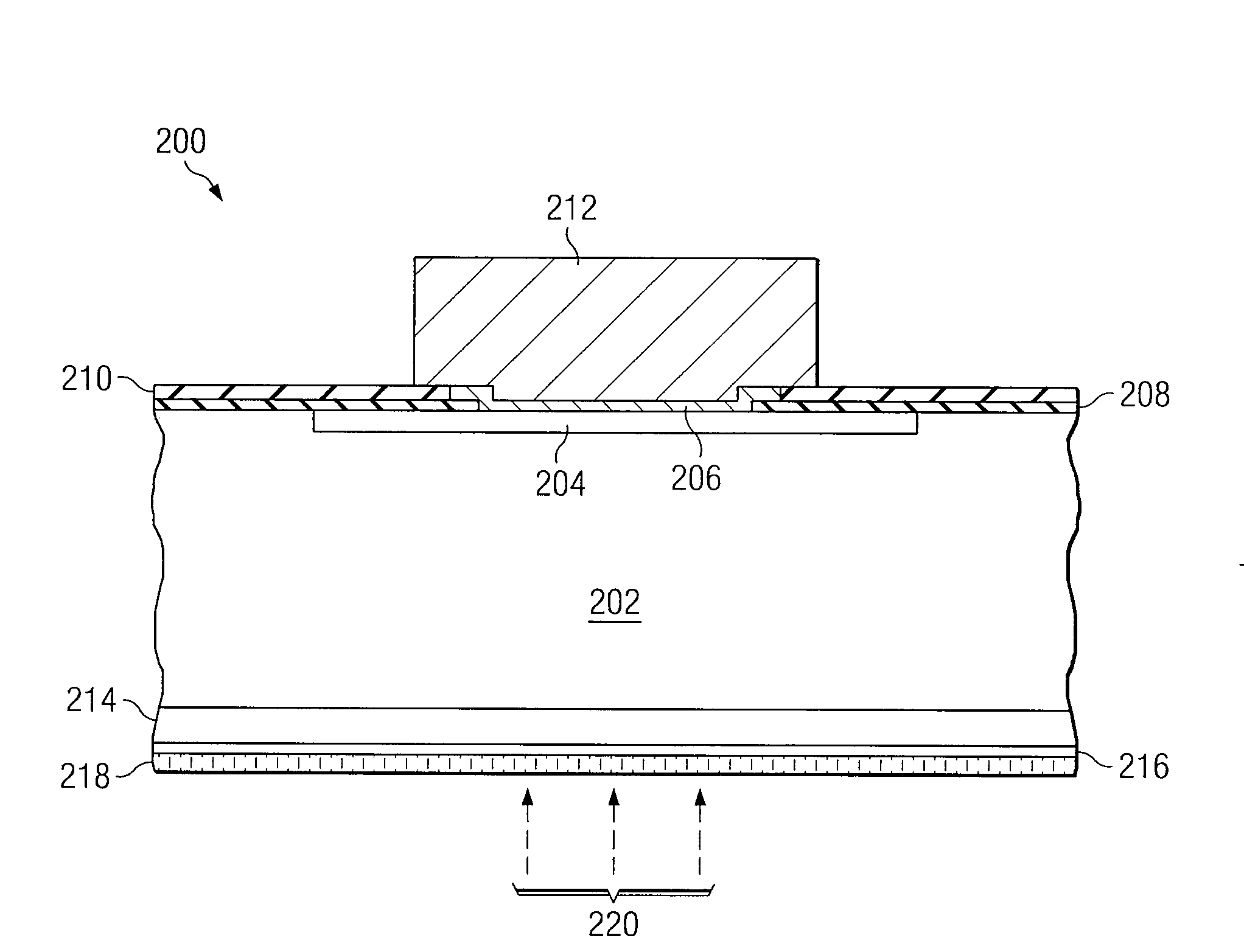

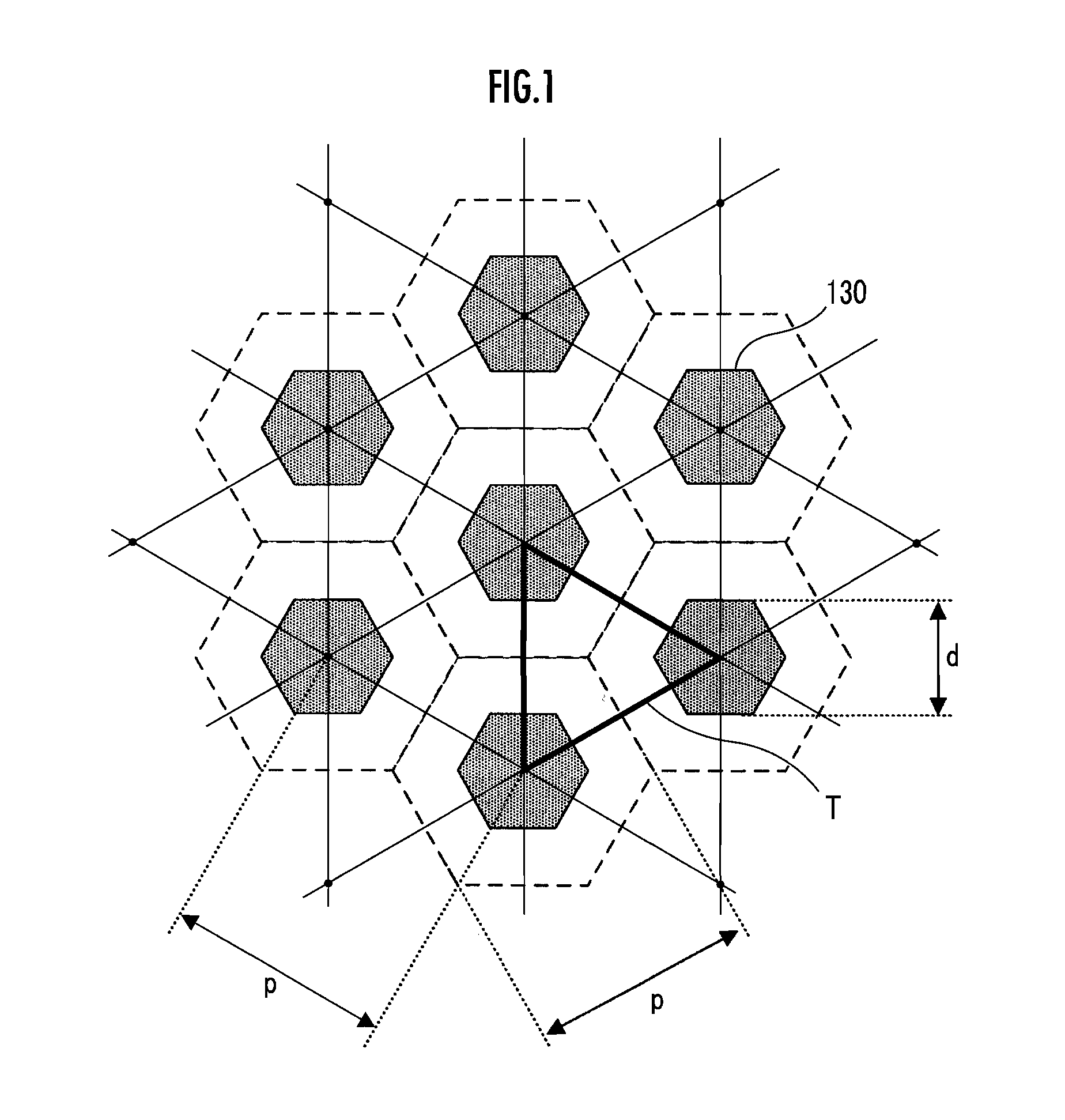

Solar Cell Element, Color Sensor and Method of Manufacturing Light Emitting Element and Light Receiving Element

A solar cell element having improved power generation efficiency is provided. A solar cell element 100 has a substrate 110, a mask pattern 120, semiconductor nanorods 130, a first electrode 150 and a second electrode 160. The semiconductor nanorods 130 are disposed in triangular lattice form as viewed in plan on the substrate 110. The ratio p / d of the center-to-center distance p between each adjacent pair of the semiconductor nanorods 130 and the minimum diameter d of the semiconductor nanorods 130 is within the range from 1 to 7. Each semiconductor nanorod 130 has a central nanorod 131 formed of a semiconductor of a first conduction type, a first cover layer 132 formed of an intrinsic semiconductor and covering the central nanorod 131, and a second cover layer 138 formed of a semiconductor of a second conduction type and covering the first cover layer 132.

Owner:HONDA MOTOR CO LTD +1

Semiconductor device

ActiveUS8421069B2Shorten driving distanceTimely controlSemiconductor/solid-state device detailsSolid-state devicesElectron donorImpurity

An object is to reduce leakage current and parasitic capacitance of a transistor used for an LSI, a CPU, or a memory. A semiconductor integrated circuit included in an LSI, a CPU, or a memory is manufactured using the transistor which is formed using an oxide semiconductor which is an intrinsic or substantially intrinsic semiconductor obtained by removal of impurities which serve as electron donors (donors) from the oxide semiconductor and has larger energy gap than a silicon semiconductor, and is formed over a semiconductor substrate. With the transistor which is formed over the semiconductor substrate and includes the highly purified oxide semiconductor layer with sufficiently reduced hydrogen concentration, a semiconductor device whose power consumption due to leakage current is low can be realized.

Owner:SEMICON ENERGY LAB CO LTD

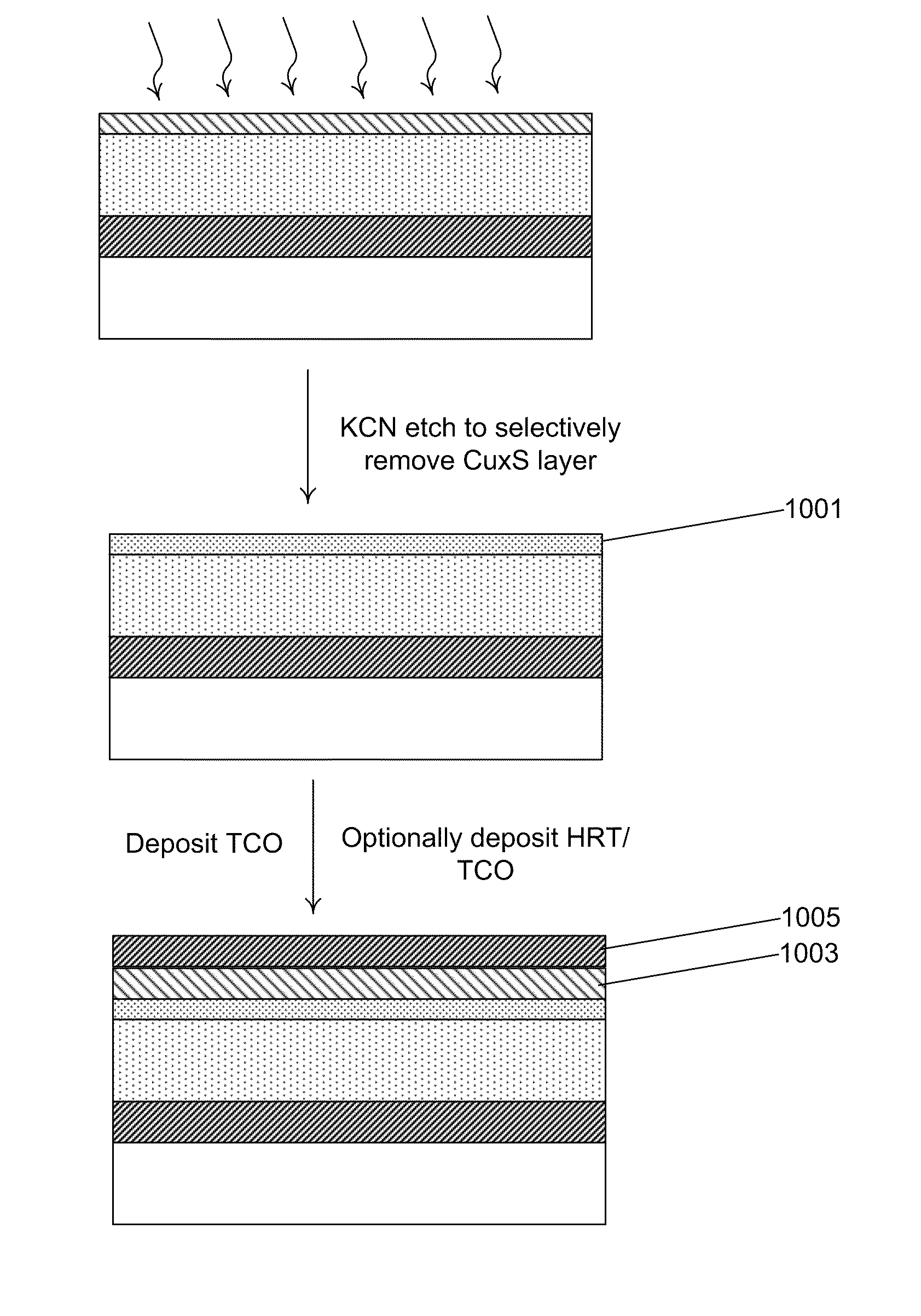

Method and structure for thin film photovoltaic cell using similar material junction

InactiveUS20100122726A1High resistivityToxic reductionFinal product manufactureSemiconductor/solid-state device manufacturingIndiumSulfur

A method for forming a thin film photovoltaic device. The method provides a transparent substrate including a surface region. A first electrode layer overlies the surface region. A copper layer is formed overlying the first electrode layer and an indium layer is formed overlying the copper layer to form a multi-layered structure. At least the multi-layered structure is subjected to a thermal treatment process in an environment containing a sulfur bearing species to forming a bulk copper indium disulfide. The bulk copper indium disulfide material has a surface region characterized by a copper poor surface region having a copper to indium atomic ratio of less than about 0.95:1 and n-type impurity characteristics. The bulk copper indium disulfide material excluding the copper poor surface region forms an absorber region and the copper poor surface region forms at least a portion of a window region for the thin film photovoltaic device. The method optionally forms a high resistivity transparent material having an intrinsic semiconductor characteristic overlying the copper poor surface region. A second electrode layer overlies the high resistivity transparent layer.

Owner:CM MFG

Transistor

InactiveUS20110121284A1Easy to operateHigh power applicationSolid-state devicesSemiconductor devicesSemiconductor materialsElectron donor

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

InactiveUS20110121288A1Easy to operateHigh power applicationSolid-state devicesSemiconductor devicesSemiconductor materialsElectron donor

Provided is a semiconductor device for high power application including a novel semiconductor material with high productivity. Alternatively, provided is a semiconductor device having a novel structure in which the novel semiconductor material is used. Provided is a vertical transistor including a channel formation region formed using an oxide semiconductor which has a wider band gap than a silicon semiconductor and is an intrinsic semiconductor or a substantially intrinsic semiconductor with impurities that can serve as electron donors (donors) in the oxide semiconductor removed. The thickness of the oxide semiconductor is greater than or equal to 1 μm, preferably greater than 3 μm, more preferably greater than or equal to 10 μm, and end portions of one of electrodes that are in contact with the oxide semiconductor is placed inside end portions of the oxide semiconductor.

Owner:SEMICON ENERGY LAB CO LTD

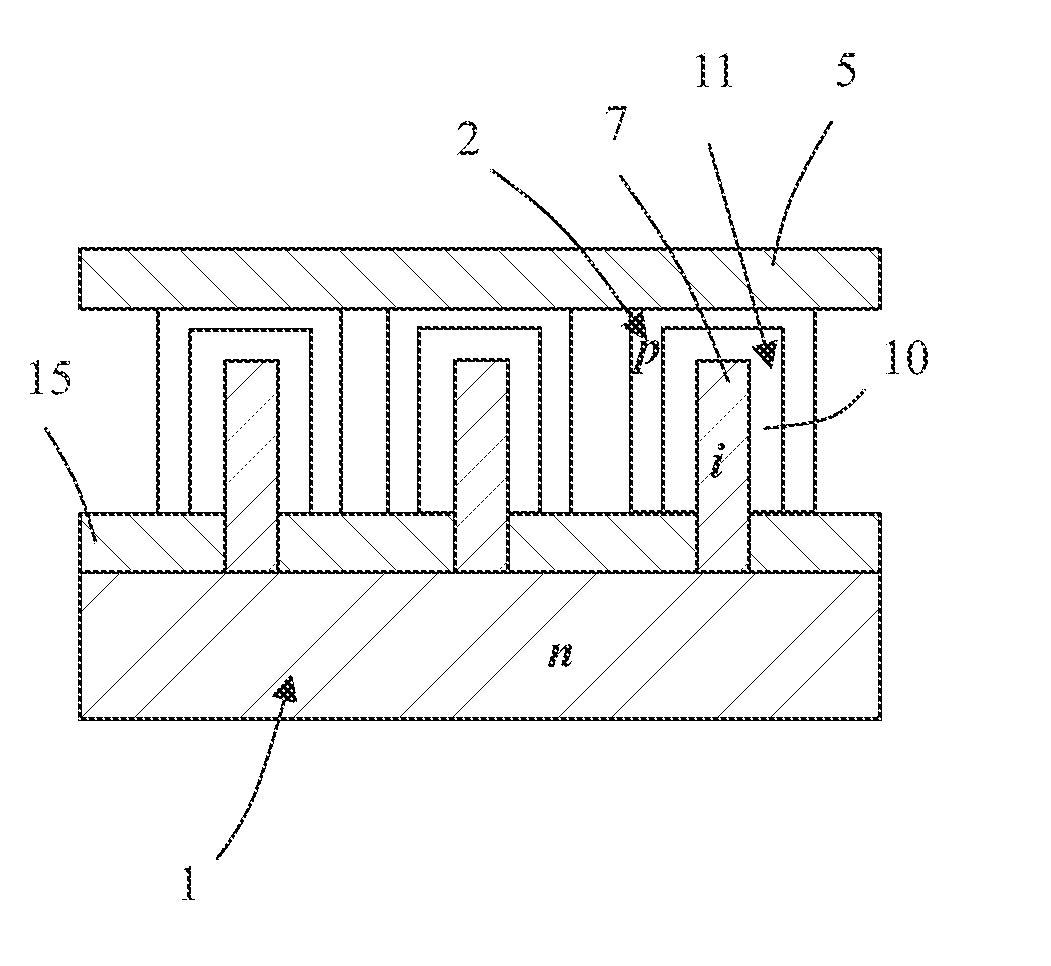

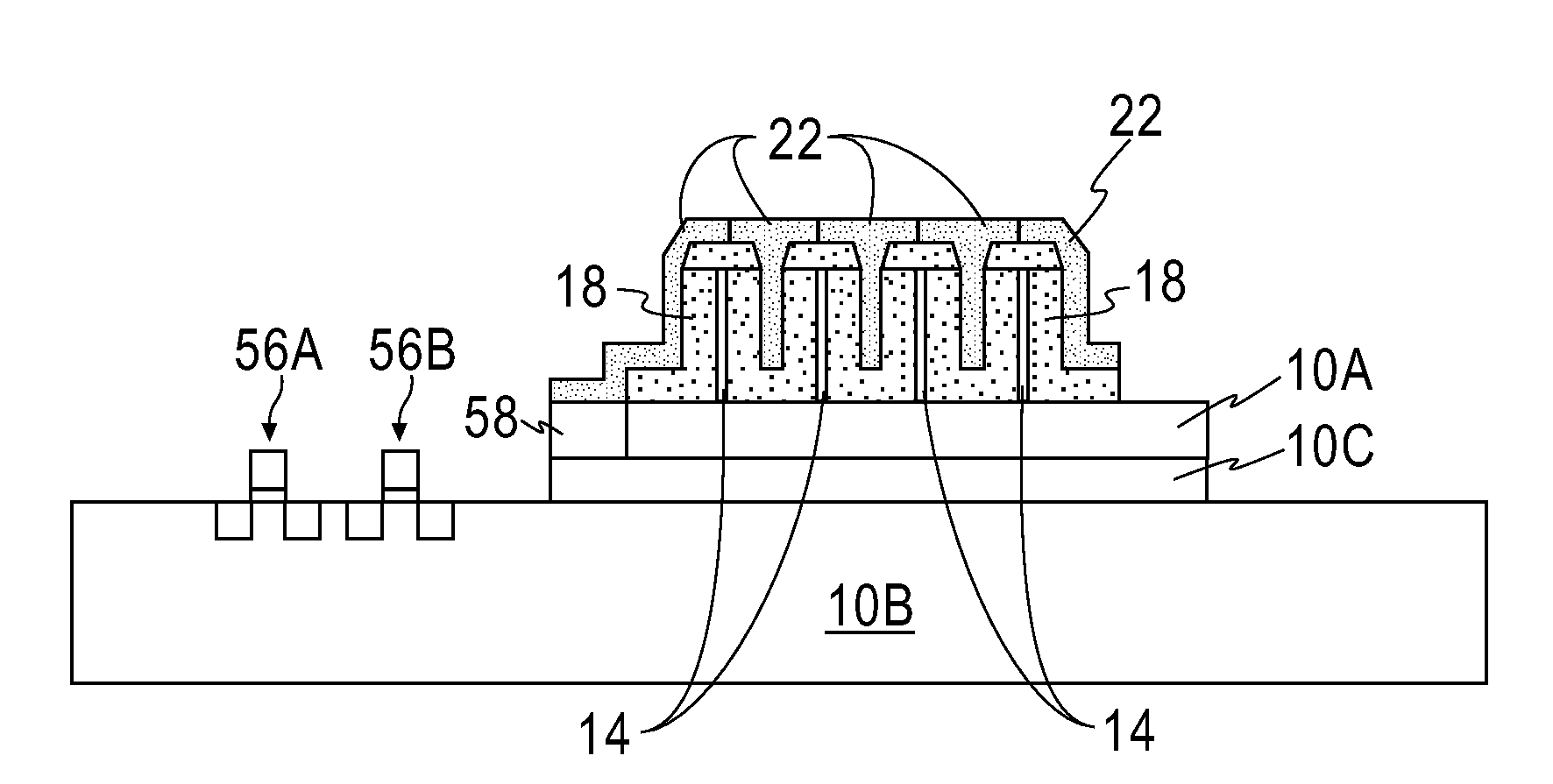

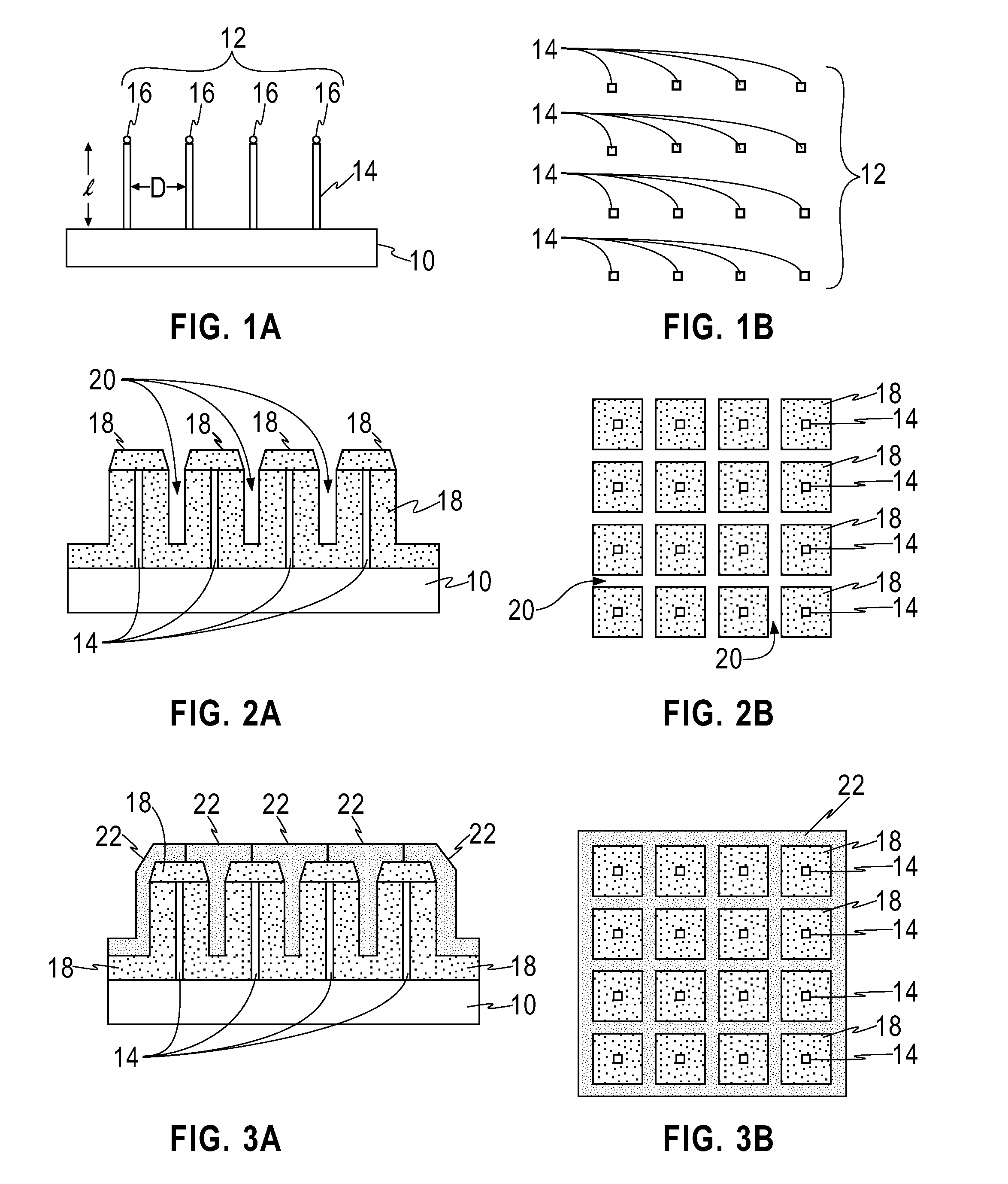

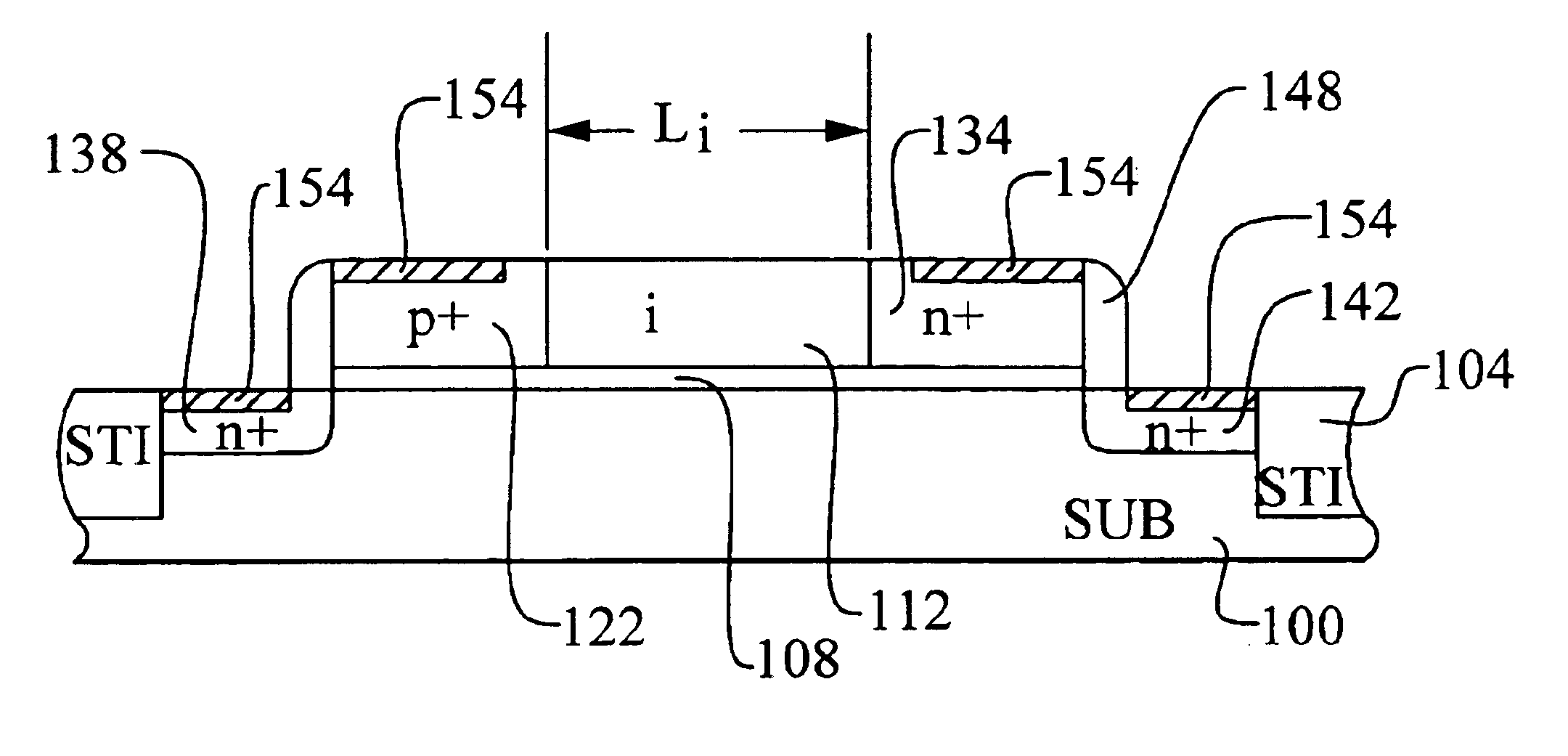

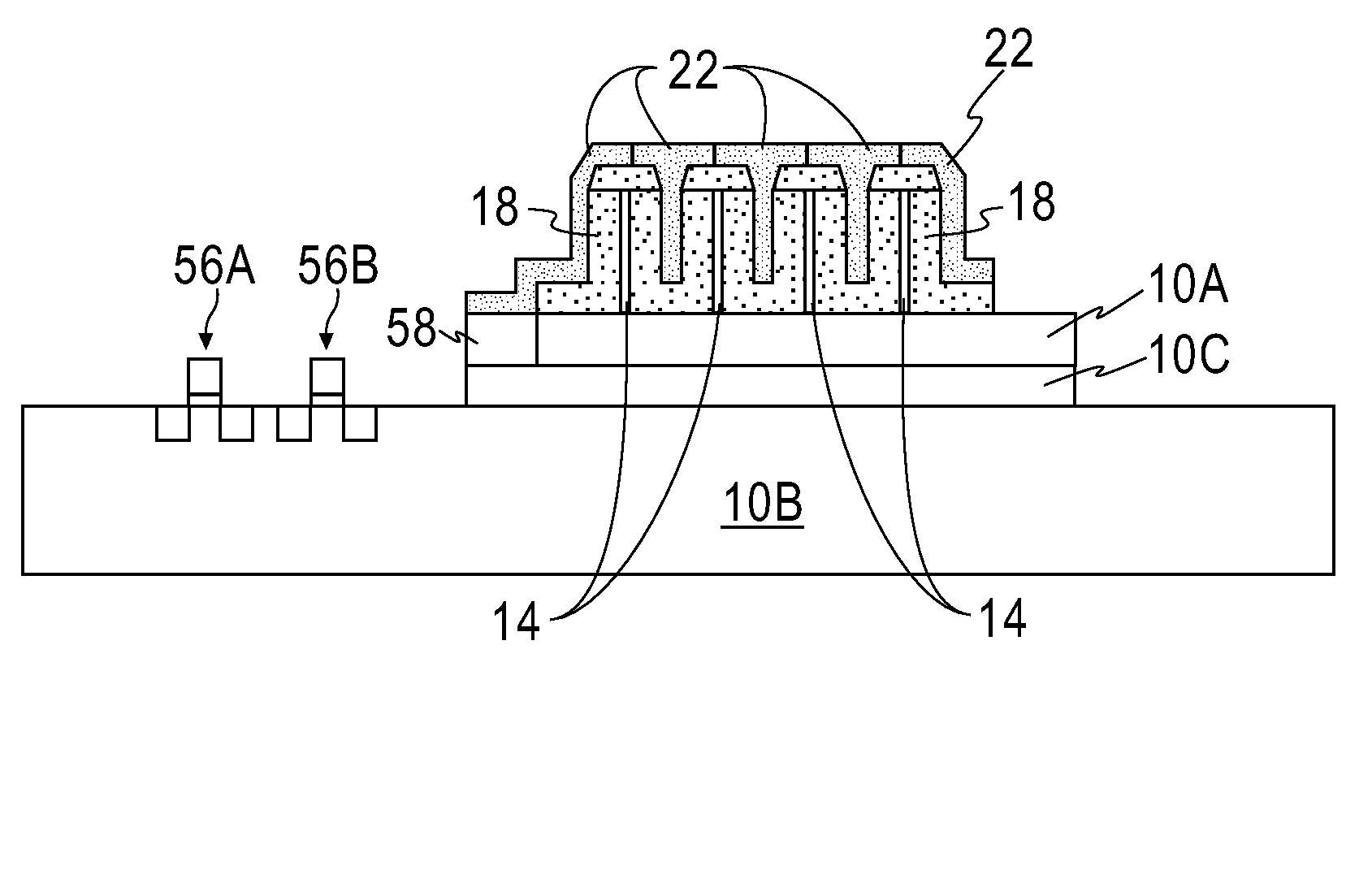

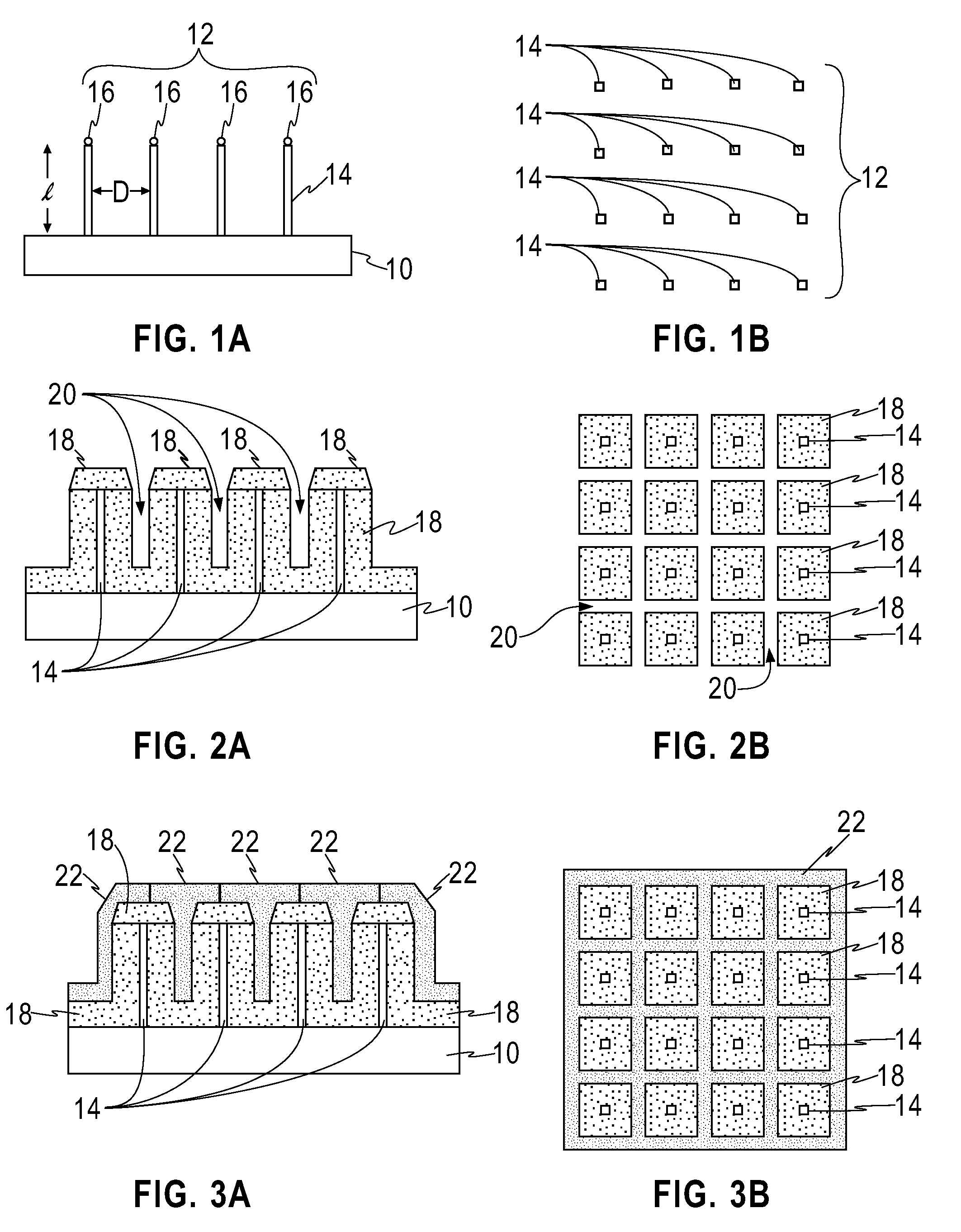

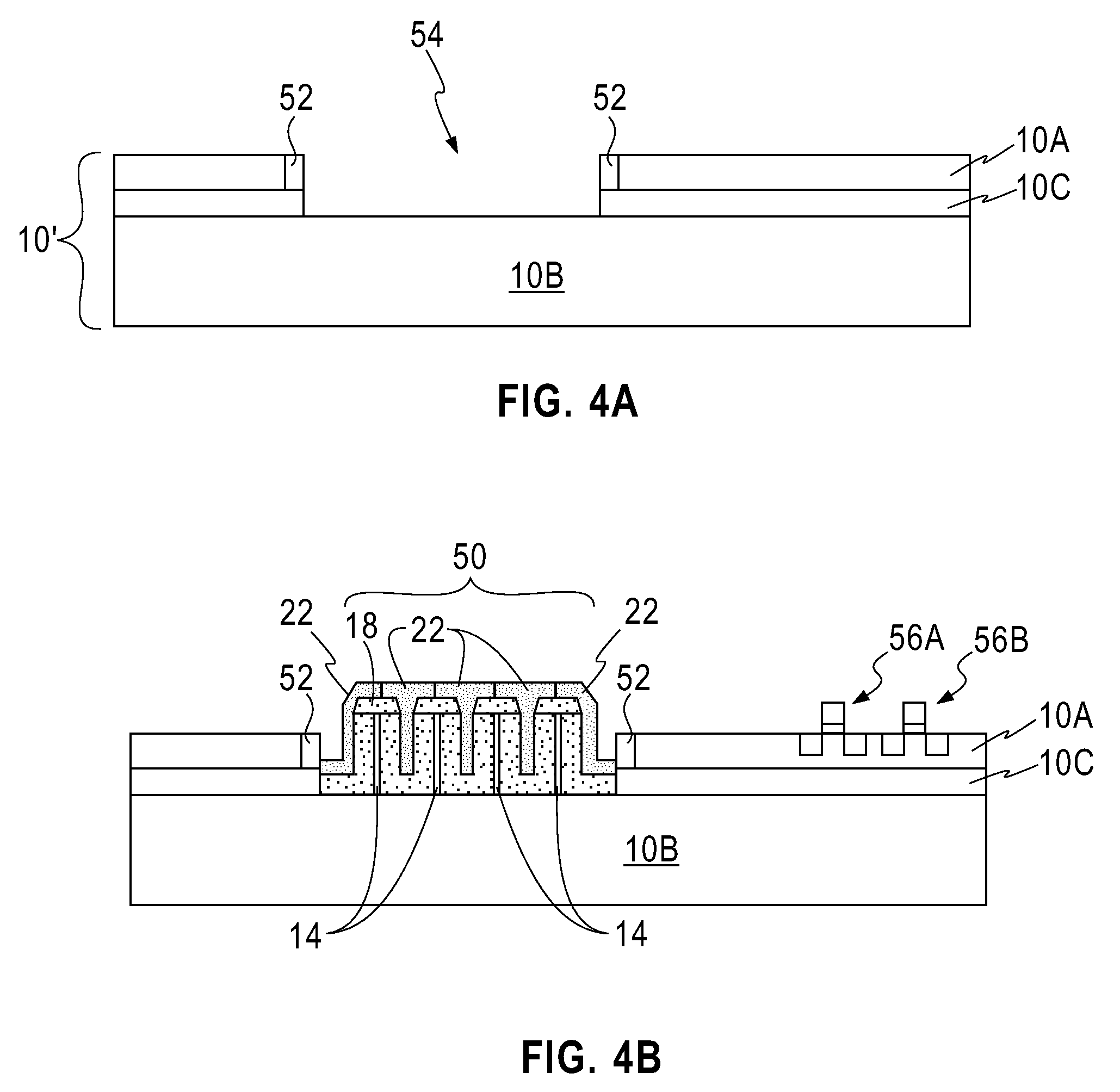

Fast p-i-n photodetector with high responsitivity

InactiveUS20090289320A1Eliminate the problemHigh recombination rateTransistorFinal product manufactureSemiconductor materialsPhotodetector

A lateral p-i-n photodetector is provided that includes an array of vertical semiconductor nanowires of a first conductivity type that are grown over a semiconductor substrate also of the first conductivity type. Each vertically grown semiconductor nanowires of the first conductivity type is surrounded by a thick epitaxial intrinsic semiconductor film. The gap between the now formed vertically grown semiconductor nanowires-intrinsic semiconductor film columns (comprised of the semiconductor nanowire core surrounded by intrinsic semiconductor film) is then filled by forming an epitaxial semiconductor material of a second conductivity type which is different from the first conductivity type. In a preferred embodiment, the vertically grown semiconductor nanowires of the first conductivity type are n+ silicon nanowires, the intrinsic epitaxial semiconductor layer is comprised of intrinsic epitaxial silicon, and the epitaxial semiconductor material of the second conductivity type is comprised of p+ silicon.

Owner:IBM CORP

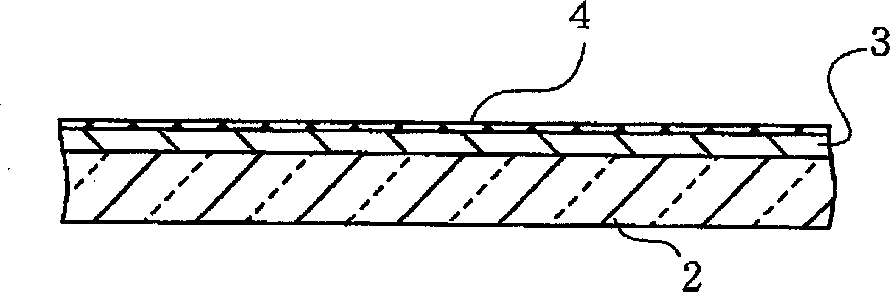

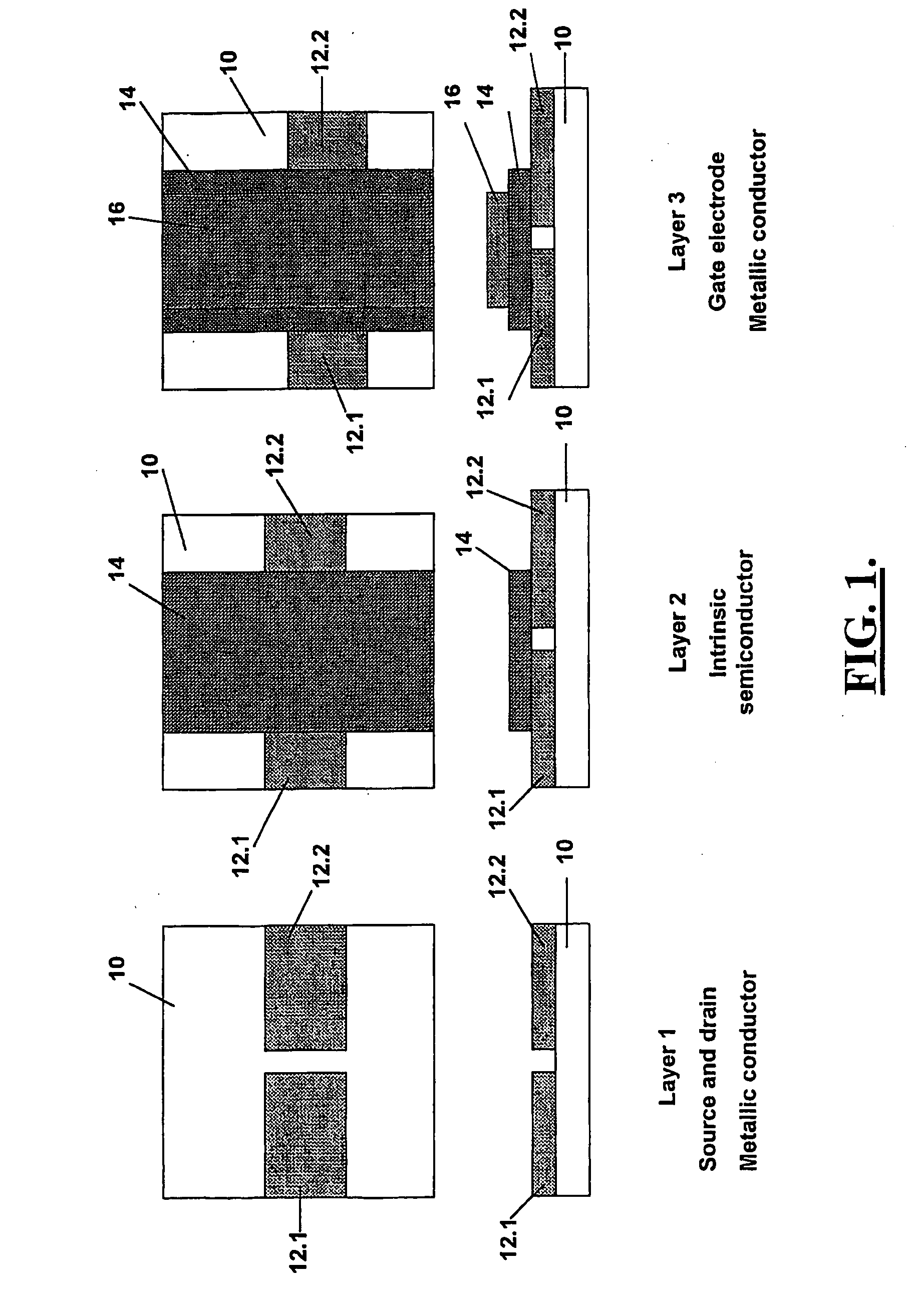

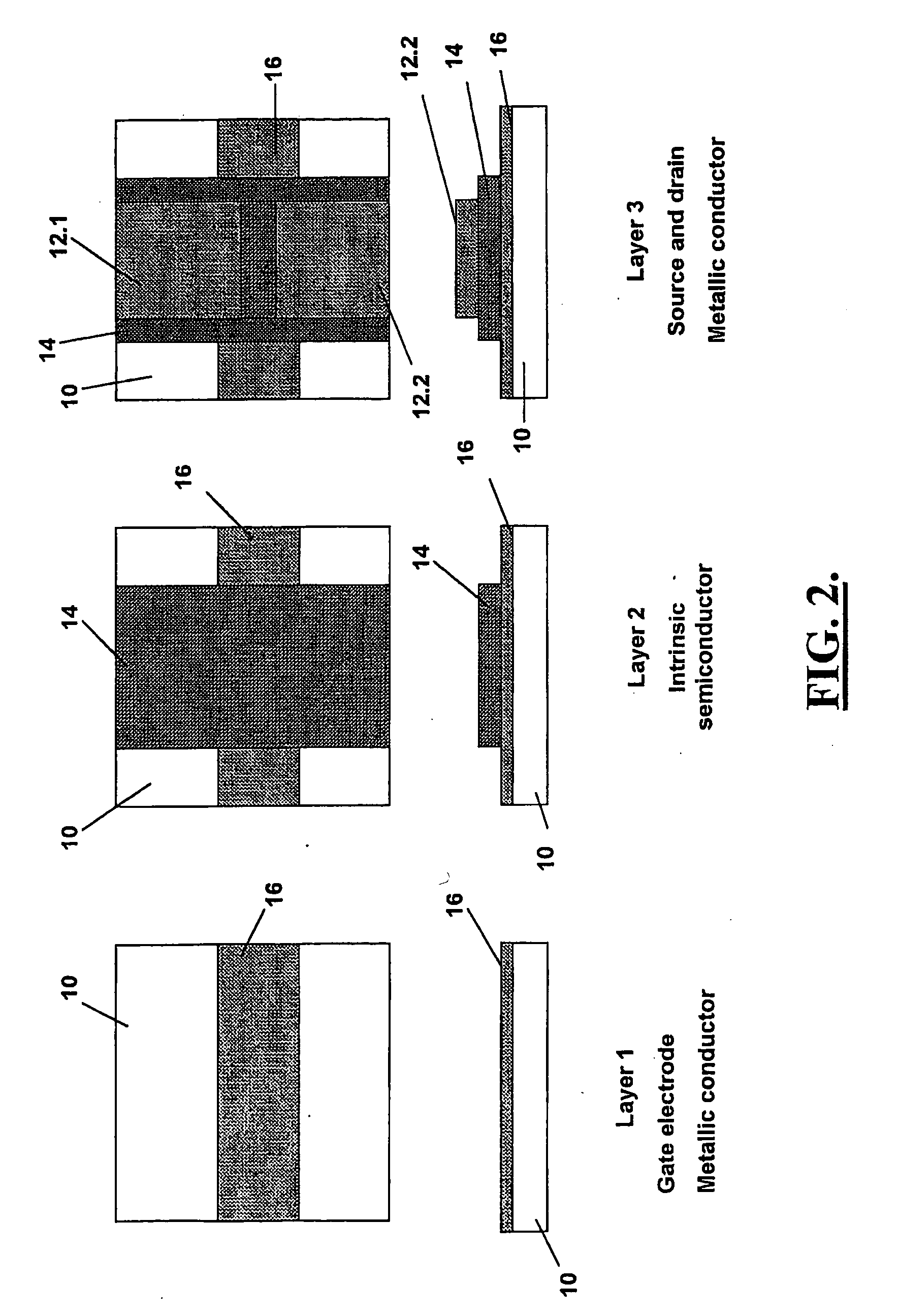

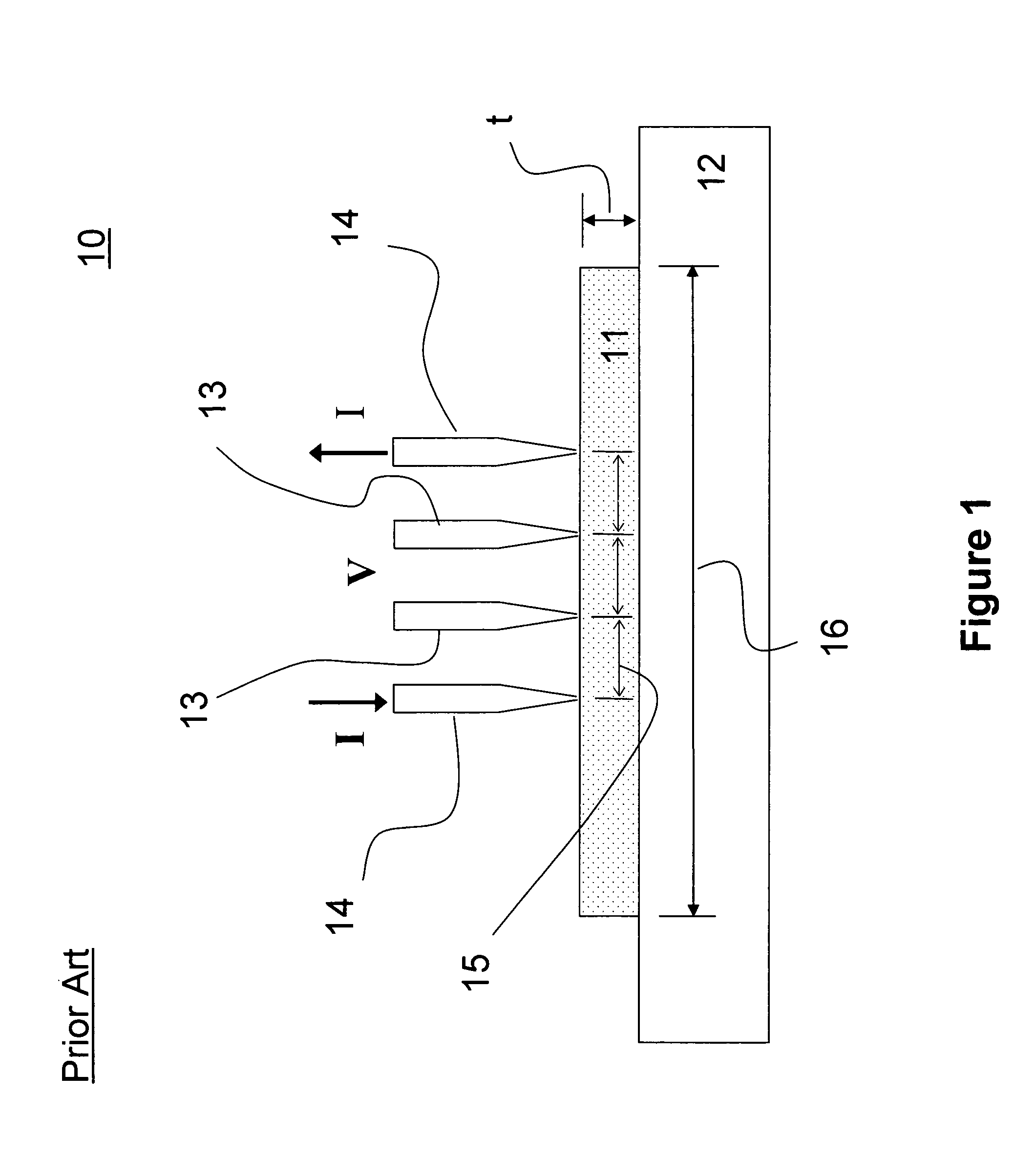

Thin film semiconductor device and method of manufacturing a thin film semiconductor device

A thin film semiconductor in the form of a metal semiconductor field effect transistor, includes a substrate 10 of paper sheet material and a number of thin film active inorganic layers that are deposited in layers on the substrate. The active layers are printed using an offset lithography printing process. A first active layer comprises source 12.1 and drain 12.2 conductors of colloidal silver ink, that are printed directly onto the paper substrate. A second active layer is an intrinsic semiconductor layer 14 of colloidal nanocrystalline silicon ink which is printed onto the first layer. A third active layer comprises a metallic conductor 16 of colloidal silver which is printed onto the second layer to form a gate electrode. This invention extends to other thin film semiconductors such as photovoltaic cells and to a method of manufacturing semiconductors.

Owner:PST SENSORS

Fast p-i-n photodetector with high responsitivity

ActiveUS20090305454A1Easy to integrateHigh rateFinal product manufactureNanoinformaticsSemiconductor materialsPhotodetector

A lateral p-i-n photodetector is provided that includes an array of vertical semiconductor nanowires of a first conductivity type that are grown over a semiconductor substrate also of the first conductivity type. Each vertically grown semiconductor nanowires of the first conductivity type is surrounded by a thick epitaxial intrinsic semiconductor film. The gap between the now formed vertically grown semiconductor nanowires-intrinsic semiconductor film columns (comprised of the semiconductor nanowire core surrounded by intrinsic semiconductor film) is then filled by forming an epitaxial semiconductor material of a second conductivity type which is different from the first conductivity type. In a preferred embodiment, the vertically grown semiconductor nanowires of the first conductivity type are n+ silicon nanowires, the intrinsic epitaxial semiconductor layer is comprised of intrinsic epitaxial silicon, and the epitaxial semiconductor material of the second conductivity type is comprised of p+ silicon.

Owner:IBM CORP

Solar cell and manufacturing method thereof

InactiveUS20130133729A1Final product manufactureSemiconductor/solid-state device manufacturingSolar cellCopper

A solar cell includes a semiconductor substrate, a first intrinsic semiconductor layer and a second intrinsic semiconductor layer on the semiconductor substrate, the first intrinsic semiconductor layer and the second intrinsic semiconductor layer being spaced apart from each other, a first conductive semiconductor layer and a second conductive semiconductor layer respectively disposed on the first intrinsic semiconductor layer and the second intrinsic semiconductor layer, and a first electrode and a second electrode, each including a bottom layer on the first conductive semiconductor layer and the second conductive semiconductor layer, respectively, the bottom layer including a transparent conductive oxide, and an intermediate layer on the bottom layer, the intermediate layer being including copper.

Owner:SAMSUNG SDI CO LTD

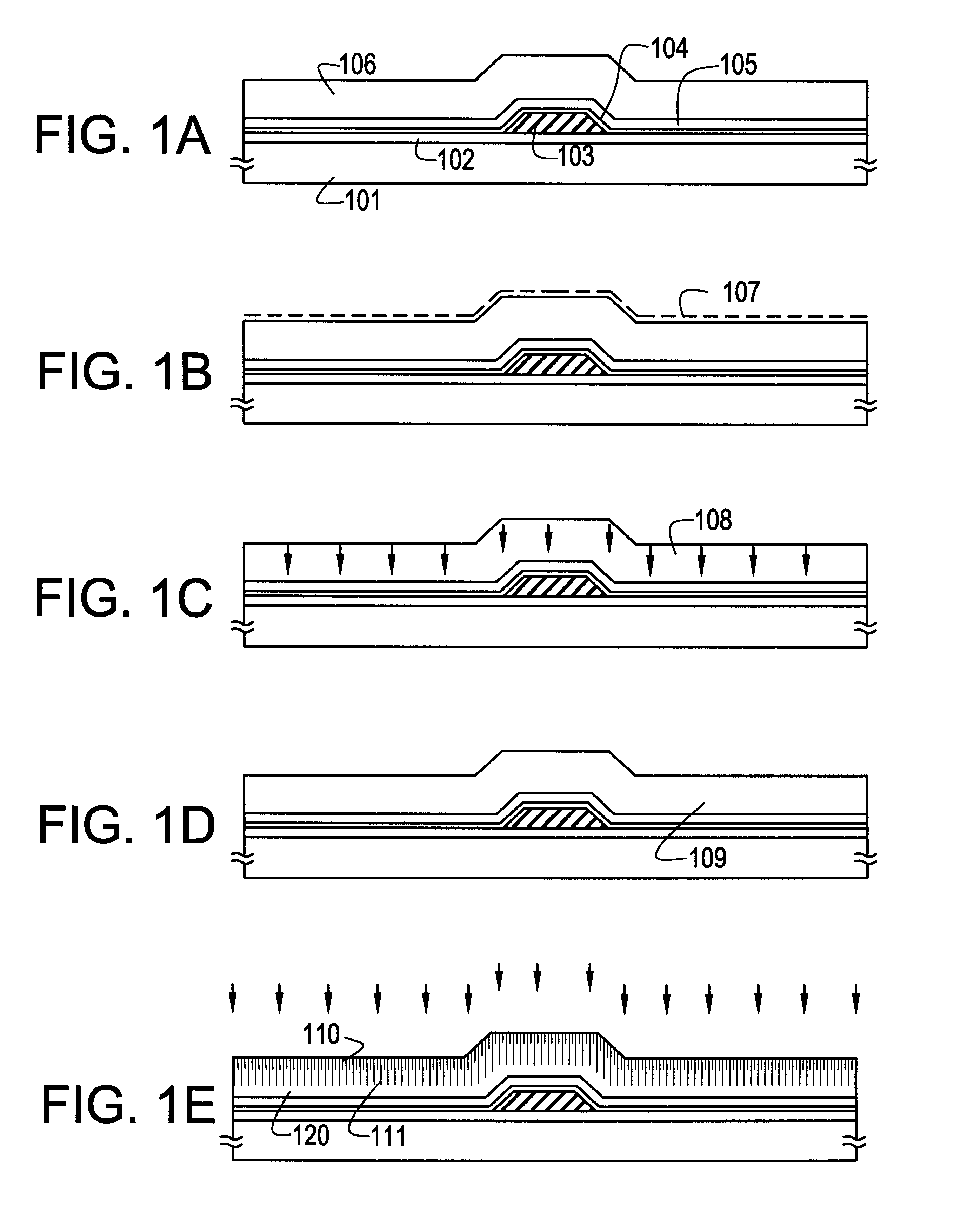

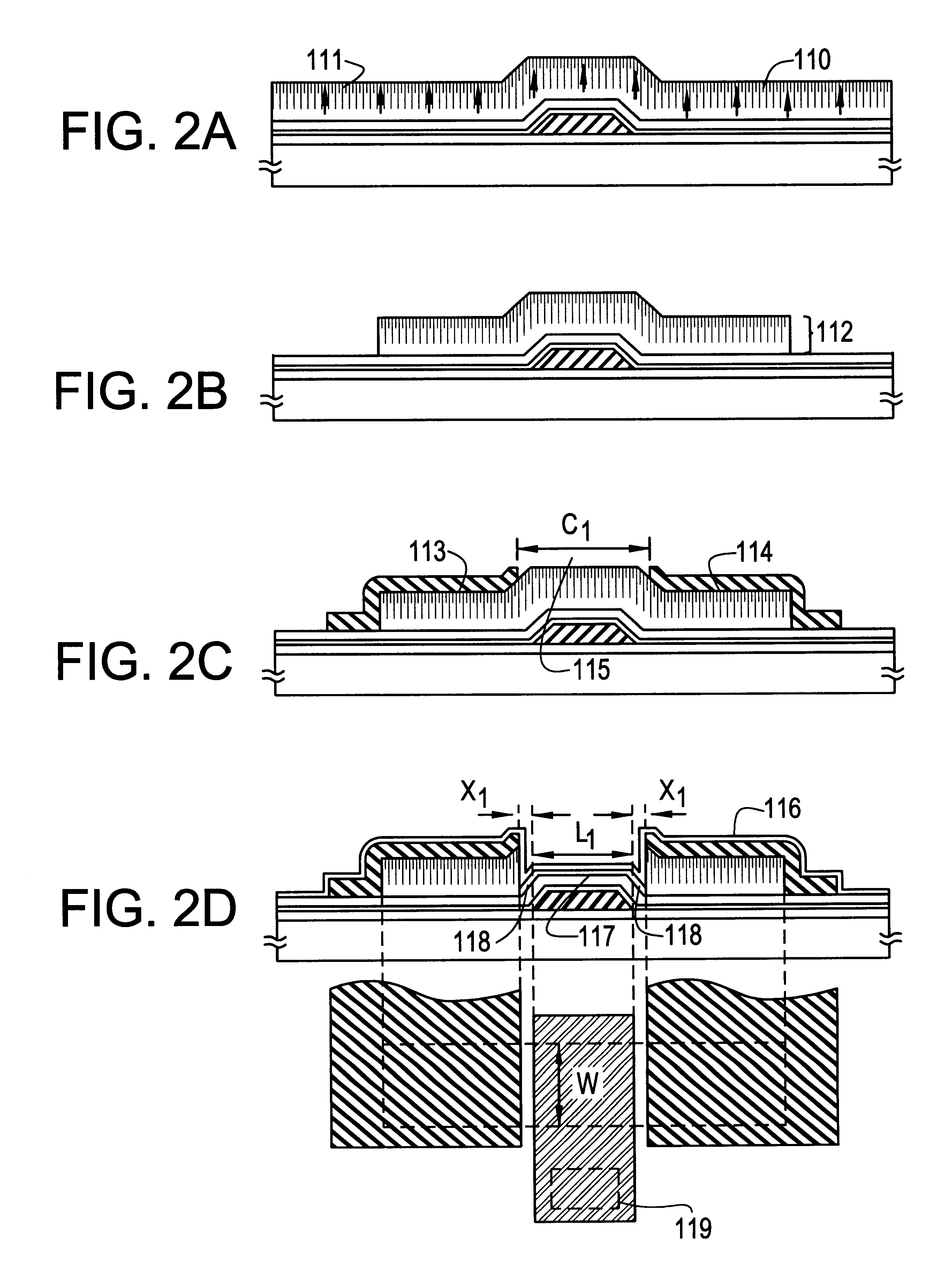

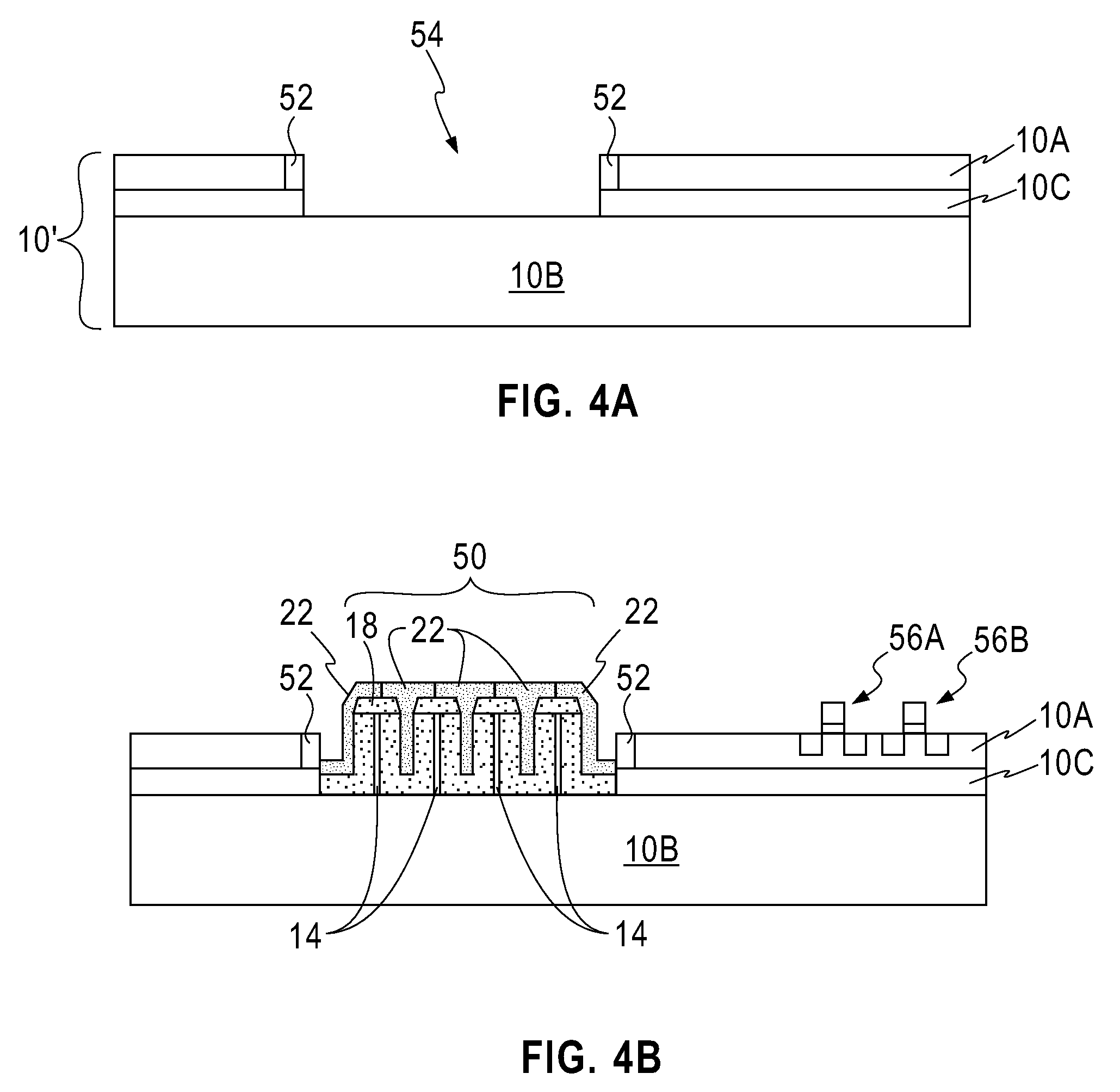

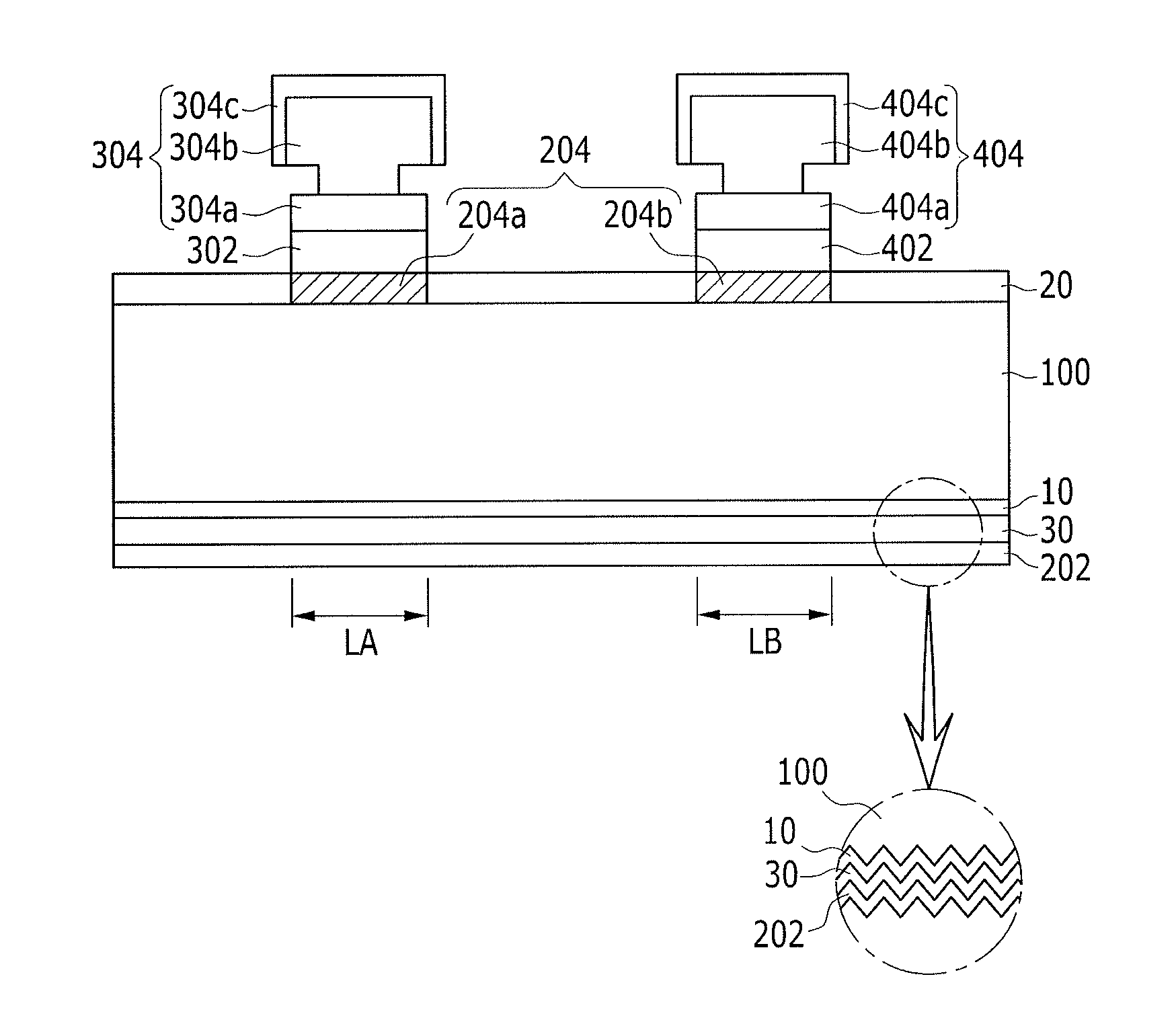

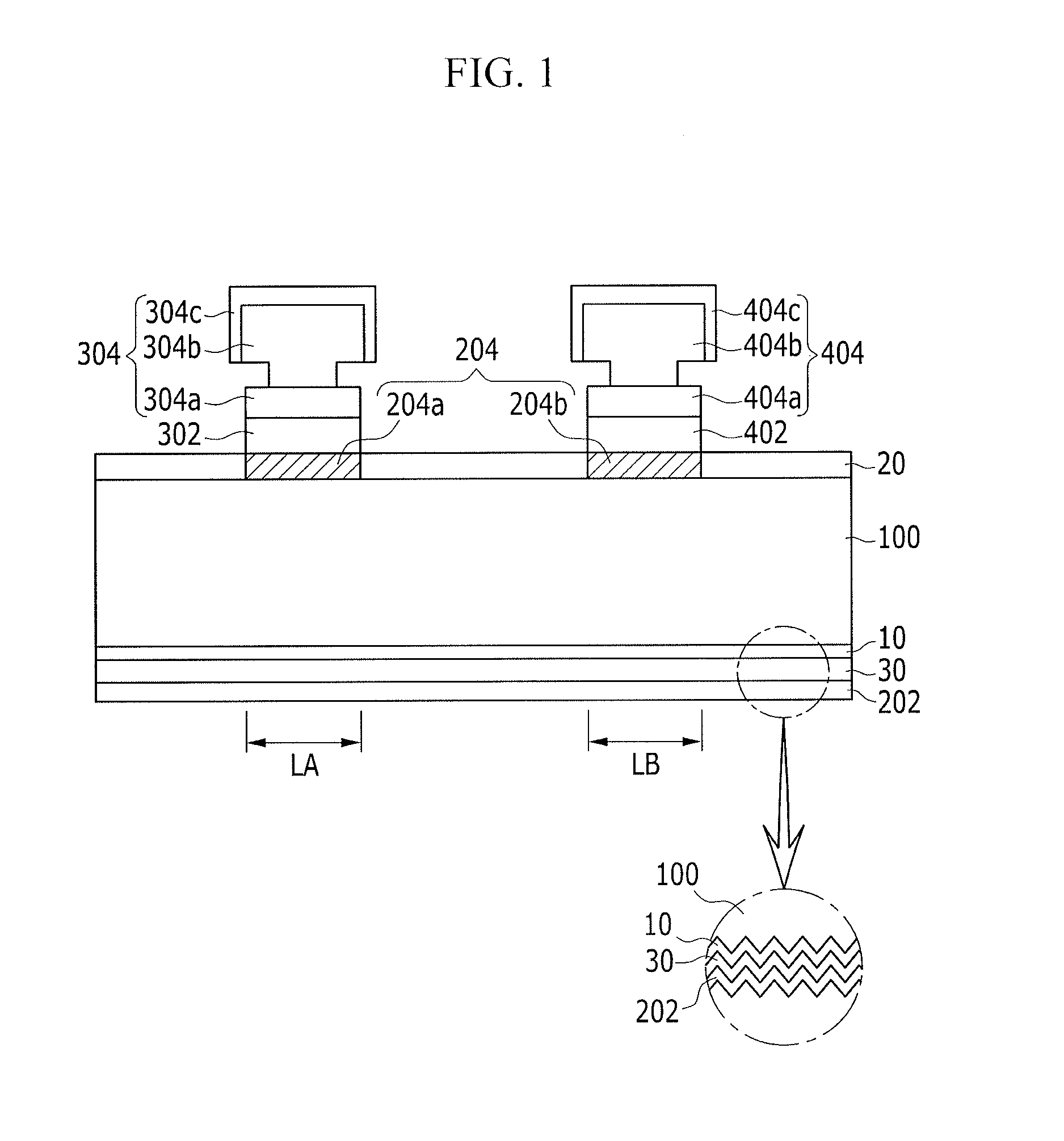

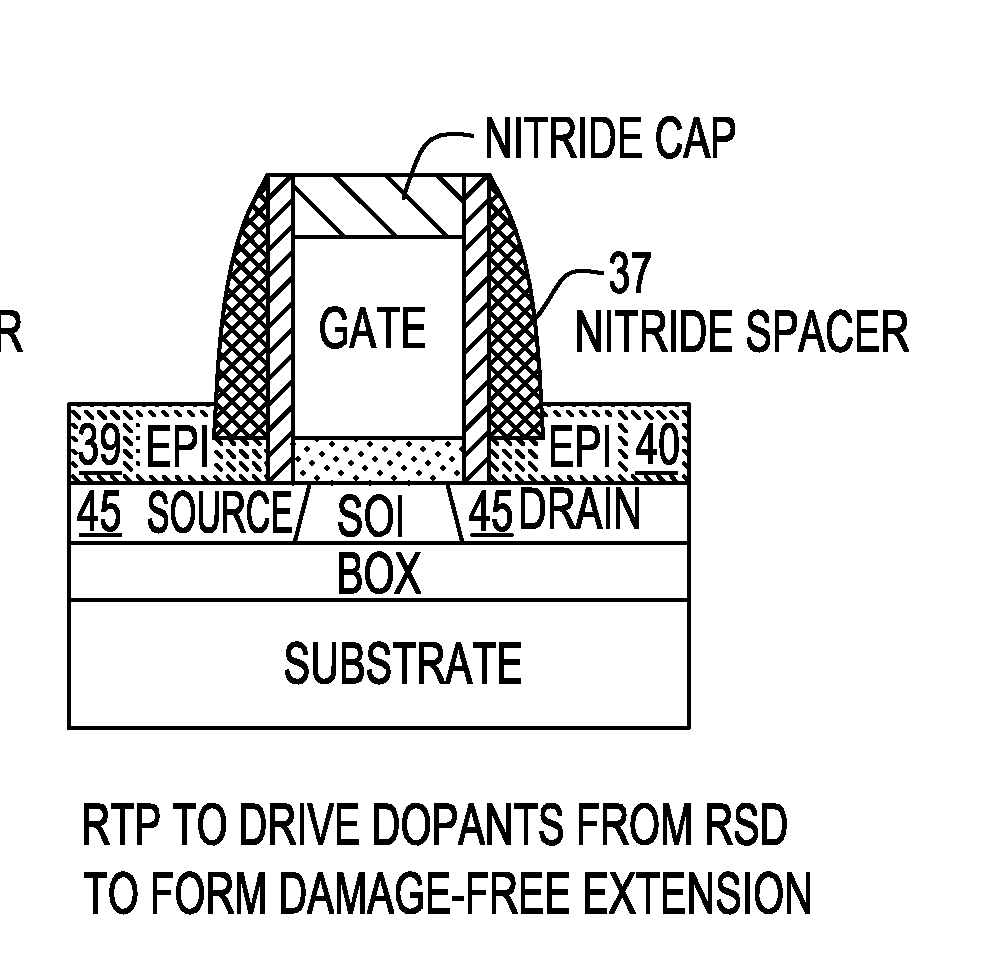

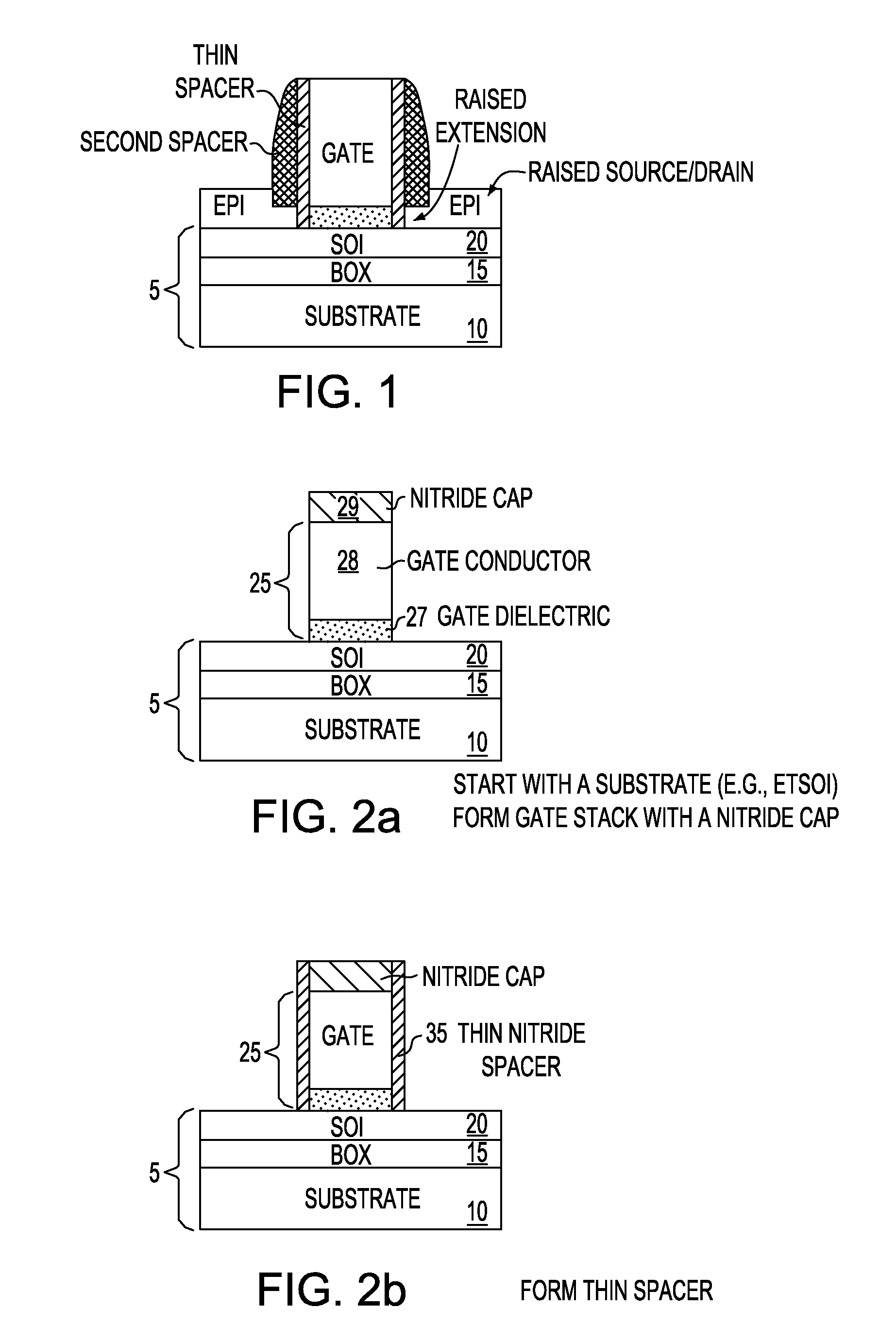

Extremely Thin Semiconductor-on-Insulator (ETSOI) FET Having a Stair-Shape Raised Source/Drain and a Method of Forming the Same

ActiveUS20120061759A1Lower extension resistanceIncrease parasitic resistanceTransistorSolid-state devicesMOSFETSoi substrate

A MOSFET device is formed on top of a semiconductor-on-insulator (SOI) substrate having a semiconductor layer with a thickness ranging from 3 nm to 20 nm. A stair-shape raised extension, a raised source region and a raised drain region (S / D) are formed on top of the SOI substrate. The thinner raised extension region abuts at a thin gate sidewall spacer, lowering the extension resistance without significantly increasing the parasitic resistance. A single epitaxial growth forms the thinner raised extension and the thicker raised S / D preferably simultaneously, reducing the fabrication cost as well as the contact resistance between the raised S / D and the extension. A method of forming the aforementioned MOSFET device is also provided.

Owner:GLOBALFOUNDRIES US INC

Semiconductor device

ActiveUS20110101331A1Reduce hydrogen concentrationReduce power consumptionSemiconductor/solid-state device detailsSolid-state devicesElectron donorElectron

An object is to reduce leakage current and parasitic capacitance of a transistor used for an LSI, a CPU, or a memory. A semiconductor integrated circuit included in an LSI, a CPU, or a memory is manufactured using the transistor which is formed using an oxide semiconductor which is an intrinsic or substantially intrinsic semiconductor obtained by removal of impurities which serve as electron donors (donors) from the oxide semiconductor and has larger energy gap than a silicon semiconductor, and is formed over a semiconductor substrate. With the transistor which is formed over the semiconductor substrate and includes the highly purified oxide semiconductor layer with sufficiently reduced hydrogen concentration, a semiconductor device whose power consumption due to leakage current is low can be realized.

Owner:SEMICON ENERGY LAB CO LTD

Organic photovoltaic cells with an electric field integrally-formed at the heterojunction interface

InactiveUS7157641B2Superior mobility and exciton diffusion lengthEasy to processPV power plantsFinal product manufactureHeterojunctionEpoxy

A bi-layer photovoltaic cell, and method (100) of making same, with an electric field applied at the p-n heterojunction interface. The cell includes a first semiconductor layer including a binder, nanocrystals of an n-type semiconductor, and spatially bound cations and a second semiconductor layer contacting the first semiconductor layer that includes a binder, nanocrystals of a p-type semiconductor, and spatially bound anions. The cell further includes a p-n heterojunction at the contacting interface between the first and second semiconductor layers. An electric field is created by the spatially bound cations and anions that are located in the layers proximal to the p-n heterojunction. The nanocrystals are single crystals of organic semiconductors that are less than 50 nanometers in size and that comprise a majority of the volume of their respective layers. The binder is a polymer matrix, such as an epoxy. The cell includes electrical contacts abutting the semiconductor layers.

Owner:ALLIANCE FOR SUSTAINABLE ENERGY

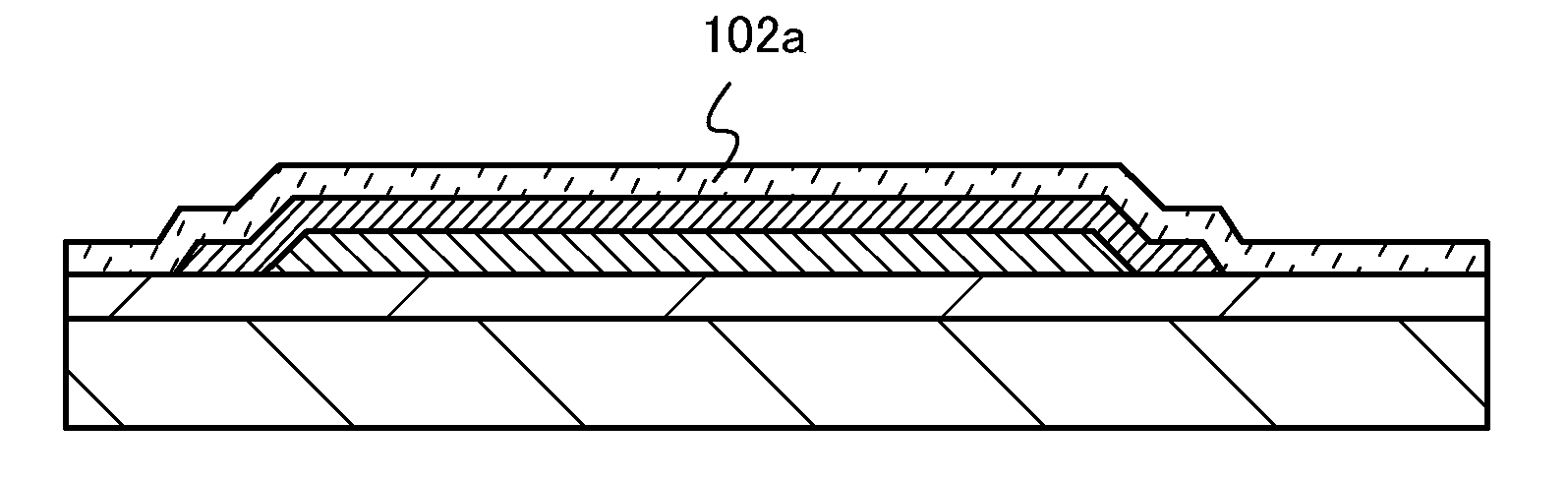

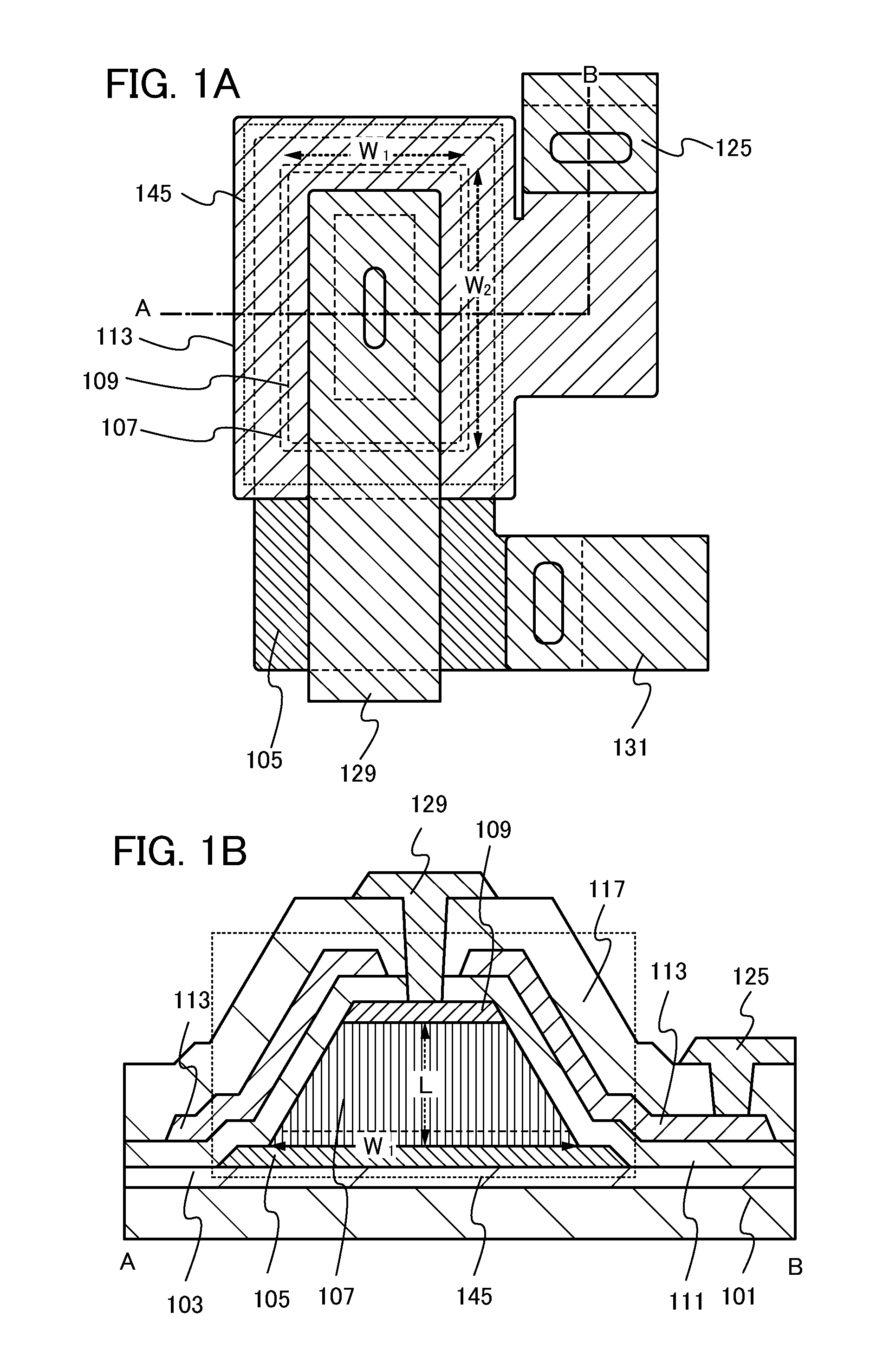

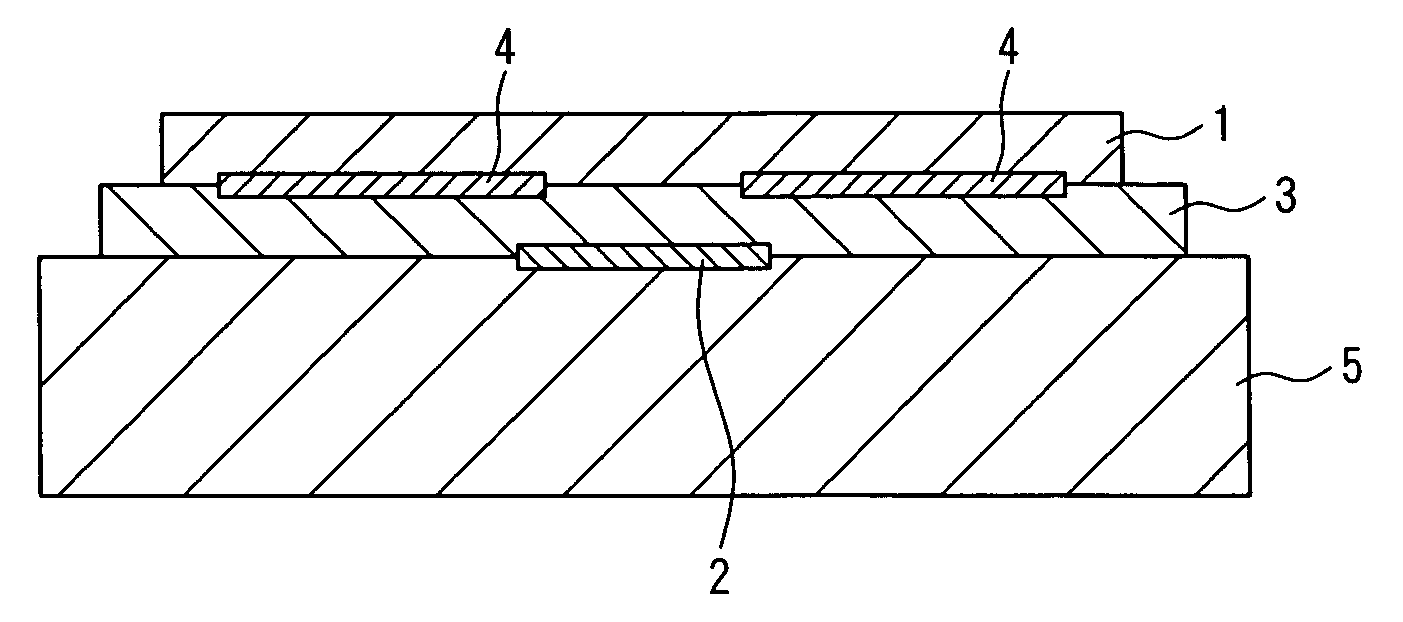

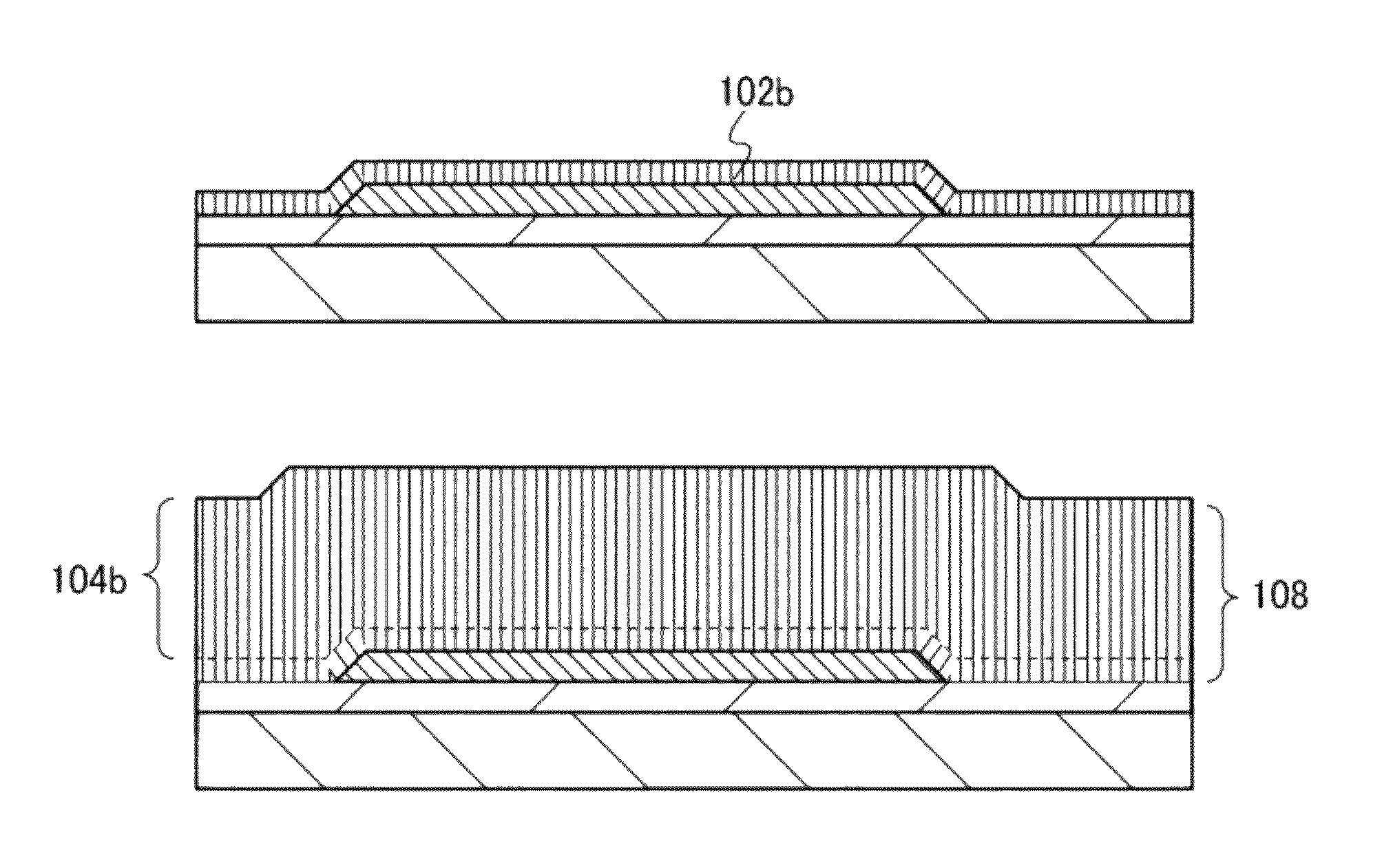

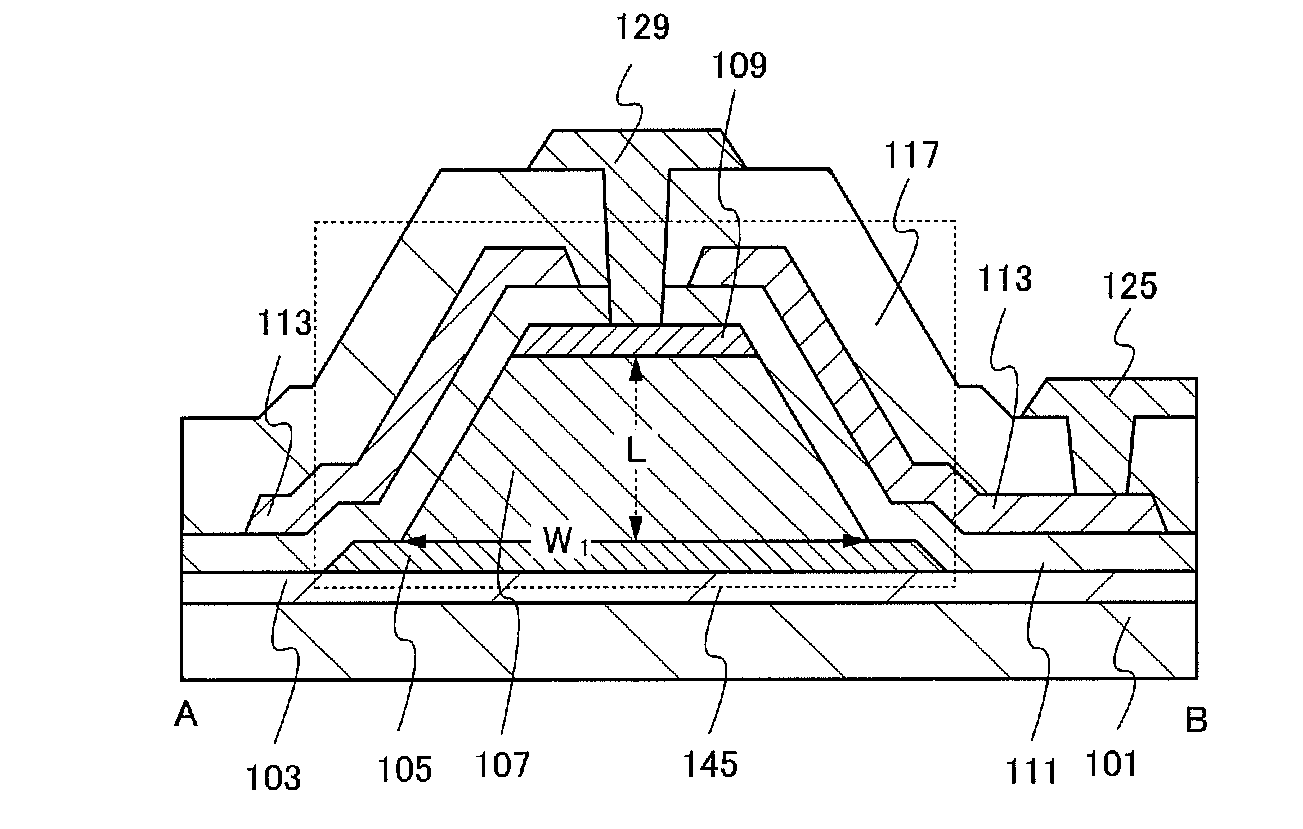

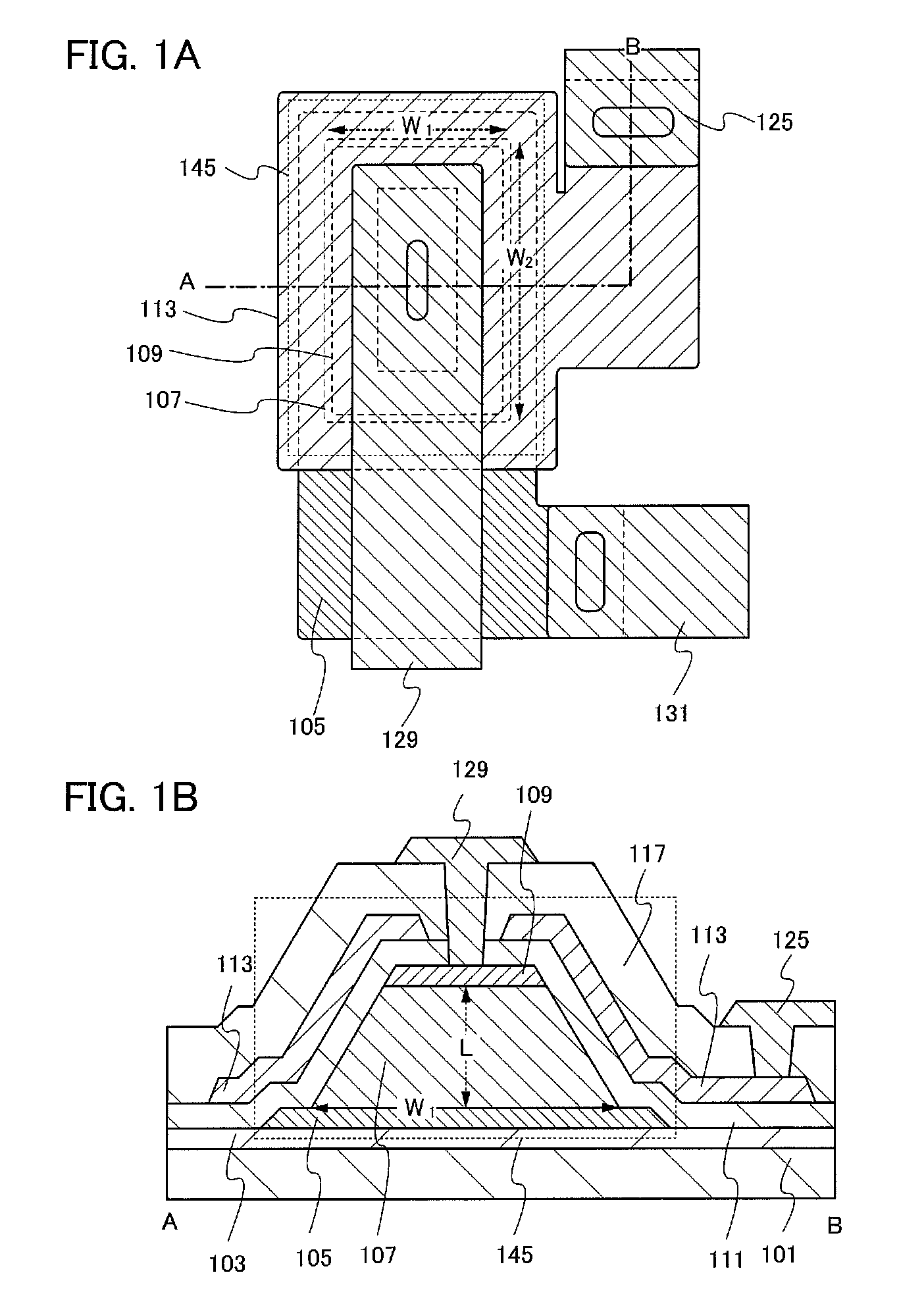

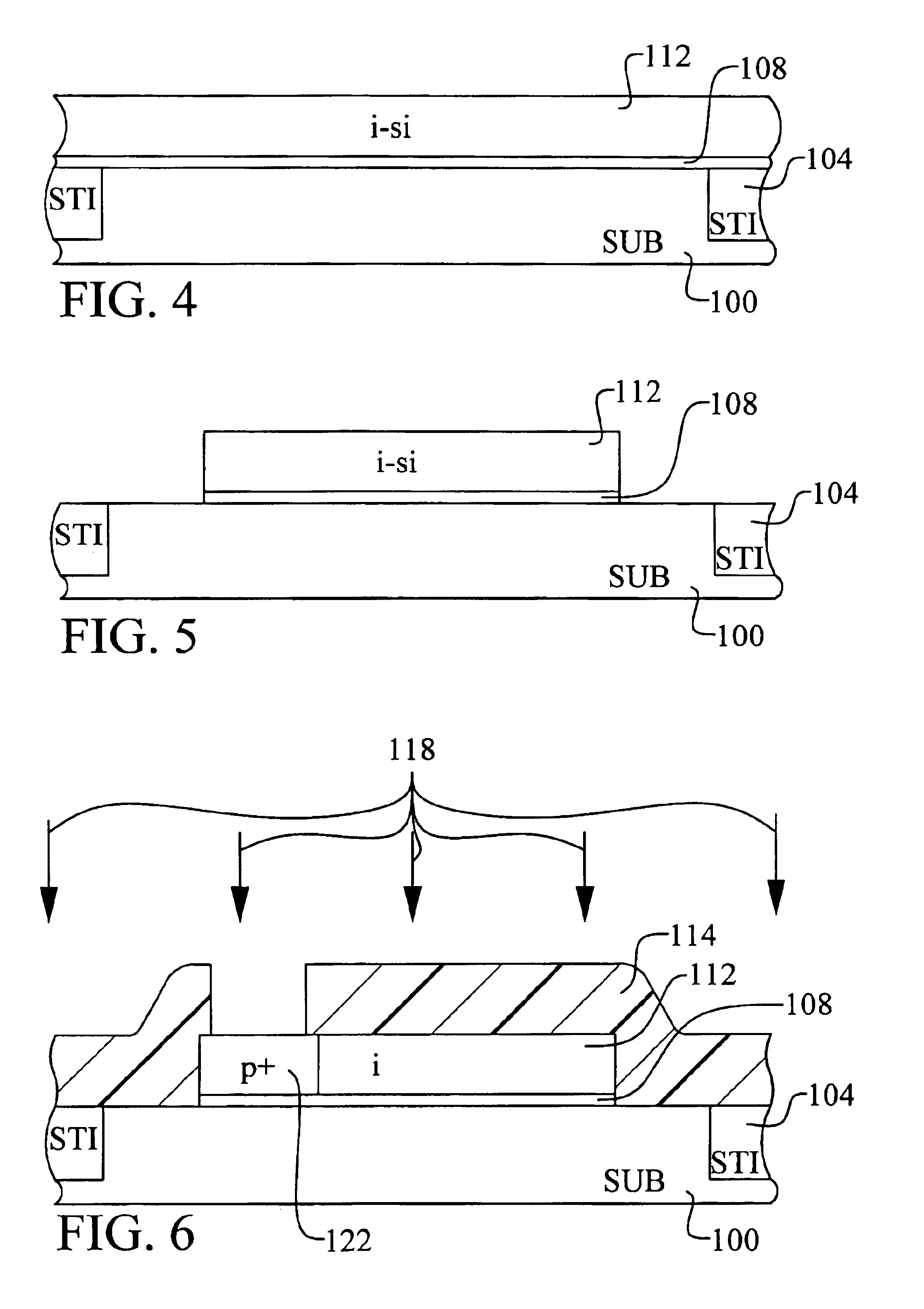

Semiconductor device and method of manufacturing the same

InactiveUS6924528B2Improve batch productivityImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingCrystal structureBottom gate

In a bottom gate type semiconductor device made of a semiconductor layer with crystal structure, source / drain regions are constructed by a lamination layer structure including a first conductive layer (n+ layer), a second conductive layer (n− layer) having resistance higher than the first conductive layer, and an intrinsic or substantially intrinsic semiconductor layer (i layer). At this time, the n− layer acts as LDD region, and the i layer acts as an offset region is a film thickness direction.

Owner:SEMICON ENERGY LAB CO LTD

ESD protection device

InactiveUS6936895B2Improve performanceIncrease the areaTransistorSemiconductor/solid-state device detailsMOSFETEngineering

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING +1

Multiple junction photovolatic devices and process for making the same

InactiveUS20100300505A1PV power plantsSemiconductor/solid-state device manufacturingForming gasGas phase

A photovoltaic device having multiple photoelectric conversion cells disposed in a tandem configuration and a chemical vapor deposition method for fabricating the same are disclosed. Each photoelectric conversion cell has a different band gap energy and includes a p-type semiconductor layer, an intrinsic semiconductor layer and an n-type semiconductor layer in sequential touching contact. Each semiconductor layer is formed of a nano-crystalline semiconductor containing silicon as a principal constituent. The semiconductor layer may be deposited by a novel chemical vapor deposition method which utilizes plasma and laser energies simultaneously to decompose a film forming gas, thereby forming a semiconductor film on a substrate. The chemical vapor deposition process may be carried out on a continuously conveying substrate, thereby permitting high throughput production of the photovoltaic device.

Owner:CHEN YUNG T

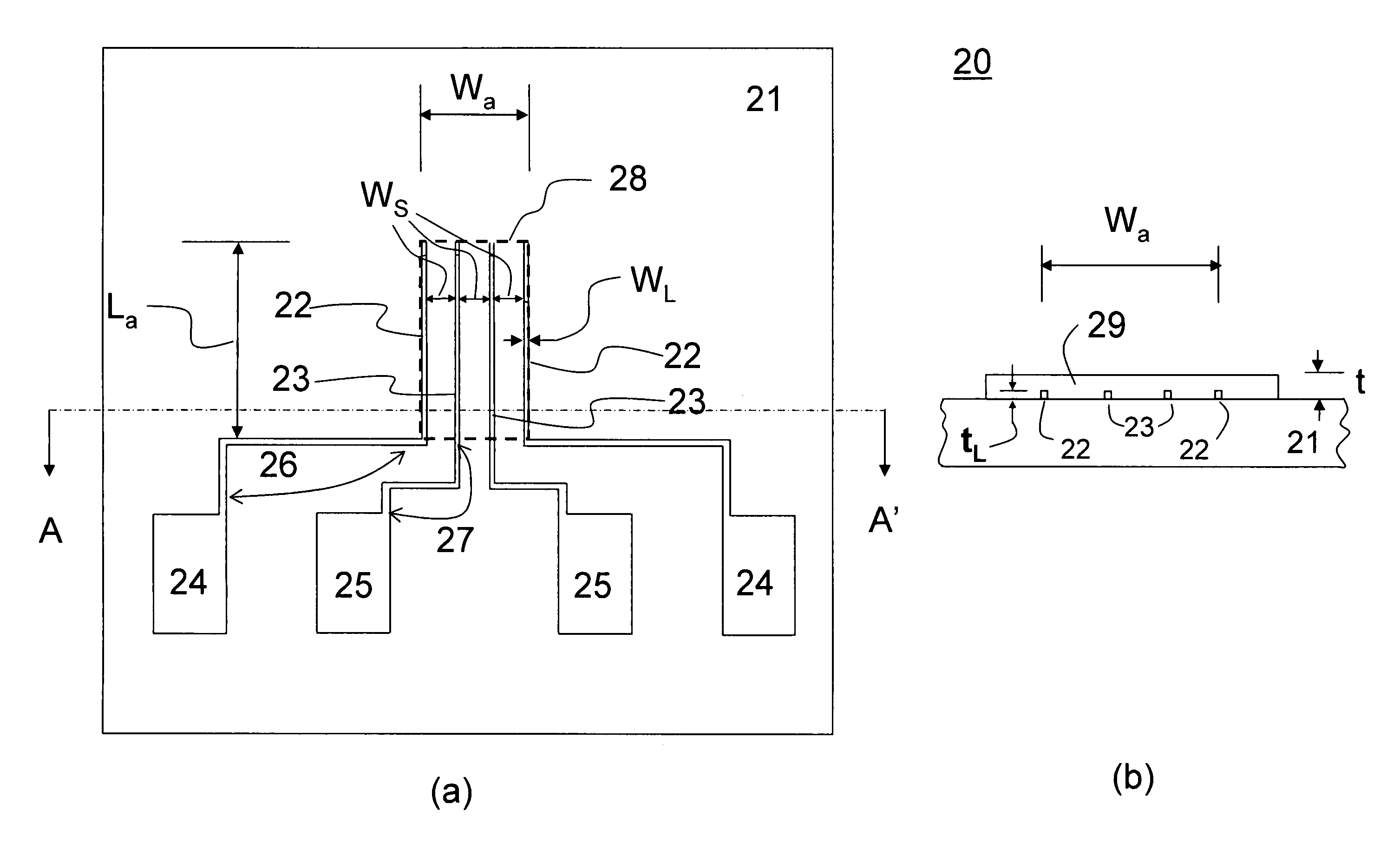

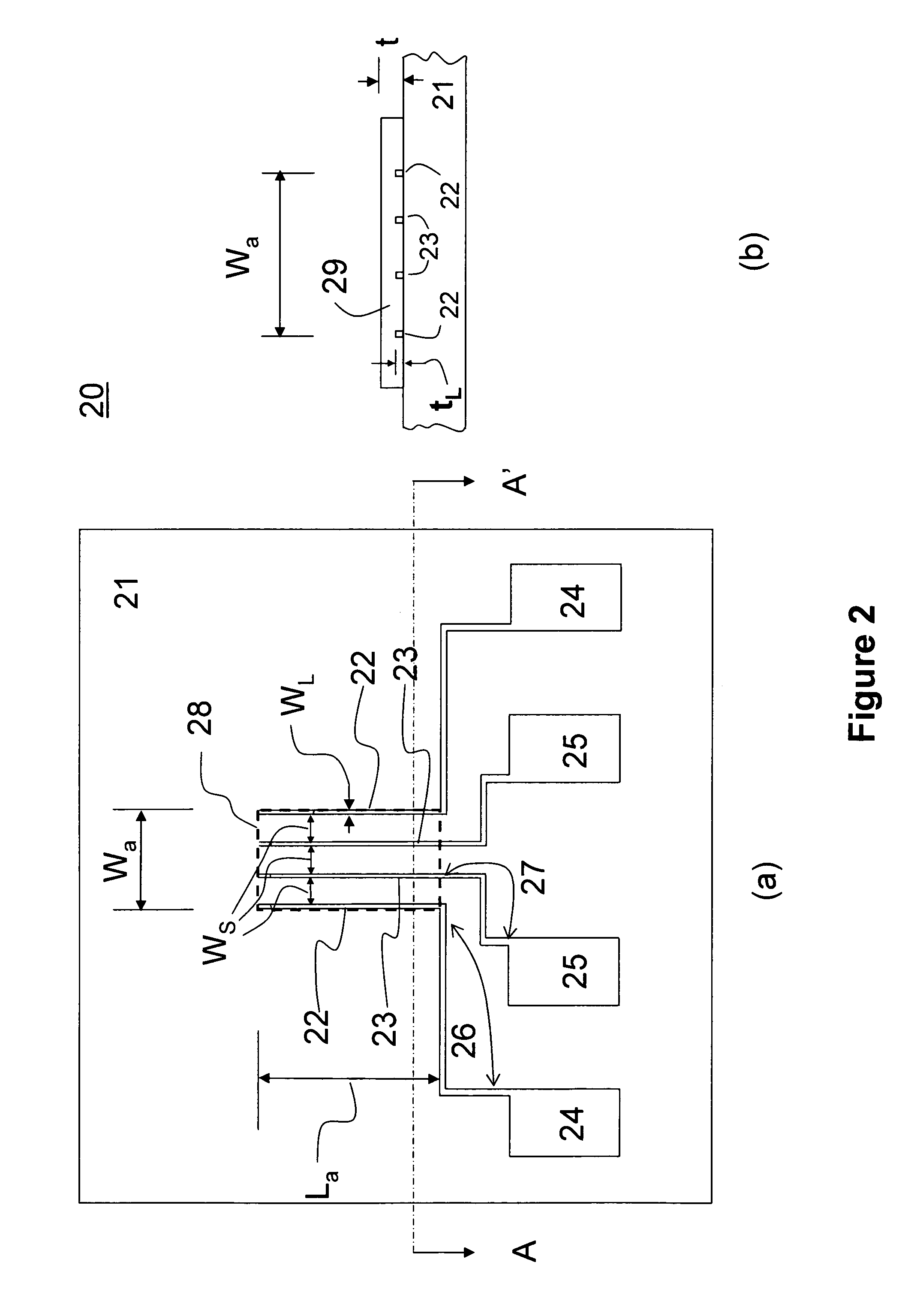

Four-terminal methods for resistivity measurement of semiconducting materials

InactiveUS7030633B1Accurately measure resistivityReduce contact resistanceSemiconductor/solid-state device testing/measurementMaterial analysis by electric/magnetic meansSemiconductor materialsOrganic semiconductor

This invention provides an innovative multi-line structure and an effective four-terminal method for the resistivity measurement of semiconductor materials. The multi-line structure and the four-terminal method not only allow one to perform resistivity measurement on any inorganic and organic semiconductor thin film conveniently, rapidly and accurately but also offer the means to study resistivity uniformity across the semiconductor thin film.

Owner:XIAO STEVEN SHUYONG

Fast P-I-N photodetector with high responsitivity

InactiveUS7902540B2Easy to integrateHigh rateTransistorFinal product manufactureSemiconductor materialsPhotodetector

A lateral p-i-n photodetector is provided that includes an array of vertical semiconductor nanowires of a first conductivity type that are grown over a semiconductor substrate also of the first conductivity type. Each vertically grown semiconductor nanowires of the first conductivity type is surrounded by a thick epitaxial intrinsic semiconductor film. The gap between the now formed vertically grown semiconductor nanowires-intrinsic semiconductor film columns (comprised of the semiconductor nanowire core surrounded by intrinsic semiconductor film) is then filled by forming an epitaxial semiconductor material of a second conductivity type which is different from the first conductivity type. In a preferred embodiment, the vertically grown semiconductor nanowires of the first conductivity type are n+ silicon nanowires, the intrinsic epitaxial semiconductor layer is comprised of intrinsic epitaxial silicon, and the epitaxial semiconductor material of the second conductivity type is comprised of p+ silicon.

Owner:INT BUSINESS MASCH CORP

LED flip chip manufacturing method and LED flip chip

InactiveCN104037277AImprove luminous efficiencySolve the problem of reduced reflection efficiencySemiconductor devicesMetallic materialsEngineering

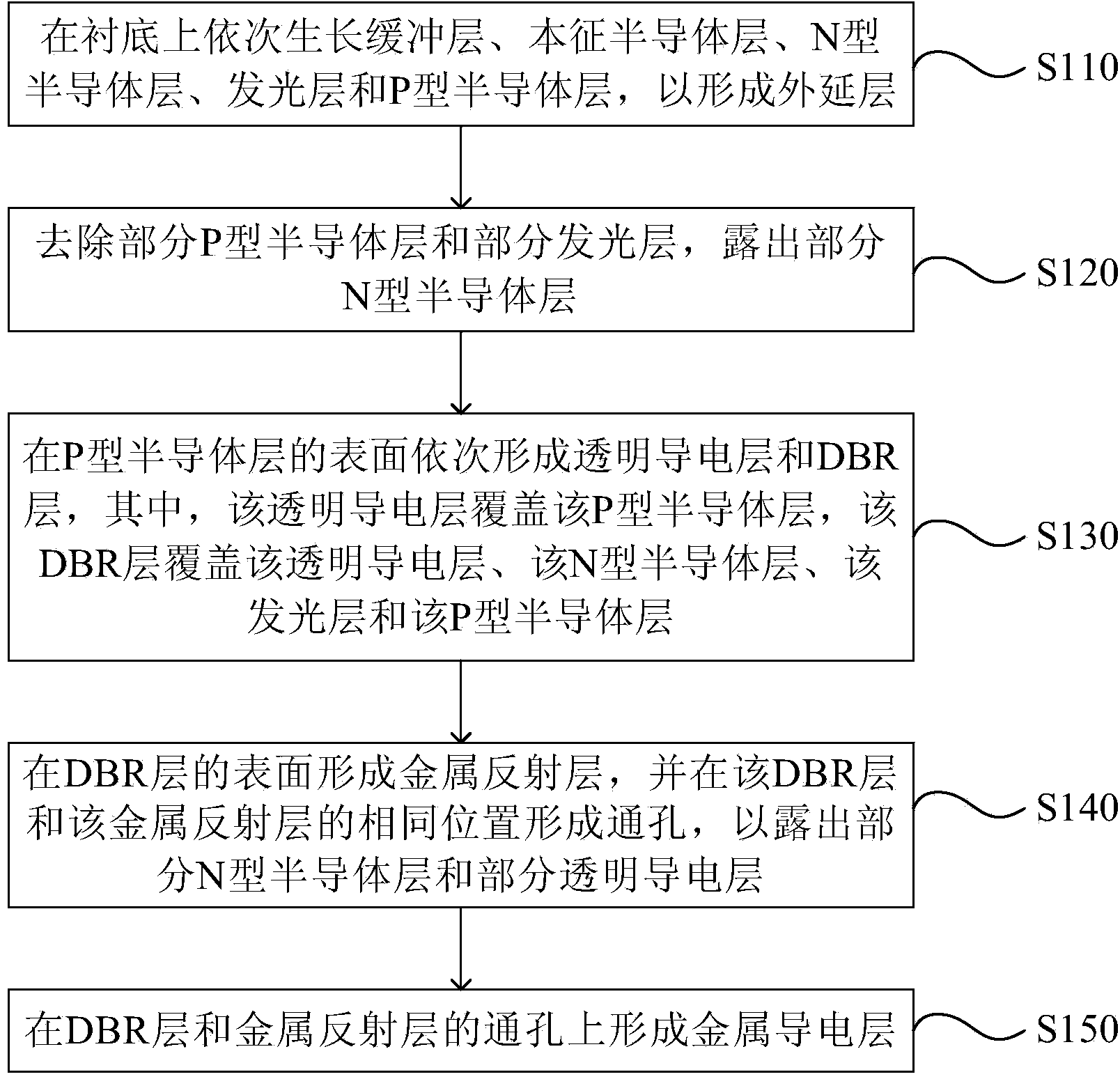

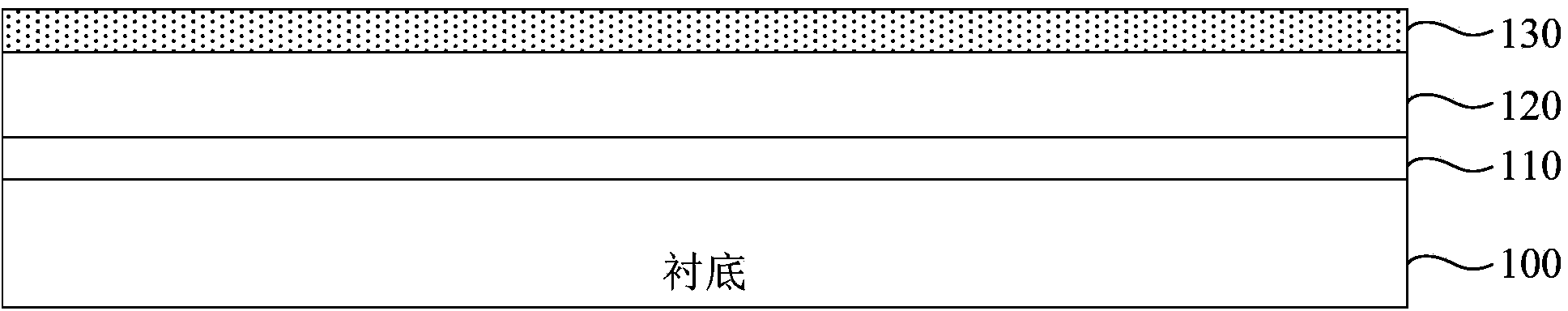

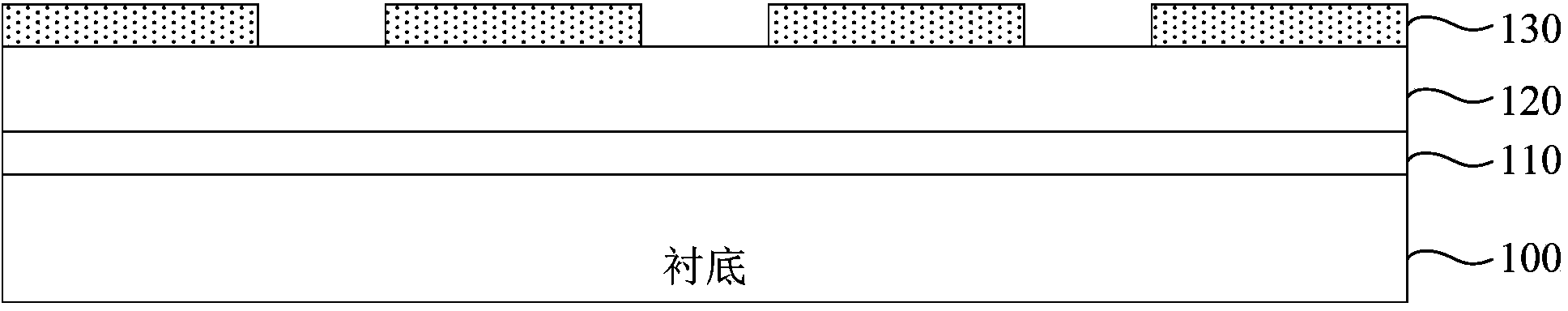

The invention provides an LED flip chip manufacturing method and an LED flip chip. The method includes the steps of sequentially growing a buffer layer, an intrinsic semiconductor layer, an N type semiconductor layer, a light-emitting layer and a P type semiconductor layer on a substrate so as to form an epitaxial layer, removing part of the P type semiconductor layer and part of the light-emitting layer to expose part of the N type semiconductor layer, sequentially forming a transparent conducting layer and a DBR layer on the surface of the P type semiconductor layer, forming a metal reflection layer on the surface of the DBR layer, forming through holes in the same positions of the DBR layer and the metal reflection layer to expose part of the N type semiconductor layer and part of the transparent conducting layer, and forming metal conducting layers on the through holes of the DBR layer and the through holes of the metal reflection layer. By means of the method, the problems that when the LED flip chip is manufactured based on the existing technology, due to the limitation of the performance of metal materials, the requirement for the reflection rate and the requirement for electrical conductivity can not be taken into consideration at the same time when the metal reflection layer is manufactured, and the reflection efficiency is lowered are solved.

Owner:EPITOP PHOTOELECTRIC TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com