Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

152 results about "Avalanche multiplication" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

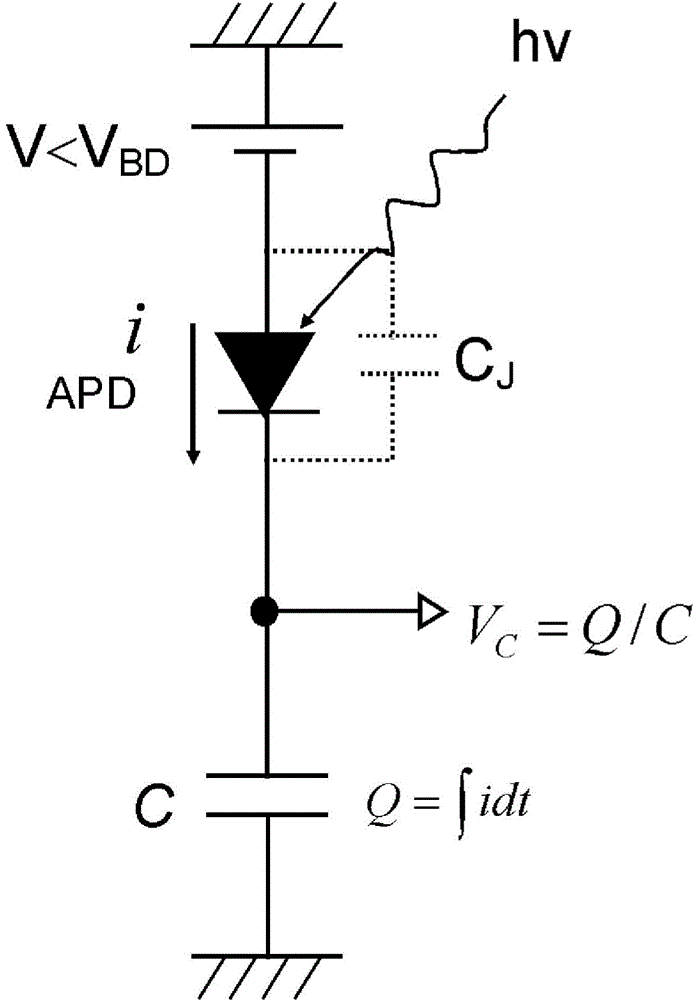

Avalanche multiplication: A current-multiplying phenomenon that occurs in a semiconductor photodiode that is reverse-biased just below its breakdown voltage.

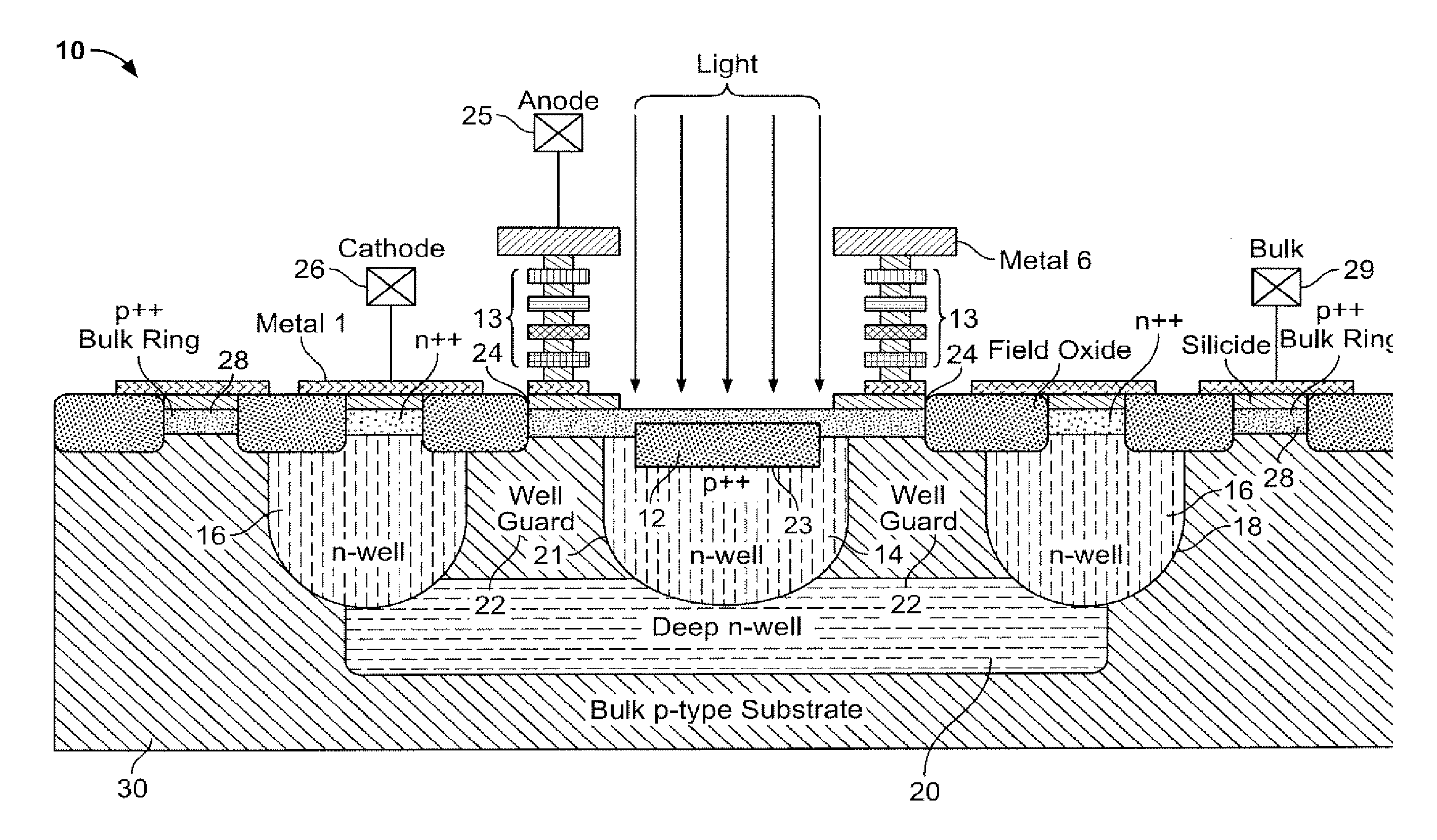

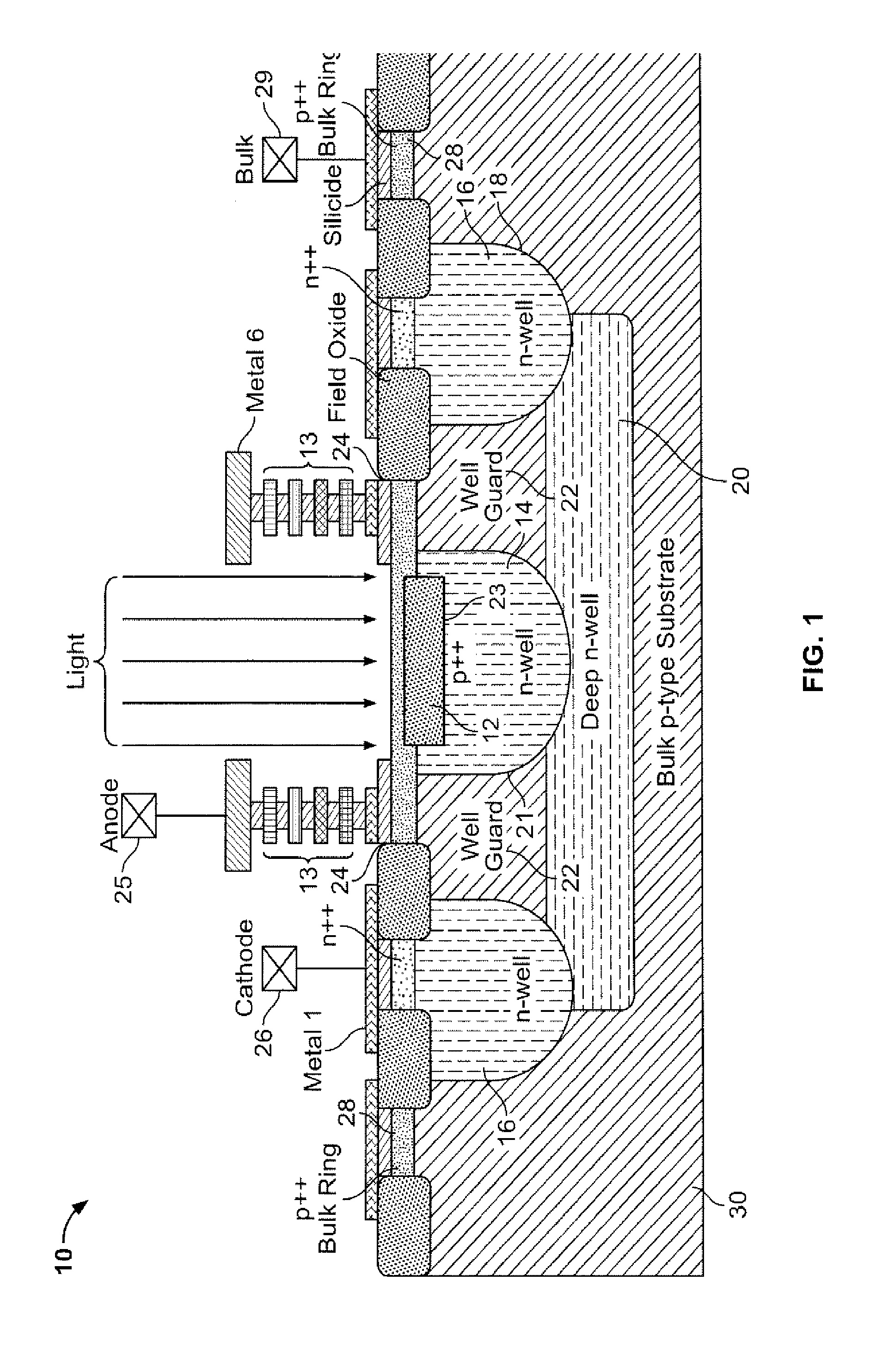

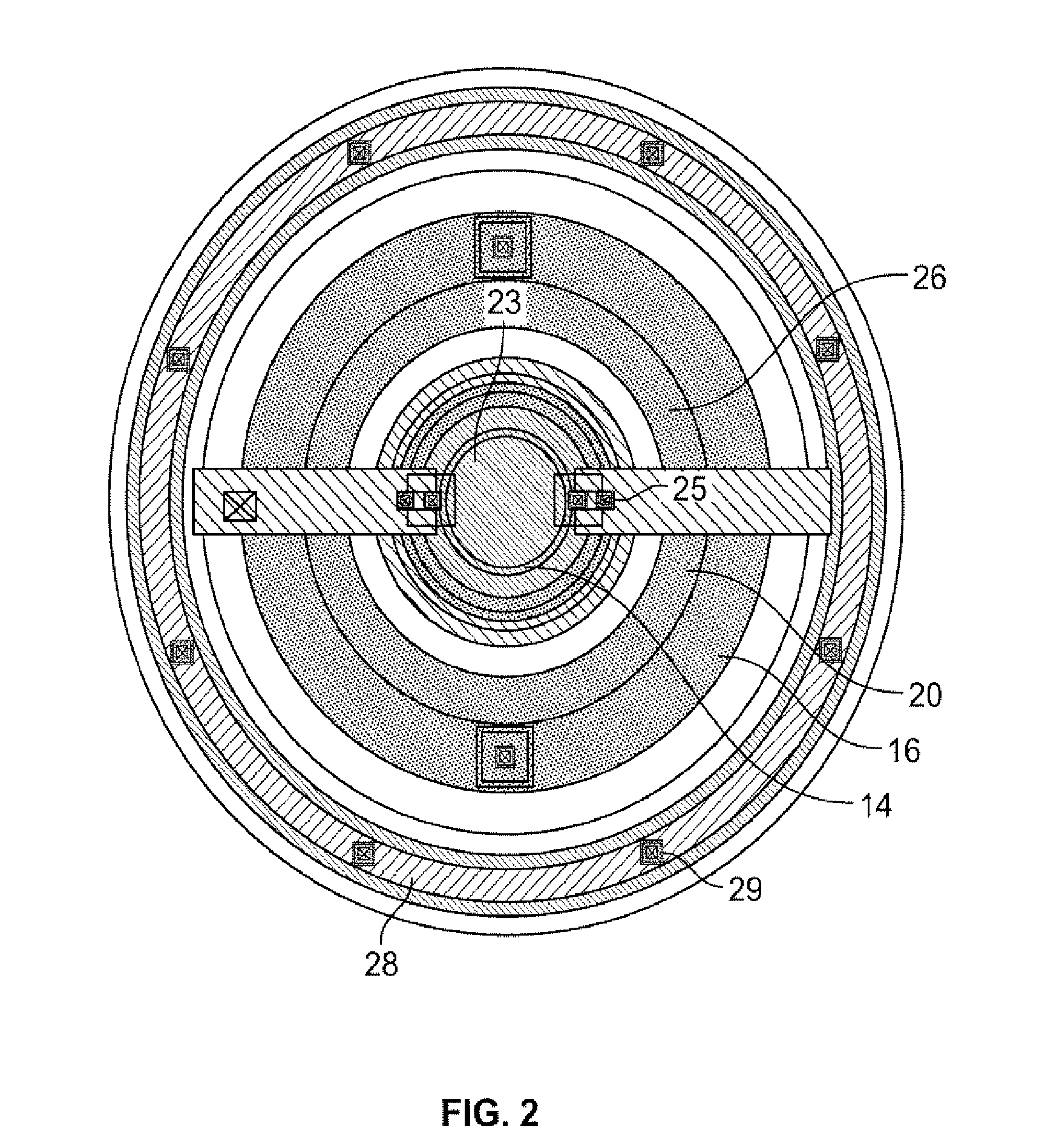

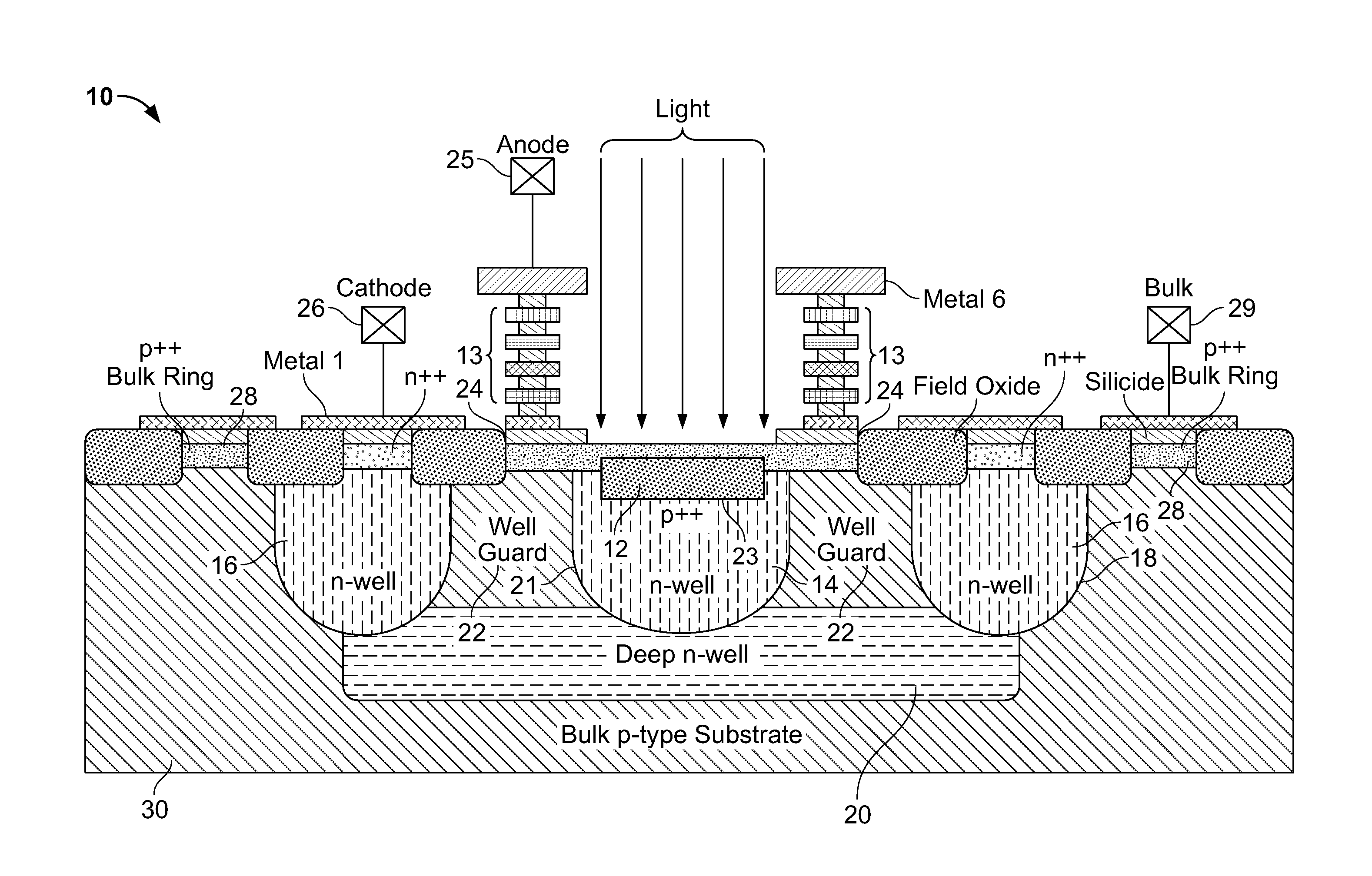

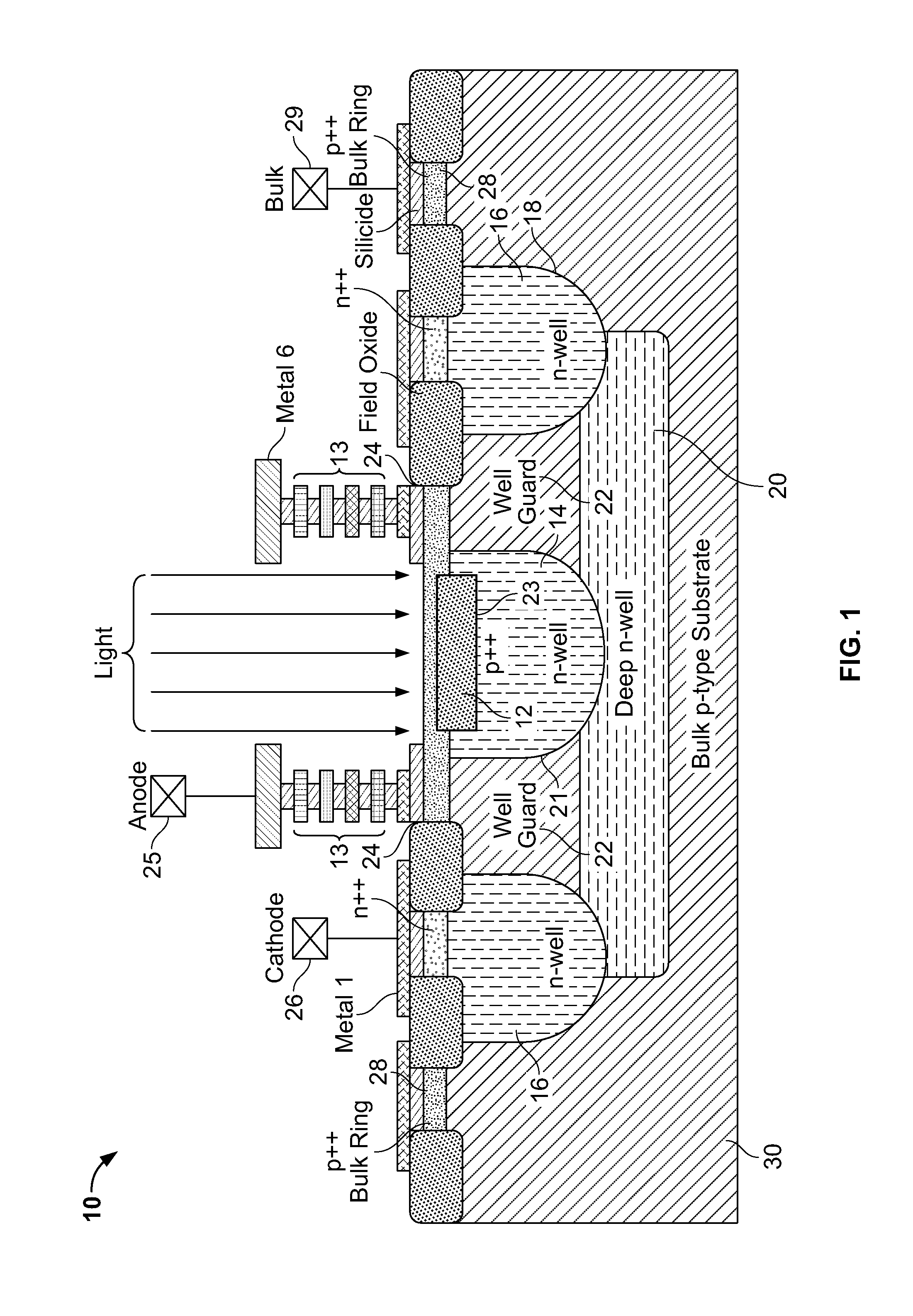

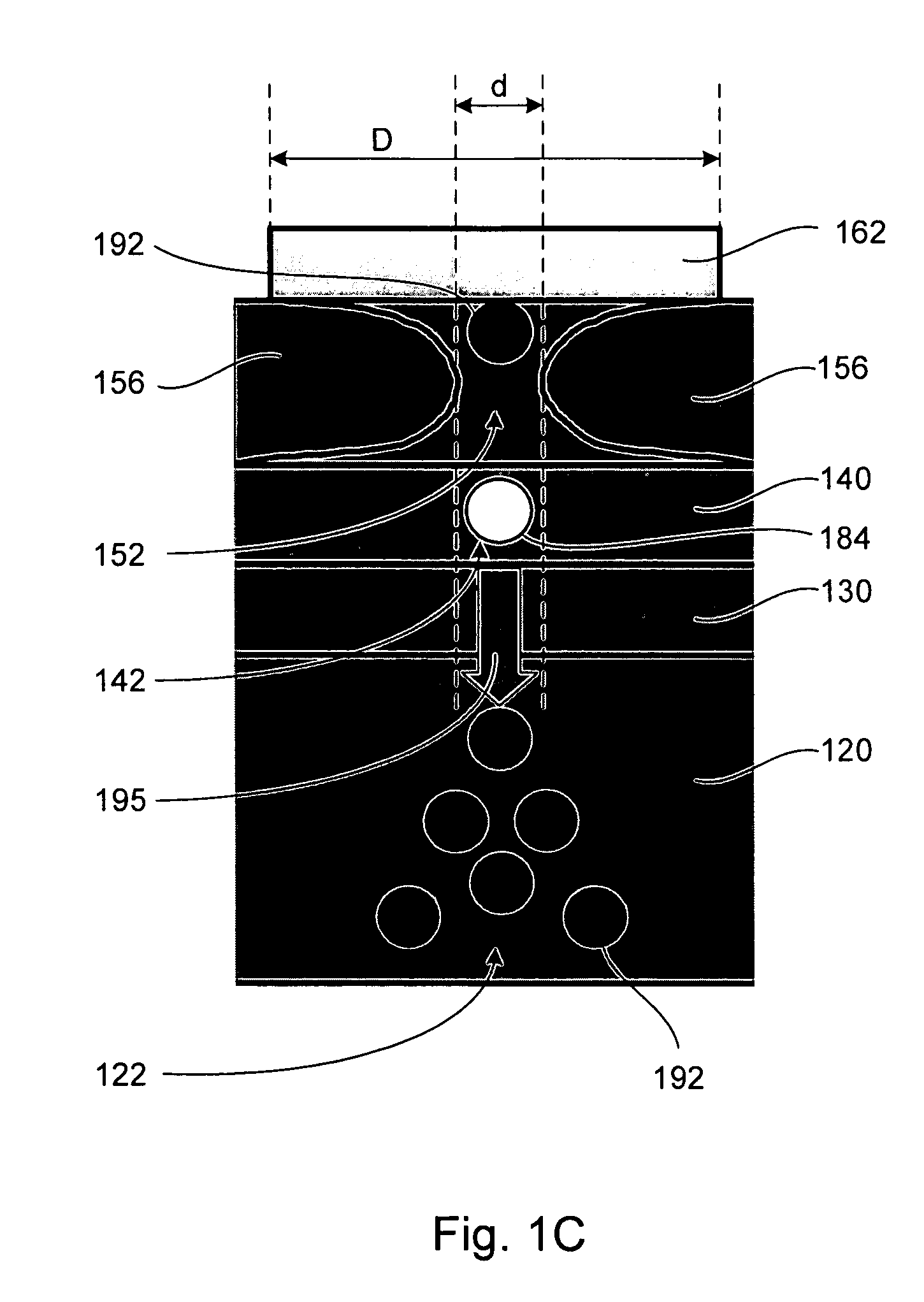

Deep submicron and NANO CMOS single photon photodetector pixel with event based circuits for readout data-rate reduction communication system

ActiveUS20100245809A1Solid-state devicesMaterial analysis by optical meansSensor arrayCommunications system

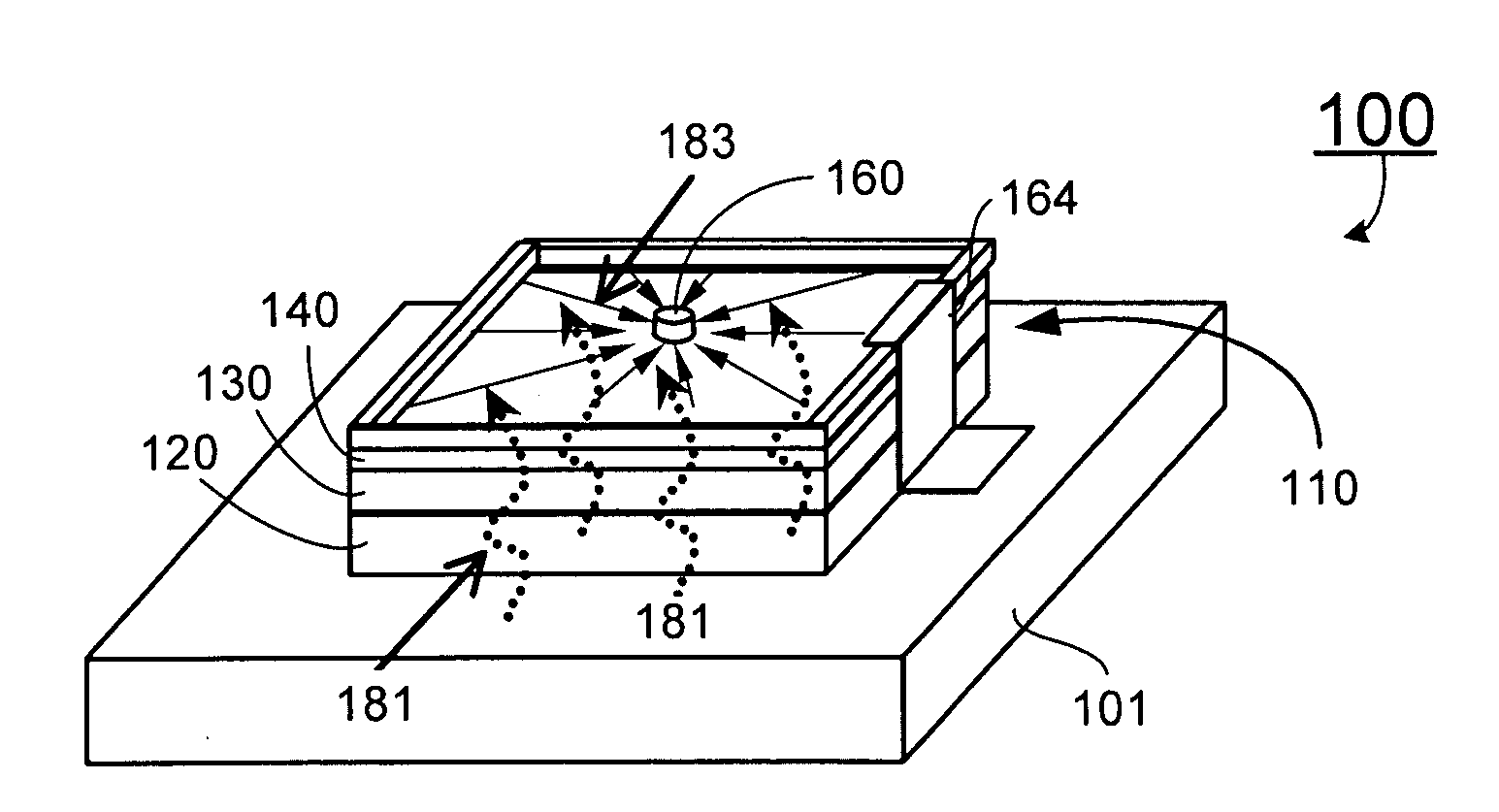

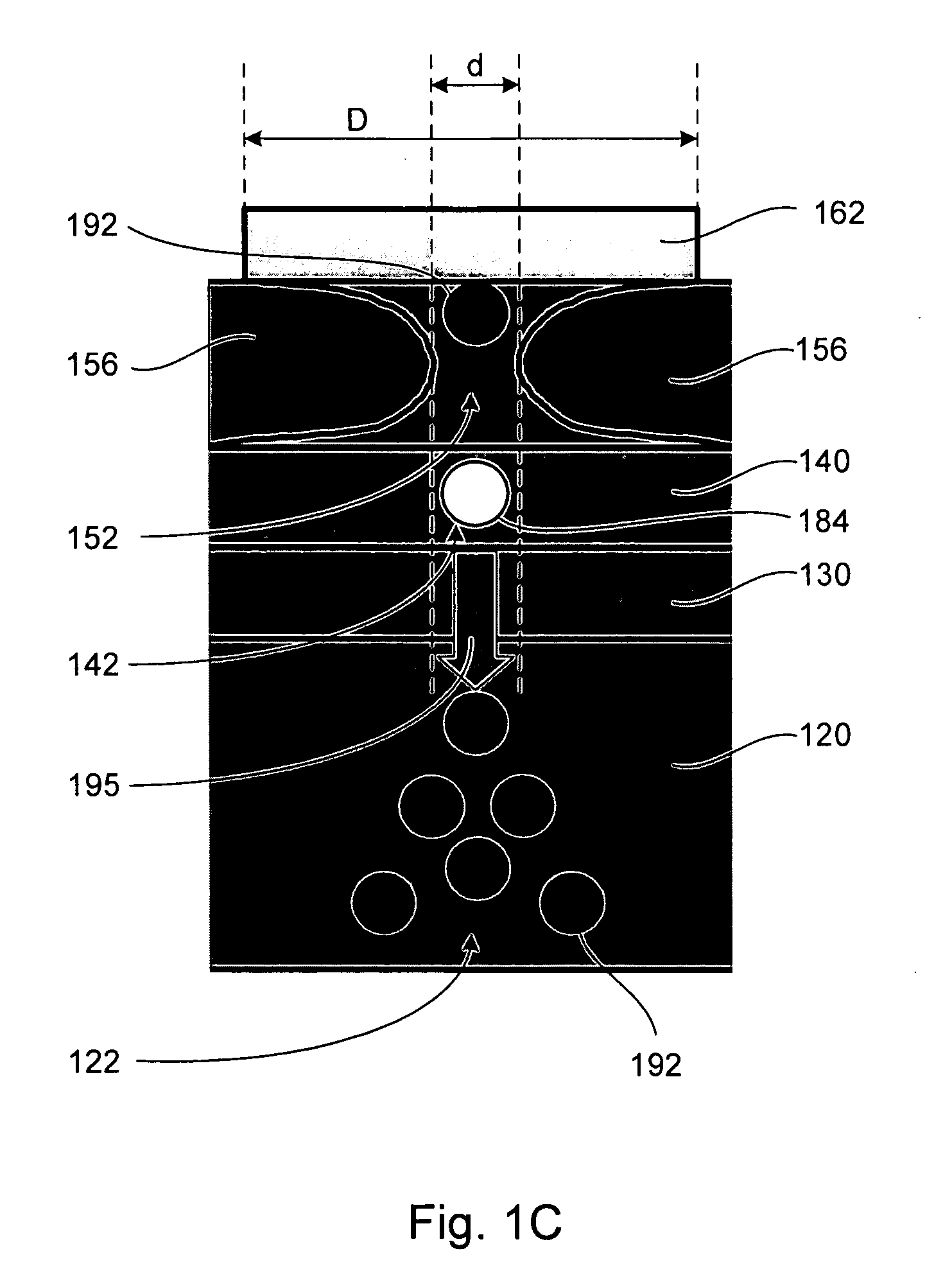

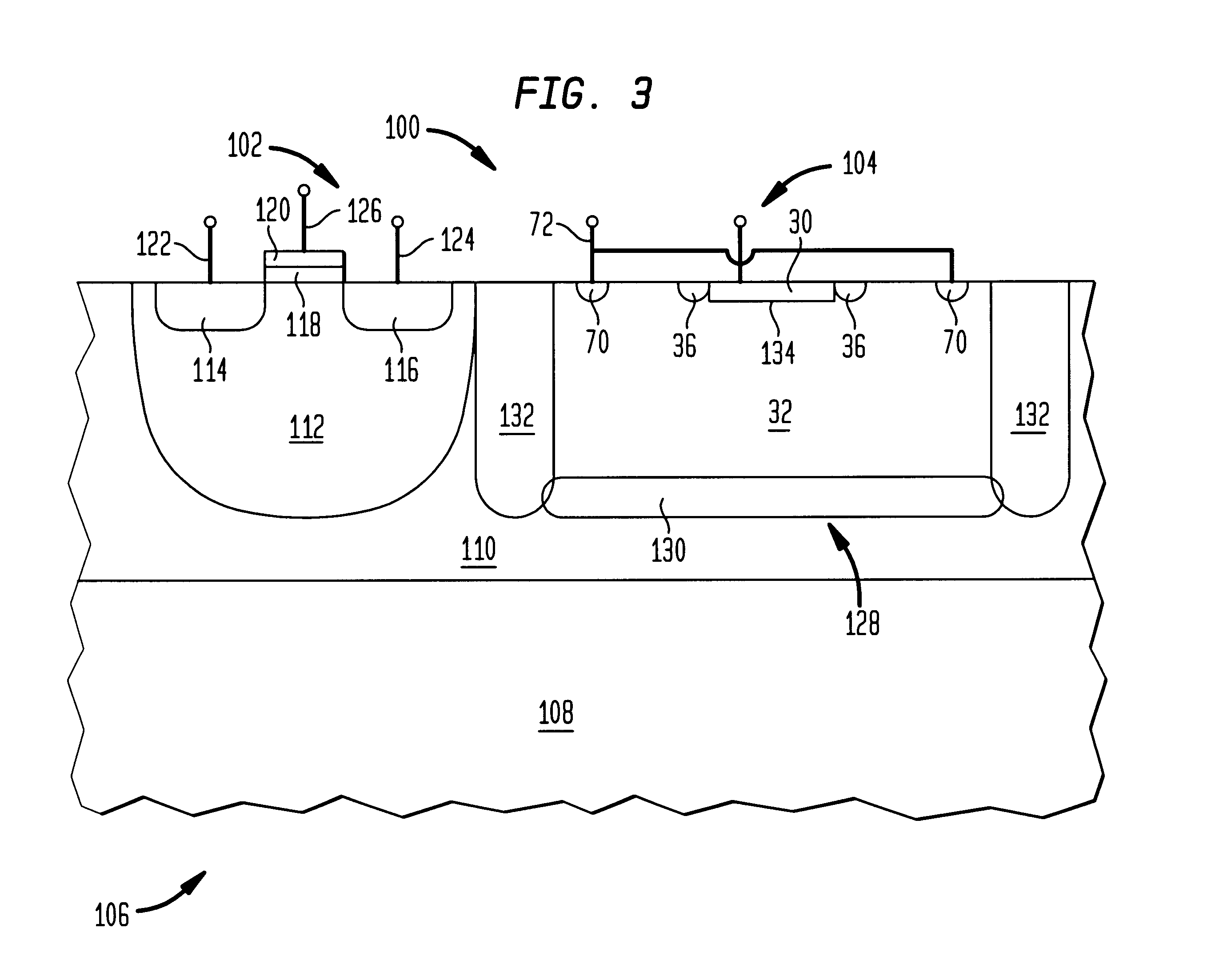

An avalanche photodiode and a sensor array comprising an array of said avalanche photodiodes is disclosed. Then avalanche photodiode comprises a substrate of a first conductivity type; a first well of a second conductivity type formed within the substrate; a second well of the second conductivity type formed substantially overlying and extending into the first well; a heavily doped region of the first conductivity type formed substantially overlying and extending into the first well, the junction between the heavily doped region and the second well forming an avalanche multiplication region; a guard ring formed from a first conductivity material positioned substantially about the periphery of the multiplication region at least partially underlying the heavily doped region; and an outer well ring of the second conductivity type formed about the perimeter of the deep well and the guard ring. The sensor array comprises a plurality of pixel elements, each of the pixel elements being configured to operate on discrete value continuous time (DVCT) basis. Each of the pixel elements can include the avalanche photodiode previously described.

Owner:THE JOHN HOPKINS UNIV SCHOOL OF MEDICINE

Deep submicron and nano CMOS single photon photodetector pixel with event based circuits for readout data-rate reduction communication system

Owner:THE JOHN HOPKINS UNIV SCHOOL OF MEDICINE

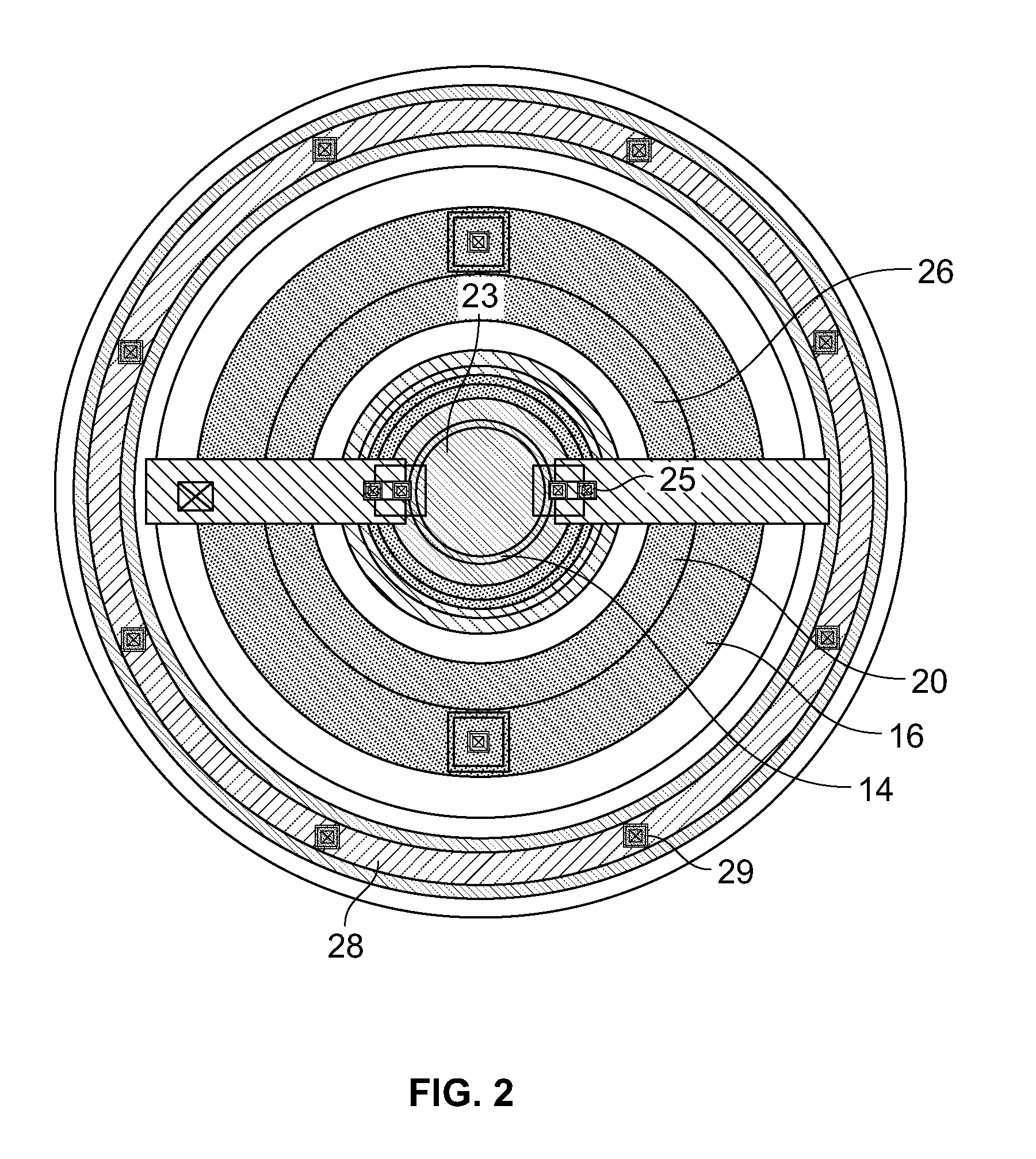

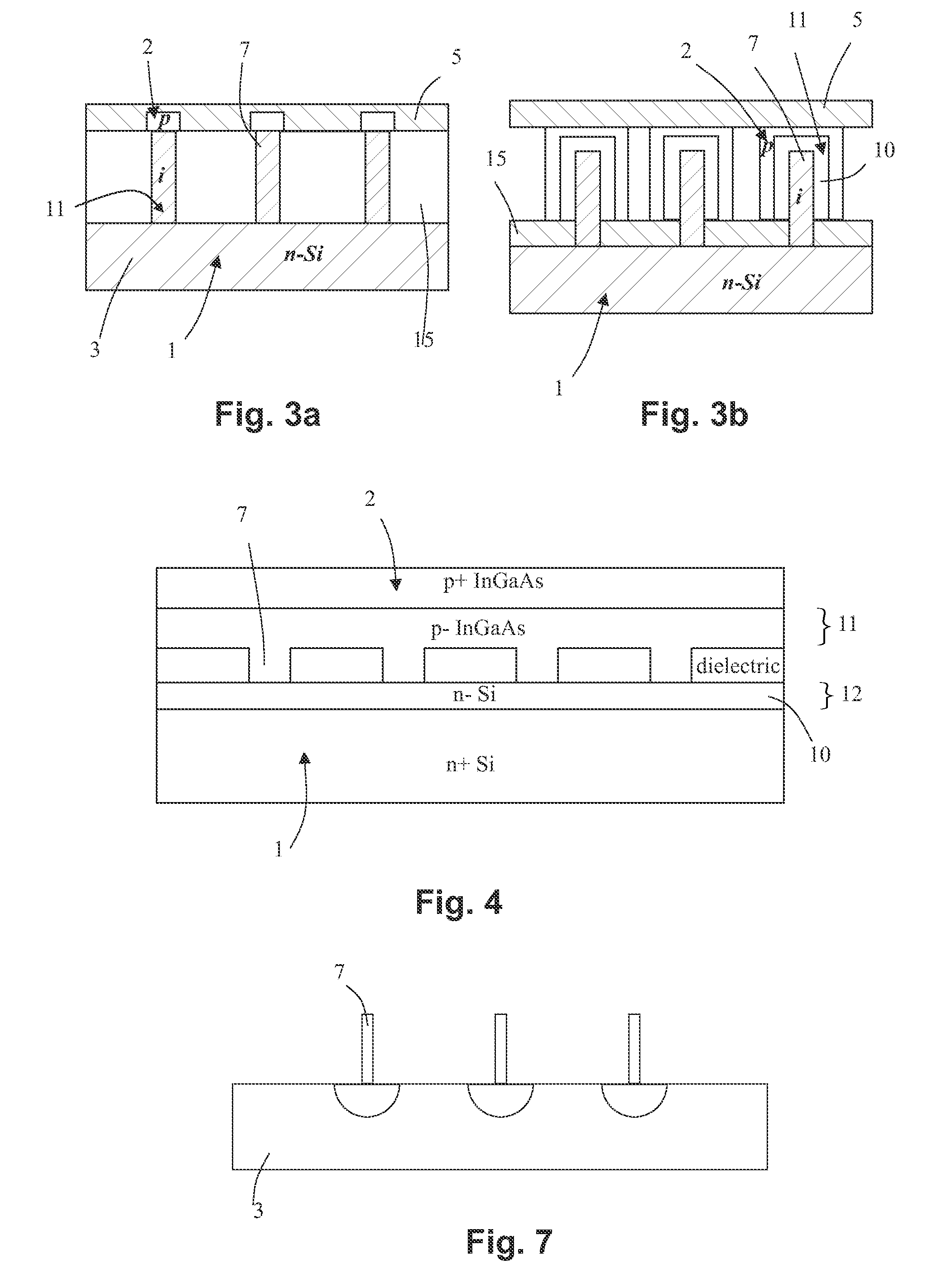

Nanostructured photodiode

InactiveUS20110180894A1Prevent excessive current leakageAvoid device failureNanosensorsPhotovoltaic energy generationNanowireSemiconductor materials

The present invention provides a photodiode comprising a p-i-n or pn junction at least partly formed by first and second regions (2) made of semiconductor materials having opposite conductivity type, wherein the p-i-n or pn junction comprises a light absorption region (11) for generation of charge carriers from absorbed light. One section of the p-i-n or pn junction is comprises by one or more nanowires (7) that are spaced apart and arranged to collect charge carriers generated in the light absorption region (11). At least one low doped region (10) made of a low doped or intrinsic semiconductor material provided between the nanowires (7) and one of said first region (1) and said second region (2) enables custom made light absorption region and / or avalanche multiplication region of the active region (9).

Owner:QUNANO

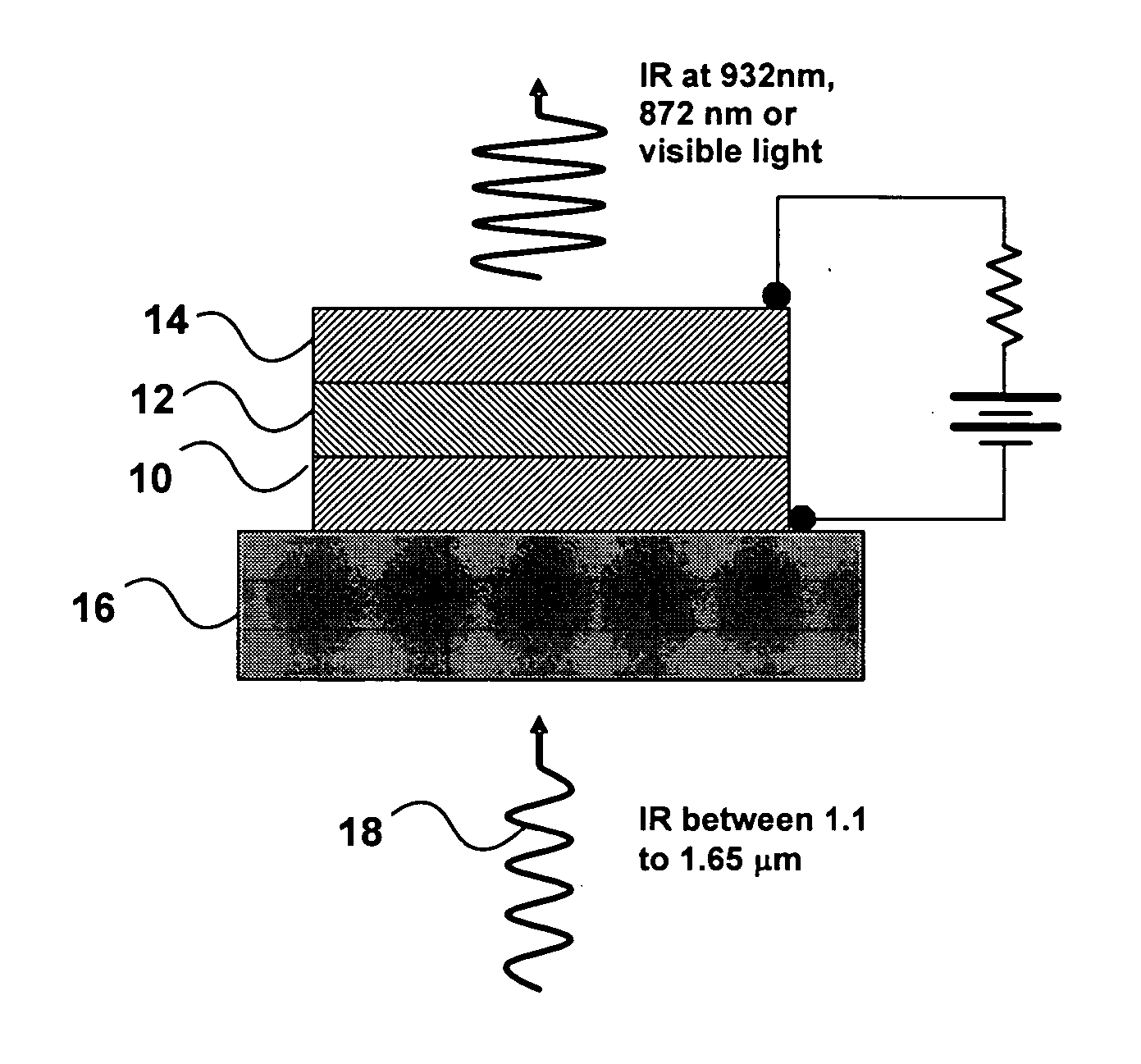

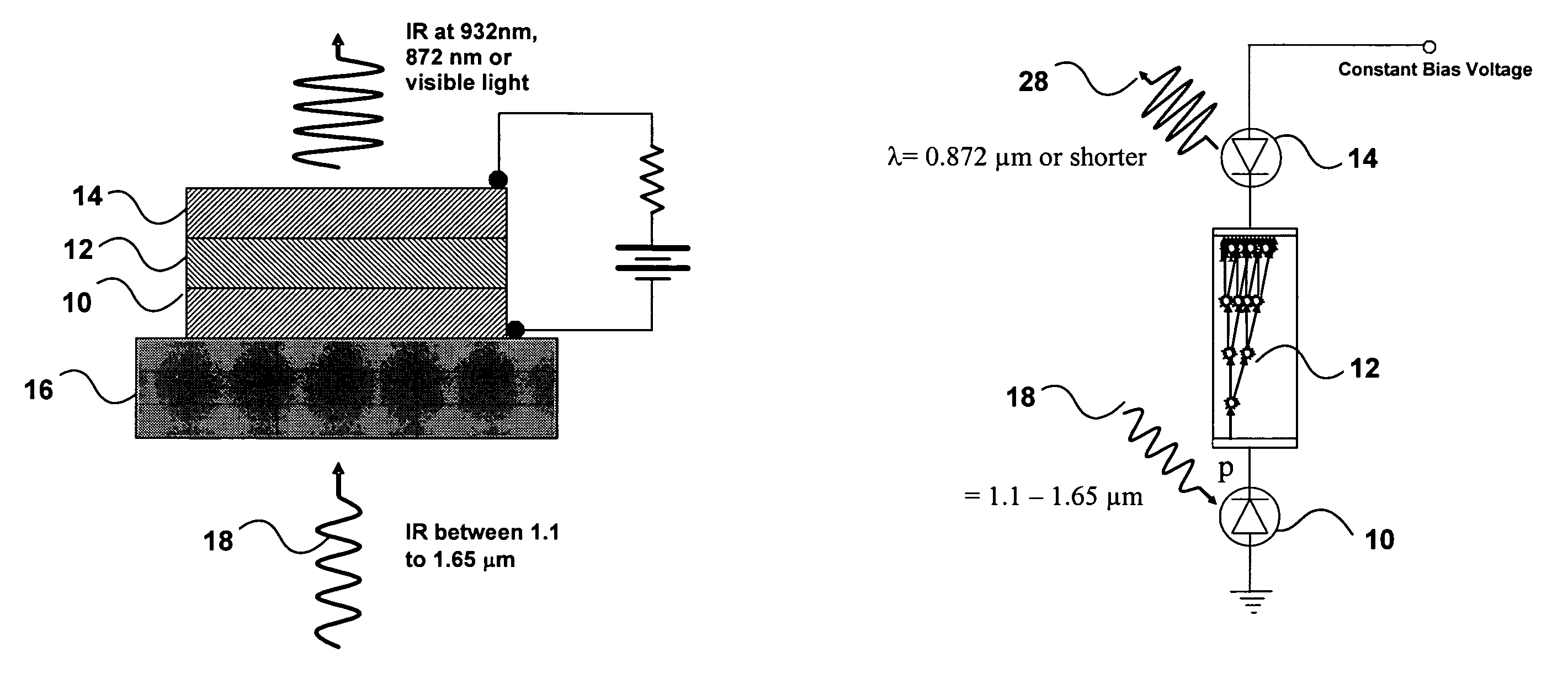

Wavelength conversion device with avalanche multiplier

InactiveUS20050083567A1Improve device performanceEfficient detectionTelevision system detailsLaser detailsPhotodetectorLength wave

A wavelength conversion device includes a photodetector for generating a photocurrent in response to the detection of radiation at a first wavelength. An avalanche multiplier amplifies the signal photocurrent and feeds this to a light emitting element that produces radiation at a second wavelength shorter than the first wavelength and corresponding to the detected radiation at the first wavelength. The components are assembled together in an integrated stacked arrangement either by epitaxial growth or wafer fusion of the individual components. The device is useful as an image intensifier or thermal imaging device.

Owner:NAT RES COUNCIL OF CANADA

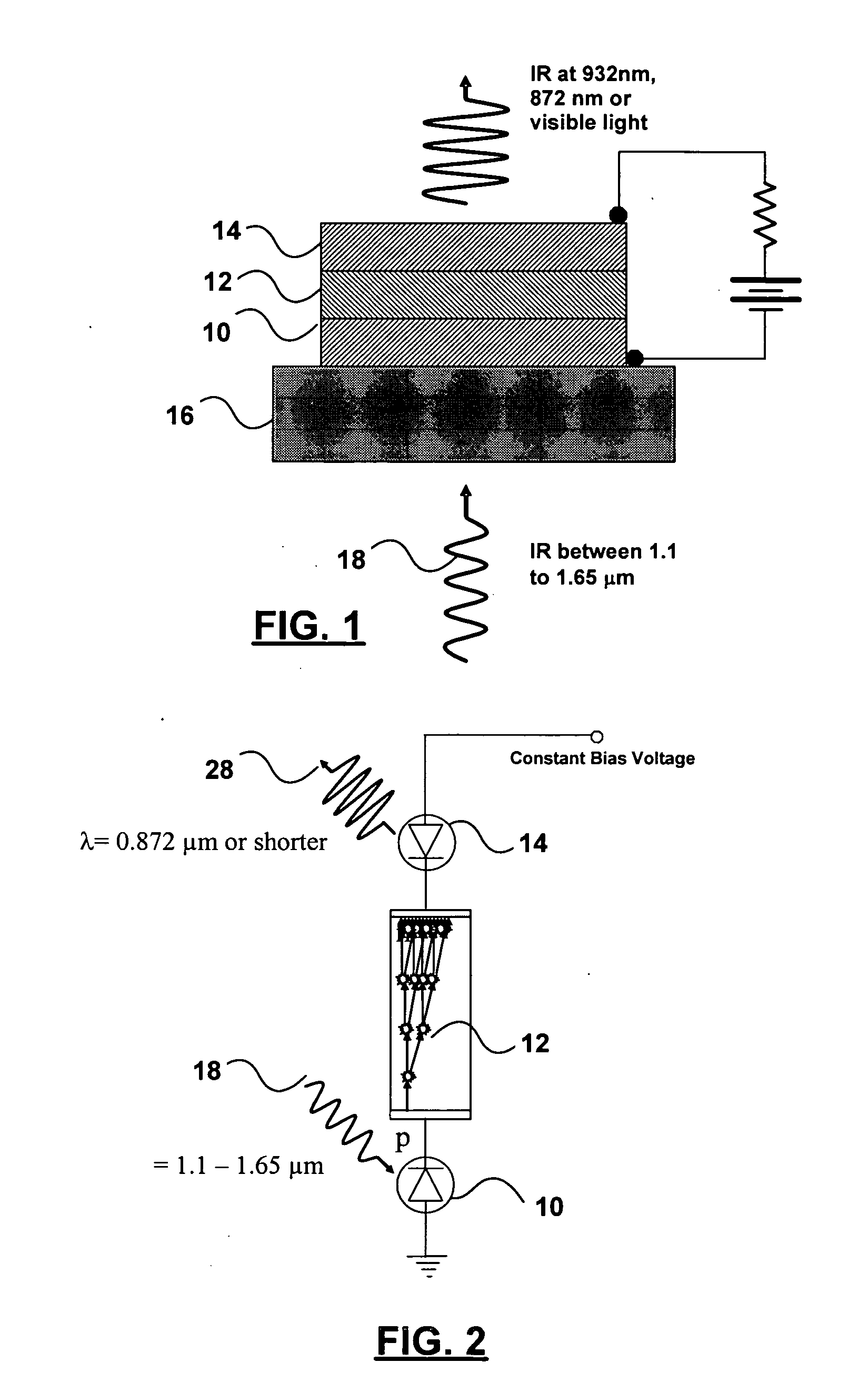

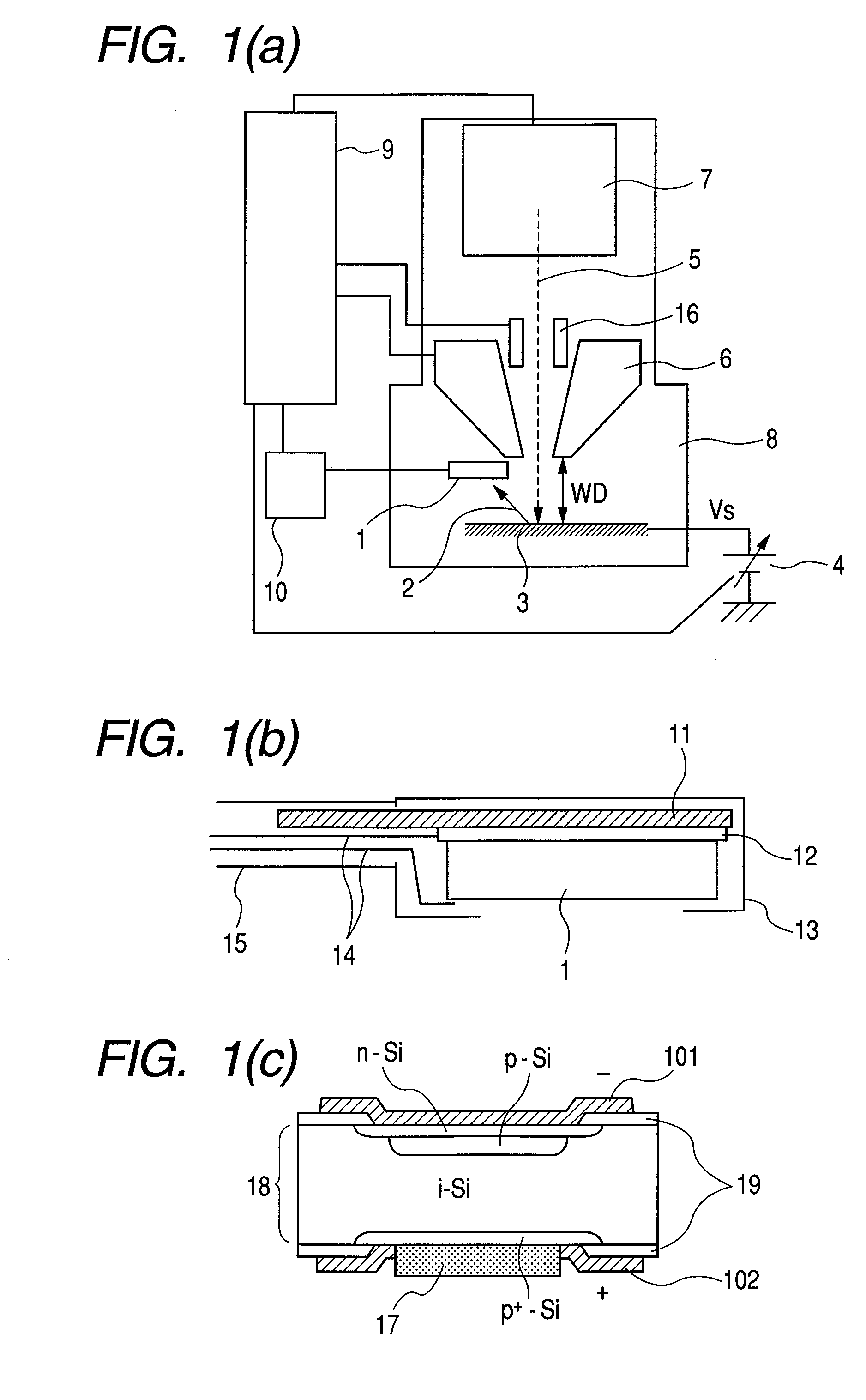

Charged particle application apparatus

InactiveUS20090101817A1Material analysis using wave/particle radiationElectric discharge tubesLow voltageElectron avalanche

The present invention provides a highly sensitive, thin detector useful for observing low-voltage, high-resolution SEM images, and provides a charged particle beam application apparatus based on such a detector. The charged particle beam application apparatus includes a charged particle irradiation source, a charged particle optics for irradiating a sample with a charged particle beam emitted from the charged particle irradiation source, and an electron detection section for detecting electrons that are secondarily generated from the sample. The electron detection section includes a diode device that is a combination of a phosphor layer, which converts the electrons to an optical signal, and a device for converting the optical signal to electrons and subjecting the electrons to avalanche multiplication, or includes a diode device having an electron absorption region that is composed of at least a wide-gap semiconductor substrate with a bandgap greater than 2 eV.

Owner:HITACHI HIGH-TECH CORP

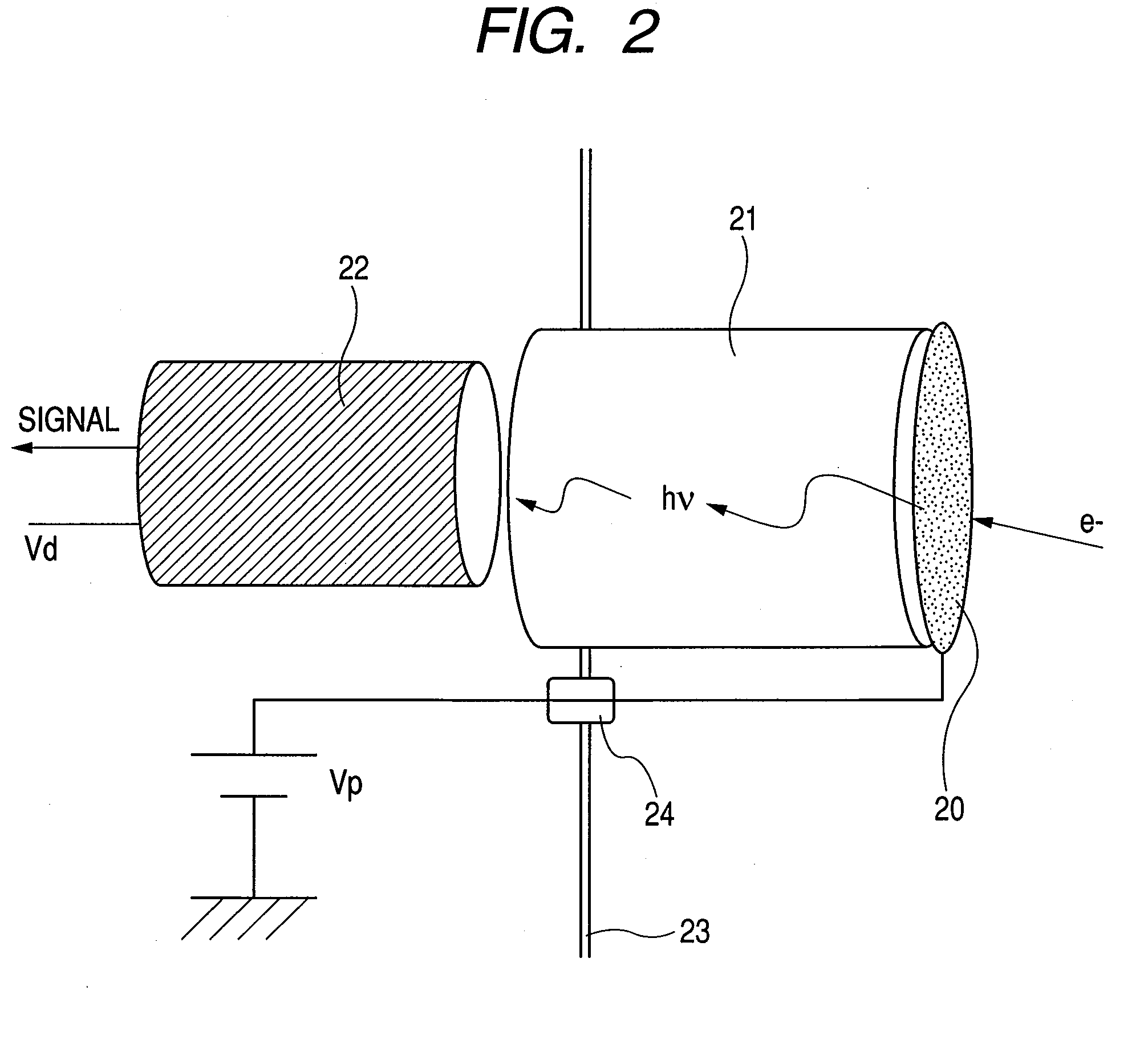

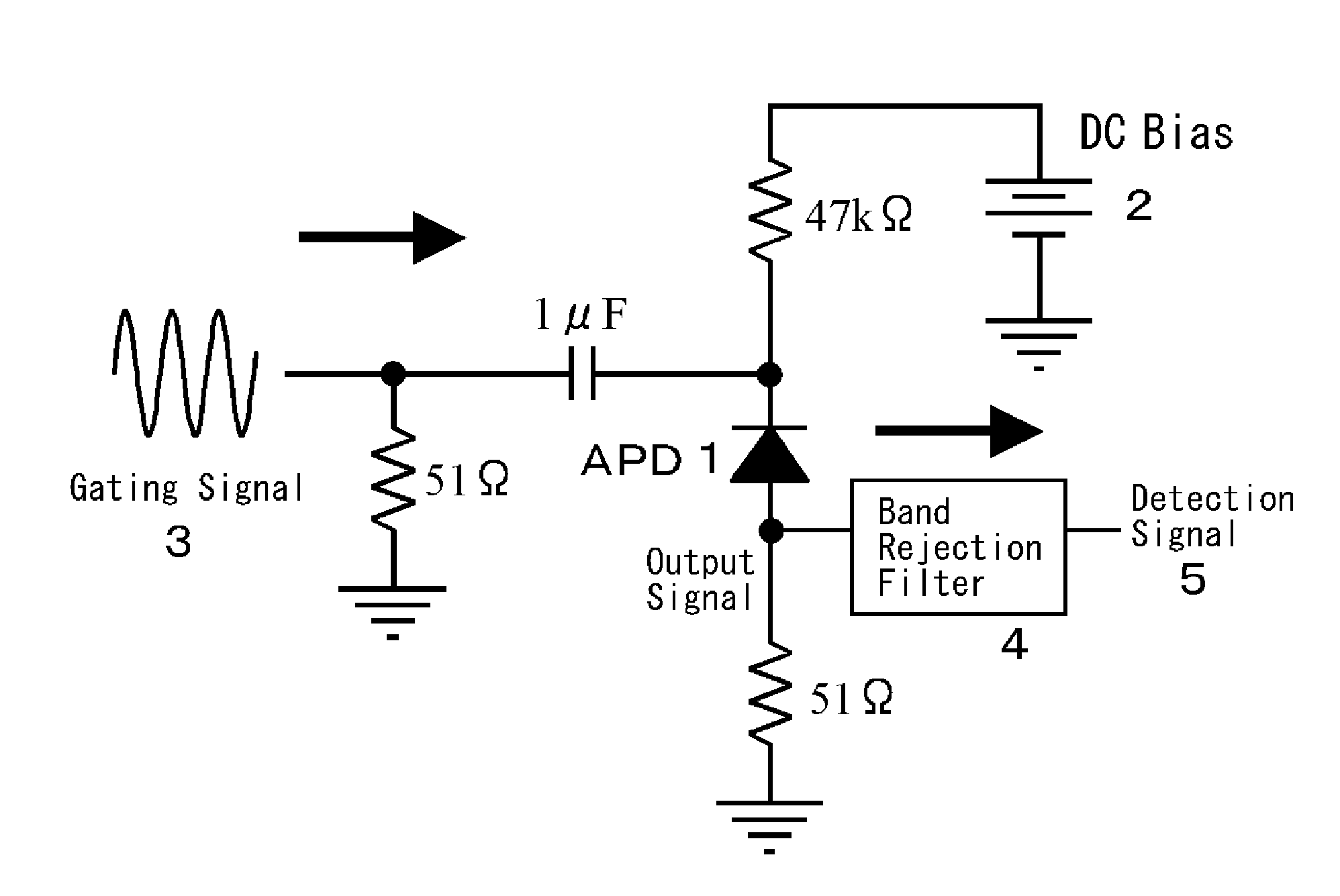

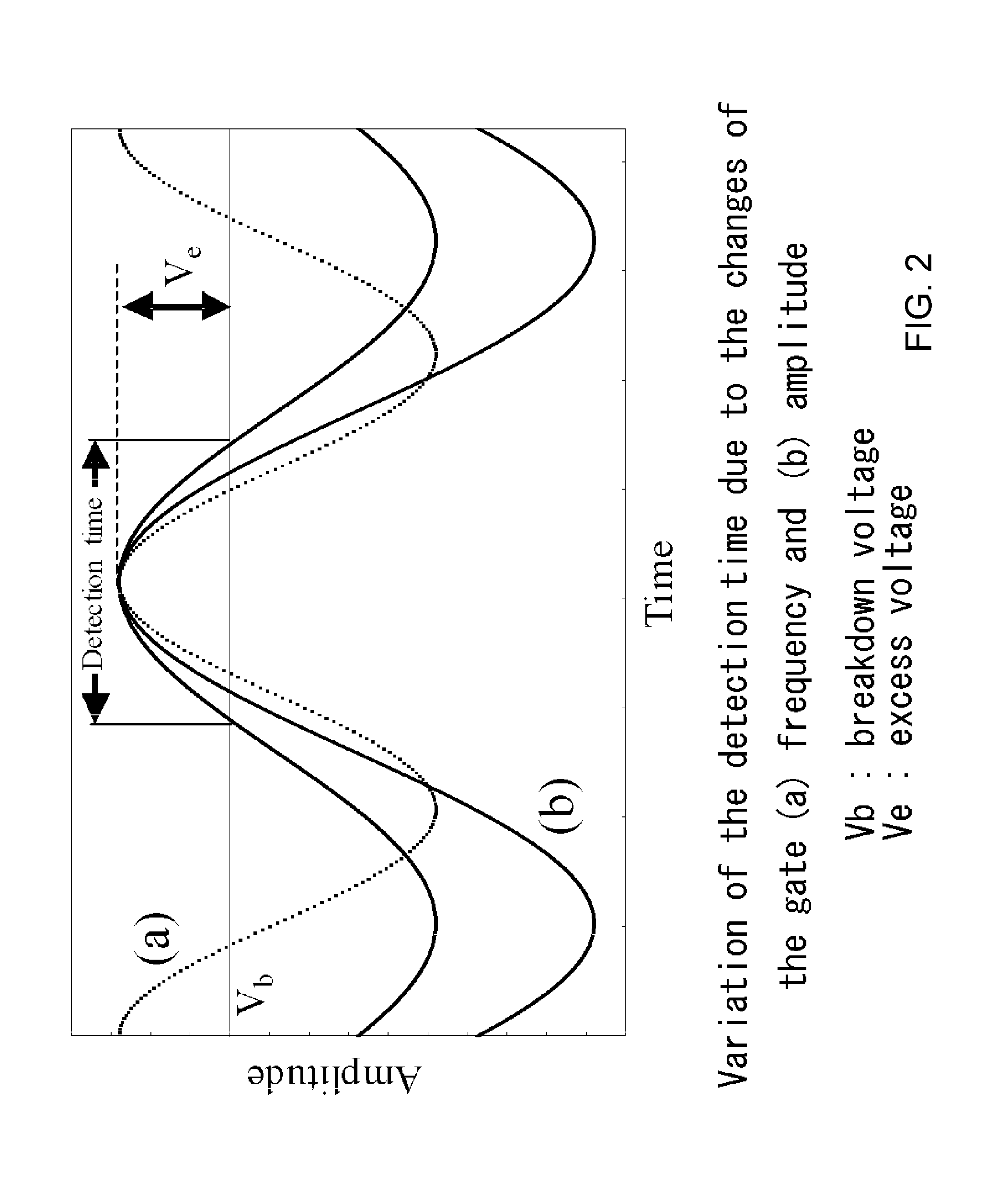

High-speed single-photon detector in telecommunication wavelength band

InactiveUS20090039237A1Reduced after pulsing probabilityHigh repetition rateMaterial analysis by optical meansElectronic switchingLength waveDc bias voltage

In order to operate a single photon detector in communication wavelength band at a high speed, a DC bias voltage 2 lower than the breakdown voltage is applied to an InGaAs / InP avalanche photodiode (APD) 1. A 500 MHz sine wave gating signal 3 is superimposed with the DC bias voltage 2 and applied to the APD so as to exceed the breakdown voltage by about 4V in a fractional time of each period. The sine wave gating signal 3 passed through the APD 1 is substantially completely removed by a filter 4, thereby improving S / N and enabling to detect a single photon even if the avalanche multiplication time is shortened to reduce the after pulse and the detection period. As a result, it achieves to detect a single photon in the 1550 nm communication band at a high speed.

Owner:NIHON UNIVERSITY

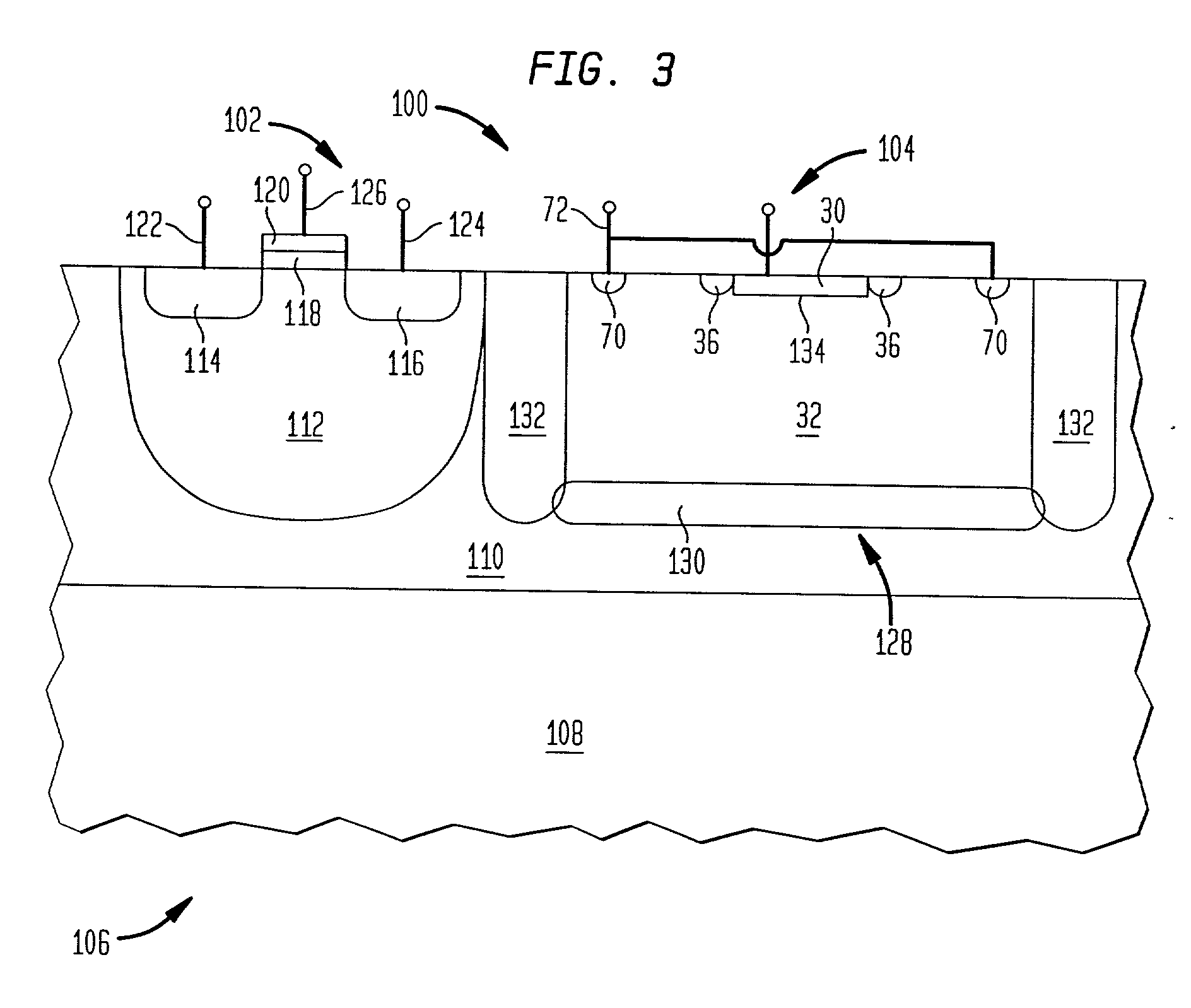

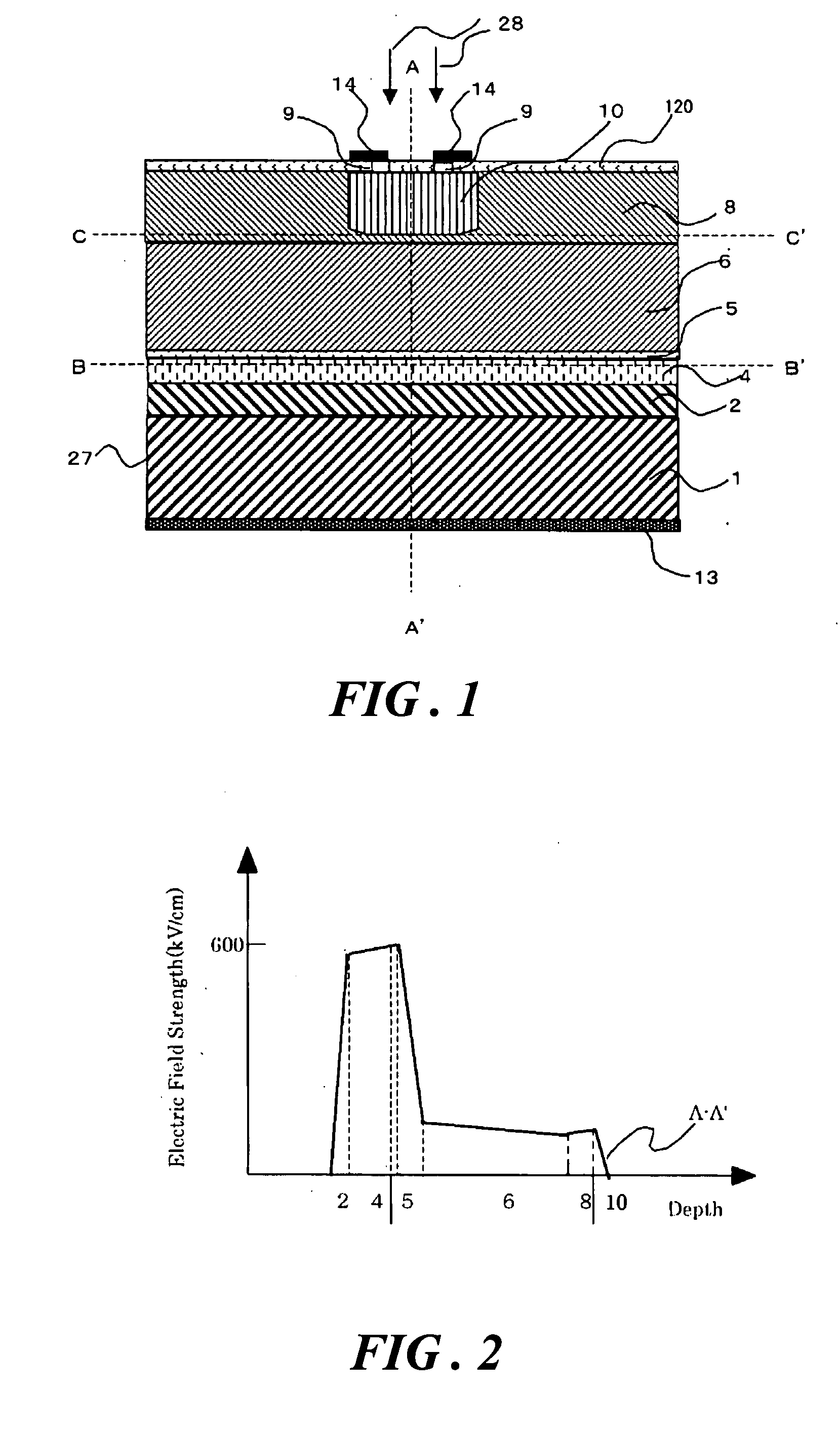

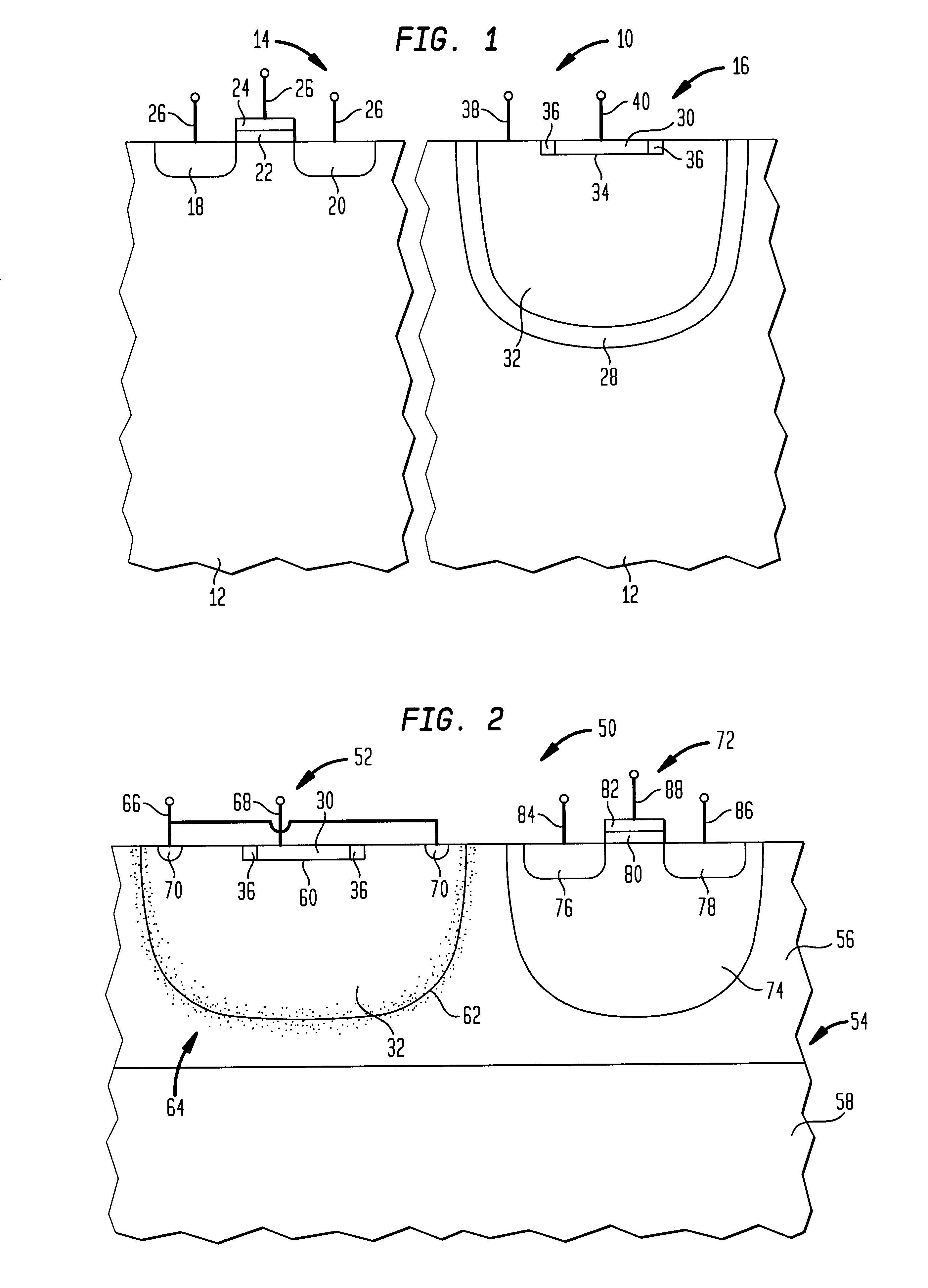

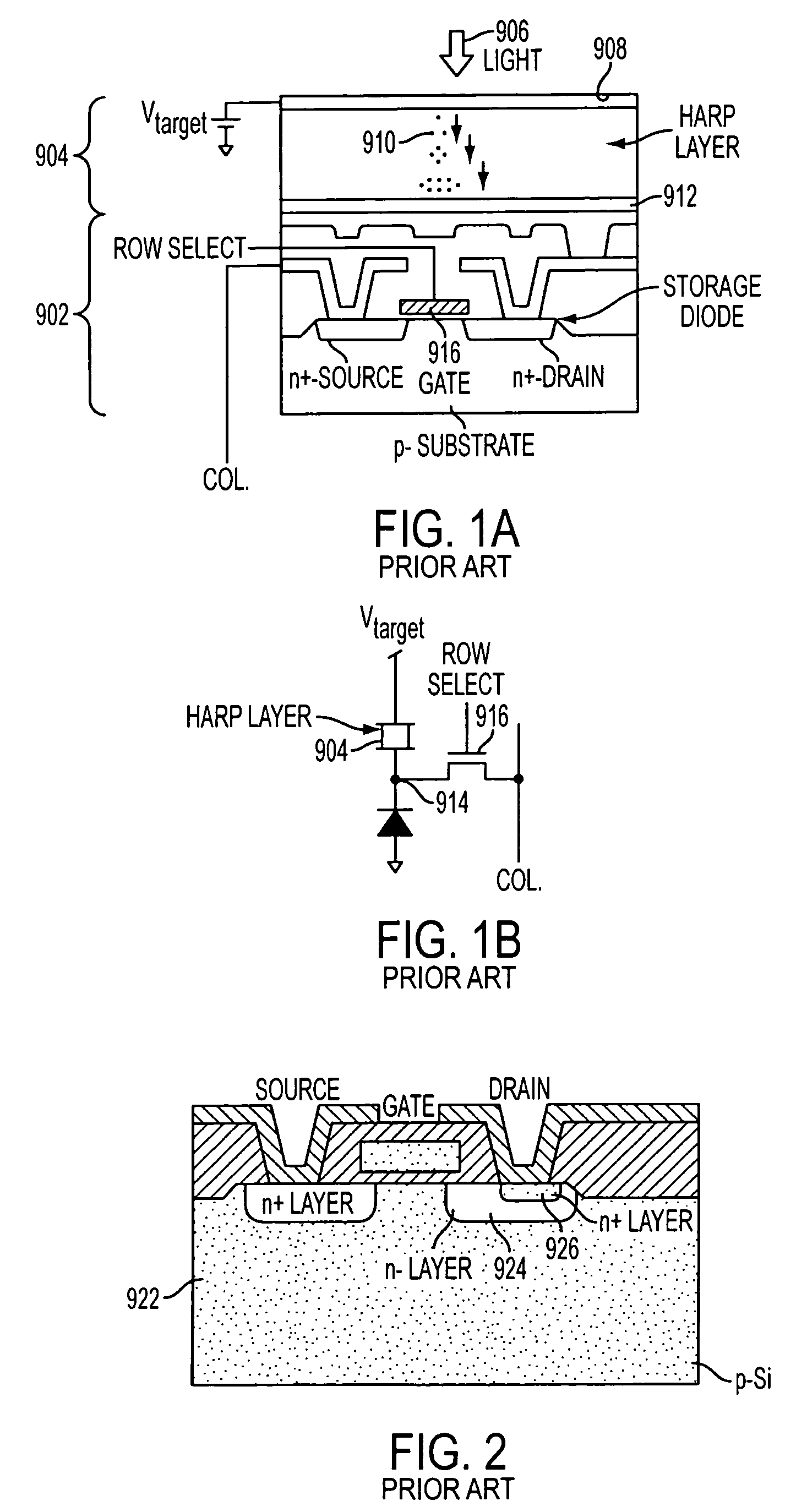

Integrated optoelectronic device with an avalanche photodetector and method of making the same using commercial CMOS processes

InactiveUS20010017786A1Reduce manufacturing costAdded complexityTransistorSemiconductor/solid-state device manufacturingMOSFETPhotodetector

An integrated optoelectronic circuit chip for optical data communication systems includes a silicon substrate, at least one MOS field effect transistor (MOSFET) formed on a portion of the silicon substrate, and an avalanche photodetector operatively responsive to an incident optical signal and formed on another portion of the substrate. The avalanche photodetector includes a light absorbing region extending from a top surface of the silicon substrate to a depth h and doped to a first conductivity type. The light absorbing region is ionizable by the incident optical signal to form freed charge carriers in the light absorbing region. A light responsive region is formed in the light absorbing region and extends from the top surface of the silicon substrate to a depth of less than h. The light responsive region is doped to a second conductivity type of opposite polarity to the first conductivity type. The light absorbing region and the light responsive region form a P-N junction at the interface therebetween such that when the light absorbing and light responsive regions are appropriately reverse biased, the freed charge carriers in the light absorbing region are amplified by avalanche multiplication.

Owner:LUCENT TECH INC

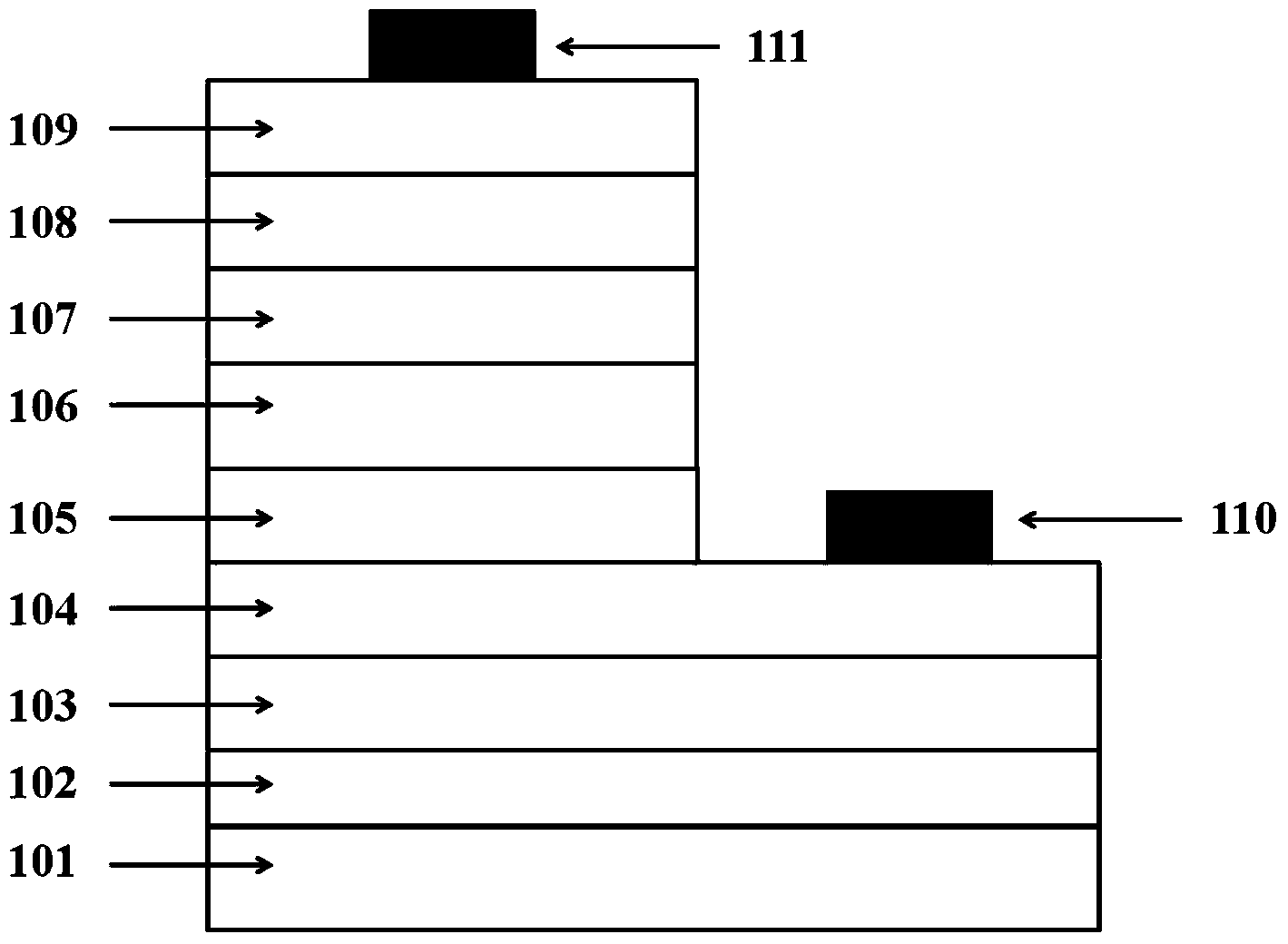

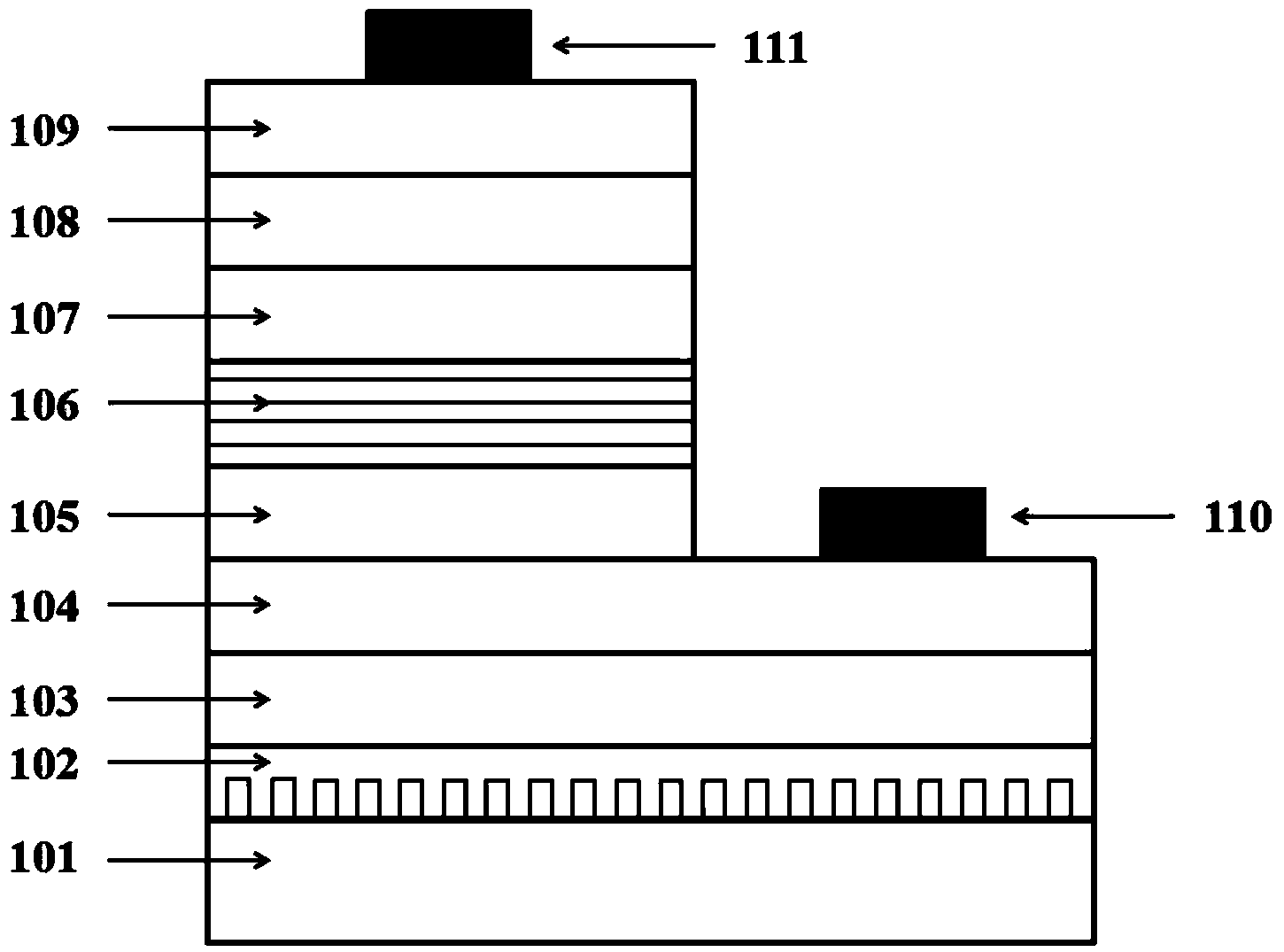

Aluminum gallium nitrogen-based solar blind ultraviolet detector and production method thereof

InactiveCN104362213AImprove quantum efficiencyImprove responsivenessSemiconductor devicesUltraviolet detectorsNitrogen

The invention discloses an aluminum gallium nitrogen-based solar blind ultraviolet detector and a production method thereof. The aluminum gallium nitrogen-based solar blind ultraviolet detector comprises a sapphire substrate, an A1N nucleating layer, an A1<x1>Ga<1-x1>N buffer layer, an n-type A1<x2>Ga<1-x2>N layer, an undoped i-type A1<x3>Ga<1-x3>N absorbing layer, an n-type A1<X4>In<y1>Ga<1-x4-y1>N / A1<x5>In<y2>Ga<1-x5-y2>N superlattice separating layer, an undoped i-type A1<x6>Ga<1-x6>N multiplication layer, a p-type A1<x7>Ga<1-x7>N layer and a p-type GaN layer which are sequentially arranged from the bottom up. An n-type ohmic electrode leads from the n type A1<x2>Ga<1-x2>N layer, and a p type ohmic electrode leads from the p type GaN layer. According to the arrangement, the absorbing layer and the multiplication layer are separated by the multi-cycle n type A1<X4>In<y1>Ga<1-x4-y1>N / A1<x5>In<y2>Ga<1-x5-y2>N superlattice separating layer, the electric field of the multiplication layer is increased, thus allowing uniform avalanche multiplication to occur under the high electric field, and avalanche multiplication factors of the solar blind ultraviolet detector are increased.

Owner:SOUTHEAST UNIV

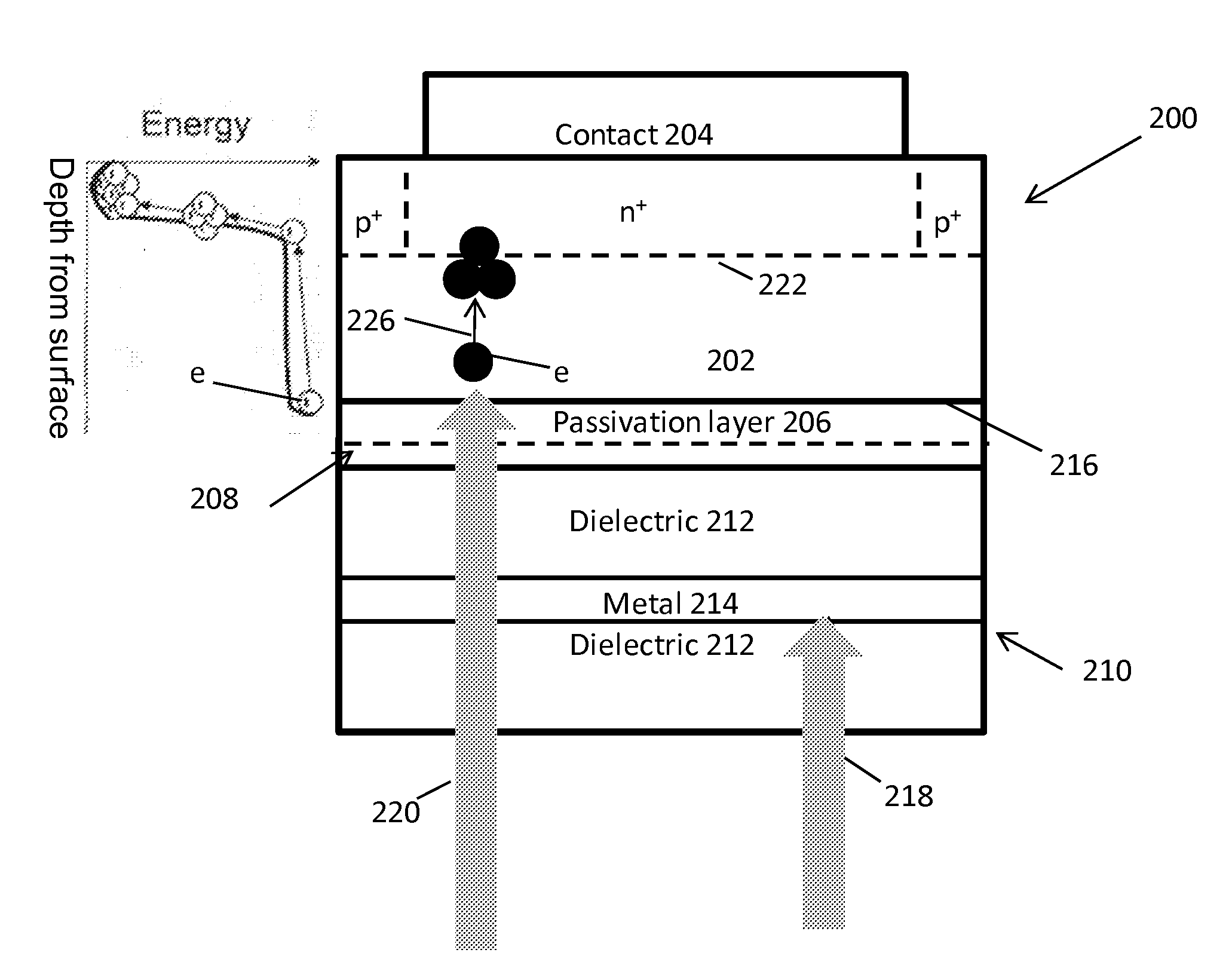

Subnanosecond scintillation detector

ActiveUS20150276947A1Avoid spreadingImprove time resolutionSolid-state devicesMaterial analysis by optical meansBandpass filteringTemporal resolution

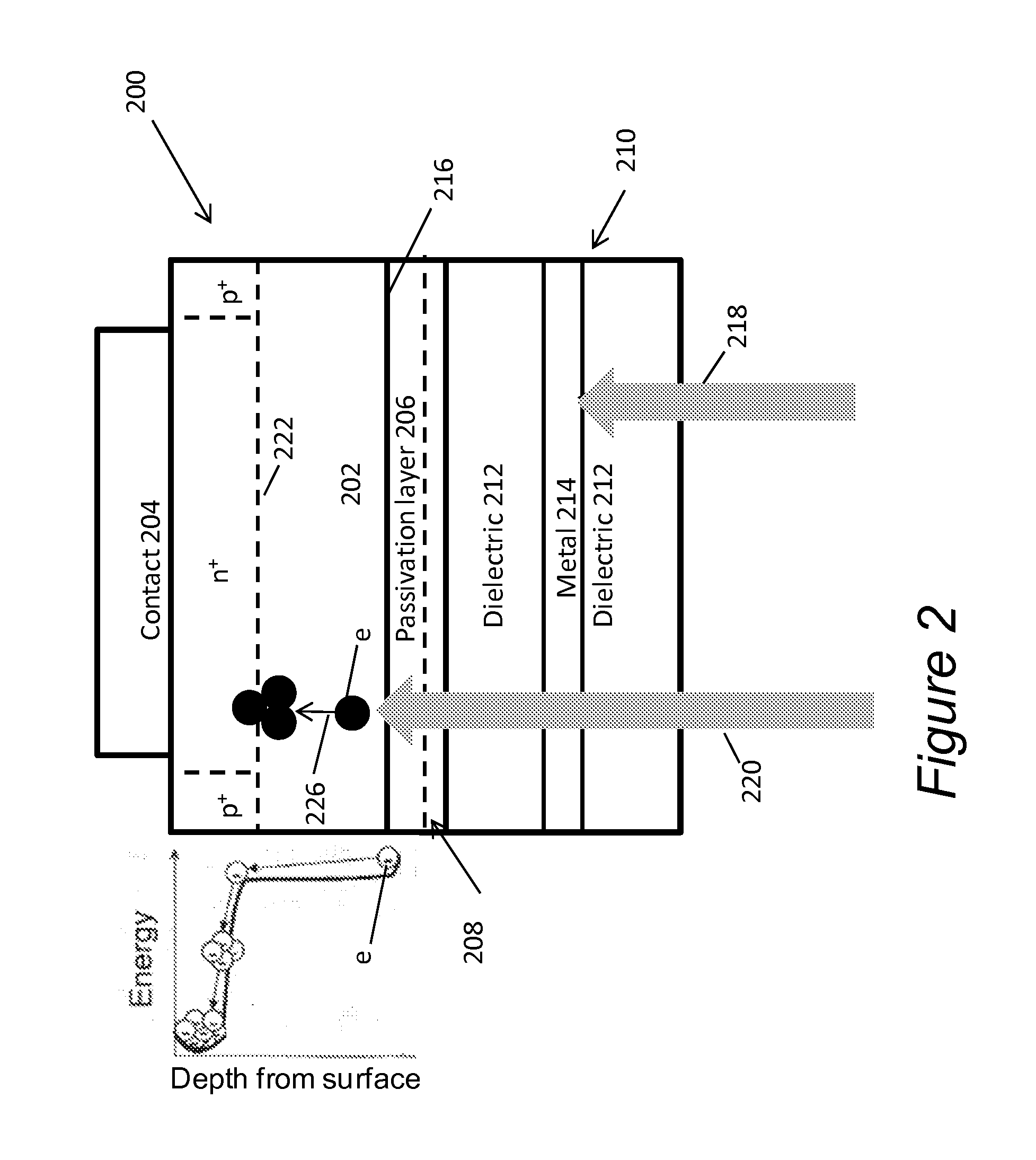

A scintillation detector, including a scintillator that emits scintillation; a semiconductor photodetector having a surface area for receiving the scintillation, wherein the surface area has a passivation layer configured to provide a peak quantum efficiency greater than 40% for a first component of the scintillation, and the semiconductor photodetector has built in gain through avalanche multiplication; a coating on the surface area, wherein the coating acts as a bandpass filter that transmits light within a range of wavelengths corresponding to the first component of the scintillation and suppresses transmission of light with wavelengths outside said range of wavelengths; and wherein the surface area, the passivation layer, and the coating are controlled to increase the temporal resolution of the semiconductor photodetector.

Owner:CALIFORNIA INST OF TECH

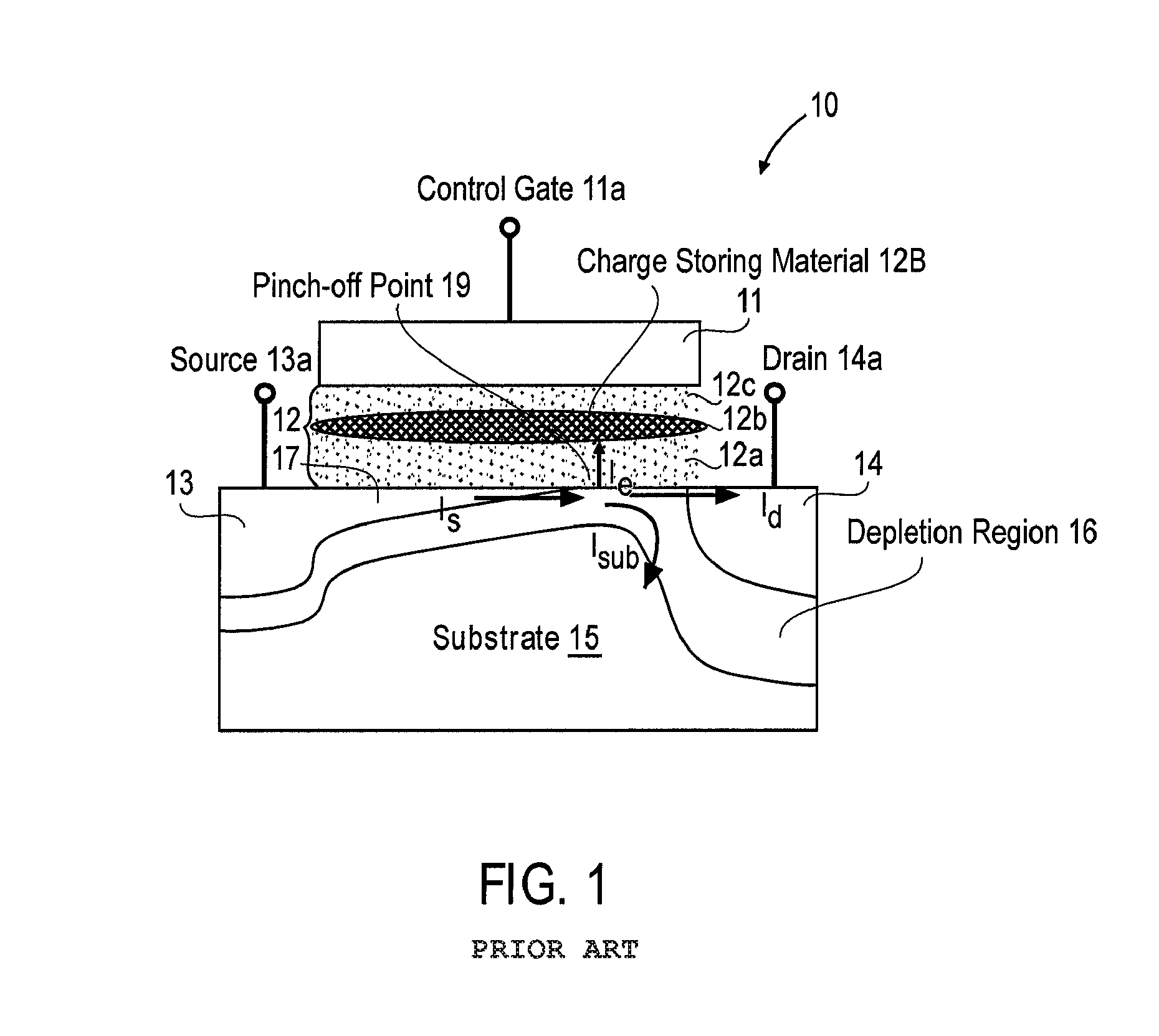

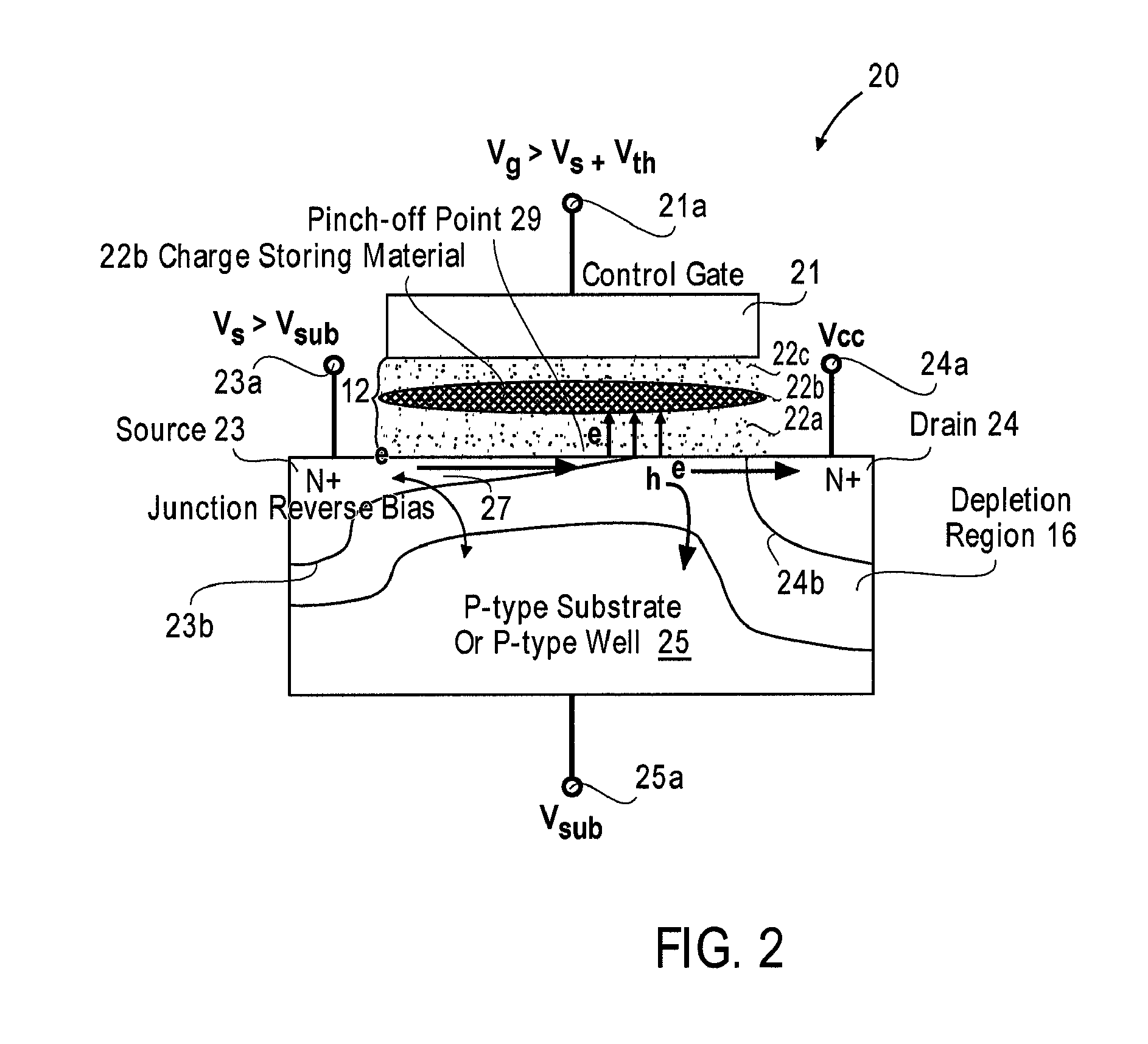

Methods and structures for highly efficient hot carrier injection programming for non-volatile memories

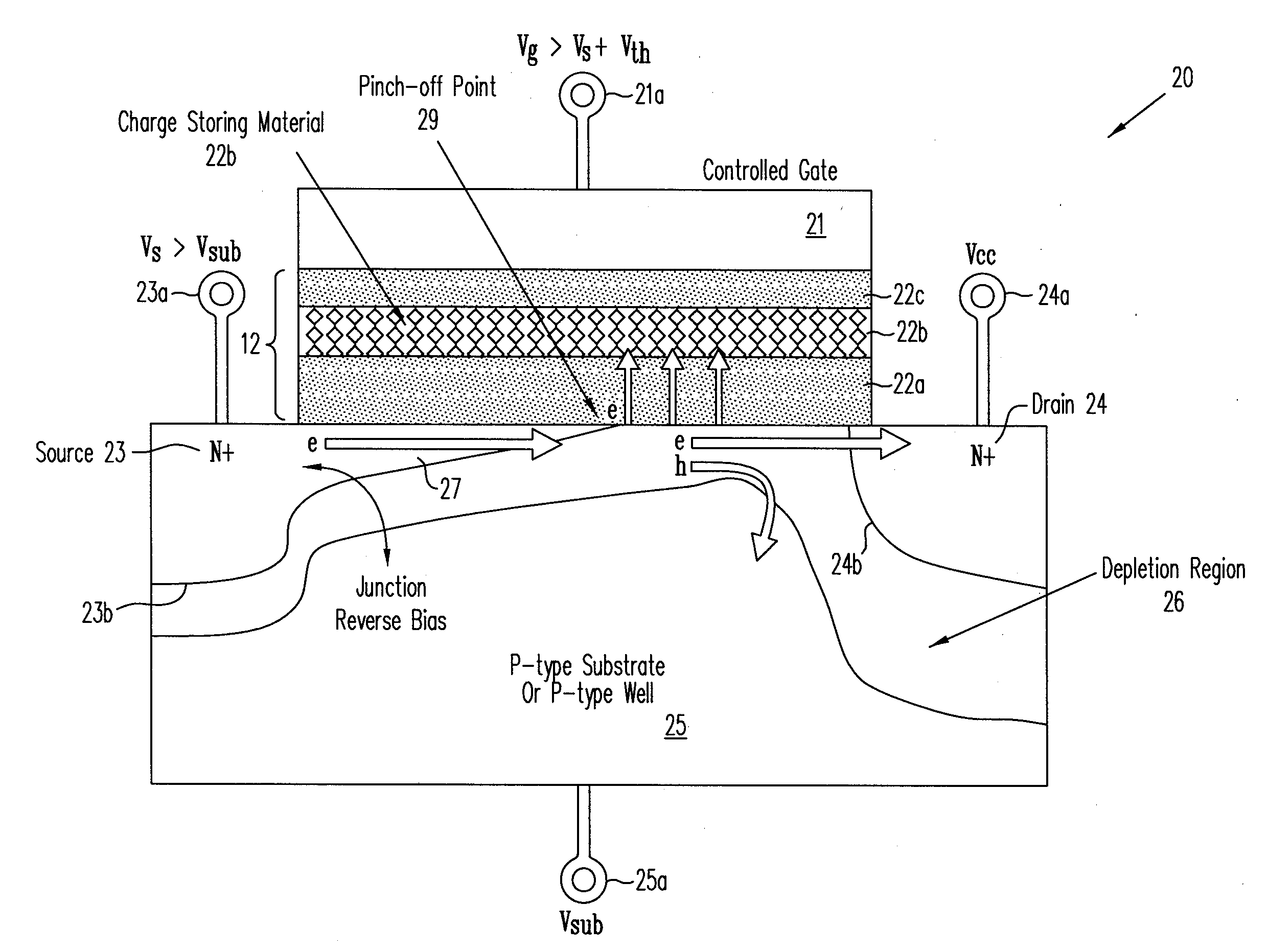

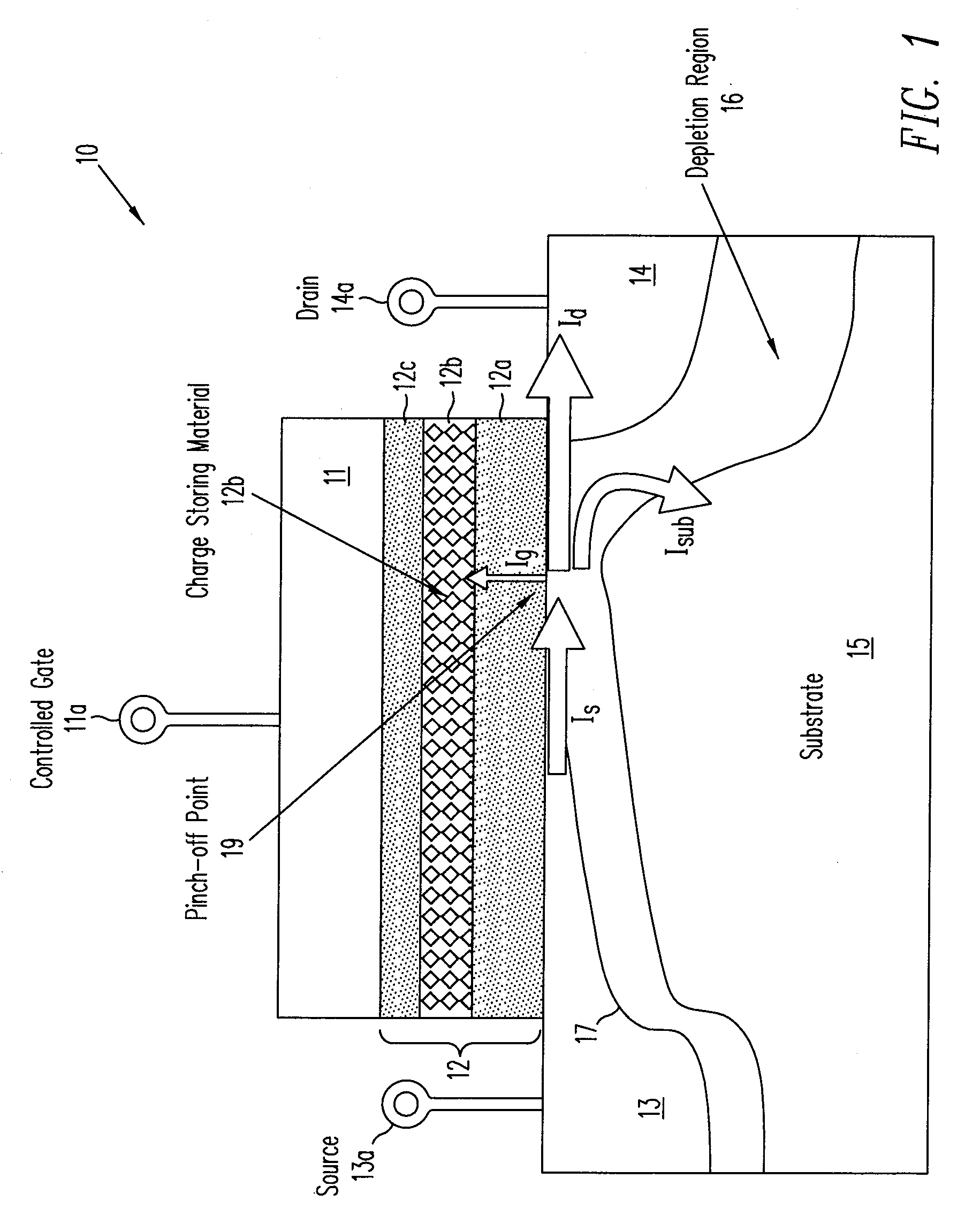

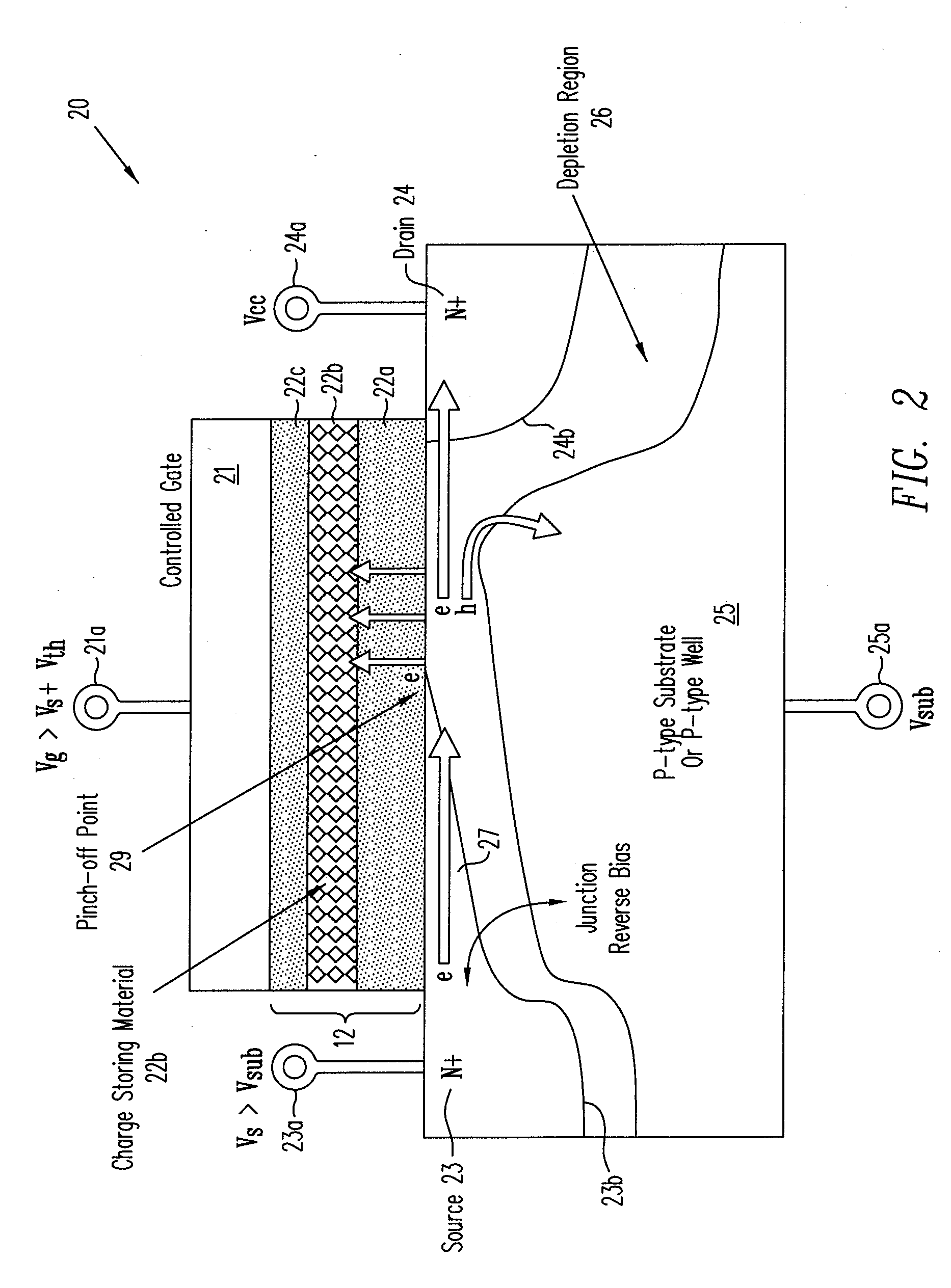

ActiveUS20090021984A1Improve programming efficiencyHigh injection rateRead-only memoriesDigital storageMOSFETVoltage amplitude

A metal oxide semiconductor field effect transistor (MOSFET) in a non-volatile memory cell has a source, a drain and a channel region between the source and the drain, all formed in a substrate of opposite conductivity type to the conductivity type of the source and drain. The MOSFET is programmed by connecting the drain electrode to the supply source of the main voltage, Vcc, provided to said non-volatile memory cell and supplying selected voltages to the source and substrate so as to invert a portion of the channel region extending from the source toward the drain. The inverted portion of the channel region ends at a pinch-off point before reaching the drain. By controlling the reverse bias across the PN junction between the source and the substrate, the pinch-off point of the inversion region is pulled back toward the source thereby to increase the programming efficiency of the MOSFET.Methods and structures for highly efficient Hot Carrier Injection (HCI) programming for Non-Volatile Memories (NVM) apply the main positive supply voltage Vcc to, the drain electrode of the NVM cell from the chip main voltage supply in contrast to the conventional method using a higher voltage than Vcc. The source electrode and substrate are reverse biased with a differential voltage relative to the drain, while a voltage pulse is applied to the control gate of the NVM cell to turn on the NVM cell for programming. To optimize the programming condition, the source voltage and the substrate voltage are then adjusted to achieve the maximum threshold voltage shifts under the same applied gate voltage pulse condition (i.e. using a gate pulse with the same voltage amplitude and duration regardless of the source voltage and the substrate voltage). The substrate voltage to the drain voltage can not exceed the avalanche multiplication junction breakdown for a small programming current during the bias voltage adjustment.

Owner:PEGASUS SEMICON SHANGHAI CO LTD

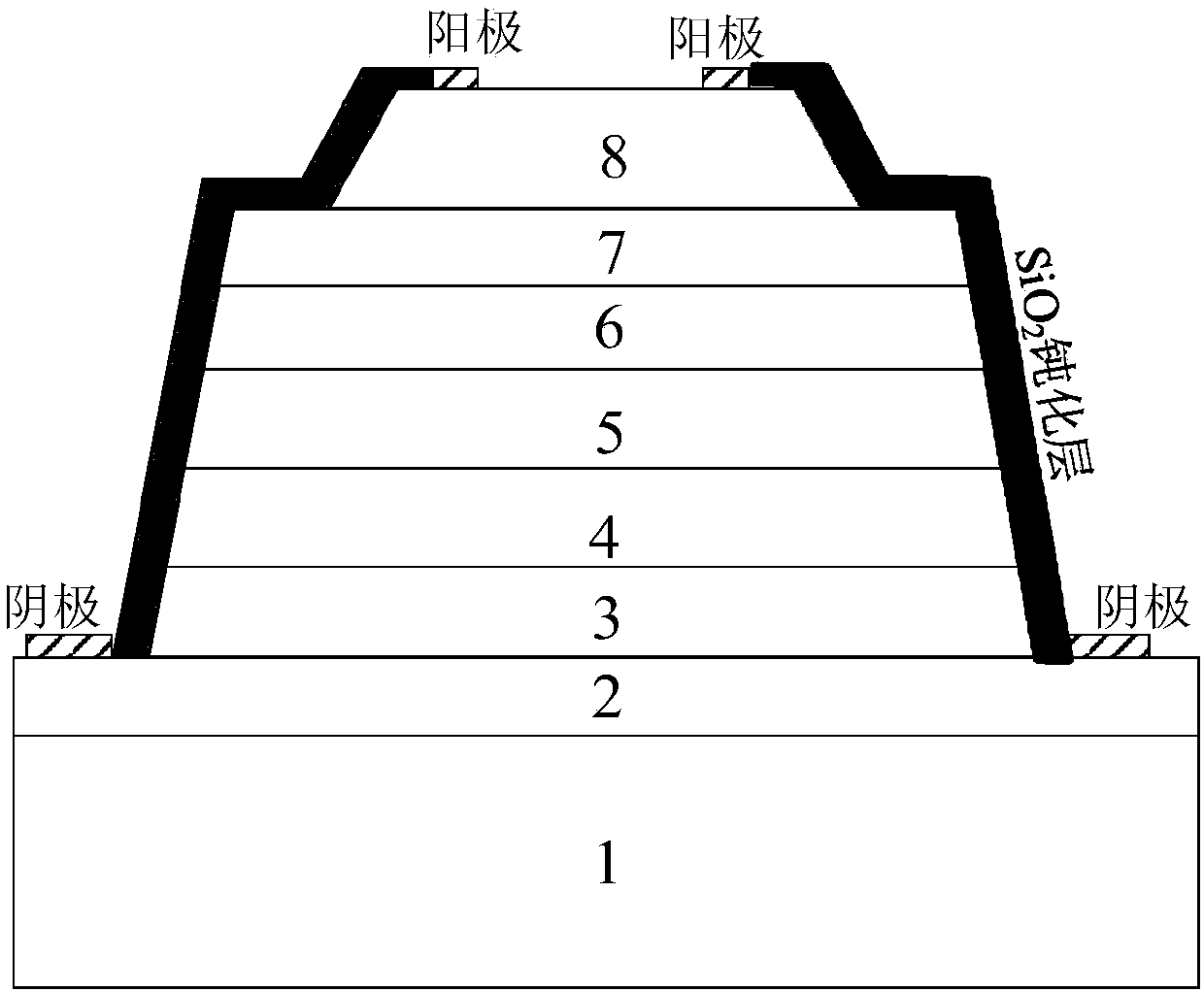

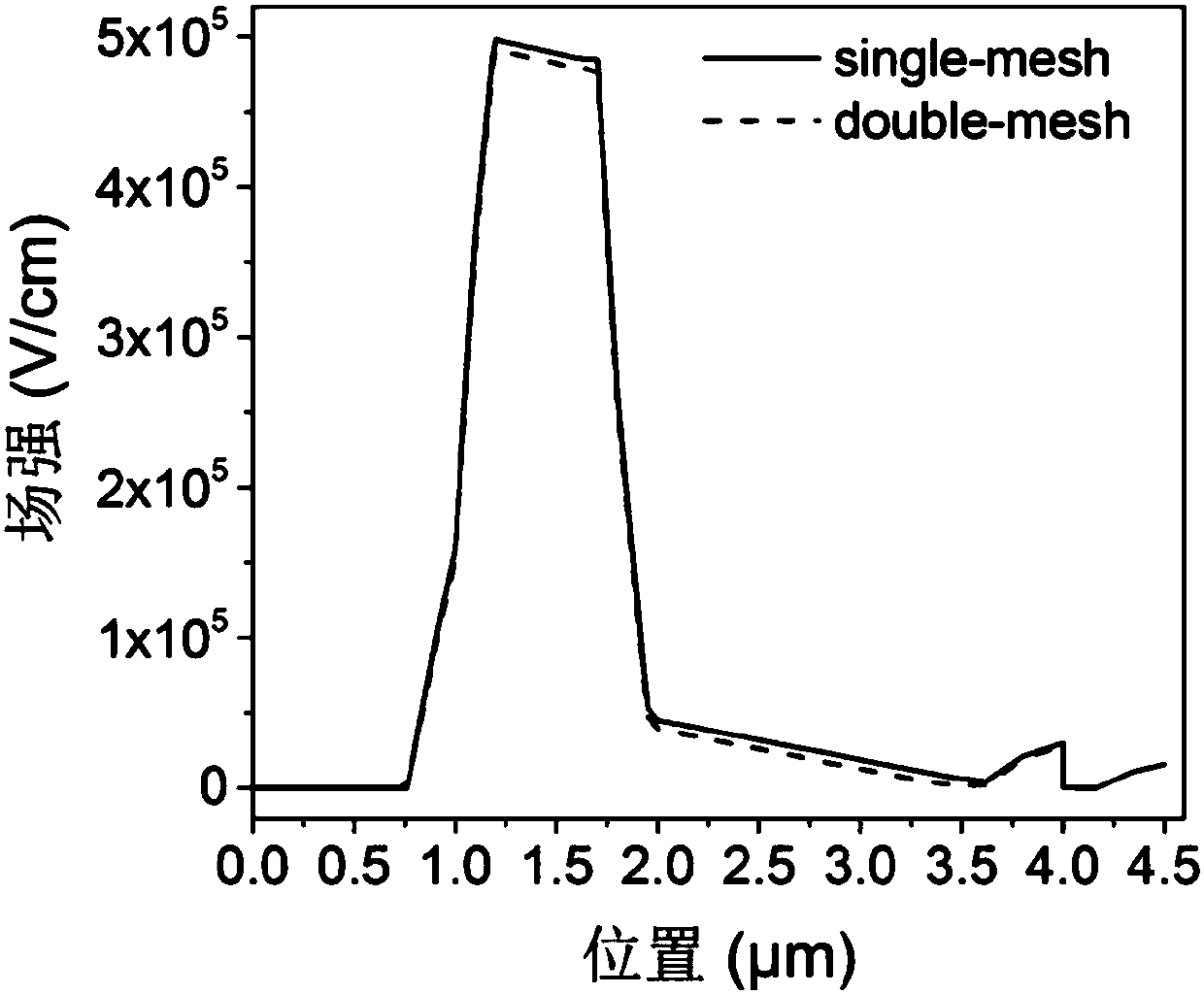

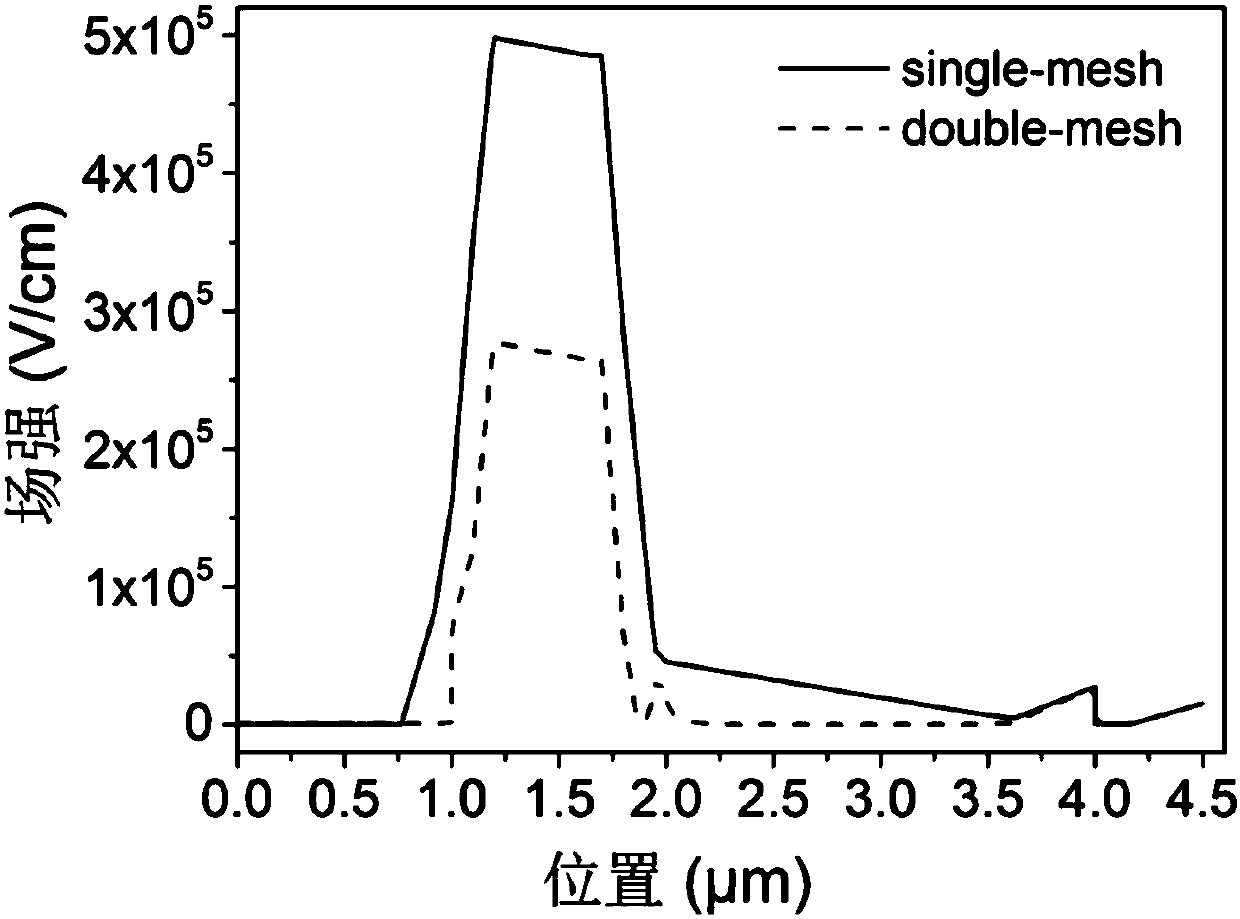

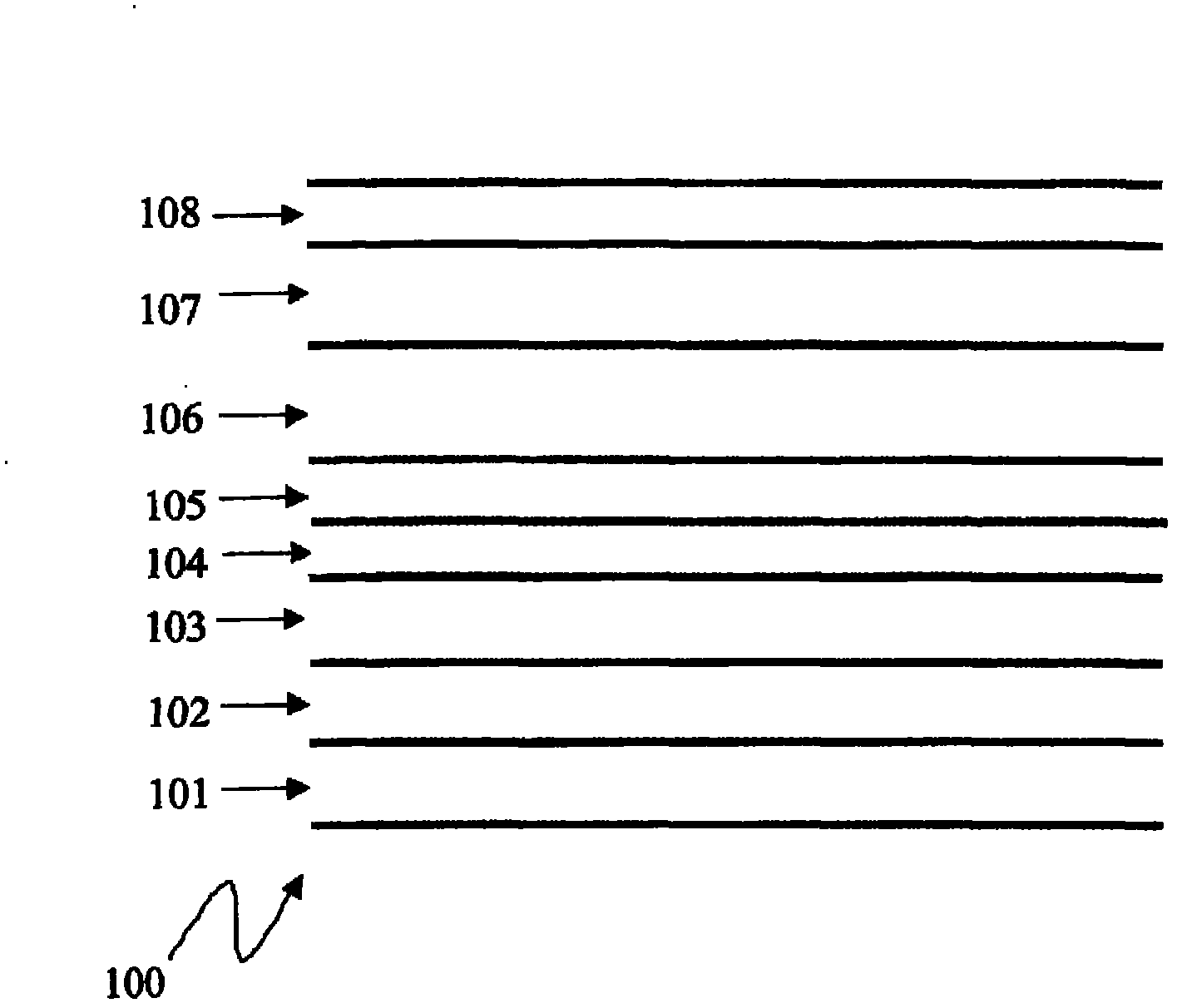

Two-stage table-top InGaAs/InP avalanche photodiode and preparation method thereof

InactiveCN107768462AReduce fringe electric fieldSuppresses edge breakdownSemiconductor devicesCharge layerContact layer

The invention belongs to the fields of photoelectric detection and image sensors, and in order to inhibit fringe field and reduce device dark current while guaranteeing a high field in the central area of the device, reference basis is provided for industrial application. The invention discloses a two-stage table-top InGaAs / InP avalanche photodiode and a preparation method thereof. The structure comprises an N<+>-InP substrate, an N-InP buffer layer, an N<->-InGaAs In0.53Ga0.47As absorbed layer, an N-InGaAsP In(1-x)GaxAsyP(1-y) component gradient layer, an N-InP charge layer, an i-InP multiplying layer, a P-InP field buffer layer and a P<+>-InP contact layer, wherein the P-InP field buffer layer forms a shallow table-top through etching, the N-InP buffer layer forms a deep table-top through etching, and constant impact ionization of photon-generated carriers inside the multiplying layer causes avalanche multiplication. The avalanche photodiode is mainly applied to the design occasionsof photoelectric detection and photoelectric sensors.

Owner:TIANJIN UNIV

A single-photon detector with a quantum dot and a nano-injector

ActiveUS20100123120A1Increase ratingsImprove concentrationDiodeSuperconductor devicesCapacitancePhotodetector

A semiconductor photodetector for photon detection without the use of avalanche multiplication, and capable of operating at low bias voltage and without excess noise. In one embodiment, the photodetector comprises a plurality of InP / AlInGaAs / AlGaAsSb layers, capable of spatially separating the electron and the hole of an photo-generated electron-hole pair in one layer, transporting one of the electron and the hole of the photo-generated electron-hole pair into another layer, focalizing it into a desired volume and trapping it therein, the desired volume having a dimension in a scale of nanometers to reduce its capacitance and increase the change of potential for a trapped carrier, and a nano-injector, capable of injecting carriers into the plurality of InP / AlInGaAs / AlGaAsSb layers, where the carrier transit time in the nano-injector is much shorter than the carrier recombination time therein, thereby causing a very large carrier recycling effect.

Owner:NORTHWESTERN UNIV

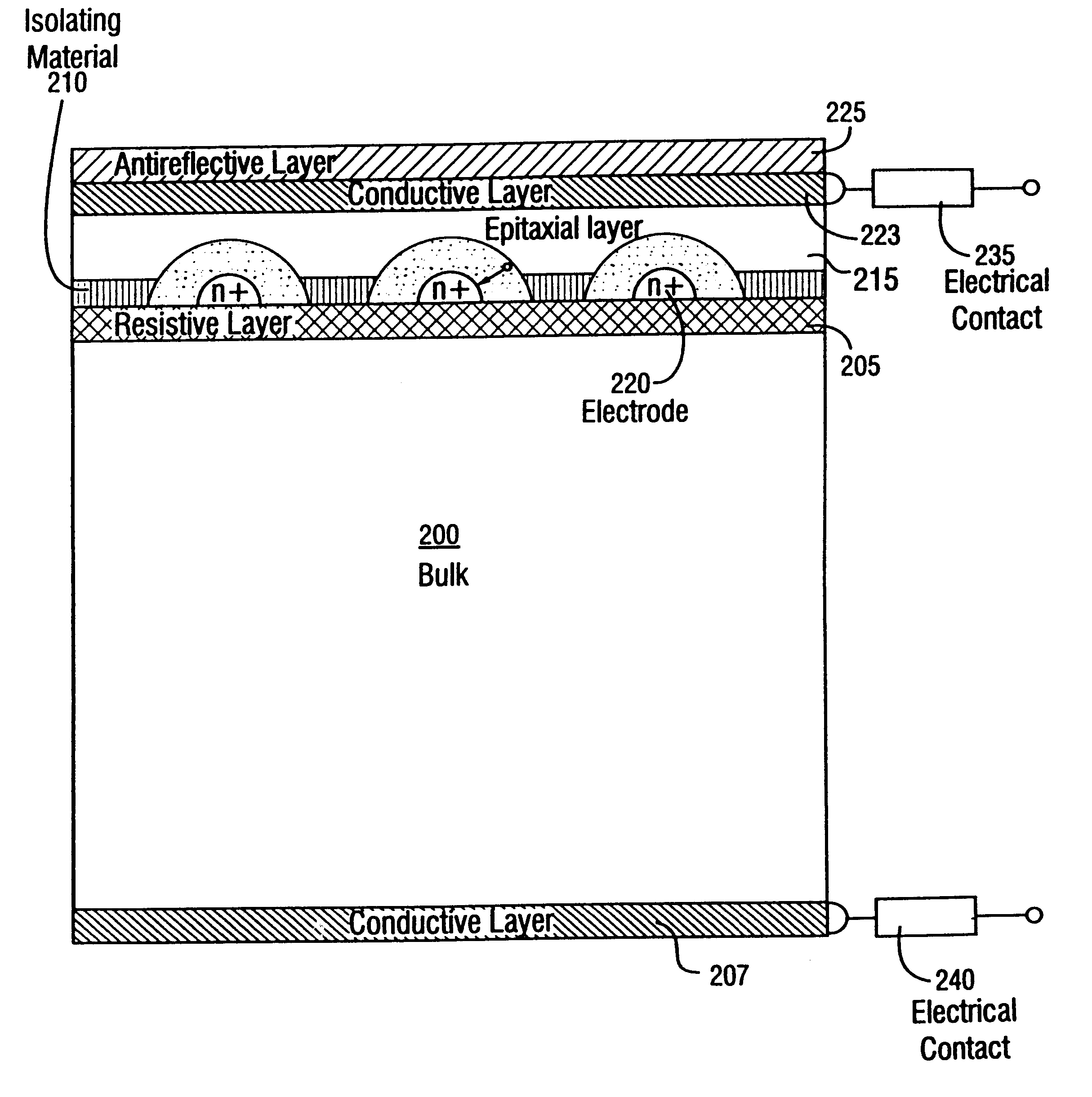

Wide wavelength range high efficiency avalanche light detector with negative feedback

A novel use of a solid state light detector with a low impedance substrate is described. Light that enters the substrate after traversing the antireflective layer creates an electron-hole pair. The electrons are collected in a crystalline epitaxial layer that spans the space charge region, or depletion layer. A high electric field accelerates free electrons inside the depletion region. The electrons collide with the lattice to free more holes and electrons resulting from the presence of an n-p junction, or diode. The diode is formed by placing the crystalline layer which has positive doping in close proximity with the electrodes which have negative doping. The continual generation of charge carriers results in avalanche multiplication with a large multiplication coefficient. During the avalanche process, electrons can be collected enabling light detection. A resistive layer is used to quench, or stop, the avalanche process.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

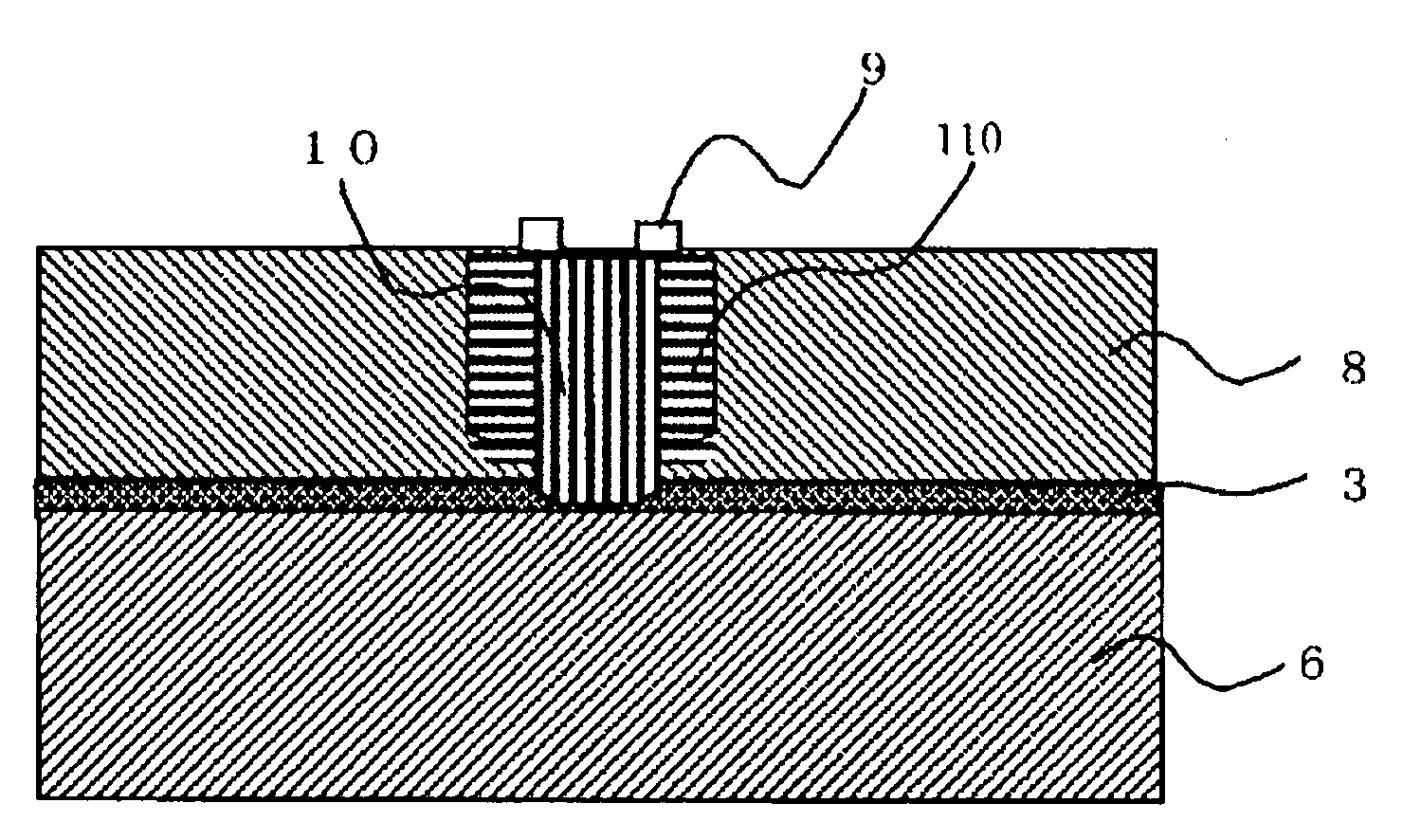

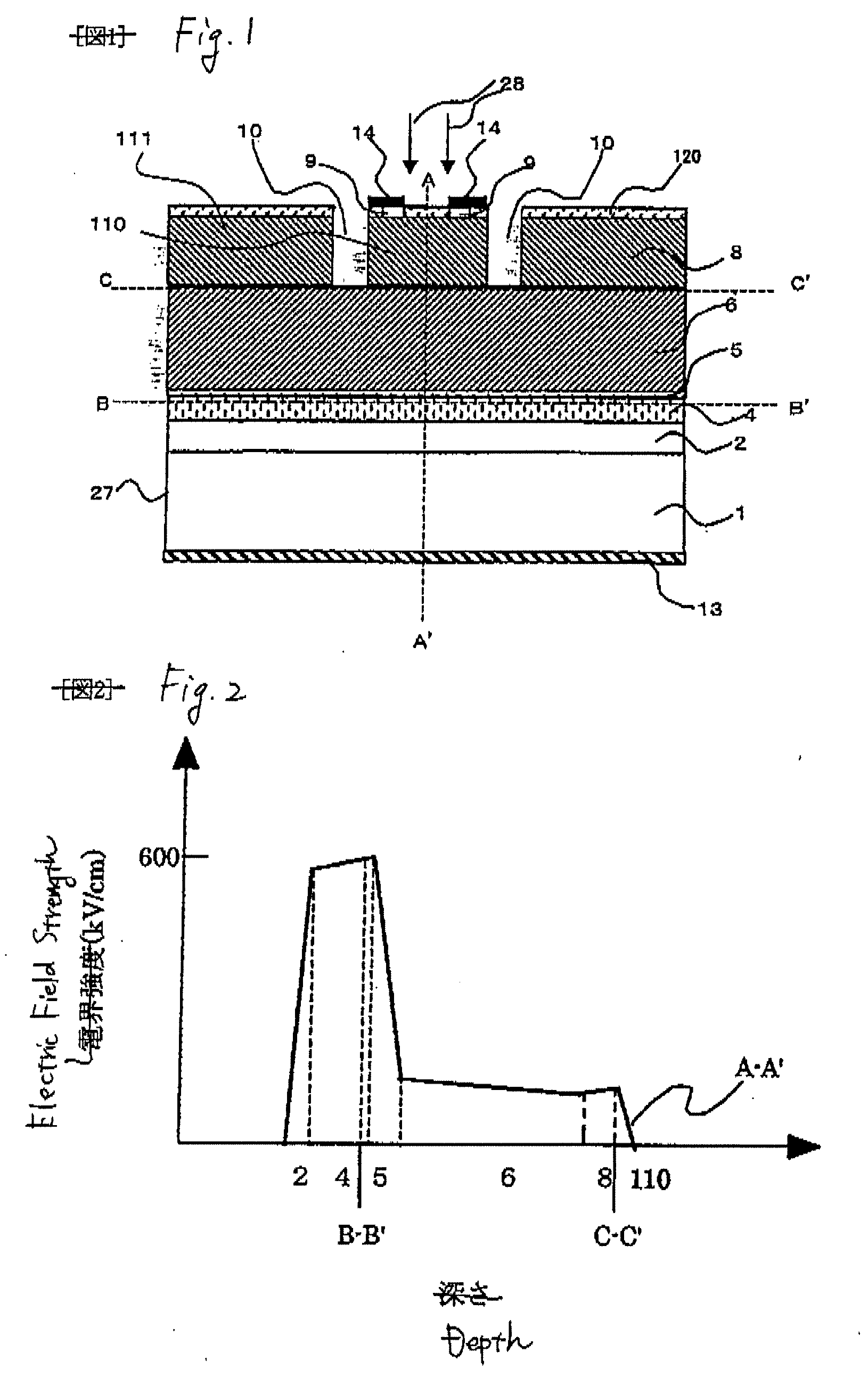

Avalanche Photodiode

ActiveUS20080121867A1Simple processEnsure reliabilityPhotovoltaic energy generationSemiconductor devicesElectrical conductorSemiconductor package

In an avalanche photodiode provided with a substrate including a first electrode and a first semiconductor layer, formed of a first conductivity type, which is connected to the first electrode, the configuration is in such a way that, at least an avalanche multiplication layer, a light absorption layer, and a second semiconductor layer having a bandgap that is larger than that of the light absorption layer are layered on the substrate; a second conductivity type conductive region is formed in the second semiconductor layer; and the second conductivity type conductive region is arranged so as to be connected to a second electrode. With the foregoing configuration, an avalanche photodiode having a small dark current and a high long-term reliability can be provided with a simple process.Additionally, the configuration is in such a way that, by removing at least the light absorption layer among the layers which are layered on the peripheral portion, of the substrate, on which the second conductivity type conductive region and the second semiconductor layer around the second conductivity type conductive region are surrounded by that layers, a side face of the light absorption layer is formed. With the configuration, the dark current can be further reduced.

Owner:MITSUBISHI ELECTRIC CORP

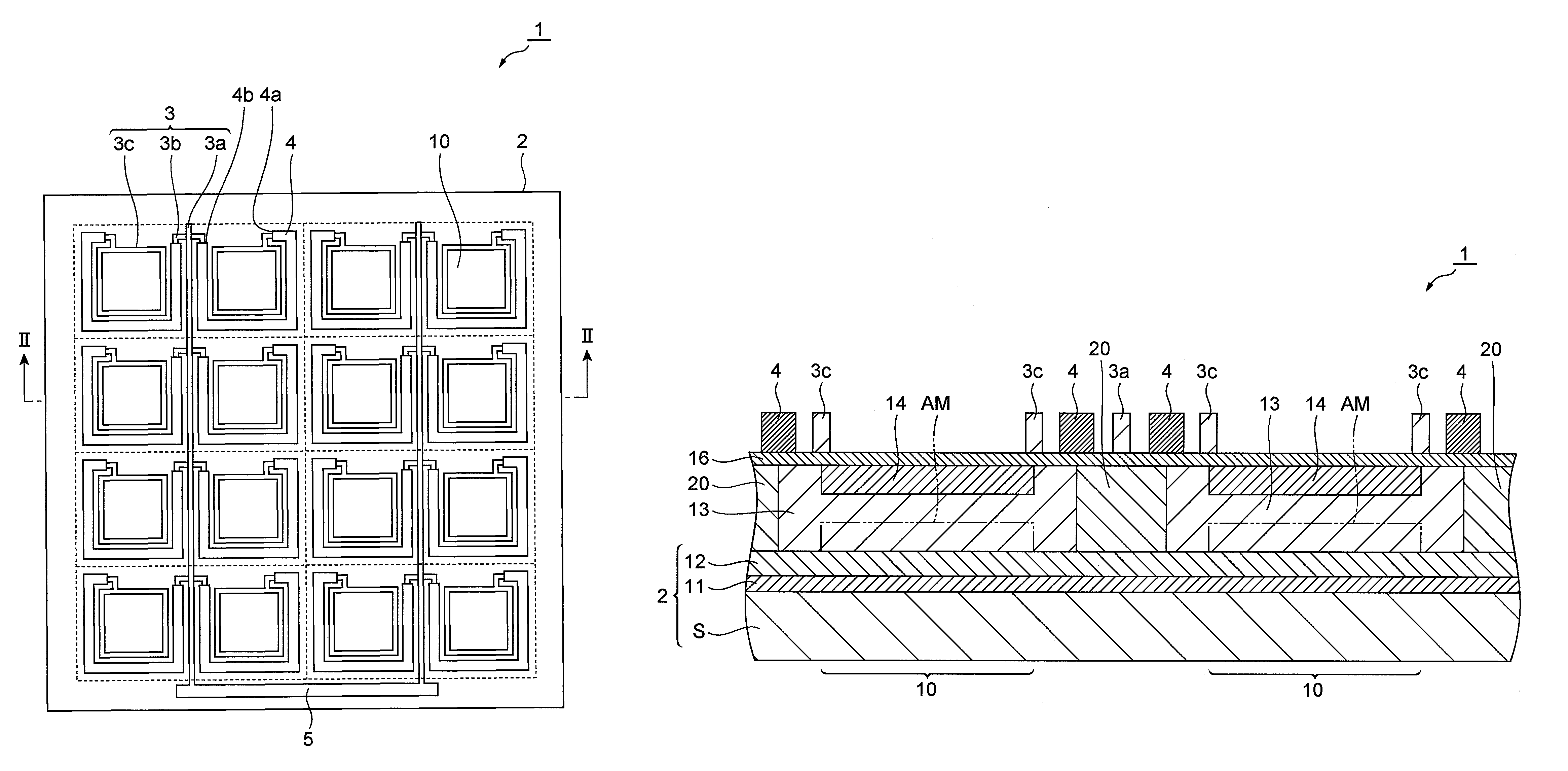

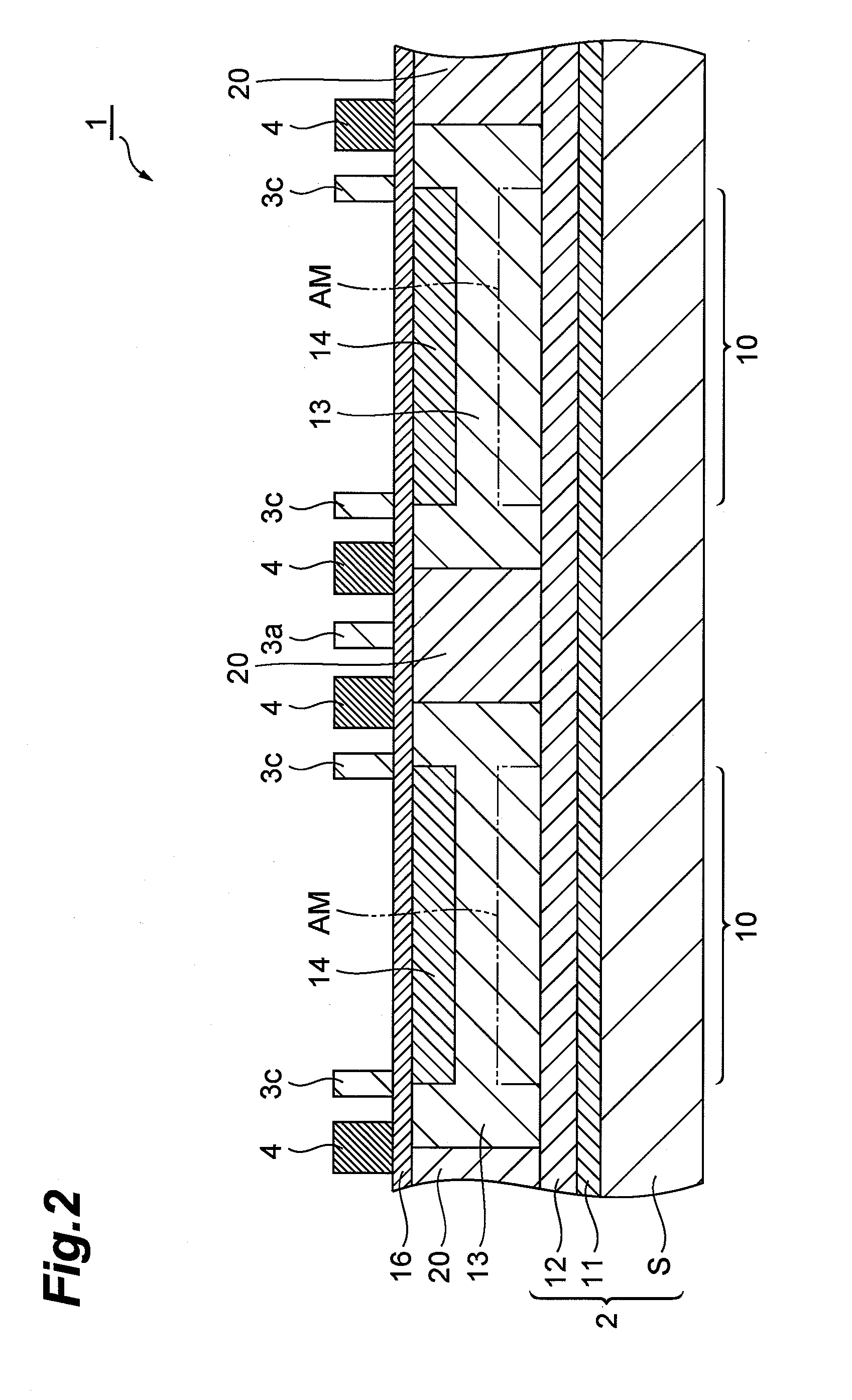

Photodiode array

ActiveUS8008741B2Improve detection efficiencyRaise the ratioSolid-state devicesRadiation controlled devicesPhotovoltaic detectorsPhotodetector

A photodiode array 1 has a plurality of photodetector channels 10 which are formed on an n-type substrate 2 having an n-type semiconductor layer 12, with a light to be detected being incident to the plurality of photodetector channels 10. The photodiode array 1 comprises: a p−-type semiconductor layer 13 formed on the n-type semiconductor layer 12 of the substrate 2; resistors 4 each of which is provided to each of the photodetector channels 10 and is connected to a signal conductor 3 at one end thereof; and an n-type separating part 20 formed between the plurality of photodetector channels 10. The p−-type semiconductor layer 13 forms a pn junction at the interface between the substrate 2, and comprises a plurality of multiplication regions AM for avalanche multiplication of carriers produced by the incidence of the light to be detected so that each of the multiplication regions corresponds to each of the photodetector channels. The separating part 20 is formed so that each of the multiplication regions AM of the p−-type semiconductor layer 13 corresponds to each of the photodetector channels 10.

Owner:HAMAMATSU PHOTONICS KK

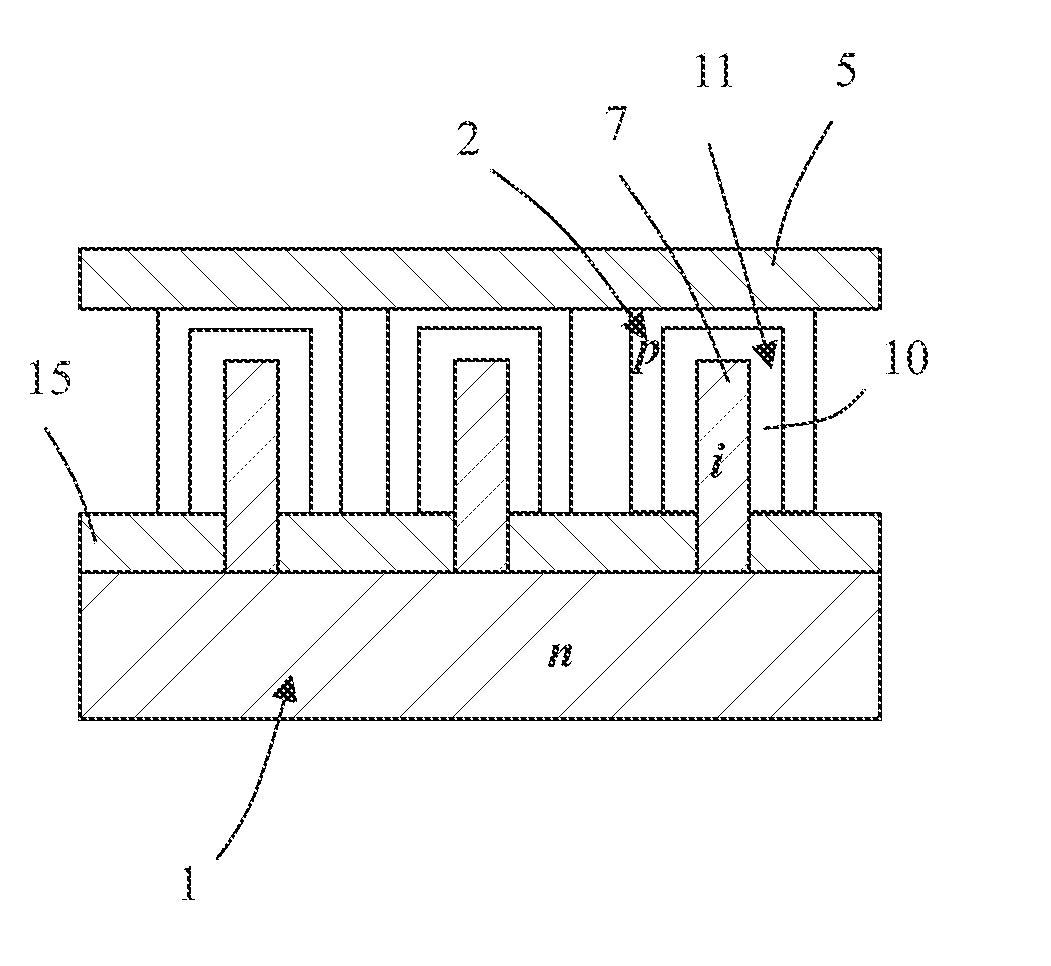

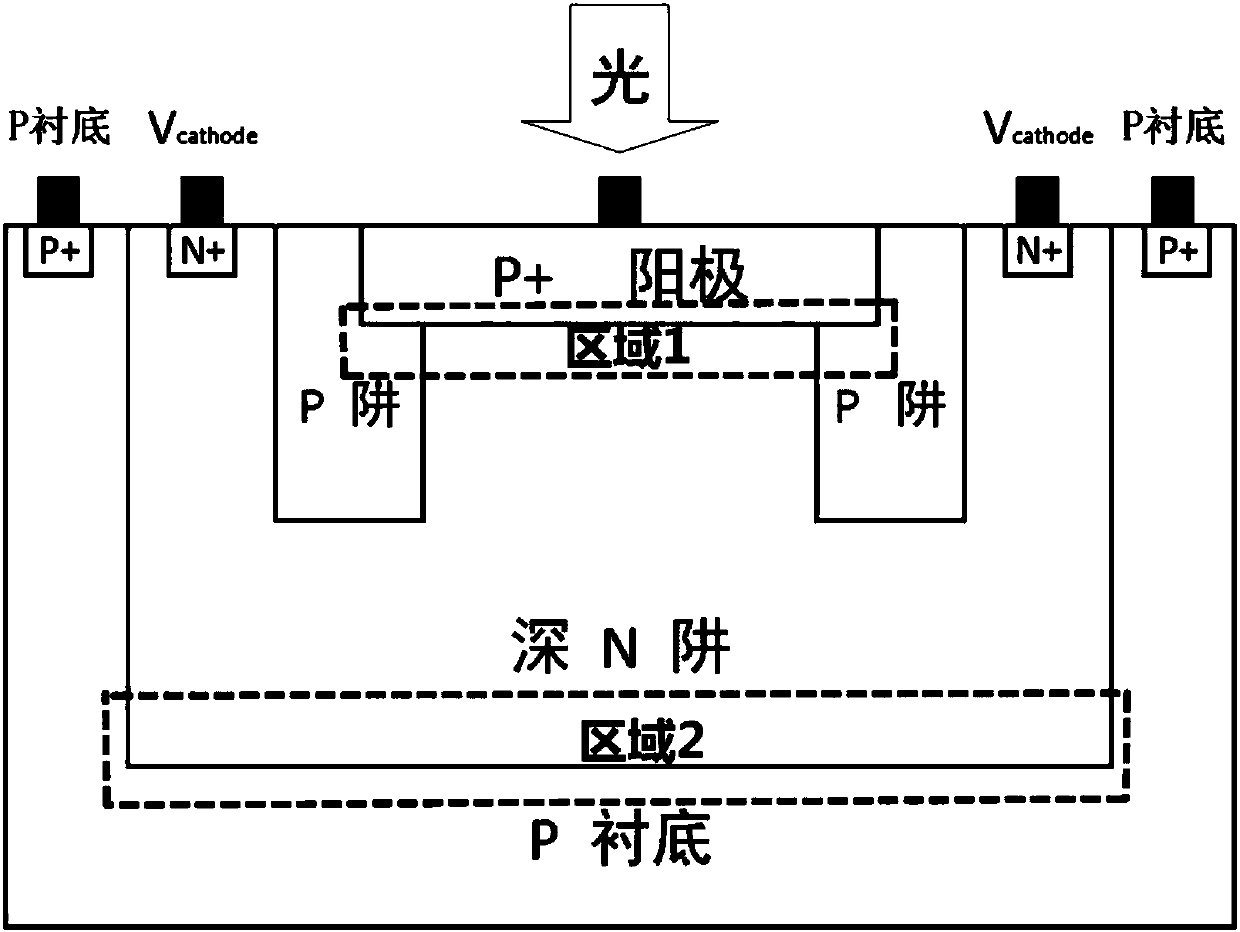

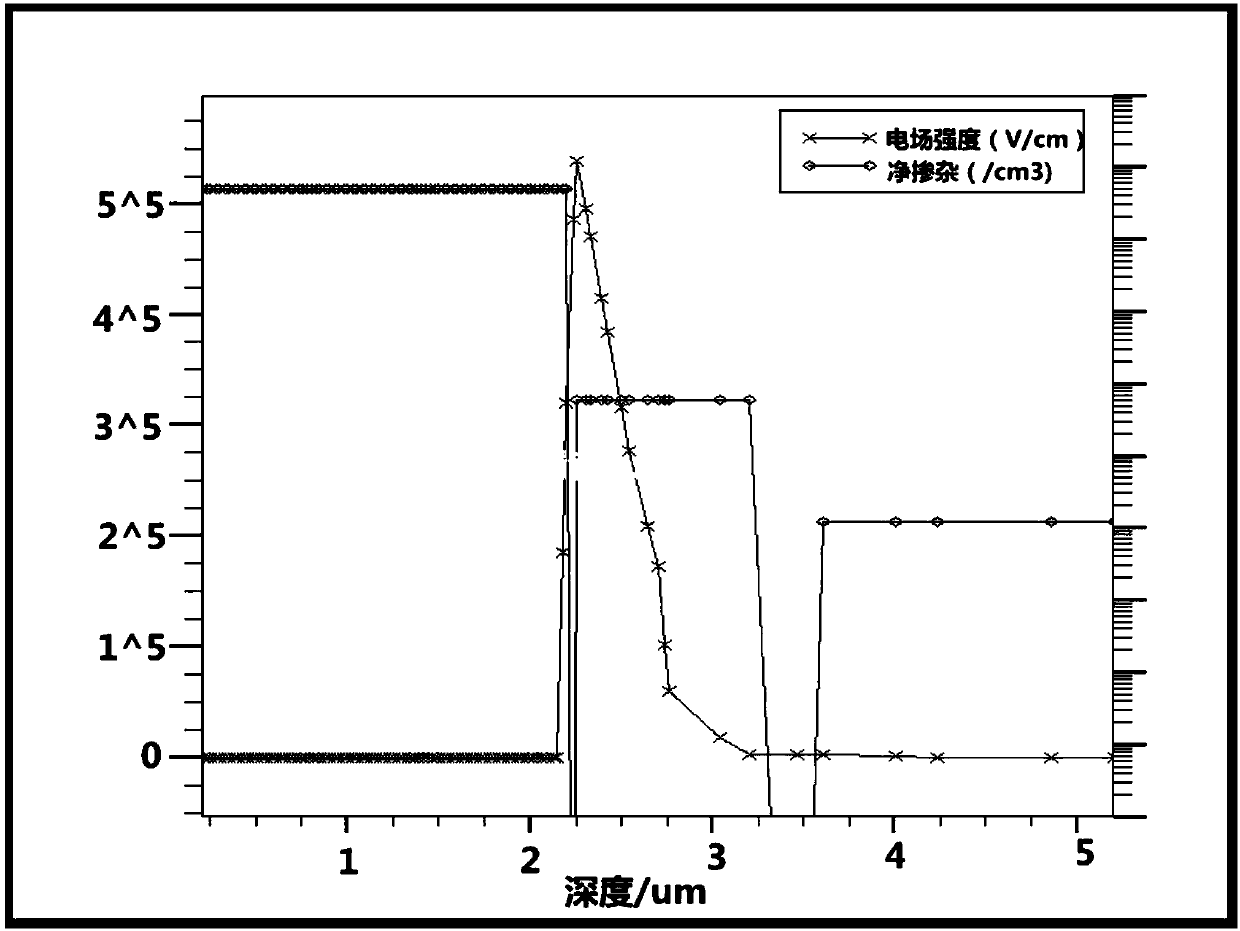

CMOS single-photon avalanche diode specific to long-wave-band weak light

InactiveCN107946389AHigh sensitivityQuick responseFinal product manufactureSemiconductor devicesElectron avalanchePhoton

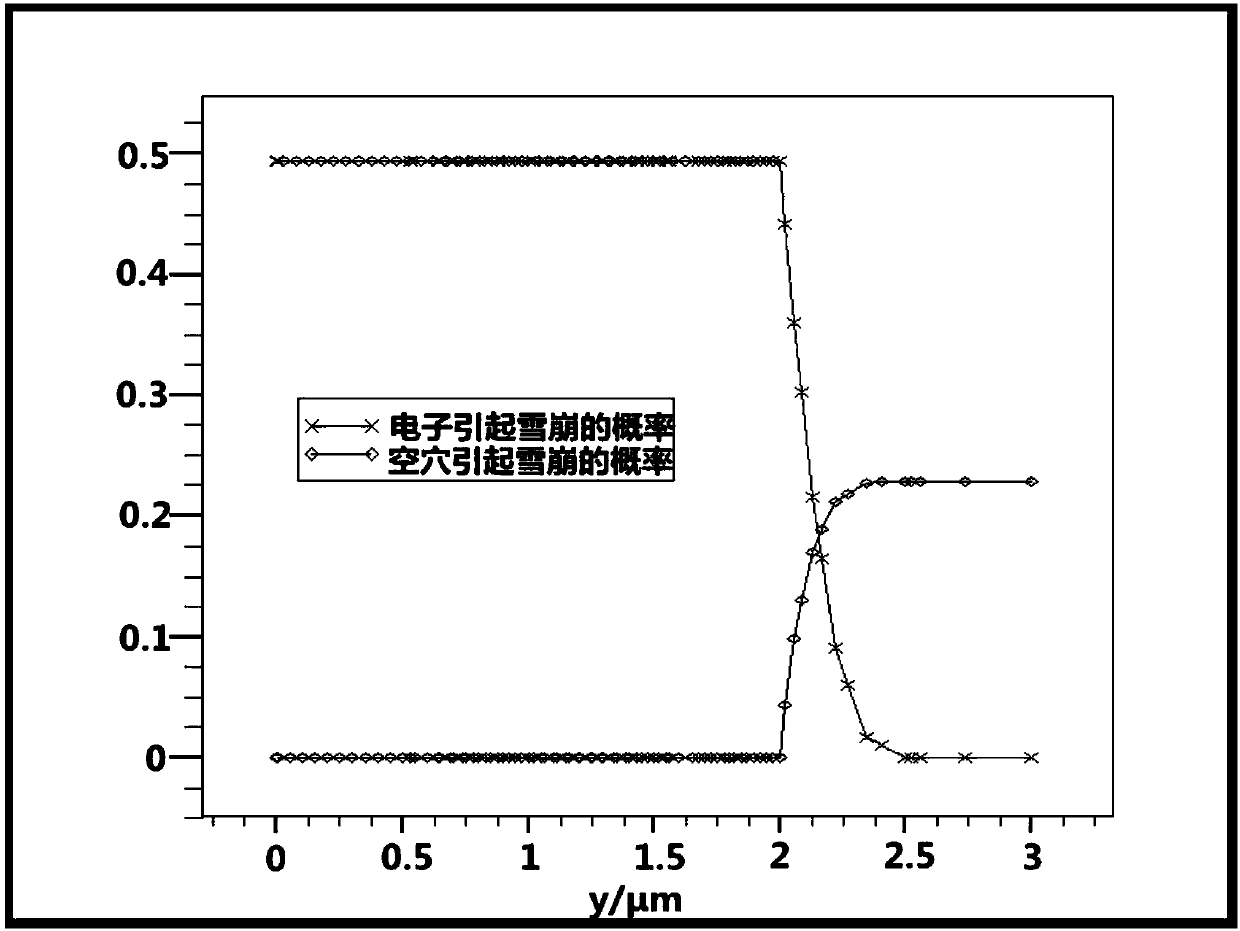

The invention provides a CMOS single-photon avalanche diode specific to long-wave-band weak light. According to the specific structure, a deep N well is manufactured on a P type substrate; next, a P type heavily doped region is manufactured in the deep N well; a PN junction is formed by a P+ layer and the deep N well to be used as an avalanche multiplication region; the P+ region is surrounded bya lightly doped P well to be used as a protection ring; and after incident light comes to a device, the deep N well region in a medium electric field strength is absorbed, and the generated photon-generated carriers move towards an avalanche multiplication region of a strong electric field region. Electron holes generated by light of relatively long waveband are formed in a relatively deep position of the device, so that the light signals can be detected effectively by the deep N well; by taking the deep N well / P substrate as a shielding diode, diffusion of the substrate photon-generated carriers to the PN junction can be prevented, thereby reducing influence of diffusion of substrate slow photon-generated carriers to the response speed of a photoelectric detector; and the absorption efficiency of the device in a long waveband can be improved.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

Avalanche Photo Diode

InactiveUS20080191240A1Reduce dark currentImprove long-term reliabilityFinal product manufacturePhotovoltaic energy generationElectrical conductorElectron avalanche

An avalanche photodiode including a first electrode; and a substrate including a first semiconductor layer of a first conduction type electrically connected to the first electrode, in which at least an avalanche multiplication layer, a light absorption layer, and a second semiconductor layer of a second conduction type with a larger band gap than the light absorption layer are deposited on the substrate. The second semiconductor layer is separated into inner and outer regions by a groove formed therein, the inner region electrically connected to a second. With the configuration, the avalanche photodiode has a low dark current and high long-term reliability. In addition, the outer region includes an outer trench, and at least the light absorption layer is removed by the outer trench to form a side face of the light absorption layer. With the configuration, the dark current can be further reduced.

Owner:MITSUBISHI ELECTRIC CORP

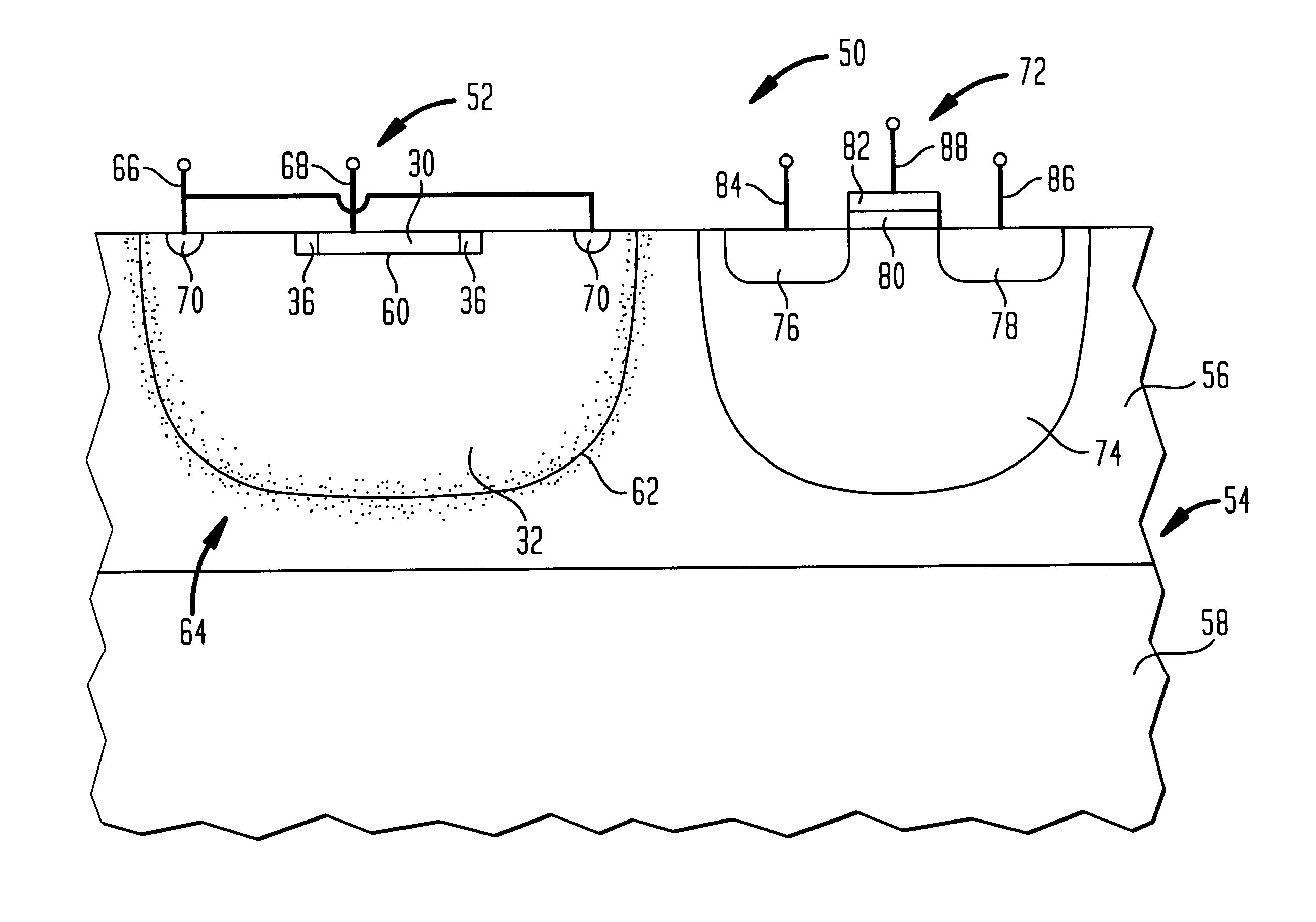

Integrated optoelectronic device with an avalanche photodetector and method of making the same using commercial CMOS processes

InactiveUS6359293B1Reduce manufacturing costAdded complexityTransistorSolid-state devicesMOSFETPhotodetector

An integrated optoelectronic circuit chip for optical data communication systems includes a silicon substrate, at least one MOS field effect transistor (MOSFET) formed on a portion of the silicon substrate, and an avalanche photodetector operatively responsive to an incident optical signal and formed on another portion of the substrate. The avalanche photodetector includes a light absorbing region extending from a top surface of the silicon substrate to a depth h and doped to a first conductivity type. The light absorbing region is ionizable by the incident optical signal to form freed charge carriers in the light absorbing region. A light responsive region is formed in the light absorbing region and extends from the top surface of the silicon substrate to a depth of less than h. The light responsive region is doped to a second conductivity type of opposite polarity to the first conductivity type. The light absorbing region and the light responsive region form a P-N junction at the interface therebetween such that when the light absorbing and light responsive regions are appropriately reverse biased, the freed charge carriers in the light absorbing region are amplified by avalanche multiplication.

Owner:LUCENT TECH INC

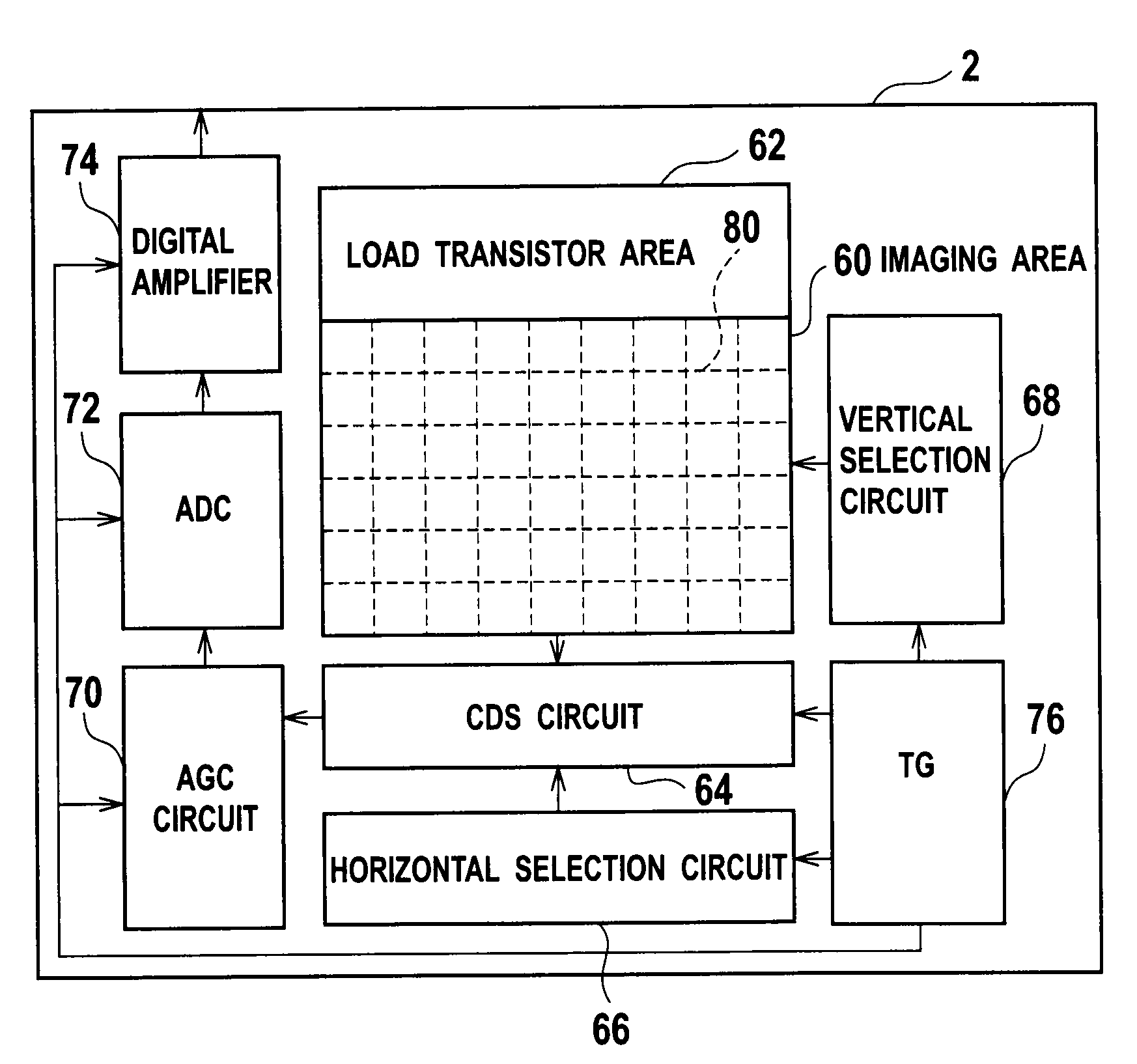

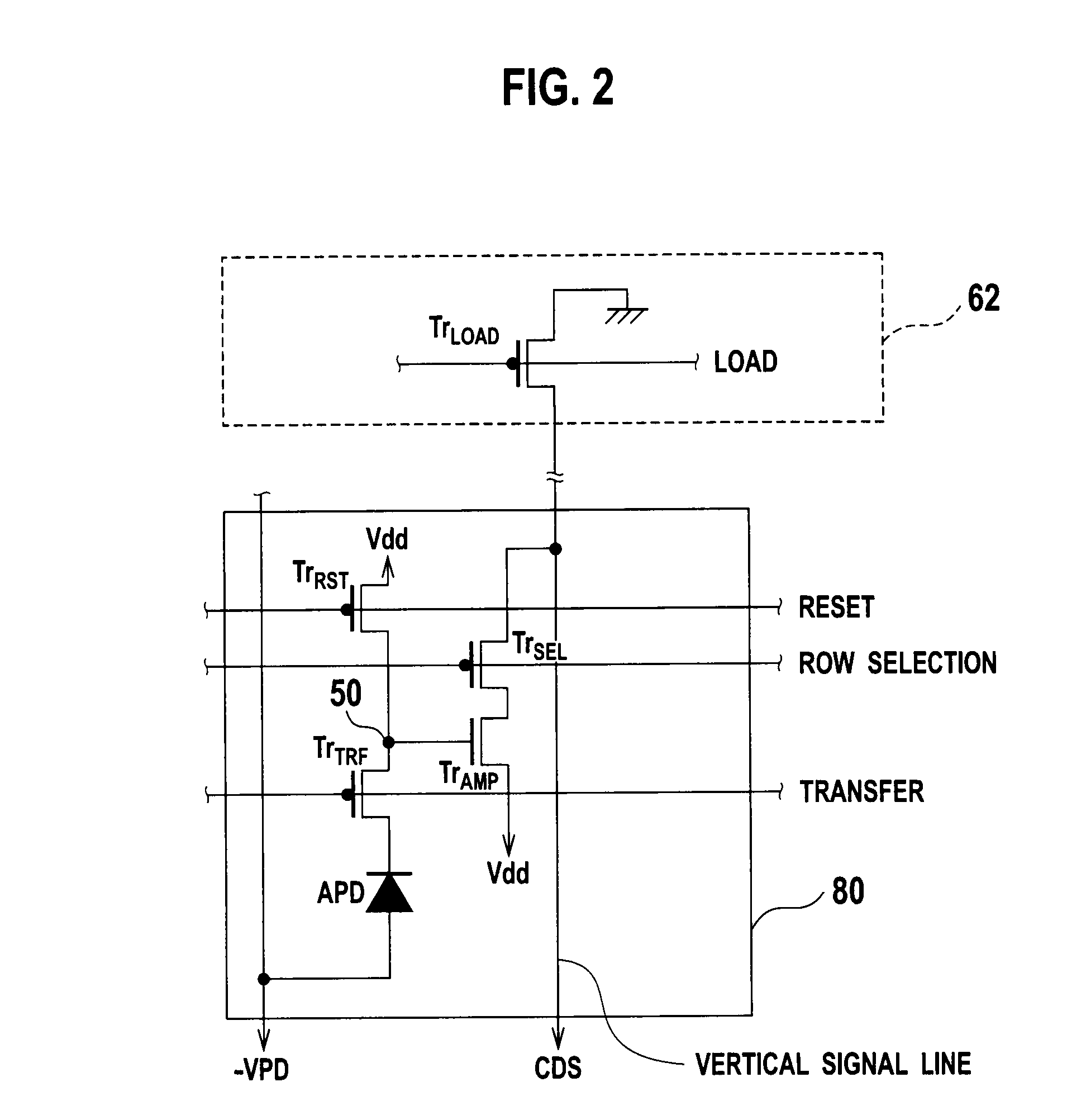

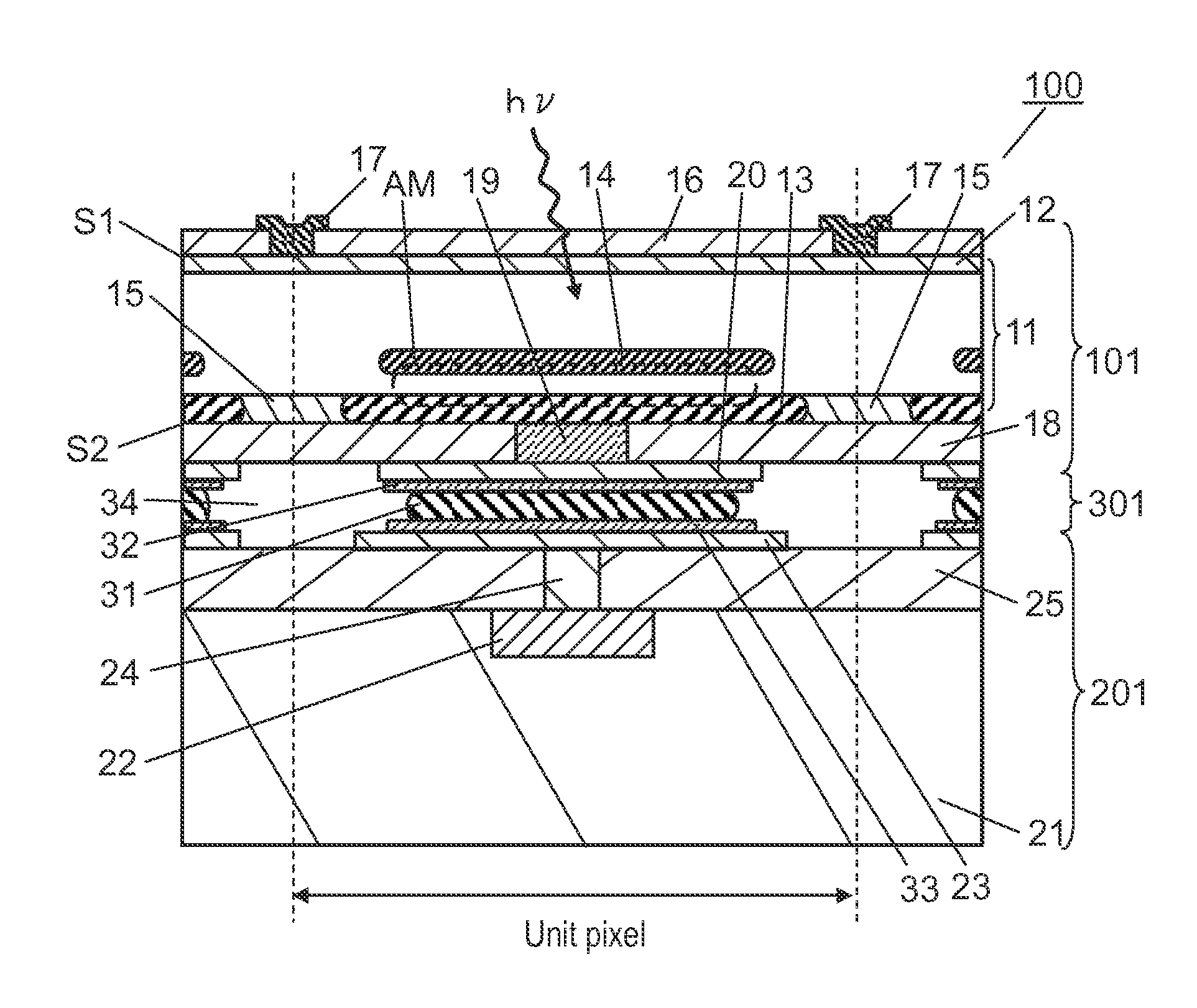

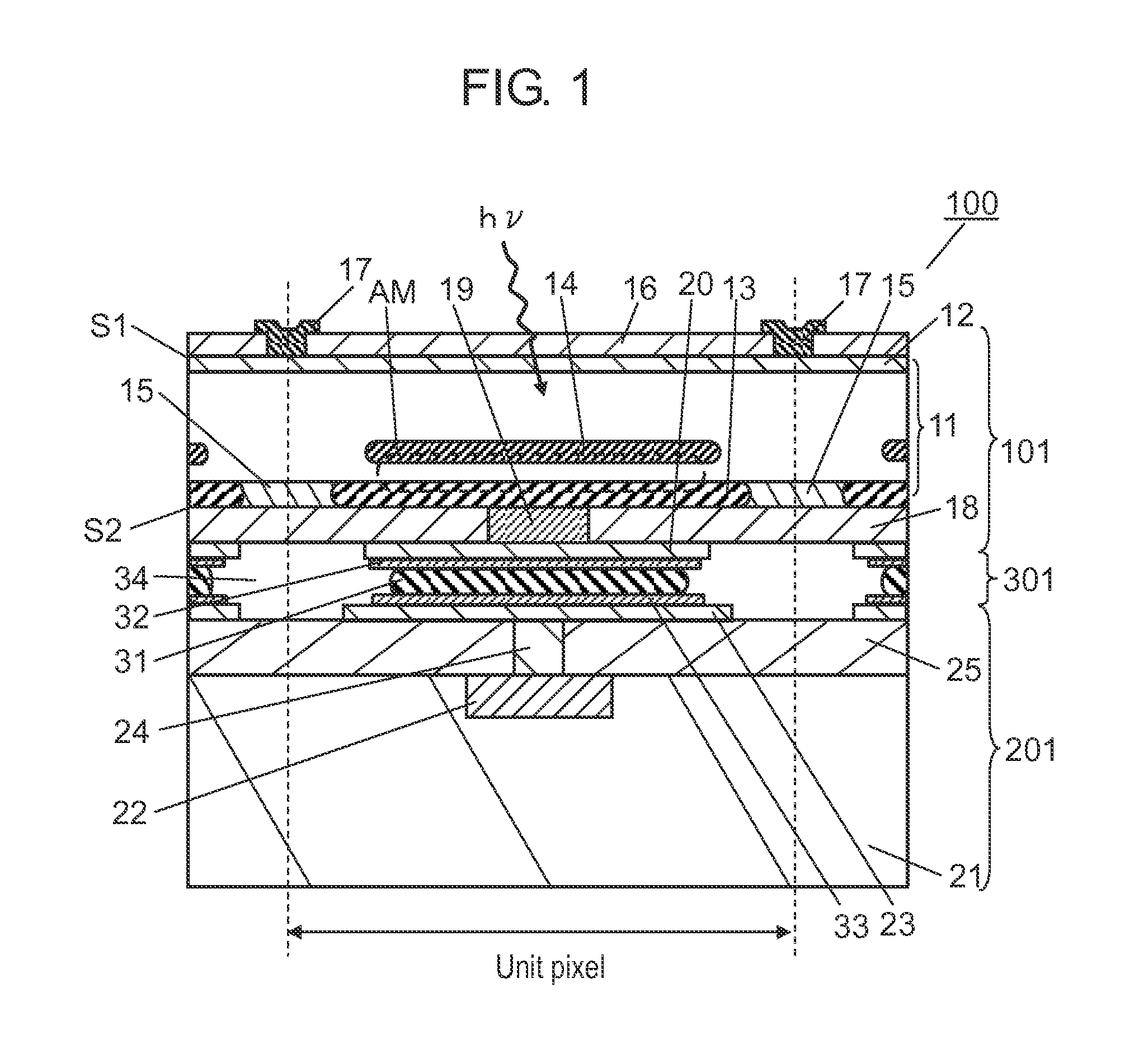

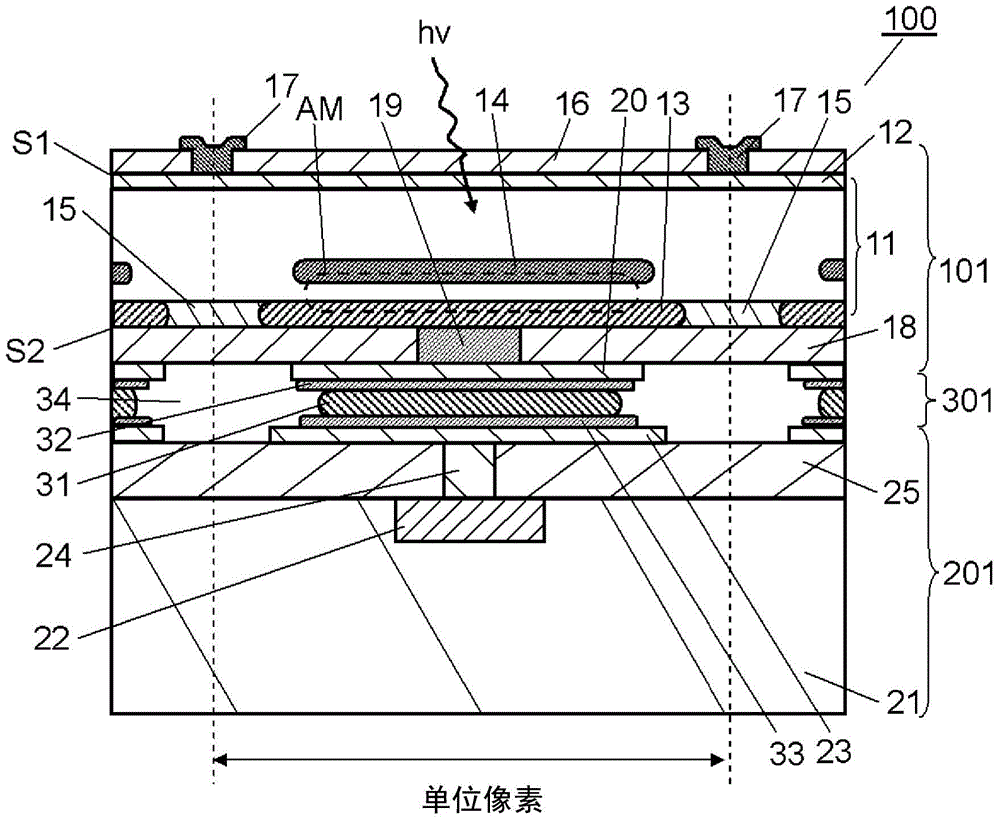

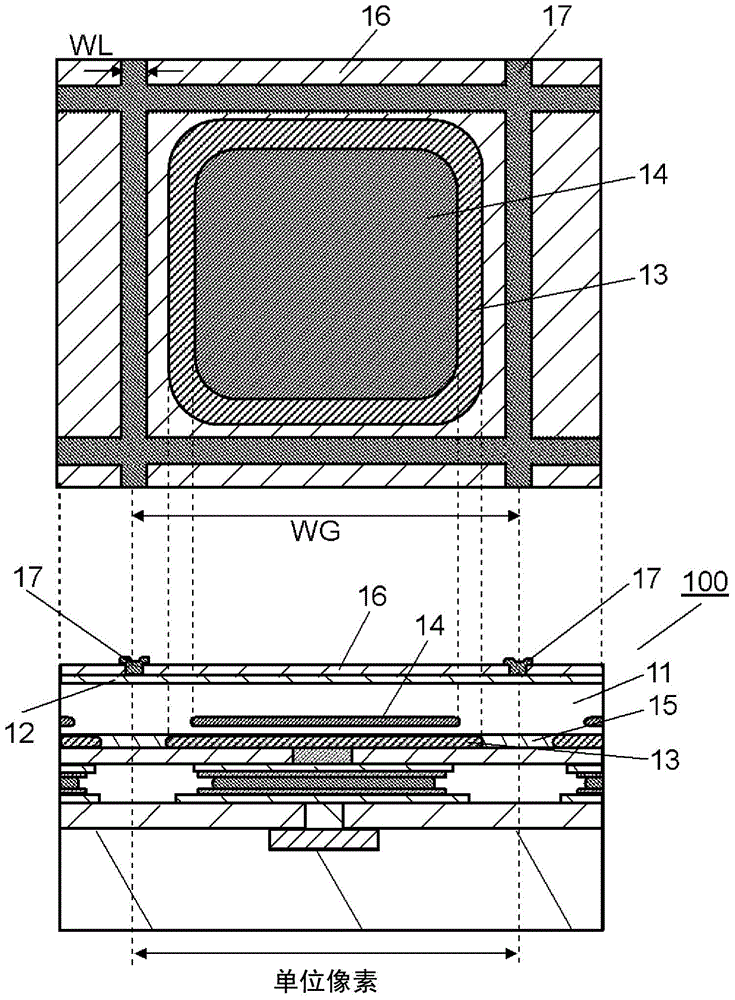

Image sensor, single-plate color image sensor, and electronic device

InactiveUS20080231738A1Decrease of change of spectralDecrease of sensitivity of spectral sensitivityTelevision system detailsTelevision system scanning detailsColor imageSingle plate

An image sensor includes an imaging area including a plurality of cells arrayed in a matrix on a semiconductor substrate, each of the cells including an avalanche photodiode, the avalanche photodiode including: an anode region buried in an upper portion of the semiconductor substrate; a cathode region buried in the upper portion of the semiconductor substrate separated from the anode region in a direction parallel to the surface of the semiconductor substrate; and an avalanche multiplication region defined between the anode and cathode regions, the avalanche multiplication region having an impurity concentration less than the anode and cathode regions; wherein depths of the anode and cathode regions from the surface of the semiconductor substrate are different from each other.

Owner:KK TOSHIBA

Wavelength conversion device with avalanche multiplier

InactiveUS7079307B2Efficient detectionImprove performanceTelevision system detailsLaser detailsPhotodetectorLength wave

A wavelength conversion device includes a photodetector for generating a photocurrent in response to the detection of radiation at a first wavelength. An avalanche multiplier amplifies the signal photocurrent and feeds this to a light emitting element that produces radiation at a second wavelength shorter than the first wavelength and corresponding to the detected radiation at the first wavelength. The components are assembled together in an integrated stacked arrangement either by epitaxial growth or wafer fusion of the individual components. The device is useful as an image intensifier or thermal imaging device.

Owner:NAT RES COUNCIL OF CANADA

Avalanche photodiode and manufacturing method thereof

ActiveCN104465853AImprove signal-to-noise ratioReduce dark currentSemiconductor devicesEtchingSignal-to-noise ratio (imaging)

The invention discloses an avalanche photodiode and a manufacturing method of the avalanche photodiode. The avalanche photodiode comprises a buffering layer at least having epitaxial growth on a substrate, an N-type ohmic contact layer, a light absorption layer, an avalanche multiplication and a P-type ohmic contact layer. The light absorption layer is made of superlattices of an InAs layer and a GaSb layer which are different in thickness and can adsorb infrared from a short wave to a long wave, meanwhile, dark current can be reduced by AlGaAsSb, the device is manufactured through mesa etching, passivation and metal evaporation, the device can respond to the infrared from the short wave to the long wave and provide certain gain, and therefore the signal-to-noise ratio of a detector can be increased.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

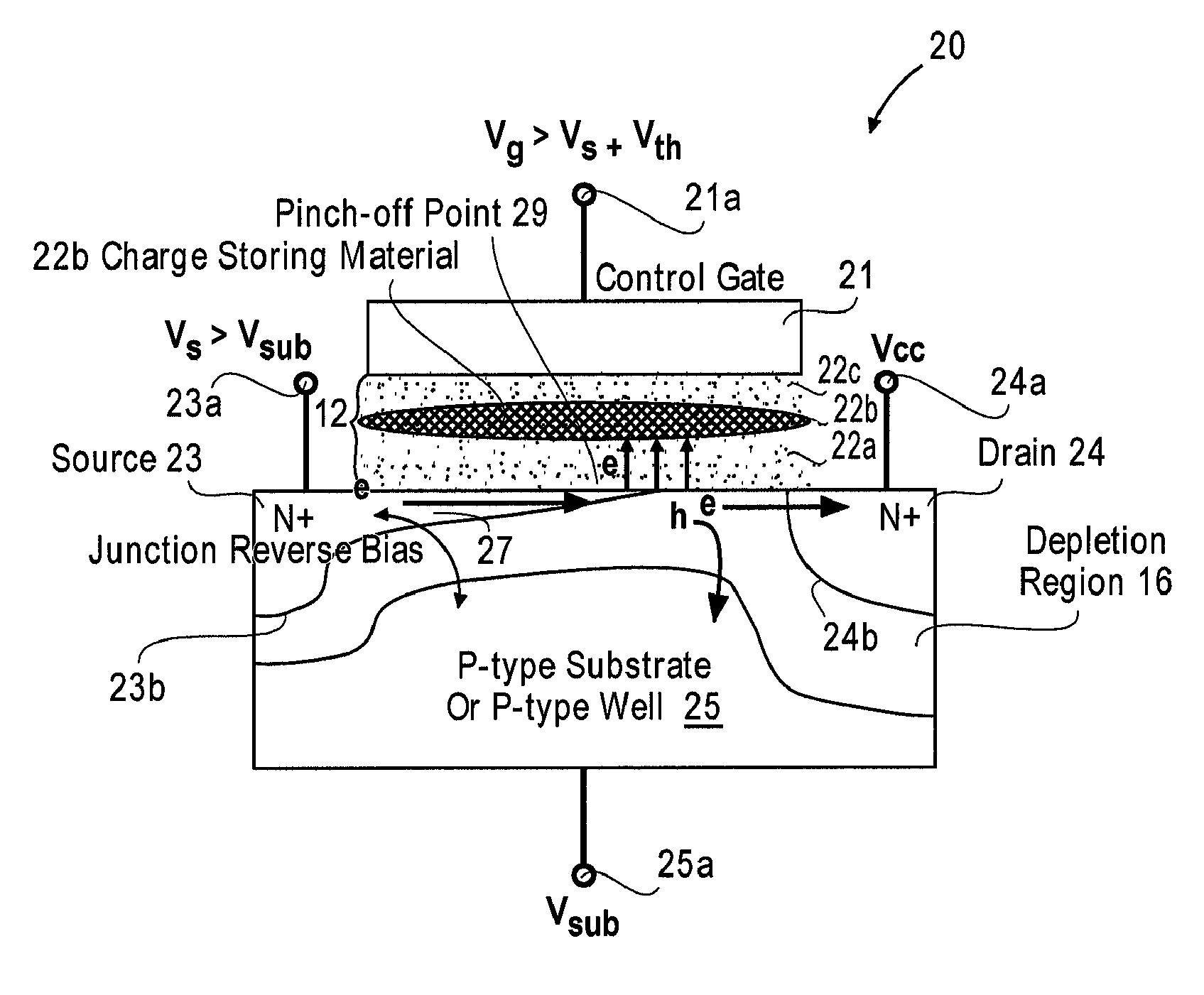

Method and structures for highly efficient hot carrier injection programming for non-volatile memories

ActiveUS7733700B2High rateReduce voltage dropRead-only memoriesDigital storageMOSFETVoltage amplitude

A method programs a memory cell by controlling a reverse bias voltage across the PN junction between a source electrode of a MOSFET in the memory cell and the substrate, and pulling back the pinch-off point of the inversion region toward the source electrode, thereby increasing the programming efficiency of the memory cell. The method applies the main positive supply voltage Vcc to, the drain electrode of the memory cell from the chip main voltage supply, rather than the conventional method of using a higher voltage than Vcc. To optimize the programming condition, the source voltage and the substrate voltage are adjusted to achieve the maximum threshold voltage shifts under the same applied gate voltage pulse condition (i.e. using the gate pulse with the same voltage amplitude and duration regardless of the source voltage and the substrate voltage). The substrate voltage to the drain voltage can not exceed the avalanche multiplication junction breakdown for a small programming current during the bias voltage adjustment.

Owner:PEGASUS SEMICON SHANGHAI CO LTD

Single-photon detector with a quantum dot and a nano-injector

ActiveUS7745816B2Increase ratingsImprove concentrationDiodeSuperconductor devicesCapacitancePhoton detection

A semiconductor photodetector for photon detection without the use of avalanche multiplication, and capable of operating at low bias voltage and without excess noise. In one embodiment, the photodetector comprises a plurality of InP / AlInGaAs / AlGaAsSb layers, capable of spatially separating the electron and the hole of an photo-generated electron-hole pair in one layer, transporting one of the electron and the hole of the photo-generated electron-hole pair into another layer, focalizing it into a desired volume and trapping it therein, the desired volume having a dimension in a scale of nanometers to reduce its capacitance and increase the change of potential for a trapped carrier, and a nano-injector, capable of injecting carriers into the plurality of InP / AlInGaAs / AlGaAsSb layers, where the carrier transit time in the nano-injector is much shorter than the carrier recombination time therein, thereby causing a very large carrier recycling effect.

Owner:NORTHWESTERN UNIV

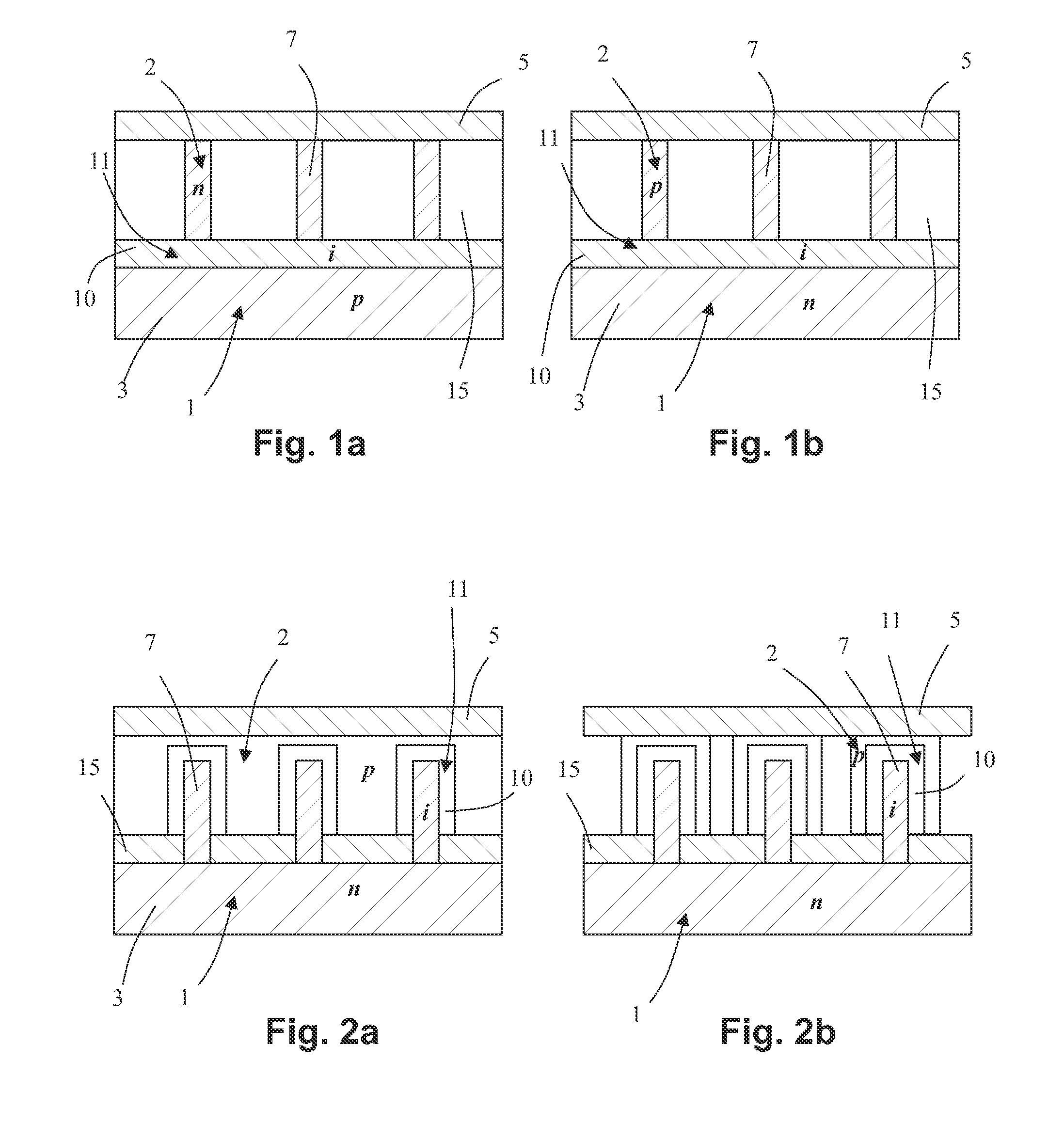

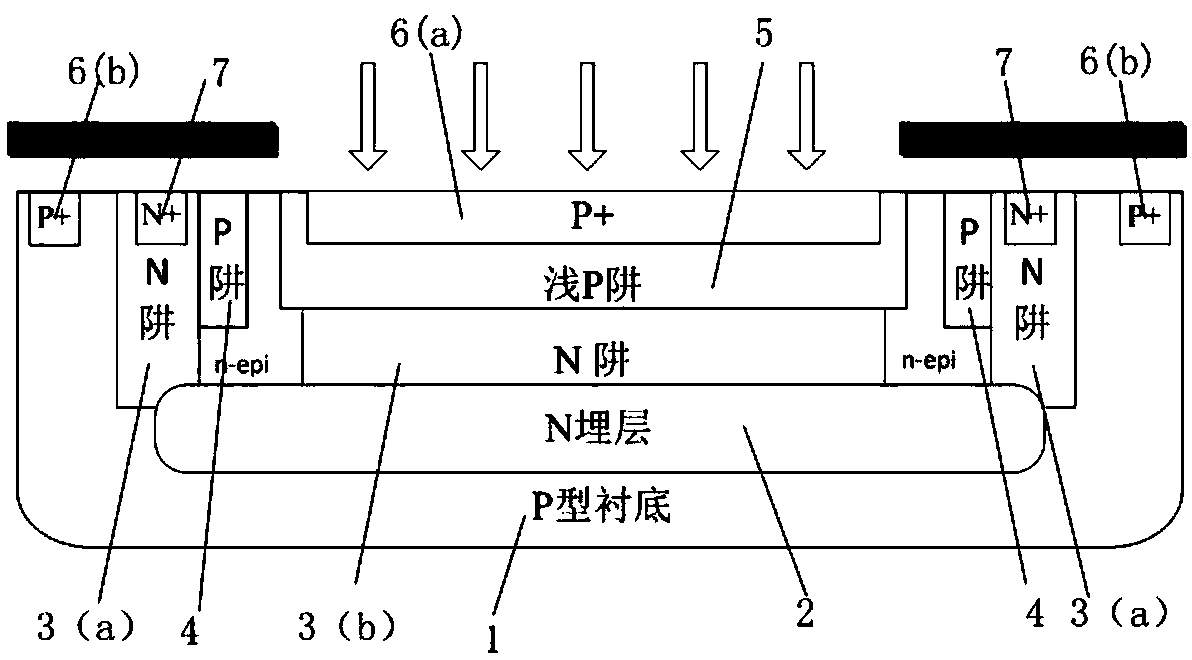

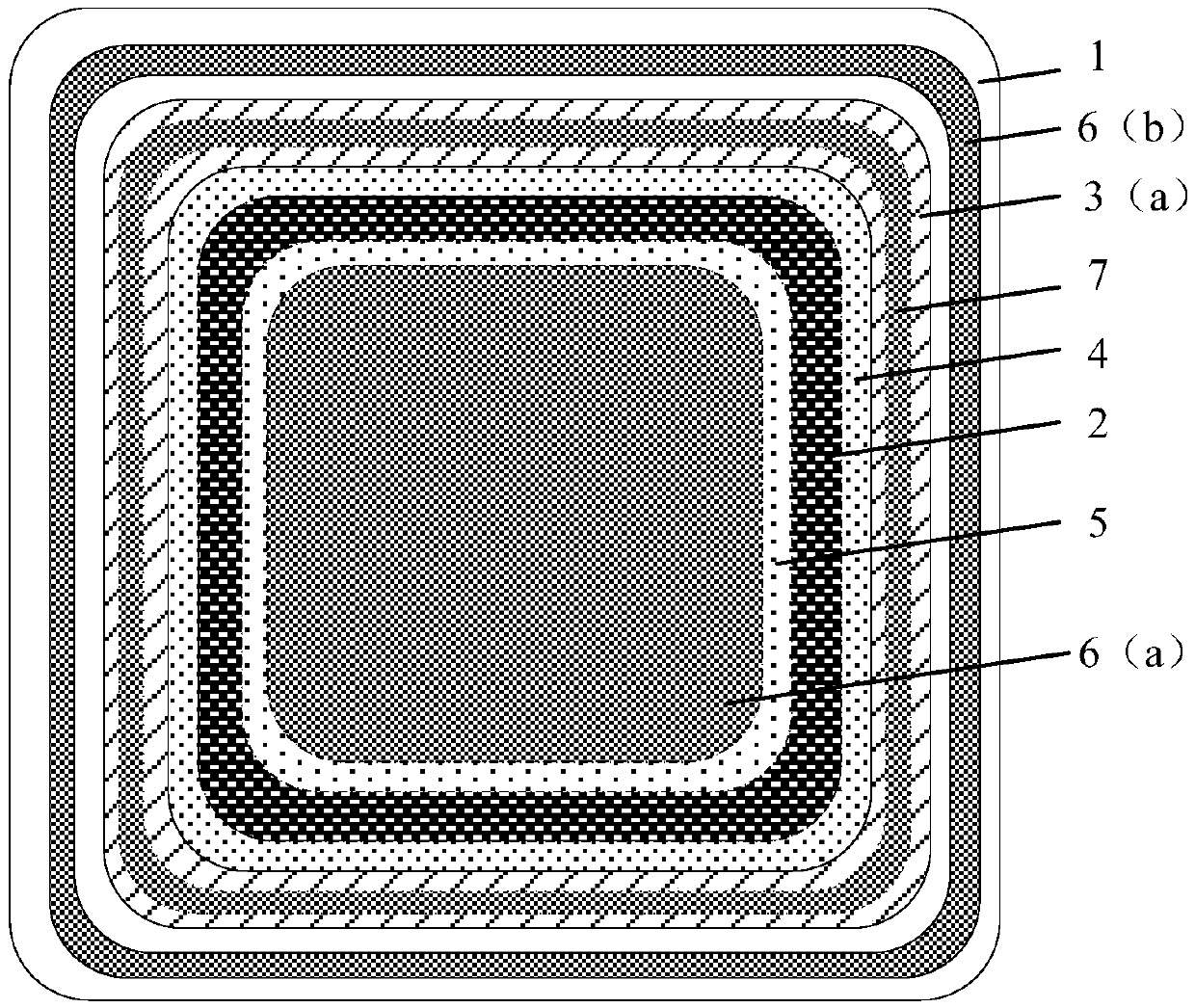

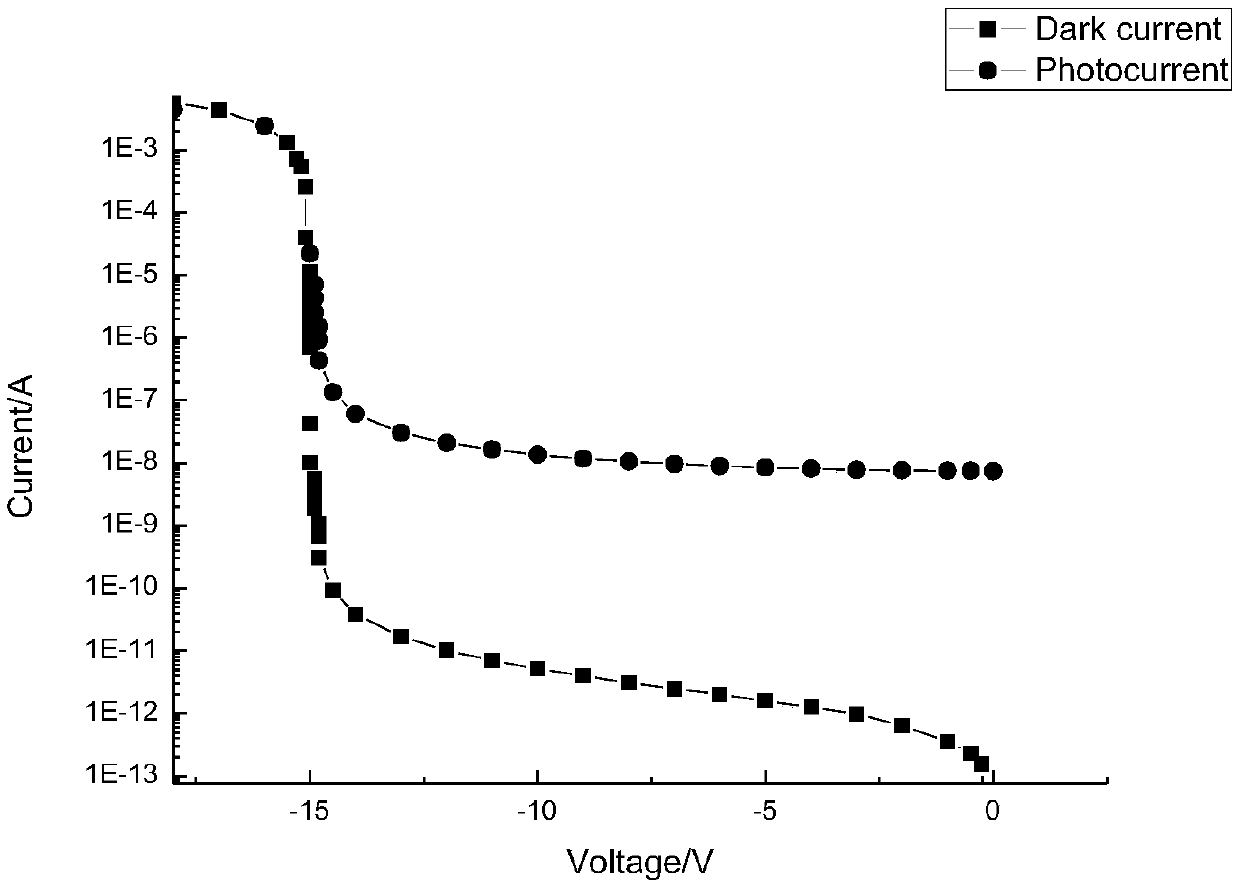

SPAD with high detection efficiency and low dark count based on standard CMOS process

InactiveCN109638092AIncrease costImprove detection efficiencySemiconductor devicesPhotodetectorProtection ring

The invention discloses an SPAD with high detection efficiency and low dark count based on a standard CMOS process. The SPAD is prepared on a P substrate that is provided based on the CMOS process; anN-buried layer is arranged on the P substrate to play an isolation role, the buried N-type injection has the characteristic of inverted doping distribution, the doping concentration increases with the increase of depth, and a virtual protection ring is formed; an N-well region, a P-well region and a heavily doped P+ region are respectively arranged in a diffusion doping region of the N-buried layer, and the N-well region is taken as a component part of a photosensitive PN junction; the P-well region serves as a protection ring; the heavily doped P+ region, a shallow P-well region and the N-type region jointly form a P+P- / N-well photosensitive PN junction, and the combination of two P-type injections with different concentrations form a gradient junction to reduce the dark count of devices; the depletion region of the PN junction is the main occurrence region of avalanche multiplication, and meanwhile, the heavily doped P+ region is also taken as an anode contact region of a photodetector; an N-well contact region is arranged in the N-well region at the edge, and the N-well contact region is a heavily doped N+ region and serves as a cathode contact region of the photodetector.

Owner:TIANJIN UNIV

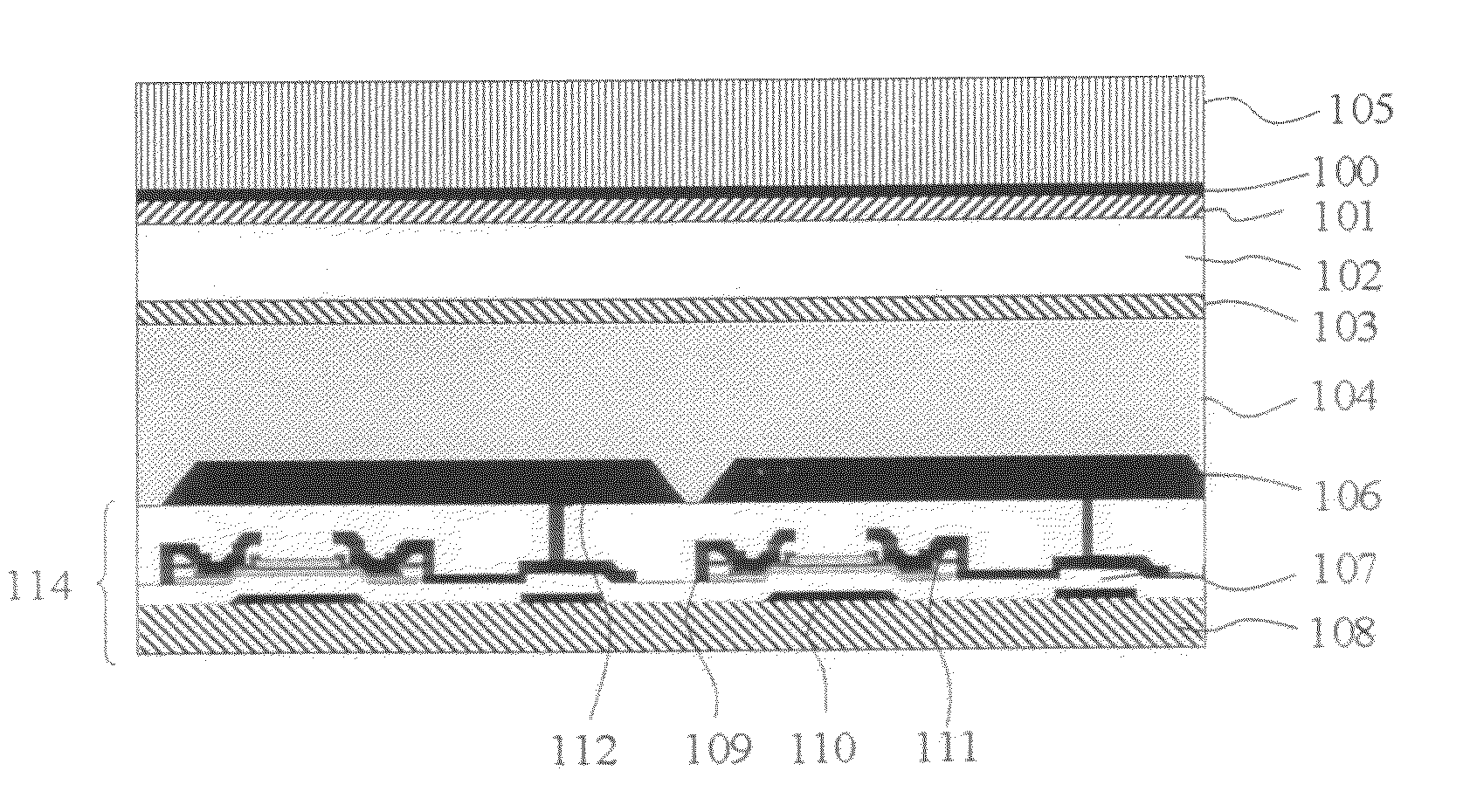

Photodetector/imaging device with avalanche gain

ActiveUS20100181487A1Solid-state devicesMaterial analysis by optical meansPhotovoltaic detectorsPhotodetector

A photodetector / imaging device comprises a layer of photoconductive material converting incident electromagnetic radiation into electrical charges, the layer of photoconductive material being capable of avalanche multiplication when an electric field of sufficient magnitude is applied thereacross; a readout layer detecting the electrical charge; and at least one interface layer between the layer of photoconductive material and the readout layer, the interface layer coupling electrical charge to or from the layer of photoconductive material and being configured to inhibit uncontrolled rises in current in the photoconductive material during avalanche multiplication.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK +1

Semiconductor photodetector

ActiveUS20150281620A1Little noiseImprove signal-to-noise ratioTransistorTelevision system detailsAudio power amplifierPhotodetector

A semiconductor photodetector has at least one unit pixel having a photoelectric conversion part, a charge storage part, and a detection circuit. The photoelectric conversion part includes a charge multiplication region in which incident light is converted into a charge, and the charge is multiplied by avalanche multiplication. The charge storage part is connected to the photoelectric conversion part and stores a signal charge from the photoelectric conversion part. The detection circuit is connected to the charge storage part, converts the signal charge stored in the charge storage part into a voltage, passes the voltage through an amplifier to amplify the voltage, and outputs the amplified voltage.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

Semiconductor optical detector

Provided is a semiconductor optical detector that is capable of detecting weak light including random light by significantly reducing dark-time noise and multiplicative noise from those in conventional semiconductor optical detectors. This semiconductor optical detector has at least one unit pixel having a photoelectric conversion section, a charge storage section, and a detecting circuit. The charge storage section photoelectrically converts inputted light, and has a charge multiplying region where charges are multiplied by means of avalanche multiplication. The charge storage section is connected to the photoelectric conversion section, and stores signal charges transmitted from the photoelectric conversion section. The detecting circuit is connected to the charge storage section, converts the signal charges stored in the charge storage section into voltage, amplifies the voltage by means of an amplifying section, and outputs the amplified voltage.

Owner:PANASONIC INTPROP MANAGEMENT CO LTD

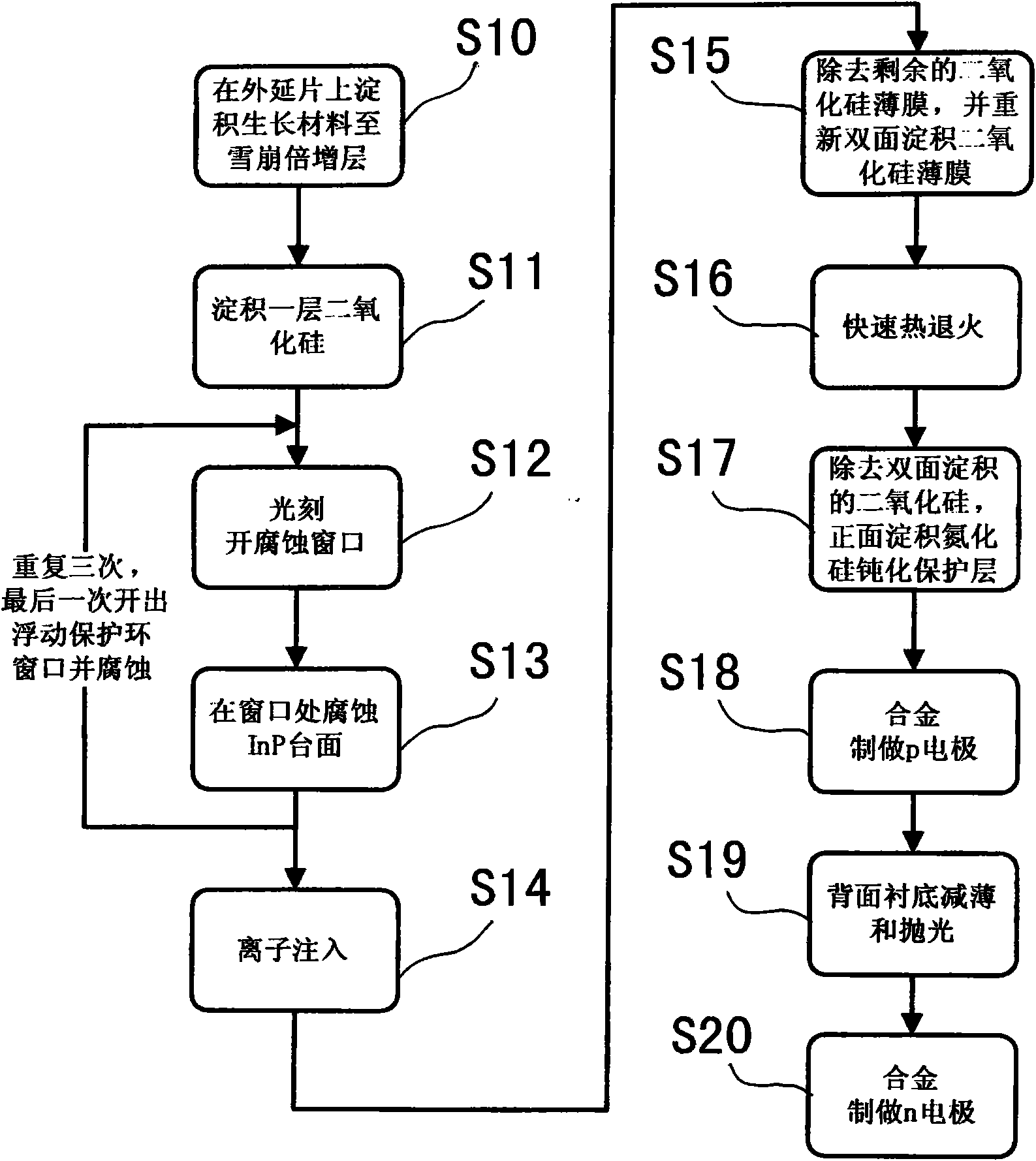

InP base plane type back incident avalanche optoelectronic diode and manufacturing method thereof

InactiveCN101552304ASuppresses edge breakdownSimple processSemiconductor devicesControl layerProtection layer

The invention relates to an InP base plane type back incident avalanche optoelectronic diode which comprises a substrate, a buffer layer manufactured on the substrate, an absorption layer manufactured on the buffer layer, a transition layer manufactured on the absorption layer, an electric field control layer manufactured on the transition layer and an avalanche multiplication layer manufactured on the electric field control layer, wherein a concave part is disposed on a central area on the avalanche multiplication layer, and the edge of the concave part is of an inverse step-shaped structure; a floating protective ring is manufactured at the outside of the concave part on the avalanche multiplication layer; the concave part comprises a P-type doped layer disposed on the bottom surface of the concave part and a passivation protecting layer disposed on the surfaces of the P-type doped layer and the avalanche multiplication layer, wherein a contact through hole is disposed in the center of the passivation protecting layer, and a P electrode is manufactured at the bottom in the middle of the passivation protecting layer; and an n electrode is manufactured on the back of the substrate, and a light incident window is disposed in the middle of the n electrode.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

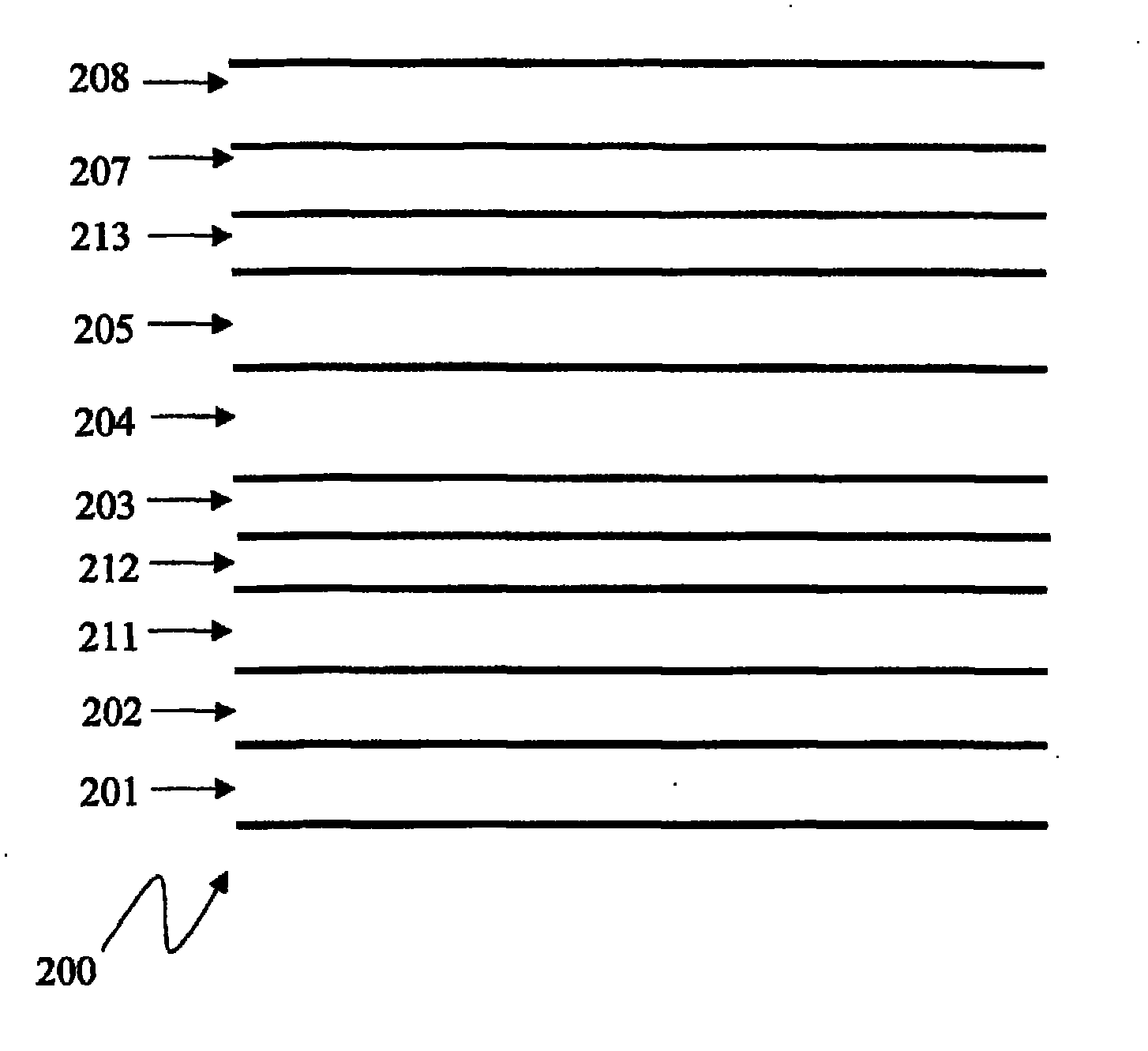

Avalanche photodiode

A single carrier avalanche photodiode (200) comprising a p-doped absorption layer (213), an unintentionally doped avalanche multiplication layer (203) and an n-doped collector layer (211) and a method of manufacturing said avalanche photodiode. The absorption layer is doped at a level that allows the photodiode to operate as a single carrier device. Therefore total delay time of the device is mainly dependent on electrons. The collector layer is in charge of reducing capacitance in the device. A built-in field layer (212) of n plus delta doped material may be provided between the two layers in order to improve the injection of electrons in the collector layer.

Owner:ALCATEL LUCENT SAS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com