Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

31 results about "Nano cmos" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

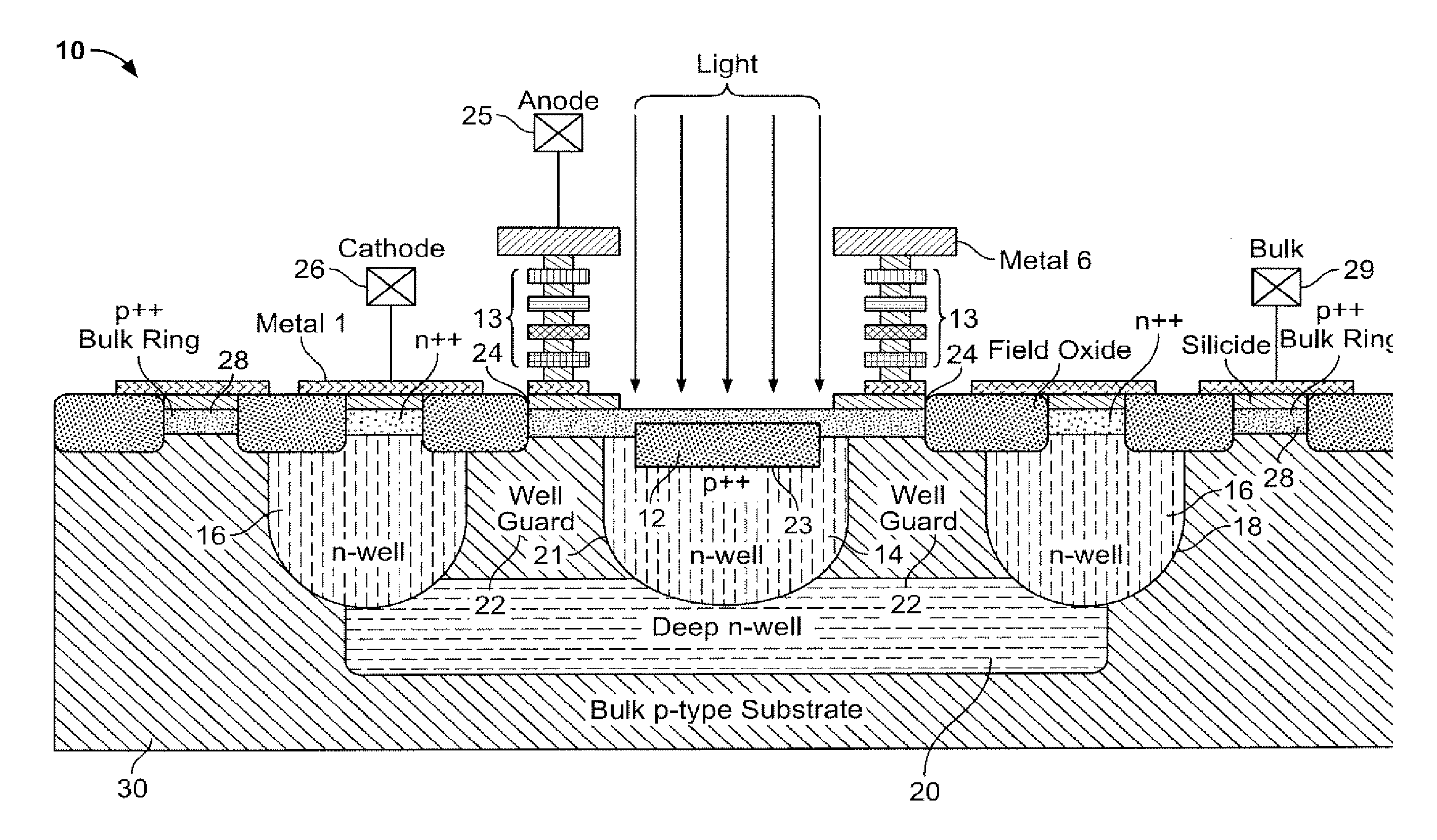

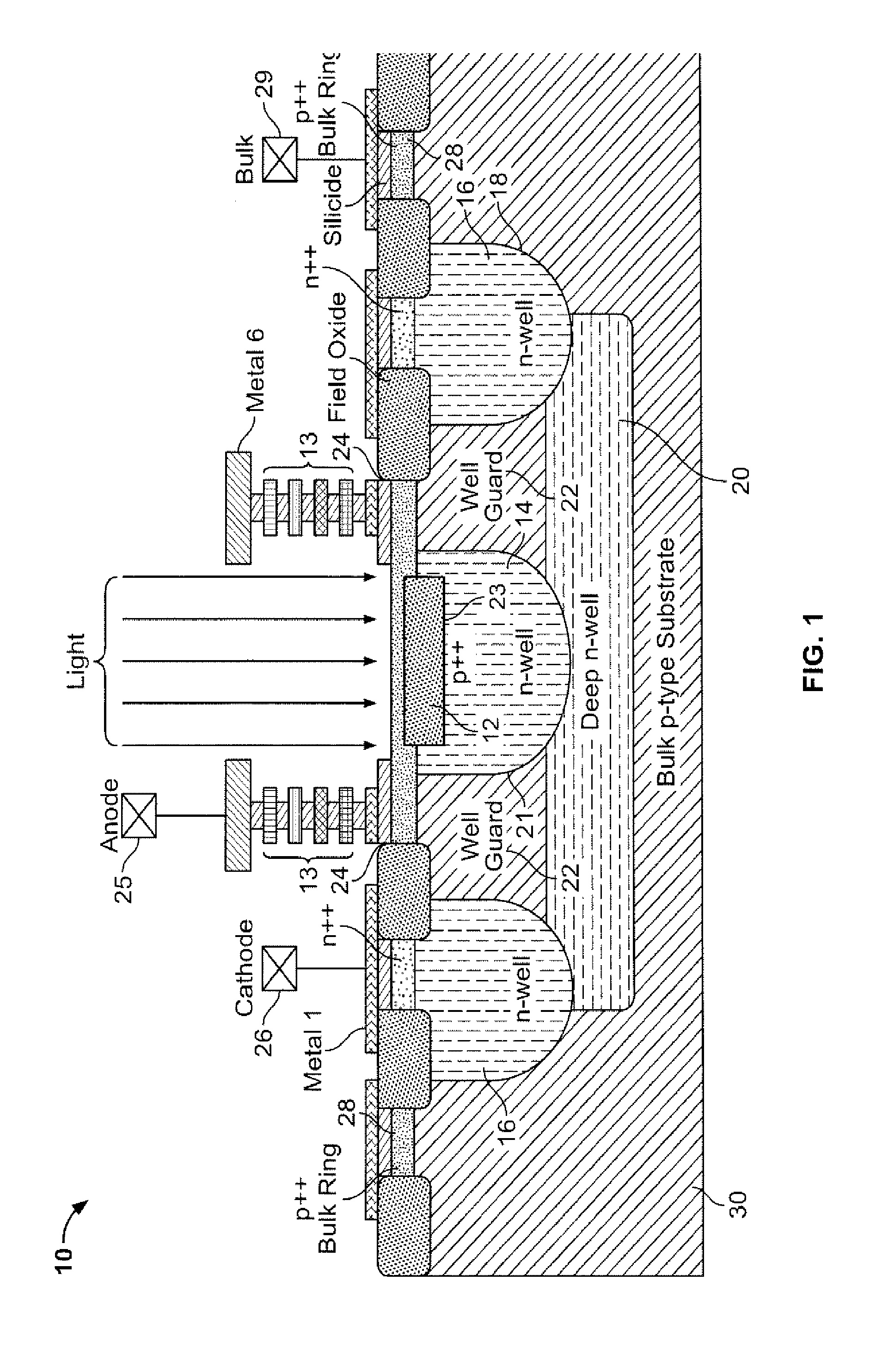

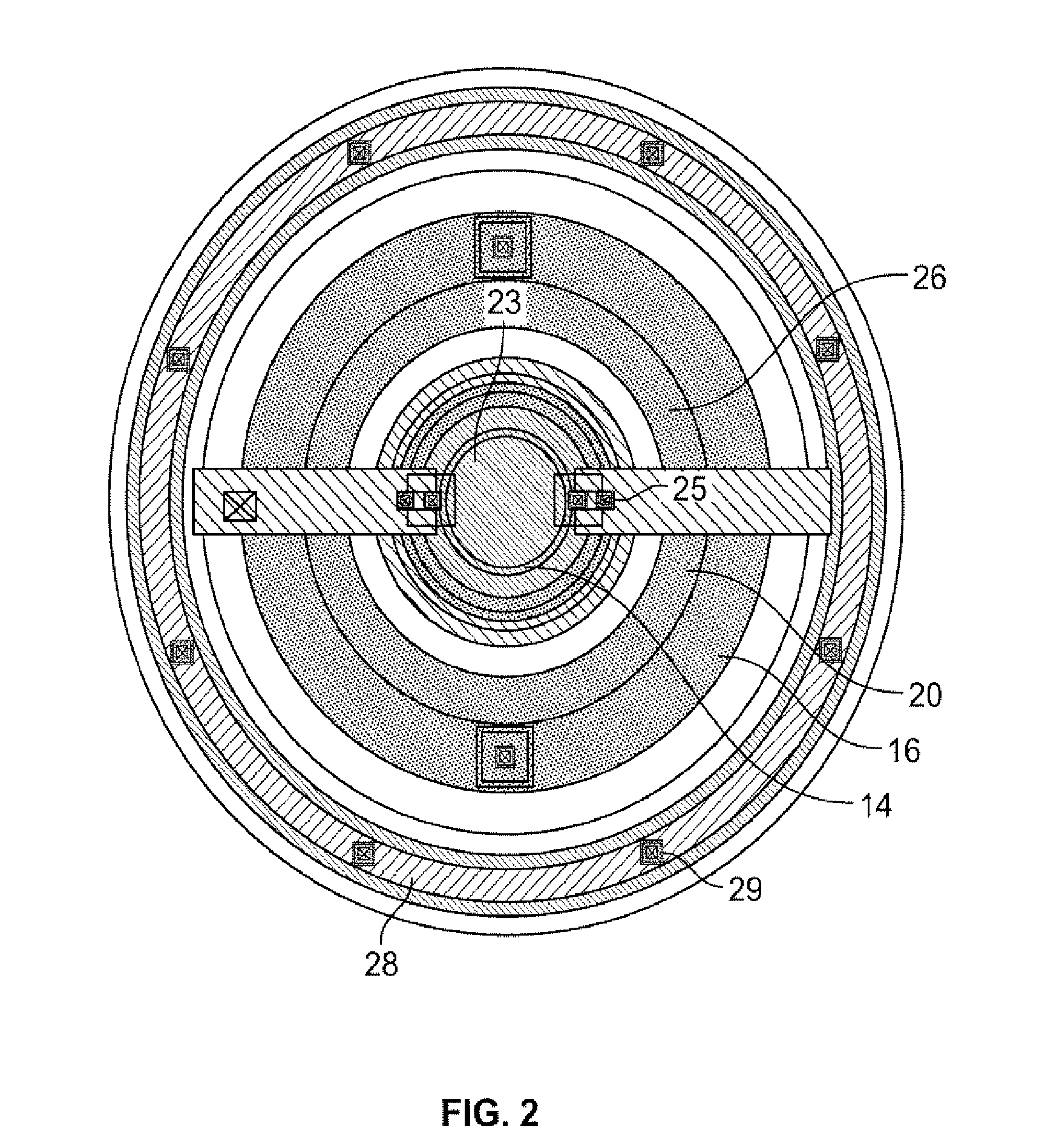

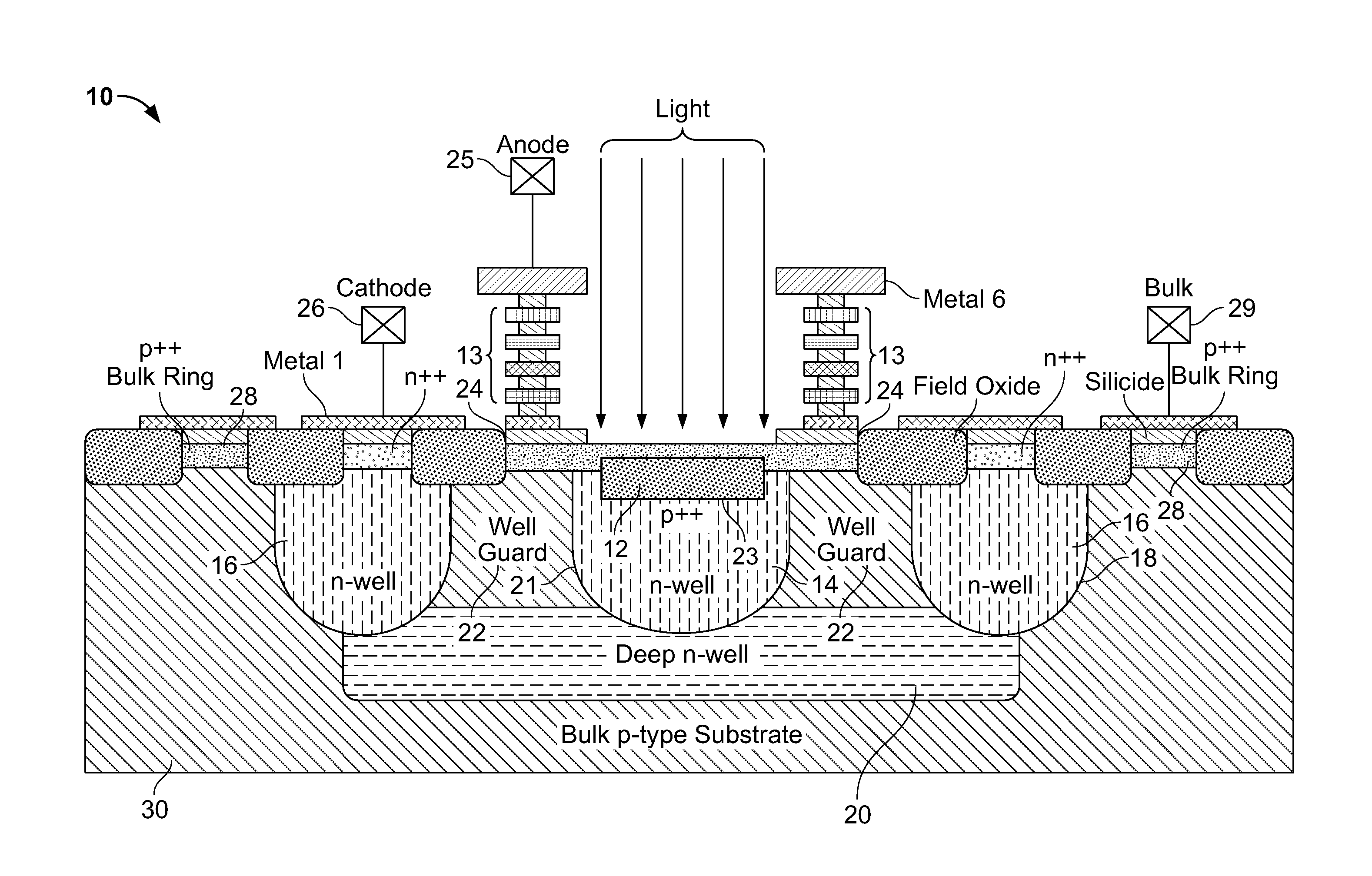

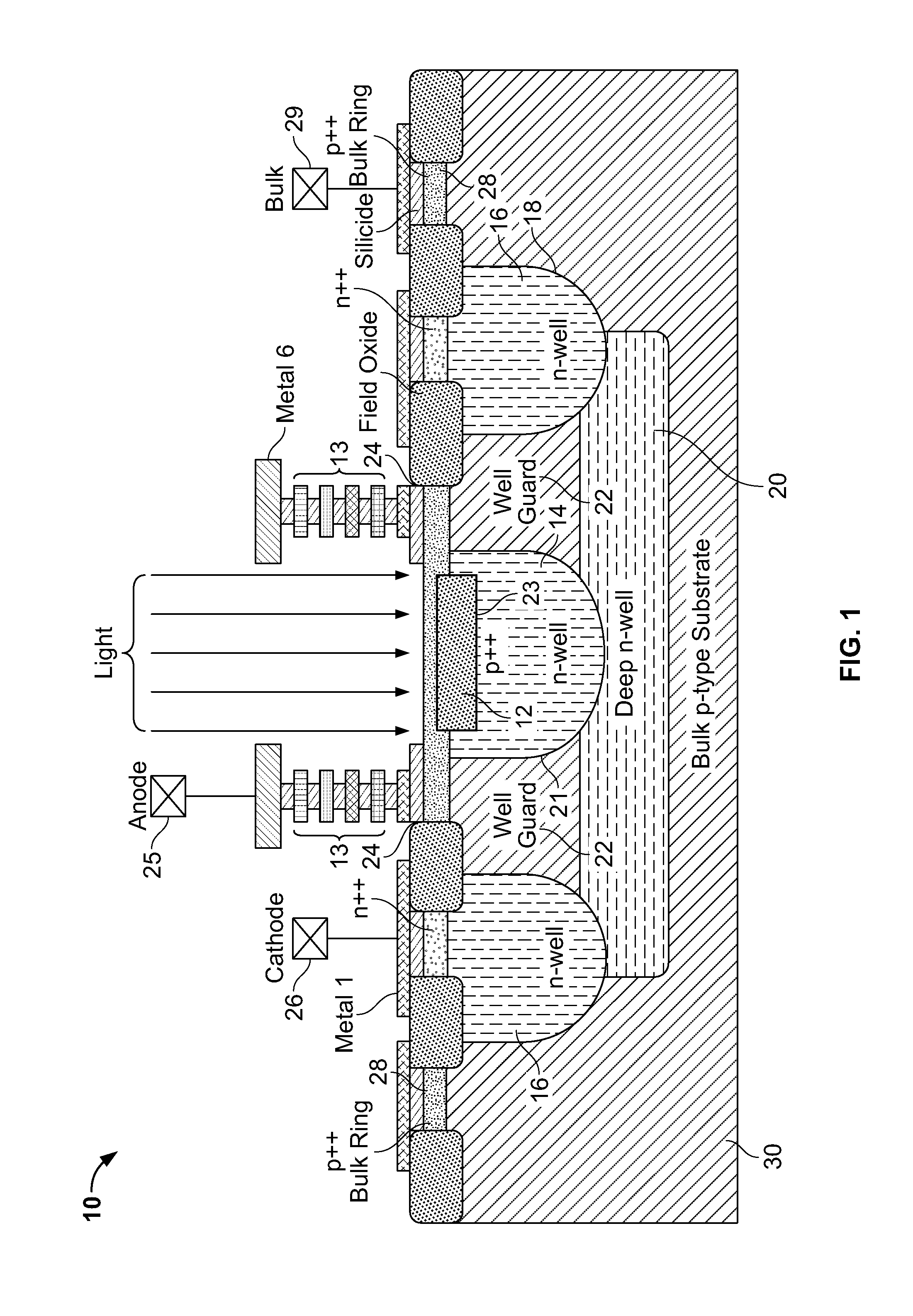

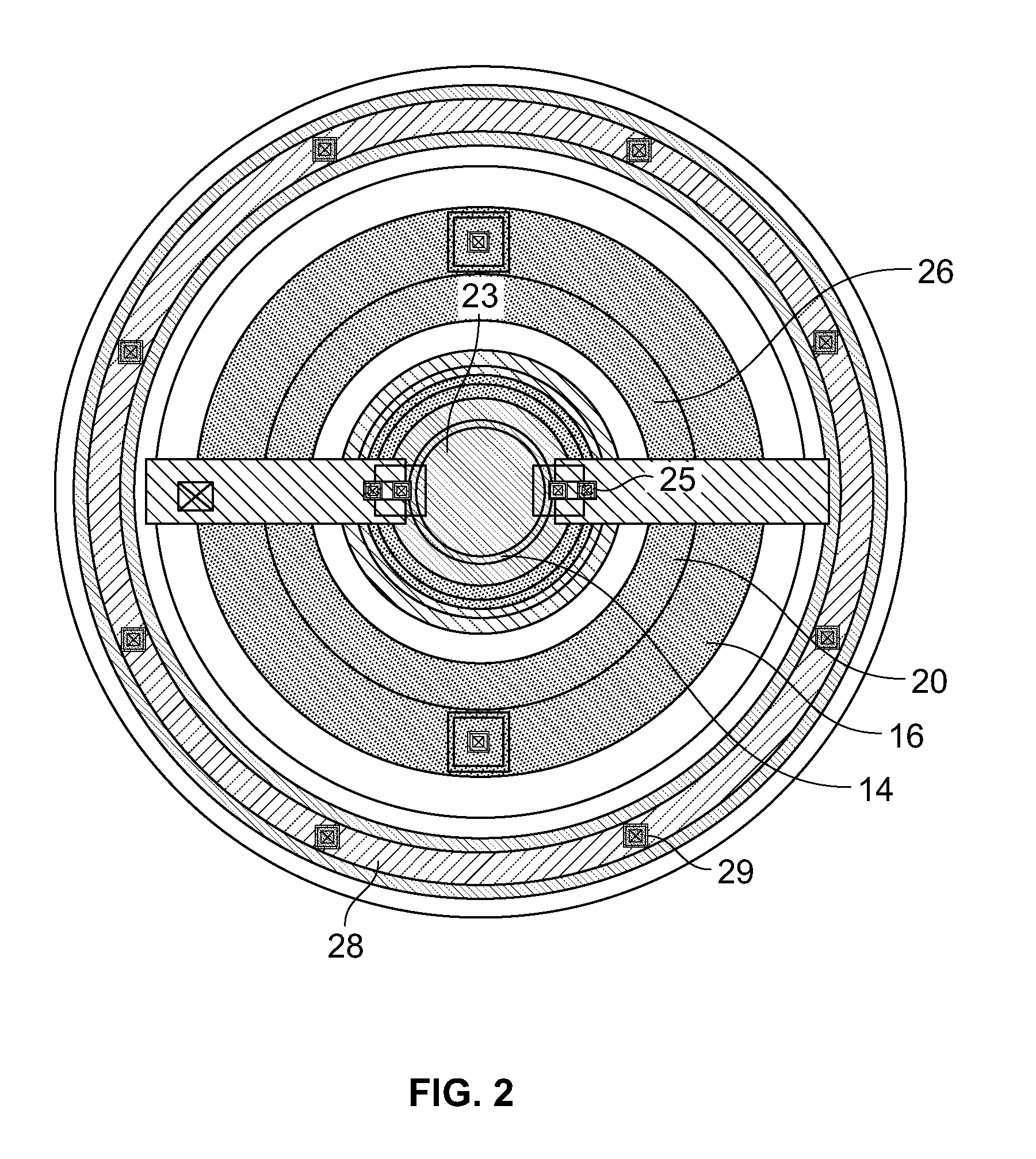

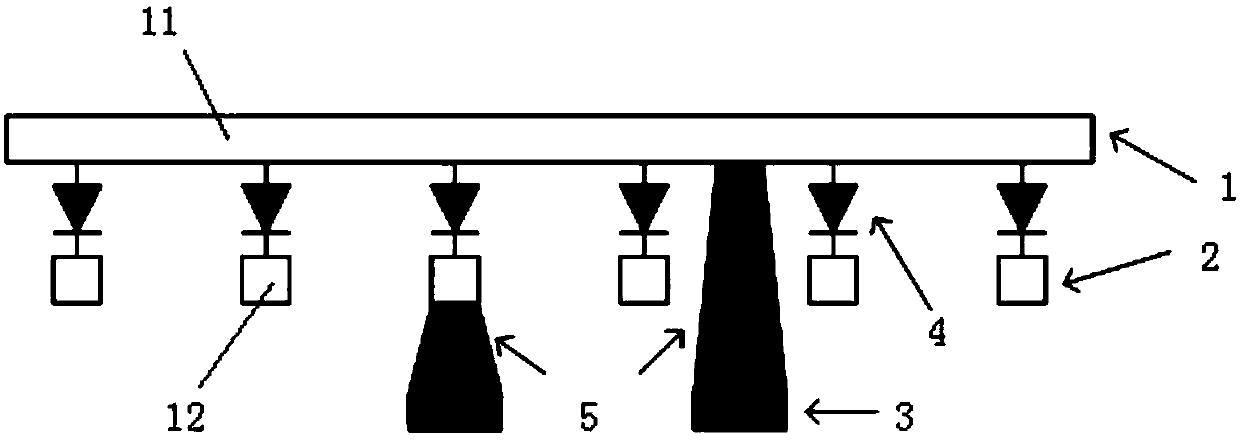

Deep submicron and NANO CMOS single photon photodetector pixel with event based circuits for readout data-rate reduction communication system

ActiveUS20100245809A1Solid-state devicesMaterial analysis by optical meansSensor arrayCommunications system

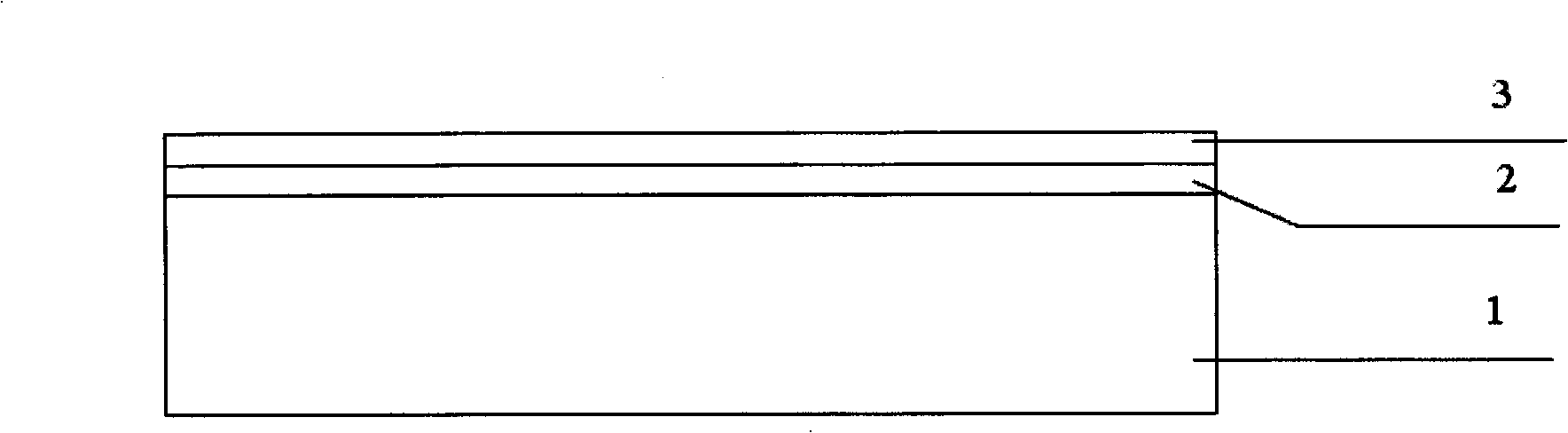

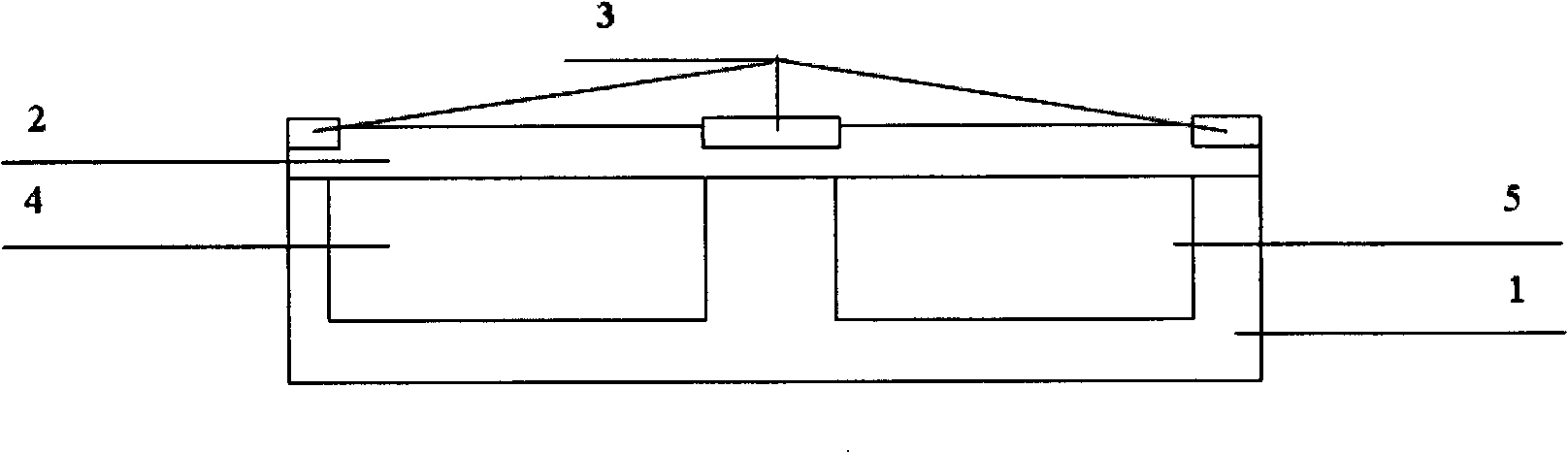

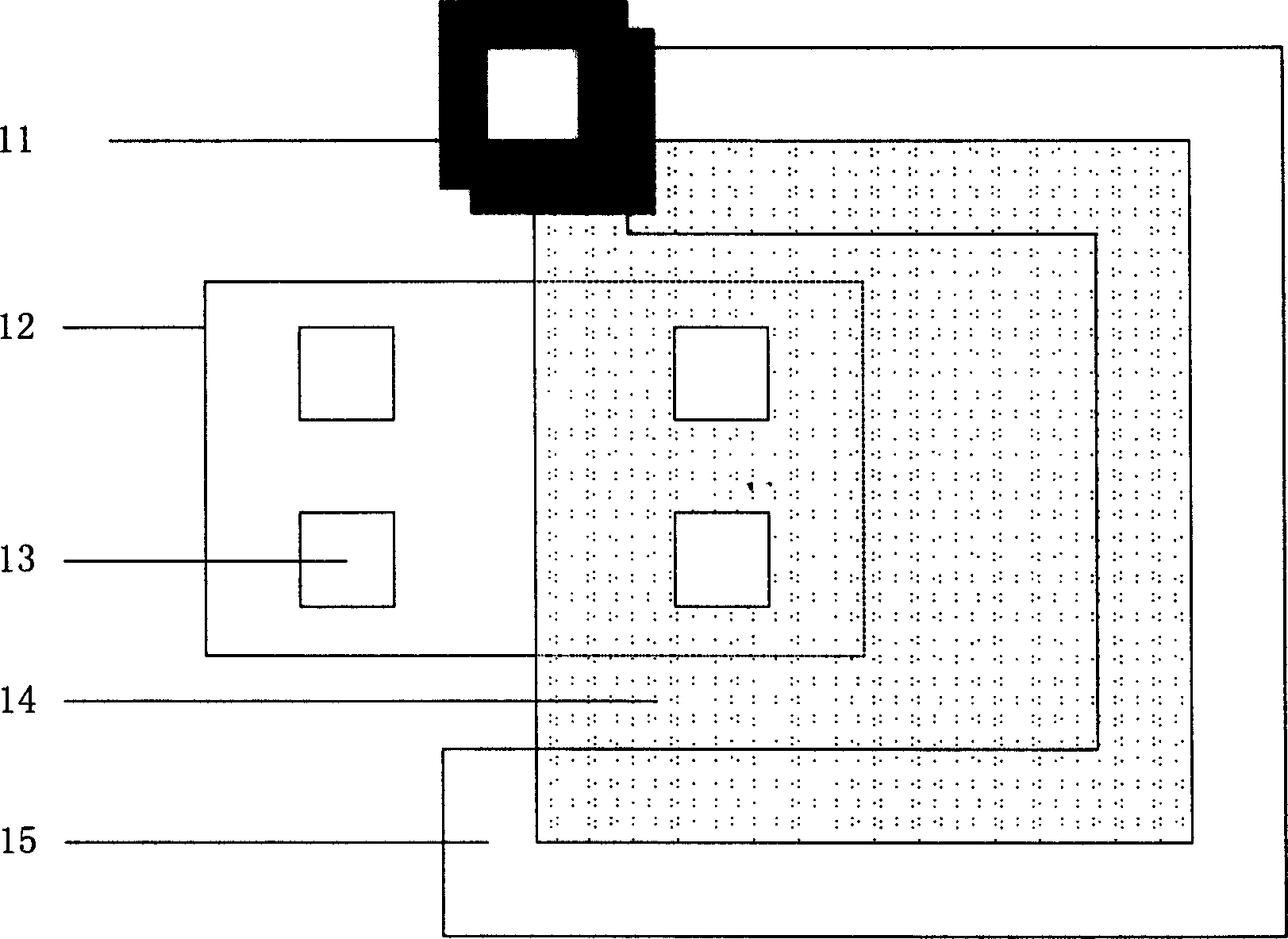

An avalanche photodiode and a sensor array comprising an array of said avalanche photodiodes is disclosed. Then avalanche photodiode comprises a substrate of a first conductivity type; a first well of a second conductivity type formed within the substrate; a second well of the second conductivity type formed substantially overlying and extending into the first well; a heavily doped region of the first conductivity type formed substantially overlying and extending into the first well, the junction between the heavily doped region and the second well forming an avalanche multiplication region; a guard ring formed from a first conductivity material positioned substantially about the periphery of the multiplication region at least partially underlying the heavily doped region; and an outer well ring of the second conductivity type formed about the perimeter of the deep well and the guard ring. The sensor array comprises a plurality of pixel elements, each of the pixel elements being configured to operate on discrete value continuous time (DVCT) basis. Each of the pixel elements can include the avalanche photodiode previously described.

Owner:THE JOHN HOPKINS UNIV SCHOOL OF MEDICINE

Deep submicron and nano CMOS single photon photodetector pixel with event based circuits for readout data-rate reduction communication system

Owner:THE JOHN HOPKINS UNIV SCHOOL OF MEDICINE

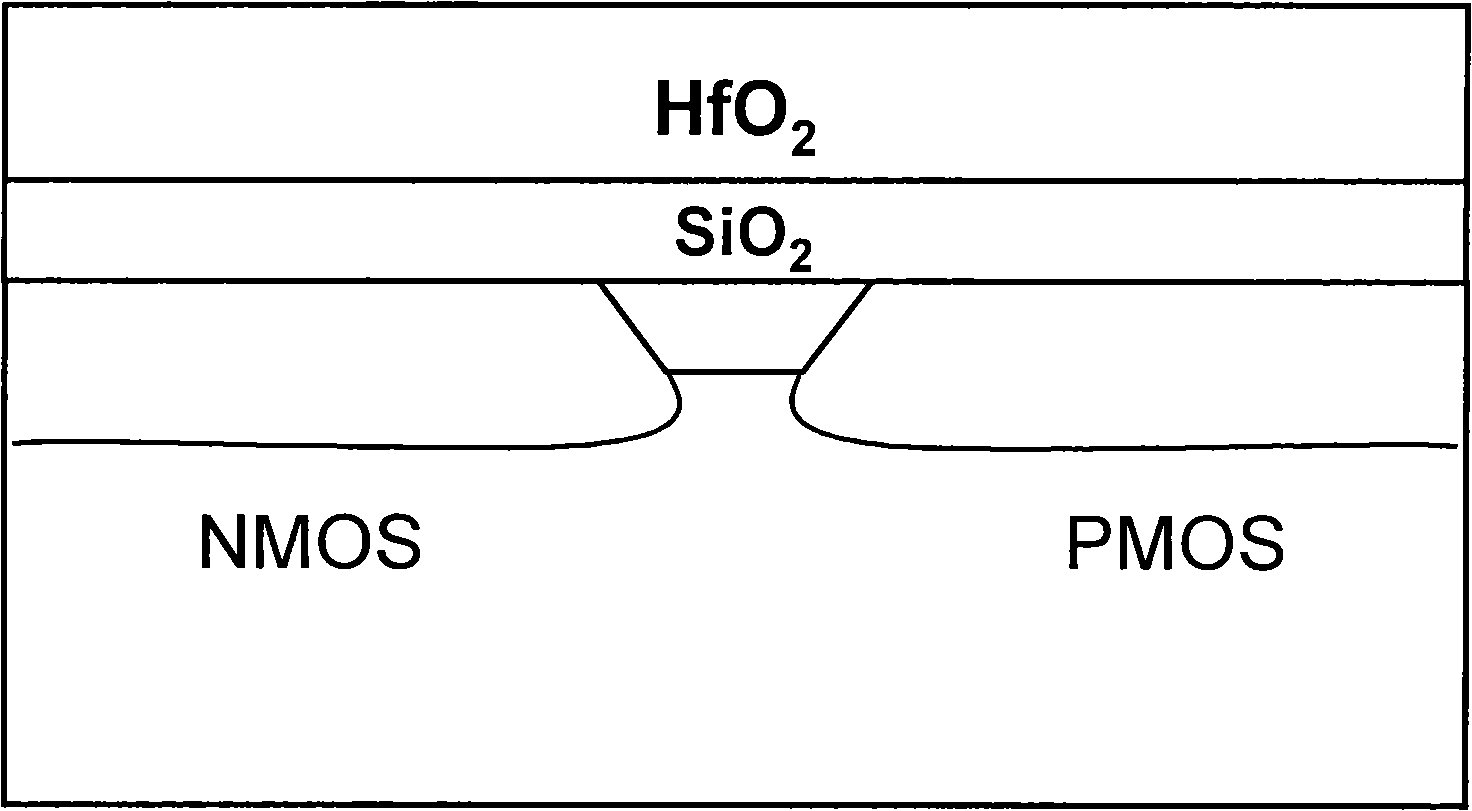

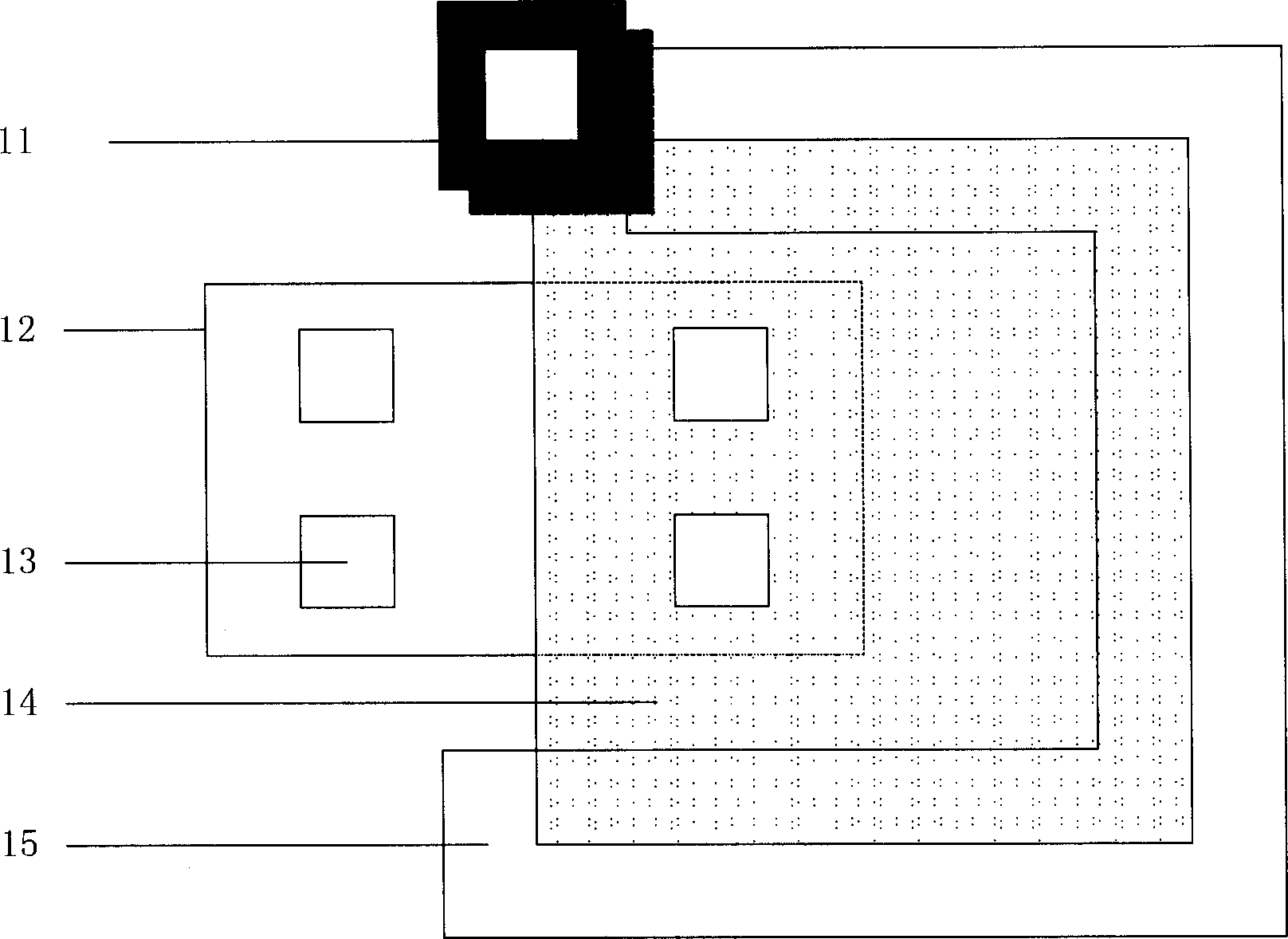

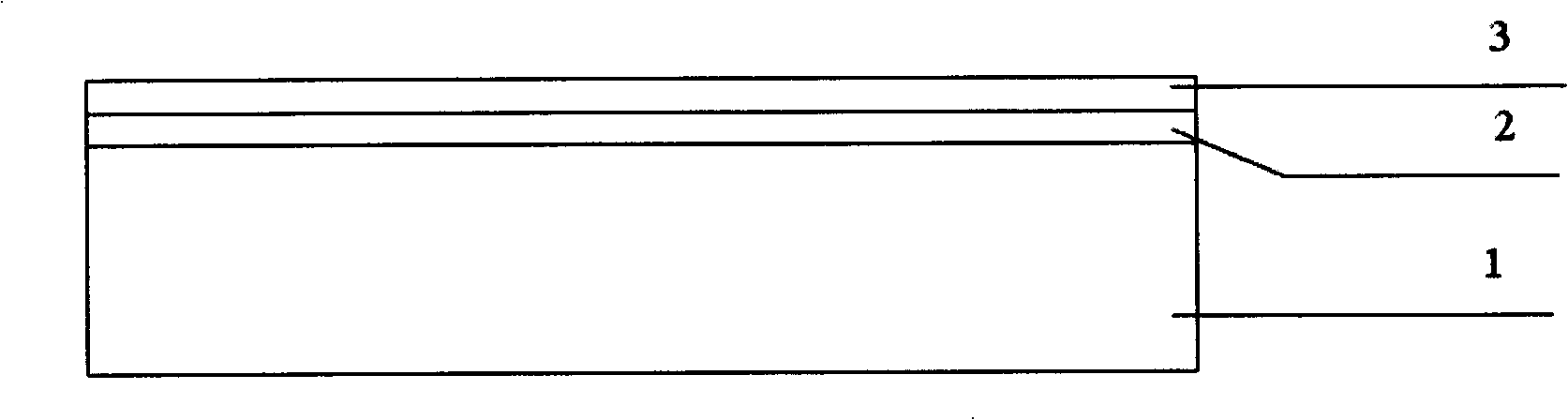

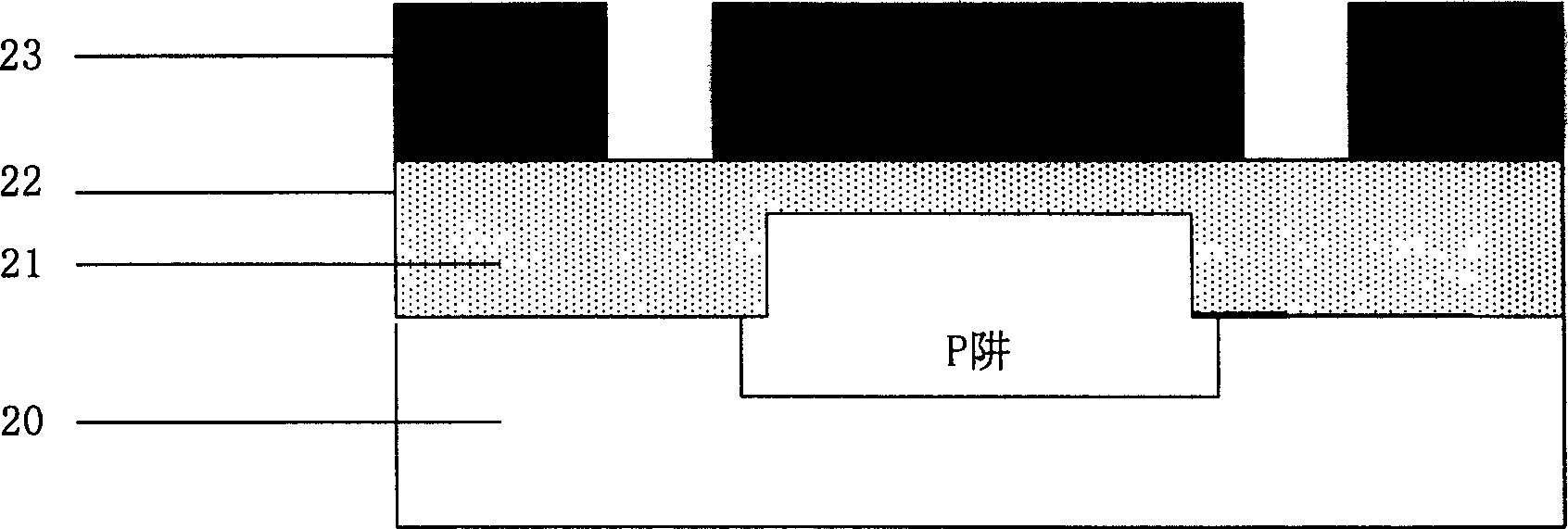

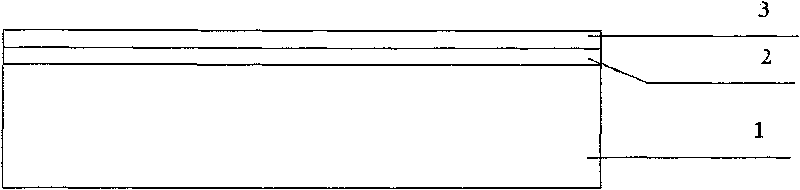

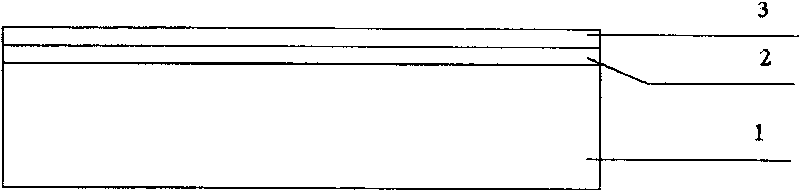

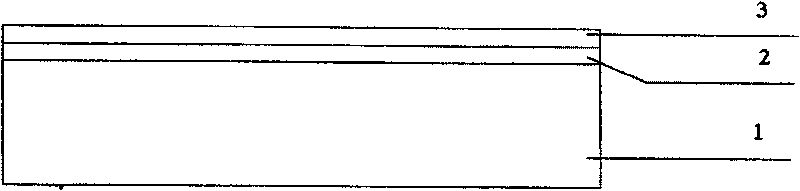

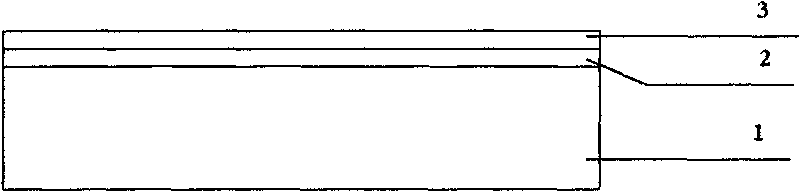

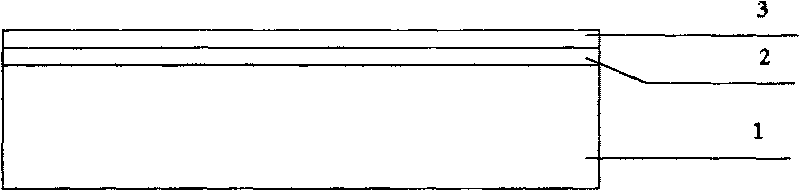

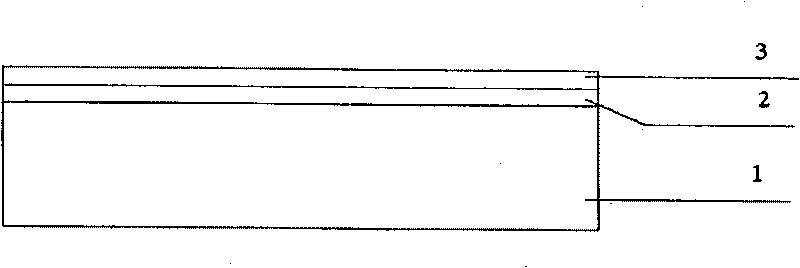

Grid structure from material with high dielectric constant and preparing technique

InactiveCN1540769AEffective isolation of diffusionPrevent penetrationTransistorSemiconductor/solid-state device manufacturingDielectricThin layer

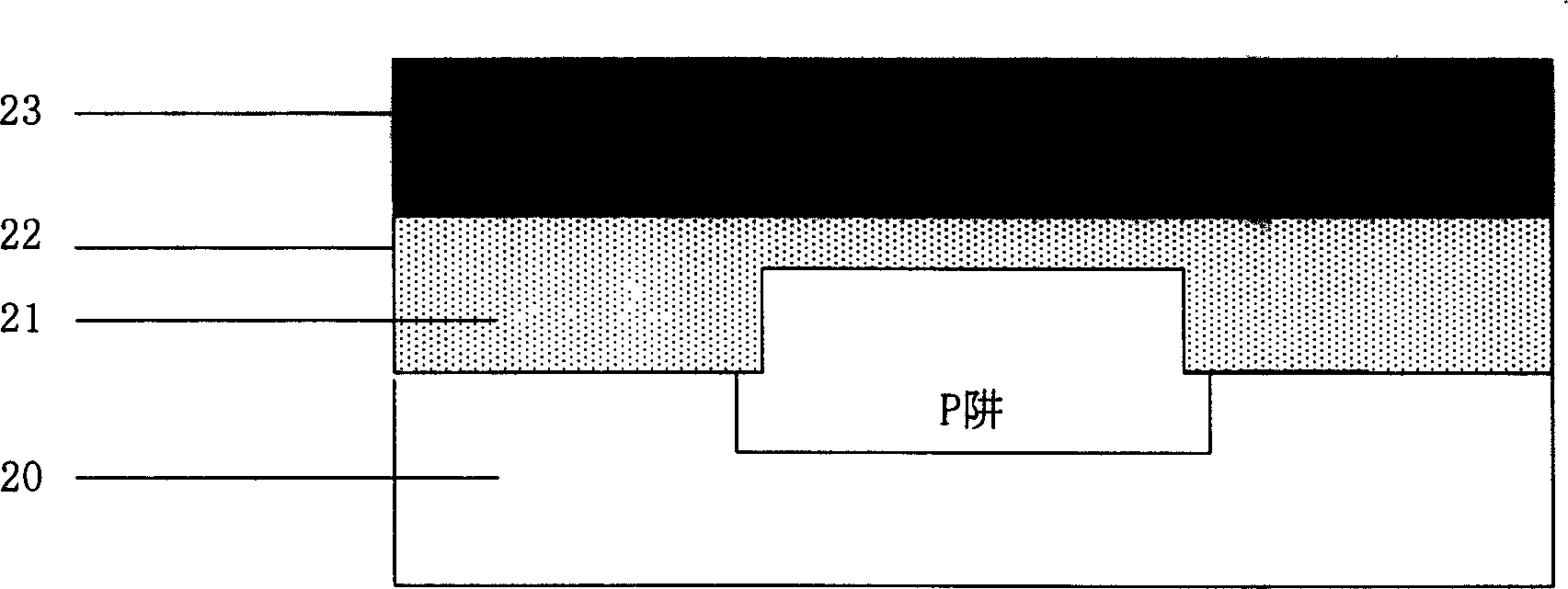

Oxidizing surface of silicon chip grows a very thin silicon oxynitride layer as a buffer of interface between material with high dielectric constant and silicon substrate in order to insulate diffusion between impurity element in material with high dielectric constant and silicon substrate. Carrying out nitrogen treatment for surface of material with high dielectric constant or depositing a thin layer of silicon nitride covers material with high dielectric constant. The nitrogen treated surface or deposited thin layer as interface layer between material with high dielectric constant and polysilicon blocks off penetration from boron P+ polycrystal. In the invention , grid structure is in sandwich type. The invention is applicable to not more than 65 Nano CMOS technique.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT +1

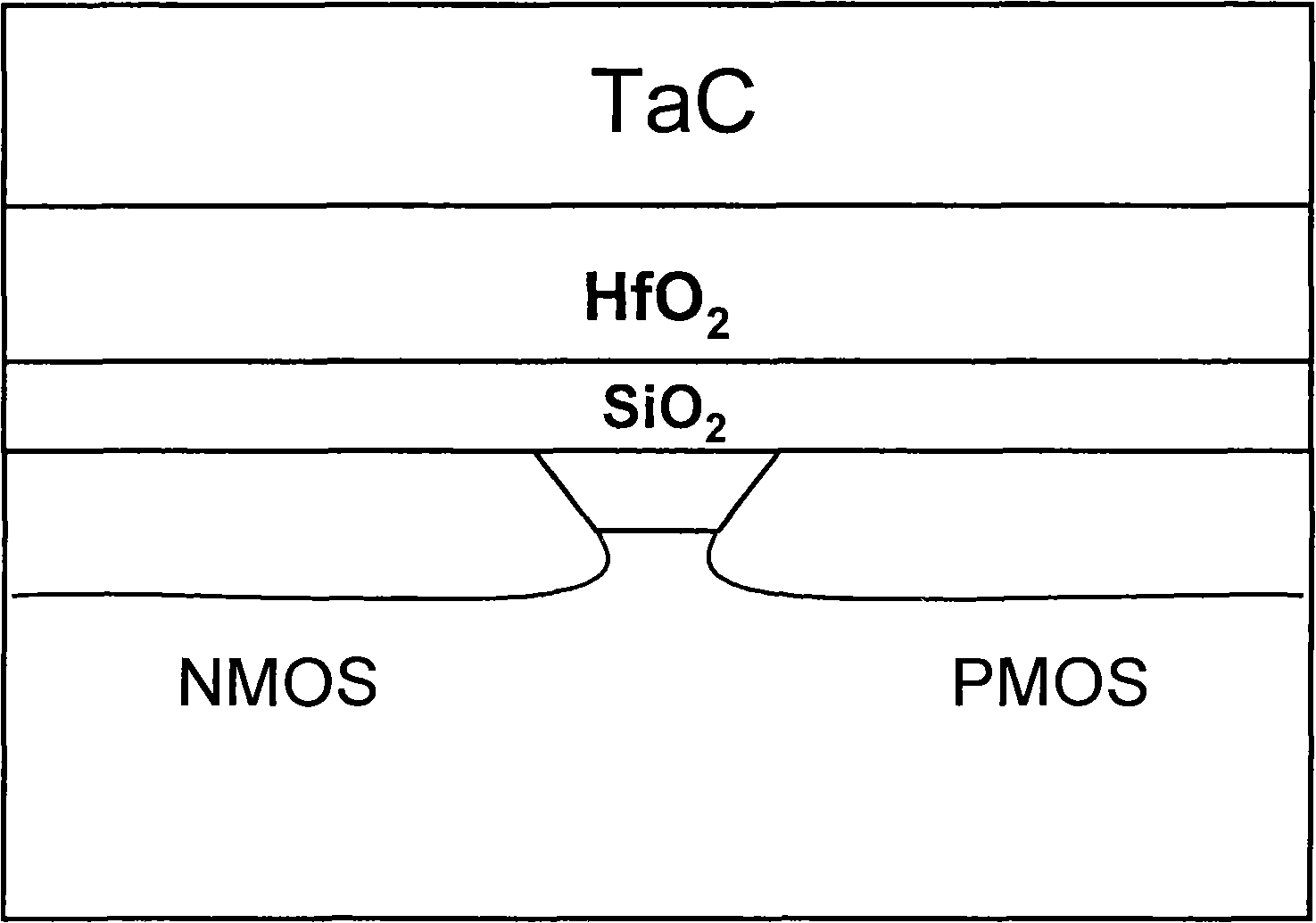

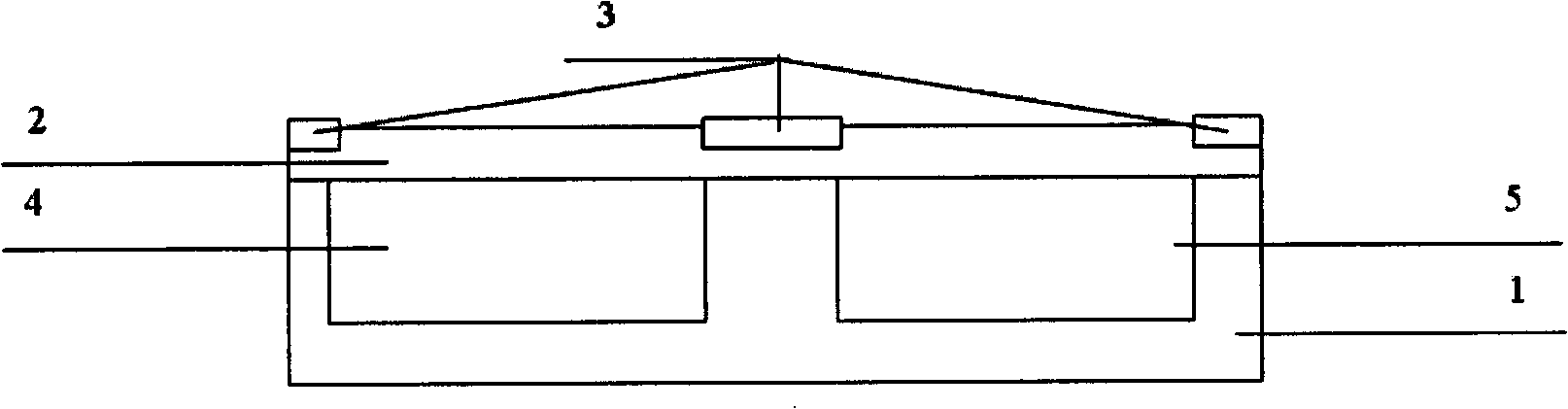

CMOS device metal grid and method for forming same

InactiveCN101494236AEasy to processReduce deposition processTransistorSemiconductor/solid-state device manufacturingDielectricEngineering

The invention provides a metal grid electrode of a CMOS element and a forming method thereof. With the technical proposal, the change of the thickness of the metal grid electrode can lead to obvious change of an effective work function value of the metal grid electrode material on the same high k (dielectric constant) grid medium, thus realizing the regulation of the effective work function value in simple and effective ways and further effectively regulating a threshold voltage of the high k grid medium / a CMOS element of a metal grid electrode structure. Therefore, the high k grid medium / the CMOS element of the metal grid electrode structure meeting the threshold voltage demands of a nano CMOS element can be obtained. Moreover, the adoption of the technical proposal can simplify the processing flow of the high k grid medium / the CMOS element of the metal grid electrode structure, thus not only reducing the deposition process of a double metal grid thin film, but also overcoming complex pattern etching problems of a double metal grid structure.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

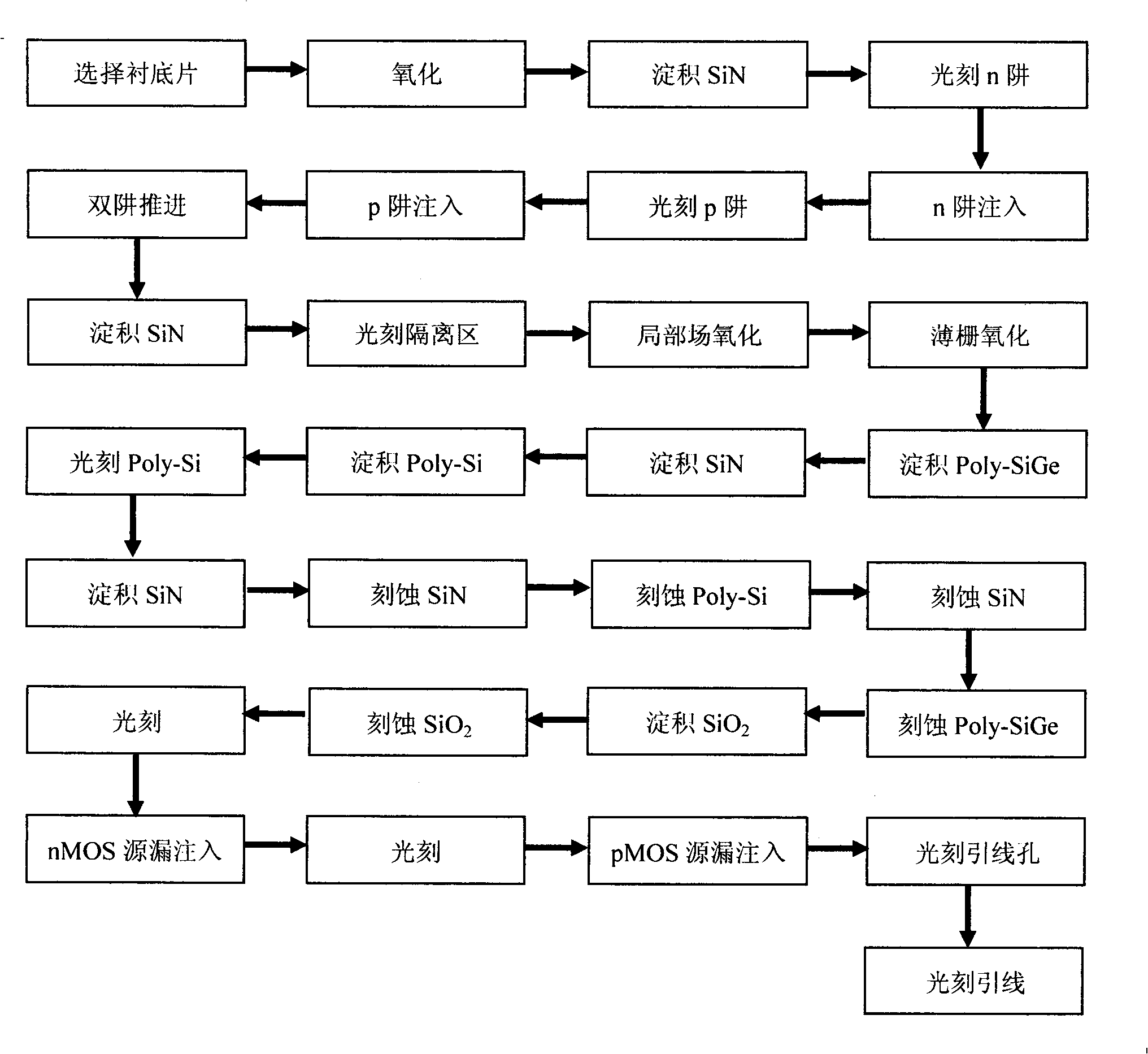

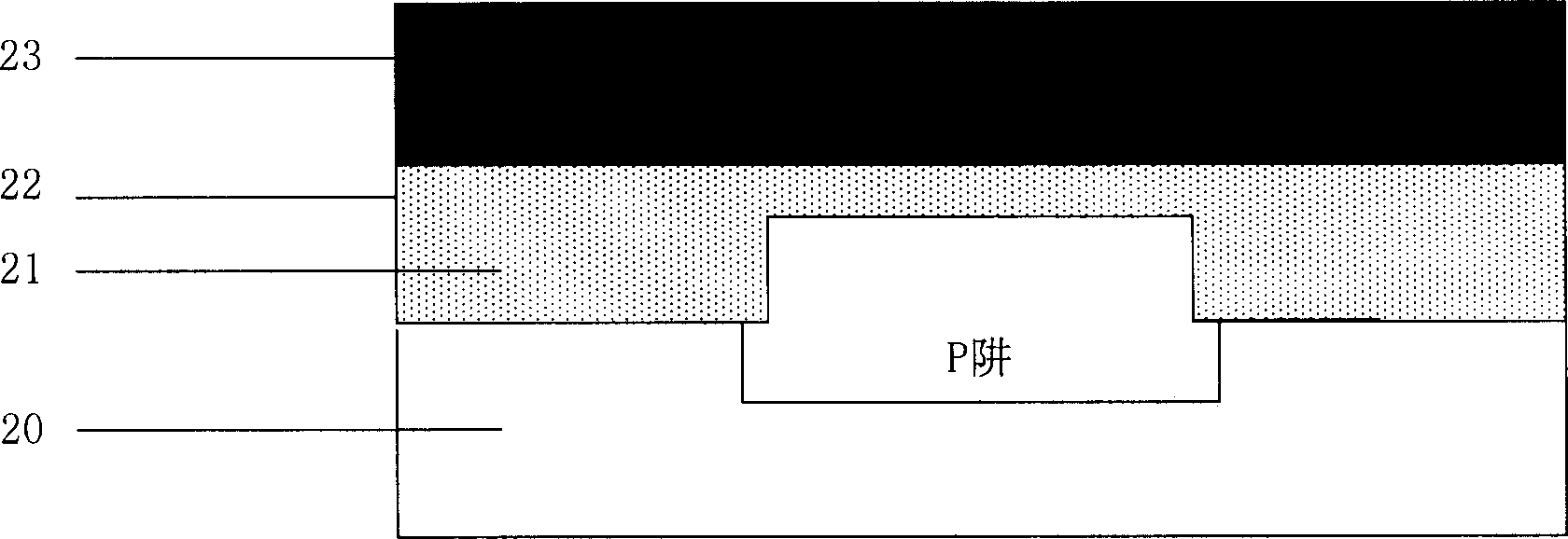

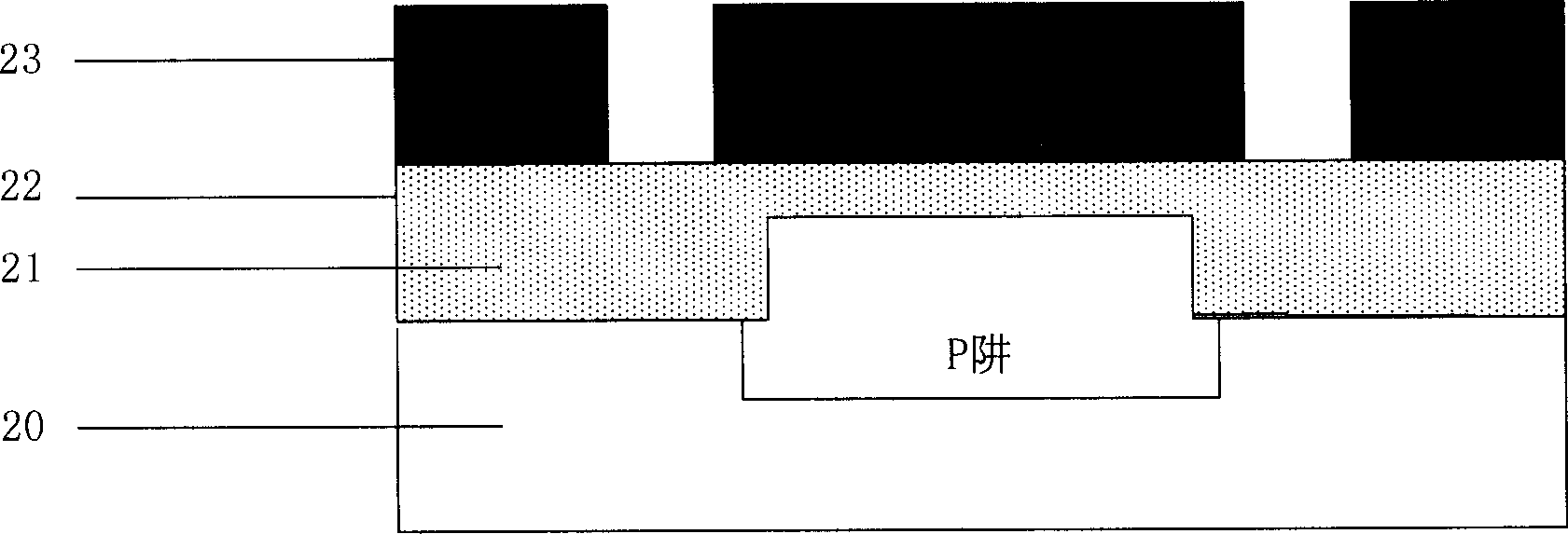

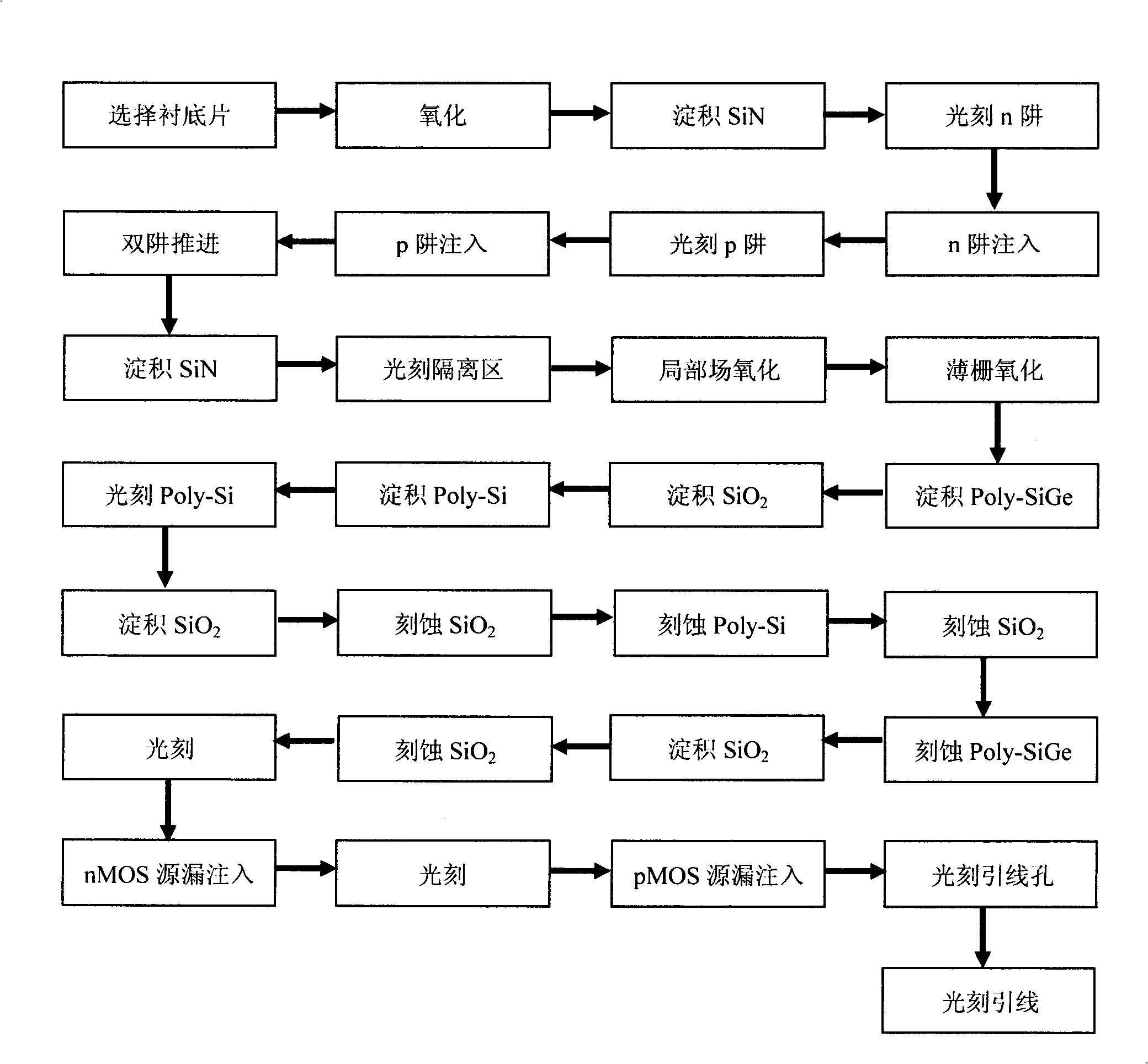

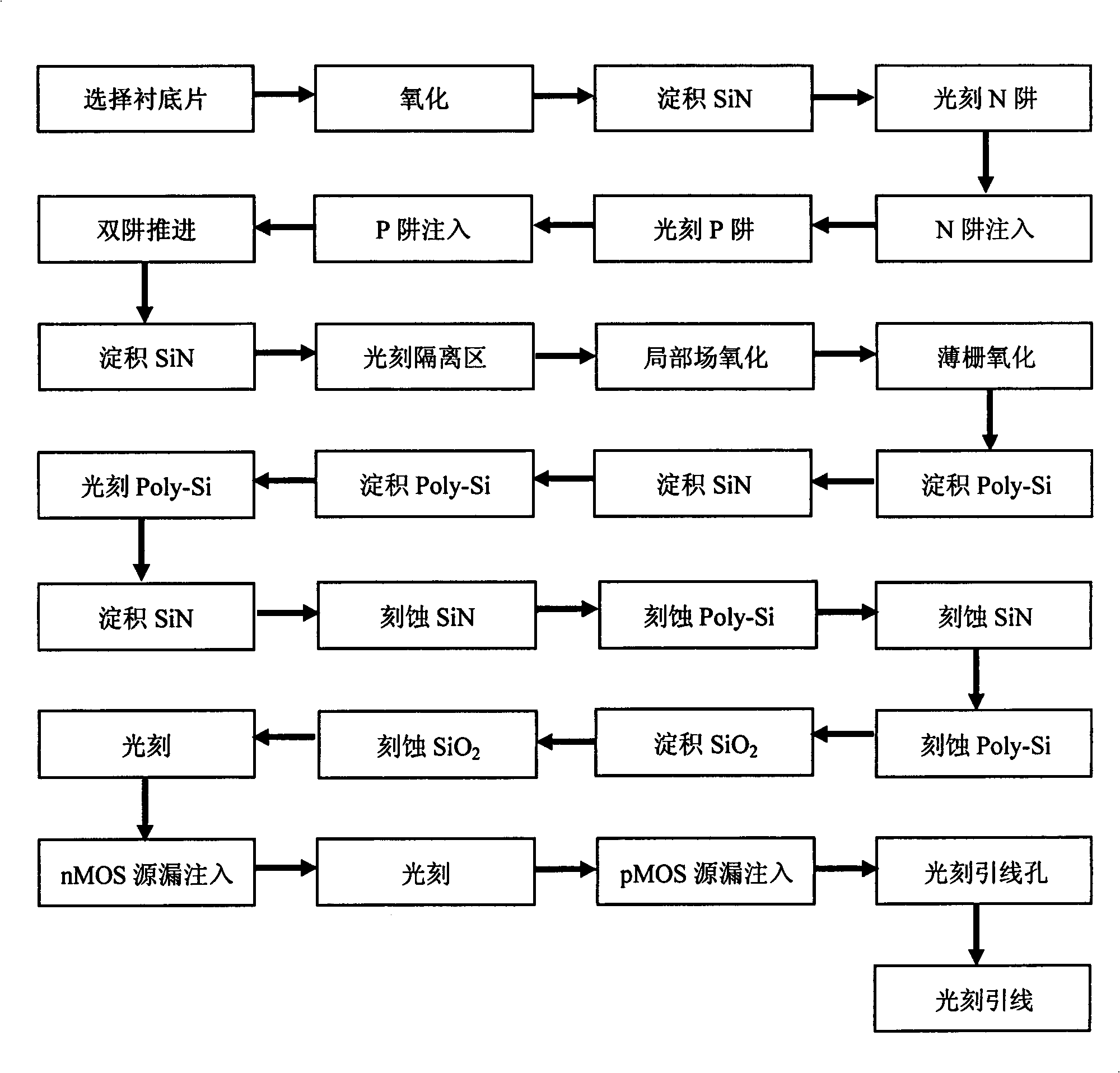

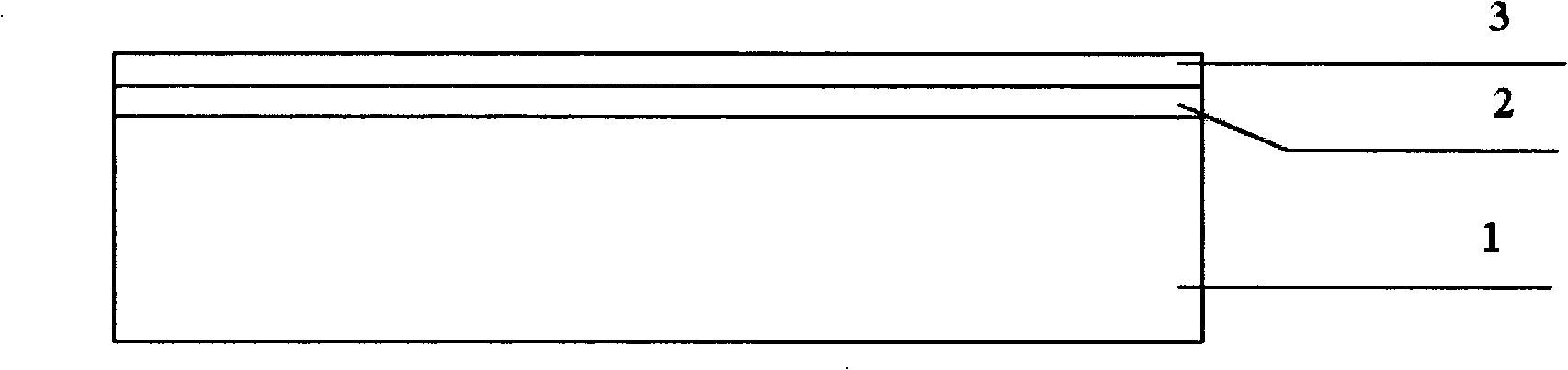

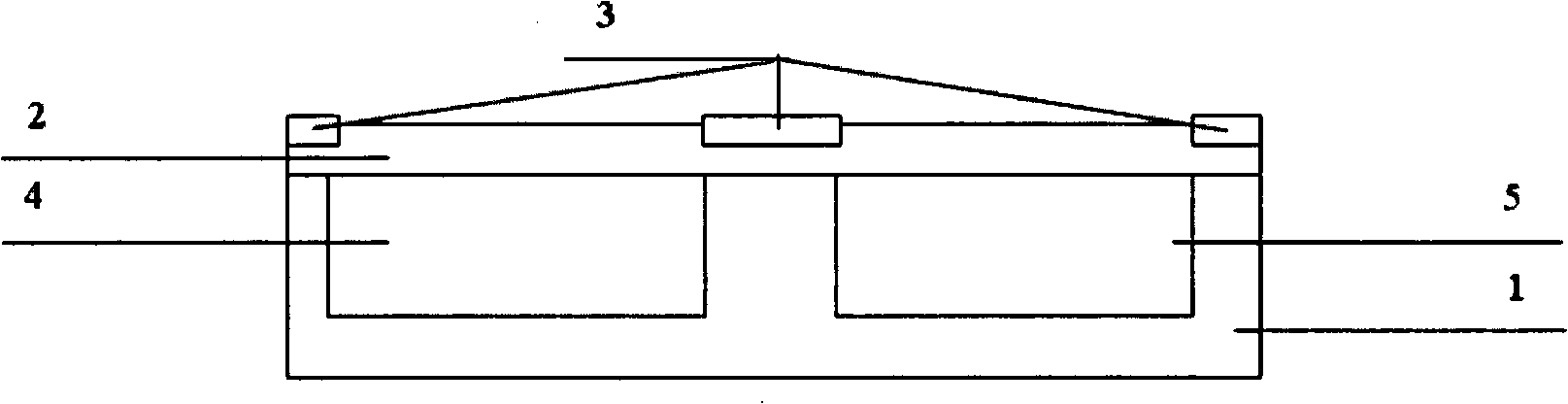

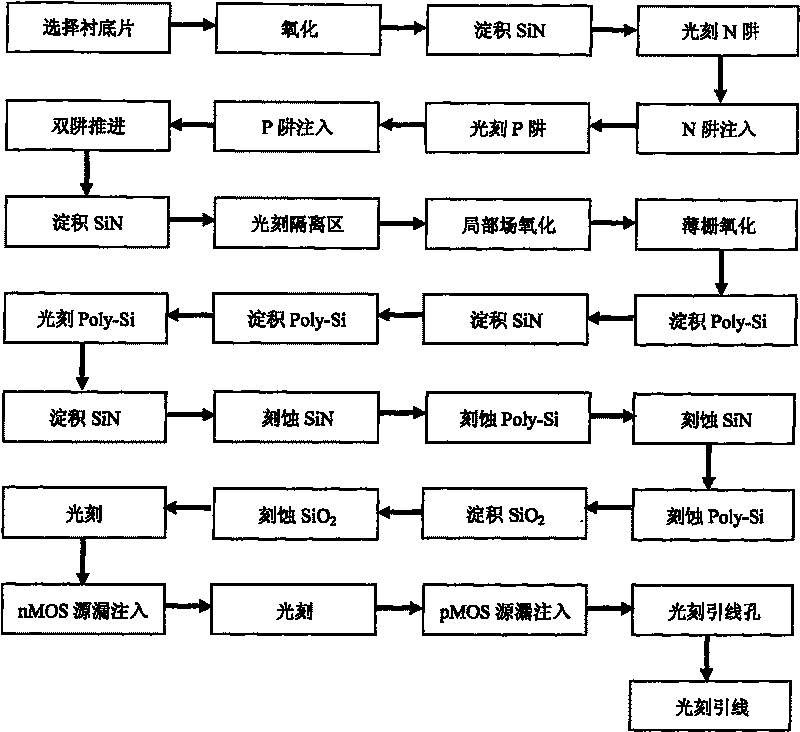

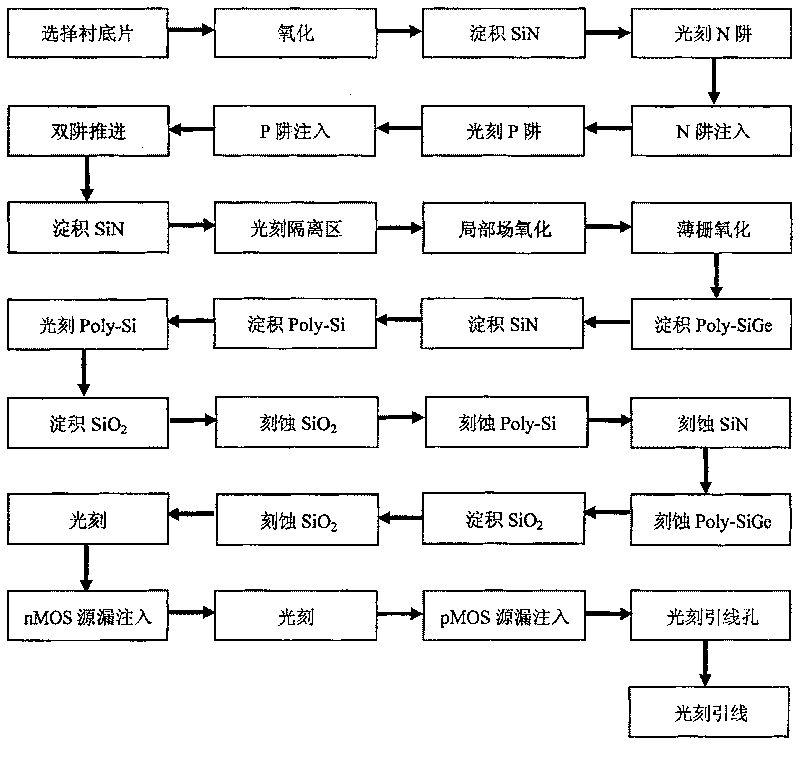

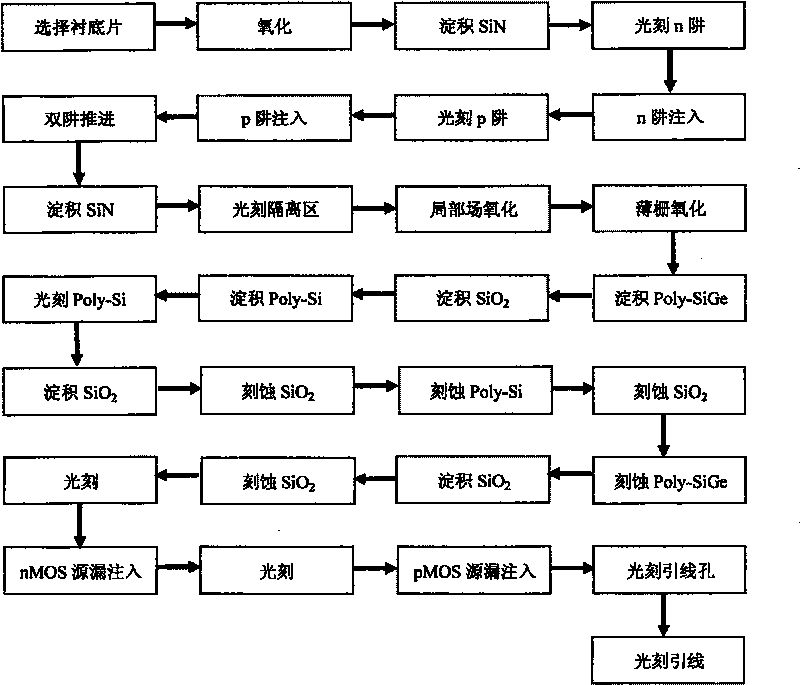

Method for preparing polycrystal SiGe gate nano CMOS integrated circuit by SiN masking technique

InactiveCN101359627AThreshold Voltage AdjustmentAchieve regulationSemiconductor/solid-state device manufacturingMOSFETMicron scale

The invention discloses a method for fabricating a nano-scale CMOS integrated circuit which has a polycrystal SiGe grid through SiN masking technique. The process includes the following steps: fabricating an N / P well and growing a Poly- SiGe / SiN / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiN; etching the SiN layer on the surface, except the SiN at the side face of the window; based on the etching ratio of Poly-Si to SiN (11:1), etching the Poly-Si at the surface of SiN and etching the SiN except on the side wall of SiN so as to expose the substrate of Poly-SiGe; based on the etching ratio of Poly-SiGe to SiN(11:1), etching the Poly-SiGe except on the side wall of the SiN so as to form an n / p MOSFET grid; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form an n / p MOSFET device; and photoetching interconnection lines of the device so as to form a CMOS integrated circuit with a conducting channel at 45-90nanometer. The method can fabricate a CMOS integrated circuit which is improved in performance by 3-5 generations on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

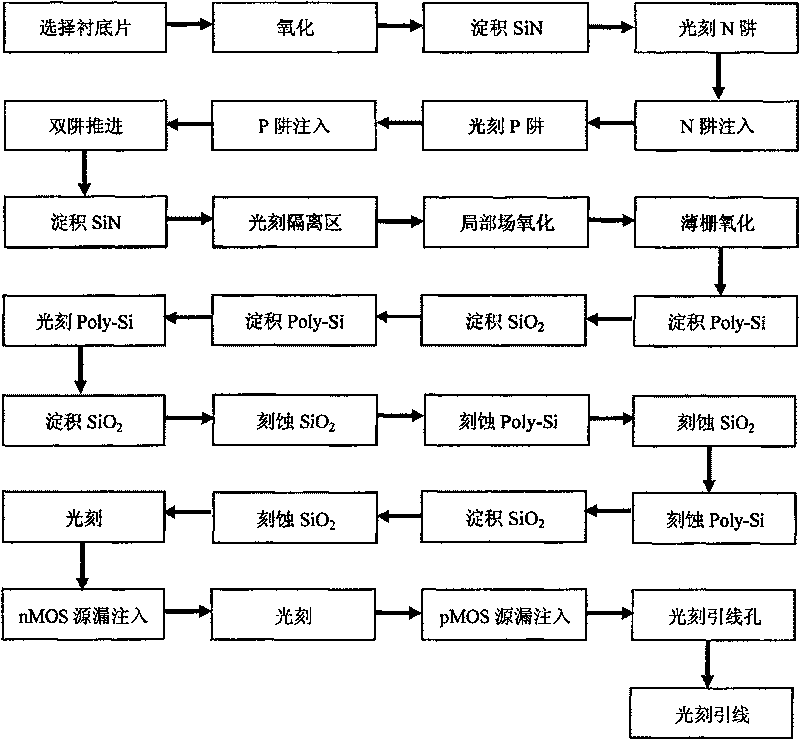

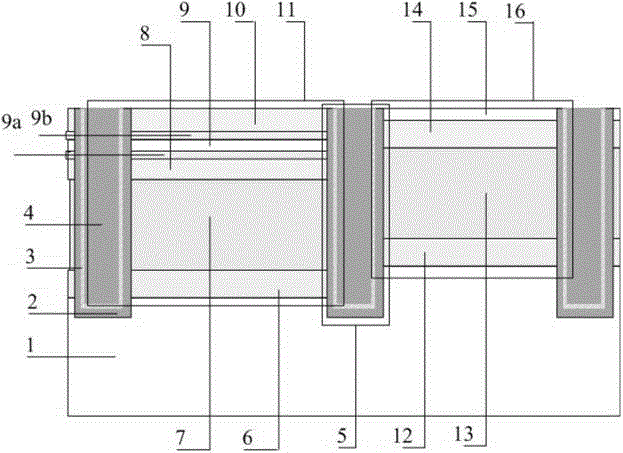

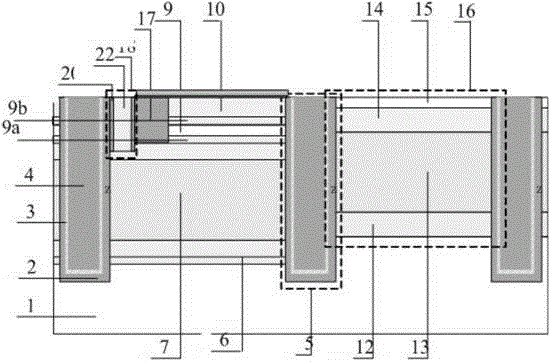

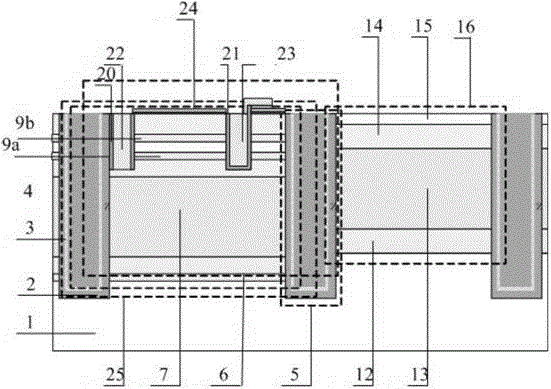

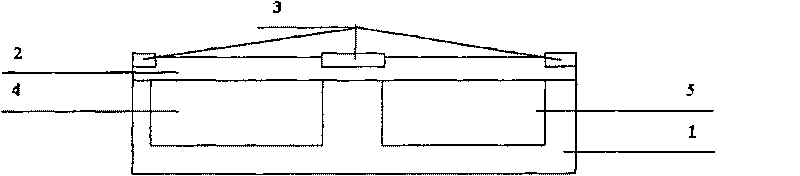

Method for preparing nano CMOS parts by using side wall and solid phase diffusion of polysilicon

InactiveCN1416168ALower requirementSemiconductor/solid-state device manufacturingEngineeringReactive-ion etching

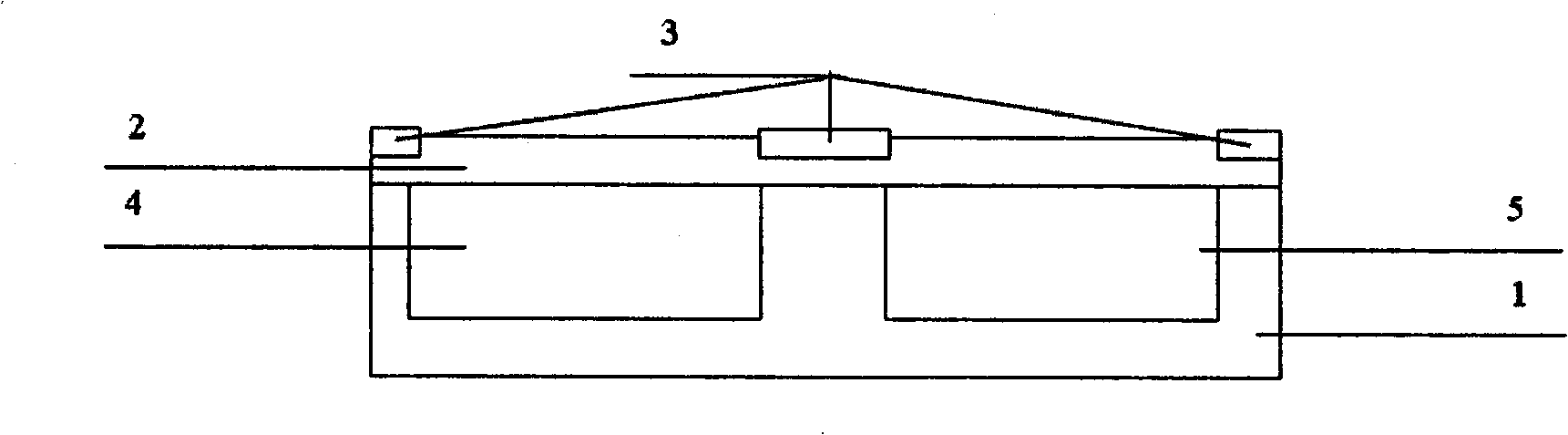

The invention relates to the technique area for manufacturing very large integrated circuit, including following steps. (1) Designing the pattern of the cell. (2) Insulating components, oxidizing grids and depositing the polysilicon of the grids, before this step, the trap is made based on the need. (3) The lines of the grids are made by using the side wall translocation (4) Depositing silicon dioxide, then reactive ion etching silicon dioxide forms the side wall. Complement area of CMOS LDD is prepared by polysilicon solid diffusion. (5) Depositing silicon dioxide, reactive ion etching silicon dioxide forms, the side wall of the final components. (6) The general following up procedures form the source and the drain electrodes. Etching the contact hole, forming the metal line to connect components.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

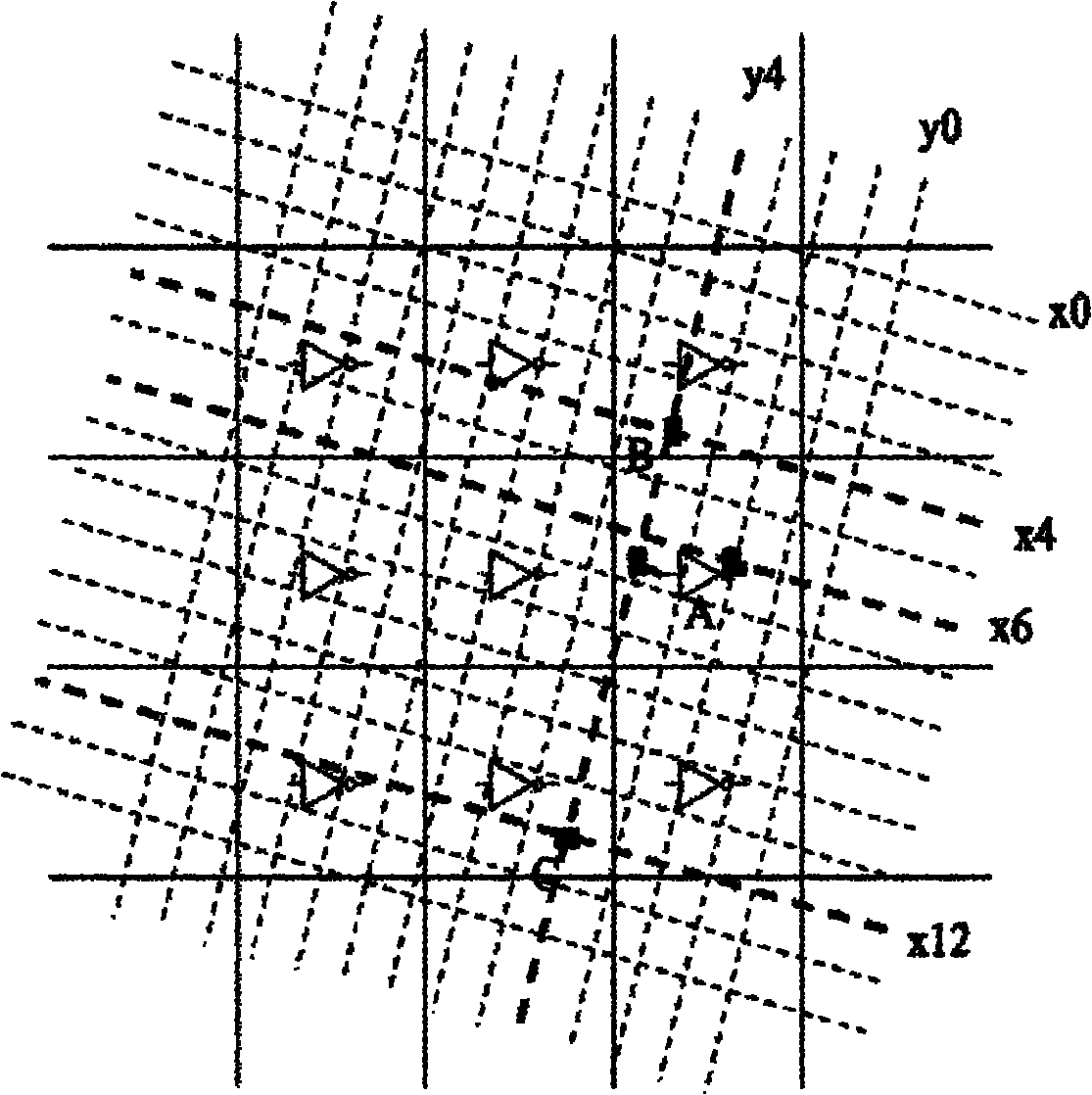

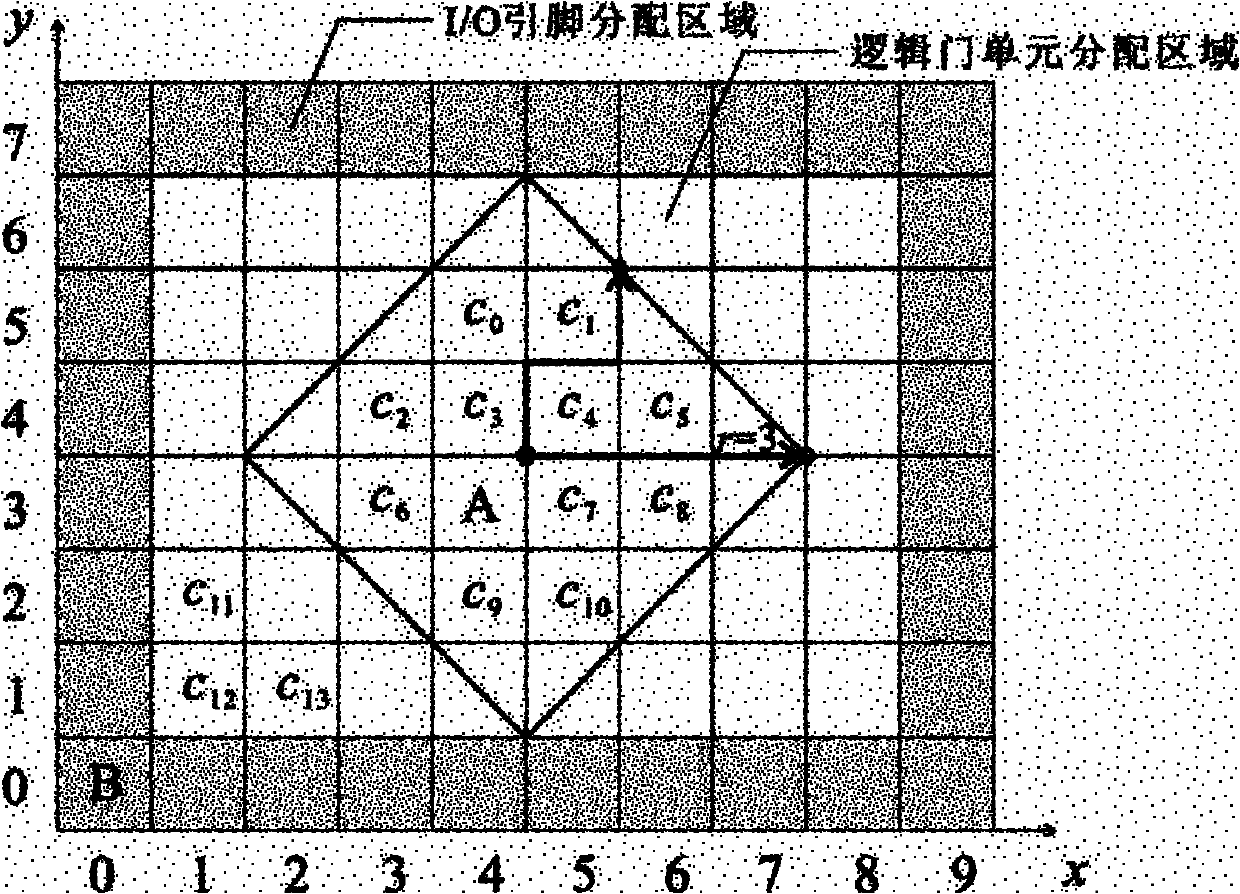

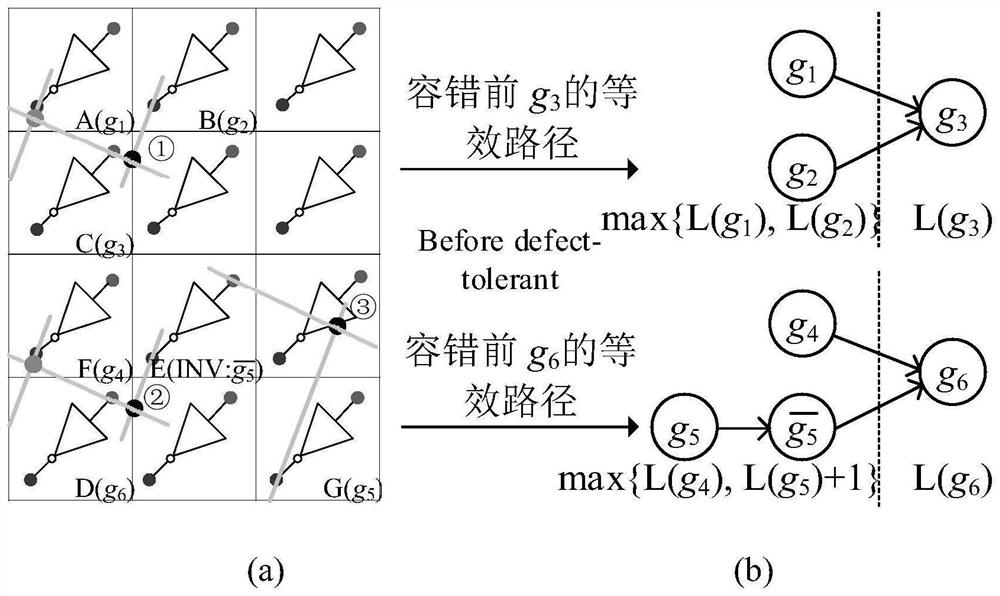

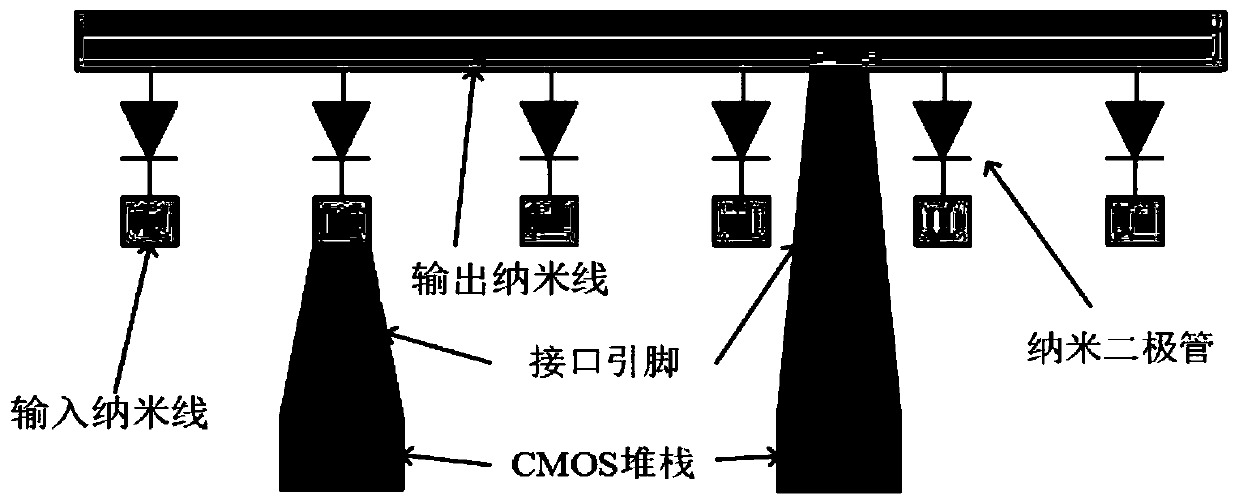

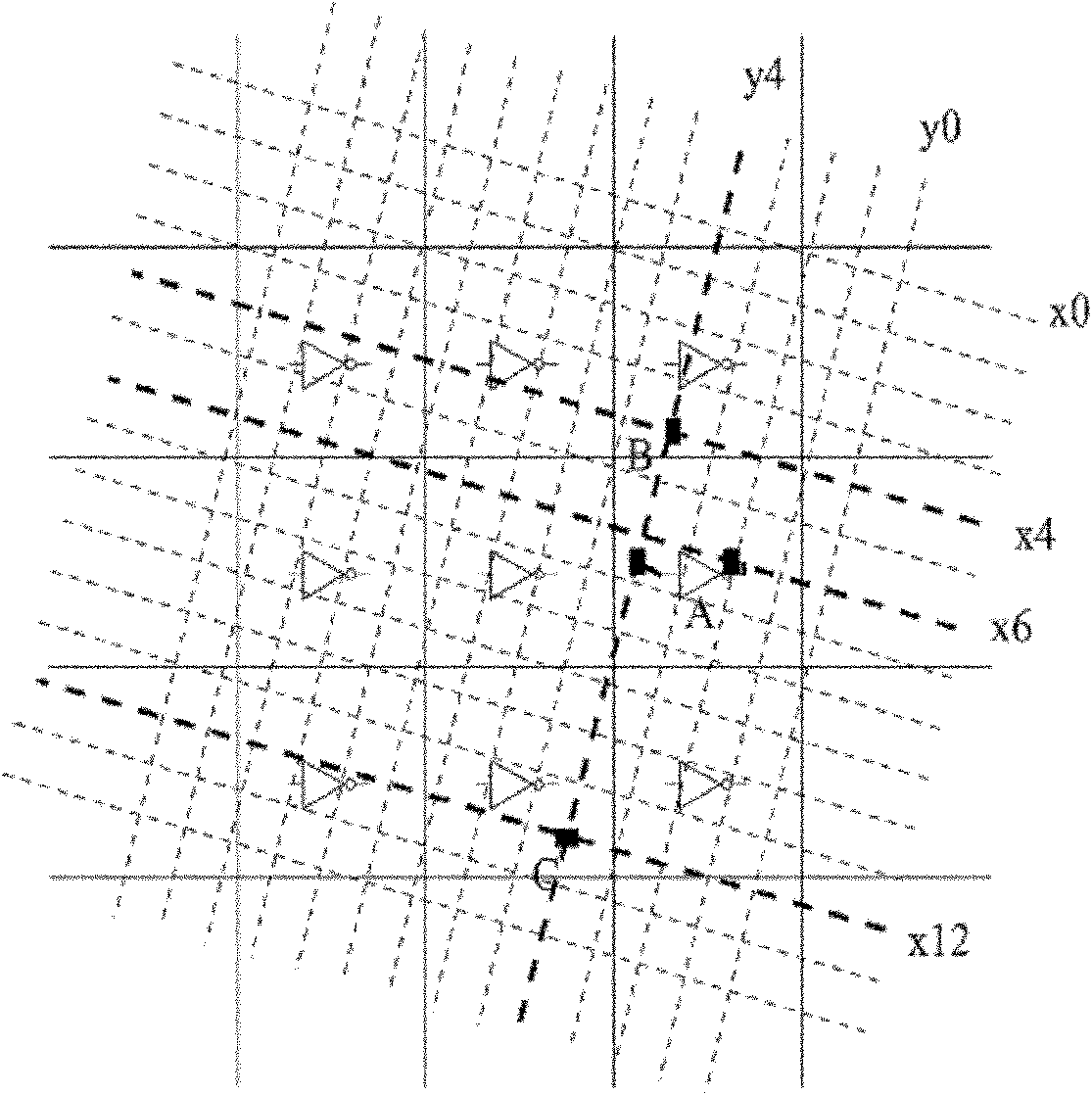

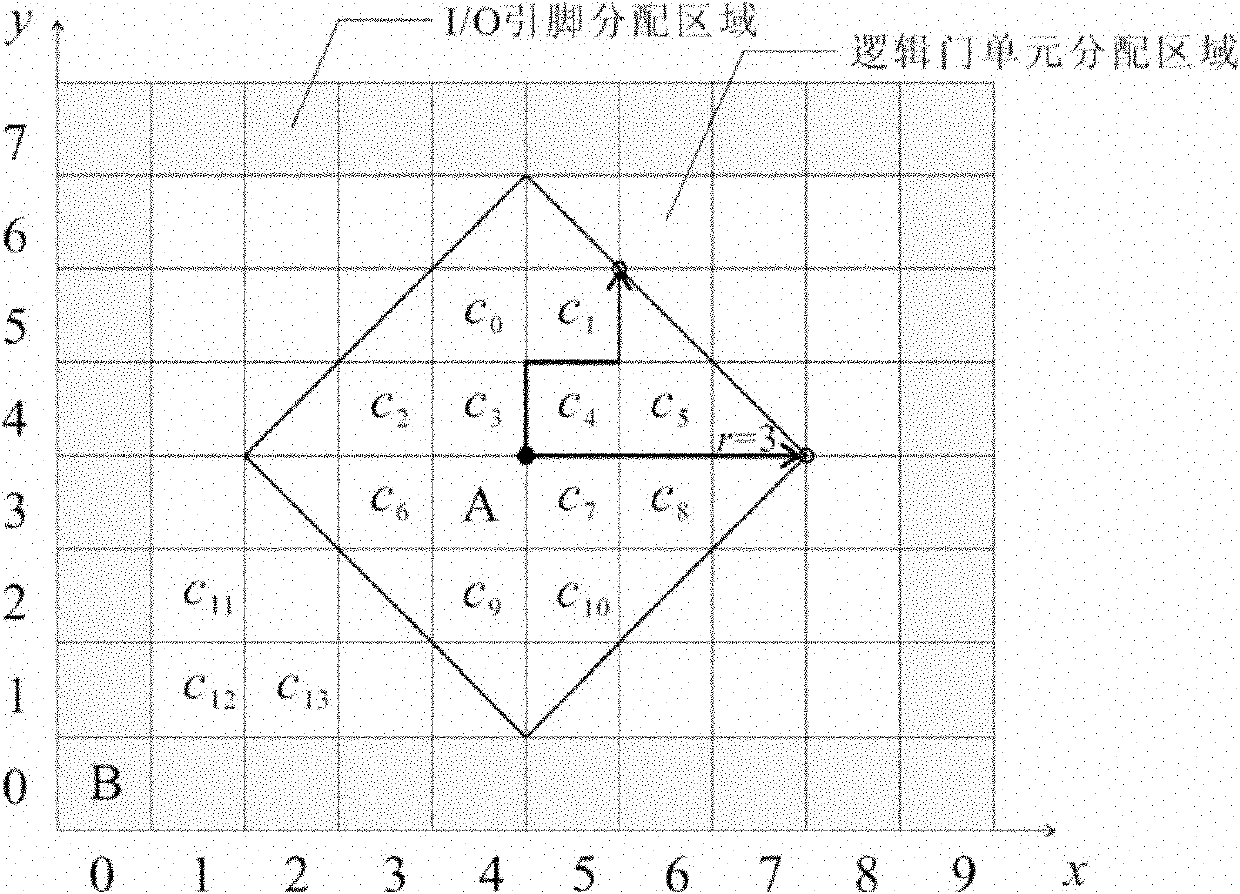

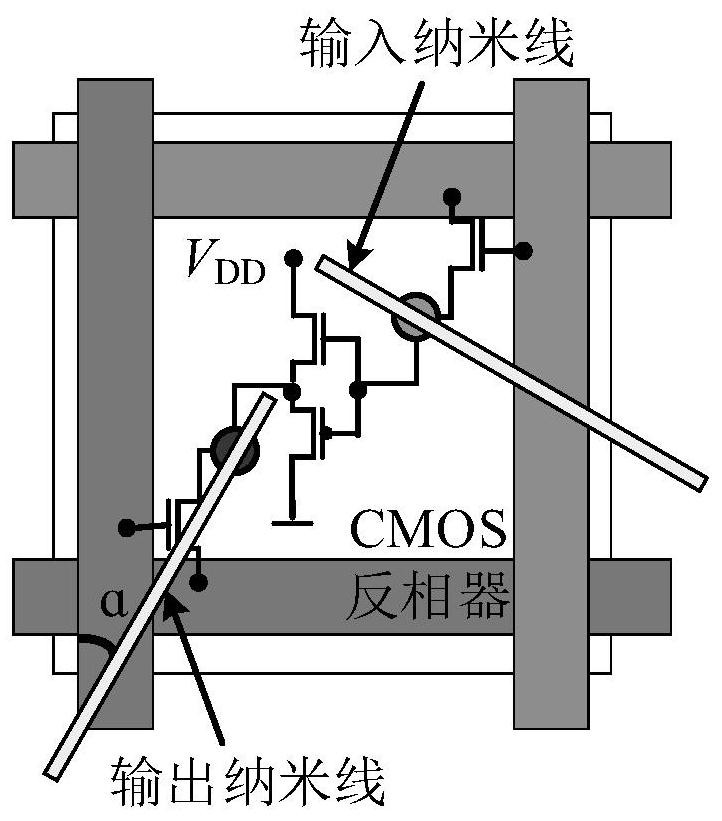

I/O (input/output)pin allotting method for nano CMOS (Complementary Metal-Oxide-Semiconductor Transistor) circuit structure

InactiveCN102103647AExpand the range of connected domainsFaster allocation timeSemiconductor/solid-state device manufacturingSpecial data processing applicationsComputer scienceMetal

The invention discloses an I / O (input / output)pin allotting method for a nano CMOS (Complementary Metal-Oxide-Semiconductor Transistor) circuit structure; the method provided by the invention has the advantages of capable of effectively solving the limited I / O pin allotting communication area of the nano CMOS circuit structure, and reducing complexity of the whole circuit. The method comprises the following steps: a fan-out degree of an input pin I is analyzed, when the fan-out degree is larger than one threshold value Dout(T), the communication area is expanded by logically copying; a fan-in degree of an output pin O is analyzed, when the fan-in degree is larger than one threshold value Din(T), the communication area is expanded by inserting a pair of inverter sets so as to ease the allotting difficulty caused by high fan-out / fan-in of the I / O pin in the circuit. The test proves that the method provided by the invention can effectively solve the problem of difficultly allotting the I / O pin of the nano CMOS circuit structure.

Owner:NINGBO UNIV

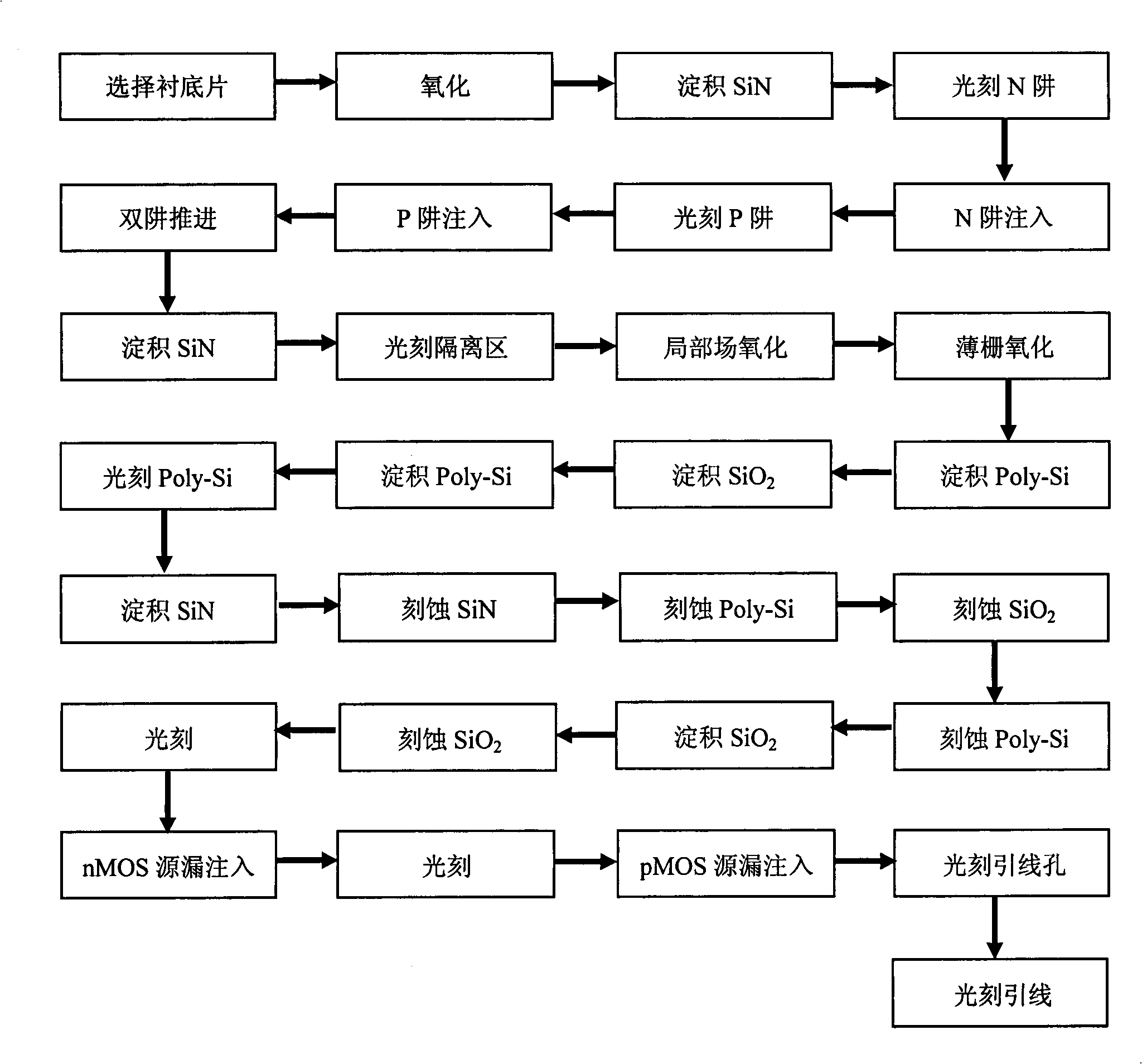

Method for preparing nano CMOS integrated circuit by SiO2 masking technique

InactiveCN101359630AImprove the preparation effectImprove performanceSemiconductor/solid-state device manufacturingMOSFETMicron scale

The invention discloses a method based on SiO2 masking technique for fabricating a nano-scale CMOS integrated circuit. The process includes the following steps: fabricating a N / P well and growing a Poly- Si / SiO2 / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiO2; etching away the SiO2 layer on the surface, except the SiO2 at the side face of the window; based on the etching ratio of Poly-Si to SiO2(50:1), etching the Poly-Si on the upper layer; etching the SiO2 on the substrate, except the SiO2 on the side wall so as to expose the substrate of Poly-Si; based on the etching ratio of Poly-Si to SiO2, etching the Poly-Si, except the Poly-Si in the protective area on the side wall of SiO2 so as to form an n / p MOSFET grid, and depositing a layer of SiO2 on the well; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form an n / p MOSFET device; and photoetching interconnection lines of the device so as to form a CMOS integrated circuit with a conducting channel at 65-90nm. The method can fabricate a CMOS integrated circuit which is improved in performance by 3-5 generations on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

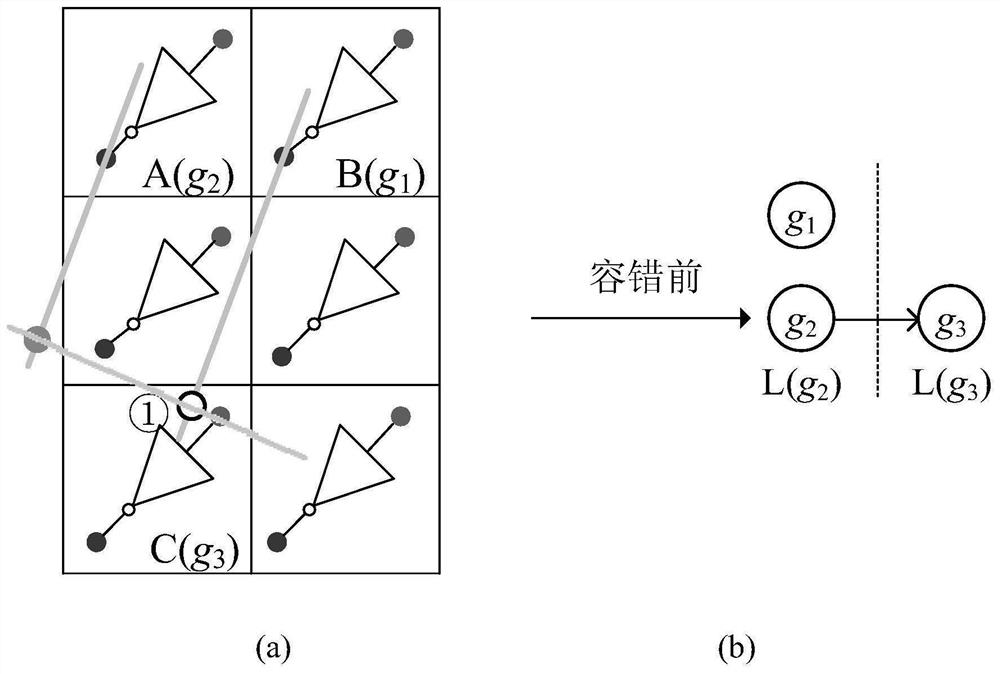

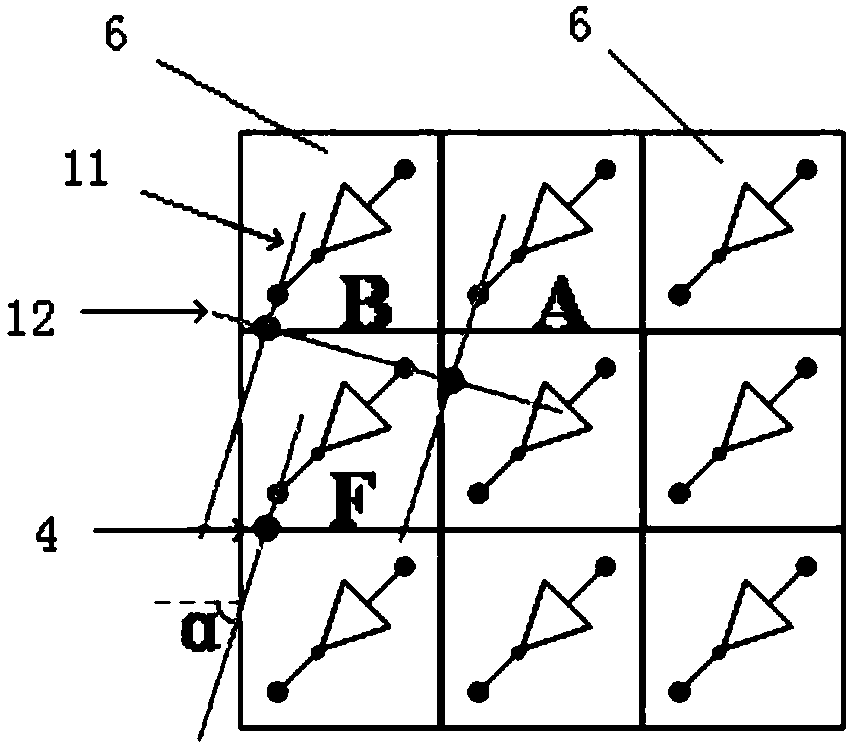

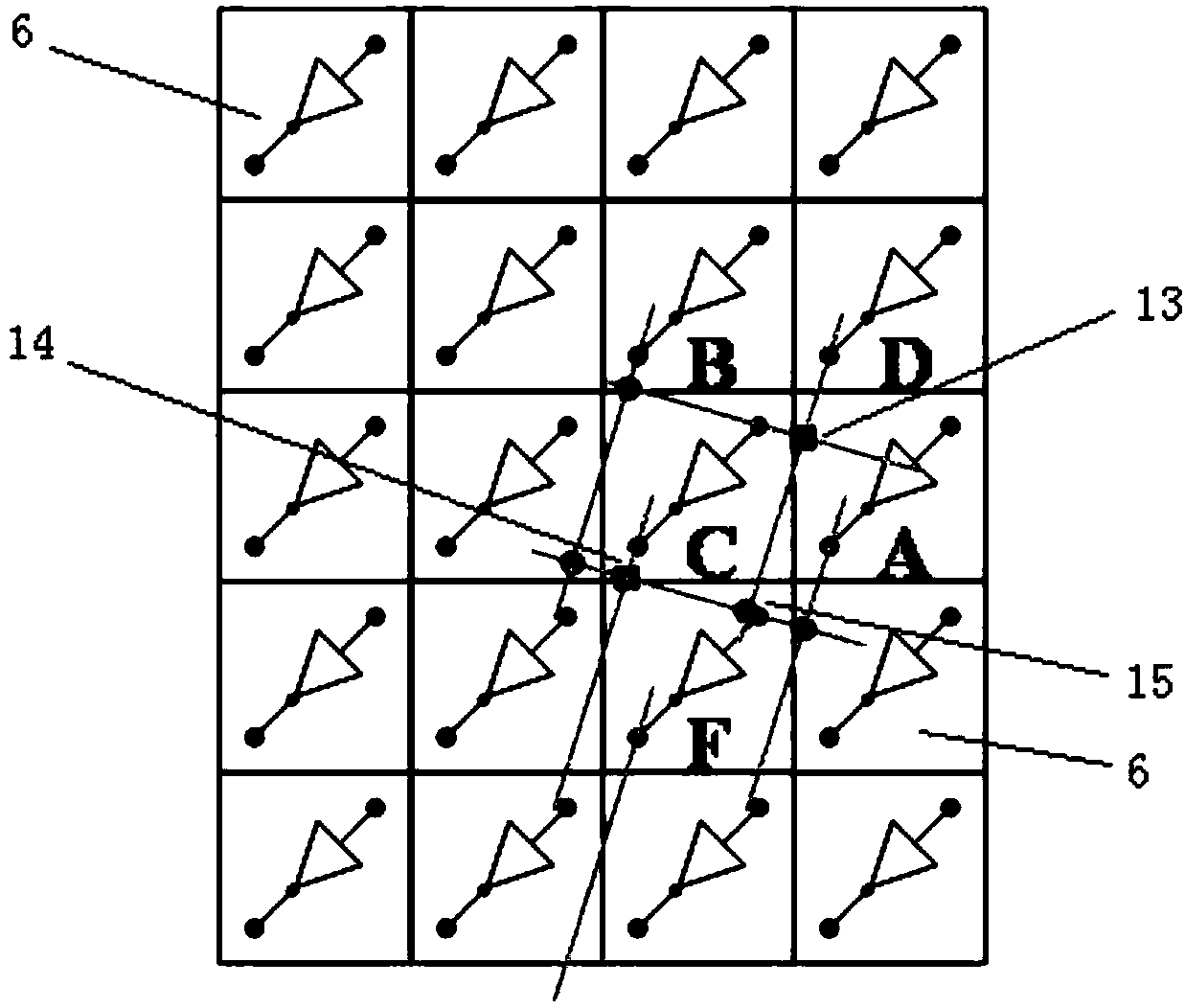

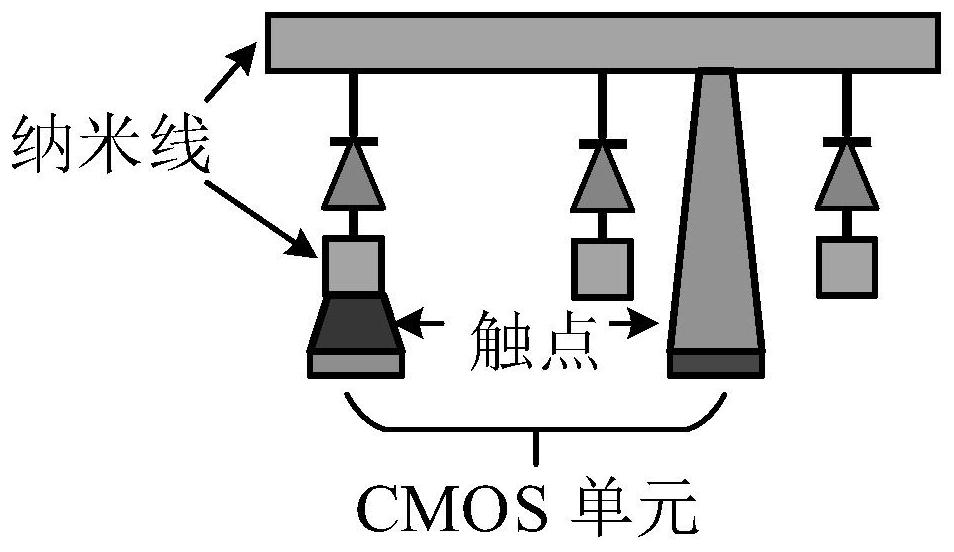

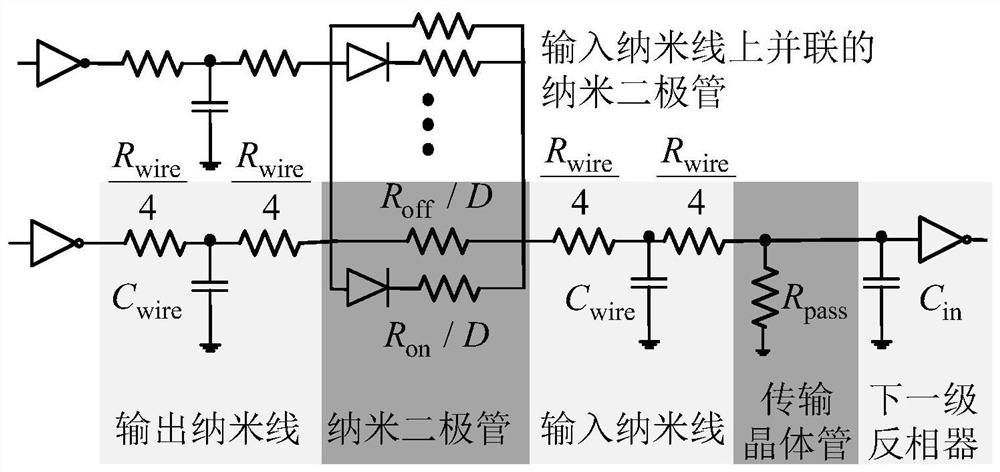

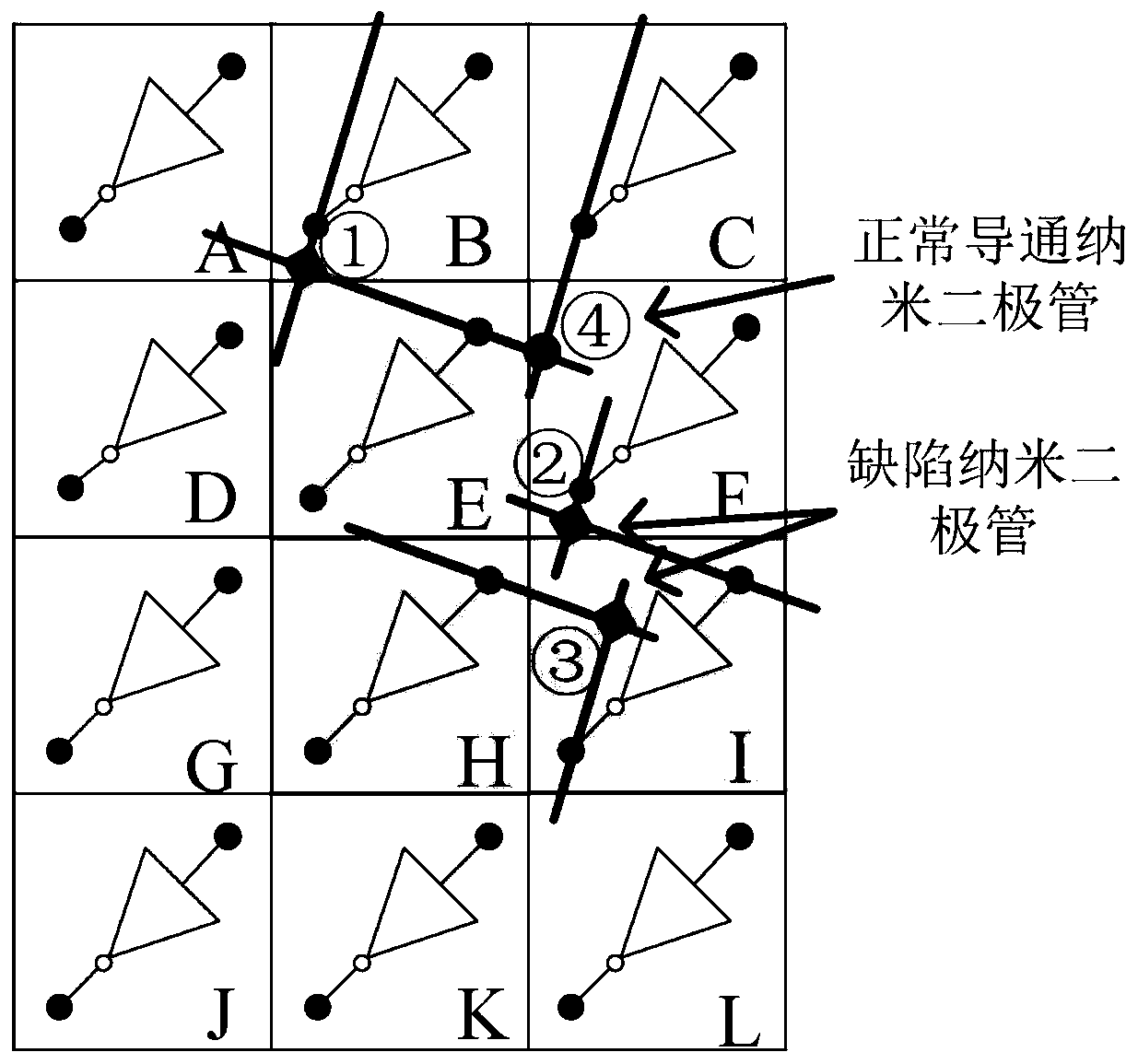

Nano CMOS circuit fault-tolerant mapping method capable of optimizing time delay

PendingCN112214946AImprove mapping abilityBig spaceSpecial data processing applicationsCAD with nanotechnologyTime delaysHemt circuits

The invention discloses a nano CMOS (Complementary Metal Oxide Semiconductor) circuit fault-tolerant mapping method capable of optimizing time delay, and aims to solve the problems of poor time delayperformance, poor solving speed, poor quality and the like in a nano CMOS circuit for realizing a correct logic function by adopting an existing fault-tolerant mapping method. Under the mapping constraints of defective nano CMOS circuit, the invention provides a nano CMOS circuit fault-tolerant mapping method capable of optimizing time delay. According to the fault-tolerant mapping method, the mapping process of a traditional nano CMOS circuit is optimized, the dividing technology of a logic level to a logic circuit to be mapped and the physical-level pre-planning technology with original input as an object are newly added, and the logic circuit is mapped by taking a path tree as a unit. Two mapping modes are adopted to be mapped into a pre-planned area in the nano CMOS circuit to optimizeeach path delay, the mapping success rate is improved by searching available defect units, and the delay performance of the delay mapping circuit is optimized on the basis of quickly eliminating theinfluence of defects on the logic function of the nano CMOS circuit.

Owner:NINGBO UNIV

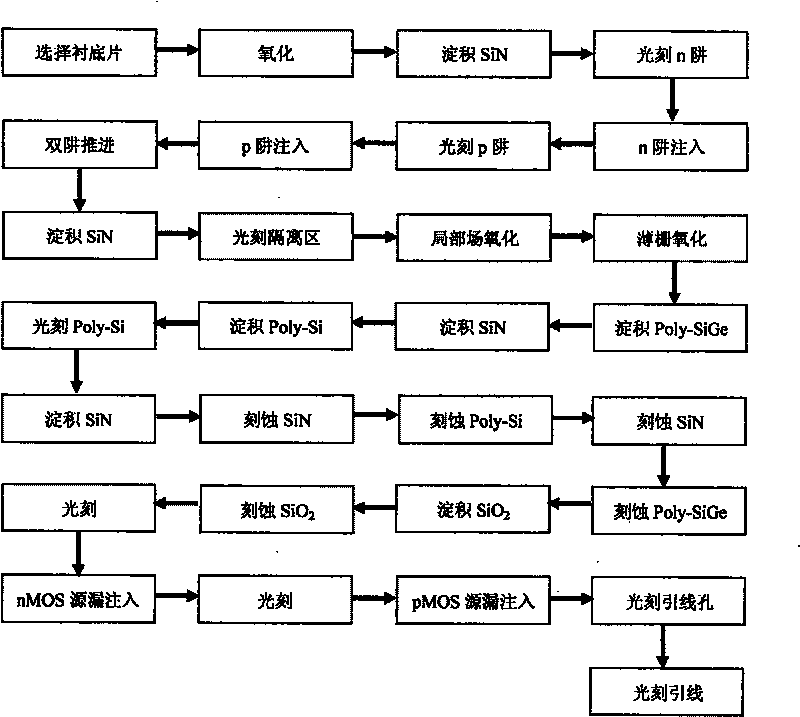

Polycrystal SiGe gate nano CMOS integrated circuit preparation based on SiO2 macking technique

InactiveCN101359629AThreshold Voltage AdjustmentAchieve regulationSemiconductor/solid-state device manufacturingMOSFETMicron scale

The invention discloses a method based on SiO2 masking technique for fabricating a nano-scale CMOS integrated circuit which has a polycrystal SiGe grid. The process includes the following steps: fabricating an N / P well and growing a Poly- SiGe / SiO2 / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiO2; etching the SiO2 layer on the surface, except the SiO2 at the side face of the window; based on the etching ratio of Poly-Si to SiO2 (50:1), etching the Poly-Si at the upper layer; based on the etching ratio of Poly-SiGe to SiO2 (50:1), etching the SiO2 and the Poly-SiGe, except the SiO2 and Poly-SiGe in the protective area at the side wall of the SiO2, preserving the SiO2 and Poly-SiGe below the side wall, forming a n / p MOSFET grid and depositing a layer of SiO2; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form an n / p MOSFET device; and photoetching interconnection lines of the device so as to form a CMOS integrated circuit with a conducting channel at 65-90nm. The method can fabricate a CMOS integrated circuit which is improved in performance by 3-5 generations on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

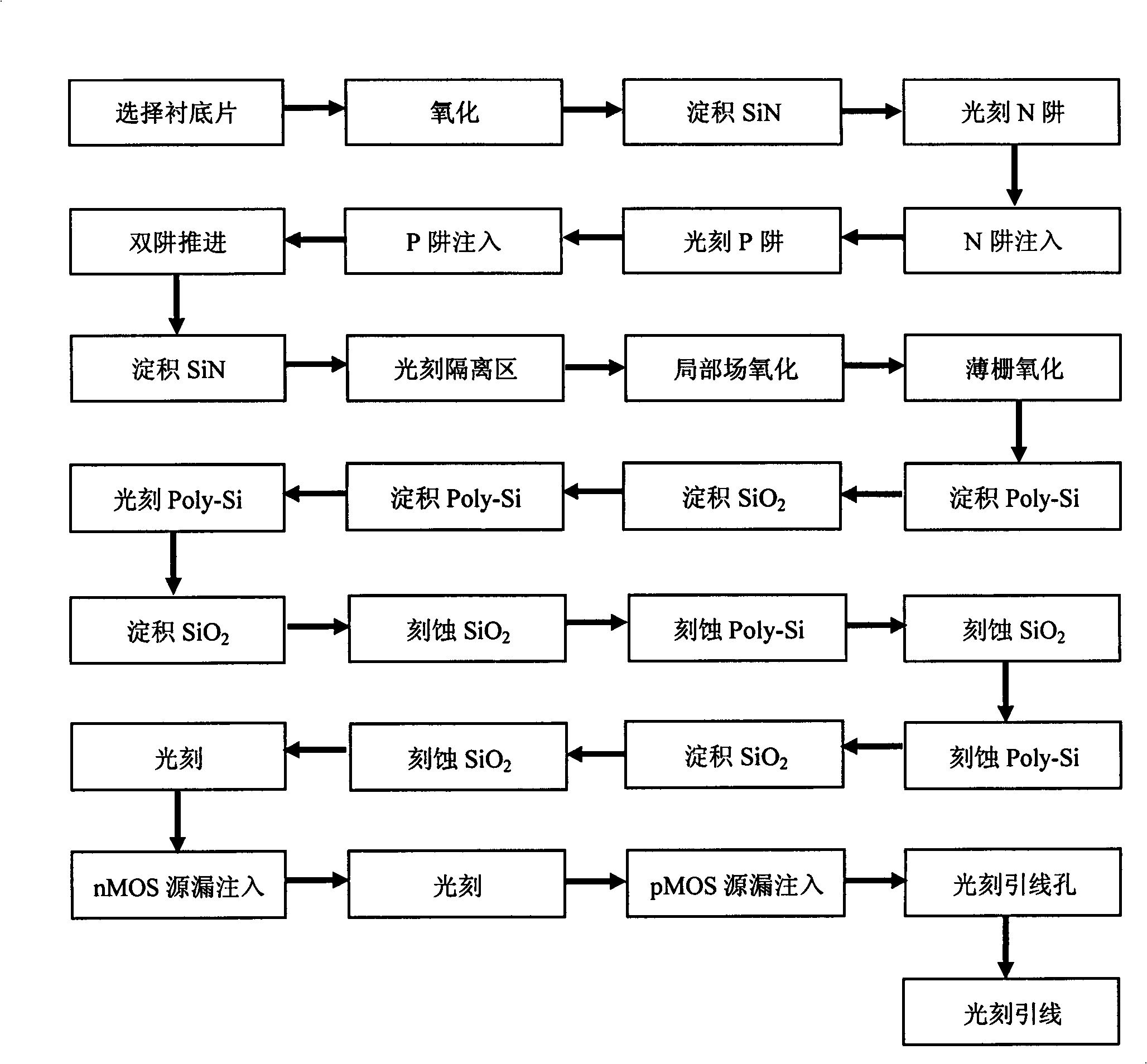

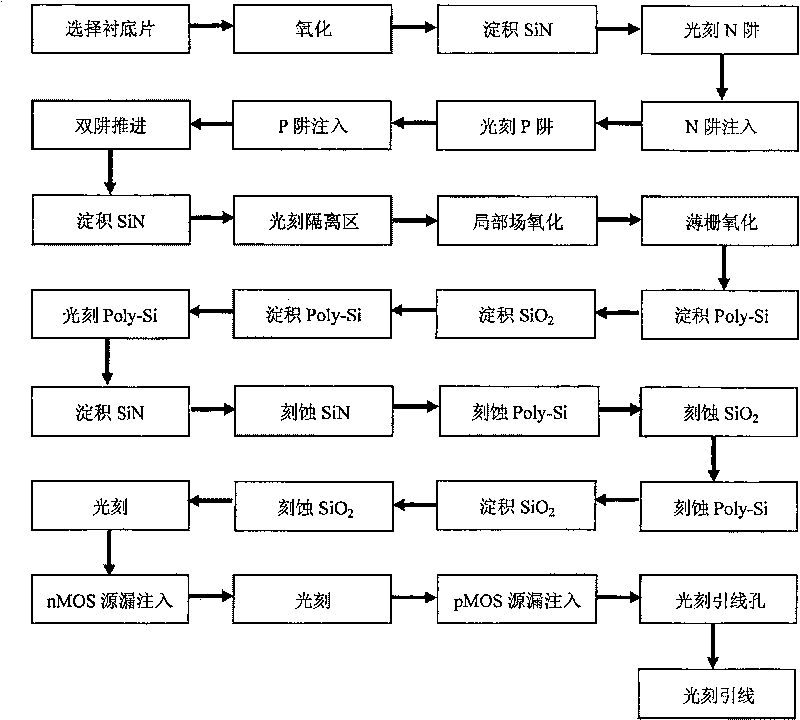

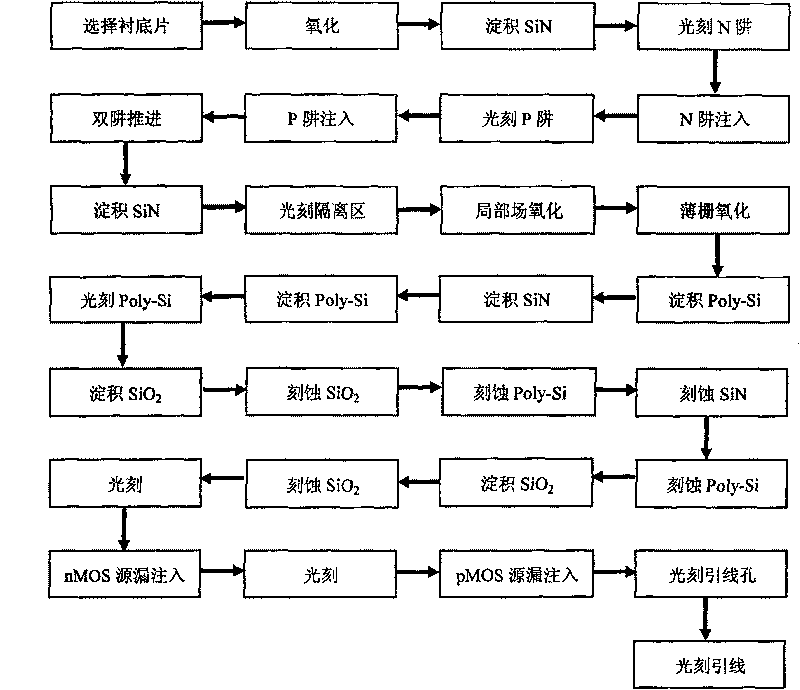

Method for preparing nano CMOS integrated circuit by SiN masking technique

InactiveCN101359632AImprove the preparation effectImprove performanceSemiconductor/solid-state device manufacturingMOSFETMicron scale

The invention discloses a method based on SiN masking technique for fabricating a nano-scale CMOS integrated circuit. The process includes the following steps: fabricating an N / P well and growing a Poly-Si / SiN / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiN; etching away the SiN on the surface of the substrate, except the SiN at the side wall of the Poly- Si; based on the etching ratio of Poly-Si to SiN(11:1), etching the Poly-Si on the surface of SiN; etching the SiN on surface of the substrate, except the SiN on the side wall of the SiN so as to expose the substrate of Poly-Si; based on the etching ratio of Poly-Si to SiN, etching the Poly-Si, except the Poly-Si in the protective area on the side wall of SiN so as to form an n / p MOSFET grid, and depositing a layer of SiO2 at the well area; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form an n / p MOSFET device; and photoetching interconnection lines of the device so as to form a CMOS integrated circuit with a conducting channel at 45-90nm. The method can fabricate a CMOS integrated circuit which is improved in performance by 3-5 generations on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

Nano CMOS integrated circuit preparation method based on SiN/SiO2 masking technique

InactiveCN101359628AImprove the preparation effectImprove performanceSemiconductor/solid-state device manufacturingMOSFETCMOS

The invention discloses a method based on SiN / SiO2 masking technique for fabricating a nano-scale CMOS integrated circuit. The process includes the following steps: fabricating an N / P well and growing a Poly- Si / SiO2 / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiN; etching the SiN layer on the surface, except the SiN at the side face of the window; based on the etching ratio of Poly-Si to SiN (11:1), etching the Poly-Si at the surface of SiN; based on the etching ratio of (4:1), etching the SiN on the surface, except the SiN on the side wall of SiO2; based on the etching ratio of Poly-Si to SiN, etching the Poly- Si, except the Poly- Si on the side wall of the SiO2 so as to form an n / p MOSFET grid; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form an n / p MOSFET device; and photoetching interconnection lines of the device so as to form a CMOS integrated circuit with a conducting channel at 65-90nanometer. The method can fabricate a CMOS integrated circuit which is improved in performance by 3-5 generations on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

Method for preparing nano CMOS parts by using side wall and solid phase diffusion of polysilicon

InactiveCN1182578CLower requirementSemiconductor/solid-state device manufacturingEngineeringReactive-ion etching

The invention relates to the technique area for manufacturing very large integrated circuit, including following steps. (1) Designing the pattern of the cell. (2) Insulating components, oxidizing grids and depositing the polysilicon of the grids, before this step, the trap is made based on the need. (3) The lines of the grids are made by using the side wall translocation (4) Depositing silicon dioxide, then reactive ion etching silicon dioxide forms the side wall. Complement area of CMOS LDD is prepared by polysilicon solid diffusion. (5) Depositing silicon dioxide, reactive ion etching silicon dioxide forms, the side wall of the final components. (6) The general following up procedures form the source and the drain electrodes. Etching the contact hole, forming the metal line to connect components.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

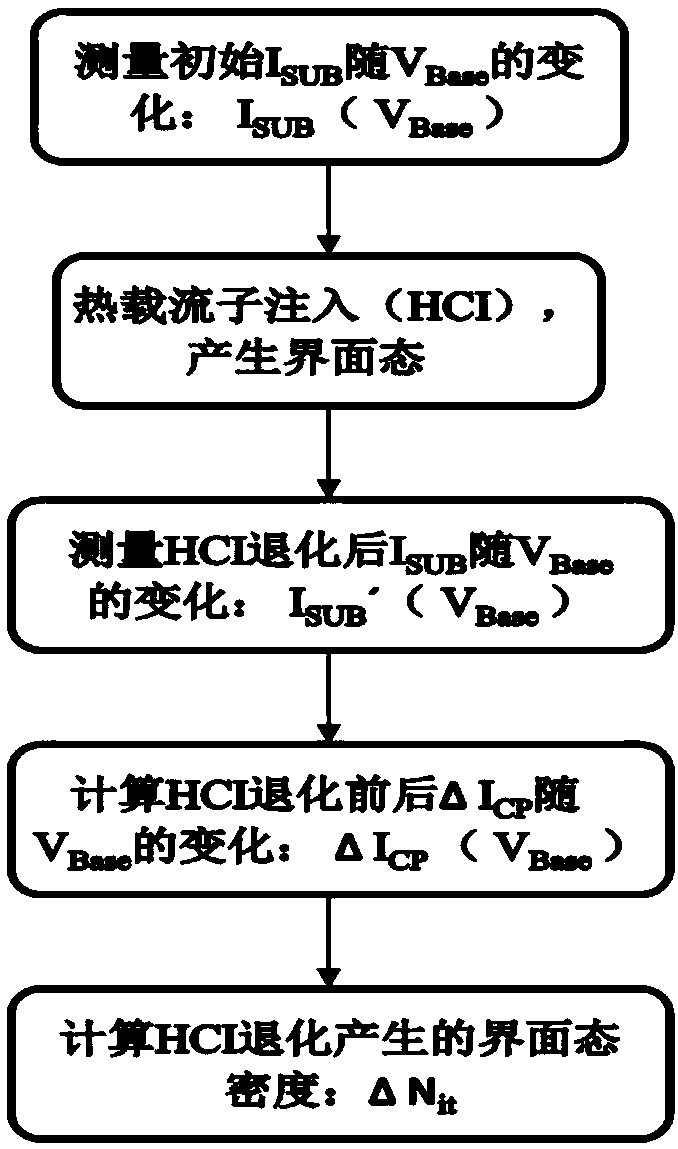

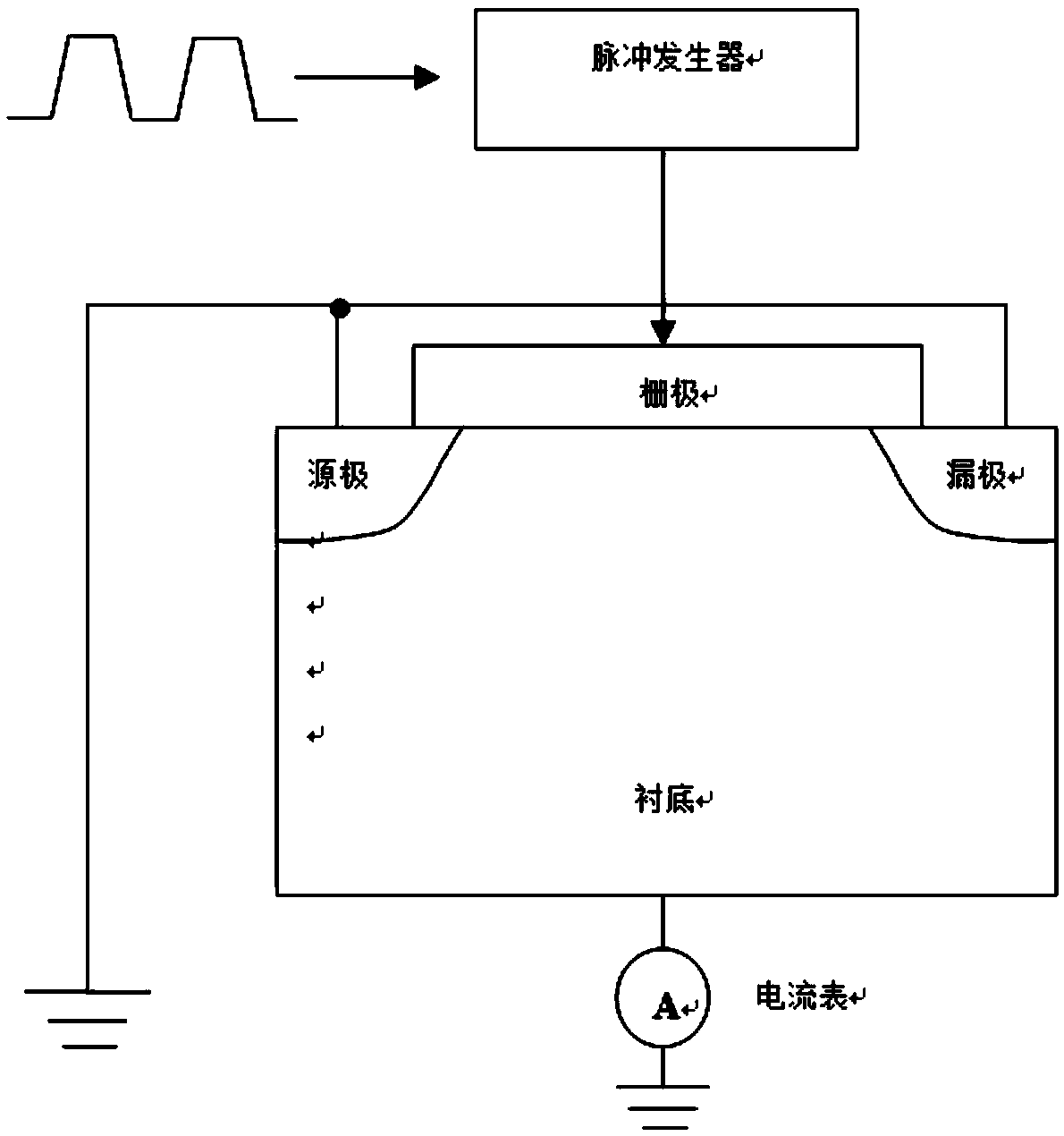

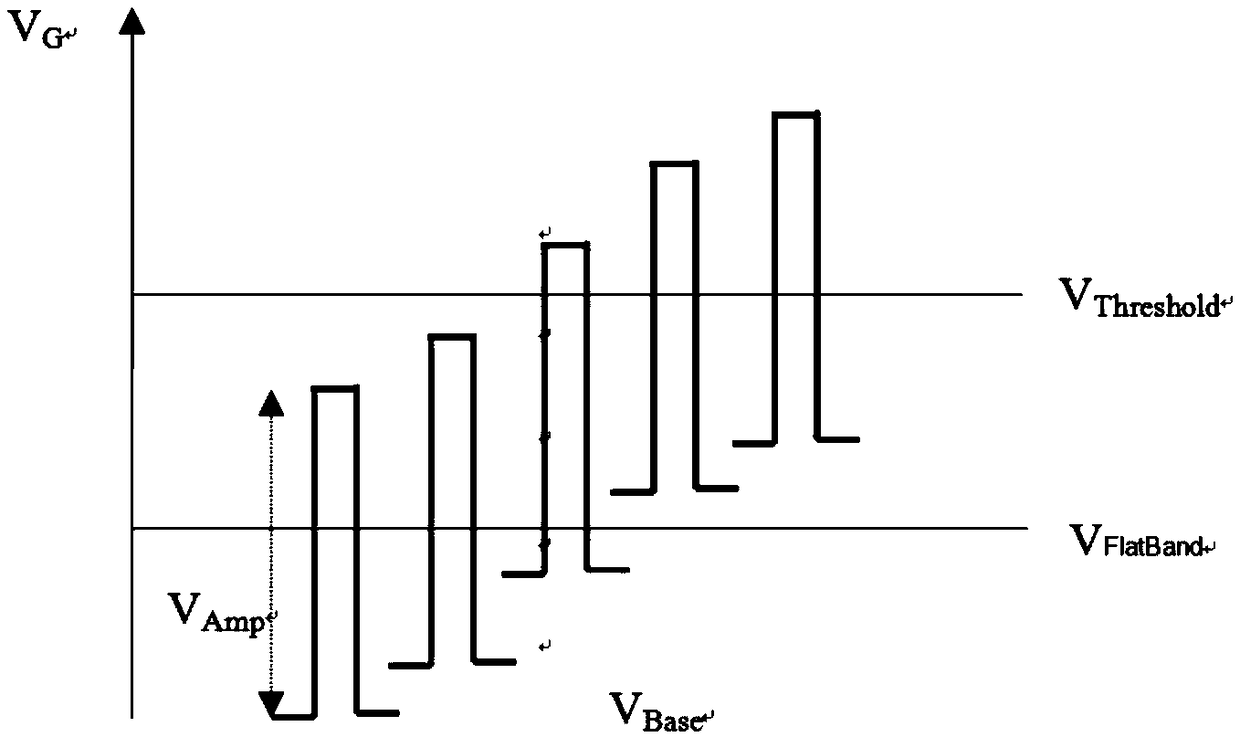

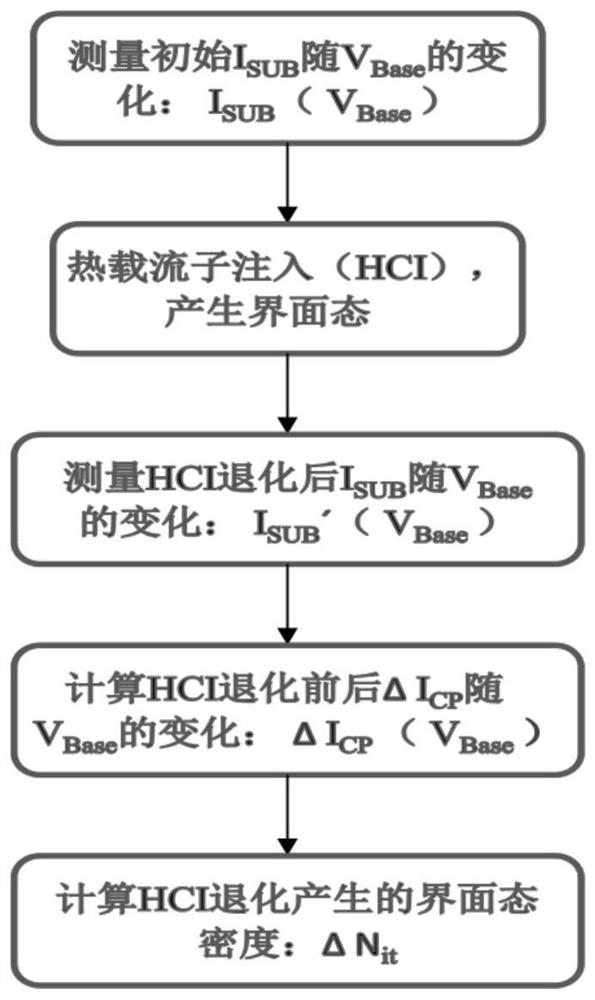

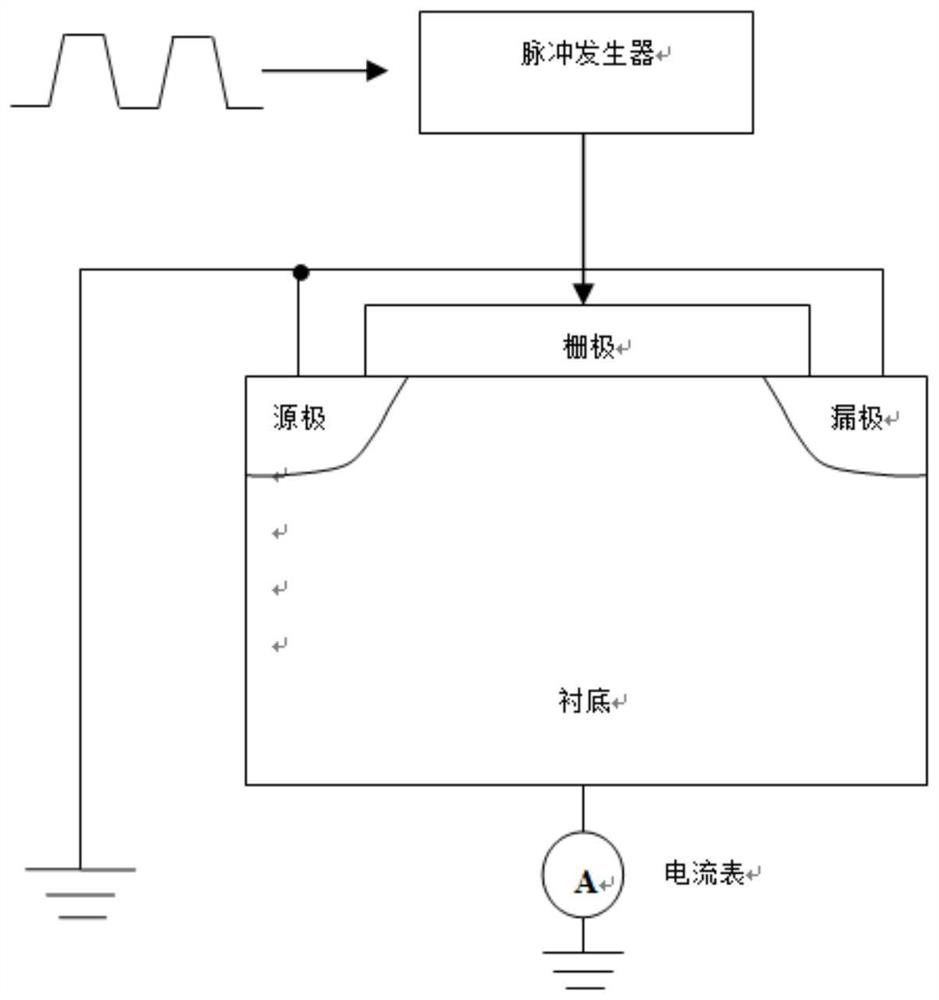

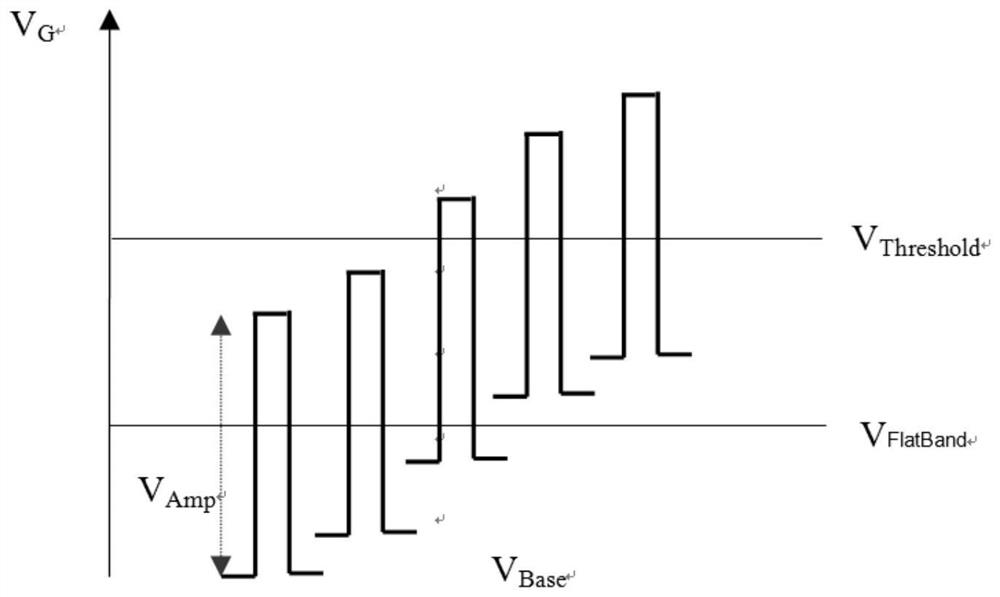

Charge pump method for calculating variable quantity of stress-induced interfacial state density in nano-CMOS device

ActiveCN109001609ADevelopment Reliability StudiesPromote Reliability ResearchSemiconductor operation lifetime testingCMOSEngineering

The invention discloses a charge pump method for calculating the variable quantity of stress-induced interfacial state density in a nano-CMOS device. On the basis of a traditional CP method, the substrate currents of the nano small-size device in an initial state and in a stress state are measured, the real charge pump current I<cp> is extracted from the substrate current, and the stress-induced interfacial defect density is calculated. The charge pump method is suitable for the nano small-size CMOS device with the large leakage current, the frequency is kept fixed in the measurement process,and measurement results are high in accuracy; and the research on a stress-induced defect characterization method of the nano-CMOS device can be further developed, and the development of reliability research of the nano small-size CMOS device is promoted advantageously.

Owner:马丽娟

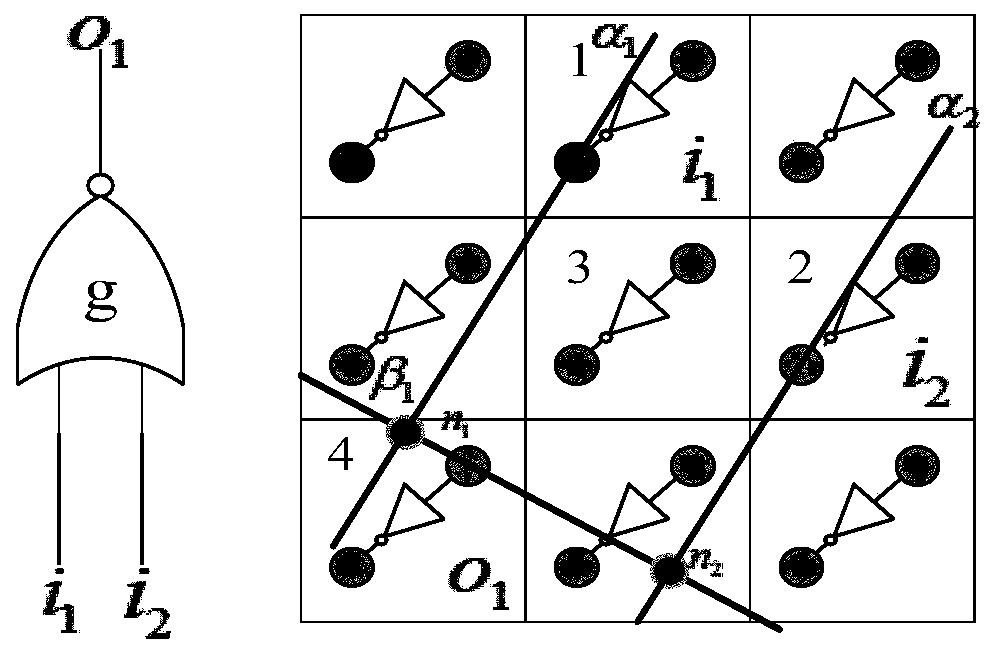

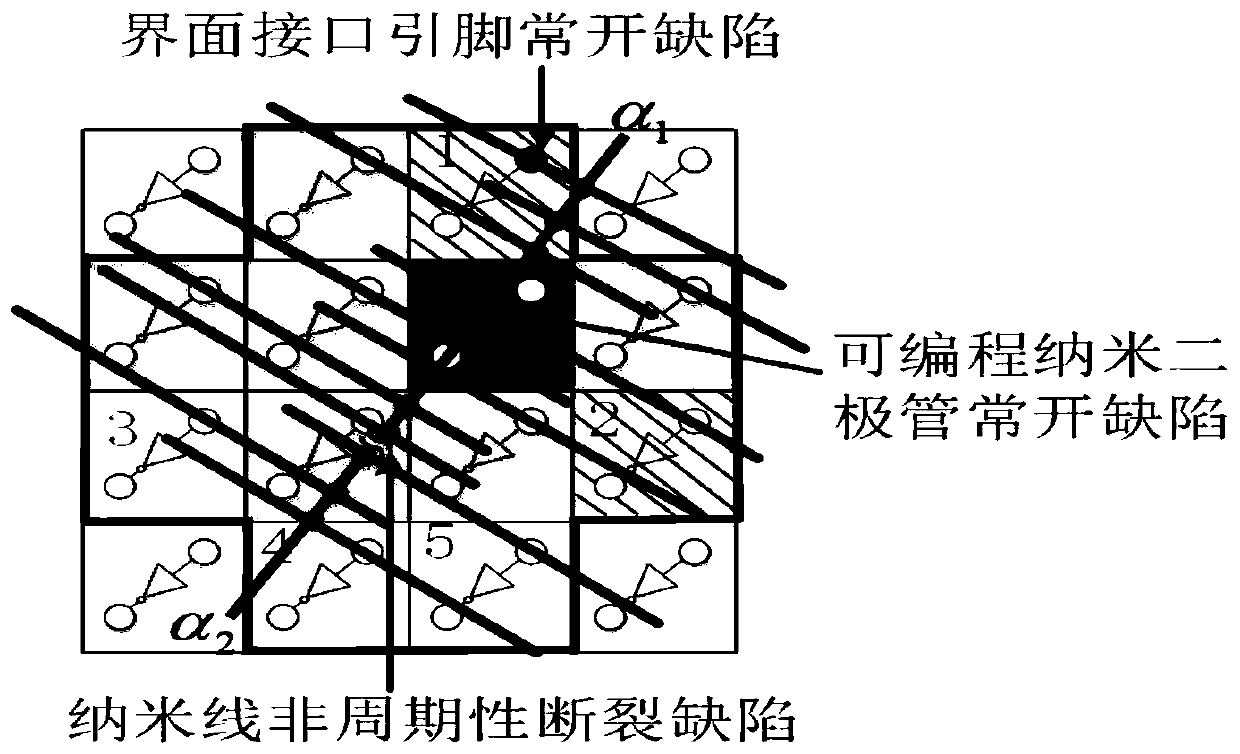

Quick mapping method for normally open defect of nano CMOS circuit represented by matrix

ActiveCN111062182AFast Fault Tolerant MappingEfficient Fault-Tolerant MappingComputer aided designSpecial data processing applicationsHemt circuitsLogic circuitry

The invention discloses a quick mapping method for normally open defects of a nano CMOS (Complementary Metal Oxide Semiconductor) circuit represented by a matrix, which comprises the following steps:defining the normally open defects of three nano CMOS circuits, and constructing a given nano CMOS circuit into a nano CMOS matrix to be represented according to the connected domain constraint and circuit defect condition of the nano CMOS circuit; then, according to the fan-in and fan-out relationship among the nodes in the logic circuit to be mapped, constructing the logic circuit into a logic matrix for representation; then, establishing matching rules of the two matrixes, and finishing searching of matchable elements between the matrixes through an evolutionary algorithm; and finally, carrying out element matching on the two matrixes to finish unit mapping. According to the invention, the circuit mapping complexity can be simplified, the circuit solving efficiency and the solving scaleare improved, the mapping area is reduced, and the influence of the normally open defect on the logic function of the nano CMOS circuit is quickly eliminated under the condition of improving the unitutilization rate and the mapping success rate, so that the fault-tolerant mapping of the normally open defect of the nano CMOS circuit is quickly and effectively completed.

Owner:NINGBO UNIV

Nano CMOS integrated circuit preparation method based on SiN/SiO2 masking technique

InactiveCN101359628BImprove the preparation effectImprove performanceSemiconductor/solid-state device manufacturingMOSFETMicron scale

The invention discloses a method based on SiN / SiO2 masking technique for fabricating a nano-scale CMOS integrated circuit. The process includes the following steps: fabricating an N / P well and growinga Poly- Si / SiO2 / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiN; etching the SiN layer on the surface, except the SiNat the side face of the window; based on the etching ratio of Poly-Si to SiN (11:1), etching the Poly-Si at the surface of SiN; based on the etching ratio of (4:1), etching the SiN on the surface, except the SiN on the side wall of SiO2; based on the etching ratio of Poly-Si to SiN, etching the Poly- Si, except the Poly- Si on the side wall of the SiO2 so as to form an n / p MOSFET grid; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form an n / p MOSFET device; and photoetching interconnection lines of the device so as to form a CMOSintegrated circuit with a conducting channel at 65-90nanometer. The method can fabricate a CMOS integrated circuit which is improved in performance by 3-5 generations on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

I/O (input/output)pin allotting method for nano CMOS (Complementary Metal-Oxide-Semiconductor Transistor) circuit structure

InactiveCN102103647BExpand the range of connected domainsFaster allocation timeSemiconductor/solid-state device manufacturingSpecial data processing applicationsComputer architectureComputer science

Owner:NINGBO UNIV

A charge-pump method for calculating stress-induced changes in interface state density in nano-cmos devices

ActiveCN109001609BDevelopment Reliability StudiesPromote Reliability ResearchSemiconductor operation lifetime testingCMOSEngineering

Owner:马丽娟

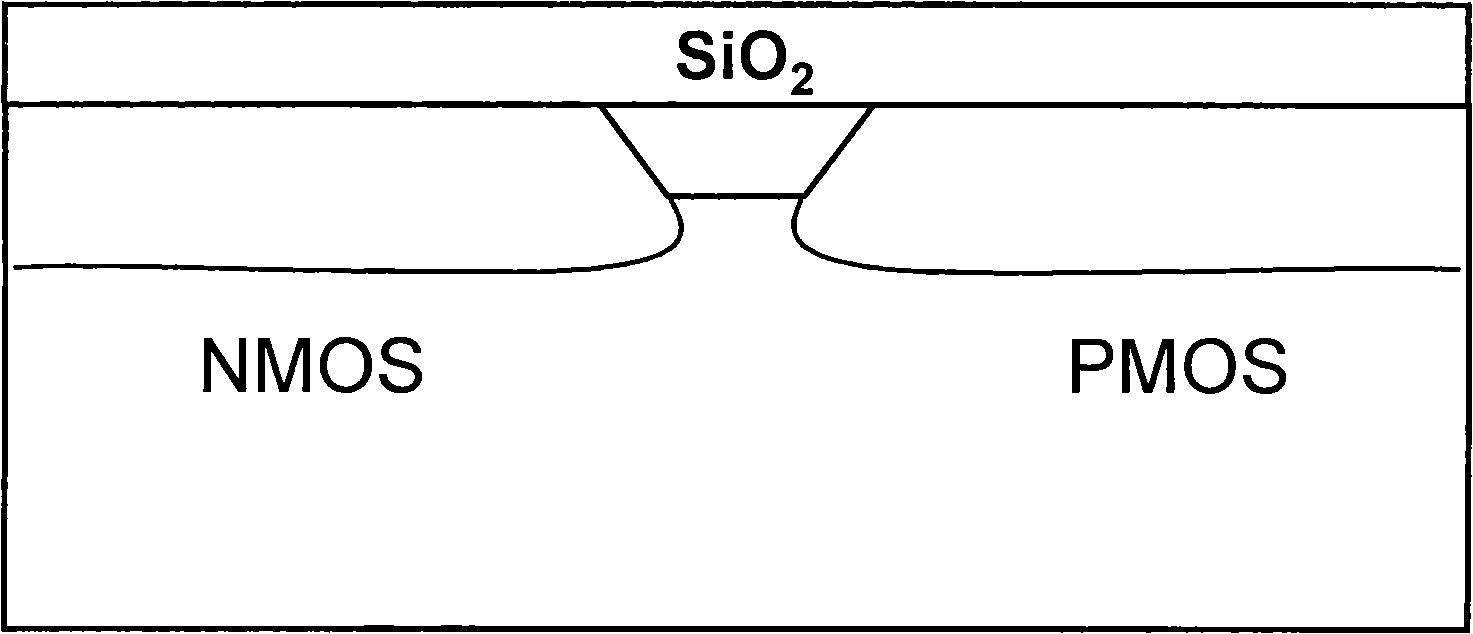

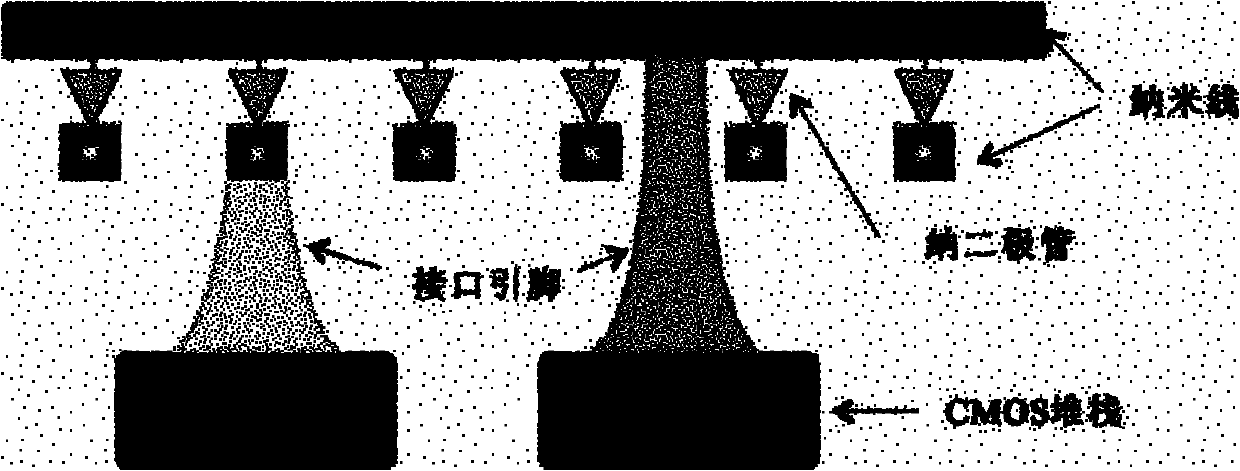

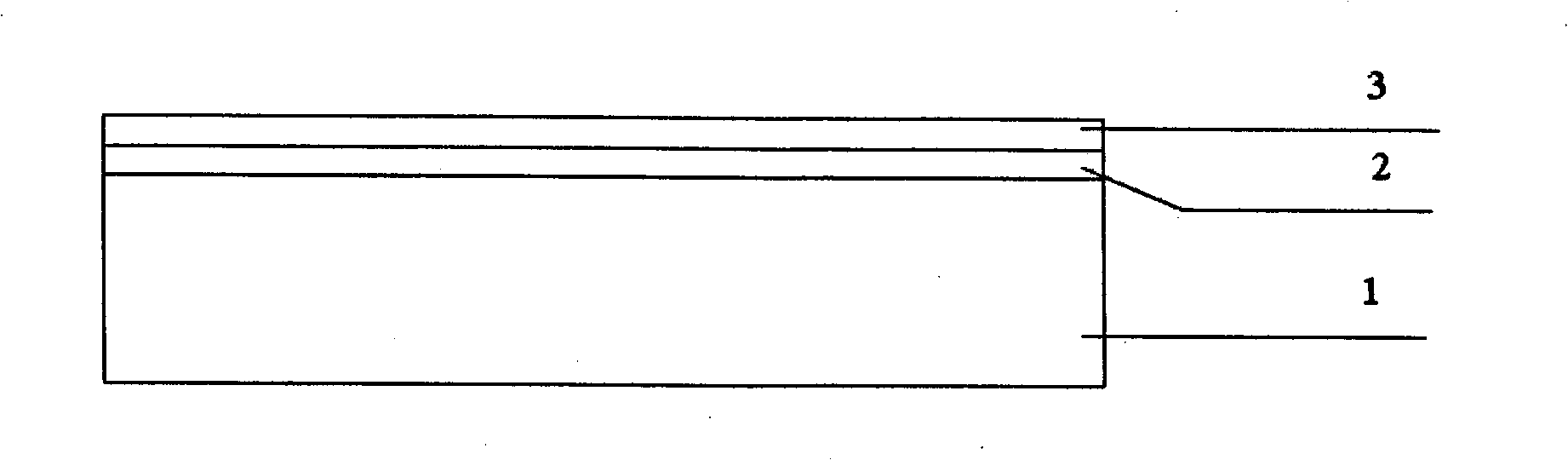

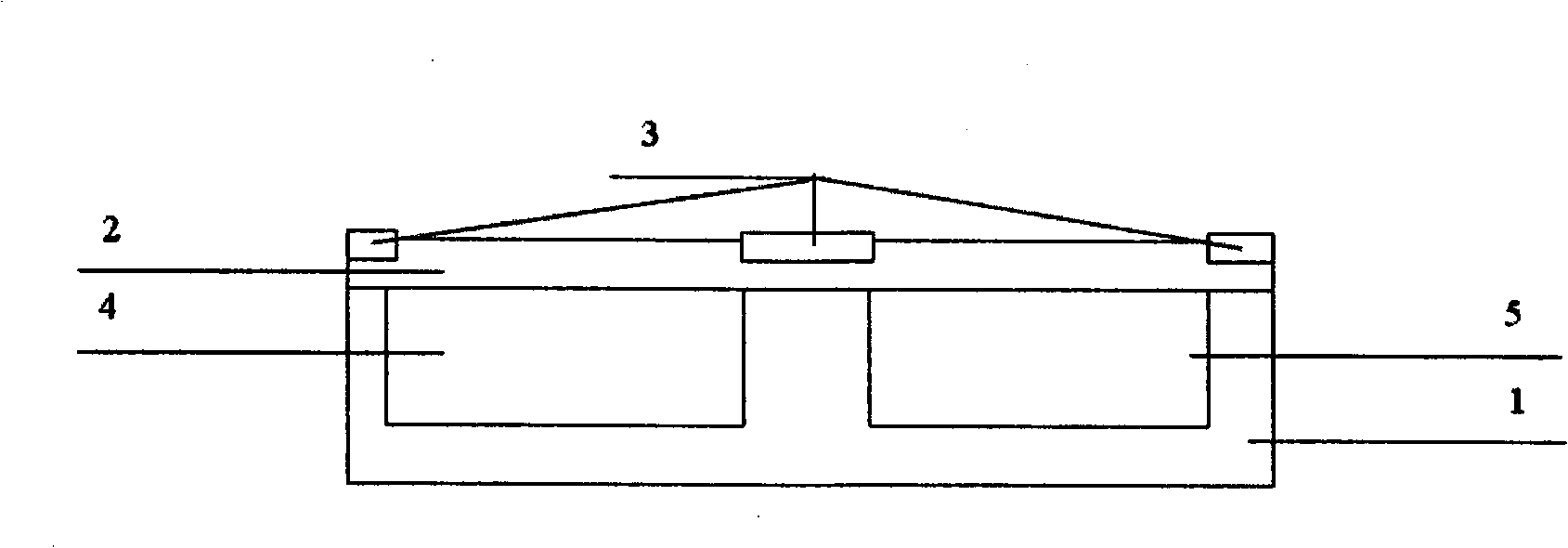

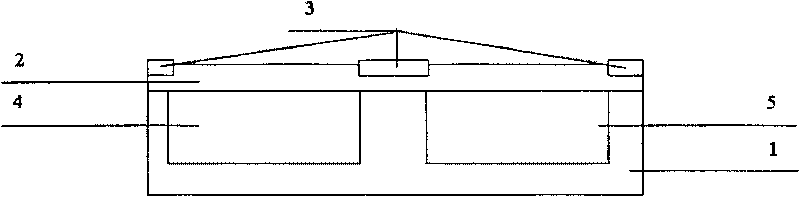

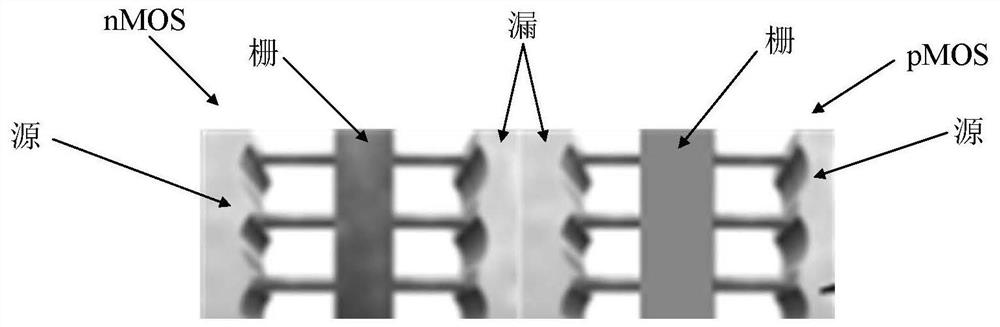

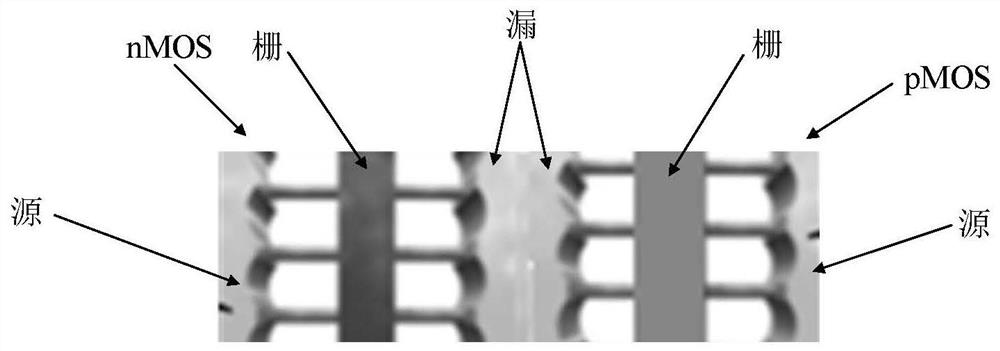

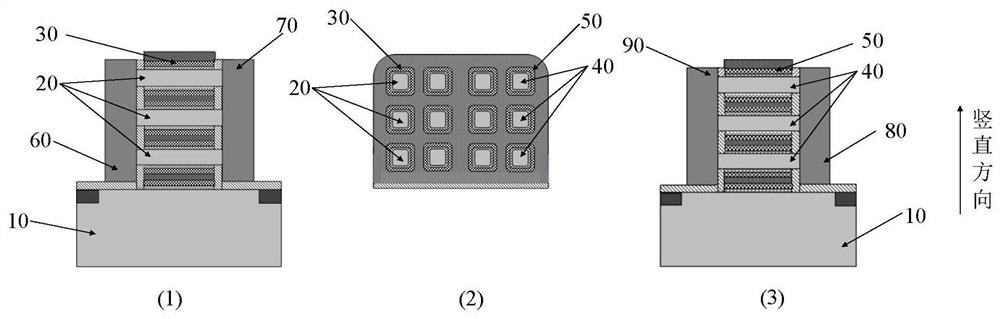

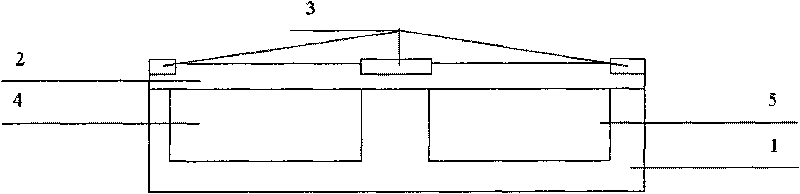

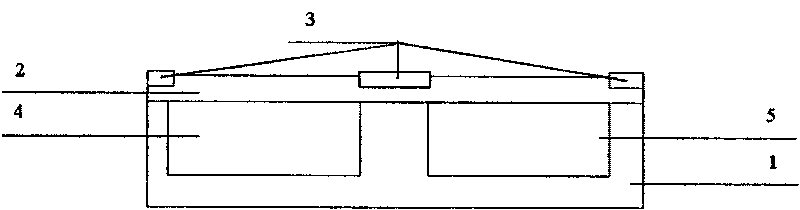

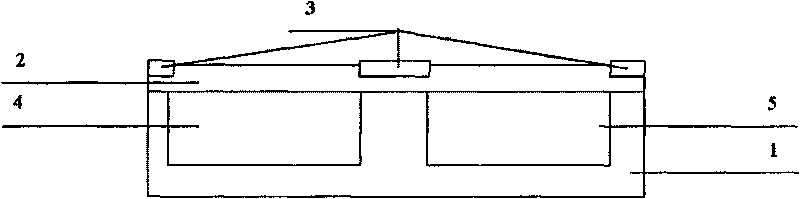

Ring gate nano CMOS structure and preparation method thereof

PendingCN112713191AReduce process stepsImprove performanceTransistorSolid-state devicesSemiconductor materialsNano structuring

The invention discloses a ring gate nano CMOS structure and a preparation method thereof. The ring gate nano CMOS structure comprises an nMOS and a pMOS, and the ring gate nano CMOS structure is characterized in that the nMOS comprises a first nano body structure arranged on a semiconductor substrate and a first gate electrode surrounding the first nano body structure, wherein the pMOS comprises a second nanobody structure arranged on the semiconductor substrate and a second gate electrode surrounding the second nanobody structure, and the first nanobody structure and the second nanobody structure are made of semiconductor materials of the same conductivity type; the first gate electrode and the second gate electrode are formed of a conductive material having the same work function. According to the ring-gate nano CMOS, process steps for preparing the ring-gate nano CMOS are reduced, and the process flow is reduced, so process difficulty and the preparation cost can be reduced, and the performance and reliability of the ring-gate nano CMOS and an integrated circuit thereof can be improved.

Owner:张鹤鸣

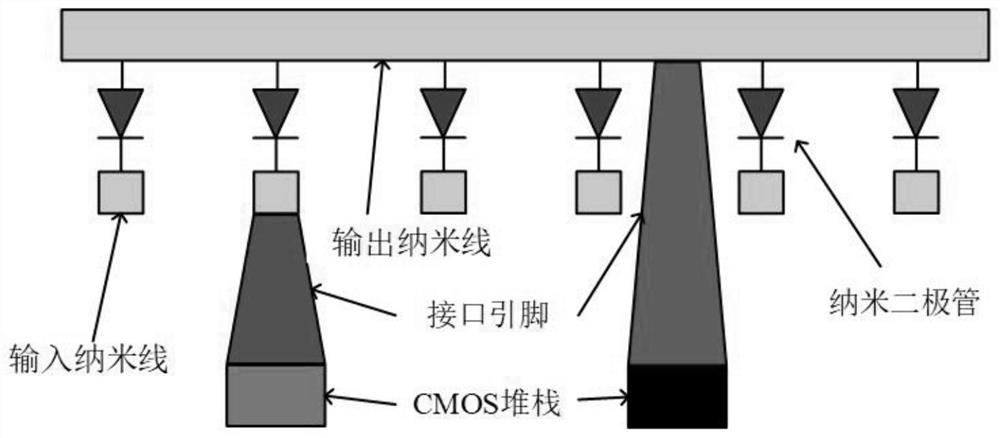

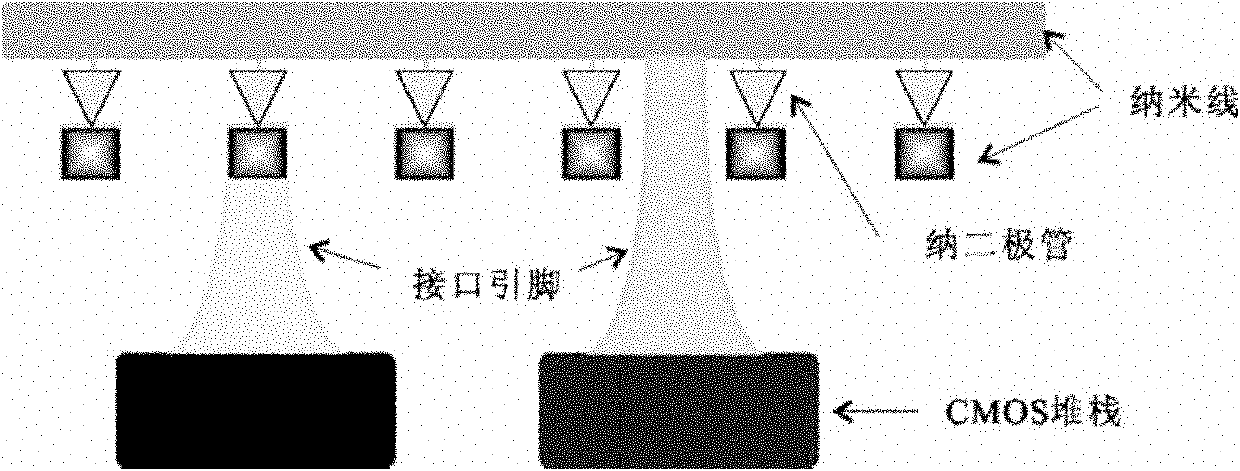

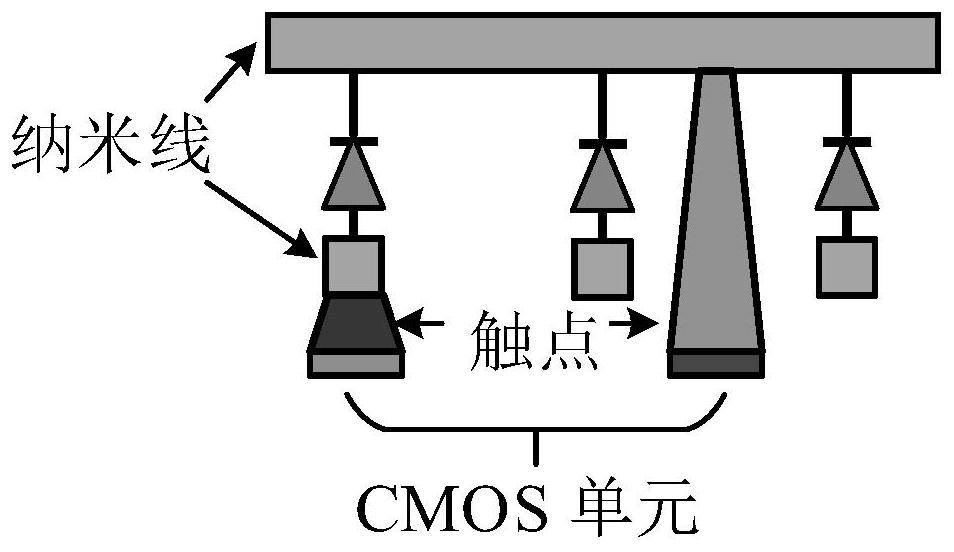

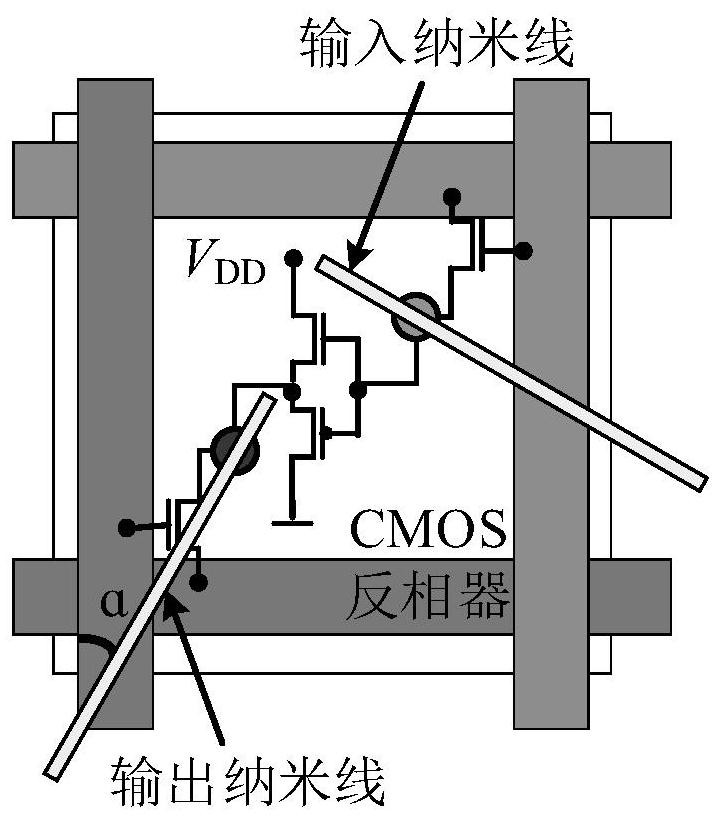

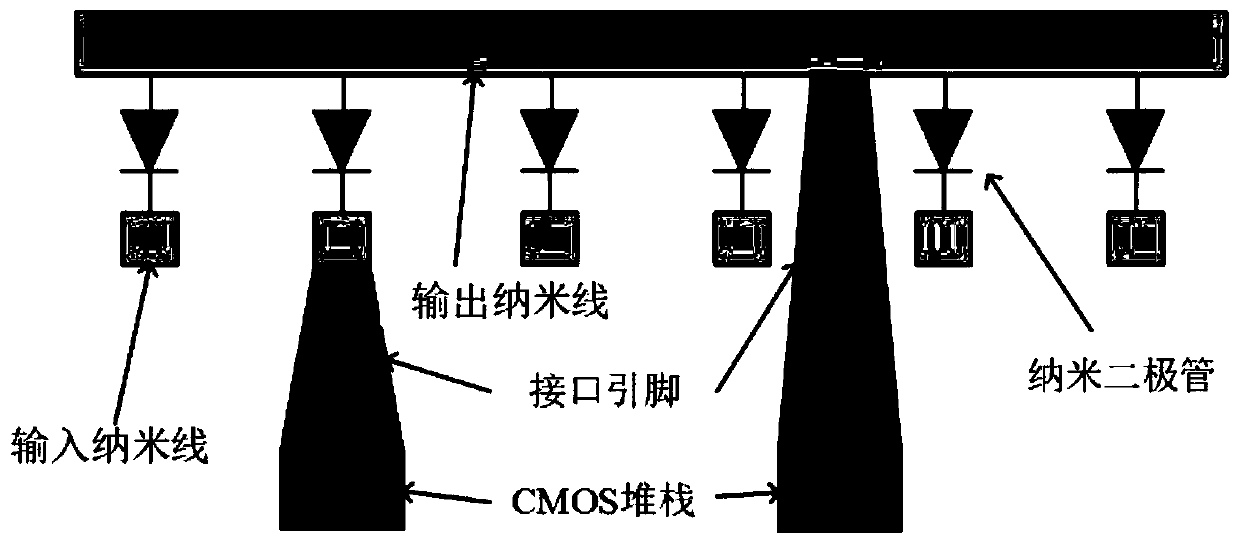

A Method of Suppressing the Propagation of Normally Connected Defects in Nano CMOS Circuits

ActiveCN106130541BAvoid spreadingReduce the impact of logic functionsLogic circuits characterised by logic functionMode of actionNanodiodes

Owner:NINGBO UNIV

Method for preparing nano CMOS integrated circuit by SiN masking technique

InactiveCN101359632BImprove the preparation effectImprove performanceSemiconductor/solid-state device manufacturingMOSFETMicron scale

The invention discloses a method based on SiN masking technique for fabricating a nano-scale CMOS integrated circuit. The process includes the following steps: fabricating an N / P well and growing a Poly-Si / SiN / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiN; etching away the SiN on the surface of the substrate, exceptthe SiN at the side wall of the Poly- Si; based on the etching ratio of Poly-Si to SiN(11:1), etching the Poly-Si on the surface of SiN; etching the SiN on surface of the substrate, except the SiN onthe side wall of the SiN so as to expose the substrate of Poly-Si; based on the etching ratio of Poly-Si to SiN, etching the Poly-Si, except the Poly-Si in the protective area on the side wall of SiNsoas to form an n / p MOSFET grid, and depositing a layer of SiO2 at the well area; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form an n / p MOSFET device; and photoetching interconnection lines of the device so as to form a CMOS integrated circuit with a conducting channel at 45-90nm. The method can fabricate a CMOS integrated circuit which is improved in performance by 3-5 generations on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

Method for preparing polycrystal SiGe gate nano CMOS integrated circuit by micro process

InactiveCN101359631BThreshold Voltage AdjustmentAchieve regulationSemiconductor/solid-state device manufacturingMicron scaleMOSFET

The invention discloses a method based on micron-scale technique for fabricating a nano-scale CMOS integrated circuit which has a polycrystal SiGe grid. The process includes the following steps: fabricating an N / P well and growing a Poly- SiGe / SiN / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiO2; etching away the SiO2layer on the surface of the substrate, except the SiO2 at the side wall of Poly-Si; based on the etching ratio of Poly-Si to SiN(11:1), etching the Poly-Si on the surface of SiN; based on the ratio of SiN to SiO2(2:1), etching the SiN, except the SiN in the protective area on the side wall of SiO2; based on the etching ratio of Poly-SiGe to SiO2(50:1), etching the Poly-SiGe, except the Poly-SiGein the protective area on the side wall of SiO2 so as to form an n / p MOSFET grid; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form ann / p MOSFET device; and photoetching interconnection lines of the device so as to form a CMOS integrated circuit with a conducting channel at 45-90nm. The method can fabricate a CMOS integrated circuitwhich has a polycrystal SiGe grid on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

Method for preparing polycrystal SiGe gate nano CMOS integrated circuit by SiN masking technique

InactiveCN101359627BThreshold Voltage AdjustmentAchieve regulationSemiconductor/solid-state device manufacturingMicron scaleMOSFET

The invention discloses a method for fabricating a nano-scale CMOS integrated circuit which has a polycrystal SiGe grid through SiN masking technique. The process includes the following steps: fabricating an N / P well and growing a Poly- SiGe / SiN / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiN; etching the SiN layer onthe surface, except the SiN at the side face of the window; based on the etching ratio of Poly-Si to SiN (11:1), etching the Poly-Si at the surface of SiN and etching the SiN except on the side wallof SiN so as to expose the substrate of Poly-SiGe; based on the etching ratio of Poly-SiGe to SiN(11:1), etching the Poly-SiGe except on the side wall of the SiN so as to form an n / p MOSFET grid; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form an n / p MOSFET device; and photoetching interconnection lines of the device so as to forma CMOS integrated circuit with a conducting channel at 45-90nanometer. The method can fabricate a CMOS integrated circuit which is improved in performance by 3-5 generations on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

A Fault-Tolerant Mapping Method for Optimizing Power Consumption in Nanoscale CMOS Circuits

ActiveCN113343614BReduce the impact of fault tolerance complexityFast solutionEnergy efficient computingComputer aided designFault toleranceHemt circuits

The invention discloses a nano-CMOS circuit fault-tolerant mapping method that can optimize power consumption. Aiming at the problem that the defects of the nano-CMOS circuit increase the power consumption of the circuit, the method of the invention first uses the packaging technology to pack the high-level constant-connected units and their The constant output is packaged into a unit package, and the associated nodes are selected to generate a certain number of node packages; then the circuit fault-tolerant mapping is completed by using the genetic algorithm, and the one-to-one matching mapping between the unit package and the node package is guaranteed through specific genetic coding methods and crossover and mutation operations , to reduce the complexity of fault tolerance, and absorb the power consumption optimization constraints into the fitness function to optimize the power consumption of the mapping solution. The method of the invention can effectively reduce the circuit fault-tolerant complexity, and realize power consumption optimization of the mapping circuit on the basis of quickly eliminating the influence of defects on the logic function of the mapping circuit.

Owner:NINGBO UNIV

Method for preparing nano CMOS integrated circuit by SiO2 masking technique

InactiveCN101359630BImprove the preparation effectImprove performanceSemiconductor/solid-state device manufacturingMicron scaleMOSFET

The invention discloses a method based on SiO2 masking technique for fabricating a nano-scale CMOS integrated circuit. The process includes the following steps: fabricating a N / P well and growing a Poly- Si / SiO2 / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiO2; etching away the SiO2 layer on the surface, except the SiO2 at the side face of the window; based on the etching ratio of Poly-Si to SiO2(50:1), etching the Poly-Si on the upper layer; etching the SiO2 on the substrate, except the SiO2 on the side wall so as to expose the substrate of Poly-Si; based on the etching ratio of Poly-Si to SiO2, etching the Poly-Si, except the Poly-Si in the protective area on the side wall of SiO2 so as to form an n / p MOSFETgrid, and depositing a layer of SiO2 on the well; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form an n / p MOSFET device; and photoetching interconnection lines of the device so as to form a CMOS integrated circuit with a conducting channel at 65-90nm. The method can fabricate a CMOS integrated circuit which is improved in performance by 3-5 generations on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

A strained Si vertical back-channel nano-CMOS integrated device and its preparation method

Owner:XIDIAN UNIV

Method for preparing nano CMOS integrated circuit by micro process

InactiveCN101359626BImprove the preparation effectImprove performanceSemiconductor/solid-state device manufacturingMicron scaleMOSFET

The invention discloses a method for fabricating a nano-scale CMOS integrated circuit based on micron-scale processing technique. The method includes the following steps: fabricating an N / P well and growing a Poly-Si / SiN / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiO2; etching the SiO2layer on the surface, except the SiO2 at the side of the window; based on the etching ratio of Poly-Si to SiN(11:1), etching the Poly-Si on the upper layer; based on the etching ratio of SiN to SiO2 (2:1), etching the SiN outside the protective area on the side wall of SiO2; based on the etching ratio of Poly-Si to SiO2(50:1), etching the Poly-Si outside the protective area on the side wall of SiO2 so as to form an n / p MOSFET grid; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form an n / p MOSFET device; and photoetching interconnection lines of the device so asto form a CMOS integrated circuit with a conducting channel at 45-90nanometer. The invention can fabricate a CMOS integrated circuit which is improved in performance by 3-5 generations on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

Polycrystal SiGe gate nano CMOS integrated circuit preparation based on SiO2 masking technique

InactiveCN101359629BThreshold Voltage AdjustmentAchieve regulationSemiconductor/solid-state device manufacturingMOSFETMicron scale

The invention discloses a method based on SiO2 masking technique for fabricating a nano-scale CMOS integrated circuit which has a polycrystal SiGe grid. The process includes the following steps: fabricating an N / P well and growing a Poly- SiGe / SiO2 / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiO2; etching the SiO2 layer on the surface, except the SiO2 at the side face of the window; based on the etching ratio of Poly-Si to SiO2 (50:1), etching the Poly-Si at the upper layer; based on the etching ratio of Poly-SiGeto SiO2 (50:1), etching the SiO2 and the Poly-SiGe, except the SiO2 and Poly-SiGe in the protective area at the side wall of the SiO2, preserving the SiO2 and Poly-SiGe below the side wall, forming an / p MOSFET grid and depositing a layer of SiO2; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form an n / p MOSFET device; and photoetching interconnection lines of the device so as to form a CMOS integrated circuit with a conducting channel at 65-90nm. The method can fabricate a CMOS integrated circuit which is improved in performanceby 3-5 generations on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

Nano CMOS circuit fault-tolerant mapping method capable of optimizing power consumption

ActiveCN113343614AReduce the impact of fault tolerance complexityFast solutionEnergy efficient computingComputer aided designGenetics algorithmsEmbedded system

The invention discloses a nano CMOS circuit fault-tolerant mapping method capable of optimizing power consumption. To solve the problem that power consumption of a circuit is increased due to the defect of a nano CMOS circuit, the method comprises the following steps of: firstly, packaging normally-connected units with higher normally-connected levels and normally-connected outputs of the normally-connected units into unit packets by packaging technology, and selecting associated nodes to generate a certain number of node packets; and completing circuit fault-tolerant mapping by a genetic algorithm, one-to-one matching mapping of a unit packet and a node packet is ensured through a specific gene coding mode and crossover and mutation operations, so that the fault-tolerant complexity is reduced, and power consumption optimization constraints are absorbed into an appropriate value function to optimize power consumption of a mapping solution. Fault-tolerant complexity of the circuit can be effectively reduced, and the power consumption optimization of the mapping circuit is realized on the basis of quickly eliminating the influence of defects on the logic function of the mapping circuit.

Owner:NINGBO UNIV

Efficient fault tolerance method for nano CMOS (Complementary Metal-Oxide-Semiconductor Transistor) circuit capable of effectively utilizing normally-closed defect unit

ActiveCN110837725AOptimize the mapping processImprove performanceCAD circuit designSpecial data processing applicationsLocal search (optimization)Fault tolerance

The invention discloses an efficient fault tolerance method for a nano CMOS (Complementary Metal-Oxide-Semiconductor Transistor) circuit capable of effectively utilizing a normally-closed defect unit.The connection relationship between the sequence input unit and the normally closed defect unit is matched with the logic relationship between nodes in the logic circuit; the normally-closed defect unit is used for mapping of logic nodes of all levels. Meanwhile, the defect information of the nano CMOS circuit is considered in the initial mapping process; the hierarchical mapping of the logic circuit fully considers the logic relationship between the gate nodes, the local optimization result is synthesized, the tabu search algorithm with strong local search capability is adopted to verify thefunctional correctness of the unit mapped by each logic level node, and the practical process of the nano CMOS circuit structure is accelerated. According to the invention, the mapping success rate is improved by using the available normally-closed defect units, the performance of the mapped nano CMOS circuit is optimized, the fault-tolerant complexity of the circuit is simplified, and the influence of the normally-closed defects on the logic function of the nano CMOS circuit is quickly eliminated under the condition of improving the unit utilization rate and the mapping success rate.

Owner:NINGBO UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com