Method for preparing nano CMOS parts by using side wall and solid phase diffusion of polysilicon

A technology of polysilicon and sidewalls, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as high surface impurity concentration, high impurity activation rate, high temperature, etc., achieve the effect of reducing requirements and overcoming technical difficulties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

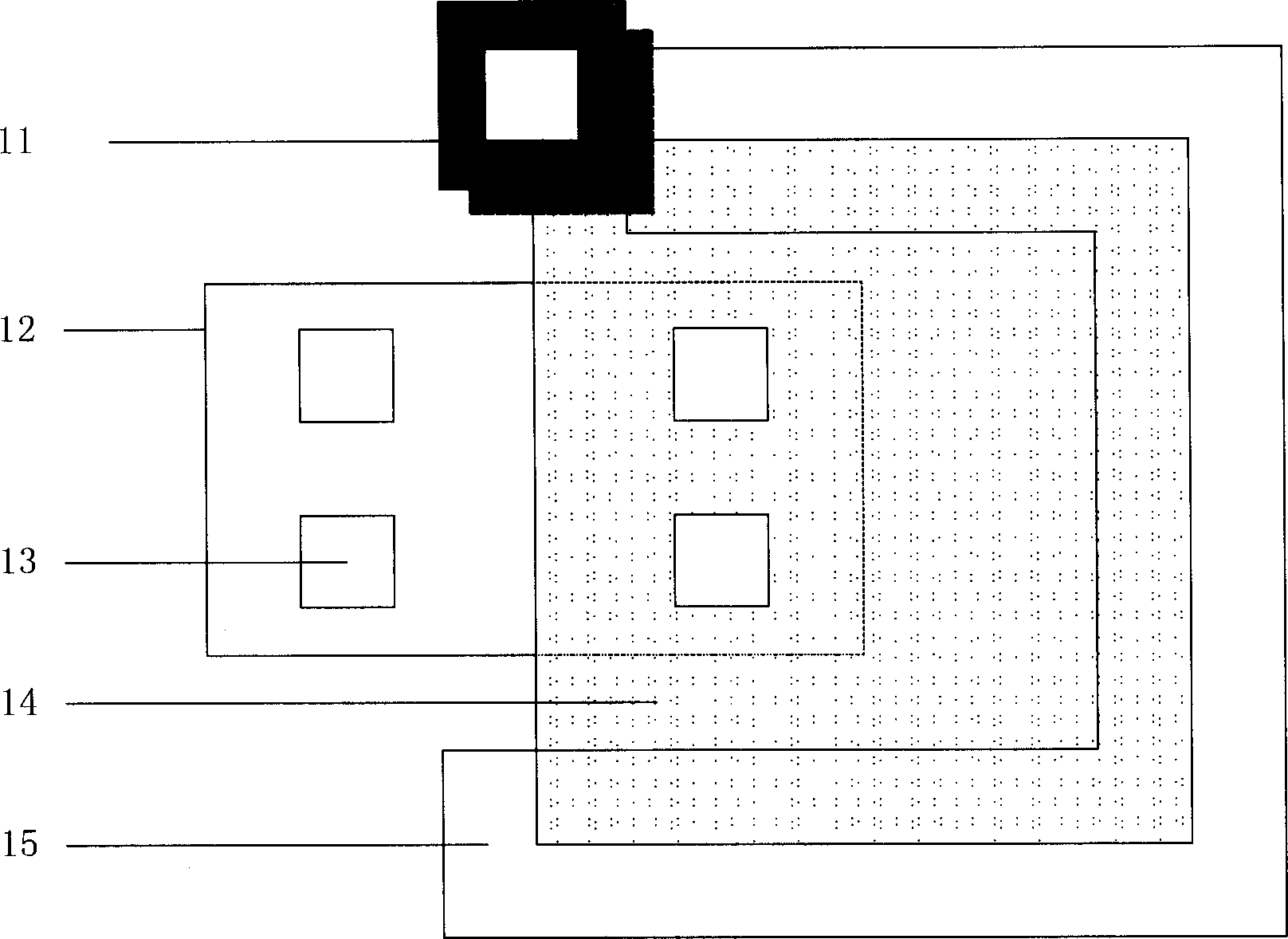

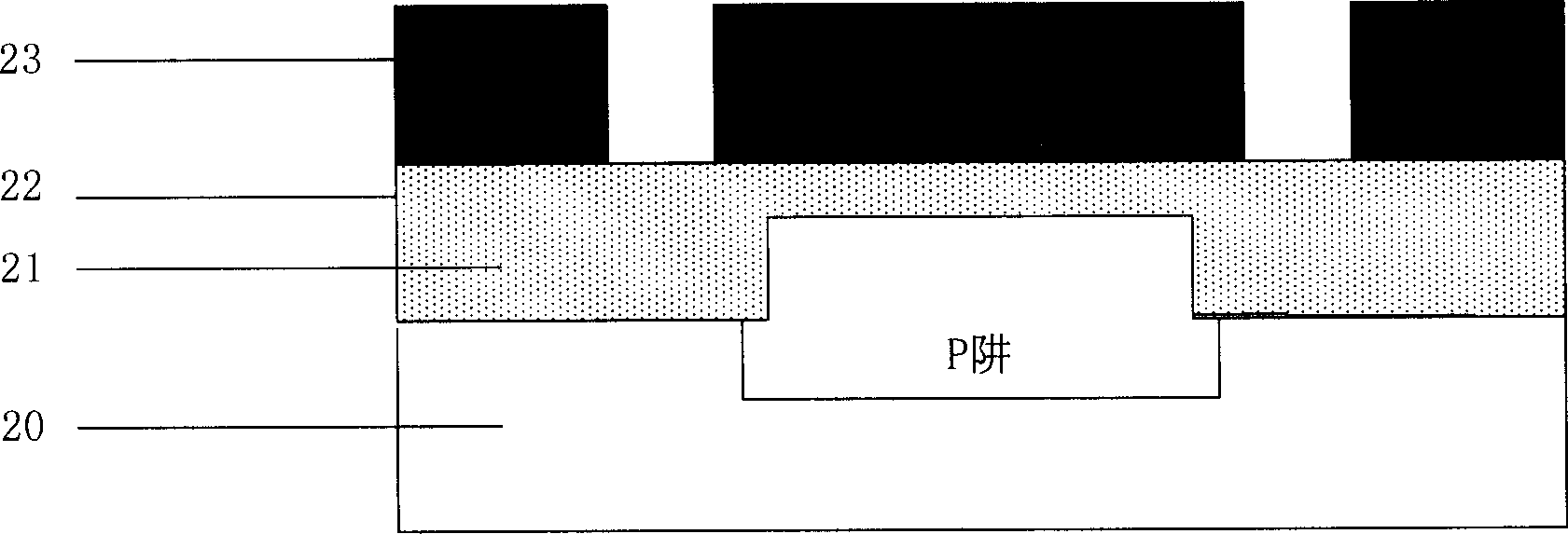

[0052] The method of the present invention is fully compatible with the traditional bulk silicon double-well CMOS process, uses sidewall transfer to make gate lines and heavily doped polysilicon as a diffusion source to form an ultra-shallow junction in the source and drain regions, and organically combines the two to finally realize Nanoscale CMOS transistors and devices. The following are specific examples.

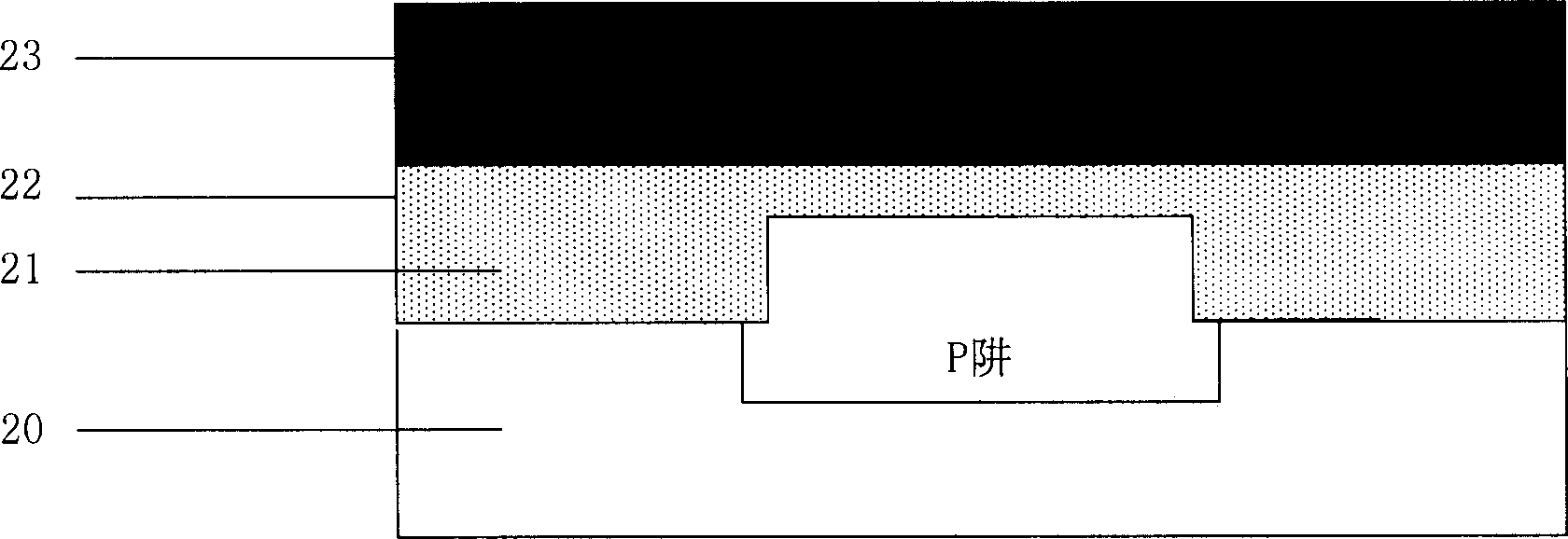

[0053] A bulk silicon P(100) silicon wafer is used, and the resistivity of the substrate 20 is 10-15Ω·cm. Of course, an SOI chip can also be used, the difference is that no well needs to be fabricated.

[0054] 1. Using double well technology, two-step well pushing method: first, photolithography N well, and then implanting phosphorus into the well, 80~120Kev, 1.0~4.0E13cm -2 , then at 1000°C, hydrogen-oxygen synthesis and oxidation of about 150-200nm silicon dioxide, and N-well advancement at the same time; followed by photolithography in the P-well area, and well im...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com