Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1564 results about "Cmos process" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

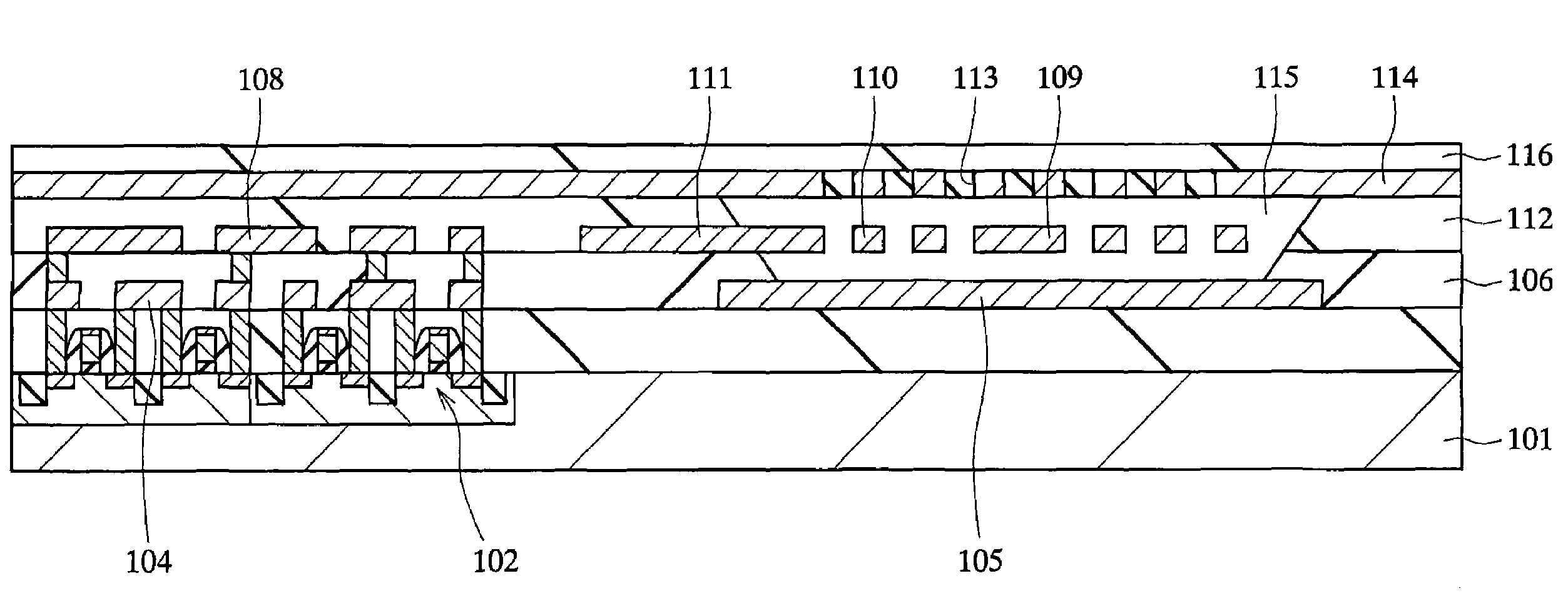

Method of manufacturing semiconductor device

ActiveUS20080299758A1Reduces yield and reliabilityReduce capacitySemiconductor/solid-state device detailsSolid-state devicesHigh densityDevice material

A high-density N-type diffusion layer 116 formed in a separation area 115 makes it possible to reduce a collector current flowing through a parasitic NPN transistor 102. Thus, a normal CMOS process can be used to provide a driving circuit and a data line driver which make it possible to improve resistance to possible noise occurring between adjacent terminals, while controlling a chip size.

Owner:PANNOVA SEMIC

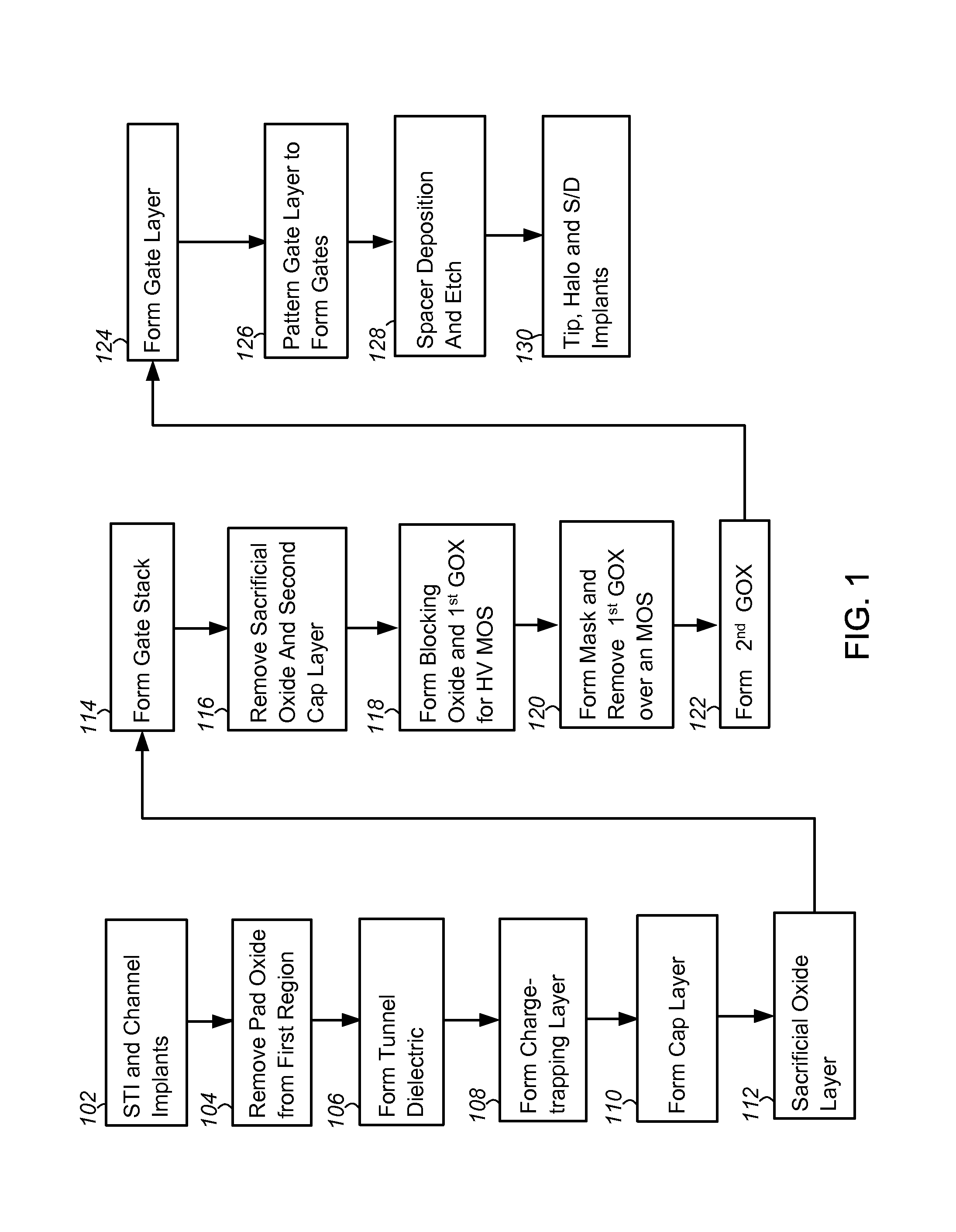

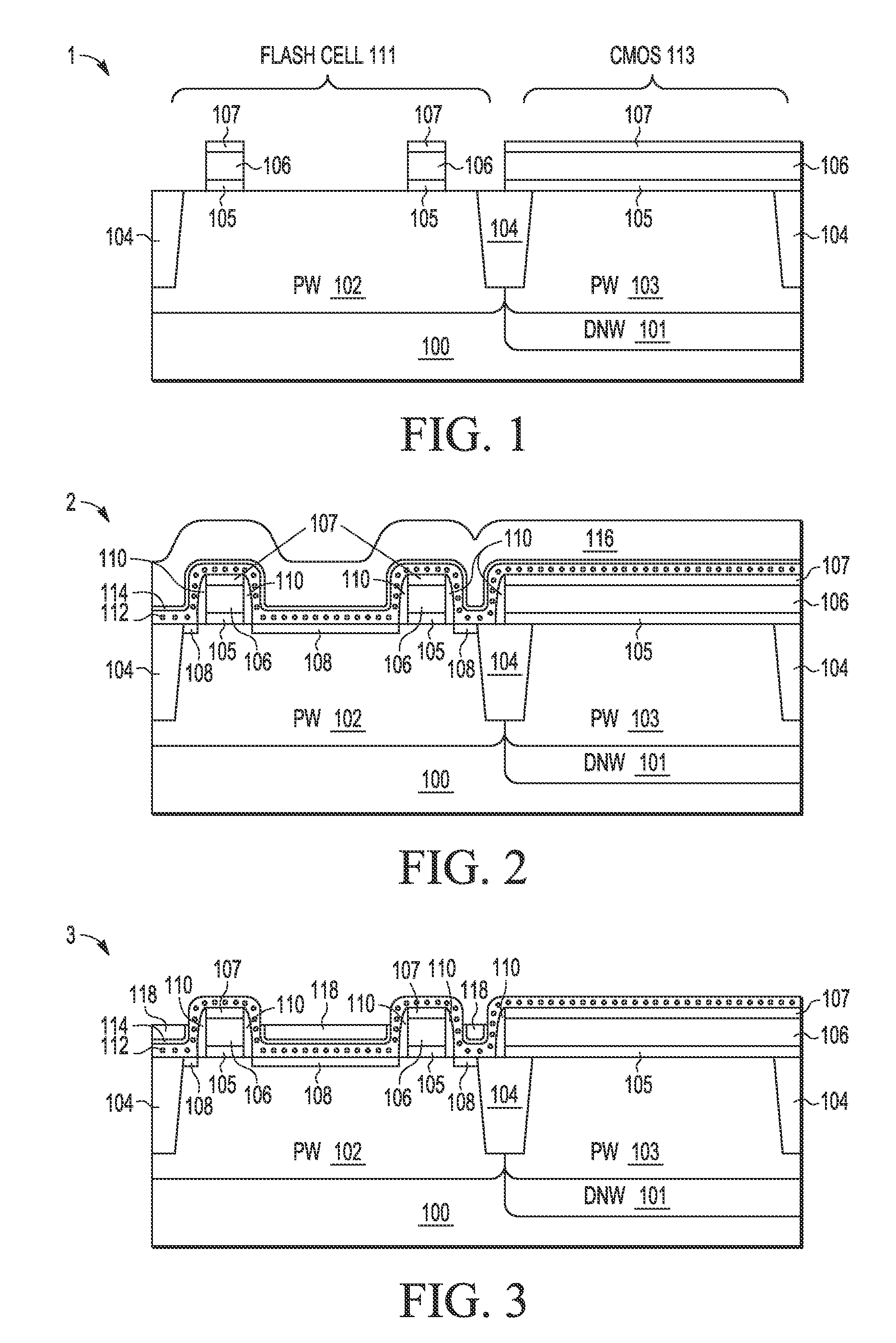

Method of fabricating a charge-trapping gate stack using a CMOS process flow

ActiveUS8993457B1Semiconductor/solid-state device manufacturingSemiconductor devicesDielectricTrapping

A method of fabricating a memory device is described. Generally, the method includes: forming on a surface of a substrate a dielectric stack including a tunneling dielectric and a charge-trapping layer overlying the tunneling dielectric; depositing a first cap layer comprising an oxide over the dielectric stack; forming a second cap layer comprising a nitride over the first cap layer; patterning the first and second cap layers and the dielectric stack to form a gate stack of a memory device; removing the second cap layer; and performing an oxidation process to form a blocking oxide over the charge-trapping layer, wherein the oxidation process consumes the first cap layer. Other embodiments are also described.

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

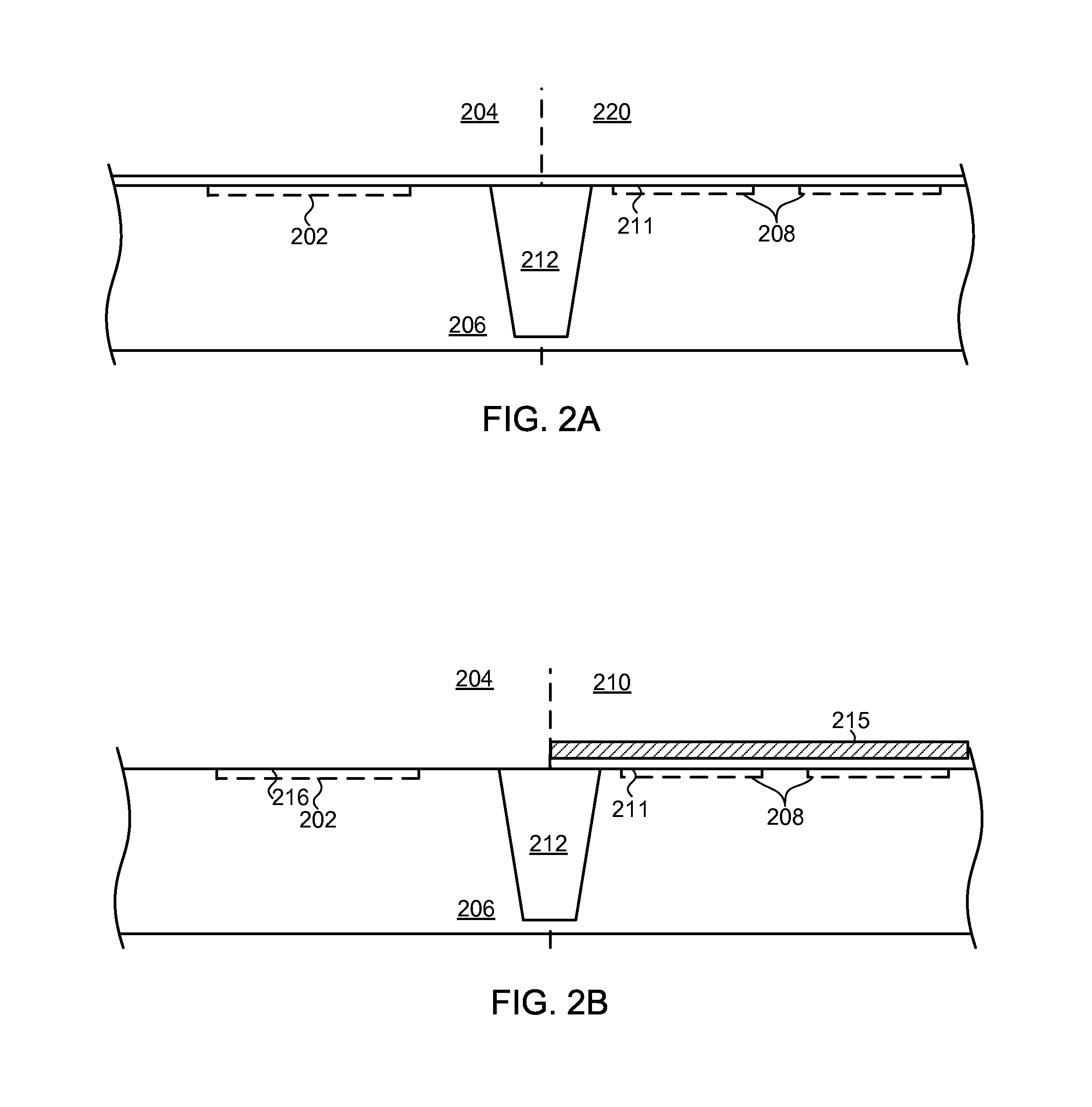

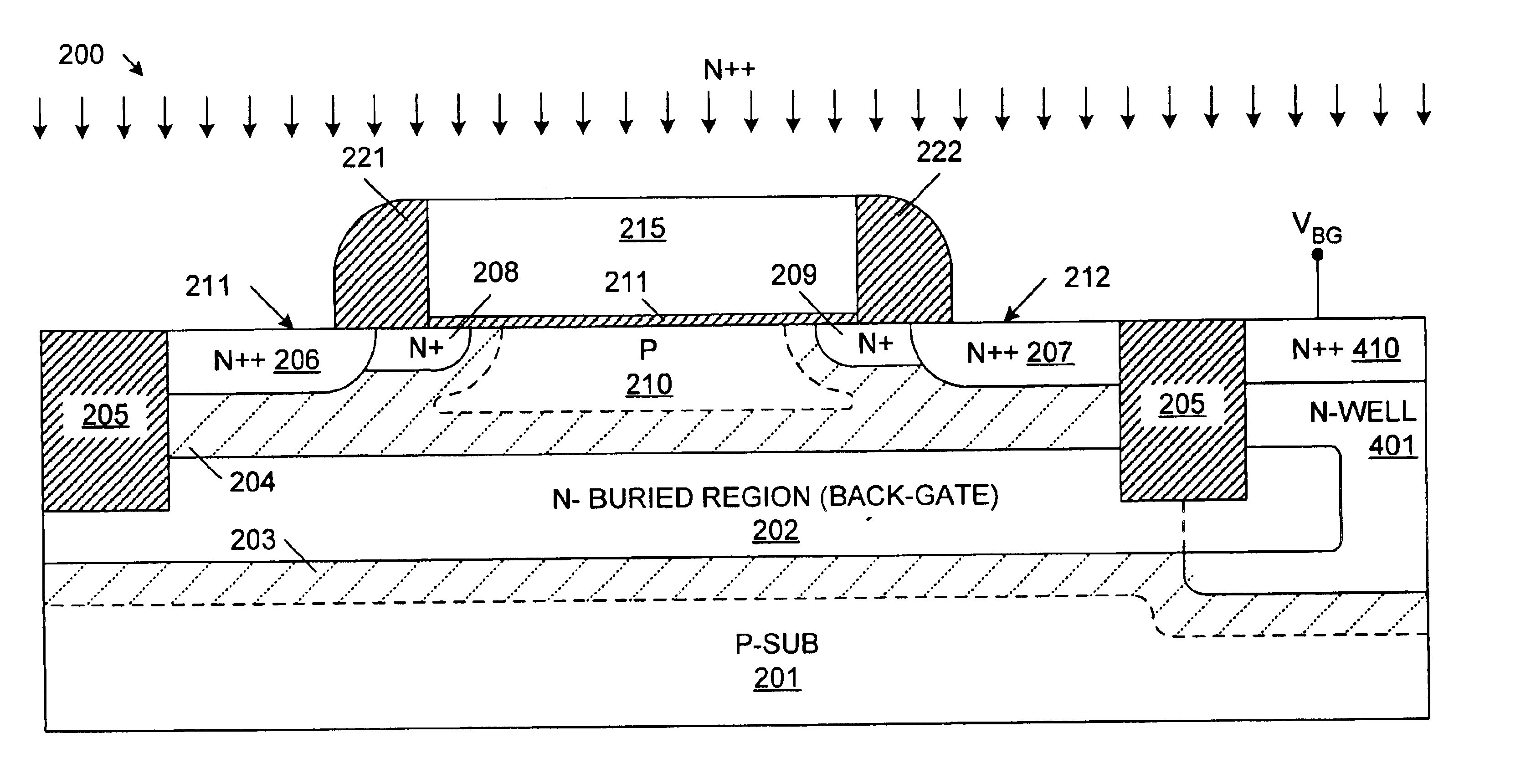

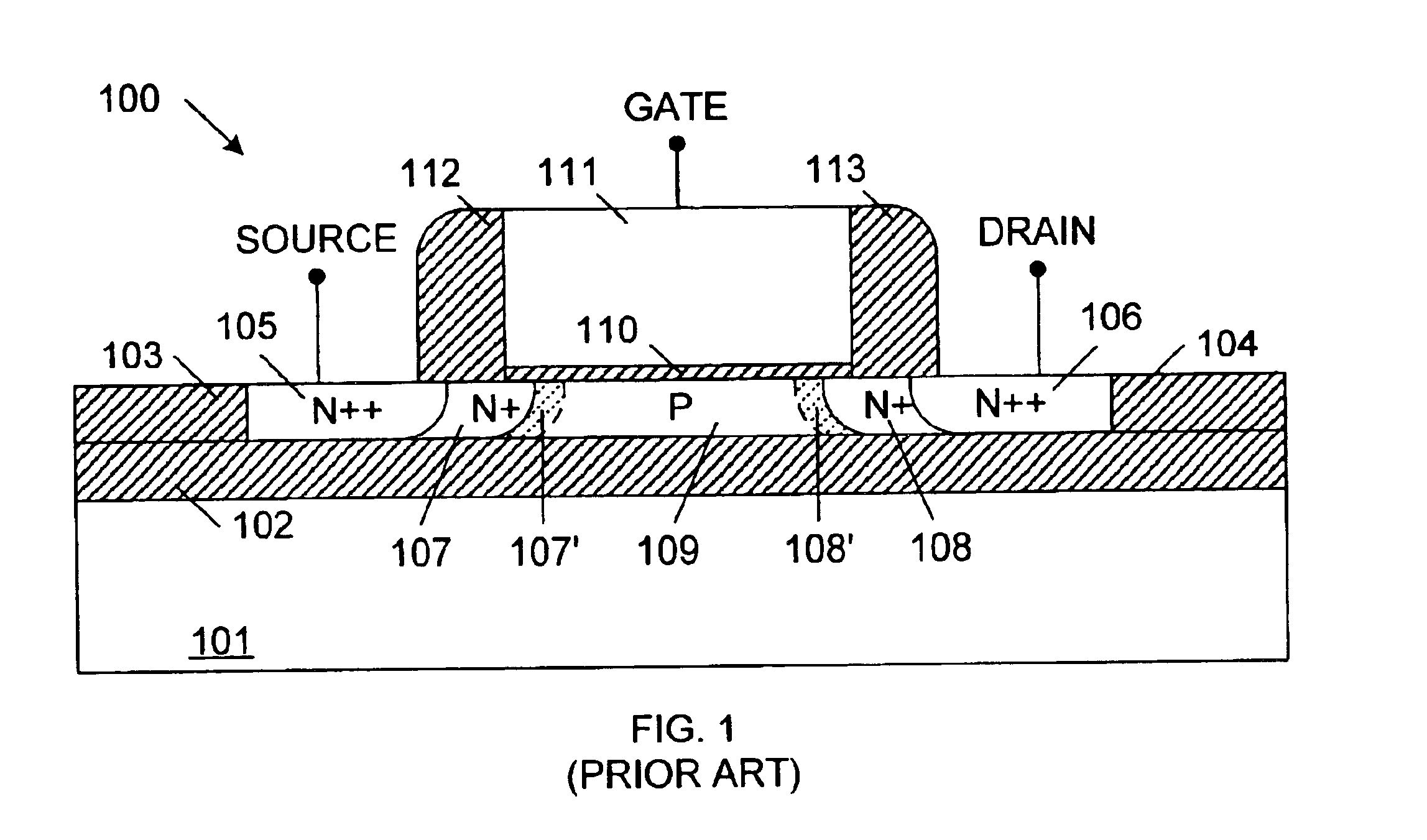

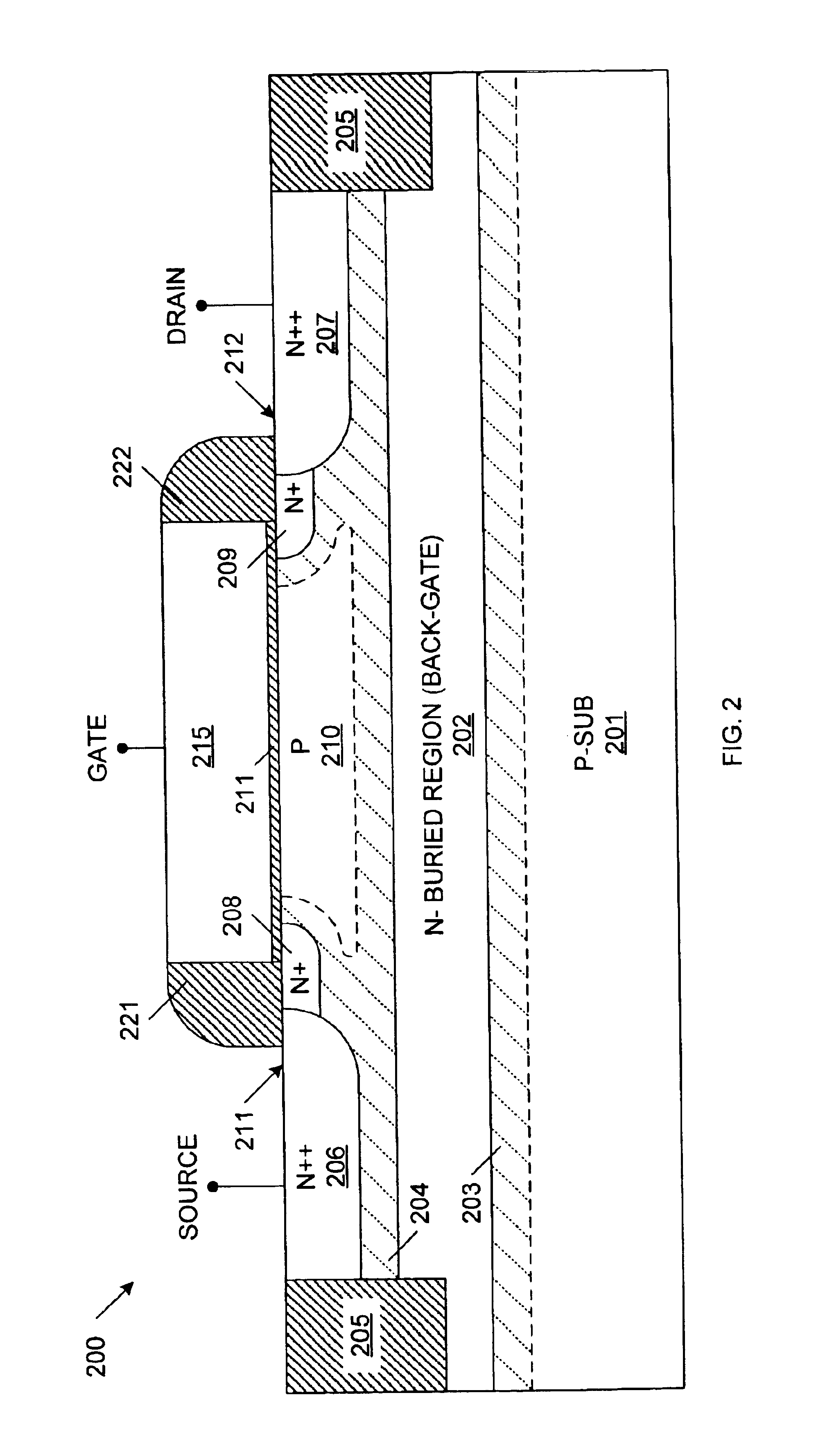

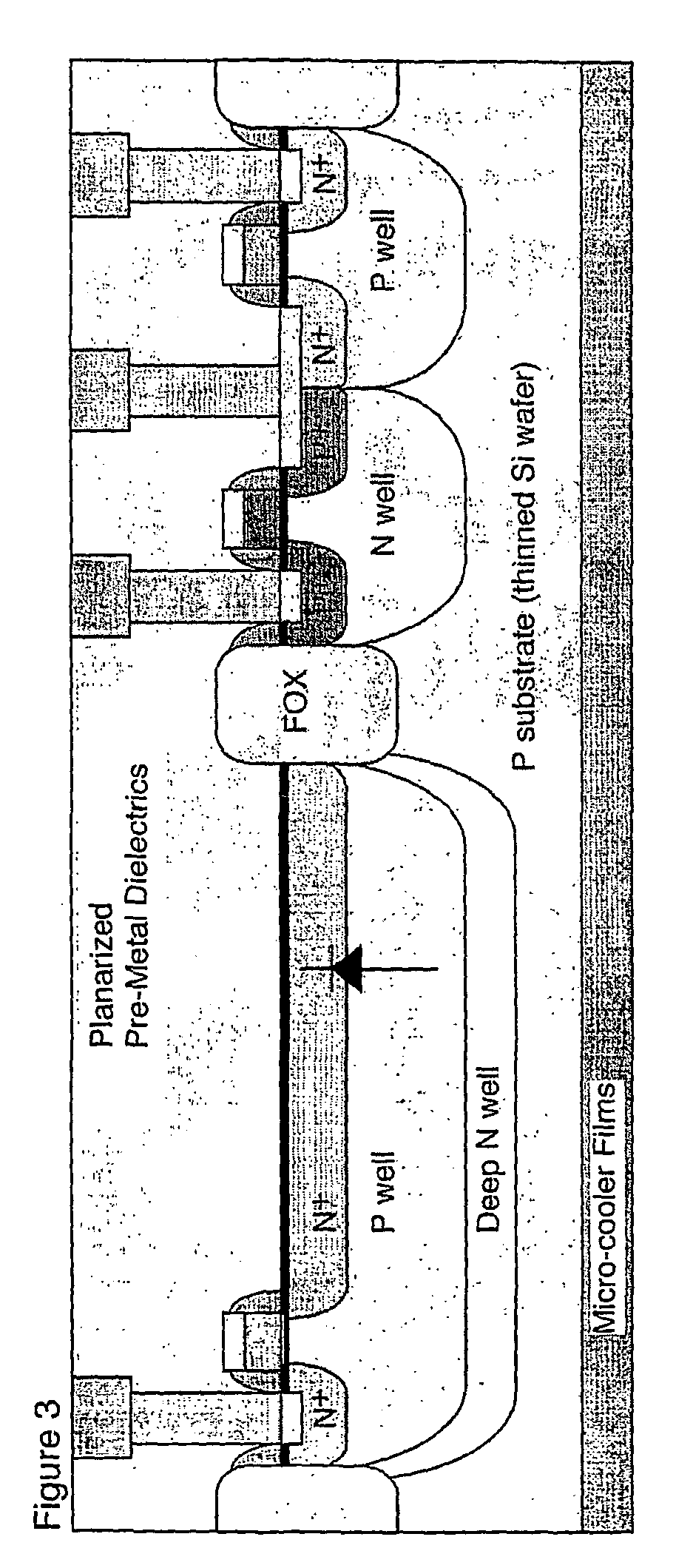

Method of fabricating a one transistor floating-body DRAM cell in bulk CMOS process with electrically isolated charge storage region

InactiveUS6913964B2Limiting leakage currentEnsure adequate isolationTransistorSolid-state devicesEngineeringField-effect transistor

A one-transistor, floating-body (1T / FB) dynamic random access memory (DRAM) cell is provided that includes a field-effect transistor fabricated using a process compatible with a standard CMOS process. The field-effect transistor includes a source region and a drain region of a first conductivity type and a floating body region of a second conductivity type, opposite the first conductivity type, located between the source region and the drain region. A buried region of the first conductivity type is located under the source region, drain region and floating body region. The buried region helps to form a depletion region, which is located between the buried region and the source region, the drain region and the floating body region. The floating body region is thereby isolated by the depletion region. A bias voltage can be applied to the buried region, thereby controlling leakage currents in the 1T / FB DRAM cell.

Owner:MOSYS INC

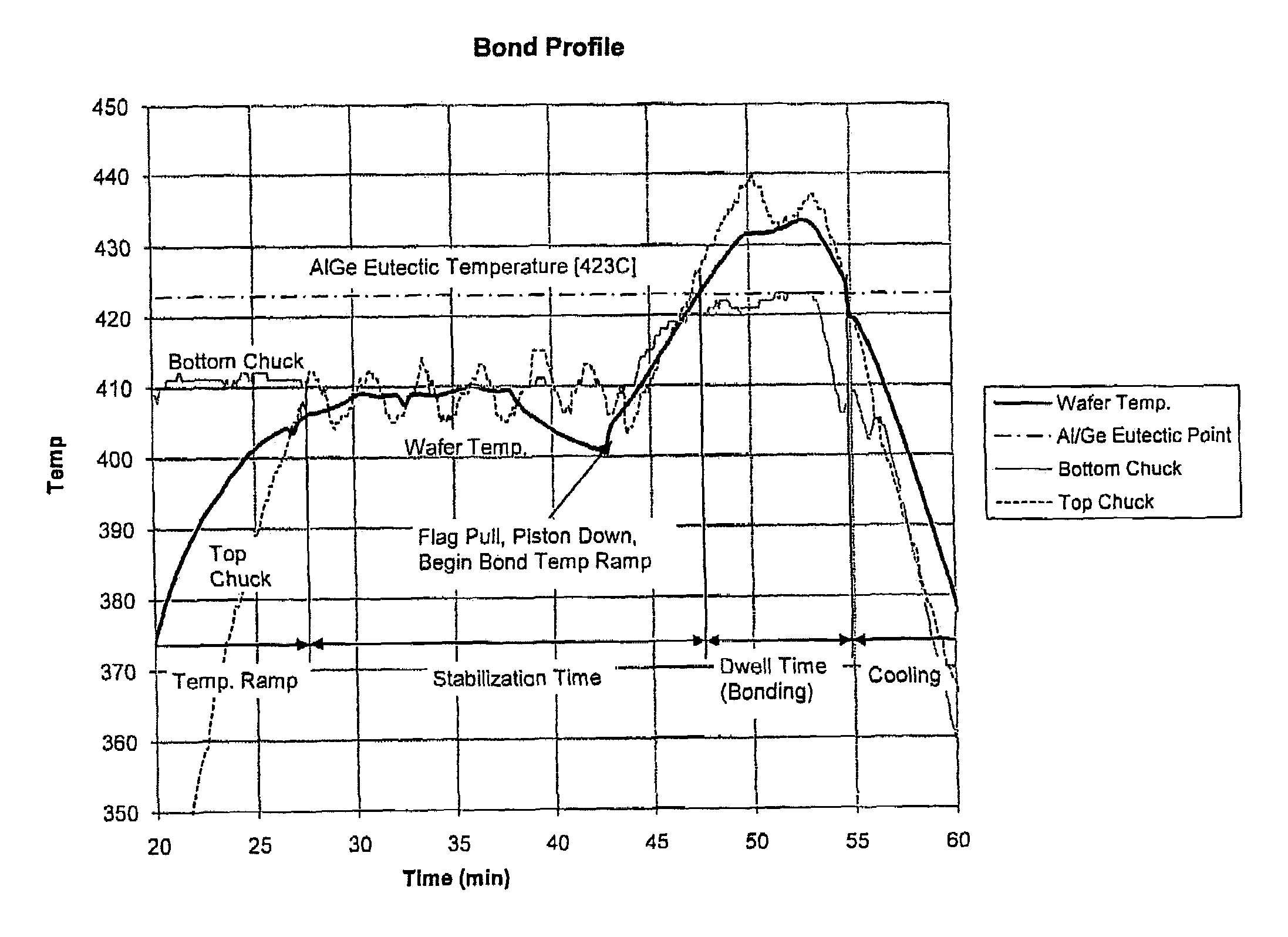

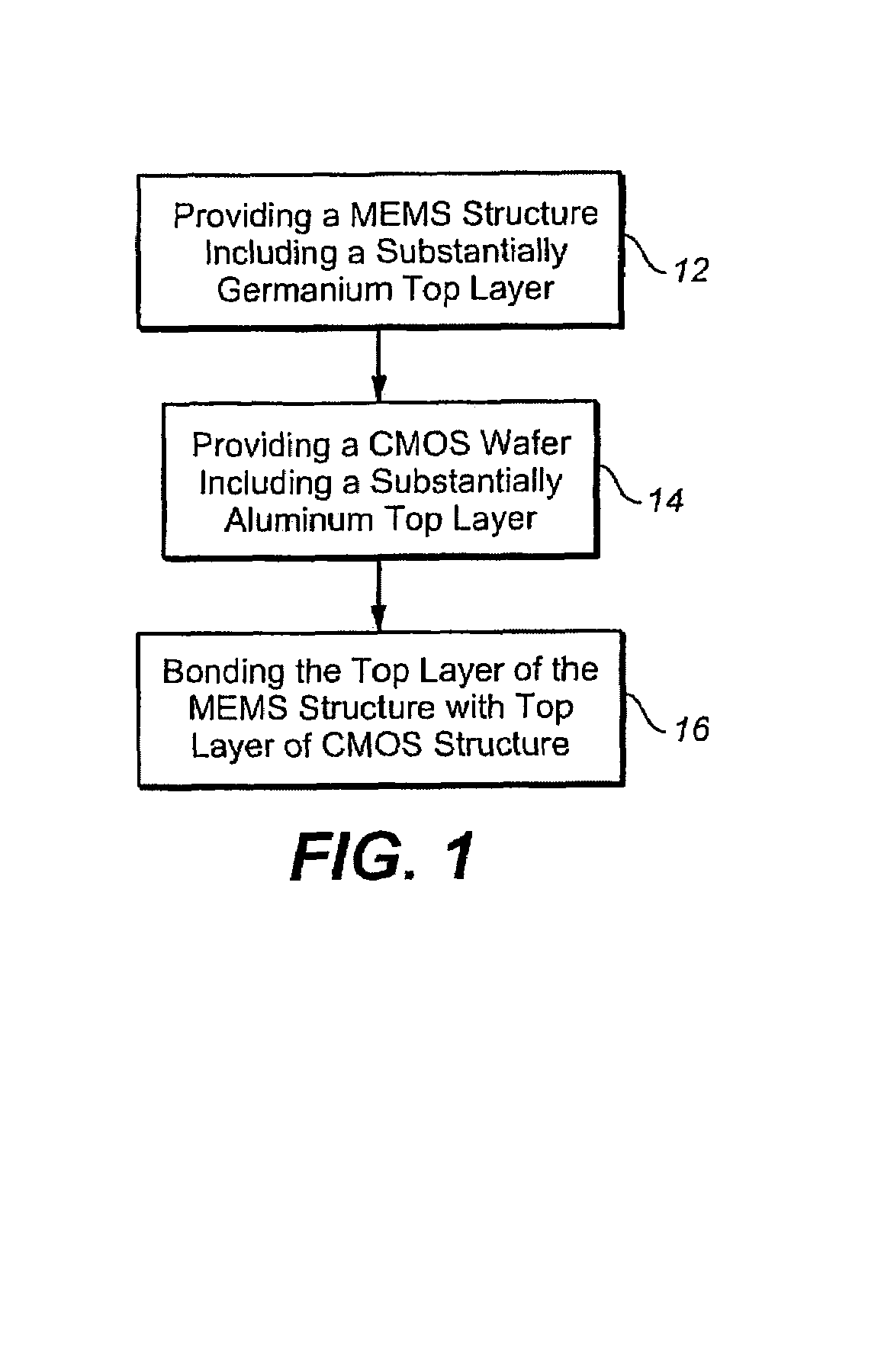

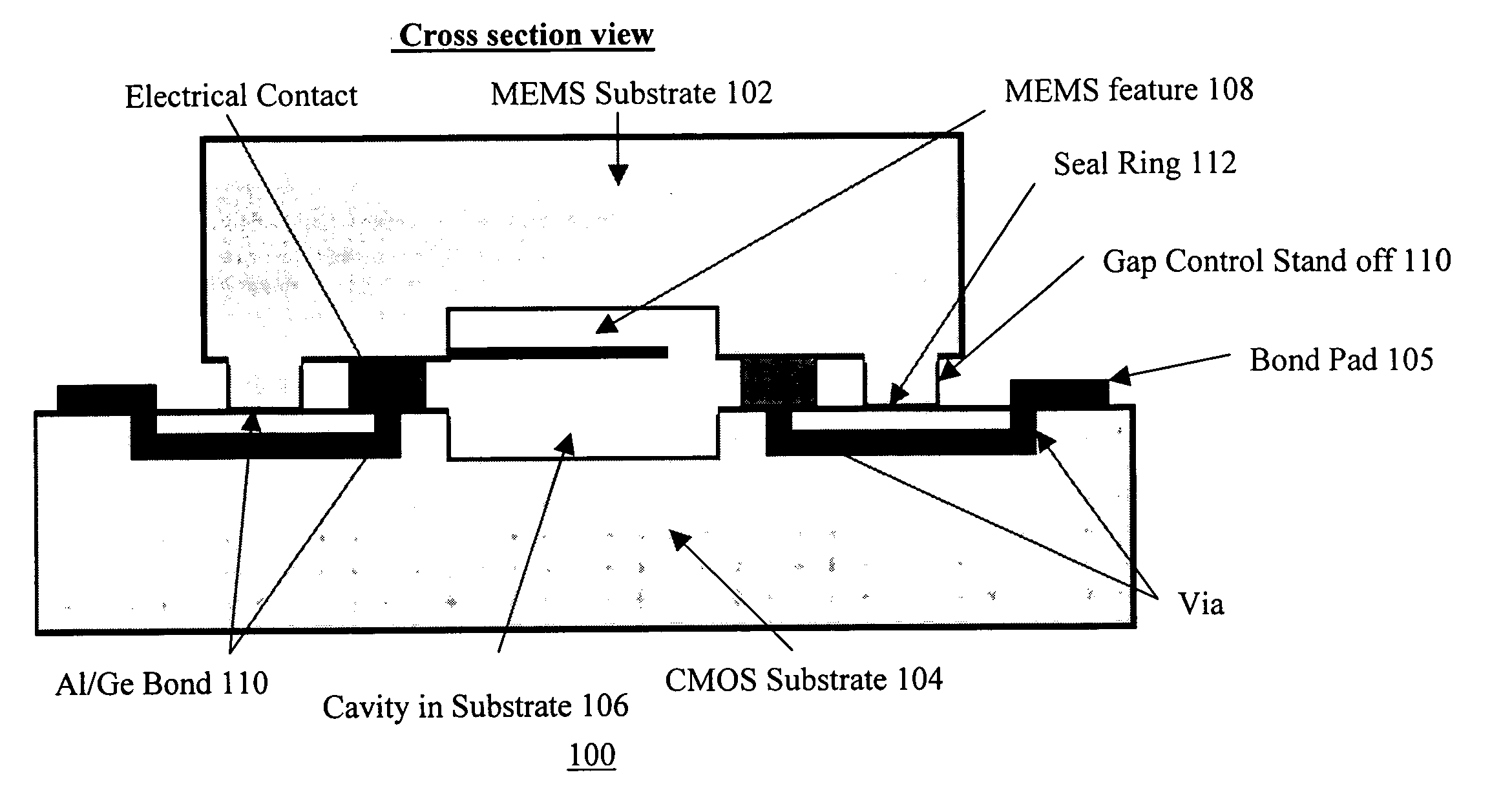

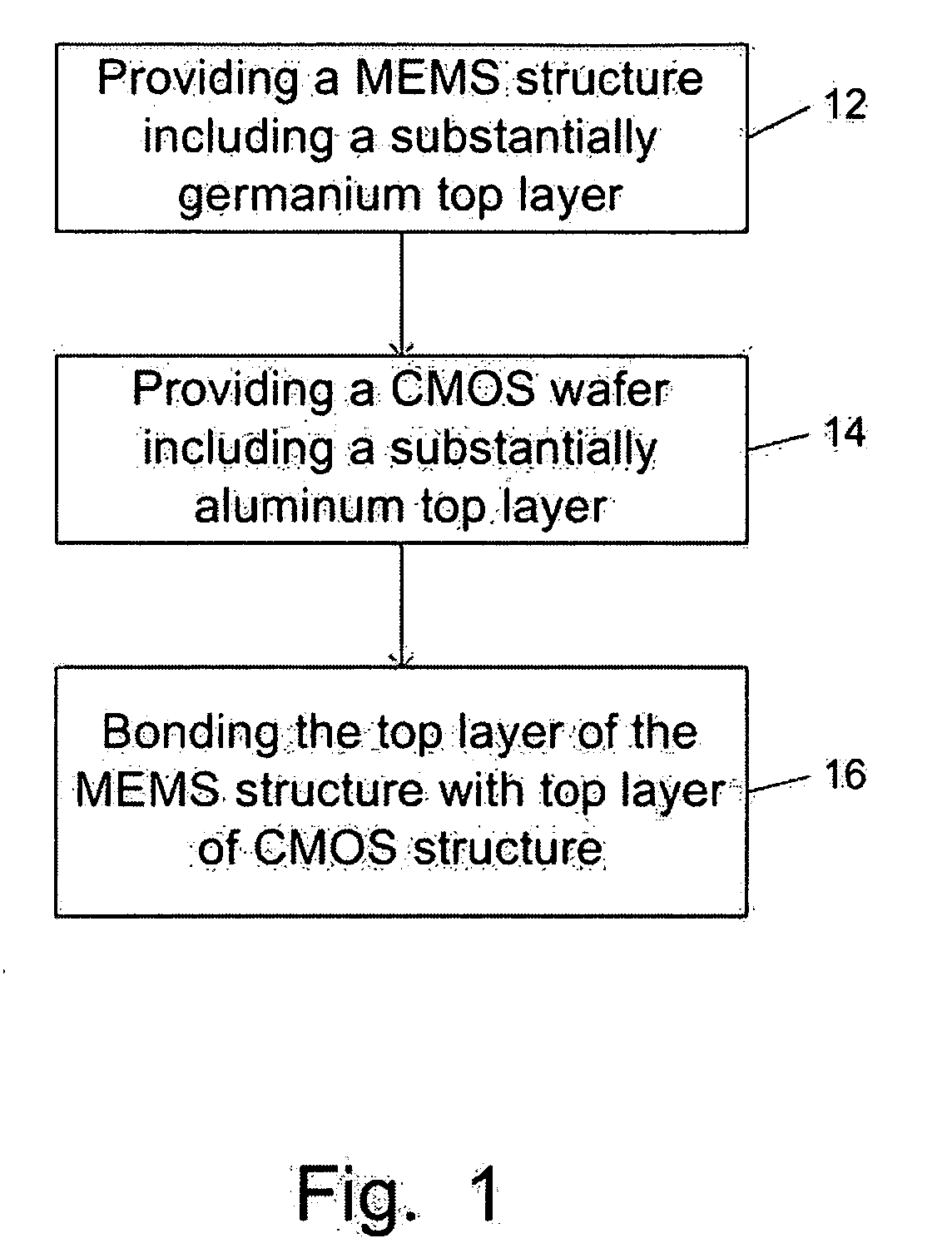

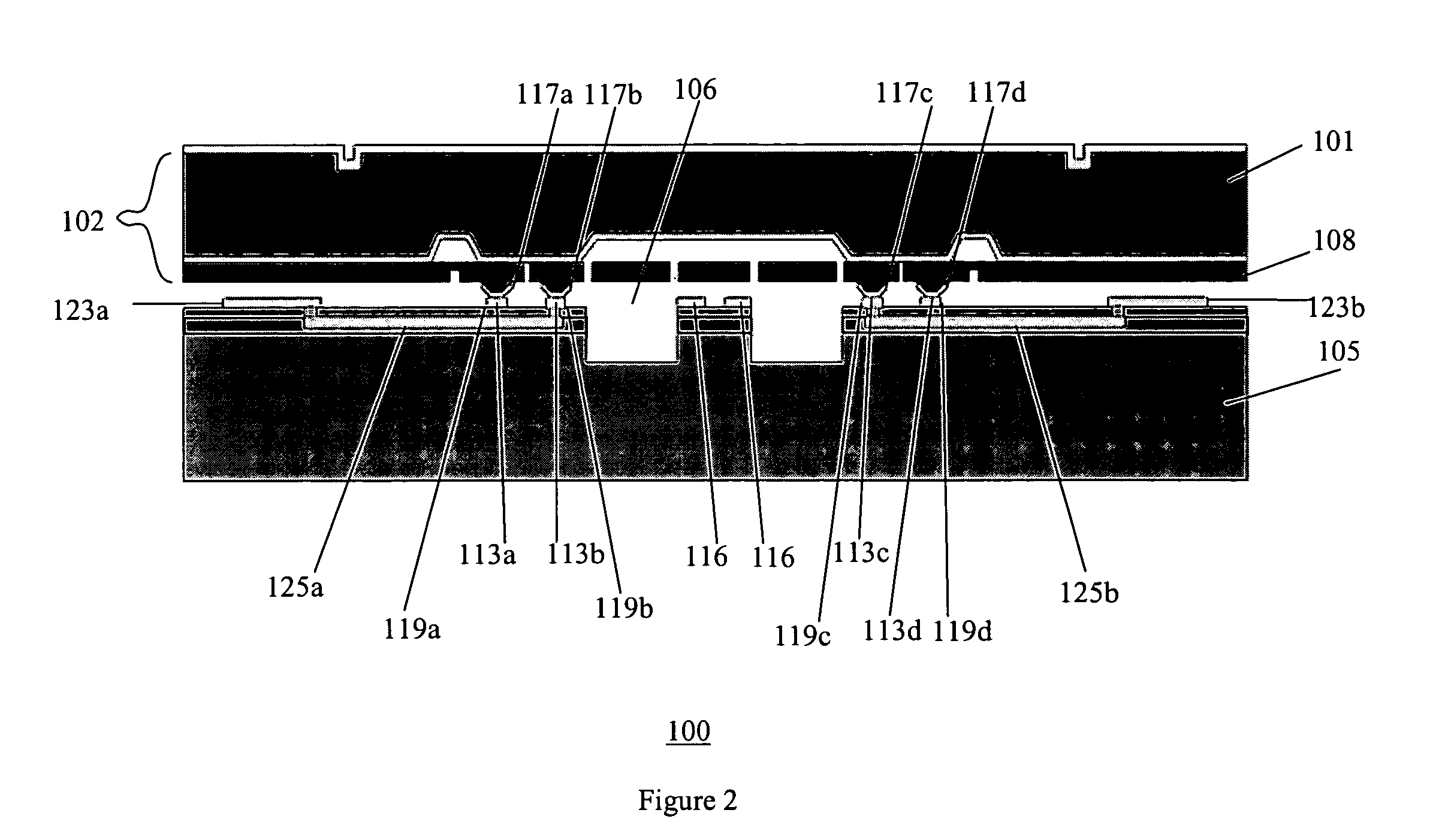

Method of fabrication of a AL/GE bonding in a wafer packaging environment and a product produced therefrom

ActiveUS7442570B2Robust and mechanical contactHighly controllableAcceleration measurement using interia forcesSemiconductor/solid-state device detailsFoundryHermetic seal

A method of bonding of germanium to aluminum between two substrates to create a robust electrical and mechanical contact is disclosed. An aluminum-germanium bond has the following unique combination of attributes: (1) it can form a hermetic seal; (2) it can be used to create an electrically conductive path between two substrates; (3) it can be patterned so that this conduction path is localized; (4) the bond can be made with the aluminum that is available as standard foundry CMOS process. This has the significant advantage of allowing for wafer-level bonding or packaging without the addition of any additional process layers to the CMOS wafer.

Owner:INVENSENSE

Method of fabrication of ai/ge bonding in a wafer packaging environment and a product produced therefrom

ActiveUS20060208326A1RobustHighly controllableAcceleration measurement using interia forcesSemiconductor/solid-state device detailsFoundryHermetic seal

A method of bonding of germanium to aluminum between two substrates to create a robust electrical and mechanical contact is disclosed. An aluminum-germanium bond has the following unique combination of attributes: (1) it can form a hermetic seal; (2) it can be used to create an electrically conductive path between two substrates; (3) it can be patterned so that this conduction path is localized; (4) the bond can be made with the aluminum that is available as standard foundry CMOS process. This has the significant advantage of allowing for wafer-level bonding or packaging without the addition of any additional process layers to the CMOS wafer.

Owner:INVENSENSE

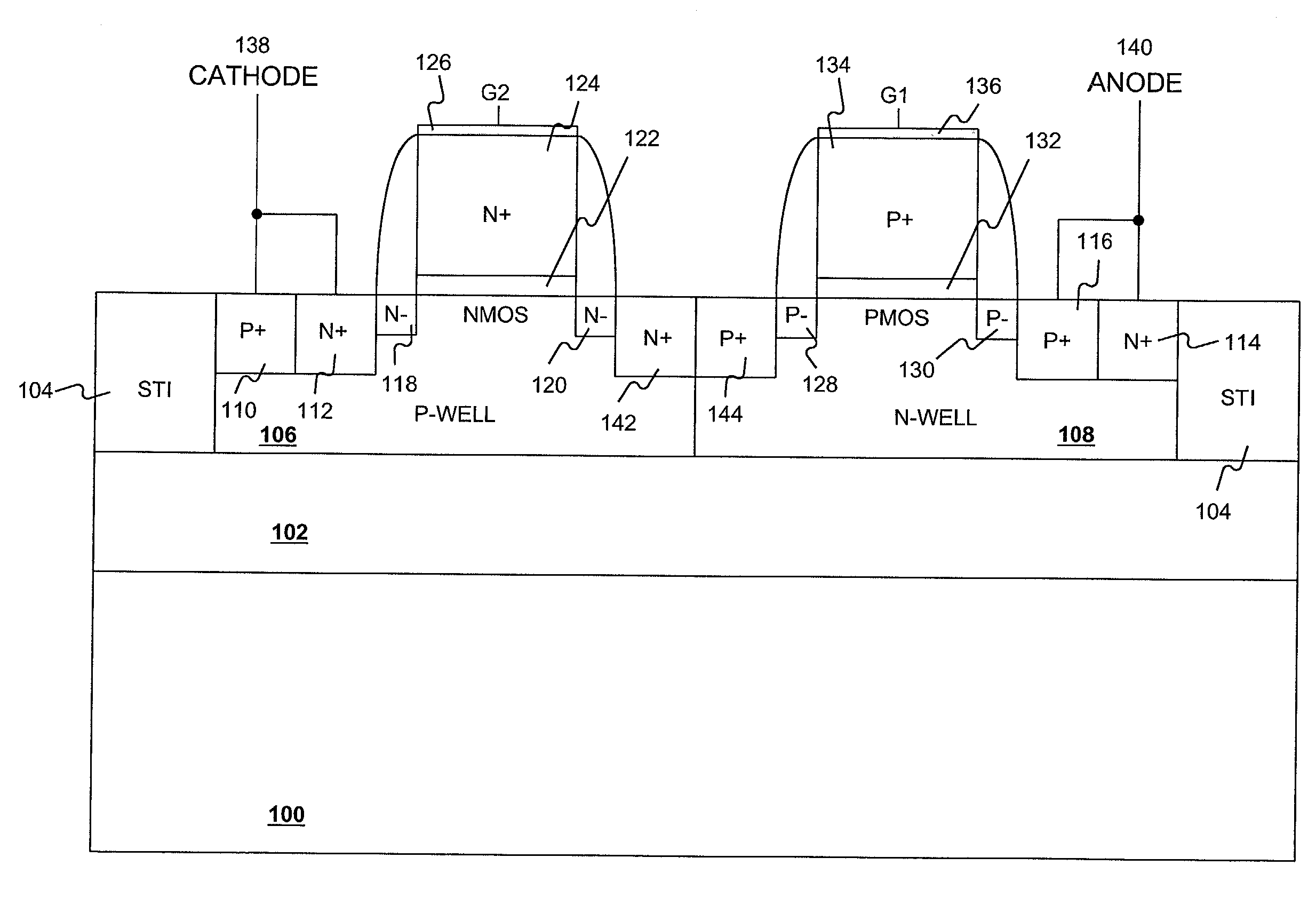

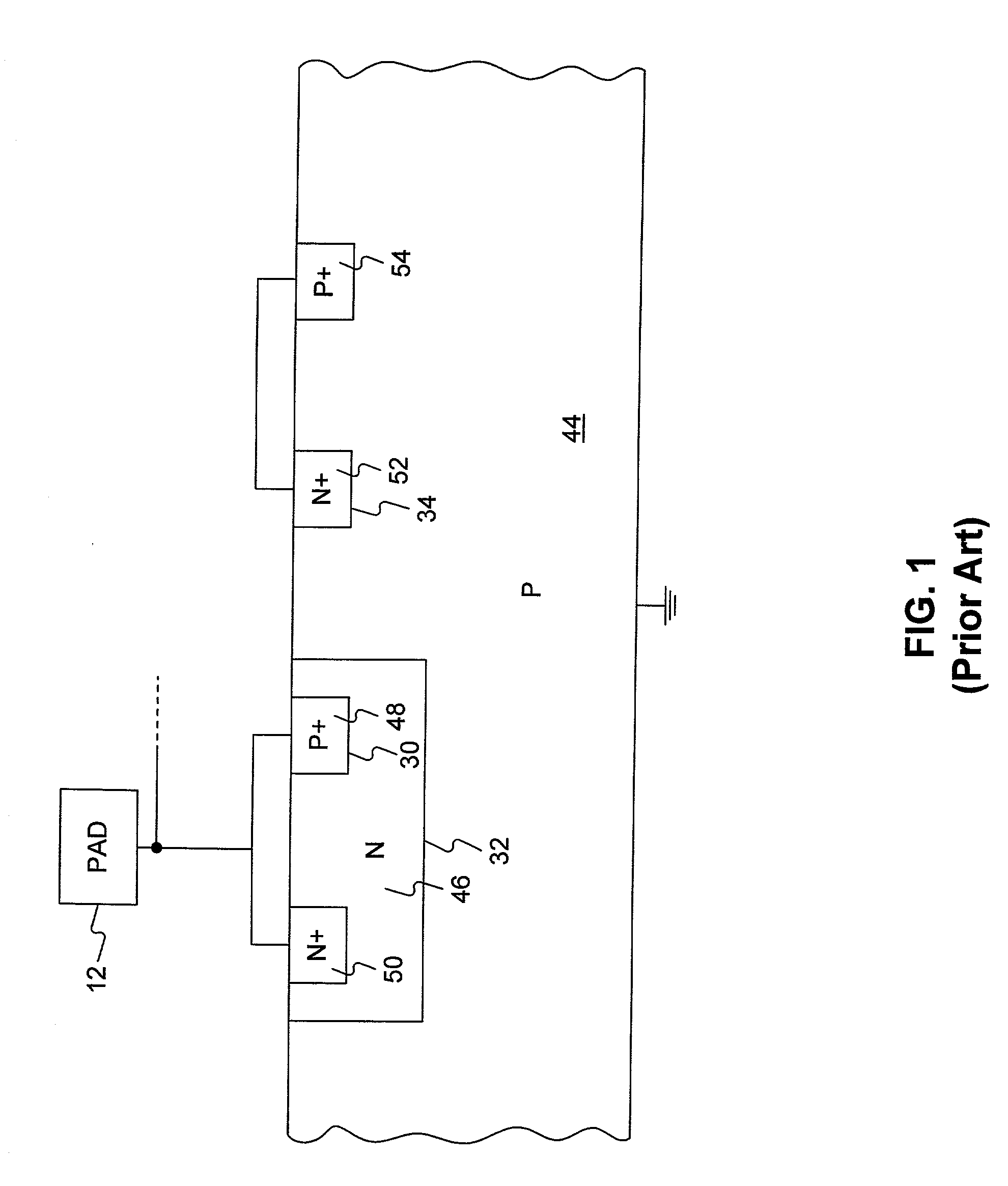

SCR devices in silicon-on-insulator CMOS process for on-chip ESD protection

InactiveUS20030146474A1TransistorSemiconductor/solid-state device detailsSilicon-controlled rectifierSilicon on insulator

A silicon-on-isolator CMOS integrated circuit device includes a semiconductor substrate, an isolation layer formed over the semiconductor substrate, an n-type MOS transistor having a gate, a drain region, and a source region formed over the isolation layer, and a p-type MOS transistor having a gate, a drain region, and a source region formed over the isolation layer and contiguous with the n-type MOS transistor, wherein the n-type MOS transistor and the p-type MOS transistor form a silicon controlled rectifier to provide electrostatic discharge protection.

Owner:TRANSPACIFIC IP LTD

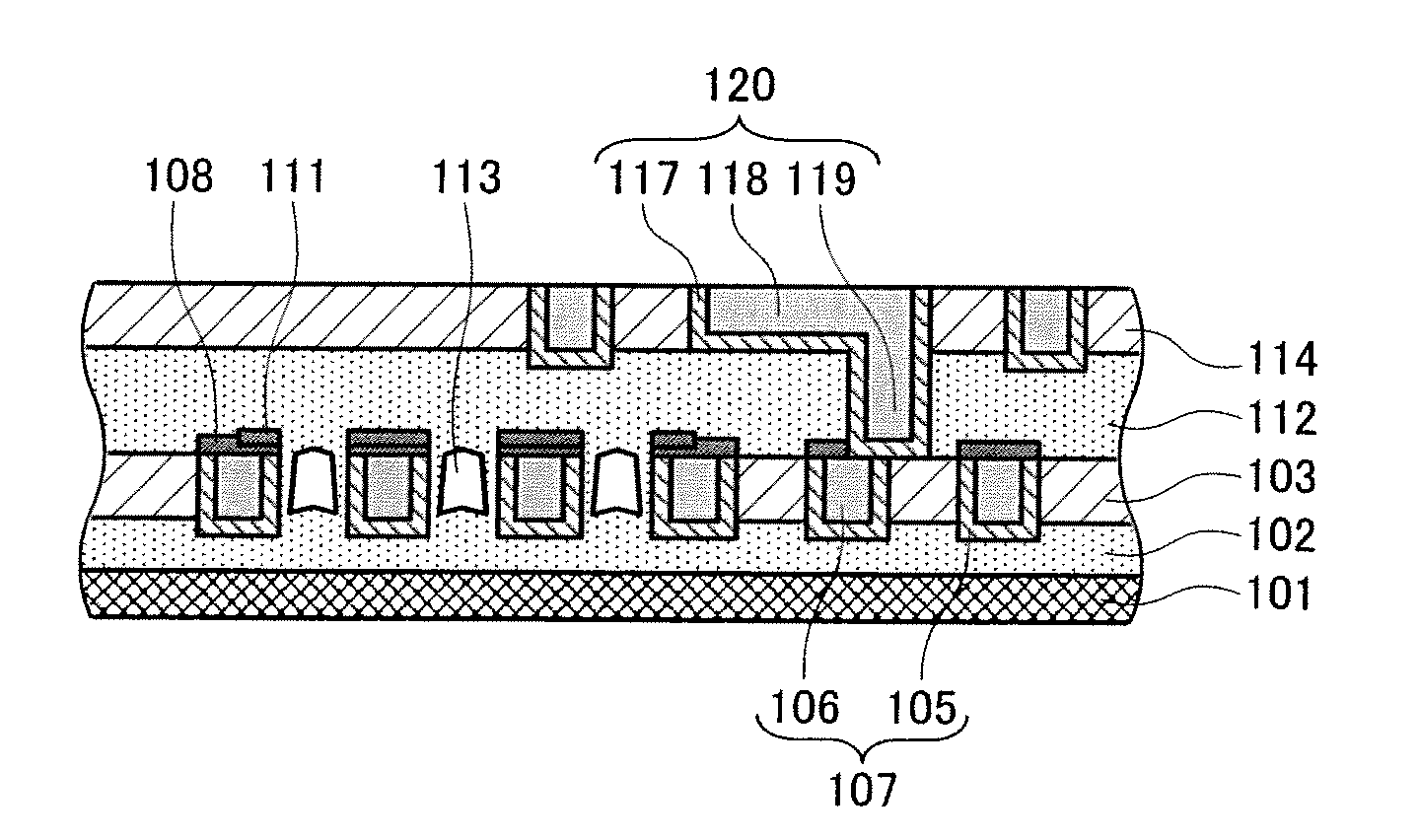

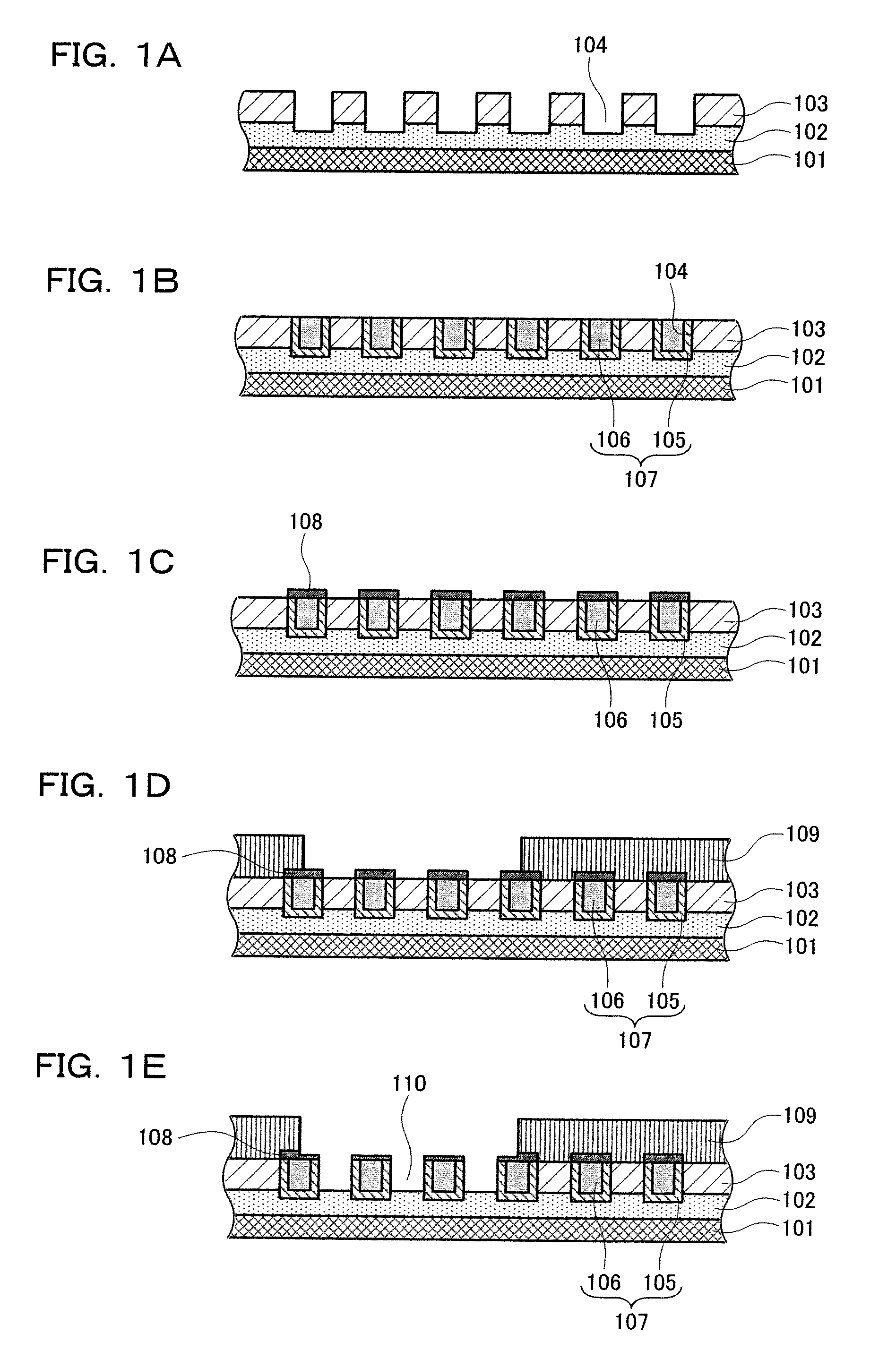

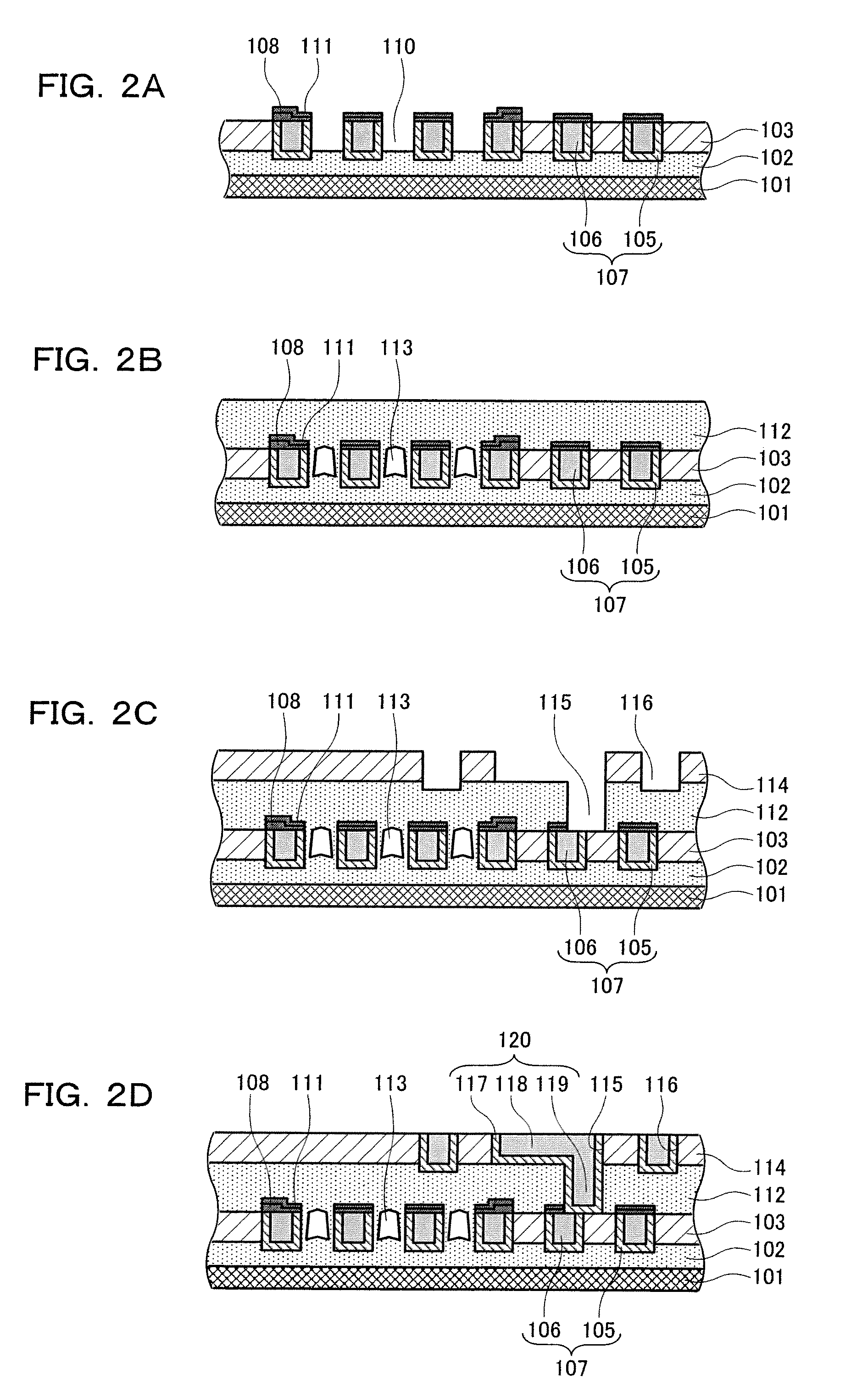

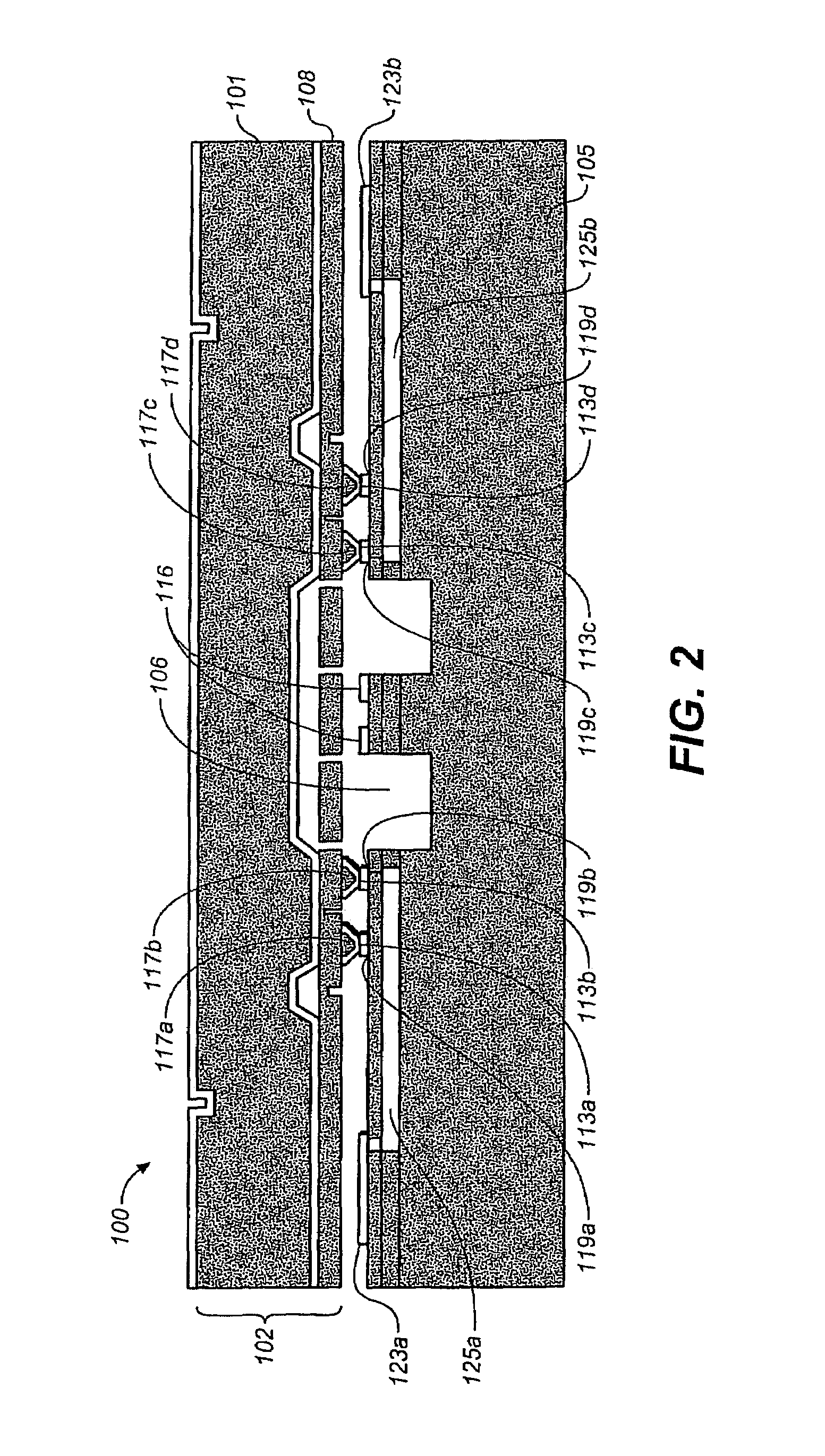

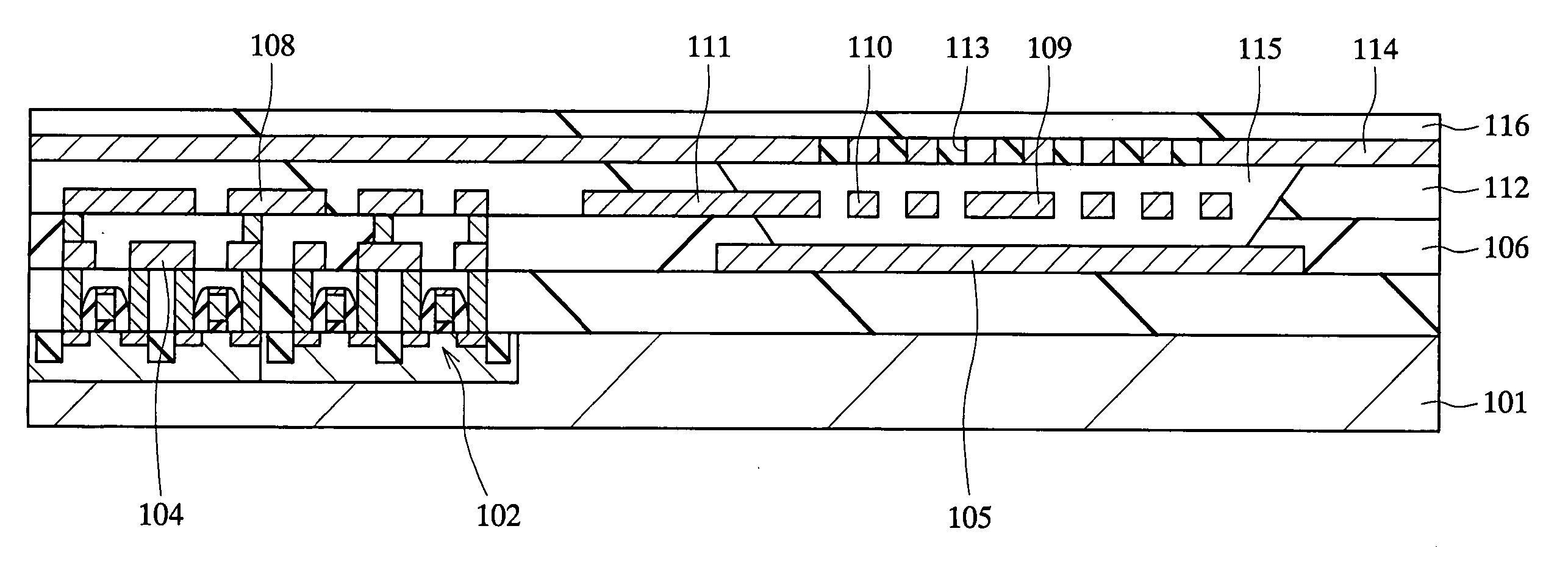

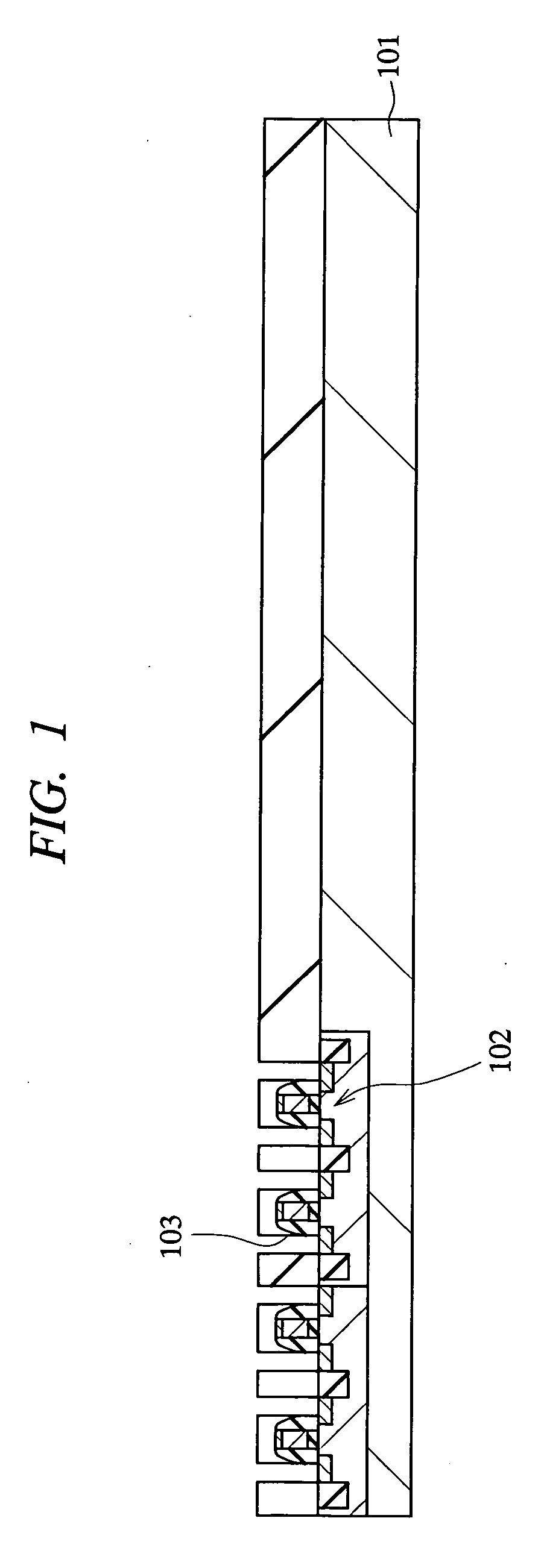

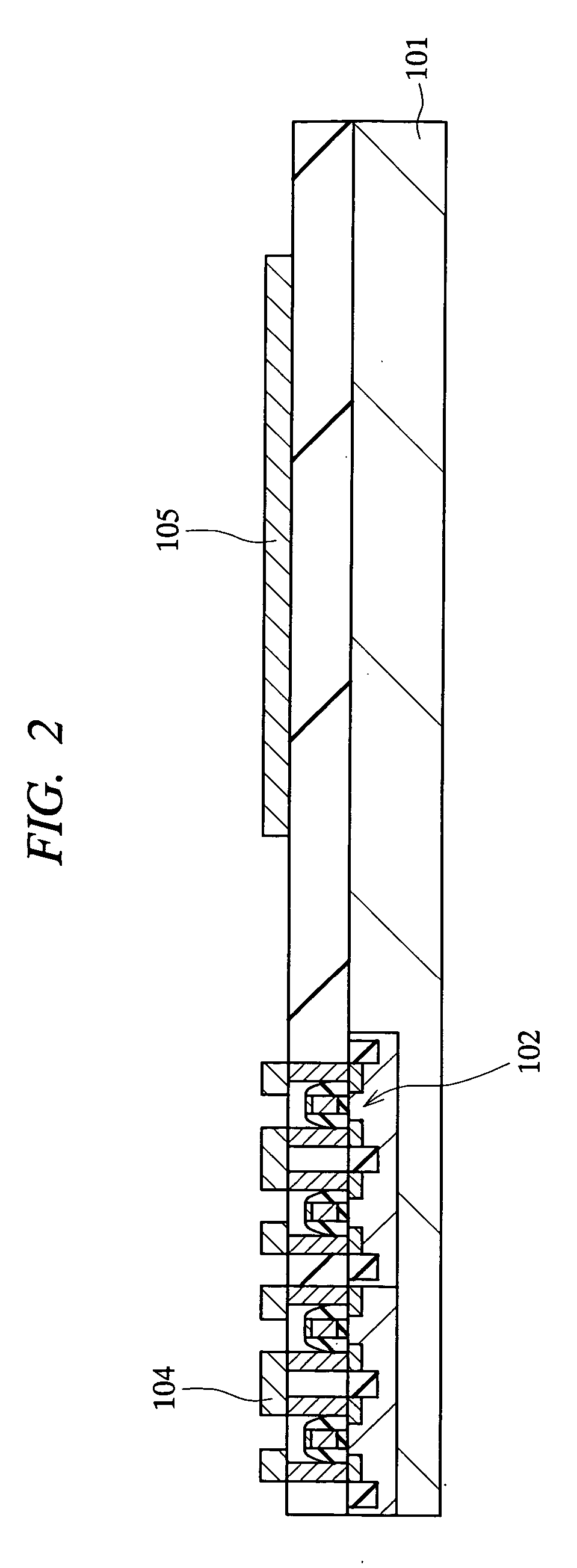

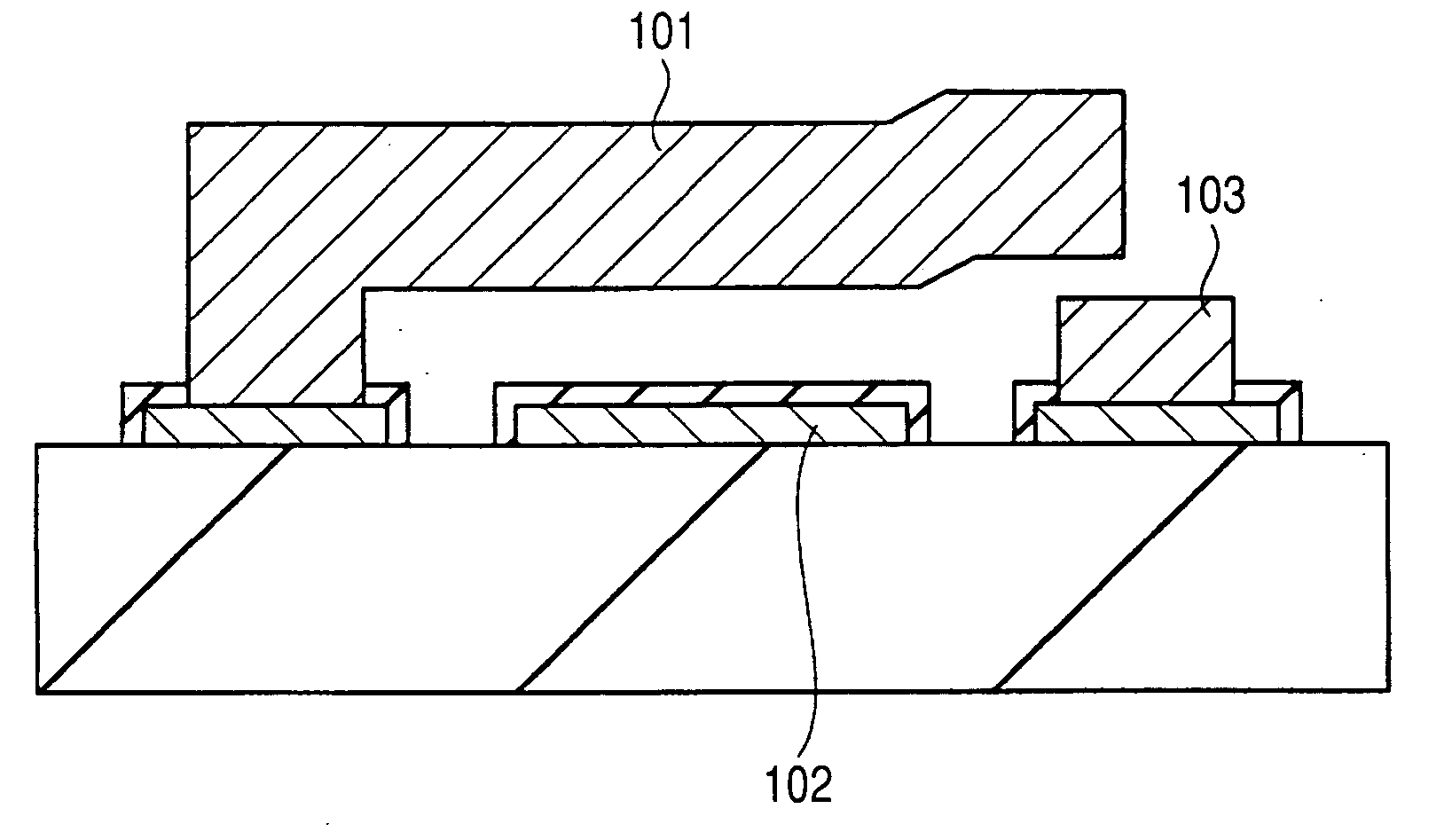

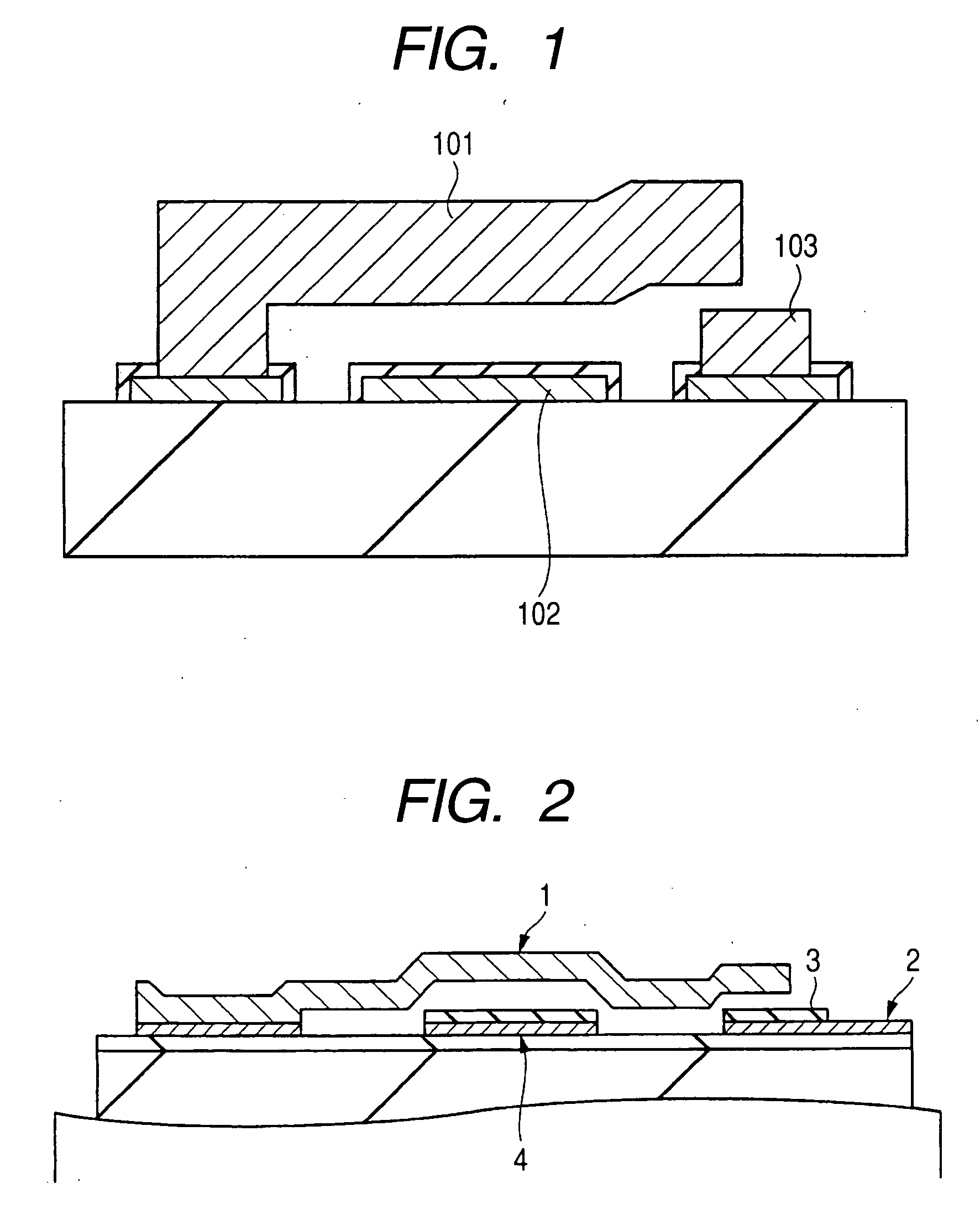

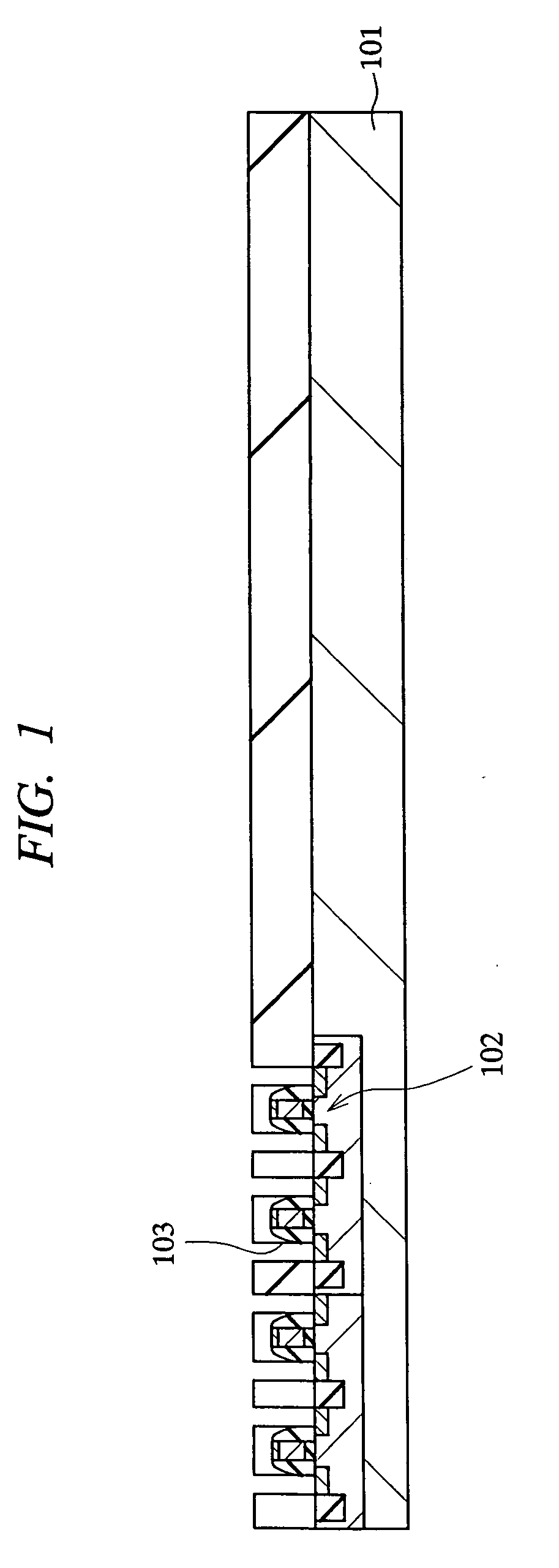

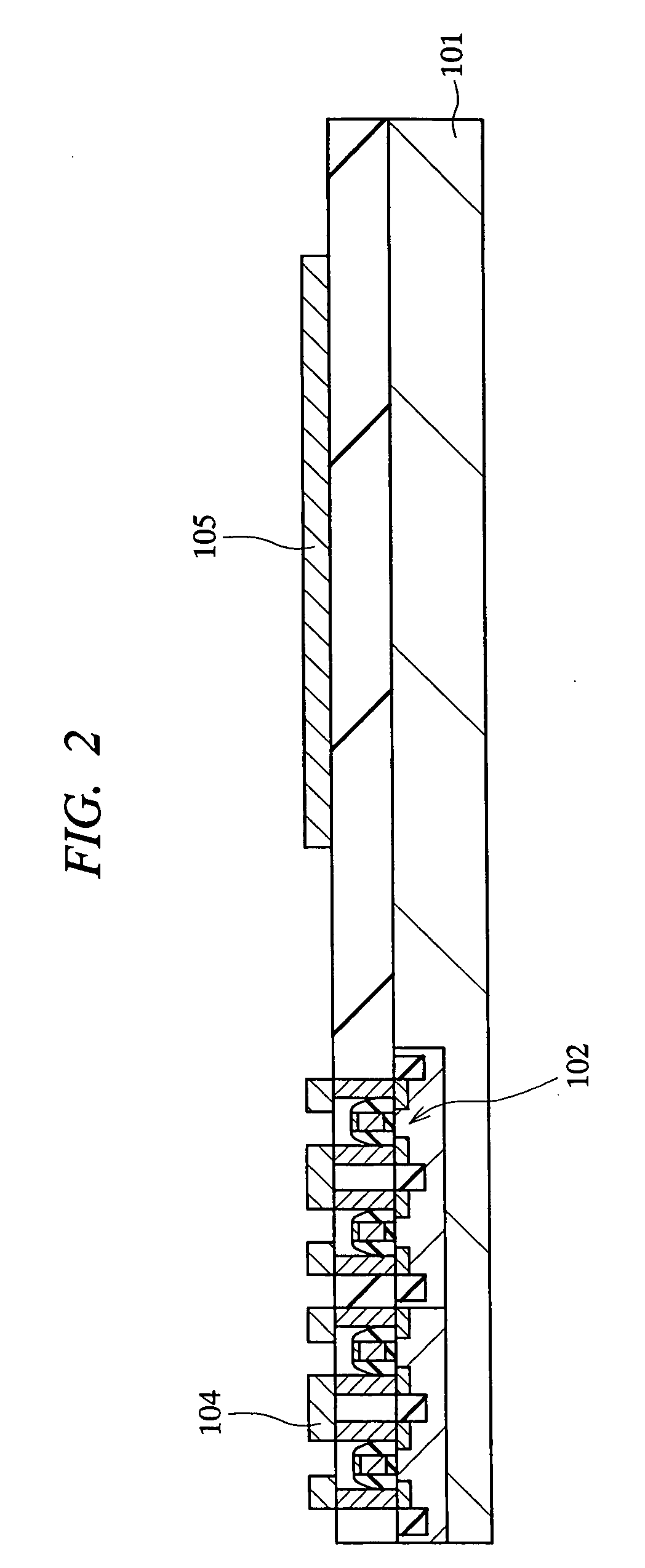

Integrated micro electro-mechanical system and manufacturing method thereof

ActiveUS20060205106A1Accurate representationHigh dimensional accuracyTelevision system detailsInflated body pressure measurementDielectricEtching

In the manufacturing technology of an integrated MEMS in which a semiconductor integrated circuit (CMOS or the like) and a micro machine are monolithically integrated on a semiconductor substrate, a technology capable of manufacturing the integrated MEMS without using a special process different from the normal manufacturing technology of a semiconductor integrated circuit is provided. A MEMS structure is formed together with an integrated circuit by using the CMOS integrated circuit process. For example, when forming an acceleration sensor, a structure composed of a movable mass, an elastic beam and a fixed beam is formed by using the CMOS interconnect technology. Thereafter, an interlayer dielectric and the like are etched by using the CMOS process to form a cavity. Then, fine holes used in the etching are sealed with a dielectric.

Owner:HITACHI ASTEMO LTD

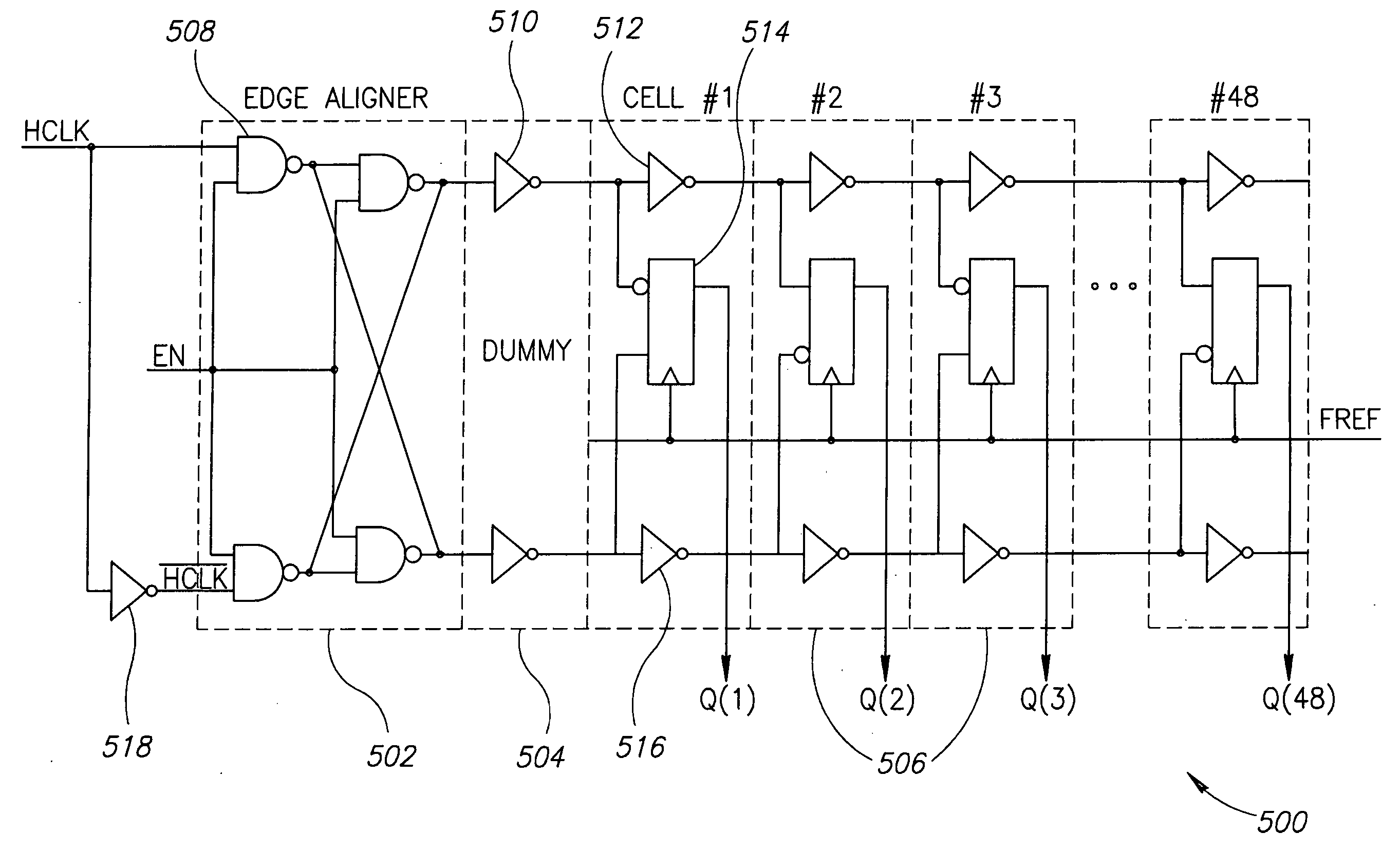

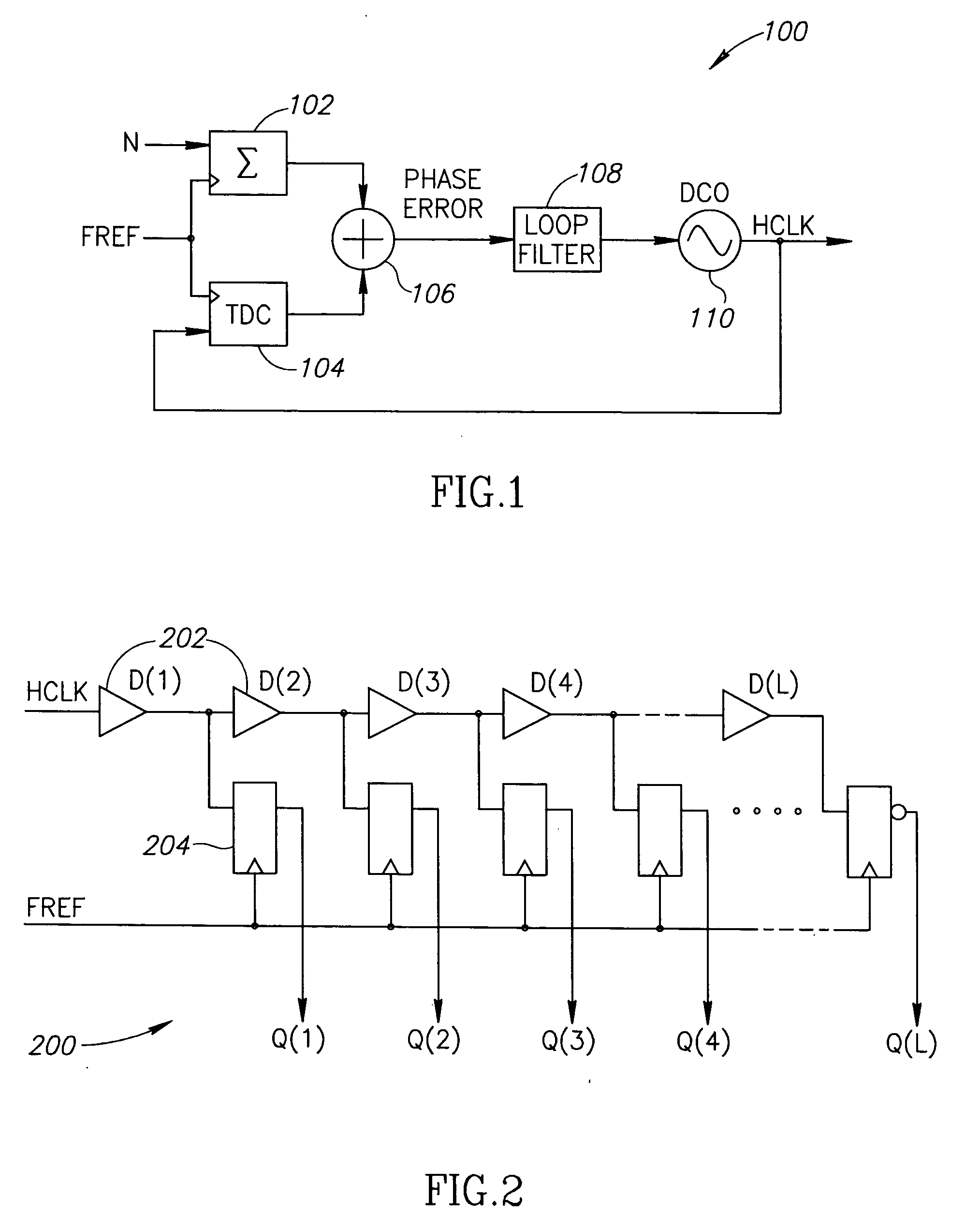

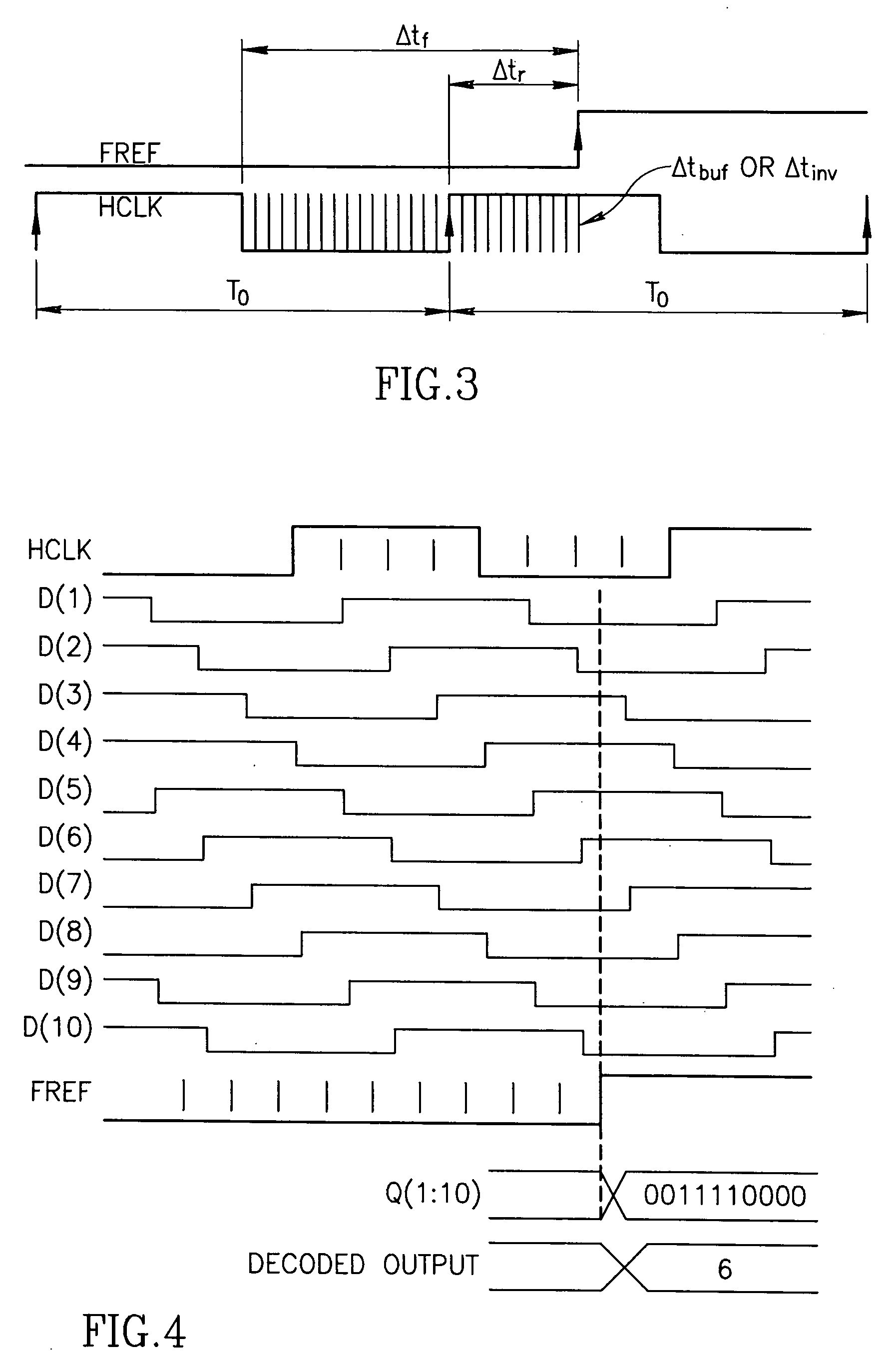

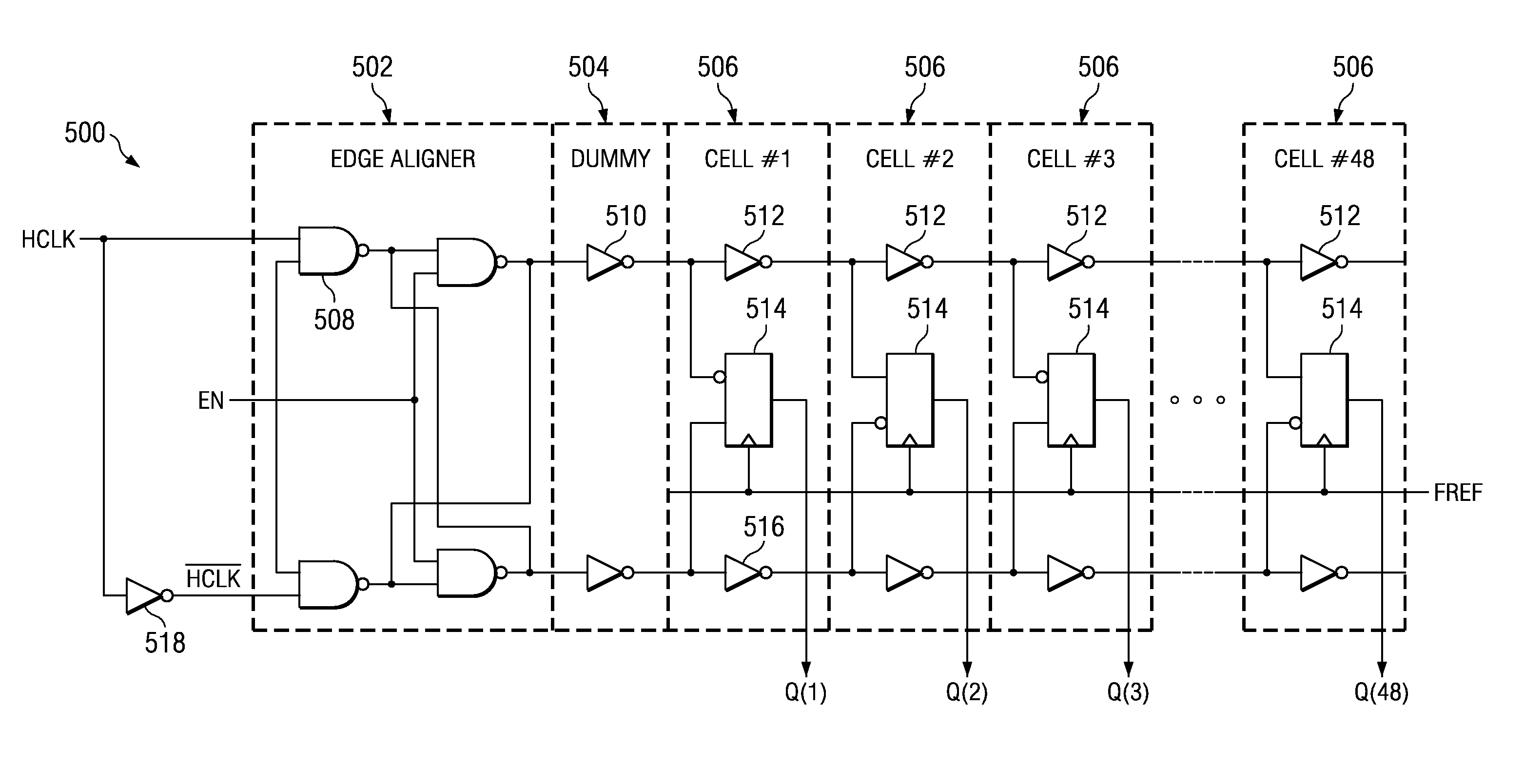

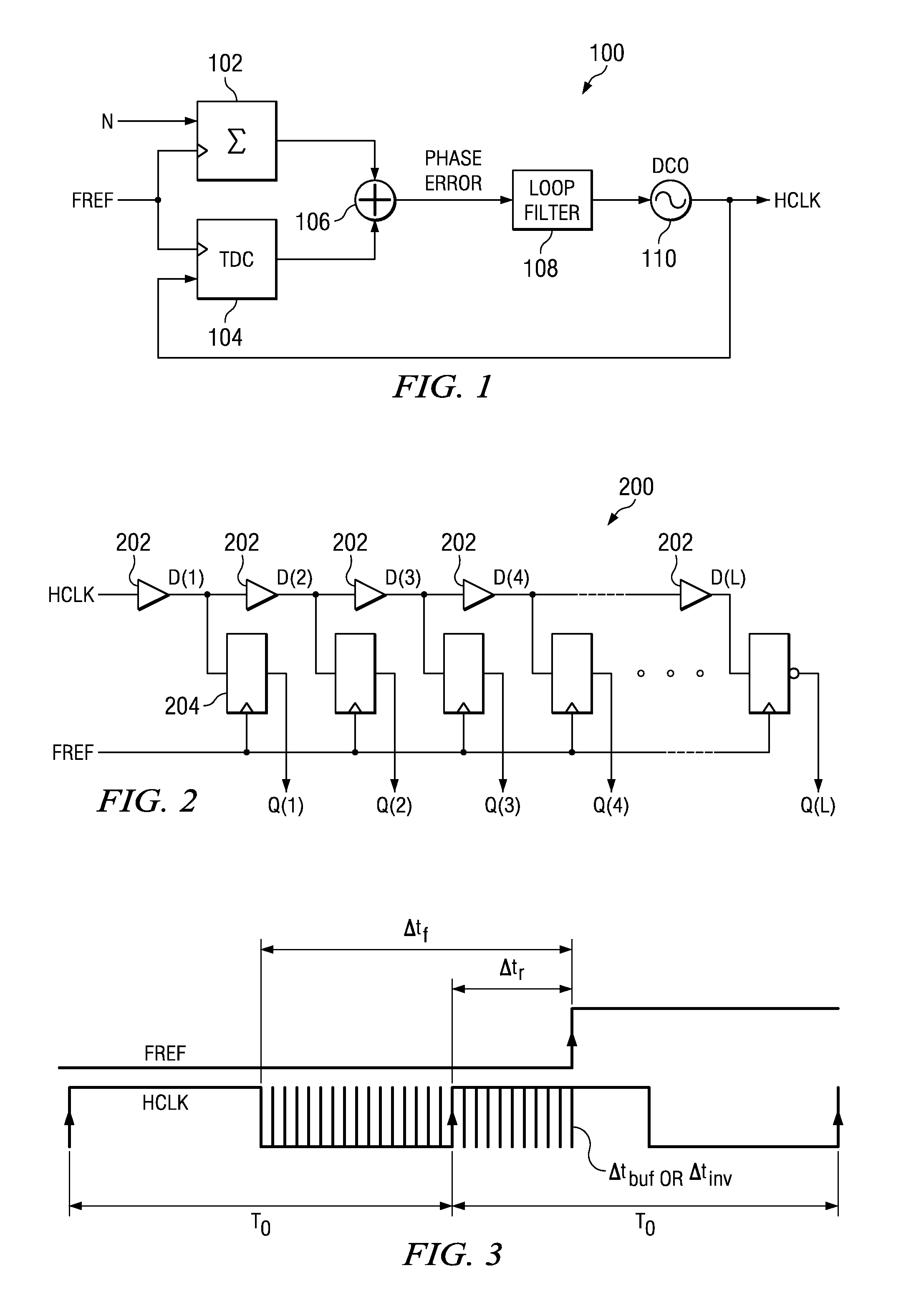

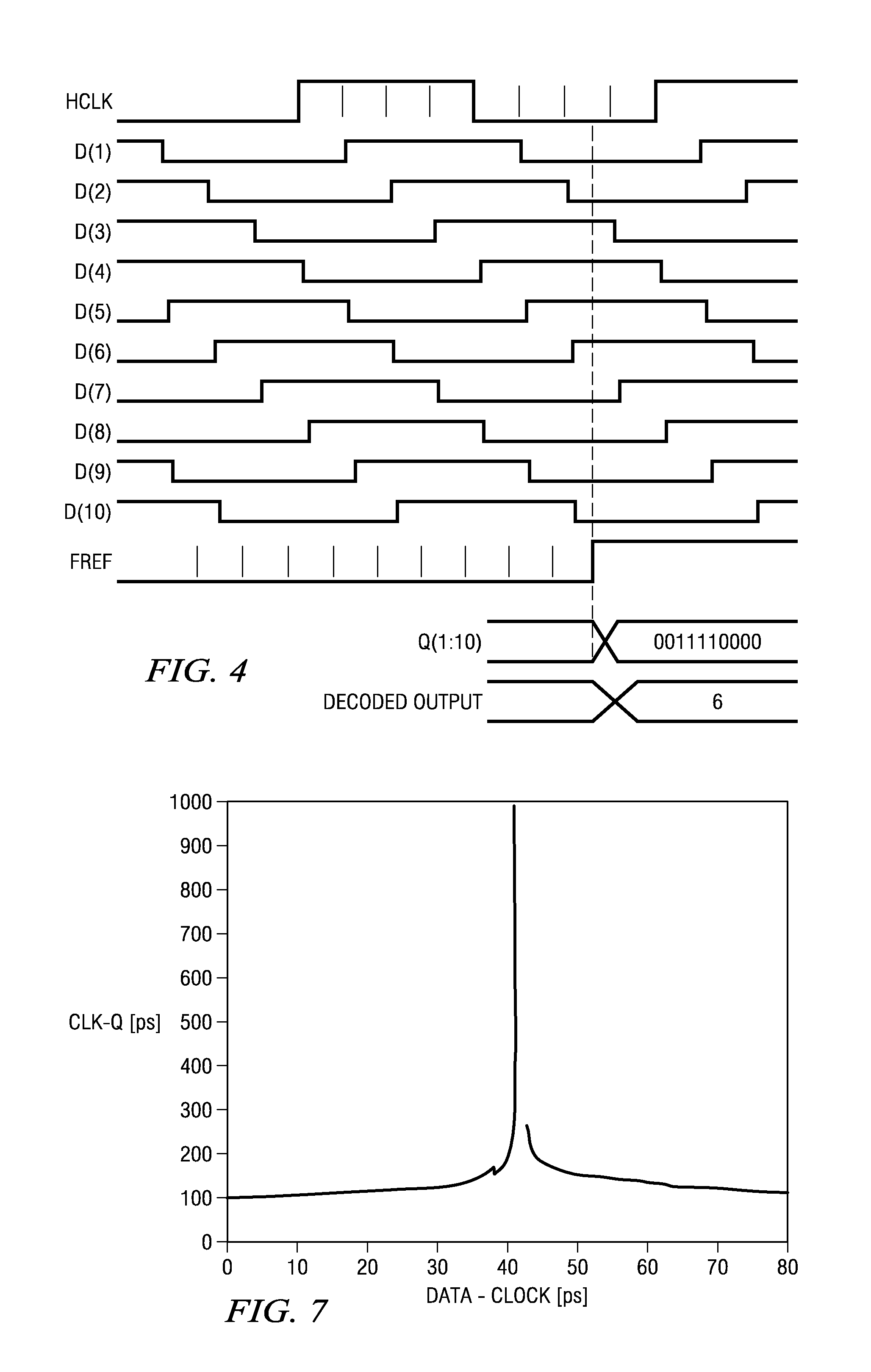

Circuit for high-resolution phase detection in a digital RF processor

ActiveUS20060103566A1Less sensitiveReduce power consumptionElectric signal transmission systemsPulse automatic controlEngineeringDigital converter

A novel time-to-digital converter (TDC) used as a phase / frequency detector and charge pump replacement in an all-digital PLL within a digital radio processor. The TDC core is based on a pseudo-differential digital architecture making it insensitive to NMOS and PMOS transistor mismatches. The time conversion resolution is equal to an inverter propagation delay, e.g., 20 ps, which is the finest logic-level regenerative timing in CMOS. The TDC is self calibrating with the estimation accuracy better than 1%. The TDC circuit can also serve as a CMOS process strength estimator for analog circuits in large SoC dies. The circuit also employs power management circuitry to reduce power consumption to a very low level.

Owner:TEXAS INSTR INC

Integrated micro electro-mechanical system and manufacturing method thereof

ActiveUS7402449B2Easy to manufactureSufficient massTelevision system detailsInflated body pressure measurementDielectricEtching

In the manufacturing technology of an integrated MEMS in which a semiconductor integrated circuit (CMOS or the like) and a micro machine are monolithically integrated on a semiconductor substrate, a technology capable of manufacturing the integrated MEMS without using a special process different from the normal manufacturing technology of a semiconductor integrated circuit is provided. A MEMS structure is formed together with an integrated circuit by using the CMOS integrated circuit process. For example, when forming an acceleration sensor, a structure composed of a movable mass, an elastic beam and a fixed beam is formed by using the CMOS interconnect technology. Thereafter, an interlayer dielectric and the like are etched by using the CMOS process to form a cavity. Then, fine holes used in the etching are sealed with a dielectric.

Owner:HITACHI ASTEMO LTD

Switch, semiconductor device, and manufacturing method thereof

InactiveUS20070018761A1Improve reliabilityElectrostatic/electro-adhesion relaysForming microstructural systemsCantilevered beamField strength

It is an objective to achieve a MEMS switch which can be mounted with a CMOS circuit and has a contact point with high reliability, both mechanically and electrically. An insulator having a compatibility with a CMOS process is formed at the contact surface of a cantilever beam constituting a MEMS switch and a fixed contact 2 opposite thereto. When the switch is used the cantilever beam is moved by applying a voltage to the pull-in electrode and the cantilever beam. After the cantilever beam makes contact with the fixed contact, a voltage exceeding the breakdown field strength of the insulator is applied to the insulator, resulting in dielectric breakdown occurring. By modifying the insulator once, the mechanical fatigue concentration point of the switch contact point is protected, and a contact point is achieved as well in which electrical signals are transmitted through the current path formed by the dielectric breakdown.

Owner:HITACHI LTD

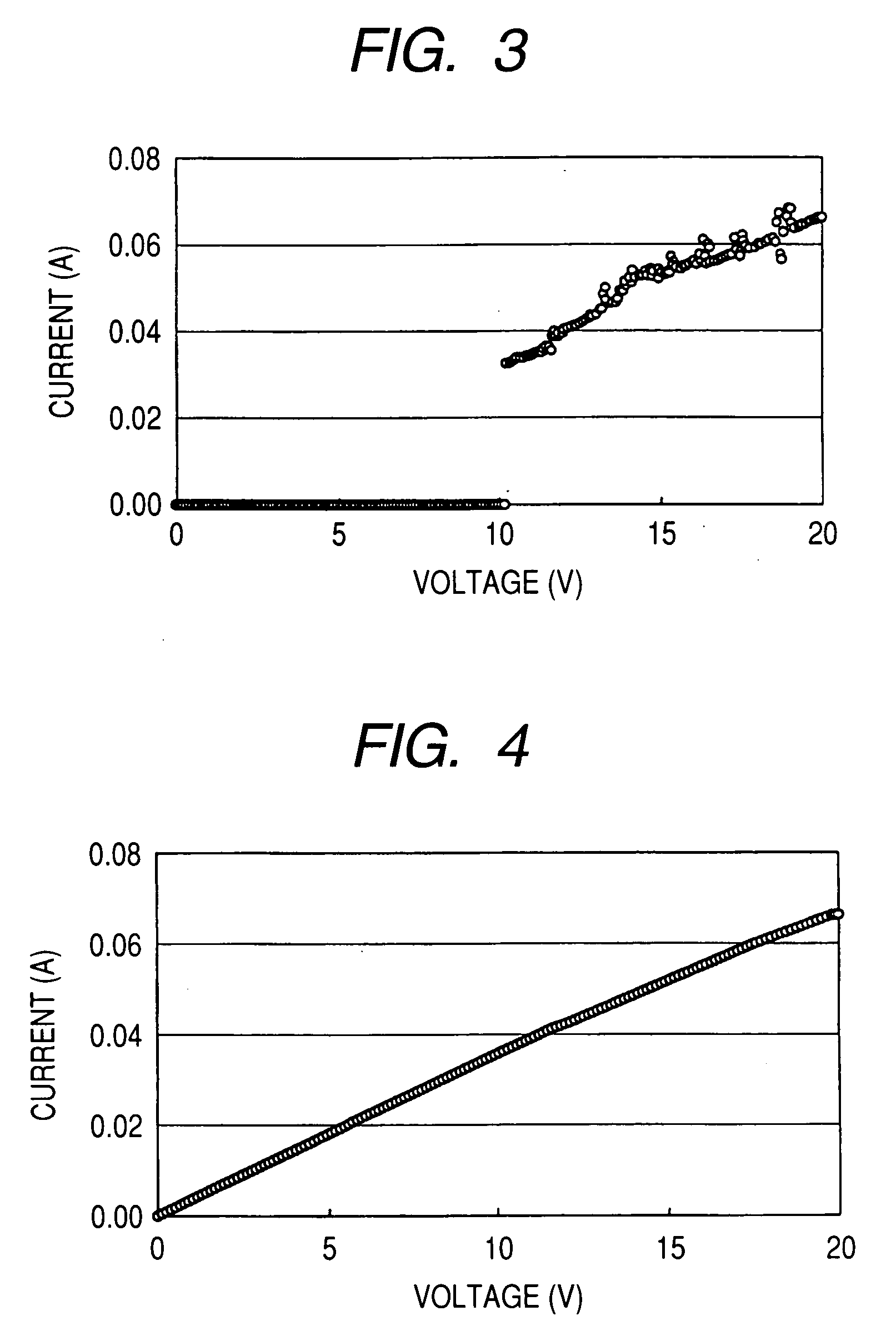

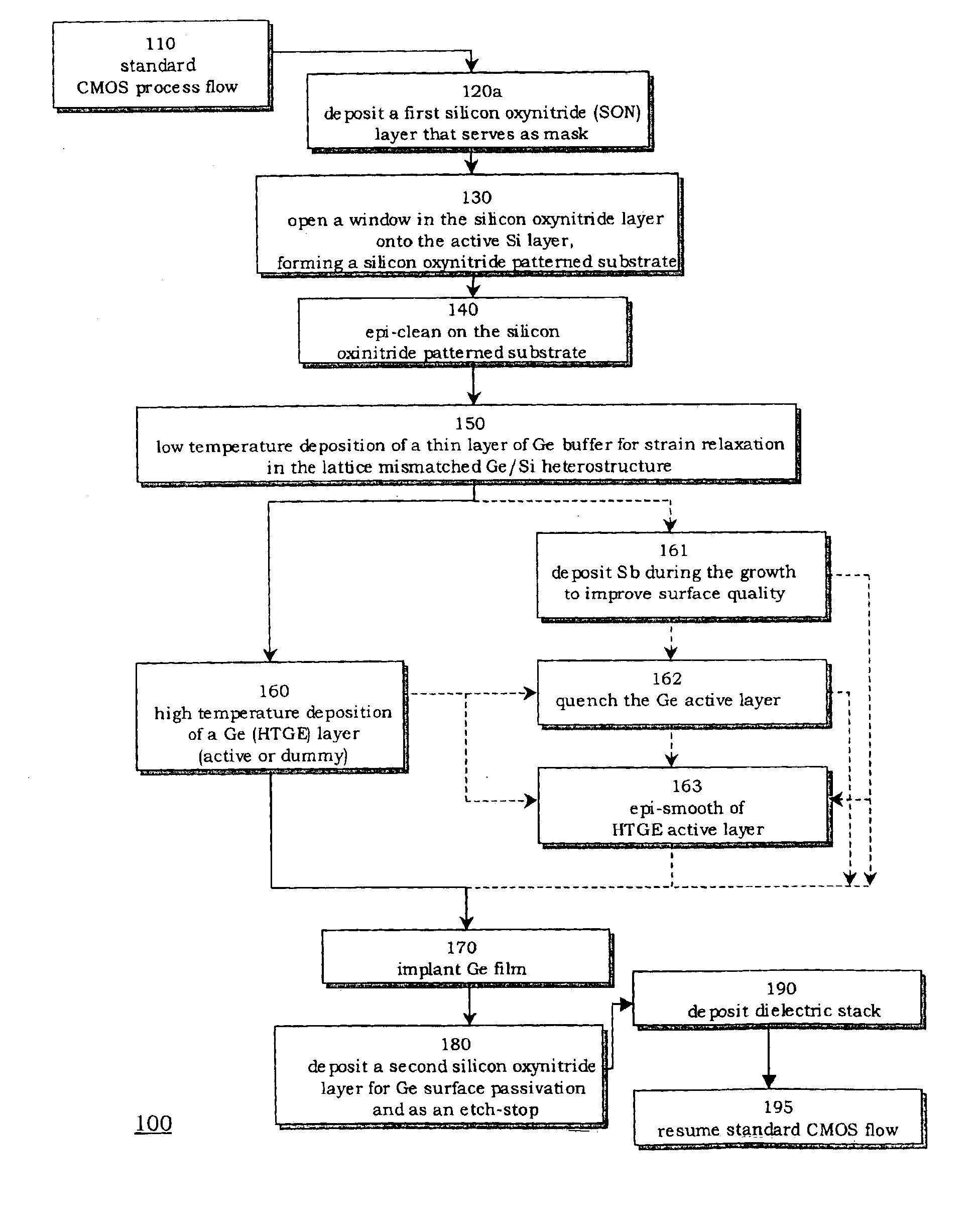

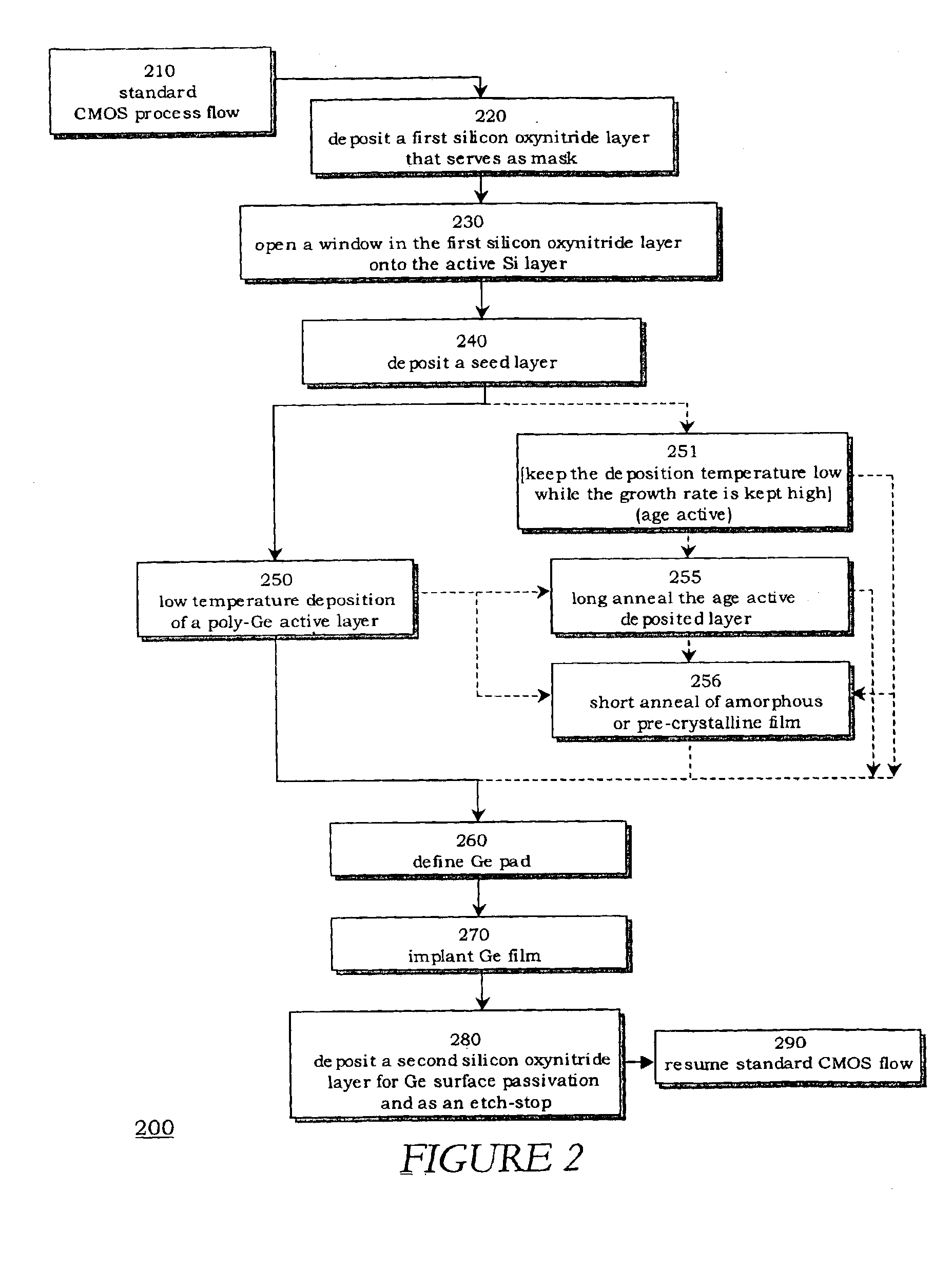

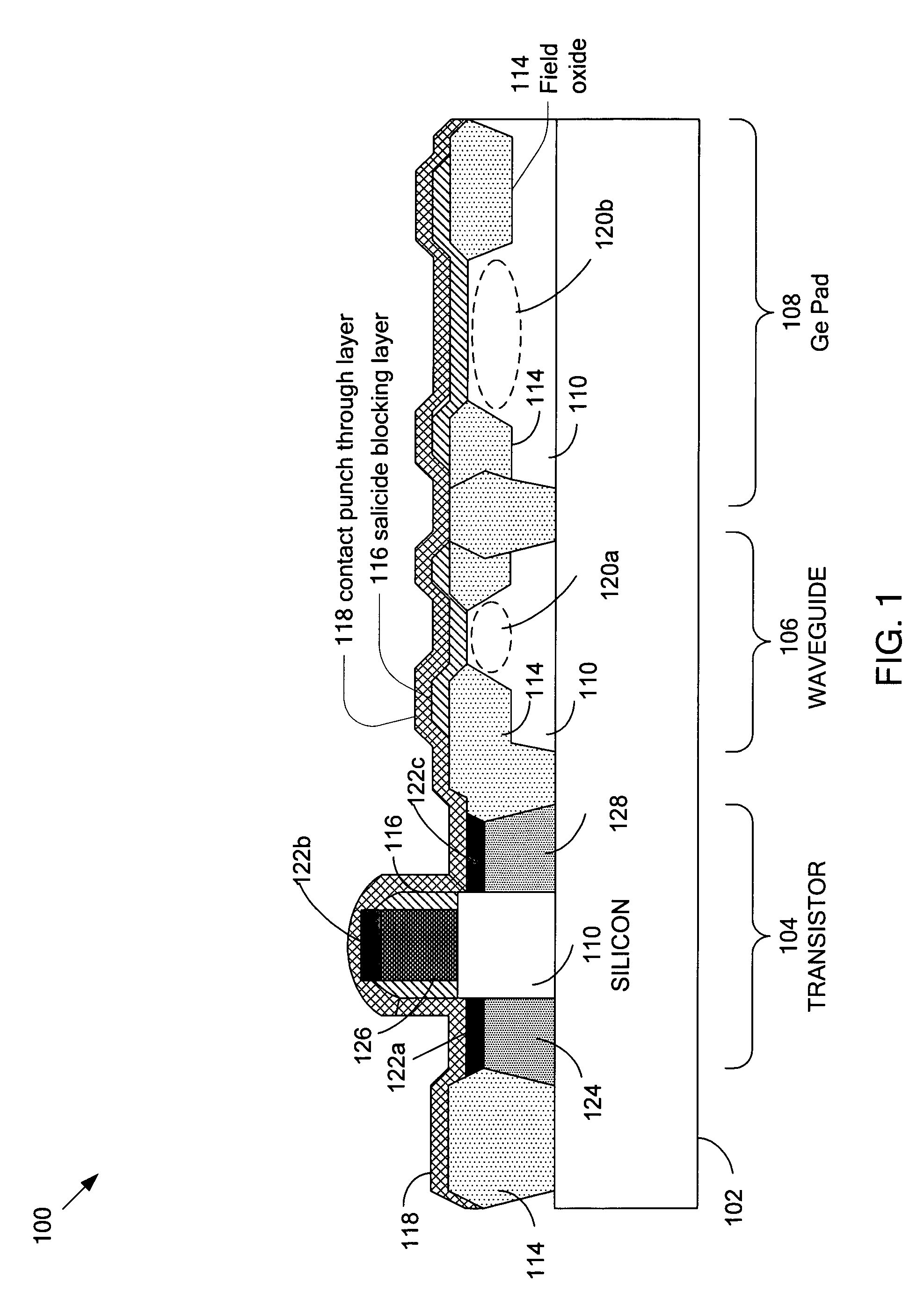

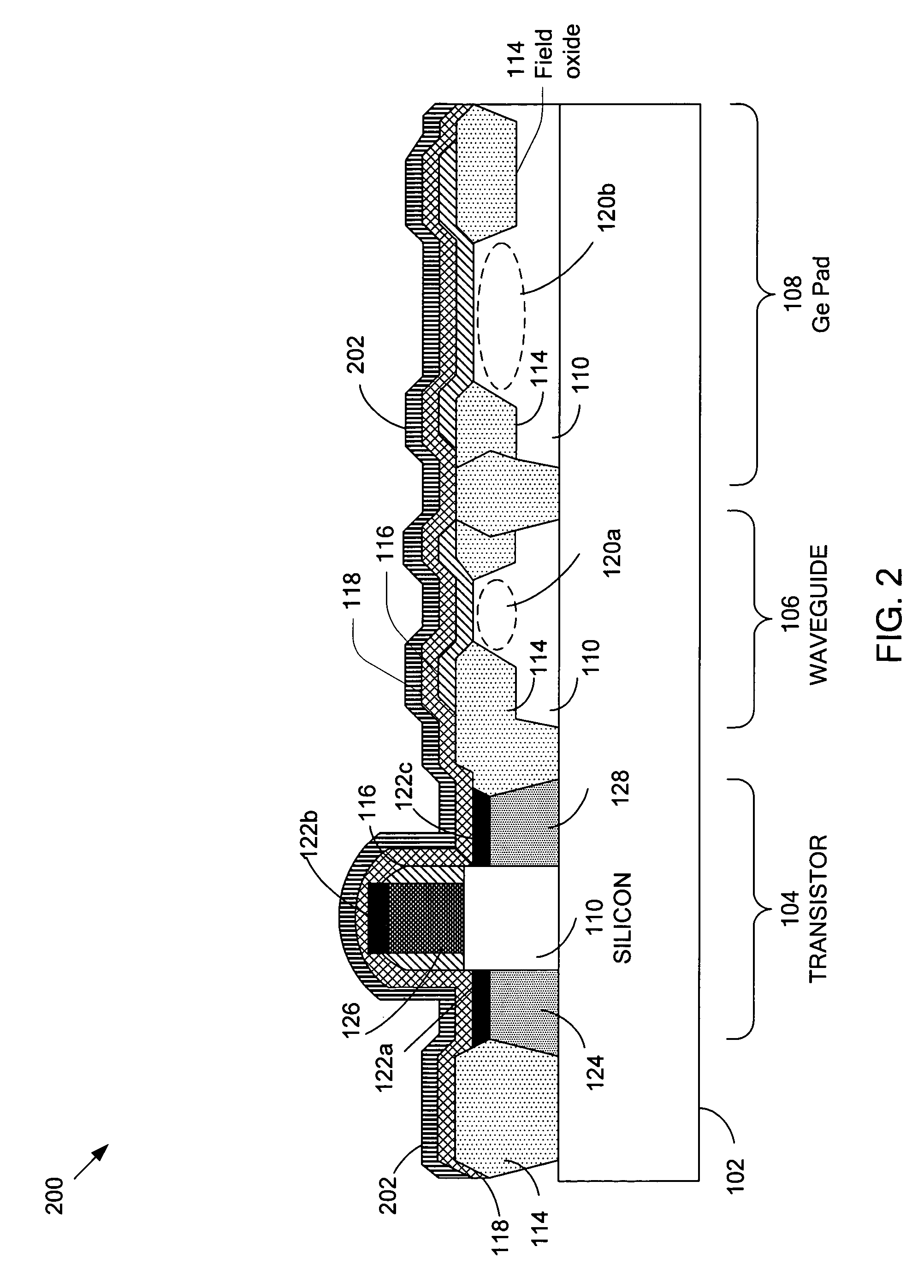

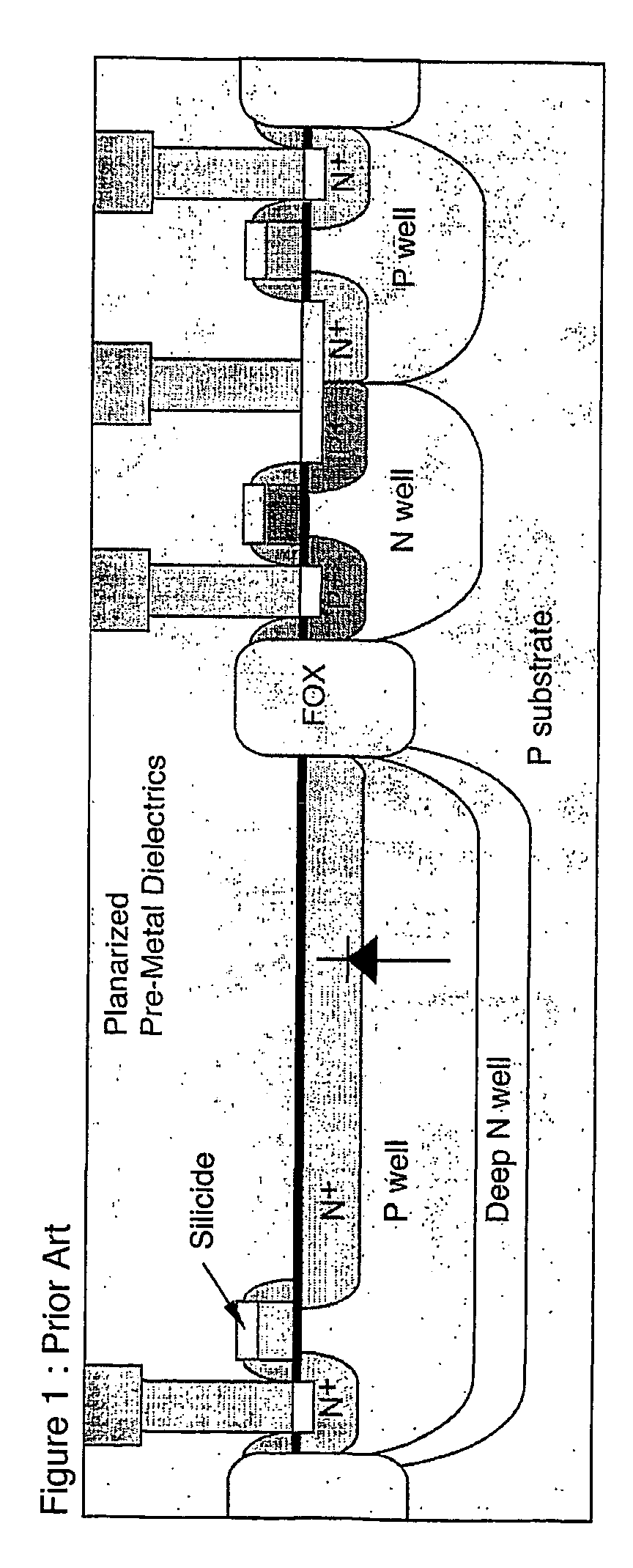

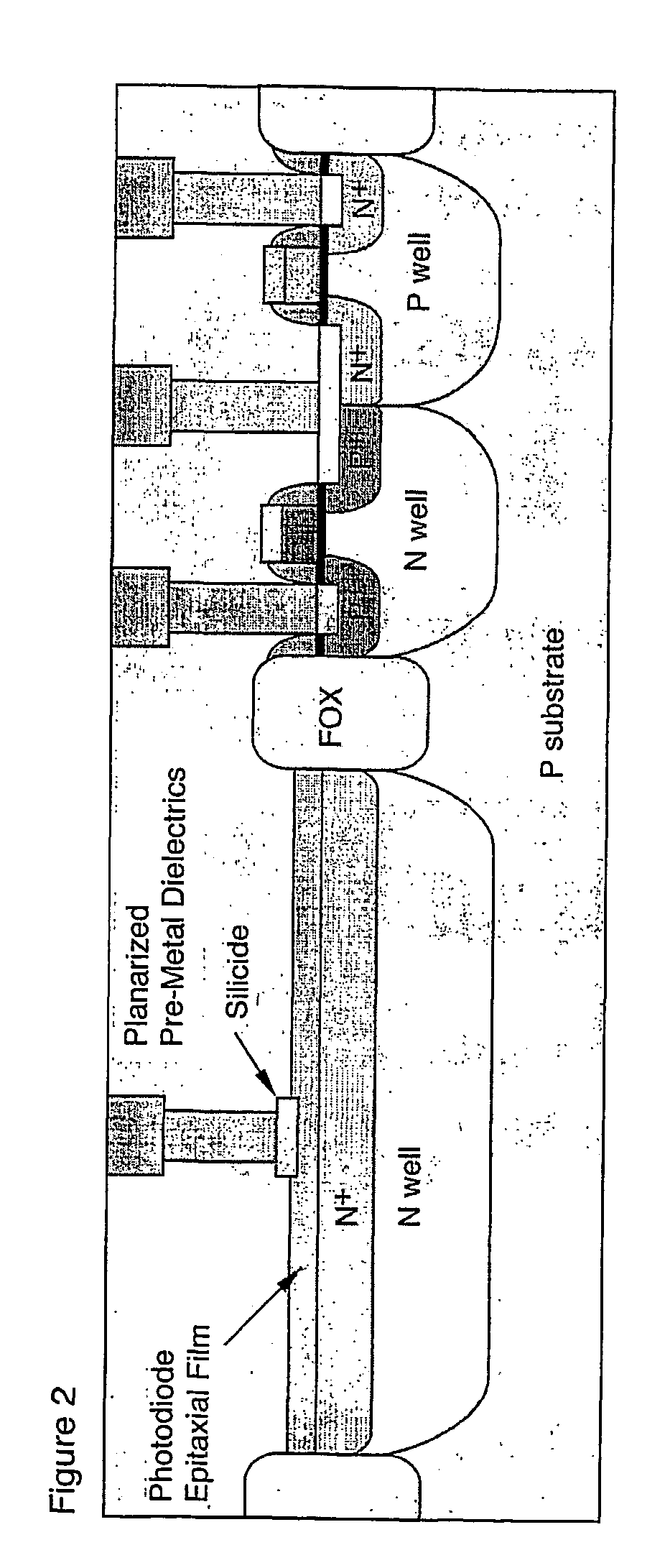

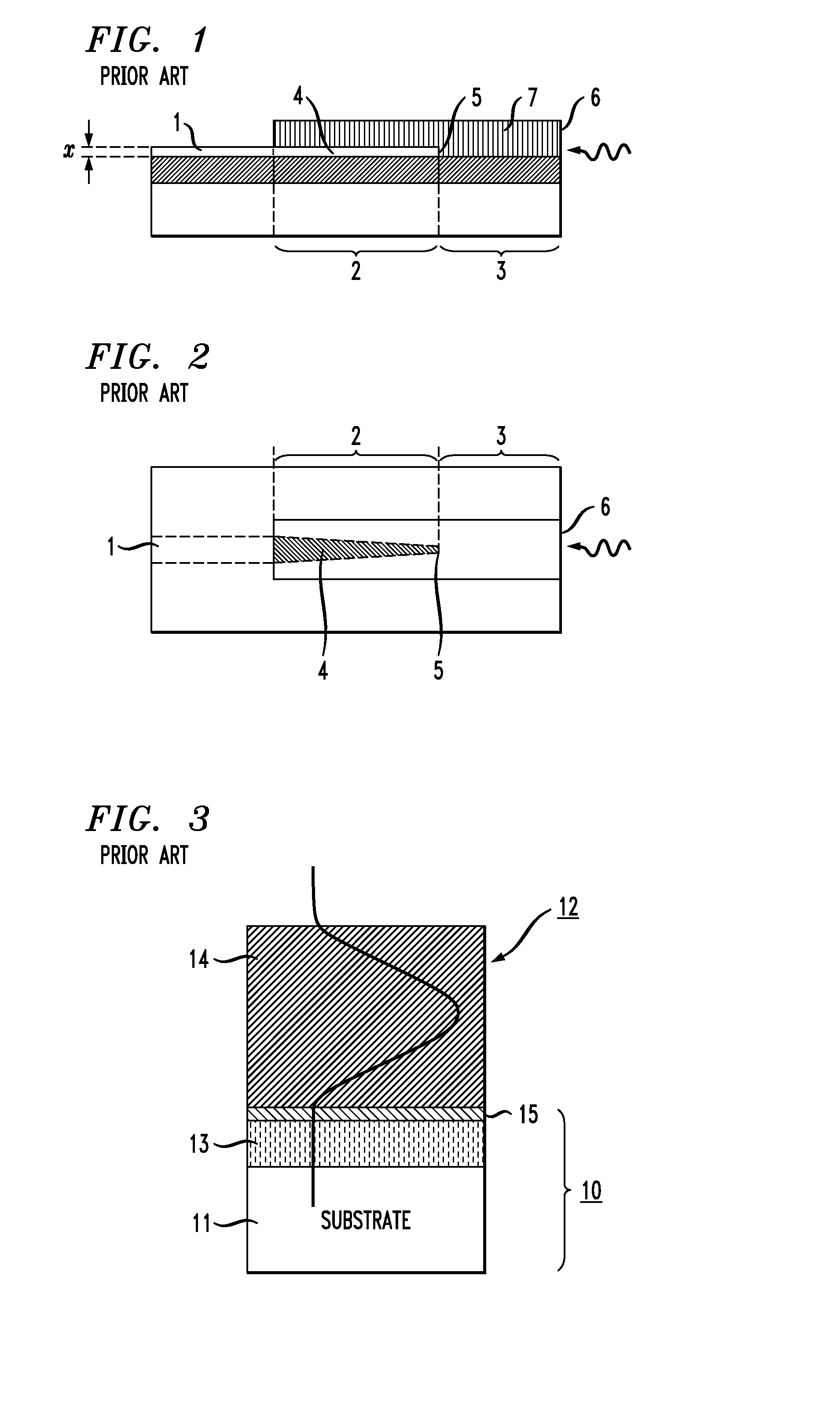

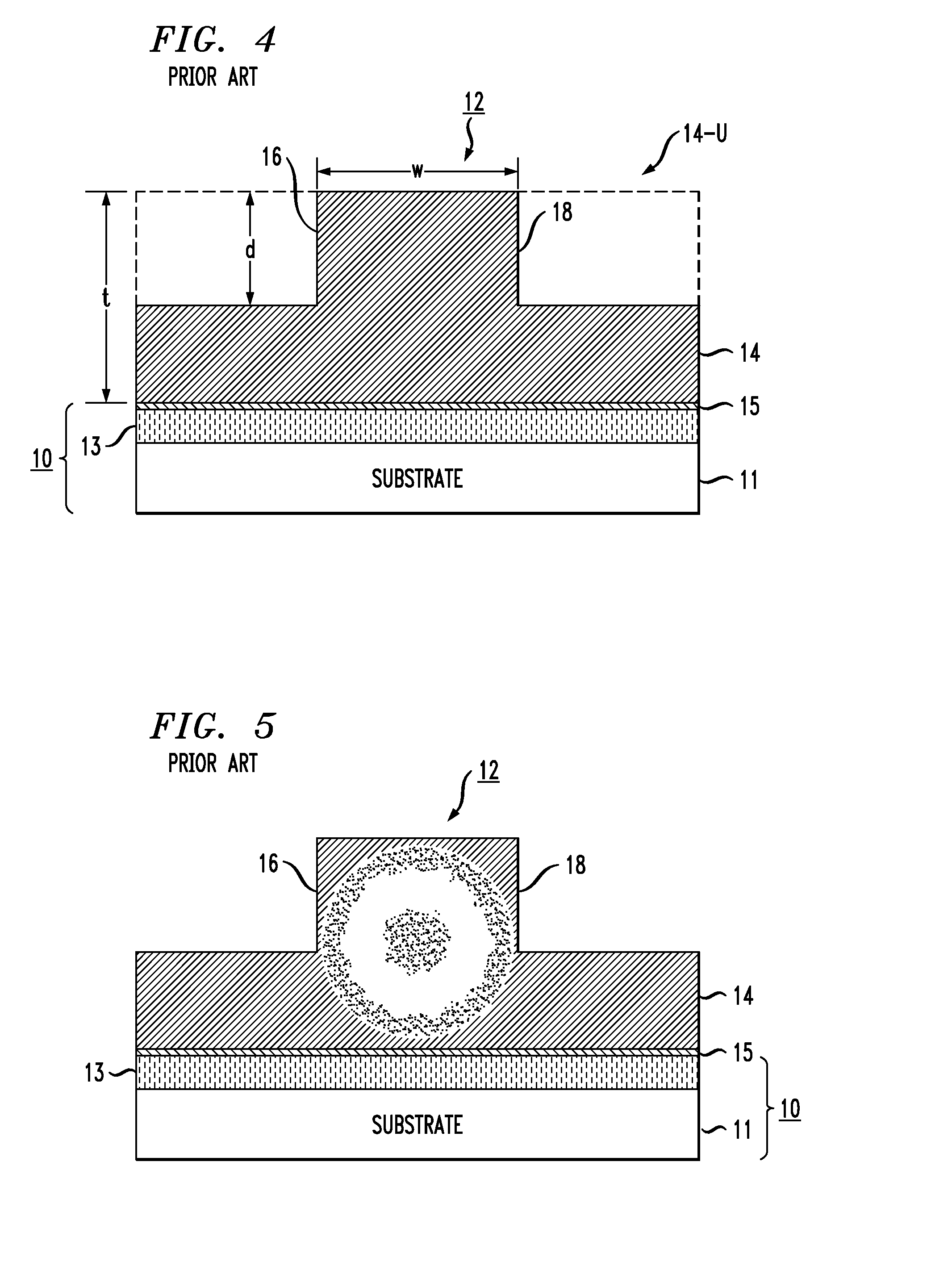

Methods of incorporating germanium within CMOS process

InactiveUS6887773B2Semiconductor/solid-state device manufacturingSemiconductor devicesMechanical engineeringCmos process

Methods for deposition of a Ge layer during a CMOS process on a monolithic device are disclosed. The insertion of the Ge layer enables the conversion of light to electrical signals easily. As a result of this method, standard metals can be attached directly to the Ge in completing an electrical circuit. Vias can also be used to connect to the Ge layer. In a first aspect of the invention, a method comprises the step of incorporating the deposition of Ge at multiple temperatures in a standard CMOS process. In a second aspect of the invention, a method comprises the step of incorporating the deposition of poly-Ge growth in a standard CMOS process.

Owner:CISCO TECH INC

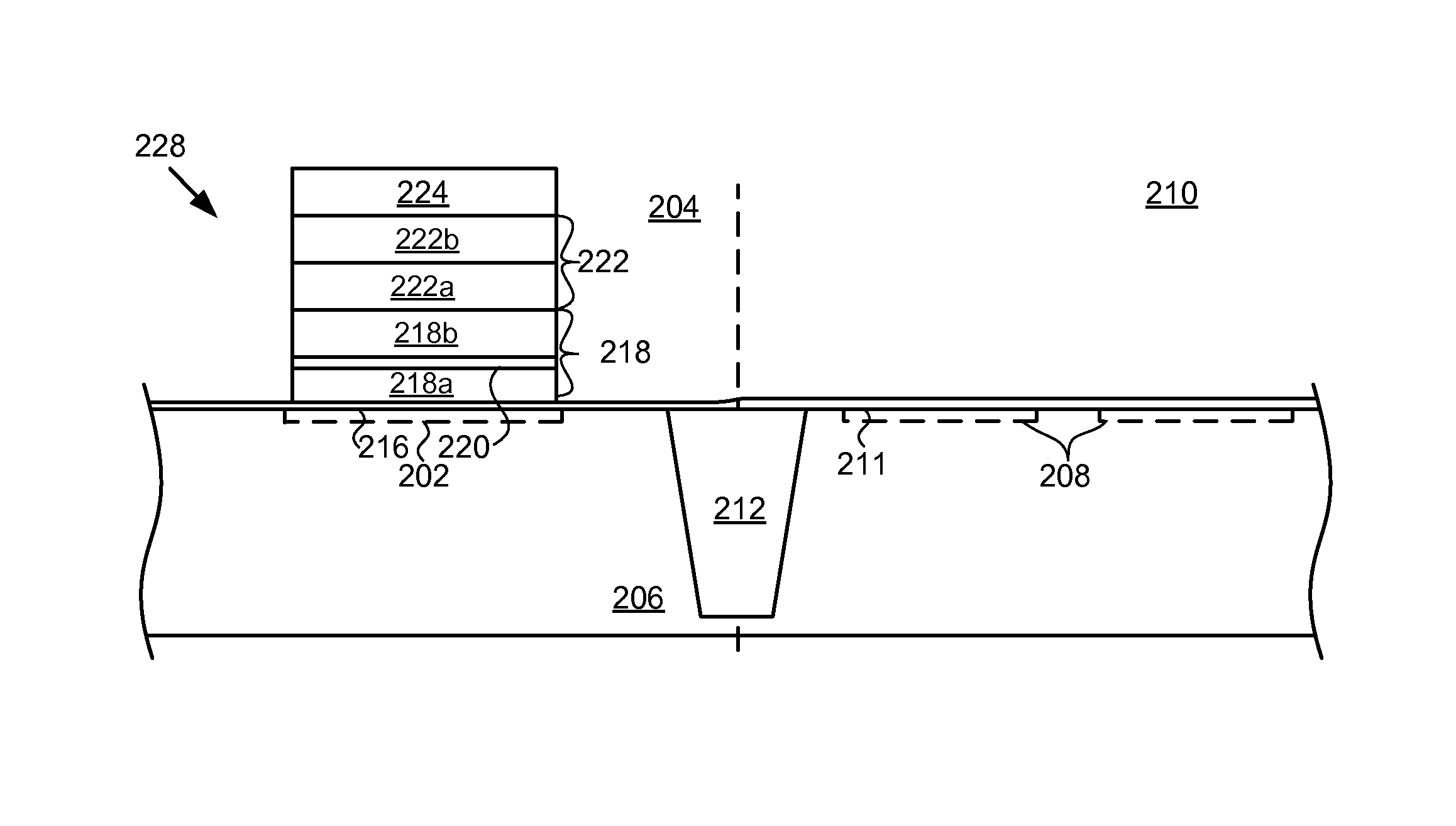

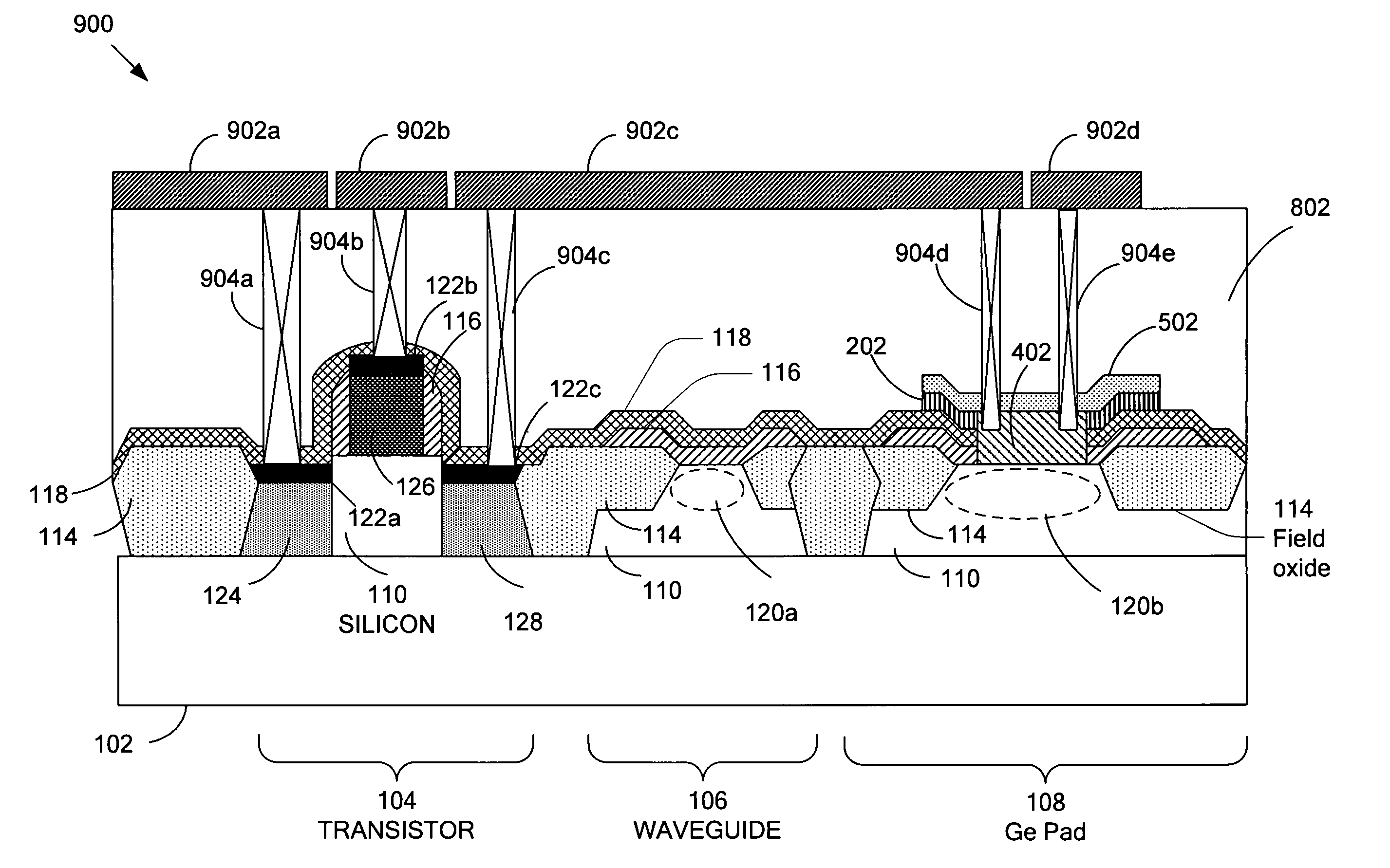

Germanium integrated CMOS wafer and method for manufacturing the same

ActiveUS7262117B1Solid-state devicesSemiconductor/solid-state device manufacturingPhotovoltaic detectorsPhotodetector

The present invention discloses an integration flow of germanium into a conventional CMOS process, with improvements in performing selective area growth, and implementing electrical contacts to the germanium, in a way that has minimal impact on the preexisting transistor devices. The present invention also provides methods to integrate the germanium without impacting the optical or electrical performance of these devices, except where intended, such as in a germanium photodetector, or germanium waveguide photodetector.

Owner:CISCO TECH INC

Circuit for high-resolution phase detection in a digital RF processor

ActiveUS7205924B2Less sensitiveReduce power consumptionElectric signal transmission systemsModulated-carrier systemsDigital converterCmos process

A novel time-to-digital converter (TDC) used as a phase / frequency detector and charge pump replacement in an all-digital PLL within a digital radio processor. The TDC core is based on a pseudo-differential digital architecture making it insensitive to NMOS and PMOS transistor mismatches. The time conversion resolution is equal to an inverter propagation delay, e.g., 20 ps, which is the finest logic-level regenerative timing in CMOS. The TDC is self calibrating with the estimation accuracy better than 1%. The TDC circuit can also serve as a CMOS process strength estimator for analog circuits in large SoC dies. The circuit also employs power management circuitry to reduce power consumption to a very low level.

Owner:TEXAS INSTR INC

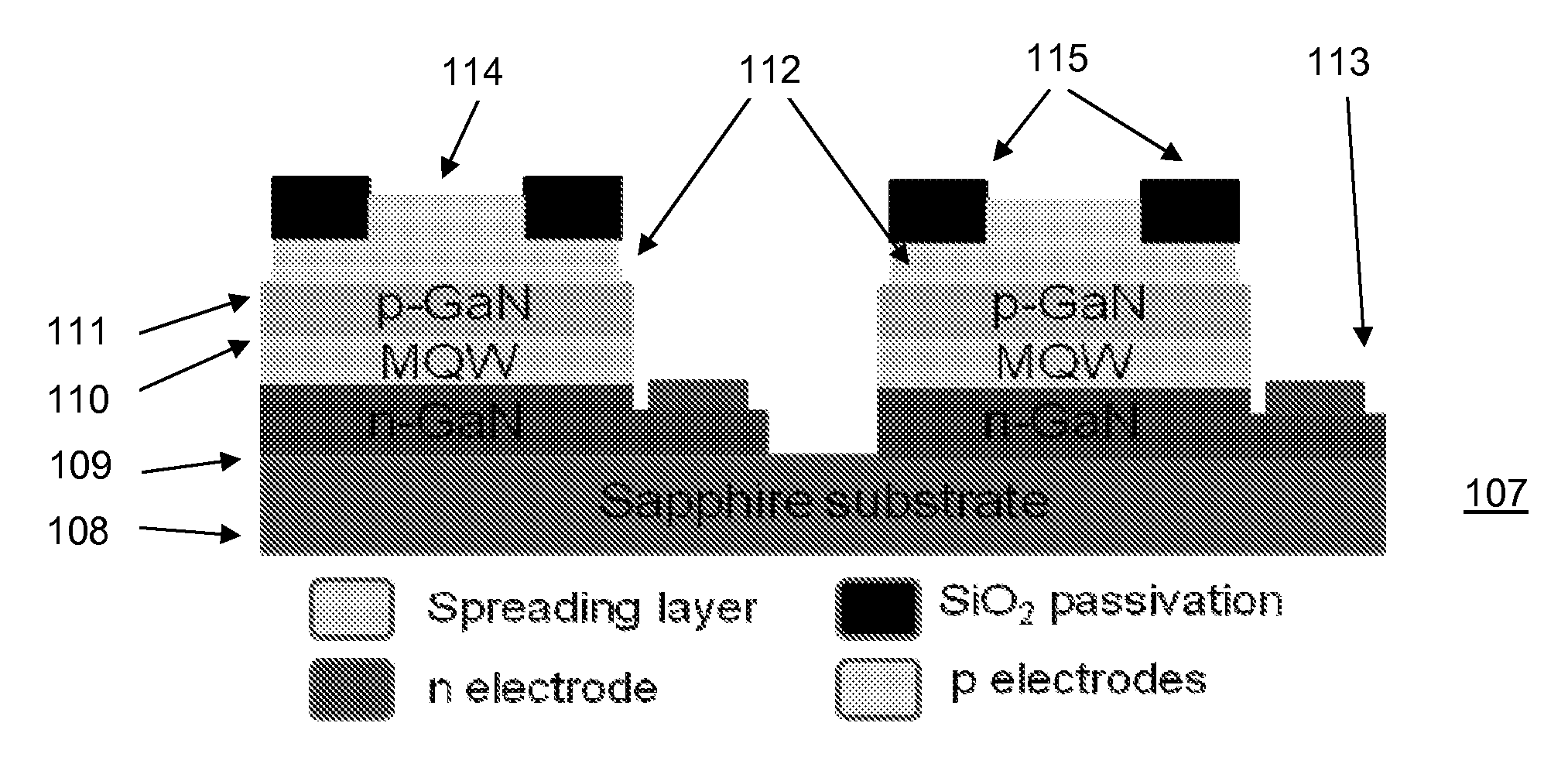

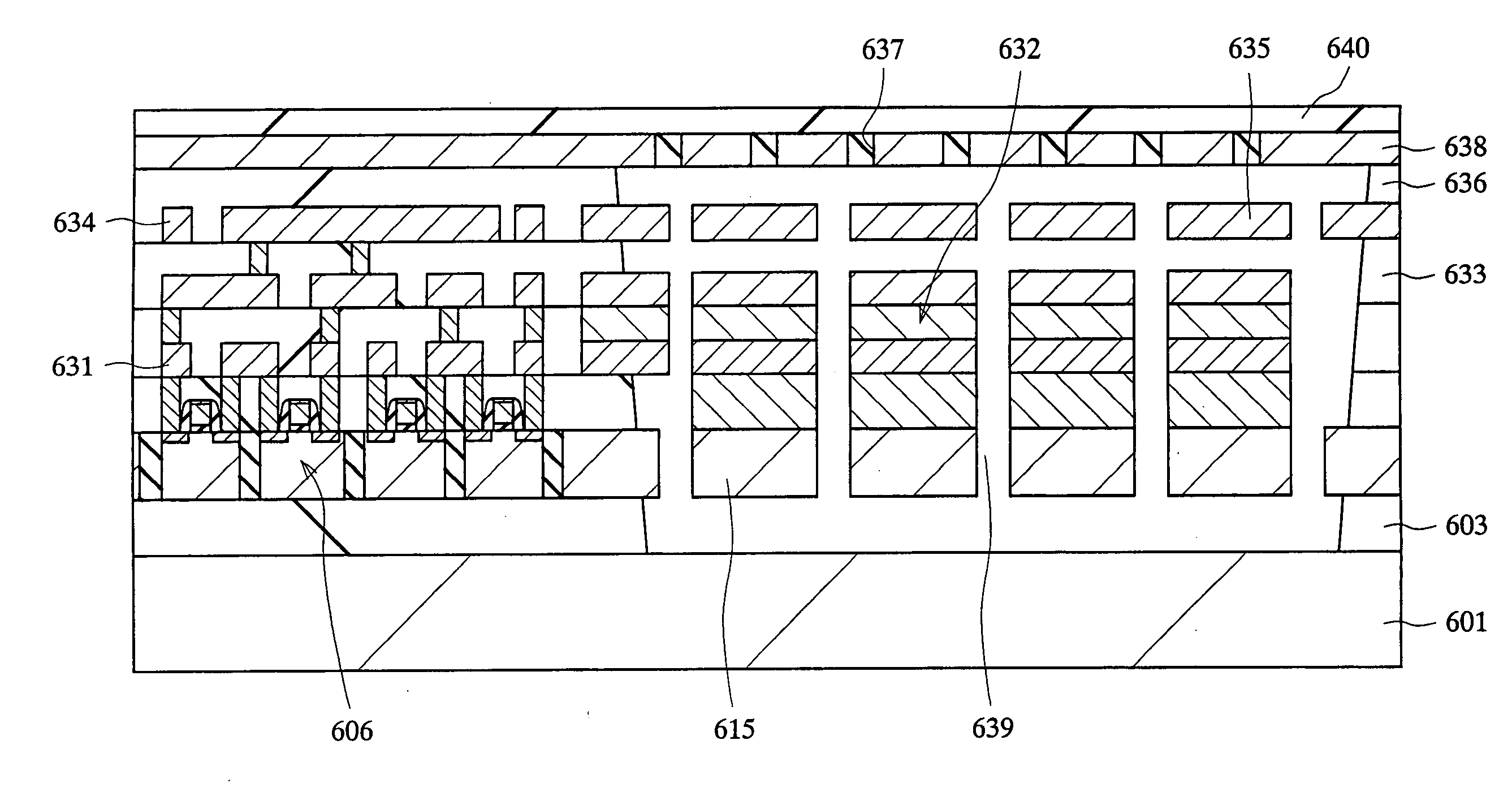

Method for manufacturing a monolithic LED micro-display on an active matrix panel using flip-chip technology and display apparatus having the monolithic LED micro-display

ActiveUS20110309378A1Solid-state devicesSemiconductor/solid-state device manufacturingActive matrixEngineering

A high-resolution, Active Matrix (AM) programmed monolithic Light Emitting Diode (LED) micro-array is fabricated using flip-chip technology. The fabrication process includes fabrications of an LED micro-array and an AM panel, and combining the resulting LED micro-array and AM panel using the flip-chip technology. The LED micro-array is grown and fabricated on a sapphire substrate and the AM panel can be fabricated using CMOS process. LED pixels in a same row share a common N-bus line that is connected to the ground of AM panel while p-electrodes of the LED pixels are electrically separated such that each p-electrode is independently connected to an output of drive circuits mounted on the AM panel. The LED micro-array is flip-chip bonded to the AM panel so that the AM panel controls the LED pixels individually and the LED pixels exhibit excellent emission uniformity. According to this constitution, incompatibility between the LED process and the CMOS process can be eliminated.

Owner:NANO & ADVANCED MATERIALS INST

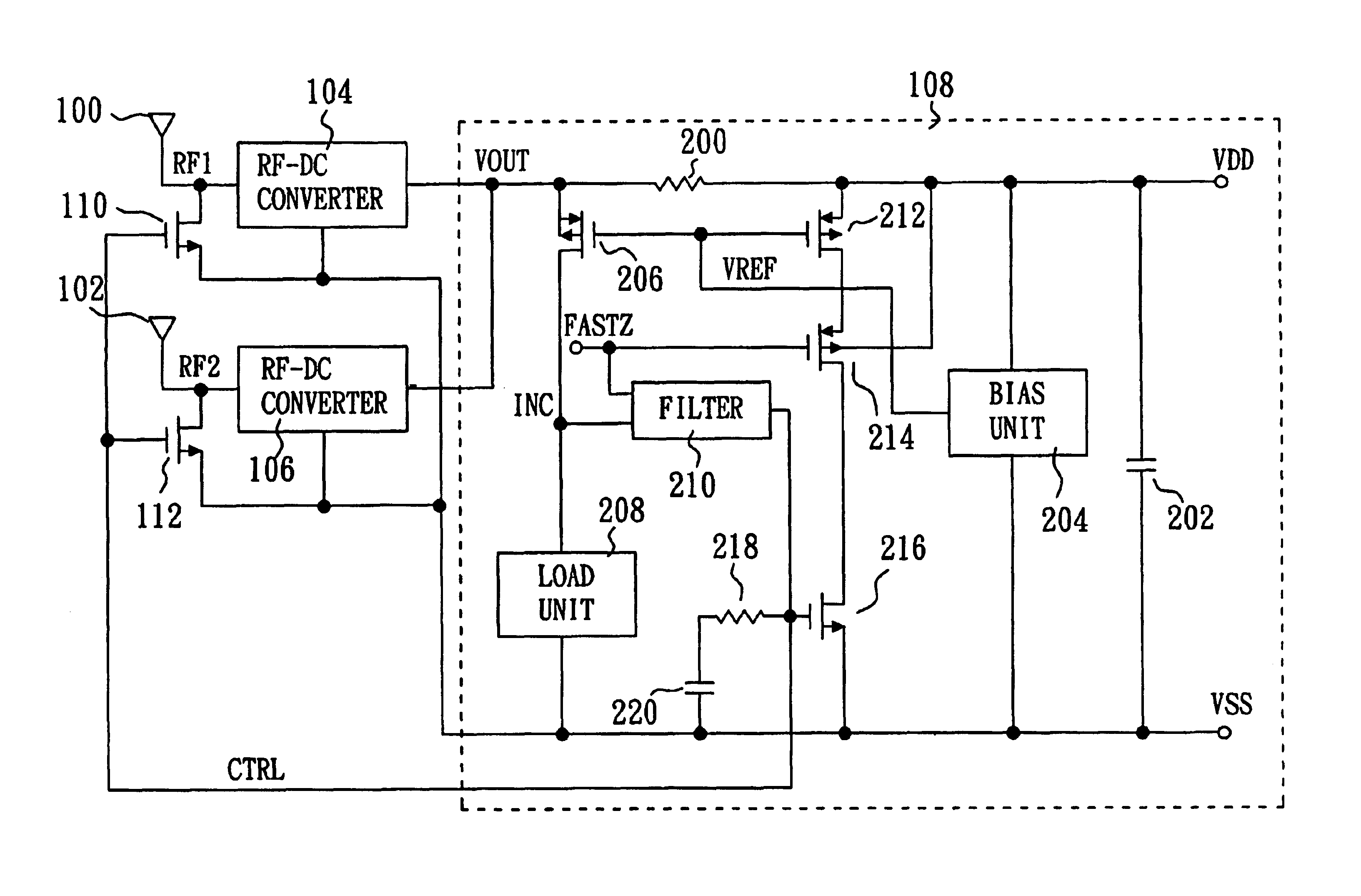

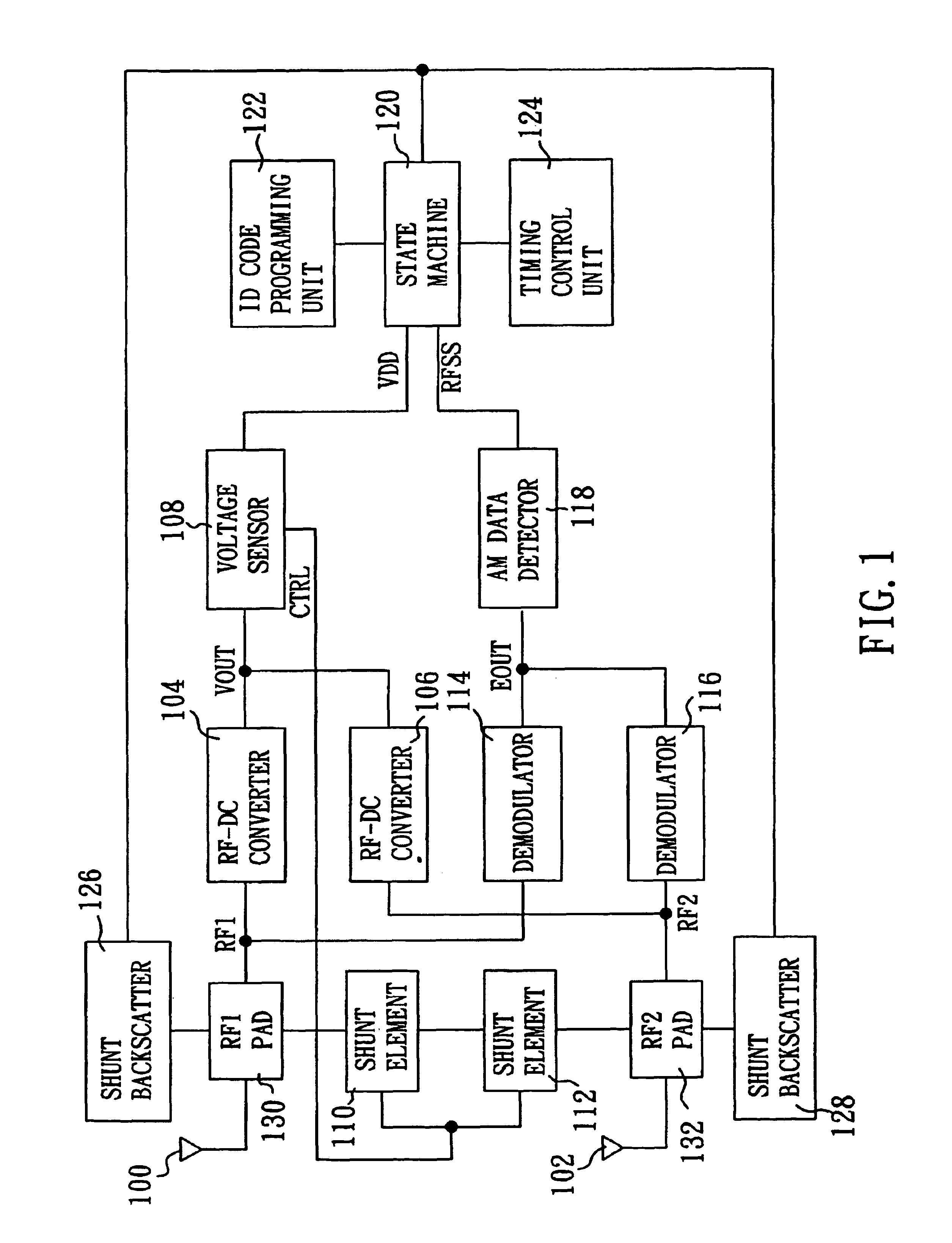

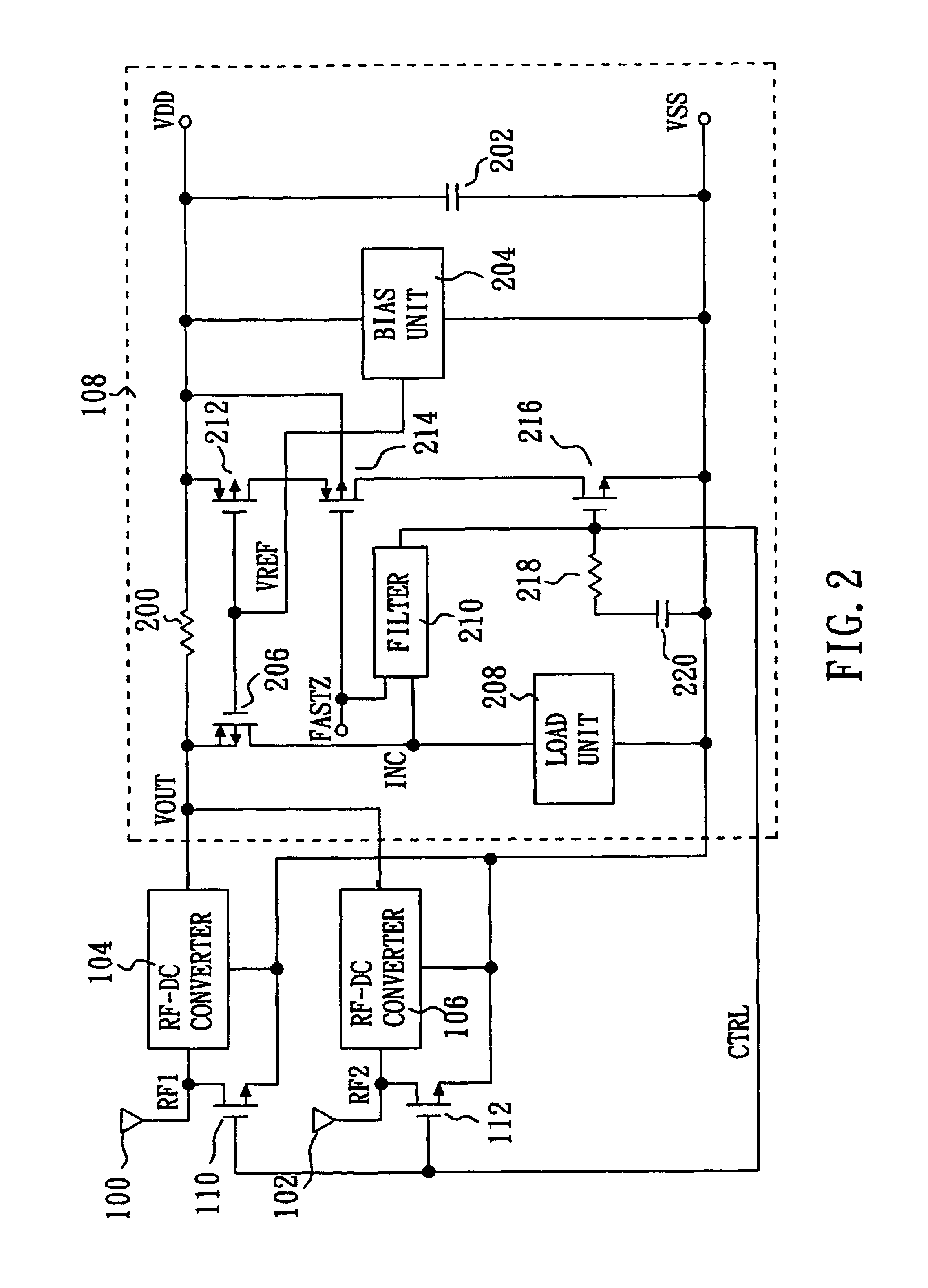

Radio frequency data communication device in CMOS process

InactiveUS6841981B2Low costFilamentary/web record carriersRecord information storageVoltage alarmEngineering

The present invention provides a passive RFID chip with on-chip charge pumps for generating electrical power for the chip from radio frequencies. The passive RFID chip comprises an analog portion and a digital portion. The analog portion primarily comprises a voltage sensor and an AM data detector. The digital portion comprises a state machine digital logic controller. Incoming RF signals enter the chip via external antennas. The RF signals are converted into regulated DC signals by RF-DC converters with the voltage sensor. The RF-DC converters provide power for all the on-chip components and hence the chip does not require external power supply. The incoming RF signals are demodulated by demodulators and enter the AM data detector where the envelope transitions are detected. A voltage alarm is provided to ensure the voltage level does not drop below an operational level of the chip. The logic signals and programming data are controlled by the state machine digital logic controller and the timing signals are provided by an on-chip oscillator.

Owner:XUESHAN TECH INC

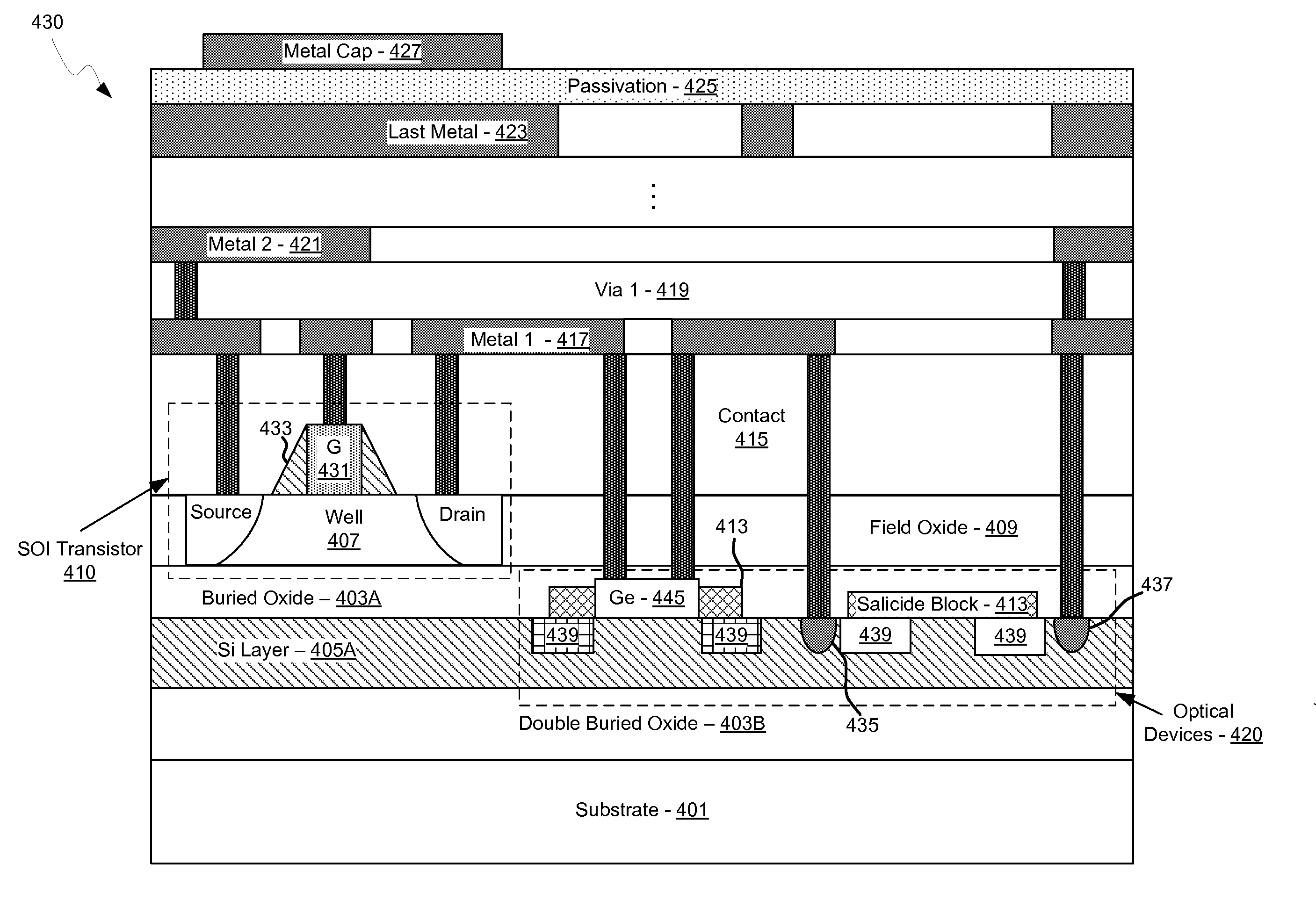

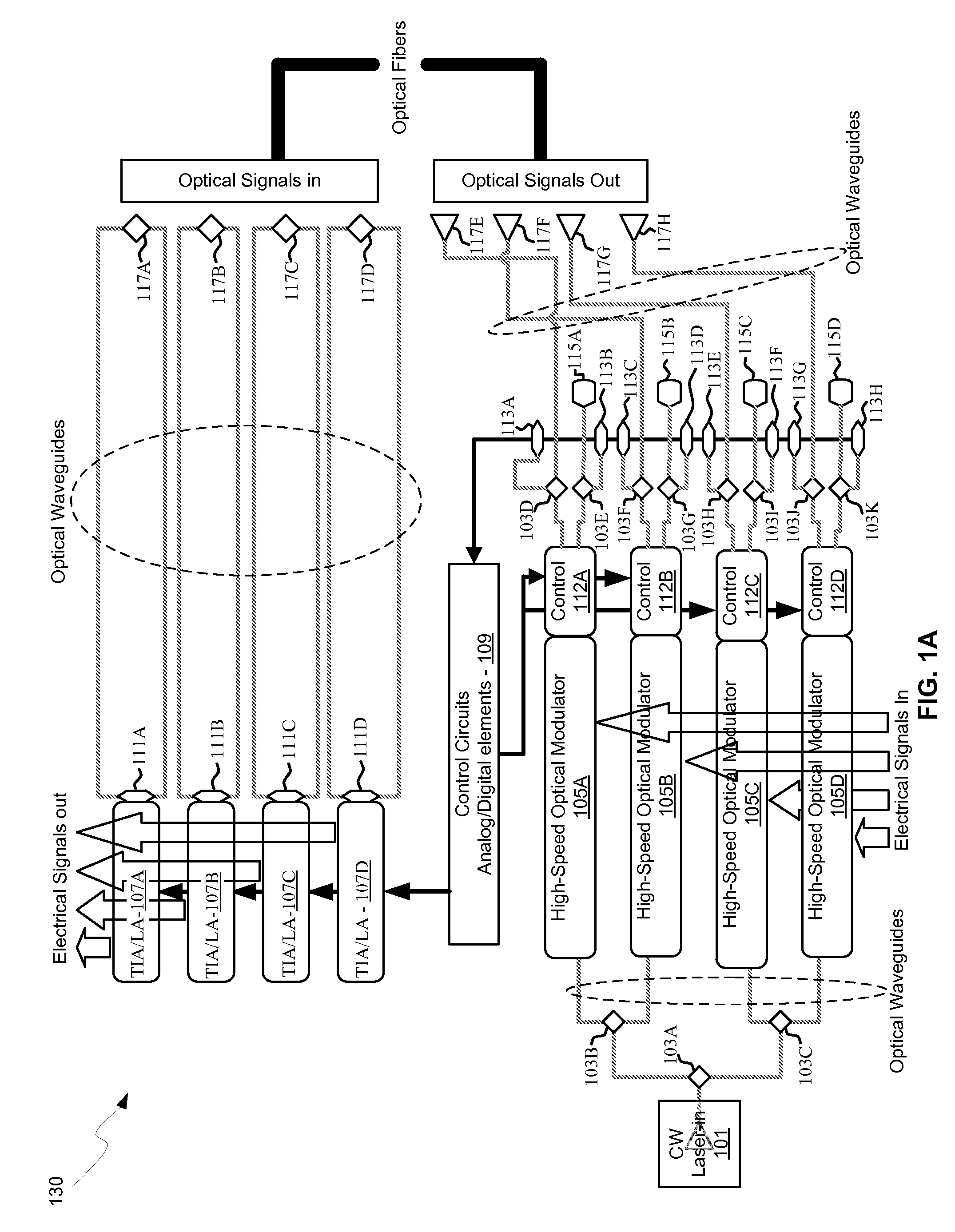

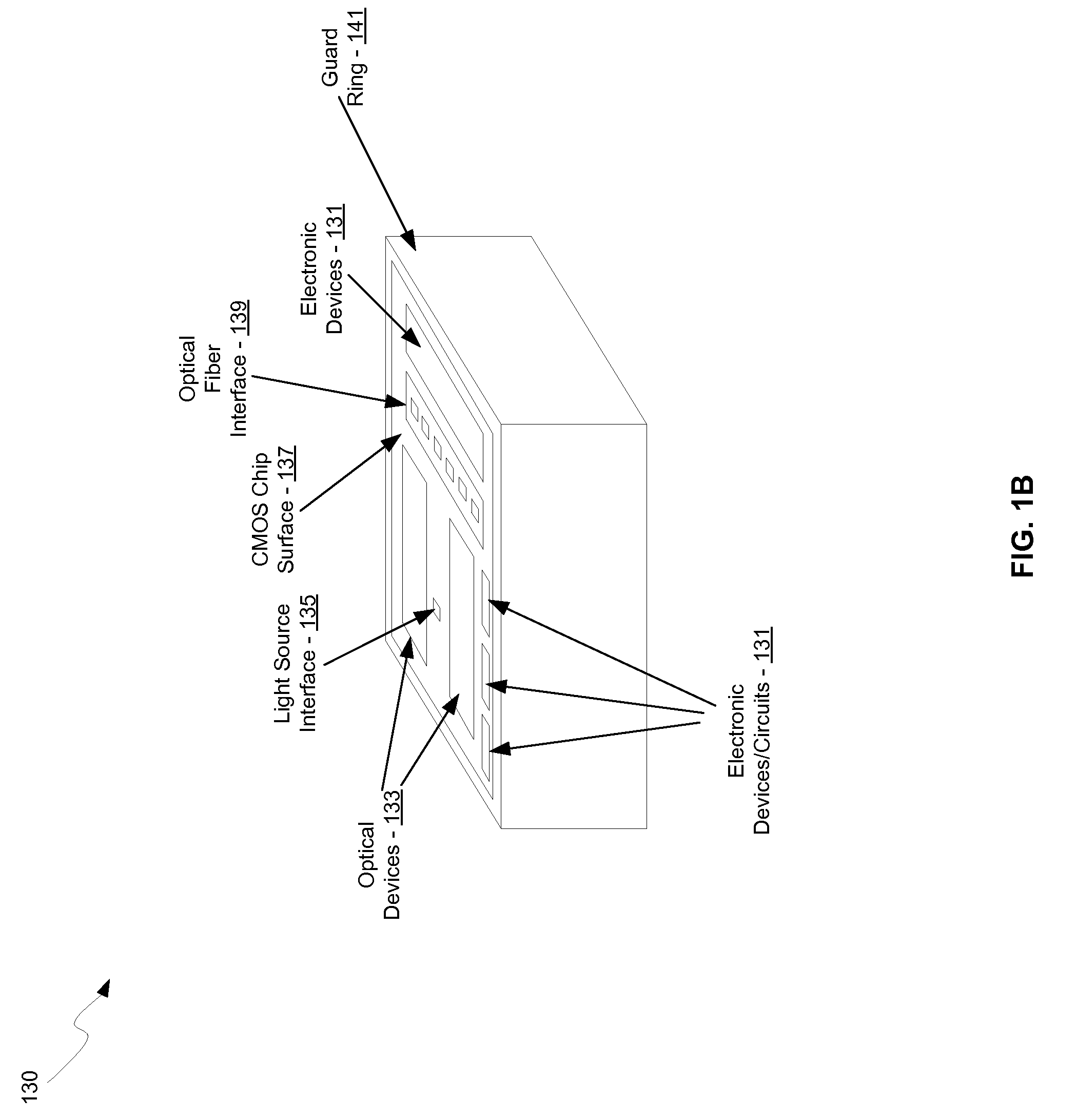

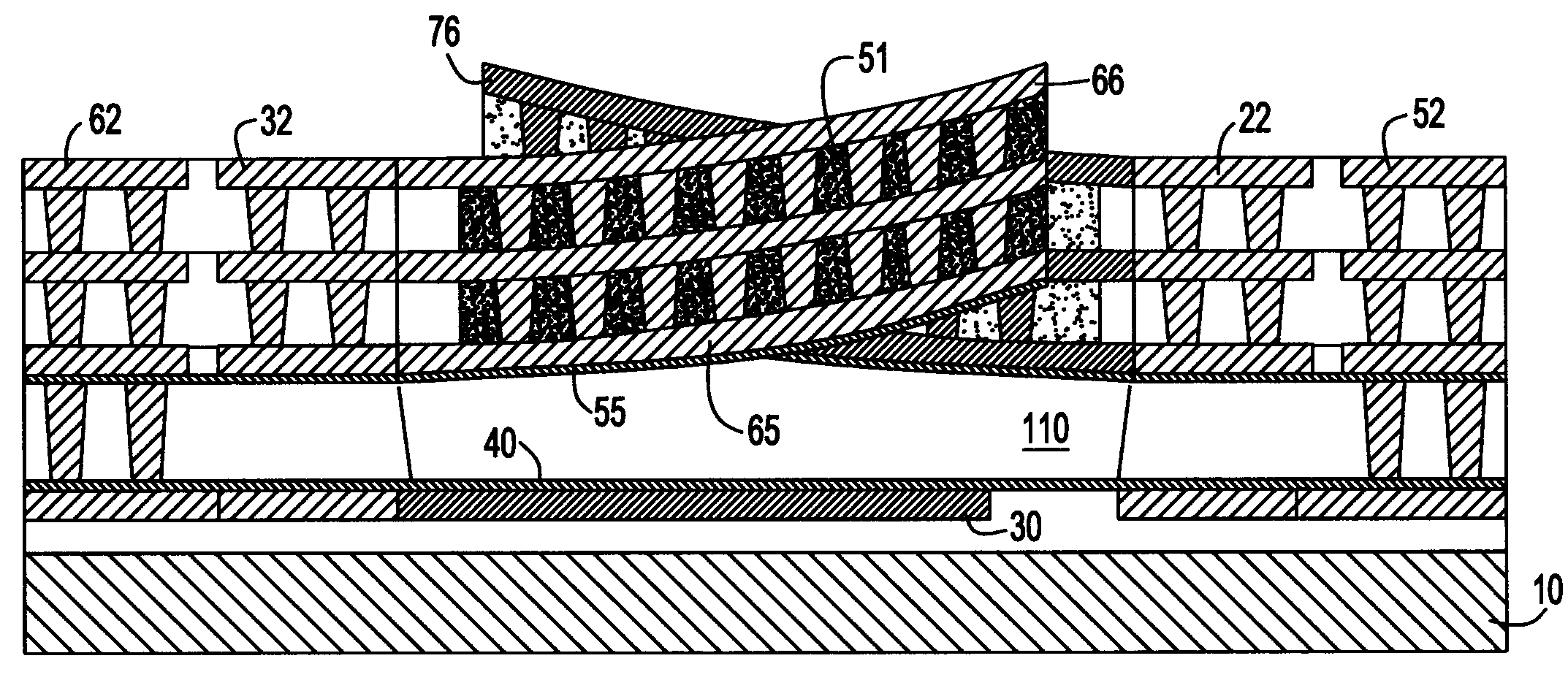

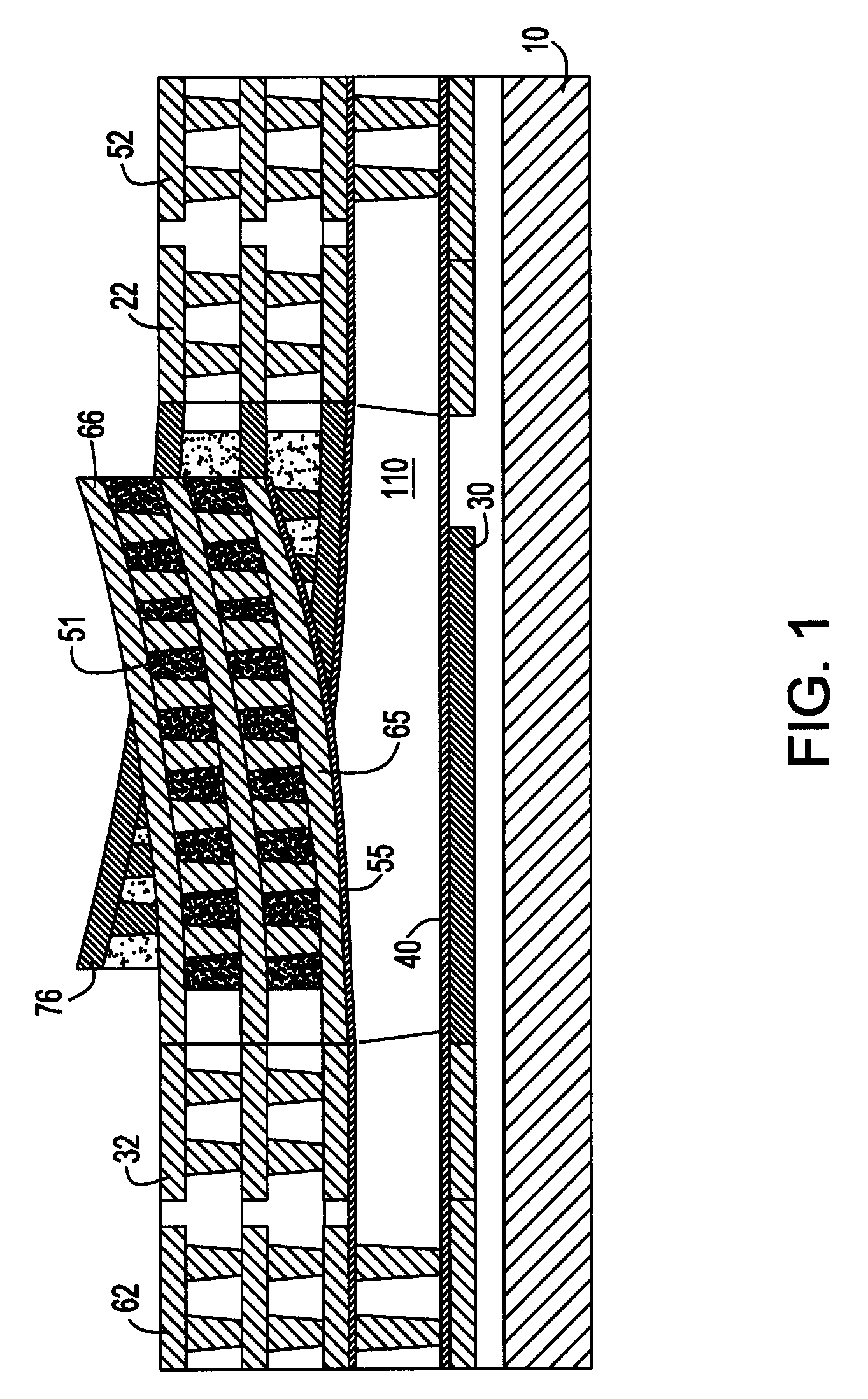

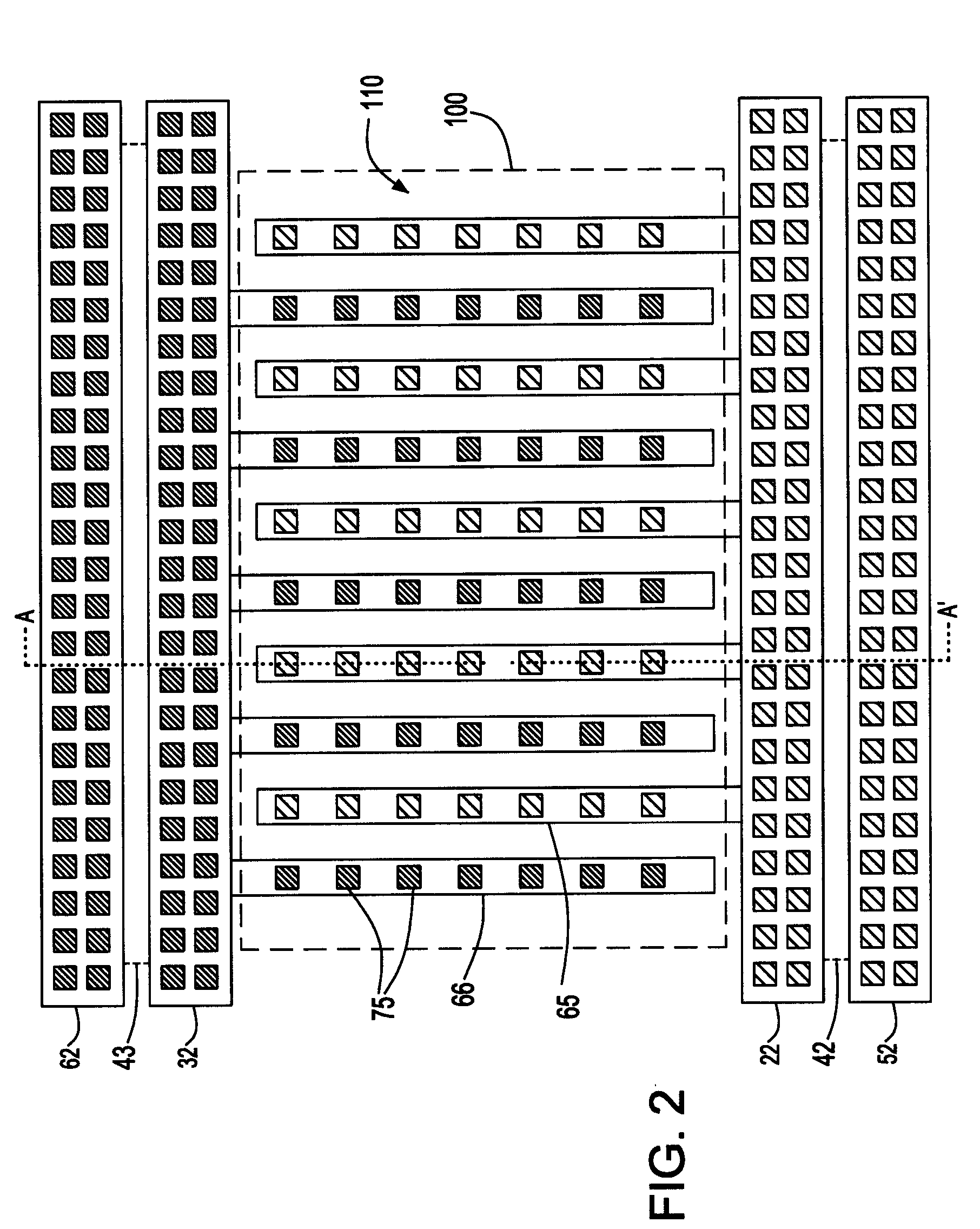

Method and system for monolithic integration of photonics and electronics in CMOS processes

ActiveUS20100059822A1Solid-state devicesSemiconductor/solid-state device manufacturingSoi cmosEtching

Methods and systems for monolithic integration of photonics and electronics in CMOS processes are disclosed and may include fabricating photonic and electronic devices on a single CMOS wafer with different silicon layer thicknesses. The devices may be fabricated on a semiconductor-on-insulator (SOI) wafer utilizing a bulk CMOS process and / or on a SOI wafer utilizing a SOI CMOS process. The different thicknesses may be fabricated utilizing a double SOI process and / or a selective area growth process. Cladding layers may be fabricated utilizing one or more oxygen implants and / or utilizing CMOS trench oxide on the CMOS wafer. Silicon may be deposited on the CMOS trench oxide utilizing epitaxial lateral overgrowth. Cladding layers may be fabricated utilizing selective backside etching. Reflective surfaces may be fabricated by depositing metal on the selectively etched regions. Silicon dioxide or silicon germanium integrated in the CMOS wafer may be utilized as an etch stop layer.

Owner:CISCO TECH INC

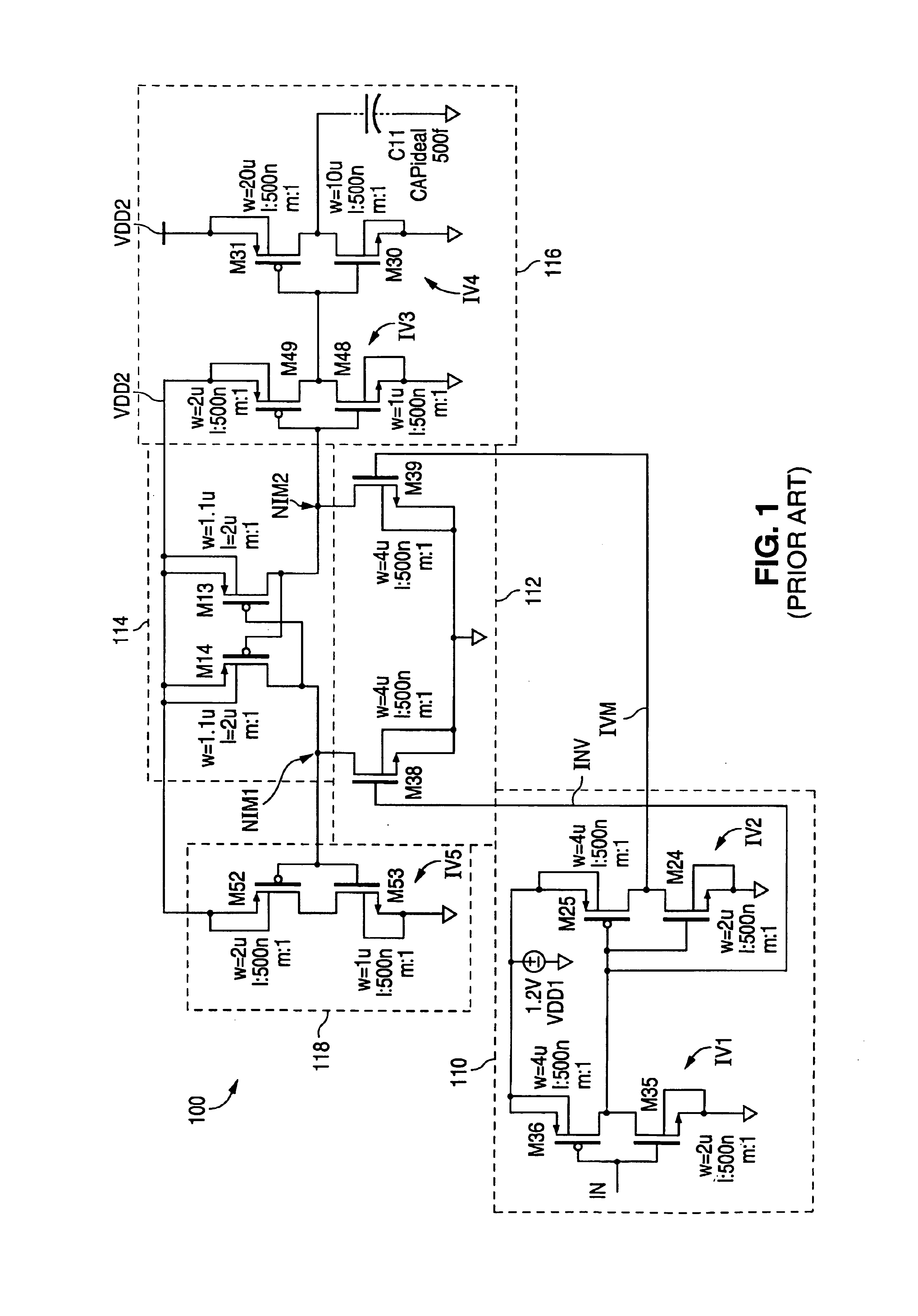

Level translator for high voltage digital CMOS process

InactiveUS6838905B1Maximum voltageLogic circuit coupling/interface arrangementsLevel converterHigh voltage

The speed of a level shifter is increased by utilizing an additional transistor to pull down the voltage on a first intermediate node, and an additional transistor to pull down the voltage on a second intermediate node. In addition, a precharge circuit is utilized to precharge the voltage on the first and second intermediate nodes to further increase the speed of the level shifter.

Owner:NAT SEMICON CORP

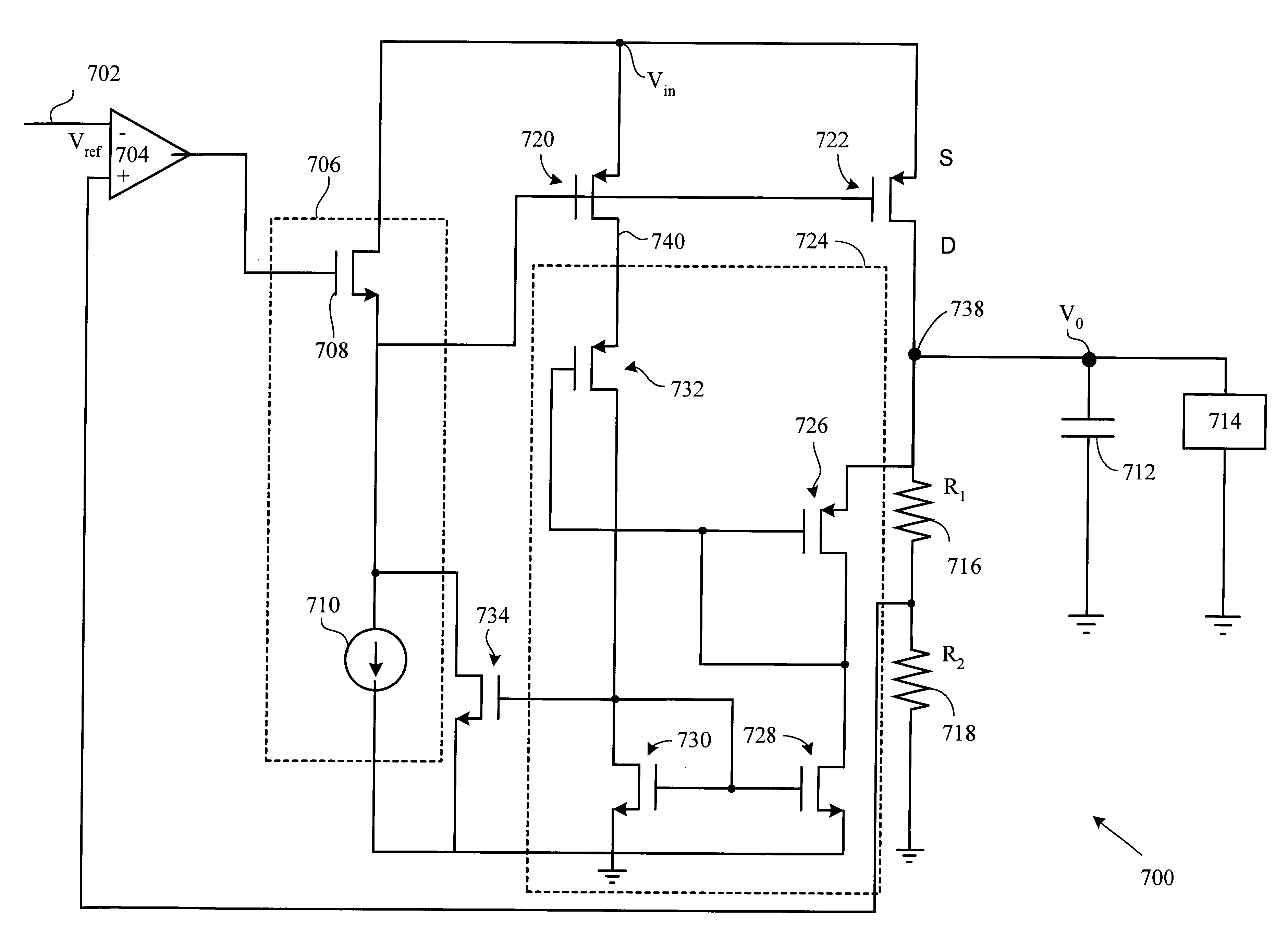

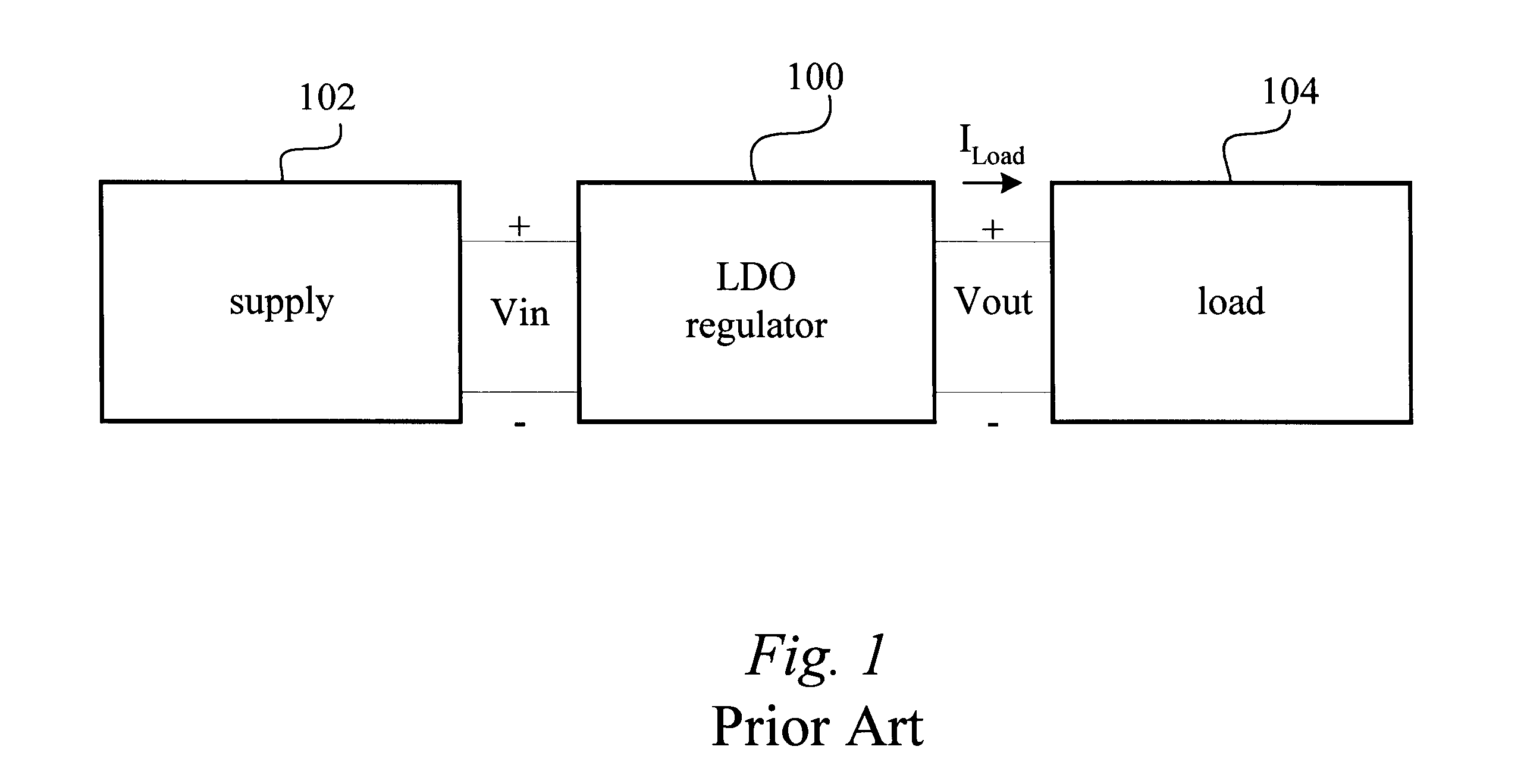

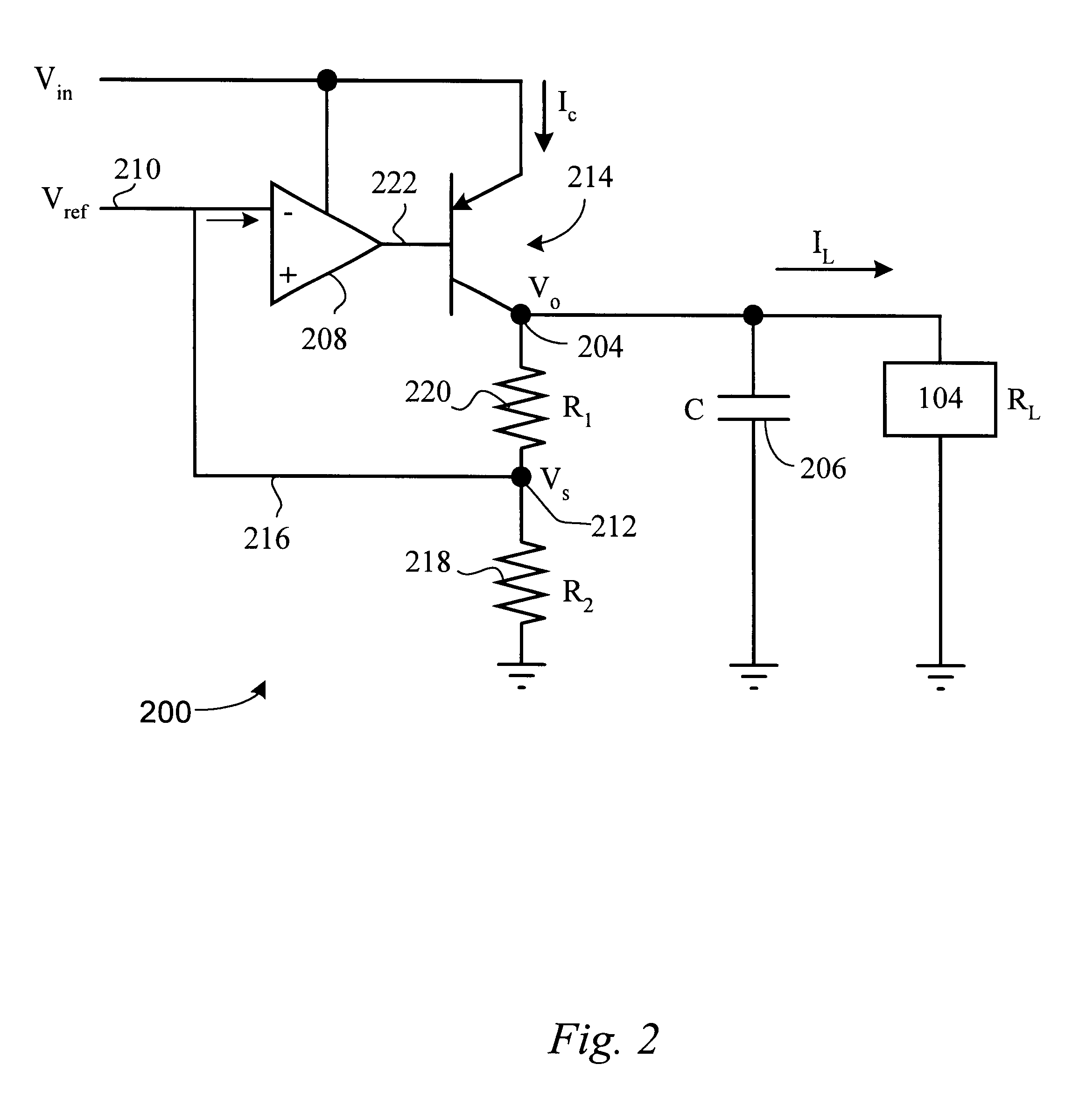

Low drop-out regulator capable of functioning in linear and saturated regions of output driver

InactiveUS6285246B1Reduce power consumptionReduce consumptionElectric variable regulationEngineeringCmos process

A low drop-out regulator and methods for producing a low drop-out voltage are provided. A driver transistor adapted for connecting to an input supply voltage and producing an output voltage is provided. In addition, a mirroring transistor is coupled to the driver transistor and a voltage differential between the drain and the source of the driver transistor is mirrored in the mirroring transistor. The low drop-out regulator operates in both linear and saturation regions of the driver transistor. The driver transistor and the mirroring transistor are implemented in a CMOS process.

Owner:SEMICON COMPONENTS IND LLC

Shielding structure for use in a metal-oxide-semiconductor device

InactiveUS20050017298A1Improve high frequency performanceLow costTransistorSemiconductor/solid-state device detailsSemiconductorCmos process

An MOS device is formed comprising a semiconductor layer of a first conductivity type, a first source / drain region of a second conductivity type formed in the semiconductor layer, and a second source / drain region of the second conductivity type formed in the semiconductor layer and spaced apart from the first source / drain region. The MOS device further comprises a gate formed proximate an upper surface of the semiconductor layer and at least partially between the first and second source / drain regions, and a shielding structure formed proximate the upper surface of the semiconductor layer and between the gate and the second source / drain region, the shielding structure being electrically connected to the first source / drain region, the shielding structure being spaced laterally from the gate and being non-overlapping relative to the gate. In this manner, the MOS device is substantially compatible with a CMOS process technology.

Owner:BELL SEMICON LLC

Method of fabricating heterojunction photodiodes integrated with cmos

A method in which thin-film p-i-n heterojunction photodiodes are formed by selective epitaxial growth / deposition on pre-designated active-area regions of standard CMOS devices. The thin-film p-i-n photodiodes are formed on active areas (for example n<+>-doped), and these are contacted at the bottom (substrate) side by the "well contact" corresponding to that particular active area. There is no actual potential well since that particular active area has only one type of doping. The top of each photodiode has a separate contact formed thereon. The selective epitaxial growth of the p-i-n photodiodes is modular, in the sense that there is no need to change any of the steps developed for the "pure" CMOS process flow. Since the active region is epitaxially deposited, there is the possibility of forming sharp doping profiles and band-gap engineering during the epitaxial process, thereby optimizing several device parameters for higher performance. This new type of light sensor architecture, monolithically integrated with CMOS, decouples the photo-absorption active region from the MOSFETs, hence the bias applied to the photodiode can be independent from the bias between the source, drain, gate and substrate (well) of the MOSFETs.

Owner:QUANTUM SEMICON

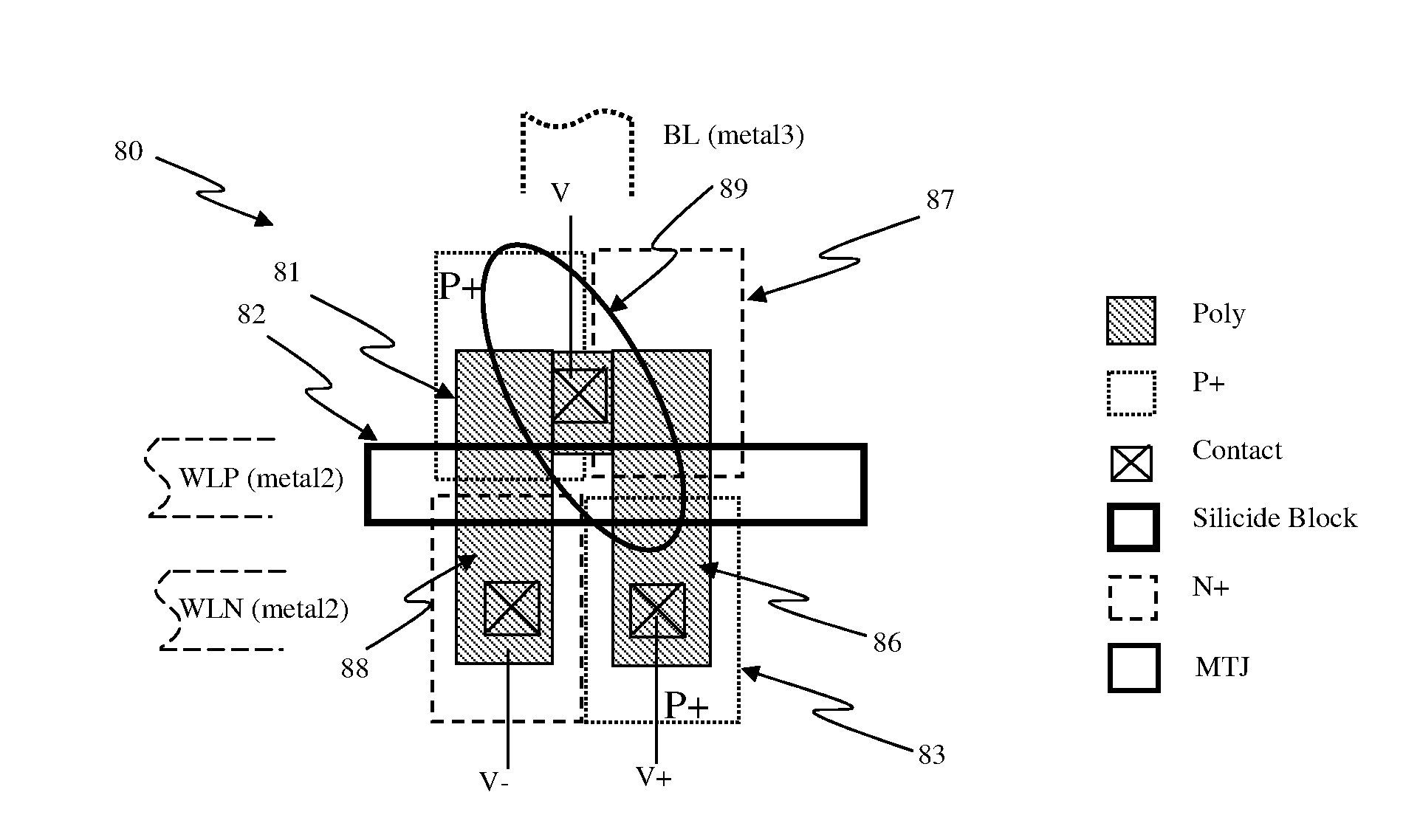

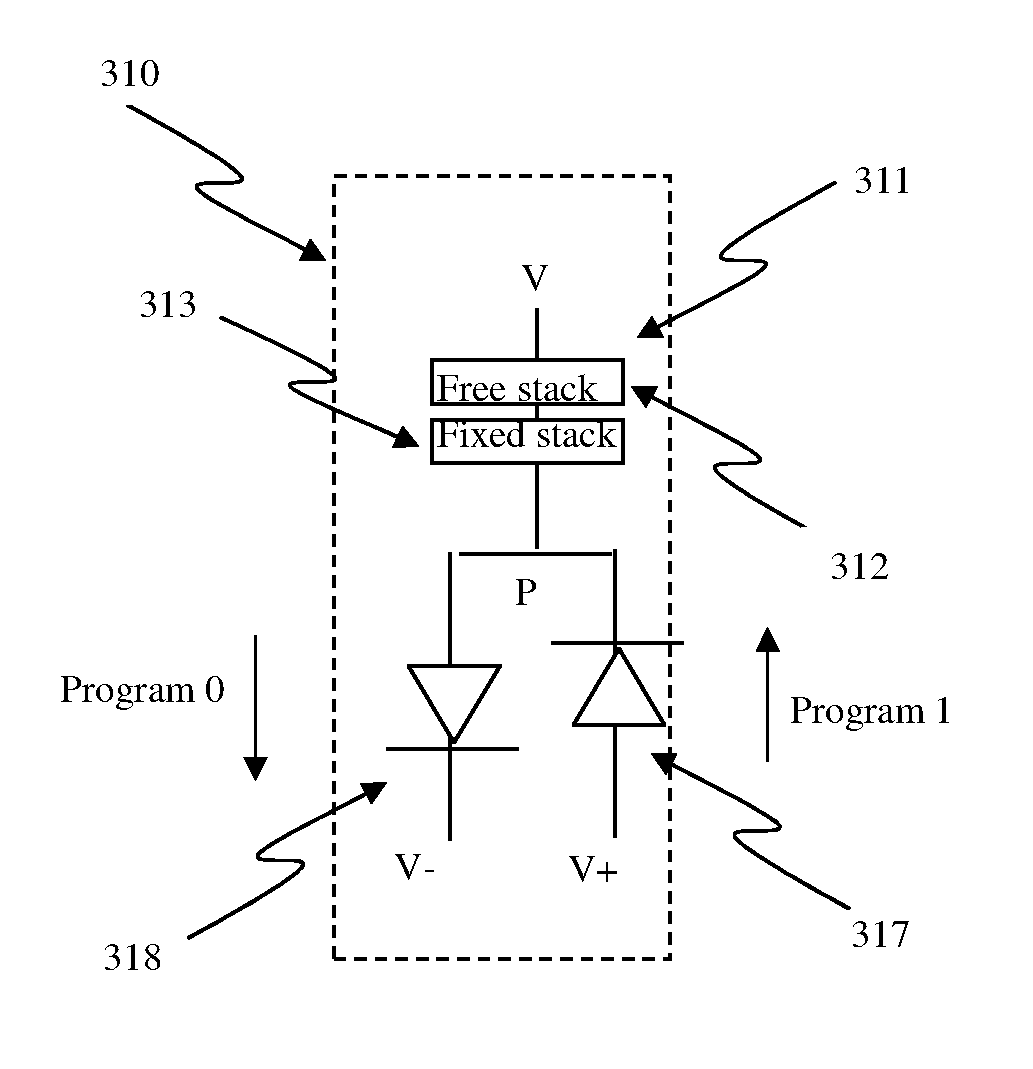

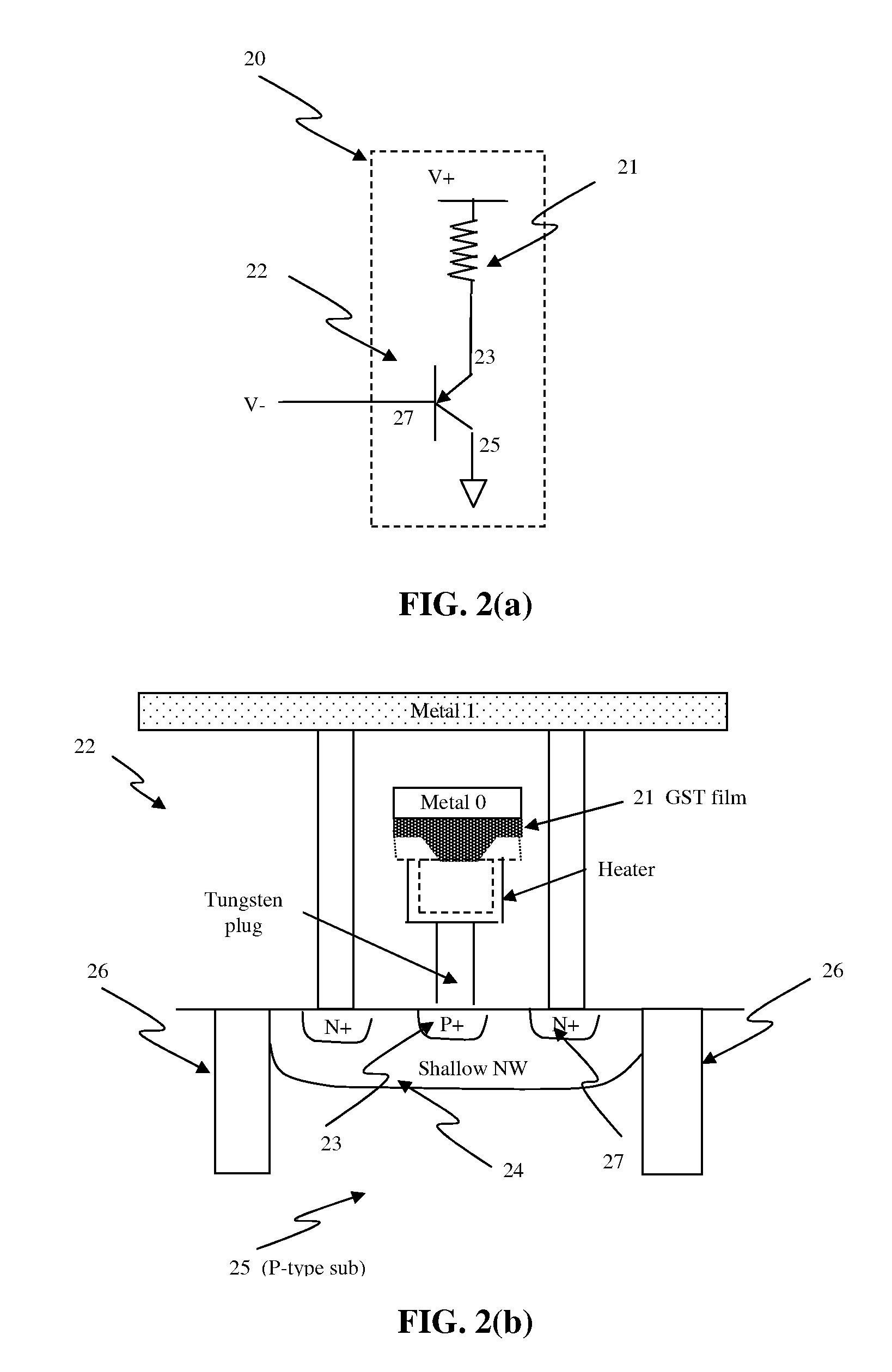

Memory using a plurality of diodes as program selectors with at least one being a polysilicon diode

ActiveUS20120044757A1Small cell sizeLow costSolid-state devicesRead-only memoriesBit lineElectrical current

Embodiments of programmable memory cells using a plurality of diodes as program selectors are disclosed for those memory cells that can be programmed based on direction of current flow. These memory cells are MRAM, RRAM, CBRAM, or other memory cells that have a programmable resistive element coupled to the P-terminal of a first diode and to the N-terminal of a second diode. At least one of the diodes can be a polysilicon diode fabricated using standard CMOS processes with P+ and N+ implants in two ends. The polysilicon diode can be constructed by P+ / N+ implants on a polysilicon substrate as a program selector. The memory cells can be used to construct a two-dimensional memory array with the N-terminals of the first diodes and the P-terminals of the second diodes in a row connected as wordline(s) and the resistive elements in a column connected as a bitline.

Owner:ATTOPSEMI TECH CO LTD

Memory devices using a plurality of diodes as program selectors with at least one being a polysilicon diode

ActiveUS8482972B2Avoid shortingSmall cell sizeSolid-state devicesRead-only memoriesPower flowCmos process

Embodiments of programmable memory cells using a plurality of diodes as program selectors are disclosed for memory cells that can be programmed based on direction of current flow. These memory cells are MRAM, RRAM, CBRAM, or other memory cells that have a programmable resistive element coupled to the P-terminal of a first diode and to the N-terminal of a second diode. At least one of the diodes can be a polysilicon diode fabricated using standard CMOS processes. The polysilicon diode can be constructed by P+ / N+ implants on a polysilicon substrate as a program selector.

Owner:ATTOPSEMI TECH CO LTD

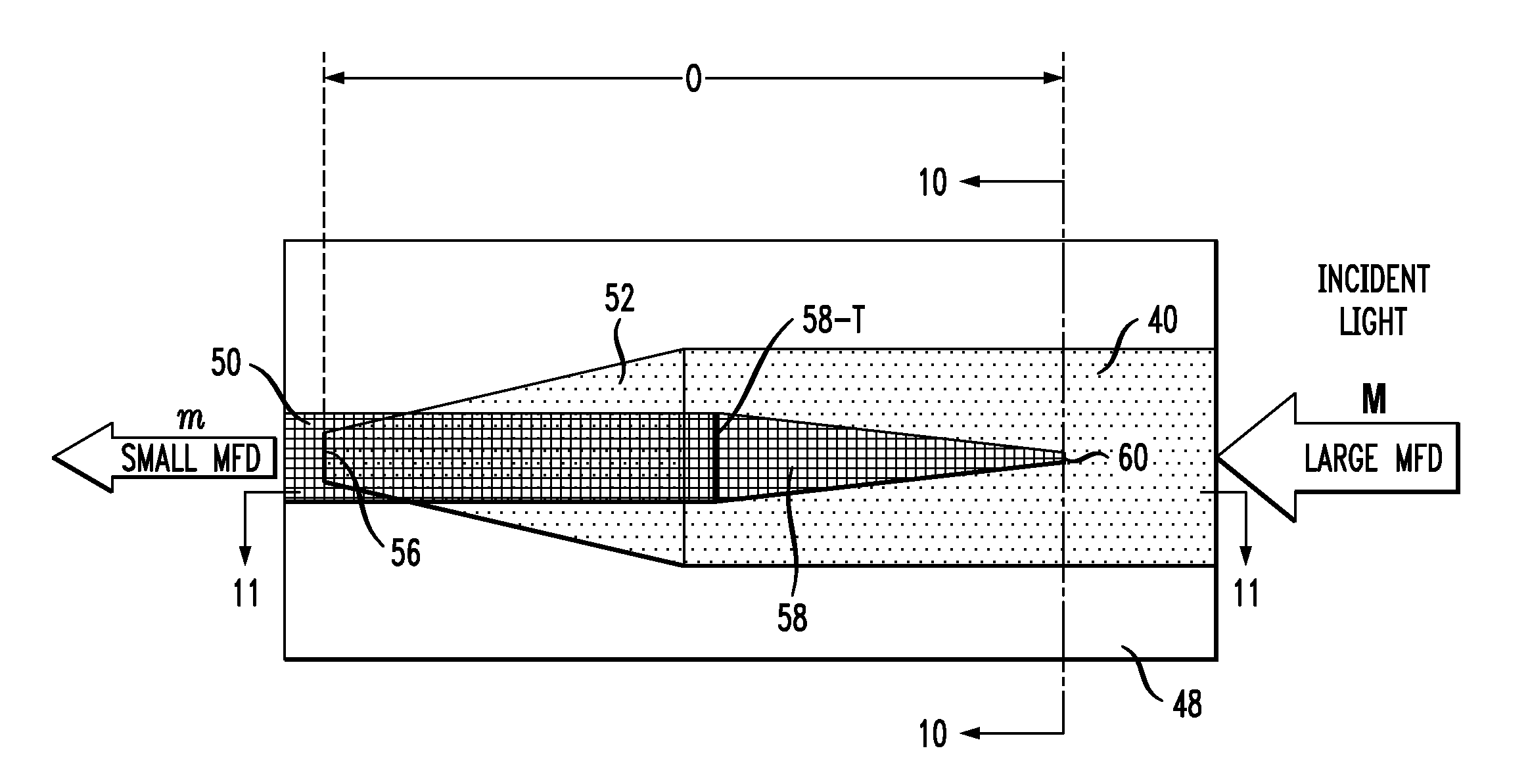

Low index, large mode field diameter optical coupler

ActiveUS20090297093A1Wide bandwidthEasy transferOptical articlesCoupling light guidesCouplingRefractive index

An optical coupler is formed of a low index material and exhibits a mode field diameter suitable to provide efficient coupling between a free space optical signal (of large mode field diameter) and a single mode high index waveguide formed on an optical substrate. One embodiment comprises an antiresonant reflecting optical waveguide (ARROW) structure in conjunction with an embedded (high index) nanotaper coupling waveguide. Another embodiment utilizes a low index waveguide structure disposed in an overlapped arrangement with a high index nanotaper coupling waveguide. The low index waveguide itself includes a tapered region that overlies the nanotaper coupling waveguide to facilitate the transfer of the optical energy from the low index waveguide into an associated single mode high index waveguide. Methods of forming these devices using CMOS processes are also disclosed.

Owner:CISCO TECH INC

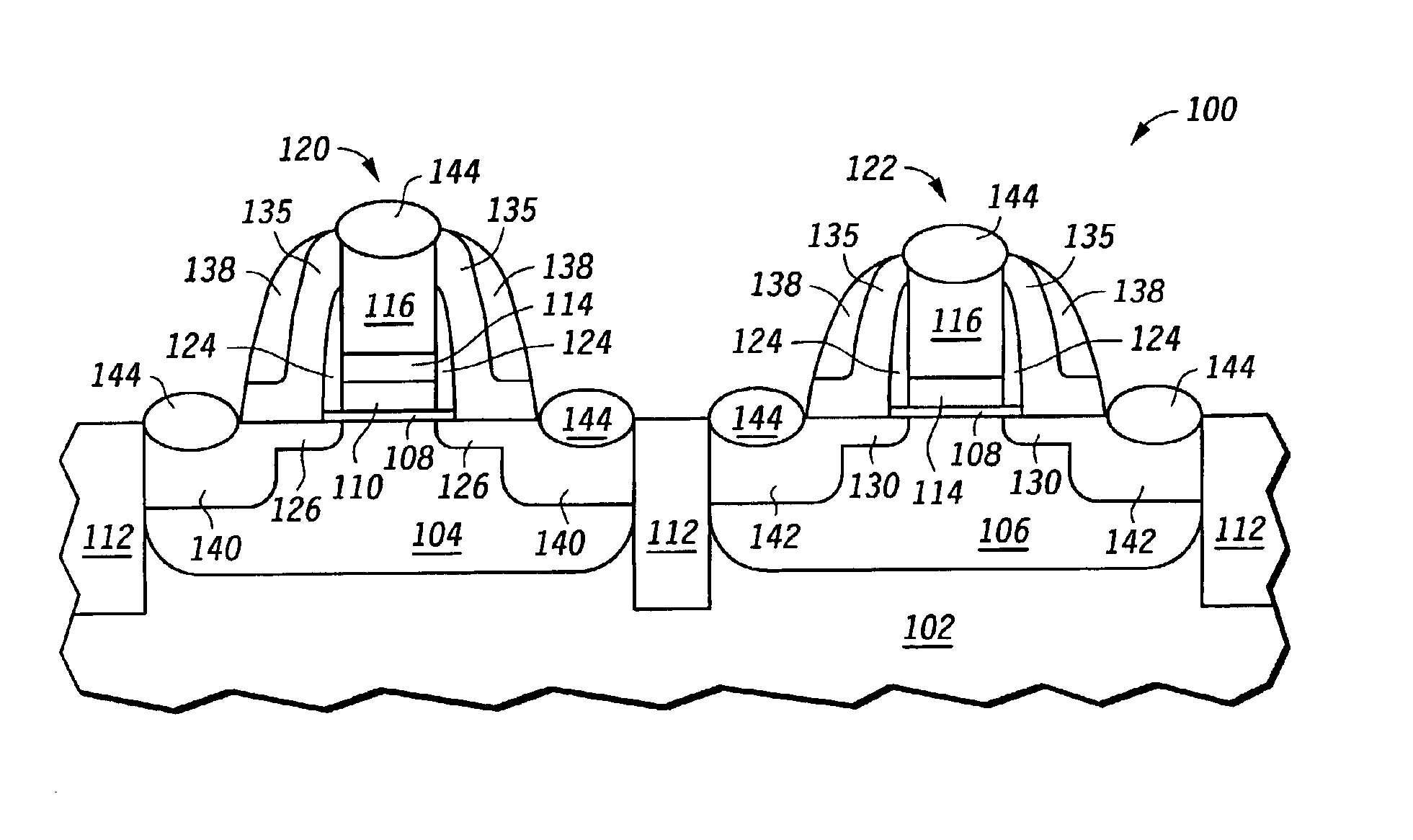

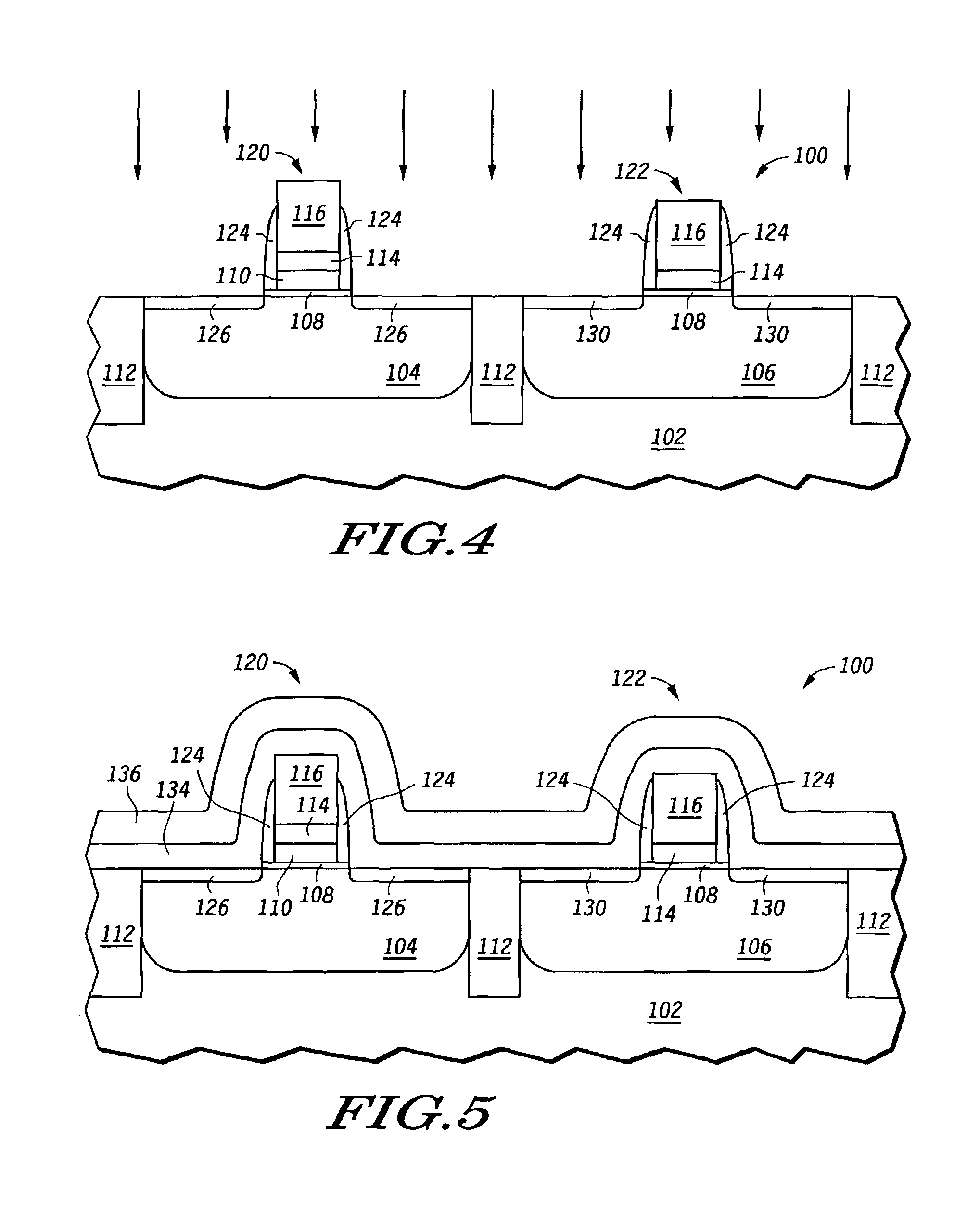

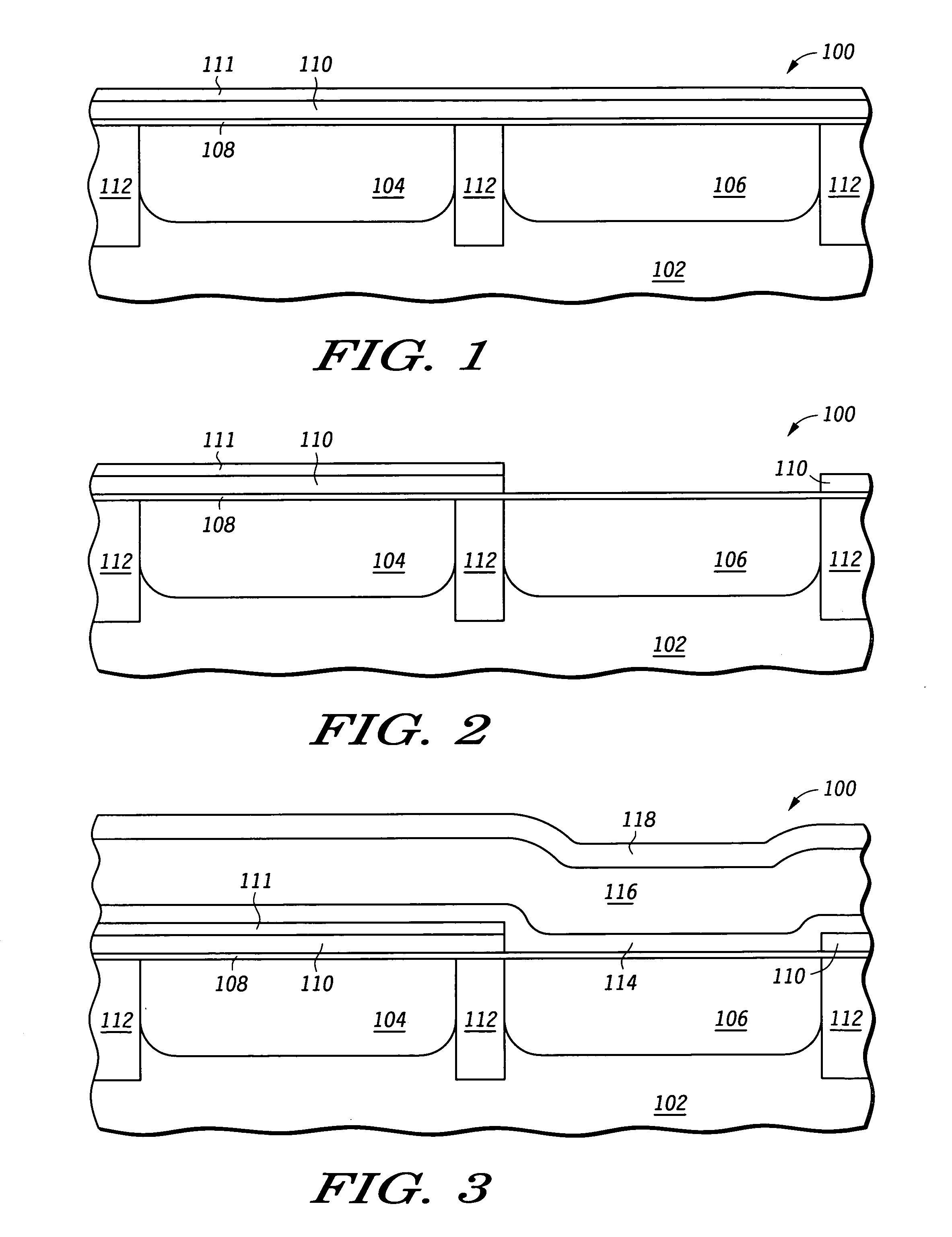

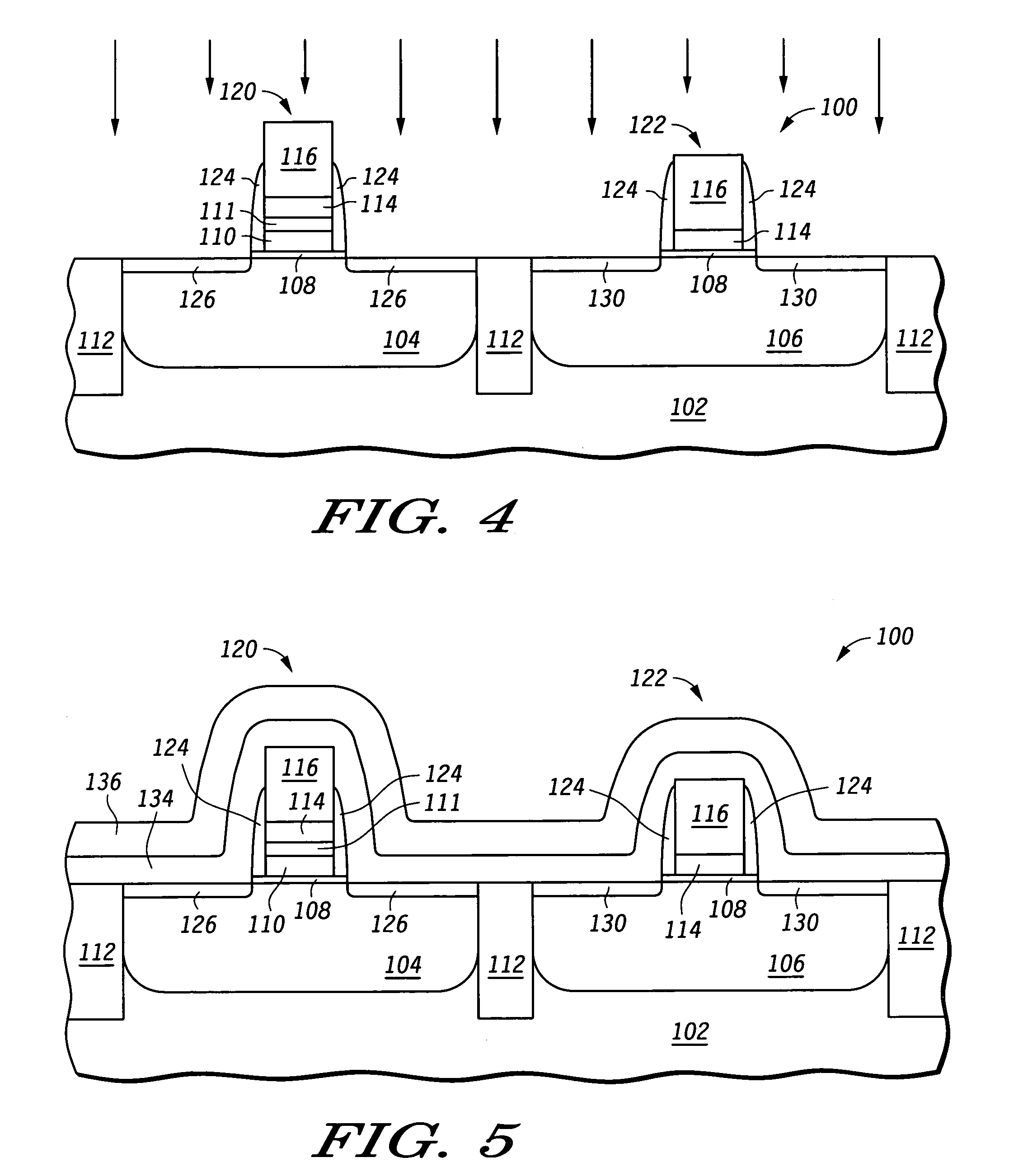

Capped dual metal gate transistors for CMOS process and method for making the same

InactiveUS6894353B2Semiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricTitanium nitride

A first gate (120) and a second gate (122) are preferably PMOS and NMOS transistors, respectively, formed in an n-type well (104) and a p-type well (106). In a preferred embodiment first gate (120) includes a first metal layer (110) of titanium nitride on a gate dielectric (108), a second metal layer (114) of tantalum silicon nitride and a silicon containing layer (116) of polysilicon. Second gate (122) includes second metal layer (114) of a tantalum silicon nitride layer on the gate dielectric (108) and a silicon containing layer (116) of polysilicon. First spacers (124) are formed adjacent the sidewalls of the gates to protect the metals from chemistries used to remove photoresist masks during implant steps. Since the chemistries used are selective to polysilicon, the spacers (124) need not protect the polysilicon capping layers, thereby increasing the process margin of the spacer etch process. The polysilicon cap also facilitates silicidation of the gates.

Owner:NXP USA INC

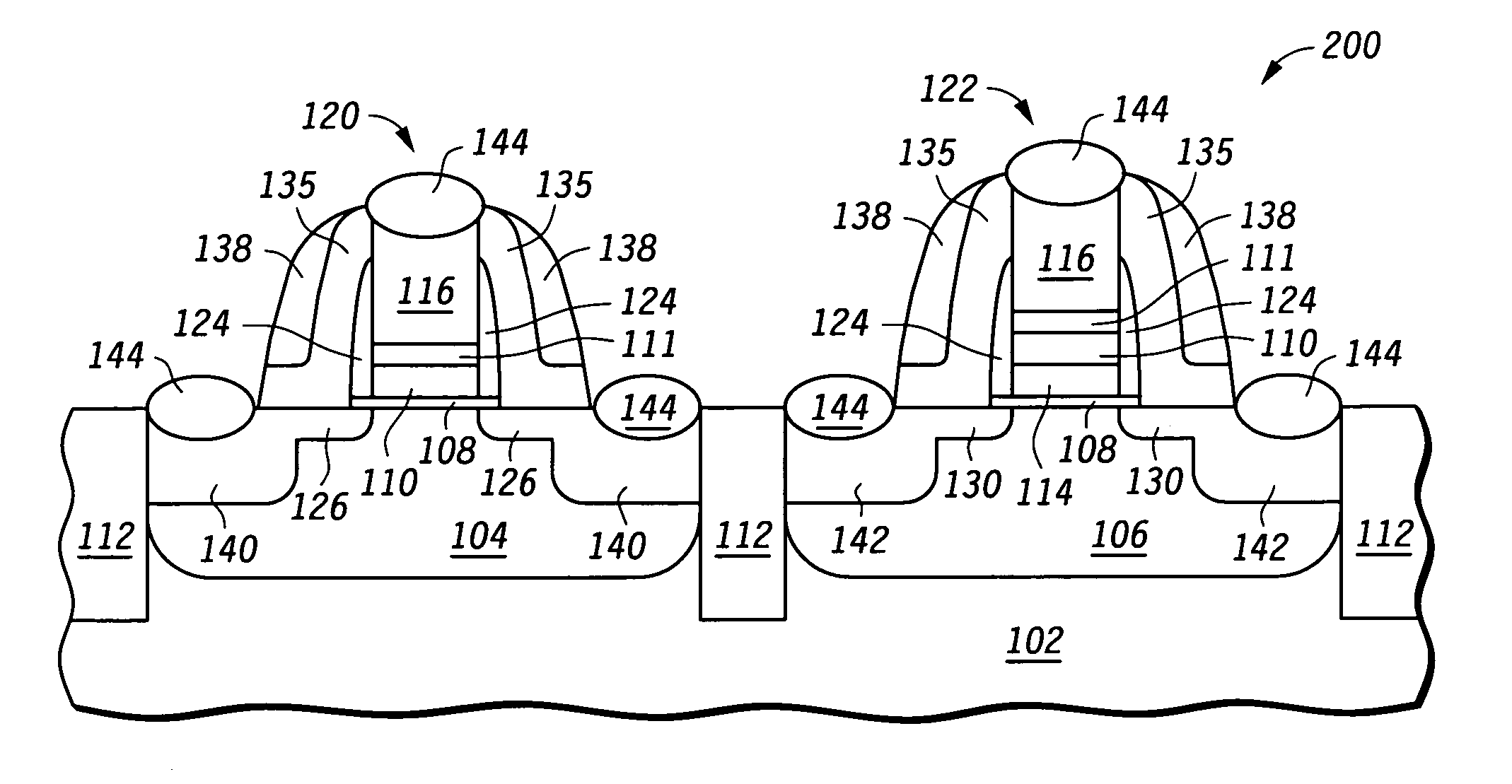

Metal gate transistor CMOS process and method for making

InactiveUS7109079B2TransistorSemiconductor/solid-state device manufacturingGate dielectricOxidation resistant

A method for forming a semiconductor device (100) includes a semiconductor substrate (102) having a first region (104), forming a gate dielectric (108) over the first region, forming a conductive metal oxide (110) over the gate dielectric, forming an oxidation resistant barrier layer (111) over the conductive metal oxide, and forming a capping layer over the oxidation resistant barrier layer. In one embodiment, the conductive metal oxide is IrO2, MoO2, and RuO2, and the oxidation resistant barrier layer includes TiN.

Owner:NORTH STAR INNOVATIONS

Elastomeric CMOS based micro electromechanical varactor

InactiveUS20060003482A1Increase capacitance densityIncreased side wall areaCapacitor with electrode distance variationMultiple capacitorsElastomerElectrical polarity

A micro electro-mechanical system (MEMS) variable capacitor is described, wherein movable comb electrodes of opposing polarity are fabricated simultaneously on the same substrate and are independently actuated. The electrodes are formed in an interdigitated fashion to maximize capacitance. The MEMS variable capacitor includes CMOS manufacturing steps in combination with elastomeric material selectively used in areas under greatest stress to ensure that the varactor will not fail as a result of stresses that may result in the separation of dielectric material from the conductive elements. The combination of a CMOS process with the conducting elastomeric material between vias increases the overall sidewall area, which provides increased capacitance density.

Owner:IBM CORP

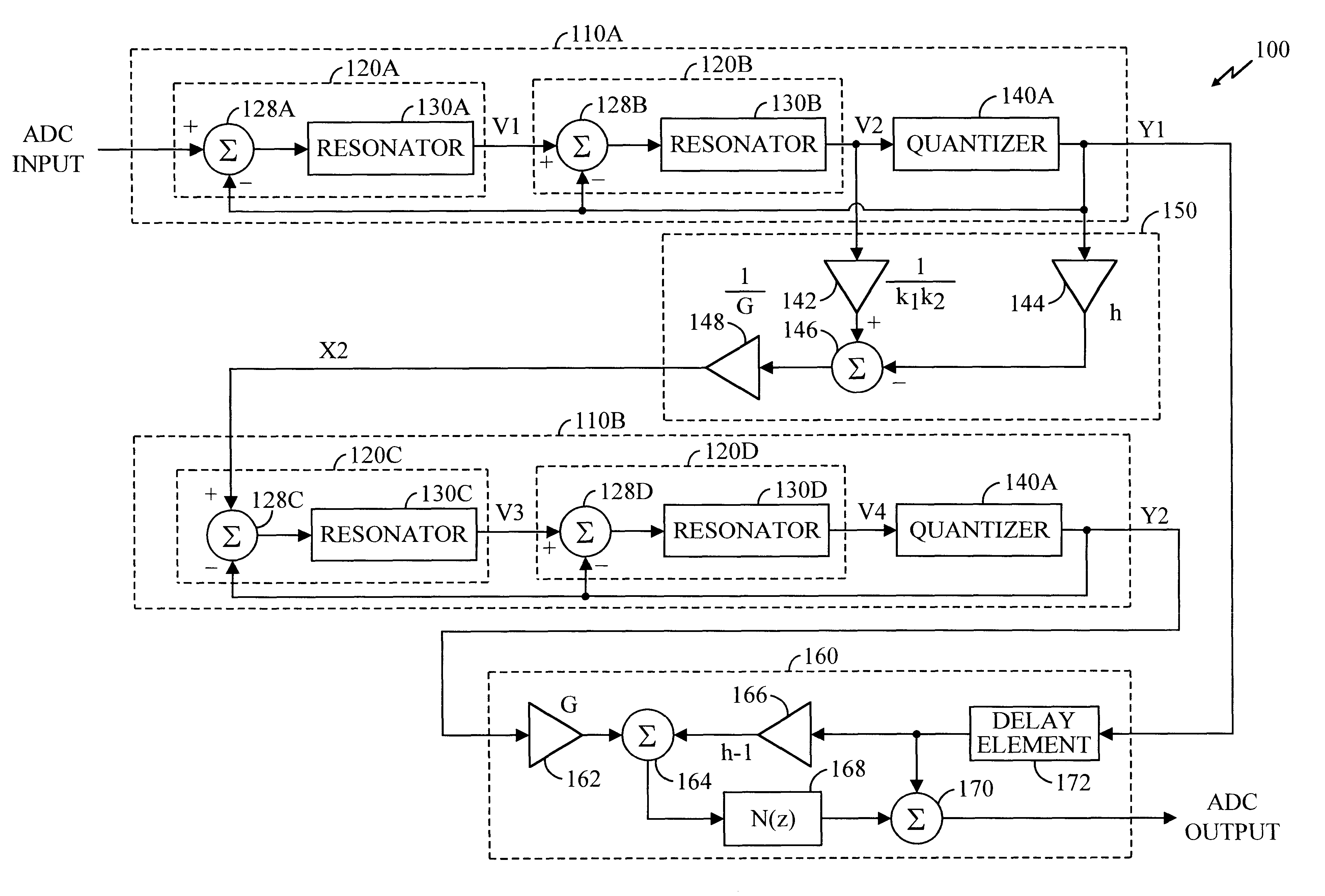

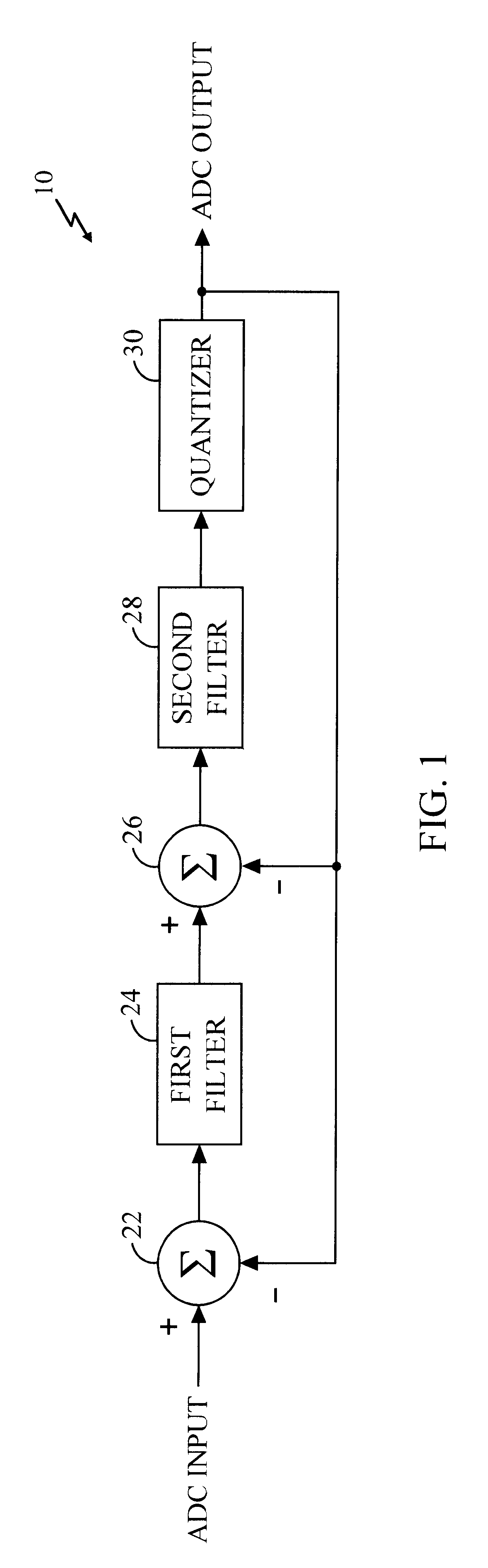

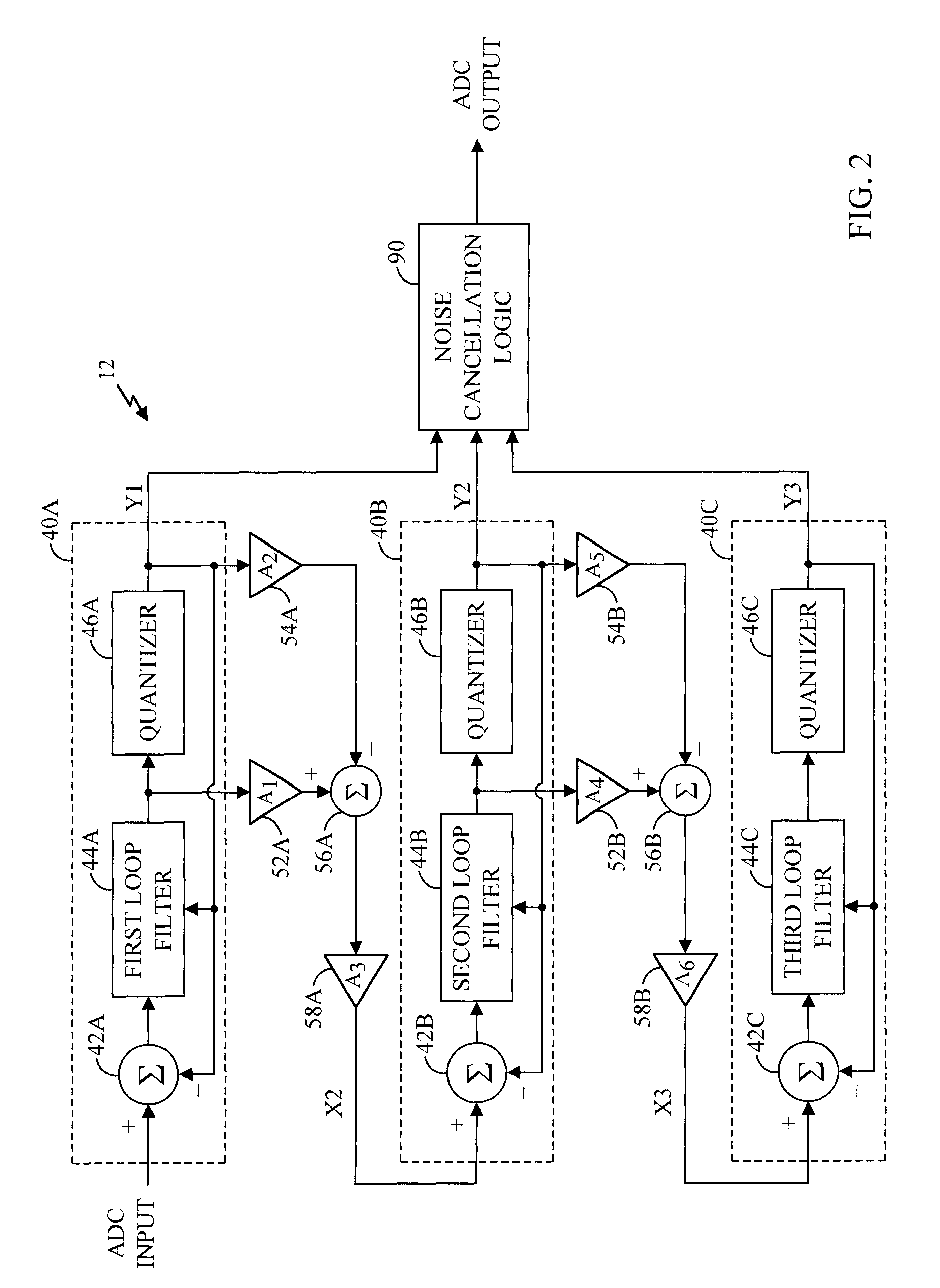

Multi-sampling SIGMA-DELTA analog-to-digital converter

A bandpass SIGMADELTA ADC utilizing either a single-loop or a MASH architecture wherein the resonators are implemented as either a delay cell resonator, a delay cell based resonator, a Forward-Euler resonator, a two-path interleaved resonator, or a four-path interleaved resonator. The resonator can be synthesized with analog circuit techniques such as active-RC, gm-C, MOSFET-C, switched capacitor, or switched current. The switched capacitor or switched current circuits can be designed using single-sampling, double-sampling, or multi-sampling circuits. The non-stringent requirement of a SIGMADELTA ADC using switched capacitor circuits allows the ADC to be implemented in a CMOS process to minimize cost and reduce power consumption. Double-sampling circuits provide improved matching and improved tolerance to sampling clock jitter. In particular, a bandpass MASH 4-4 SIGMADELTA ADC provides a simulated signal-to-noise ratio of 85 dB at an oversampling ratio of 32 for a CDMA application. The bandpass SIGMADELTA ADC can also be used in conjunction with undersampling to provide a frequency downconversion.

Owner:QUALCOMM INC

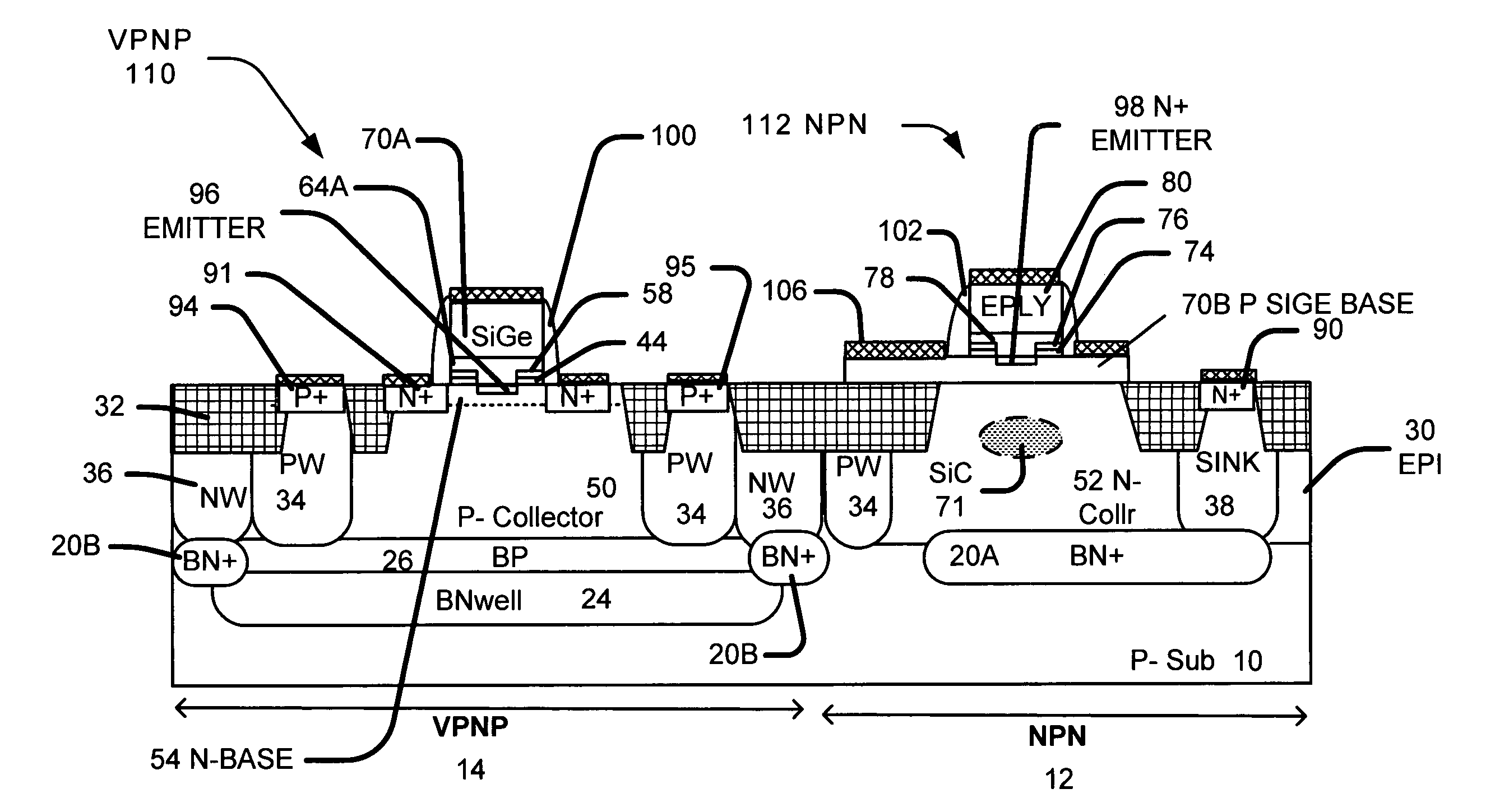

Self-aligned vertical PNP transistor for high performance SiGe CBiCMOS process

A structure and a process for a self-aligned vertical PNP transistor for high performance SiGe CBiCMOS process. Embodiments include SiGe CBiCMOS with high-performance SiGe NPN transistors and PNP transistors. As the PNP transistors and NPN transistors contained different types of impurity profile, they need separate lithography and doping step for each transistor. The process is easy to integrate with existing CMOS process to save manufacturing time and cost. As plug-in module, fully integration with SiGe BiCMOS processes. High doping Polysilicon Emitter can increase hole injection efficiency from emitter to base, reduce emitter resistor, and form very shallow EB junction. Self-aligned N+ base implant can reduce base resistor and parasitical EB capacitor. Very low collector resistor benefits from BP layer. PNP transistor can be Isolated from other CMOS and NPN devices by BNwell, Nwell and BN+ junction.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

Nonvolatile Memory Bitcell With Inlaid High K Metal Select Gate

ActiveUS20150041875A1Solid-state devicesSemiconductor/solid-state device manufacturingDielectricProcess integration

A process integration is disclosed for fabricating non-volatile memory (NVM) cells having recessed control gates (118, 128) on a first substrate area (111) which are encapsulated in one or more planar dielectric layers (130) prior to forming in-laid high-k metal select gates and CMOS transistor gates (136, 138) in first and second substrate areas (111, 113) using a gate-last HKMG CMOS process flow without interfering with the operation or reliability of the NVM cells.

Owner:NXP USA INC

Integrated micro electro-mechanical system and manufacturing method thereof

InactiveUS20090049911A1Easy to manufactureSufficient massTelevision system detailsInflated body pressure measurementDielectricEtching

In the manufacturing technology of an integrated MEMS in which a semiconductor integrated circuit (CMOS or the like) and a micro machine are monolithically integrated on a semiconductor substrate, a technology capable of manufacturing the integrated MEMS without using a special process different from the normal manufacturing technology of a semiconductor integrated circuit is provided. A MEMS structure is formed together with an integrated circuit by using the CMOS integrated circuit process. For example, when forming an acceleration sensor, a structure composed of a movable mass, an elastic beam and a fixed beam is formed by using the CMOS interconnect technology. Thereafter, an interlayer dielectric and the like are etched by using the CMOS process to form a cavity. Then, fine holes used in the etching are sealed with a dielectric.

Owner:HITACHI LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com