Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

263results about How to "Increase capacitance density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

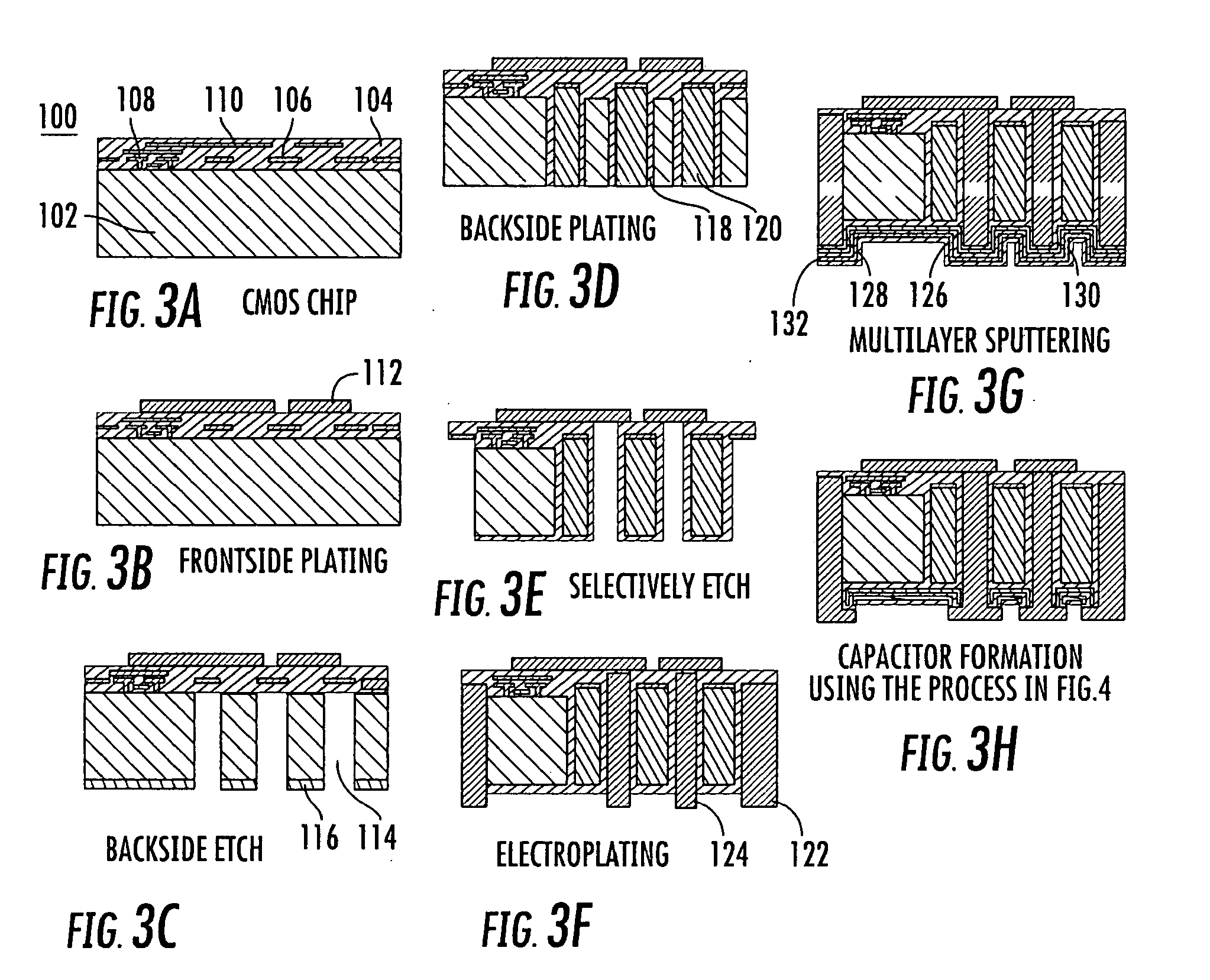

Integration substrate with a ultra-high-density capacitor and a through-substrate via

ActiveUS20100244189A1Simple to introduce into existing production lineIncrease capacitance densitySemiconductor/solid-state device detailsSolid-state devicesMicrometerEngineering

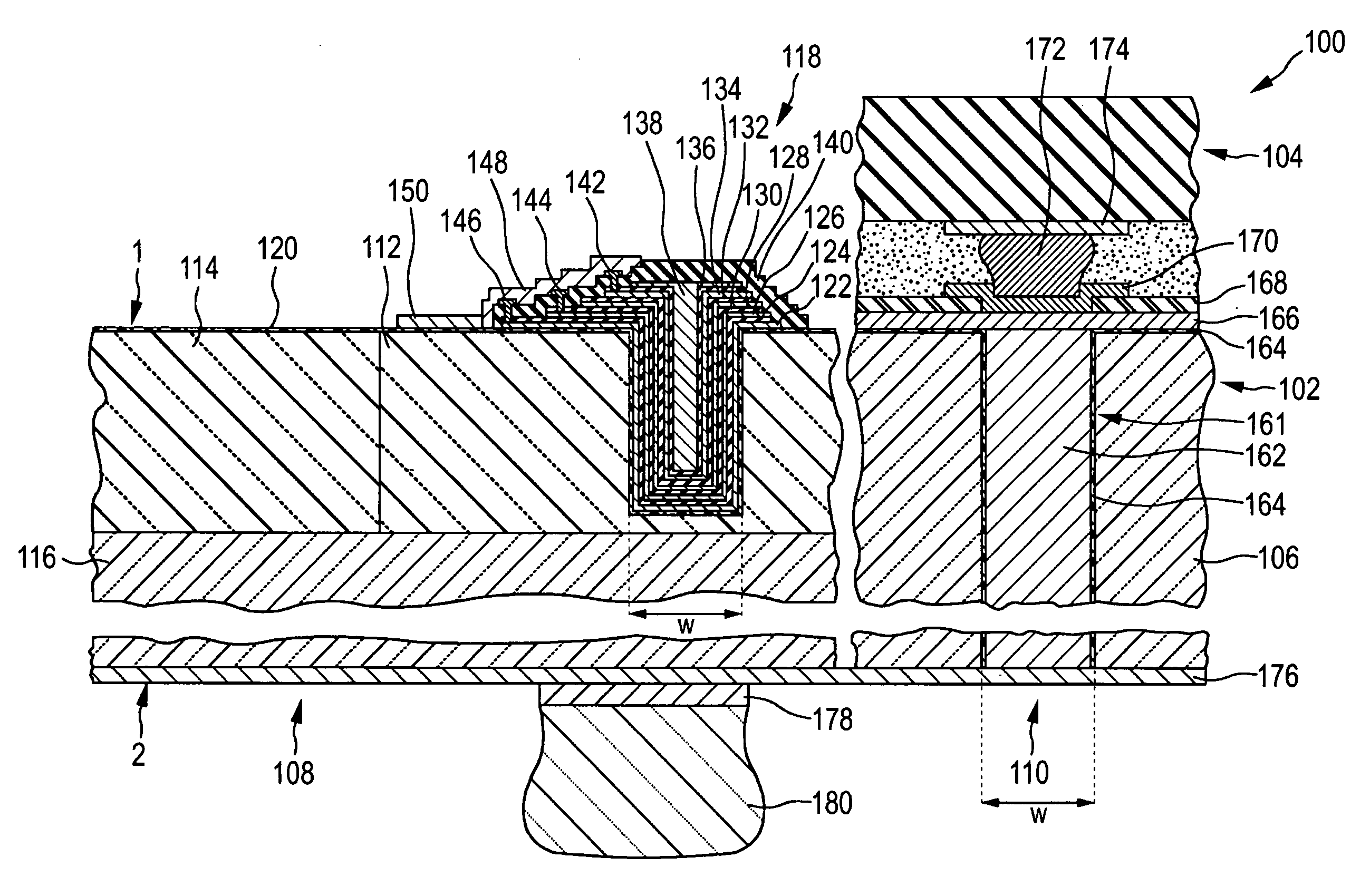

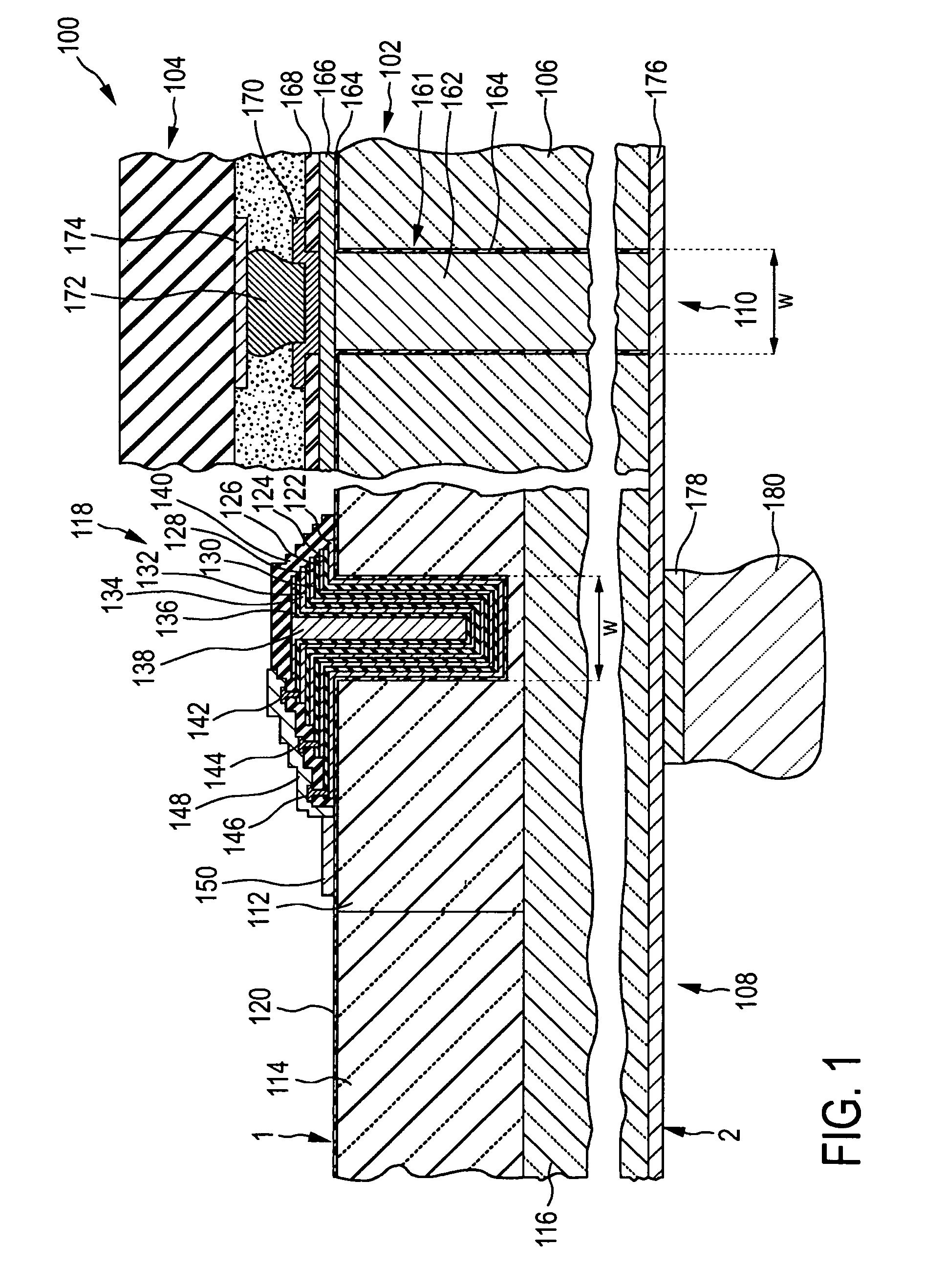

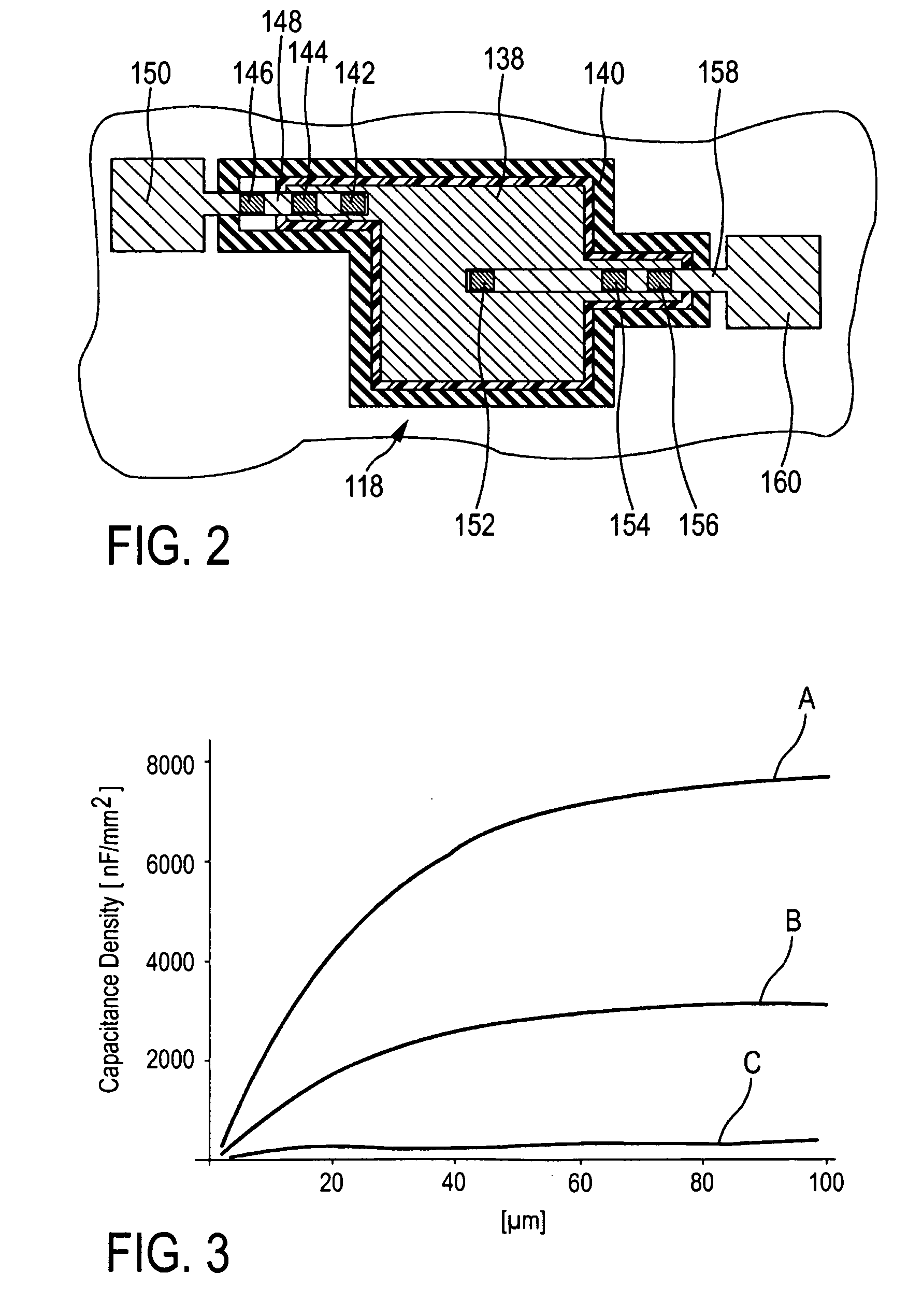

An integration substrate for a system in package comprises a through-substrate via and a trench capacitor wherein with a trench filling that includes at least four electrically conductive capacitor-electrode layers in an alternating arrangement with dielectric layers. —The capacitor-electrode layers are alternatingly connected to a respective one of two capacitor terminals provided on the first or second substrate side. The trench capacitor and the through-substrate via are formed in respective trench openings and via openings in the semiconductor substrate, which have an equal lateral extension exceeding 10 micrometer. This structure allows, among other advantages, a particularly cost-effective fabrication of the integration substrate because the via openings and the trench openings in the substrate can be fabricated simultaneously.

Owner:MURATA INTEGRATED PASSIVE SOLUTIONS

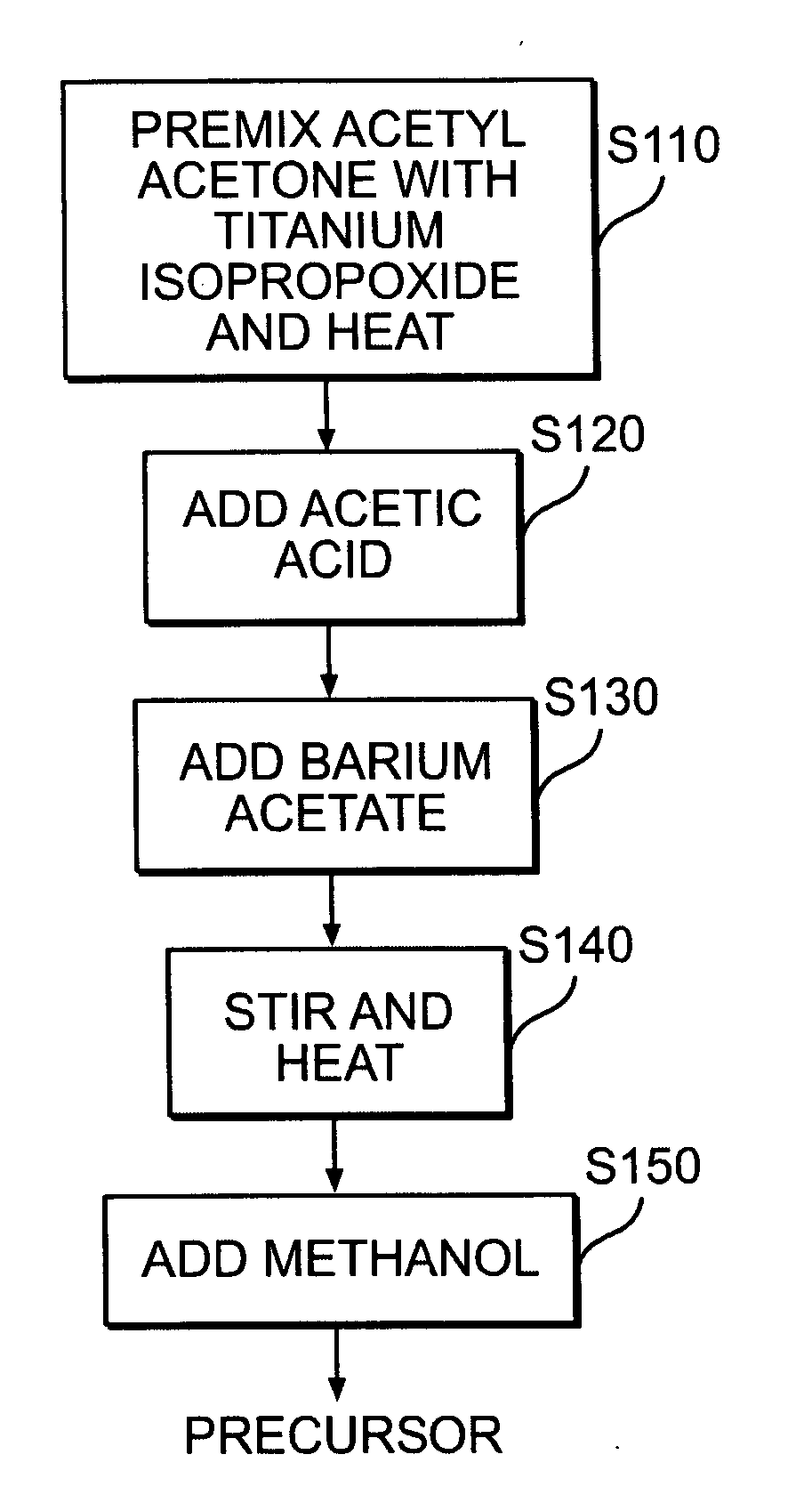

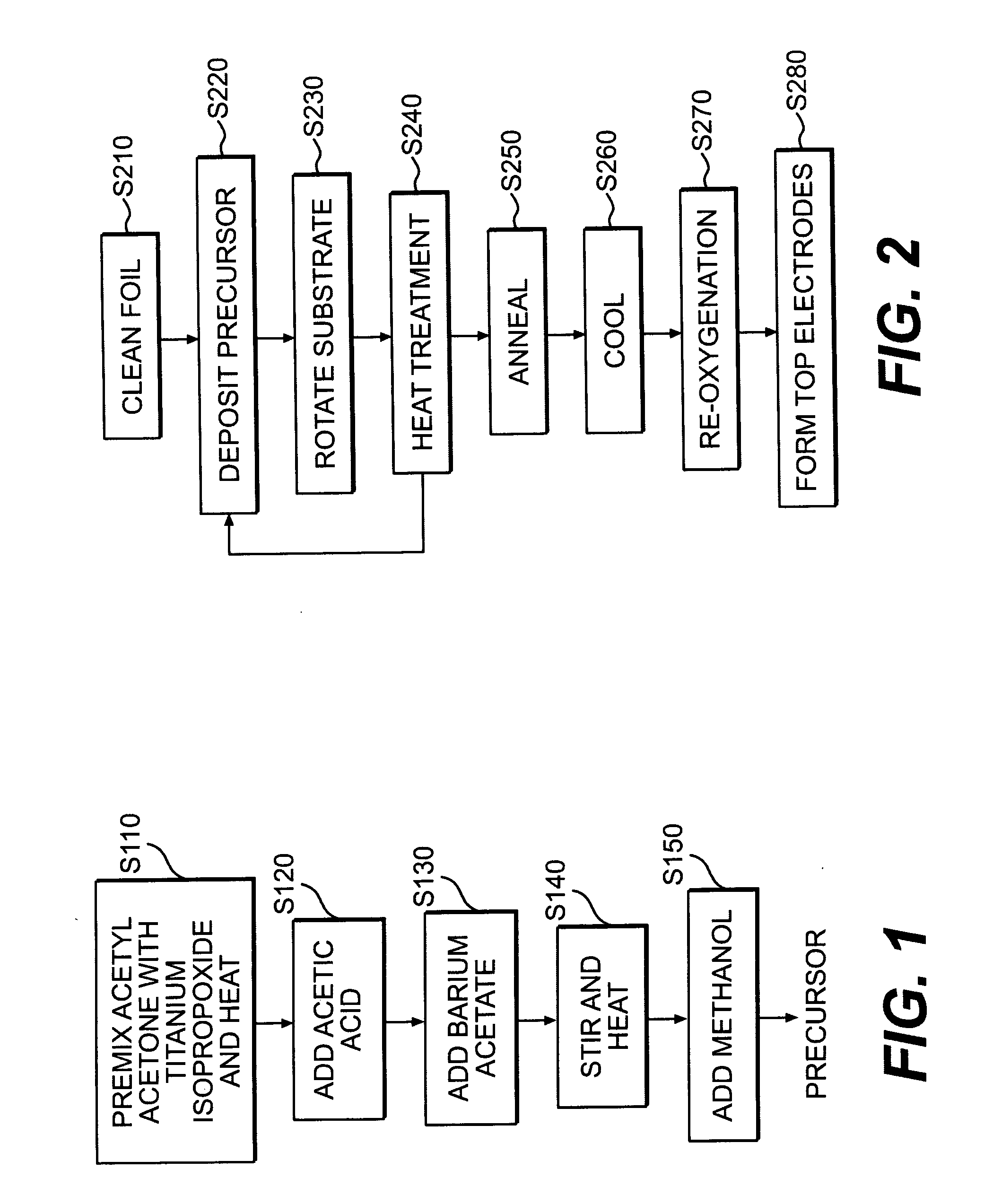

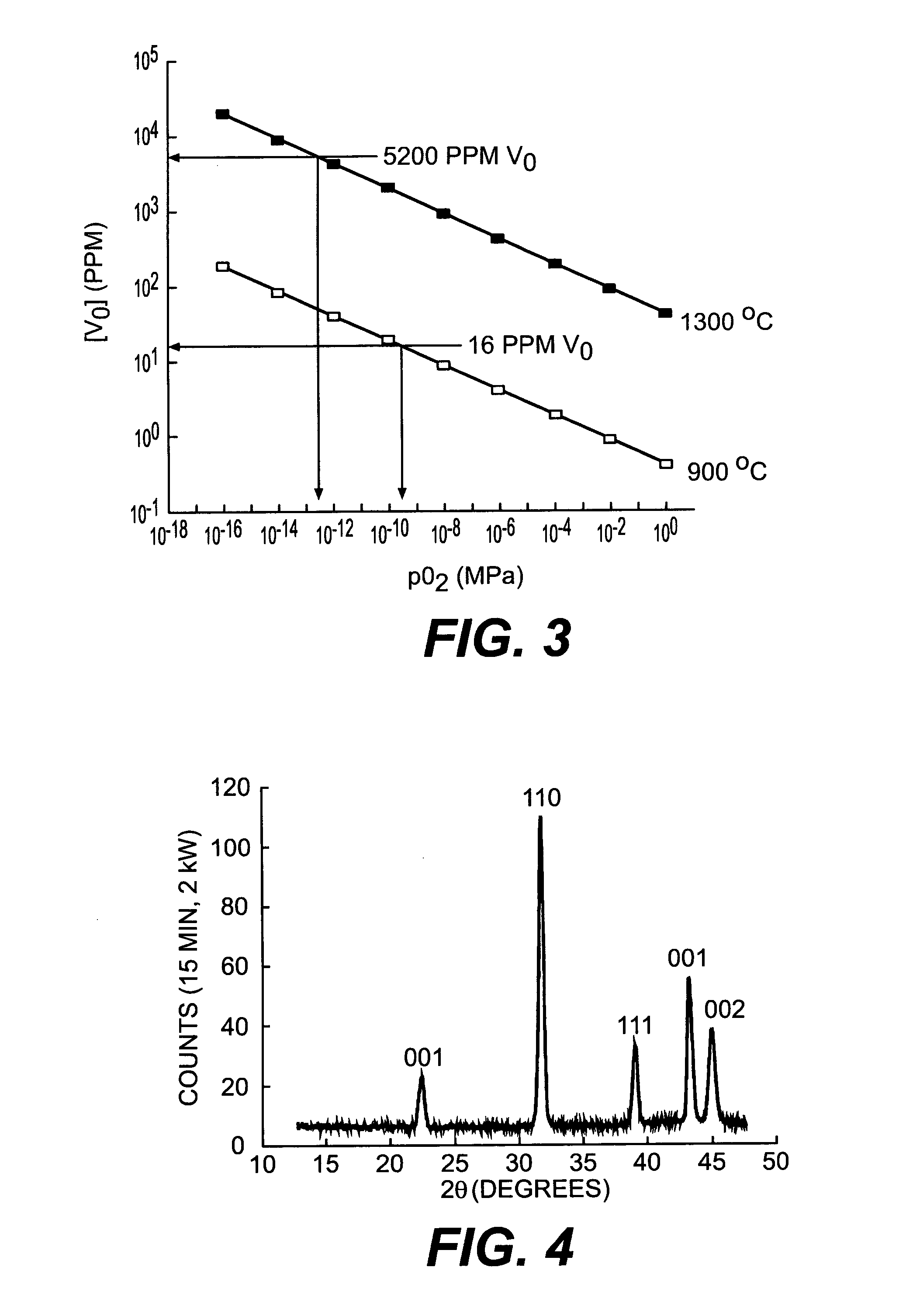

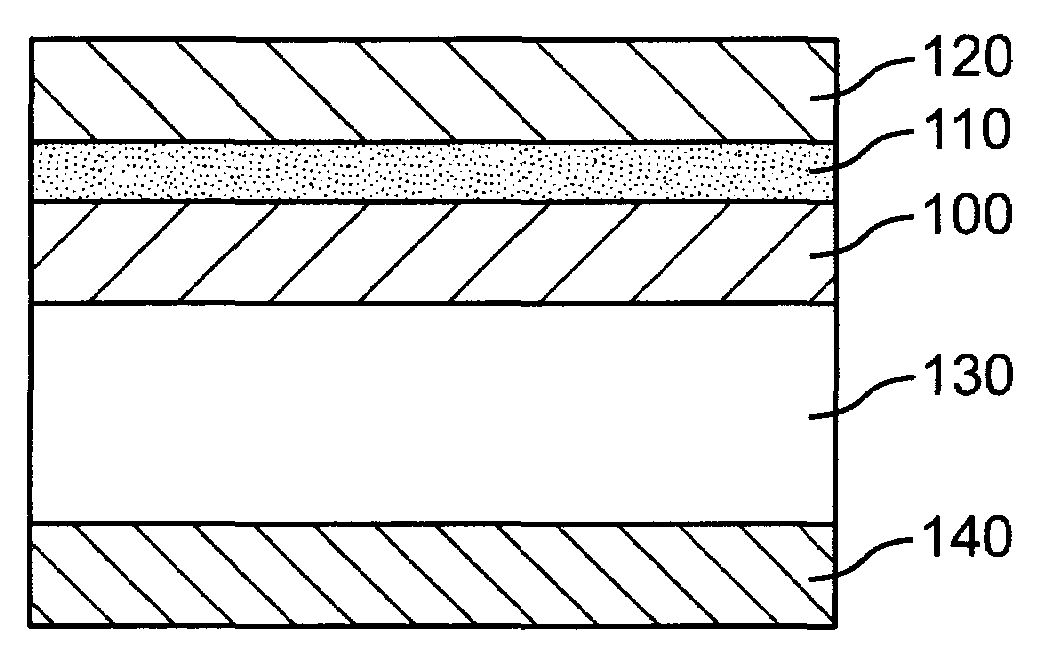

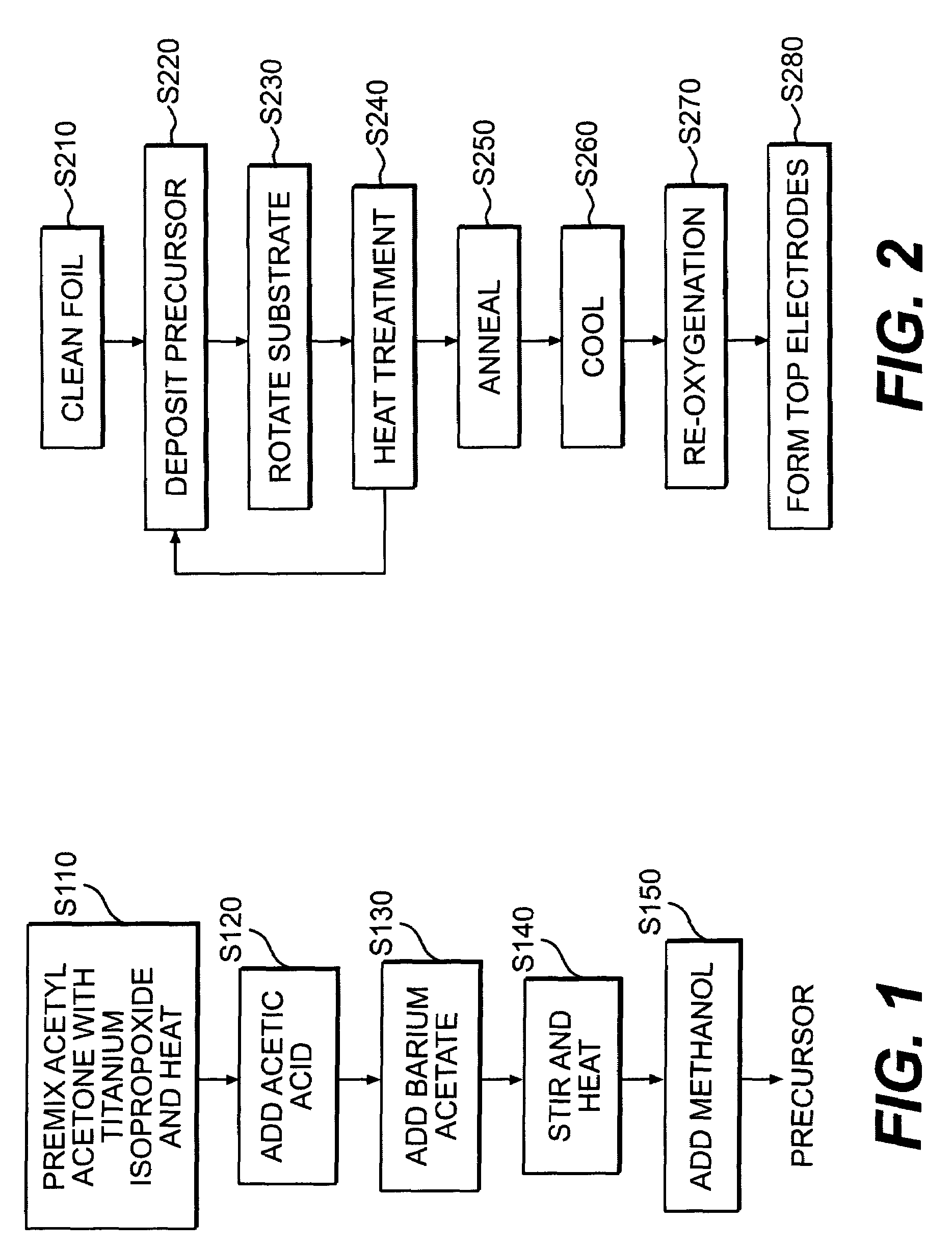

Thin film dielectrics for capacitors and methods of making thereof

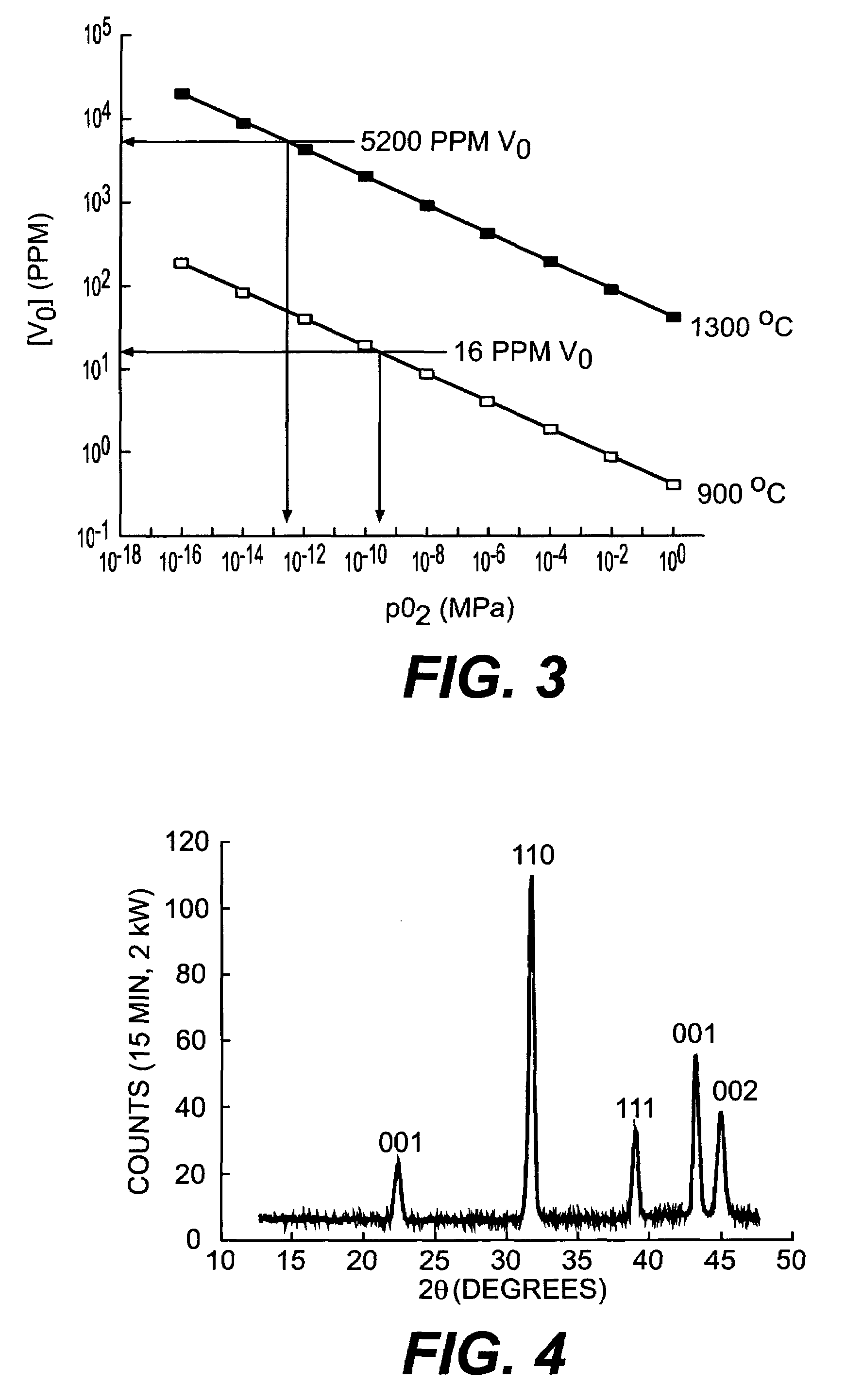

ActiveUS20050011857A1Increase capacitance densityLow loss tangentFixed capacitor dielectricPrinted circuit aspectsCopper foilHigh dielectric permittivity

Dielectrics are formed having high dielectric constants, low loss tangents, and other desirable electrical and physical properties. The dielectrics are annealed at temperatures allowing the use of copper foil substrates, and at low oxygen partial pressures.

Owner:NYTELL SOFTWARE LLC

Thin film dielectrics for capacitors and methods of making thereof

ActiveUS7029971B2Increase capacitance densityLow loss tangentFixed capacitor dielectricPrinted circuit aspectsDielectricCopper foil

Dielectrics are formed having high dielectric constants, low loss tangents, and other desirable electrical and physical properties. The dielectrics are annealed at temperatures allowing the use of copper foil substrates, and at low oxygen partial pressures.

Owner:NYTELL SOFTWARE LLC

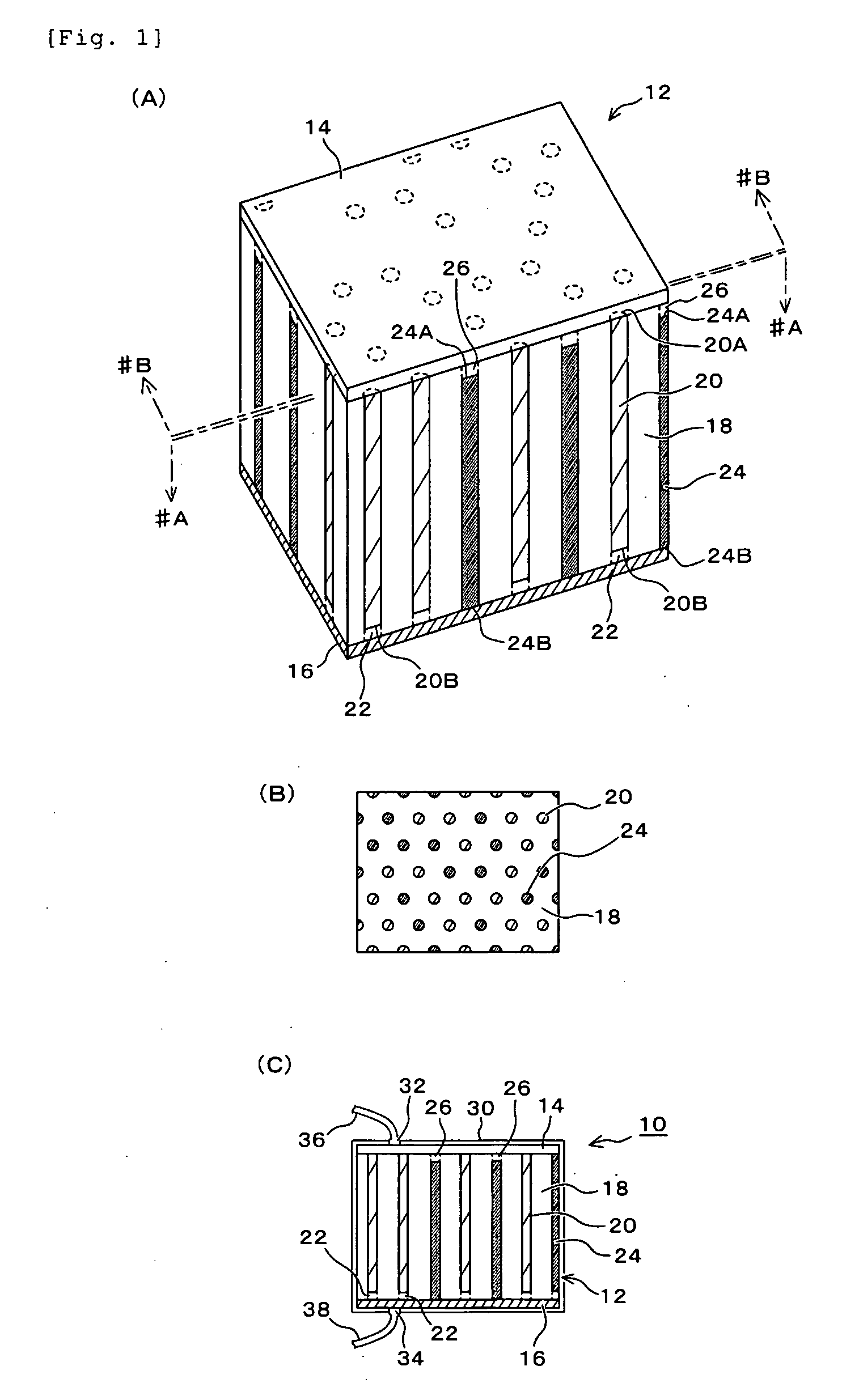

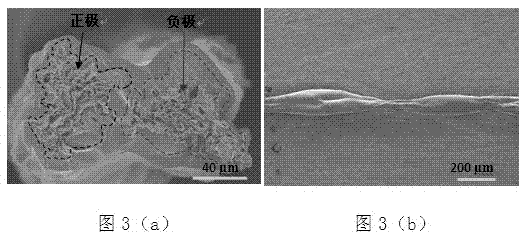

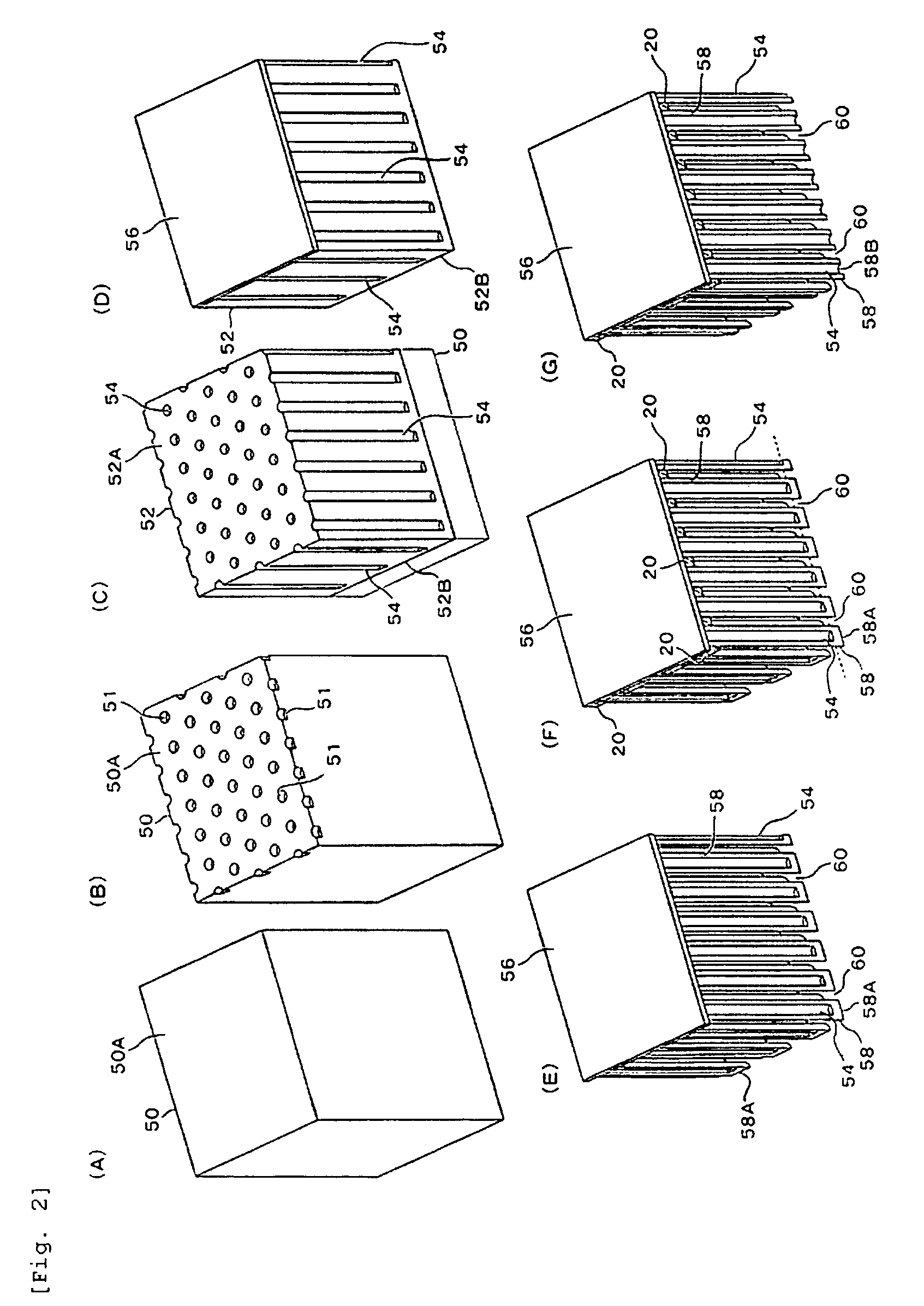

Electric double layer capacitor and process for its production

InactiveUS6906911B2Increase capacitance densityMaintained satisfactorilyHybrid capacitor separatorsHybrid capacitor electrodesEngineeringElectric double-layer capacitor

An electric double layer capacitor includes, contained in a casing, an electrolyte, a positive electrode and a negative electrode each being an electrode containing carbon black, to form an electric double layer at the interface with the electrolyte, and a separator interposed between the positive electrode and the negative electrode. At least one electrode of the positive electrode and the negative electrode has protruded portions or bent portions formed continuously in the height direction against the bottom face of the casing. Further, a space due to the height of the protruded portions or the bent portions is formed between the at least one electrode and the separator.

Owner:MITSUBISHI ELECTRIC CORP +1

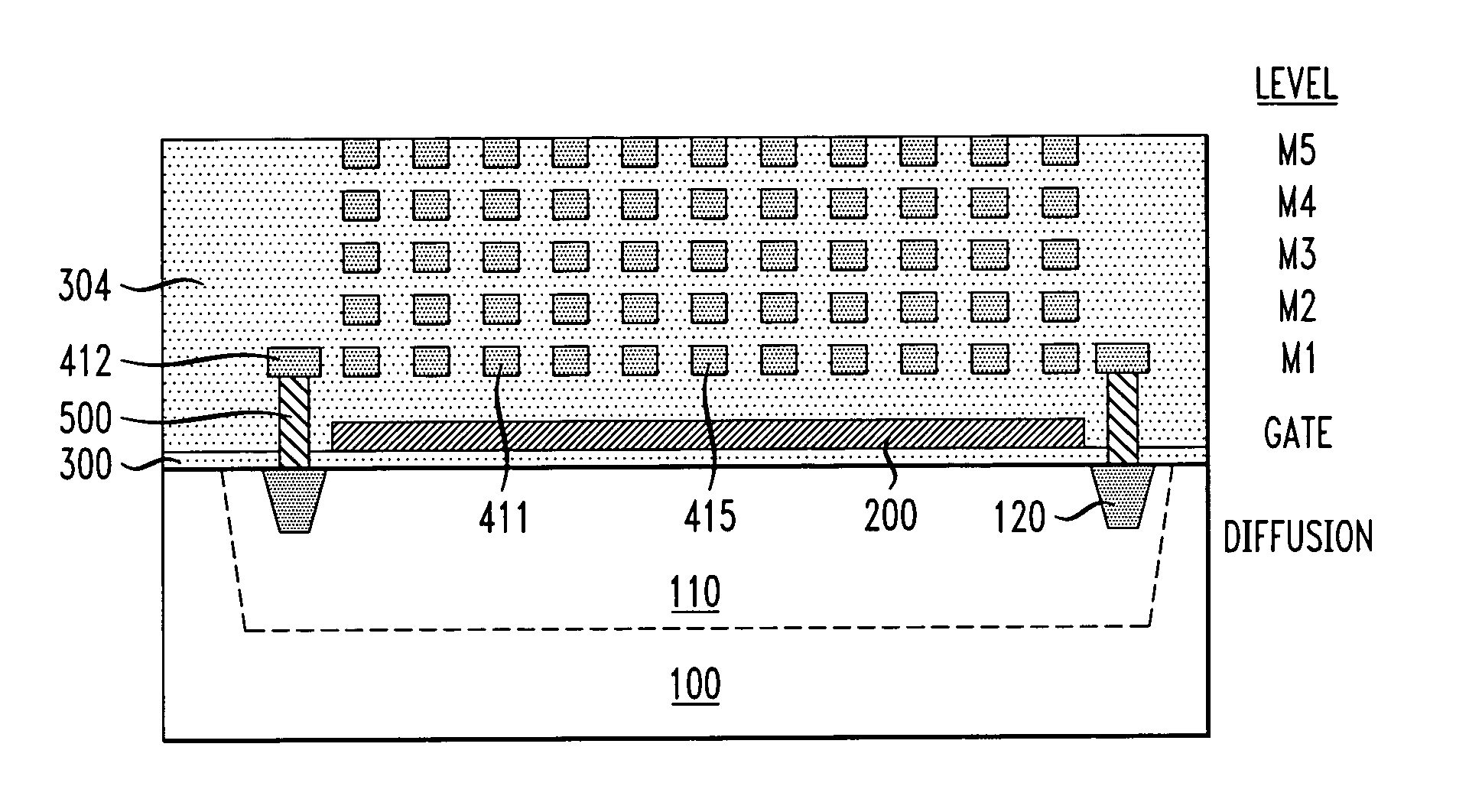

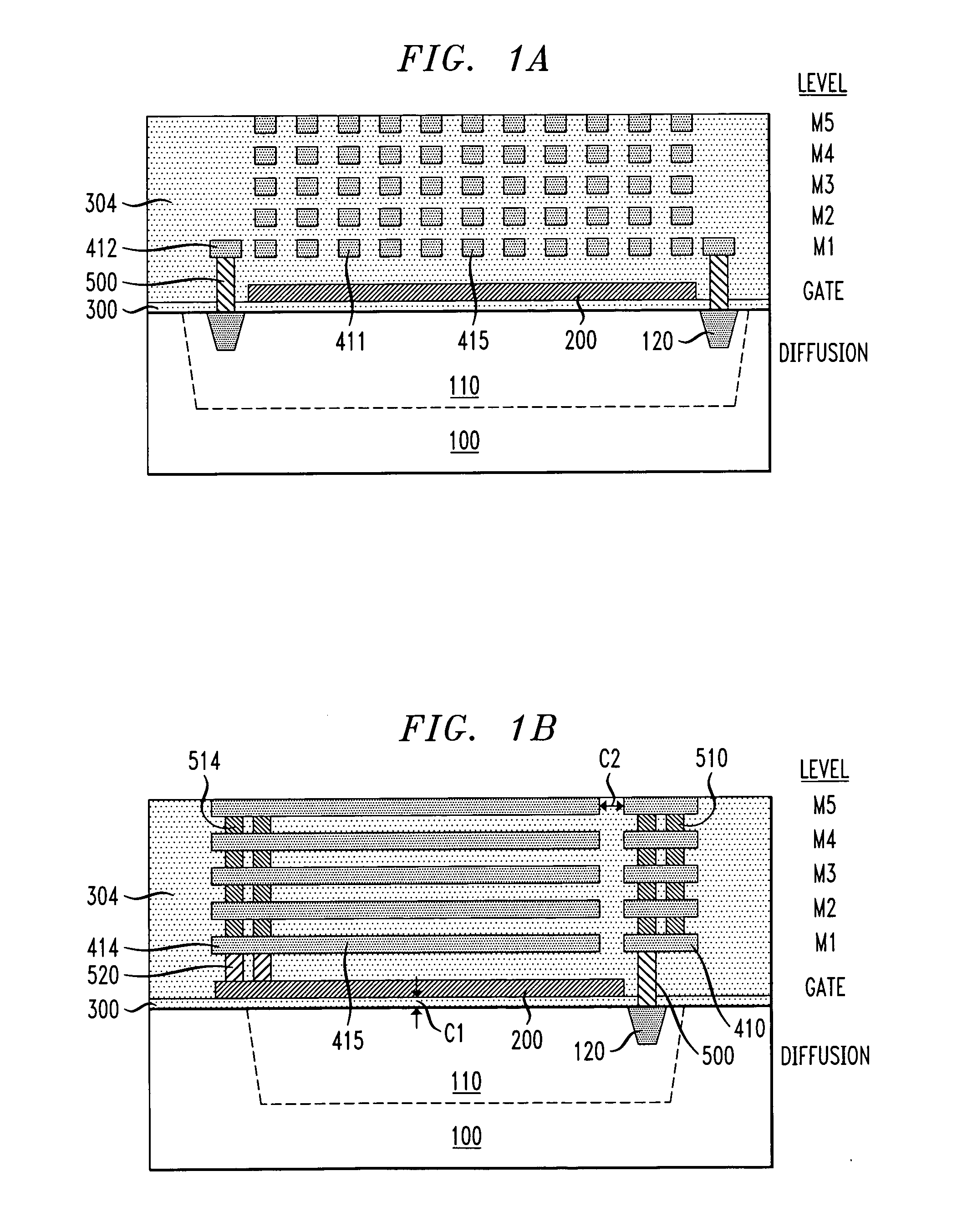

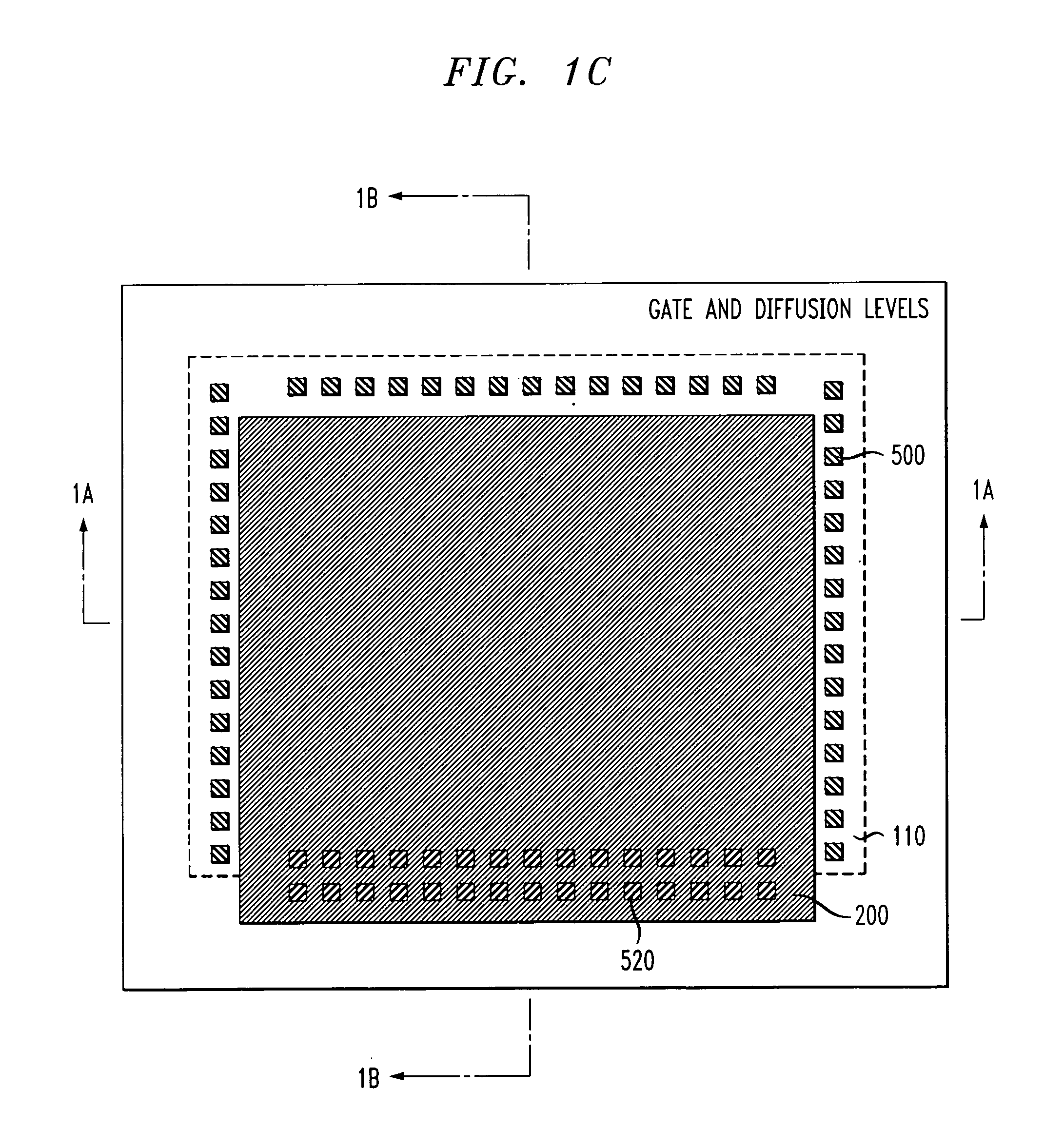

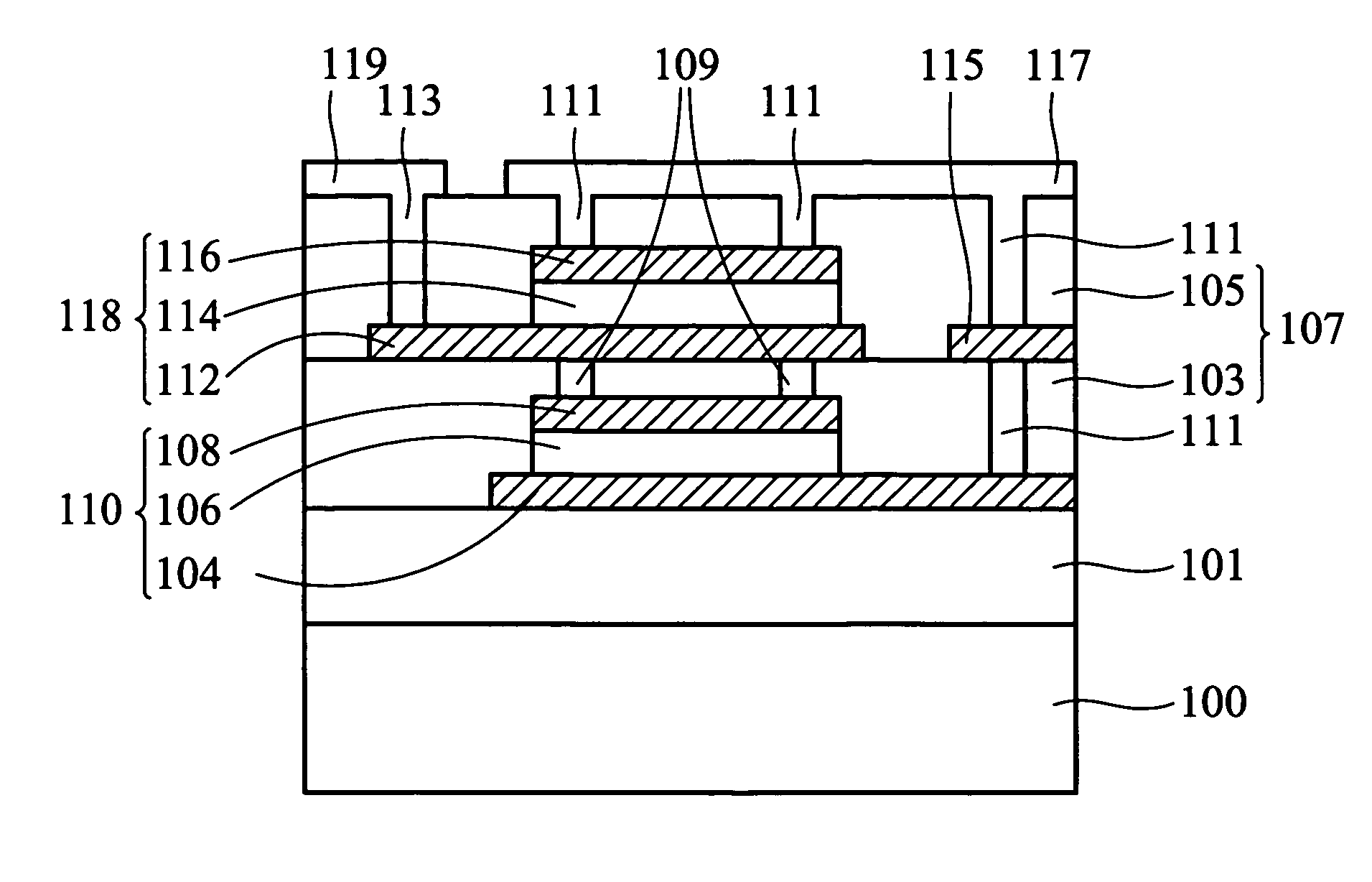

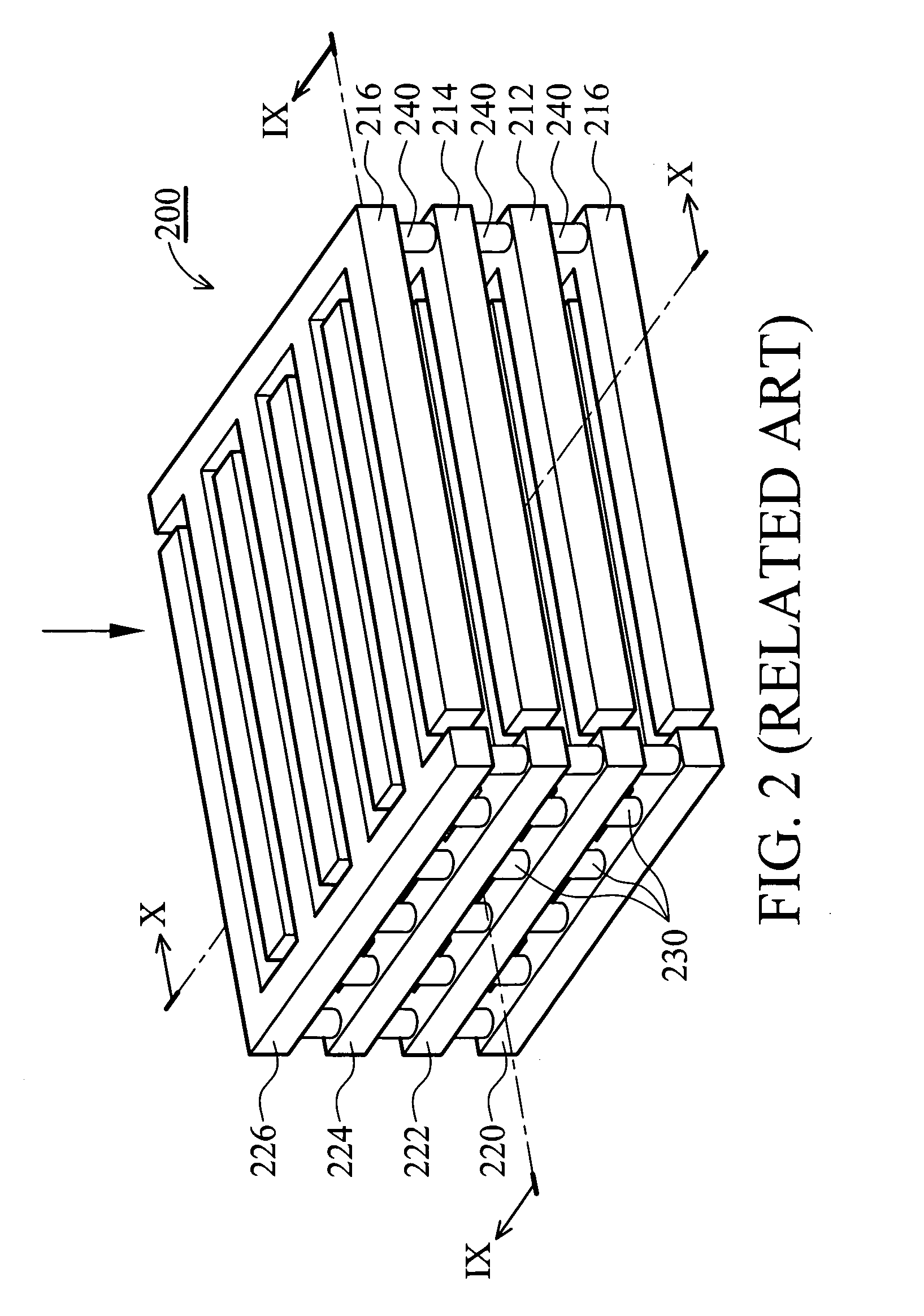

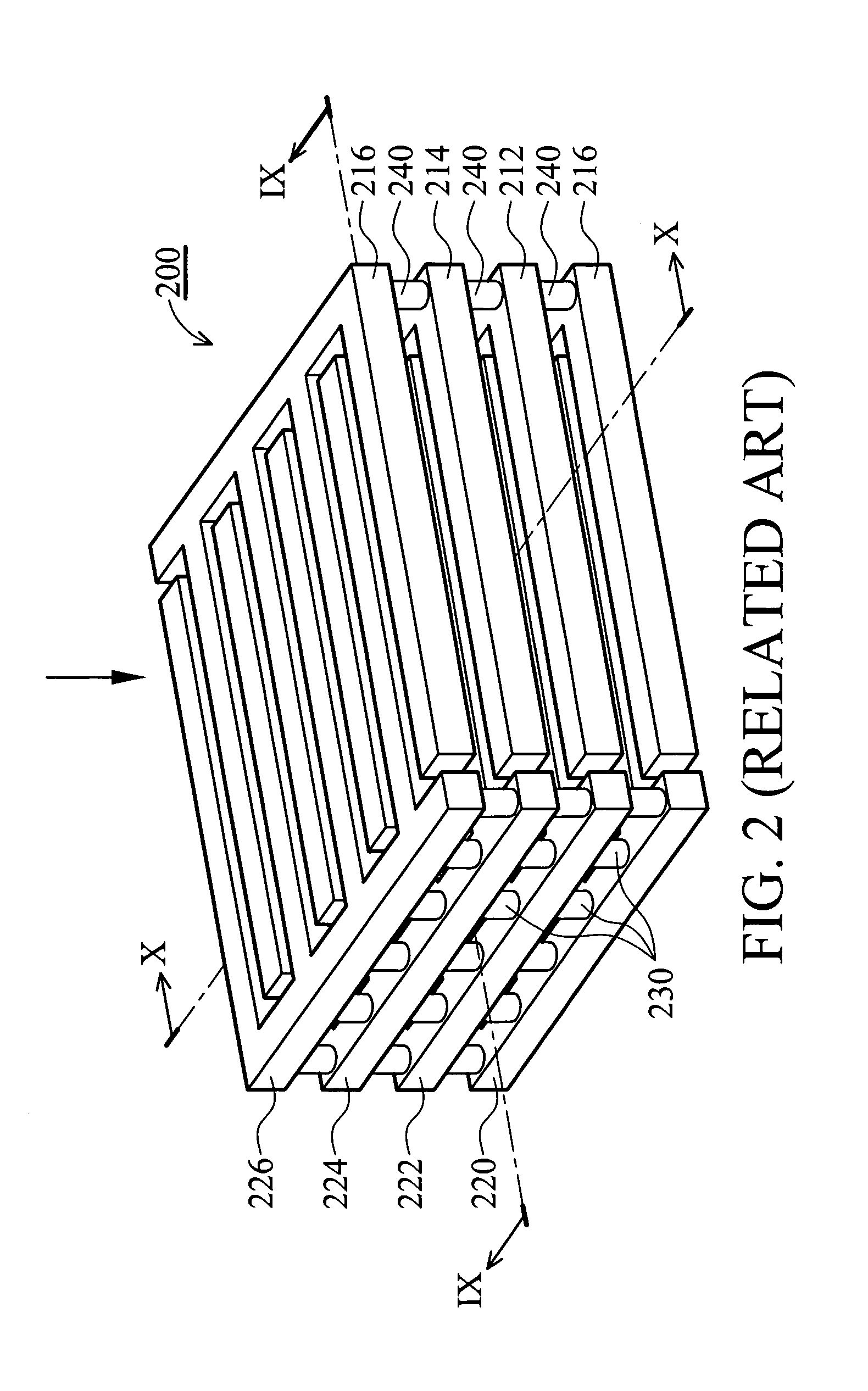

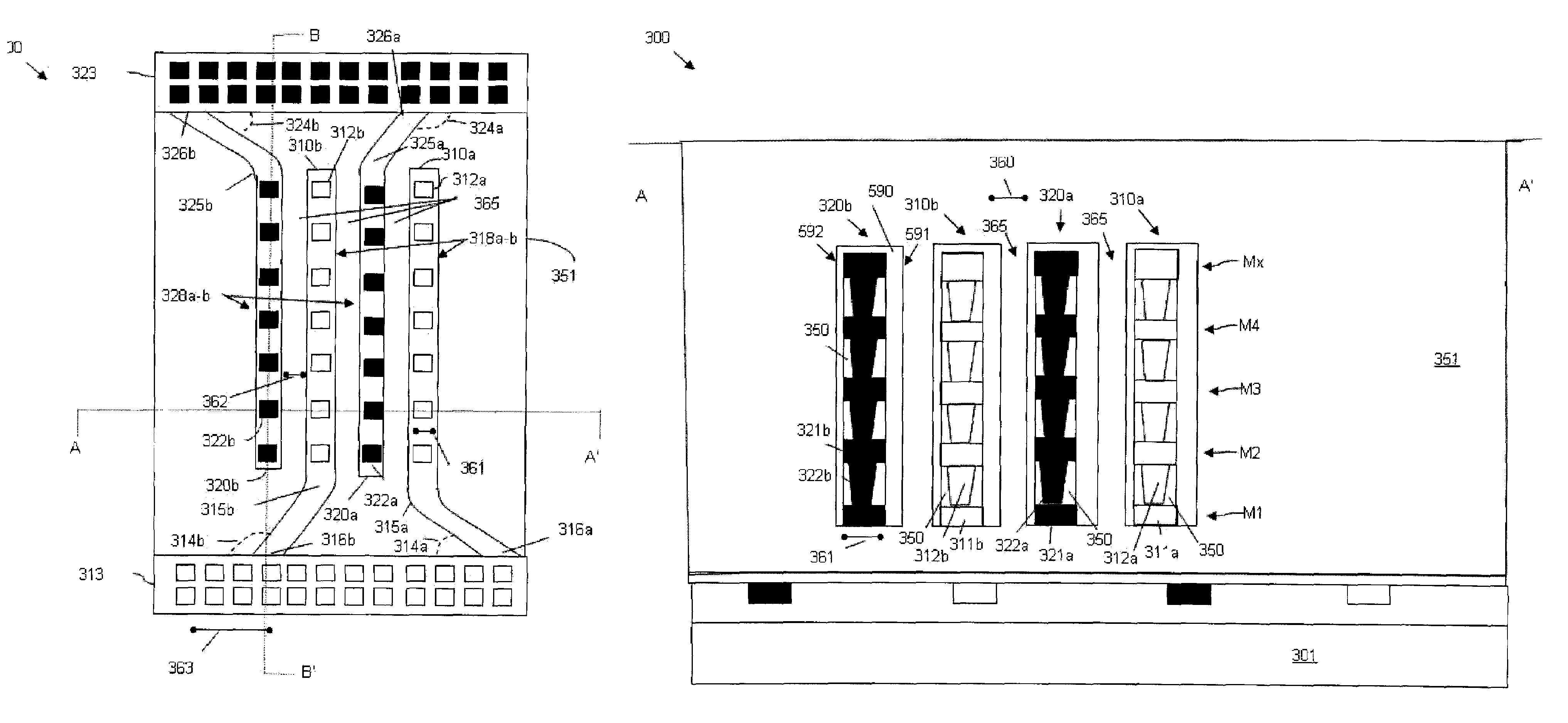

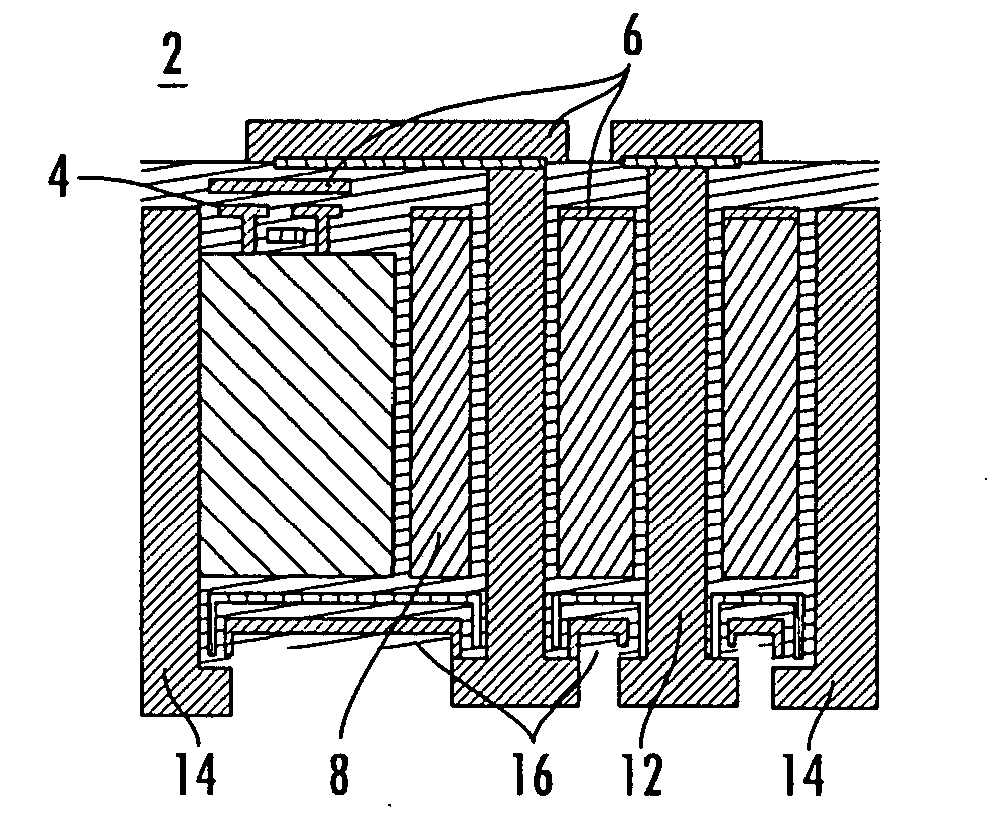

Metal capacitor stacked with a MOS capacitor to provide increased capacitance density

InactiveUS20060024905A1Increase capacitance densityIncrease processing costTransistorSemiconductor/solid-state device detailsCapacitanceMetal interconnect

An on-chip capacitive device comprises a semiconductor substrate, a MOS capacitor formed on the semiconductor substrate, and a metal interconnect capacitor formed at least in part in a region above the MOS capacitor. The MOS capacitor and the metal interconnect capacitor are connected in parallel to form a single capacitive device. The capacitance densities of the MOS capacitor and the metal interconnect capacitor are, thereby, combined. Advantageously, significant capacitance density gains can be achieved without additional processing steps.

Owner:BELL SEMICON LLC

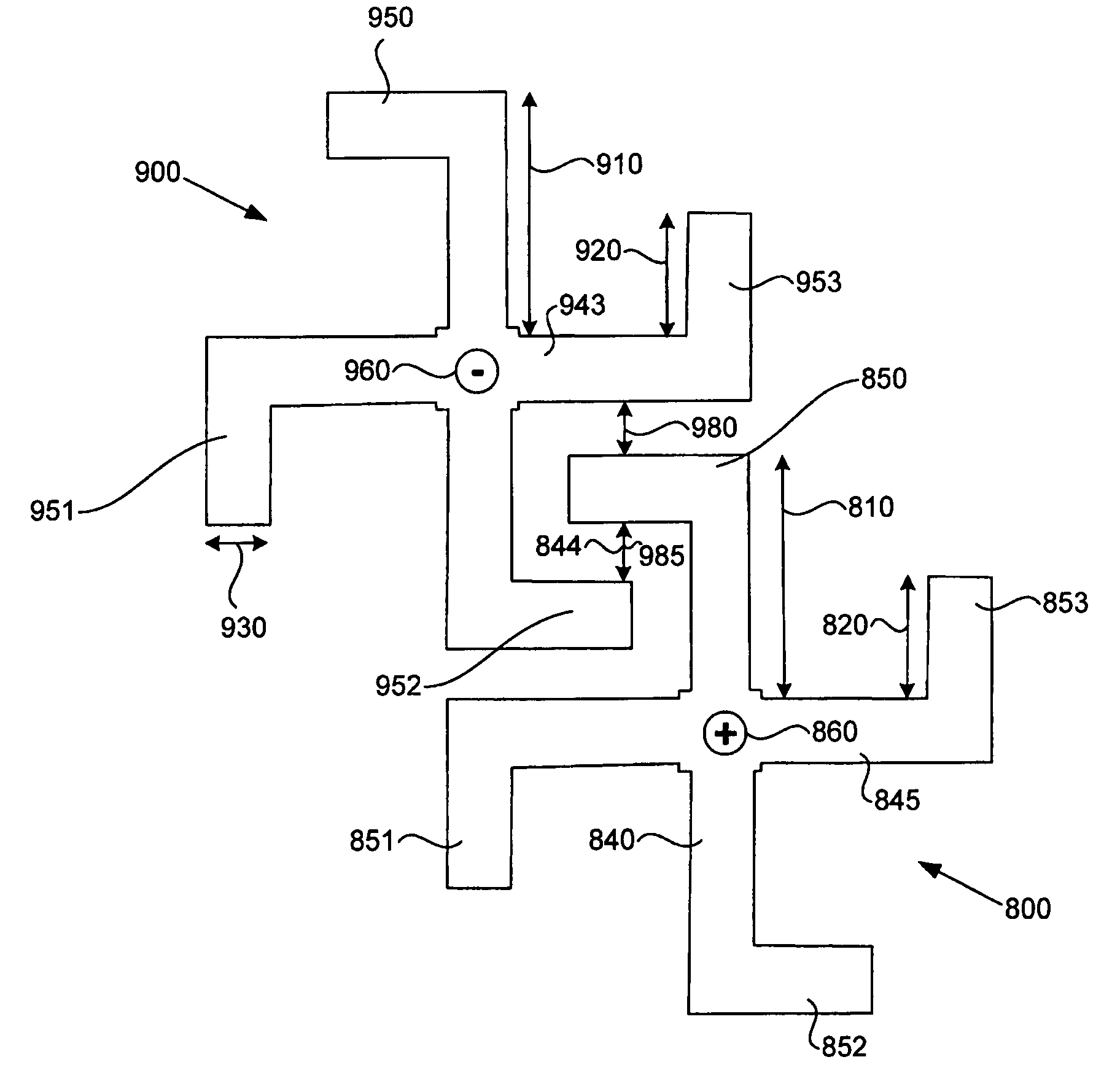

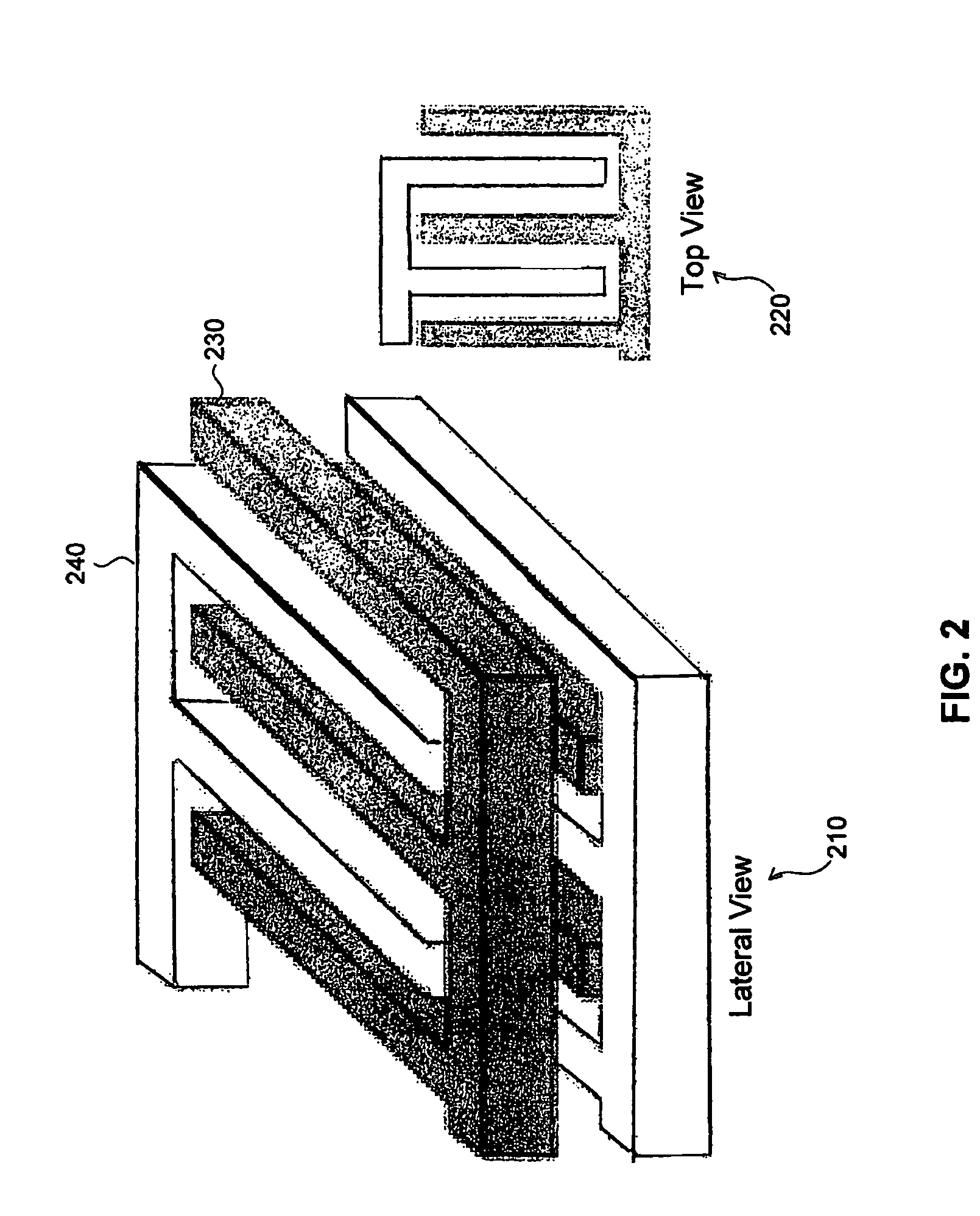

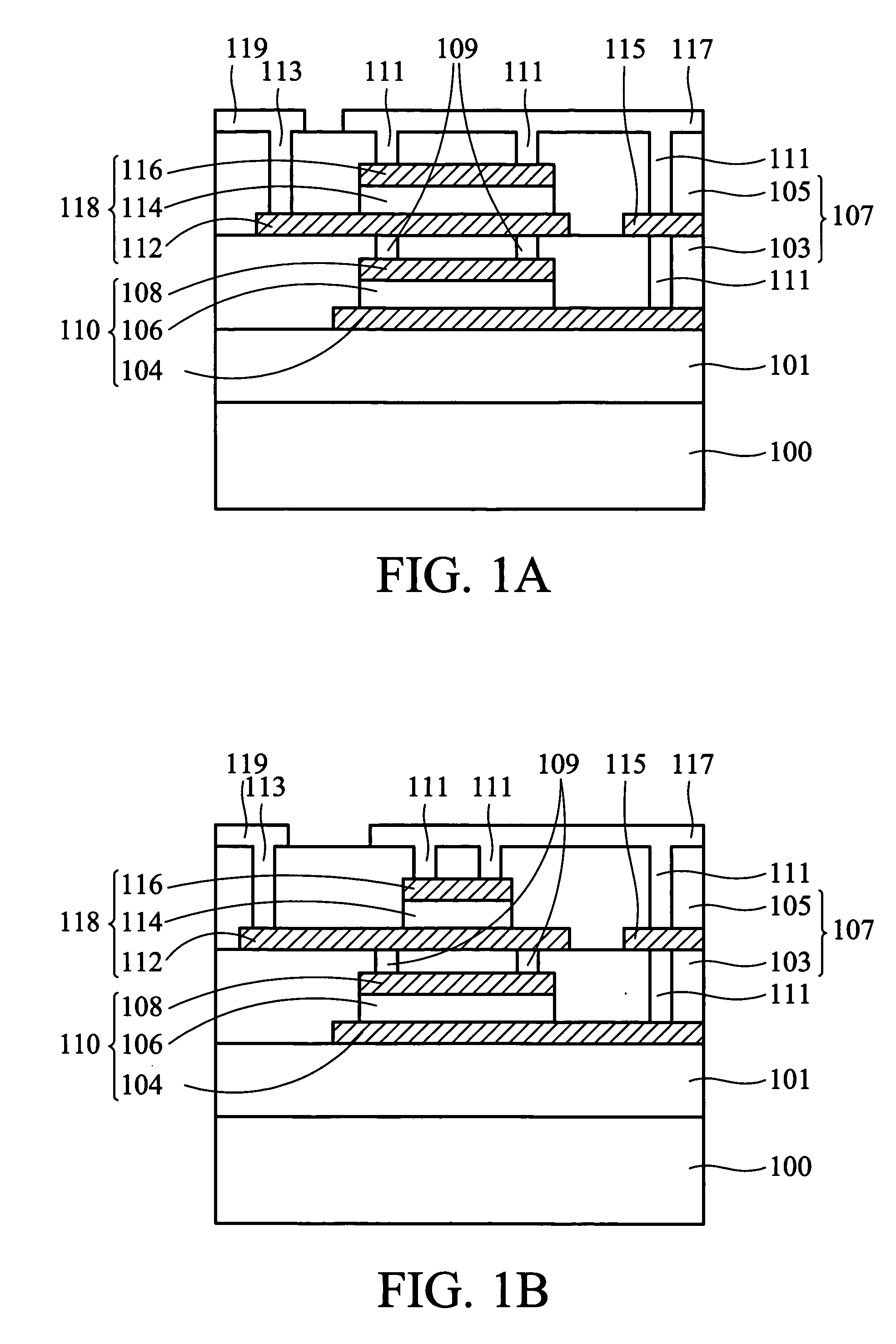

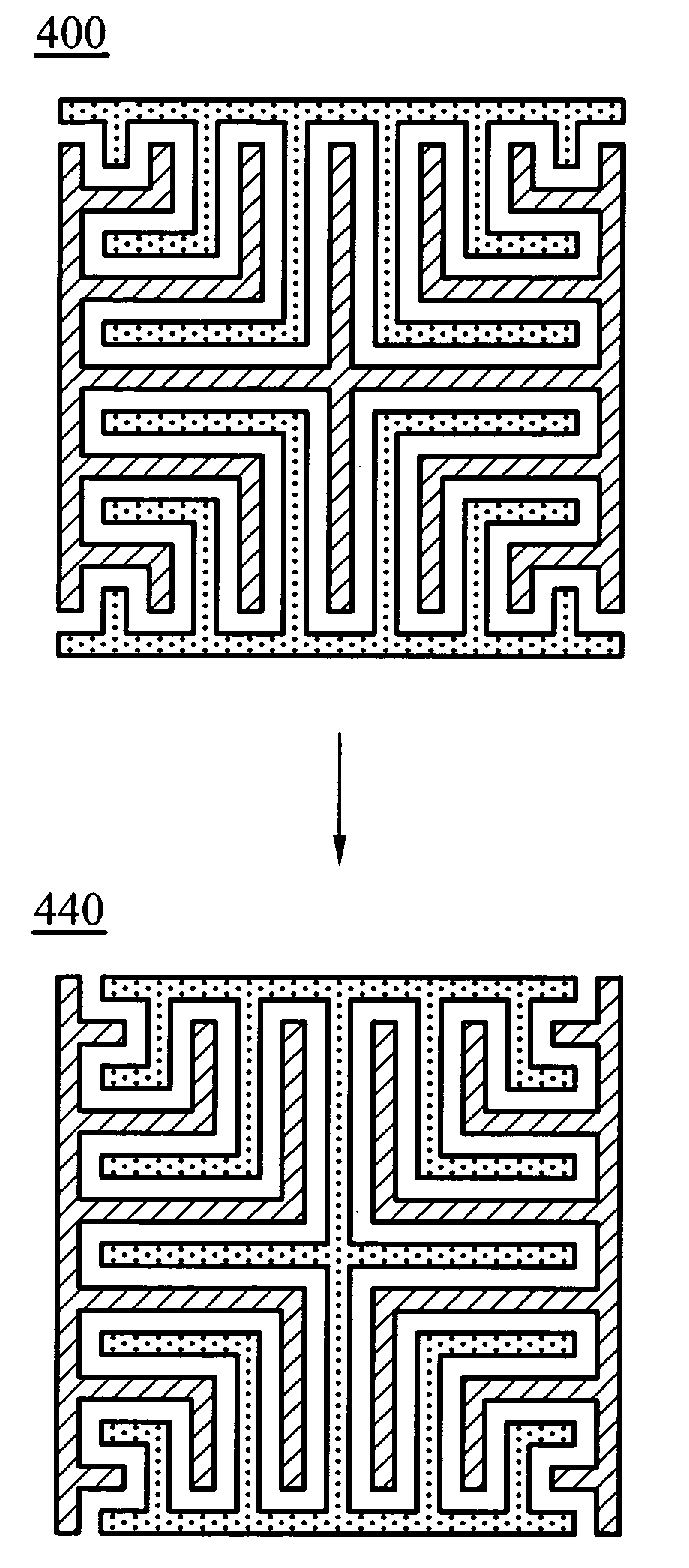

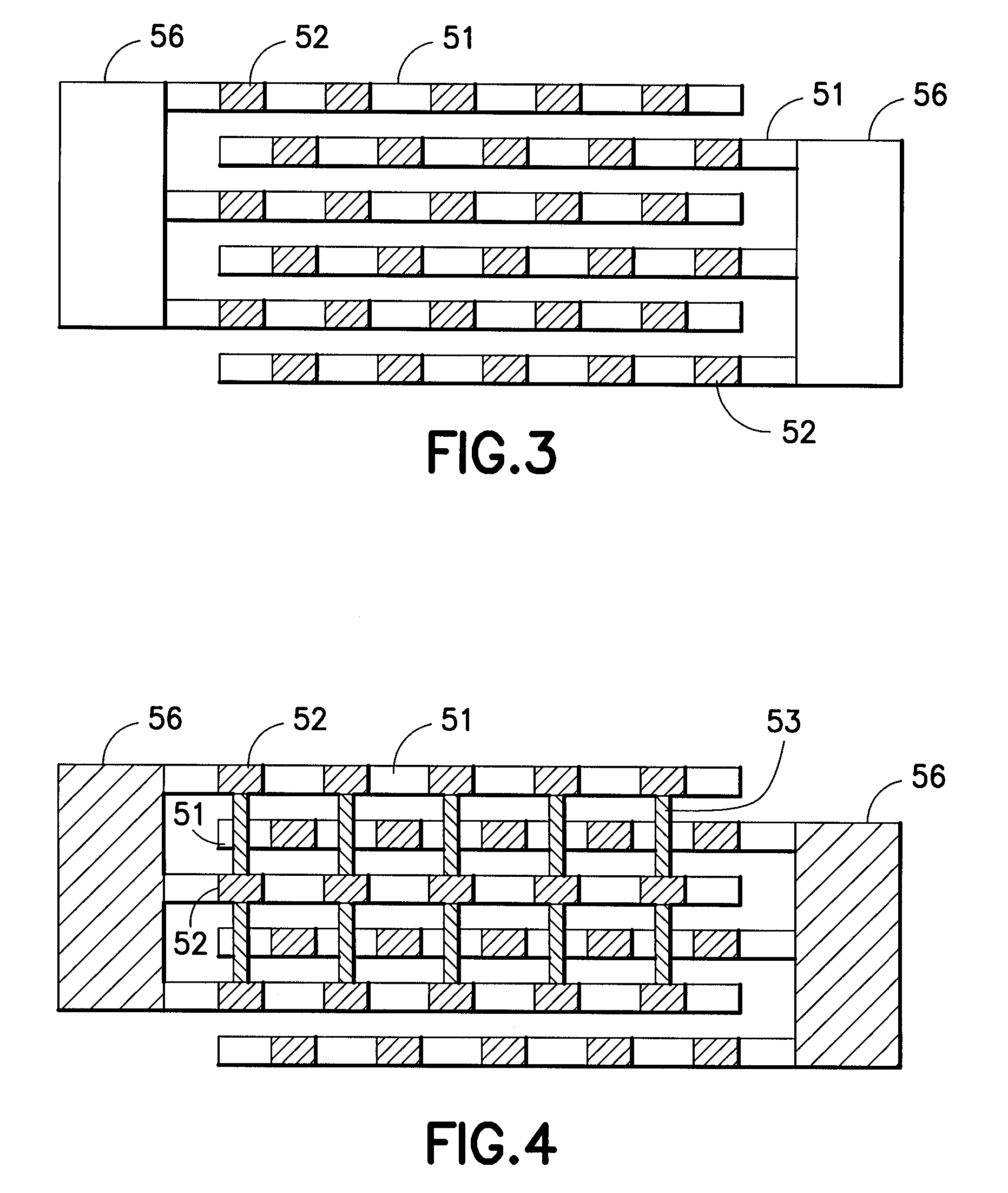

High density metal-to-metal maze capacitor with optimized capacitance matching

InactiveUS7009832B1Increase capacitance densityImproves capacitance capacitance matchingTransistorMultiple fixed capacitorsCapacitanceHigh density

A capacitor including a first and second component capacitor structure disposed on a substrate. A component capacitor structure includes an upright arm, a transverse arm, and a via. The upright arm has a top end and a bottom end that extend at substantially right angles to a central axis of the upright arm. The transverse arm has a left and right end that extend at substantially right angles to a central axis of the transverse arm. The upright arm and the transverse arm intersect to form a cross-like pattern and the top, bottom, left and right ends all extend in the same rotary direction. The via is electrically coupled to an area of intersection of the upright and transverse arms.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

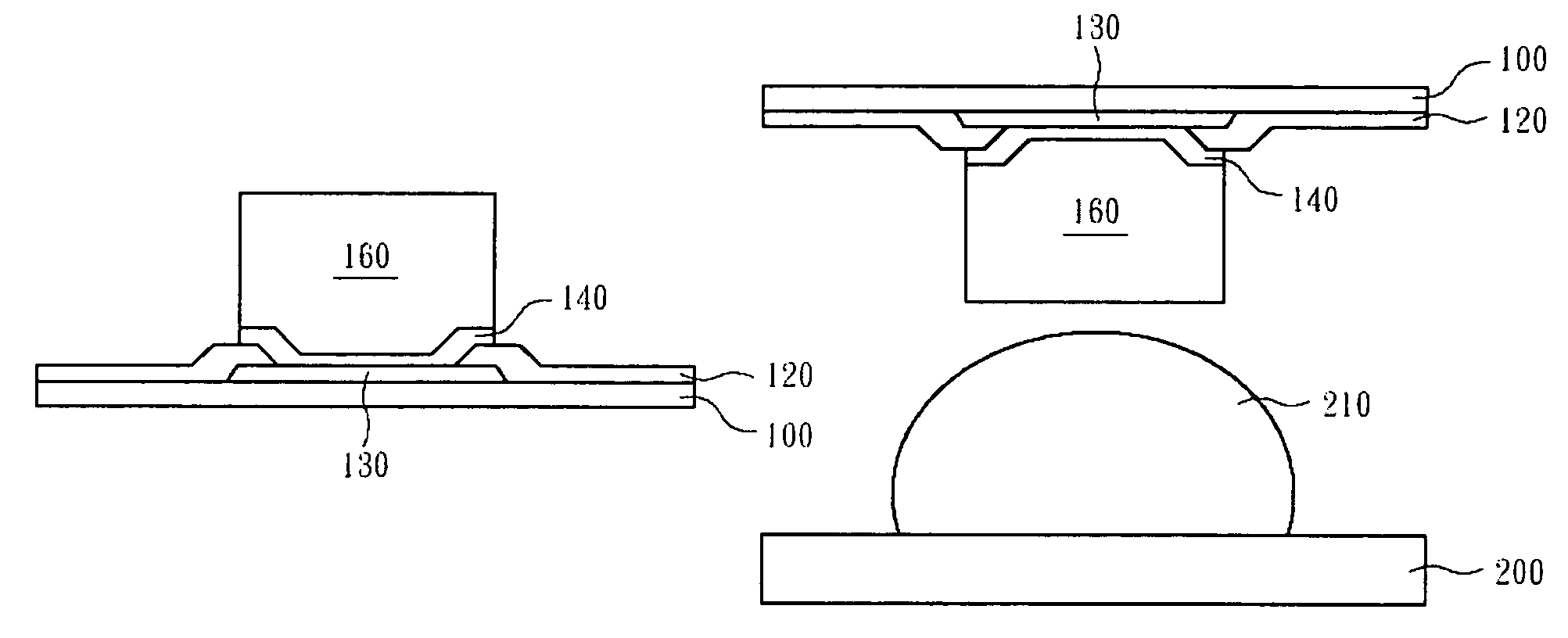

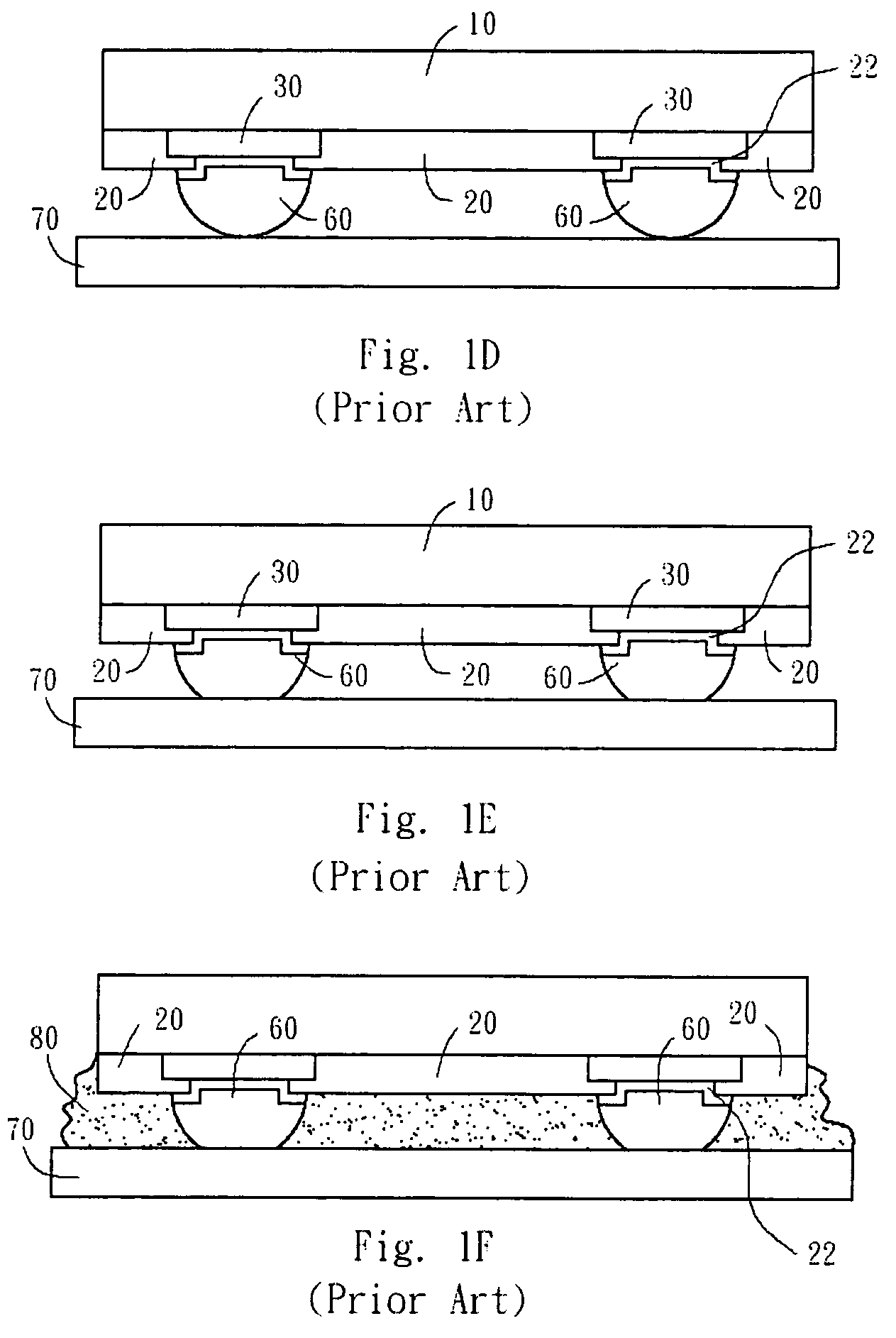

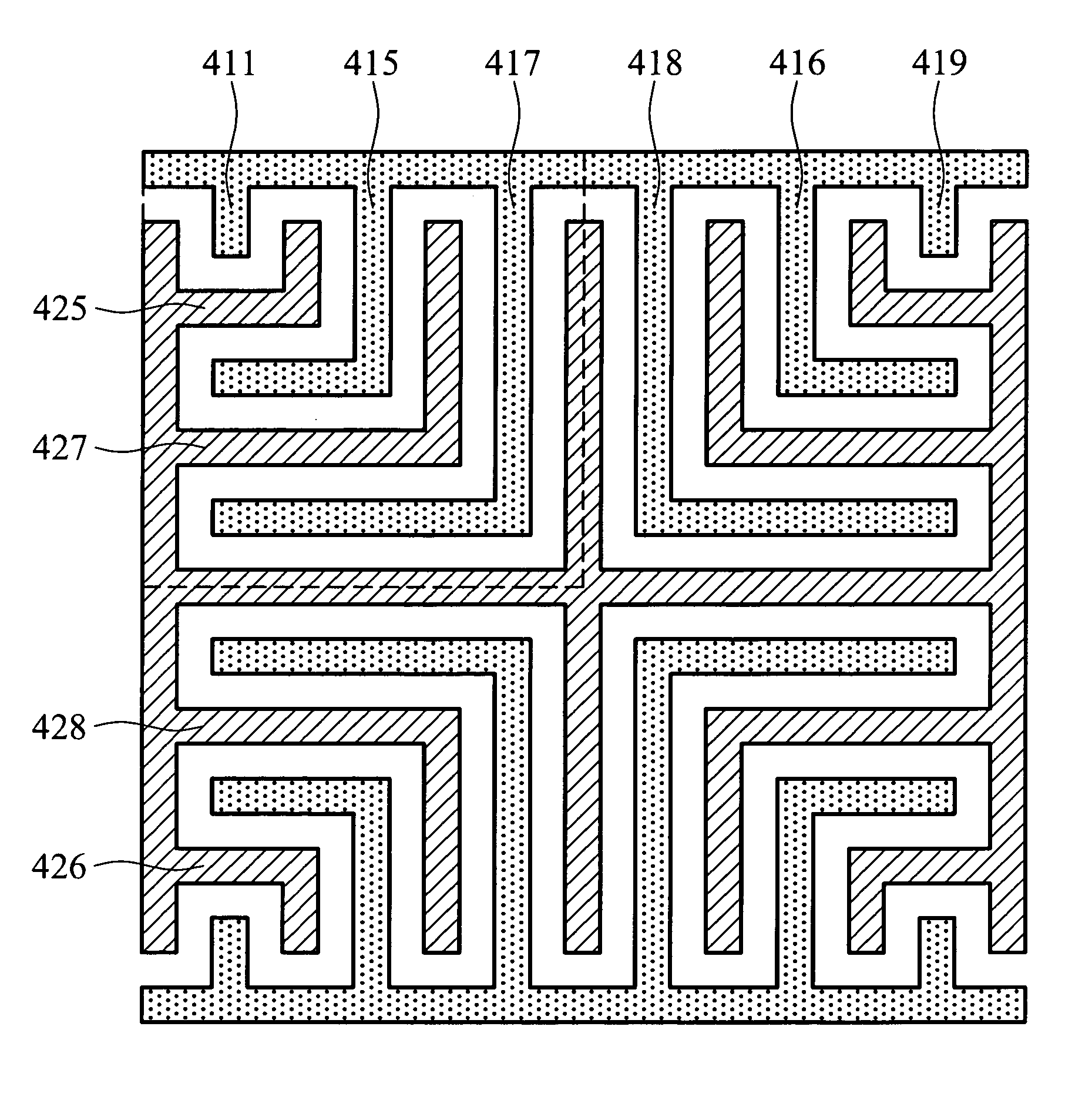

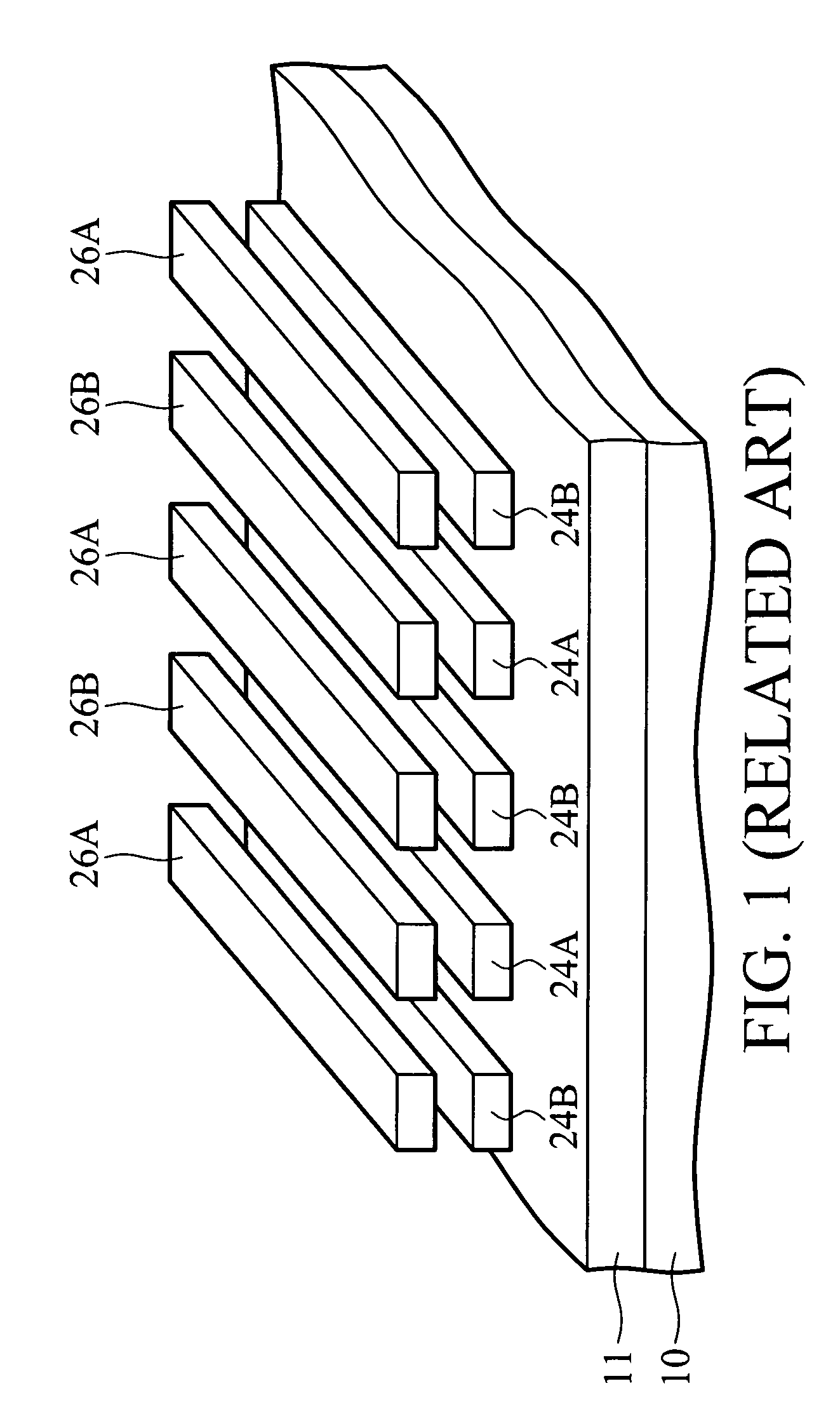

Flip-chip packaging process using copper pillar as bump structure

ActiveUS7476564B2Improve controllabilityPrevent oxidationFinal product manufactureSemiconductor/solid-state device detailsPrismCopper

A flip-chip packaging process is disclosed. The present invention is featured in forming a copper pillar on a wafer, forming a solder on a substrate; and enabling the solder to substantially cover the entire externally-exposed surface of the copper pillar, thereby connecting the copper pillar to the substrate. The copper pillar of the present invention can be such as a prism or a cylinder.

Owner:ADVANCED SEMICON ENG INC

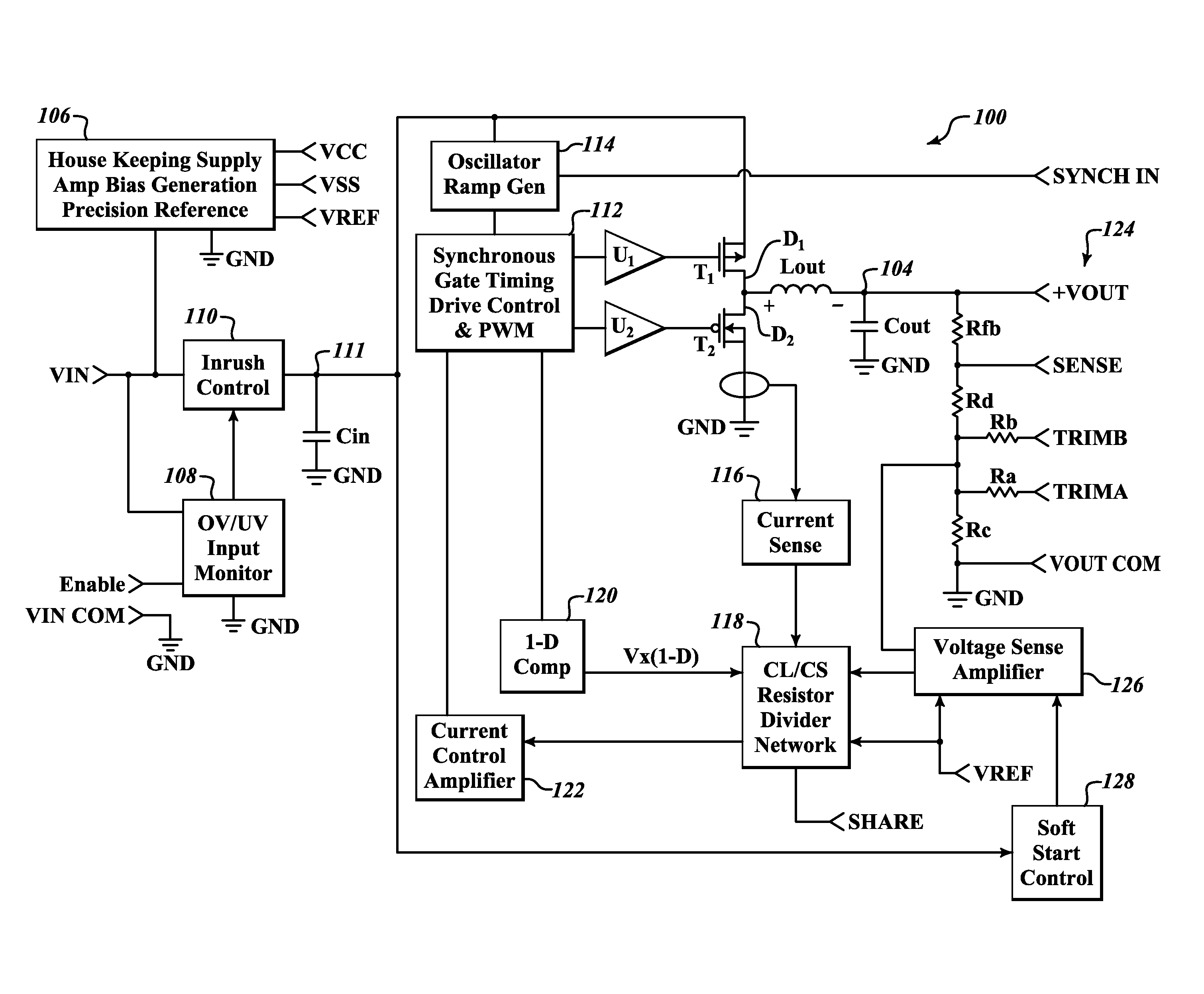

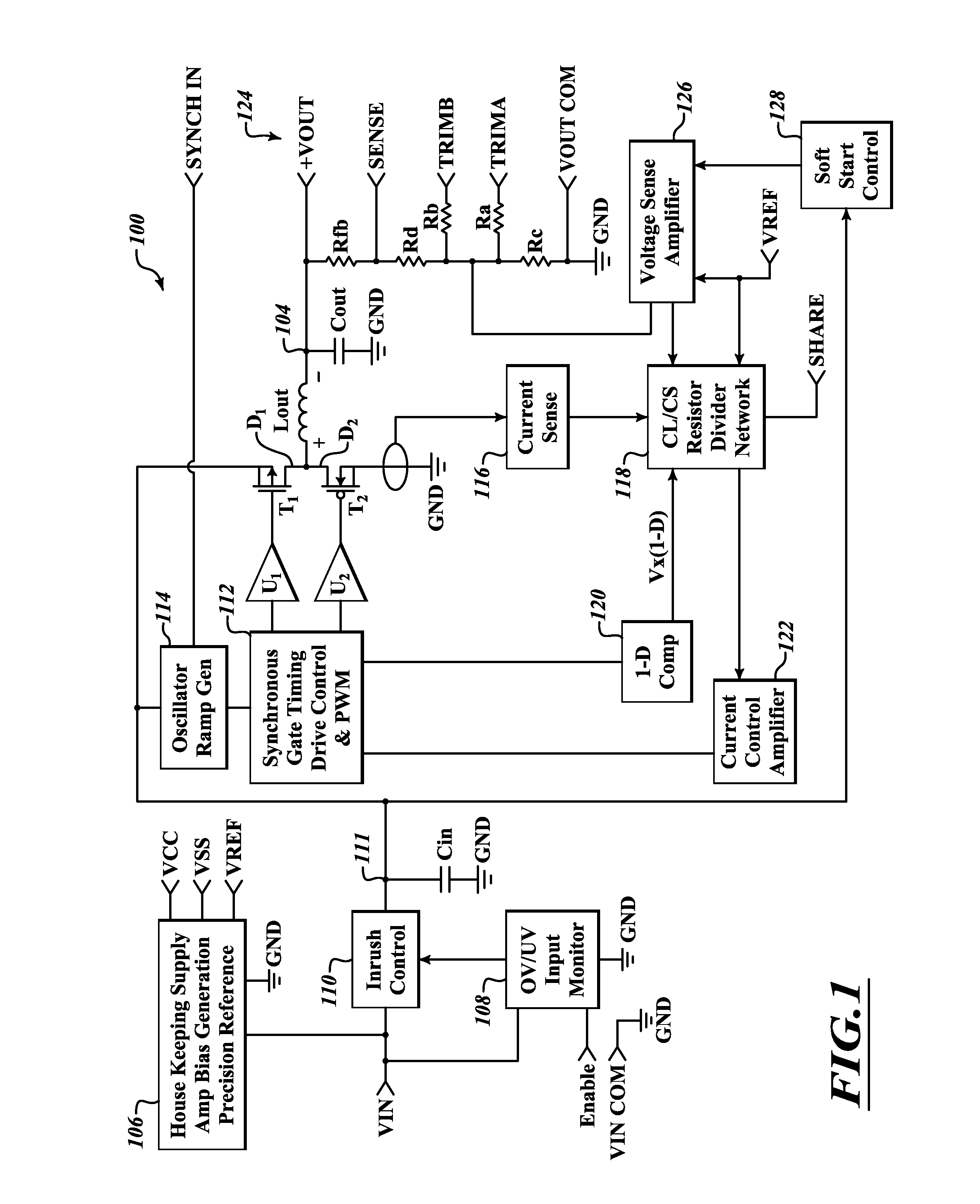

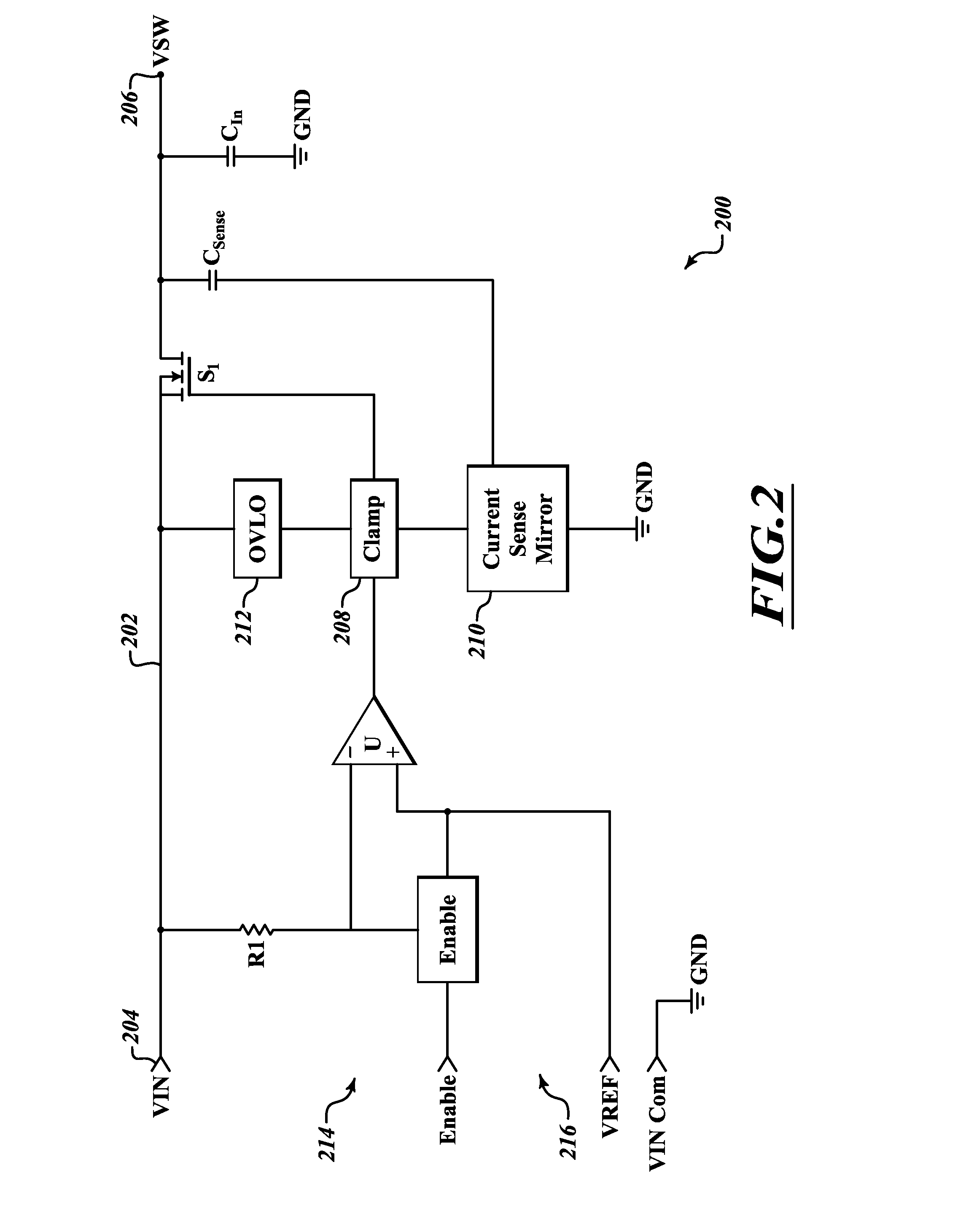

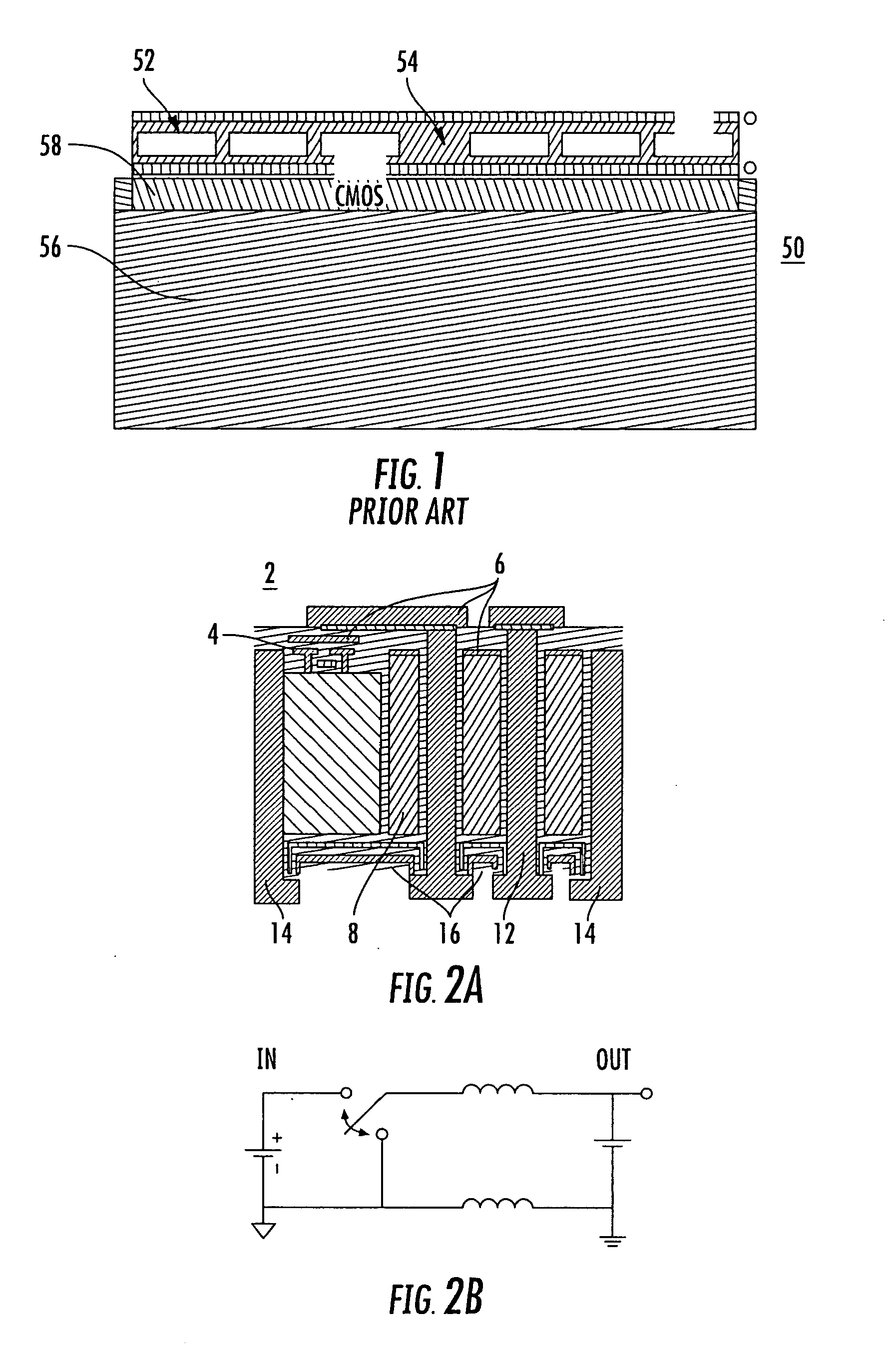

Input control apparatus and method with inrush current, under and over voltage handling

ActiveUS20130021702A1Improve reliabilityIncrease capacitance densityDc-dc conversionEmergency protective arrangements for limiting excess voltage/currentInput controlEngineering

Control circuitry handles inrush current, and may provide under voltage and / or over voltage monitoring and handling, as well as remote enable handling. The circuitry may advantageously employ a sense capacitor in parallel with an input capacitor (e.g., bulk input filter capacitor), and a current mirror to produce a signal proportional to input current. A clamp circuit may control a series pass device to regulate current in response to the proportional signal, or to interrupt current flow in response to an under voltage or over voltage condition or receipt of a signal indicative of a disable state. An enable signal may be summed into a comparator that handles under voltage condition determination.

Owner:CRANE ELECTRONICS INC

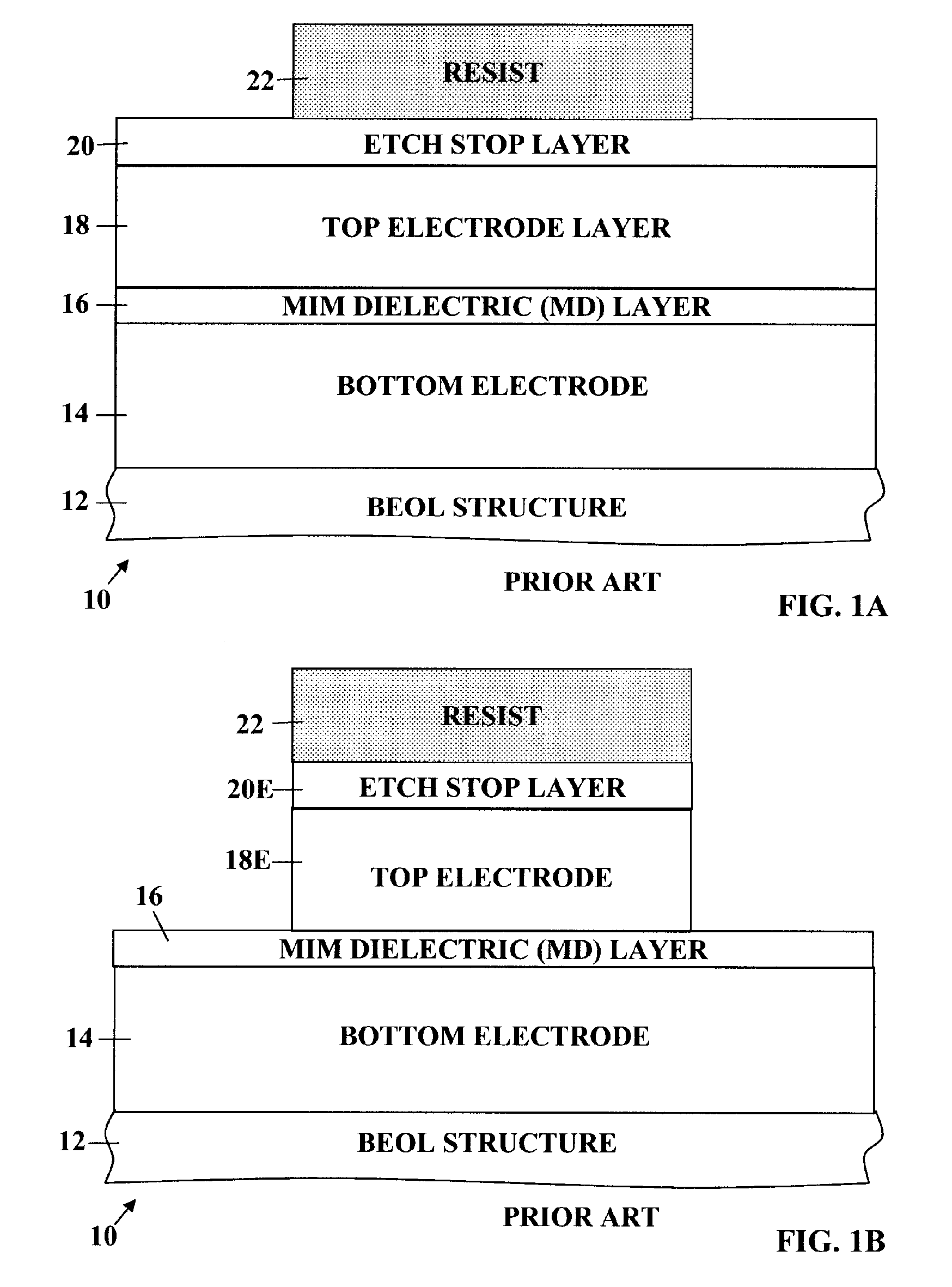

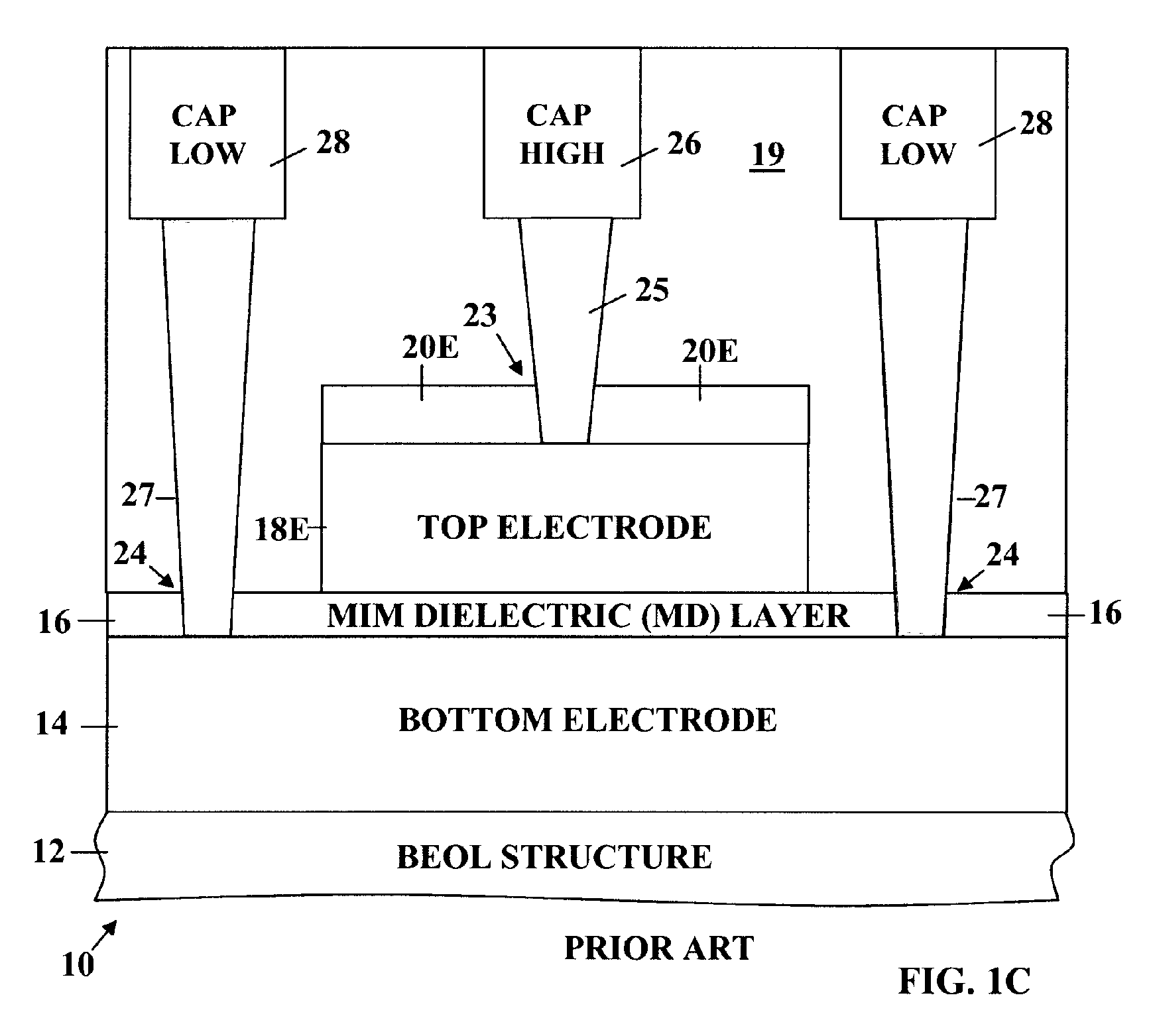

Metal-insulator-metal capacitor structure having low voltage dependence

InactiveUS20070152295A1Extended working voltage rangeIncrease capacitance densityTransistorSemiconductor/solid-state device detailsCapacitanceLow voltage

A semiconductor capacitor device. A dielectric layer is on a substrate. A stack capacitor structure is disposed in the dielectric layer and comprises first and overlying second MIM capacitors electrically connected in parallel. The first and second MIM capacitors have individual upper and lower electrode plates and different compositions of capacitor dielectric layers.

Owner:TAIWAN SEMICON MFG CO LTD

Interdigitized capacitor

ActiveUS20070126078A1Series parasitic resistanceQuality improvementTransistorSemiconductor/solid-state device detailsCapacitorAtomic physics

An interdigitized capacitor comprising first and second electrodes. The first electrode comprises two combs symmetrical to a first mirror plane. The fingers of the combs extend toward the first mirror plane. The second electrode comprises two combs and a linear plate. The combs are symmetrical to a second mirror plane and the fingers thereof extend toward the second mirror plane. The linear plate is located at the second mirror plane and connected to one finger of the combs of the second electrode. The first and second mirror planes are orthogonal. The fingers of the combs of the first and second electrodes are interdigitized.

Owner:NUVOTON

Interdigitized capacitor

ActiveUS7485914B2Series parasitic resistanceQuality improvementTransistorSemiconductor/solid-state device detailsCapacitorAtomic physics

An interdigitized capacitor comprising first and second electrodes. The first electrode comprises two combs symmetrical to a first mirror plane. The fingers of the combs extend toward the first mirror plane. The second electrode comprises two combs and a linear plate. The combs are symmetrical to a second mirror plane and the fingers thereof extend toward the second mirror plane. The linear plate is located at the second mirror plane and connected to one finger of the combs of the second electrode. The first and second mirror planes are orthogonal. The fingers of the combs of the first and second electrodes are interdigitized.

Owner:NUVOTON

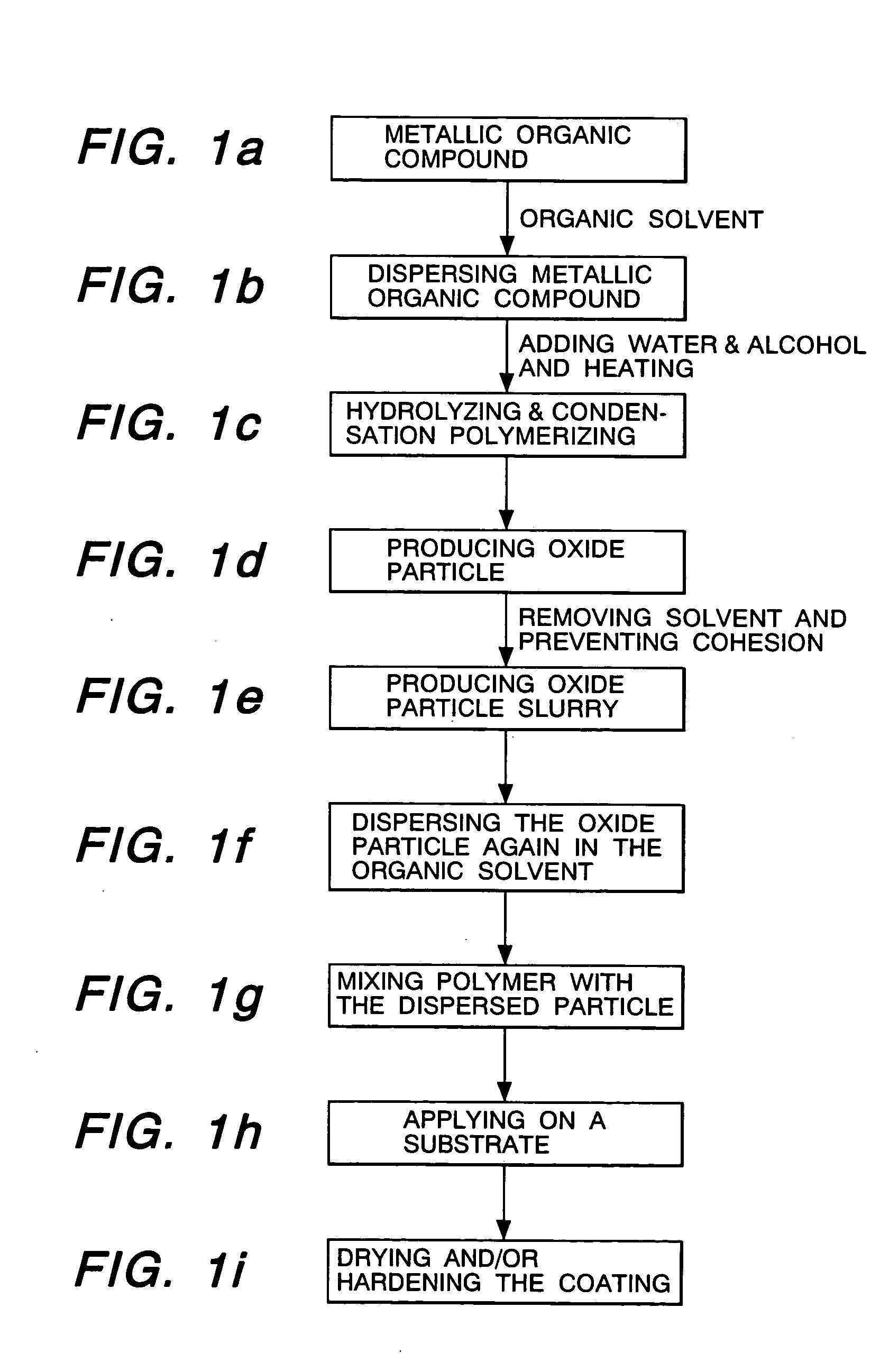

Organic/inorganic oxide mixed film, passive device contained electronic substrate using the film, and method of manufacturing organic/inorganic oxide mixed film

InactiveUS20050029515A1High insulation resistanceLarge capacityThin/thick film capacitorFixed capacitor dielectricCapacitanceCapacitor

An organic / inorganic oxide mixture has high capacitance density so as to realize a capacitor material that can be self-contained in a substrate. The mixture film made of inorganic oxide particle has a mean particle size of less than 90 nm dispersed in organic polymer, of which relative dielectric constant is more than 10 and thickness is less than 900 nm.

Owner:HITACHI LTD

Integration of a MIM capacitor over a metal gate or silicide with high-k dielectric materials

InactiveUS20070057343A1Eliminate needImprove linearityTransistorSolid-state devicesCapacitanceMetal-insulator-metal

A Metal Insulator-Metal (MIM) capacitor is formed on a semiconductor substrate with a base comprising a semiconductor substrate having a top surface and including regions formed in the surface selected from a Shallow Trench Isolation (STI) region and a doped well having exterior surfaces coplanar with the semiconductor substrate. An ancillary MIM capacitor plate is selected either a lower electrode formed on the STI region in the semiconductor substrate or a doped well formed in the top surface of the semiconductor substrate. A capacitor HiK dielectric layer is formed on or above the MIM capacitor lower plate. A second MIM capacitor plate is formed on the HiK dielectric layer above the MIM capacitor lower plate.

Owner:GLOBALFOUNDRIES INC

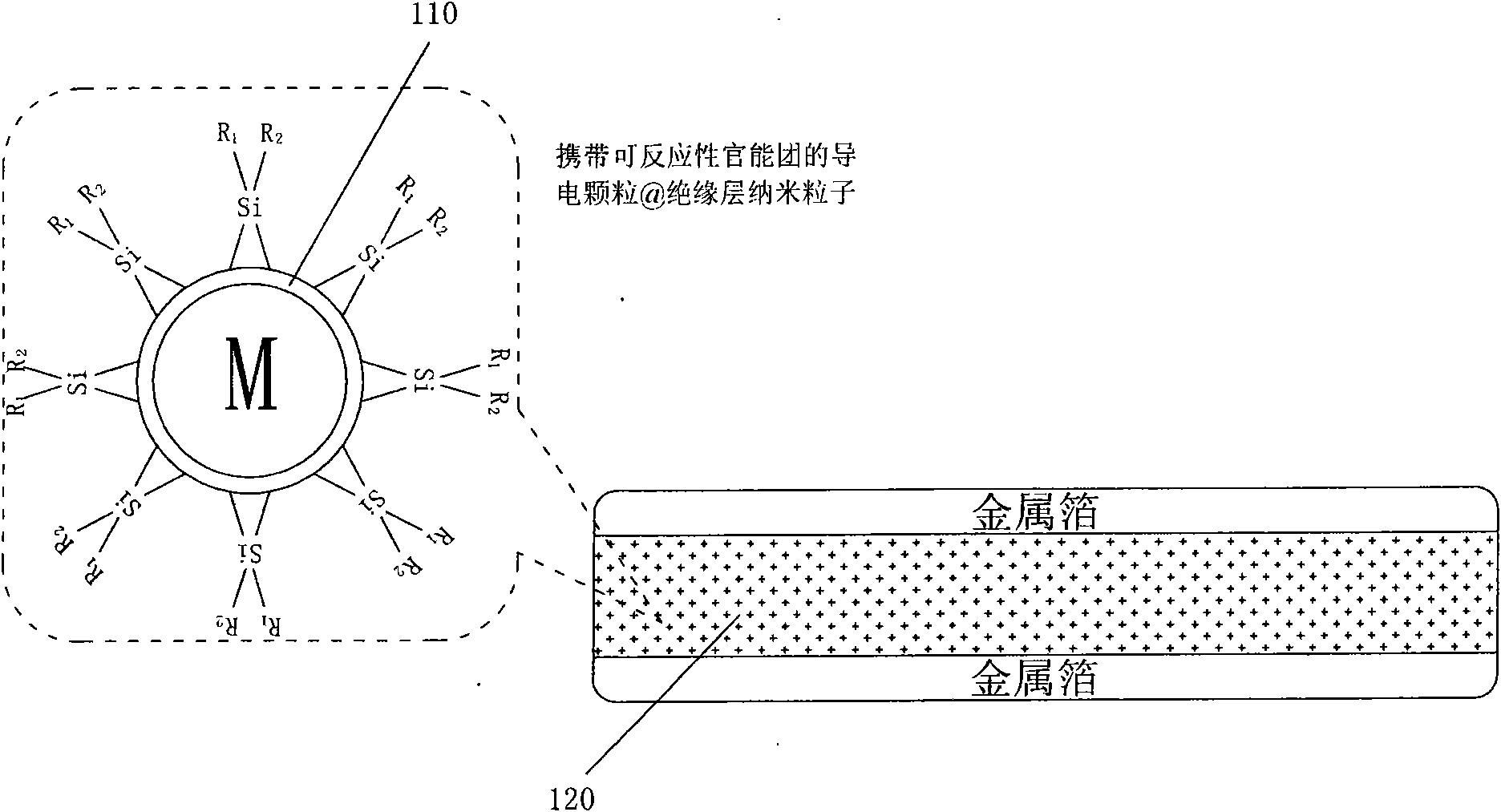

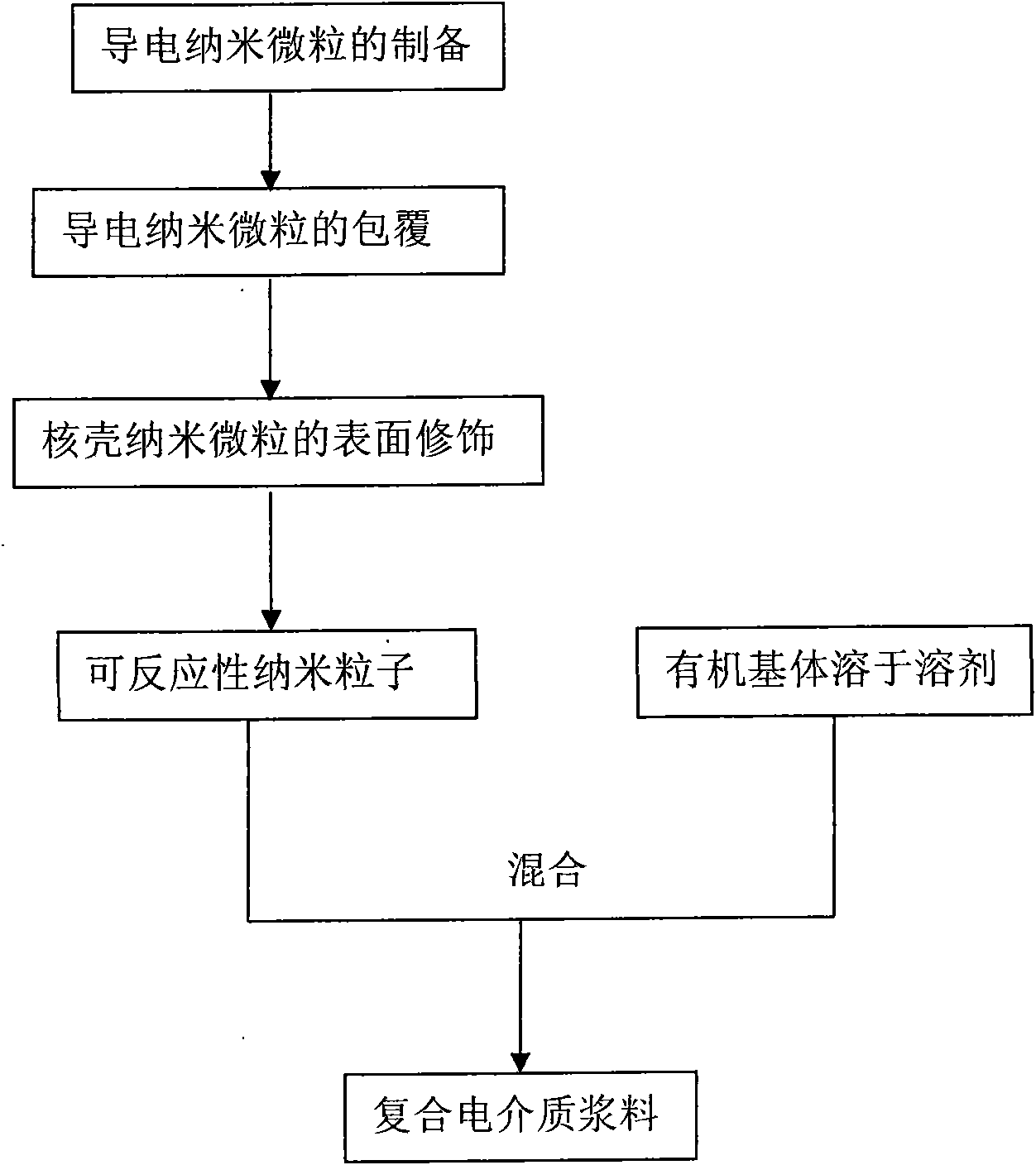

Polymer-matrix composite dielectric material and plate capacitor

ActiveCN101677033AIncrease capacitance densityHigh dielectric constantPlastic/resin/waxes insulatorsFixed capacitor electrodesElectronic componentCore shell

The invention discloses a plate capacitor and polymer-matrix composite dielectric material which can be filled with reactive nano particles, belonging to the technical field of the electronic materialand the electronic component. The reactive nano particles are conductive nano particles in core shell structures, the surface of each conductive nano particle is coated with a layer of insulating coating, and the surface of the insulating coating can carry reactive functional groups. The nano particles can be organically combined with polymer through the reactive functional groups and can be evenly dispersed in the matrix of the polymer. The polymer-matrix composite dielectric material which can be filled with the conductive nano particles can be used as the dielectric layer and flexible foilsheets can be used the upper electrode and the lower electrode of the plate capacitor.

Owner:SHENZHEN INST OF ADVANCED TECH

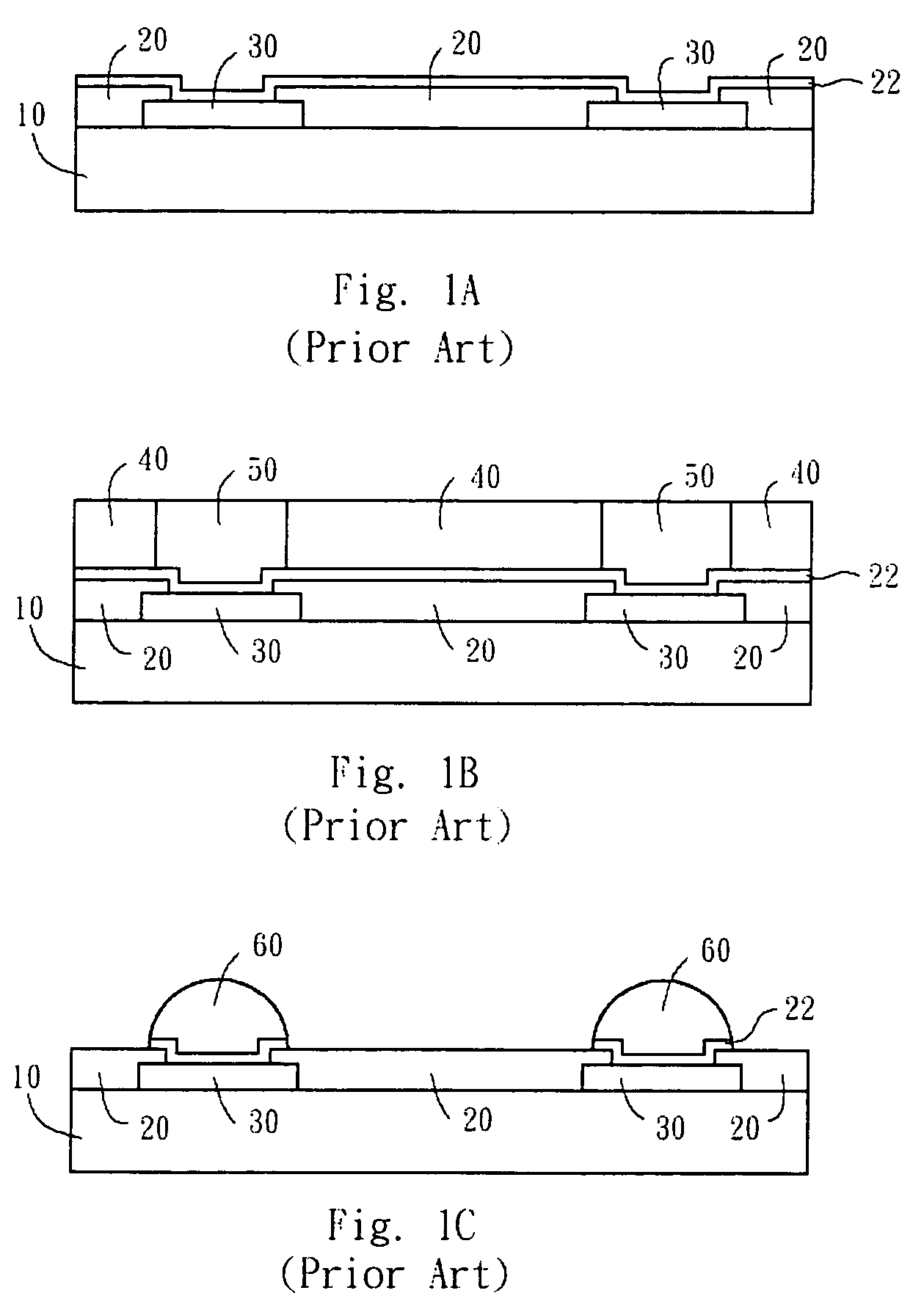

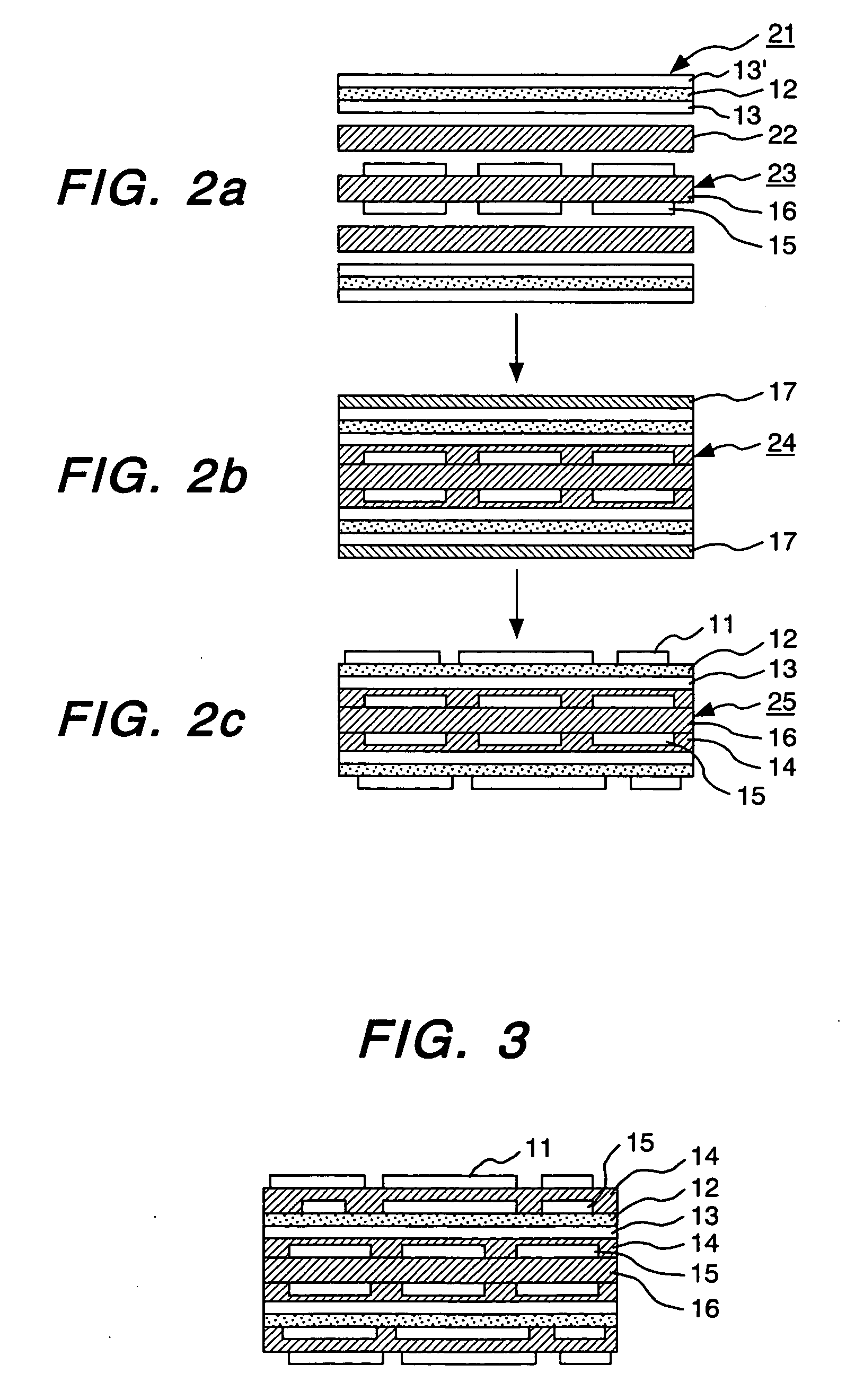

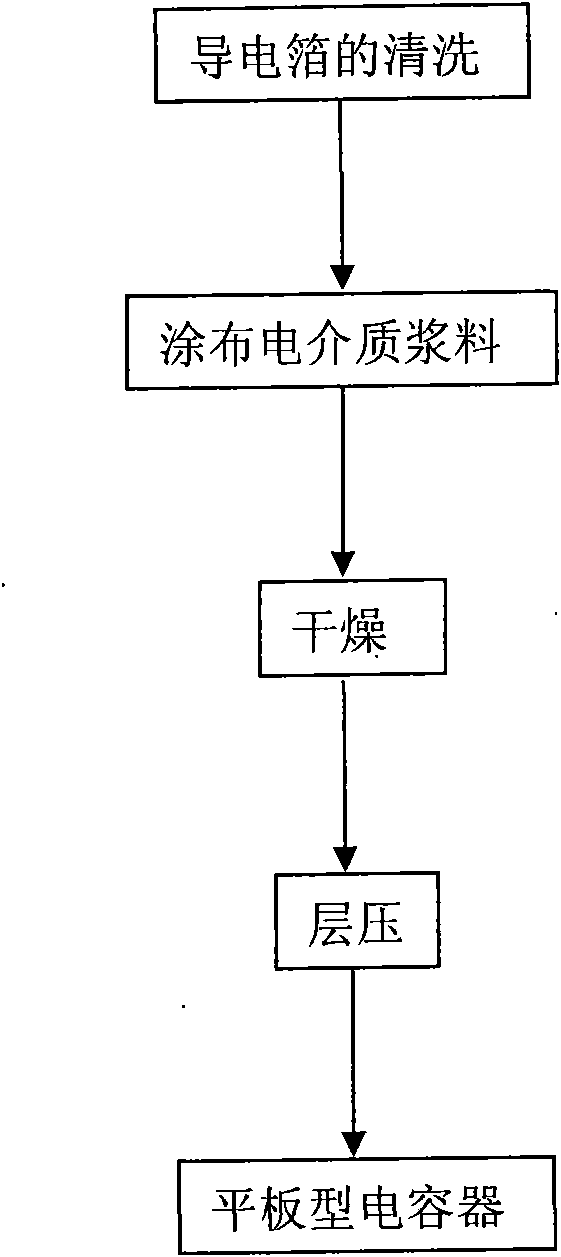

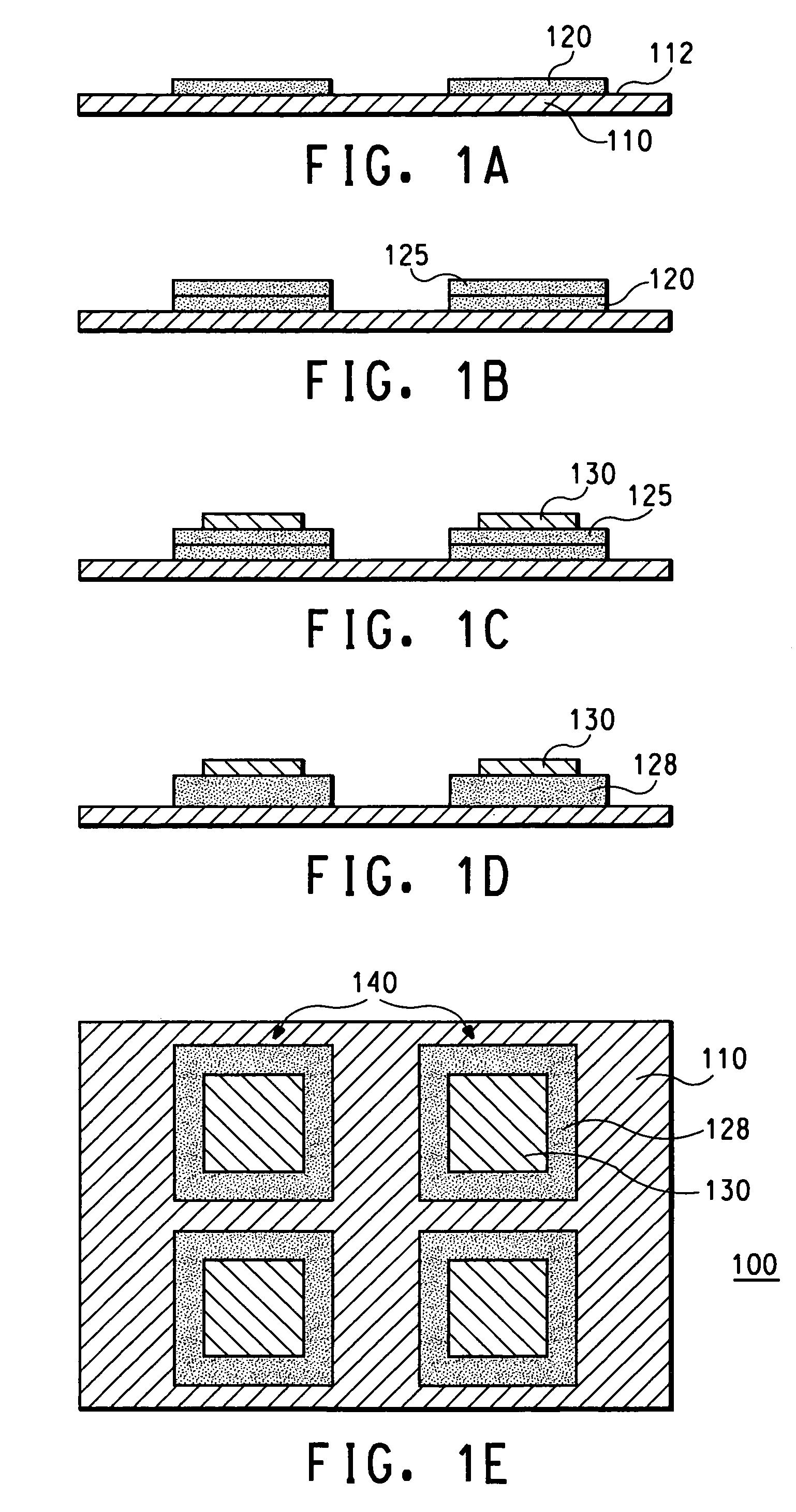

Co-fired ceramic capacitor and method for forming ceramic capacitors for use in printed wiring boards

InactiveUS7072167B2Increase capacitance densityAnti-noise capacitorsFixed capacitor electrodesDielectricCeramic capacitor

A capacitor structure is fabricated by forming a pattern of first dielectrics over a foil, forming first electrodes over the first dielectrics, and co-firing the first dielectrics and the first electrodes. Co-firing of the dielectrics and the electrodes alleviates cracking caused by differences in thermal coefficient of expansion (TCE) between the electrodes and the dielectrics. Co-firing also ensures a strong bond between the dielectrics and the electrodes. In addition, co-firing allows multi-layer capacitor structures to be constructed, and allows the capacitor electrodes to be formed from copper.

Owner:CHEMTRON RES

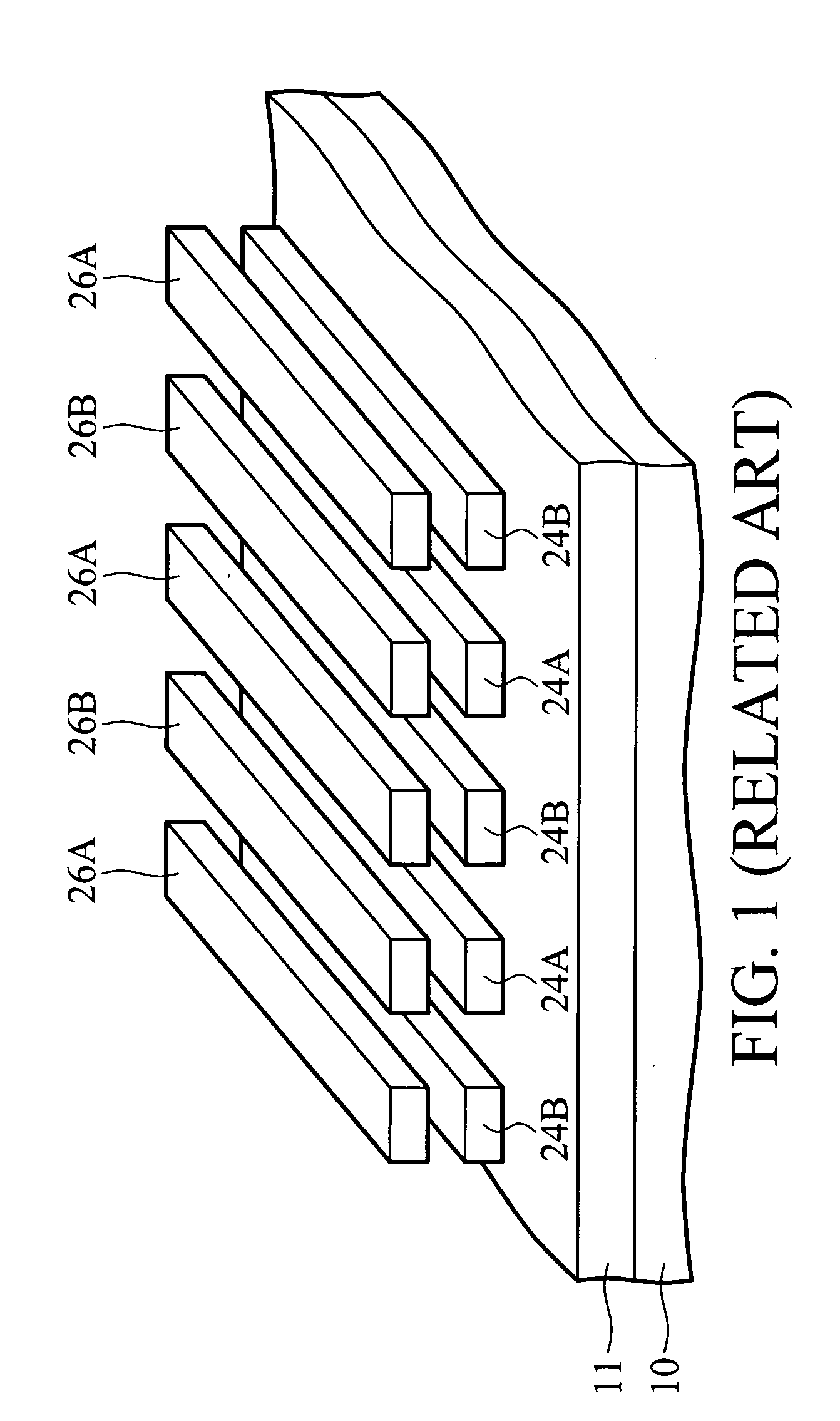

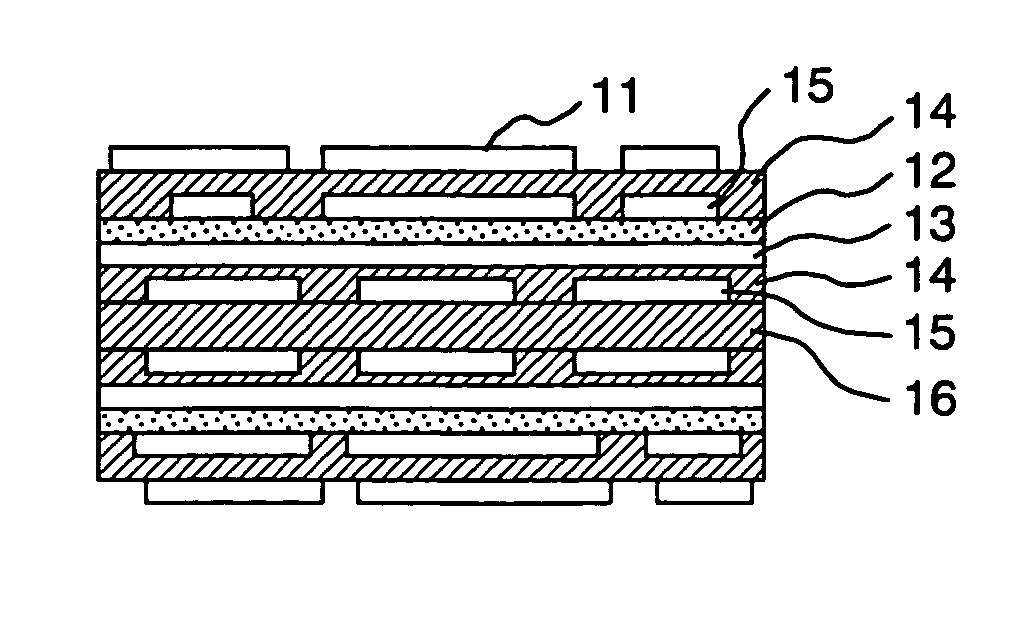

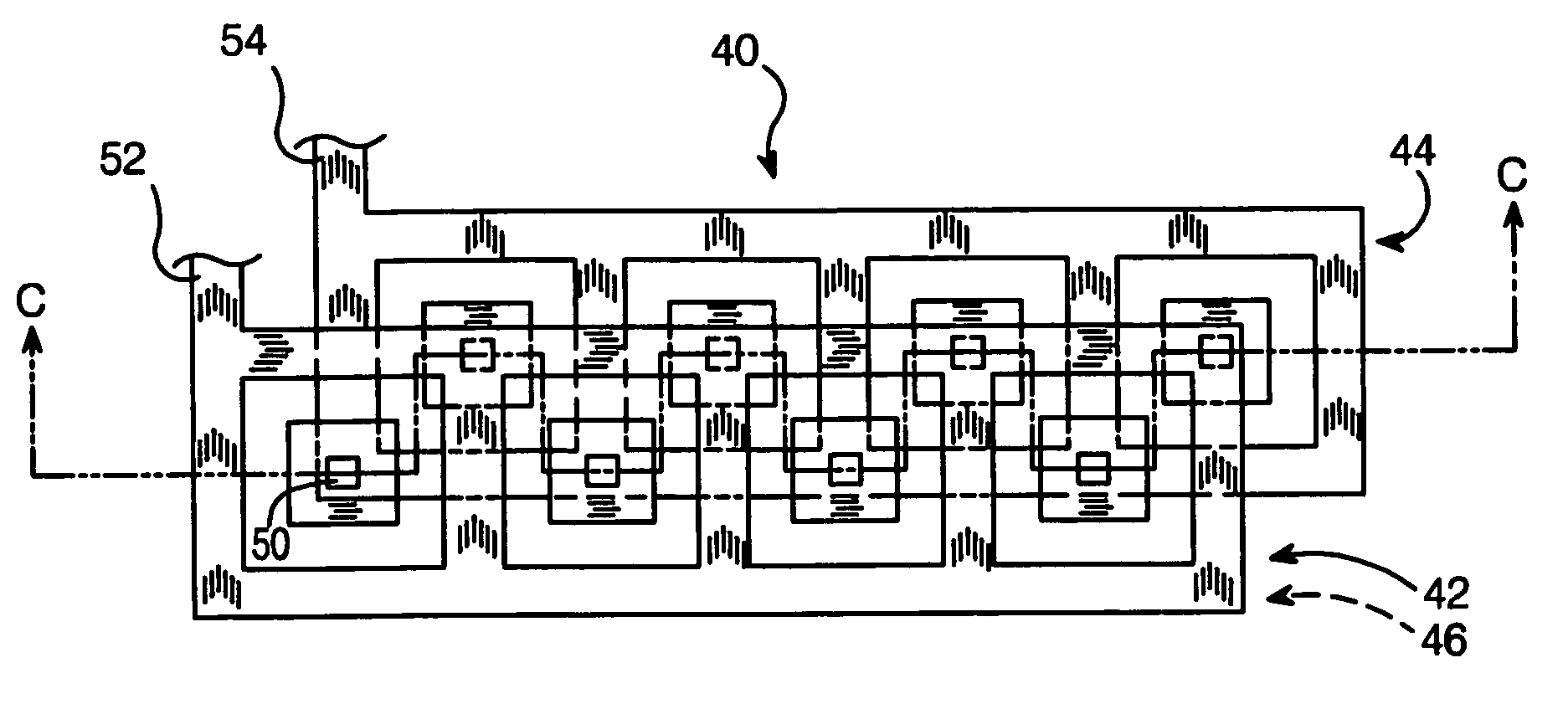

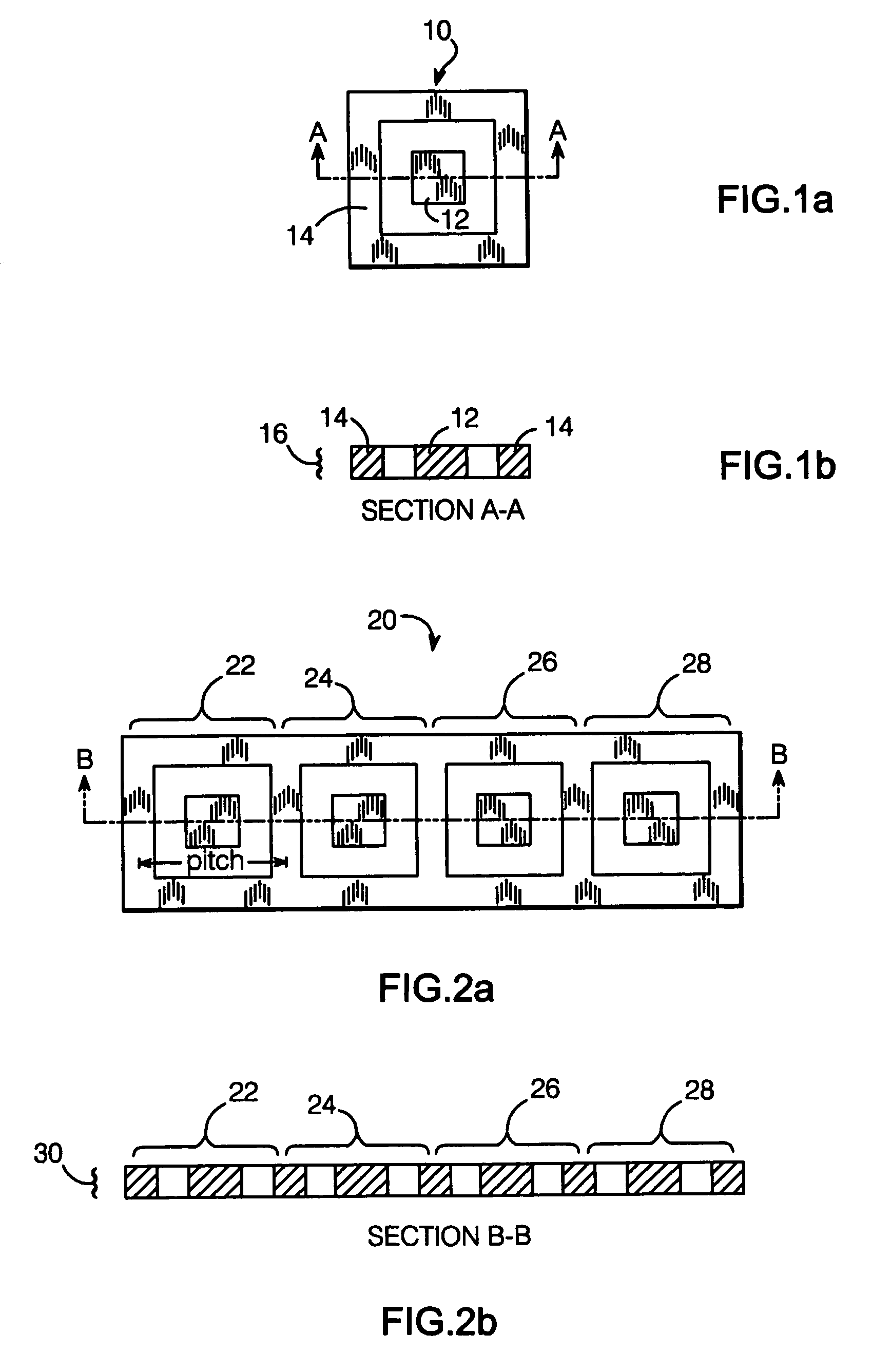

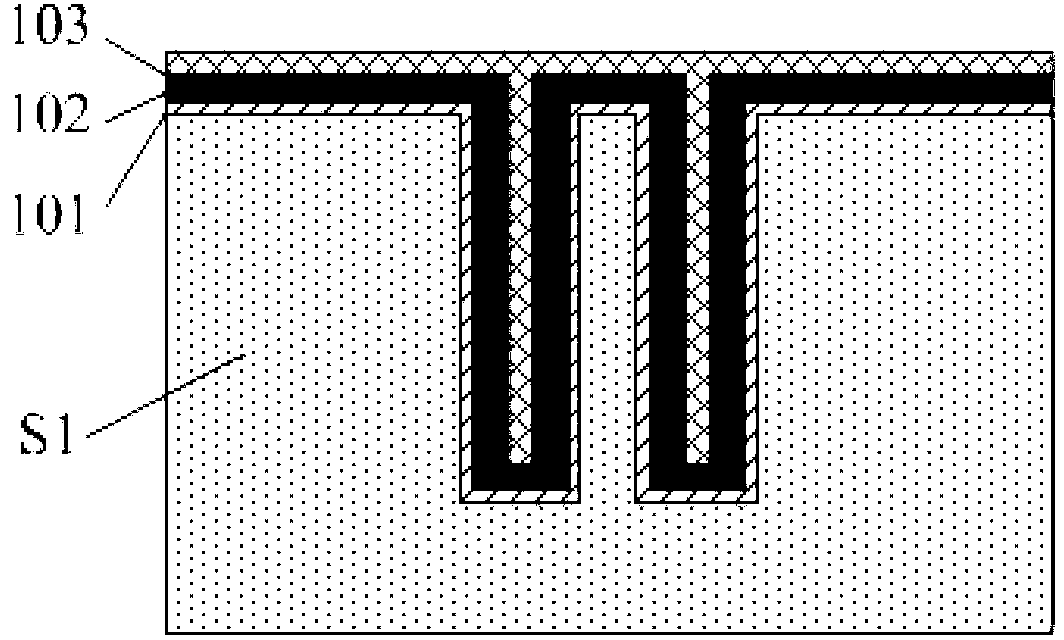

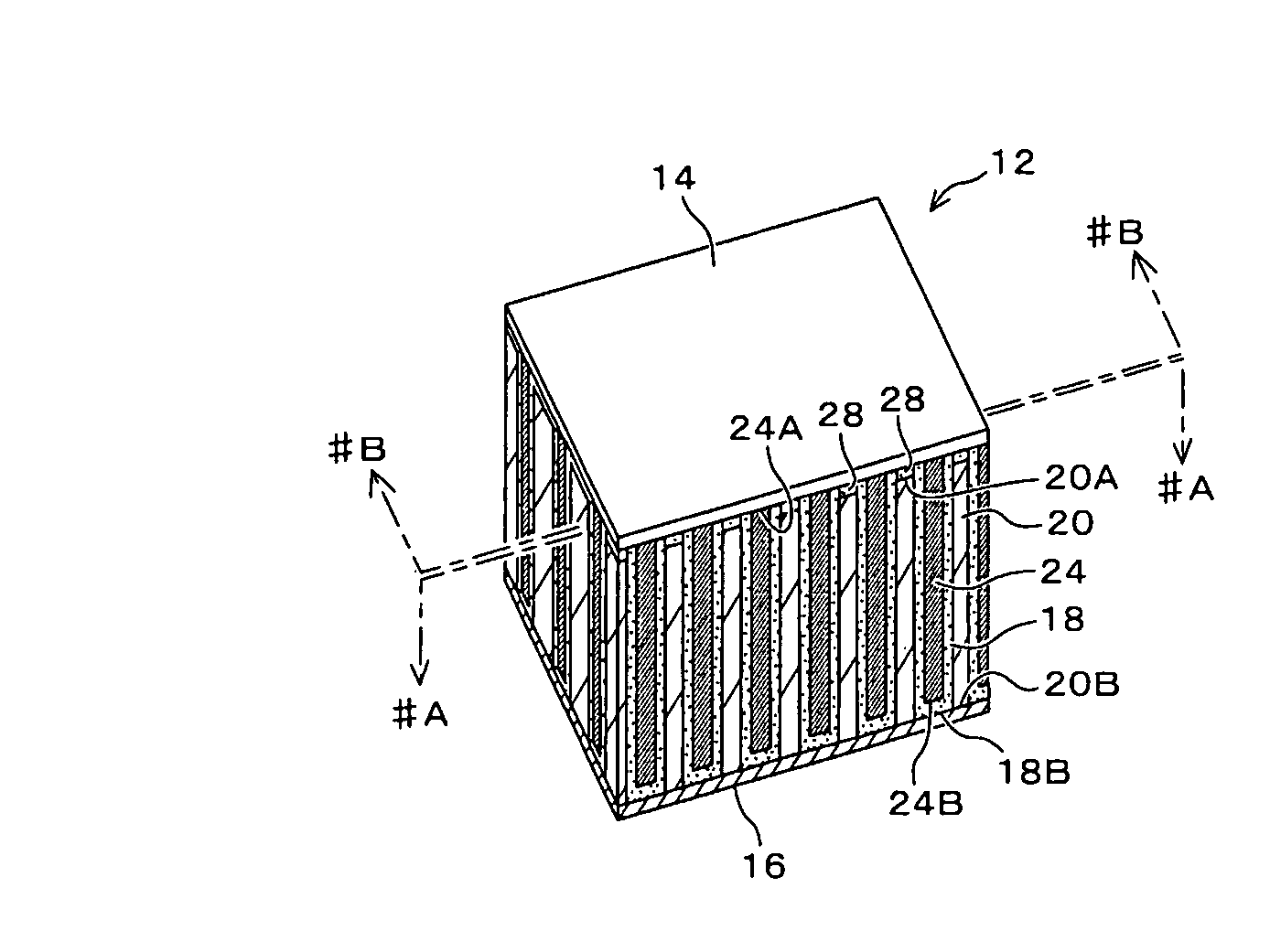

Three-dimensional integrated capacitance structure

ActiveUS7161228B1Increase capacitance densitySemiconductor/solid-state device detailsSolid-state devicesCapacitanceElectrical conductor

A three-dimensional integrated capacitance structure comprises at least two arrays of “unit cells” on respective layers of an IC, with each unit cell comprising a center conductor and a conducting ring which surrounds the center conductor. Each array comprises a plurality of unit cells, tiled on a given IC layer at a predetermined pitch. The arrays are arranged vertically such that adjacent vertical arrays are offset in the x and y dimensions by a predetermined fraction—preferably ½—of the unit cells' pitch. The structure includes vias arranged to interconnect the arrays such that each center conductor is connected to a conducting ring of the array immediately above and / or below the center conductor, and such that each conducting ring is connected to a center conductor of the array immediately above and / or below the conducting ring.

Owner:ANALOG DEVICES INC

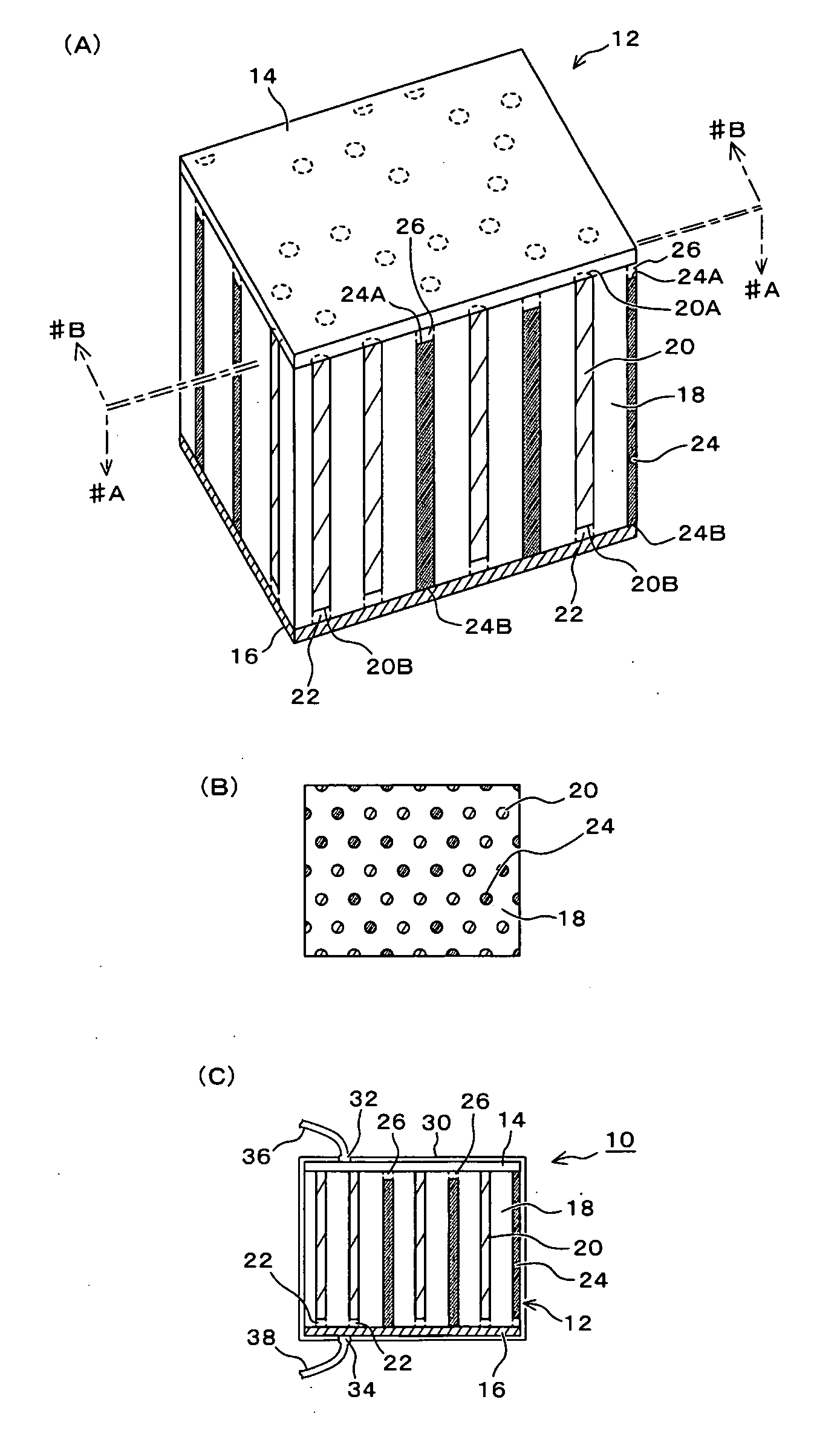

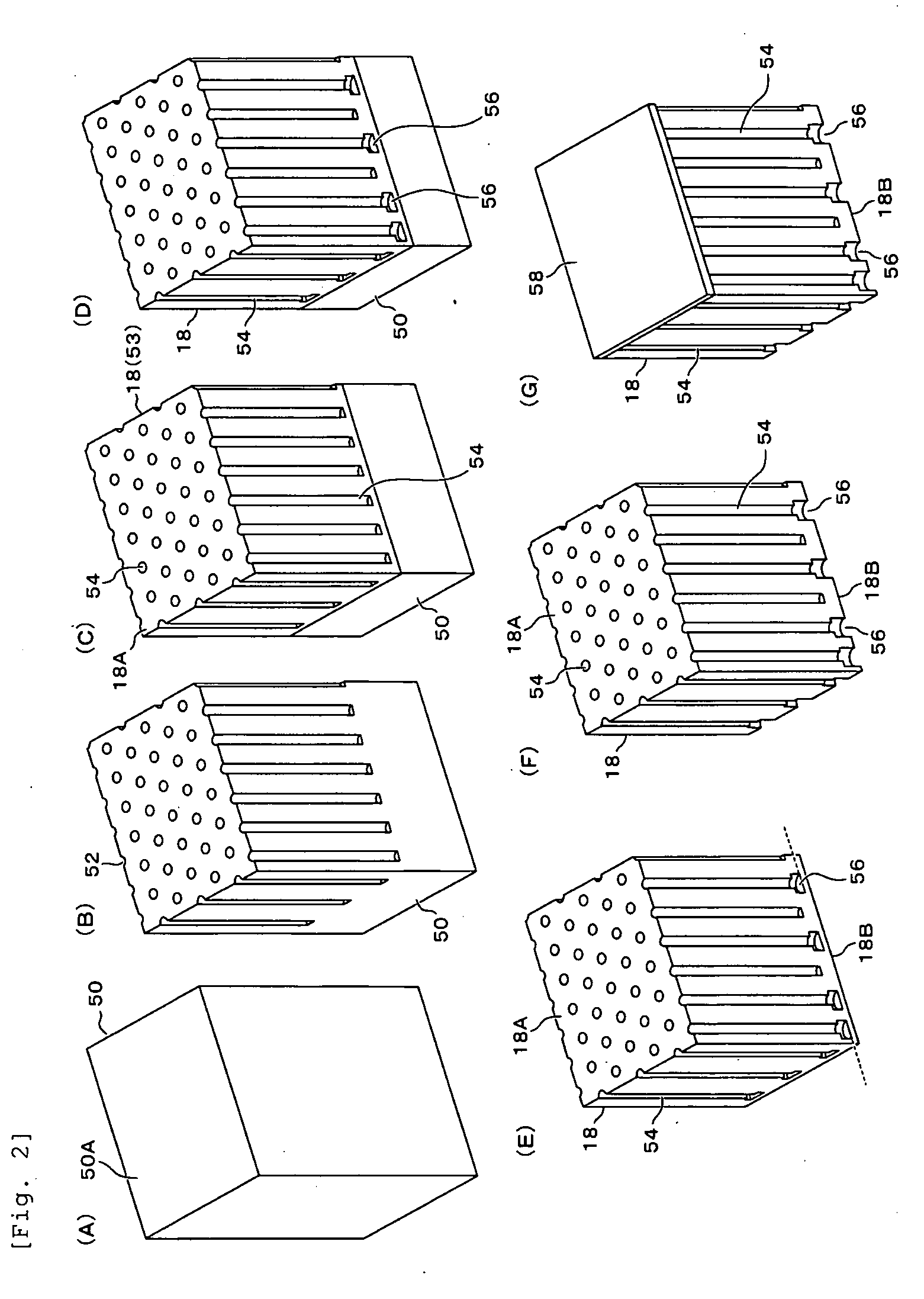

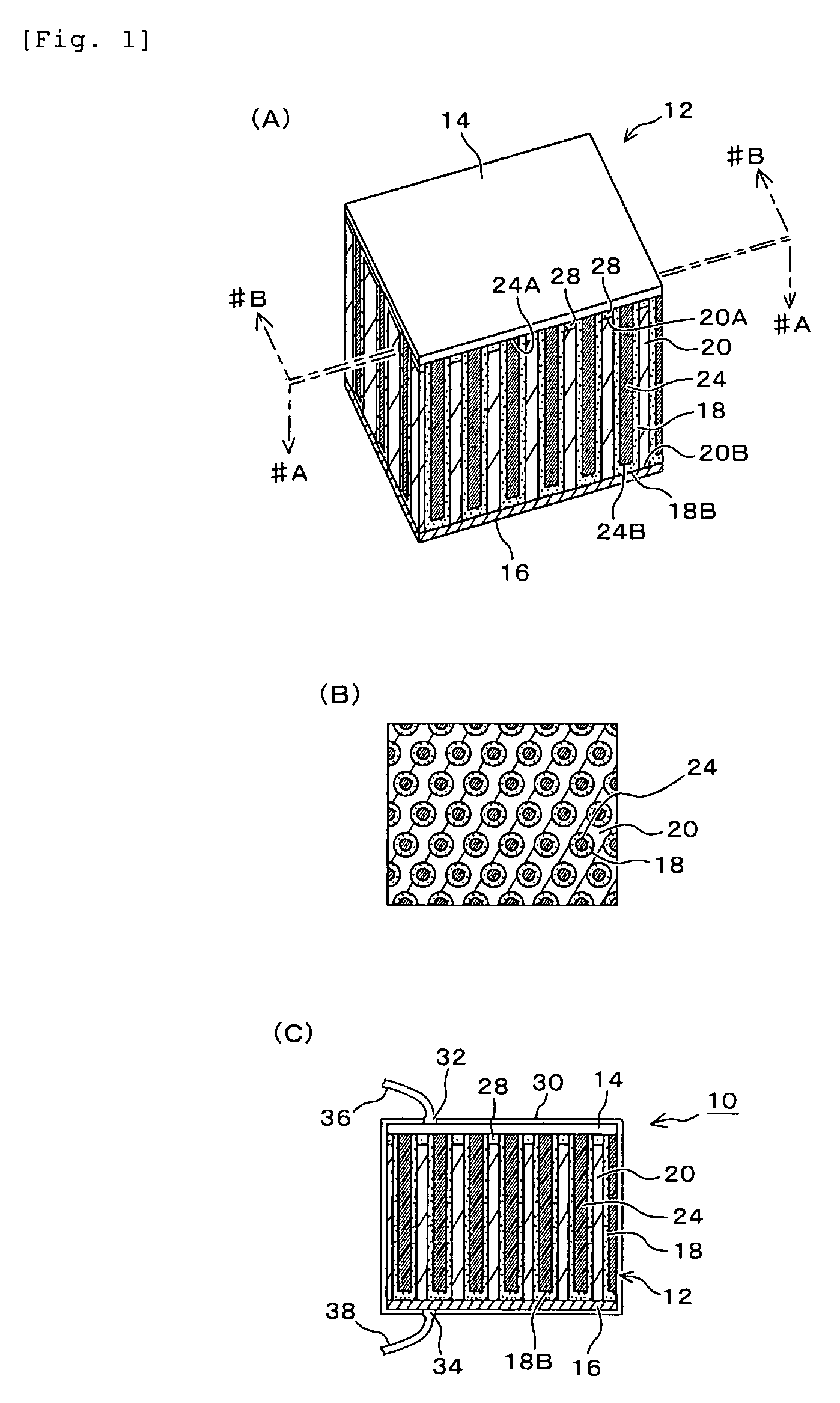

Capacitor and method of manufacturing the same

ActiveUS20090086404A1High selectivitySimple manufacturing processFixed capacitor electrodesFixed capacitor dielectricCapacitorMetal substrate

A capacitor element includes a pair of conductive layer, a plurality of first electrodes and second electrodes, and insulation caps for insulating these electrodes from the conductive layers. By anodizing a metal substrate in two stages, holes filled with the first electrodes and holes filled with the second electrodes are randomly distributed

Owner:TAIYO YUDEN KK

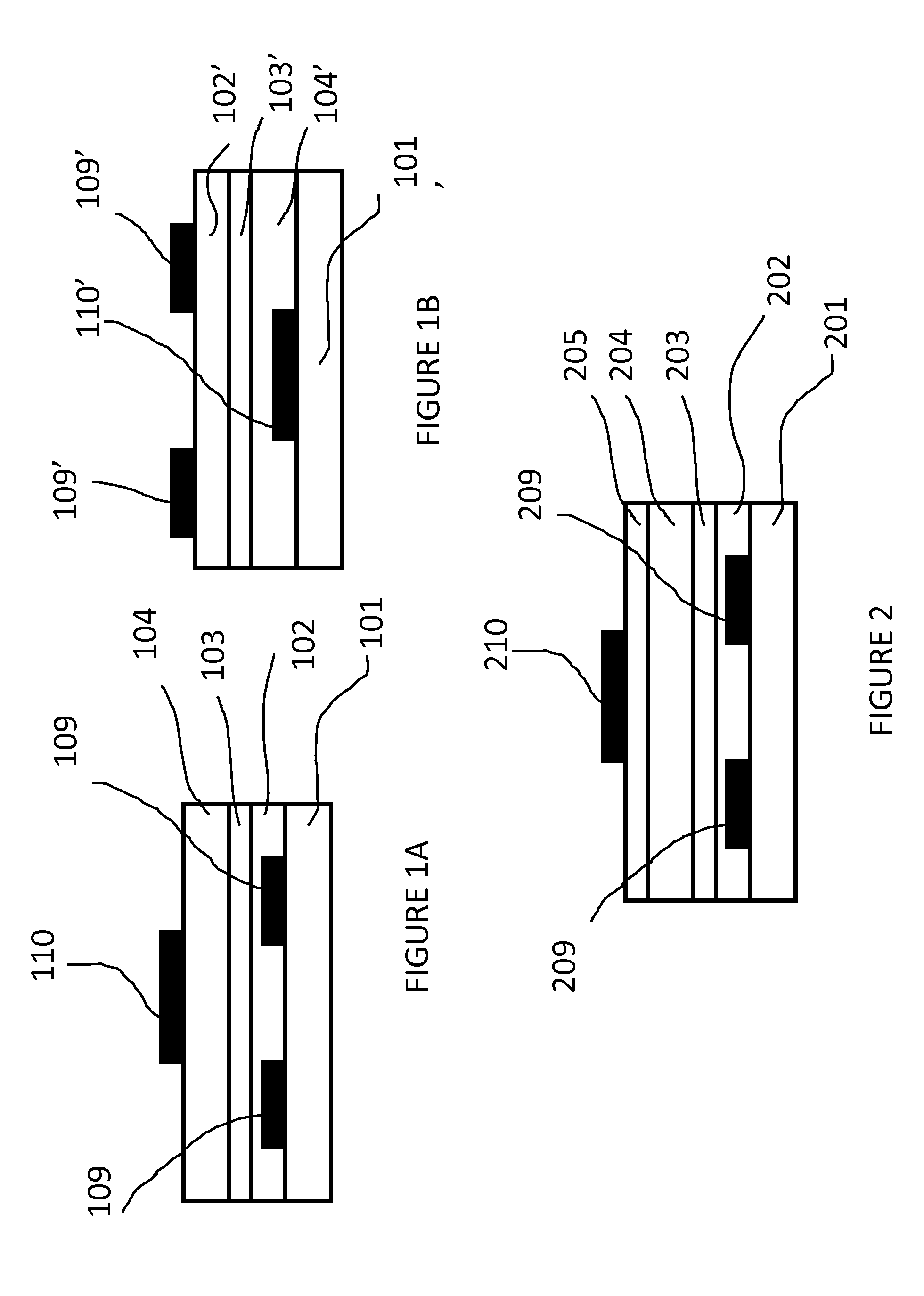

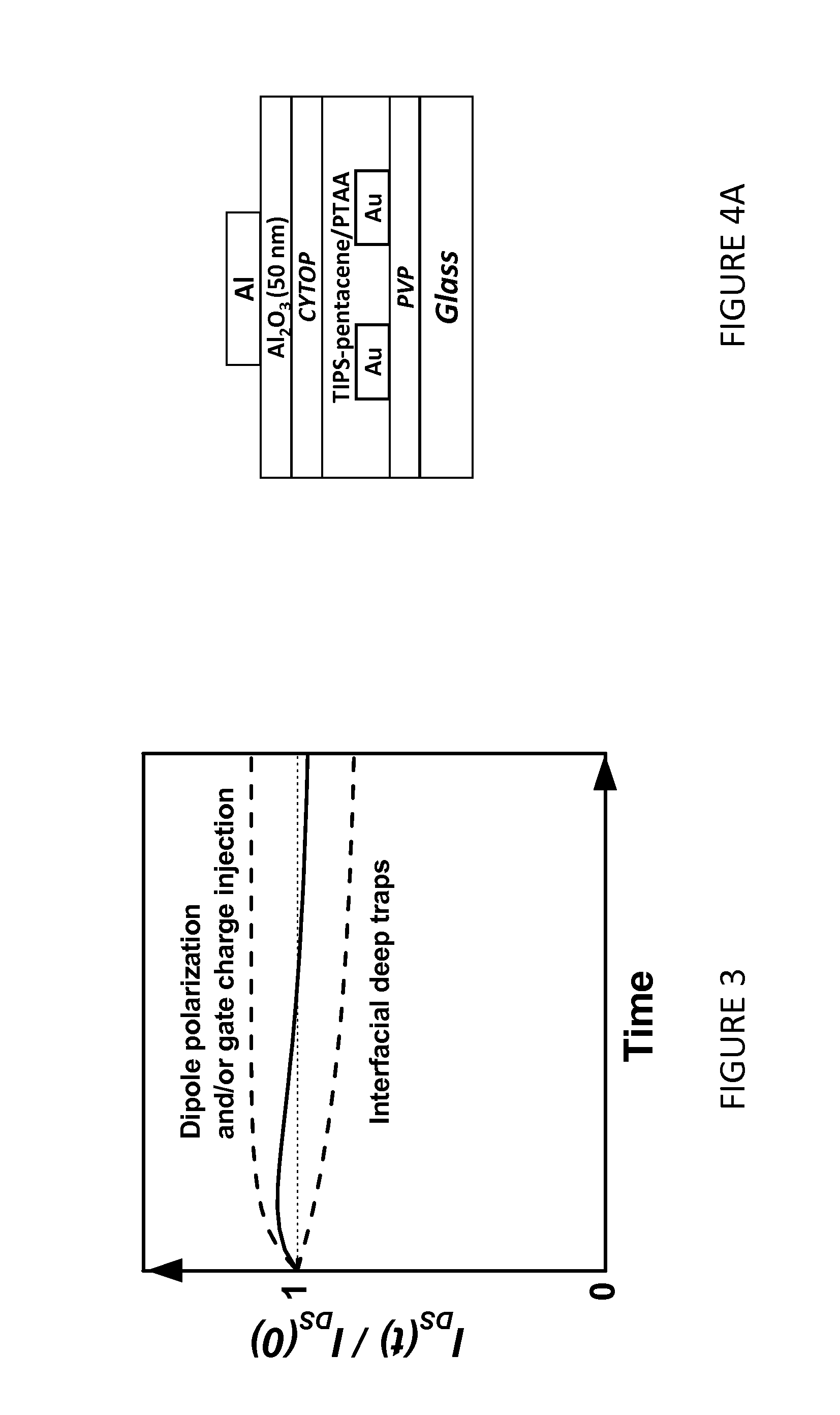

Field-effect transistor and manufacturing process thereof

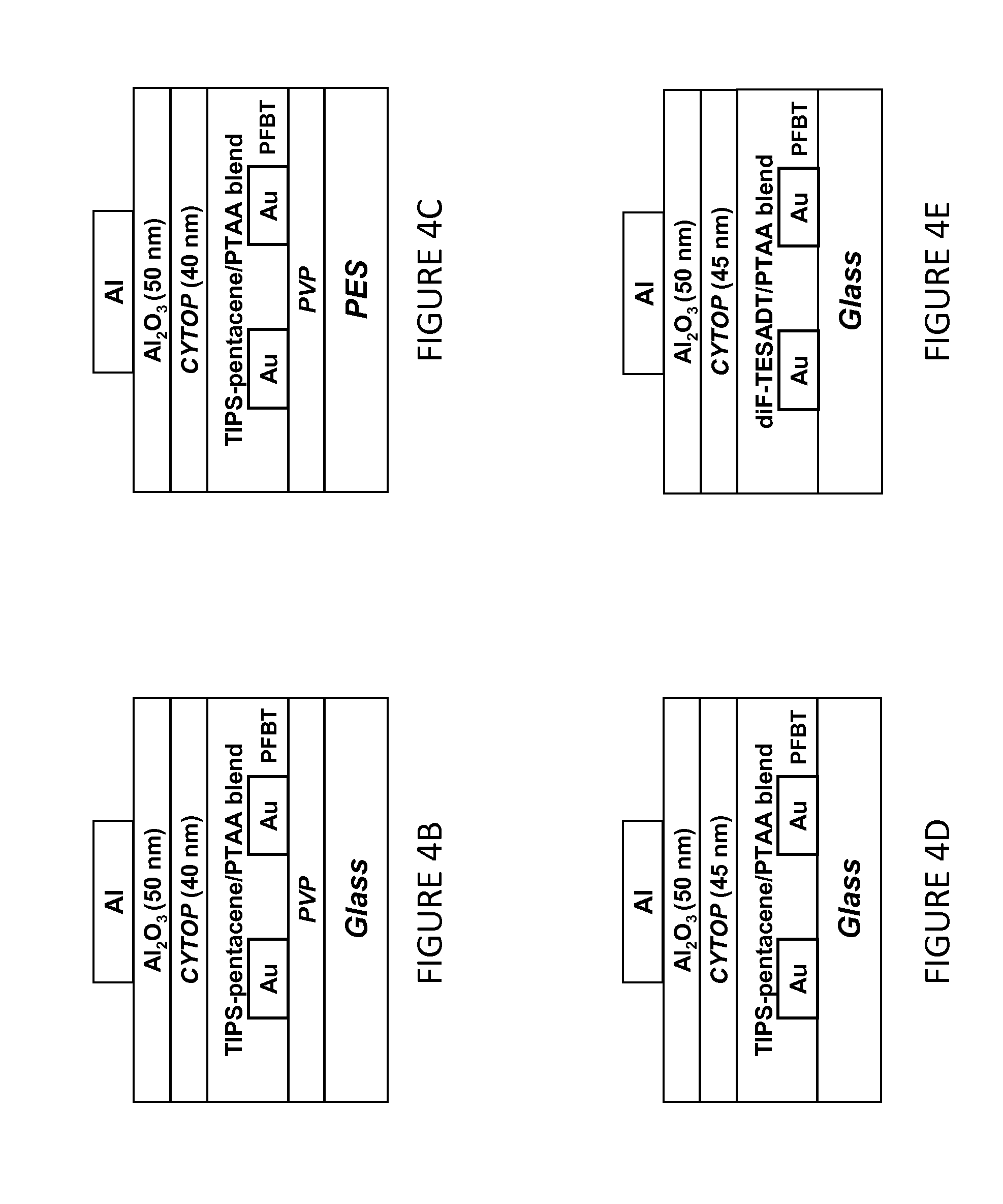

ActiveUS20130270534A1High electrical stabilityImprove performanceOrganic chemistrySolid-state devicesSecondary layerField-effect transistor

A field-effect transistor includes a gate, a source and a drain; a semiconductor layer between the source and the drain; and a gate insulator between the gate and the semiconductor layer. The gate insulator comprises a first layer adjoining the semiconductor layer; and a second layer. The first layer is formed from an amorphous fluoropolymer having a first dielectric constant and a first thickness. The second layer has a second dielectric constant and a second thickness. The first dielectric constant is smaller than 3, the first thickness is smaller than 200 nm, the second dielectric constant is higher than 5, and the second thickness is smaller than 500 nm.

Owner:GEORGIA TECH RES CORP

Elastomeric CMOS based micro electromechanical varactor

InactiveUS7265019B2Increase capacitance densityIncreased side wall areaCapacitor with electrode distance variationSemiconductor/solid-state device manufacturingElastomerElectrical polarity

A micro electro-mechanical system (MEMS) variable capacitor is described, wherein movable comb electrodes of opposing polarity are fabricated simultaneously on the same substrate and are independently actuated. The electrodes are formed in an interdigitated fashion to maximize capacitance. The MEMS variable capacitor includes CMOS manufacturing steps in combination with elastomeric material selectively used in areas under greatest stress to ensure that the varactor will not fail as a result of stresses that may result in the separation of dielectric material from the conductive elements. The combination of a CMOS process with the conducting elastomeric material between vias increases the overall sidewall area, which provides increased capacitance density.

Owner:IBM CORP

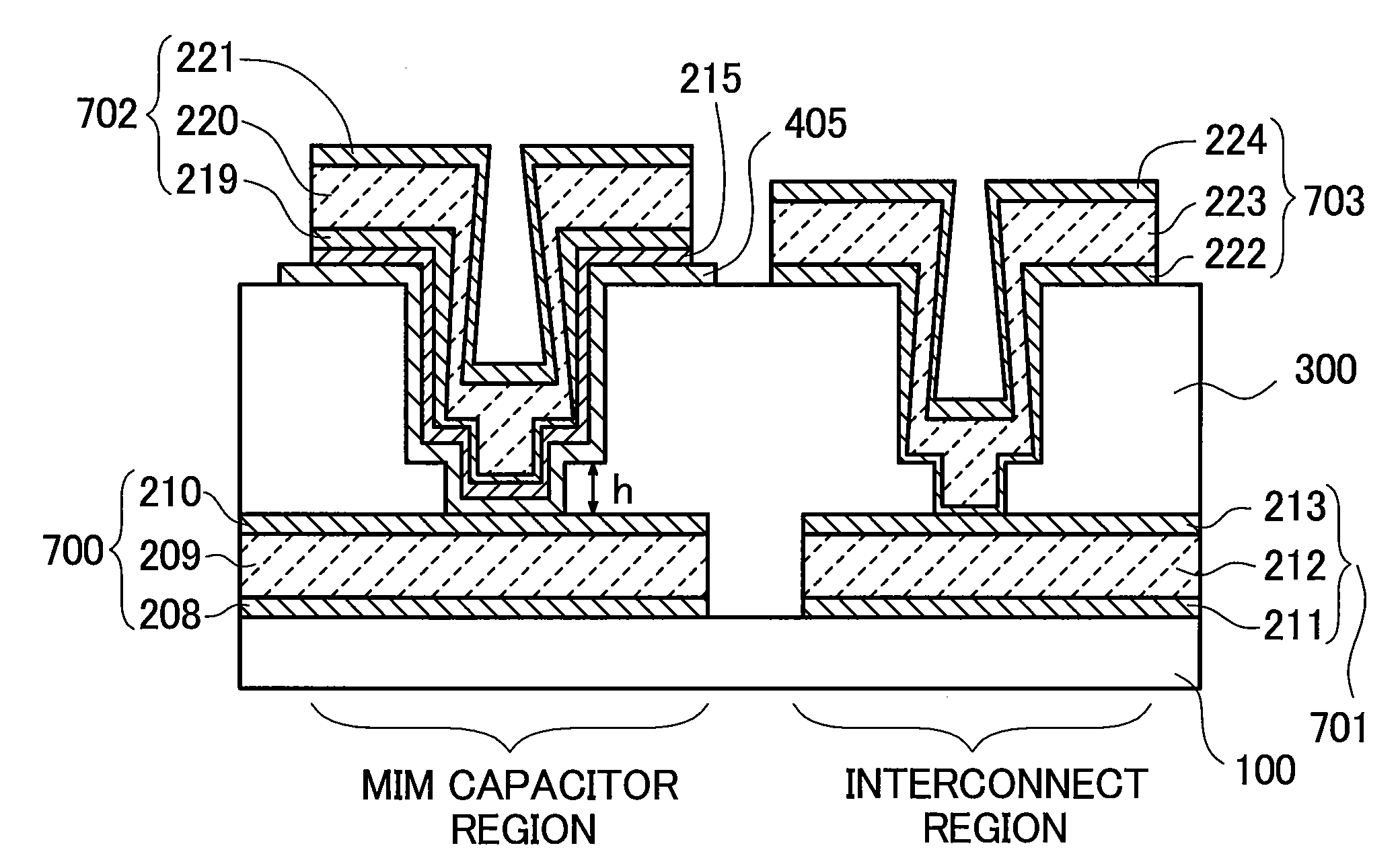

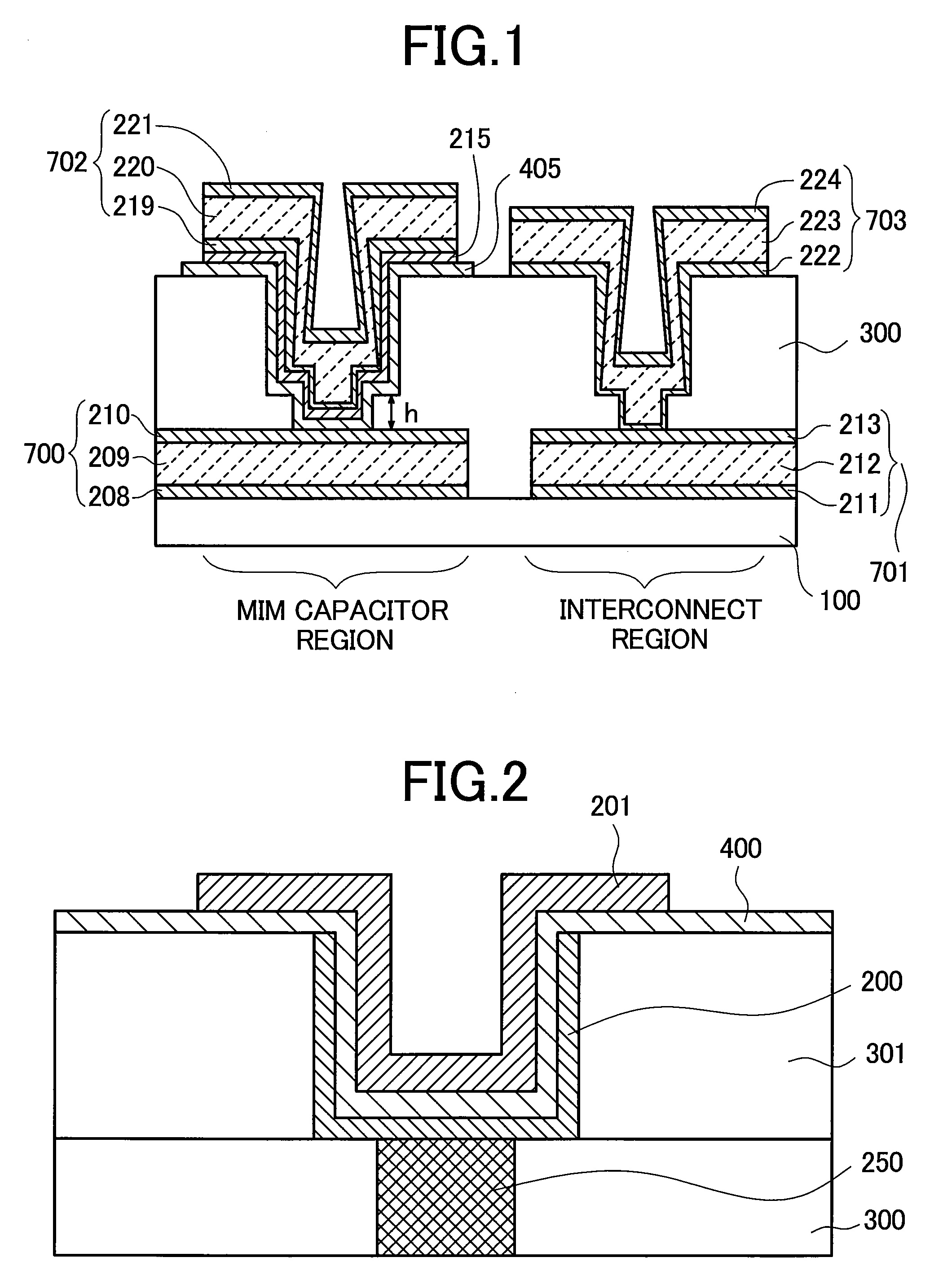

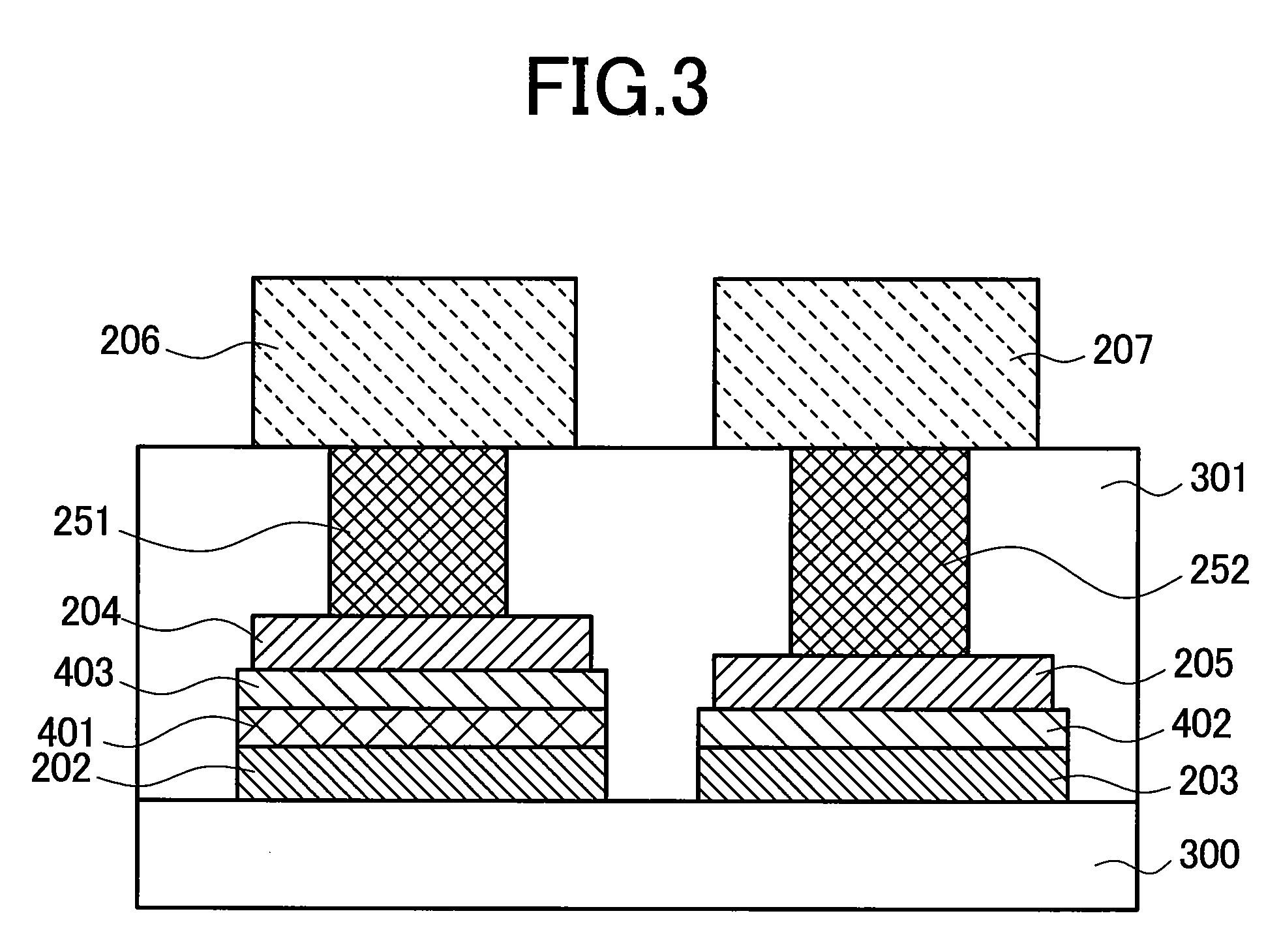

Manufacturing method of semiconductor device

InactiveUS20080020540A1Small sizeIncrease capacitanceSemiconductor/solid-state device detailsSolid-state devicesCapacitanceMetal interconnect

The present invention provides an MIM capacitor using a high-k dielectric film preventing degradation of breakdown field strength of the MIM capacitor and suppressing the increase of the leakage current. The MIM capacitor comprises a first metal interconnect, a fabricated capacitance film, a fabricated upper electrode, and a third metal interconnect. The MIM capacitor is realized by forming an interlayer dielectric film comprising silicon oxide so as to cover the first metal interconnect, then forming a first opening in the interlayer dielectric film to a region corresponding to a via hole layer in the interlayer dielectric film just above the first metal interconnect so as not to expose the upper surface of the first metal interconnect, then forming a second opening to the inside of the first opening so as to expose the surface of the first metal interconnect and then forming a capacitance film and a third metal interconnect.

Owner:HITACHI LTD

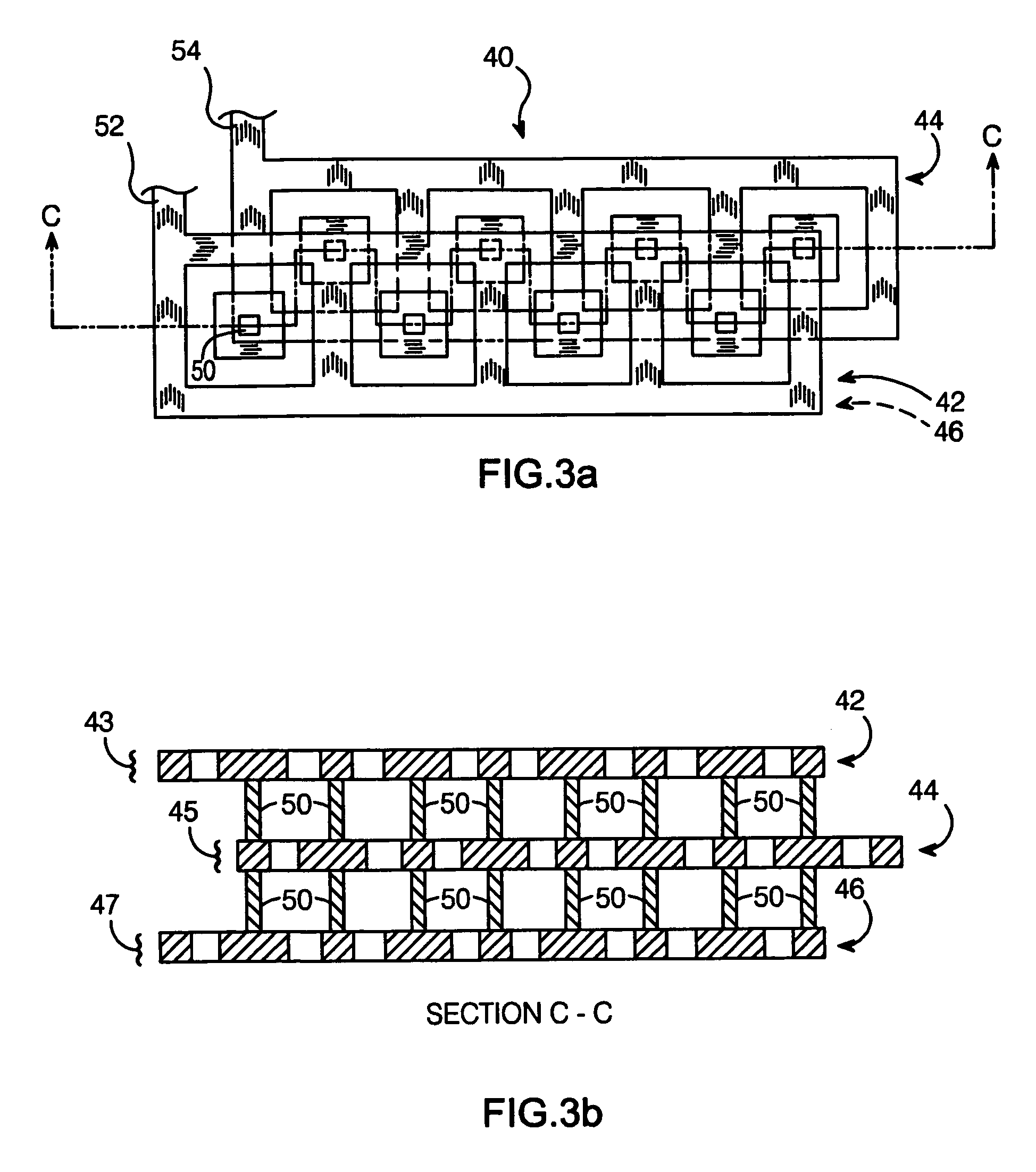

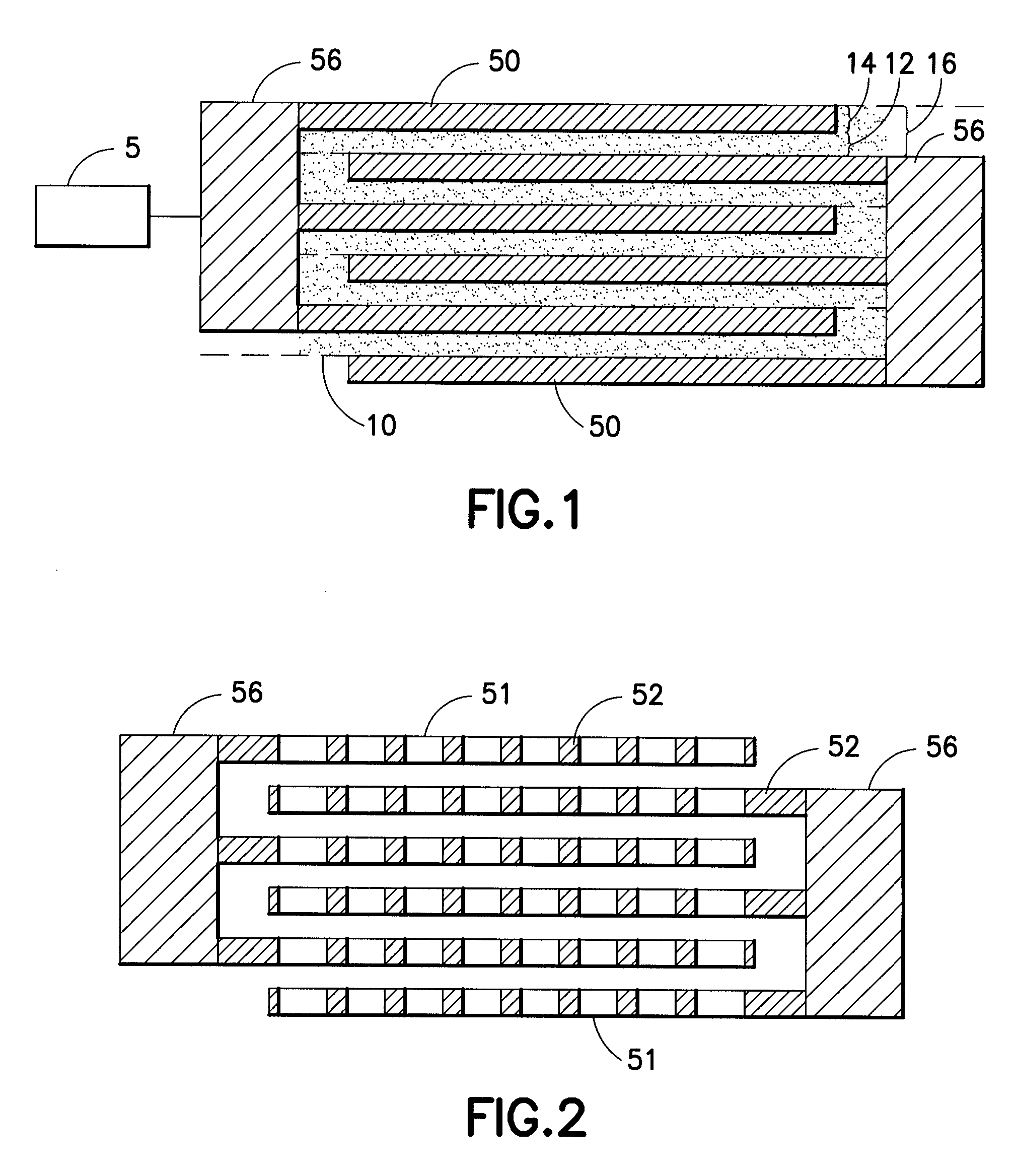

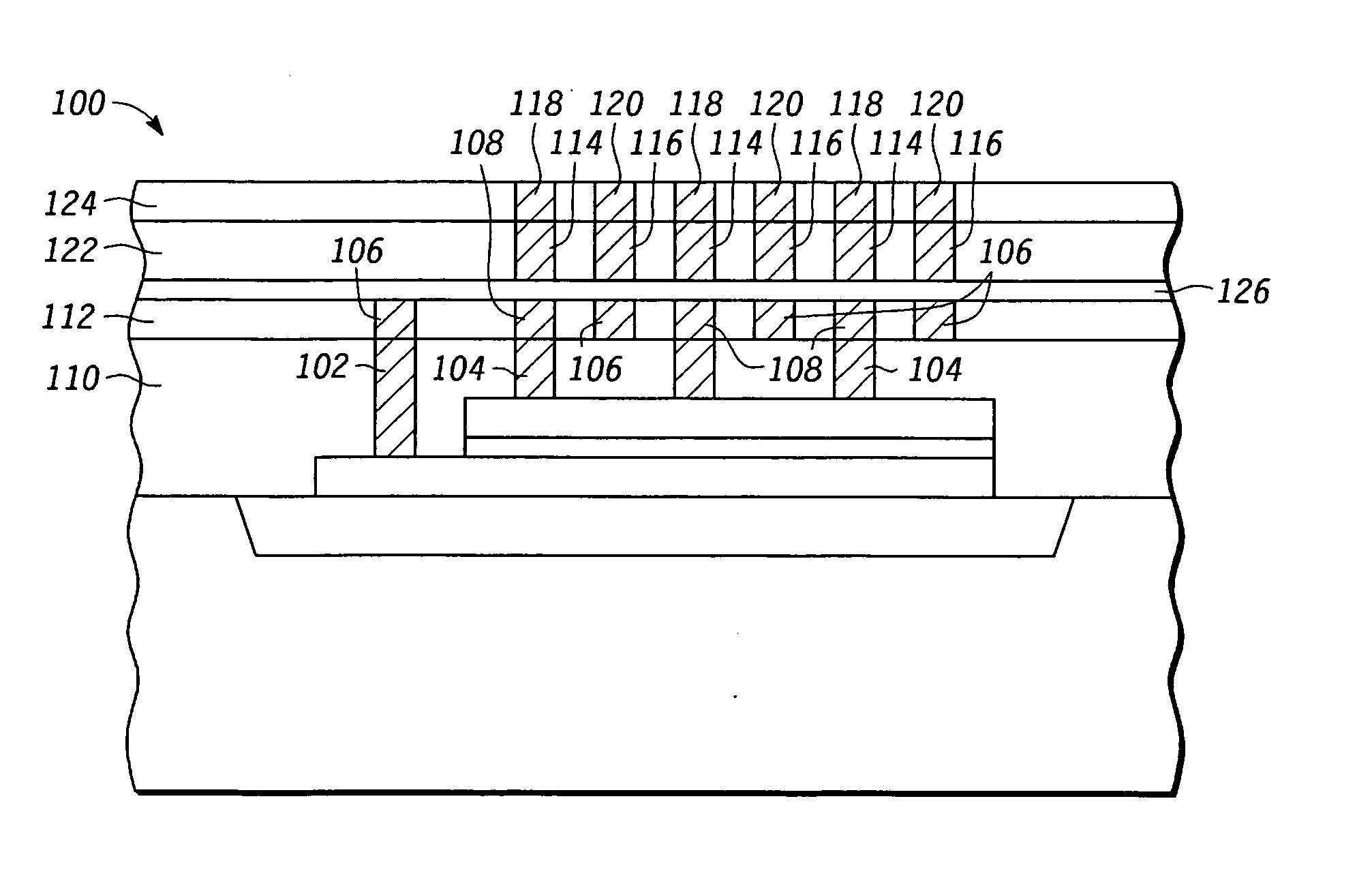

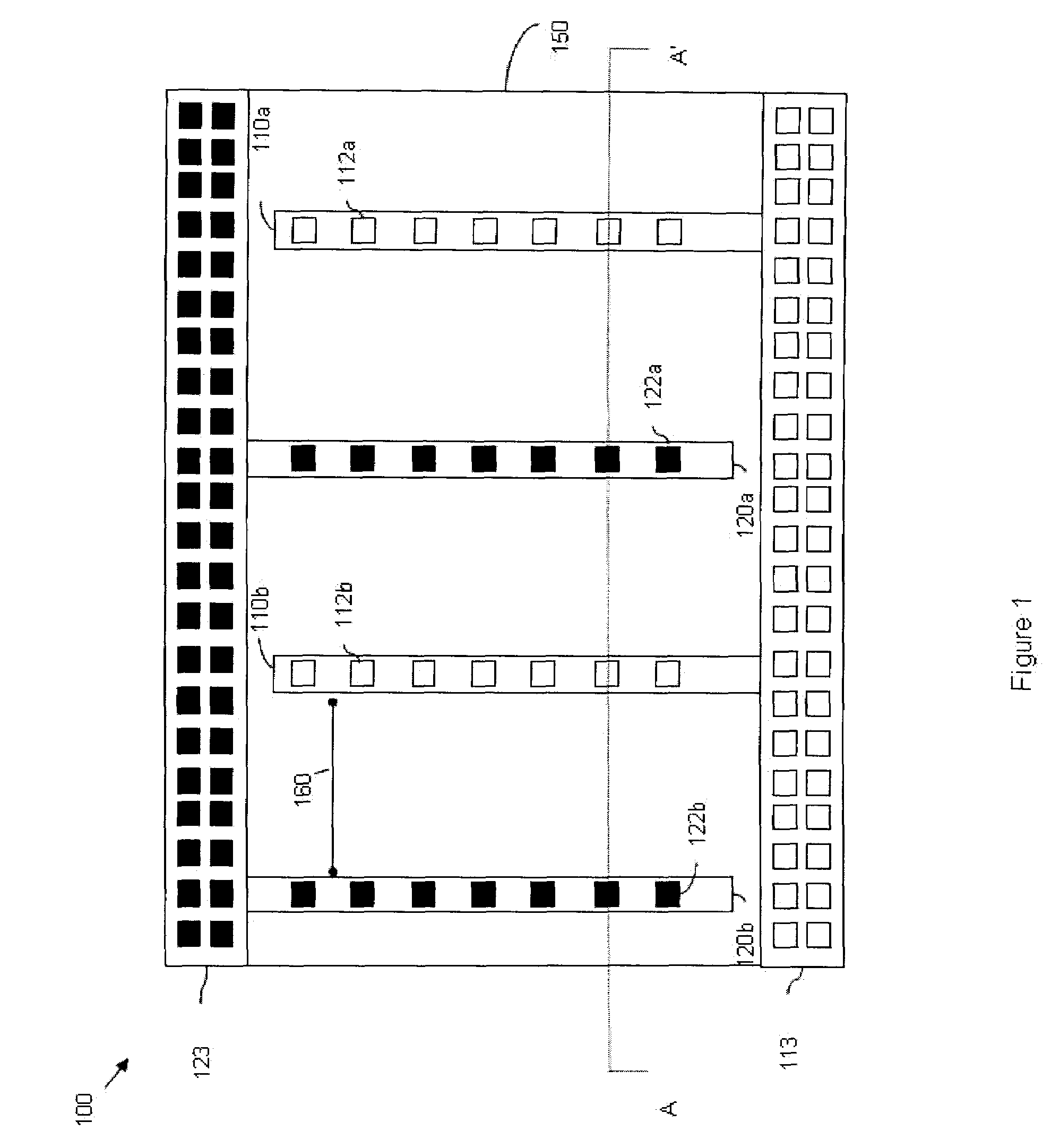

Integrated parallel plate capacitors

ActiveUS20070190760A1Improve performanceResistance of MIM plates according to the present invention is extremely lowTransistorSemiconductor/solid-state device detailsDielectricParallel plate

A parallel plate capacitor formed in the back end of an integrated circuit employs conductive capacitor plates that are formed simultaneously with the other interconnects on that level of the back end (having the same material, thickness, etc). The capacitor plates are set into the interlevel dielectric using the same process as the other interconnects on that level of the back end (preferably dual damascene). Some versions of the capacitors have perforations in the plates and vertical conductive members connecting all plates of the same polarity, thereby increasing reliability, saving space and increasing the capacitive density compared with solid plates.

Owner:IBM CORP

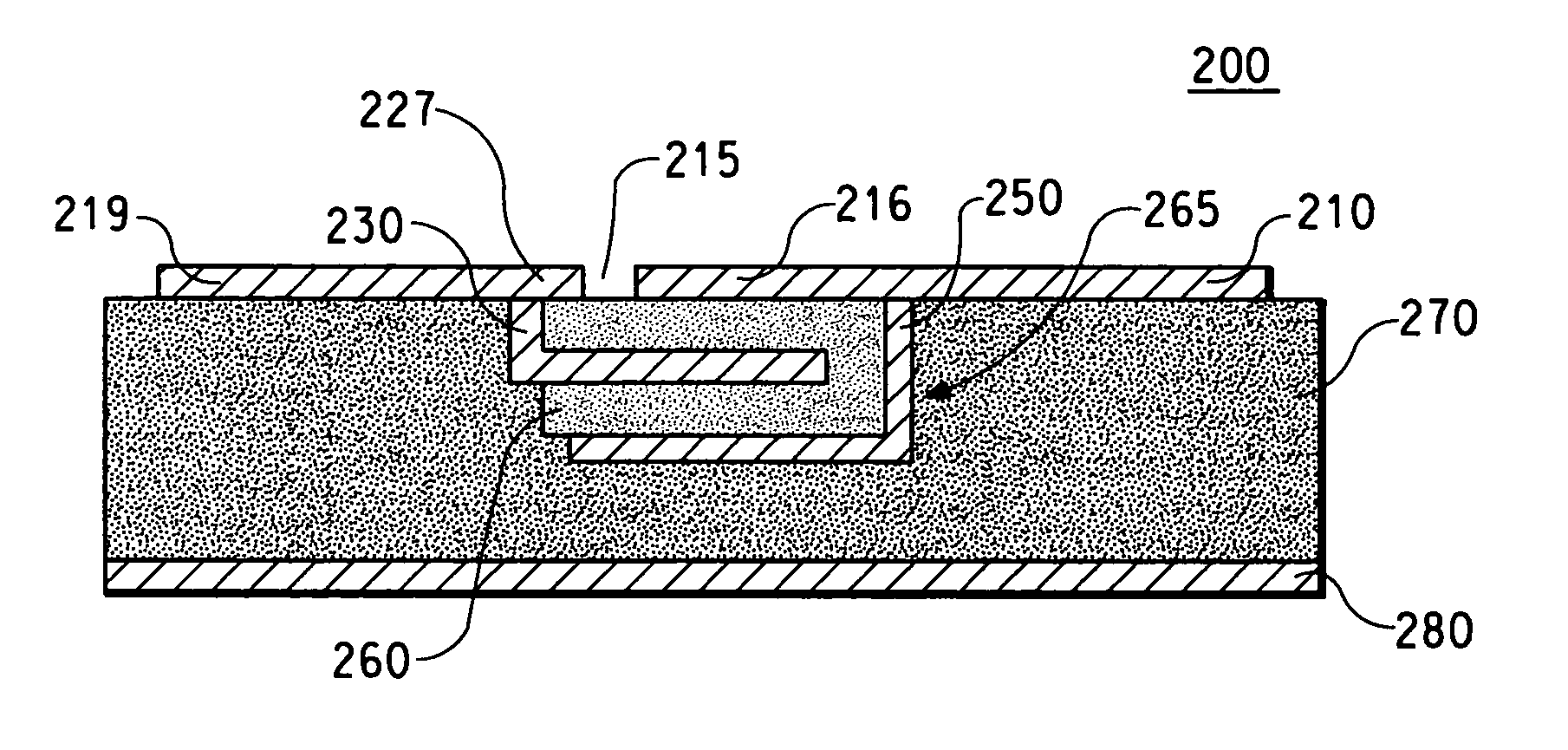

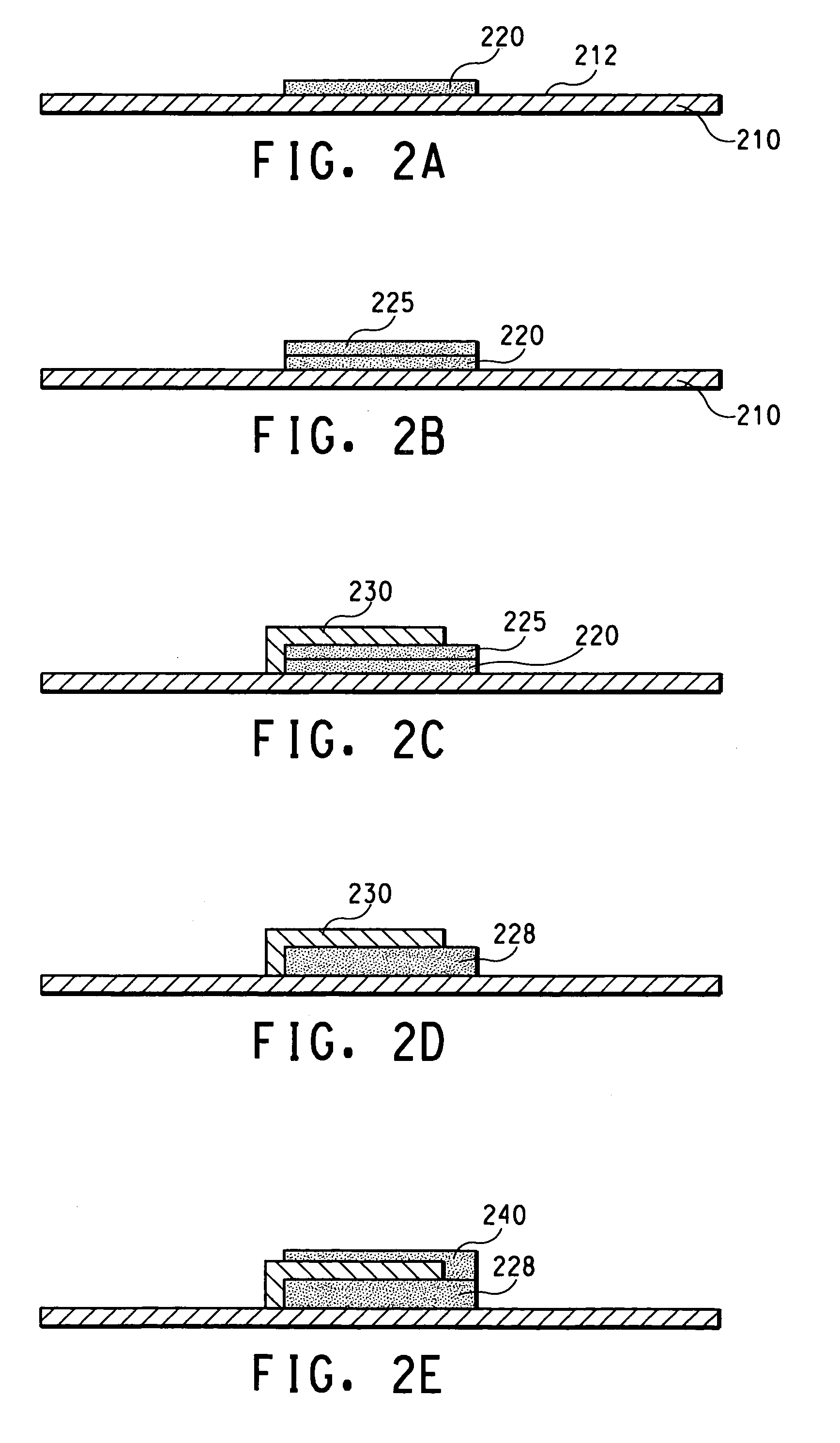

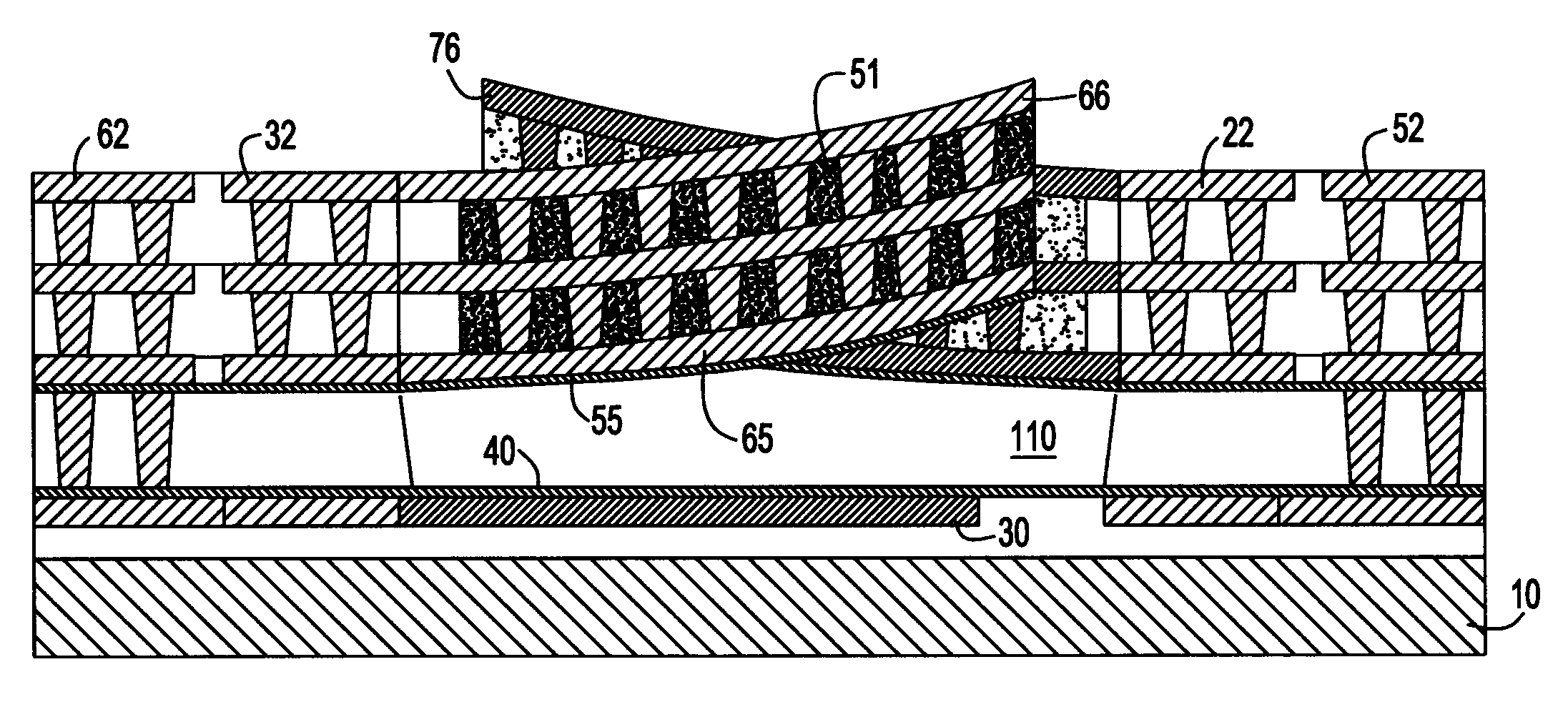

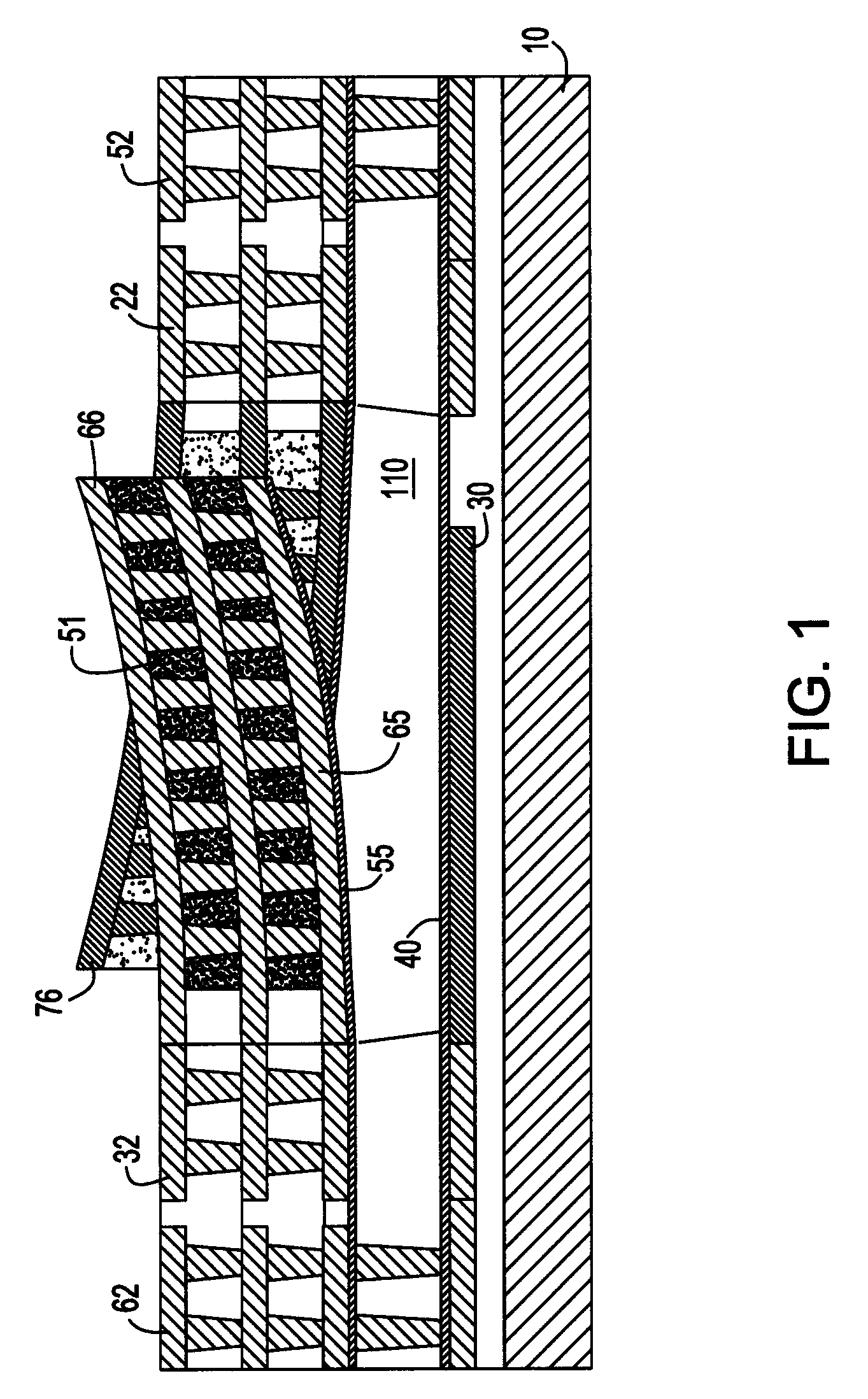

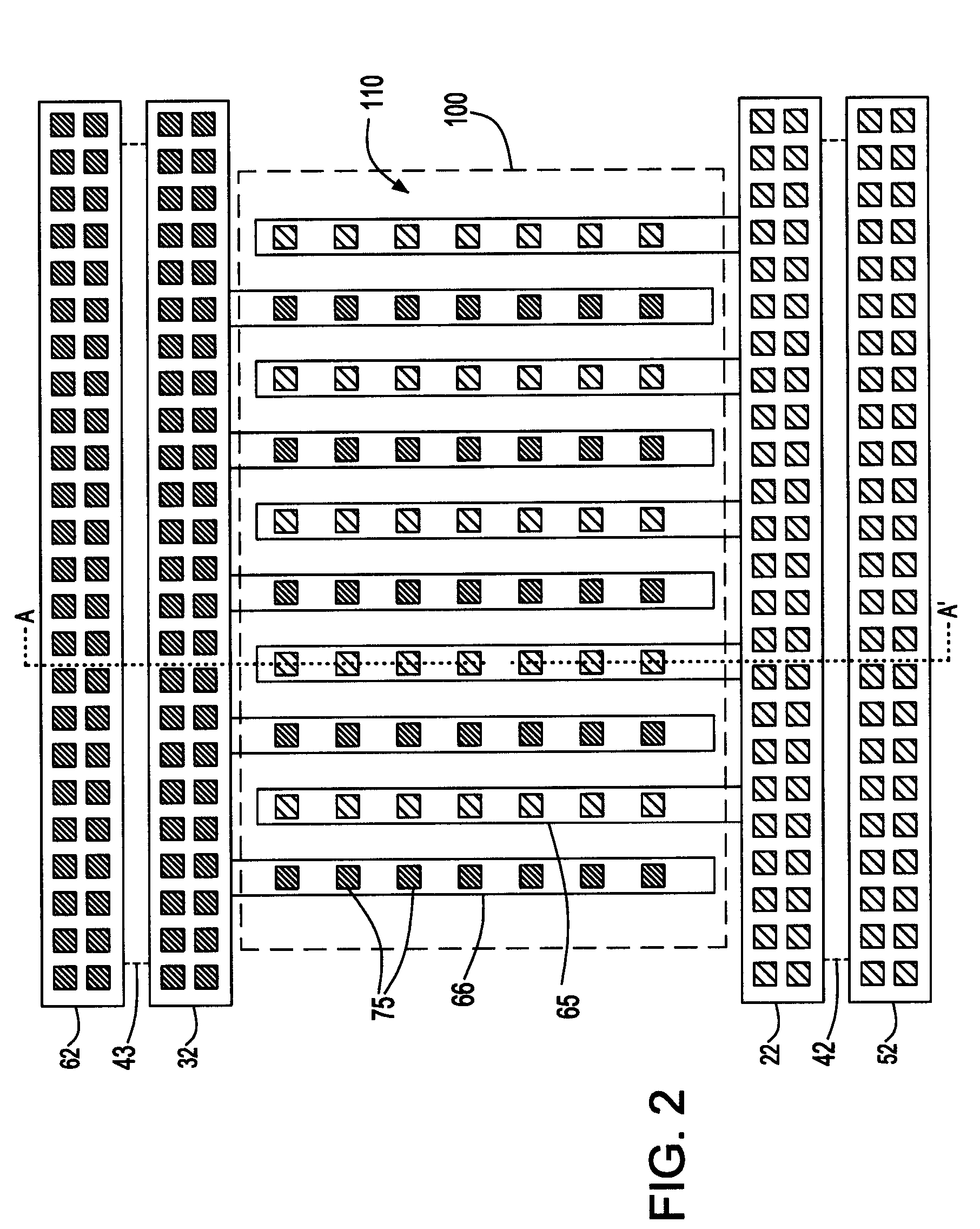

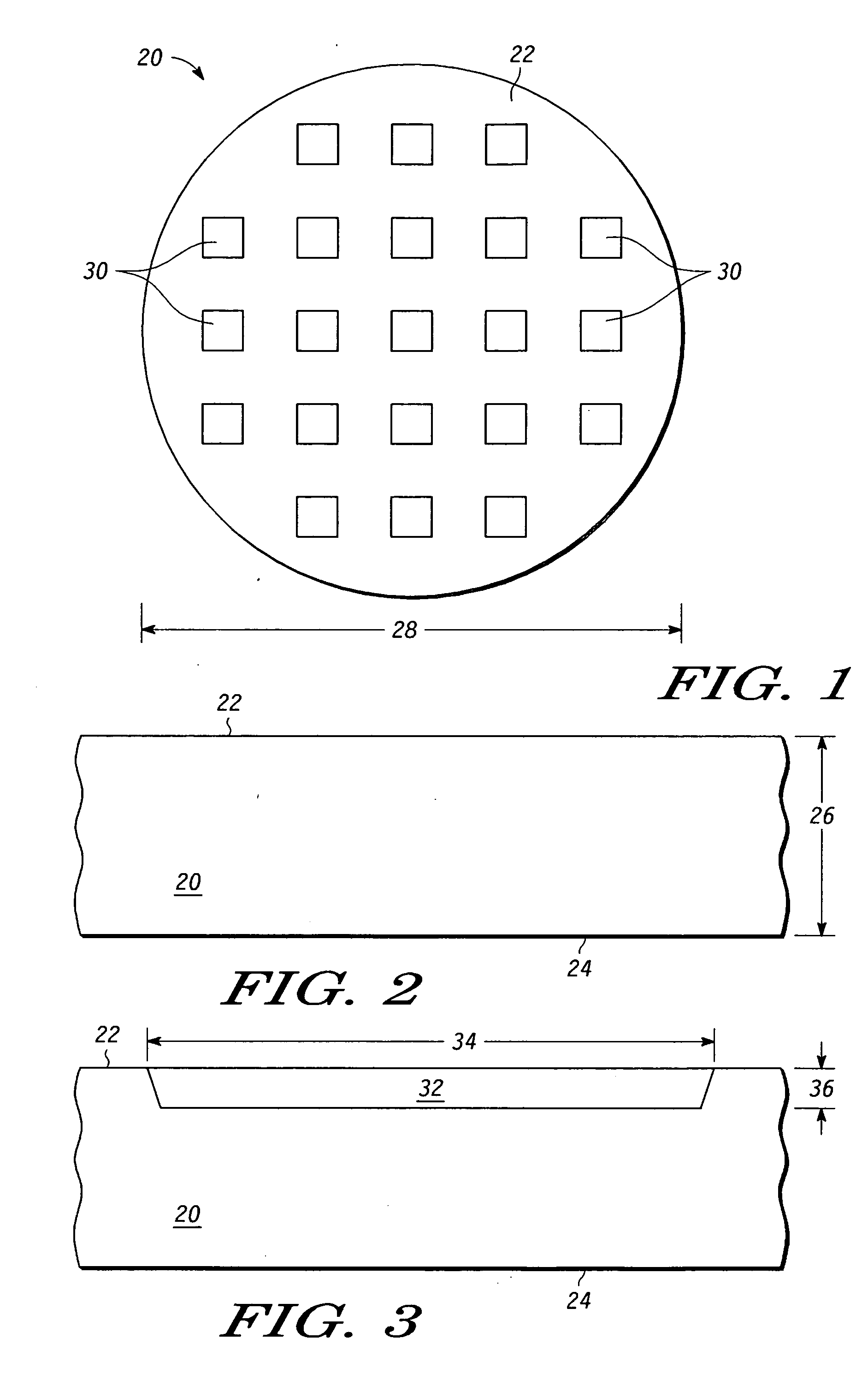

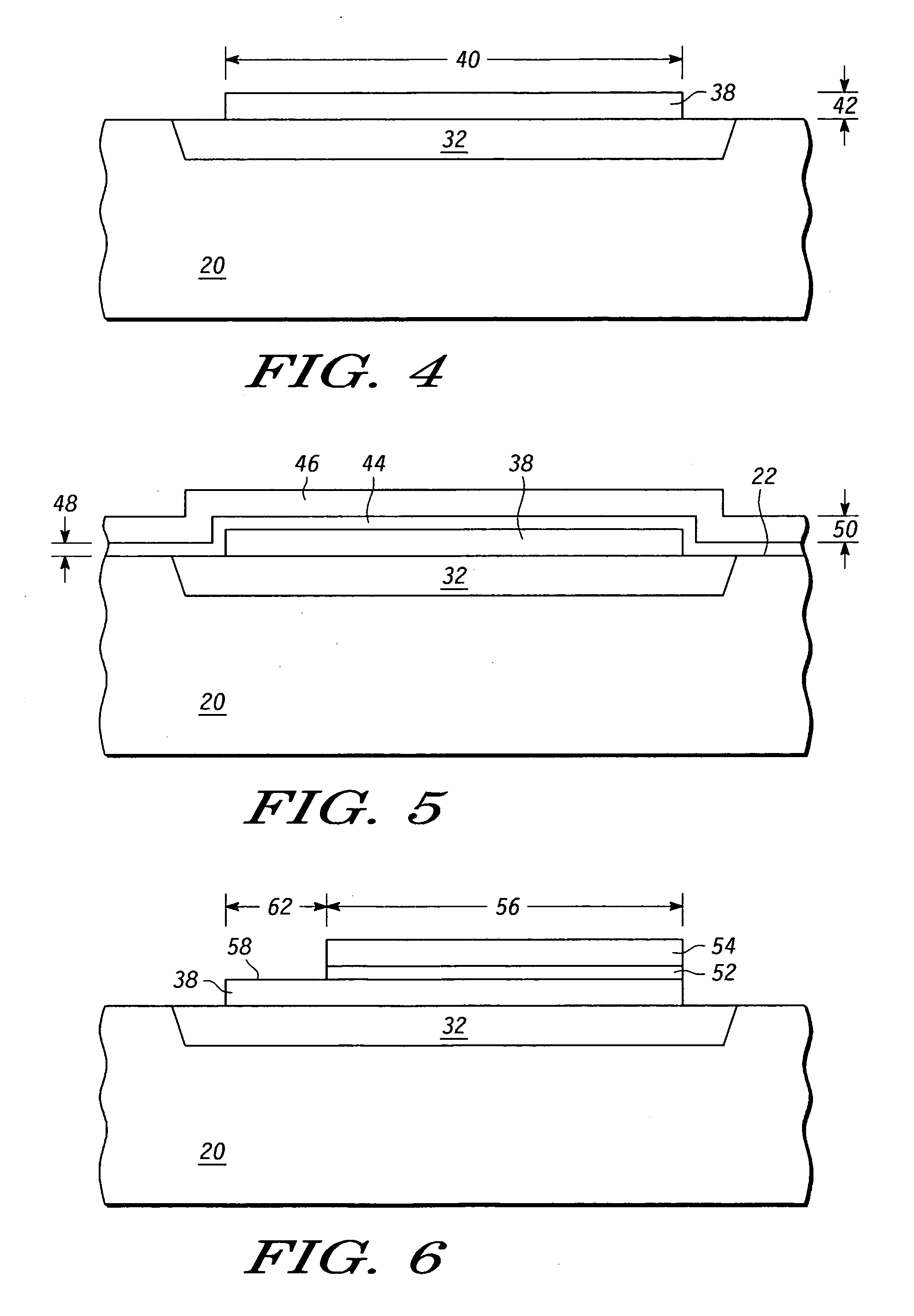

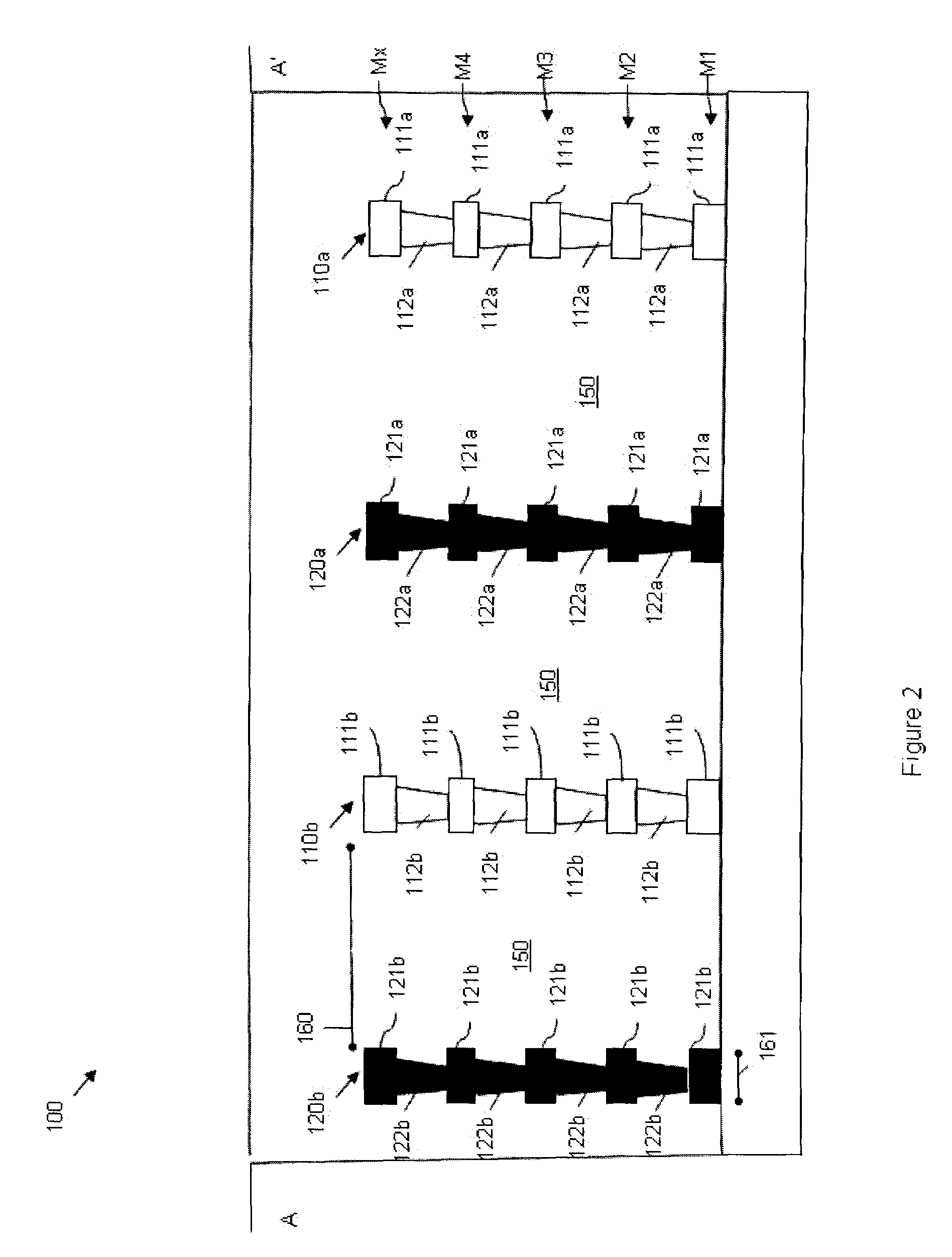

Composite capacitor and method for forming the same

ActiveUS20070228506A1Increase capacitance densityReduce capacitanceThin/thick film capacitorSemiconductor/solid-state device detailsElectrical conductorEngineering

An electronic assembly (98) includes a substrate (20), a capacitor having first and second conductors (38,54) formed over the substrate, a first set of conductive members (76) formed over the substrate and being electrically connected to the first conductor of the capacitor, and a second set of conductive members (78) formed over the substrate and being electrically connected to the second conductor of the capacitor.

Owner:NXP USA INC

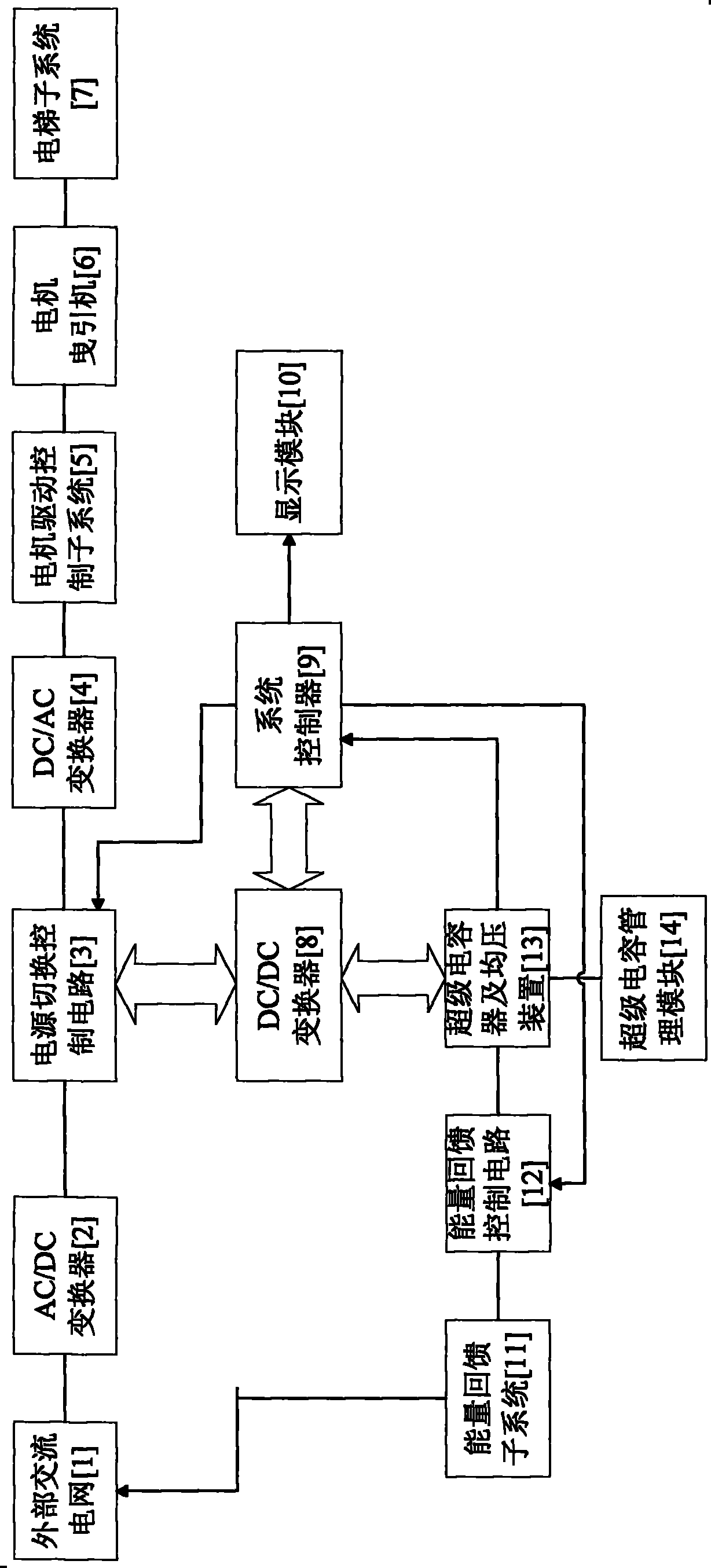

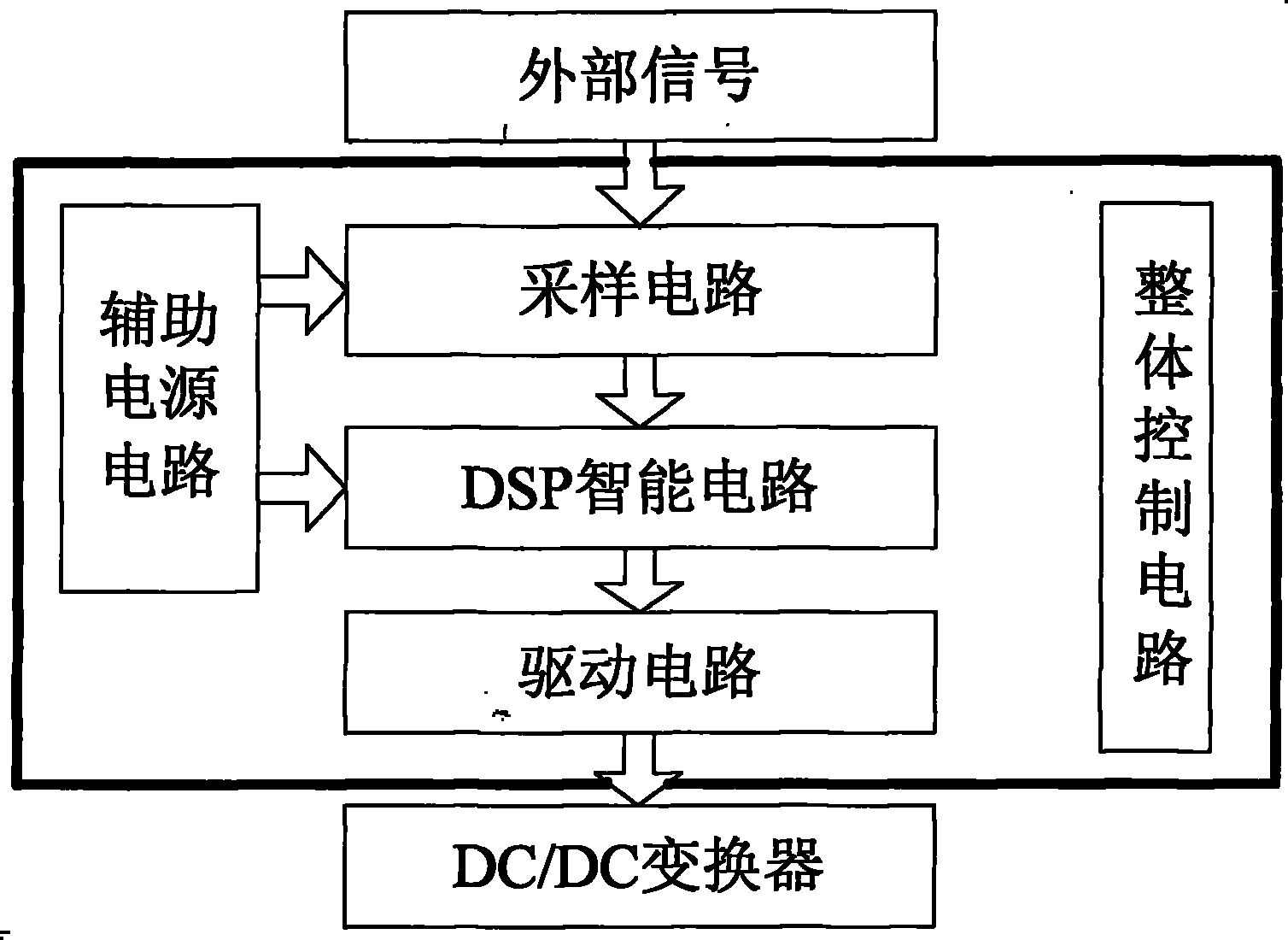

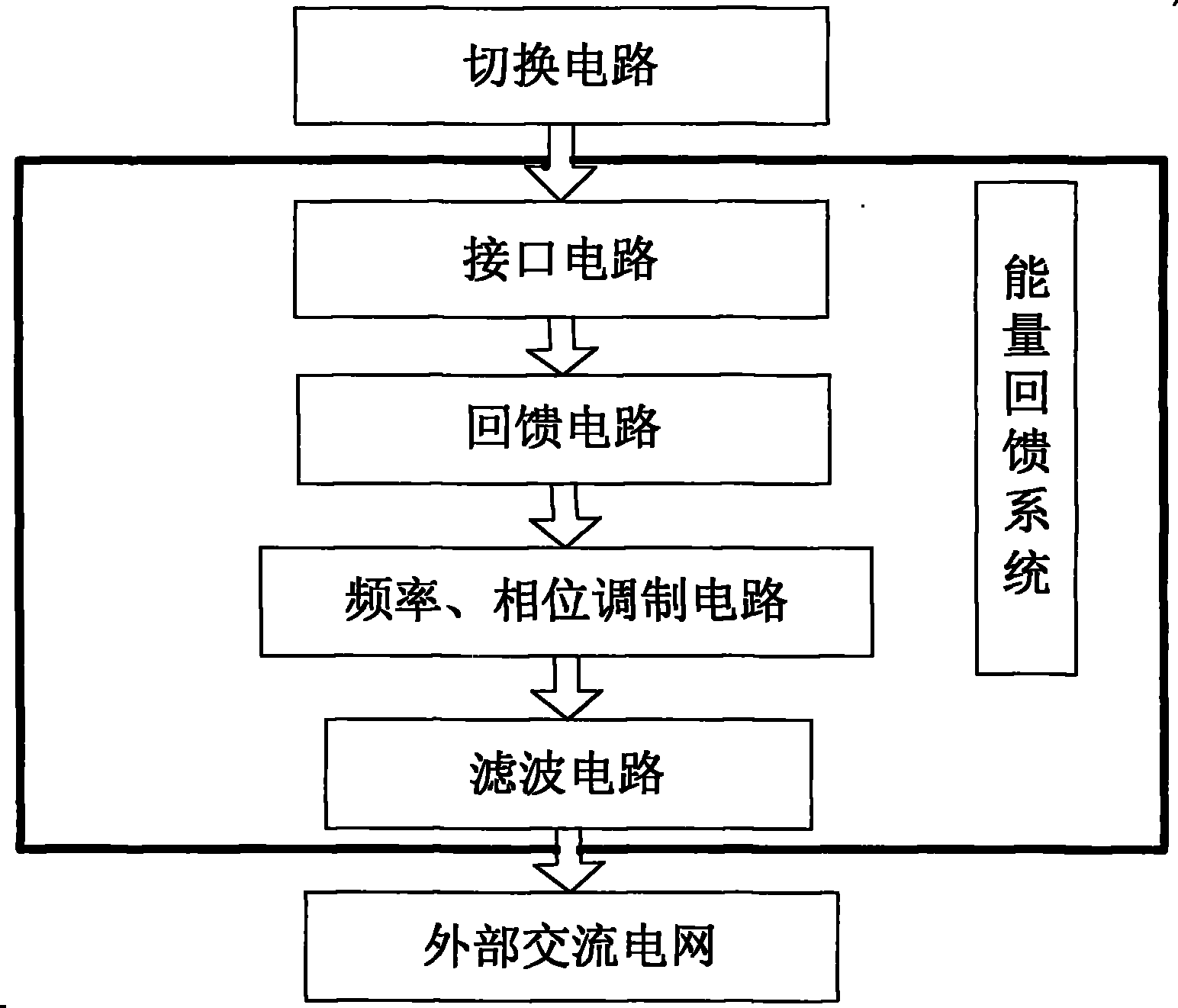

Energy saving system of elevator

ActiveCN101807821AImprove securityImprove power densityElectrical storage systemPower network operation systems integrationCapacitanceEngineering

The invention discloses an energy saving system of an elevator. In the system, a super capacitor group is utilized as a regenerative braking energy storage device of an elevator sub-system and a power supply source for operating the elevator sub-system, energy is stored in the braking process of operating the elevator sub-system, a power source switching control circuit is controlled by a system controller to realize the switching between the super capacitor group and an external alternating current network for supplying the electricity to the elevator sub-system so as to achieve the purpose of saving energy. The system fully utilizes the characteristics of heavy current discharge of a super capacitor, lowers the requirements on the level of the external alternating current network and can synchronously satisfy a peak value power generated when the elevator sub-system is operated, and the super capacitor presents the advantages of long service life, short charging and discharging time, large capacitance density and the like. The system saves energy and synchronously improves the safety of the elevator operation and has very high social benefit and economic benefit.

Owner:NANJING UNIV OF SCI & TECH

Process for producing polyradical compound and battery cell

InactiveUS20100255372A1High capacitance densityLarge quantityLi-accumulatorsNon-aqueous electrolyte accumulator electrodesSingle bondPhenylene

Disclosed is a polyradical compound which can be used as an electrode active material for at least one of a positive electrode and a negative electrode. The polyradical compound has a repeating unit represented by general formula (1) and is crosslinked using a bifunctional crosslinking agent having two polymerizing groups in the molecule represented by general formula (2), wherein R1 to R3 each independently represent hydrogen or methyl group; R4 to R7 each independently represent C1 to C3 alkyl group; X represents single bond, linear, branched or cyclic C1 to C15 alkylenedioxy group, alkylene group, phenylenedioxy group, phenylene group or structure represented by general formula (3); and R8 to R13 each independently represent hydrogen or methyl group, and k represents an integer of 2 to 5.

Owner:NEC CORP

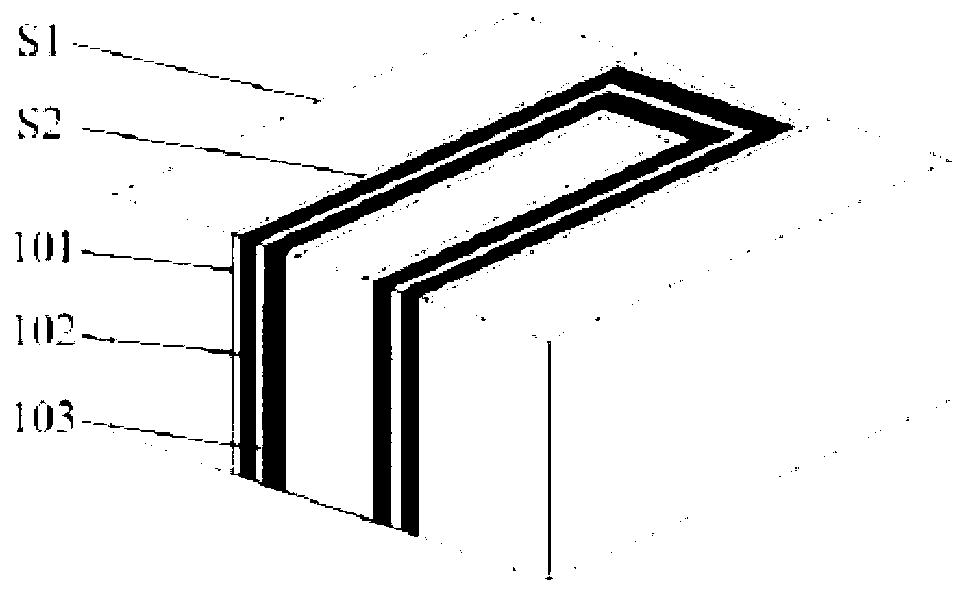

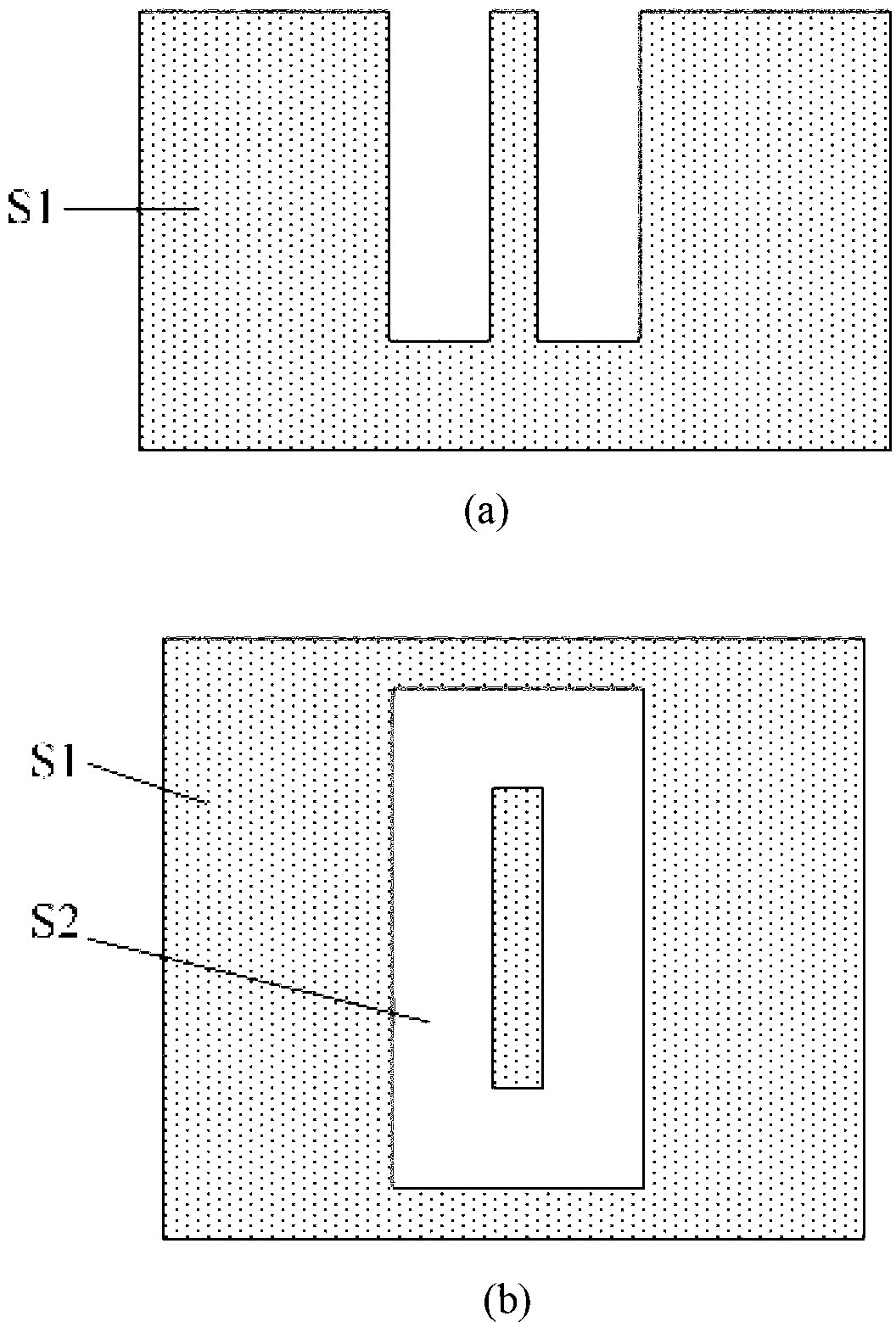

Vertical-type capacitor structure and manufacturing method thereof

InactiveCN103346148AHighly integratedReduce areaSemiconductor/solid-state device detailsSolid-state devicesCapacitanceEngineering

The invention relates to a vertical-type capacitor structure and a manufacturing method of the vertical-type capacitor structure, and belongs to the technical field of micro-electronic passive devices. The vertical-type capacitor structure structurally and specifically comprises a deep-groove structure, insulating layers, conducting layers and a dielectric layer, wherein the deep-groove structure is located inside a wafer substrate, the insulating layers and the conducting layers are sequentially deposited on the inner side wall of a deep groove, and the dielectric layer is filled between the conducting layers. The insulating layers, the conducting layers, the dielectric layer and the deep groove are the same in height. On the basis of the principle that the area of a capacitor is expanded in the direction perpendicular to the substrate, the area of an plate electrode in the perpendicular direction is utilized, the processes such as sputtering and electroplating are adopted to manufacture a metal plate electrode, and the plate electrode is made of low electrical resistivity materials, like metal. With the combination of a silicon through hole technology, the vertical-type capacitor with a large depth-to-width ratio is achieved. With the combination of a substrate back thinning technology, the vertical-type capacitor structure penetrates through the substrate, the vertical-type capacitor structure can be used as a high-frequency channel between multi-layer chips, the area of the plate can be greatly saved, and the integration level of an integrated circuit is improved.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

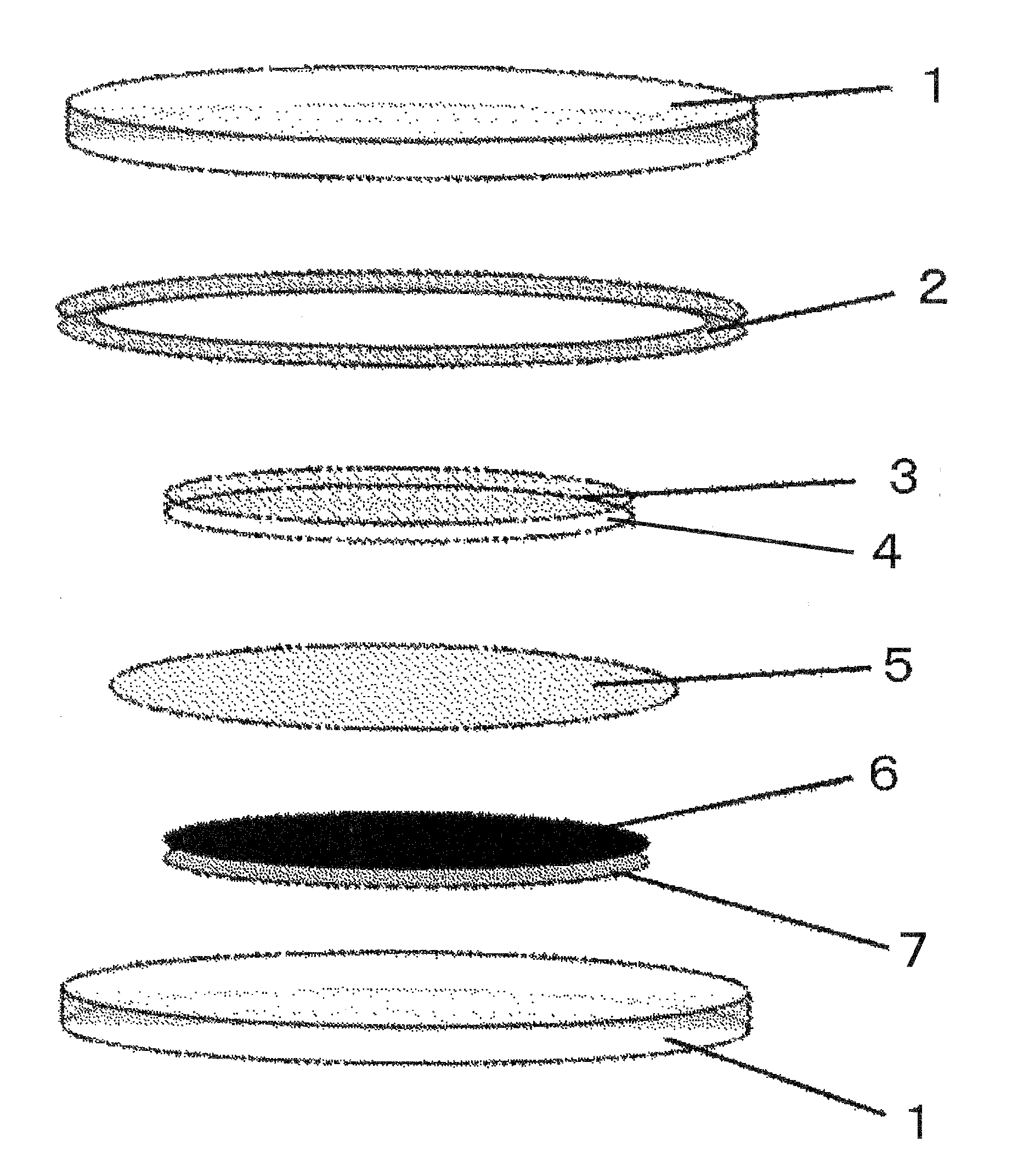

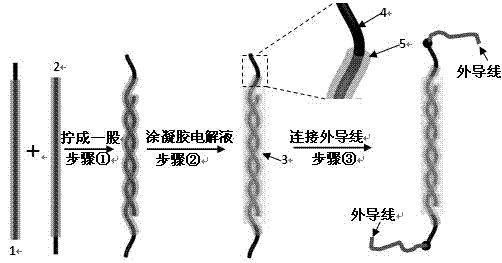

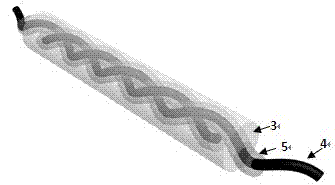

Linear secure high-energy-density supercapacitor and preparation method thereof

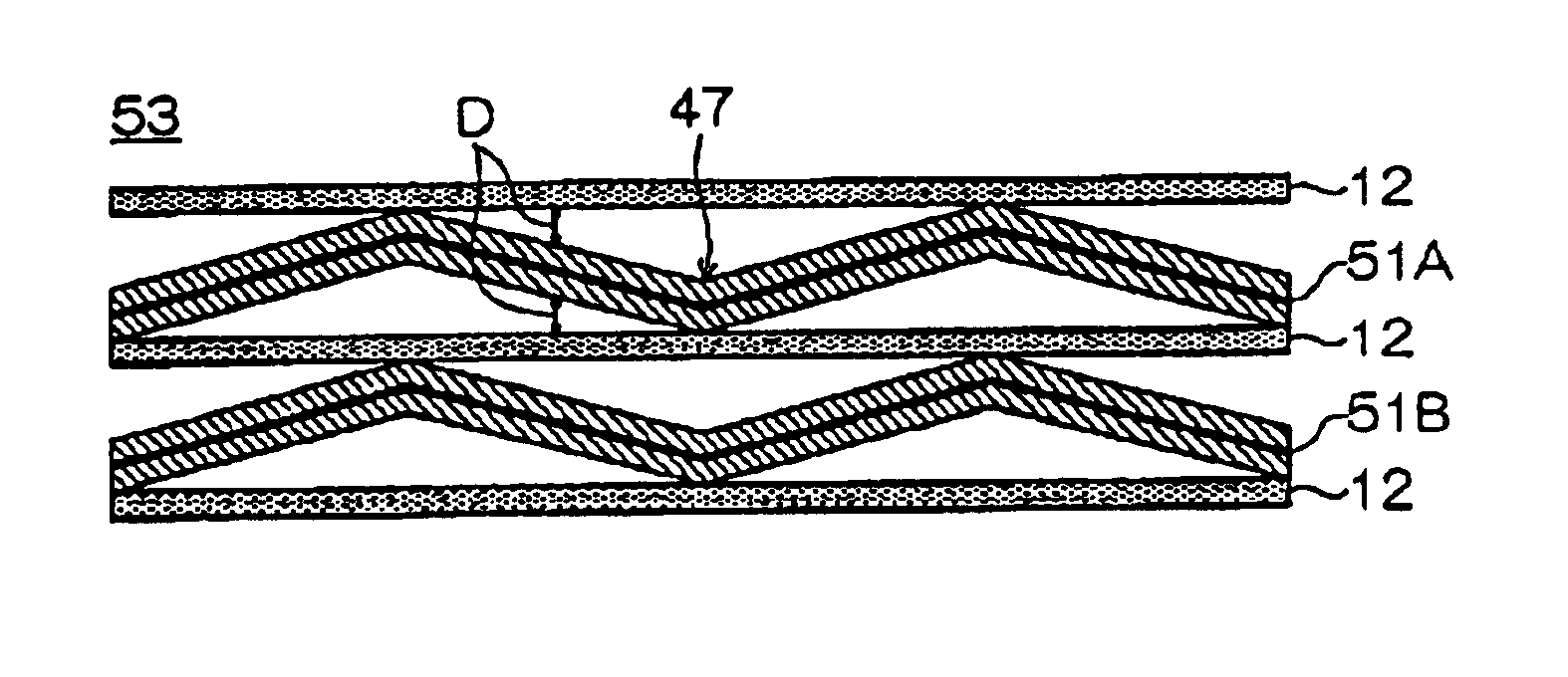

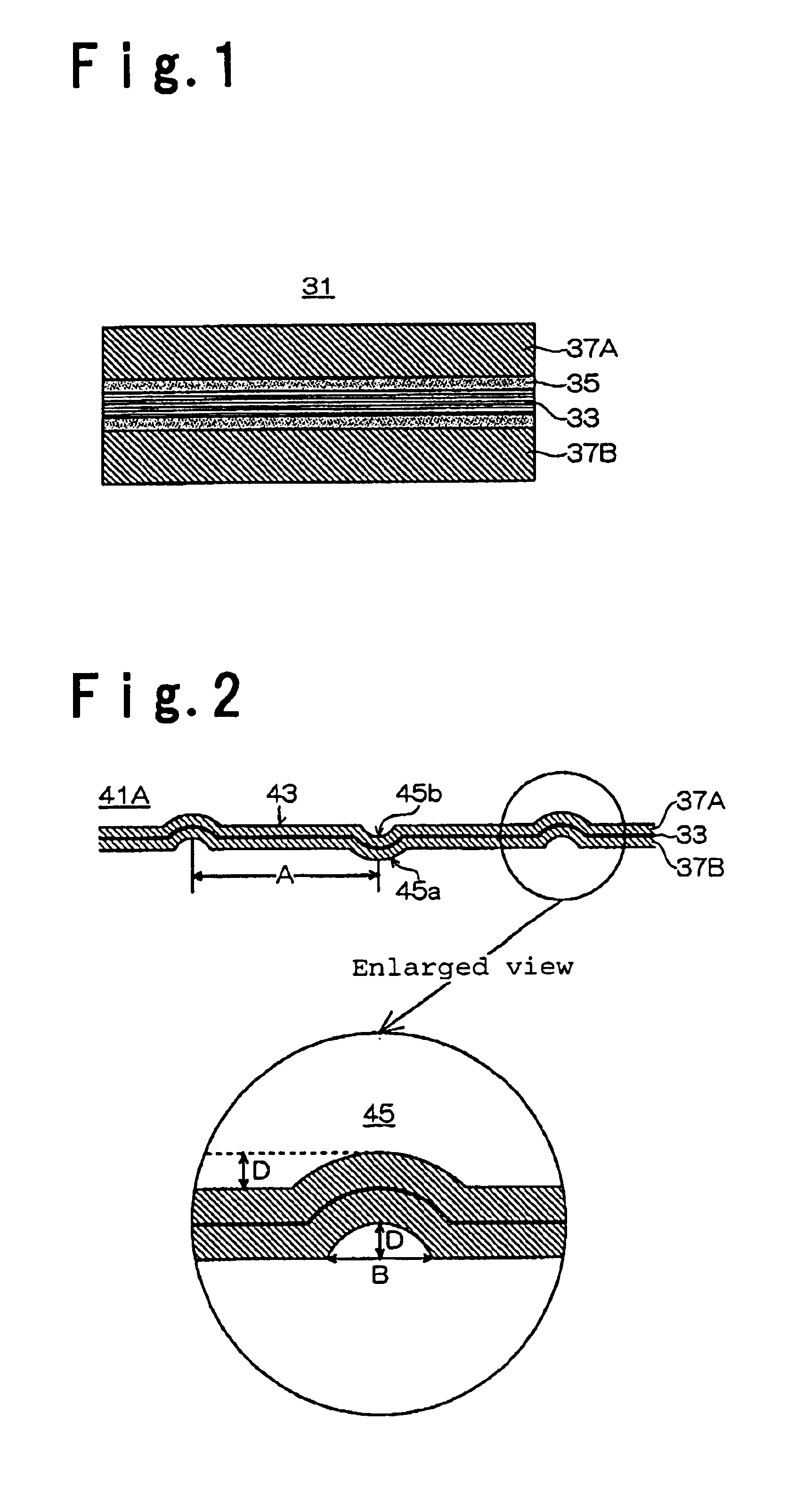

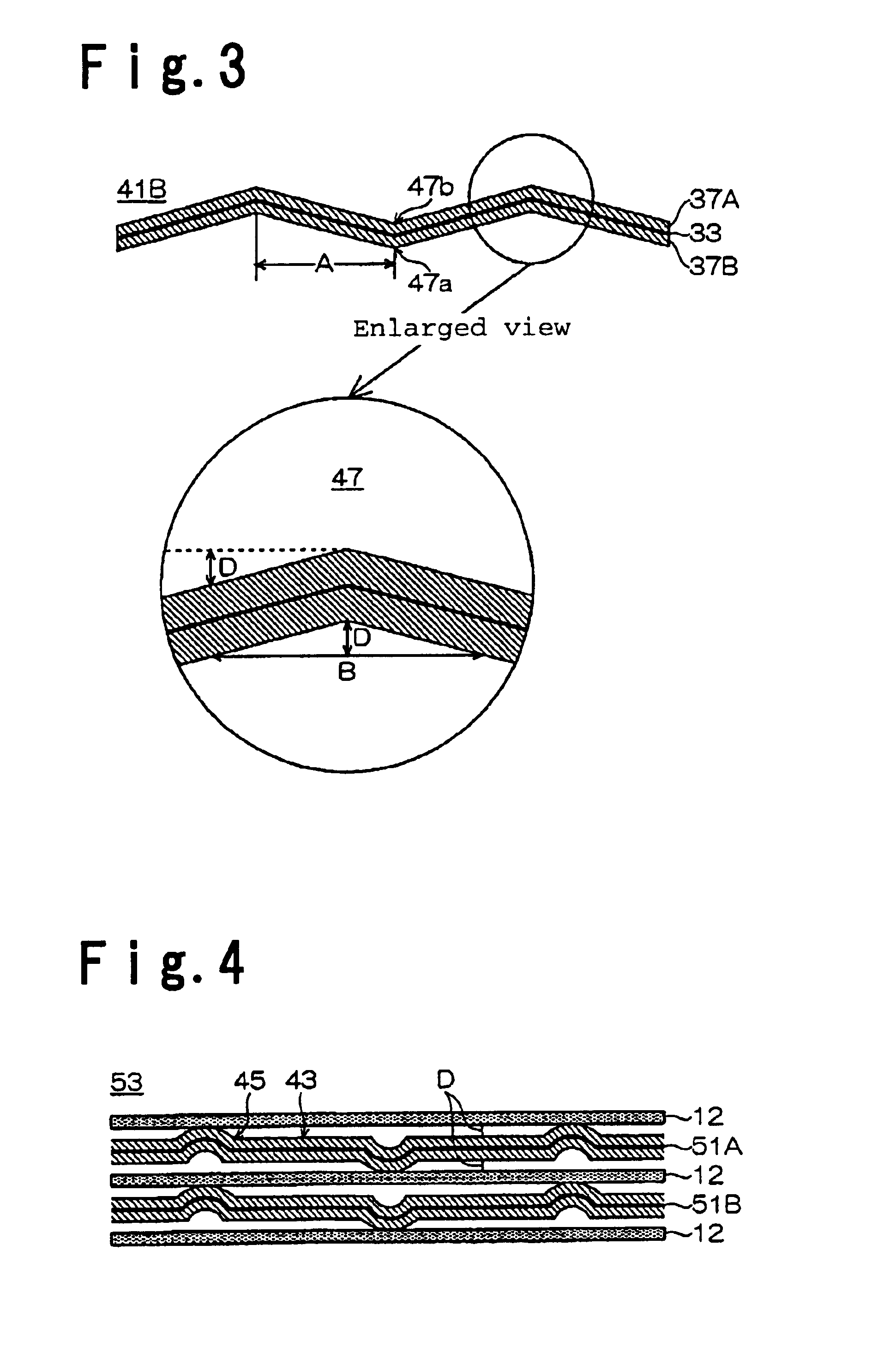

InactiveCN103714972AEasy to buyAvoid short circuit problemsLiquid electrolytic capacitorsFiberHigh energy

The invention discloses a linear secure high-energy-density supercapacitor and a preparation method thereof. The method comprises the following steps of 1) respectively taking two conducting fibers which are in core-shell structures as the anode and the cathode of the linear supercapacitor and twisting the two conducting fibers together to form the intertwisted anode and cathode; 2) coating gel electrolyte onto the surface of the anode and cathode and curing the gel electrolyte to form a gel electrolyte layer; 3) connecting the intertwisted anode and cathode coated with the gel electrolyte layer with lead wires respectively through conductive adhesive bonding or tin scolding methods. The preparation method is simple and is low in cost, strong in applicability, and suitable for large-scale industrial production. The produced linear supercapacitor is characterized by lightweight, security, high energy density, good flexibility, intertwining capability, and the like. The produced linear supercapacitor is applicable to flexible energy storage devices, lightweight portable electronic devices, military-use electronic clothes, and other fields.

Owner:ZHEJIANG UNIV

High capacitance density vertical natural capacitors

InactiveUS7466534B2Effective gap distanceIncrease capacitance densityTransistorThin/thick film capacitorDielectricCapacitance

Disclosed are embodiments of a capacitor with inter-digitated vertical plates and a method of forming the capacitor such that the effective gap distance between plates is reduced. This gap width reduction significantly increases the capacitance density of the capacitor. Gap width reduction is accomplished during back end of the line processing by masking connecting points with nodes, by etching the dielectric material from between the vertical plates and by etching a sacrificial material from below the vertical plates. Etching of the dielectric material from between the plates forms air gaps and various techniques can be used to cause the plates to collapse in on these air gaps, once the sacrificial material is removed. Any remaining air gaps can be filled by depositing a second dielectric material (e.g., a high k dielectric), which will further increase the capacitance density and will encapsulate the capacitor in order to make the reduced distance between the vertical plates permanent.

Owner:GLOBALFOUNDRIES INC

Capacitor having microstructures

ActiveUS7903387B2Increase capacitance densityLower ESLFixed capacitor electrodesFixed capacitor dielectricElectrical conductorPermittivity

A capacitor element includes a pair of conductor layers, a plurality of generally tube-shaped dielectric substances, a first electrode outside the dielectric substances and second electrodes in the insides thereof, and insulation caps for insulating the first electrode from the conductor layer, wherein an electrode material is filled in gaps of a structure of an oxide base material resulting from anodic oxidation of a metal, and then, the structure is removed and replaced by a high permittivity material.

Owner:TAIYO YUDEN KK

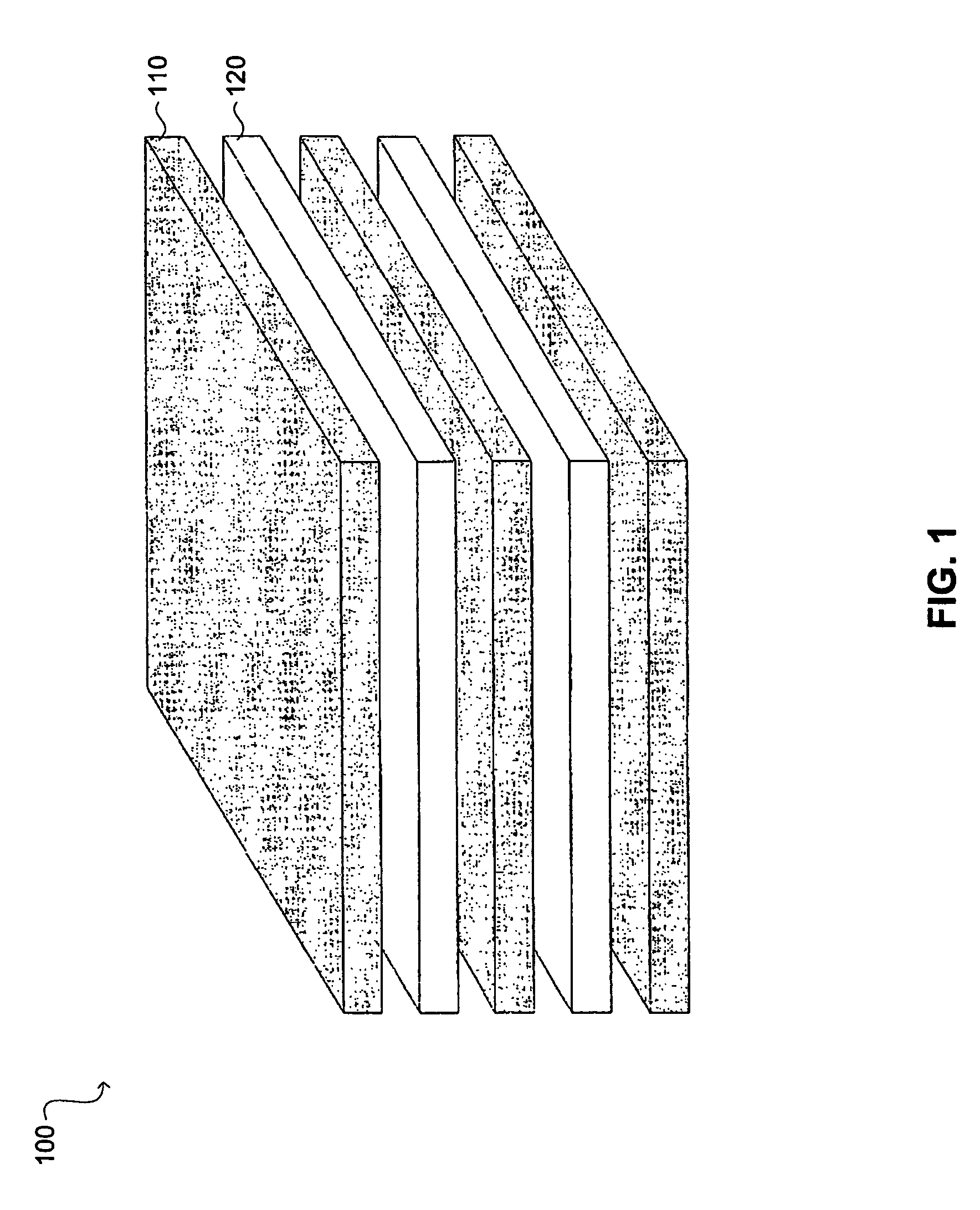

Integrated Power Passives

InactiveUS20100020509A1Reduce areaIncrease capacitance densityElectrolytic capacitorsDecorative surface effectsCapacitanceInductor

A multi-layer film-stack and method for forming the multilayer film-stack is given where a series of alternating layers of conducting and dielectric materials are deposited such that the conducting layers can be selectively addressed. The use of the method to form integratable high capacitance density capacitors and complete the formation of an integrated power system-on-a-chip device including transistors, conductors, inductors, and capacitors is also given.

Owner:UNIV OF FLORIDA RES FOUNDATION INC

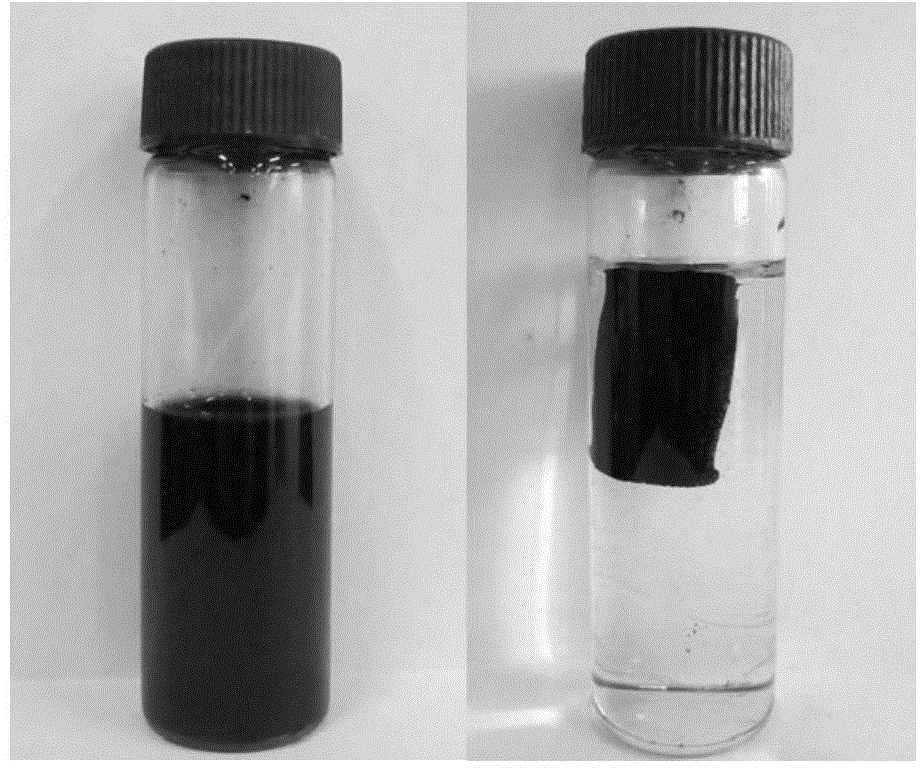

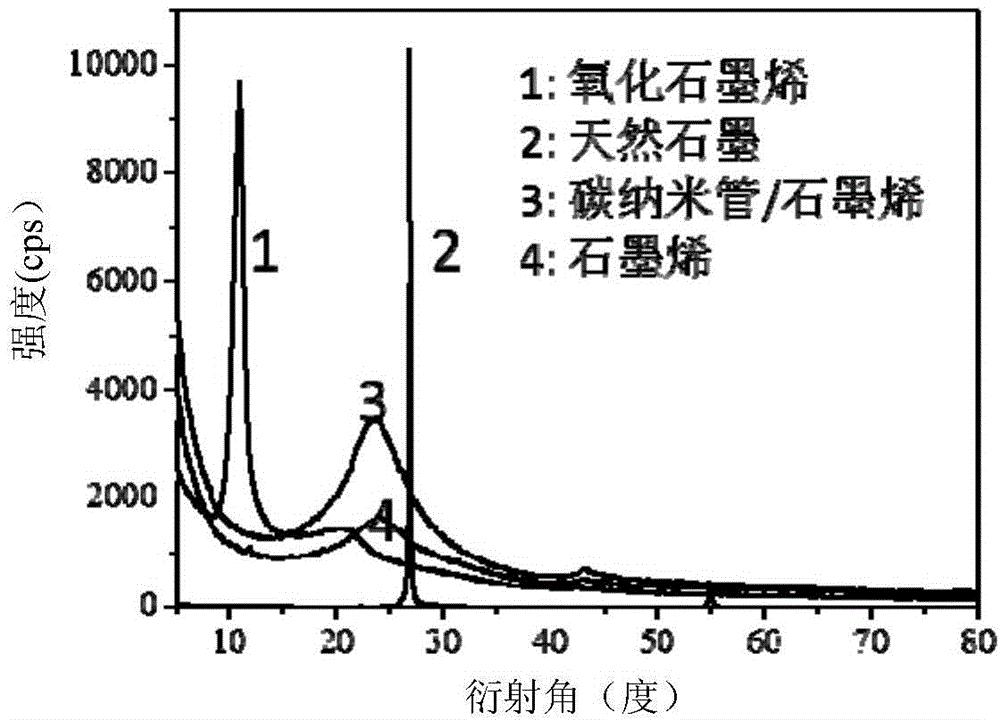

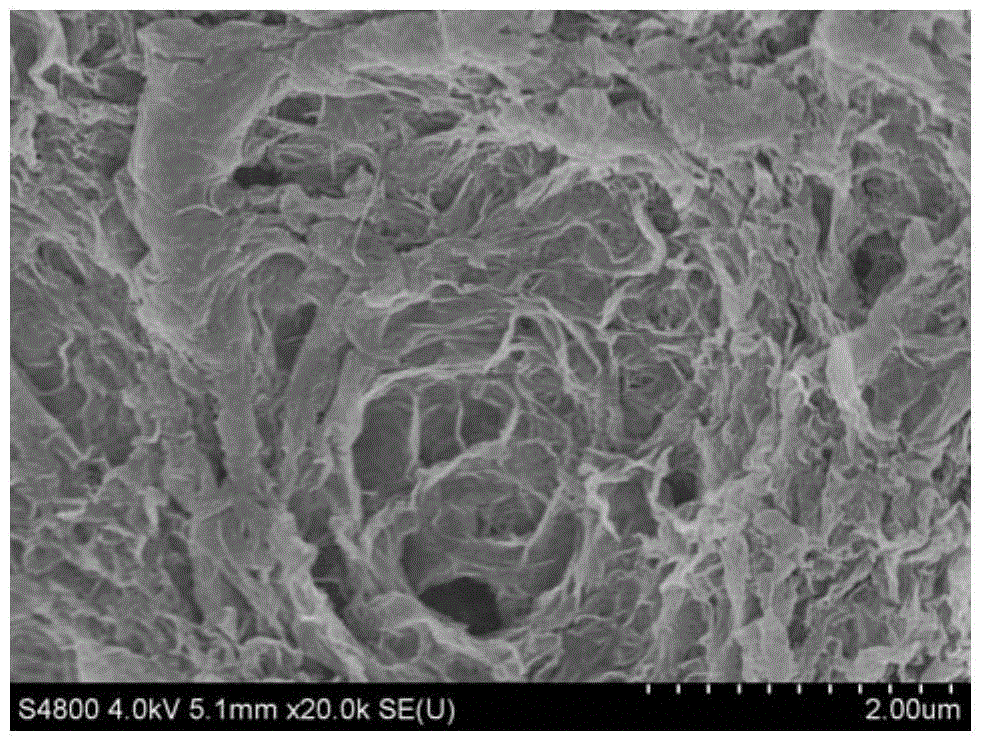

Carbon nanotube/graphene composite gel and preparation method thereof

InactiveCN105590757AAvoid reunionRaised Surface Area LowHybrid capacitor electrodesHybrid/EDL manufactureCarbon nanotubeCapacitance

The invention provides a carbon nanotube / graphene composite gel. In the carbon nanotube / graphene composite gel, carbon nanotubes are inserted into the graphene gel to form three-dimensional porous structure, thereby contributing to prevention of graphene interlayer agglomeration, increasing surface area, and improving the electrochemical performance of the carbon nanotube / graphene composite gel. A method for preparing the carbon nanotube / graphene composite gel comprises adding carbon nanotubes to a graphene oxide aqueous solution and dispersing the carbon nanotubes uniformly by a hydrothermal method; obtaining the carbon nanotube / graphene oxide composite gel by using thermal treatment; and obtaining the carbon nanotube / graphene composite gel by using reducing, cleaning, and drying methods. An experiment testifies that the carbon nanotube / graphene composite gel has higher conductivity than graphene gel and can be used as an electrode material. Used as the electrode material of a super capacitor, the carbon nanotube / graphene composite gel increases the specific capacitance and the power density of the super capacitor.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com