Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

104results about How to "Cost-effective fabrication" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

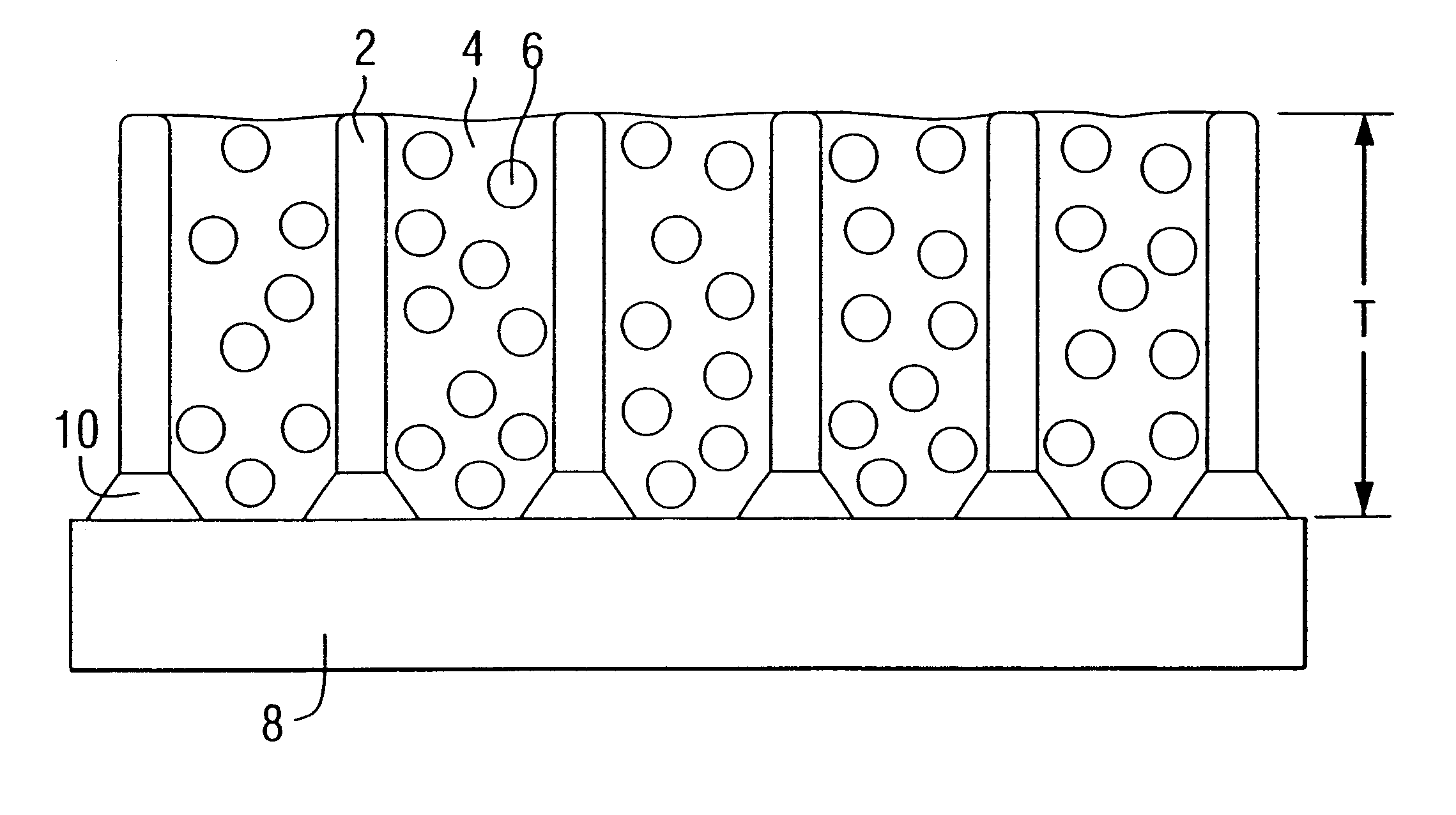

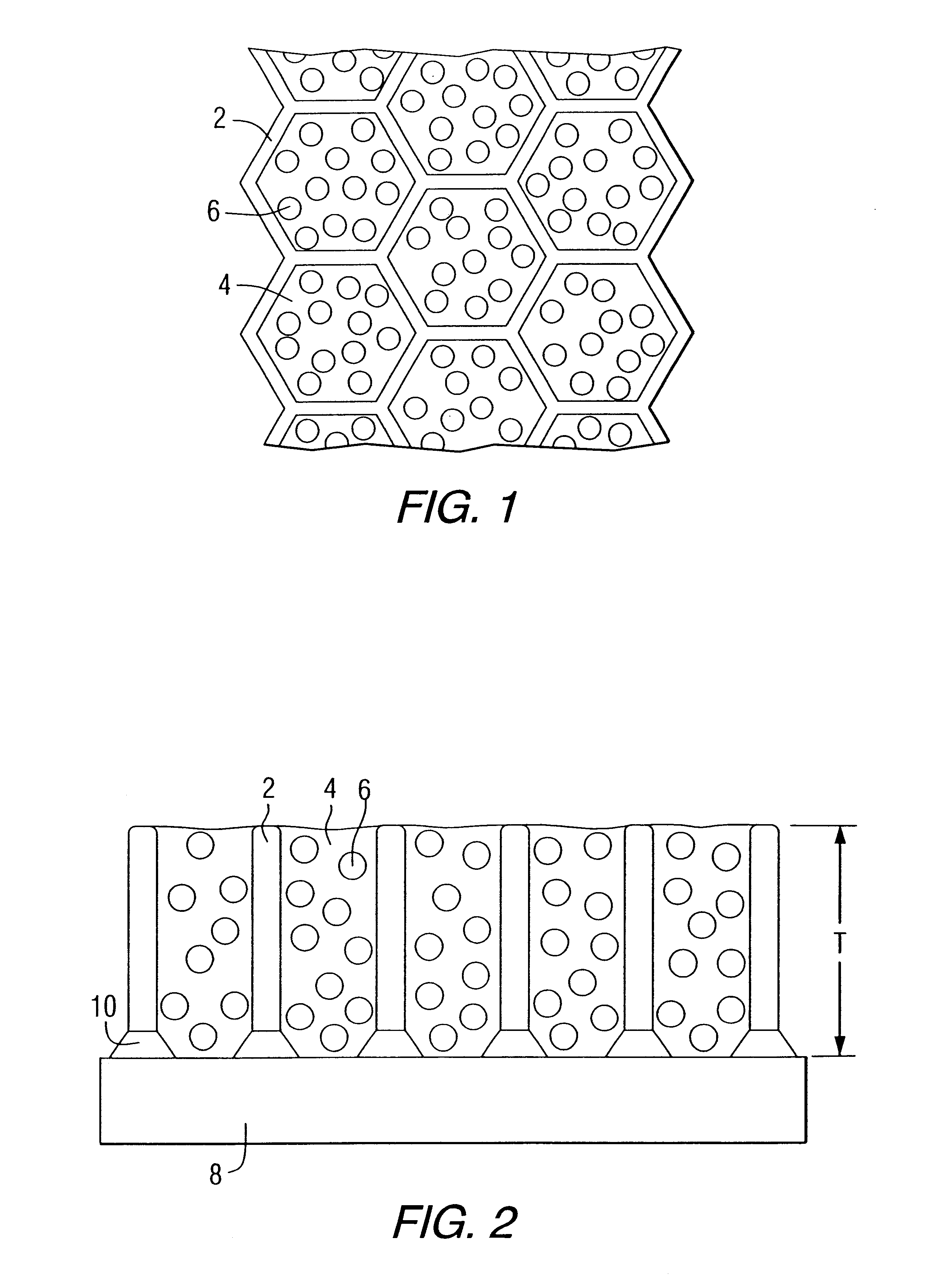

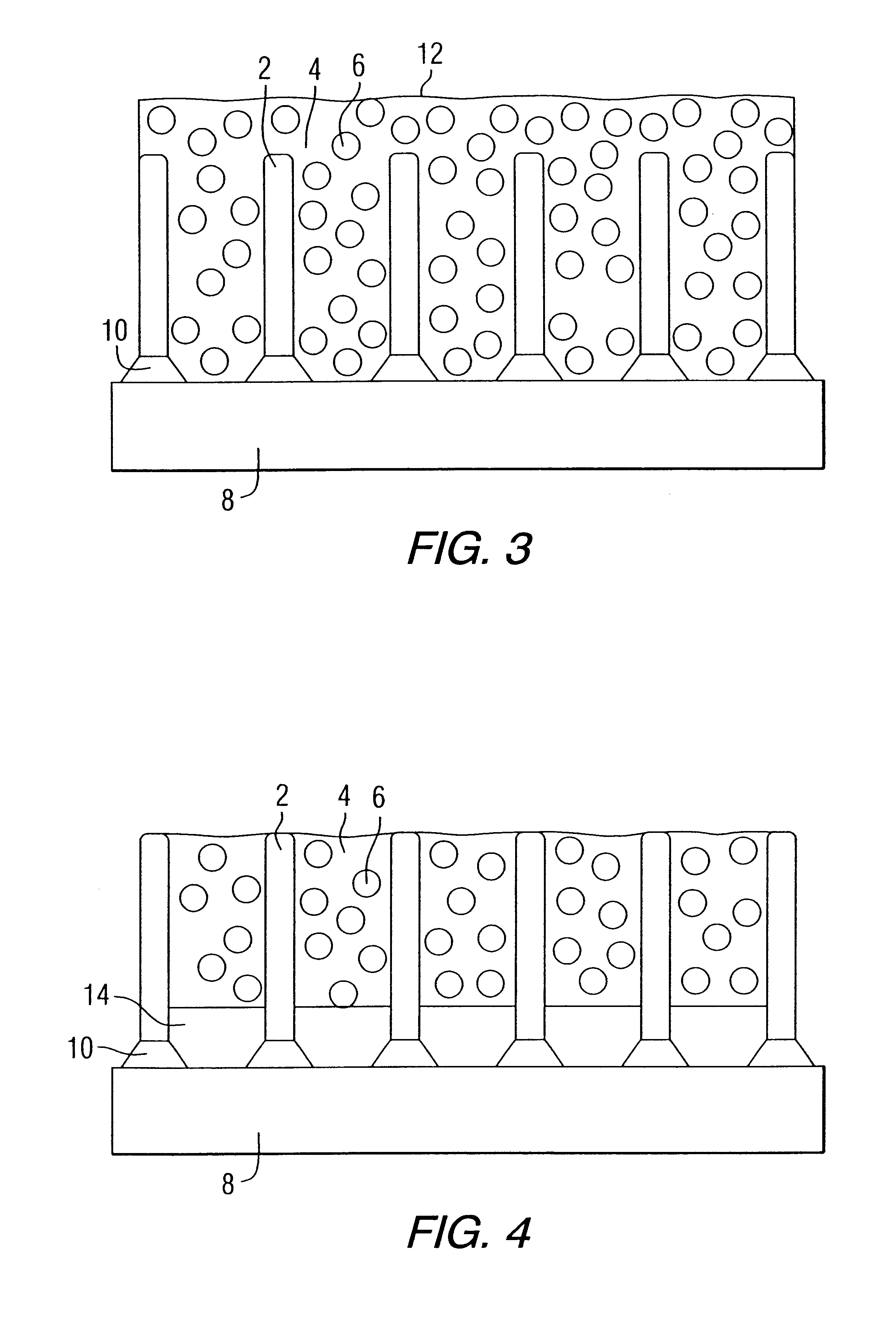

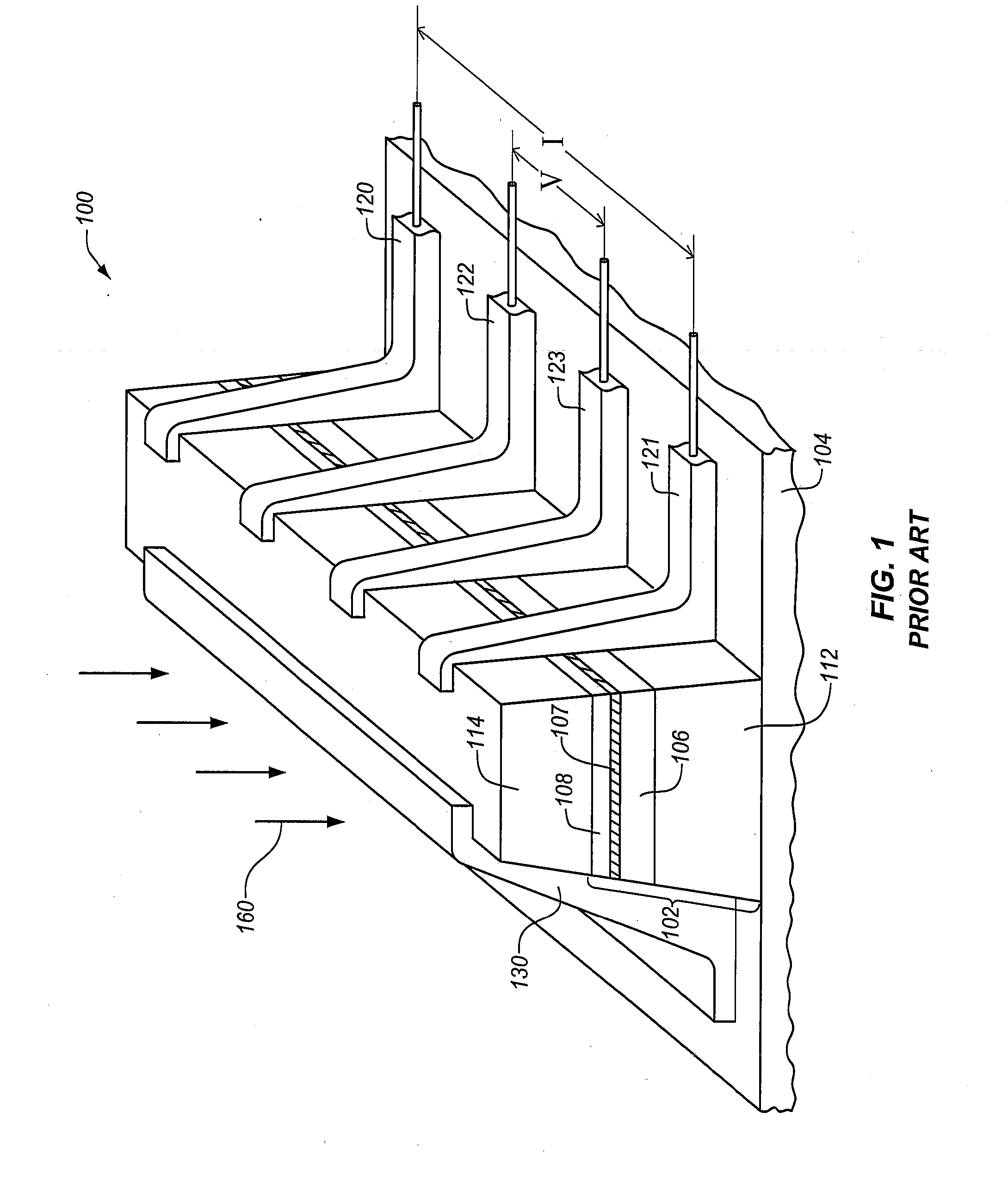

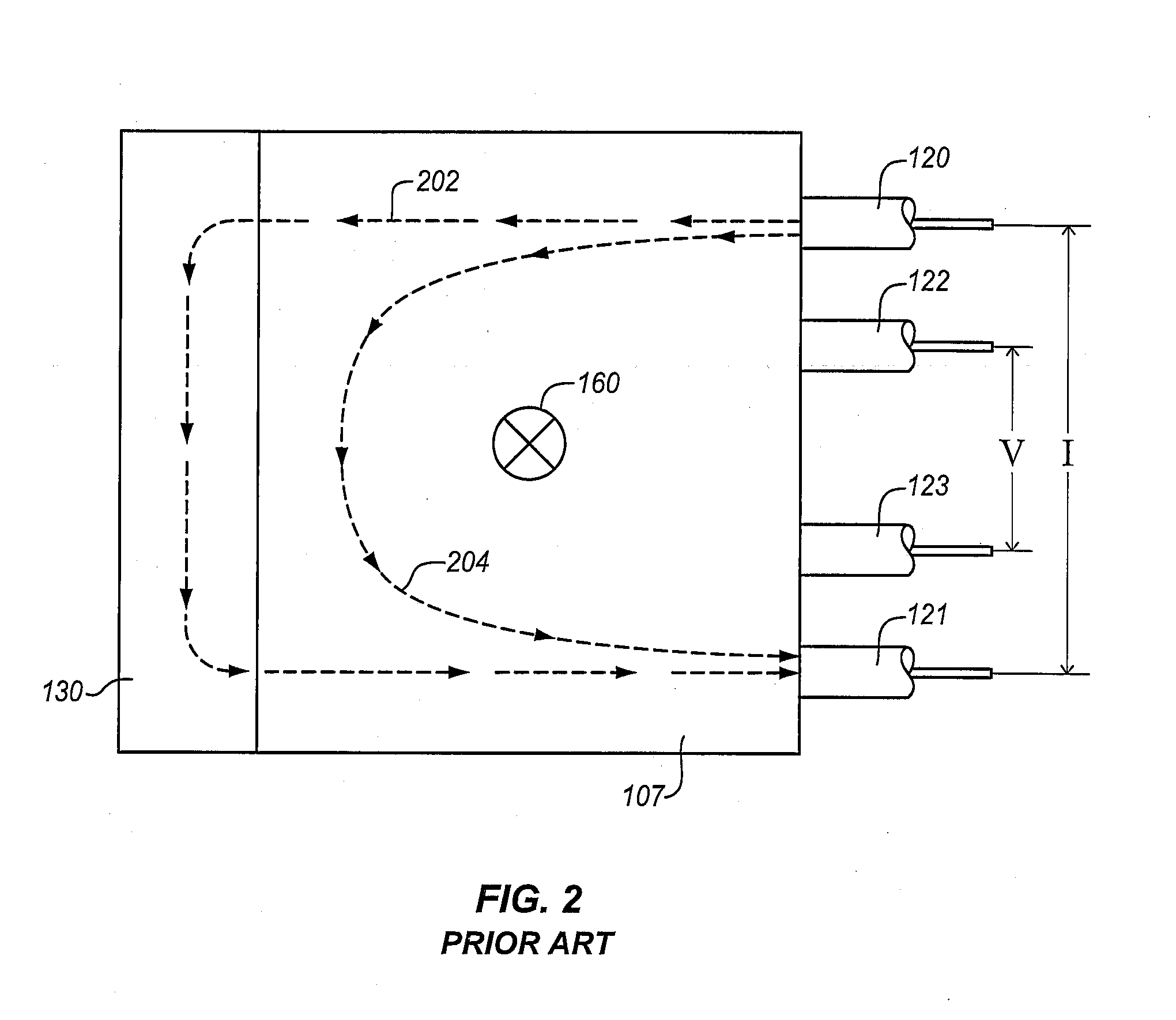

High temperature erosion resistant, abradable thermal barrier composite coating

InactiveUS6235370B1Improve wear resistanceImprove adhesionMolten spray coatingPump componentsCombustorHoneycomb

A composite thermal barrier coating system includes a honeycomb metallic structure filled with high thermal expansion ceramic hollow spheres in a phosphate bonded matrix. The composite thermal barrier coating system may be manufactured to thicknesses in excess of current thermal barrier coating systems, thereby imparting greater thermal protection. Superior erosion resistance and abrasion properties are also achieved. The composite thermal barrier coating is useful on combustion turbine components such as ring seal segments, vane segment shrouds, transitions and combustors.

Owner:SIEMENS ENERGY INC

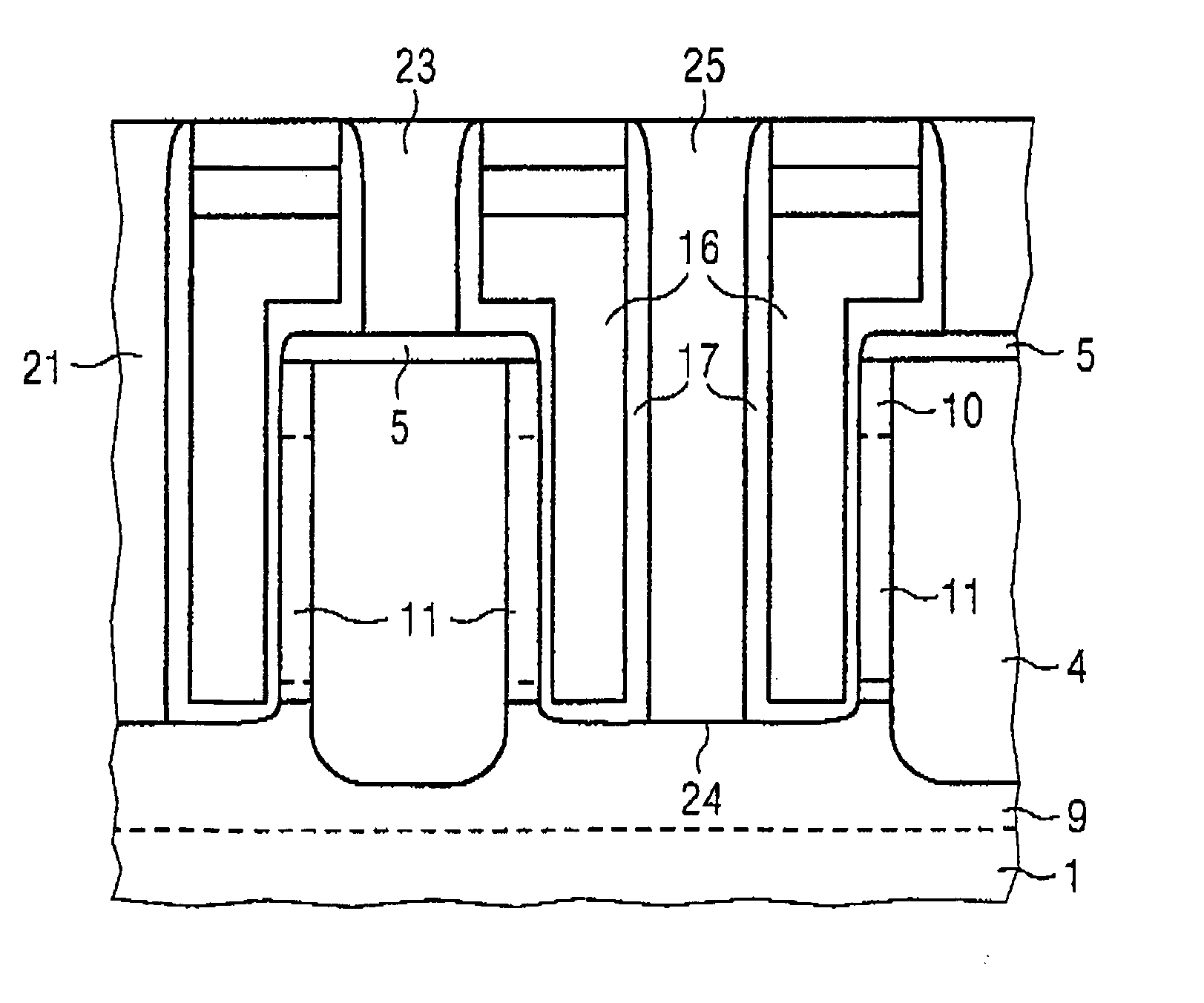

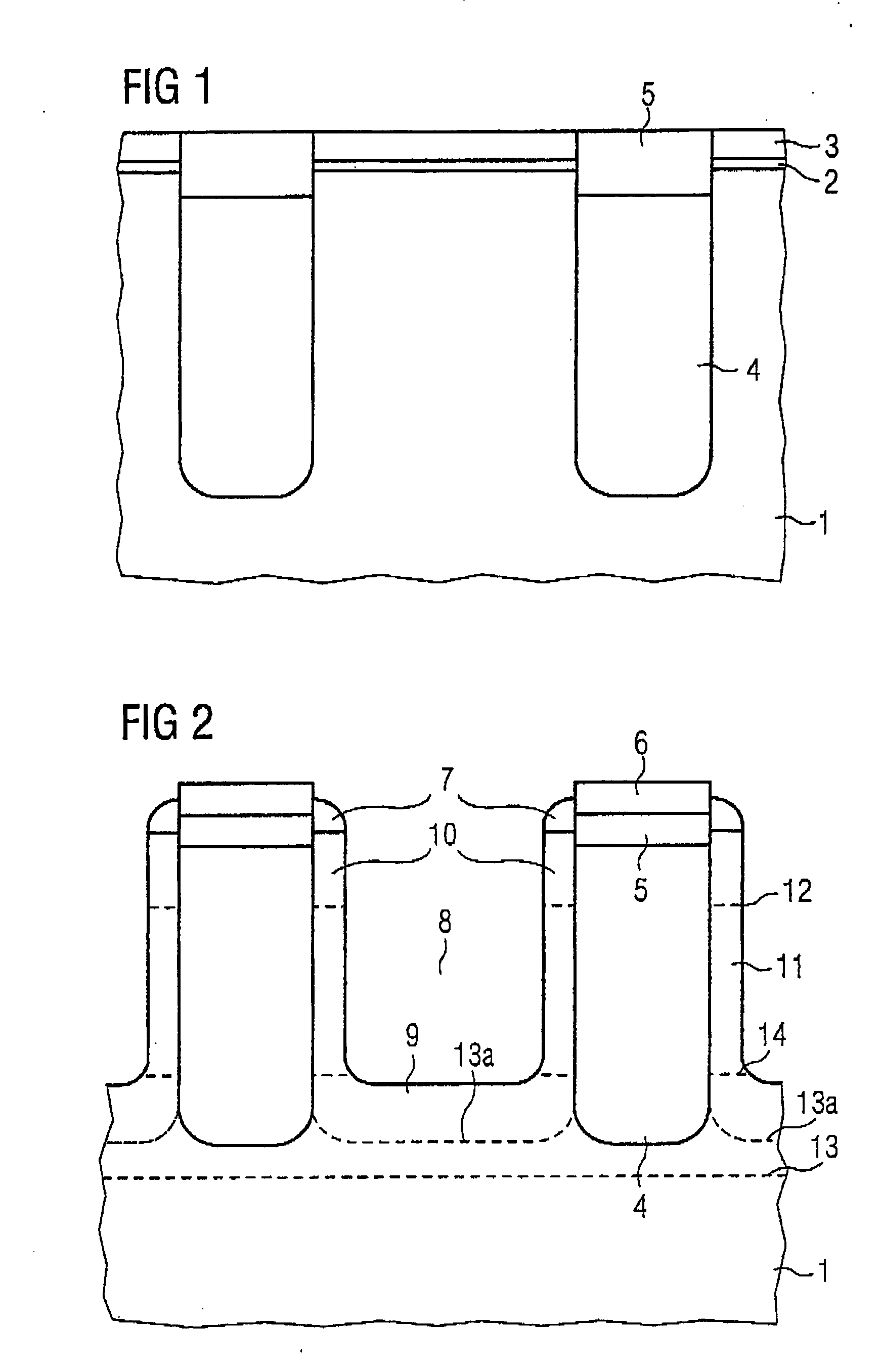

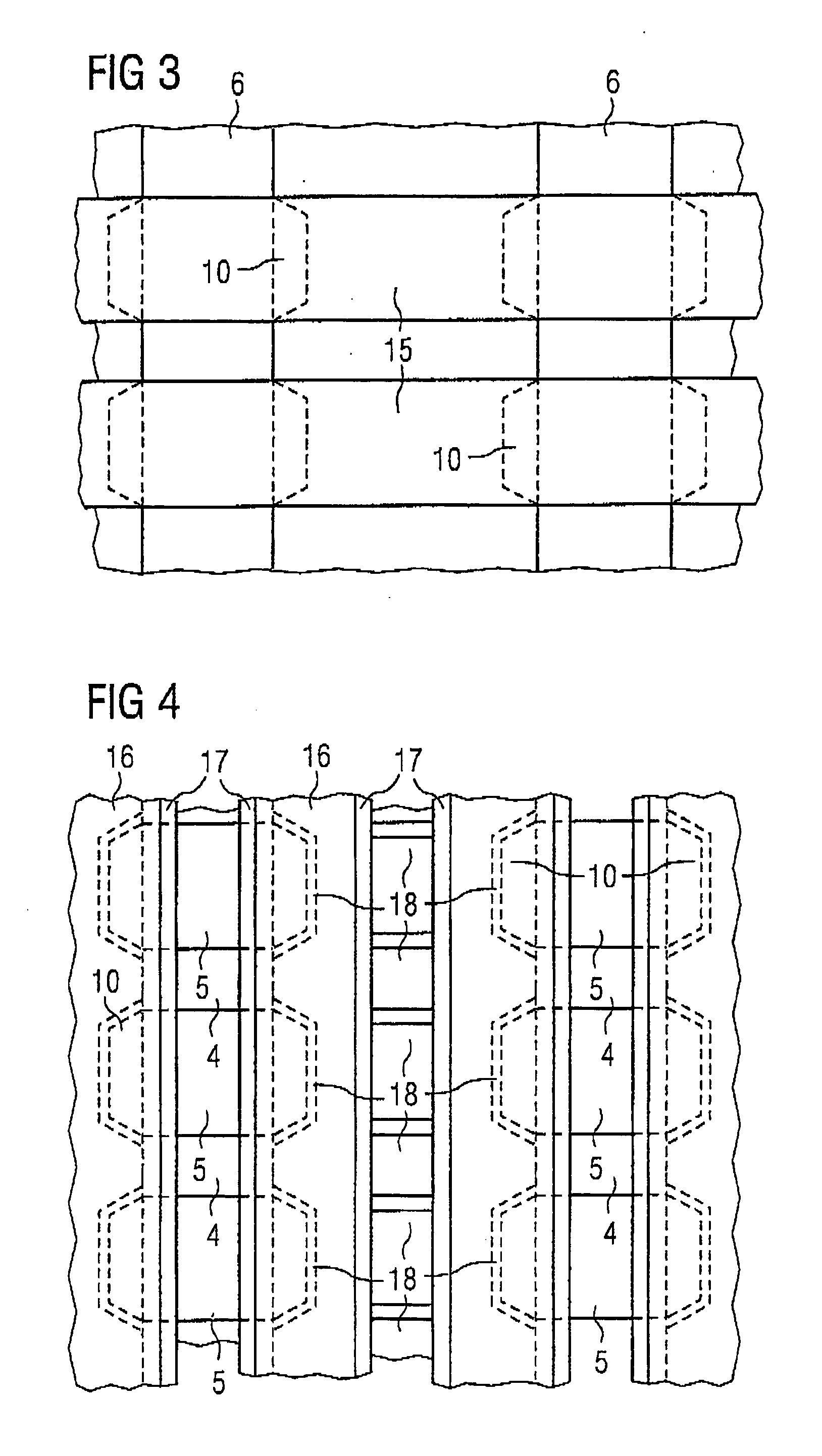

Capacitorless 1-transistor DRAM cell and fabrication method

InactiveUS20050064659A1Cost-effectiveCost-effective fabricationTransistorSolid-state devicesCapacitanceGate dielectric

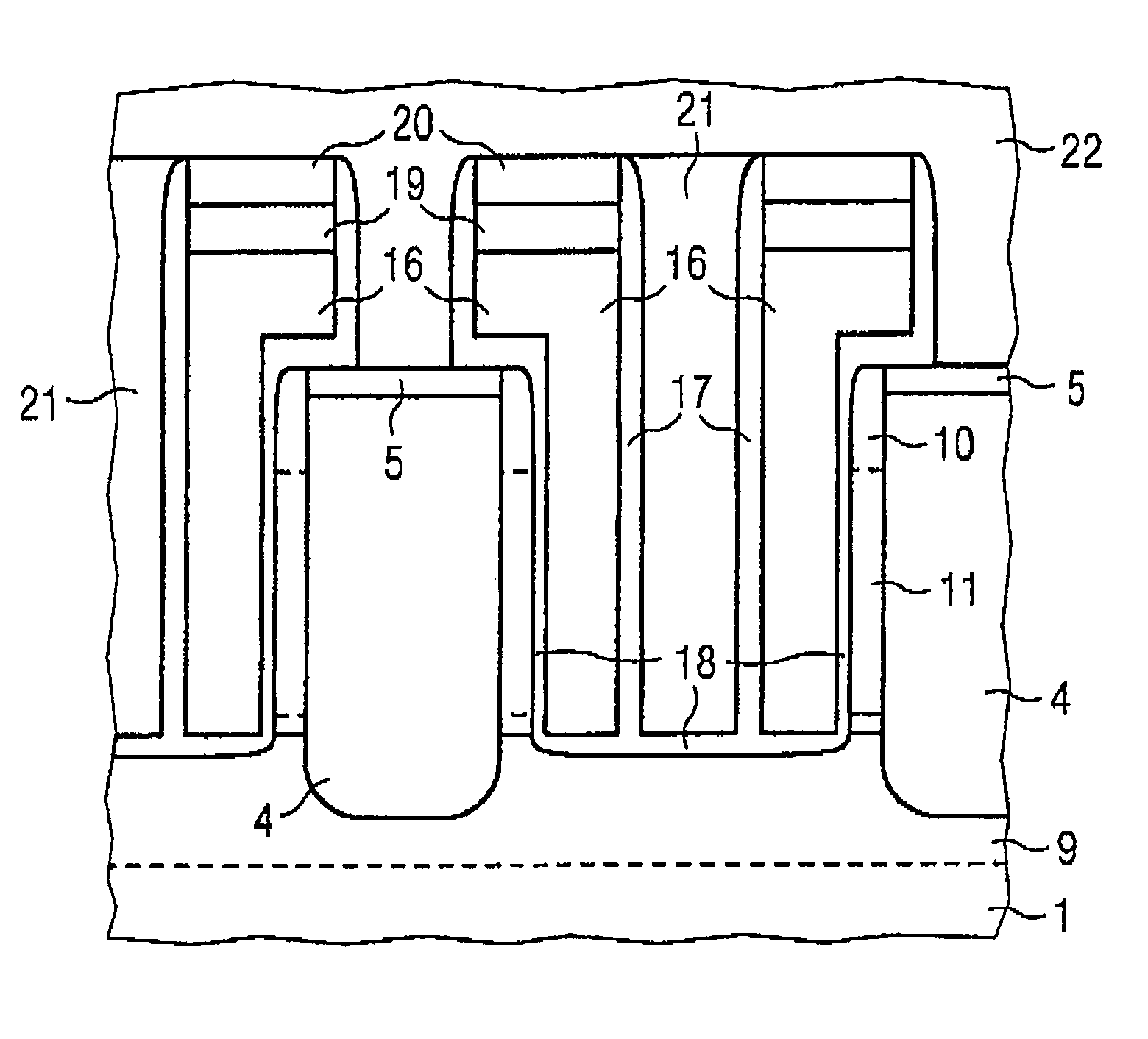

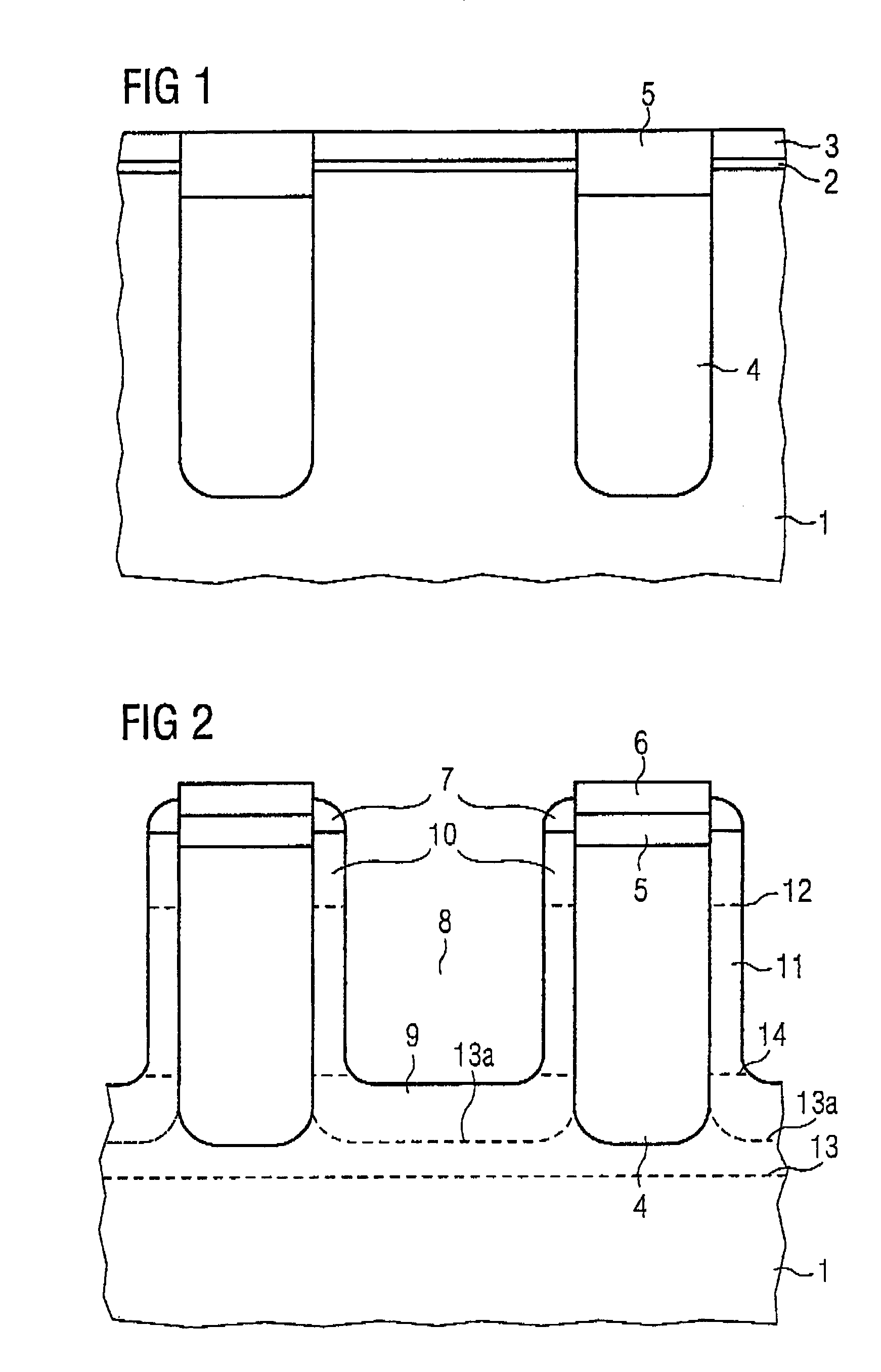

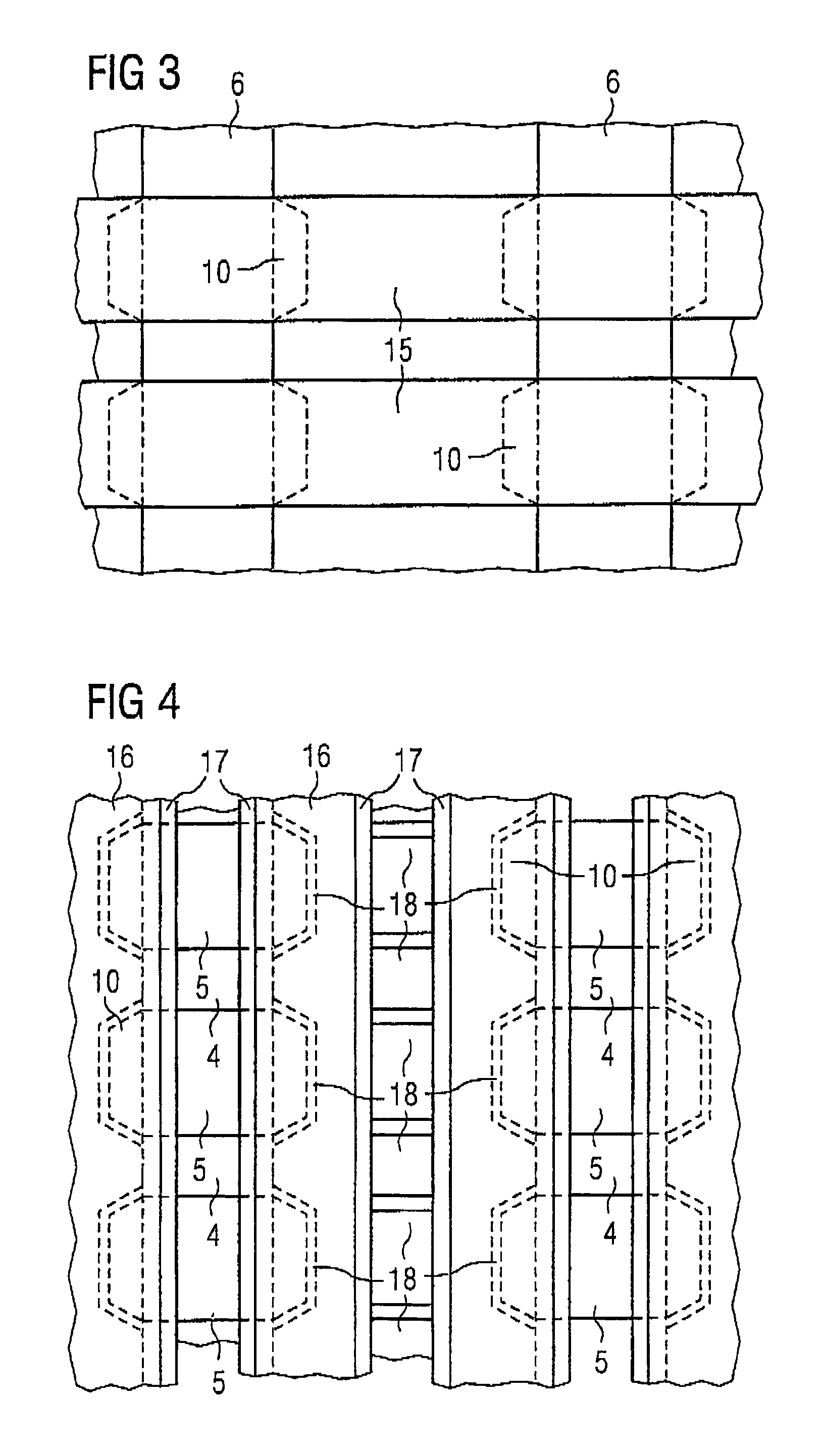

The channel region (11) and the source-drain regions (9, 10) are arranged vertically at a sidewall of a dielectric trench filling (4). On the opposite side, the semiconductor material is bounded by the gate dielectric (18) and the gate electrode (16), which is arranged in a cutout of the semiconductor material. A memory cell array comprises a multiplicity of vertically oriented strip-type semiconductor regions in which source-drain regions are implanted at the top and bottom and a channel region embedded in insulating material on all sides is present in between as a floating body.

Owner:POLARIS INNOVATIONS

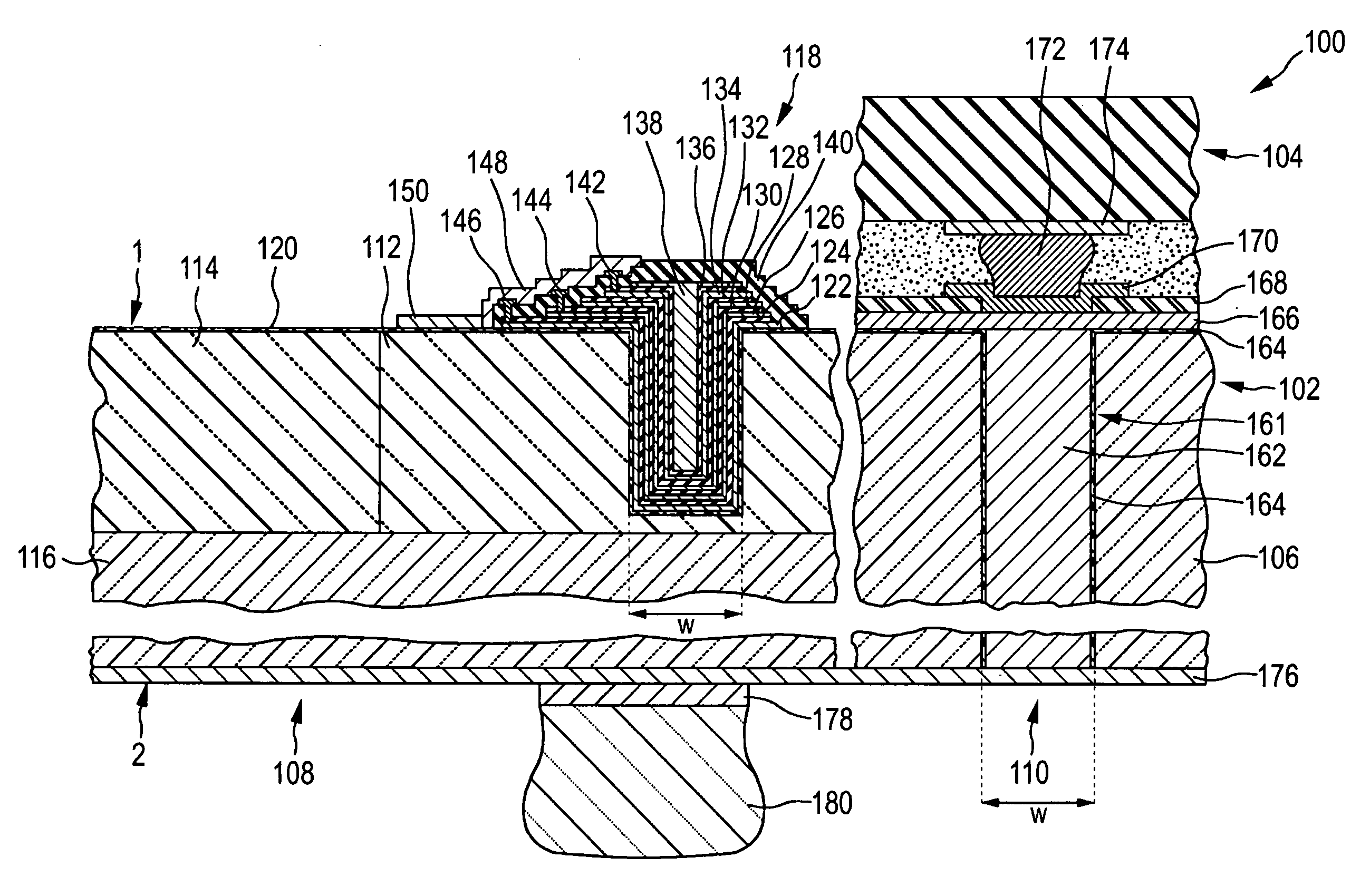

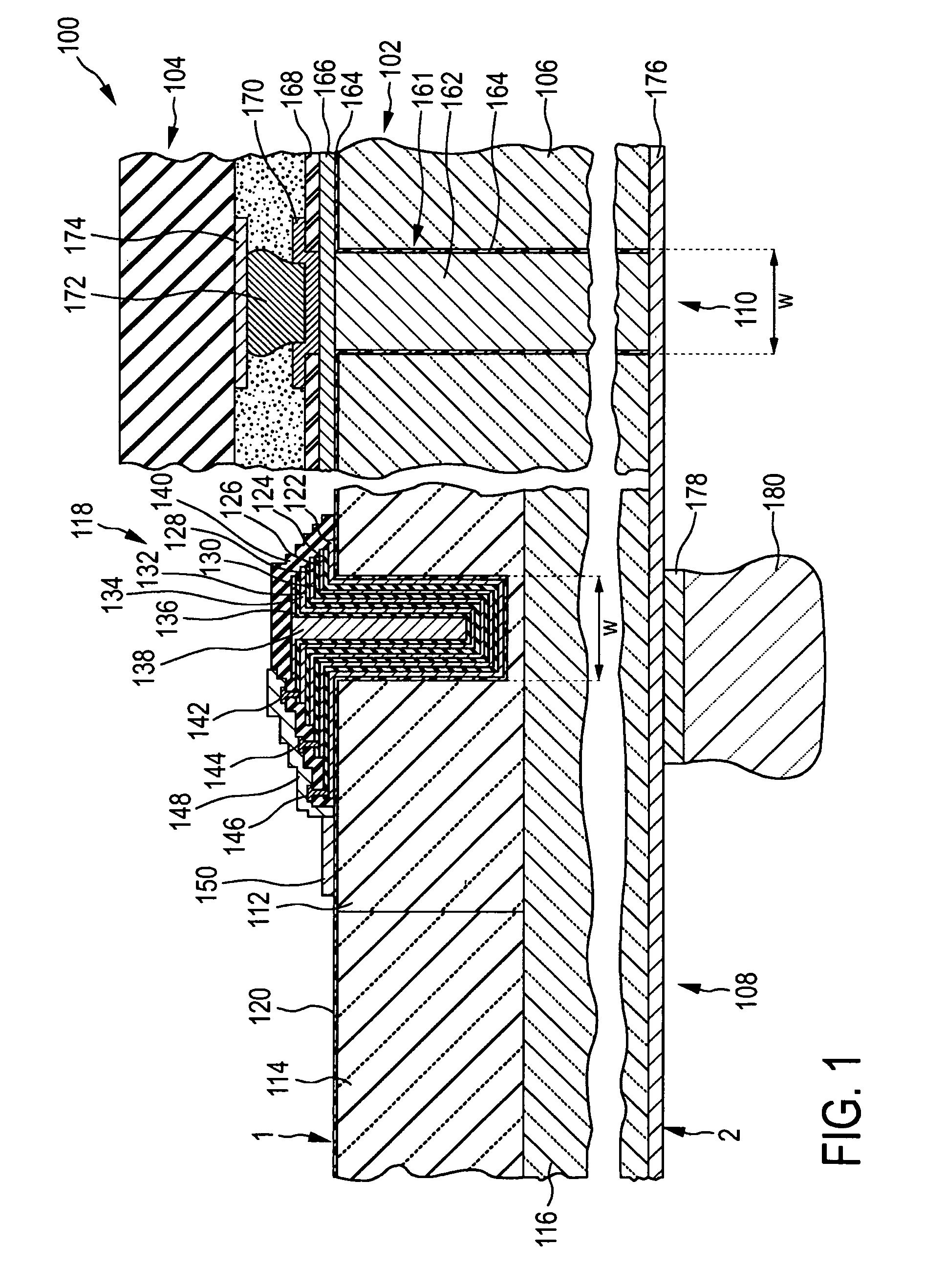

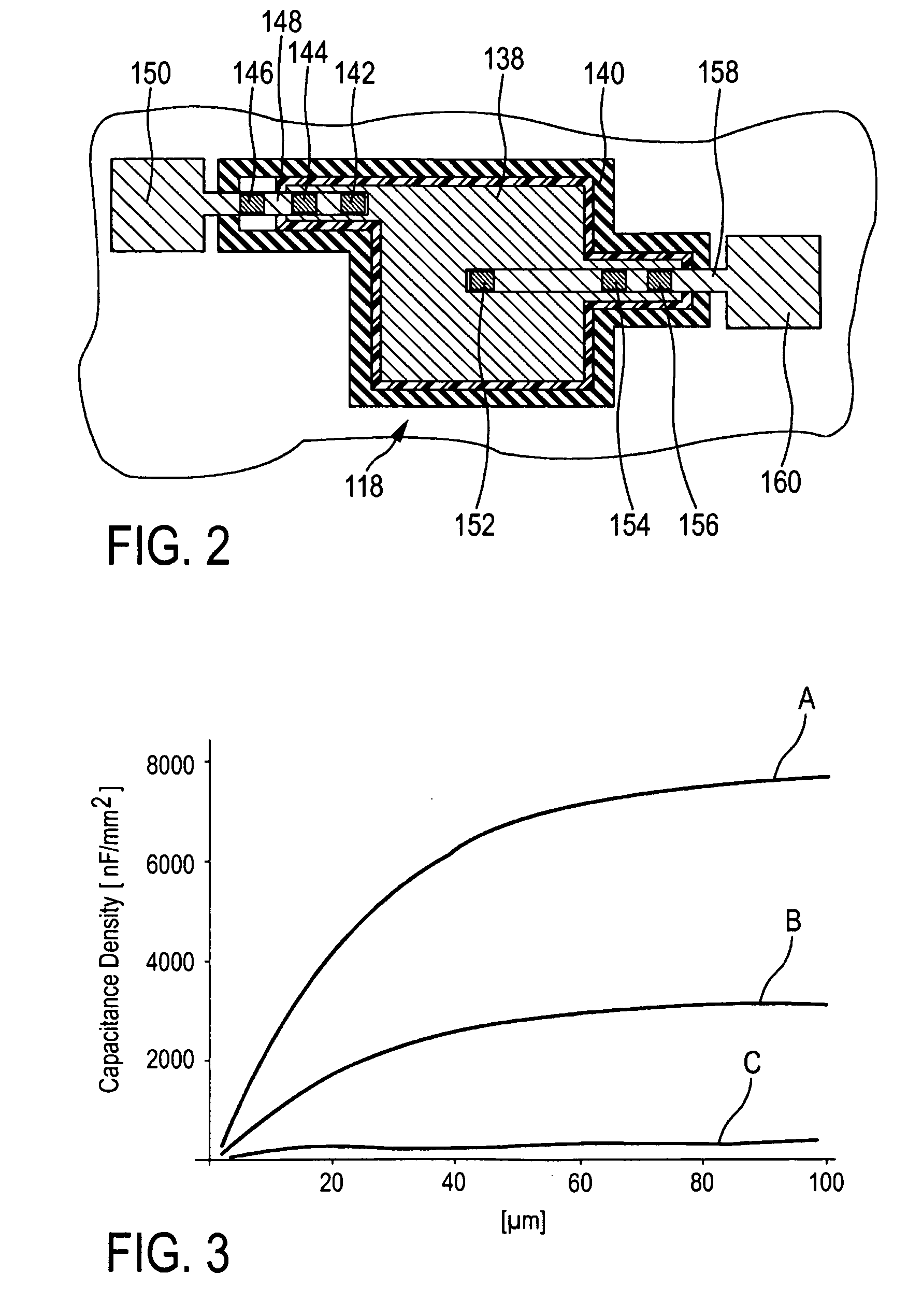

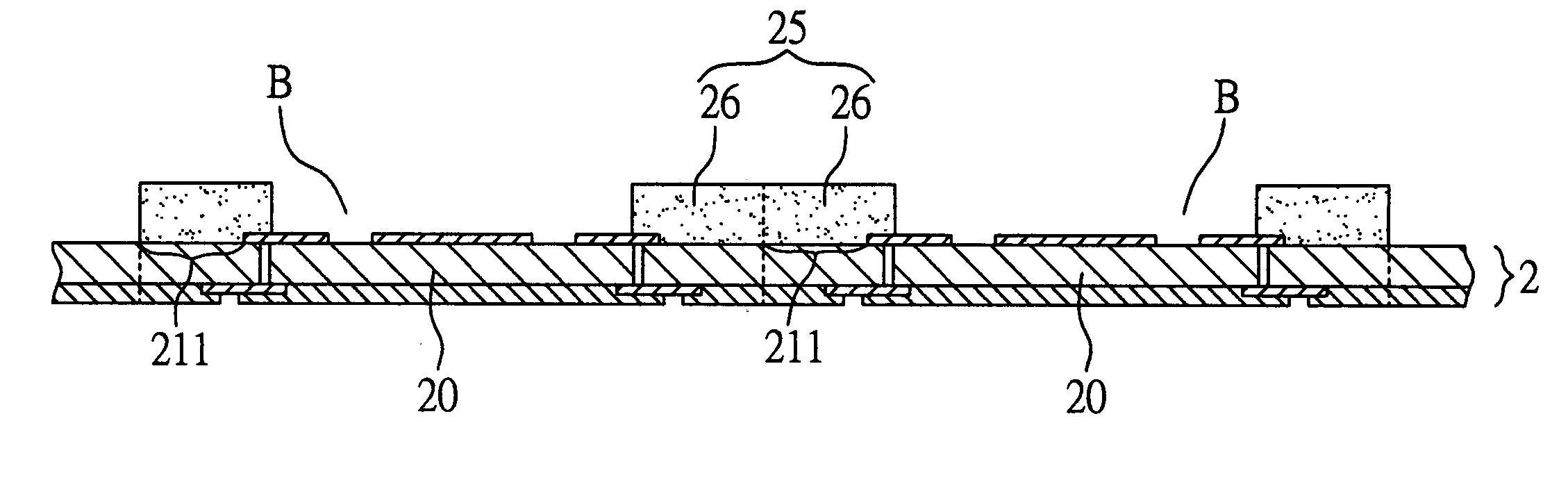

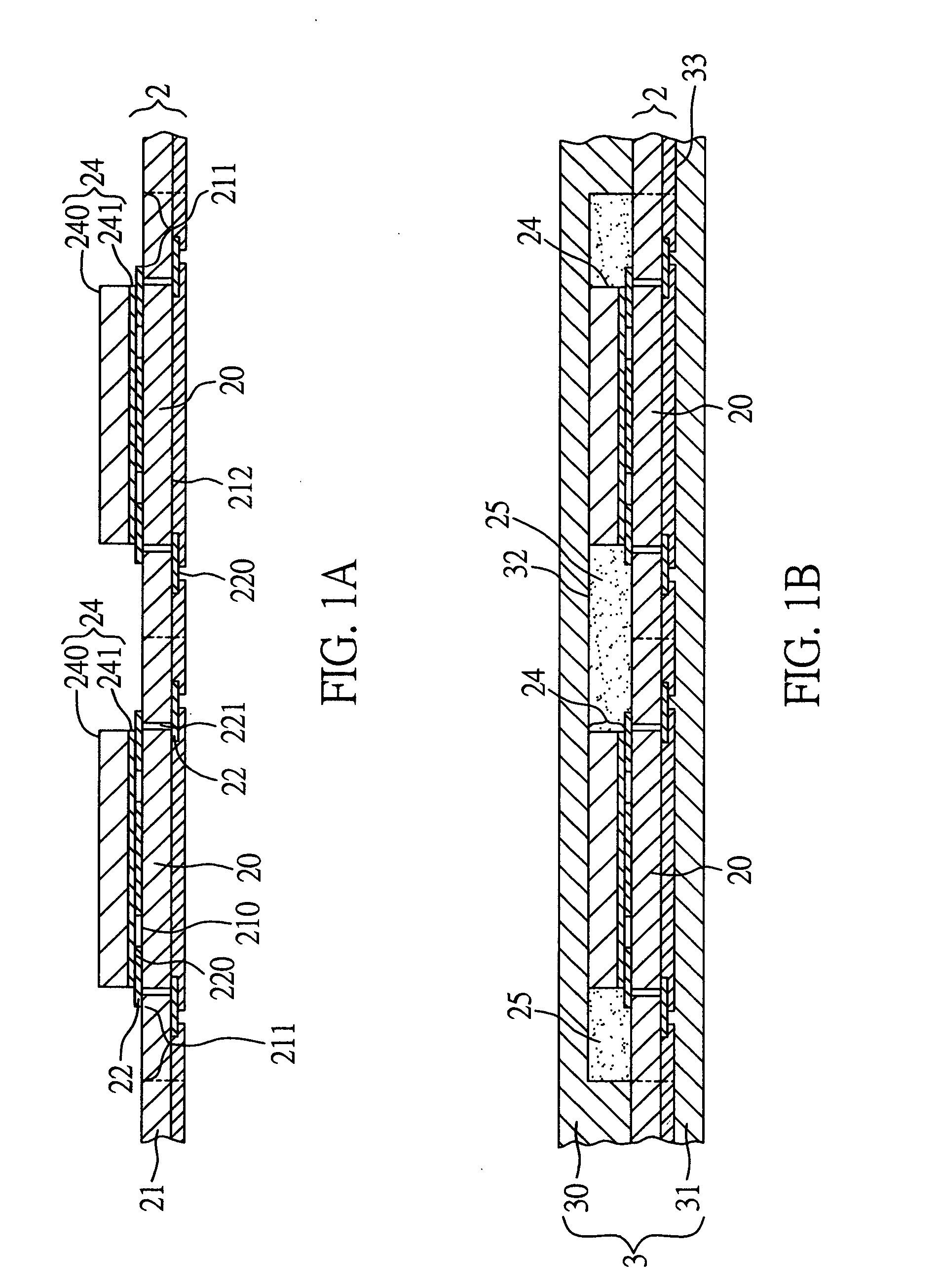

Integration substrate with a ultra-high-density capacitor and a through-substrate via

ActiveUS20100244189A1Simple to introduce into existing production lineIncrease capacitance densitySemiconductor/solid-state device detailsSolid-state devicesMicrometerEngineering

An integration substrate for a system in package comprises a through-substrate via and a trench capacitor wherein with a trench filling that includes at least four electrically conductive capacitor-electrode layers in an alternating arrangement with dielectric layers. —The capacitor-electrode layers are alternatingly connected to a respective one of two capacitor terminals provided on the first or second substrate side. The trench capacitor and the through-substrate via are formed in respective trench openings and via openings in the semiconductor substrate, which have an equal lateral extension exceeding 10 micrometer. This structure allows, among other advantages, a particularly cost-effective fabrication of the integration substrate because the via openings and the trench openings in the substrate can be fabricated simultaneously.

Owner:MURATA INTEGRATED PASSIVE SOLUTIONS

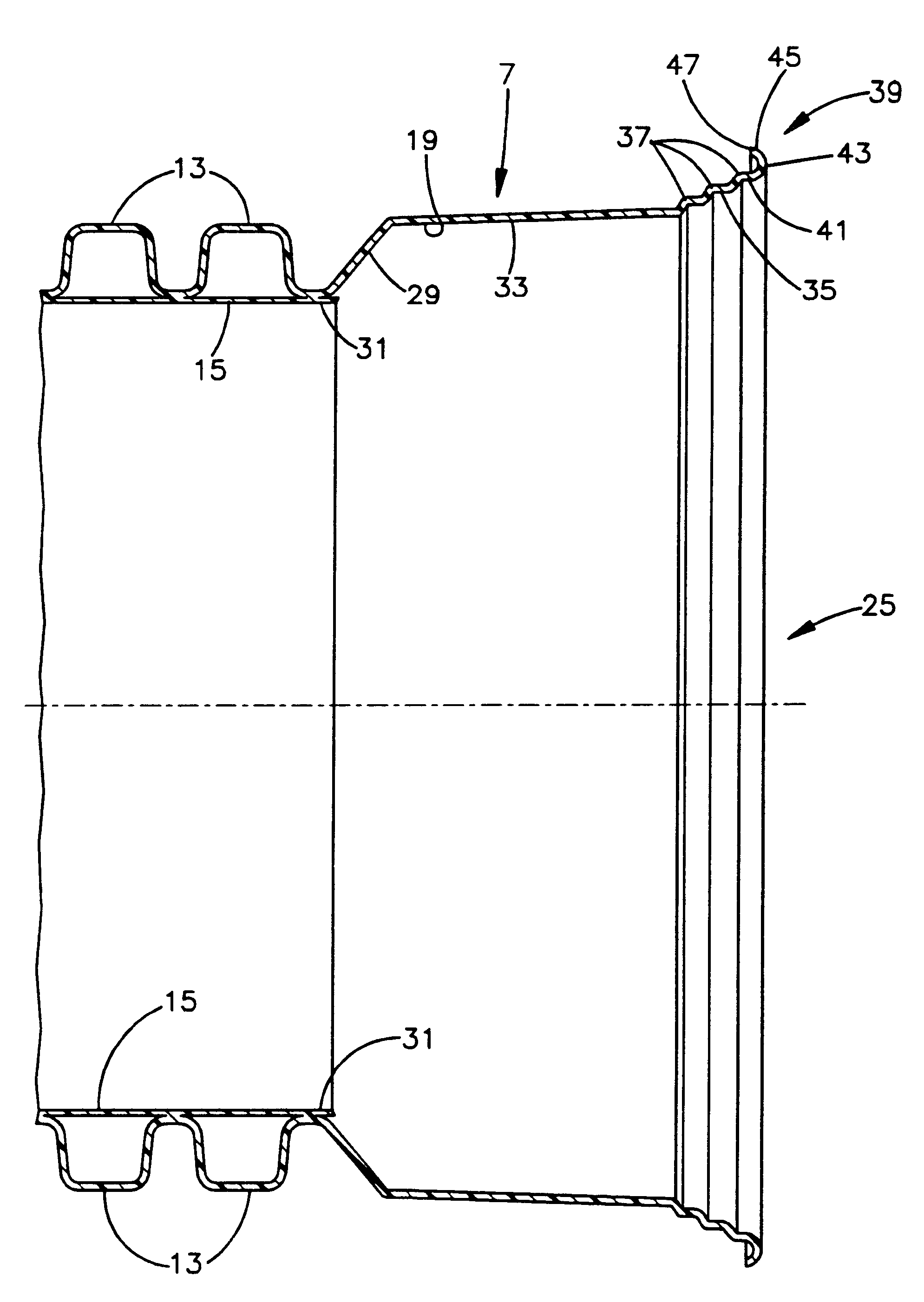

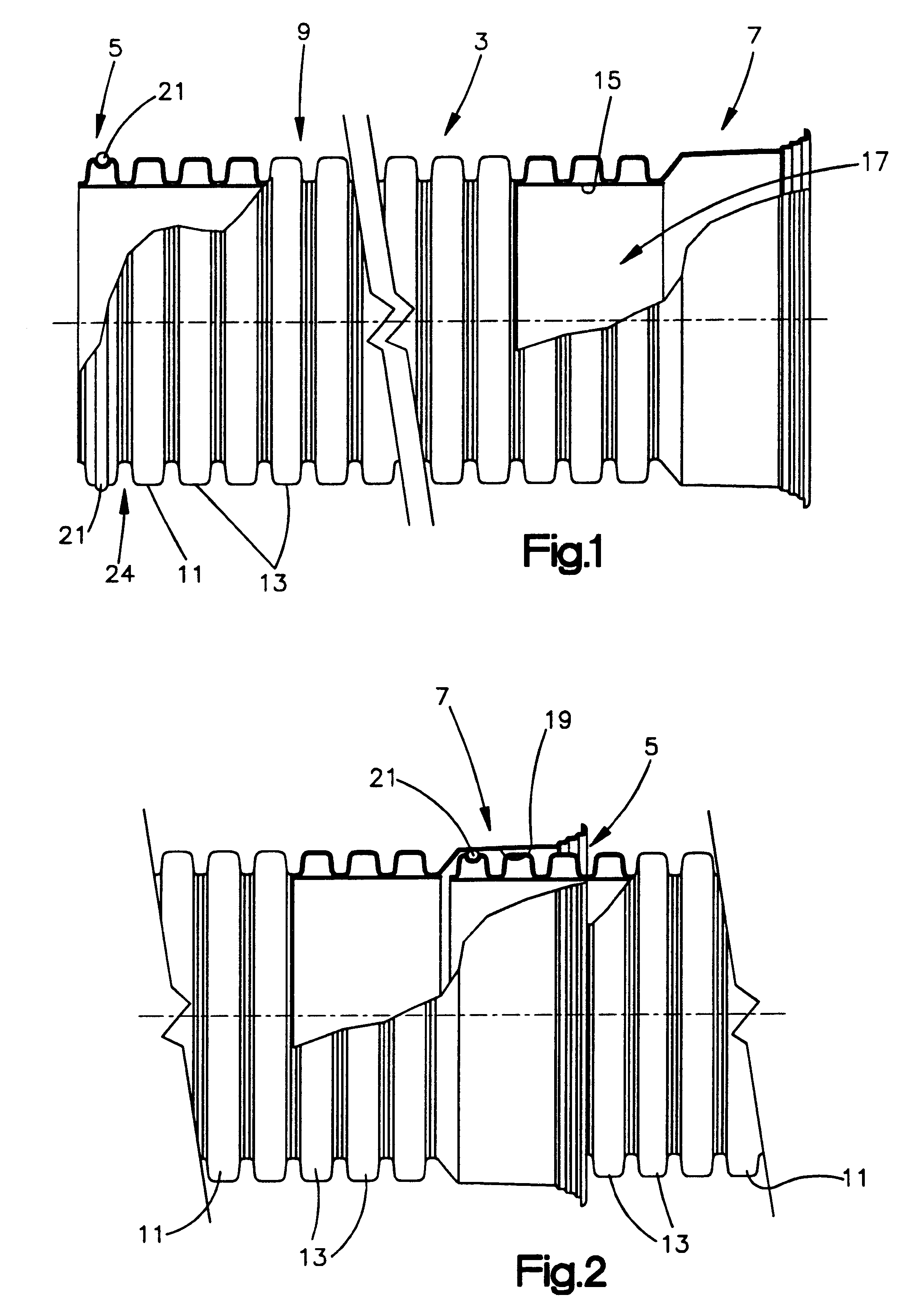

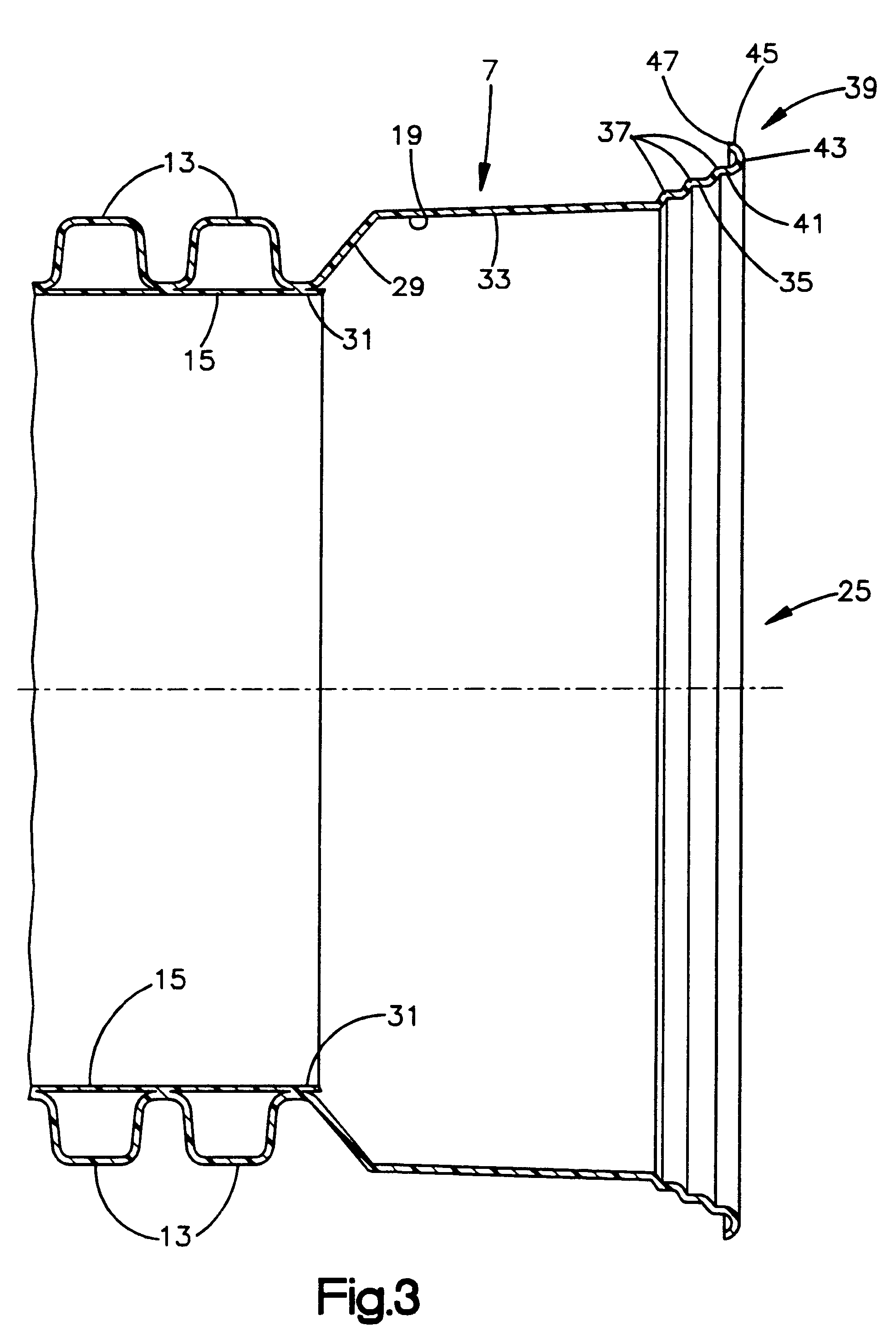

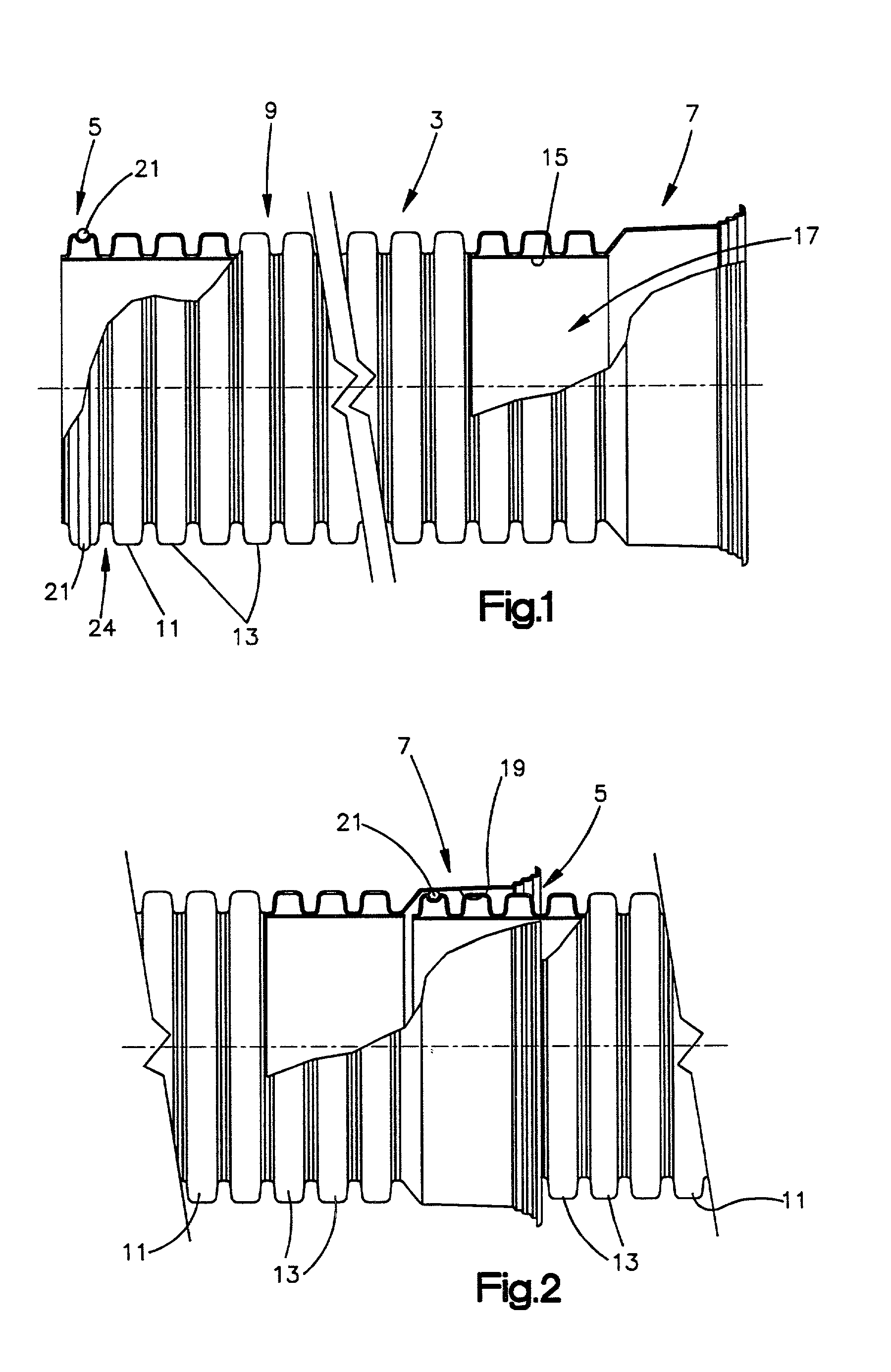

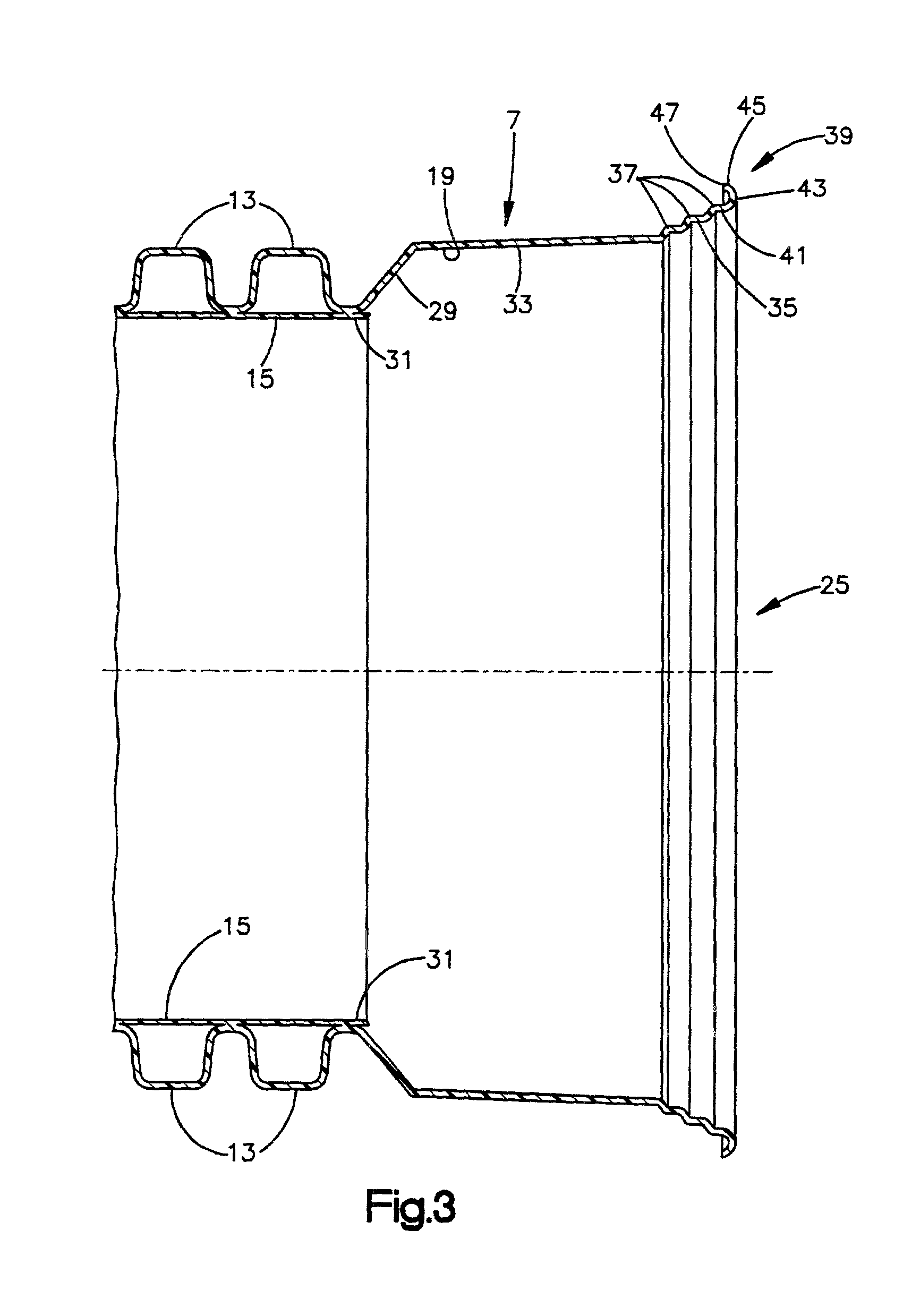

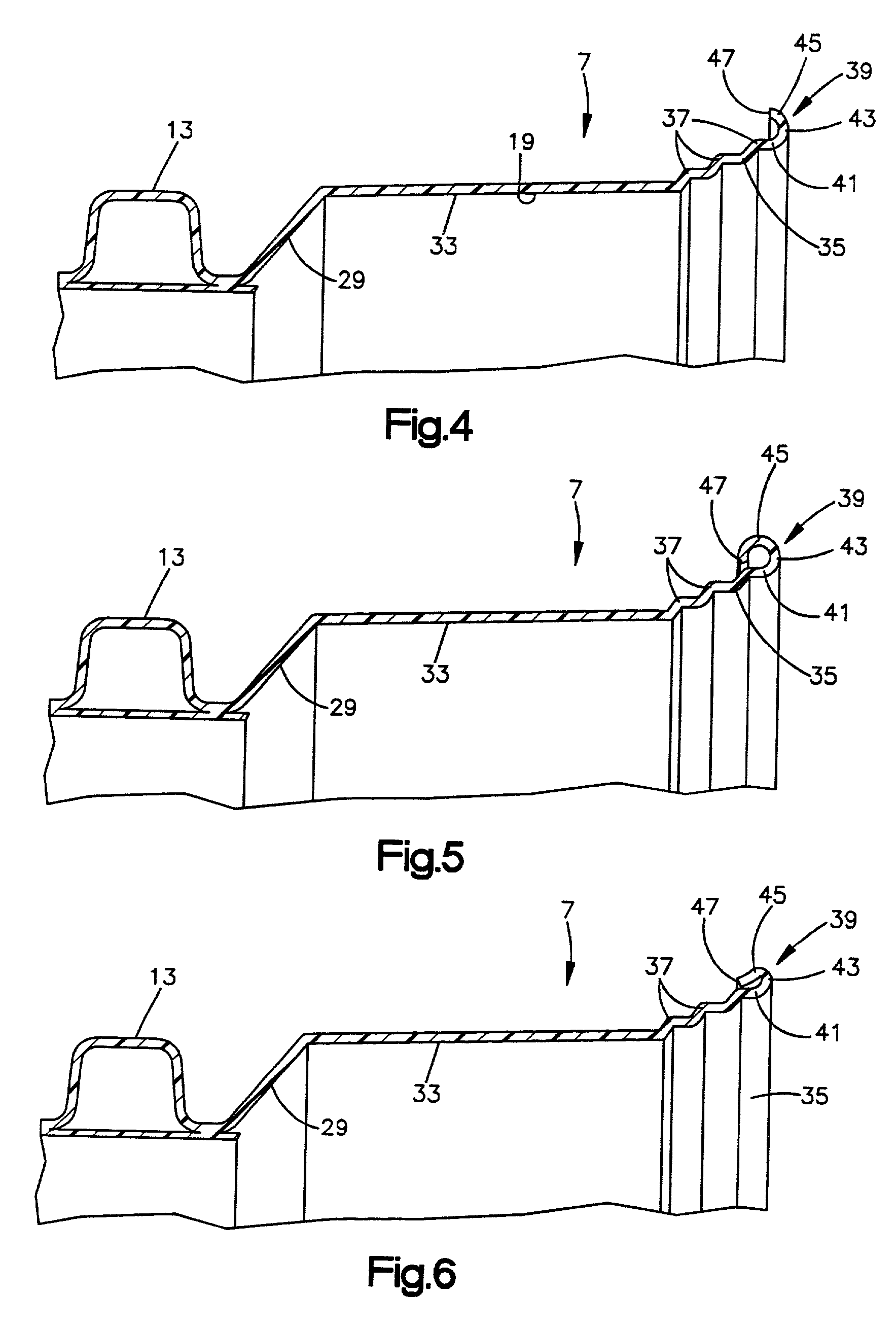

Pipe structure and method of manufacture

InactiveUS6199592B1Reliably sealed against leakageEfficient and cost-effectiveFlexible pipesPipe-jointsEngineeringMechanical engineering

A pipe section formed of a polymeric material which has a substantially constant thickness throughout, the terminal edge of the female connection having a reinforcement structure which rigidifies the end of the female connection and prevents deformation, the pipe section preferably having a flared end, and the reinforcement structure preferably being a semicircular channel formed at the end of the pipe section by a mandrel after initial extrusion of the pipe section; along with a method and apparatus for forming the pipe section, a pipe assembly including such pipe section, and a method of forming the pipe assembly.

Owner:HANCOR

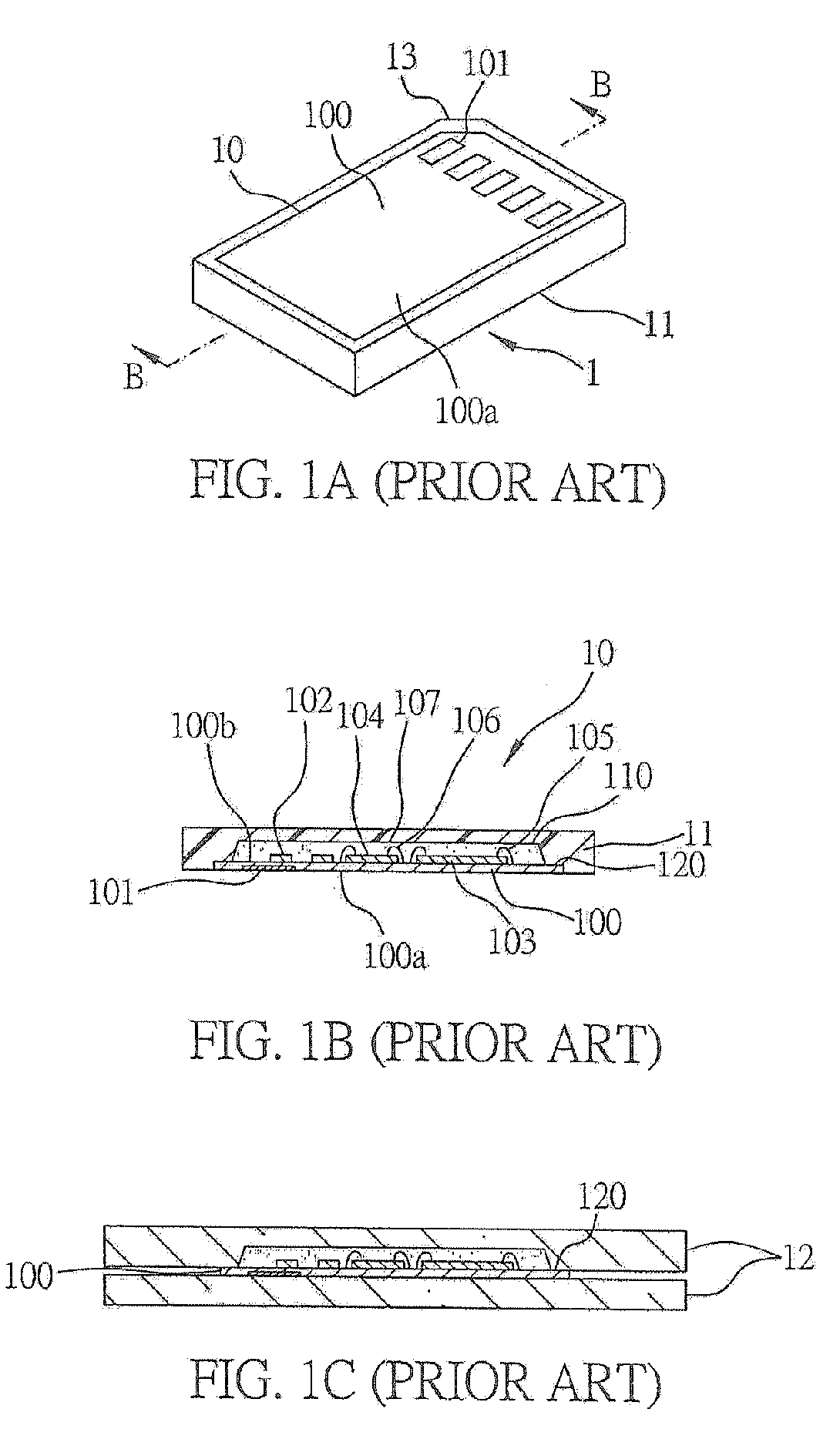

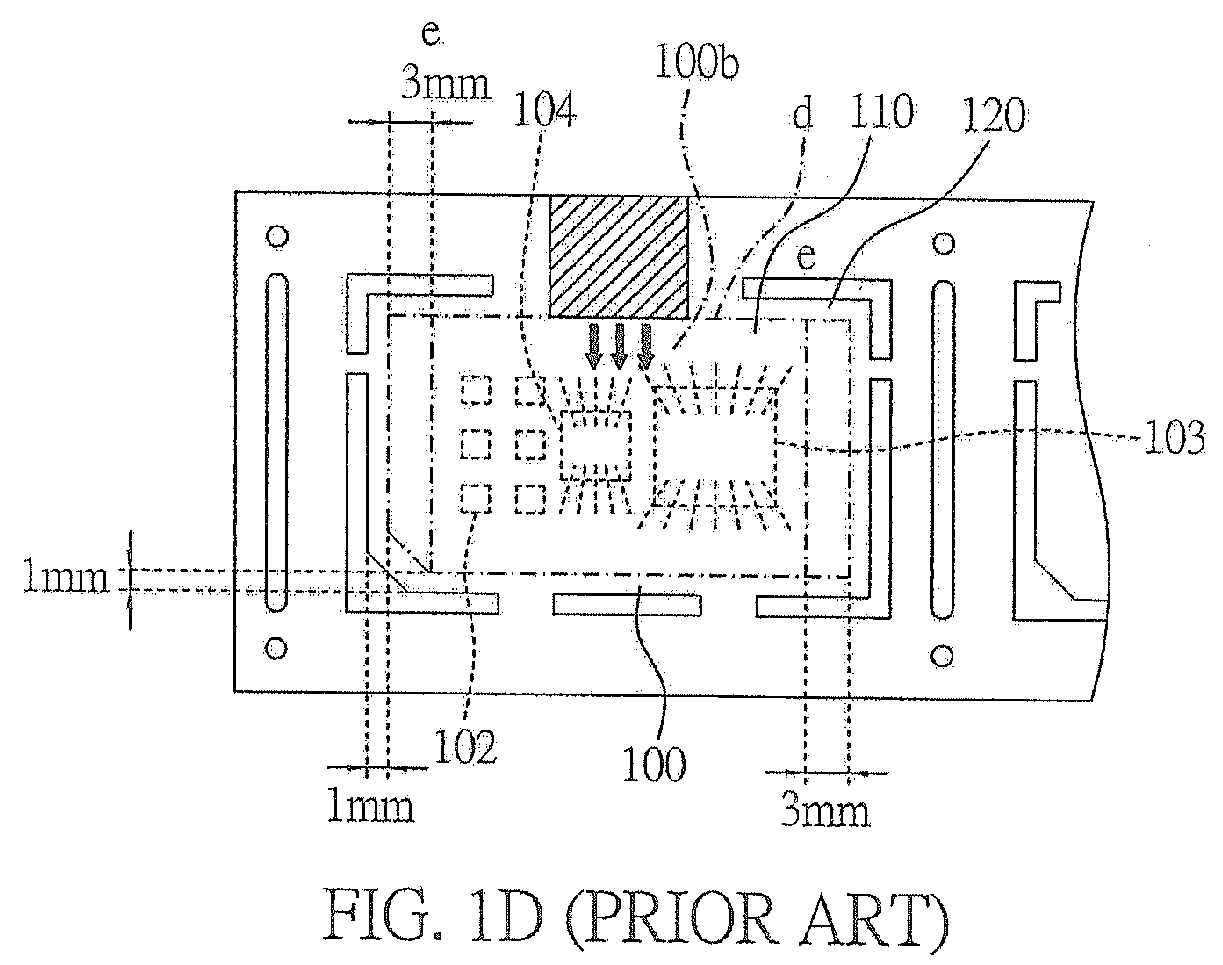

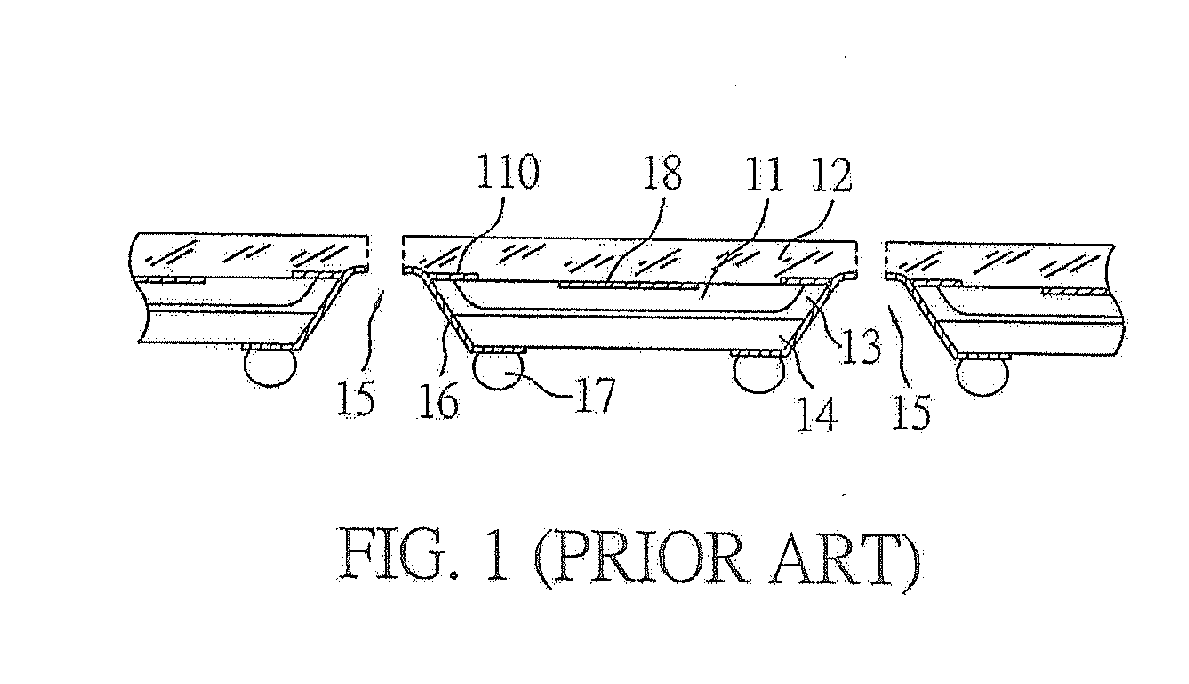

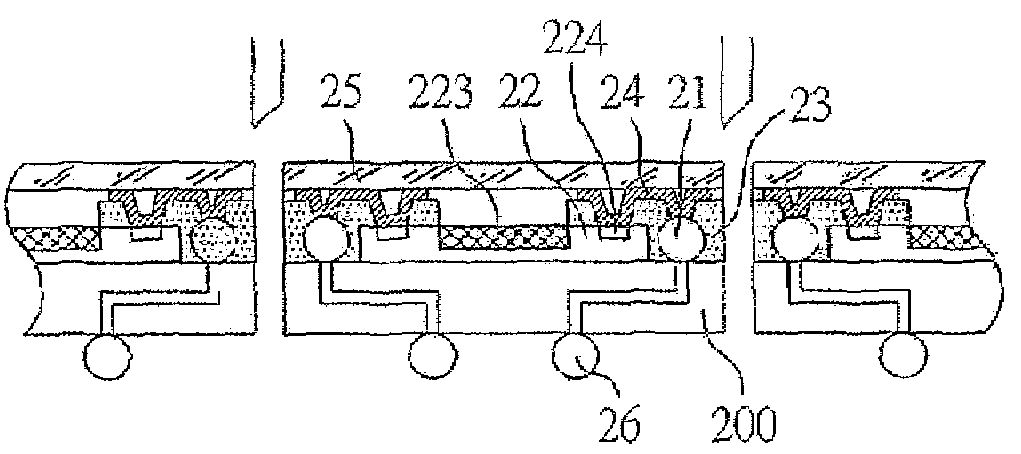

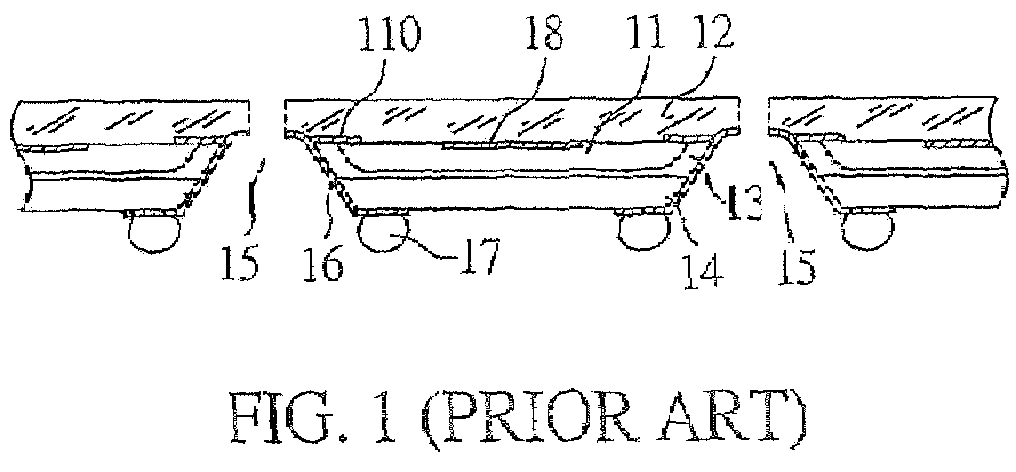

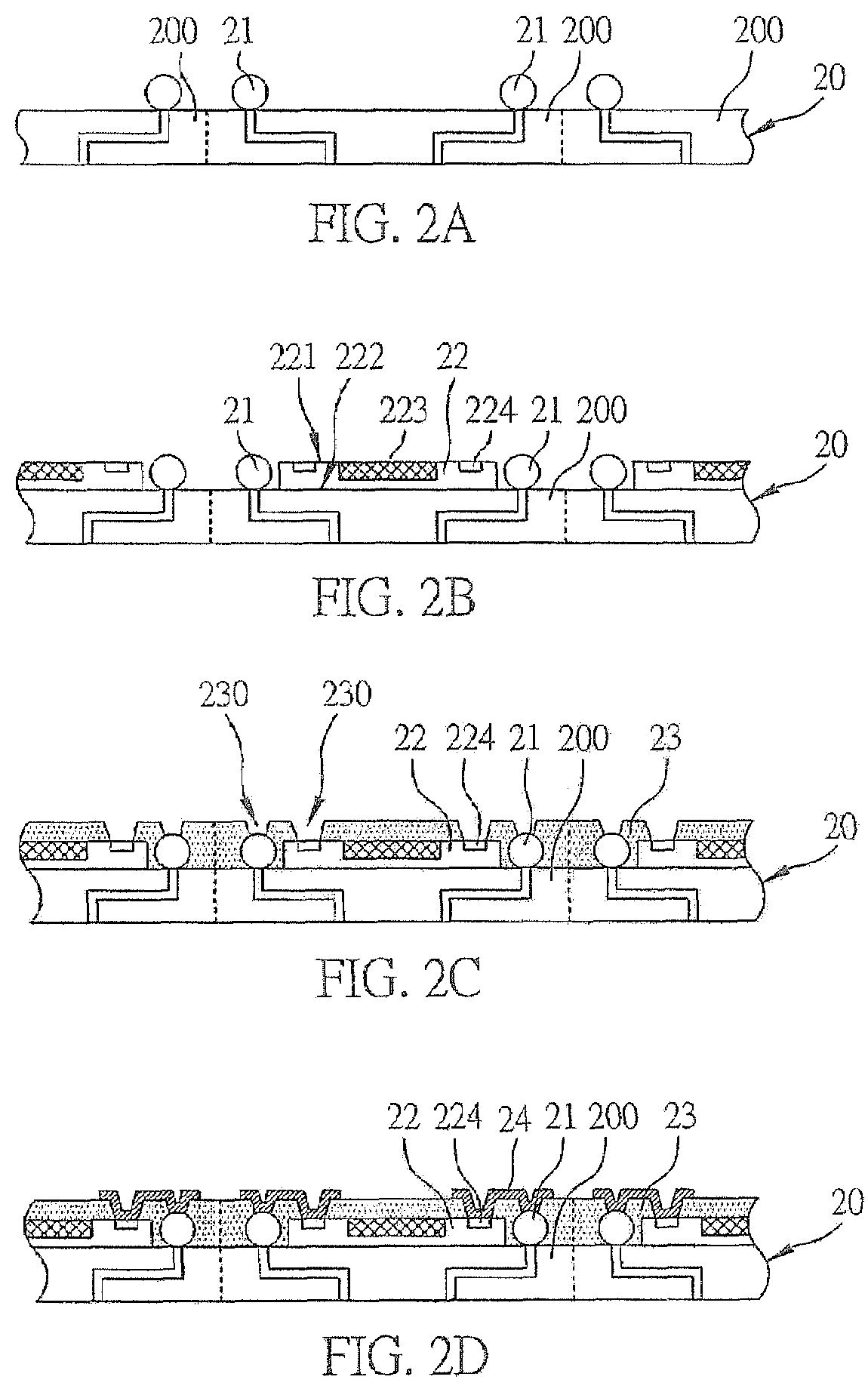

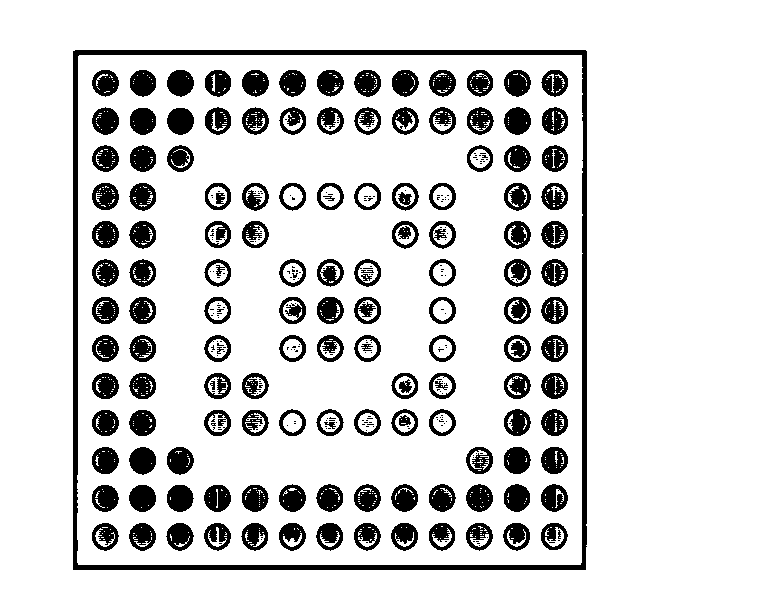

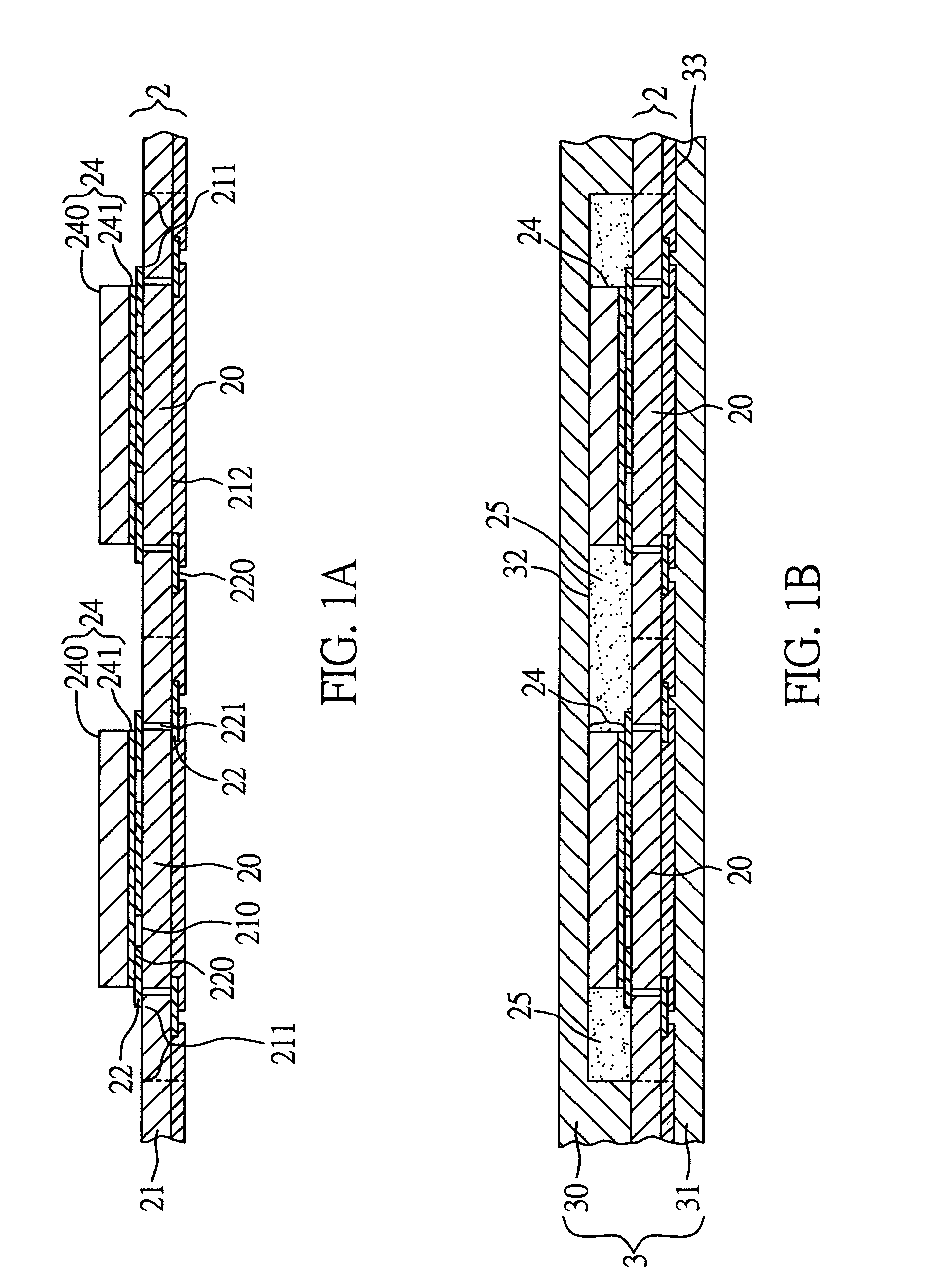

Semiconductor device for use as multimedia memory card, has encapsulant with chamfer such that portion of substrate and chamfer are exposed from encapsulant and remaining portion of surface of substrate is covered by encapsulant

InactiveUS7443016B2Cost-effective fabricationIncrease memory capacitySemiconductor/solid-state device detailsPrinted circuit aspectsMultimedia storageSealant

A semiconductor device and a fabrication method thereof are provided. An opening having at least one slanted side is formed on a substrate. At least one chip and at least one passive component are mounted on the substrate. An encapsulant having a cutaway corner is formed on the substrate to encapsulate the chip and the passive component, wherein the cutaway corner of the encapsulant is spaced apart from the slanted side of the opening by a predetermined distance. A singulation process is performed to cut the encapsulant to form a package with a chamfer. The package is embedded in a lid to form the semiconductor device, wherein a portion of the substrate located between the slanted side of the opening and the cutaway corner of the encapsulant is exposed from the encapsulant to form an exposed portion. The present invention also provides a carrier for the semiconductor device.

Owner:SILICONWARE PRECISION IND CO LTD

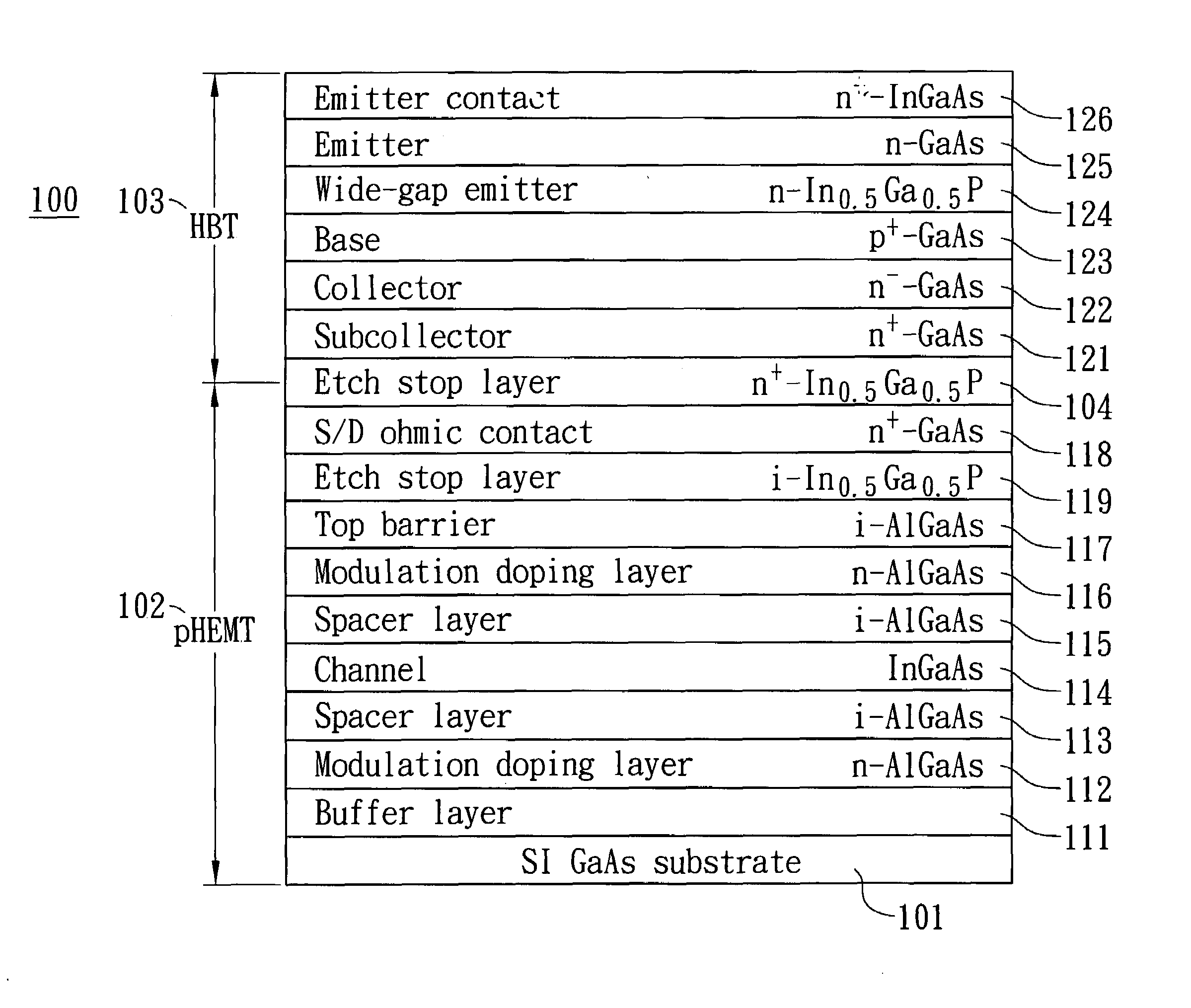

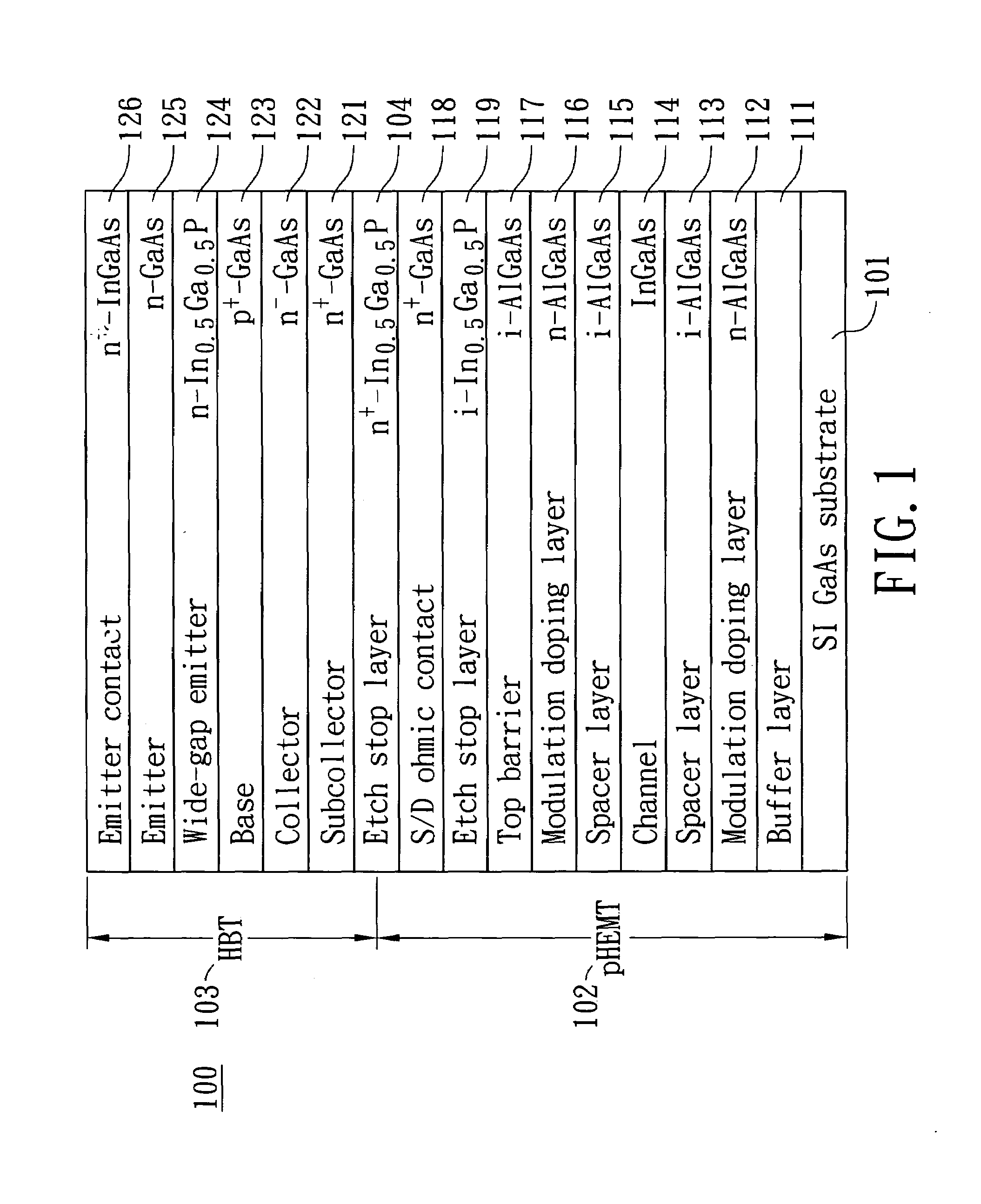

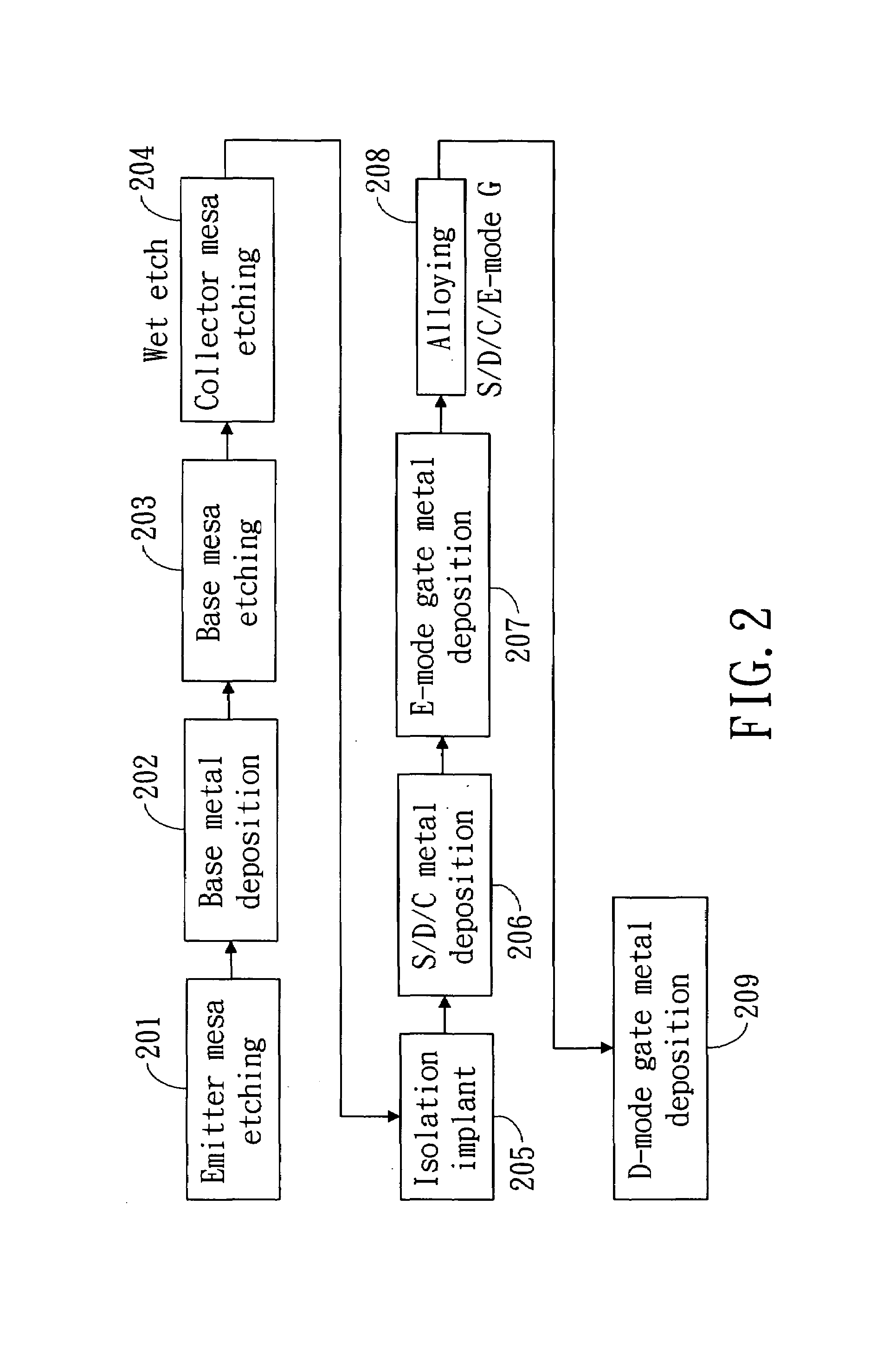

Structure and a method for monolithic integration of HBT, depletion-mode HEMT and enhancement-mode HEMT on the same substrate

InactiveUS20070278523A1Easy to integrateCost-effective fabricationSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringElectrical and Electronics engineering

An epitaxial layers structure and a method for fabricating HBTs and HEMTs on a common substrate are disclosed. The epitaxial layers comprise generally a set of HBT layers on the top of a set of HEMT layers. The method can be used to fabricate HBT, E-mode HEMT and D-mode HEMT as well as passive devices, that enabling monolithic integration of a significant number of devices on a common substrate by a cost-effective way.

Owner:WIN SEMICON

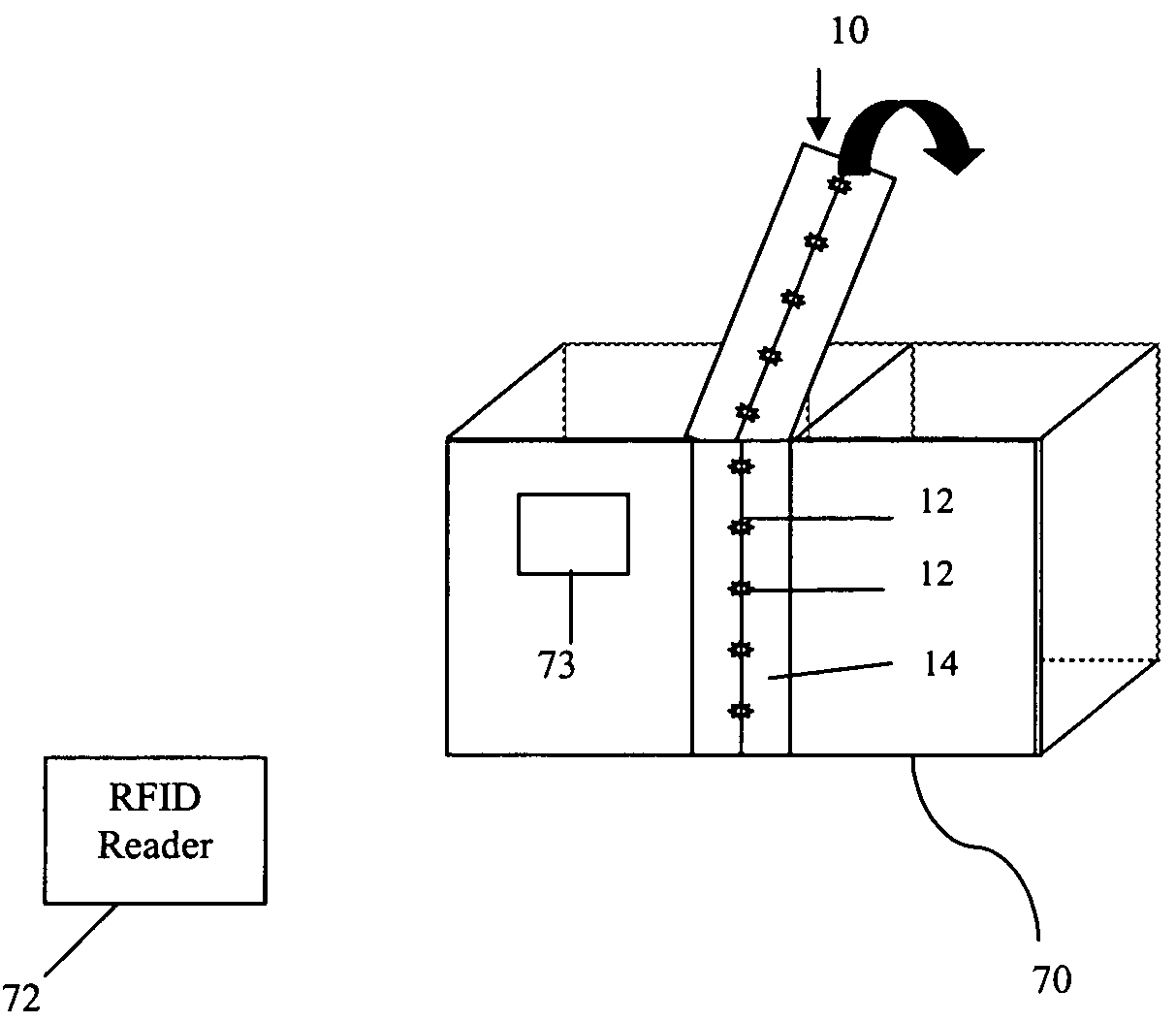

RFID devices for verification of correctness, reliability, functionality and security

InactiveUS7712674B1Effective monitoringCost-effective designMultiplex system selection arrangementsSubscribers indirect connectionNetwork sizeTransceiver

The present invention differs from the prior art in that the present invention provides one or a network of passive or active radio frequency identification (RFID) transceivers and antenna elements in different numbers, in various network sizes, in different configurations and on various substrates. The RFID transceiver can be co-located with standard semiconductor devices, for cost-effective circuit design and non-destructive fabrication test and analysis of integrated circuits and printed circuit boards after fabrication, and to locate, track and identify the integrated circuit, printed circuit boards and products in which they are implemented. The RFID transceivers can be coupled to substrates containing matter in gas, liquid, or solid form, such as medical devices like breast implants, for effective monitoring of the substrates to ensure that the substrate is in an unaltered state and the matter is still contained securely within. The RFID transceivers can be coupled to secure tapes of various lengths and widths and mesh bags or sheets of various sizes and they can be applied at the carton-level using them to locate, track and identify the integrated circuit, printed circuit boards and products in which they are implemented and / or the cartons in which they were placed.

Owner:EIGENT TECH

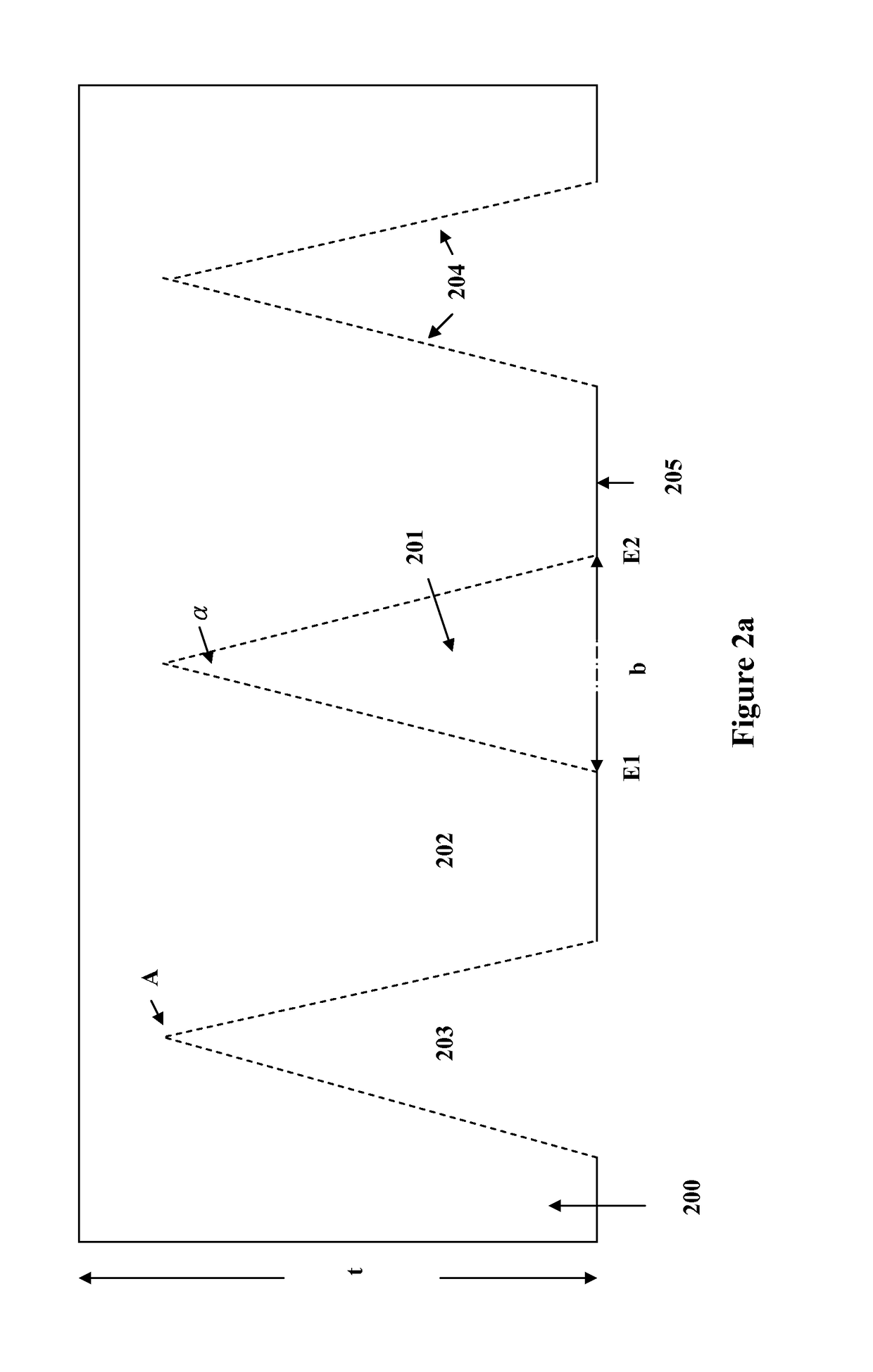

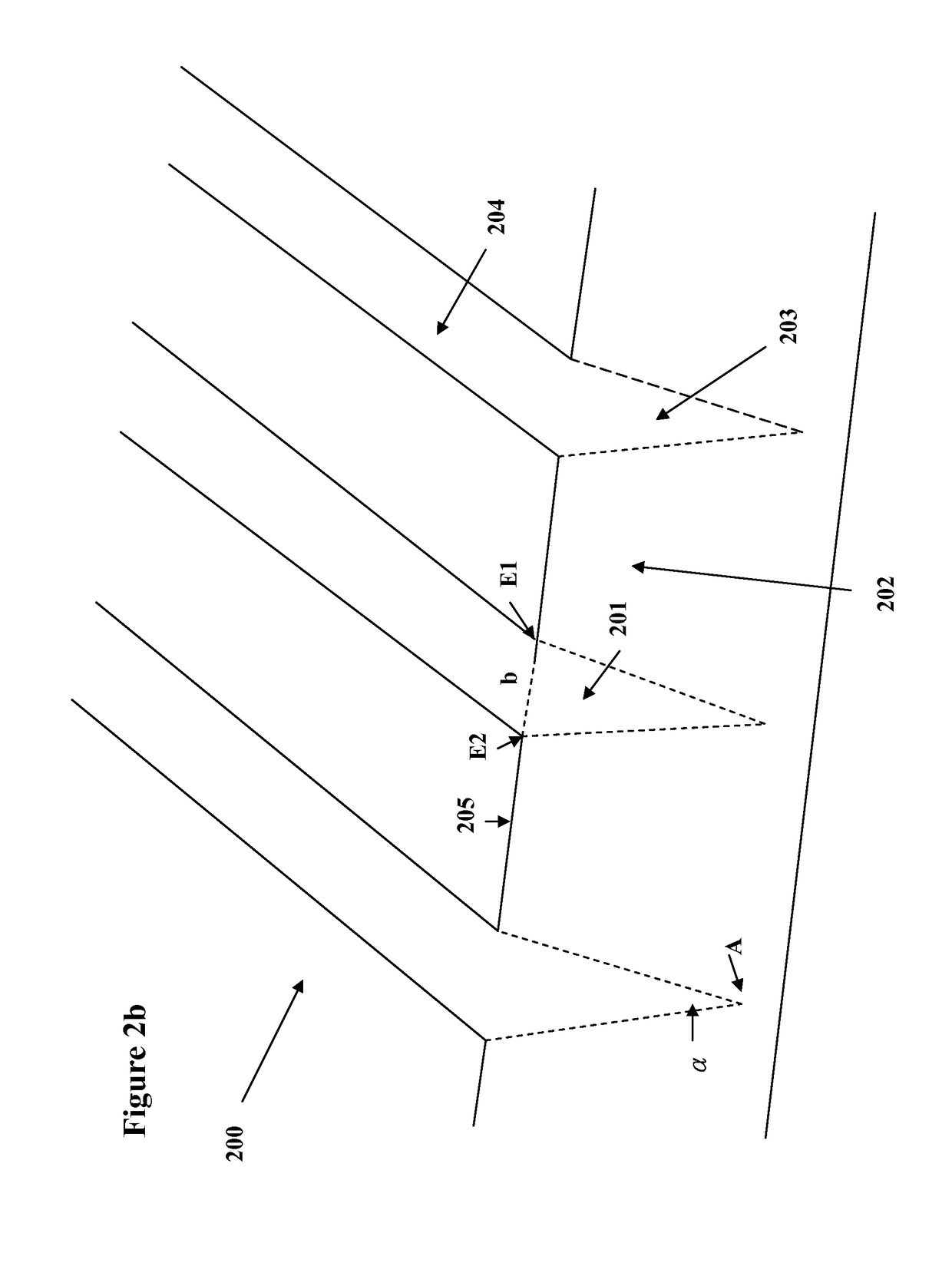

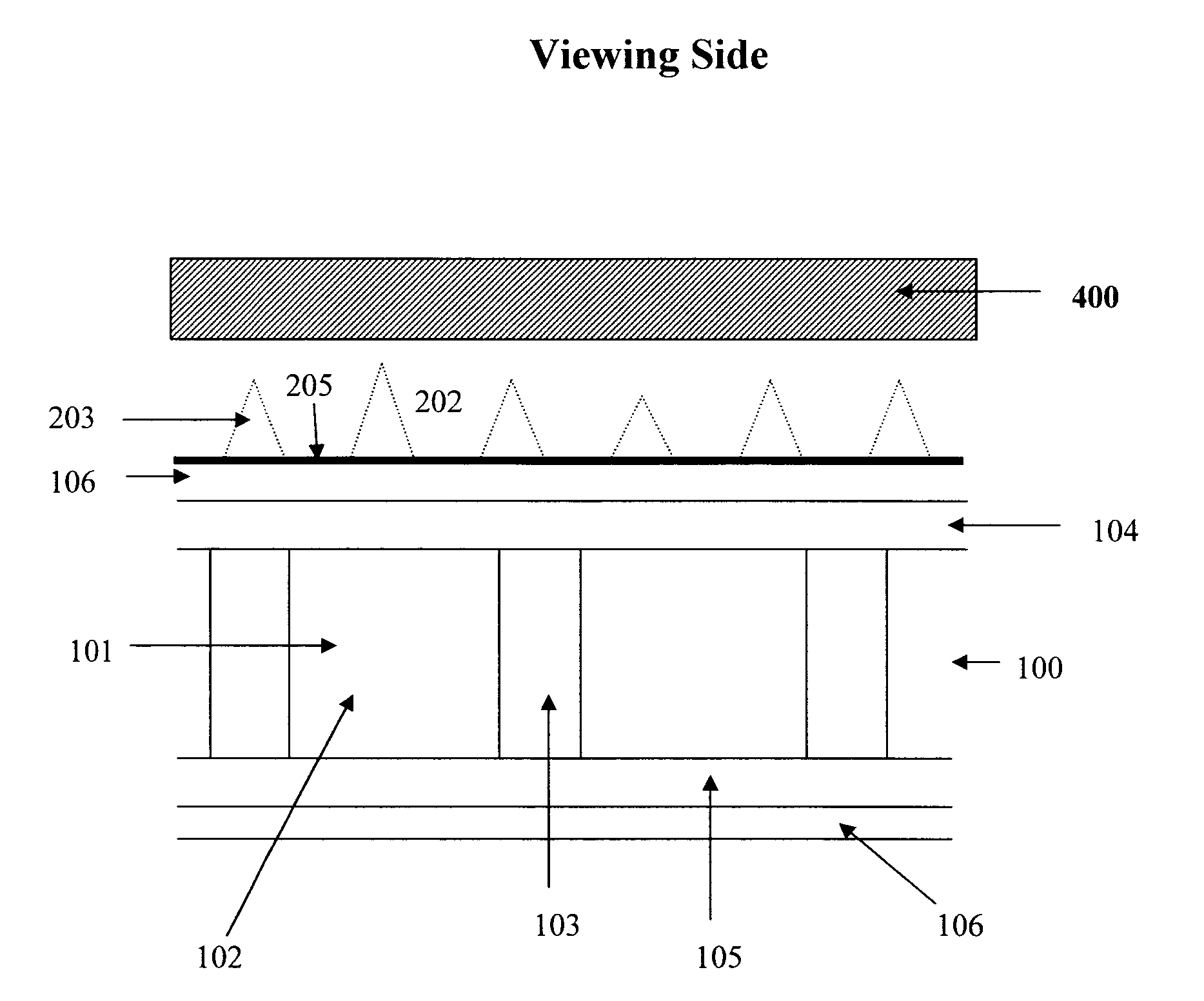

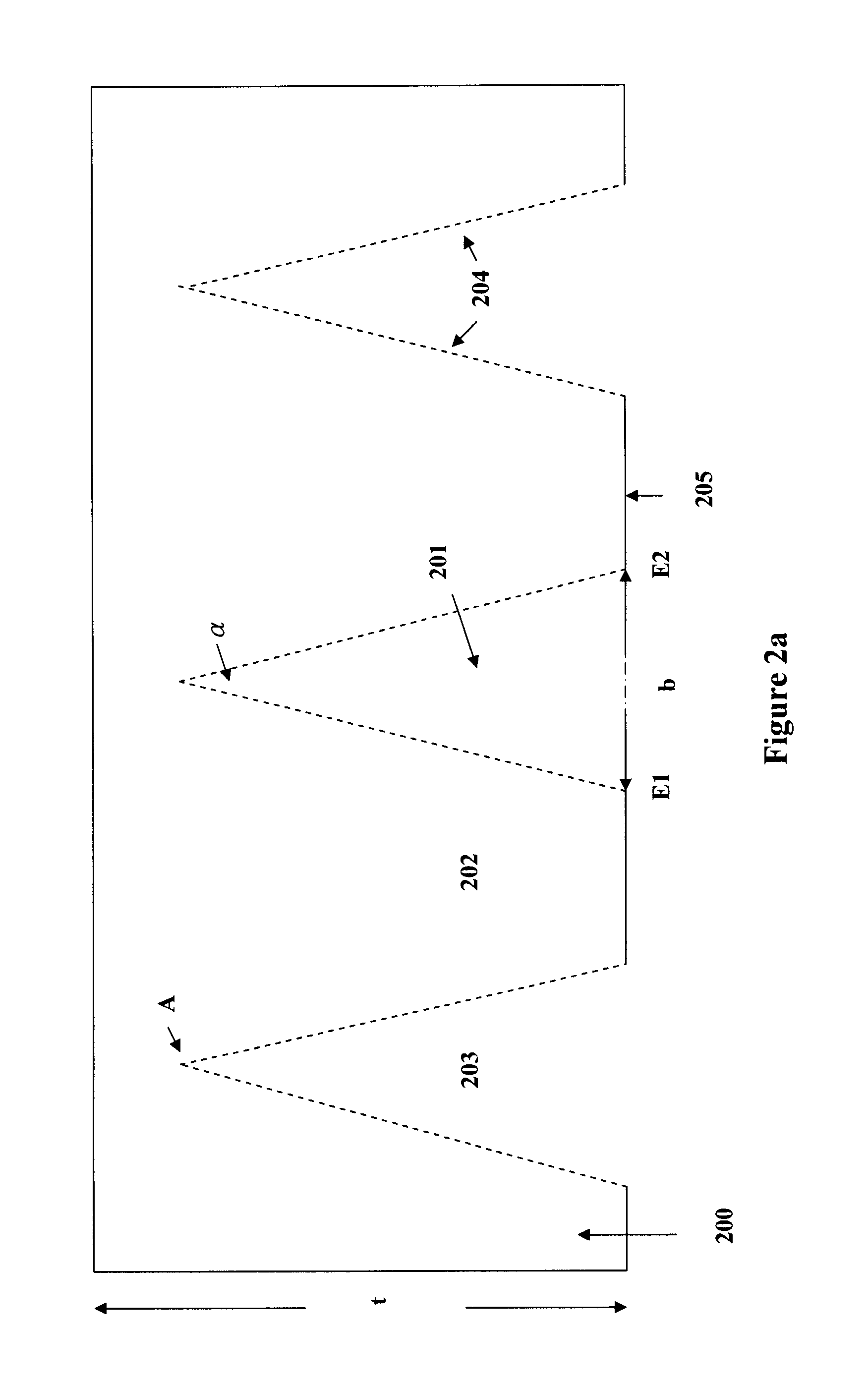

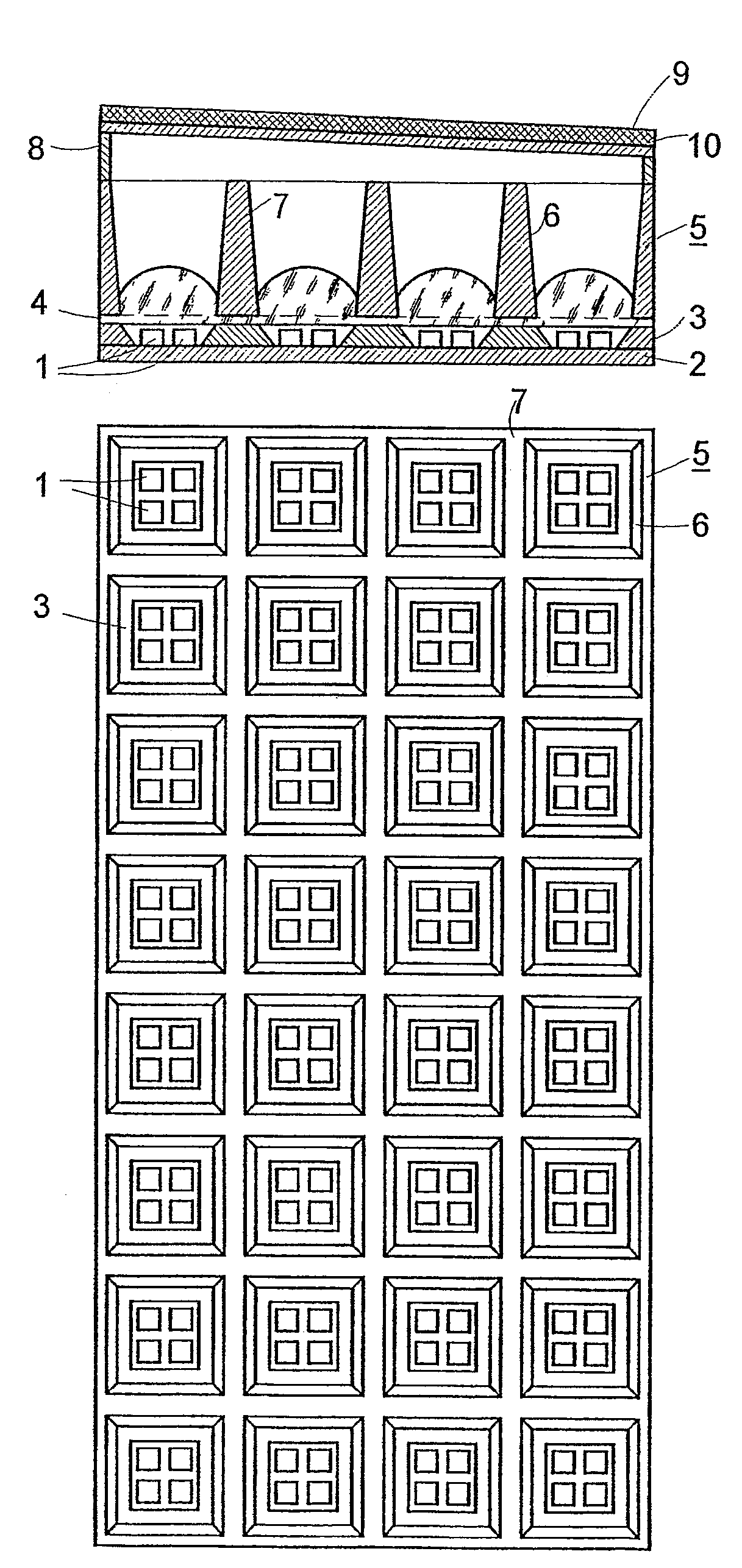

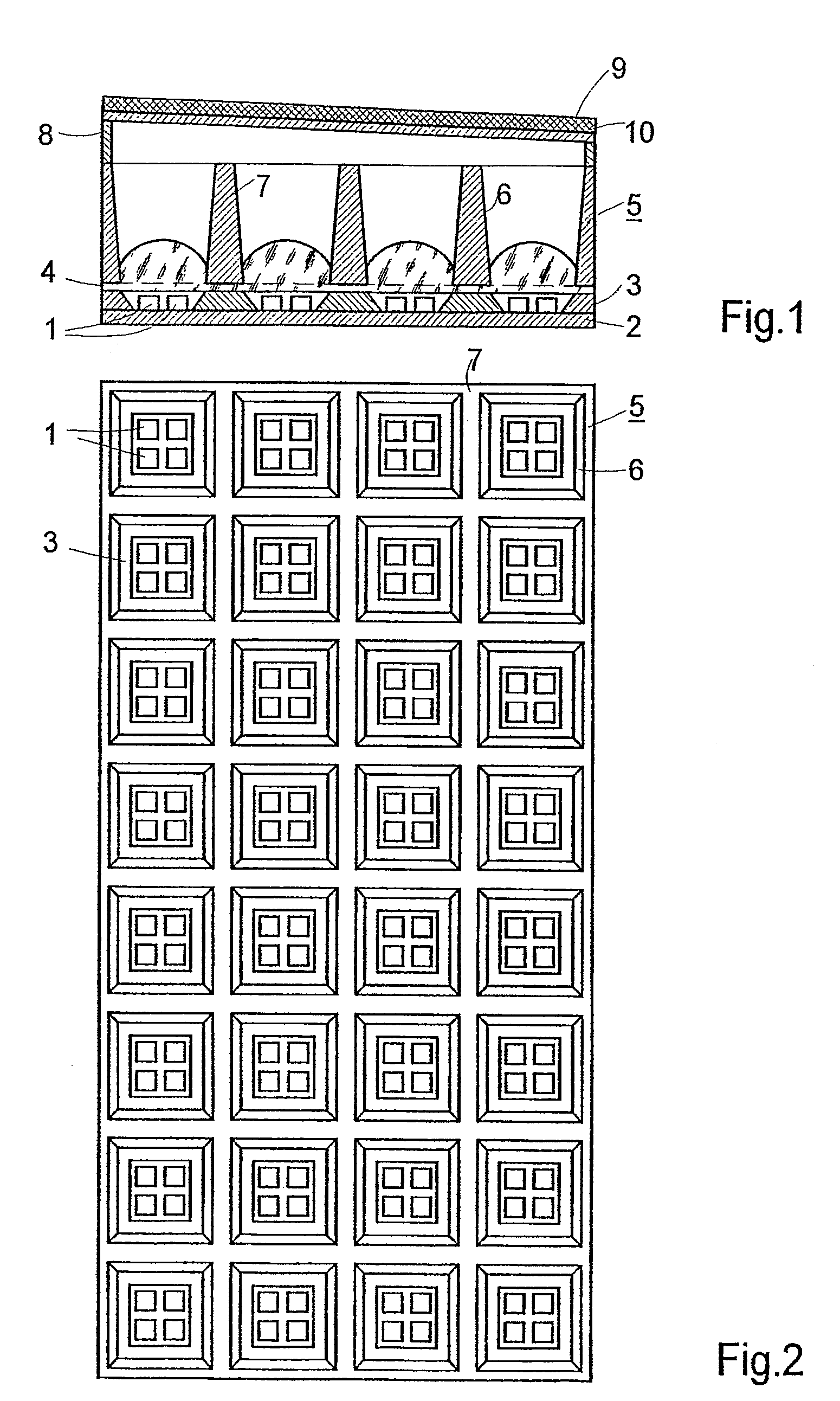

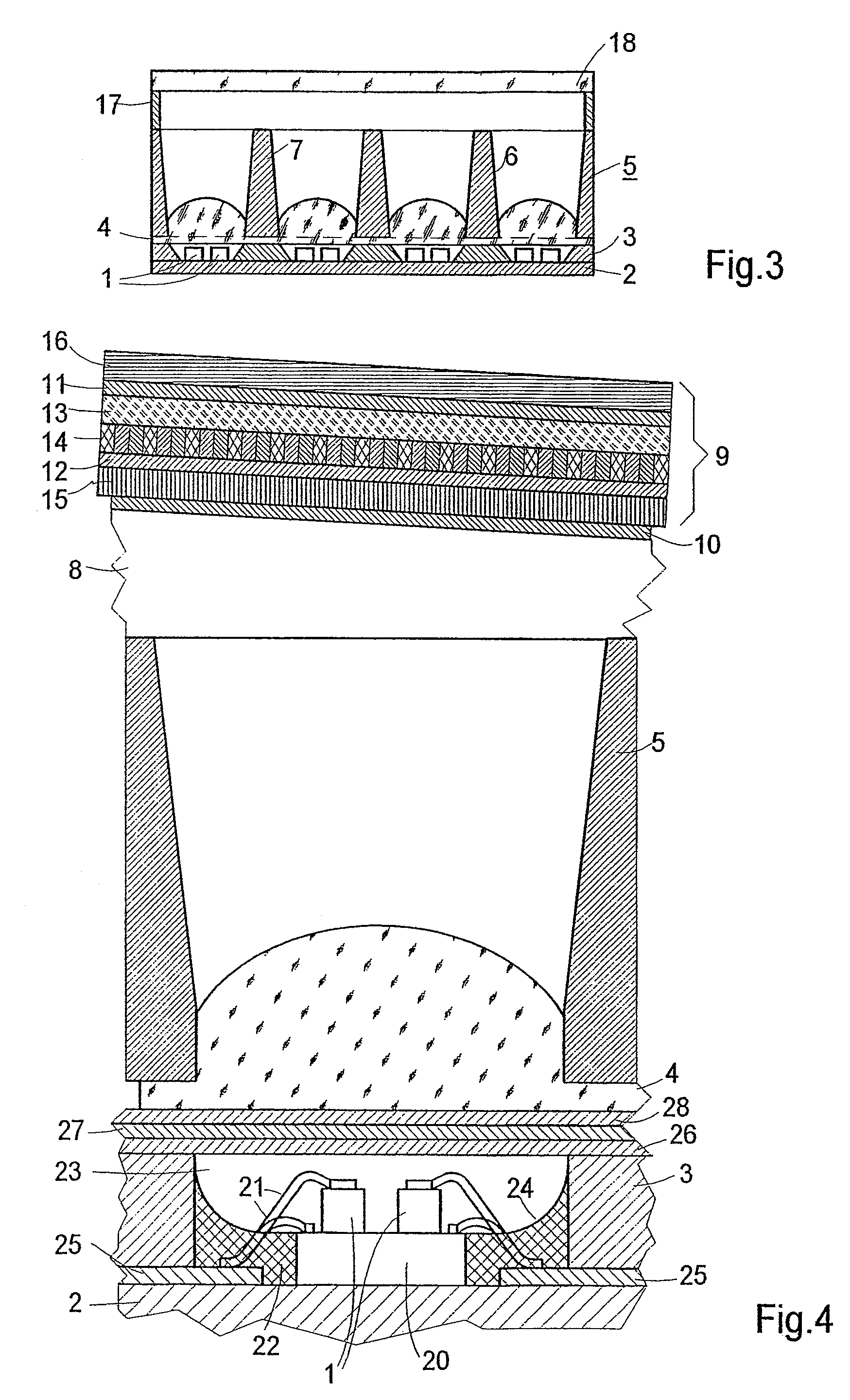

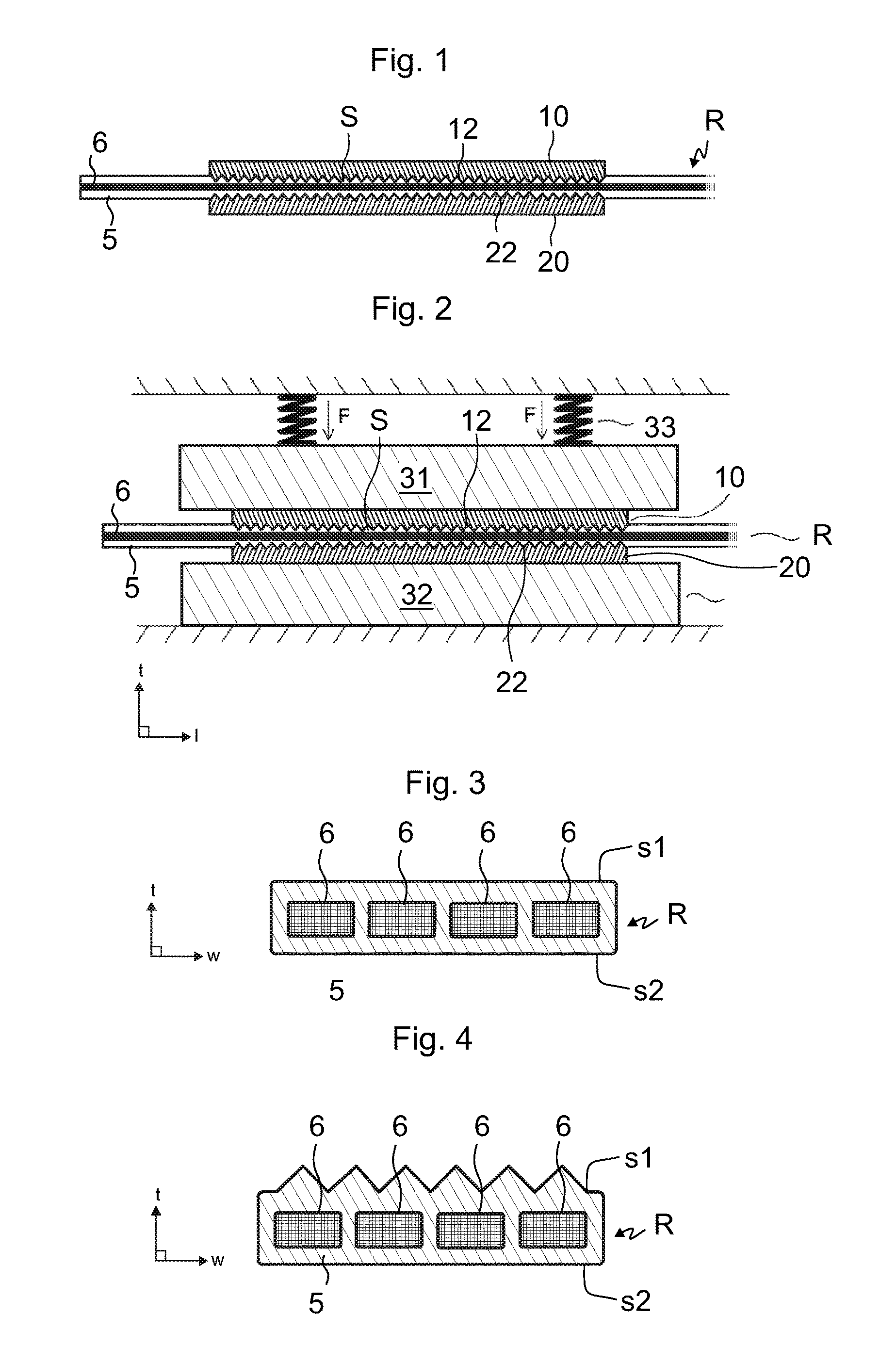

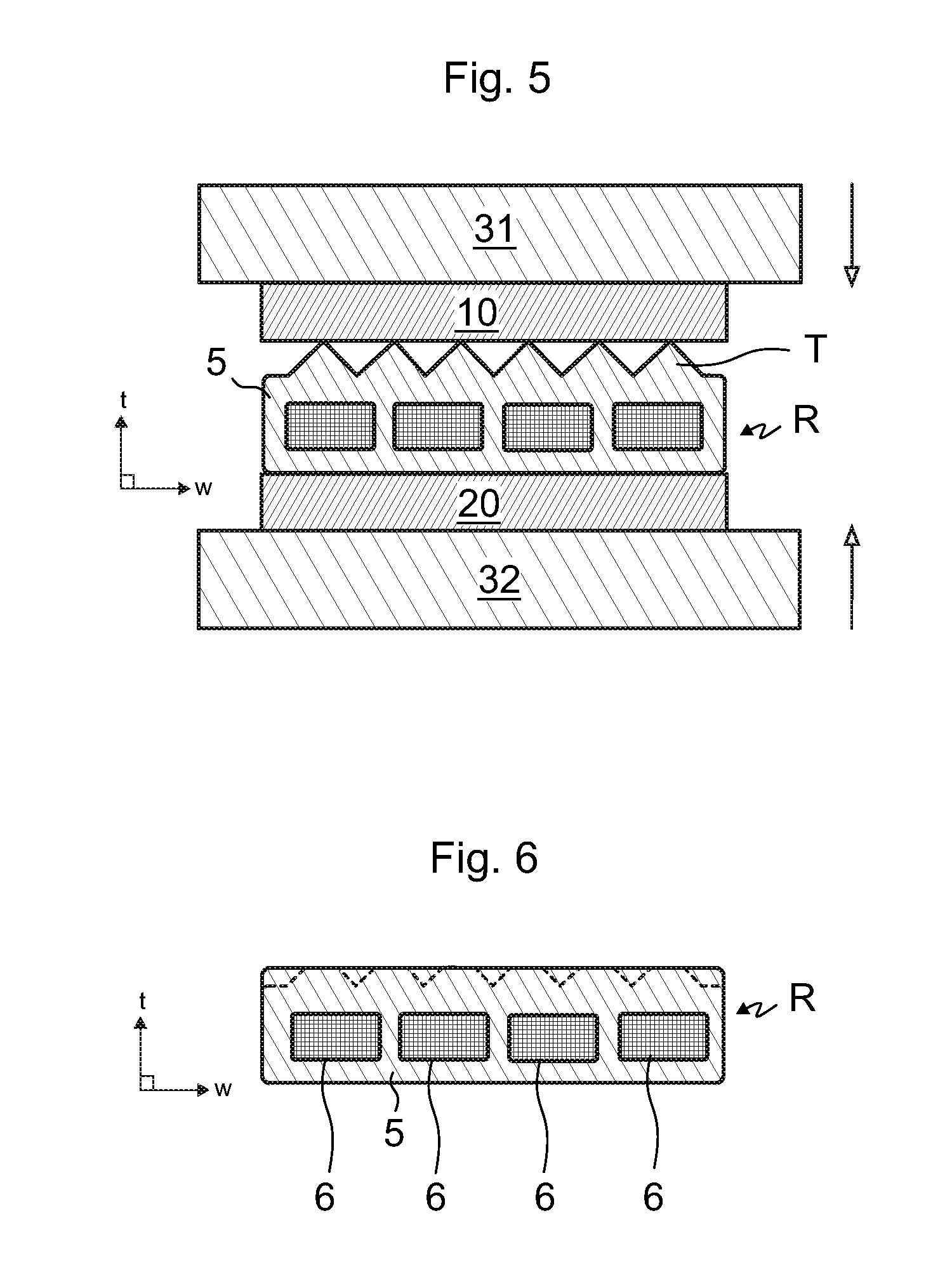

Luminance enhancement structure for reflective display devices

ActiveUS8120836B2Enhancement structure increases the overall reflectanceReduce reflectionStatic indicating devicesNon-linear opticsTotal internal reflectionDisplay device

The present invention is directed to luminance enhancement structures for reflective display devices. The structure comprises columns and grooves, wherein each of said grooves has a cross-section comprising an apex angle and two edge lines. The structure increases the overall reflectance by reducing the total internal reflection, and as a result, the brightness of a display device is increased.

Owner:E INK CORPORATION

Display devices with grooved luminance enhancement film

ActiveUS8714780B2Enhancement structure increases the overall reflectanceReduce reflectionStatic indicating devicesGlobesDisplay deviceComputer science

Owner:E INK CORPORATION

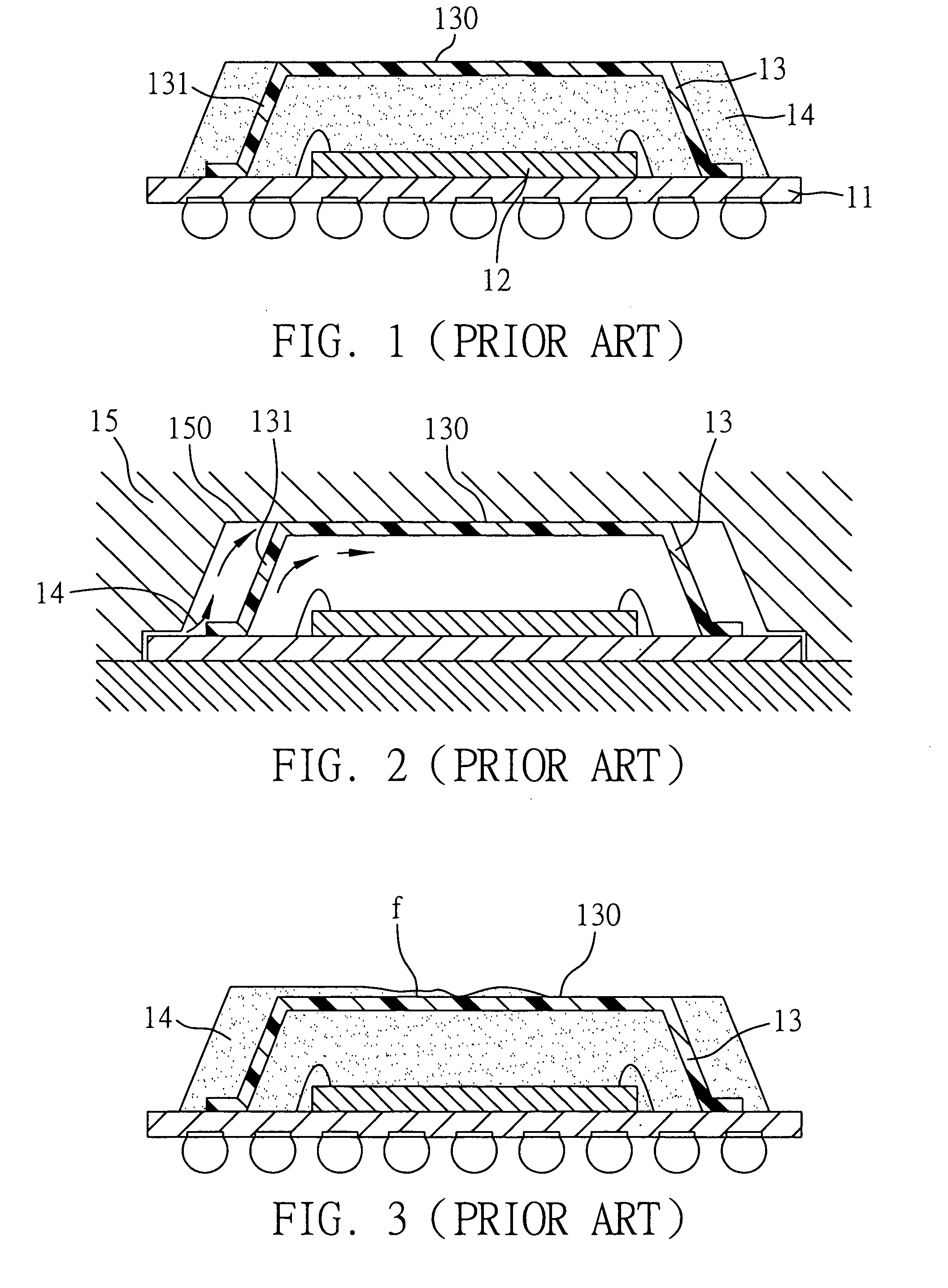

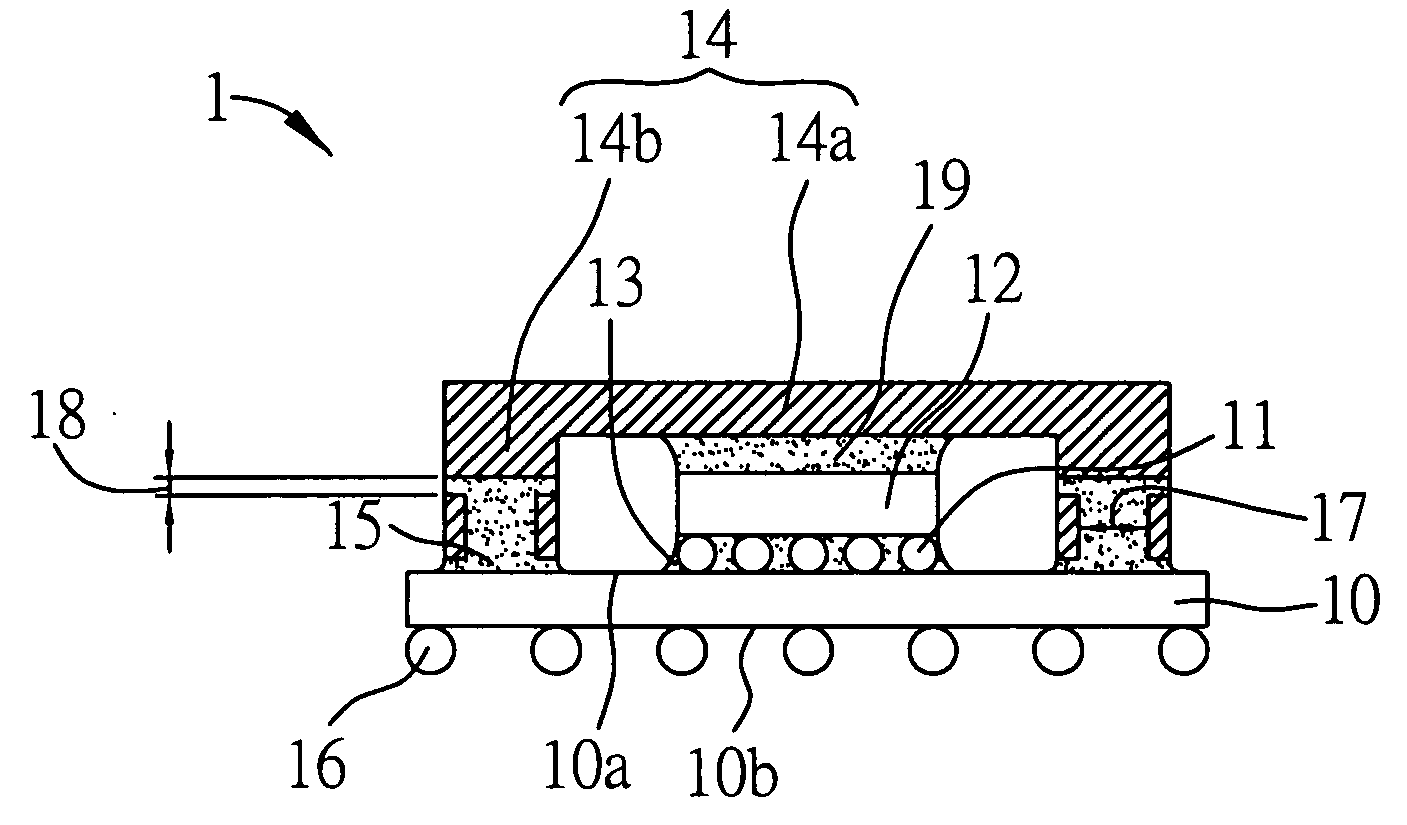

Semiconductor package with exposed heat sink and the heat sink thereof

InactiveUS20050285258A1Guaranteed cooling efficiencyReduce flow rateSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A semiconductor package with an exposed heat sink and the heat sink thereof are proposed. A carrier having a first surface and a second surface is provided. At least one chip is mounted on the first surface of the carrier and electrically connected to the carrier. A heat sink includes a flat portion having an exposed surface, and a support portion extended peripherally from the flat portion and attached to the first surface of the carrier, wherein the flat portion, the support portion and the carrier form a space where the chip is received, and the flat portion is peripherally formed with a stepped structure having at least one flash preventing groove located at a position adjacent to the exposed surface so as to prevent resin flashes on the exposed surface of the heat sink during a molding process for forming an encapsulant that encapsulates the chip.

Owner:SILICONWARE PRECISION IND CO LTD

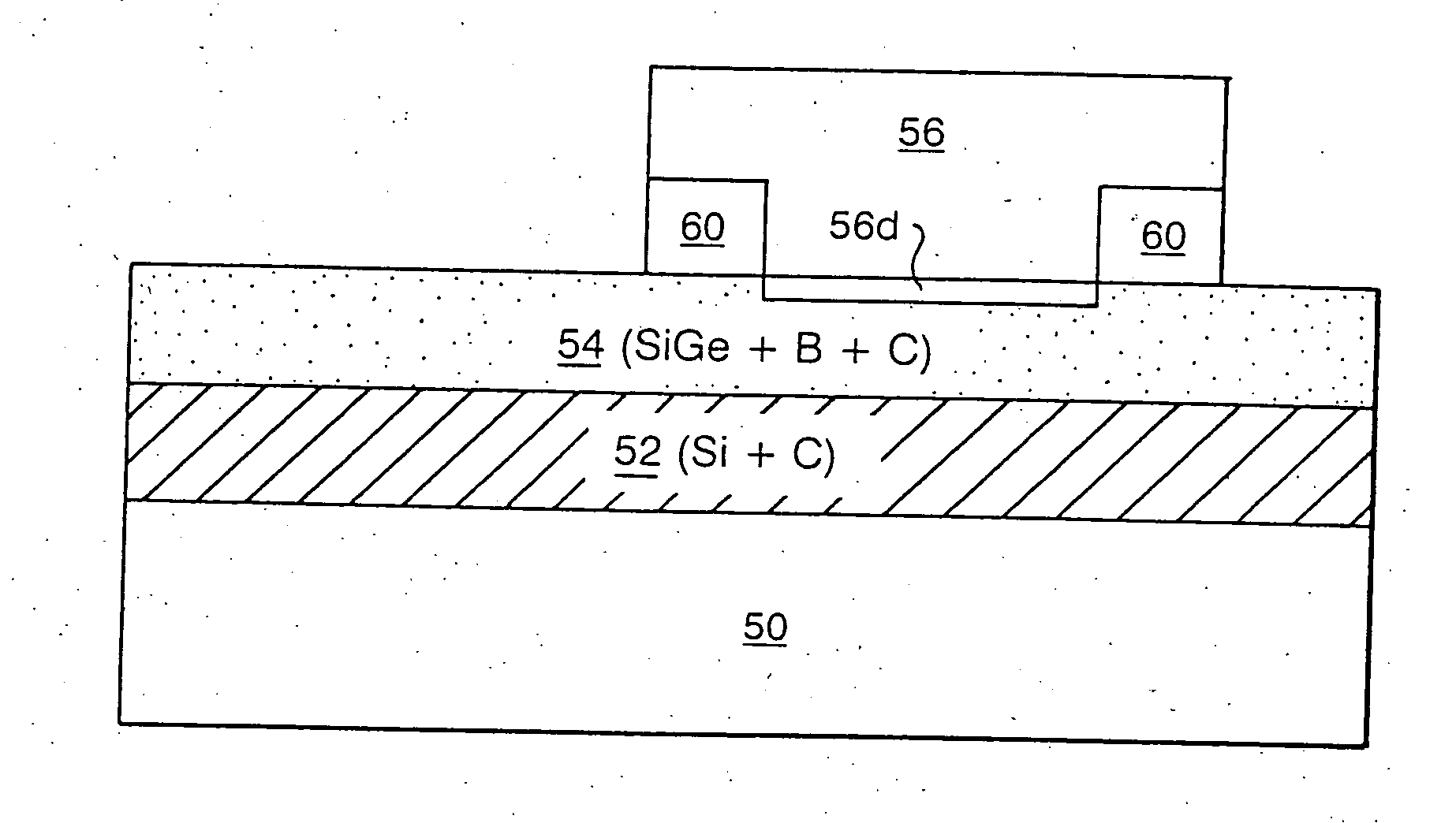

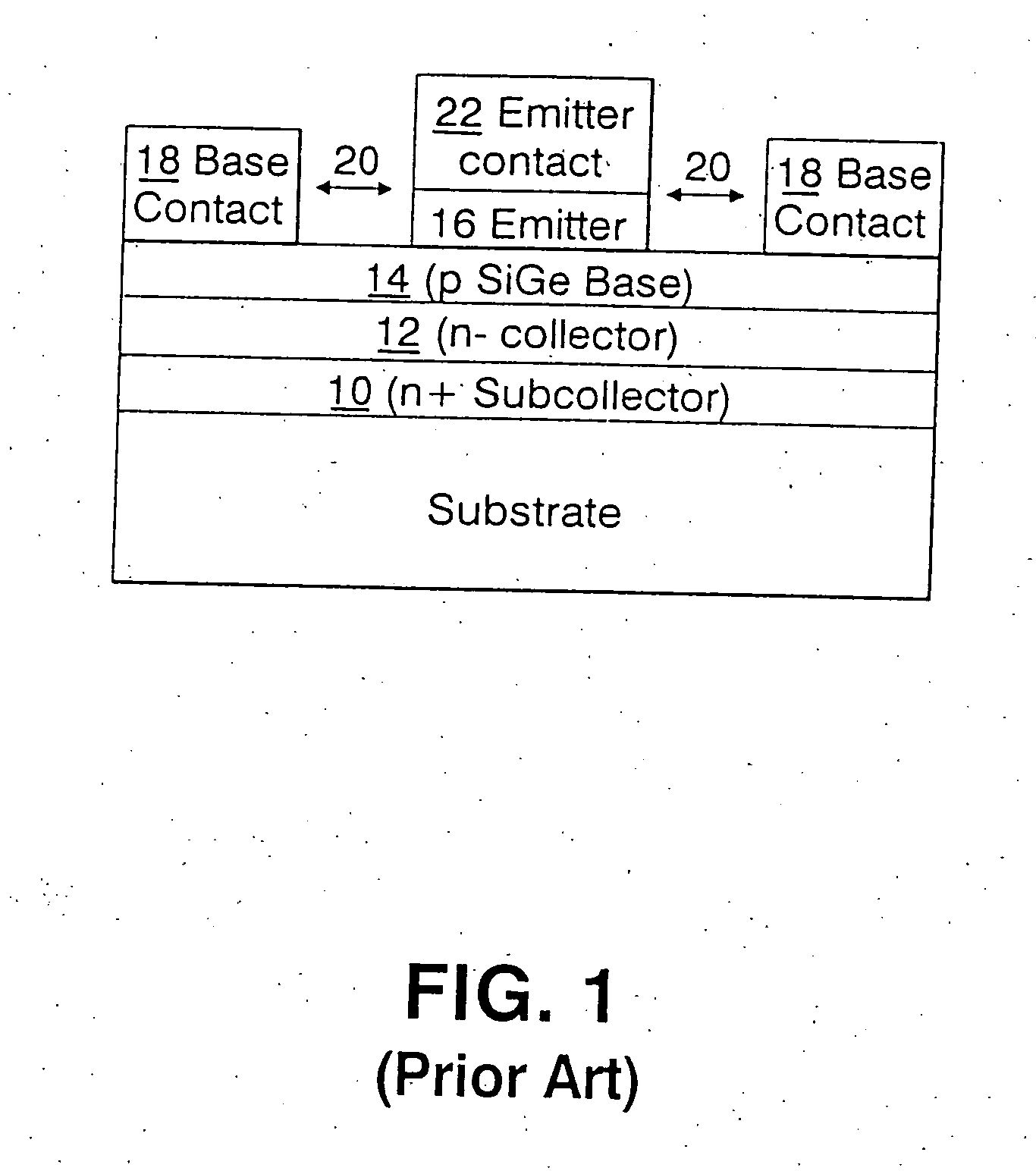

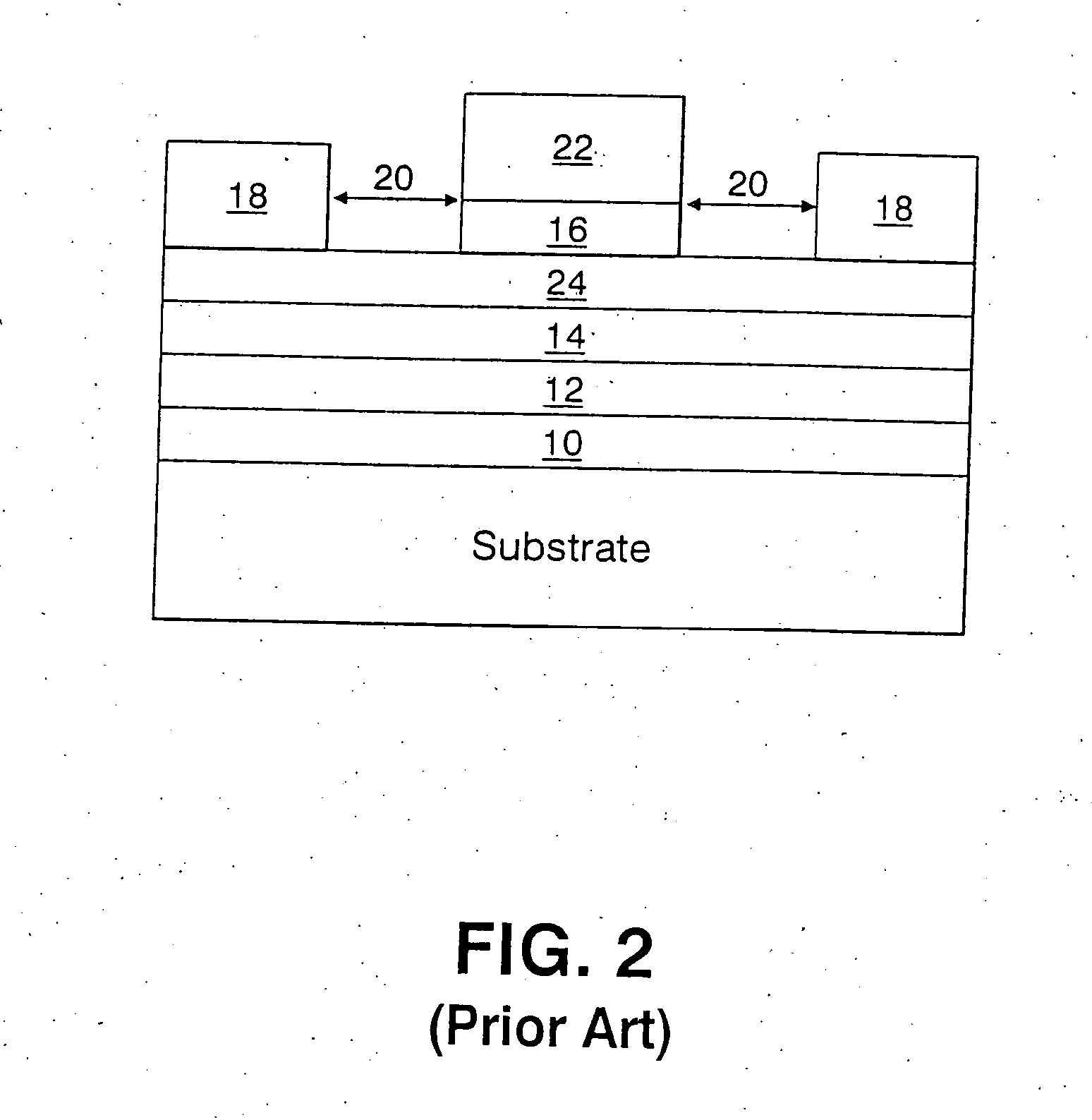

Incorporation of carbon in silicon/silicon germanium epitaxial layer to enhance yield for Si-Ge bipolar technology

InactiveUS20050054171A1Suppressed dislocationAvoid problemsSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringBoron

A SiGe bipolar transistor containing substantially no dislocation defects present between the emitter and collector region and a method of forming the same are provided. The SiGe bipolar transistor includes a collector region of a first conductivity type; a SiGe base region formed on a portion of said collector region; and an emitter region of said first conductivity type formed over a portion of said base region, wherein said collector region and said base region include carbon continuously therein. The SiGe base region is further doped with boron.

Owner:GLOBALFOUNDRIES US INC

Head-up display

ActiveUS7312927B2Small sizeLittle power lossMeasurement apparatus componentsLighting support devicesHead-up displayEngineering

A straw holder for supporting a drinking straw in the mouth of a bottle is presented. The holder includes a straw support portion dimensioned for placement across the mouth of a bottle. The straw support portion includes an aperture designed to receive a straw therethrough and to vertically support the straw with respect to the support portion. The holder further includes a bottle retaining portion that includes at least one turn extending around the retaining portion. The at least one turn includes a first turn having an end attached to the straw support portion.

Owner:OSRAM OLED

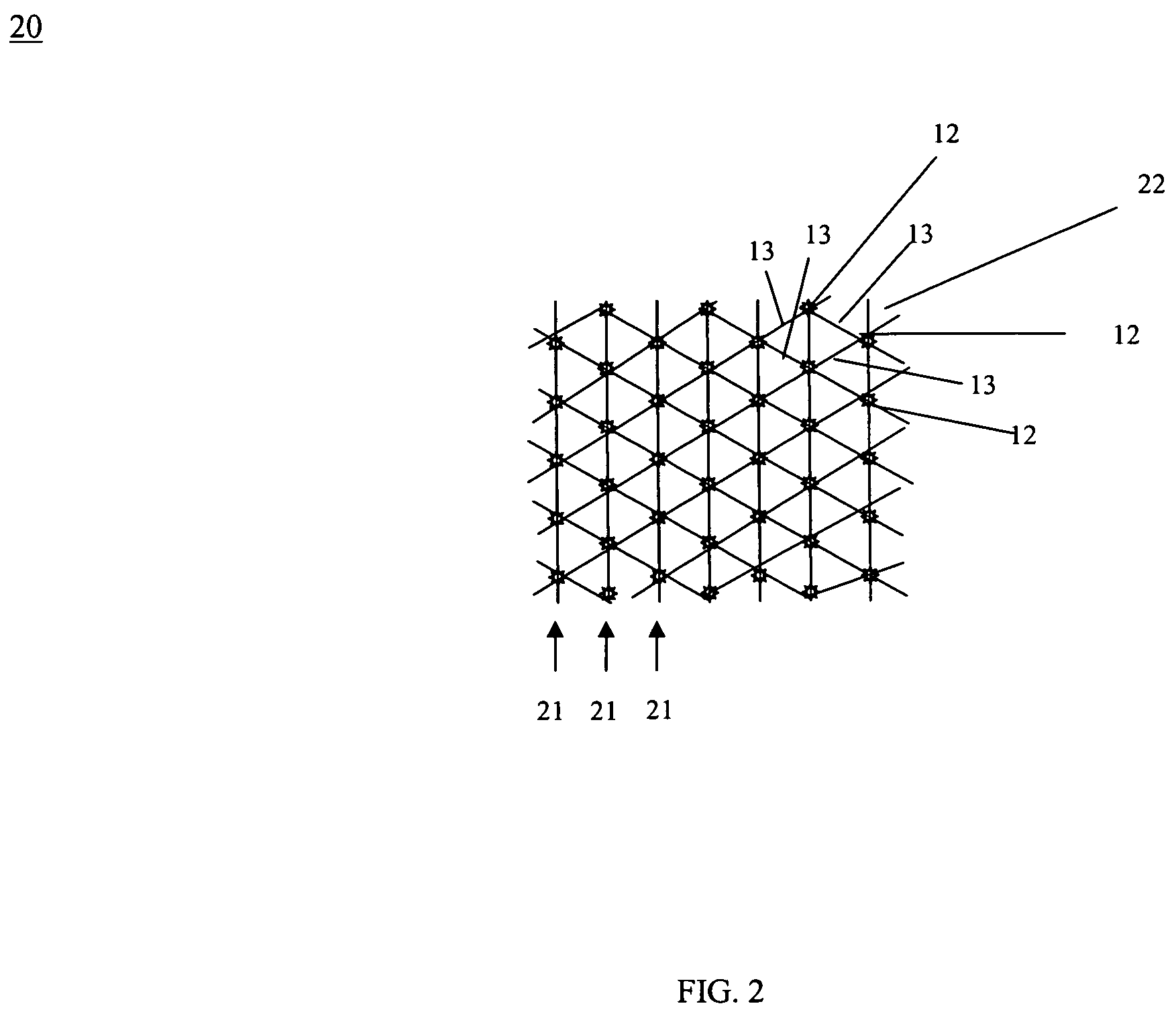

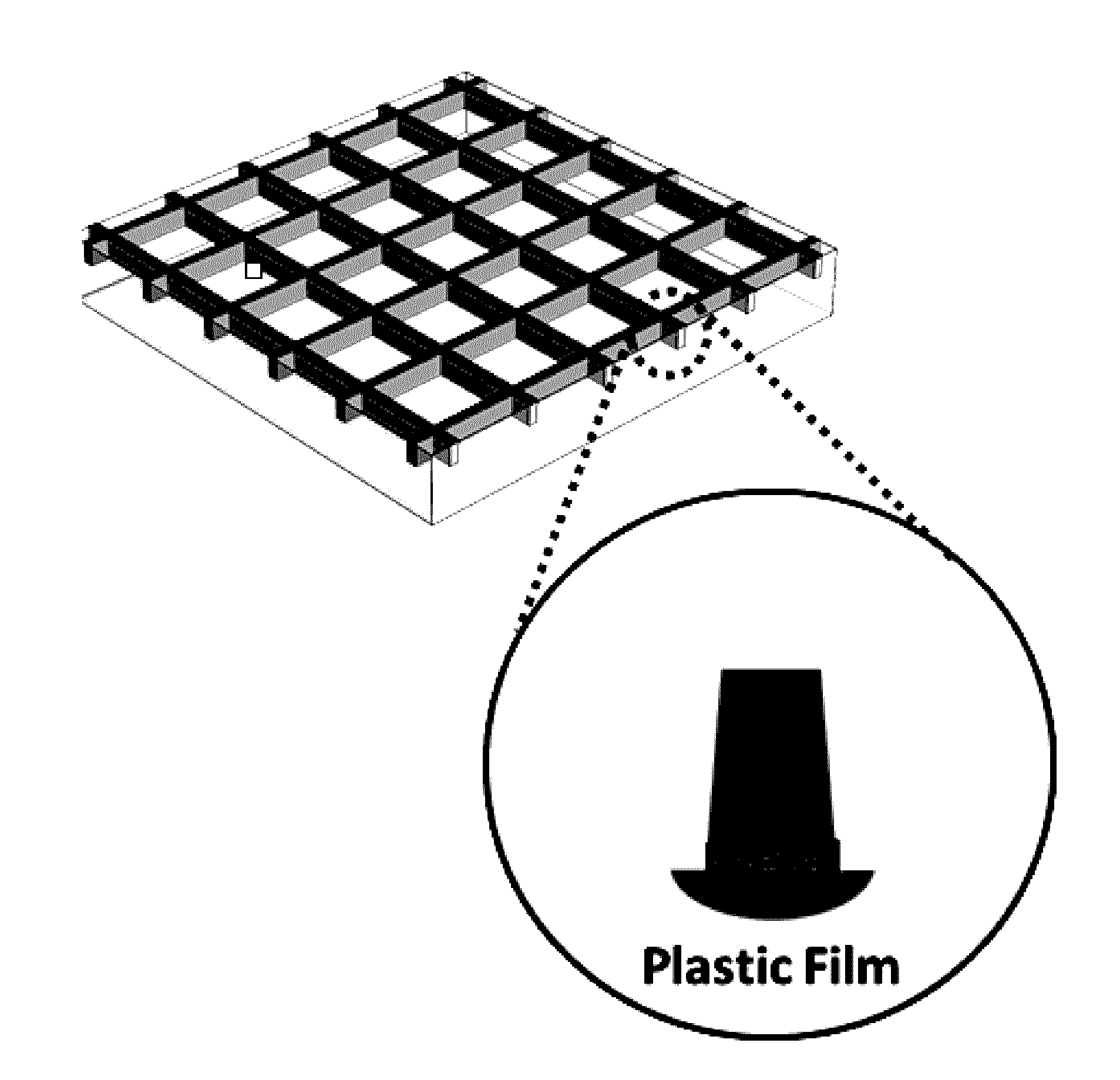

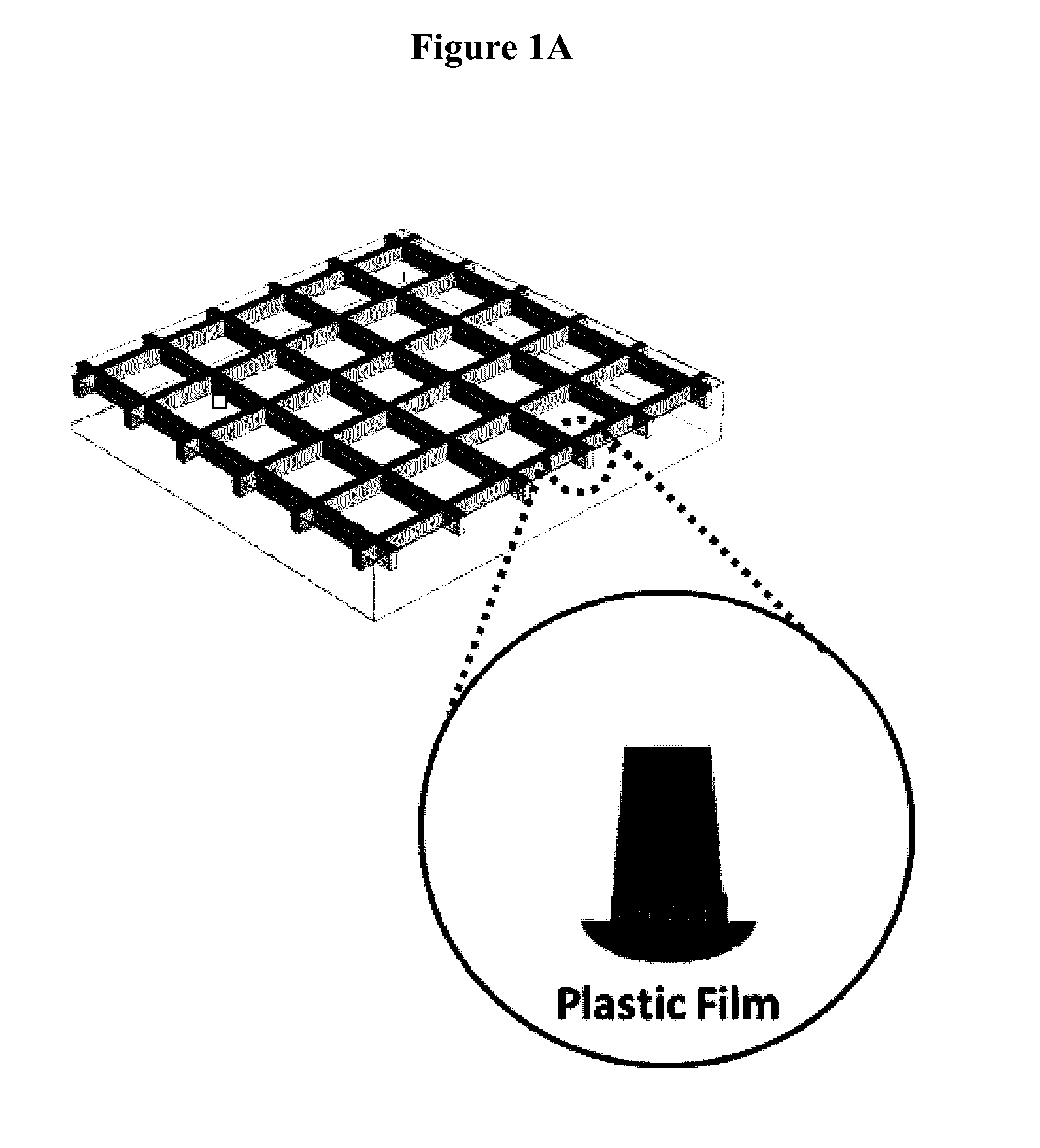

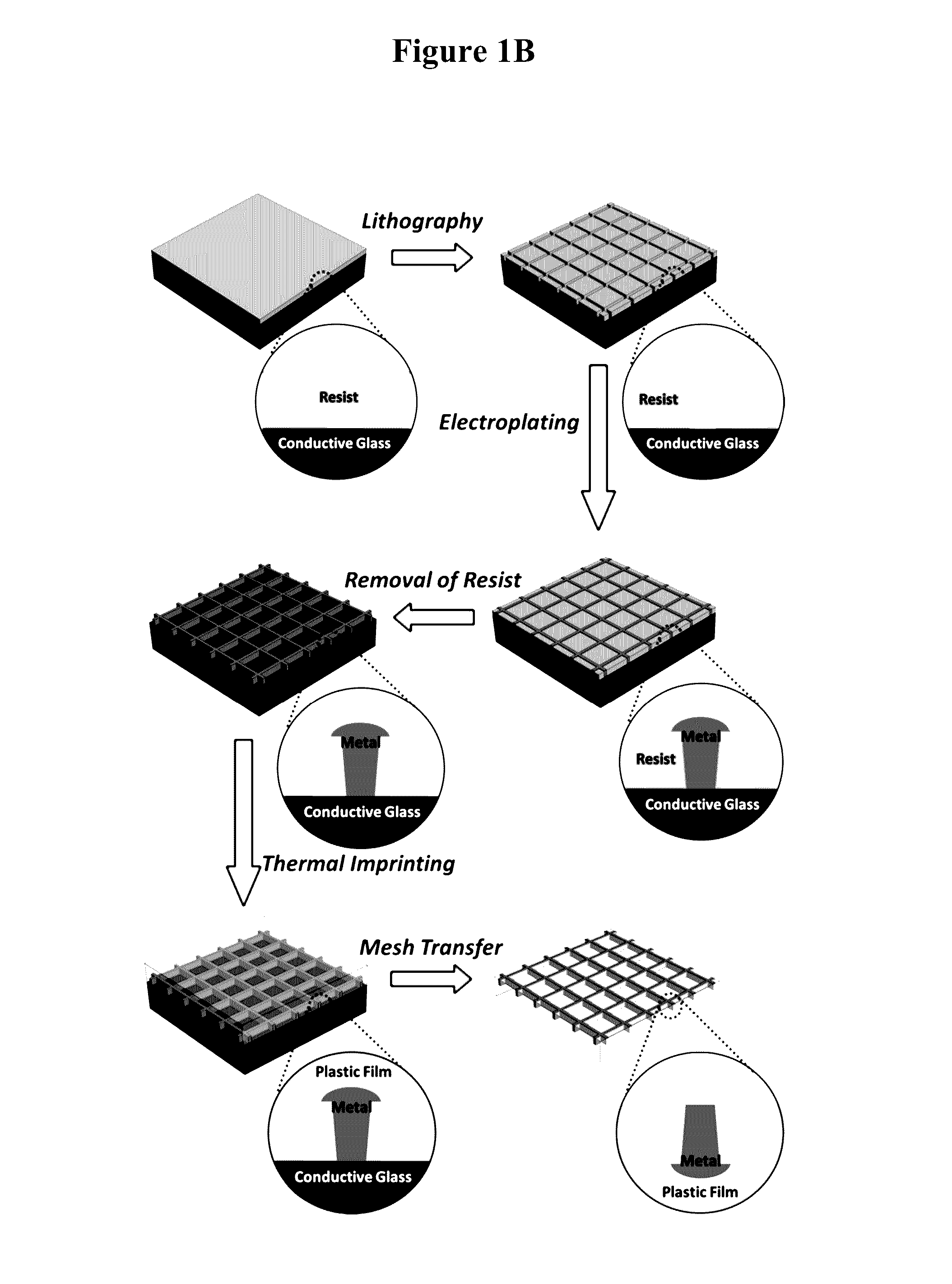

Transparent conductive films with embedded metal grids

ActiveUS20160345430A1Improve stabilityHigh strengthConductive layers on insulating-supportsCircuit optical detailsMechanical stabilityTransparent conducting film

A transparent conductive film with a metal mesh embedded in a substrate and a method of fabrication thereof is provided. The metal mesh has a cap that is pressed and embedded in a substrate or a deformable material on a substrate, providing superior mechanical stability by mechanical interlocking. The embedding mechanism also provides superior chemical and environmental stability. A fabrication method is provided and includes a vacuum-free and low-cost process for large-volume manufacturing of the transparent conductive film with tunable performance.

Owner:VERSITECH LTD

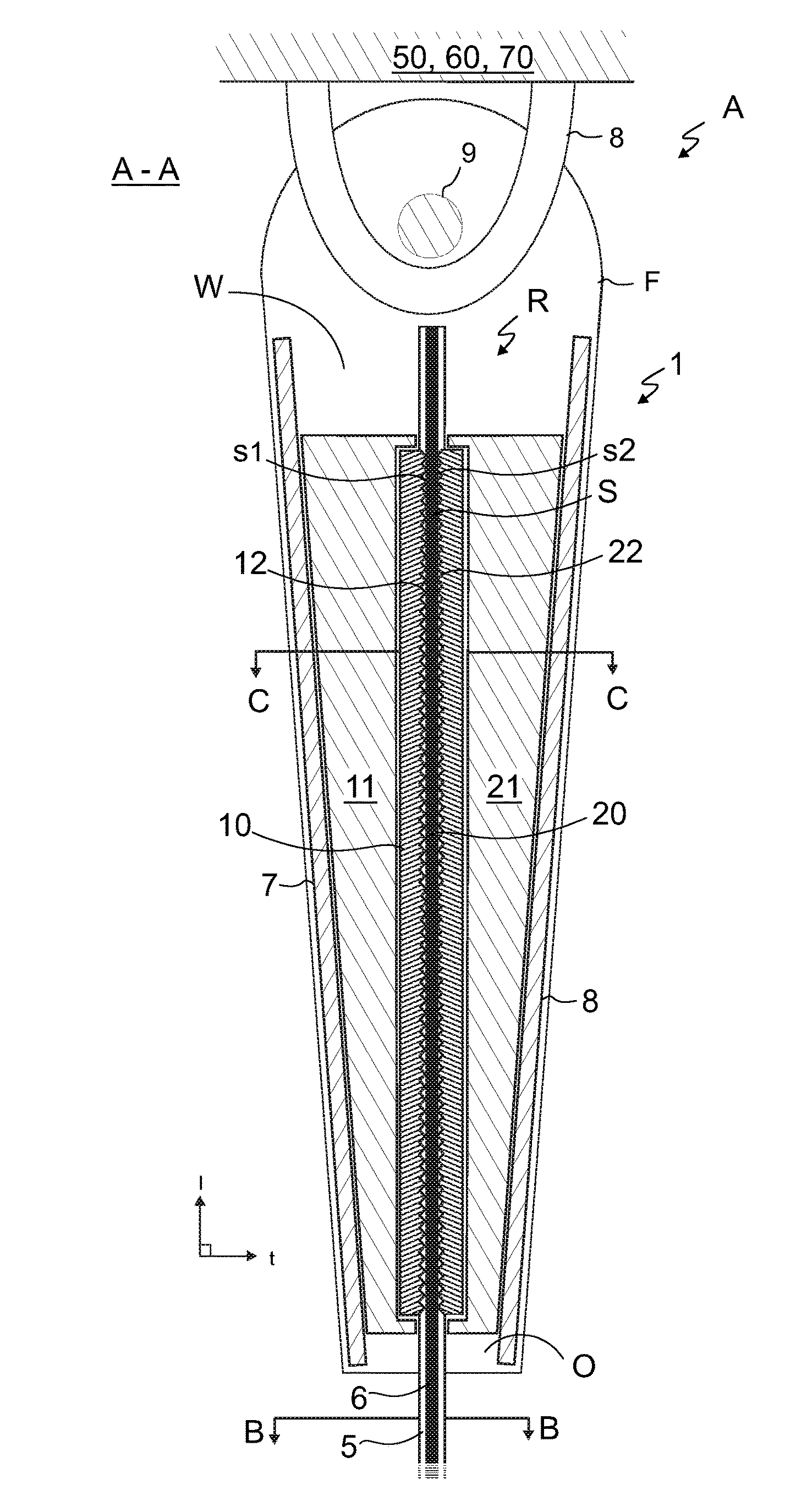

Method, a rope terminal arrangement and an elevator

InactiveUS20170036891A1Easy to installIncreased riskRopes and cables for vehicles/pulleyElevatorsBand shapeMechanical engineering

The invention relates to a method for fabricating a rope terminal arrangement of an elevator, comprisingproviding a belt-shaped elevator rope comprising a coating forming the outer surface of the rope;providing at least one gripping member having a gripping face;providing a wedge frame delimiting a wedge-shaped space;placing the gripping face of each said gripping member against the coating of a rope section of the belt-shaped rope;bonding the gripping face of each said gripping member and the coating of the rope section together;wedging the at least one gripping member and the rope section in the wedge shaped space.The invention furthermore relates to a rope terminal arrangement fabricated with the method, as well as to an elevator implementing the rope terminal arrangement.

Owner:KONE CORP

Capacitorless 1-transistor DRAM cell and fabrication method

InactiveUS7034336B2Cost-effective fabricationTransistorSolid-state devicesGate dielectricSemiconductor materials

Owner:POLARIS INNOVATIONS LTD

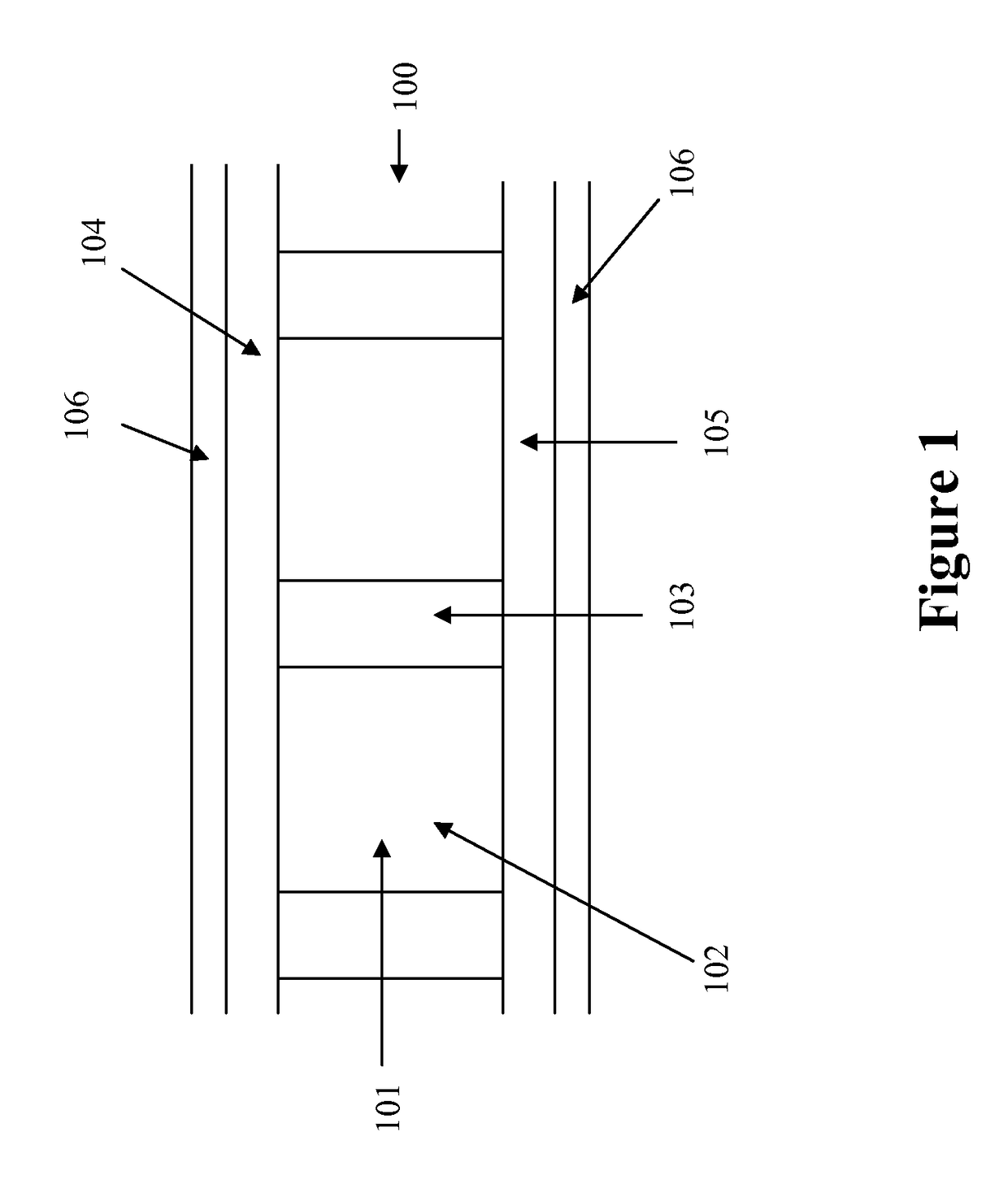

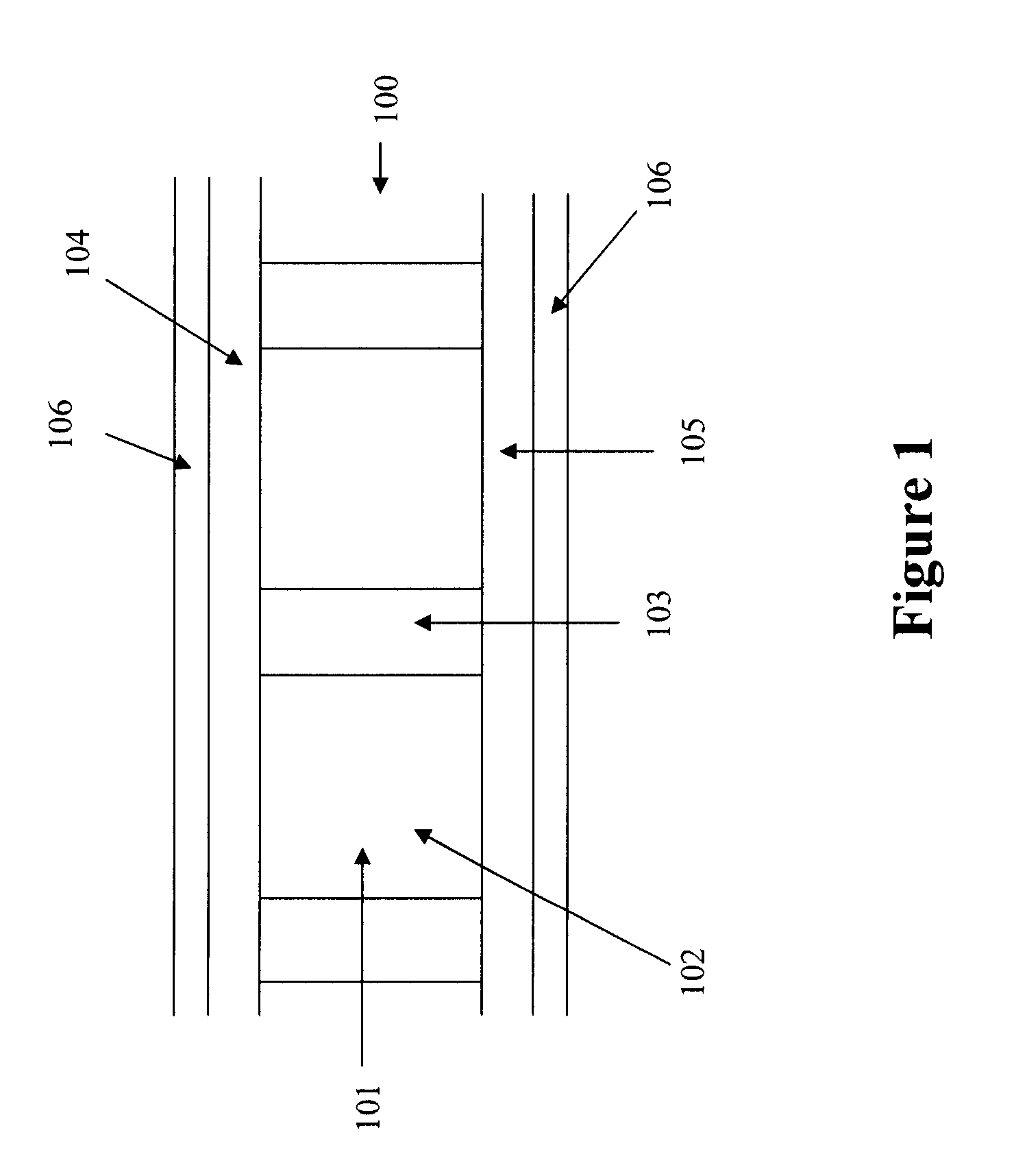

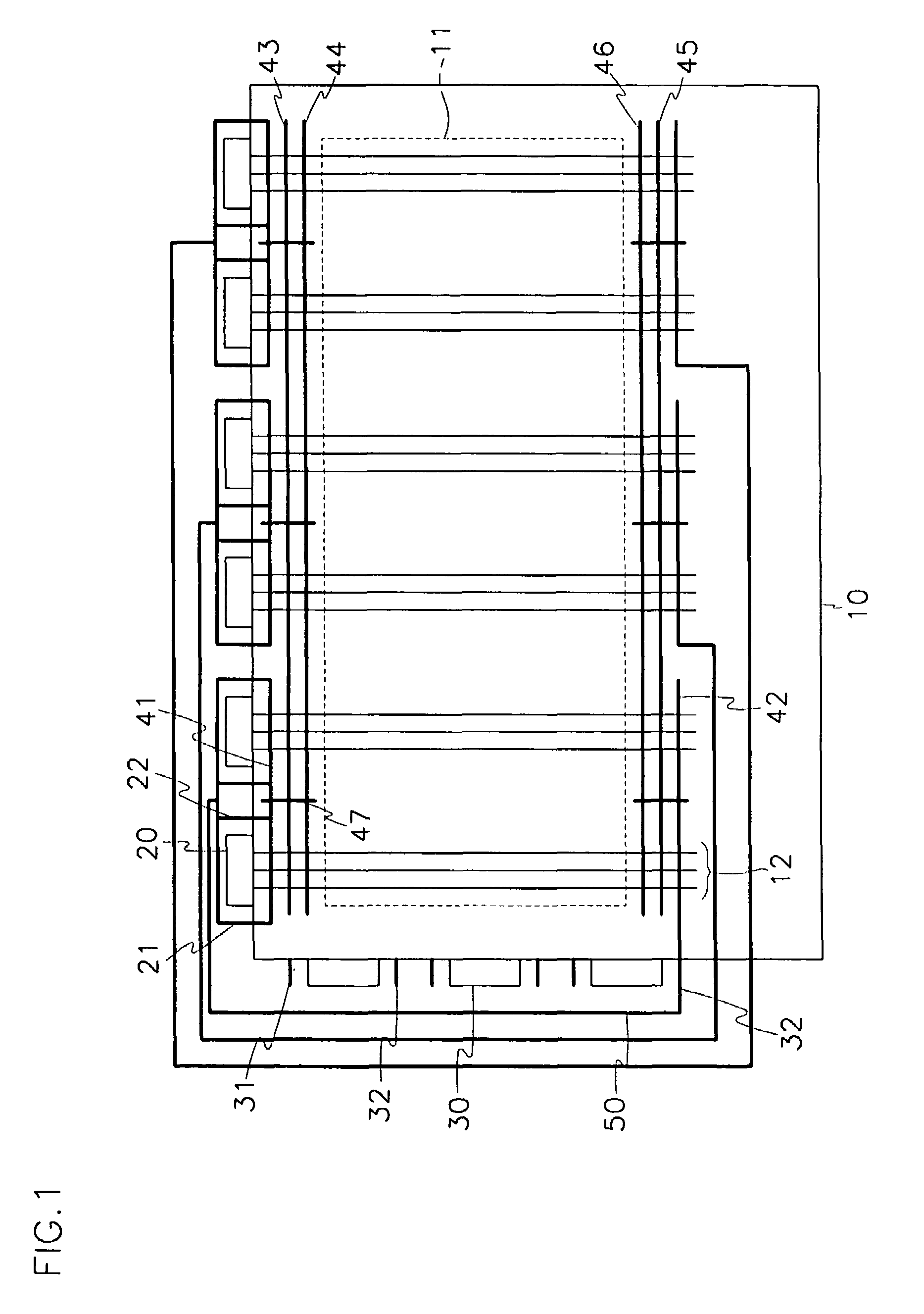

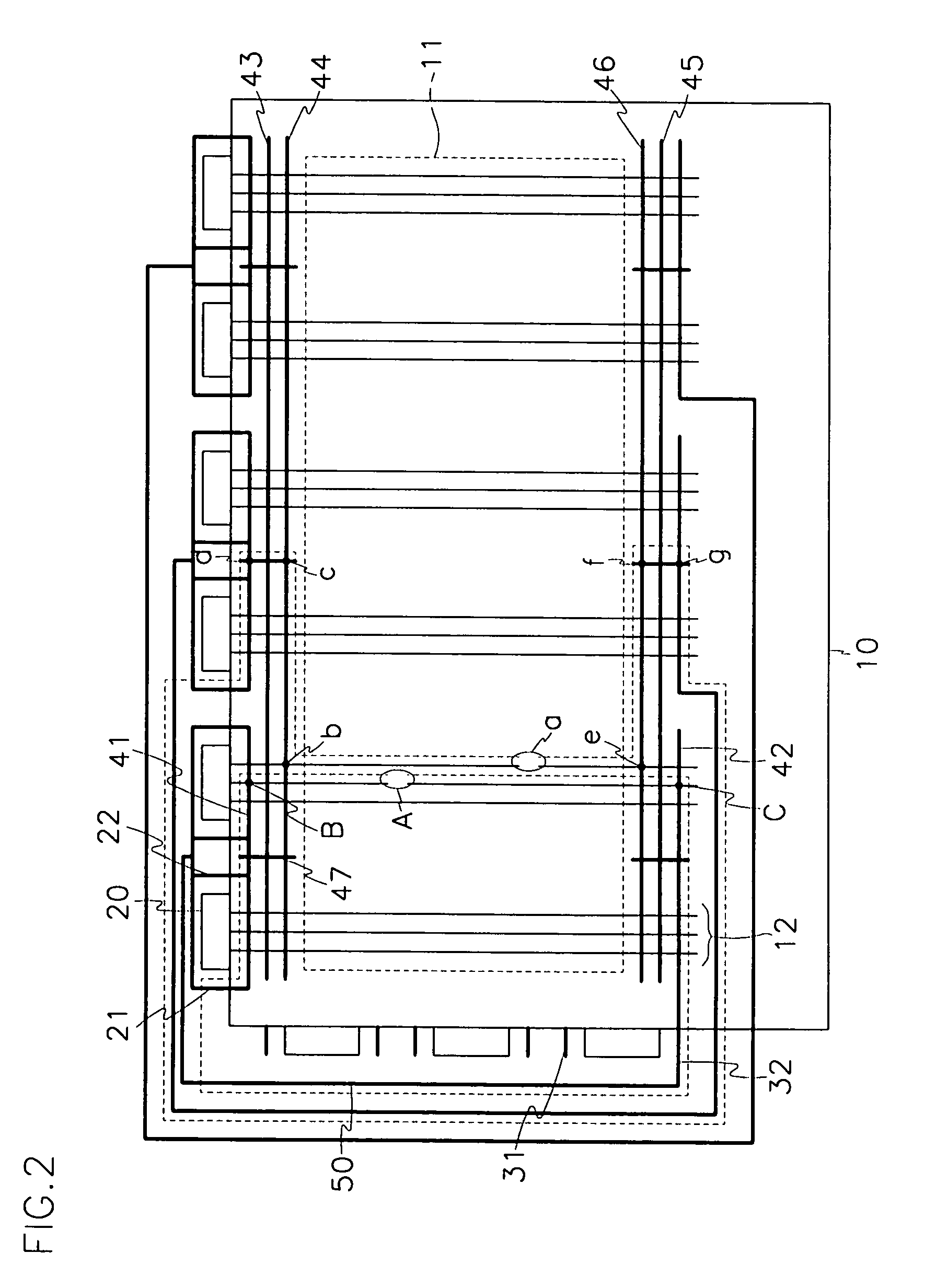

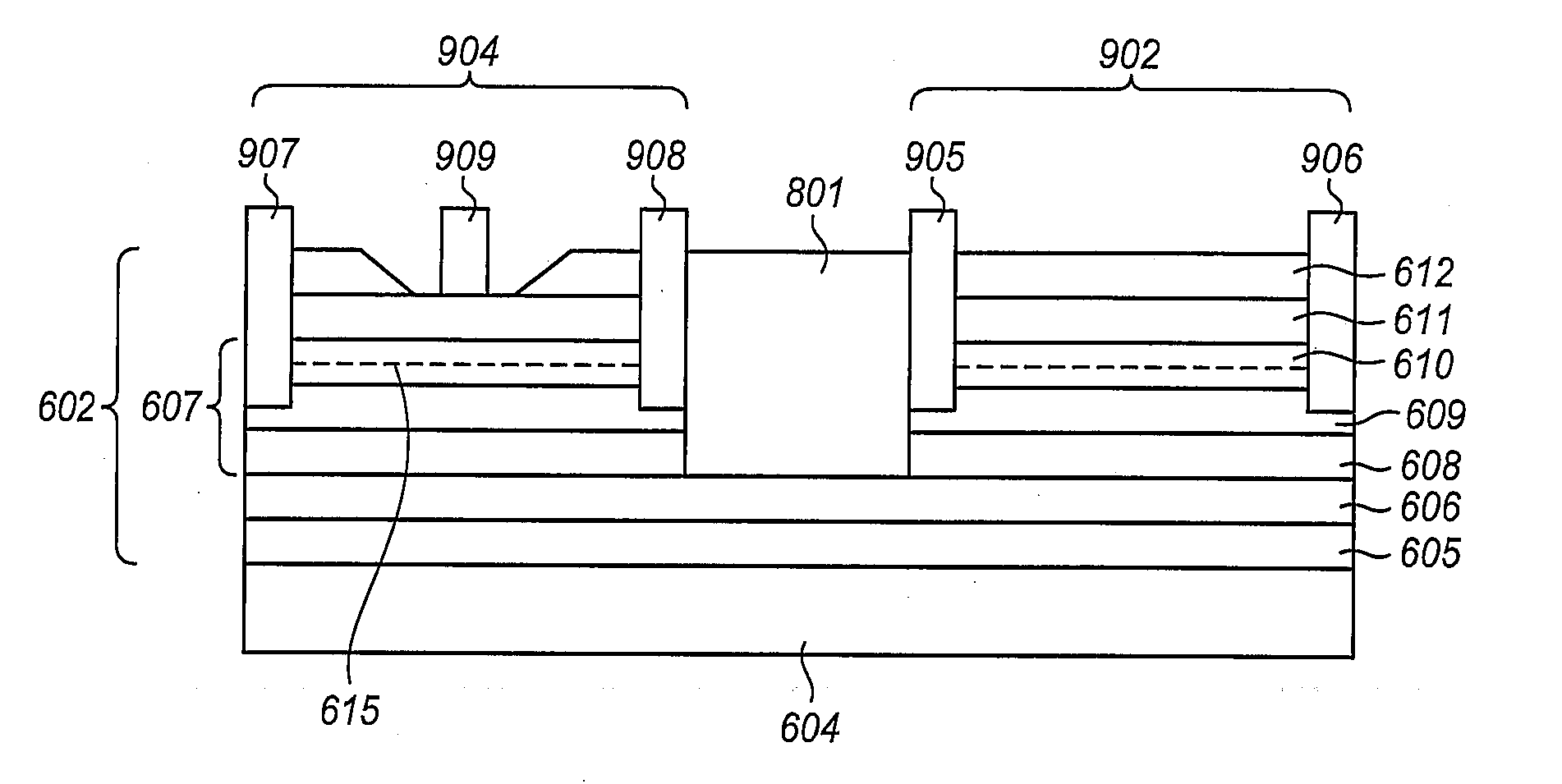

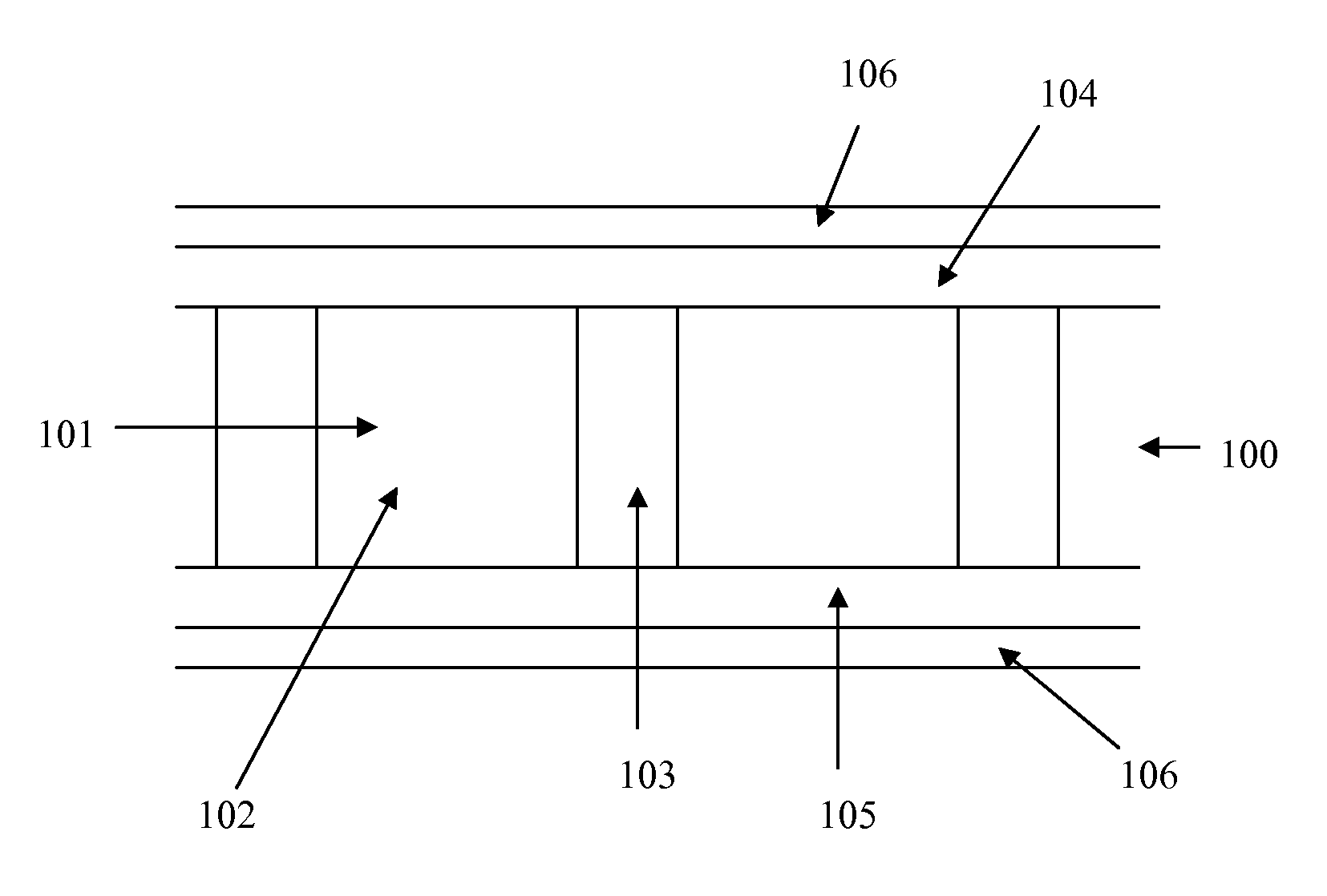

Thin film transistor array substrate for a liquid crystal display having repair lines

InactiveUS6943374B1Cost-effective fabricationSolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayEngineering

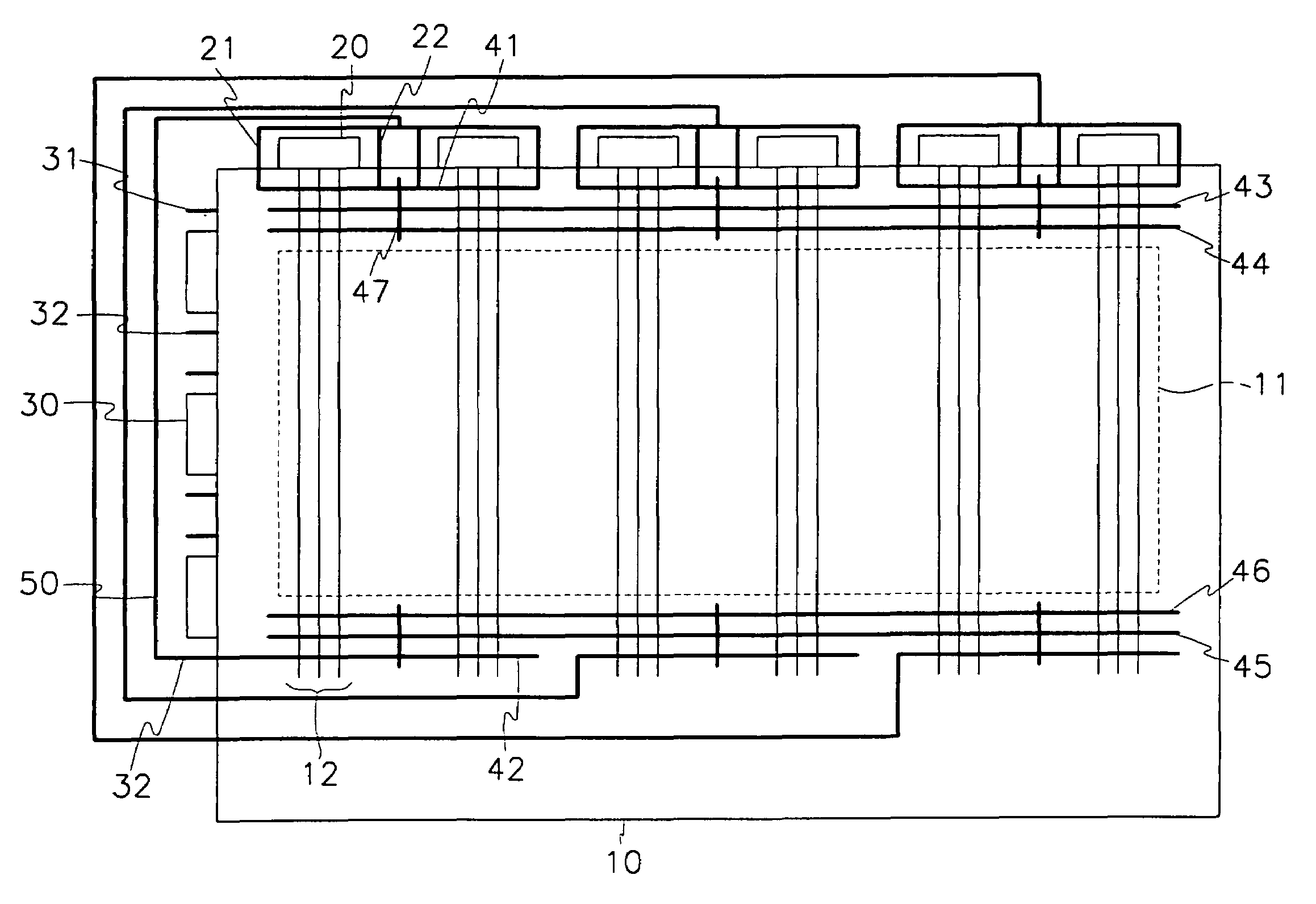

A thin film transistor array substrate for a liquid crystal display includes an insulating substrate with a display area and a peripheral area surrounding the display area. The peripheral area has an upper region above the display area and a lower region below the display area. Signal lines are formed on the substrate such that the signal lines are bundled into a plurality of blocks. Each block has a predetermined number of signal lines. A plurality of first upper repair lines is formed at the upper peripheral region of the substrate, crossing one or more blocks of the signal lines. A plurality of second upper repair lines is formed at the upper peripheral region of the substrate, crossing all of the signal lines. A plurality of first lower repair lines are formed at the lower peripheral region of the substrate, connected to the corresponding first upper repair lines. The first lower repair lines cross the signal lines crossed by the first upper repair lines. A plurality of second lower repair lines is formed at the lower peripheral region of the substrate, crossing all of the signal lines. A plurality of upper connection members crosses the first upper repair lines and the second upper repair lines. A plurality of lower connection members crosses the first lower repair lines and the second lower repair lines. In this structure, even though line breakage is concentrated at a particular area, such line breakage can be collectively repaired using the spare neighboring repair lines and interconnection lines interconnecting the repair lines efficiently.

Owner:SAMSUNG DISPLAY CO LTD

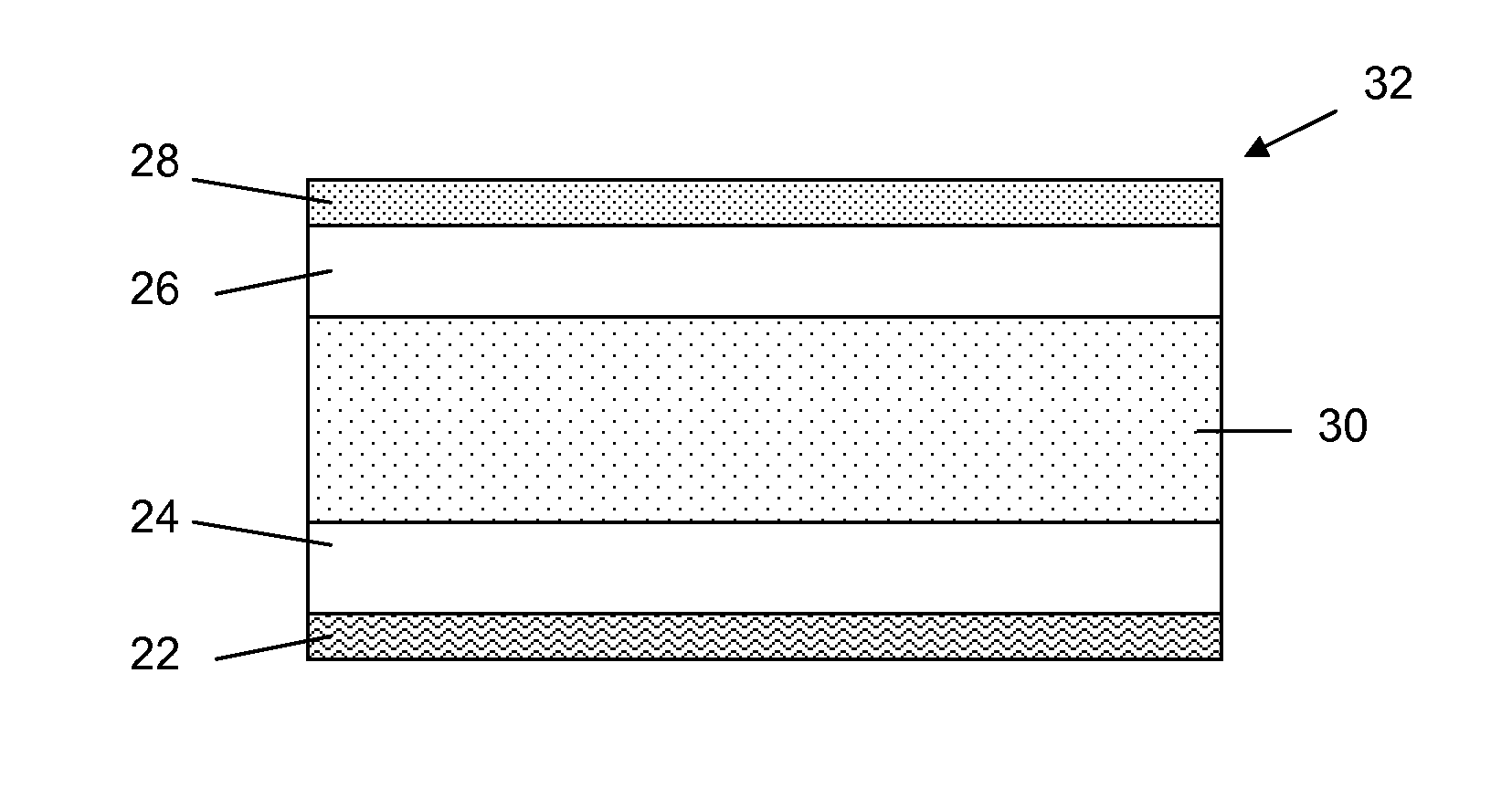

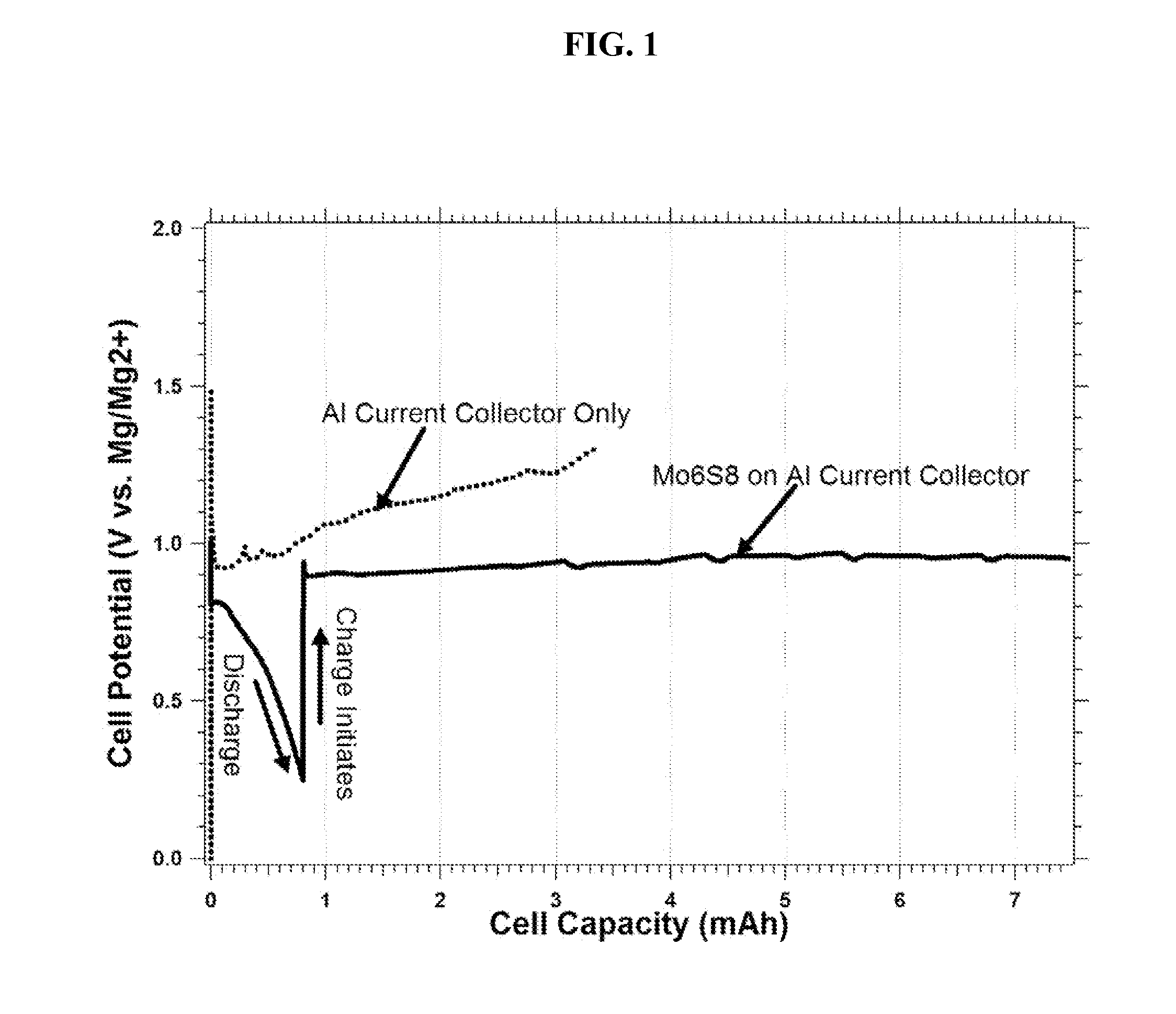

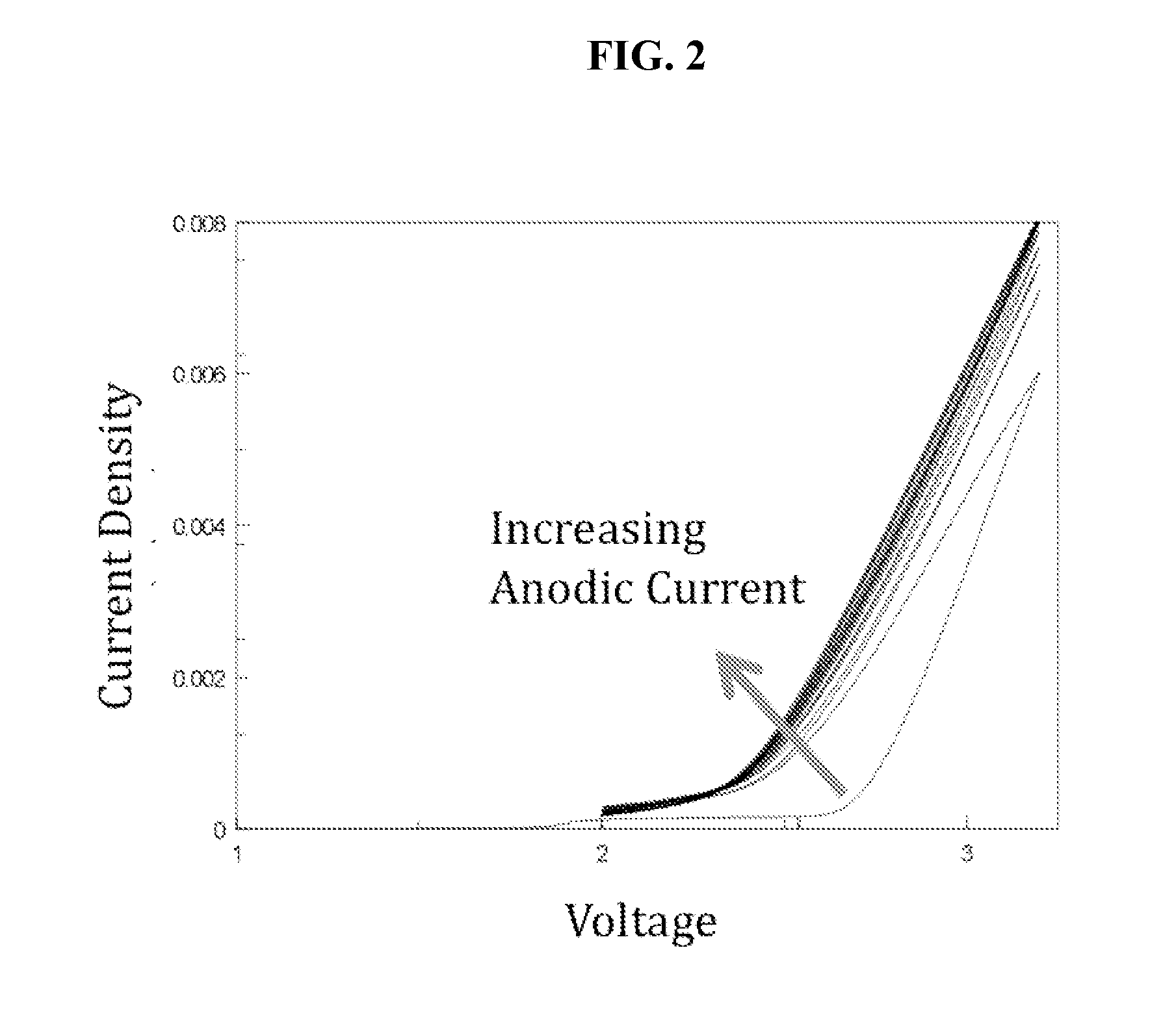

Rechargeable magnesium ion cell components and assembly

InactiveUS20130115521A1Improve chemical inertnessImproves anodic stabilityElectrode carriers/collectorsOrganic electrolyte cellsCorrosion reactionMagnesium ion

A magnesium battery electrode assembly is described, including a current collector comprising a metal, an overlayer material on the metal and an electrode layer comprising an electrode active material disposed on the current collector. The overlayer material passivates the metal, or inhibits a corrosion reaction that would occur between the metal and an electrolyte in the absence of the overlayer material.

Owner:PELLION TECH

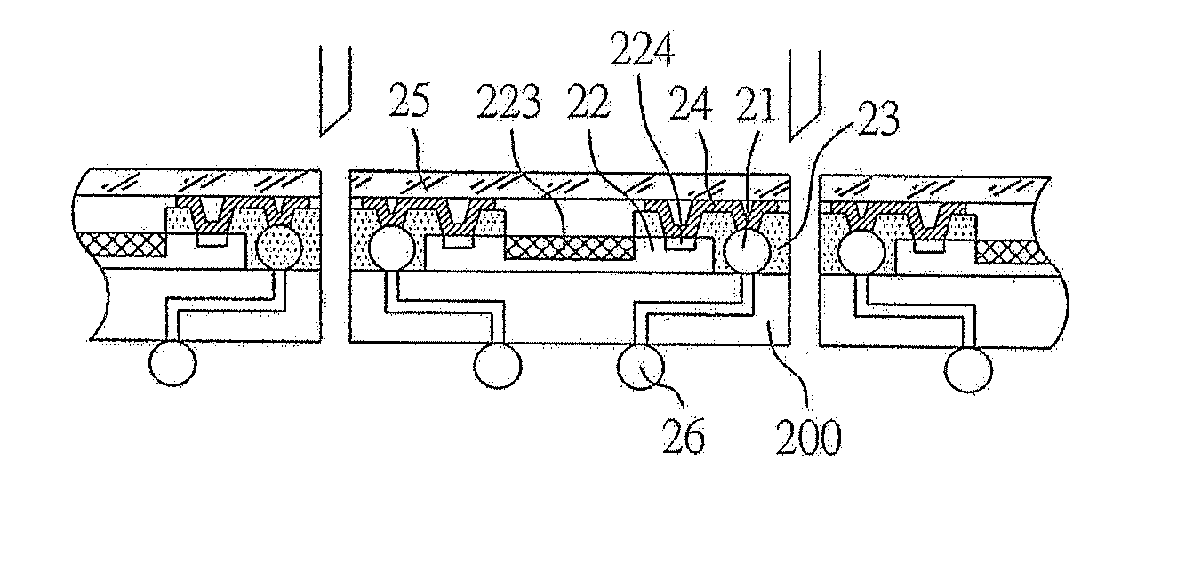

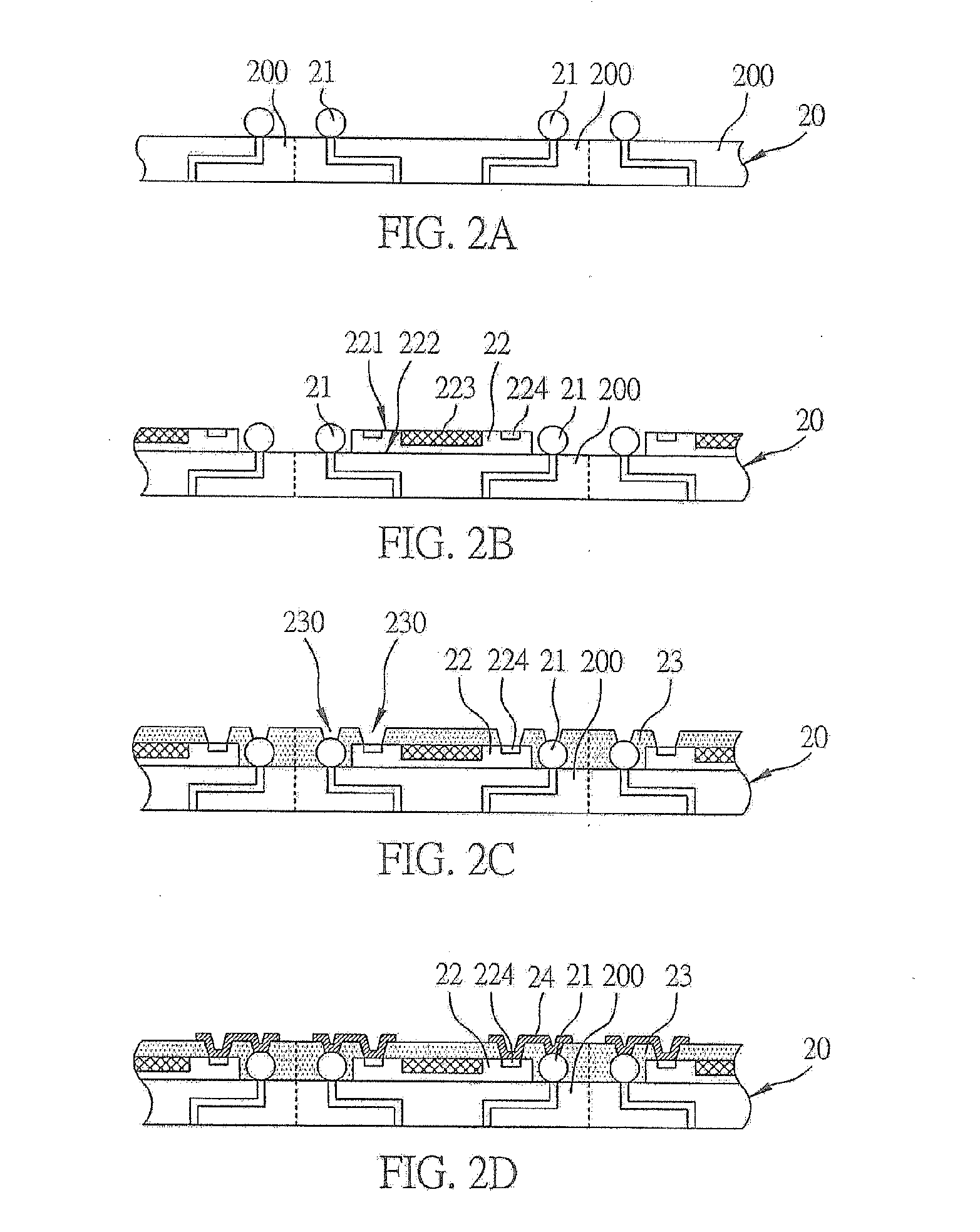

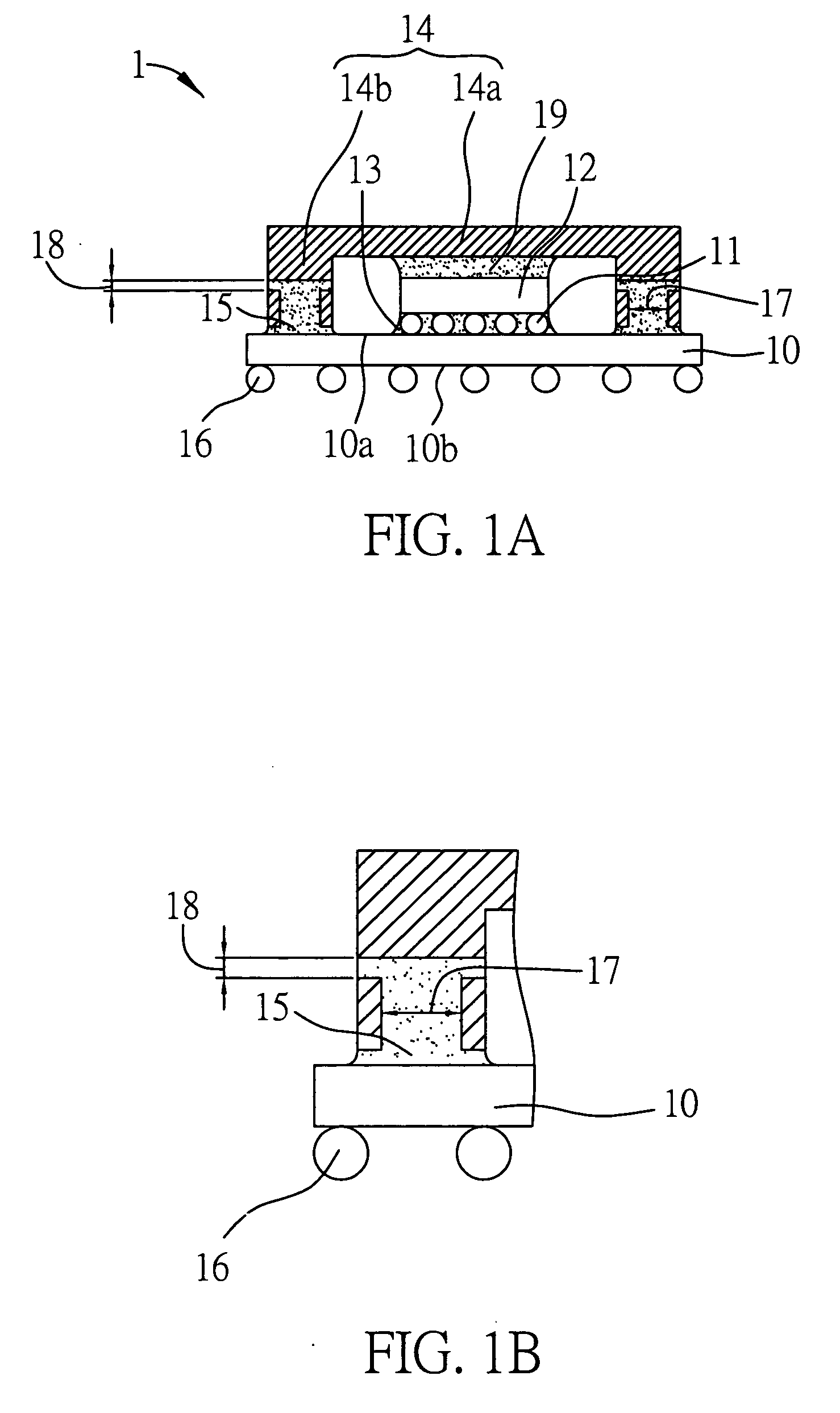

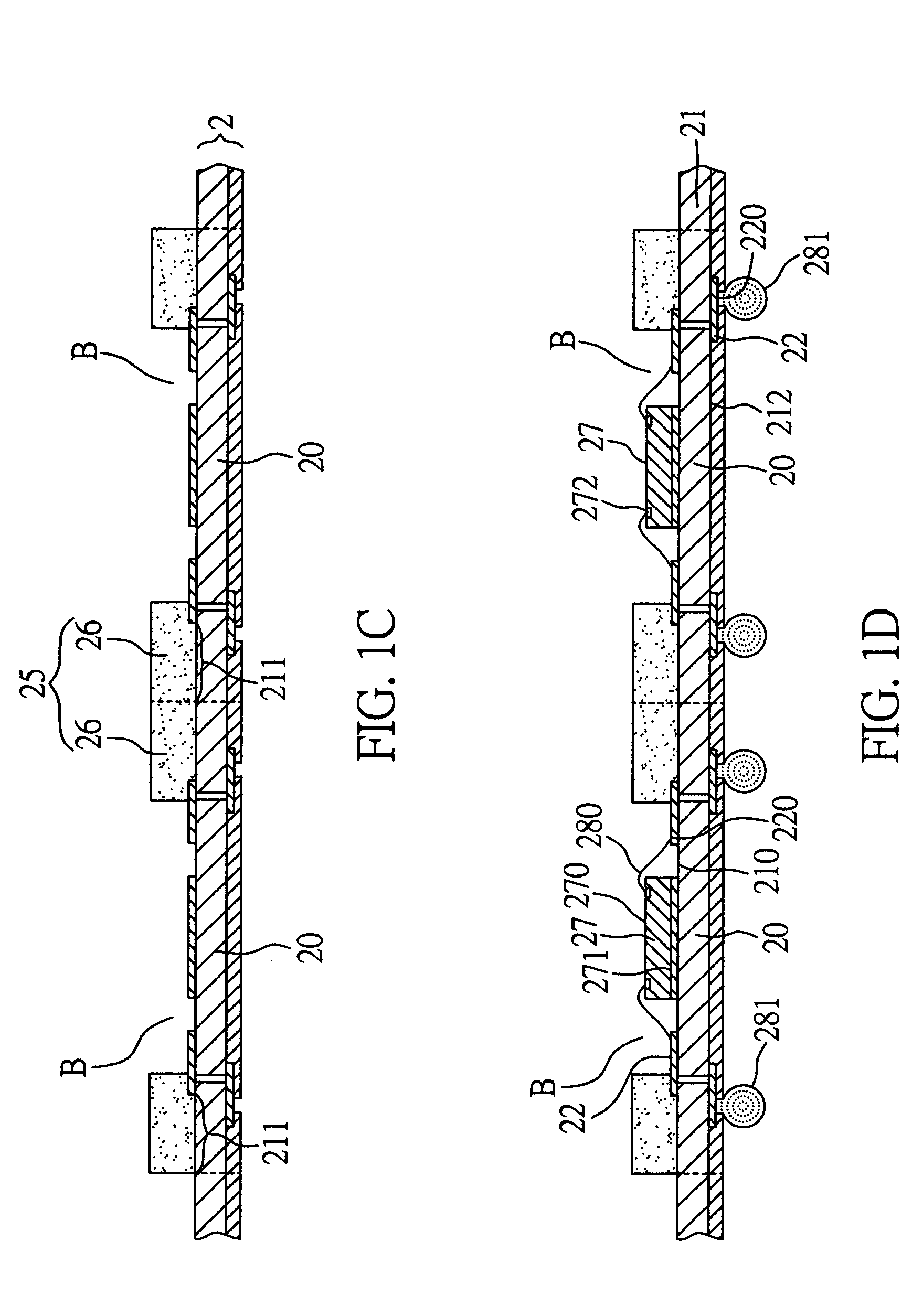

Sensor semiconductor device and method for fabricating the same

ActiveUS20060270089A1Avoid problemsImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesDevice materialSolder ball

A sensor semiconductor device and a method for fabricating the same are proposed. A plurality of metal bumps and a sensor chip are mounted on a substrate. A dielectric layer and a circuit layer are formed on the substrate, wherein the circuit layer is electrically connected to the metal bumps and the sensor chip. Thus, the sensor chip is electrically connected to the substrate via the circuit layer and the metal bumps. The dielectric layer is formed with an opening for exposing a sensor region of the sensor chip. A light-penetrable lid covers the opening of the dielectric layer, such that light is able to penetrate the light-penetrable lid to reach the sensor region and activate the sensor chip. A plurality of solder balls are mounted on a surface of the substrate free of mounting the sensor chip, for electrically connecting the sensor chip to an external device.

Owner:SILICONWARE PRECISION IND CO LTD

Emr sensor and transistor formed on the same substrate

InactiveUS20080088982A1Cost-effective fabricationCompact designRecord information storageManufacture of flux-sensitive headsQuantum wellData signal

Magnetic sensing chips and methods of fabricating the magnetic sensing chips are disclosed. A magnetic sensing chip as described herein includes an EMR sensor formed on a substrate from multiple semiconductor layers. One or more of the semiconductor layers form a quantum well comprising a two-dimensional electron gas (2DEG) or hole gas (2DHG). The magnetic sensing chip also includes one or more transistors formed on the substrate from the multiple semiconductor layers. The transistor(s) likewise include a quantum well comprising a 2DEG or 2DHG. The EMR sensor and the transistor(s) are connected by one or more connections so that the transistor(s) amplifies data signals from the EMR sensor.

Owner:WESTERN DIGITAL TECH INC

Pipe structure and method of manufacture

InactiveUS20010013673A1Reliably sealed against leakageEfficient and cost-effectiveAssembly machinesFilament/thread formingEngineeringMechanical engineering

A pipe section formed of a polymeric material which has a substantially constant thickness throughout, the terminal edge of the female connection having a reinforcement structure which rigidifies the end of the female connection and prevents deformation, the pipe section preferably having a flared end, and the reinforcement structure preferably being a semicircular channel formed at the end of the pipe section by a mandrel after initial extrusion of the pipe section; along with a method and apparatus for forming the pipe section, a pipe assembly including such pipe section, and a method of forming the pipe assembly.

Owner:ADVANCED DRAINAGE SYST

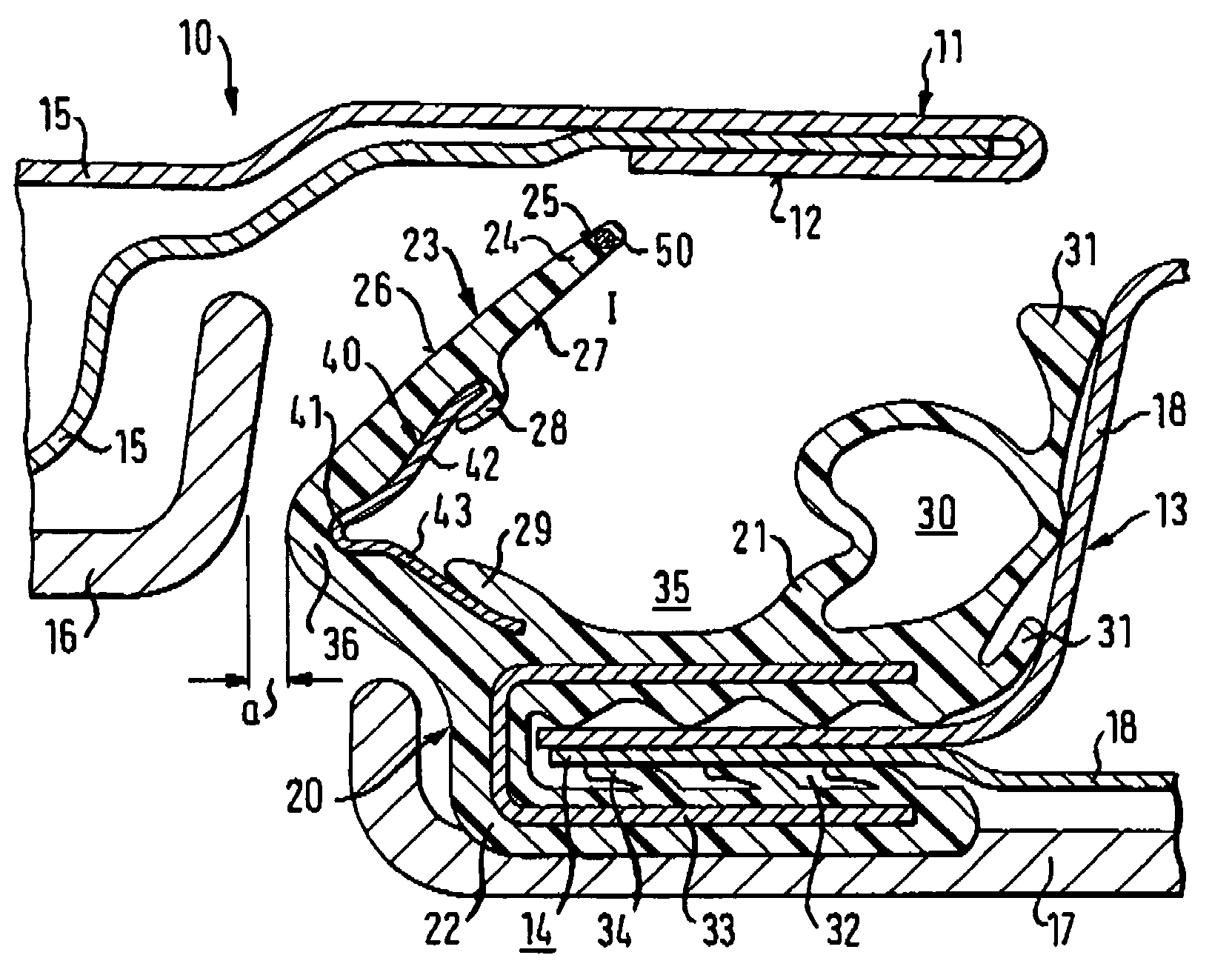

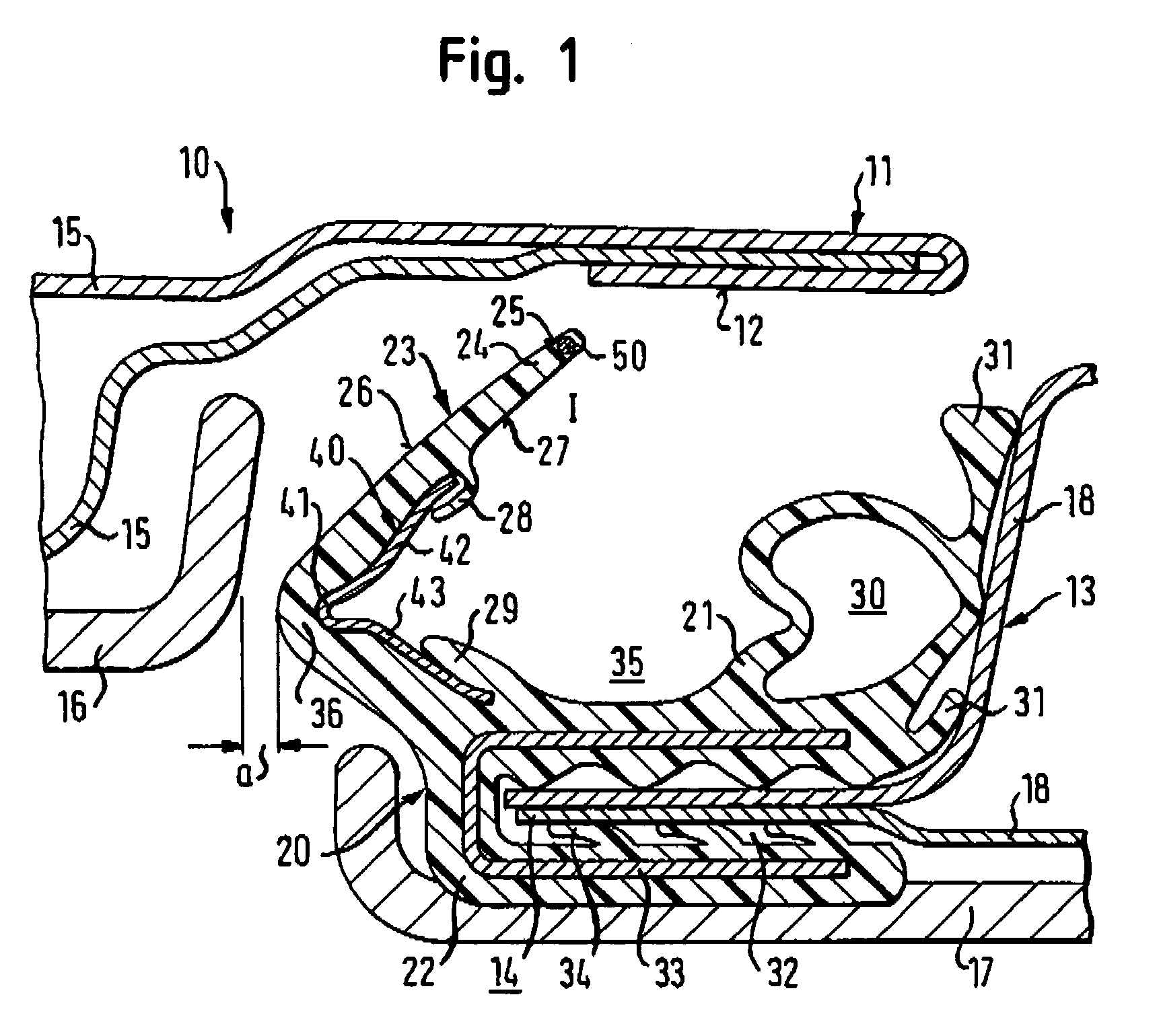

Sealing device especially for sealing the folding roof of a car

InactiveUS7380862B2Durable restoring responseSatisfactory sealEngine sealsSealing arrangementsMobile vehicleEngineering

The invention relates to a weatherstrip assembly which is used particularly for sealing a folding hardtop (10) of a motor vehicle and comprises a joint consisting of sealing section (21) and fastening section (22) parts. The sealing section (21) is provided with a sealing lip (23), which is made of elastically deformable material, can be moved from the first position (I) to the second position (II) thereof and is provided with at least one restoring element (40). In order to ensure a durable, efficient and reliable restoring response of the sealing lip (23), it is provided with a tensioning element (50) in the form of a hose on the end thereof.

Owner:COOPER STANDARD

Method for fabricating sensor semiconductor device

ActiveUS7271024B2Avoid crackingAvoid problemsSemiconductor/solid-state device detailsSolid-state devicesSolder ballDielectric layer

A sensor semiconductor device and a method for fabricating the same are proposed. A plurality of metal bumps and a sensor chip are mounted on a substrate. A dielectric layer and a circuit layer are formed on the substrate, wherein the circuit layer is electrically connected to the metal bumps and the sensor chip. Thus, the sensor chip is electrically connected to the substrate via the circuit layer and the metal bumps. The dielectric layer is formed with an opening for exposing a sensor region of the sensor chip. A light-penetrable lid covers the opening of the dielectric layer, such that light is able to penetrate the light-penetrable lid to reach the sensor region and activate the sensor chip. A plurality of solder balls are mounted on a surface of the substrate free of mounting the sensor chip, for electrically connecting the sensor chip to an external device.

Owner:SILICONWARE PRECISION IND CO LTD

Device packages

InactiveUS20090042382A1Easily and precisely locatedLow costSemiconductor/solid-state device manufacturingNon-printed masksSolder ballEngineering

Low volume production of electronic devices having ball attachments, e.g. solder ball arrays, is advantageously achieved using a specific method. In particular a stencil having holes in, for example, the ball grid array pattern is formed by laser ablation of the holes in materials such as paper and polymers. The stencil holes are aligned with corresponding pads on the electronic device. Balls such as solder balls are introduced into the holes and heated to induce adhesion of the balls to the corresponding pads.

Owner:AGERE SYST INC

Heat dissipating structure and semiconductor package with the same

InactiveUS20050056926A1Easy to checkImprove bond reliabilitySemiconductor/solid-state device detailsSolid-state devicesAdhesiveSemiconductor package

A heat dissipating structure and a semiconductor package with the same are proposed. A substrate is used to accommodate at least one chip thereon, and the chip is electrically connected to the substrate. A heat dissipating structure having a flat portion and a support portion is mount on the substrate via the support portion by means of an adhesive. At least one groove is formed on the support portion and at least one air vent is formed around the groove to allow the groove to communicate with the outside via the air vent, such that the adhesive is allowed to fill the groove to expel air from the groove to the atmosphere through the air vent, thereby preventing the air from trapped in the groove.

Owner:SILICONWARE PRECISION IND CO LTD

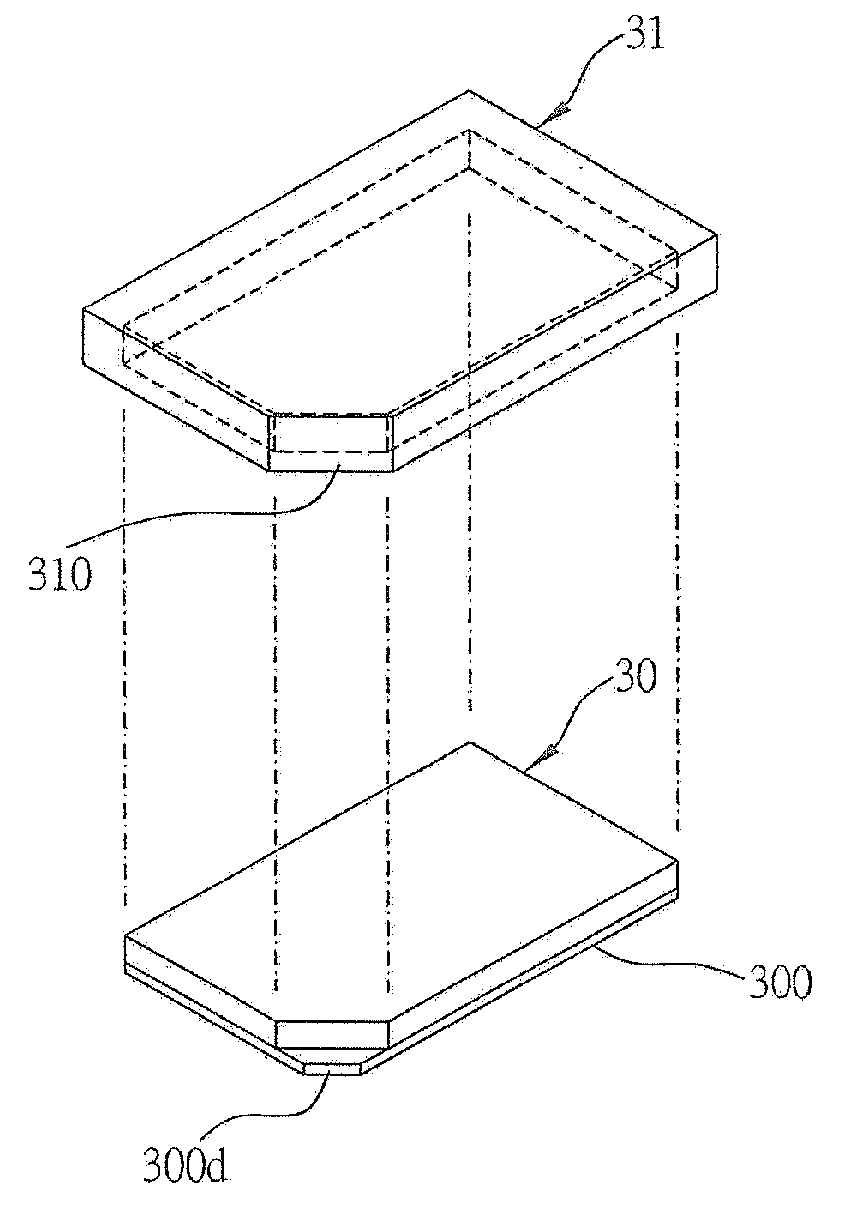

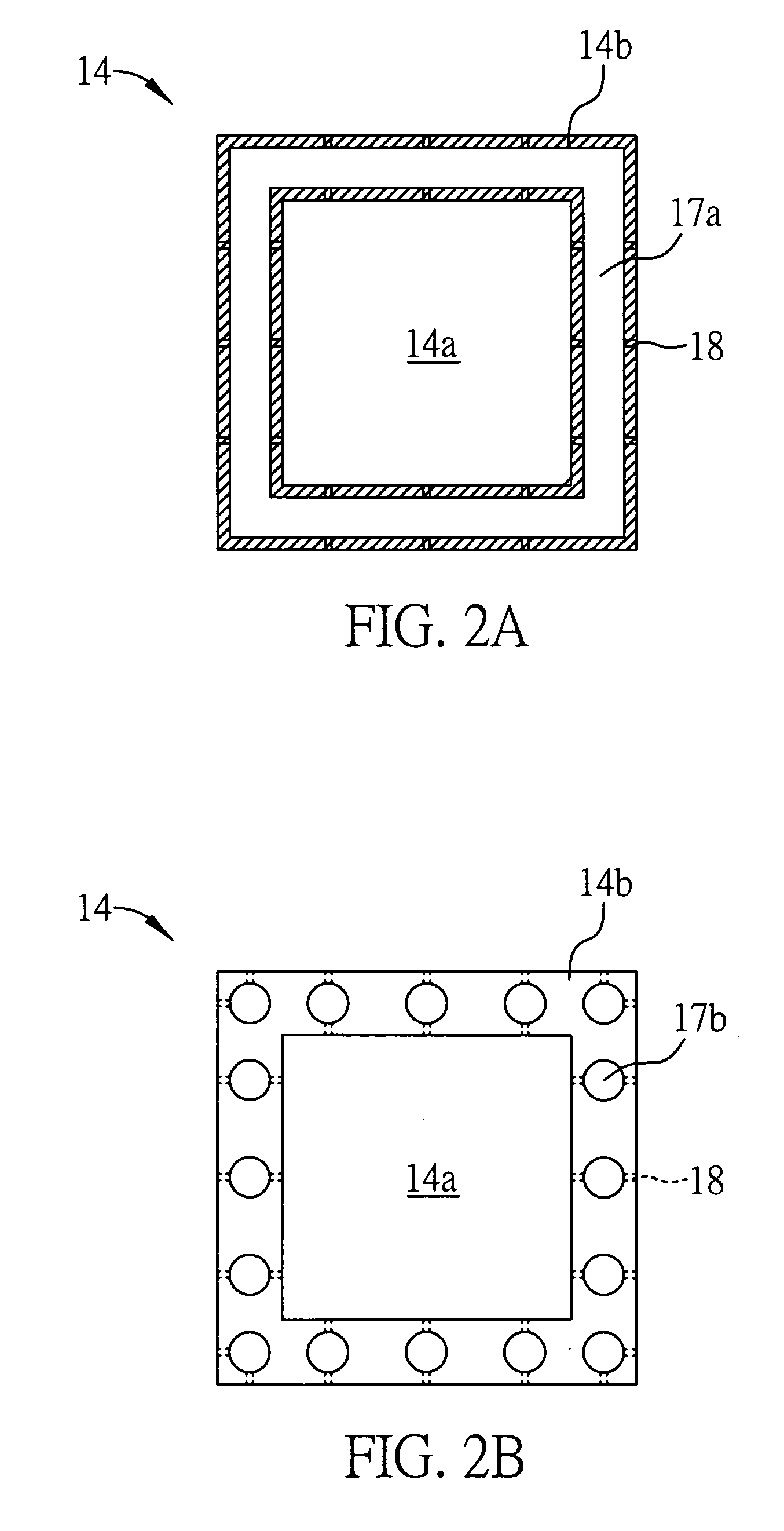

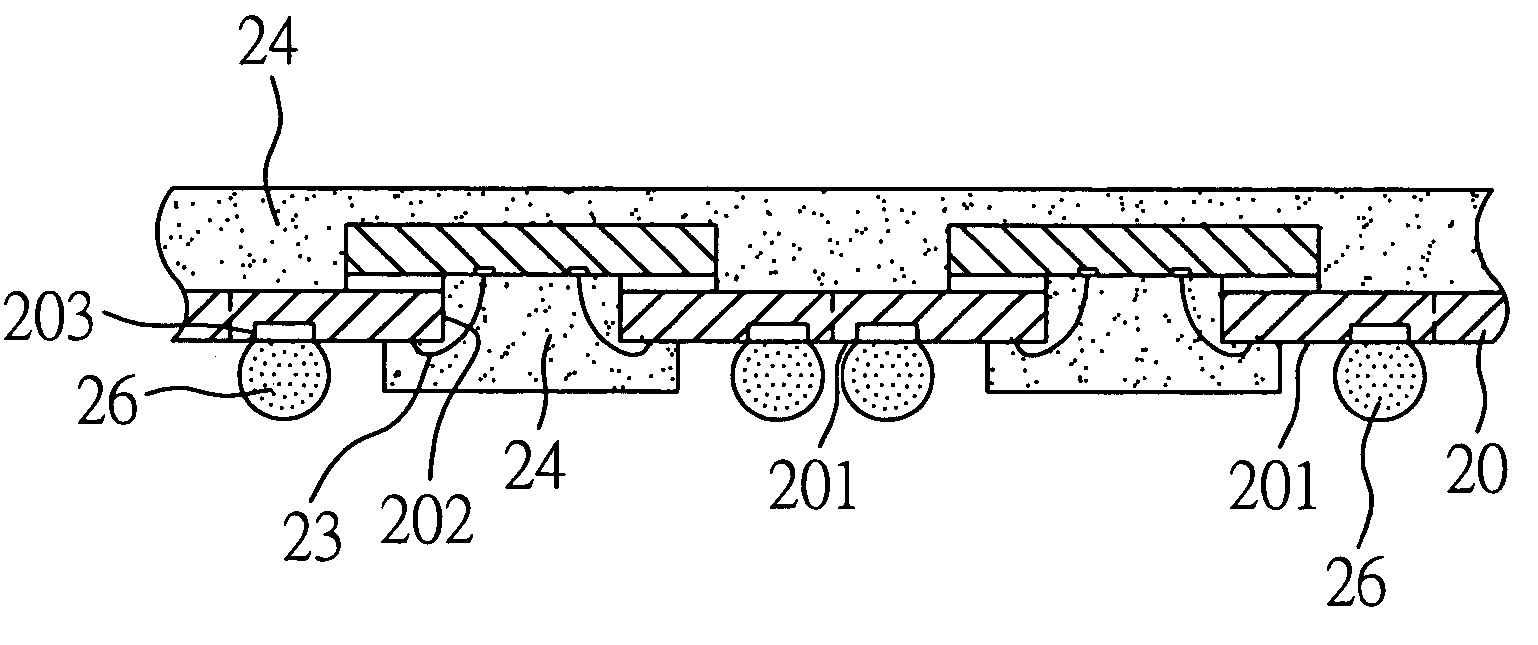

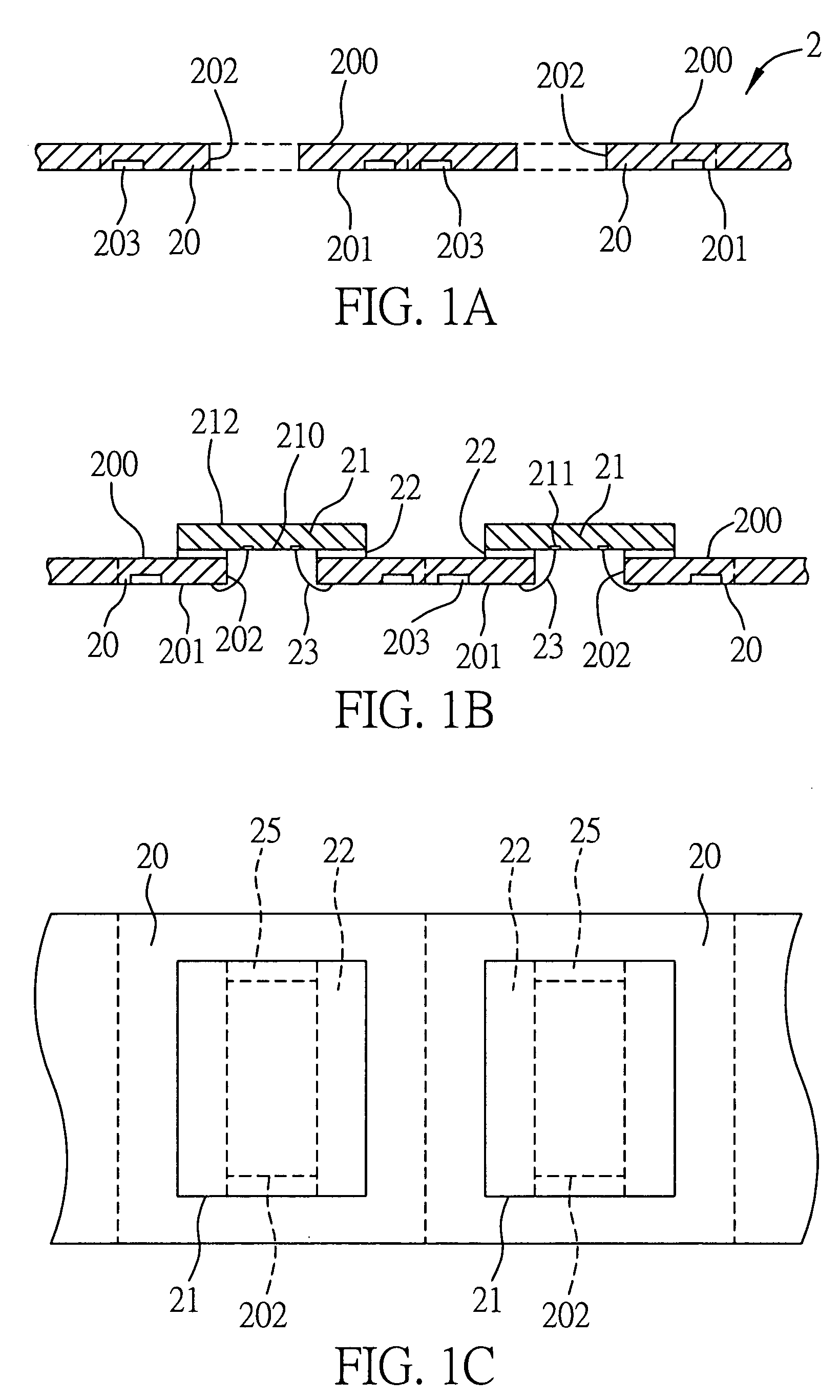

Fabrication method of semiconductor package with photosensitive chip

InactiveUS6989296B2Reduce manufacturing costSimplify the manufacturing processSemiconductor/solid-state device detailsSolid-state devicesInterposerSemiconductor package

A fabrication method of a semiconductor package with a photosensitive chip is provided. A substrate having a core is prepared. An interposer is mounted on the substrate, with a peripheral portion of the substrate exposed from the interposer. A molding process is performed and the substrate is clamped between an upper mold and a lower mold, with the interposer received in an upwardly-recessed cavity of the upper mold. A molding compound is injected into the upwardly-recessed cavity to form a dam on the peripheral portion of the substrate. Then the upper and lower molds and the interposer are removed from the substrate to expose area covered by the interposer on the substrate. At least one photosensitive chip is mounted on the exposed area of the substrate. A lid seals the dam such that the chip is received in a space defined by the substrate, the dam and the lid.

Owner:SILICONWARE PRECISION IND CO LTD

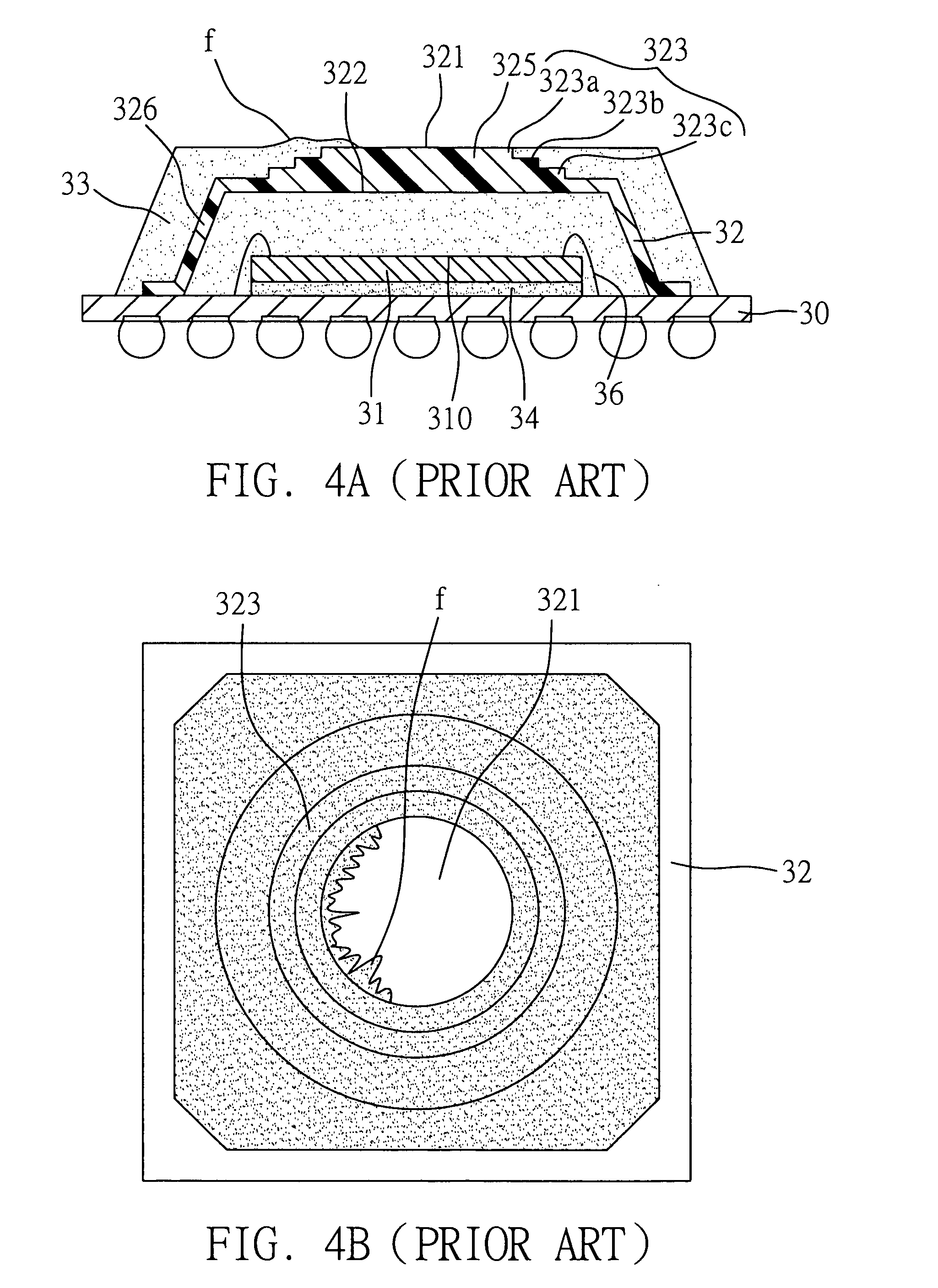

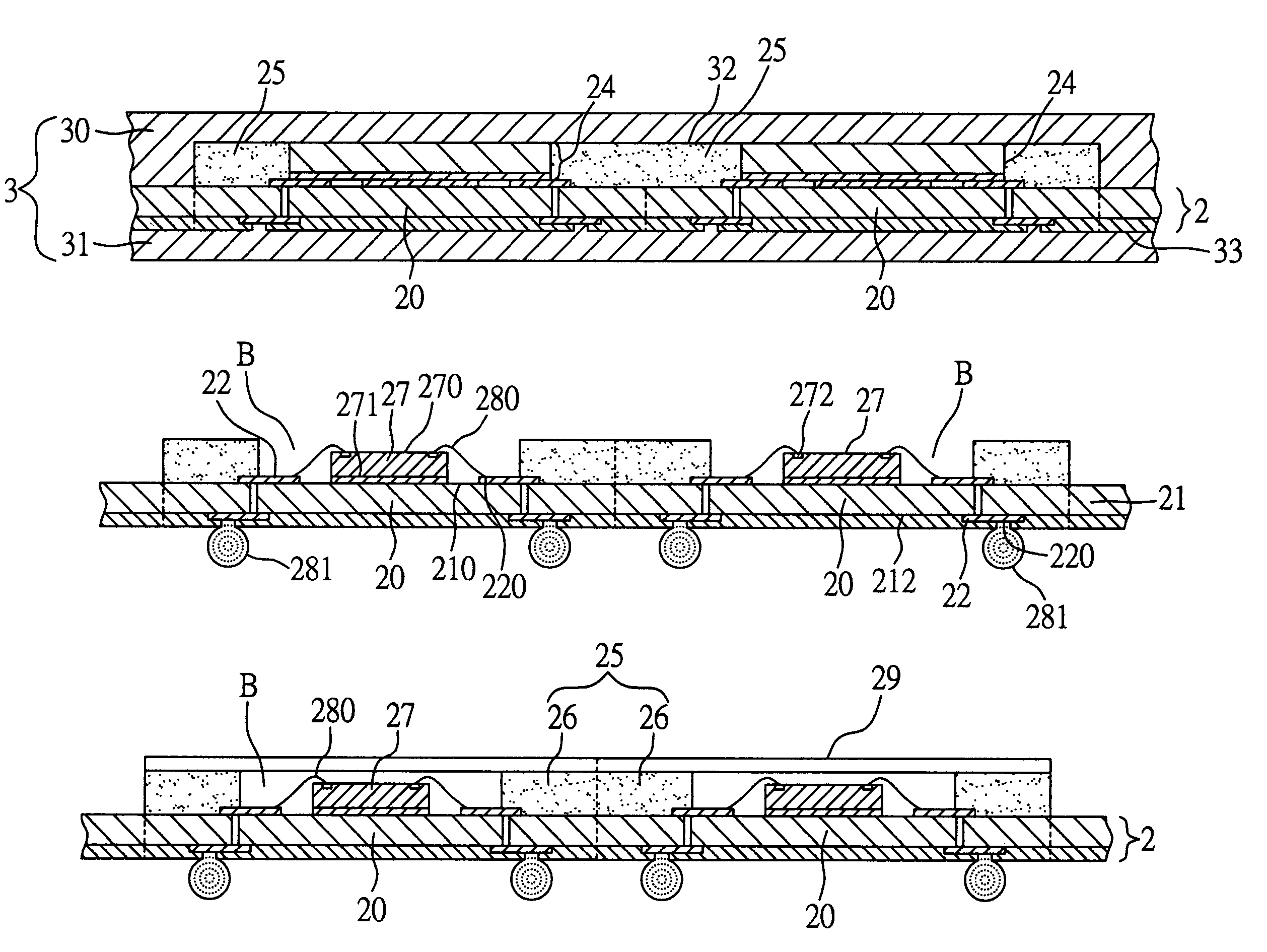

Method for fabricating window ball grid array semiconductor package

ActiveUS20050208707A1Inexpensive to fabricateFabrication cost is increasedSemiconductor/solid-state device detailsSolid-state devicesAdhesiveSemiconductor package

A method for fabricating a window ball grid array (WBGA) semiconductor package is provided. A substrate is prepared having a through opening and ball pads on a lower surface thereof. A chip is mounted over the opening of the substrate via an adhesive, with gaps not applied with the adhesive left between the chip and substrate. The chip is electrically connected to the substrate via bonding wires through the opening. A spacer is attached to the lower surface of the substrate and has a through hole and a recessed portion around the through hole. During molding, the spacer is clamped between the substrate and a mold, and the recessed portion is located between the ball pads and the opening, such that a resin material for forming an encapsulation body encapsulates the chip and flows through the gaps to encapsulate the bonding wires. The recessed portion holds resin flash therein.

Owner:UTAC HEADQUARTERS PTE LTD

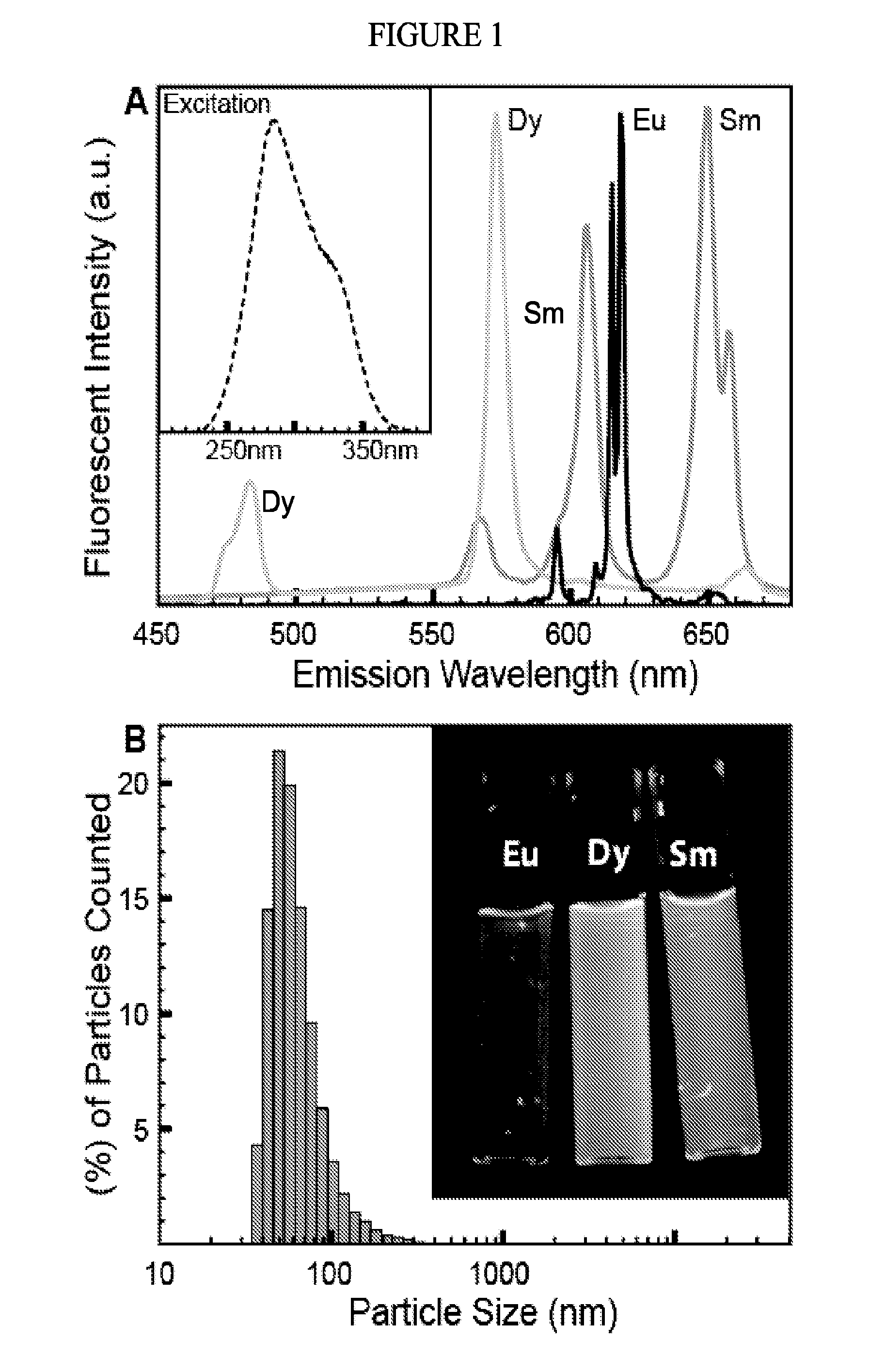

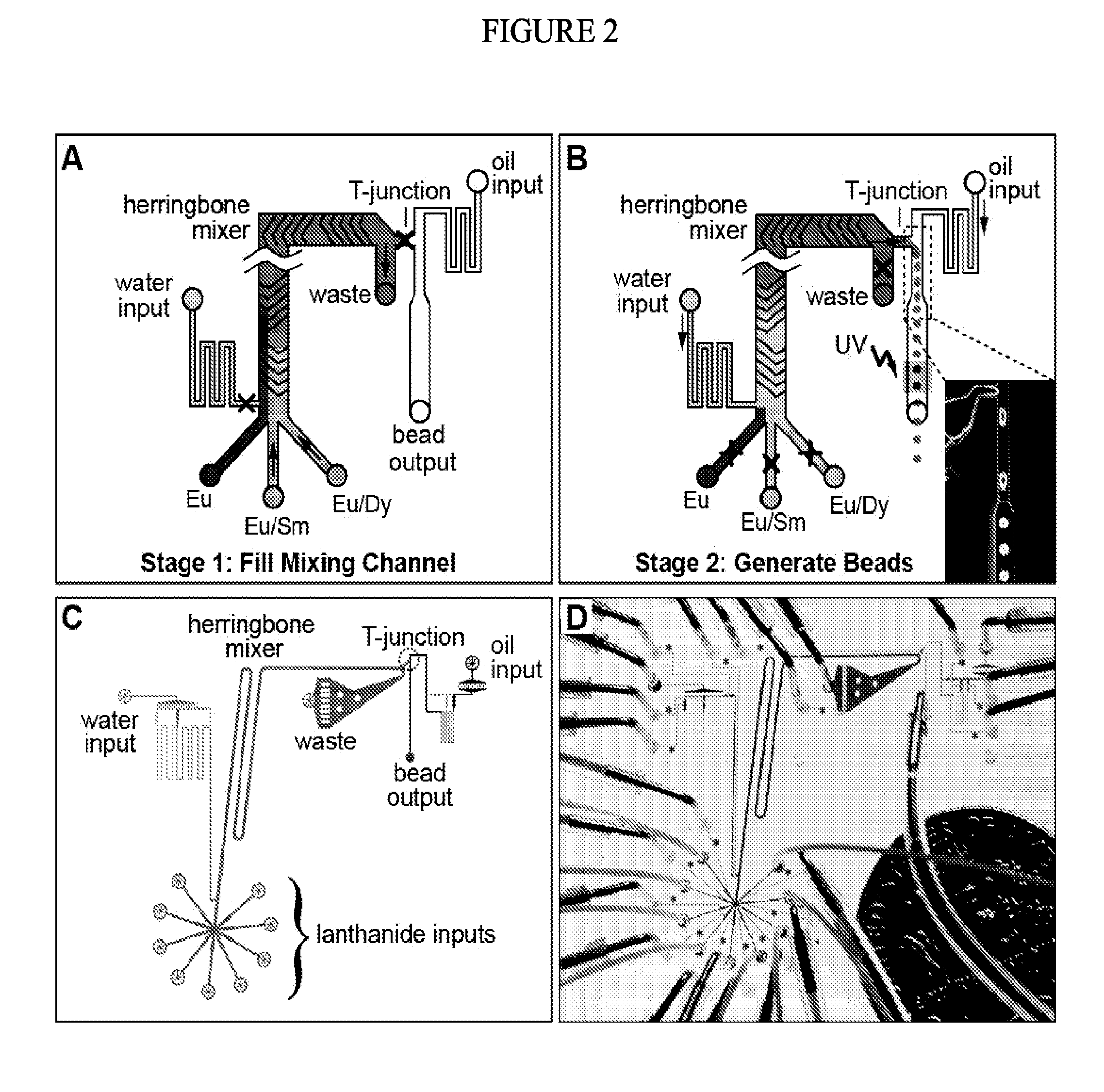

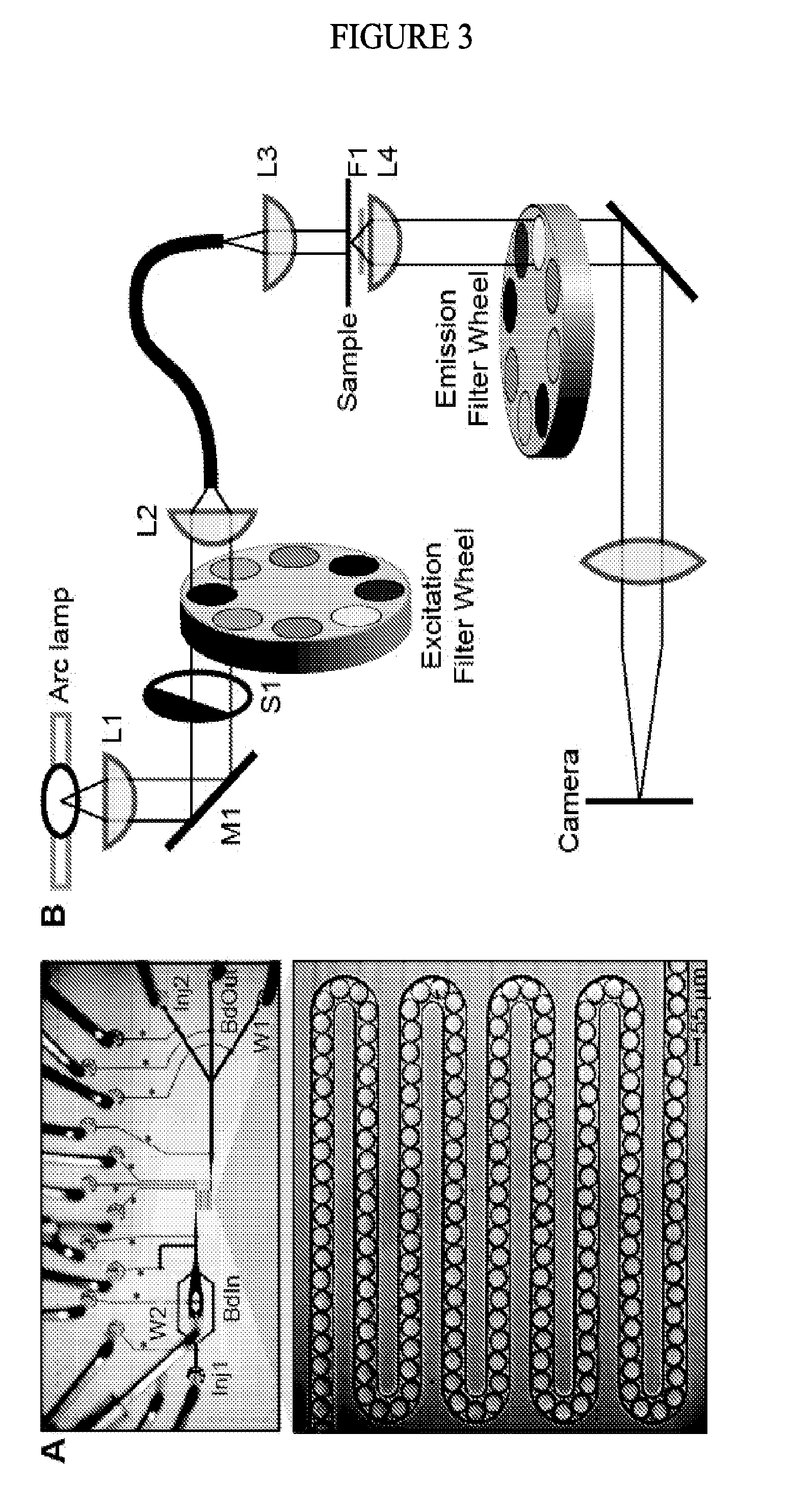

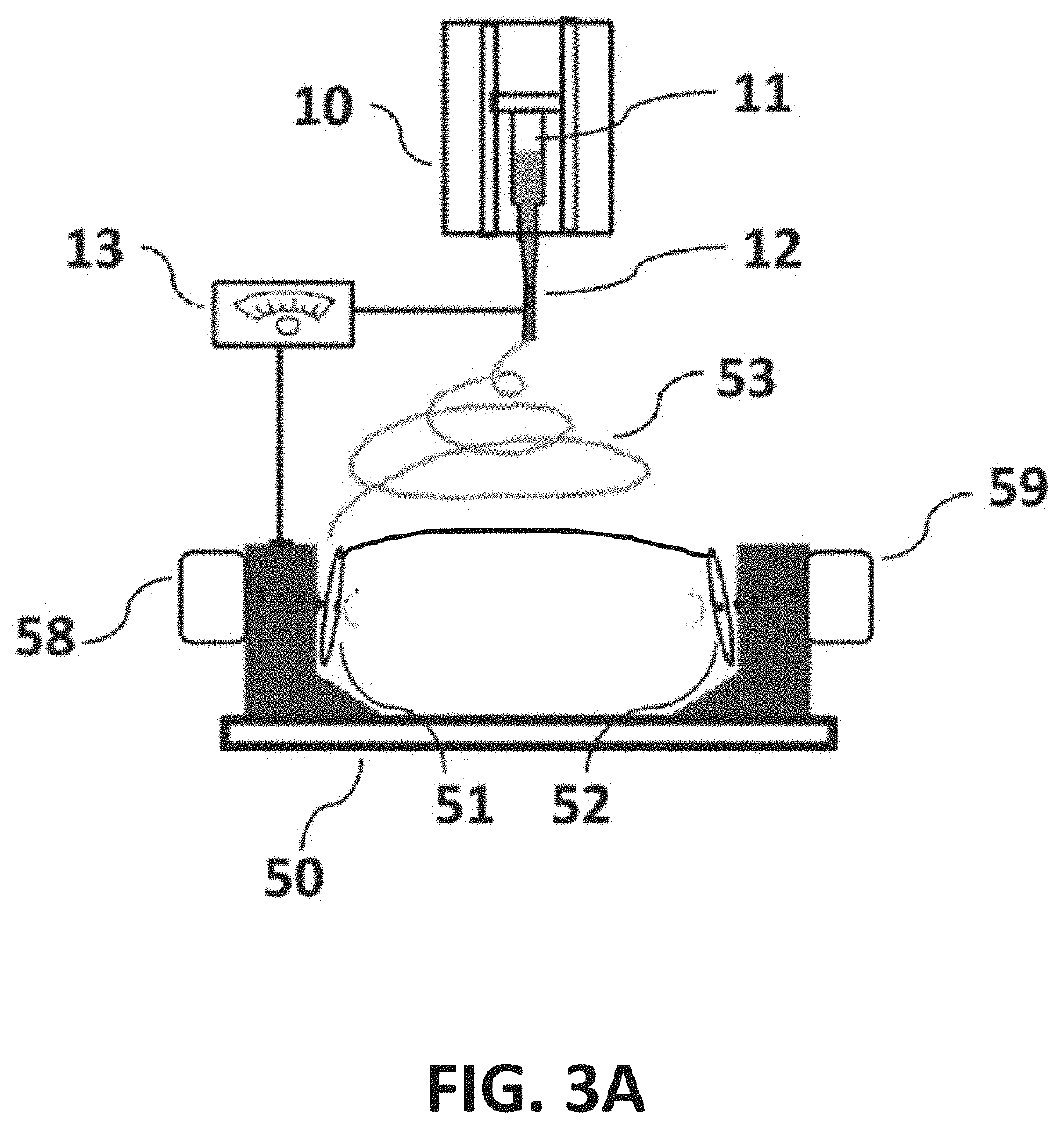

Spectrally encoded microbeads and methods and devices for making and using same

ActiveUS20150192518A1Easy to prepareEasy to useMaterial nanotechnologyFlow mixersMultiplexingHigh flux

Spectrally encoded microbeads and methods and devices for making and using spectrally encoded microbeads are provided. The disclosed methods and devices facilitate the preparation and use of microbeads containing multiple lanthanide nanoparticles, which microbeads have uniquely identifiable spectral codes. The disclosed microbeads, and the methods and devices for making and using same, find use in multiplexing and high-throughput biomarker analysis.

Owner:RGT UNIV OF CALIFORNIA

Fabrication method of semiconductor package with photosensitive chip

InactiveUS20050170561A1Reduce manufacturing costSimplify the manufacturing processSemiconductor/solid-state device detailsSolid-state devicesInterposerSemiconductor package

A fabrication method of a semiconductor package with a photosensitive chip is provided. A substrate having a core is prepared. An interposer is mounted on the substrate, with a peripheral portion of the substrate exposed from the interposer. A molding process is performed and the substrate is clamped between an upper mold and a lower mold, with the interposer received in an upwardly-recessed cavity of the upper mold. A molding compound is injected into the upwardly-recessed cavity to form a dam on the peripheral portion of the substrate. Then the upper and lower molds and the interposer are removed from the substrate to expose area covered by the interposer on the substrate. At least one photosensitive chip is mounted on the exposed area of the substrate. A lid seals the dam such that the chip is received in a space defined by the substrate, the dam and the lid.

Owner:SILICONWARE PRECISION IND CO LTD

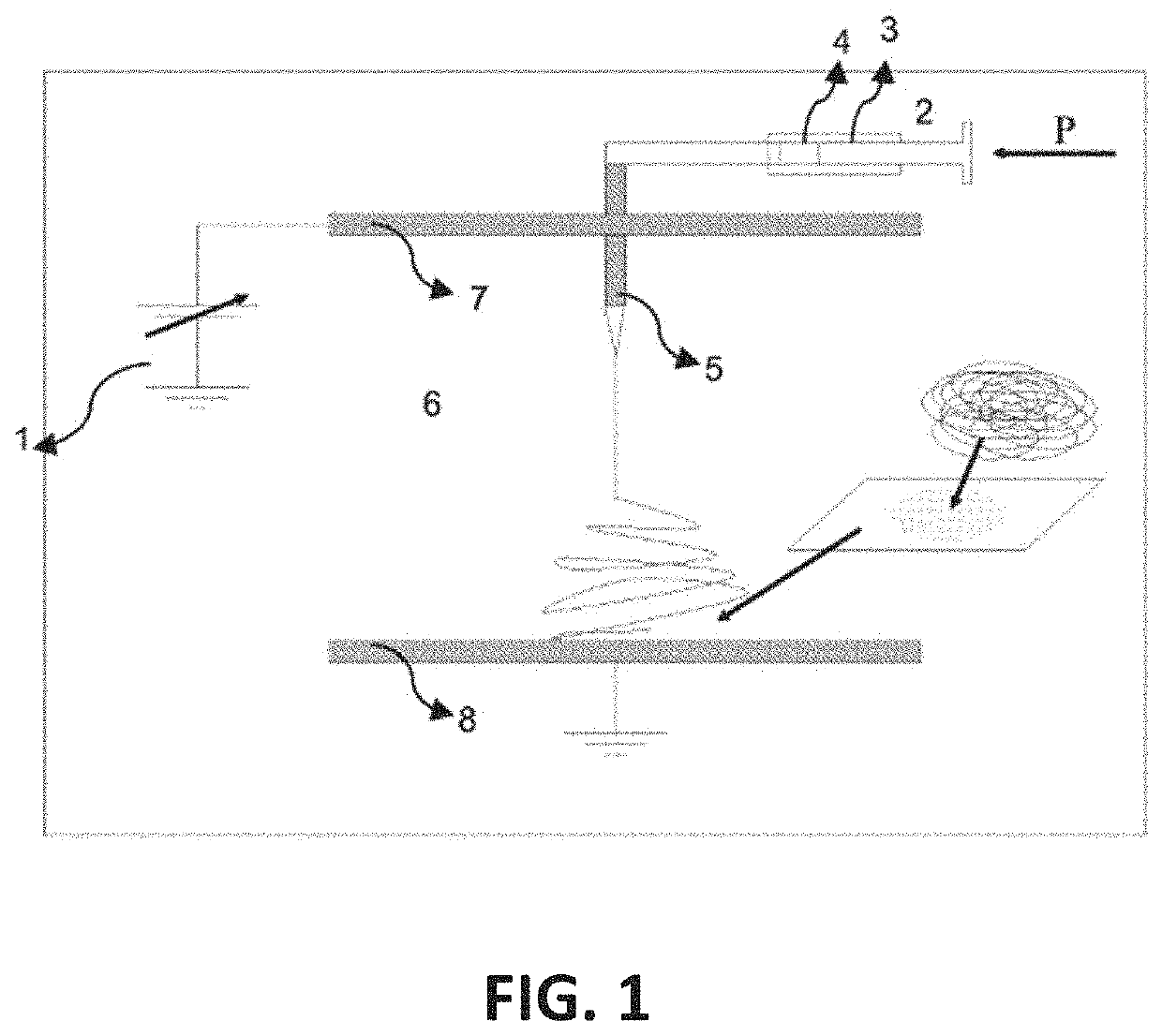

Method and apparatus for accumulating cross-aligned fiber in an electrospinning device

ActiveUS10640888B1Maximize surface contactHigh porosityLiquid spraying plantsSpraying power supplyFiberElectrical conductor

An apparatus for accumulating cross-aligned fiber in an electrospinning device, comprising a multiple segment collector including at least a first segment, a second segment, and an intermediate segment, the intermediate segment positioned between the first and second segment to collectively present an elongated cylindrical structure; at least one electrically chargeable edge conductor circumferentially resident on the first segment and circumferentially resident on the second segment; a connection point on the first segment and on the second segment, the connection points usable for mounting the elongated cylindrical structure on a drive unit to rotate around a longitudinal axis; the elongated cylindrical structure holding electrospun fiber substantially aligned with the longitudinal axis when the edge conductors are excited with a charge of opposite polarity relative to charged fiber, and attracting electrospun fiber on to its surface around the longitudinal axis at least when the edge conductors are absent a charge or grounded.

Owner:UNIVERSITY OF CENTRAL OKLAHOMA

Luminance enhancement structure for reflective display devices

ActiveUS20100225999A1Reduce internal reflectionsIncrease display brightnessNon-linear opticsOptical elementsTotal internal reflectionDisplay device

The present invention is directed to luminance enhancement structures for reflective display devices. The structure comprises columns and grooves, wherein each of said grooves has a cross-section comprising an apex angle and two edge lines. The structure increases the overall reflectance by reducing the total internal reflection, and as a result, the brightness of a display device is increased.

Owner:E INK CALIFORNIA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com