Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

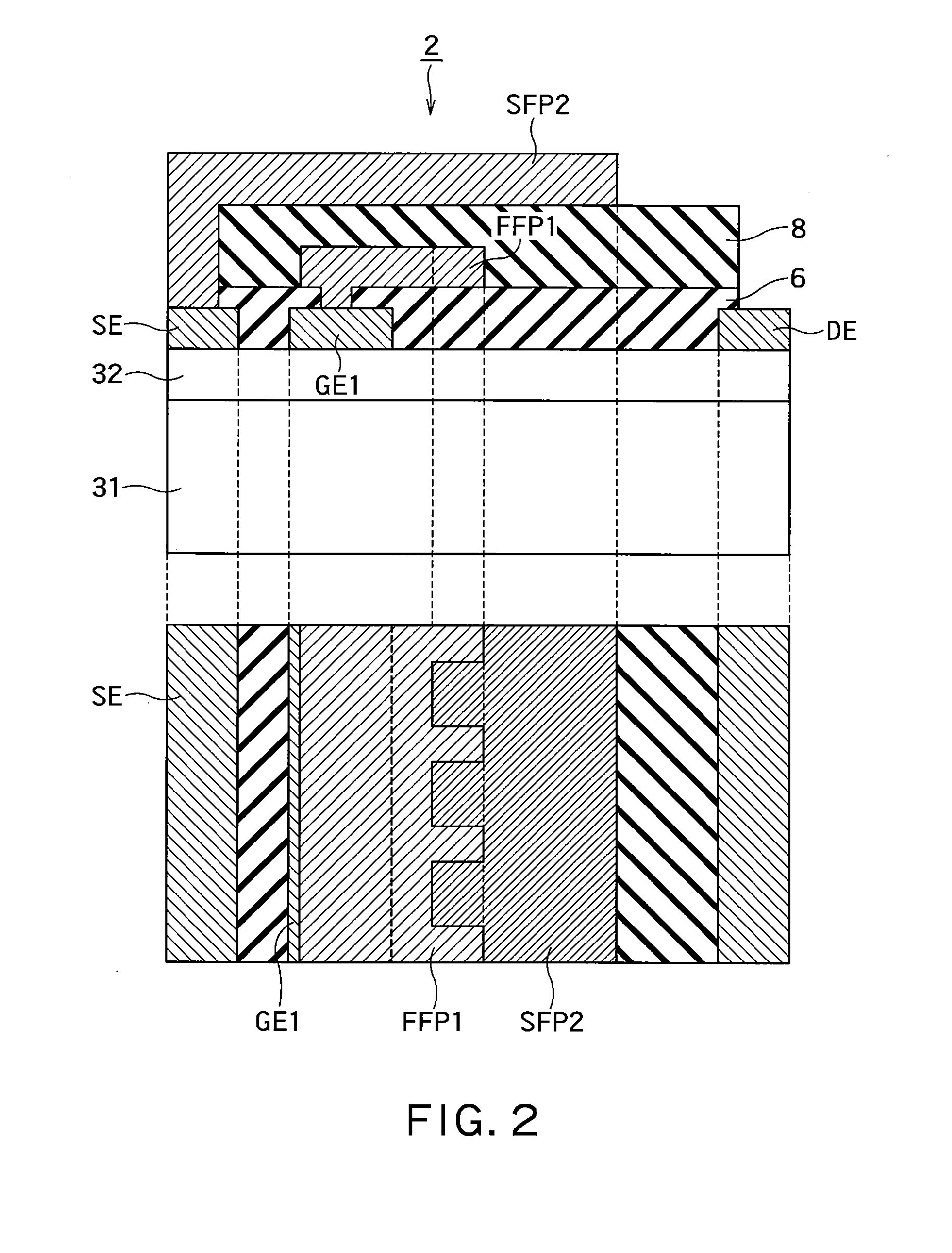

1895 results about "Plate electrode" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A plate, usually called anode in Britain, is a type of electrode that forms part of a vacuum tube. It is usually made of sheet metal, connected to a wire which passes through the glass envelope of the tube to a terminal in the base of the tube, where it is connected to the external circuit. The plate is given a positive potential, and its function is to attract and capture the electrons emitted by the cathode. Although it is sometimes a flat plate, it is more often in the shape of a cylinder or flat open-ended box surrounding the other electrodes.

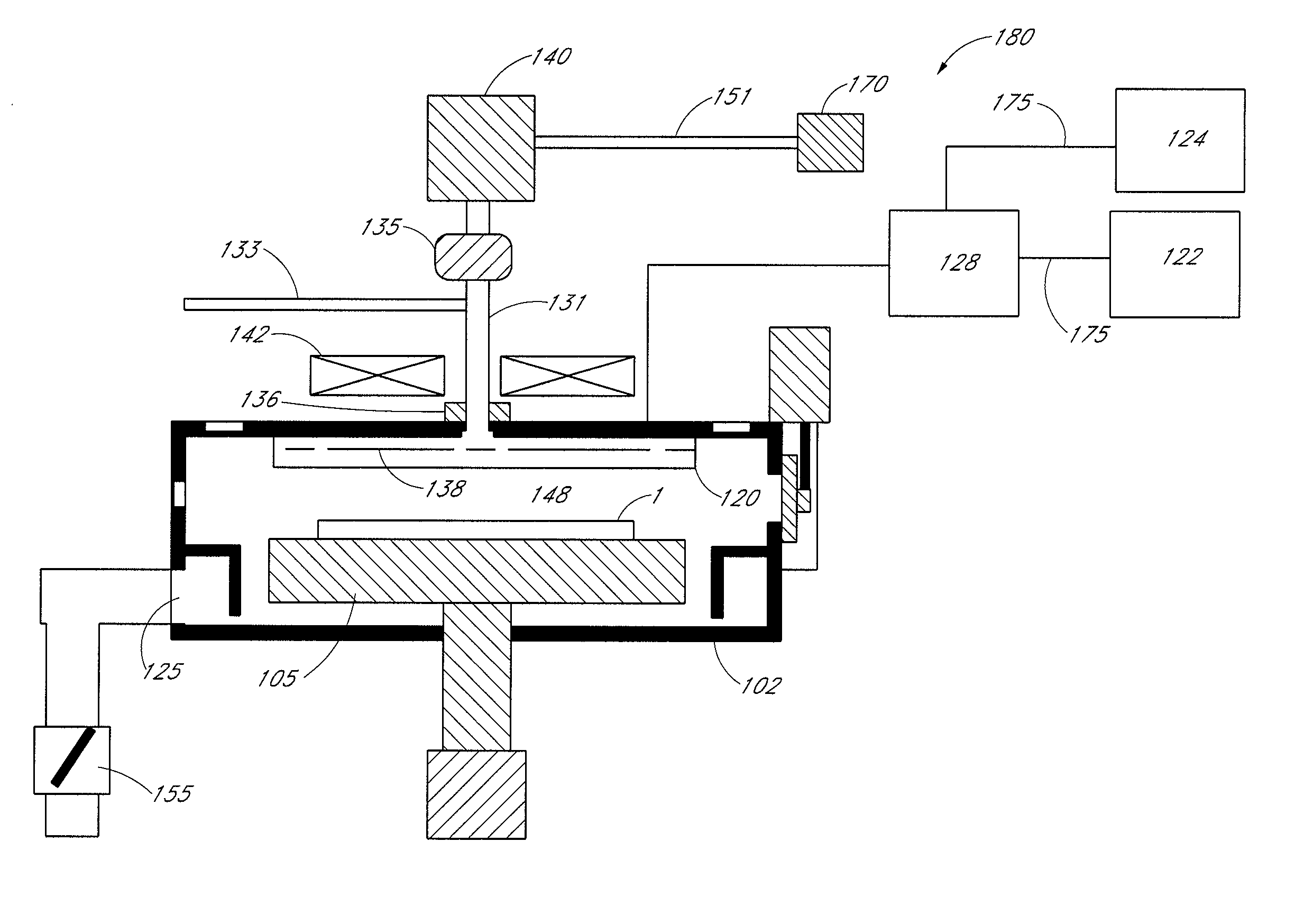

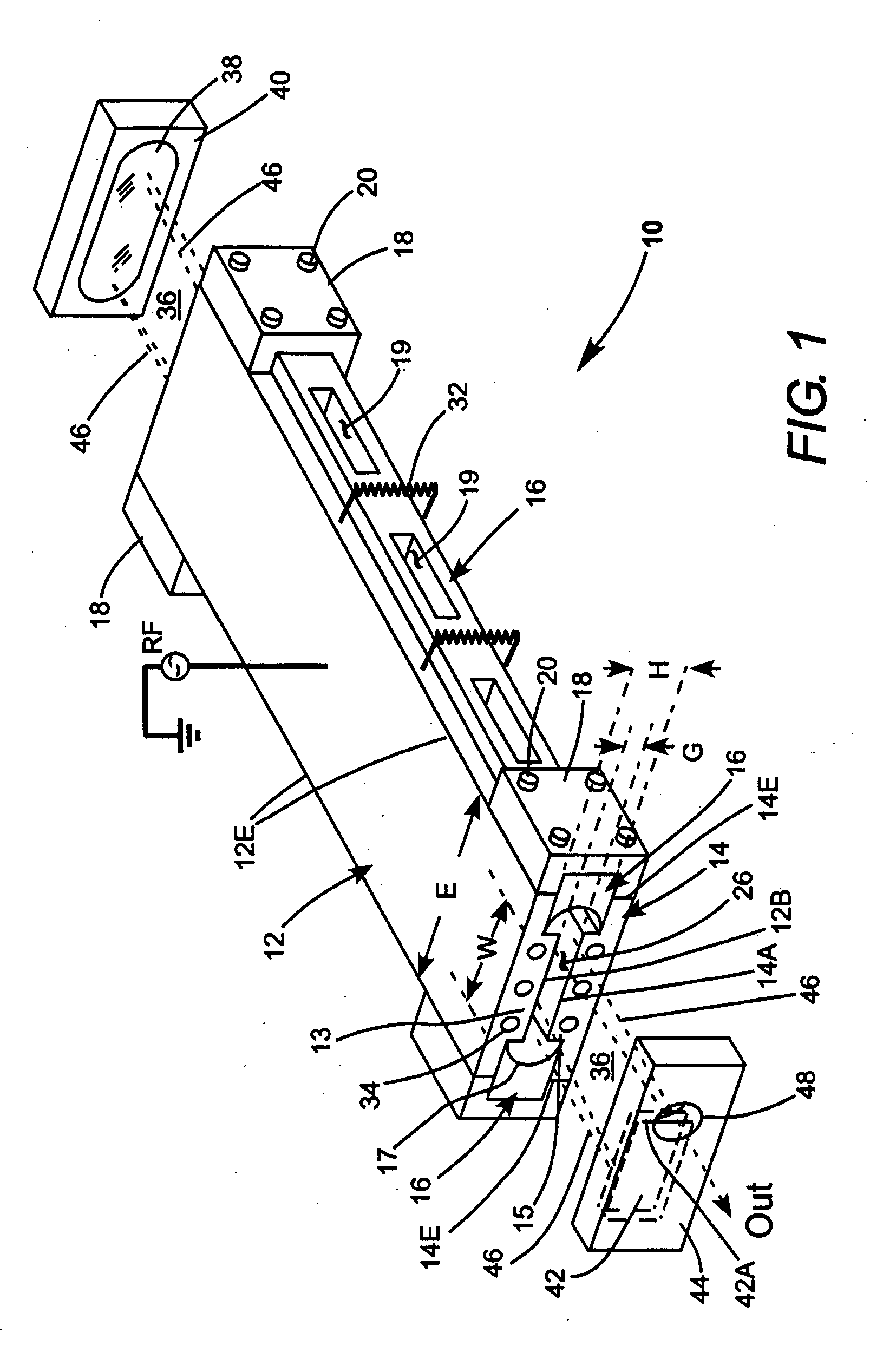

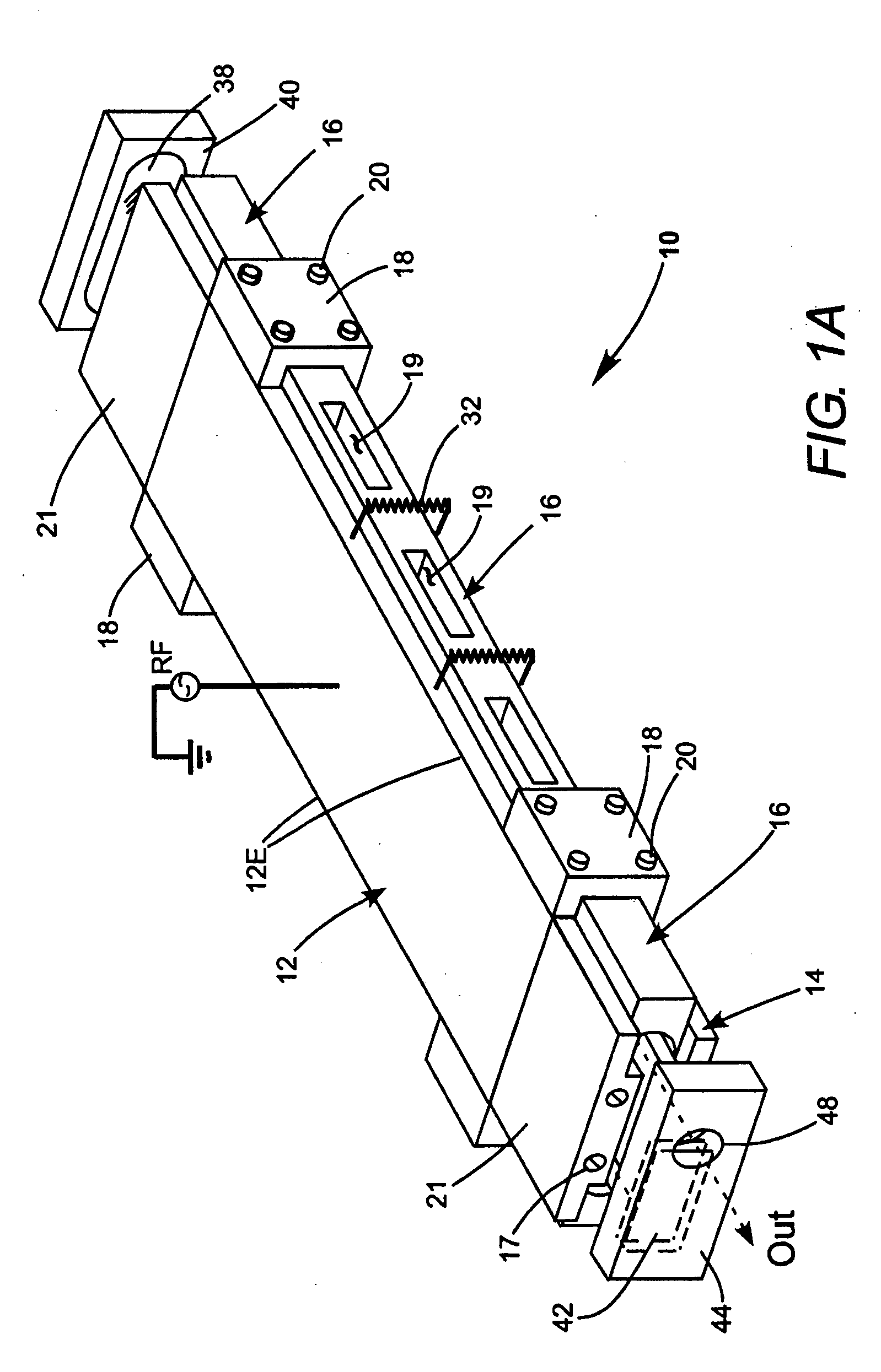

Shower plate electrode for plasma CVD reactor

InactiveUS20090155488A1Uniform cross-sectional areaElectrostatic cleaningChemical vapor deposition coatingMachined surfaceEngineering

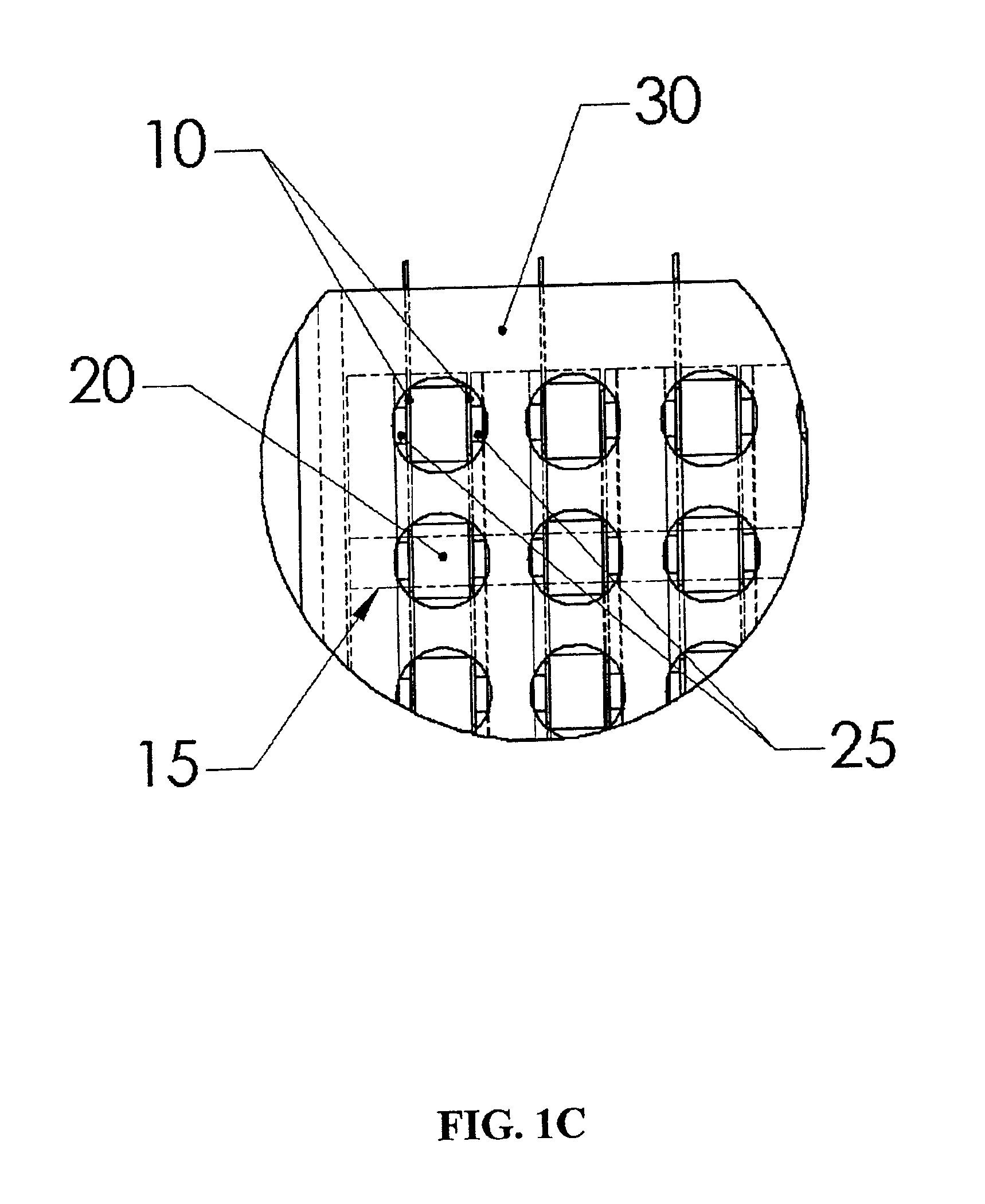

Methods and apparatuses for plasma chemical vapor deposition (CVD). In particular, a plasma CVD apparatus having a cleaning function, has an improved shower plate with holes having a uniform cross-sectional area to yield a high cleaning rate. The shower plate may serve as an electrode, and may have an electrically conductive extension connected to a power source. The shower plate, through which both cleaning gases and reaction source gases flow, may include a hole machined surface area with a size different than conventionally used to ensure a good film thickness uniformity during a deposition process. The size of the hole machined surface area may vary based on the size of a substrate to be processed, or the size of the entire surface of the shower plate.

Owner:ASM JAPAN

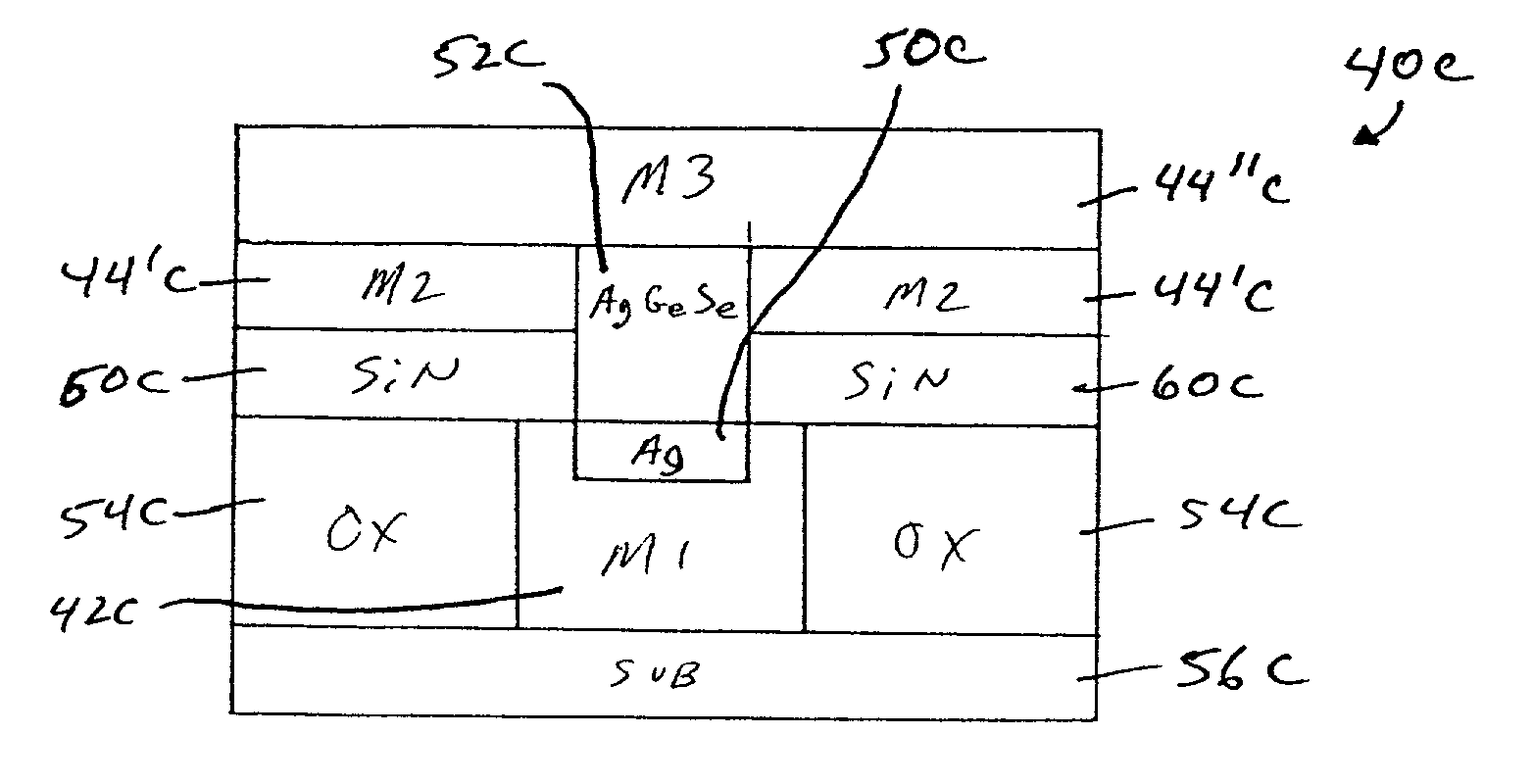

PCRAM memory cell and method of making same

InactiveUS20020168852A1Semiconductor/solid-state device manufacturingBulk negative resistance effect devicesConductive materialsCopper

An inverted PCRAM cell is formed by plating the bottom electrode, made of copper for example, with a conductive material, such as silver. Chalcogenide material is disposed over the plated electrode and subjected to a conversion process so that ions from the plated material diffuse into the chalcogenide material.

Owner:OVONYX MEMORY TECH LLC

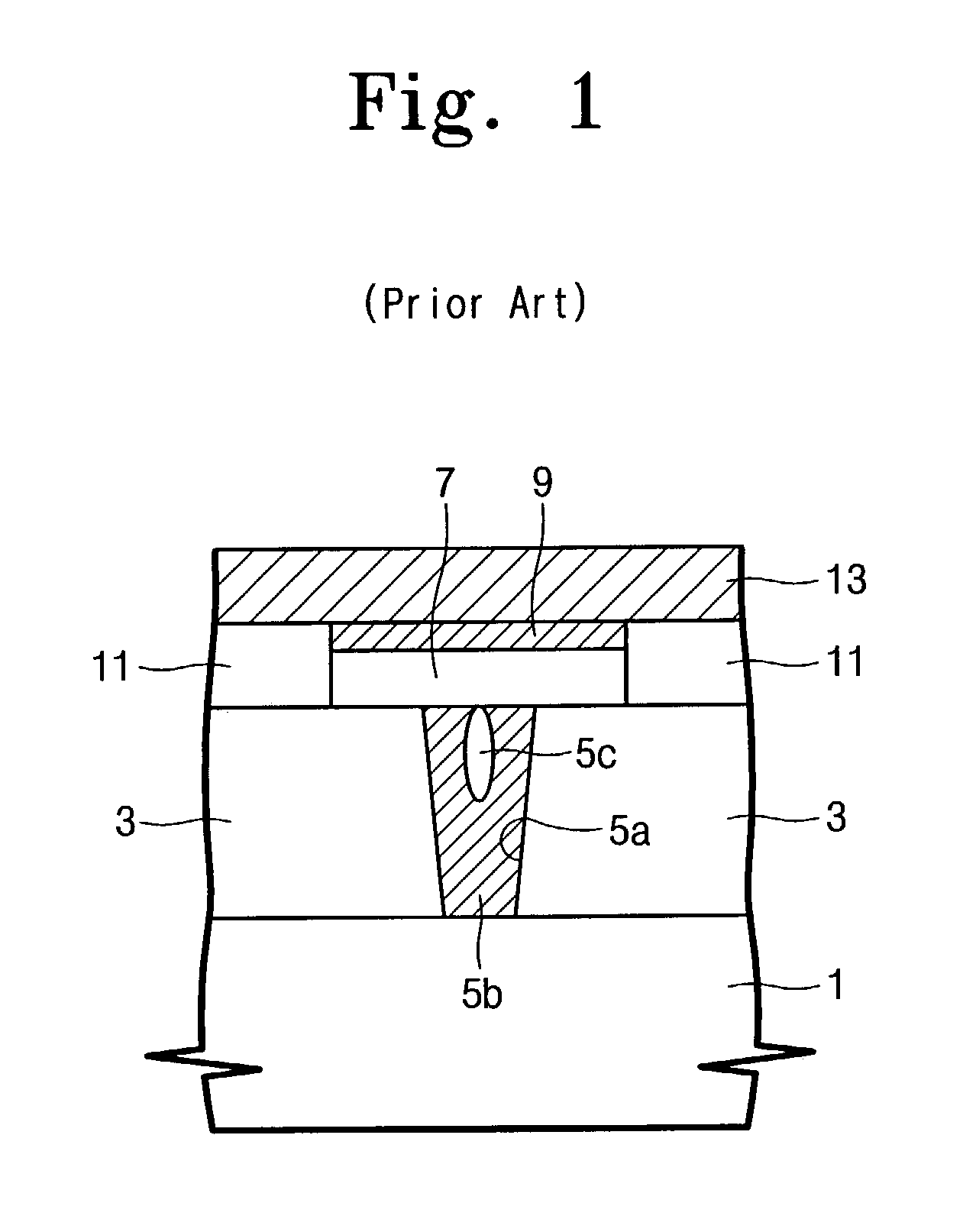

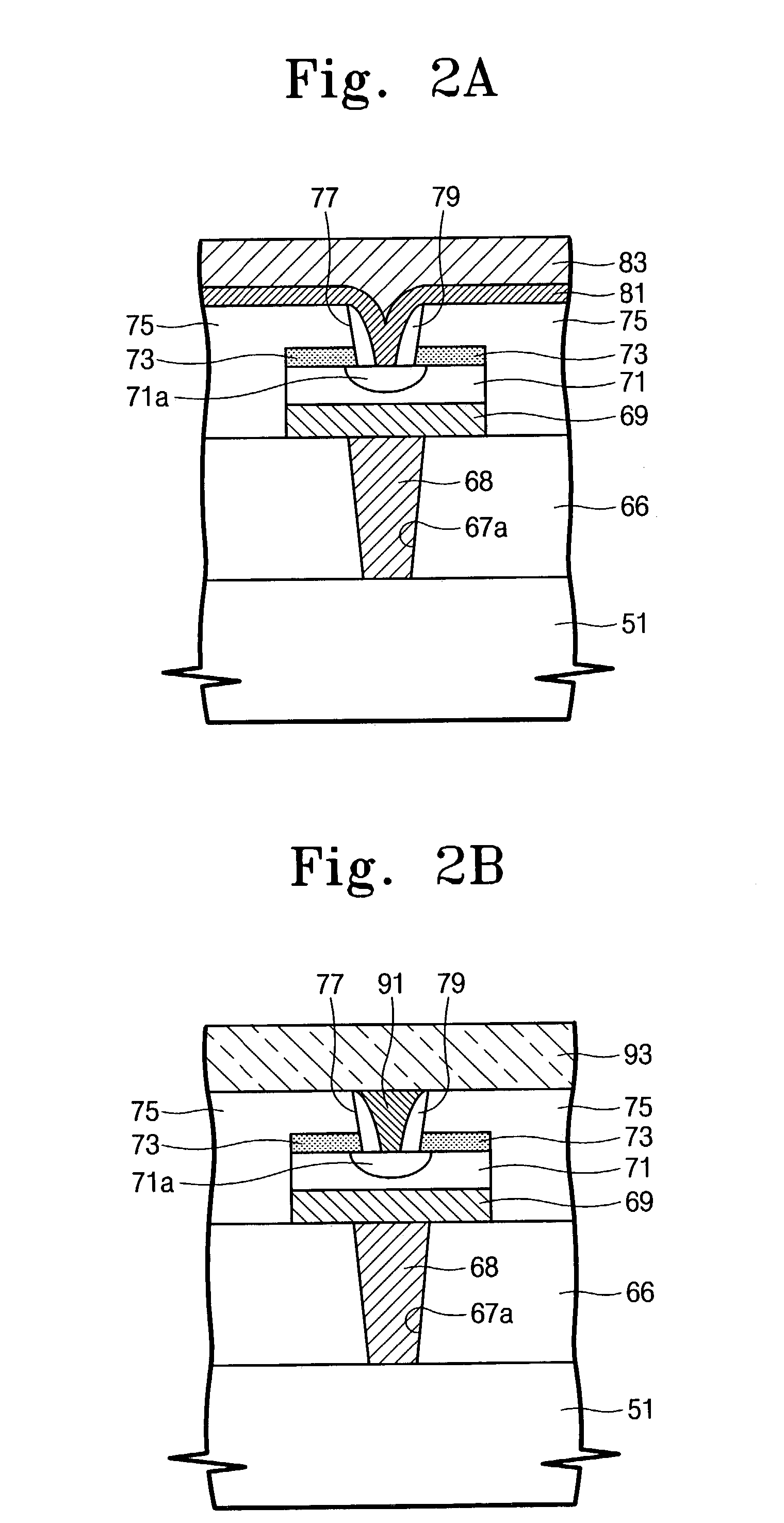

Semiconductor memory device

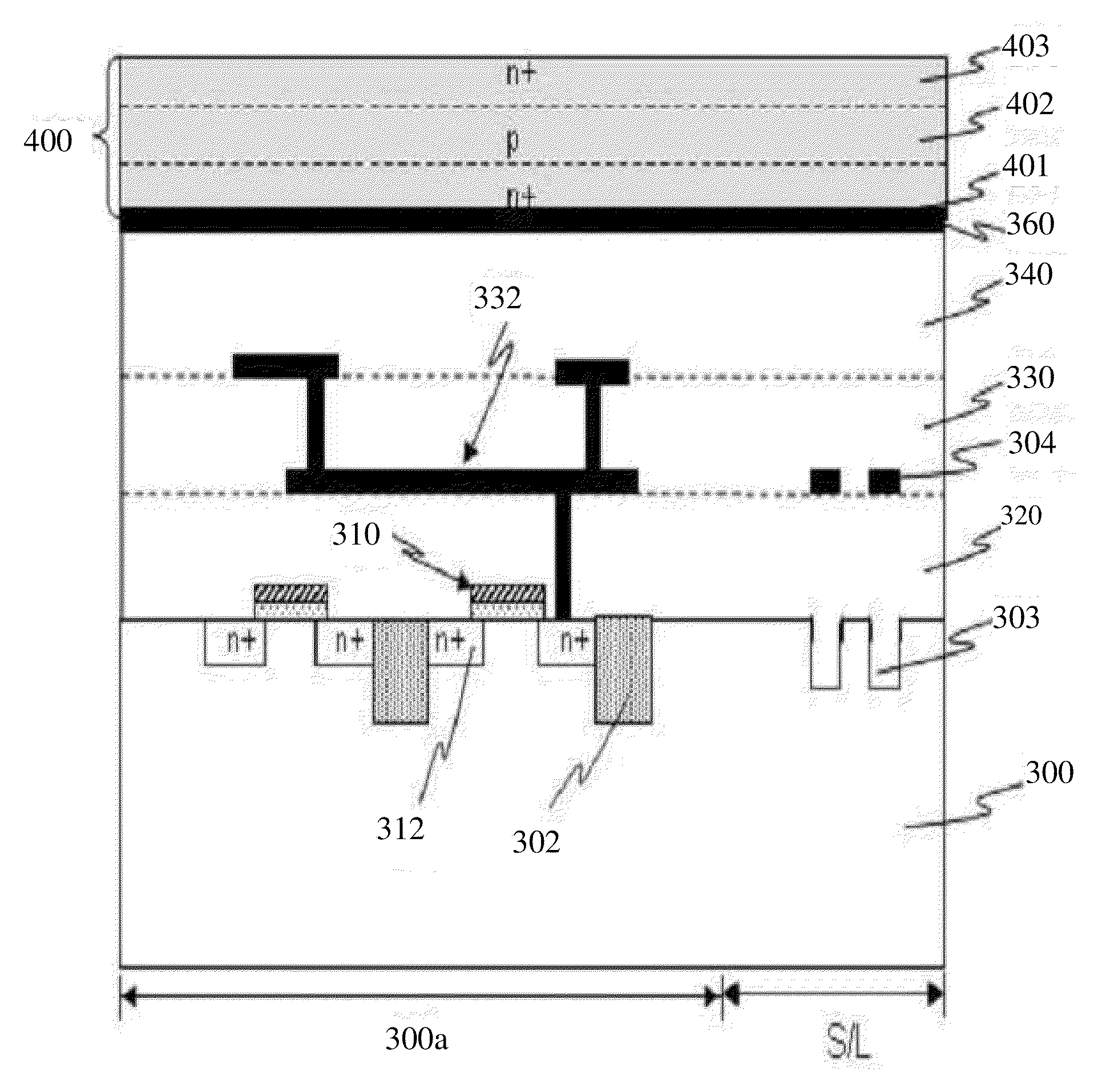

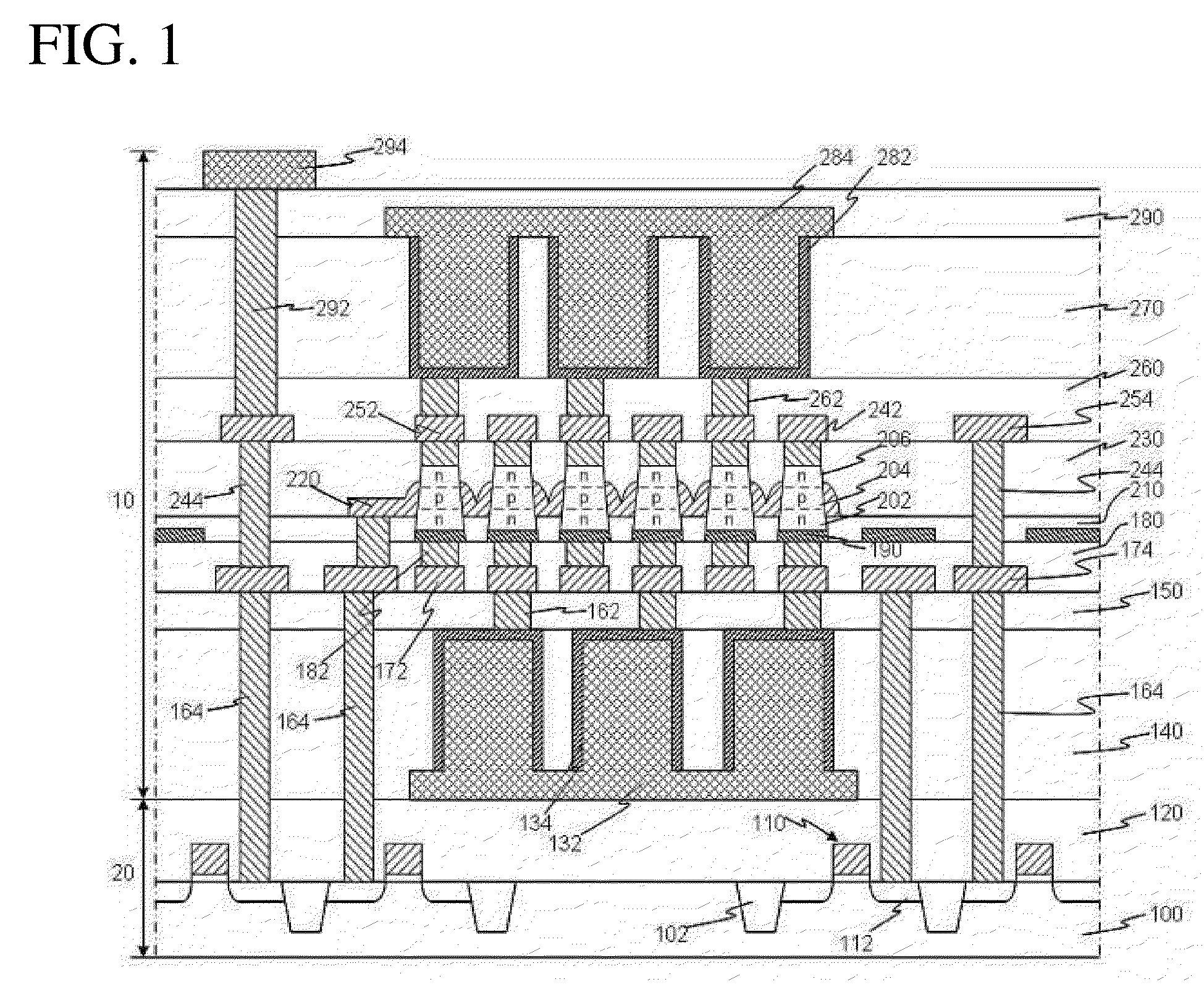

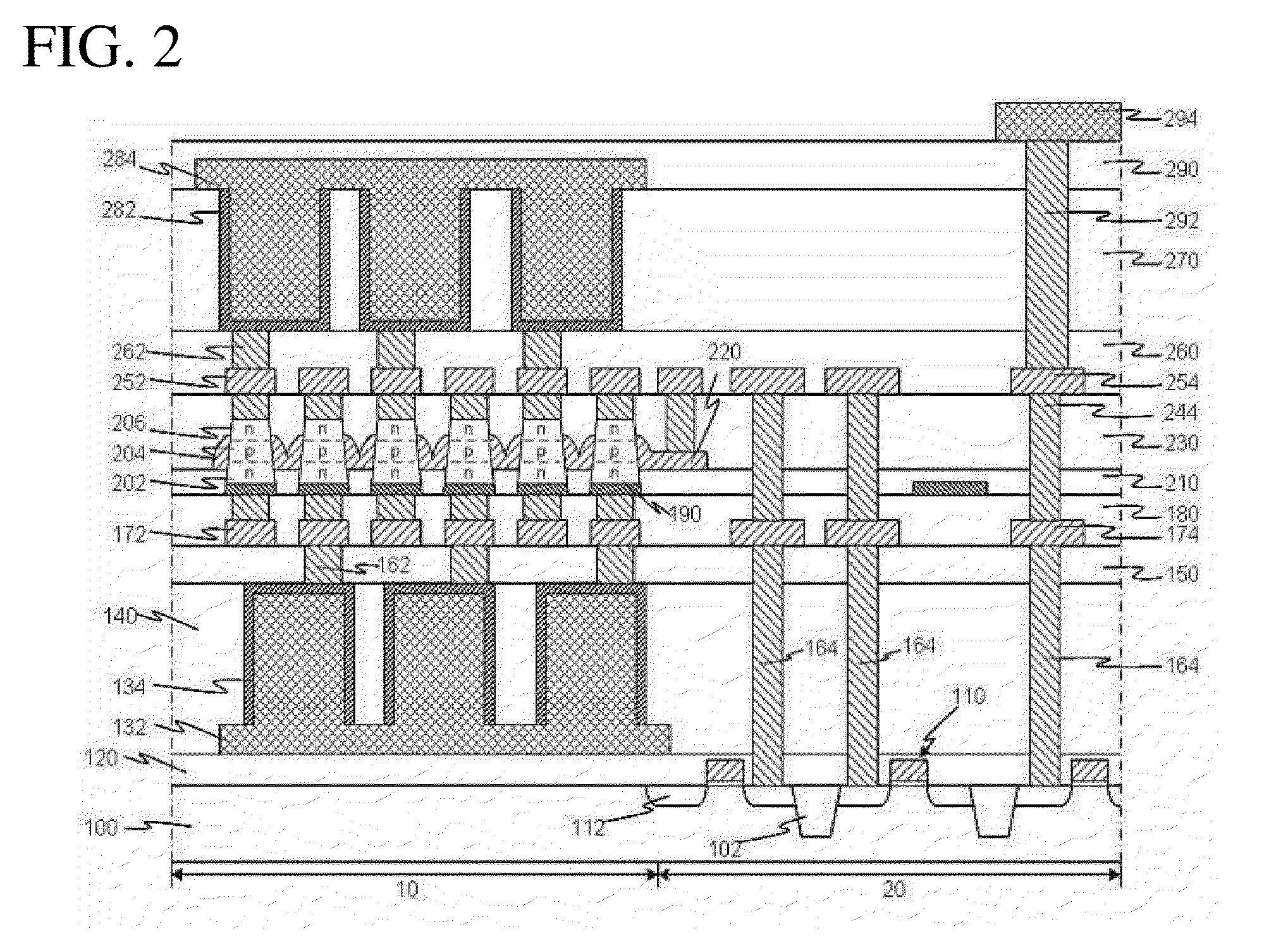

InactiveUS20100112753A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringVertical channel

A method includes forming a switching device which includes a vertical channel spaced apart from a semiconductor substrate, and forming a storage device which is positioned on opposed sides of the switching device. The storage device includes a cylindrically shaped storage node, a plate electrode coupled to the storage node, and a dielectric film which is formed between the storage node and plate electrode, the storage nodes being electrically connected to the switching device.

Owner:BESANG

Semiconductor memory device

InactiveUS7867822B2Solid-state devicesSemiconductor/solid-state device manufacturingVertical channelSemiconductor

A method includes forming a switching device which includes a vertical channel spaced apart from a semiconductor substrate, and forming a storage device which is positioned on opposed sides of the switching device. The storage device includes a cylindrically shaped storage node, a plate electrode coupled to the storage node, and a dielectric film which is formed between the storage node and plate electrode, the storage nodes being electrically connected to the switching device.

Owner:BESANG

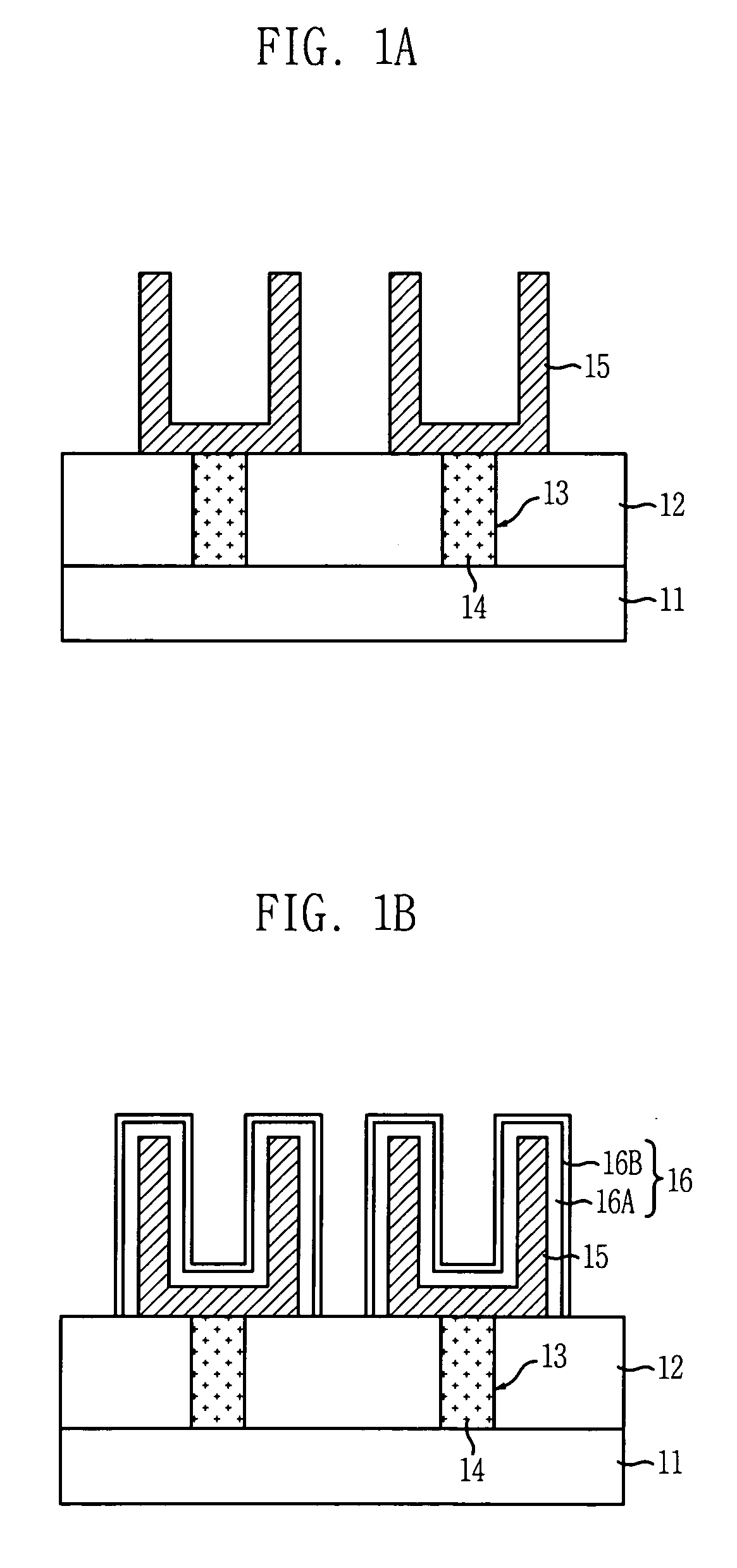

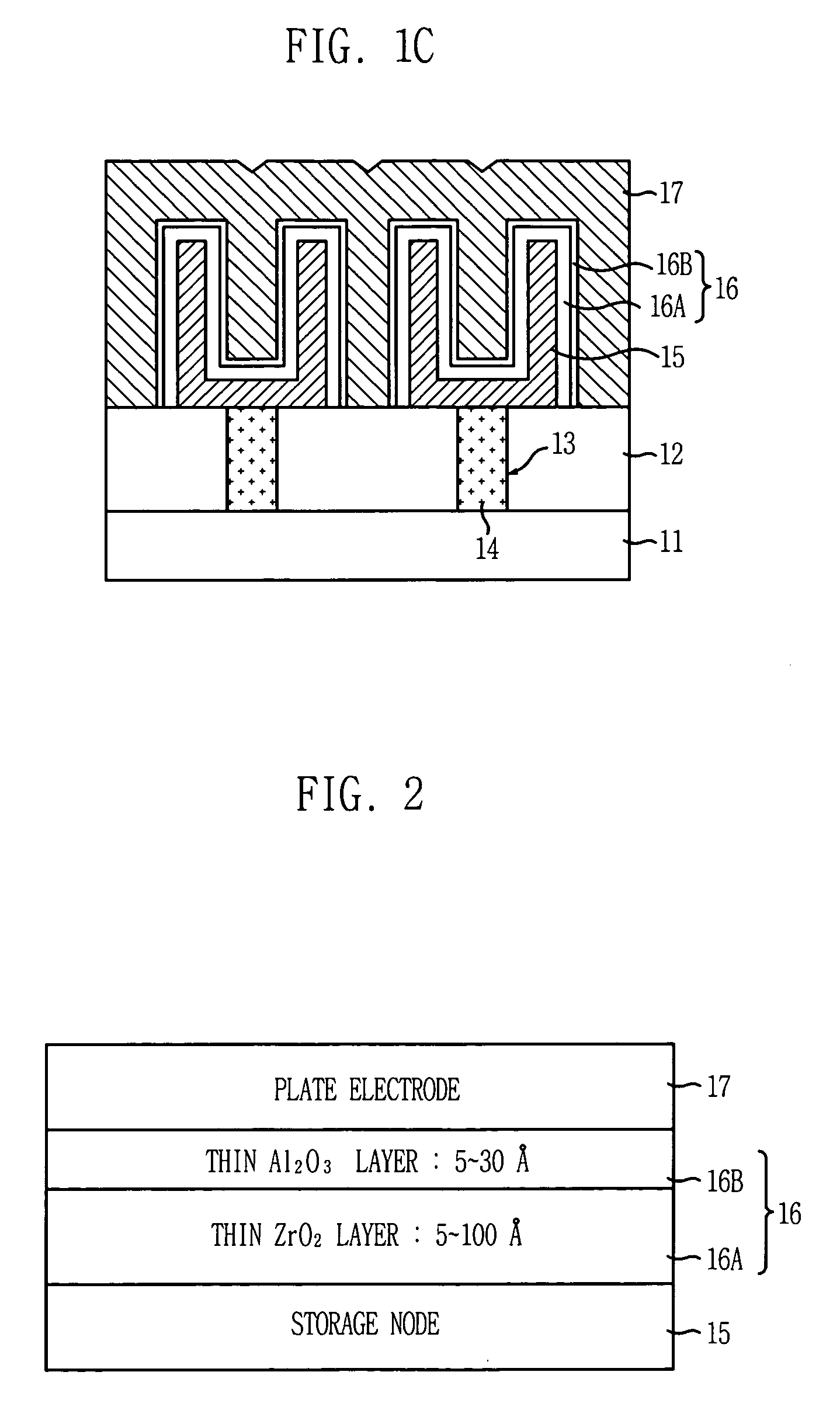

Capacitor with zirconium oxide and method for fabricating the same

ActiveUS20060097305A1Secure leakage current characteristicSecure capacitance levelTransistorSolid-state devicesOptoelectronicsDielectric structure

A capacitor with zirconium oxide and a method for fabricating the same are provided. The method includes: forming a storage node; forming a multi-layered dielectric structure on the storage node, the multi-layered dielectric structure including a zirconium oxide (ZrO2) layer and an aluminum oxide (Al2O3) layer; and forming a plate electrode on the multi-layered dielectric structure.

Owner:SK HYNIX INC

PCRAM memory cell and method of making same

An inverted PCRAM cell is formed by plating the bottom electrode, made of copper for example, with a conductive material, such as silver. Chalcogenide material is disposed over the plated electrode and subjected to a conversion process so that ions from the plated material diffuse into the chalcogenide material.

Owner:MICRON TECH INC

Multi-well plate and electrode assemblies for ion channel assays

InactiveUS6969449B2Immobilised enzymesBioreactor/fermenter combinationsElectrical field strengthEngineering

Plate and electrode assemblies include configurations allowing for relatively uniform electric field production. The electrodes may comprise strips of conductive material plated onto the bottom surface of sample wells or they may comprise plate electrodes extending down into the well. In some embodiments, the electric field strength varies by less than about 10% from a mean field intensity over at least about 20% of the surface area of the bottom surface of a sample well.

Owner:VERTEX PHARMA SAN DIEGO LLC

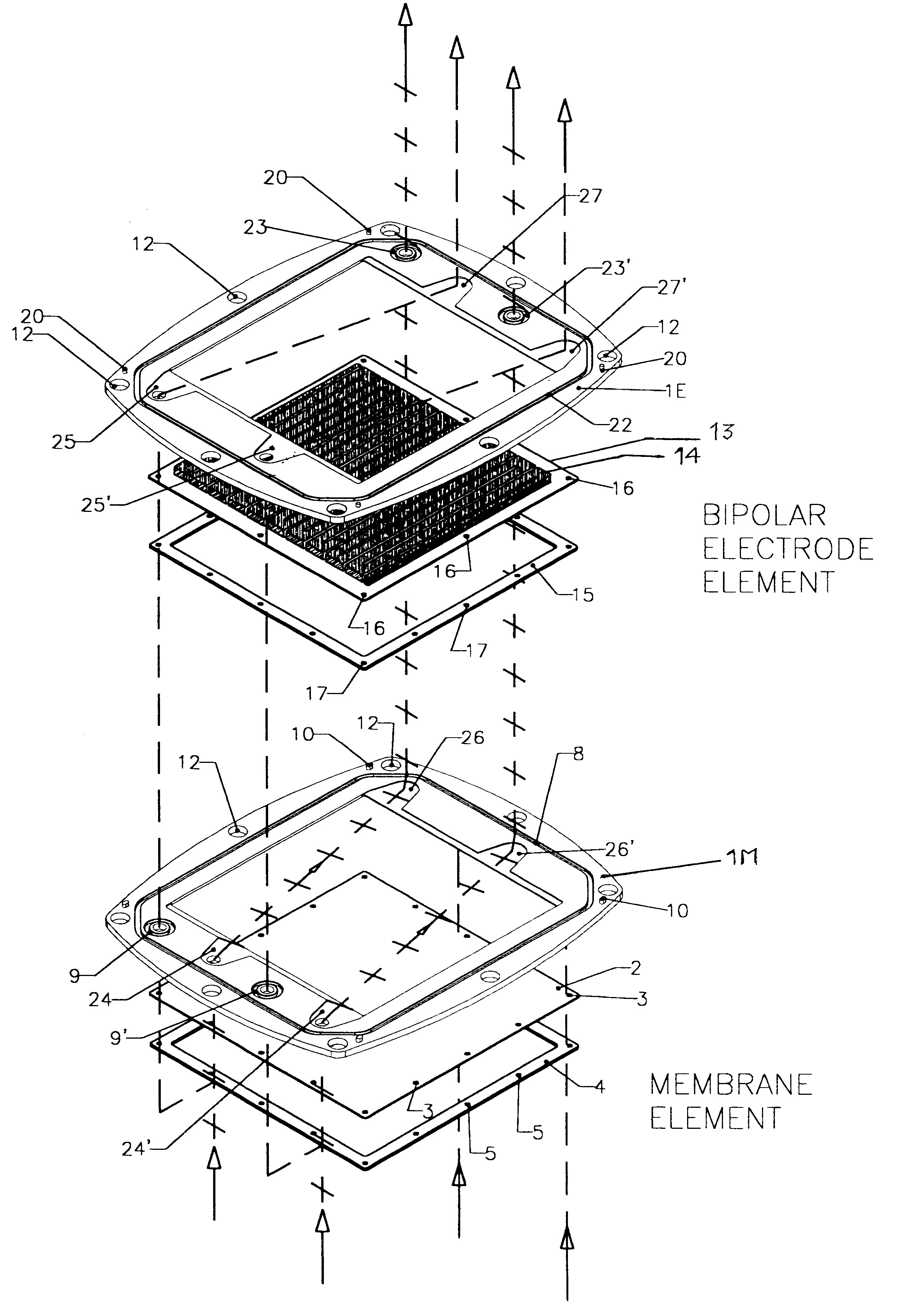

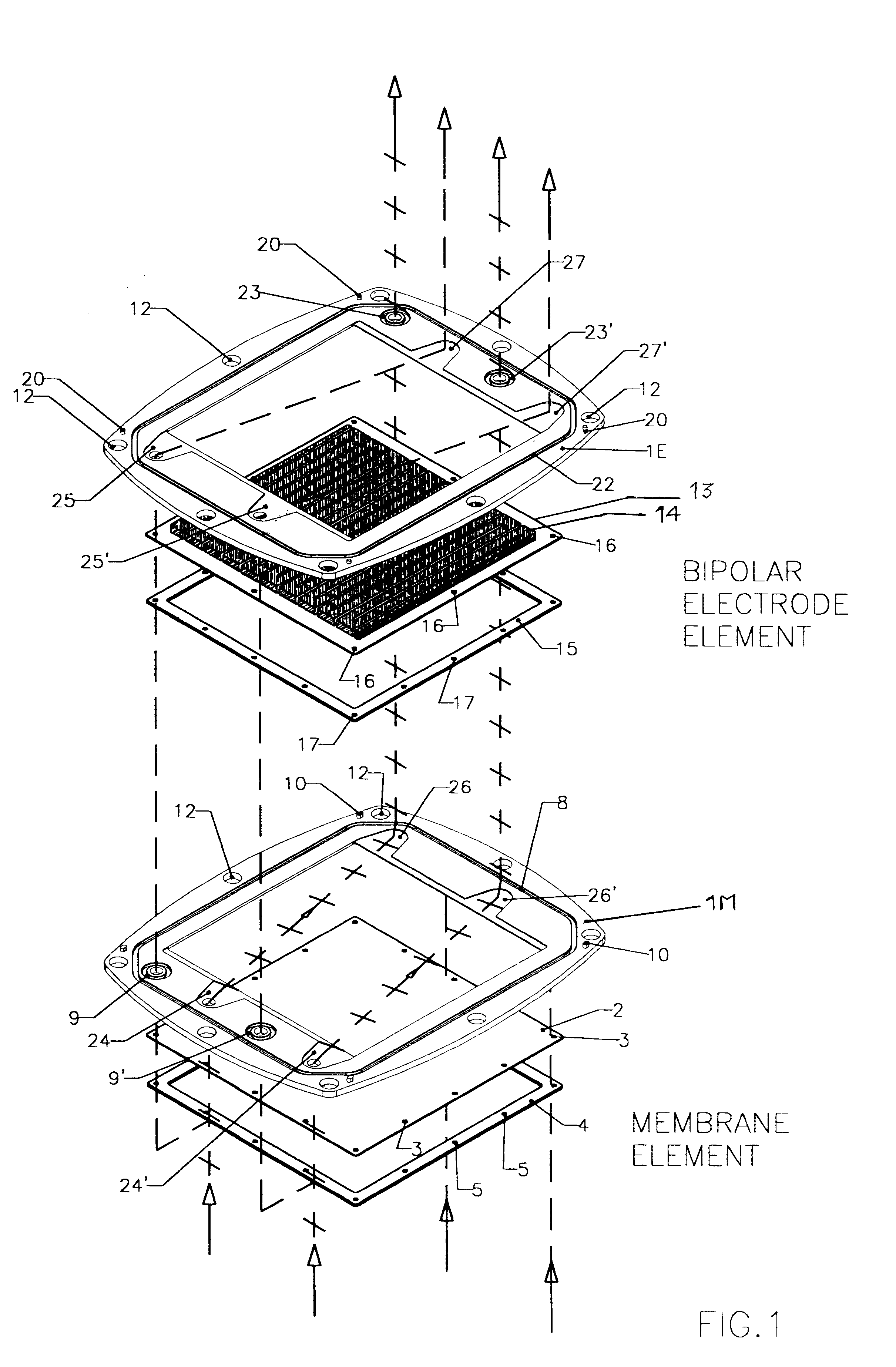

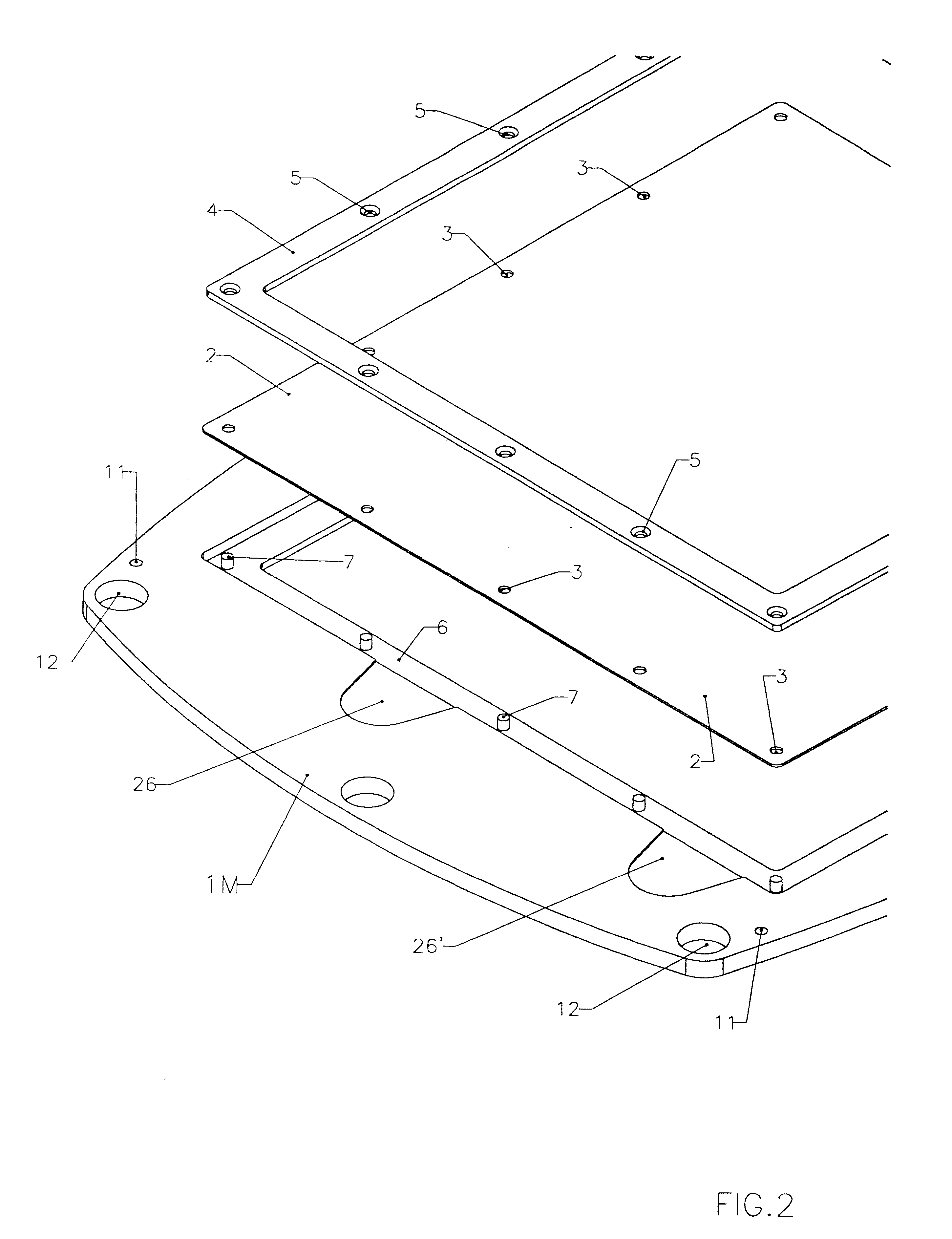

Membrane-separated, bipolar multicell electrochemical reactor

InactiveUS6555267B1Improve electrochemical performanceLower overall pressure dropFuel cells groupingFuel cell auxillariesPlastic materialsIon-exchange membranes

A multicell assembly is constituted by alternately stacking two types of pre-assembled elements: a bipolar electrode holding subassembly and a membrane holding subassembly. The alternate stack of elements is piled over a bottom end element and the stack is terminated by placing over the last membrane holding element a top end electrode element. Each bipolar plate electrode holding element and each ion exchange membrane separator holding element includes a substantially similar rectangular frame piece, made of an electrically nonconductive and chemically resistant material, typically of molded plastic material, having on its upper (assembly) face grooves for receiving O-ring type gasket means, and having through holes and recesses in coordinated locations disposed along two opposite sides of the rectangular frame forming, upon completion of the assembling, ducts for the separate circulation of the negative electrolyte and of the positive electrolyte through all the negative electrolyte flow chambers and all positive electrolyte flow chambers, respectively, in cascade.

Owner:SQUIRREL HLDG

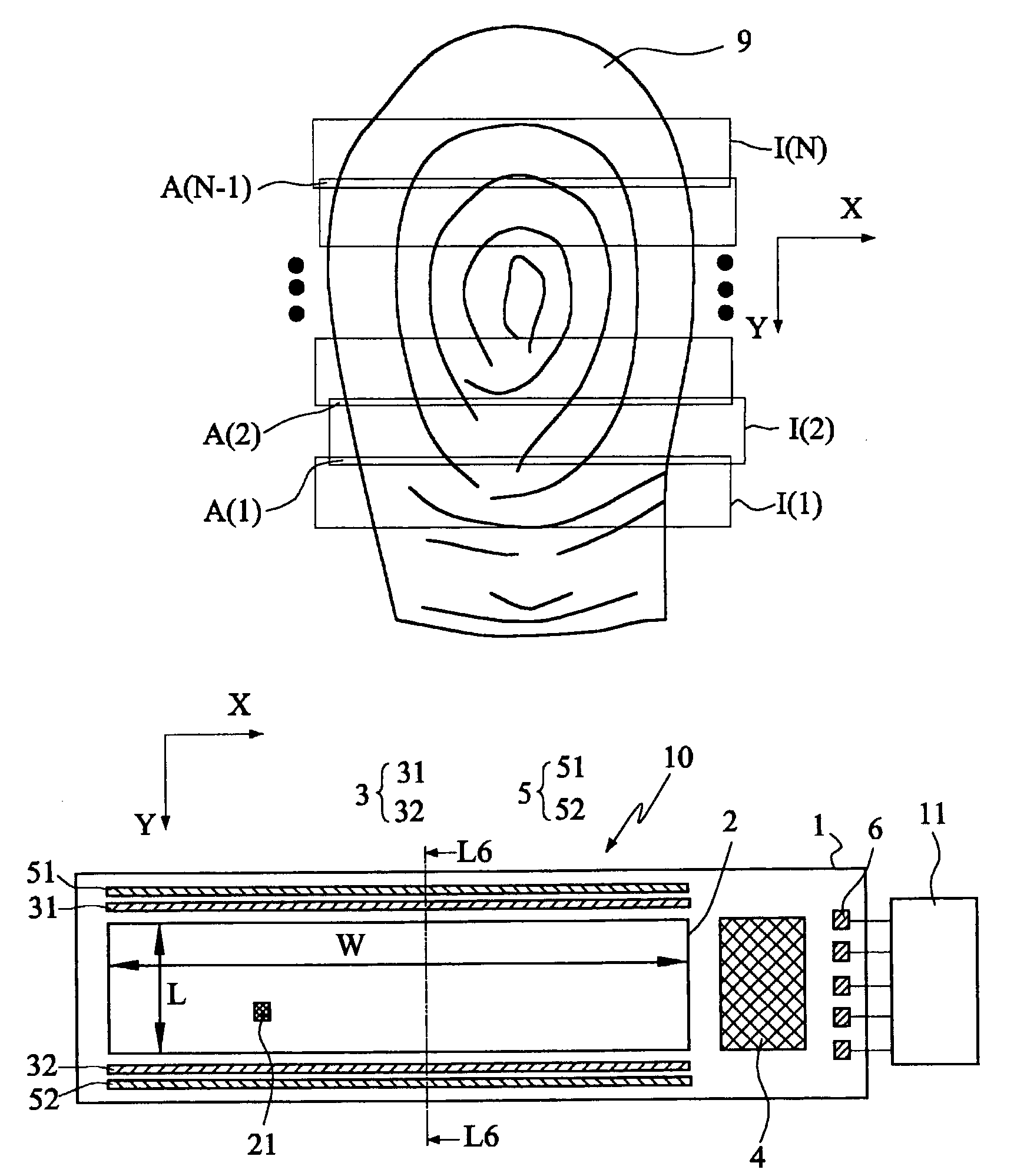

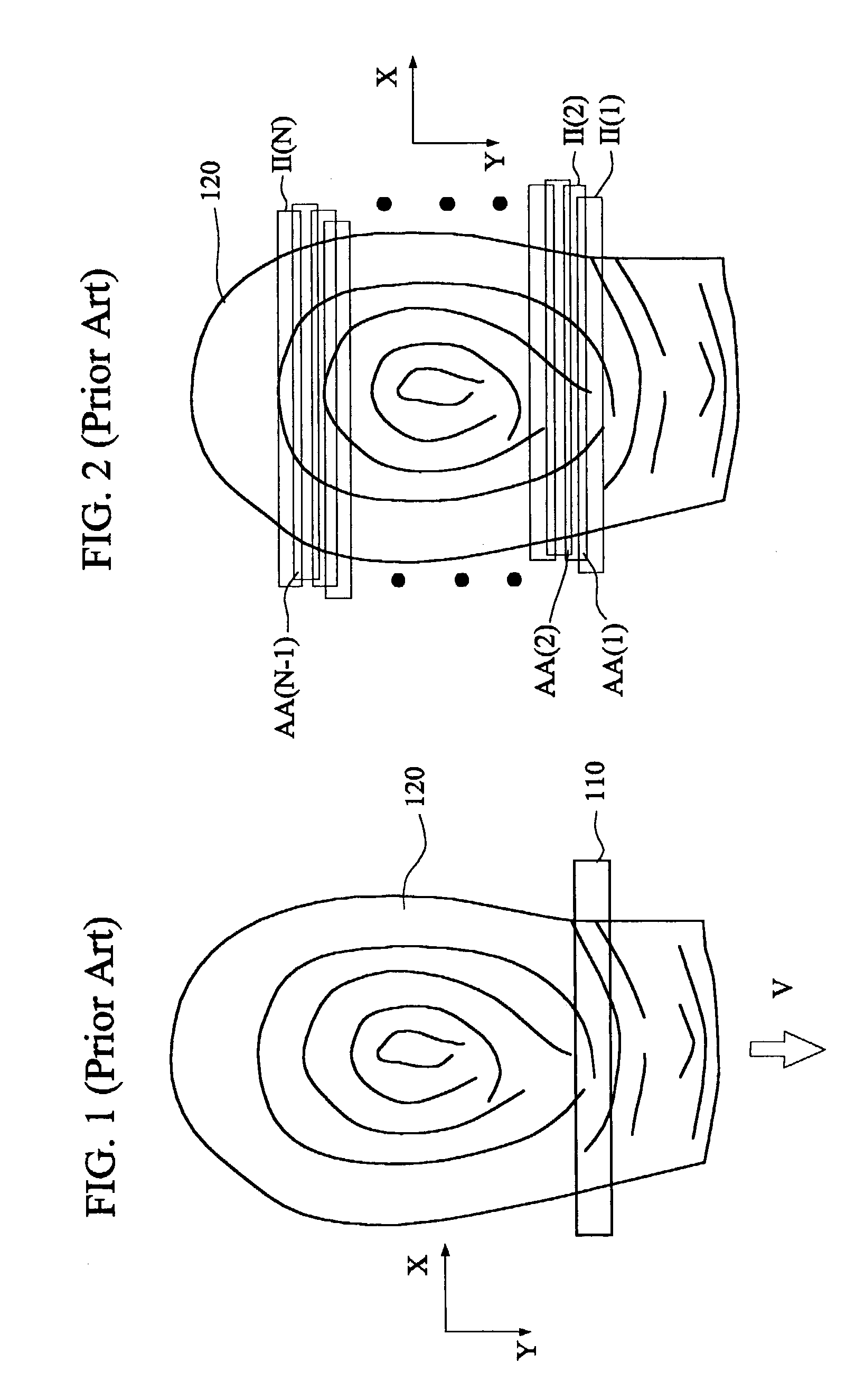

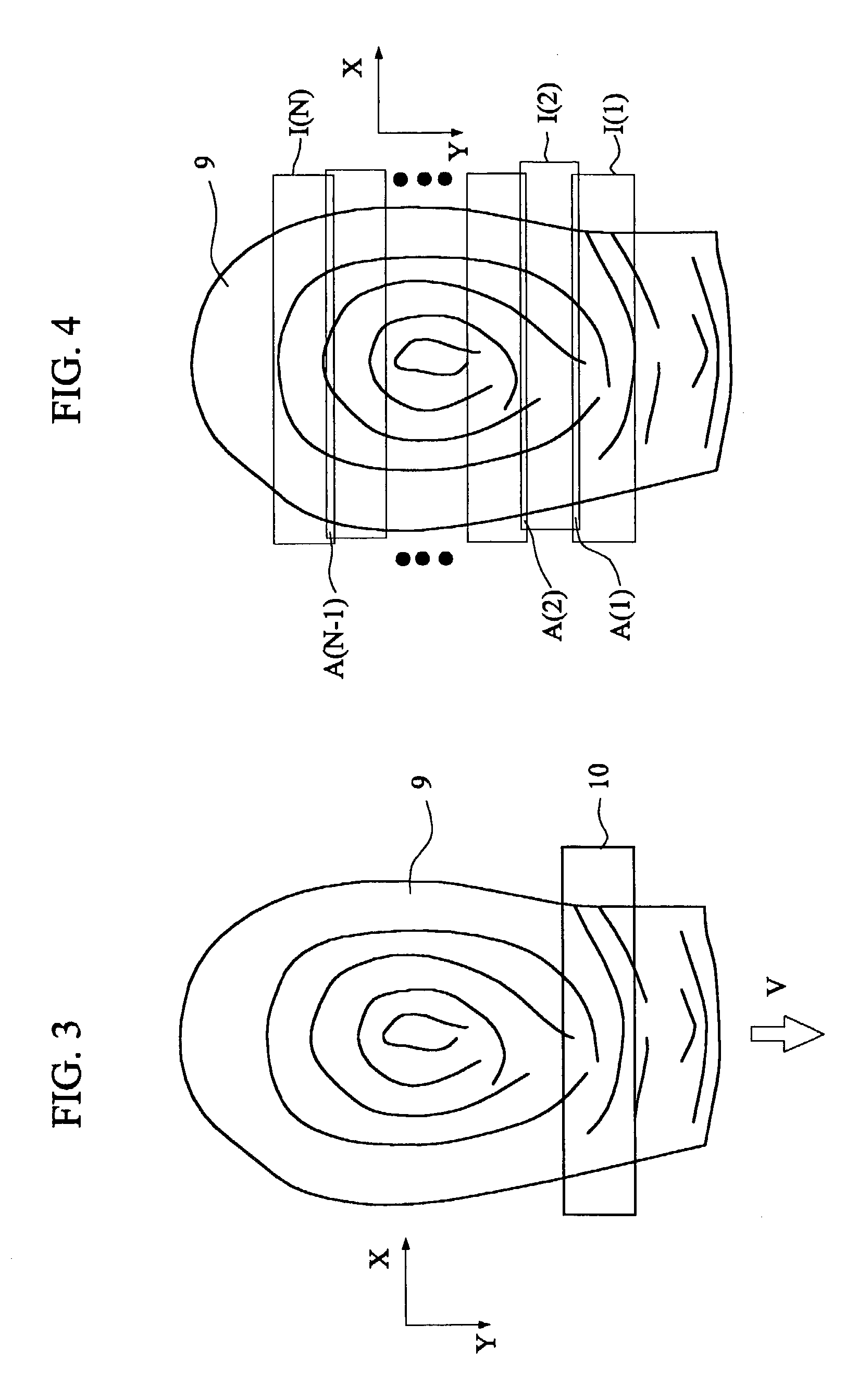

Sweep-type fingerprint sensor module

ActiveUS7200250B2Reduce in quantitySimplify image processingPrint image acquisitionTime differenceComputer science

A sweep-type fingerprint sensor module includes a microprocessor and a sweep-type fingerprint sensor, which includes a substrate, and a sensing members array, a speed-detecting unit, and a processing circuit on the substrate. The array is composed of plural fingerprint sensing members. When the finger sweeps across the fingerprint sensor, the array sequentially acquires plural fingerprint fragment images from the finger with a sampling time interval. The speed-detecting unit is composed of first and second plate electrodes. The processing circuit processes and then outputs signals from the array and the speed-detecting unit. The microprocessor electrically connected to the processing circuit derives a sweeping speed of the finger by the time difference when the finger sweeps across the sensor surface and sequentially contacts the first and second plate electrodes, determines the sampling time interval and minimize the number of captured fragment images for re-construction of the initial complete fingerprint image.

Owner:EGIS TECH

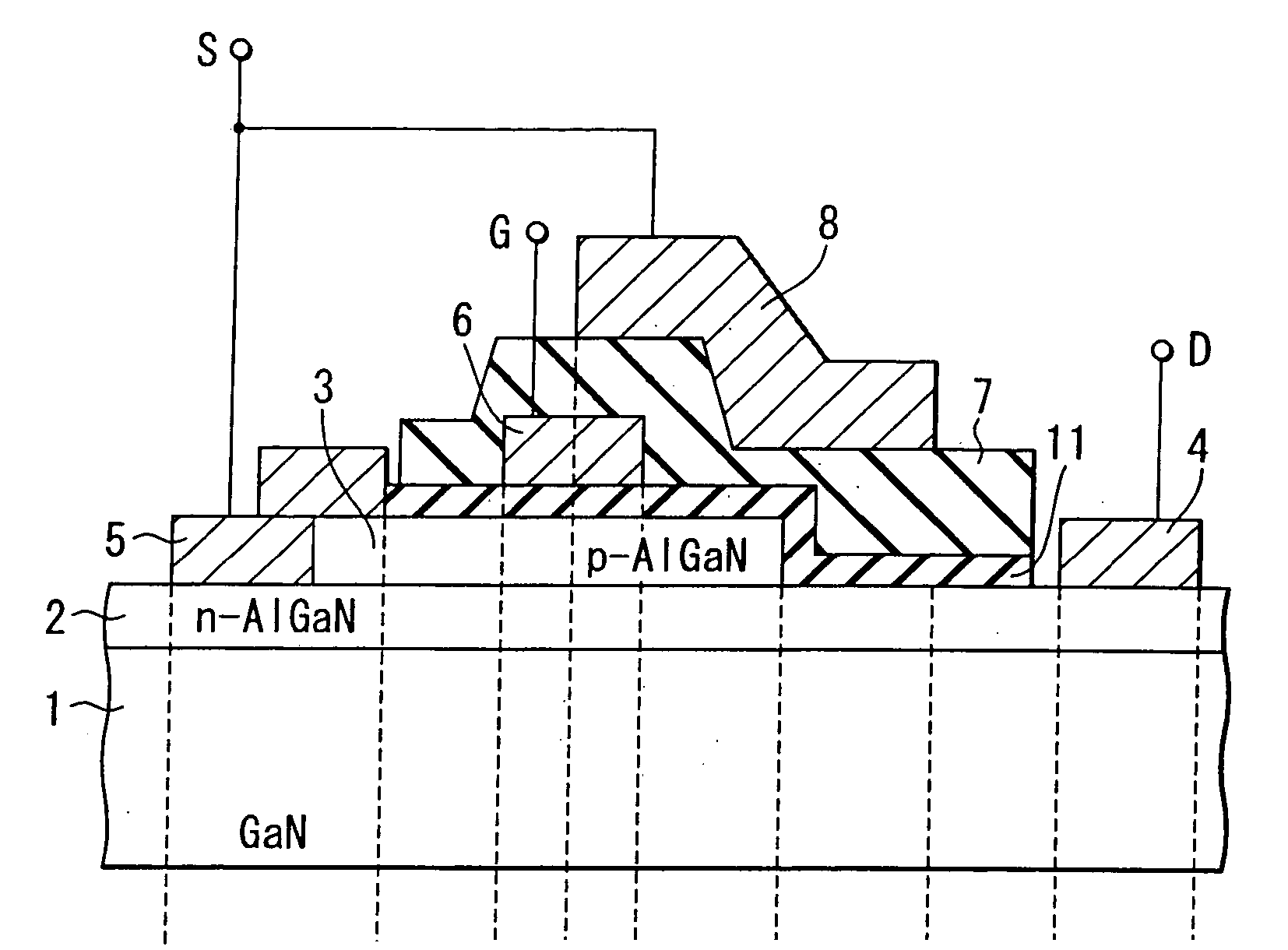

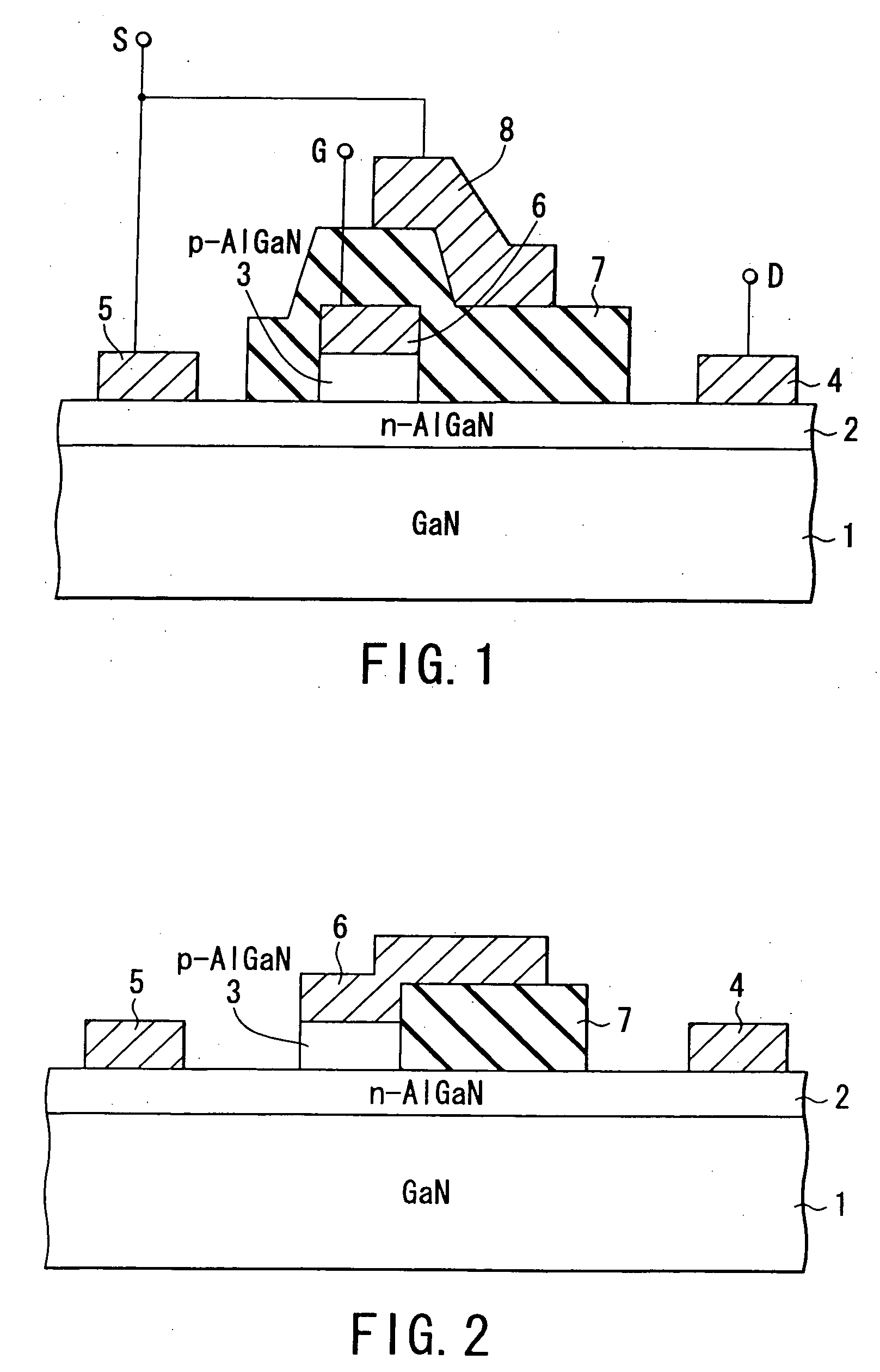

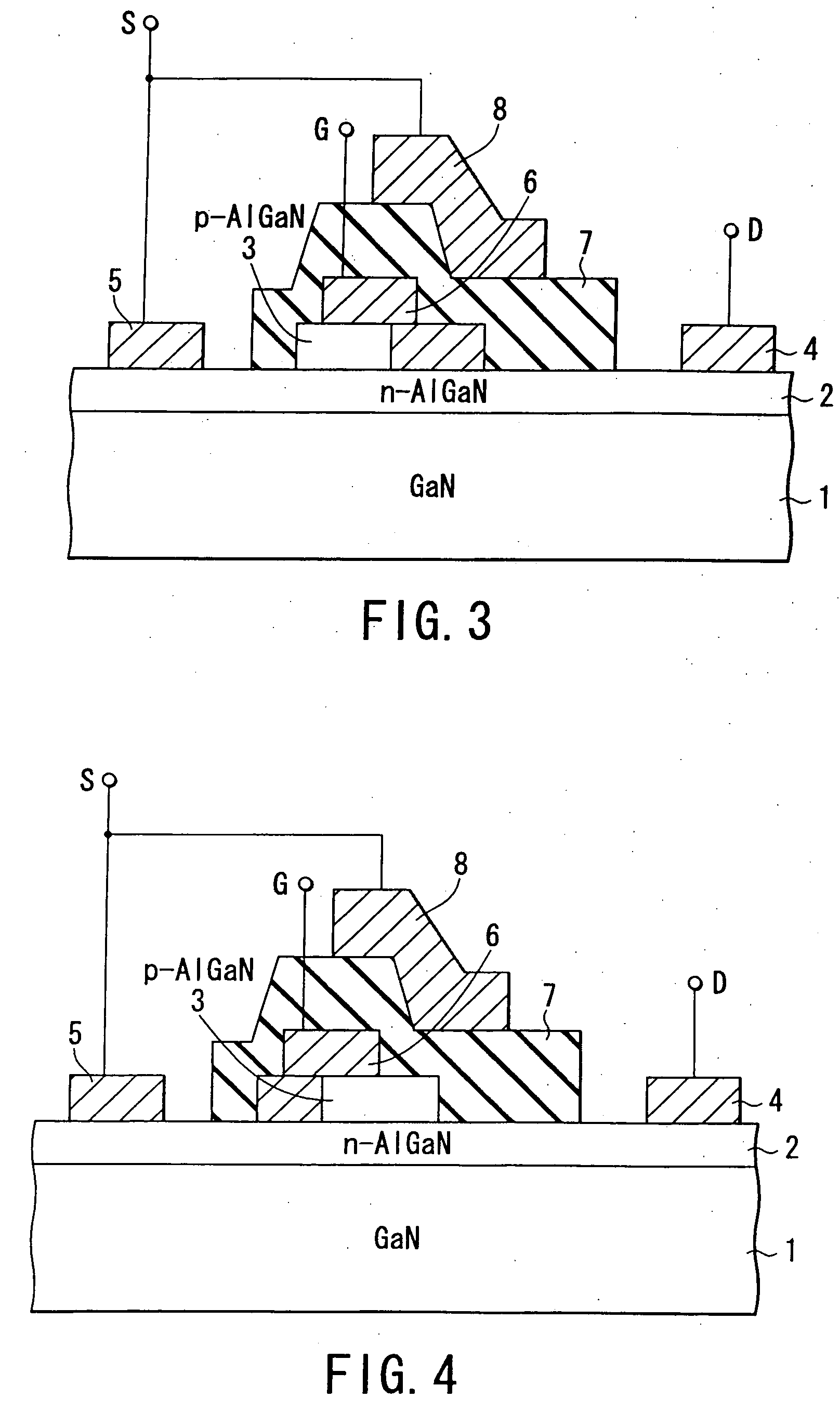

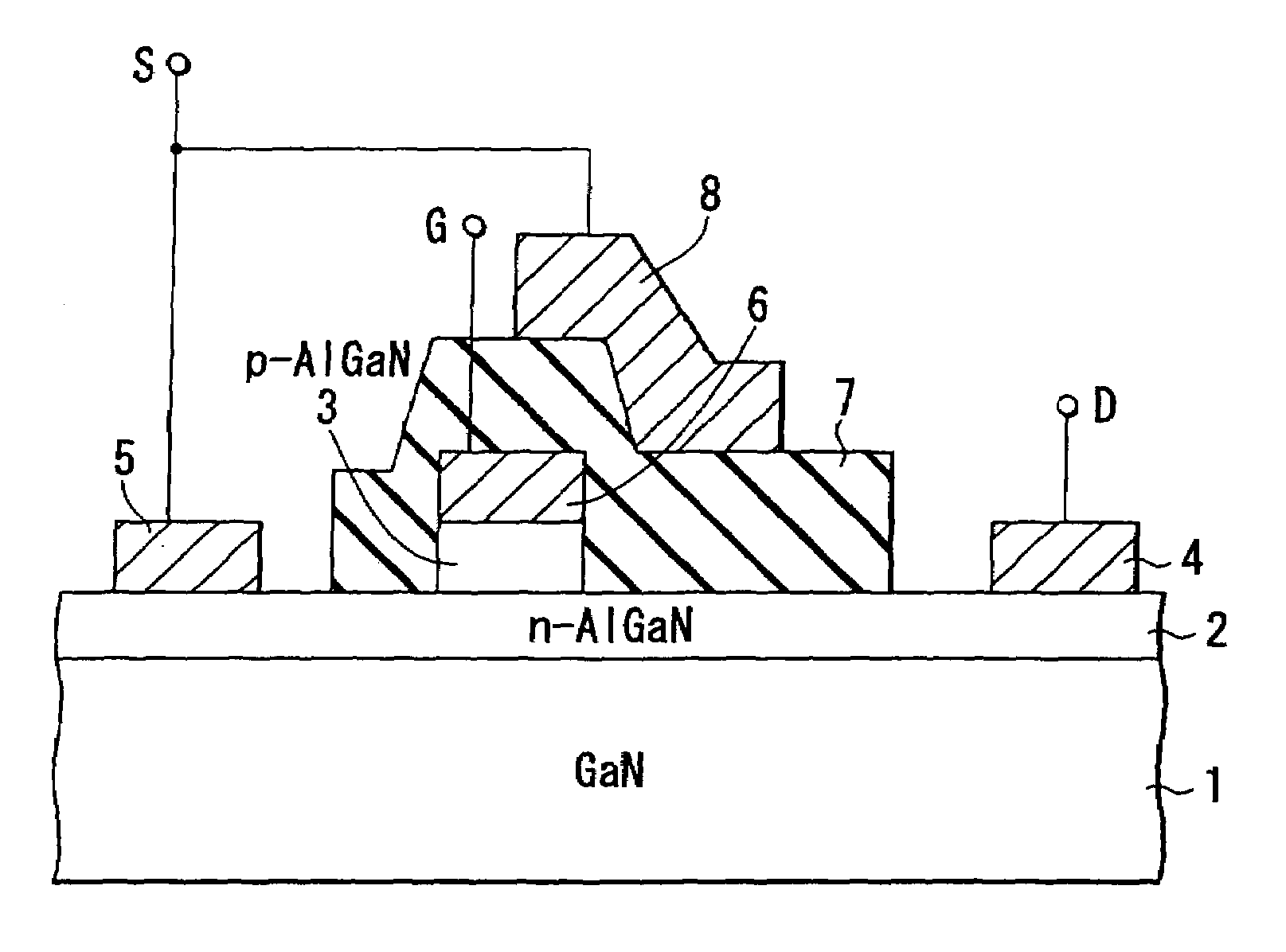

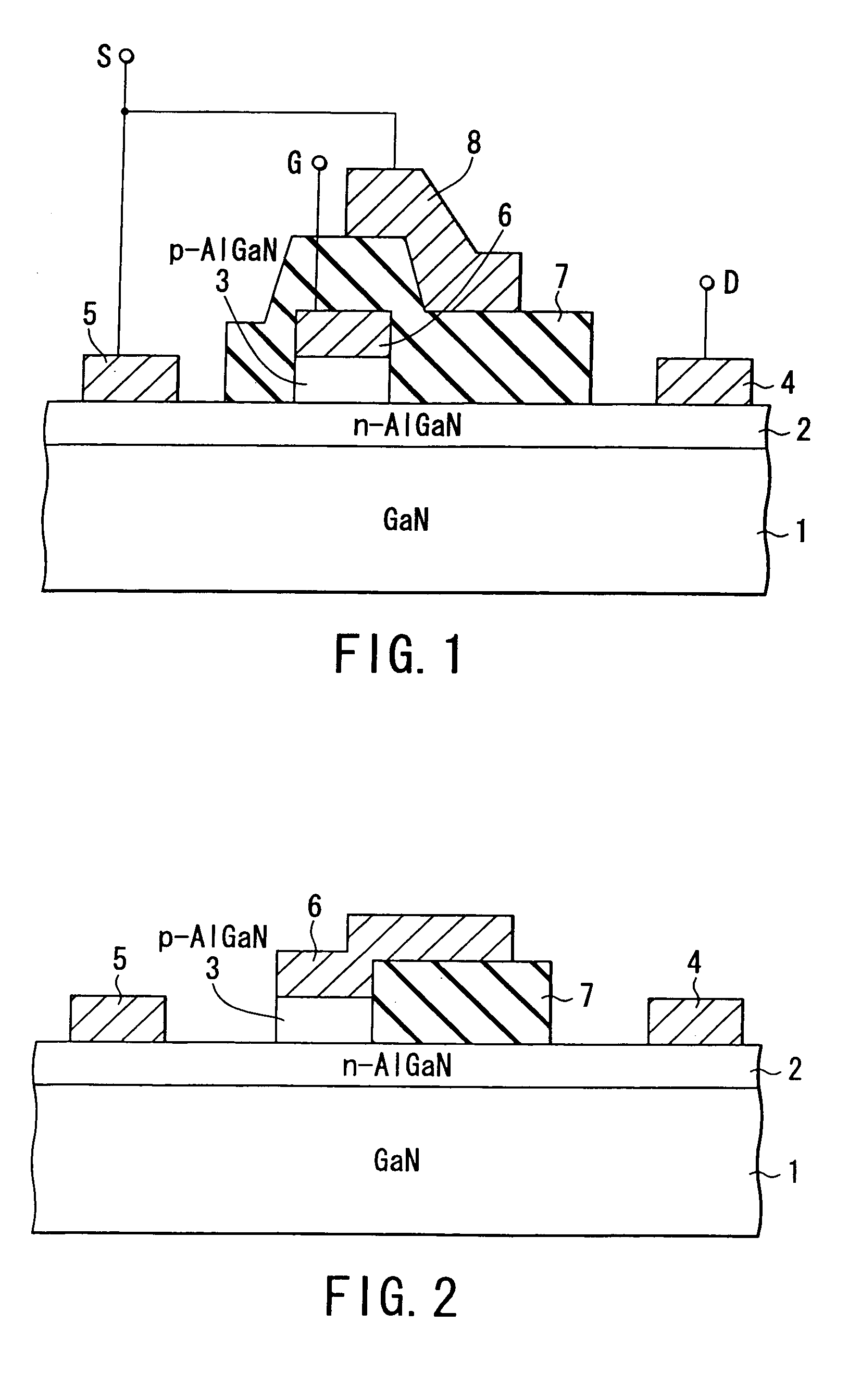

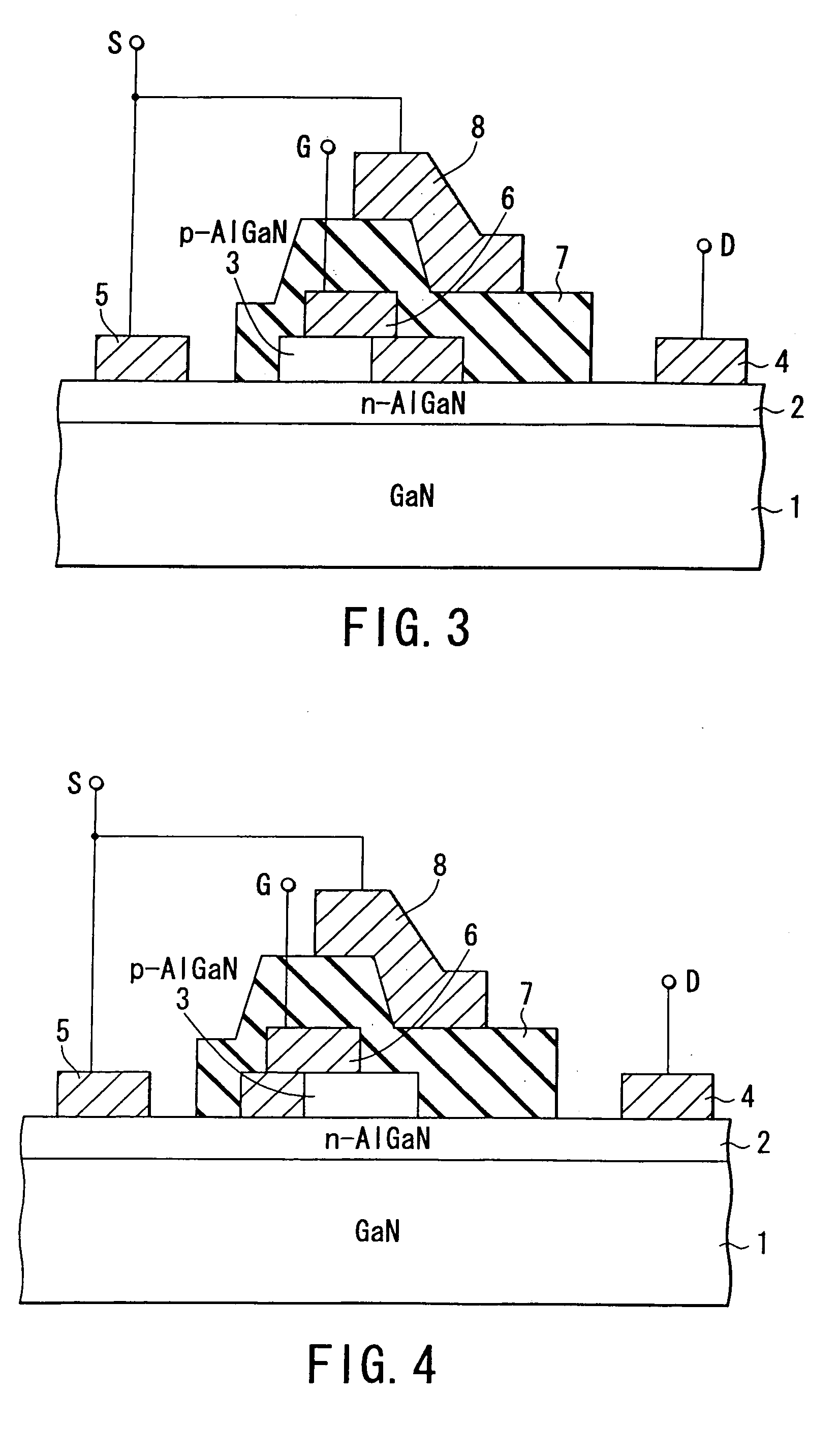

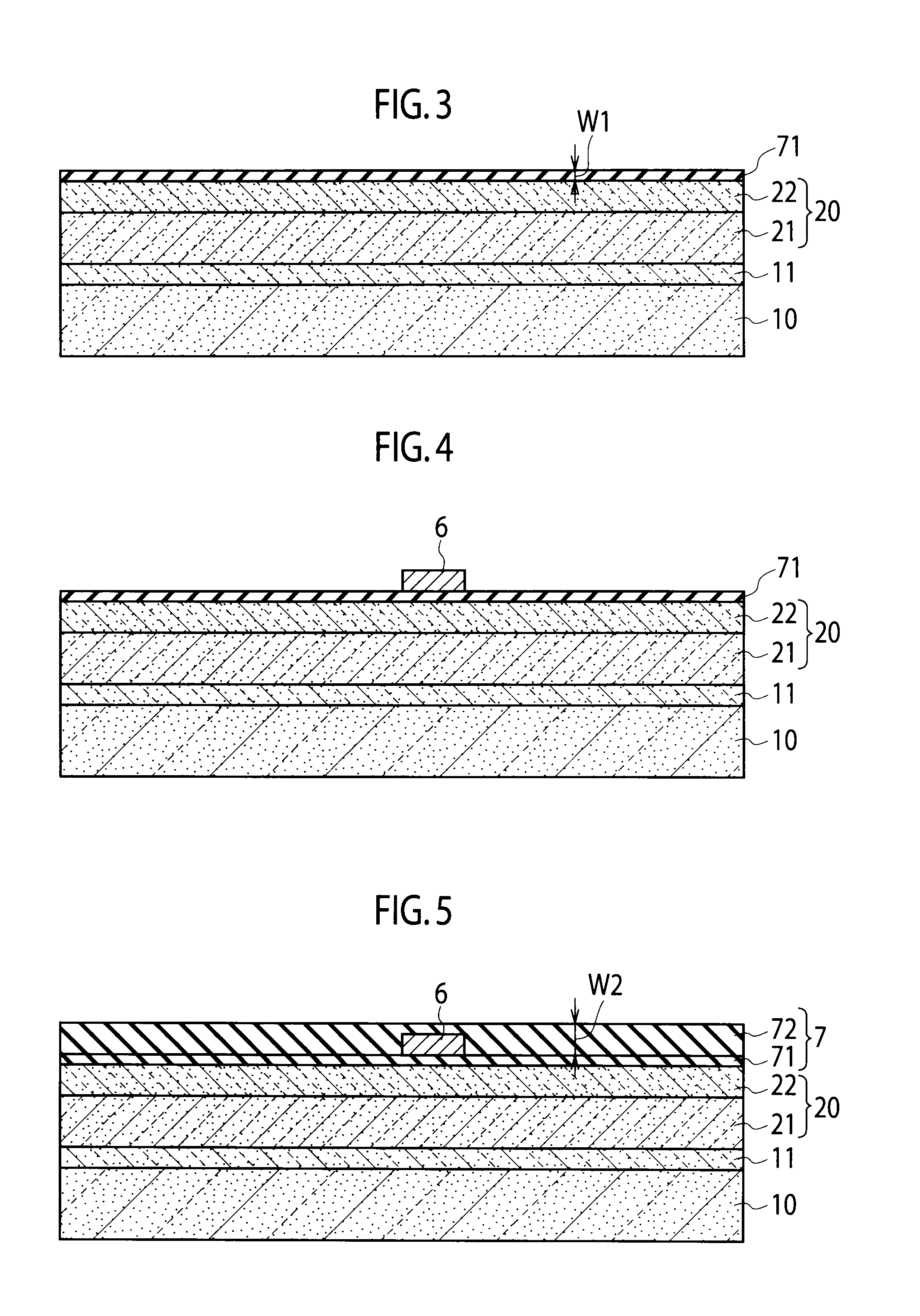

Power semiconductor device

InactiveUS20050110042A1Improve rendering capabilitiesResistanceTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceNon doped

A power semiconductor device including a non-doped GaN channel layer, an n-type Al0.2Ga0.8N barrier layer formed on the channel layer, a p-type Al0.1Ga0.9N semiconductor layer selectively formed on the barrier layer, a drain electrode positioned at one of both sides of the semiconductor layer and formed on the barrier layer, an insulating film formed on the barrier layer adjacent to the semiconductor layer between at least semiconductor layer and drain electrode, and a field plate electrode formed on the insulating film.

Owner:KK TOSHIBA

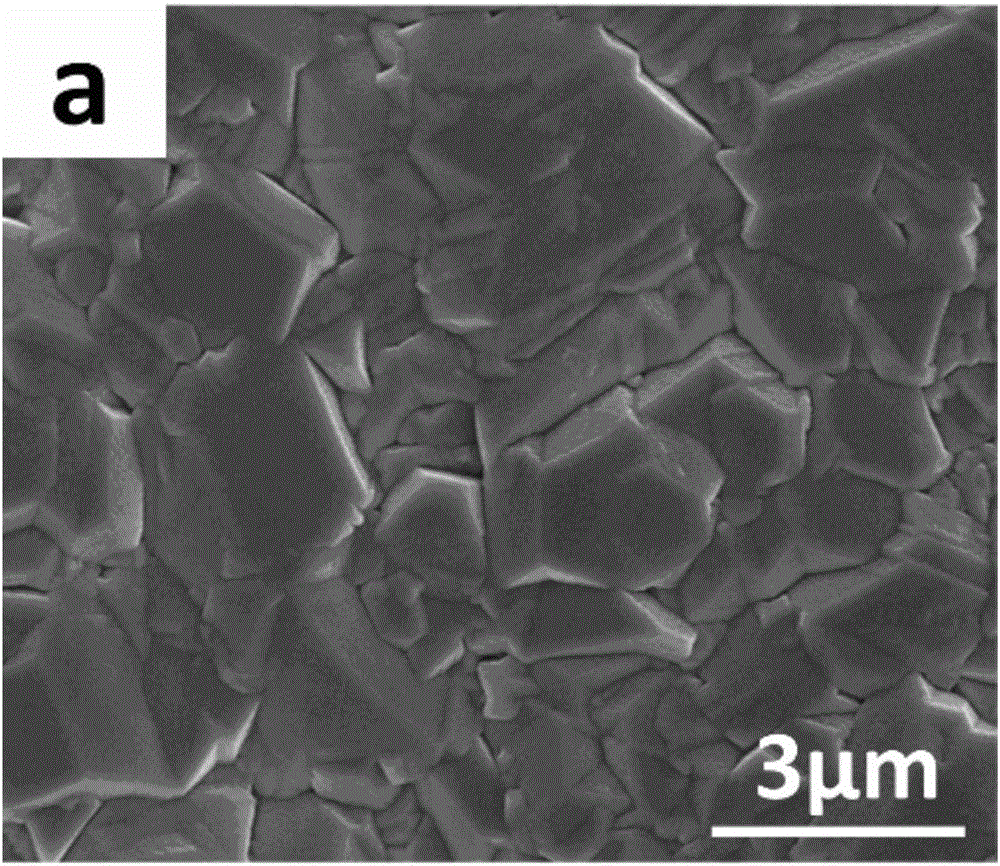

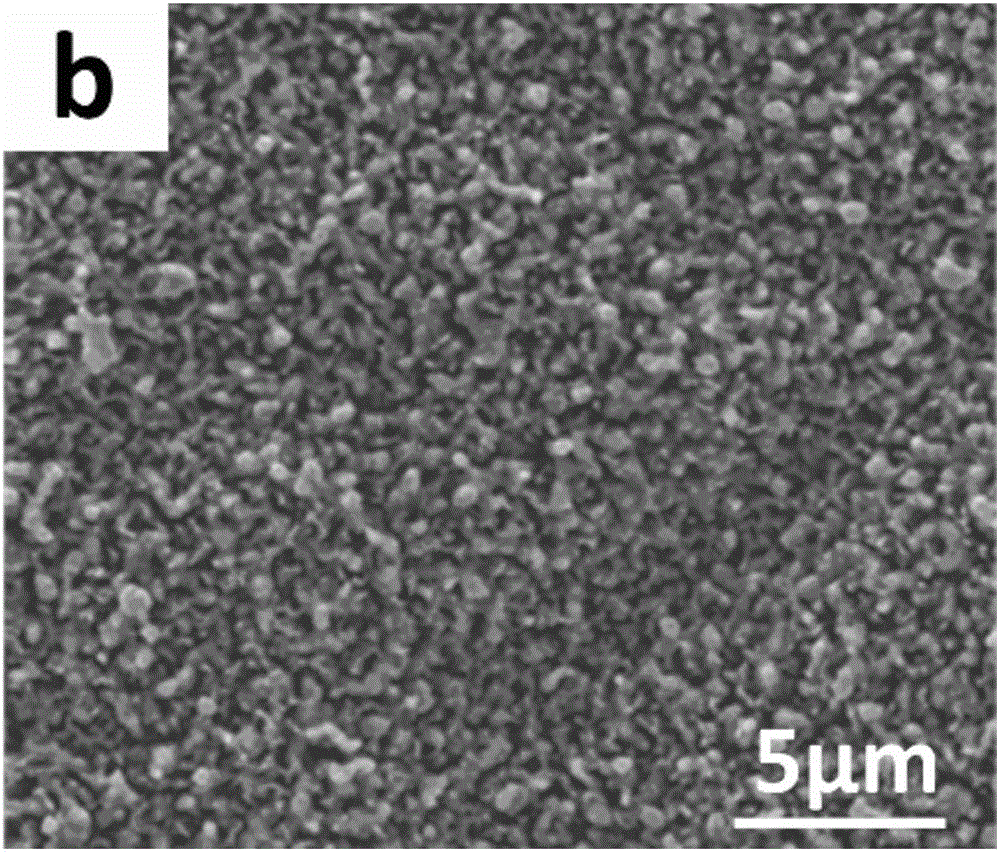

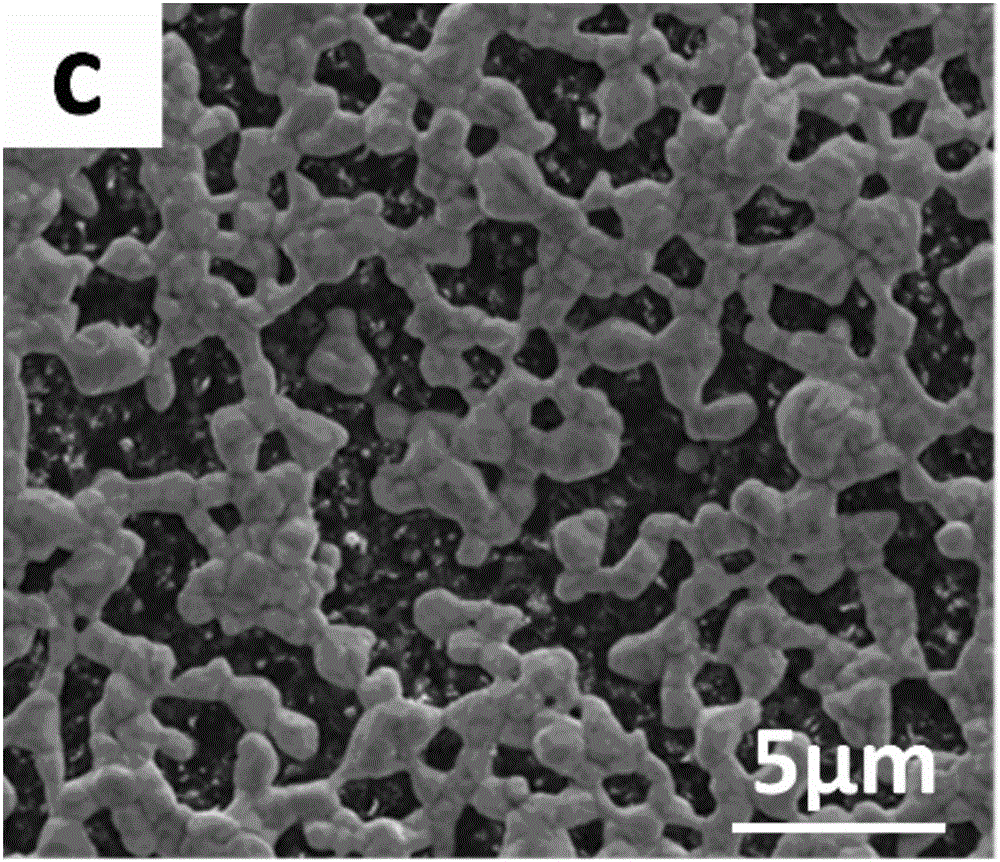

High-specific-surface-area boron-doped diamond electrode and preparation method and application thereof

ActiveCN106435518AHigh activityLarge electrochemical reaction interfaceWater contaminantsWater/sewage treatmentElectrochemical biosensorDiamond electrodes

The invention discloses a high-specific-surface-area boron-doped diamond (BDD) electrode which comprises an electrode substrate. A boron-doped diamond layer is arranged on the surface of the electrode substrate. Or, a transition layer is arranged on the surface of the substrate, and then a boron-doped diamond layer is arranged on the surface of the transition layer. Metal particles are distributed in the diamond layer, and tiny holes and / or pointed cones are distributed on the surface of the diamond layer. Compared with a traditional plate electrode, the boron-doped diamond electrode contains a large number of tiny holes and pointed cones and has the extremely high specific surface area, and the large current intensity is provided through the low current intensity; and meanwhile, due to the different electrode configurations of the substrate and modification of surface graphene and / or carbon nano tubs (CNT), the mass transfer process can be greatly improved, the current efficiency and the electrochemical property are greatly improved, and the BDD electrode with high electrocatalytic activity and high using efficiency is prepared. The electrode can be widely applied in the fields of electrochemical wastewater purification treatment, electrochemical biosensors, strong oxidant electrochemical synthesis, electrochemical detection and the like.

Owner:NANJING DAIMONTE TECH CO LTD

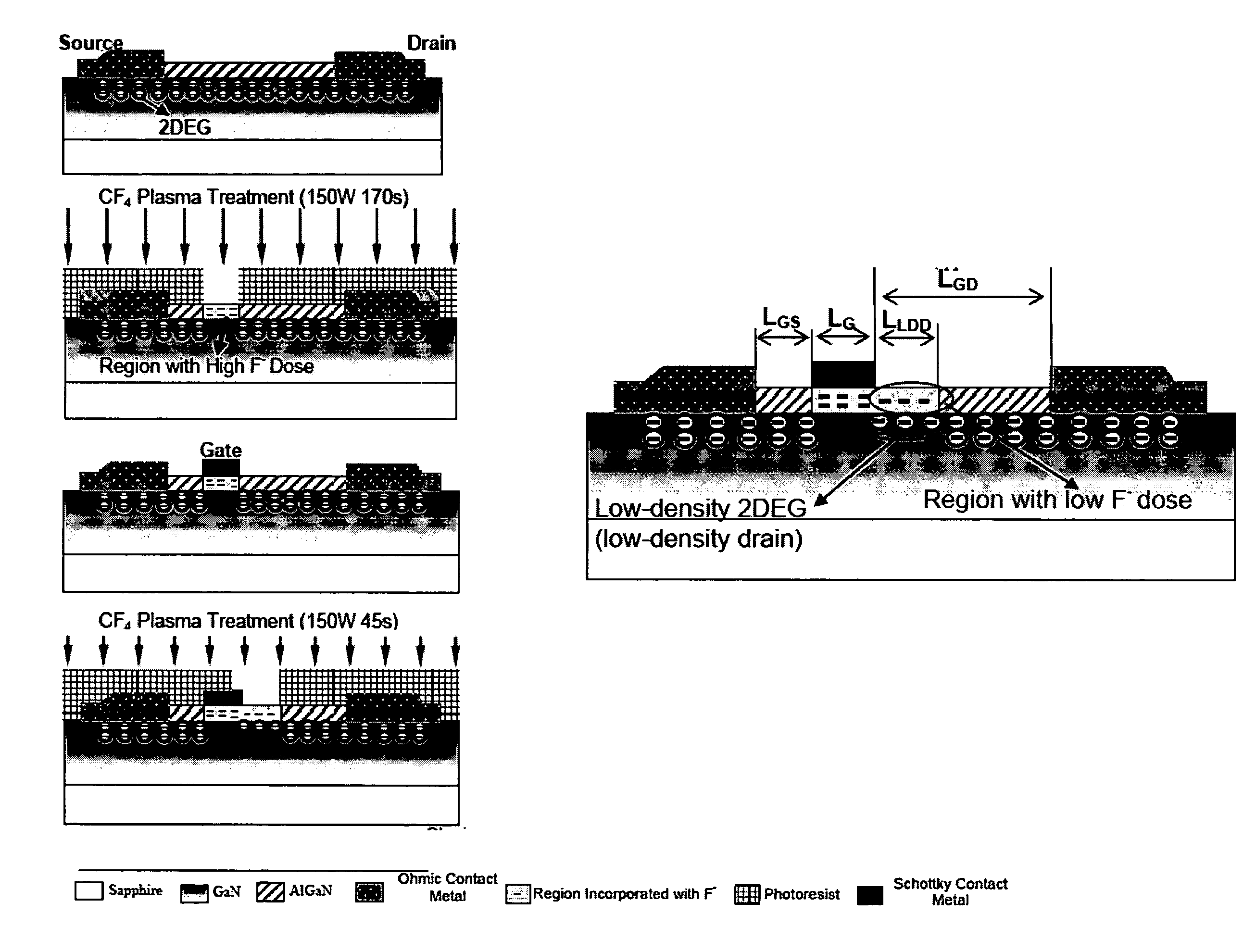

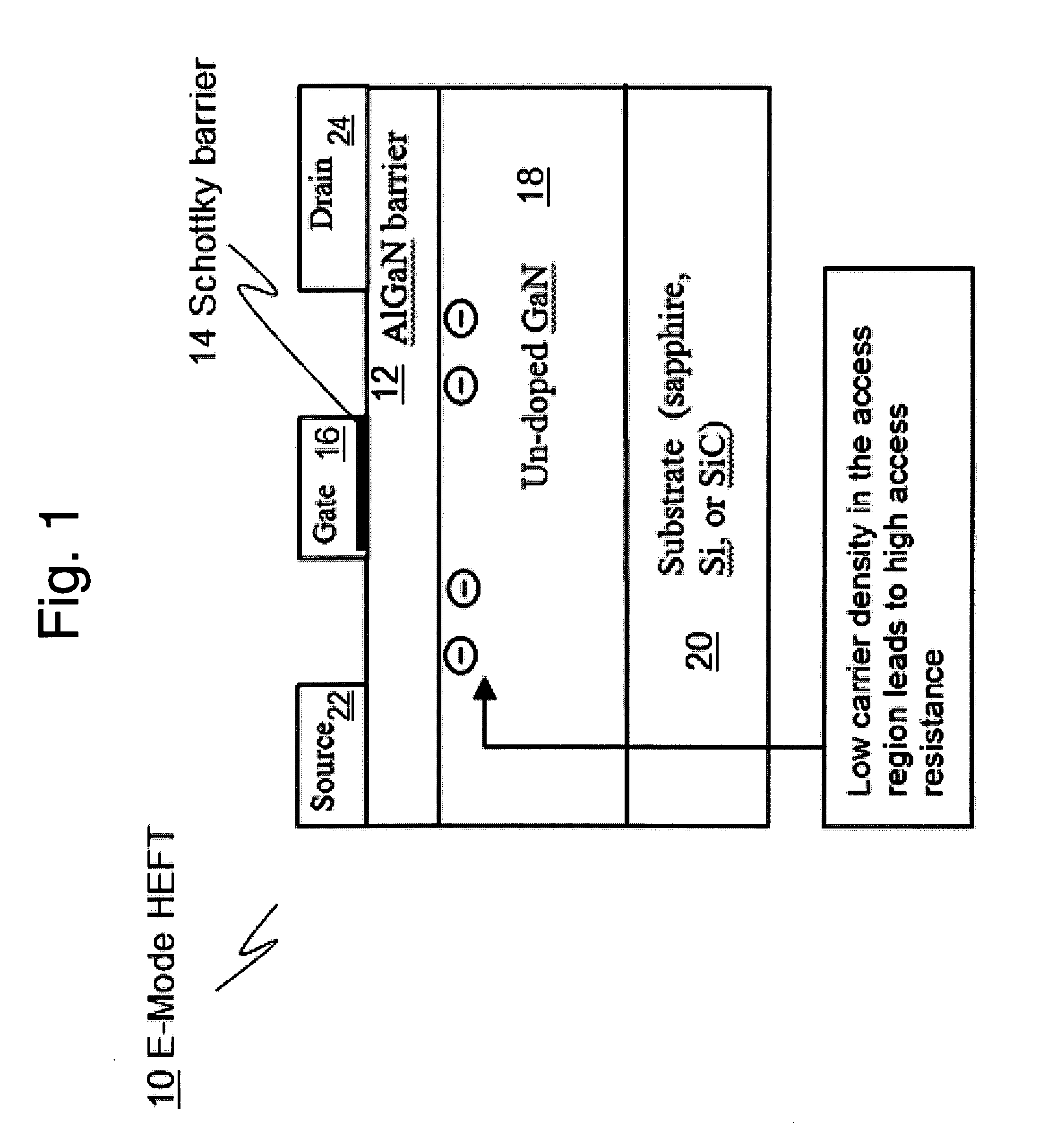

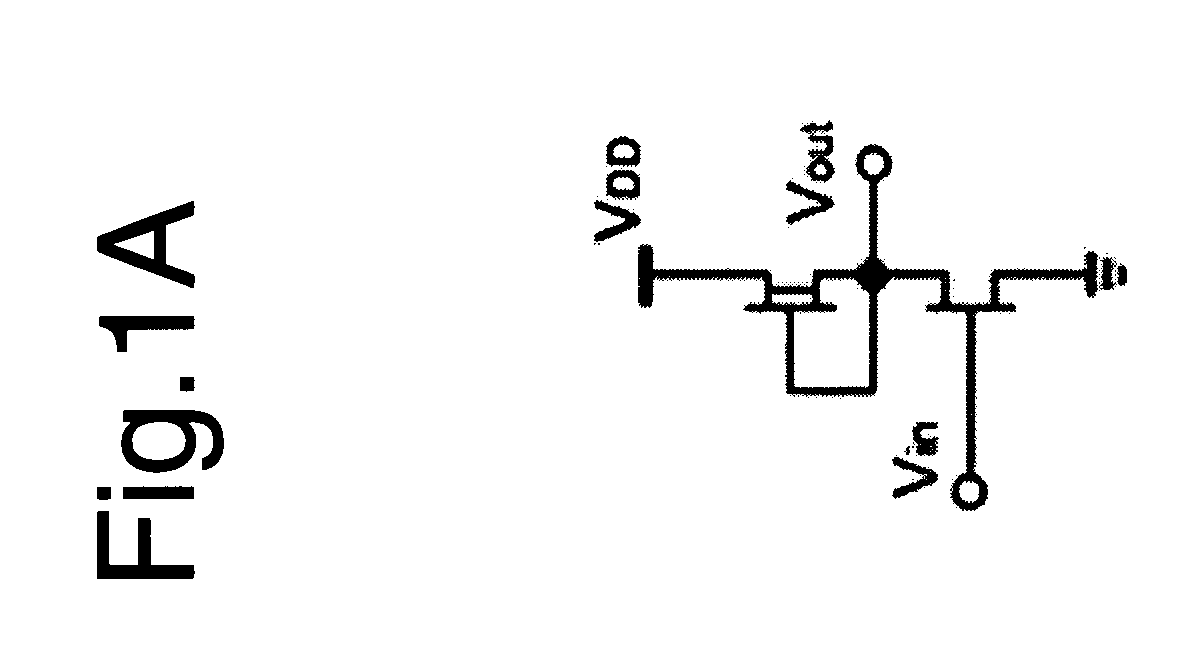

Low Density Drain HEMTs

ActiveUS20070295993A1Simple circuit configurationFavorable operating condition for device safetySemiconductor/solid-state device manufacturingSemiconductor devicesIon implantationBreakdown voltage

Methods and devices for fabricating AlGaN / GaN normally-off high electron mobility transistors (HEMTs). A fluorine-based (electronegative ions-based) plasma treatment or low-energy ion implantation is used to modify the drain-side surface field distribution without the use of a field plate electrode. The off-state breakdown voltage can be improved and current collapse can be completely suppressed in LDD-HEMTs with no significant degradation in gains and cutoff frequencies.

Owner:THE HONG KONG UNIV OF SCI & TECH

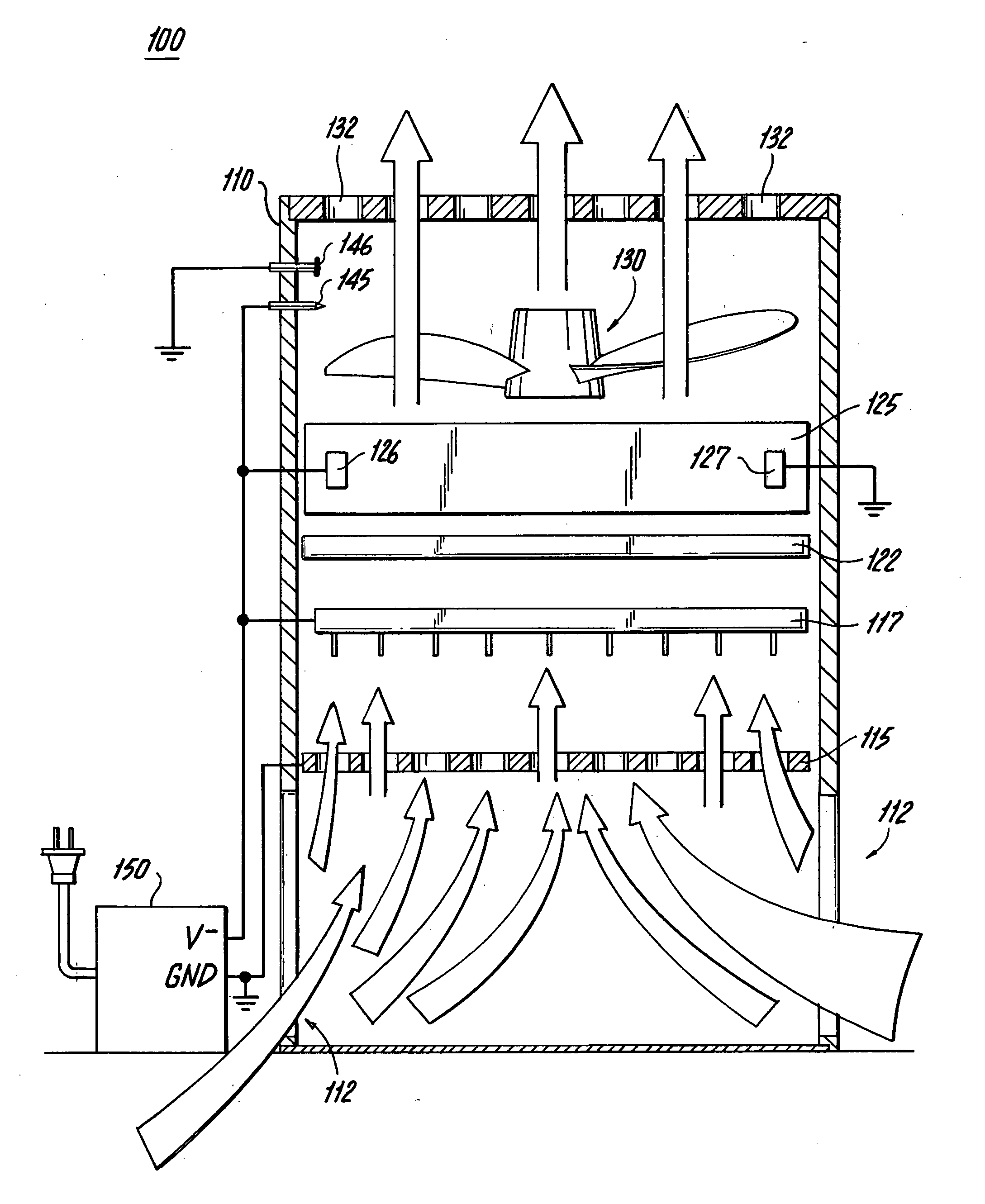

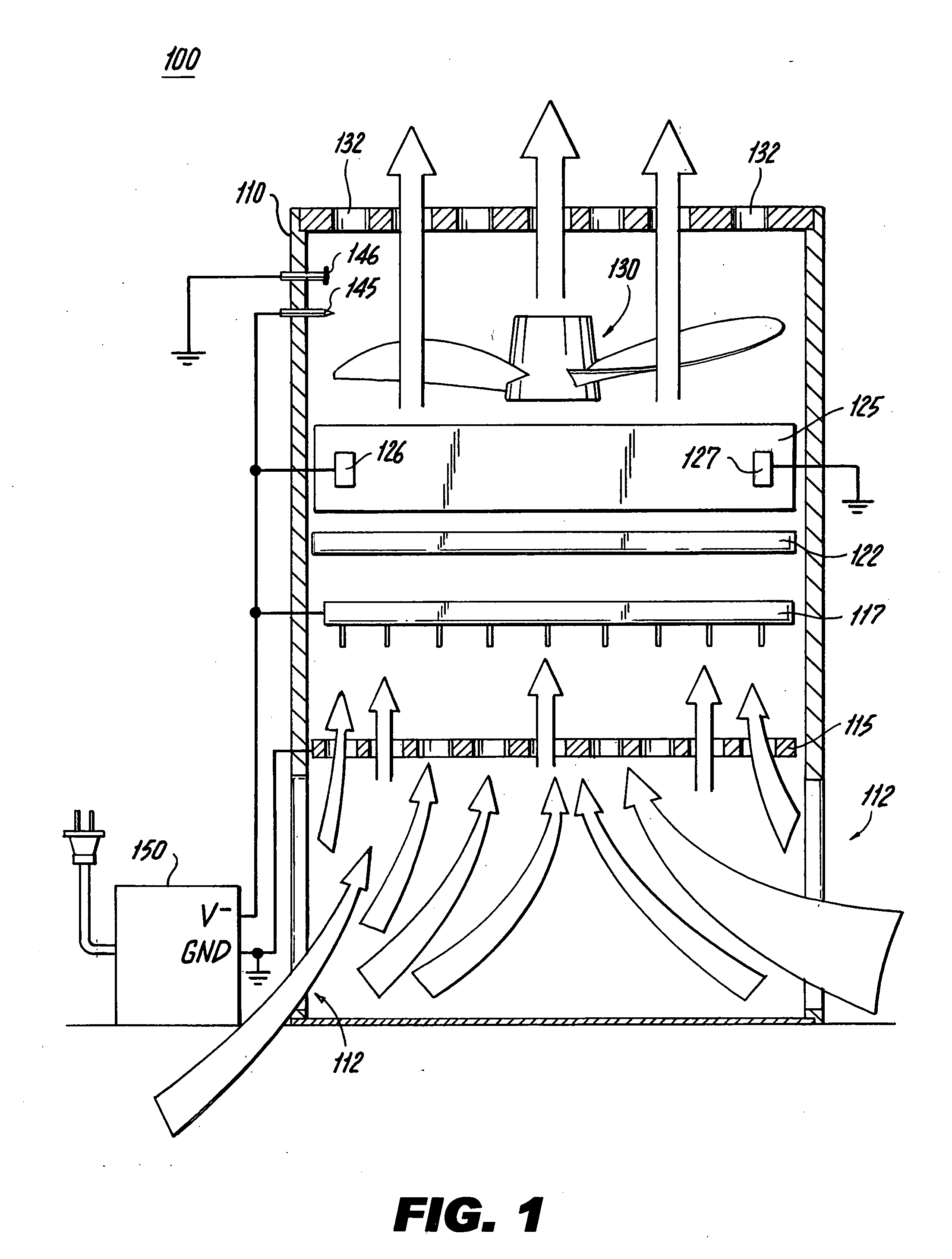

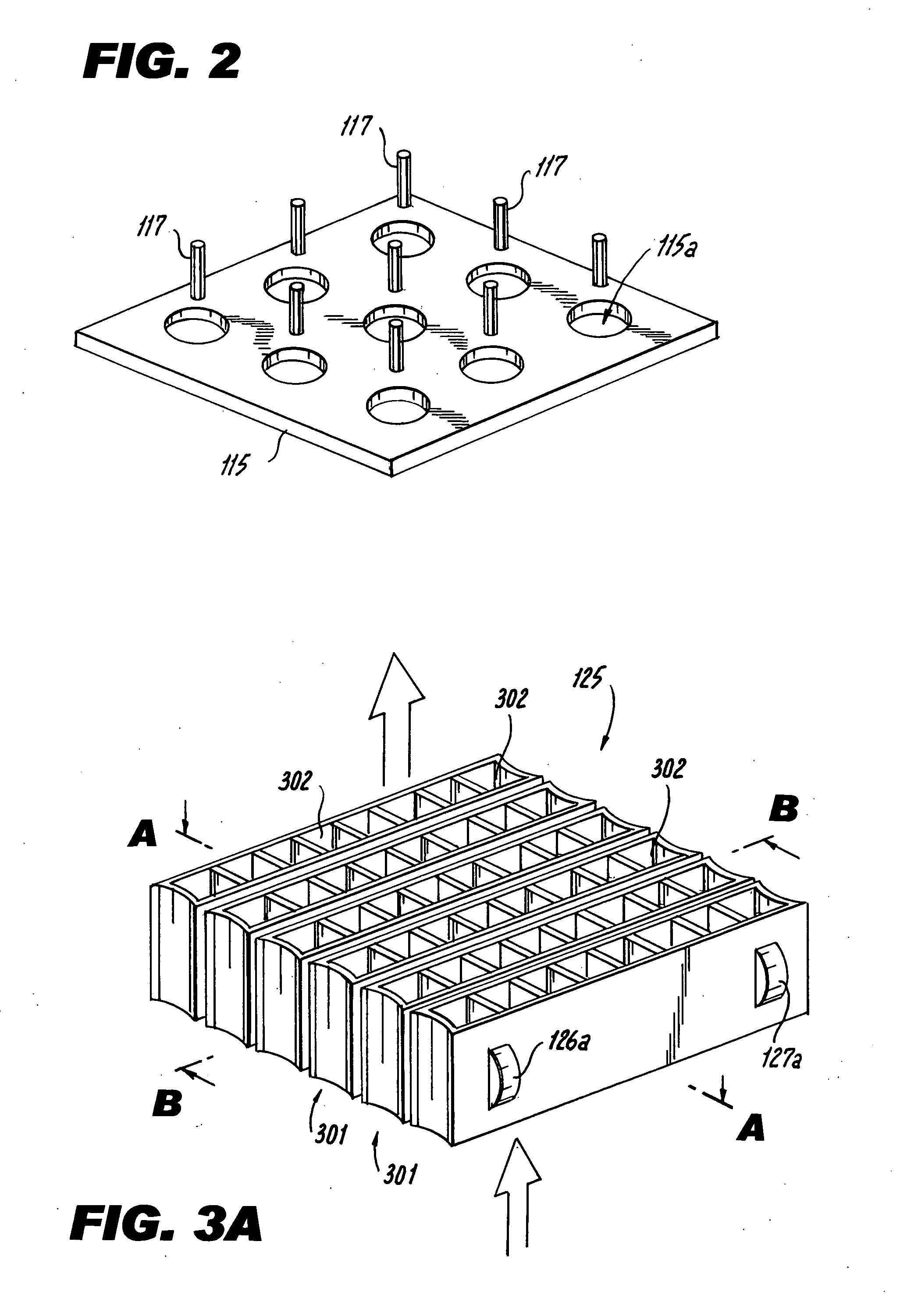

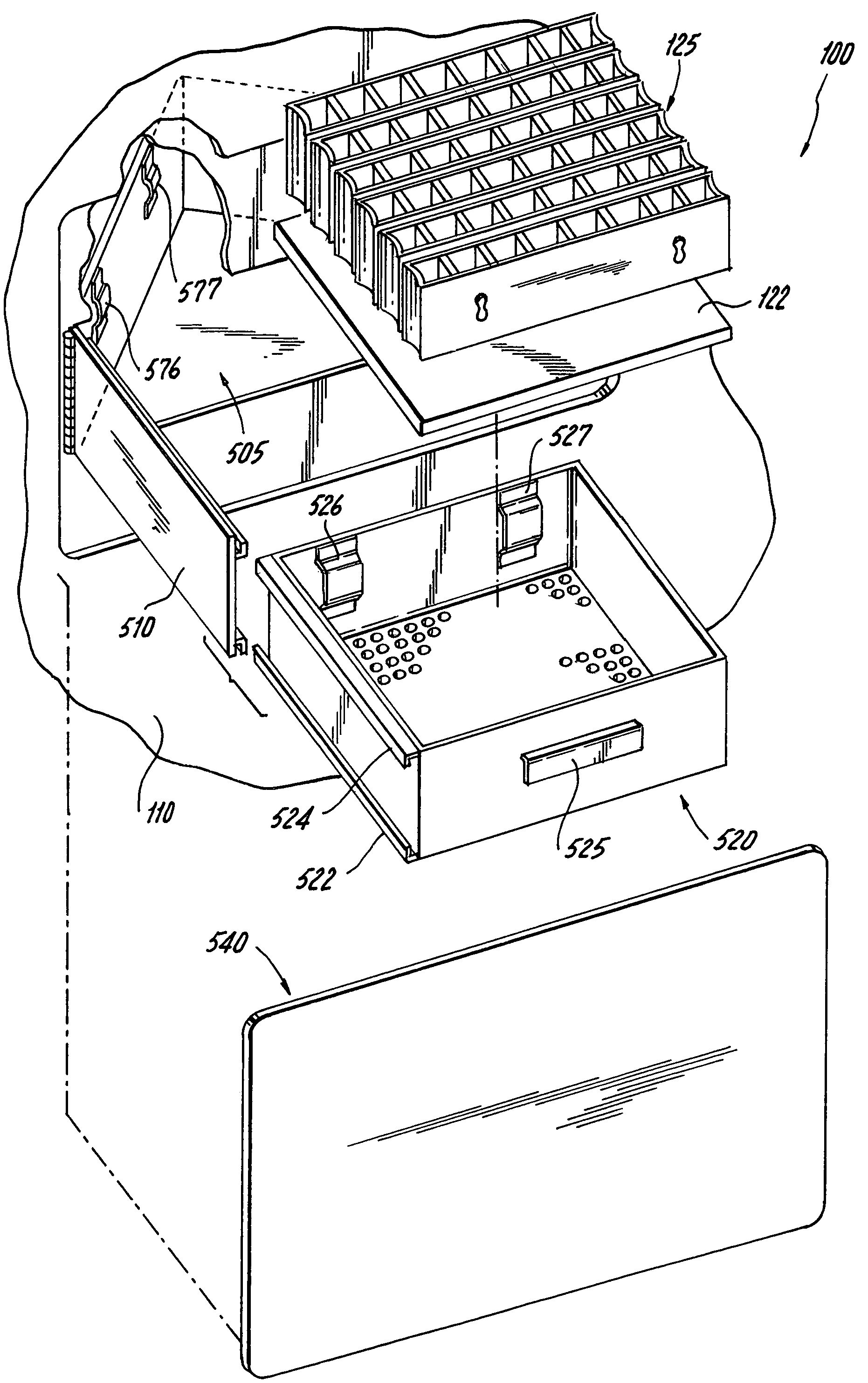

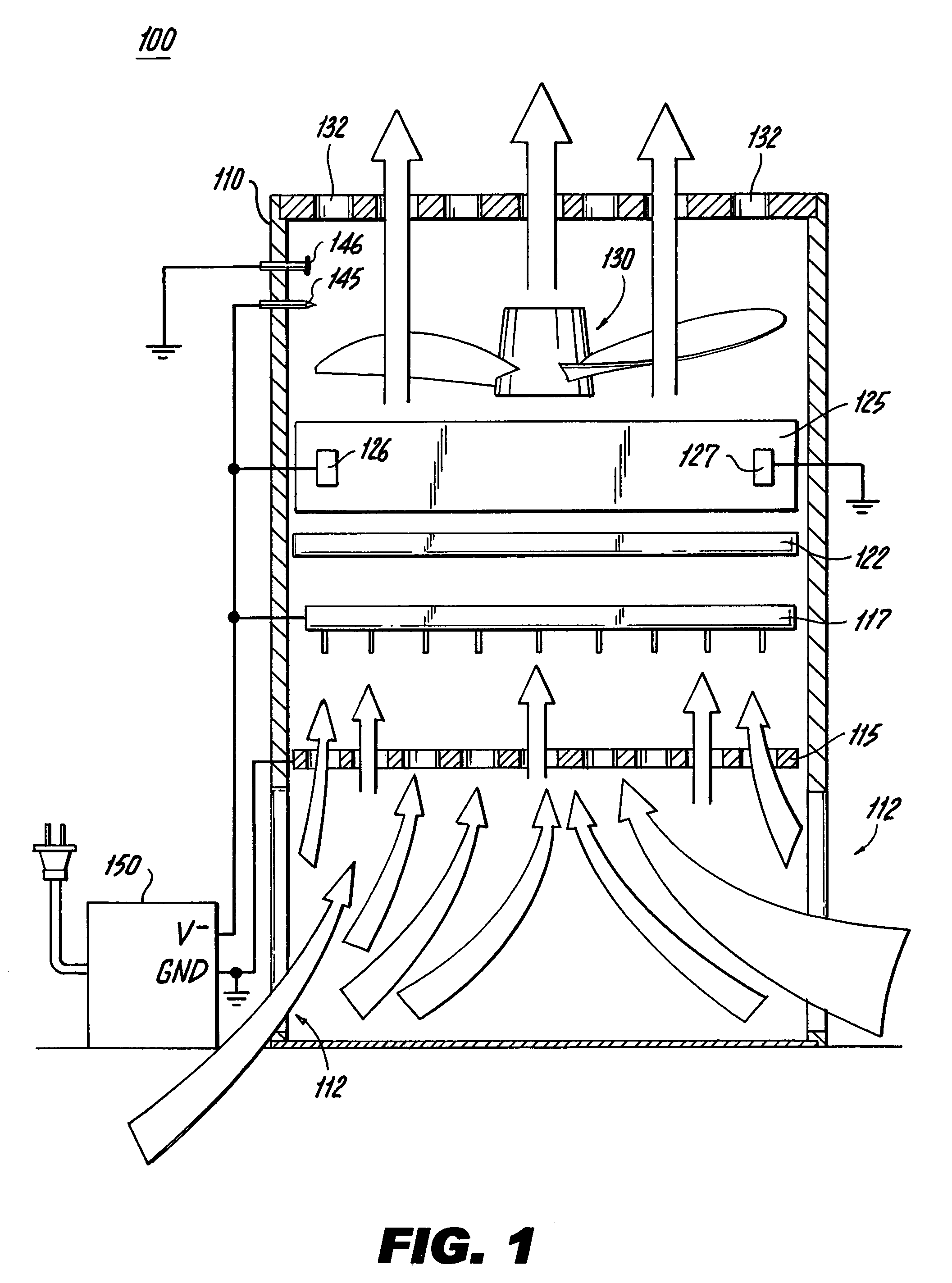

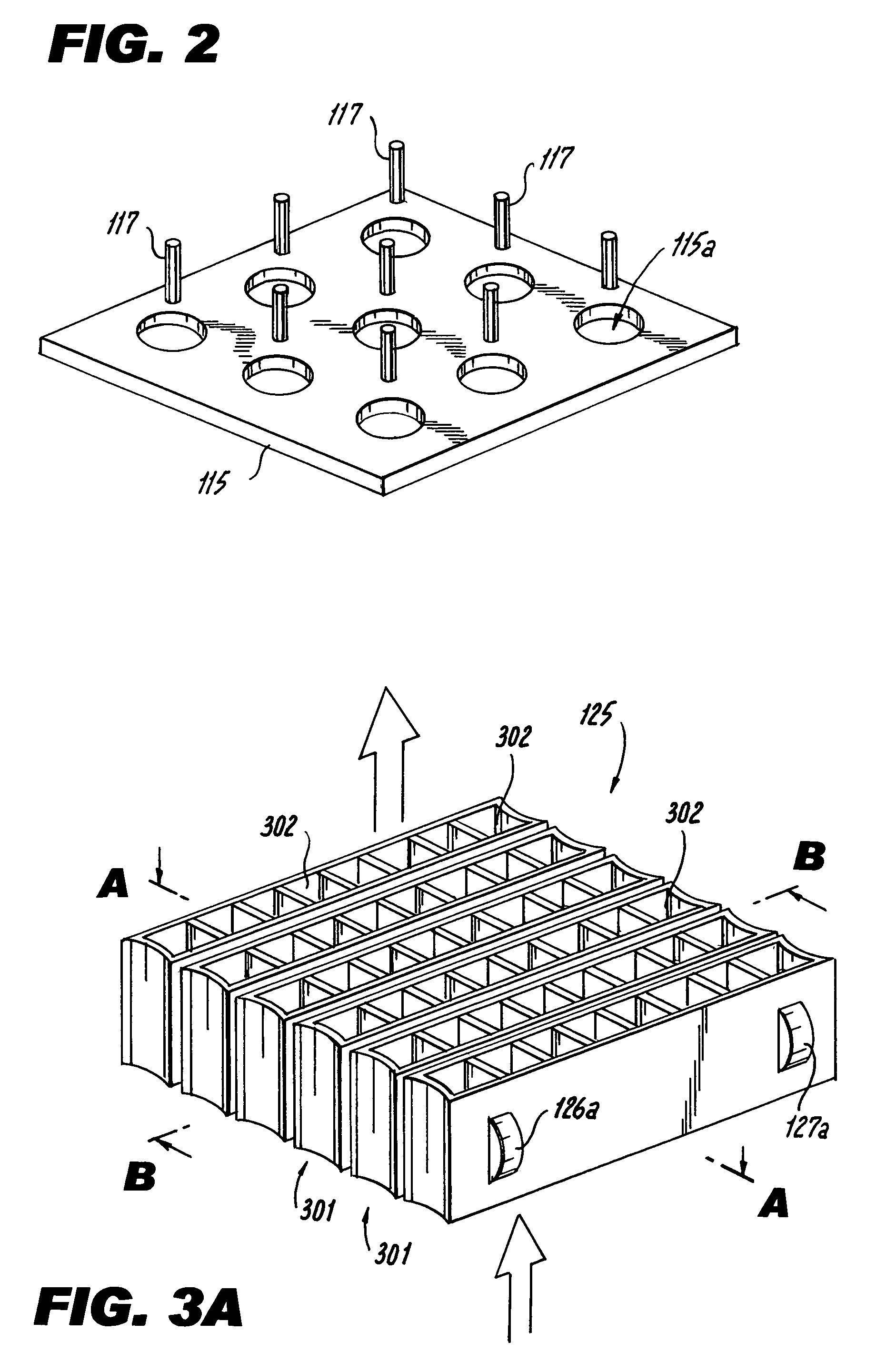

Air cleaner

An improved filter element for use in an electrostatic precipitation air cleaning device, the filter element including rod electrodes arranged through a stack of alternating fluted plastic sheets and plate electrodes. Successive plate electrodes are arranged to make contact with an alternating one or the other of the rod electrodes. The plate and rod electrodes may be composed of high impedance materials such as paper and plastic, respectively. An arrangement for removably inserting a filter element into an air cleaning device is provided. The arrangement also removably provides electrical connectivity between the filter element and the air cleaning device. The filter element can thus be readily removed and re-installed by a user.

Owner:HELEN OF TROY LIMITED

Power semiconductor device

InactiveUS6933544B2Improve rendering capabilitiesResistanceTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceNon doped

A power semiconductor device including a non-doped GaN channel layer, an n-type Al0.2Ga0.8N barrier layer formed on the channel layer, a p-type Al0.1Ga0.9N semiconductor layer selectively formed on the barrier layer, a drain electrode positioned at one of both sides of the semiconductor layer and formed on the barrier layer, an insulating film formed on the barrier layer adjacent to the semiconductor layer between at least semiconductor layer and drain electrode, and a field plate electrode formed on the insulating film.

Owner:KK TOSHIBA

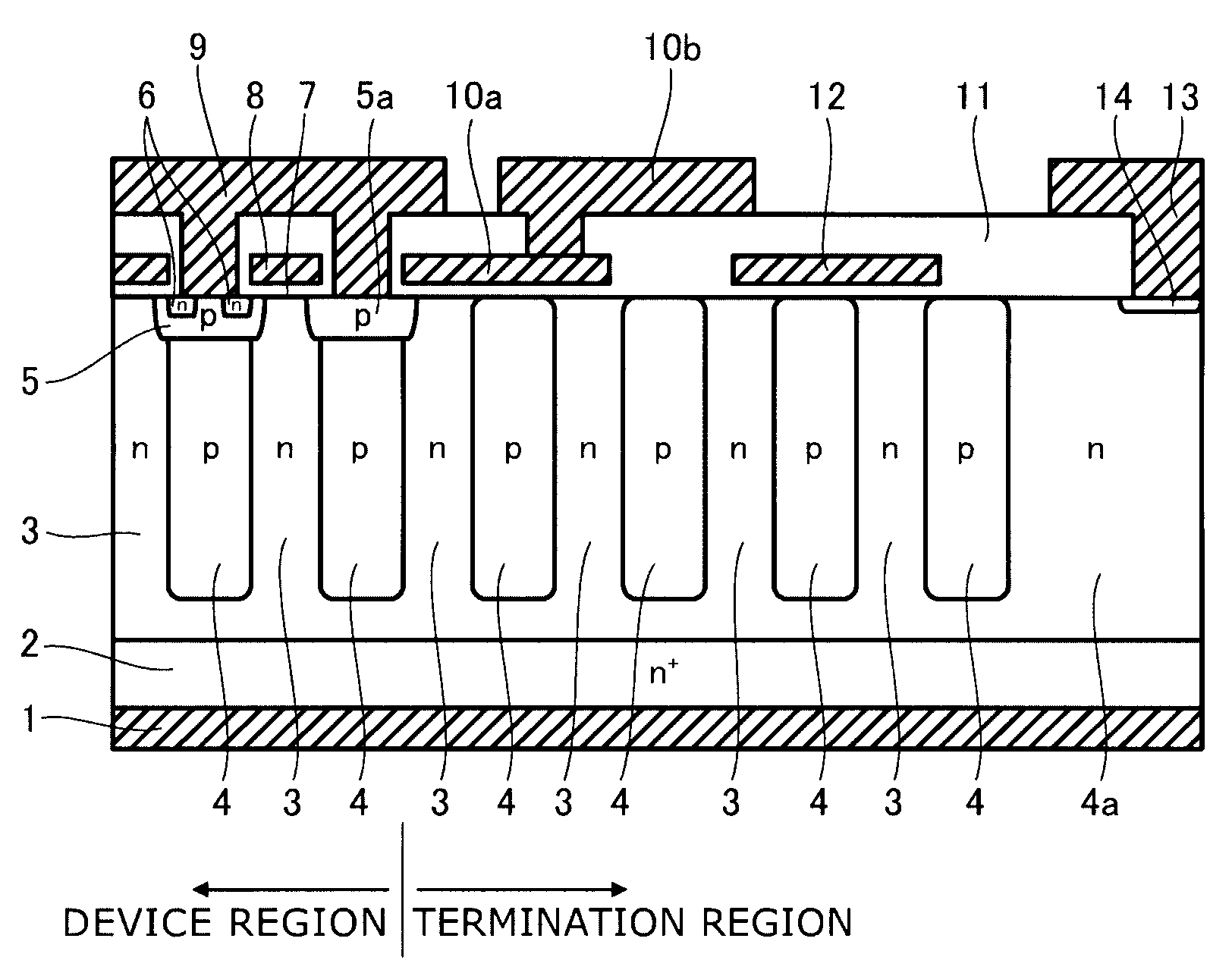

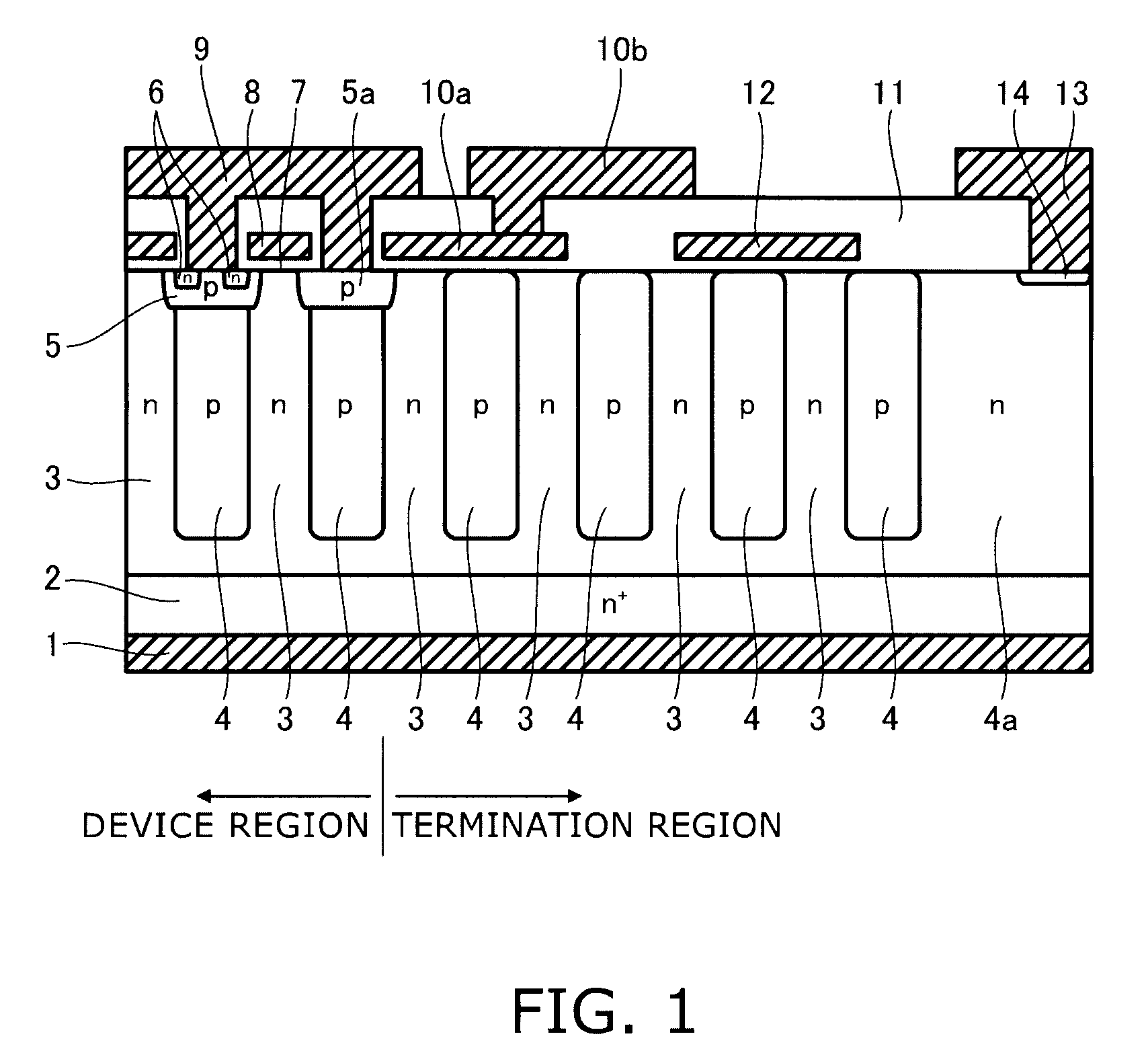

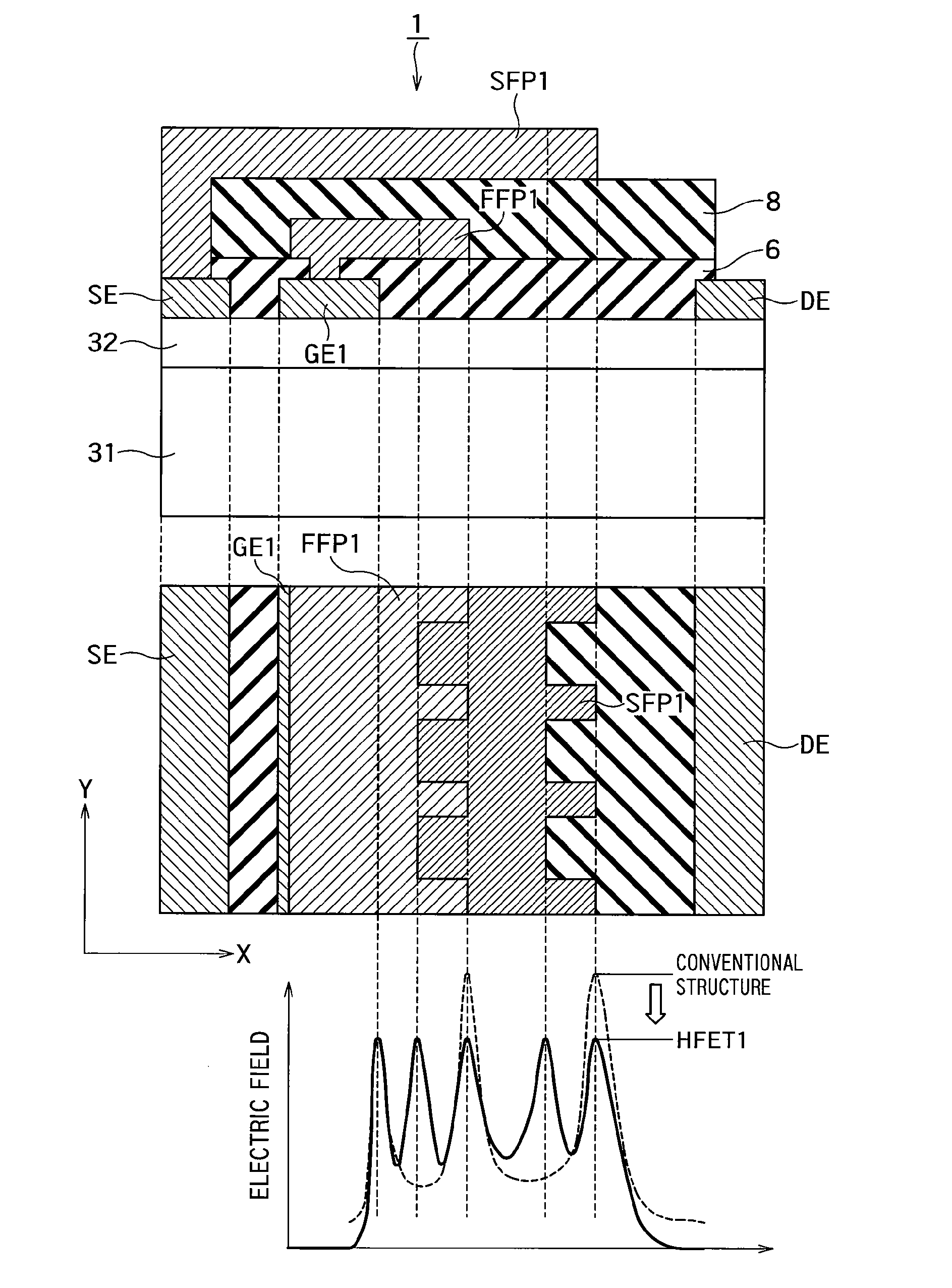

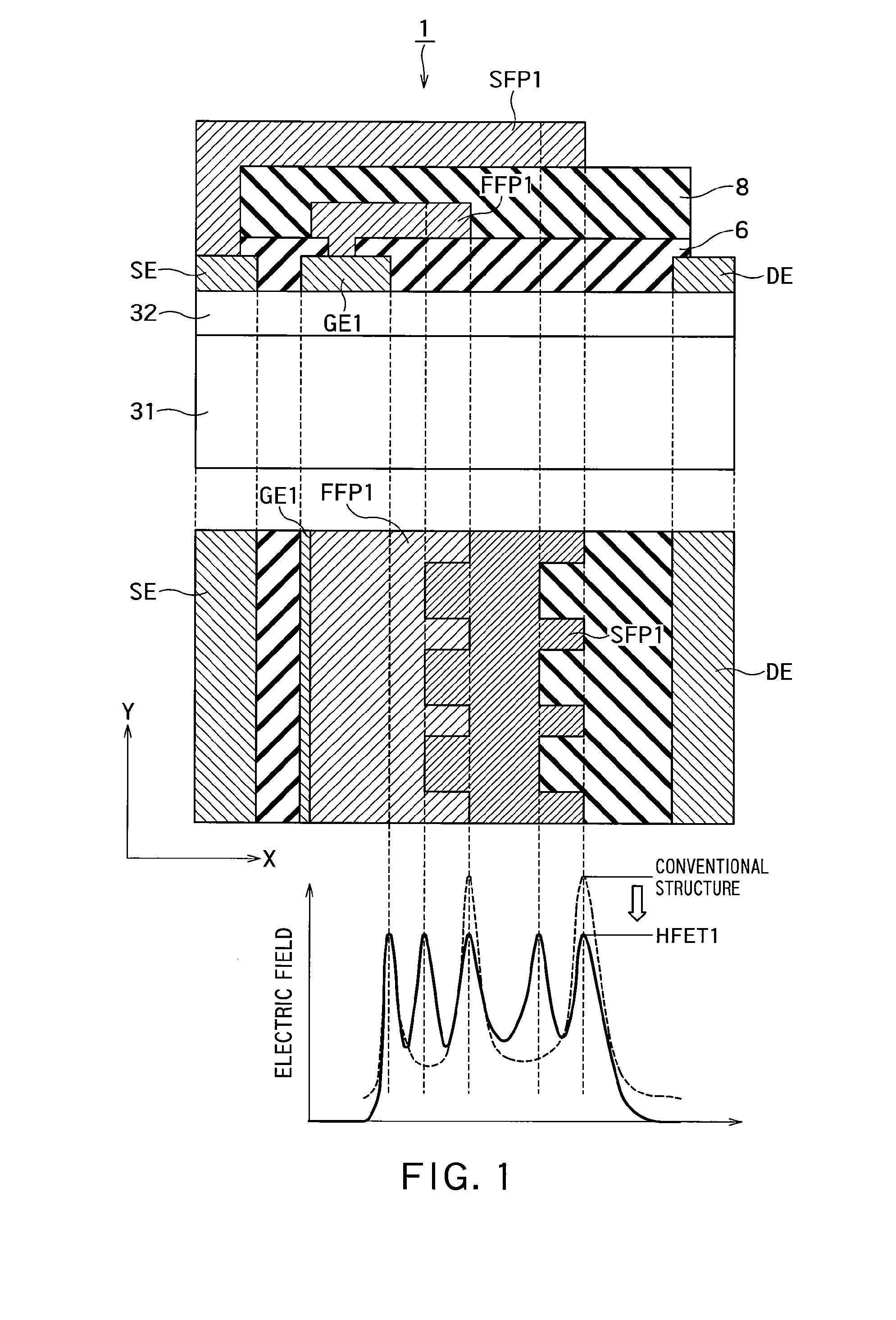

Semiconductor apparatus

A semiconductor apparatus includes: a first first-conductivity-type semiconductor layer; a second first-conductivity-type semiconductor layer provided on a major surface of the first first-conductivity-type semiconductor layer in a device region and a termination region outside the device region; a third second-conductivity-type semiconductor layer being adjacent to the second first-conductivity-type semiconductor layer, forming a periodic array structure; a field insulating film provided on the second first-conductivity-type semiconductor layer and the third second-conductivity-type semiconductor layer in the termination region; a first field plate electrode provided on the field insulating film and connected to the second main electrode or the control electrode; and a second field plate electrode. The second field plate electrode partly overlies the first field plate electrode through intermediary of an insulating film and extends on the field insulating film outside the first field plate electrode. The second field plate electrode is floating in potential.

Owner:KK TOSHIBA

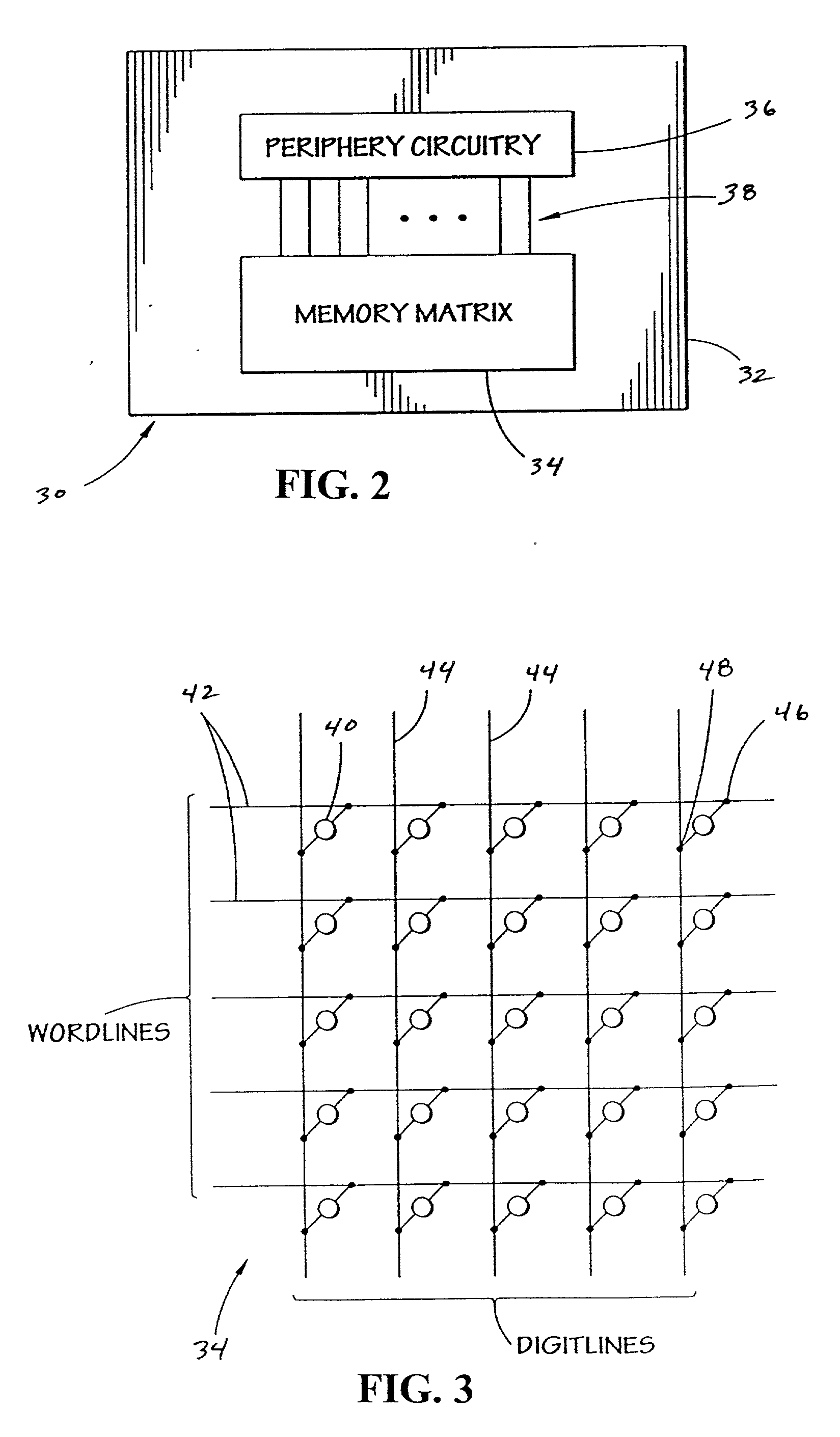

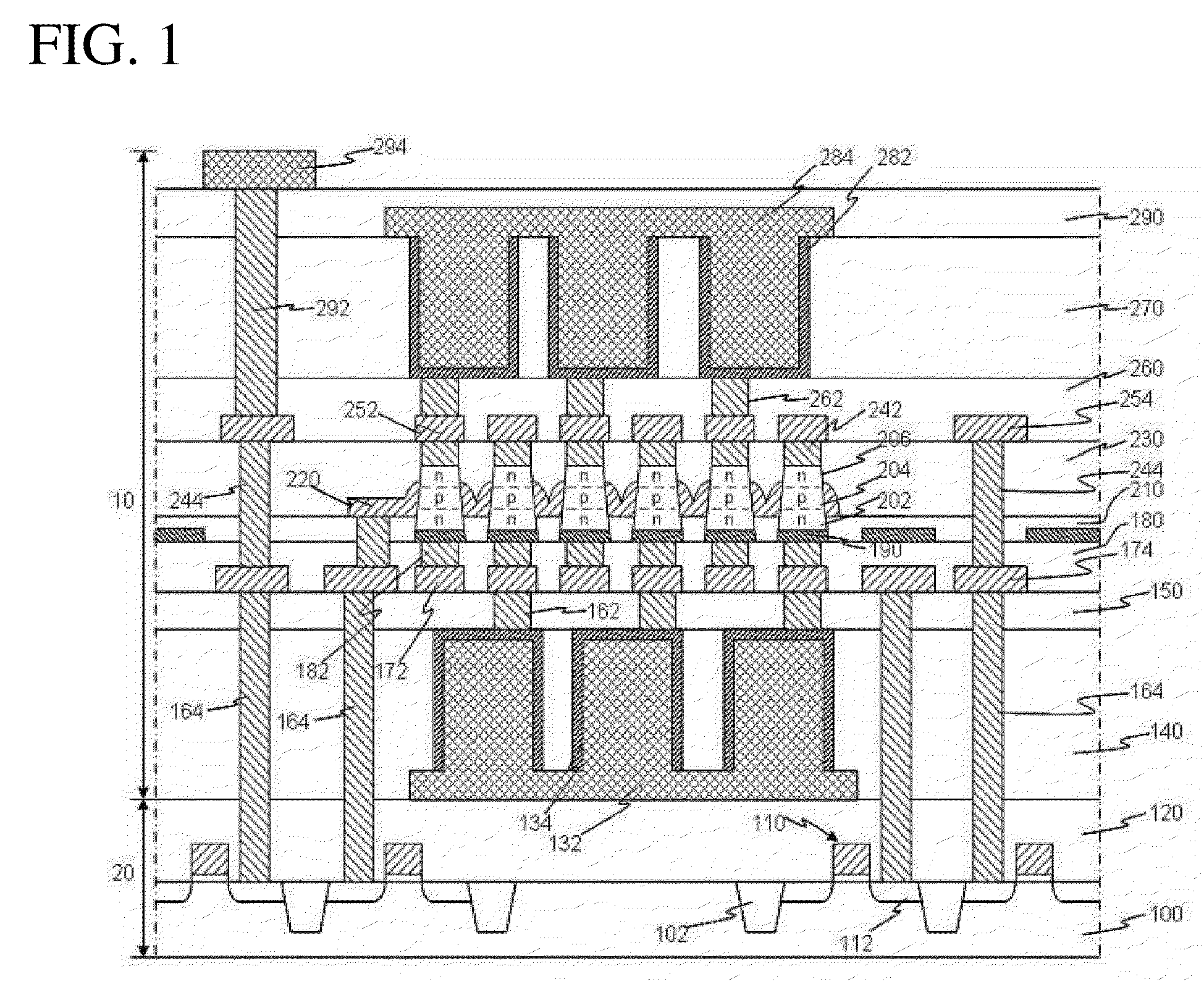

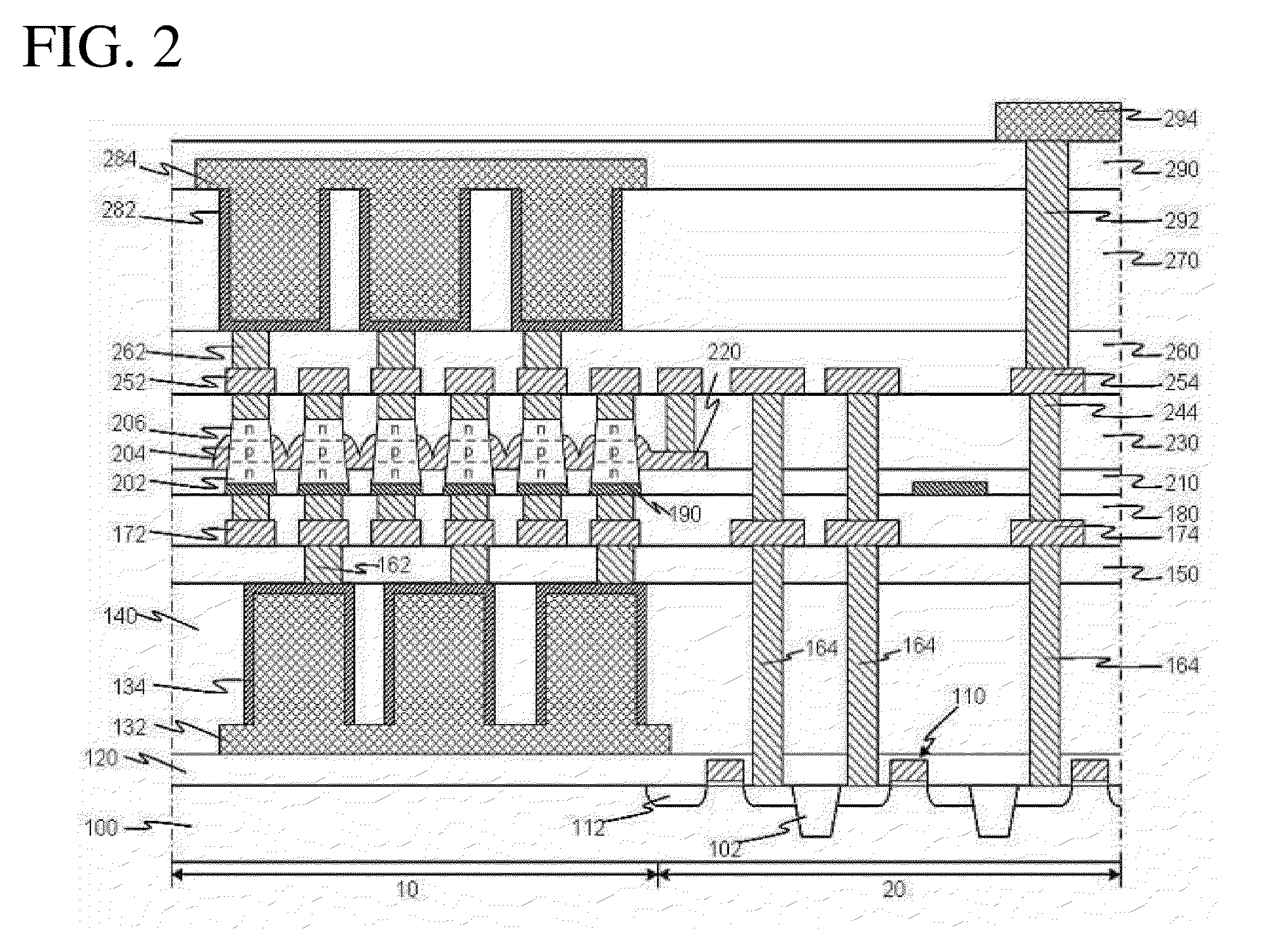

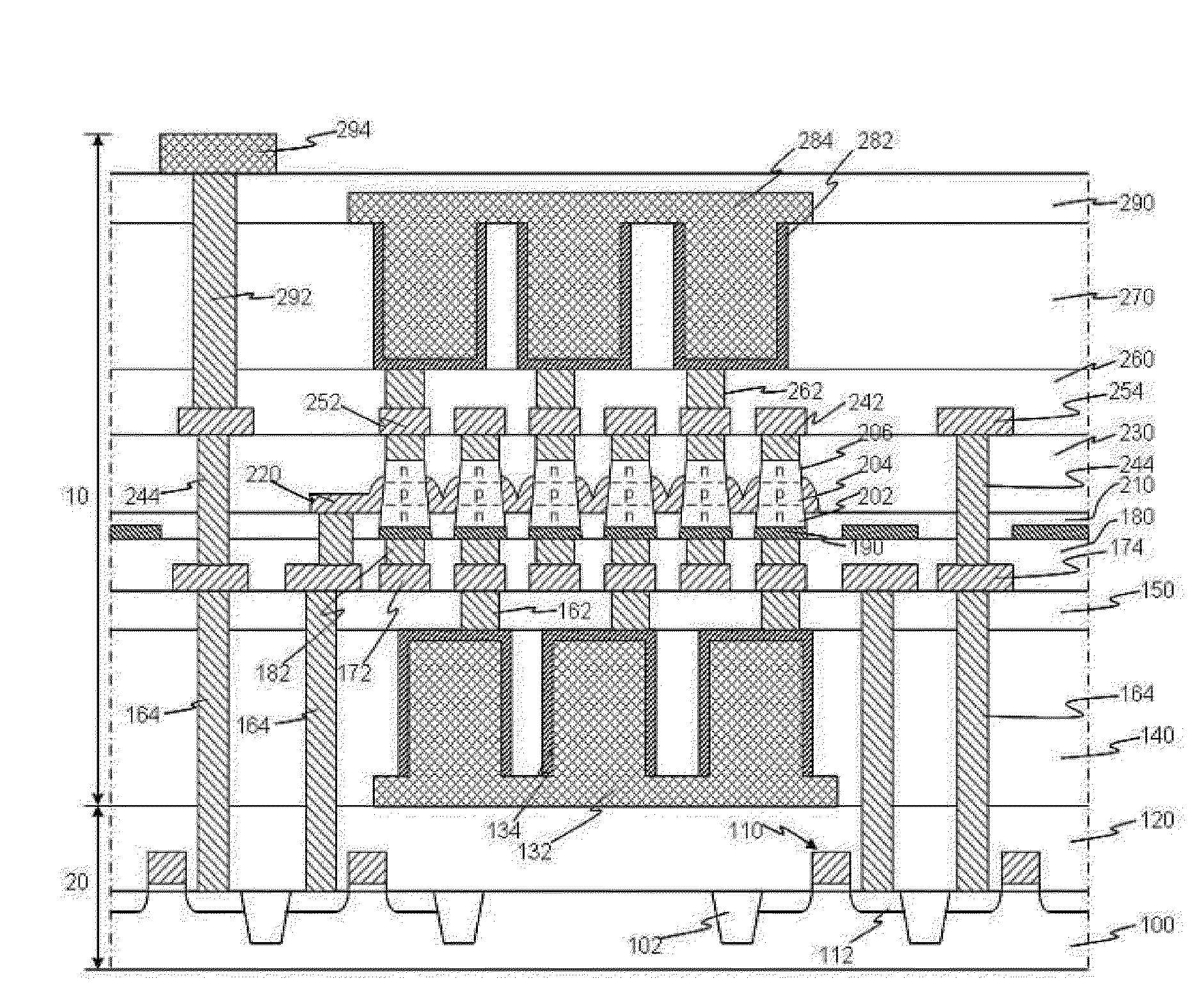

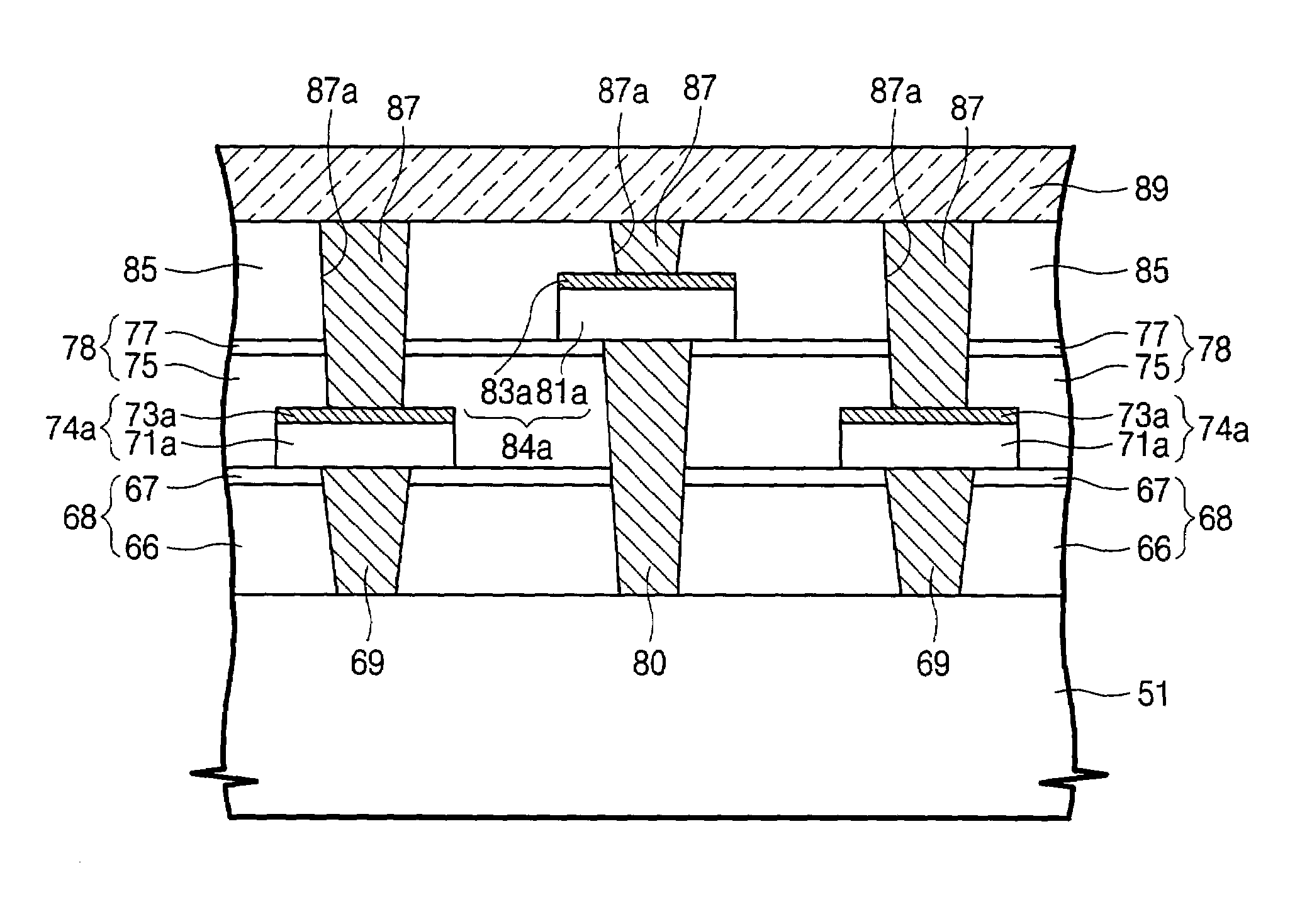

Phase changeable memory devices having multi-level data storage elements and methods of fabricating the same

ActiveUS7037762B2Semiconductor/solid-state device detailsSolid-state devicesPhase-change memoryDielectric layer

A phase changeable memory device includes a lower interlayer dielectric layer on a semiconductor substrate. A plurality of first phase changeable data storage elements is disposed on the lower interlayer dielectric layer. A middle interlayer dielectric layer covers the first phase changeable data storage elements and the lower interlayer dielectric layer. A plurality of second phase changeable data storage elements is disposed on the middle interlayer dielectric layer. The first and second phase changeable data storage elements are arrayed in rows and columns such that respective first phase changeable data storage elements are disposed between respective adjacent second phase changeable data storage elements in the rows and columns. A plate electrode overlies the first and second phase changeable data storage elements and is electrically connected to the first and second phase changeable data storage elements. Related fabrication methods are also disclosed.

Owner:SAMSUNG ELECTRONICS CO LTD

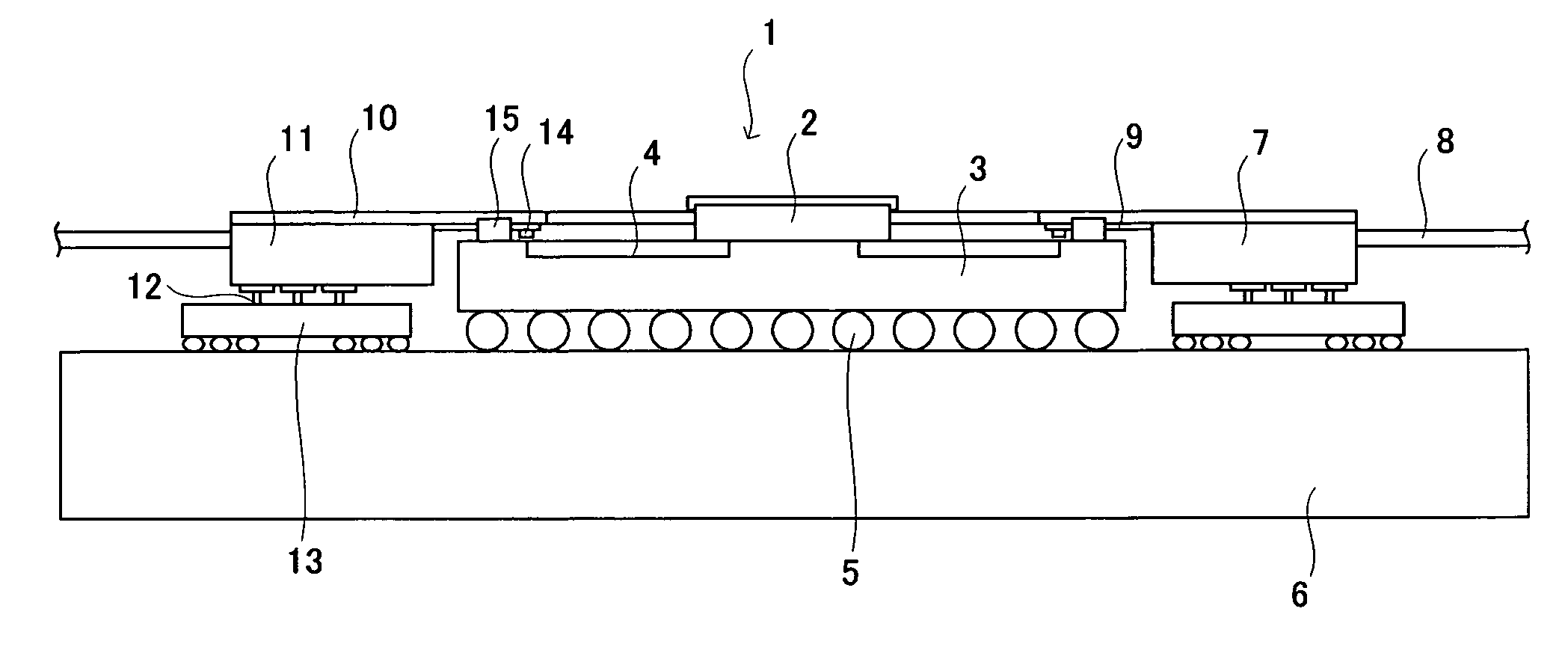

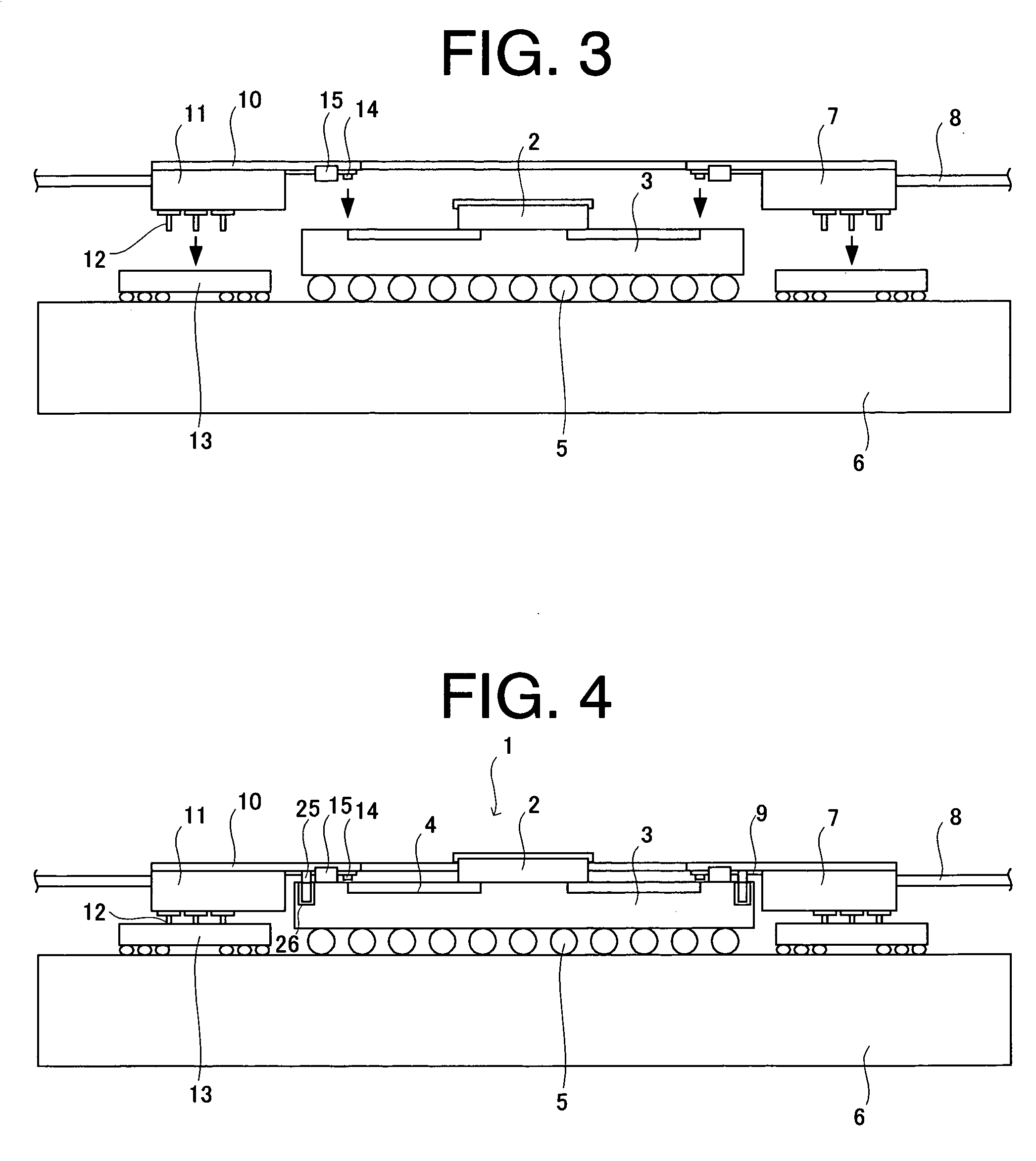

LSI package with interface module, transmission line package, and ribbon optical transmission line

InactiveUS20060050493A1Final product manufactureHigh frequency circuit adaptationsInterposerElectrostatic coupling

According to an aspect of the present invention, there is provided an LSI package with an interface module including: an interposer, on which a signal processing LSI is mounted, having a mounting board connecting electrical terminal; and an interface module having a transmission line to wire a high-speed signal to the exterior and a socket connecting electrical terminal corresponding to a mounting board connecting socket, in which the interposer and the interface module have at least either loop electrodes or plate electrodes, respectively, and the interposer and the interface module are electrically connected by inductive coupling, electrostatic coupling, or combined coupling of these two couplings by at least either the loop electrodes or the plate electrodes.

Owner:KK TOSHIBA

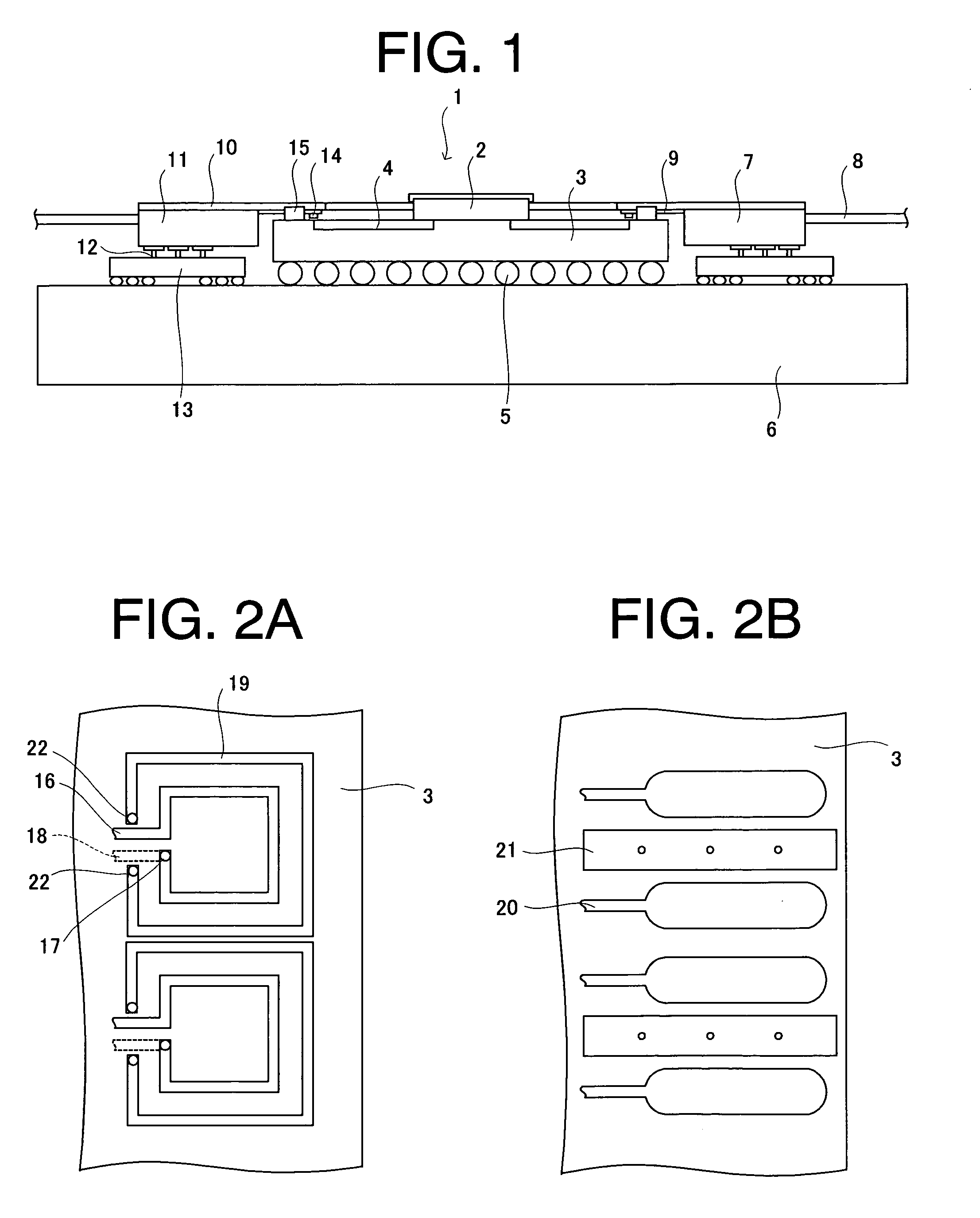

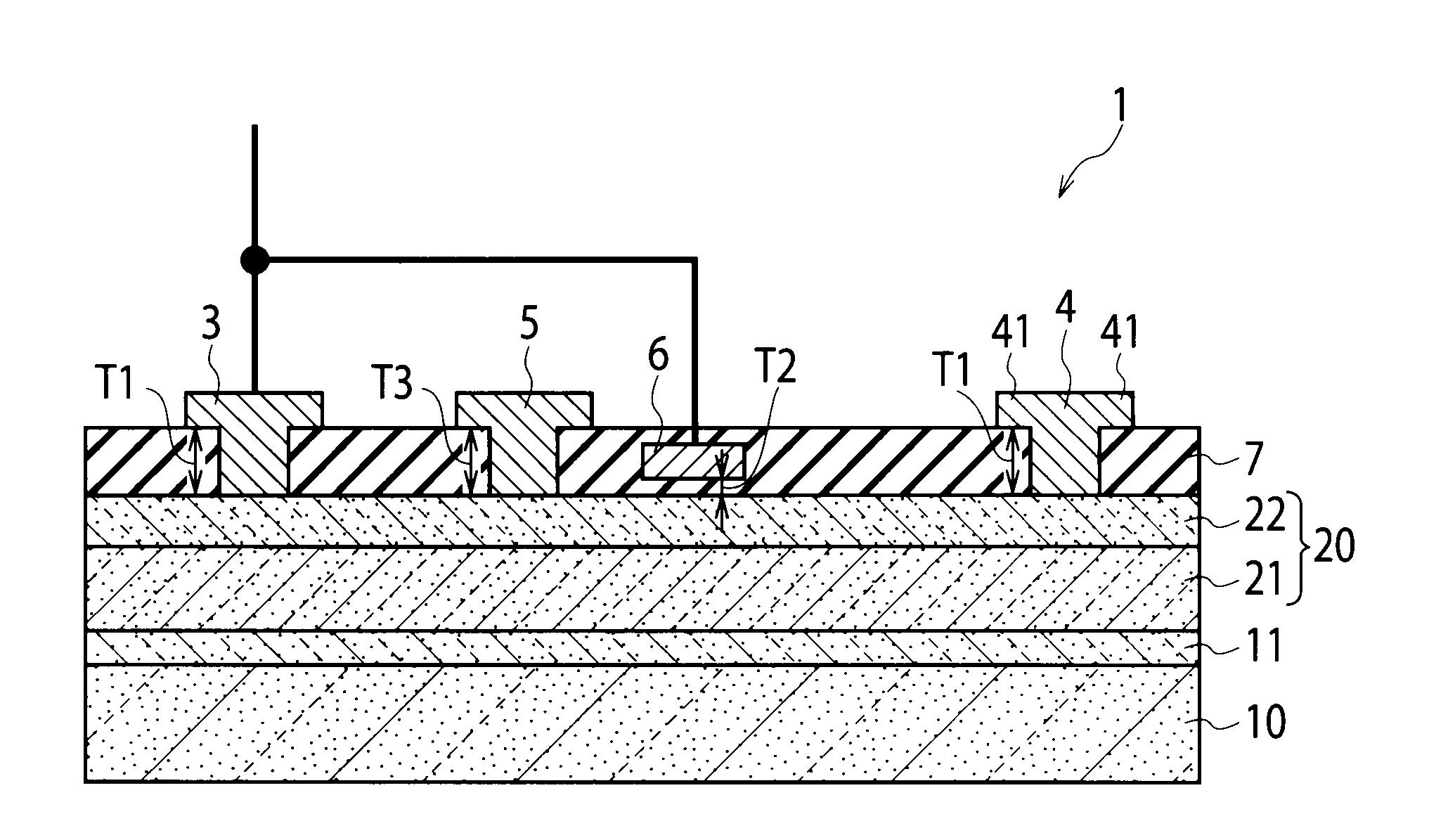

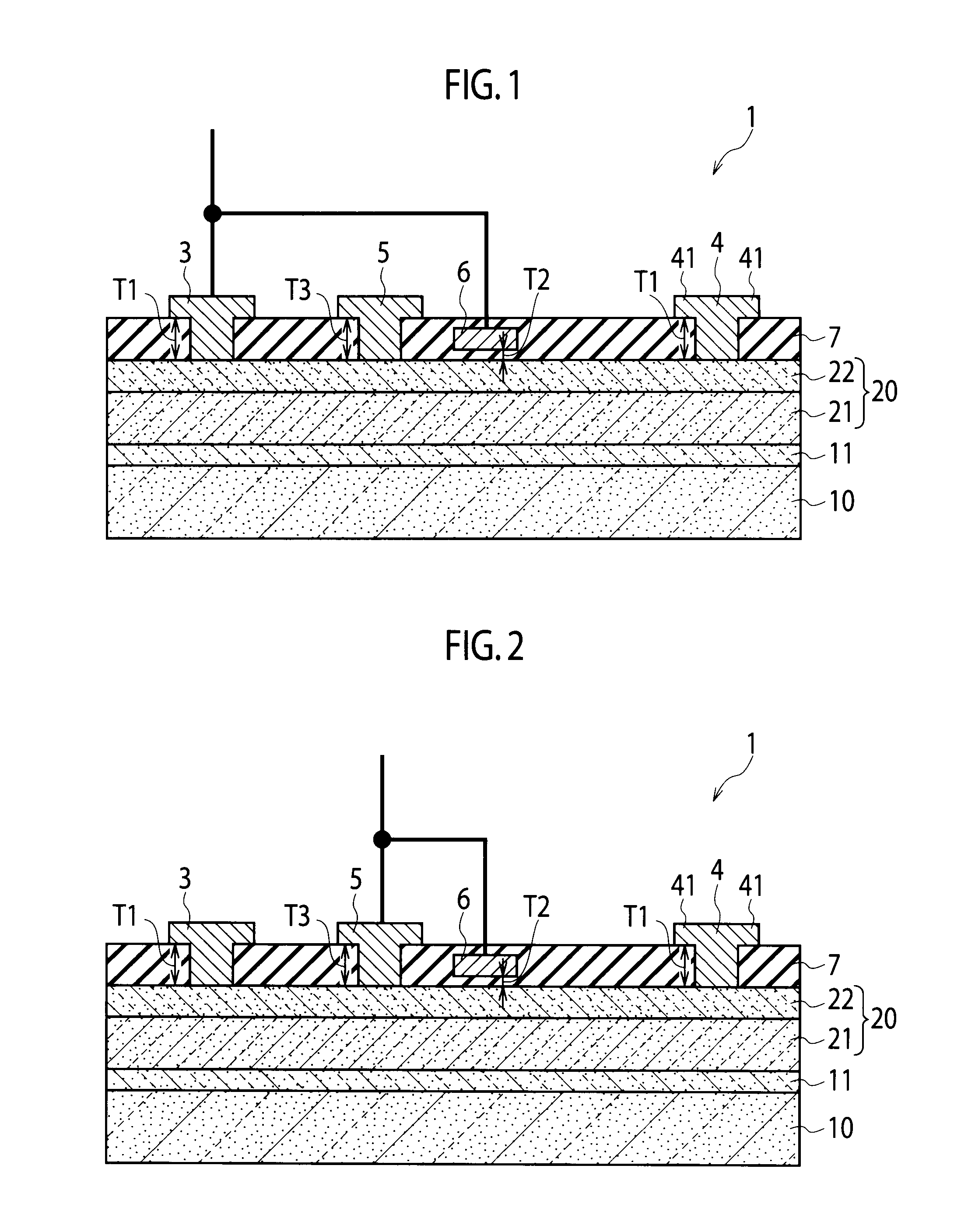

Piezoelectric acoustic transducer

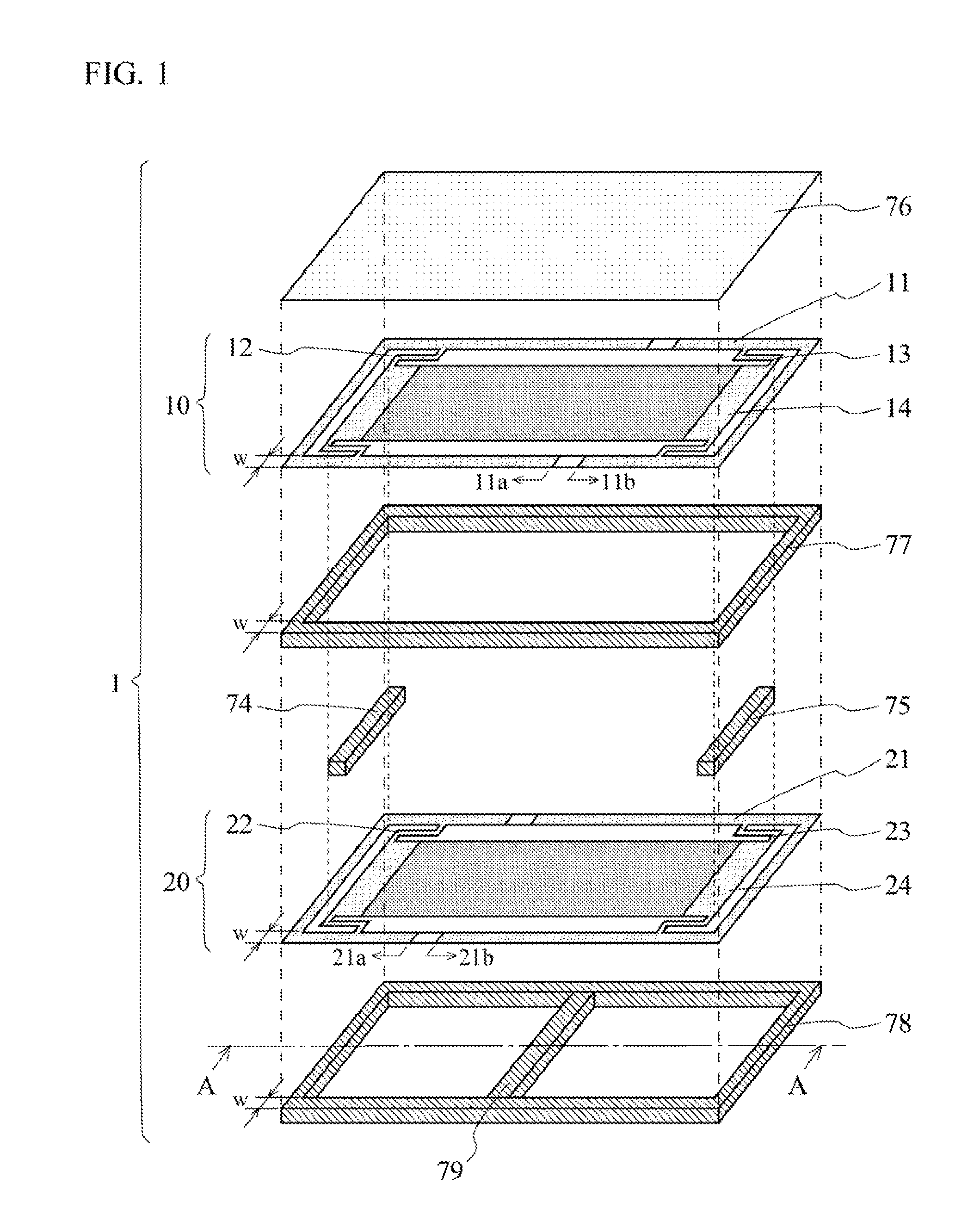

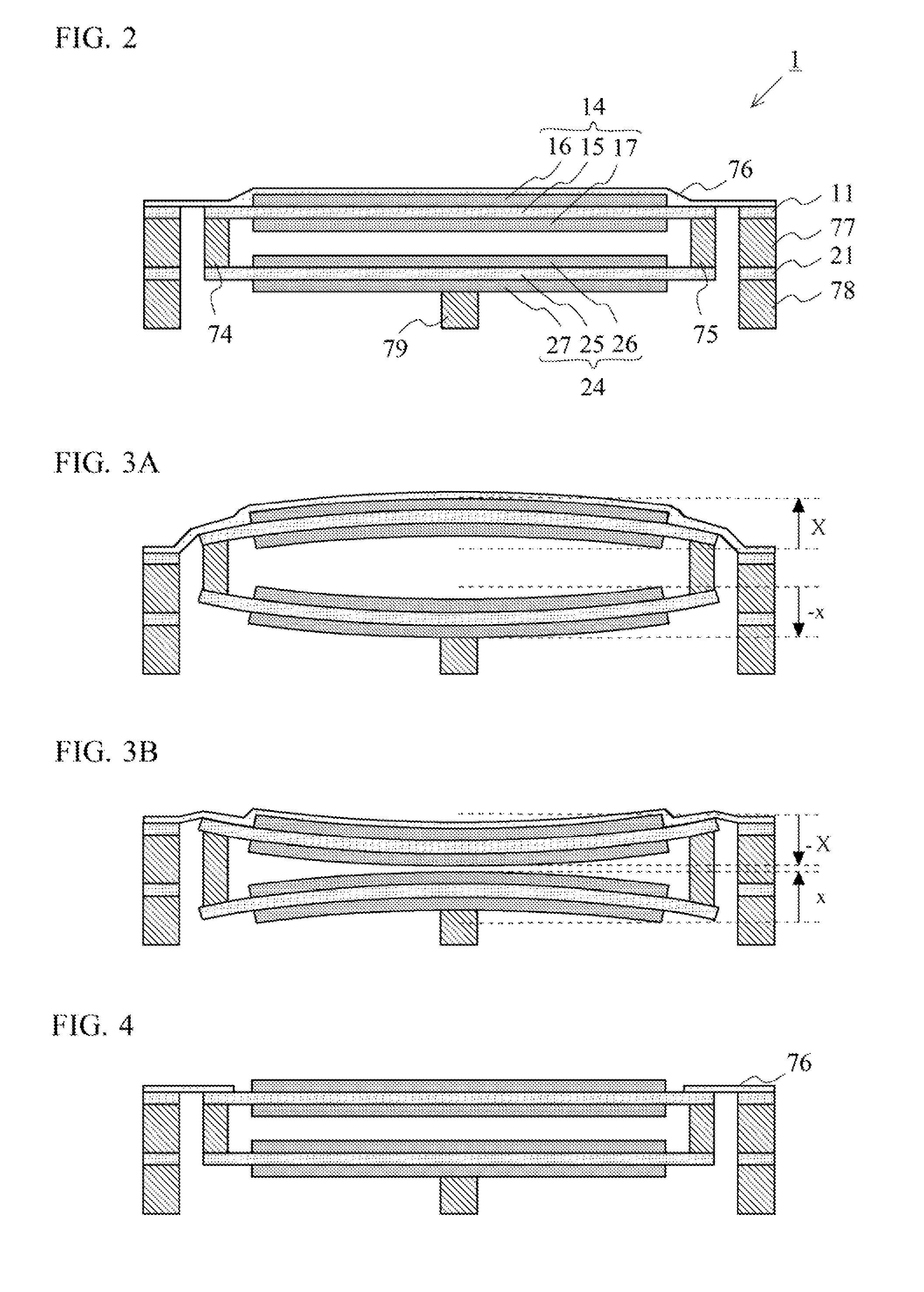

ActiveUS20120057730A1Large displacementImprove voltage sensitivityTransducer detailsPiezoelectric/electrostrictive transducersTransducerEngineering

A piezoelectric acoustic transducer (1) of the present invention includes a lower frame (78), a lower speaker circuit (20), an upper frame (77), an upper speaker circuit (10), and a surround (76). The upper speaker circuit (10) has a piezoelectric diaphragm (14) in which piezoelectric elements (16, 17), each having a structure that flat plate electrodes are disposed on top and bottom of a piezoelectric member, are mounted on top and bottom surfaces of a board (15). The lower speaker circuit (20) has a piezoelectric diaphragm (24) in which piezoelectric elements (26, 27), each having the same structure, are mounted on a top surface and a bottom surface of a board (25). The piezoelectric diaphragms (14, 24) are coupled to each other via coupling members (74, 75). At an application of a voltage, the piezoelectric diaphragms (14, 24) are caused to curve in directions opposite to each other. Having this structure, the piezoelectric acoustic transducer (1) has an increased displacement in a thickness direction thereof, and thereby achieving high quality sound with space-saving.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

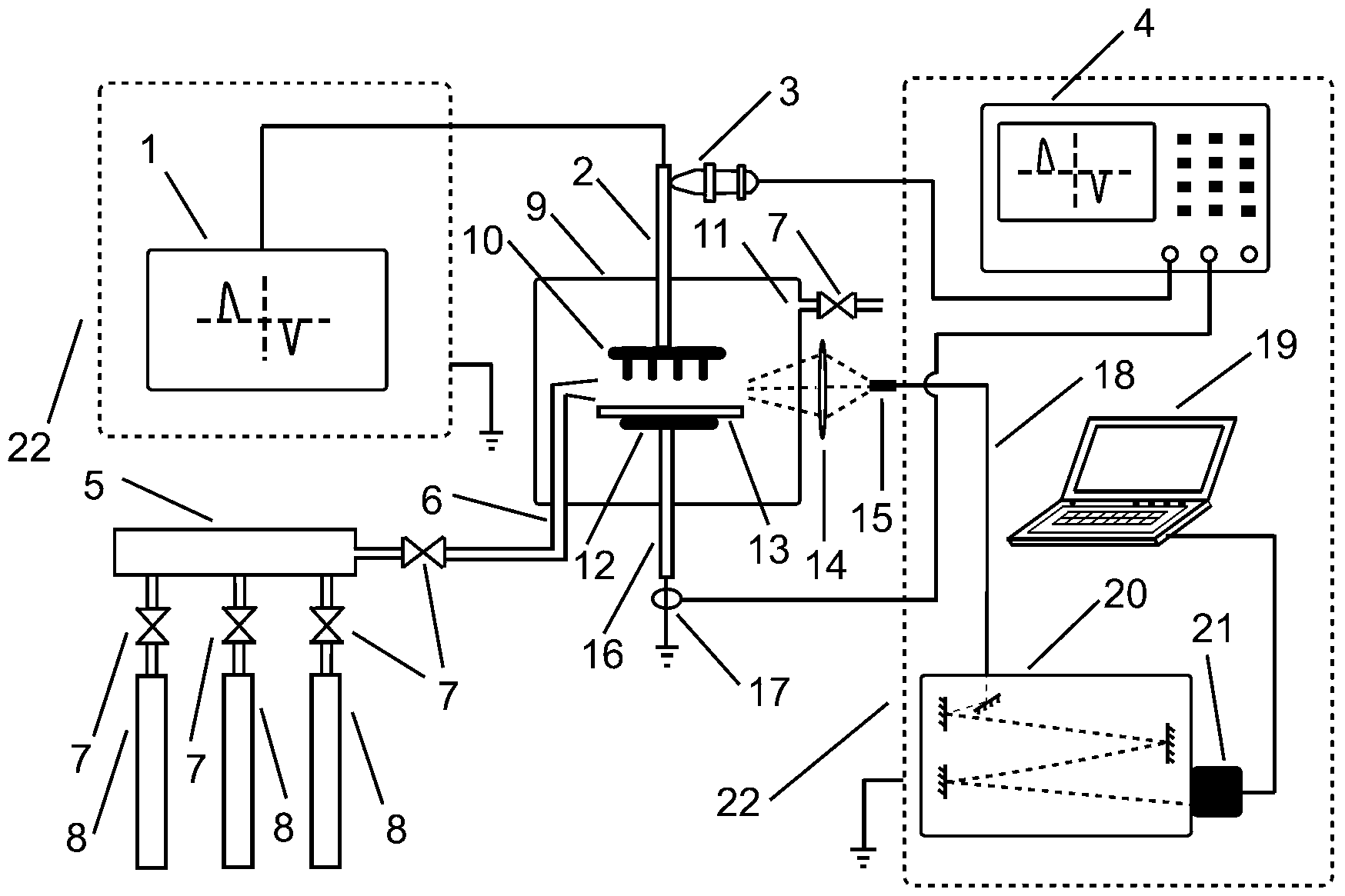

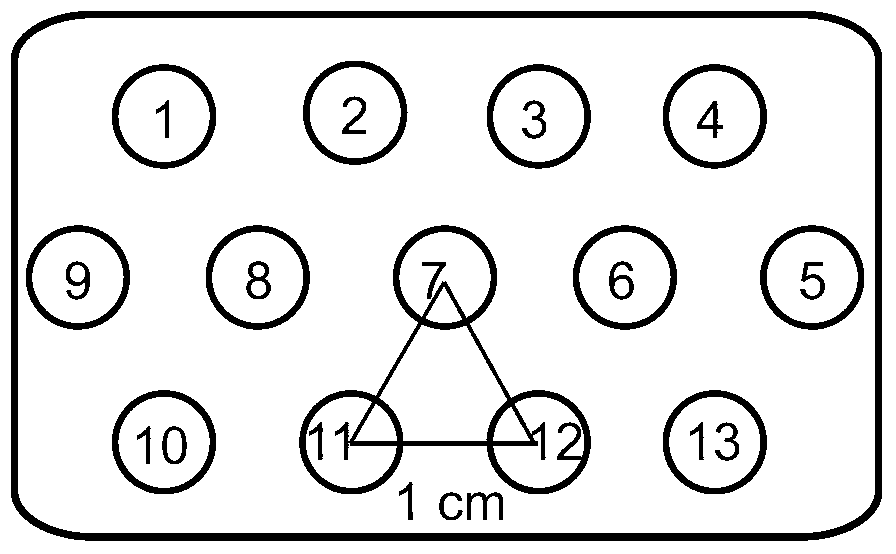

Experimental apparatus for acquiring large-area uniform discharge plasmas

InactiveCN103245655AIncrease electron densityImprove energy utilizationAnalysis by thermal excitationPlasma techniqueDischarge measurementsElectron density

The invention relates to an experimental apparatus for acquiring large-area uniform discharge plasmas, which belongs to the technical field of plasmas. The experimental apparatus comprises a bipolar nanosecond pulse power supply, a reactor, multi-needle-to-plate electrodes, a gas distribution system, a spectral measurement system and a discharge measurement system, wherein the bipolar nanosecond pulse power supply drives dielectric barrier discharge of air and other gas mixtures among the multi-needle-to-plate electrodes in the reactor, and the gas mixtures are input to the reactor through the gas distribution system; the spectral measurement system collects photonic information of plasma discharge in real time and inputs the photonic information to a computer for spectral analysis; and the discharge measurement system collects discharge voltage and current of the high-voltage nanosecond pulse power supply in real time, and the discharge voltage and current are displayed through a digital oscilloscope. By virtue of the bipolar nanosecond narrow-pulse power supply, the large-area discharge plasmas are generated without a magnetic field; and the generated plasmas are uniform, diffusive, high in electron density, high in energy utilization ratio, low in energy consumption and easy to control in a discharge process.

Owner:DALIAN UNIV OF TECH

Air cleaner

Owner:HELEN OF TROY LTD

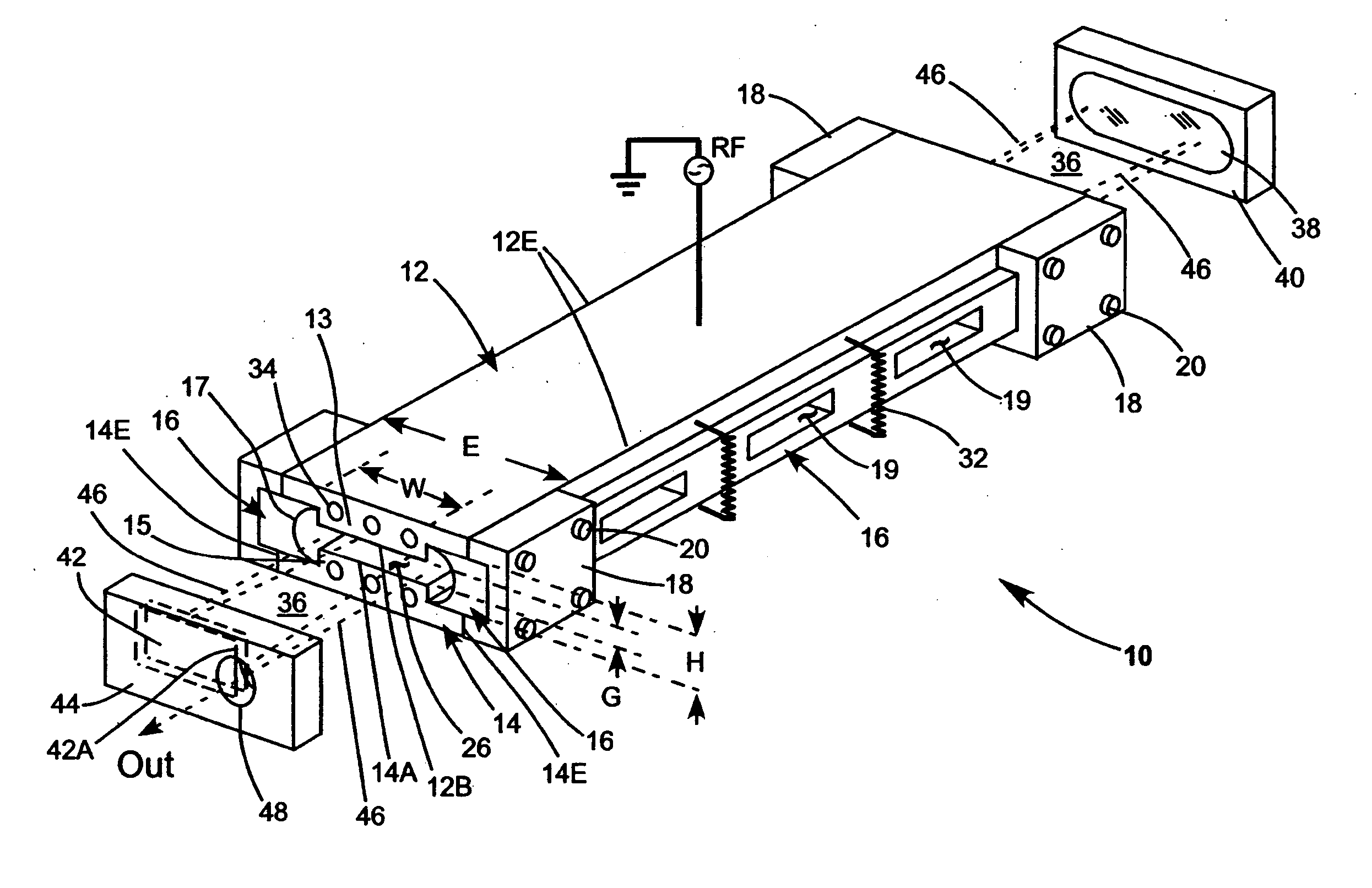

Dielectric coupled CO2 slab laser

InactiveUS20050175054A1Extension of timeDecreases difference in impedanceActive medium materialLaser cooling arrangementsCapacitanceDielectric

An slab CO2 laser includes spaced-apart elongated slab electrodes. A lasing gas fills a discharge gap between the electrodes. An RF power supply is connected across the electrodes and sustains an electrical discharge in the lasing gas in the discharge gap. Either one or two ceramic inserts occupy a portion of width of the electrodes and in contact with the electrodes. A discharge gap is formed between the portions of the width of the electrodes not occupied by the insert or inserts. Provision of the ceramic insert or inserts increases the resistance-capacitance (RC) time constant of the electrode impedance by increasing the capacitive component of the time constant. This hinders the formation of arcs in the discharge, which, in turn enables the inventive laser to operate with higher excitation power or higher lasing-gas pressure than would be possible without the dielectric insert. The ceramic insert also decreases the difference in impedance of the electrodes with and without a discharge. This leads to a better-behaved discharge, and a discharge that is easier to light.

Owner:COHERENT INC

Compound semiconductor device having insulation film with different film thicknesses beneath electrodes

A compound semiconductor device includes a group-III nitride semiconductor layer; an insulation film located on the group-III nitride semiconductor layer; a drain electrode located in a position which is a first distance away from an upper surface of the group-III nitride semiconductor layer; a source electrode located in a position which is the first distance away from the upper surface of the group-III nitride semiconductor layer; a gate electrode located between the drain electrode and the source electrode; and a field plate electrode located between the drain electrode and the gate electrode at a position which is a second distance away from the upper surface of the group-III nitride semiconductor layer, the second distance is shorter than the first distance.

Owner:SANKEN ELECTRIC CO LTD

Semiconductor device

ActiveUS20100230717A1Solid-state devicesSemiconductor devicesElectrical conductorSemiconductor package

A semiconductor device includes: a first semiconductor layer of non-doped AlXGa1-XN (0≦X<1); a second semiconductor layer of non-doped or n-type AlYGa1-YN (0<Y≦1, X<Y) on the first semiconductor layer; a first electrode on the second semiconductor layer; a second electrode on the second semiconductor layer that is separated from the first electrode and electrically connected to the second semiconductor layer; a first insulating film covering the first and second electrodes; a first field plate electrode electrically connected to the first electrode and covered by a second insulating film; and a second field plate electrode on the second insulating film, wherein a length of at least one of the first and second field plate electrodes in a first direction from the first electrode toward the second electrode changes periodically in a second direction intersecting the first direction.

Owner:KK TOSHIBA

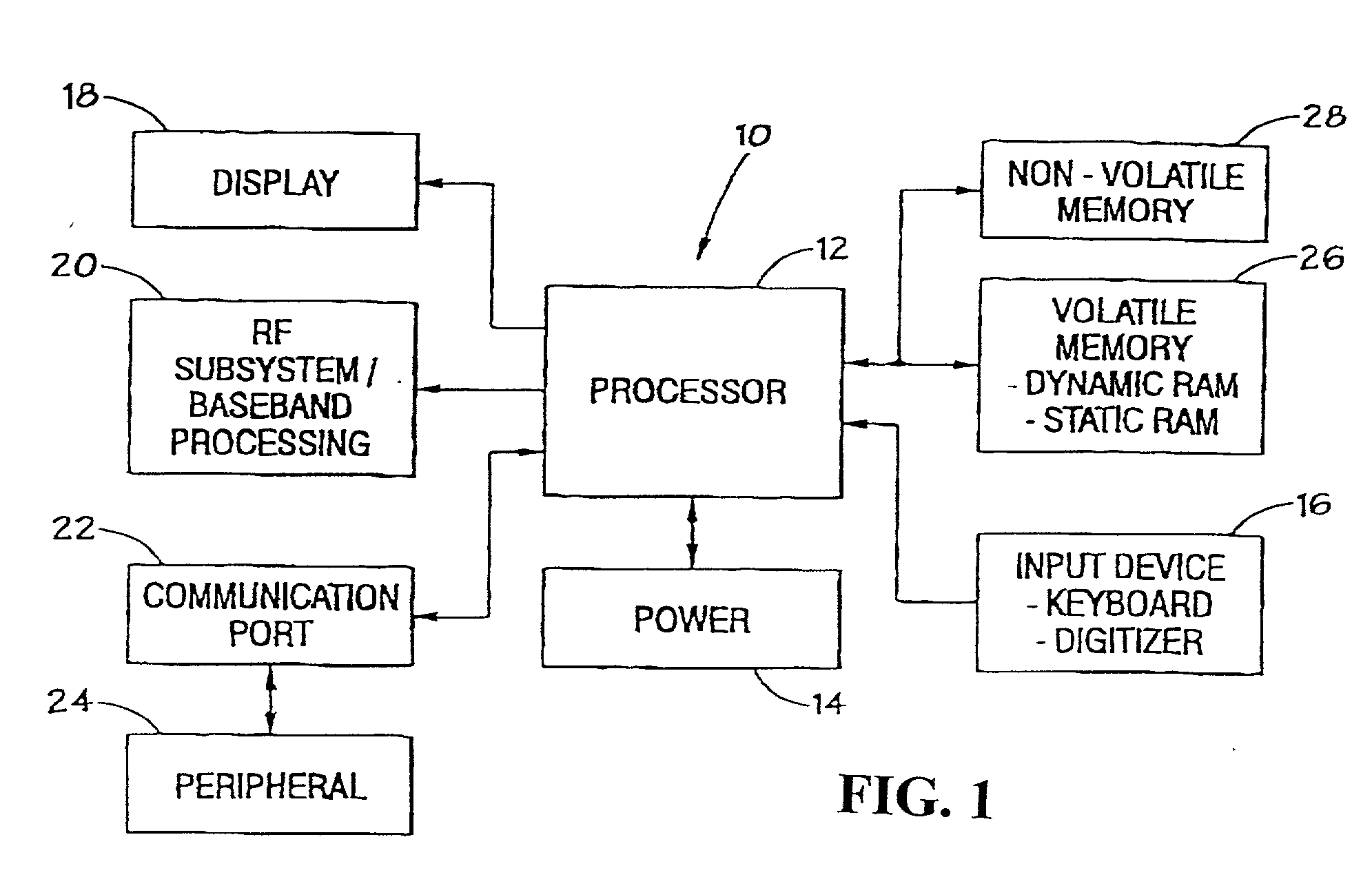

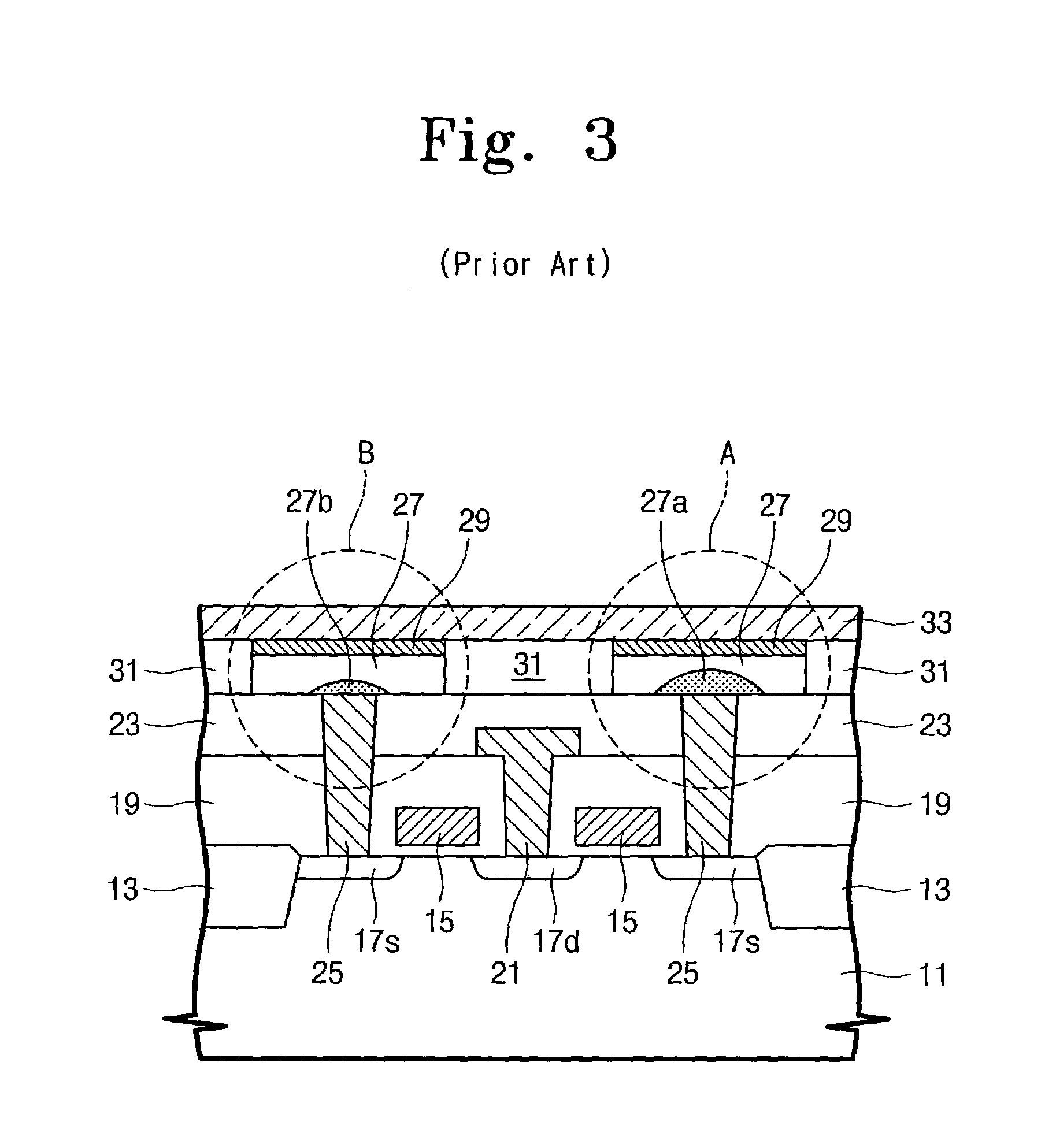

Integrated circuit memory devices having memory cells therein that utilize phase-change materials to support non-volatile data retention

InactiveUS7038261B2Efficient executionAvoid pollutionTransistorSolid-state devicesPhase changePhase-change material

An integrated circuit memory device includes a semiconductor substrate and a first electrically insulating layer that extends on the semiconductor substrate and has a first contact hole extending therethrough. An electrically conductive plug is provided in the first contact hole. A phase-change material layer pattern is provided as a non-volatile storage medium. The phase-change material layer pattern has a bottom surface that is electrically connected to the electrically conductive plug. A second electrically insulating layer is provided on the phase-change material layer pattern. The second electrically insulating layer has a second contact hole therein. This contact hole exposes a portion of an upper surface of the phase-change material layer pattern. To improve data writing efficiency, the area of the exposed portion of the upper surface of the phase-change material layer pattern is less than a maximum cross-sectional area of the electrically conductive plug. A plate electrode is also provided. This plate electrode is electrically connected to the phase-change material layer pattern. Barrier layers may also be provided directly on the plug and directly on the exposed portion of the upper surface.

Owner:SAMSUNG ELECTRONICS CO LTD

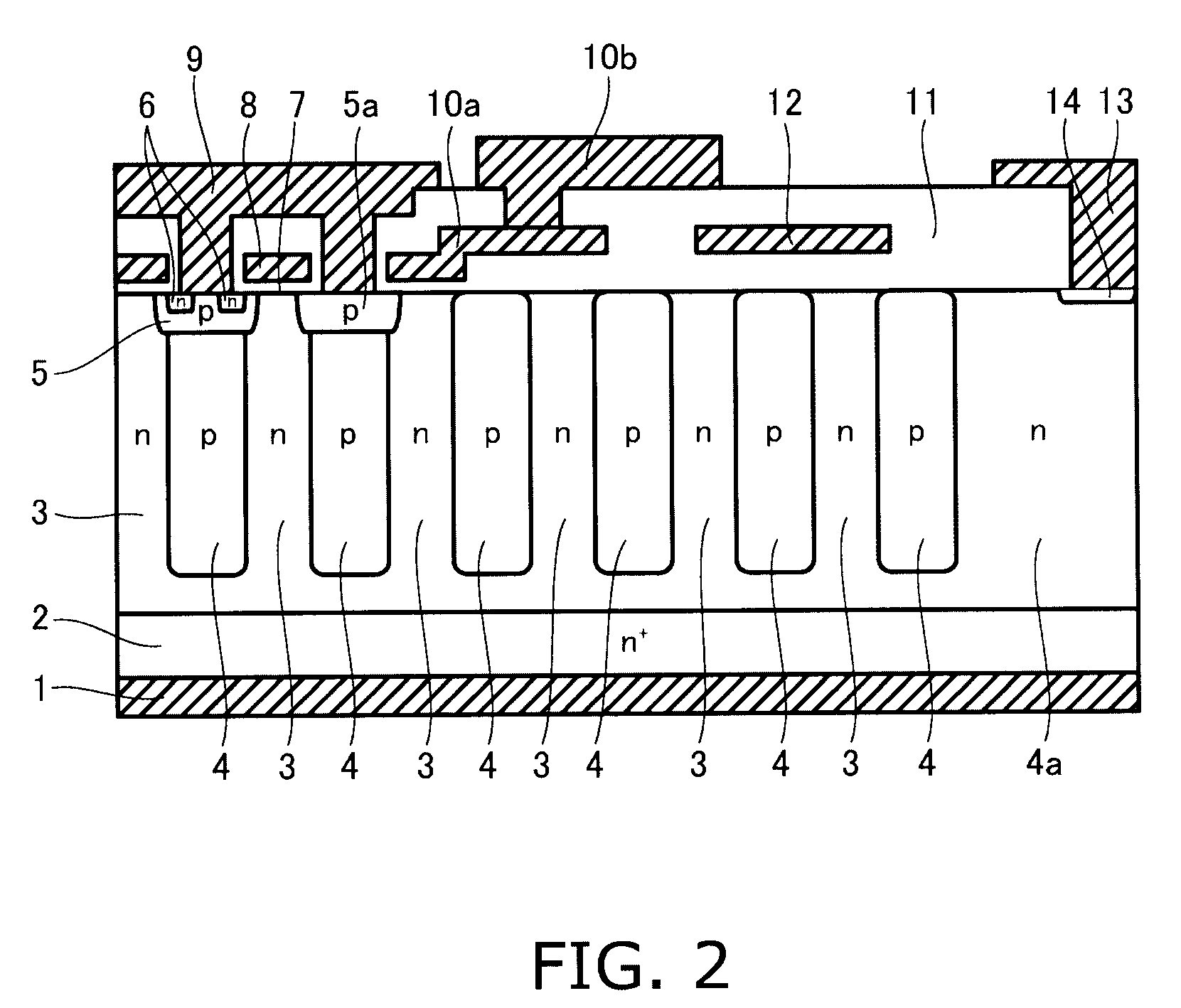

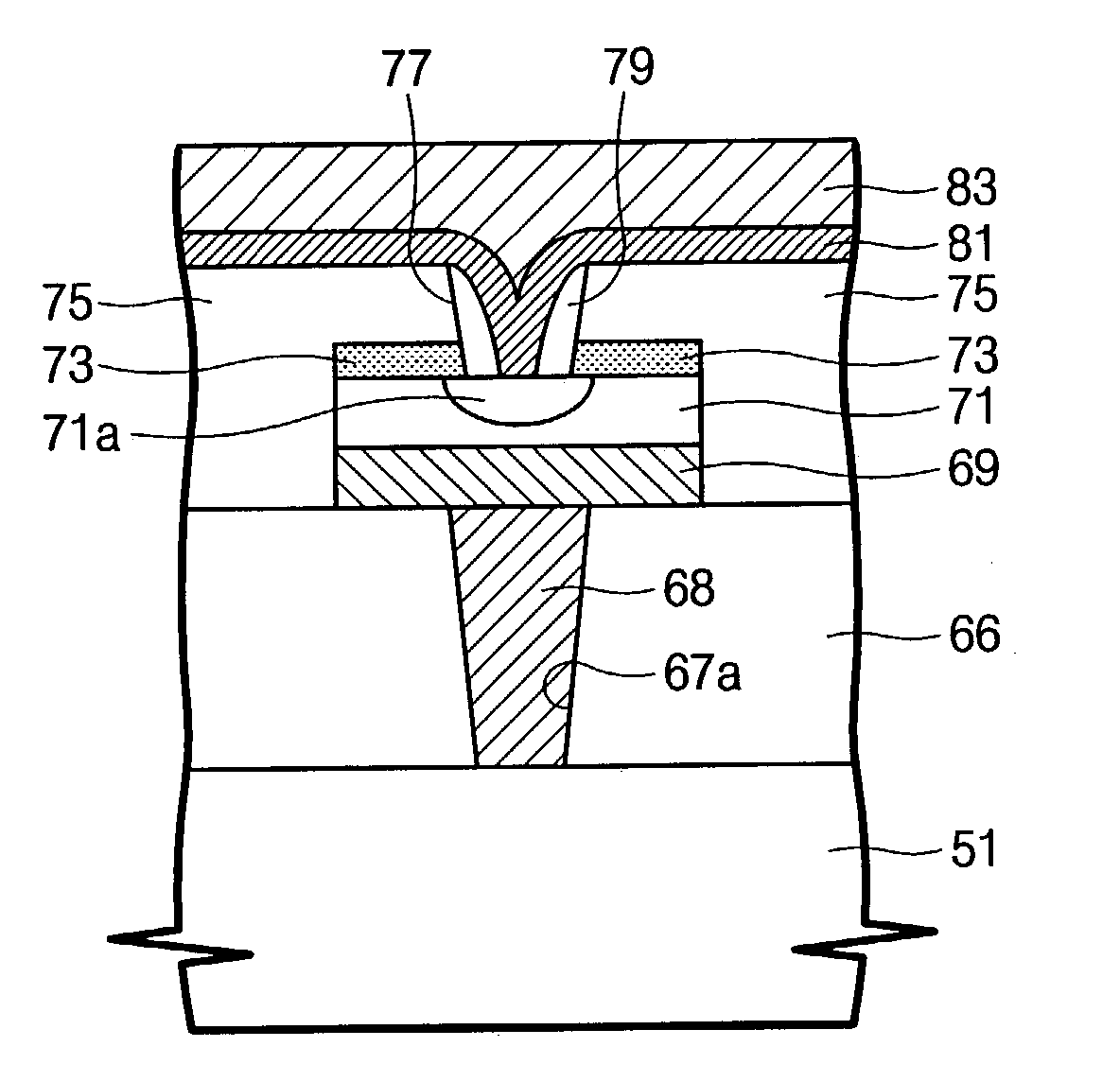

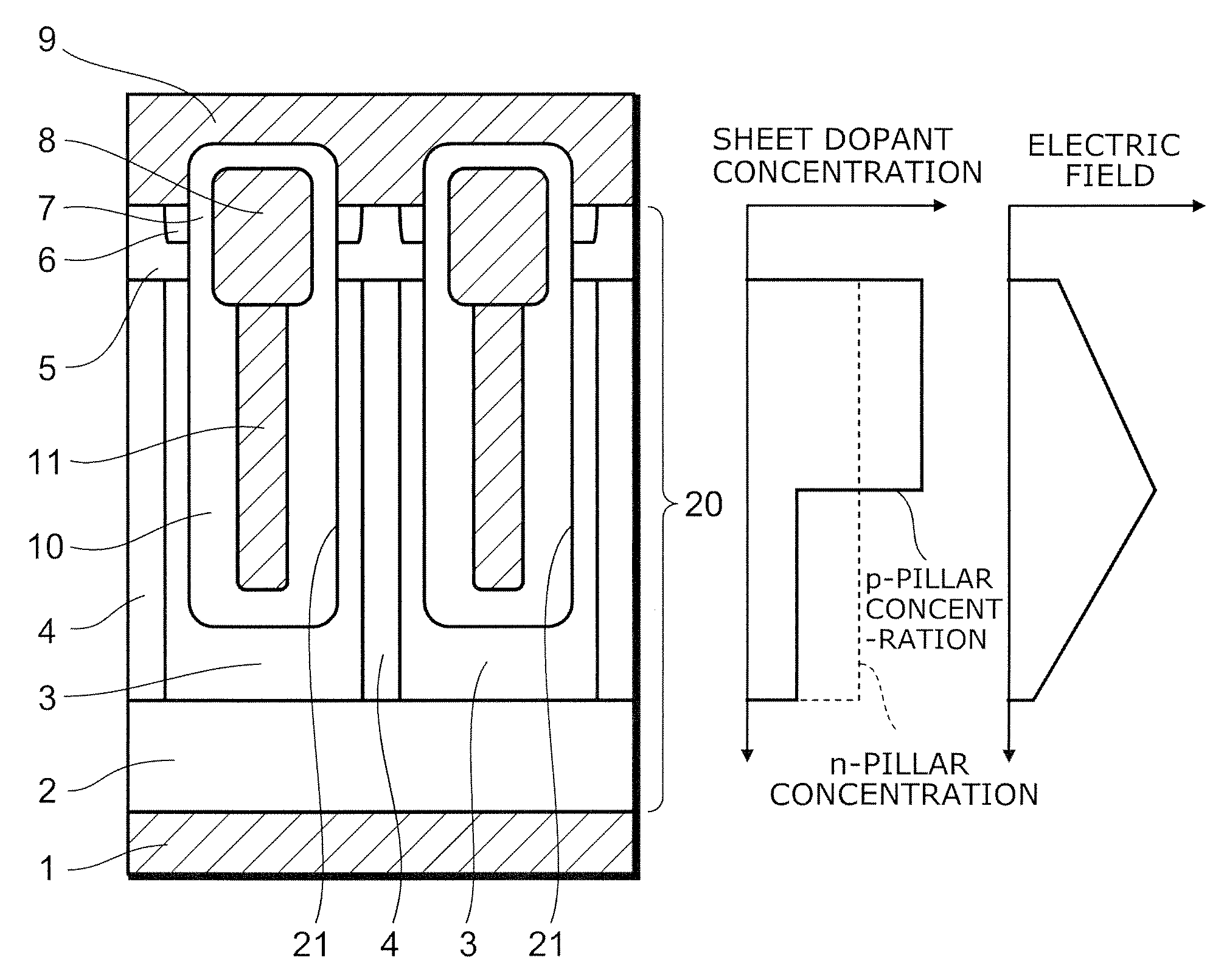

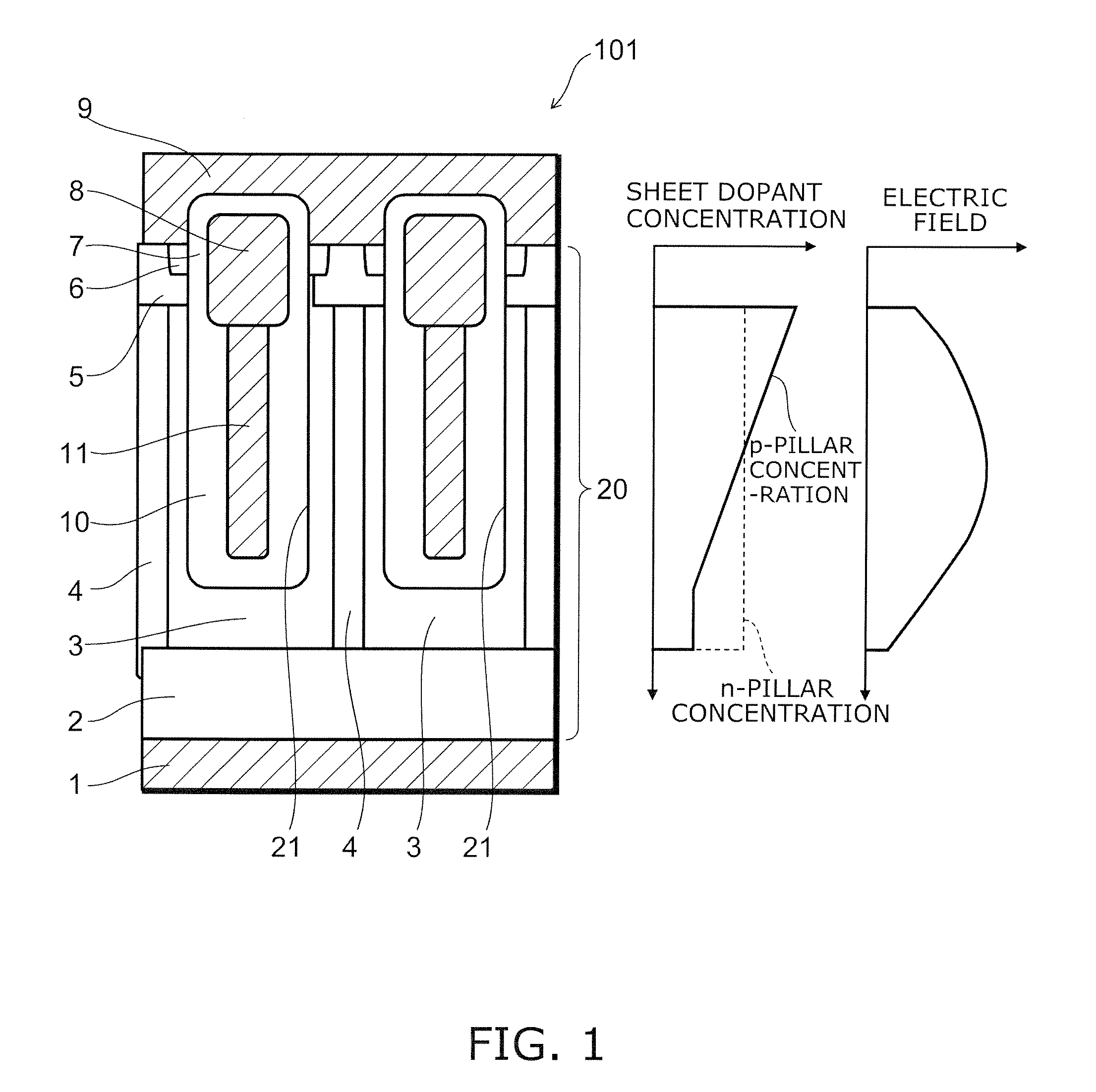

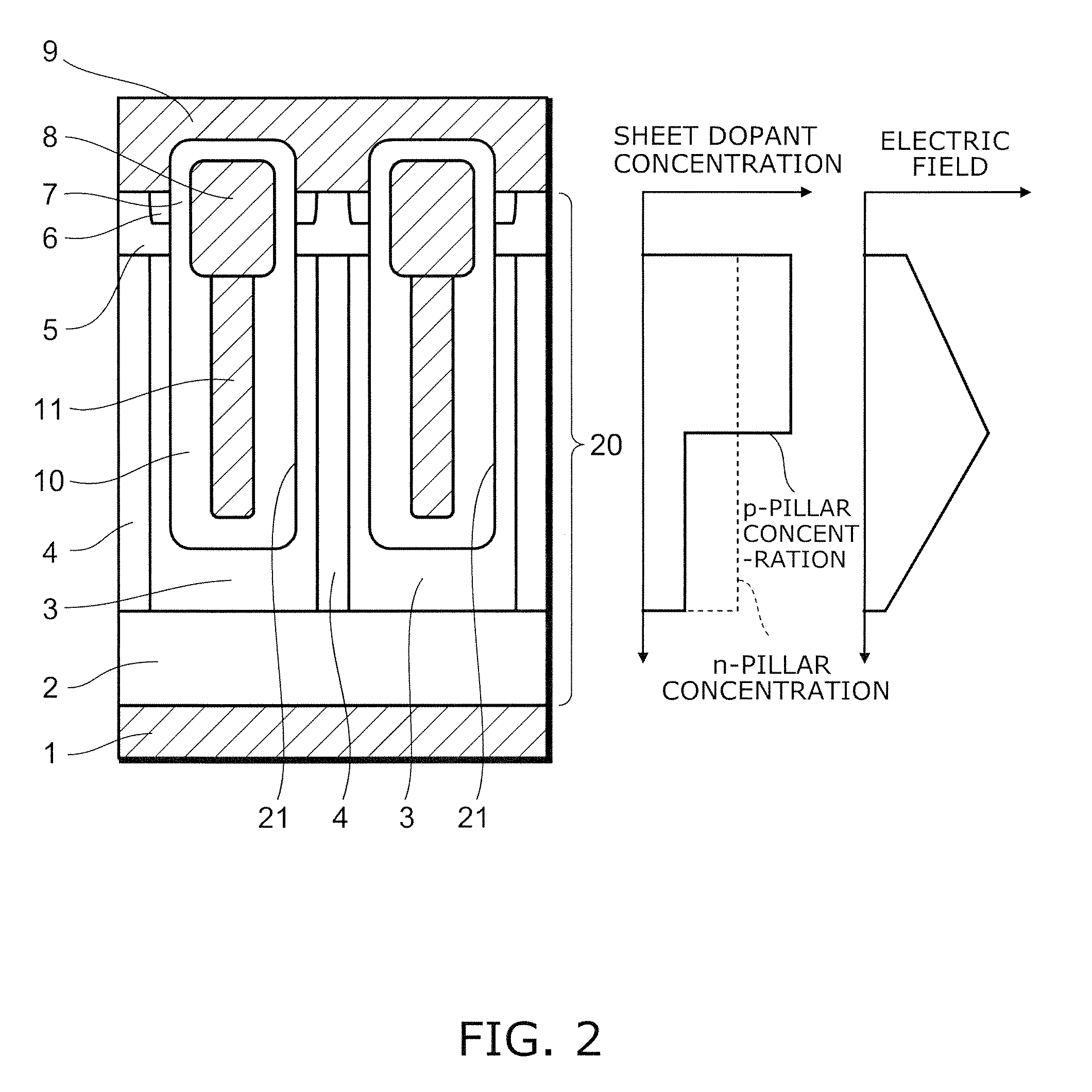

Power semiconductor device

InactiveUS7642597B2TransistorSemiconductor/solid-state device detailsPower semiconductor deviceDopant

A power semiconductor device includes a semiconductor substrate having a plurality of trenches formed in an upper surface thereof; a buried insulating film; a buried field plate electrode; a control electrode; a first main electrode provided on a lower side of the semiconductor substrate; and a second main electrode provided on an upper side of the semiconductor substrate. The semiconductor substrate includes: a first semiconductor; a second semiconductor layer of the first conductivity type and a third semiconductor layer of a second conductivity type; a fourth semiconductor layer; and a fifth semiconductor layer. The buried insulating film is thicker than a gate insulating film. At least one of the second semiconductor layer and the third semiconductor layer has a portion with its sheet dopant concentration varying along a depth direction of the semiconductor substrate.

Owner:KK TOSHIBA

Method for fabricating capacitor of semiconductor device

The invention relates to a method for fabricating a capacitor of a semiconductor device including the steps of: forming storage nodes for being connected with predetermined portions of a semiconductor substrate; forming a surface nitride layer by performing a surface nitrification process for preventing formation of an oxide layer on the surface of the storage nodes that deteriorates dielectric characteristic of the layer; forming an alumina (Al2O3) layer as a dielectric layer on the surface nitride layer in a perovskite structure with superior electrical and mechanical strength; and forming a plate electrode on the dielectric layer, thereby forming a capacitor with capacitance high enough to achieve high integration of the semiconductor device.

Owner:INTELLECTUAL DISCOVERY CO LTD

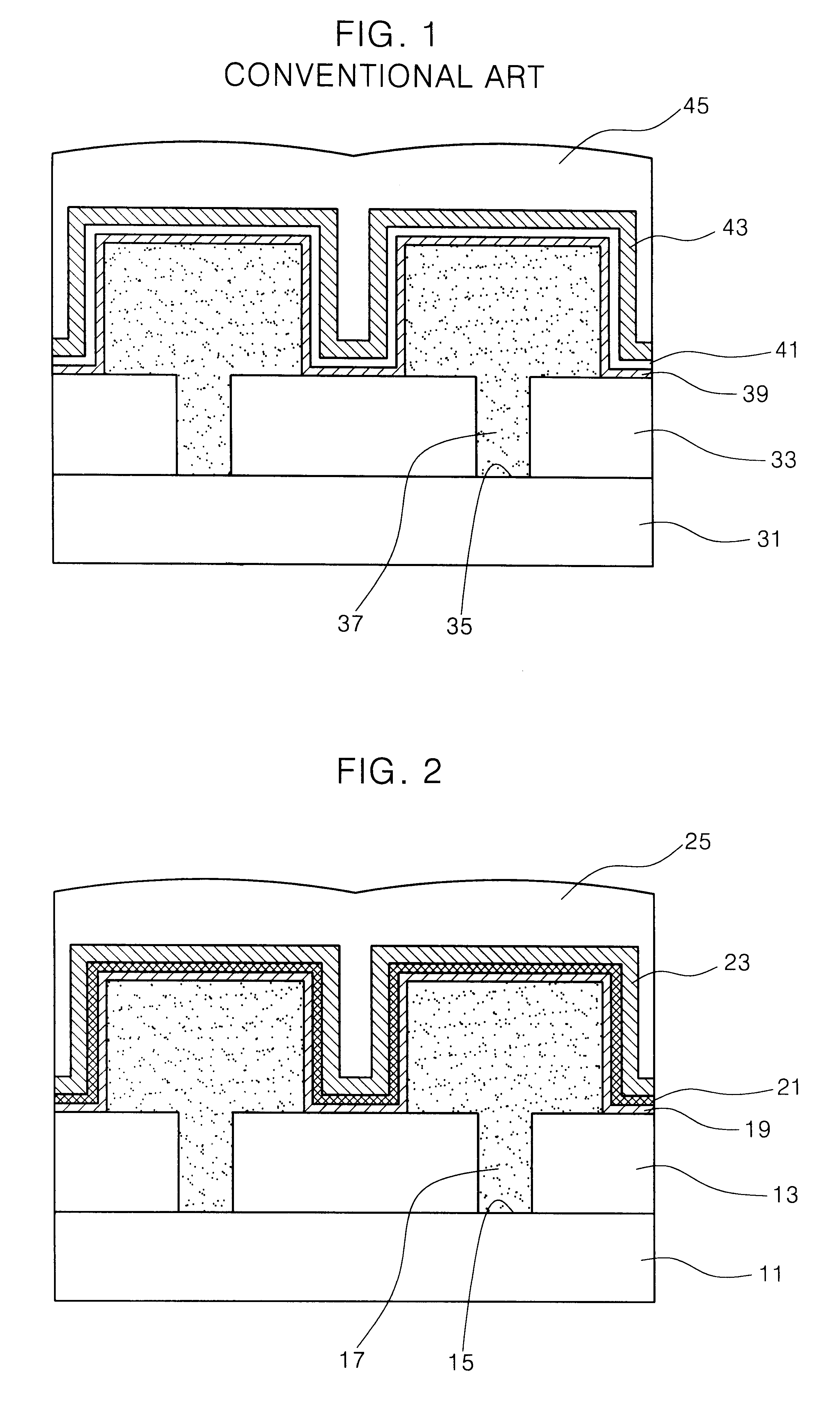

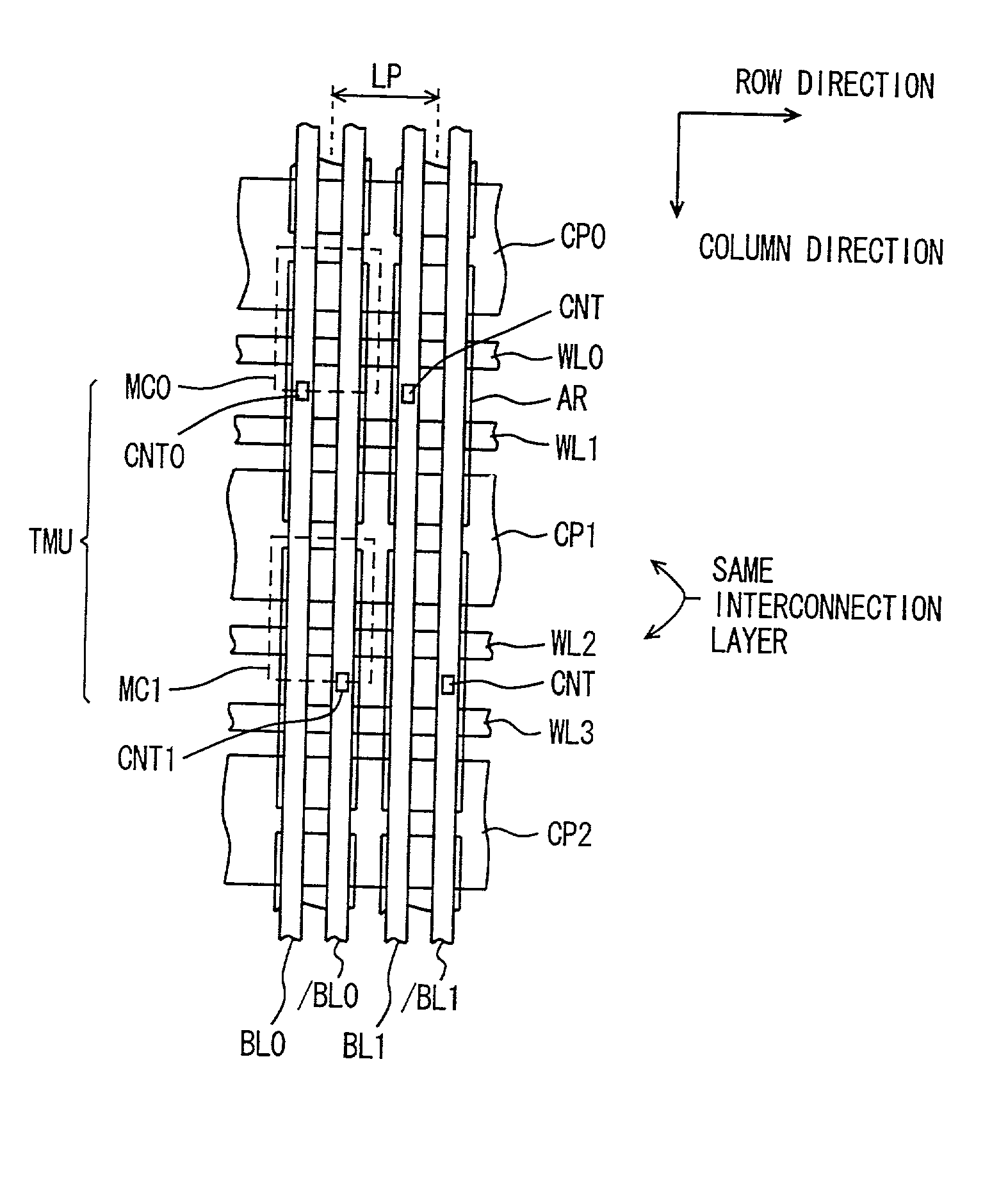

Semiconductor memory device

InactiveUS20020172070A1Reduce step heightReduce manufacturing stepsTransistorSolid-state devicesCapacitanceEngineering

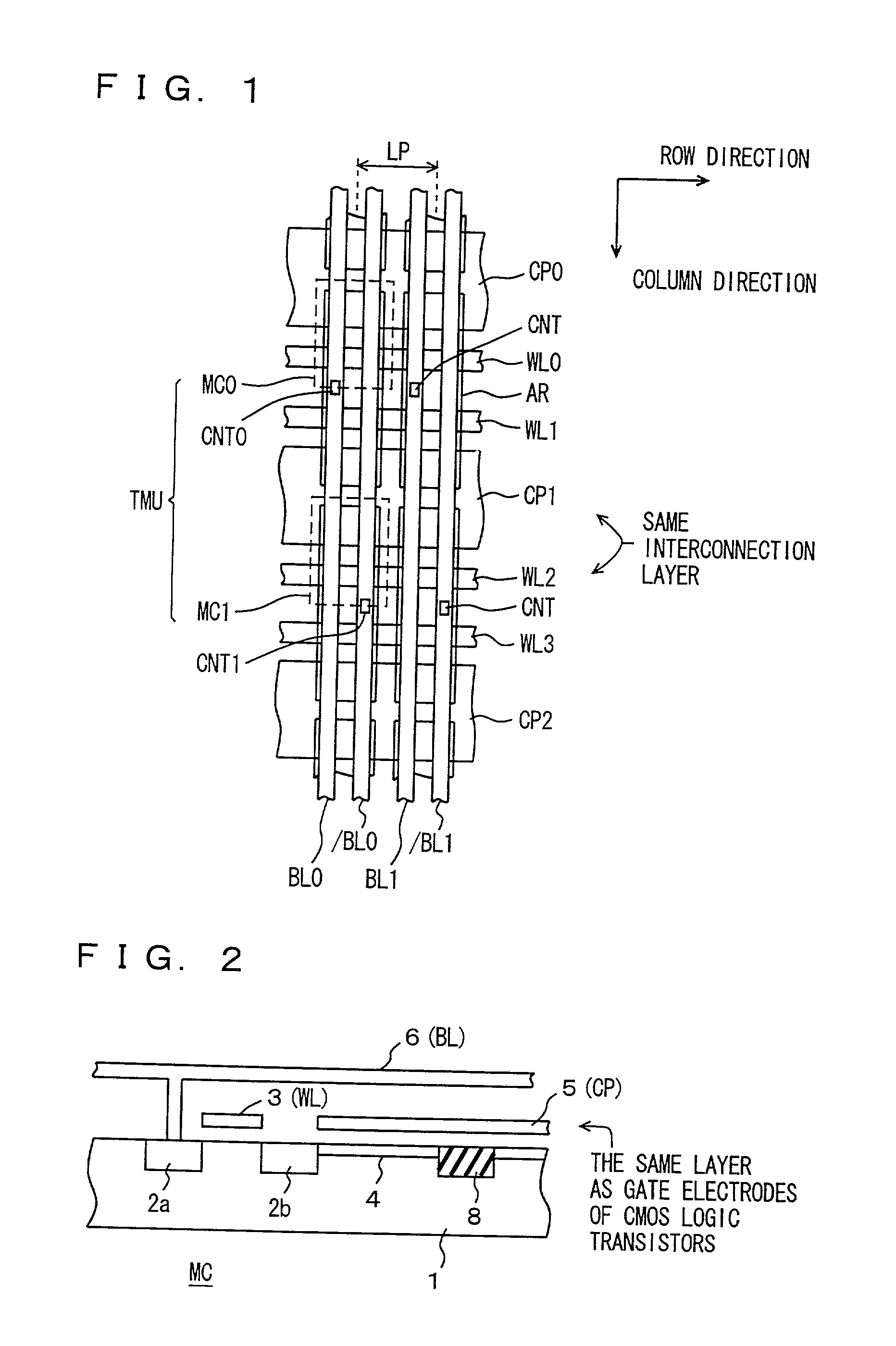

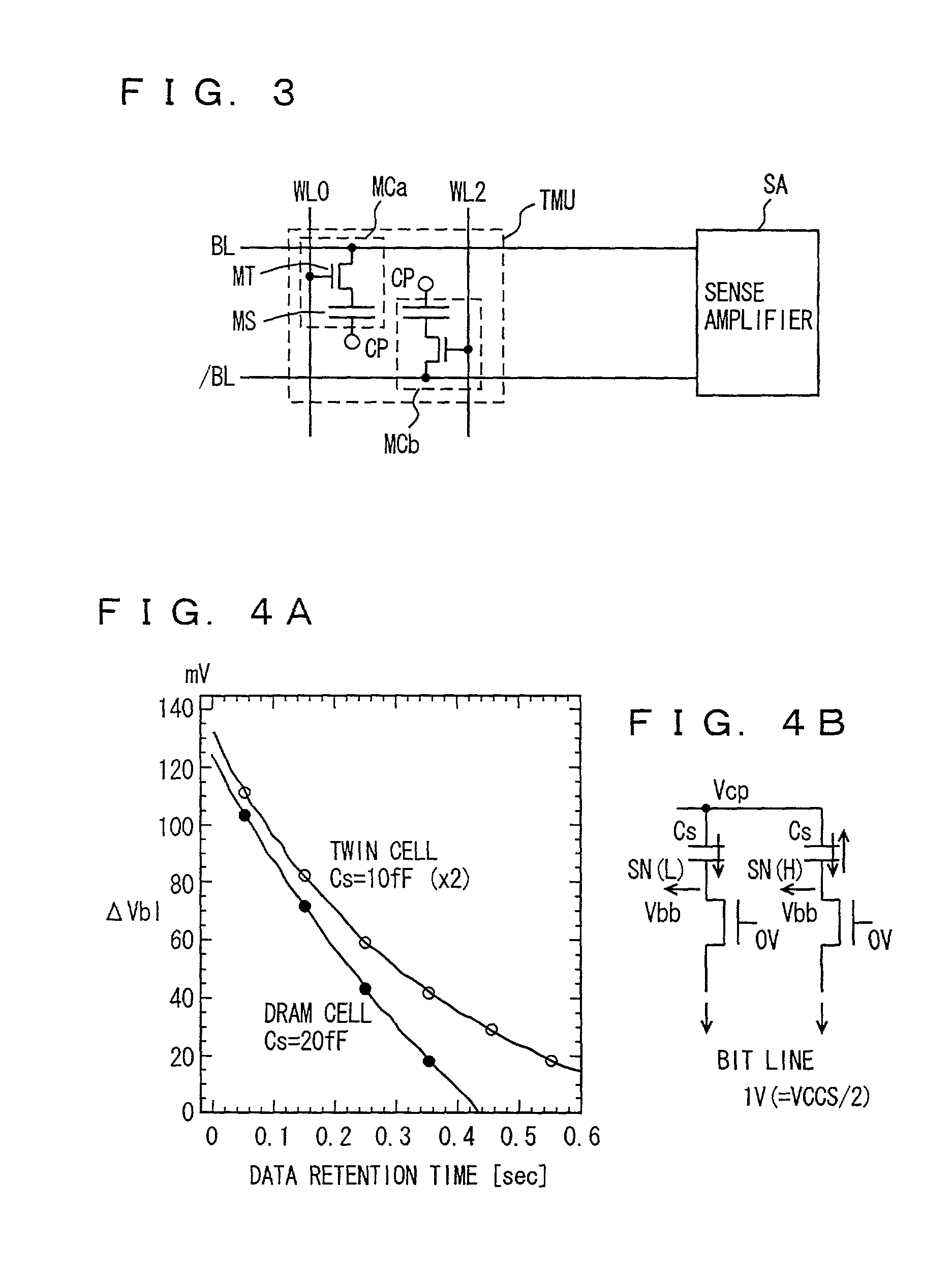

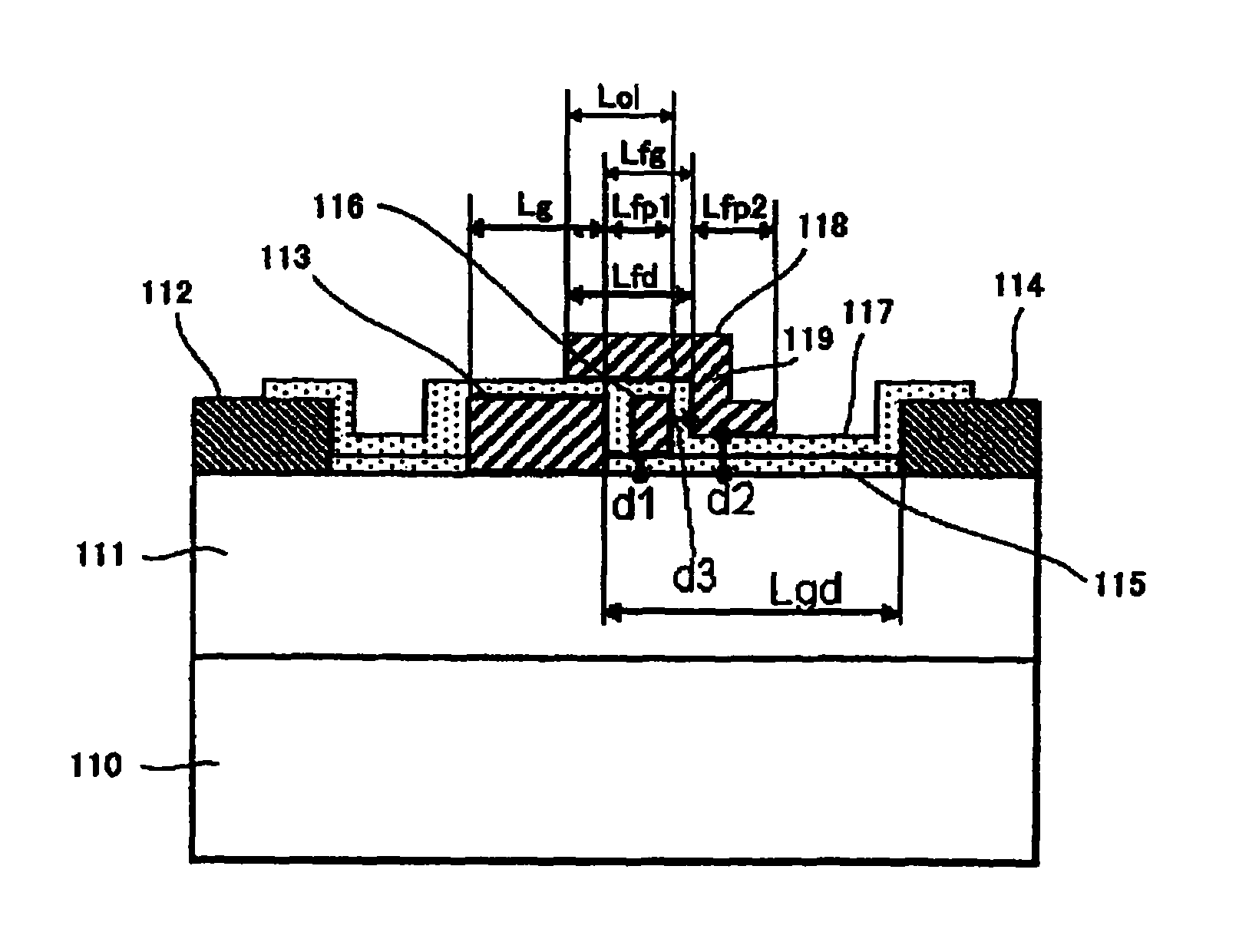

Conductive lines constituting word lines of memory cells and conductive lines constituting memory cell plate electrodes are formed in the same interconnecting layer in a memory device including a plurality of memory cells each including a capacitor for storing data in an electrical charge form. By forming the capacitors of the memory cells into a planar capacitor configuration, a step due to the capacitors is removed. Thus. a dynamic semiconductor memory device can be formed through CMOS process, and a dynamic semiconductor memory device suitable for merging with logic is achieved. Data of 1 bit is stored by two memory cells, and data can be reliably stored even if the capacitance value of the memory cell is reduced due to the planar type capacitor.

Owner:RENESAS ELECTRONICS CORP

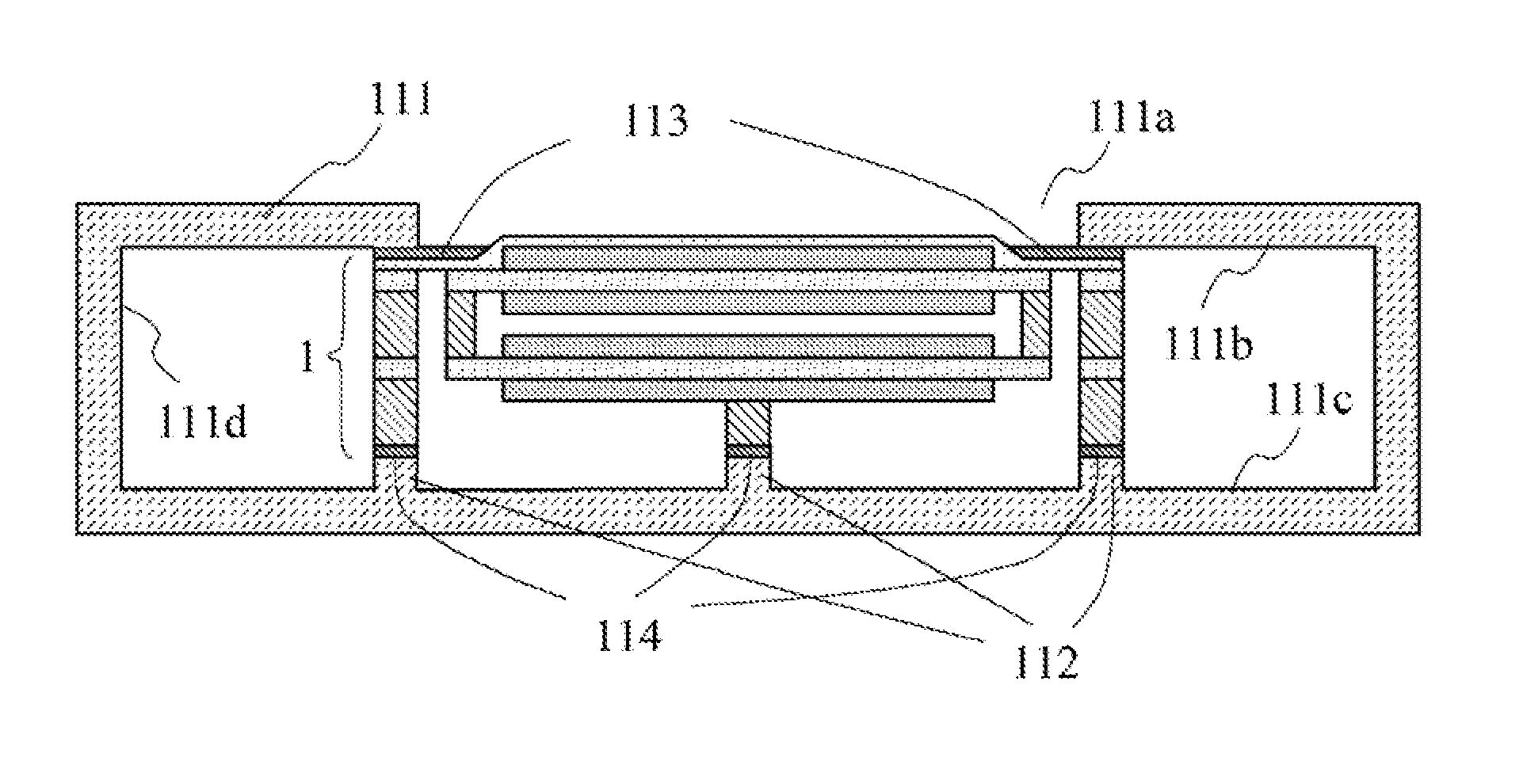

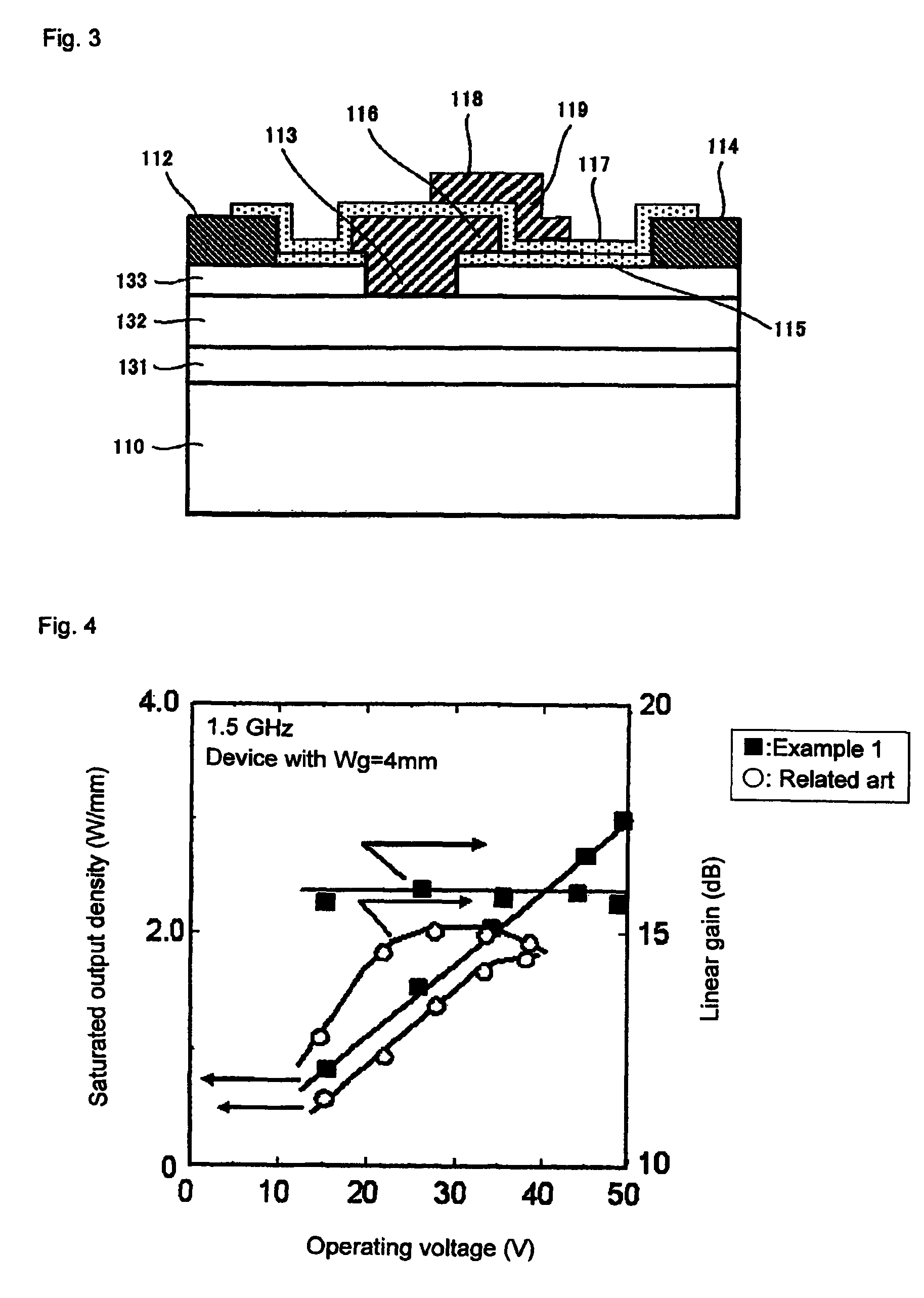

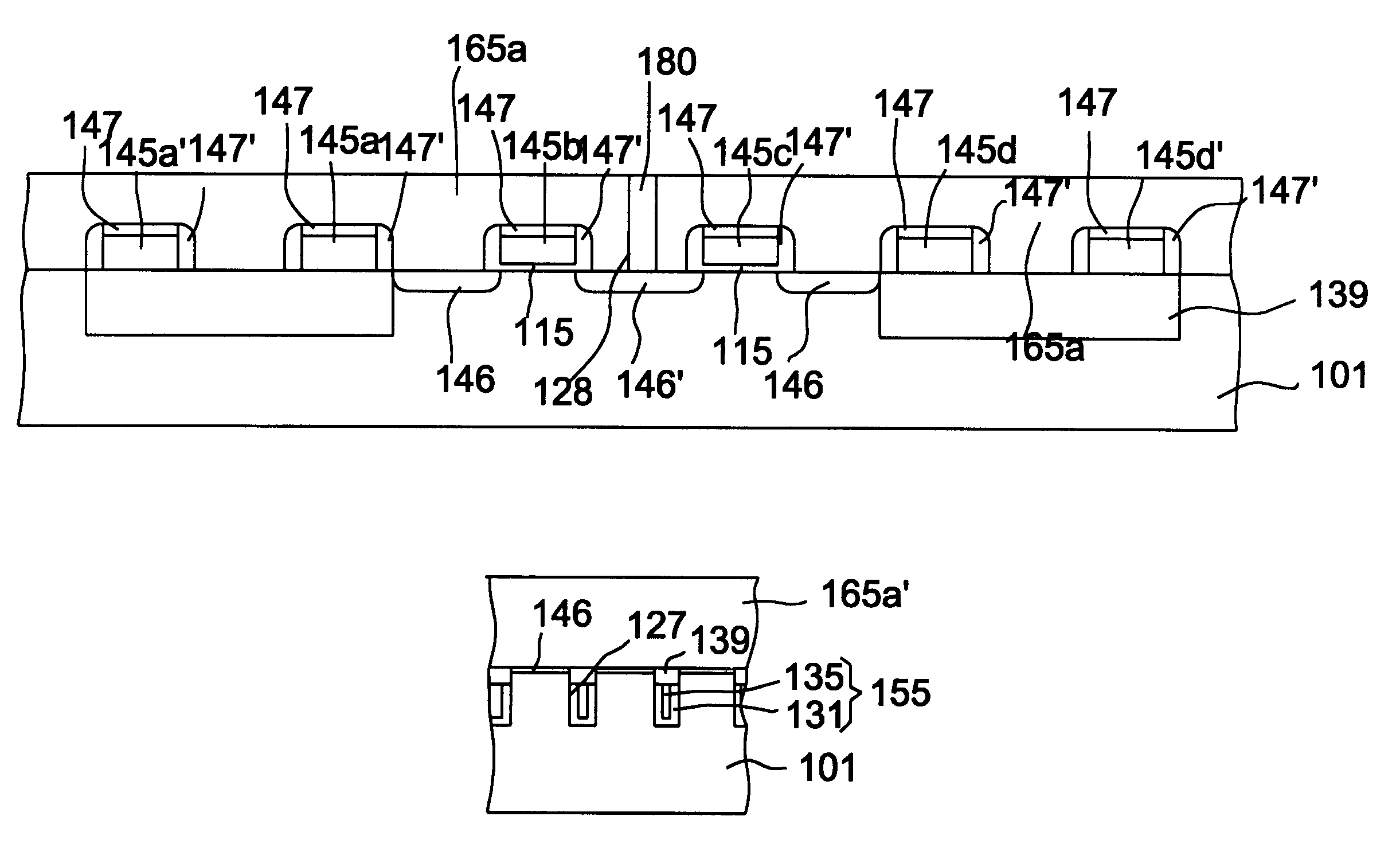

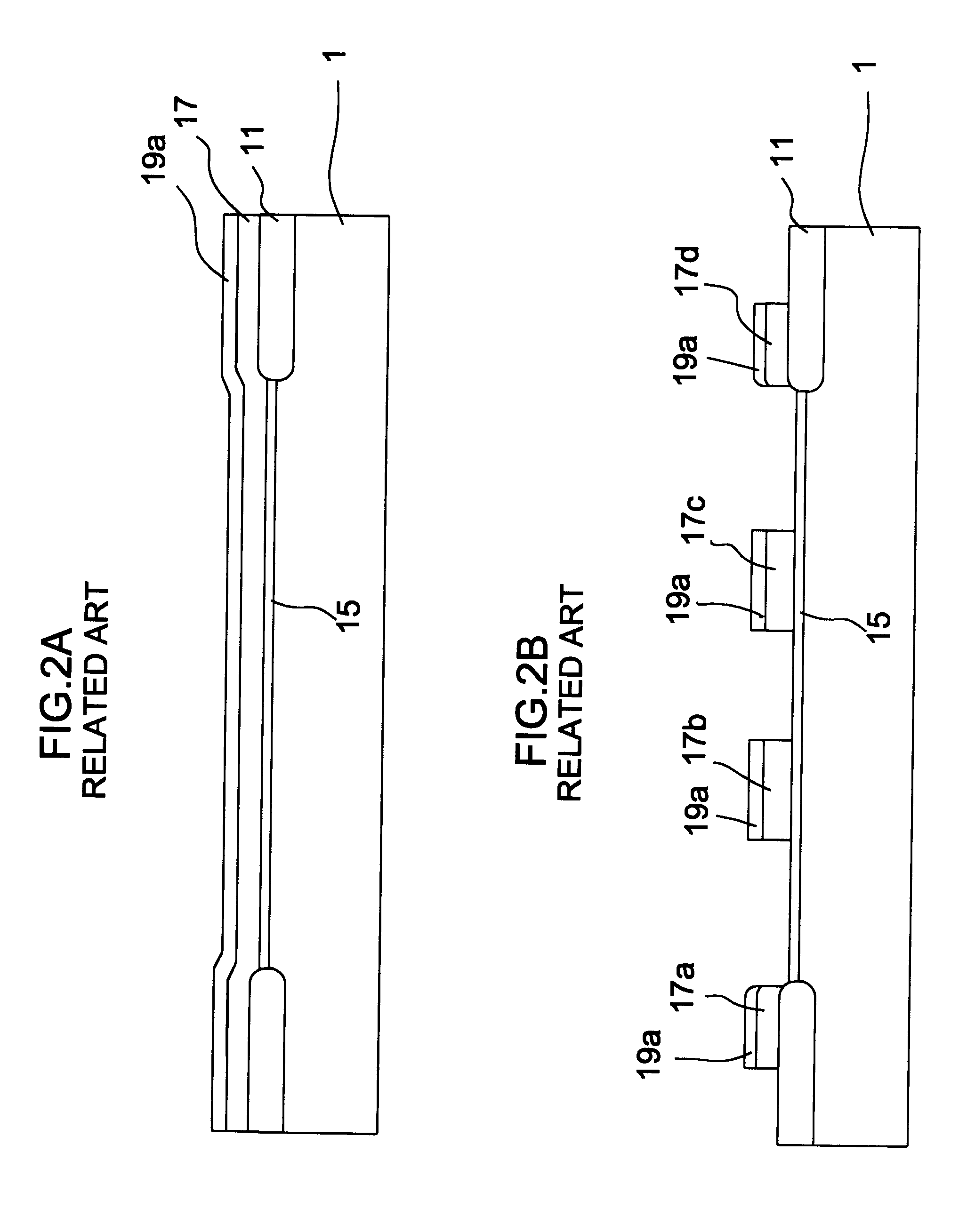

Field effect transistor

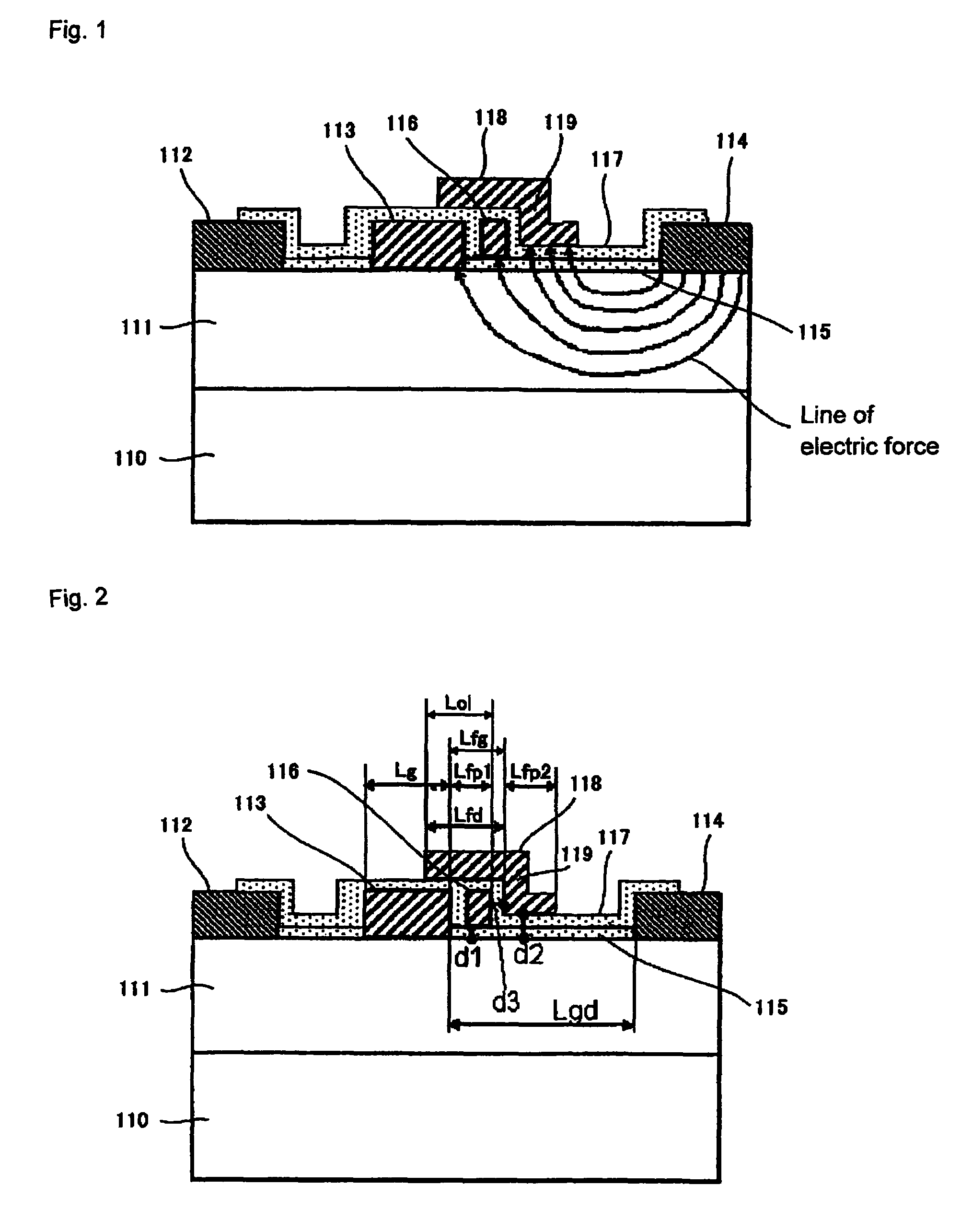

InactiveUS7800131B2Improve performanceSemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorCondensed matter physics

A field effect transistor includes a layer structure made of compound semiconductor (111) provided on a semiconductor substrate (110) made of GaAs or InP, as an operation layer, and employs a first field plate electrode (116) and a second field plate electrode (118). The second field plate electrode includes a shielding part (119) located in the region between the first field plate electrode and a drain electrode (114), and serves to shield the first field plate electrode from the drain electrode. When, in the cross sectional view in the gate length direction, the length in the gate length direction of an overlap region, in which the second field plate electrode overlaps the upper part of a structure composed of the first field plate electrode and a gate electrode (113), is designated as Lol, and the gate length is Lg, the relation expressed as 0≦Lol / Lg≦1 holds.

Owner:NEC CORP

Method for fabricating dynamic random access memory cells

A method for fabricating DRAM cells according to the present invention includes the steps of: forming a trench within a semiconductor substrate using a stacked layer as a mask, said stacked layer composed of a silicon oxide film and a silicon nitride film formed in an active region of said semiconductor substrate; forming a first insulation layer on a bottom and sides of said trench; depositing a first conductive layer on whole surface of said semiconductor substrate including said trench; etching back said conductive layer to be recessed from a top surface of said semiconductor substrate and forming bit lines of said first conductive layer on said bottom of said trench in a direction of column; filling a second insulation layer in said trench; removing said stacked layer and a part of said second insulation layer to expose said semiconductor substrate in said active region and planarizing said semiconductor substrate simultaneously; forming a gate insulation layer on said semiconductor substrate;forming a gate structure of a second conductive layer on said gate insulation layer; forming a spacer of an insulation layer on said sides of said gate structure of said second conductive layer; forming source and drain regions on both sides of said gate structure of said second conductive layer;forming a third insulation layer on said semiconductor substrate; connecting said bit lines to a first one of said source and drain regions with a plug of a third conductive layer filled in a contact hole inside said third insulation layer and said second insulation layer; forming a storage node electrode connected to a second one of said source and drain regions; andforming a plate electrode overlying a dielectric layer disposed said storage node electrode.Accordingly, the present invention has the buried bit lines in the trench, making it easy to secure a process margin in the subsequent process, maintaining a constant width of the bit lines to lower the resistance thereof. Furthermore, the bit lines disposed under the word lines has an advantage over patterning the node contact due to the low step height, with enhanced capacitance of the capacitor.

Owner:HYUNDAI ELECTRONICS IND CO LTD

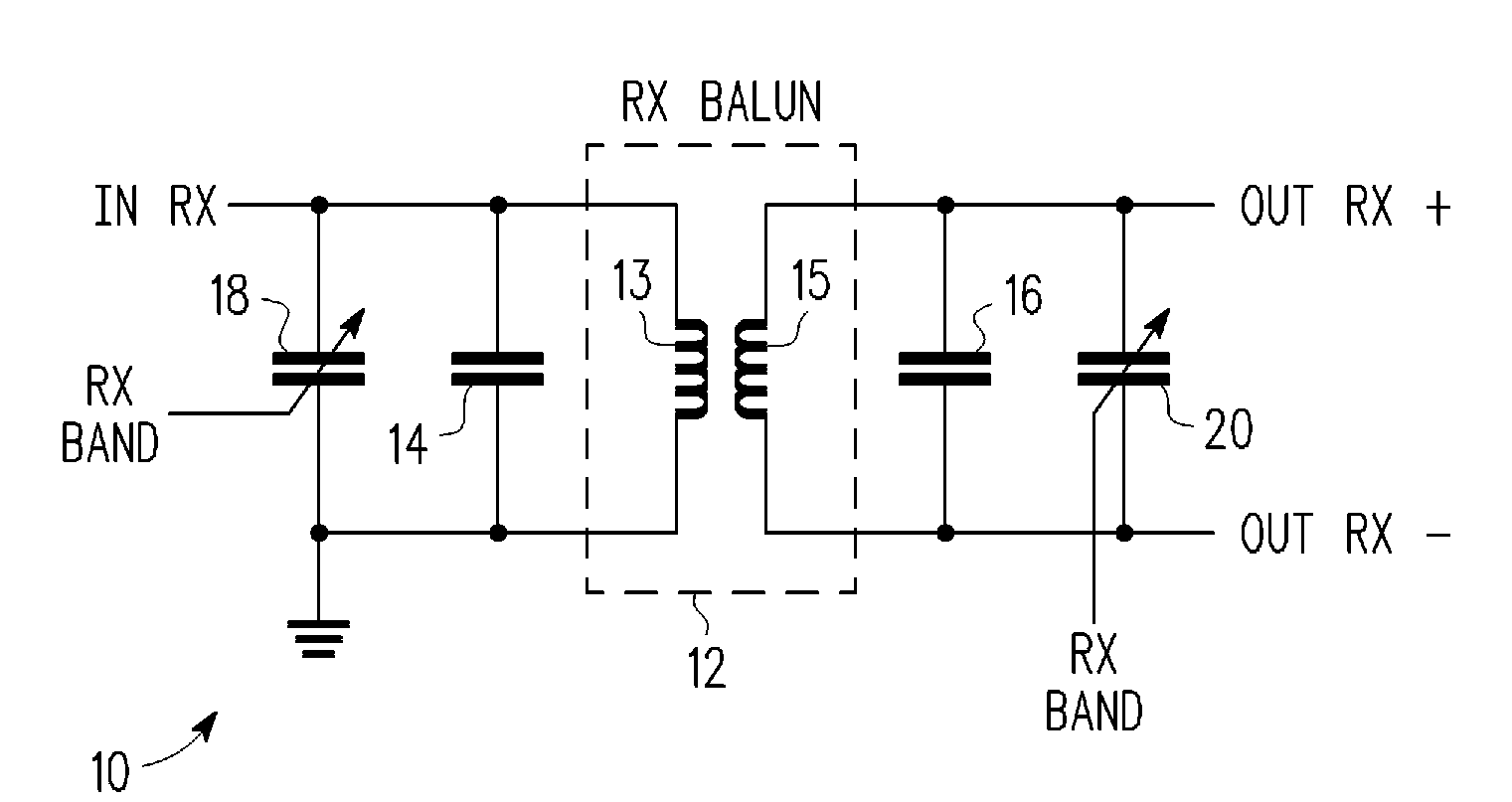

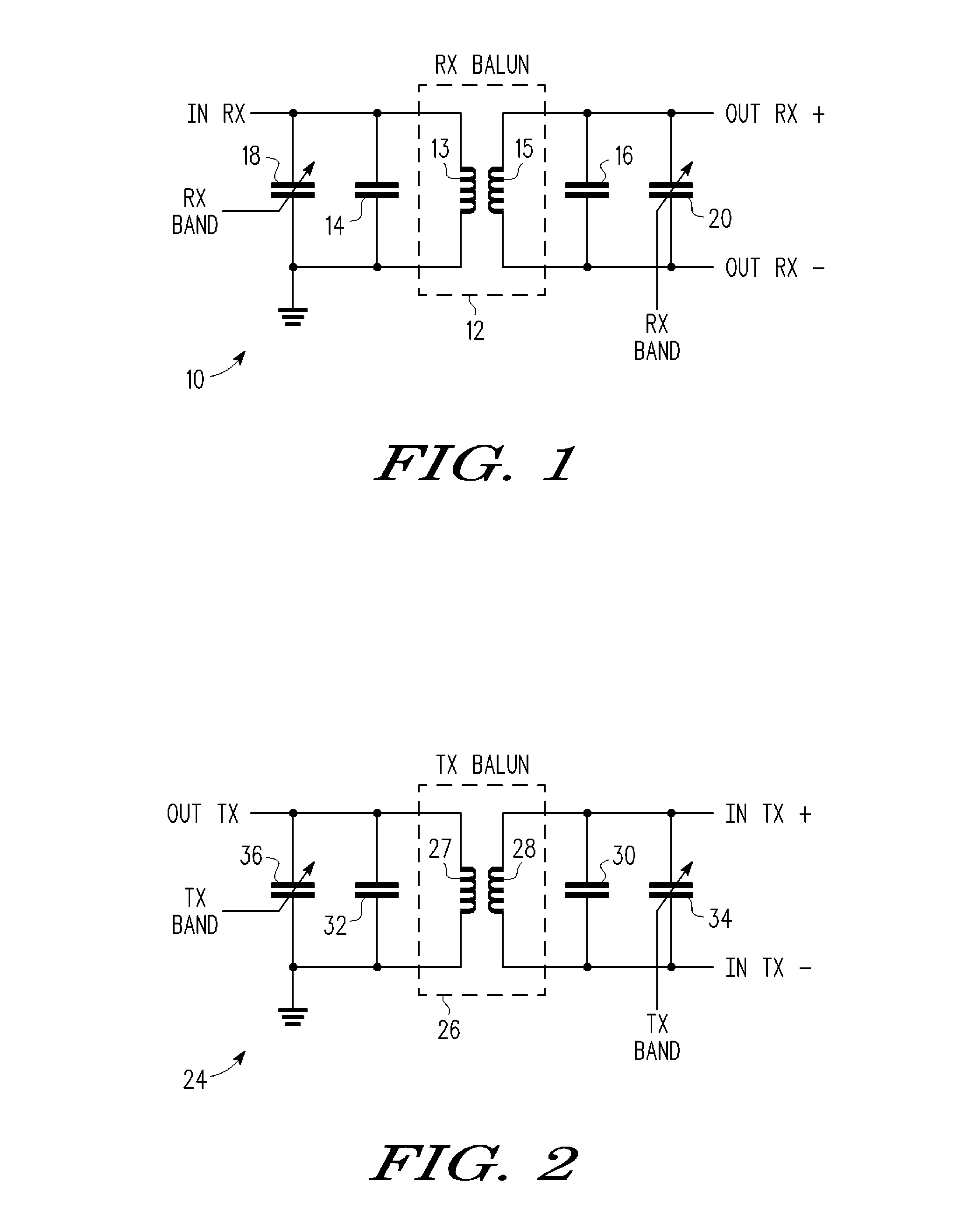

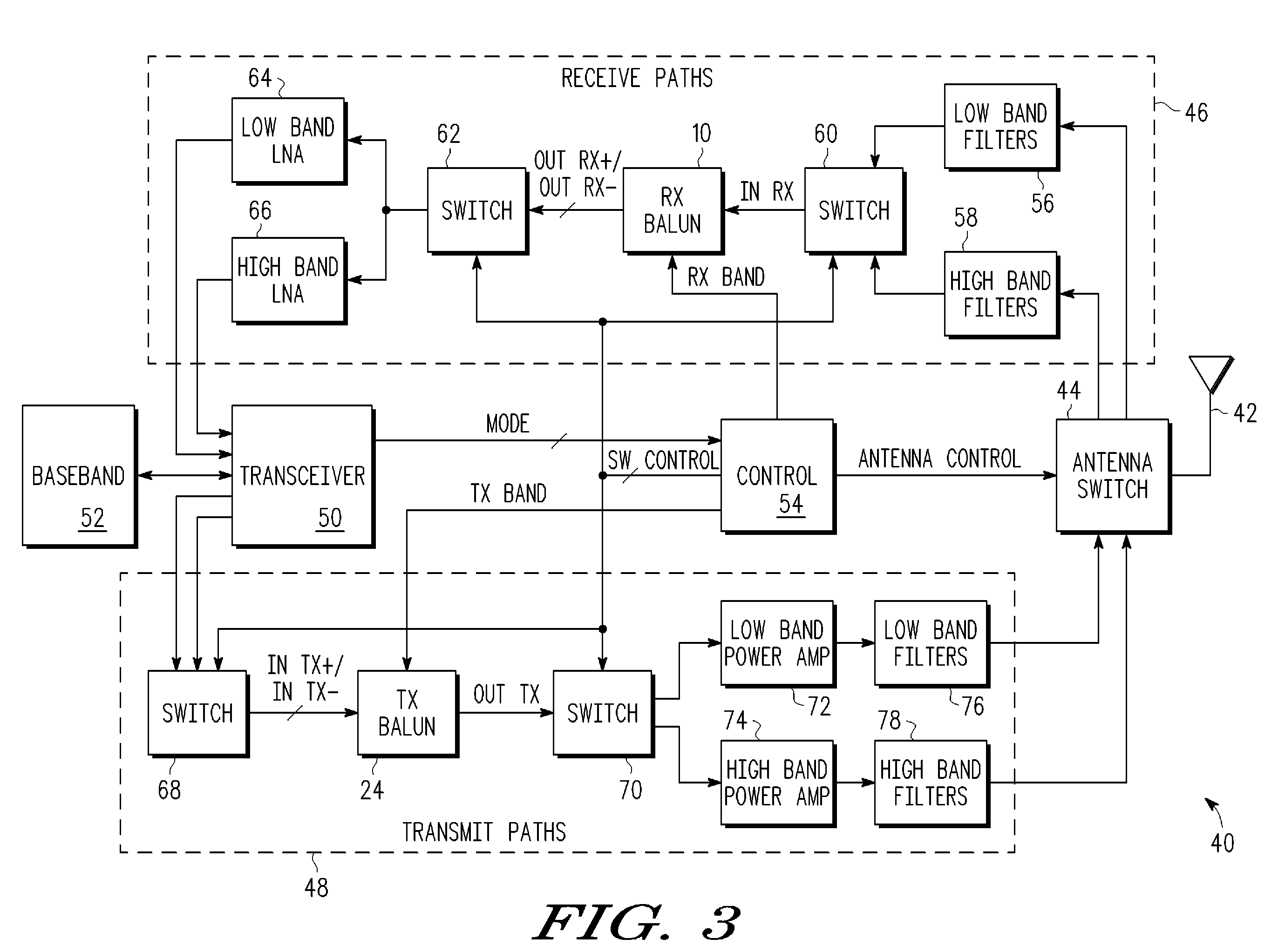

Integrated circuit having re-configurable balun circuit and method therefor

A balun circuit comprises a balun transformer having first and second windings, and first and second variable capacitors. The first variable capacitor has a first plate electrode coupled to the first terminal of the first winding, and a second plate electrode coupled to the second terminal of the first winding. The second variable capacitor has a first plate electrode coupled to the first terminal of the second winding, and a second plate electrode coupled to the second terminal of the second winding. The first variable capacitor is tunable between first and second capacitance values. The second variable capacitor is tunable between third and fourth capacitance values. Tuning the variable capacitors allows the balun circuit to be re-configurable to operate in both the first frequency band and the second frequency band.

Owner:FREESCALE SEMICON INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com