Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

674 results about "Non doped" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

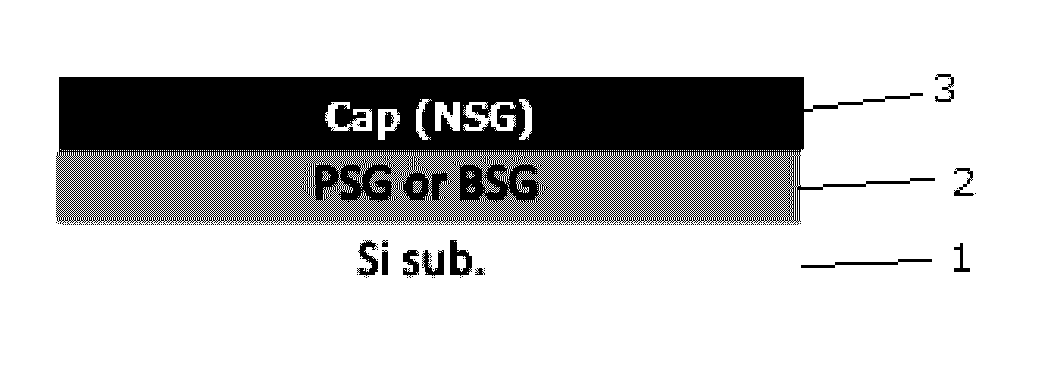

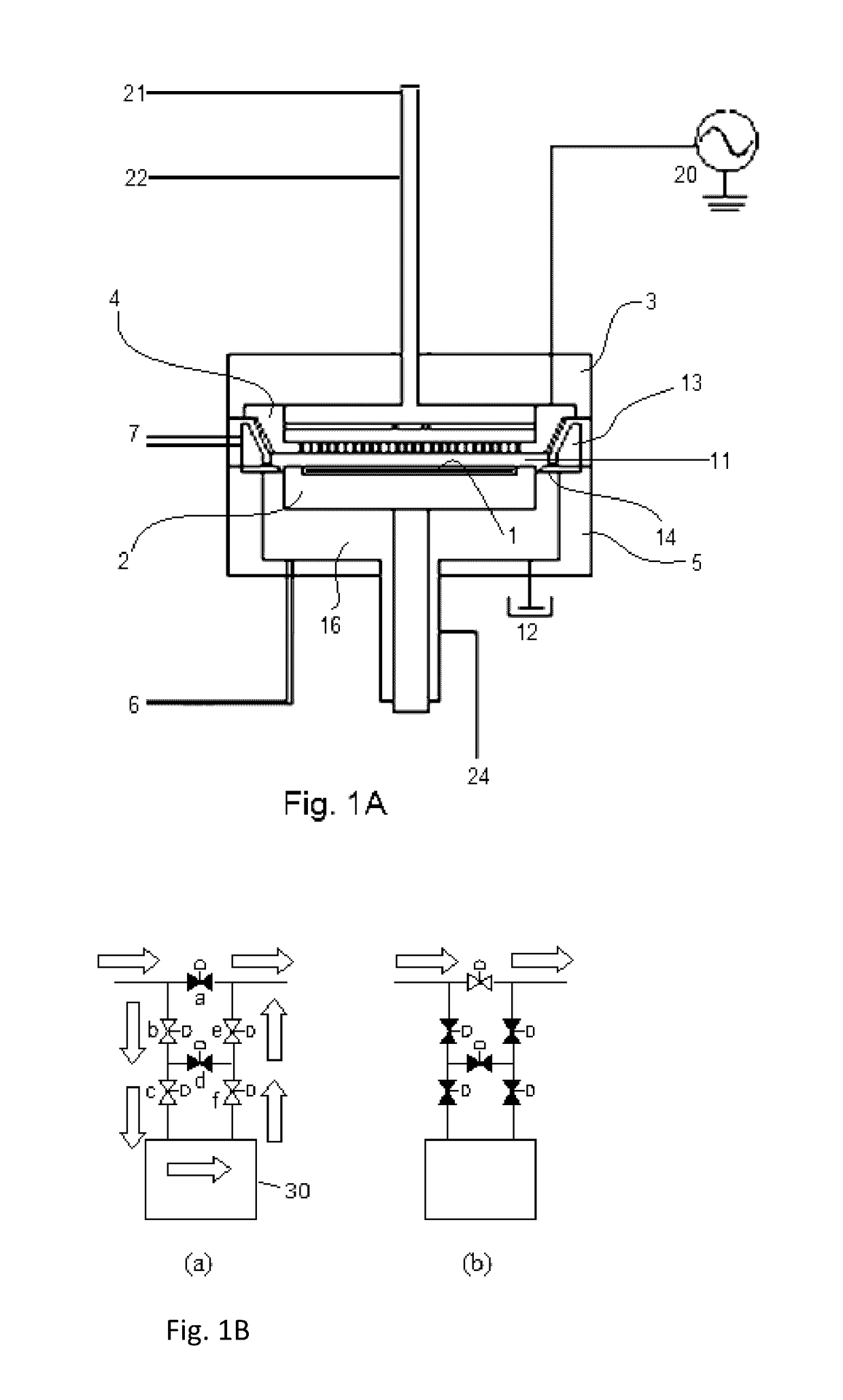

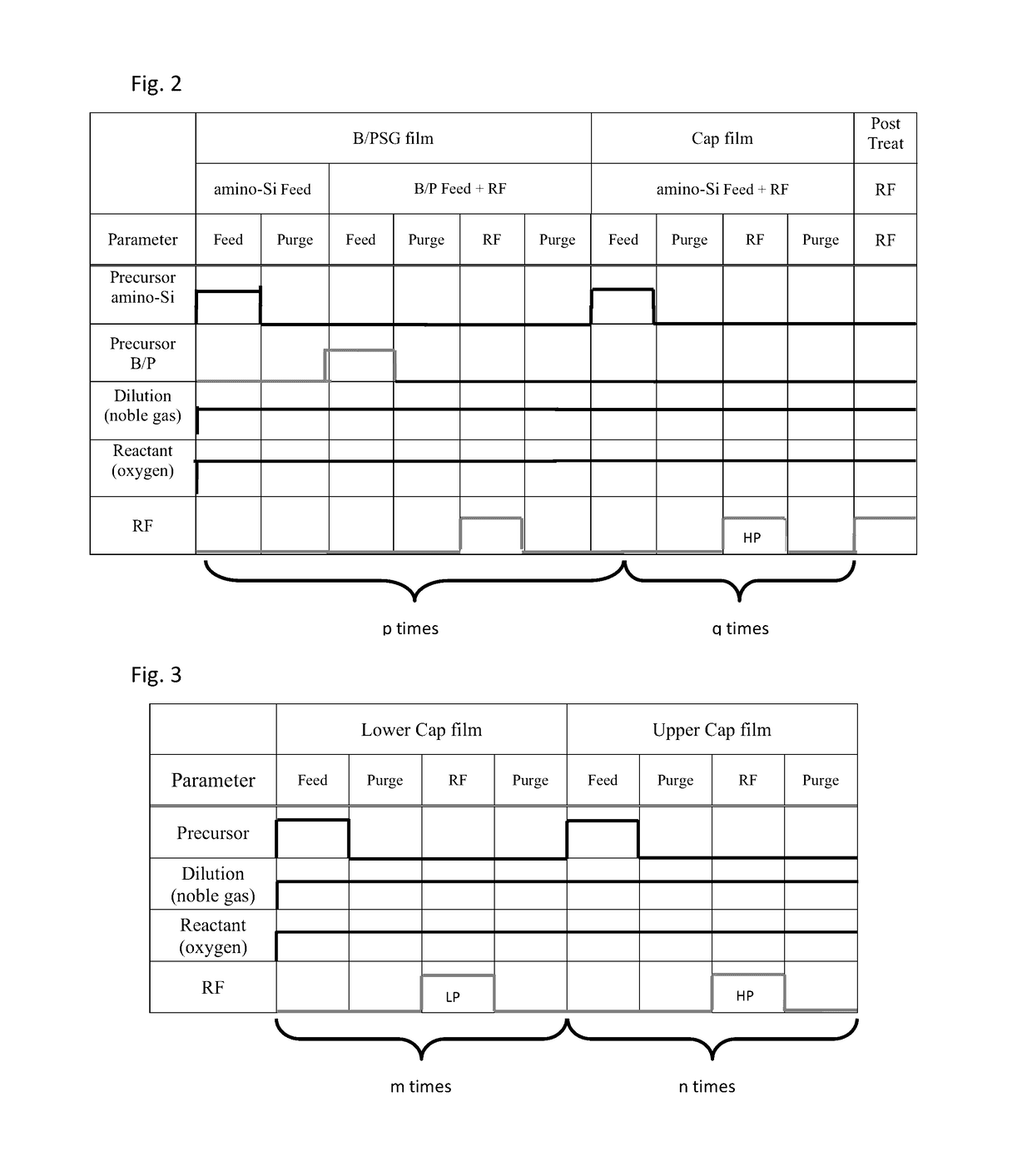

Method for forming silicon oxide cap layer for solid state diffusion process

ActiveUS9607837B1Avoid dissipationQuality improvementSemiconductor/solid-state device manufacturingPlasma techniqueMetallurgySilicate glass

Owner:ASM IP HLDG BV

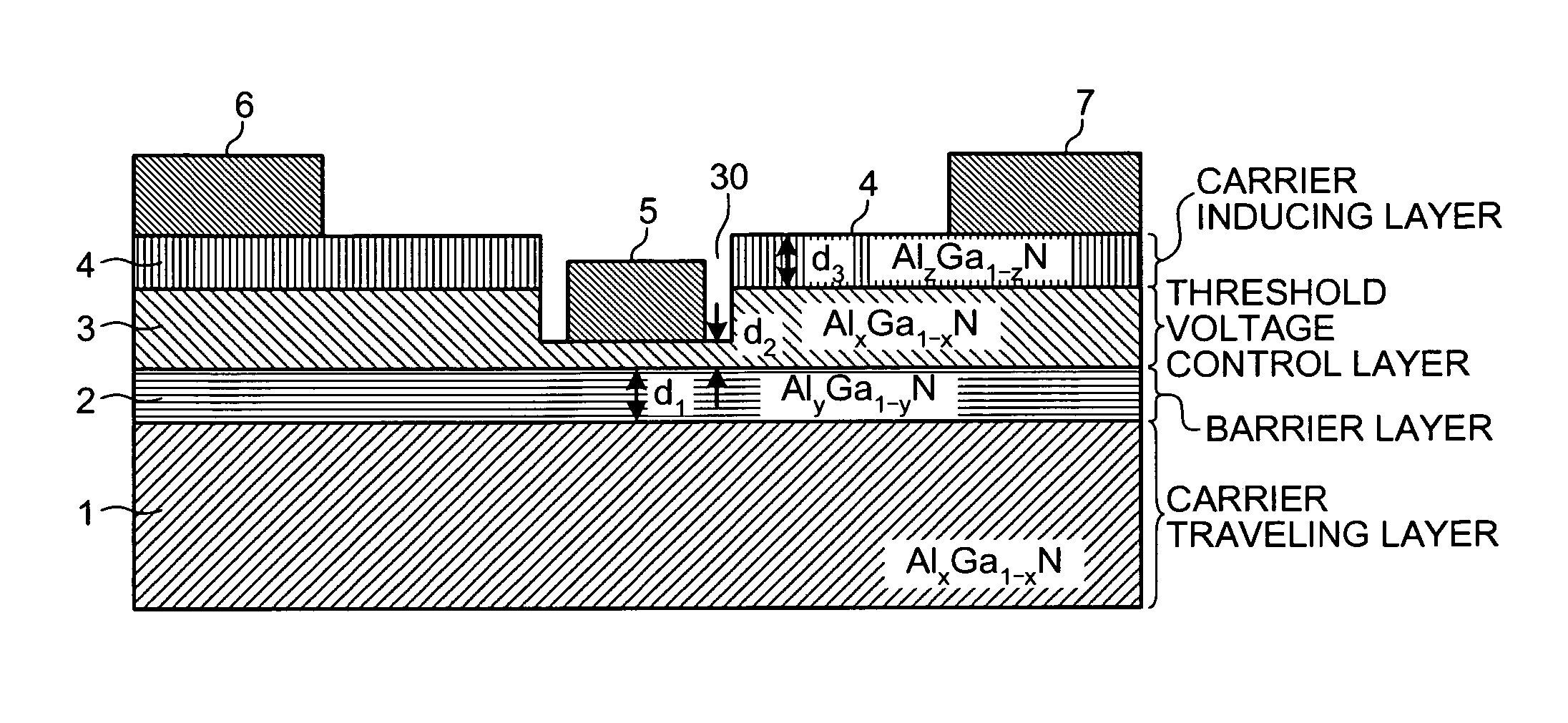

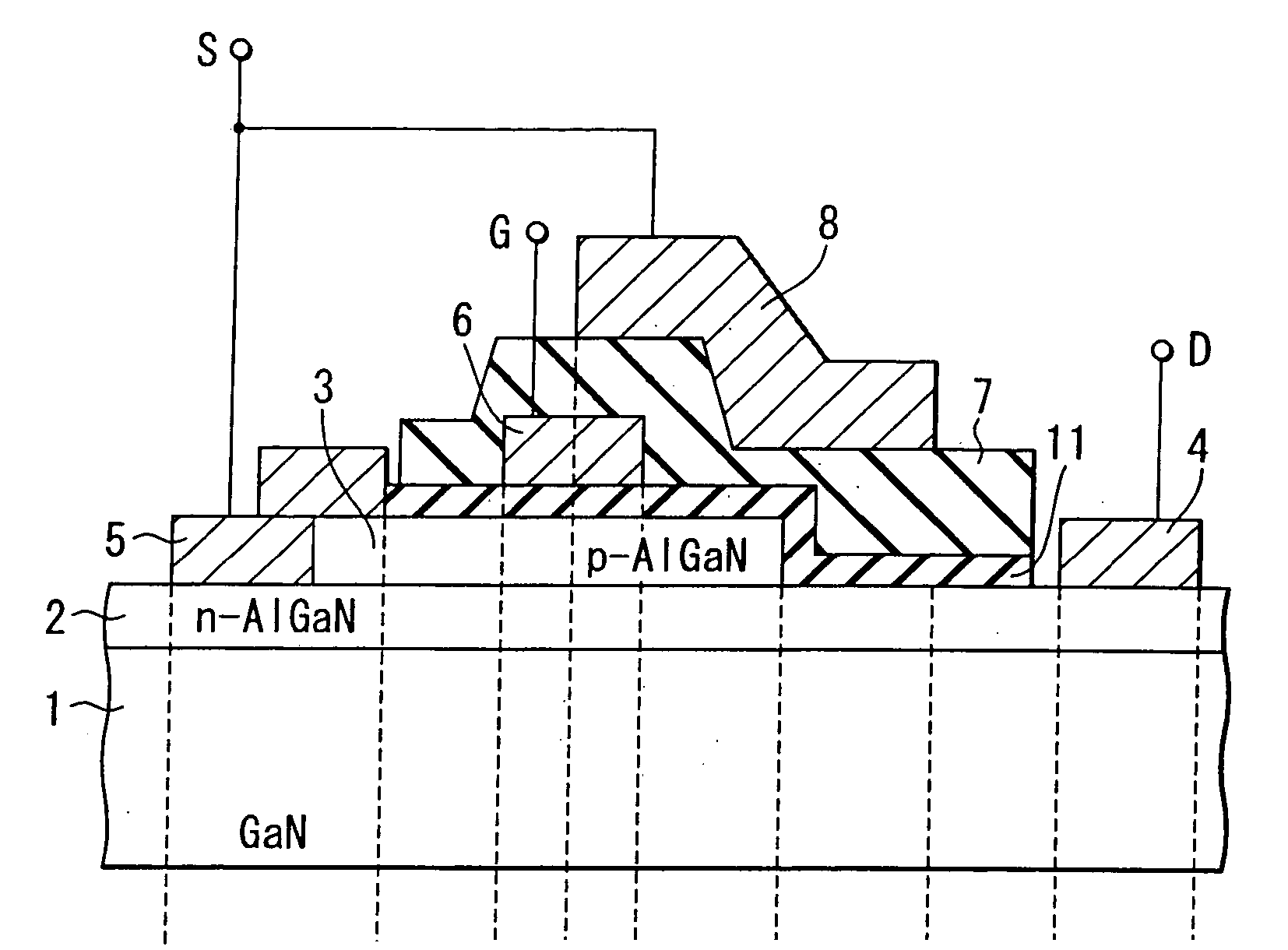

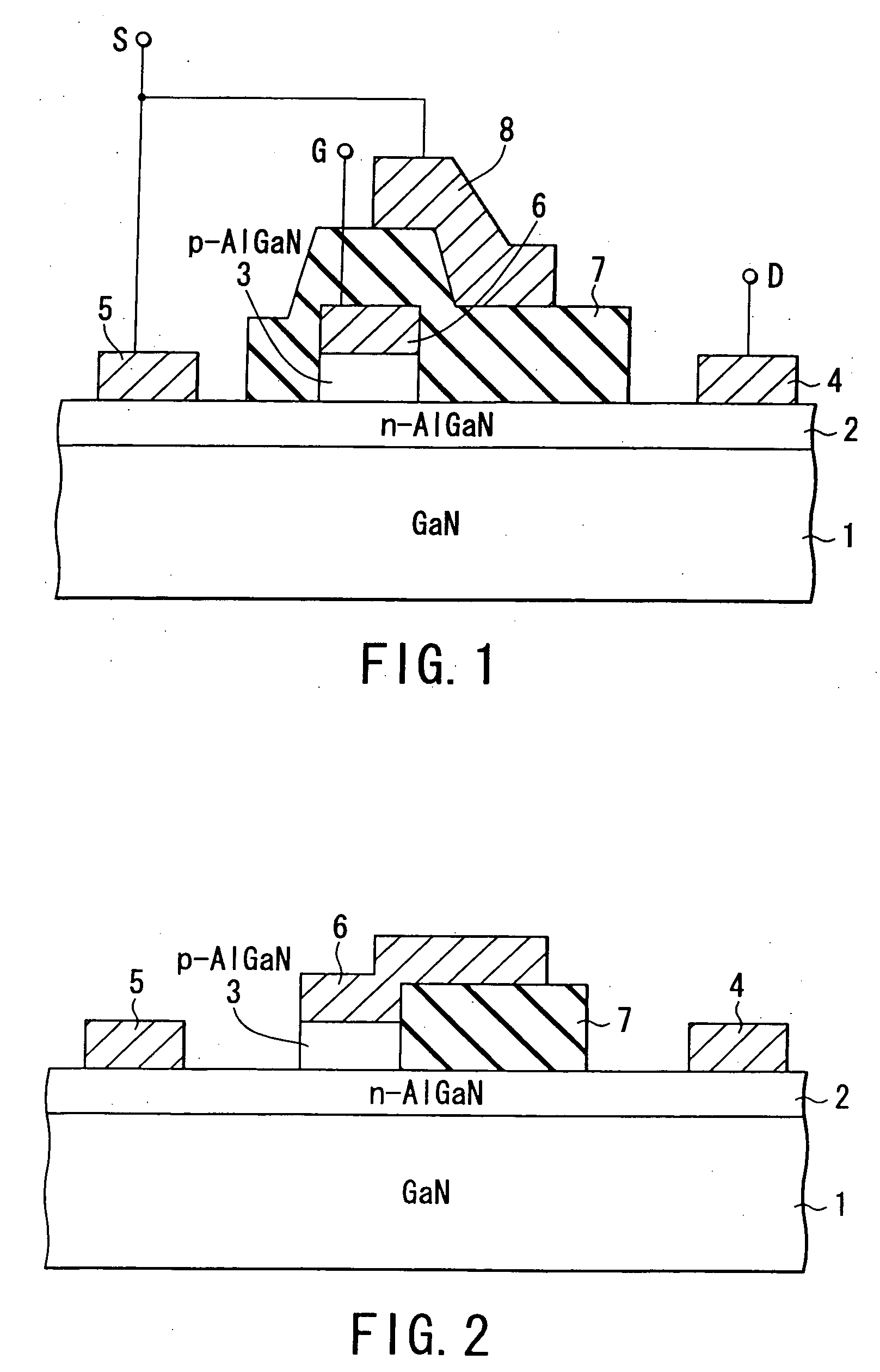

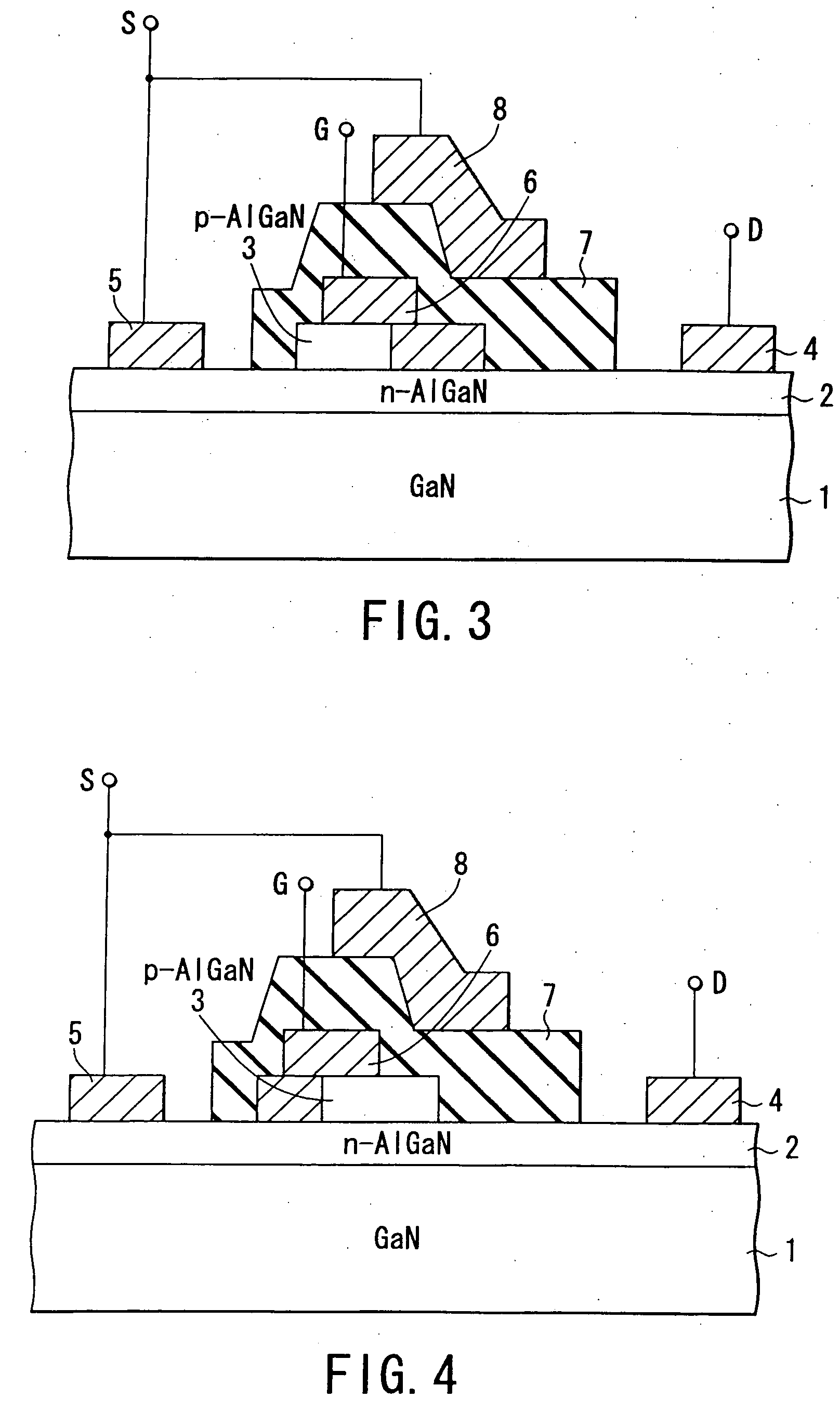

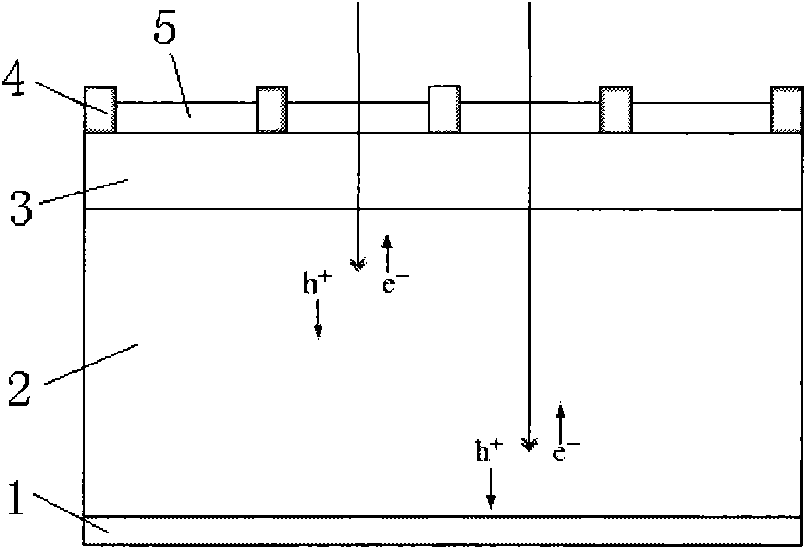

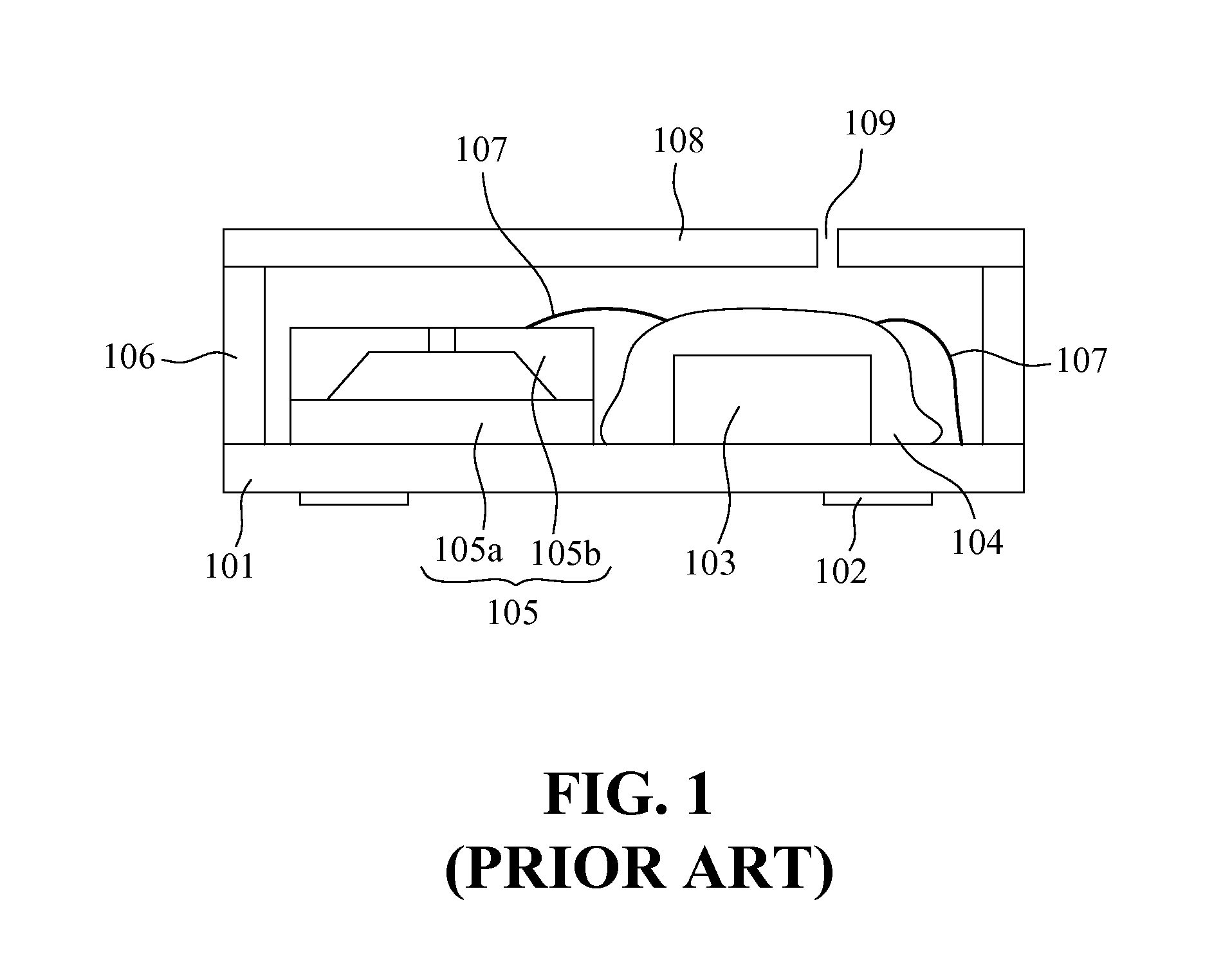

Nitride-based semiconductor device and method of manufacturing the same

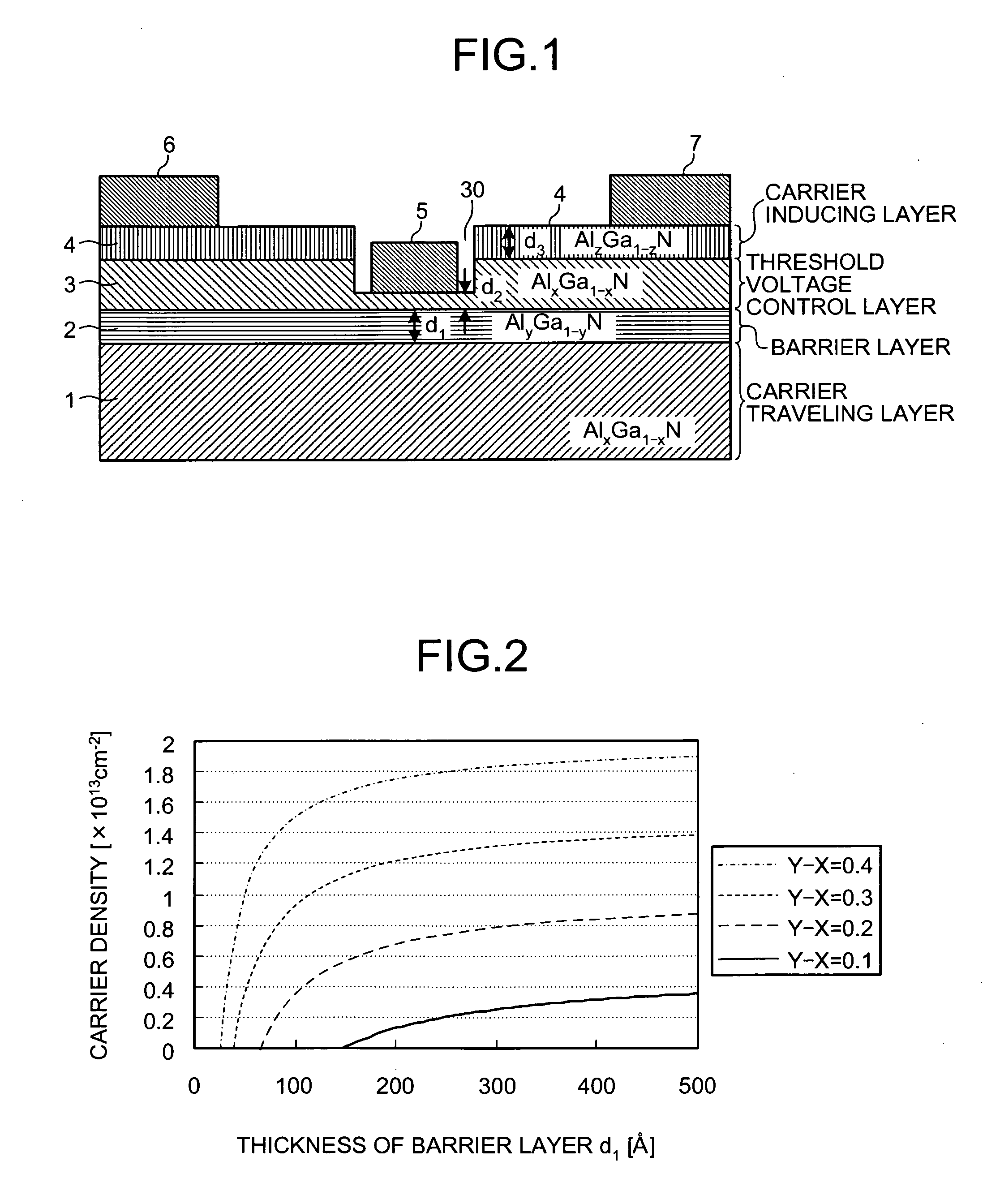

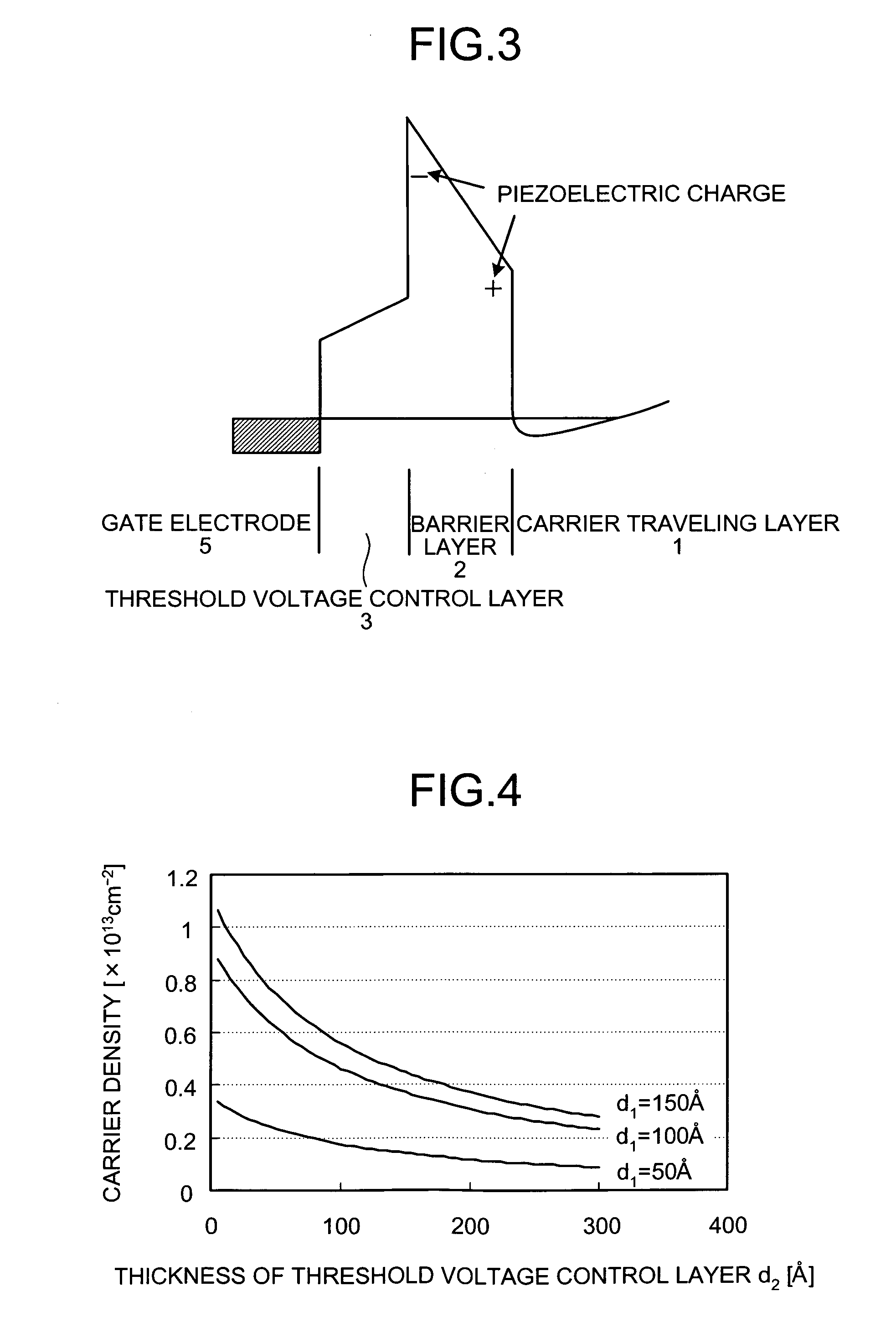

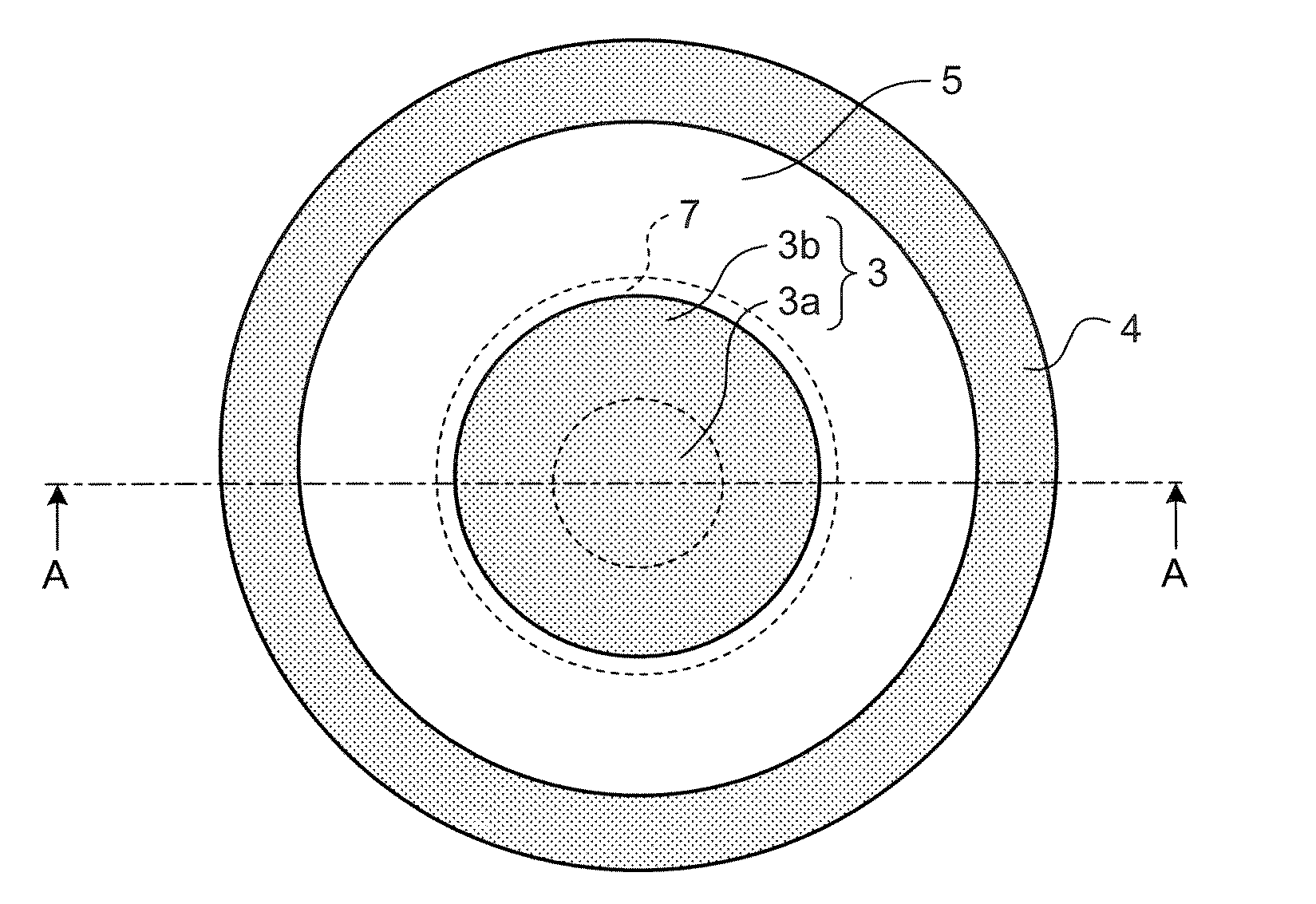

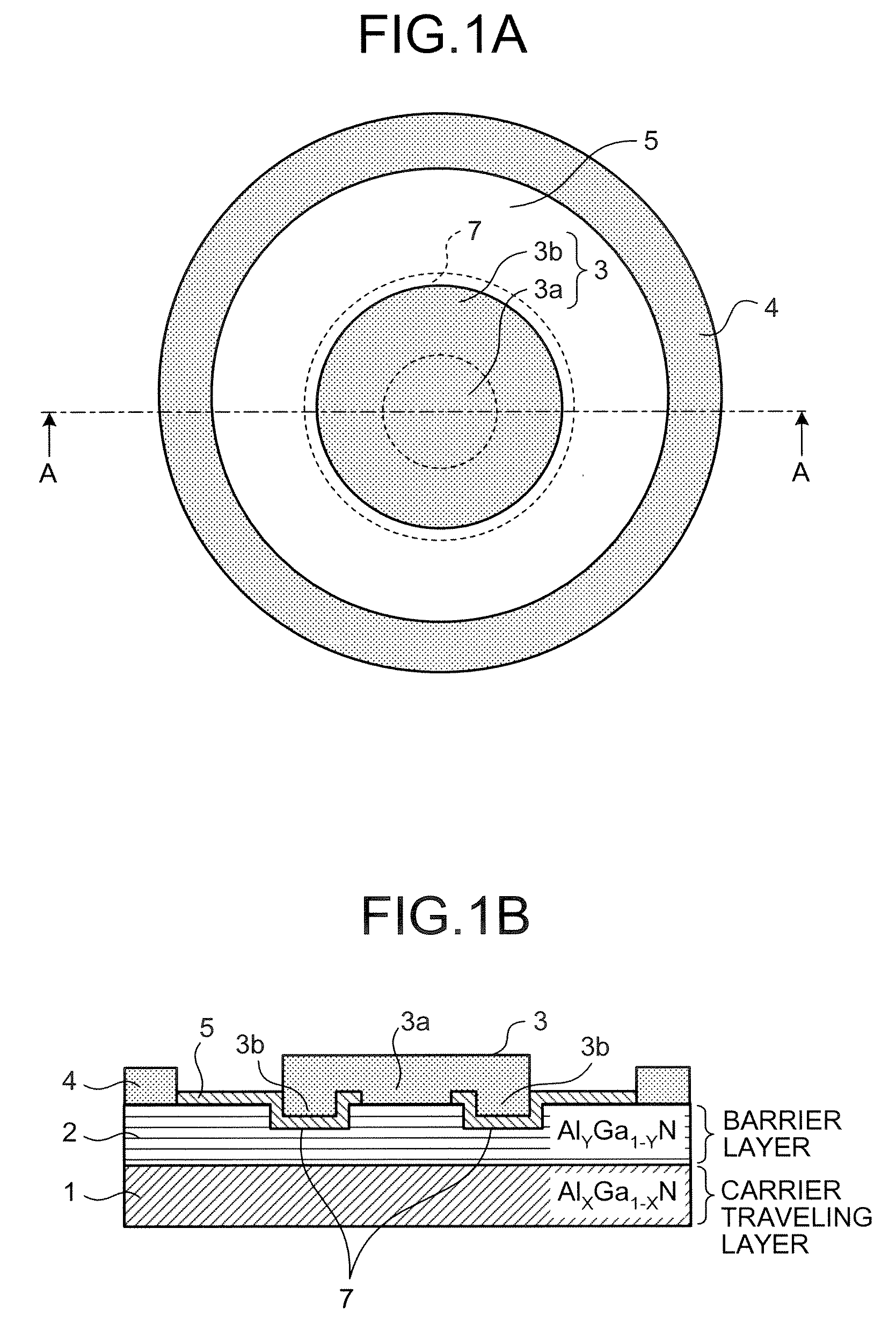

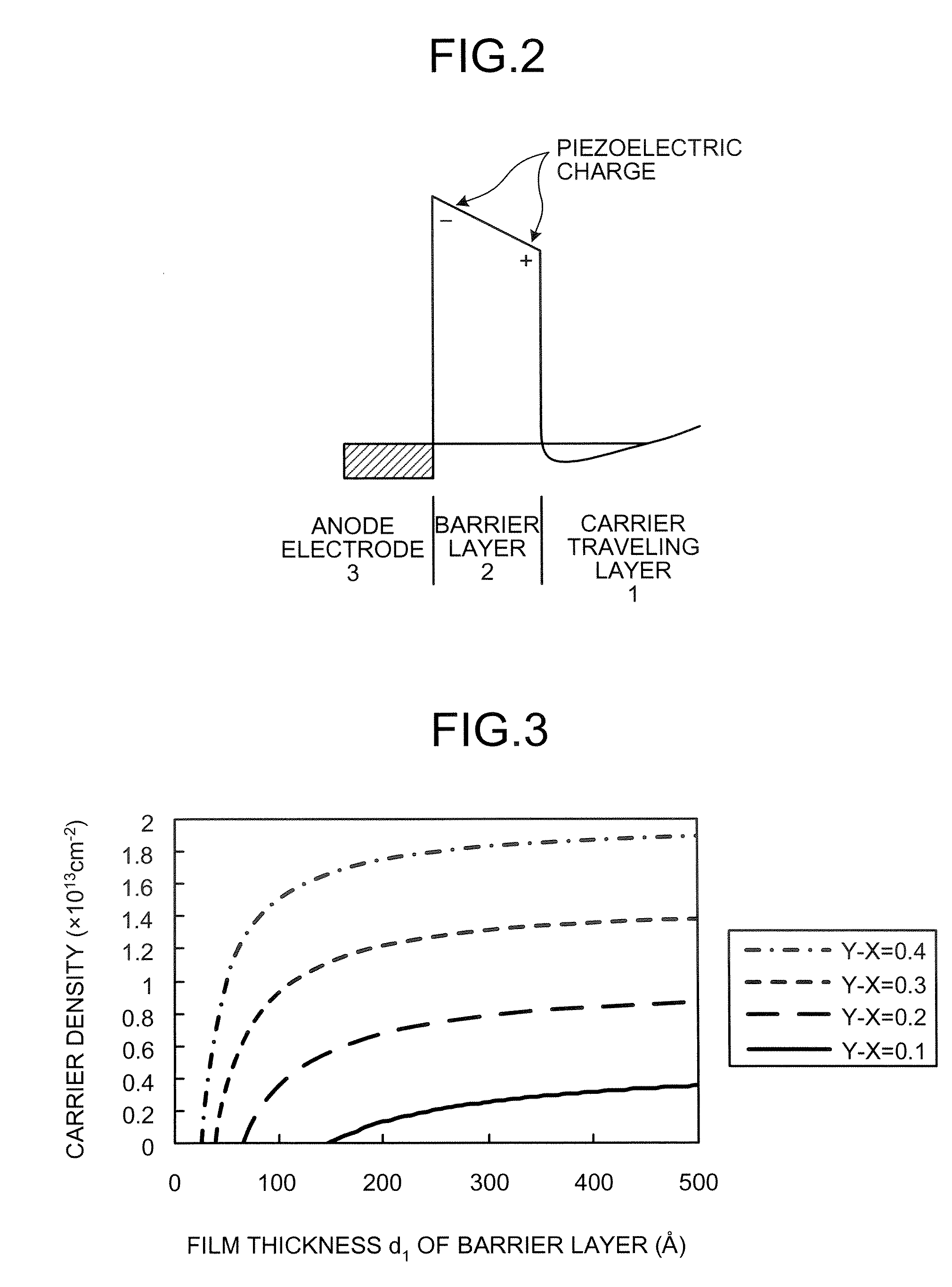

The nitride-based semiconductor device includes a carrier traveling layer 1 composed of non-doped AlxGa1-xN (0≦X<1); a barrier layer 2 formed on the carrier traveling layer 1 and composed of non-doped or n-type AlYGa1-YN (0<Y≦1, X<Y) having a lattice constant smaller than that of the carrier traveling layer 1; a threshold voltage control layer 3 formed on the barrier layer 2 and composed of a non-doped semiconductor having a lattice constant equal to that of the carrier traveling layer 1; and a carrier inducing layer 4 formed on the threshold voltage control layer 3 and composed of a non-doped or n-type semiconductor having a lattice constant smaller than that of the carrier traveling layer 1. The nitride-based semiconductor device further includes a gate electrode 5 formed in a recess structure, a source electrode 6 and a drain electrode 7.

Owner:KK TOSHIBA

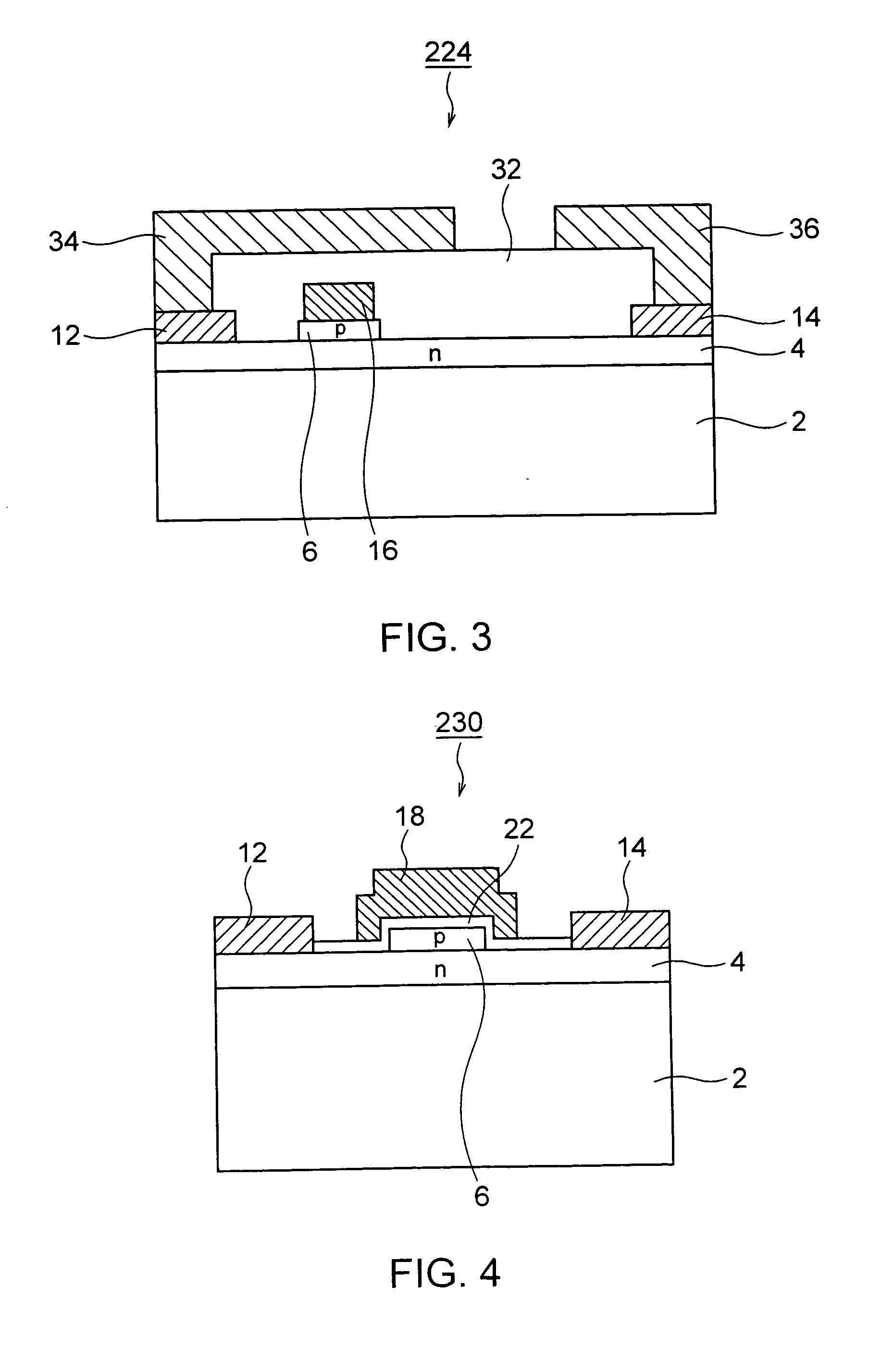

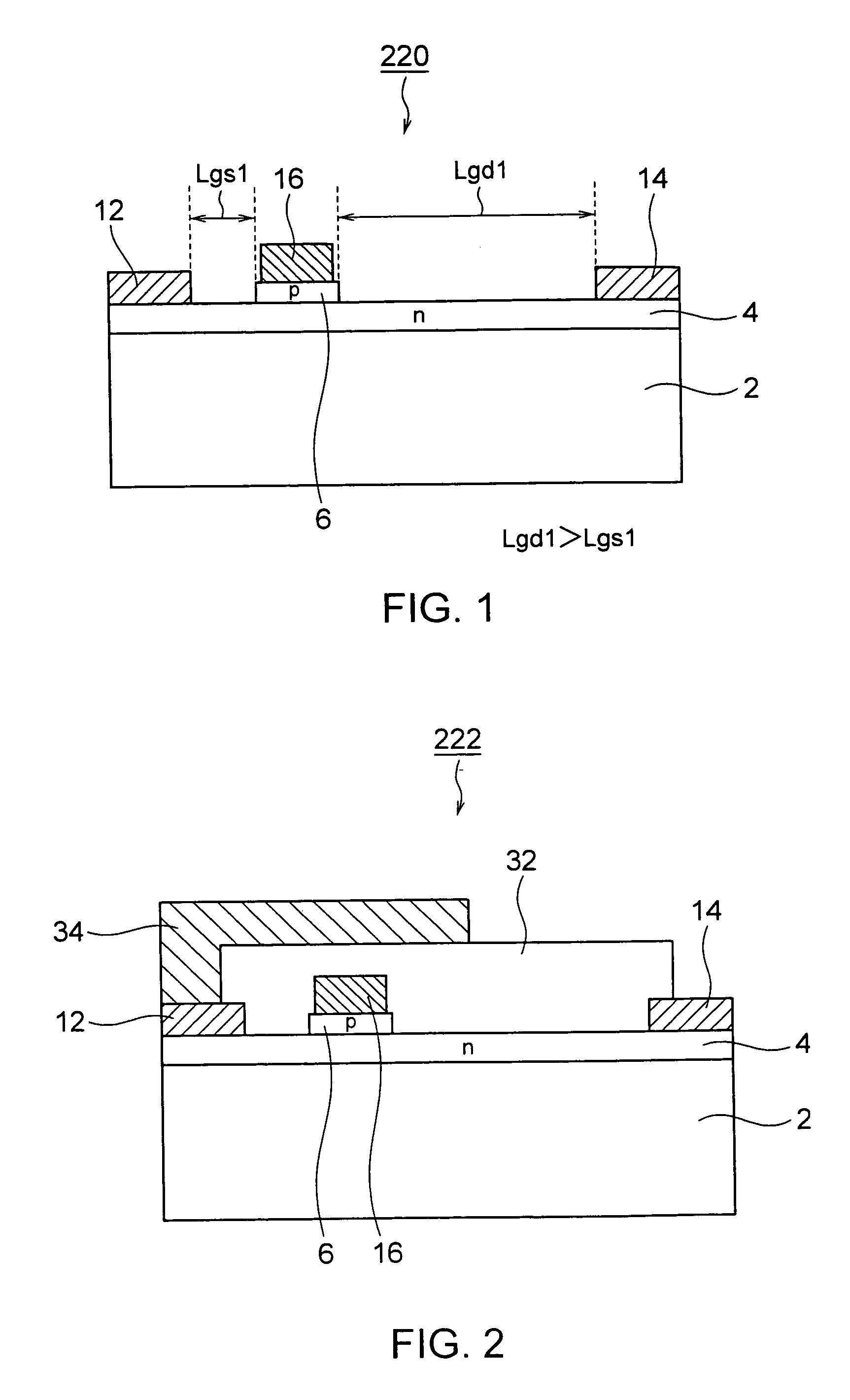

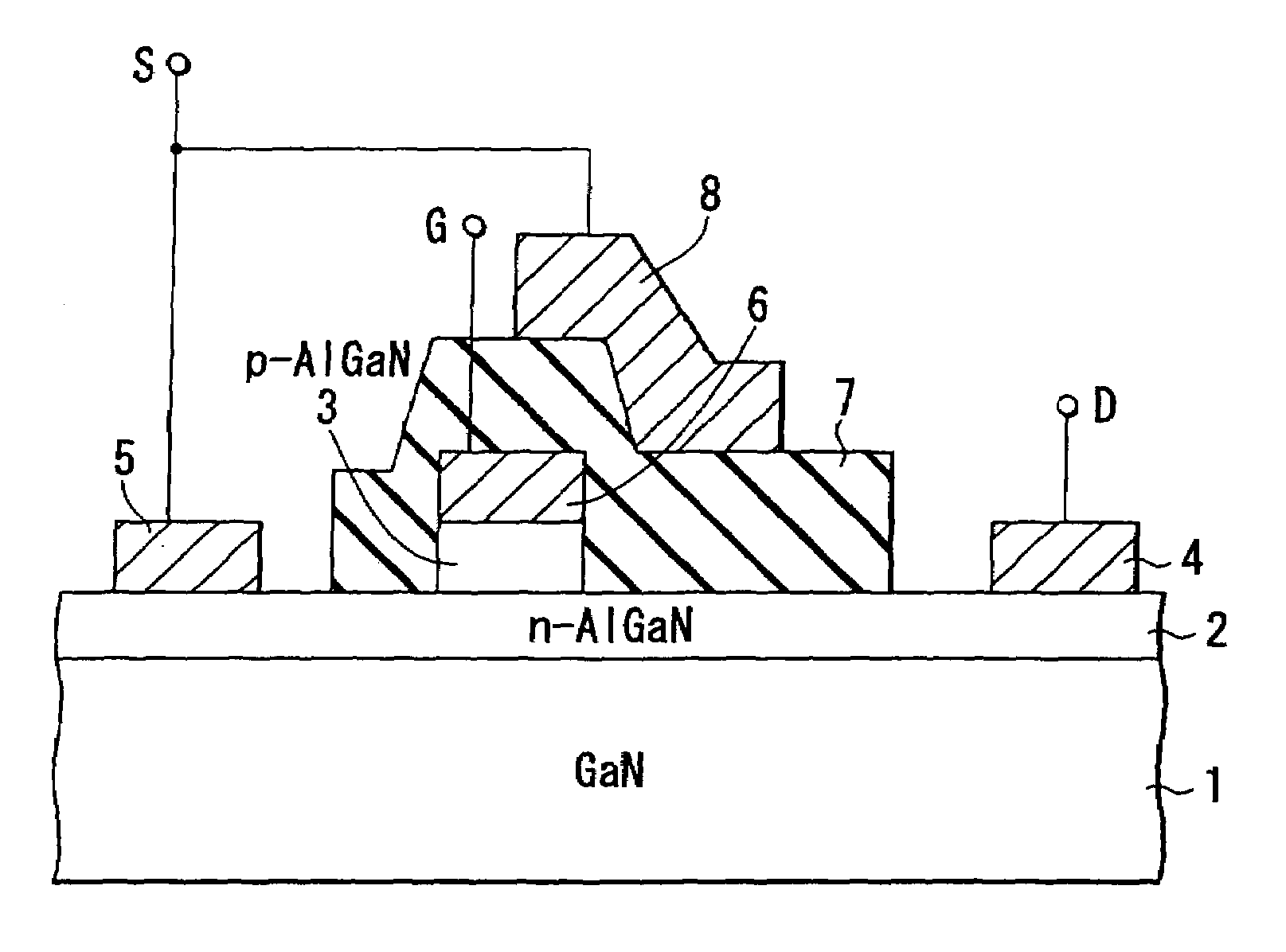

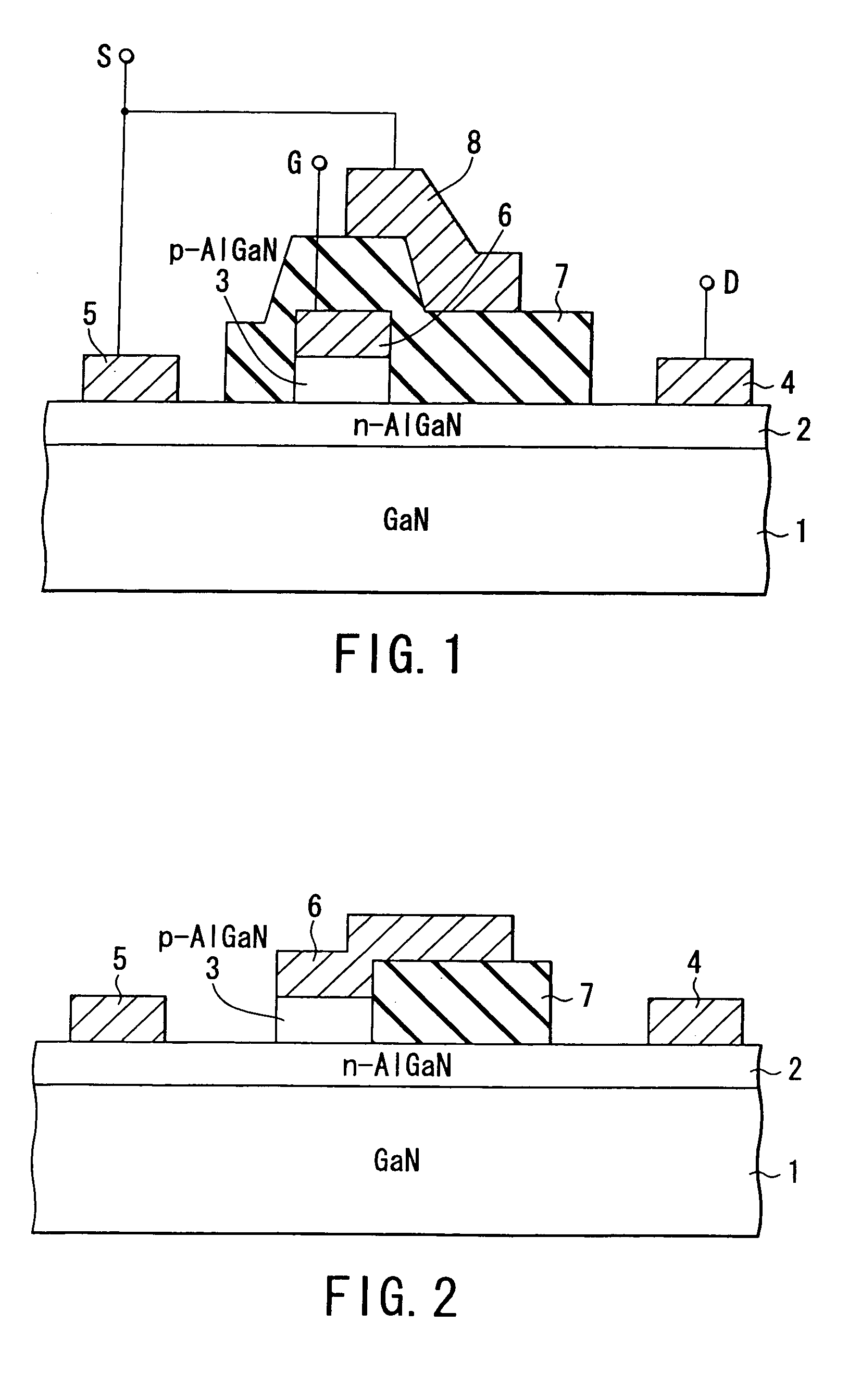

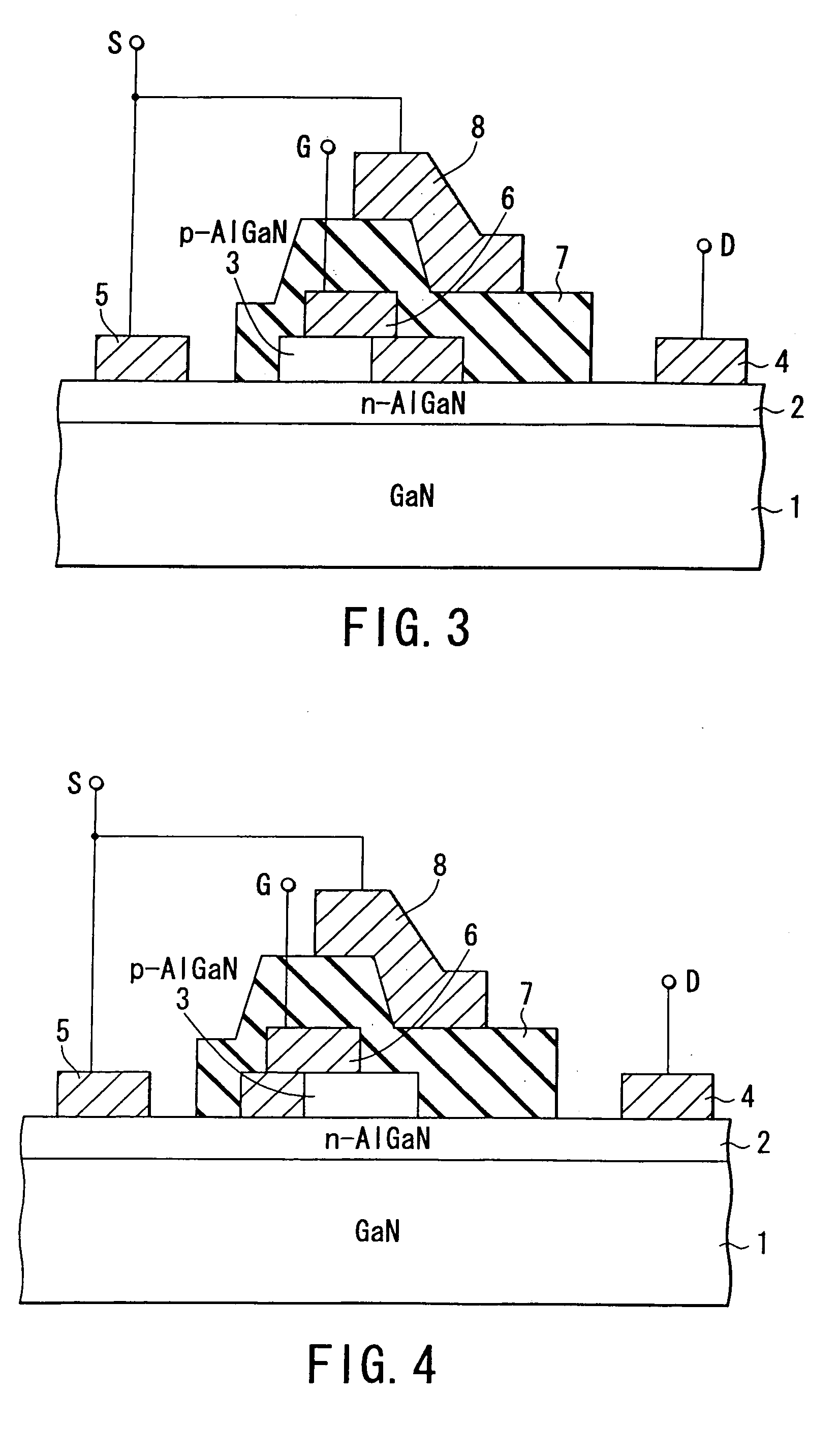

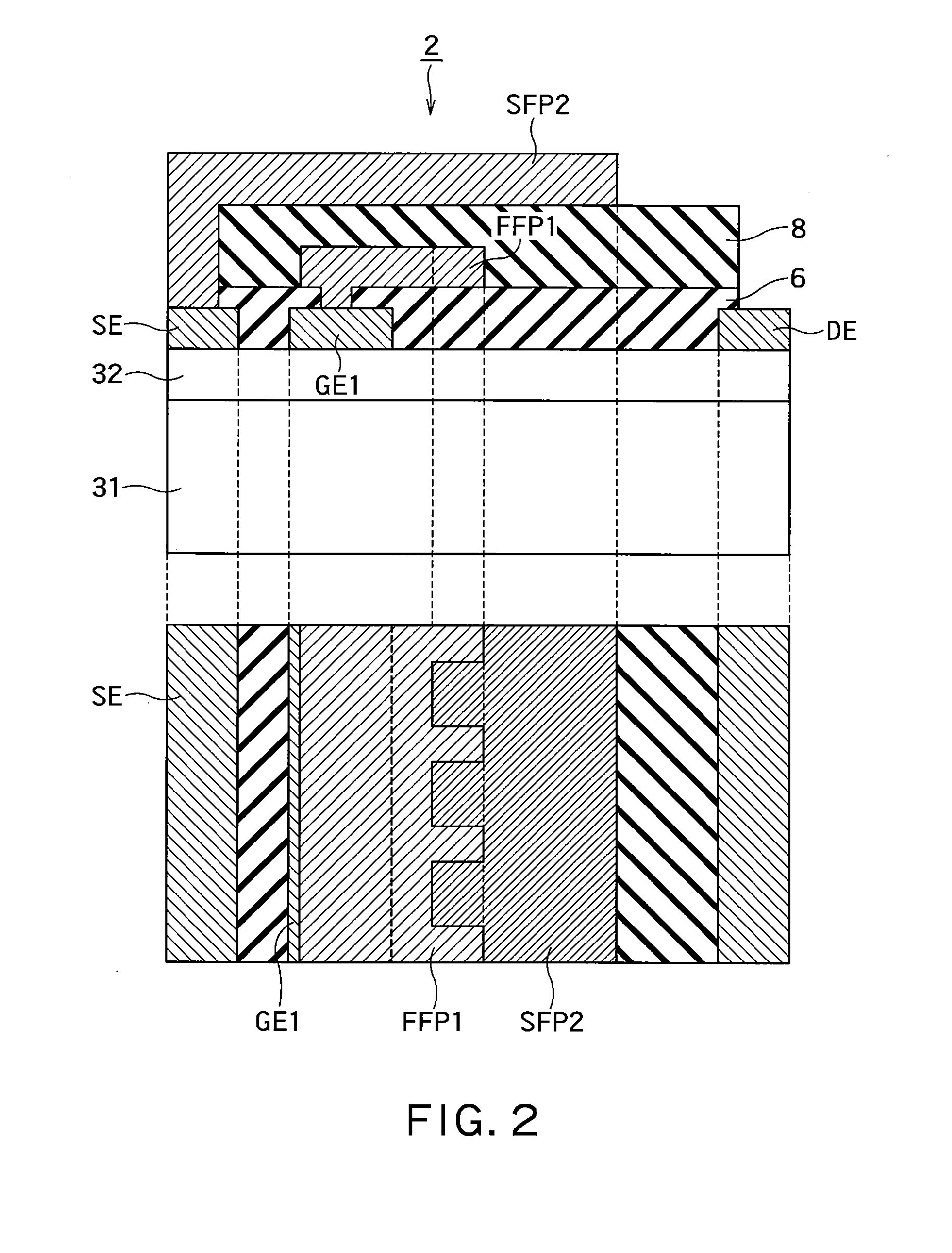

Semiconductor device

ActiveUS20050189559A1Semiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorDevice material

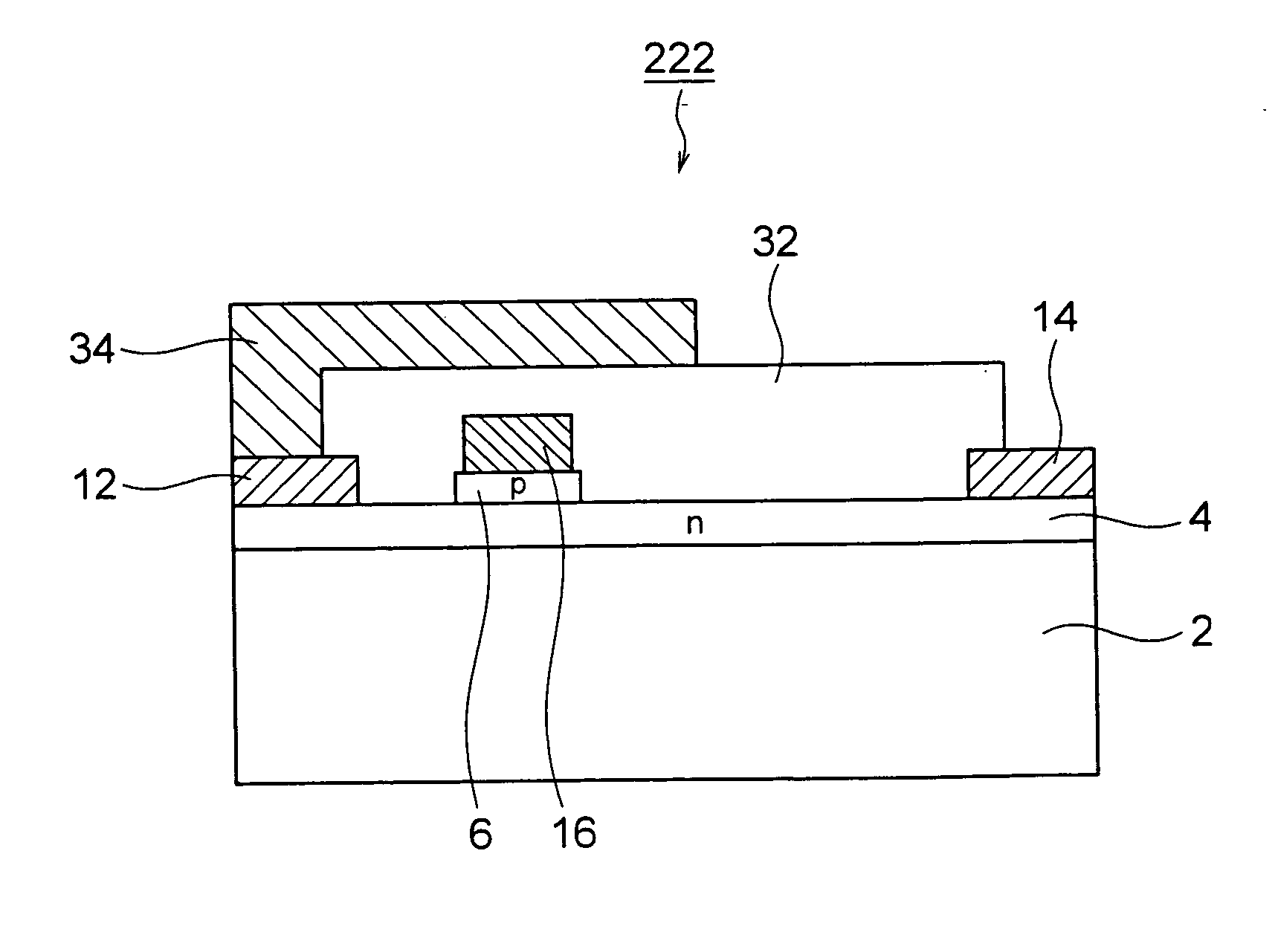

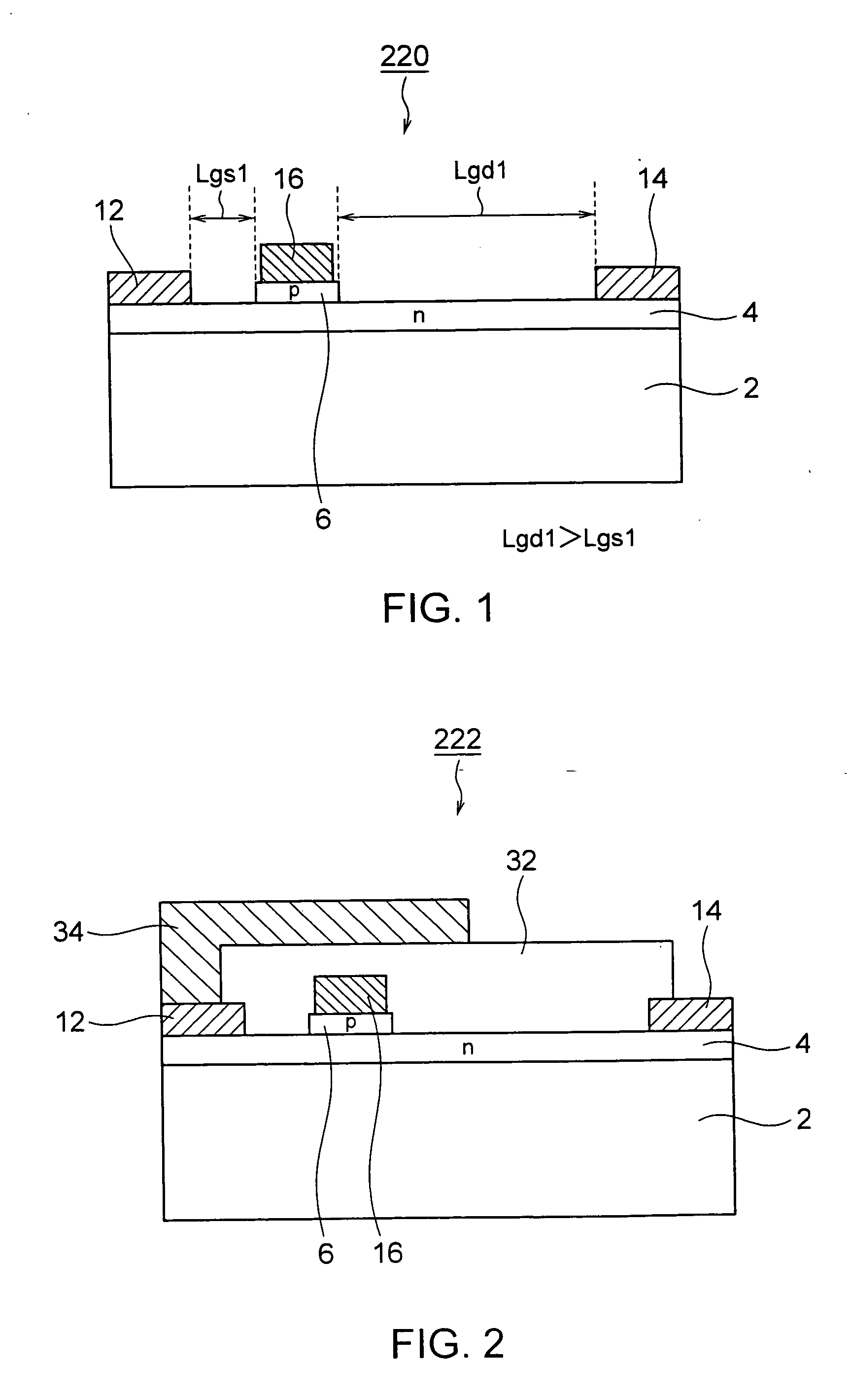

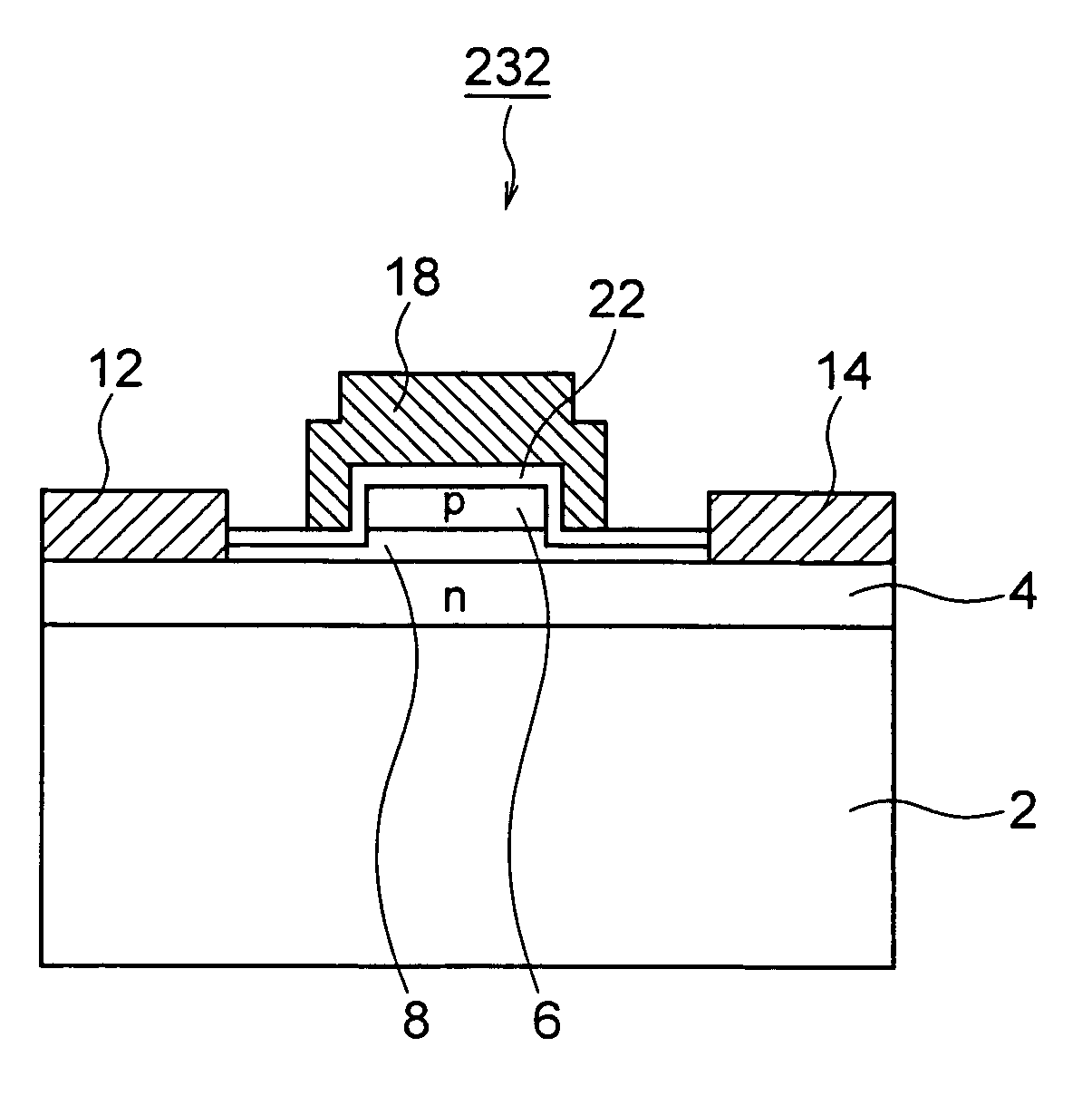

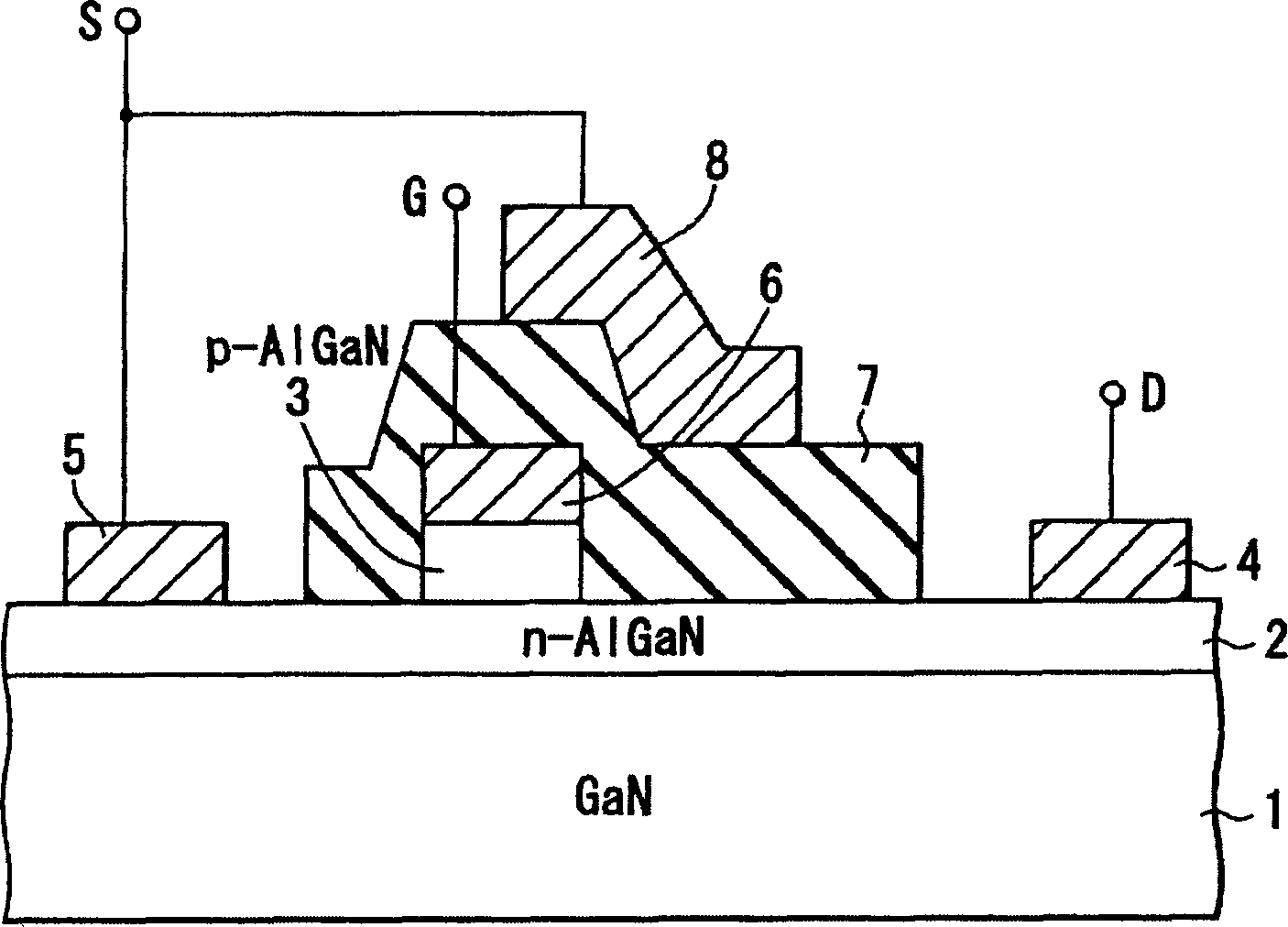

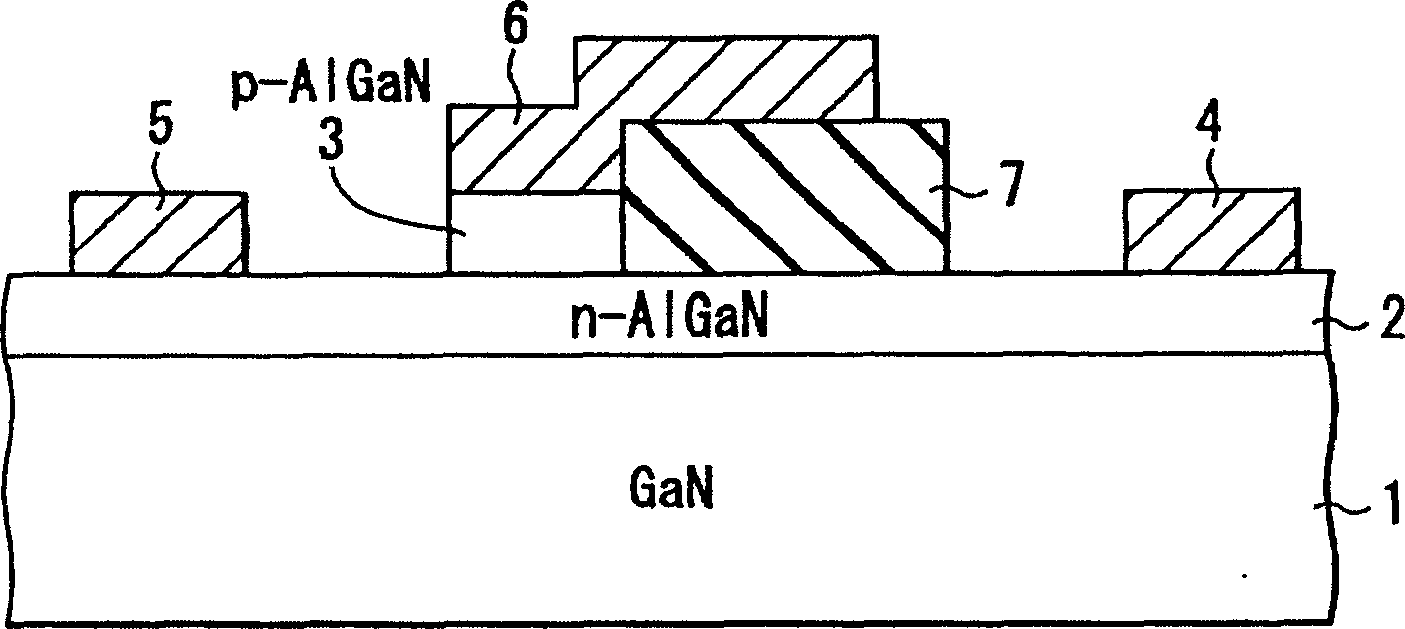

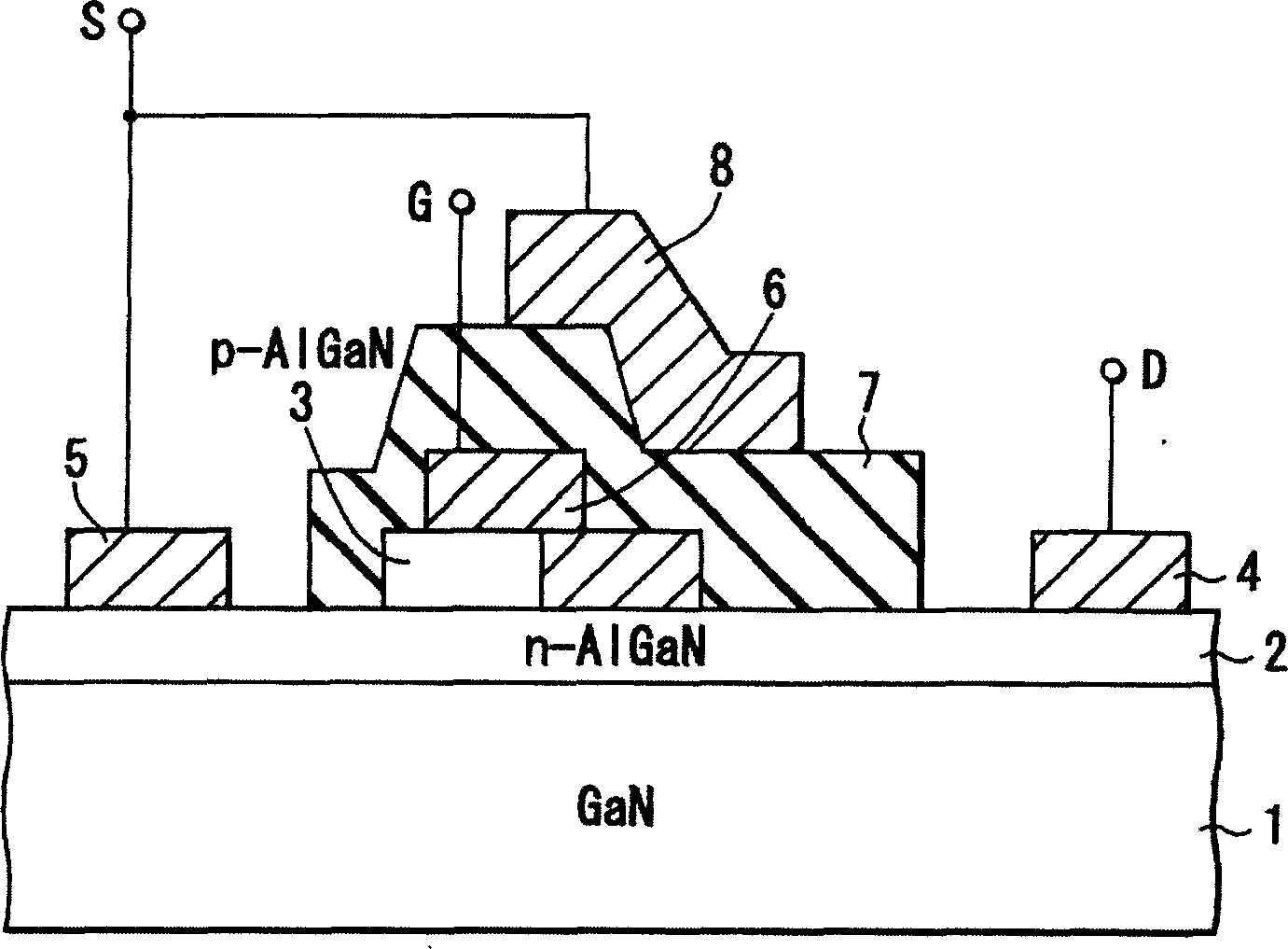

A semiconductor device includes: a first semiconductor layer represented by a composition formula AlxGa1-xN(0≦x≦1); a first conductivity type or non-doped second semiconductor layer represented by a composition formula AlyGa1-yN (0≦y≦1, x<y) and is formed on the first semiconductor layer; a second conductivity type third semiconductor layer represented by a composition formula AlxGa1-xN (0≦x≦1) and is selectively formed on the second semiconductor layer; a gate electrode formed on the third semiconductor layer; a source electrode electrically connected to the second semiconductor layer; and a drain electrode electrically connected to the second semiconductor layer; wherein the distance between the drain electrode and the third semiconductor layer is longer than the distance between the source electrode and the third semiconductor layer.

Owner:KK TOSHIBA

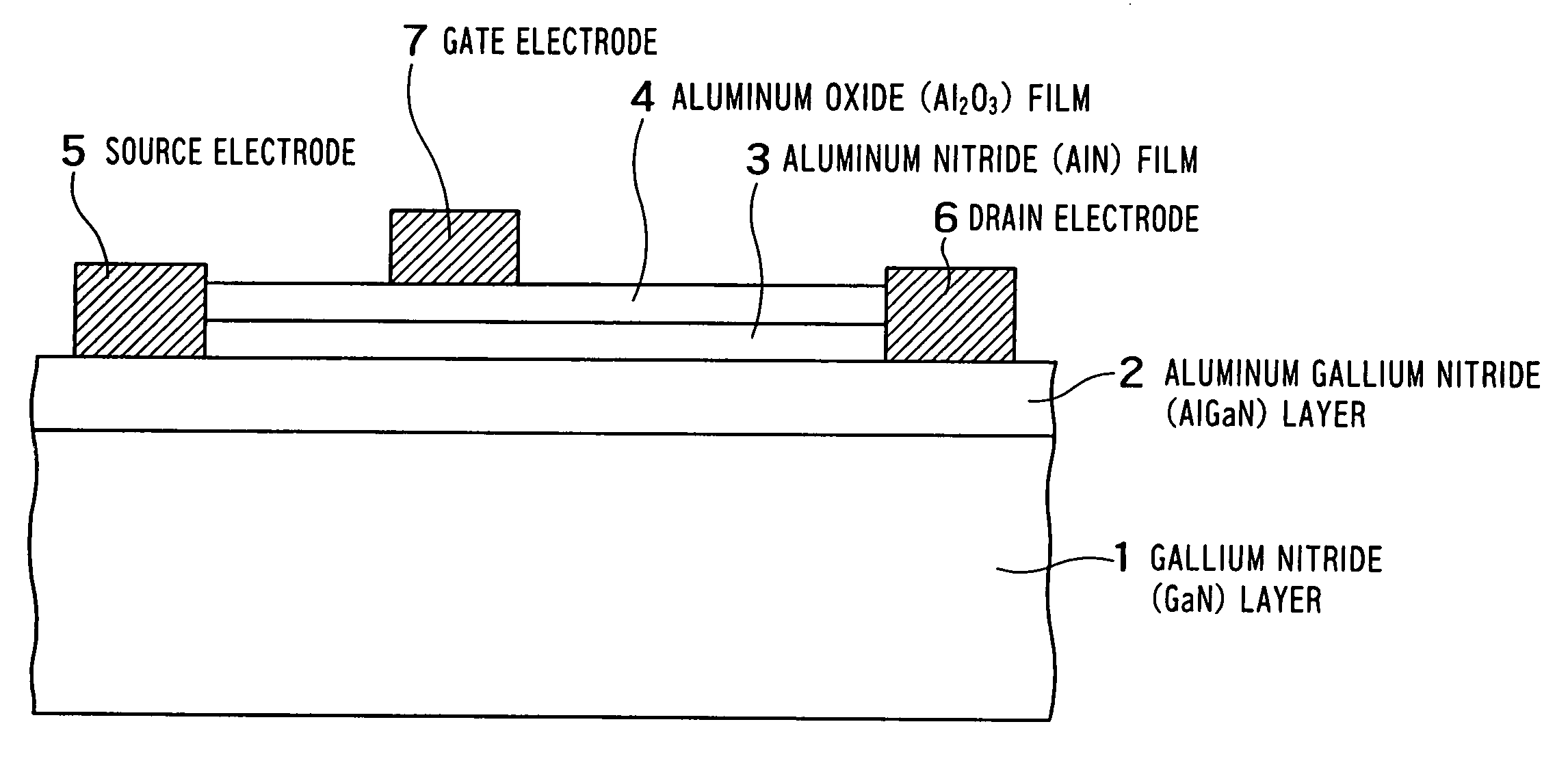

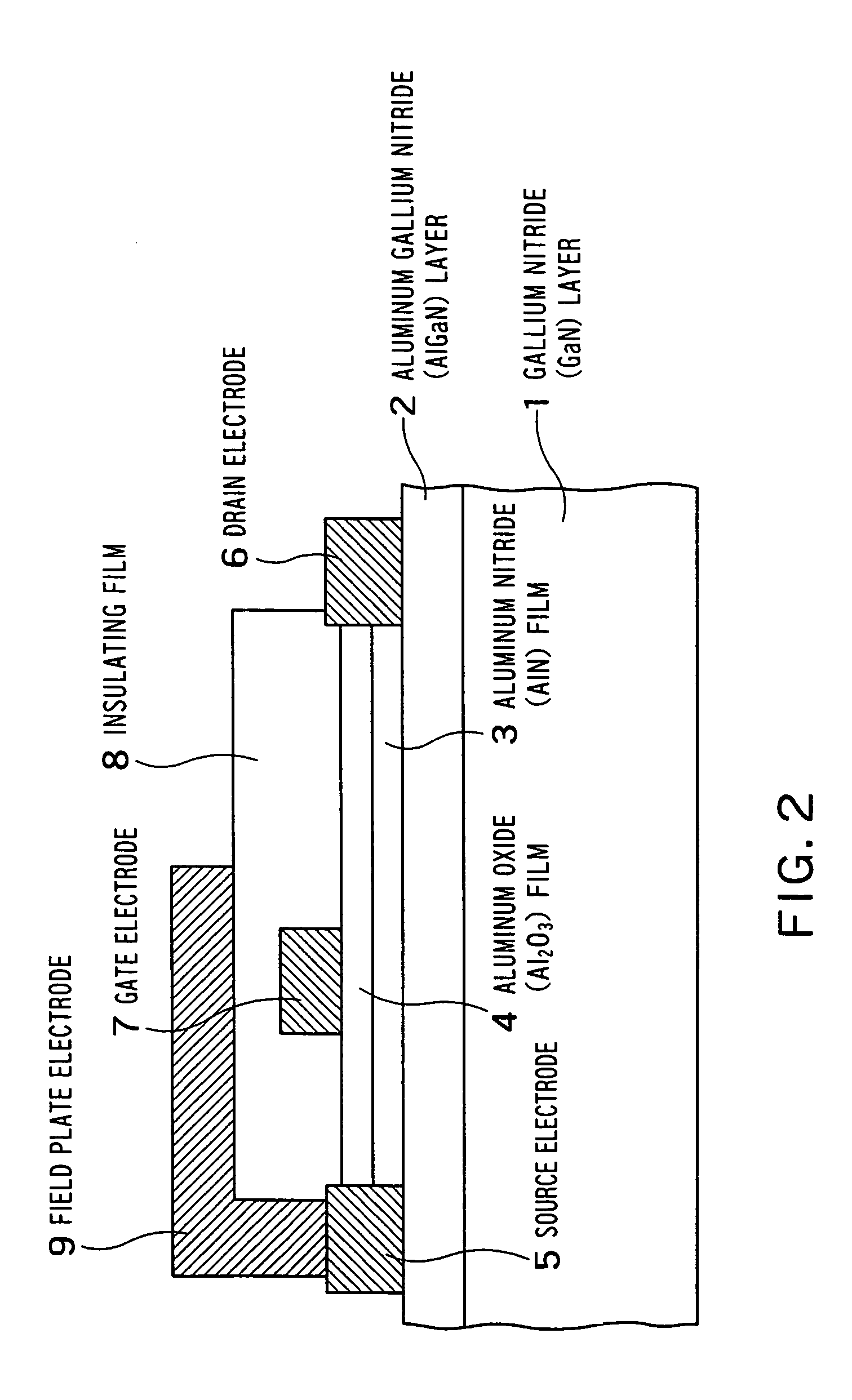

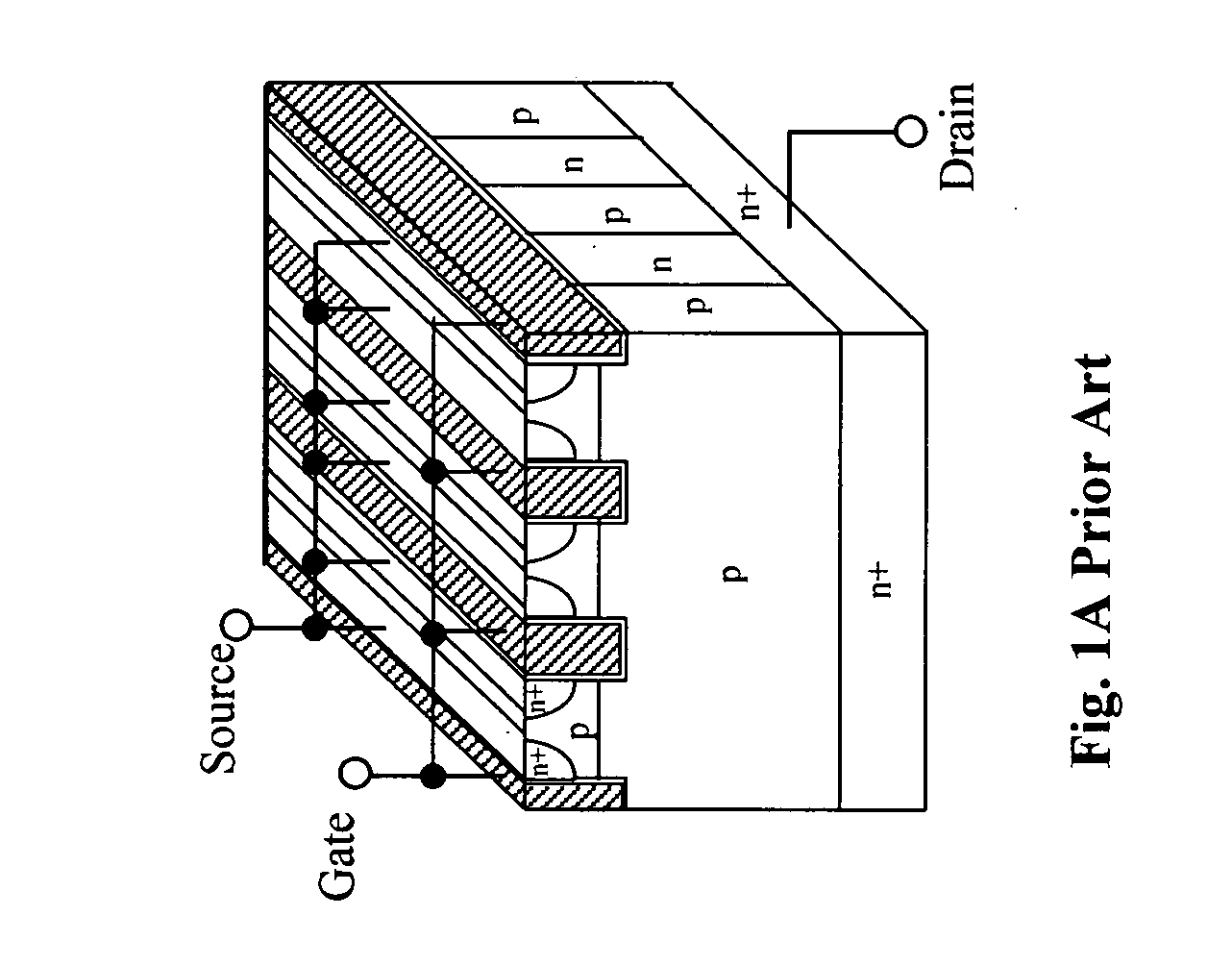

Nitride semiconductor device such as transverse power FET for high frequency signal amplification or power control

InactiveUS7304331B2Semiconductor/solid-state device manufacturingSemiconductor devicesNon dopedSignal amplification

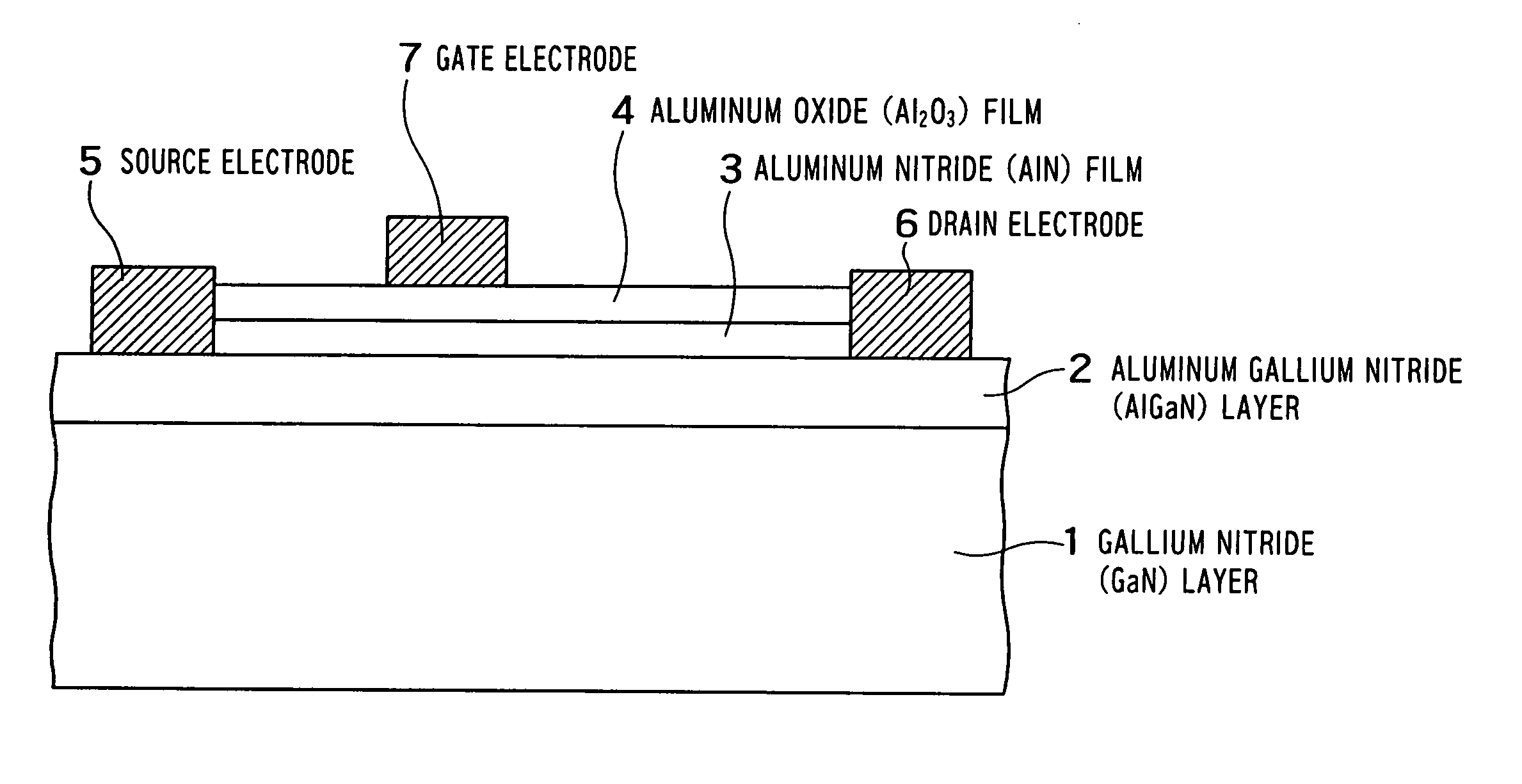

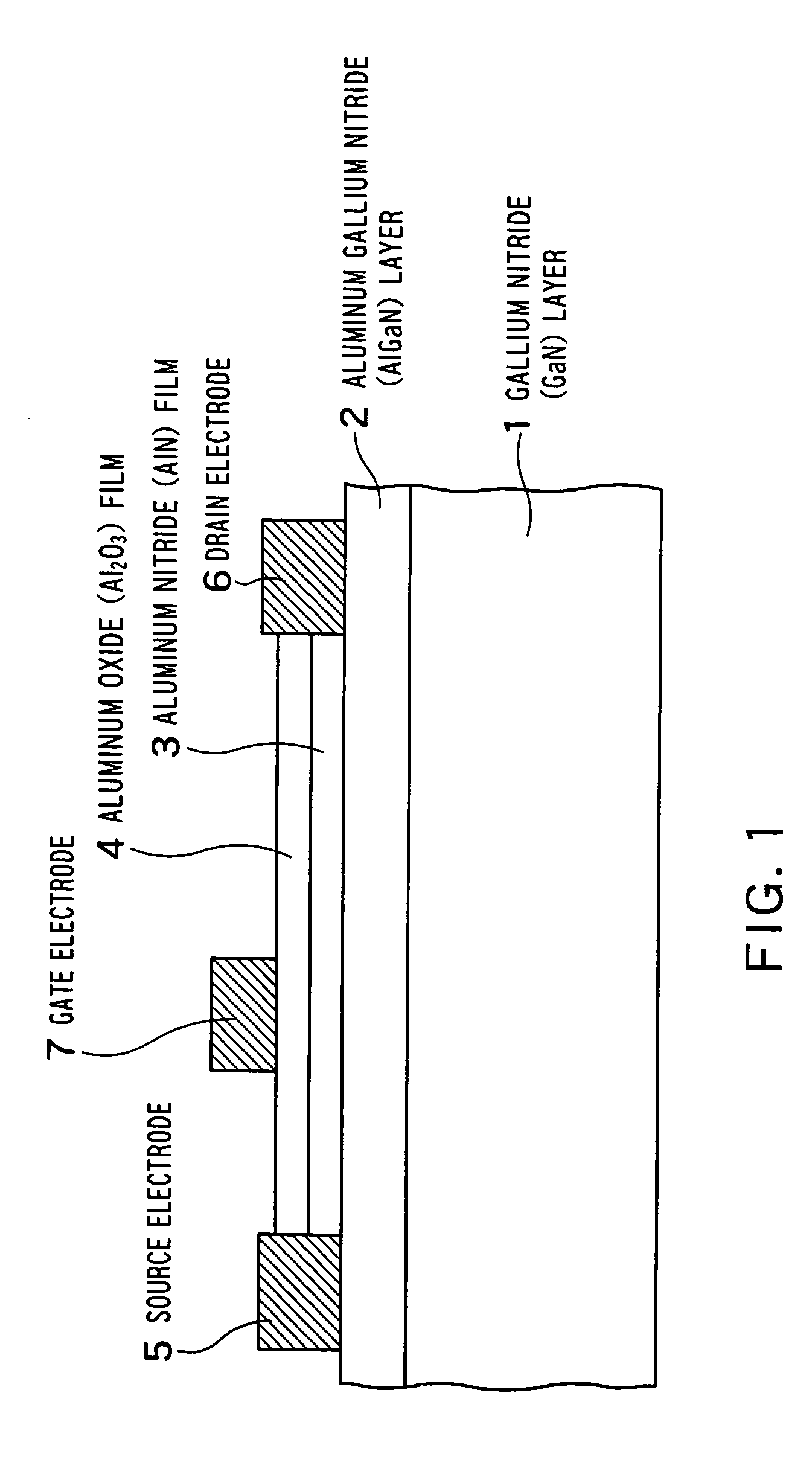

A nitride semiconductor device according to one embodiment of the present invention includes: a non-doped first aluminum gallium nitride (AlxGa1-xN (0≦x≦1)) layer which is formed as a channel layer; a non-doped or n type second aluminum gallium nitride (AlyGa1-yN (0≦y≦1, x <y)) layer which is formed on the first aluminum gallium nitride layer as a barrier layer; an aluminum nitride (AlN) film which is formed on the second aluminum gallium nitride layer as a gate insulating film lower layer; an aluminum oxide (AL2O3) film which is formed on the aluminum nitride film as a gate insulating film upper layer; a source electrode and a drain electrode which are formed as first and second main electrodes to be electrically connected to the second aluminum gallium nitride layer, respectively; and a gate electrode which is formed on the aluminum oxide film as a control electrode.

Owner:KK TOSHIBA

Nitride semiconductor device

InactiveUS20060011915A1Semiconductor/solid-state device manufacturingSemiconductor devicesNon dopedNitride semiconductors

A nitride semiconductor device according to one embodiment of the present invention comprises: a non-doped first aluminum gallium nitride (AlxGa1-xN (0≦x≦1)) layer which is formed as a channel layer; a non-doped or n type second aluminum gallium nitride (AlyGa1-yN (0≦x≦1,x<y)) layer which is formed on the first aluminum gallium nitride layer as a barrier layer; an aluminum nitride (AlN) film which is formed on the second aluminum gallium nitride layer as a gate insulating film lower layer; an aluminum oxide (Al2O3) film which is formed on the aluminum nitride film as a gate insulating film upper layer; a source electrode and a drain electrode which are formed as first and second main electrodes to be electrically connected to the second aluminum gallium nitride layer, respectively; and a gate electrode which is formed on the aluminum oxide film as a control electrode.

Owner:KK TOSHIBA

Semiconductor device using a nitride semiconductor

ActiveUS7038252B2Semiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorDevice material

Owner:KK TOSHIBA

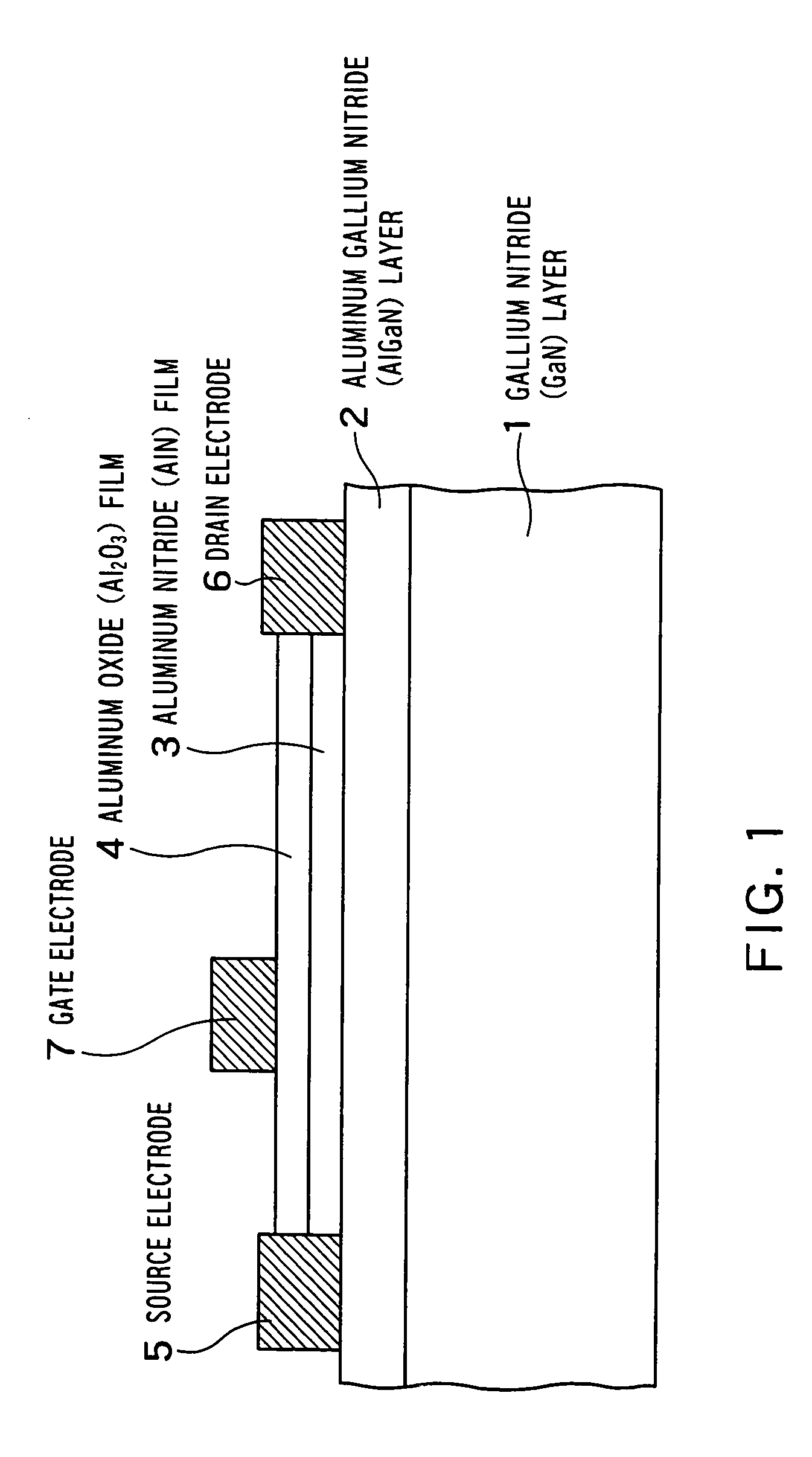

Power semiconductor device

InactiveUS20050110042A1Improve rendering capabilitiesResistanceTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceNon doped

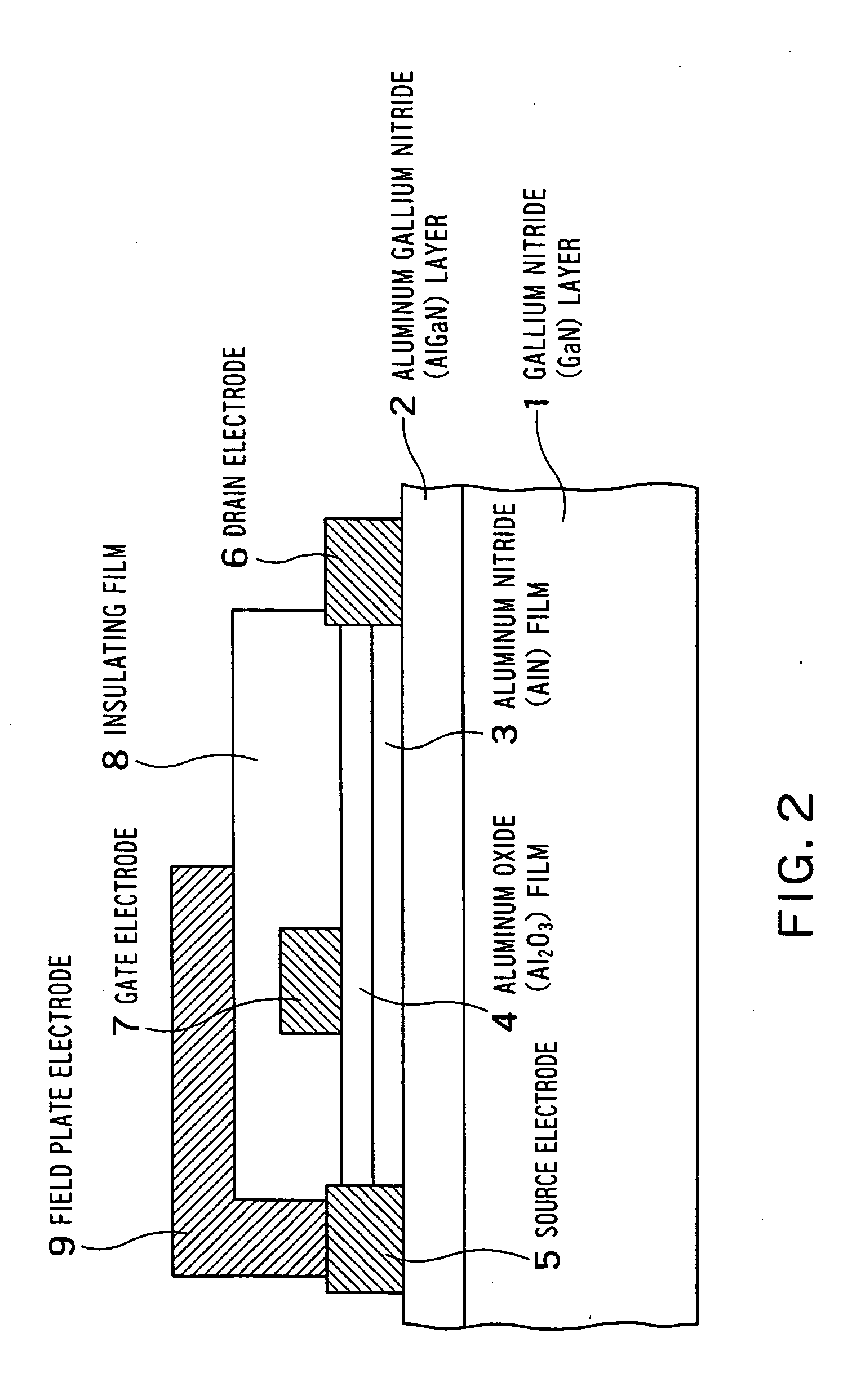

A power semiconductor device including a non-doped GaN channel layer, an n-type Al0.2Ga0.8N barrier layer formed on the channel layer, a p-type Al0.1Ga0.9N semiconductor layer selectively formed on the barrier layer, a drain electrode positioned at one of both sides of the semiconductor layer and formed on the barrier layer, an insulating film formed on the barrier layer adjacent to the semiconductor layer between at least semiconductor layer and drain electrode, and a field plate electrode formed on the insulating film.

Owner:KK TOSHIBA

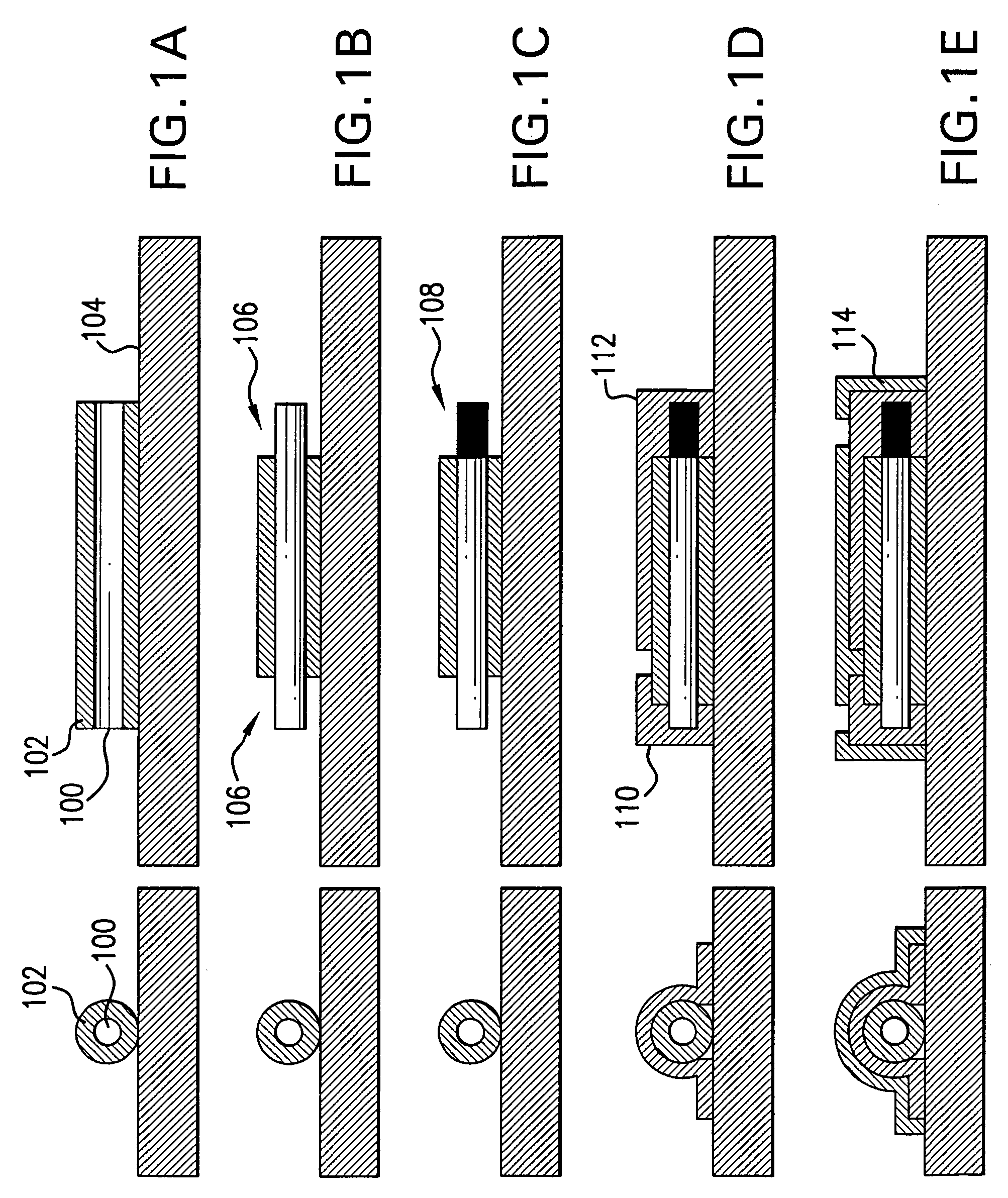

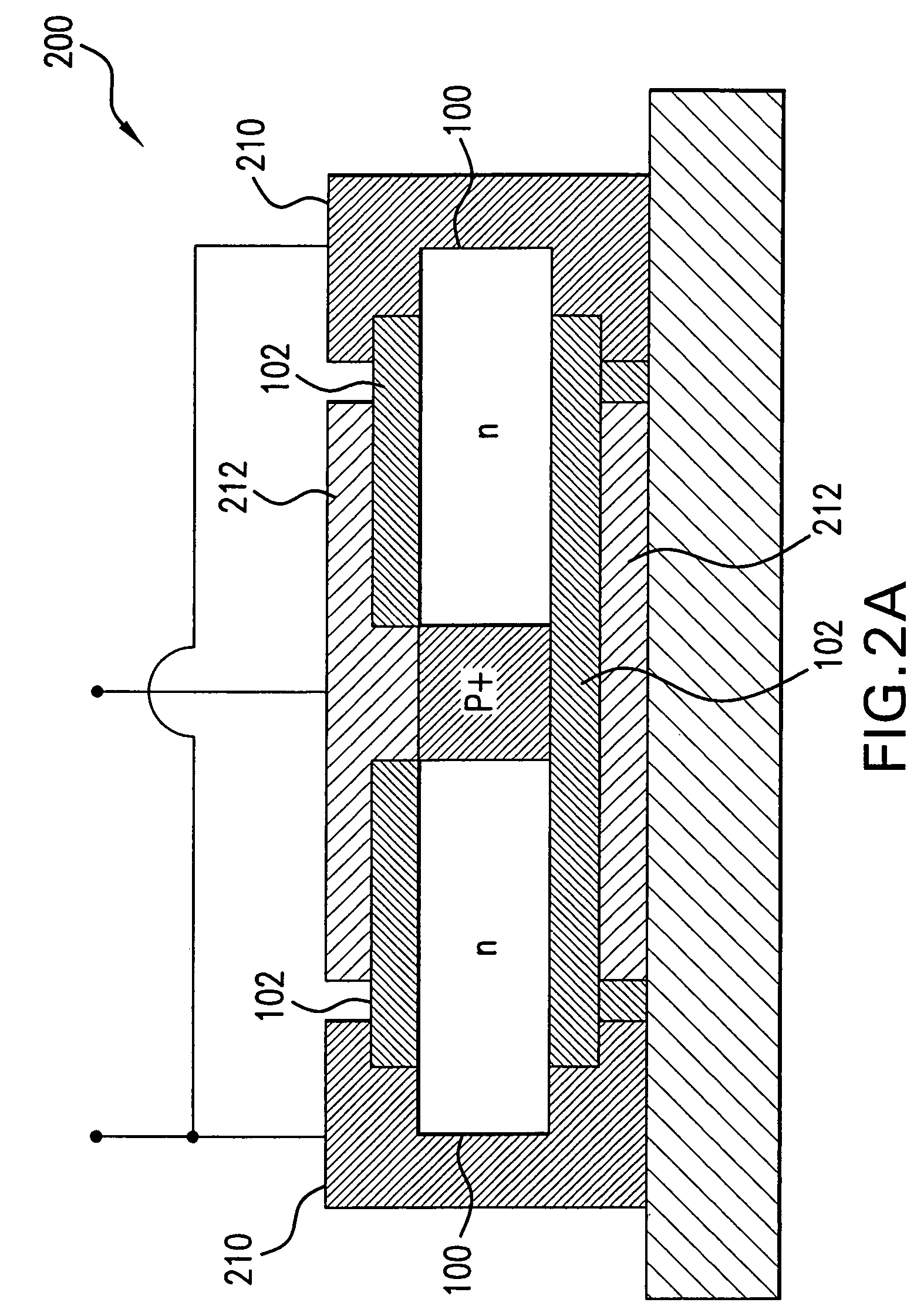

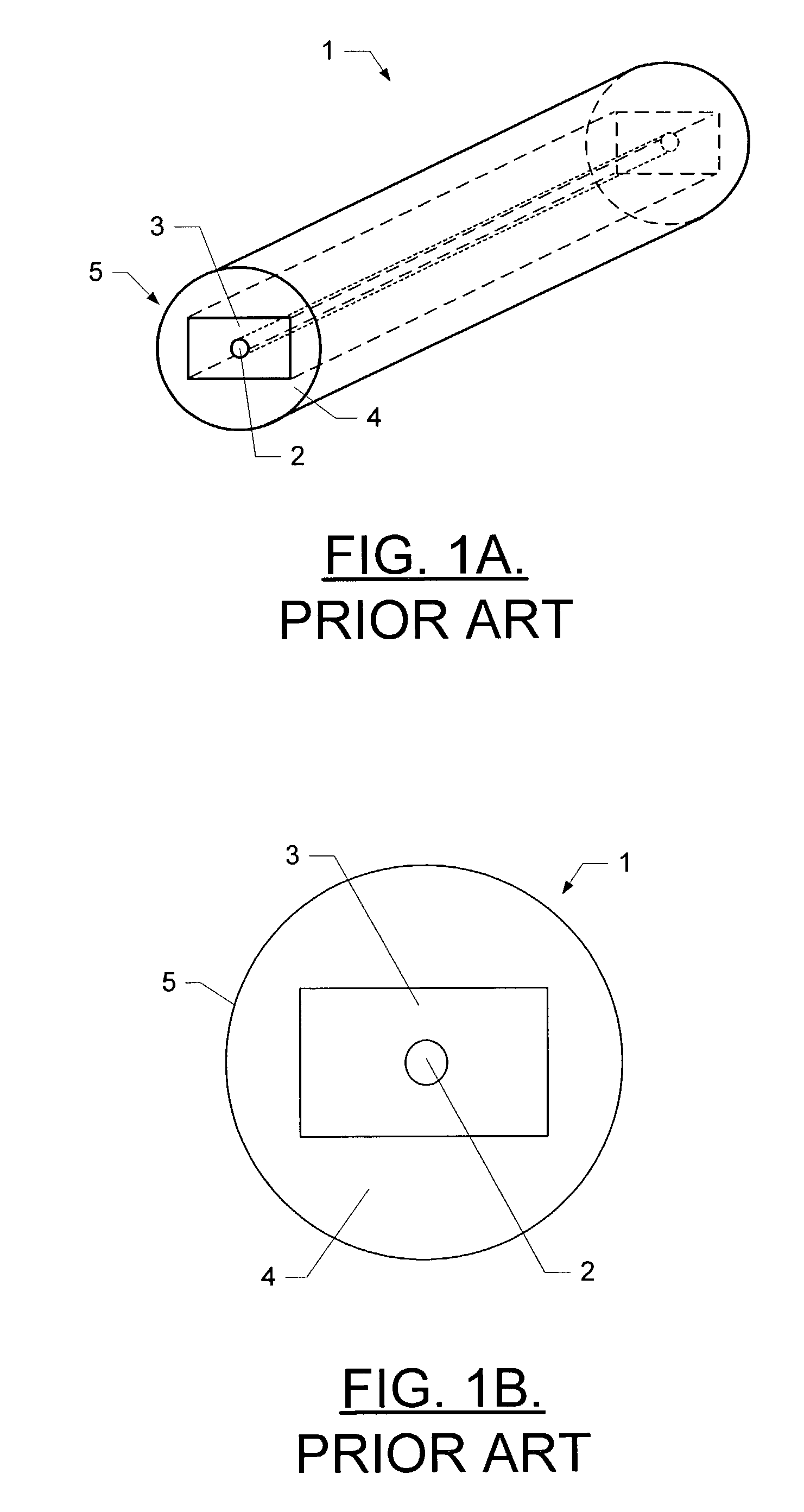

Nanowire varactor diode and methods of making same

InactiveUS7115971B2Facilitate conductionNanoinformaticsSemiconductor/solid-state device manufacturingNanowireNon doped

A nanowire varactor diode and methods of making the same are disclosed. The structure comprises a coaxial capacitor running the length of the semiconductor nanowire. In one embodiment, a semiconductor nanowire of a first conductivity type is deposited on a substrate. An insulator is formed on at least a portion of the nanowire's surface. A region of the nanowire is doped with a second conductivity type material. A first electrical contact is formed on at least part of the insulator and the doped region. A second electrical contact is formed on a non-doped potion of the nanowire. During operation, the conductivity type at the surface of the nanowire inverts and a depletion region is formed upon application of a voltage to the first and second electrical contacts. The varactor diode thereby exhibits variable capacitance as a function of the applied voltage.

Owner:NANOSYS INC

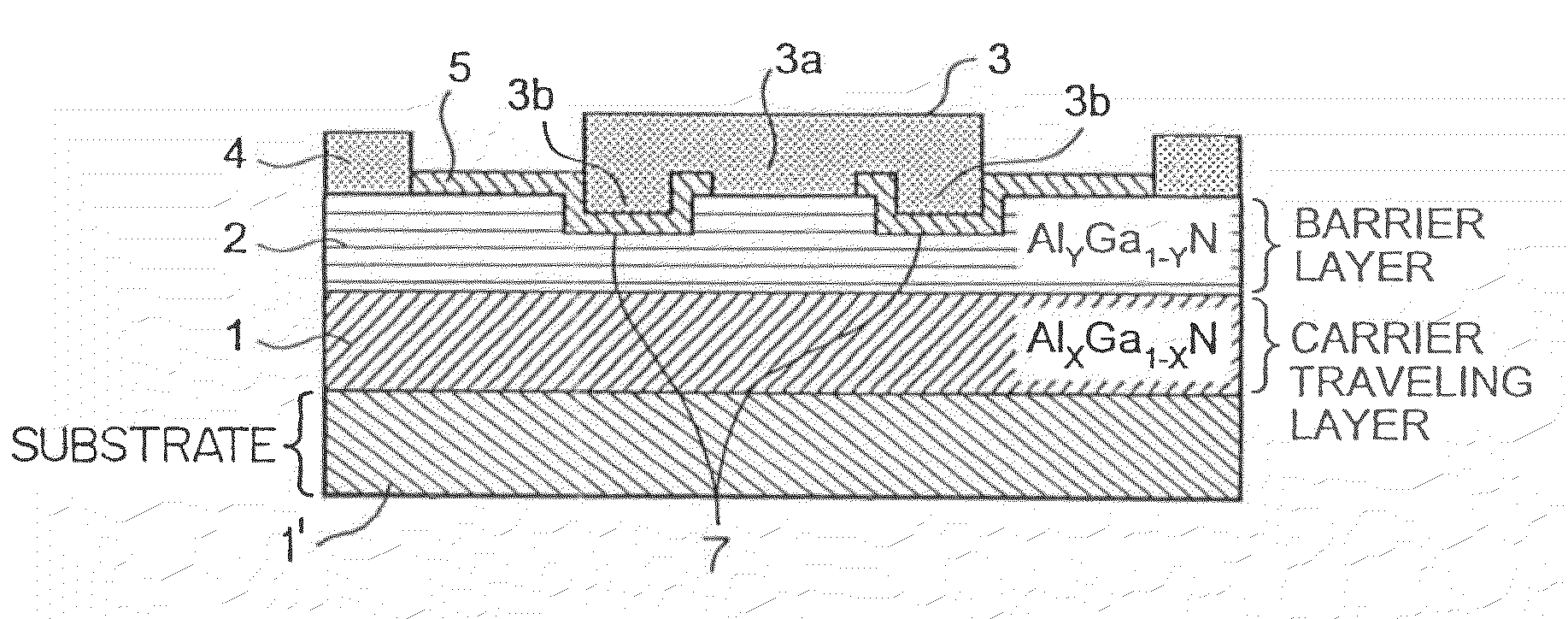

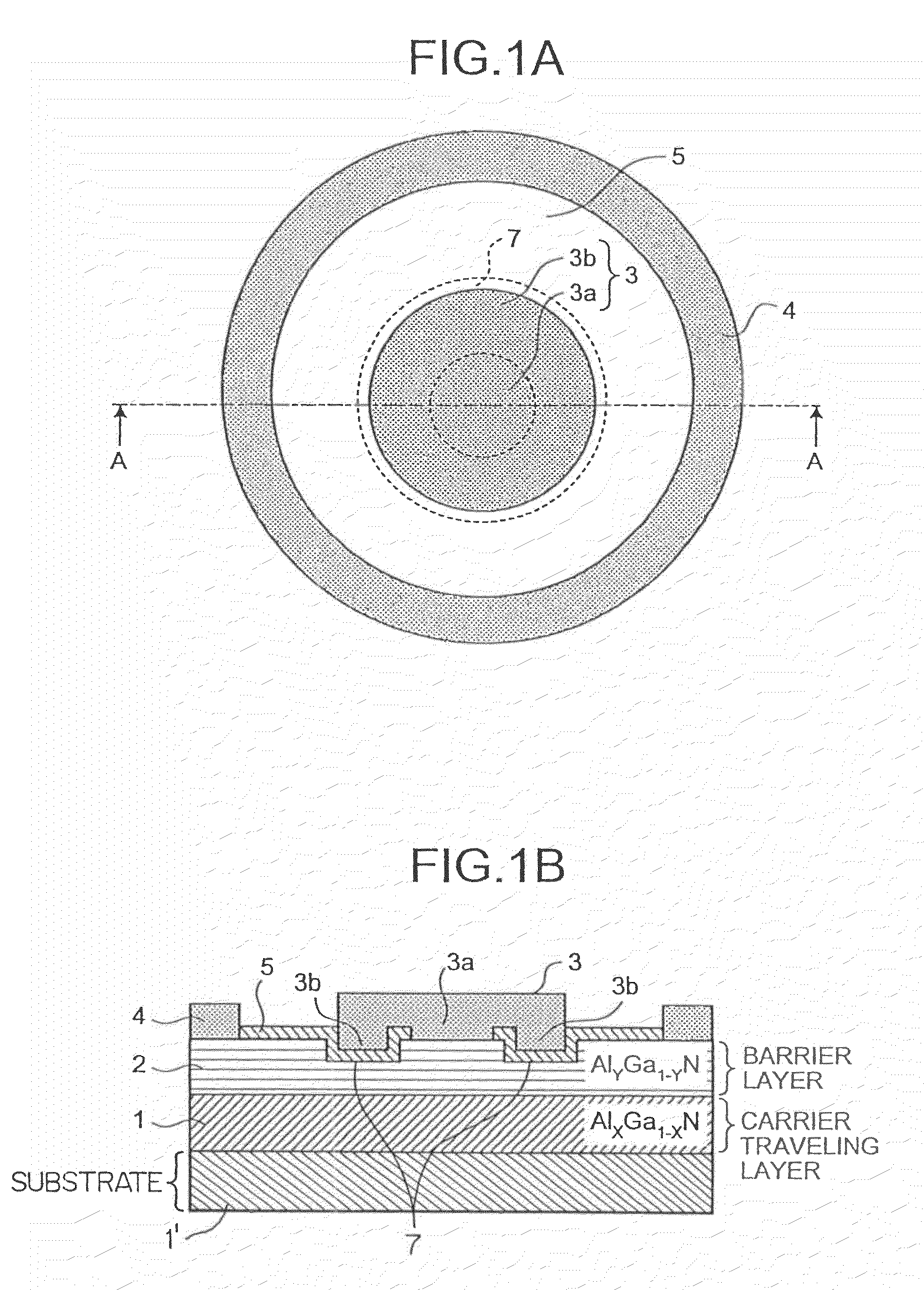

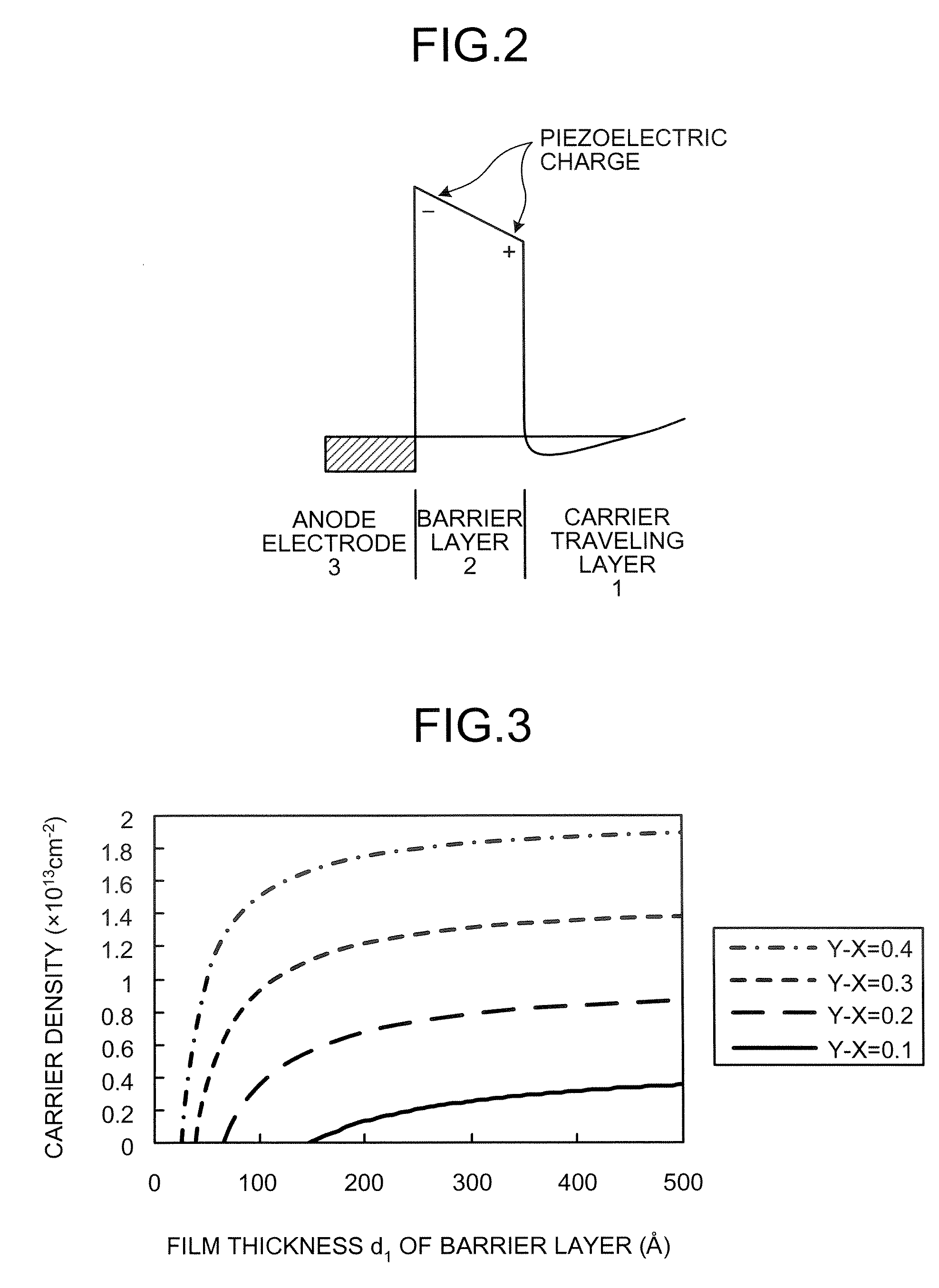

Nitride-based semiconductor device

ActiveUS20070145390A1Solid-state devicesSemiconductor/solid-state device manufacturingDevice materialNon doped

A nitride-based semiconductor device includes a diode provided on a semiconductor substrate. The diode contains a first nitride-based semiconductor layer made of non-doped AlXGa1-XN (0≦X<1); a second nitride-based semiconductor layer made of non-doped or n-type AlYGa1-YN (0≦Y≦1, X<Y) having a lattice constant smaller than that of the first nitride-based semiconductor layer; a first electrode formed on the second nitride-based semiconductor layer; a second electrode formed on the second nitride-based semiconductor layer; and an insulating film that covers the second nitride-based semiconductor layer below a peripheral portion of the first electrode. In the diode, a recess structure portion is formed at a position near the peripheral portion of the first electrode on the second nitride-based semiconductor layer, and the first electrode covers the second nitride-based semiconductor layer and at least a part of the insulating film.

Owner:KK TOSHIBA

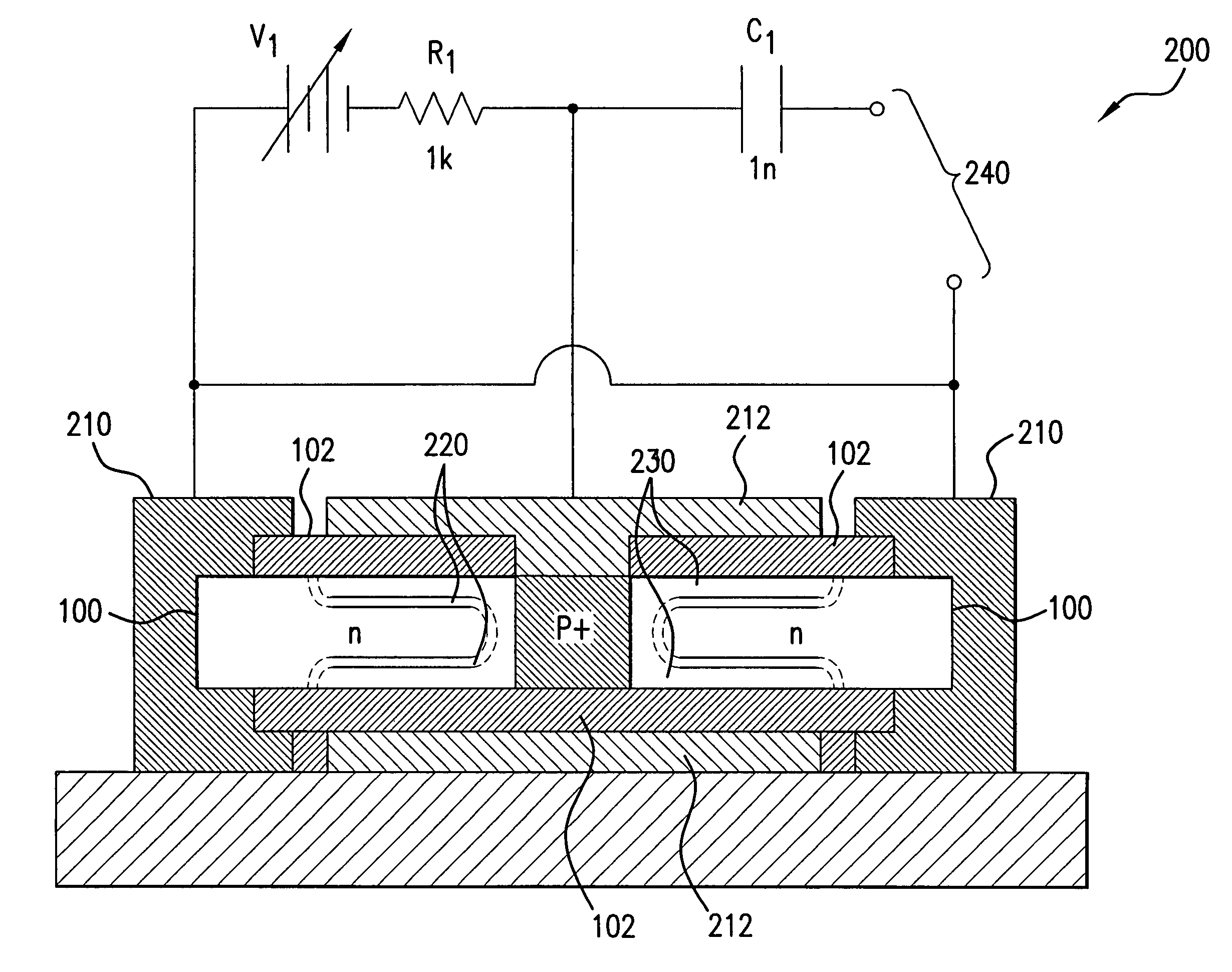

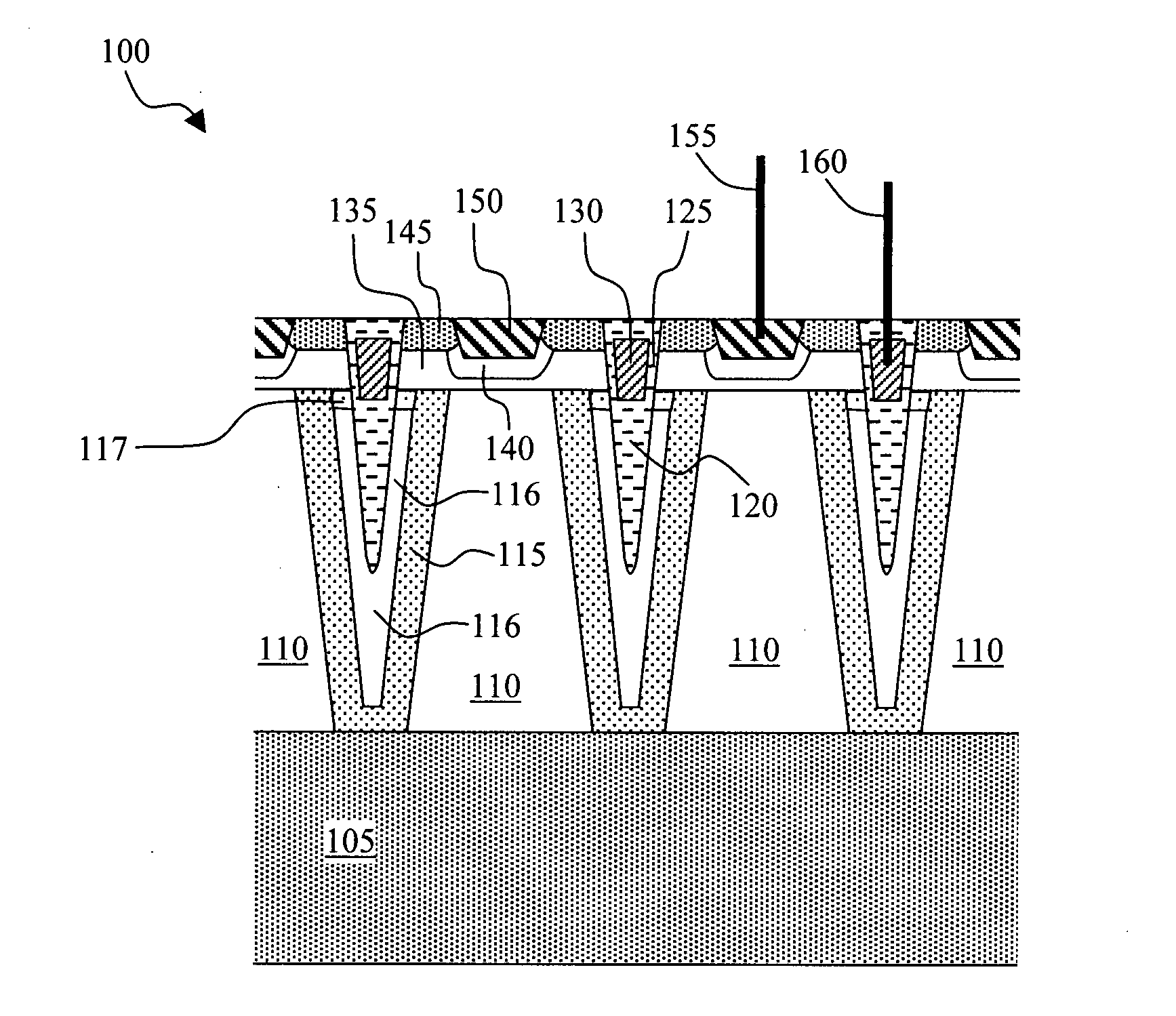

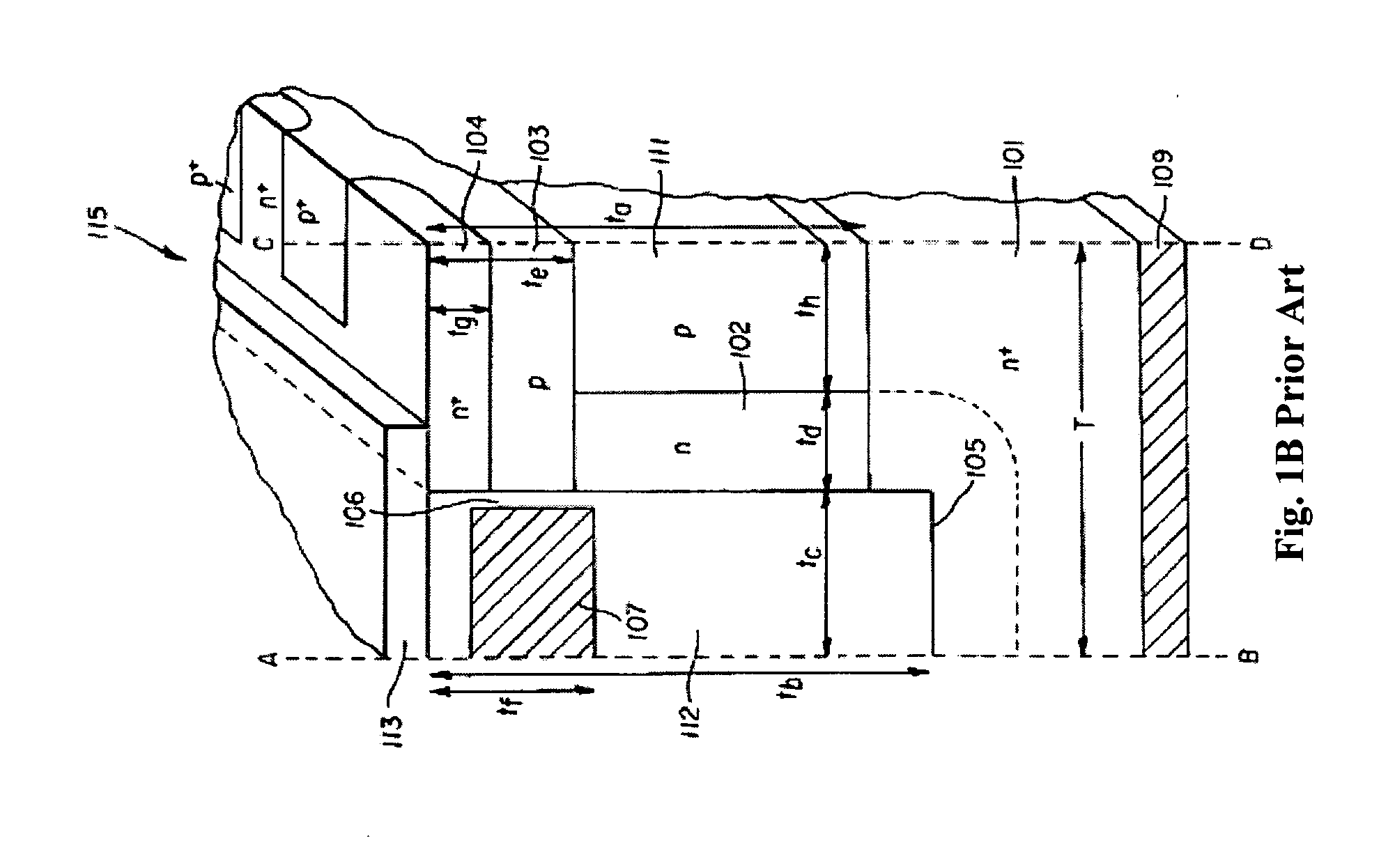

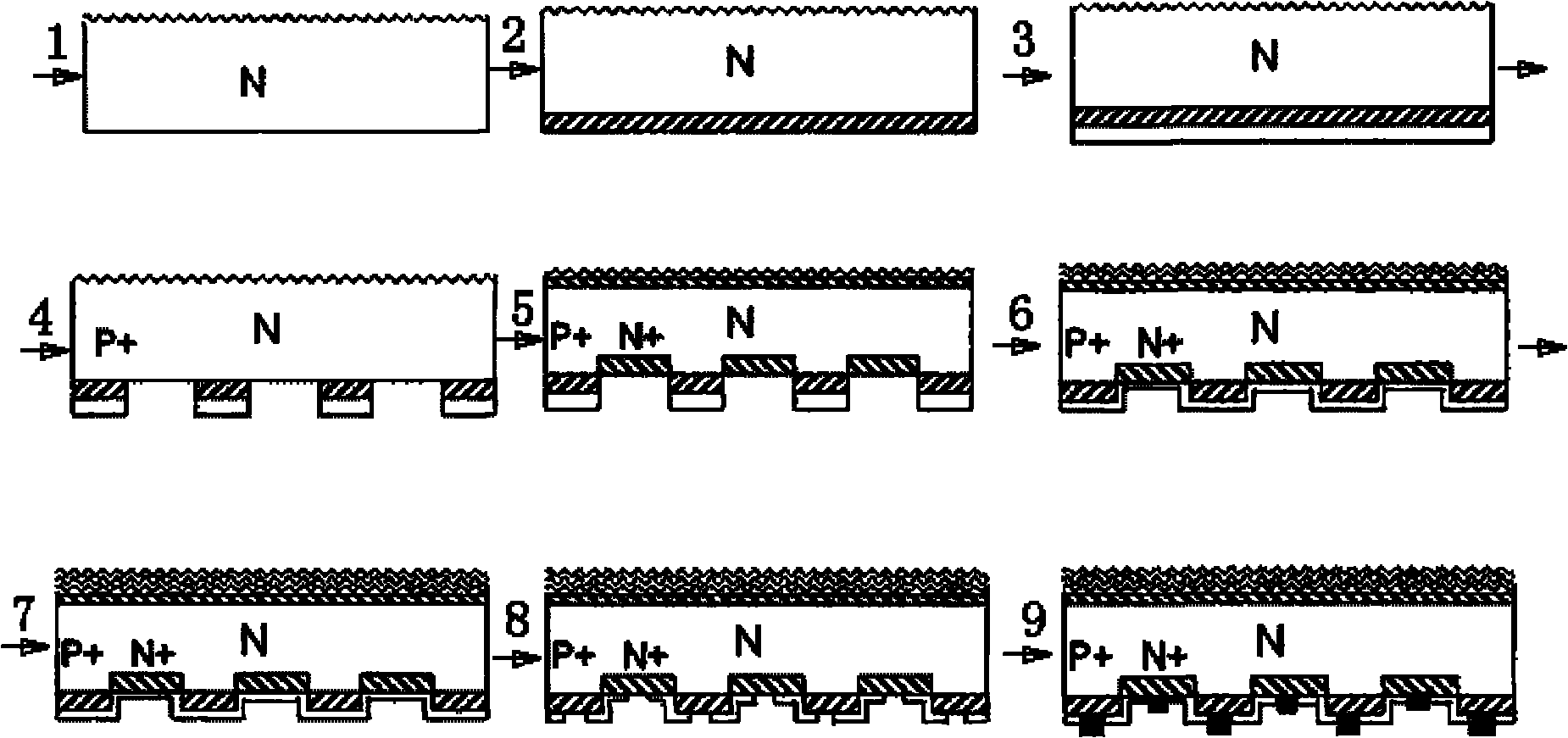

Configurations and methods for manufacturing devices with trench-oxide-nano-tube super-junctions

ActiveUS20100314682A1High production costEasy to fillSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringNon doped

This invention discloses semiconductor power device disposed on a semiconductor substrate of a first conductivity type. The semiconductor substrate supports an epitaxial layer of a second conductivity type thereon wherein the semiconductor power device is supported on a super-junction structure. The super-junction structure comprises a plurality of trenches opened from a top surface in the epitaxial layer; wherein each of the trenches having trench sidewalls covered with a first epitaxial layer of the first conductivity type to counter charge the epitaxial layer of the second conductivity type. A second epitaxial layer may be grown over the first epitaxial layer. Each of the trenches is filled with a non-doped dielectric material in a remaining trench gap space. Each of the trench sidewalls is opened with a tilted angle to form converging U-shaped trenches.

Owner:ALPHA & OMEGA SEMICON INC

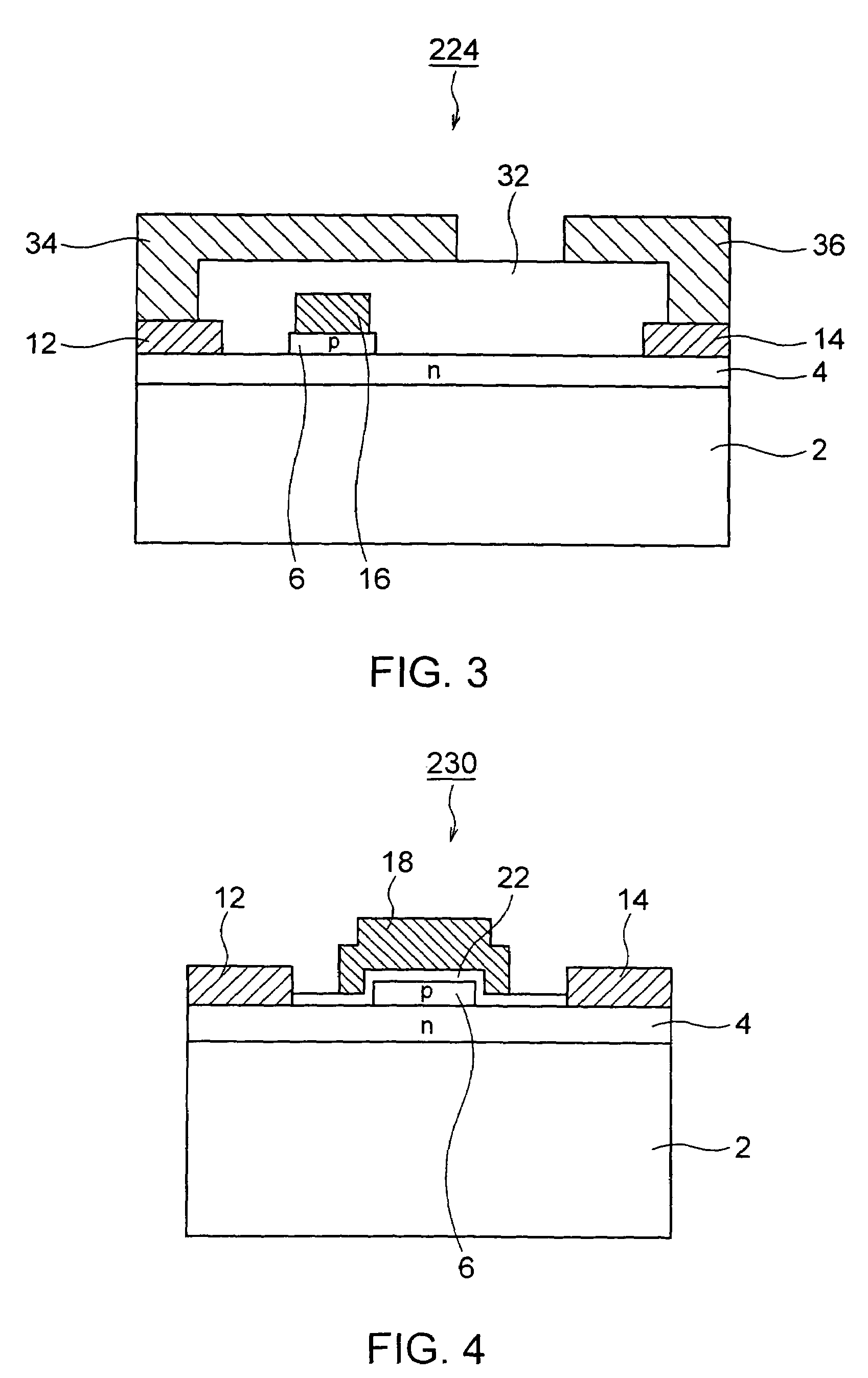

Power semiconductor device

InactiveUS6933544B2Improve rendering capabilitiesResistanceTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceNon doped

A power semiconductor device including a non-doped GaN channel layer, an n-type Al0.2Ga0.8N barrier layer formed on the channel layer, a p-type Al0.1Ga0.9N semiconductor layer selectively formed on the barrier layer, a drain electrode positioned at one of both sides of the semiconductor layer and formed on the barrier layer, an insulating film formed on the barrier layer adjacent to the semiconductor layer between at least semiconductor layer and drain electrode, and a field plate electrode formed on the insulating film.

Owner:KK TOSHIBA

Nitride-based semiconductor device

ActiveUS7449730B2Solid-state devicesSemiconductor/solid-state device manufacturingNon dopedLattice constant

A nitride-based semiconductor device includes a diode provided on a semiconductor substrate. The diode contains a first nitride-based semiconductor layer made of non-doped AlXGa1-XN (0≦X<1); a second nitride-based semiconductor layer made of non-doped or n-type AlYGa1-YN (0<Y≦1, X<Y) having a lattice constant smaller than that of the first nitride-based semiconductor layer; a first electrode formed on the second nitride-based semiconductor layer; a second electrode formed on the second nitride-based semiconductor layer; and an insulating film that covers the second nitride-based semiconductor layer below a peripheral portion of the first electrode. In the diode, a recess structure portion is formed at a position near the peripheral portion of the first electrode on the second nitride-based semiconductor layer, and the first electrode covers the second nitride-based semiconductor layer and at least a part of the insulating film.

Owner:KK TOSHIBA

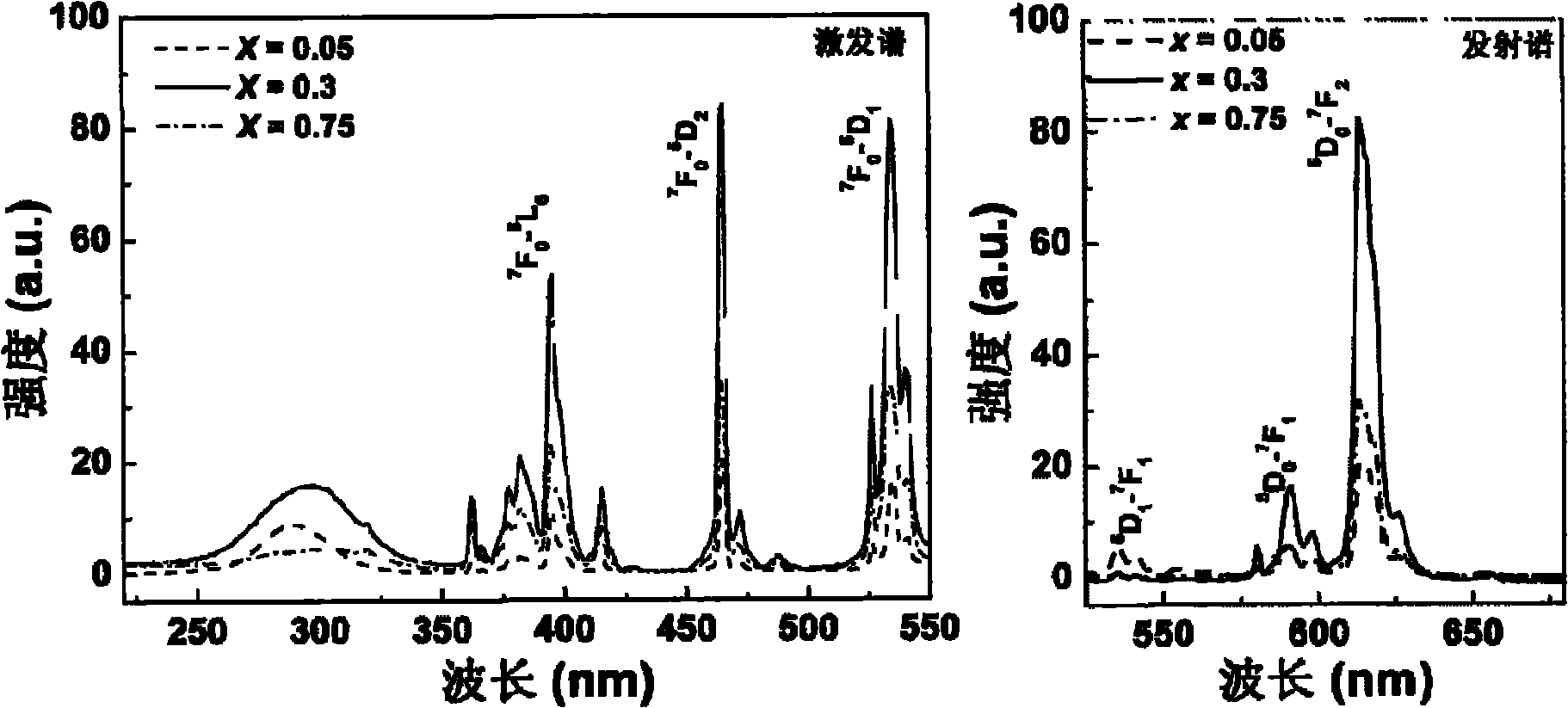

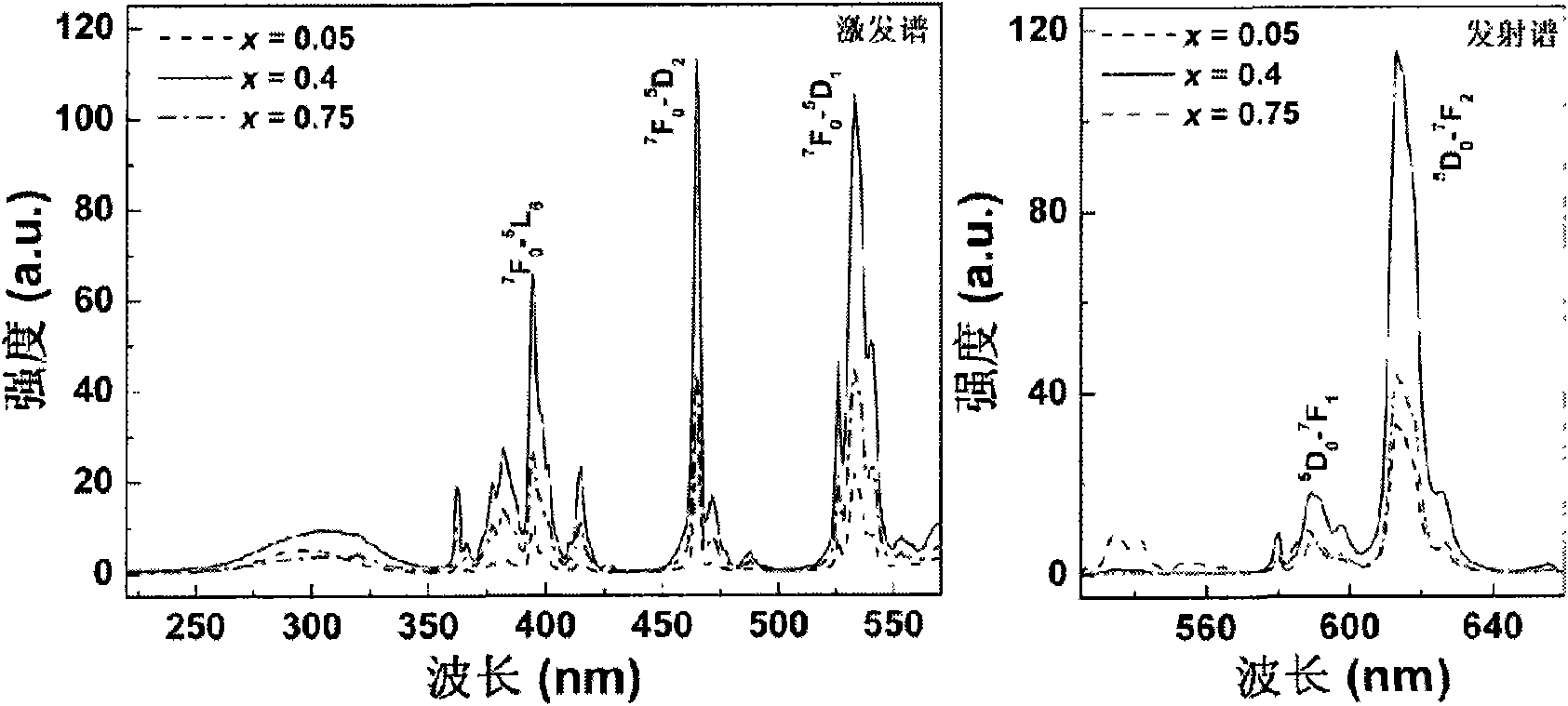

Niobate or tantalite fluorescent material used for white light LED and preparation method thereof

InactiveCN101921589AVariable crystal structureAdjustable Crystal Field StrengthGas discharge lamp usageLuminescent compositionsRare-earth elementEffect light

The invention relates to a niobate or tantalite fluorescent material used for a white light LED and a preparation method thereof. The material comprises the following components: non-doped niobate or tantalite, transition metal doped niobate or tantalite, T1 like ion doped niobate or tantalite with an s2 configuration, rare-earth element doped niobate or tantalite and T1 like ion and rear earth codoped niobate or tantalite. The materials in the invention can be used for the white light LED and related display and lighting devices. The invention has cheap and easy available materials, simple preparation process, stable material chemical property and excellent luminescence performance, and the prepared niobate or tantalite flourescent material is an ideal fluorescent powder candidate material for the white light LED.

Owner:SHANGHAI INST OF CERAMIC CHEM & TECH CHINESE ACAD OF SCI

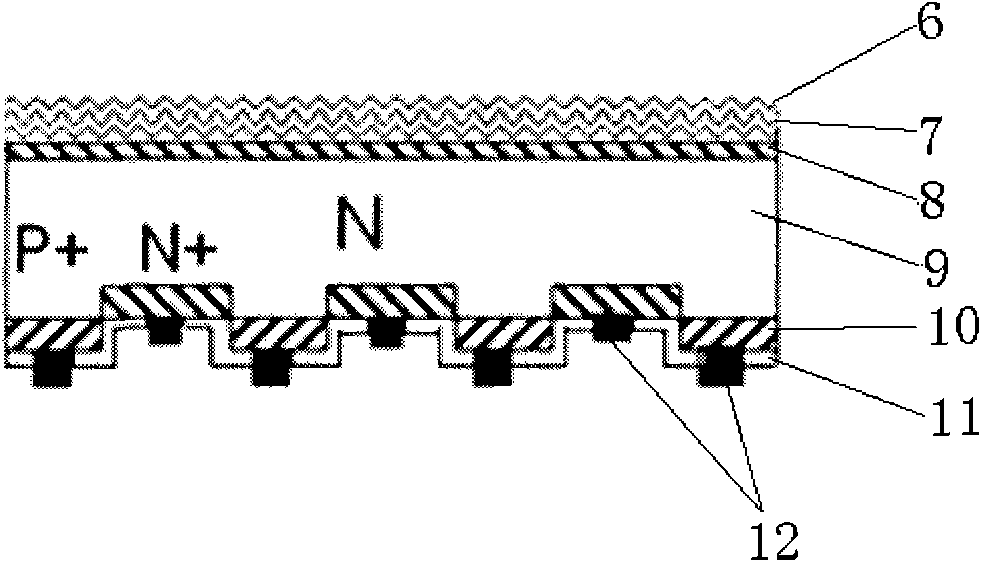

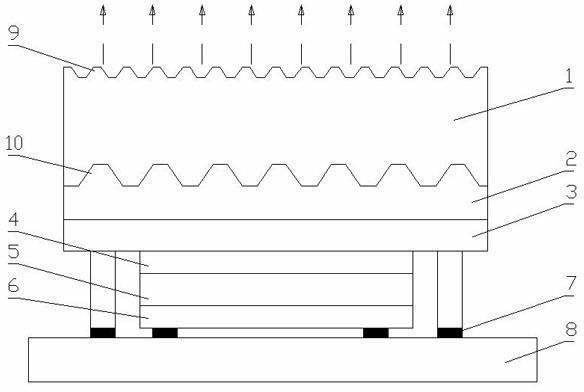

Method for manufacturing back contact solar energy batteries

ActiveCN101777603ASimple processEasy to implementFinal product manufactureSemiconductor devicesNon dopedSolar cell

The invention discloses a method for manufacturing back contact solar energy batteries, comprises the following steps of: firstly growing a P type doped silicon dioxide layer on an N type silicon chip; then growing a non-doped silicon dioxide layer on a P type doped layer; after that, printing a corrosive agent or an anti corrosive agent on the non-doped silicon dioxide layer to corrode the P type doped silicon dioxide layer and the non-doped silicon dioxide layer so as to form required patterns; and finally carrying out N type adulteration on the back face and the front face of the silicon chip to form an N type doped layer. The P type doped layer is protected by the non-doped silicon dioxide layer, and an N front surface field on the front face of the battery and a PN alternating doped layer on the back face of the battery are realized in the N type doped step at the same time, thereby reducing the diffusion step, reducing the cost and simplifying the process.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

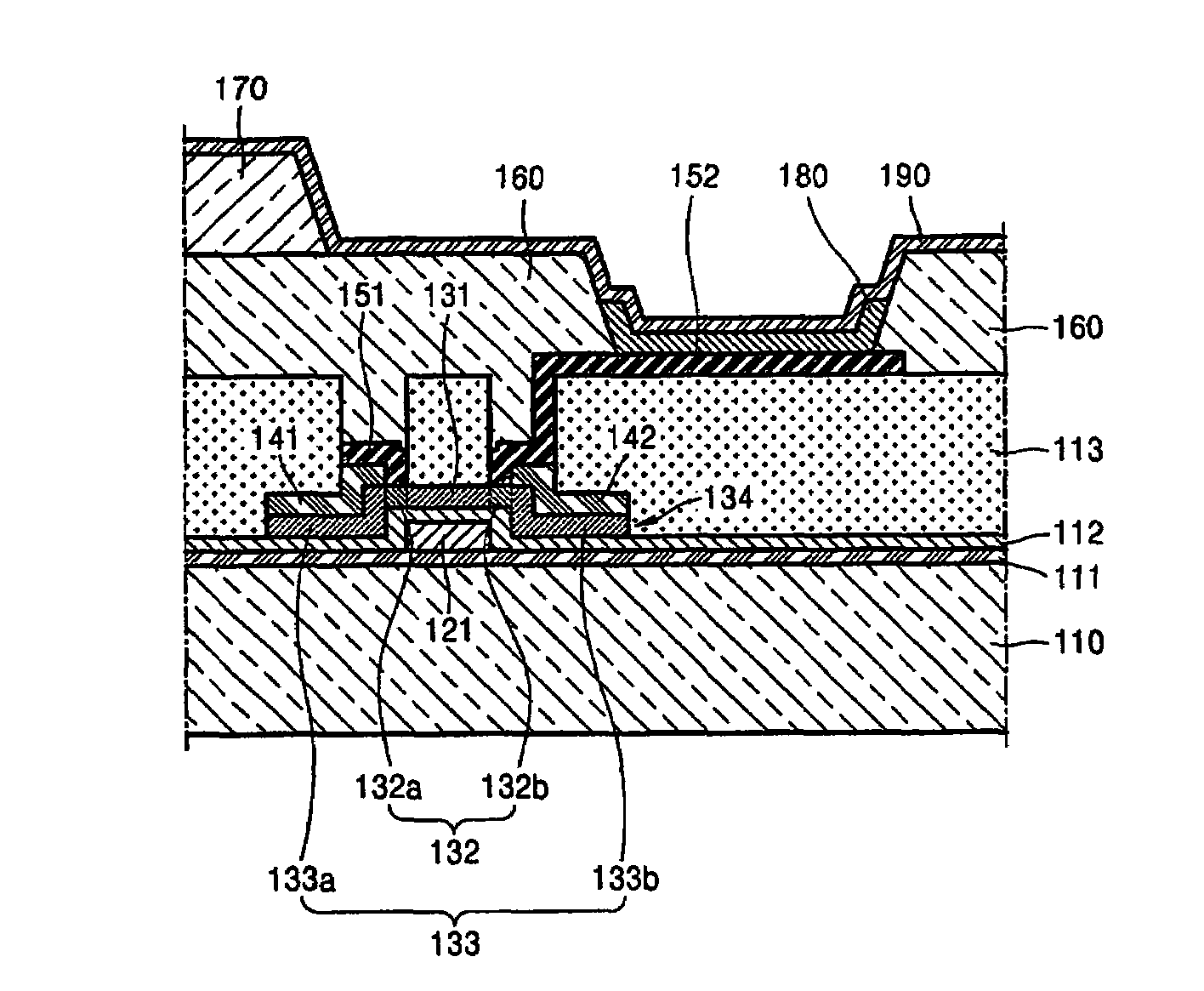

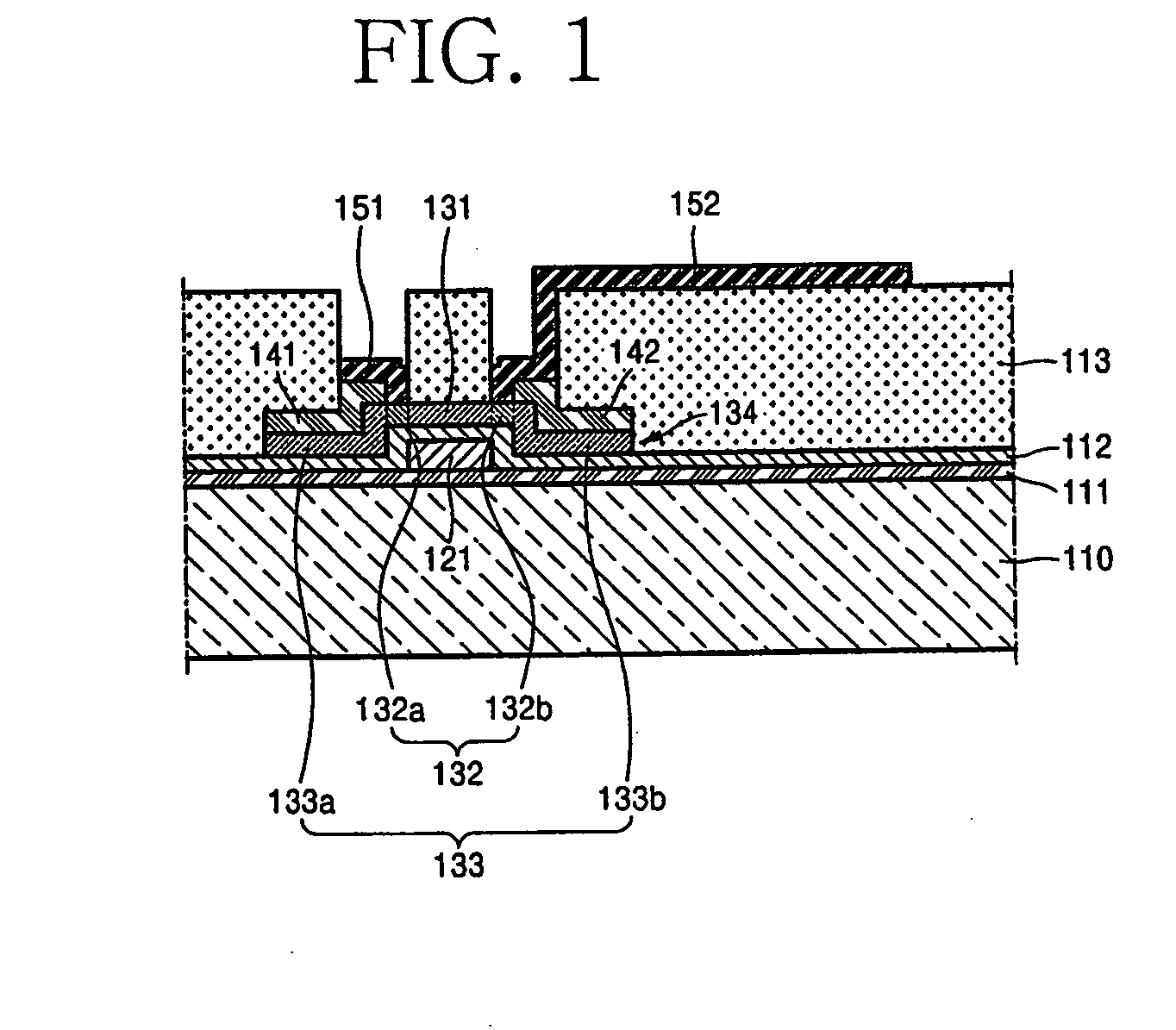

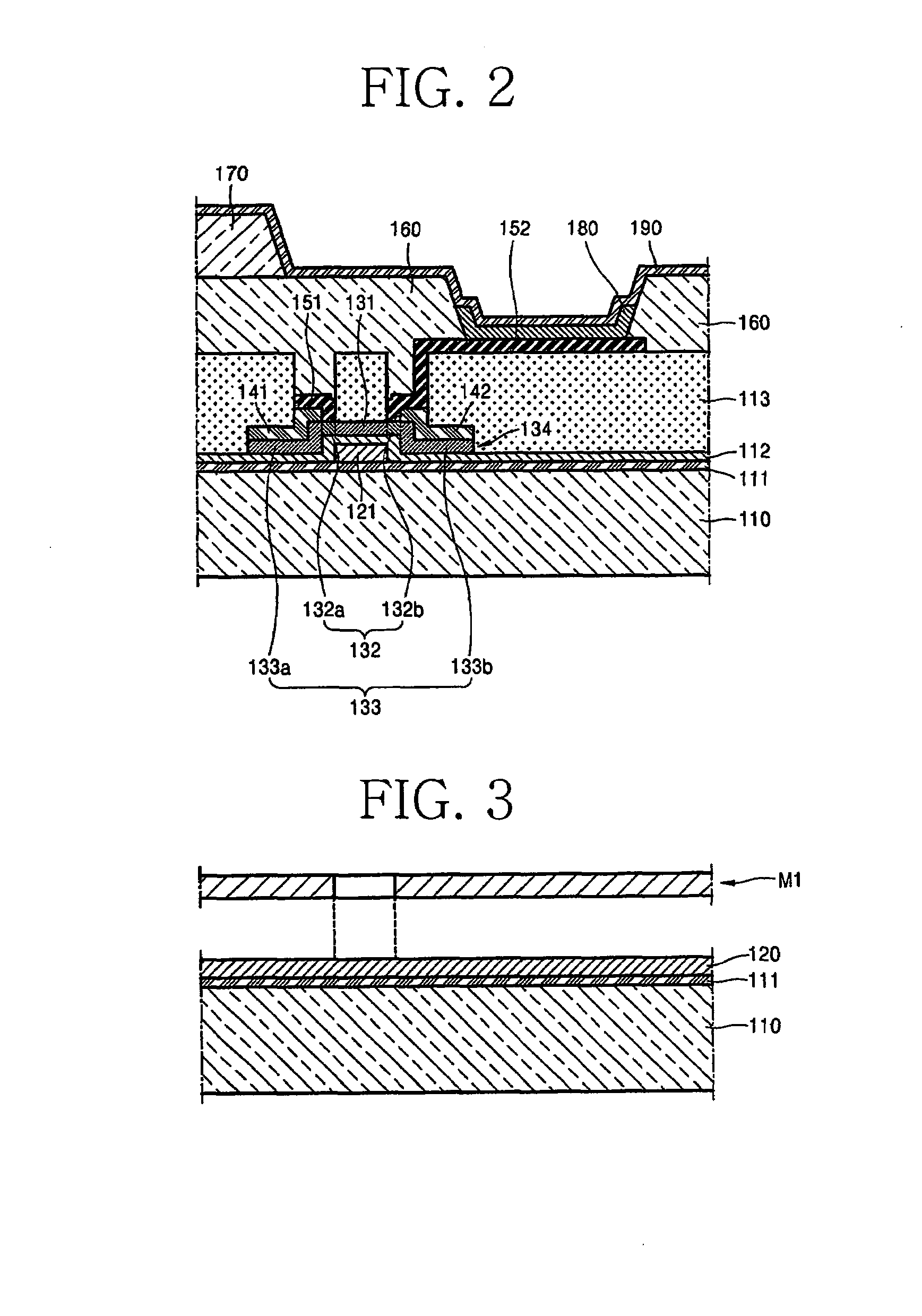

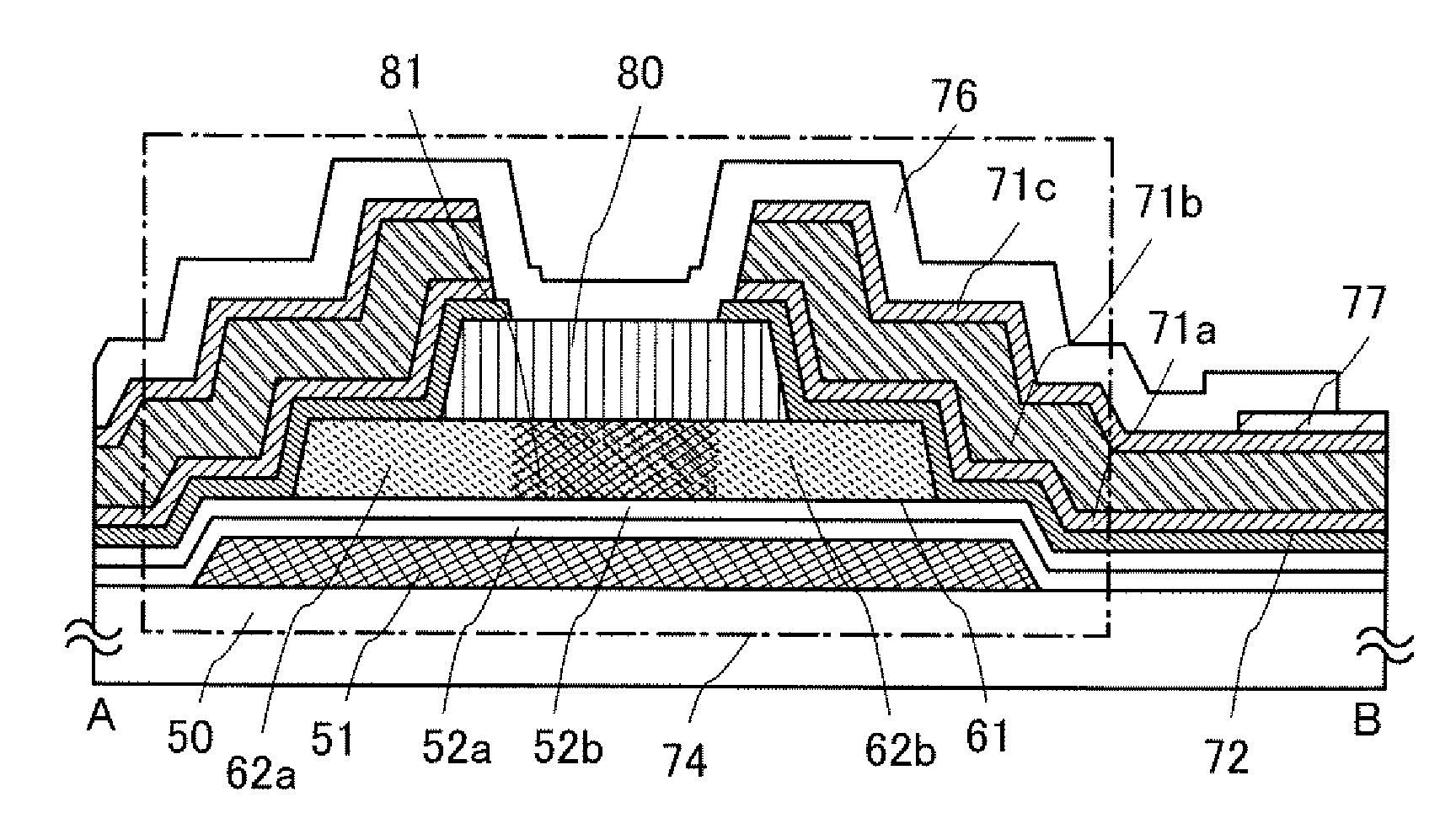

Thin film transistor, organic light emitting display device including the same, and method of manufacturing the organic light emitting display device

ActiveUS20080277666A1Reduce processing stepsReduce in quantitySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceNon doped

A thin film transistor (TFT) may include a substrate, a gate electrode on the substrate, a gate insulating layer on the gate electrode, and a semiconductor layer on the gate insulating layer. The semiconductor layer may include a top surface, a channel area aligned in a vertical direction with the gate electrode, a plurality of doped areas proximate to the channel area, and a plurality of non-doped areas. Source and drain electrodes may be on the top surface of the semiconductor layer aligned above respective ones of the plurality of non-doped areas of the semiconductor layer. A planarization layer may be on the gate insulating layer, the source and drain electrodes and the semiconductor layer channel area, and may include a plurality of openings respectively exposing the plurality of doped areas of the semiconductor layer and a portion of the source electrode and the drain electrode.

Owner:SAMSUNG DISPLAY CO LTD

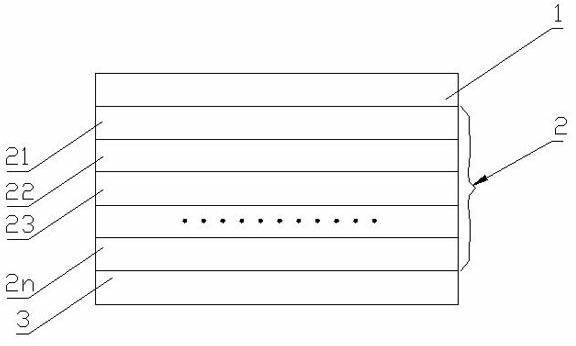

Epitaxial structure and growing method for improving gallium nitride (GaN) based light-emitting diode (LED) lighting efficiency

InactiveCN103066174AImprove crystal qualityStress reliefSemiconductor devicesPotential wellEffect light

The invention discloses an epitaxial structure and a growing method for improving gallium nitride (GaN) based light-emitting diode (LED) lighting efficiency. The order of the epitaxial structure from bottom to up is that a substrate, a low-temperature GaN buffer layer, a GaN non-doping layer, a N-shaped GaN layer, a multiple quantum well (MQW) structure, a multiple quantum well active layer, a low-temperature P-shaped GaN layer, a P-shaped aluminum (AL) GaN layer, a high-temperature P-shaped GaN layer and a P-shaped contact layer, wherein the order of the multiple quantum well active layer from bottom to up comprises a InyGa1-yN potential well layer, a InN layer and a barrier layer in sequence. The growing method of the multiple quantum well active layer structure is that by inserting the InN layer and a low-temperature annealing step in the growing process of a InyGa1 potential well layer and a GaN barrier layer, so that the composition of In quantum dot in the barrier layer is advanced and crystalline quality of the quantum well is improved, therefore, gallium nitride based LED lighting efficiency is improved.

Owner:合肥彩虹蓝光科技有限公司

Semiconductor device

ActiveUS20100230717A1Solid-state devicesSemiconductor devicesElectrical conductorSemiconductor package

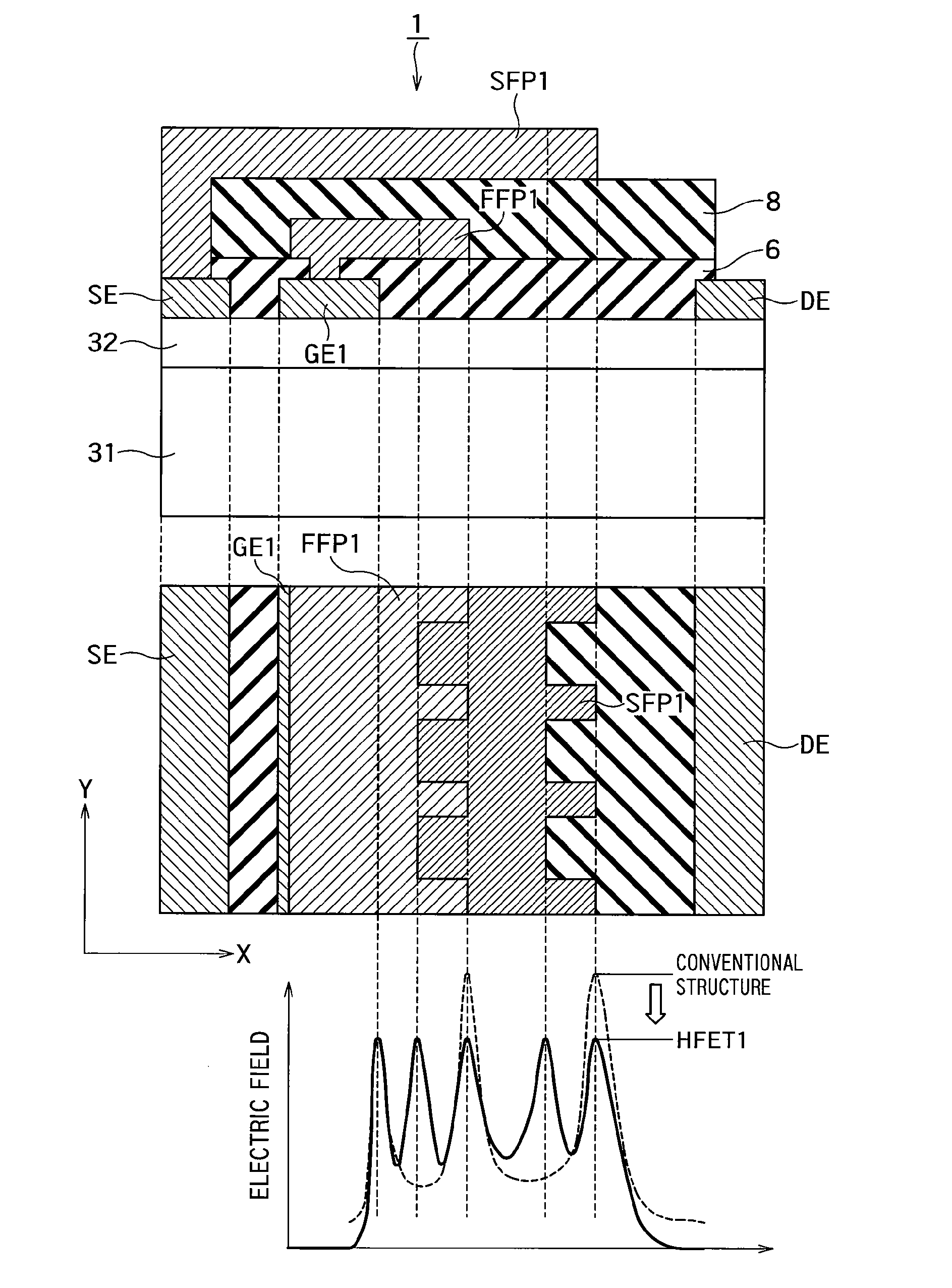

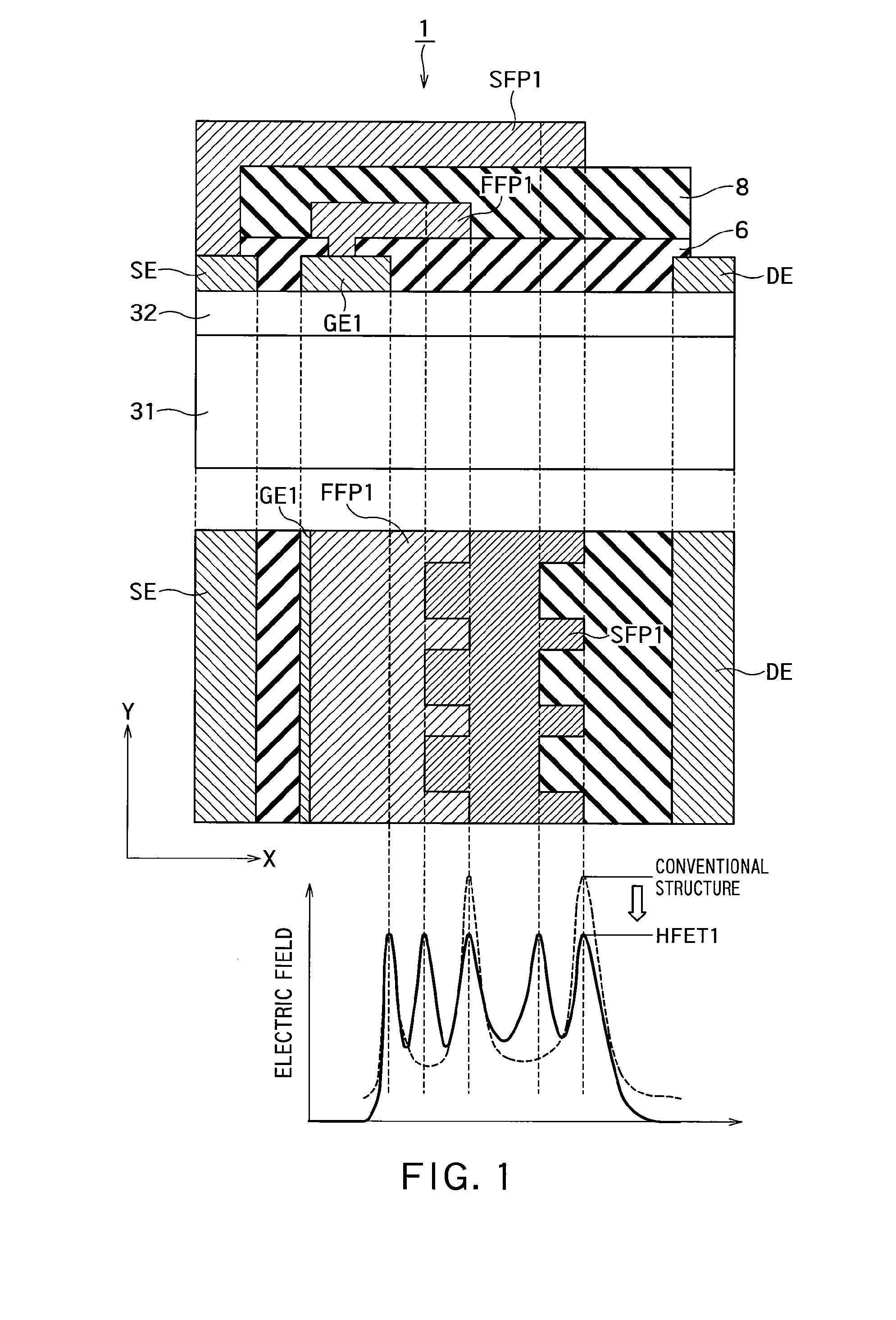

A semiconductor device includes: a first semiconductor layer of non-doped AlXGa1-XN (0≦X<1); a second semiconductor layer of non-doped or n-type AlYGa1-YN (0<Y≦1, X<Y) on the first semiconductor layer; a first electrode on the second semiconductor layer; a second electrode on the second semiconductor layer that is separated from the first electrode and electrically connected to the second semiconductor layer; a first insulating film covering the first and second electrodes; a first field plate electrode electrically connected to the first electrode and covered by a second insulating film; and a second field plate electrode on the second insulating film, wherein a length of at least one of the first and second field plate electrodes in a first direction from the first electrode toward the second electrode changes periodically in a second direction intersecting the first direction.

Owner:KK TOSHIBA

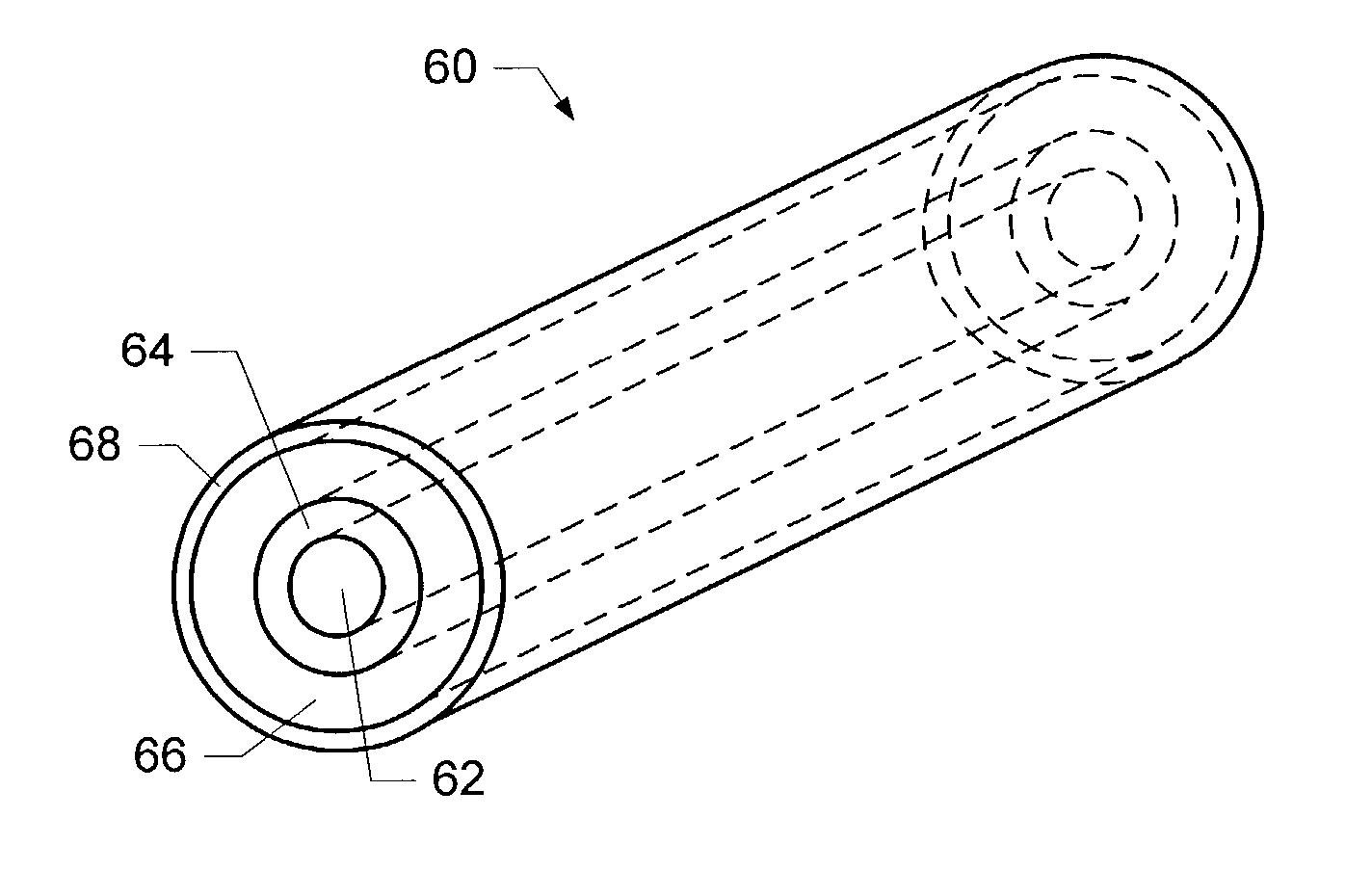

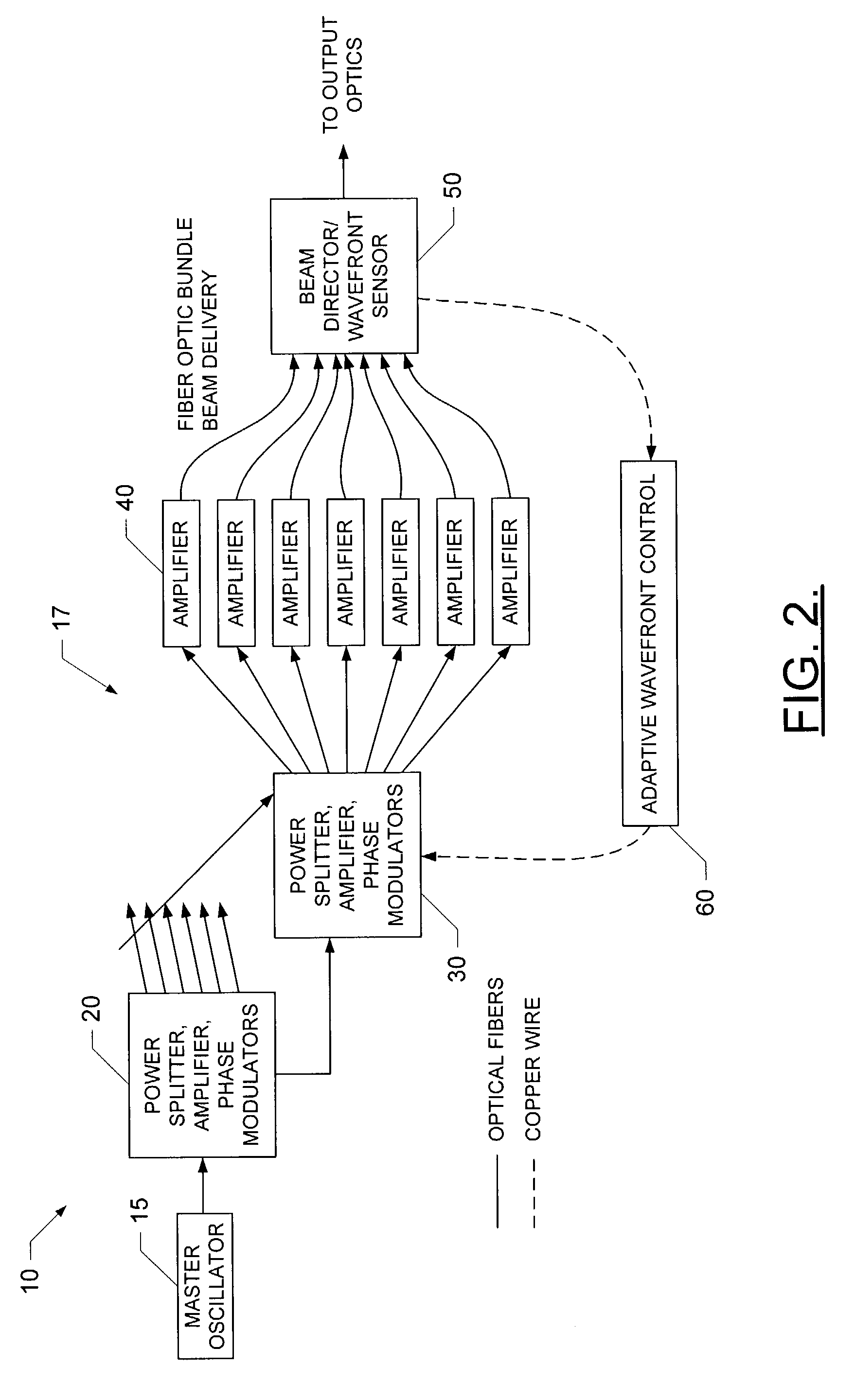

Fiber amplifier having a non-doped inner core and at least one doped gain region

ActiveUS6965469B2Minimizes waste heatOvercomes inherent intensity limitationLaser using scattering effectsFibre transmissionNon dopedEngineering

A fiber amplifier includes at least one longitudinally extending non-doped inner core capable of transmitting signals. At least partially surrounding the inner core and extending at least partially therealong, the fiber amplifier also includes at least one gain region capable of amplifying signals propagating therethrough. The fiber amplifier also includes an outer core surrounding the gain region and the inner core and extending longitudinally therealong. The outer core is capable of transmitting pump energy such that the pump energy at least partially amplifies signals propagating through the inner core according to a nonlinear amplification process, such as a Raman or a Brillouin amplification process.

Owner:THE BOEING CO

Power semiconductor device

InactiveCN1639875AImprove reliabilityAvoid instabilityTransistorPower semiconductor deviceOptoelectronics

A power semiconductor device including a non-doped GaN channel layer, an n-type Al0.2Ga0.8N barrier layer formed on the channel layer, a type-Al0.1Ga0.9N semiconductor layer selectively formed on the barrier layer a drain electrode positioned at one of both sides of the semiconductor layer and formed on the barrier layer an insulating film formed on the barrier layer adjacent to the semiconductor layer between at least semiconductor layer and drain electrode, and a field plate electrode formed on the insulating film.

Owner:KK TOSHIBA

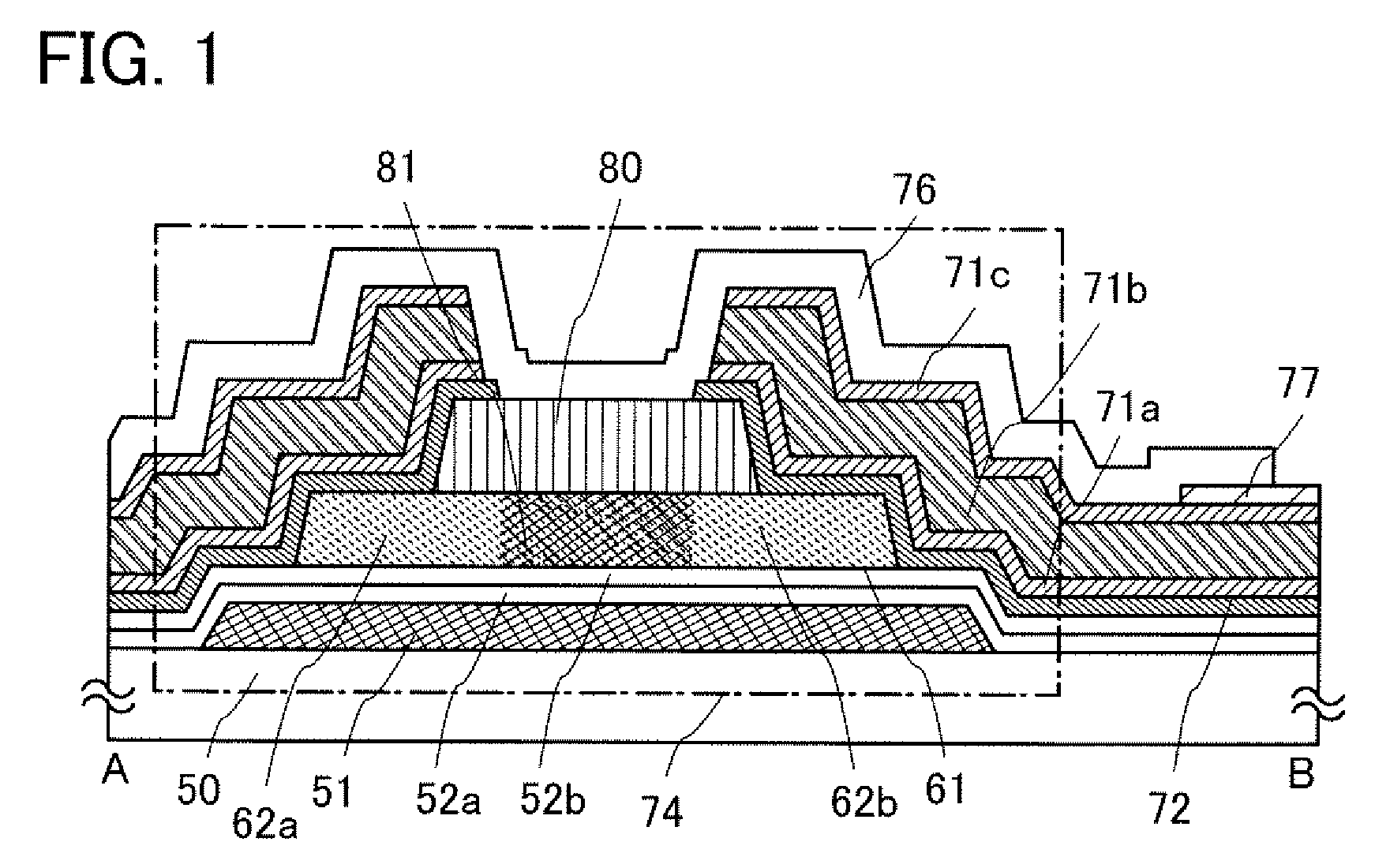

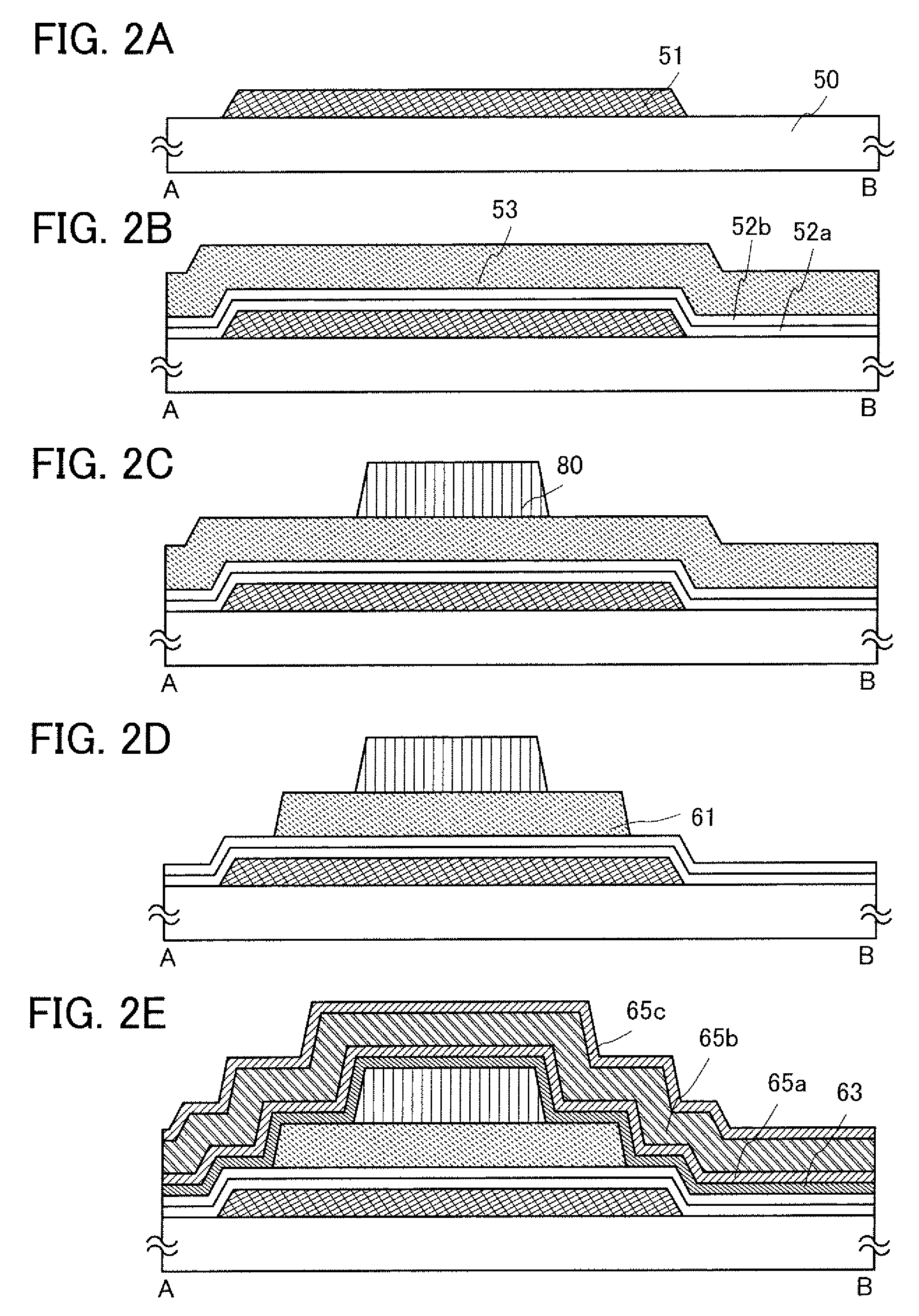

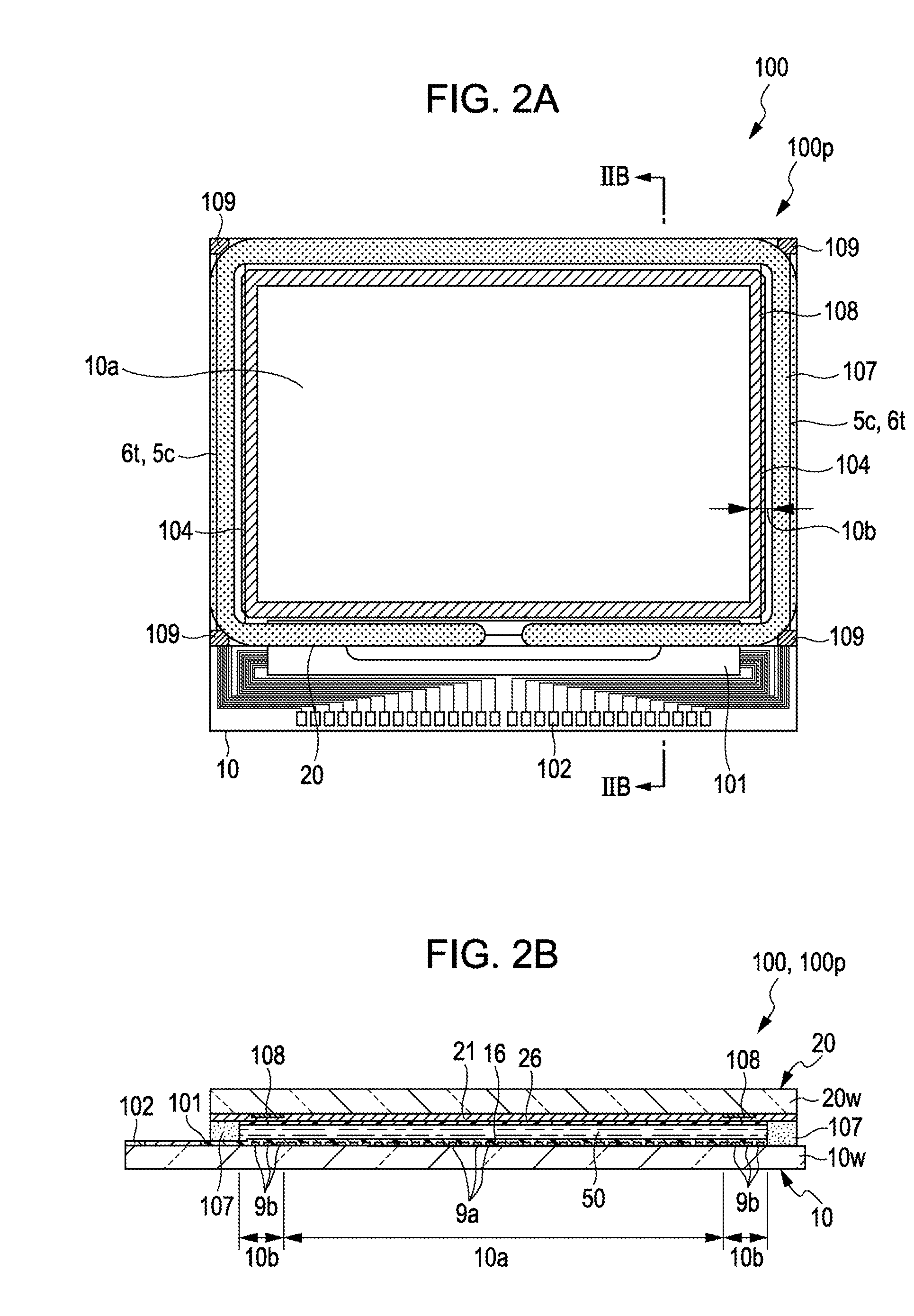

Display device and manufacturing method thereof

InactiveUS7791075B2Improve featuresImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

A display device including a thin film transistor with high electric characteristics and high reliability, and a method for manufacturing the display device in high yield are proposed. In a display device including a channel stop thin film transistor with an inverted-staggered structure, the channel stop thin film transistor with the inverted-staggered structure includes a microcrystalline semiconductor film including a channel formation region. An impurity region including an impurity element imparting one conductivity type is formed as selected in a region in the channel formation region of the microcrystalline semiconductor film which does not overlap with a source electrode or a drain electrode. In the channel formation region, a non-doped region, to which the impurity element imparting one conductivity type is not added, is formed between the impurity region, which is a doped region to which the impurity element is added, and the source region or the drain region.

Owner:SEMICON ENERGY LAB CO LTD

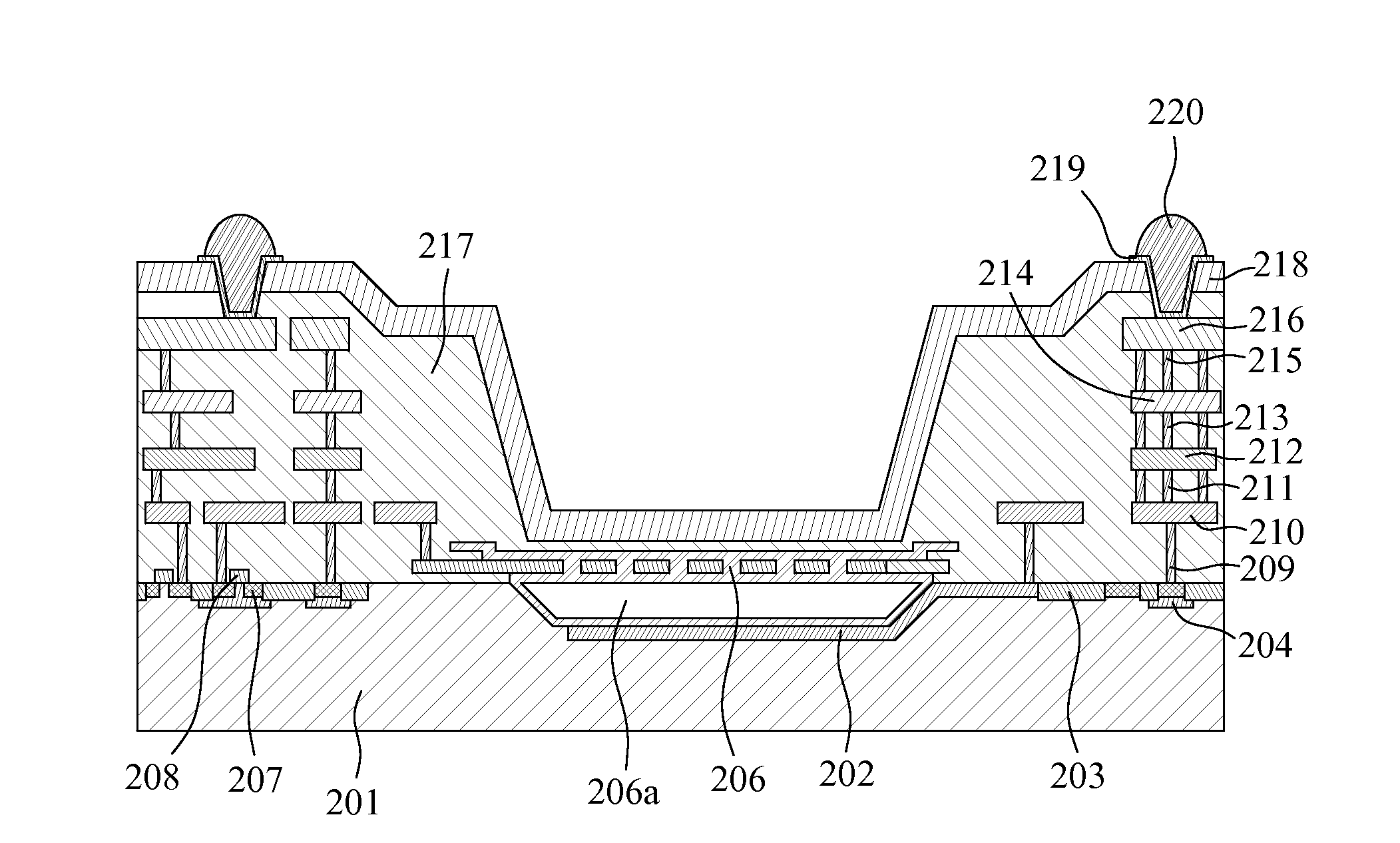

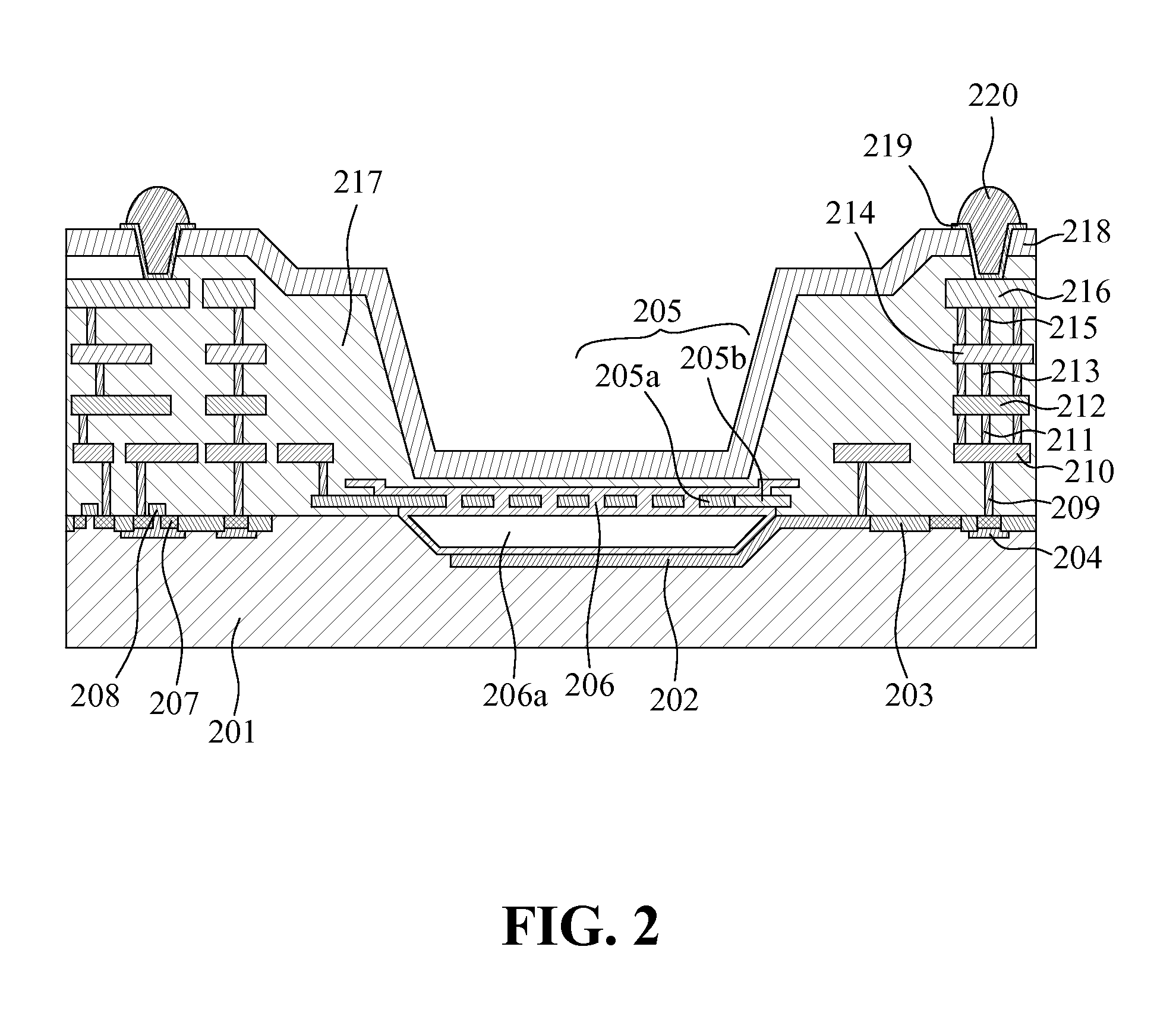

Integrated MEMS pressure sensor with mechanical electrical isolation

InactiveUS20150060956A1Improve reliabilityReduce manufacturing costDecorative surface effectsFluid pressure measurement by electric/magnetic elementsContact layerEngineering

An integrated MEMS pressure sensor is provided, including, a CMOS substrate layer, an N+ implant doped silicon layer, a field oxide (FOX) layer, a plurality of implant doped silicon areas forming CMOS wells, a two-tier polysilicon layer with selective ion implantation forming a membrane, including an implant doped polysilicon layer and a non-doped polysilicon layer, a second non-doped polysilicon layer, a plurality of implant doped silicon areas forming CMOS source / drain, a gate poly layer made of polysilicon forming CMOS transistor gates, said CMOS wells, CMOS transistor sources / drains and CMOS gates forming CMOS transistors, an oxide layer embedded with an interconnect contact layer, a plurality of metal layers interleaved with a plurality of via hole layers, a Nitride deposition layer, an under bump metal (UBM) layer and a plurality of solder spheres. N+ implant doped silicon layer and implant doped / un-doped composition polysilicon layer forming a sealed vacuum chamber.

Owner:WINDTOP TECH CORP

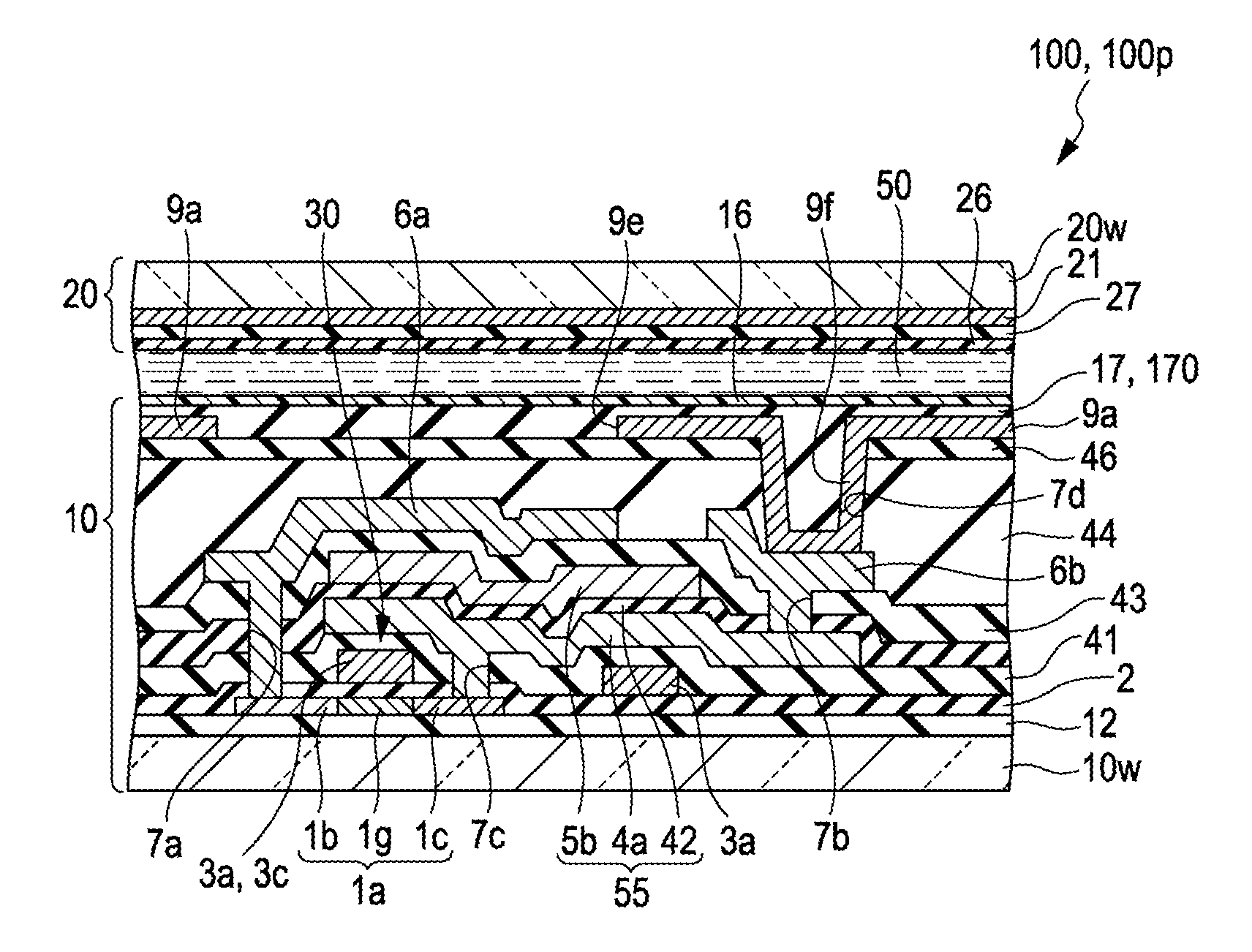

Electro-optic device and projection-type display apparatus

ActiveUS20120120357A1Preventing a defect such as hillockReduce generationNon-linear opticsStress relievingSilicon oxide

An electro-optic device is provided with an substrate, in which a stress relieving film formed of a doped silicon oxide film is formed between a third interlayer insulating film formed of a non-doped silicon oxide film and a pixel electrode formed of an aluminum film or the like. The stress relieving film is formed of the doped silicon oxide film, has a thermal expansion coefficient different from that of the third interlayer insulating film, comes in contact with the third interlayer insulating film, has a thermal expansion coefficient different from that of the pixel electrode, and comes in contact with the pixel electrode. The thermal expansion coefficients are in the following relation of Third Interlayer Insulating Film<Stress relieving Film<Pixel Electrode.

Owner:SEIKO EPSON CORP

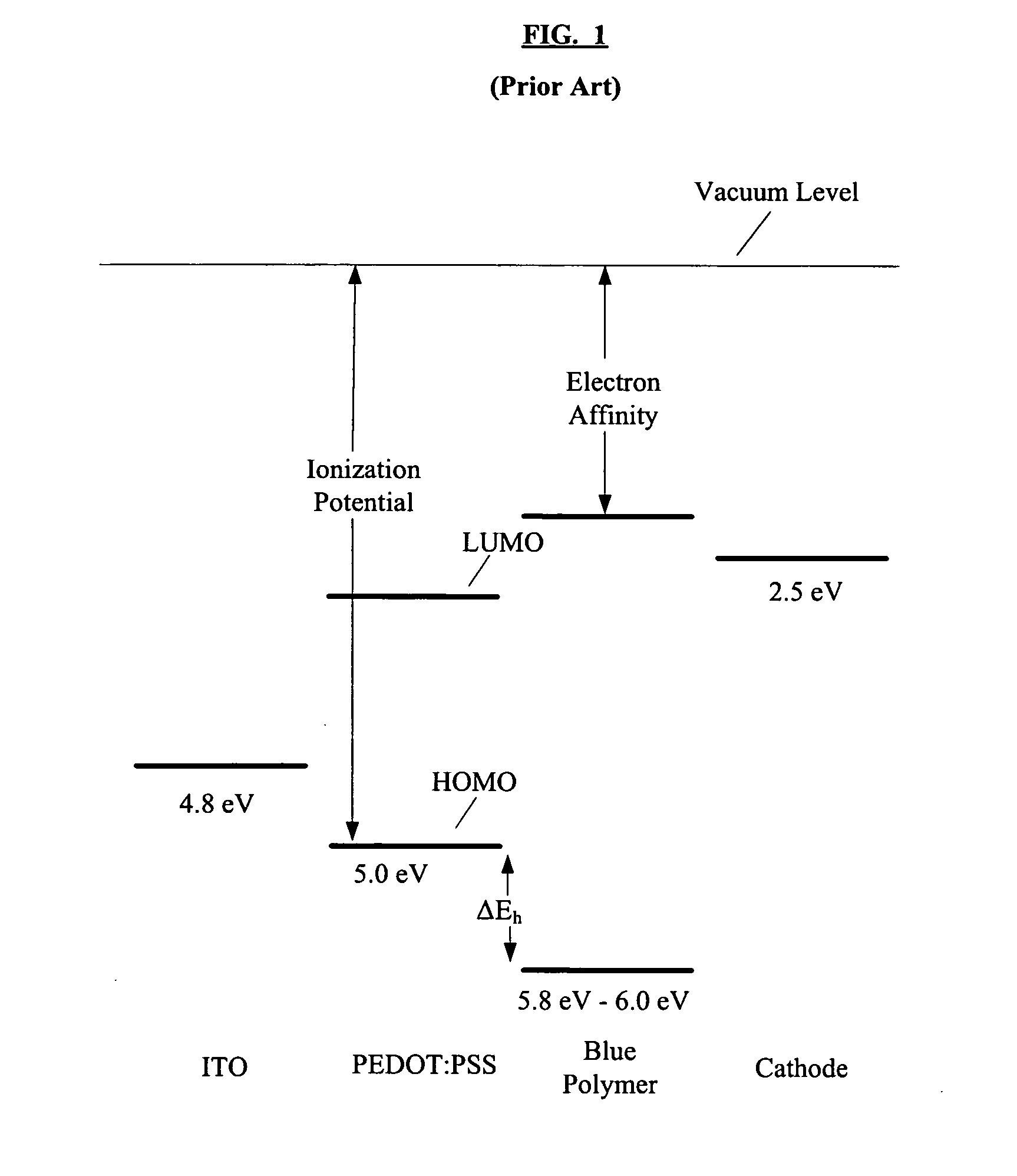

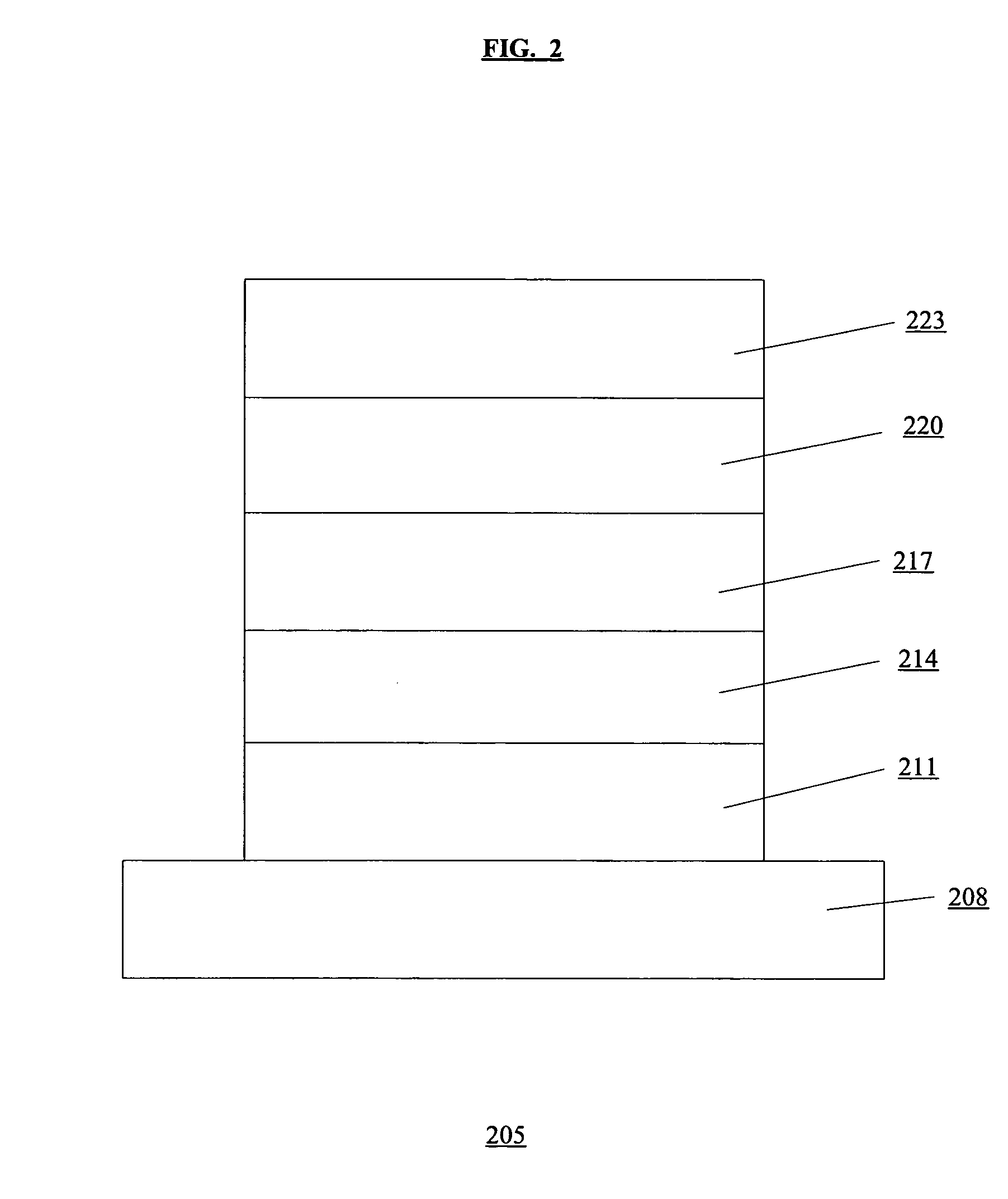

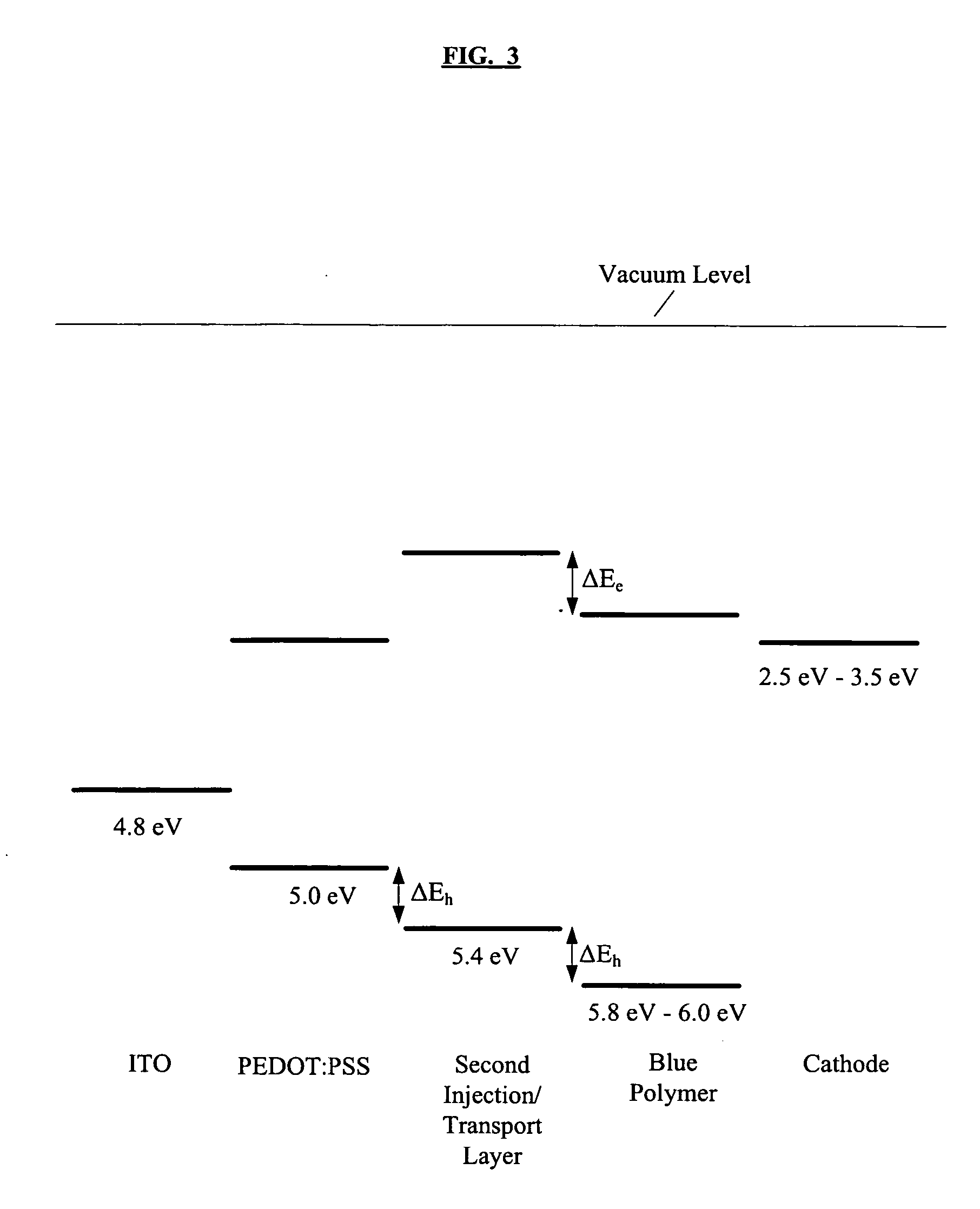

Light emitting polymer devices with improved efficiency and lifetime

InactiveUS20050048314A1Discharge tube luminescnet screensElectroluminescent light sourcesDopantTransport layer

In one embodiment of an OLED device, a hole injection / transport layer is added to the device structure in order to increase the number of holes injected into the emissive layer and reduce the number of electrons injected into the added hole injection / transport layer. In a first configuration of the added hole injection / transport layer, the added hole injection / transport layer is comprised of a non-doped hole transporting material that has an IP range between the highest IP value of the adjacent layer on the anode-end and the lowest IP value of the adjacent layer on the “emissive layer”-end. Optionally, in addition, nearly all electron affinities of the added hole injection / transport layer are less than the lowest electron affinity of the adjacent layer on the “emissive layer”-end. In a second configuration of the added hole injection / transport layer, this layer is formed by doping the hole transport material. The dopant is able to abstract electrons from the hole transporting material. By doping the hole transport material, the IP range of the hole transporting material is broadened. In addition or alternatively, the doping produces more HOMO energy states thus allowing more holes to occupy these intermediate states at any one time.

Owner:OSRAM OPTO SEMICONDUCTORS GMBH

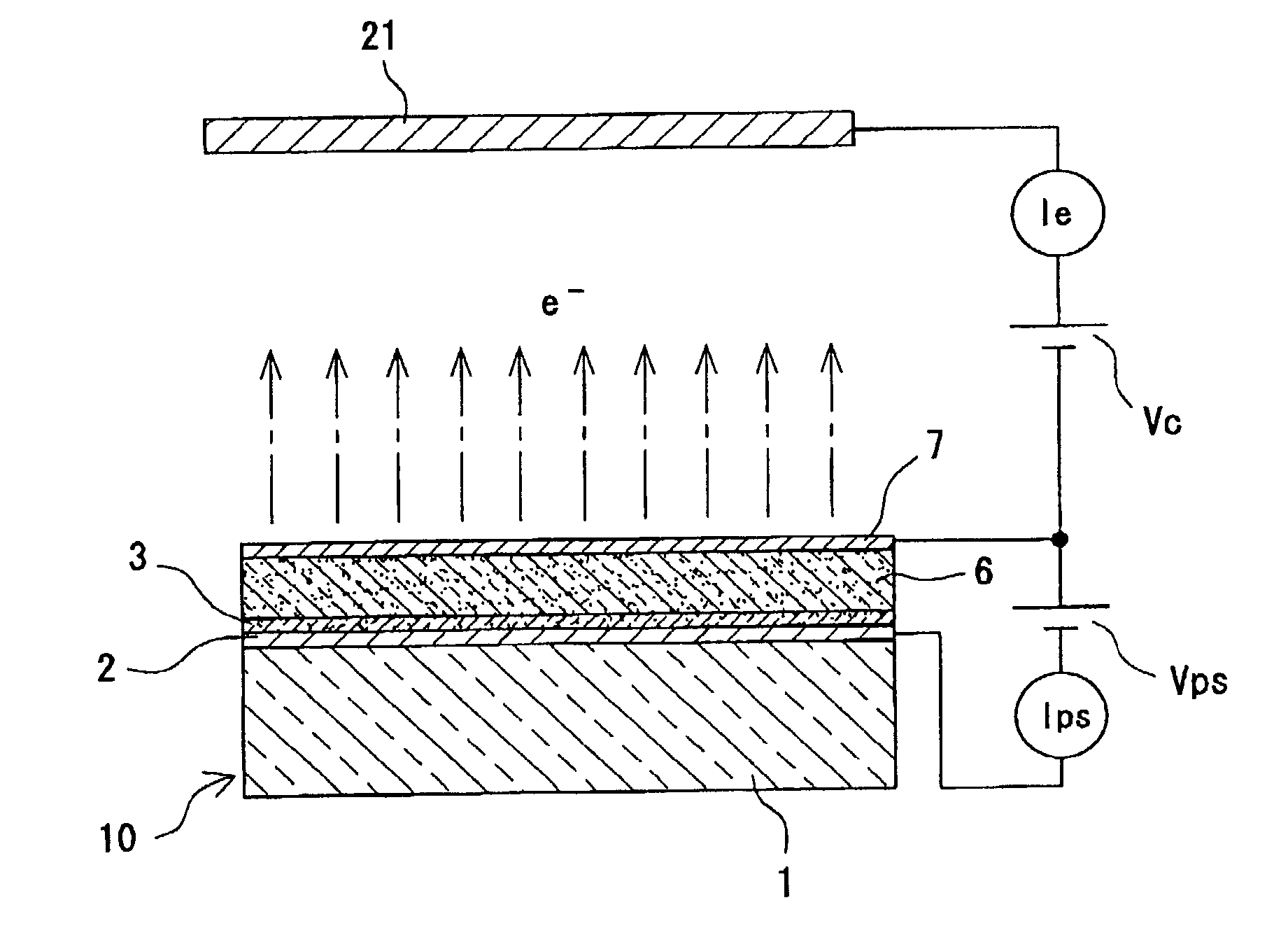

Field emission-type electron source

InactiveUS20030076023A1Increase resistanceImprove featuresDischarge tube luminescnet screensElectric discharge tubesOptoelectronicsNon doped

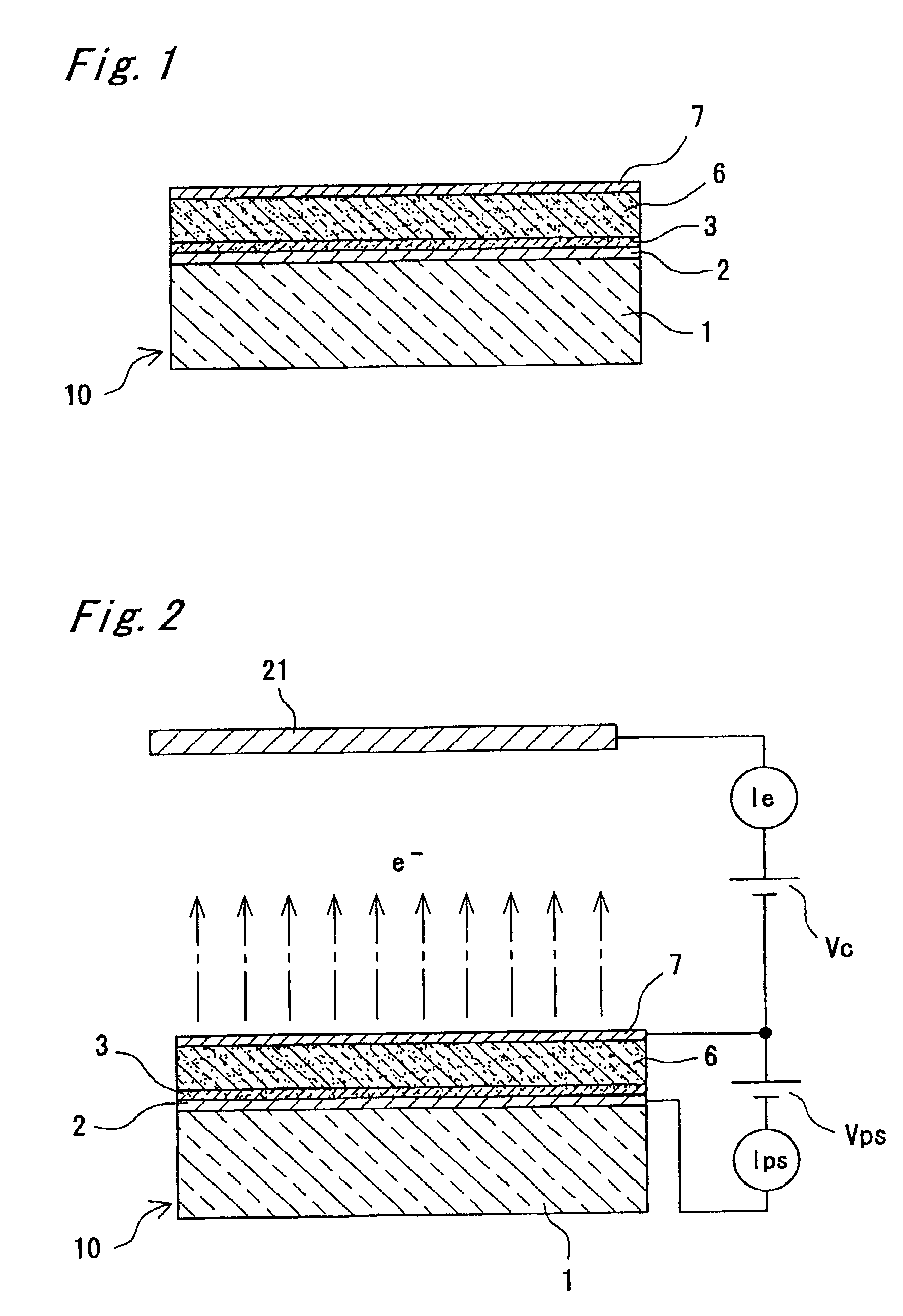

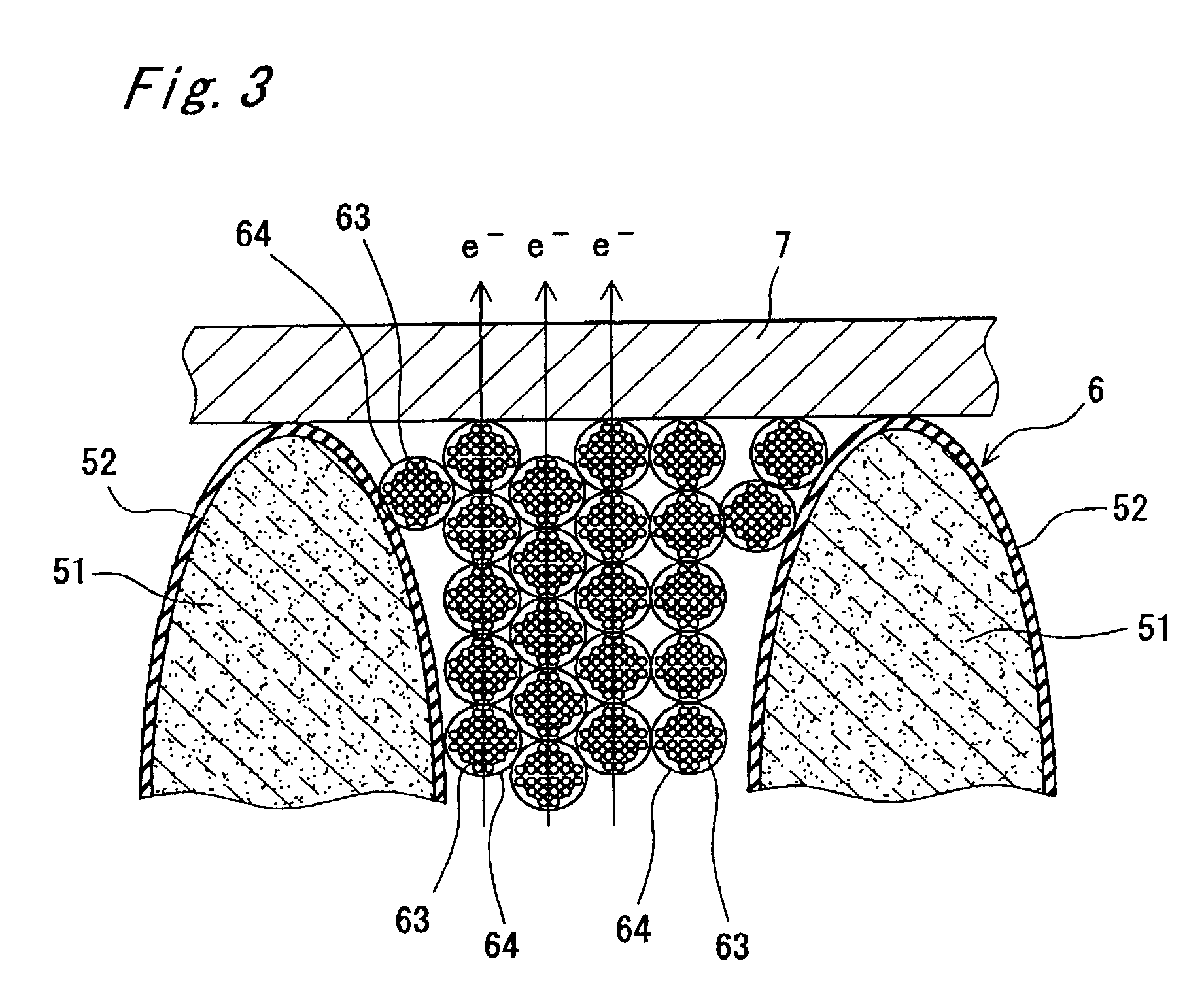

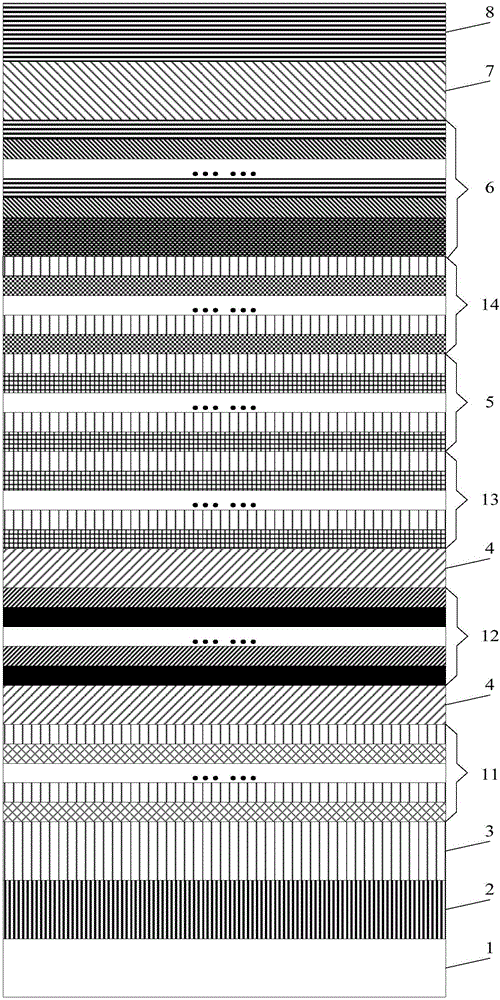

A lower electrode (2) and surface electrode (7) composed of a layer-structured conductive carbide layer is formed on one principal surface side of the substrate (1) composed of an insulative substrate such as a glass or ceramic substrate. A non-doped polycrystalline silicon layer (3) is formed on the lower electrode (2), An electron transit layer (6) composed of an oxidized porous polycrystalline silicon is formed on the polycrystalline silicon layer (3). The electron transit layer (6) is composed of a composite nanocrystal layer including polycrystalline silicon and many nanocrystalline silicons residing adjacent to a grain boundary of the polycrystalline silicon. When voltage is applied between the lower electrode (2) and the surface electrode (7) such that the surface electrode (7) has a higher potential, electrons are injected from the lower electrode (2) toward the surface electrode (7), and emitted through the surface electrode (7) through the electron transit layer (6).

Owner:MATSUSHITA ELECTRIC WORKS LTD

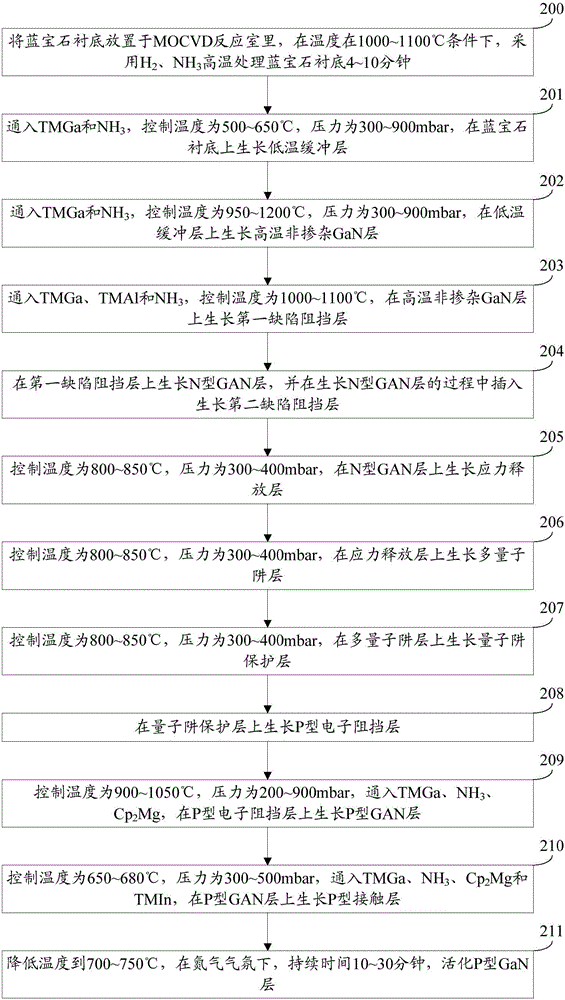

Light-emitting diode epitaxial wafer and preparation method thereof

The invention discloses a light-emitting diode epitaxial wafer and a preparation method thereof, and belongs to the technical field of semiconductors. The light-emitting diode epitaxial wafer comprises a sapphire substrate, a low-temperature buffer layer, a high-temperature non-doped GaN layer, a first defect barrier layer, an N-type GaN layer, a stress release layer, a multi-quantum well layer, a P-type electron blocking layer, a P-type GaN layer and a P-type contact layer, wherein the low-temperature buffer layer, the high-temperature non-doped GaN layer, the first defect barrier layer, the N-type GaN layer, the stress release layer, the multi-quantum well layer, the P-type electron blocking layer, the P-type GaN layer and the P-type contact layer are sequentially laminated on the sapphire substrate; a second defect barrier layer is inserted into the N-type GaN layer; the first defect barrier layer comprises alternately laminated AlGaN layers and GaN layers; the second defect barrier layer comprises alternately laminated SiN films and N-type AlGaN layers; and the stress release layer comprises alternately laminated InGaN layers and GaN layers. According to the light-emitting diode epitaxial wafer, extension of defects formed by lattice mismatch into the multi-quantum well layer is effectively suppressed; stress release is enhanced; the crystal quality is improved; leakage passages are reduced; the anti-static electricity capacity of an LED chip is improved; and the product yield is improved.

Owner:HC SEMITEK SUZHOU

Inverted mounting LED chip based on double-faced shrinkage pool substrate and component gradual change buffer layer

InactiveCN102157654AImprove radiative recombination luminous efficiencyReduce defect densitySemiconductor devicesQuantum efficiencyQuantum well

The invention discloses an inverted mounting LED chip based on double-faced shrinkage pool substrate and component gradual change buffer layer, wherein the chip comprises a sapphire substrate distributed with 102-104 shrinkage pools at upper and lower surfaces, an AlxGa1-xN component gradual change buffer layer composed of an unit layer formed by k non-doping AlxGa1-xN epitaxial materials, a n-type GaN epitaxial layer, an InGaN / GaN multi-quantum well, a p-type GaN layer, a transparent ITO (indium tin oxide) conductive film, an inverted mounting welding electrode and a silicon substrate from upper to lower. The LED chip disclosed by the invention uses the shrinkage pool structure for improving the emergent probability of LED emergent lights, and increasing the heat radiation area and growth stress acting range of the substrate, so that the GaB epitaxial quality and the radiation composite luminous efficiency are improved; the buffer layer of the n-type GaN epitaxial layer is manufactured by the AlxGa1-xN with gradually reduced Al component, so that the light-emitting efficiency and the internal quantum efficiency of the LED are improved, and a relatively high light output power is obtained.

Owner:CHONGQING UNIV

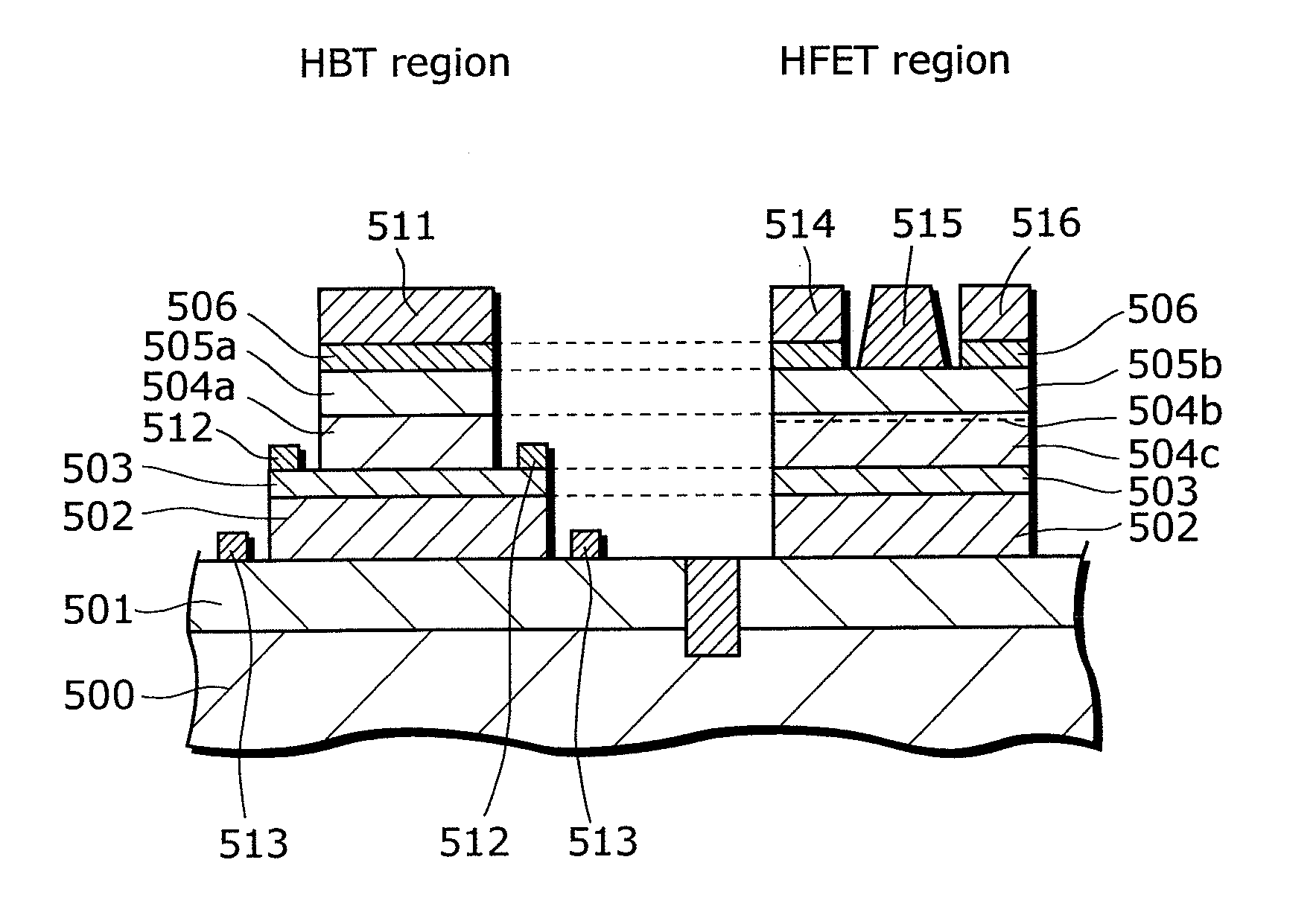

Semiconductor device and manufacturing method thereof

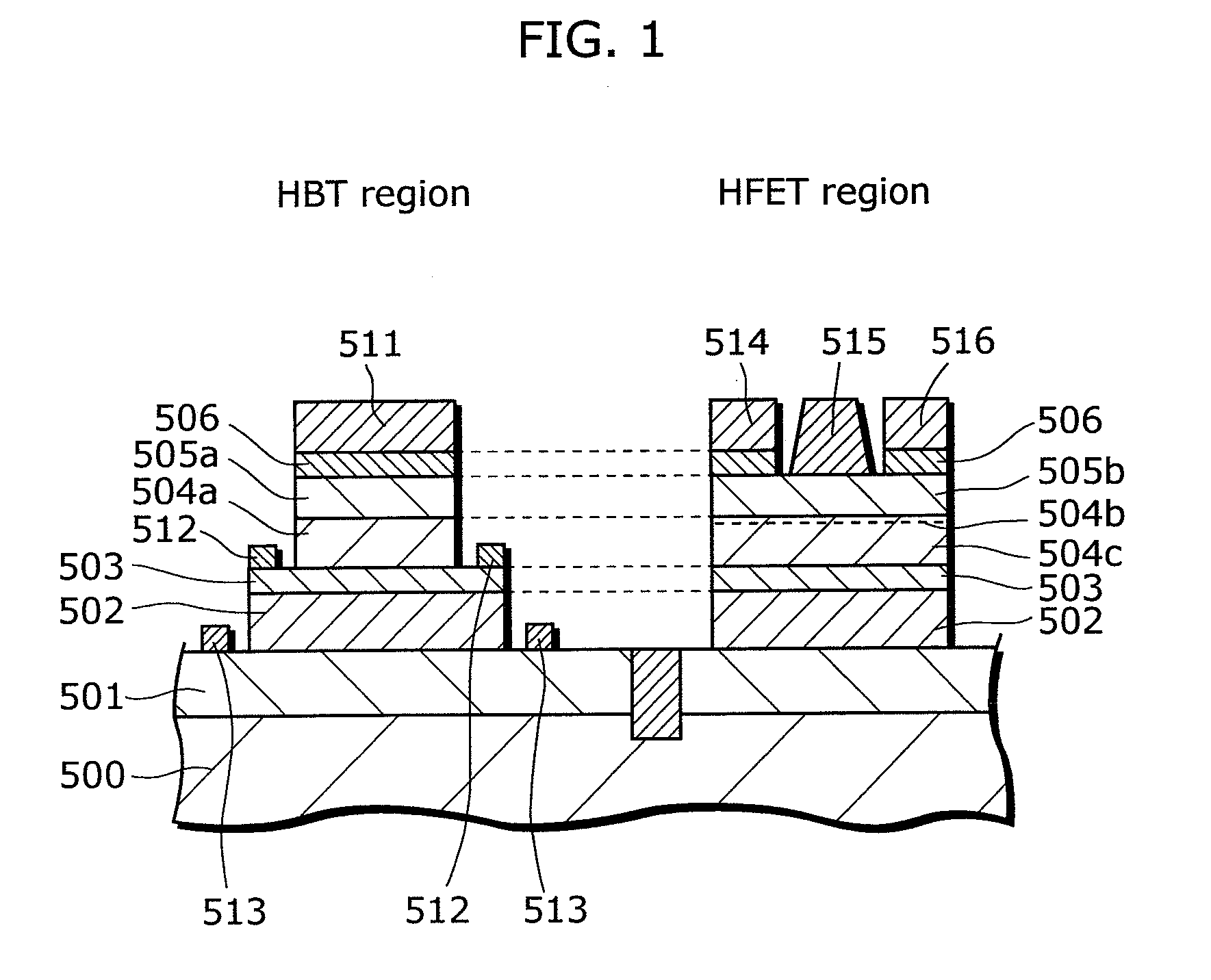

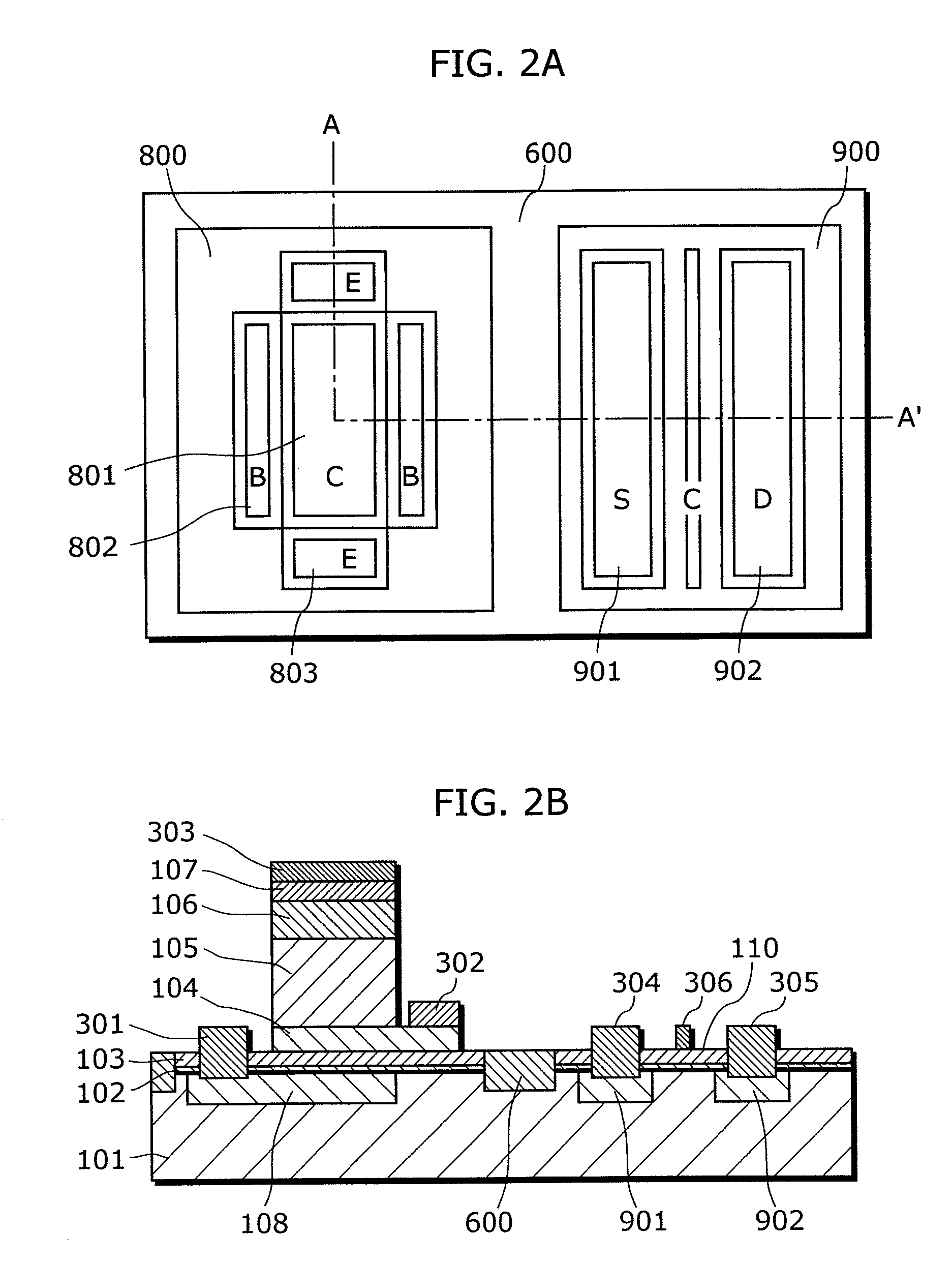

InactiveUS20080296624A1Improve breakdown voltageReduce collector resistanceTransistorSolid-state devicesElectron donorNon doped

The object of the present invention is to provide a semiconductor device and the manufacturing method thereof which are capable of preventing decrease in the collector breakdown voltage and reducing the collector resistance. The semiconductor device according to the present invention includes: a HBT formed on a first region of a semiconductor substrate; and an HFET formed on a second region of the semiconductor substrate, wherein the HBT includes: an emitter layer of a first conductivity; a base layer of a second conductivity that has a band gap smaller than that of the emitter layer; a collector layer of the first conductivity or a non-doped collector layer; and a sub-collector layer of the first conductivity which are formed sequentially on the first region, and the HFET includes an electron donor layer including a part of the emitter layer, and a channel layer formed under the electron donor layer.

Owner:COLLABO INNOVATIONS INC

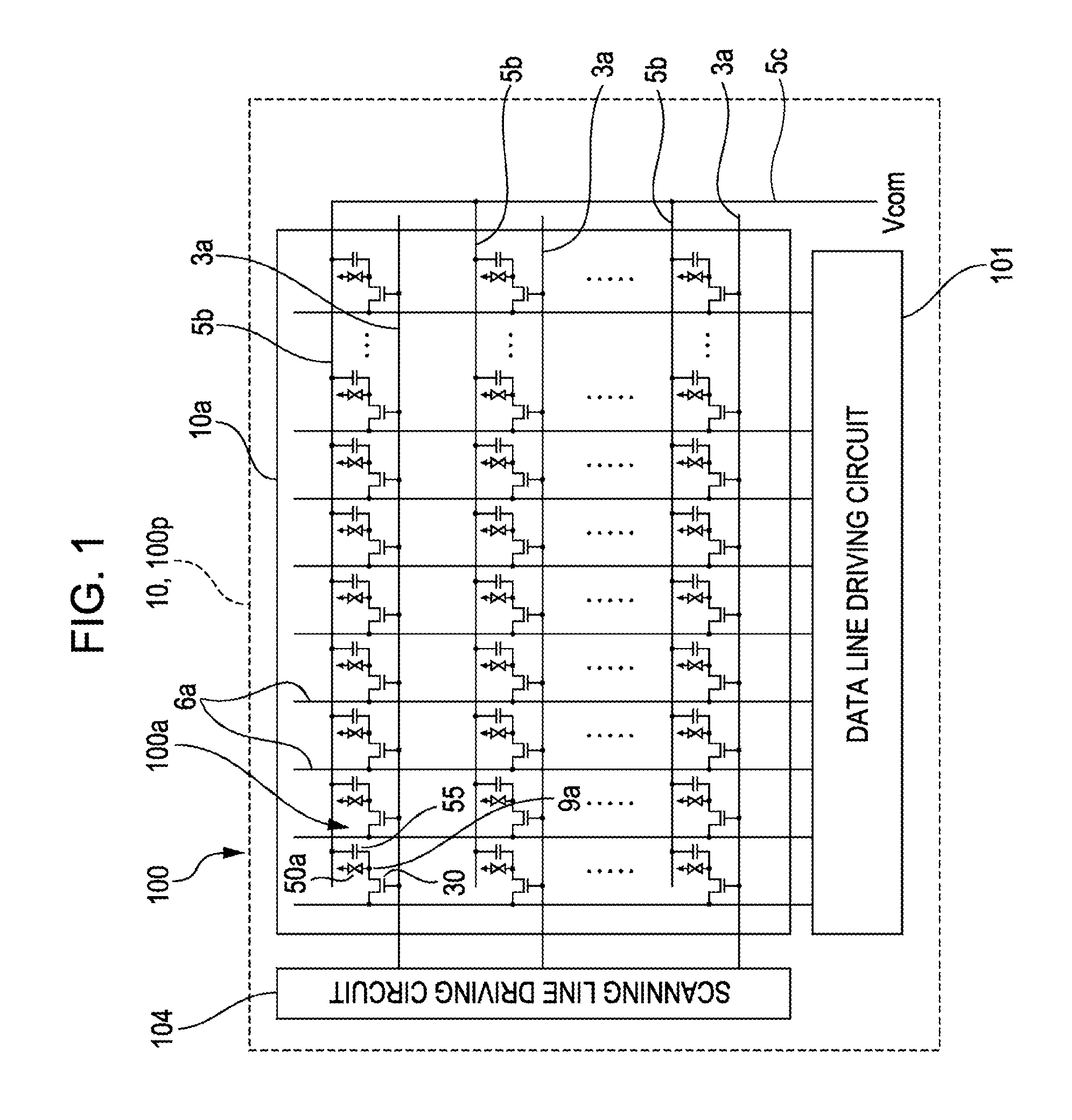

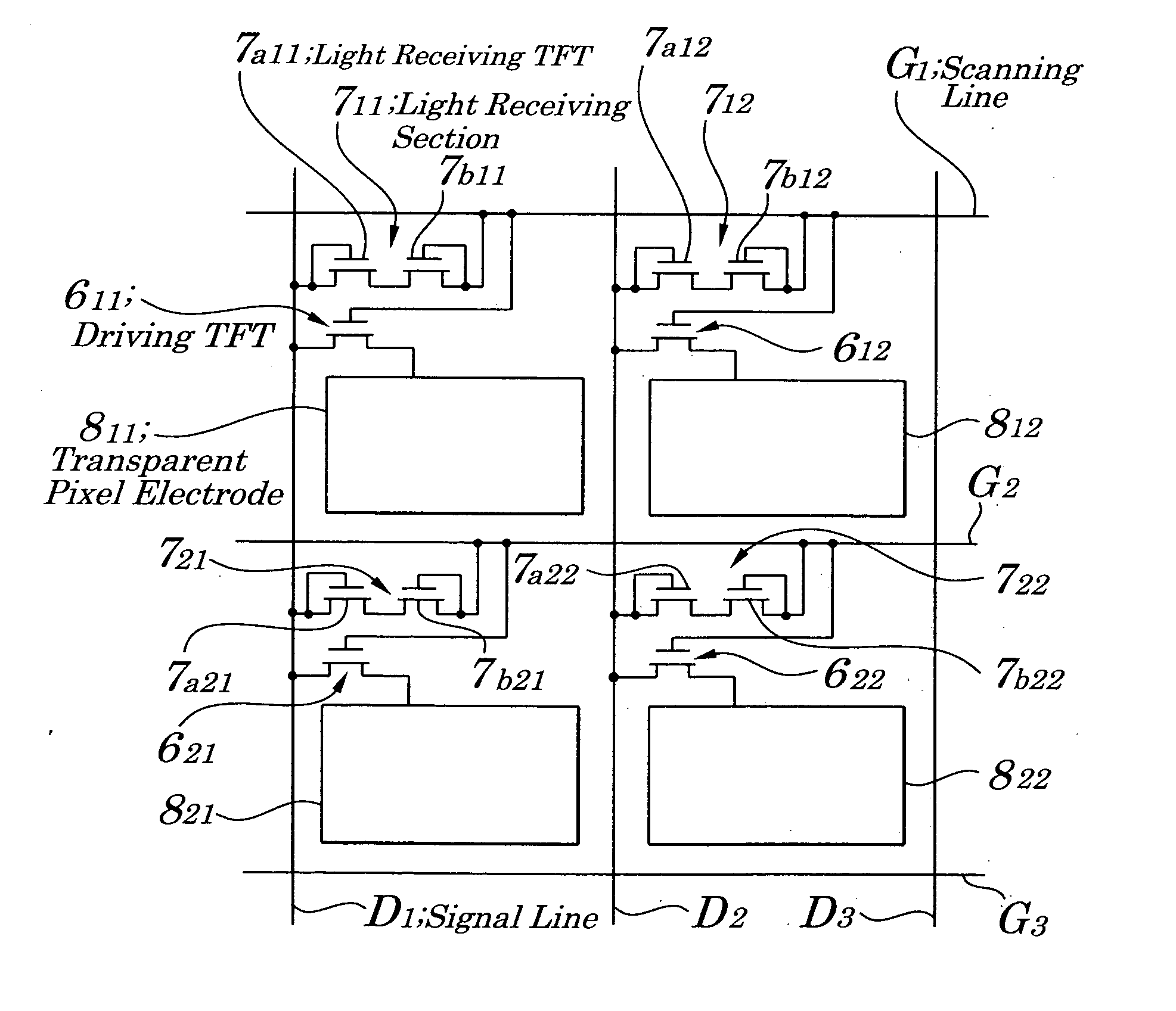

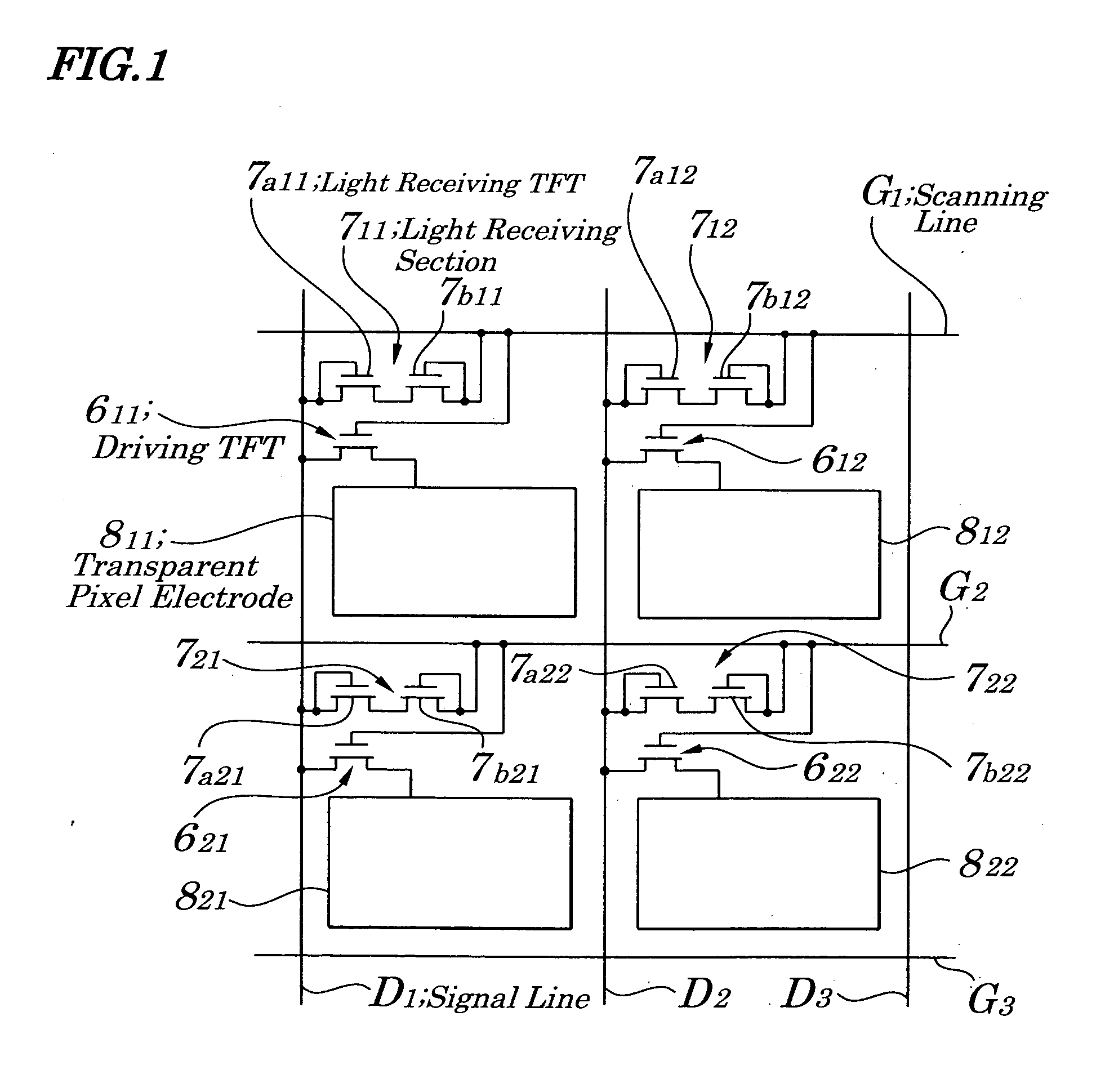

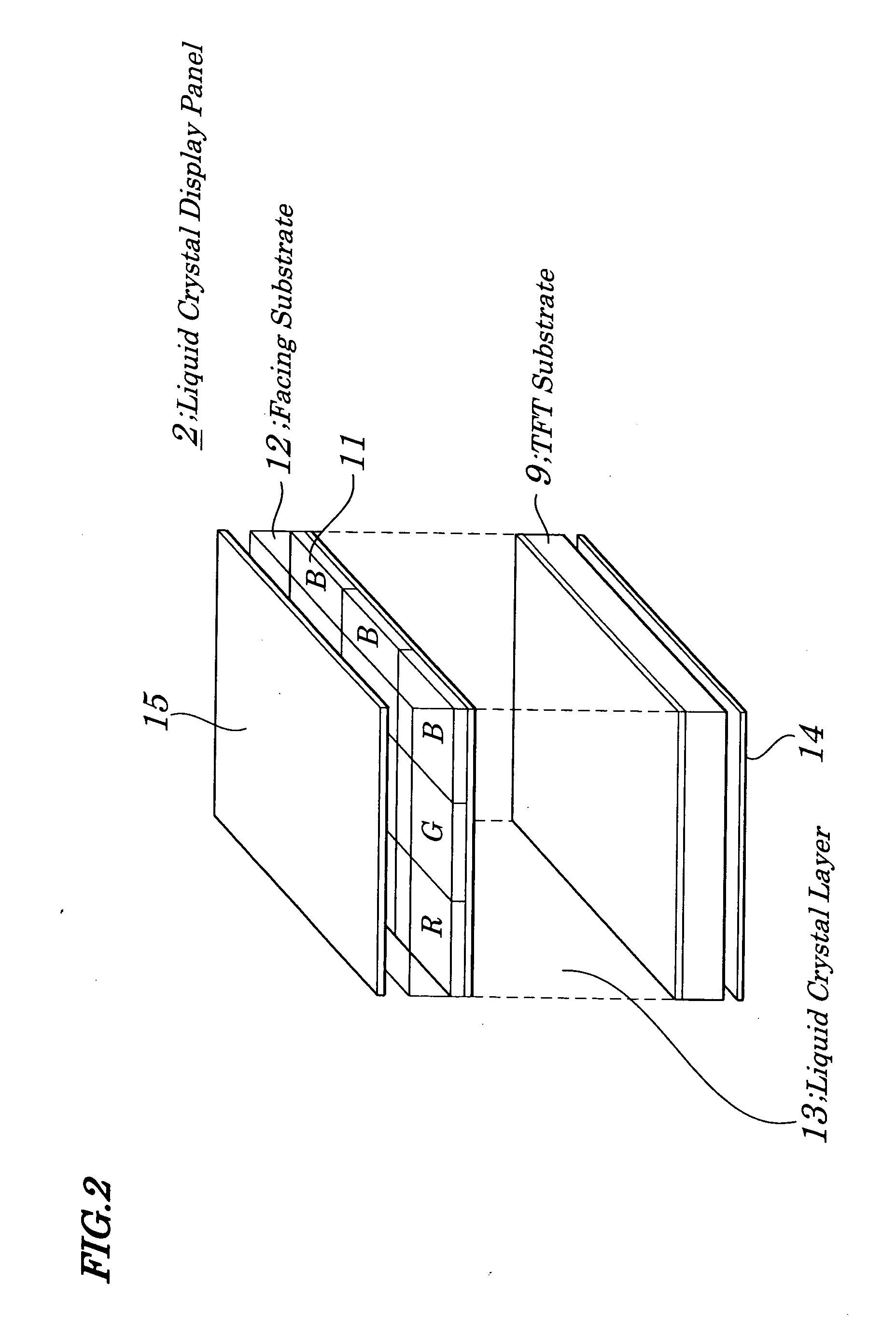

Liquid crystal display device with tablet function

InactiveUS20060267948A1Avoid failureReliably preventing malfunctionInput/output for user-computer interactionCathode-ray tube indicatorsLiquid-crystal displayAmorphous silicon

A liquid crystal display device having a tablet function is provided which is capable of reliably preventing malfunction. Light receiving devices are made up of TFTs (Thin Film Transistors) having approximately the same structure as driving switching elements. A semiconductor layer making up the light receiving devices, in particular, is made up of a non-doped a-Si (amorphous silicon) layer and a doped n+-type a-Si layer. A gate electrode of each of light receiving TFTs is connected to its own source electrode and to its own drain electrode. This prevents each of the light receiving TFTs from being put, in error, into an ON state. The light receiving TFTs can be kept reliably in an OFF state irrespective of setting of a bias level, which prevents reliably malfunction. By detecting optical currents generated in the light receiving devices, light input positions can be identified accurately and reliably.

Owner:NEC LCD TECH CORP

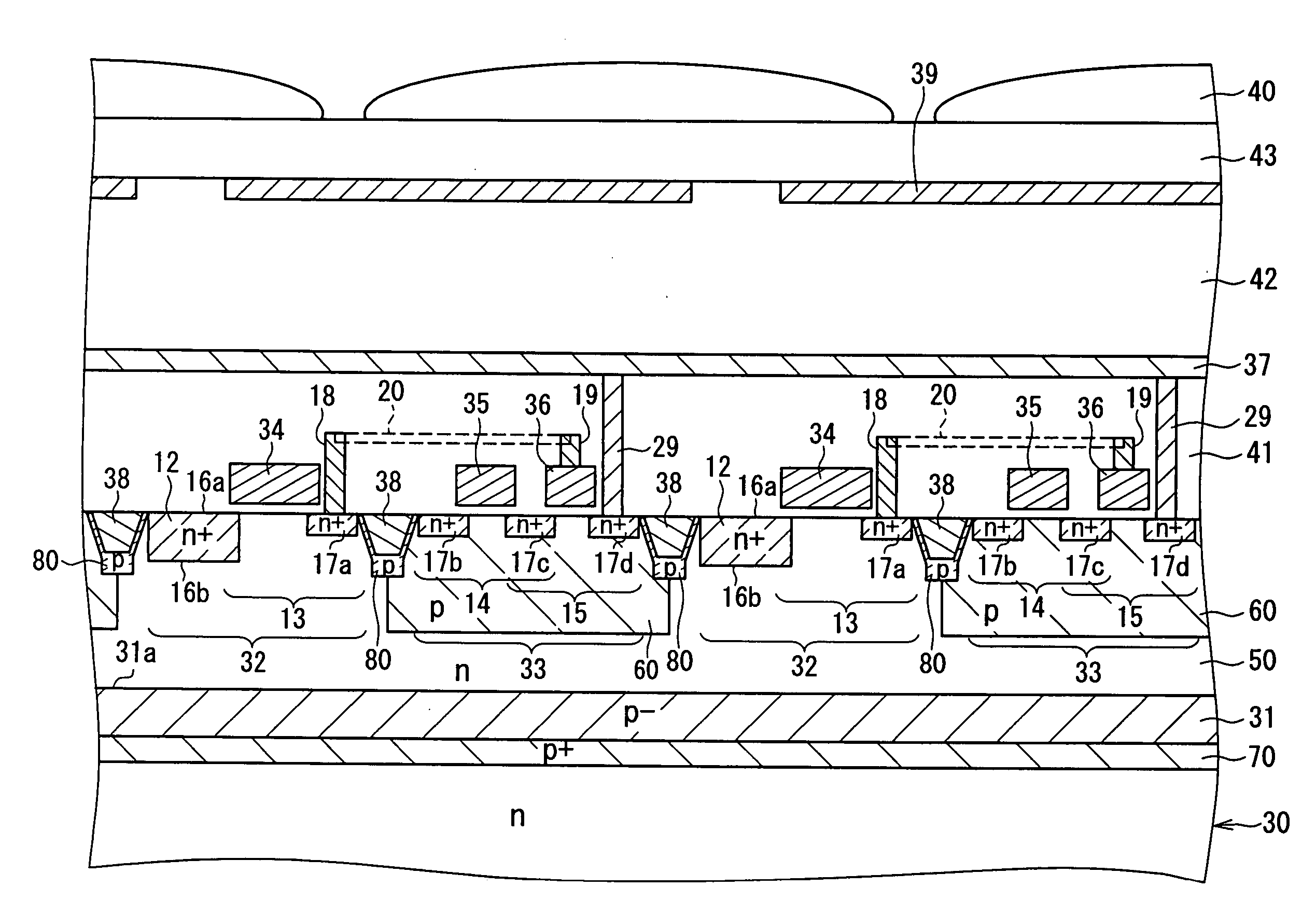

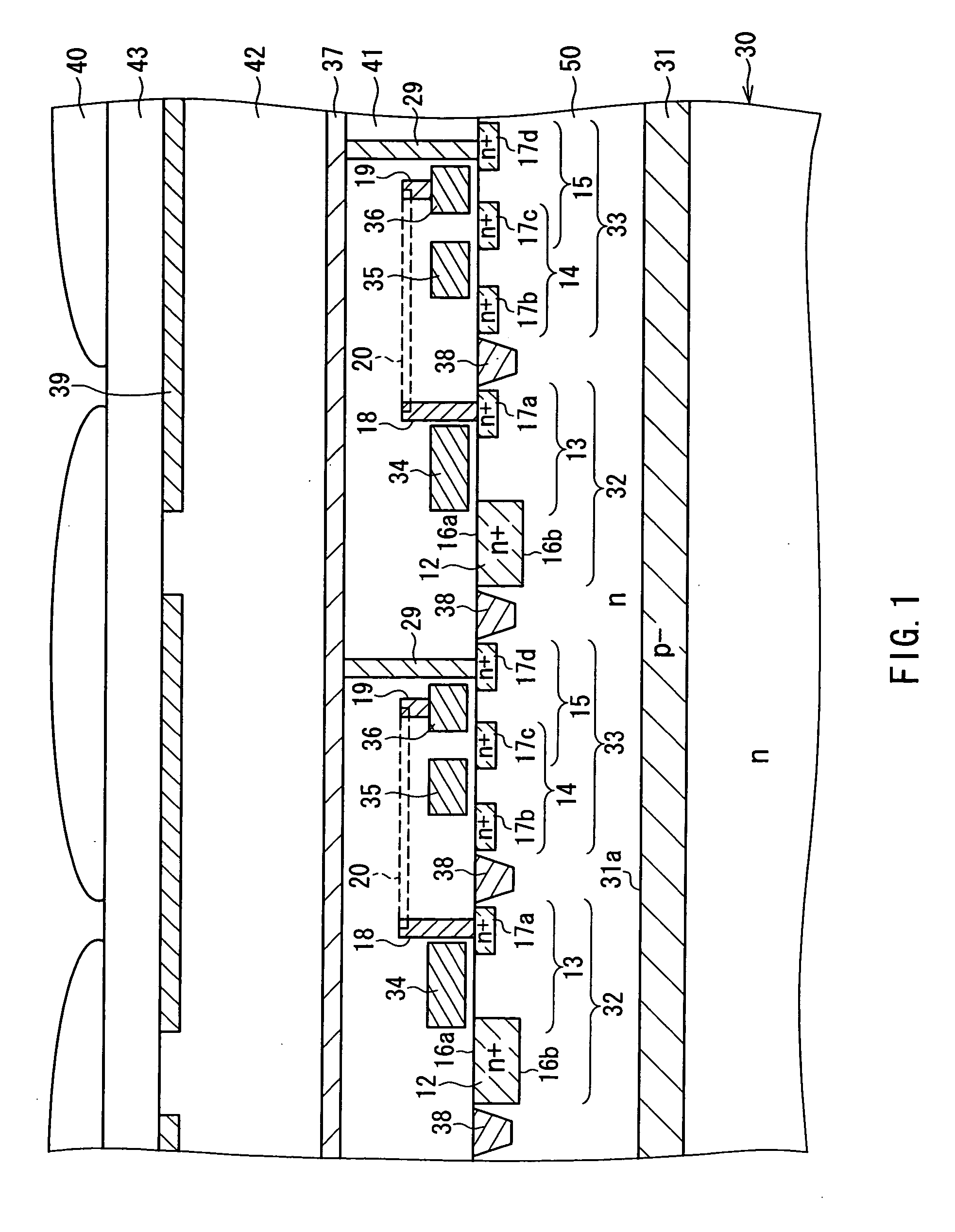

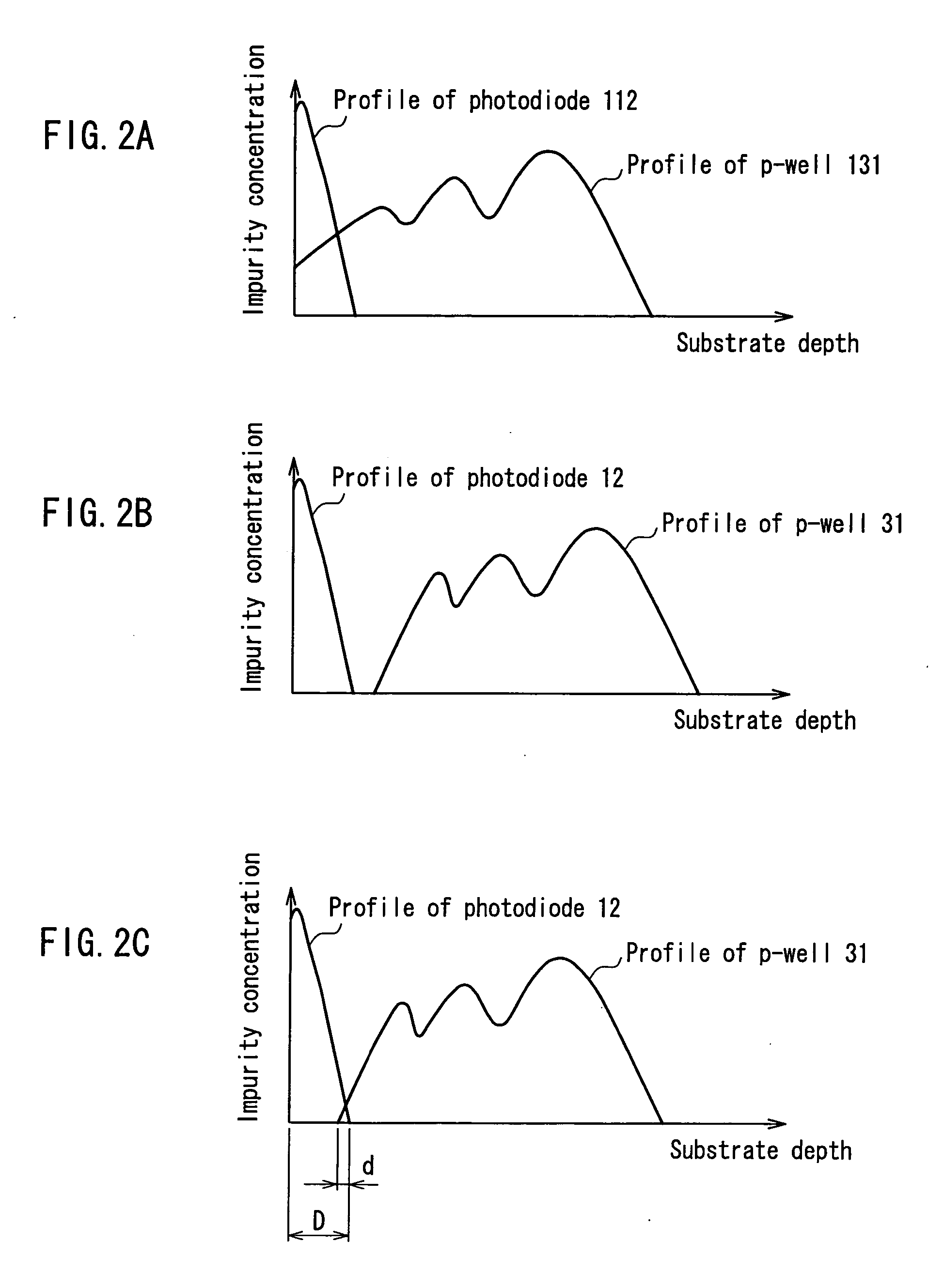

Solid-state imaging device

InactiveUS20060226438A1InhibitionSuppresses deterioration of image qualityTelevision system detailsSolid-state devicesEngineeringNon doped

A solid-state imaging device including an n-type semiconductor substrate including a photoelectric conversion portion, and a signal detection portion for detecting a signal charge is used. The photoelectric conversion portion is provided with a photodiode, and a p-well that overlaps the photoelectric conversion portion and the signal detection portion when viewed in a thickness direction of the semiconductor substrate is formed in the semiconductor substrate. The p-well is formed so that a surface side interface is located below a surface side interface of the photodiode. Preferably, the surface side interface of the p-well is located below a lower side interface of the photodiode and an impurity profile of the p-well does not overlap that of the photodiode. At this time, a non-dope region is present between the photodiode and the p-well.

Owner:PANASONIC CORP

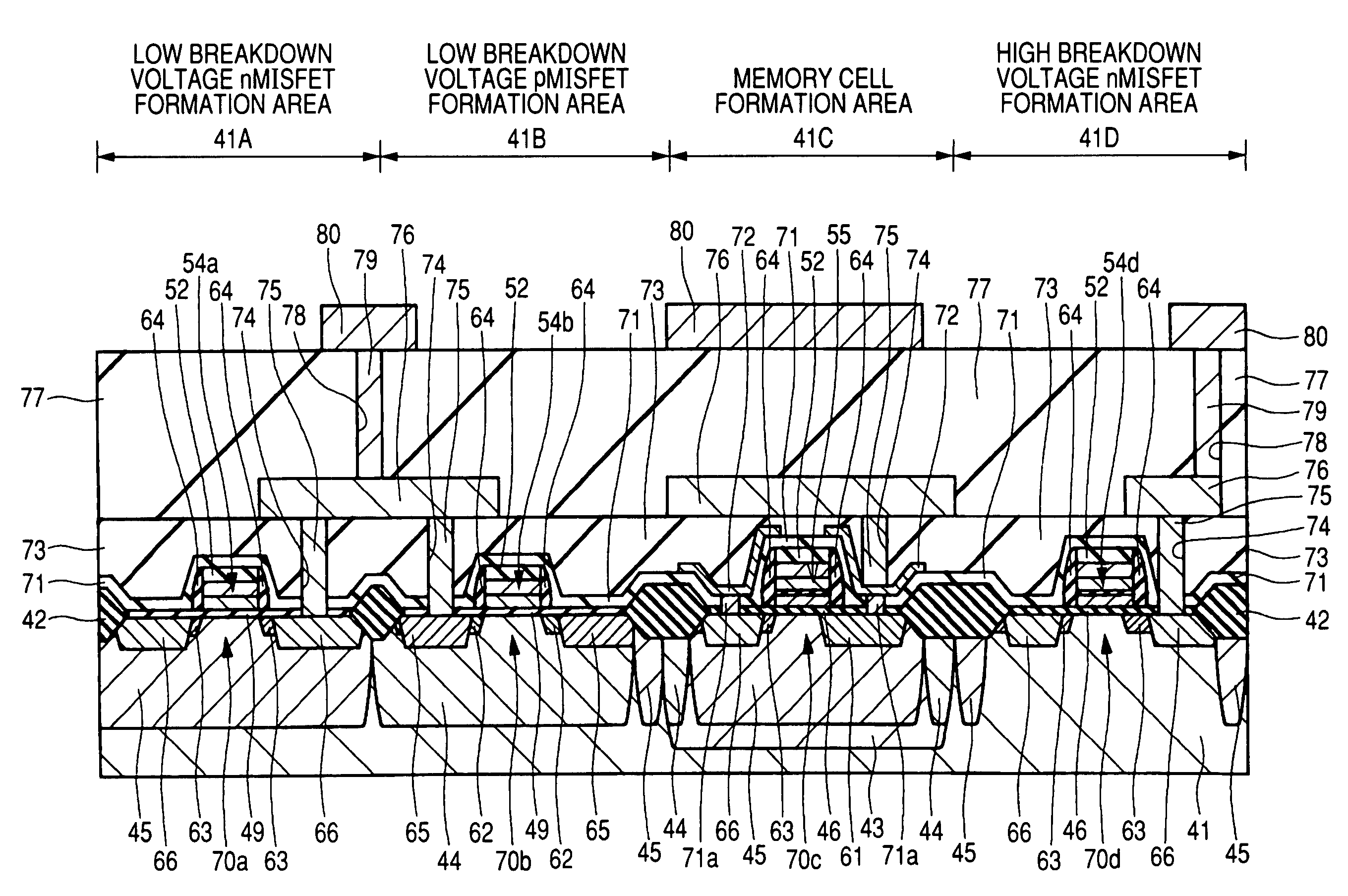

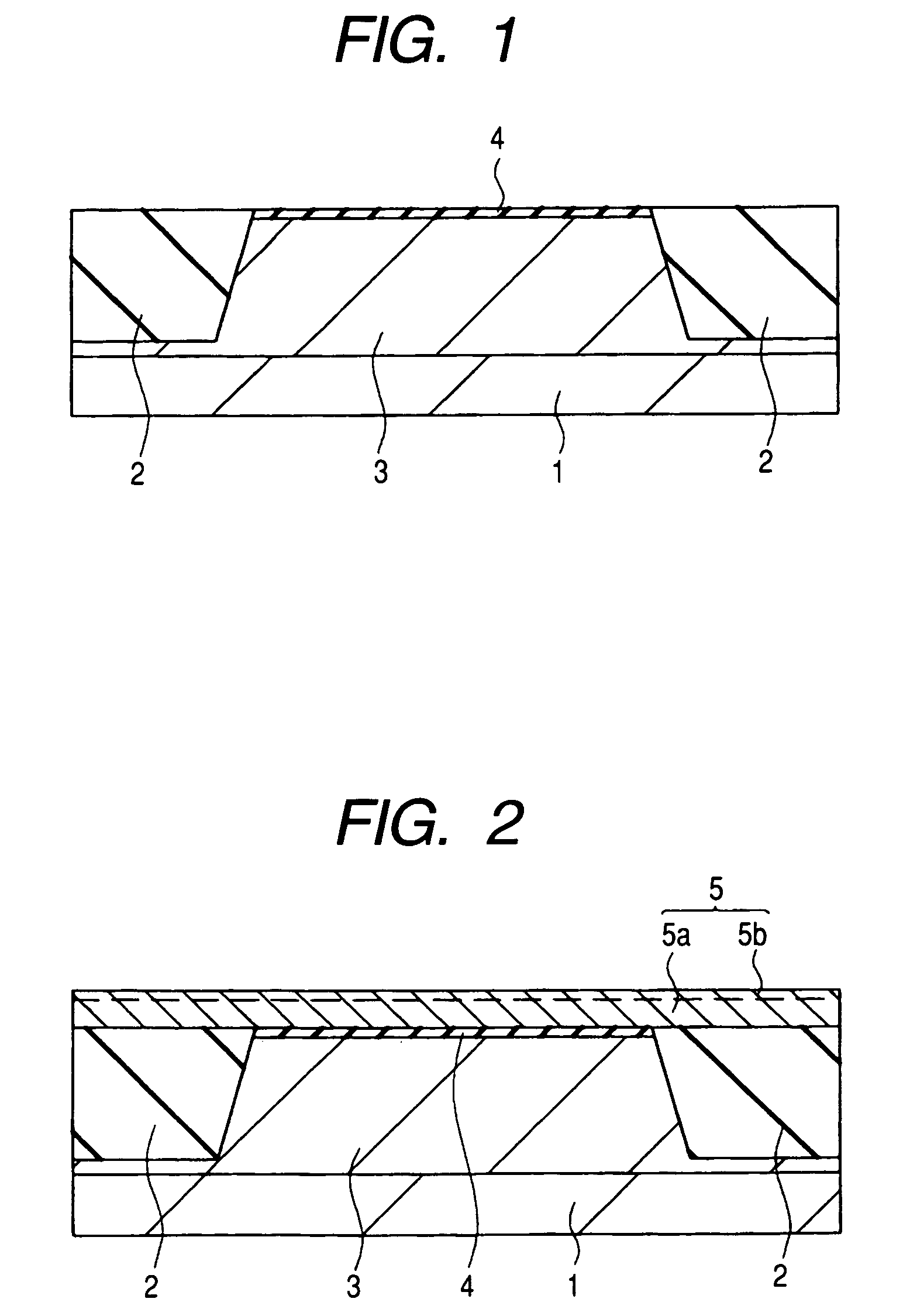

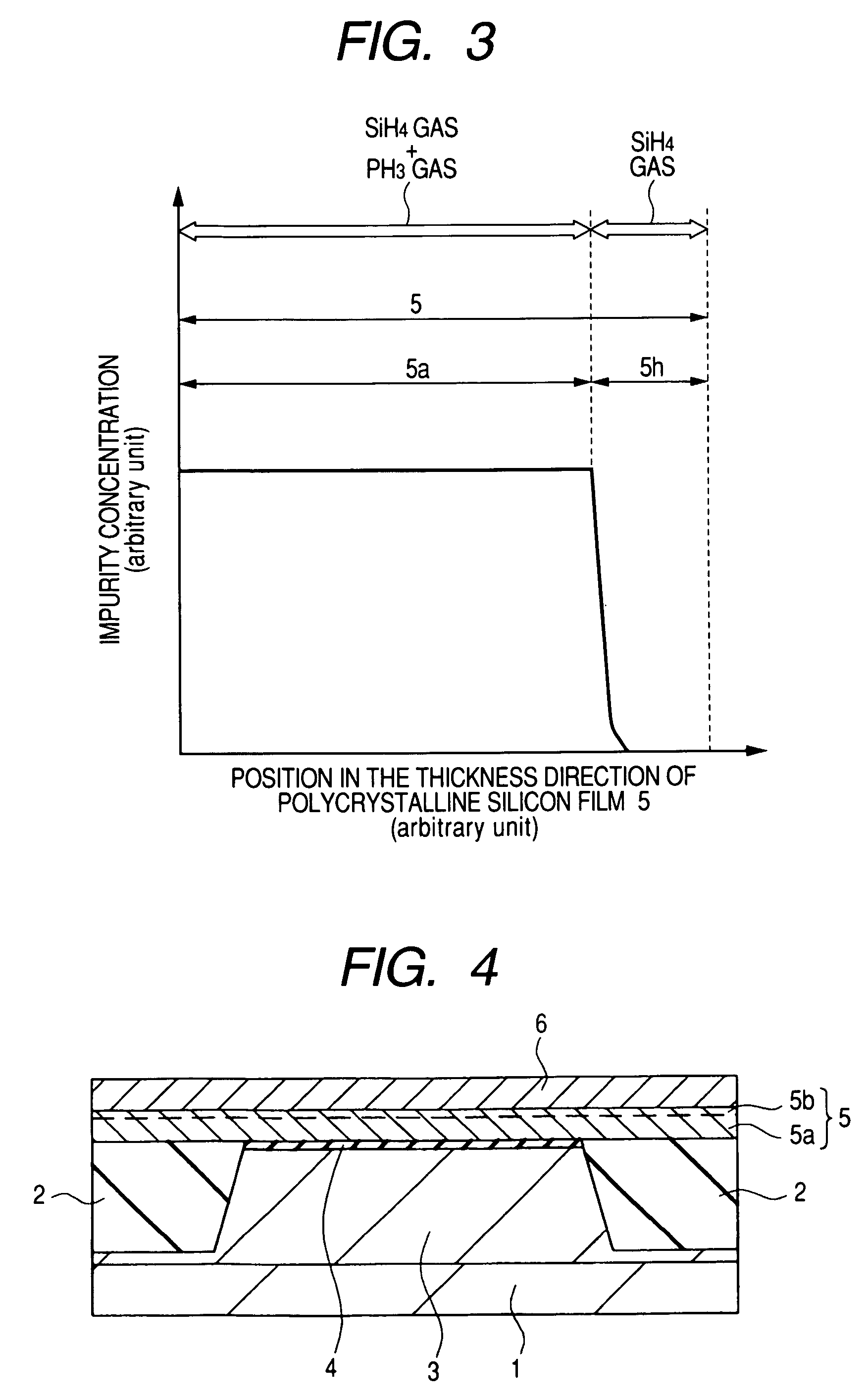

Method of manufacturing a semiconductor device

ActiveUS7256125B2Lower gate resistanceLow reliabilityTransistorSolid-state devicesNon dopedSemiconductor

For improving the reliability of a semiconductor device having a stacked structure of a polycrystalline silicon film and a tungsten silicide film, the device is manufactured by forming a polycrystalline silicon film, a tungsten silicide film and an insulating film successively over a gate insulating film disposed over the main surface of a semiconductor substrate, and patterning them to form a gate electrode having a stacked structure consisting of the polycrystalline silicon film and tungsten silicide film. The polycrystalline silicon film has two regions, one region formed by an impurity-doped polycrystalline silicon and the other one formed by non-doped polycrystalline silicon. The tungsten silicide film is deposited so that the resistivity of it upon film formation would exceed 1000 μΩcm.

Owner:RENESAS ELECTRONICS CORP +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com