Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

39results about How to "Reduce collector resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

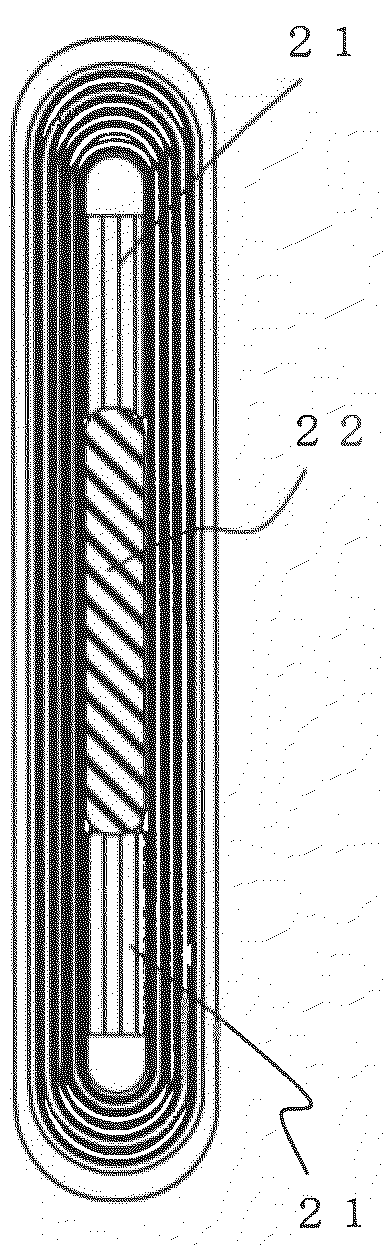

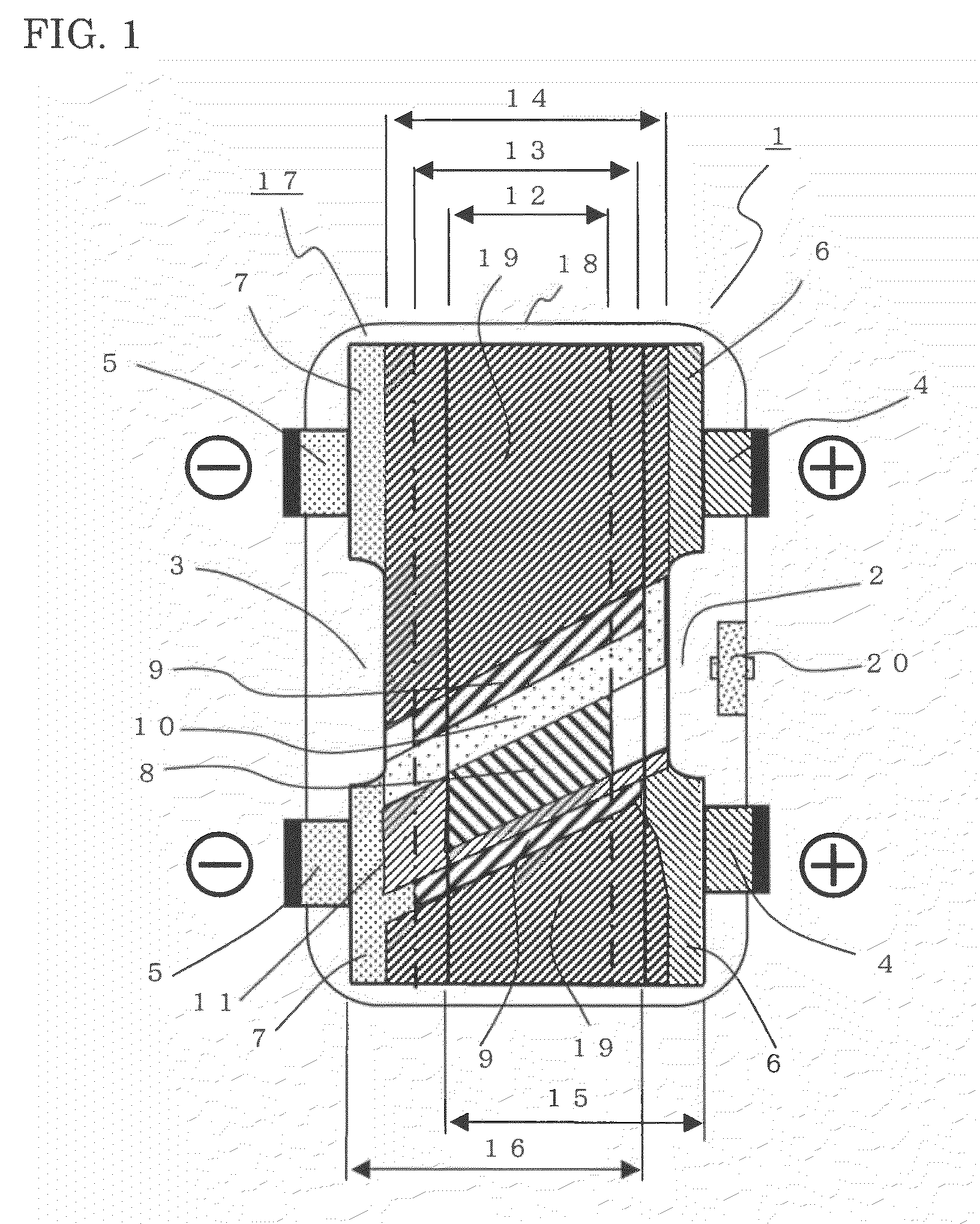

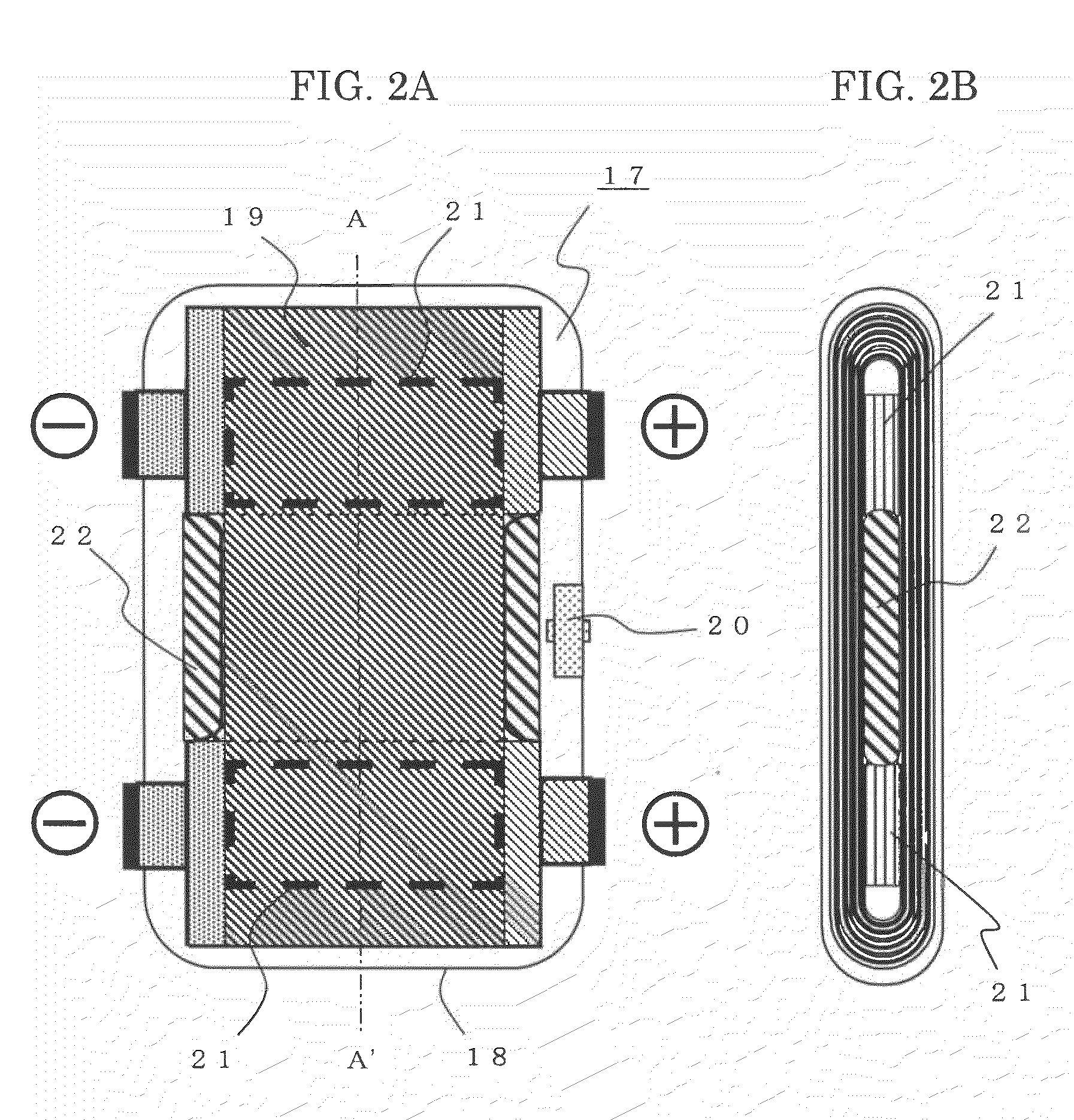

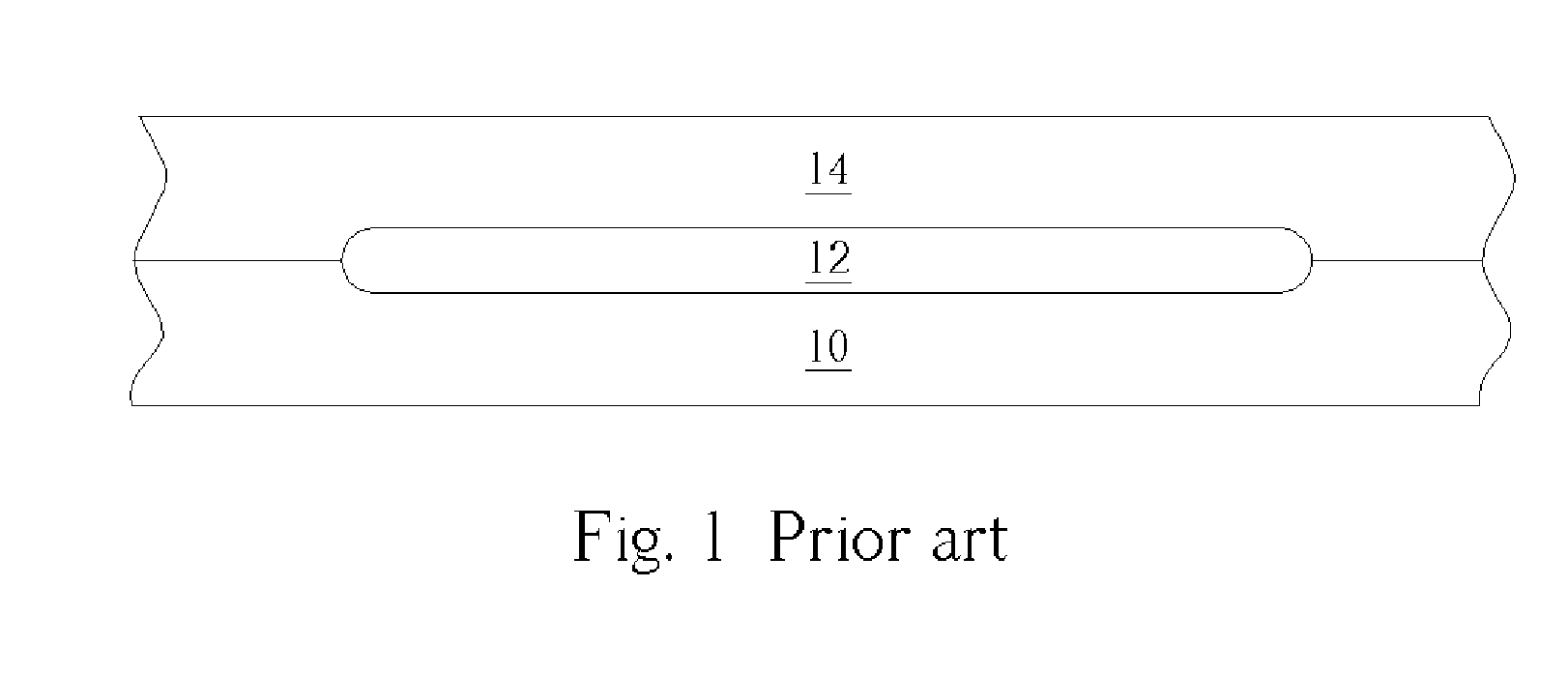

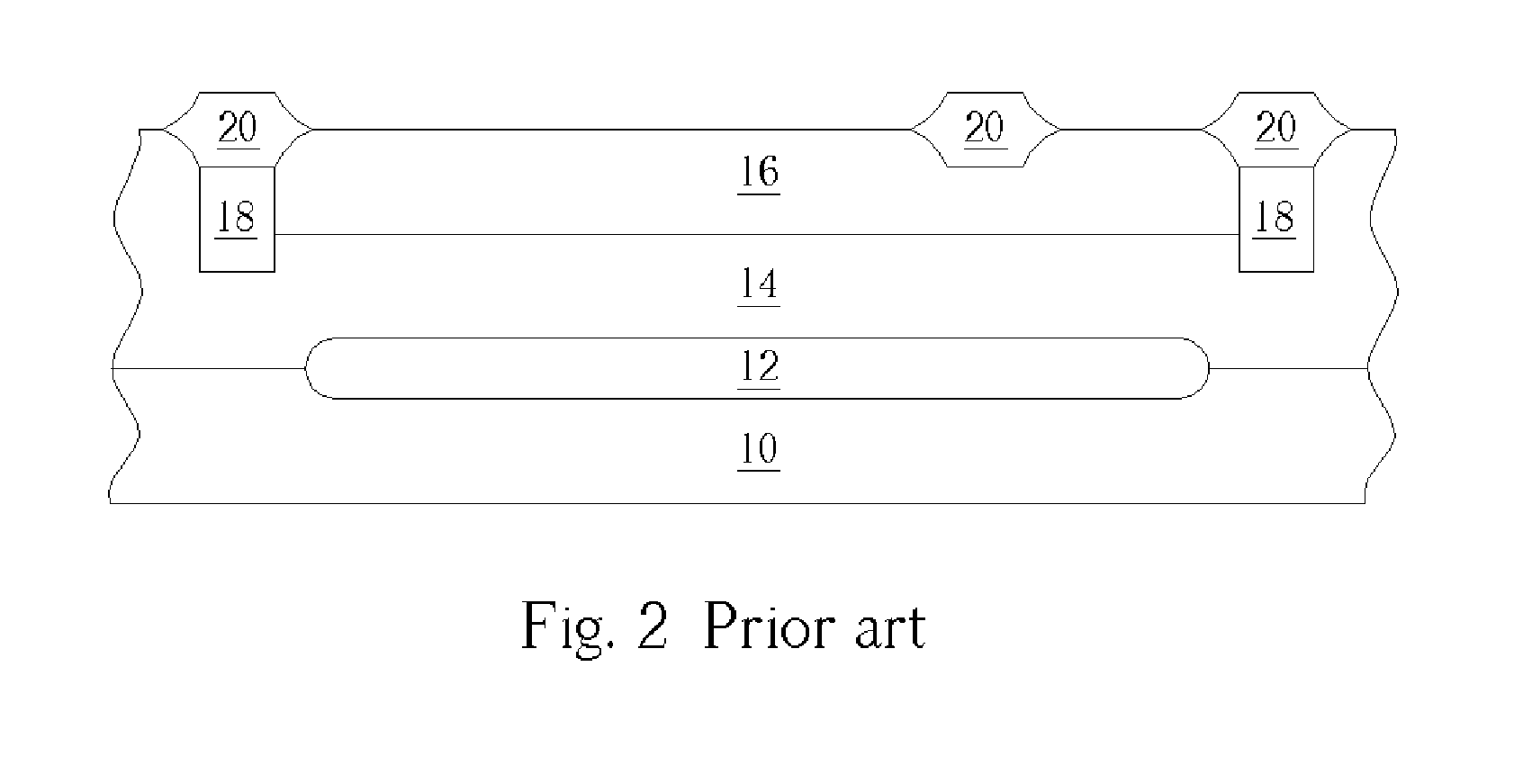

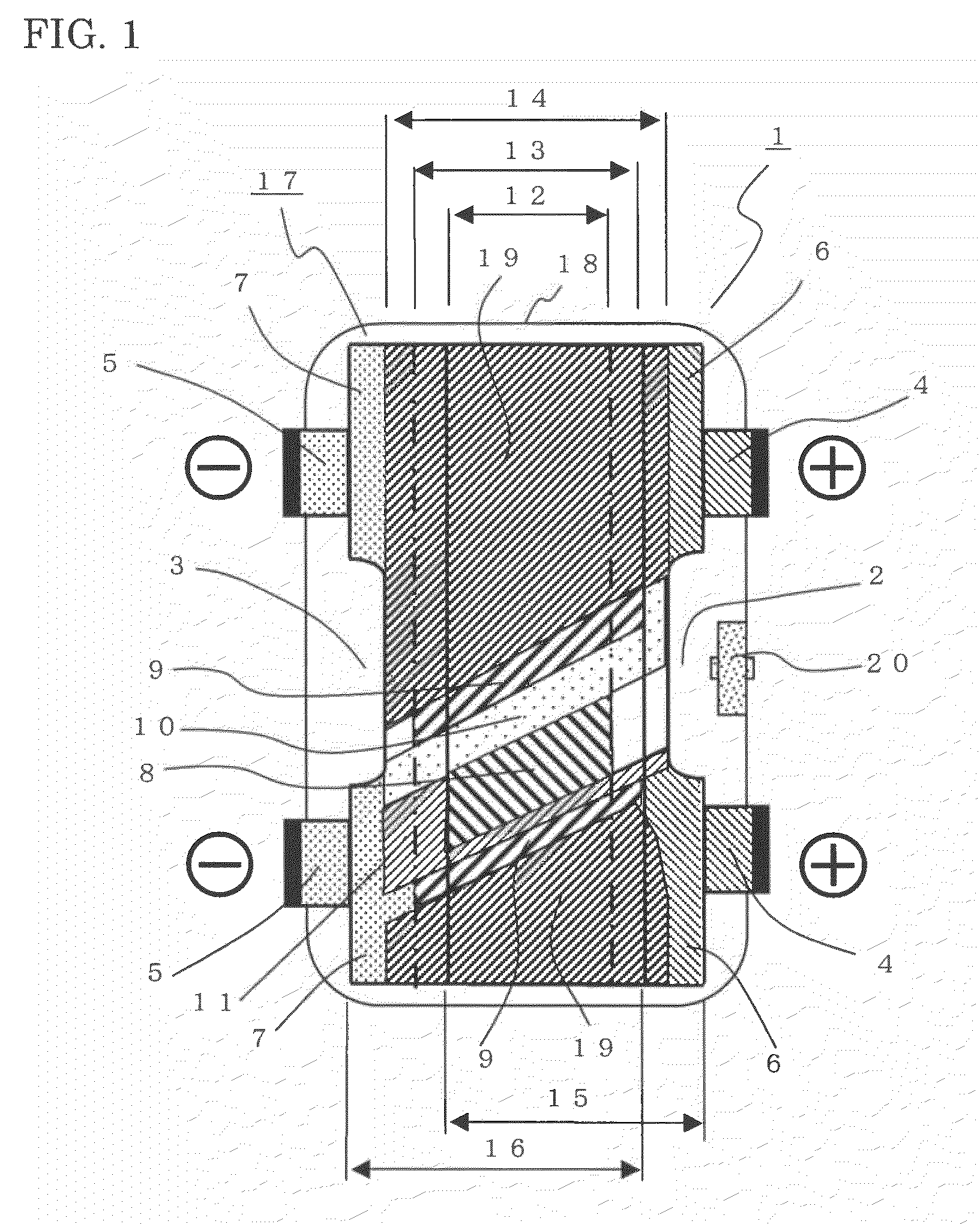

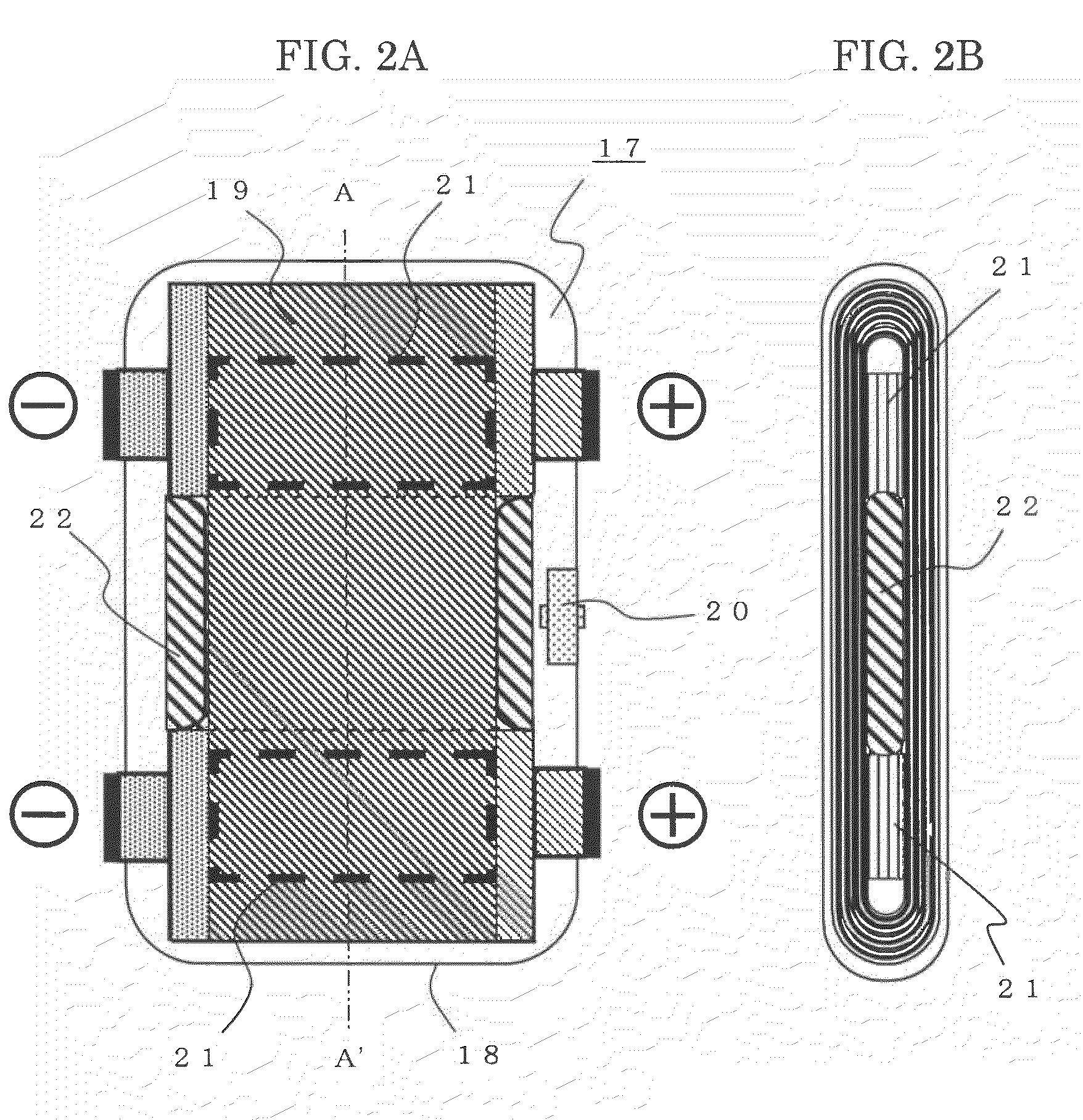

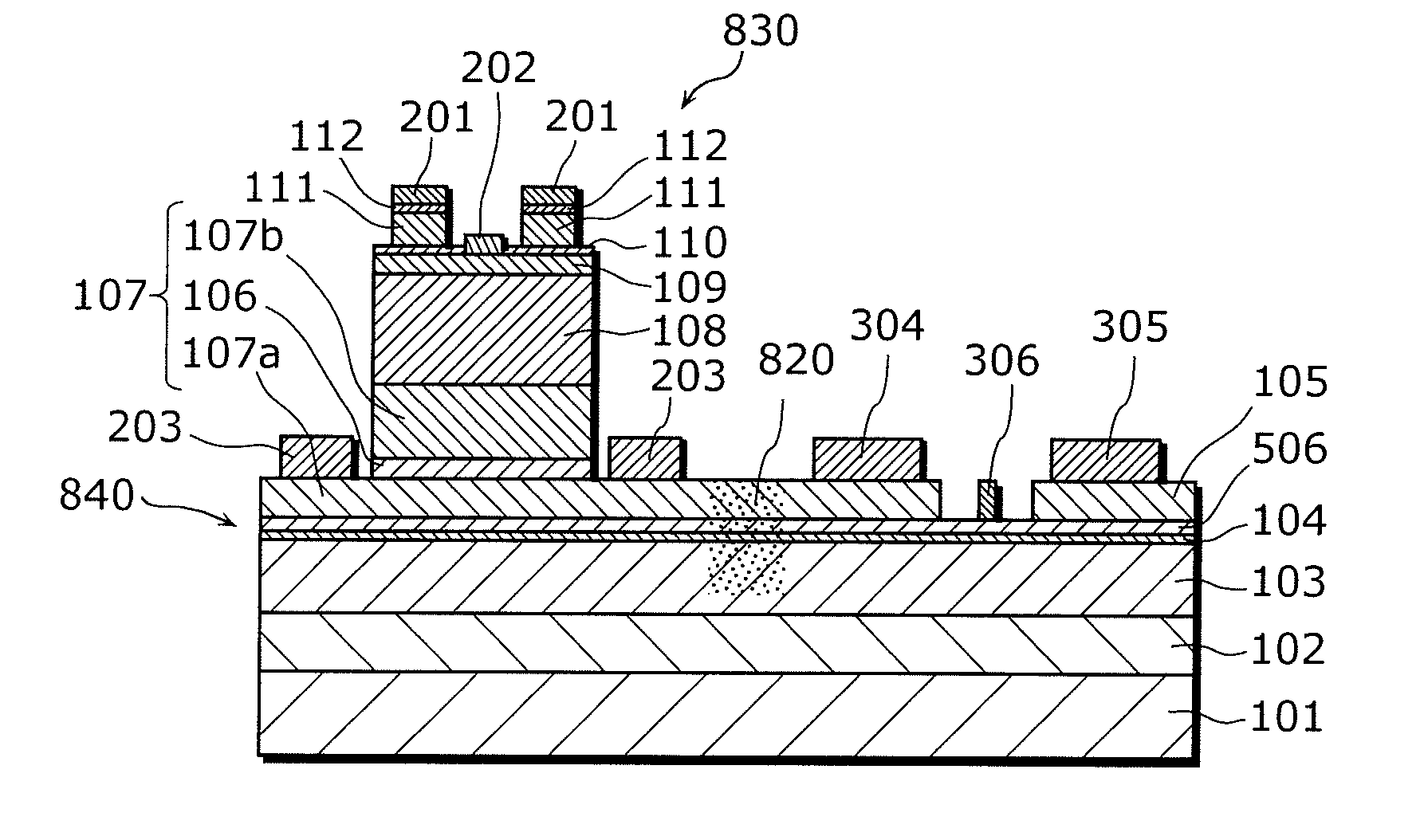

Electrical energy storage cell and electrical energy storage module including the same

InactiveUS20090136832A1Efficiently internally generated heatReduce collector resistancePrimary cell to battery groupingFinal product manufacturePositive currentStorage cell

The storage cell comprises a flat roll electrode that includes a strip of positive electrode having a positive electrode current collector foil and a positive electrode layer formed thereon, a strip of negative electrode having an electrode current collector foil and a negative electrode layer formed, and a strip of electrically insulated separator, the strip of positive electrode and the strip of negative electrode being wound into a flat roll configuration with the strip of electrically insulated separator sandwiched therebetween; a sealed casing that hermetically seals the flat roll electrode impregnated with an electrolyte; a positive terminal and a negative terminal each electrically insulated from the sealed casing, connected to the positive current collector foil and the negative current collector foil, respectively.

Owner:MITSUBISHI ELECTRIC CORP

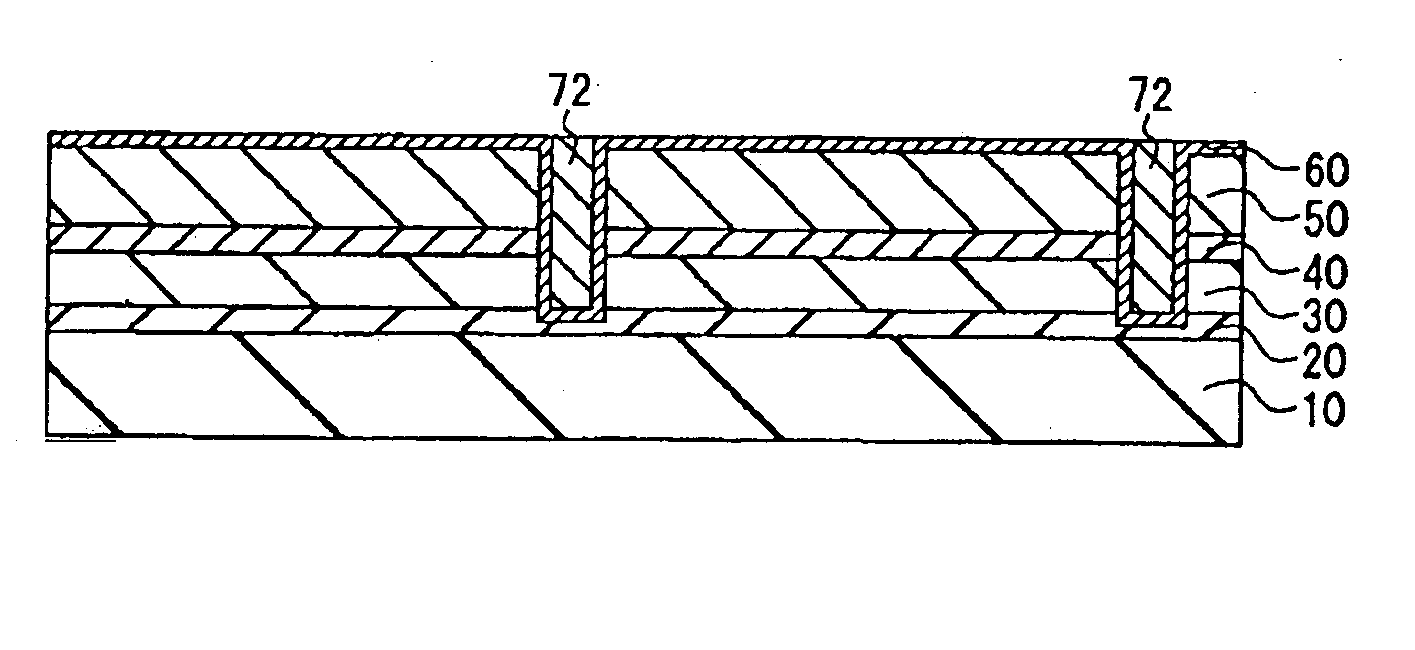

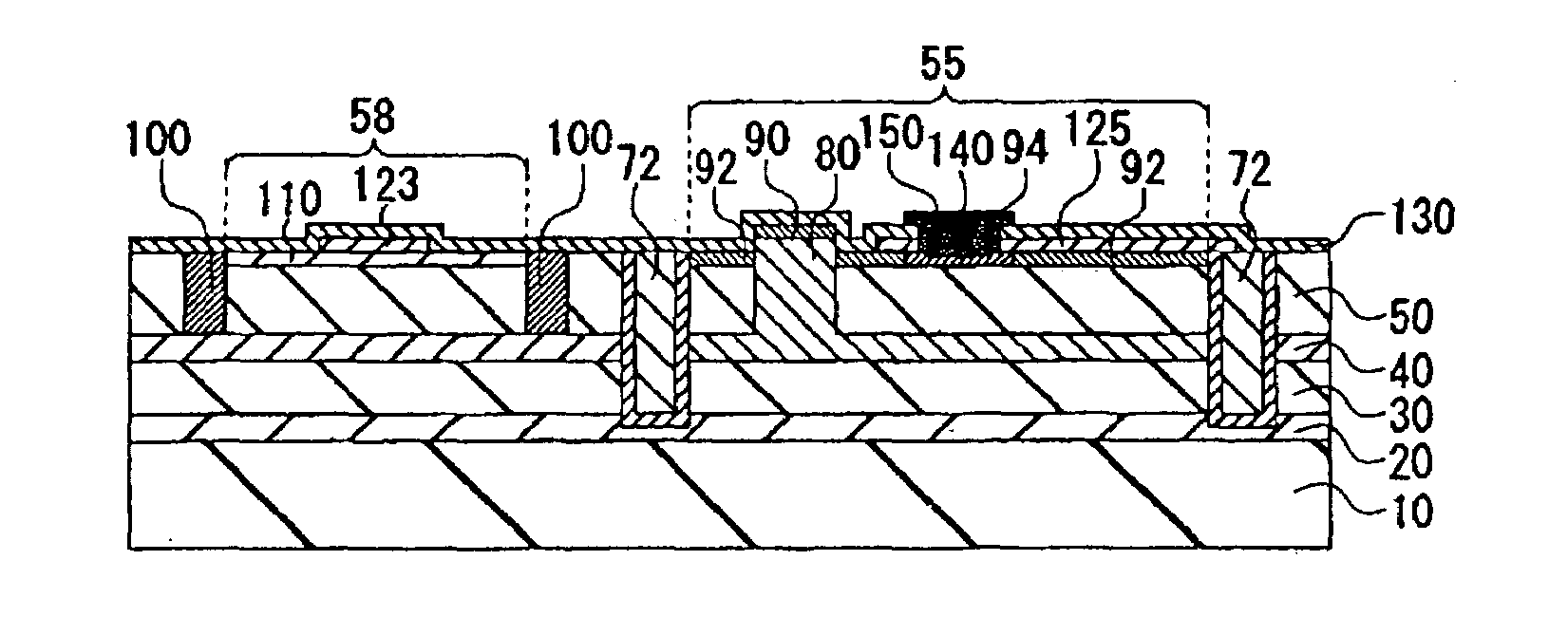

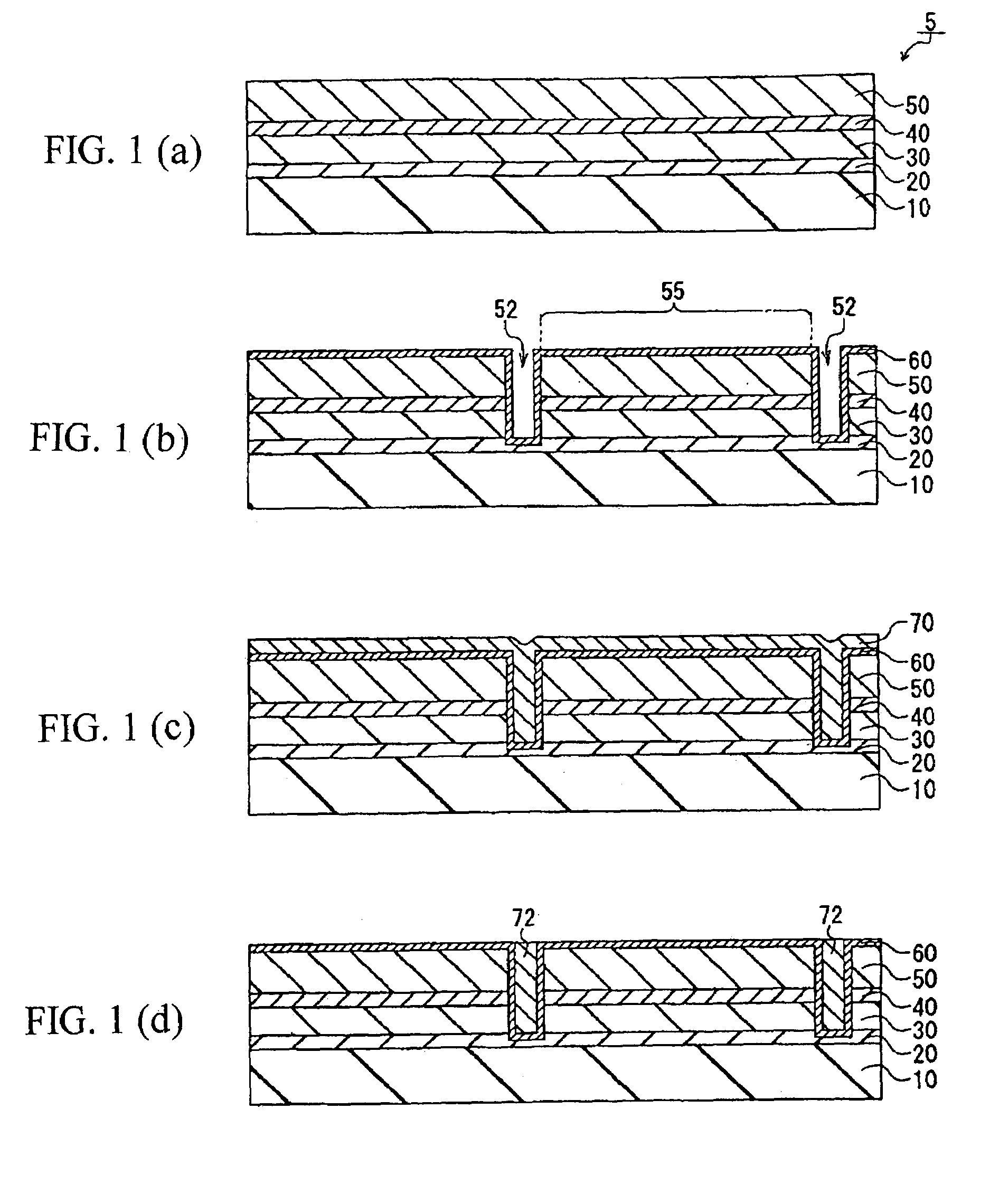

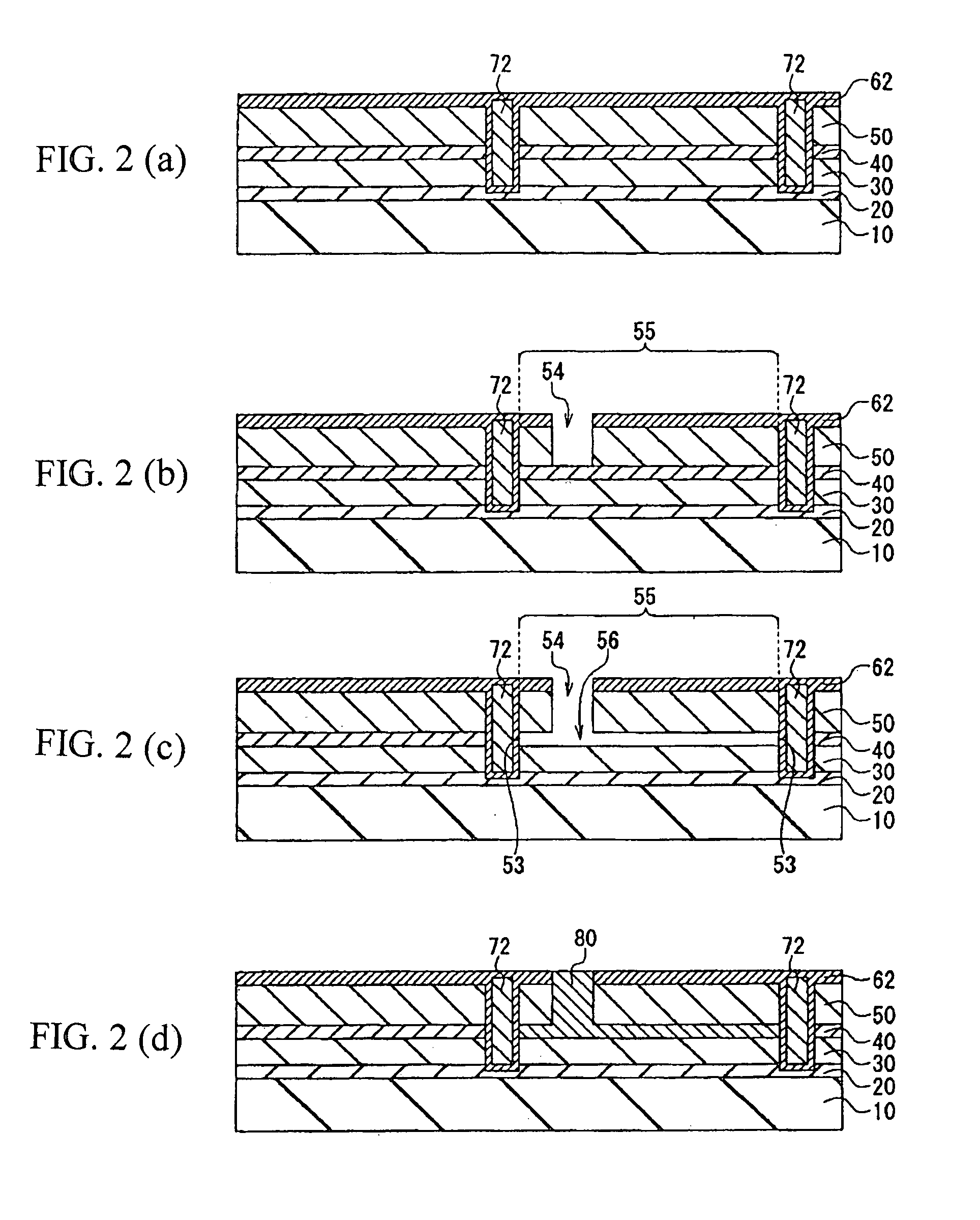

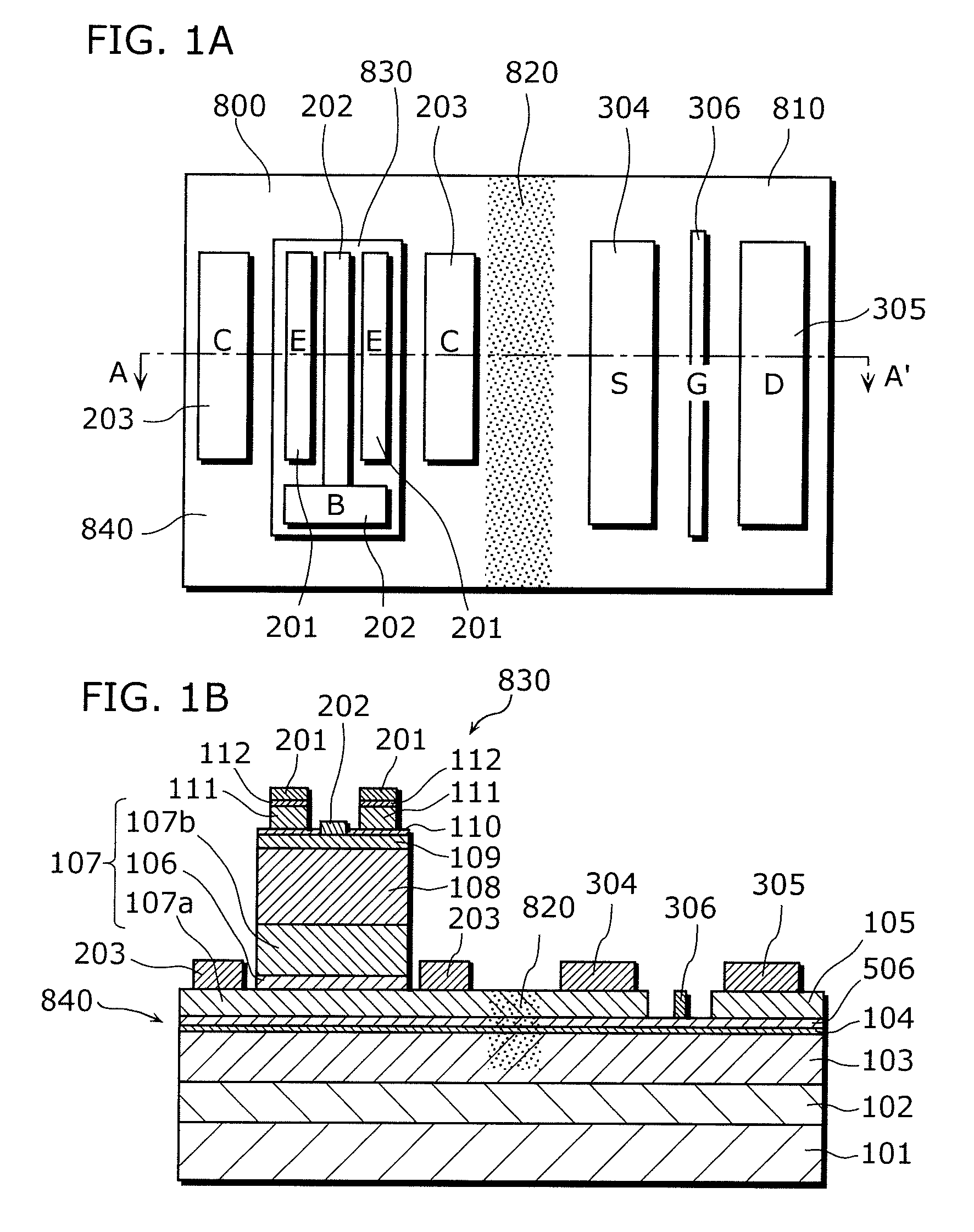

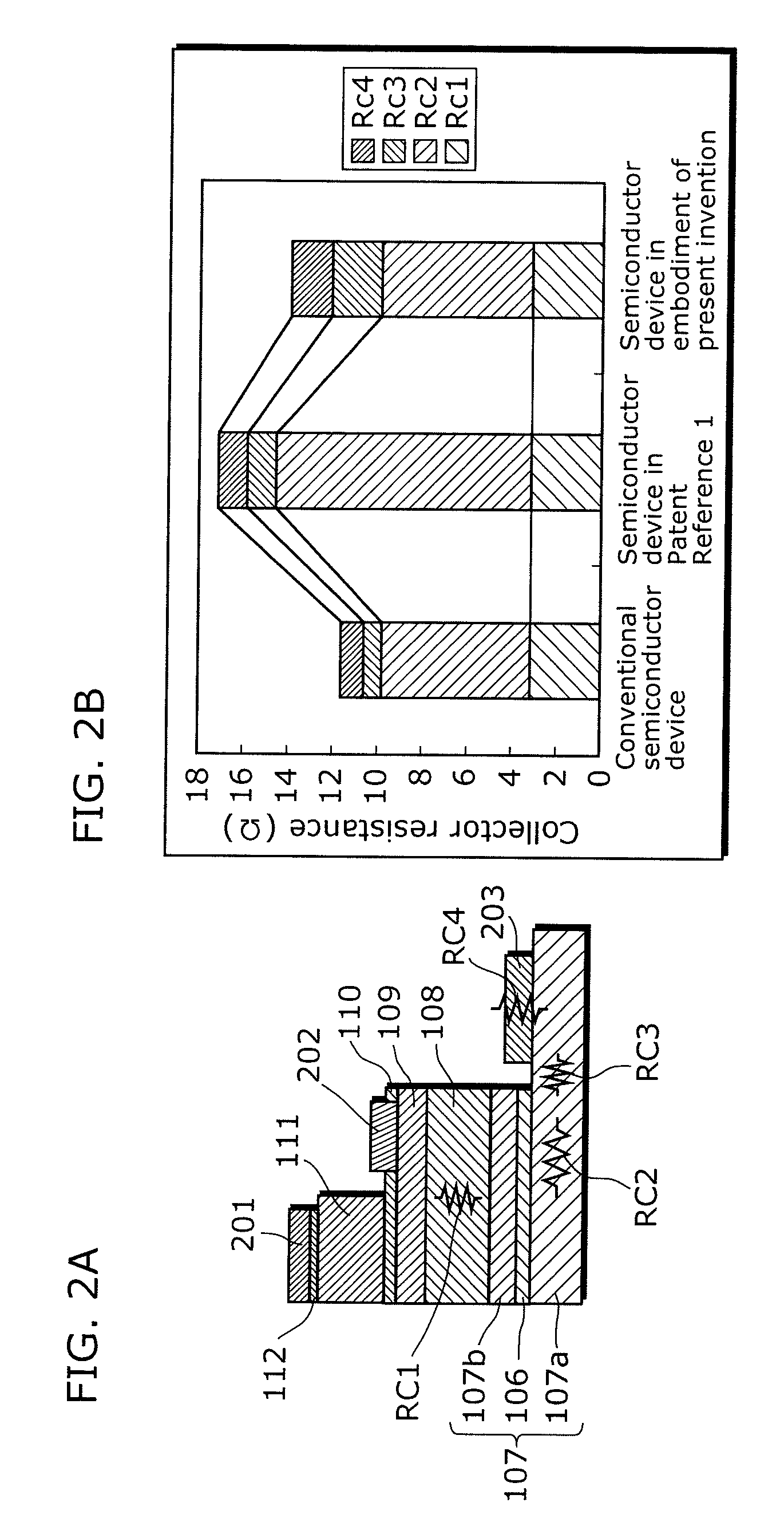

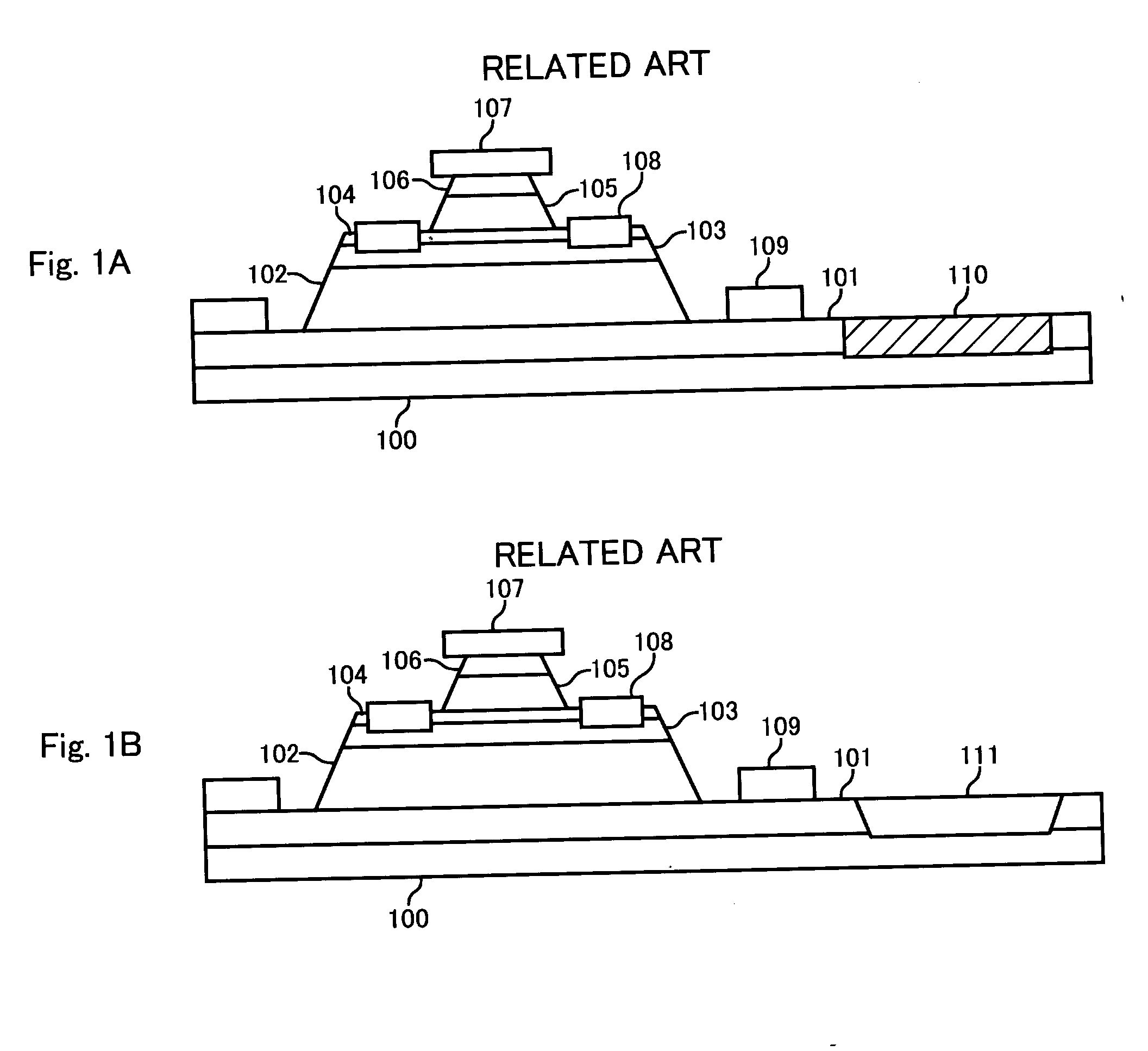

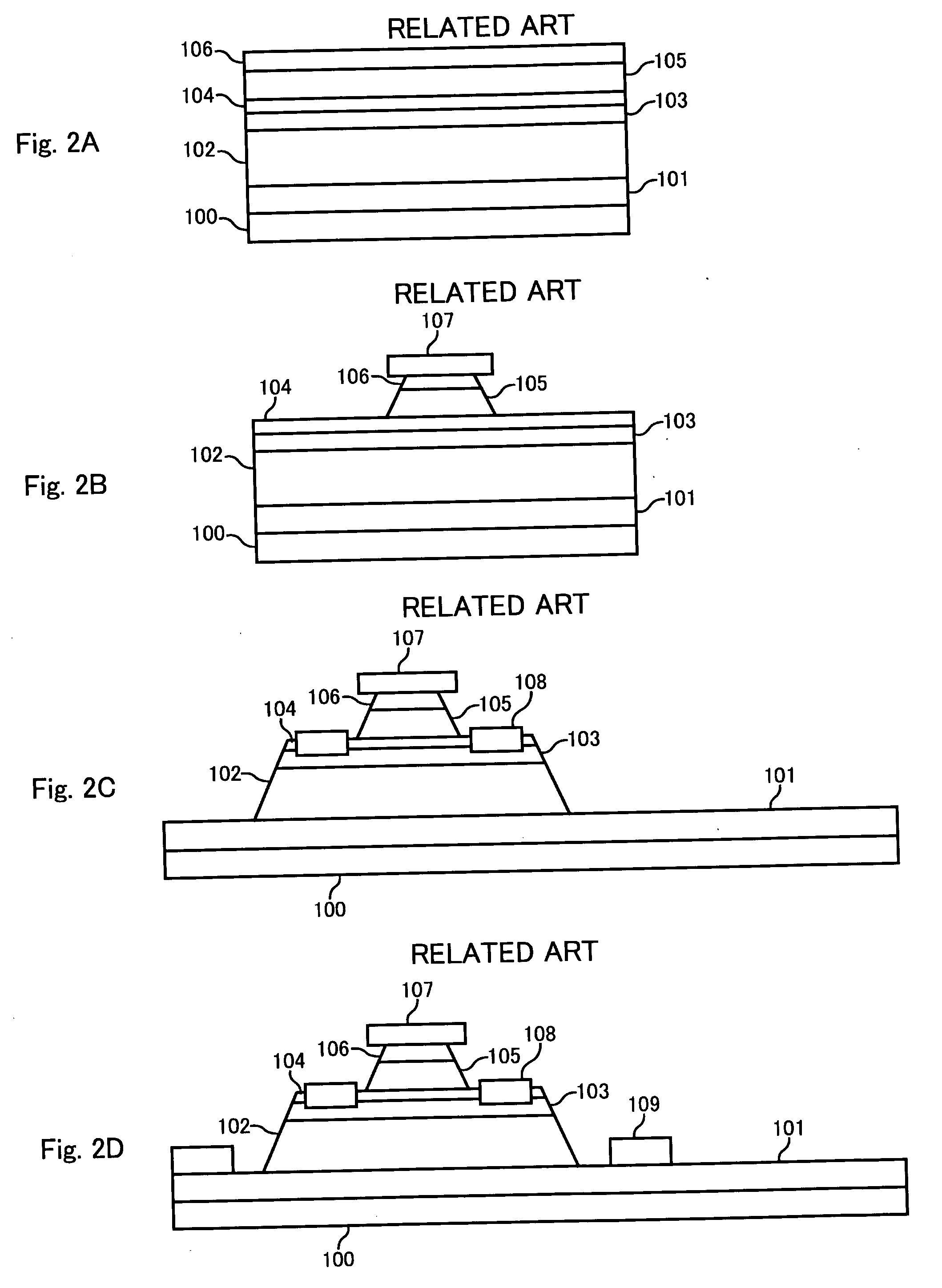

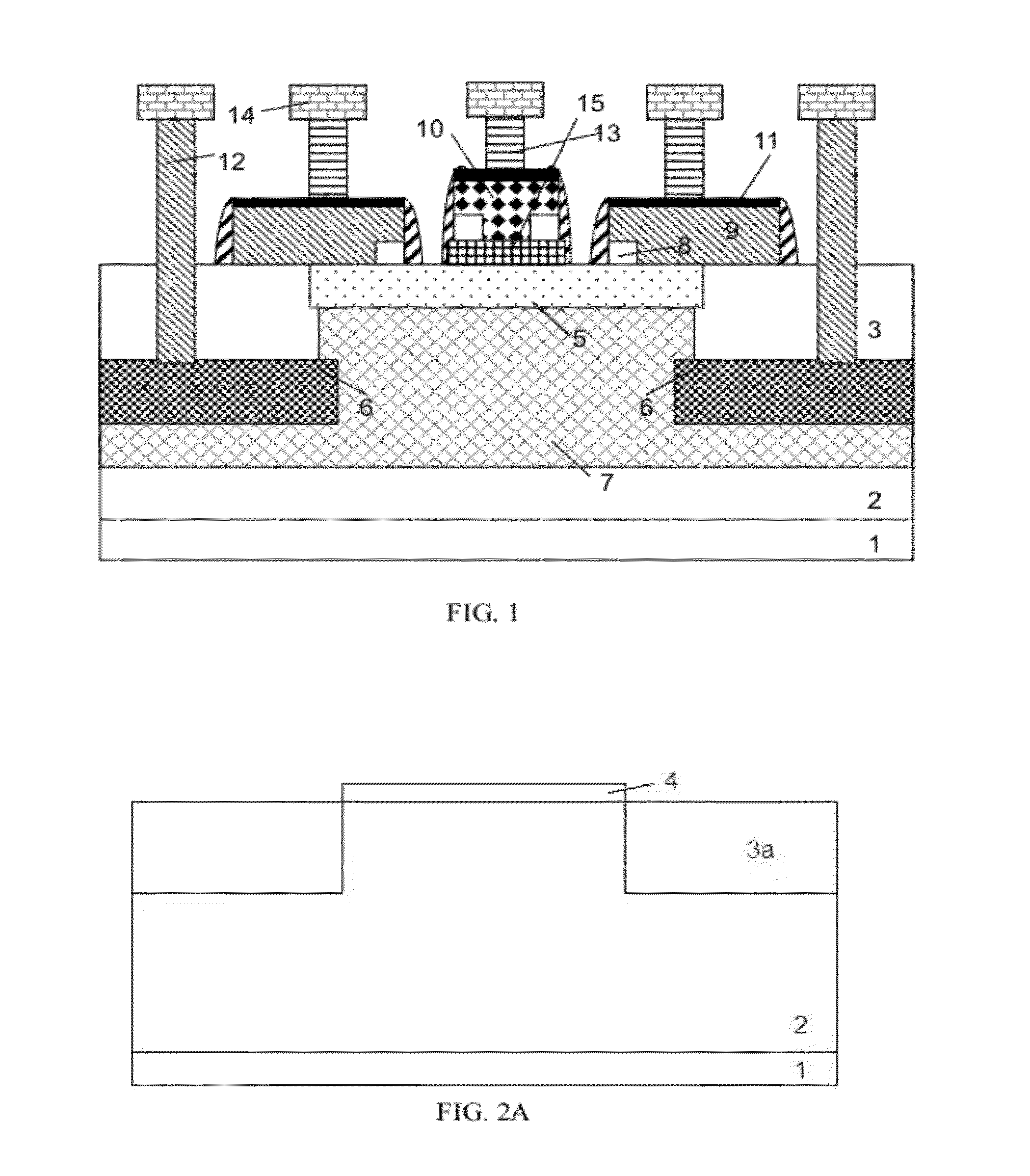

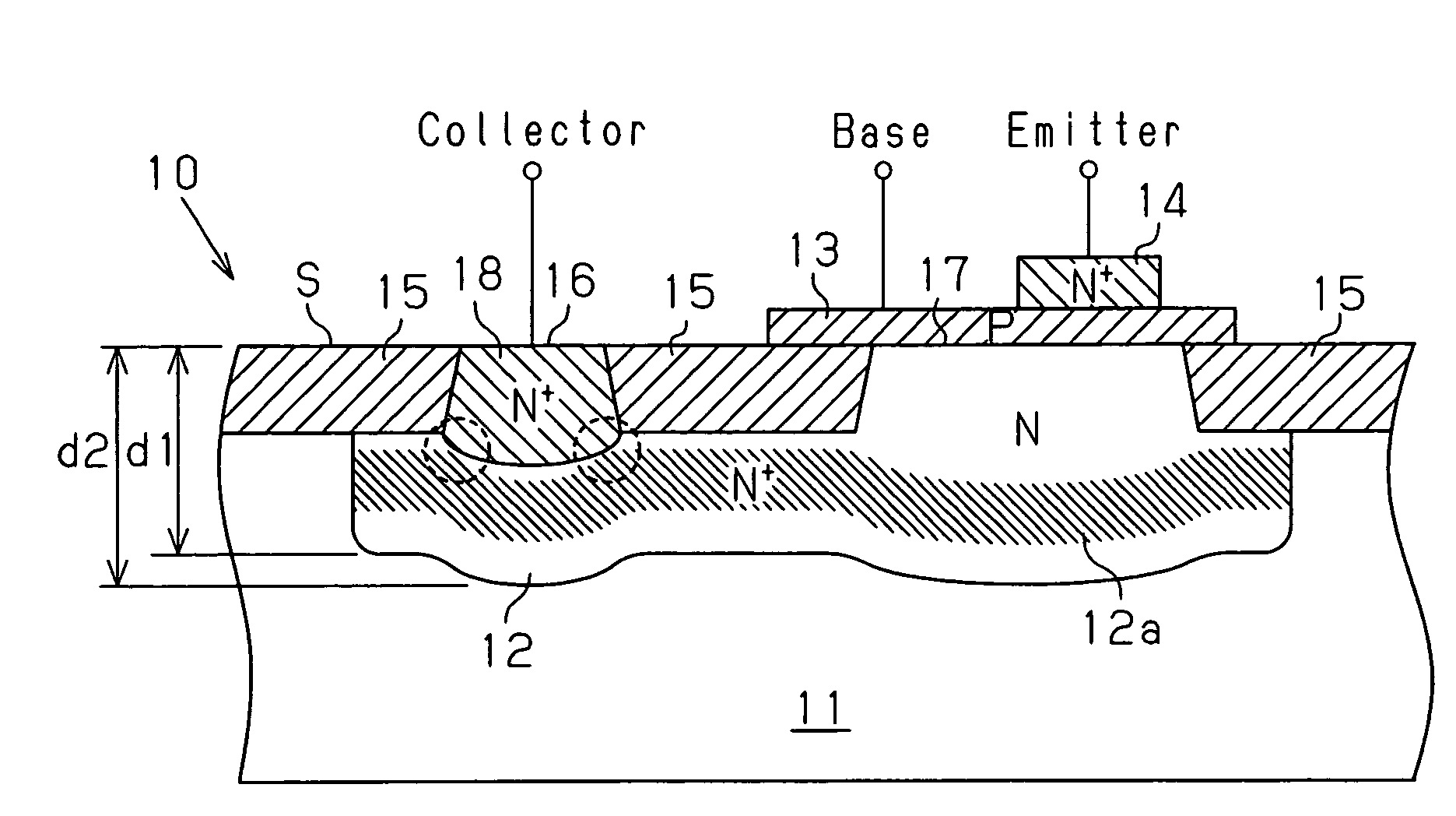

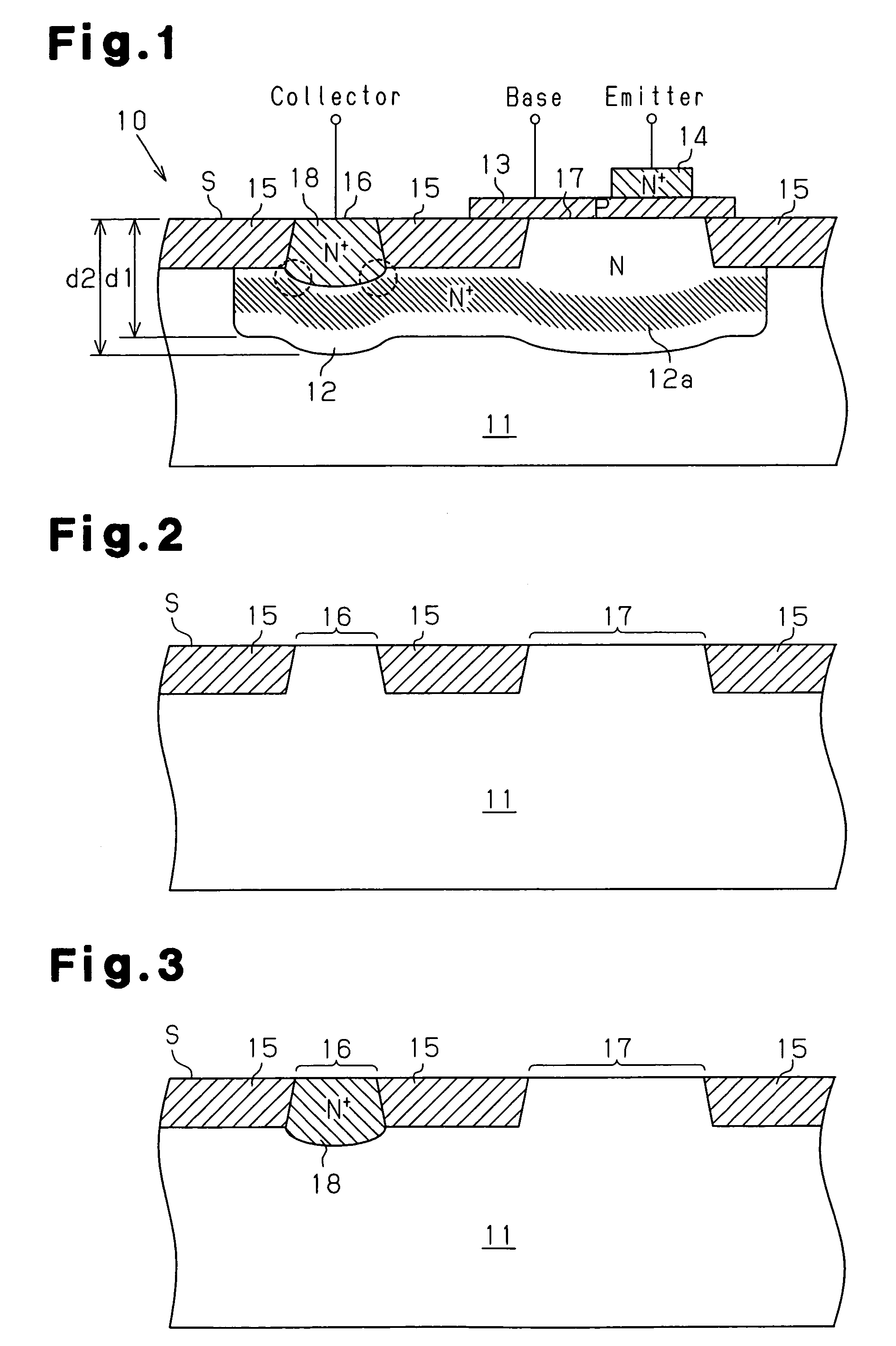

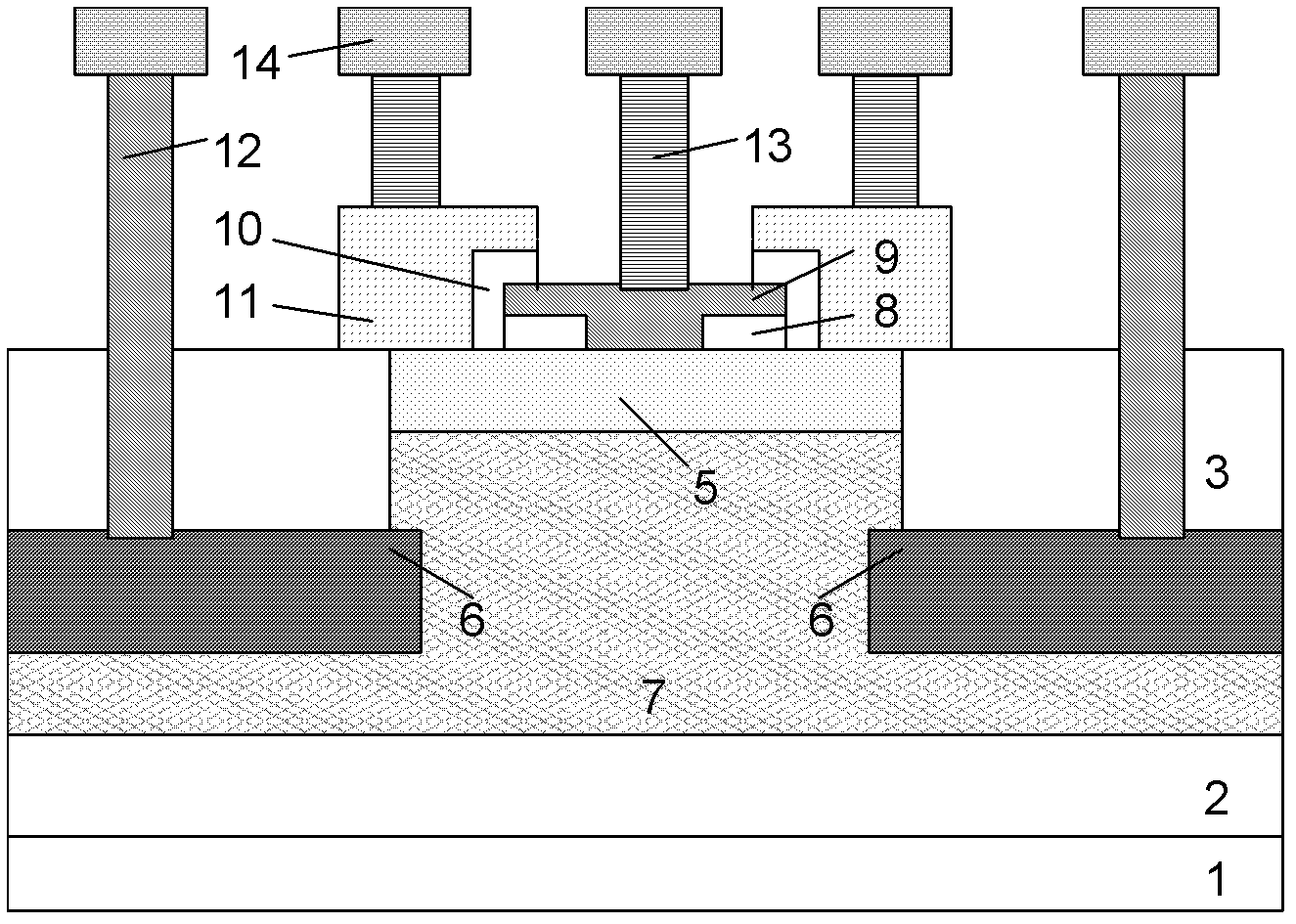

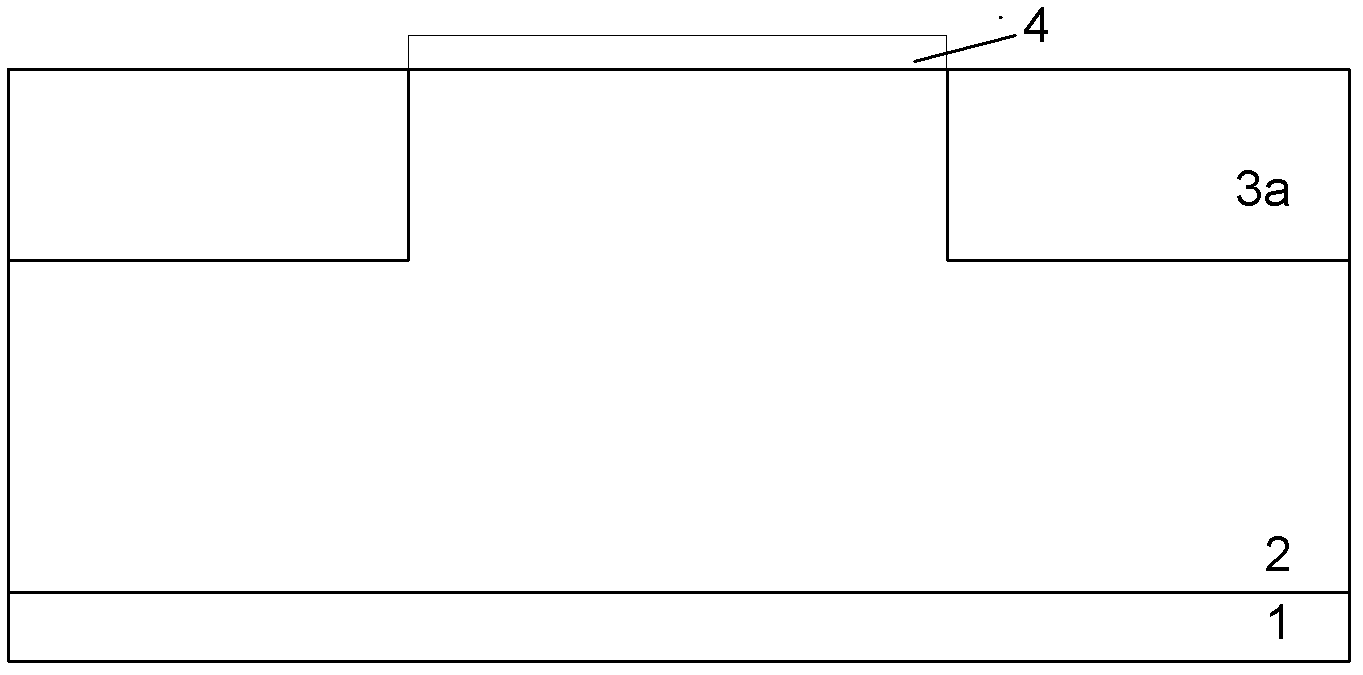

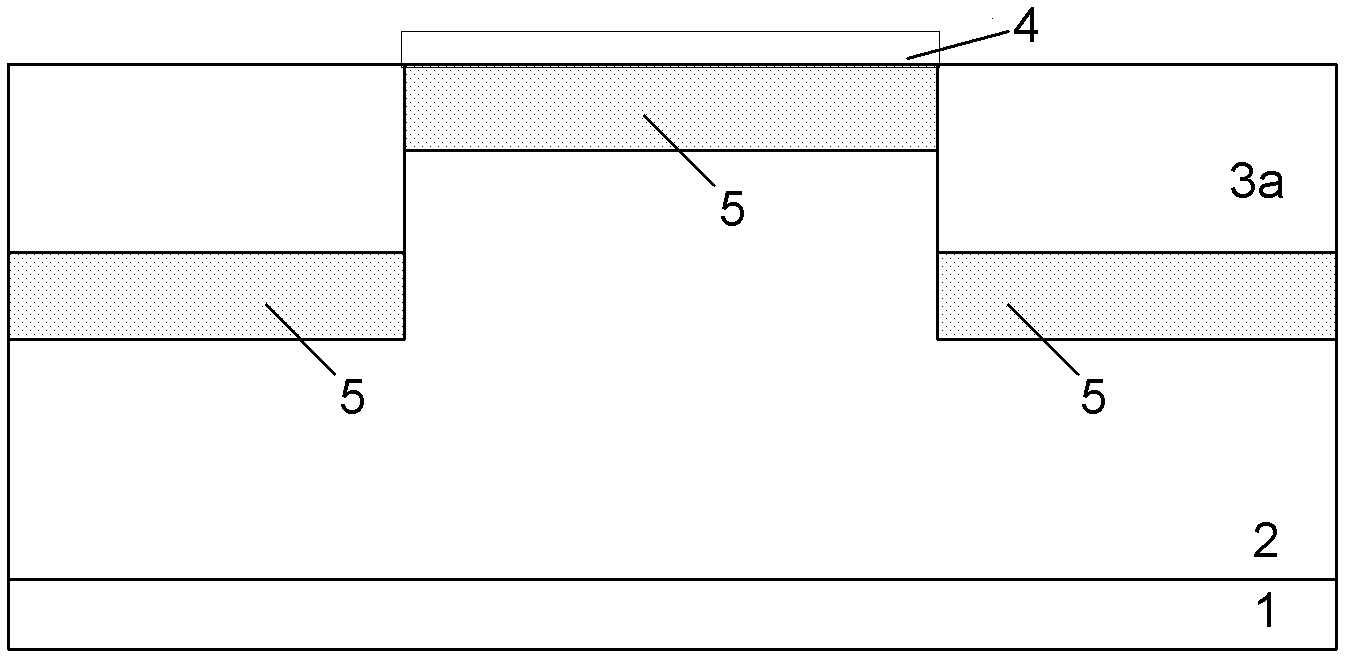

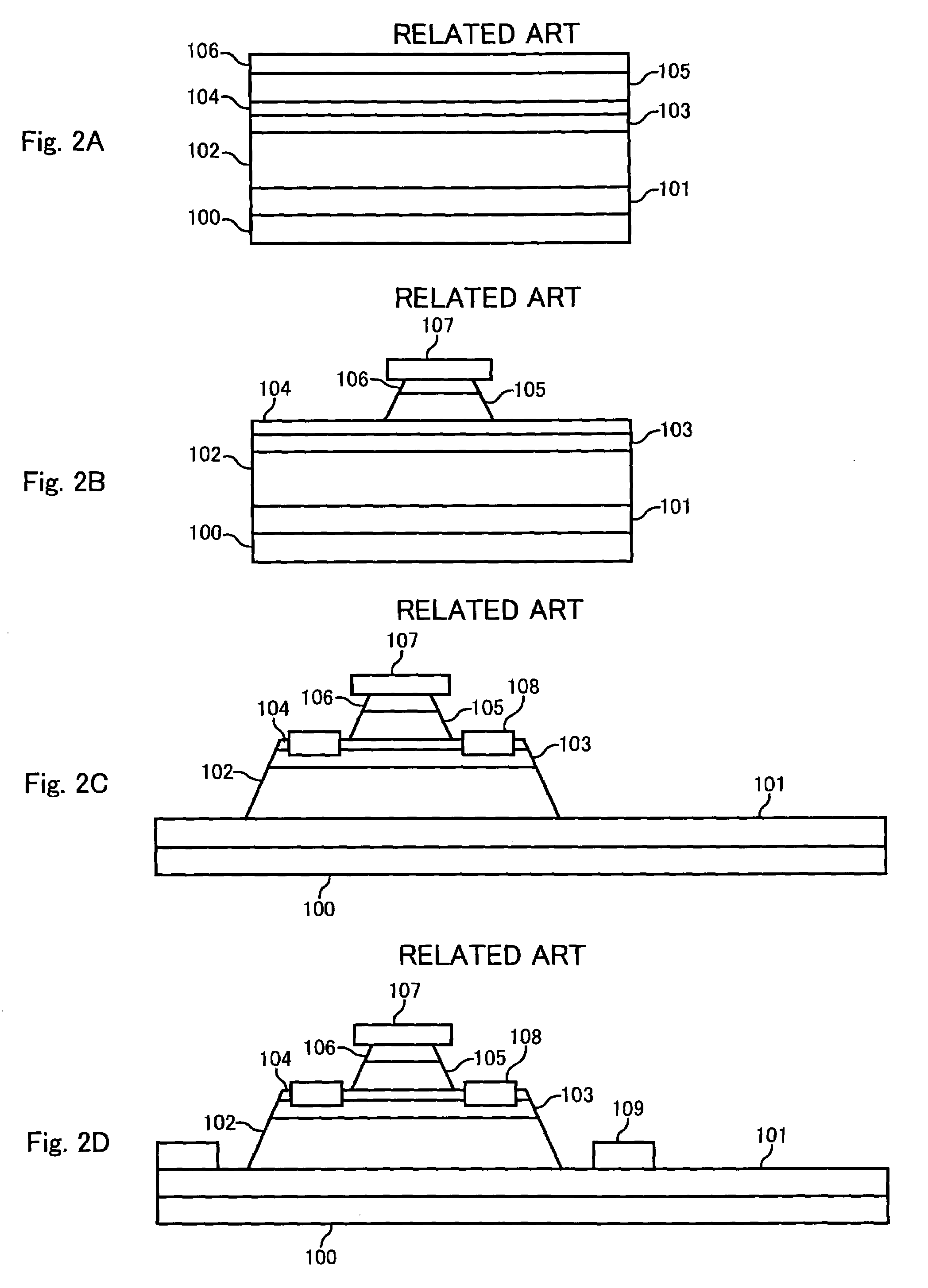

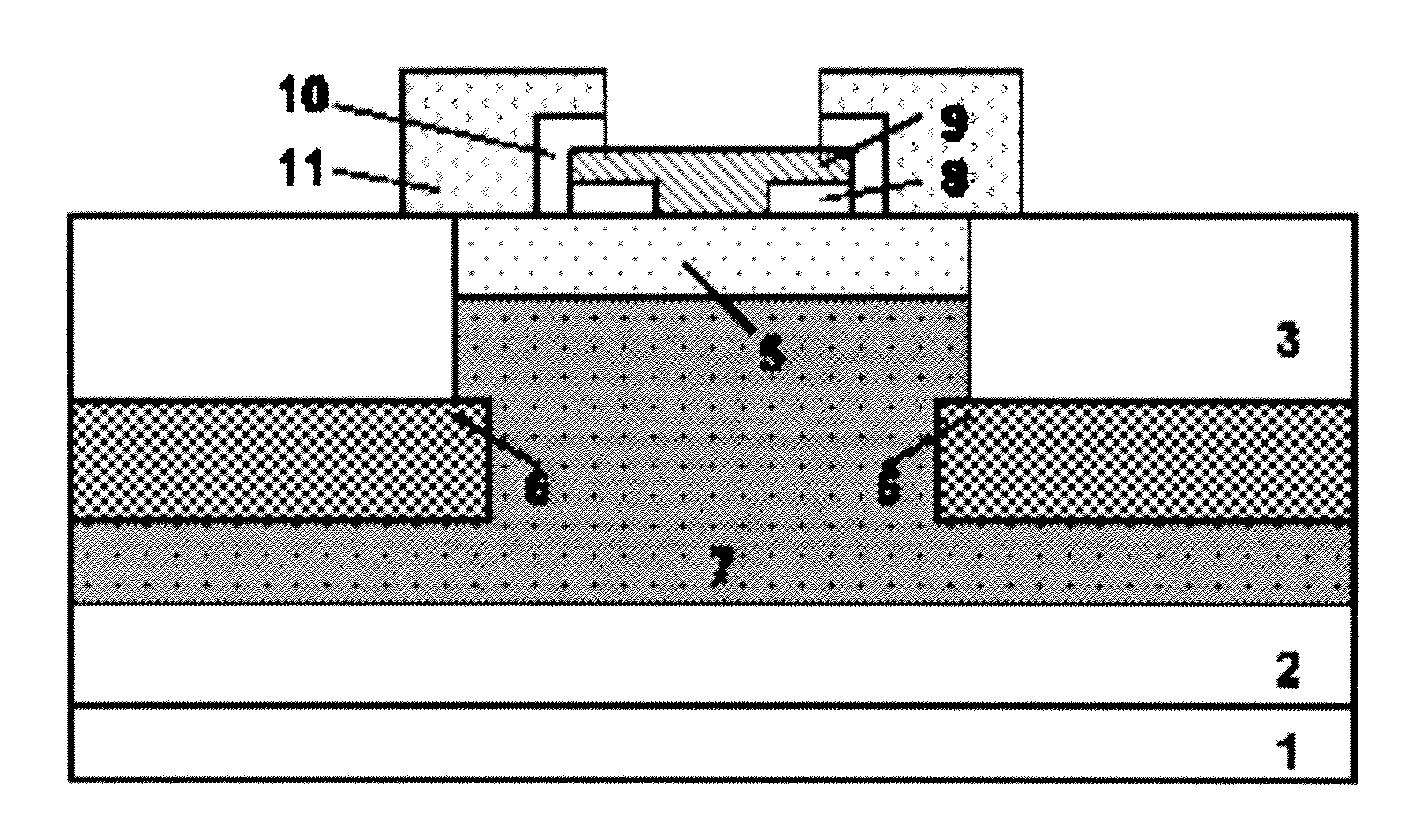

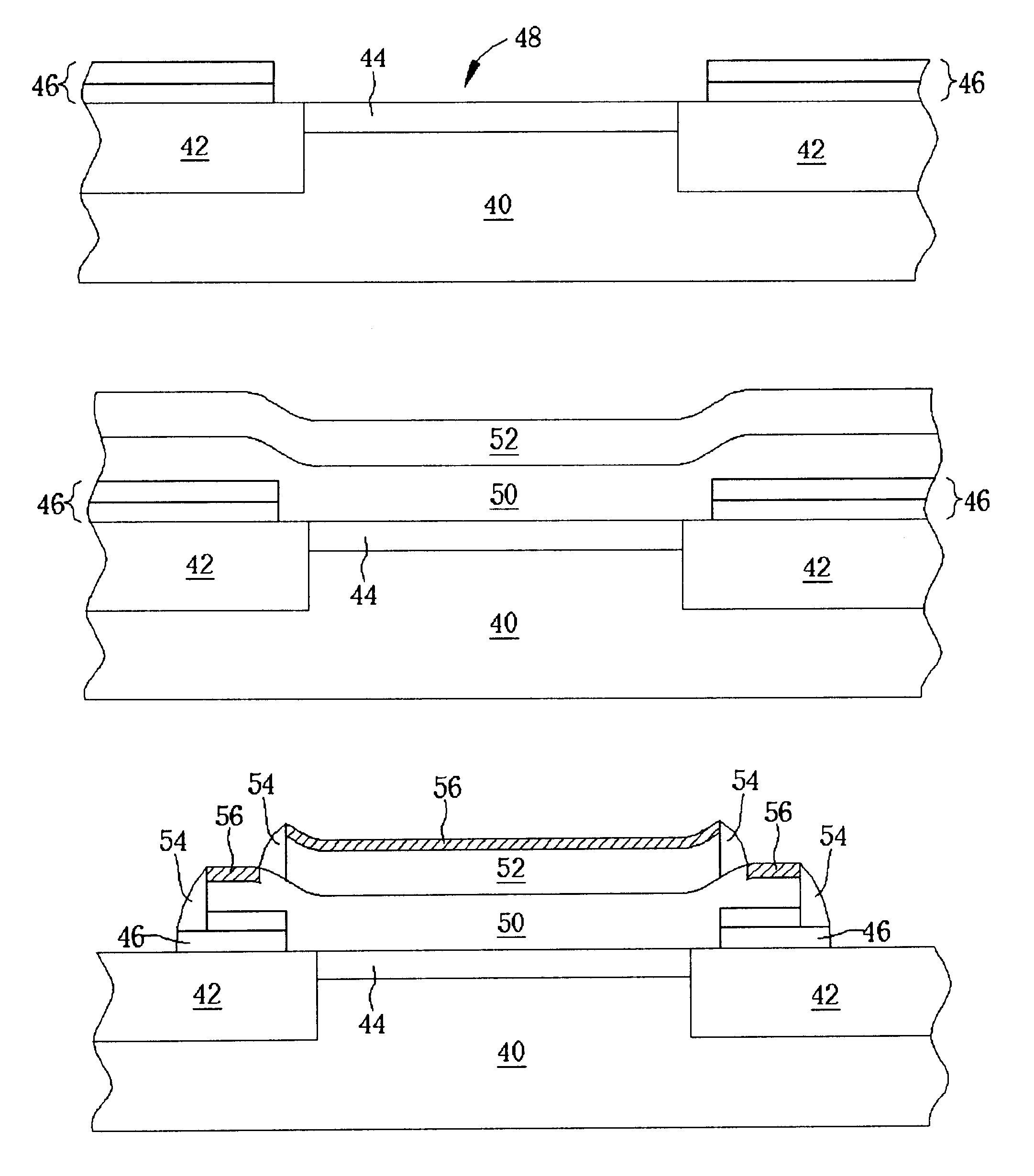

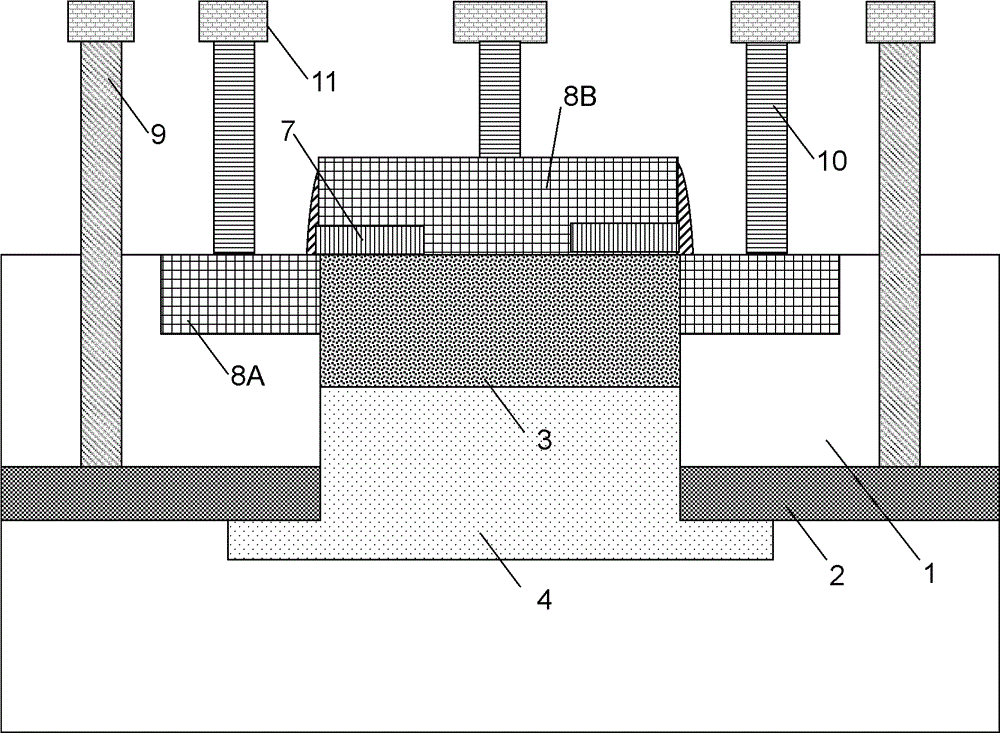

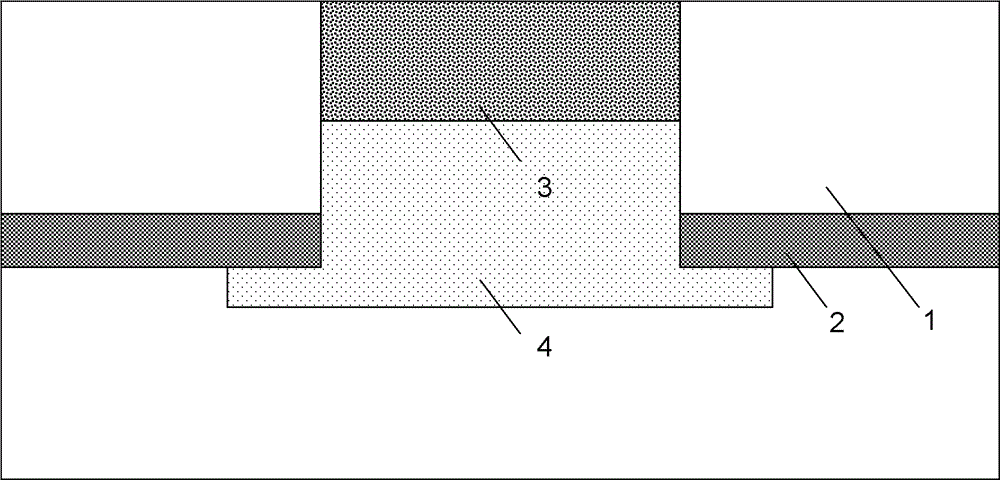

Semiconductor device and method of producing the same

InactiveUS20060046409A1Reduce collector resistanceSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialOptoelectronics

A method of producing a semiconductor device includes the steps of: preparing a double SOI substrate, forming a deep trench, filling the deep trench, forming an opening, forming a cavity, depositing a polycrystalline silicon layer, and forming a bipolar transistor.

Owner:LAPIS SEMICON CO LTD

Semiconductor device and method of producing the same

InactiveUS7205587B2Reduce collector resistanceSolid-state devicesSemiconductor/solid-state device manufacturingSoi substrateSemiconductor

A method of producing a semiconductor device includes the steps of: preparing a double SOI substrate, forming a deep trench, filling the deep trench, forming an opening, forming a cavity, depositing a polycrystalline silicon layer, and forming a bipolar transistor.

Owner:LAPIS SEMICON CO LTD

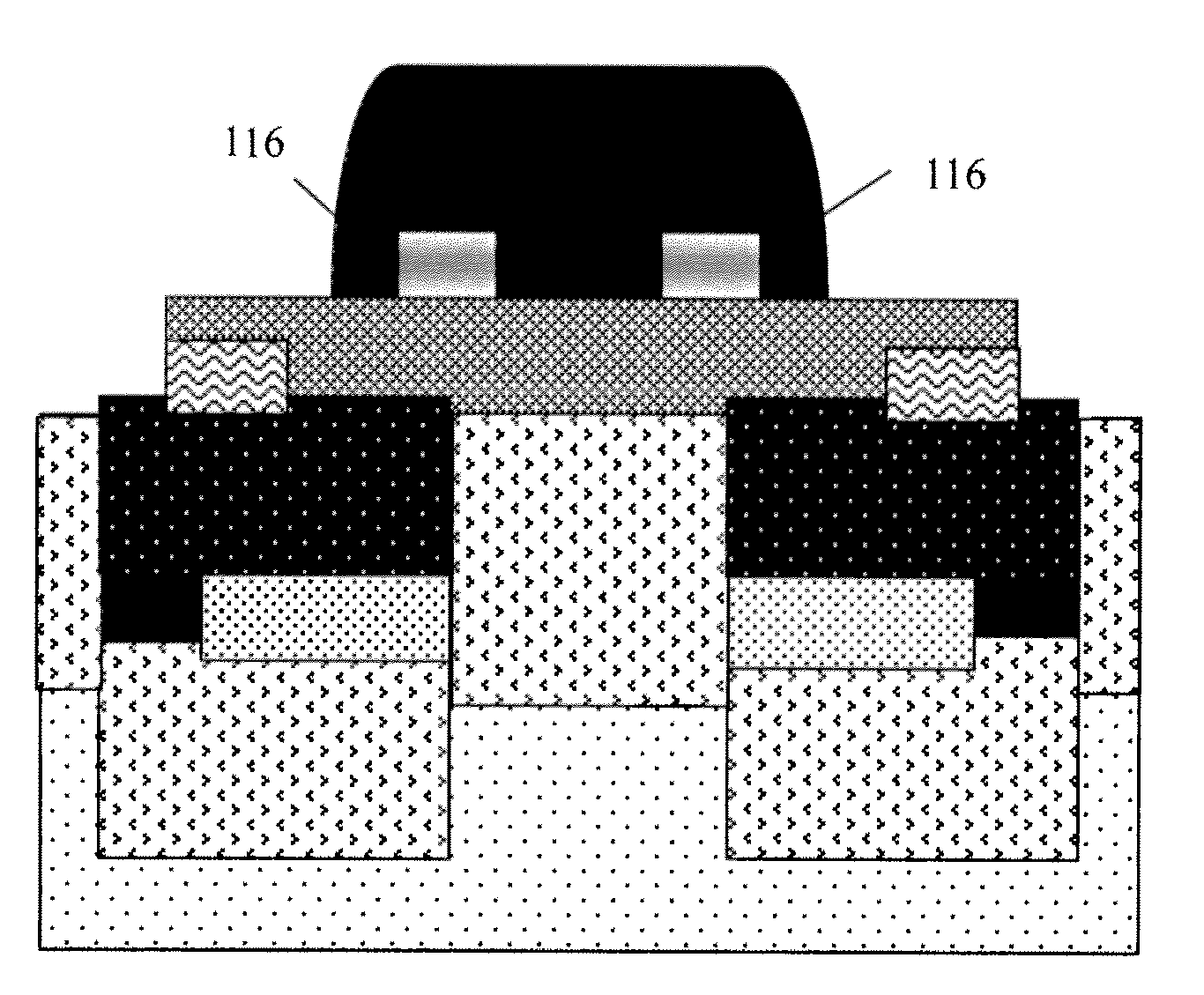

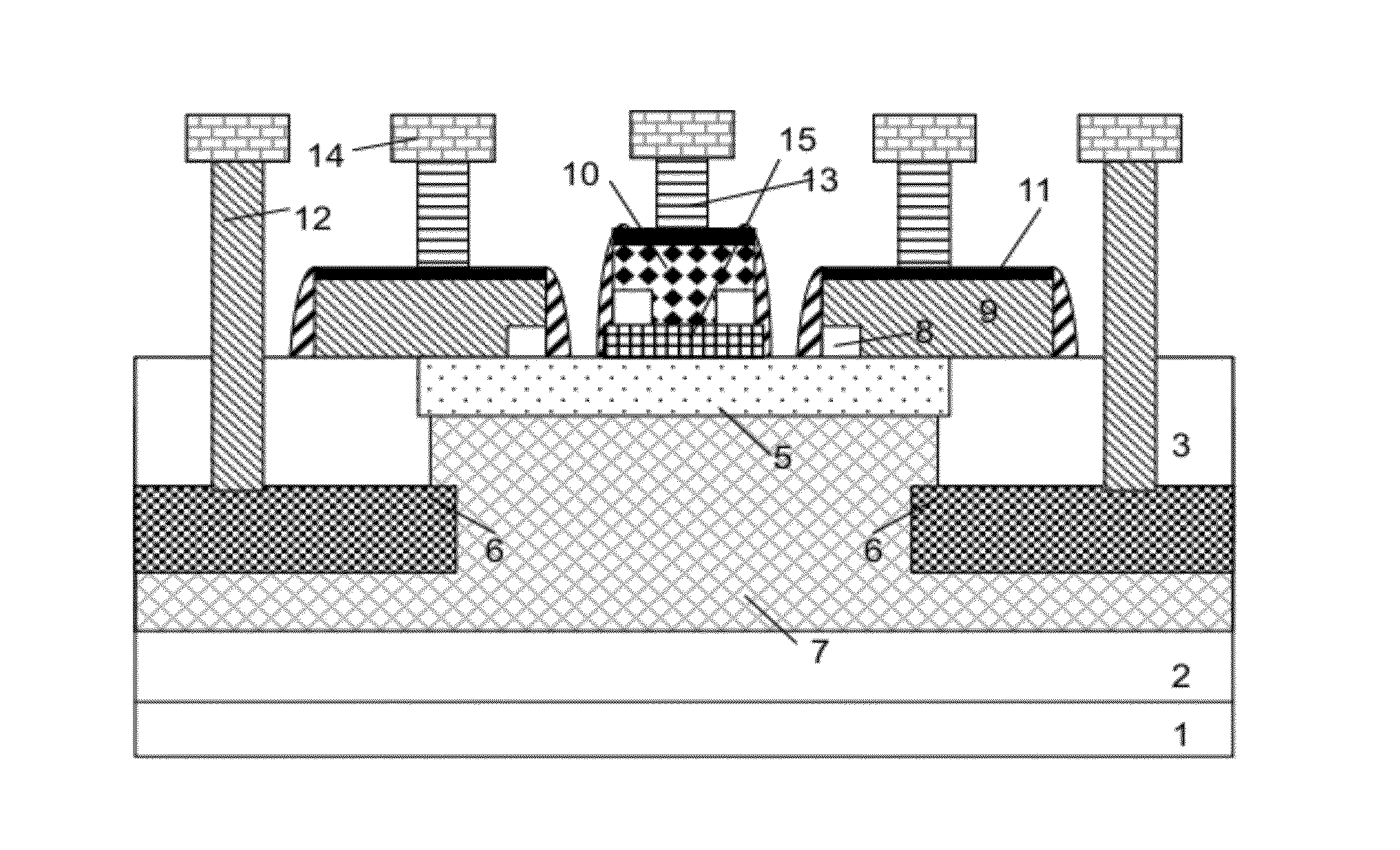

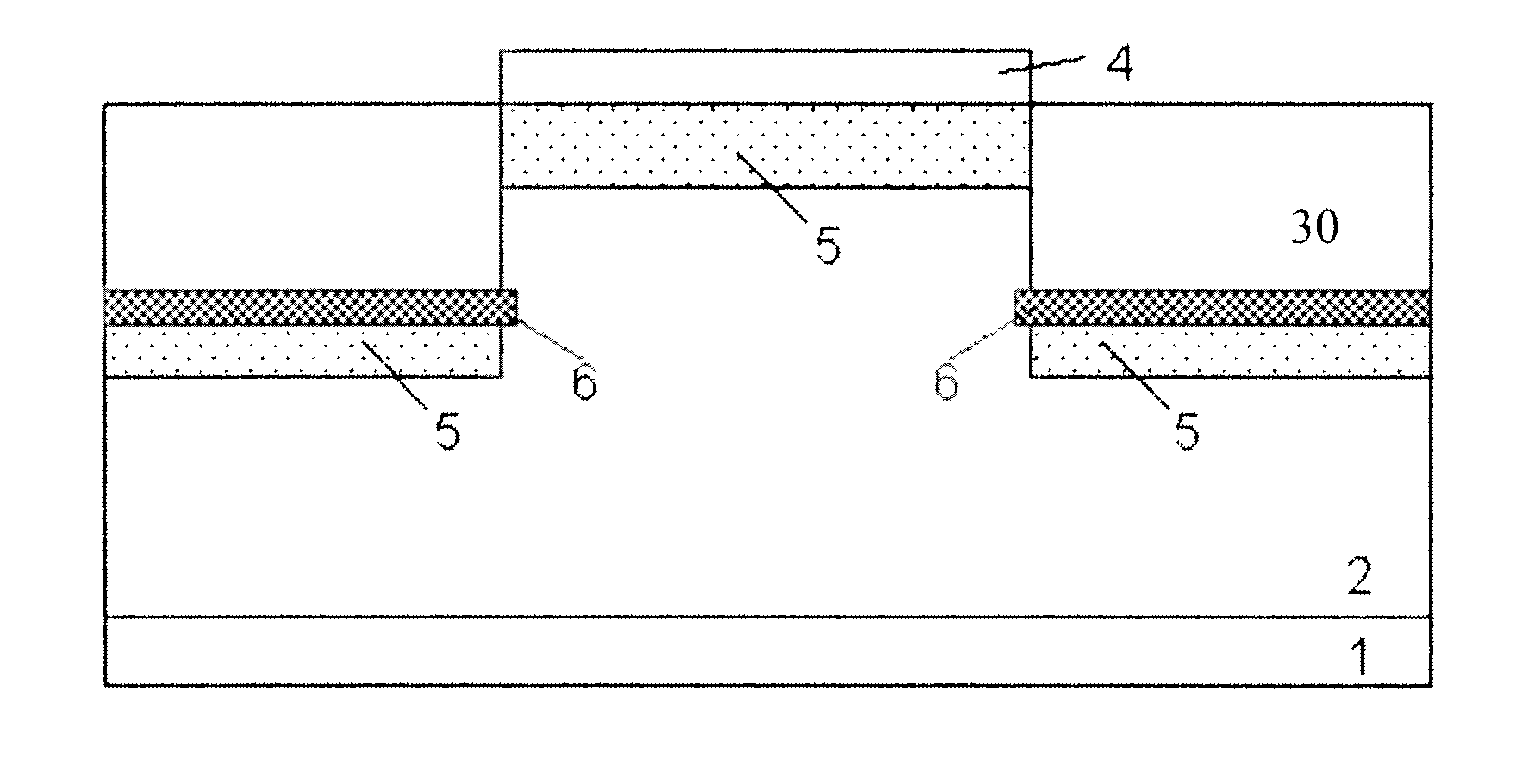

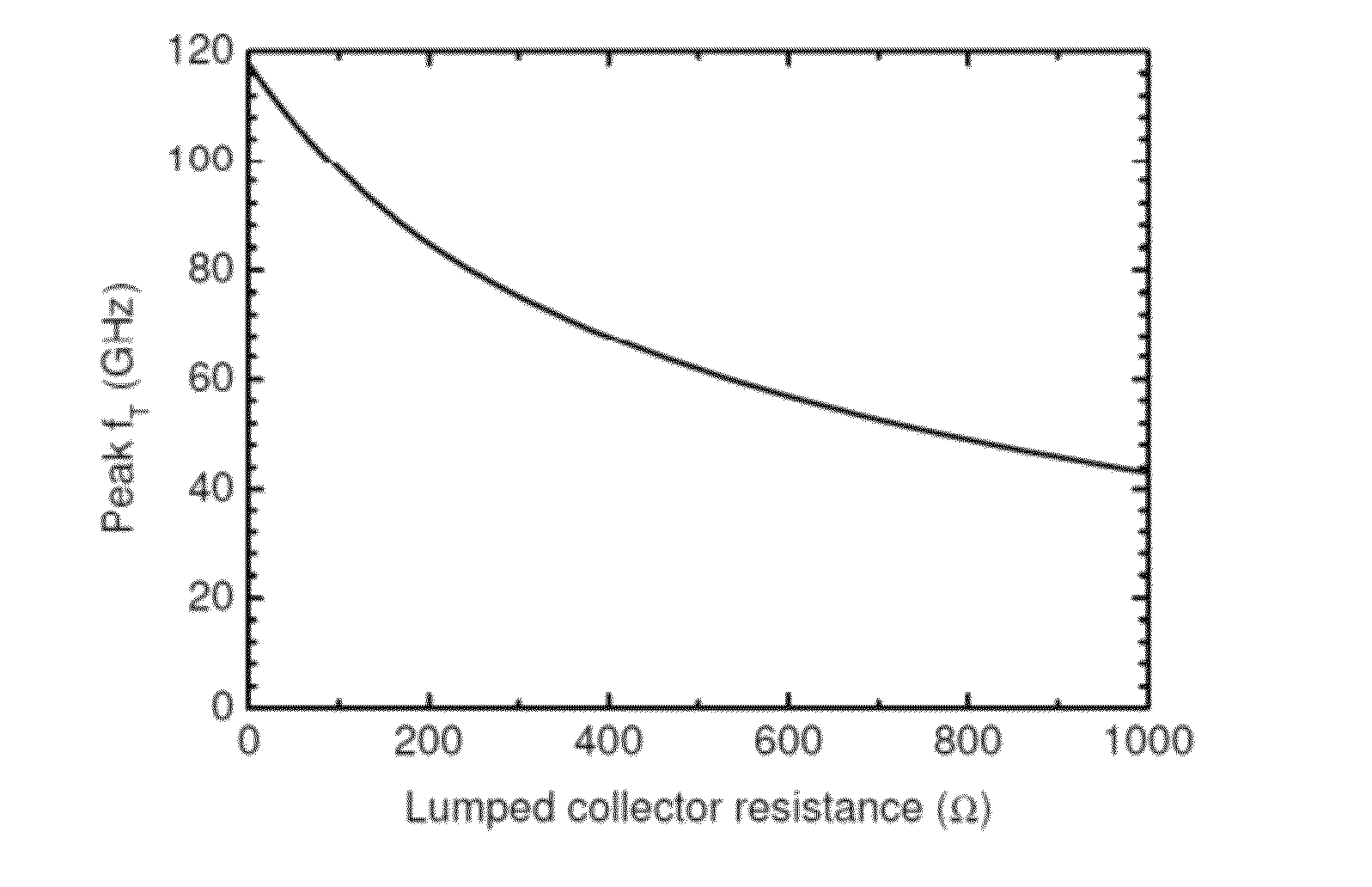

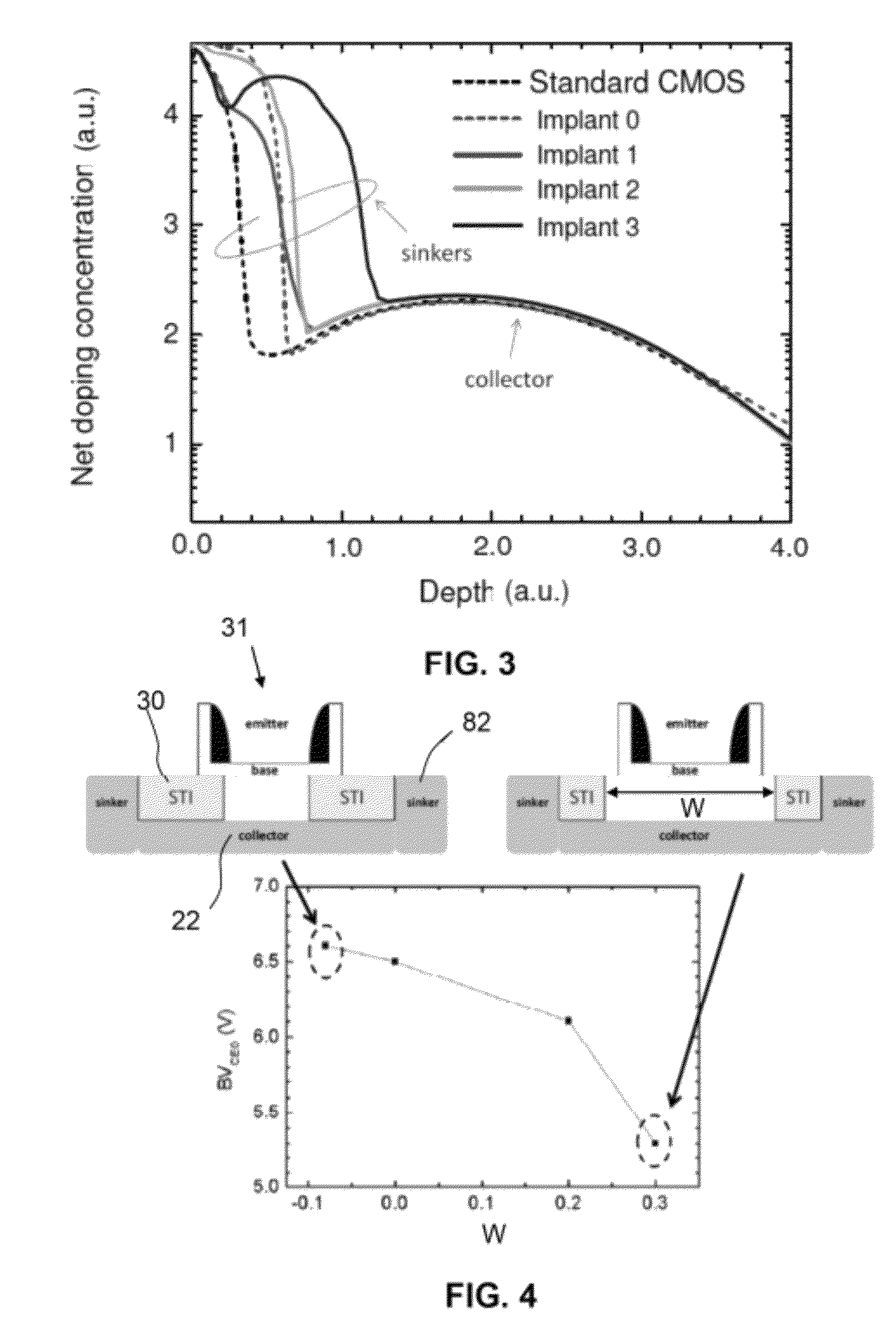

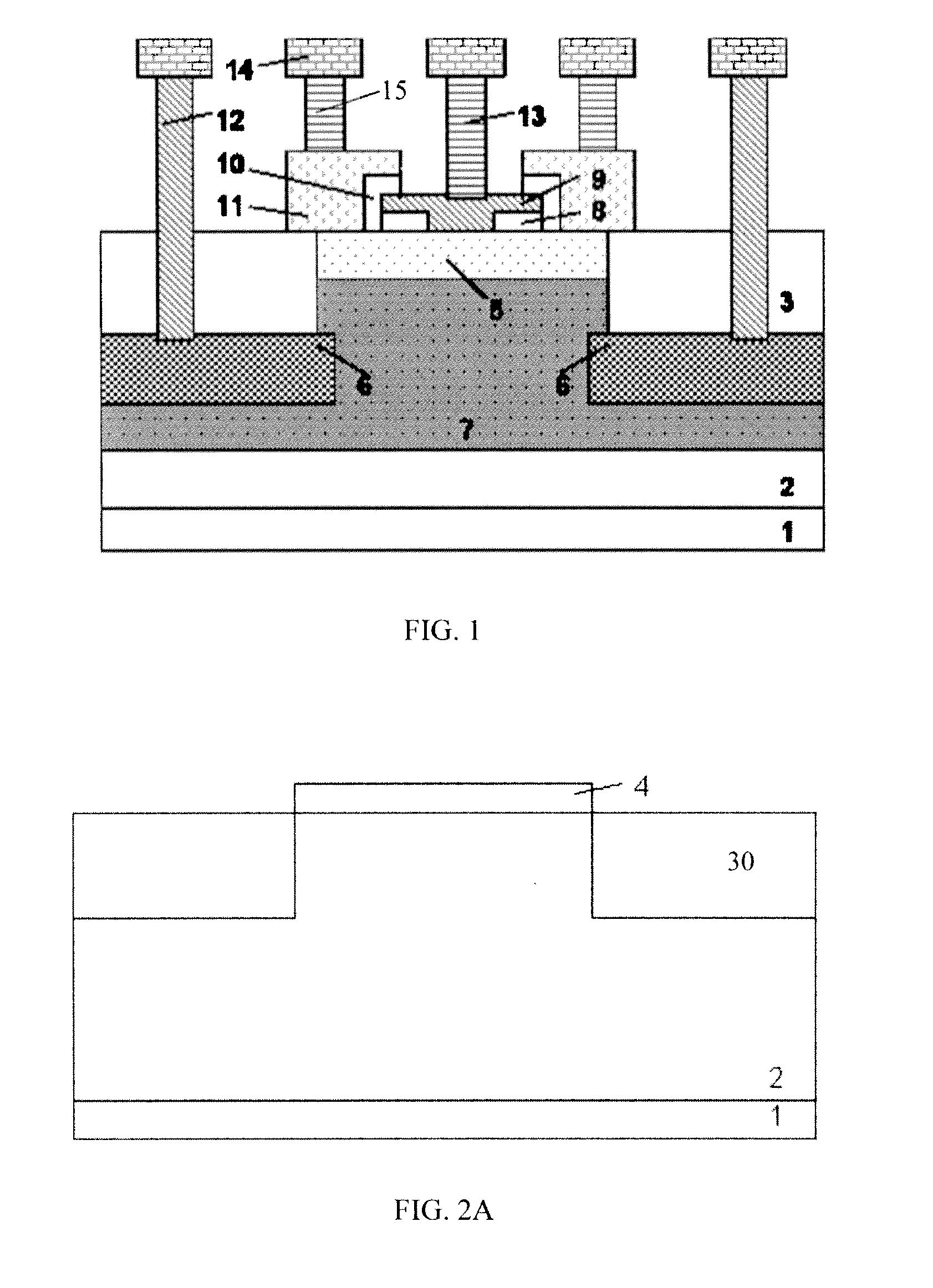

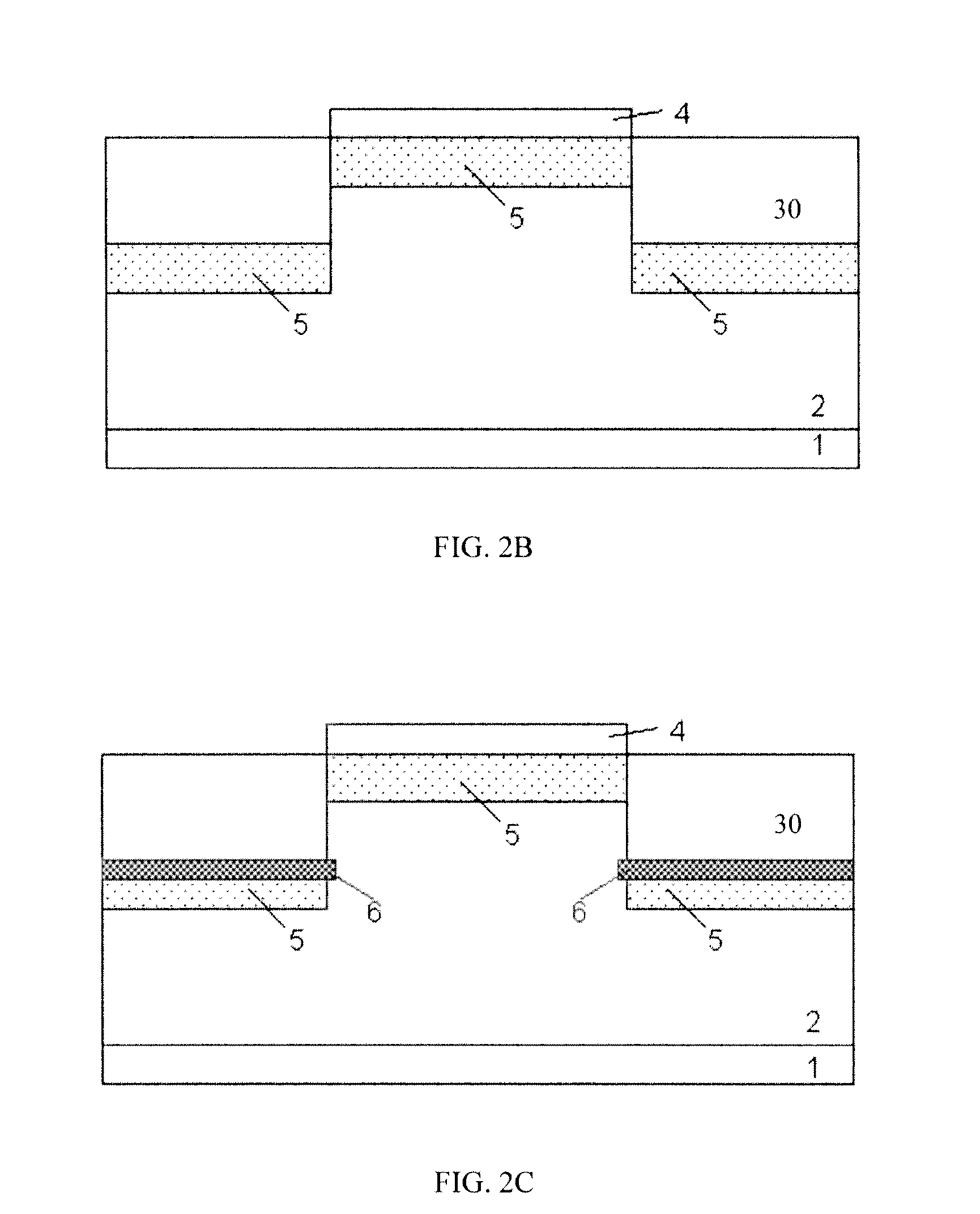

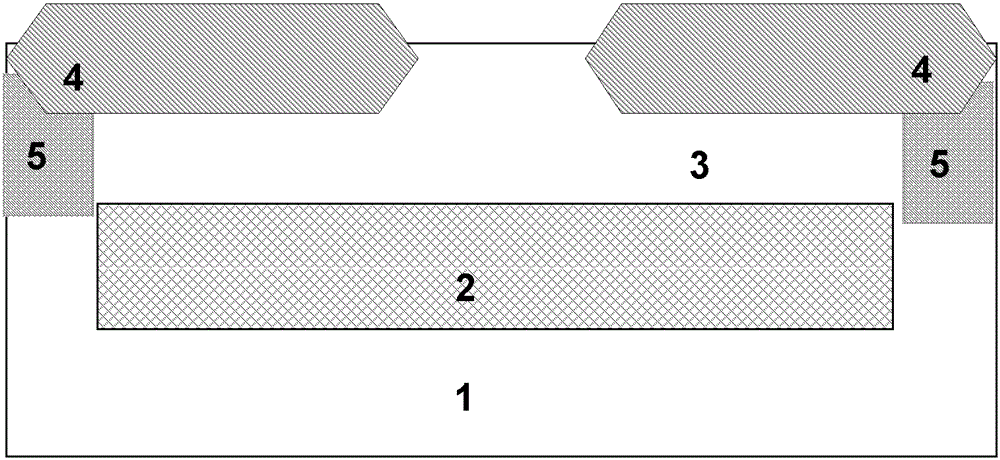

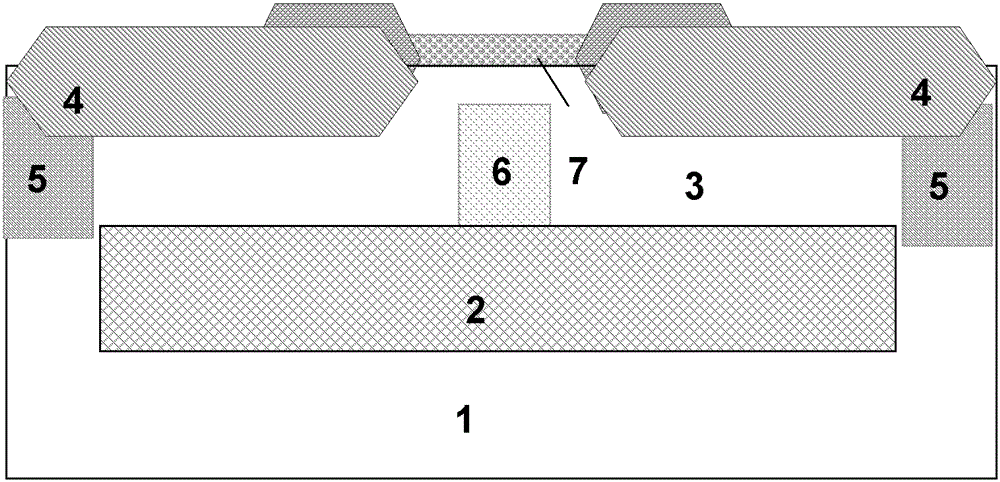

Silicon-germanium heterojunction bipolar transistor

ActiveUS20120091509A1Improve breakdown voltageRaise the cutoff frequencySemiconductor/solid-state device manufacturingSemiconductor devicesIon implantationJunction depth

A SiGe HBT is disclosed. A collector region consists of a first ion implantation region in an active area as well as second and third ion implantation regions respectively at bottom of field oxide regions. Each third ion implantation region has a width smaller than that of the field oxide region, has one side connected to first ion implantation region and has second side connected to a pseudo buried layer; each second ion implantation region located at bottom of the third ion implantation region and pseudo buried layer is connected to them and has a width equal to that of the field oxide region. Third ion implantation region has a higher doping concentration and a smaller junction depth than those of first and second ion implantation regions. Deep hole contacts are formed on top of pseudo buried layers in field oxide regions to pick up collector region.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Silicon-germanium heterojunction bipolar transistor and manufacturing method of the same

InactiveUS20120032233A1Improve breakdown voltageIncrease in sizeSemiconductor/solid-state device manufacturingSemiconductor devicesBreakdown voltageDeep hole

A Silicon-Germanium heterojunction bipolar transistor (SiGe HBT) formed on a silicon substrate, wherein, an active region is isolated by field oxide regions, a collector region is formed in the active region and extends into the bottom of the field oxide regions; pseudo buried layers are formed at the bottom of the field oxide regions. Each of the pseudo buried layers is a lateral distance away from the active region and contacts with a part of the collector region. Deep-hole contacts are formed in the field oxide regions located on top of the pseudo buried layers to pick up the collector region. The present invention can adjust the breakdown voltage of devices through adjusting the lateral distance. A method for manufacturing the SiGe HBT is also disclosed.

Owner:SHANGHAI HUA HONG NEC ELECTRONICS

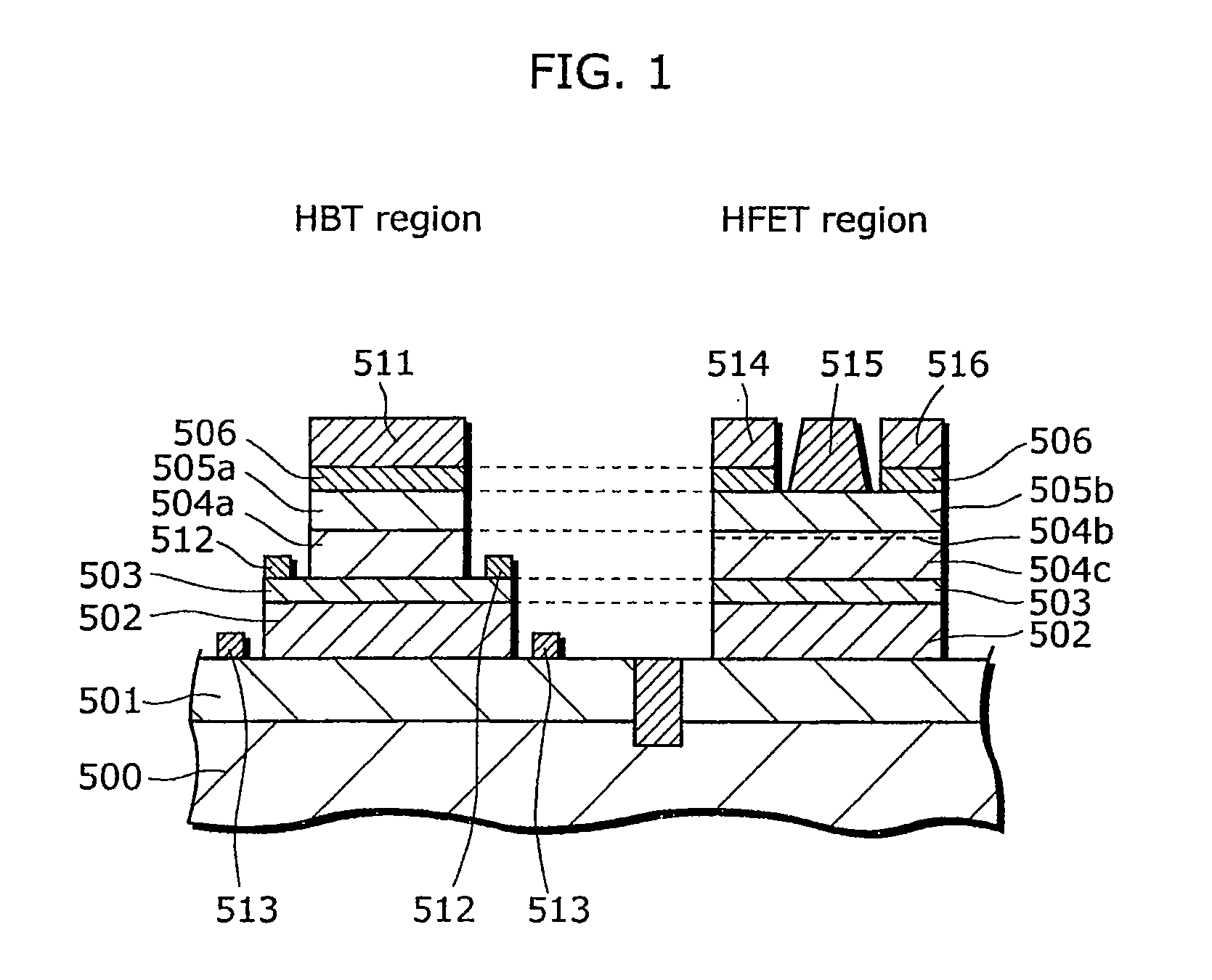

Semiconductor device having a hetero-junction bipolar transistor and manufacturing method thereof

InactiveUS7989845B2Reduce voltageReduce collector resistanceTransistorSolid-state devicesElectron donorEngineering

The object of the present invention is to provide a semiconductor device and the manufacturing method thereof which are capable of preventing decrease in the collector breakdown voltage and reducing the collector resistance. The semiconductor device according to the present invention includes: a HBT formed on a first region of a semiconductor substrate; and an HFET formed on a second region of the semiconductor substrate, wherein the HBT includes: an emitter layer of a first conductivity; a base layer of a second conductivity that has a band gap smaller than that of the emitter layer; a collector layer of the first conductivity or a non-doped collector layer; and a sub-collector layer of the first conductivity which are formed sequentially on the first region, and the HFET includes an electron donor layer including a part of the emitter layer, and a channel layer formed under the electron donor layer.

Owner:COLLABO INNOVATIONS INC

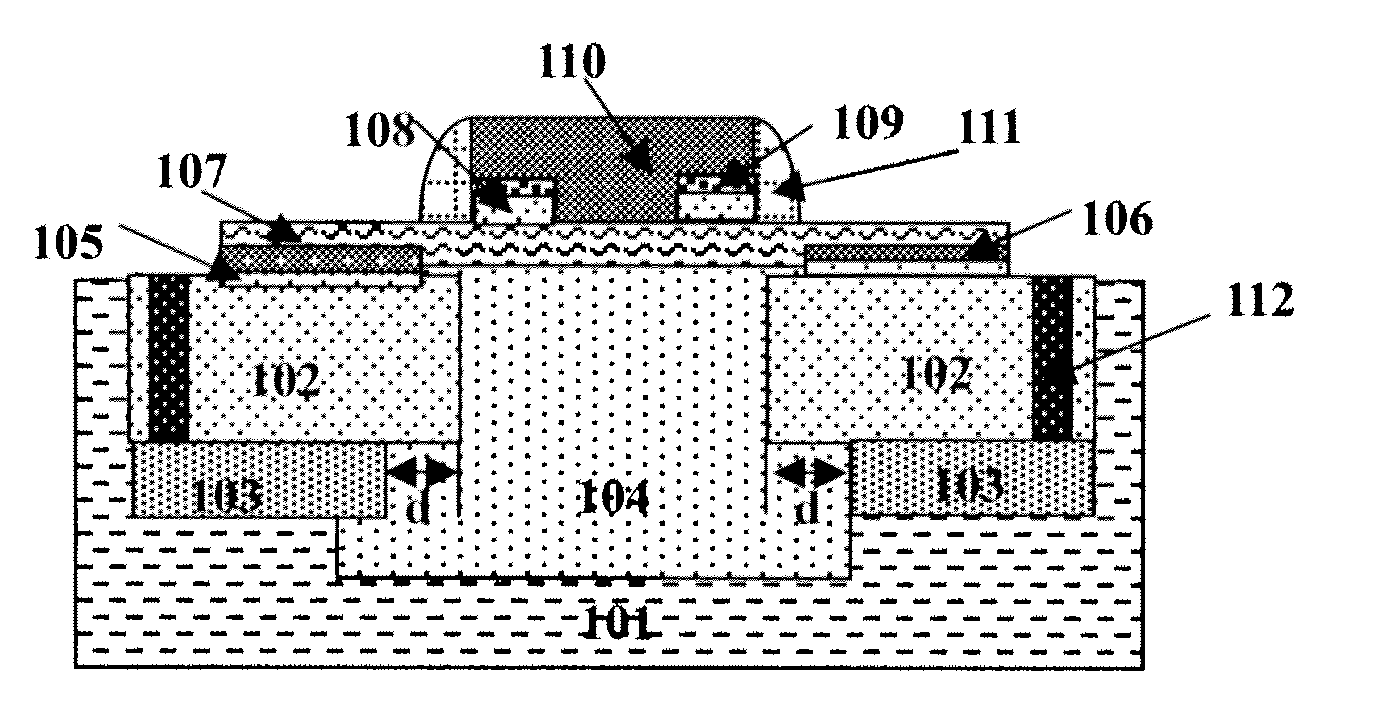

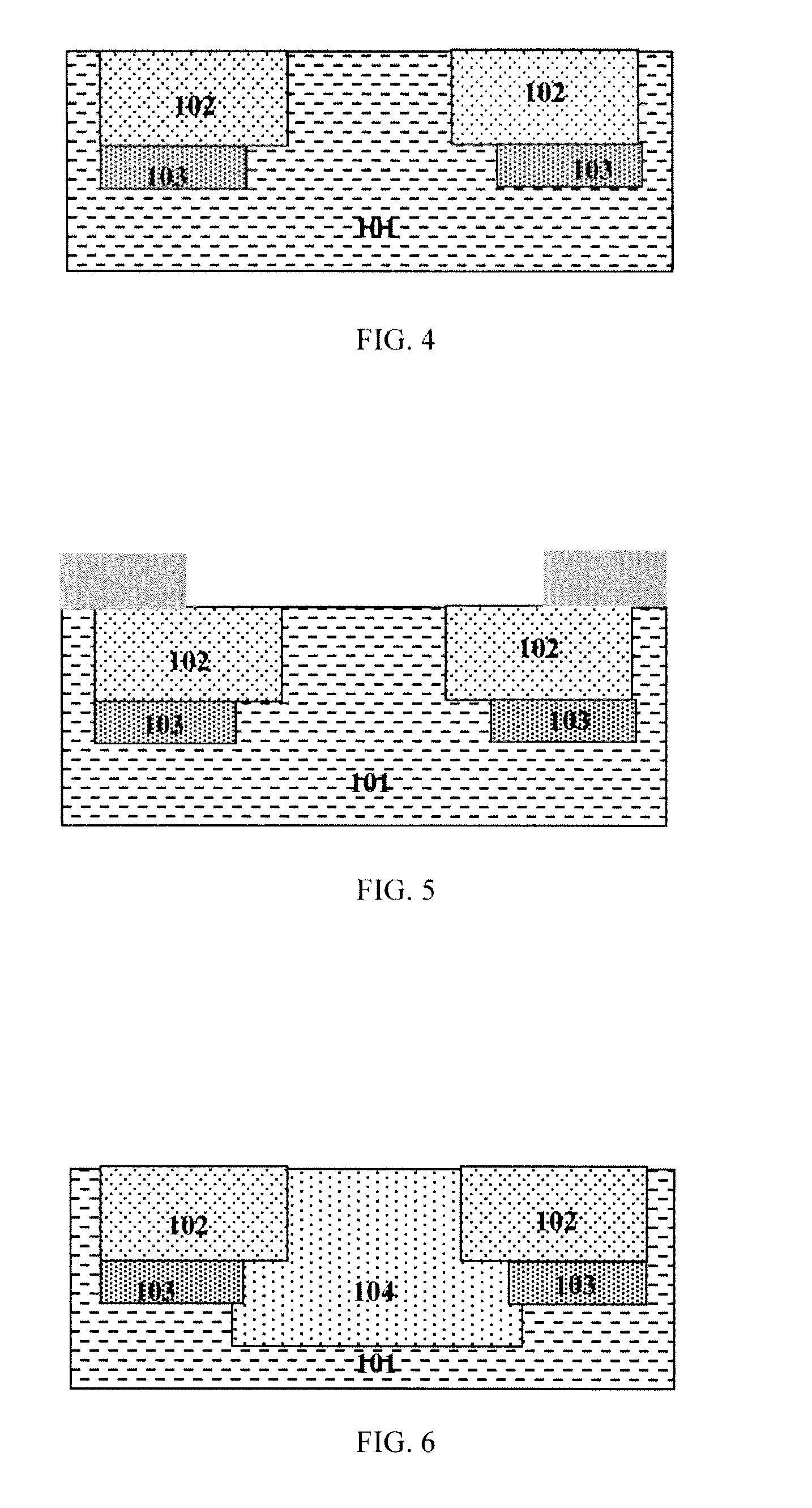

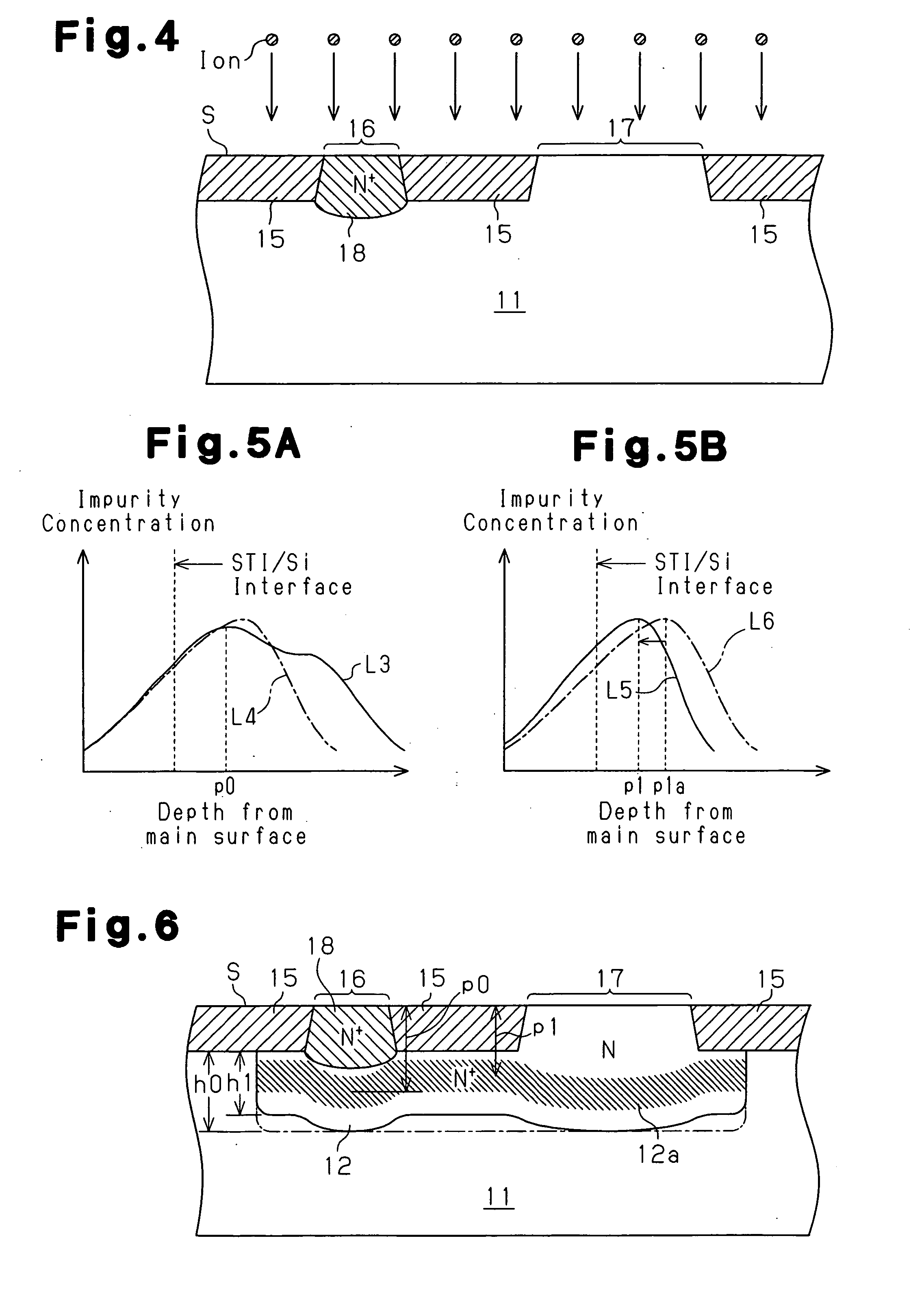

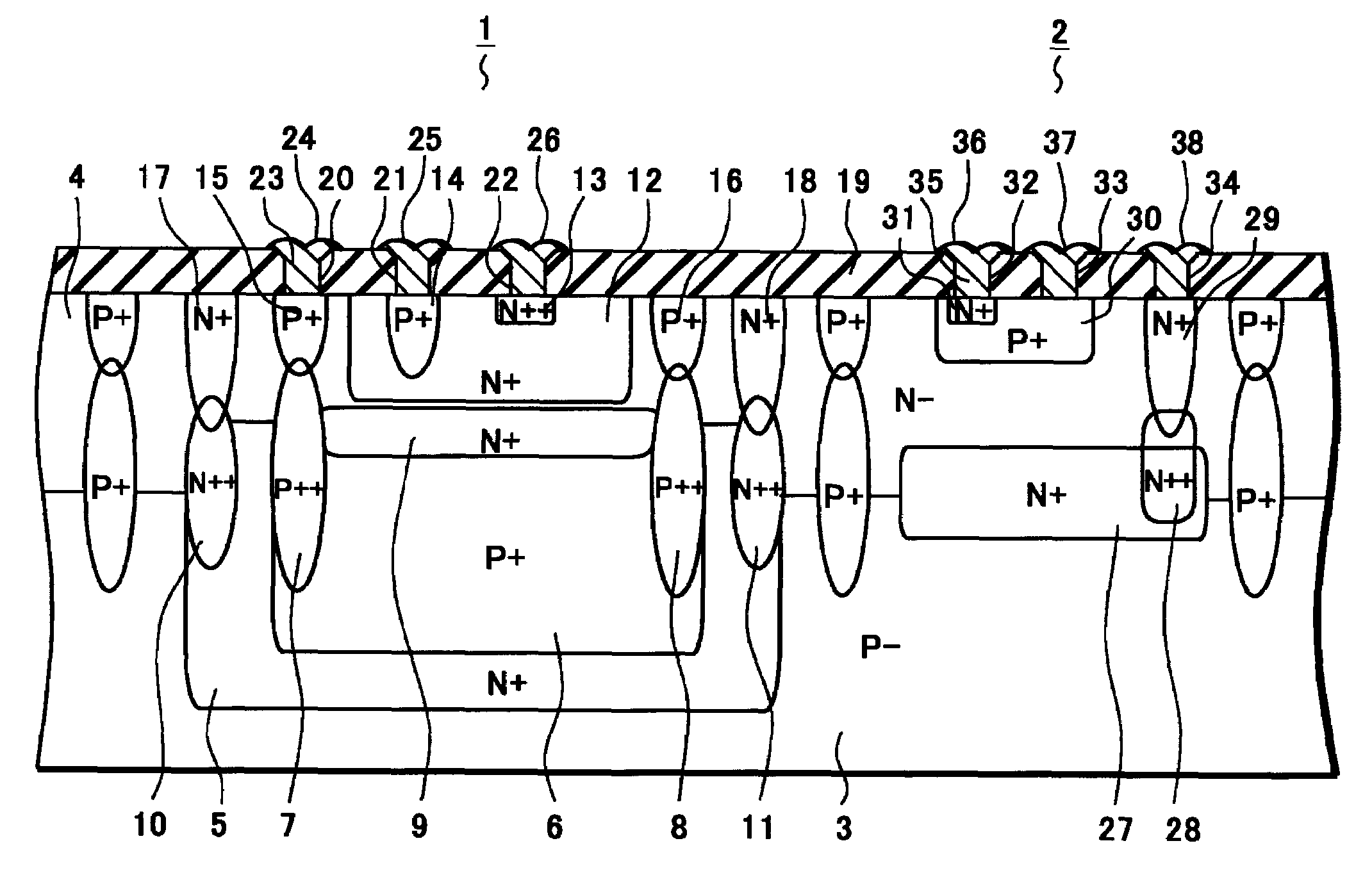

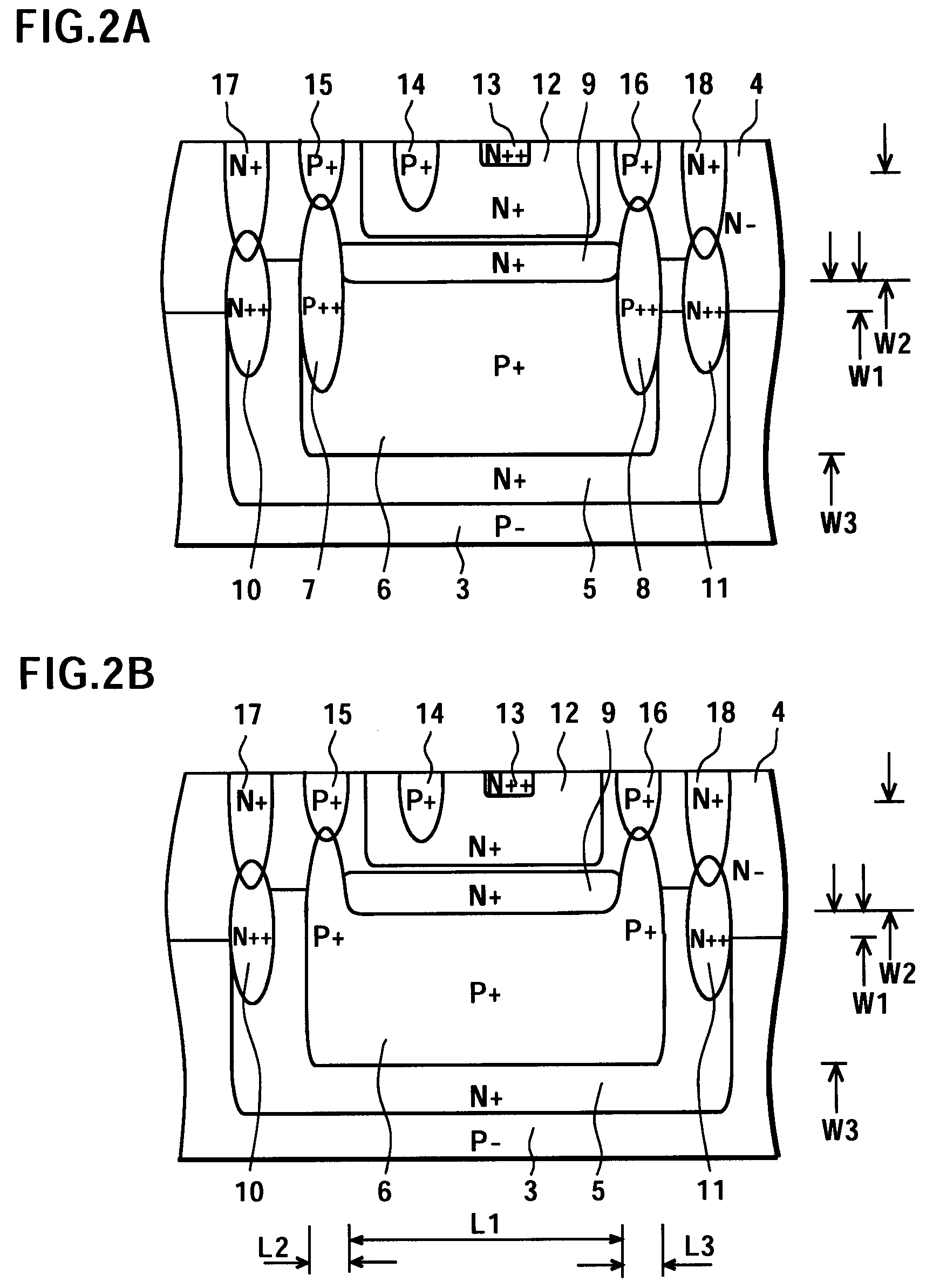

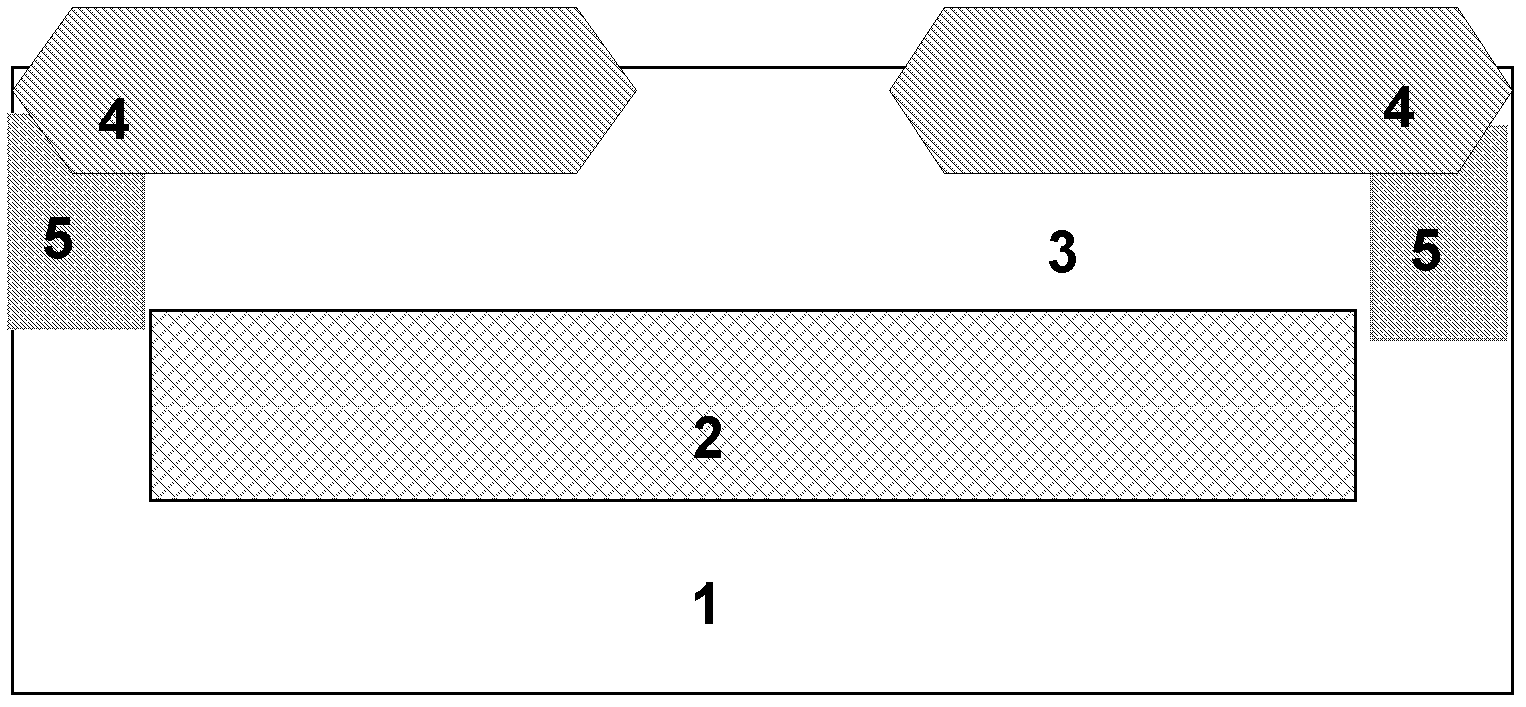

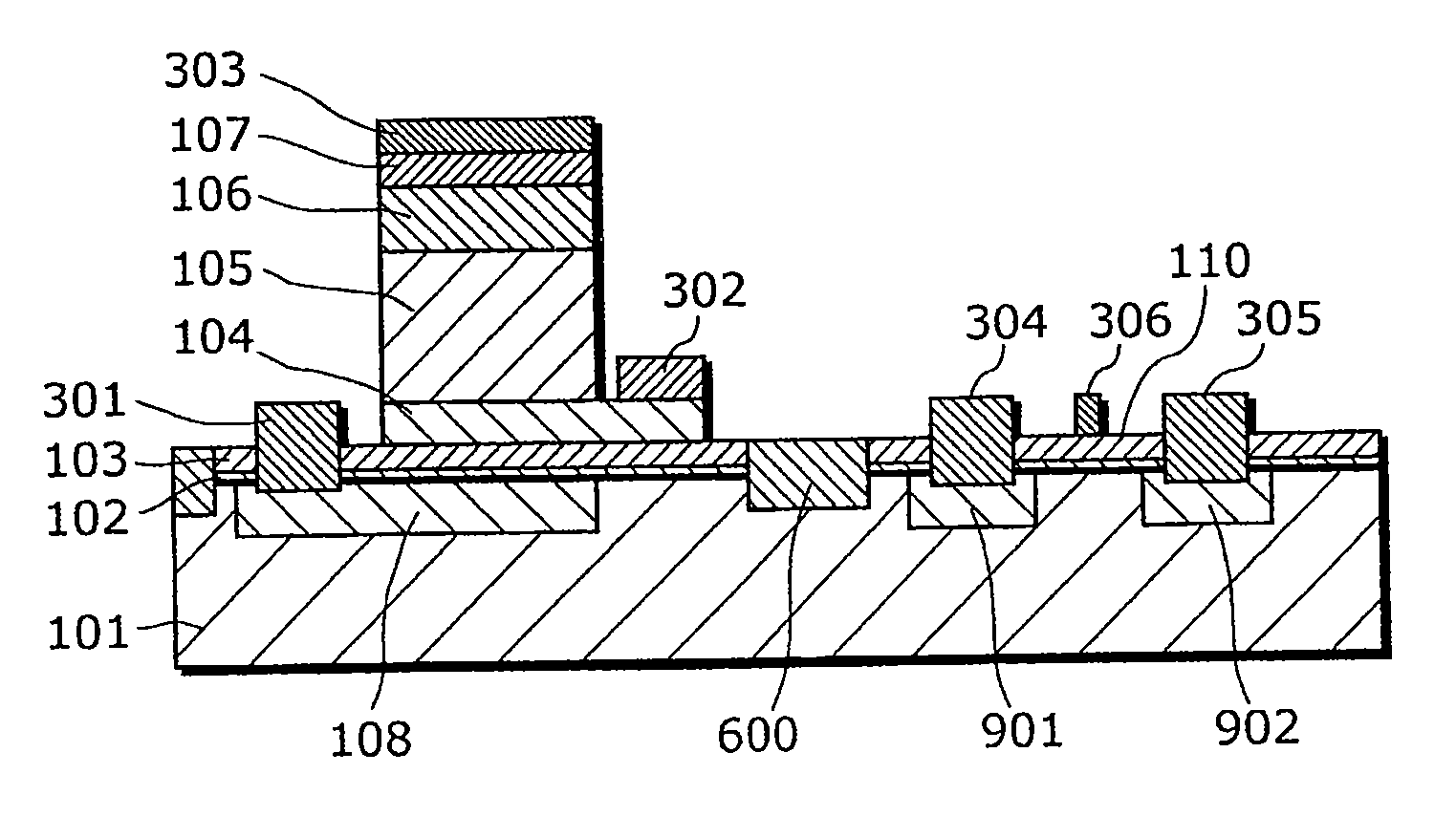

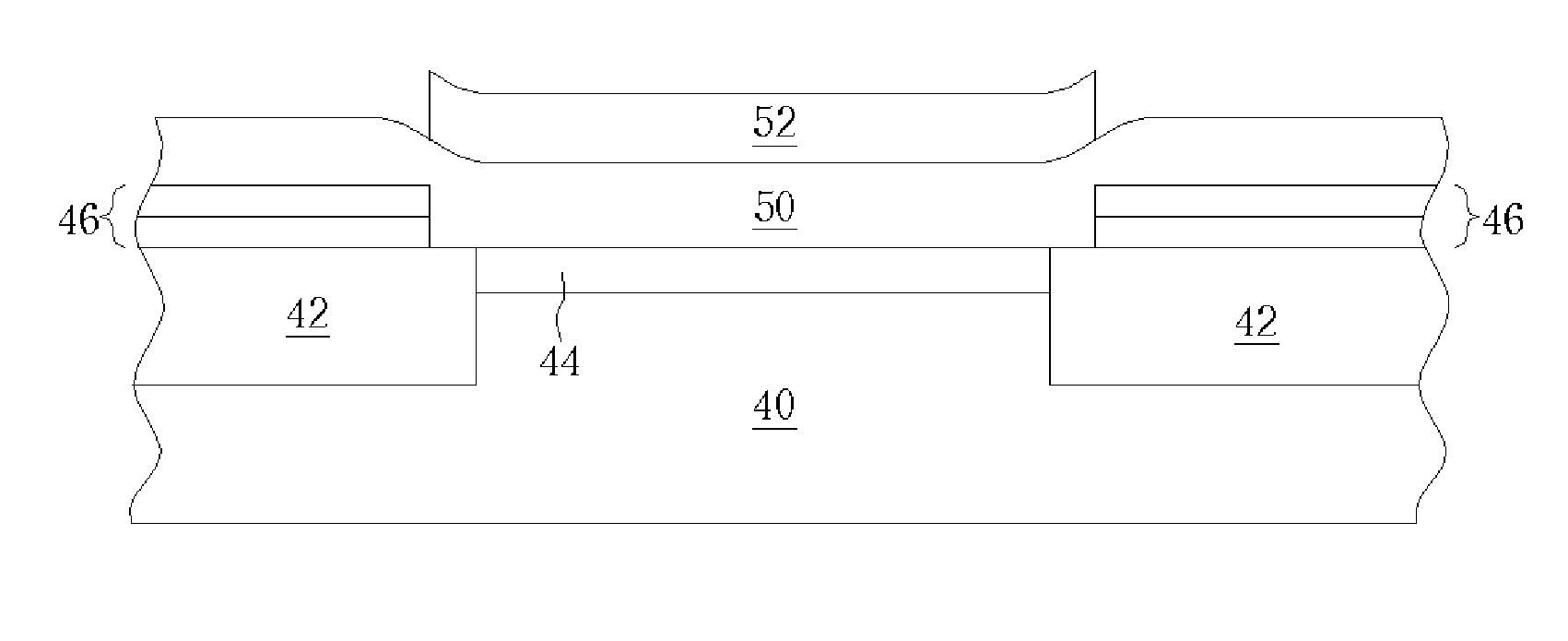

Semiconductor device and method for manufacturing the same

ActiveUS20060220104A1Reduce collector resistanceTransistorSemiconductor/solid-state device manufacturingDevice materialEngineering

A semiconductor device including a bipolar transistor in which the collector resistance. The bipolar transistor includes a first conduction type semiconductor substrate having a main surface. A second conduction type collector region is formed in the semiconductor substrate. A shallow trench isolation structure isolates the main surface of the semiconductor substrate into two insulated active regions. A collector leading portion is formed in one of the active regions. A first conduction type base region and a second conduction type emitter region are formed on the other one of the active regions. The collector region has a first depth from the main surface immediately below the shallow trench isolation structure, and the collector region has a second depth from the main surface immediately below the two active regions. The first depth is less than the second depth.

Owner:SEMICON COMPONENTS IND LLC

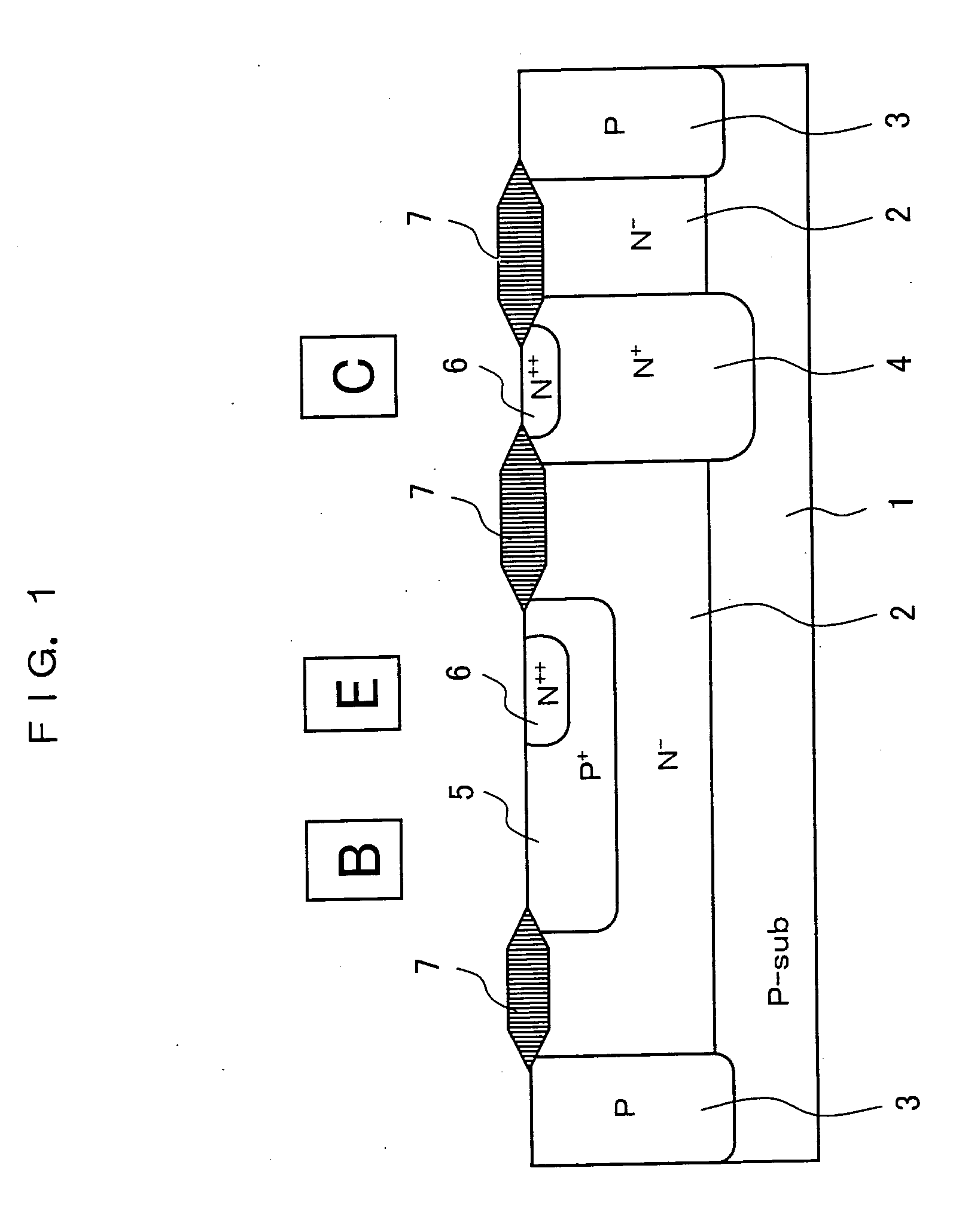

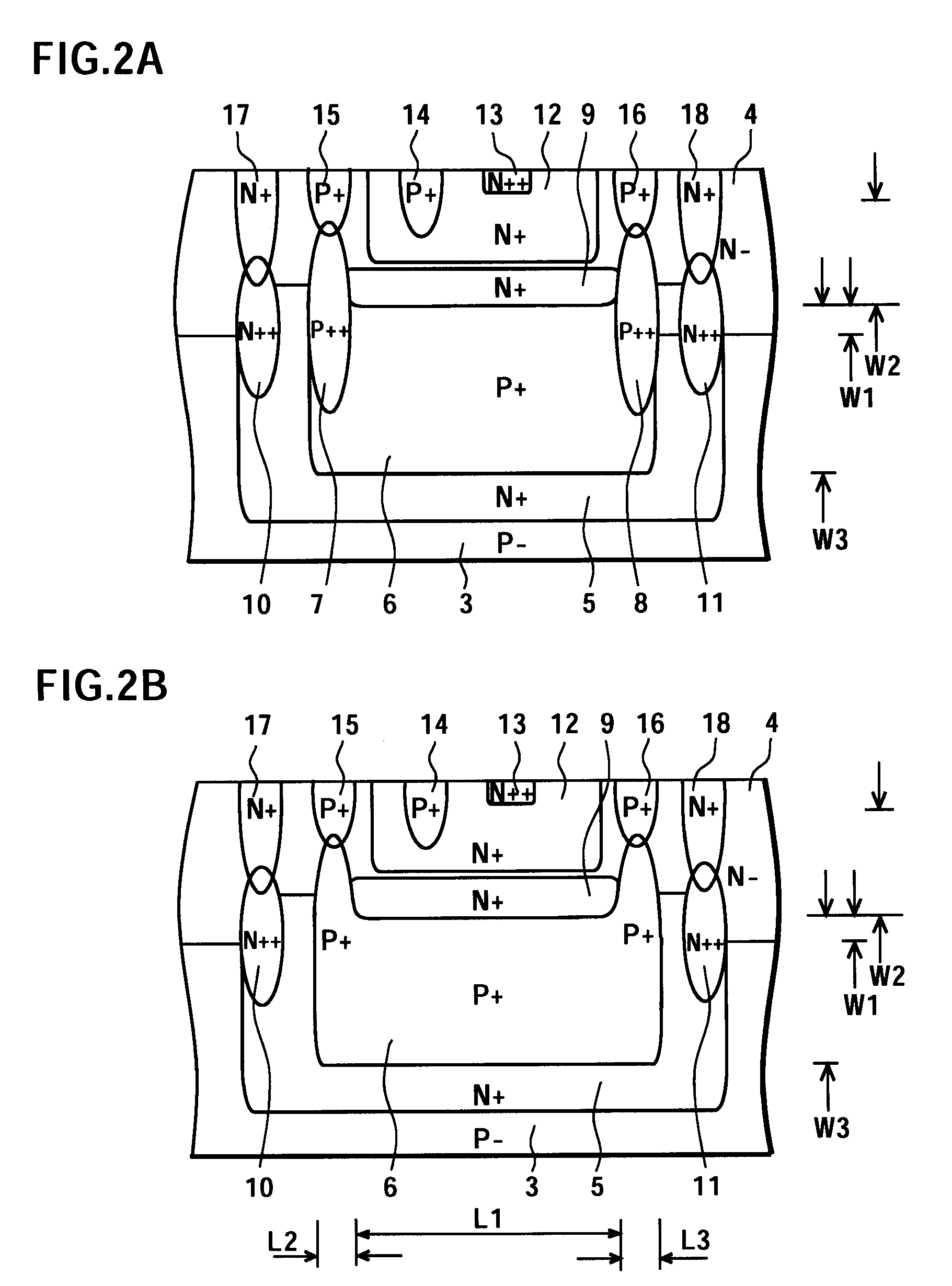

Semiconductor device and method of manufacturing the same

ActiveUS7619299B2Reduce collector resistanceReduce horizontal widthTransistorThyristorDiffusion layerBreakdown voltage

Owner:SEMICON COMPONENTS IND LLC

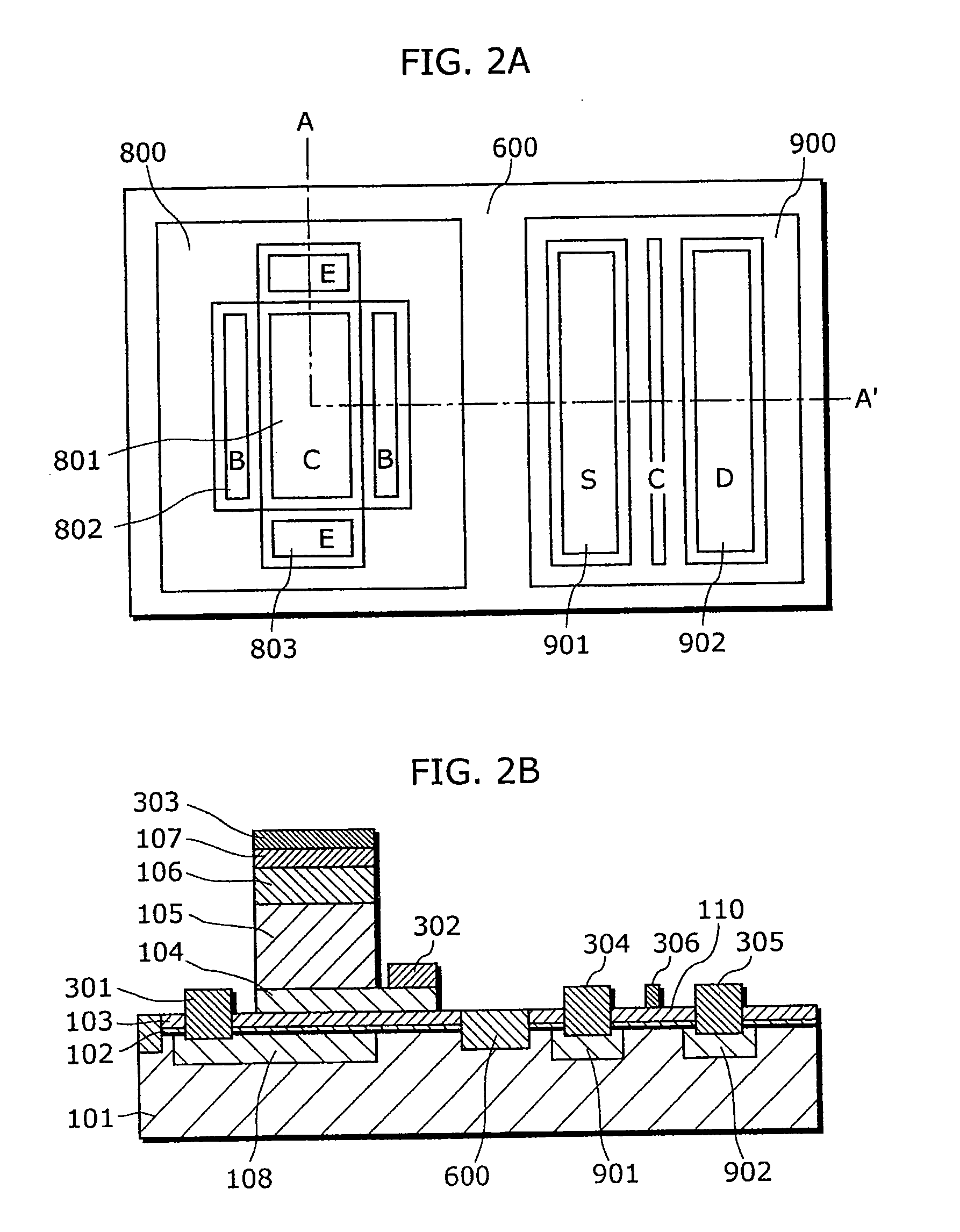

Semiconductor device and manufacturing method thereof

ActiveUS20090230431A1Reduce in quantityLower on-resistanceTransistorSolid-state devicesEngineeringTrade offs

The present invention has as an objective to provide: a semiconductor device to satisfy both of the trade-off characteristic advantages of the HBT; and the HFET and a manufacturing method thereof. The semiconductor device in the present invention is an HBT and HFET integrated circuit. The HBT includes a sub-collector layer, a GaAs collector layer, a GaAs base layer, and an InGaP emitter layer which are sequentially stacked. The sub-collector layer includes a GaAs external sub-collector region, and a GaAs internal sub-collector region disposed on the GaAs external sub-collector region. A mesa-shaped collector part and a collector electrode are separately formed on the GaAs external sub-collector region. The HFET includes a GaAs cap layer, a source electrode, and a drain electrode, the GaAs cap layer including portion of the GaAs external sub-collector region, and the source electrode and the drain electrode being formed on the GaAs cap layer.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

Semiconductor device and method of manufacturing the same

ActiveUS20050110045A1Reduce collector resistanceThe implementation process is simpleTransistorSolid-state devicesDevice materialIon implantation

A semiconductor device includes a sub-collector layer, a collector layer, a base layer, an emitter layer, and an emitter cap layer, which are sequentially laminated on a substrate. It also includes an emitter electrode, a base electrode, and a collector electrode, which are respectively formed on the emitter cap layer, the base layer, and the sub-collector layer. The sub-collector layer is made up of a first sub-collector layer adjacent to the substrate and a second sub-collector layer adjacent to the collector layer. In the area between adjacent device elements, the first sub-collector layer has an element insulating region created by ion implantation, and the second sub-collector layer has a recess-shaped element insulating region.

Owner:RENESAS ELECTRONICS CORP

Vertical parasitic pnp device in a silicon-germanium hbt process and manufacturing method of the same

InactiveUS20120181579A1Reduce areaReduce resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField oxide

A vertical parasitic PNP device in a SiGe HBT process is disclosed which comprises a collector region, a base region, an emitter region, P-type pseudo buried layers and N-type polysilicons. The pseudo buried layers are formed at bottom of shallow trench field oxide regions around the collector region and contact with the collector region; deep hole contacts are formed on top of the pseudo buried layers to pick up collector electrodes. The N-type polysilicons are formed on top of the base region and are used to pick up base electrodes. The emitter region comprises a P-type SiGe epitaxial layer and a P-type polysilicon both of which are formed on top of the base region. A manufacturing method of a vertical parasitic PNP device in a SiGe HBT process is also disclosed.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

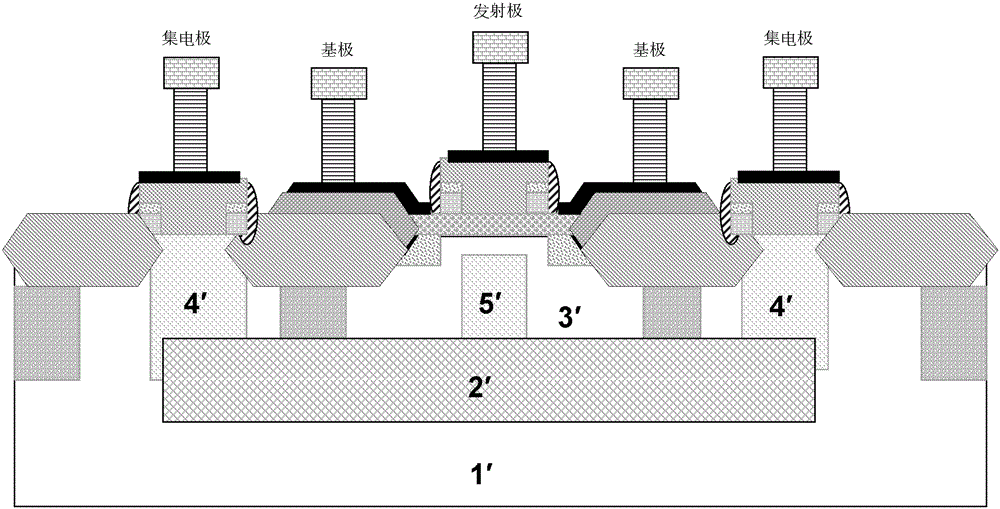

Germanium-silicon heterojunction bipolar transistor (HBT) single tube structure, manufacture method thereof and germanium-silicon HBT multi-finger structure

ActiveCN103123928ALower resistanceReduce spacingSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceSilicon heterojunction

The invention discloses a germanium-silicon heterojunction bipolar transistor (HBT) single tube structure. A collector region C is manufactured through a low-doping N type epitaxy technique, and the bottom of the collector region C is extracted by a heavy N type doping buried layer; a base region B is composed of a boron heavy doping germanium-silicon epitaxial layer; a transmitting region E is formed by etching media deposited on the base region to form a window and then depositing N type doping polycrystalline silicon; an N type epitaxy at the bottom of field oxide under outer base region polycrystalline silicon is converted to a P type region through P type ion injection and high-temperature annealing; and a collector electrode is extracted by a deep groove contact hole and metals. The invention further discloses a multi-finger structure in a CBEBE...BEBC or CEBECBE...CEBEC mode. The deep groove contact hole penetrates through the field oxide and the N type epitaxy to penetrate into the N type buried layer, the space of two transmitting electrodes can be greatly reduced, the collector resistance of device is reduced, and junction capacitance of the collector electrode for the base region and a silicon substrate is reduced. A P type ion injection region is not communicated with a P type ion injection region arranged outside the device, so that base electrode-collector electrode medium capacitance is reduced. The multi-finger structure can obtain the largest output power and power gain.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

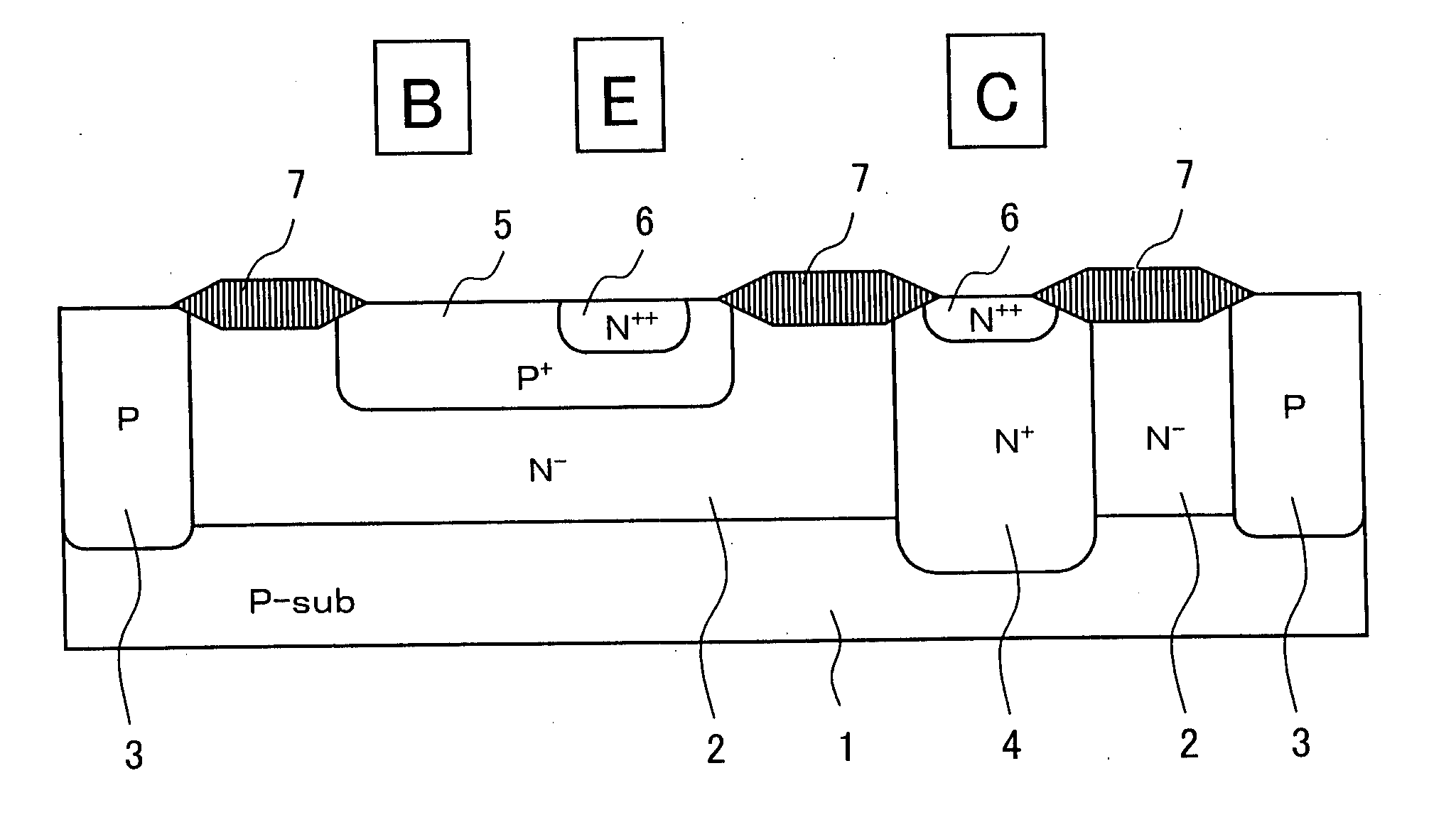

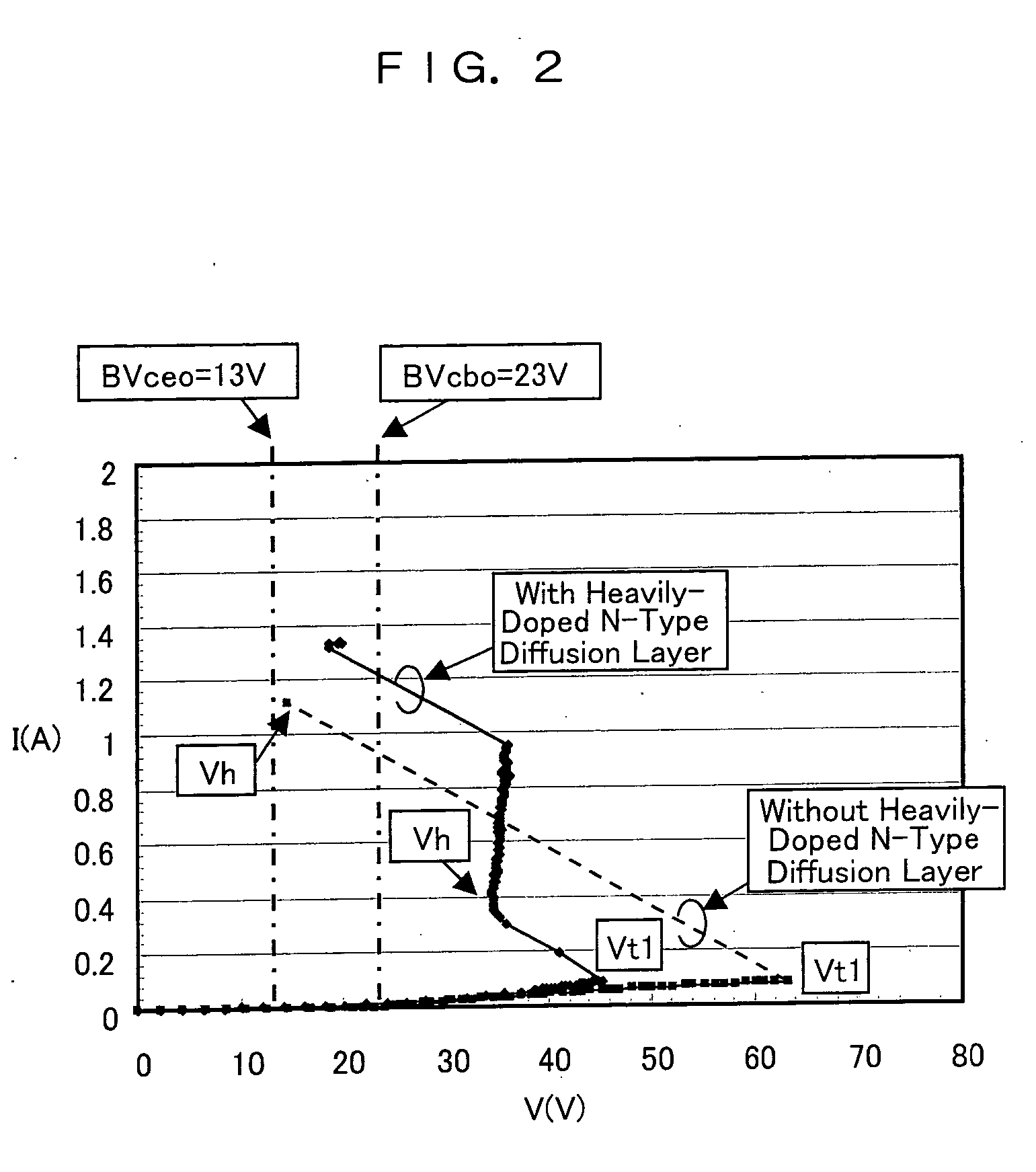

Electrostatic protective element of semiconductor integrated circuit

InactiveUS20060086983A1Improve electrostatic protection abilityReduce collector resistanceTransistorSemiconductor/solid-state device detailsContact formationEngineering

An electrostatic protective element of the present invention comprises: a second-conductive-type and lightly-doped first diffusion layer to be a collector, which is formed to be in contact with a first conductive type semiconductor substrate; a first-conductive-type second diffusion layer to be a base, which is formed on the first diffusion layer; a second-conductive-type third diffusion layer to be an emitter, which is formed on the second diffusion layer, wherein the bottom face of the first diffusion layer is in contact with the semiconductor substrate. Further, the electrostatic protective element comprises a second-conductive-type and heavily-doped fourth diffusion layer, which is formed deeper than the second diffusion layer in a contact area of the first diffusion layer.

Owner:PANASONIC CORP

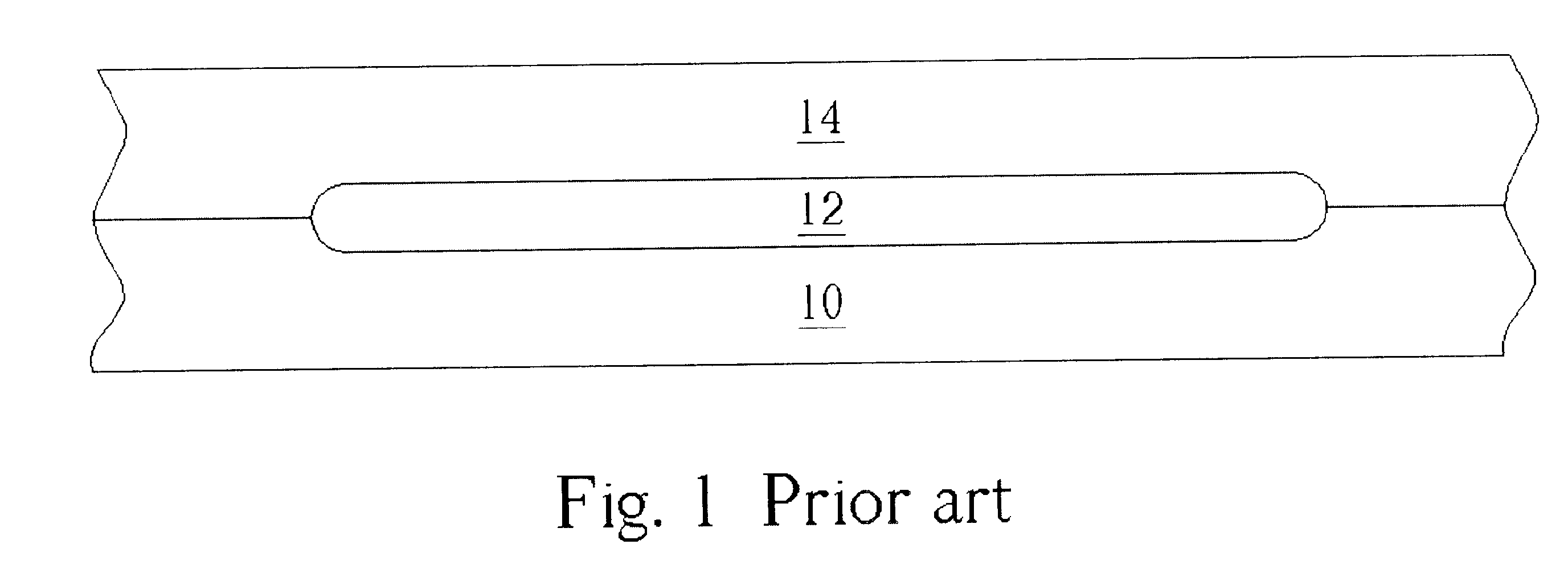

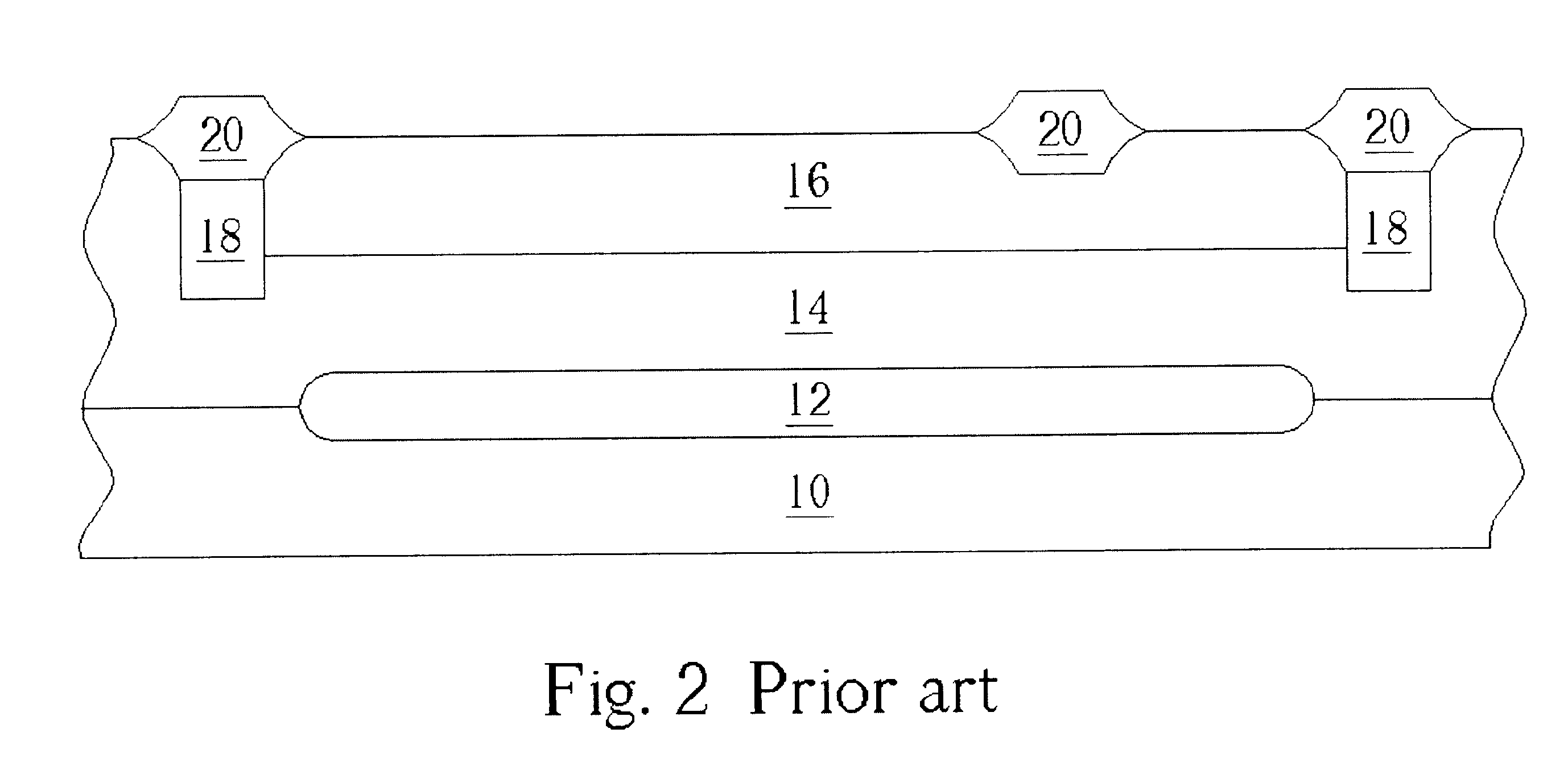

Method of fabricating a bipolar junction transistor

InactiveUS6881638B1The process steps are simpleLow production costSemiconductor/solid-state device manufacturingSemiconductor devicesProtection layerIon implantation

A substrate with a plurality of isolation structures for defining at least an active area thereon is provided. Ions of a first conductive type are implanted into the substrate to form a doping region in the active area. Following that, a protective layer is formed on the substrate, the protective layer having an opening to expose the doping region. A first doping layer of a second conductive type and a second doping layer of the first conductive type are formed on the doping region, respectively, to complete fabrication of a bipolar junction transistor.

Owner:UNITED MICROELECTRONICS CORP

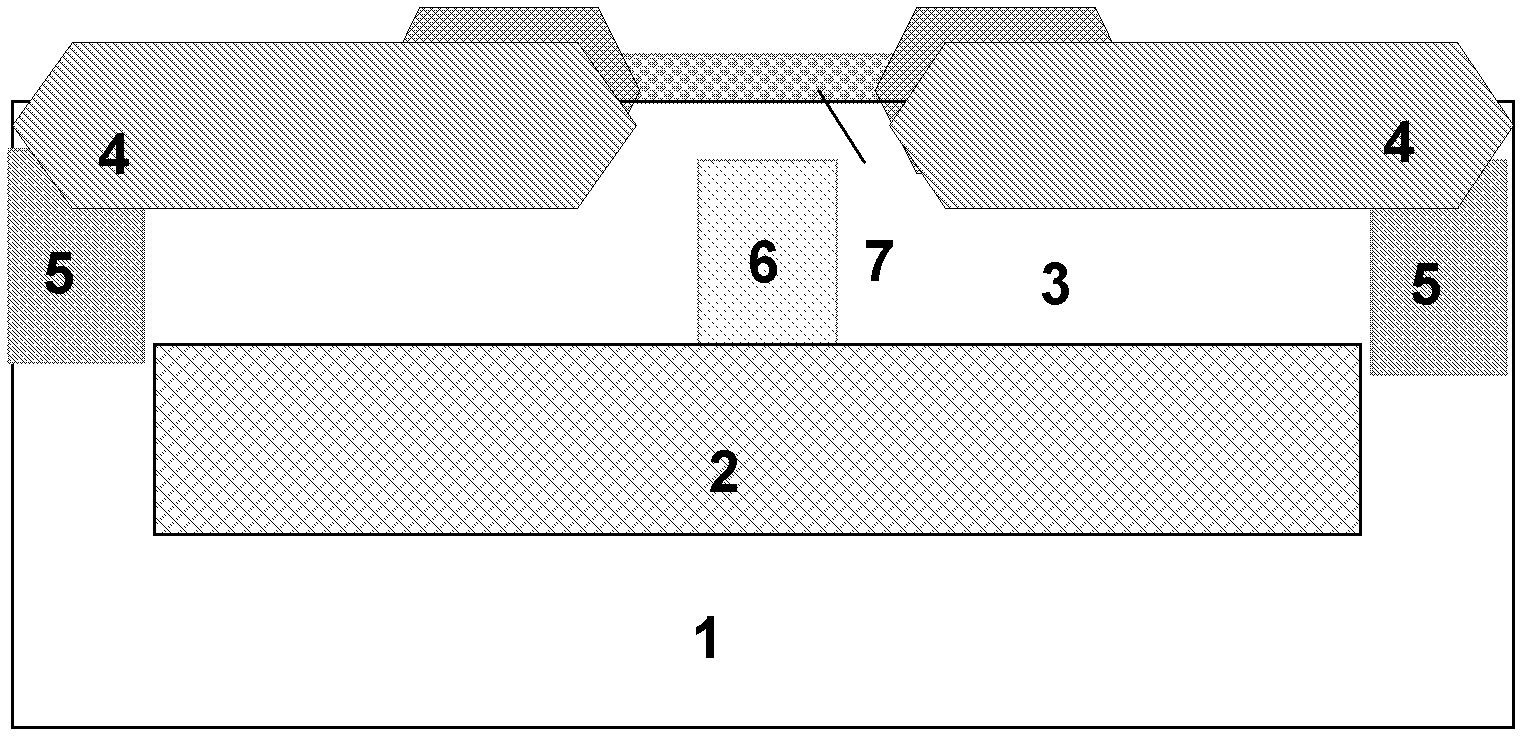

Semiconductor device and method of manufacturing the same

ActiveUS20070123006A1Reduce collector resistanceReduce horizontal widthThyristorSolid-state devicesDevice materialDiffusion layer

In a semiconductor device of the present invention, an N type epitaxial layer is formed on a P type single crystal silicon substrate. In the substrate and the epitaxial layer, an N type buried diffusion layer is formed on a P type buried diffusion layer. With this structure, an upward expansion of the P type buried diffusion layer is checked and a thickness of the epitaxial layer can be made small while maintaining the breakdown voltage characteristics of a power semiconductor element. Accordingly, a device size of a control semiconductor element can be reduced.

Owner:SEMICON COMPONENTS IND LLC

Semiconductor device having a hetero-junction bipolar transistor and manufacturing method thereof

InactiveUS20110250726A1Reduce voltageReduce collector resistanceTransistorSolid-state devicesNon dopedSemiconductor

Method for manufacturing a semiconductor device. A channel layer is formed by epitaxially growing a semiconductor layer, in which an ion species of a first conductivity is implanted on a semiconductor substrate. A source region, a drain region, and an emitter region which are of the first conductivity, are formed by activating, using annealing, a portion of the semiconductor substrate in which the ion species has been implanted. An emitter layer of the first conductivity, a base layer of a second conductivity having a band gap smaller than a band gap of the emitter layer, and a collector layer of the first conductivity or a non-doped collector layer are sequentially and epitaxially grown on the channel layer.

Owner:PANASONIC CORP

Method of fabricating a bipolar junction transistor

InactiveUS20050112837A1The process steps are simpleLow production costSemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsIon implantation

A substrate with a plurality of isolation structures for defining at least an active area thereon is provided. Ions of a first conductive type are implanted into the substrate to form a doping region in the active area. Following that, a protective layer is formed on the substrate, the protective layer having an opening to expose the doping region. A first doping layer of a second conductive type and a second doping layer of the first conductive type are formed on the doping region, respectively, to complete fabrication of a bipolar junction transistor.

Owner:UNITED MICROELECTRONICS CORP

Semiconductor bipolar transistor

ActiveUS7459766B2Reduce collector resistanceTransistorSemiconductor/solid-state device manufacturingSemiconductor deviceTransistor

A semiconductor device including a bipolar transistor in which the collector resistance. The bipolar transistor includes a first conduction type semiconductor substrate having a main surface. A second conduction type collector region is formed in the semiconductor substrate. A shallow trench isolation structure isolates the main surface of the semiconductor substrate into two insulated active regions. A collector leading portion is formed in one of the active regions. A first conduction type base region and a second conduction type emitter region are formed on the other one of the active regions. The collector region has a first depth from the main surface immediately below the shallow trench isolation structure, and the collector region has a second depth from the main surface immediately below the two active regions. The first depth is less than the second depth.

Owner:SEMICON COMPONENTS IND LLC

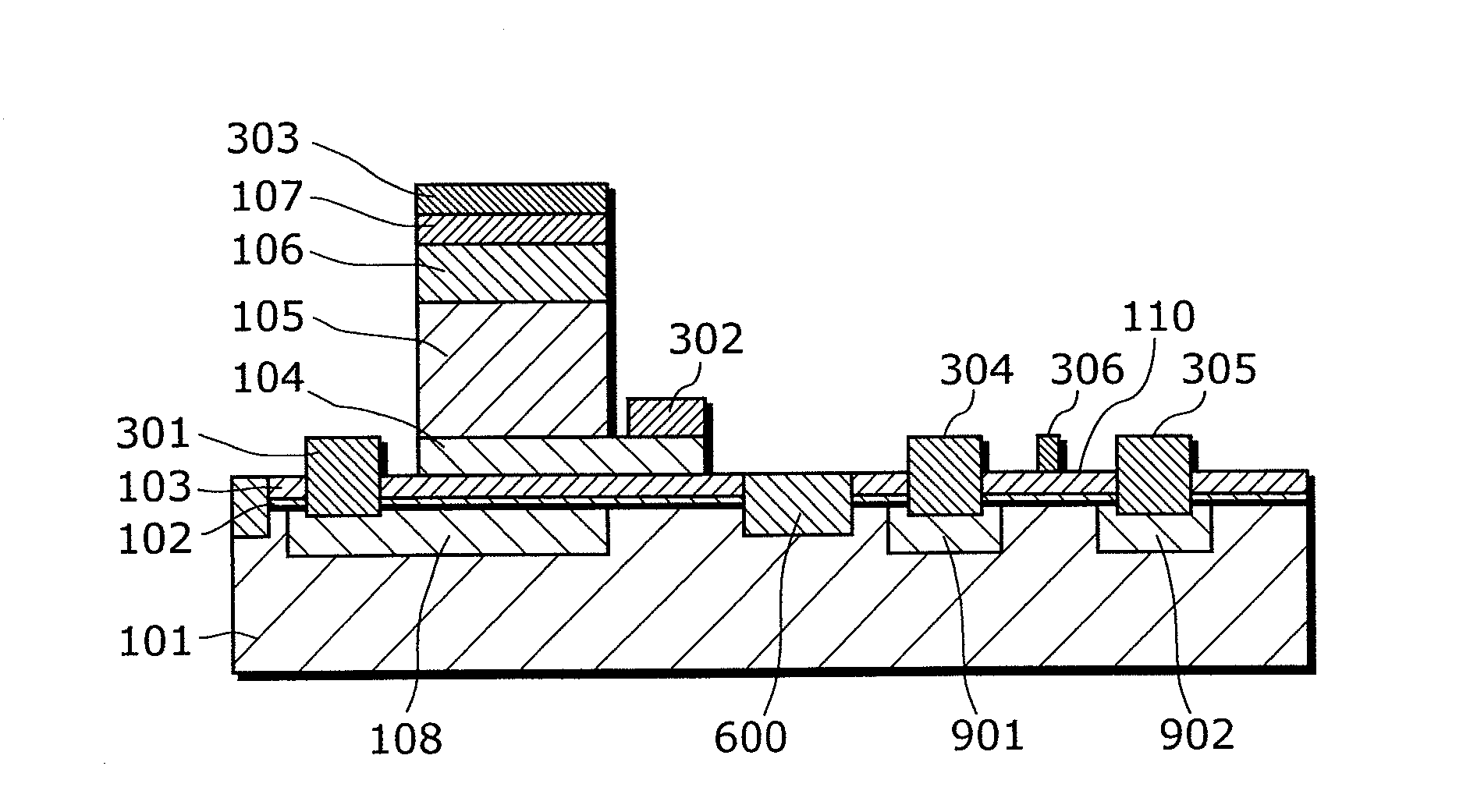

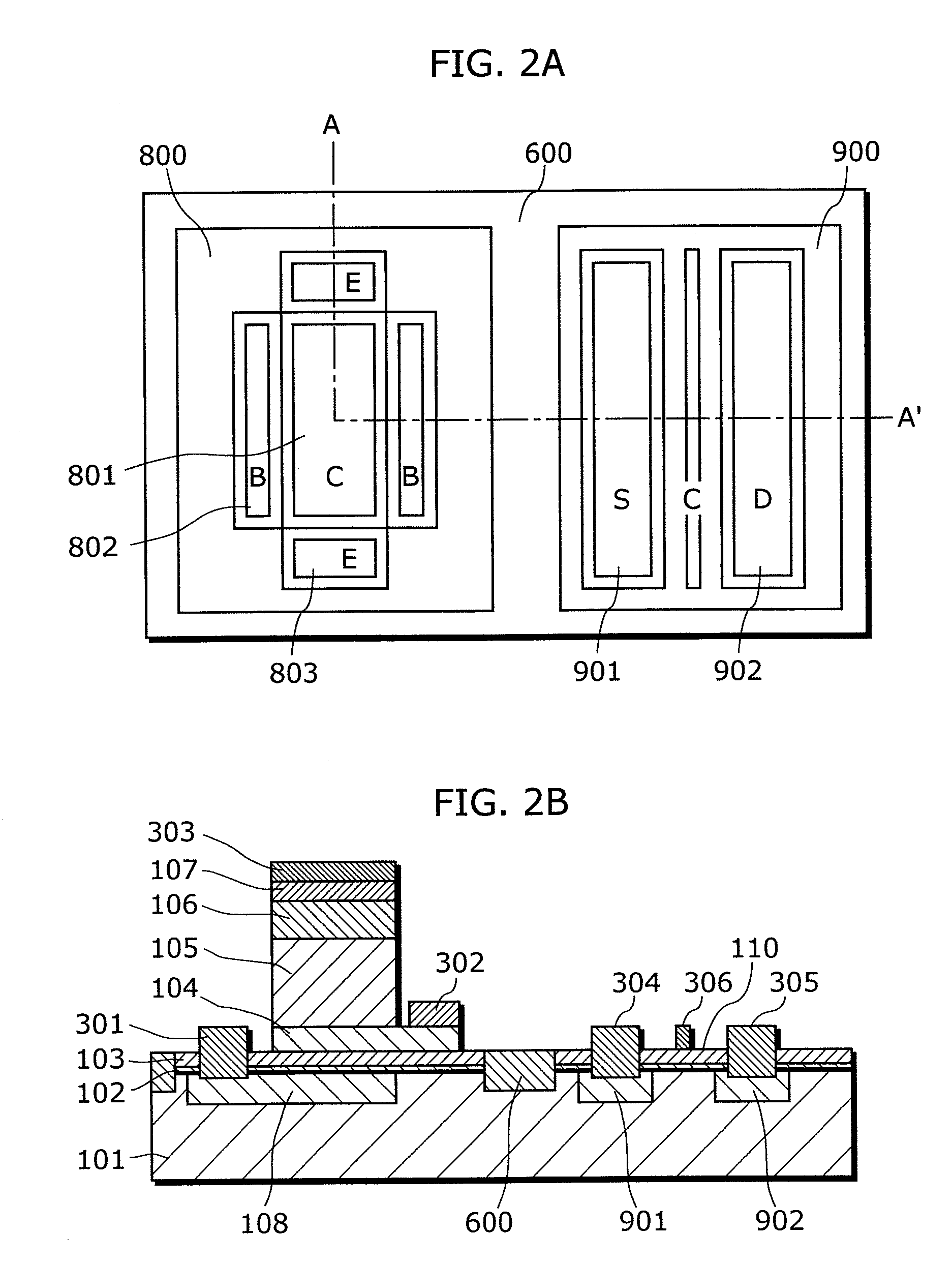

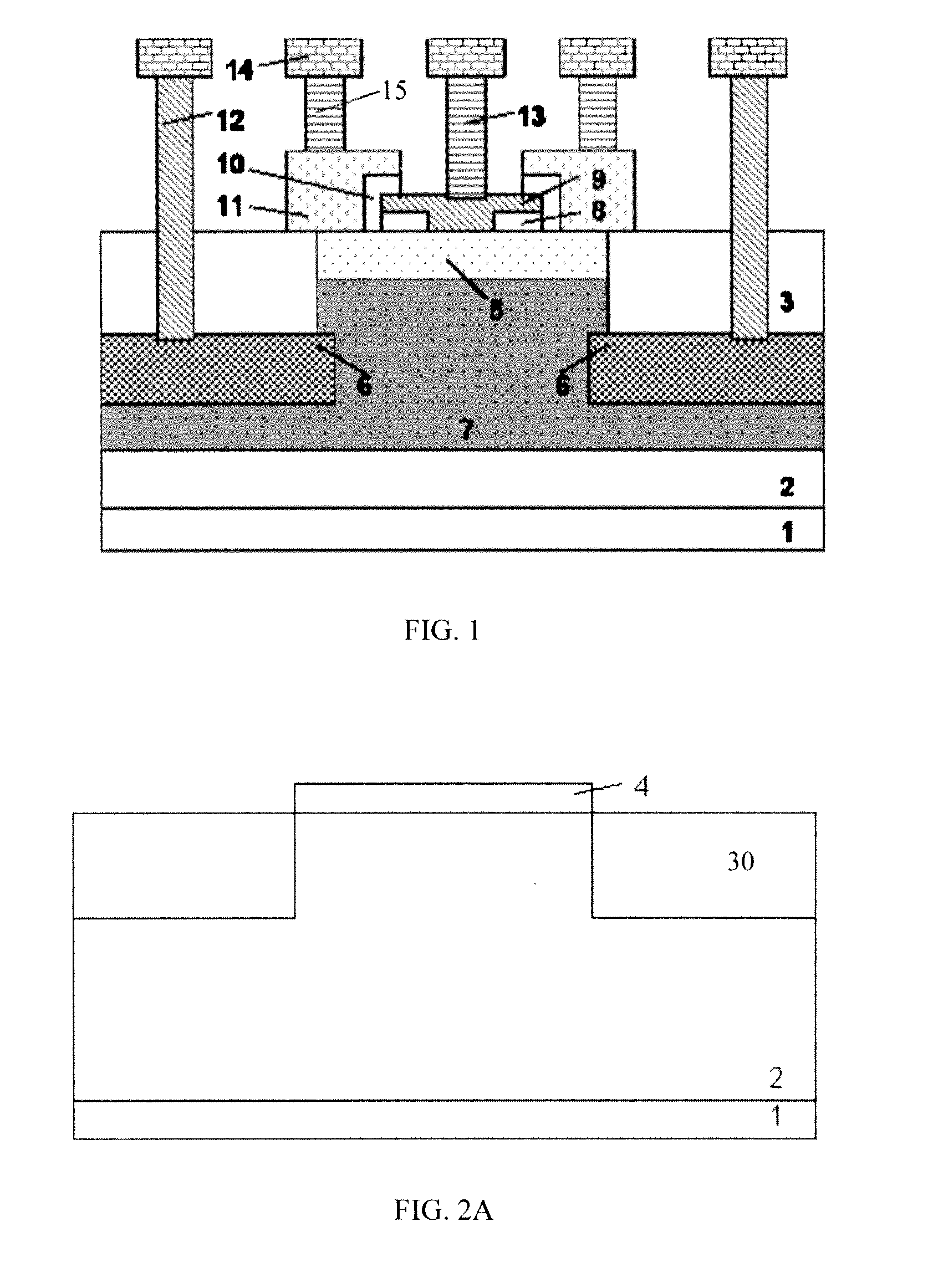

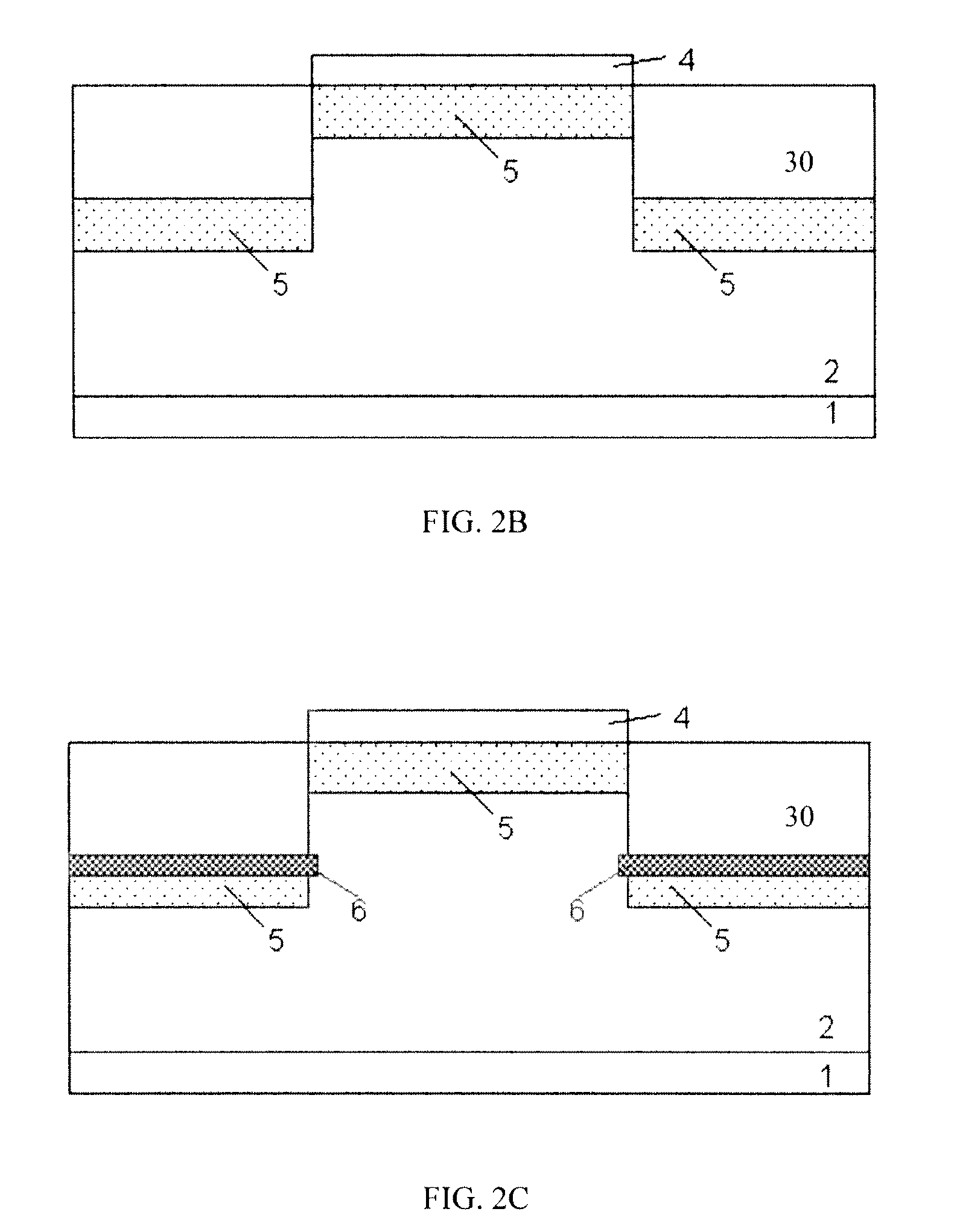

Vertical parasitic PNP device in a BiCMOS process and manufacturing method of the same

ActiveUS8637959B2Reduce device areaReduce collector resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHigh velocityBicmos process

The invention discloses a vertical parasitic PNP transistor in a BiCMOS process and manufacturing method of the same, wherein an active region is isolated by STIs. The transistor includes a collector region, a base region, an emitter region, pseudo buried layers, and N-type polysilicon. The pseudo buried layers, formed at the bottom of the STIs located on both sides of the collector region, extend laterally into the active region and contact with the collector region, whose electrodes are picked up through making deep-hole contacts in the STIs. The N-type polysilicon is formed on the base region and contacts with it, whose electrodes are picked up through making metal contacts on the N-type polysilicon. The transistors can be used as output devices in high-speed and high-gain circuits, efficiently reducing the transistors area, diminishing the collector resistance, and improving the transistors performance. The method can reduce the cost without additional technological conditions.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Vertical parasitic type plug-and-play (PNP) audion in germanium silicon heterojunction bipolar transistor (HBT) technology and manufacture method

ActiveCN103165667AImprove emission efficiencyImprove parasitic effectsSemiconductor/solid-state device manufacturingSemiconductor devicesSilicon heterojunctionTransistor

The invention discloses a vertical parasitic type plug-and-play (PNP) audion in a germanium silicon heterojunction bipolar transistor (HBT) technology. A window defining germanium before growth in a trapezoid shape is adopted and germanium silicon layers in an emitter region can be in a polycrystalline structure, and therefore dosage concentration in the emitter region can be improved, emitting efficiency and amplification coefficient of a device is improved, and cut-off frequency of the device is increased. Due to the fact that the advanced deep hole contact technology and the P-type buried layer technology are adopted, area of an active region can be greatly saved, parasitic effect of the device is improved, collector resistance of the device is reduced, and performance of the device is improved. The invention further discloses a manufacture method of the vertical parasitic type PNP audion in the germanium silicon HBT technology. The manufacture method can be integrated with the technology of the PNP audion in the germanium silicon HBT technology and reduce production cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Silicon-germanium heterojunction bipolar transistor

ActiveUS8395188B2Reduce collector resistanceImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesIon implantationJunction depth

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Semiconductor device and method of manufacturing the same

ActiveUS7038244B2Reduce collector resistanceThe implementation process is simpleTransistorSolid-state devicesOptoelectronicsSemiconductor

A semiconductor device includes a sub-collector layer, a collector layer, a base layer, an emitter layer, and an emitter cap layer, which are sequentially laminated on a substrate. It also includes an emitter electrode, a base electrode, and a collector electrode, which are respectively formed on the emitter cap layer, the base layer, and the sub-collector layer. The sub-collector layer is made up of a first sub-collector layer adjacent to the substrate and a second sub-collector layer adjacent to the collector layer. In the area between adjacent device elements, the first sub-collector layer has an element insulating region created by ion implantation, and the second sub-collector layer has a recess-shaped element insulating region.

Owner:RENESAS ELECTRONICS CORP

Heterojunction bipolar transistor manufacturing method and integrated circuit comprising a heterojunction bipolar transistor

ActiveUS8872237B2Lower breakdown voltageIncreased complexitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringImpurity

Owner:NXP BV

Electrical energy storage cell and electrical energy storage module including the same

InactiveUS8173289B2Improve cooling effectEasy to migrateLiquid electrolytic capacitorsFinal product manufactureEngineeringPositive current

The storage cell includes a flat roll electrode that includes a strip of positive electrode having a positive electrode current collector foil and a positive electrode layer formed thereon, a strip of negative electrode having an electrode current collector foil and a negative electrode layer formed, and a strip of electrically insulated separator, the strip of positive electrode and the strip of negative electrode being wound into a flat roll configuration with the strip of electrically insulated separator sandwiched therebetween; a sealed casing that hermetically seals the flat roll electrode impregnated with an electrolyte; a positive terminal and a negative terminal each electrically insulated from the sealed casing, connected to the positive current collector foil and the negative current collector foil, respectively.

Owner:MITSUBISHI ELECTRIC CORP

Semiconductor device

ActiveUS8017975B2Reduce in quantityLower on-resistanceTransistorSolid-state devicesPower semiconductor deviceTrade offs

A semiconductor device and manufacturing method satisfies both of the trade-off characteristic advantages of the HBT and the HFET. The semiconductor device is an HBT and HFET integrated circuit. The HBT includes a sub-collector layer, a GaAs collector layer, a GaAs base layer, and an InGaP emitter layer that are sequentially stacked. The sub-collector layer includes a GaAs external sub-collector region, and a GaAs internal sub-collector region disposed on the GaAs external sub-collector region. A mesa-shaped collector part and a collector electrode are separately formed on the GaAs external sub-collector region. The HFET includes a GaAs cap layer, a source electrode, and a drain electrode. The GaAs cap layer includes a portion of the GaAs external sub-collector region. The source electrode and the drain electrode are formed on the GaAs cap layer.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

Vertical parasitic pnp device in a bicmos process and manufacturing method of the same

ActiveUS20120049327A1Good frequency characteristicReduce device areaSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringElectrical and Electronics engineering

The invention discloses a vertical parasitic PNP transistor in a BiCMOS process and manufacturing method of the same, wherein an active region is isolated by STIs. The transistor includes a collector region, a base region, an emitter region, pseudo buried layers, and N-type polysilicon. The pseudo buried layers, formed at the bottom of the STIs located on both sides of the collector region, extend laterally into the active region and contact with the collector region, whose electrodes are picked up through making deep-hole contacts in the STIs. The N-type polysilicon is formed on the base region and contacts with it, whose electrodes are picked up through making metal contacts on the N-type polysilicon. The transistors can be used as output devices in high-speed and high-gain circuits, efficiently reducing the transistors area, diminishing the collector resistance, and improving the transistors performance. The method can reduce the cost without additional technological conditions.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

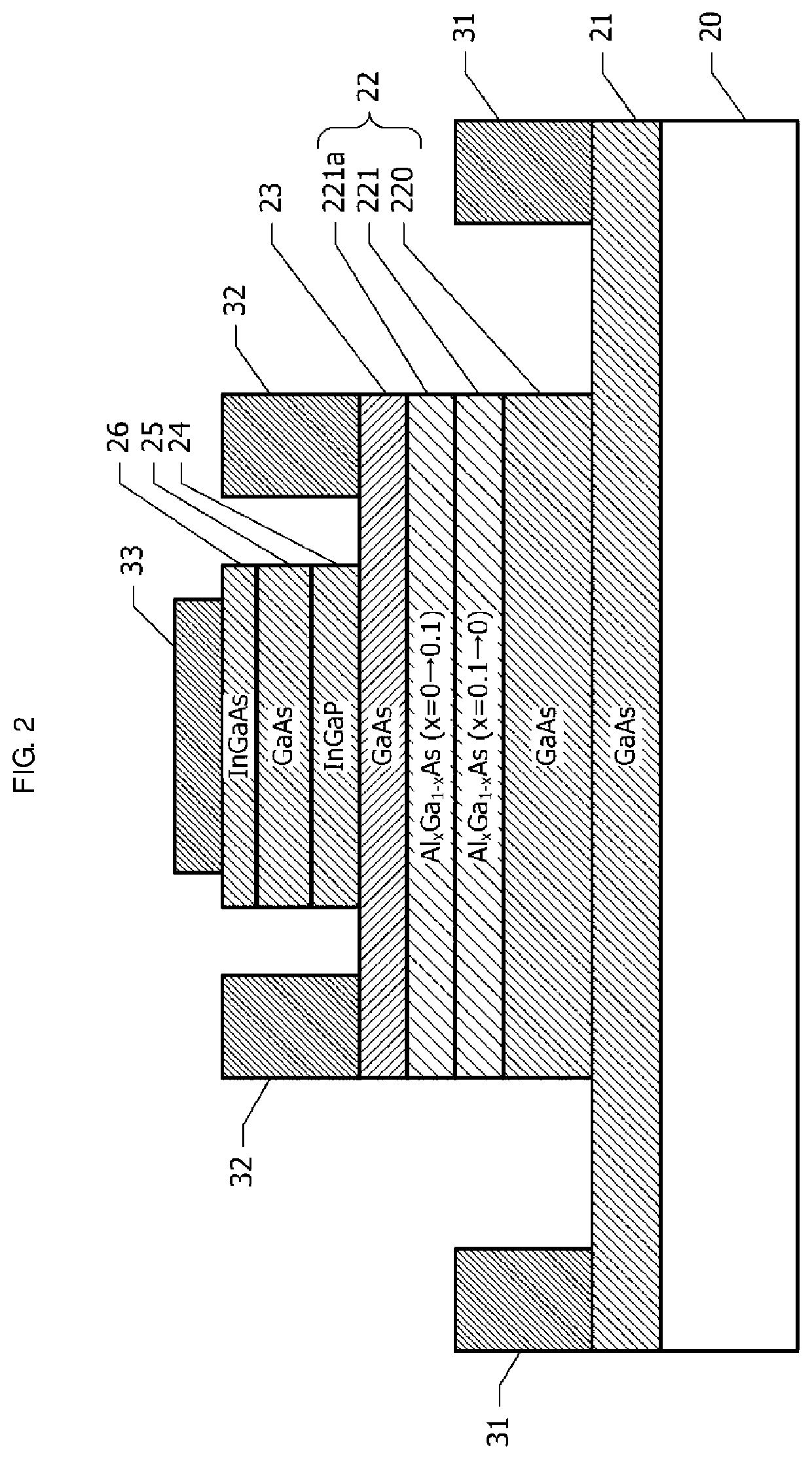

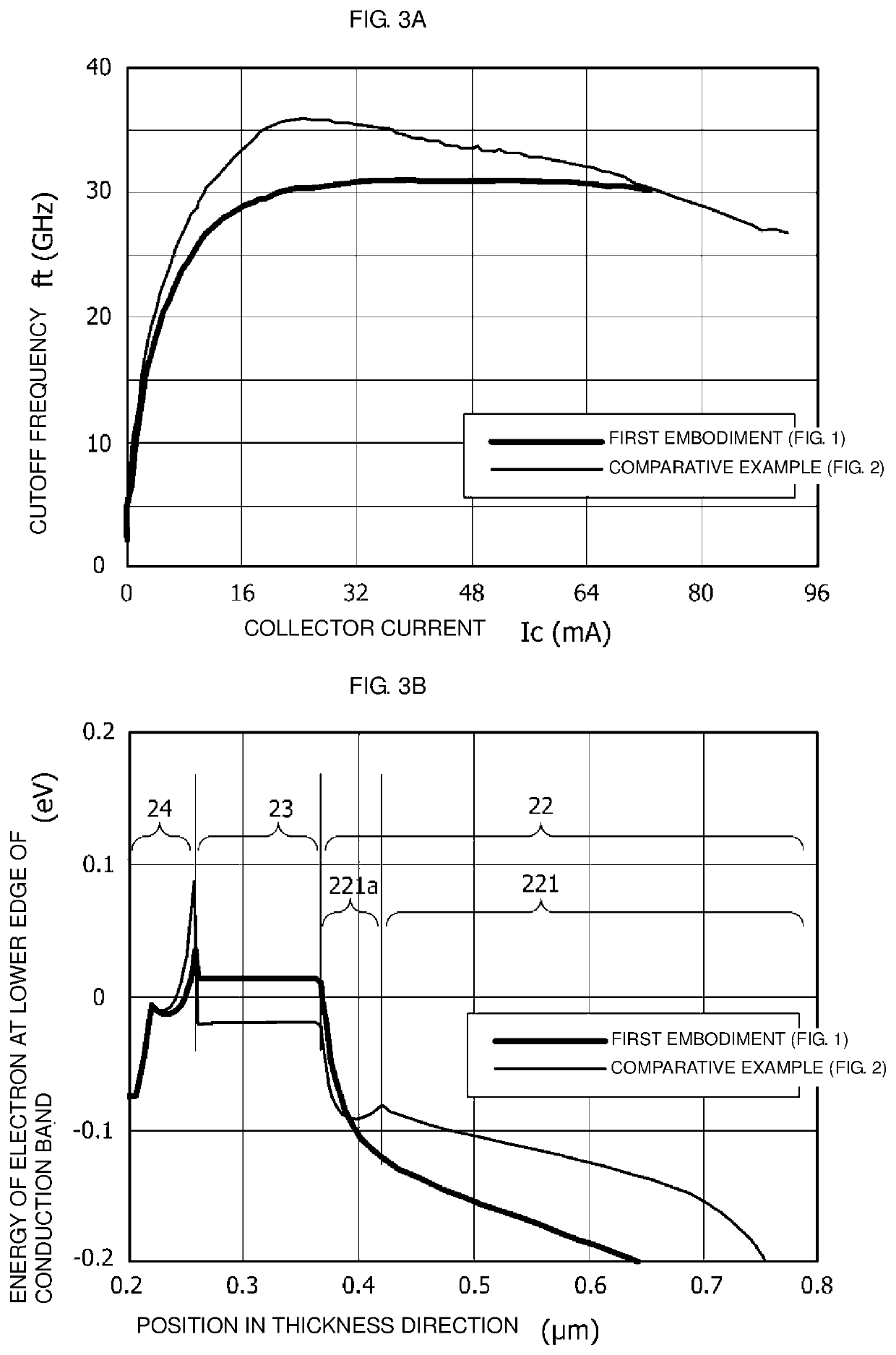

Heterojunction bipolar transistor

ActiveUS10777669B2Reduced Linearity RequirementsImprove power efficiencyPower amplifiersSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A heterojunction bipolar transistor includes a collector layer, a base layer, and an emitter layer that are stacked on a substrate. The collector layer includes a graded semiconductor layer in which an electron affinity increases from a side closer to the base layer toward a side farther from the base layer. An electron affinity of the base layer at an interface closer to the collector layer is equal to an electron affinity of the graded semiconductor layer at an interface closer to the base layer.

Owner:MURATA MFG CO LTD

Method of fabricating a bipolar junction transistor

InactiveUS6949438B2The process steps are simpleLow production costSemiconductor/solid-state device manufacturingSemiconductor devicesProtection layerIon implantation

A substrate with a plurality of isolation structures for defining at least an active area thereon is provided. Ions of a first conductive type are implanted into the substrate to form a doping region in the active area. Following that, a protective layer is formed on the substrate, the protective layer having an opening to expose the doping region. A first doping layer of a second conductive type and a second doping layer of the first conductive type are formed on the doping region, respectively, to complete fabrication of a bipolar junction transistor.

Owner:UNITED MICROELECTRONICS CORP

Vertical parasitic PNP transistor in silicon-germanium BICMOS (Bipolar Complementary Metal Oxide Semiconductor) technique and fabrication method

ActiveCN102412279BImprove parasitic effectsReduce collector resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDopantEngineering

The invention discloses a vertical parasitic PNP transistor in the silicon-germanium BICMOS technique. A groove which is in contact with a base region is formed in a shallow trench field oxide around the base region, the depth of the groove is smaller than or equal to the depth of the base region, polycrystalline silicon is filled in the groove and doped with N-type dopant, the polycrystalline silicon doped with the N-type dopant is formed into an outer base region, which is in contact with the side of the base region, and a metal contact is formed on the outer base region, and leads out a base. The invention also discloses a fabrication method for the vertical parasitic PNP transistor in the silicon-germanium BICMOS technique. The vertical parasitic PNP transistor can be used as an output device in a high-speed, high-gain HBT (heterojunction bipolar transistor) circuit, so that one more type of device is provided as an option for the circuit, the area of the device can be effectively reduced, the parasitic effect of the device can be effectively decreased, the collector resistance of the PNP transistor can be effectively decreased, and the performance of the device can be effectively enhanced; and the method does not need additional process conditions, and can reduce the production cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

SiGe hbt single tube structure, its manufacturing method and SiGe hbt multi-finger structure

ActiveCN103123928BLower resistanceReduce spacingSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceSilicon heterojunction

The invention discloses a germanium-silicon heterojunction bipolar transistor (HBT) single tube structure. A collector region C is manufactured through a low-doping N type epitaxy technique, and the bottom of the collector region C is extracted by a heavy N type doping buried layer; a base region B is composed of a boron heavy doping germanium-silicon epitaxial layer; a transmitting region E is formed by etching media deposited on the base region to form a window and then depositing N type doping polycrystalline silicon; an N type epitaxy at the bottom of field oxide under outer base region polycrystalline silicon is converted to a P type region through P type ion injection and high-temperature annealing; and a collector electrode is extracted by a deep groove contact hole and metals. The invention further discloses a multi-finger structure in a CBEBE...BEBC or CEBECBE...CEBEC mode. The deep groove contact hole penetrates through the field oxide and the N type epitaxy to penetrate into the N type buried layer, the space of two transmitting electrodes can be greatly reduced, the collector resistance of device is reduced, and junction capacitance of the collector electrode for the base region and a silicon substrate is reduced. A P type ion injection region is not communicated with a P type ion injection region arranged outside the device, so that base electrode-collector electrode medium capacitance is reduced. The multi-finger structure can obtain the largest output power and power gain.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com