Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

85 results about "Interconnect technology" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

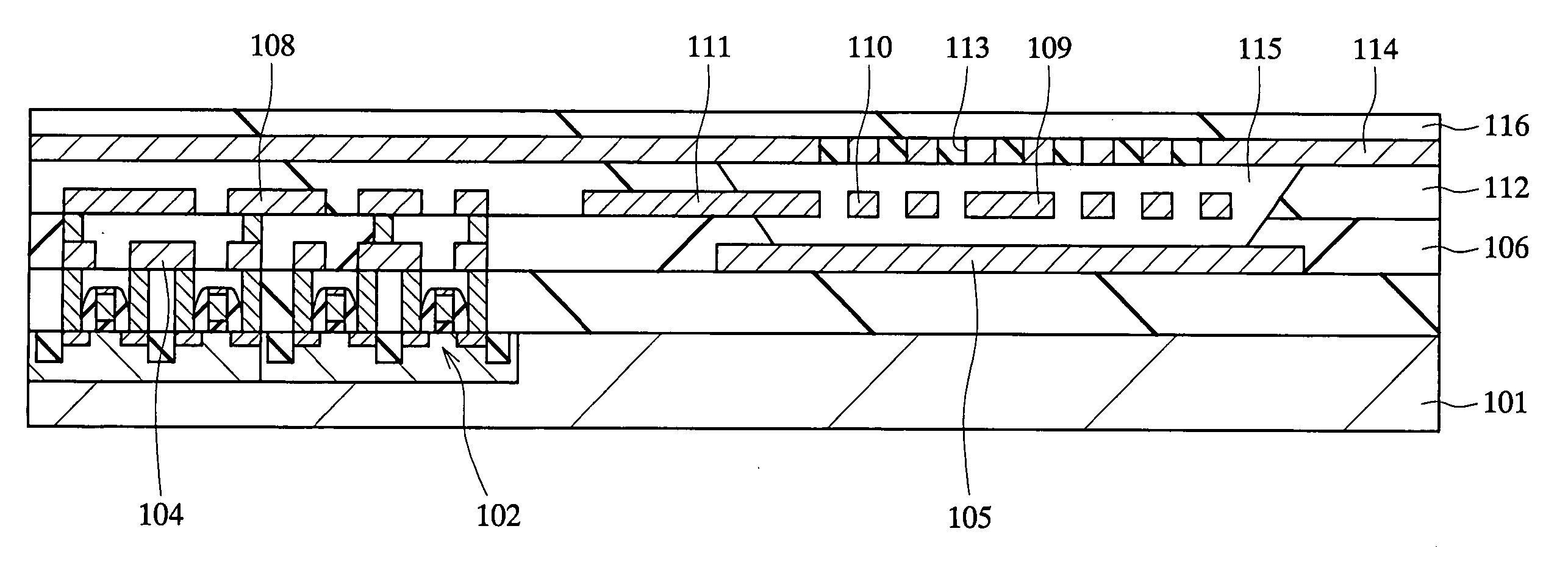

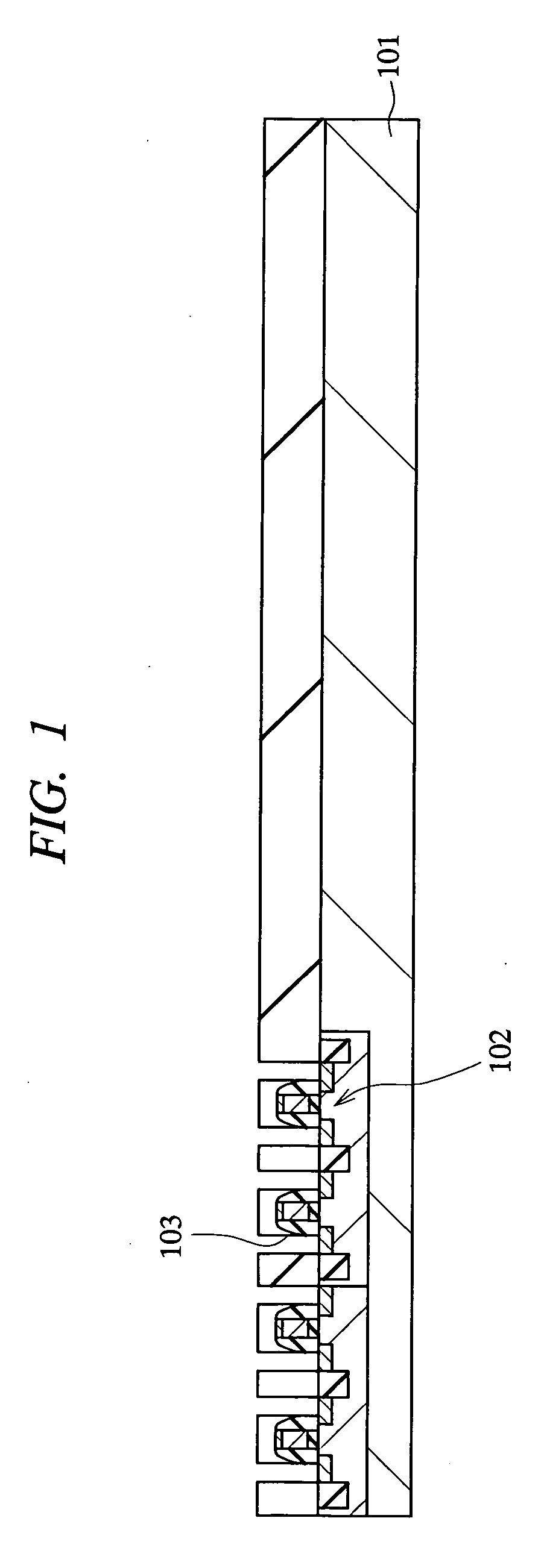

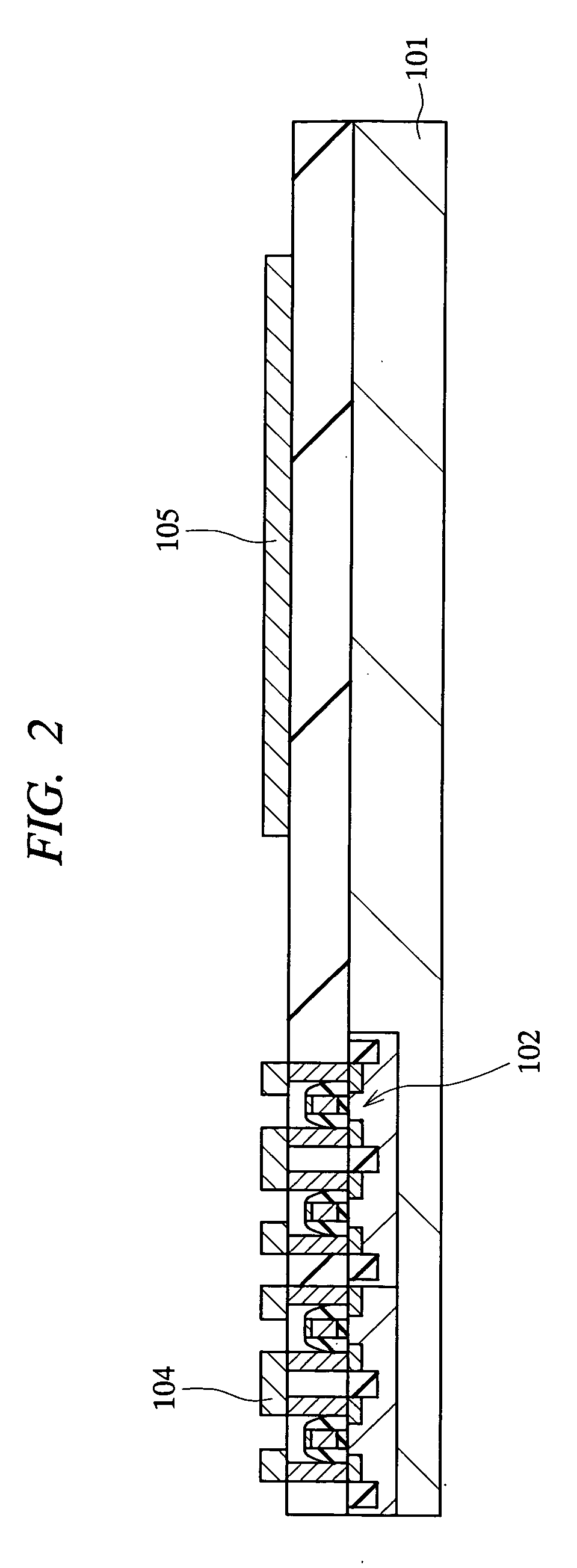

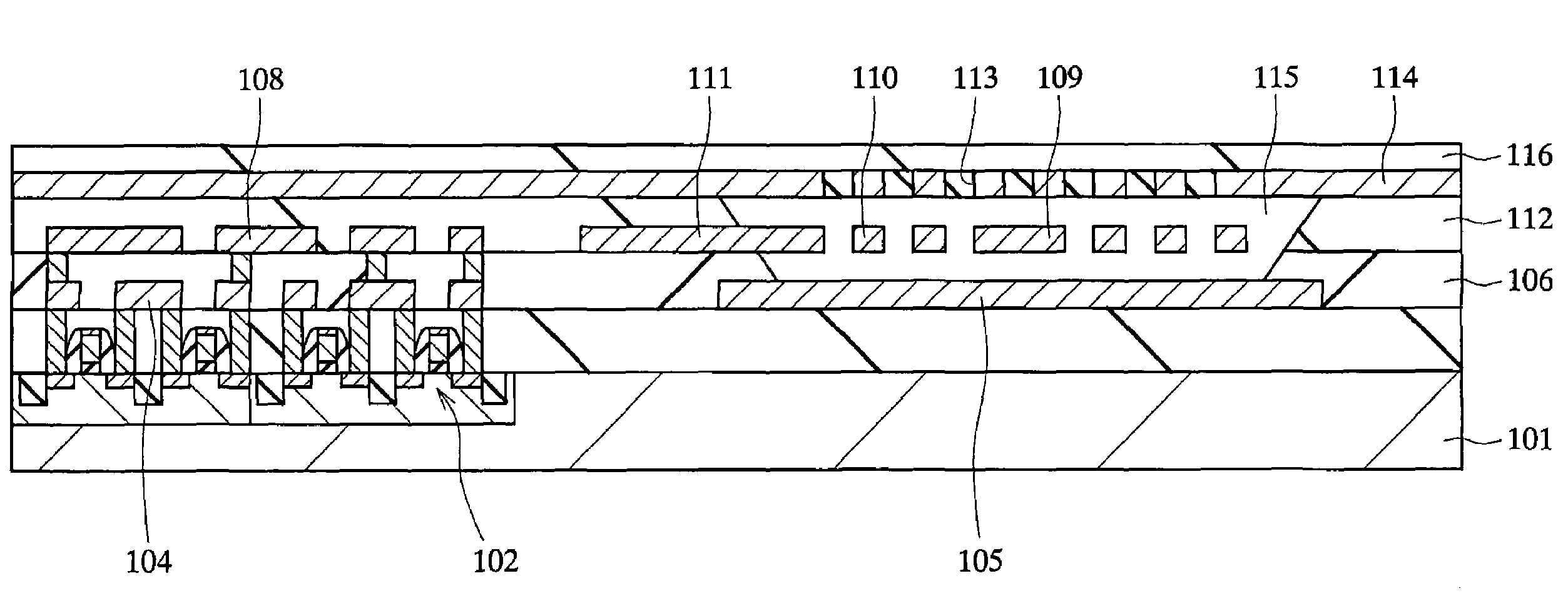

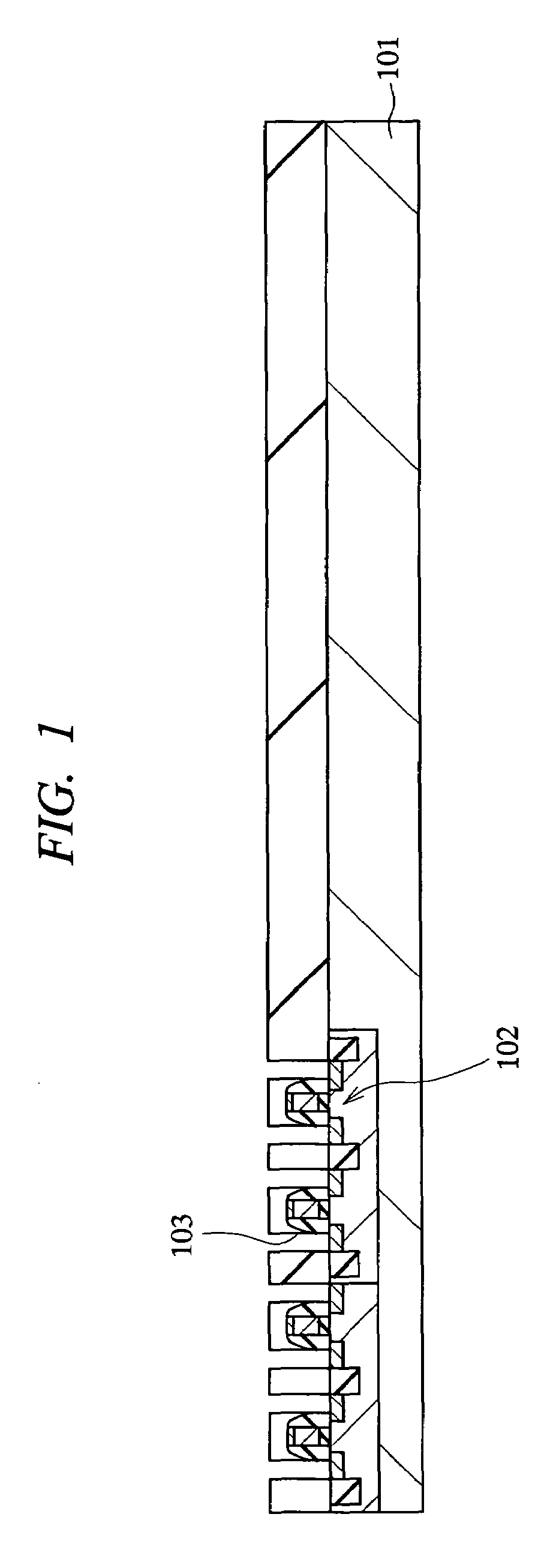

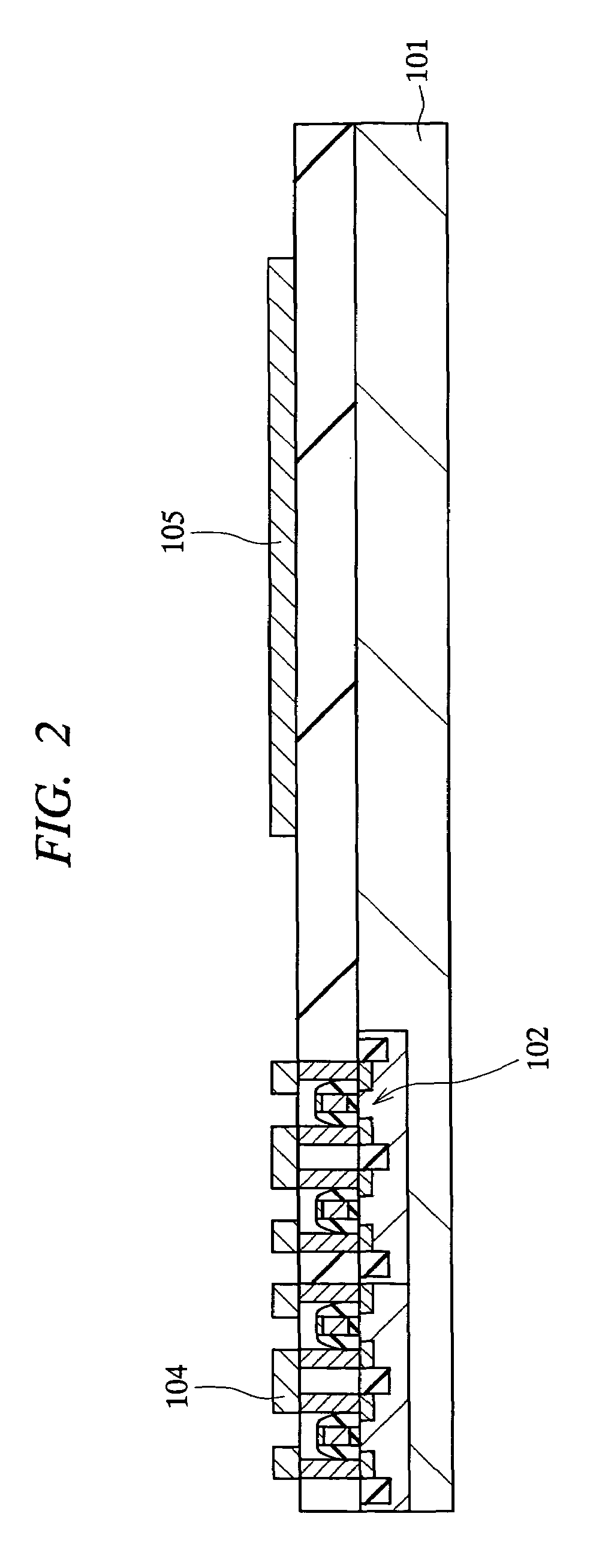

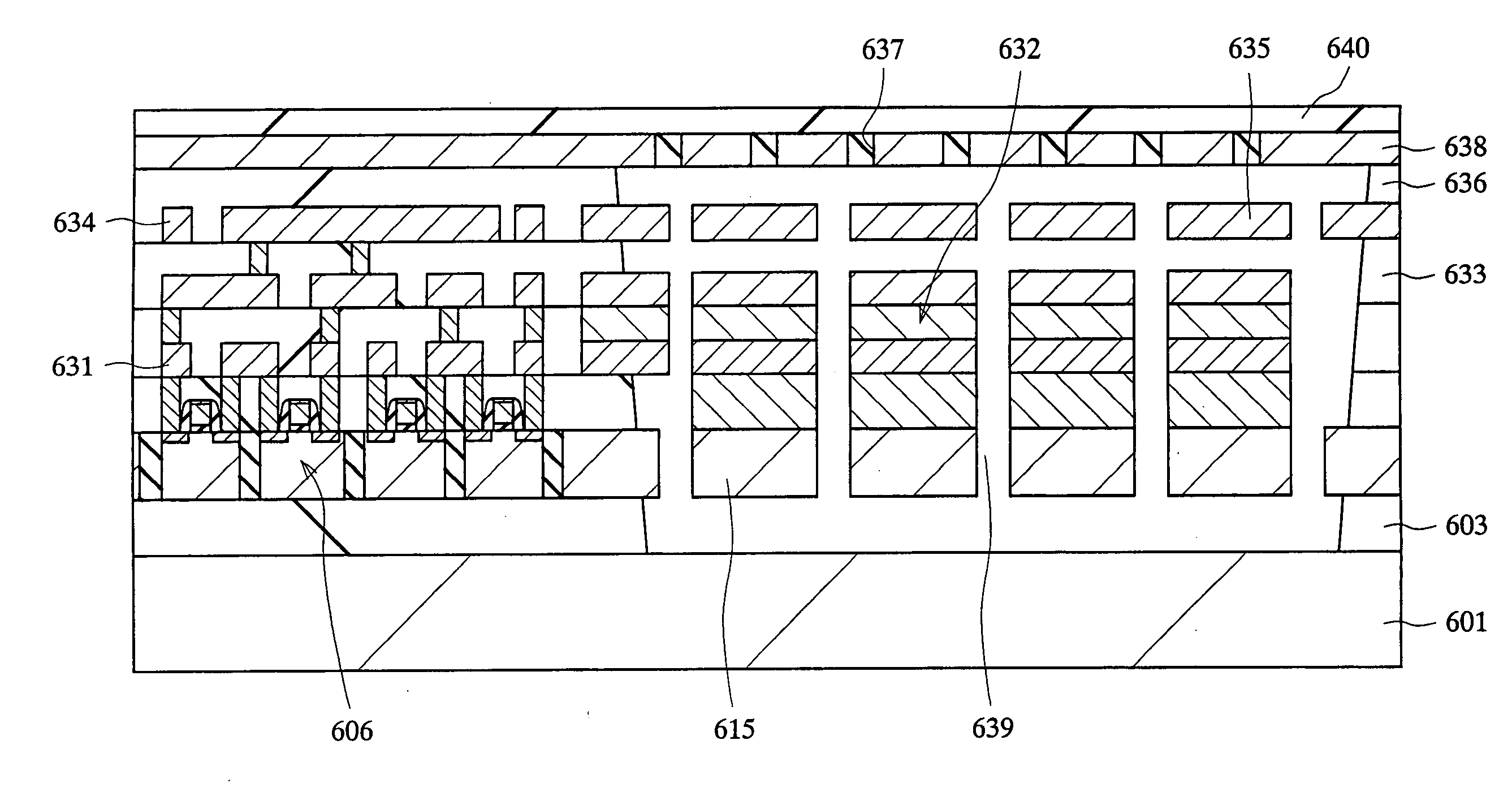

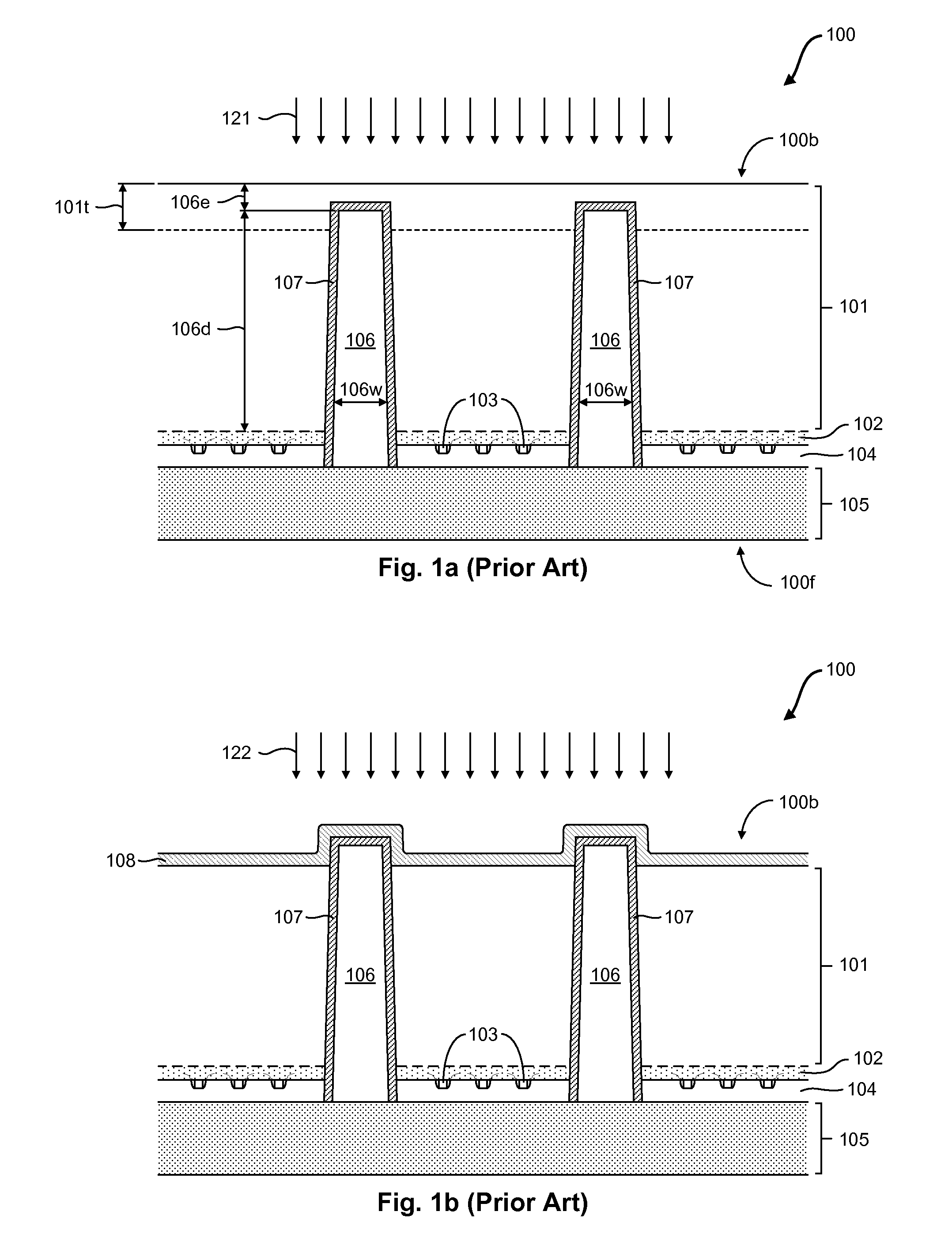

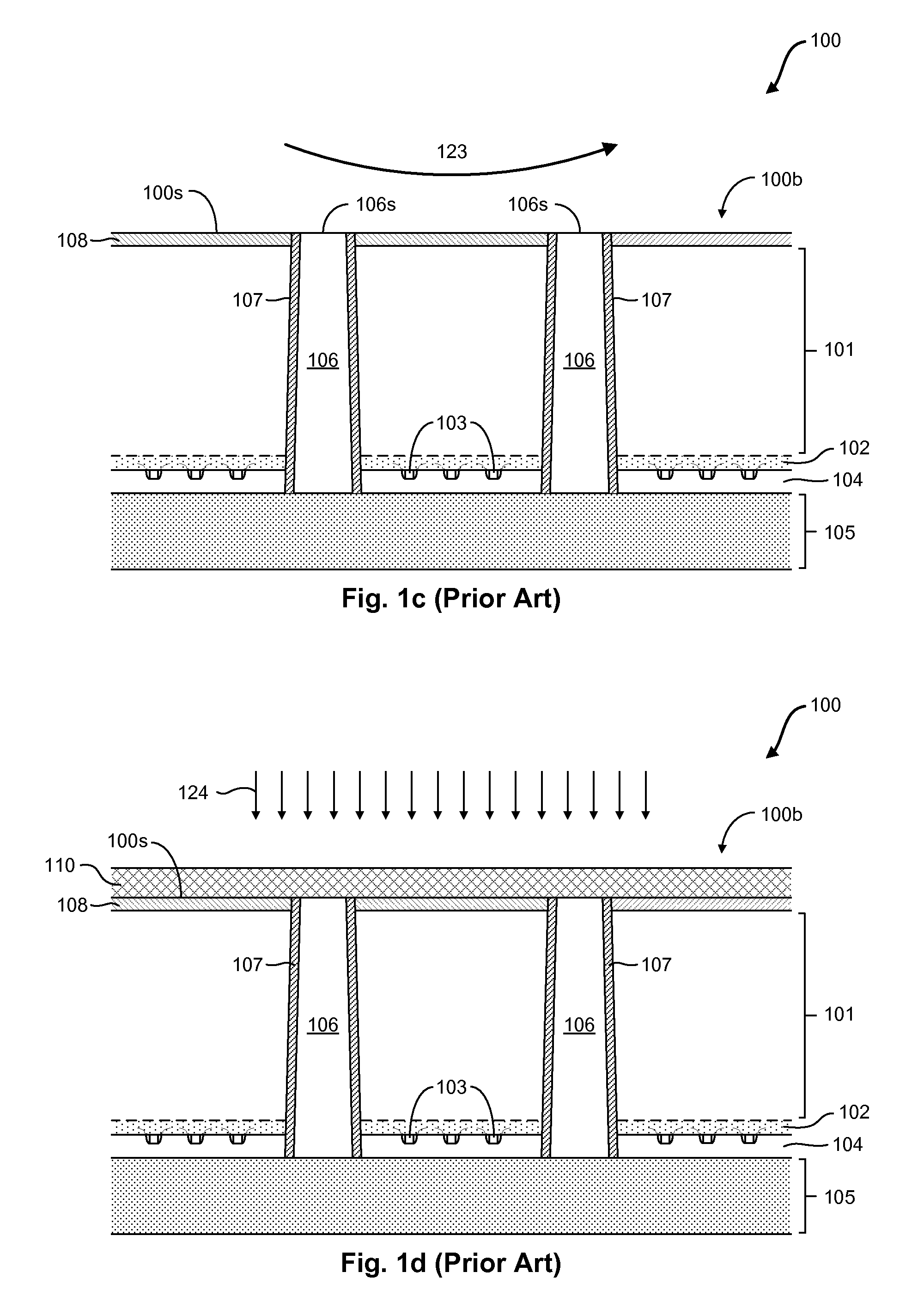

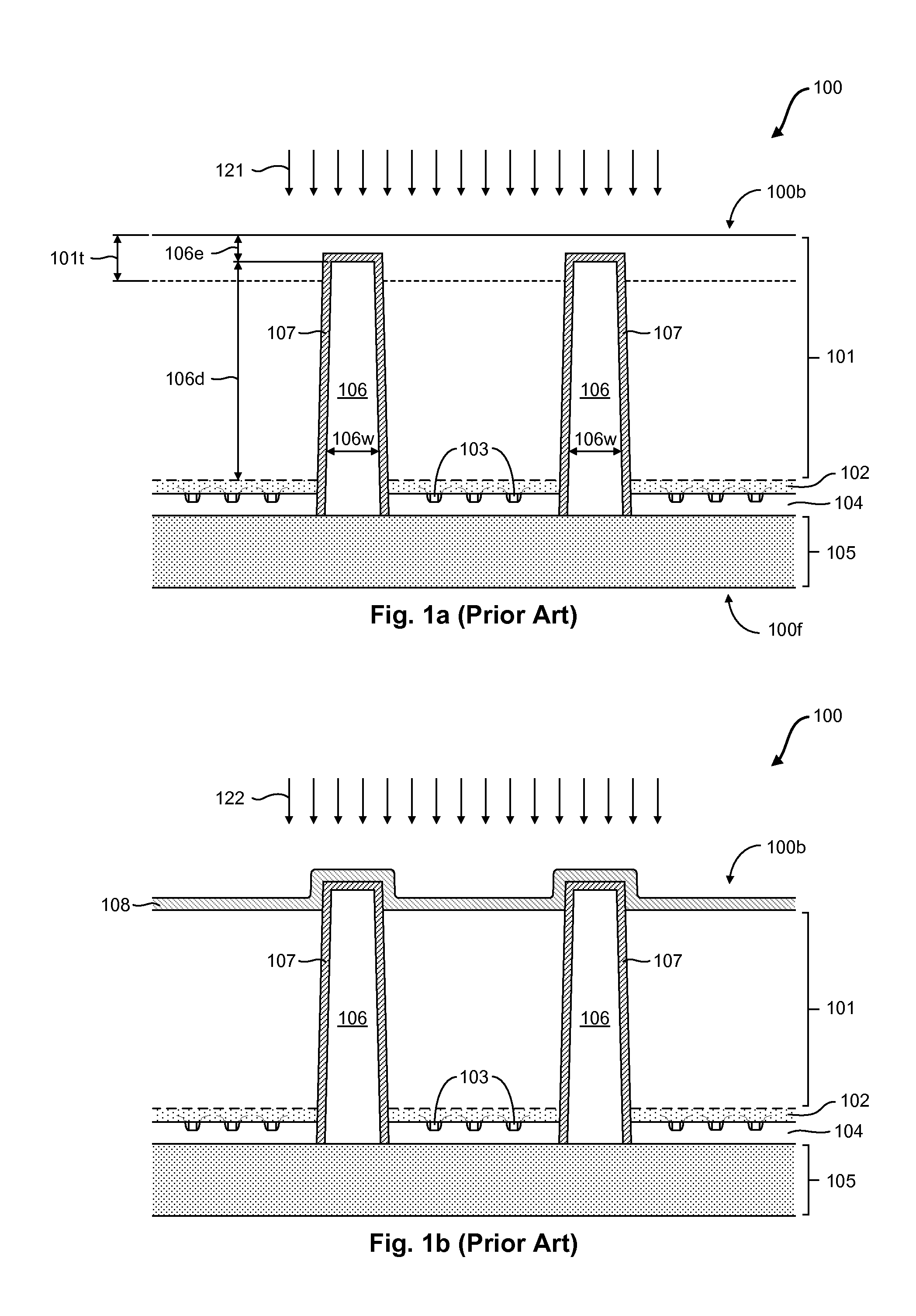

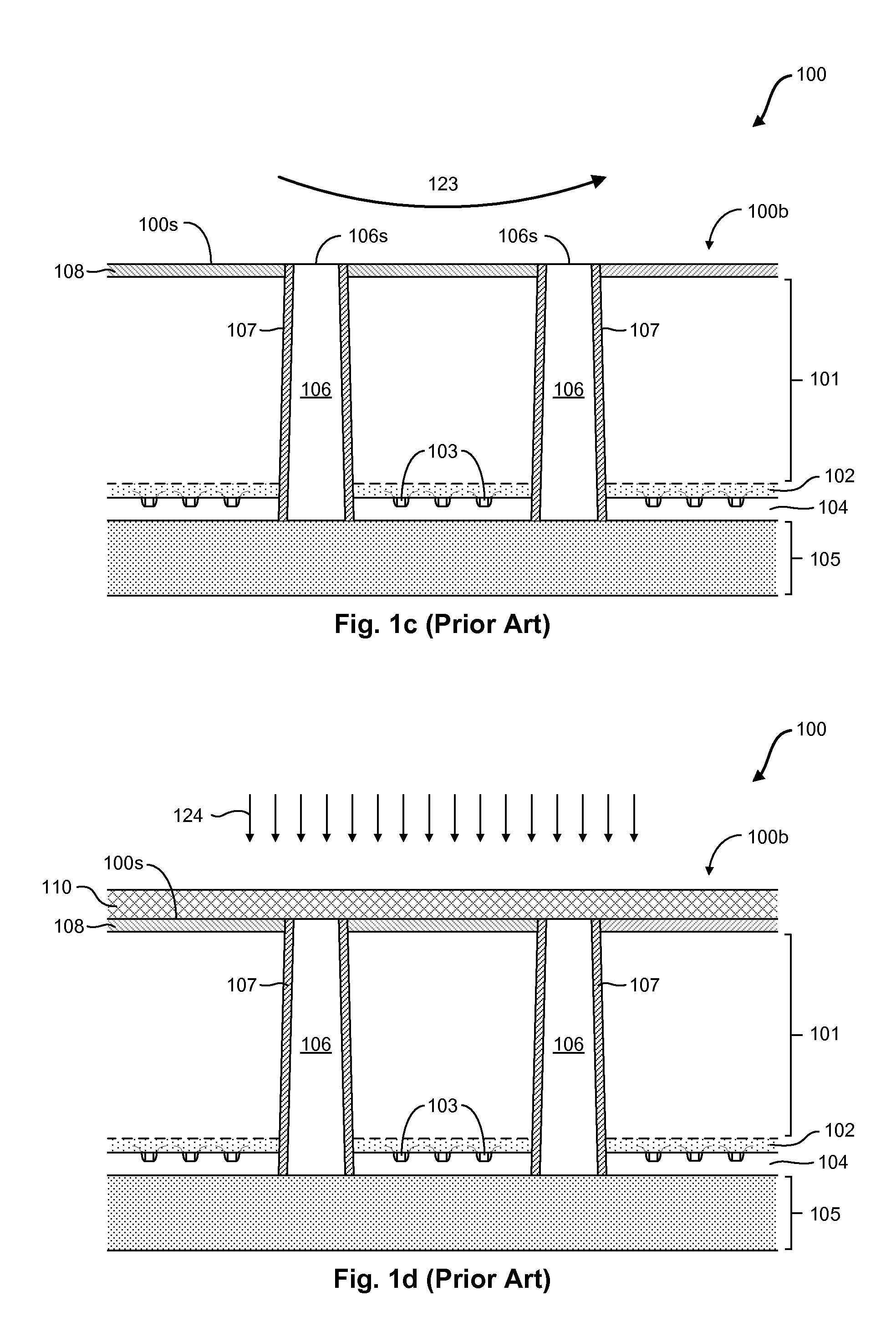

Integrated micro electro-mechanical system and manufacturing method thereof

ActiveUS20060205106A1Accurate representationHigh dimensional accuracyTelevision system detailsInflated body pressure measurementDielectricEtching

In the manufacturing technology of an integrated MEMS in which a semiconductor integrated circuit (CMOS or the like) and a micro machine are monolithically integrated on a semiconductor substrate, a technology capable of manufacturing the integrated MEMS without using a special process different from the normal manufacturing technology of a semiconductor integrated circuit is provided. A MEMS structure is formed together with an integrated circuit by using the CMOS integrated circuit process. For example, when forming an acceleration sensor, a structure composed of a movable mass, an elastic beam and a fixed beam is formed by using the CMOS interconnect technology. Thereafter, an interlayer dielectric and the like are etched by using the CMOS process to form a cavity. Then, fine holes used in the etching are sealed with a dielectric.

Owner:HITACHI ASTEMO LTD

Integrated micro electro-mechanical system and manufacturing method thereof

ActiveUS7402449B2Easy to manufactureSufficient massTelevision system detailsInflated body pressure measurementDielectricEtching

In the manufacturing technology of an integrated MEMS in which a semiconductor integrated circuit (CMOS or the like) and a micro machine are monolithically integrated on a semiconductor substrate, a technology capable of manufacturing the integrated MEMS without using a special process different from the normal manufacturing technology of a semiconductor integrated circuit is provided. A MEMS structure is formed together with an integrated circuit by using the CMOS integrated circuit process. For example, when forming an acceleration sensor, a structure composed of a movable mass, an elastic beam and a fixed beam is formed by using the CMOS interconnect technology. Thereafter, an interlayer dielectric and the like are etched by using the CMOS process to form a cavity. Then, fine holes used in the etching are sealed with a dielectric.

Owner:HITACHI ASTEMO LTD

Integrated micro electro-mechanical system and manufacturing method thereof

InactiveUS20090049911A1Easy to manufactureSufficient massTelevision system detailsInflated body pressure measurementDielectricEtching

In the manufacturing technology of an integrated MEMS in which a semiconductor integrated circuit (CMOS or the like) and a micro machine are monolithically integrated on a semiconductor substrate, a technology capable of manufacturing the integrated MEMS without using a special process different from the normal manufacturing technology of a semiconductor integrated circuit is provided. A MEMS structure is formed together with an integrated circuit by using the CMOS integrated circuit process. For example, when forming an acceleration sensor, a structure composed of a movable mass, an elastic beam and a fixed beam is formed by using the CMOS interconnect technology. Thereafter, an interlayer dielectric and the like are etched by using the CMOS process to form a cavity. Then, fine holes used in the etching are sealed with a dielectric.

Owner:HITACHI LTD

Microelectronic cleaning composition containing halogen oxygen acids, salts and derivatives thereof

ActiveUS20050176603A1Improve compatibilityImproved and superior cleaningSurface-active detergent compositionsDetergent mixture composition preparationIridiumHafnium

Microelectronic cleaning compositions for cleaning microelectronic substrates, and particularly cleaning compositions useful with and having improved compatibility with microelectronic substrates characterized by silicon dioxide, sensitive low-κ or high-κ dielectrics and copper, tungsten, tantalum, nickel, gold, cobalt, palladium, platinum, chromium, ruthenium, rhodium, iridium, hafnium, titanium, molybdenum, tin and other metallization, as well as substrates of Al or Al(Cu) metallizations and advanced interconnect technologies, are provided by microelectronic cleaning compositions comprising halogen acids, salts and derivatives thereof.

Owner:AVANTOR PERFORMANCE MATERIALS LLC

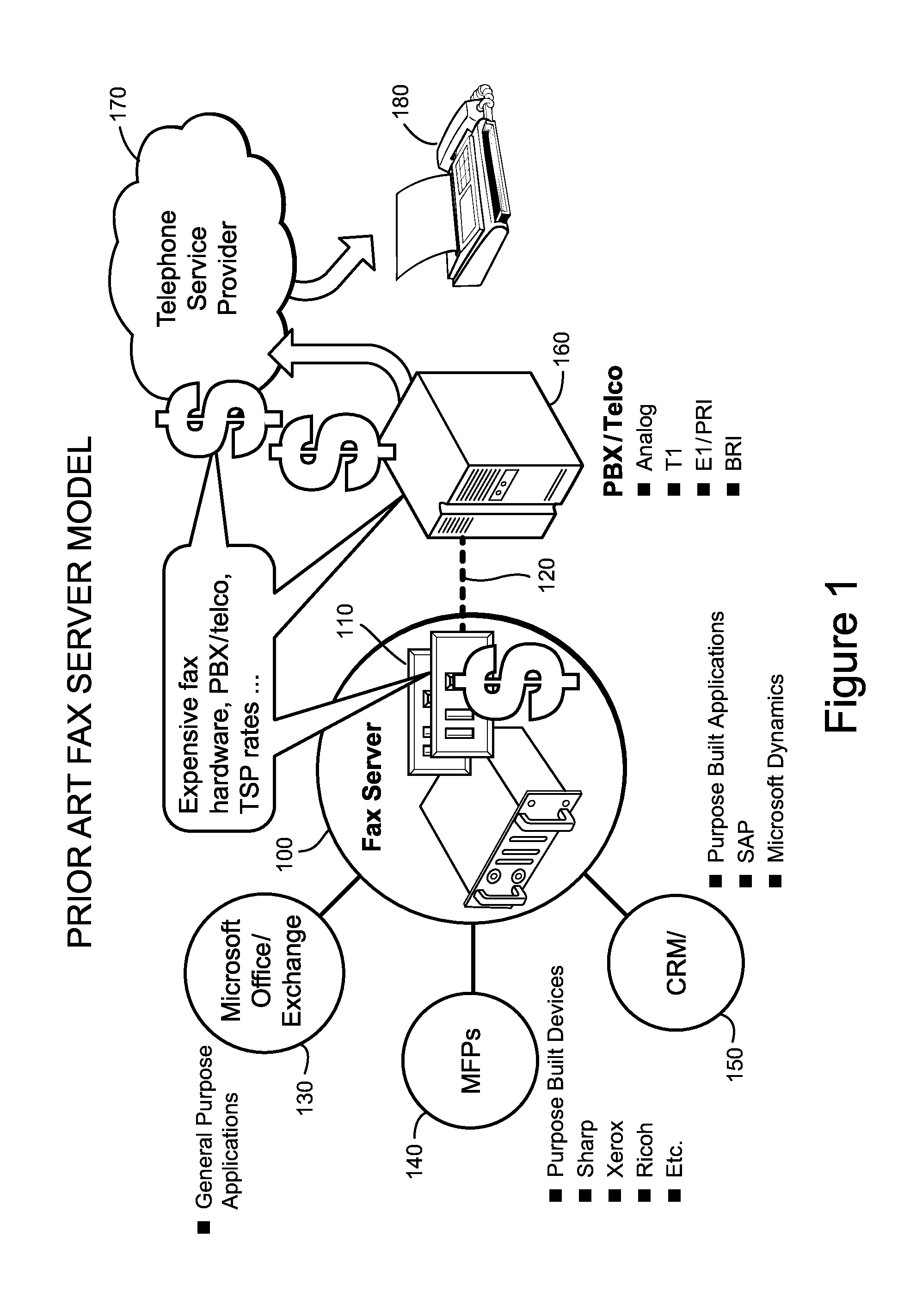

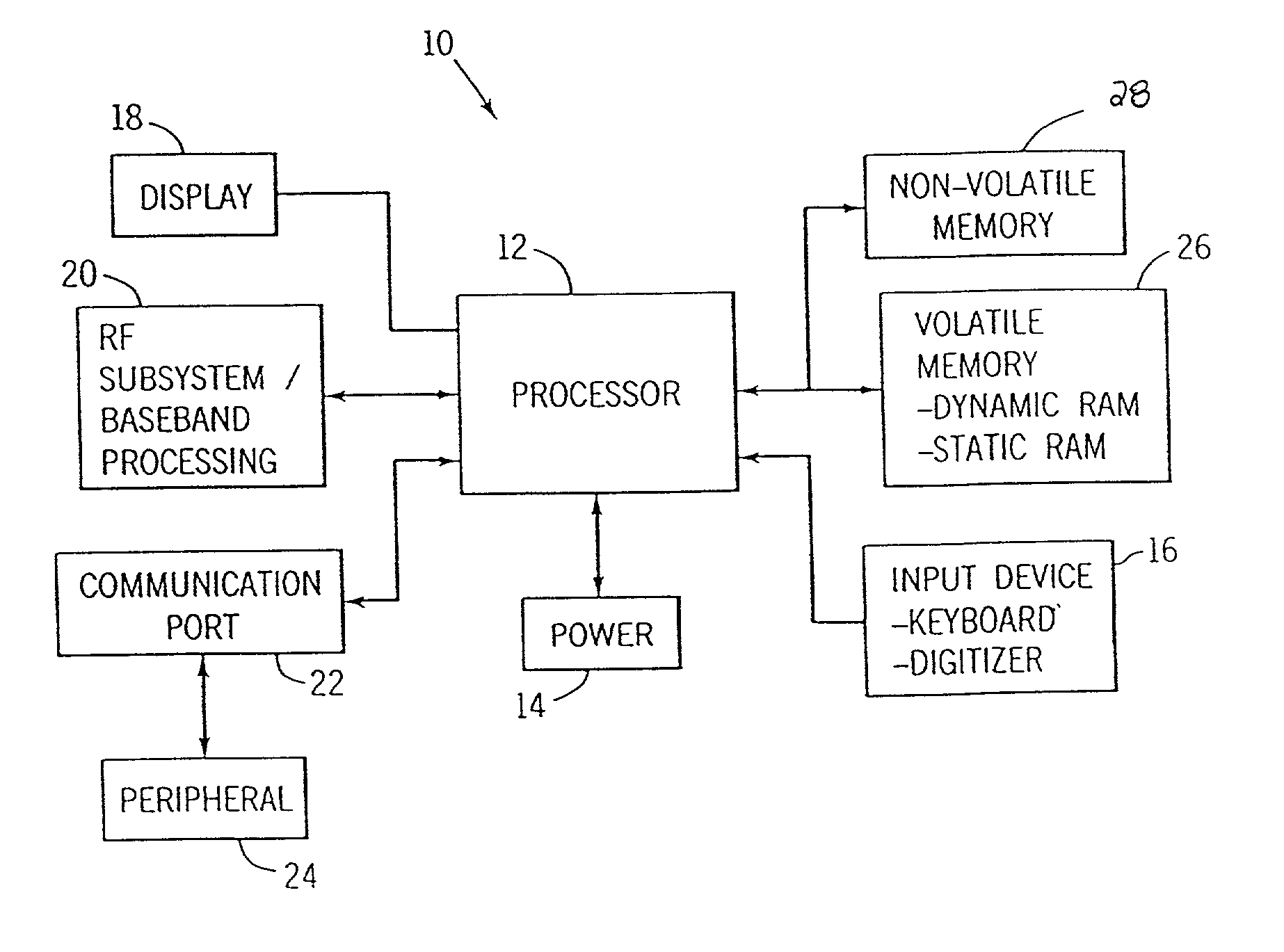

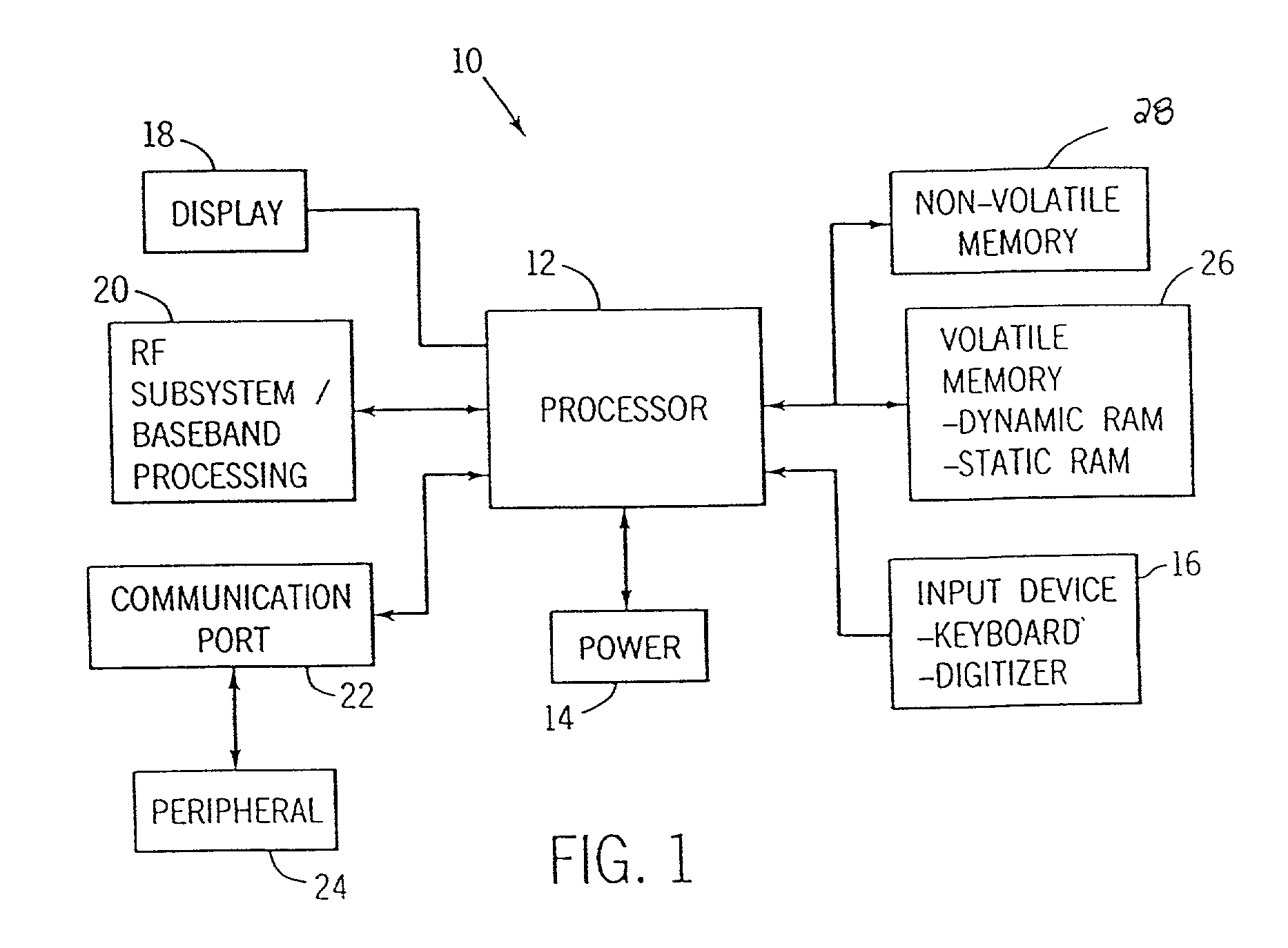

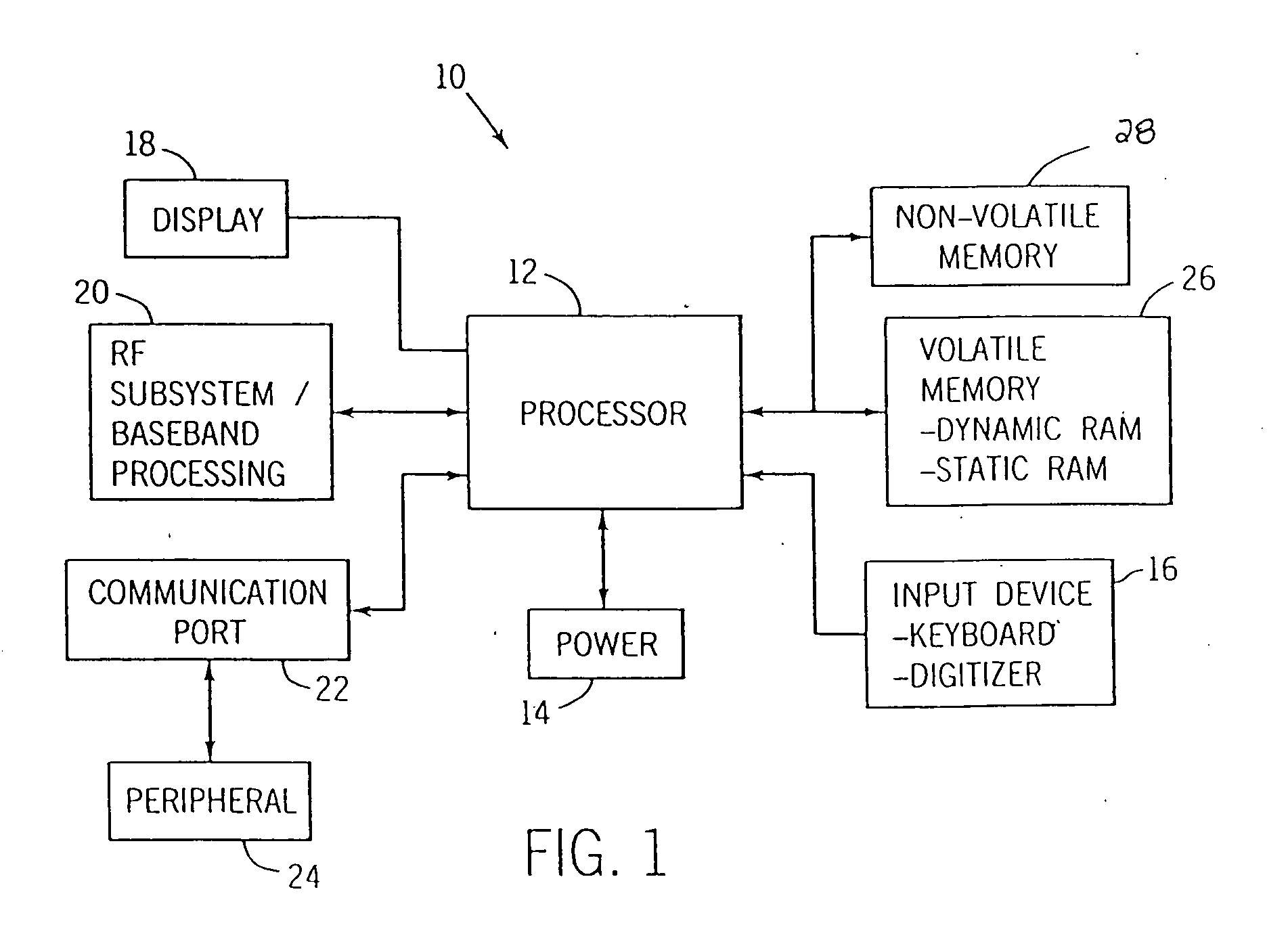

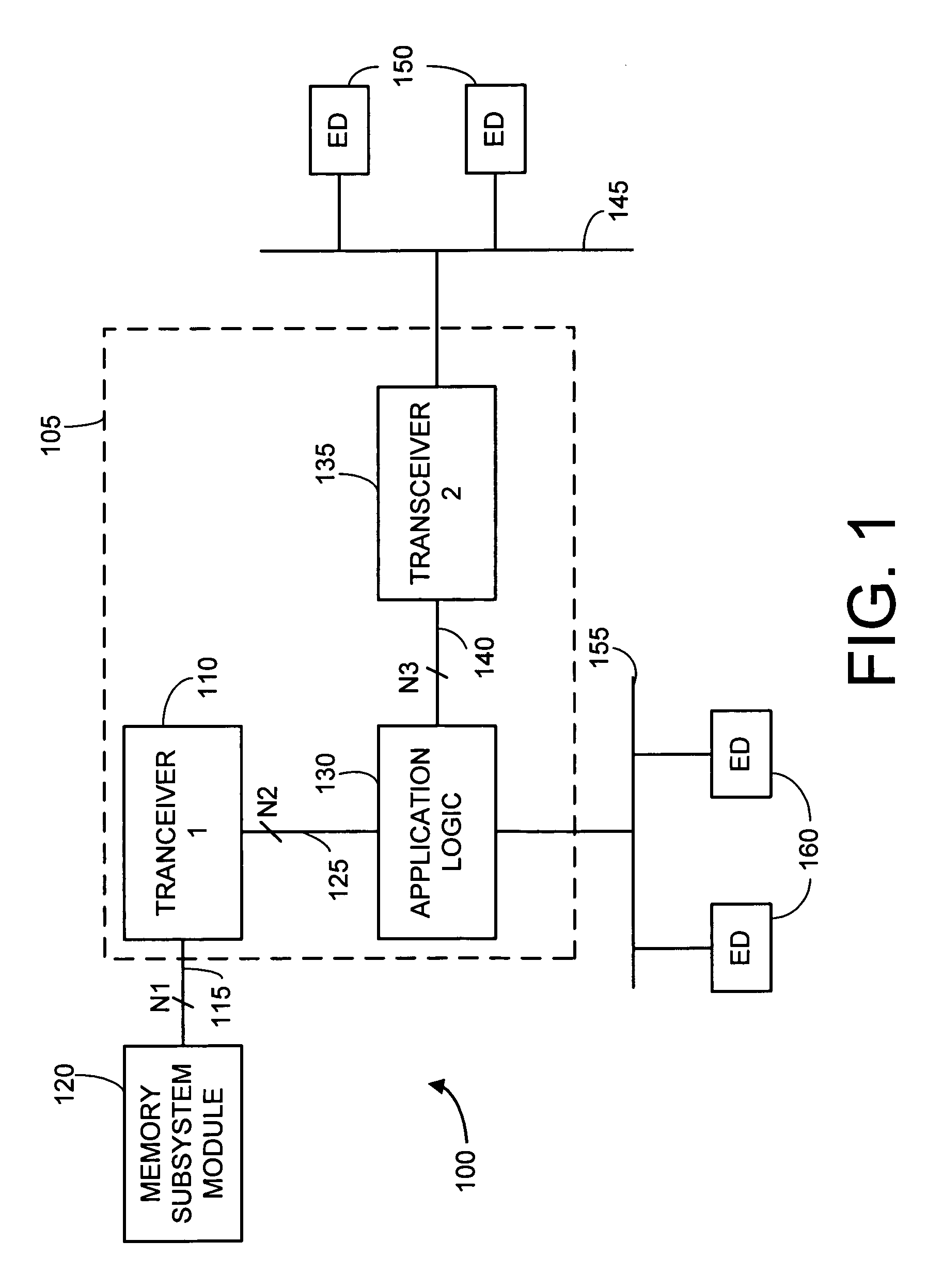

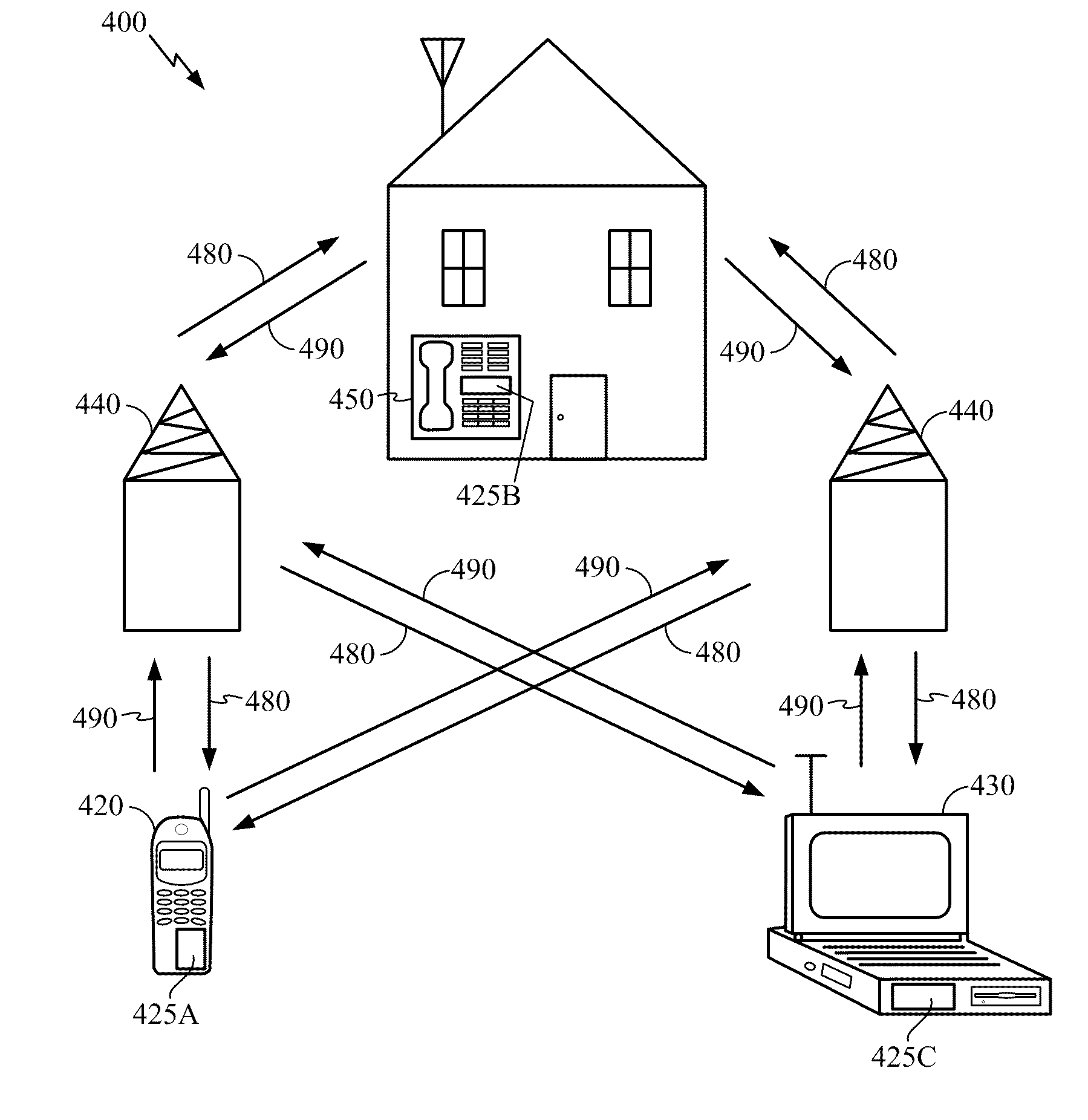

System and method of remote fax interconnect technology

ActiveUS20130287189A1Reduce overheadTelephonic communicationPictoral communicationVirtualizationTTEthernet

The present invention provides systems and methods for the virtualization, aggregation, and distributed processing of facsimile communications. The Remote FAX Interconnect known as etherFAX® is a system and method that allows for the reception and delivery of information based on cloud computing infrastructure to or from one or more facsimile systems using Internet / web based communication protocols such as HTTP(S) as the transport between a facsimile capable application or hardware and the remotely accessible etherFAX® services.

Owner:ETHERFAX

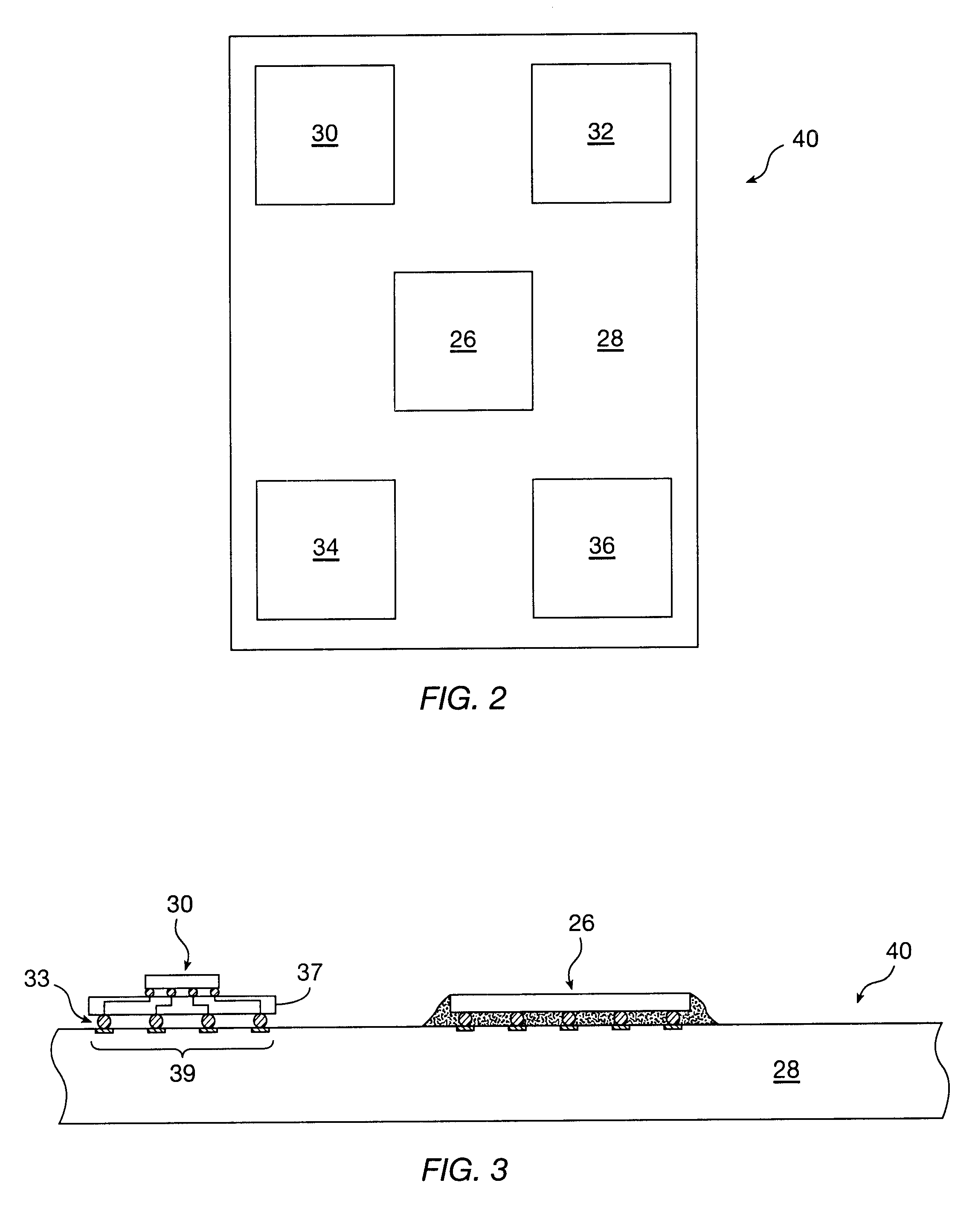

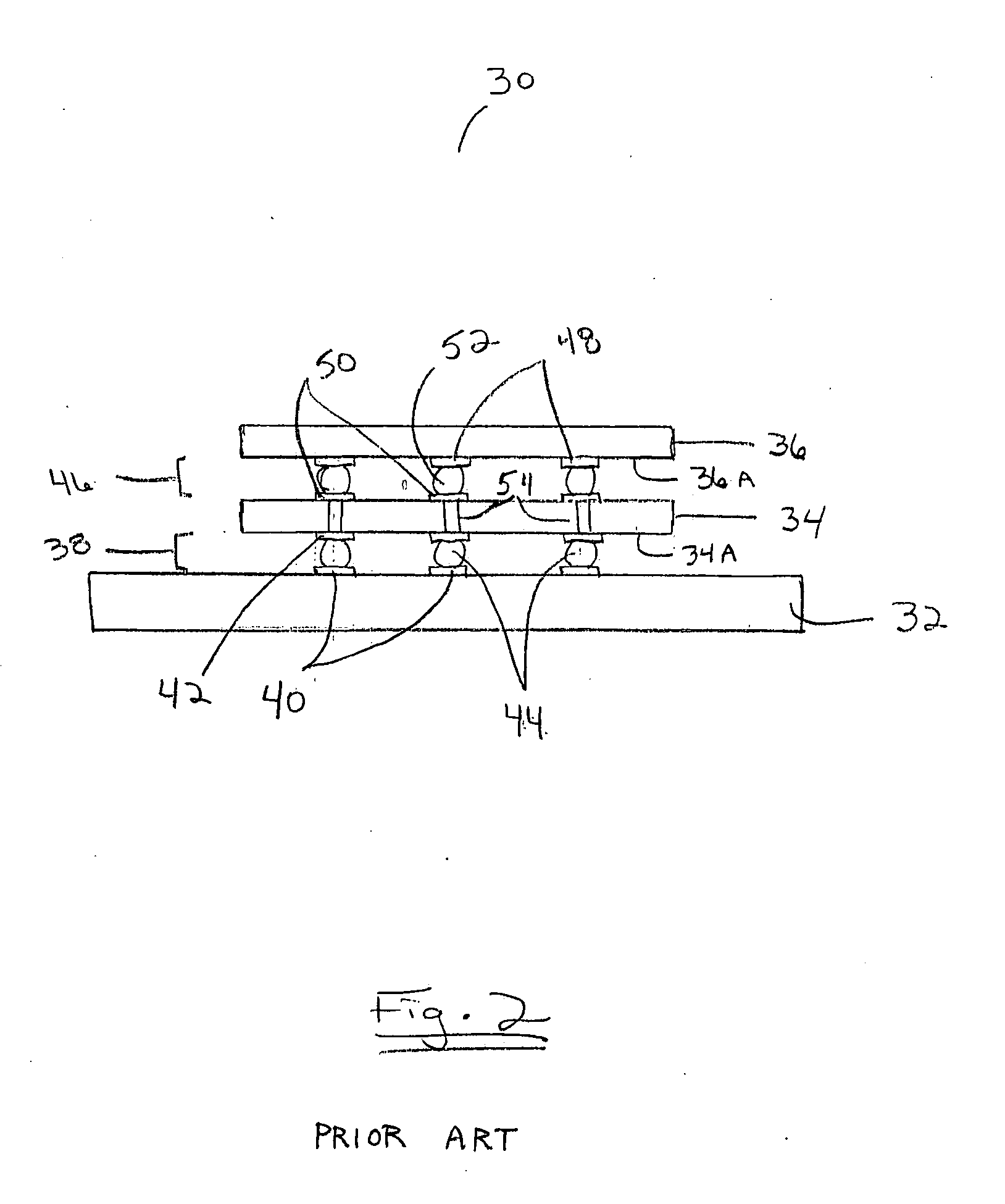

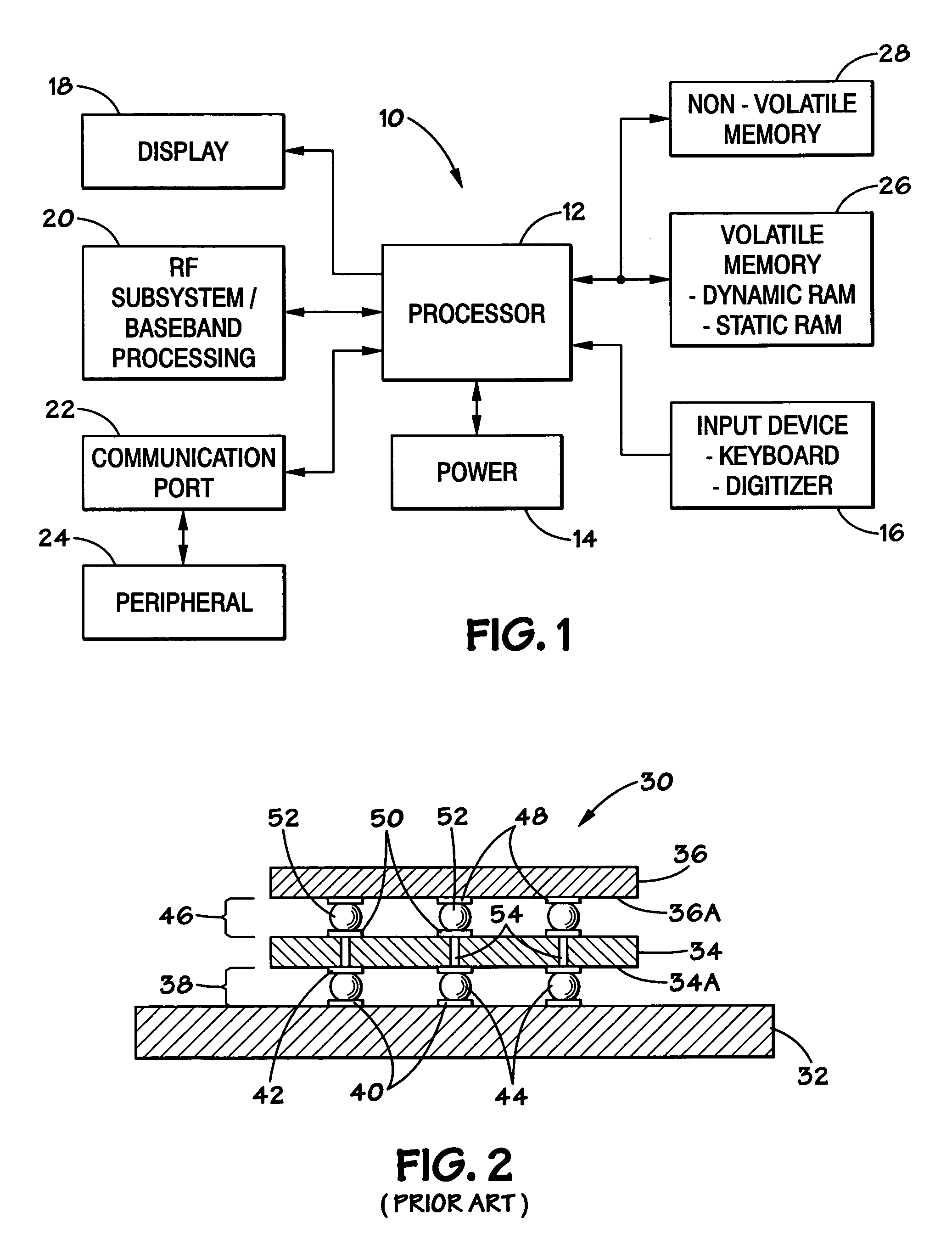

Flip chip and packaged memory module

InactiveUS6475830B1Printed circuit assemblingSemiconductor/solid-state device testing/measurementMemory chipSolder ball

A multi-chip, module (MCM) having one or more high value chips such as ASICs, CPUs, DSPs or the like attached to the MCM substrate via a direct attach technology (such as flip chip) and one or more memory chips attached to the MCM substrate via a reworkable technology such as connector and receptacle-based package, wirebond package, chip scale package (CSP), leaded package, ball grid array package, or fine pitch ball grid array package. The MCM substrate may, in turn, be attached to a motherboard via solder balls (ball grid array); leads and / or connector interconnect technologies (such as compression sockets).

Owner:CISCO TECH INC

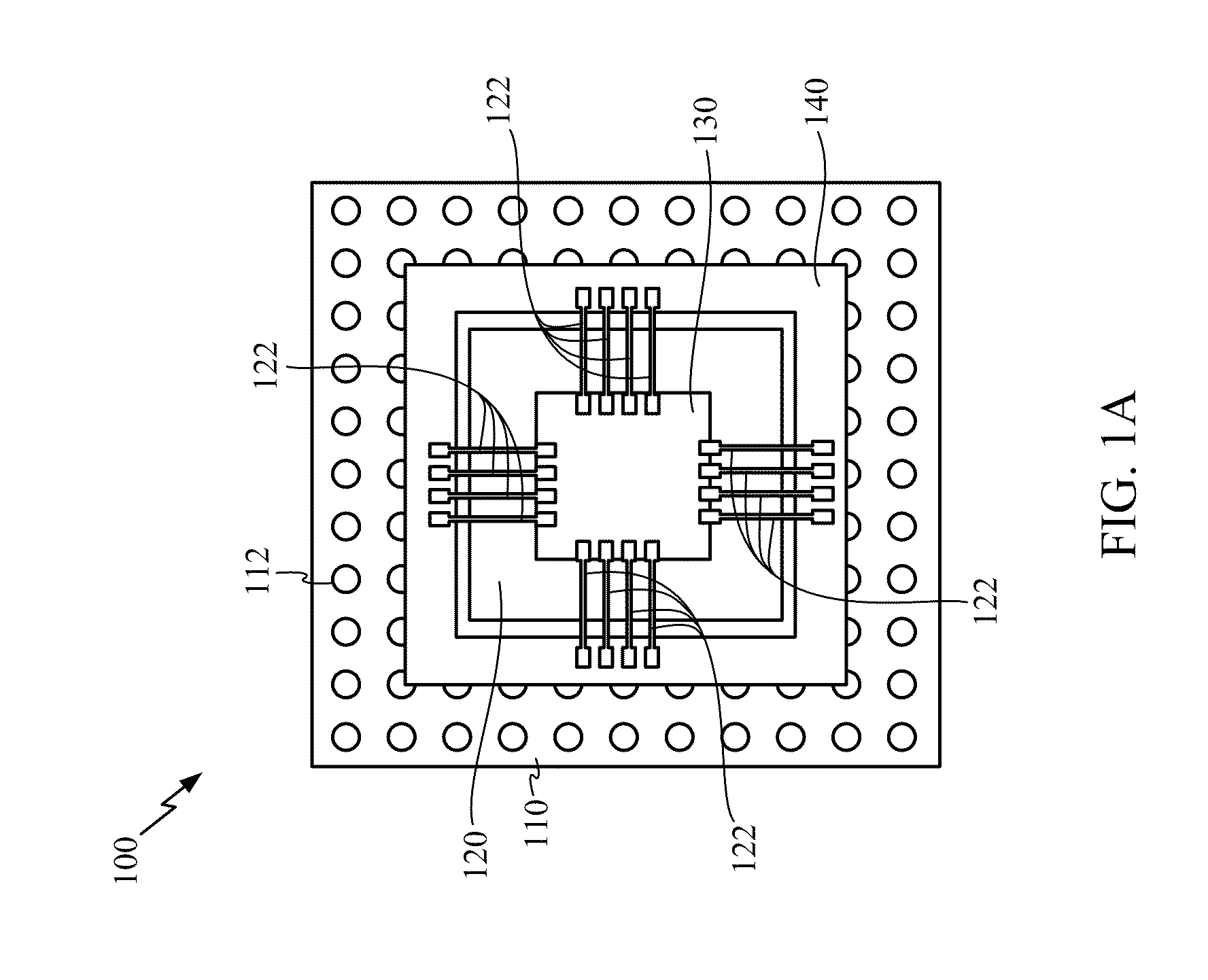

Integrated circuit package having reduced interconnects

InactiveUS20030197281A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringInterconnect technology

A technique for making an integrated circuit package. Specifically, a stacked memory device is provided with minimal interconnects. Memory die are stacked on top of each other and electrically coupled to a substrate. Thru vias are provided in the substrate and / or memory die to facilitate the electrical connects without necessitating a complex interconnect technology between each of the interfaces. Wire bonds are used to complete the circuit package.

Owner:ROUND ROCK RES LLC

Integrated circuit package having reduced interconnects

InactiveUS20060014317A1Semiconductor/solid-state device detailsSolid-state devicesMemory chipLead bonding

A technique for making an integrated circuit package. Specifically, a stacked memory device is provided with minimal interconnects. Memory die are stacked on top of each other and electrically coupled to a substrate. Thru vias are provided in the substrate and / or memory die to facilitate the electrical connects without necessitating a complex interconnect technology between each of the interfaces. Wire bonds are used to complete the circuit package.

Owner:ROUND ROCK RES LLC

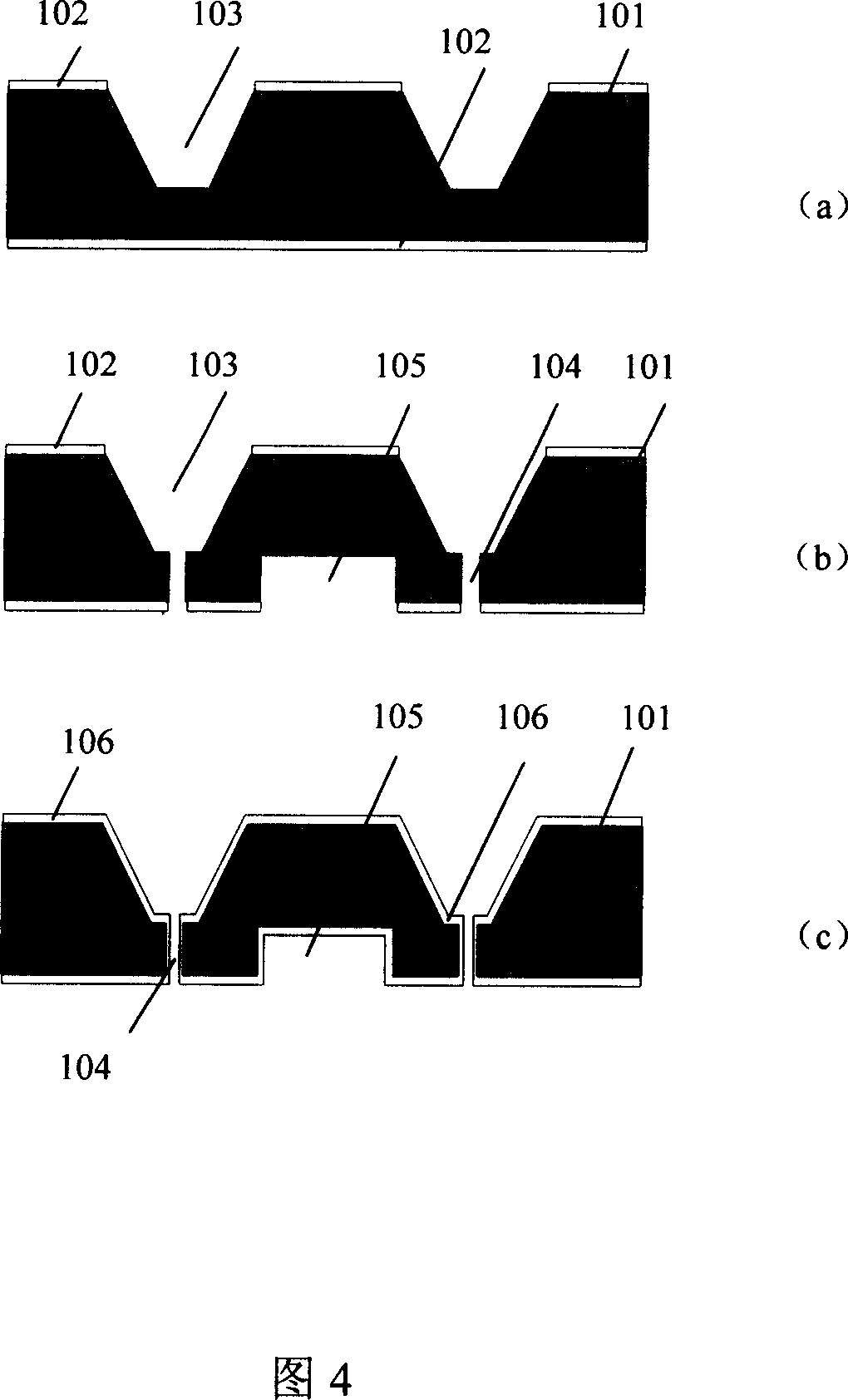

Micro electromechanical system chip size airtight packaging vertical interconnecting structure and its manufacturing method

InactiveCN1935630AImprove reliabilitySo as not to damagePrecision positioning equipmentSoldering apparatusElectricityCopper plating

The invention relates to a micro electromechanical systems (MEMS) chip size airtight package vertical-interconnection structure and the making method thereof, characterized in putting forward a novel wafer-level chip size package structure, where the chip interconnection adopts through hole vertical interconnection techniques: thin silicon wafer thorugh hole etching technique of integrating KOH corrosion and DRIE, through hole metallizing technique of copper plating from the bottom up, and thorugh interconnection technique of integrating pure Sn solder airtight bonding and bump preparation. The whole process matches with IC process and is completed on the wafer-level basis, and has higher vertical thorugh hole interconnection density. And the structure reduces package cost, increases package density, and can effectively protect MEMS devices against damage, reduce impedance, parasitic effect and noise of MEMS device connection, and improve quality of output signals of MEMS devices.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Nanoelectronic and microelectronic cleaning compositions

InactiveUS20090163396A1Improved and superior cleaningImproved and superior and stripping photoresistElectrostatic cleaningOrganic/inorganic per-compounds compounding agentsHafniumSolvent

Nanoelectronic and microelectronic cleaning compositions for cleaning nanoelectronic and microelectronic substrates under supercritical fluid state conditions, and particularly cleaning compositions useful with and having improved compatibility with nanoelectronic and microelectronic substrates characterized by silicon dioxide, sensitive low-κ or high-κ dielectrics and copper, tungsten, tantalum, nickel, gold, cobalt, palladium, platinum, chromium, ruthenium, rhodium, iridium, hafnium, titanium, molybdenum, tin and other metallization, as well as substrates of Al or Al(Cu) metallizations and advanced interconnect technologies, are provided by nanoelectronic and microelectronic cleaning compositions comprising nanoelectronic and microelectronic cleaning compositions of this invention are provided by compositions comprising: (1) a supercritical main fluid reaching a supercritical fluid state at a temperature of 250° C. or less and a pressure of 600 bars or less (592.2 atm, 8702.3 psi), and (2) as a secondary fluid, a modifier formulation selected from the following formulations: a) a formulation comprising: an oxidizing agent; a polar organic solvent selected from the group consisting of amides, sulfones, sulfolenes, selenones and saturated alcohols; and optionally other components; b) a silicate free formulation comprising: a polar organic solvent selected from the group consisting of amides, sulfones, selenones and saturated alcohols; a strong alkaline base; and optionally other components; c) a formulation comprising: from about 0.05% to 30% by weight of one or more non-ammonium producing strong base containing non-nucleophilic, positively charged counter ions; from about 0.5 to about 99.95% by weight of one or more corrosion inhibiting solvent compounds, said corrosion inhibiting solvent compound having at least two sites capable of complexing with metals; and optionally other components; d) a formulation comprising: from about 0.05 to 20% by weight of one or more non-ammonium producing, non-HF producing fluoride salt; from about 5 to about 99.95% by weight of water, organic solvent or both water and organic solvent; and optionally other components; and e) a formulation comprising: from about 0.05% to 30% by weight of one or more non-ammonium producing strong base containing non-nucleophilic, positively charged counter ions; from about 5 to about 99.95% by weight of one or more steric hindered amide solvents; and optionally other components.

Owner:AVANTOR PERFORMANCE MATERIALS LLC

Microelectronic cleaning composition containing halogen oxygen acids, salts and derivatives thereof

ActiveUS7521406B2Improve compatibilityImprove abilitiesSurface-active detergent compositionsDetergent mixture composition preparationIridiumHafnium

Microelectronic cleaning compositions for cleaning microelectronic substrates, and particularly cleaning compositions useful with and having improved compatibility with microelectronic substrates characterized by silicon dioxide, sensitive low-κ or high-κ dielectrics and copper, tungsten, tantalum, nickel, gold, cobalt, palladium, platinum, chromium, ruthenium, rhodium, iridium, hafnium, titanium, molybdenum, tin and other metallization, as well as substrates of Al or Al(Cu) metallizations and advanced interconnect technologies, are provided by microelectronic cleaning compositions comprising halogen acids, salts and derivatives thereof.

Owner:AVANTOR PERFORMANCE MATERIALS LLC

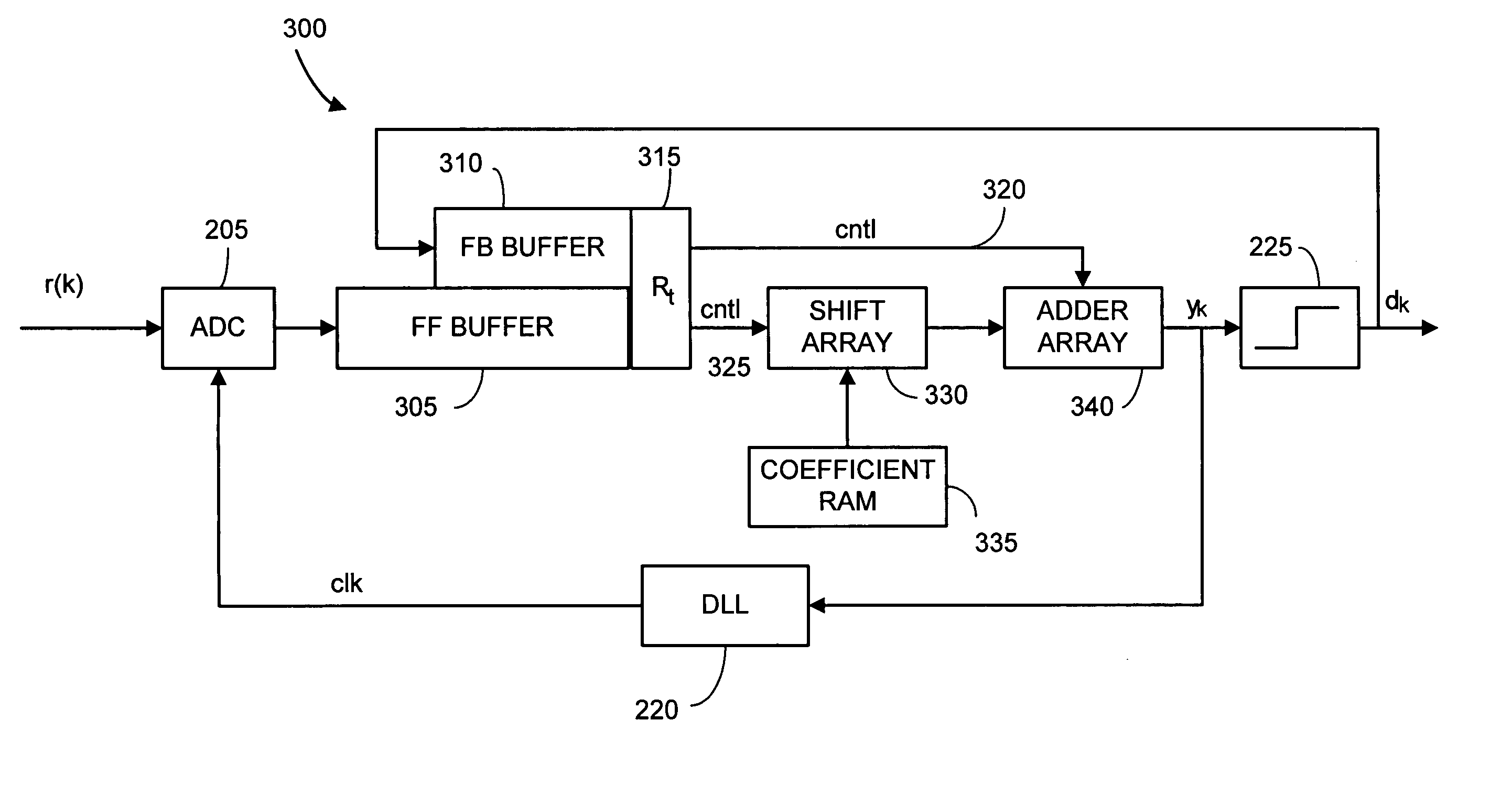

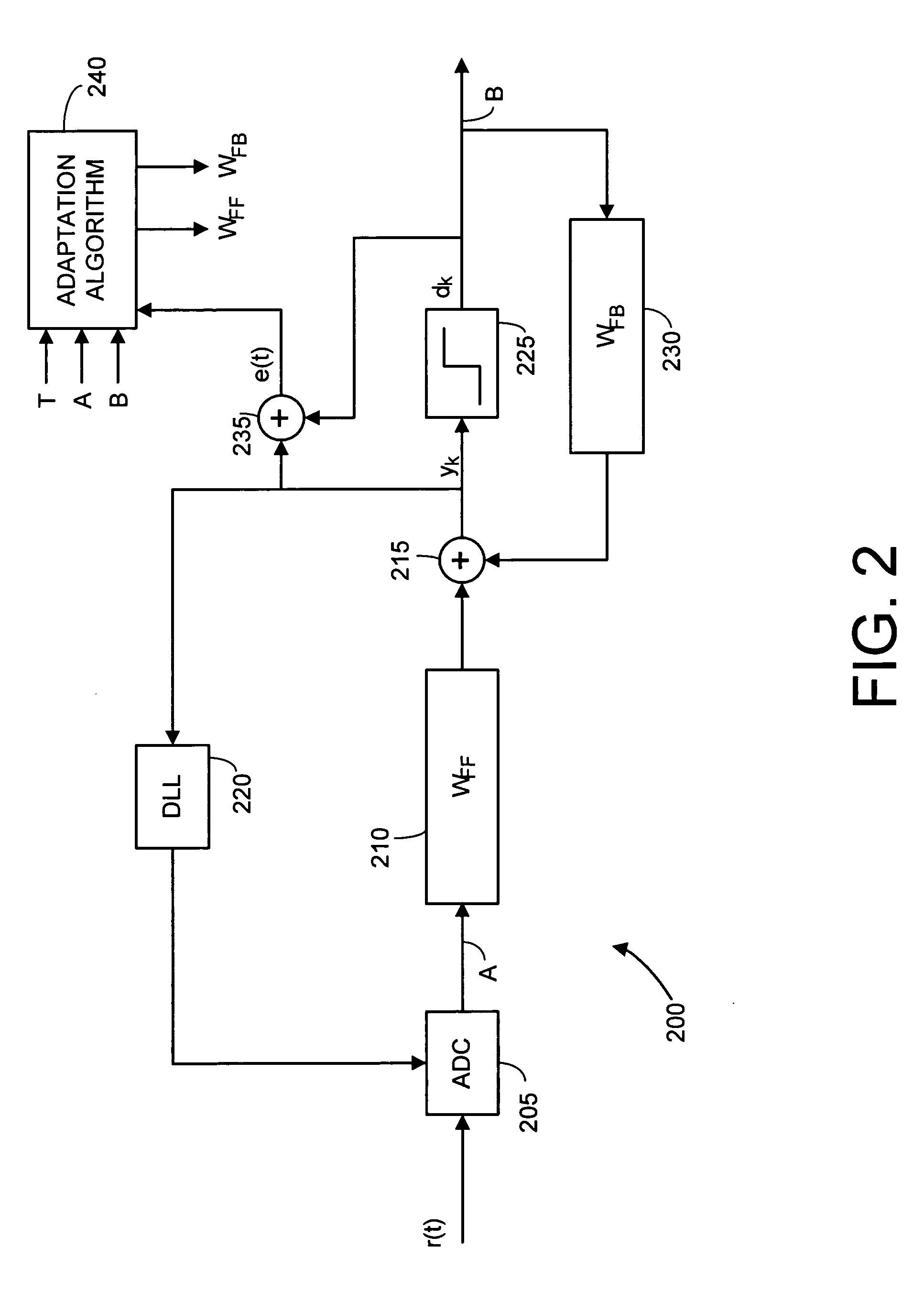

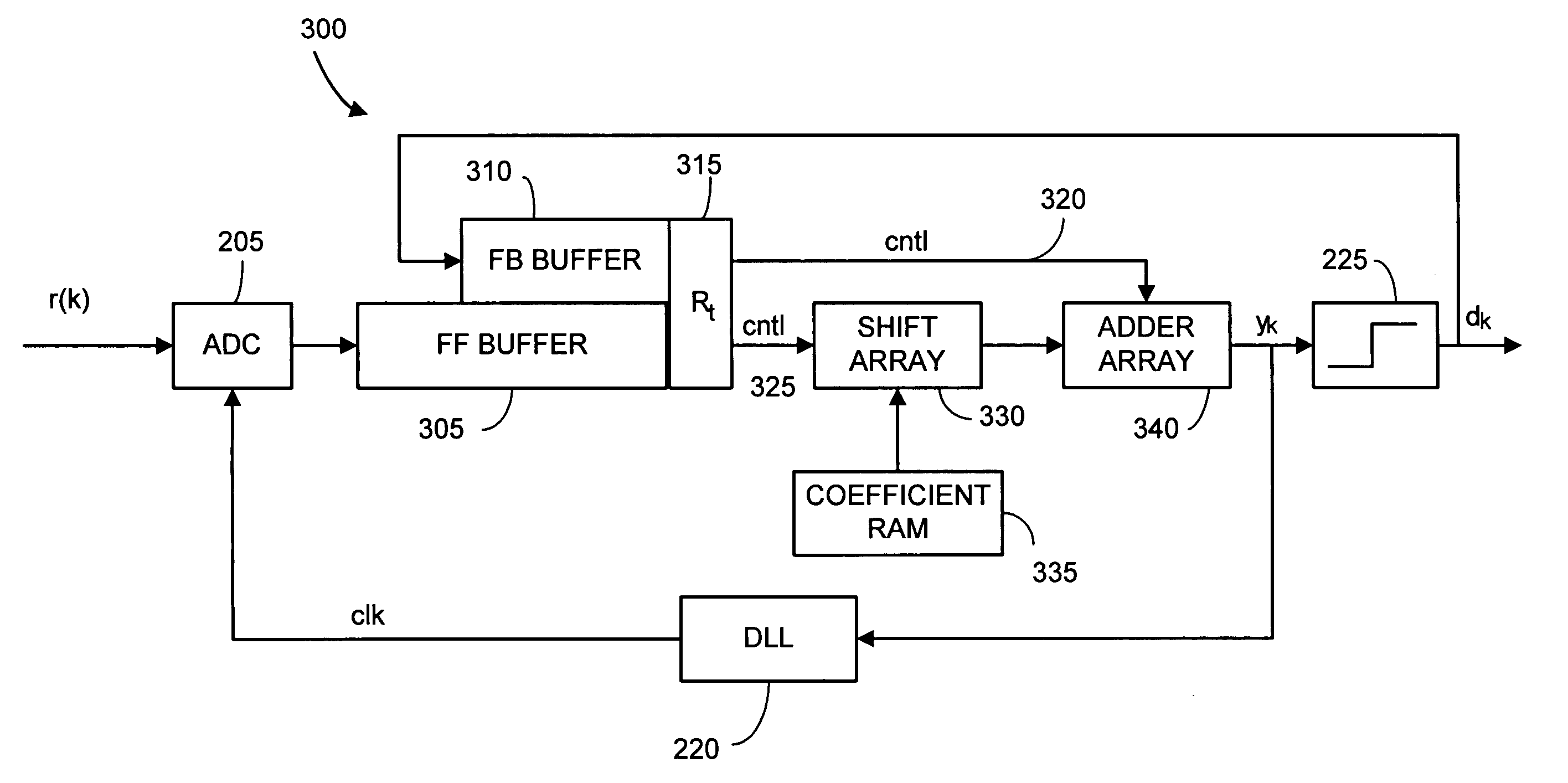

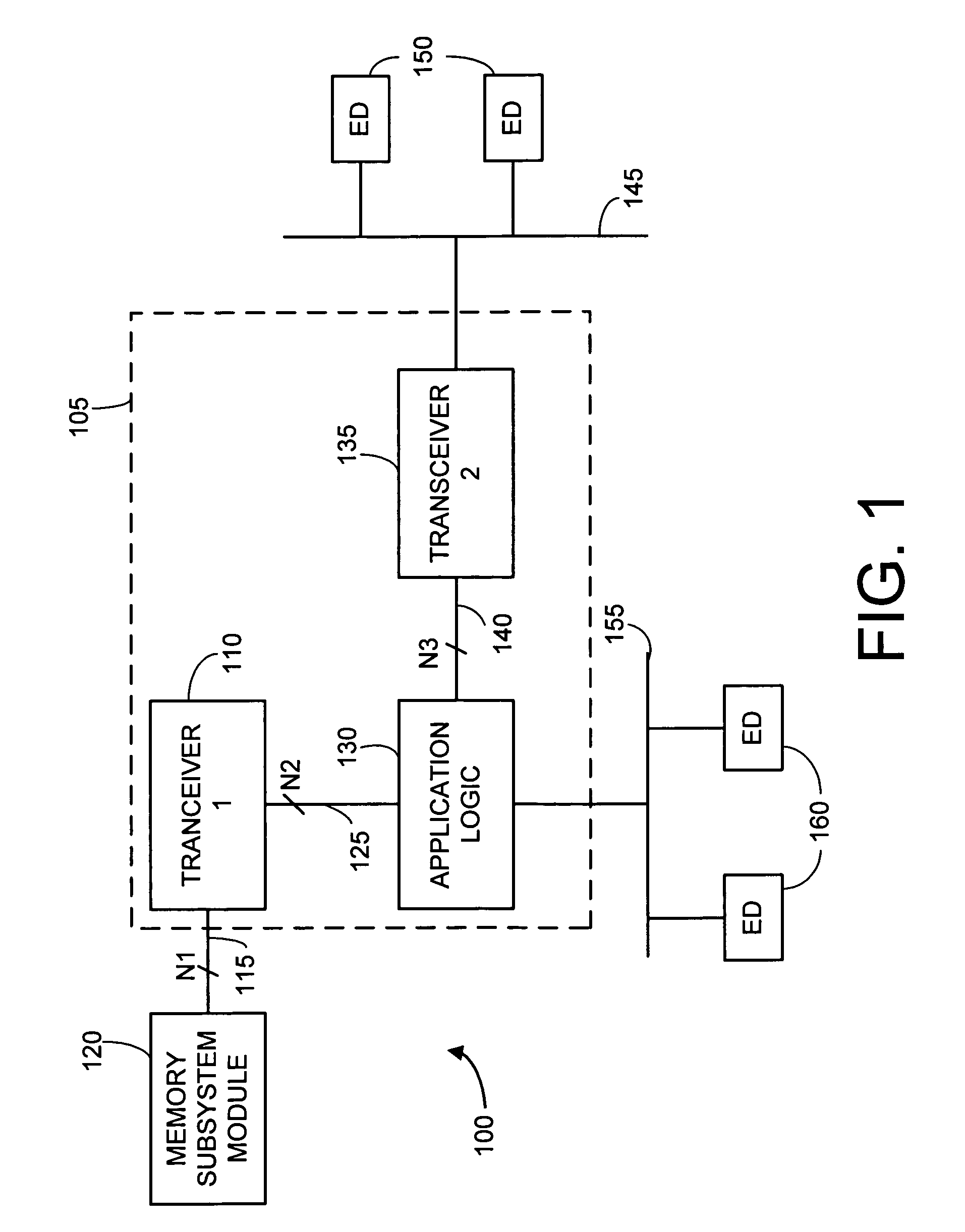

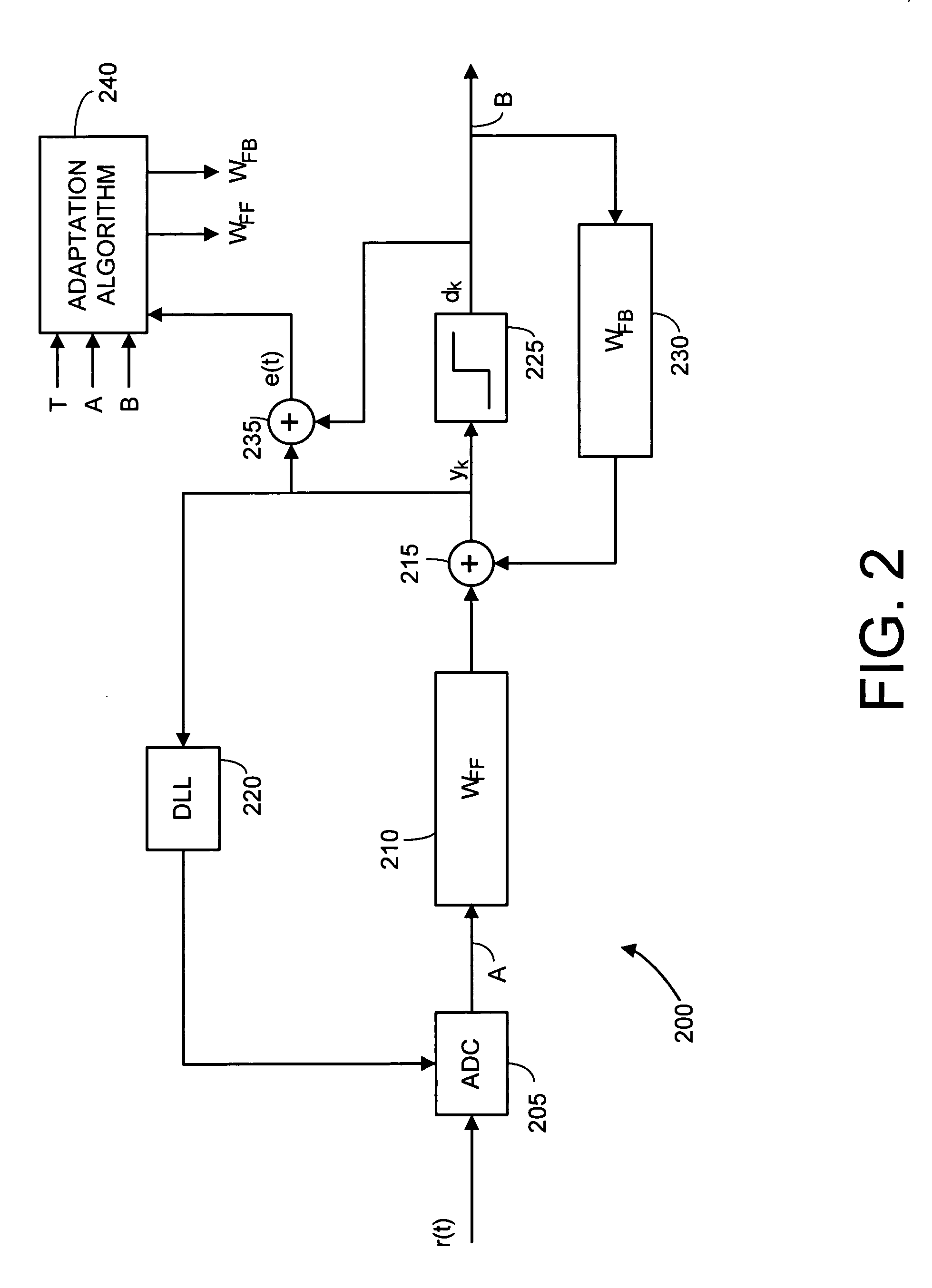

High-speed adaptive interconnect architecture with nonlinear error functions

InactiveUS20050220185A1Low costIncrease speedMultiple-port networksDelay line applicationsData rateError function

A low cost and high speed equalizing receiver structure is provided for improved inter-chip and inter-module communications. The receiver is able to recover data from a corrupted waveform from a signal wire such as one found on data, address or control wires in a microsystem architecture. The receiver can be used with binary as well as mary pulse amplitude modulation schemes. The receiver can be used to increase the sustainable data rate between chips or can be used to sustain a given data rate over a poorer quality channel as compared to prior art interconnect technologies. Methods for training and operating the receiver structure are provided. A novel structure called the decision feedback equalizer and cross talk canceller (DFE-CTC) is introduced and methods to compute the coefficients to minimize error in terms of the l2 norm, the l∞ norm, and statistical probability of error functions are also disclosed.

Owner:RPX CORP

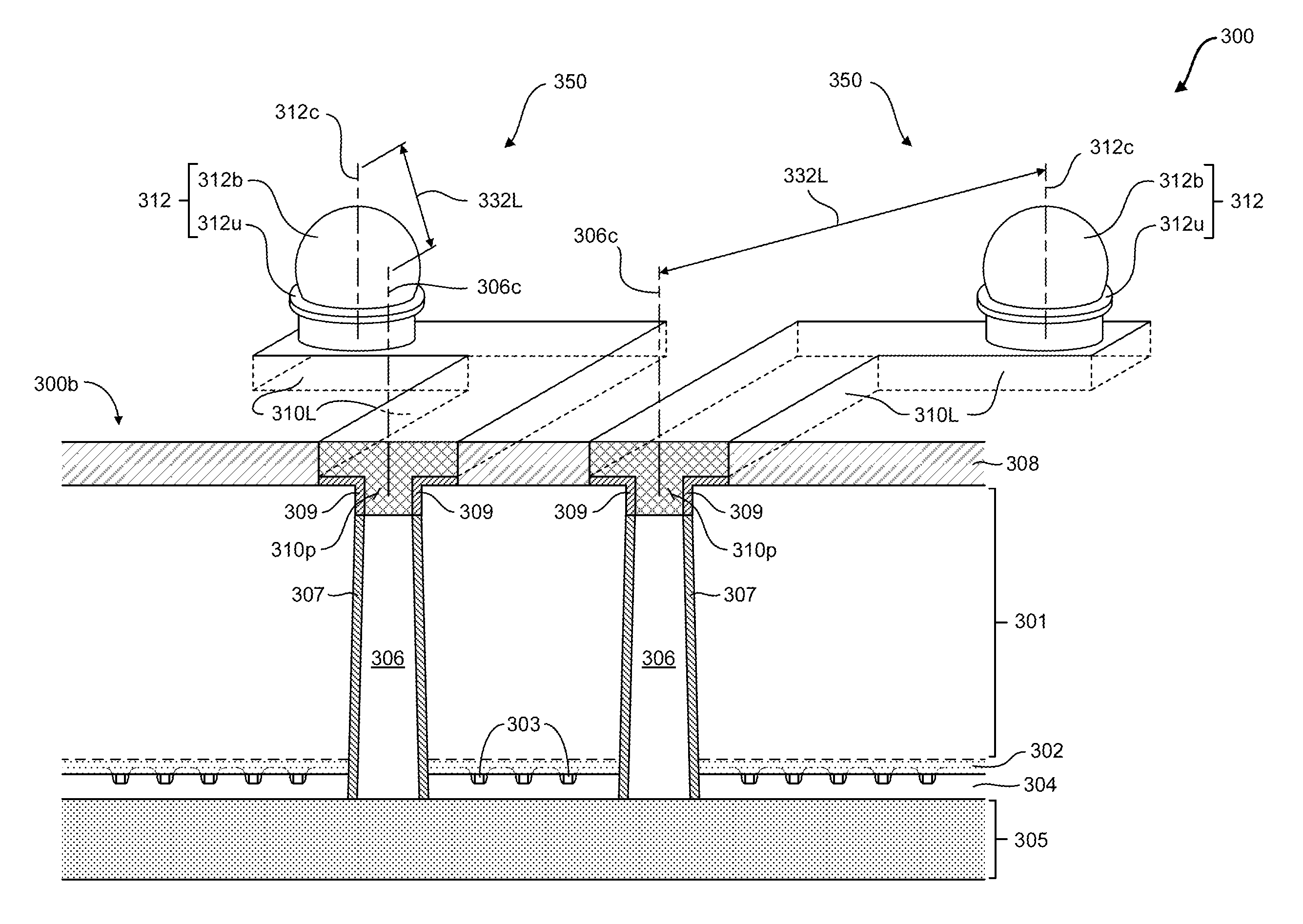

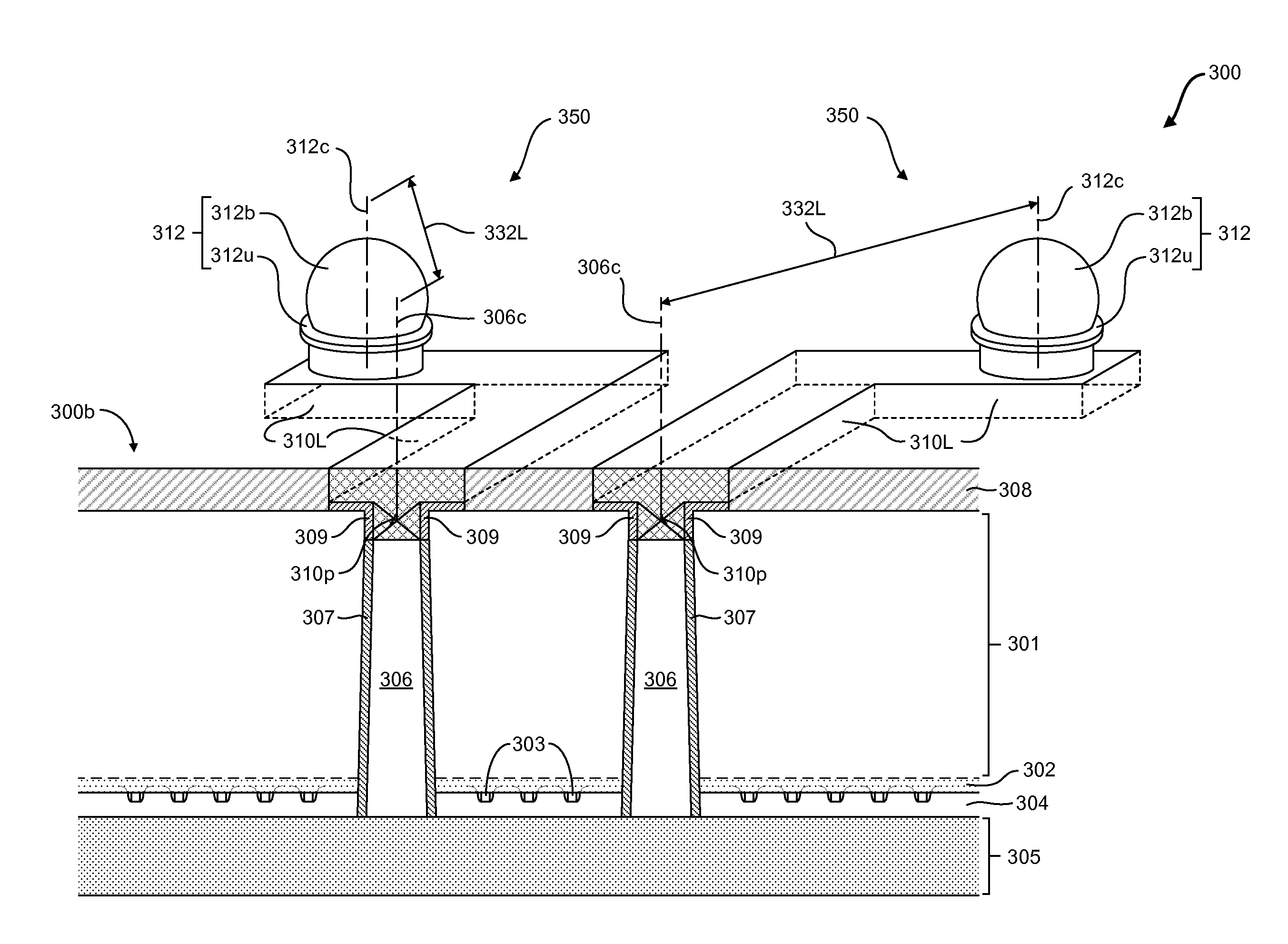

TSV backside processing using copper damascene interconnect technology

ActiveUS8466062B2Semiconductor/solid-state device detailsSolid-state devicesSubject matterSemiconductor chip

Generally, the subject matter disclosed herein relates to interconnect structures used for making electrical connections between semiconductor chips in a stacked or 3D chip configuration, and methods for forming the same. One illustrative method disclosed herein includes forming a conductive via element in a semiconductor substrate, wherein the conductive via element is formed from a front side of the semiconductor substrate so as to initially extend a partial distance through the semiconductor substrate. The illustrative method also includes forming a via opening in a back side of the semiconductor substrate to expose a surface of the conductive via element, and filling the via opening with a layer of conductive contact material.

Owner:GLOBALFOUNDRIES SINGAPORE PTE LTD

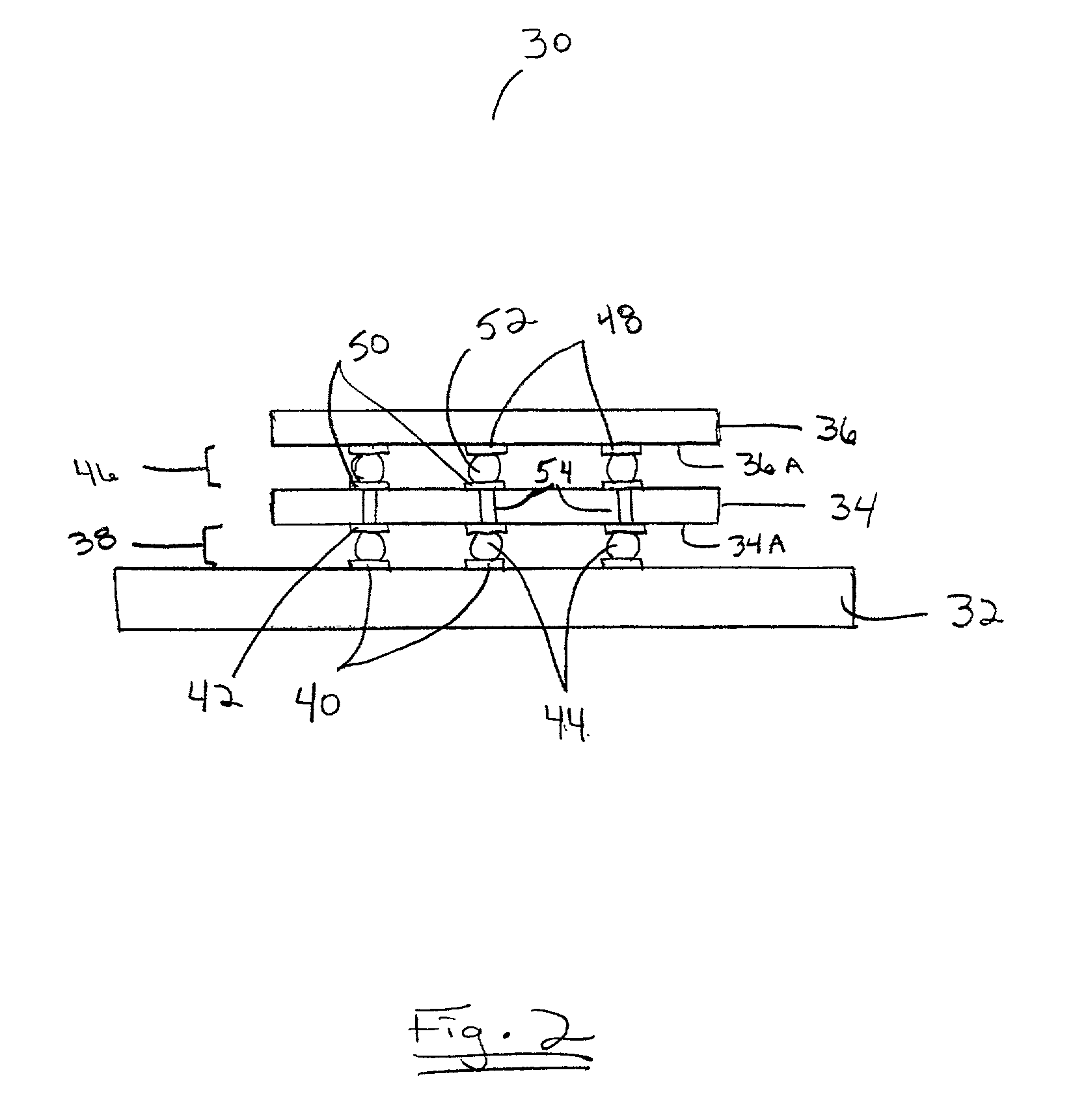

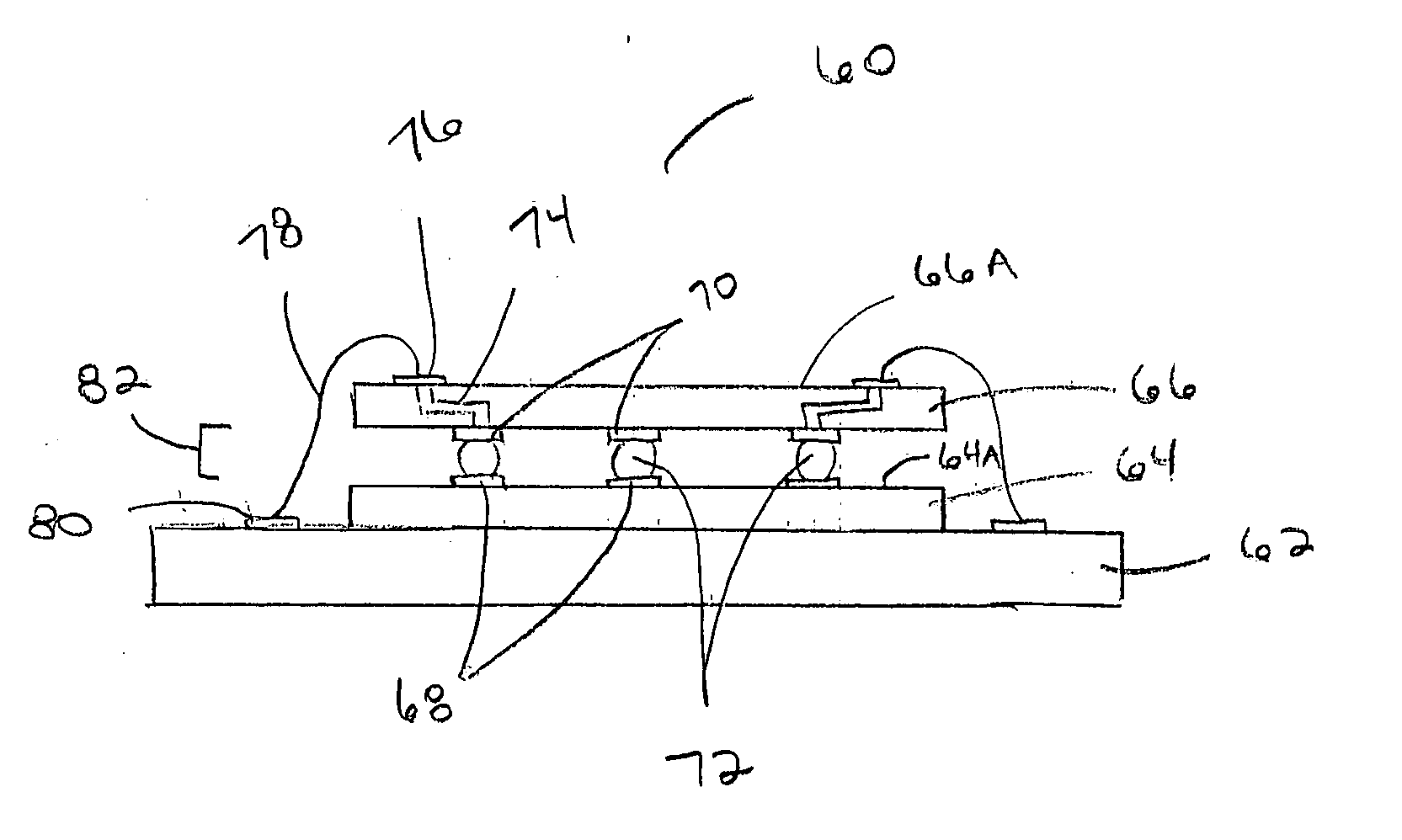

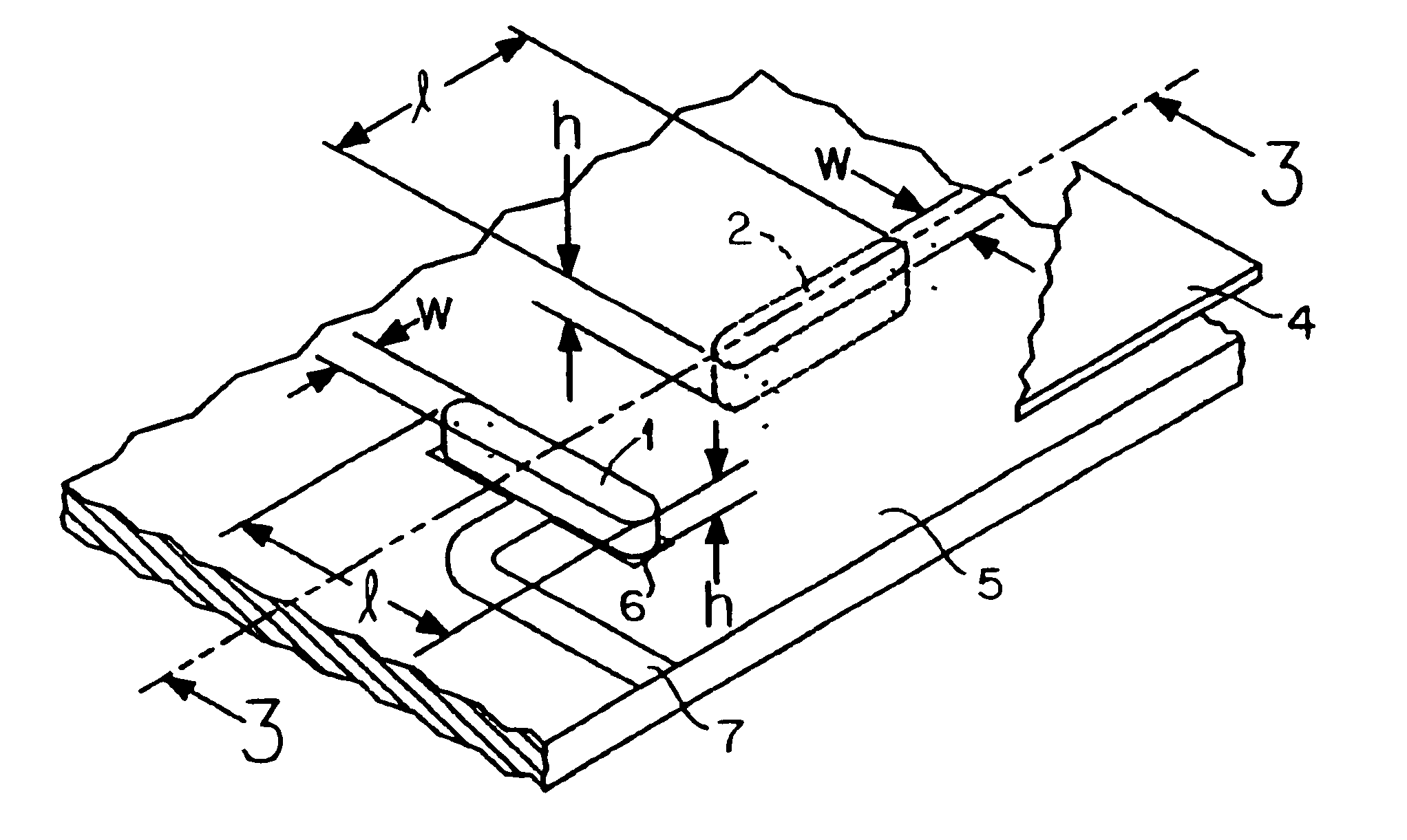

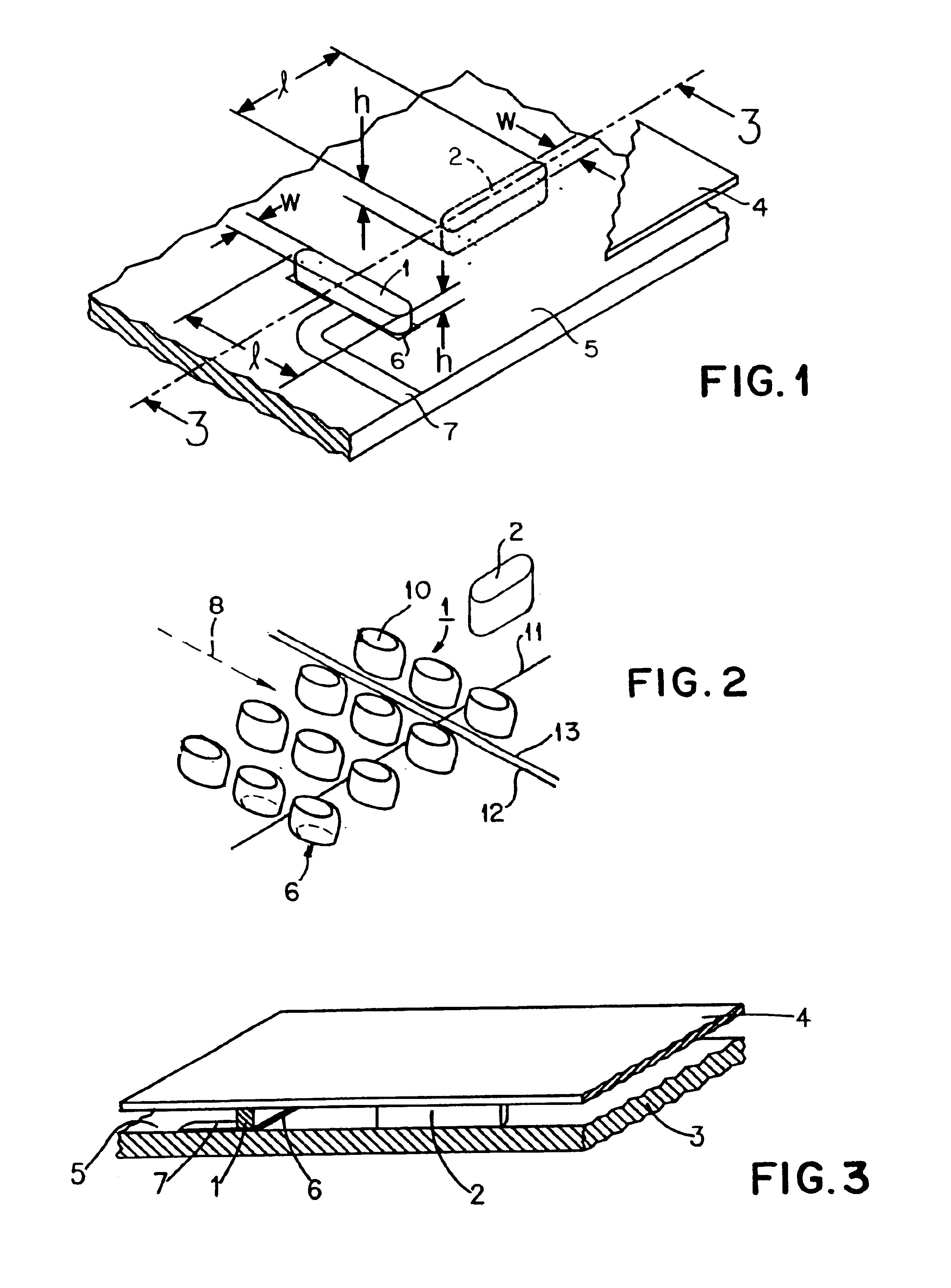

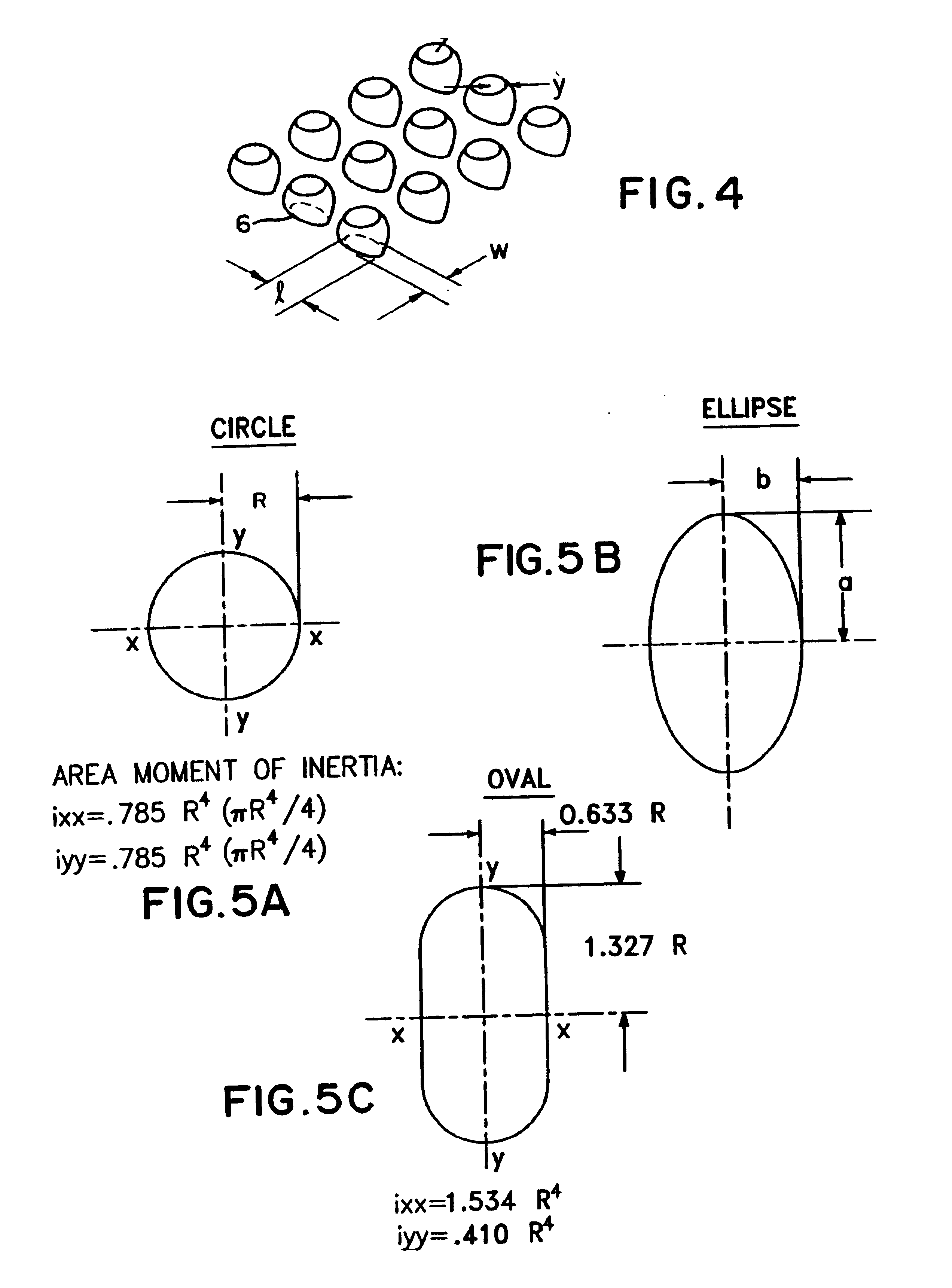

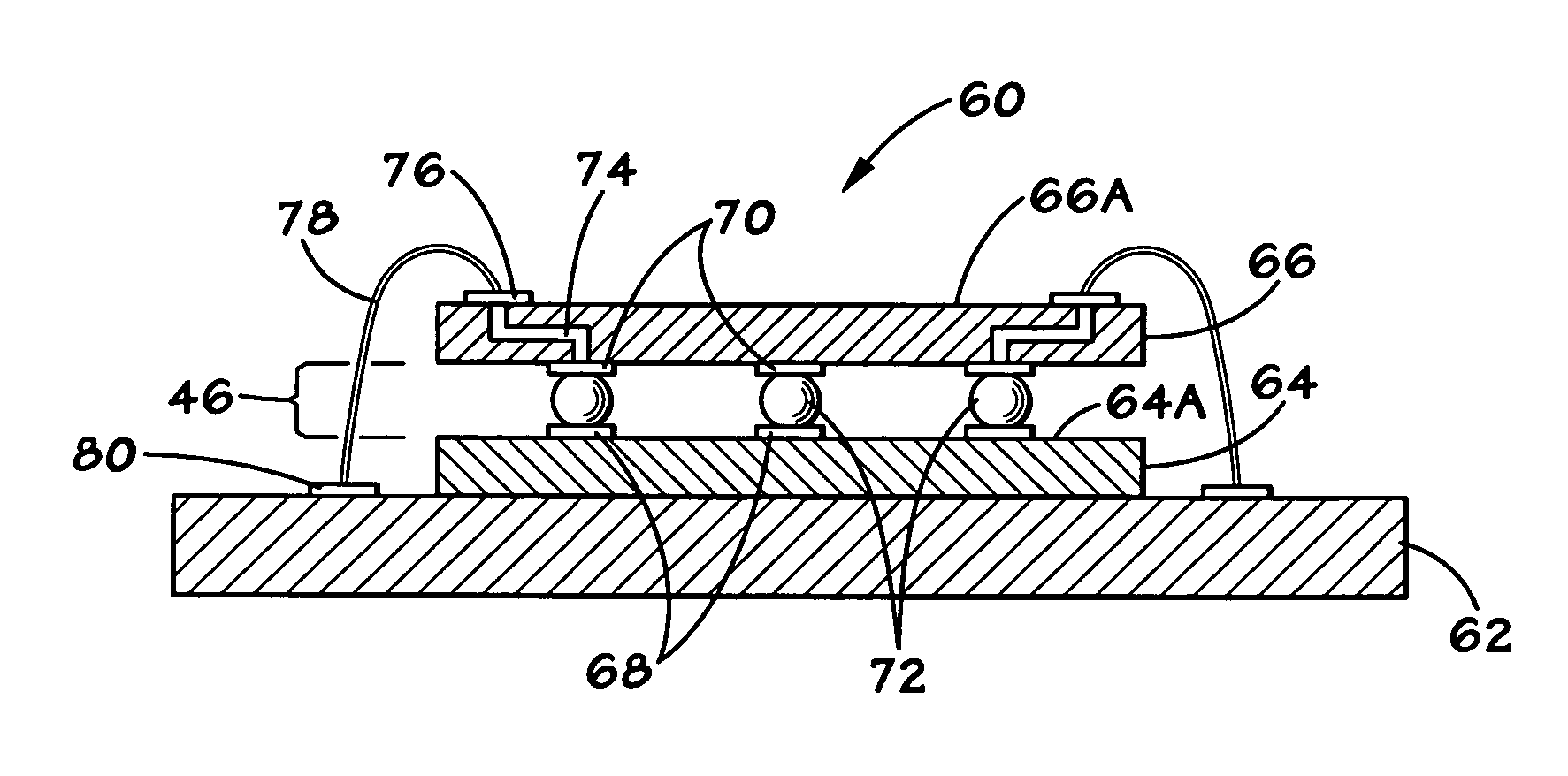

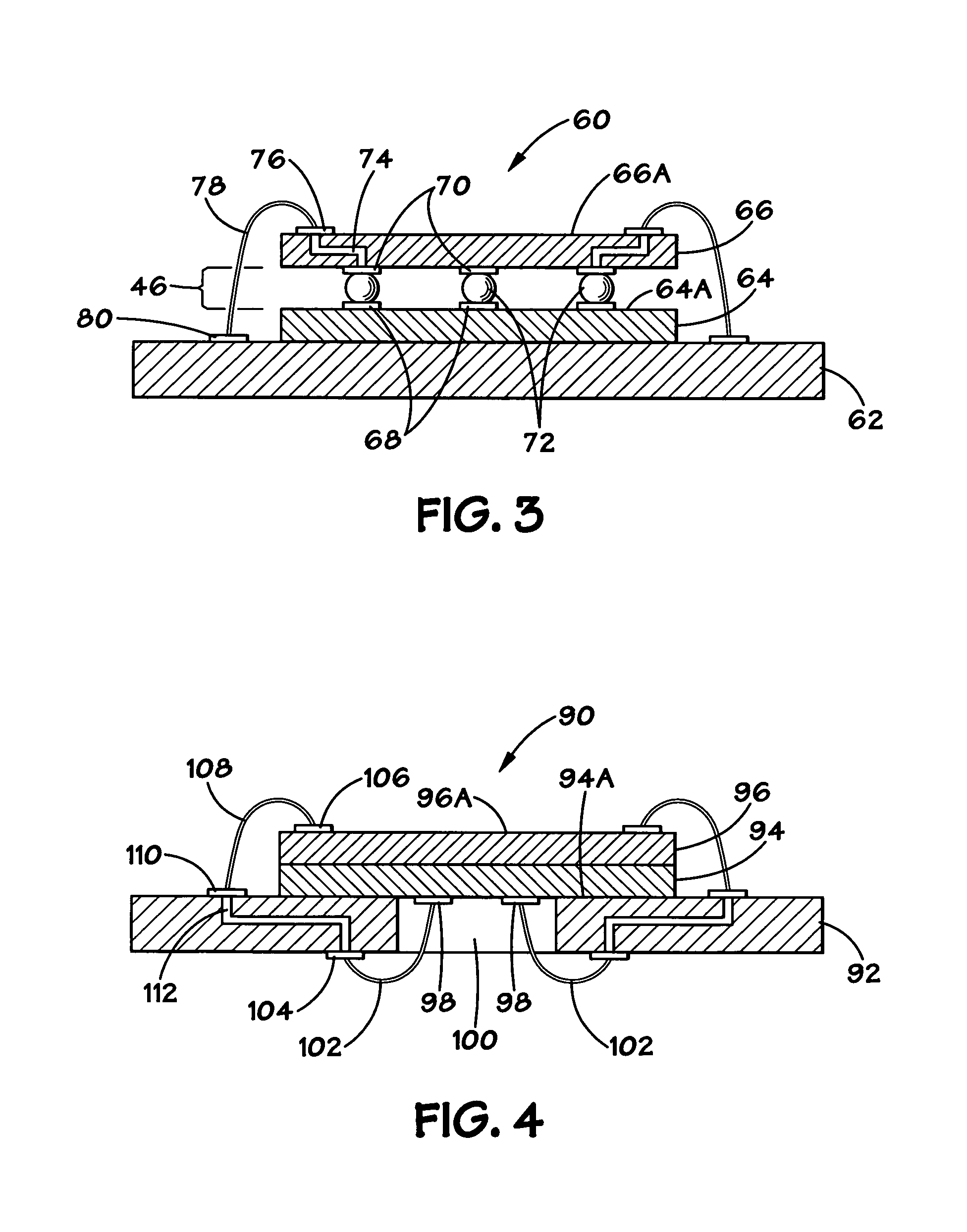

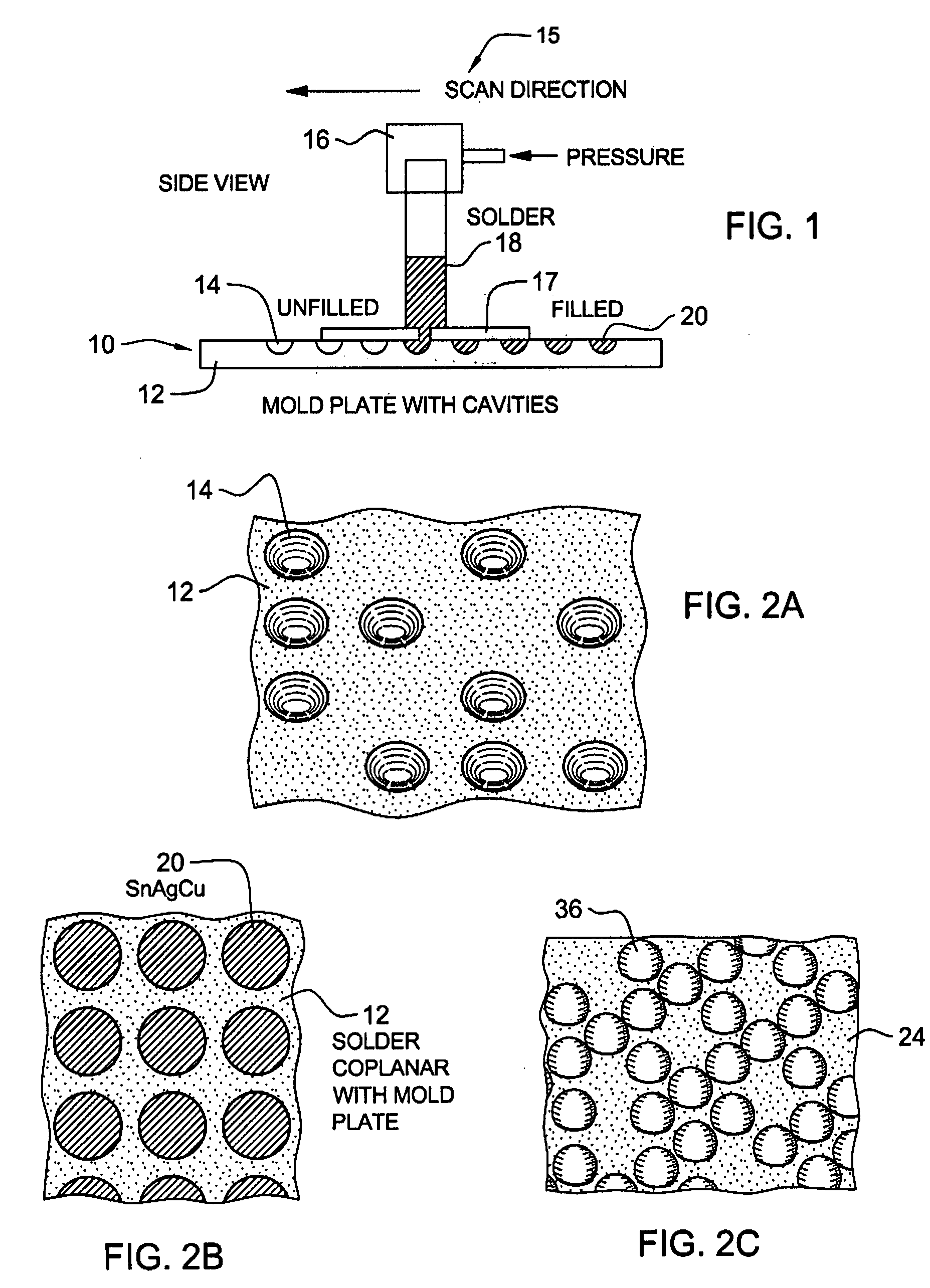

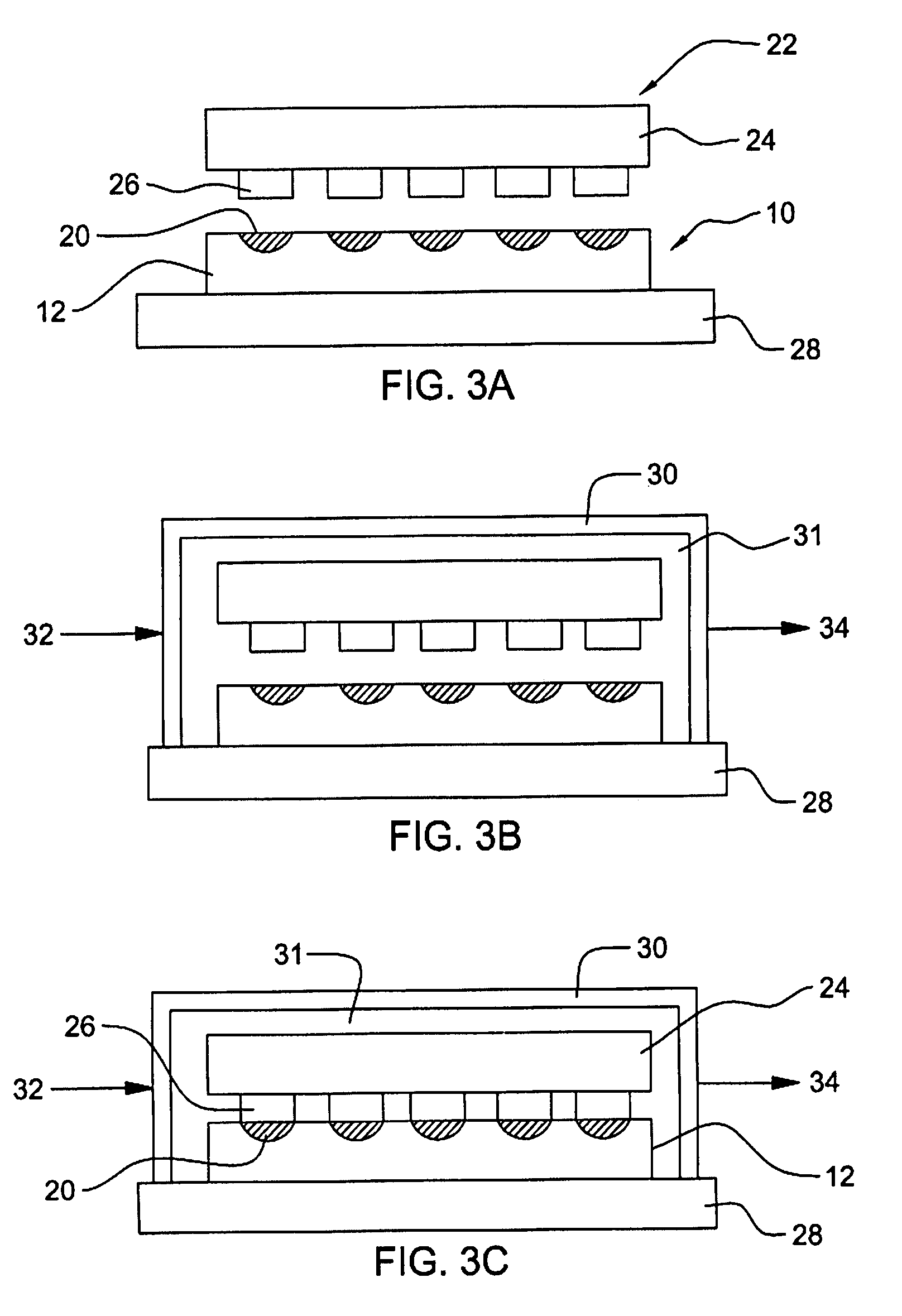

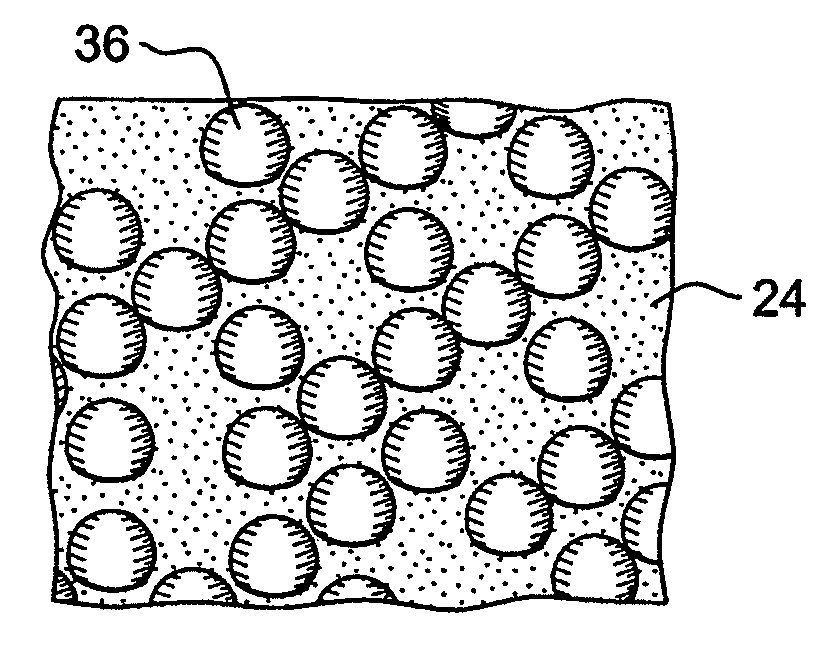

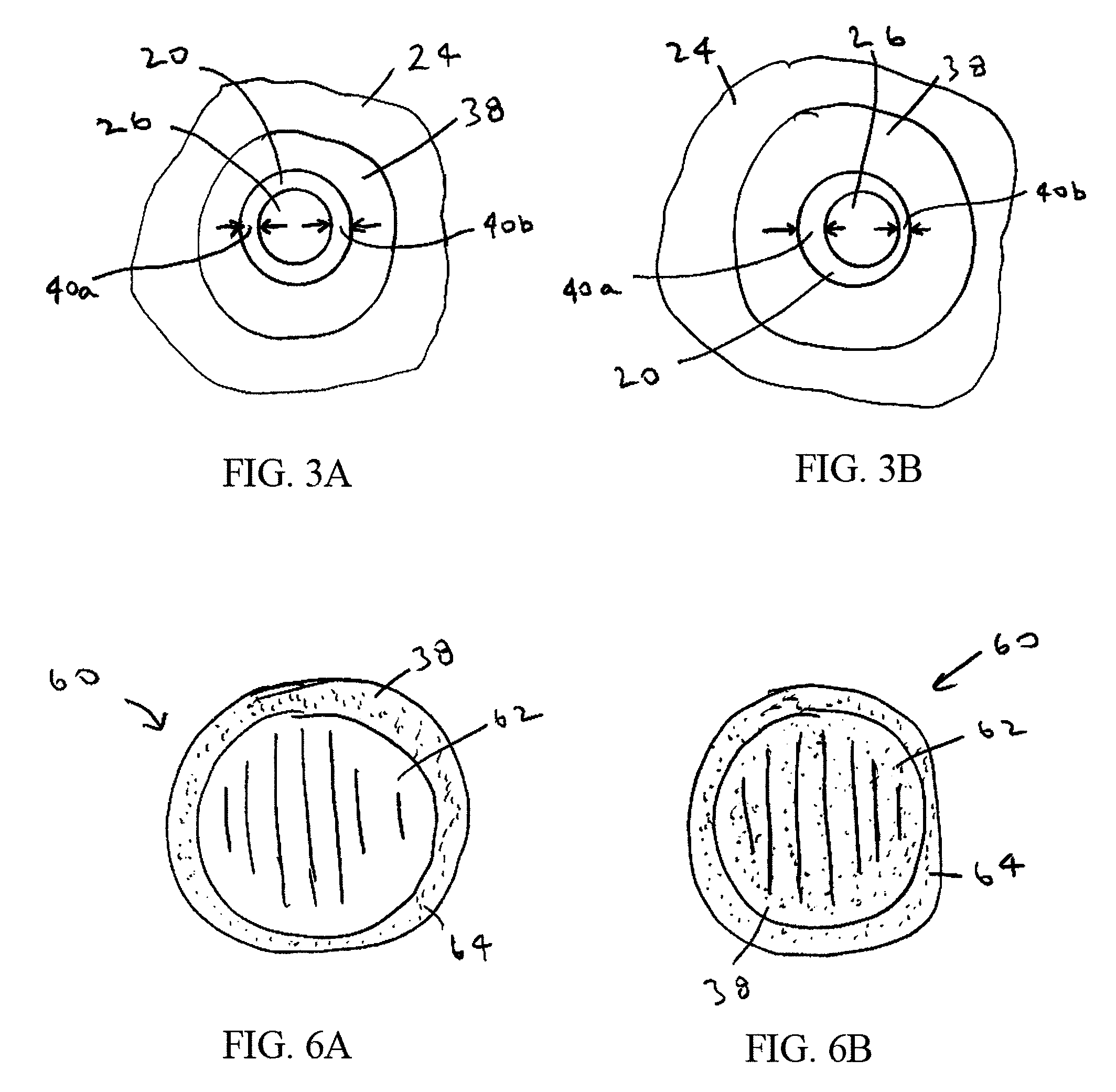

Stress accommodation in electronic device interconnect technology for millimeter contact locations

InactiveUS6919515B2Increase the number ofImprove resistance to stress damagePrinted circuit assemblingFinal product manufactureSurface mountingSlurry

The providing of an array interface of conductive joint members for use in forming interconnections between mating surfaces such as a pad on a surface mount electronic device and contacts on a circuit card where one portion of the conductive joint members are of a relatively elongated or oval outline and are oriented with the longer dimension in one direction to accommodate wiring spacing and another portion oriented in a different direction for accommodating expansion stress. In manufacturing when the relatively elongated shape is oriented with the longer dimension along the wiping motion direction in a screen type forming of the conductive joint members the slurry of material that is to be the conductive joint members fills the openings in the screen more reliably and the areas of the conductive members are more uniform. The invention provides the advantages of an increase in the number of wiring lines, an increase in uniformity of wiped screen deposition conductive joint member formation, ability to employ more than one out of chip and wiring levels in expansion mismatch stress relief, and ability by conductive joint member dimensional alignment to improve reliability and flexibility.

Owner:INVENSAS CORP

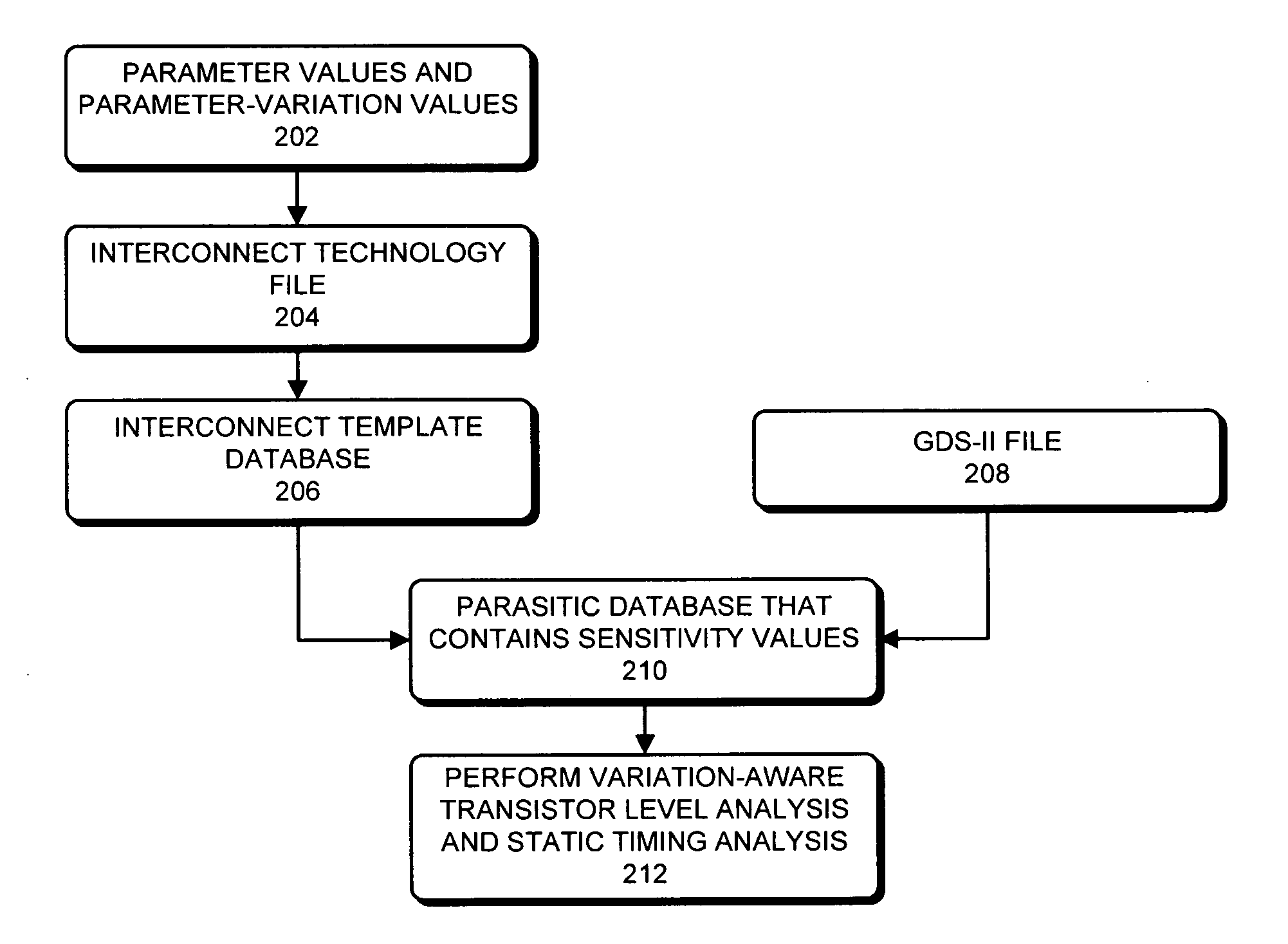

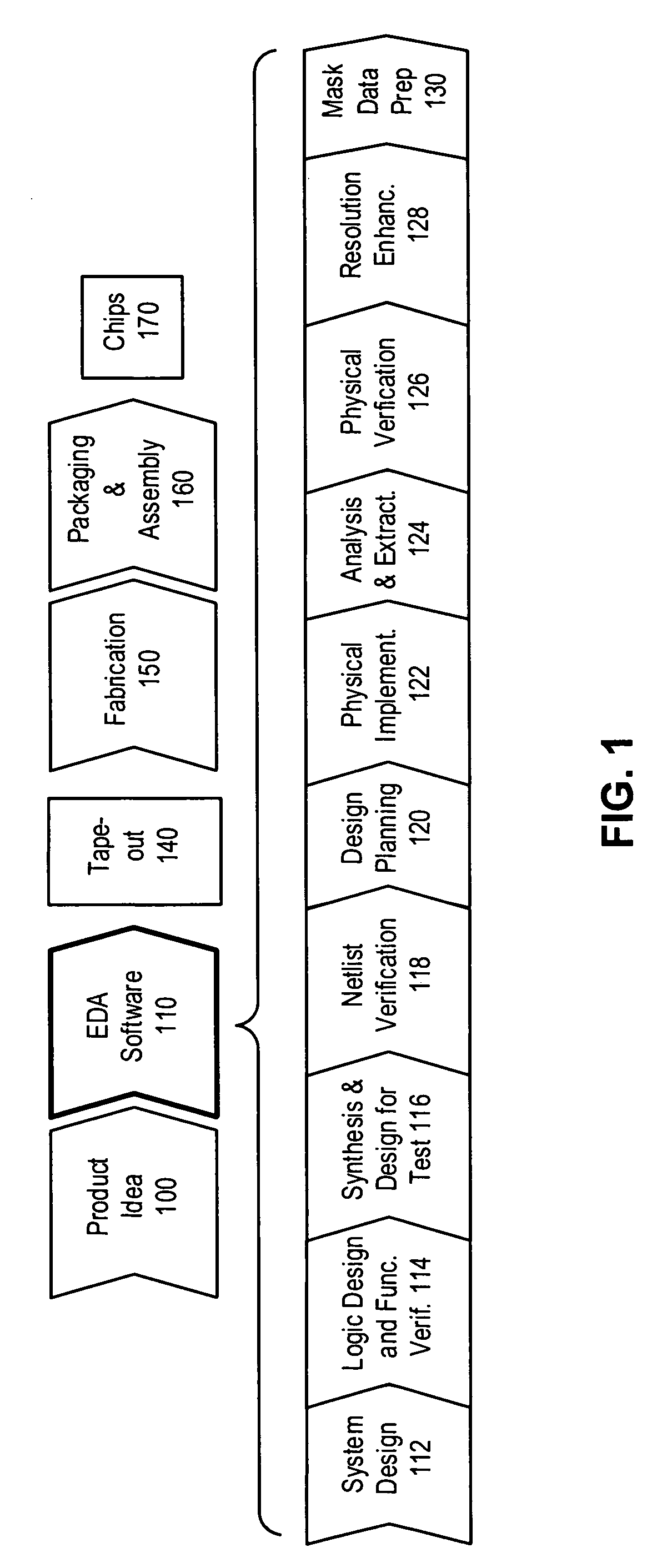

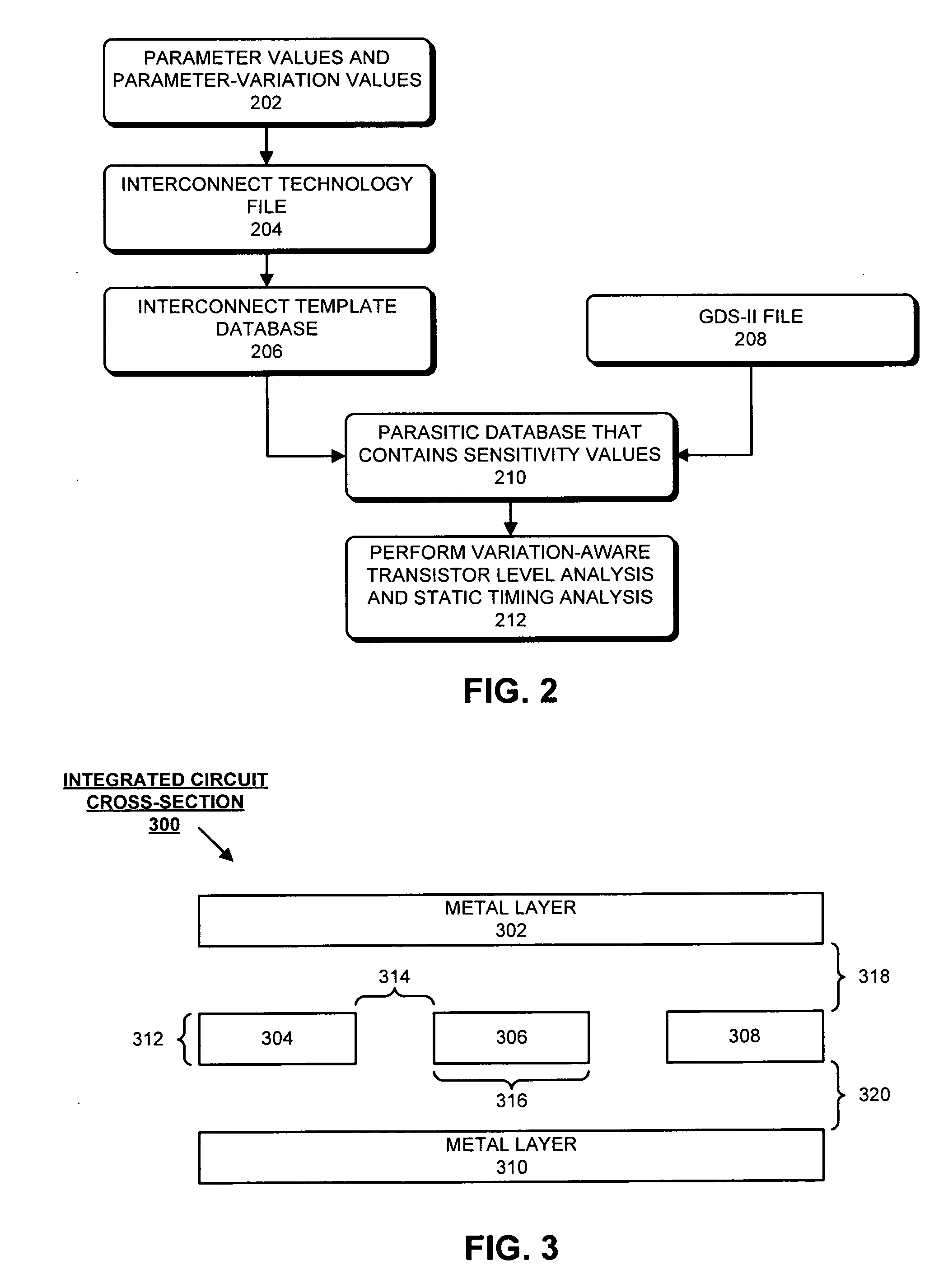

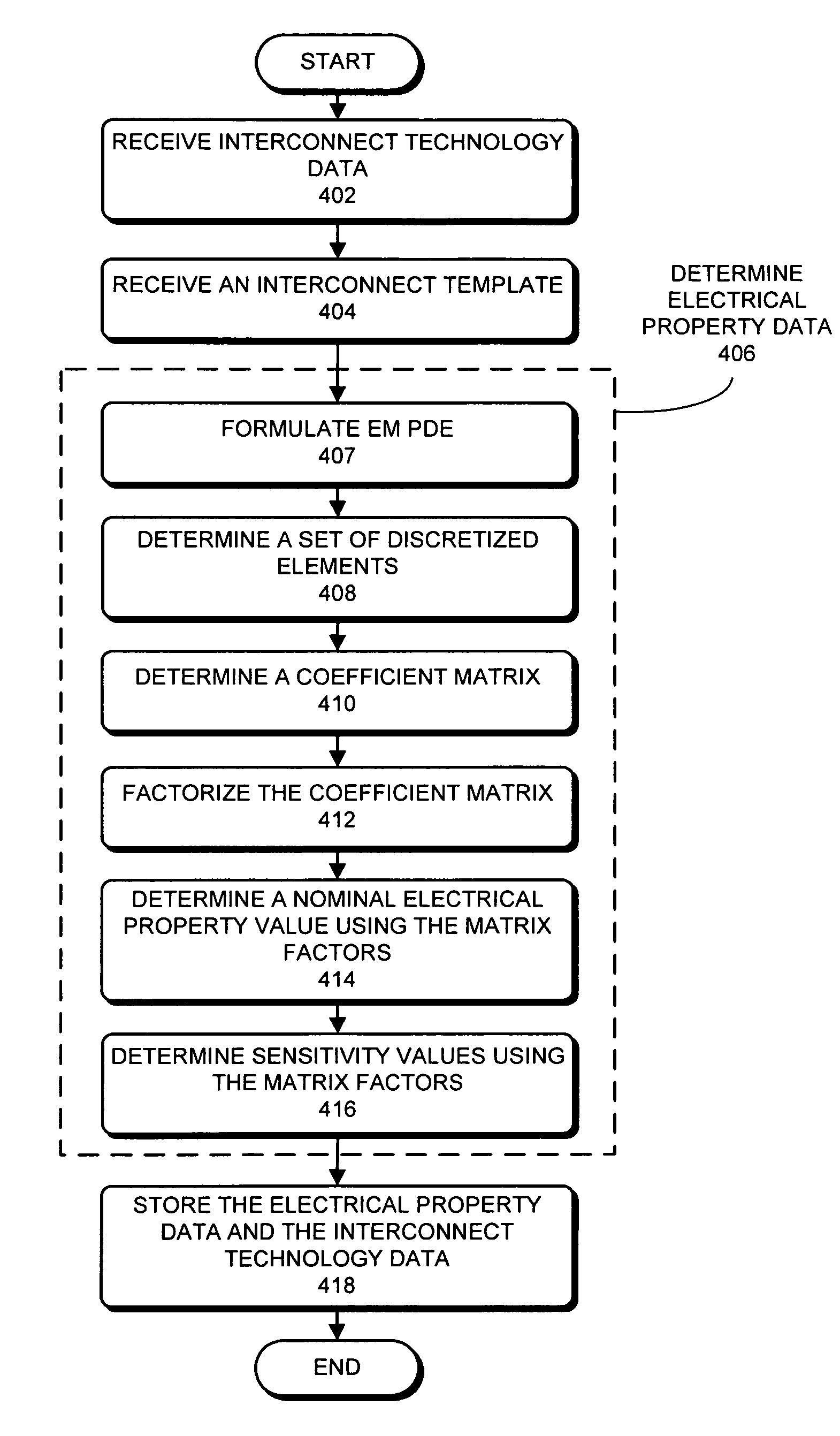

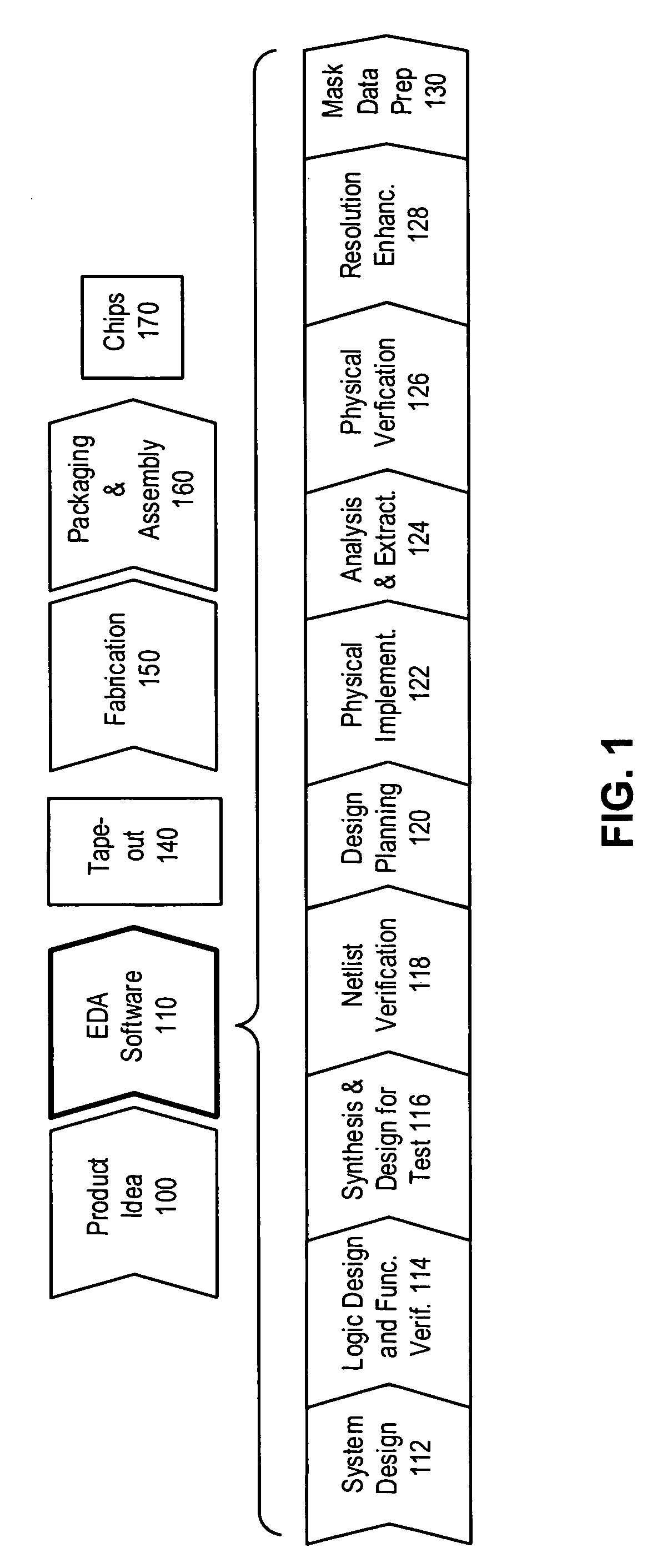

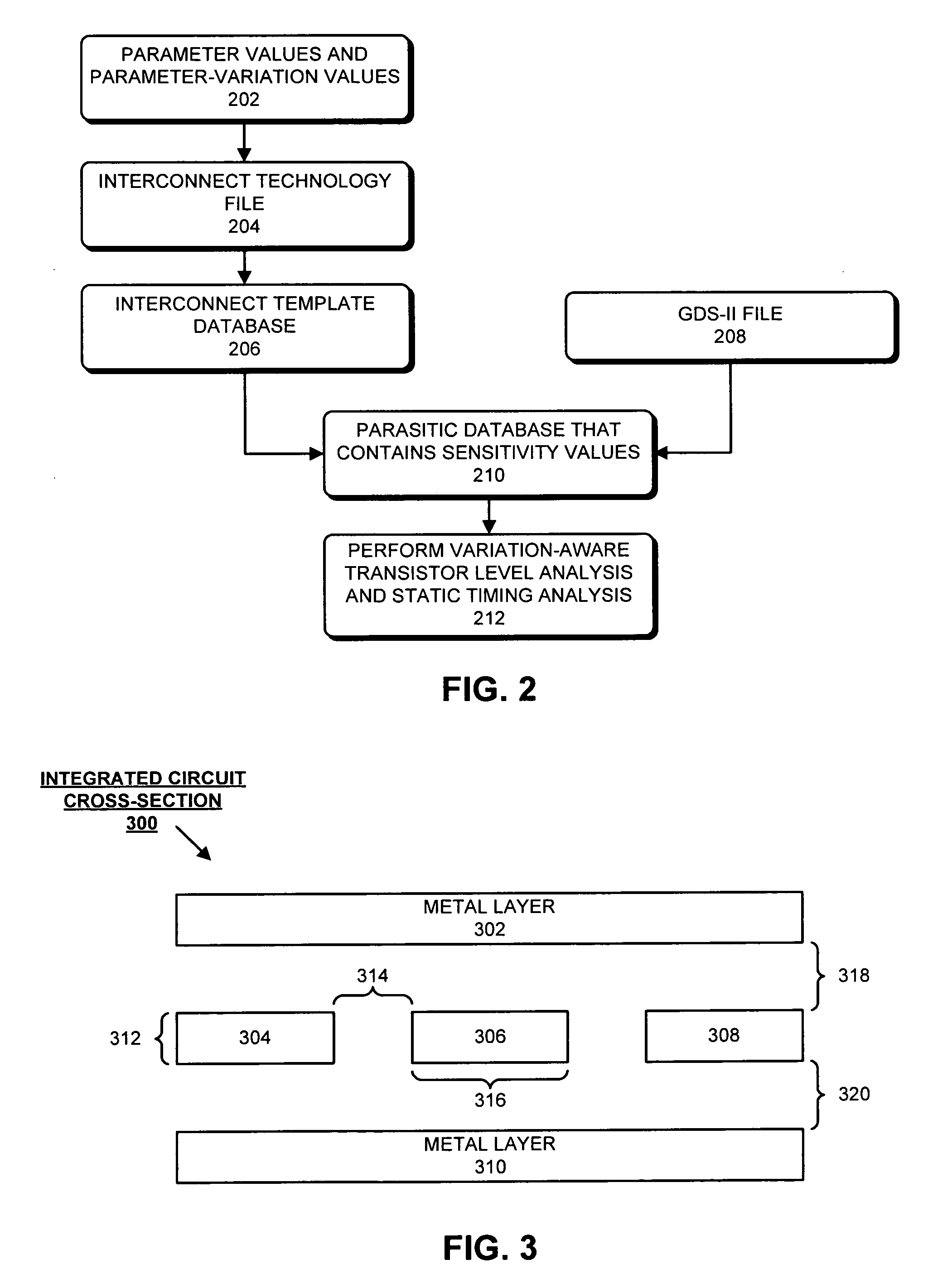

Method and apparatus for facilitating variation-aware parasitic extraction

ActiveUS20070124707A1Generate accuratelyDetecting faulty computer hardwareDesign optimisation/simulationElectricityProperty value

One embodiment of the present invention provides a system for determining an electrical property for an interconnect layer. During operation, the system receives interconnect technology data which includes nominal parameter values for a first interconnect layer, and parameter-variation values which represent variations in the nominal parameter values due to random process variations. Next, the system receives an interconnect template which describes the geometry of a portion of a second interconnect layer. The system then determines electrical property data for the interconnect template using the interconnect technology data. The electrical property data can include a nominal electrical property value, and sensitivity values which represent the sensitivities of the nominal electrical property value to variations in the nominal parameter values. Next, the system stores the electrical property data and the interconnect technology data in a storage.

Owner:SYNOPSYS INC

Integrated circuit package having reduced interconnects

InactiveUS6979904B2Semiconductor/solid-state device detailsSolid-state devicesEngineeringInterconnect technology

A technique for making an integrated circuit package. Specifically, a stacked memory device is provided with minimal interconnects. Memory die are stacked on top of each other and electrically coupled to a substrate. Thru vias are provided in the substrate and / or memory die to facilitate the electrical connects without necessitating a complex interconnect technology between each of the interfaces. Wire bonds are used to complete the circuit package.

Owner:ROUND ROCK RES LLC

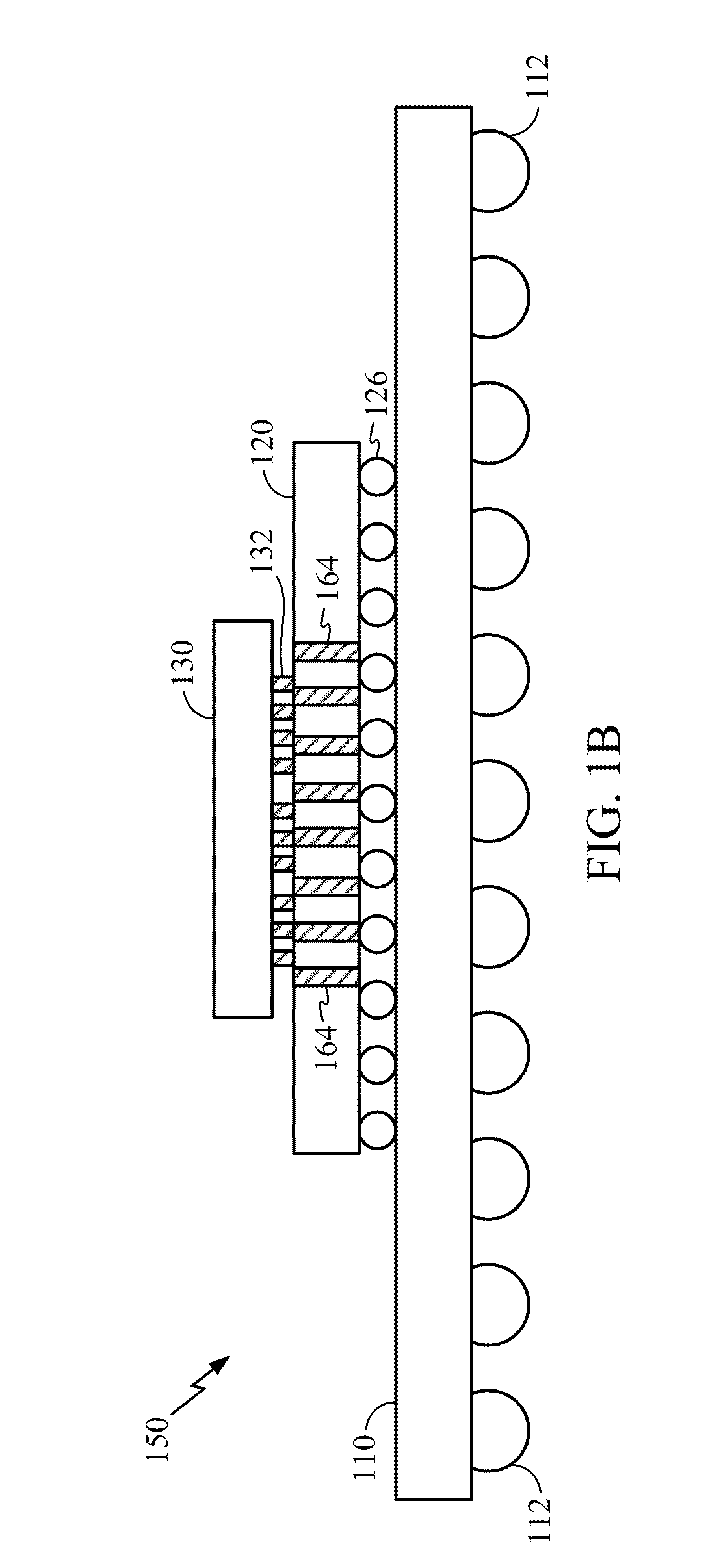

Hybrid Package Construction With Wire Bond And Through Silicon Vias

ActiveUS20110115064A1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerLead bonding

A hybrid interconnect includes a through silicon via and a wire bond. Hybrid interconnects enable better layout of a stacked IC by combining benefits from both interconnect technologies. In one hybrid interconnect, wire bonds couples a second tier die mounted on a first tier die to a redistribution layer in the first tier die. Through silicon vias in the first tier die are coupled to the wire bonds to provide communication. In another hybrid interconnect, a wire bond couples a redistribution layer on a first tier die to a packaging substrate on which the first tier die is mounted. The redistribution layer couples to a second tier die mounted on the first tier die to provide a power supply to the second tier die. Through silicon vias in the first tier die couple to the second tier die to provide communication from the packaging substrate to the second tier die.

Owner:QUALCOMM INC

TSV Backside Processing Using Copper Damascene Interconnect Technology

ActiveUS20130105968A1Well formedSemiconductor/solid-state device detailsSolid-state devicesSubject matterSemiconductor chip

Generally, the subject matter disclosed herein relates to interconnect structures used for making electrical connections between semiconductor chips in a stacked or 3D chip configuration, and methods for forming the same. One illustrative method disclosed herein includes forming a conductive via element in a semiconductor substrate, wherein the conductive via element is formed from a front side of the semiconductor substrate so as to initially extend a partial distance through the semiconductor substrate. The illustrative method also includes forming a via opening in a back side of the semiconductor substrate to expose a surface of the conductive via element, and filling the via opening with a layer of conductive contact material.

Owner:GLOBALFOUNDRIES SINGAPORE PTE LTD

High-speed adaptive interconnect architecture with nonlinear error functions

InactiveUS7158566B2Low costLow structural requirementsMultiple-port networksDelay line applicationsEngineeringError function

A low cost and high speed equalizing receiver structure is provided for improved inter-chip and inter-module communications. The receiver is able to recover data from a corrupted waveform from a signal wire such as one found on data, address or control wires in a microsystem architecture. The receiver can be used with binary as well as m-ary pulse amplitude modulation schemes. The receiver can be used to increase the sustainable data rate between chips or can be used to sustain a given data rate over a poorer quality channel as compared to prior art interconnect technologies. Methods for training and operating the receiver structure are provided. A novel structure called the decision feedback equalizer and cross talk canceller (DFE-CTC) is introduced and methods to compute the coefficients to minimize error in terms of the l2 norm, the l∞ norm, and statistical probability of error functions are also disclosed.

Owner:RPX CORP

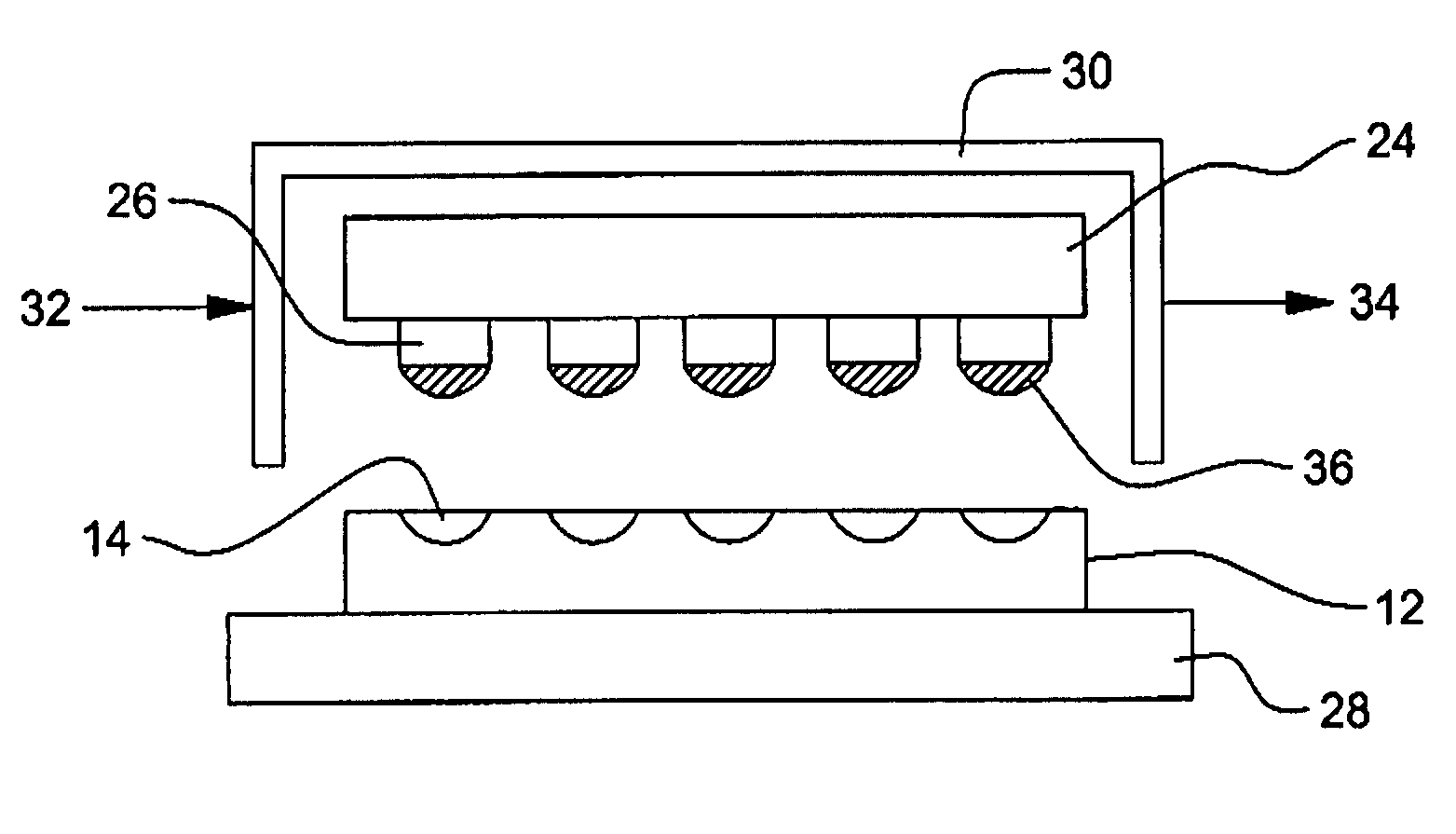

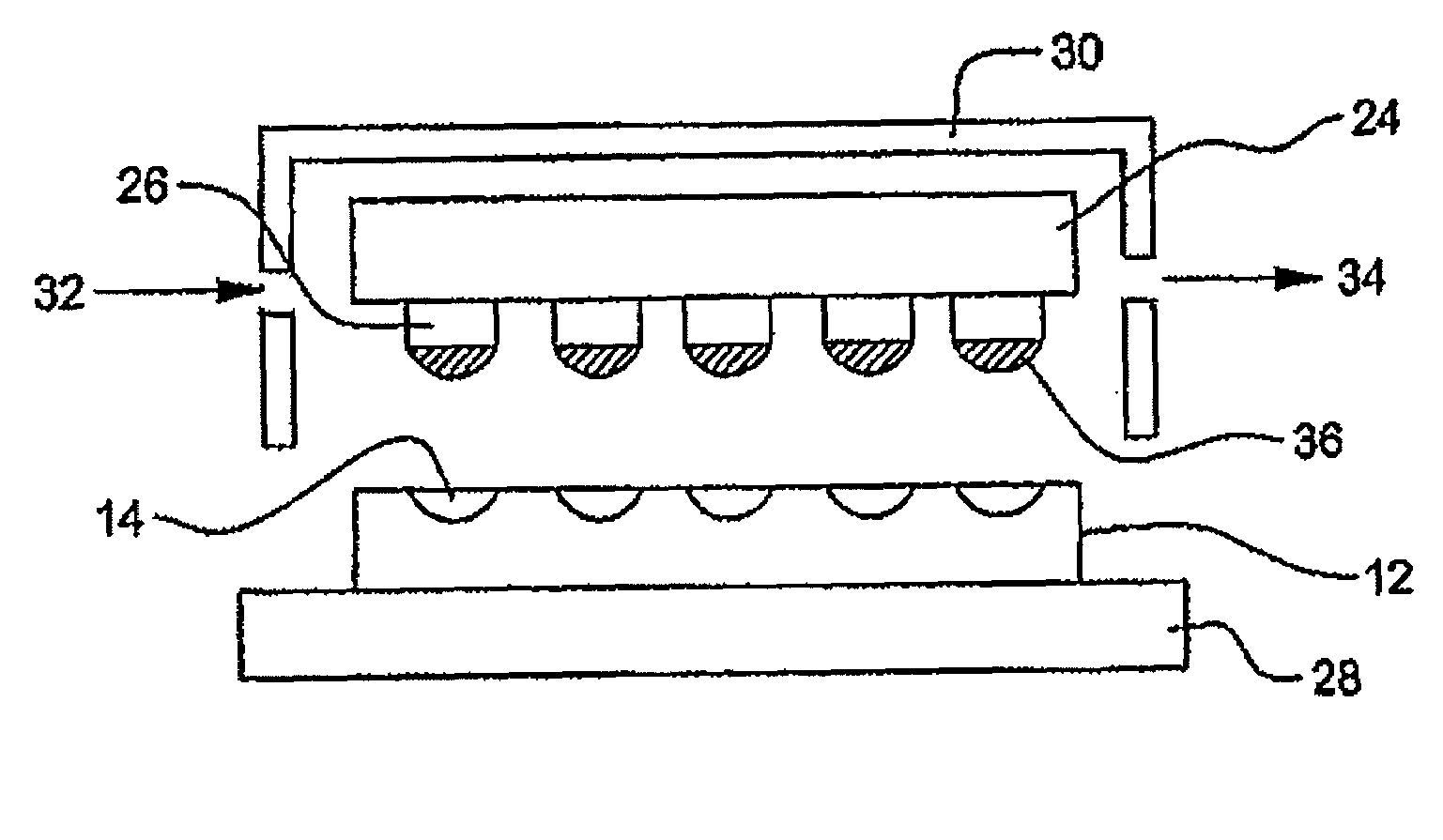

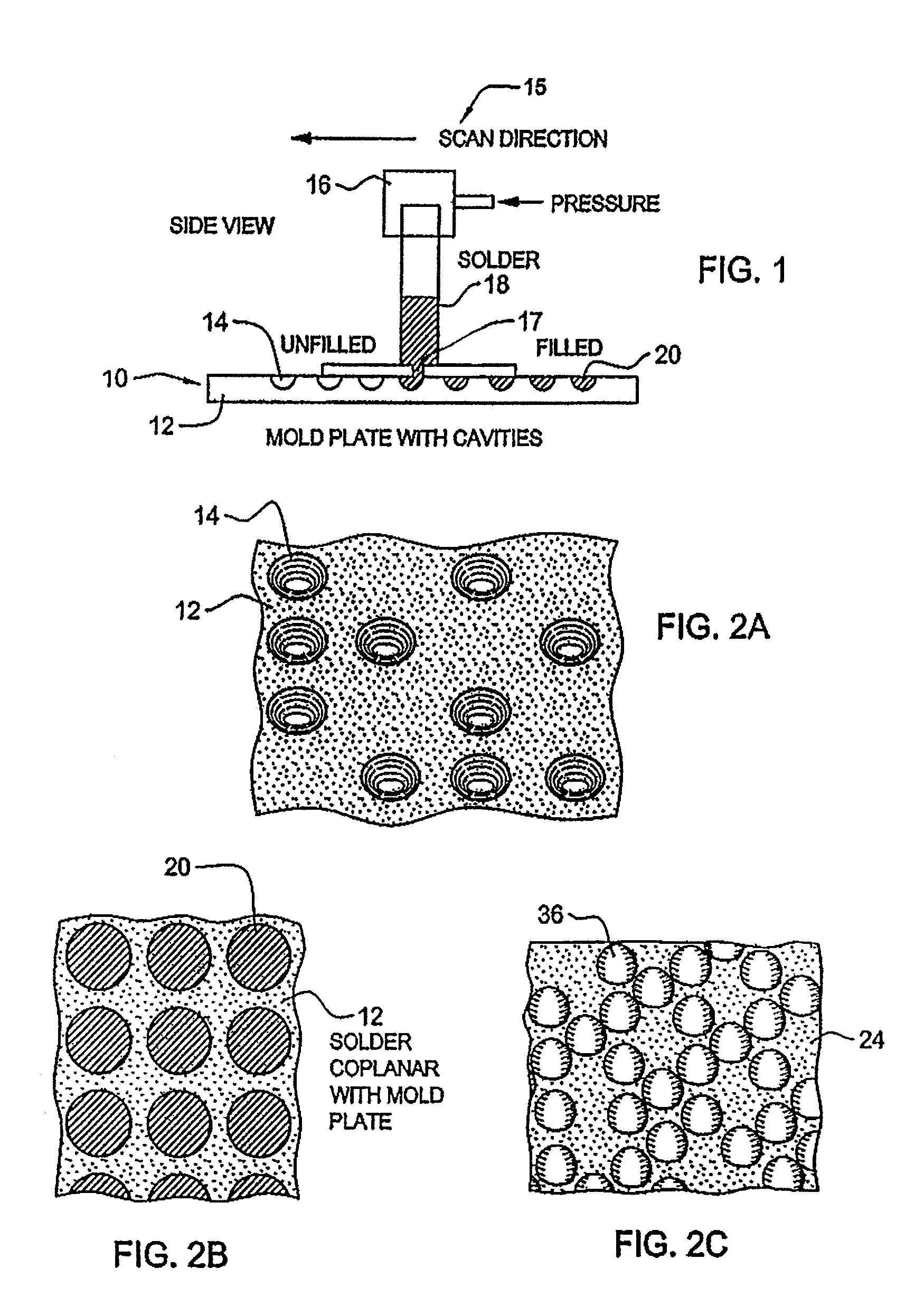

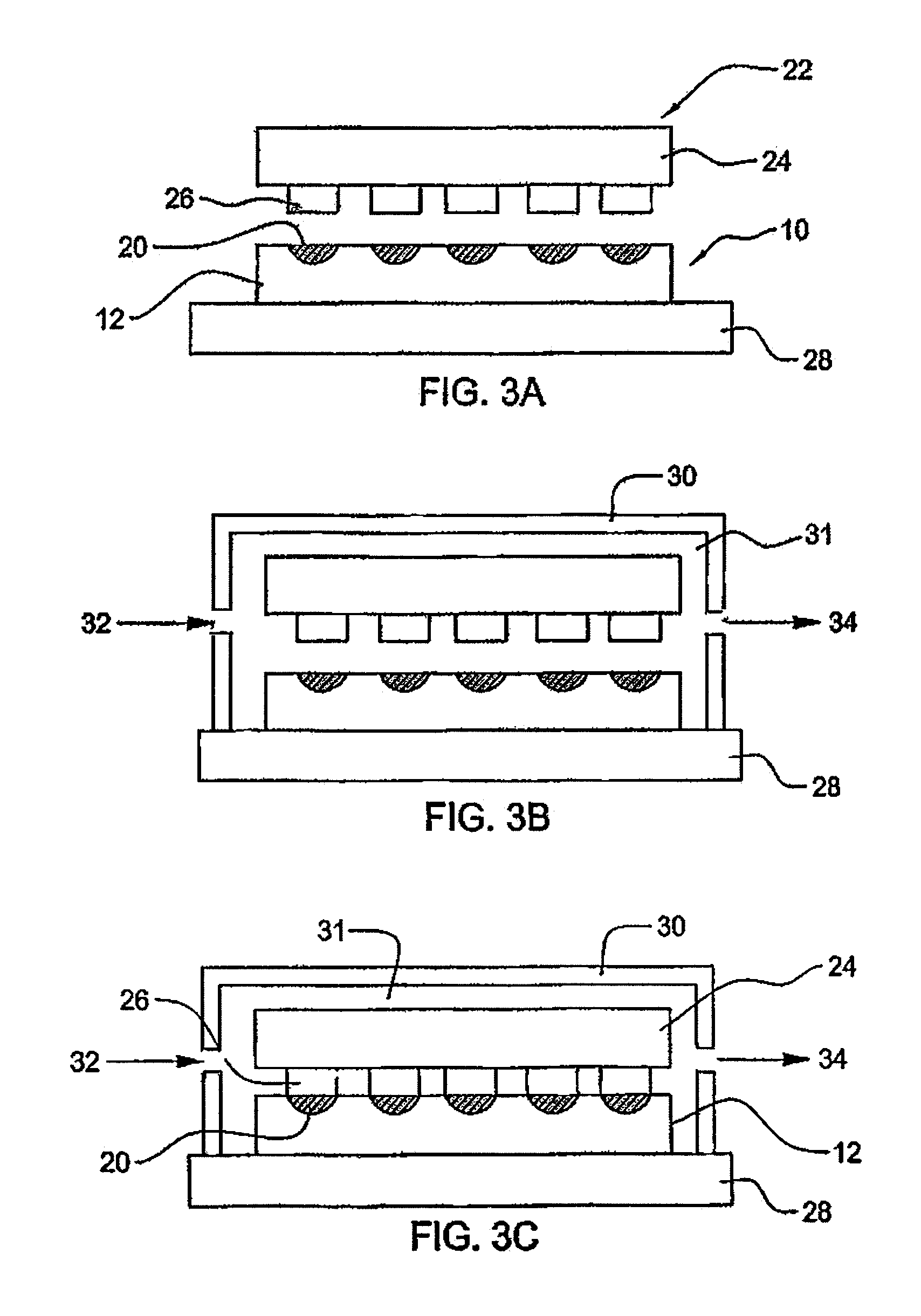

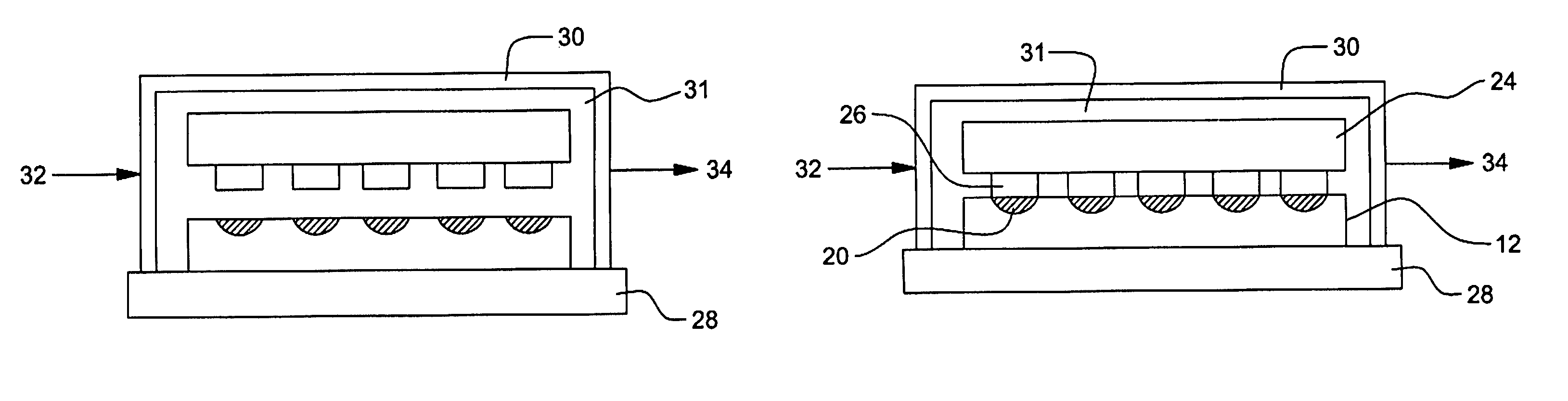

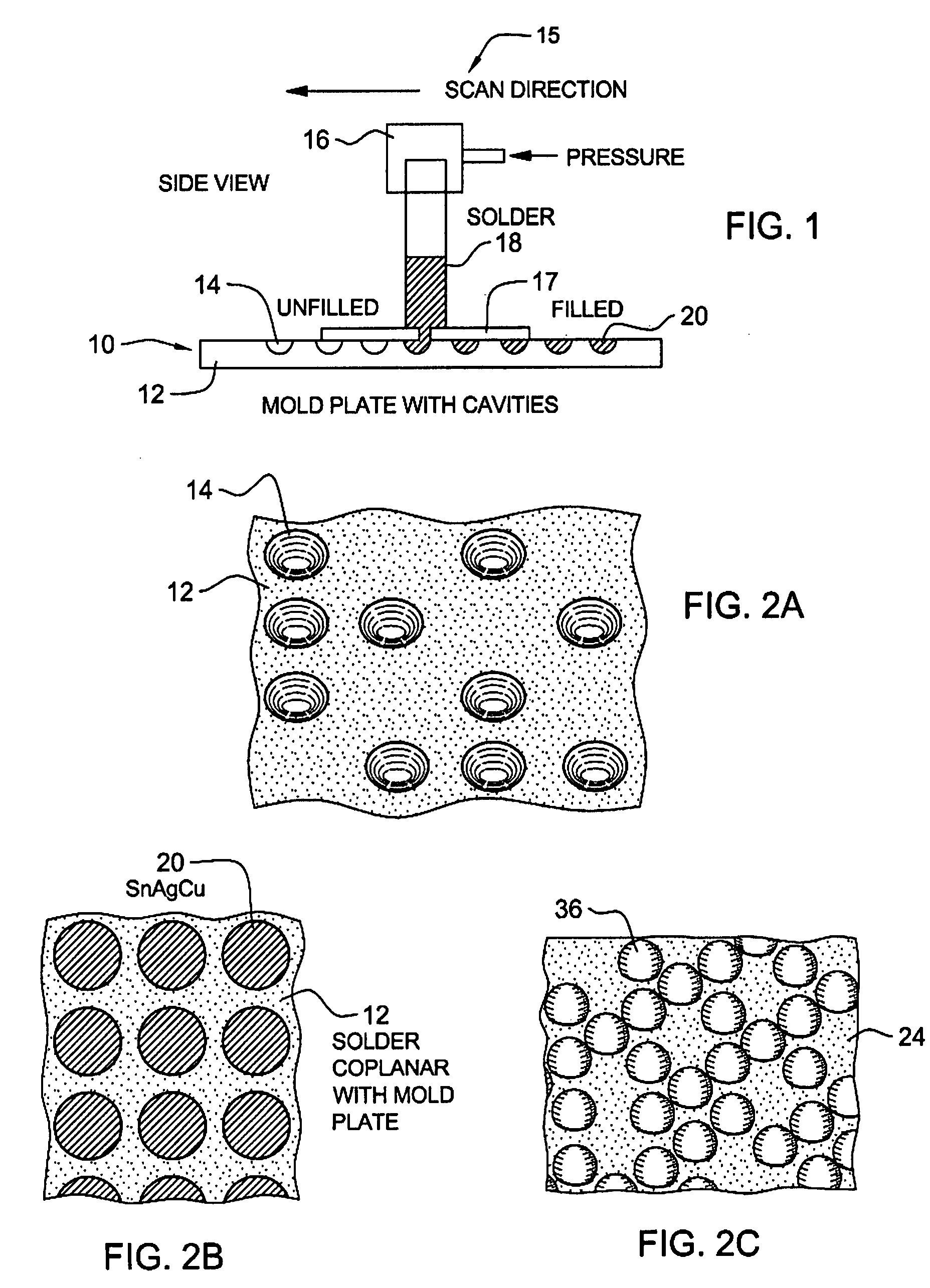

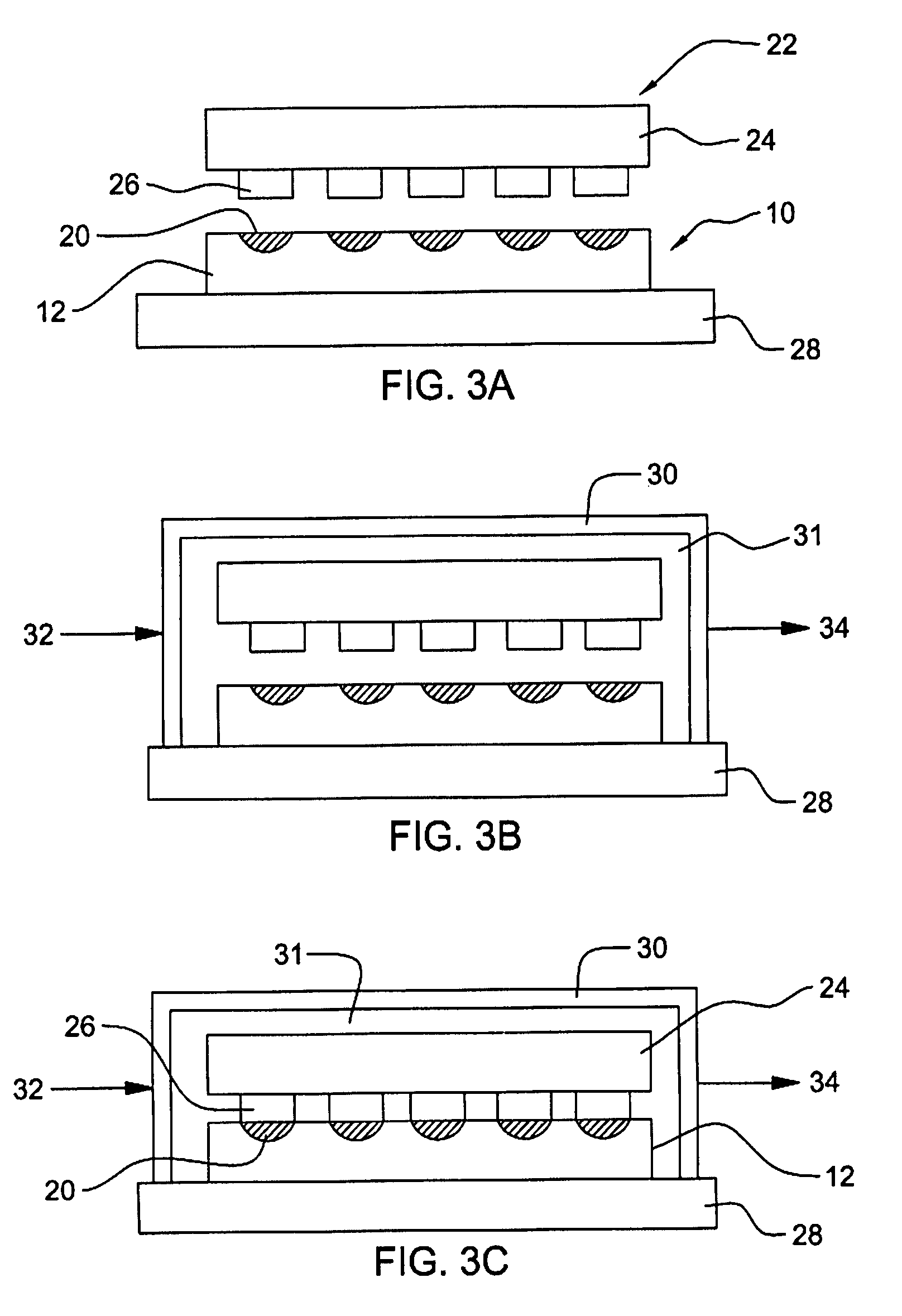

PROCESS FOR MAKING INTERCONNECT SOLDER Pb-FREE BUMPS FREE FROM ORGANO-TIN/TIN DEPOSITS ON THE WAFER SURFACE

InactiveUS20090020590A1Exhaust apparatusSilencing apparatusInterconnect technologyMelting temperature

A method is provided for making of interconnect solder bumps on a wafer or other electronic device without depositing any significant amount of tin or other solder component from the solder onto the wafer surface which tin can cause shorts or other defects in the wafer. The method is particularly useful for well-known C4NP interconnect technology. In one aspect of the invention, a reducing gas flow rate is used to remove oxides from the solder surfaces and wafer pad surfaces and is of a sufficient determined or pre-determined flow and / or chamber or mold / wafer spacing to provide a gas velocity across the solder surfaces and wafer pad surfaces so that Sn or other contaminants do not deposit on the wafer surface during solder transfer. In another aspect, the transfer contact is performed below the melting point of the solder and subsequently heated to above the melting temperature while in transfer contact. The heated solder in contact with the wafer pads is transferred to the wafer pads.

Owner:ULTRATECH INT INC

High tin solder etching solution

InactiveUS20090120999A1Decorative surface effectsSemiconductor/solid-state device detailsSulfateAlloy

A method is provided for the removal of tin or tin alloys from substrates such as the removal of residual tin solder from the molds used in the making of interconnect solder bumps on a wafer or other electronic device. The method is particularly useful for the well-known C4NP interconnect technology and uses an etchant composition comprising cupric ions and HCl. Cupric chloride and cupric sulfate are preferred. A preferred method regenerates cupric ions by bubbling air or oxygen through the etchant solution during the cleaning process.

Owner:GLOBALFOUNDRIES INC

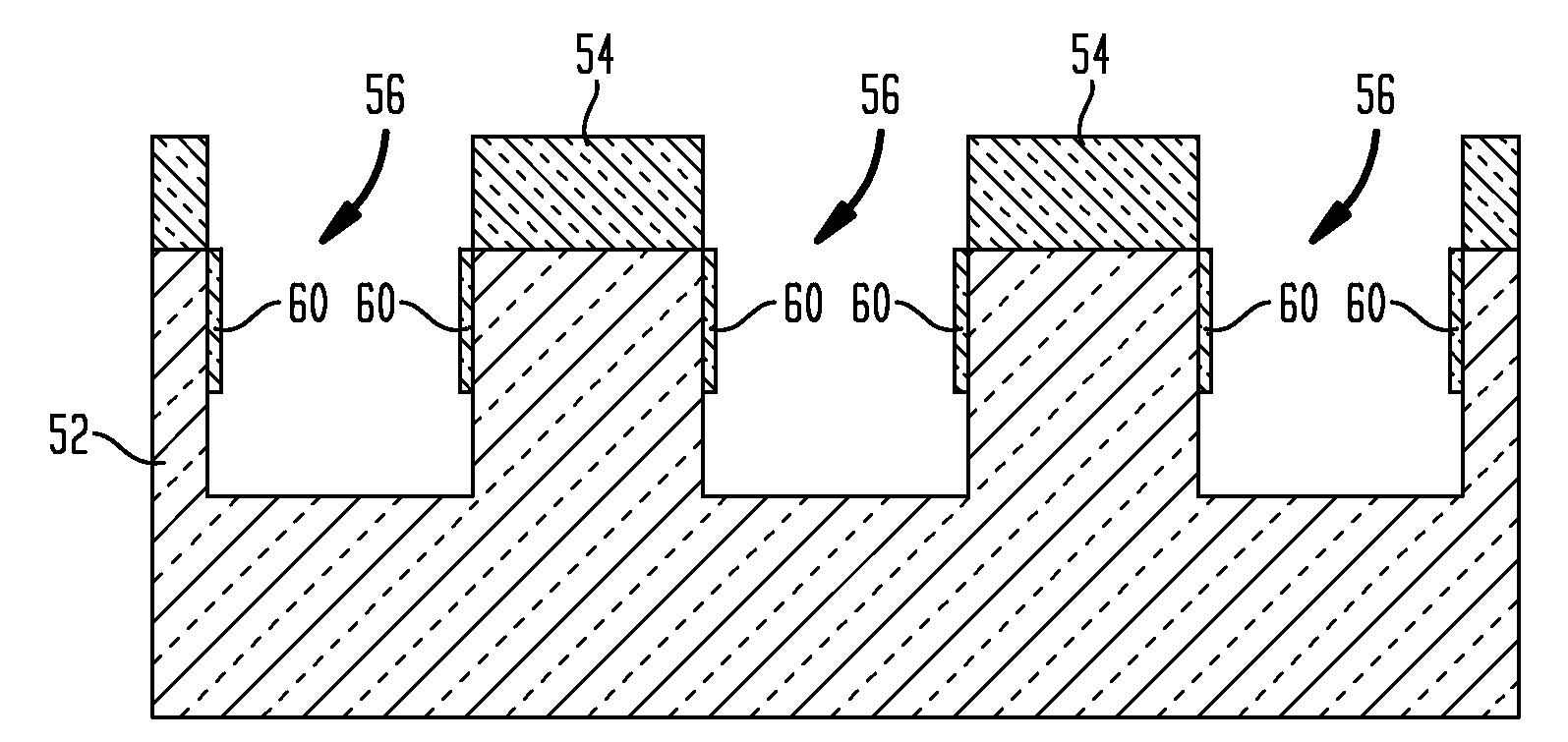

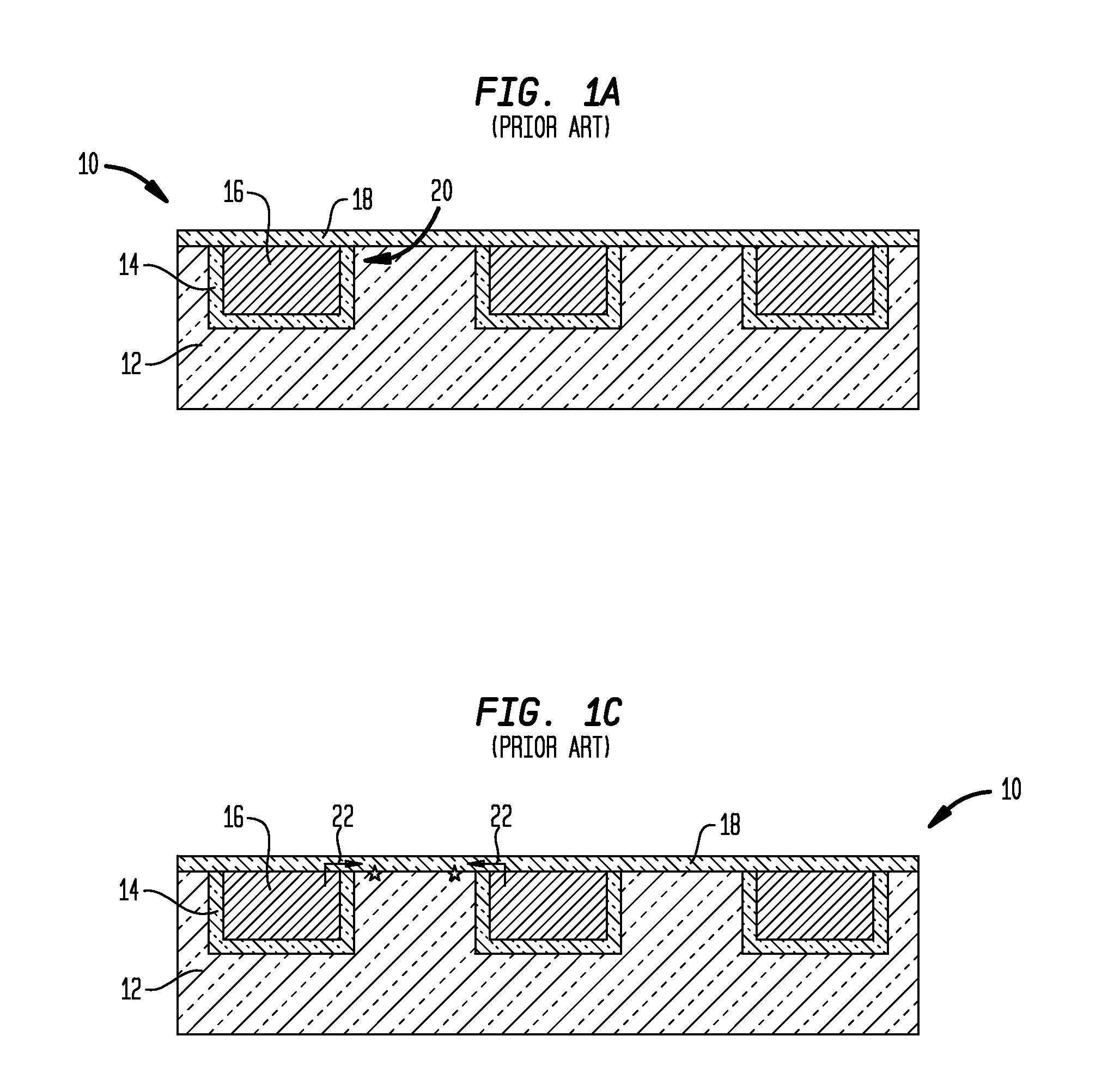

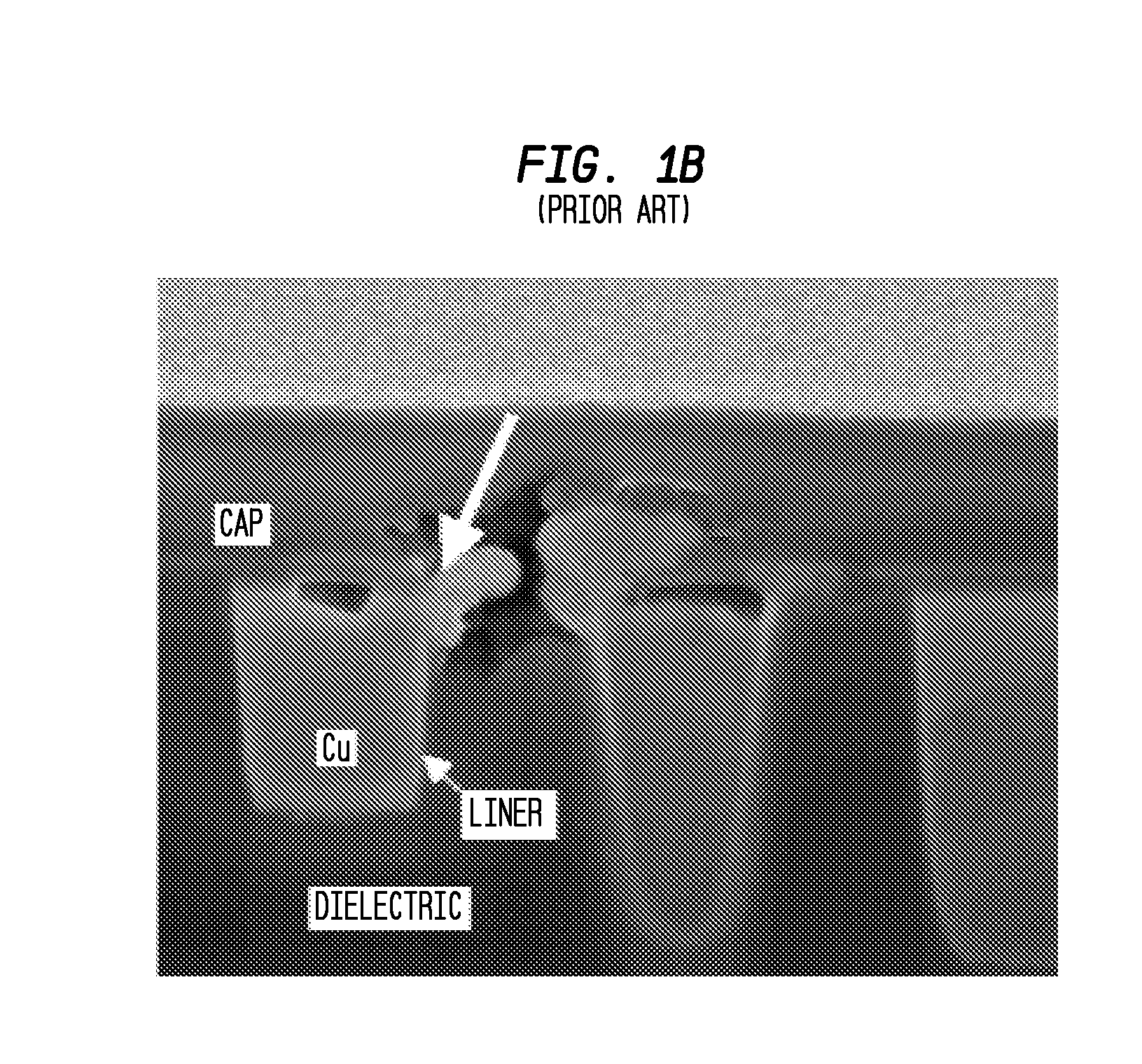

Interconnect structure for beol applications

ActiveUS20080026554A1High mechanical integrity strengthImprove circuit reliabilitySemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceInterconnect technology

A semiconductor interconnect structure is provided that includes a new capping layer / dielectric material interface which is embedded inside the dielectric material. In particular, the new interface is an air gap that is located in the upper surface of a dielectric material that is adjacent to a conductive region or feature. The air gap may be unfilled, partially filled or completely filled with either a dielectric capping layer or an upper dielectric material. The presence of the air gap in the upper surface of the dielectric material that is adjacent to the conductive region or feature provides a new interface that has a high mechanical strength and thus the resultant structure is highly reliable. Moreover, the new interface provided in the present invention has a high dielectric breakdown resistance which is important for future technology extendibility. Moreover, it is noted that the new interface is provided utilizing processing steps that are compatible with existing interconnect technology without added cost.

Owner:GLOBALFOUNDRIES US INC

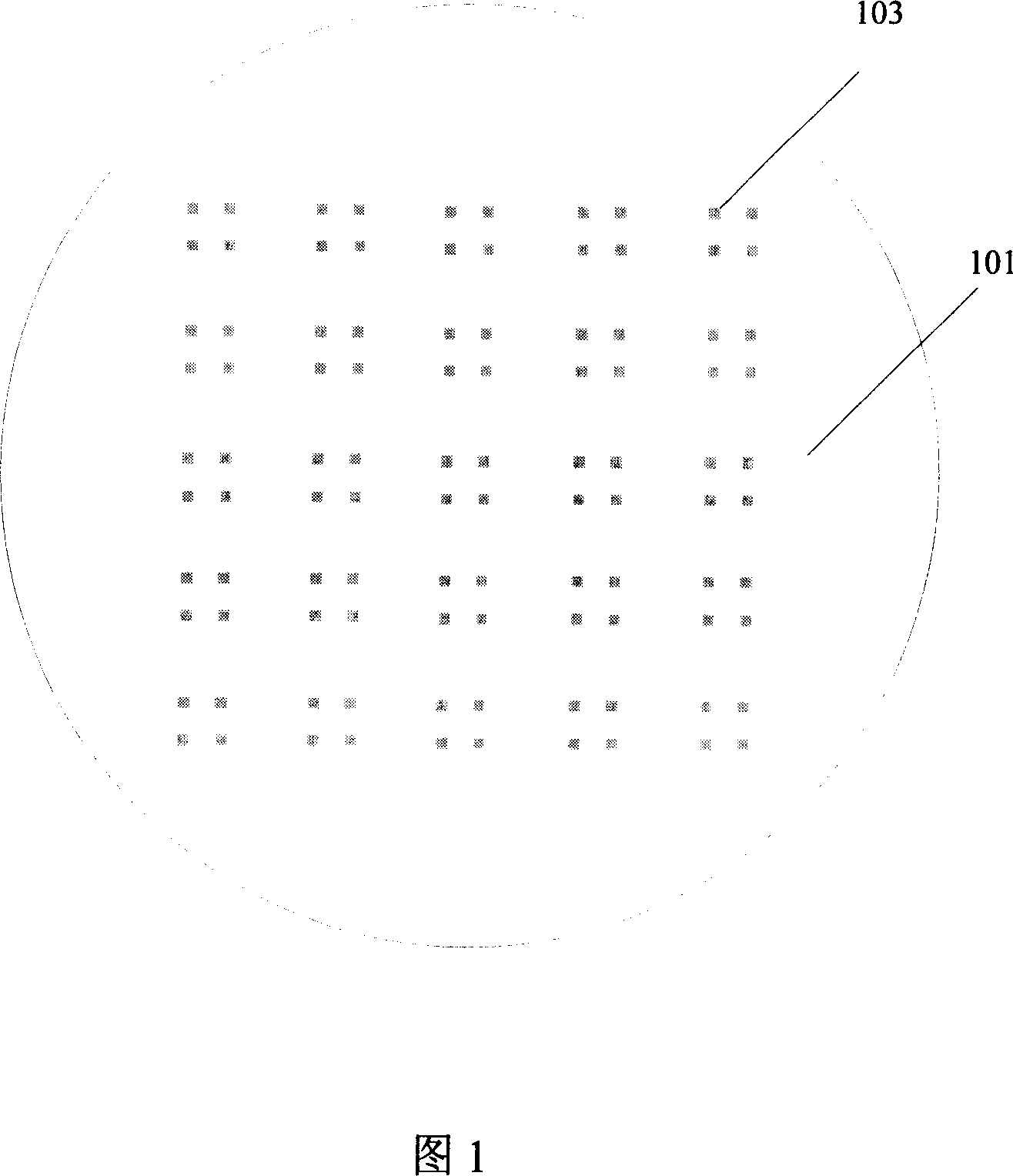

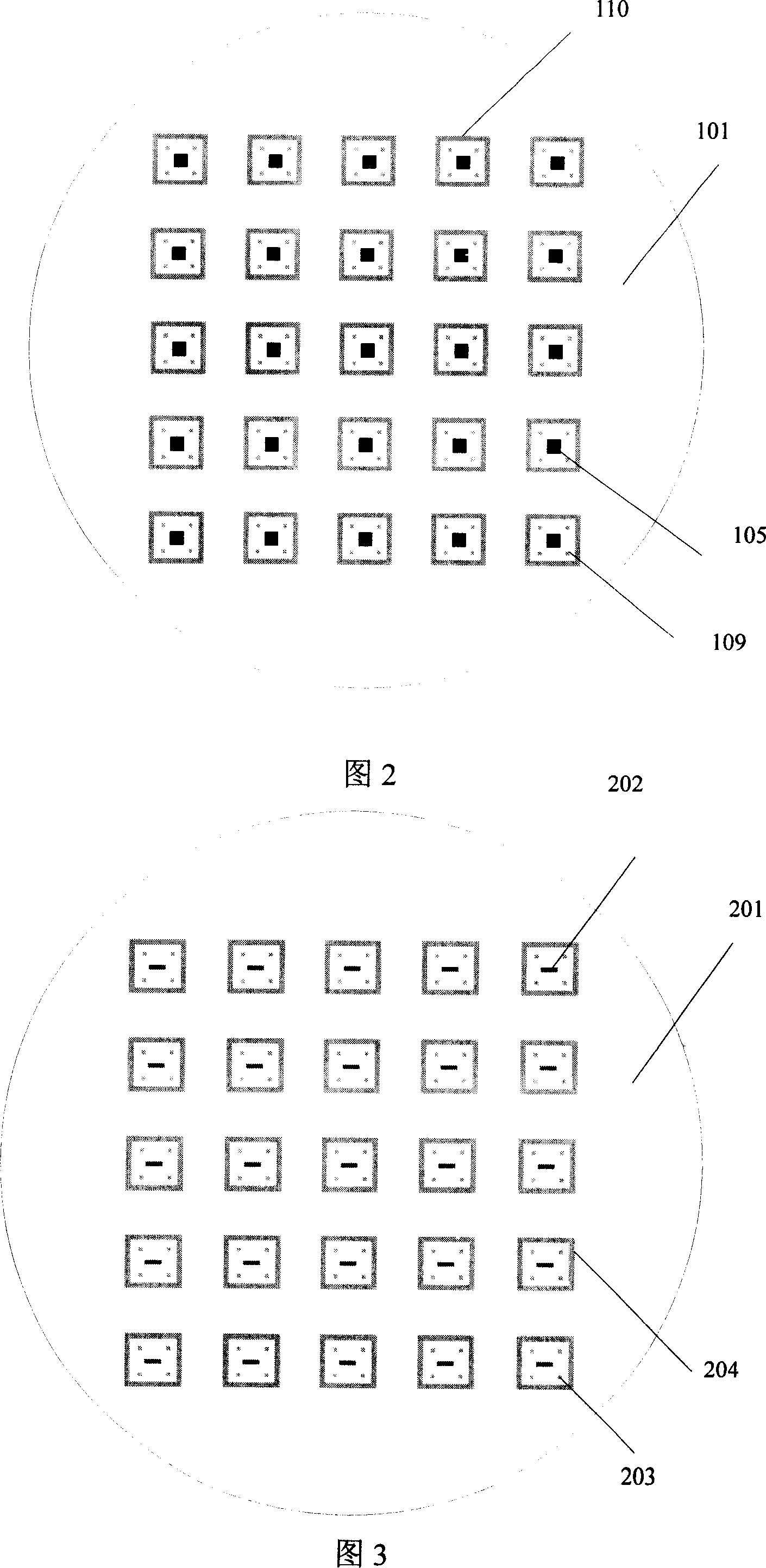

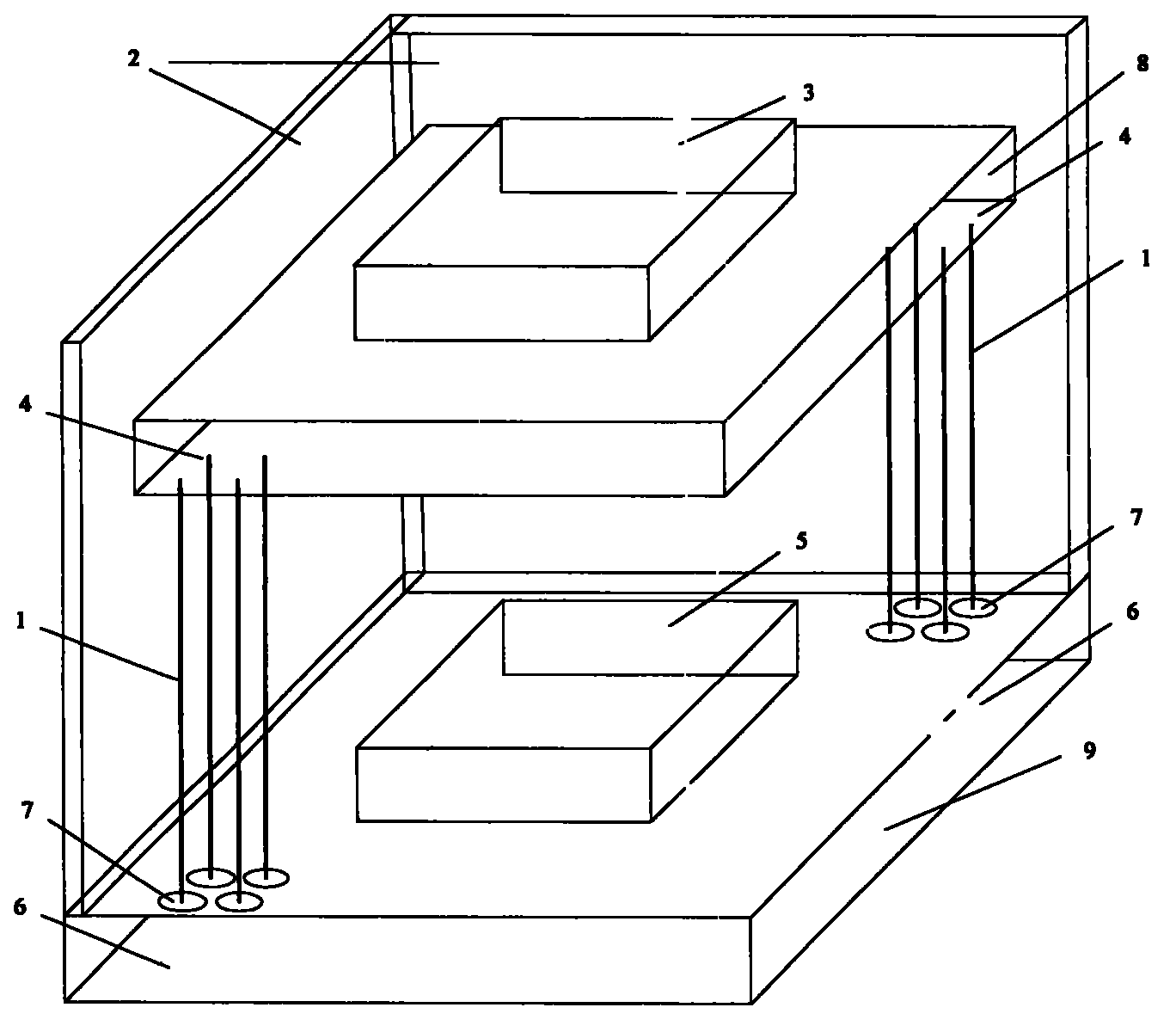

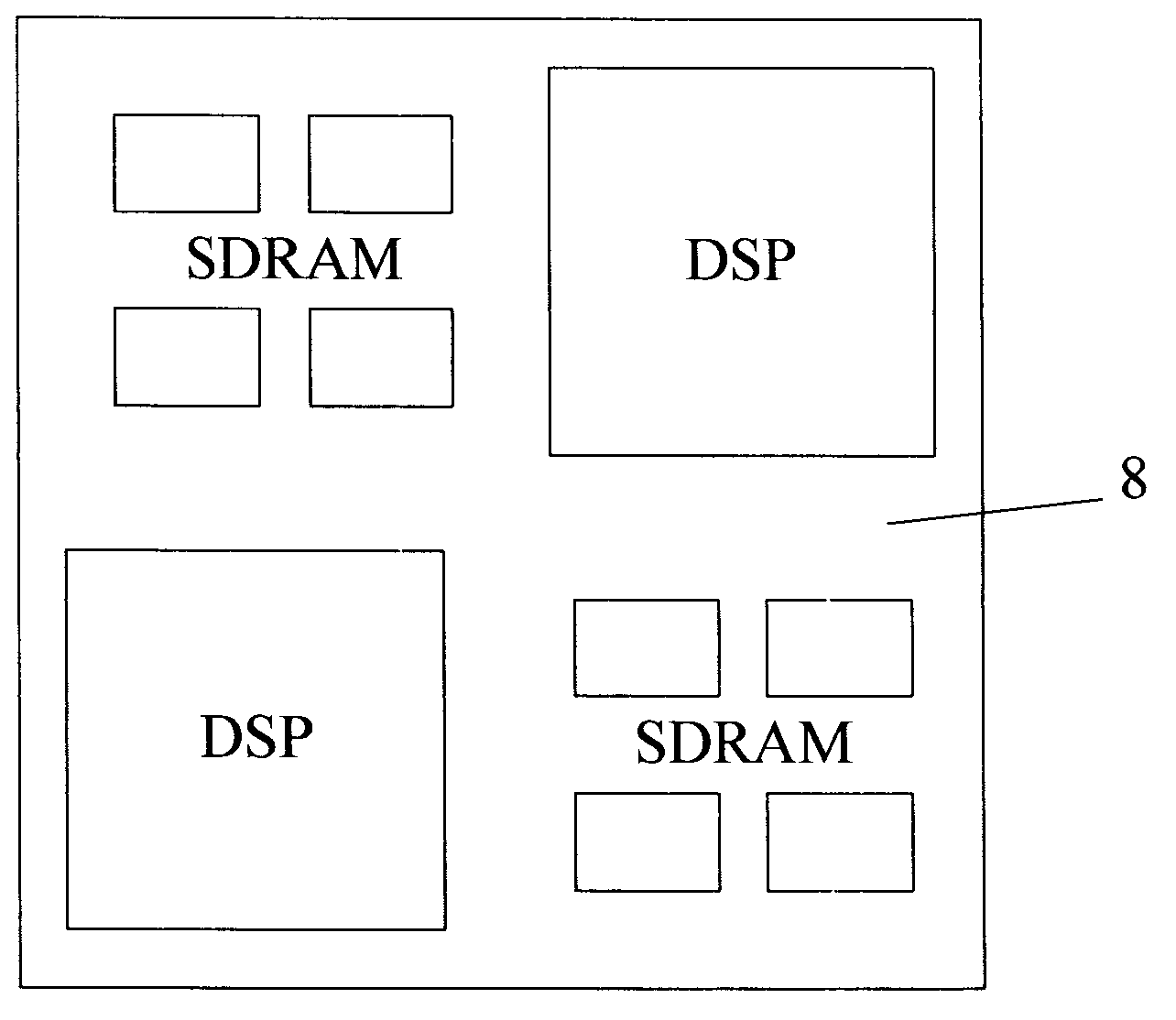

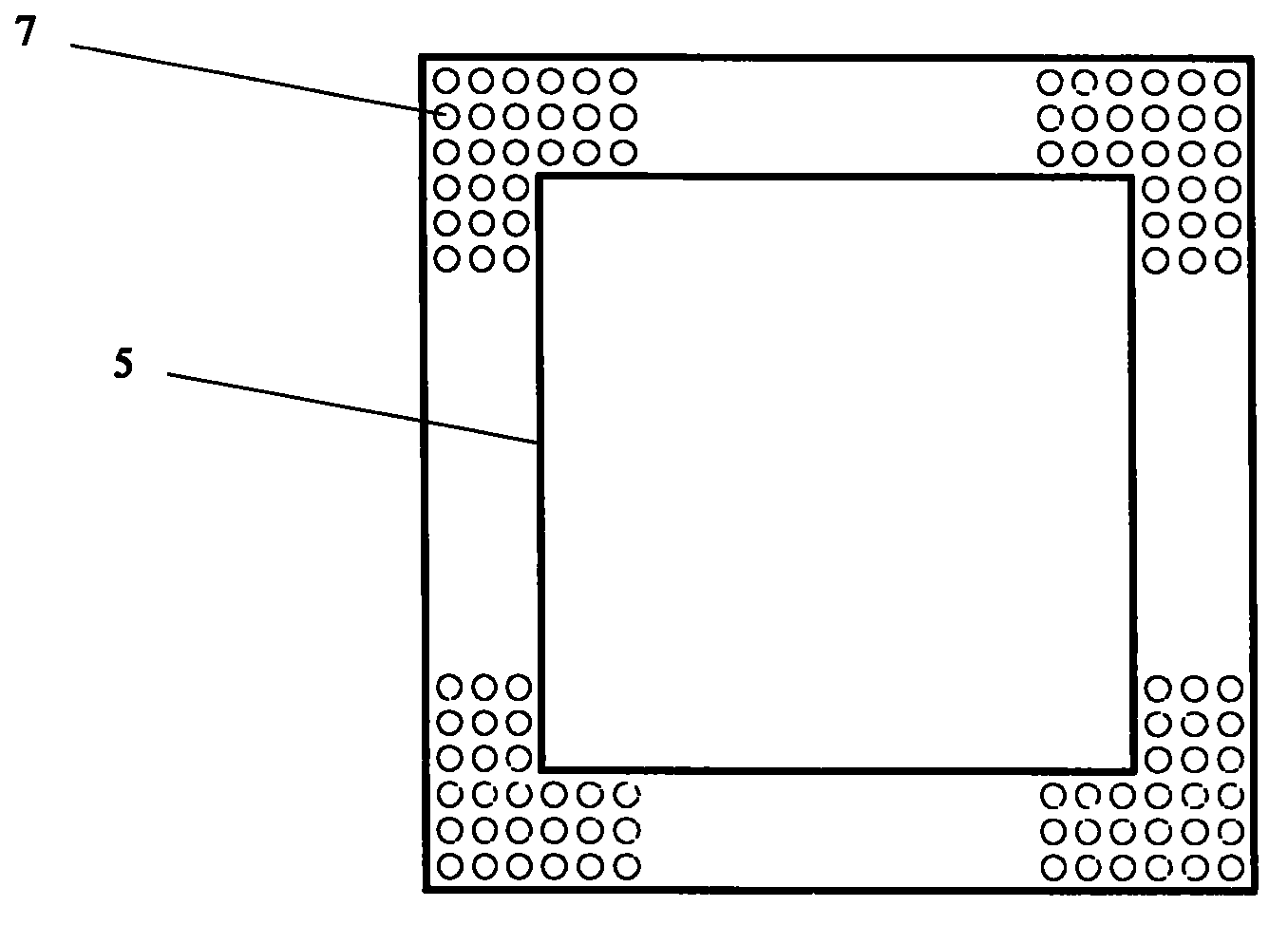

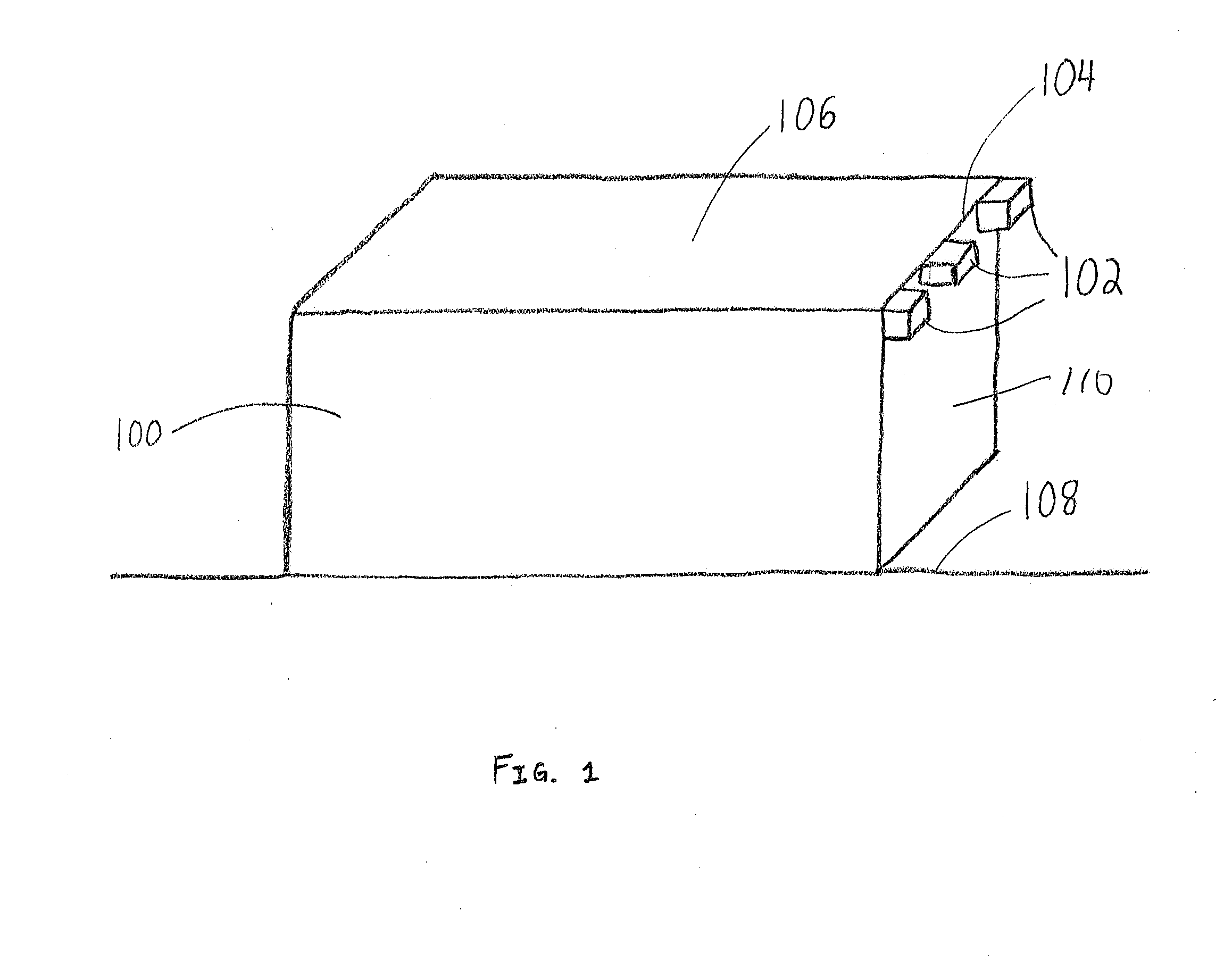

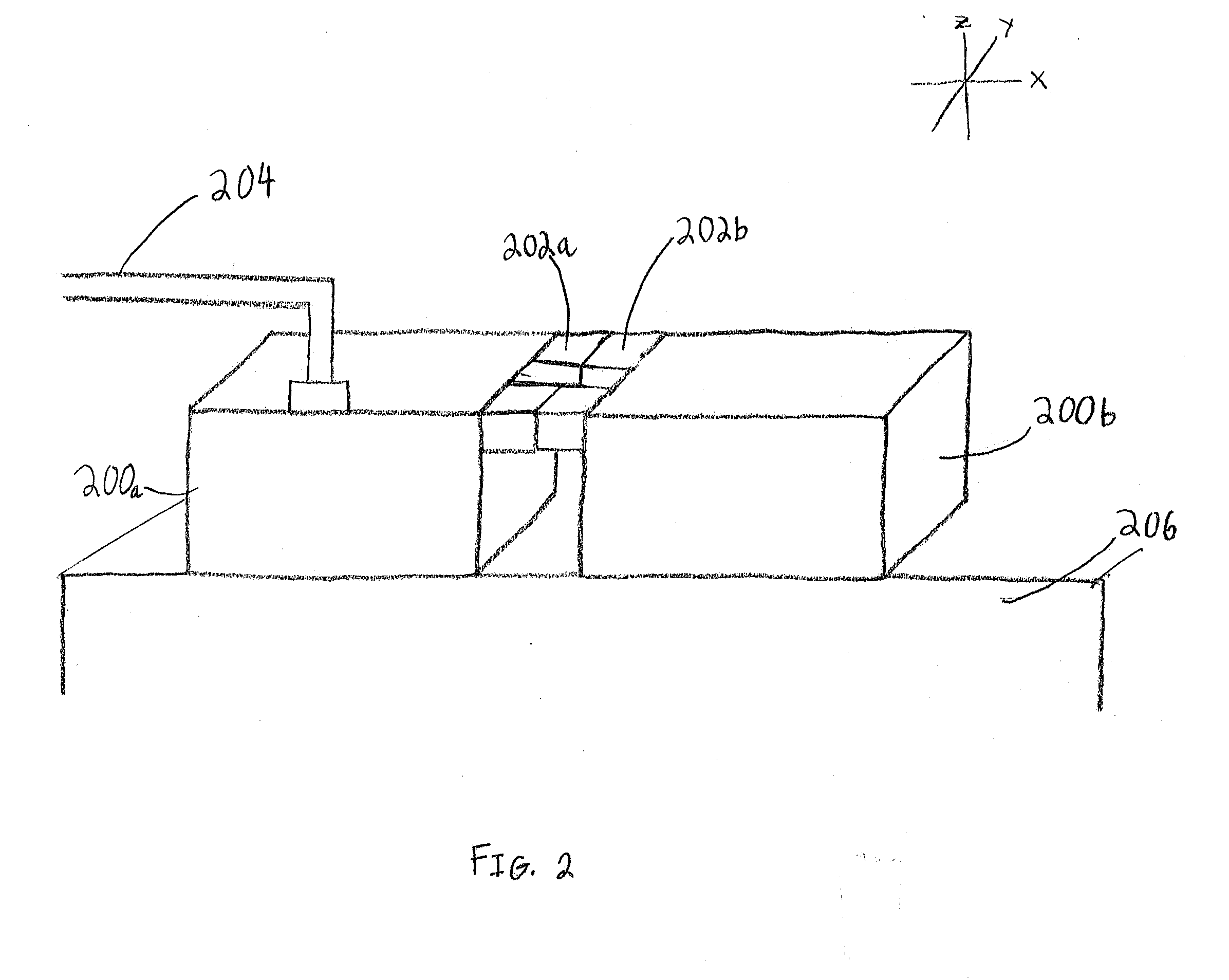

Laminated 3D-MCM (3-dimensional multiple chip module) structure based on peripheral vertical interconnect technology

ActiveCN103022005AQuality improvementIncrease transfer speedSemiconductor/solid-state device detailsSolid-state devicesHigh densityMiniaturization

The invention discloses a laminated 3D-MCM (3-dimensional multiple chip module) structure based on peripheral vertical interconnect technology. The laminated 3D-MCM structure comprises an upper multiple chip module (MCM), peripheral vertical interconnected welded columns (1), a lower MCM and a packaging shell (2), wherein the upper MCM is formed by an upper chip holding area, upper ball grid arrays and a high-density multilevel interconnected substrate, the lower MCM is formed by a lower chip holding area, lower ball grid arrays, interconnected ball grid arrays and a high-density multilevel interconnected substrate, and the upper MCM and the lower MCM are interconnected via the peripheral vertical interconnected welded columns and share the packaging shell, thus the 3-dimensional multiple chip module (3D-MCM) is formed. The laminated 3D-MCM structure based on the peripheral vertical interconnect technology can meet requirements for miniaturization and high performance and reliability of a complicated electronic circuit system.

Owner:XIDIAN UNIV

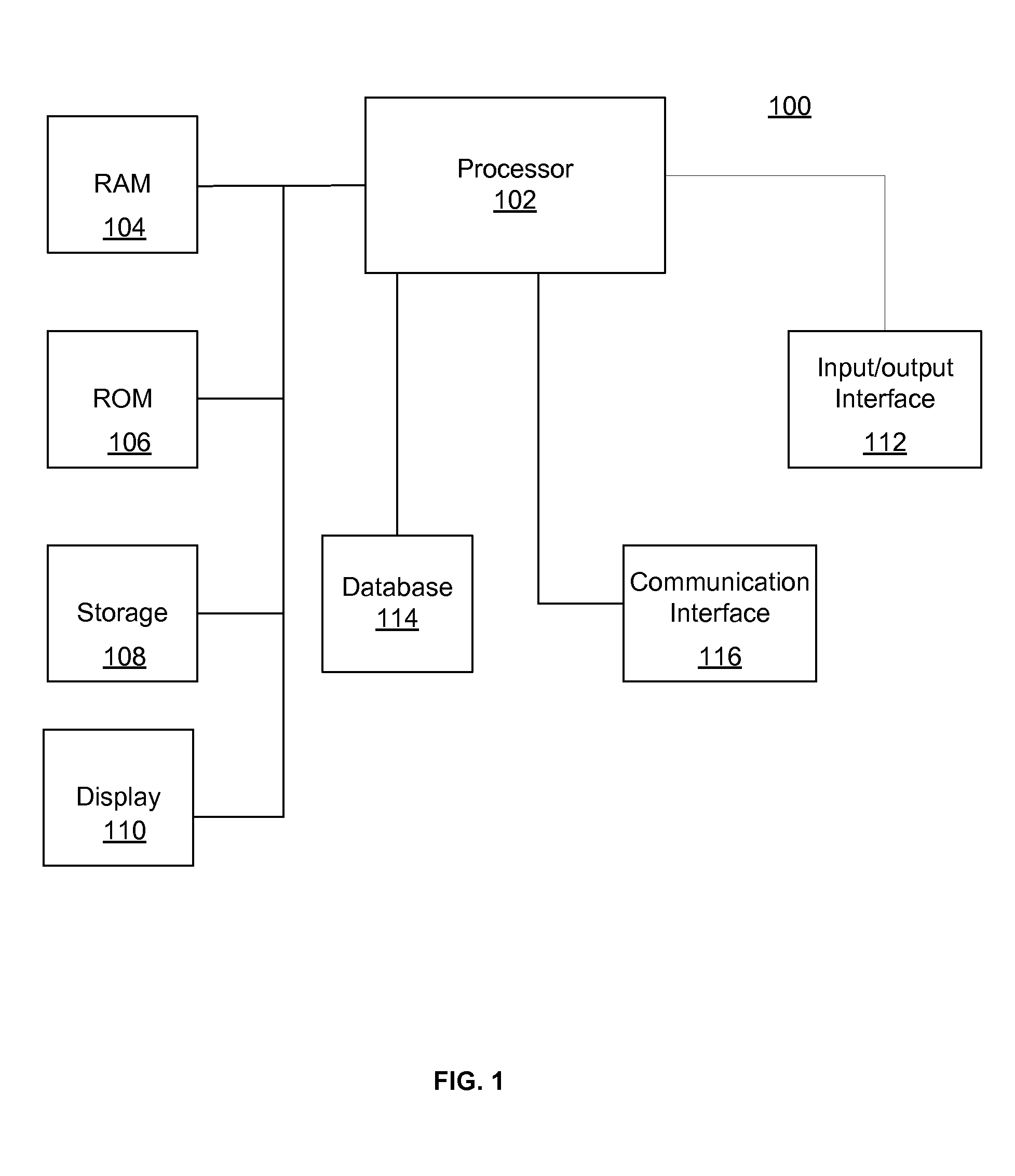

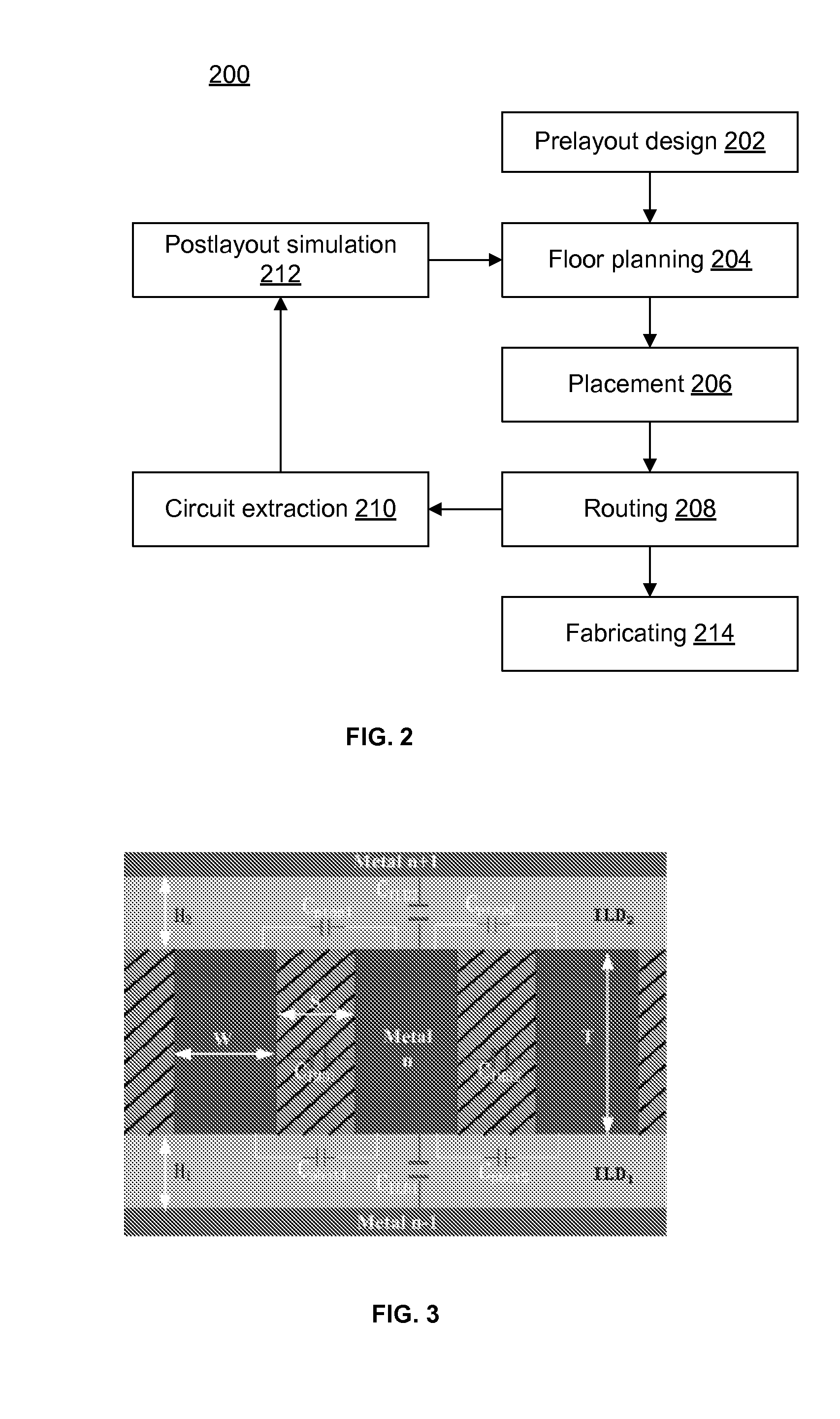

Integrated circuit (IC) design method with enhanced circuit extraction models

ActiveUS20140351779A1Improve reliabilityCareful calibrationDesign optimisation/simulationCAD circuit designCircuit extractionEngineering

A method is provided for designing an IC chip. The method includes receiving data from a pre-layout design process for the IC chip, routing a plurality of interconnecting wires to connect various devices of the IC chip, and extracting various circuit parameters. The method also includes simulating the IC chip using the extracted various circuit parameters to detect logic or timing error in the IC chip. The extracting the various circuit parameters includes establishing a statistical interconnect technology profile (ITP) file containing at least interconnect parasitic parameters based on correlations of interconnect layer geometric parameter variations.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

Method and apparatus for facilitating variation-aware parasitic extraction

ActiveUS7587691B2Generate accuratelyDetecting faulty computer hardwareDesign optimisation/simulationElectricityProperty value

One embodiment of the present invention provides a system for determining an electrical property for an interconnect layer. During operation, the system receives interconnect technology data which includes nominal parameter values for a first interconnect layer, and parameter-variation values which represent variations in the nominal parameter values due to random process variations. Next, the system receives an interconnect template which describes the geometry of a portion of a second interconnect layer. The system then determines electrical property data for the interconnect template using the interconnect technology data. The electrical property data can include a nominal electrical property value, and sensitivity values which represent the sensitivities of the nominal electrical property value to variations in the nominal parameter values. Next, the system stores the electrical property data and the interconnect technology data in a storage.

Owner:SYNOPSYS INC

Nanoelectronic and microelectronic cleaning compositions

InactiveUS7767636B2Improve compatibilityImproved and superior cleaning and stripping photoresistElectrostatic cleaningOrganic/inorganic per-compounds compounding agentsIridiumDielectric

Nanoelectronic and microelectronic cleaning corn positions for cleaning nanoelectronic and microelectronic substrates under supercritical fluid state conditions, and particularly cleaning compositions useful with and having improved compatibility with nanoelectronic and microelectronic substrates characterized by silicon dioxide, sensitive low-n or high-K dielectrics and copper, tungsten, tantalum, nickel, gold, cobalt, palladium, platinum, chromium, ruthenium, rhodium, iridium, hafnium, titanium, molybdenum, tin and other metallization, as well as substrates of A1 or Al(Cu) metallizations and advanced interconnect technologies, are provided by nanoelectronic and microelectronic cleaning compositions.

Owner:AVANTOR PERFORMANCE MATERIALS LLC

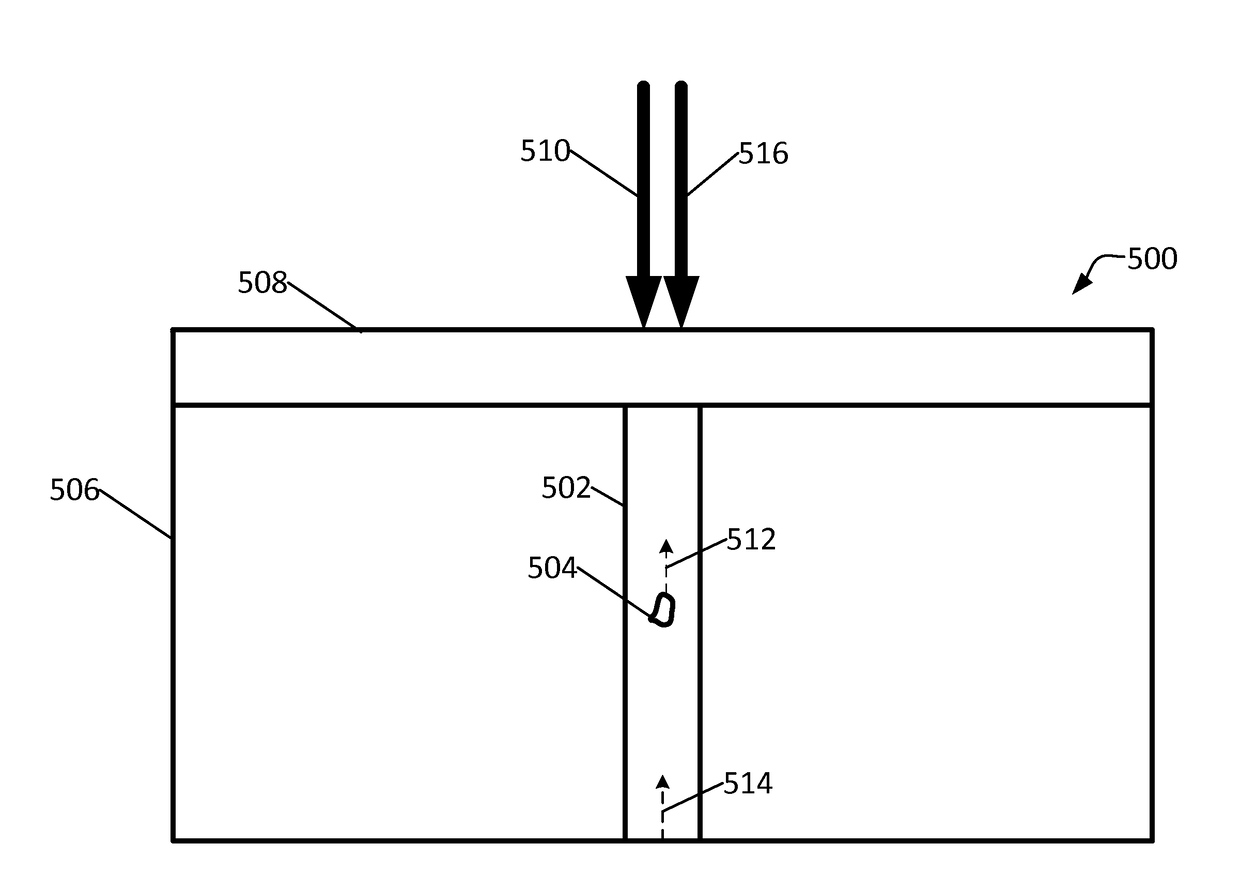

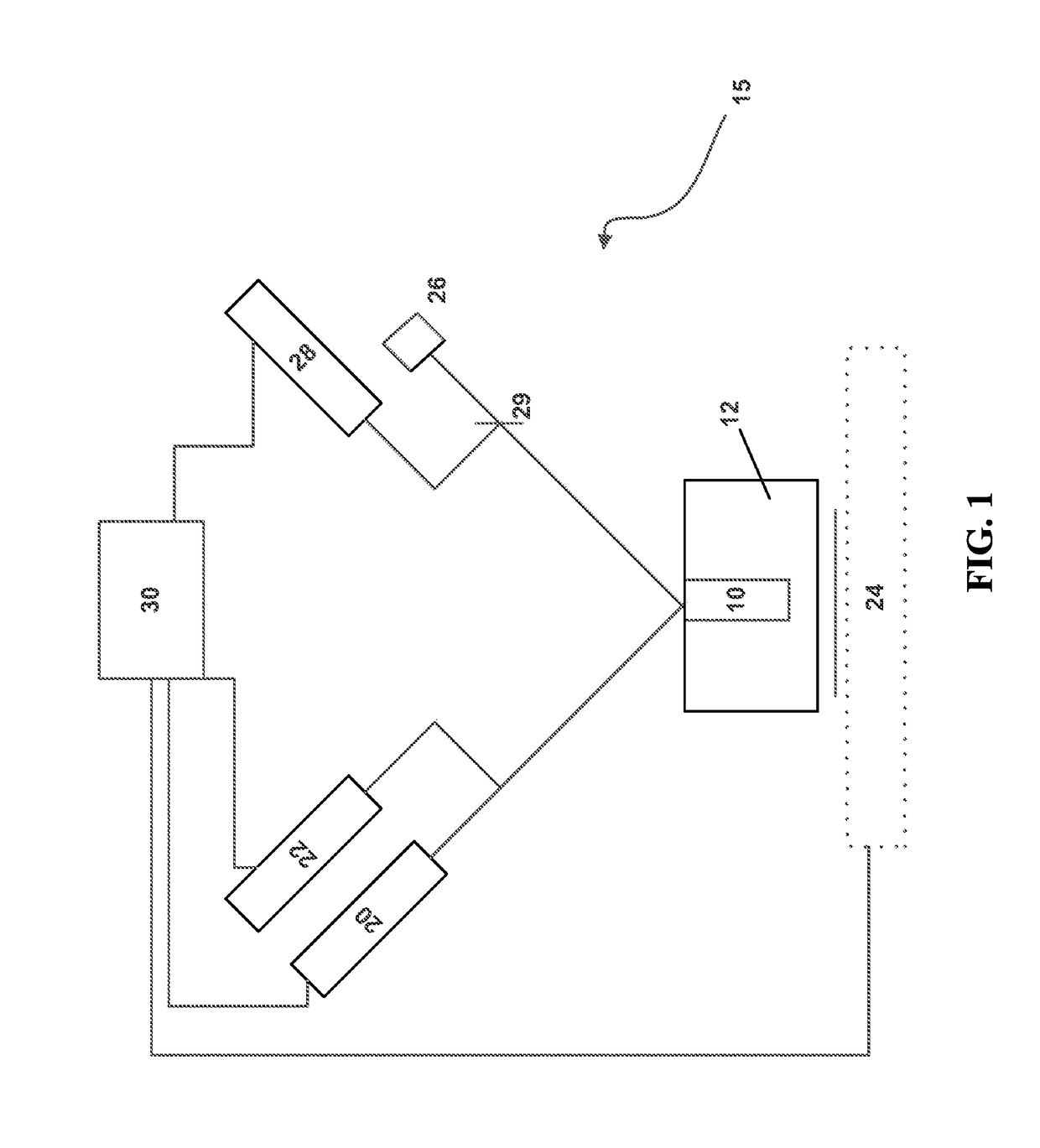

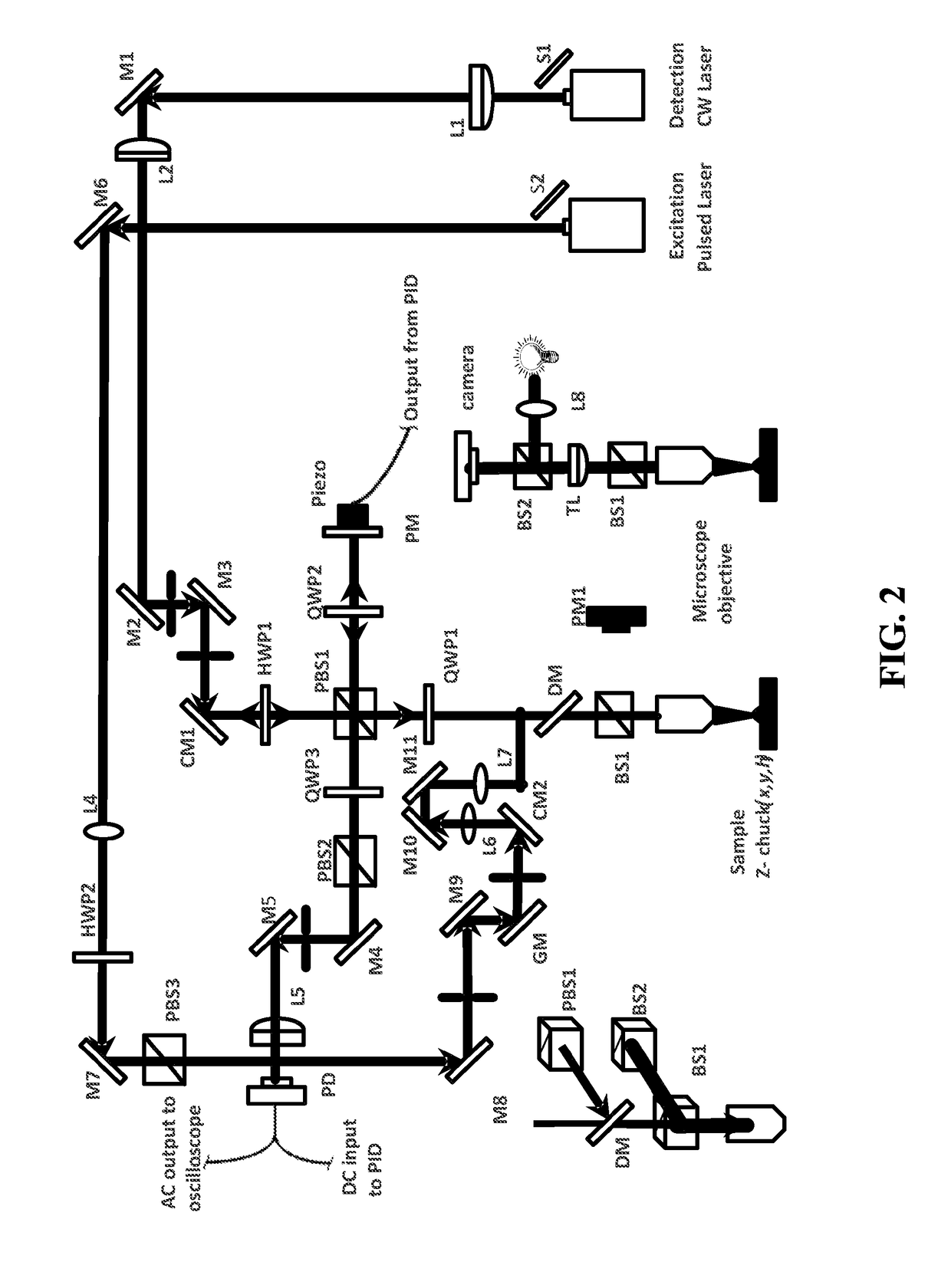

Non-destructive acoustic metrology for void detection

ActiveUS20170221778A1Improve performanceData transfer speed is fastAnalysing solids using sonic/ultrasonic/infrasonic wavesSemiconductor/solid-state device testing/measurementNon destructiveMetrology

Advanced interconnect technologies such as Through Silicon Vias (TSVs) have become an integral part of 3-D integration. Methods and systems and provided for laser-based acoustic techniques in which a short laser pulse generates broadband acoustic waves that propagate in the TSV structure. An optical interferometer detects the surface displacement caused by the acoustic waves reflecting within the structure as well as other acoustic waves traveling near the surface that has information about the structure dimensions and irregularities, such as voids. Features of voids, such as their location, are also identified based on the characteristics of the acoustic wave as it propagates through the via. Measurements typically take few seconds per site and can be easily adopted for in-line process monitoring.

Owner:UNIV OF COLORADO THE REGENTS OF +1

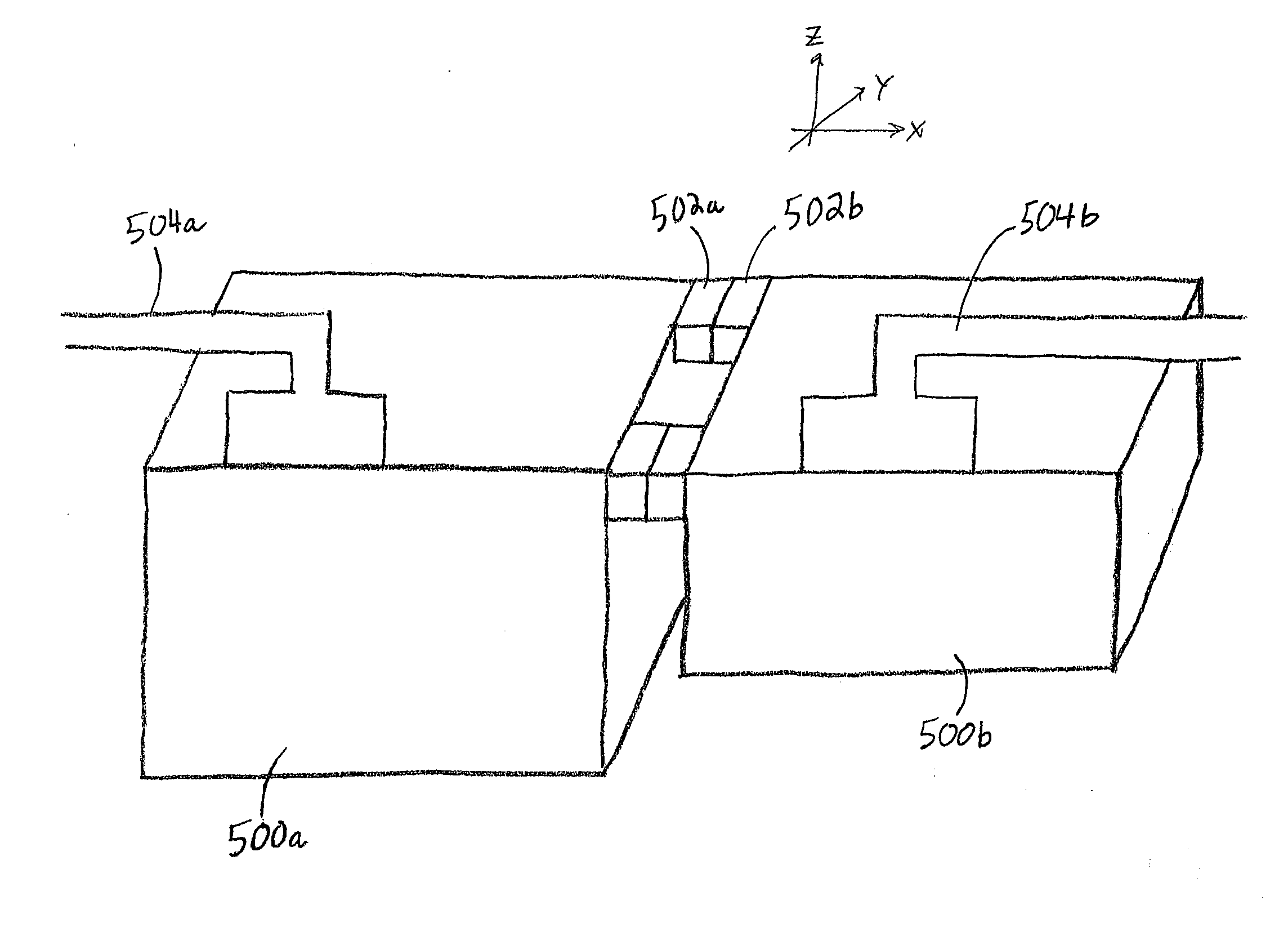

Assembling and Handling Edge Interconnect Packaging System

ActiveUS20140268592A1Printed circuit assemblingFinal product manufactureMechanical engineeringInterconnect technology

Apparatuses and methods related to the field of microchip assembly and handling, in particular to devices and methods for assembling and handling microchips manufactured with solid edge-to-edge interconnects, such as Quilt Packaging® interconnect technology. Specialized assembly tools are configured to pick up one or more microchips, place the microchips in a specified location aligned to a substrate, package, or another microchip, and facilitate electrical contact through one of a variety of approaches, including solder reflow. This specialized assembly tooling performs heating functions to reflow solder to establish electrical and mechanical interconnections between multiple microchips. Additionally, the interconnected microchips may be arranged in an arbitrarily large array.

Owner:INDIANA INTEGRATED CIRCUITS

Alignment verification for c4np solder transfer

InactiveUS20090181533A1Solid-state devicesSemiconductor/solid-state device manufacturingCost effectivenessCopper

A method is provided for the making of interconnect solder bumps on a wafer or other electronic device. The method is particularly useful for the well-known C4NP interconnect technology and determines if any off-set resulted between the solder mold array and the wafer capture array during the transfer process. The amount of off-set enables the operator to adjust the transfer tool before solder transfer to compensate for the off-set caused by the transfer process and provides a more cost-effective and efficient solder transfer process. A solder reactive material surrounding the capture pads is used to determine where the solder reacts with the solder reactive material showing the off-set resulting from the transfer process. Copper is a preferred solder reactive material.

Owner:IBM CORP

Process for making interconnect solder Pb-free bumps free from organo-tin/tin deposits on the wafer surface

A method is provided for making of interconnect solder bumps on a wafer or other electronic device without depositing any significant amount of tin or other solder component from the solder onto the wafer surface which tin can cause shorts or other defects in the wafer. The method is particularly useful for well-known C4NP interconnect technology. In one aspect of the invention, a reducing gas flow rate is used to remove oxides from the solder surfaces and wafer pad surfaces and is of a sufficient determined or pre-determined flow and / or chamber or mold / wafer spacing to provide a gas velocity across the solder surfaces and wafer pad surfaces so that Sn or other contaminants do not deposit on the wafer surface during solder transfer. In another aspect, the transfer contact is performed below the melting point of the solder and subsequently heated to above the melting temperature while in transfer contact. The heated solder in contact with the wafer pads is transferred to the wafer pads.

Owner:ULTRATECH INT INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com