Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

100results about How to "Improve circuit reliability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

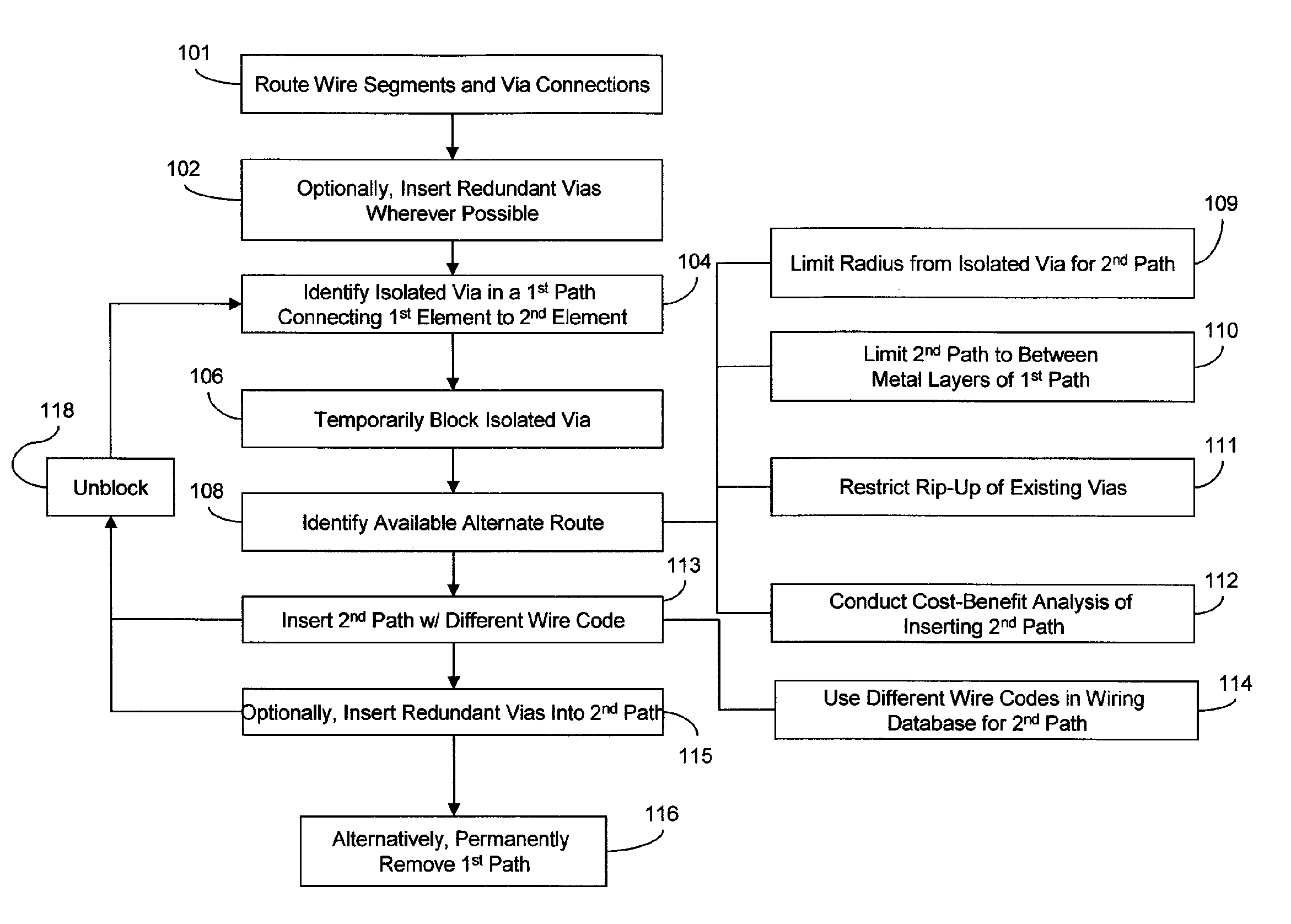

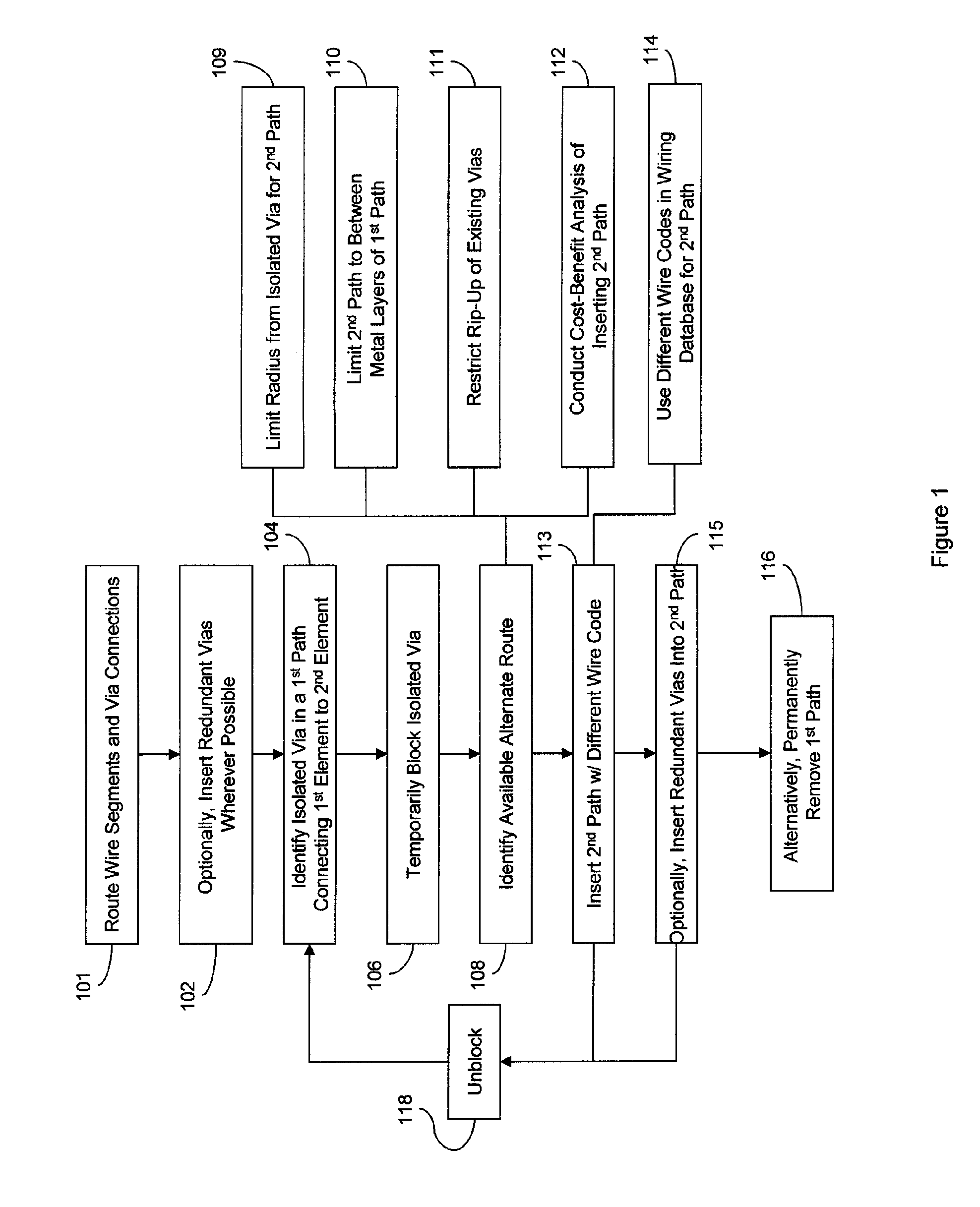

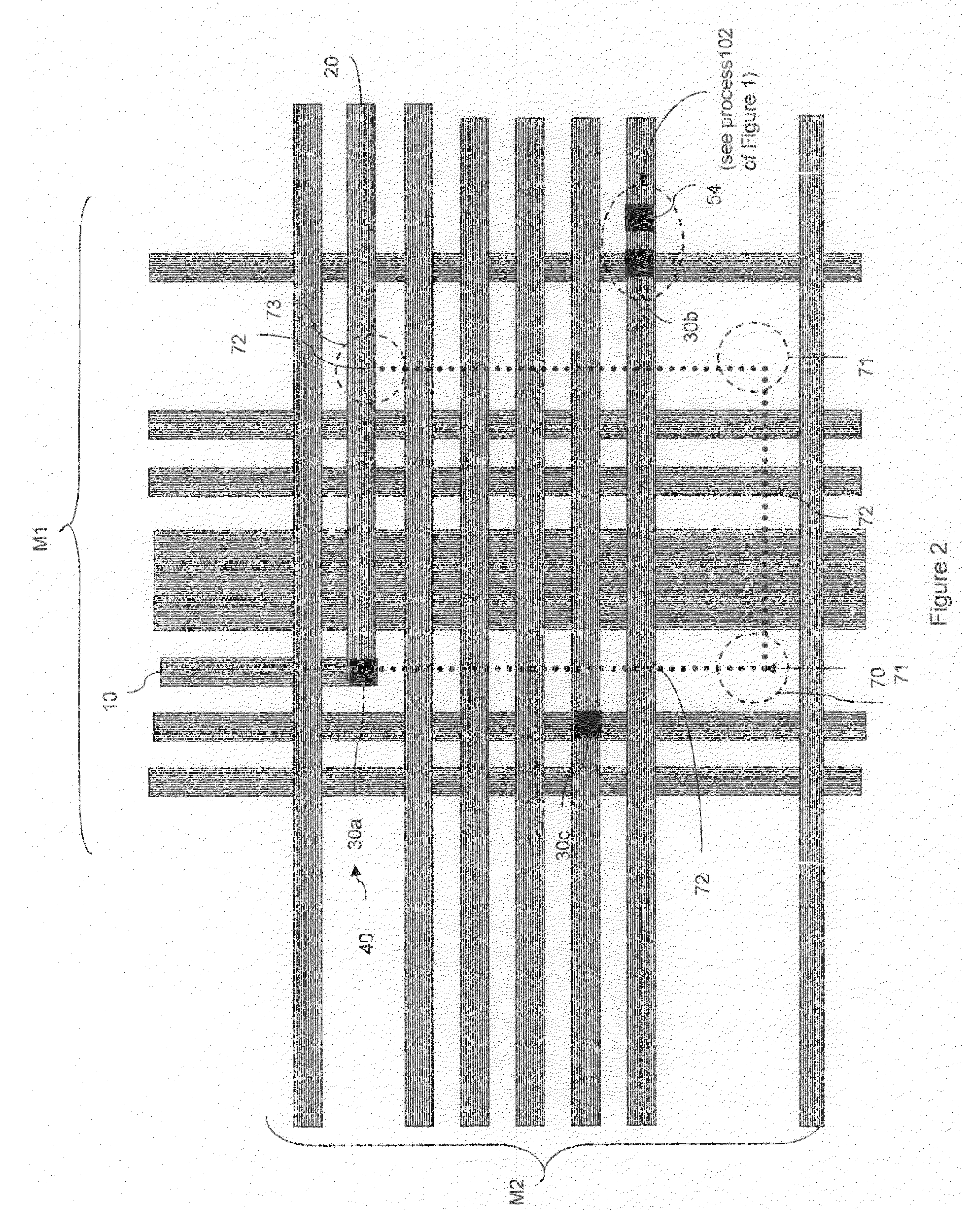

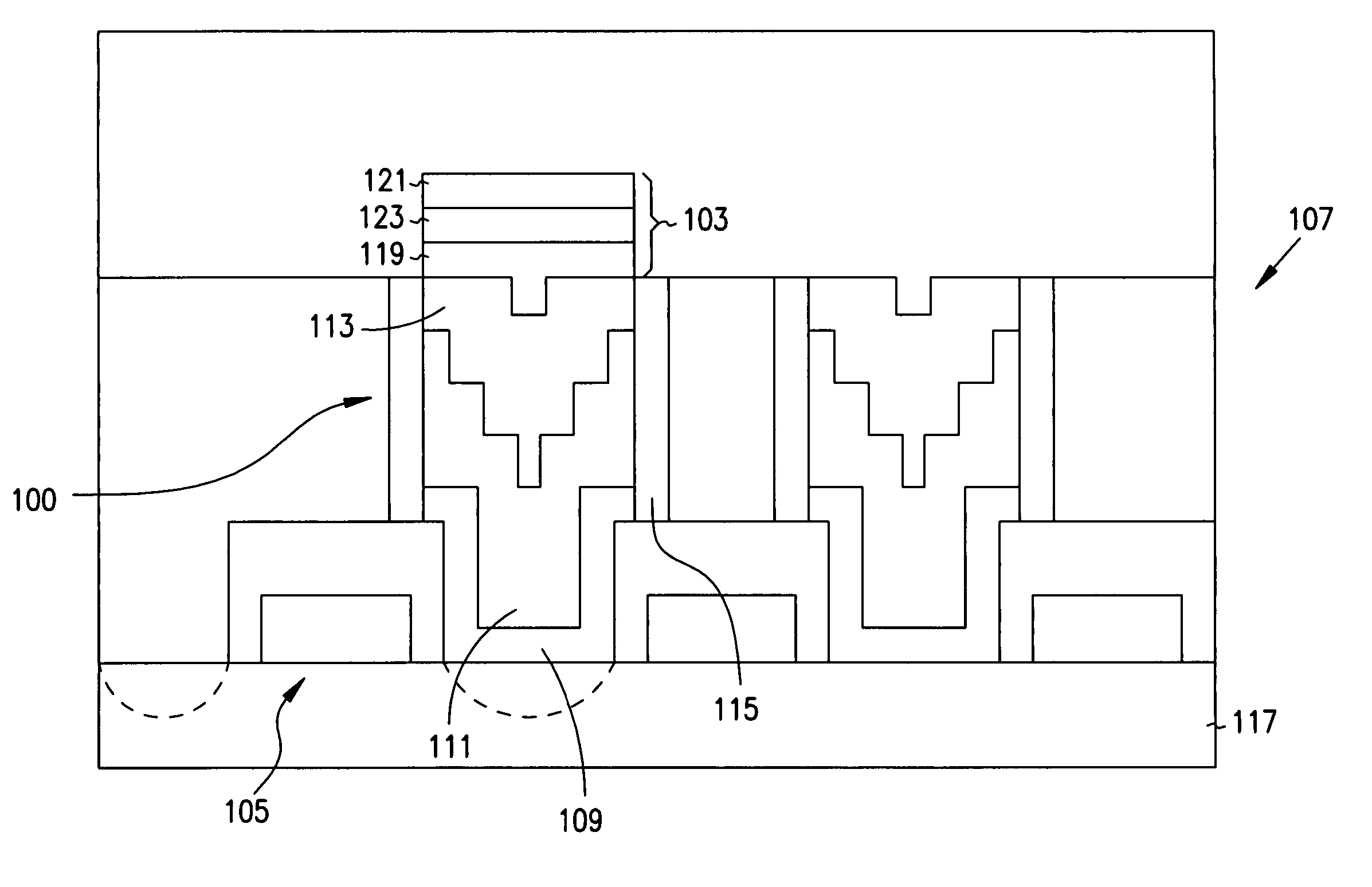

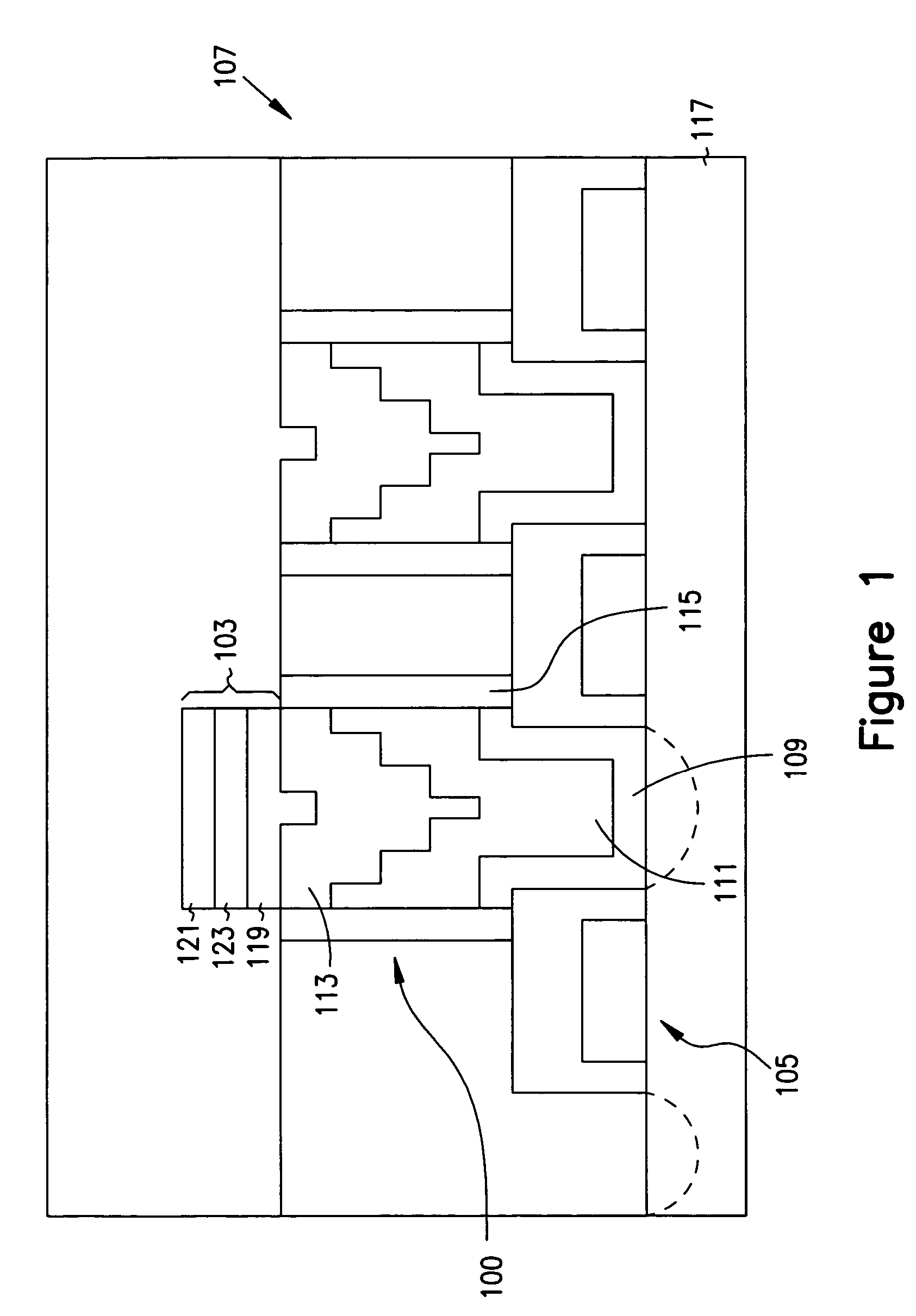

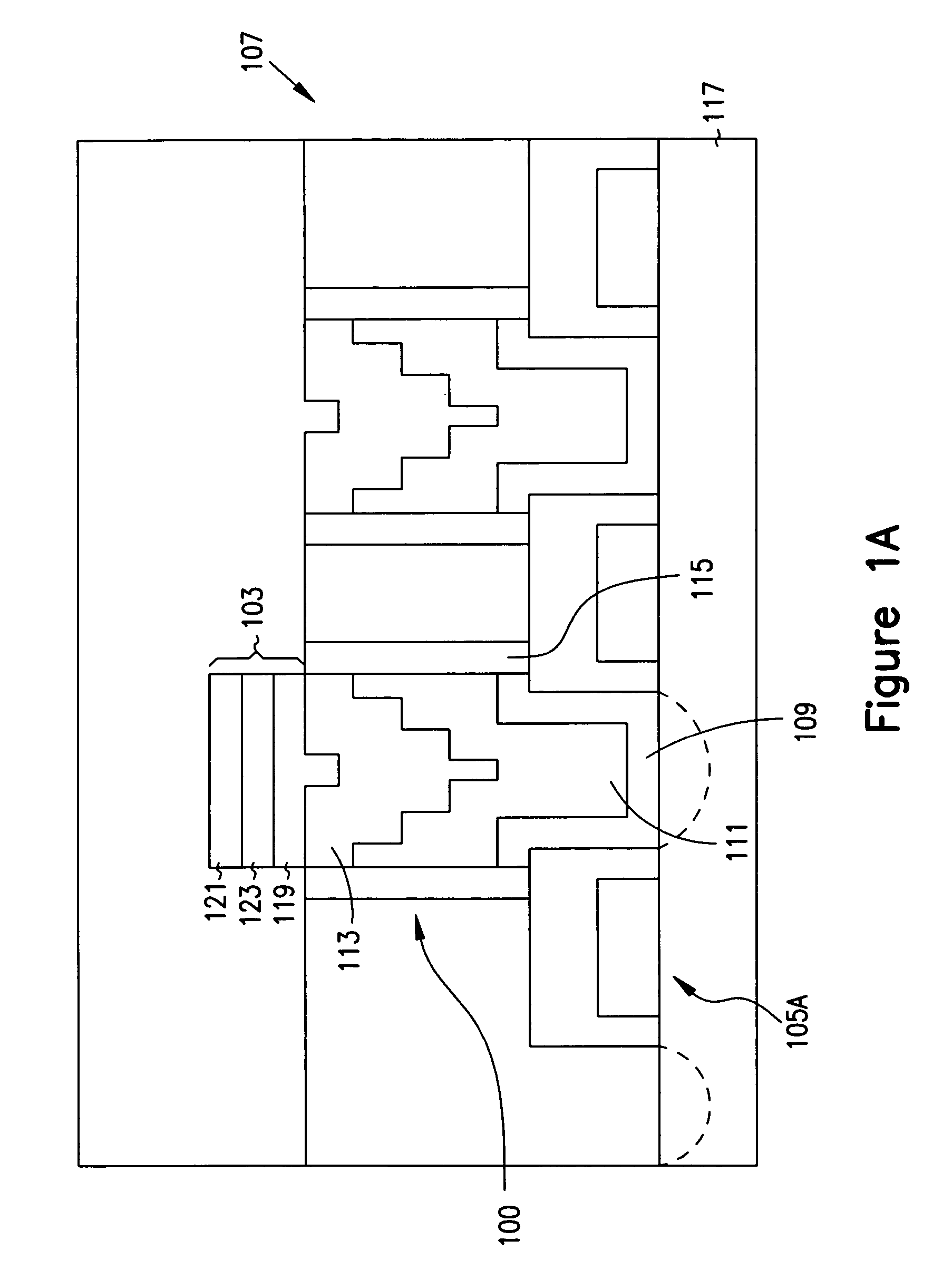

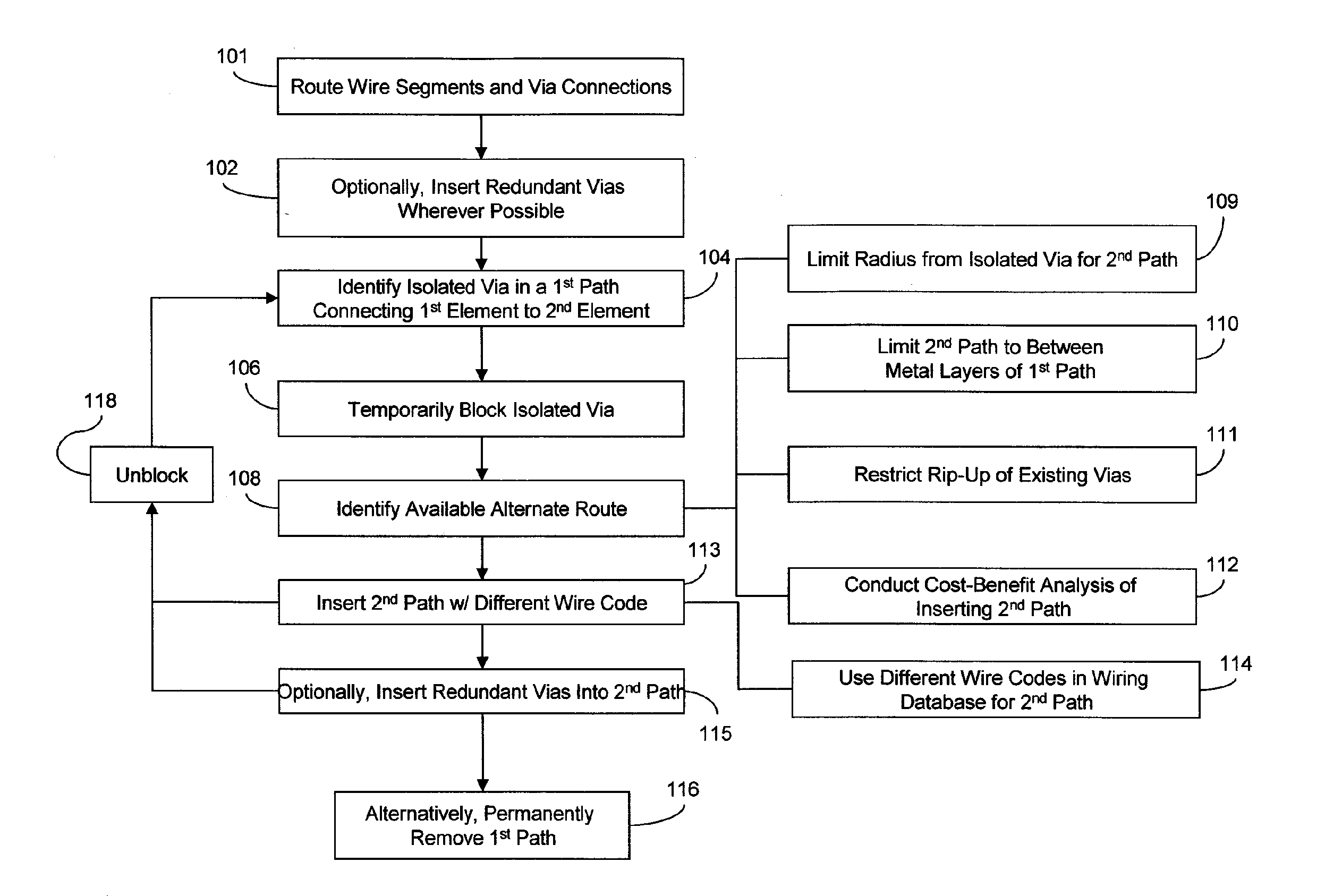

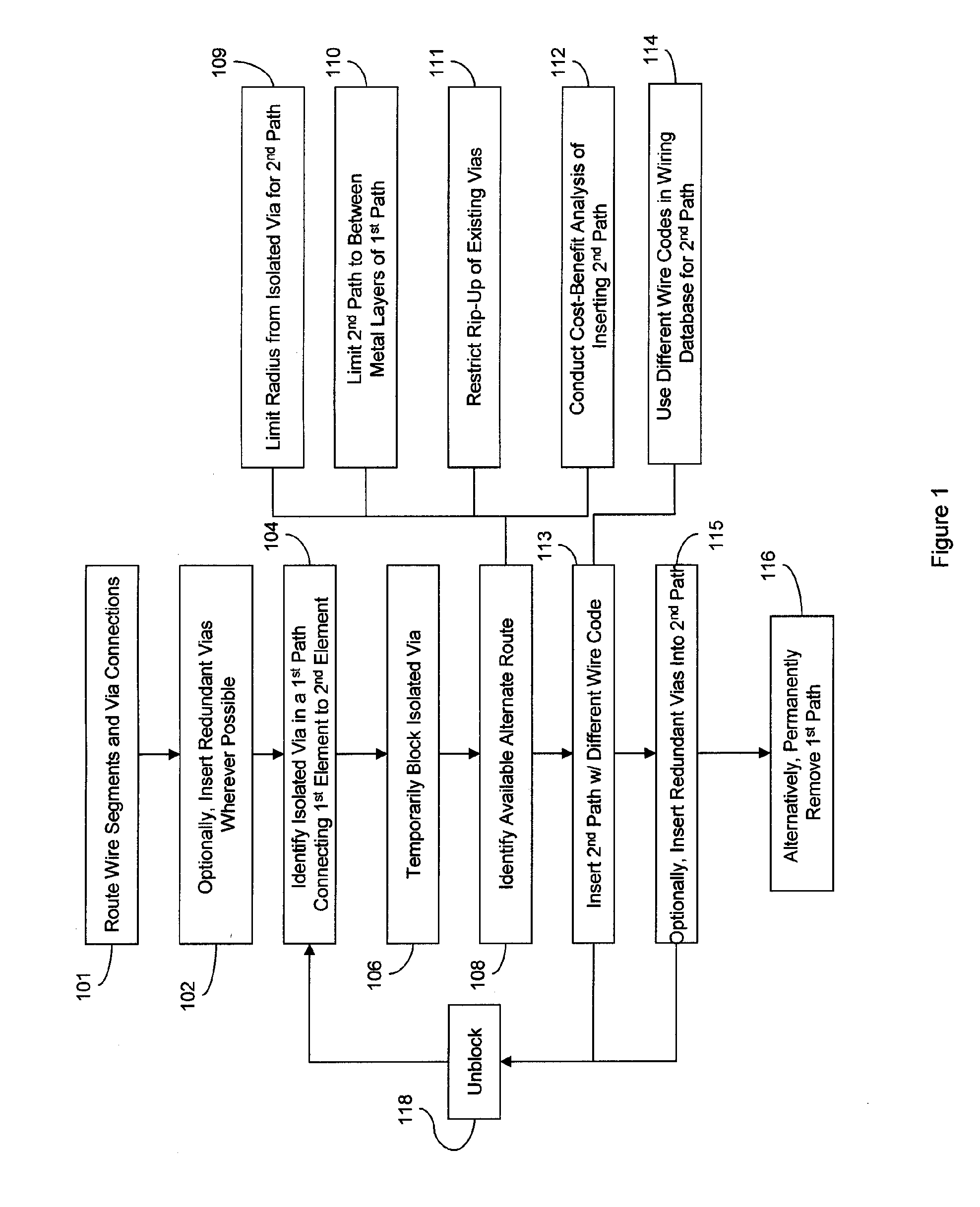

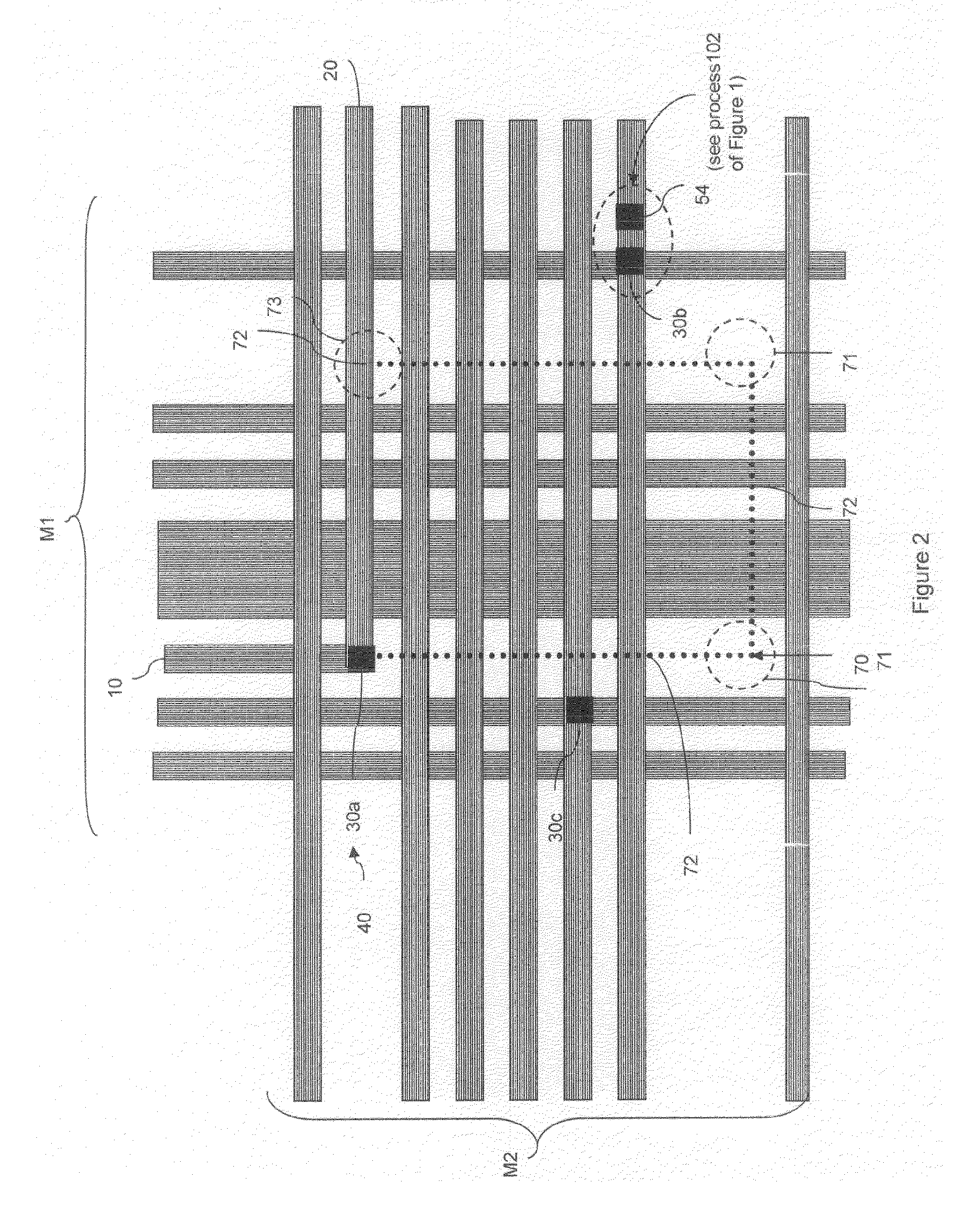

Use of redundant routes to increase the yield and reliability of a VLSI layout

ActiveUS7308669B2Increase redundancyReduce sensitivityCAD circuit designSoftware simulation/interpretation/emulationEngineeringVlsi layout

Disclosed is a method and system for inserting redundant paths into an integrated circuit. Particularly, the invention provides a method for identifying a single via in a first path connecting two elements, determining if an alternate route is available for connecting the two elements (other than a redundant via), and for inserting a second path into the available alternate route. The combination of the first and second paths provides greater redundancy than inserting a redundant via alone. More importantly, such redundant paths provide for redundancy when congestion prevents a redundant via from being inserted adjacent to the single via. An embodiment of the method further comprises removing the single via and any redundant wire segments, if all of the additional vias used to form the second path can be made redundant.

Owner:GLOBALFOUNDRIES US INC

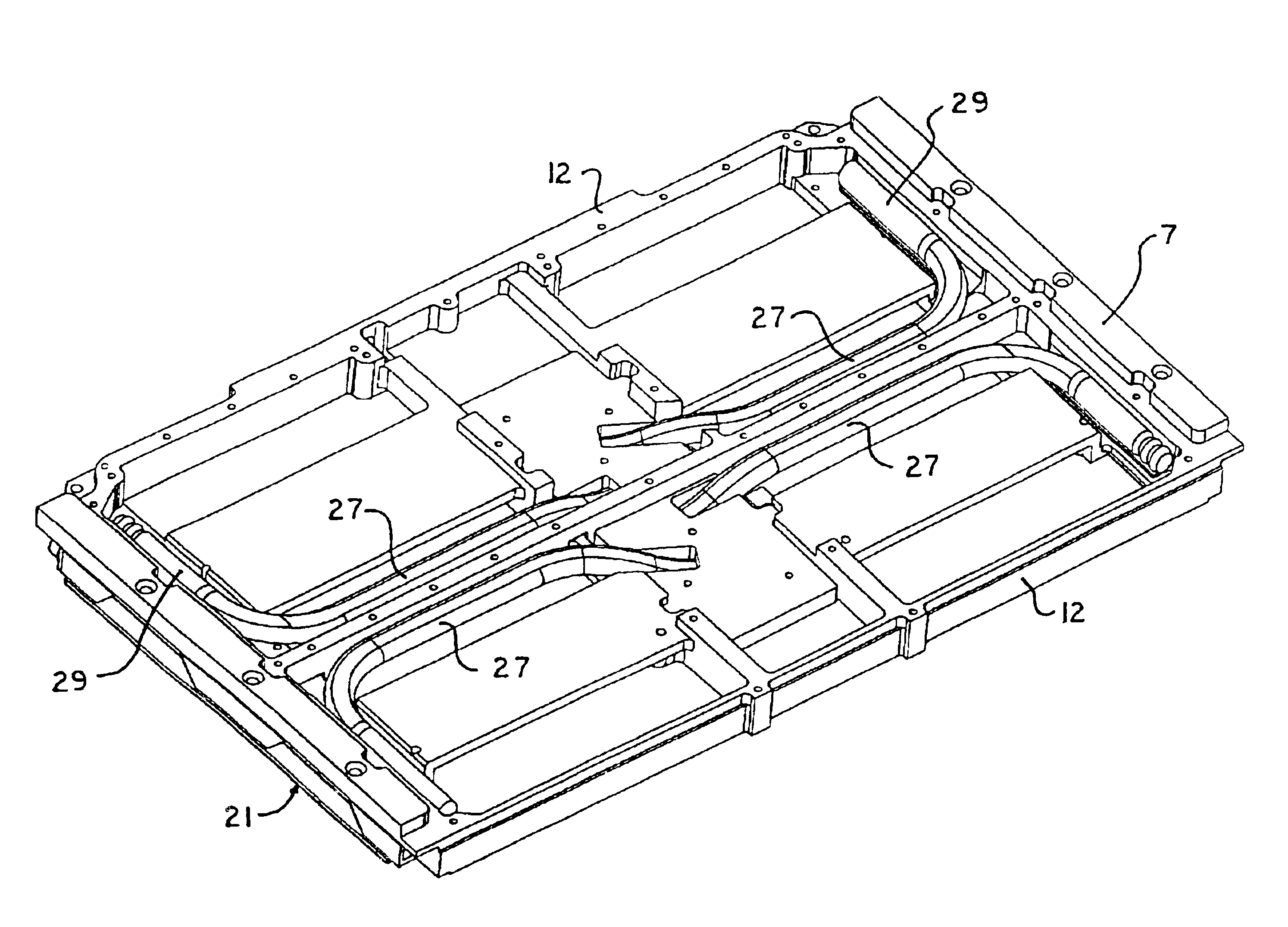

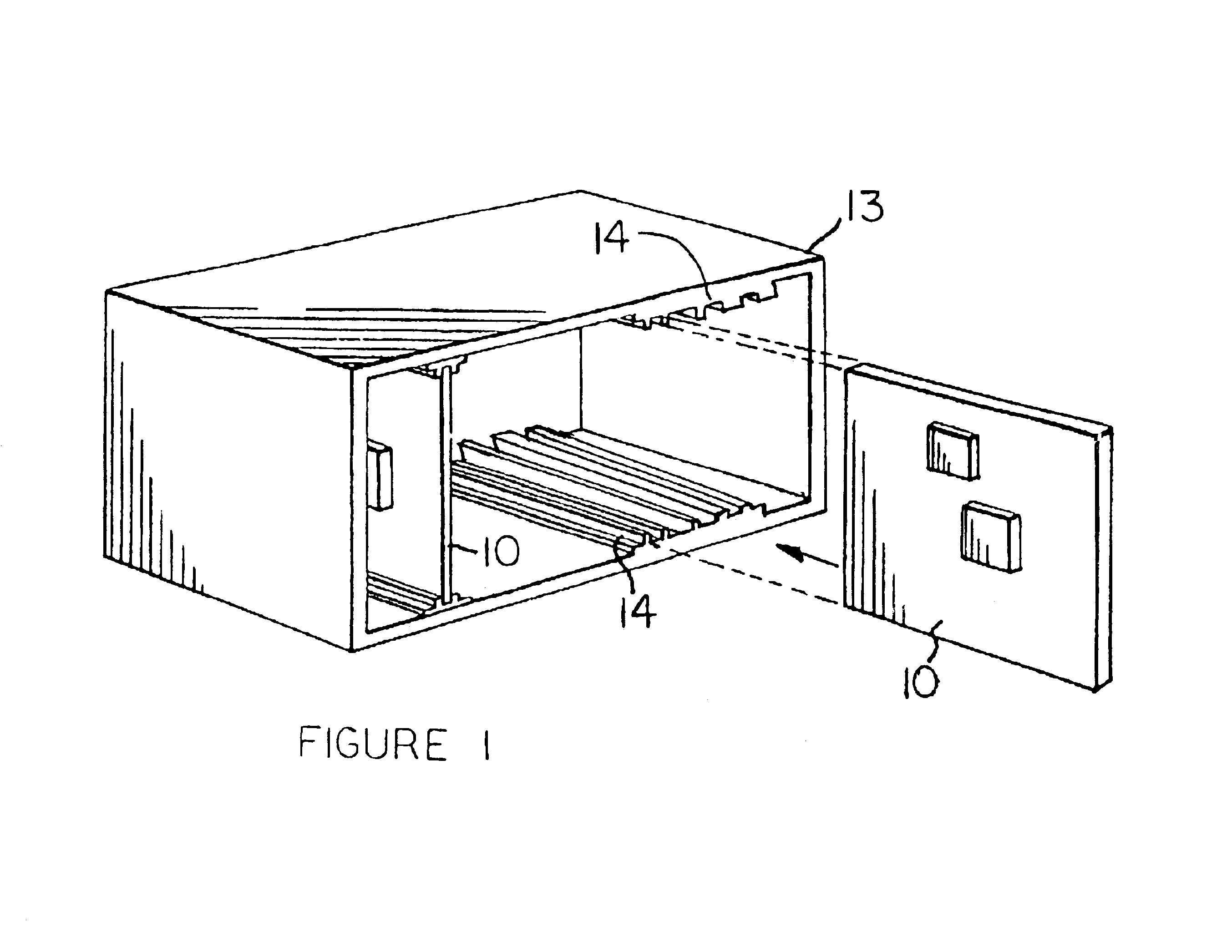

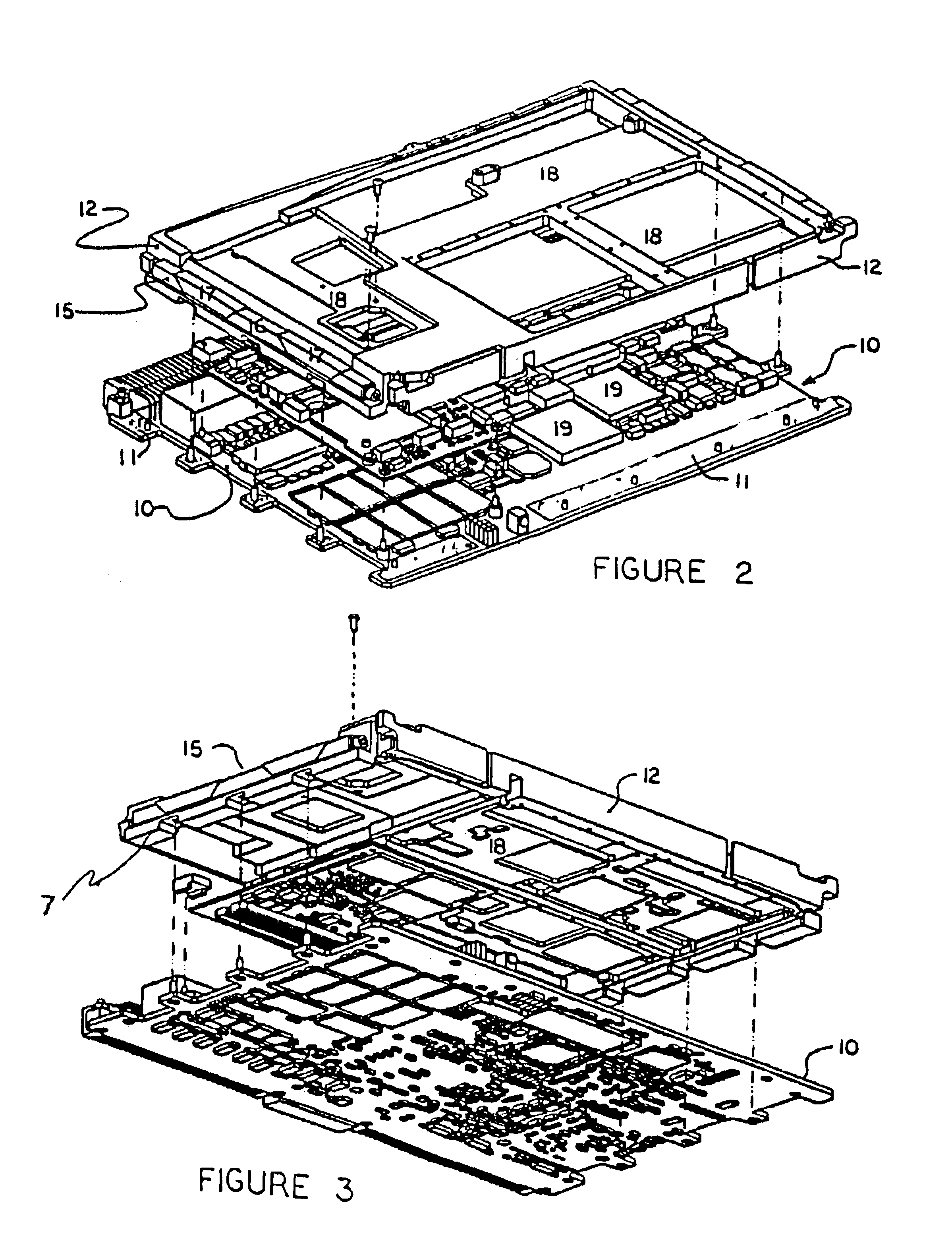

Embedded heat pipe for a conduction cooled circuit card assembly

InactiveUS6839235B2Improve signal integrityReduce electromagnetic radiationSemiconductor/solid-state device detailsSolid-state devicesCollector deviceConduction cooling

One or more heat pipes are connected between a component on a circuit card and the frame of a circuit card assembly for transfer of heat to the frame of the circuit card assembly. Circuit cards are typically held in place in channels in a chassis by an expansion type retention device. The circuit cards also include a heat frame for collecting the heat produced by the card components and channeling the heat from the card through the heat frame to the chassis. The retention device presses the heat frame in to thermal contact with one side of the channel. Heat collector can be attached to the heat generating components of a circuit card between the heat pipe and the component to provide improved thermal transfer. A number of heat collectors with pairs of heat pipes extending in opposite directions from the collector to the frame can be used to allow the heat pipes to effectively dissipate heat form the circuit card assembly regardless of the orientation of the circuit card assembly.

Owner:DY 4 SYST

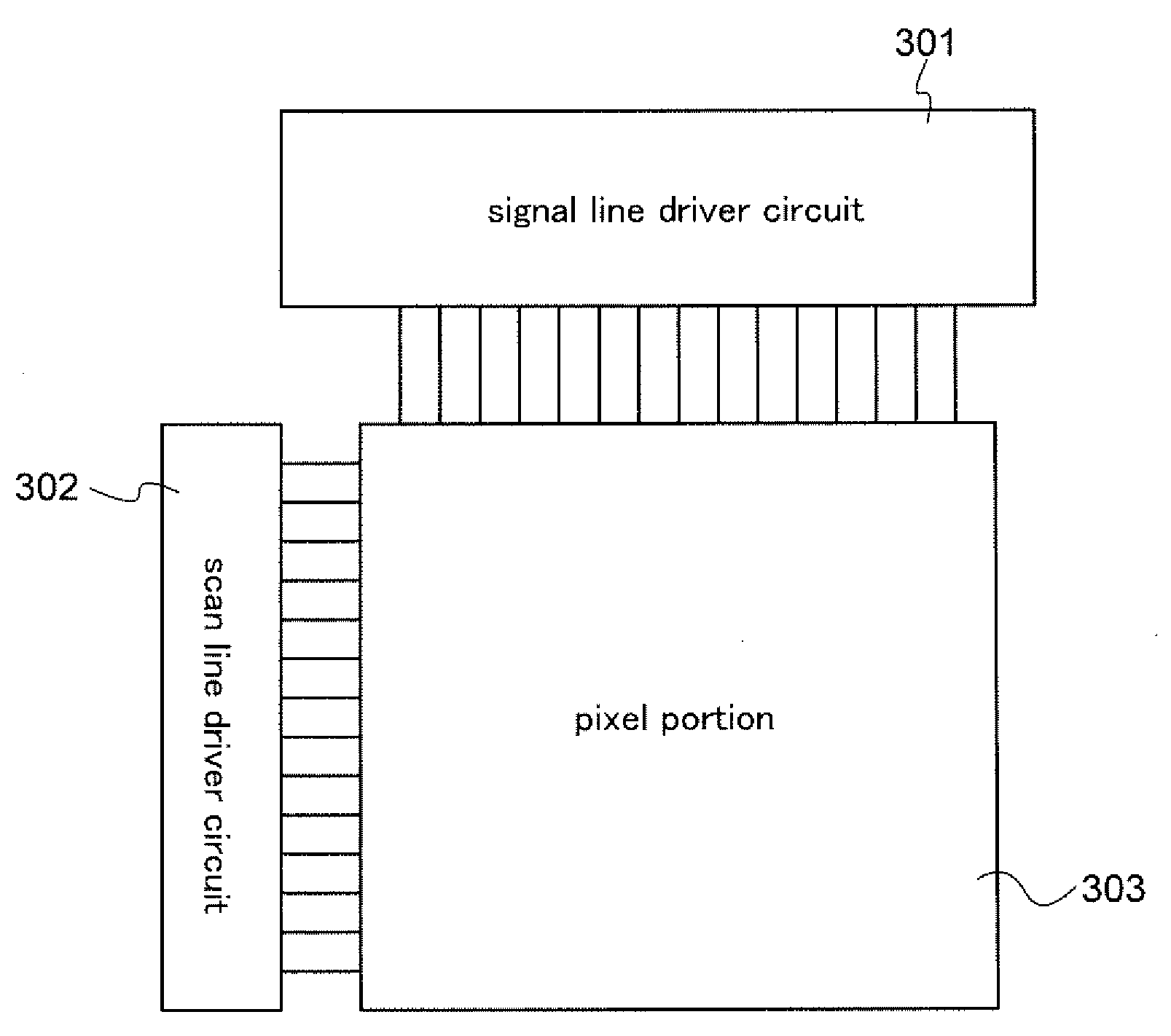

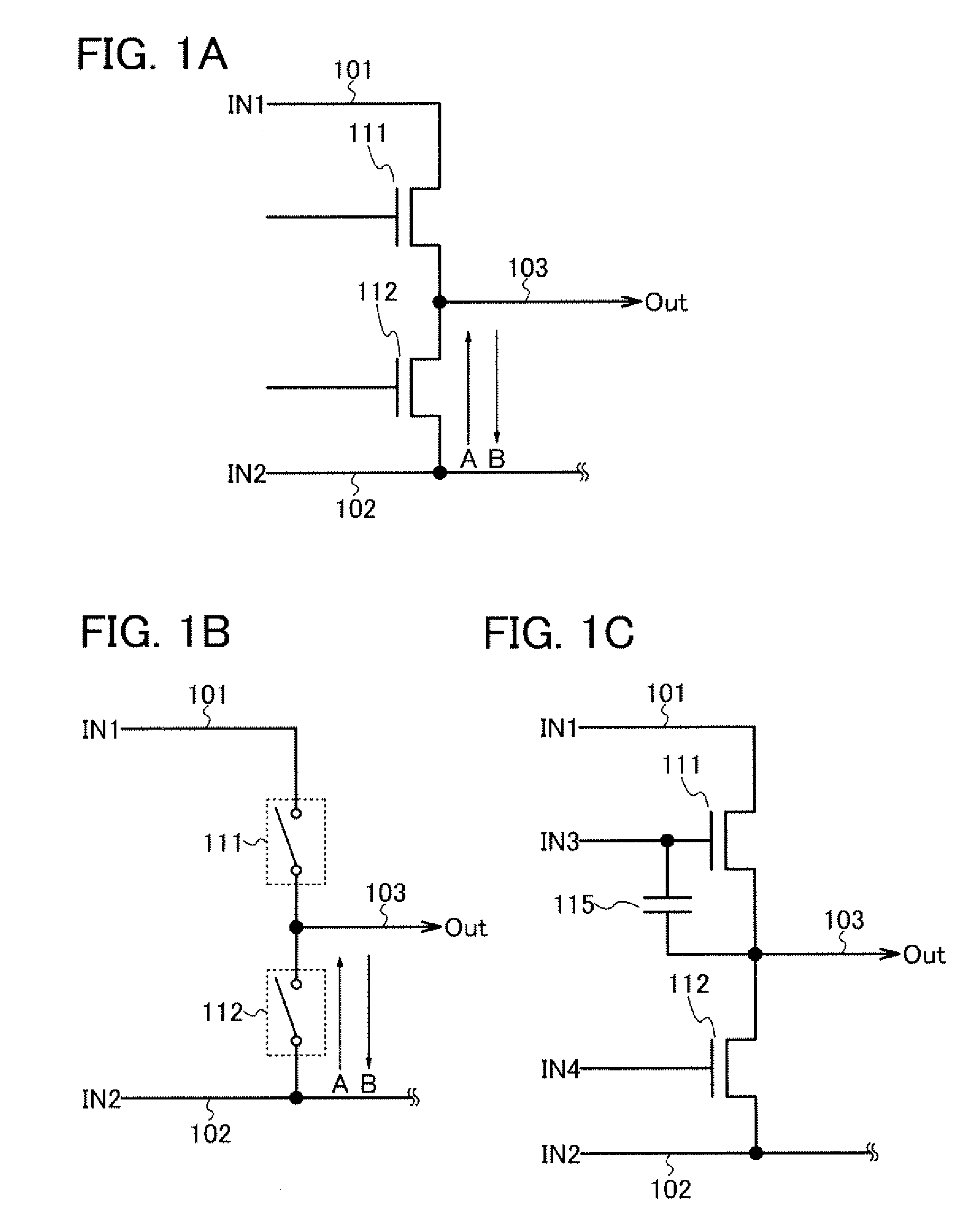

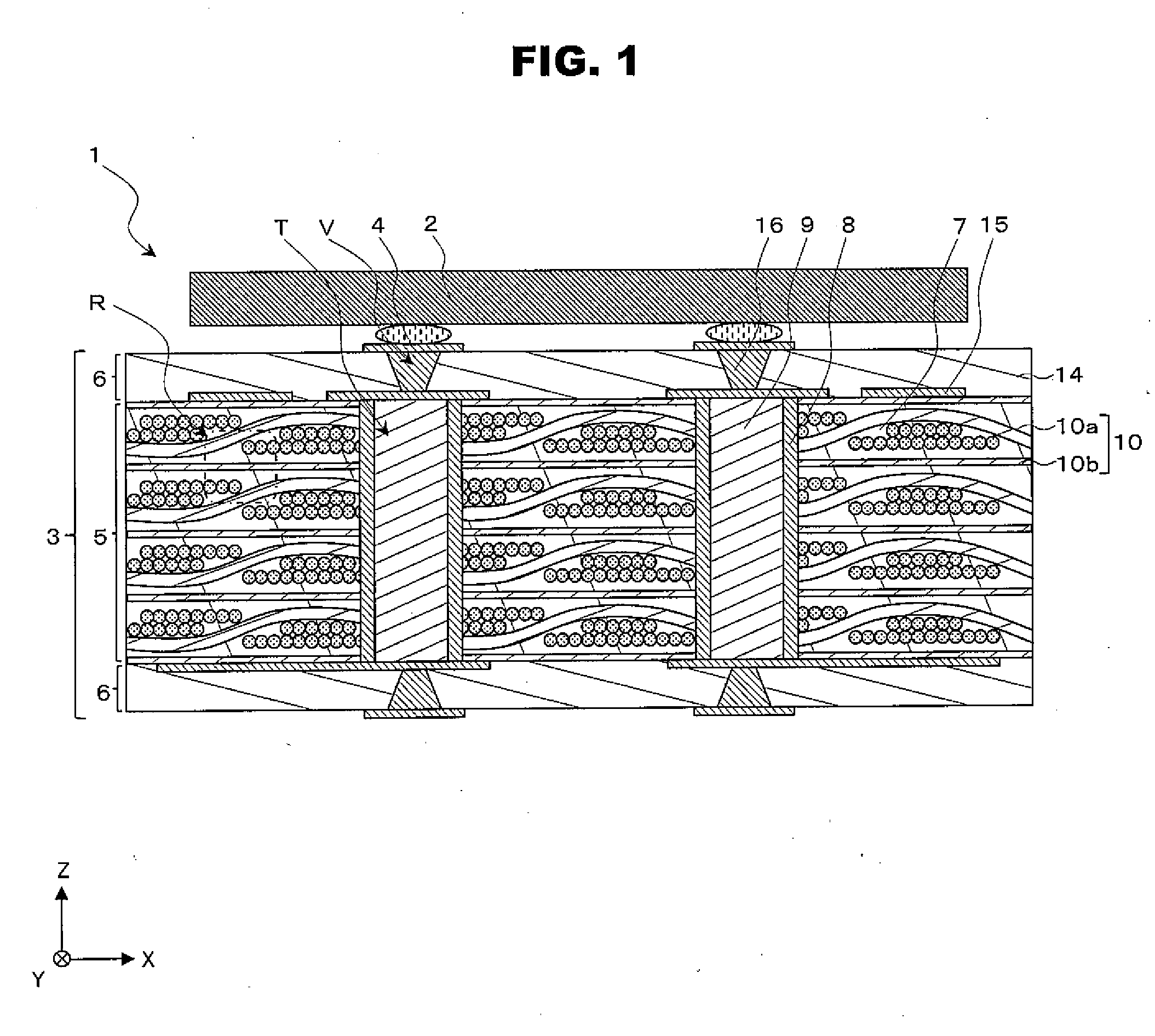

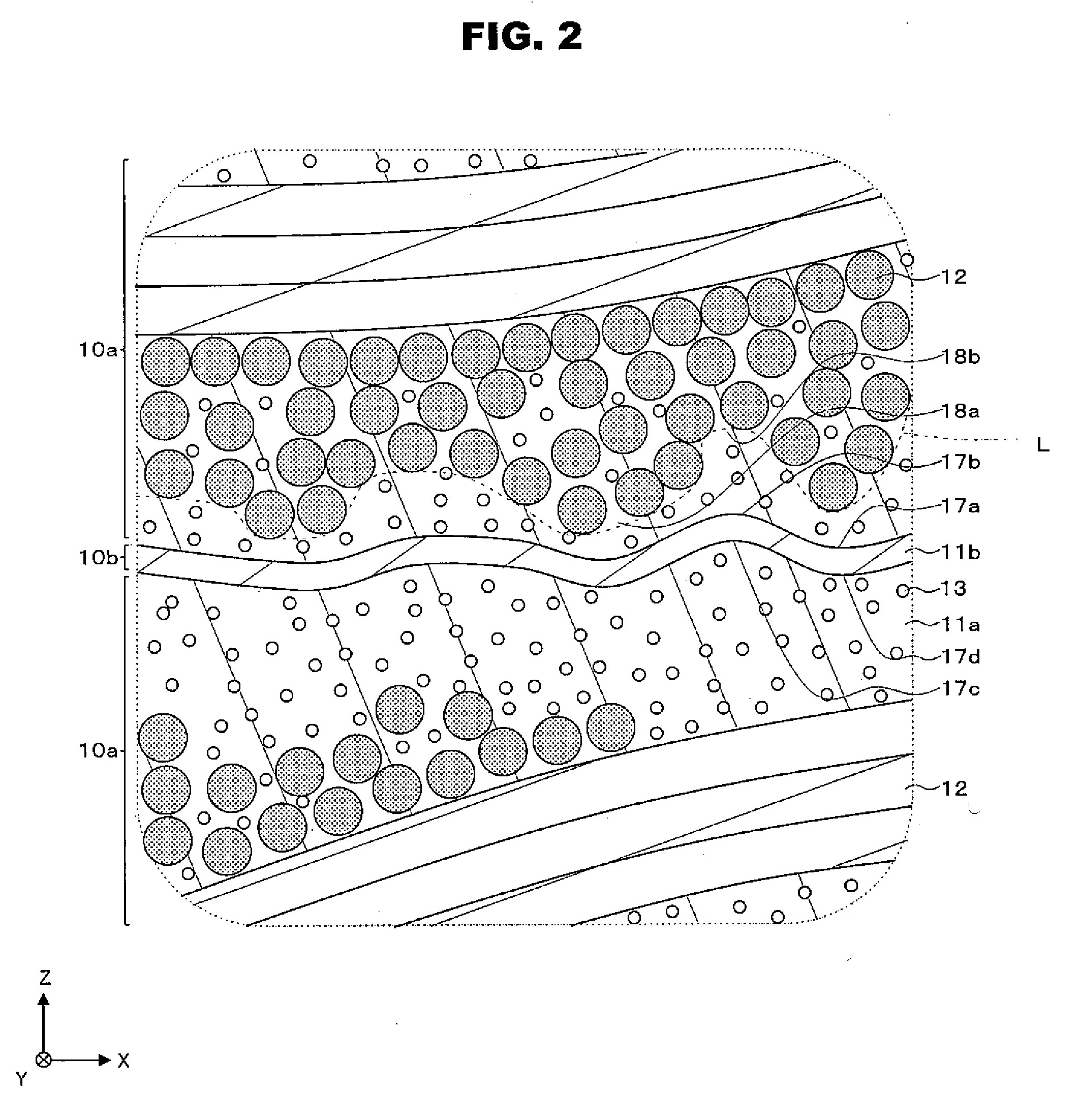

Liquid crystal display device

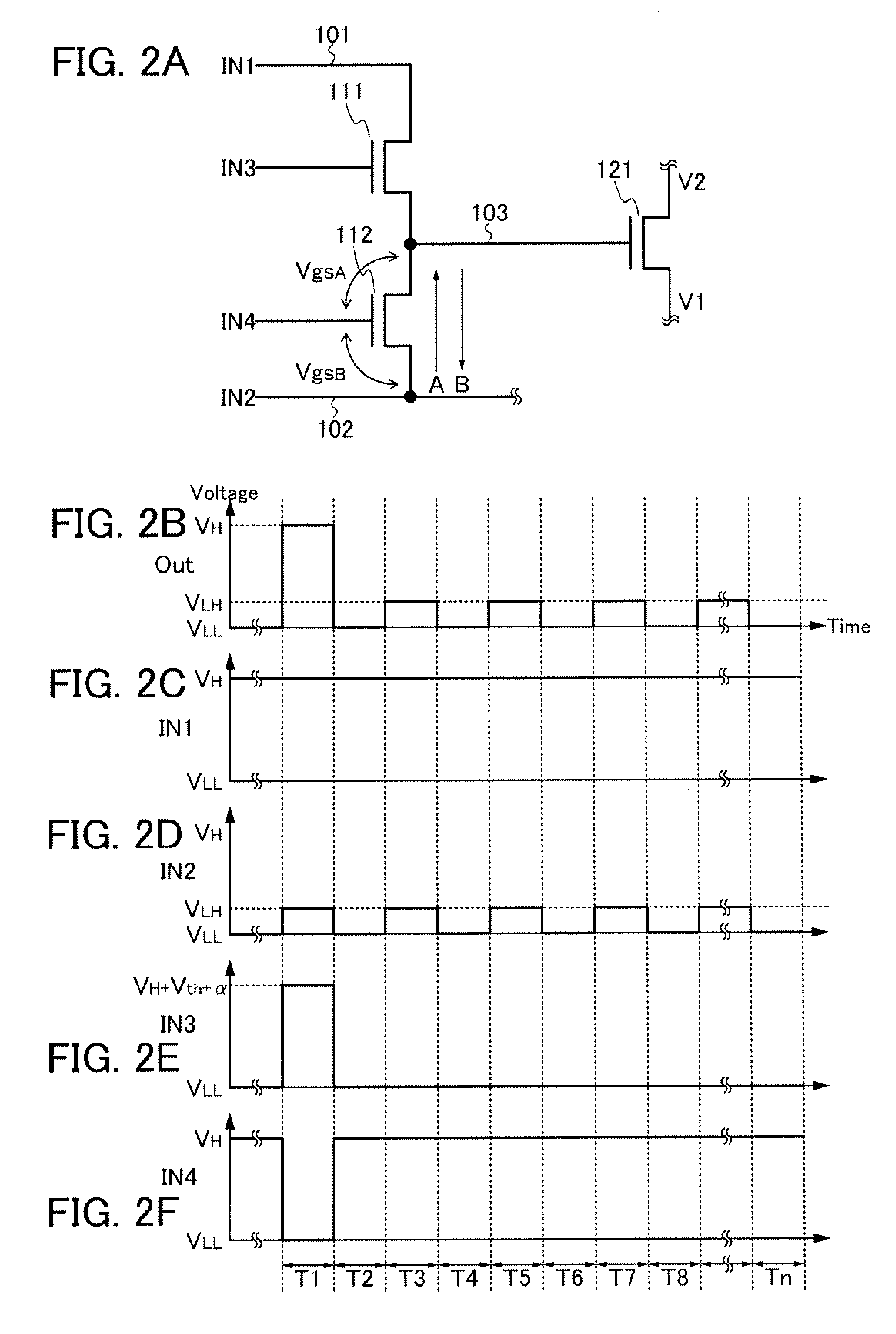

ActiveUS20100123654A1Improve circuit reliabilityImprove reliabilityStatic indicating devicesDigital storageLiquid-crystal displayHemt circuits

To suppress a malfunction of a circuit due to deterioration in a transistor. In a transistor which continuously outputs signals having certain levels (e.g., L-level signals) in a pixel or a circuit, the direction of current flowing through the transistor is changed (inverted). That is, by changing the level of voltage applied to a first terminal and a second terminal (terminals serving as a source and a drain) every given period, the source and the drain are switched every given period. Specifically, in a portion which successively outputs signals having certain levels (e.g., L-level signals) in a circuit including a transistor, L-level signals having a plurality of different potentials (L-level signals whose potentials are changed every given period) are used as the signals having certain levels.

Owner:SEMICON ENERGY LAB CO LTD

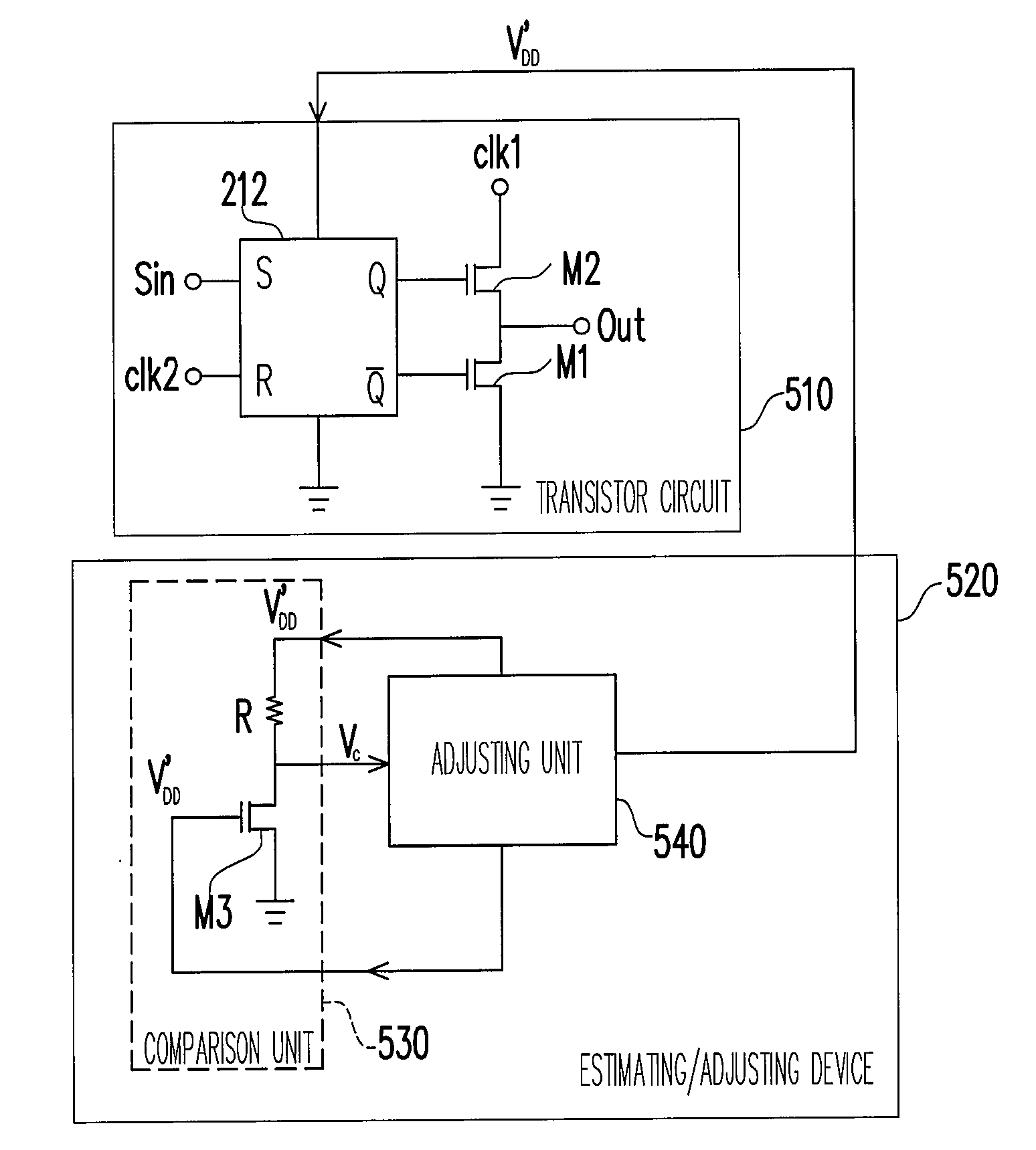

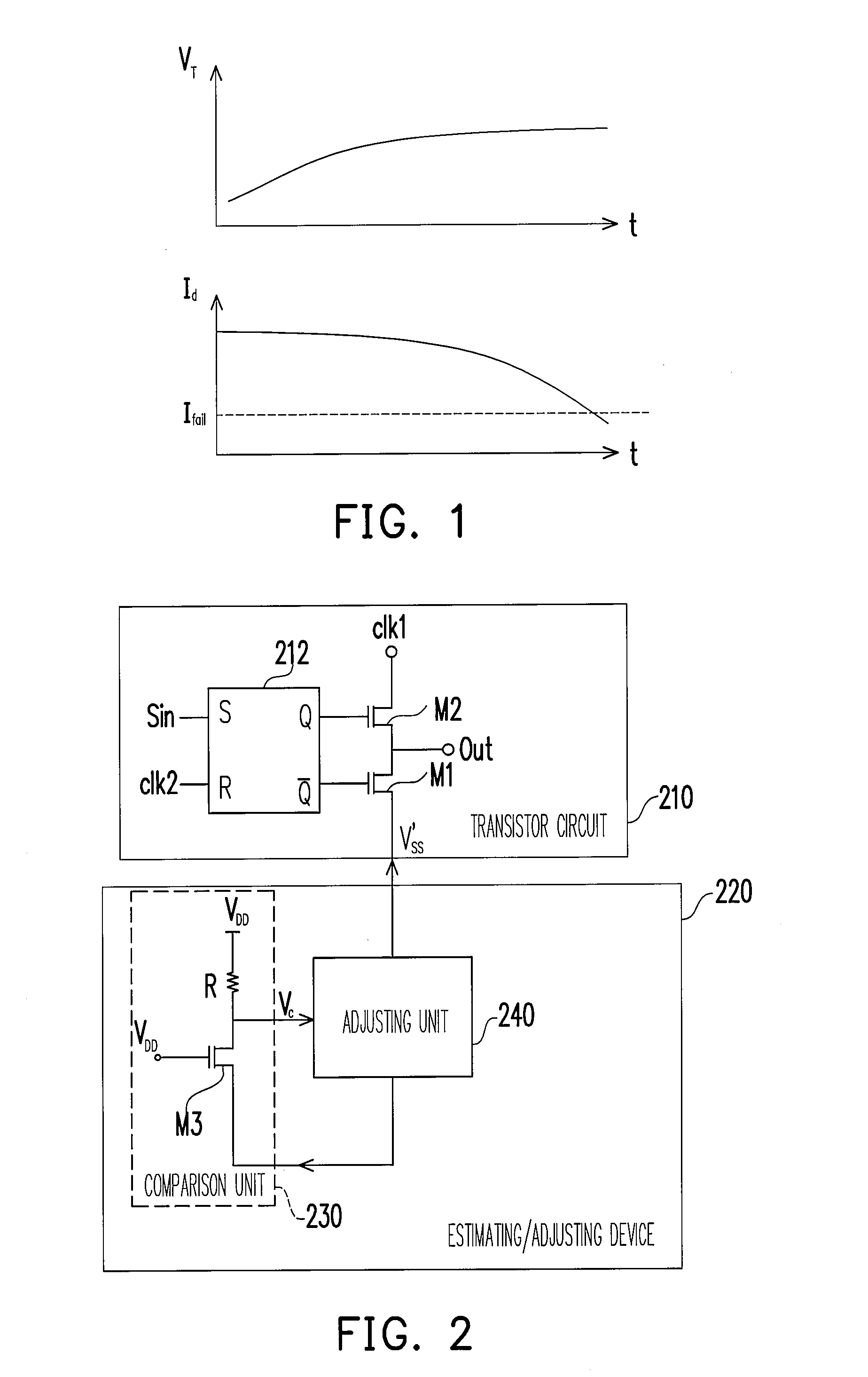

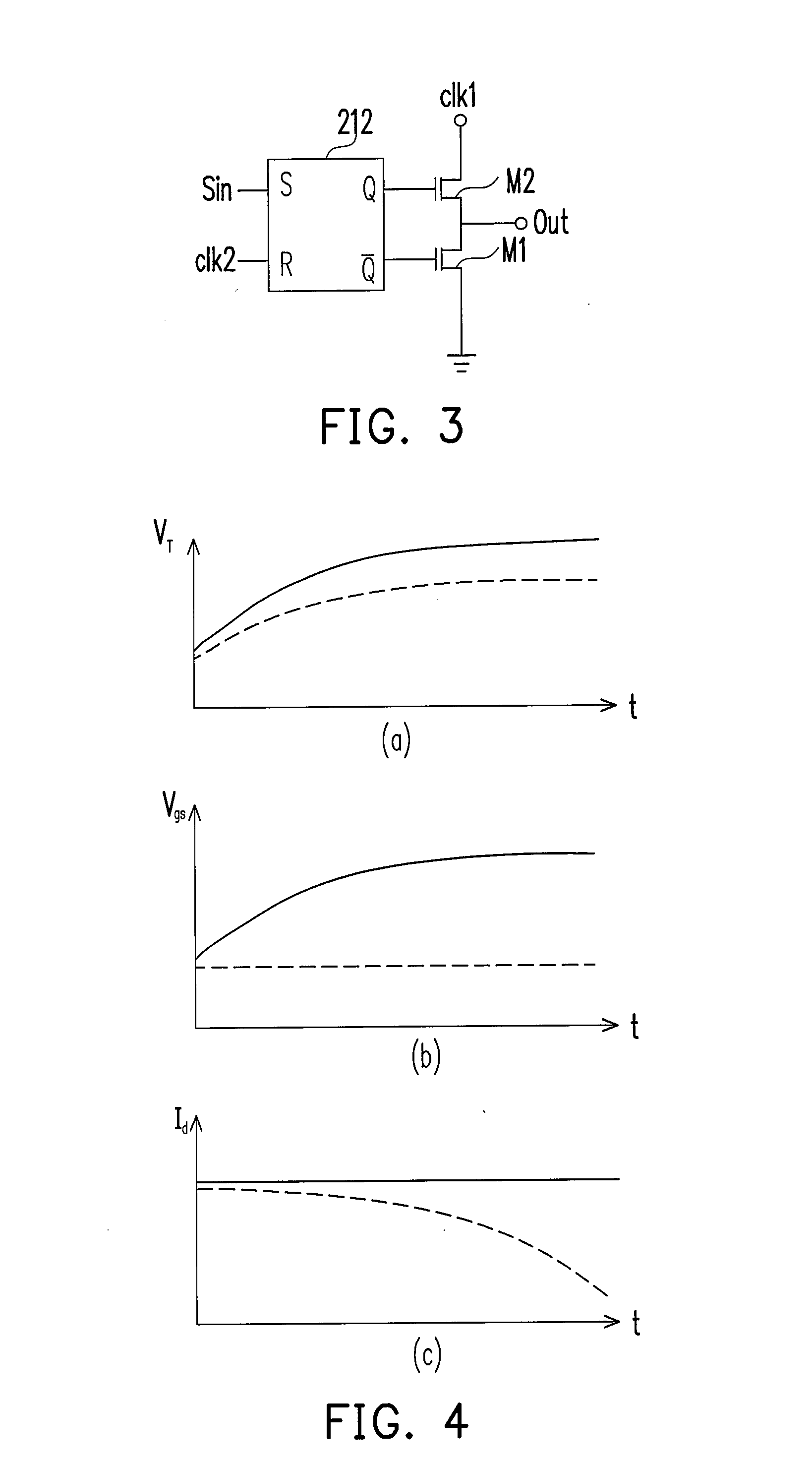

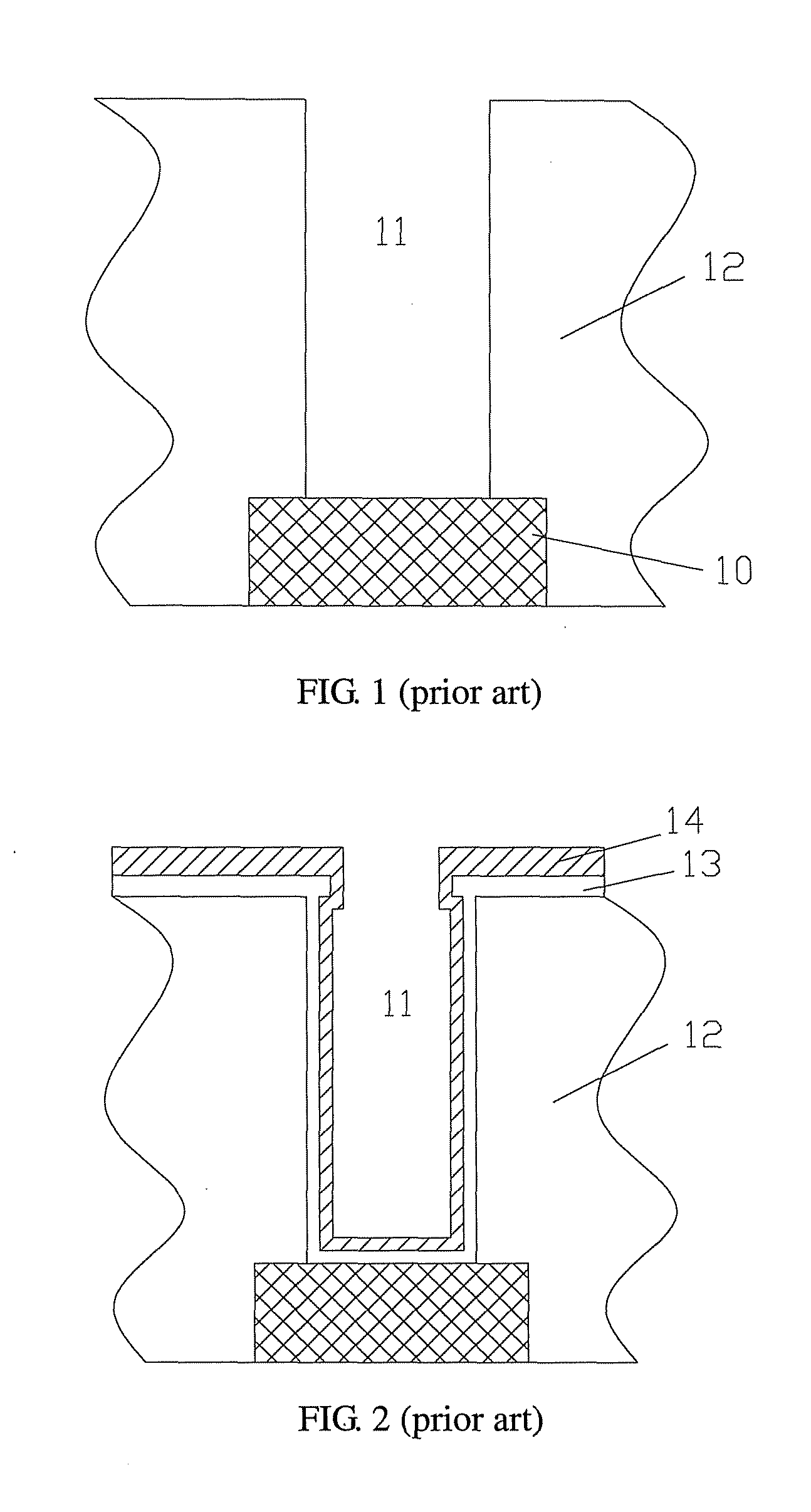

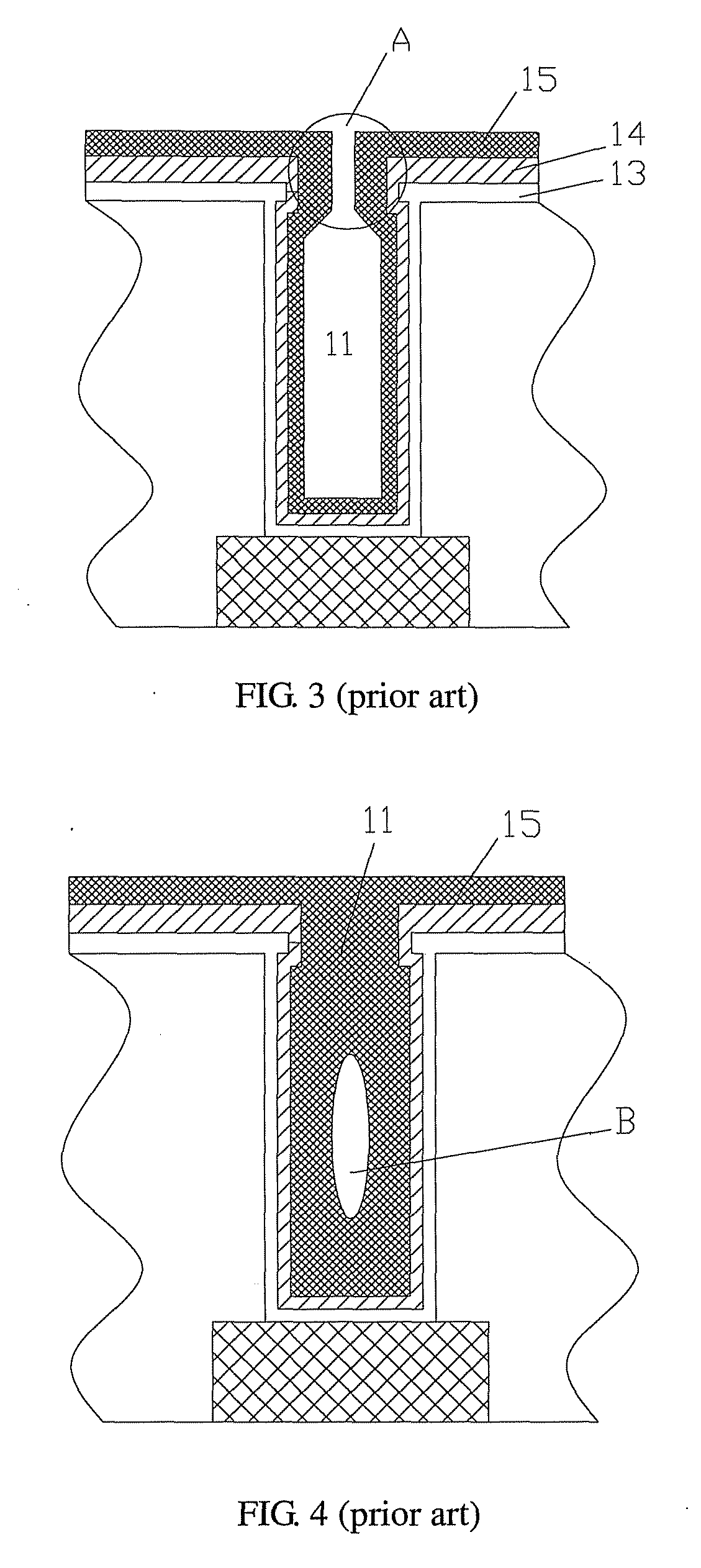

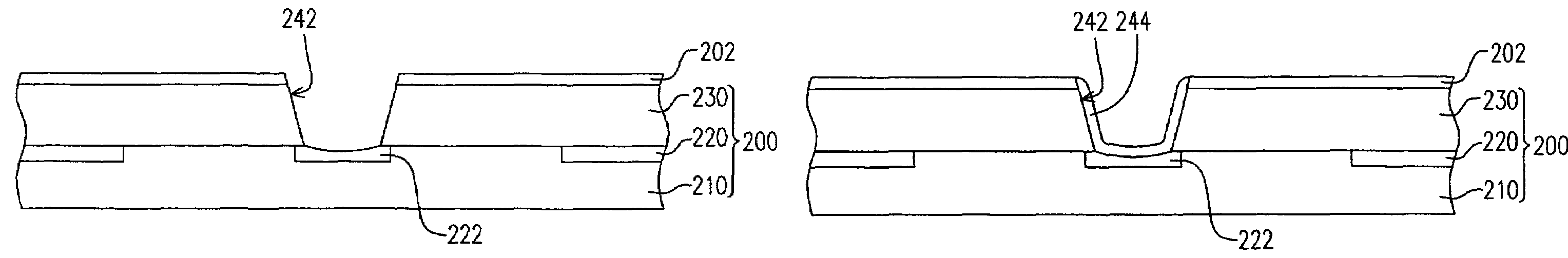

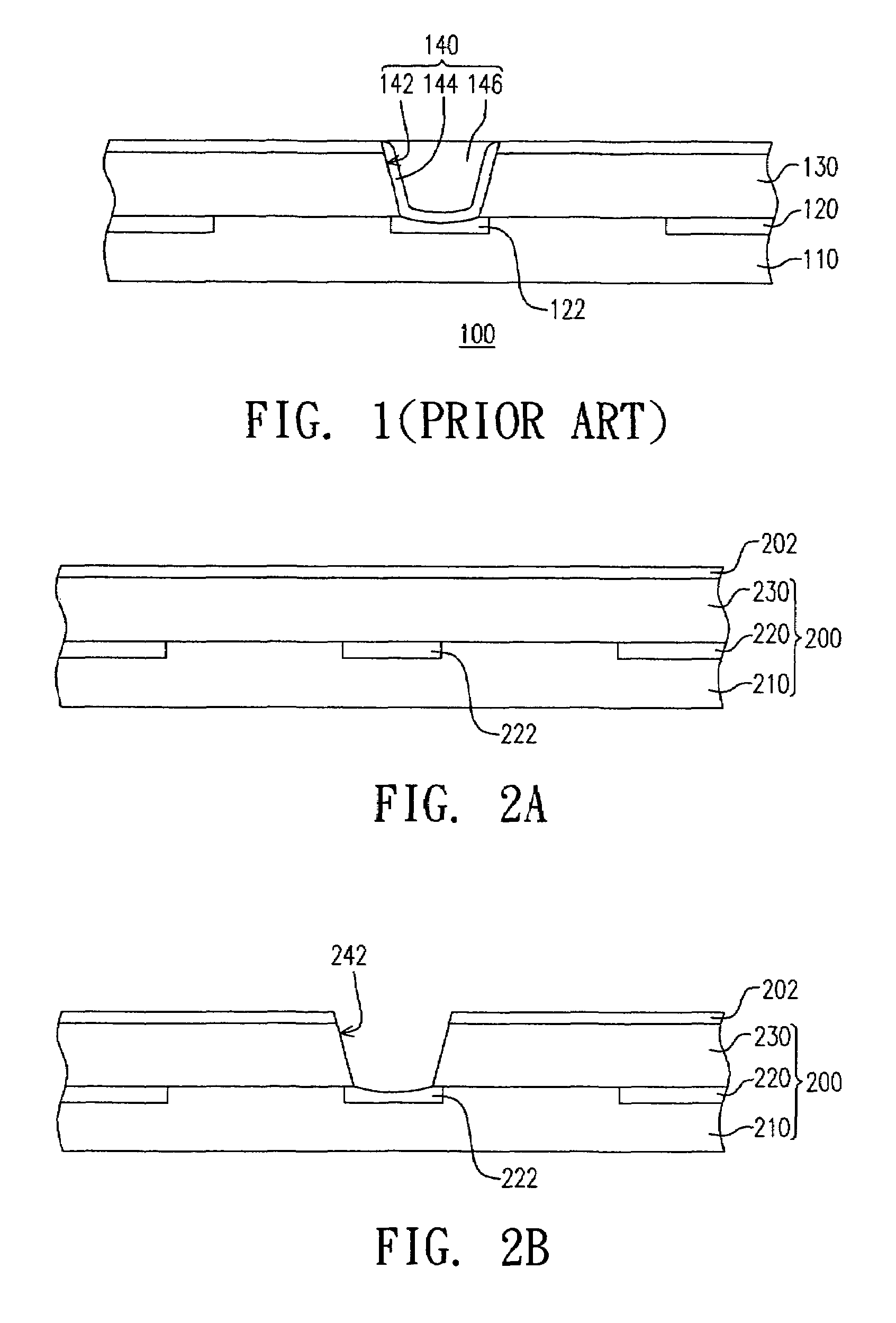

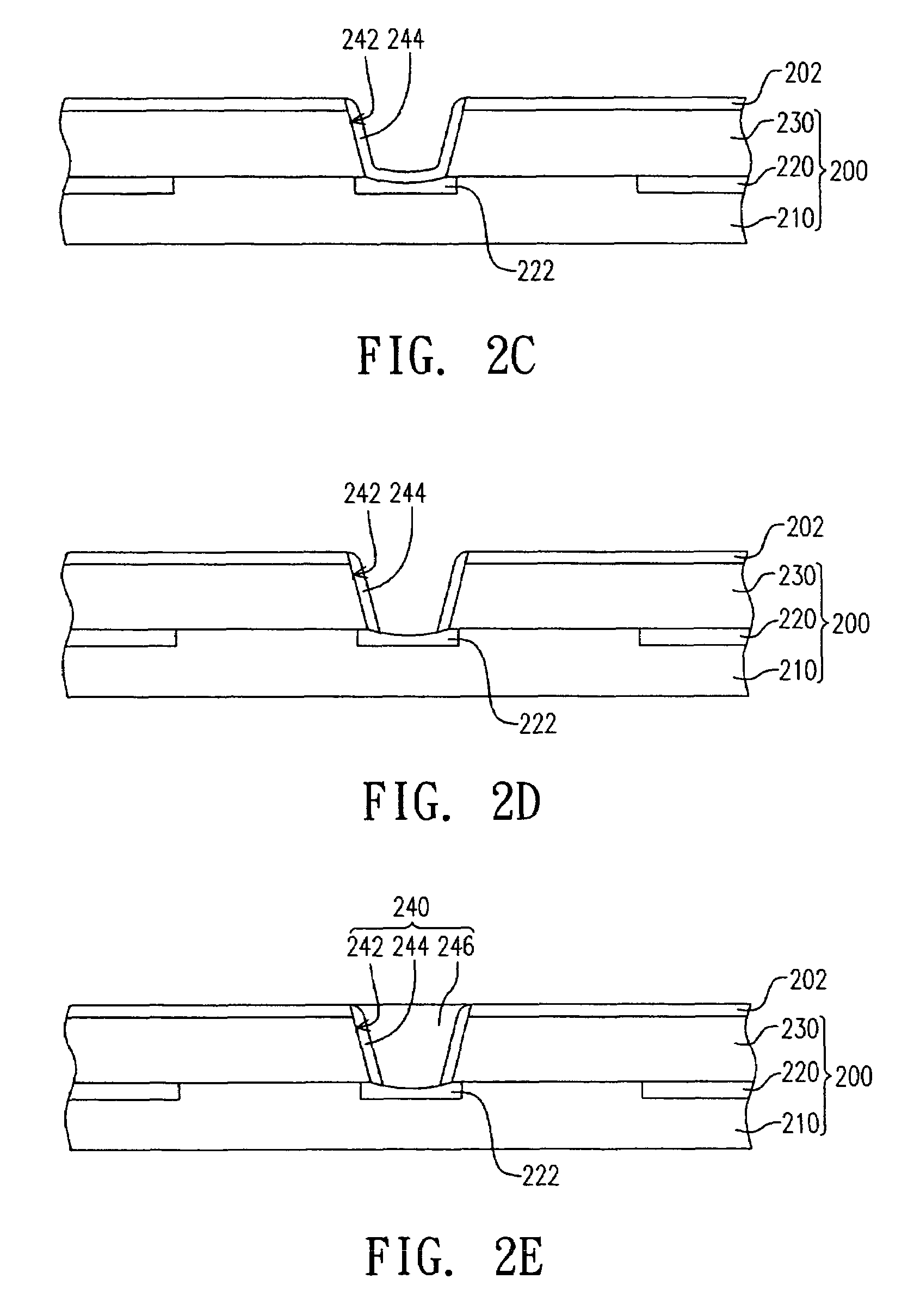

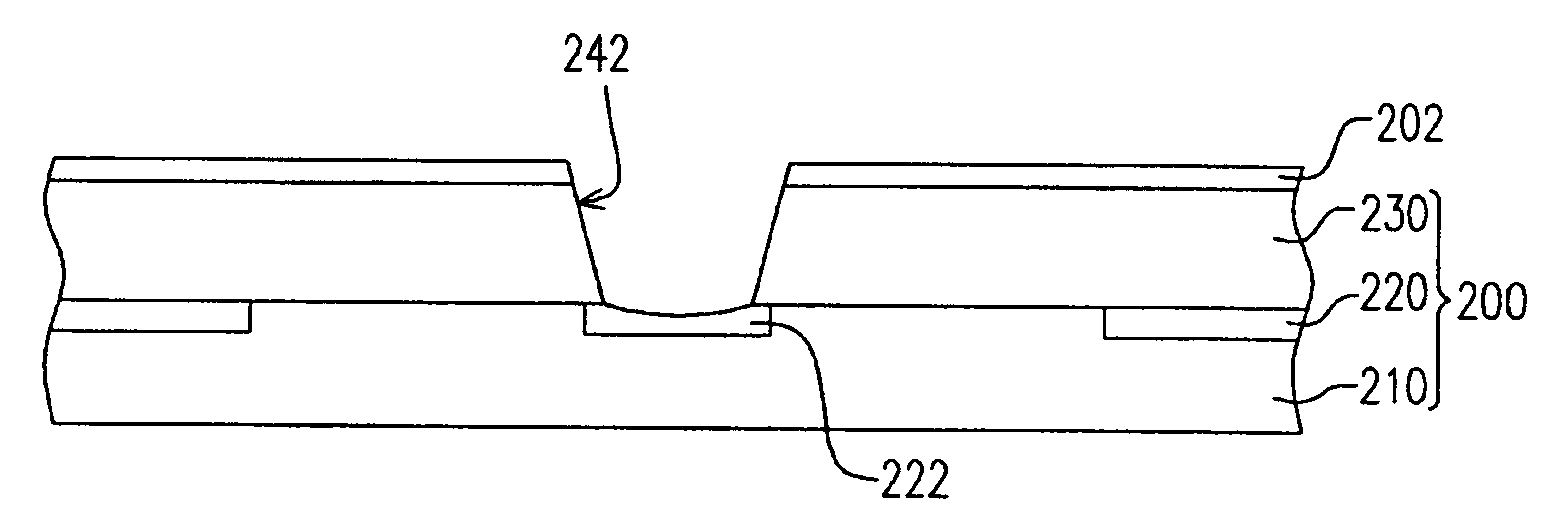

System for increasing circuit reliability and method thereof

InactiveUS20080062106A1Improve circuit reliabilityMaintain the driving ability of the TFTStatic indicating devicesCircuit reliabilityEngineering

A system for increasing circuit reliability and a method thereof are disclosed. A second thin film transistor (TFT) is used as a contrastive group of a first TFT in the circuit, and variations of device parameters of the first TFT are estimated through the contrastive group. The operation environment of the first TFT is adjusted according to the variations of device parameters of the first TFT so as to compensate the variations of device parameters of the first TFT. Thereby the driving ability of the first TFT can be maintained.

Owner:IND TECH RES INST

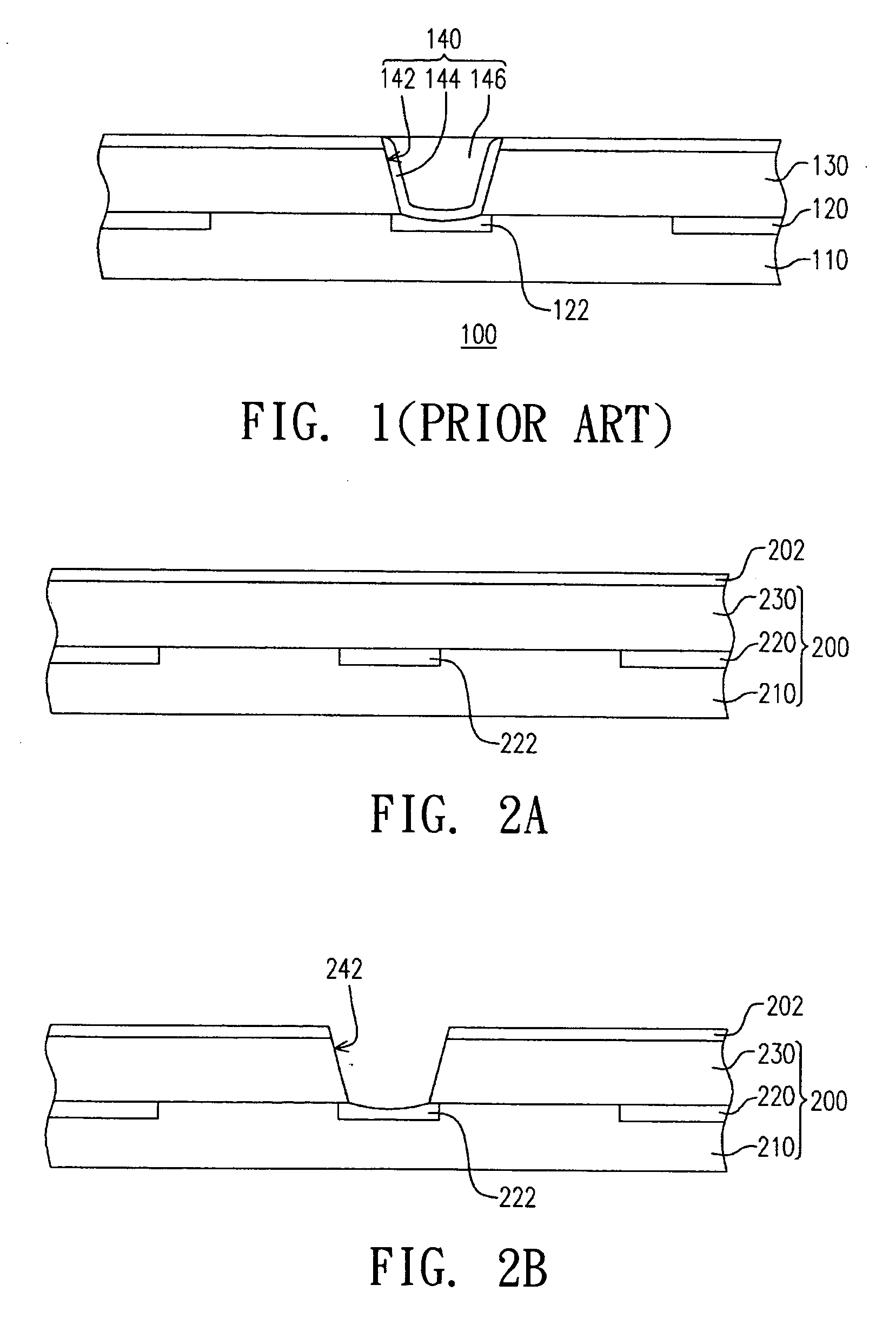

Method of forming a contact structure including a vertical barrier structure and two barrier layers

InactiveUS7071055B2Improve circuit reliabilityAvoid electrical propertiesTransistorThyristorTungsten nitrideIntegrated circuit

This invention relates to contact structures for use in integrated circuits and methods of fabricating contact structures. In one embodiment, a contact structure includes a conductive layer, one or more barrier layers formed above the conductive layer, and a barrier structure encircling the polysilicon layer and the one or more barrier layers. In an alternate embodiment, a contact structure is fabricated by forming a polysilicon layer on a substrate, forming a tungsten nitride layer above the polysilicon layer, and etching the polysilicon layer and the tungsten nitride layer to a level below the surface of a substrate structure. A silicon nitride layer is formed above the tungsten nitride layer, and a ruthenium silicide layer is formed above the silicon nitride layer. The ruthenium silicide layer is then polished.

Owner:MICRON TECH INC

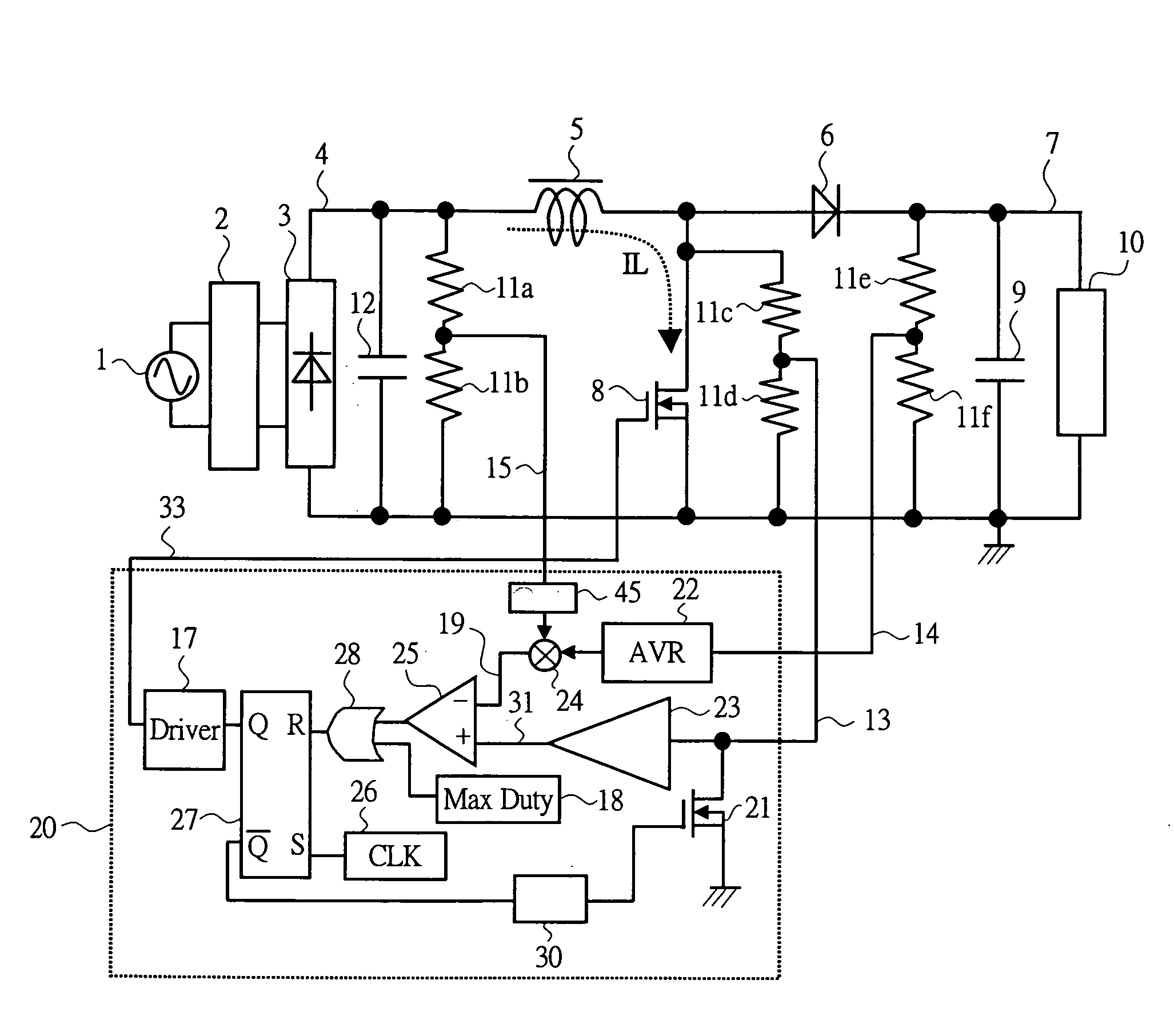

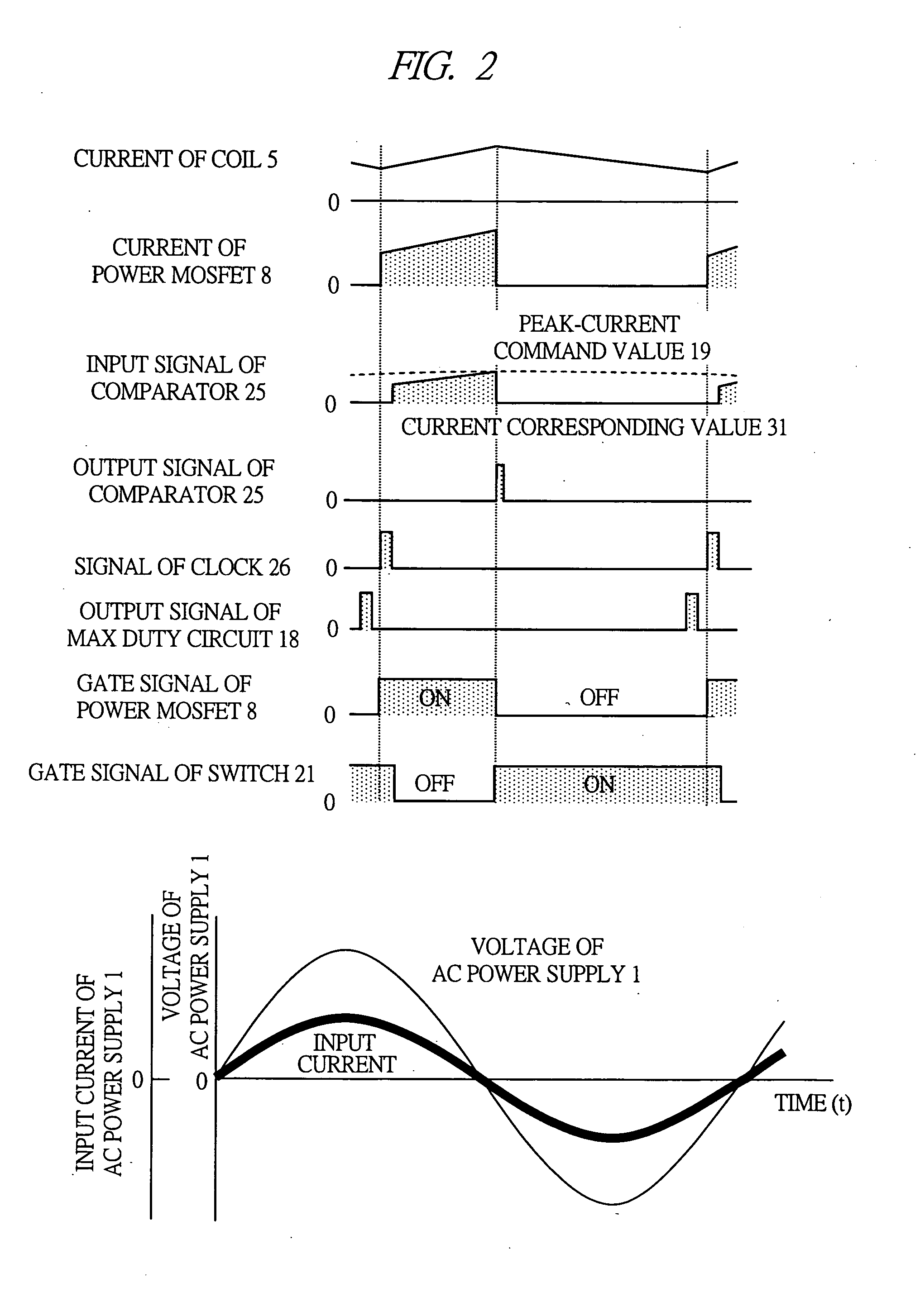

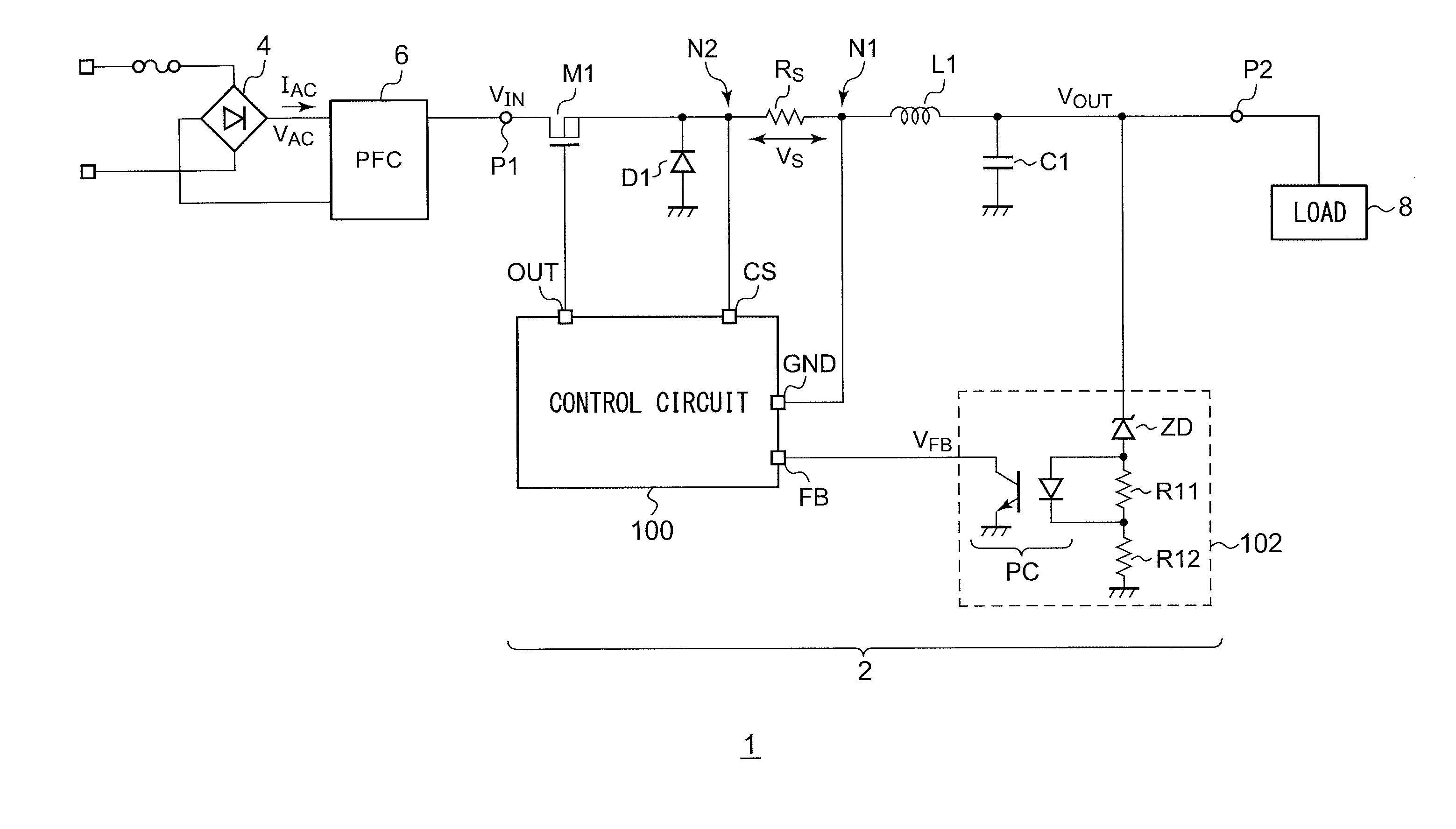

Switching power supply

InactiveUS20080290846A1Eliminate the problemReduce lossesEfficient power electronics conversionElectric variable regulationAudio power amplifierBoost rectifier

A switching power supply capable of correcting a power factor without using a shunt resistor is provided. The switching power supply includes a rectifier for rectifying an AC power supply, boosting means including a power MOSFET for boosting an output of the rectifier, a smoothing capacitor for smoothing an output of the boosting means, voltage-dividing resistors for detecting a voltage between main terminals of the power MOSFET, a switch for selecting only the voltage by which the power MOSFET is in on-state from voltages detected by the voltage-dividing resistors, an amplifier for amplifying the voltage selected by the switch and outputting the same as a current corresponding value of a current flowing in the power MOSFET, voltage-dividing resistors for detecting the output voltage, and driving means which form a pulse signal based on the current corresponding value and the output voltage for driving the power MOSFET by the pulse signal.

Owner:RENESAS ELECTRONICS CORP

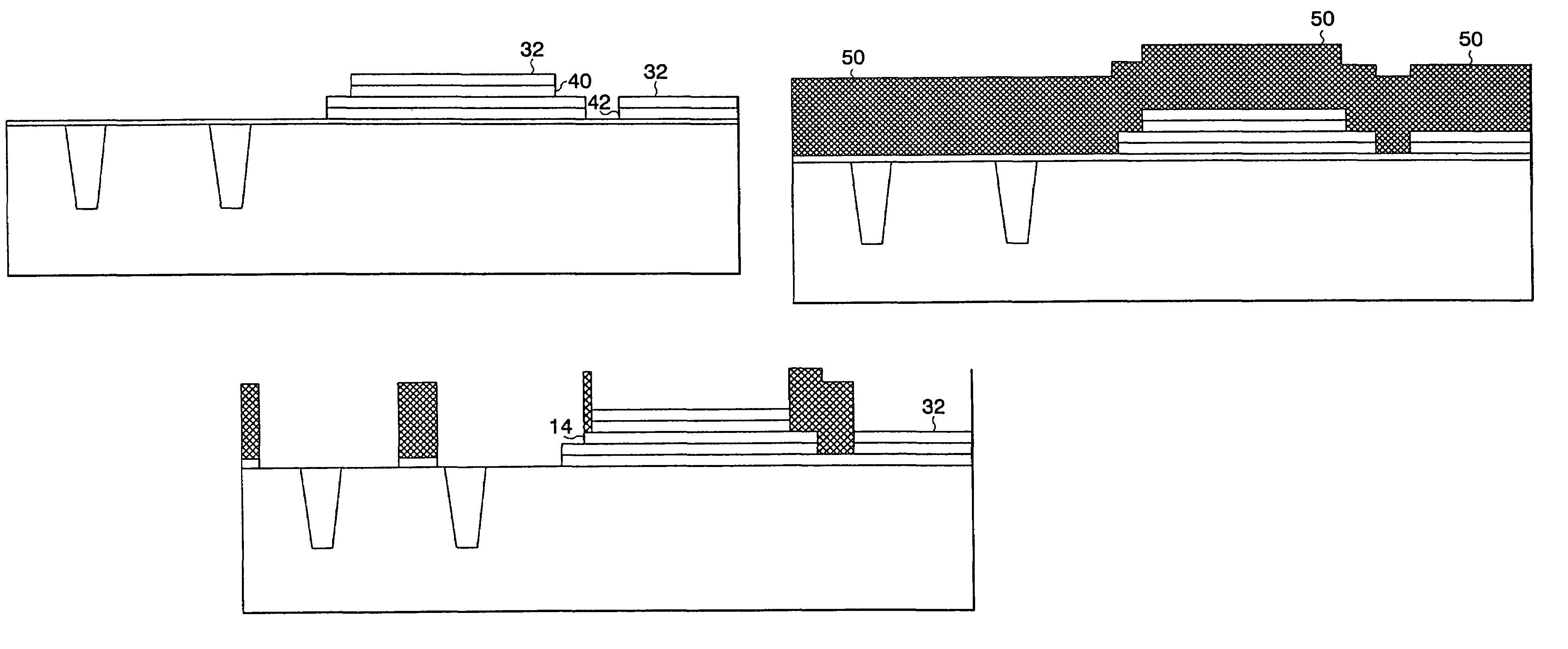

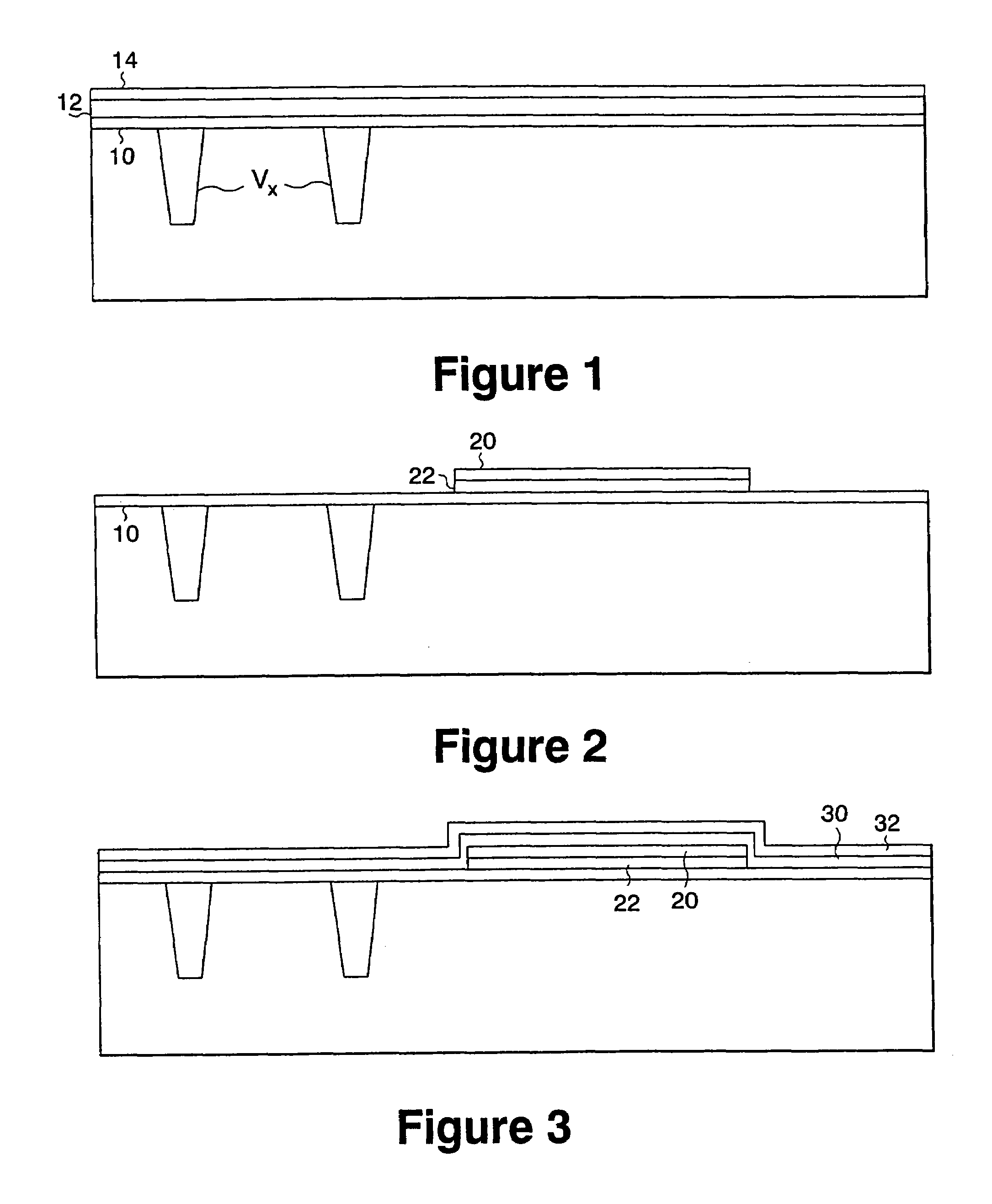

The use of redundant routes to increase the yield and reliability of a VLSI layout

ActiveUS20060265684A1Increase redundancyReduce sensitivityCAD circuit designSoftware simulation/interpretation/emulationPathPingVlsi layout

Disclosed is a method and system for inserting redundant paths into an integrated circuit. Particularly, the invention provides a method for identifying a single via in a first path connecting two elements, determining if an alternate route is available for connecting the two elements (other than a redundant via), and for inserting a second path into the available alternate route. The combination of the first and second paths provides greater redundancy than inserting a redundant via alone. More importantly, such redundant paths provide for redundancy when congestion prevents a redundant via from being inserted adjacent to the single via. An embodiment of the method further comprises removing the single via and any redundant wire segments, if all of the additional vias used to form the second path can be made redundant.

Owner:GLOBALFOUNDRIES US INC

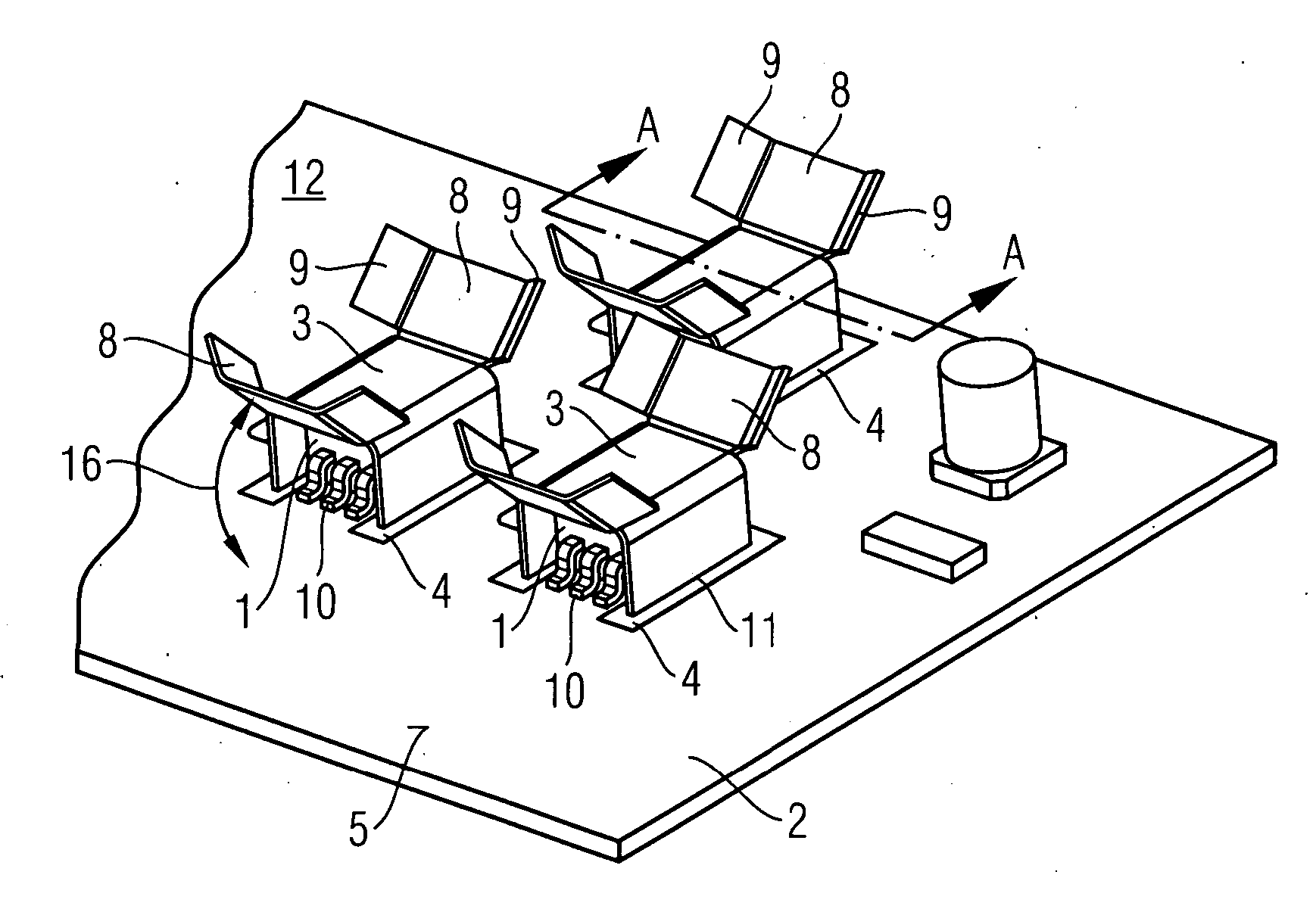

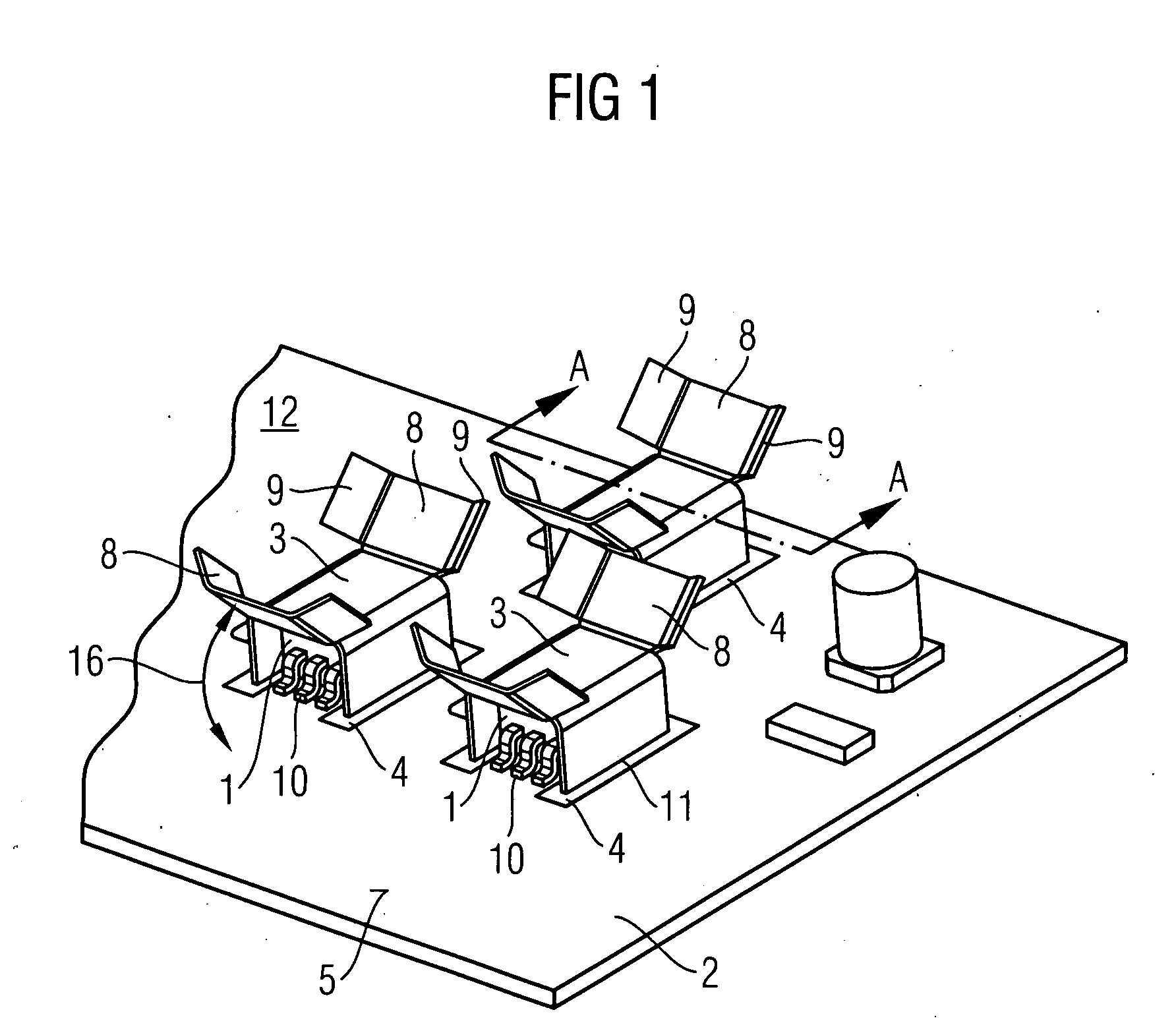

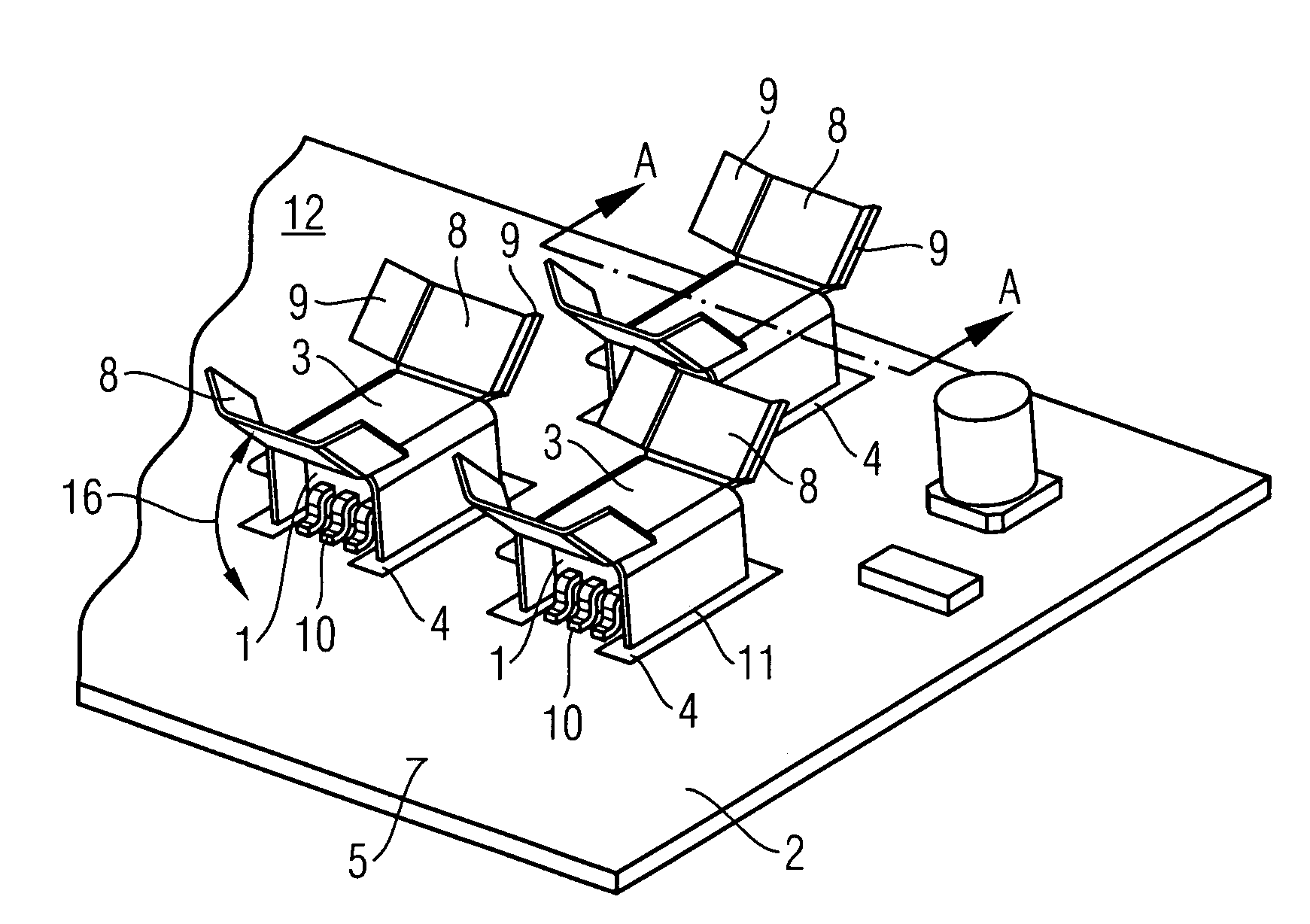

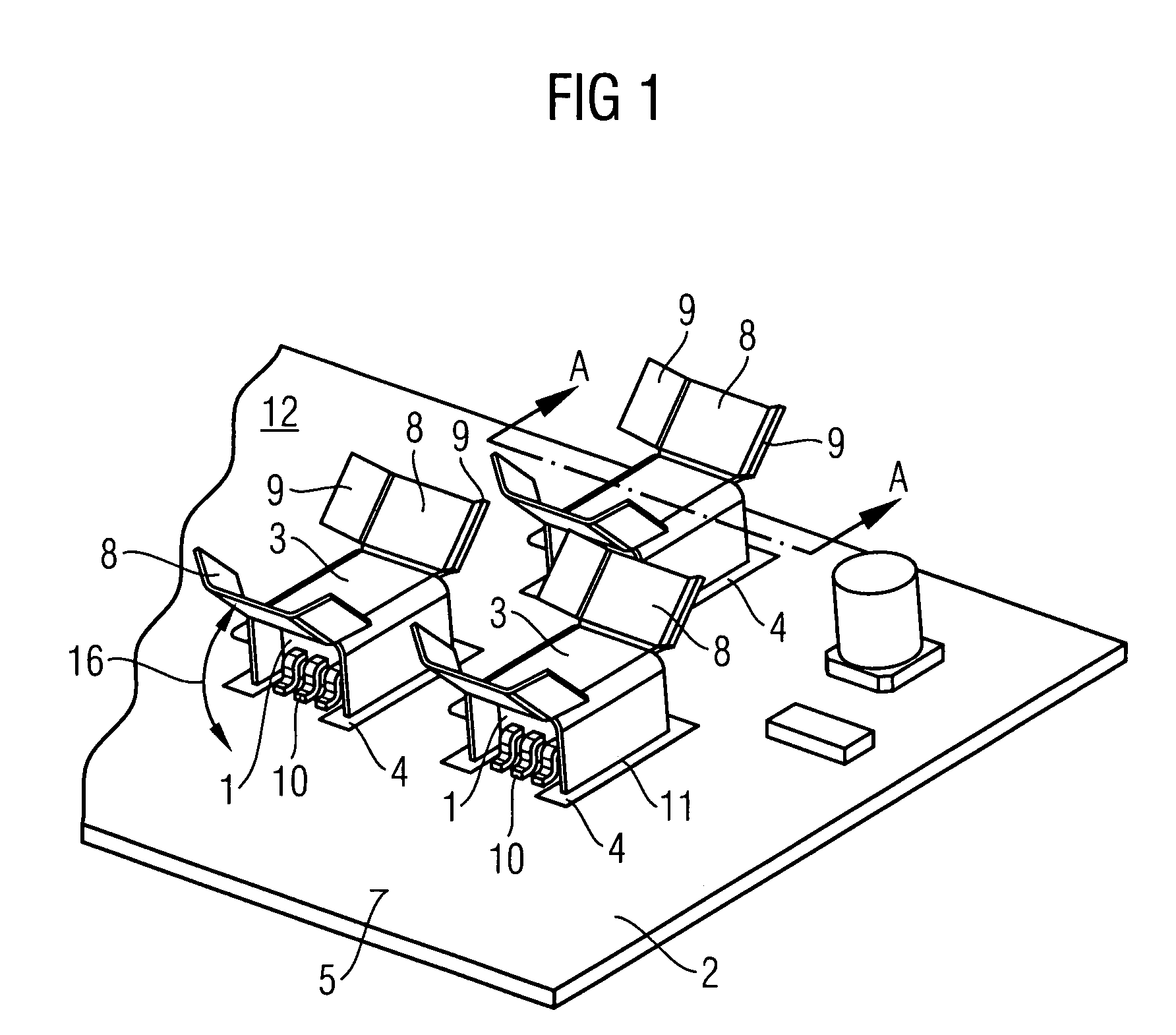

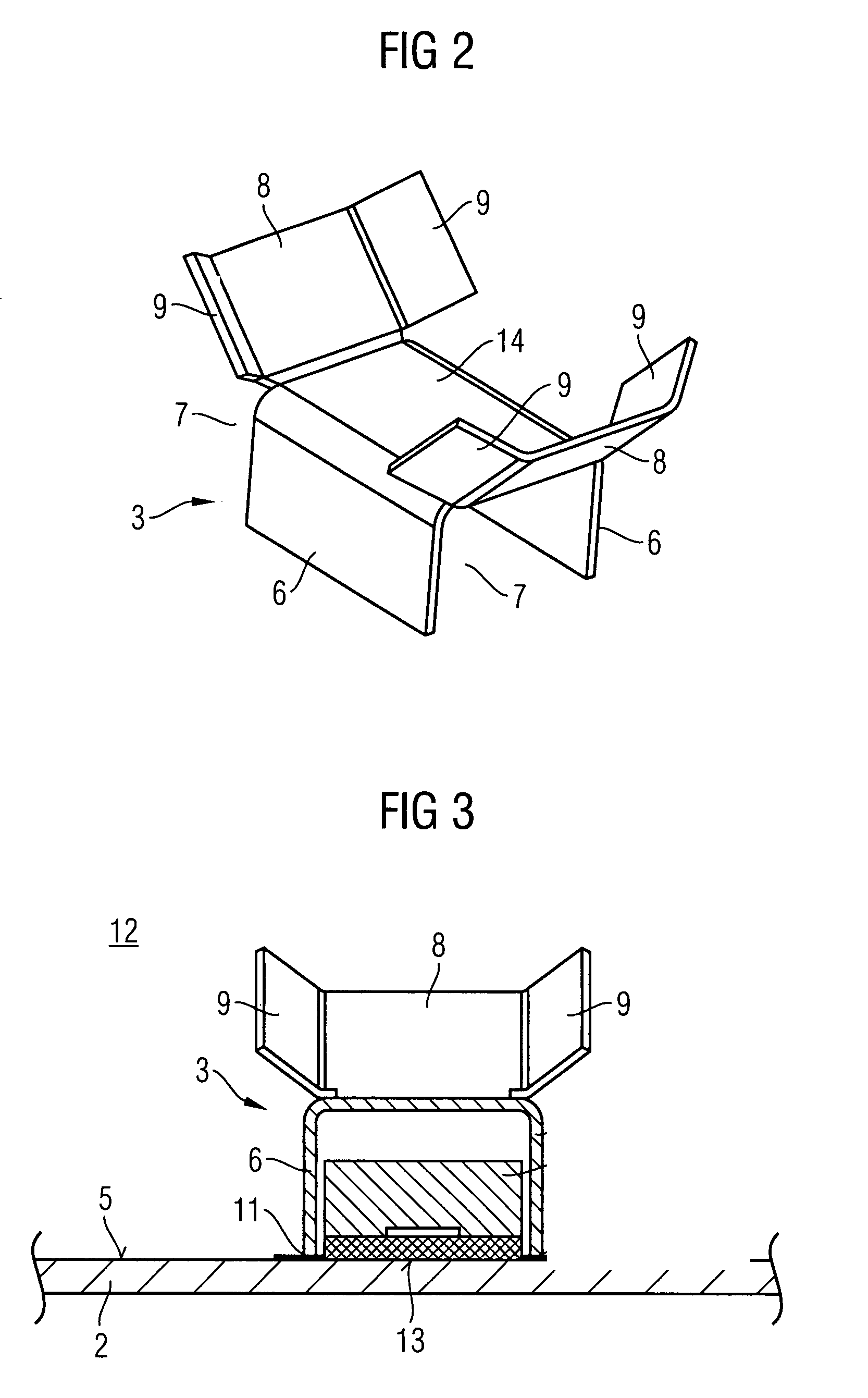

Arrangement for cooling SMD power components on a printed circuit board

InactiveUS20070206357A1Simple and inexpensive to manufactureReduces positional dependenceSemiconductor/solid-state device detailsSolid-state devicesPower componentElectronic component

There is described an arrangement for cooling electrical components disposed on a board-shaped mounting substrate, particularly SMD power components on a printed circuit board, wherein at least one heat sink assigned to a component is present which is disposed on the same side as the components and which is connected in a thermally conductive manner to the assigned component by means of a thermally conductive layer implemented on the mounting substrate. The heat sink is implemented as a bent sheet-metal part and is connected to the thermally conductive layer by means of a solder joint, wherein the bent sheet-metal part has at least one heat sink element which extends in a longitudinal direction and said longitudinal direction is oriented obliquely to the plane of the board-shaped substrate.

Owner:SIEMENS AG OESTERR

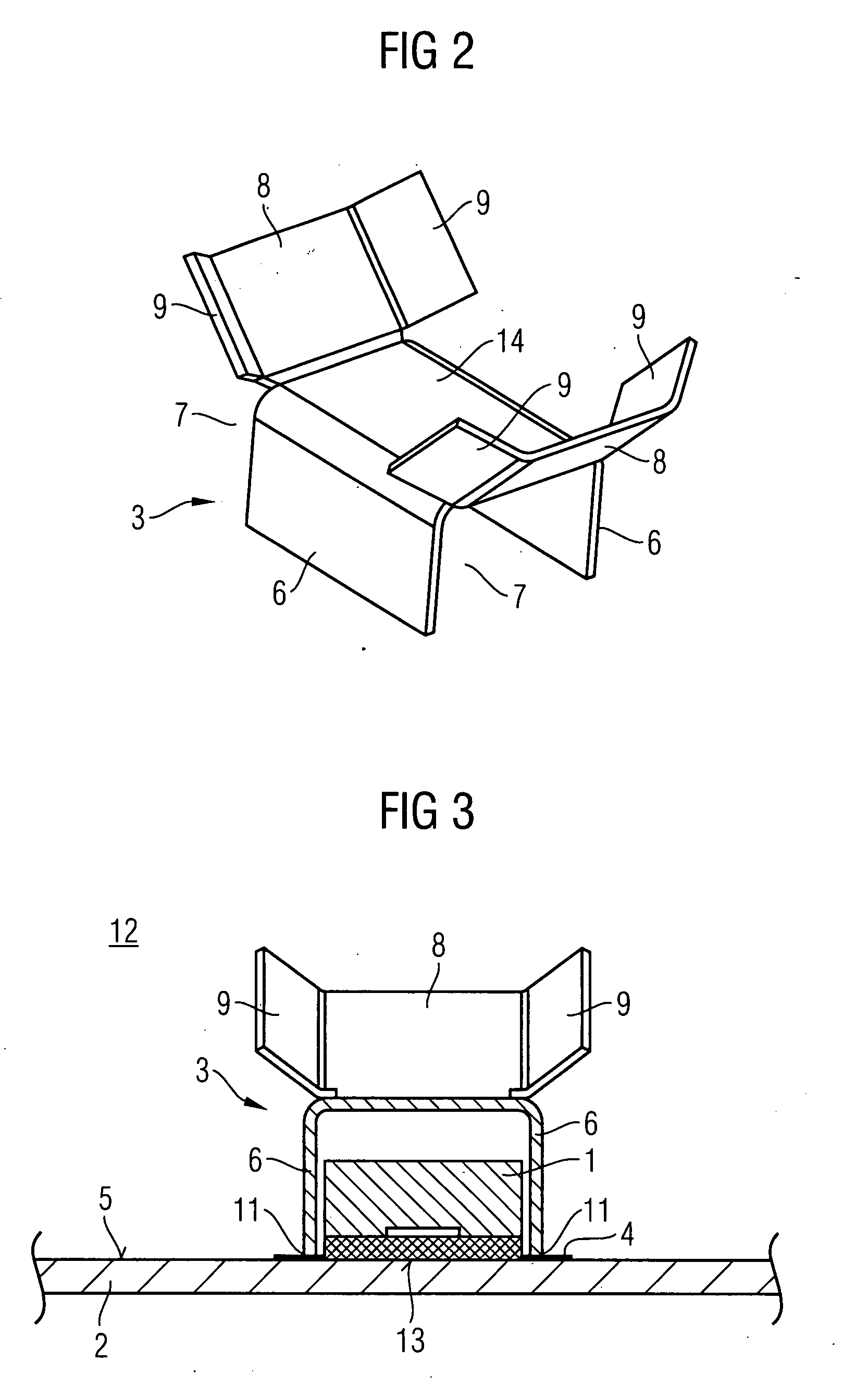

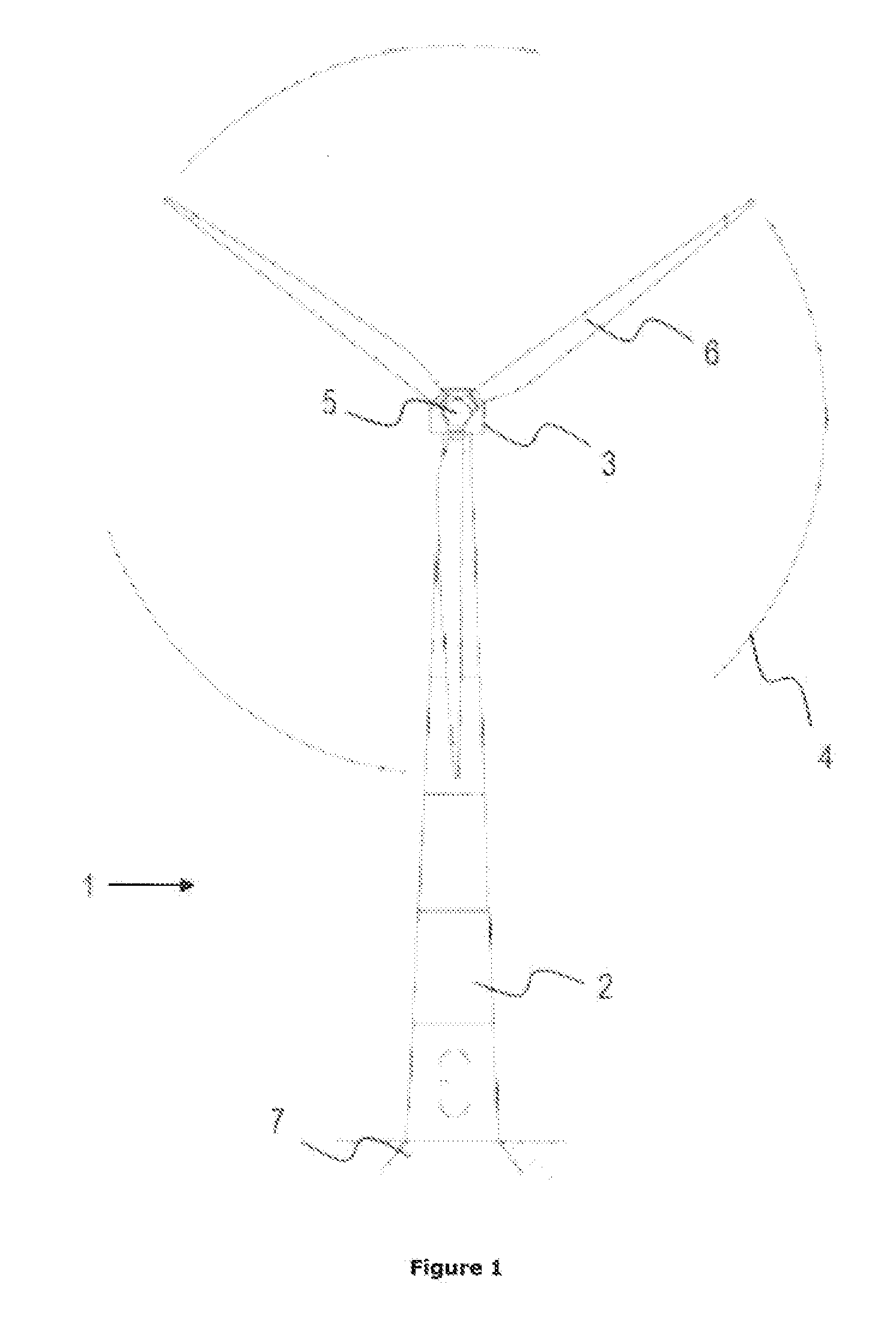

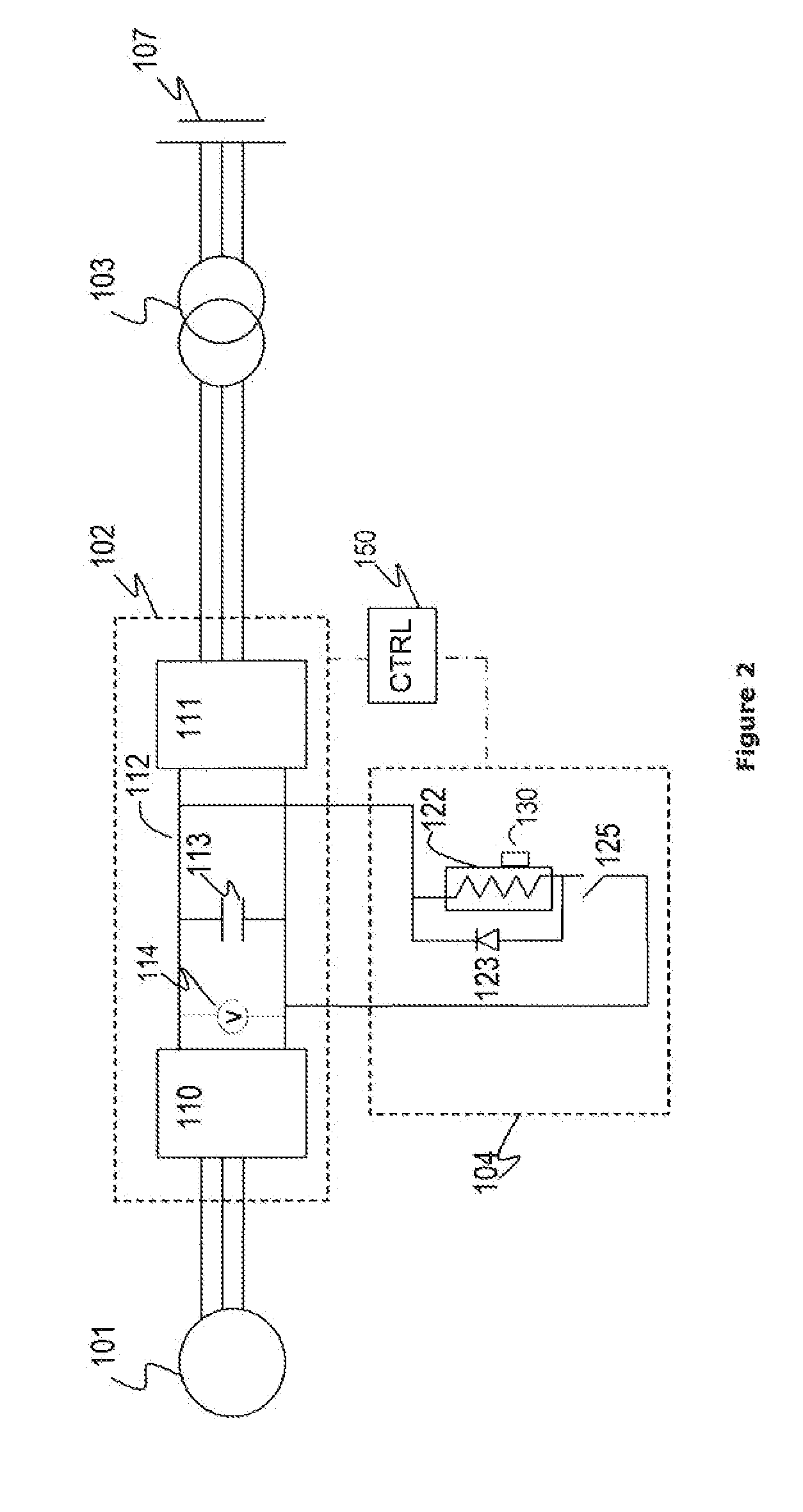

Test system for wind turbine dump load

ActiveUS20130033268A1Improve circuit reliabilityImprove rendering capabilitiesElectronic circuit testingEngine fuctionsAutomotive engineeringElectric generator

The present invention relates to a dump load applied in a wind turbine generator; normally it is only operating to absorb the energy during faults. Therefore in the majority time of wind turbine generator operation, the dump load is not applied, and its health condition is unknown. This invention is about a method to check the dump load condition during normal operation.

Owner:VESTAS WIND SYST AS

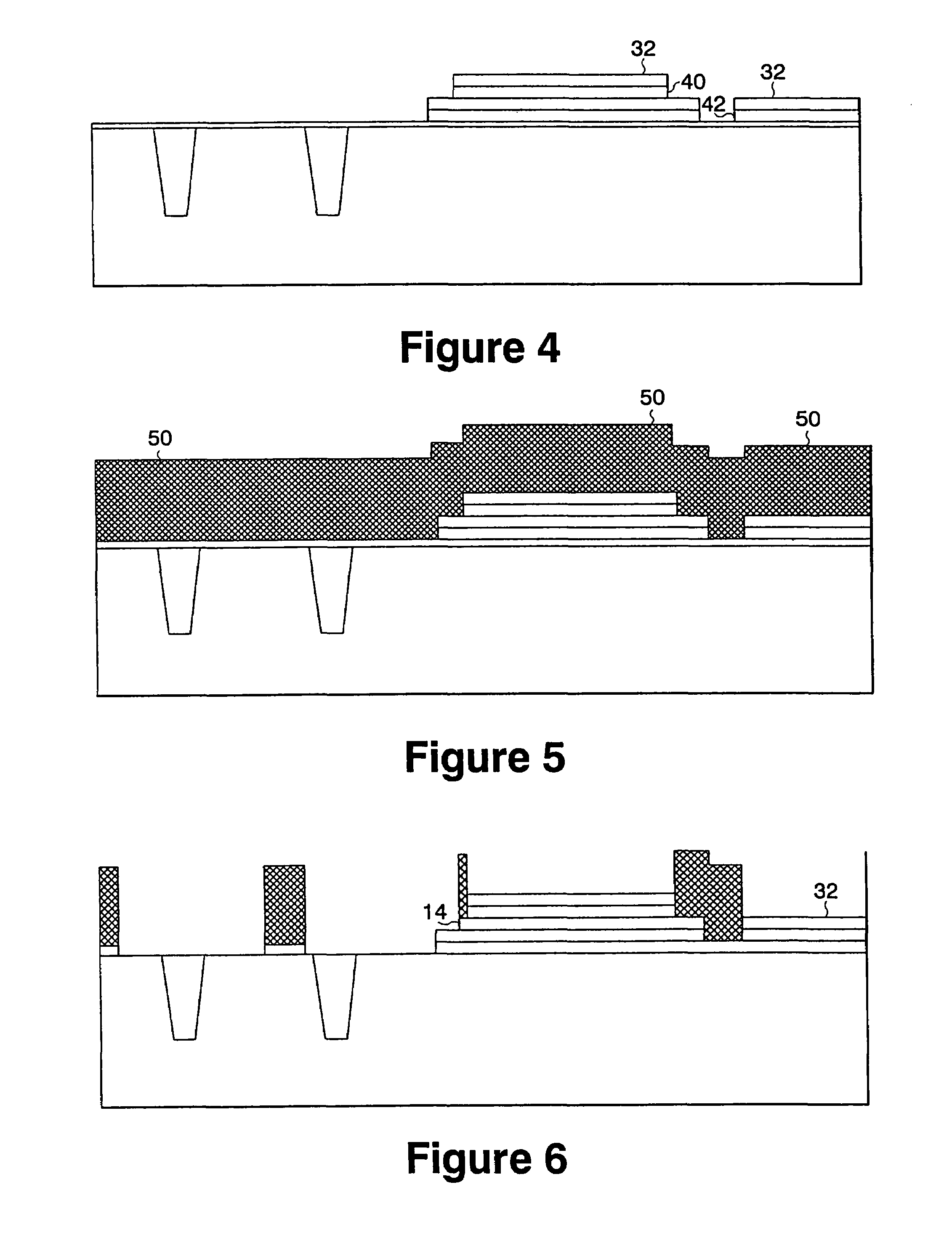

Method of fabrication of MIMCAP and resistor at same level

InactiveUS7022246B2Reduce parasitismEasy to useElectrolytic capacitorsDecorative surface effectsFront end of lineCapacitor

A method is disclosed of fabricating a MIMCAP (a capacitor (CAP) formed by successive layers of metal, insulator, metal (MIM)) and a thin film resistor at the same level. A method is also disclosed of fabricating a MIMCAP and a thin film resistor at the same level, and a novel integration scheme for BEOL (back-end-of-line processing) thin film resistors which positions them closer to FEOL (front-end-of-line processing) devices.

Owner:GLOBALFOUNDRIES US INC

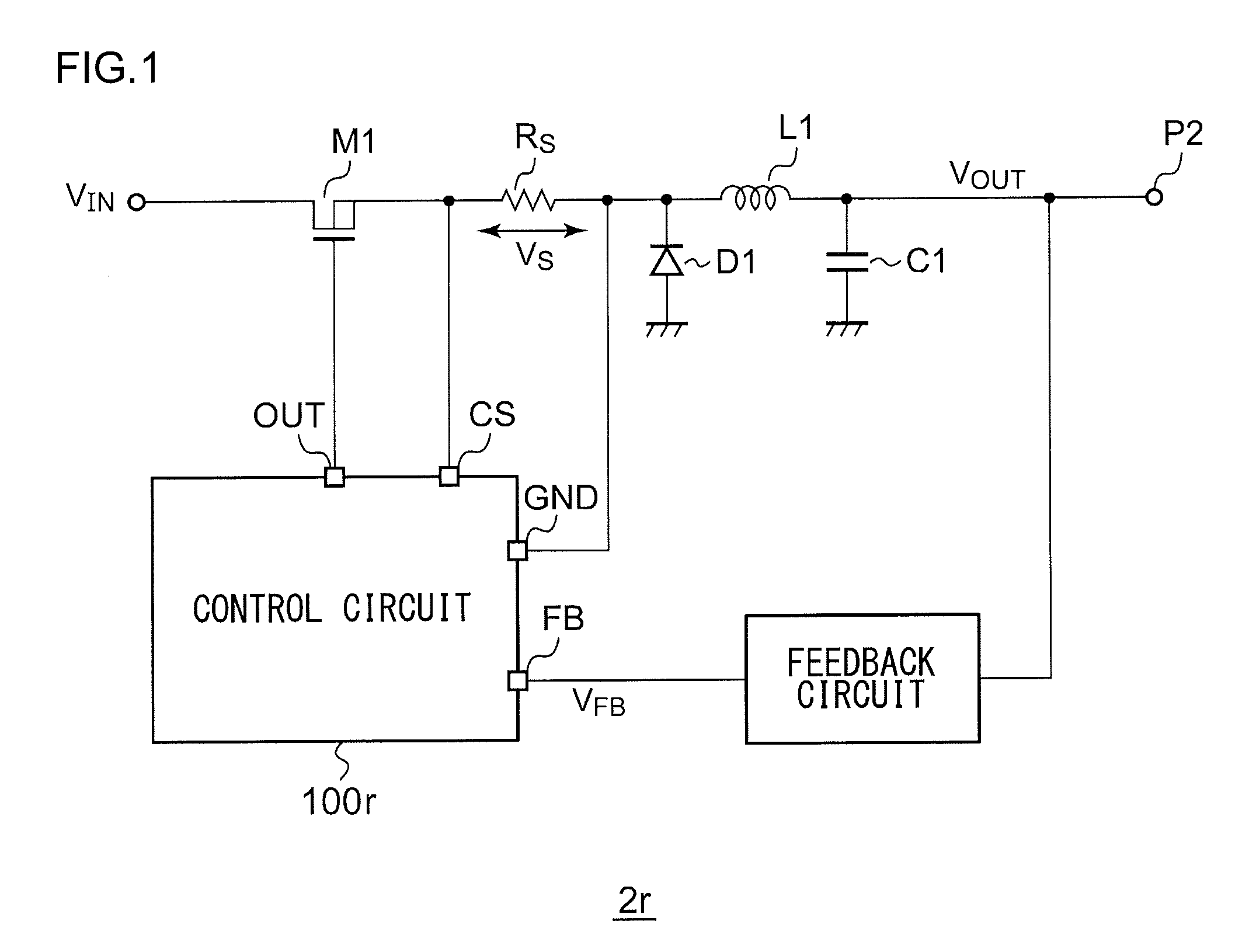

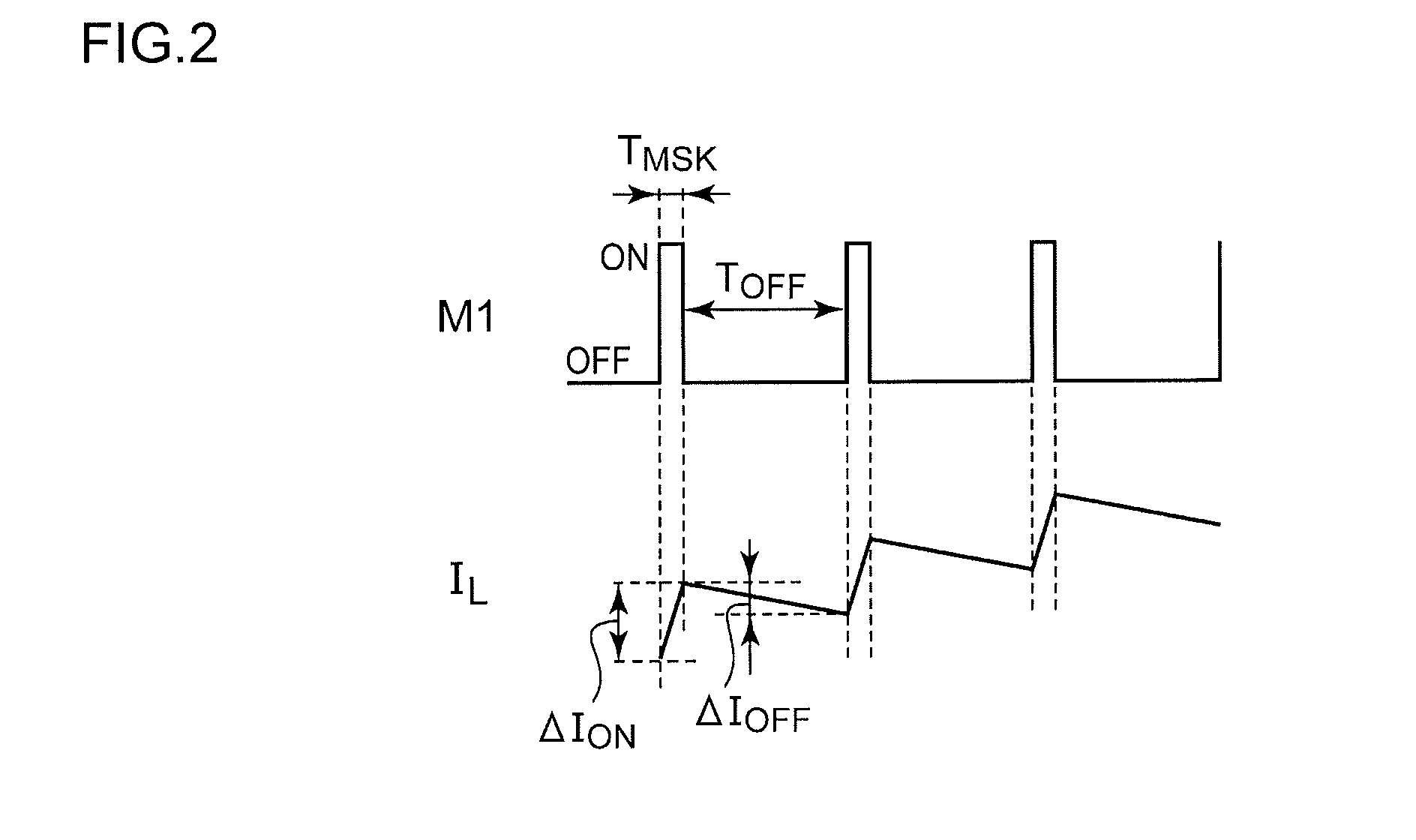

Step down switching regulator

ActiveUS20140218988A1Improve circuit reliabilityInhibit currentAc-dc conversion without reversalDc-dc conversionCurrent limitingComparator

A current limiting comparator generates a current limiting signal SLIM which is asserted when a detection voltage Vs at a detection terminal CS is higher than a predetermined threshold voltage VTH. A mask signal generating unit generates a mask signal SMSK which is asserted after a predetermined delay time TMSK elapses after a switching transistor is turned on. A pulse signal generating unit has: a function (a) in which, when the set signal SSET is asserted in a period in which the current limiting signal SLIM is negated, a pulse signal SPWM is switched to a first level; and a function (b) in which, when the reset signal SRST is asserted, or when the current limiting signal SLIM is asserted in a period in which the mask signal SMSK is negated, the pulse signal SPWM is switched to a second level.

Owner:ROHM CO LTD

Arrangement for cooling SMD power components on a printed circuit board

InactiveUS7746650B2Simple and inexpensive to manufactureReduces positional dependenceSemiconductor/solid-state device detailsSolid-state devicesElectronic componentPower component

There is described an arrangement for cooling electrical components disposed on a board-shaped mounting substrate, particularly SMD power components on a printed circuit board, wherein at least one heat sink assigned to a component is present which is disposed on the same side as the components and which is connected in a thermally conductive manner to the assigned component by means of a thermally conductive layer implemented on the mounting substrate. The heat sink is implemented as a bent sheet-metal part and is connected to the thermally conductive layer by means of a solder joint, wherein the bent sheet-metal part has at least one heat sink element which extends in a longitudinal direction and said longitudinal direction is oriented obliquely to the plane of the board-shaped substrate.

Owner:SIEMENS AG OESTERR

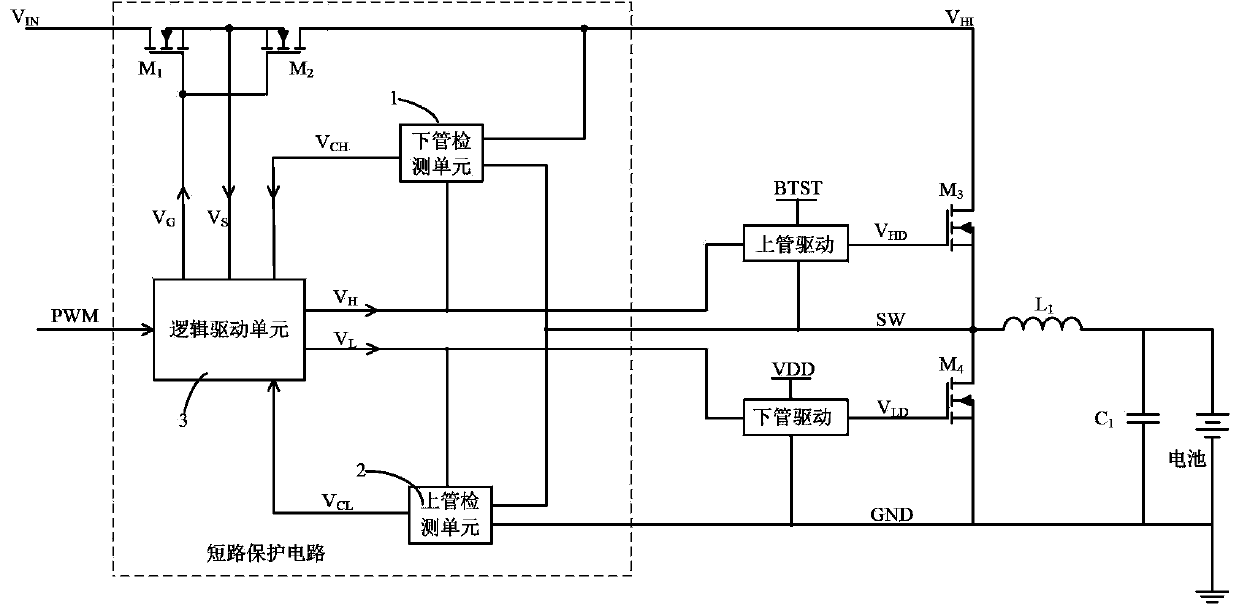

Short-circuit protection circuit for driving tubes and inductor in switch-type charge management chip

ActiveCN103401541AGuaranteed circuit response speedImprove circuit reliabilityElectronic switchingOxide semiconductorInductor

The invention discloses a short-circuit protection circuit for driving tubes and an inductor in a switch-type charge management chip, which mainly solves the problem of incorrect detection of an existing short-circuit protection circuit. The short-circuit protection circuit comprises two high-voltage NMOS (N-channel Metal Oxide Semiconductor) tubes, a lower tube detection unit (1), an upper tube detection unit (2) and a logic drive unit (3), wherein the lower tube detection unit (1) is used for carrying out short-circuit detection on a lower driving tube when an upper driving tube is switched on and outputting a lower tube short-circuit signal to the logic drive unit (3); the upper tube detection unit (2) is used for carrying out the short-circuit detection on the upper driving tube and the inductor when the lower driving tube is switched on and outputting an upper tube short-circuit signal to the logic drive unit (3); the logic driving unit (3) controls the upper driving tube and the lower driving tube to be switched off when short circuit happens and controls the high-voltage NMOS tubes to switch off a charge power supply if a short-circuit phenomenon continues. According to the short-circuit protection circuit disclosed by the invention, a short-circuit detection circuit is mutually independent of an over-current detection circuit, the detection accuracy and the circuit reliability are increased, and the short-circuit protection circuit can be used for the switch-type charge management chip in large charge current.

Owner:深圳德信微电子有限公司

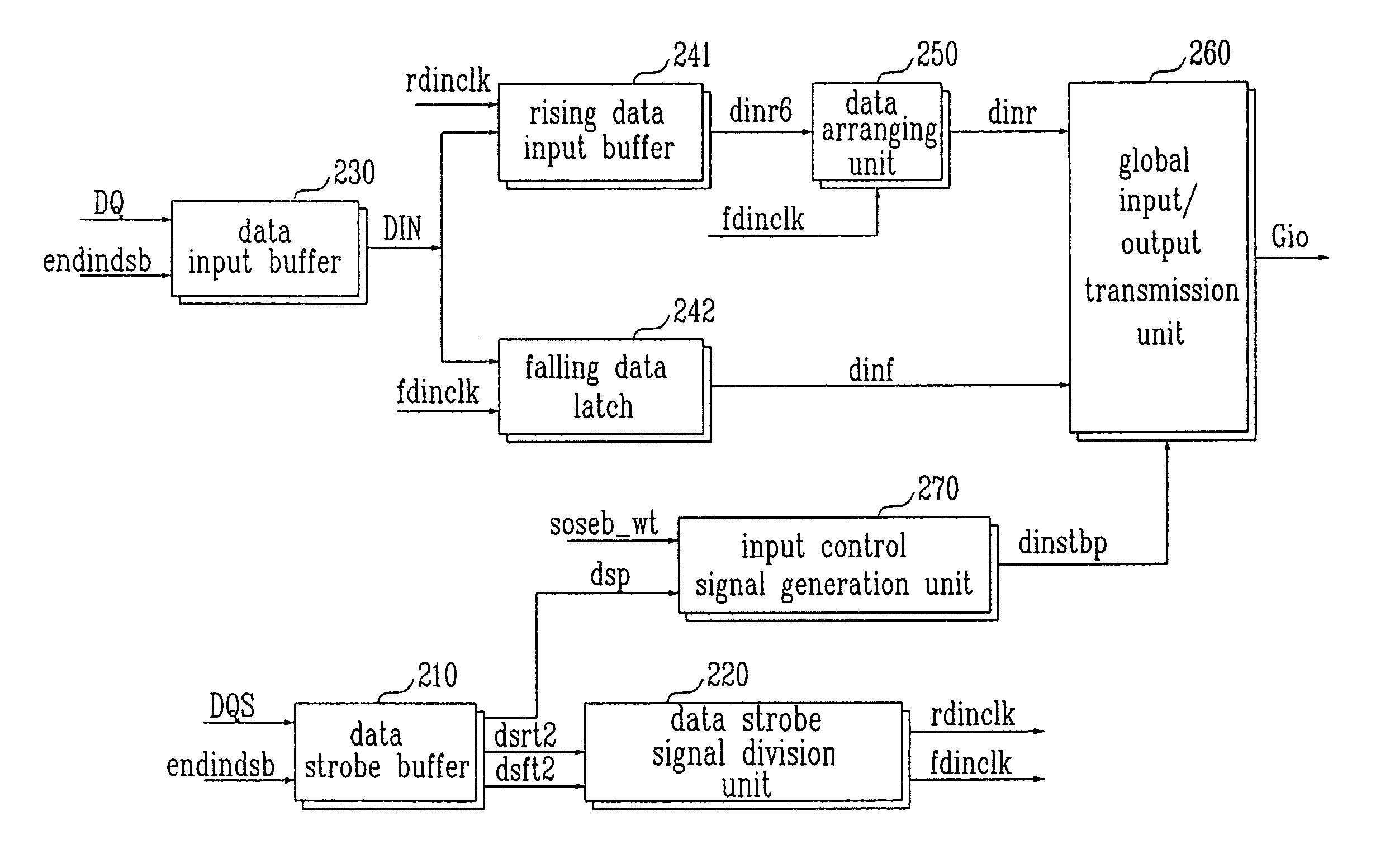

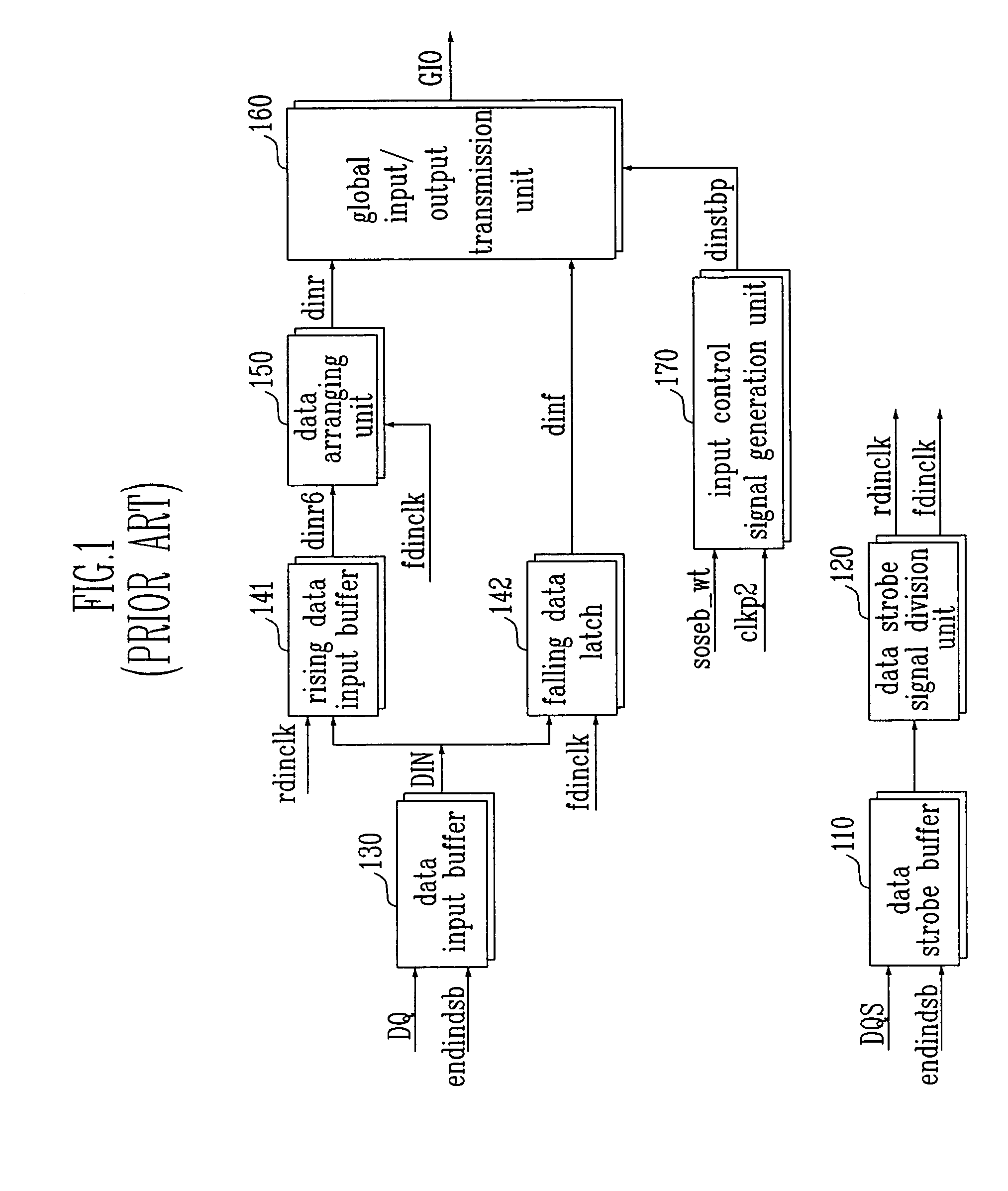

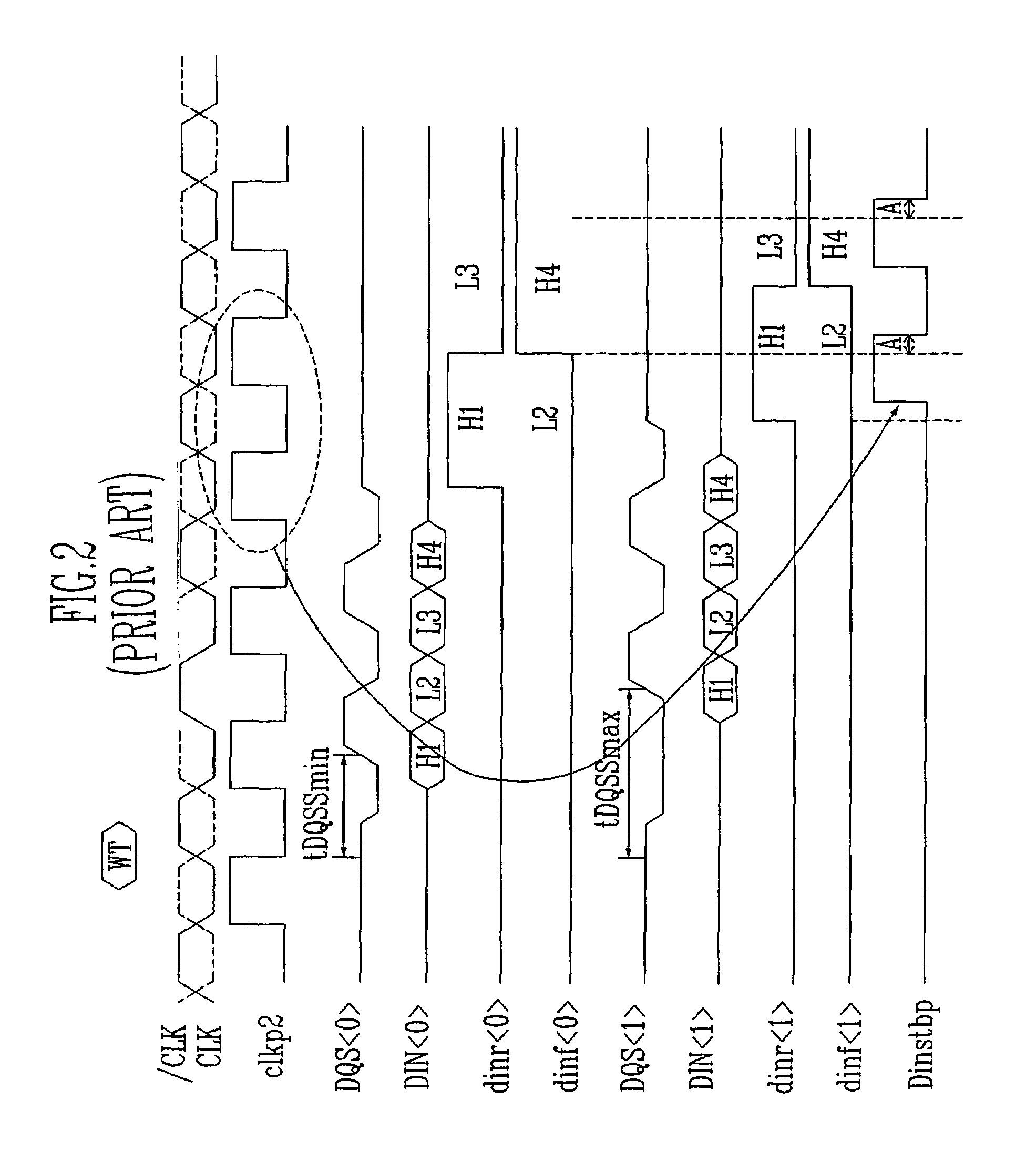

Data input apparatus of DDR SDRAM and method thereof

InactiveUS7050352B2Improve circuit reliabilityDoor/window protective devicesDigital storageTime differenceComputer science

Provided is directed to a data input apparatus and a method of DDR SDRAM which can improve reliability of a circuit operation by transferring data inputted after applying a data strobe signal DQS to an input / output bus GIO by a exact timing, by means of correctly arranging the data strobe signal DQS and a data input strobe pulse dinstbp regardless of time difference of inputting the data strobe signal DQS after a write command, in response to generating a data input strobe pulse dinstbp used to load data to the input / output bus GIO as a data strobe pulse dsp identical to the data strobe signal DQS.

Owner:SK HYNIX INC

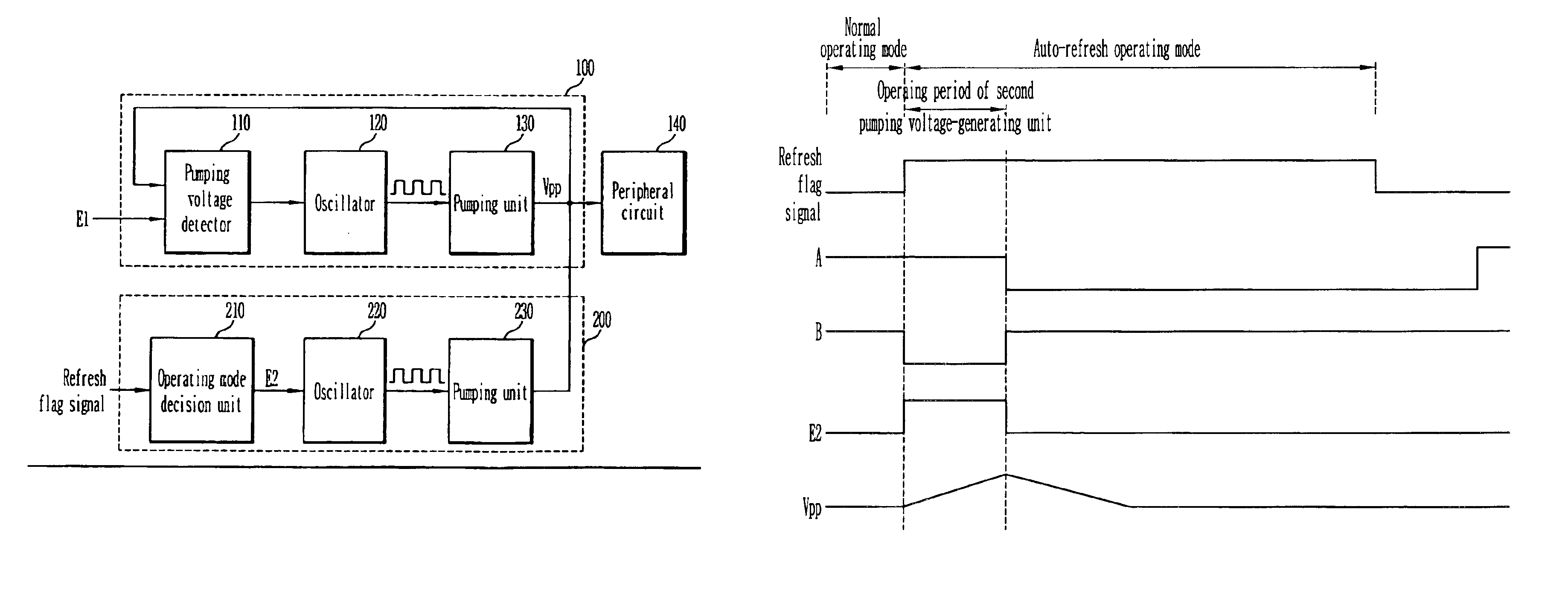

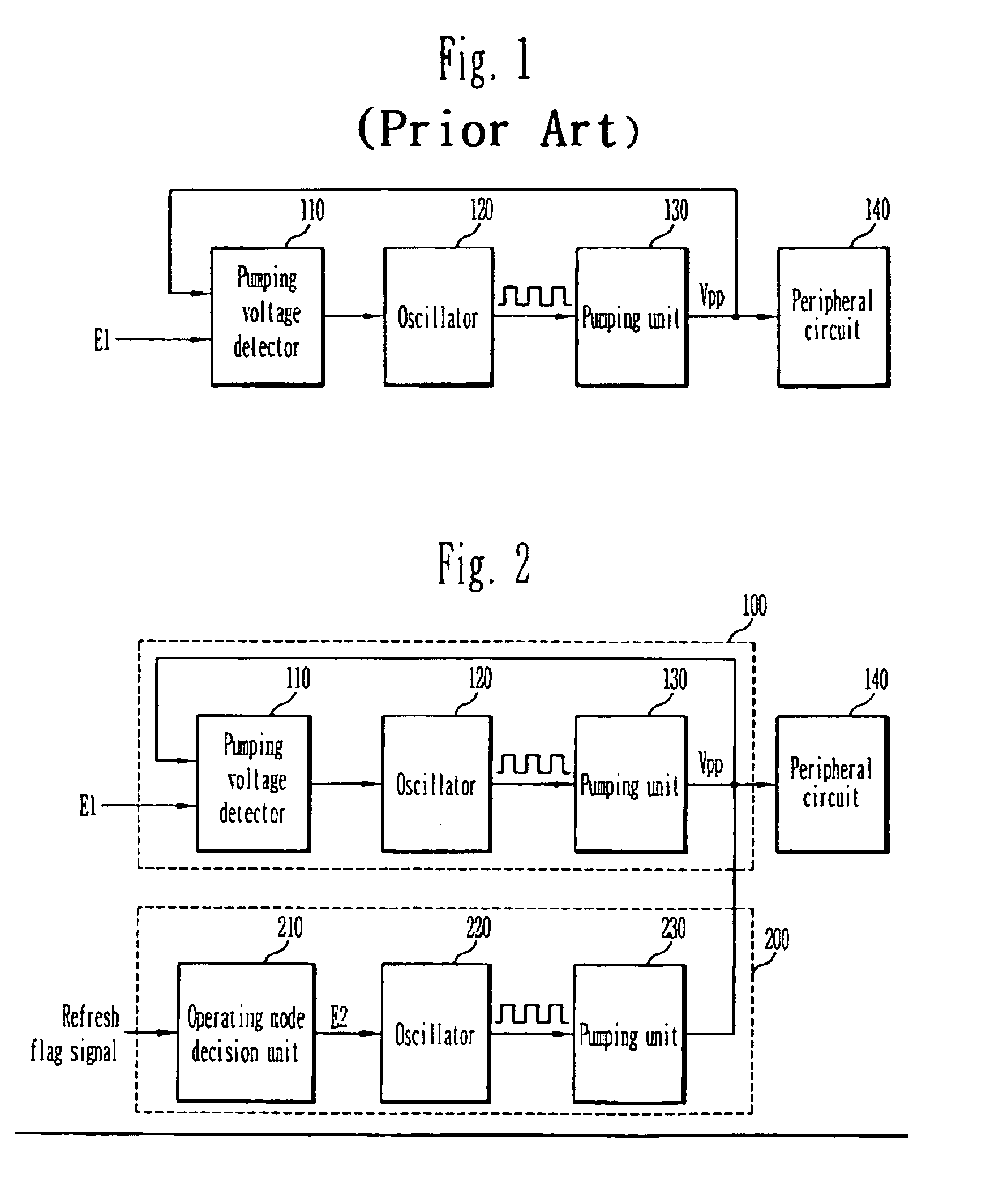

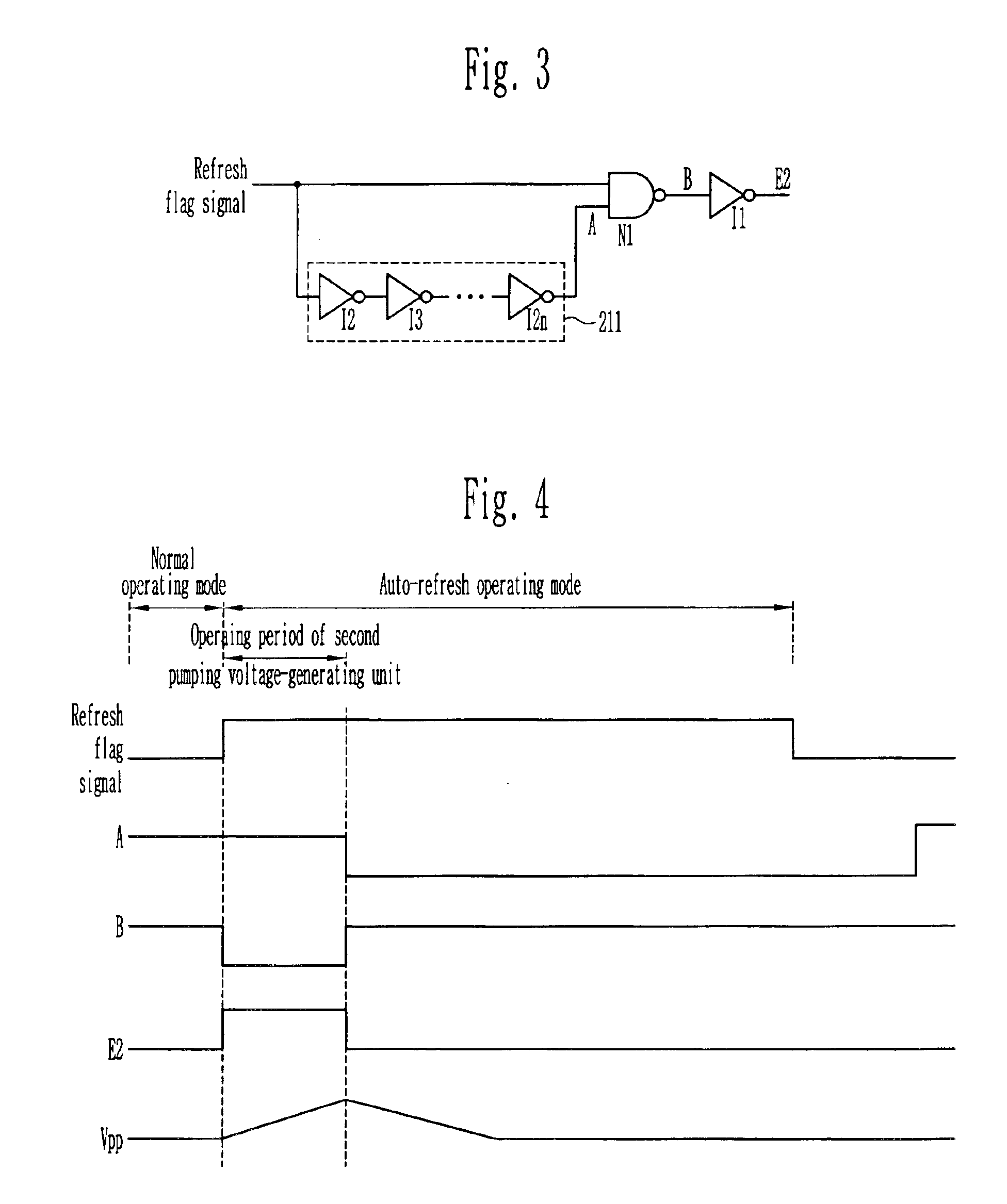

High voltage supply circuit and a method of supplying high voltage

InactiveUS6930535B2Improve circuit reliabilityImprove reliabilityEfficient power electronics conversionApparatus without intermediate ac conversionCurrent consumptionEngineering

A high voltage supply circuit and method of supplying a high voltage are disclosed. A second pumping voltage-generating unit, in addition to a primary pumping voltage-generating unit for generating a pumping voltage, is provided. The second pumping voltage-generating unit is operated for a certain time simultaneously with the primary voltage-generating unit when a normal operating mode is switched to an auto-refresh operating mode where current consumption is abruptly increased in order to raise the pumping voltage higher than a target voltage. Therefore, the resulting pumping voltage is prevented from being lower than the target voltage even if the operating mode where current consumption is abruptly increased is entered, and the reliability of the circuit is therefore increased.

Owner:MOSAID TECH

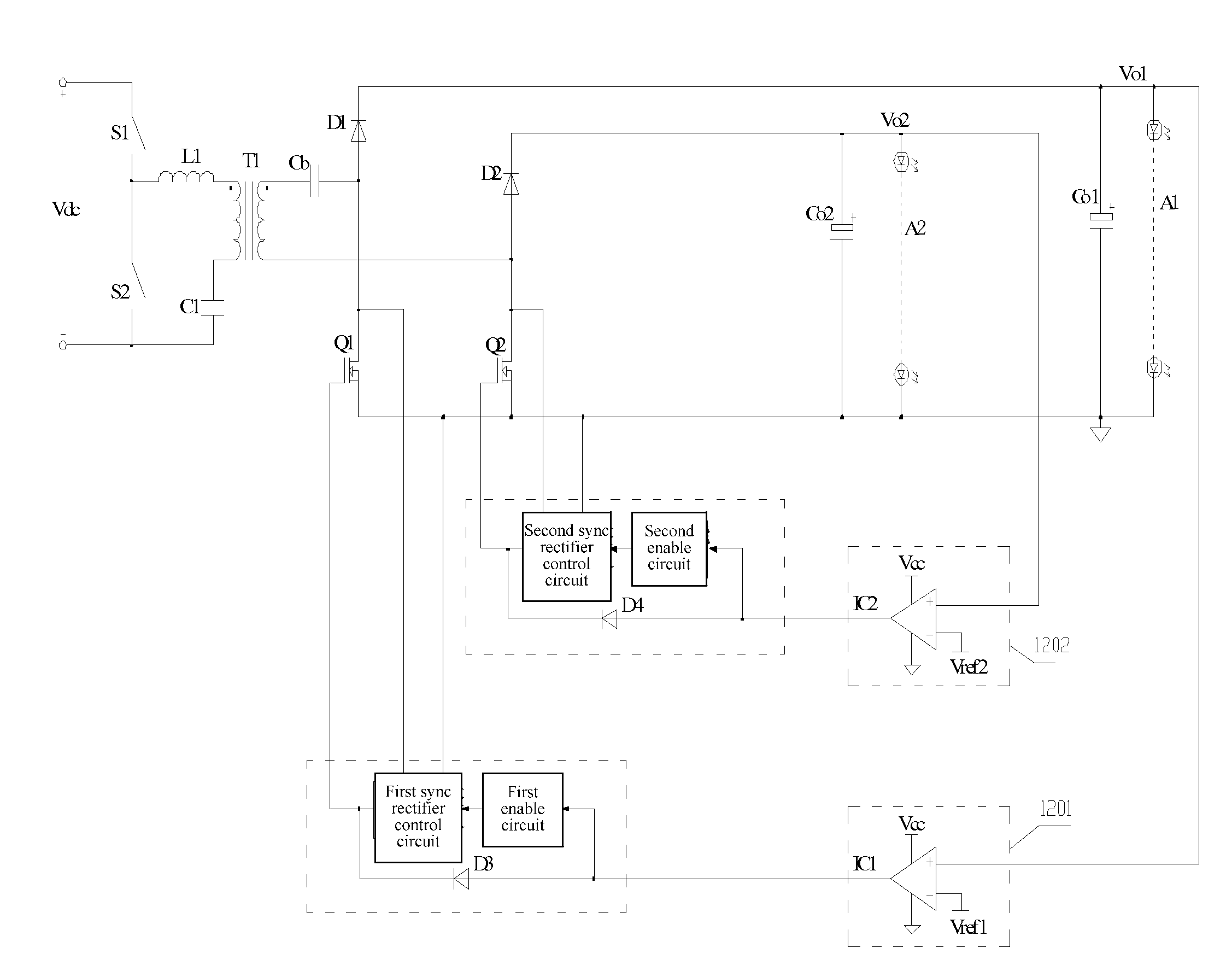

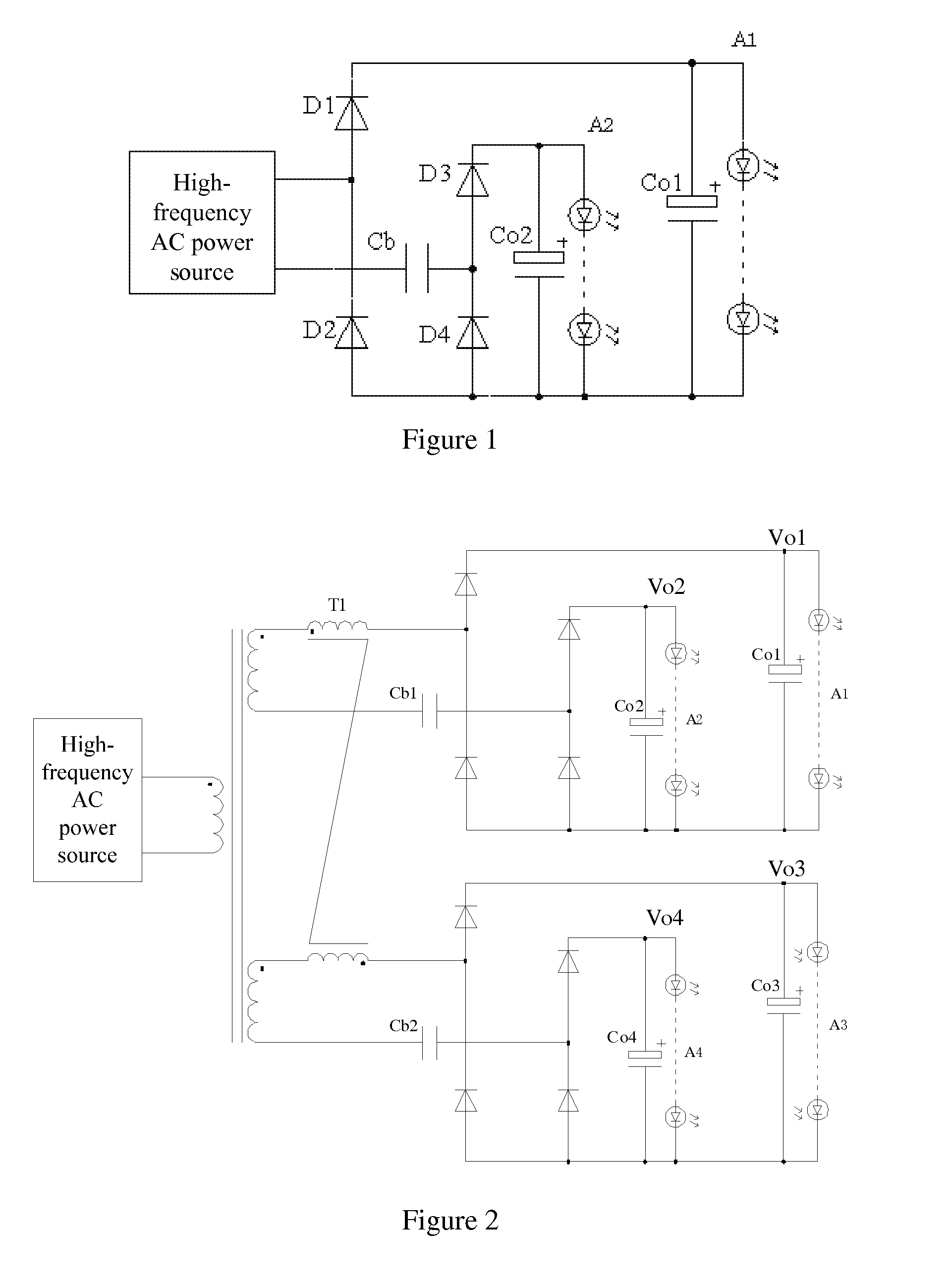

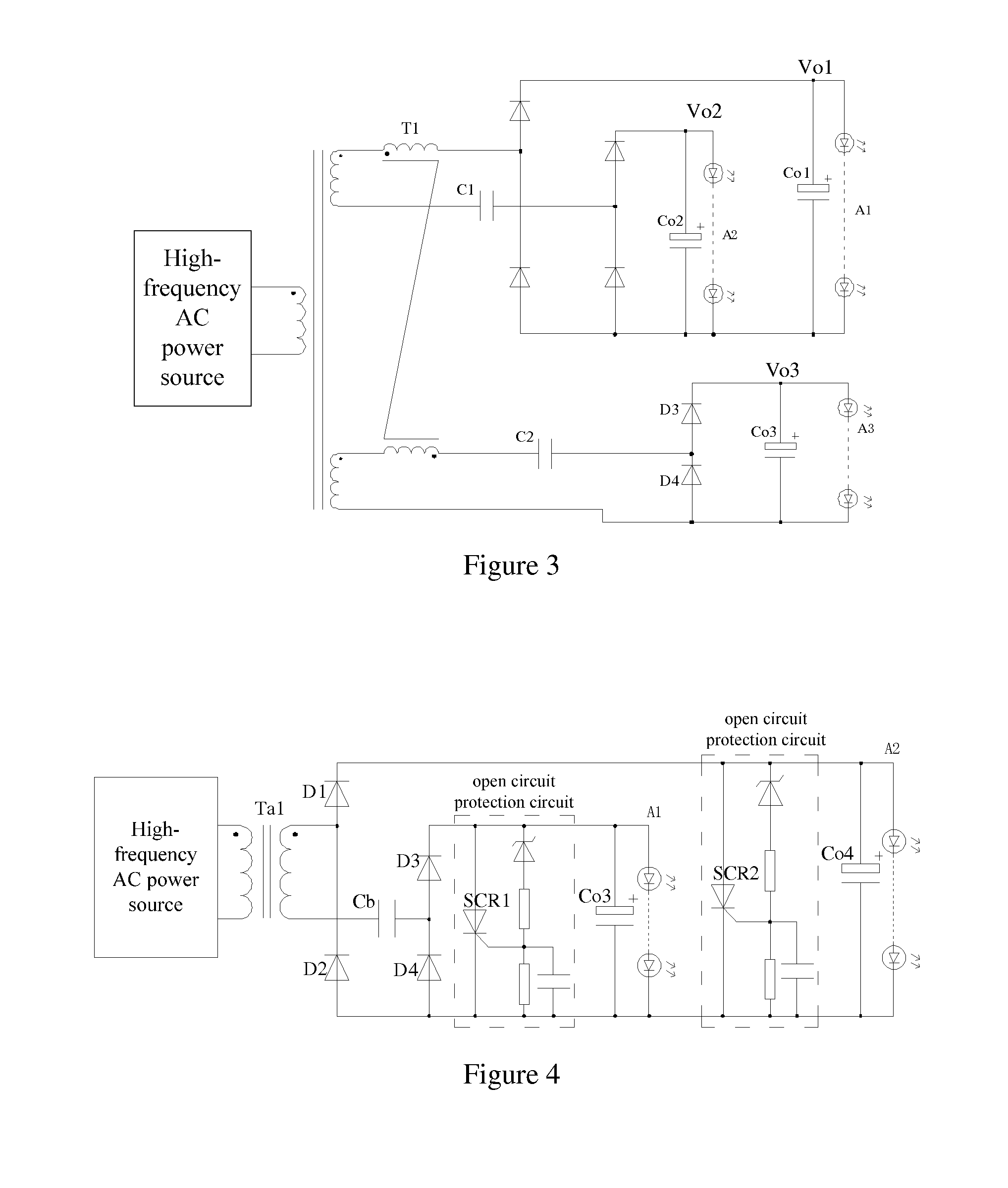

Power supply circuit for multi-path light-emitting diode (LED) loads

ActiveUS20130127343A1Total current dropImprove circuit reliabilityElectrical apparatusElectroluminescent light sourcesPower circuitsMulti path

The present invention discloses a power supply circuit for multi-path light-emitting diode (LED) loads. The two ports of the second diode are connected in parallel with the first switch tube, and the two ports of the forth diode are connected in parallel with the second switch tube. The conduction mode of the second and forth diodes is controlled by controlling the switch status of the first and second switch tubes. When the system is on a normal state, the first and second switch tubes are both switched off. When the load output of any path needs to be turned off, the corresponding switch tube should be controlled to switch on, which makes the diode connected in parallel with the switch tube short-circuited. The present invention can avoid a strong impulse current produced in filtering capacitor when the load of any path is directly short-circuited. Therefore, the present invention can reduce the current stress in circuits, improve the reliability of circuits, and reduce the cost.

Owner:INVENTRONICS HANGZHOU

Circuit board and process for fabricating the same

InactiveUS20110155441A1Improve reliabilityReduce height differenceRadiation applicationsDecorative surface effectsBiological activationDielectric layer

A process for fabricating a circuit board is provided. A circuit substrate having a first surface and a first circuit layer is provided. A first dielectric layer having a second surface is formed on the circuit substrate and covers the first surface and the first circuit layer. An antagonistic activation layer is formed on the second surface. The antagonistic activation layer is irradiated by a laser beam to form at least a blind via extended from the antagonistic activation layer to the first circuit layer and an intaglio pattern. A first conductive layer is formed inside the blind via. A second conductive layer is formed in the intaglio pattern and the blind via. The second conductive layer covers the first conductive layer and is electrically connected with the first circuit layer through the first conductive layer. The antagonistic activation layer is removed to expose the second surface.

Owner:UNIMICRON TECH CORP

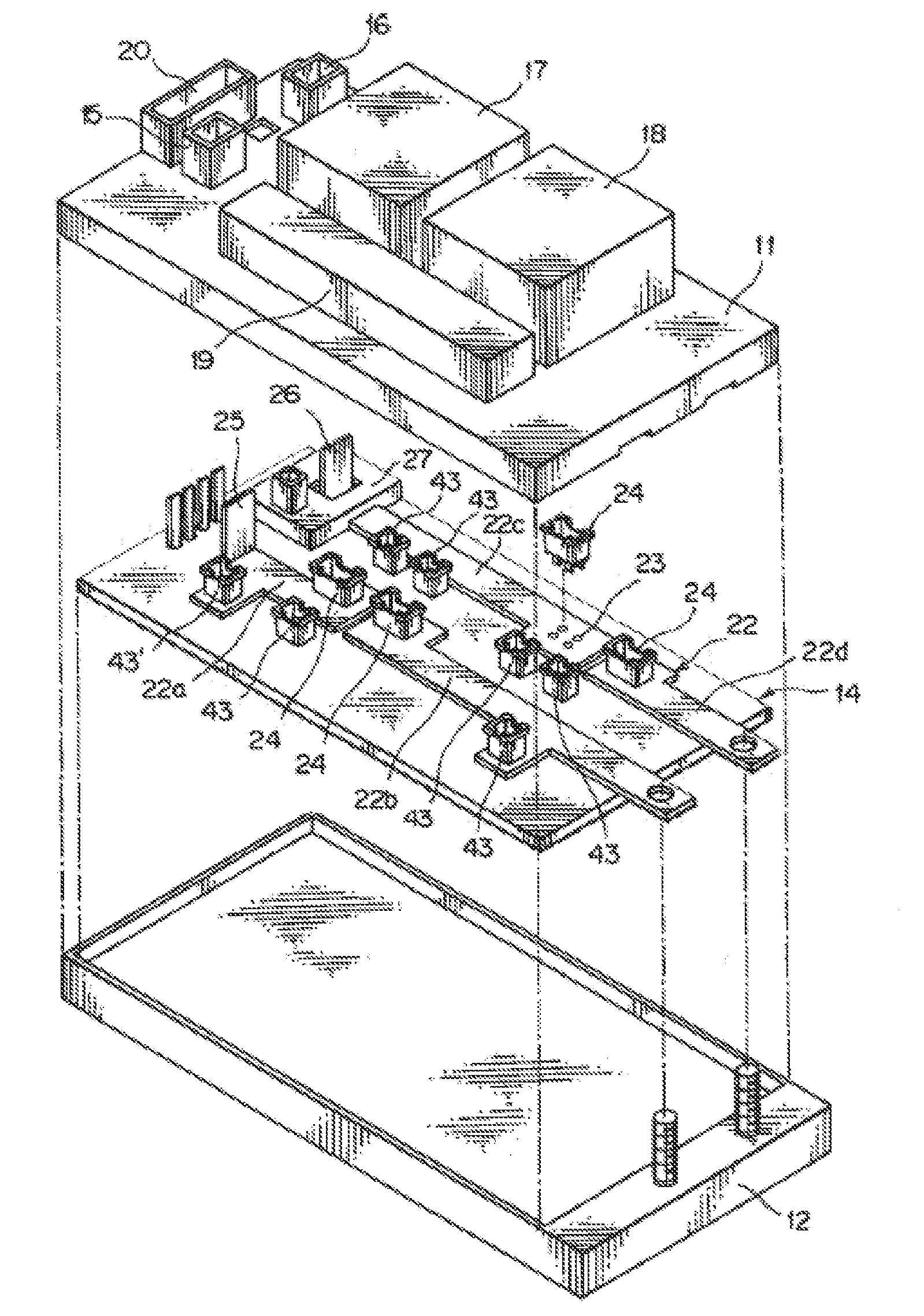

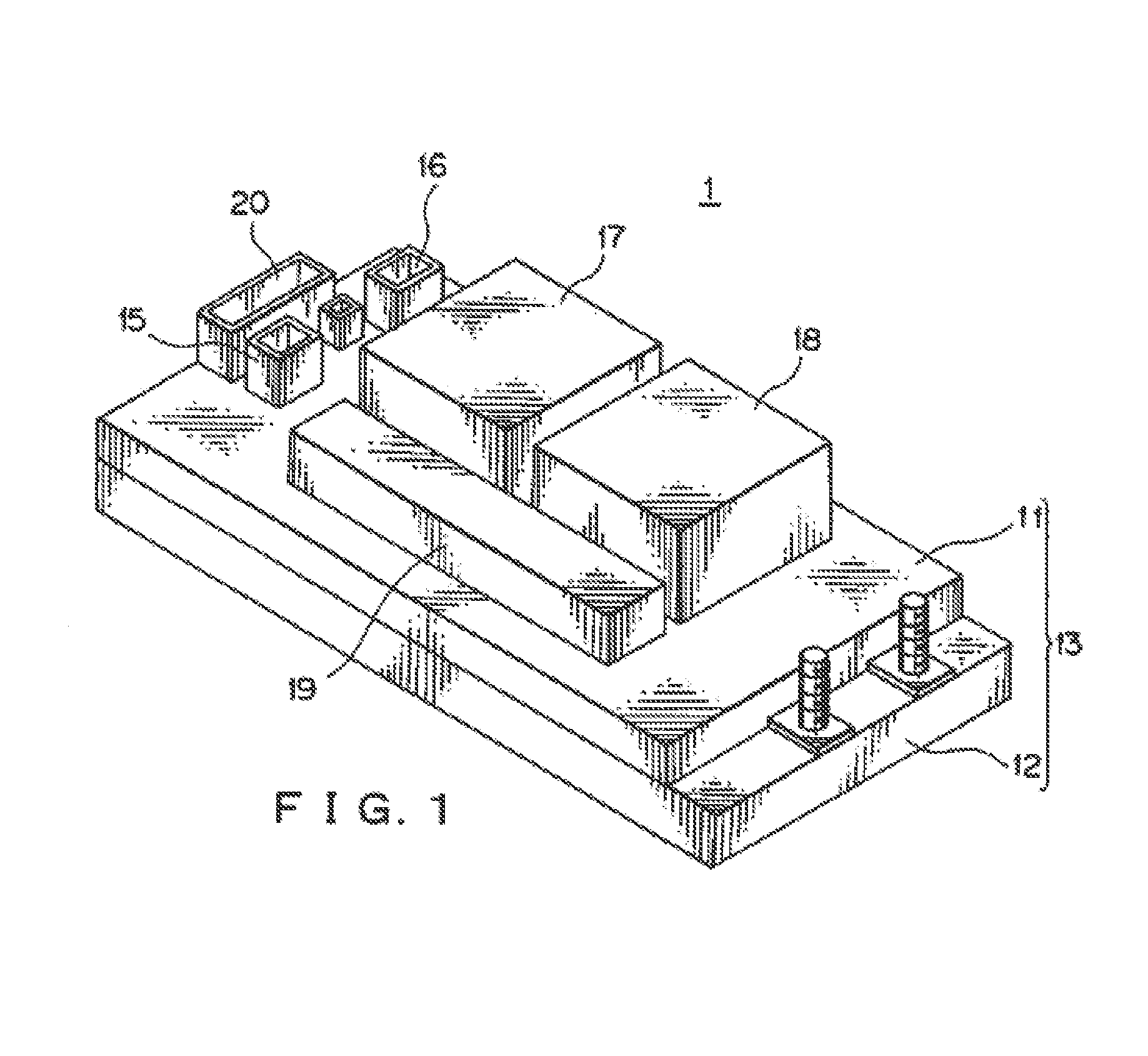

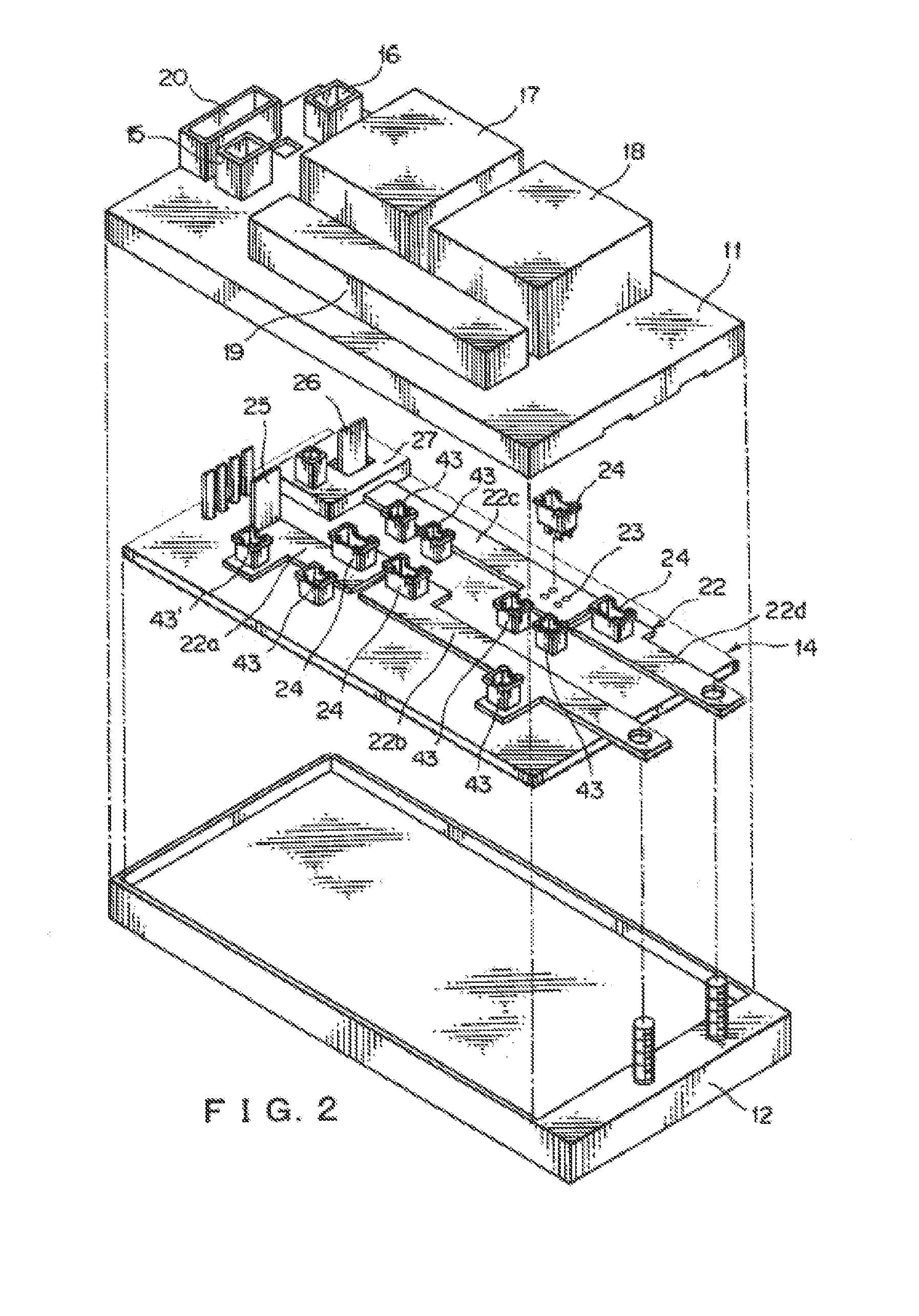

High-voltage electrical junction box

ActiveUS20140273554A1Easy to assembleReduce component countPrinted circuitsElectric/fluid circuitElectrical junctionHigh pressure

A high-voltage electrical junction box includes a box body having an insulating property, a board having an insulating property, the board being accommodated in the box body, a bus bar that is disposed on one surface of the board, a printed pattern that is formed on another surface of the board, a first through hole that is formed to penetrate through the bus bar, the board and the printed pattern, and a first connection piece that is inserted through the first through hole, the first connection piece being connected to the bus bar, the board and the printed pattern.

Owner:FURUKAWA ELECTRIC CO LTD +1

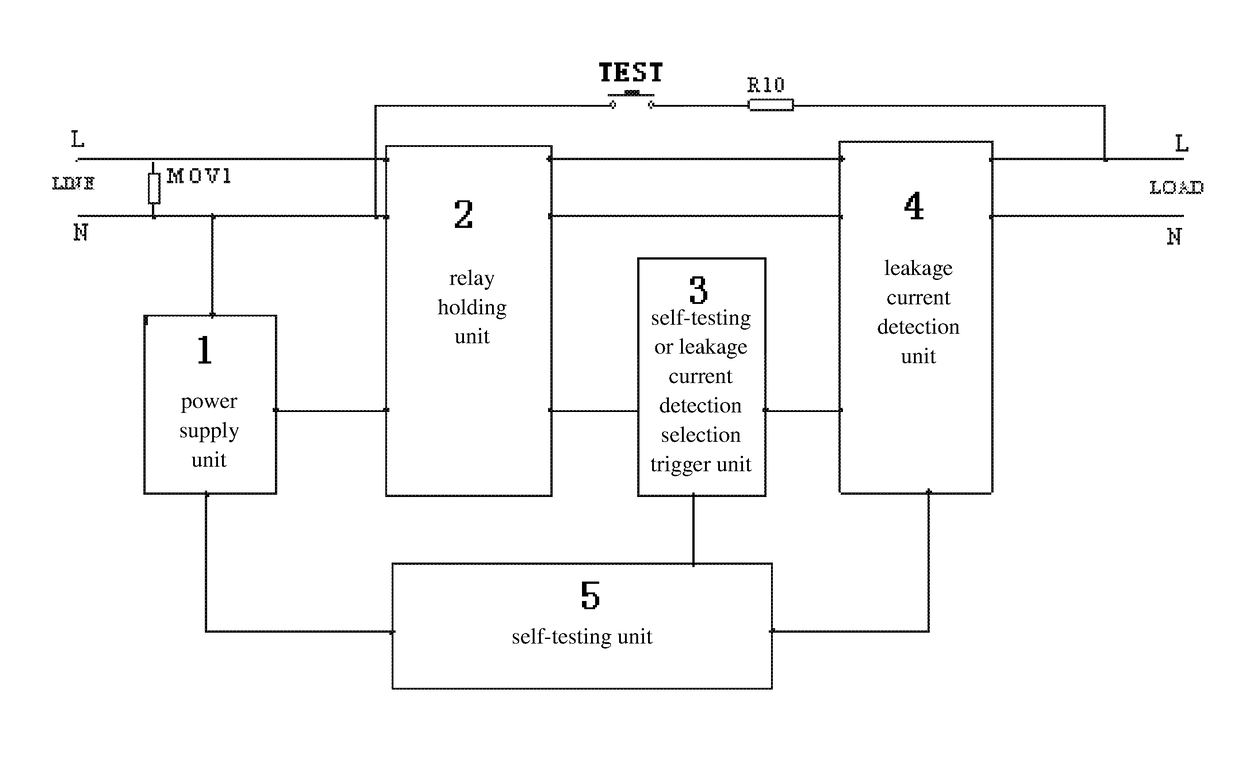

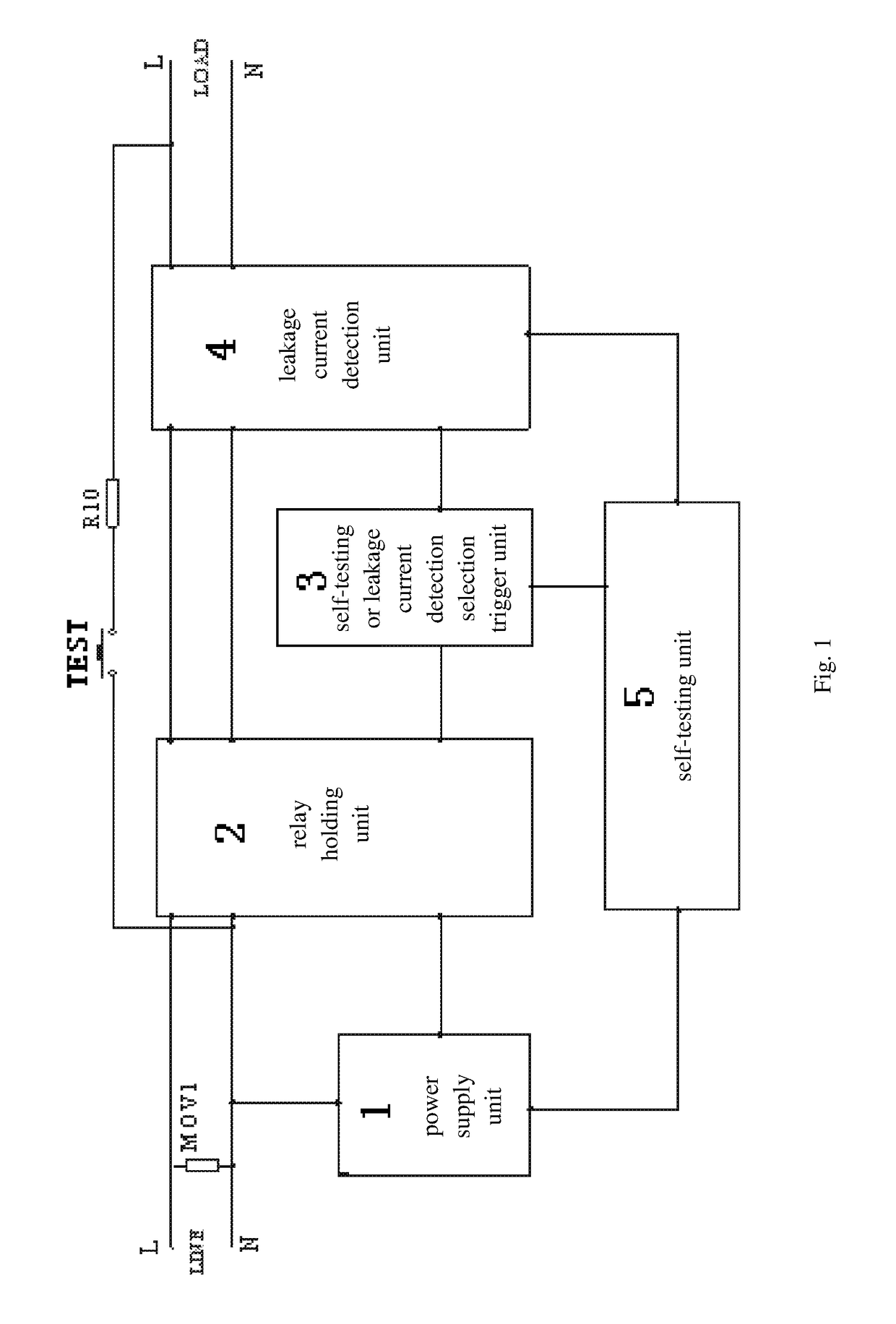

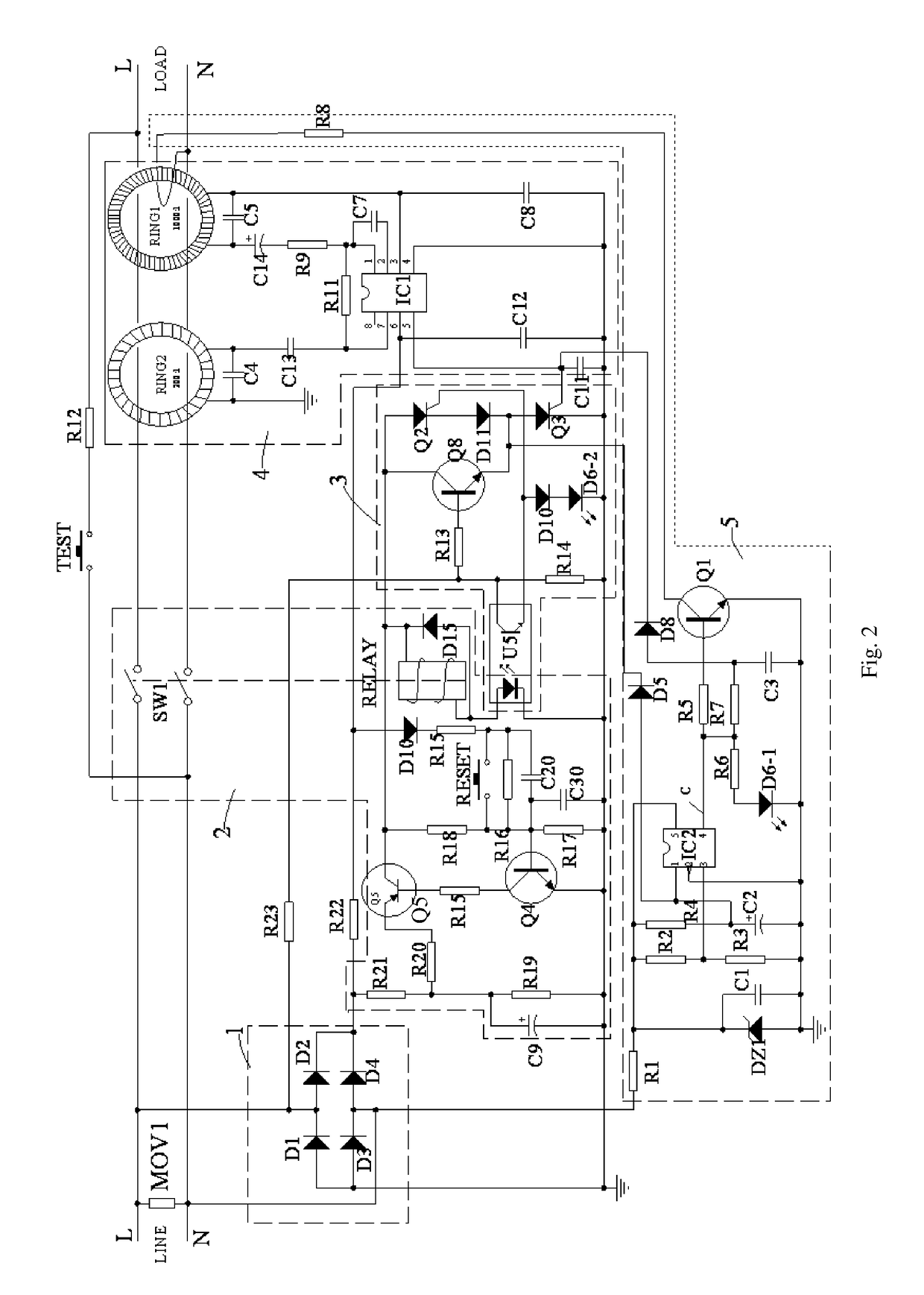

Leakage current detection device for appliances

ActiveUS20170222425A1Protective function is improvedLeakage is detectedArrangements responsive to excess currentEmergency protective arrangements for limiting excess voltage/currentPower flowEngineering

A leakage current detection device connected between a power source and a load, which includes a self-testing or leakage current detection selection trigger unit, for selecting a leakage current detection mode or a self-testing mode; a self-testing unit, for periodically generating a simulated leakage current signal in the self-testing mode; and a leakage current detection unit, for detecting a leakage current signal in the leakage current detection mode and detecting the simulated leakage current signal in the self-testing mode. The selection trigger unit further causes the power source to be disconnected from the load when a leakage current signal is detected, and sends a self-testing result to the self-testing unit depending on whether the leakage current detection unit detects the simulated leakage current signal. The self-testing unit displays an indication of the self-testing result.

Owner:LI CHENGLI

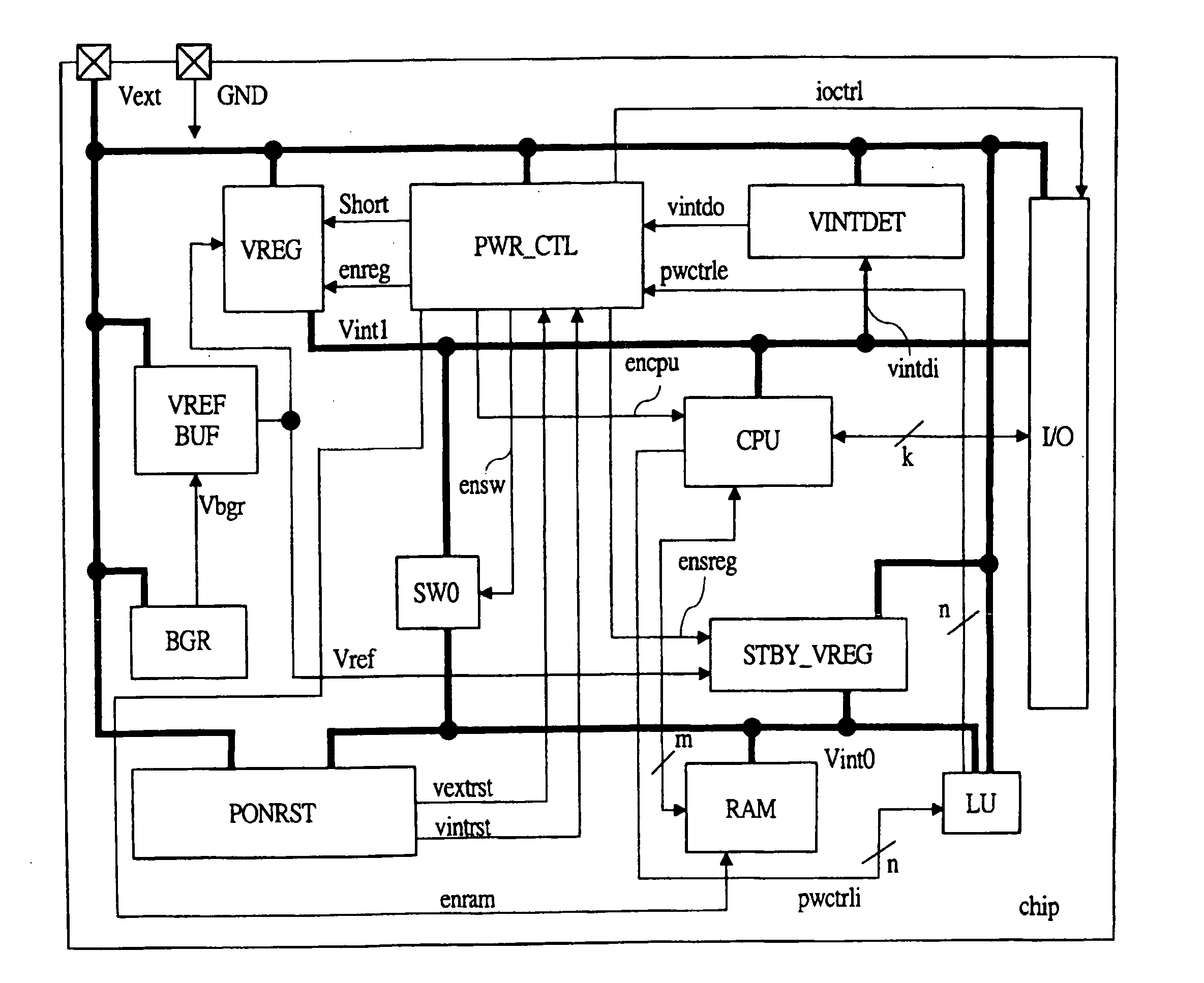

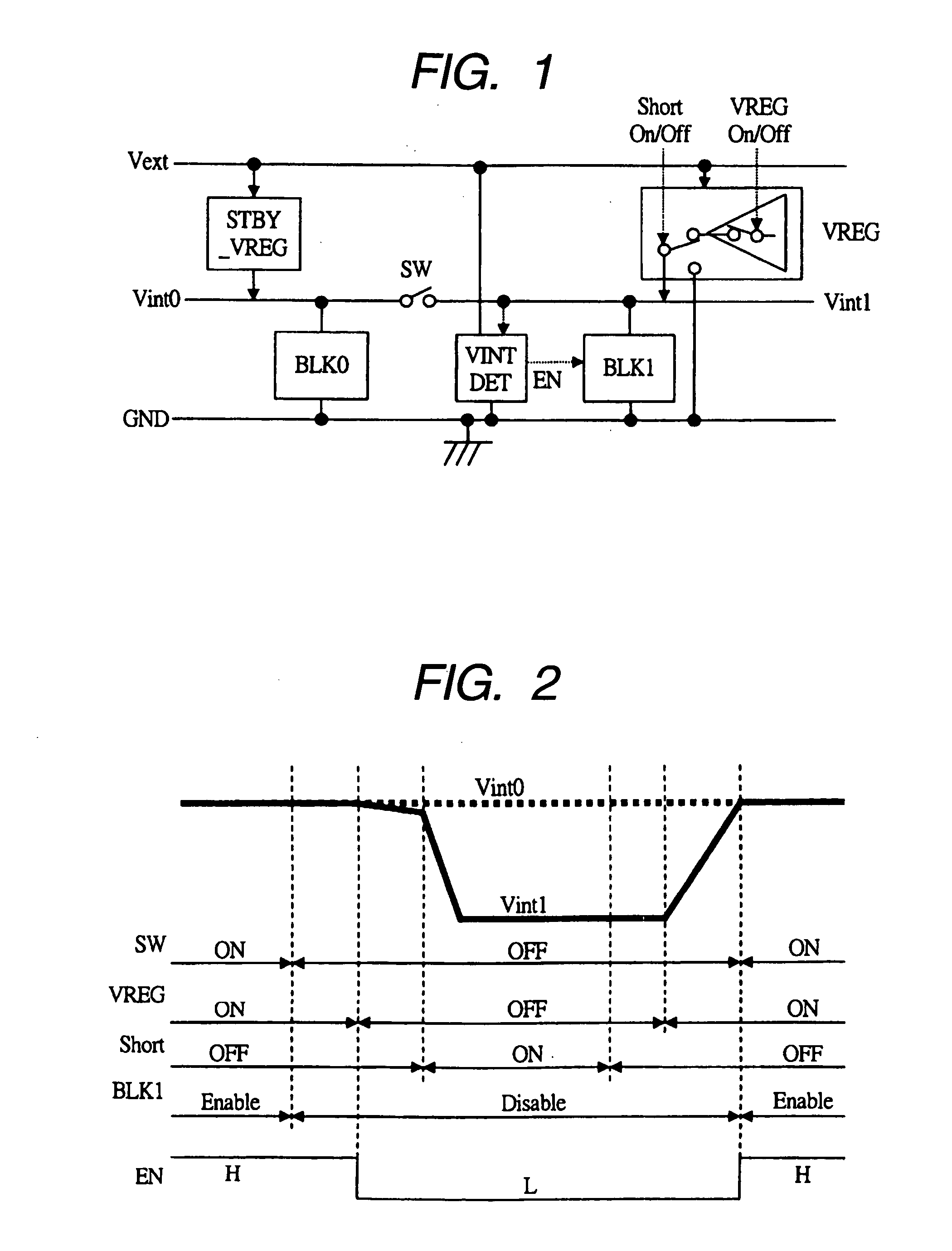

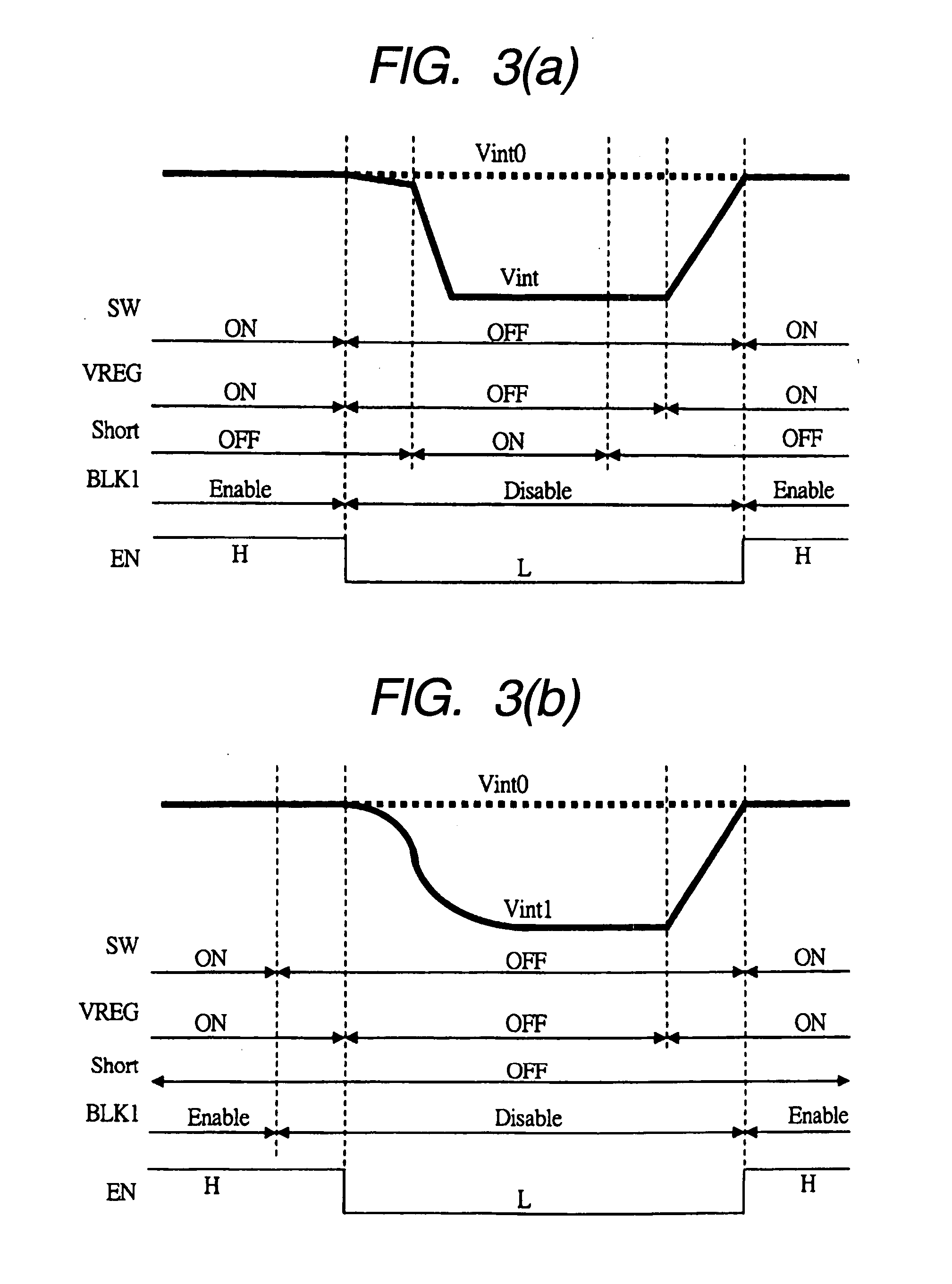

Semicondustor device

InactiveUS20060235630A1Improve reliabilityReduce areaEnergy efficient ICTElectric devicesDevice materialPower switching

The present invention provides a semiconductor device capable of realizing power saving and improvement in reliability or reduction in area. A semiconductor device includes: a power switch connecting an internal power supply in which power is not shut down and an internal power supply in which power is shut down; and an internal voltage determining circuit for determining voltage of the internal power supply in which power is shut down. Voltage of the internal power supply in which power is shut down is generated from voltage of an external power supply by using a regulator circuit. When the power of the internal power supply is interrupted, the power switch is turned off, the regulator circuit is turned off, and an output of the regulator circuit is shorted to a ground potential. When the power of the internal power supply is resumed, the regulator circuit is turned on, shorting is cancelled, the increased voltage of the internal power supply is determined by the internal voltage determining circuit, operation of a circuit block is started, and the switch is turned on.

Owner:RENESAS ELECTRONICS CORP

Circuit board and manufacturing method thereof

ActiveUS9635757B1Improve reliabilityInhibition formationPrinted circuit aspectsNon-printed masksDielectric matrixDielectric substrate

A circuit board and a manufacturing method thereof are provided. The circuit board includes a dielectric substrate, a circuit pattern and a dielectric layer. The circuit pattern is disposed on the dielectric substrate. The dielectric layer is disposed on the dielectric substrate and covers the circuit pattern. The dielectric layer includes a dielectric matrix and a mesh-shaped fiber structure disposed in the dielectric matrix. There is no mesh-shaped fiber structure on a portion of the dielectric substrate exposed by the circuit pattern.

Owner:UNIMICRON TECH CORP

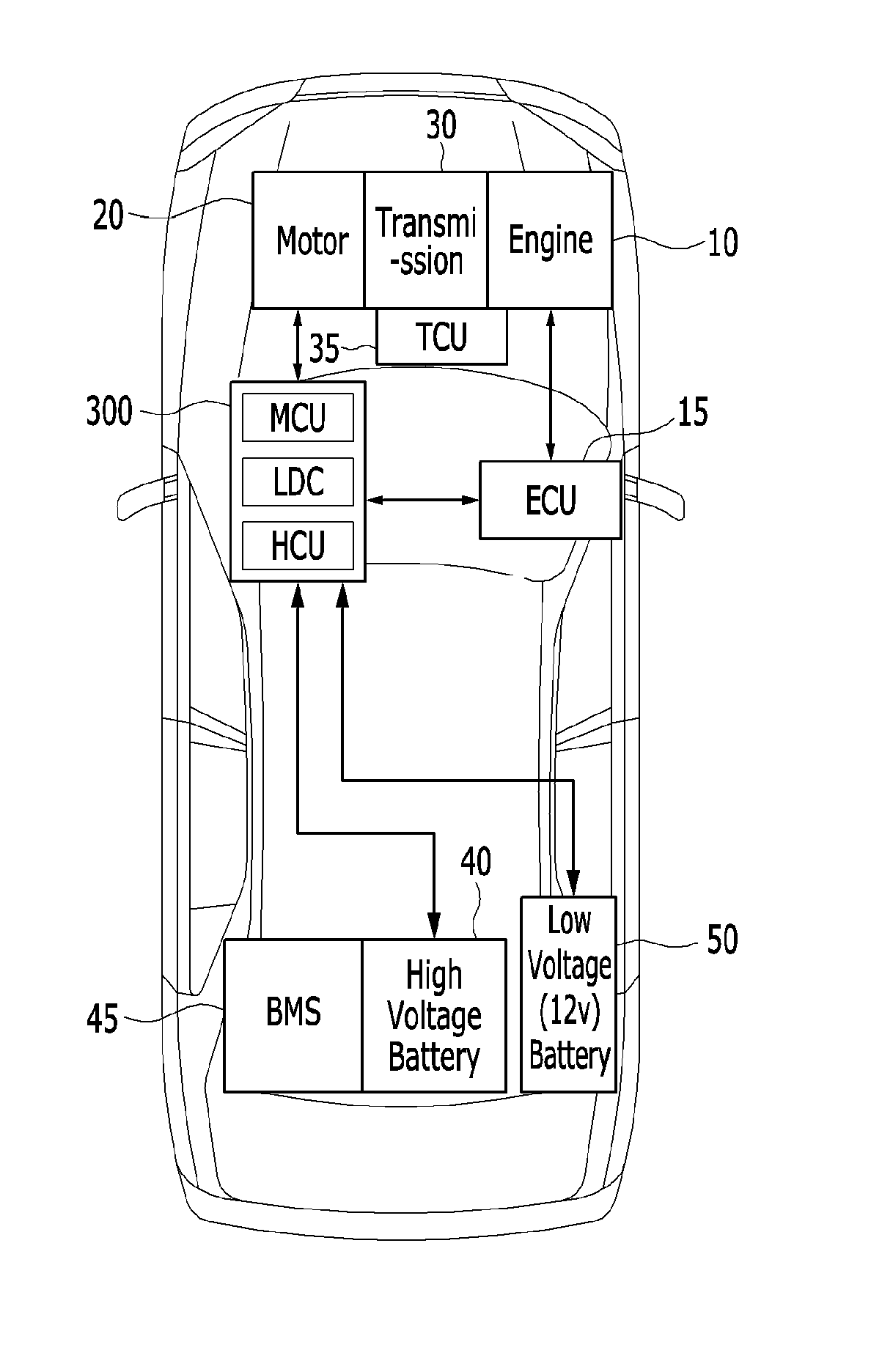

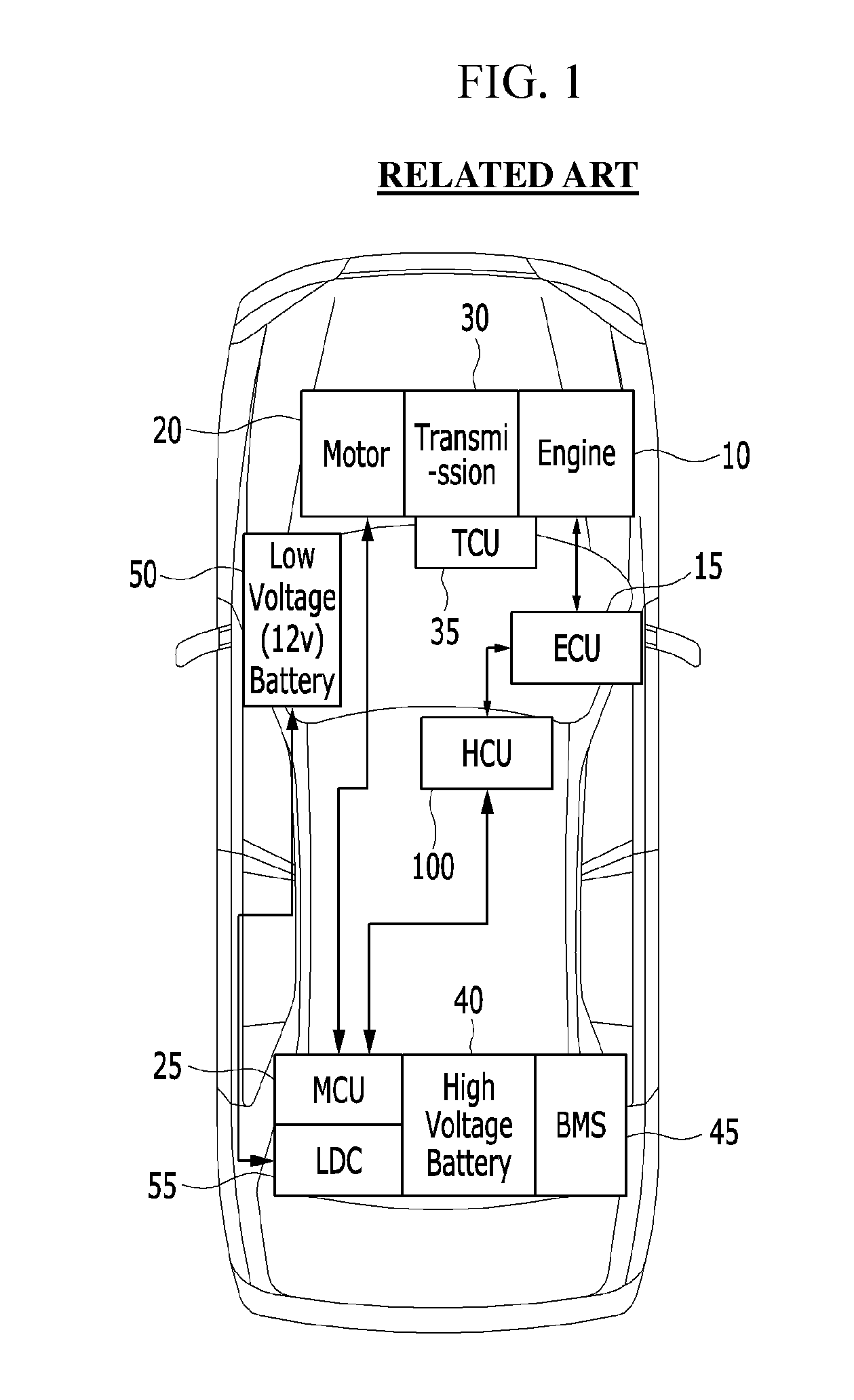

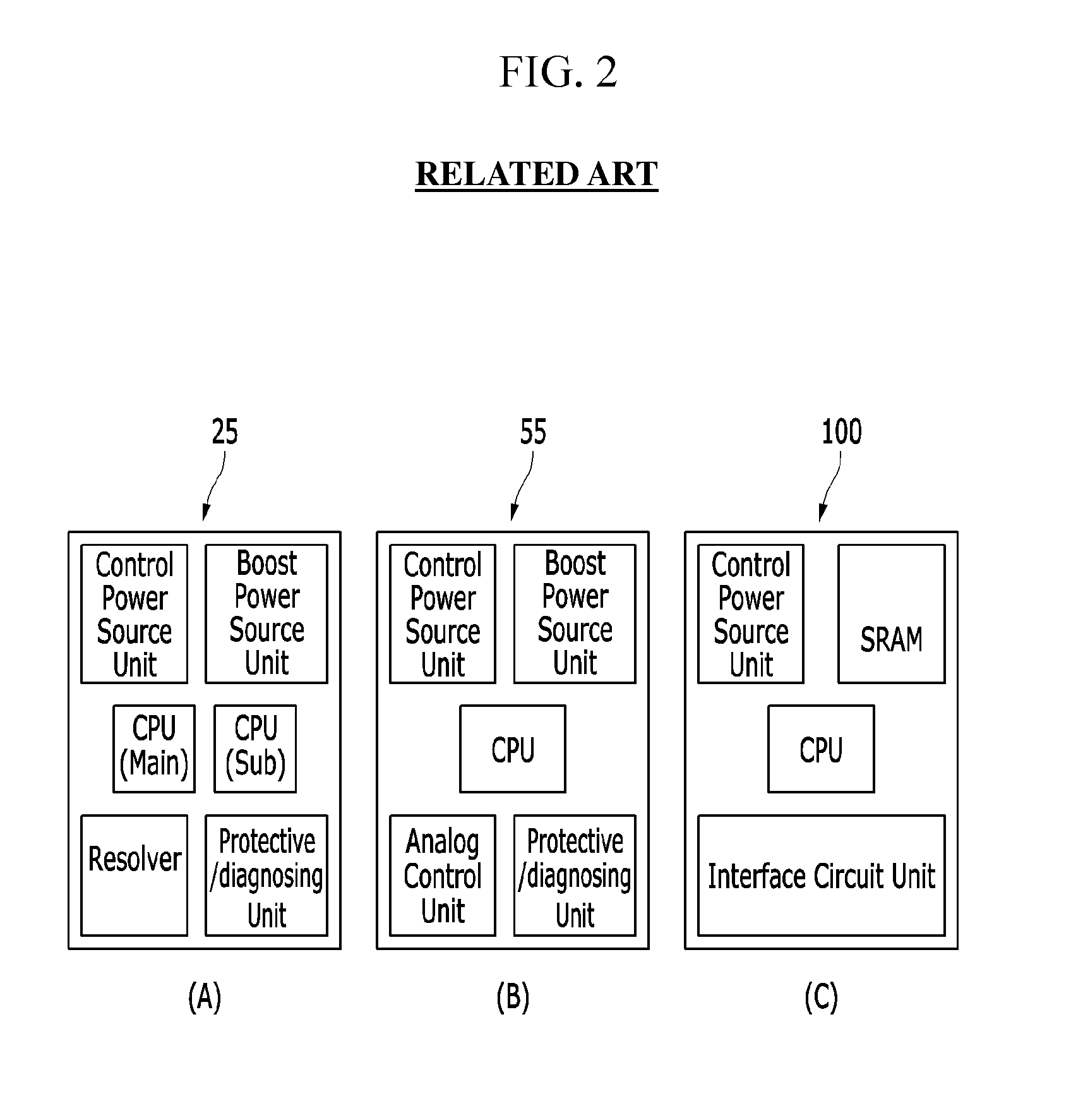

Integrated electronic power control unit of environmentally-friendly vehicle

InactiveUS20140222266A1Improve space utilizationLow costHybrid vehiclesDigital data processing detailsDc dc converterLow voltage

An integrated electronic power control unit of an environmentally-friendly vehicle that may reduce costs and enhance structure and space utilization by integrally configuring at least two or more electronic power control units (EPCUs) disposed within the environmentally-friendly vehicle. The integrated electronic power control unit (EPCU) includes a plurality of EPCUs such as a motor control unit (MCU), a low voltage DC-DC converter (LDC), or a hybrid control unit (HCU), wherein at least one or more components of the plurality of EPCUs are integrated. In addition, the integrated electronic power control unit includes a hardware failure management unit (HFM) that is configured to detect and manage a failure of hardware including the at least one or more integrated components.

Owner:HYUNDAI MOTOR CO LTD +1

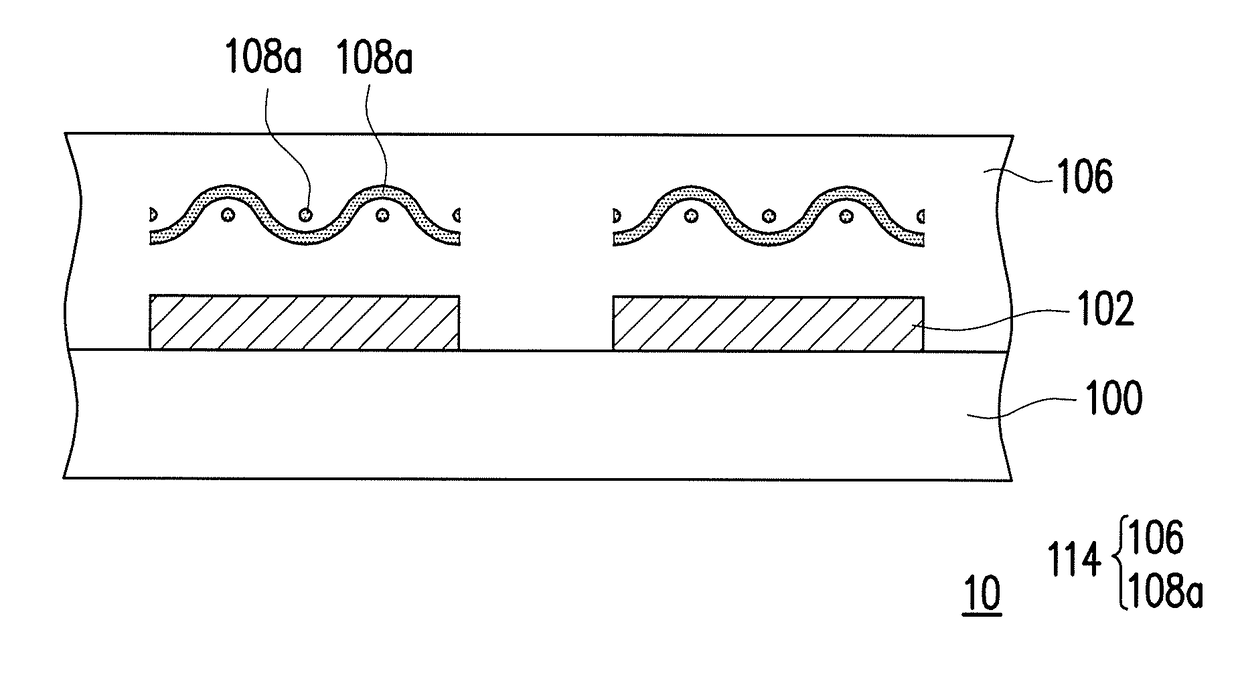

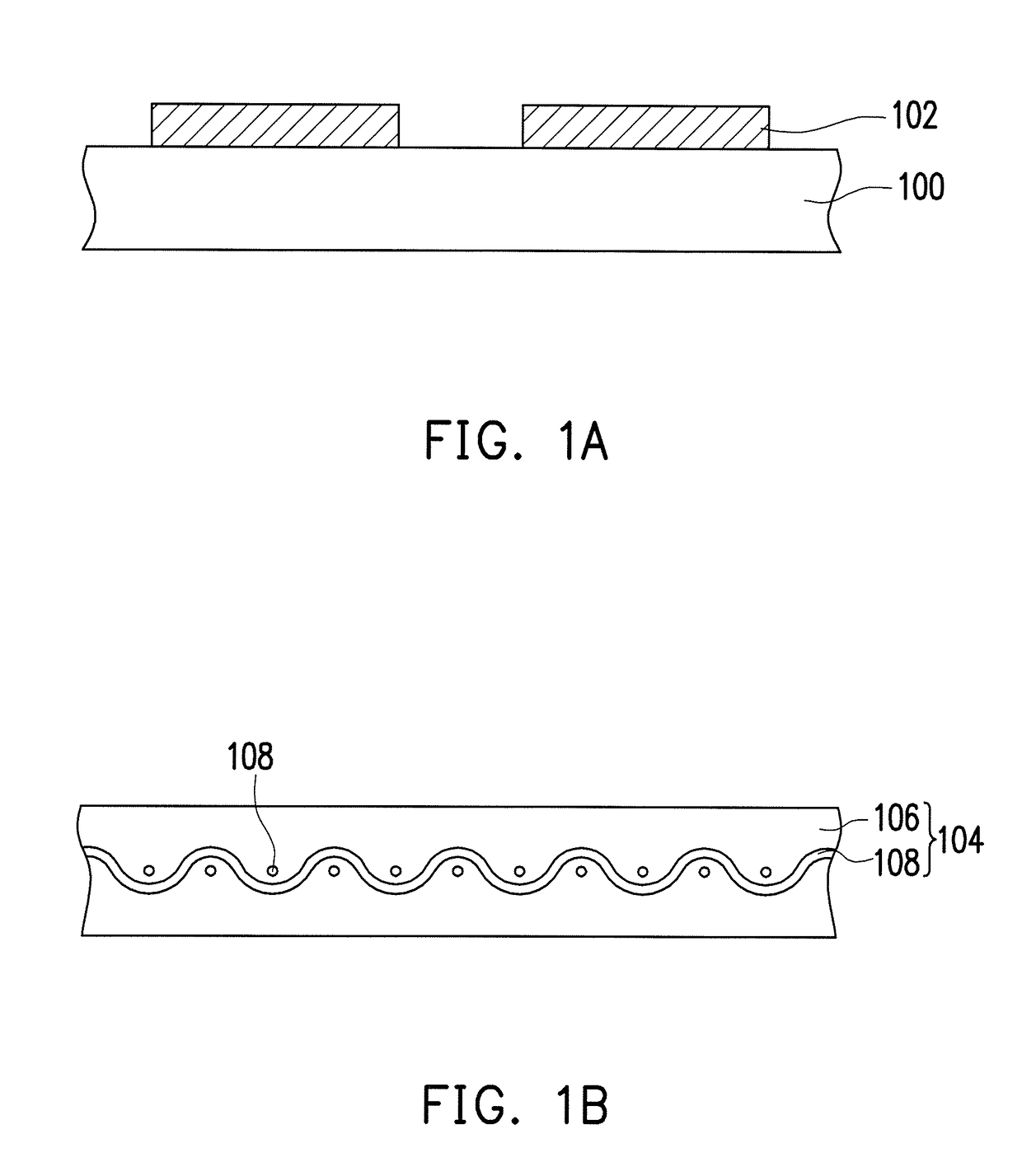

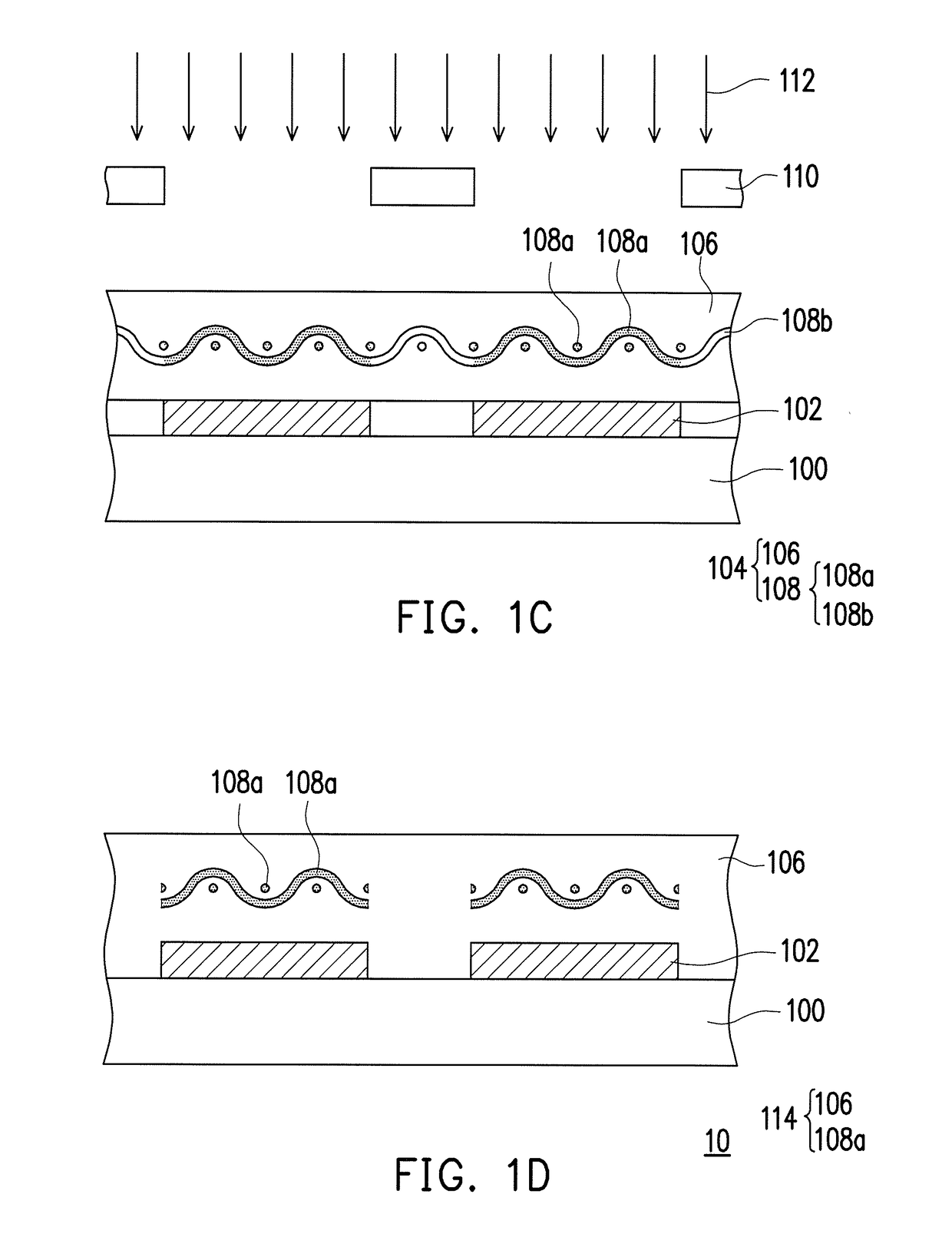

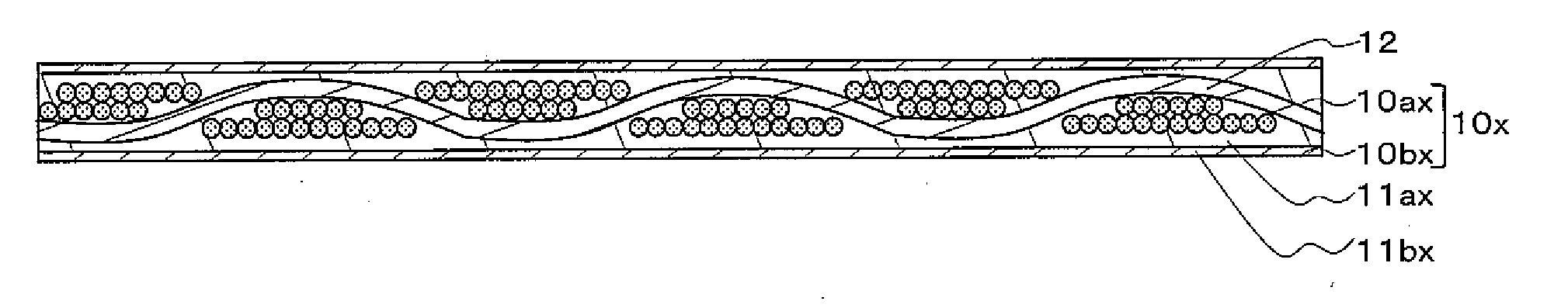

Circuit Substrate and Structure Using the Same

InactiveUS20110024170A1Suppress growth of crackHigh electric reliabilityPrinted electric component incorporationPrinted circuit aspectsMaterials scienceComposite material

A circuit substrate comprises a base and conductive layers disposed on lower and upper surfaces of the substrate. The base includes resin layers and the conductive layers overlapping with each other in a plan view. The resin layers include first resin layers and a second resin layer interposed between the first resin layers. The first resin layer has a filler and the second resin layer has no filler or a filler whose amount is 1 volume % or less and smaller than an amount of the filler in the first resin layer.

Owner:KYOCERA CORP

Method for filling a gap

InactiveUS20120190188A1Reduce and eliminate possibility to produce voidImprove circuit reliabilitySemiconductor/solid-state device detailsSolid-state devicesMetal interconnectDielectric layer

A method for filling a gap includes: providing a semiconductor substrate, at least having an metal interconnect layer and an insulating dielectric layer on top of the underlying metal interconnect layer, the insulating dielectric layer having a gap; forming a diffusion bather layer and a seed layer sequentially in the gap and on a surface of the insulating dielectric layer outside the gap; forming a mask layer on a surface of the seed layer outside of the gap; and depositing a metal layer on the semiconductor substrate with the mask layer, the metal layer filling the gap.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method for fabricating conductive blind via of circuit substrate

ActiveUS7698813B2Improve reliabilityHigh bonding strengthDecorative surface effectsLiquid/solution decomposition chemical coatingConductive materialsCopper

A method for fabricating a conductive blind via of a circuit substrate including the following steps is provided. First, the circuit substrate including a first dielectric layer, a patterned circuit layer and a second dielectric layer are provided. The patterned circuit layer including at least a capture pad is disposed between the first dielectric layer and the second dielectric layer. Next, a blind via exposing the capture pad is formed in the second dielectric layer. Then, an electroless plating process is performed to form an electroless copper layer on the capture pad and an inner wall of the blind via. Next, the electroless copper layer on the capture pad is removed. Finally, the blind via is filled with a conductive material to form the conductive blind via.

Owner:ADVANCED SEMICON ENG INC

Method for fabricating conductive blind via of circuit substrate

ActiveUS20070163112A1Increase reliabilityImprove reliabilityDecorative surface effectsLiquid/solution decomposition chemical coatingElectroless platingConductive materials

A method for fabricating a conductive blind via of a circuit substrate including the following steps is provided. First, the circuit substrate including a first dielectric layer, a patterned circuit layer and a second dielectric layer are provided. The patterned circuit layer including at least a capture pad is disposed between the first dielectric layer and the second dielectric layer. Next, a blind via exposing the capture pad is formed in the second dielectric layer. Then, an electroless plating process is performed to form an electroless copper layer on the capture pad and an inner wall of the blind via. Next, the electroless copper layer on the capture pad is removed. Finally, the blind via is filled with a conductive material to form the conductive blind via.

Owner:ADVANCED SEMICON ENG INC

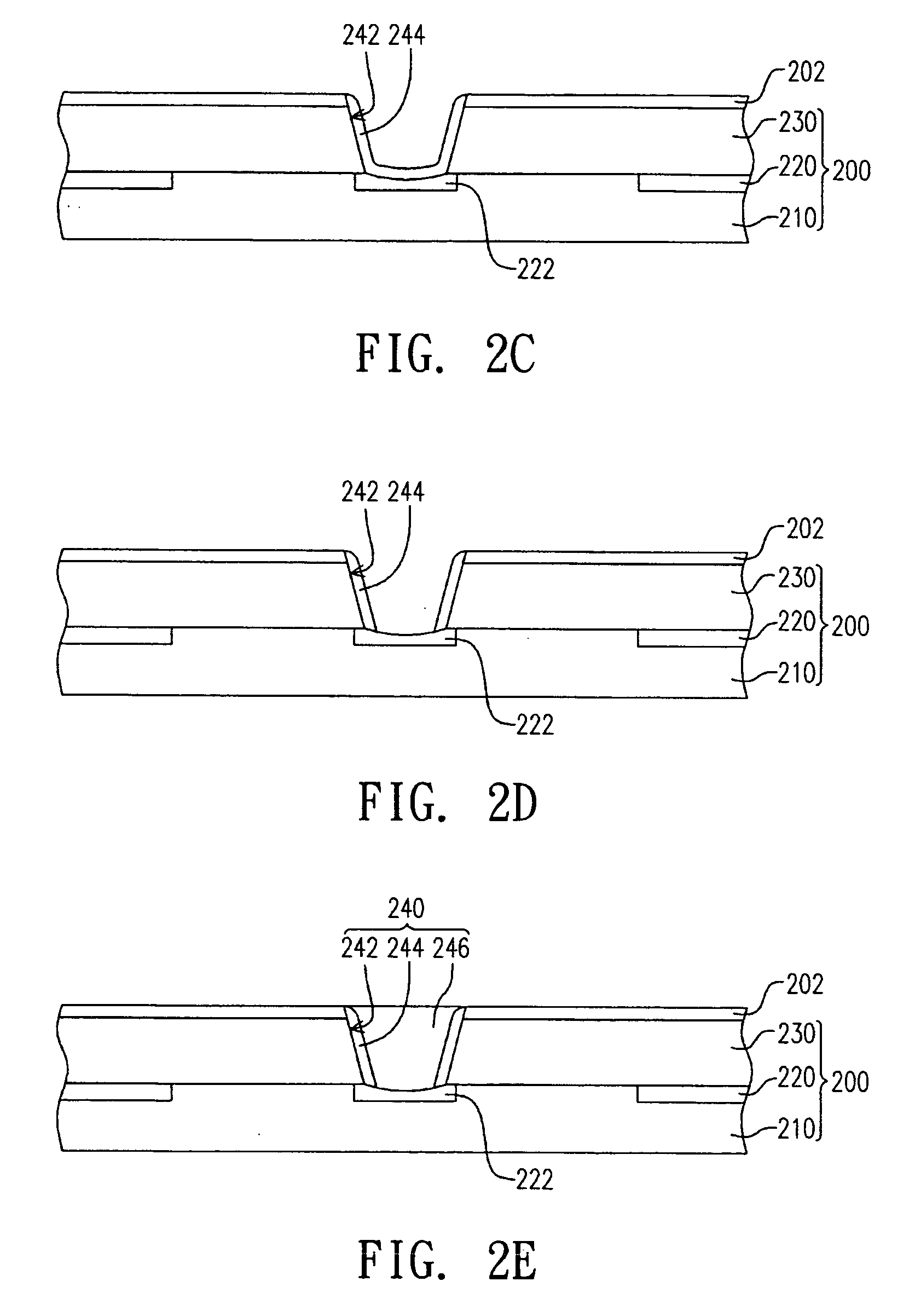

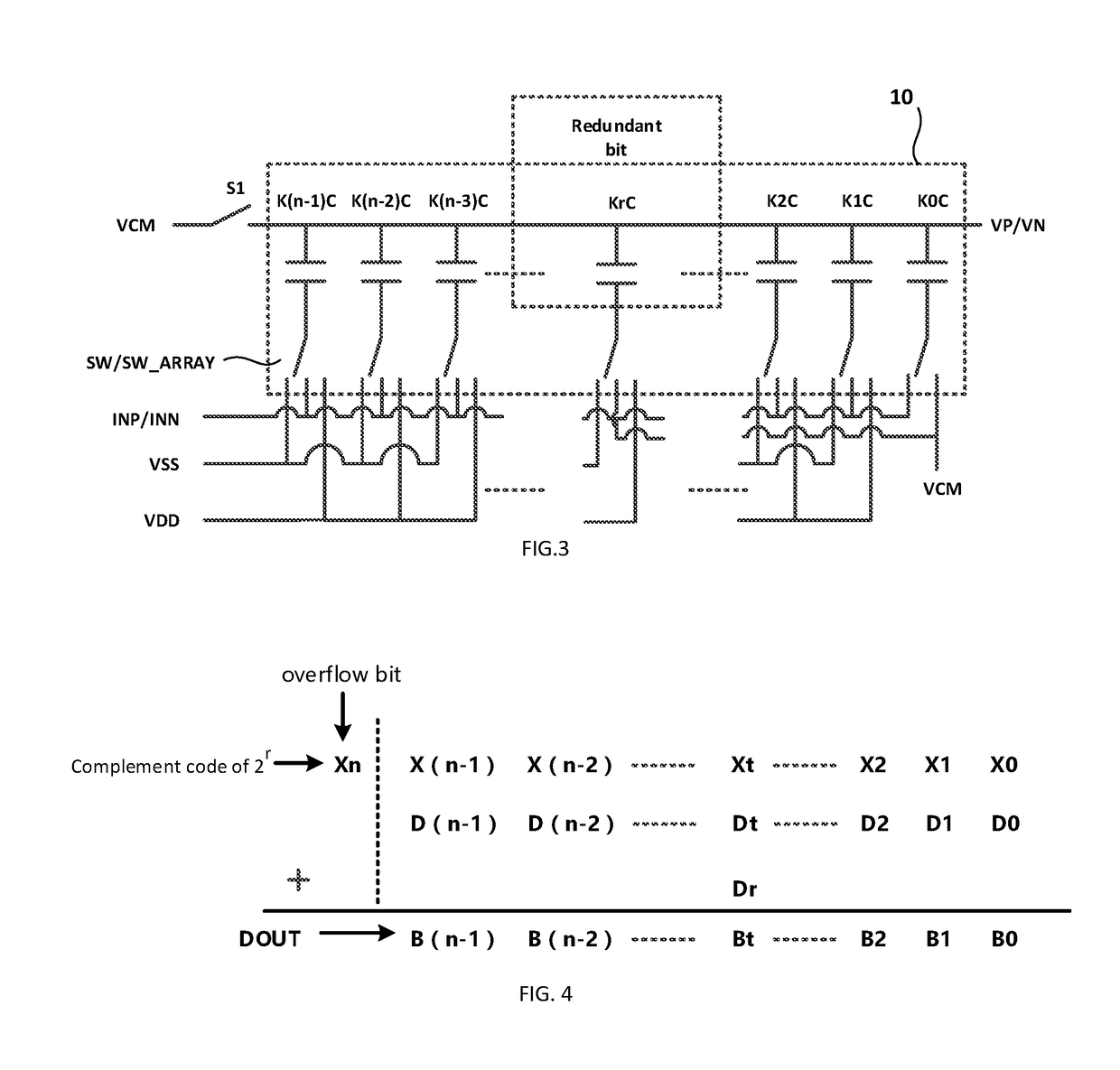

Analogue-digital converter of non-binary capacitor array with redundant bit and its chip

ActiveUS20180041221A1Overall design flexibilitySimple designElectric signal transmission systemsAnalogue-digital convertersCapacitanceA d converter

An analog-to-digital converter of non-binary capacitor array with redundancy bits and its chip. The non-binary capacitor array with redundancy bits comprises a common-mode voltage, analog signal input, no less than one redundancy bit capacitor and multiple capacitors; each capacitor of capacitors with redundancy bits and multiple capacitors is connected in parallel between common-mode voltage and analog signal input and marked in a sequence from highest to lowest / lowest to highest bit; the sum of the capacitance of capacitors from the lowest bit capacitor to an random capacitor must be no less than the capacitance of the higher bit capacitor adjacent to the random capacitor. The ratio of the capacitance of each capacitor to the capacitance of unit capacitor is set to be positive. The capacitor array is applied into an analog-to-digital converter or fabricated as a chip.

Owner:CETC CHIPS TECH GRP CO LTD

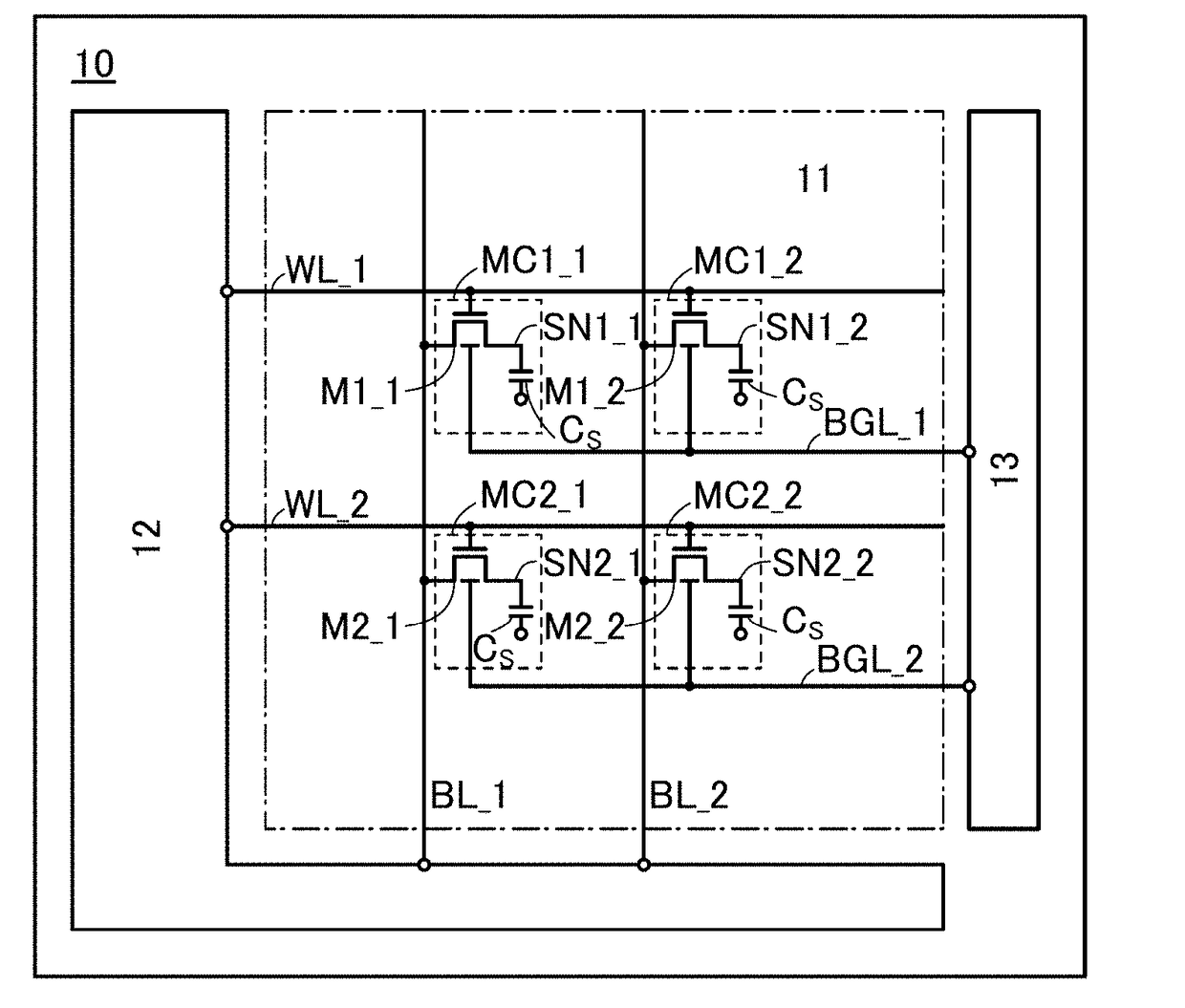

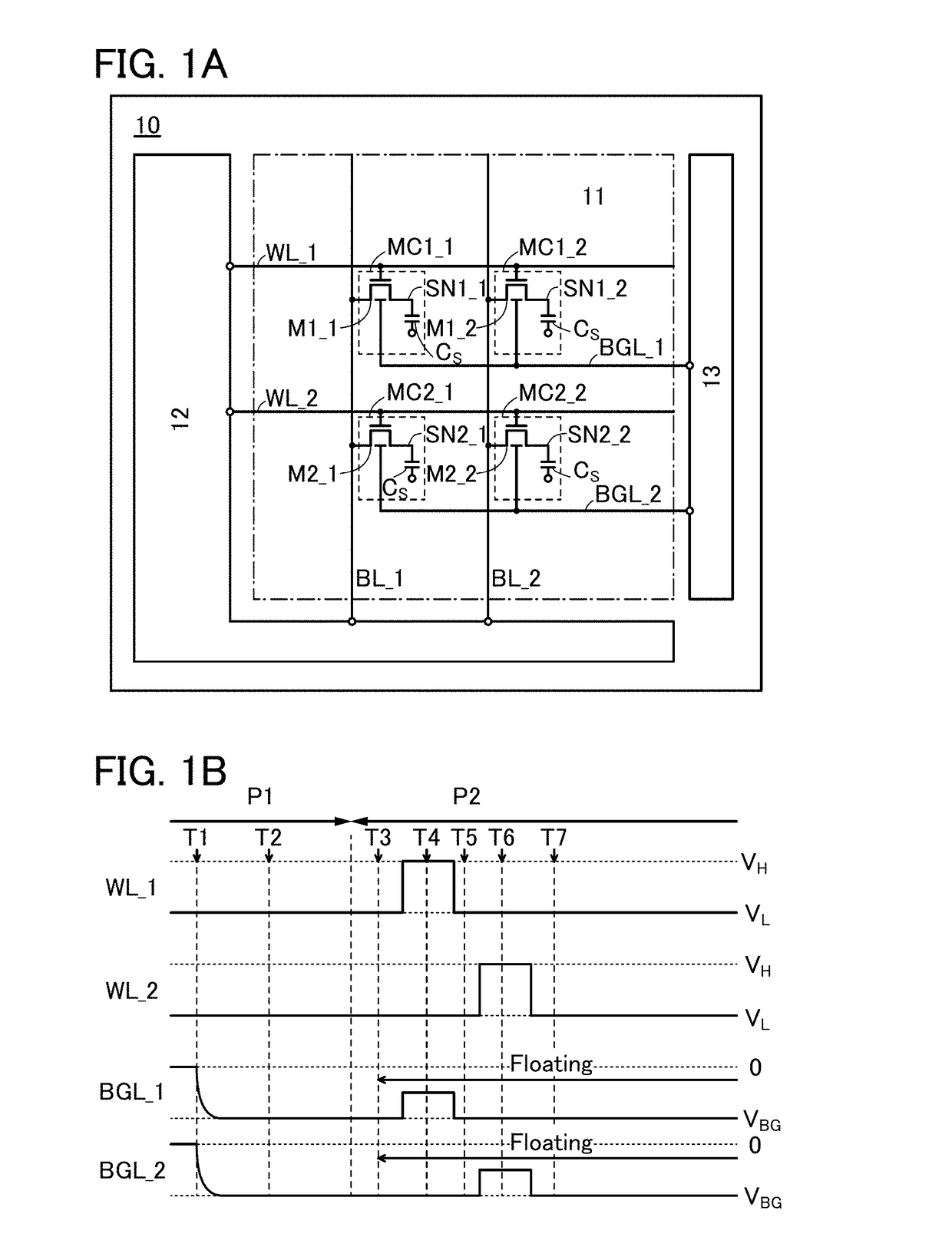

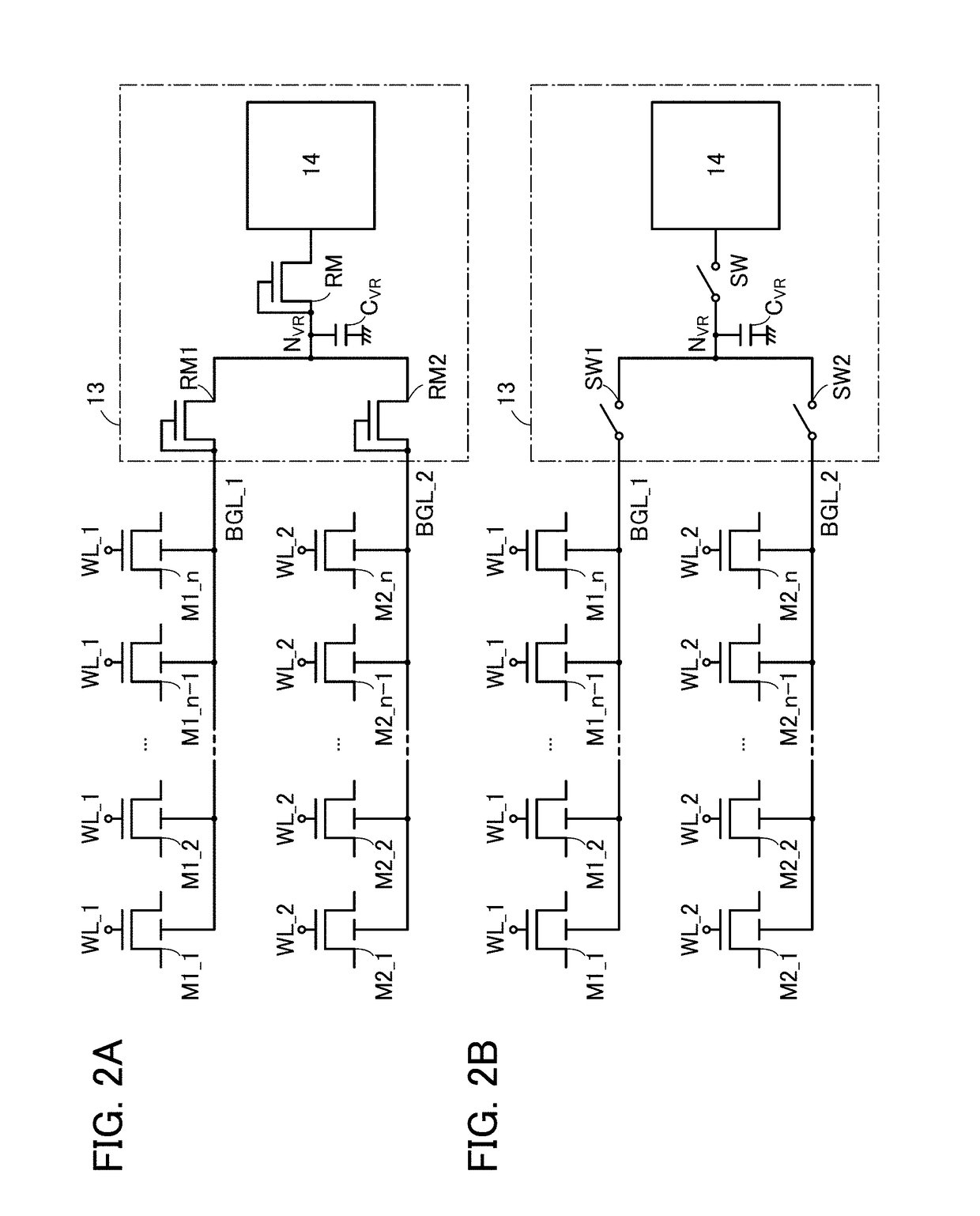

Semiconductor device, semiconductor wafer, and electronic device

ActiveUS20170271516A1Increase currentIncrease power consumptionTransistorSolid-state devicesDevice materialEngineering

A semiconductor device is provided in which the power consumption can be reduced by reducing the driving voltage and the on-state current can be increased in a period in which a transistor having an extremely low off-state current is brought into an electrically floating state. The semiconductor device comprises a memory cell, a first circuit, and a second circuit. The memory cell includes a first transistor. The first transistor includes a first semiconductor layer, a first gate electrode, and a first back gate electrode. The first gate electrode is connected to a word line. The first back gate electrode is connected to a back gate line. The first circuit supplies a signal for controlling the conduction state of the first transistor to the word line. The second circuit supplies a voltage for controlling the threshold voltage of the first transistor to the back gate line. The second circuit has a function of bringing the back gate line into an electrically floating state in a period in which a signal for controlling the conduction state of the first transistor is supplied to the word line.

Owner:SEMICON ENERGY LAB CO LTD

Circuit board process

InactiveUS20080196934A1Added fabricationImprove alignment accuracyPrinted circuit assemblingPrinted circuit aspectsEngineeringDielectric layer

A circuit board process is provided. First, multiple carriers is provided, and a first conductive layer having multiple concave structures is formed on each carrier. A dielectric layer is then provided, and the carriers with the first conductive layers are laminated on a first and a second surface of the dielectric layer respectively, wherein portions of the first conductive layers are embedded in the first and second surfaces. Next, the carriers are removed. Thereafter, the first conductive layer corresponding to at least one concave is removed to expose a portion of the dielectric layer. Next, the exposed dielectric layer is removed to form an opening. A second conductive layer is then formed on the inner wall of the opening, wherein the second conductive layer is electrically connected to the first conductive layers on both sides of the dielectric layer.

Owner:UNIMICRON TECH CORP

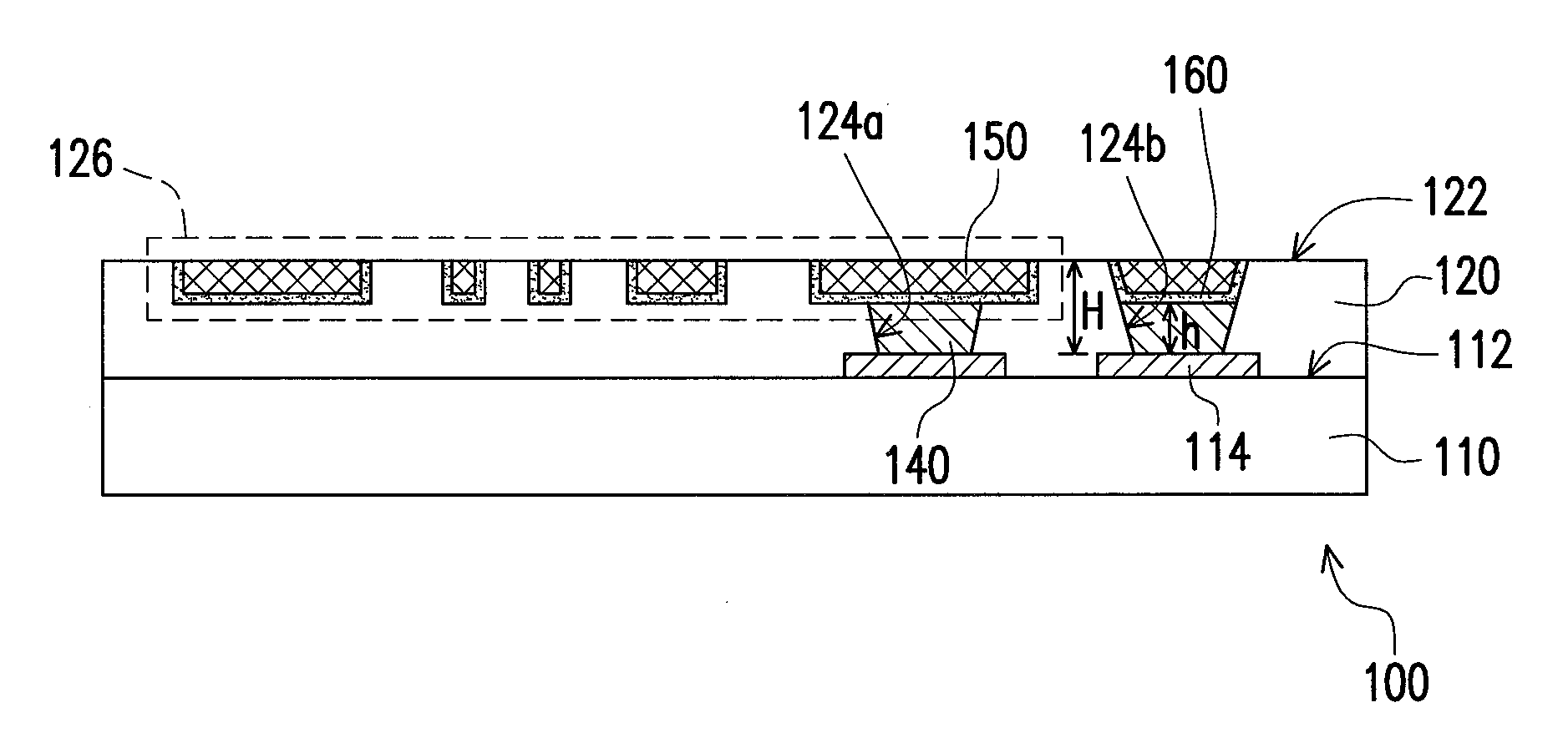

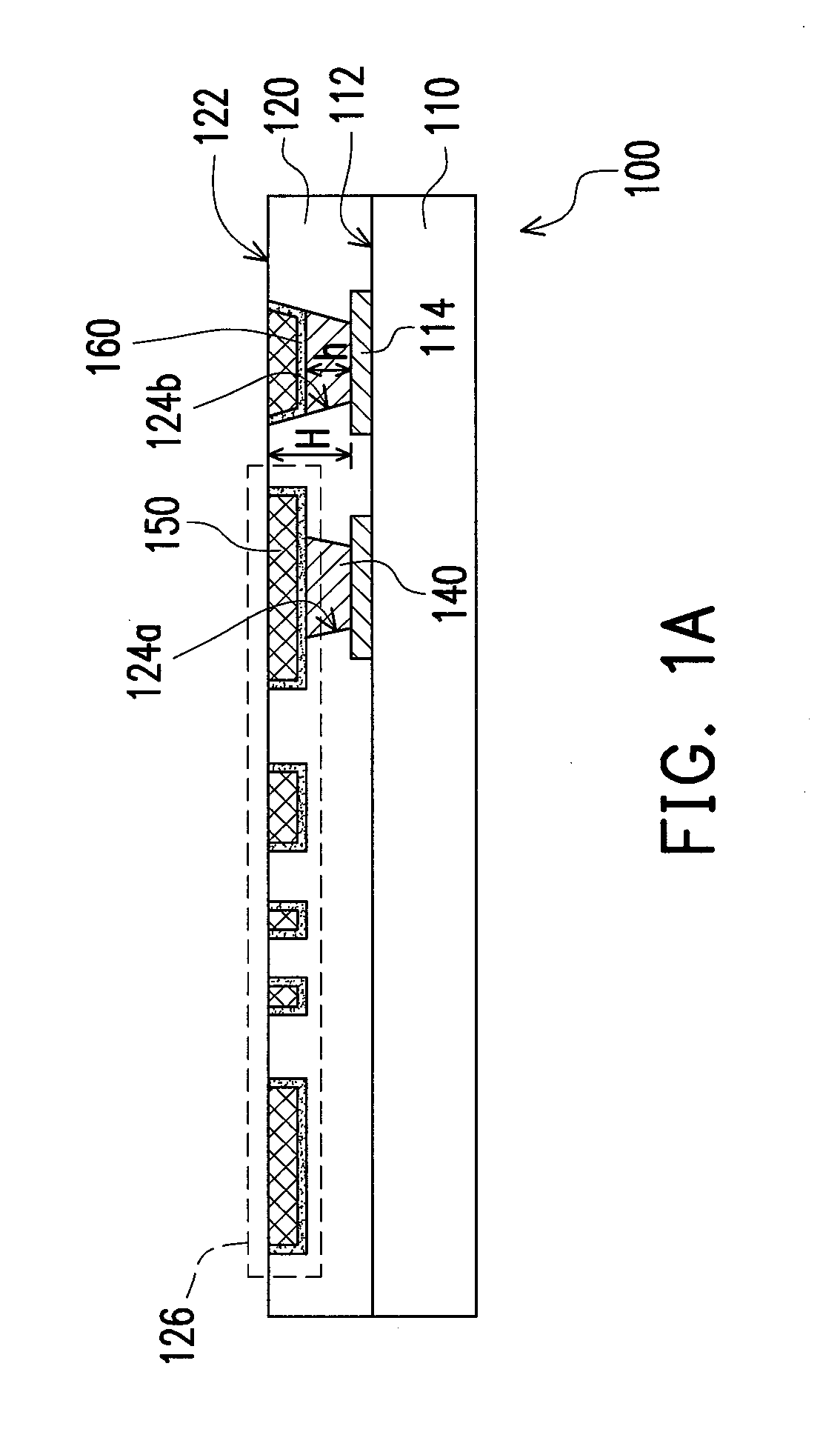

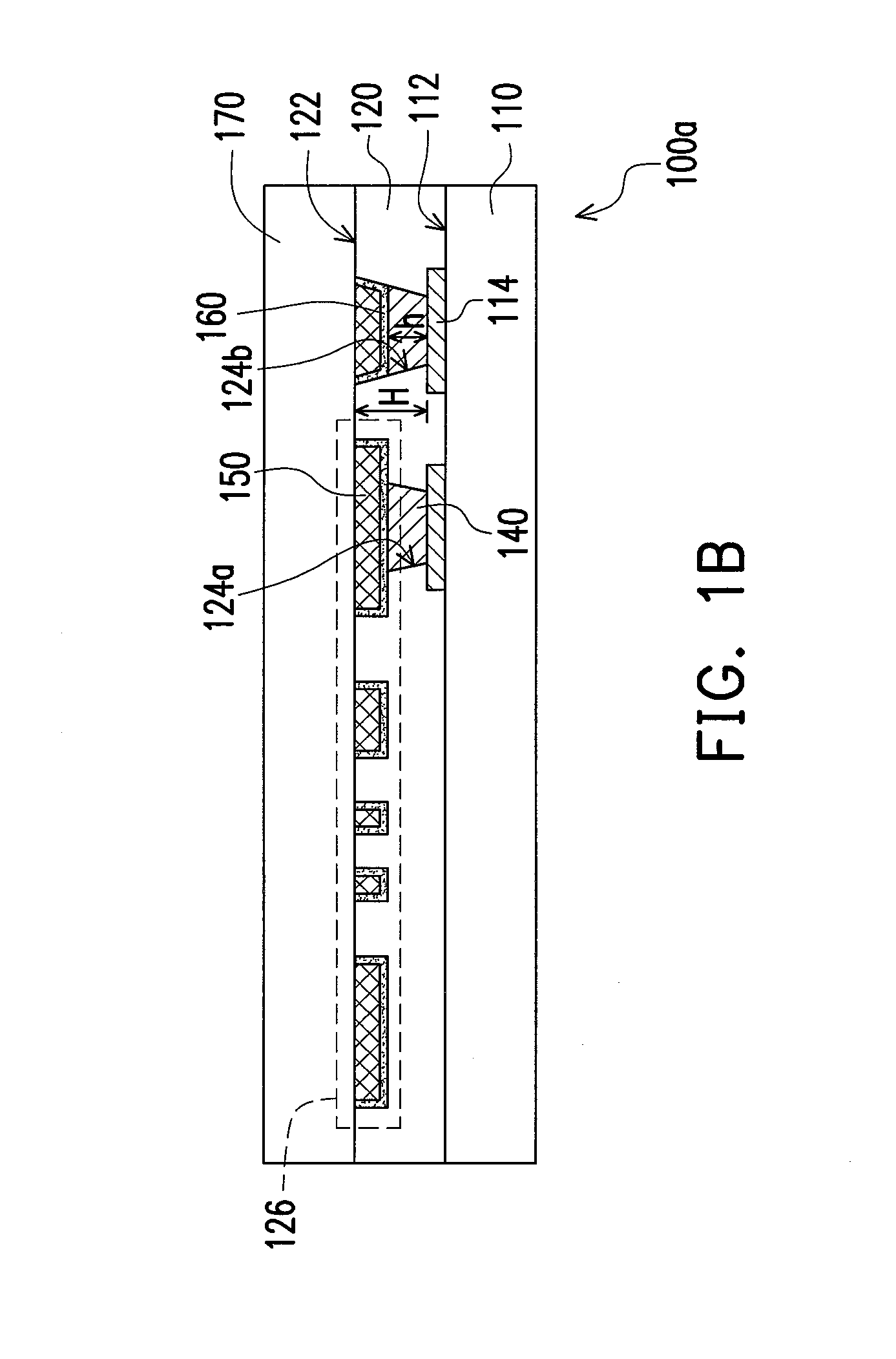

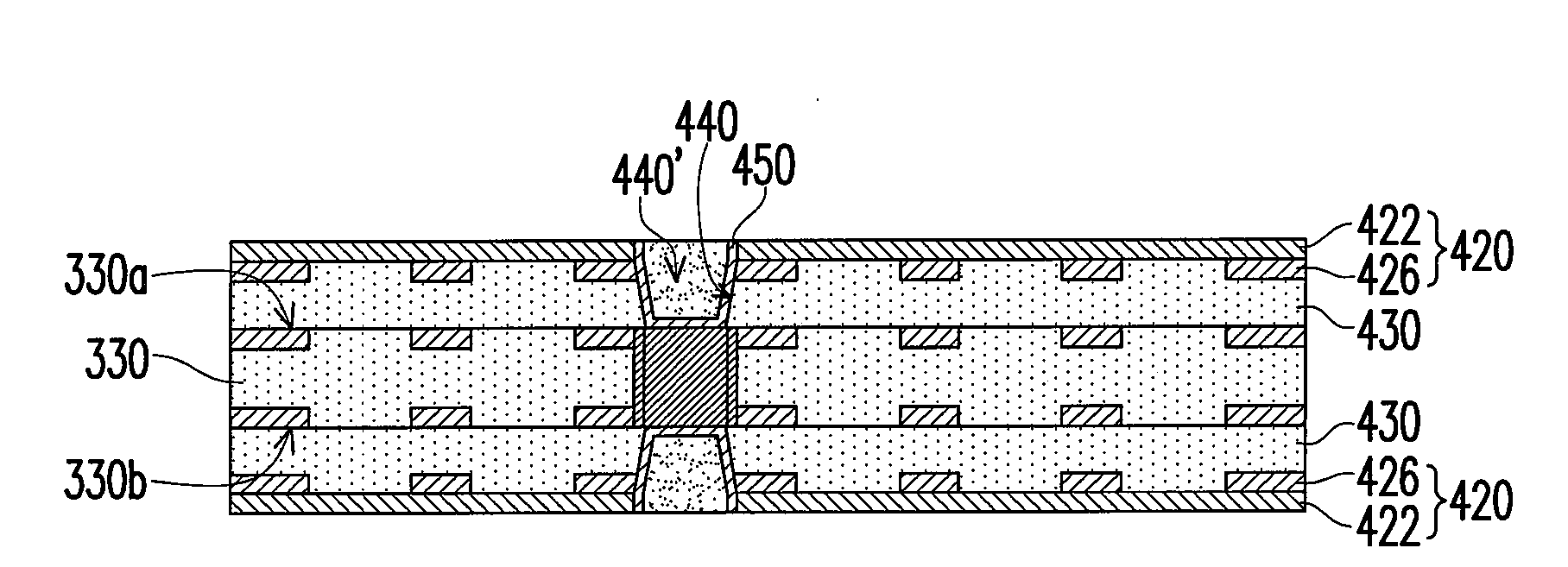

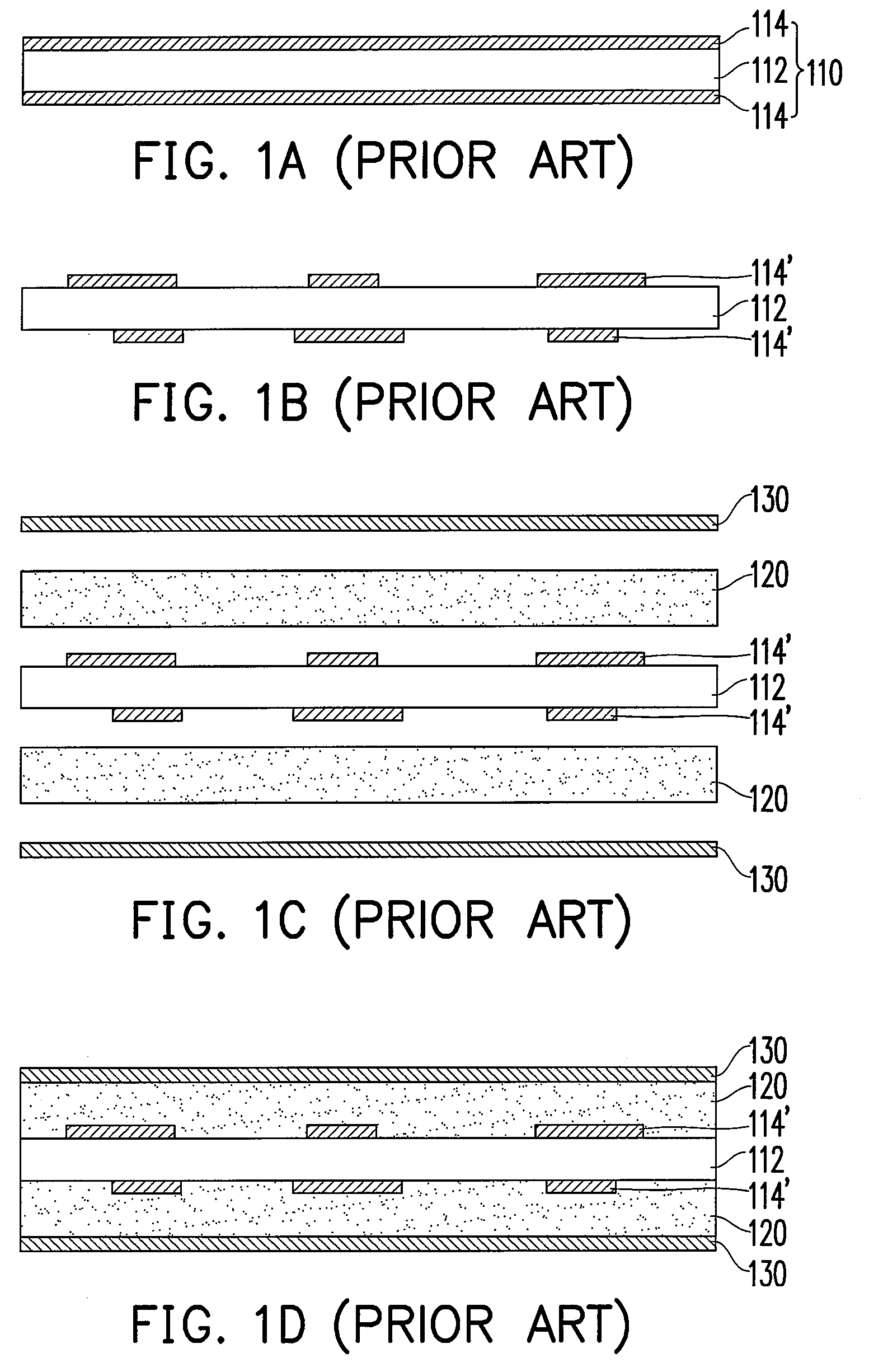

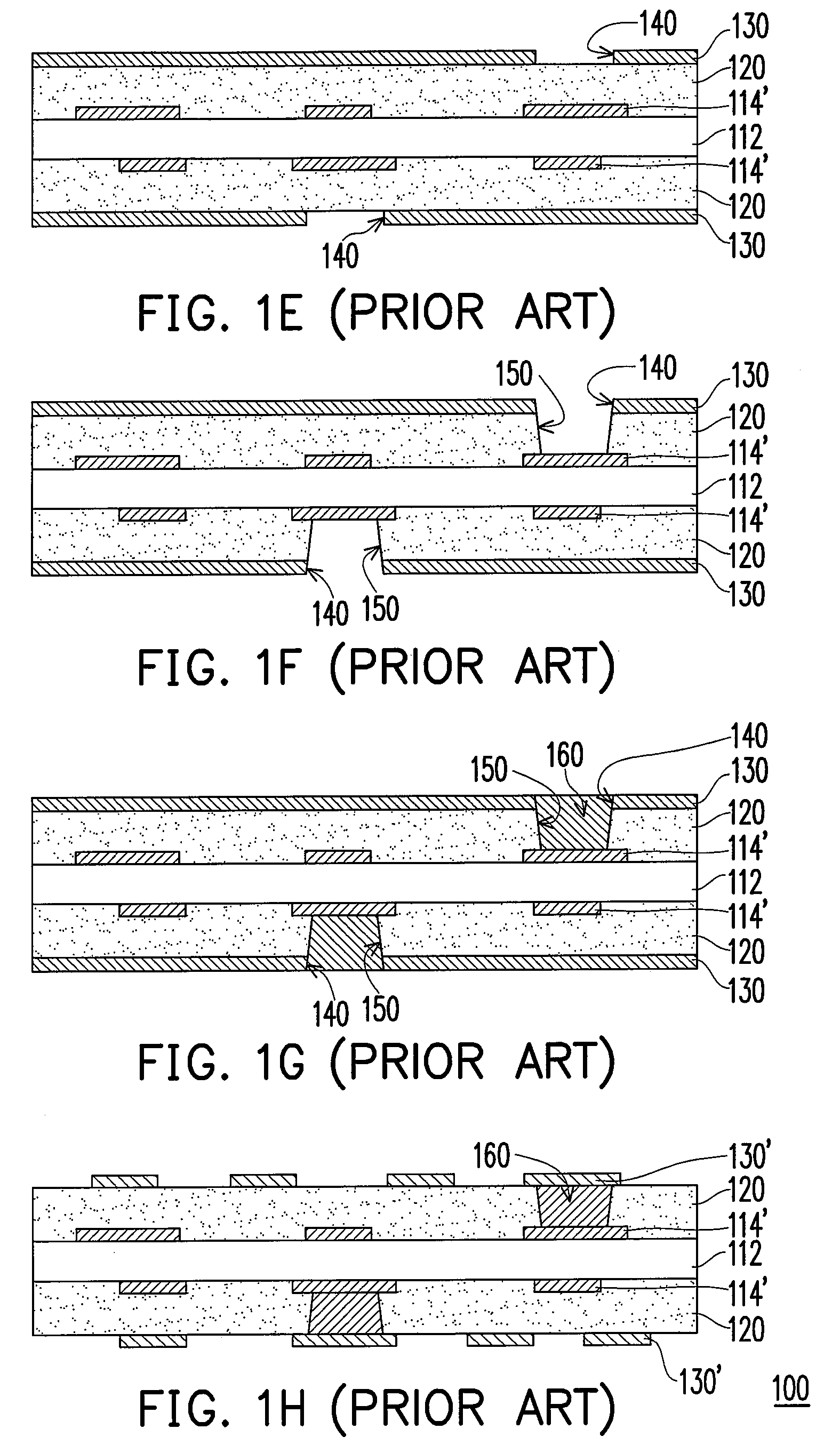

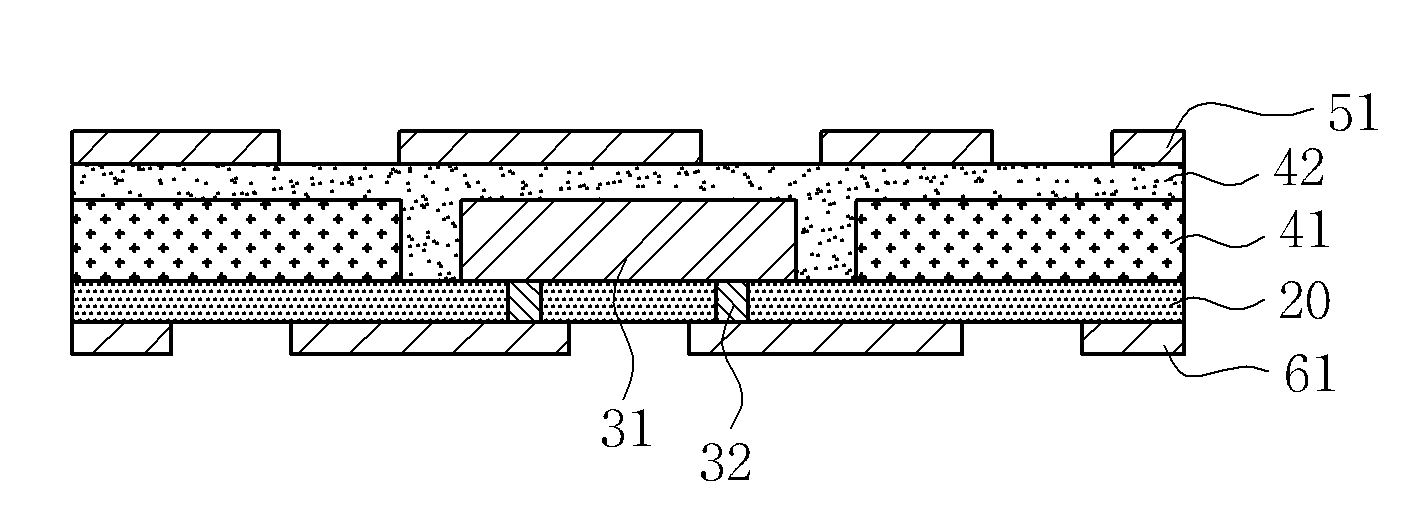

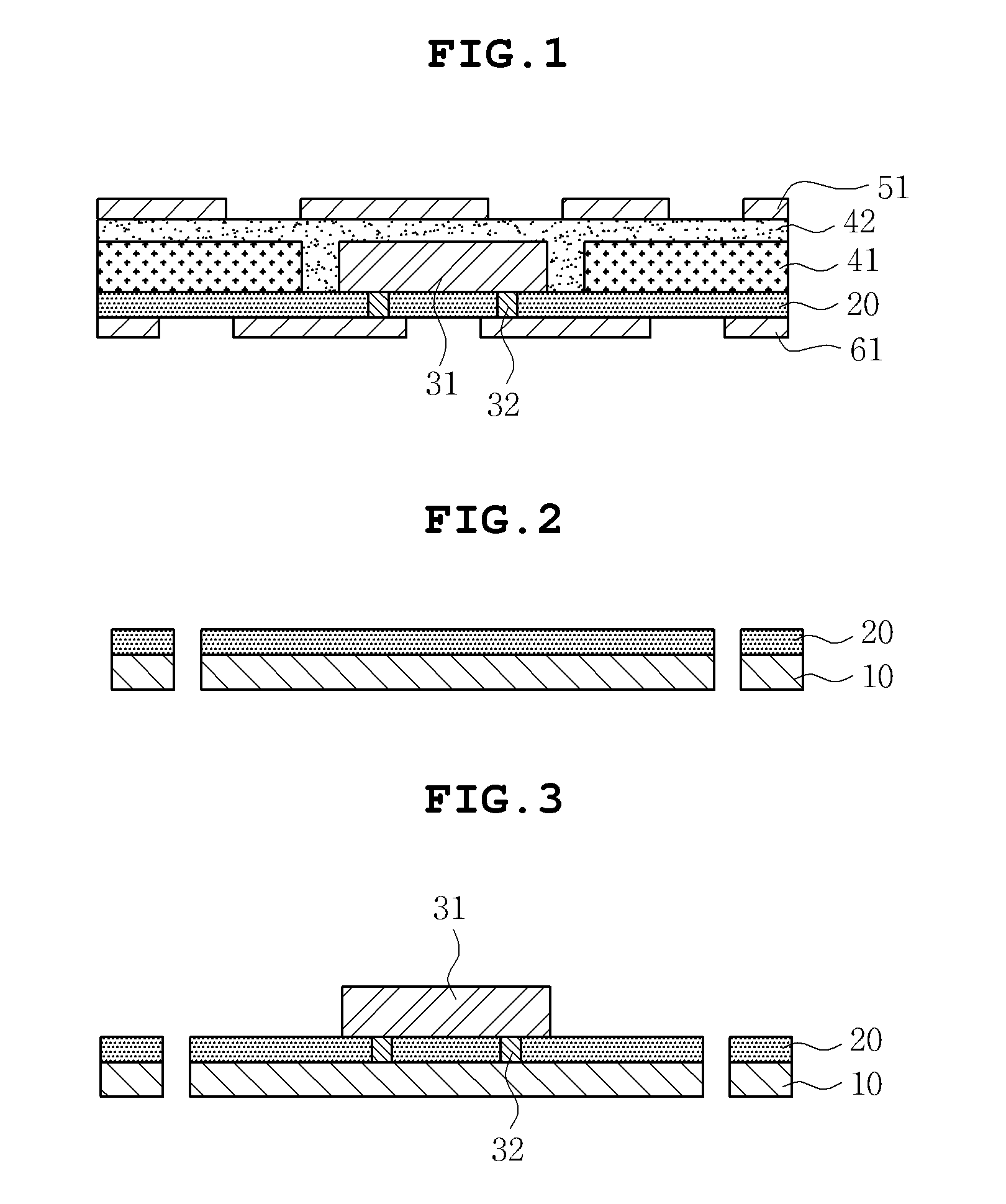

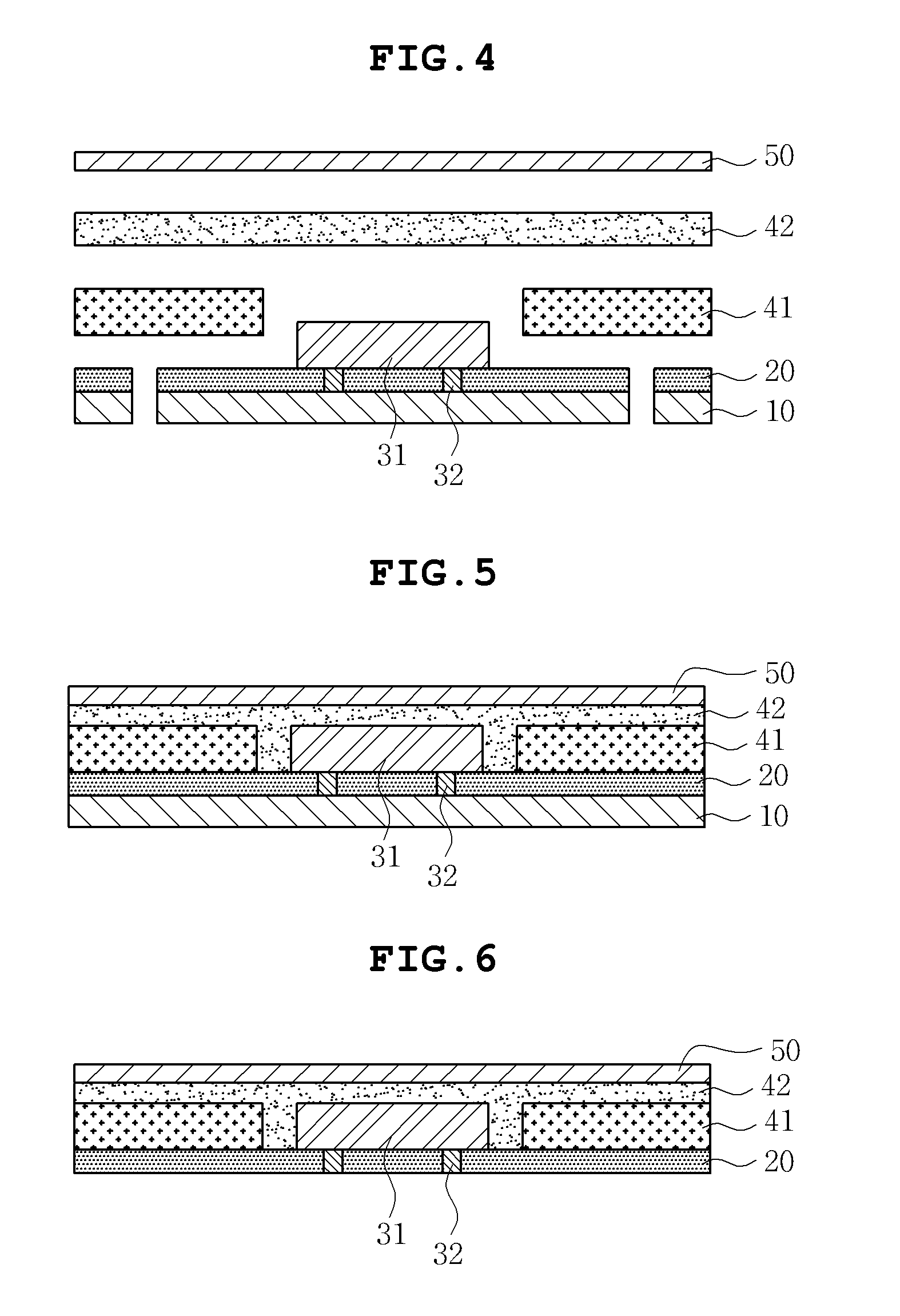

Printed circuit board having embedded electronic component and method of manufacturing the same

InactiveUS20120160550A1Improve electrical reliabilityImprove circuit reliabilityPrinted circuit assemblingSemiconductor/solid-state device detailsPrinted circuit boardEmbedded electronics

Disclosed is a printed circuit board having an embedded electronic component, which includes a first insulating layer, an electronic component disposed in an opening formed in a thickness direction of the first insulating layer and having a metal bump, a polymer layer formed on one side of the first insulating layer and on which the electronic component is seated so that the metal bump of the electronic component perforates the polymer layer, a second insulating layer formed on the other side of the first insulating layer so as to embed the electronic component, a first circuit layer formed on the second insulating layer, and a second circuit layer formed on the polymer layer so as to be directly electrically connected to the metal bump that perforates the polymer layer, and in which roughness is formed on the polymer layer so that the force of adhesion of the polymer layer to a plating layer is enhanced, thus ensuring reliability of the electrical connection of a circuit layer which is subsequently formed.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com