Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

84 results about "Dielectric matrix" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

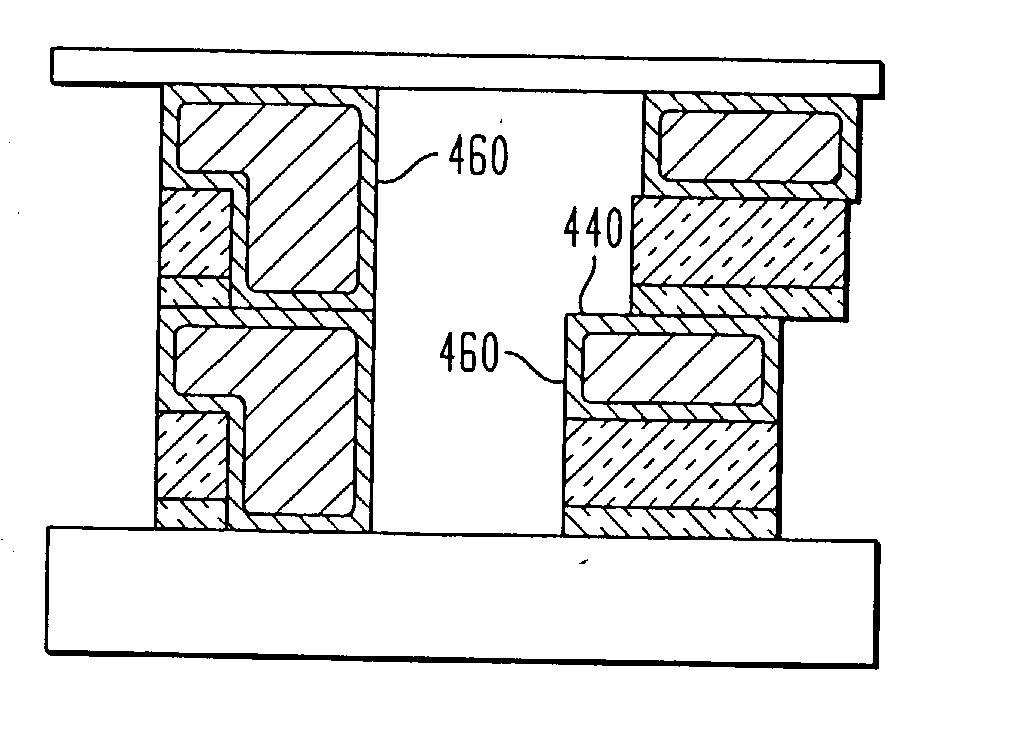

Multilevel interconnect structure containing air gaps and method for making

InactiveUS20020127844A1Maximizes air gap volume fractionQuantity minimizationSemiconductor/solid-state device detailsSolid-state devicesDielectric matrixEngineering

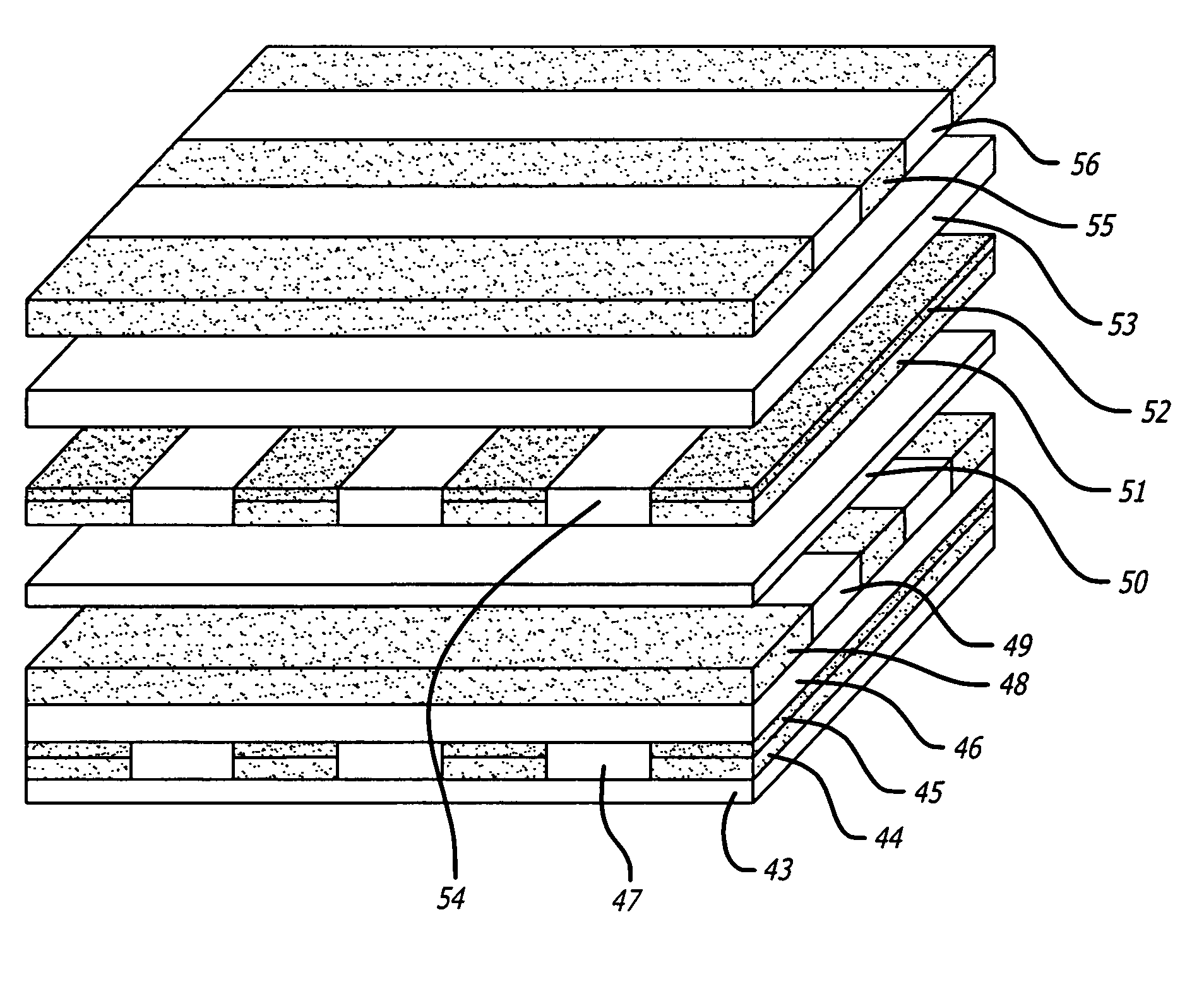

A method for forming a multilayer interconnect structure on a substrate that include interconnected conductive wiring and vias spaced apart by a combination of solid or gaseous dielectrics. The inventive method includes the steps of: (a) forming a first planar via plus line level pair embedded in a dielectric matrix formed from one or more solid dielectrics and comprising a via level dielectric and a line level dielectric on a substrate, wherein, at least one of said solid dielectrics is at least partially sacrificial; (b) etching back sacrificial portions of said at least partially sacrificial dielectrics are removed to leave cavities extending into and through said via level, while leaving, at least some of the original via level dielectric as a permanent dielectric under said lines; (c) partially filling or overfilling said cavities with a place-holder material which may or may not be sacrificial; (d) planarizing the structure by removing overfill of said place-holder material; (e) repeating, as necessary, steps (a)-(d); (f) forming a dielectric bridge layer over the planar structure; and (g) forming air gaps by at least partially extracting said place-holder material.

Owner:GLOBALFOUNDRIES US INC

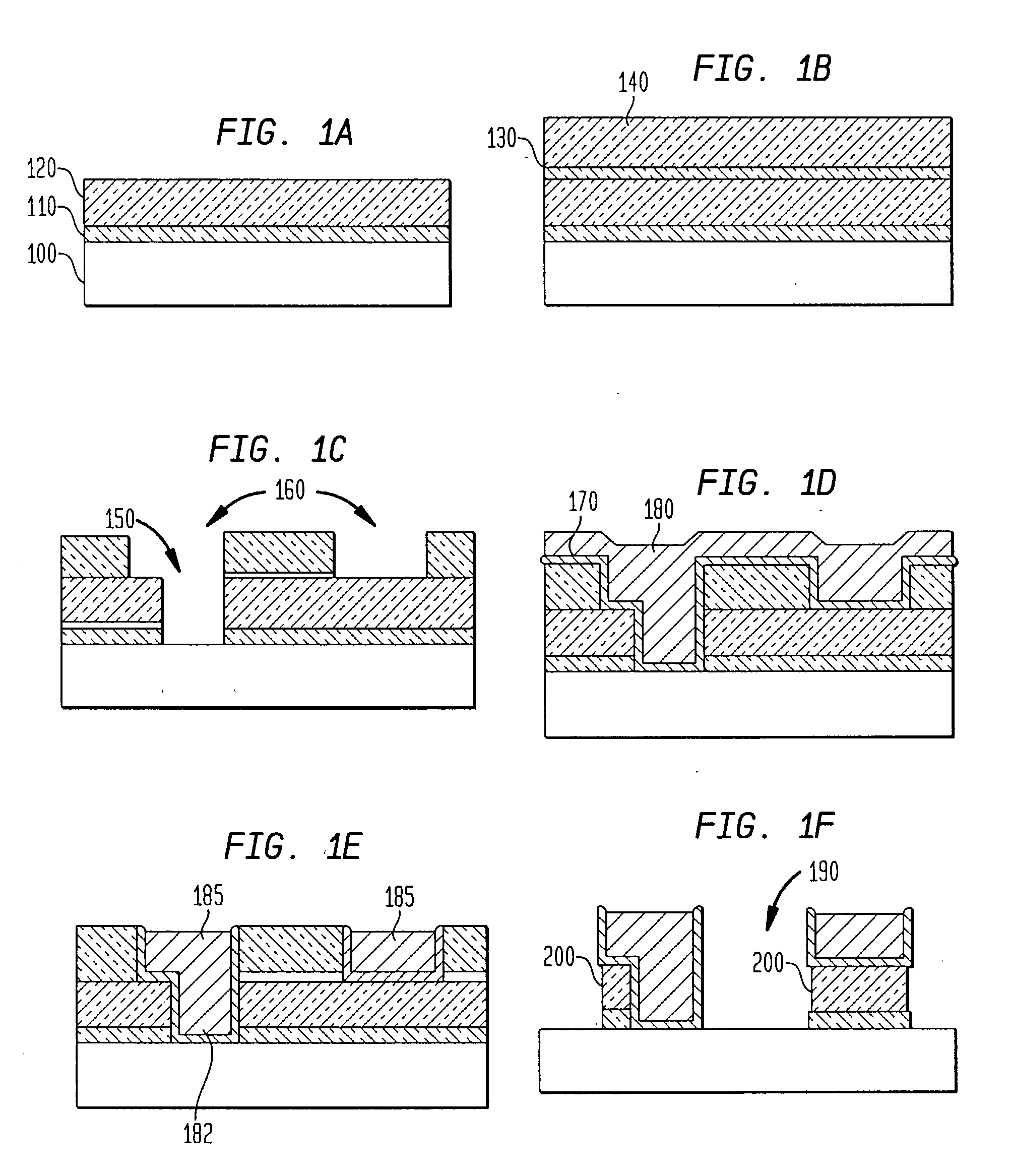

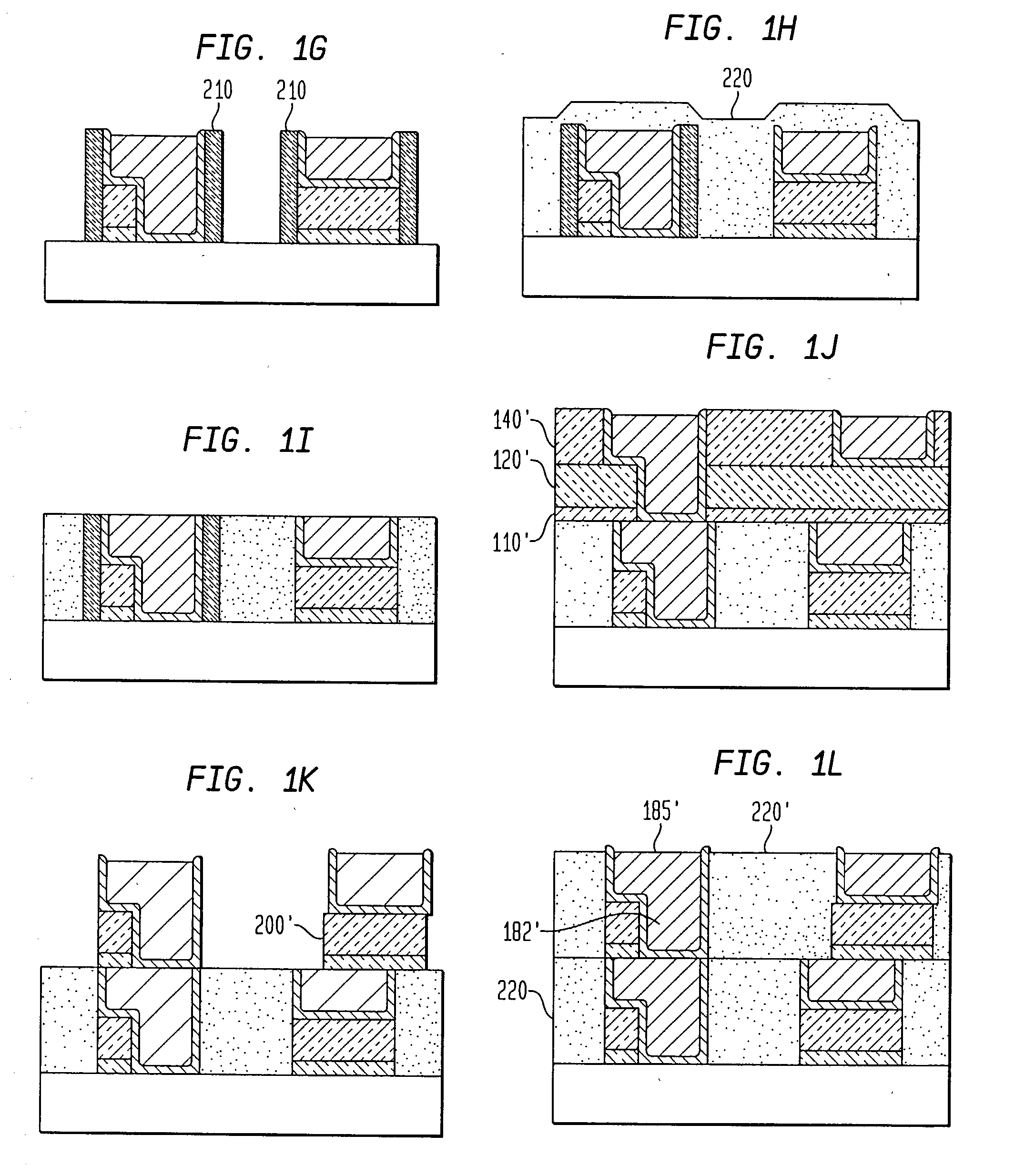

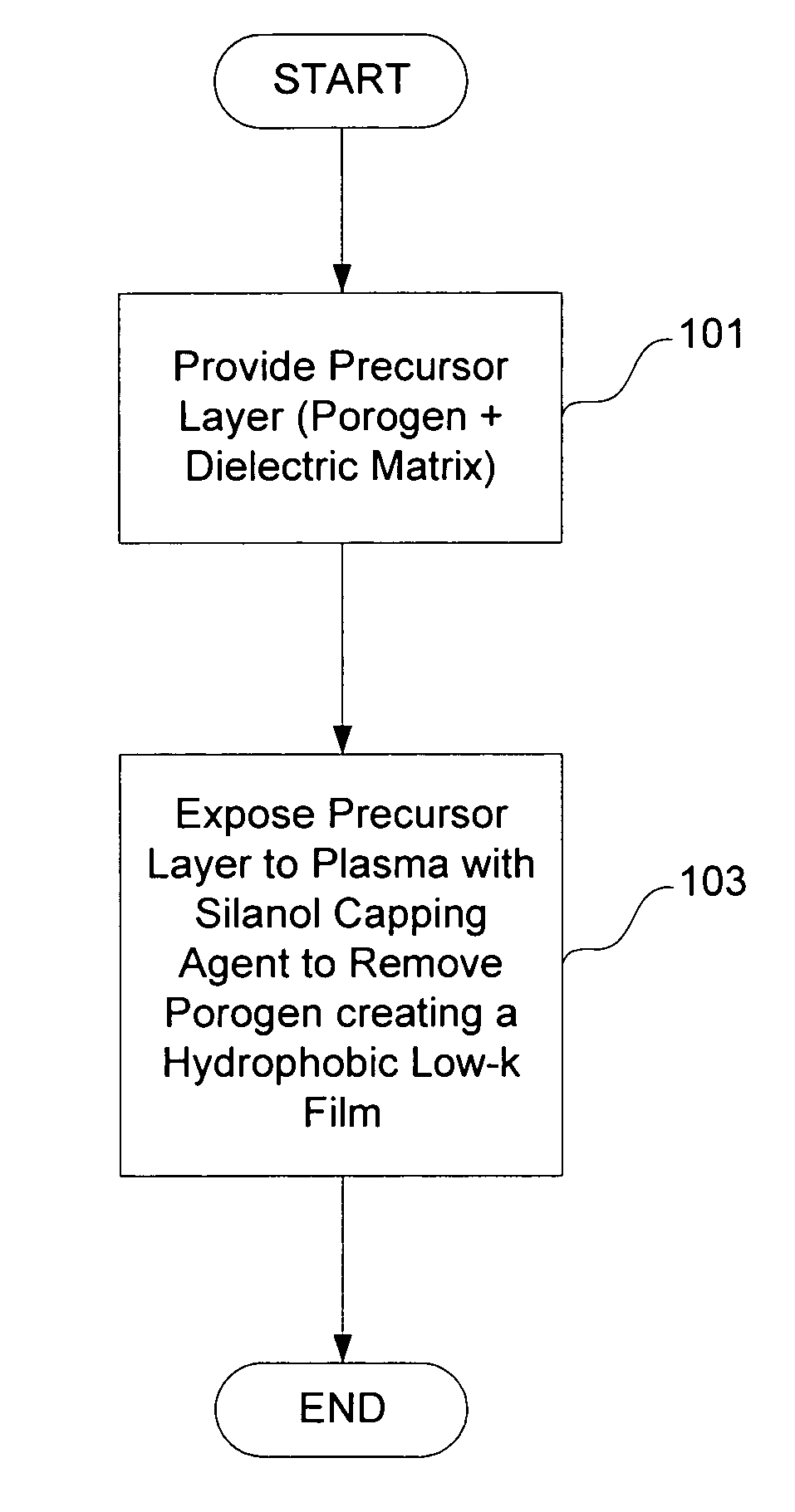

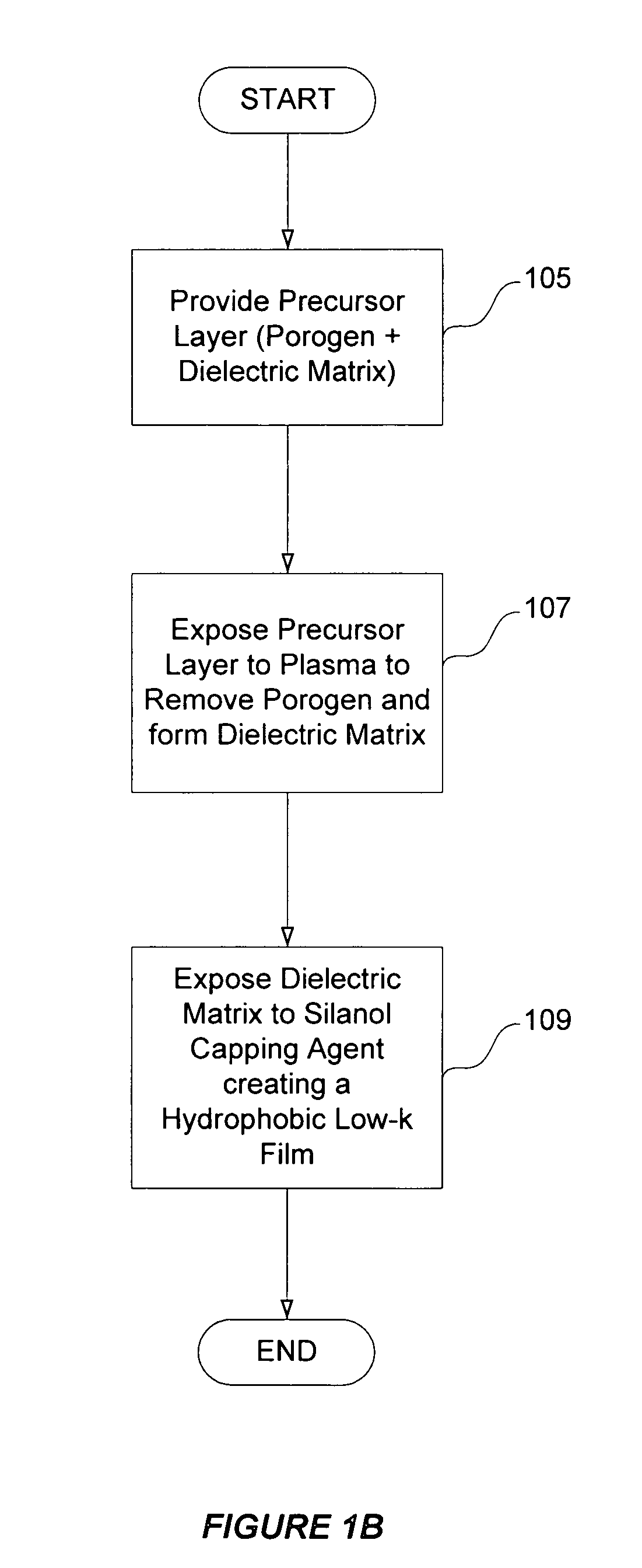

Plasma detemplating and silanol capping of porous dielectric films

InactiveUS7176144B1Creating voidSemiconductor/solid-state device manufacturingDielectric matrixSilanol

Methods of preparing a low-k dielectric material on a substrate are provided. The methods involve using plasma techniques to remove porogen from a precursor layer comprising porogen and a dielectric matrix and to protect the dielectric matrix with a silanol capping agent, resulting in a low-k dielectric matrix. Porogen removal and silanol capping can occur concurrently or sequentially. If performed sequentially, silanol capping is performed without first exposing the dielectric matrix to moisture or ambient conditions.

Owner:NOVELLUS SYSTEMS

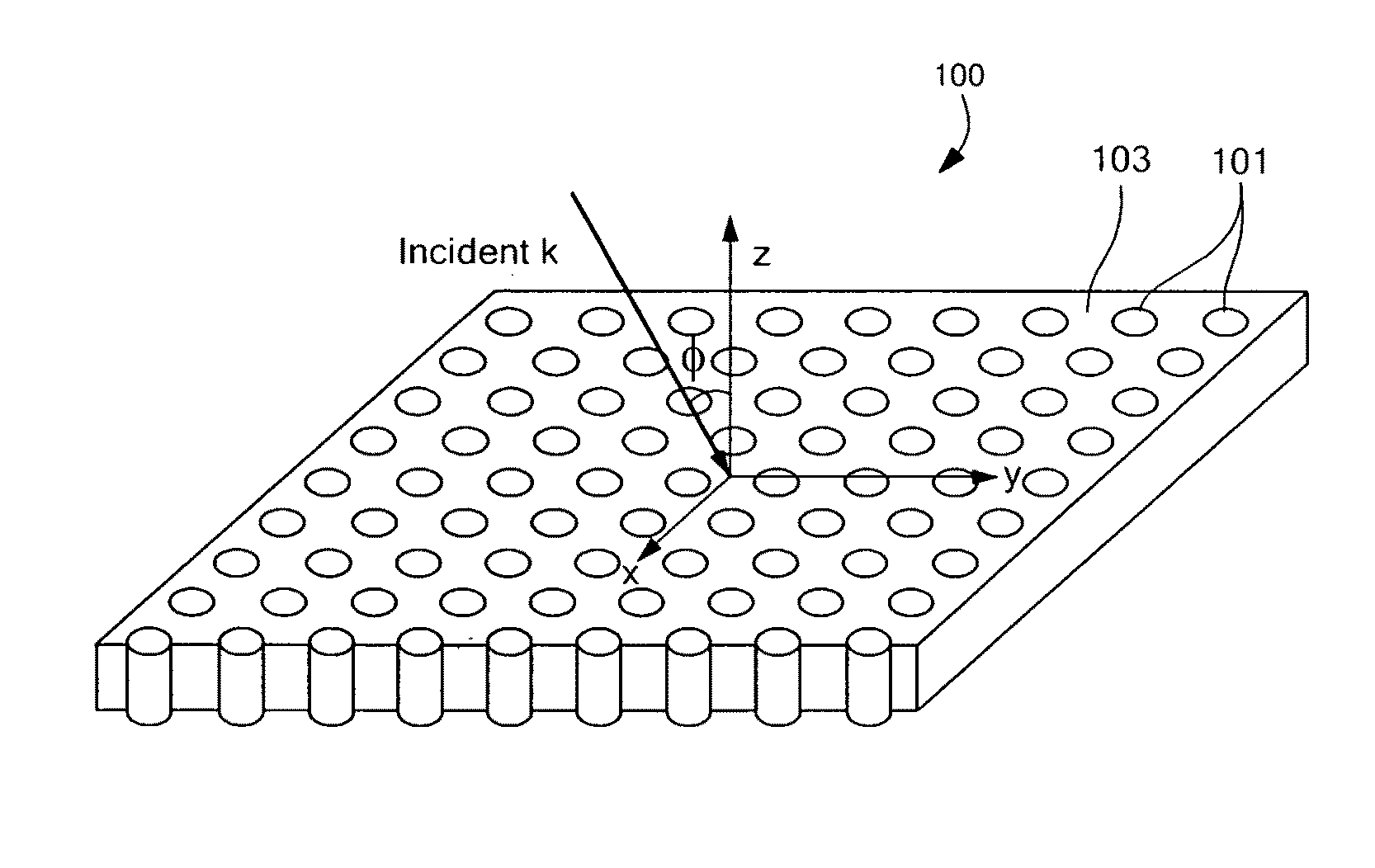

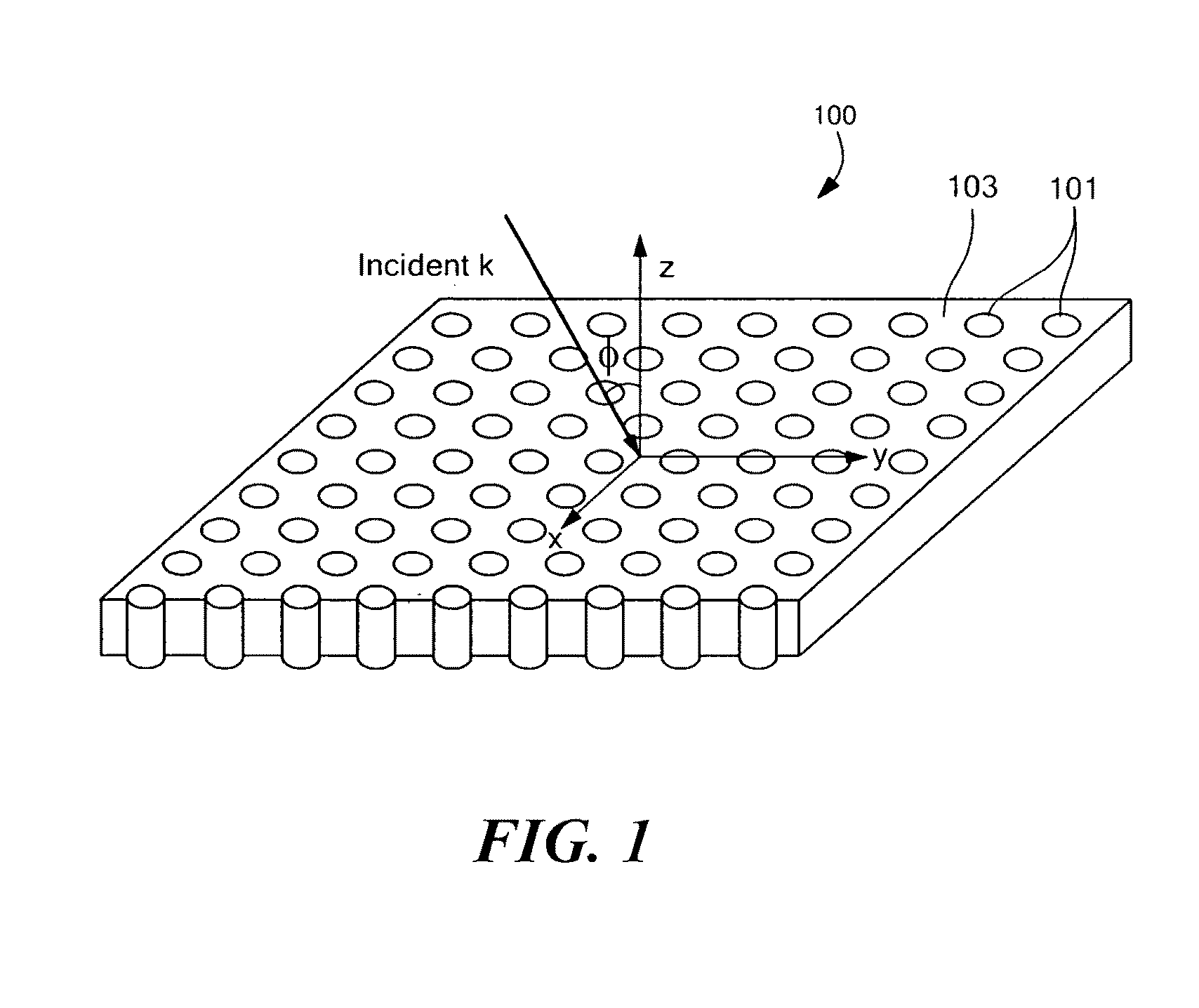

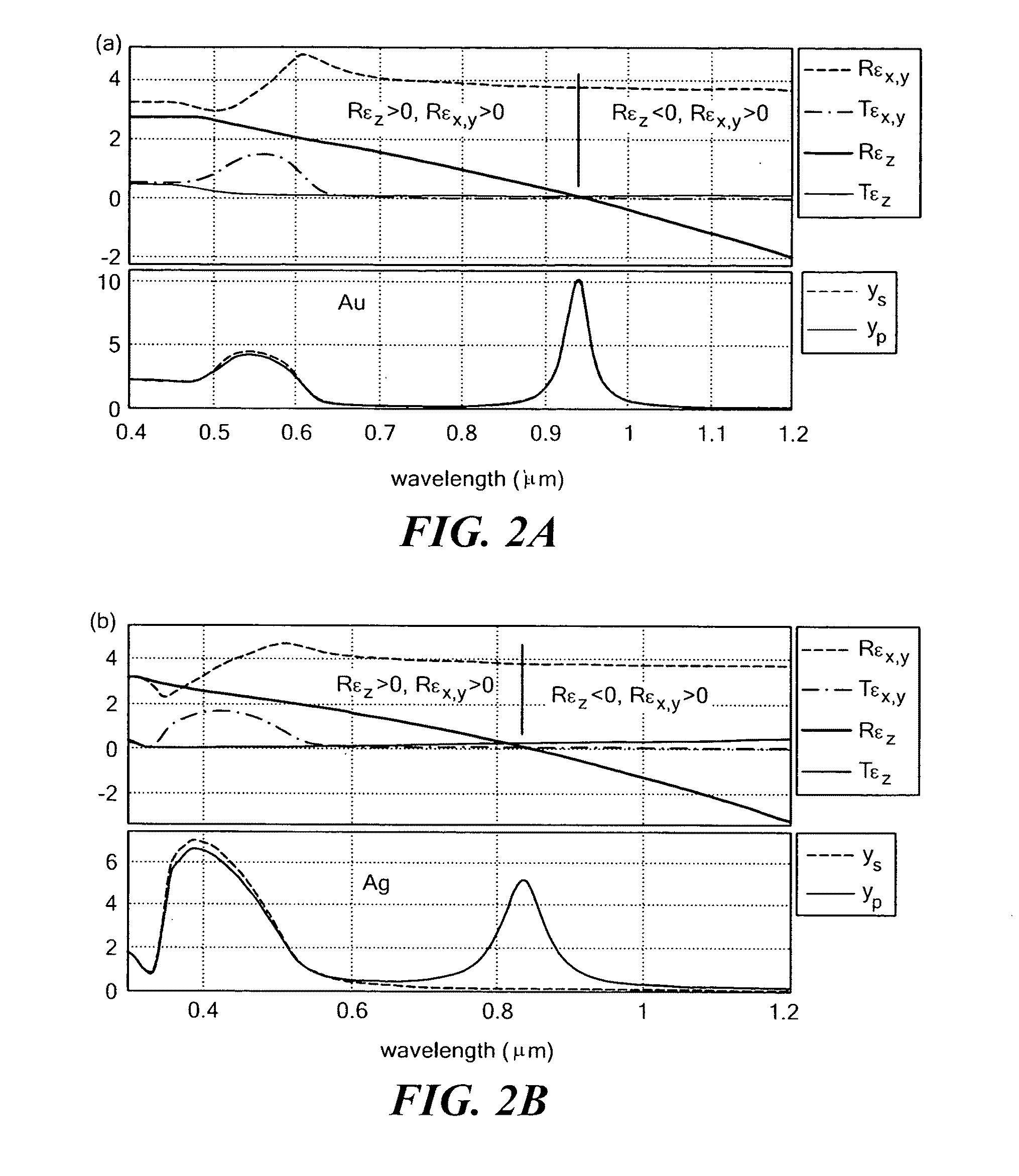

Anisotropic metal-dielectric metamaterials for broadband all-angle negative refraction and superlens imaging

InactiveUS20090040132A1Easy to makeEasy to customizeLiquid surface applicatorsCoatingsNegative refractionDielectric matrix

A metamaterial comprises a plurality of metallic nanowires embedded in a dielectric matrix. The metamaterial composite media provide broadband all-angle negative refraction and flat lens, superlens and curved hyperlens imaging in specific spectral regions over a wide range of frequencies including, for example, from deep infrared to ultraviolet frequencies.

Owner:NORTHEASTERN UNIV

Memory devices based on electric field programmable films

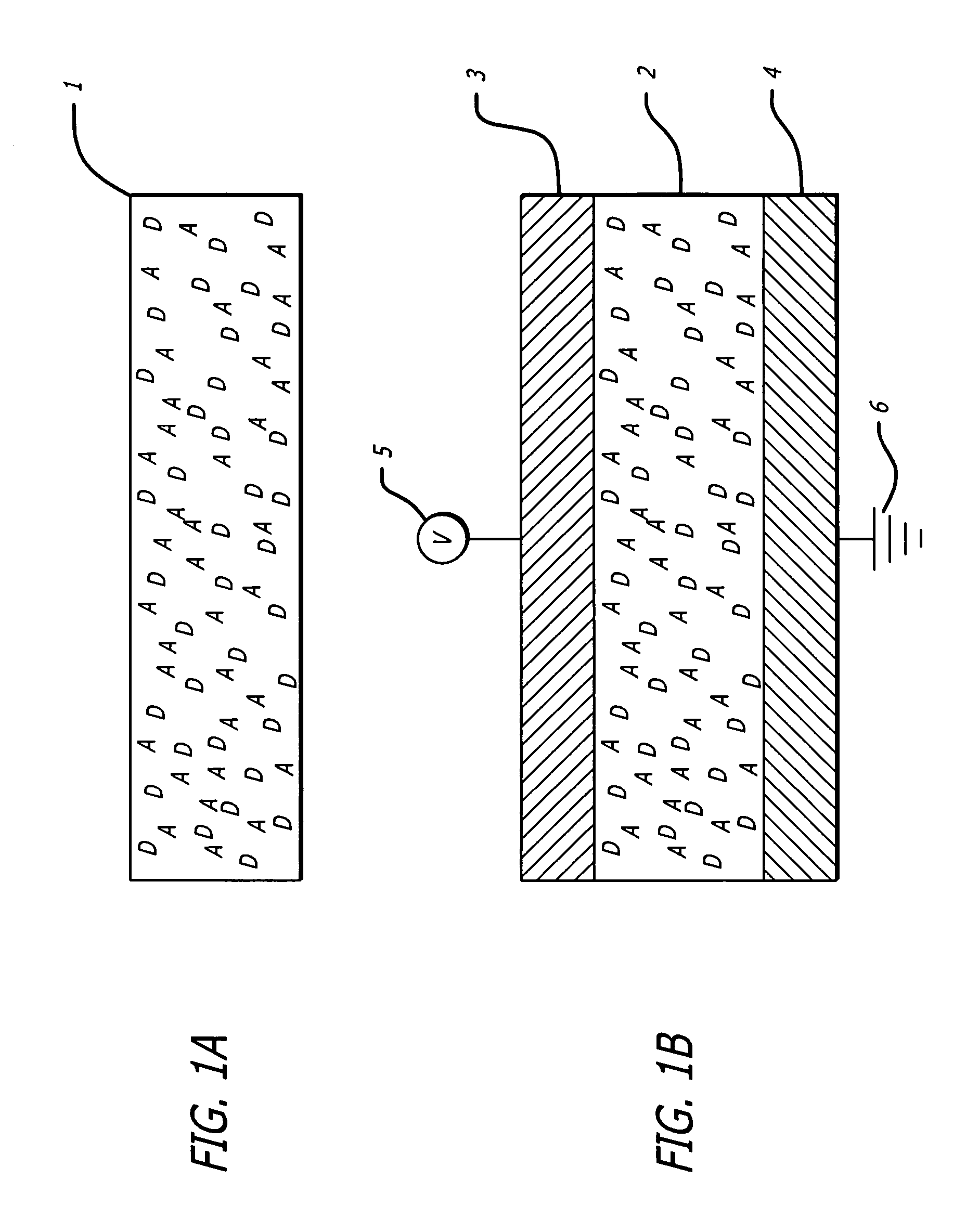

InactiveUS20050058009A1Easy to manufactureImprove device densityNanoinformaticsSolid-state devicesDielectric matrixElectricity

A composition for the formation of an electric field programmable film, the composition comprising a matrix precursor composition or a dielectric matrix material, wherein the dielectric matrix material comprises an organic polymer and / or a inorganic oxide; and an electron donor and an electron acceptor of a type and in an amount effective to provide electric field programming. The films are of utility in data storage devices.

Owner:RGT UNIV OF CALIFORNIA

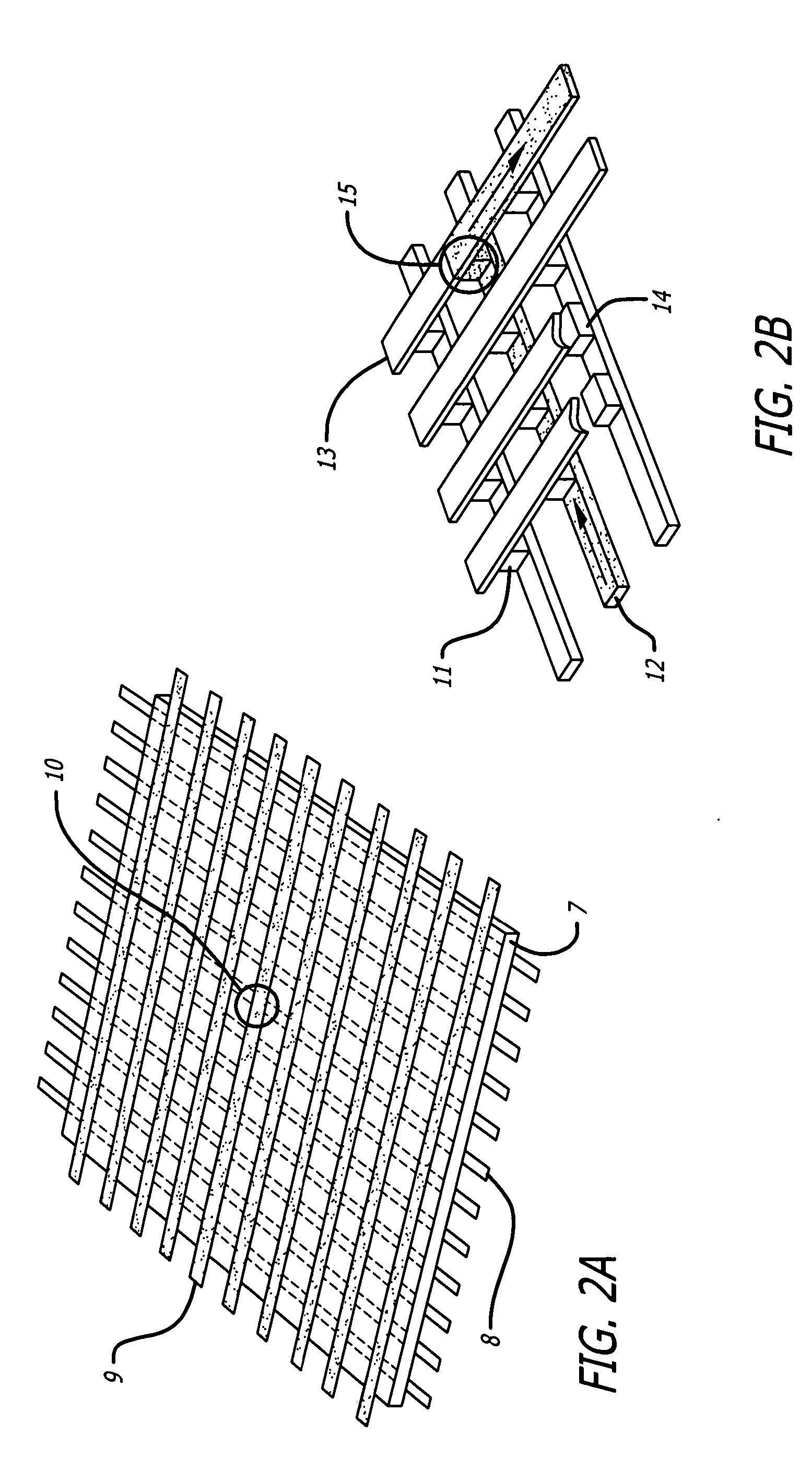

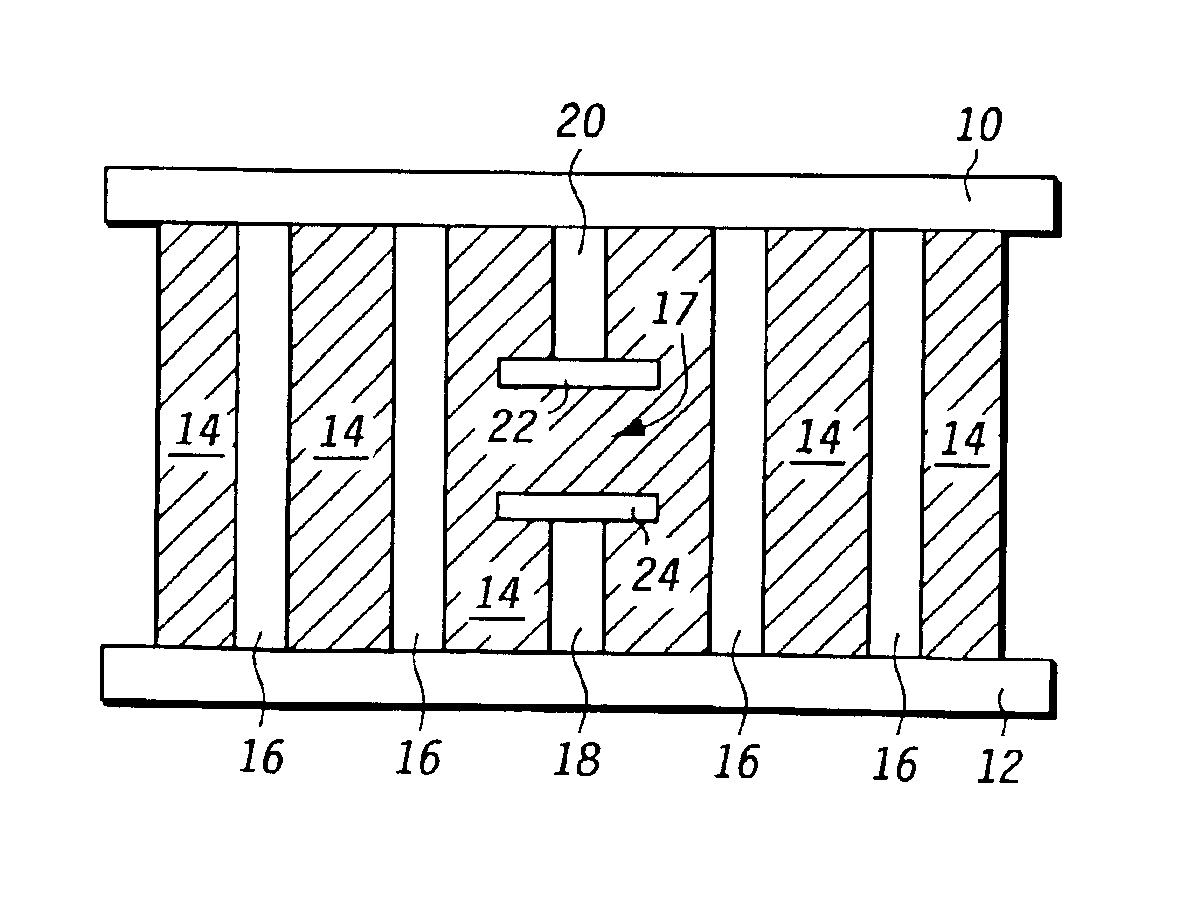

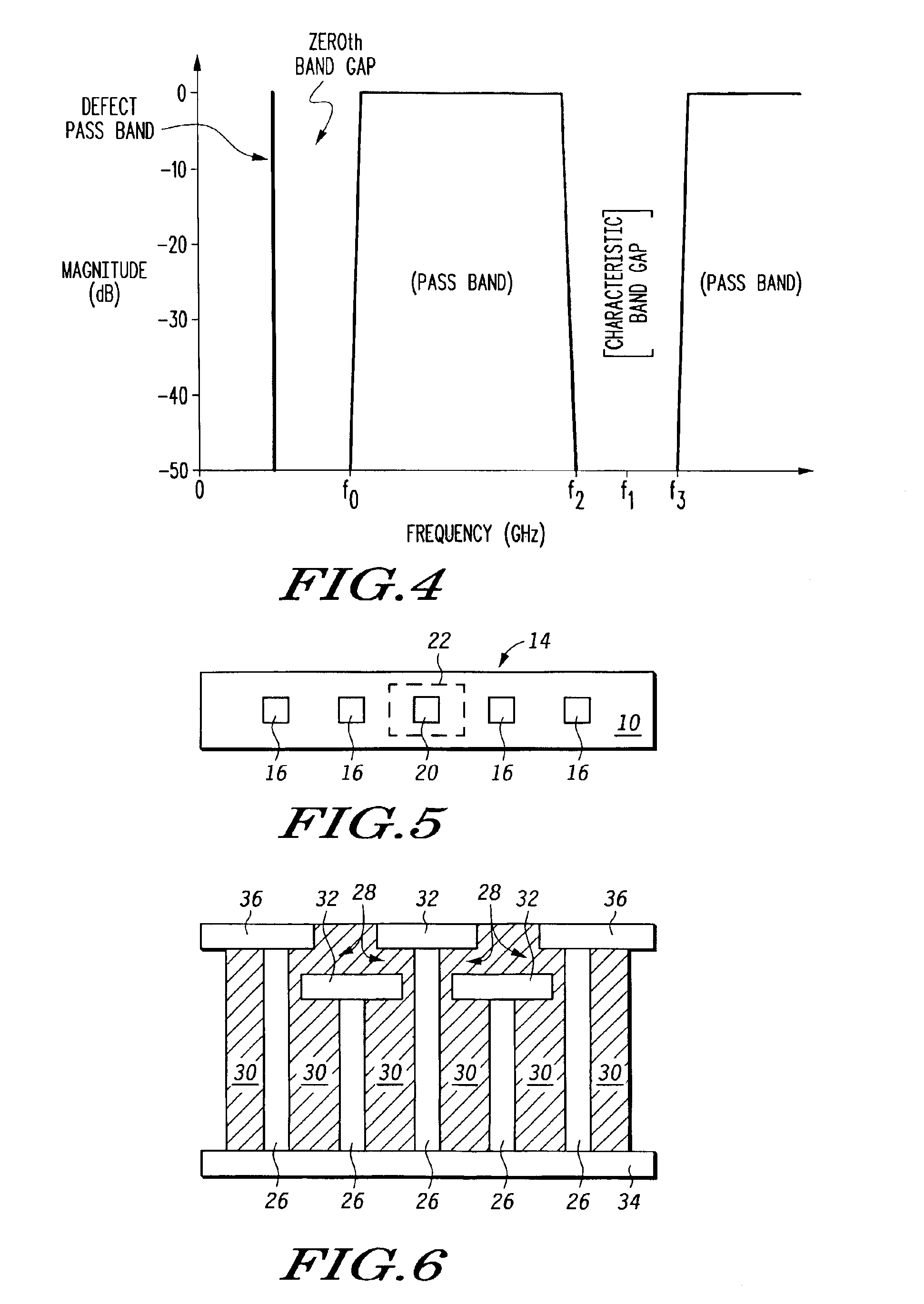

Electromagnetic band gap microwave filter

A microwave filter is formed from an electromagnetic band gap structure. The electromagnetic band gap structure includes a periodic array of metal features (16, 42, 44, 50) formed within a dielectric matrix (14, 52). A defect feature (17, 48) is formed within the periodic array of metal features (16, 42, 44, 50) in order to create a pass band within a stop band region.

Owner:NXP USA INC

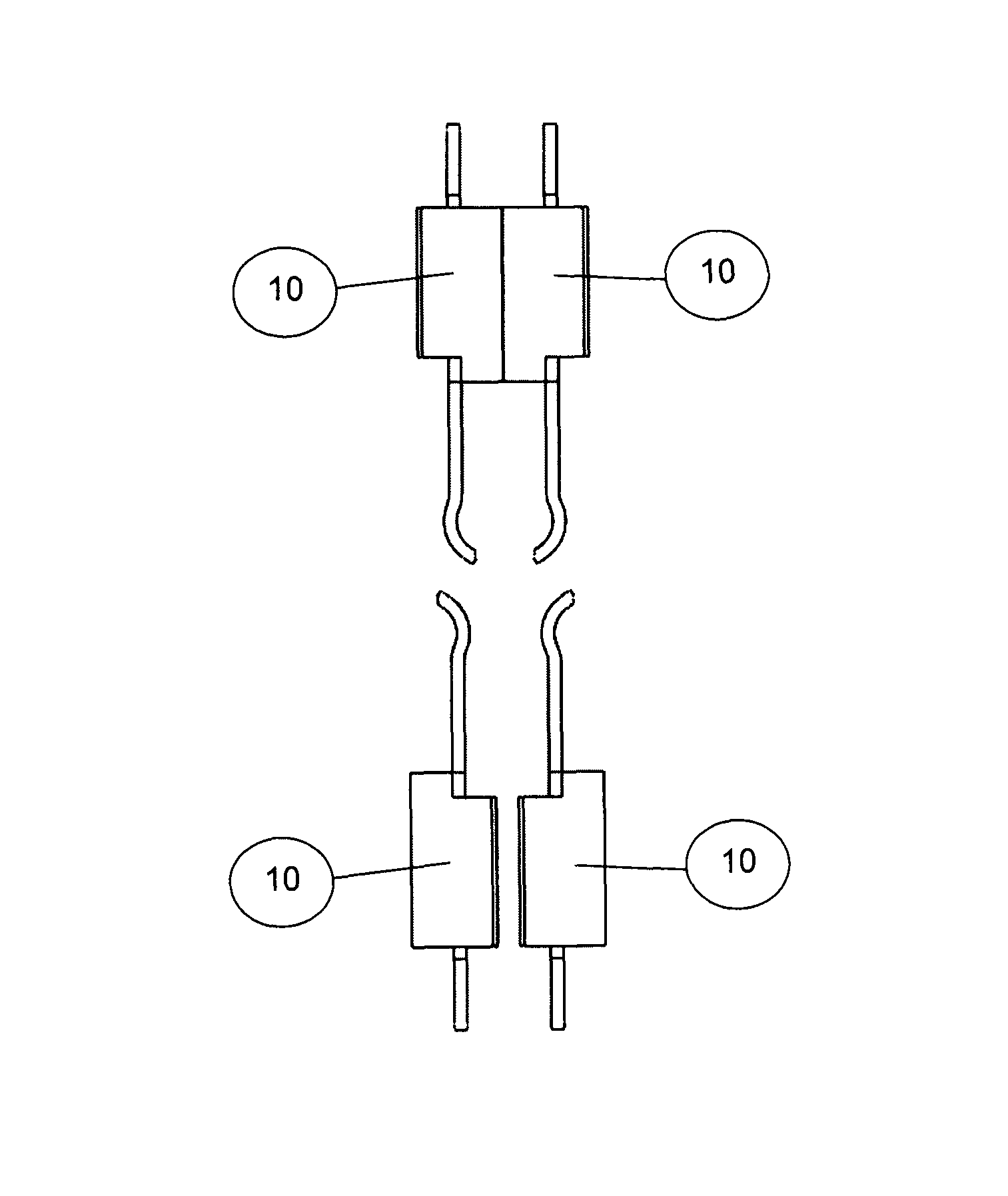

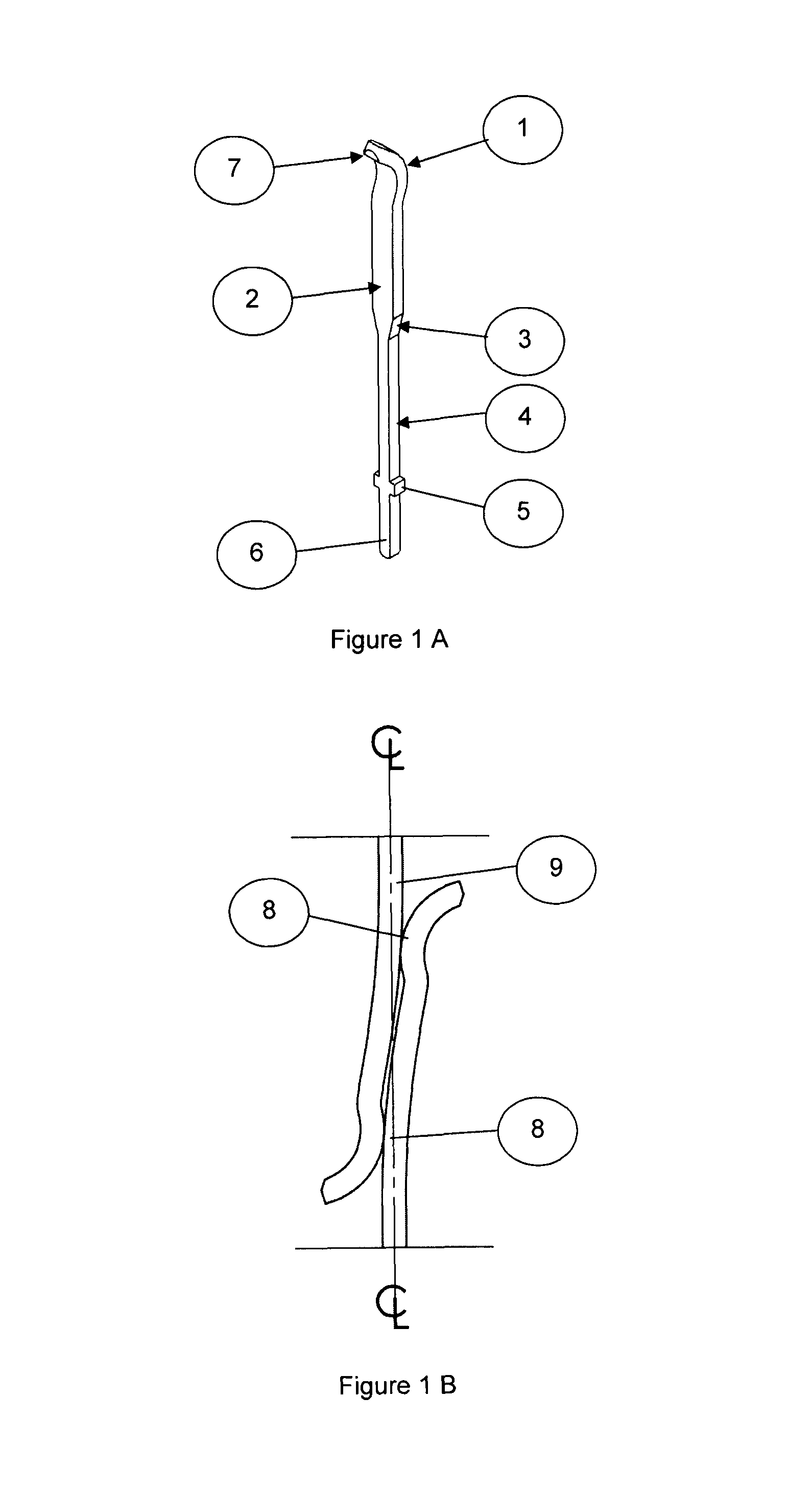

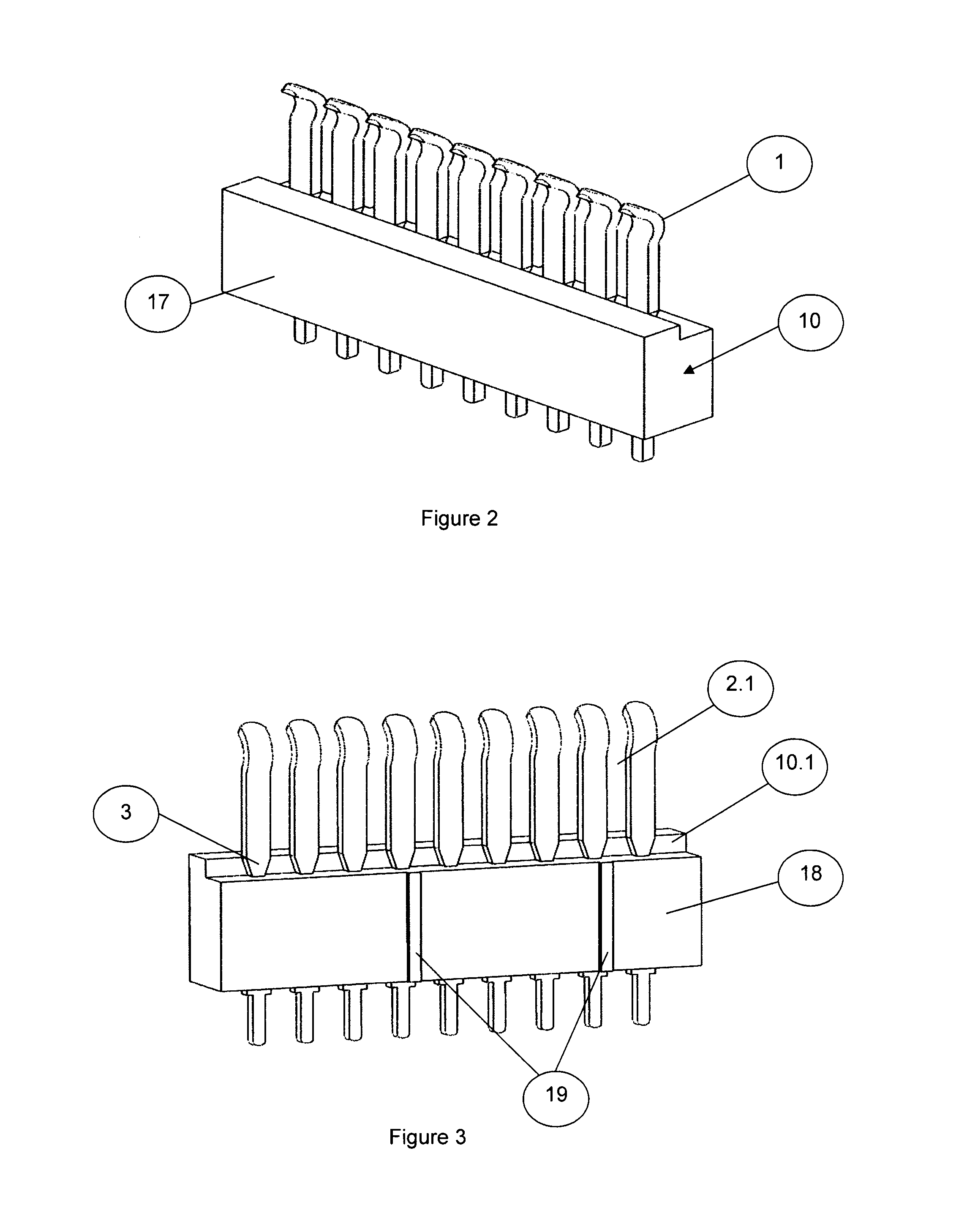

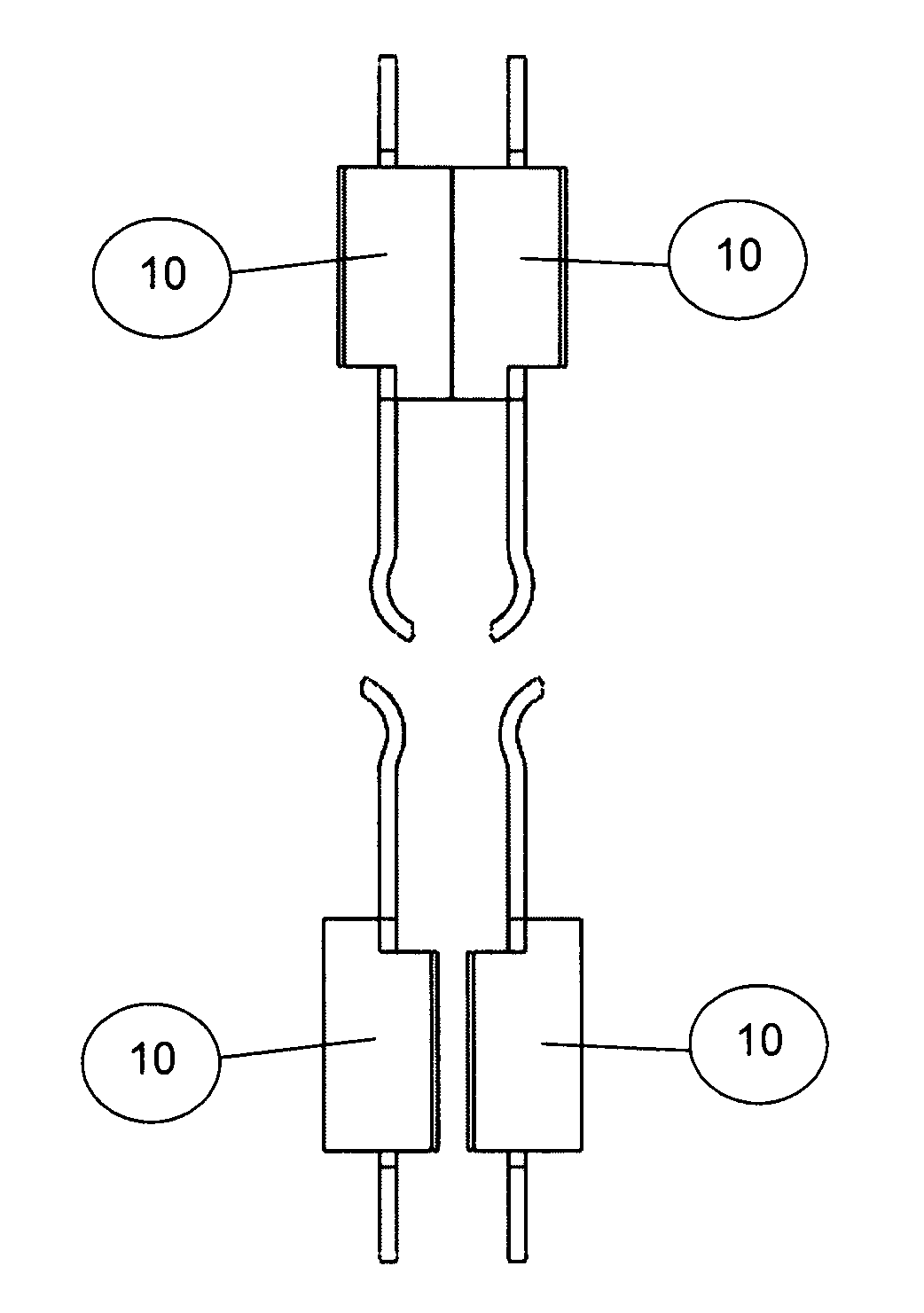

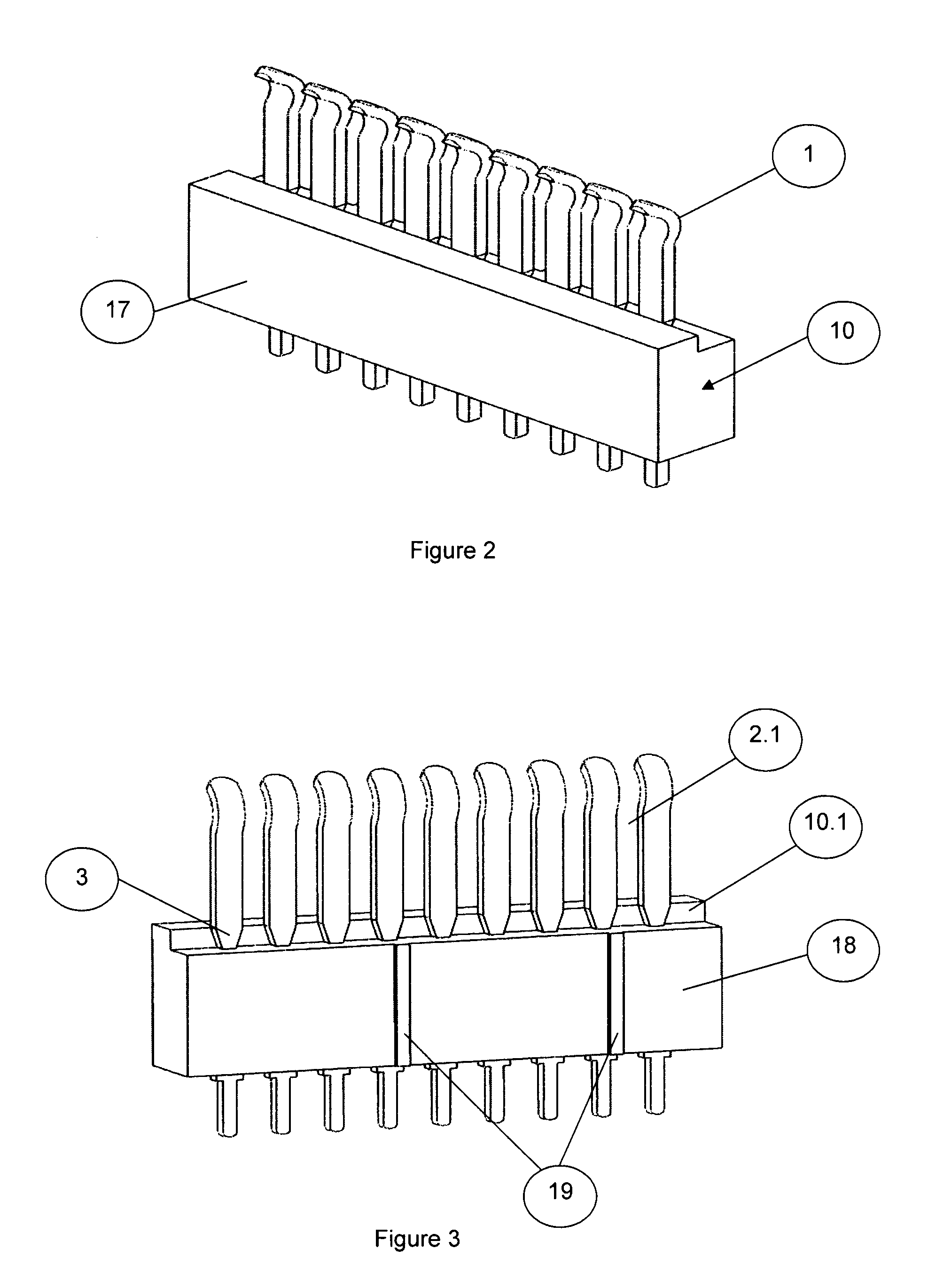

Hermaphroditic interconnect system

ActiveUS8998645B2Reduced metalReduce impactCoupling contact membersTwo-part coupling devicesDielectric matrixElectricity

An electrical interconnect system employs electrical connectors in which the contacts are identical for both the male and the female side of the connection. Contacts are arranged in a linear header and multiple header pairs are arranged in a dielectric matrix or grid. The grid is an external dielectric frame capable of providing load bearing and geometry requirements. This arrangement results in a cost-effective construction that features very high electrical bandwidth capabilities and an extremely rugged product.

Owner:OHIO ASSOCD ENTERPRISES

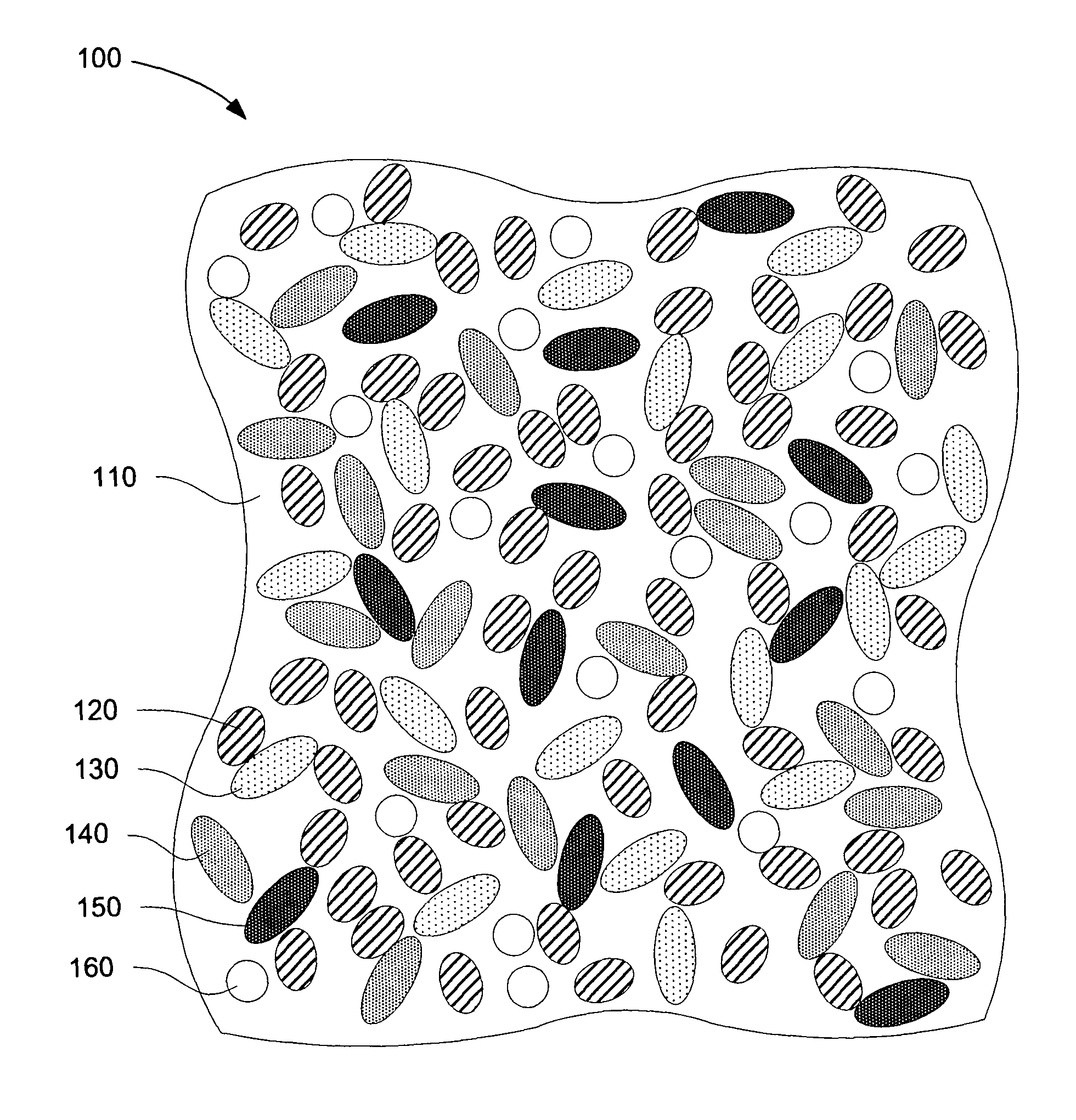

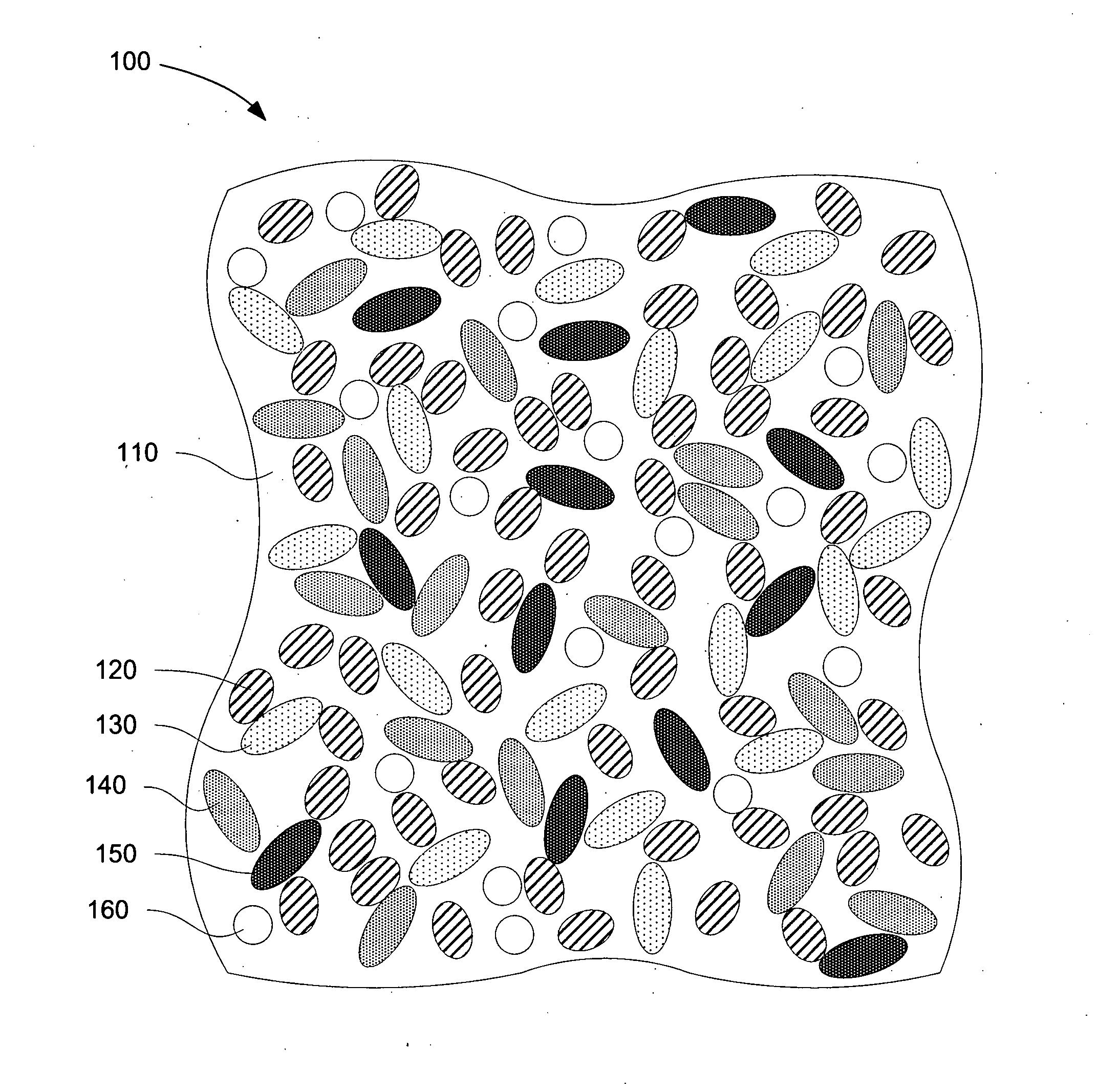

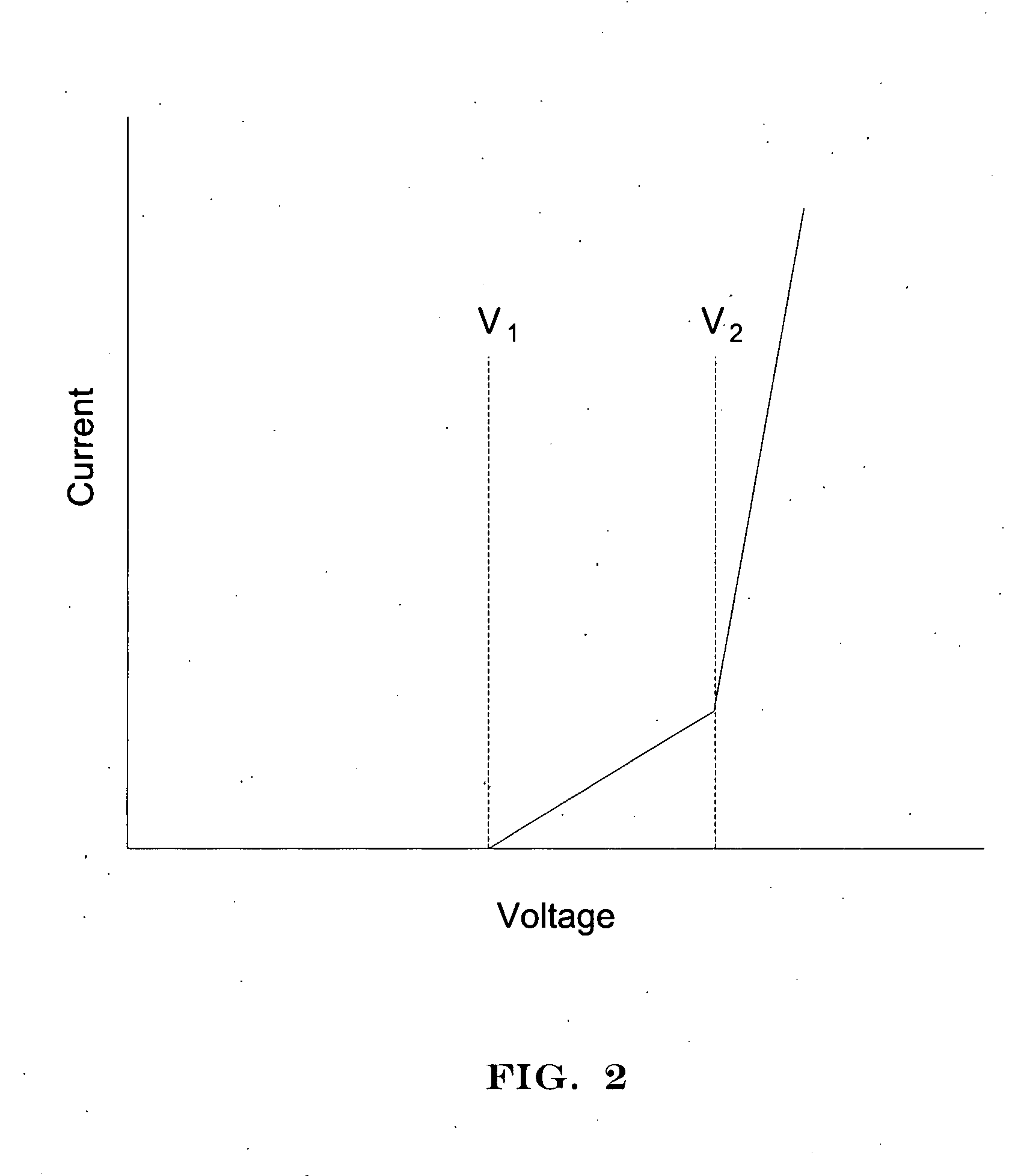

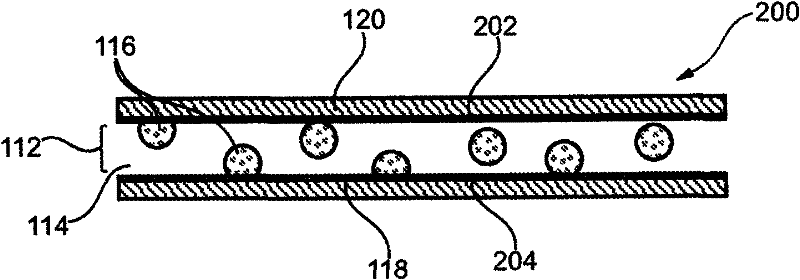

Formulations for voltage switchable dielectric material having a stepped voltage response and methods for making the same

Formulations for voltage switchable dielectric materials include two or more different types of semiconductive materials uniformly dispersed within a dielectric matrix material. The semiconductive materials are selected to have different bandgap energies in order to provide the voltage switchable dielectric material with a stepped voltage response. The semiconductive materials can comprise inorganic particles, organic particles, or an organic material that is soluble in, or miscible with, the dielectric matrix material. Formulations optionally can also include electrically conductive materials. At least one of the conductive or semiconductive materials in a formulation can comprise particles characterized by an aspect ratio of at least 3 or greater.

Owner:LITTELFUSE INC

Formulations for voltage switchable dielectric material having a stepped voltage response and methods for making the same

InactiveUS20100270588A1Material nanotechnologyConductive materialDielectric matrixInorganic particle

Formulations for voltage switchable dielectric materials include two or more different types of semiconductive materials uniformly dispersed within a dielectric matrix material. The semiconductive materials are selected to have different bandgap energies in order to provide the voltage switchable dielectric material with a stepped voltage response. The semiconductive materials can comprise inorganic particles, organic particles, or an organic material that is soluble in, or miscible with, the dielectric matrix material. Formulations optionally can also include electrically conductive materials. At least one of the conductive or semiconductive materials in a formulation can comprise particles characterized by an aspect ratio of at least 3 or greater.

Owner:LITTELFUSE INC

Hermaphroditic interconnect system

ActiveUS20130102199A1Avoid stacking toleranceKeep distanceCoupling contact membersTwo-part coupling devicesDielectric matrixElectricity

An electrical interconnect system employs electrical connectors in which the contacts are identical for both the male and the female side of the connection. Contacts are arranged in a linear header and multiple header pairs are arranged in a dielectric matrix or grid. The grid is an external dielectric frame capable of providing load bearing and geometry requirements. This arrangement results in a cost-effective construction that features very high electrical bandwidth capabilities and an extremely rugged product.

Owner:OHIO ASSOCD ENTERPRISES

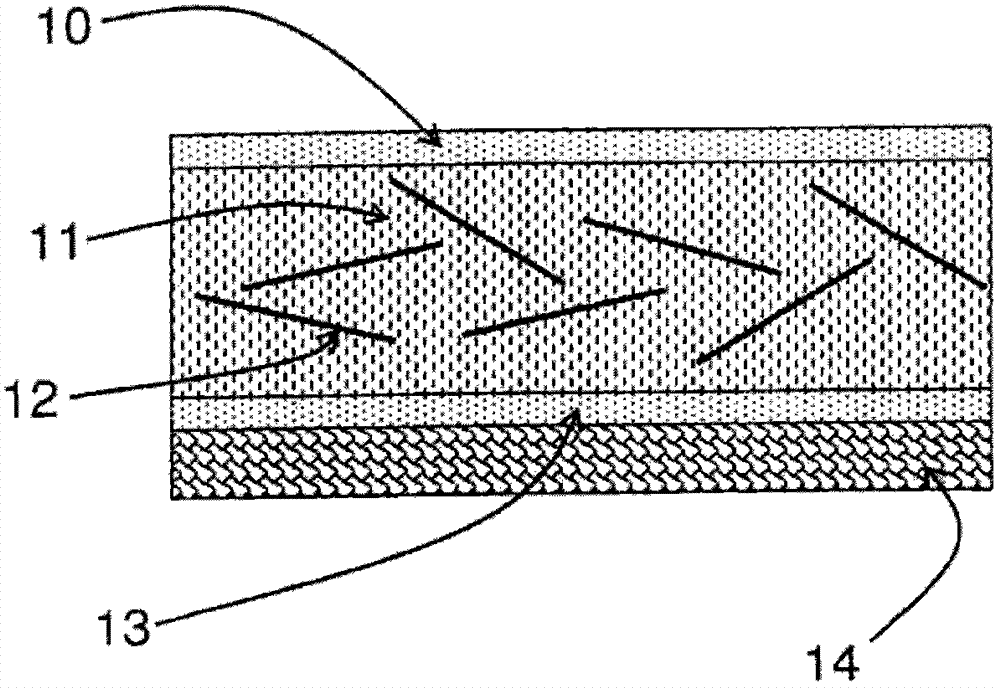

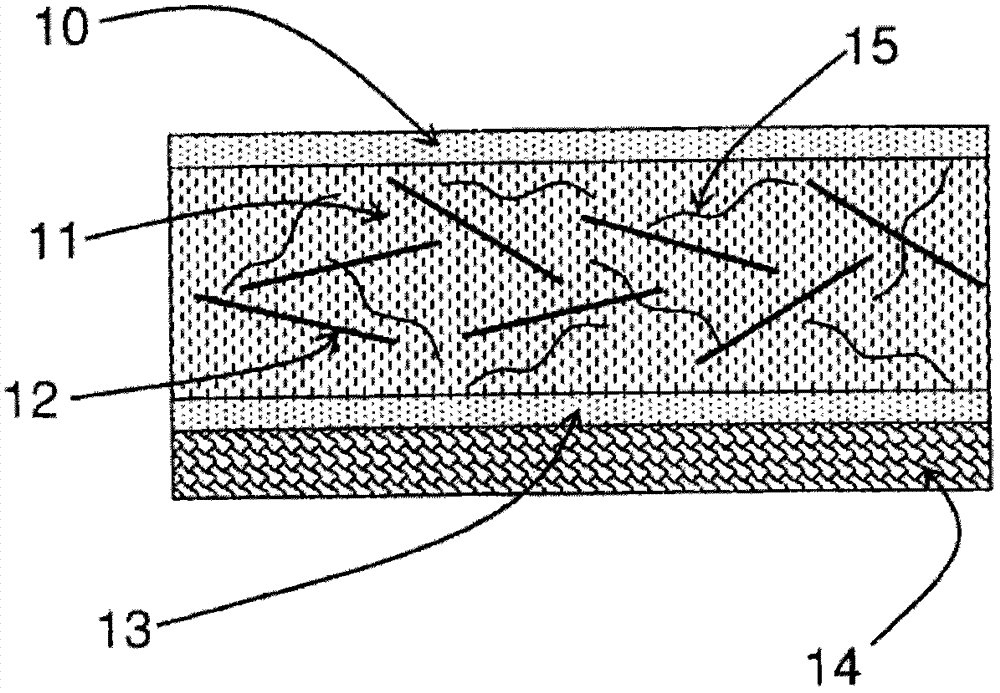

Piezoelectric and/or pyroelectric composite solid material, method for obtaining same and use of such a material

InactiveCN102792476AMaterial nanotechnologyPiezoelectric/electrostrictive device manufacture/assemblyMetallurgyMixed materials

The invention relates to a piezoelectric and / or pyroelectric composite solid material, referred to as a hybrid material, including: a solid dielectric matrix (11), a filler of at least one inorganic piezoelectric and / or pyroelectric material, characterised in that said filler includes filiform nanoparticles (12) distributed throughout the volume of the solid dielectric matrix (11) with an amount by volume of less than 50%, and in that the main directions of elongation of the filiform nanoparticles (12) of the inorganic filler distributed in the dielectric matrix (11) have a substantially isotropic distribution in the solid dielectric matrix (11). The invention also relates to a method for manufacturing and using such a hybrid material for the production of structural parts and supported films deposited on the surface of such a substrate for the purpose of: detecting mechanical stress by direct piezoelectric effect; detecting temperature variations by direct pyroelectric effect; creating a mechanical wave by reverse piezoelectric effect in a flexible audio device, in a de-icing device or in a mechanical anti-fouling device; and manufacturing a soundproof material.

Owner:UNIV PAUL SABATIER TOULOUSE III

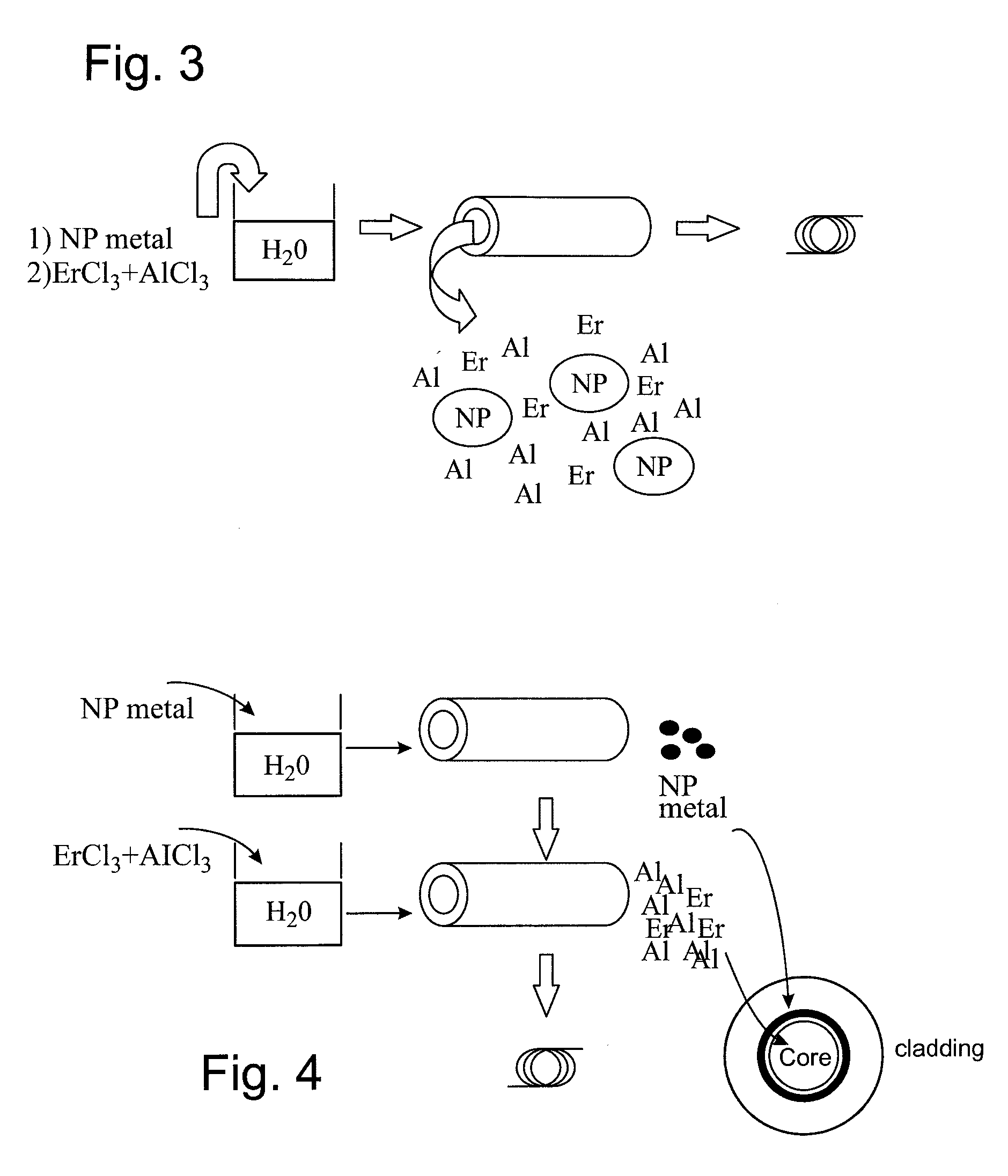

Amplifier optical fiber comprising nanoparticles and production method

InactiveUS20090207486A1Enhanced signal amplificationGlass making apparatusLaser detailsFiberDielectric matrix

An amplifier optical fiber comprising a central core of a dielectric matrix doped with at least one element ensuring the amplification of an optical signal transmitted in the fiber and a cladding surrounding the central core and suitable for confining the optical signal transmitted in the core. The fiber also comprises metallic nanostructures suitable for generating an electronic surface resonance in the dielectric matrix of central core, the wavelength of said electronic surface resonance corresponding to an excitation level of the element ensuring the amplification.

Owner:DRAKA COMTEQ BV

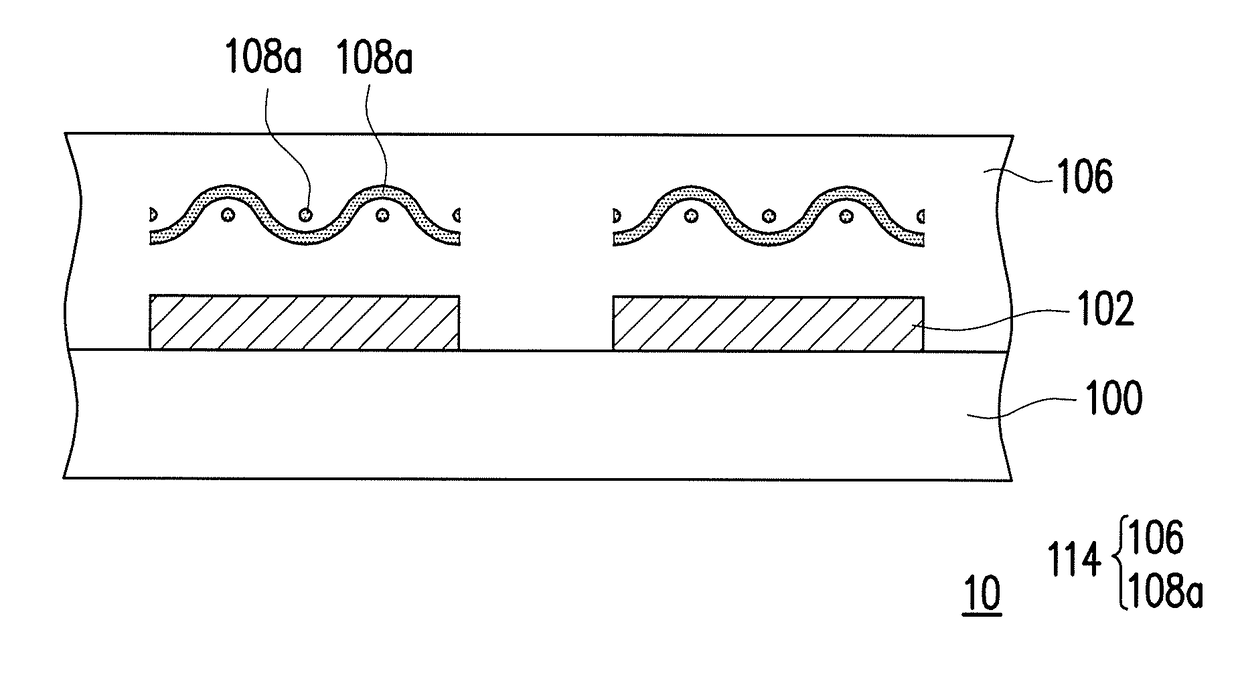

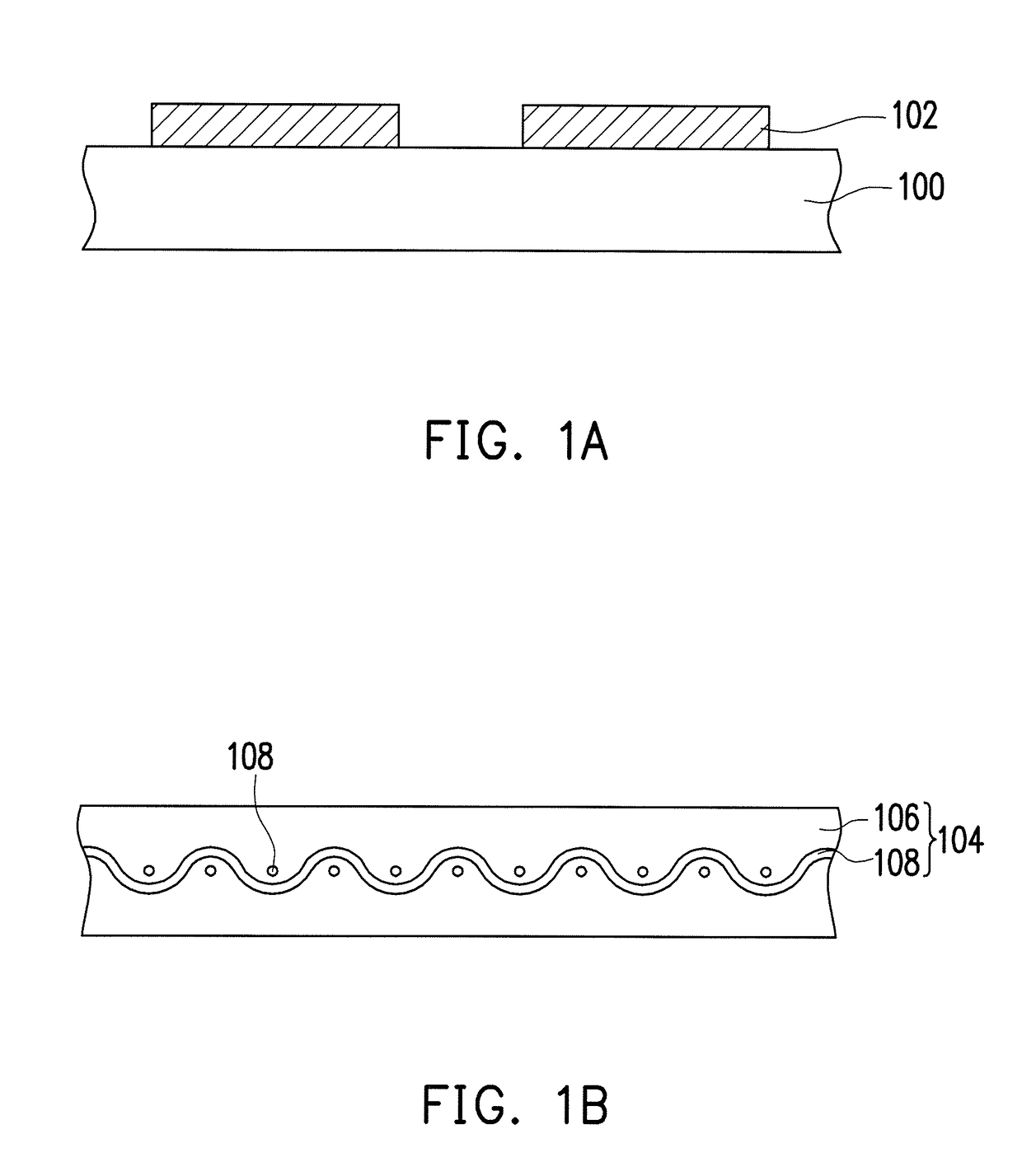

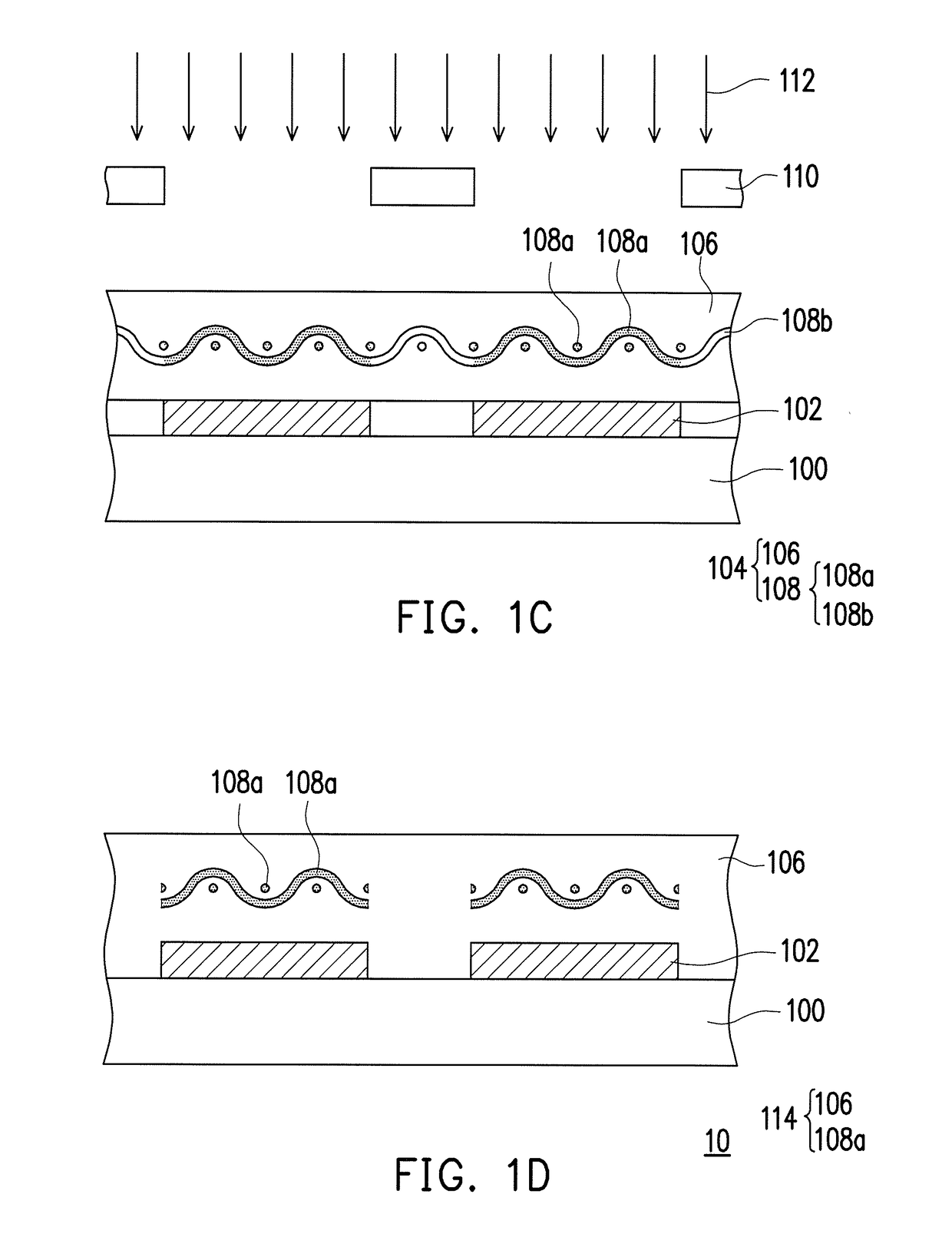

Circuit board and manufacturing method thereof

ActiveUS9635757B1Improve reliabilityInhibition formationPrinted circuit aspectsNon-printed masksDielectric matrixDielectric substrate

A circuit board and a manufacturing method thereof are provided. The circuit board includes a dielectric substrate, a circuit pattern and a dielectric layer. The circuit pattern is disposed on the dielectric substrate. The dielectric layer is disposed on the dielectric substrate and covers the circuit pattern. The dielectric layer includes a dielectric matrix and a mesh-shaped fiber structure disposed in the dielectric matrix. There is no mesh-shaped fiber structure on a portion of the dielectric substrate exposed by the circuit pattern.

Owner:UNIMICRON TECH CORP

Capacitor and a method of manufacturing the same

ActiveUS20110147891A1Increase capacitanceFixed capacitor dielectricSemiconductor/solid-state device manufacturingDielectric matrixSpontaneous nucleation

A capacitor (110), wherein the capacitor (110) comprises a capacitor dielectric (112) comprising a dielectric matrix (114) of a first value of permittivity, and a plurality of nanoclusters (116) of a second value of permittivity which is larger than the first value of permittivity which are at least partially embedded in the dielectric matrix (114), wherein the plurality of nanoclusters (116) are formed in the dielectric matrix (114) by spontaneous nucleation.

Owner:NXP BV

Reactive cyclodextrin derivatives as pore-forming templates, and low dielectric materials prepared by using the same

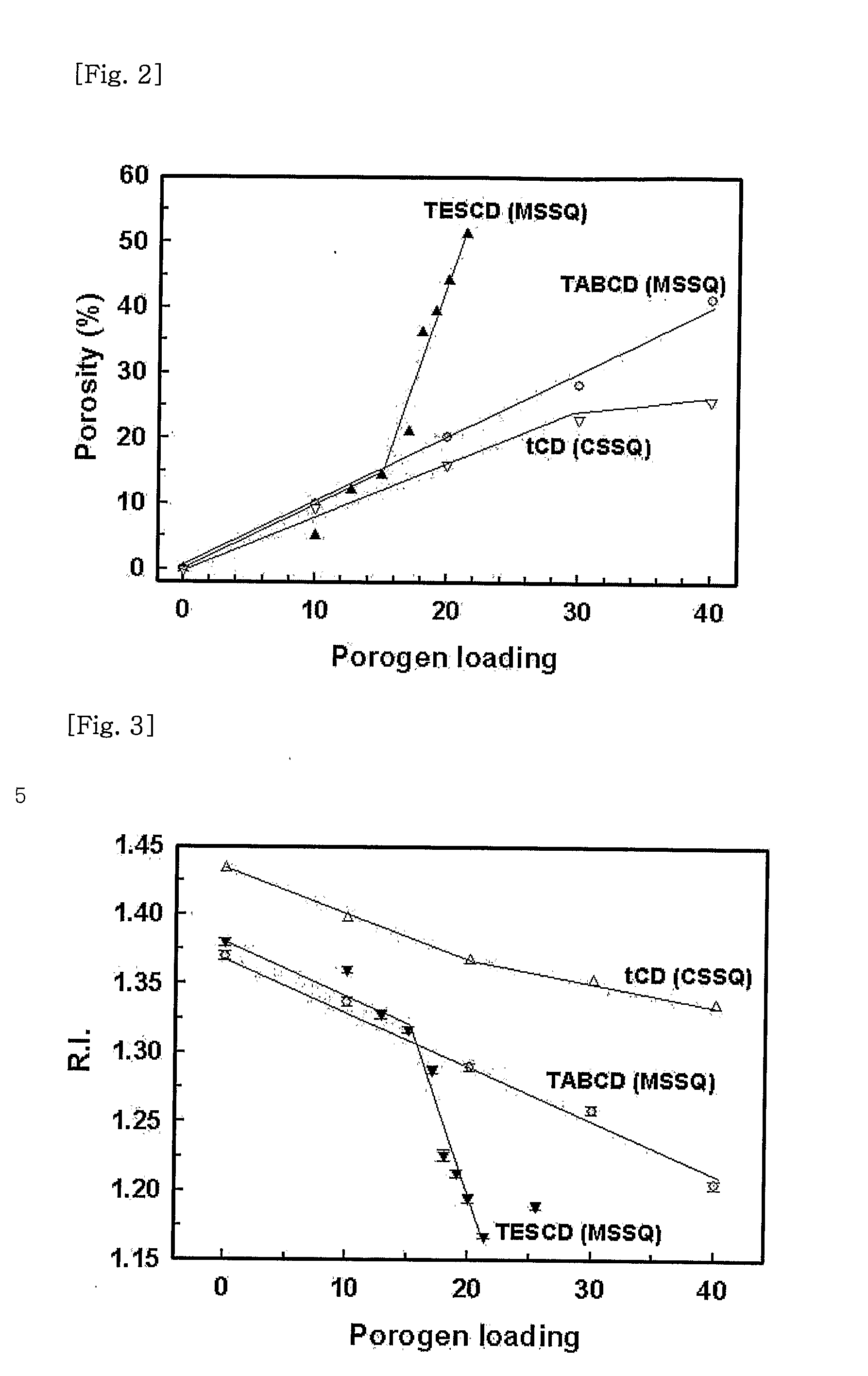

ActiveUS7462659B2Improve compatibilityExcellent dielectric propertiesPlastic/resin/waxes insulatorsSemiconductor/solid-state device detailsDielectric matrixPorosity

Owner:IND UNIV COOPPERATION FOUND SOGANG UNIV

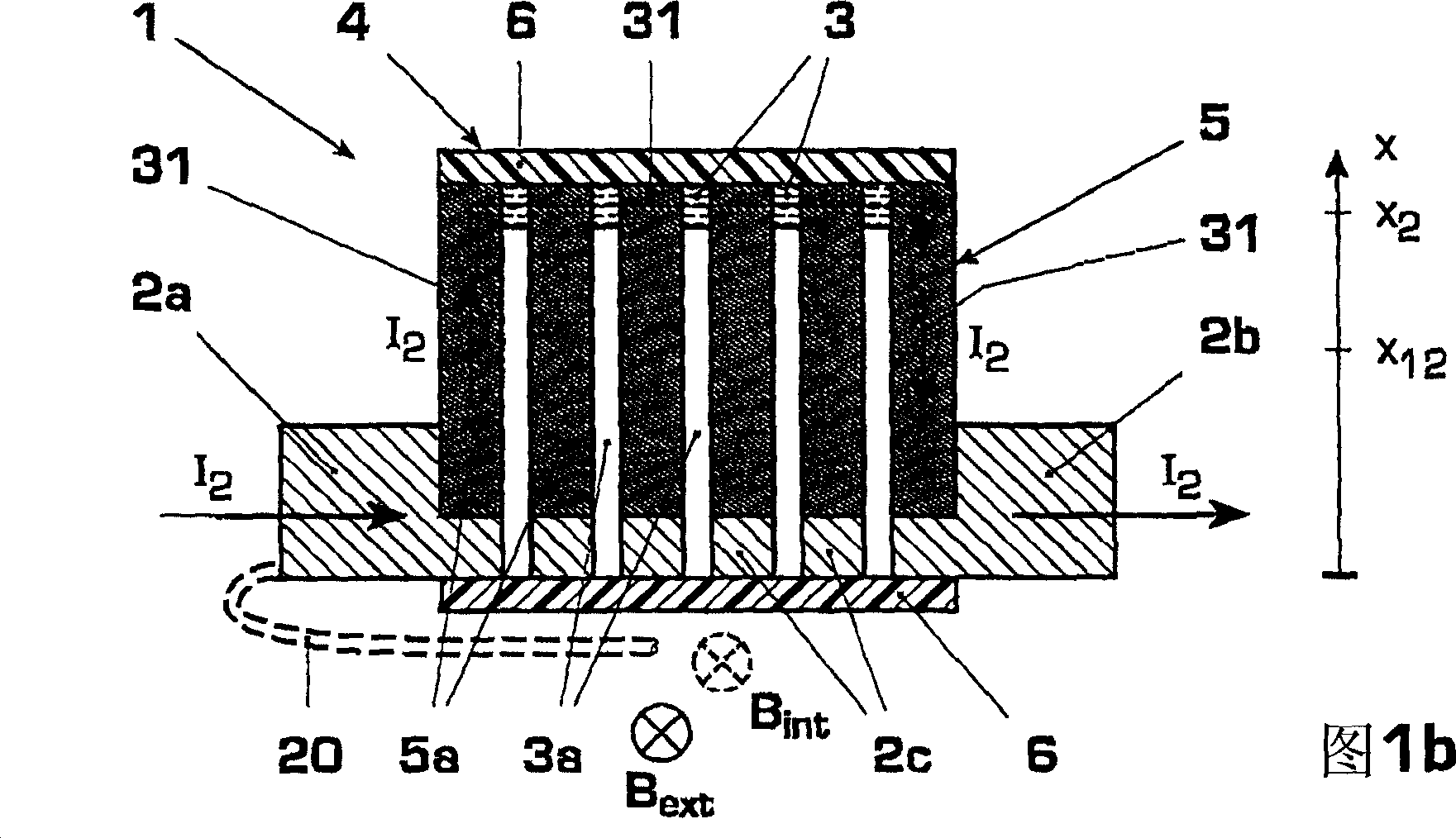

Method and device for limiting the current in a liquid metal current limiter

InactiveCN1820341AAgainst short circuit currentThe short-circuit current is suitable for limitingCircuit-breaking switches for excess currentsHigh-tension/heavy-dress switchesElectric networkLiquid metal

The invention relates to a current limiting method, a current limiting device (1), and a switchgear comprising such a device (1). According to the invention, liquid metal (3) is directed along a resistor element (5) for the current limiting path (31) so as to obtain arc-free current limitation for mains-related fault currents (i(t)). Examples of embodiments include, among other things: an electrical resistance (Rx) that increases in a non-linear manner in the direction of movement (x) of the liquid metal (3) for a smooth current limiting characteristic; a resistor element (5) in the form of a dielectric matrix (5) comprising channels (3a) for the liquid metal (3), and a combined current limiter-circuit breaker (1). Advantages include, among other things: arc-free, reversible current limitation and optional power shutdown; suitable also for high voltages and currents; fast reaction times; reduced wear; and maintenance-friendly.

Owner:ABB RES LTD

Insulating compositions and devices incorporating the same

InactiveUS20110017494A1Windings insulation materialWindings insulation shape/form/constructionDielectric matrixHost material

Provided are compositions that include a dielectric matrix material defining multiple voids of substantially uniform respective dimension and configured as a substantially uniform array. The voids may be configured such that charges that accumulate at surfaces of at least some of the voids when the composition is immersed in a uniform external electric field interact with charges that accumulate at surfaces of at least others of the voids to cause movement of the respective charges in a direction having a component transverse to the electric field. Hollow particles may be disposed within respective voids of the array of voids defined by the matrix material, and particles, such as, for example, ceramic, varistor, and / or inorganic dielectric particles, may be incorporated within the matrix material. Associated devices are also provided.

Owner:GENERAL ELECTRIC CO

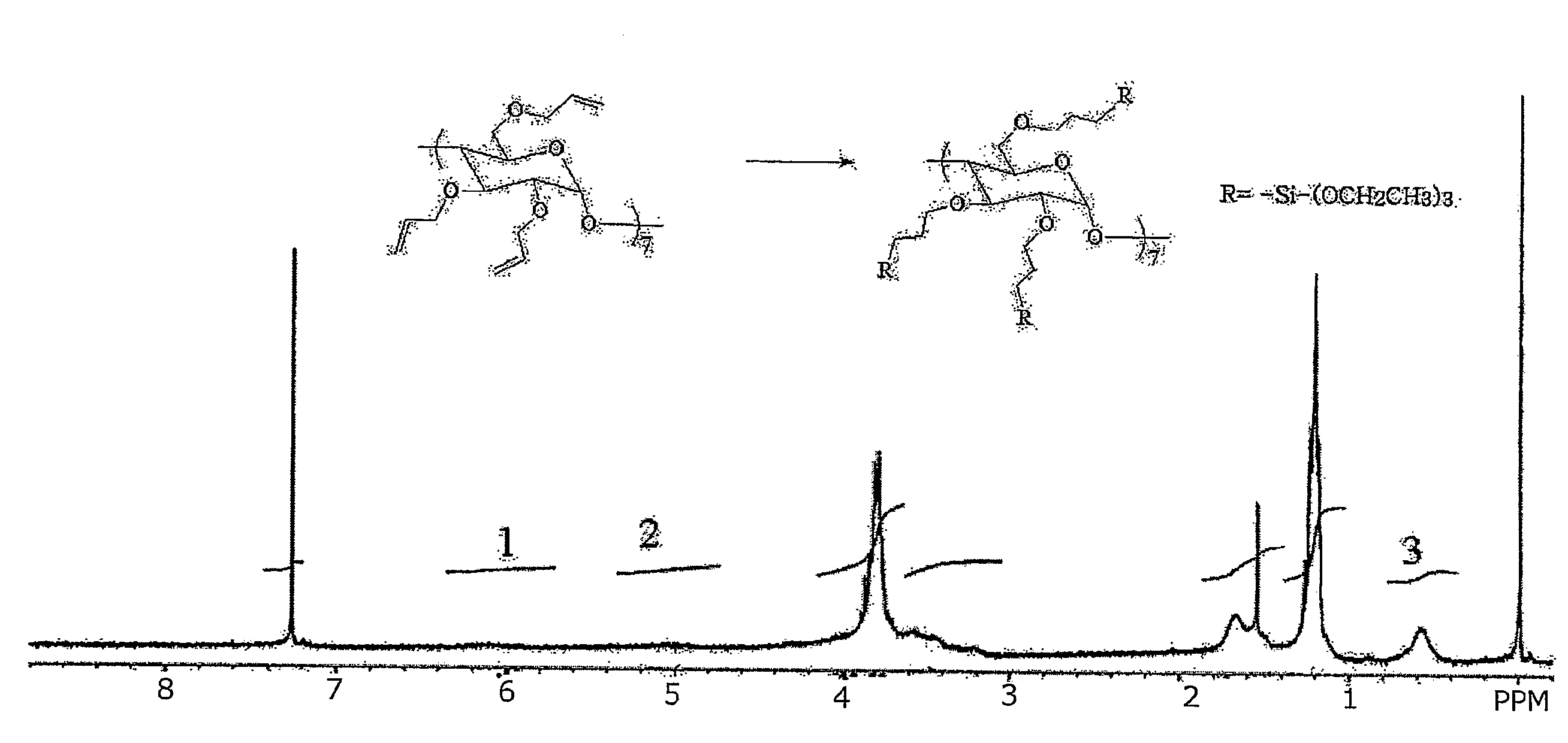

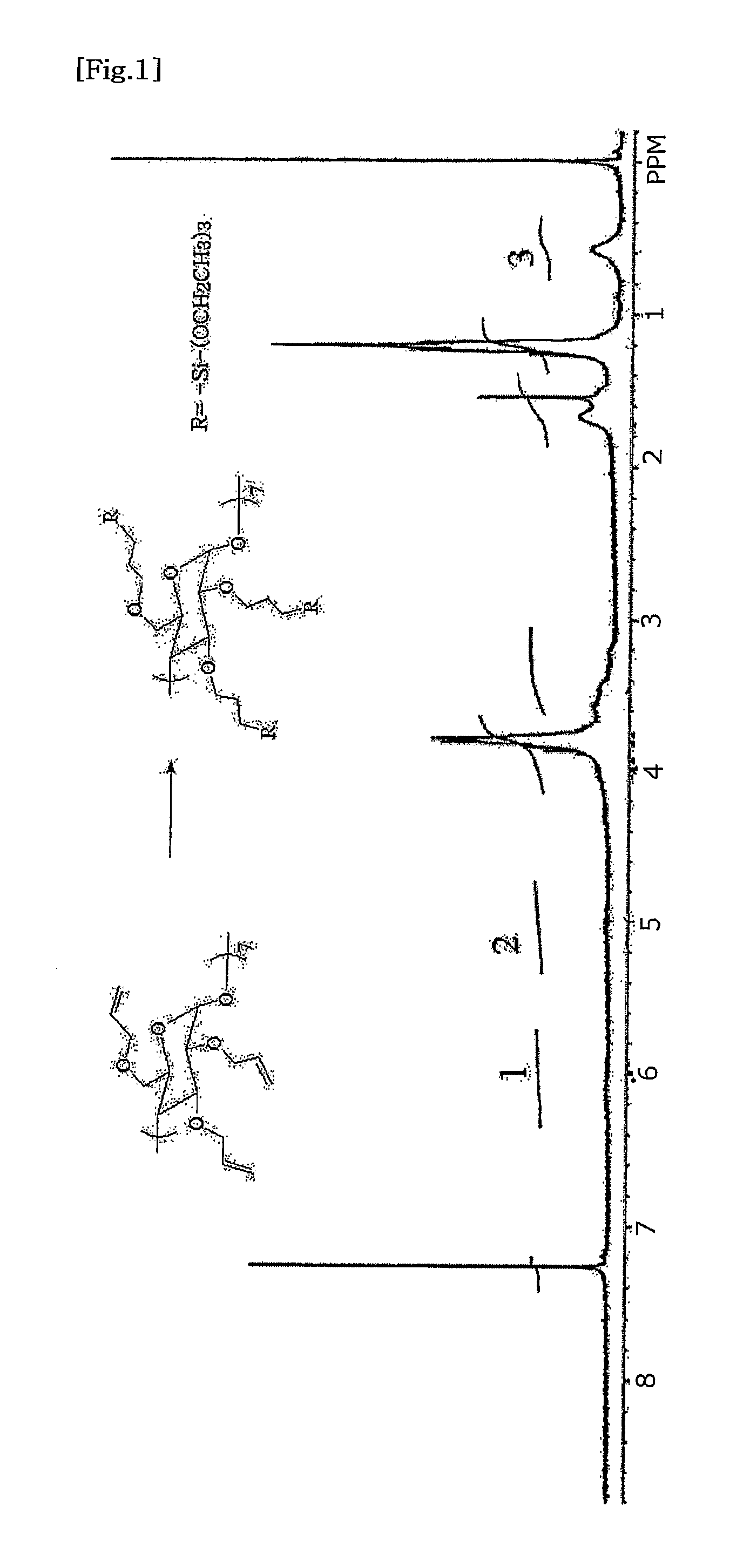

Reactive cyclodextrin derivatives as pore-forming templates, and low dielectric materials prepared by using the same

ActiveUS20070128879A1Improve compatibilityExcellent dielectric propertiesPlastic/resin/waxes insulatorsSemiconductor/solid-state device detailsDielectric matrixPorosity

This invention is related to a reactive nanoparticular cyclodextrin derivative useful as a porogen and a low dielectric matrix, with excellent mechanical properties and uniformly distributed nanopores, manufactured by sol-gel reaction of the above reactive cyclodextrin. Furthemore, this invention also is related to an ultralow dielectric film, with uniformly distributed nanopores, a relatively high porosity of 51%, and a relatively low dielectric constant of 1.6, manufactured by thin-filming of the conventional organic or inorganic silicate precursor by using the above reactive cyclodextrin as a porogen.

Owner:IND UNIV COOPPERATION FOUND SOGANG UNIV

A capacitor and a method of manufacturing the same

InactiveCN102132367AIncrease capacitanceReduce leakage currentFixed capacitor dielectricDielectric matrixSpontaneous nucleation

A capacitor (110), wherein the capacitor (110) comprises a capacitor dielectric (112) comprising a dielectric matrix (114) of a first value of permittivity, and a plurality of nanoclusters (116) of a second value of permittivity which is larger than the first value of permittivity which are at least partially embedded in the dielectric matrix (114), wherein the plurality of nanoclusters (116) are formed in the dielectric matrix (114) by spontaneous nucleation.

Owner:NXP BV

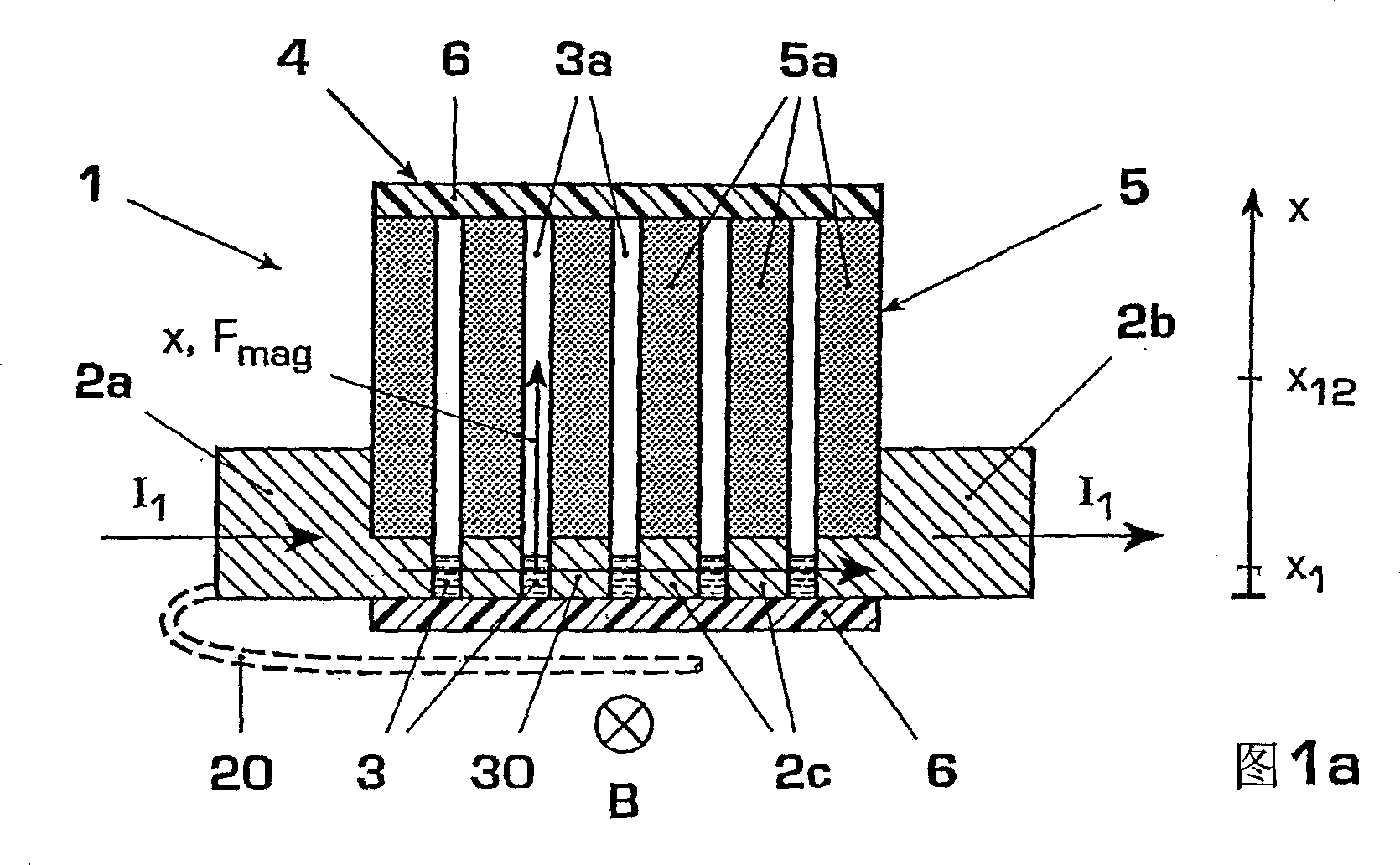

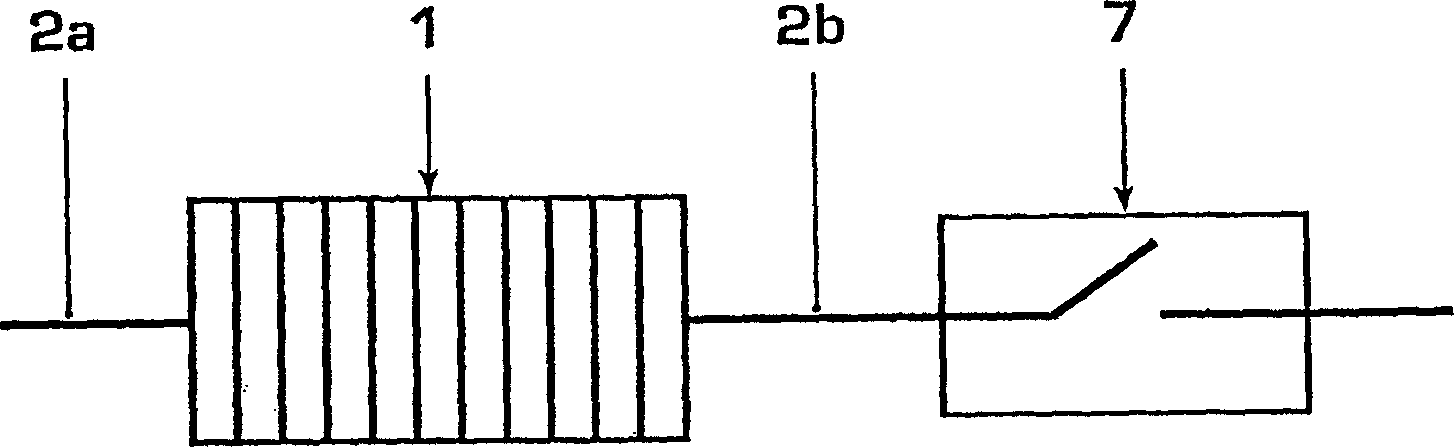

Method and device for current limitation with an automatic current limiter

InactiveCN1820340AOptimize layoutReasonable maintenanceCircuit-breaking switches for excess currentsElectric switchesElectrical resistance and conductanceDielectric matrix

The invention relates to a method and a device (1) for combined current limitation and power breaking and to a switchgear having said device (1). In a combined current limiter / power braker (1) according to the invention, a movable electrode (3, 3') is guided automatically along a resistance element (5) for the current limiting path (31) by an overcurrent-dependent force (Fmag) for the purpose of current limitation and brought to an insulator (8) in a serial arrangement for power breaking purposes. Examples of embodiments are, inter alia, the utilization of Lorenz force for automatic current limitation; movable electrodes (3, 3') realized by means of liquid metal (3) or a movable solid conductor (3'); an electrical resistance (RX) increasing non-linearly in the direction of movement (x) for smooth power limitation characteristics and a resistance element (5) in the form of a dielectric matrix (5) with several channels (3a) for the liquid metal (3). Amongst the advantages achieved are electric arc-free, reversible current limitation and power breaking, which is also suitable for high voltages and currents, rapid reaction times, little wear and easy maintenance.

Owner:ABB RES LTD

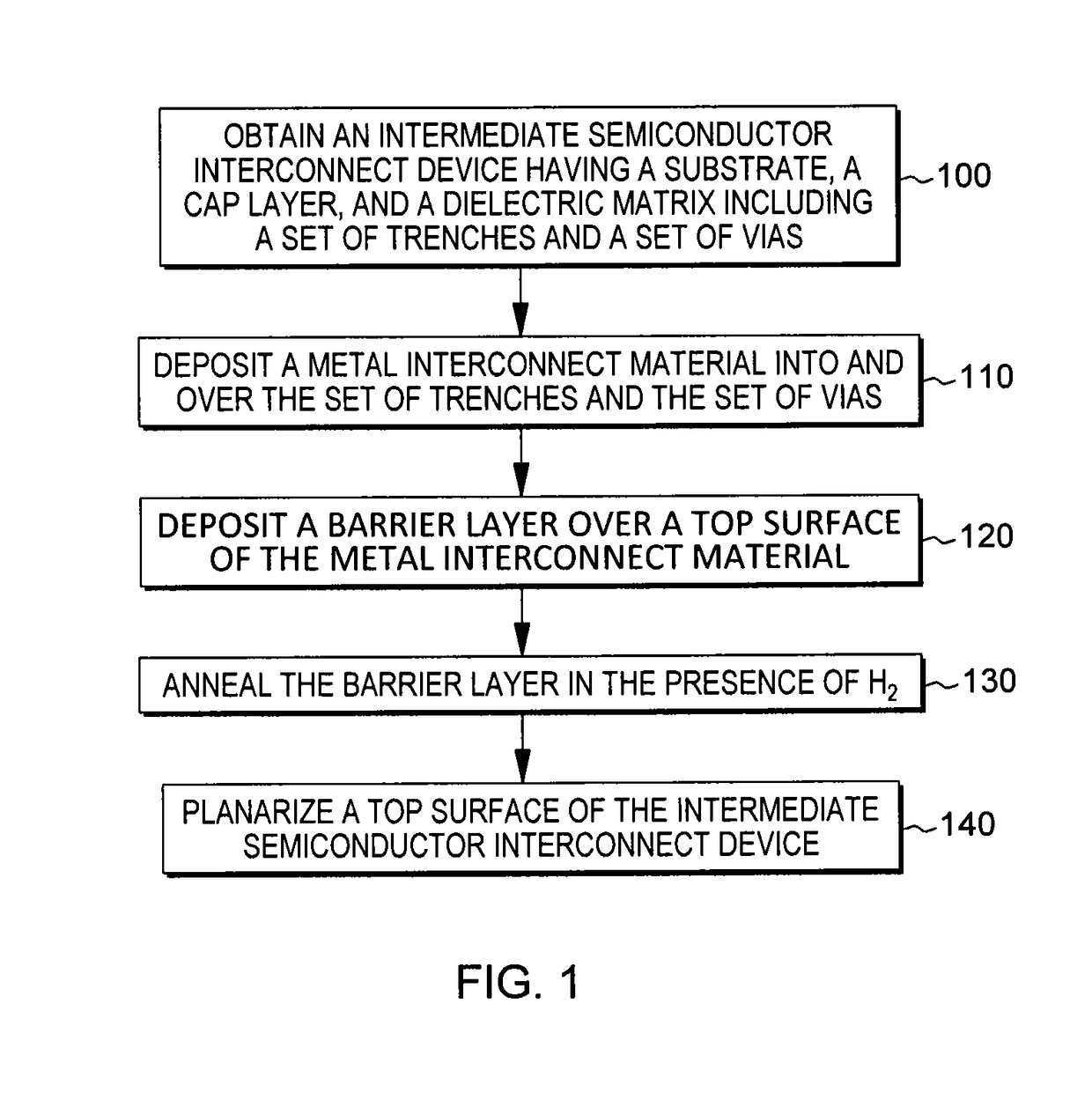

Devices and methods of forming low resistivity noble metal interconnect with improved adhesion

InactiveUS20170345766A1Overcomes shortcomingEnhanced advantageSemiconductor/solid-state device detailsSolid-state devicesDielectric matrixMetal interconnect

Devices and methods of fabricating integrated circuit devices for forming low resistivity interconnects with improved adhesion are provided. One method includes, for instance: obtaining an intermediate semiconductor interconnect device having a substrate, a cap layer, and a dielectric matrix including a set of trenches and a set of vias; depositing a metal interconnect material directly over and contacting a top surface of the dielectric matrix, wherein the metal interconnect material fills the set of trenches and the set of vias; depositing a barrier layer over a top surface of the device; annealing the barrier layer to diffuse the barrier layer to a bottom surface of the metal interconnect material; planarizing a top surface of the intermediate semiconductor interconnect device; and depositing a dielectric cap over the intermediate semiconductor interconnect device.

Owner:GLOBALFOUNDRIES INC

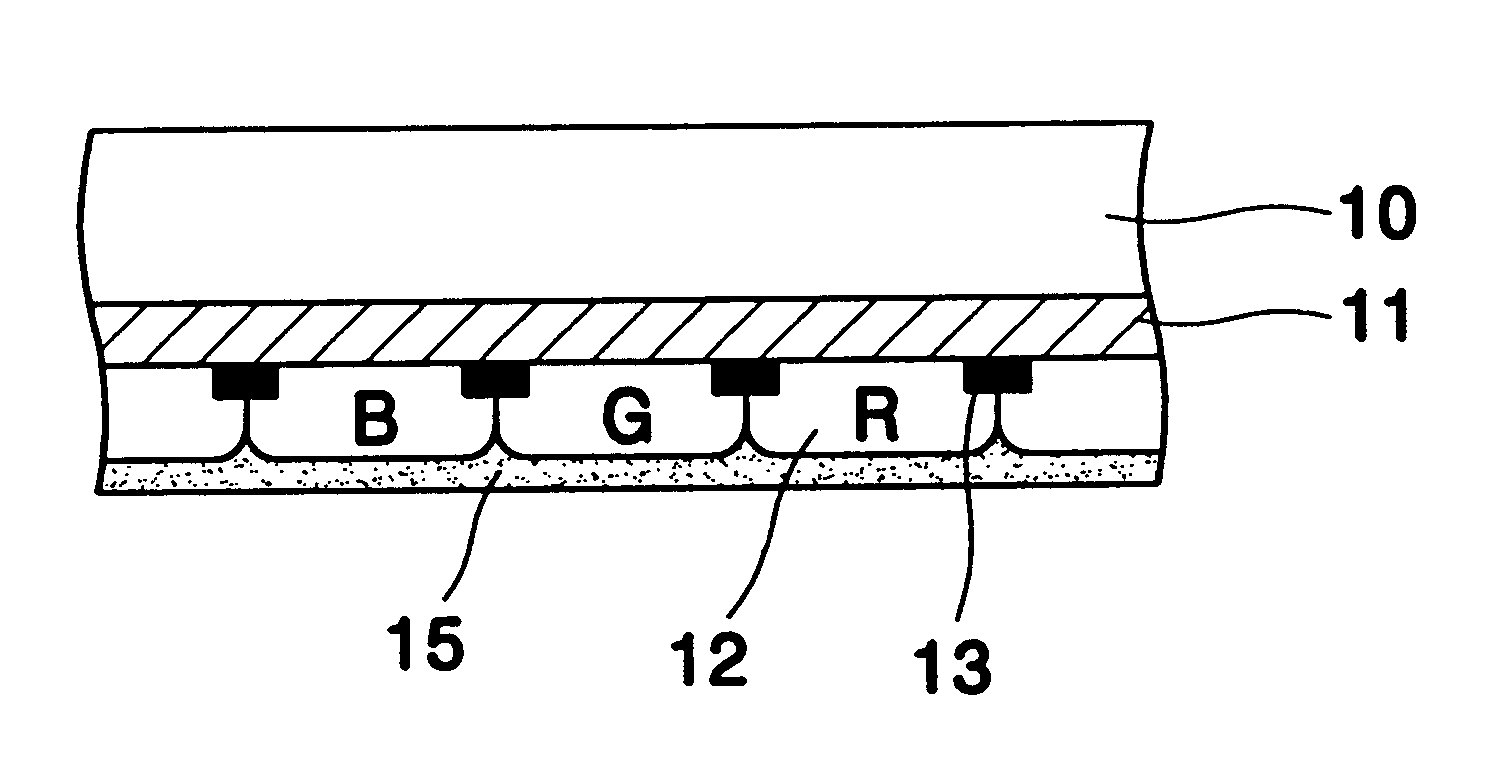

Cathode ray tube

InactiveUS6479928B1Minimize ambient light reflectionMinimizing reflection of lightTube/lamp screens manufactureTelevision system detailsNano sizeMetal particle

A CRT has an improved contrast with a provision of a filter layer where nano-sized metal particles are dispersed in a dielectric matrix to selectively absorb light in predetermined wavelengths, specifically wavelengths between peak wavelengths of primary colors emitted by phosphors coated on the inner surface of the face plate. The improved contrast is a result of the metal particles in a dielectric matrix resonating with particular wavelengths and thus absorbing them.

Owner:SAMSUNG ELECTRONICS DEVICES CO LTD

Anisotropic electrically conductive structure

InactiveCN101151728AAvoid short circuitFirmly connectedConductive layers on insulating-supportsSemiconductor/solid-state device detailsDielectric matrixAdhesive

Owner:3M INNOVATIVE PROPERTIES CO

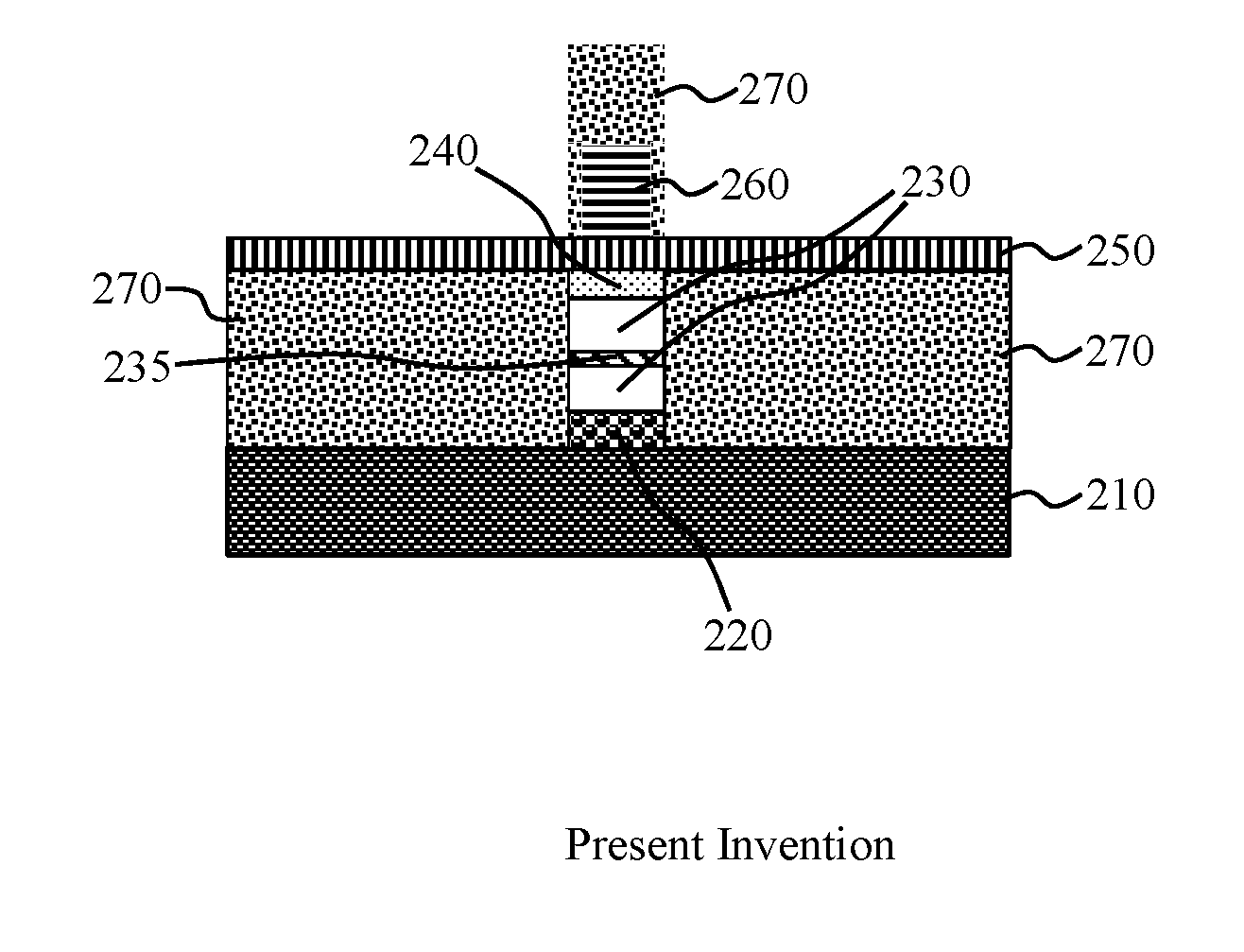

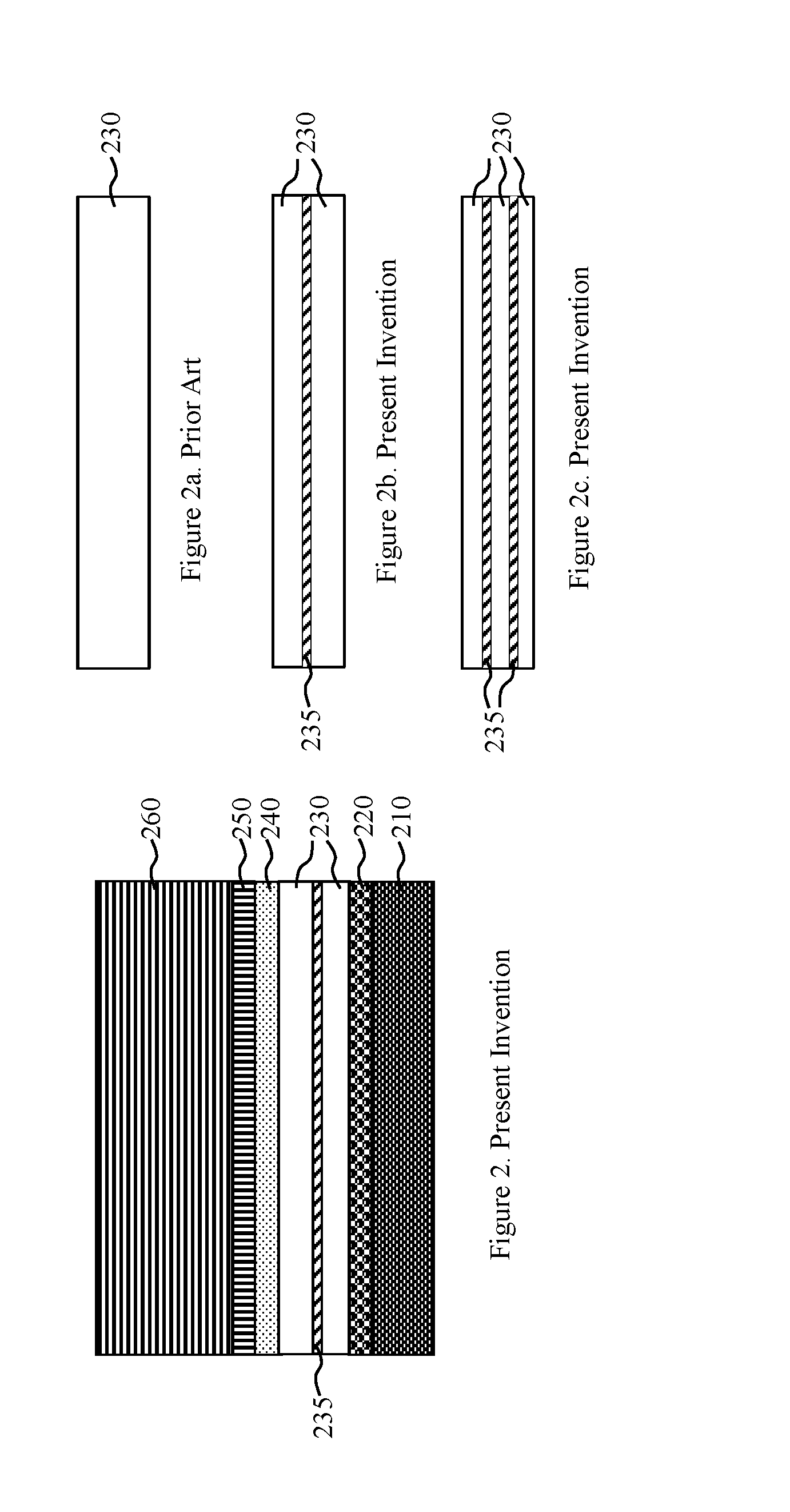

An improved method to make of fabricating ic/mram using oxygen ion implantation

InactiveUS20160172585A1Efficient captureThicker OGLsGalvano-magnetic material selectionSemiconductor/solid-state device manufacturingMagnetic memoryOxygen ions

A method to make magnetic random access memory (MRAM), in particular, perpendicular spin transfer torque MRAM or p-STT-MRAIVI is provided. Electrically isolated memory cell is formed by ion implantation instead of etching and dielectric refill. Oxygen ion implantation is used to convert the photolithography exposed areas into metal oxide dielectric matrix. An ultrathin single-layer or multiple-layer of oxygen-getter, selected from Mg, Zr, Y, Th, Ti, Al, Ba is inserted into the active magnetic memory layer in addition to putting a thicker such material above and below the memory layer to effectively capture the impinged oxygen ions. Oxygen is further confined within the core device layer by adding oxygen stopping layer below the bottom oxygen-getter. After a high temperature anneal, a uniformly distributed and electrically insulated metal oxide dielectric is formed across the middle device layer outside the photolithography protected device area, thus forming MRAM cell without any physical deformation and damage at the device boundary.

Owner:T3MEMORY

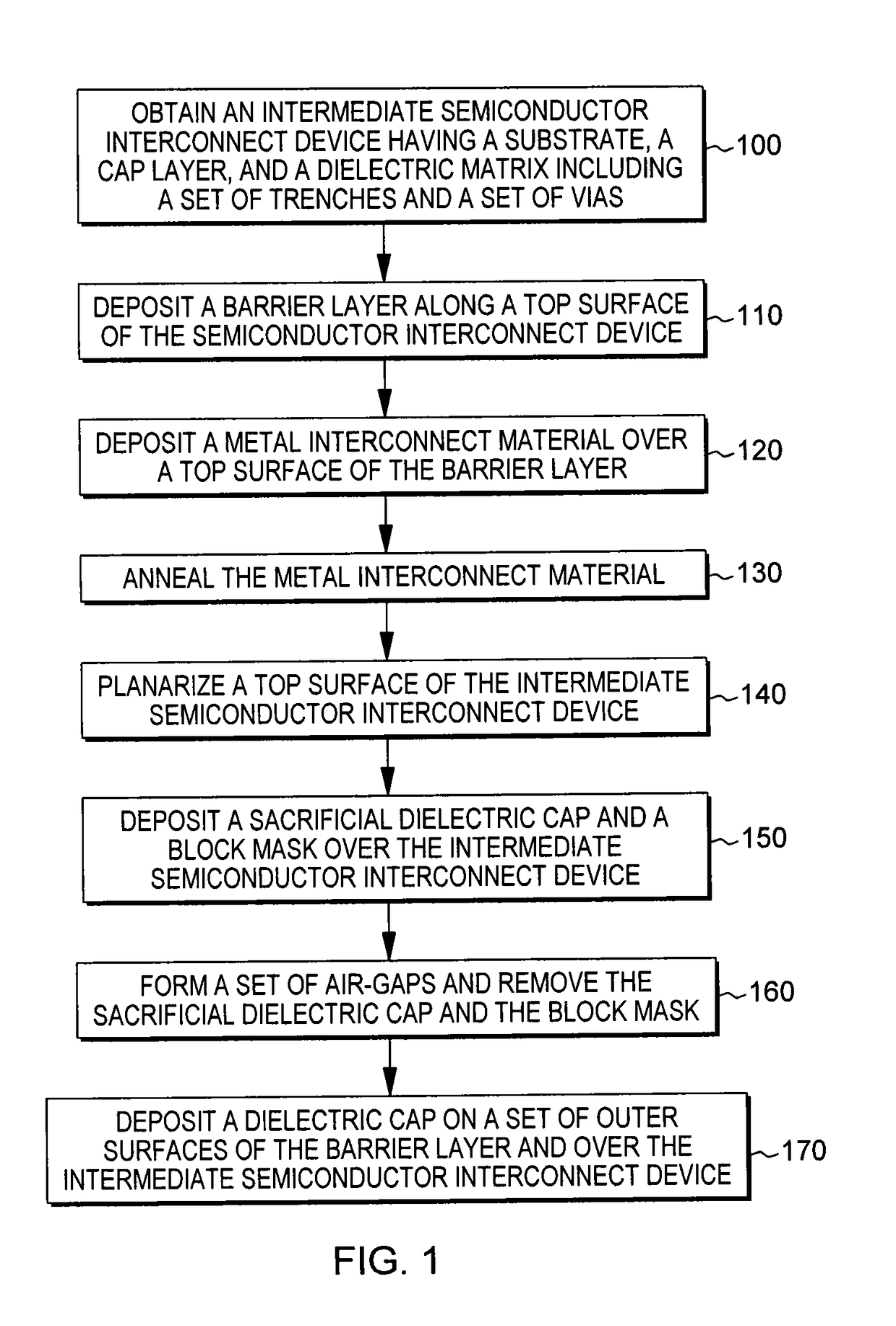

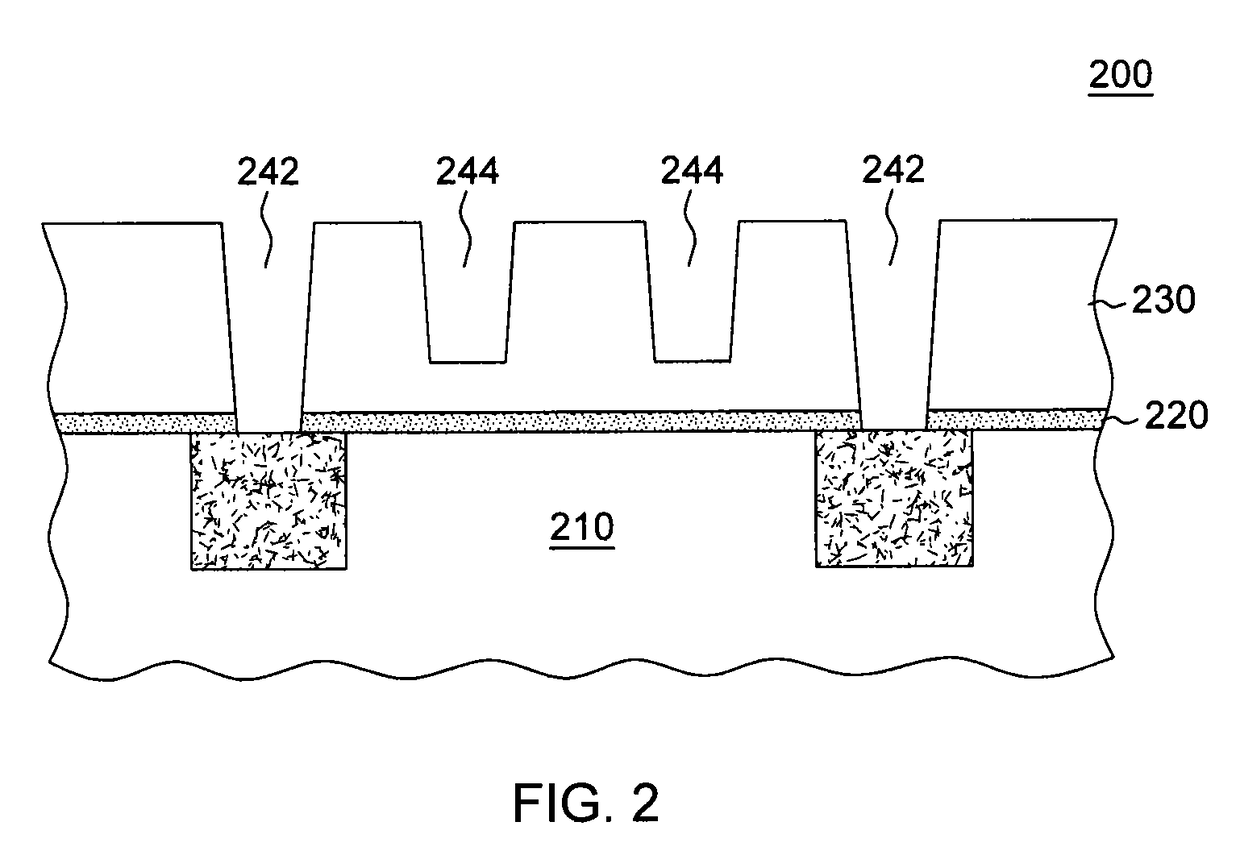

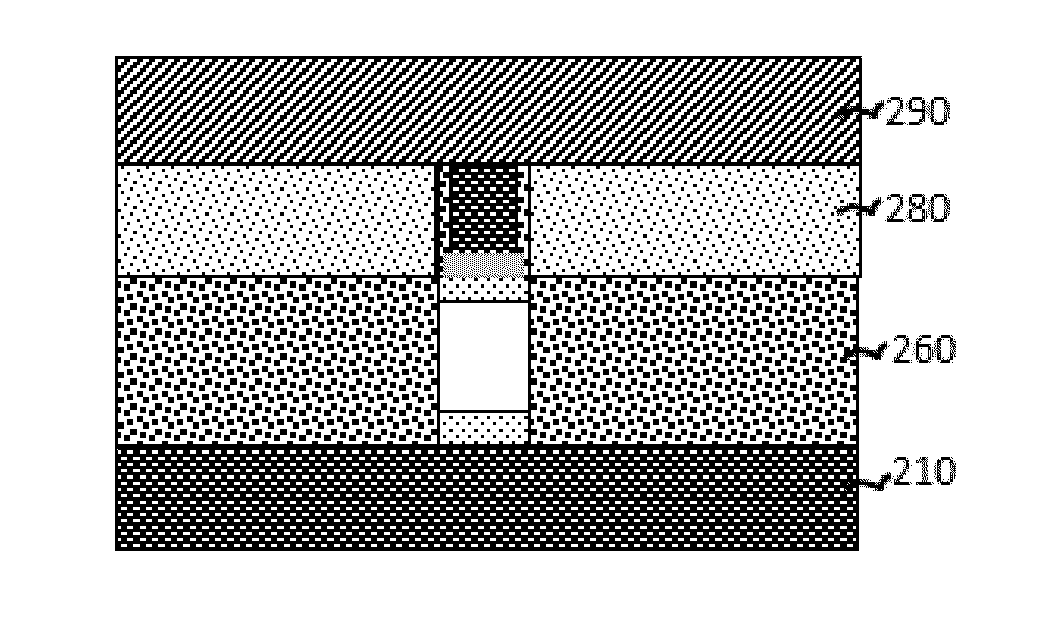

Devices and methods of forming low resistivity noble metal interconnect

ActiveUS20170345752A1Semiconductor/solid-state device detailsSolid-state devicesDielectric matrixMetal interconnect

Devices and methods of fabricating integrated circuit devices for forming low resistivity interconnects are provided. One method includes, for instance: obtaining an intermediate semiconductor interconnect device having a substrate, a cap layer, and a dielectric matrix including a set of trenches and a set of vias; depositing a barrier layer along a top surface of the semiconductor interconnect device; depositing and annealing a metal interconnect material over a top surface of the barrier layer, wherein the metal interconnect material fills the set of trenches and the set of vias; planarizing a top surface of the intermediate semiconductor interconnect device; exposing a portion of the barrier layer between the set of trenches and the set of vias; and depositing a dielectric cap. Also disclosed is an intermediate device formed by the method.

Owner:GLOBALFOUNDRIES U S INC

Capacitor and a method of manufacturing the same

ActiveUS8697516B2Increase capacitanceFixed capacitor dielectricSemiconductor/solid-state device manufacturingDielectric matrixSpontaneous nucleation

A capacitor (110), wherein the capacitor (110) comprises a capacitor dielectric (112) comprising a dielectric matrix (114) of a first value of permittivity, and a plurality of nanoclusters (116) of a second value of permittivity which is larger than the first value of permittivity which are at least partially embedded in the dielectric matrix (114), wherein the plurality of nanoclusters (116) are formed in the dielectric matrix (114) by spontaneous nucleation.

Owner:NXP BV

Method to make integrated device using oxygen ion implantation

InactiveUS20140306304A1Efficient captureSemiconductor/solid-state device manufacturingGalvano-magnetic device detailsDielectric matrixChemical physics

A method to make magnetic random access memory (MRAM), or integrated device in general, is provided. Oxygen ion implantation is used to convert the photolithography exposed areas into metal oxide dielectric matrix. To confine the oxygen ions within the desired region, heavy metals with large atomic number, such as Hf, Ta, W, Re, Os, Ir, Pt, Au is used as ion mask and bottom ion-stopping layer. An oxygen gettering material, selected from Mg, Zr, Y, Th, Ti, Al, Ba is added above and below the active device region to effectively capture the impinging oxygen. After a high temperature anneal, a buried metal oxide layer with sharp oxygen boundaries across the active device region can be obtained.

Owner:GUO YIMIN

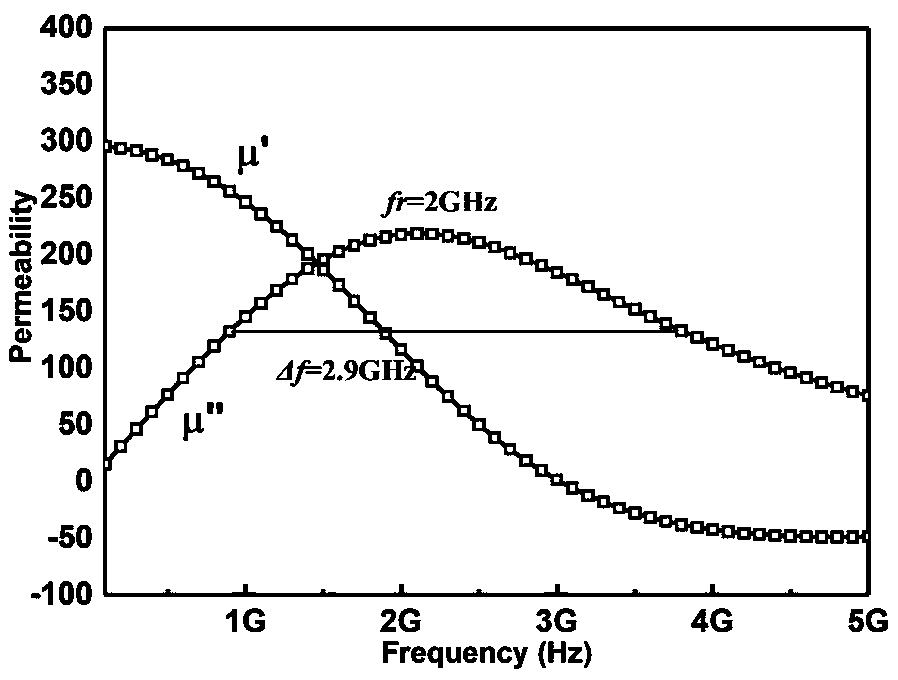

Ultrathin EMI-resistant thin film and preparation method thereof

PendingCN108617161ASpecial face anisotropyAdjusting Impedance Matching CharacteristicsMagnetic/electric field screeningDielectric matrixMicrometer

The invention discloses an ultrathin EMI-resistant thin film and a preparation method thereof. The main structure of the ultrathin EMI-resistant thin film comprises substrate / metal reflection layer / composite gradient layer, wherein the ultrathin composite gradient layer is provided with a structure of which magnetic particles are dispersed in a dielectric matrix and is in gradient distribution along a thickness direction of the thin film, impedance matching is favorably achieved, and the application frequency and the EMI-resistant frequency are improved. By the ultrathin EMI-resistant thin film, the ultrathin EMI-resistant thin film with the thickness blew 12 micrometers can be prepared, the ultrathin EMI-resistant thin film can have favorable EMI-resistant performance within a frequency band above 1GHz, and miniaturization and integration of an electronic product are very facilitated.

Owner:白国华

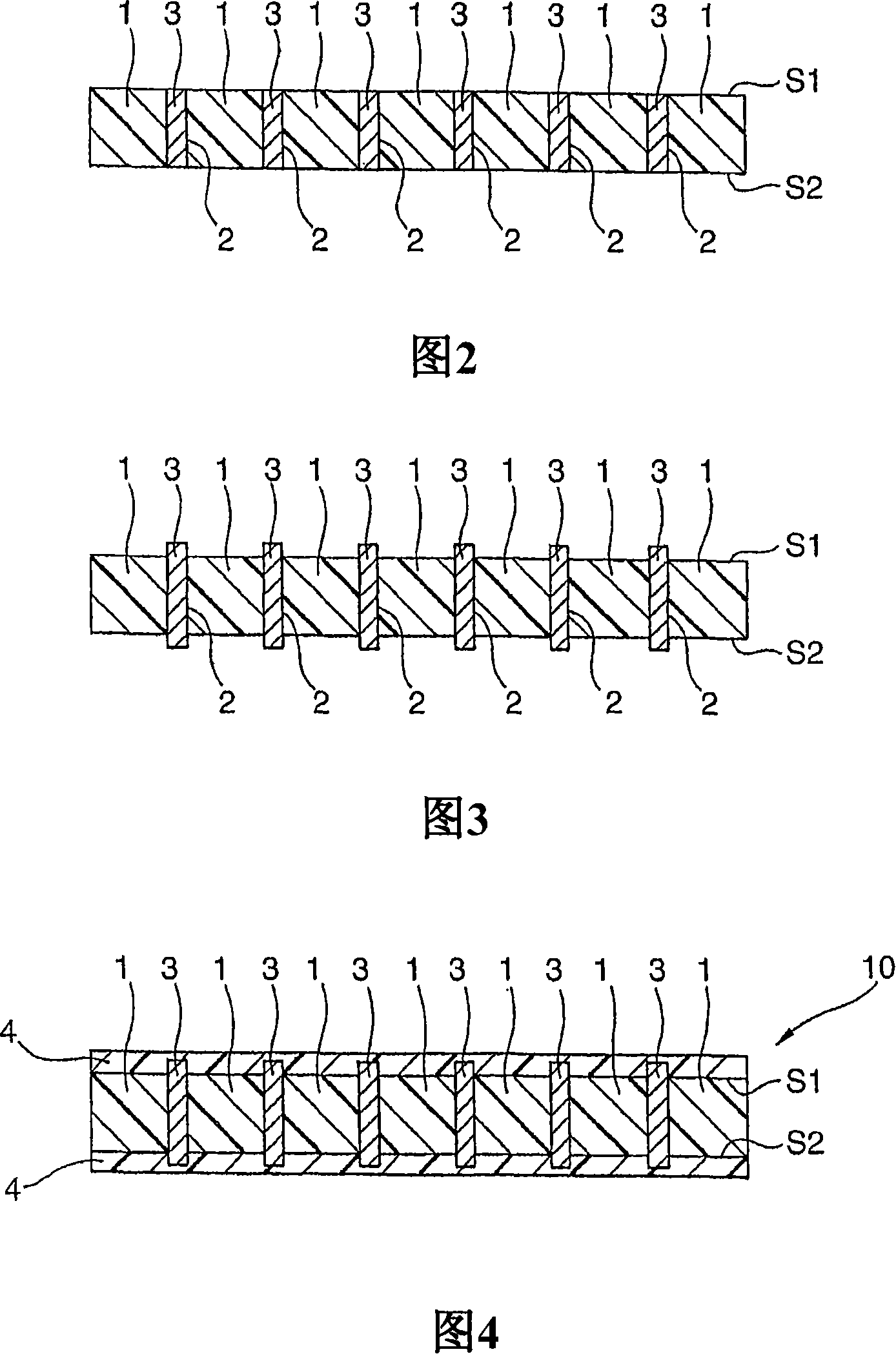

Integrated ingot for TSV substrates and method for making the same

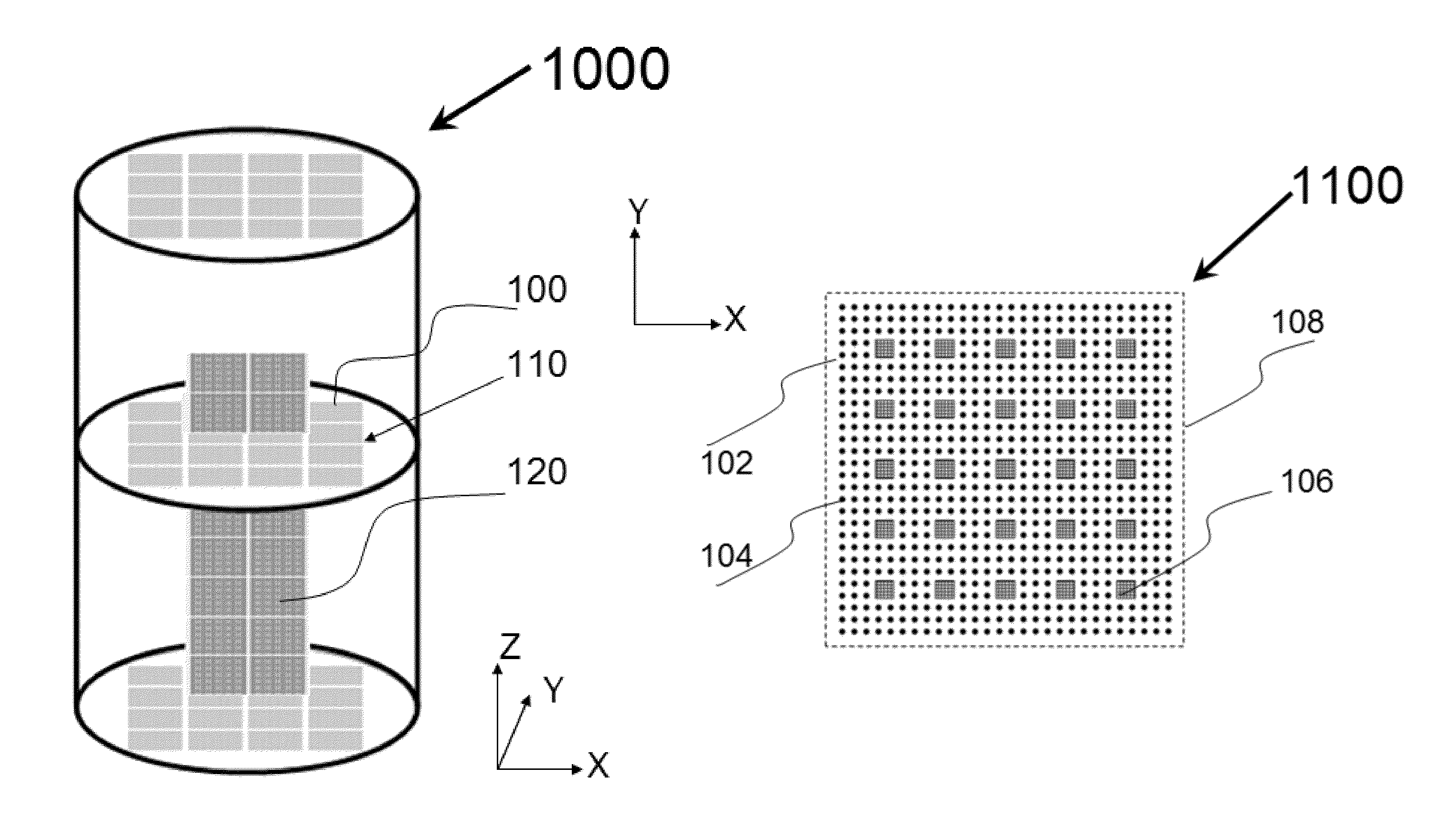

ActiveUS9397035B2Efficient productionSmall diameterSemiconductor/solid-state device detailsSolid-state devicesDielectric matrixIngot

The disclosure describes a metal-wire-based method for making an integrated ingot, which basically comprises a dielectric matrix and a patterned array of metal wires, and may further comprise other additive elements at desired locations. After sawing the integrated ingot into slices, a plurality of substrates containing through substrate metal pillars and other additive elements at desired locations are produced in a batch way. The metal-wire-based method comprises the key steps: forming a patterned array of metal wires, precisely integrating other additive elements at desired locations when needed, forming a solid dielectric material in the empty space among and around metal wires and other additive elements. Furthermore, a guidance metal wire method is described for precisely integrating other additive elements at desired locations in a patterned array of metal wires.

Owner:IC CHIP COOLING TECH LLC

Low dielectric constant composite material containing nano magnetic particles, and optical and semiconductor devices using the low dielectric constant composite material

InactiveUS6849926B2Low dielectric constantNanomagnetismSemiconductor/solid-state device detailsIndiumPolymethyl methacrylate

A composite containing nano magnetic particles is provided. The composite includes nano magnetic particles in a dielectric matrix. The matrix is made of an inorganic material such as silica, alumina, or hydrosilsesquioxane, or an organic material such as polyimide, polymethyl methacrylate, or methyl silsesquioxane. The nano magnetic particles consist of Fe2O3, chromium oxide, europium oxide, NiZn-ferrite, MnZn-ferrite, yttrium-iron garnet, or indium In.

Owner:POHANG UNIV OF SCI & TECH

Printed temperature sensor

ActiveUS20200020467A1Provide stabilitySuitable for printingThermometers using electric/magnetic elementsResistor mounting/supportingDielectric matrixHemt circuits

A printed temperature sensor (10) comprising a substrate (1) with an electrical circuit (2) comprising a pair of electrodes (2a, 2b) separated by an electrode gap (G). A sensor material (3) is disposed between the electrodes (2a, 2b) to fill the electrode gap (G), wherein the sensor material (3) comprises semi-conducting micro-particles (3p) comprising an NTC material with a negative temperature coefficient (NTC), wherein the micro-particles (3p) are mixed in a dielectric matrix (3m) functioning as a binder for printing the sensor material (3); wherein the micro-particles (3p) contact each other to form an interconnected network through the dielectric matrix (3m), wherein the interconnected network of micro-particles (3p) acts as a conductive pathway with negative temperature coefficient between the electrodes (2a, 2b).

Owner:NEDERLANDSE ORG VOOR TOEGEPAST-NATUURWETENSCHAPPELIJK ONDERZOEK (TNO)

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com