Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

625 results about "Microsystem" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Microsystem is the name commonly used in Europe to describe the same technology which goes under the name MEMS in the US. In Japan, this field is often termed micromachines. Microsystems are miniaturized devices which perform non-electronic functions: typically sensing and actuation. Typical microsystems have mechanical parts, like microbridges in RF switches or bending cantilevers in atomic force microscopes; electrical parts like piezoresistors in airbag sensors or capacitors in pressure sensors; or thermal, optical and fluidic structures like heaters and nozzles in inkjet printer or flow sensors. In biomicrosystems cells or microbeads are handled by fluidic streams, magnetic and electric fields, thermal gradients etc. In chemical microsystems operations like sample pretreatment, separation and detection are built on microchips. This field is also known as microfluidics or lab-on-a-chip. Today it is possible to build up microsystems without any tooling needed by computer-aided direct parallel batch processing technologies called RMPD Rapid Micro Product Development. Microsystems with advanced capabilities and own intelligence are commonly referred to as smart systems.

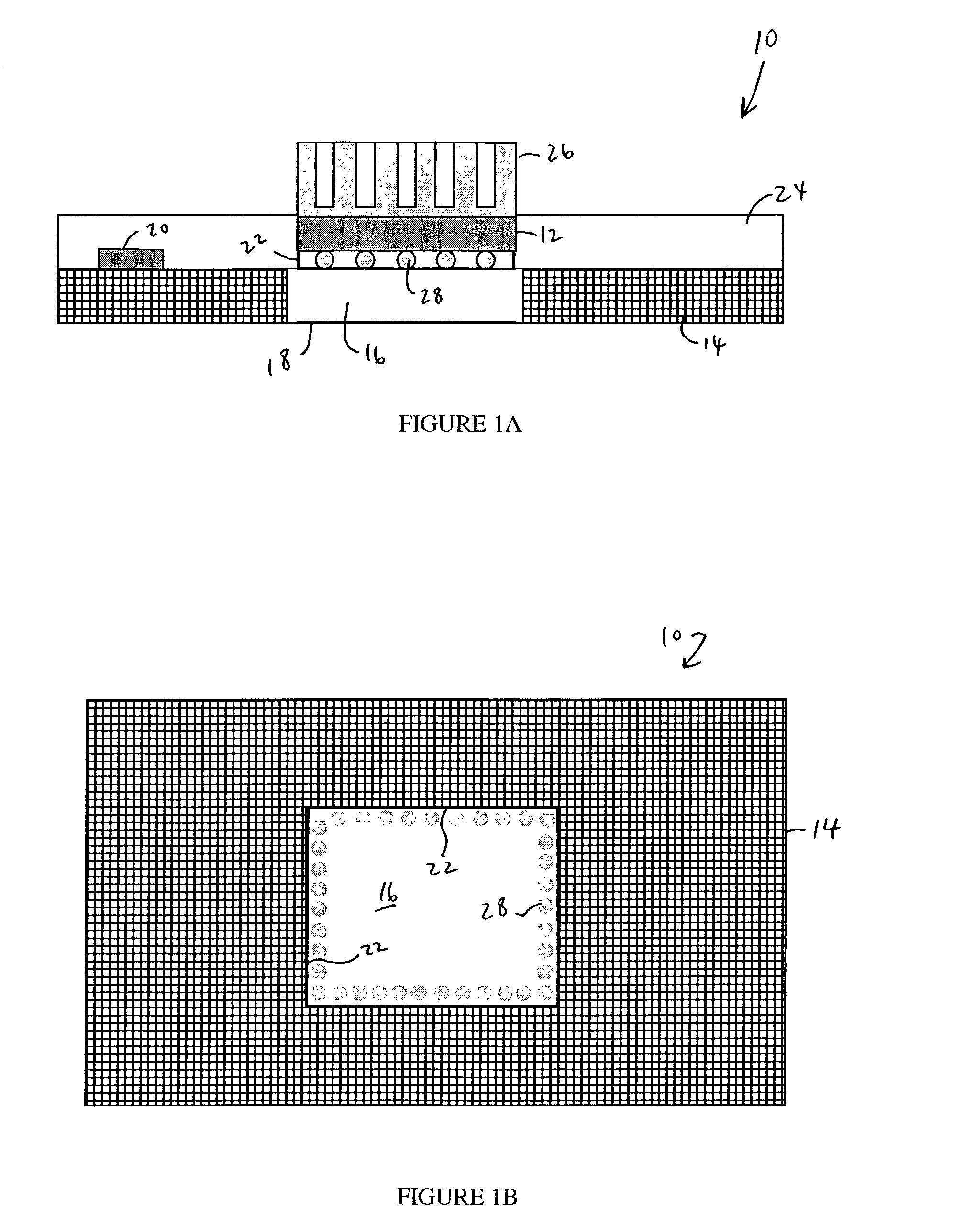

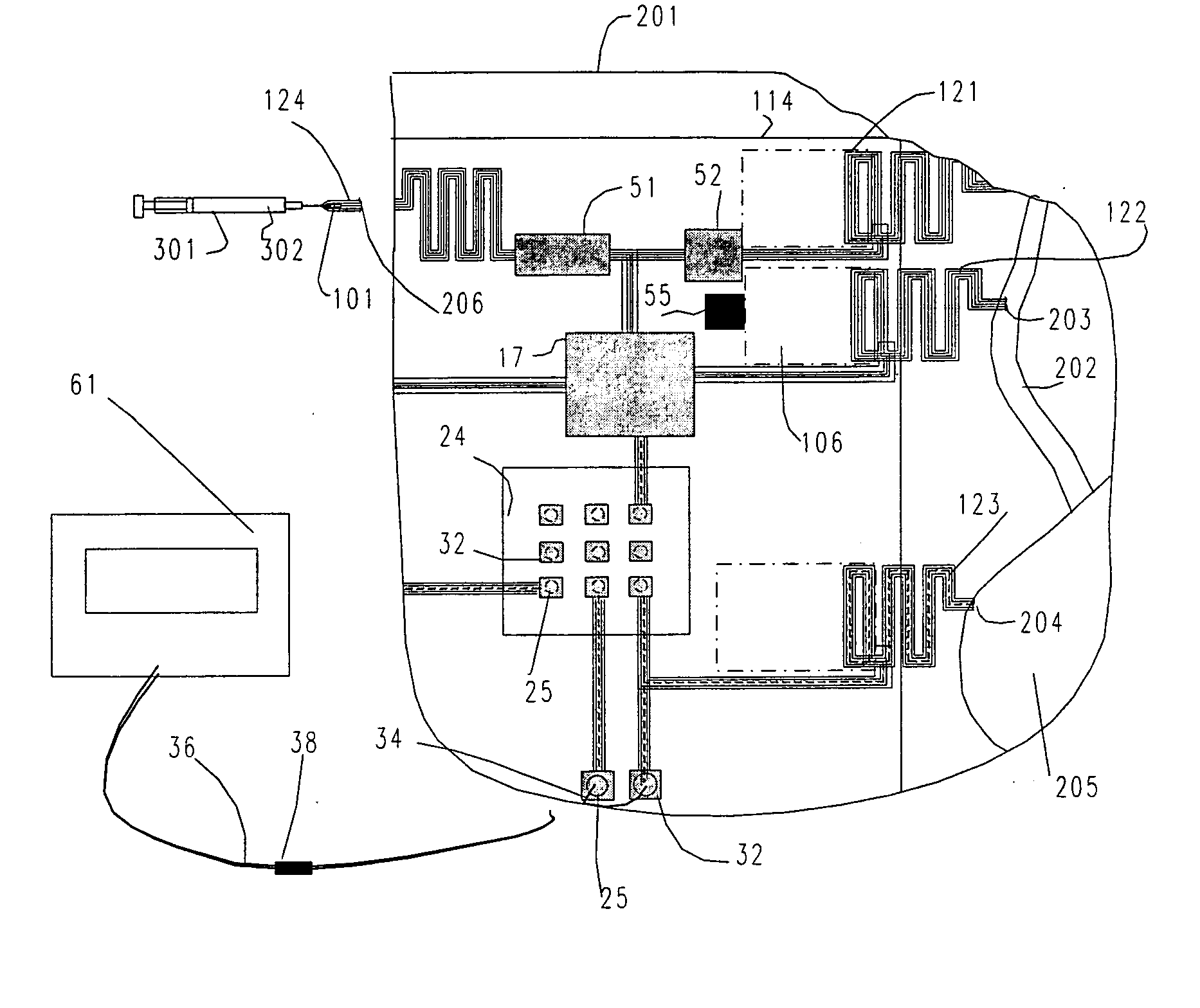

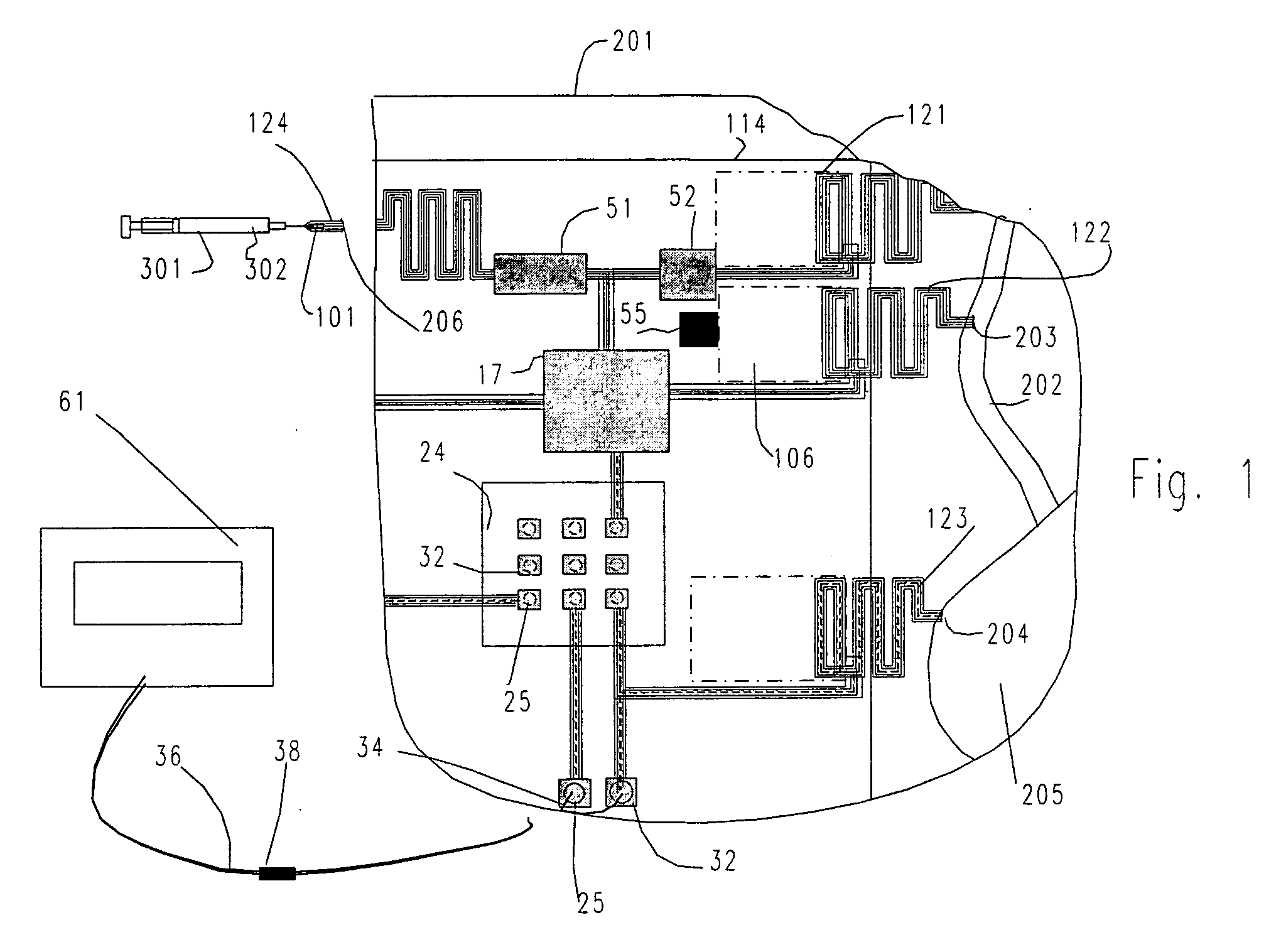

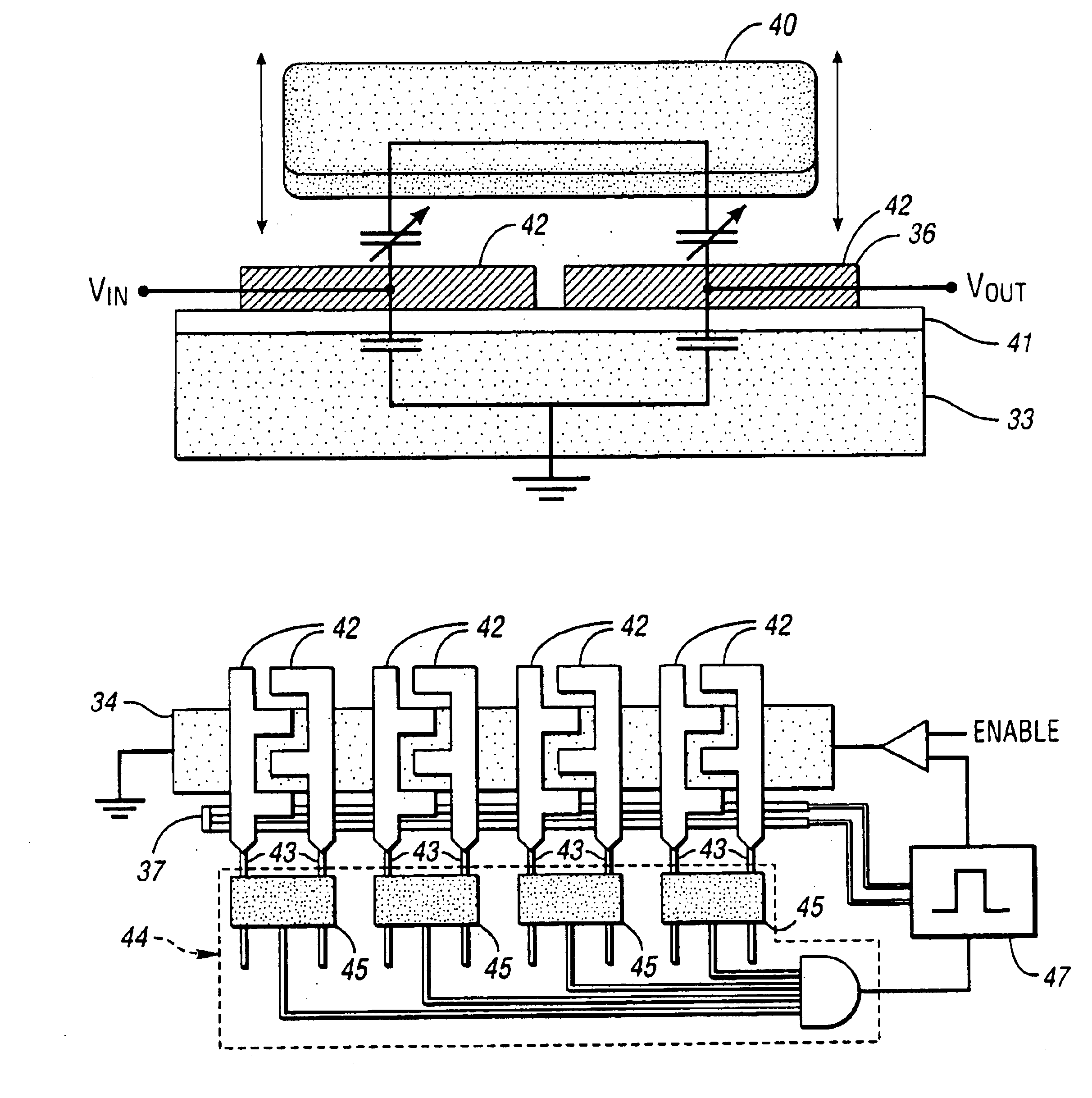

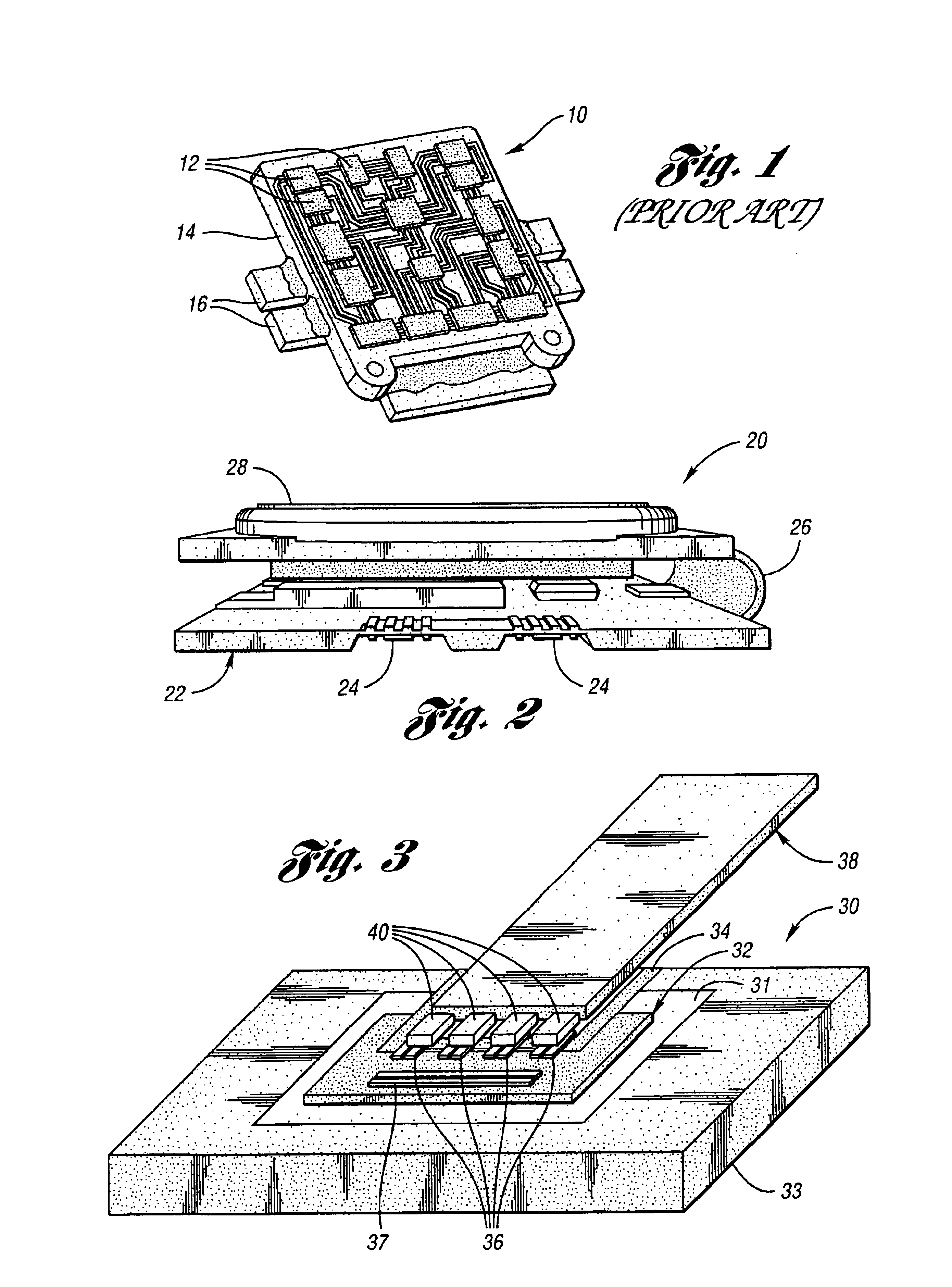

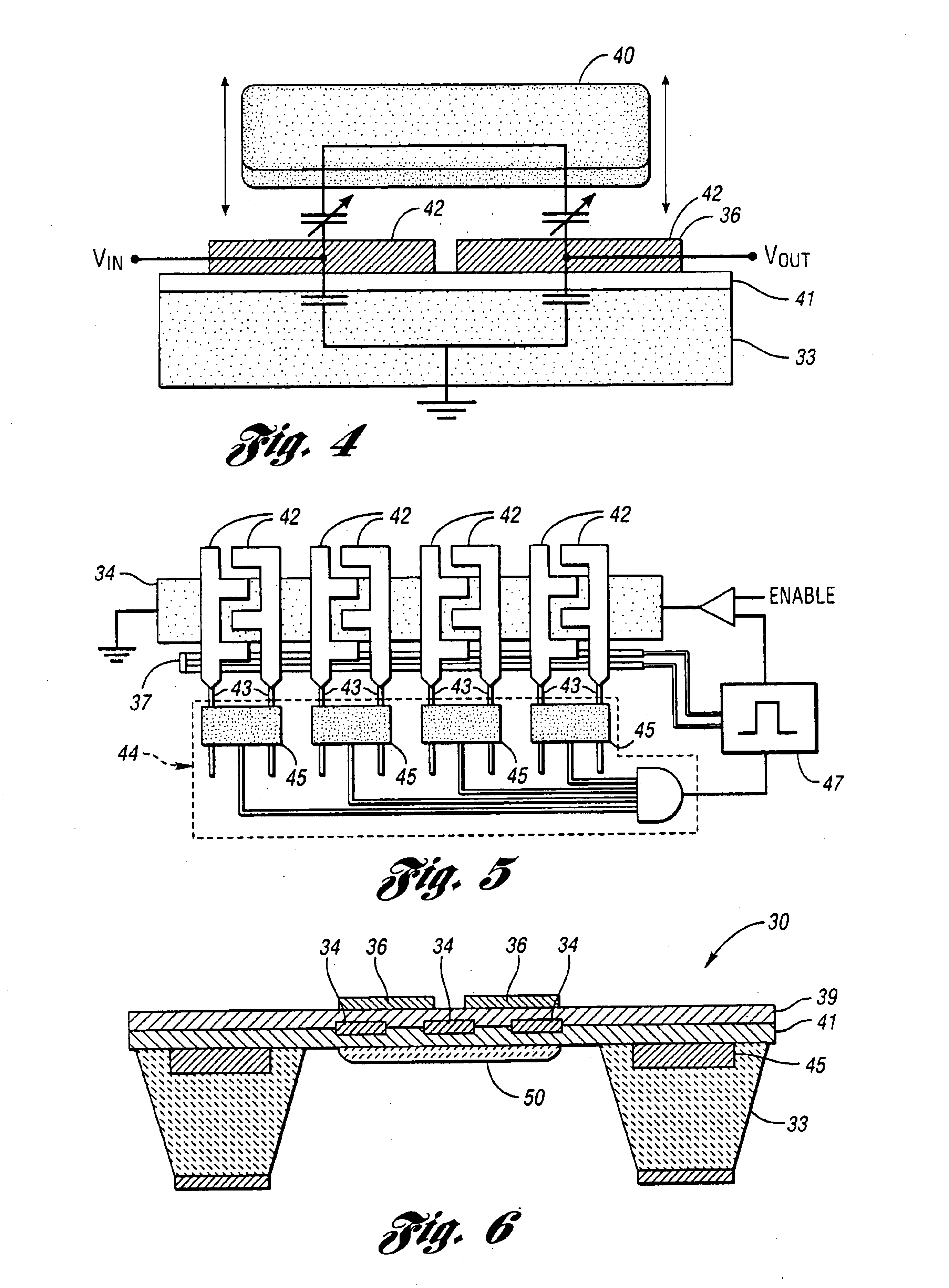

Heterogeneously integrated microsystem-on-a-chip

ActiveUS7335972B2Electronic circuit testingSemiconductor/solid-state device detailsMiniaturizationInterconnection

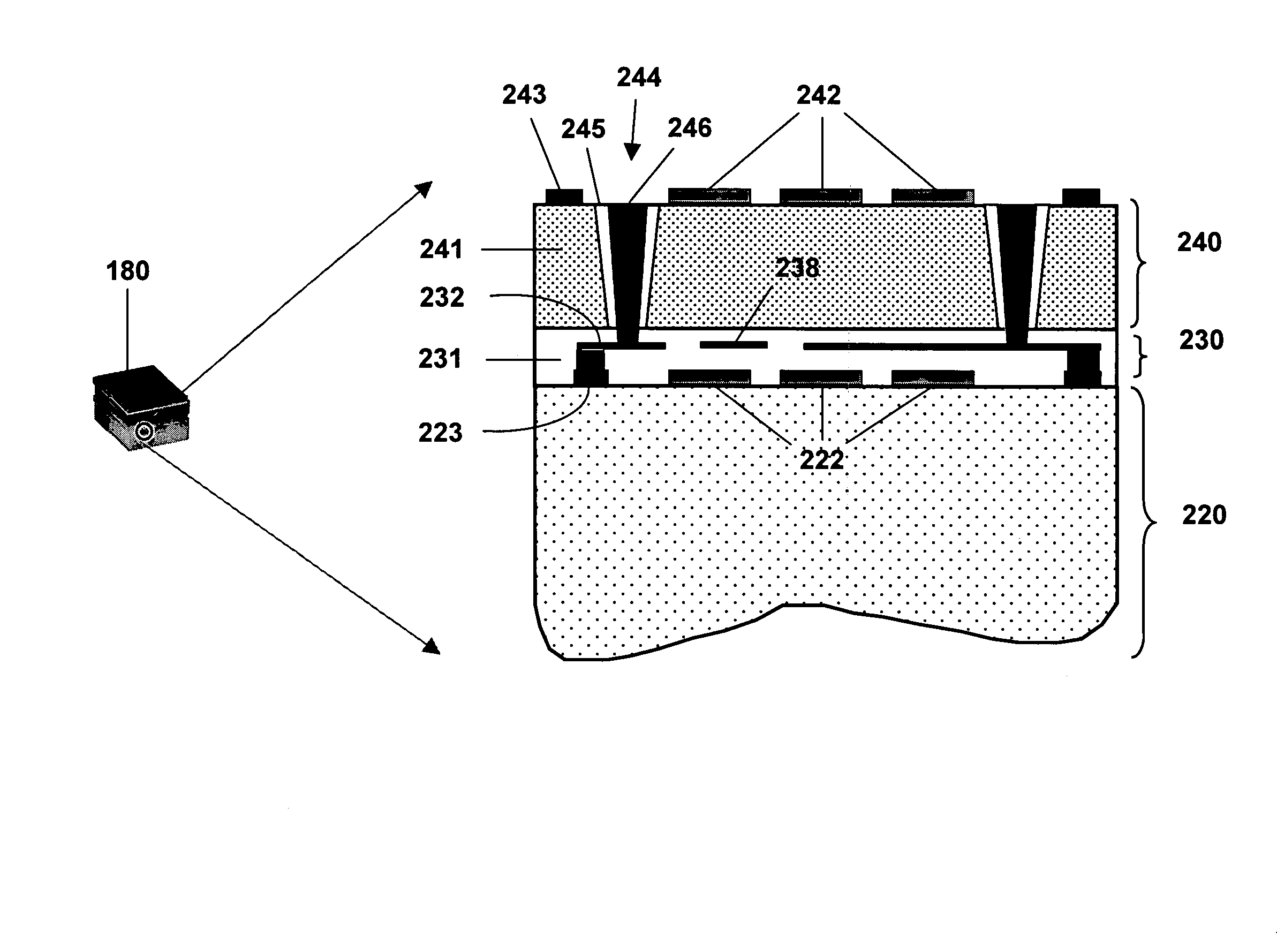

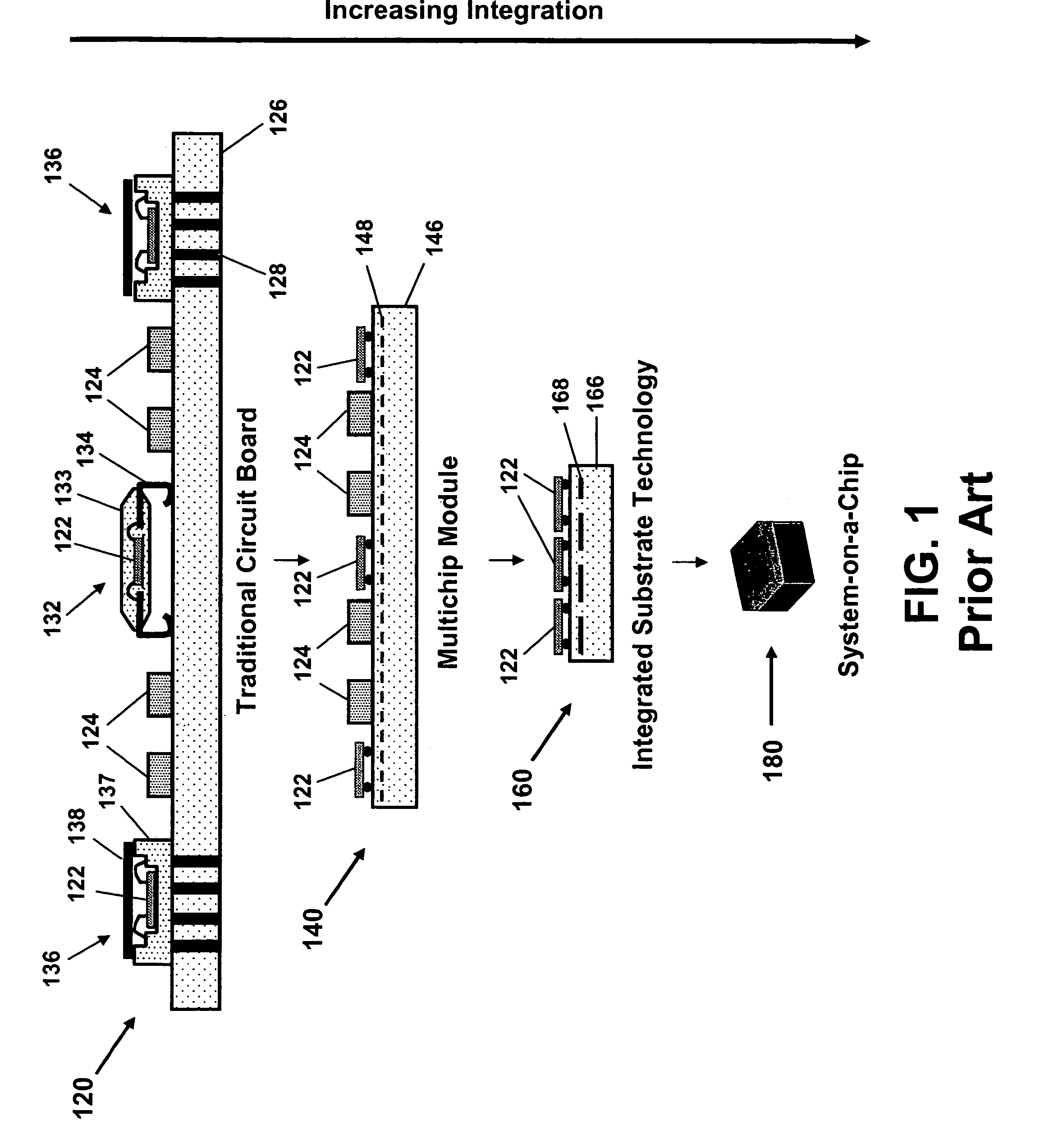

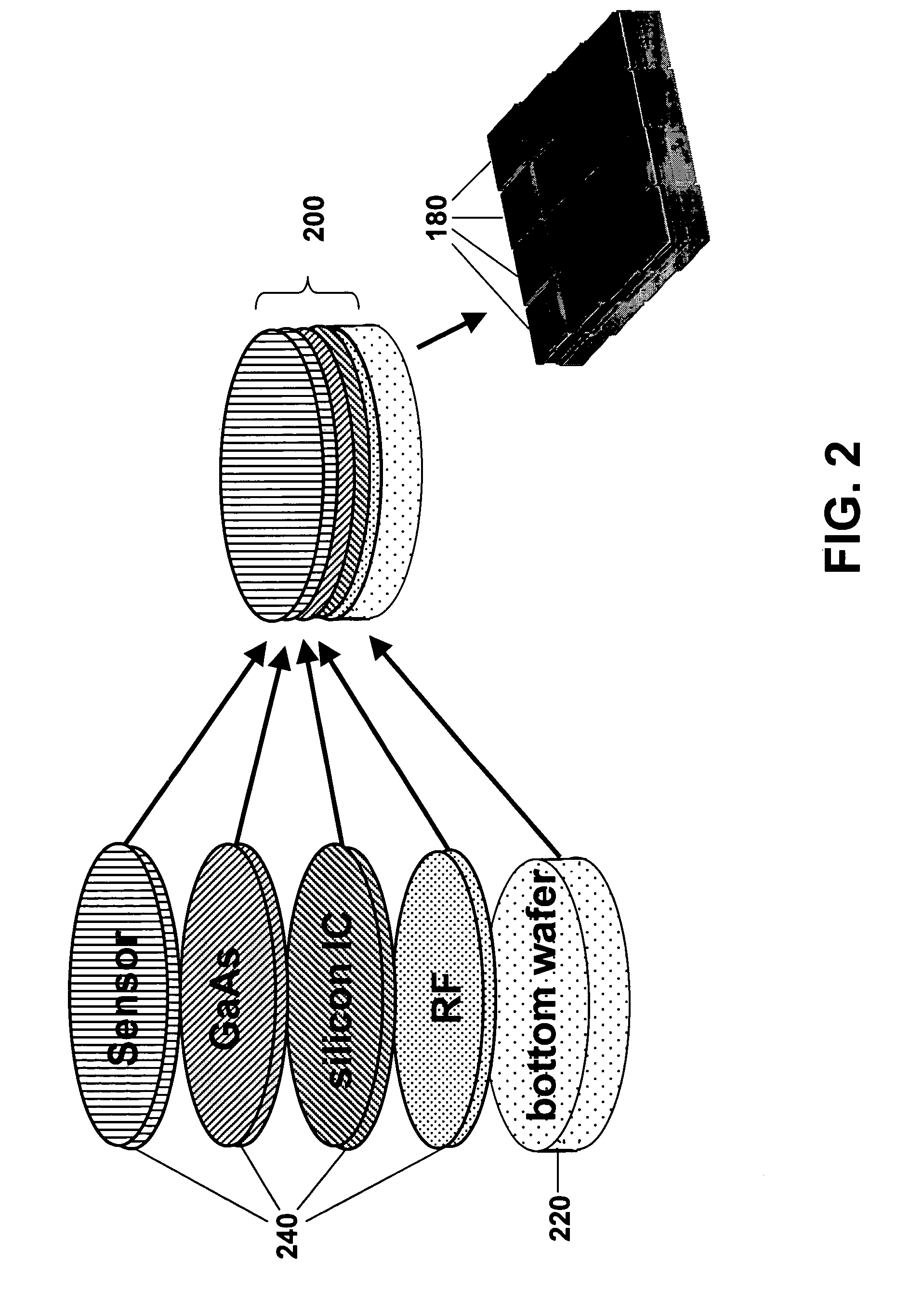

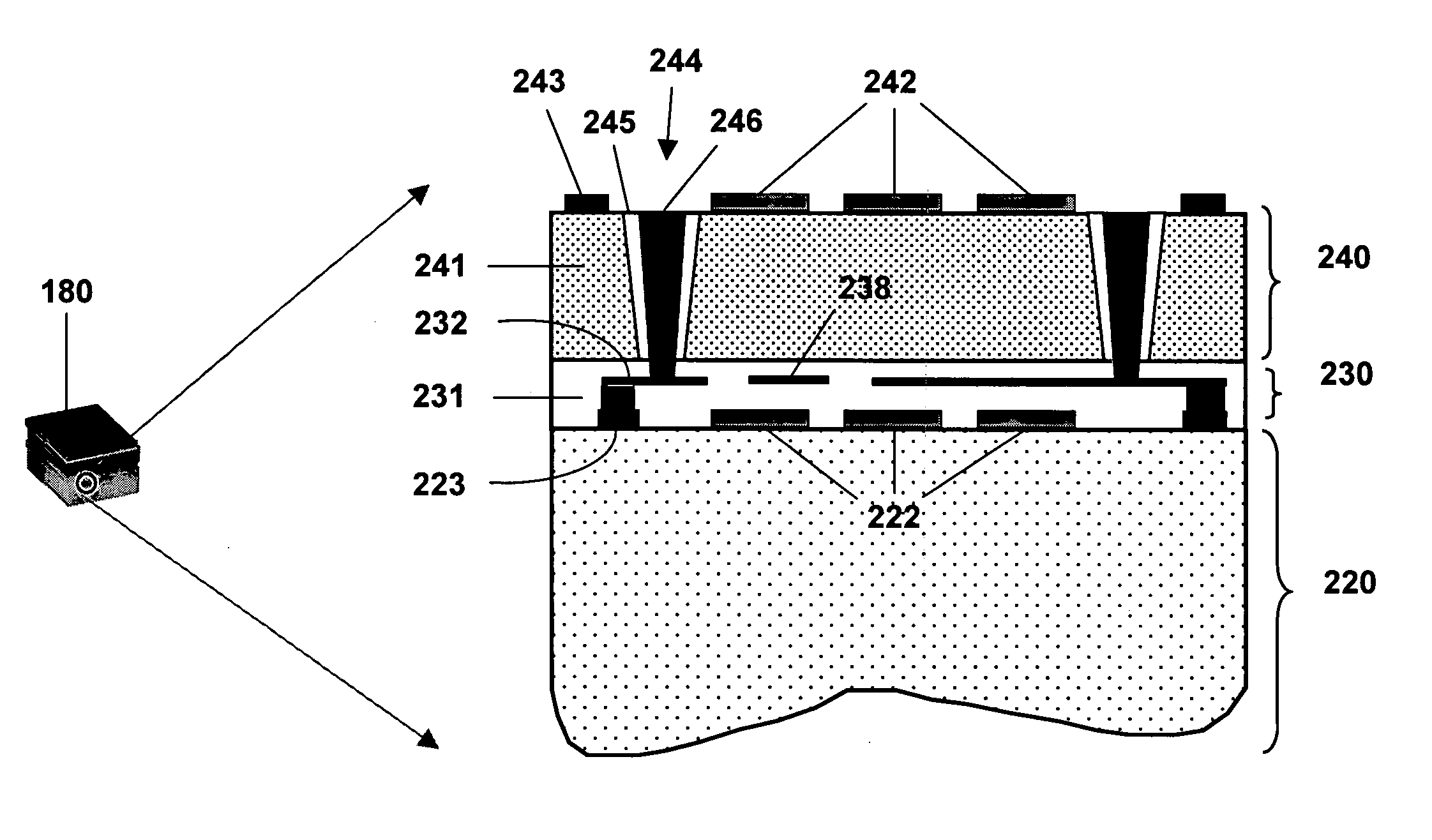

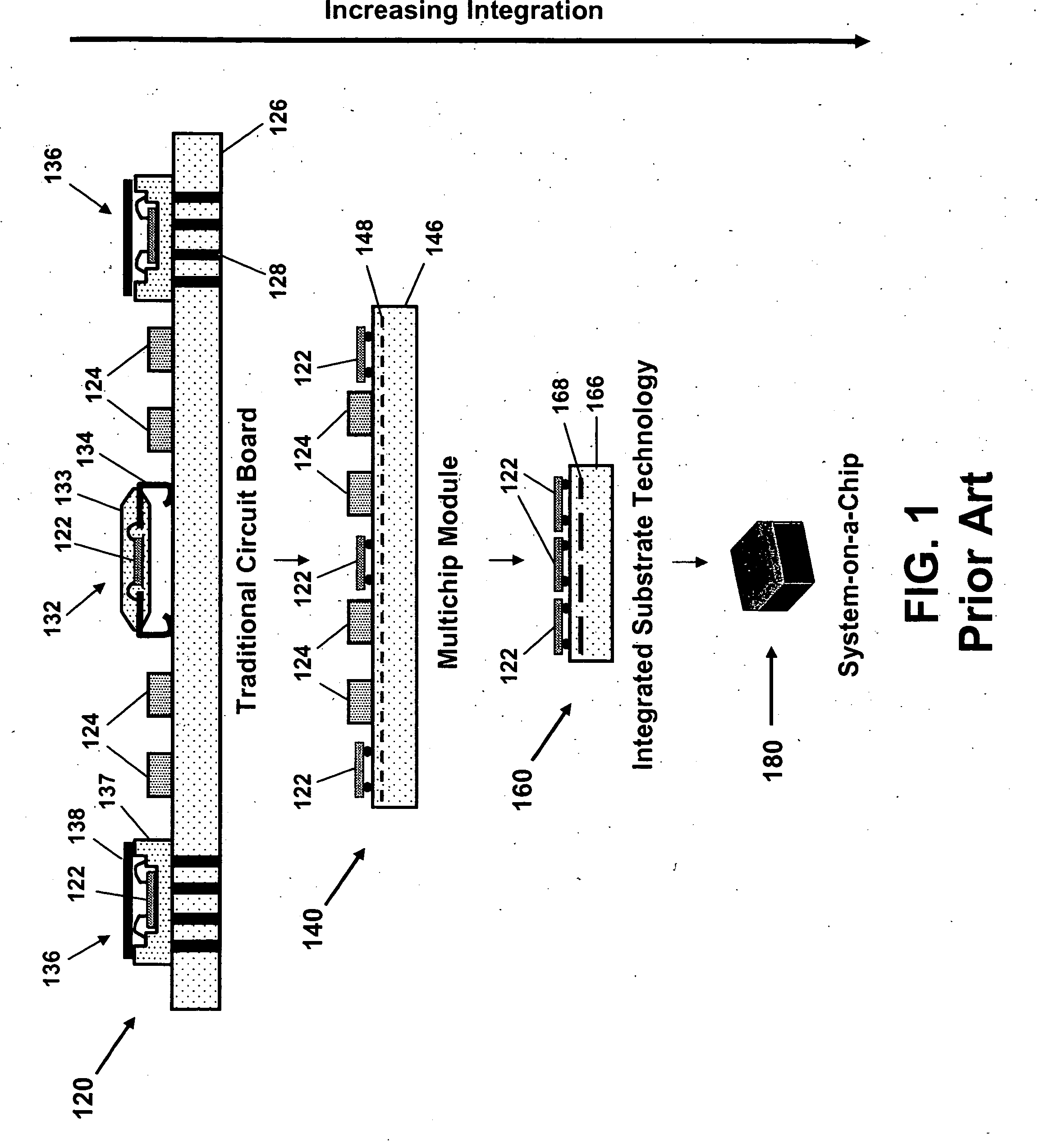

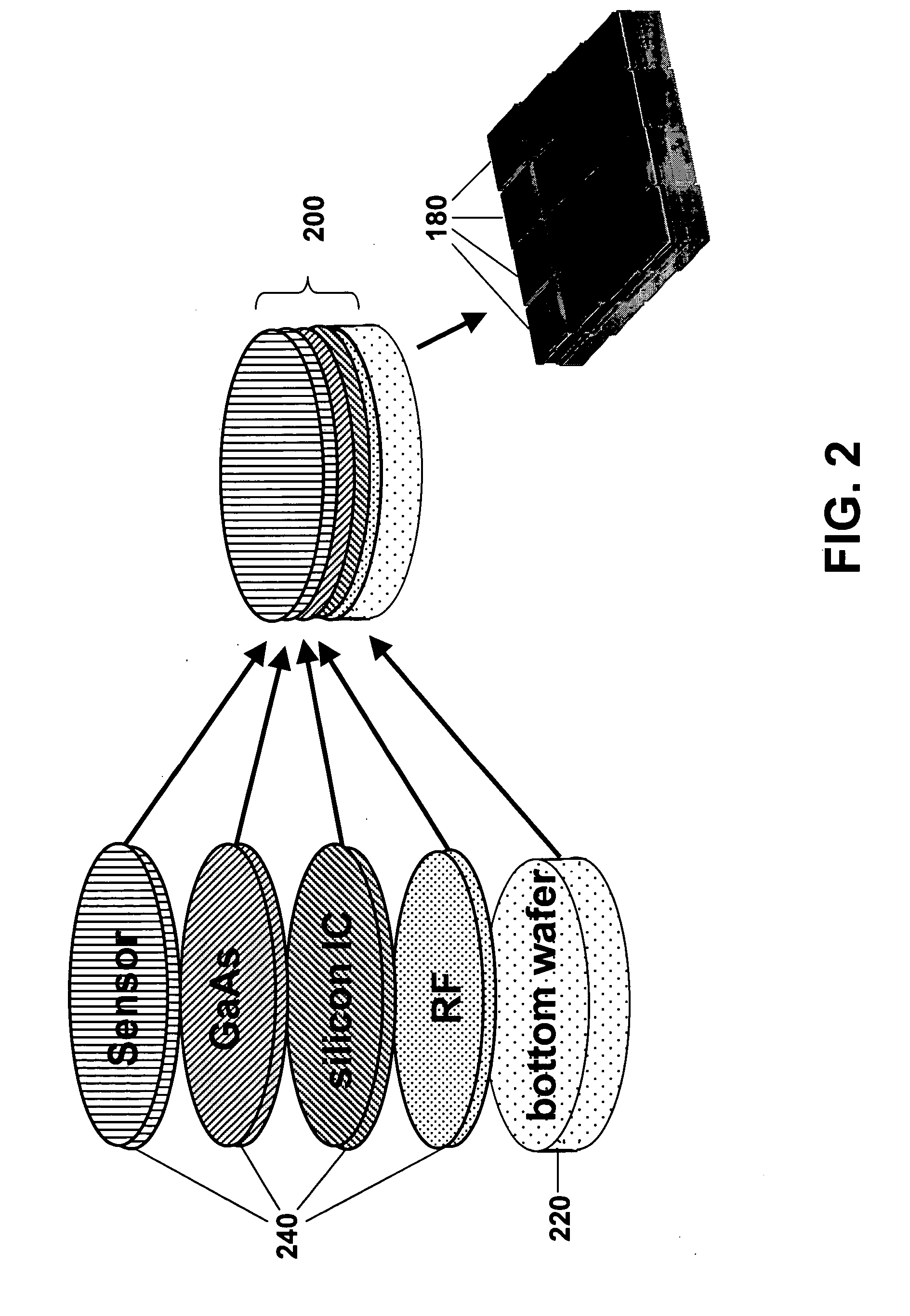

A microsystem-on-a-chip comprises a bottom wafer of normal thickness and a series of thinned wafers can be stacked on the bottom wafer, glued and electrically interconnected. The interconnection layer comprises a compliant dielectric material, an interconnect structure, and can include embedded passives. The stacked wafer technology provides a heterogeneously integrated, ultra-miniaturized, higher performing, robust and cost-effective microsystem package. The highly integrated microsystem package, comprising electronics, sensors, optics, and MEMS, can be miniaturized both in volume and footprint to the size of a bottle-cap or less.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

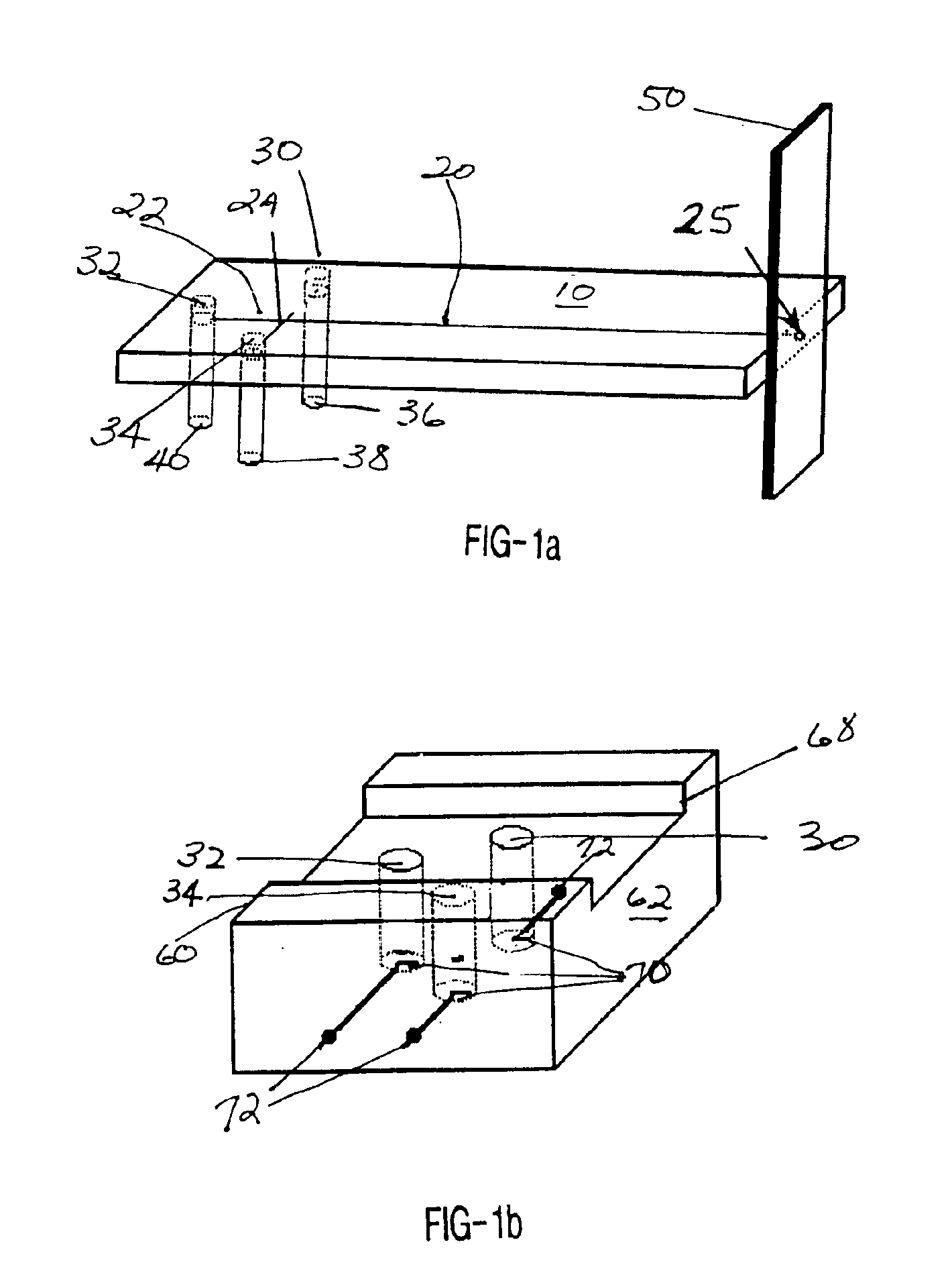

Microfluidic devices with thick-film electrochemical detection

InactiveUS6878255B1Reduce usageCost advantageSludge treatmentVolume/mass flow measurementAnalyteMicrofluidic channel

An apparatus for conducting a microfluidic process and analysis, including at least one elongated microfluidic channel, fluidic transport means for transport of fluids through the microfluidic channel, and at least one thick-film electrode in fluidic connection with the outlet end of the microfluidic channel. The present invention includes an integrated on-chip combination reaction, separation and thick-film electrochemical detection microsystem, for use in detection of a wide range of analytes, and methods for the use thereof.

Owner:ARROWHEAD CENT

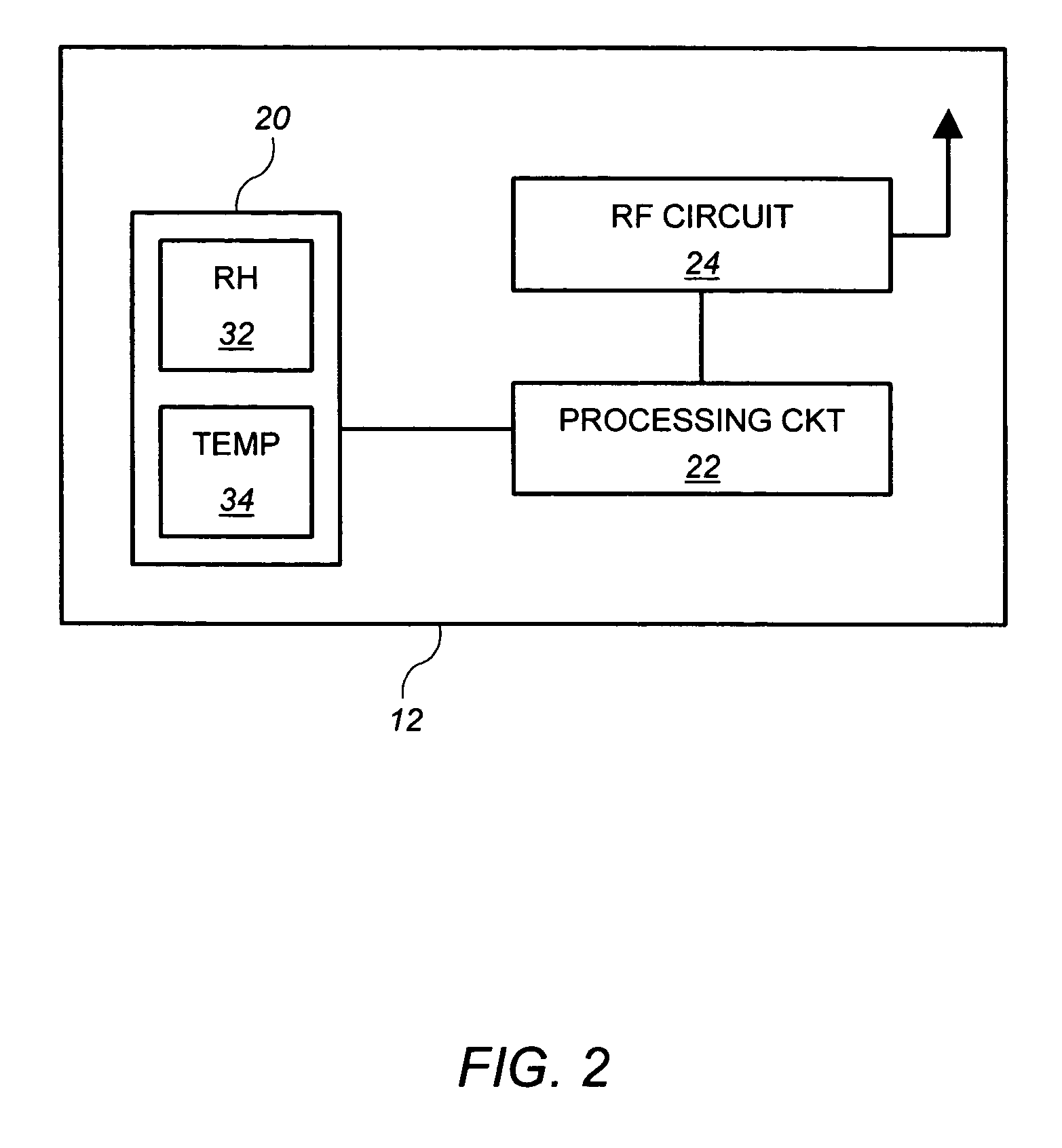

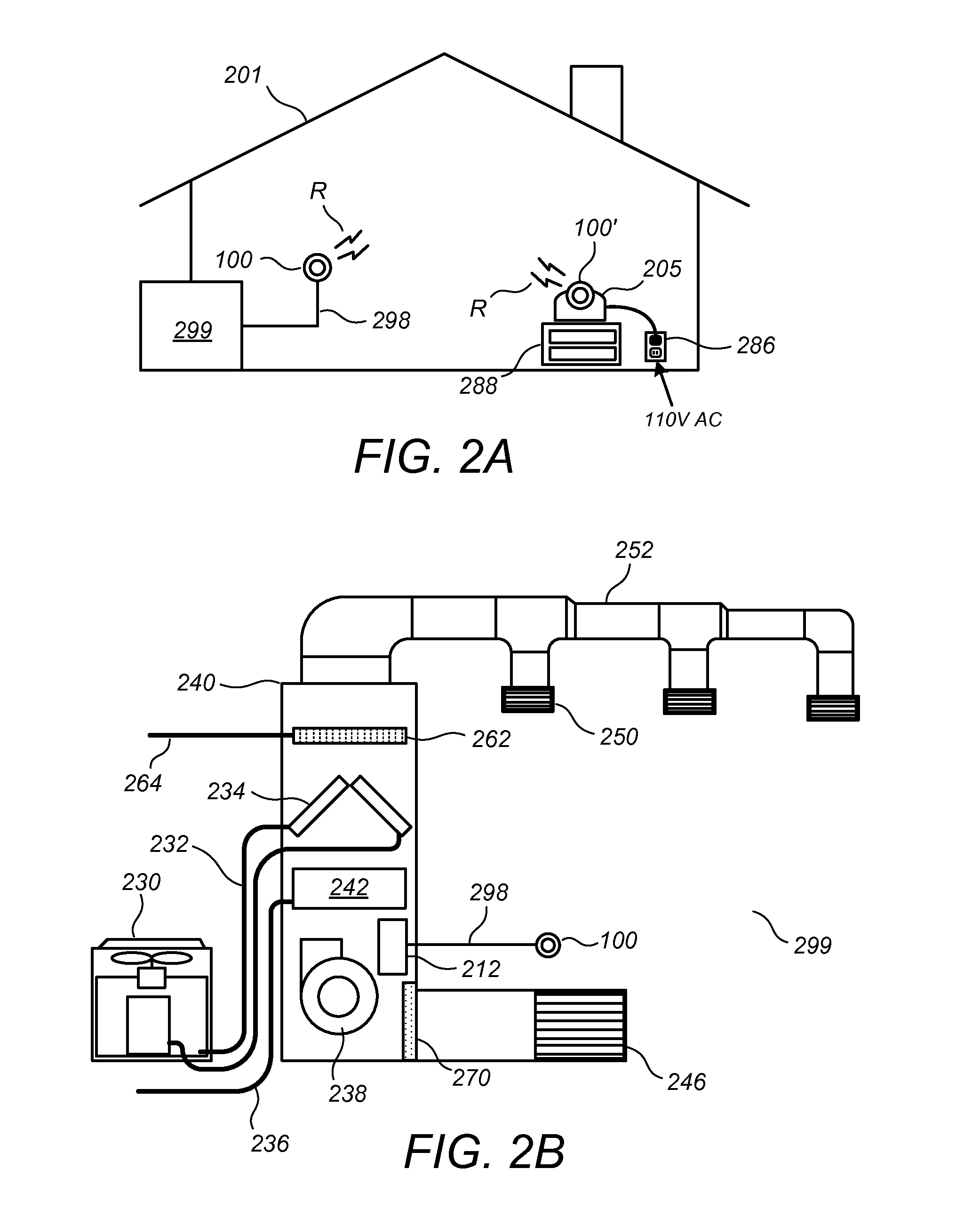

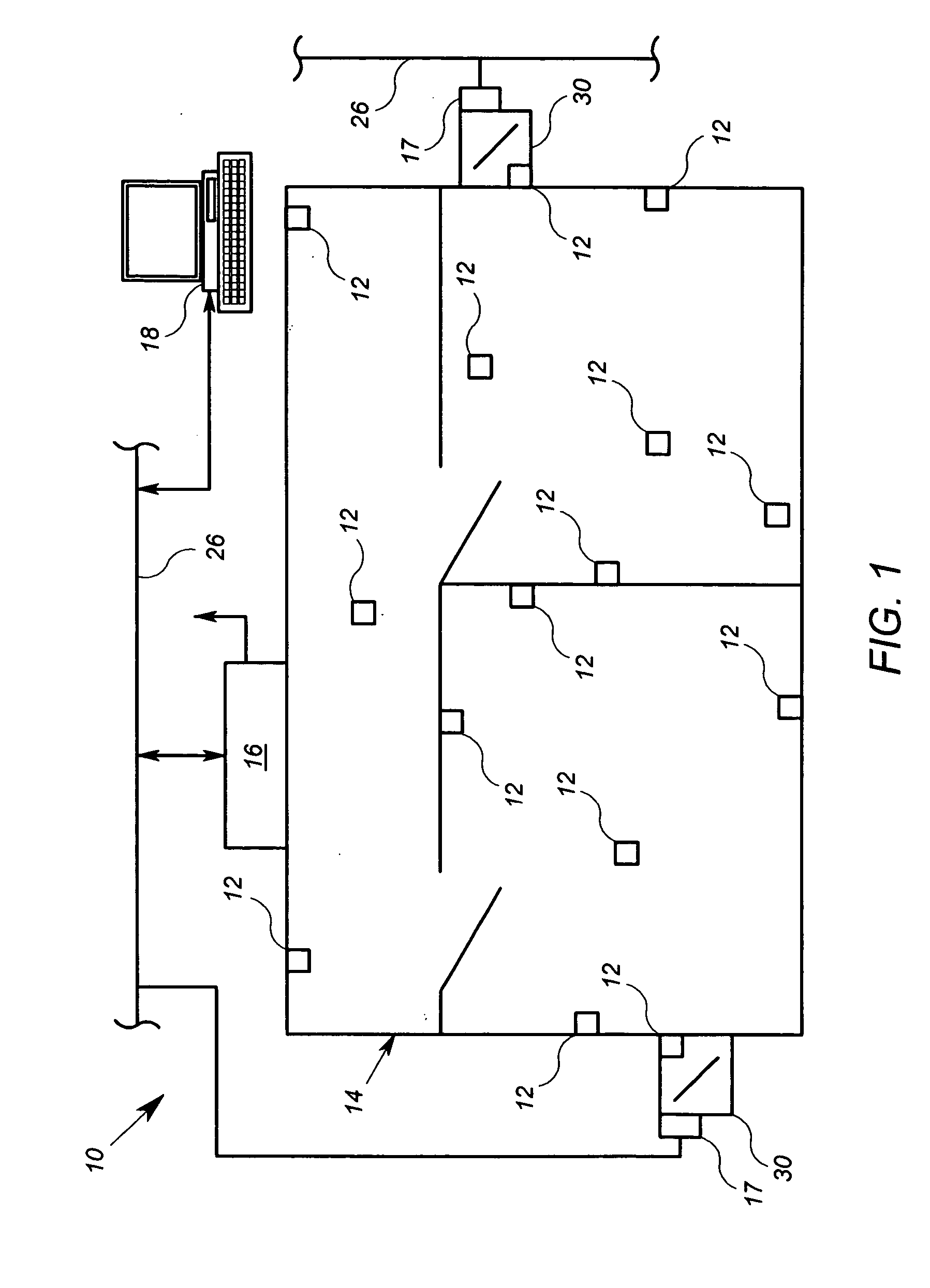

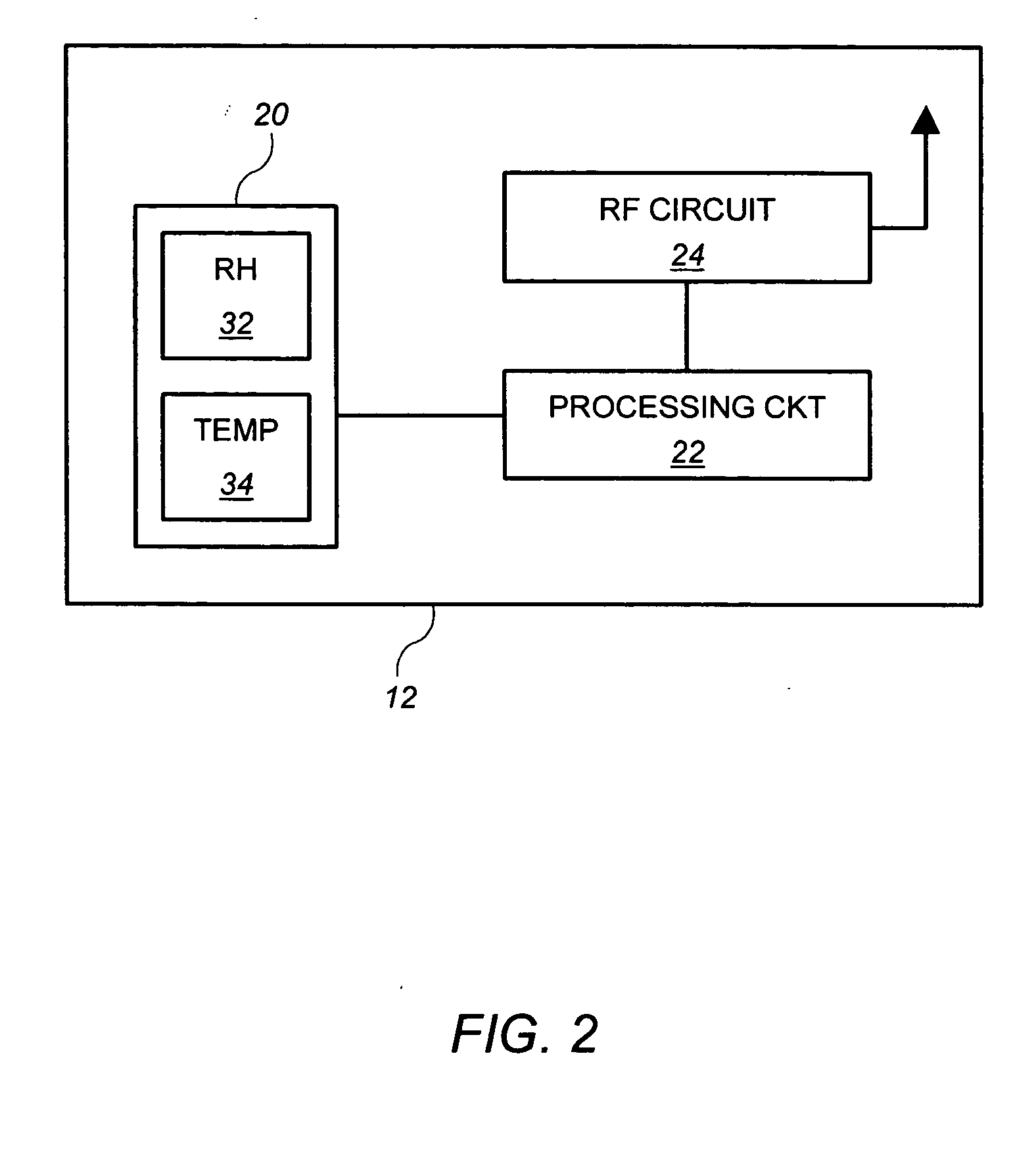

Application of microsystems for comfort control

ActiveUS7854389B2Reduce laborReduce materialMechanical apparatusTemperatue controlEngineeringRelative humidity

An arrangement includes a plurality of wireless microsystems. Each microsystem is operable to measure at least relative humidity and temperature, and to communicate temperature and relative humidity information wirelessly to a network device. The network device is operable to communicate the temperature and relative humidity information to at least a first processor configured to cause a change in a building control condition based on the information.

Owner:SIEMENS IND INC

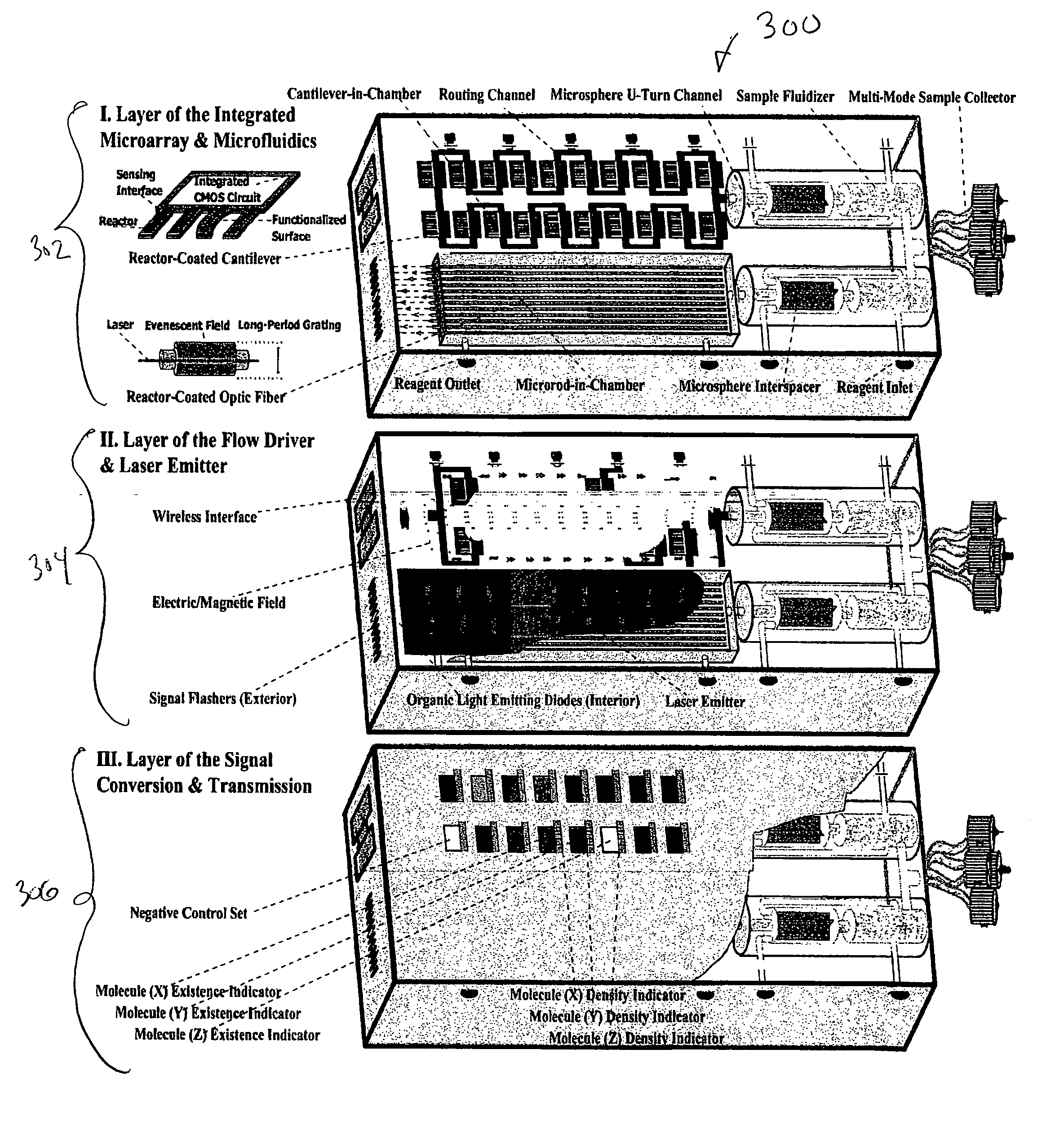

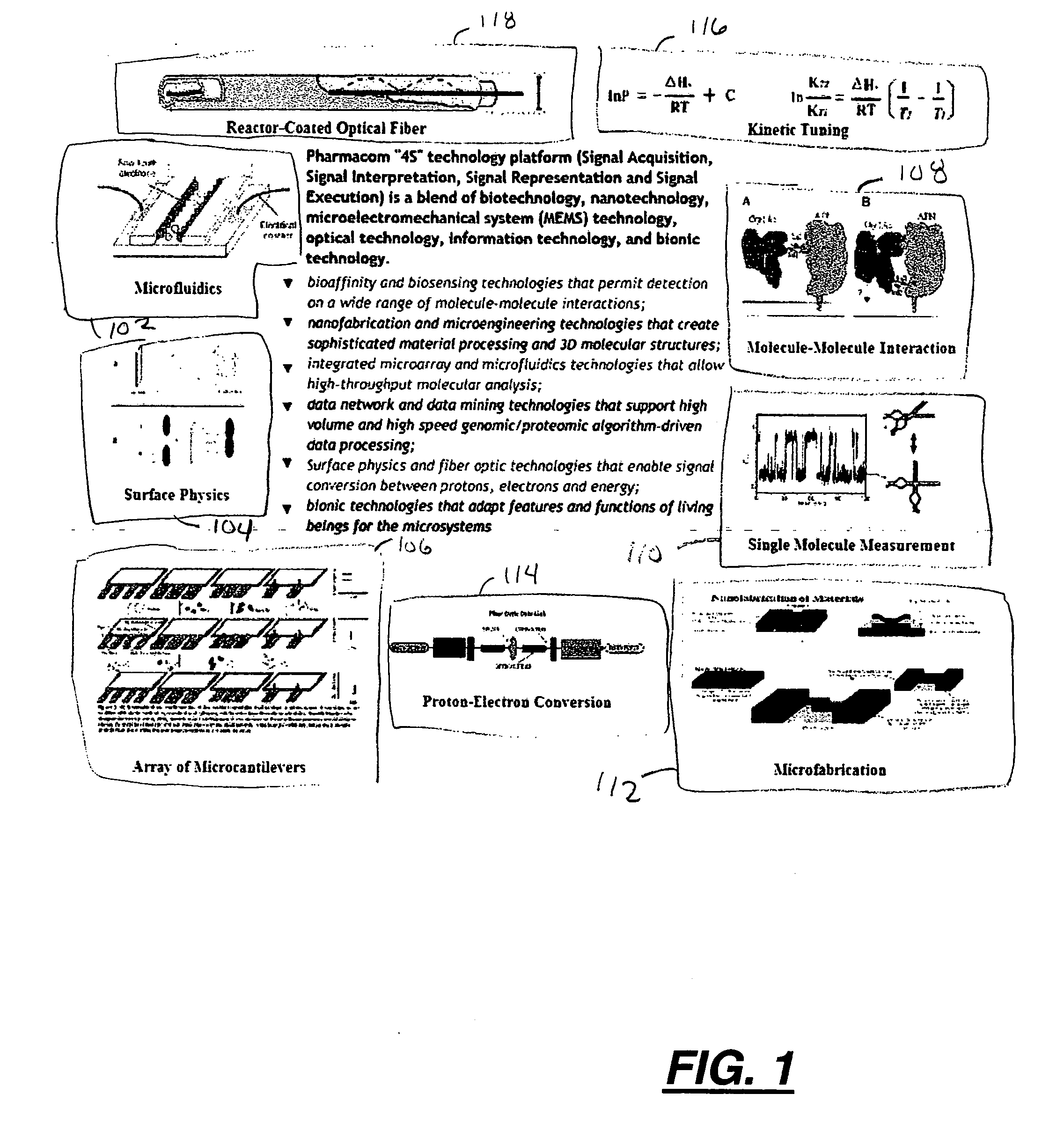

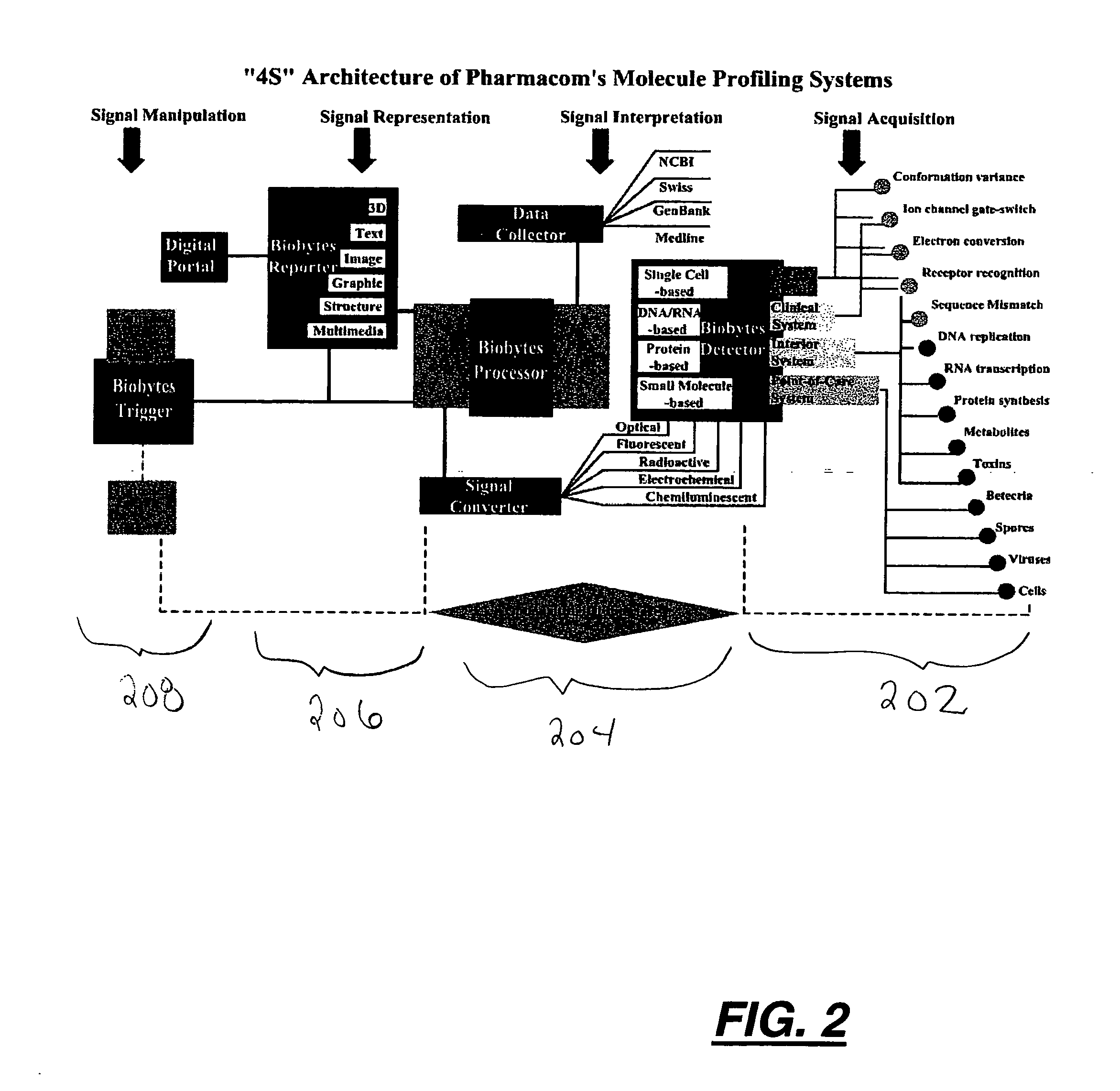

Microsystems that integrate three-dimensional microarray and multi-layer microfluidics for combinatorial detection of bioagent at single molecule level

InactiveUS20070116607A1Reduce resultHigh detection sensitivityAnalysis using chemical indicatorsWithdrawing sample devicesBiological bodyHigh-Throughput Screening Methods

Stand-alone microsystems adapted for performing combinatorial detection of bioagents at single molecule level wherein the microsystems are featured with three-dimensional microarray and multi-layer microfluidics to thereby provide high throughput screening and high content screening sufficient to allow for substantially real-time performance of the microsystem. Methods for detection of bioagents at a single molecule level or single organism level include providing a reconfigurable microsystem adapted for performing combinatorial detection of bioagents at a single molecule level and reconfiguring the reconfigurable microsystem for various environments.

Owner:PHARMACOM MICROELECTRONICS

Heterogeneously integrated microsystem-on-a-chip

ActiveUS20070158787A1Semiconductor/solid-state device detailsSolid-state devicesCost effectivenessMiniaturization

A microsystem-on-a-chip comprises a bottom wafer of normal thickness and a series of thinned wafers can be stacked on the bottom wafer, glued and electrically interconnected. The interconnection layer comprises a compliant dielectric material, an interconnect structure, and can include embedded passives. The stacked wafer technology provides a heterogeneously integrated, ultra-miniaturized, higher performing, robust and cost-effective microsystem package. The highly integrated microsystem package, comprising electronics, sensors, optics, and MEMS, can be miniaturized both in volume and footprint to the size of a bottle-cap or less.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

Microsystem packaging and associated methods

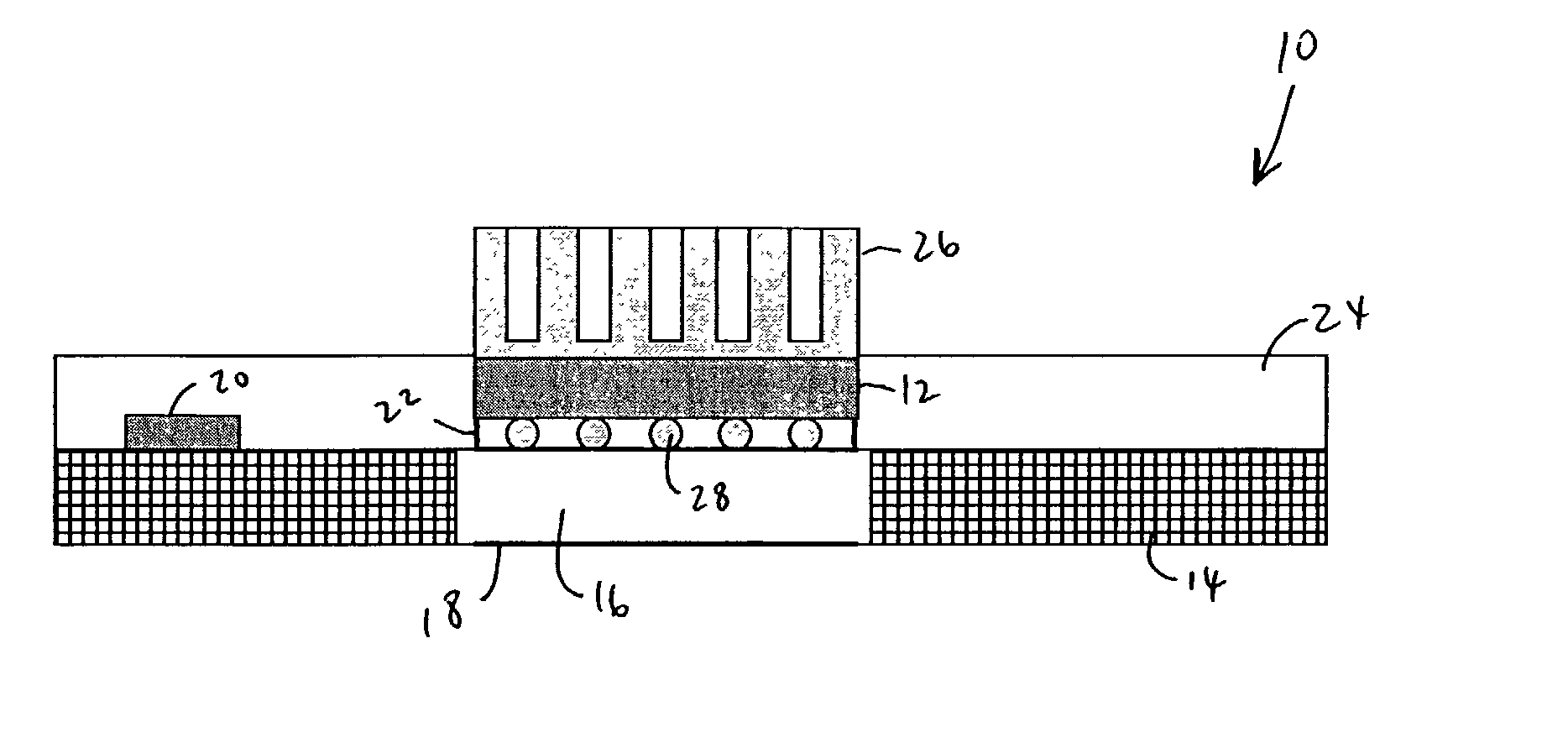

InactiveUS20040046248A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringMechanical engineering

Methods and apparatus are provided for sealing and reducing warpage in a microsystem device. The microsystem device is assembled with a substrate and packaged.

Owner:CORNING INC

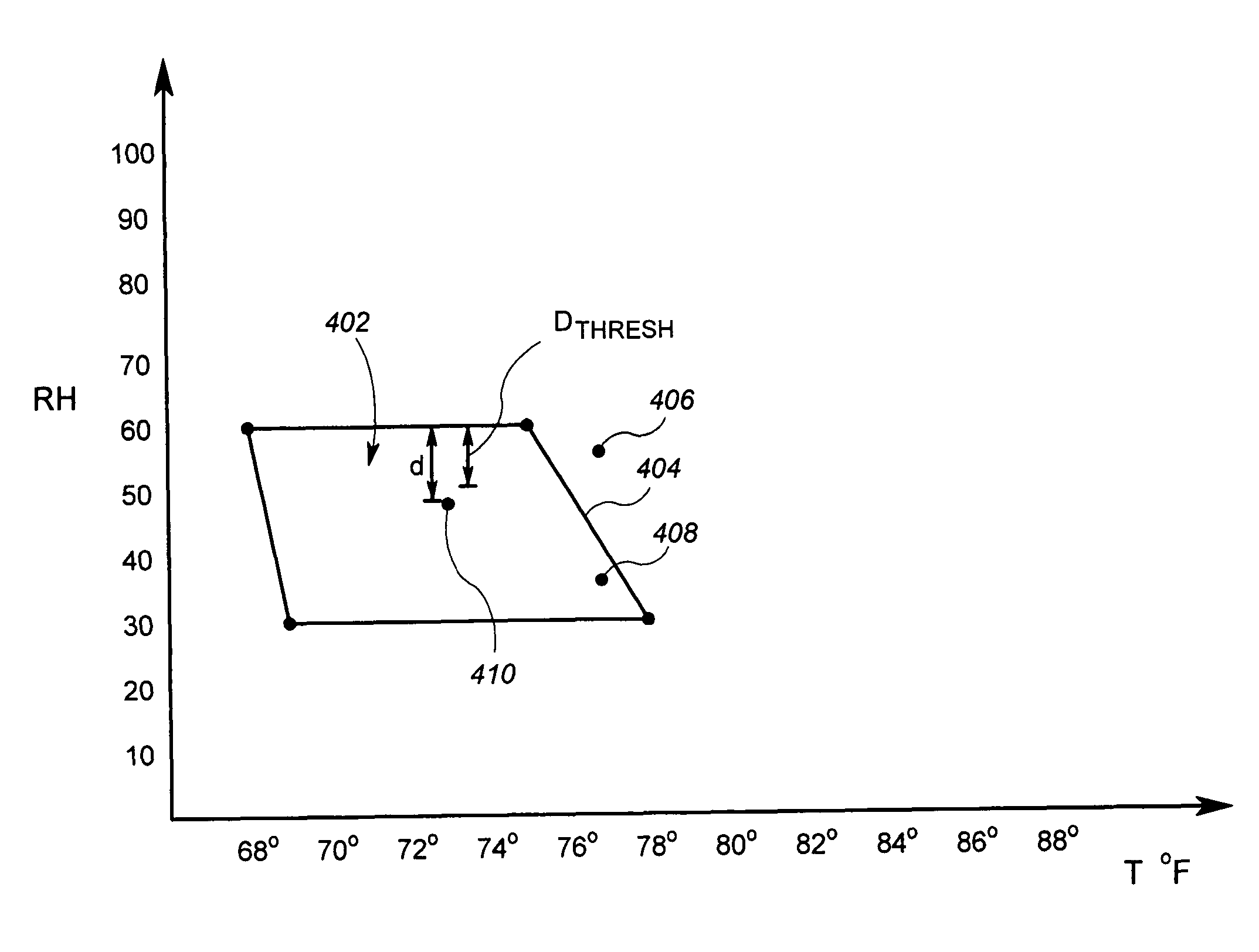

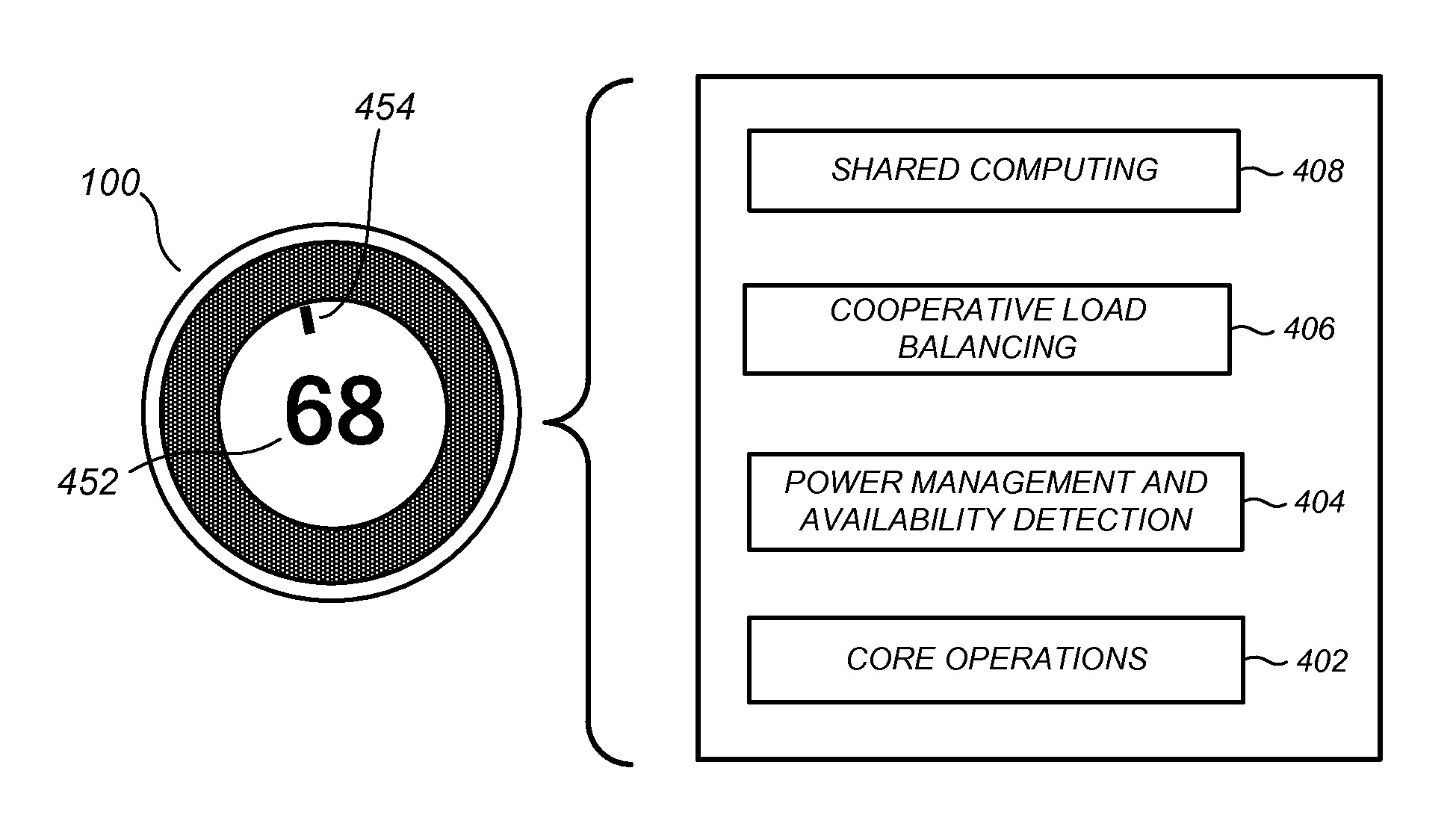

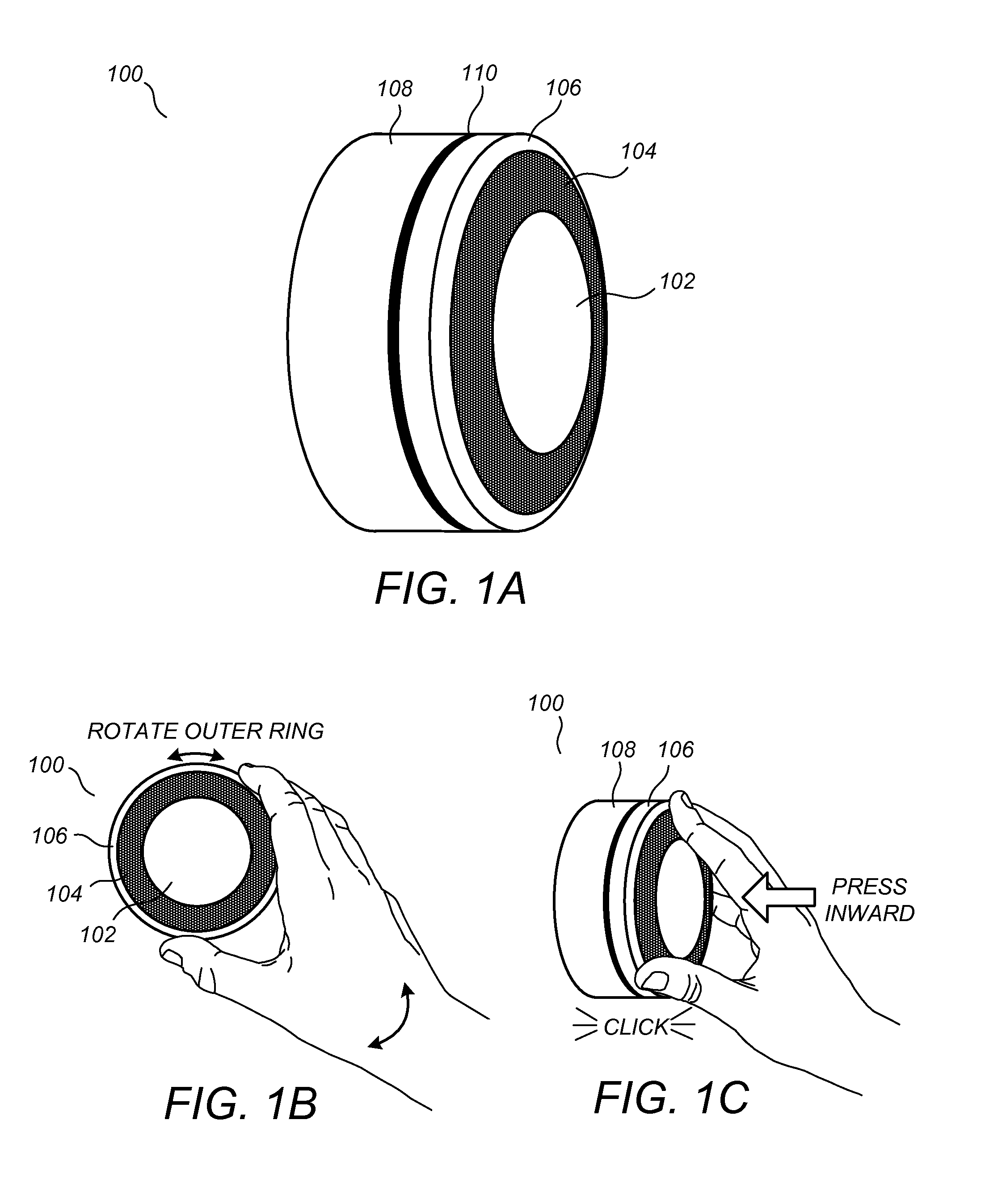

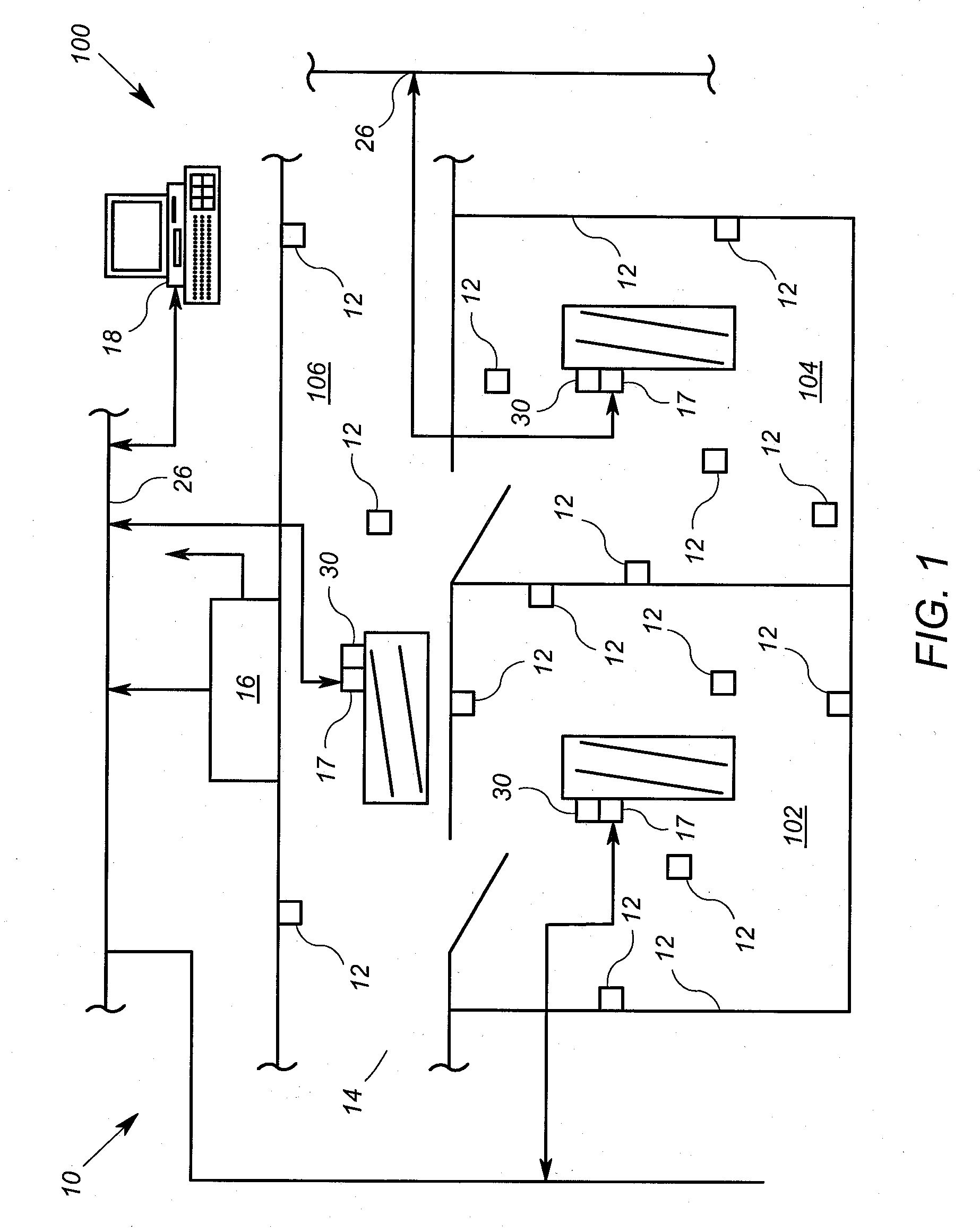

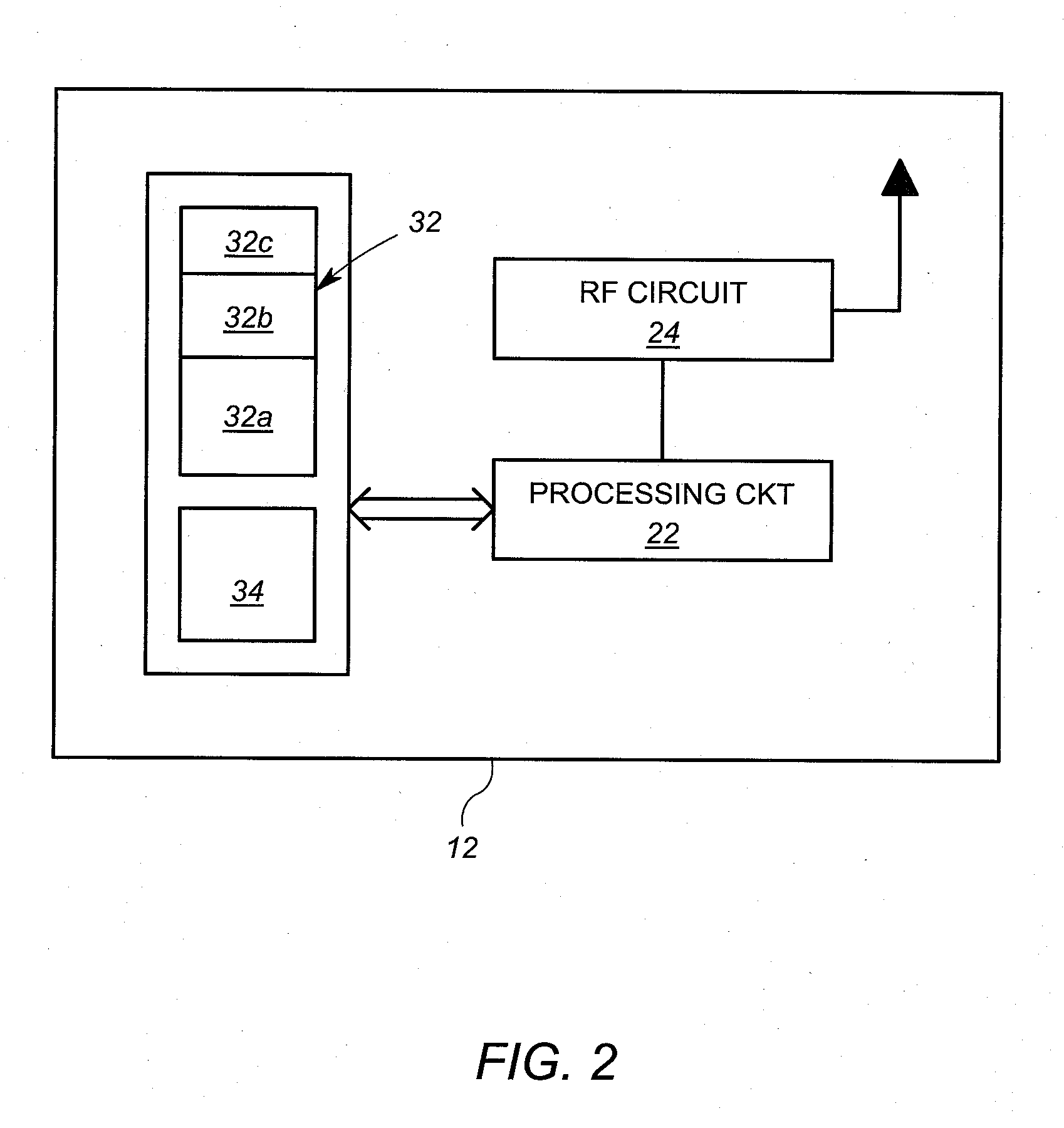

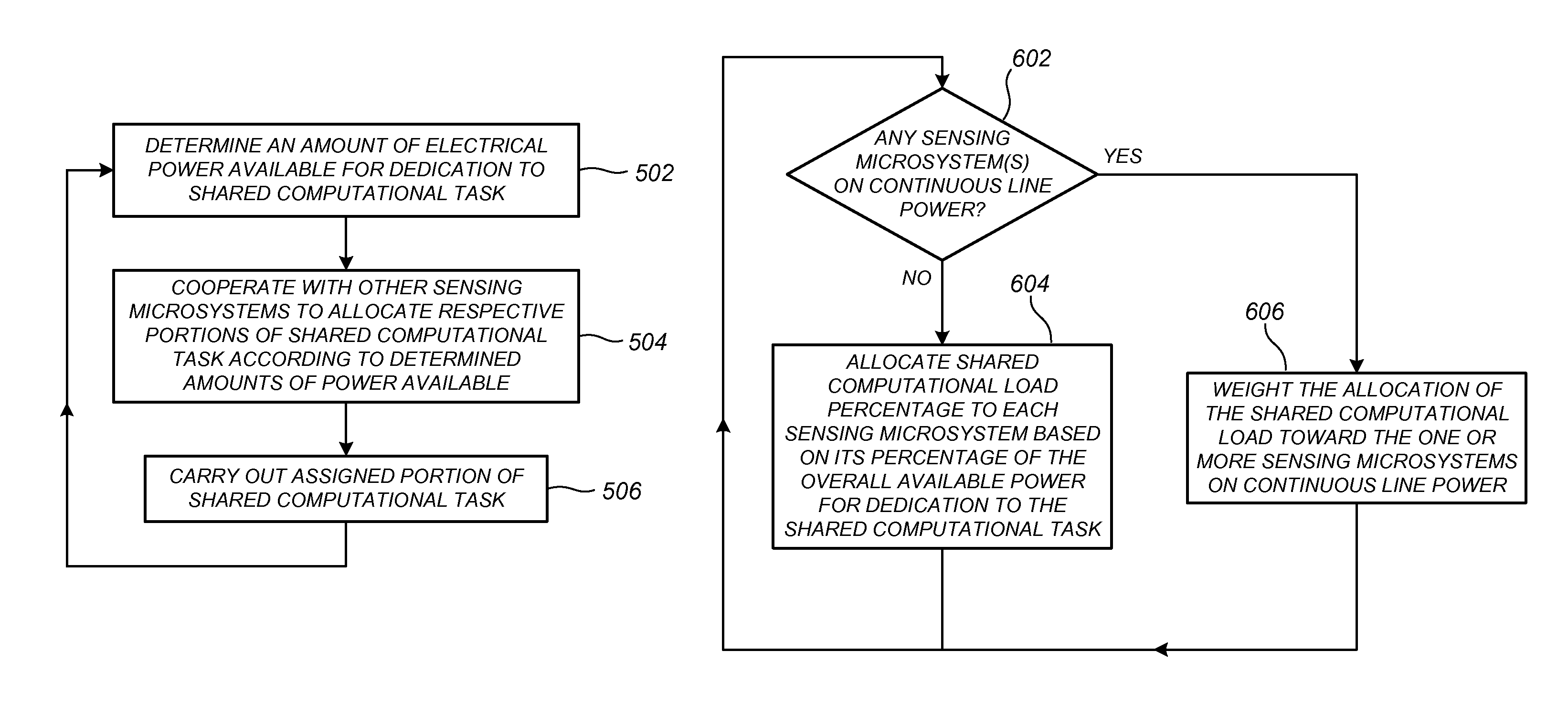

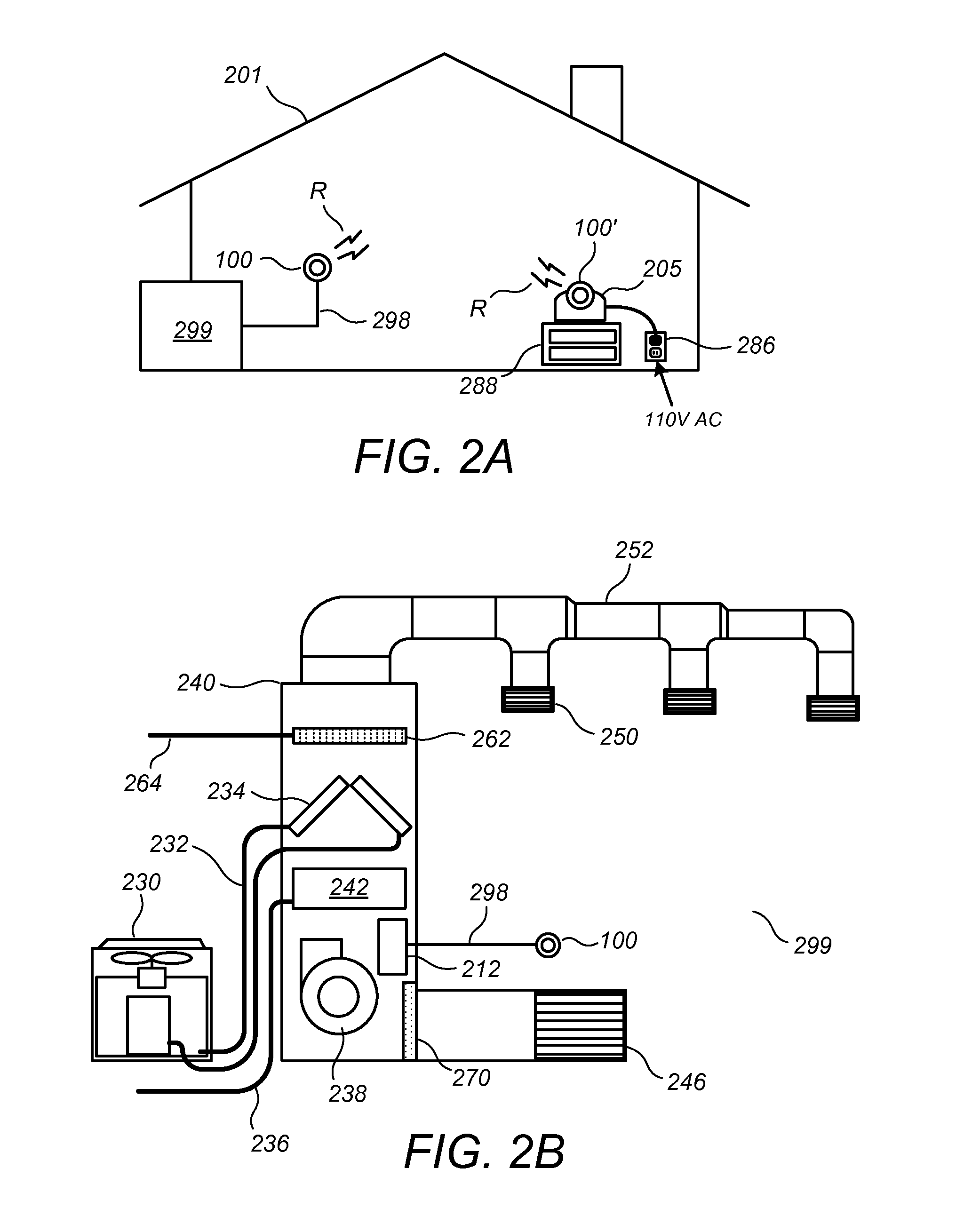

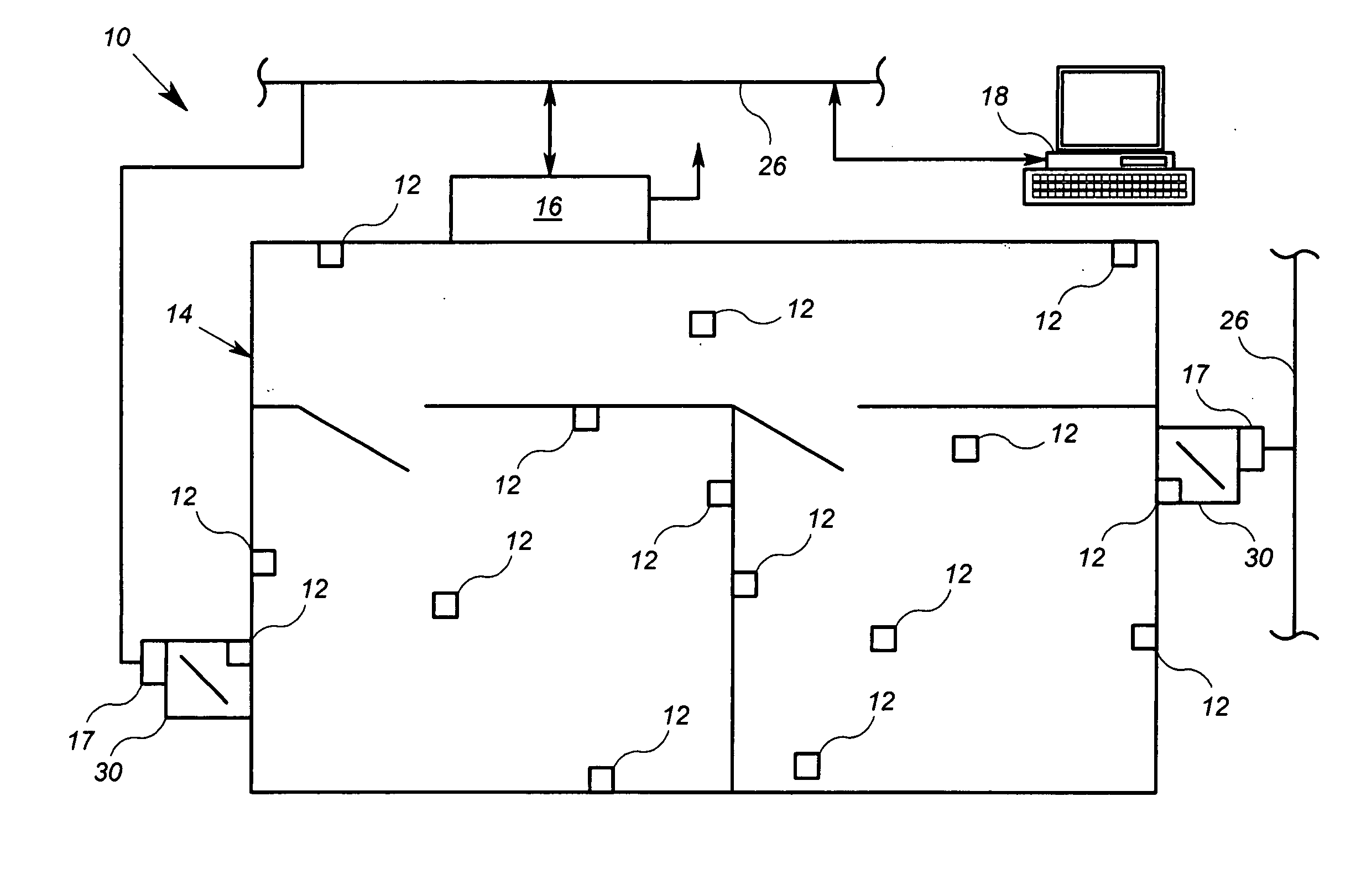

Computational load distribution in a climate control system having plural sensing microsystems

ActiveUS20120130548A1Improve energy efficiencyLarge energy expenseSampled-variable control systemsElectrically conductive connectionsControl systemEngineering

Systems, methods, and related computer program products for controlling one or more HVAC systems using a distributed arrangement of wirelessly connected sensing microsystems are described. A plurality of wirelessly communicating sensing microsystems is provided, each sensing microsystem including a temperature sensor and a processor, at least one of the sensing microsystems being coupled to an HVAC unit for control thereof. The plurality of sensing microsystems is configured to jointly carry out at least one shared computational task associated with control of the HVAC unit. Each sensing microsystem includes a power management circuit configured to determine an amount of electrical power available for dedication to the at least one shared computational task. The at least one shared computational task is apportioned among respective ones of the plurality of sensing microsystems according to the amount of electrical power determined to be available for dedication thereto at each respective sensing microsystem.

Owner:GOOGLE LLC

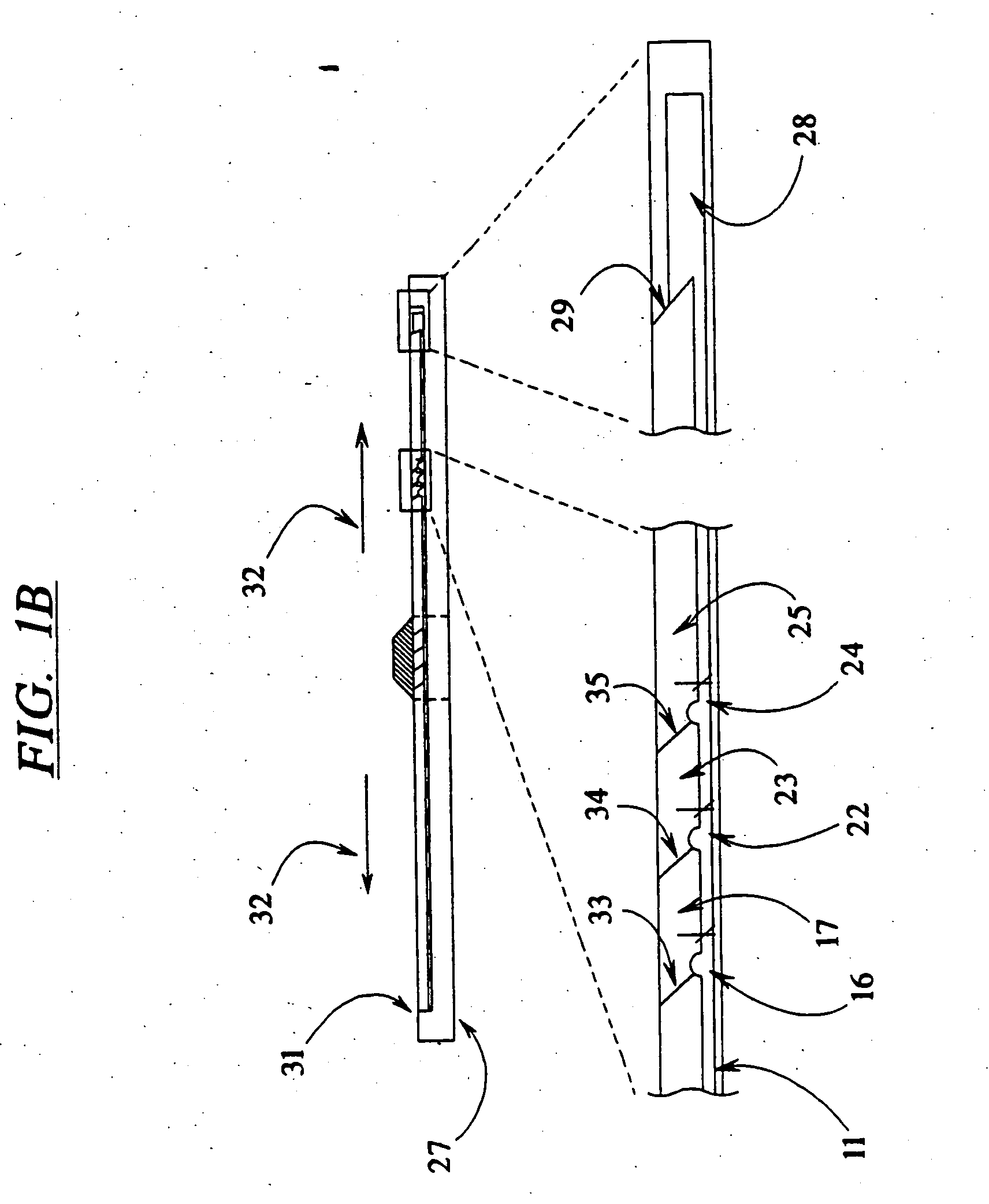

Integrally manufactured micro-electrofluidic cables

Owner:FREEMAN ALEX

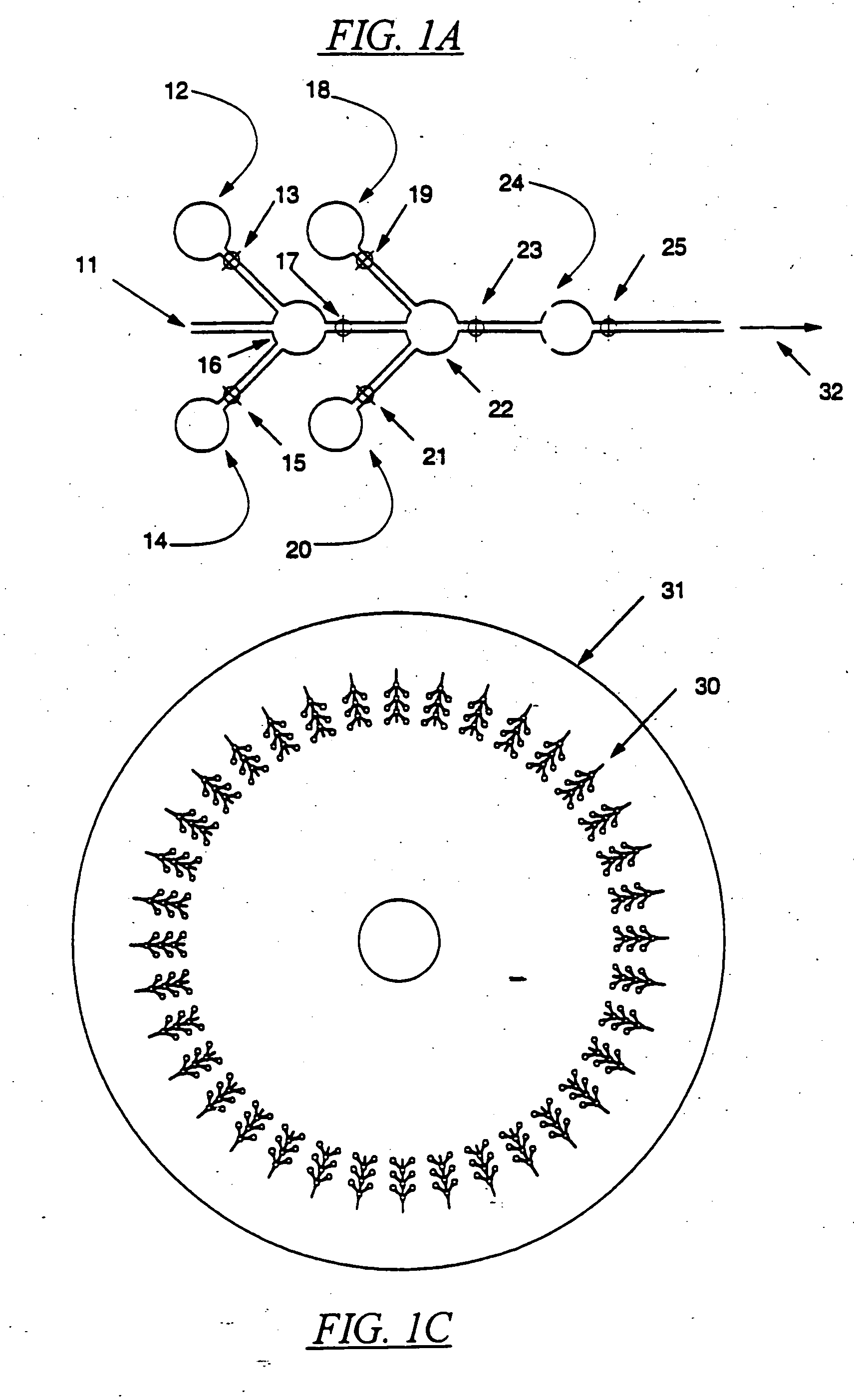

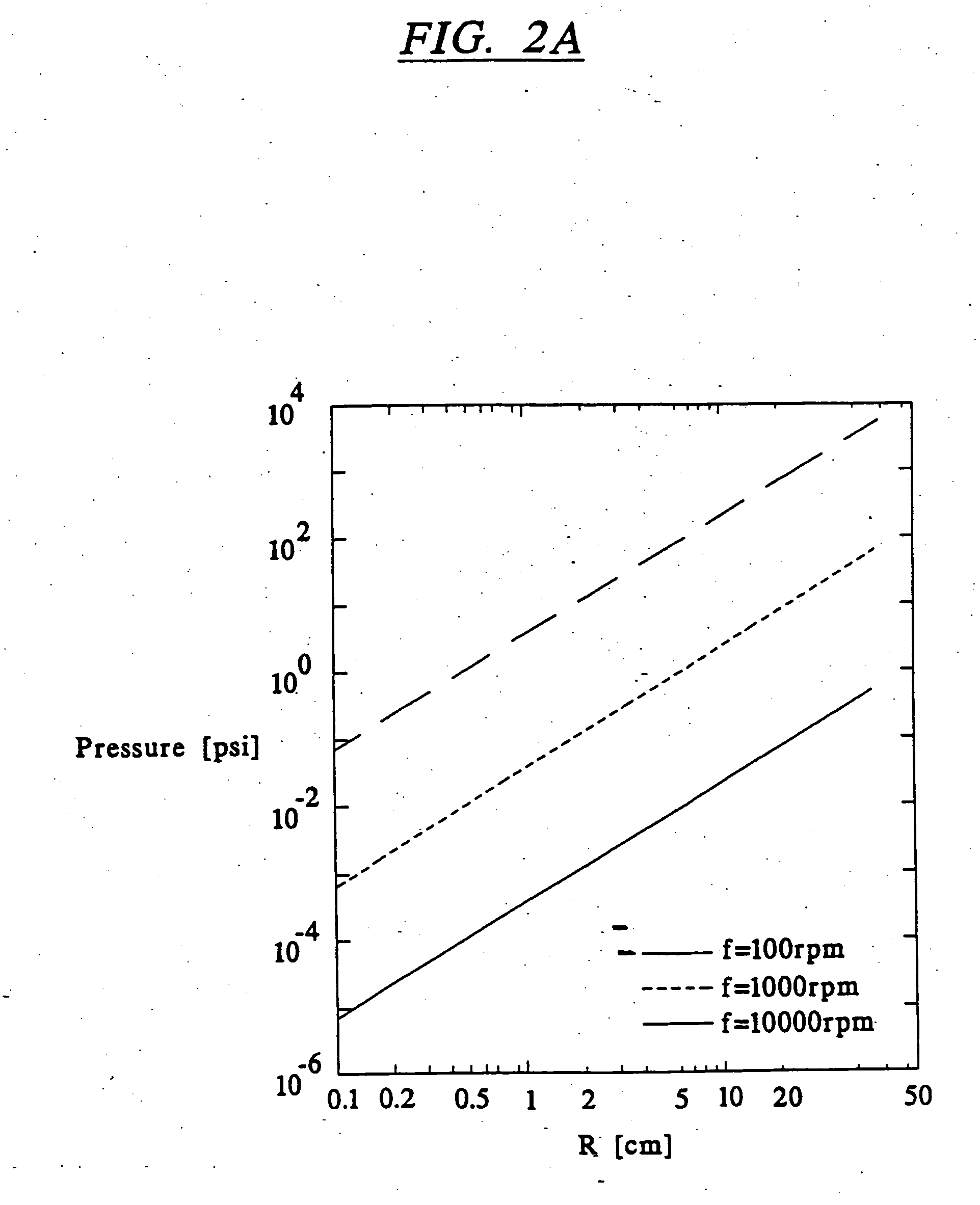

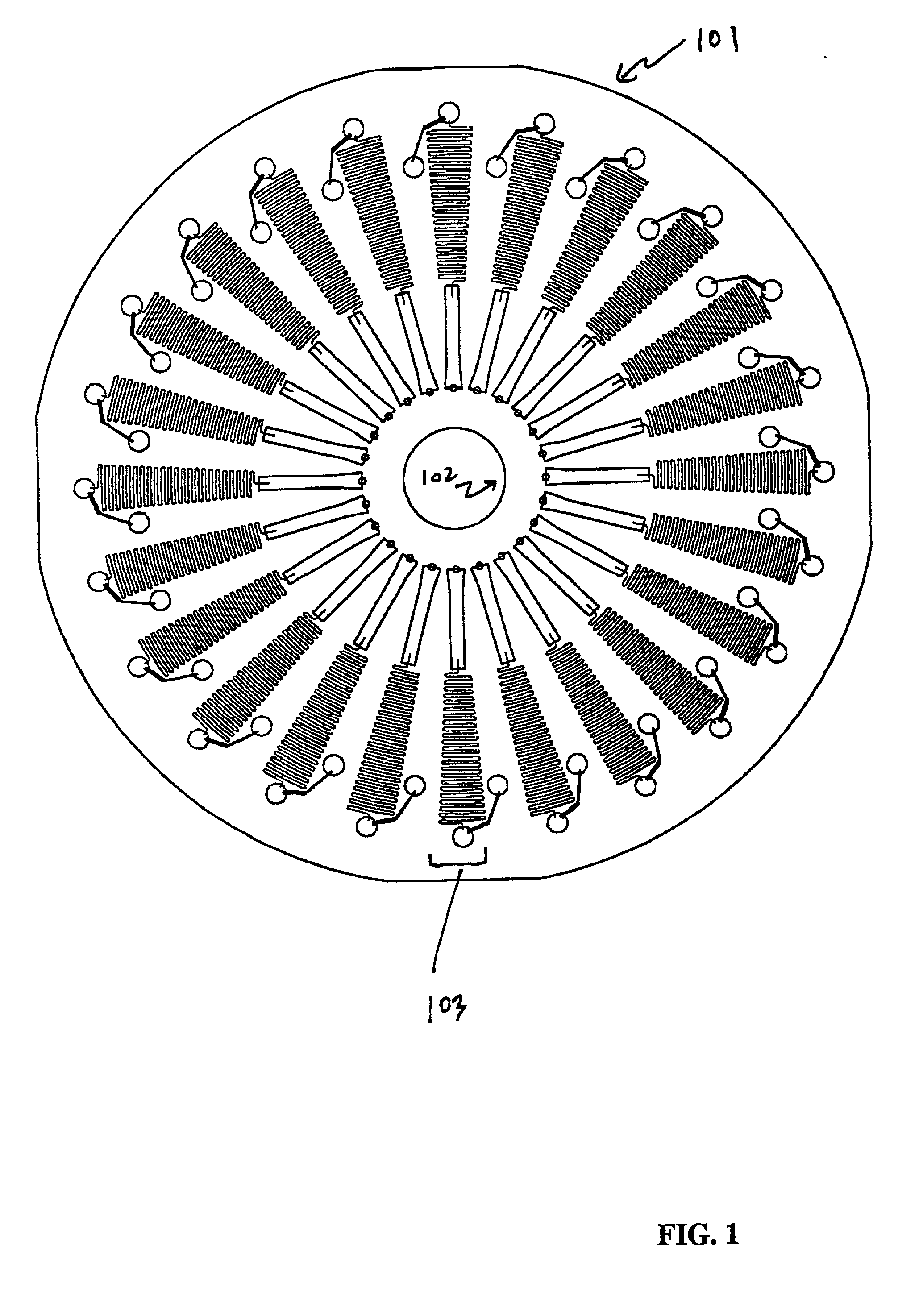

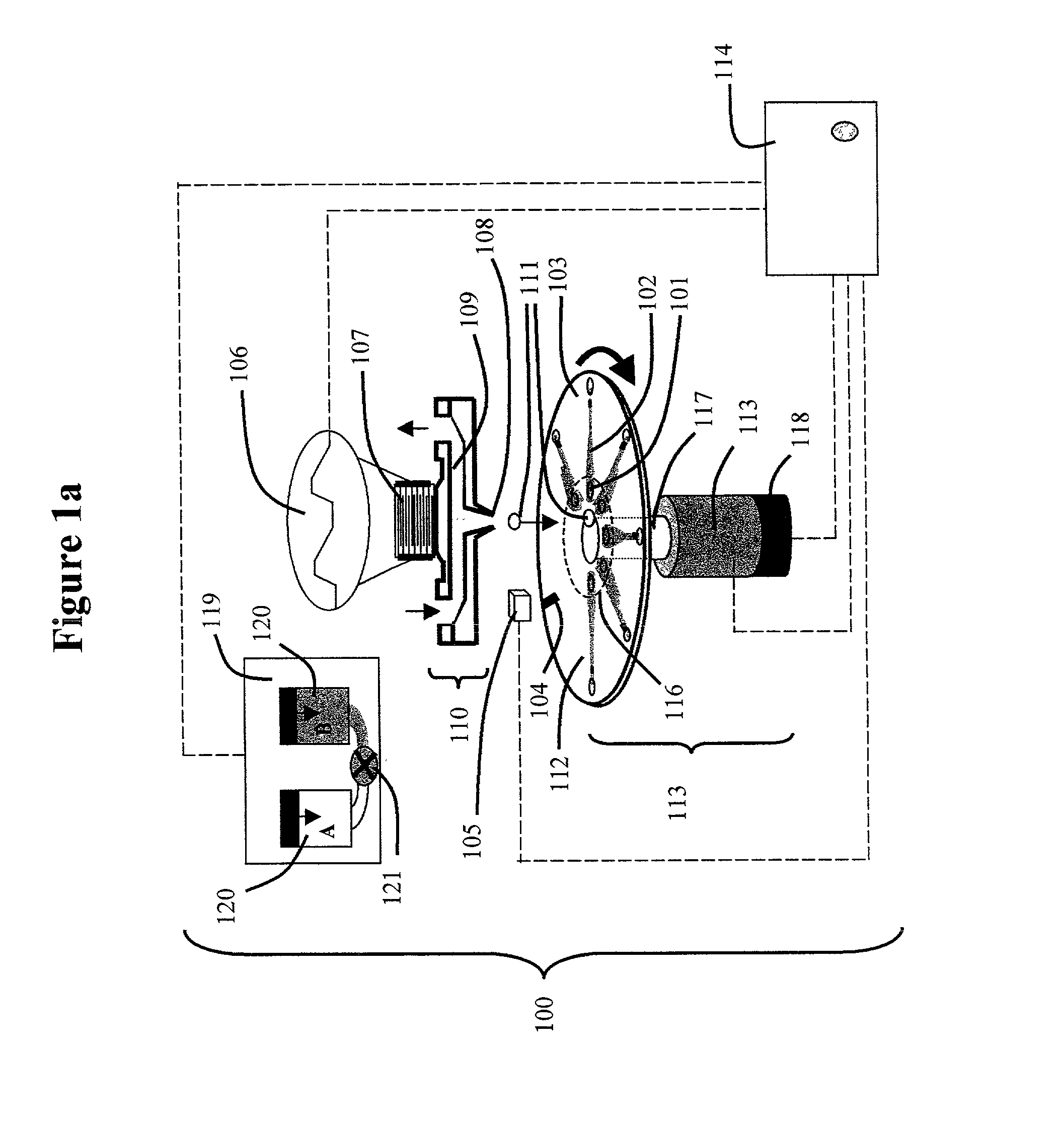

Devices and methods for using centripetal acceleration to drive fluid movement in a microfluidics system

InactiveUS20050069913A1Promote sportsBioreactor/fermenter combinationsValve arrangementsMicrofluidicsData acquisition

This invention relates to methods and apparatus for performing microanalytic and microsynthetic analyses and procedures. The invention provides a microsystem platform and a micromanipulation device for manipulating the platform that utilizes the centripetal force resulting from rotation of the platform to motivate fluid movement through microchannels. The microsystem, platforms of the invention are also optionally provided having system informatics and data acquisition, analysis and storage and retrieval informatics encoded on the surface of the disk opposite to the surface containing the fluidic components. Methods specific for the apparatus of the invention for performing any of a wide variety of microanalytical or microsynthetic processes are provided.

Owner:TECAN TRADING AG TECAN GRP LTD

Devices and methods for the performance of miniaturized in vitro amplification assays

InactiveUS20040259237A1Temperature controlEfficient use ofBioreactor/fermenter combinationsBiological substance pretreatmentsAssayBiomedical engineering

This invention relates to methods and apparatus for performing microanalytic and microsynthetic analyses and procedures. The invention provides a microsystem platform and a micromanipulation device for manipulating the platform that utilizes the centripetal force resulting from rotation of the platform to motivate fluid movement through microchannels. The invention specifically provides devices and methods for performing miniaturized in vitro amplification assays such as the polymerase chain reaction. Methods specific for the apparatus of the invention for performing PCR are provided.

Owner:TECAN TRADING AG

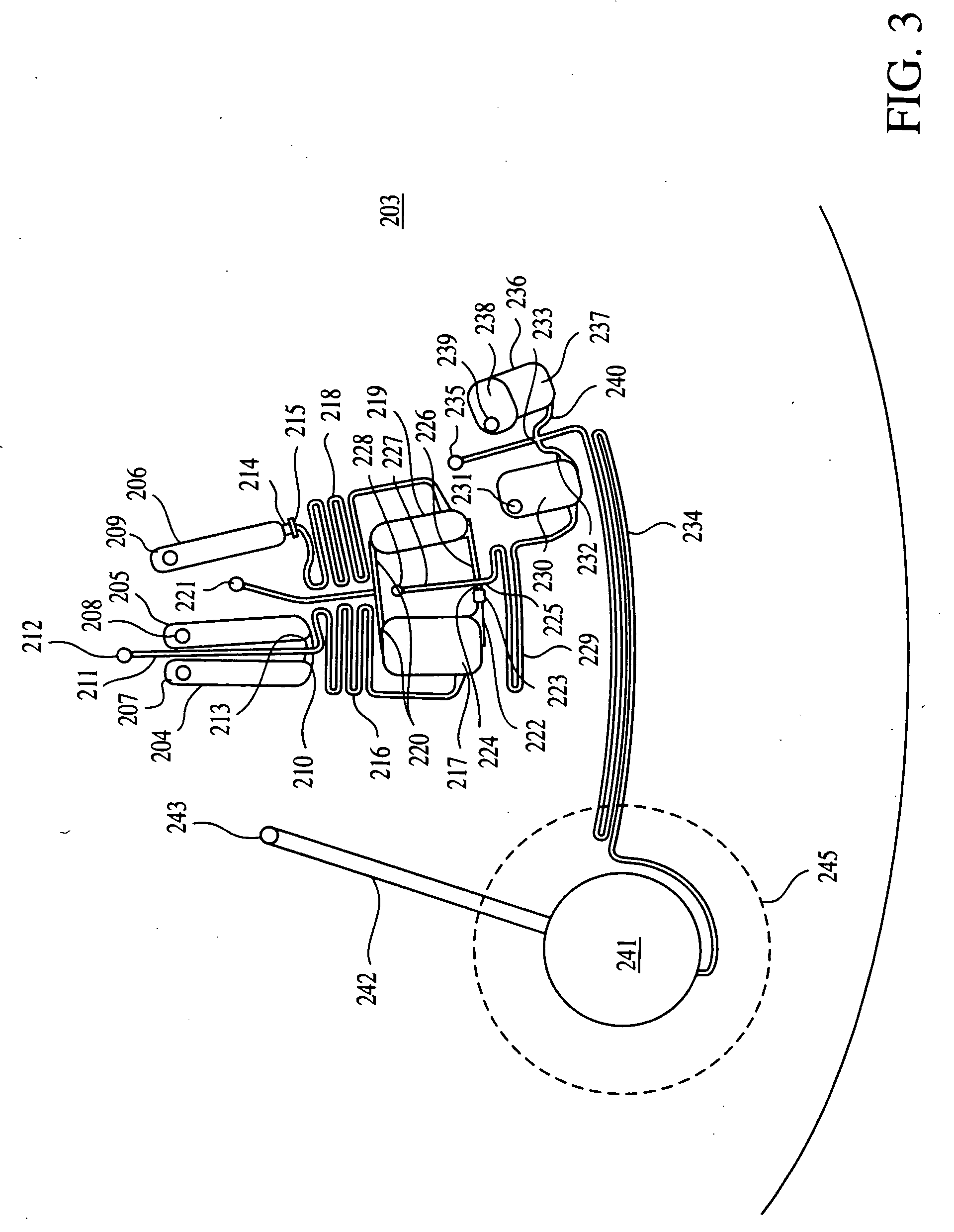

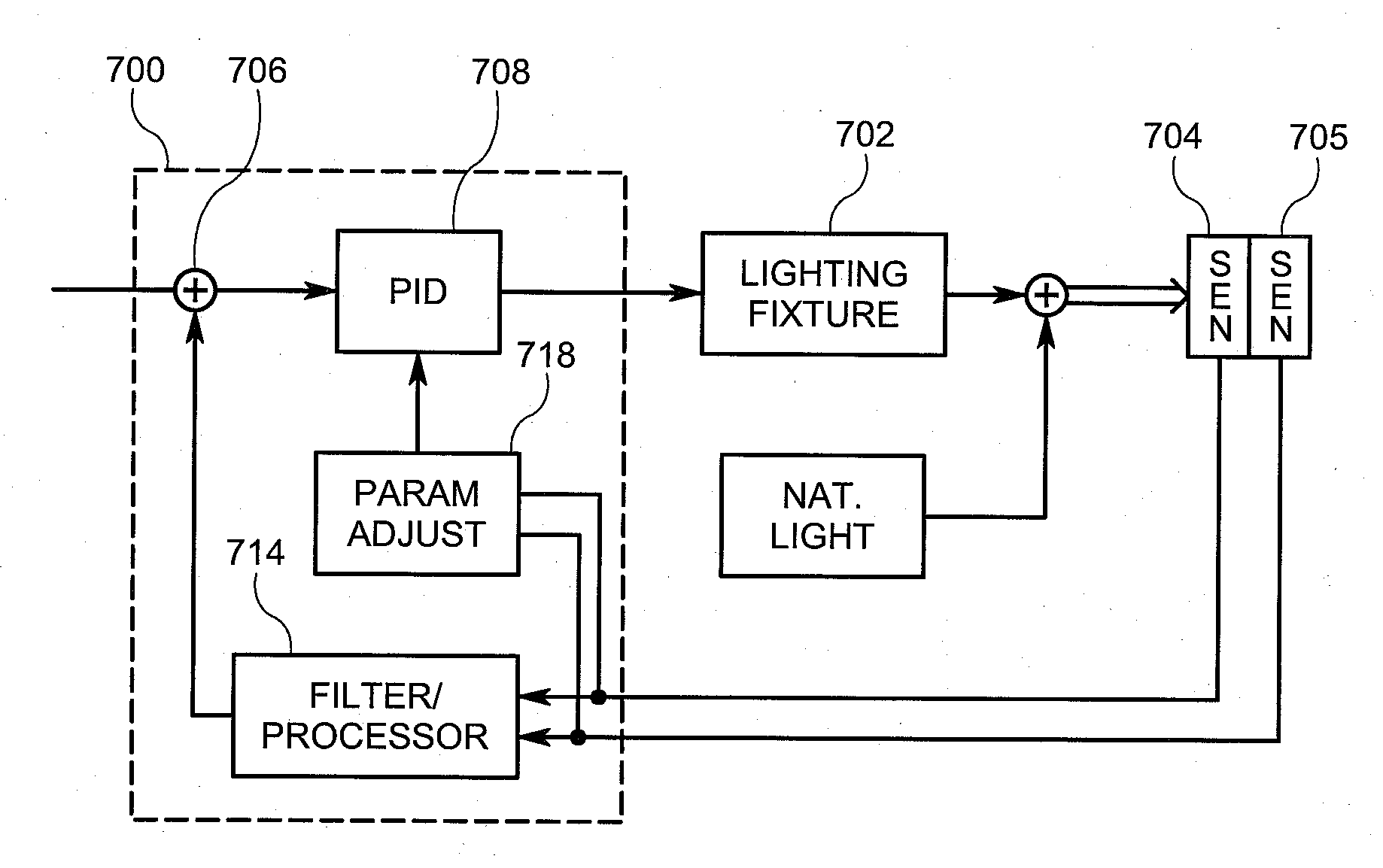

Application of Microsystems for Lighting Control

ActiveUS20080074059A1Improve efficiencyReduce laborSampled-variable control systemsElectrical apparatusEffect lightControl theory

An arrangement includes a plurality of microsystems and a controller. Each of the plurality of wireless microsystems is operable to measure at least one parameter of a space, and to transmit the at least one parameter wirelessly. The controller is operably coupled to receive the information corresponding to the at least one parameter directly or indirectly. The controller is operable to cause a change in a lighting control level based at least in part on the information. The wireless microsystems may suitably measure light levels and / or occupancy regarding the space.

Owner:SIEMENS IND INC

Cell sorting device

InactiveUS20110212440A1Large widthWell representedBioreactor/fermenter combinationsBiological substance pretreatmentsAcousticsMicrosystem

An integrated microsystem, comprising: a microchannel, a field generator to create a magnetic field in at least one first portion of the microchannel having a direction substantially collinear with the direction of flow in the portion of the microchannel, the magnetic field also presenting a gradient, wherein the microsystem additionally comprises a detection area in fluid connection with the microchannel,

Owner:CNRS DAE +3

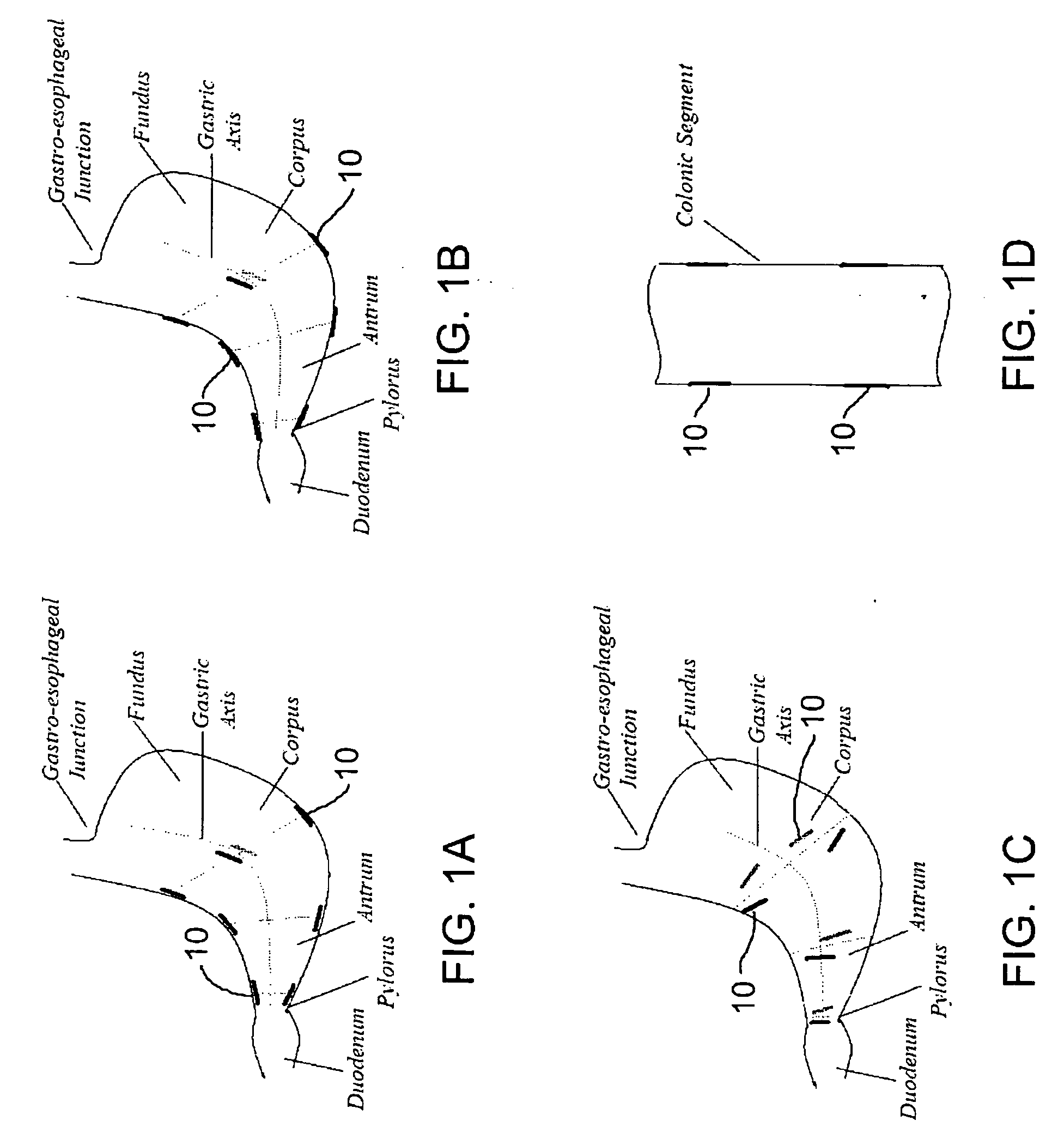

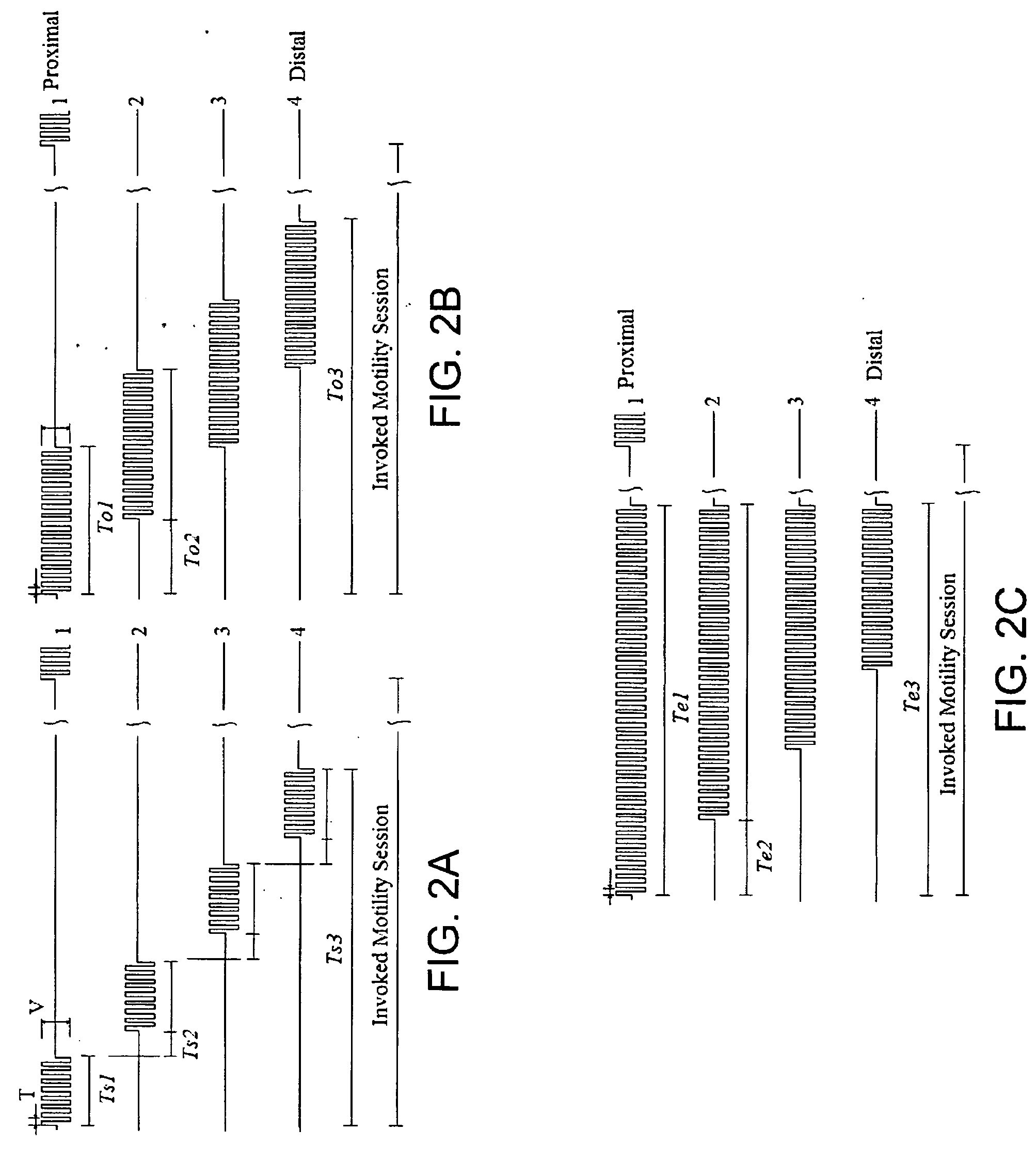

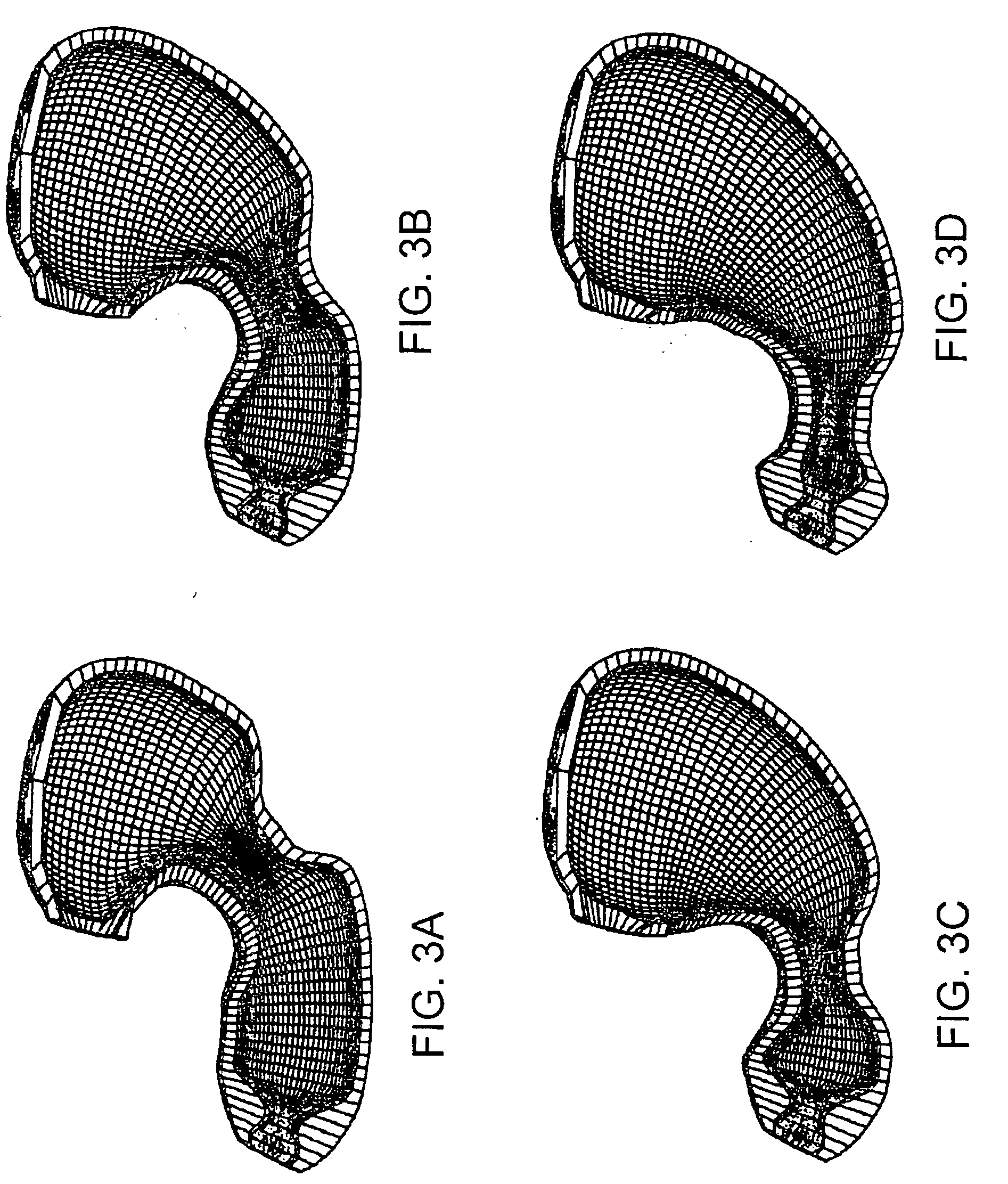

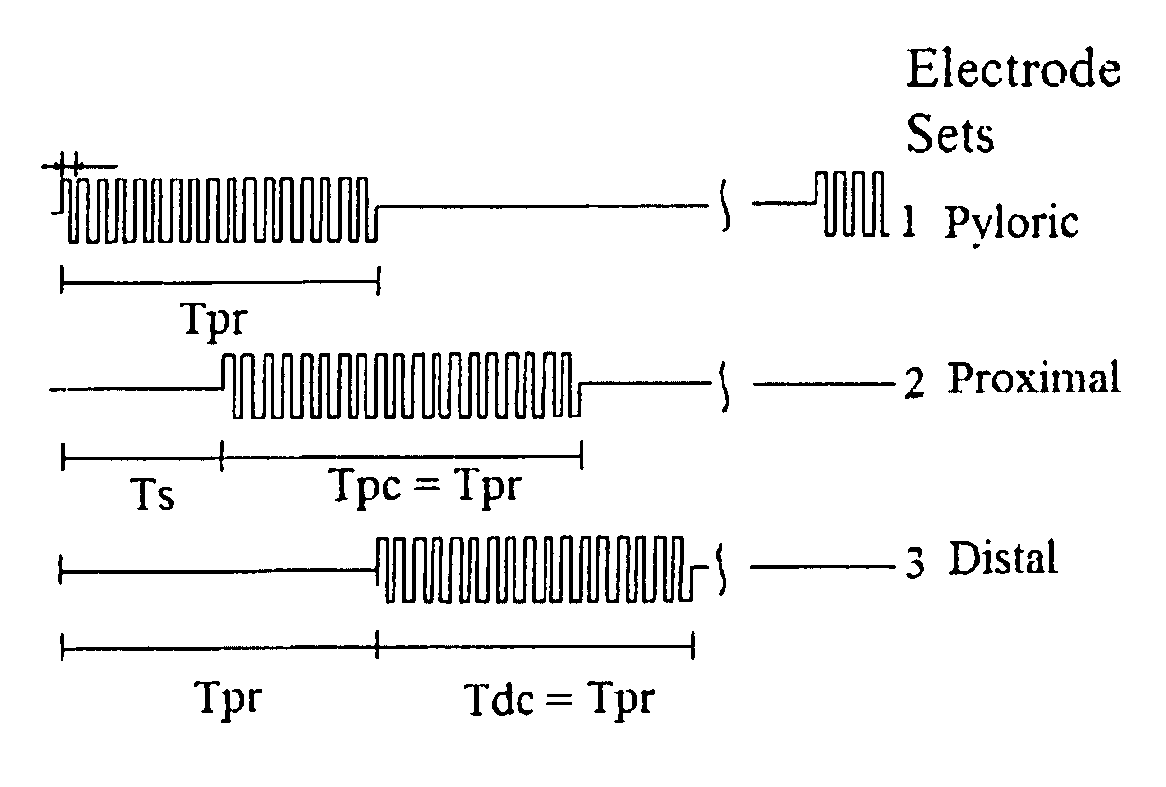

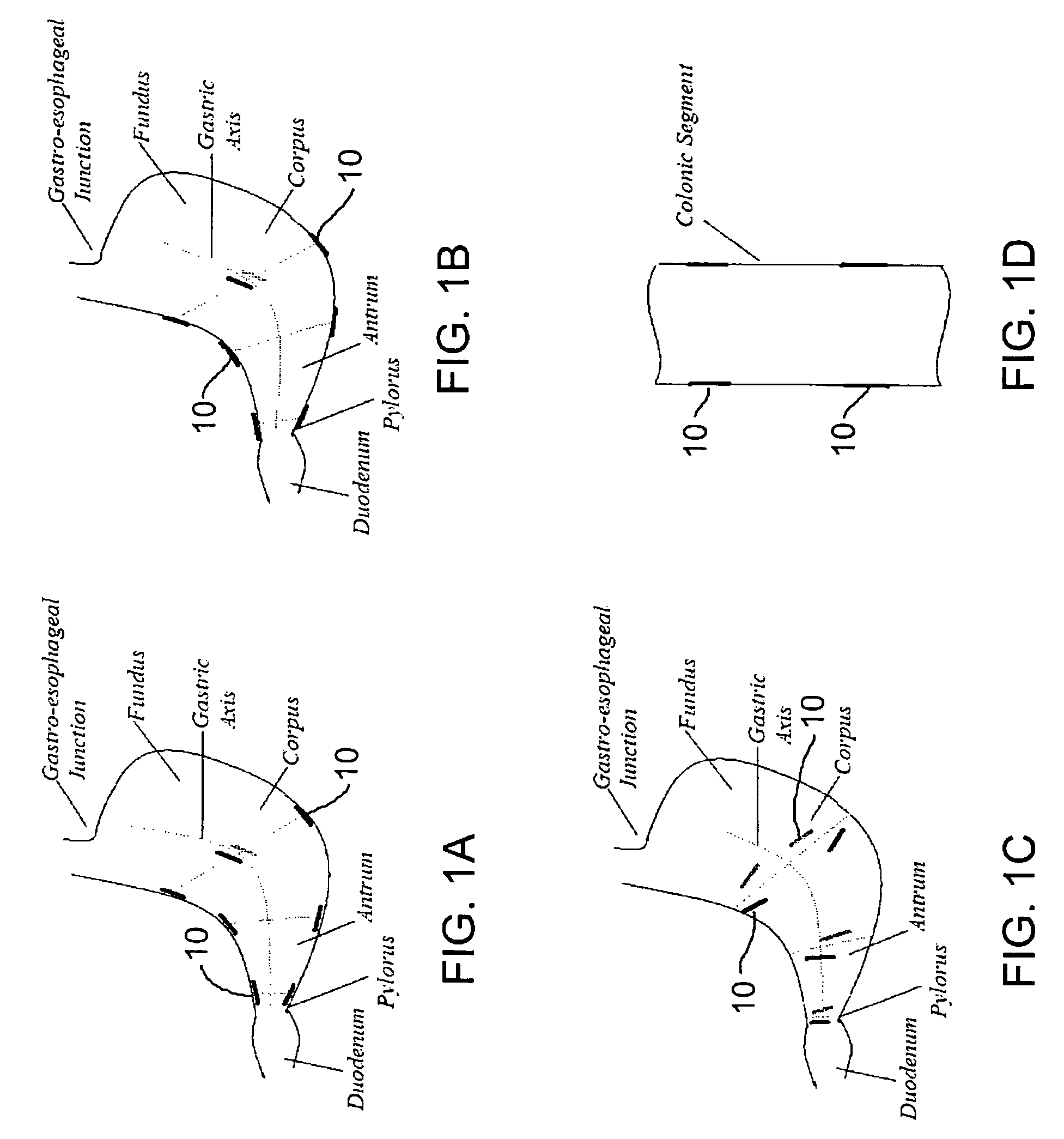

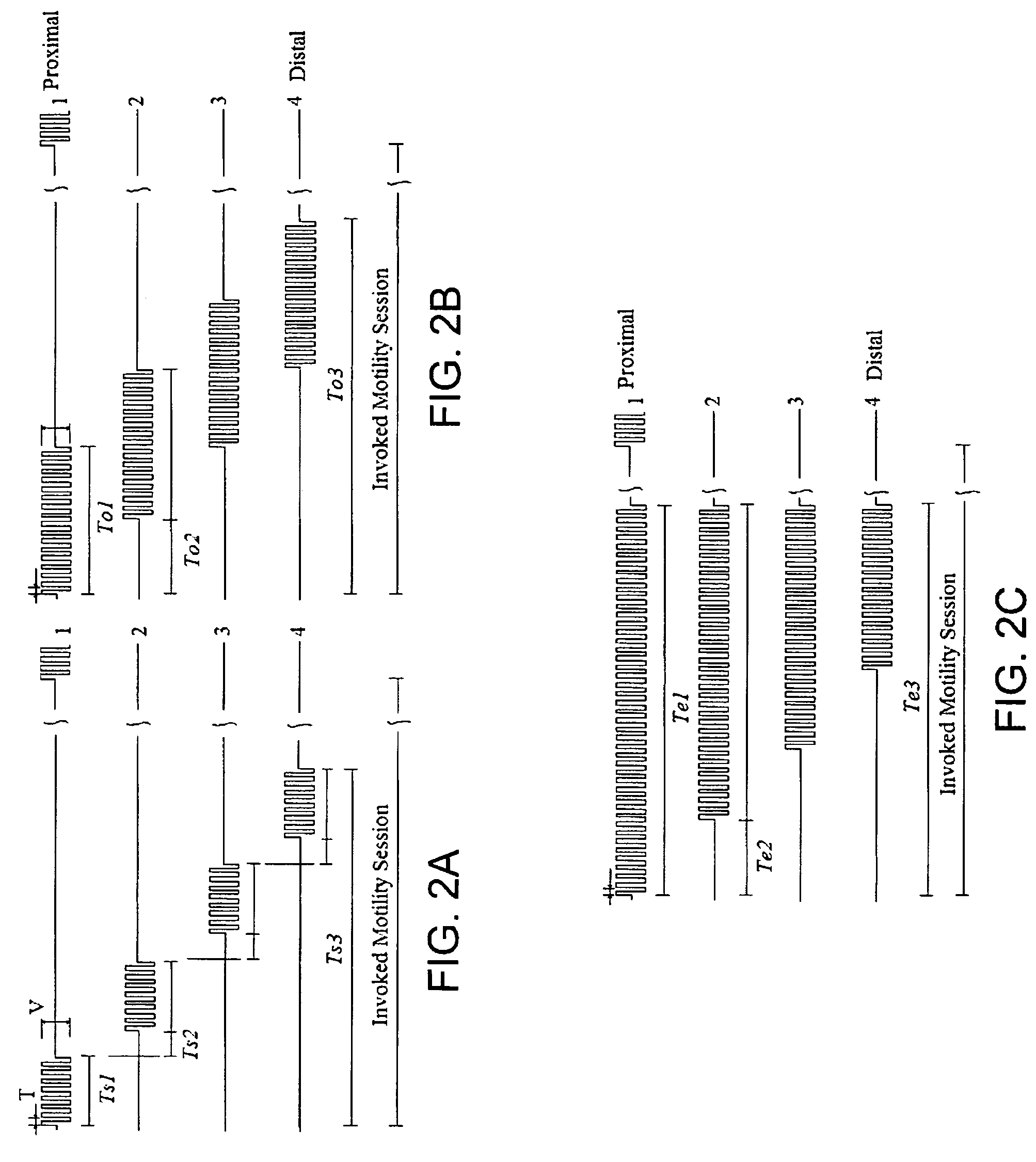

Gastrointestinal motility control

A method and a multichannel implantable device are described for partial or complete restoration of impaired gastrointestinal motility, or for disturbing and / or partially or completely blocking normal gastrointestinal motility using one or multiple microsystem-controlled channels of circumferentially arranged sets of two or more electrodes which provide externally-invoked synchronized electrical signals to the smooth muscles via the neural pathways.

Owner:UTI LLP

Computational load distribution in a climate control system having plural sensing microsystems

ActiveUS8478447B2Improve energy efficiencyLarge energy expenseDispersed particle filtrationSpace heating and ventilationControl systemEngineering

Systems, methods, and related computer program products for controlling one or more HVAC systems using a distributed arrangement of wirelessly connected sensing microsystems are described. A plurality of wirelessly communicating sensing microsystems is provided, each sensing microsystem including a temperature sensor and a processor, at least one of the sensing microsystems being coupled to an HVAC unit for control thereof. The plurality of sensing microsystems is configured to jointly carry out at least one shared computational task associated with control of the HVAC unit. Each sensing microsystem includes a power management circuit configured to determine an amount of electrical power available for dedication to the at least one shared computational task. The at least one shared computational task is apportioned among respective ones of the plurality of sensing microsystems according to the amount of electrical power determined to be available for dedication thereto at each respective sensing microsystem.

Owner:GOOGLE LLC

Bidirectional flow centrifugal microfluidic devices

This invention relates to methods and apparatus for performing microanalytic and microsynthetic analyses and procedures. The invention particularly provides microsystem platforms for achieving efficient mixing of one or a plurality of fluids on the surface of the platform when fluid flow is motivated by centripetal force produce by rotation.

Owner:TECAN TRADING AG

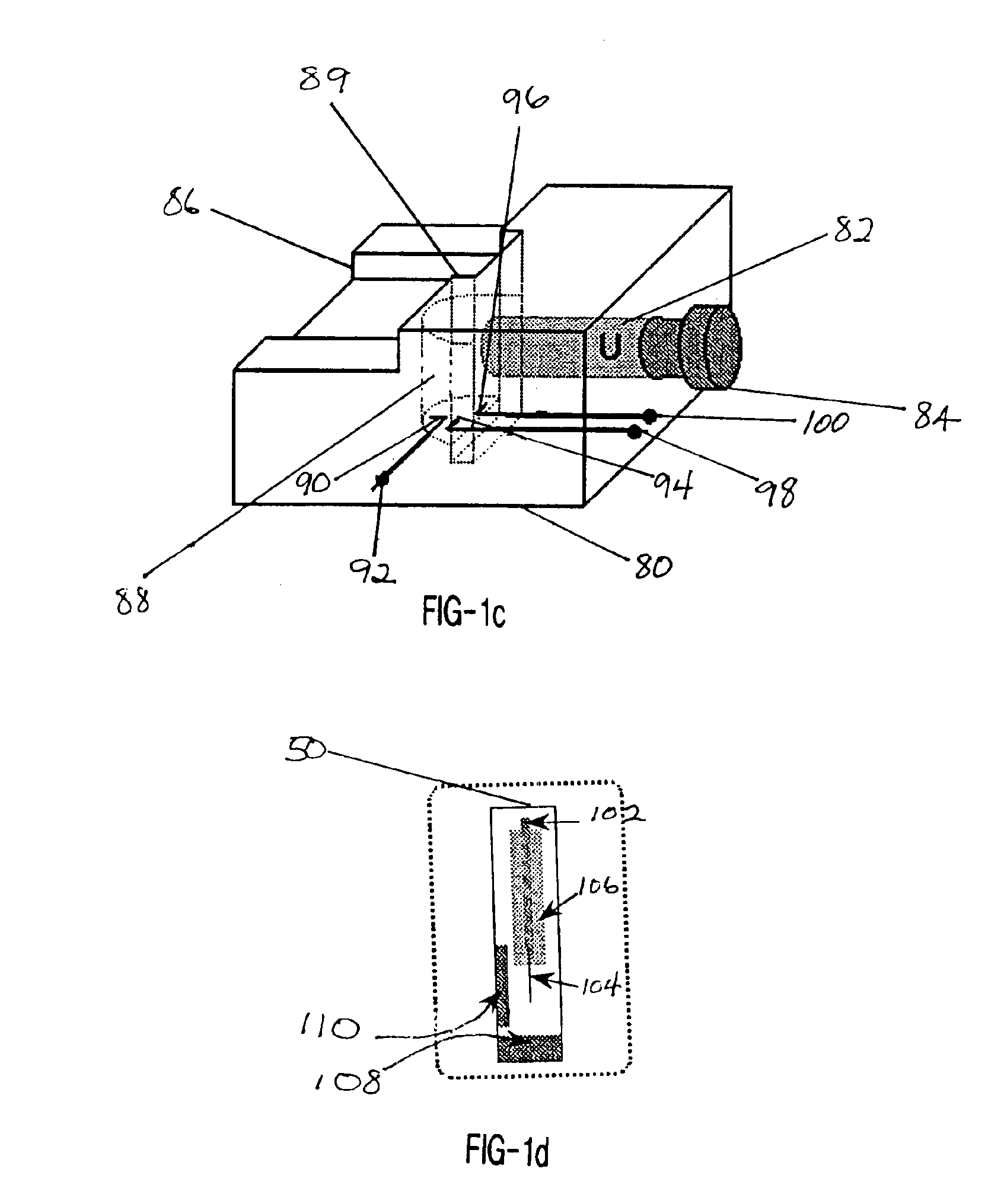

Application of microsystems for comfort control

ActiveUS20070084937A1Reduce laborReduce material costsMechanical apparatusTemperatue controlEngineeringRelative humidity

An arrangement includes a plurality of wireless microsystems. Each microsystem is operable to measure at least relative humidity and temperature, and to communicate temperature and relative humidity information wirelessly to a network device. The network device is operable to communicate the temperature and relative humidity information to at least a first processor configured to cause a change in a building control condition based on the information.

Owner:SIEMENS IND INC

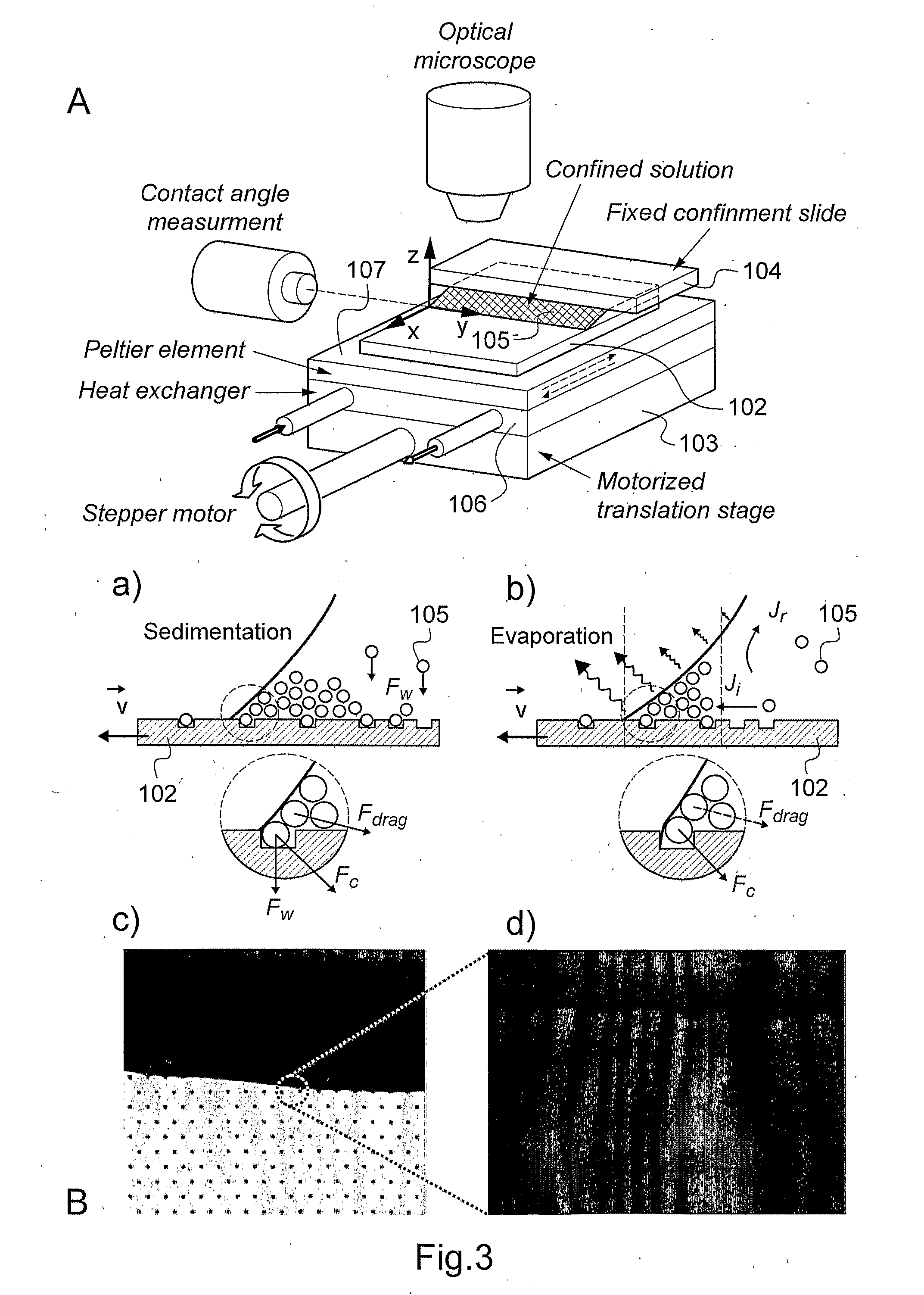

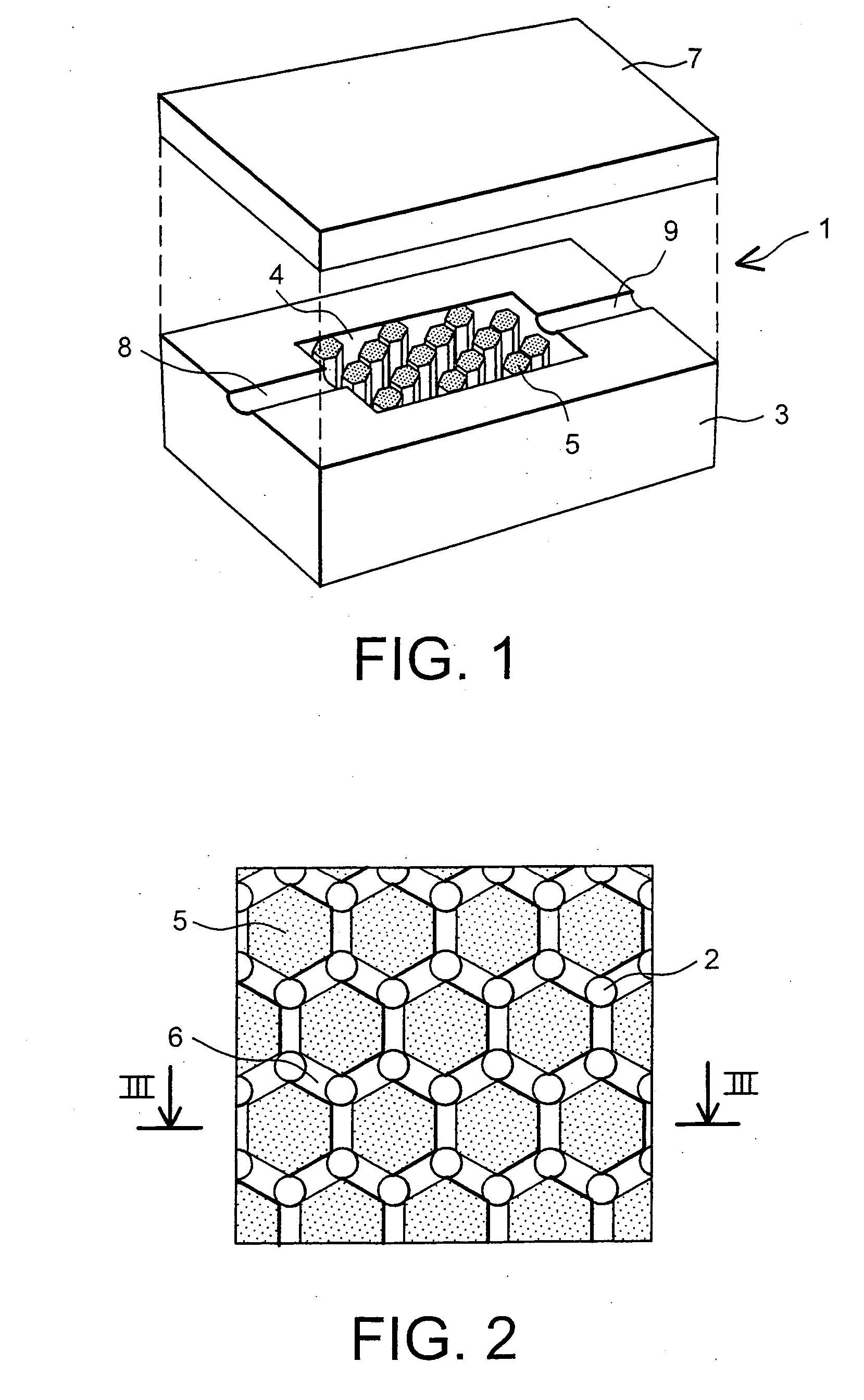

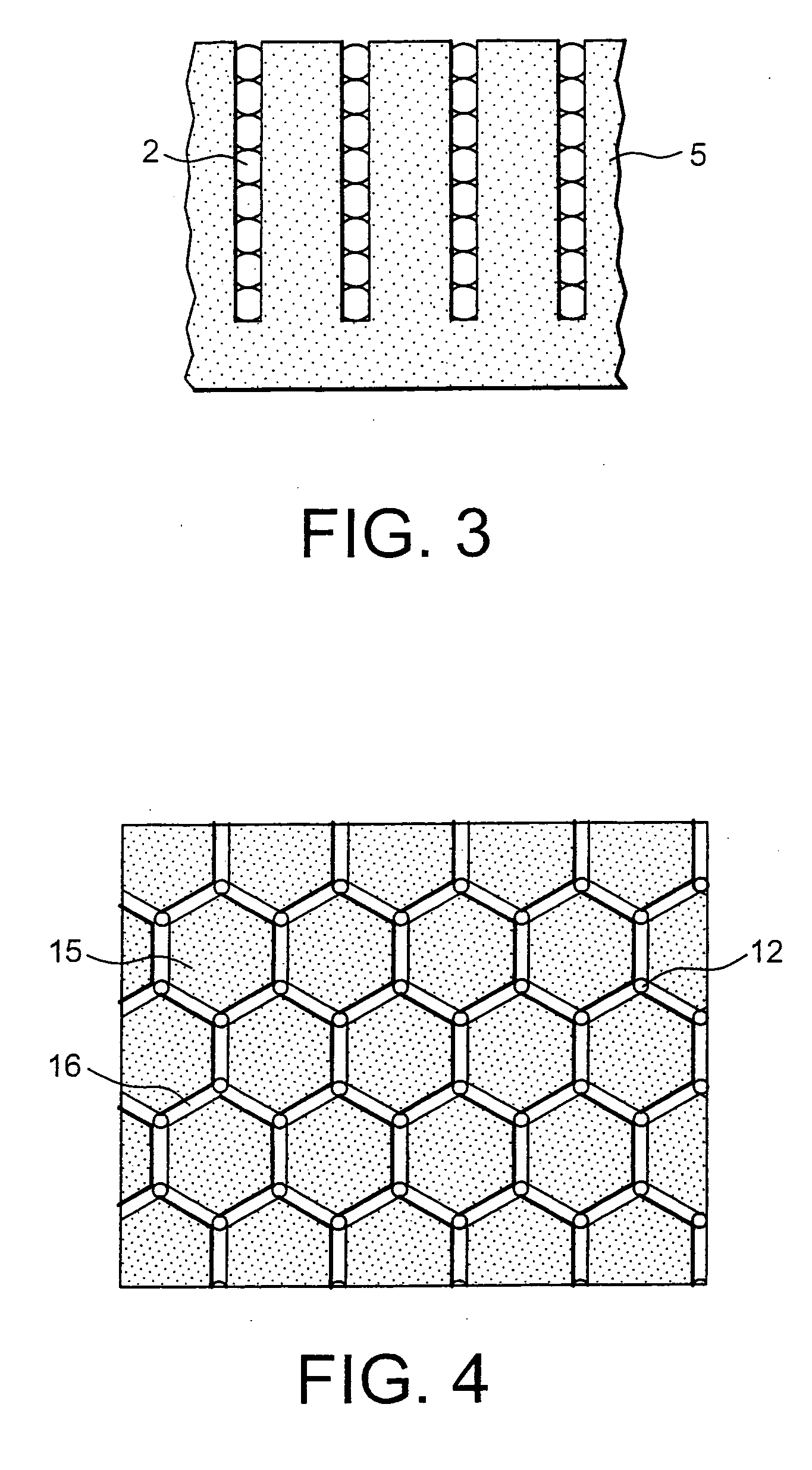

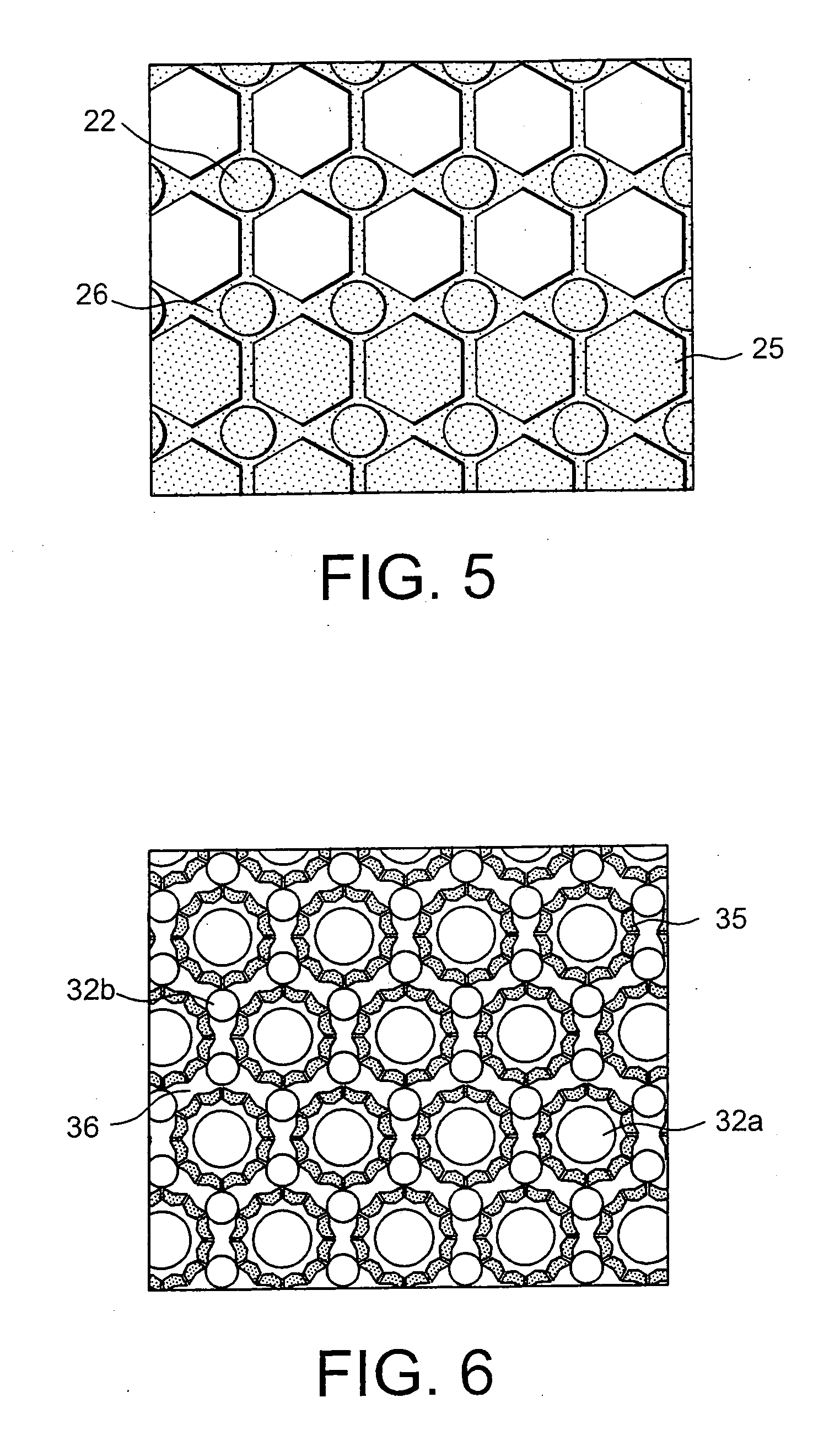

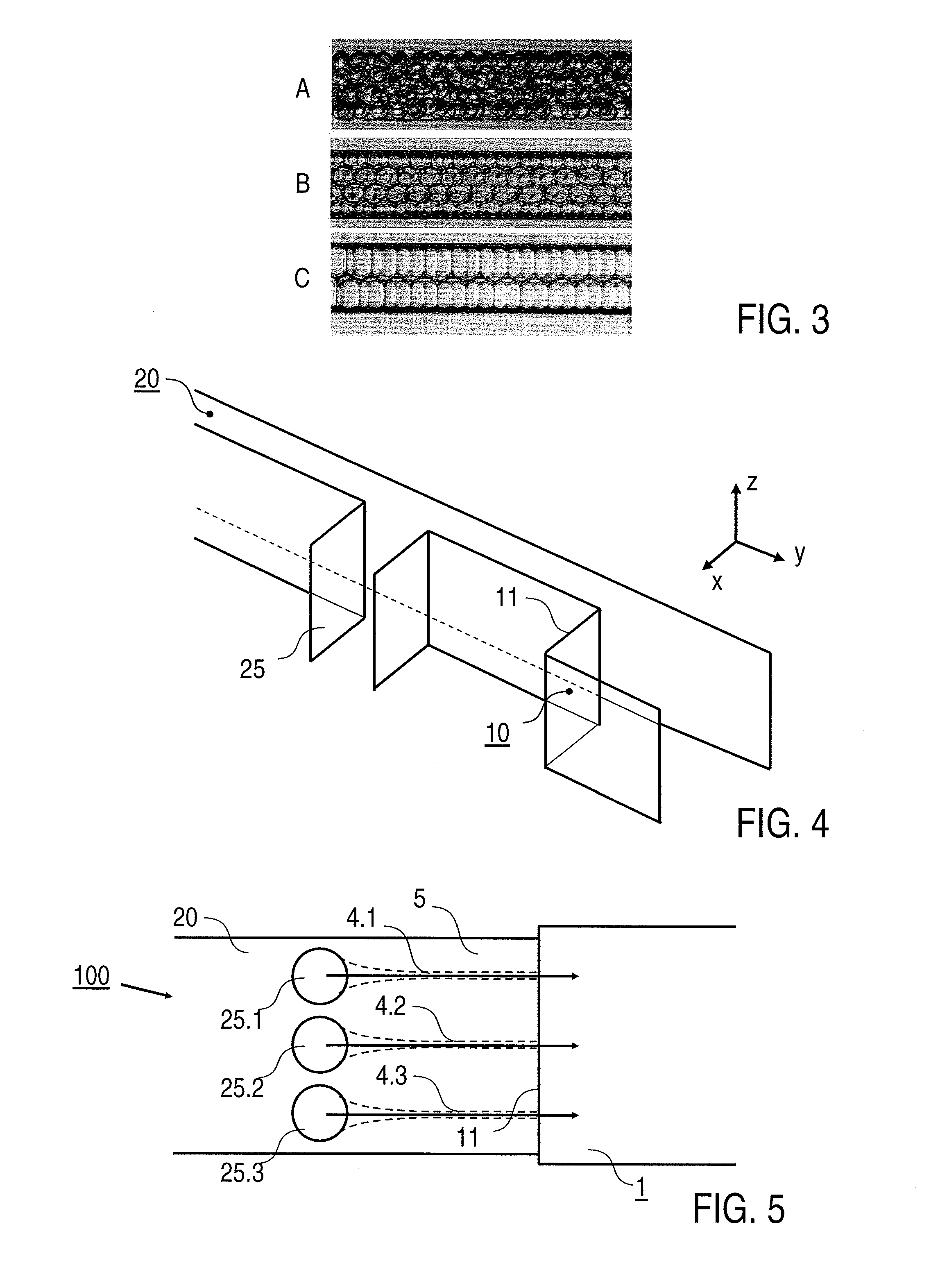

Microbead-filled microsystem and production method thereof

InactiveUS20060068450A1Easy filling stageHelps to expelBioreactor/fermenter combinationsBiological substance pretreatmentsMicrosystemWaste management

The invention relates to a micro-system intended to receive beads and to obtain a precise positioning of the beads at preset locations in the micro-system. This micro-system comprises a tank that has a cavity, the cavity being fitted with blocking elements allowing the beads to be ordered and stacked in the interstices between the blocking elements, the interstices constituting the preset locations. It also comprises a cap anchored hermetically to the tank and input means and output means allowing a fluid to flow in the cavity. The invention also relates to the implementation and use of the bead-filled micro-system.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

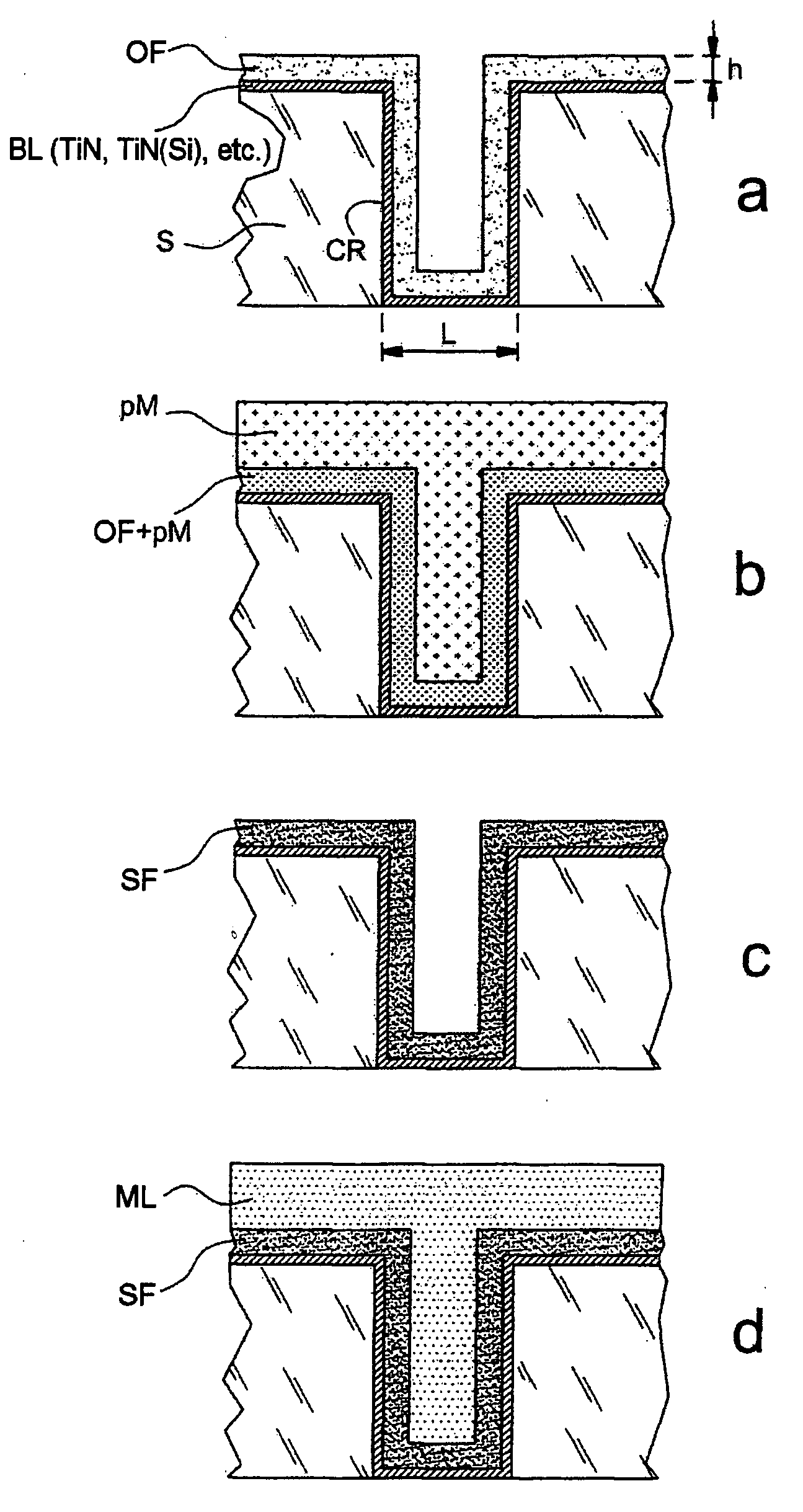

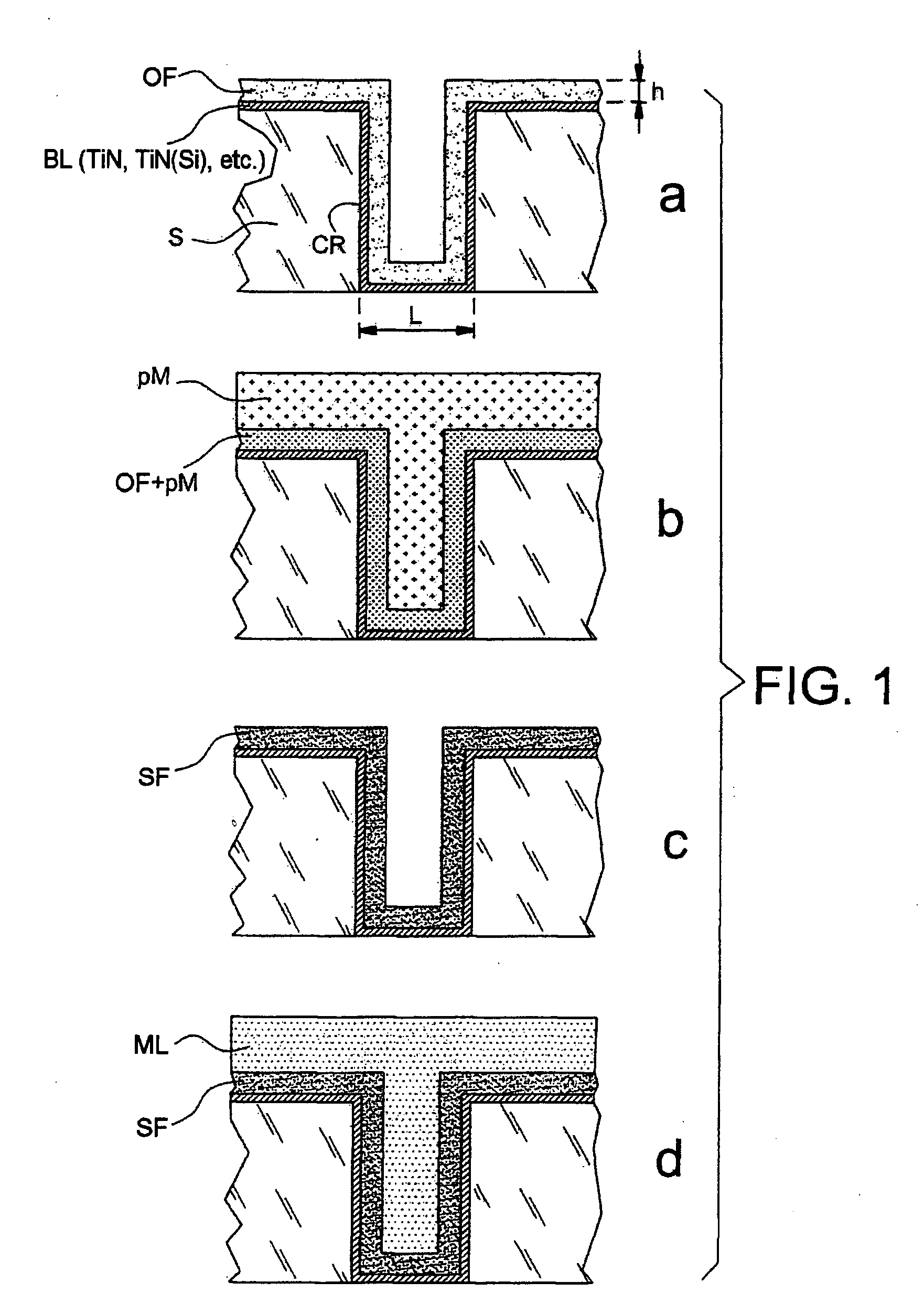

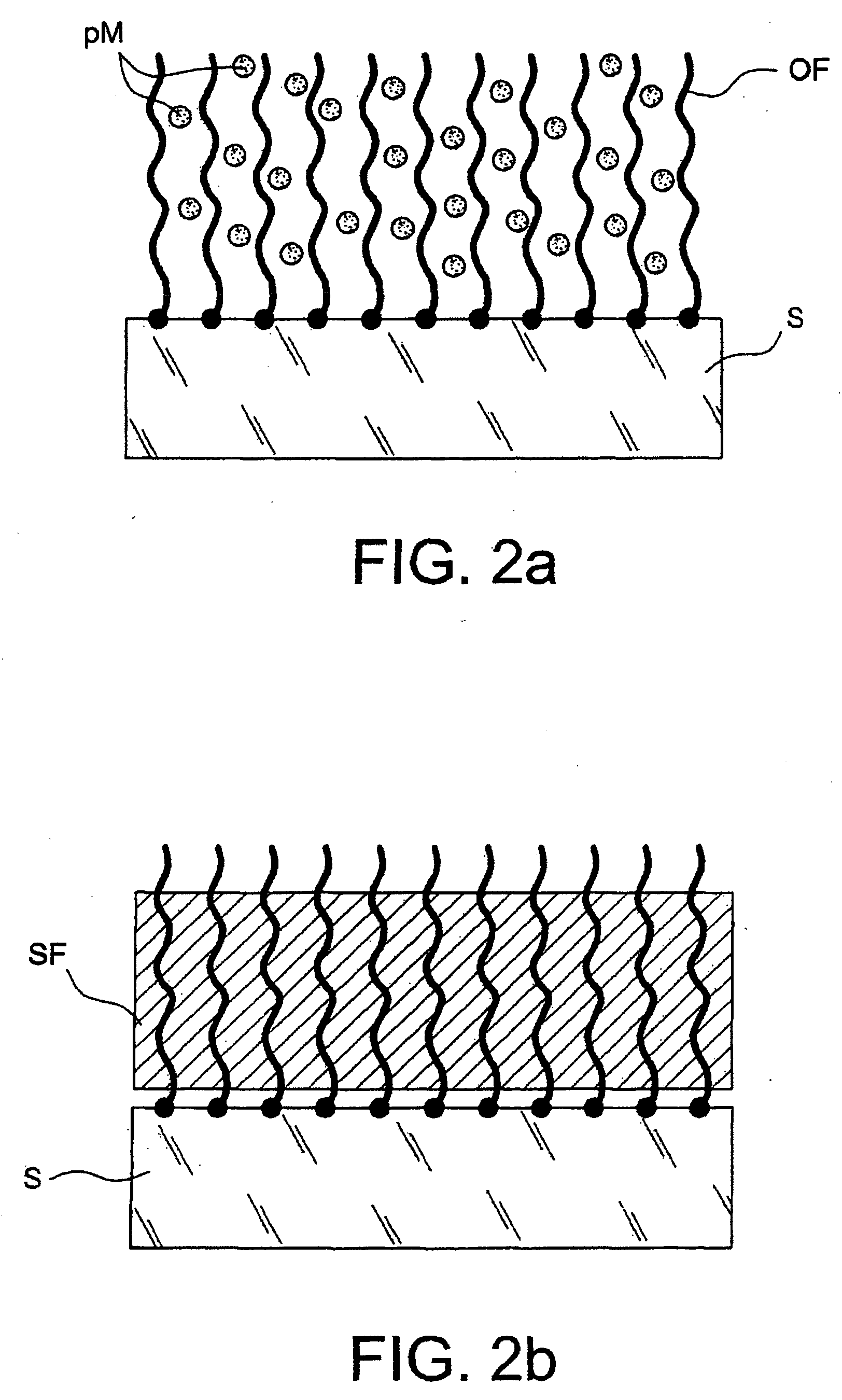

Surface-coating method, production of microelectronic interconnections using said method and integrated circuits

InactiveUS20060211236A1Overcome irregularitiesFacilitated releaseSemiconductor/solid-state device manufacturingLiquid/solution decomposition chemical coatingOrganic filmMetallic materials

The present invention relates to a process for coating a surface of a substrate with a seed film of a metallic material, the said surface being an electrically conductive or semiconductive surface and having recesses and / or projections. The process comprises the following: an organic film is placed on the said surface, the said film having a thickness such that the free face of this film conformally follows the recesses and / or projections of the said electrically conductive or semiconductive surface on which it is placed; a precursor of the metallic material is inserted within the said organic film placed on the said surface at the same time as, or after, the step consisting in placing the said organic film on the said surface; and the said precursor of the metallic material inserted within the said organic film is converted into the said metallic material. This process allows integrated circuits, interconnects in microelectronics and microsystems to be fabricated.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES +1

Gastrointestinal motility control

A method and a multichannel implantable device are described for partial or complete restoration of impaired gastrointestinal motility, or for disturbing and / or partially or completely blocking normal gastrointestinal motility using one or multiple microsystem-controlled channels of circumferentially arranged sets of two or more electrodes which provide externally-invoked synchronized electrical signals to the smooth muscles via the neural pathways.

Owner:UTI LLP

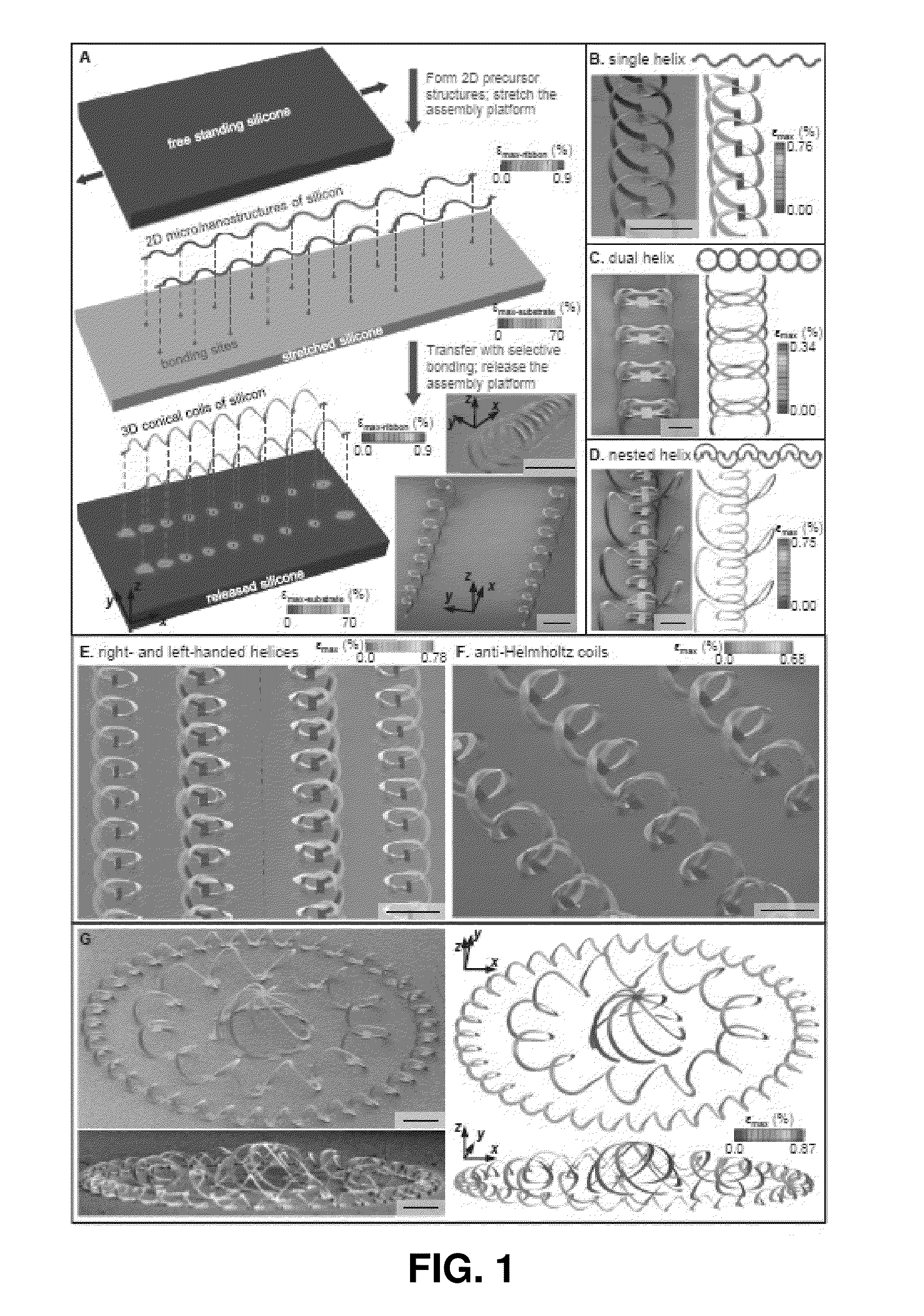

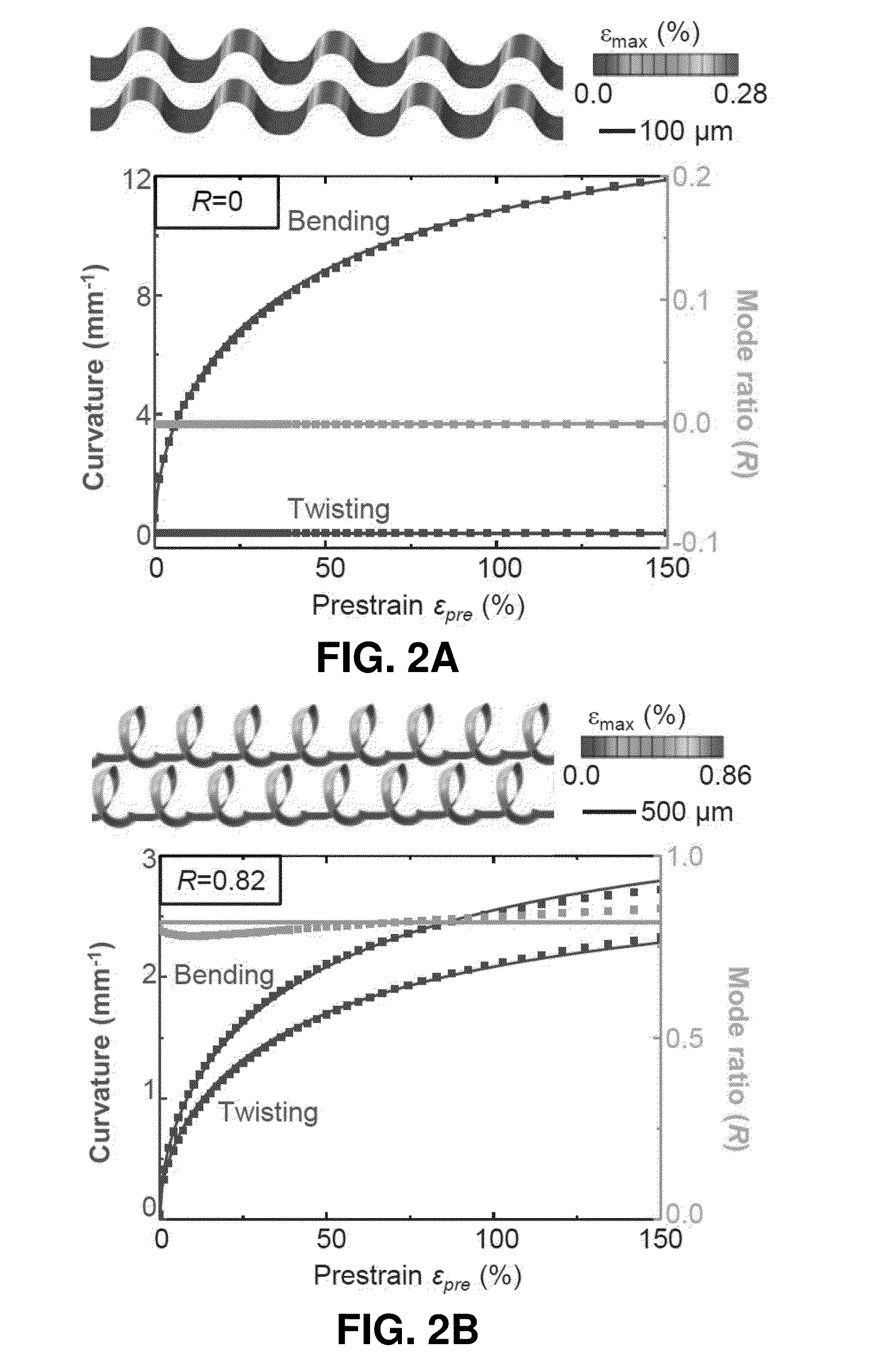

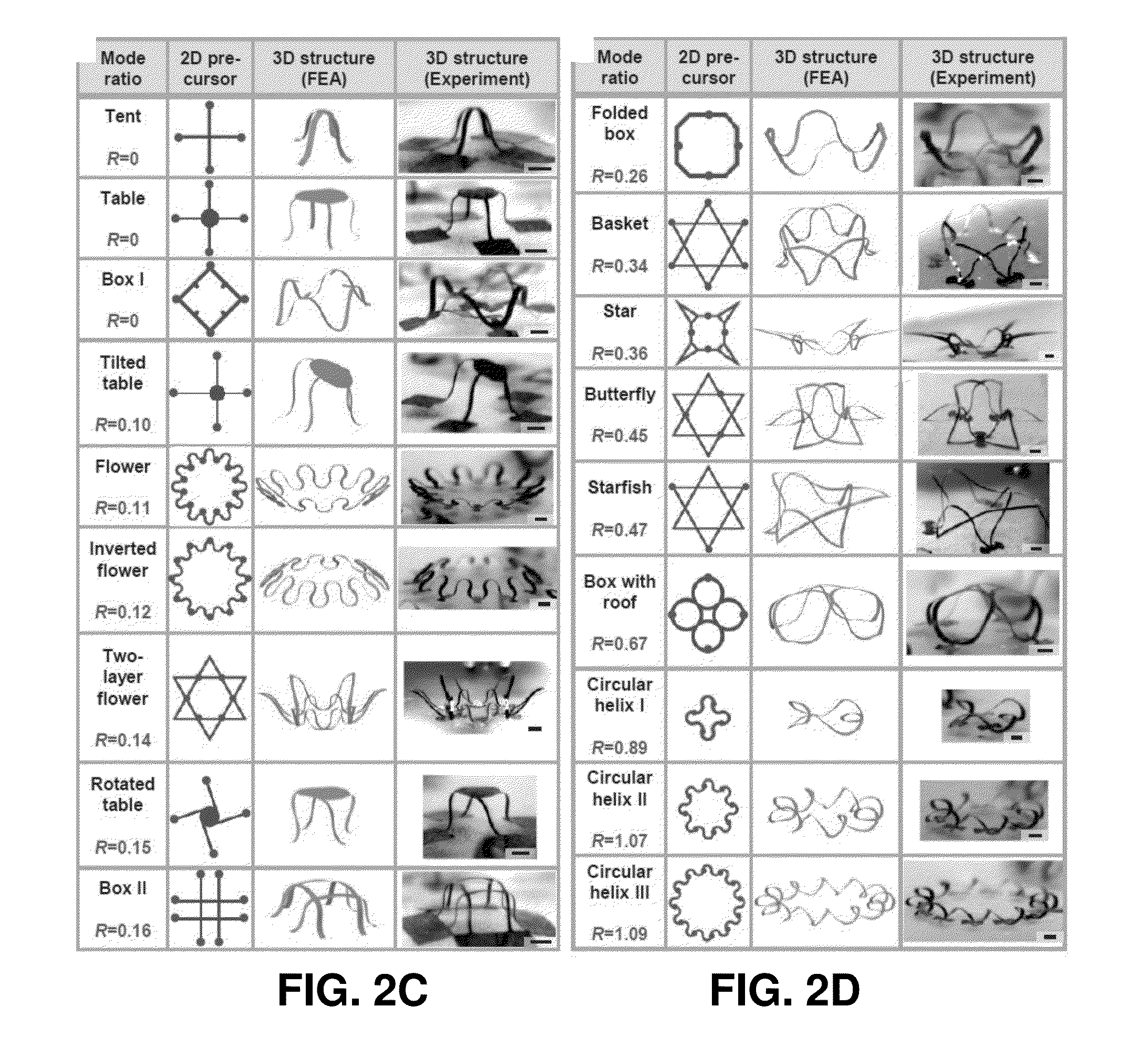

Deterministic assembly of complex, three-dimensional architectures by compressive buckling

ActiveUS20160136877A1Reduce the amount requiredReduces stateCircuit bendability/stretchabilitySynthetic resin layered productsThree dimensional architectureEngineering

Origami- and Kirigami-inspired assembly of predetermined three-dimensional forms is presented in comprehensive theoretical and experimental studies, with examples of a broad range of topologies and material compositions. The resulting engineering options in the construction of functional 3D structures have important implications for advanced microsystem technologies.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS +1

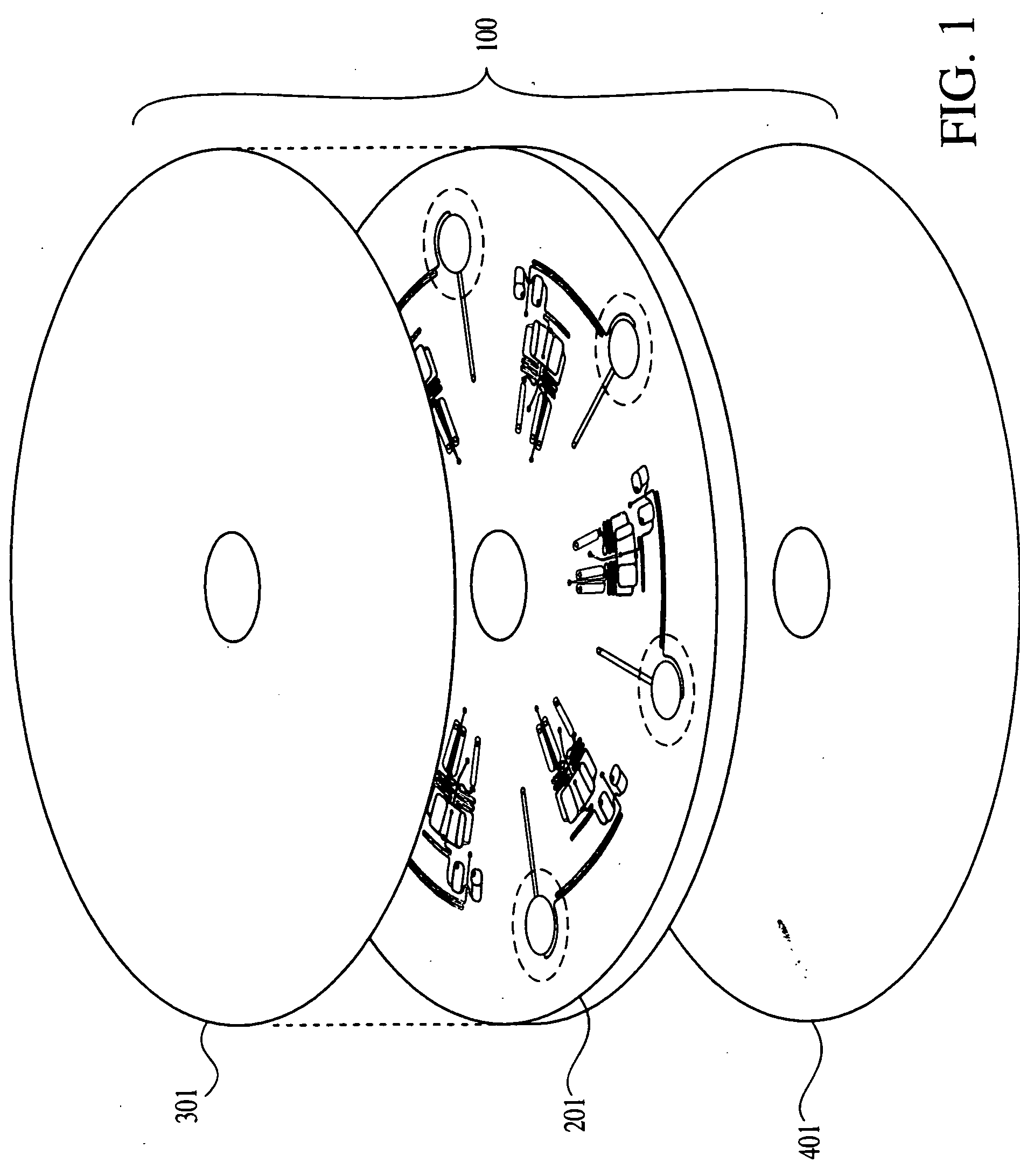

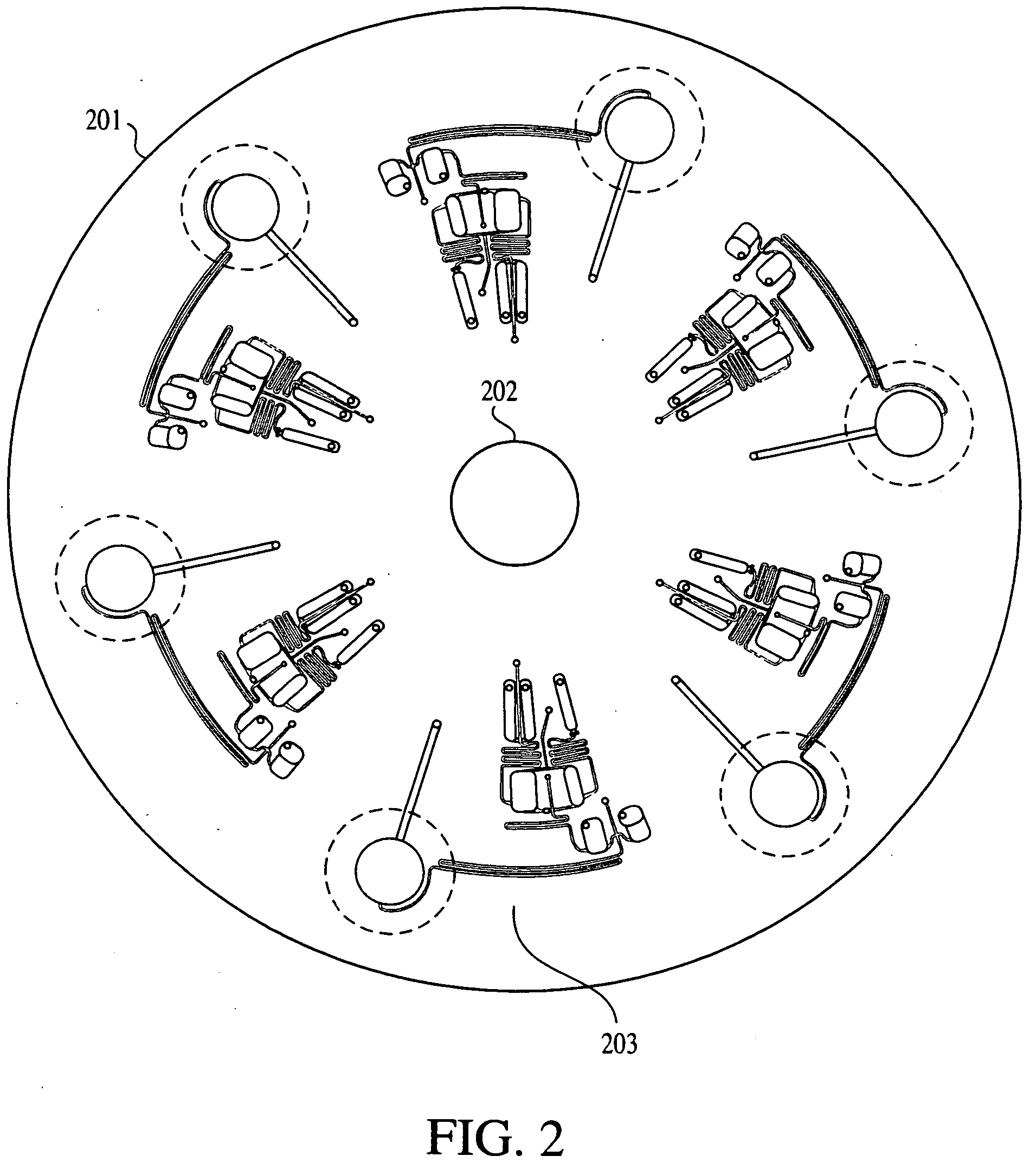

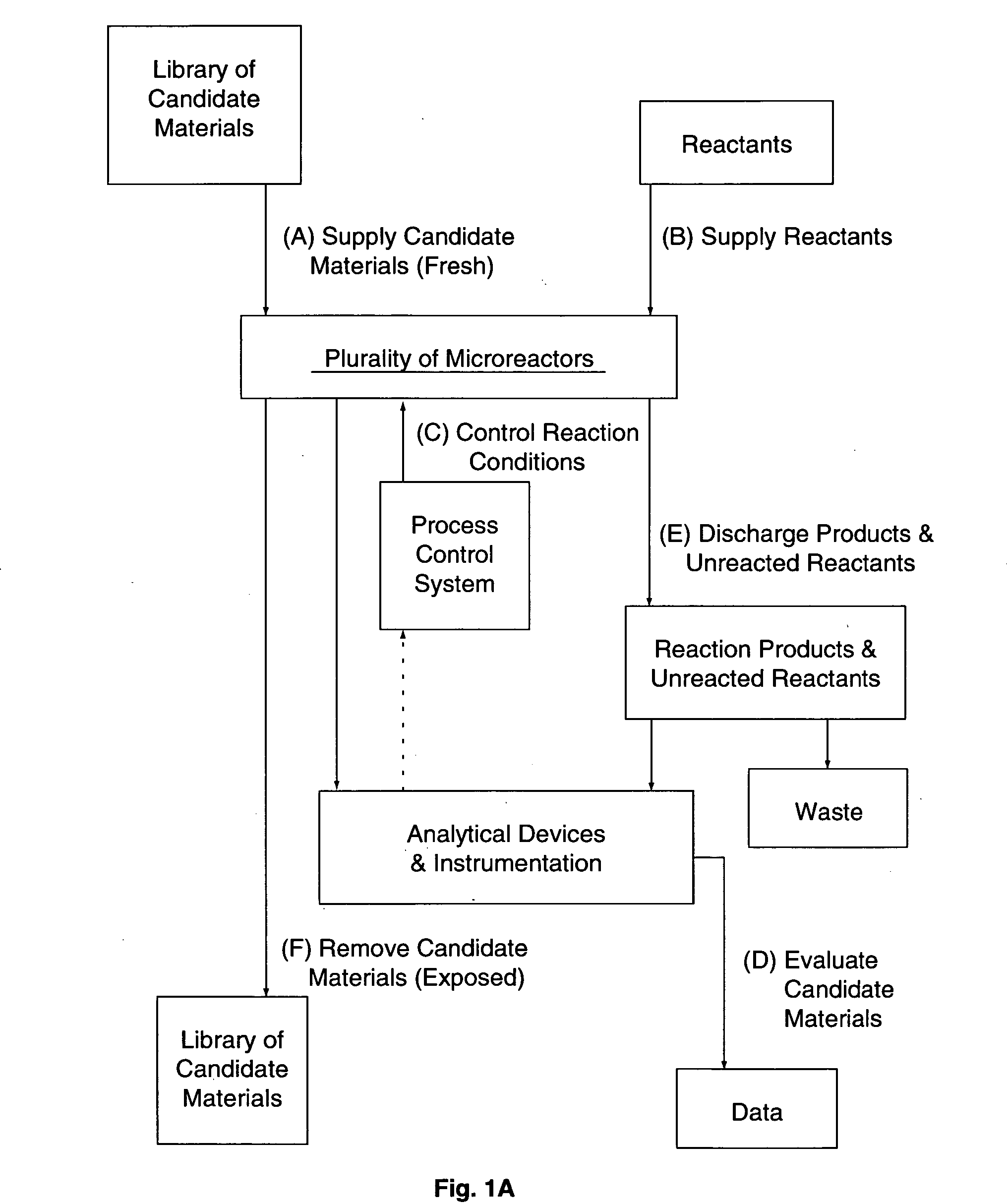

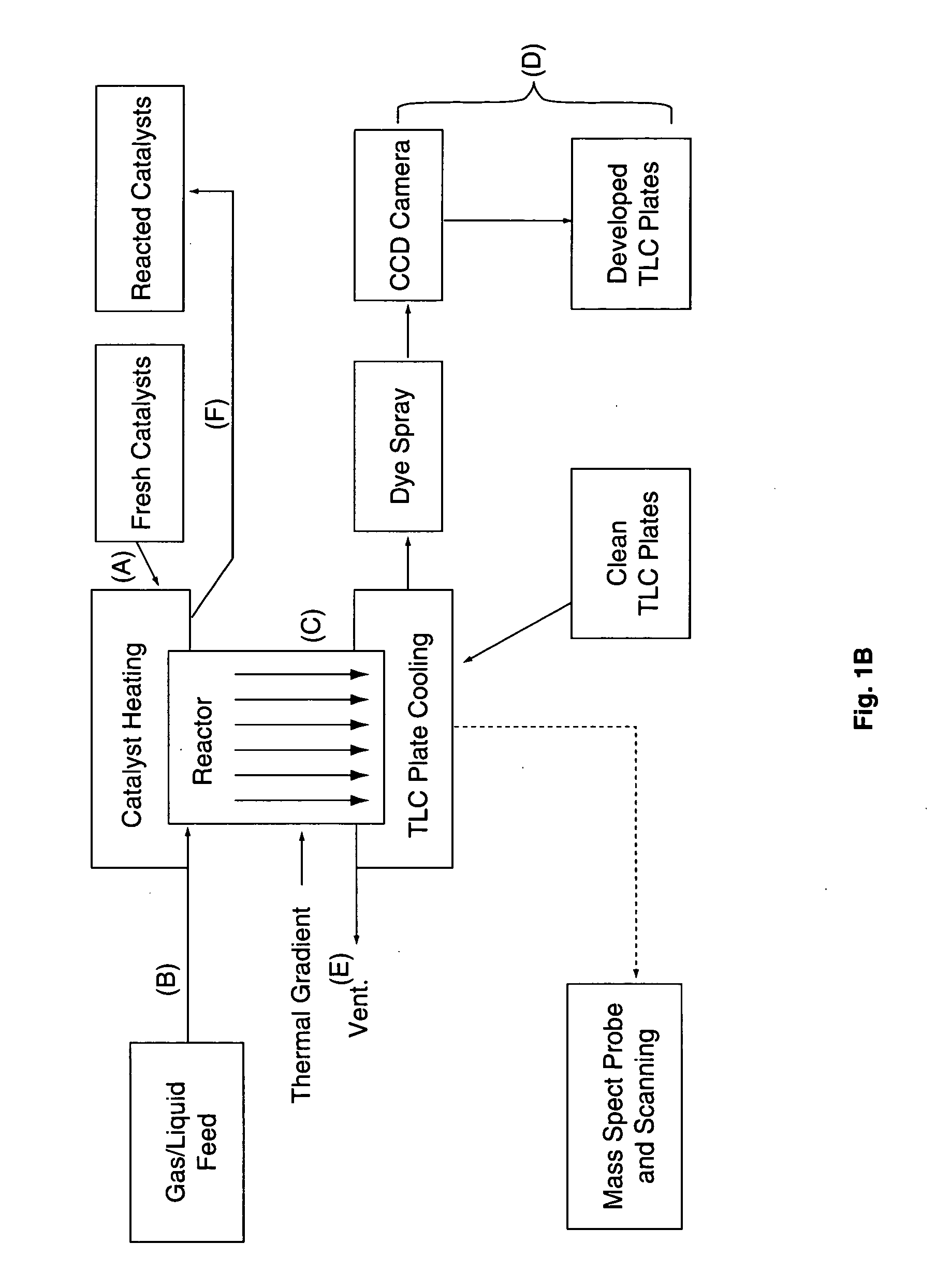

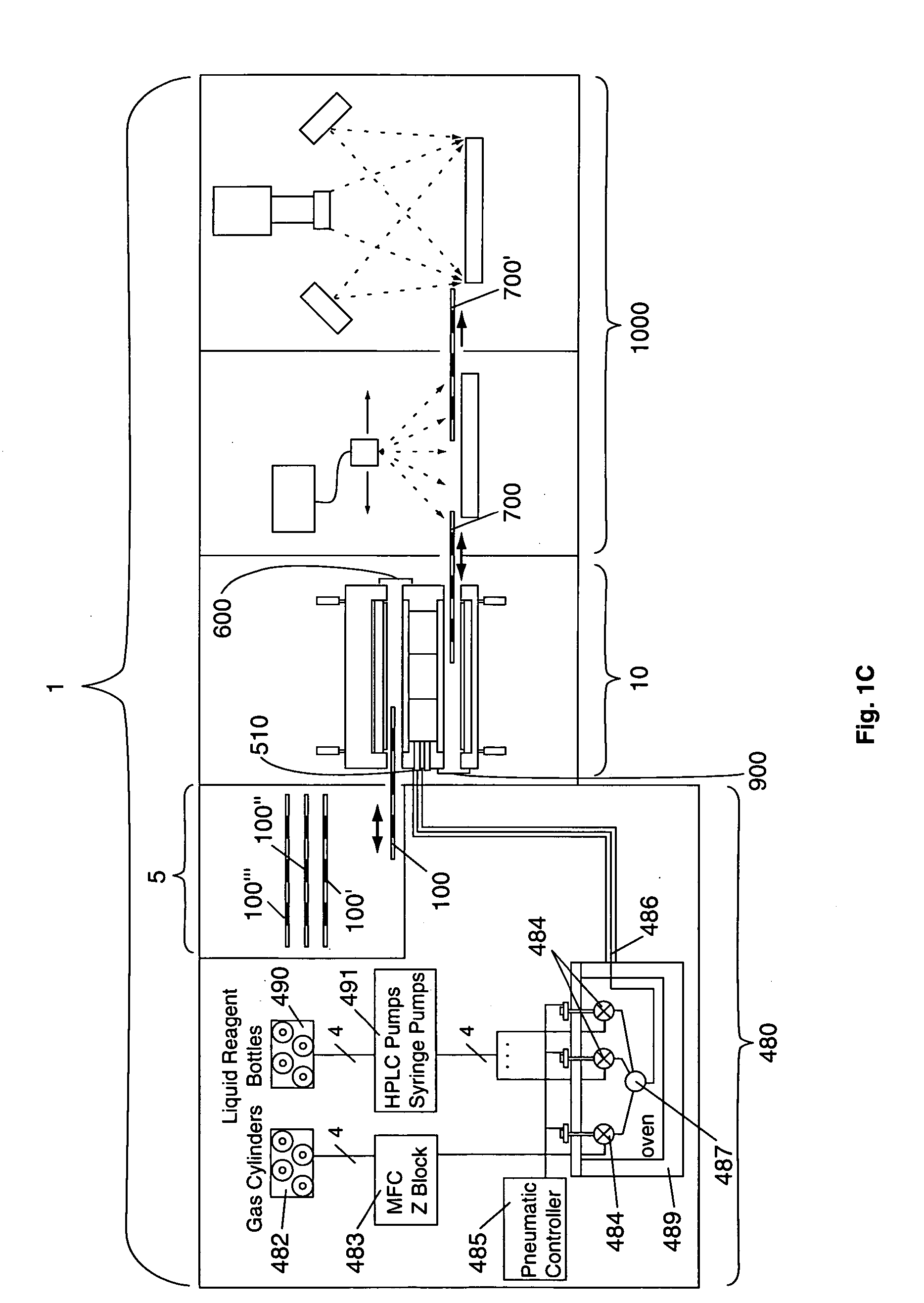

Chemical processing microsystems comprising high-temperature parallel flow microreactors

InactiveUS20050009175A1Large degree of analytical flexibilityReduce manufacturing costBioreactor/fermenter combinationsSequential/parallel process reactionsChemical treatmentMicroreactor

A chemical processing microsystem useful for identifying and optimizing materials (e.g., catalysts) that enhance chemical processes or for characterizing and / or optimizing chemical processes is disclosed. The chemical processing microsystem comprises a plurality of microreactors 600 and, in a preferred embodiment, a plurality of microseparators 900 integral with the chemical processing microsystem 10. The microreactors 600 are preferably diffusion-mixed microreactors formed in a plurality of laminae that include a modular, interchangeable candidate-material array 100. The material array 100 comprises a plurality of different candidate materials (e.g., catalysts), preferably arranged at separate, individually addressable portions of a substrate (e.g., wafer). The microseparators 900 are similarly formed in a plurality of laminae that include a modular, interchangeable adsorbent array 700. The adsorbent array 700 comprises one or more adsorbents, preferably arranged at separate, individually addressable portions of a substrate to spatially correspond to the plurality of different candidate materials. Modular microfluidic distribution systems are also disclosed. The chemical processing microsystem can be integrated into a material evaluation system that enables a comprehensive combinatorial material science research program.

Owner:FREESLATE

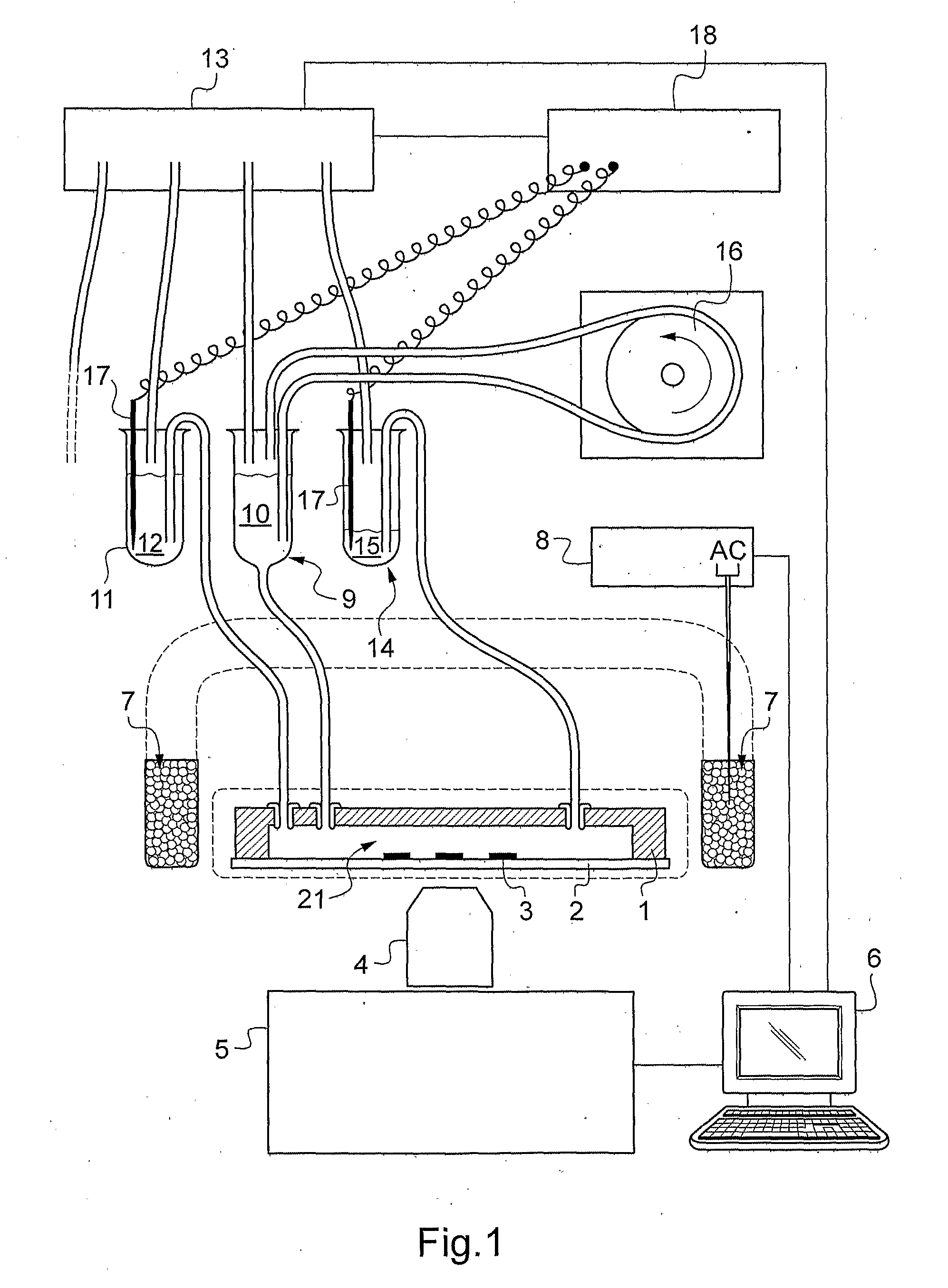

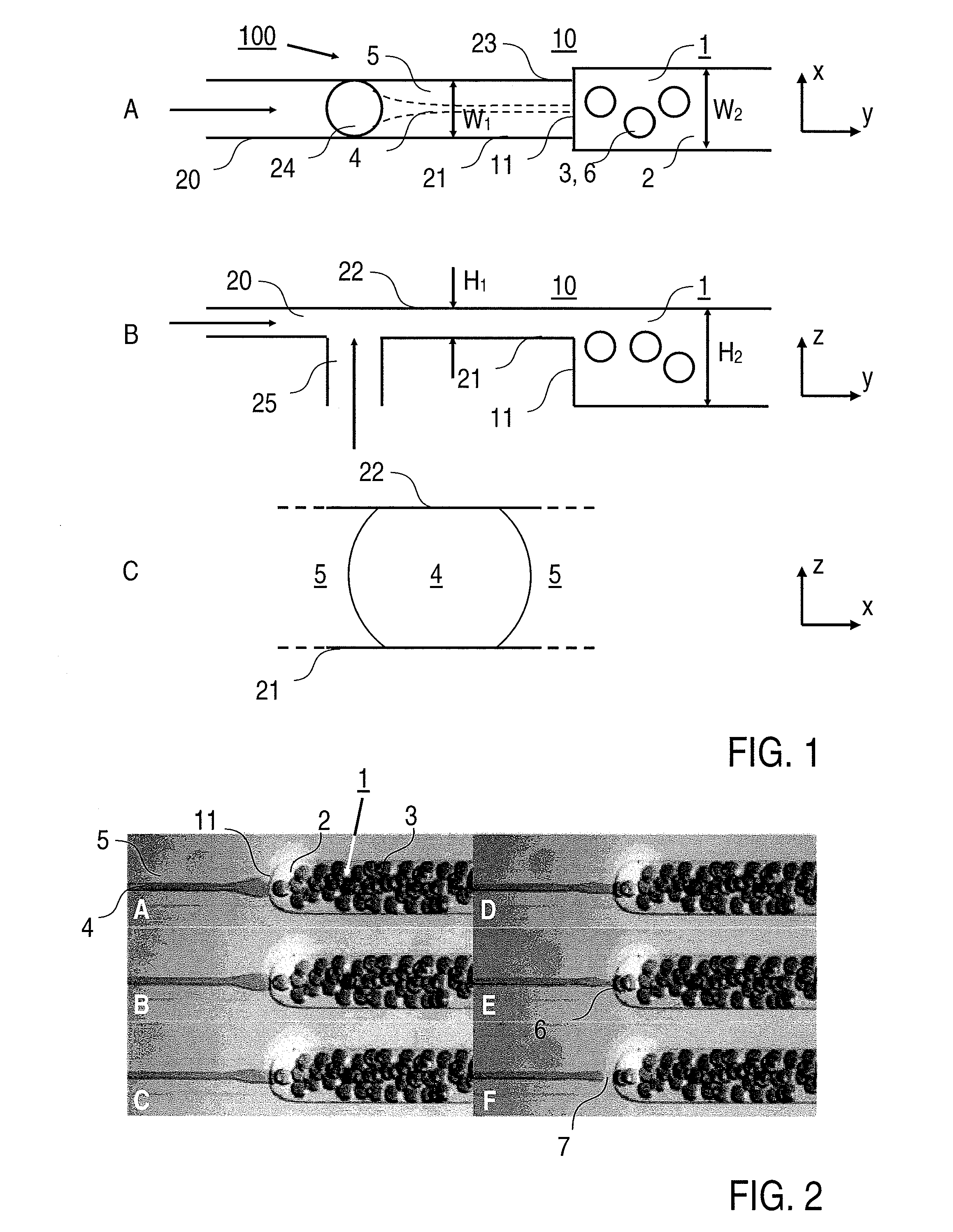

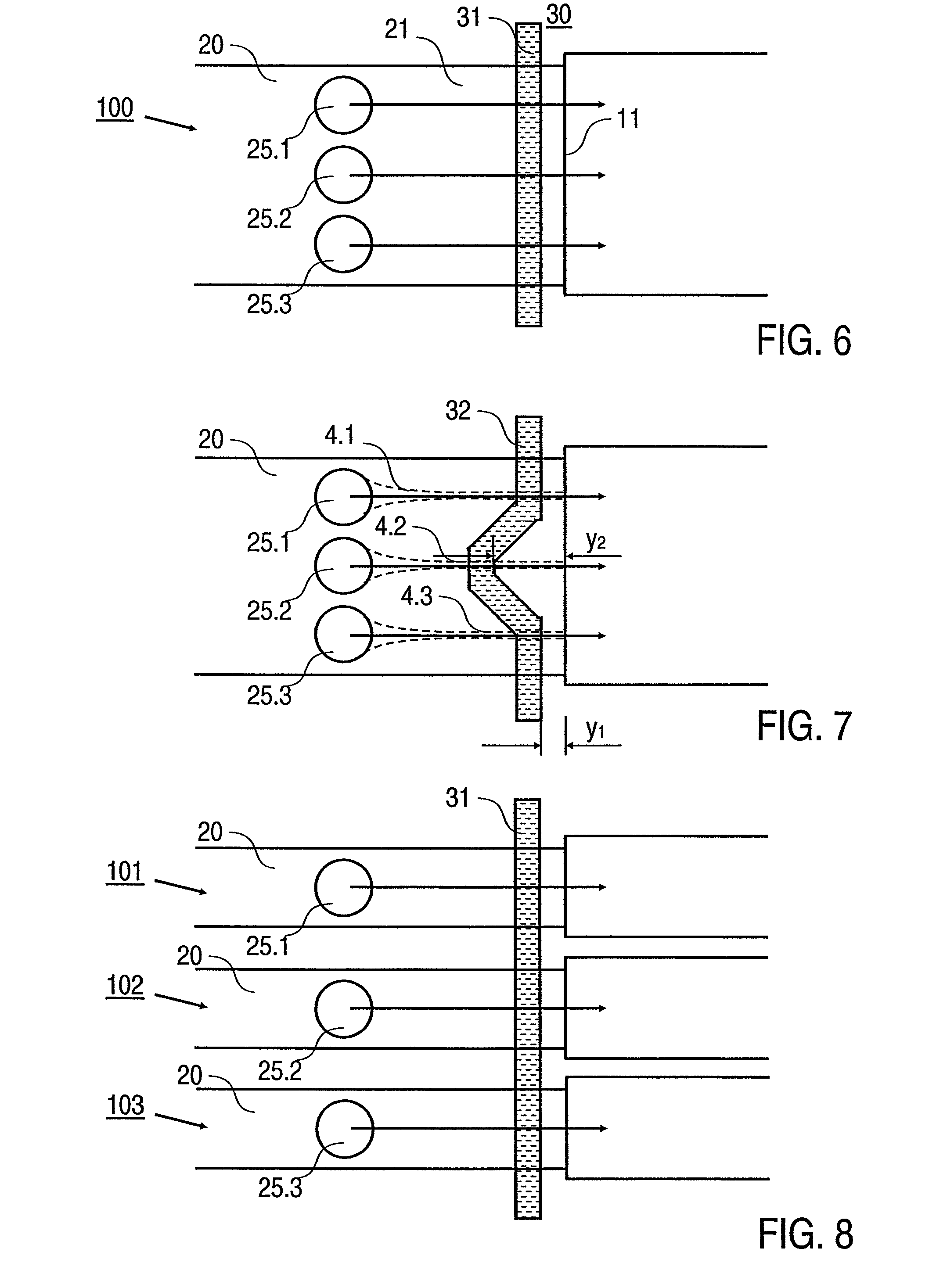

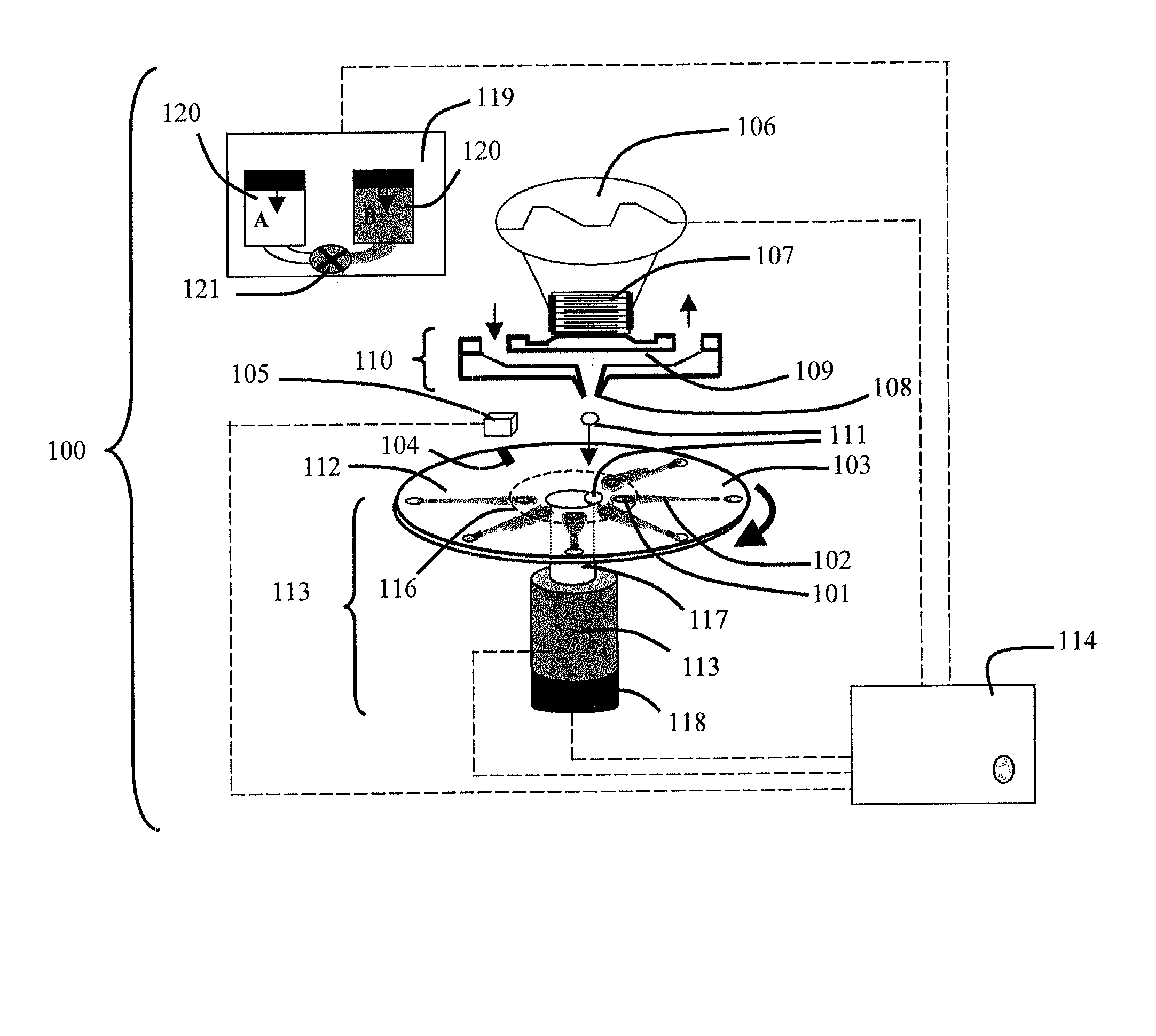

Formation of an emulsion in a fluid microsystem

InactiveUS7943671B2Promote fragmentationHigh degreeFrom normal temperature solutionsLiquid separation by electricityEmulsionEngineering

There is described a method for forming an emulsion (1) containing at least one dispersed phase (3) and a continuous phase (2) in a fluidic microsystem (100), said method comprising the steps: forming flows (4, 5) of different liquids which flow towards a dispersion region (10), and forming the emulsion (1) from the liquids in the dispersion region (10), wherein the flows (4, 5) run through a common channel (20) to the dispersion region (10) and the flows (4, 5) are arranged next to one another relative to a first reference direction, and wherein the emulsion (1) is produced as the liquids flow through a cross-sectional widening (11) provided in the dispersion region (10), at which the cross section of the channel (20) widens in a second reference direction different from the first reference direction. A fluidic microsystem for forming an emulsion (1) containing a continuous phase (2) and at least one dispersed phase (3) is also described. A fusion of droplets in electric fields is also described.

Owner:MAX PLANCK GESELLSCHAFT ZUR FOERDERUNG DER WISSENSCHAFTEN EV

Ceramic hollow fibers made from nanomscale powder particles

The invention relates to a method for producing ceramic hollow fibers from nanoscale particles and to hollow fibers produced in such a manner. The inventive method is characterized in that the ceramic material has a solids content of >25% by volume, preferably >30% by volume and is processed by means of extrusion and spinning. The hollow fiber is sintered according to conventional sintering methods. A hollow fiber produced in this manner is used for metal, polymer and ceramic matrix reinforcements, for artificial organs, for microsystems technology components, for fiber optical waveguides, for ceramic membranes, for solid electrolyte in fuel cells (SOFC), for tissue engineering and for producing extremely light ceramic parts, such as heat shields or brake systems, that are subjected to temperature stresses. The inventive ceramic batch can also be processed by means of silk screening whereby resulting in the production of filigree structures over the ceramic silk screening.

Owner:ITN NANOVATION AG

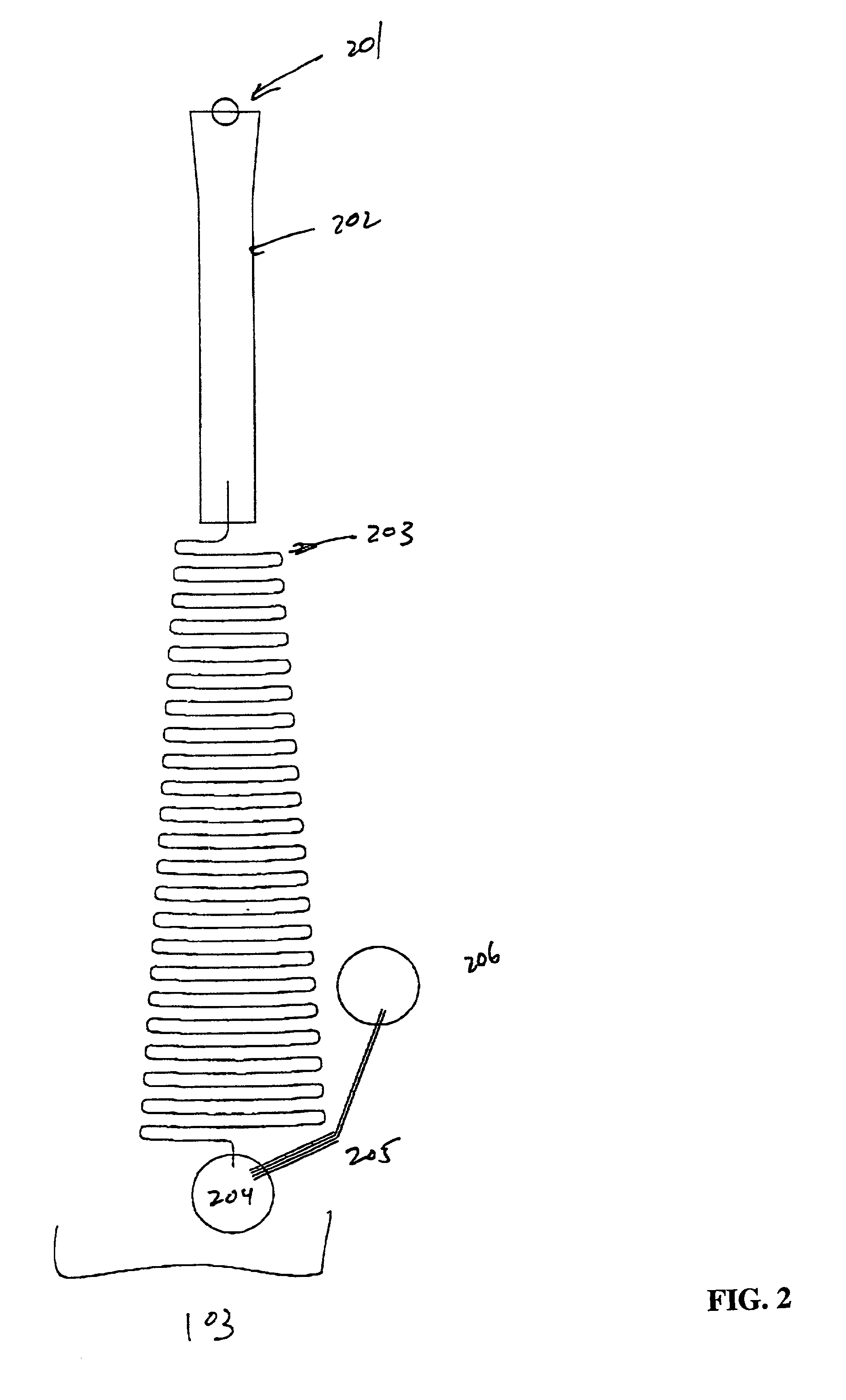

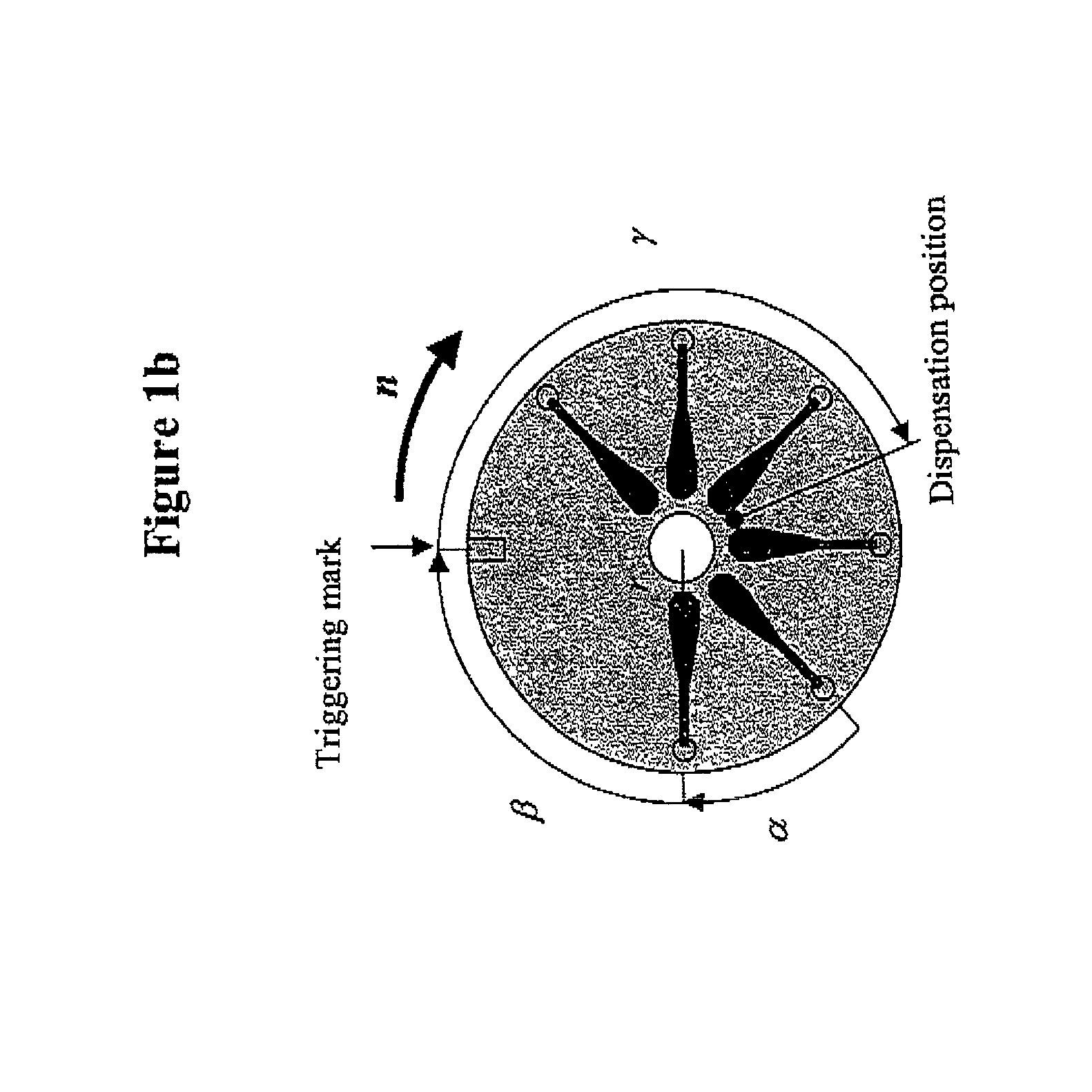

Method and instrumentation for micro dispensation of droplets

InactiveUS20030094502A1Easy to mass producePrevent leakageBurnersLiquid handlingMechanical engineeringInstrumentation

A method for dispensing droplets of a liquid to a microsystem in the form of a disc comprising a target area (TA0I) in its surface, said disc preferably being a microfluidic disc comprising a microchannel structure with an inlet port that is a target area (TA0I). The method is characterized by comprising the steps of: i) providing (1) said disc which has a triggering mark, and (2) a dispenser arrangement comprising: a) a spinner for rotating the disc around its axis, b) a drop dispenser permitting dispensation of droplets to inlet port I, c) a fixed trigger position outside the disc, and d) a controller which is capable of triggering the dispensation of a droplet into (TA0I) as a function of the triggering mark passing the trigger position; ii) placing the disc in the spinner and programming the controller with values for dispensing parameters that will give dispensation of the droplets to TA0I; iii) dispensing the droplets. The invention also comprises the dispenser arrangement as such.

Owner:GYROS

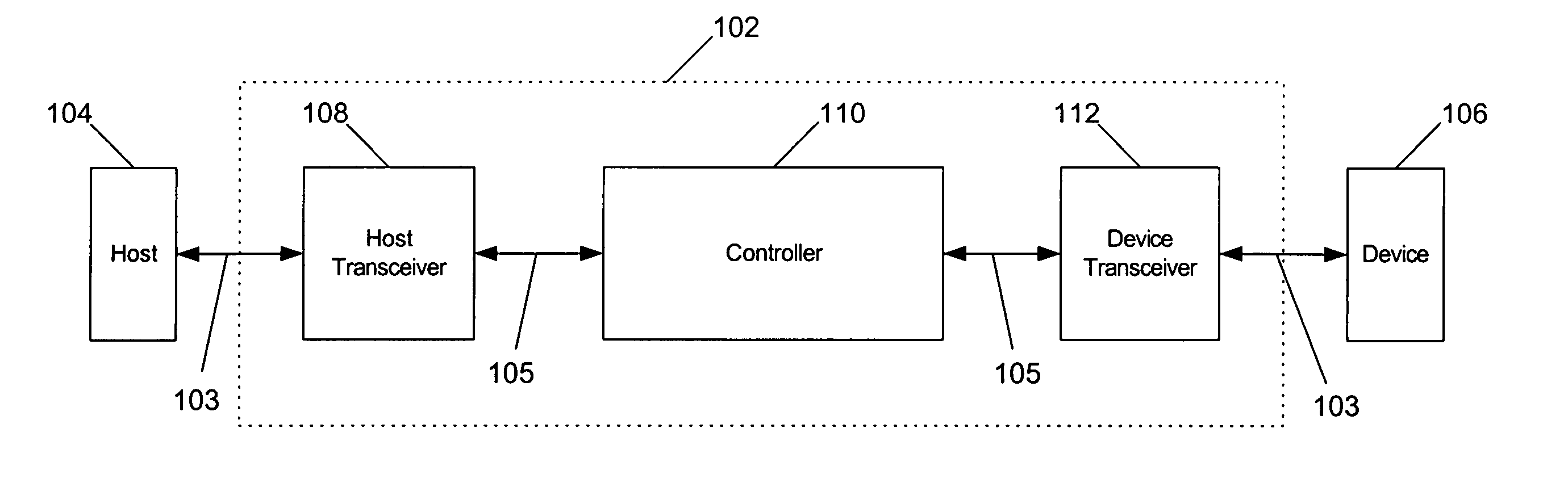

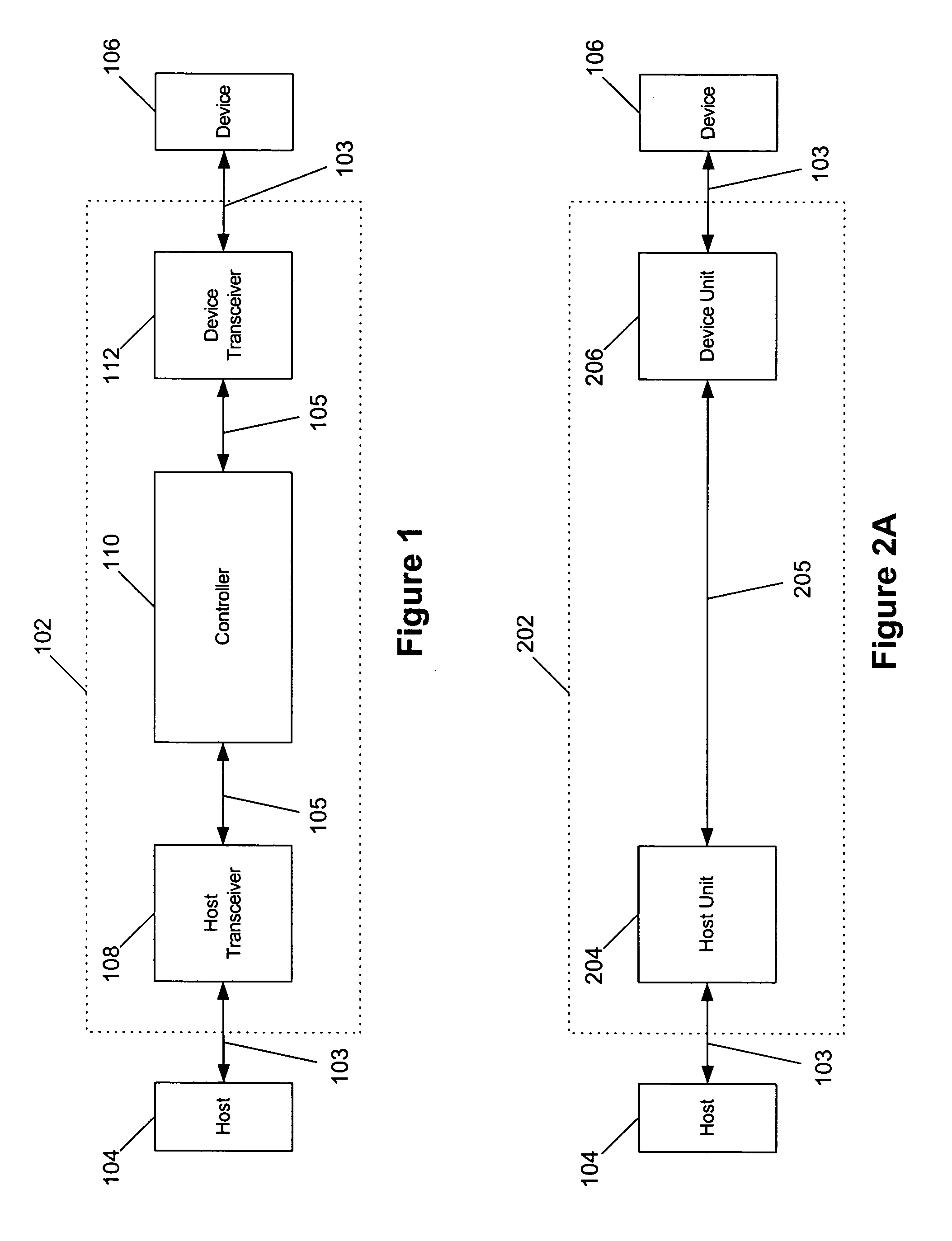

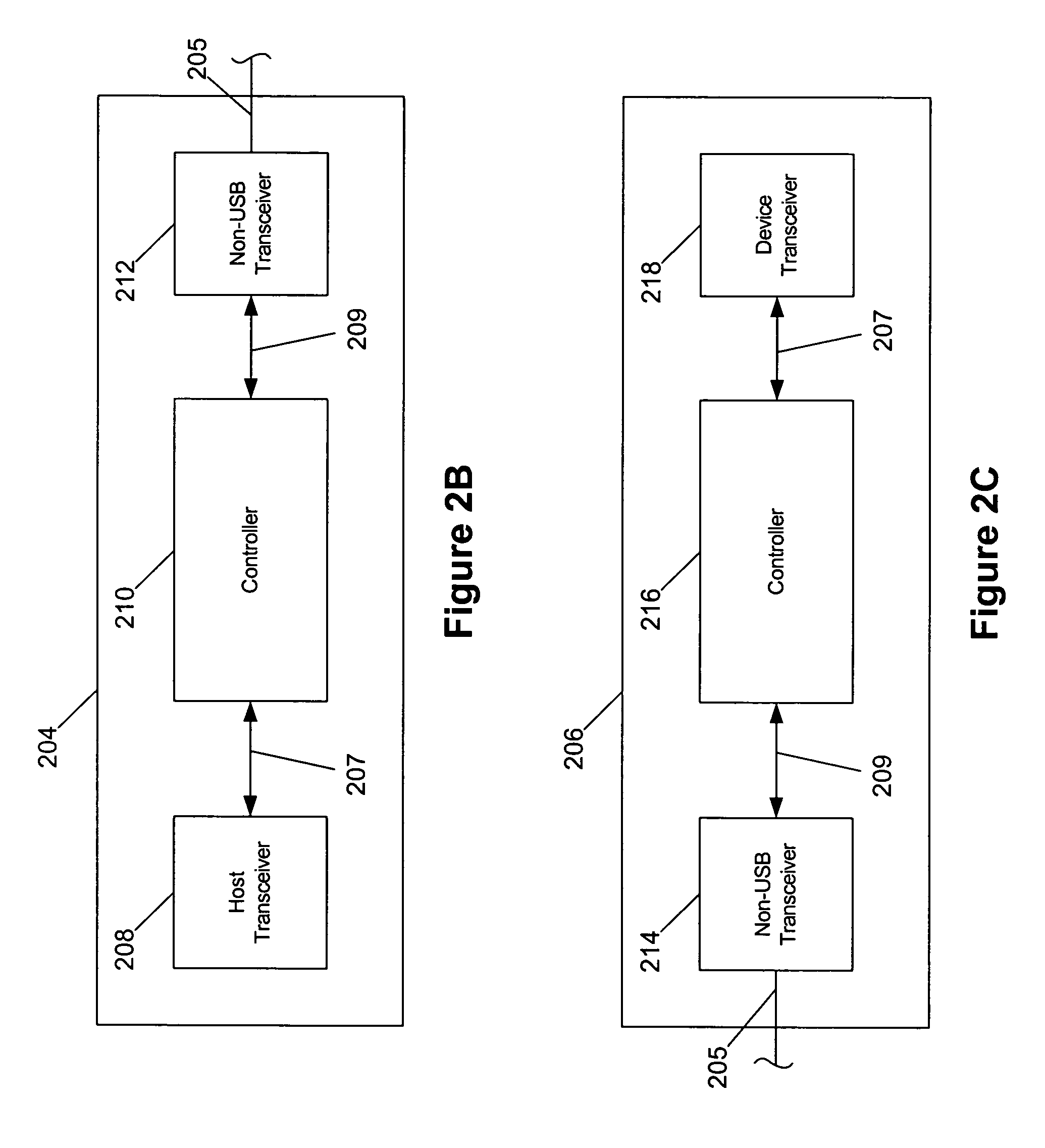

USB extender

InactiveUS20050027889A1Increase distanceMultiple digital computer combinationsElectric digital data processingSun MicrosystemsEngineering

The present invention relates to a system and method for extending USB connections. Provided are both active USB extenders and passive USB extenders that include functionality for accepting both standard and / or non-standard USB commands. The passive extender functions on a USB communications channel and the active extender functions to extend USB communications over a non-USB communications channel. Both types of extenders are configured to handle non-standard USB commands, such as a Macintosh power-on command or a Sun Microsystems reset, suspend, or wake-up command.

Owner:VIDEO PRODS

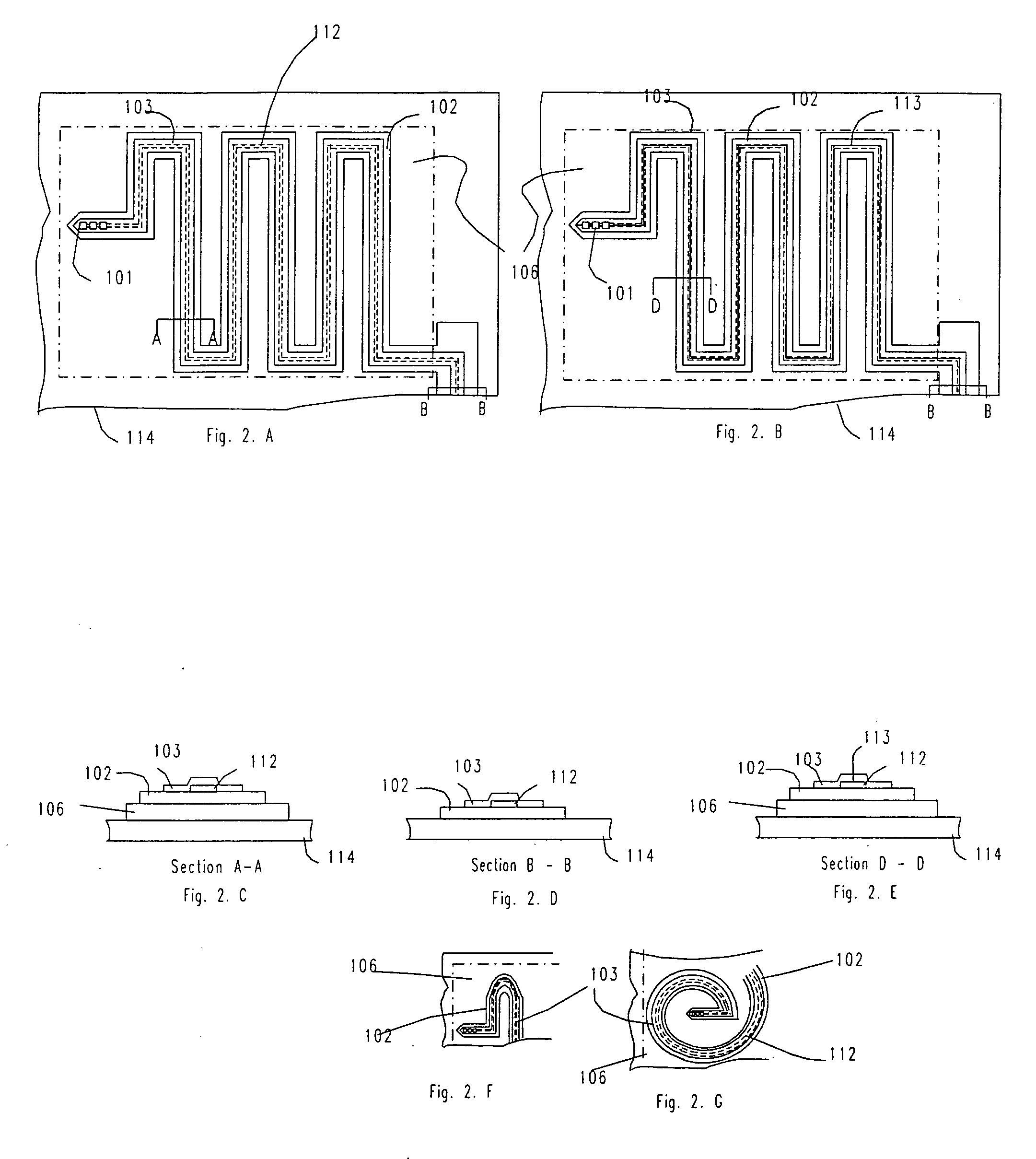

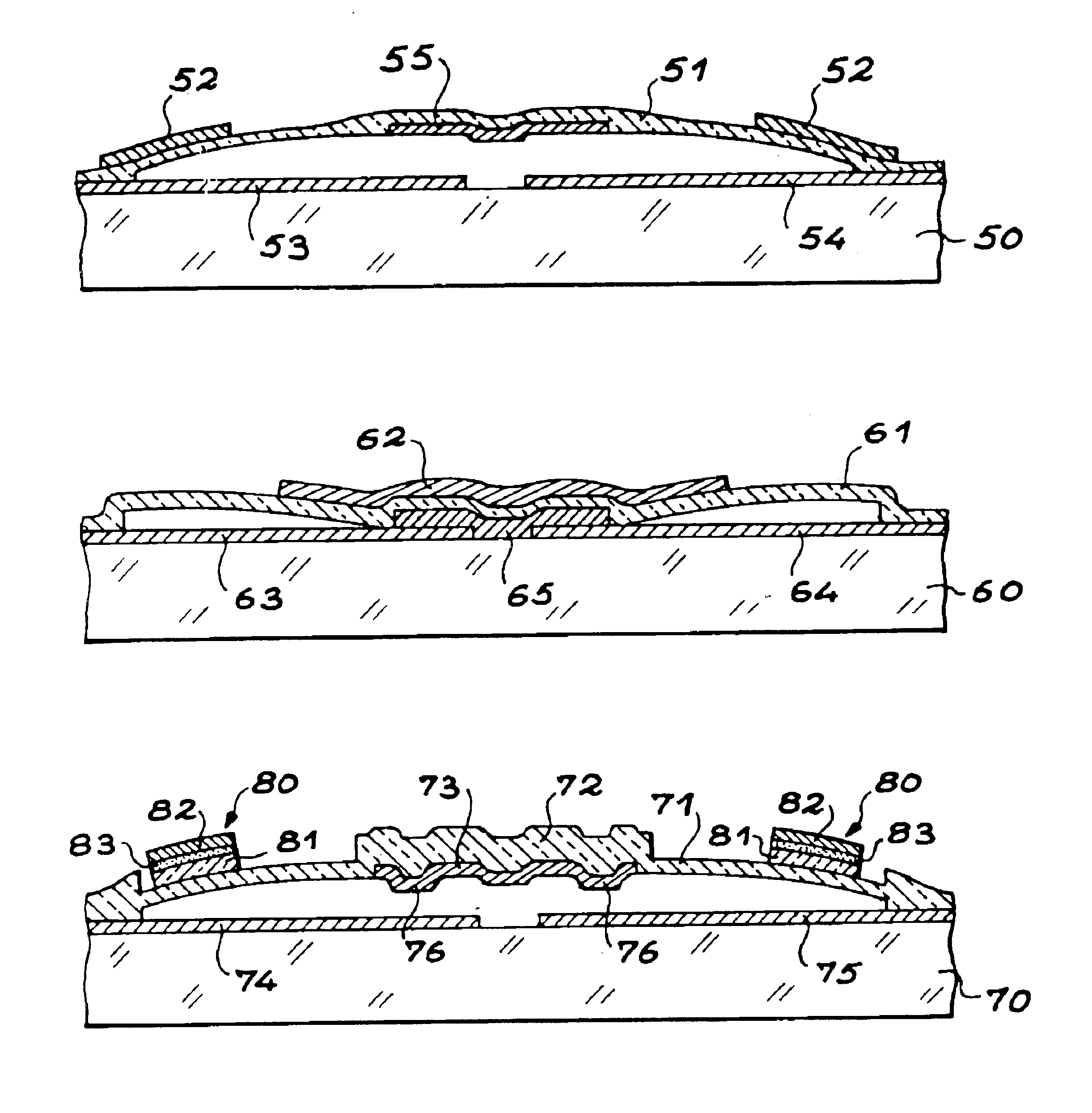

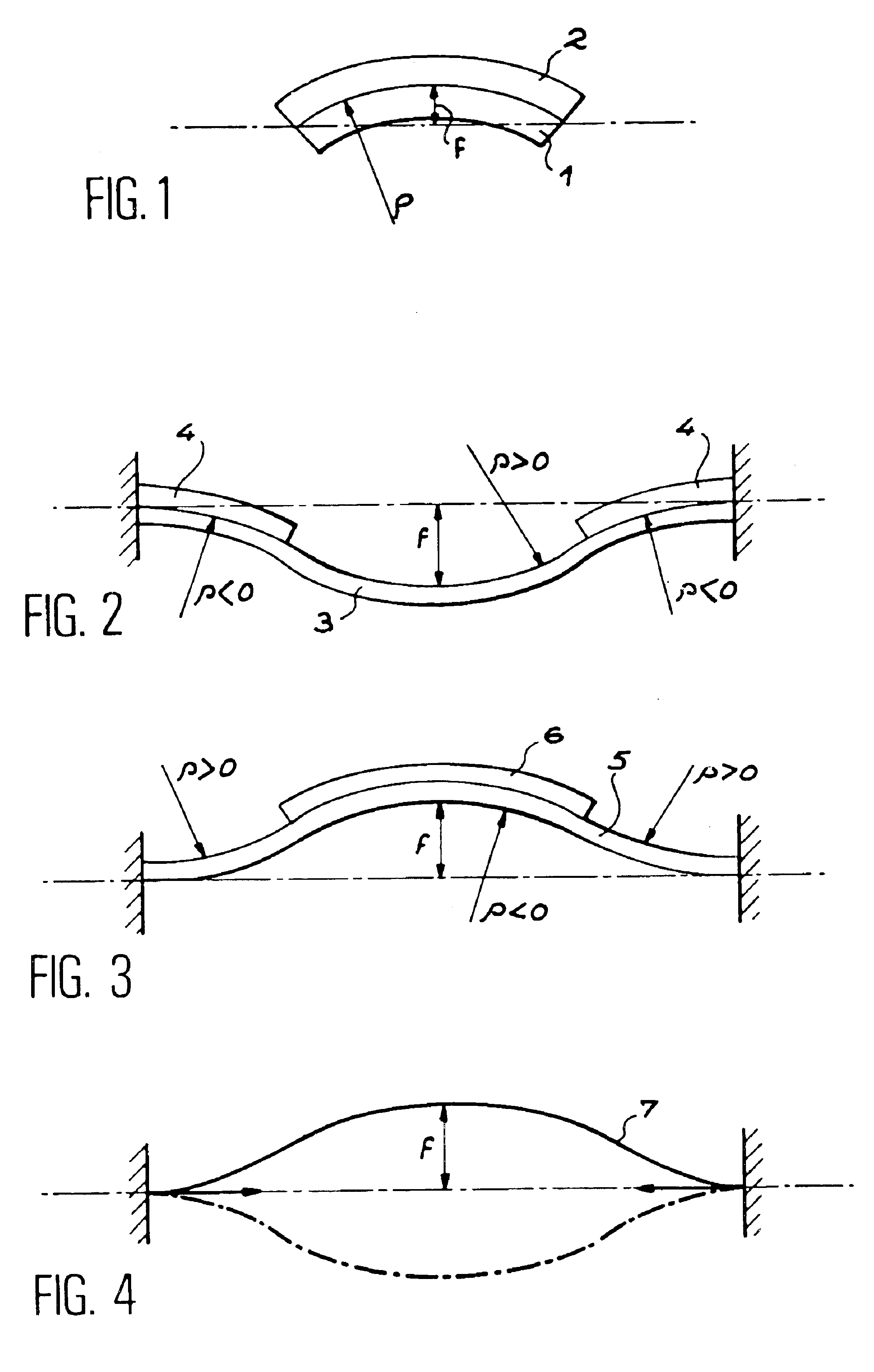

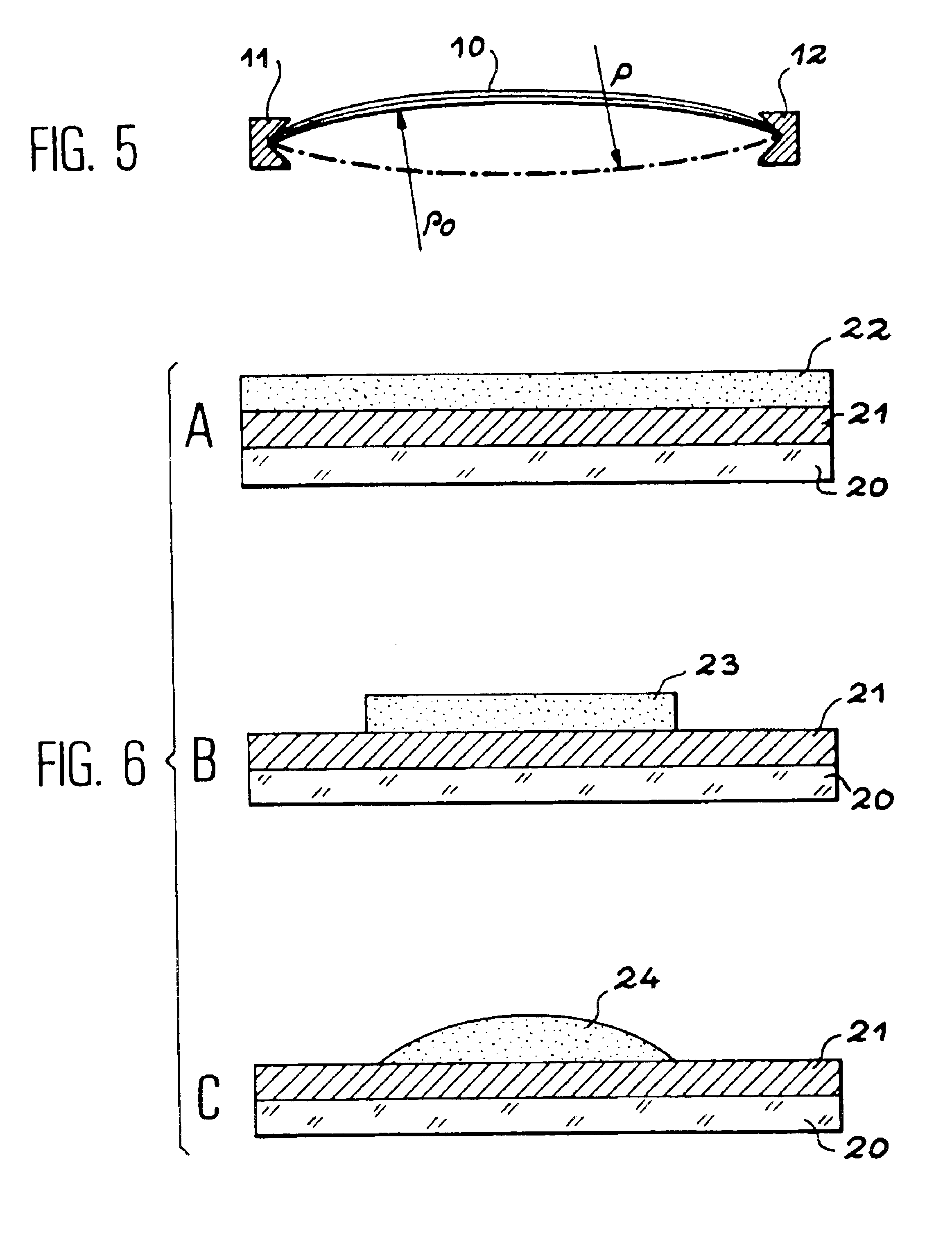

Microsystem with element deformable by the action of heat-actuated device

InactiveUS6812820B1Electrothermal relaysCapacitor with electrode distance variationEngineeringMicrosystem

The invention concerns a microsystem, in particular for producing microswitches or microvalves, constituted on a substrate (50) and used for producing a shift between a first operating state and a second operating state by means of a heat actuated device with bi-metal switch effect. The heat-actuated device comprises a deformable element (51) connected, by opposite ends, to the substrate (50) so as to present naturally a deflection without stress relative to the substrate surface which faces it, said natural deflection determining the first operating state, the second operating state being produced by the heat-actuated device which induces, by the effect of temperature variation, a deformation of the deformable element (51) tending to reduce its deflection and submitting it to a compressive stress by buckling effect in a direction opposite to its natural deflection.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

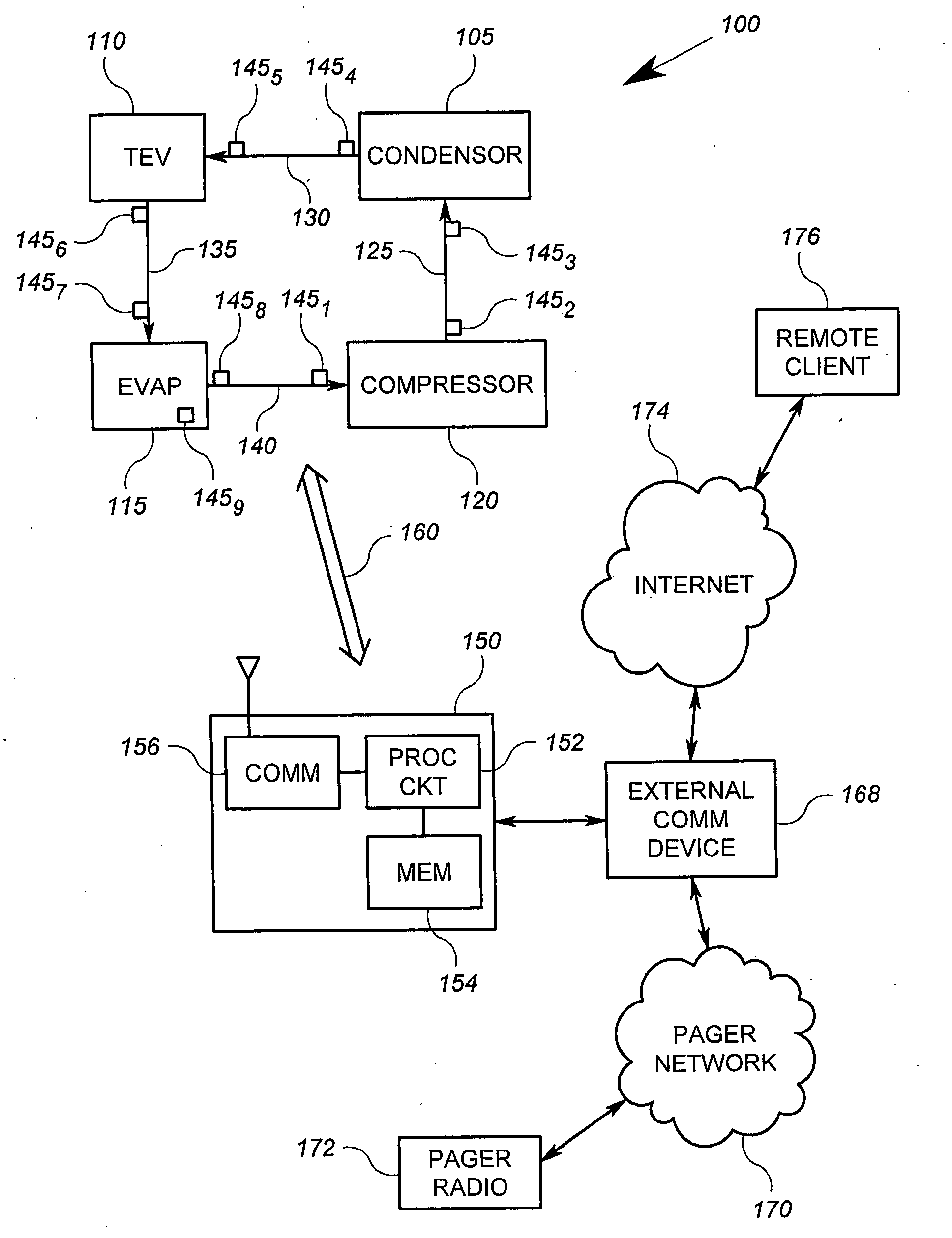

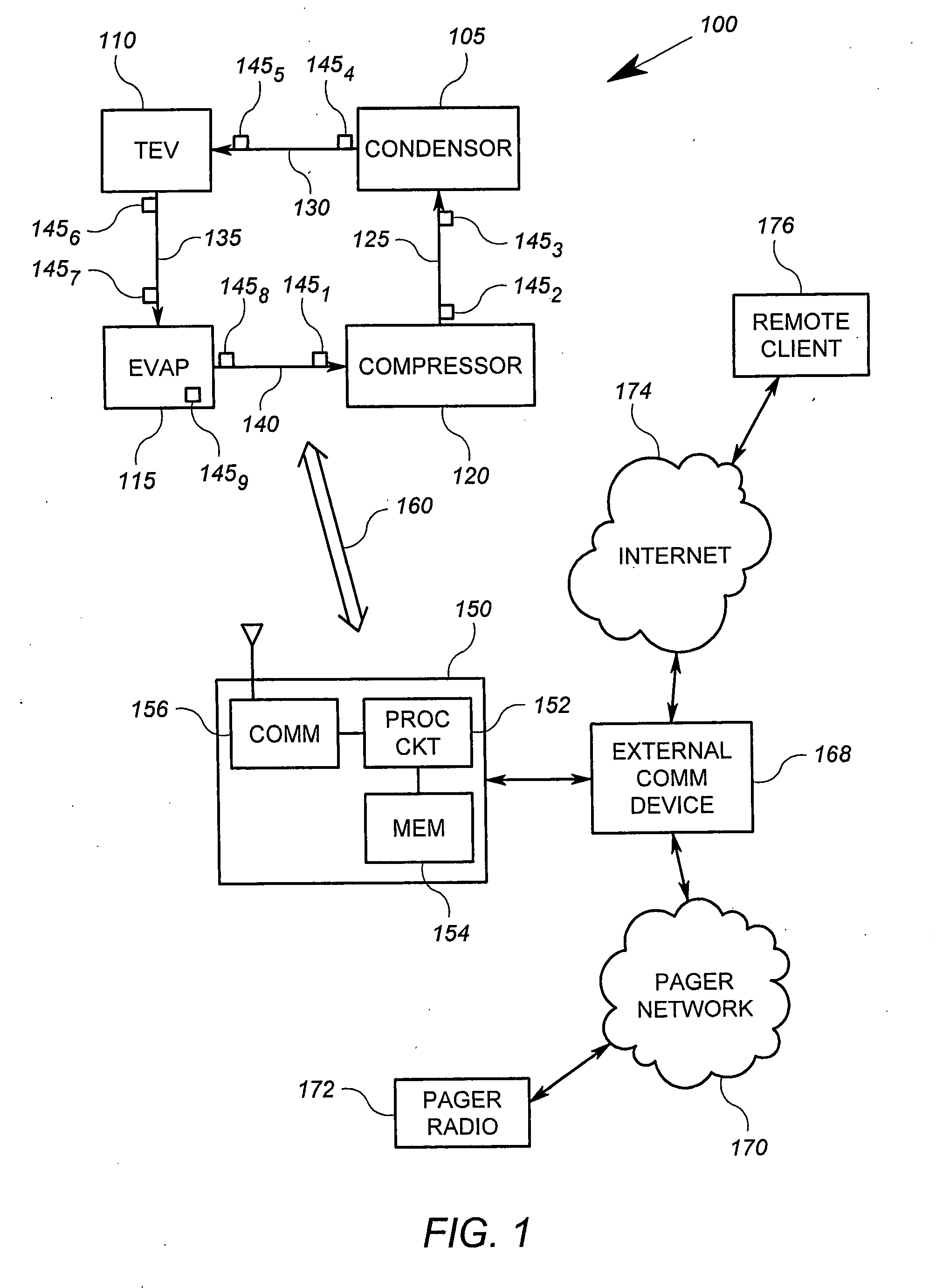

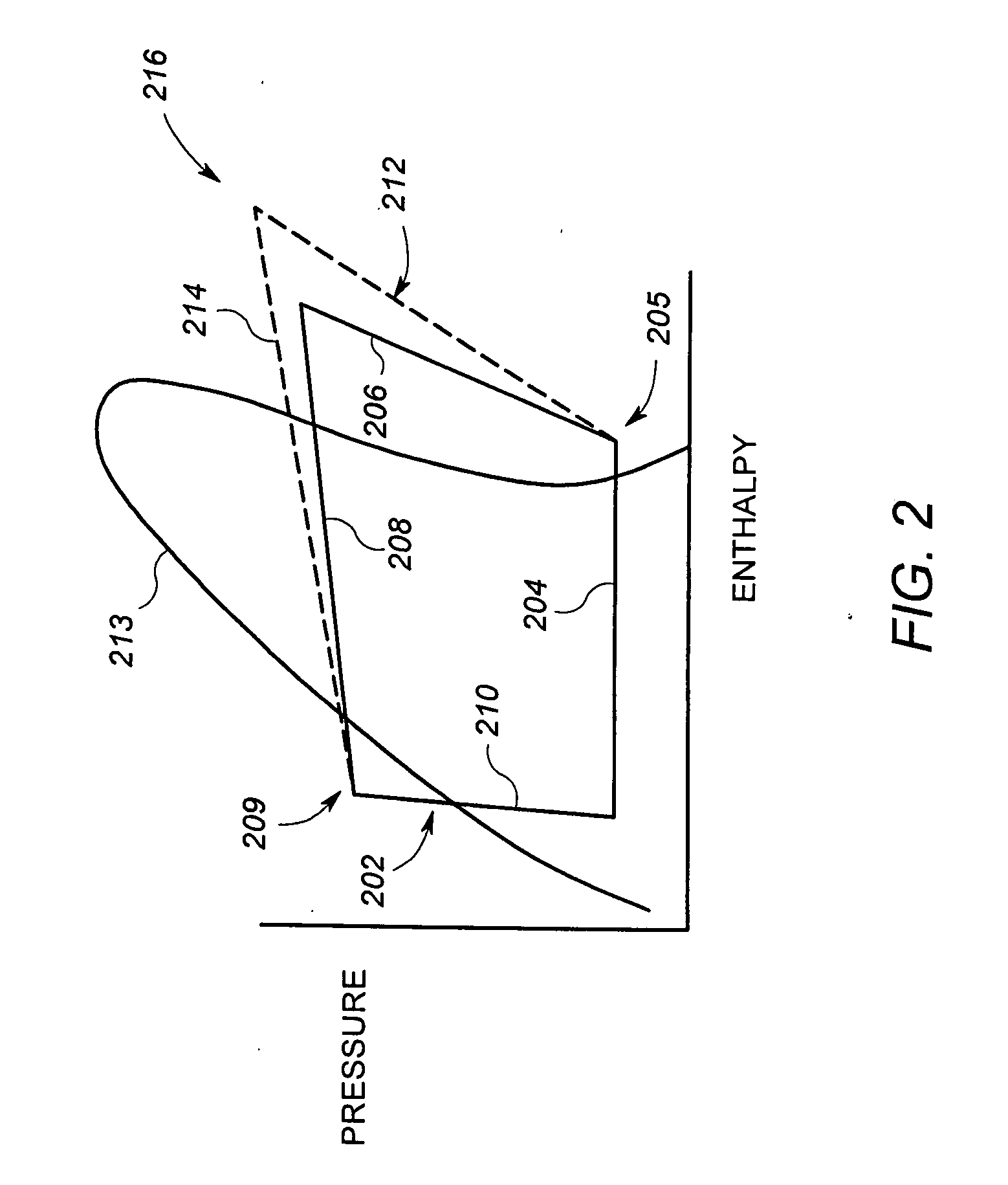

Refrigeration system fault detection and diagnosis using distributed microsystems

InactiveUS20080077260A1Readily and permanentlyDeterioration in system operationPump controlThermometer applicationsMems sensorsNormal conditions

A method and / or apparatus determines whether a refrigeration (or other cooling) related system is operating within normal parameters by comparing reference data derived from ideal or normal conditions within the system. Data regarding the actual operating parameters of the system is provided via a set of microsystem sensors disposed throughout the refrigeration or cooling system. The sensors are in some embodiments wireless, and in some advantageous embodiments includes MEMs sensors.

Owner:SIEMENS IND INC

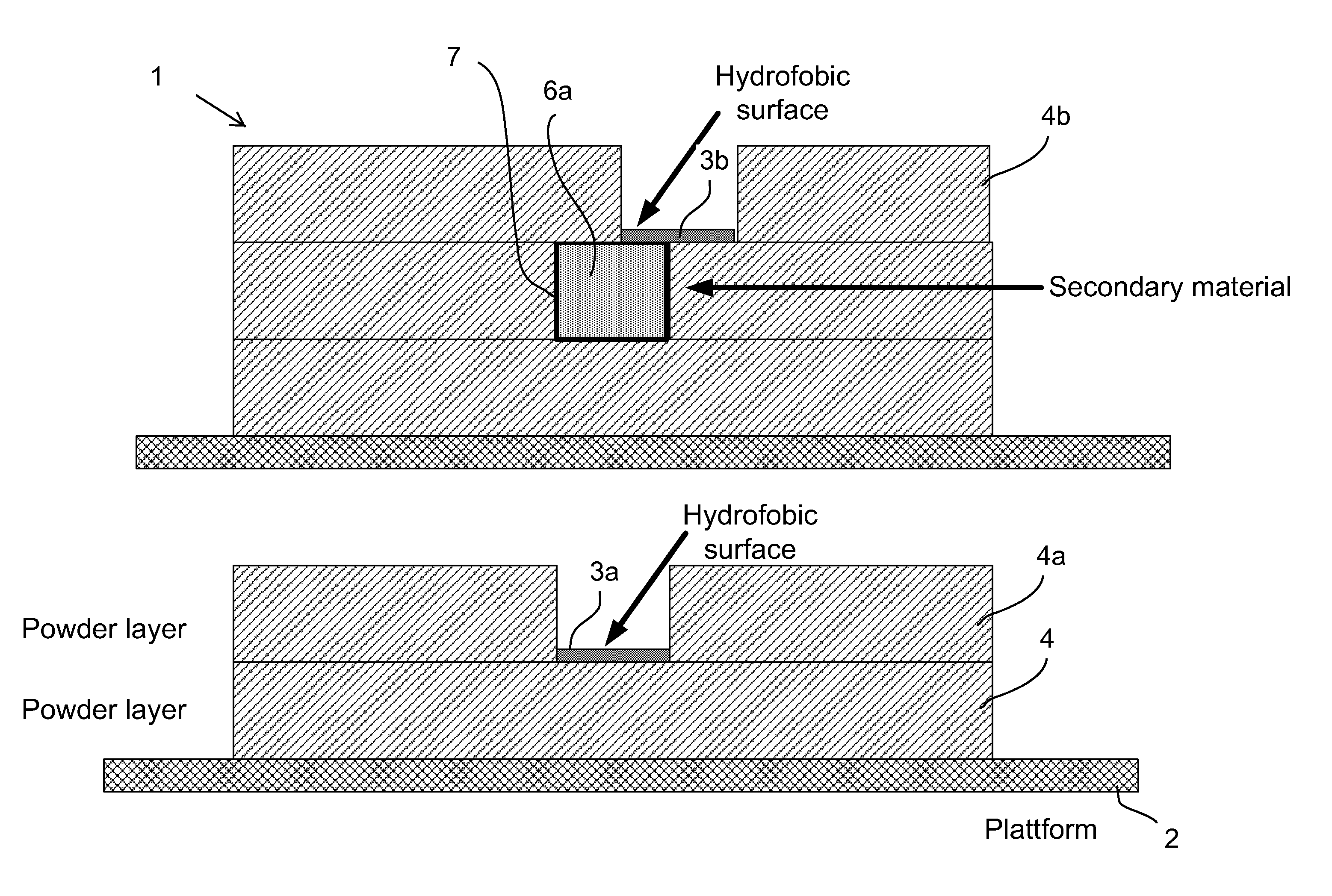

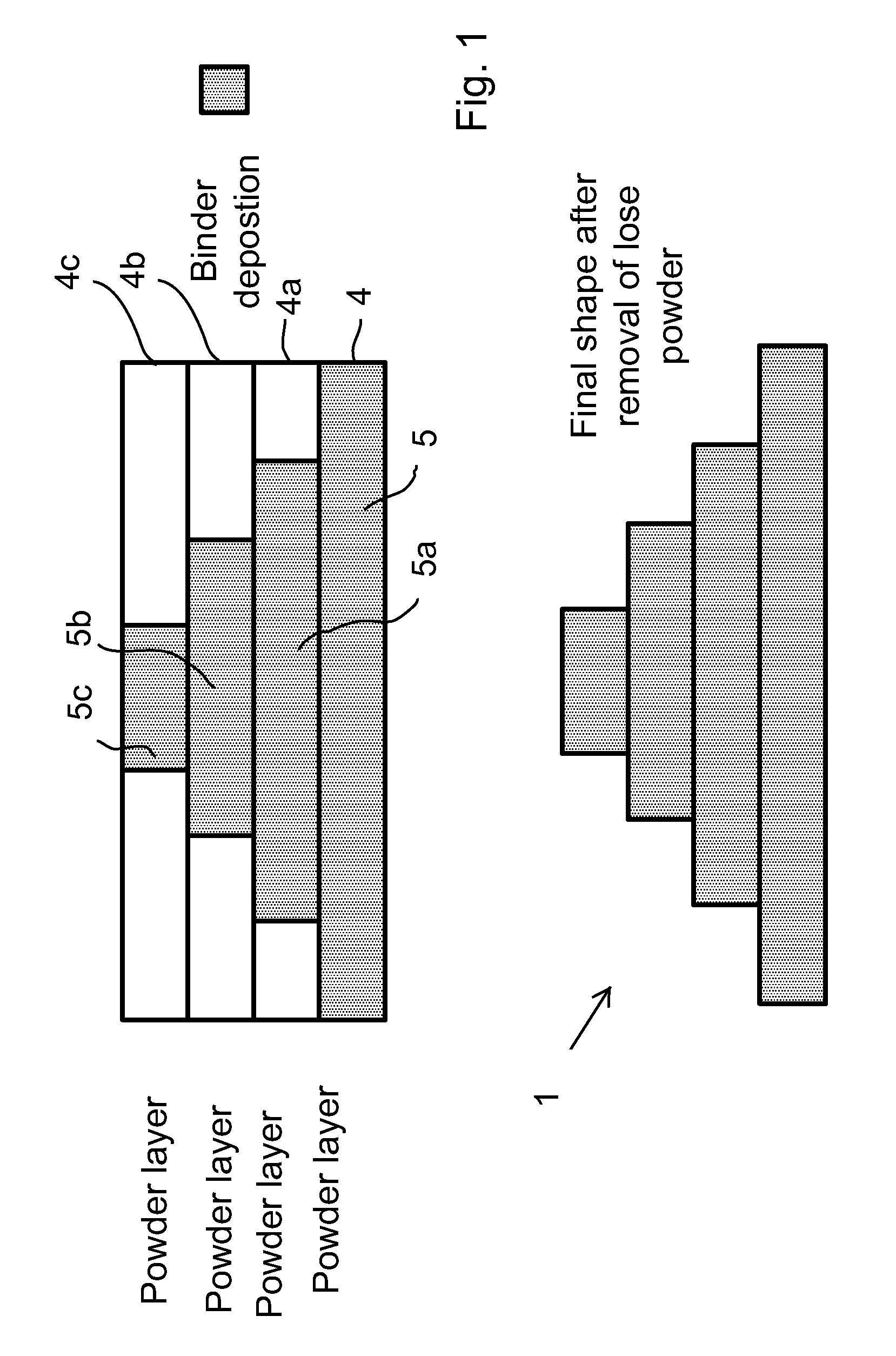

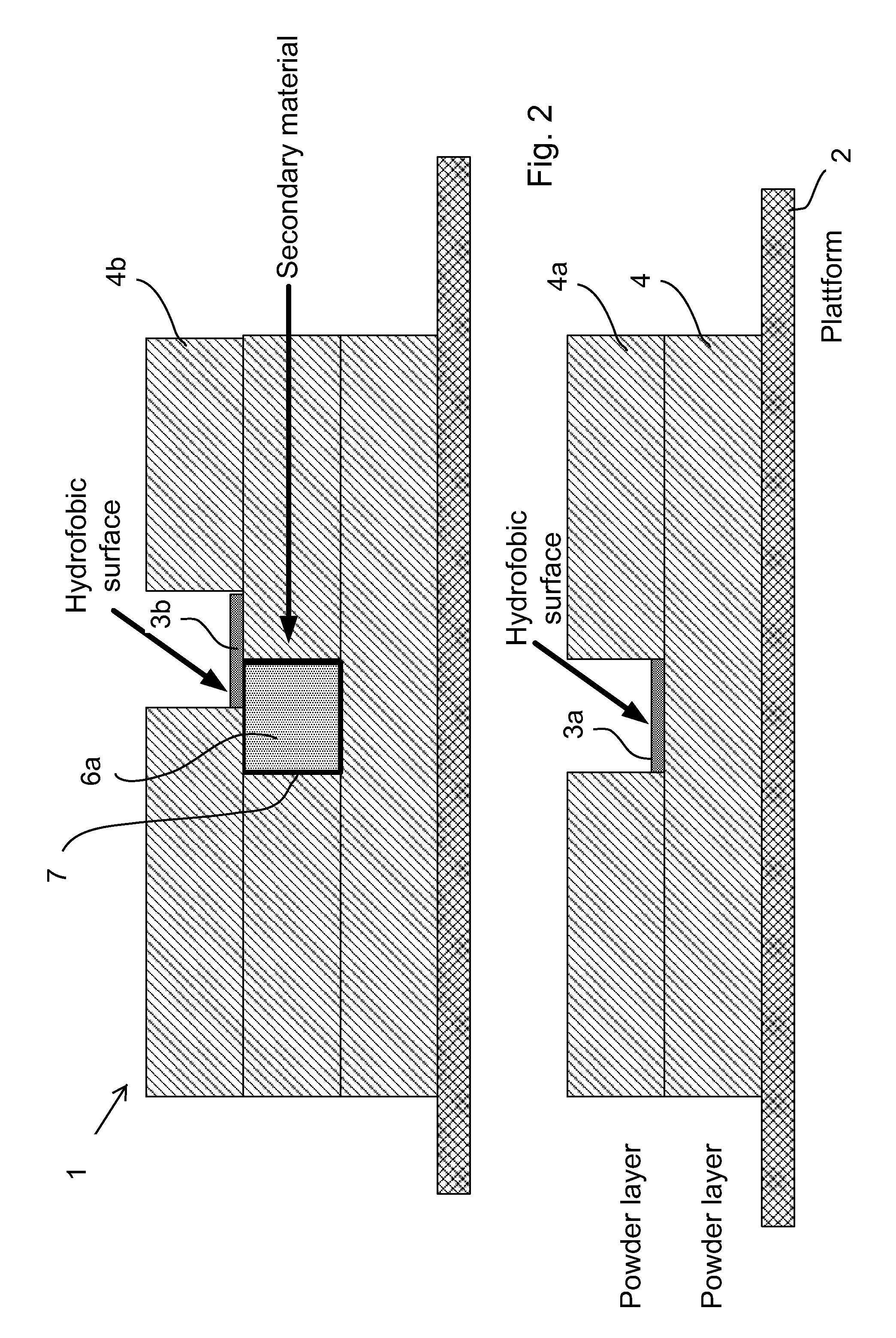

Layered manufacturing of free-form multi-material micro-components

ActiveUS20150306664A1Efficient productionAdditive manufacturing apparatusCircuit optical detailsMulti materialElectricity

The present invention relates to layer manufacturing, more particularly to a method for additive layer manufacturing of objects comprised of more than one material with free-form capability for all included materials. The invention can for example be used for producing packaging for Microsystems where the ceramic acts as an insulator and the secondary material is used to produce electrical or optical 3D conductor lines or electrical or optical 3D vias. The fine powder used in this method enables it to be used for building components with small feature size and demand for high precision. Other intended uses for this method is to build small mechanical precision parts or grinding tools, dental objects or medical implants.

Owner:DIGITAL METAL

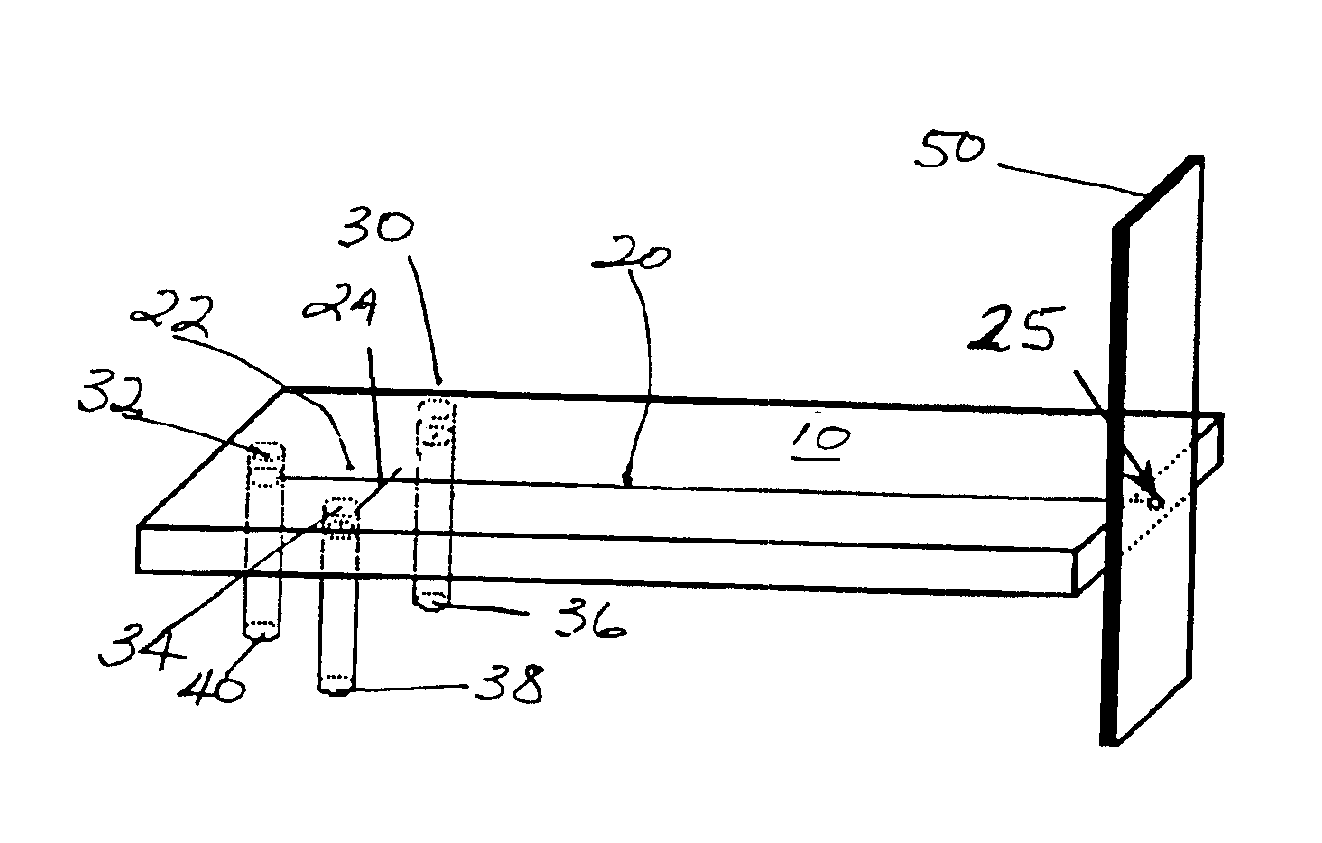

Method for electrically and mechanically connecting microstructures using solder

InactiveUS6893885B2Printed circuit assemblingSemiconductor/solid-state device testing/measurementDevice formEngineering

A method and system for locally connecting microstructures and devices formed thereby are provided wherein localized solder-bonding creates bonds between pairs of microstructures found on miniature flexible cables and silicon microsystem platforms. Multi-lead contact to the pads are detected automatically, triggering an embedded heater or heaters to initiate solder melting. This approach enables delicate microstructures to be connected and disconnected from microsystem platforms in the field, and is implemented with a process that is compatible with monolithic integration of circuits.

Owner:RGT UNIV OF MICHIGAN

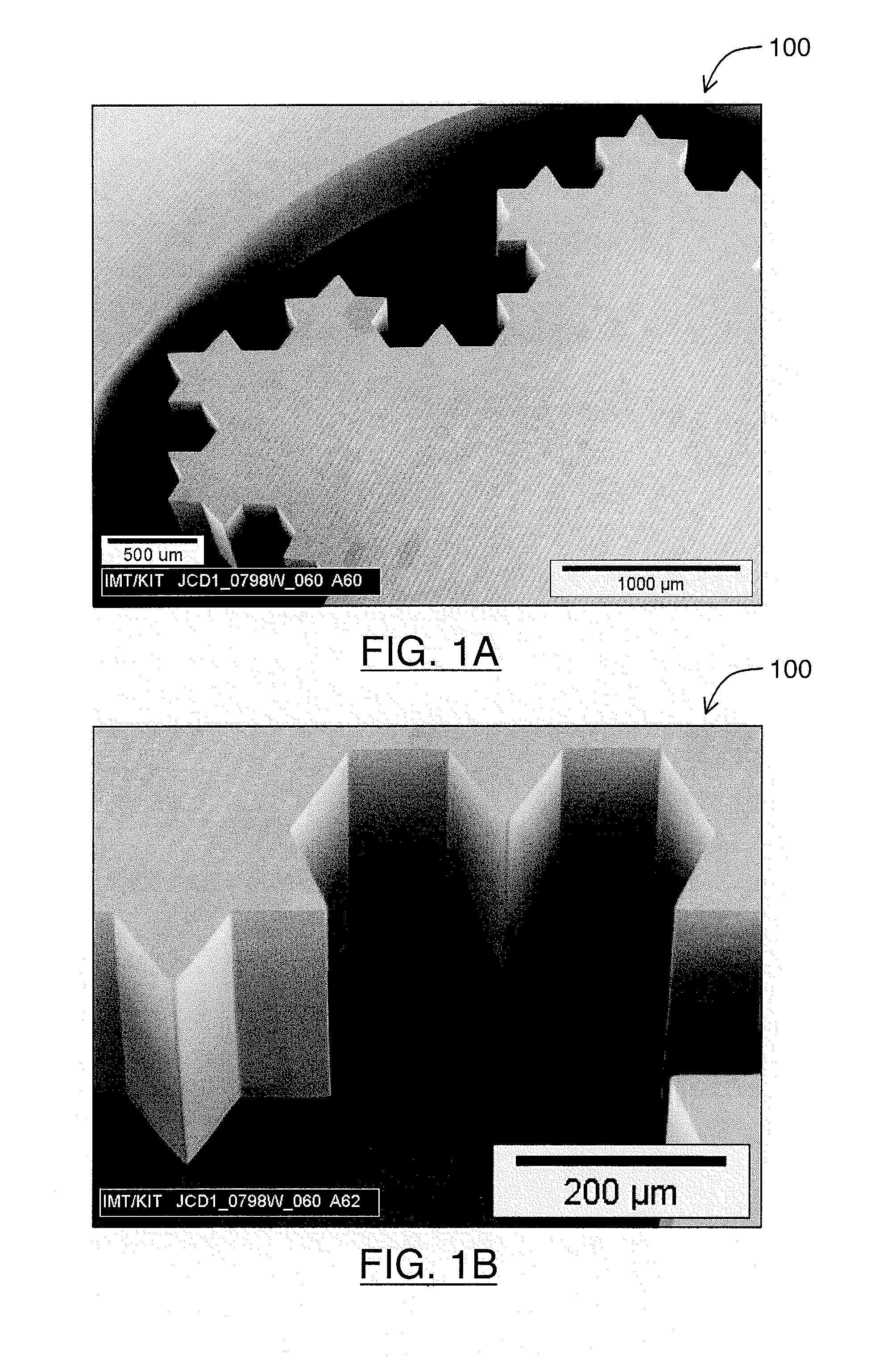

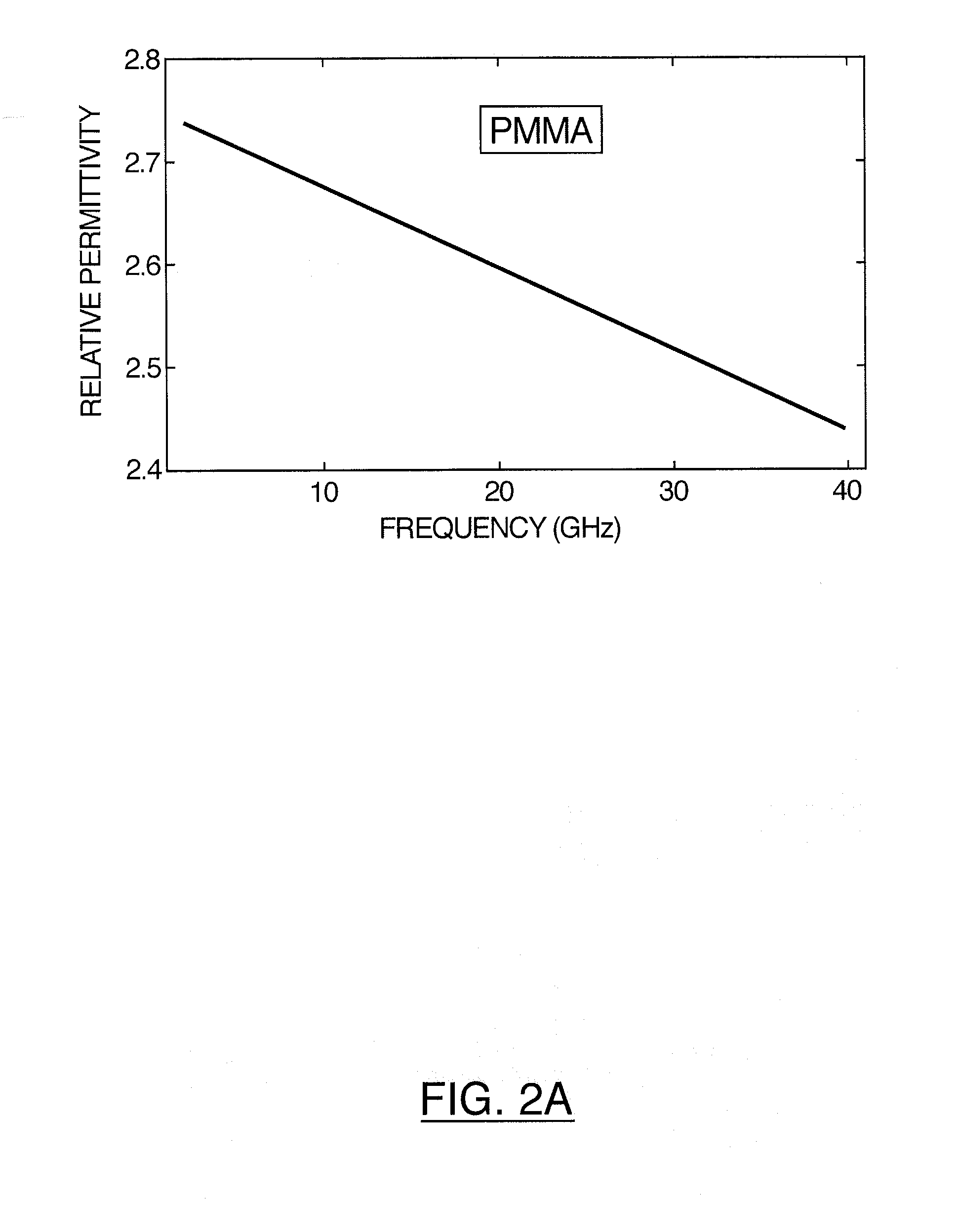

Polymer-based resonator antennas

ActiveUS20140327597A1Improve the effective dielectric constantPhotosensitive material processingAntennas earthing switches associationDielectric resonator antennaDielectric resonator

Dielectric resonator antennas suitable for use in compact radiofrequency (RF) antennas and devices, and methods of fabrication thereof. Described are dielectric resonator antennas fabricated using polymer-based materials, such as those commonly used in lithographic fabrication of integrated circuits and microsystems. Accordingly, lithographic fabrication techniques can be employed in fabrication. The polymer-based dielectric resonator antennas can be excited using tall metal vertical structures, which are also fabricated using techniques adapted from integrated circuit and microsystems fabrication.

Owner:UNIVERSITY OF SASKATCHEWAN +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com