Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

64 results about "Interconnection density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

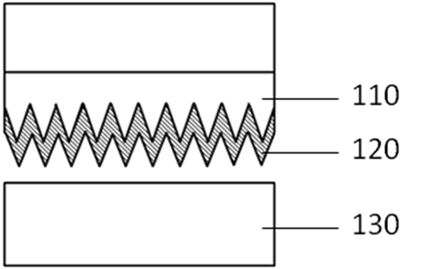

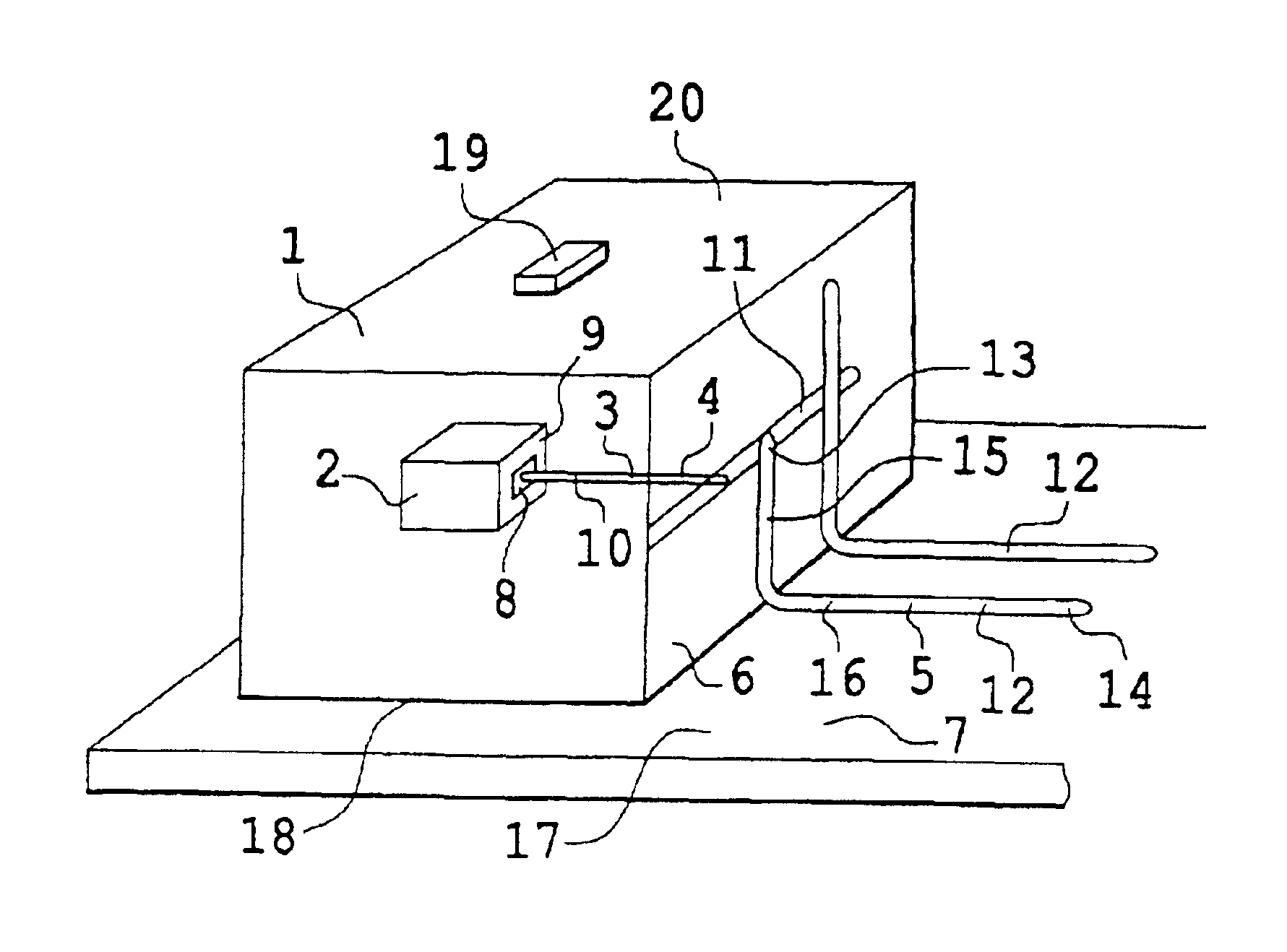

Method and apparatus for rapid thermal processing and bonding of materials using RF and microwaves

ActiveUS20070108195A1Heating fastMicrowave heating is fastSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceInterconnection density

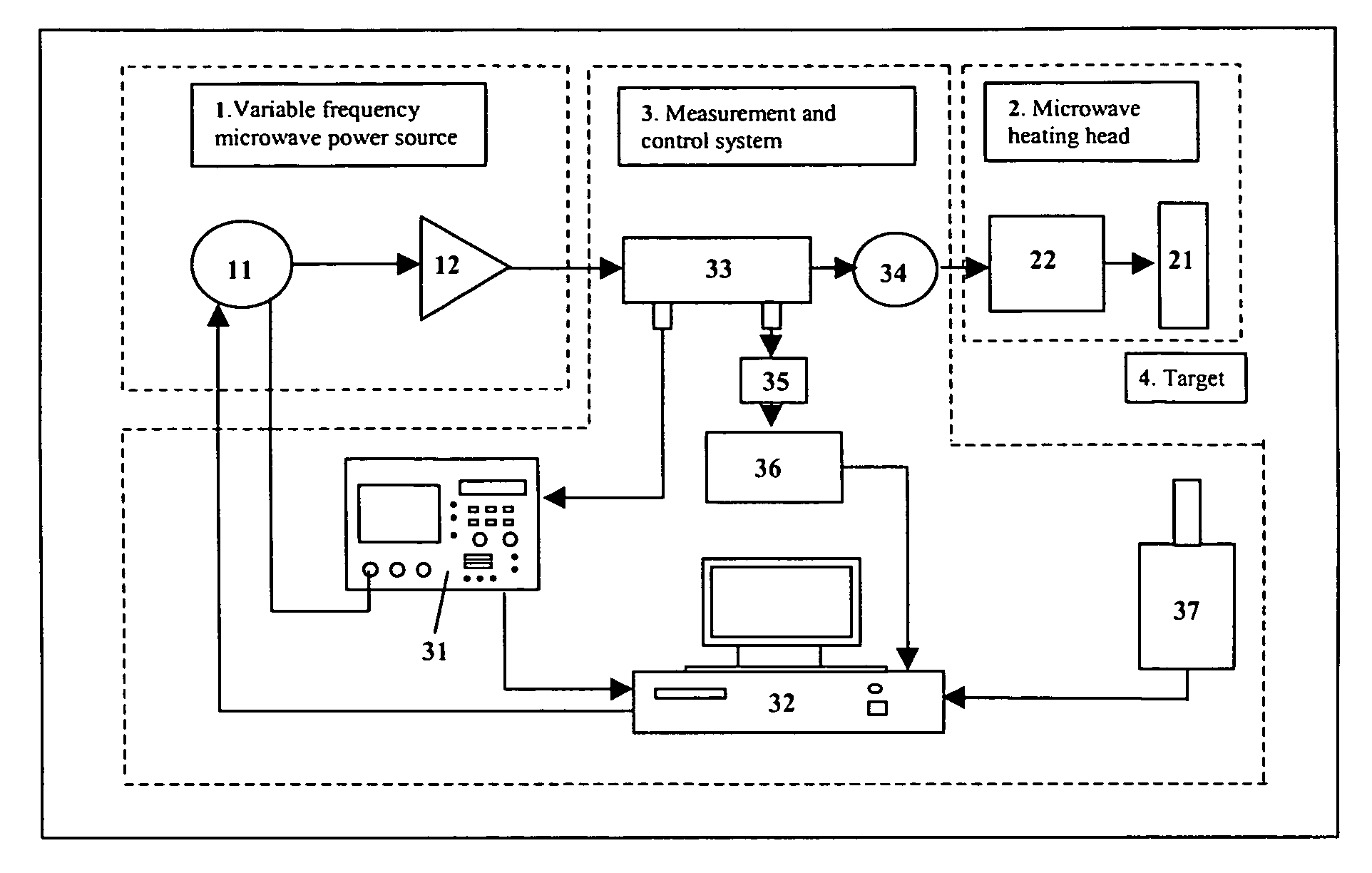

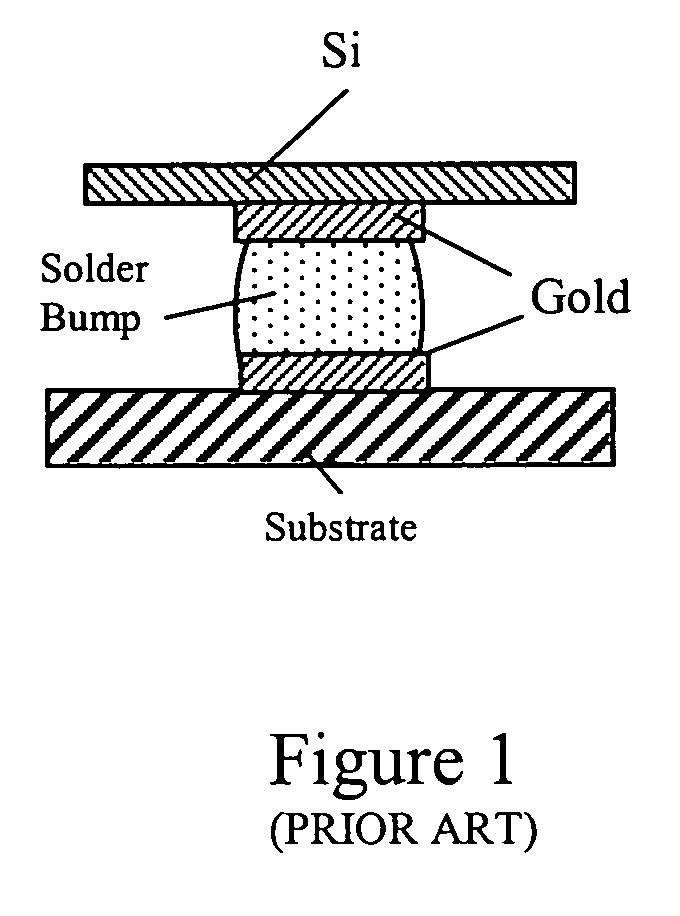

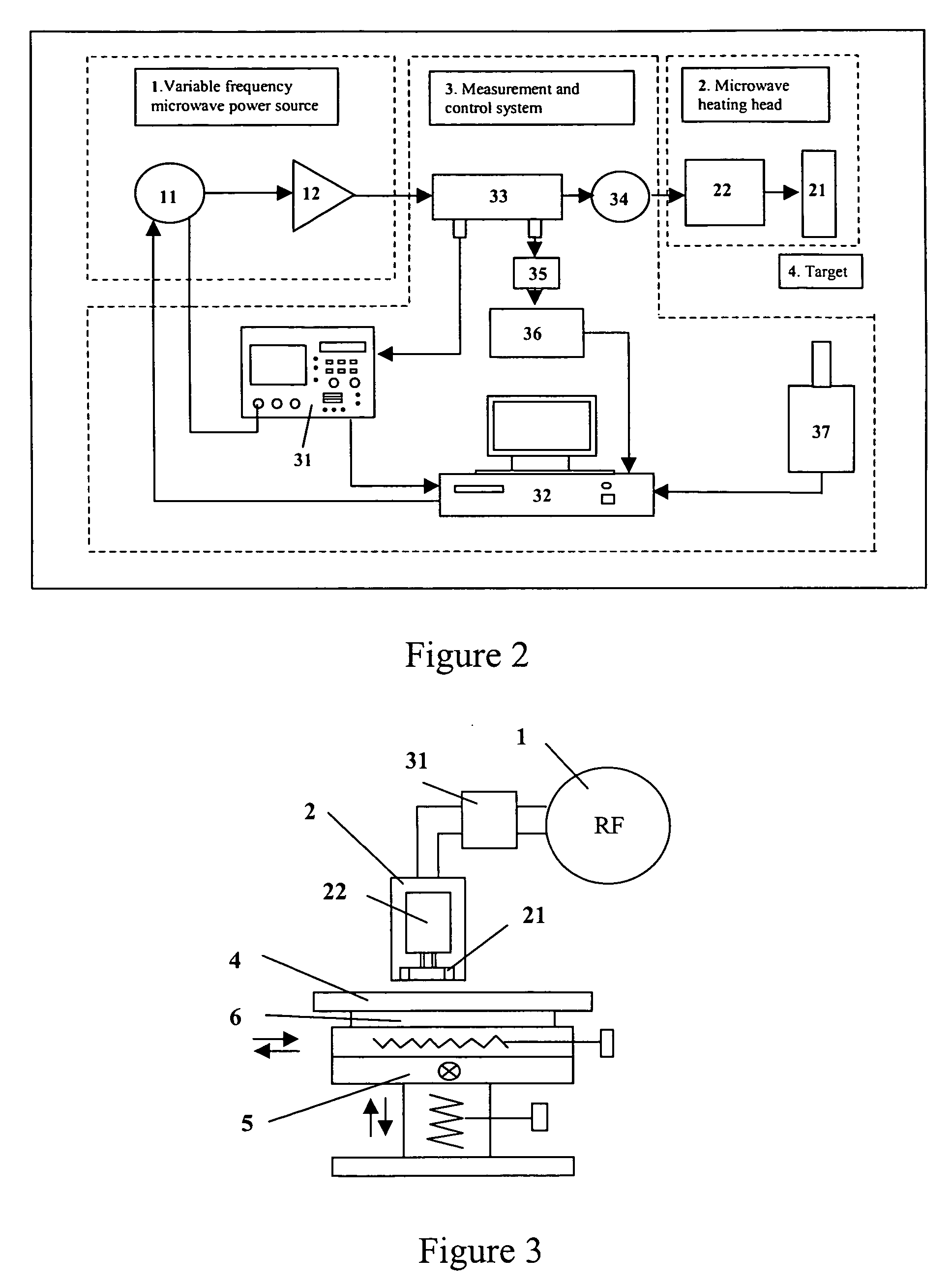

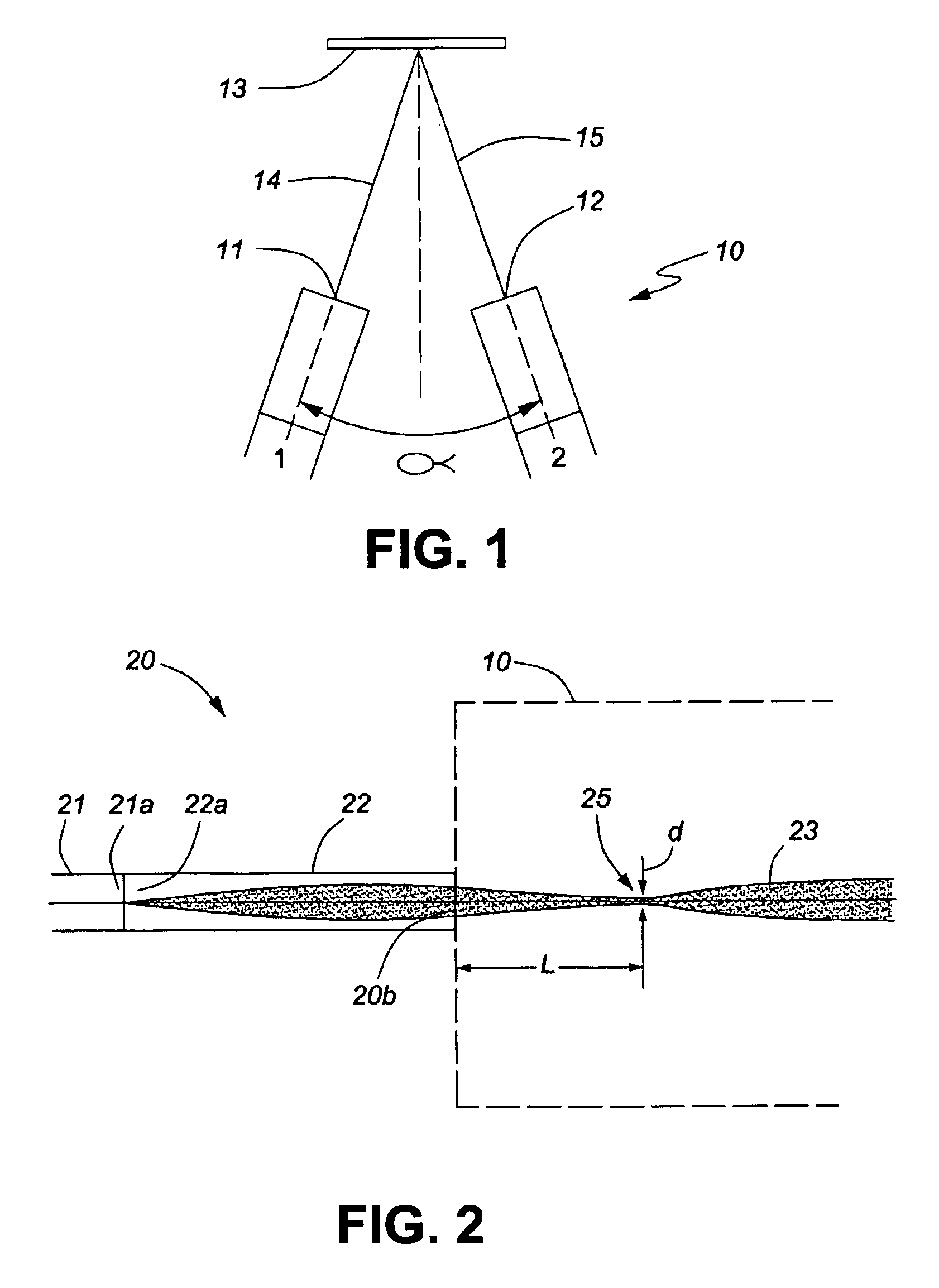

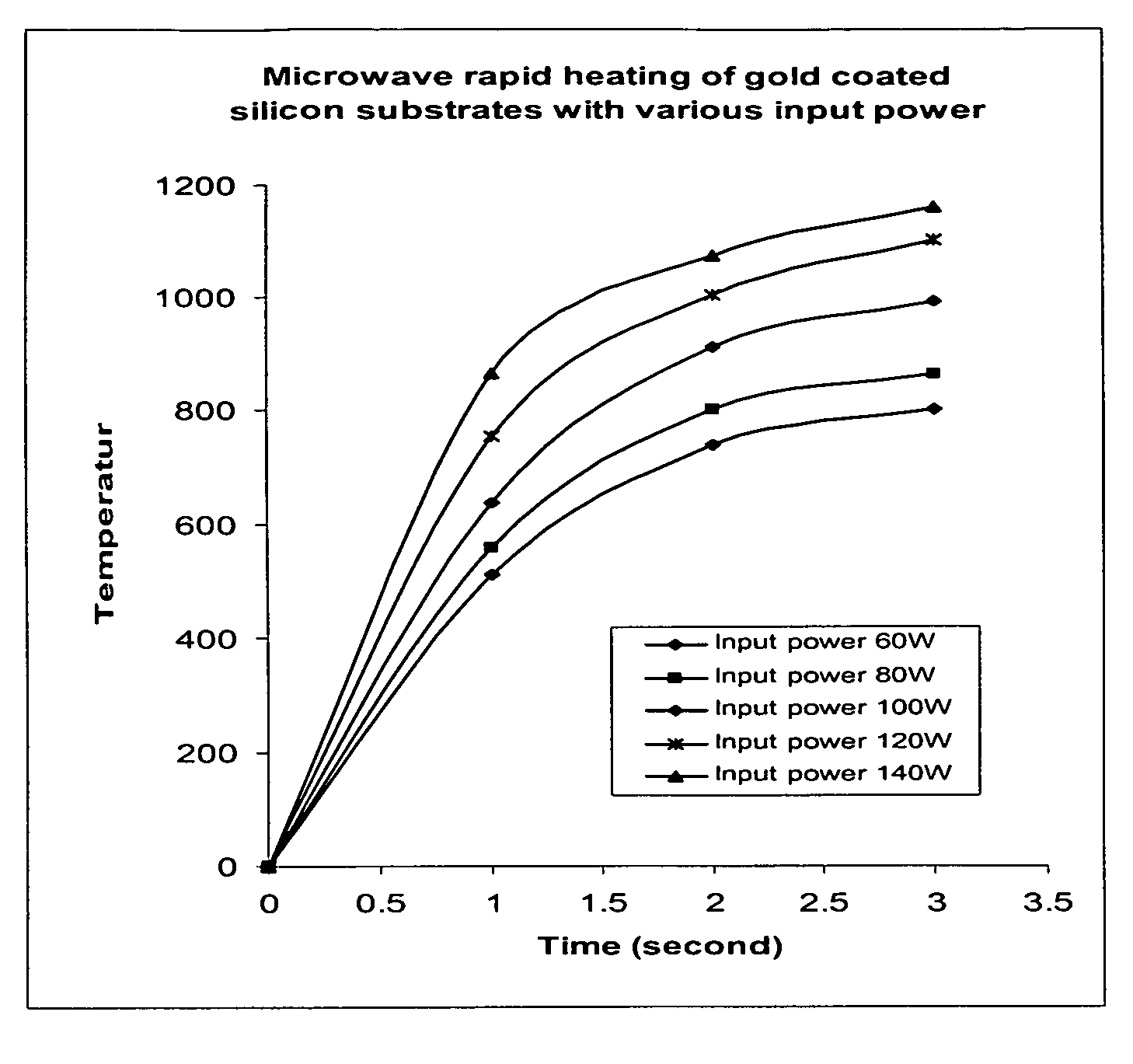

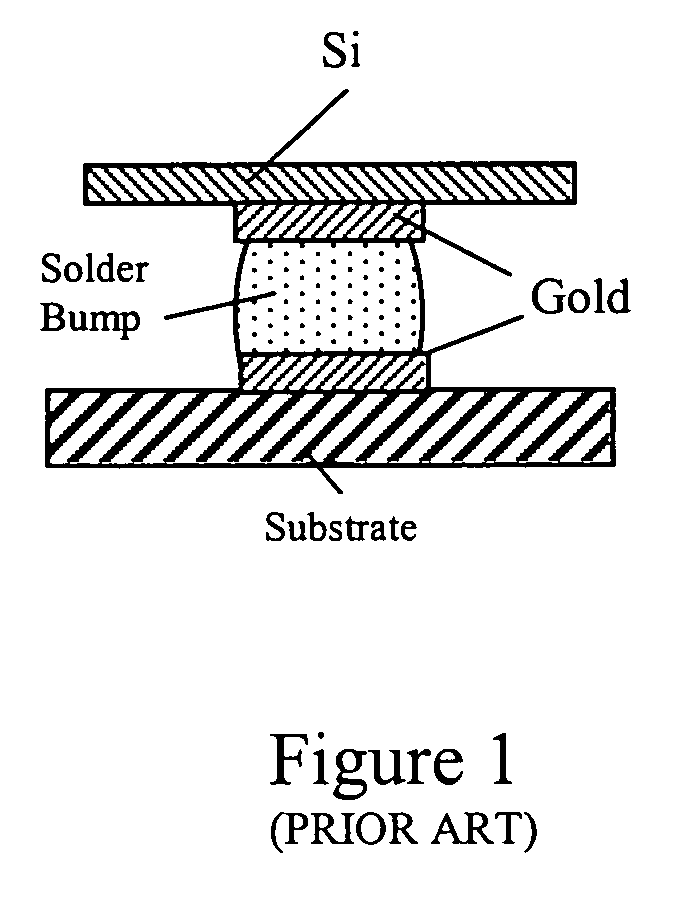

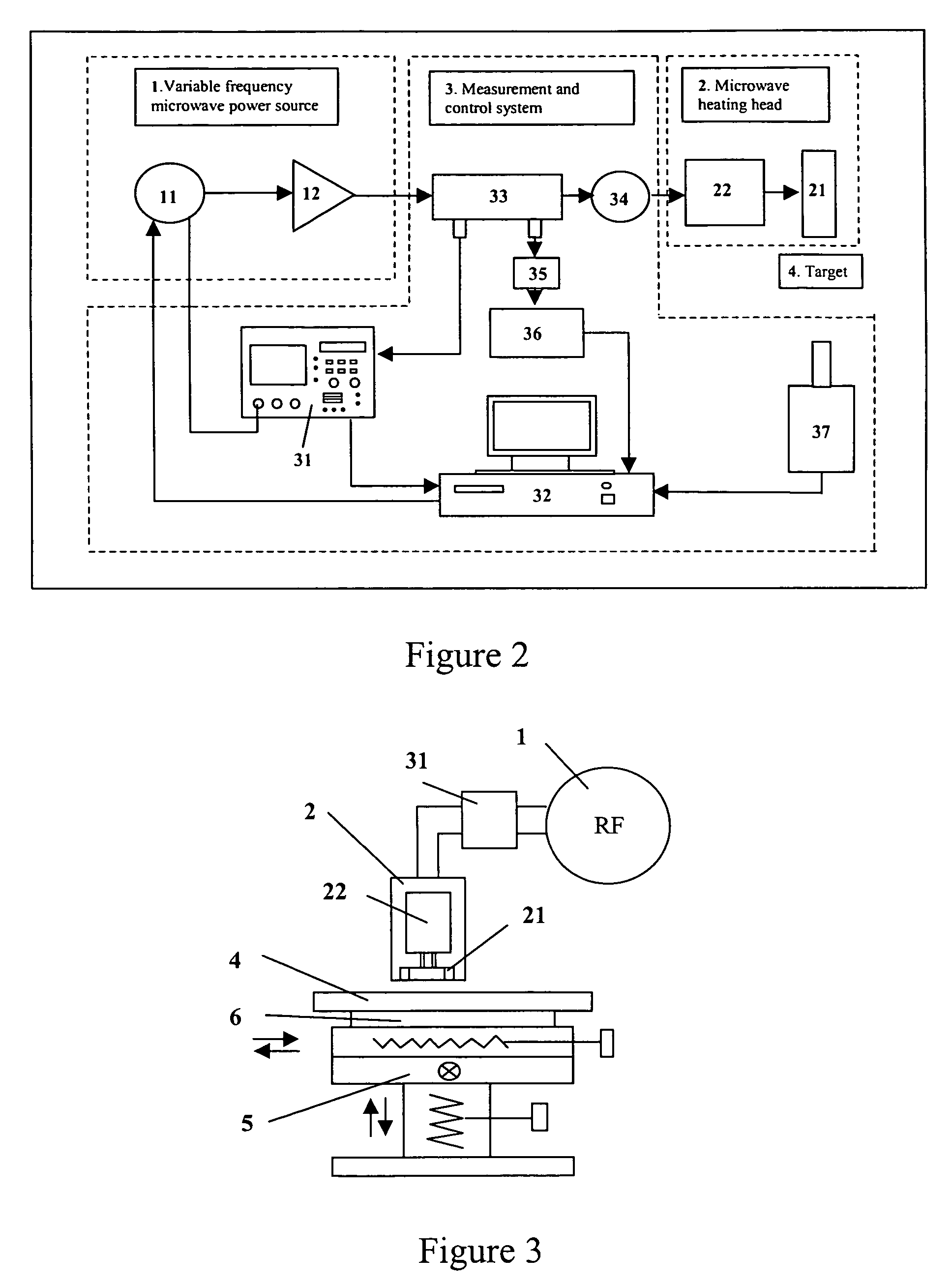

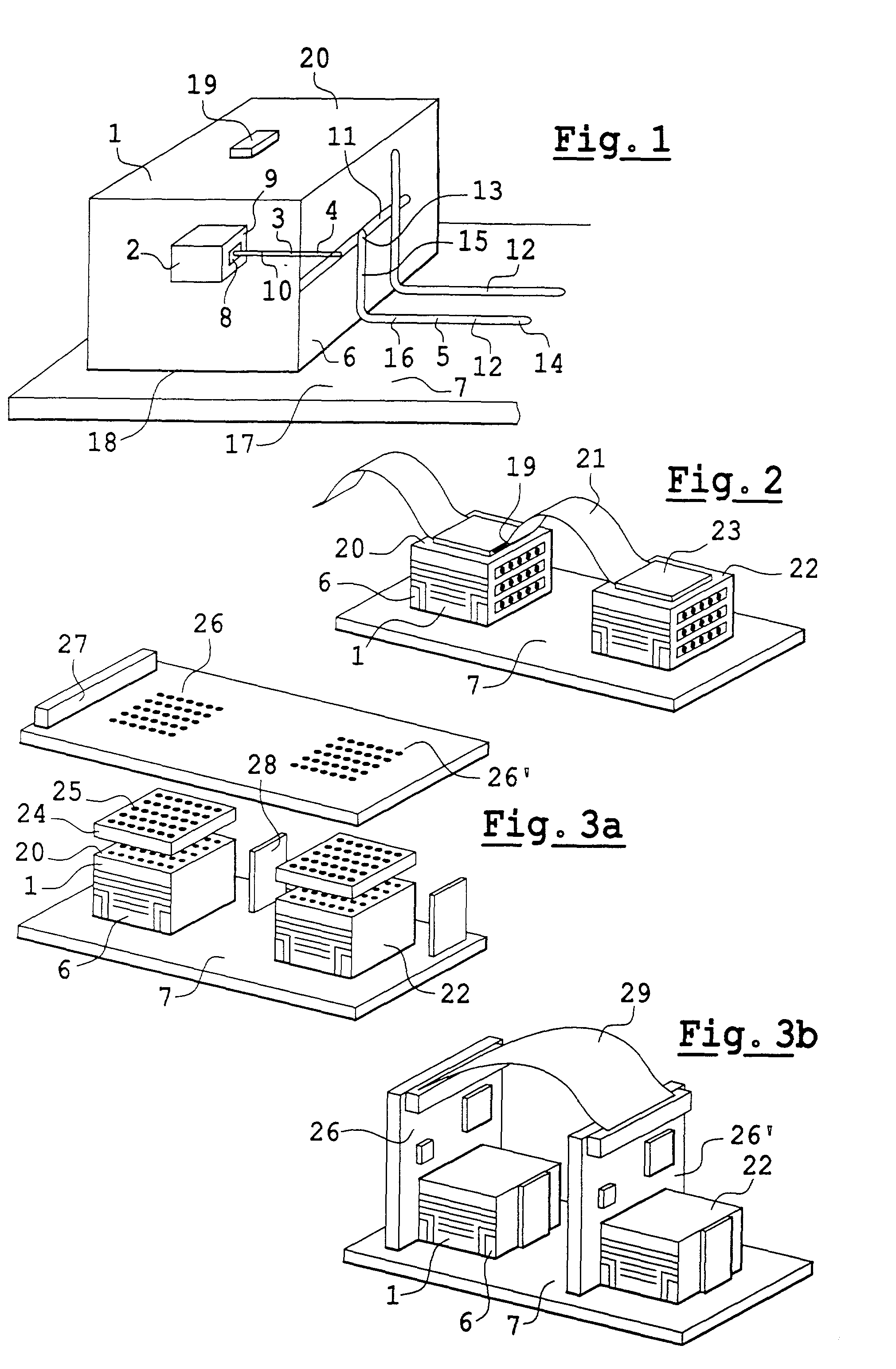

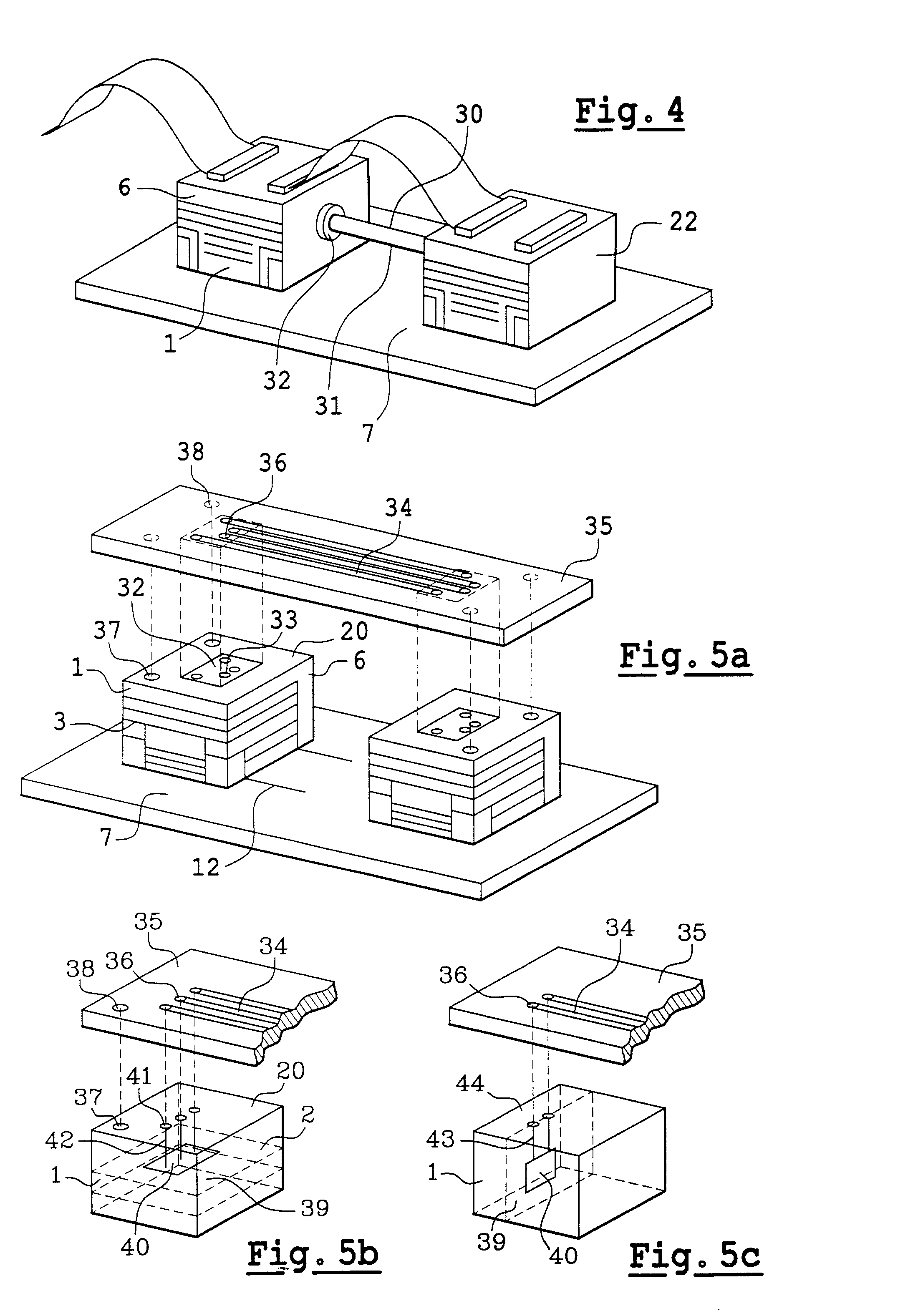

A method and apparatus for rapid and selective heating of materials using variable frequency RF and microwaves. The apparatus uses variable frequency solid state electronics as a microwave power source, a novel microwave heating head to couple microwave energy to the target materials and a match-up network to tune the frequency and impedance match between the microwave source and the load. An electronic and computer measurement and control system is employed to monitor and control the microwave heating process. The method teaches the use of inductive microwave coupling for thin conductive materials such as metal film and impurity doped silicon wafers. The method also teaches the use of capacitive microwave coupling for dielectric material such as glass and ceramics. The method further teaches the use of rapid and selective heating of heterostructure for bonding and sealing of mems and integrated circuits. The method and apparatus can provide ultra-high heating speed along with ultra-high heating temperatures for rapid thermal processing of semiconductors and other materials. It also allows the use of bonding materials with high melting temperature for strong bonding and sealing of mems and IC devices. The apparatus further provides for high interconnection density of integrated circuits as connections are made without the use of solder bumps.

Owner:TIAN YONGLAI +1

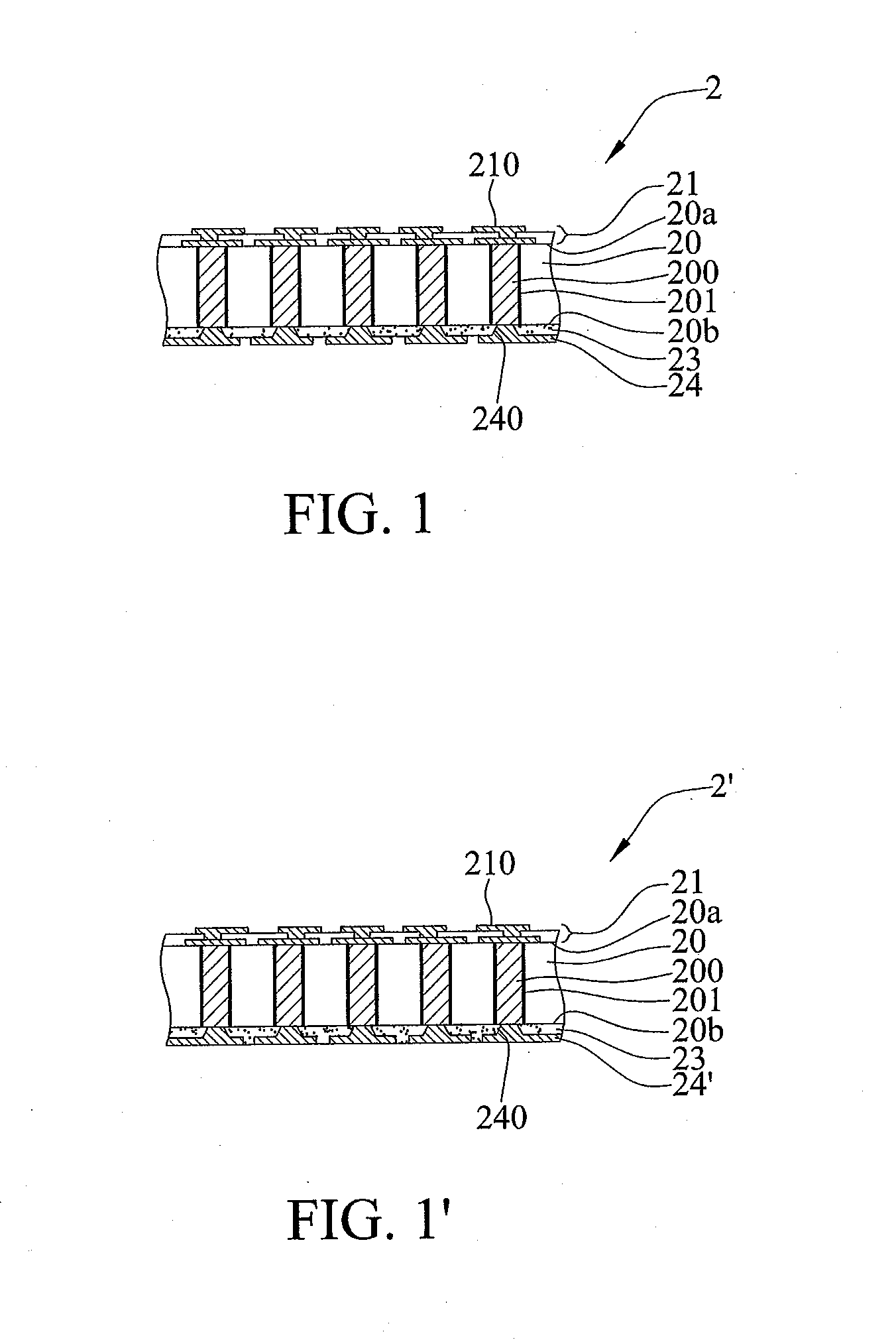

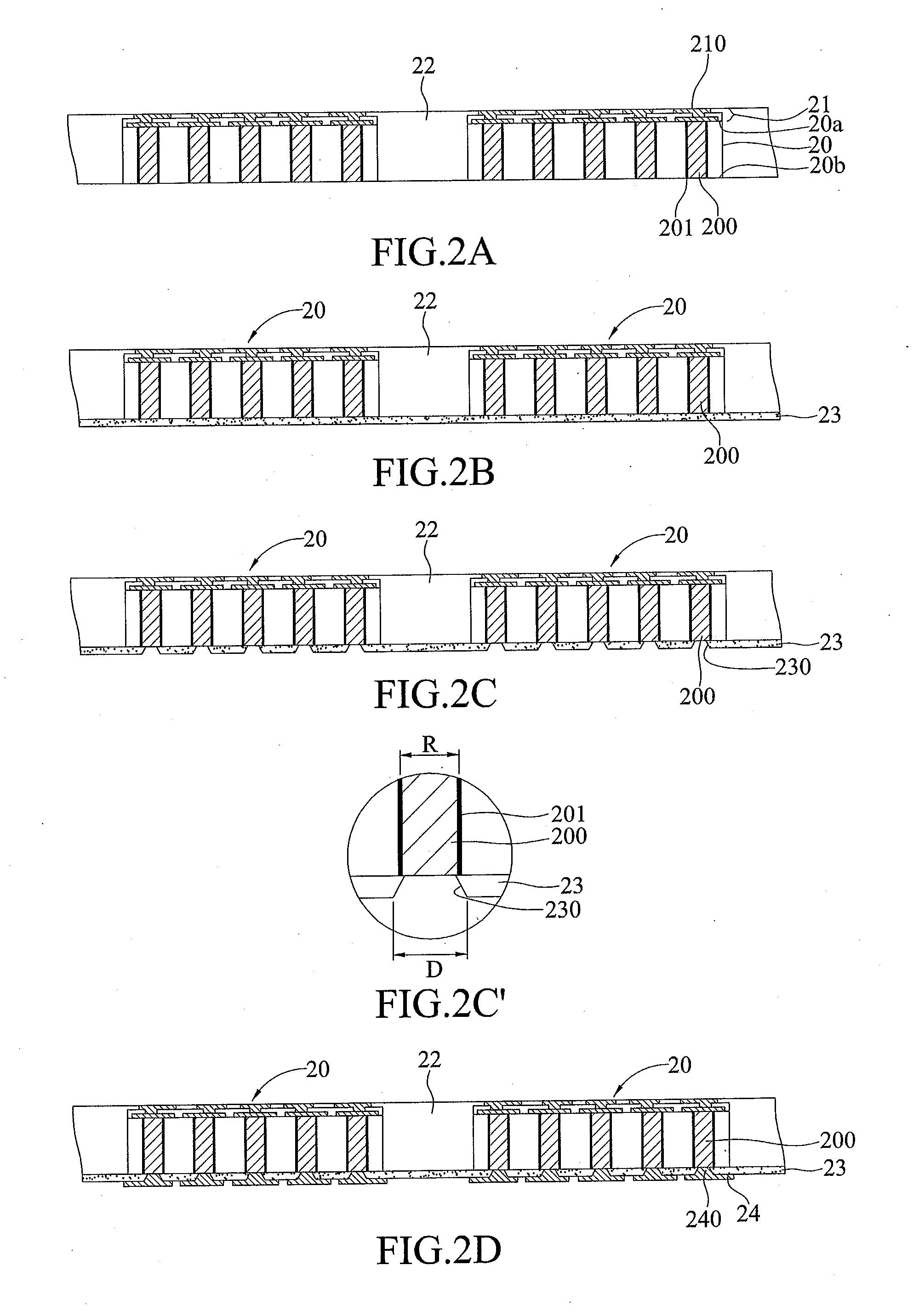

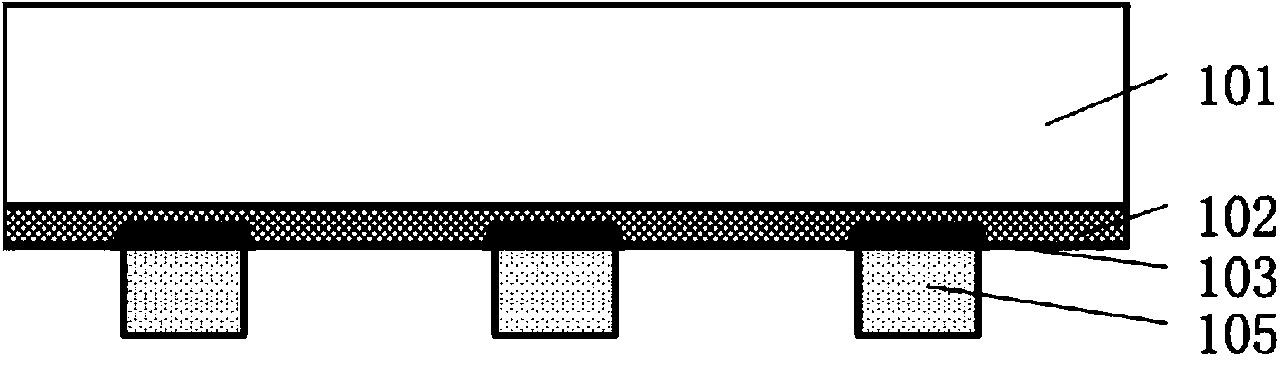

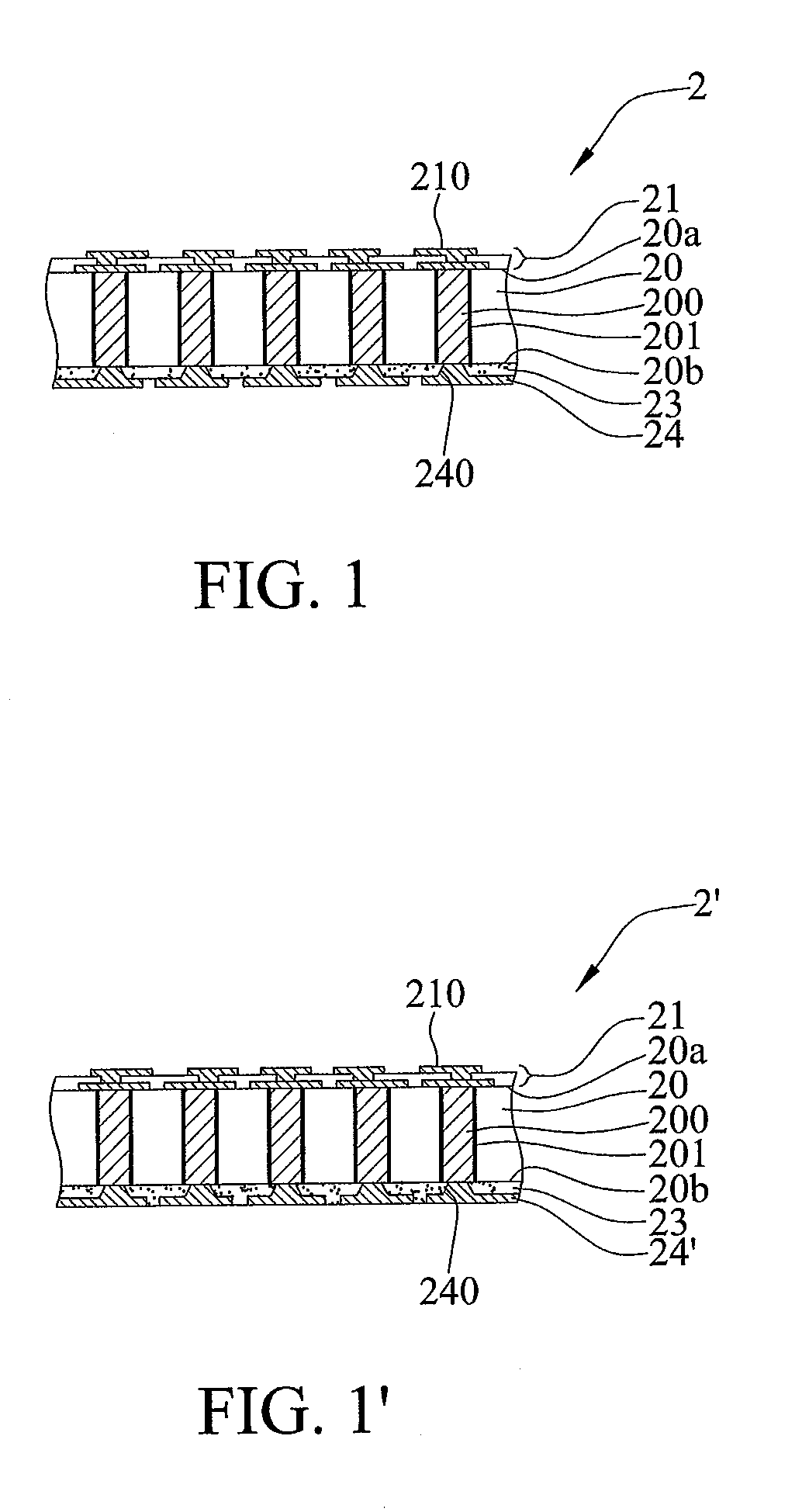

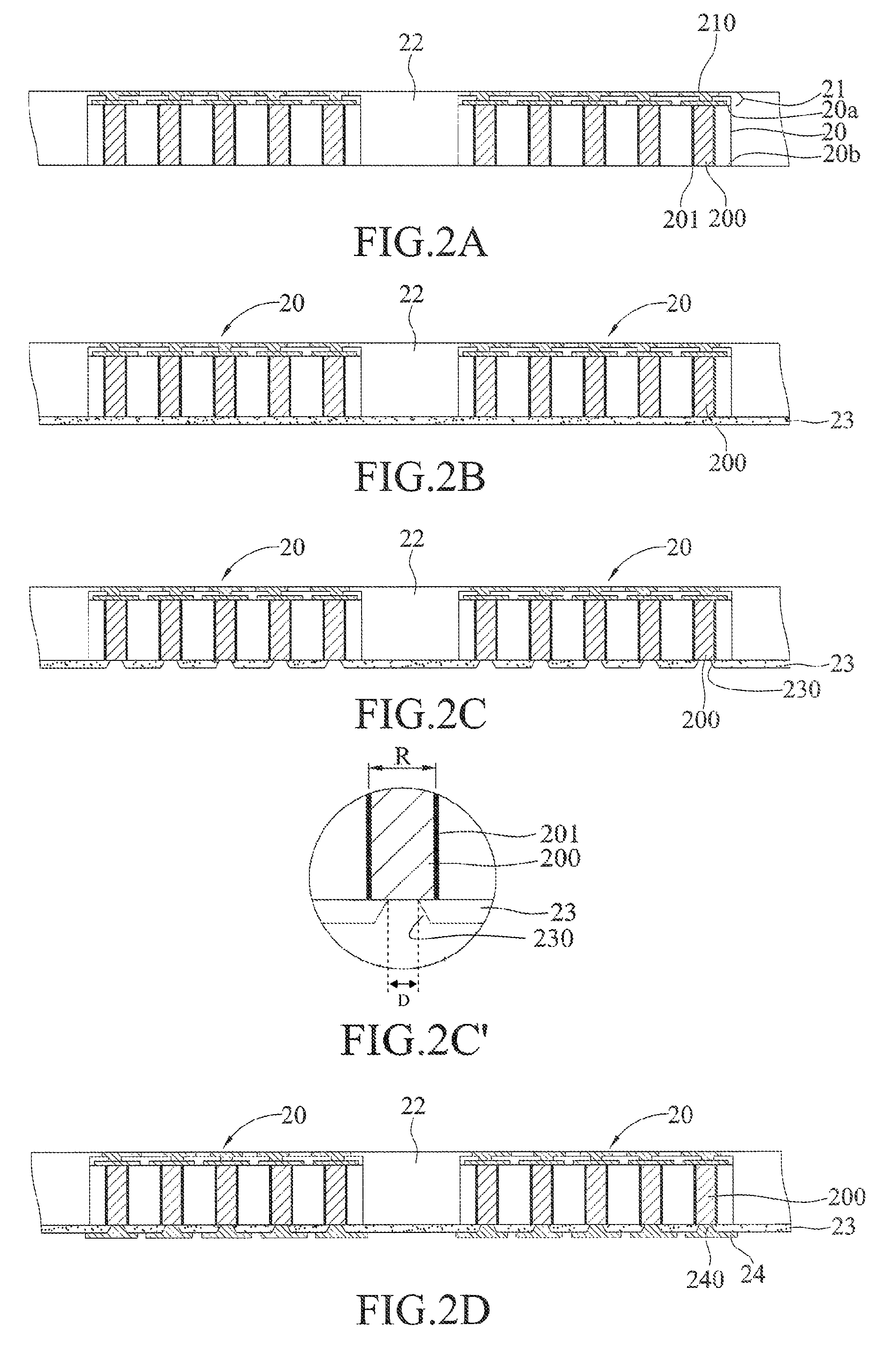

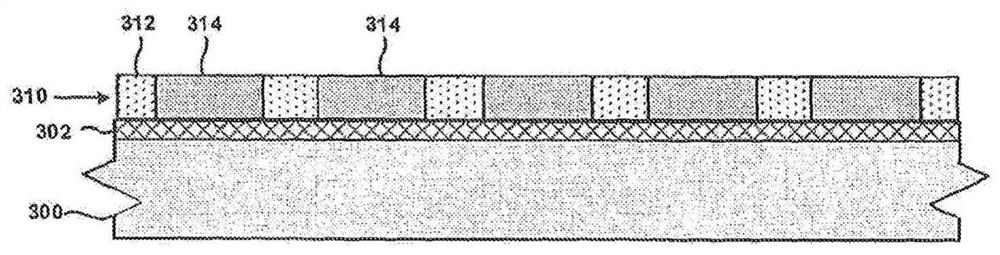

Package substrate and method of fabricating the same

ActiveUS20140102777A1Semiconductor/solid-state device detailsSolid-state devicesLithography processInterposer

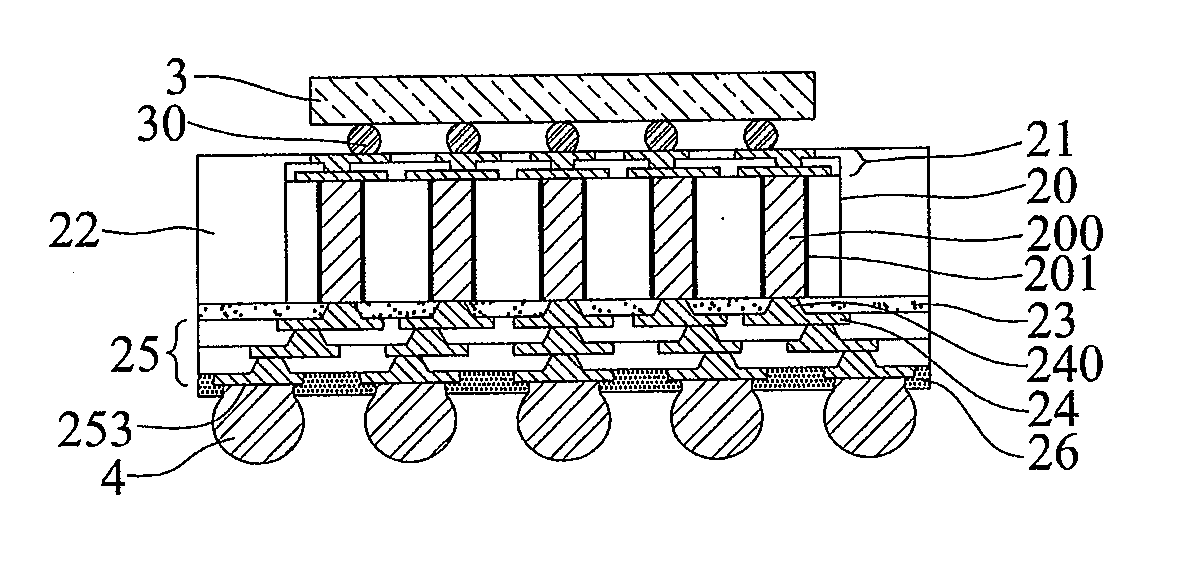

A package substrate and a method of fabricating the package substrate are provided. The package substrate may include an interposer having at least one conductive through via, a photo-sensitive dielectric layer formed on one side of the interposer, and at least one conductive via formed in the photo-sensitive dielectric layer and electrically connected to the conductive through via. By means of a photo lithography process with high alignment accuracy, at least one via with an extremely small diameter can be formed on the photo-sensitive dielectric layer and align with the conductive through via. Therefore, the conductive through via can have its diameter reduced as required, without considering the alignment with the at least one via. Accordingly, the interconnection density of the conductive through via on the interposer is increased.

Owner:IND TECH RES INST +1

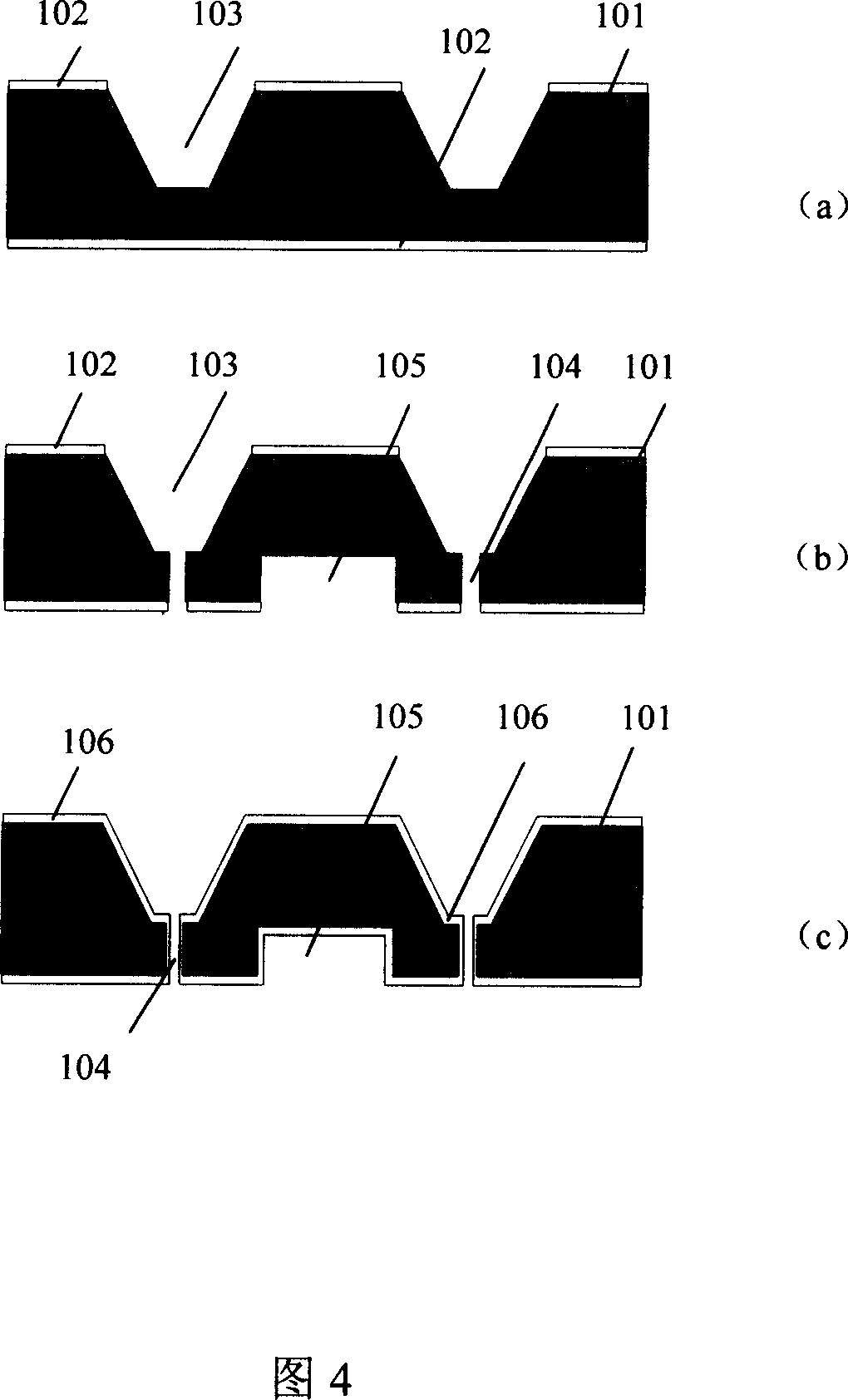

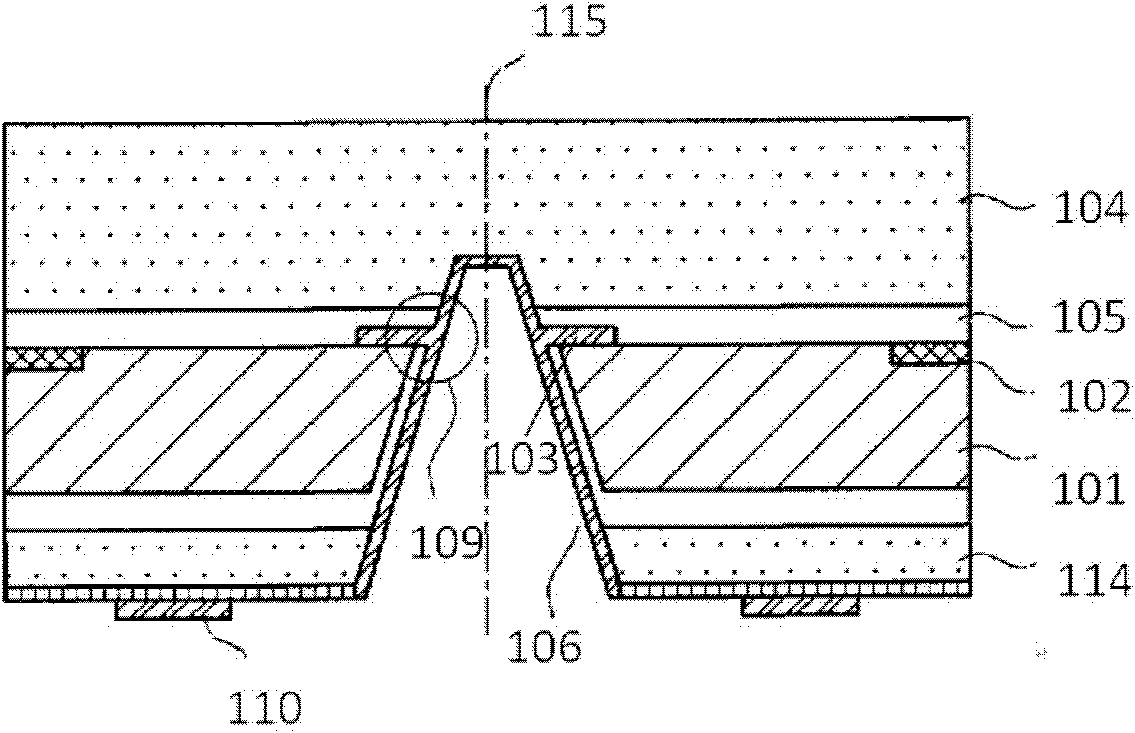

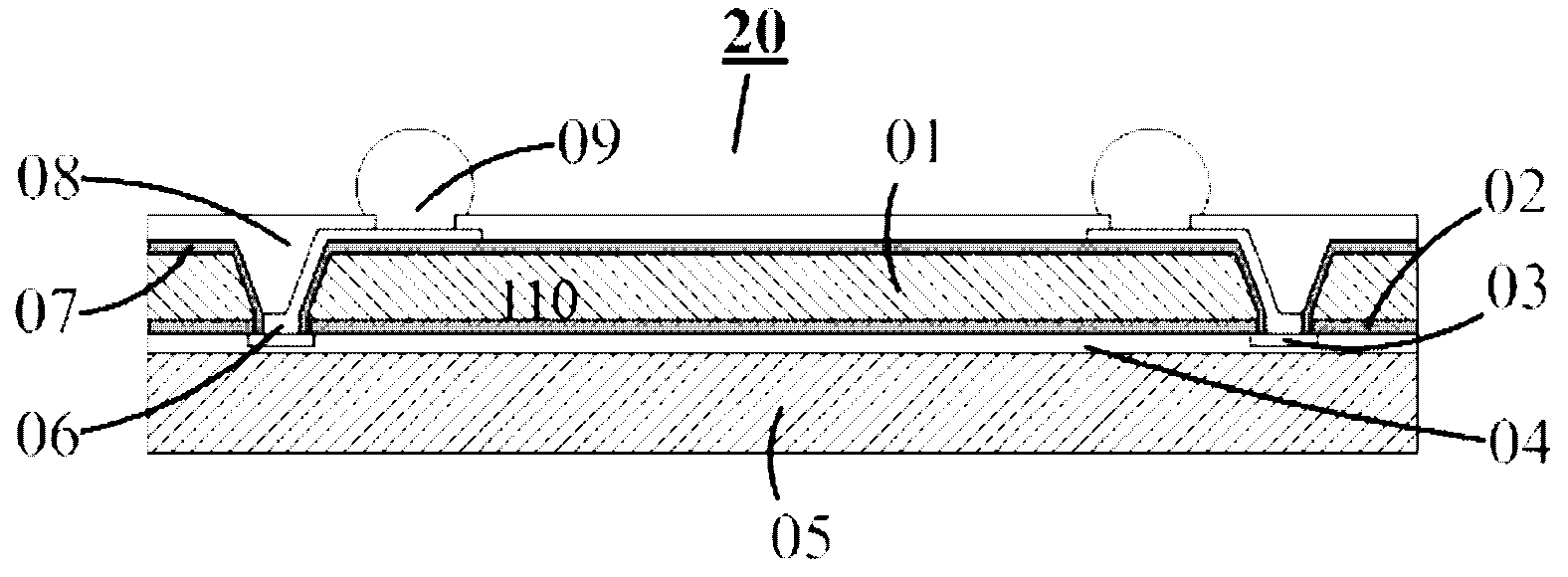

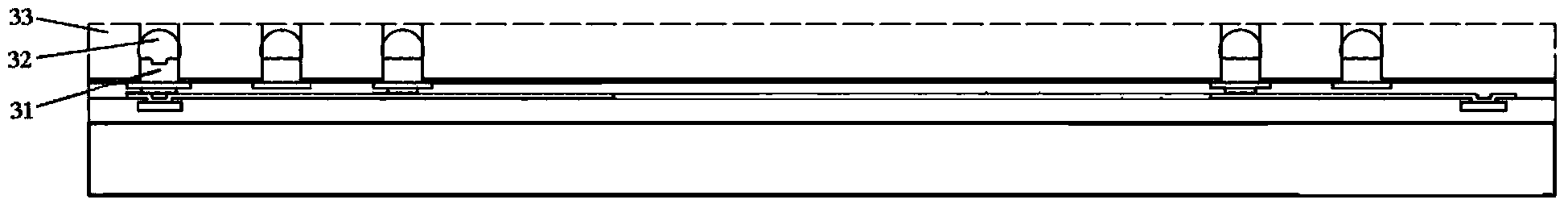

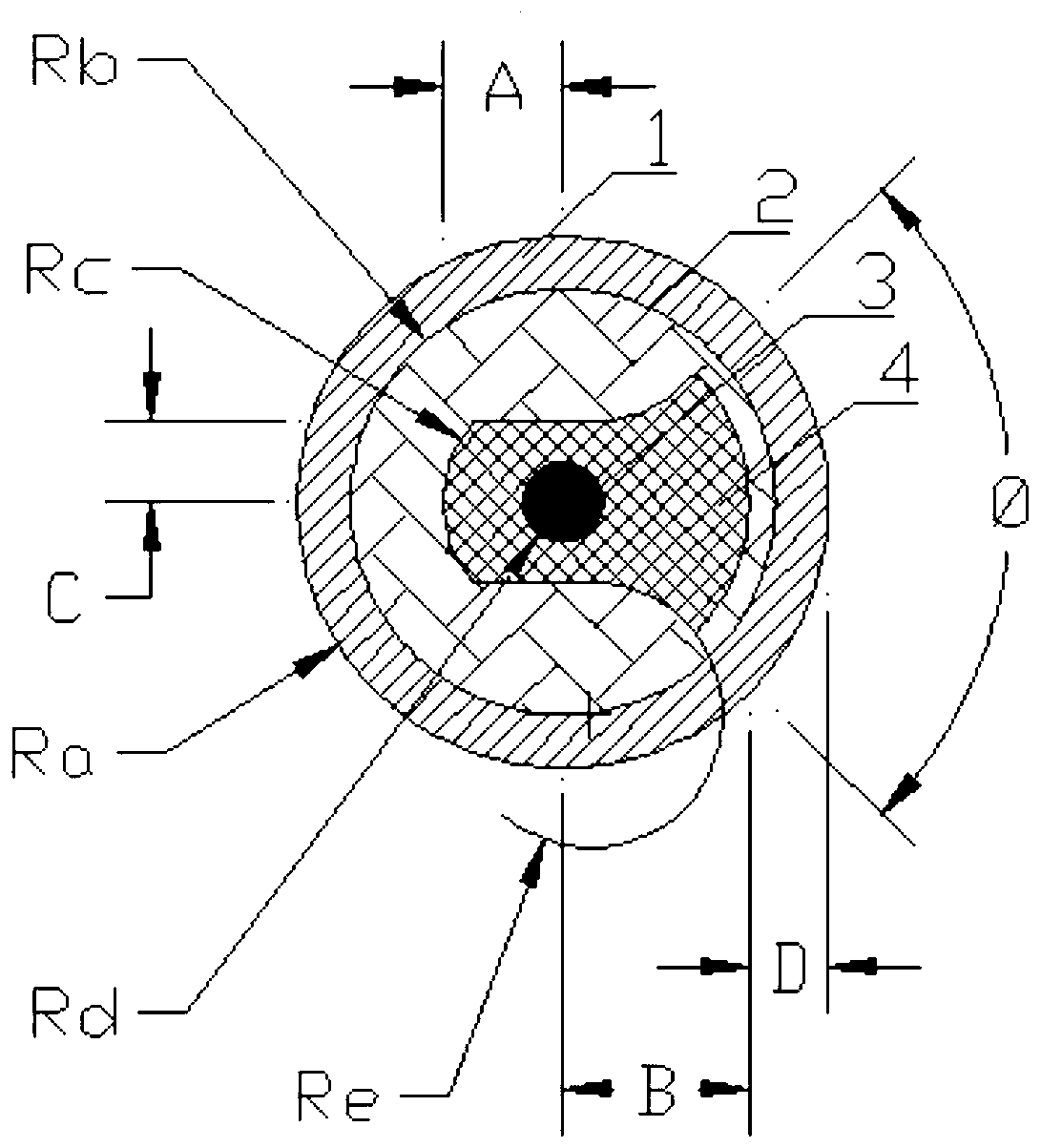

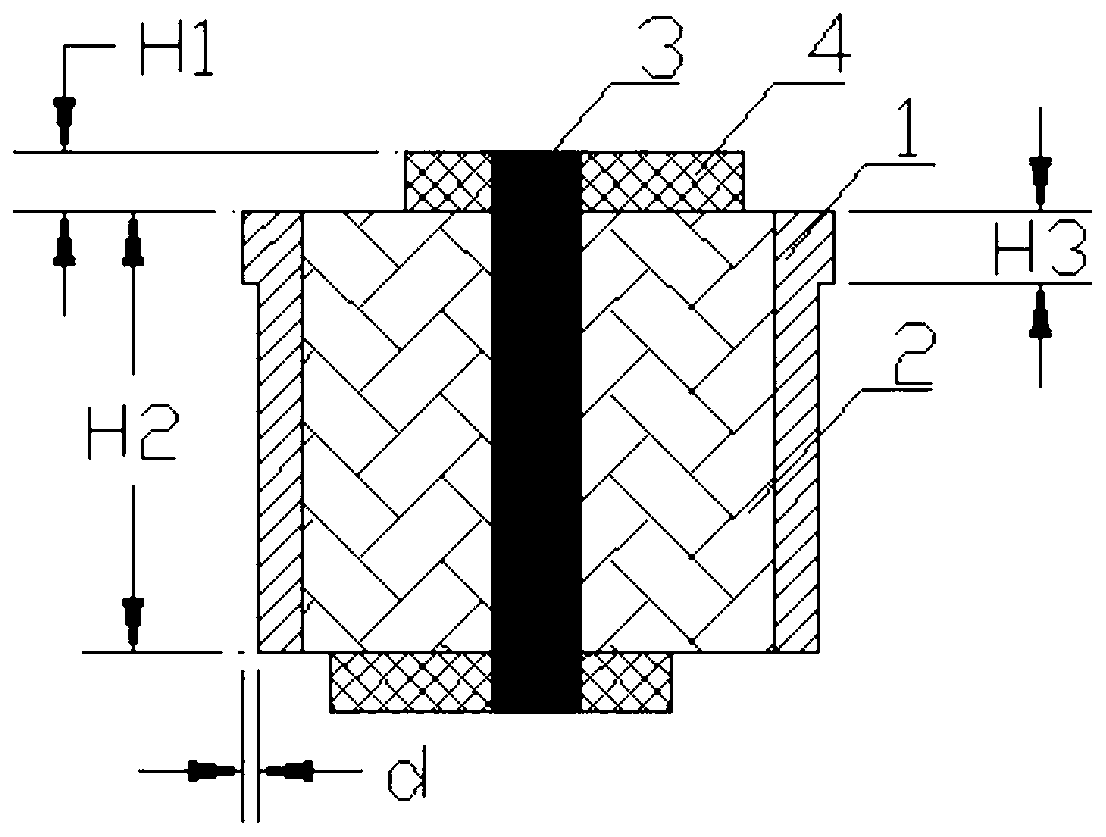

Micro electromechanical system chip size airtight packaging vertical interconnecting structure and its manufacturing method

InactiveCN1935630AImprove reliabilitySo as not to damagePrecision positioning equipmentSoldering apparatusElectricityCopper plating

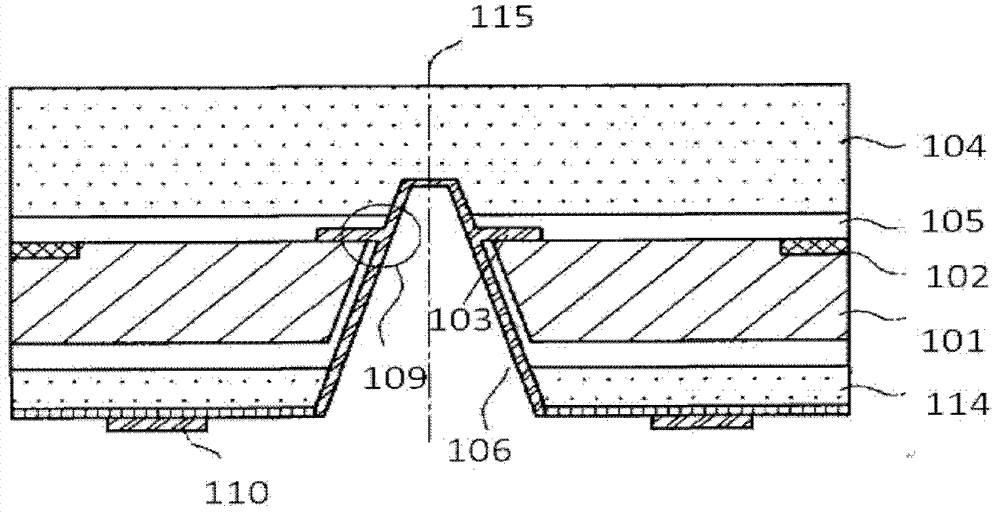

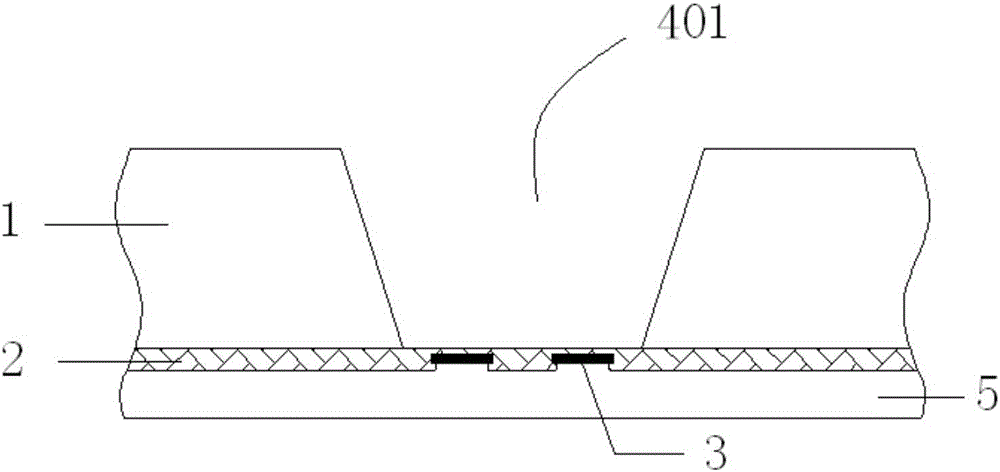

The invention relates to a micro electromechanical systems (MEMS) chip size airtight package vertical-interconnection structure and the making method thereof, characterized in putting forward a novel wafer-level chip size package structure, where the chip interconnection adopts through hole vertical interconnection techniques: thin silicon wafer thorugh hole etching technique of integrating KOH corrosion and DRIE, through hole metallizing technique of copper plating from the bottom up, and thorugh interconnection technique of integrating pure Sn solder airtight bonding and bump preparation. The whole process matches with IC process and is completed on the wafer-level basis, and has higher vertical thorugh hole interconnection density. And the structure reduces package cost, increases package density, and can effectively protect MEMS devices against damage, reduce impedance, parasitic effect and noise of MEMS device connection, and improve quality of output signals of MEMS devices.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

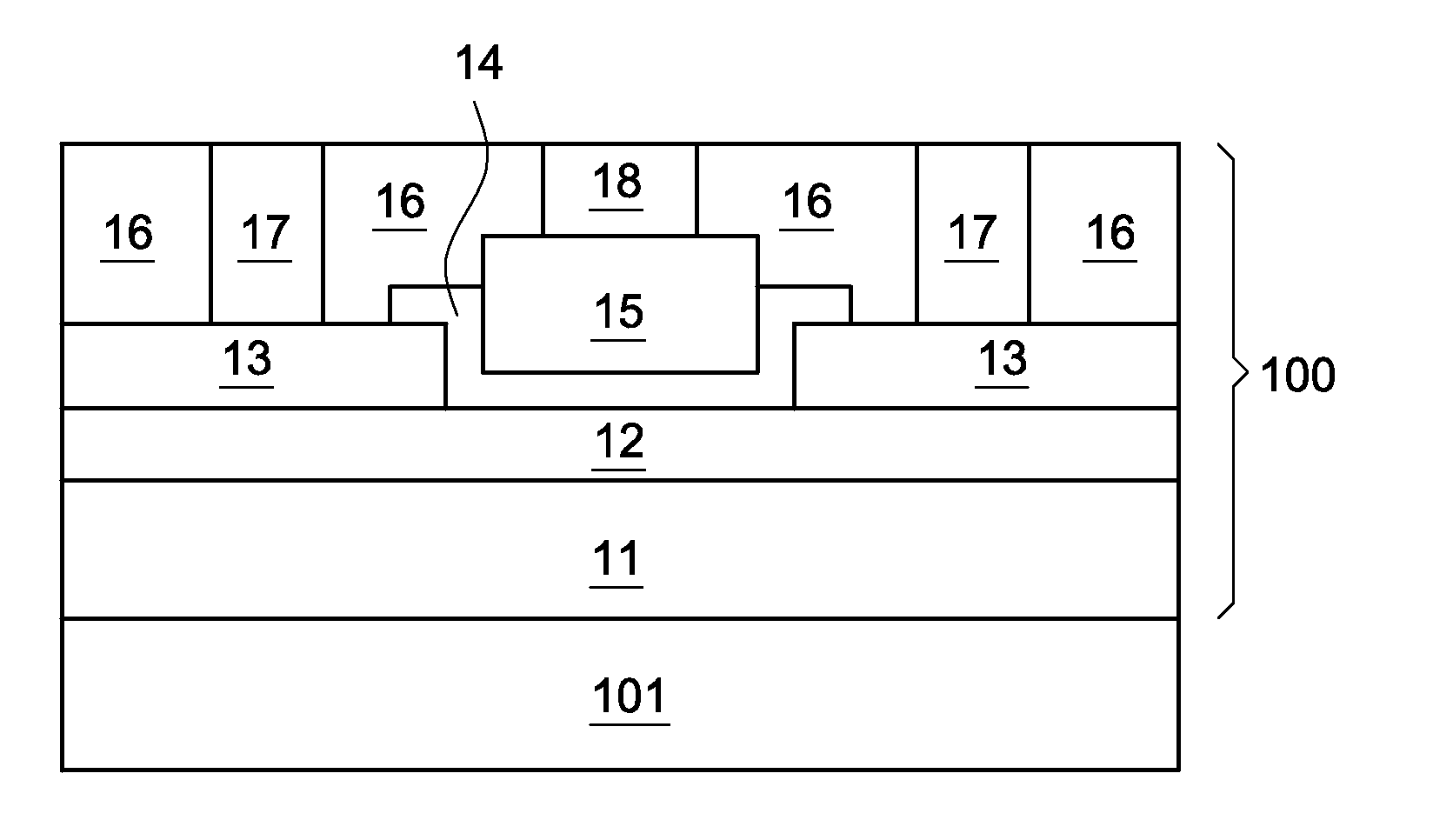

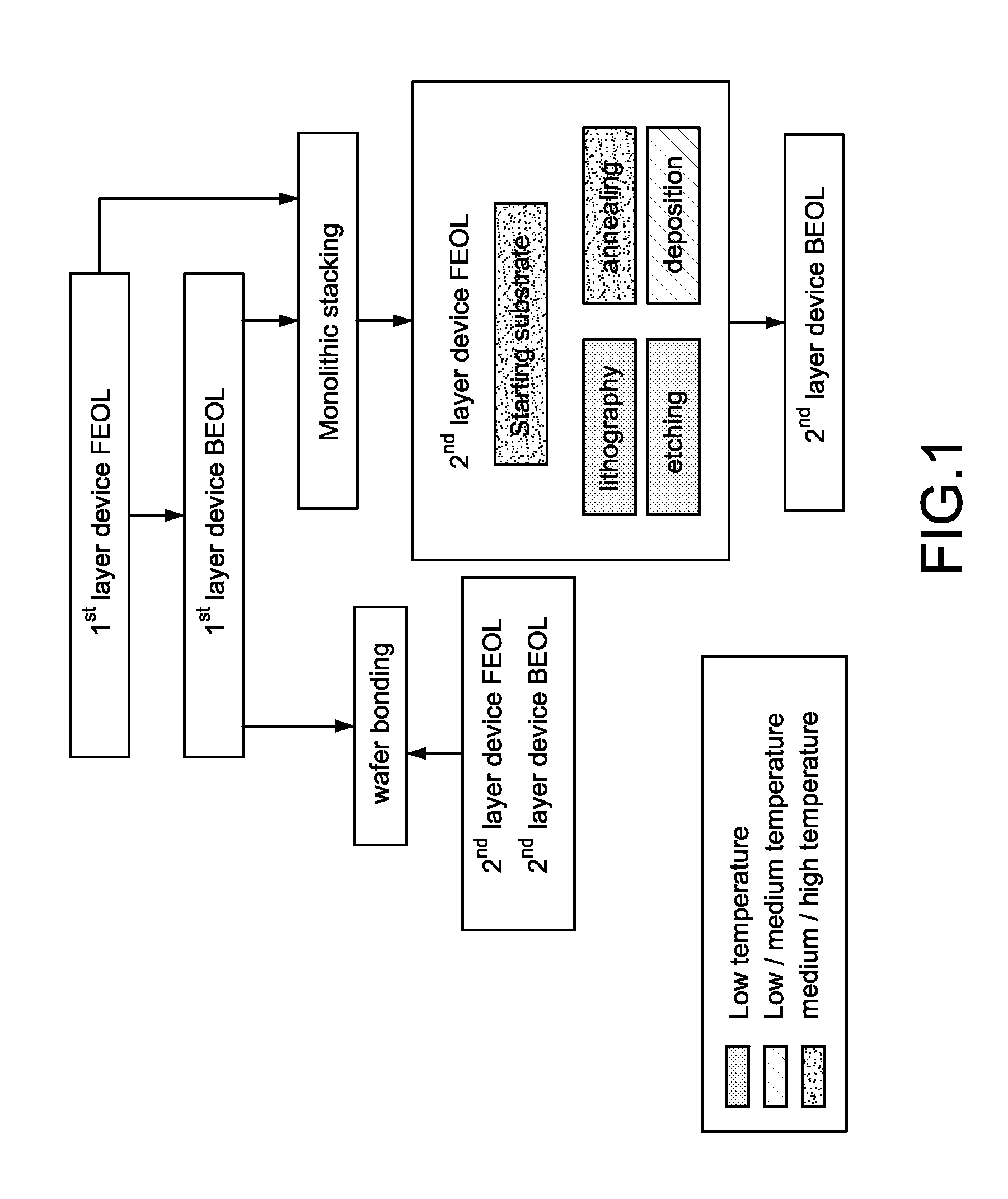

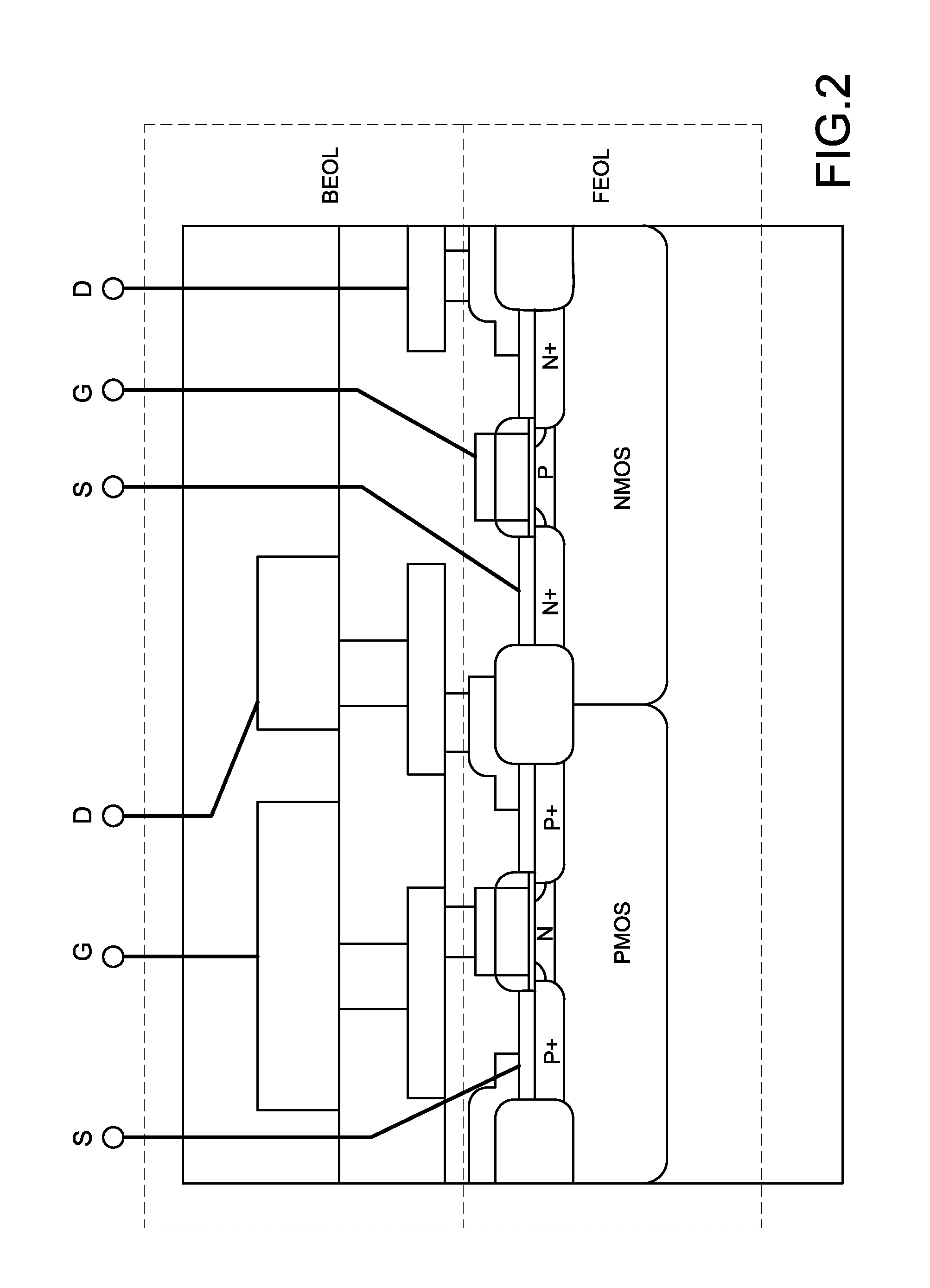

Electrical switch using gated resistor structures and three-dimensional integrated circuits using the same

ActiveUS20120056258A1Low thermal budgetImprove interconnect densityTransistorSolid-state devicesElectrical resistance and conductanceIsolation layer

An electrical switch using a gated resistor structure includes an isolation layer, a doped silicon layer arranged on the isolation layer and having a recessed portion with reduced thickness, the doped silicon layer having a predetermined doping type and a predetermined doping profile; a gate layer arranged corresponding to the recessed portion. The recessed portion in the doped silicon layer has such thickness that a channel defined under the gate can be fully depleted to form a high resistivity region. The recessed channel gated resistor structure can be advantageously used to achieve high interconnect density with low thermal budget for 3D integration.

Owner:CHEN SHU LU

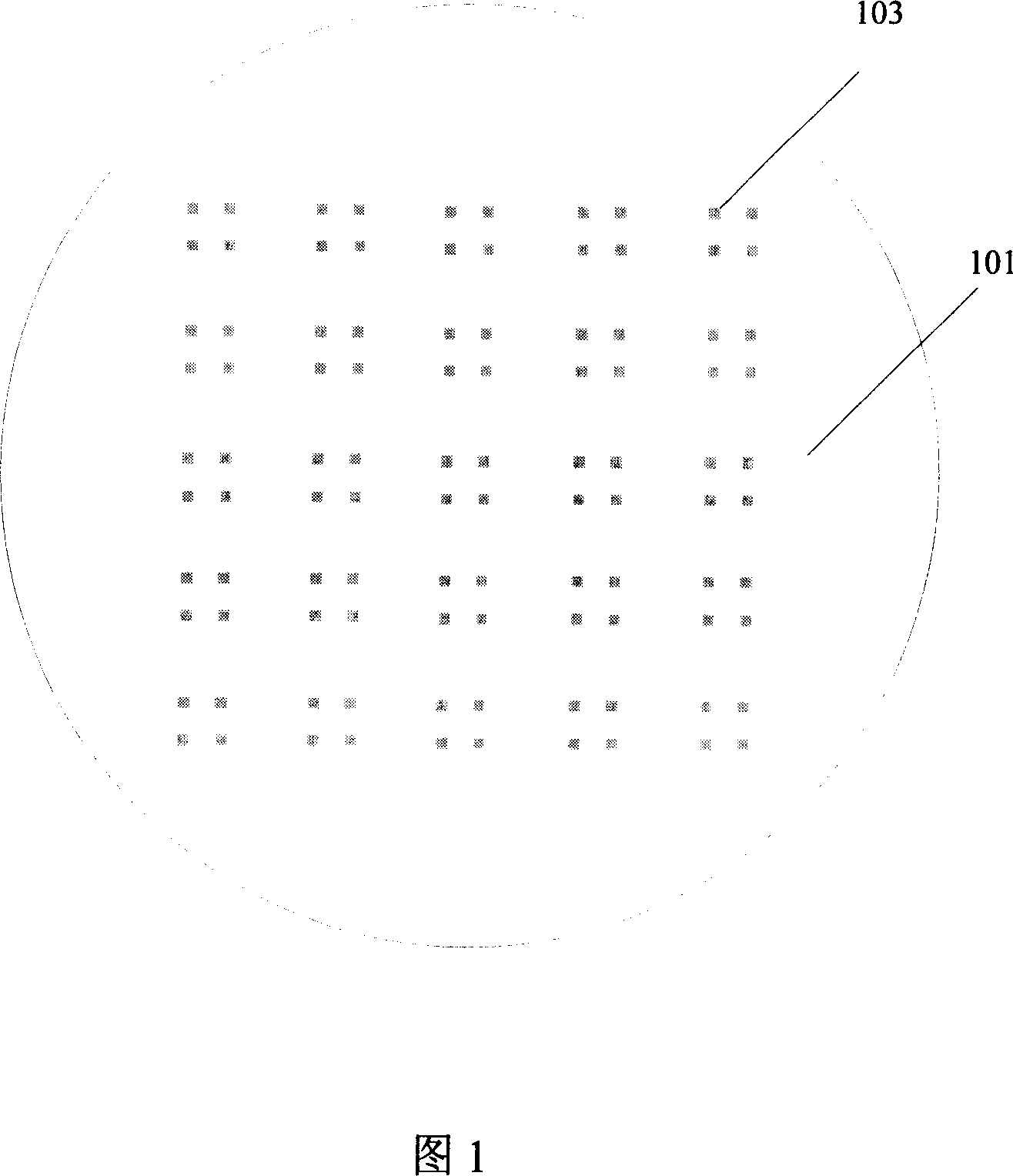

Method utilizing TSV (Through-Silicon-Via) to realize wafer level package of GaAs (gallium arsenide) image sensor

InactiveCN102544040AReduce volumeImprove package reliabilitySemiconductor/solid-state device manufacturingRadiation controlled devicesEtchingInterconnection density

The invention relates to a method utilizing TSV (Through-Silicon-Via) to realize wafer level package of a GaAs (gallium arsenide) image sensor. The method comprises the following steps: combining wet etching with mechanical machining to machine a groove; manufacturing a resin insulating layer in the groove; then manufacturing a through hole in resin by using a laser method; electroplating the inner part of the groove and the inner part of the through hole to realize the back extraction of the electrode of a front wafer surface; and making a passivating layer and solder bumps. The whole process is completed at a wafer level, and the interconnection density is high while the package cost is reduced. Meanwhile, a manufactured interconnection structure has high reliability.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

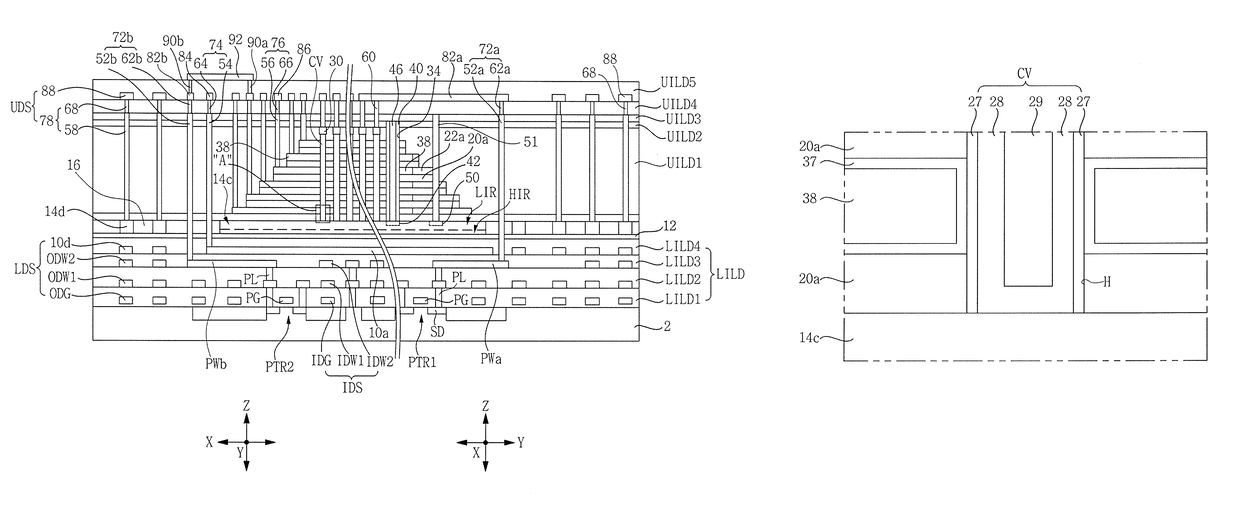

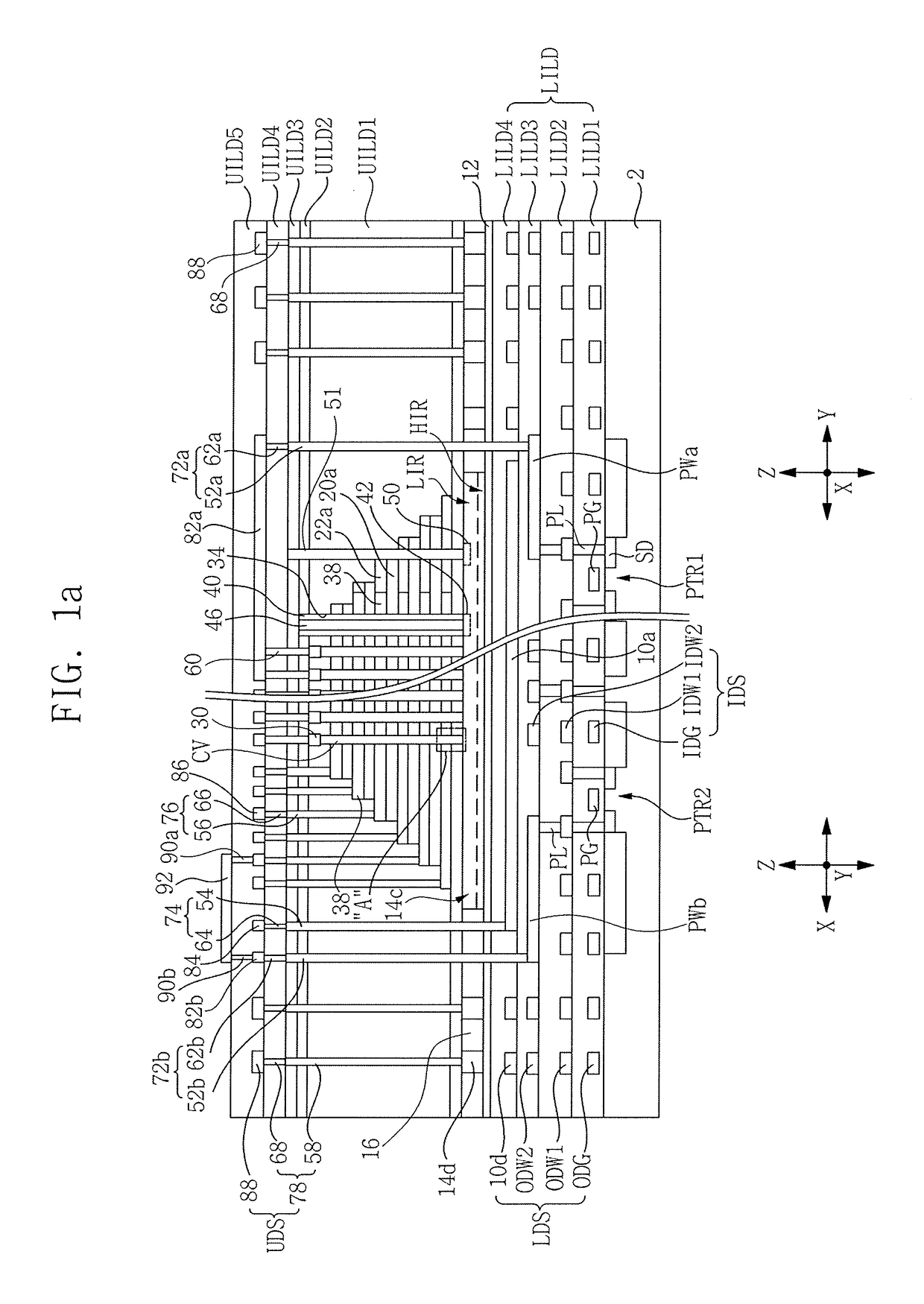

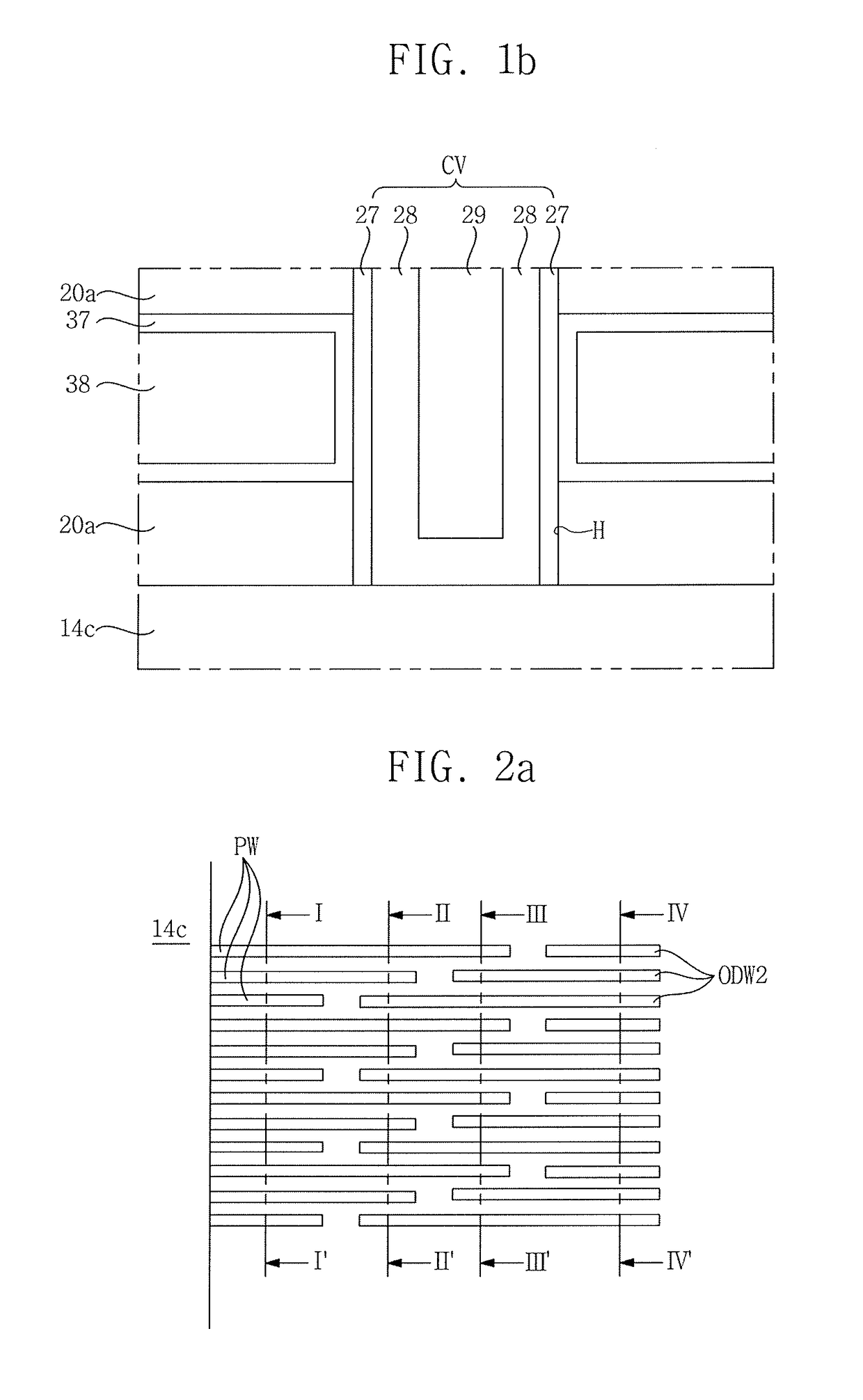

Semiconductor device with an interconnection structure having interconnections with an interconnection density that decreases moving away from a cell semiconductor pattern

ActiveUS10115667B2Semiconductor/solid-state device detailsSolid-state devicesInterconnection densityEngineering

A semiconductor device includes a cell semiconductor pattern disposed on a semiconductor substrate. A semiconductor dummy pattern is disposed on the semiconductor substrate. The semiconductor dummy pattern is co-planar with the cell semiconductor pattern. A first circuit is disposed between the semiconductor substrate and the cell semiconductor pattern. A first interconnection structure is disposed between the semiconductor substrate and the cell semiconductor pattern. A first dummy structure is disposed between the semiconductor substrate and the cell semiconductor pattern. Part of the first dummy structure is co-planar with part of the first interconnection structure. A second dummy structure not overlapping the cell semiconductor pattern is disposed on the semiconductor substrate. Part of the second dummy structure is co-planar with part of the first interconnection structure. A conductive shielding pattern is disposed between the cell semiconductor pattern and the semiconductor substrate and above the first circuit and the first interconnection structure.

Owner:SAMSUNG ELECTRONICS CO LTD

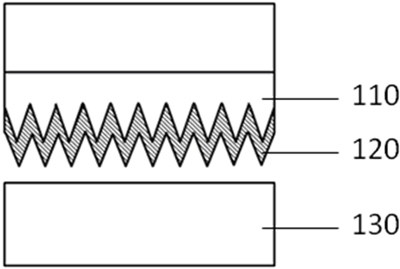

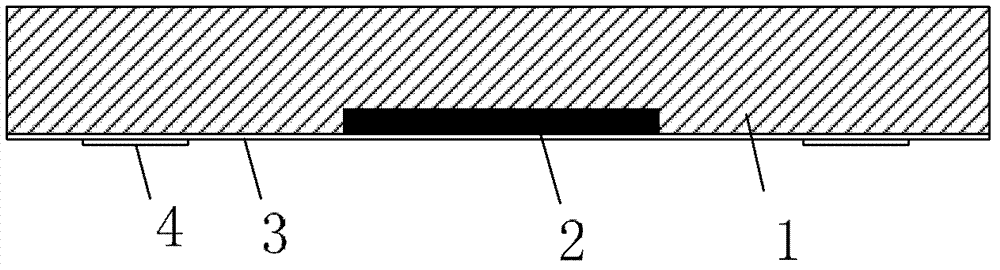

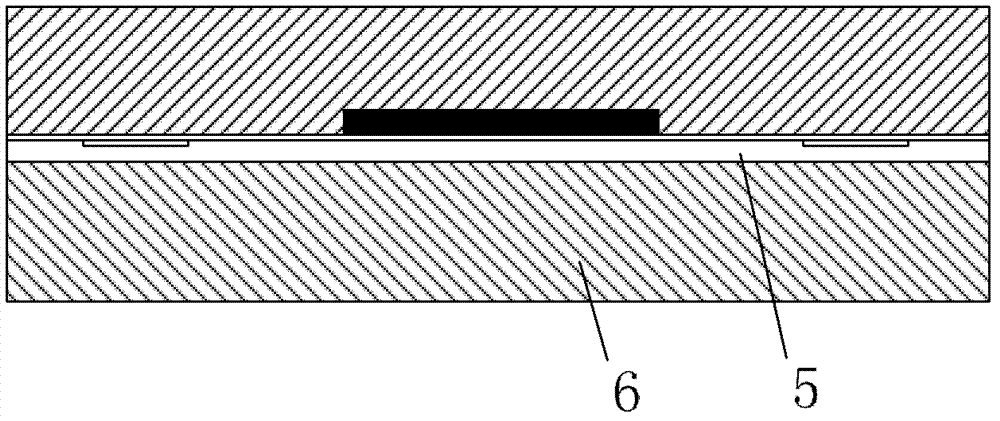

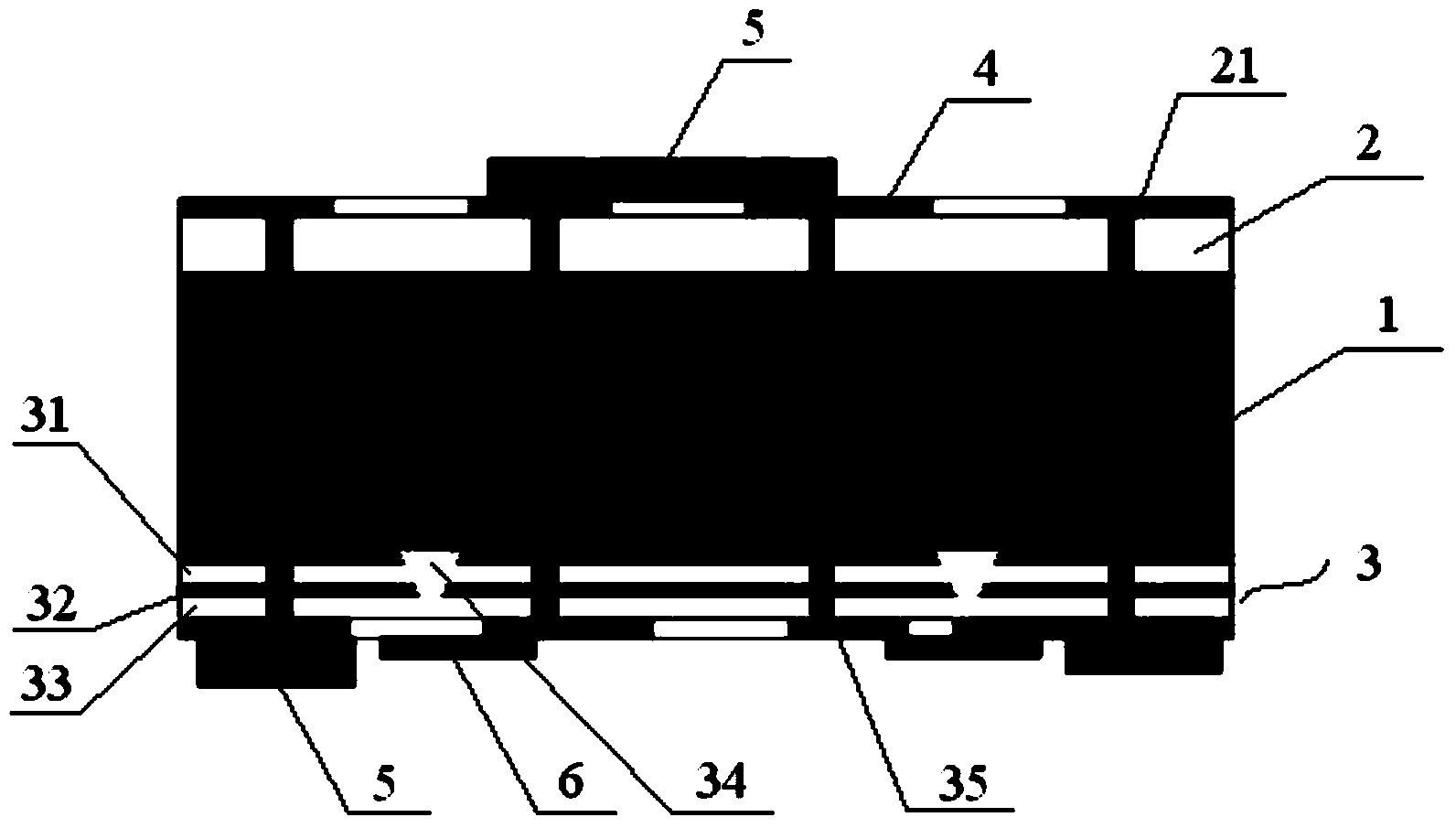

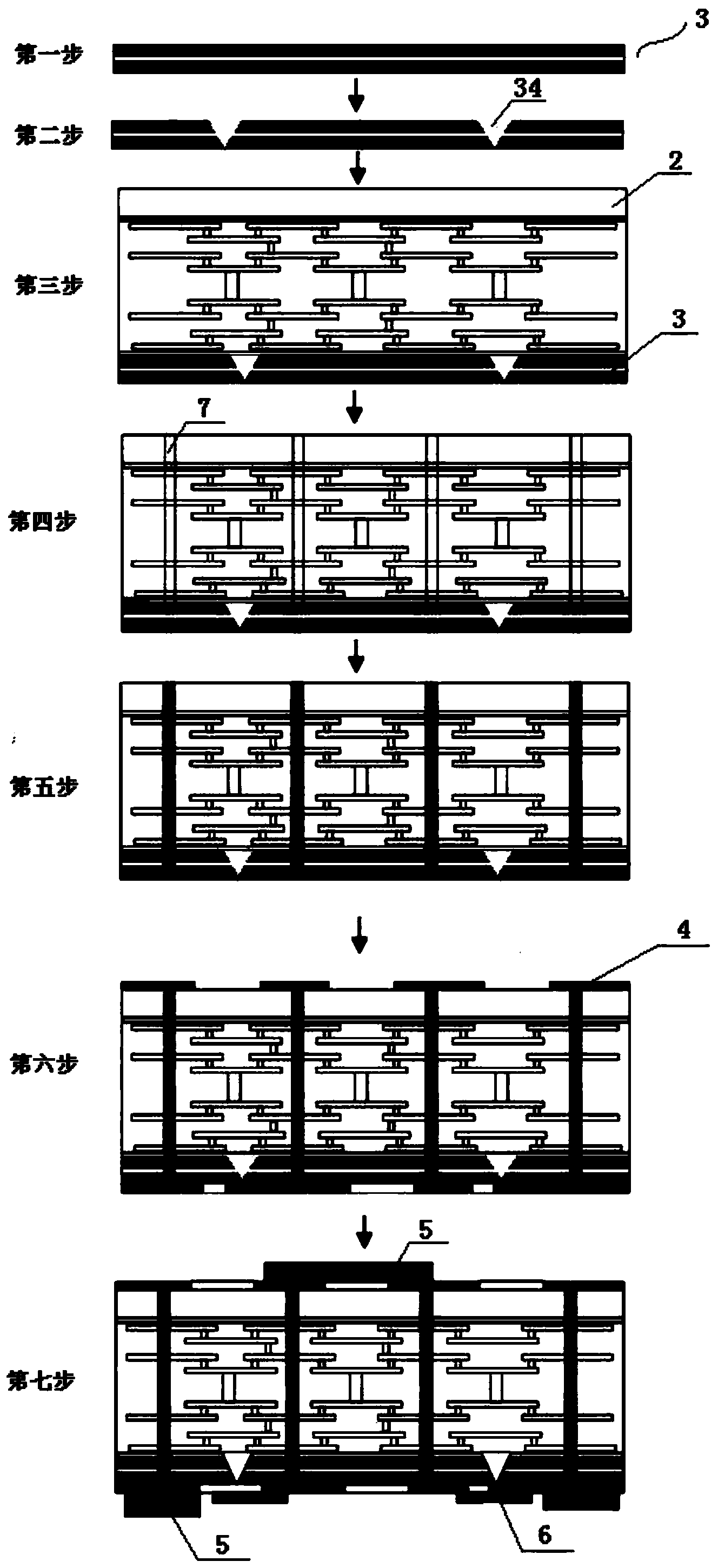

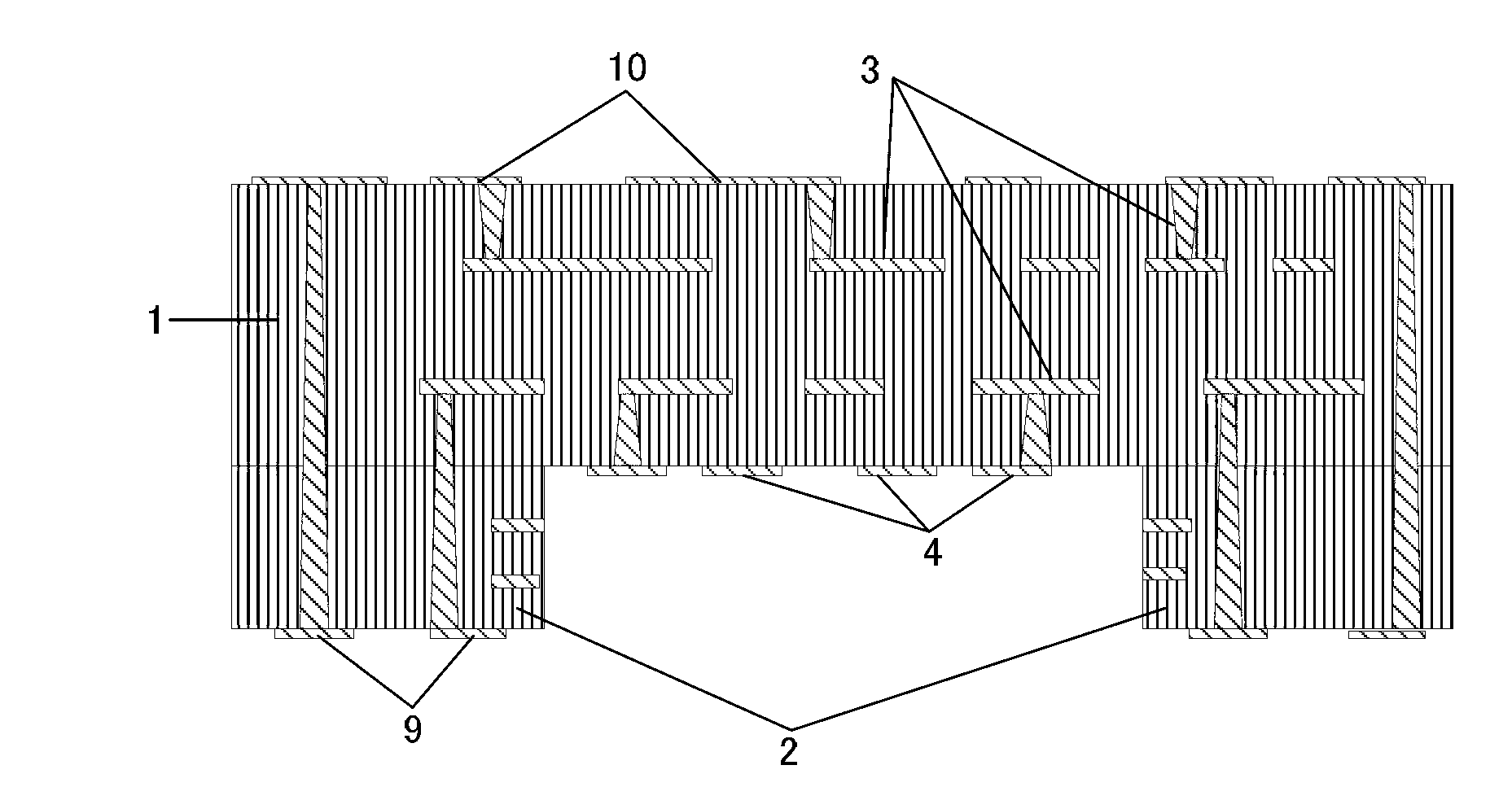

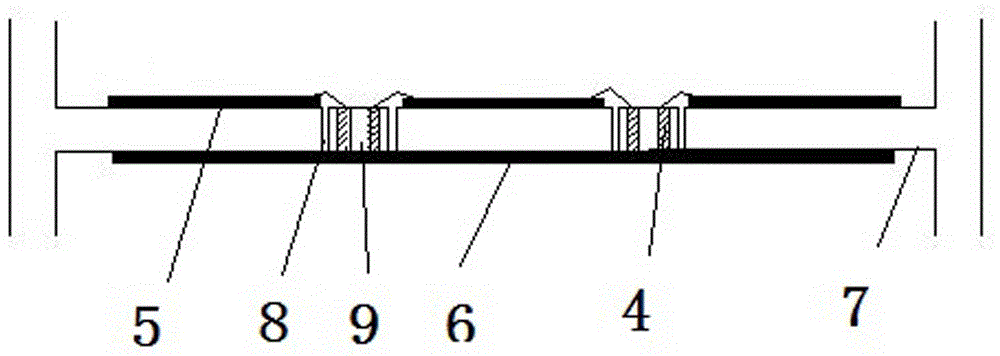

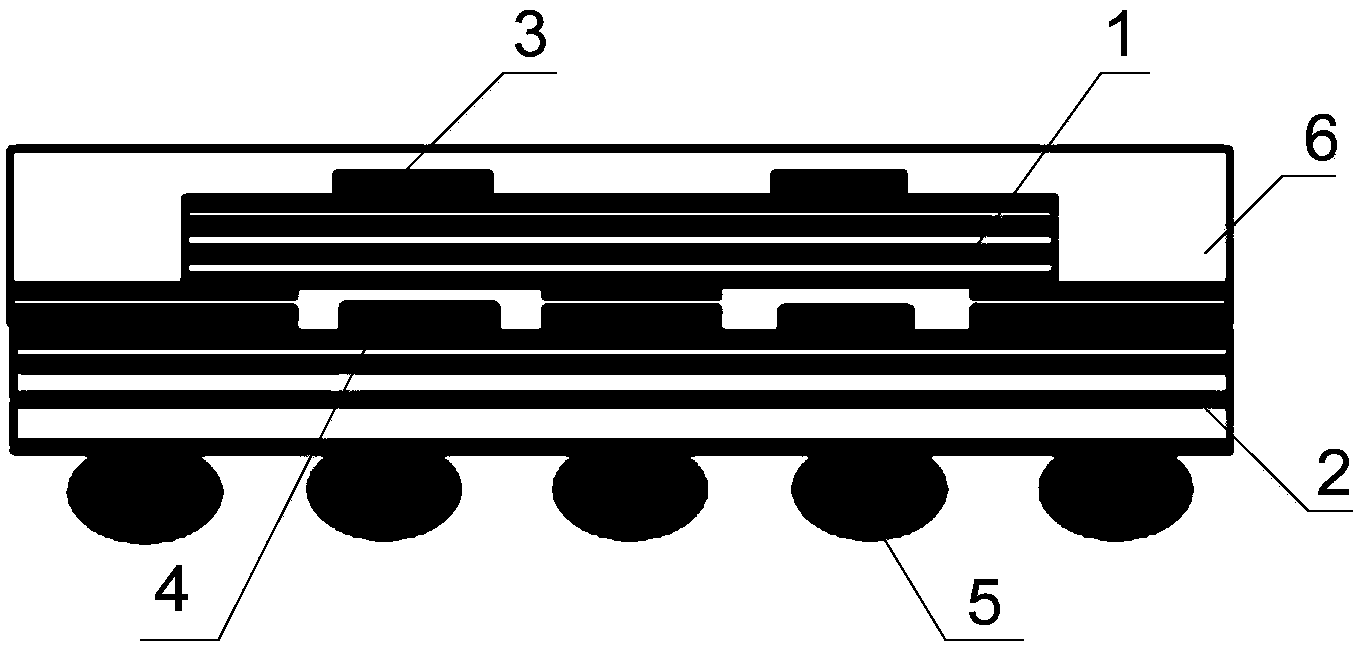

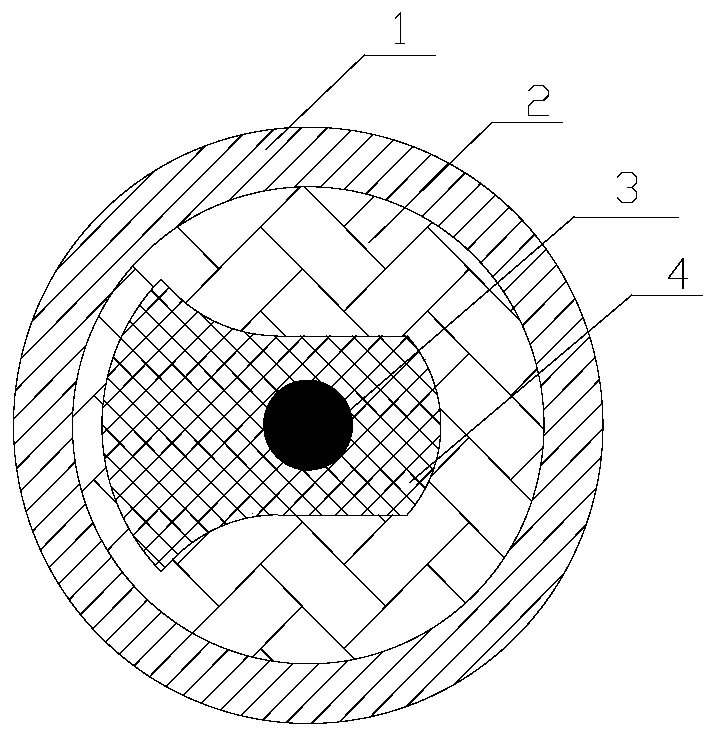

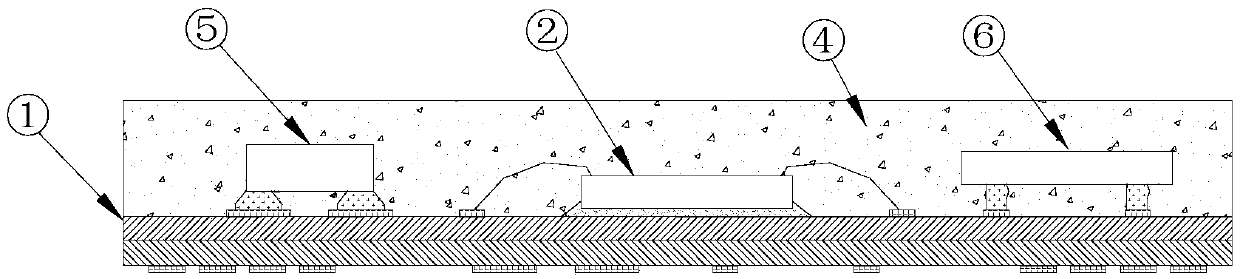

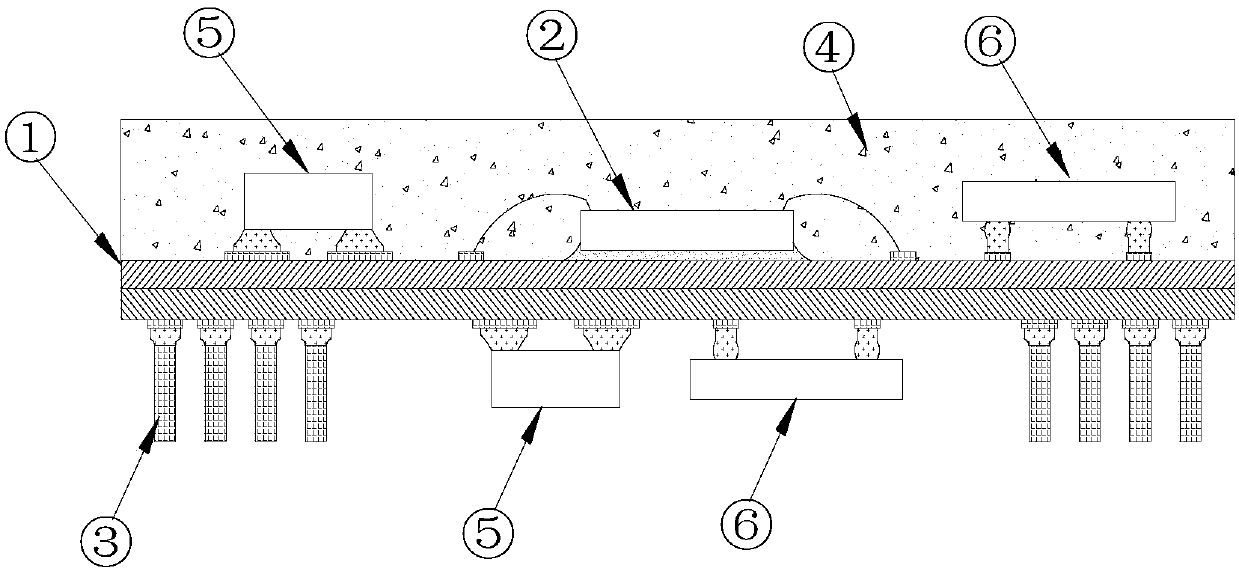

Packaging and interconnecting structure and method for copper protruded points filled up with double layers of underfill

ActiveCN104078431AAchieve high densityGuaranteed fillingSemiconductor/solid-state device detailsSolid-state devicesInterconnection densityYoung's modulus

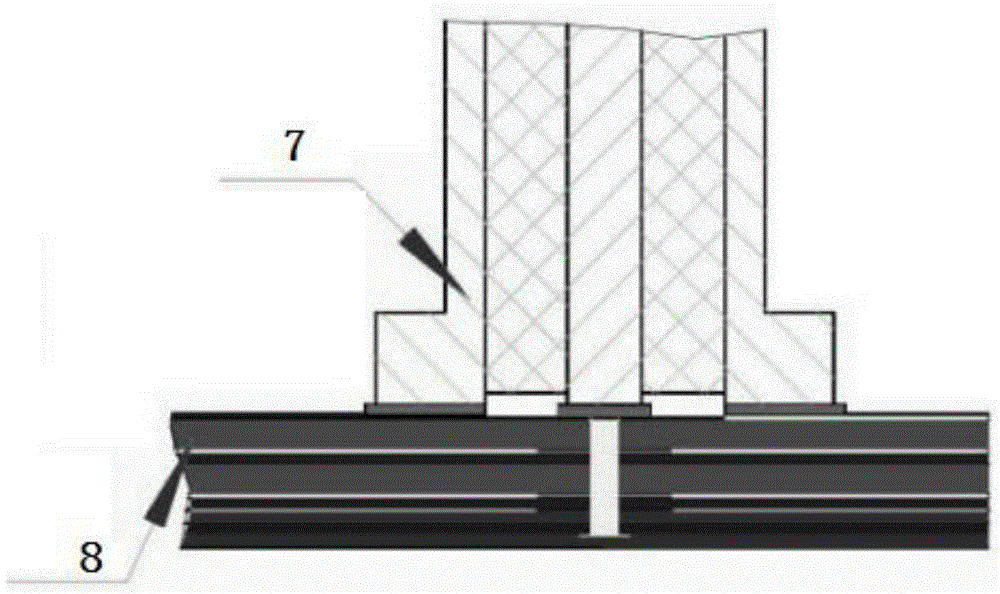

The invention relates to a packaging and interconnecting structure and method for copper protruded points filled up with double layers of underfill. The packing and interconnecting structure is characterized in that the chip end is filled up with the first layer of underfill, the first layer of underfill is manufactured on a wafer through spin coating process, the substrate end is filled up with the second layer of underfill, the substrate end is filled through capillary effects after flip-chip welding is finished, the glass transition temperature and the Young modulus of the first layer of underfill are lower than those of the second layer of the underfill, a chip and a substrate are connected through the copper protruded points and tin-contained solder protruded points to achieve high-density connection, and the copper protruded points are manufactured in twice to guarantee that the first layer underfill is completely filled and the contact between the protruded points and the tin-contained solder is enough. The whole technological process is compatible with existing IC process and has higher vertical interconnection density, better electric connection characteristics and higher mechanical stability. Heating thermal circulation tests show that the service life of chips of the packaging structures is greatly prolonged.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Compact optical fiber coupler

InactiveUS6873768B2Improve interconnect densityMinimize polarizationOptical fibre with graded refractive index core/claddingCoupling light guidesCouplingInterconnection density

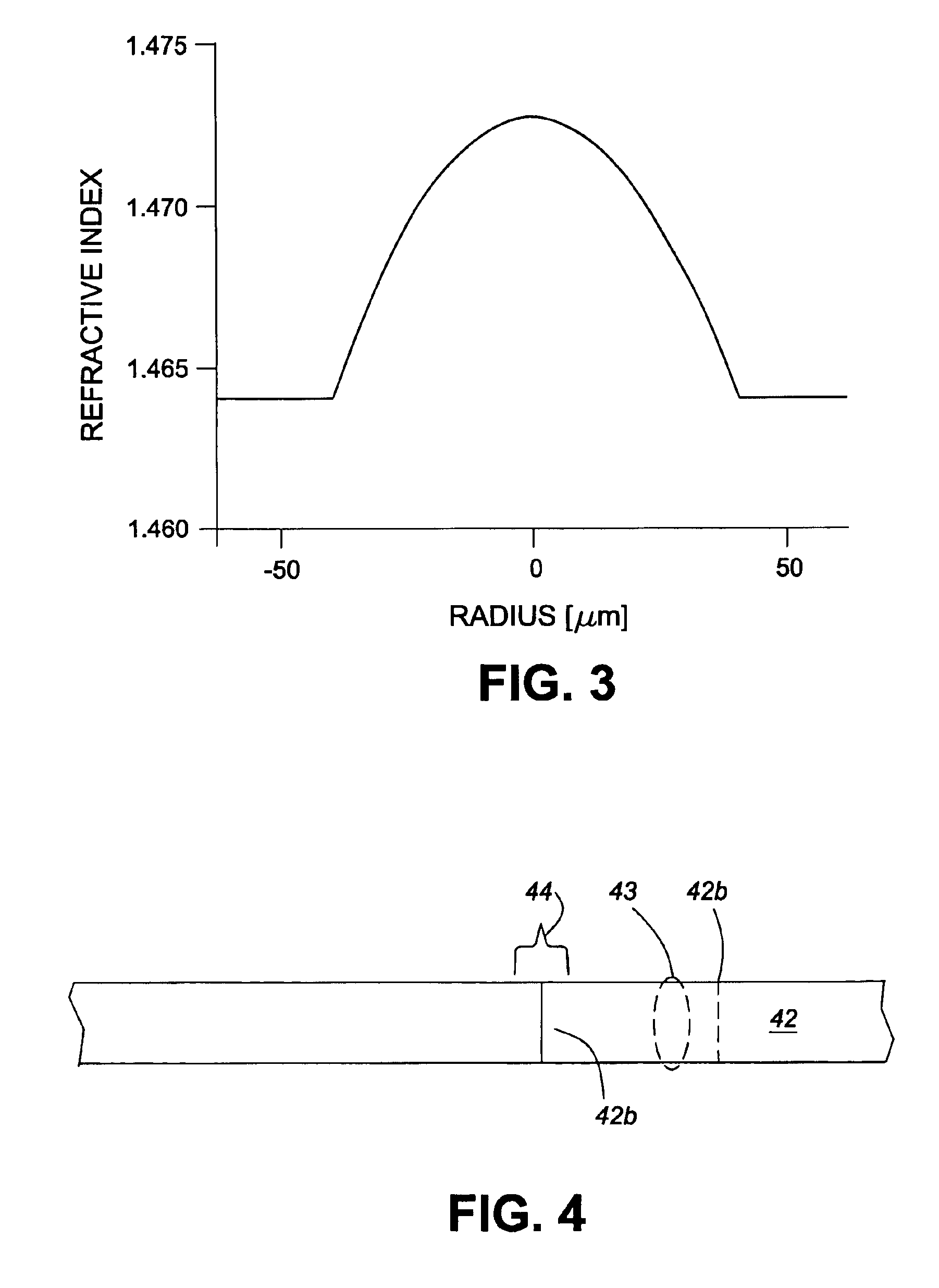

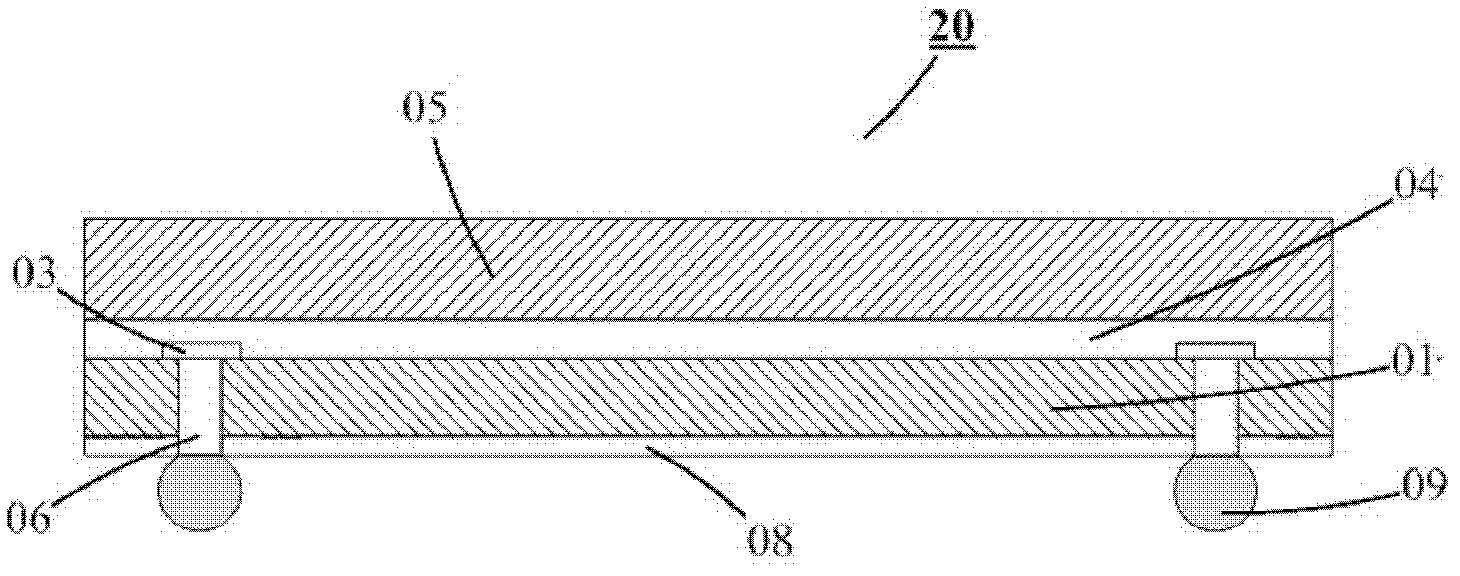

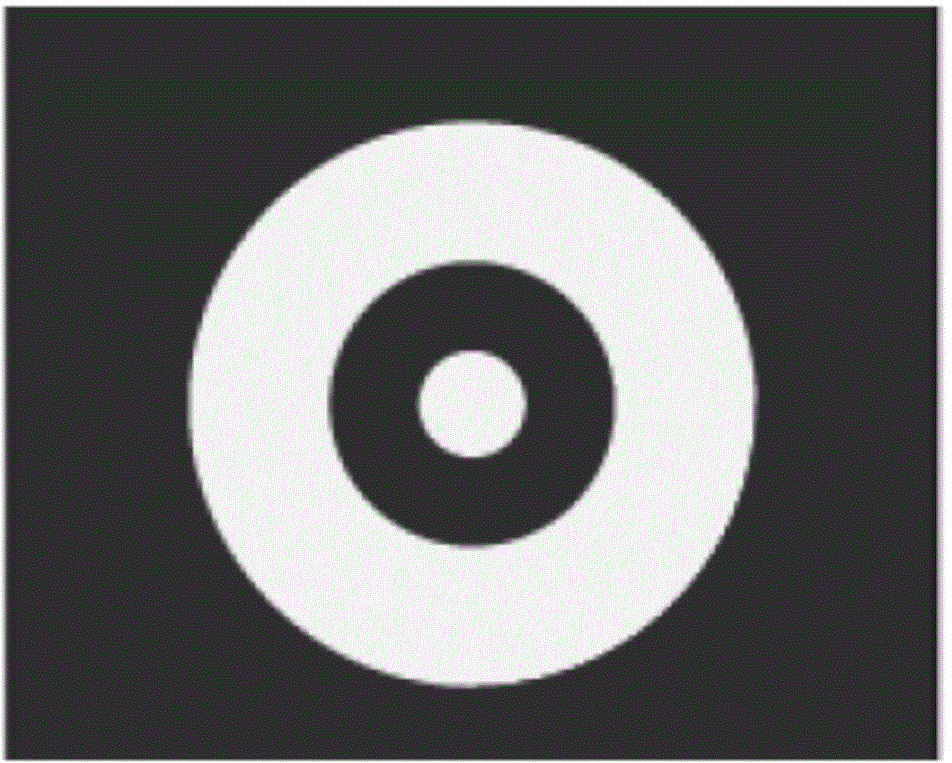

The inventive coupling device enables a high interconnection density of single mode optical fiber in active and passive devises used in a fiber optic telecommunication system. The coupling device comprise a micro-lens formed by terminating a single mode optical fibers with an optimized gradient index fiber, thus avoiding a significant increase in fiber diameter. The gradient index is optimized to provide a long working distance to the minimum spot size so that efficient coupling can be achieved in a free space interconnection between either multiple single mode fibers or a single mode fiber to a transmitting or receiving device.

Owner:JDS UNIPHASE CORP

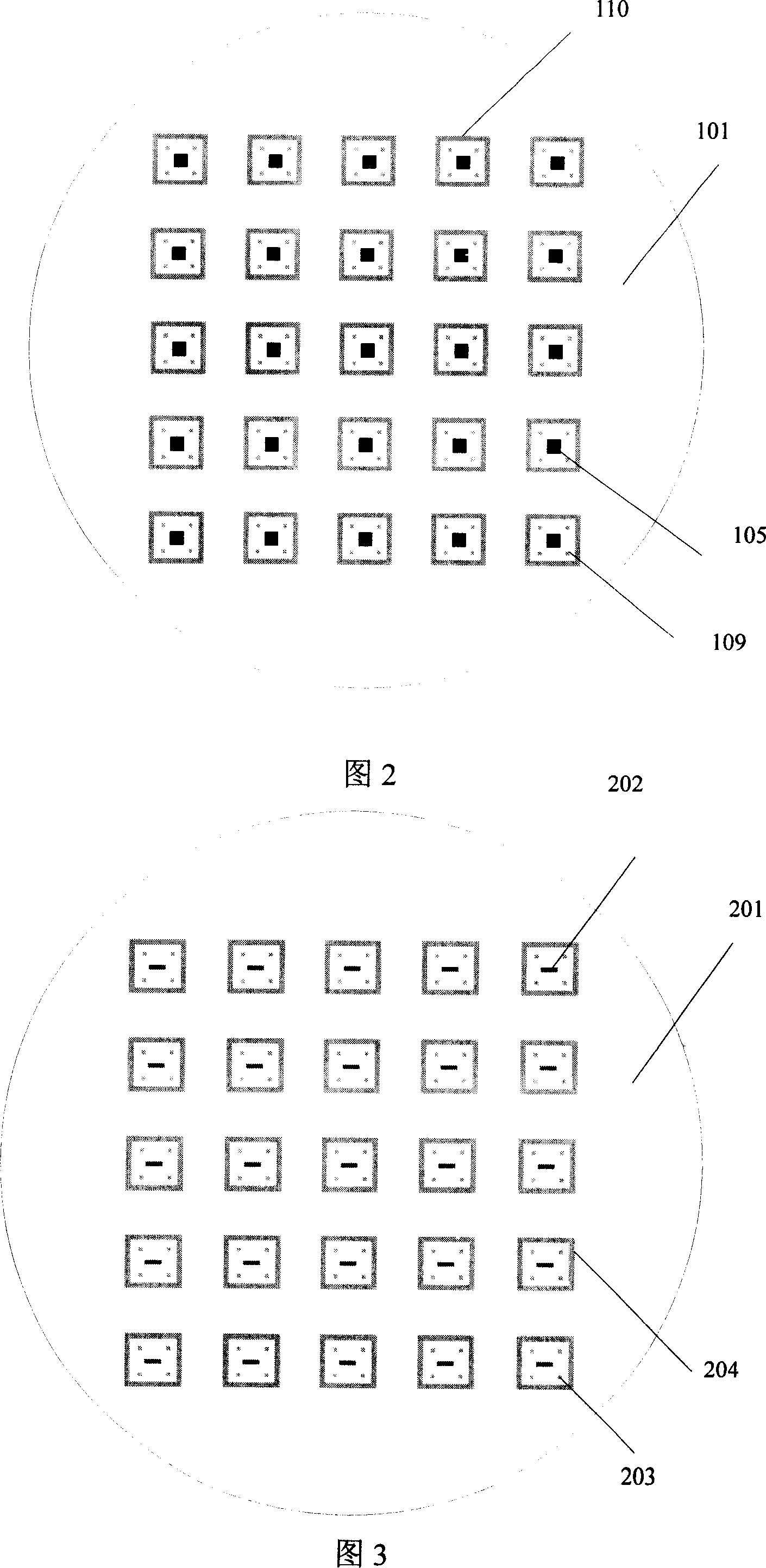

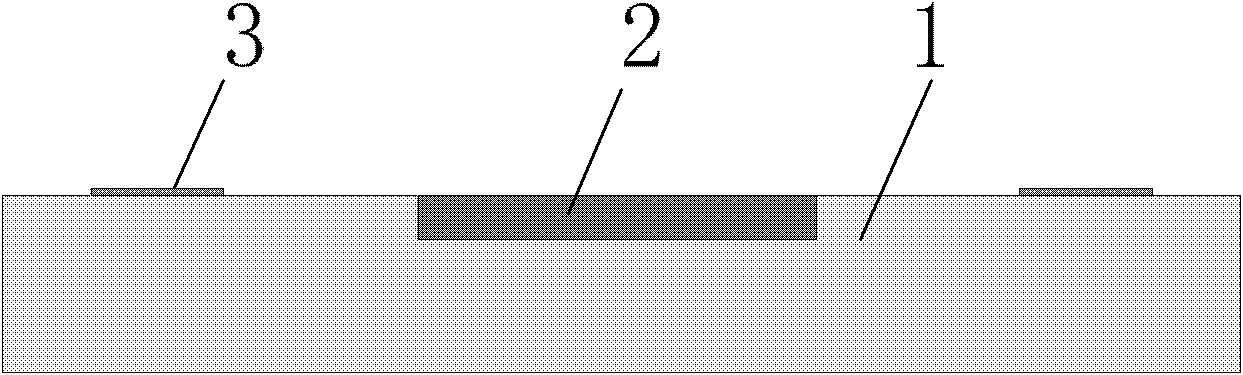

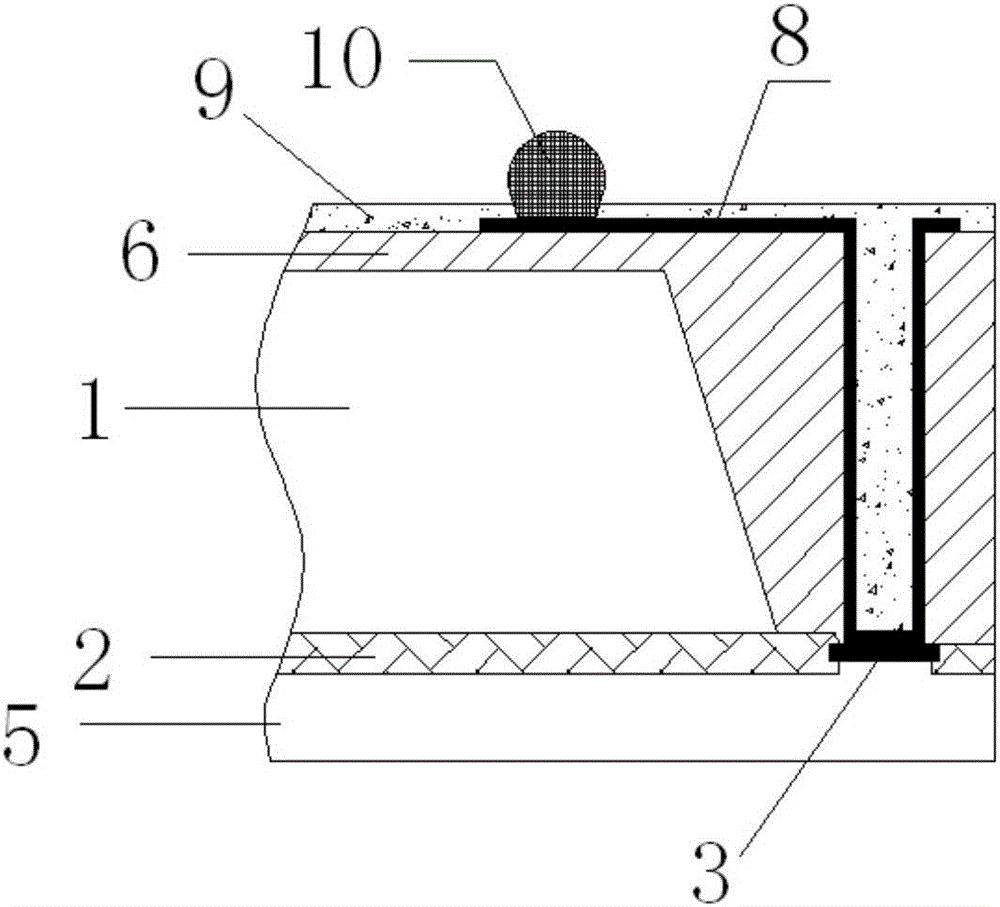

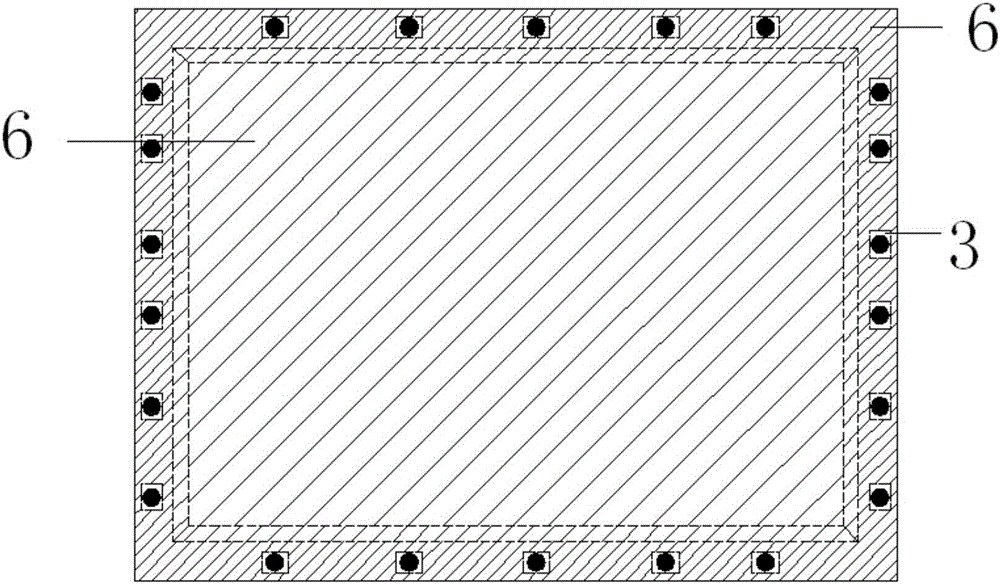

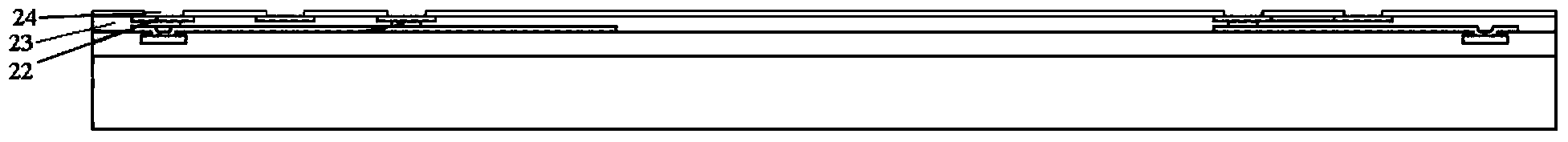

Wafer-level chip size encapsulation technology for GaAs (gallium arsenide) CCD (Charge Coupled Device) image sensor

ActiveCN102509718AImprove interconnect densityFirm packagingDecorative surface effectsSemiconductor/solid-state device manufacturingInterconnection densityCharge couple device

The invention relates to a wafer-level chip size encapsulation technology for a GaAs (gallium arsenide) CCD (Charge Coupled Device) image sensor. The technology is characterized by comprising the following steps of: (1) firstly bonding a glass wafer and a GaAs wafer through a resin adhesive so as to protect the active surface of a chip and improve the strength of a chip wafer; (2) manufacturing a trapezoidal-slot structure by a wet corrosion or physical method so as to reduce the lining thickness of a chip interconnection area; (3) manufacturing vertical interconnected through holes by a dry etching technology so as to expose a pad on the active surface of the chip; (4) sputtering seed-layer metal and electroplating, and manufacturing a hole metalizing and RDL layer to realize circuit interconnection from the active surface to the back surface of the chip; (5) manufacturing a passivation layer, a UBM layer and raised points; and (6) finally scribing to form an independent encapsulation chip. As the trapezoidal-slot structure on the back realizes thickness reduction only in the area with the pad, the cost is effectively lowered; and through the interconnection of the vertical through holes, the encapsulation interconnection density can be improved, and the signal transmission path is shortened.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

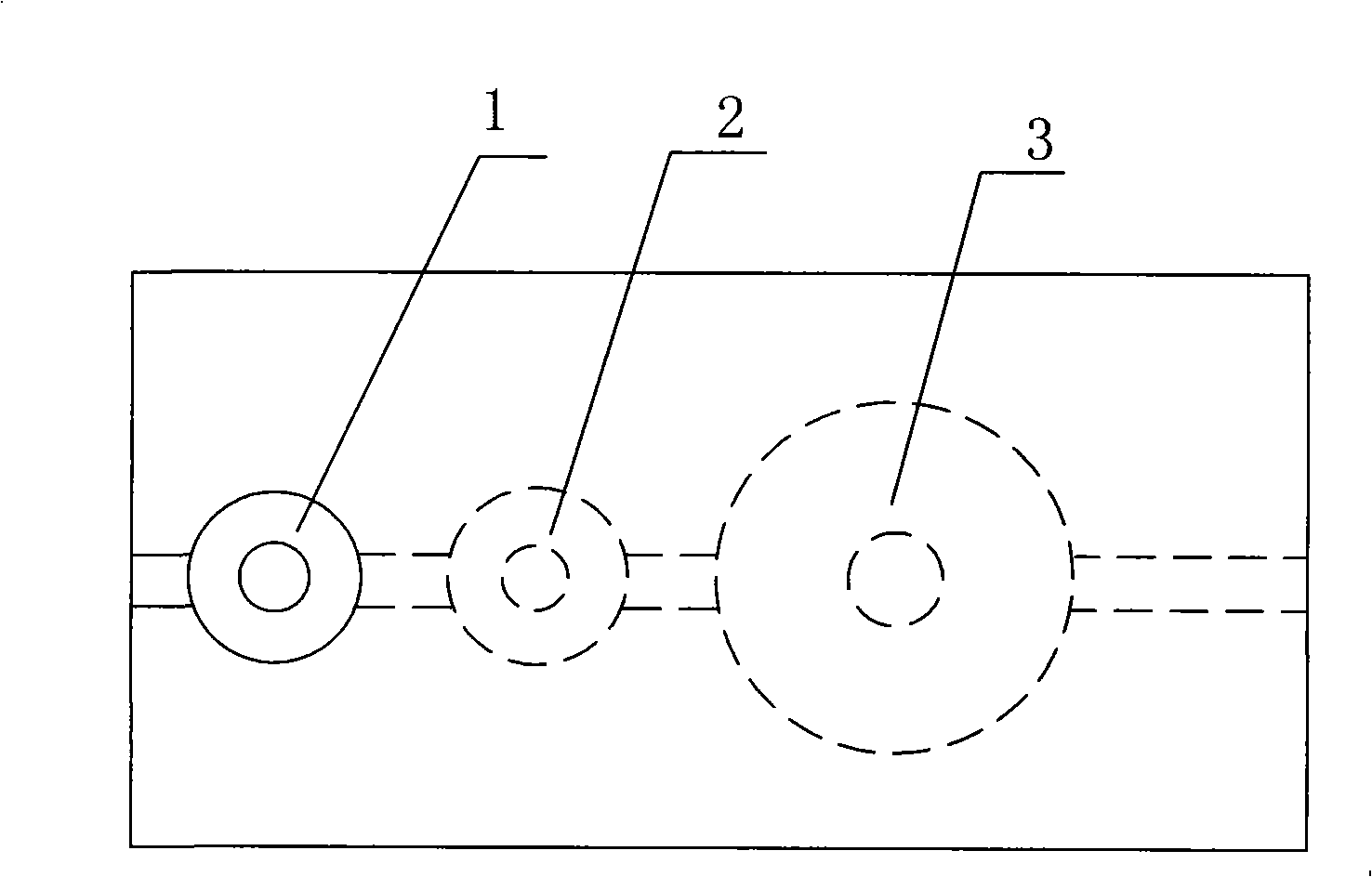

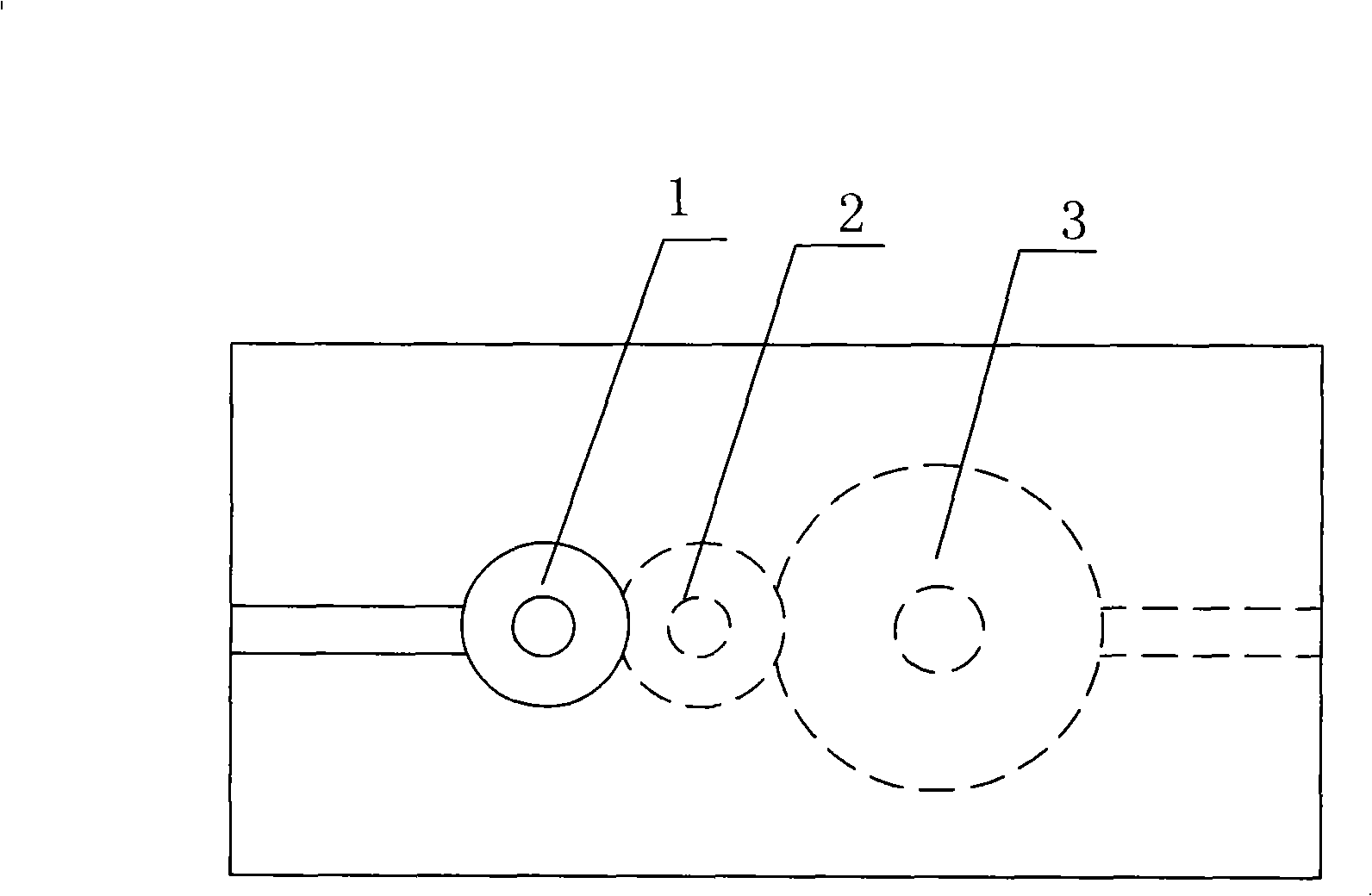

Multi-layer printed circuit board, design method thereof, and final product of mainboard

ActiveCN101309559ASmall footprintImprove interconnect densityElectrical connection printed elementsSpecial data processing applicationsInterconnection densityEngineering

The invention discloses a multi-layered printed circuit board and a design method thereof and a terminal product motherboard, which are invented for solving the problems that the space occupied by through holes can be saved, and the interconnection density can be improved. In the multilayered printed circuit board, the terminal pad center distance of the signal communication through holes between two different interlamination insulating layers at the position of replacing layers is larger than the terminal pad radius of any one of the signal communication through holes thereof, and less than the sum of the terminal pad radius of the two signal communication through holes. The terminal product motherboard adopts the multilayered printed circuit board; the design method of the multilayered printed circuit board comprises the steps that the terminal pad center distance of the two adjacent signal communication through holes is punched in a simulation model, the terminal pad center distance is larger than any one of the terminal pad radius thereof, and less than the replaced layer signal communication through hole of the sum of the terminal pad radius of the two signal communication through holes. The embodiment of the invention is applied in the manufacture and the design of the multilayered printed circuit board.

Owner:HUAWEI DEVICE CO LTD

Method for low-temperature solid bonding of semiconductor device

InactiveCN102610537AAvoid heat damageHigh densitySolid-state devicesSemiconductor/solid-state device manufacturingDevice materialInterconnection density

The invention discloses a method for the low-temperature solid bonding of a semiconductor device. The method comprises the following steps: 1) selecting at least two elements to be bonded of electric interconnection pads which are matched with each other; 2), forming copper microneedle cone groups on a plurality of pads of one element to be bonded; 3) forming salient points with at least the surfaces provided with low-hardness second metal points on a plurality of pads of the other element to be bonded; 4) contacting the salient points with the copper microneedle cone groups, heating the contact parts of the salient points and the copper microneedle cone groups to be a first temperature, and applying bonding pressure so as to electrically inter connect and bond the salient points and the copper microneedle cone groups. Compared with the prior art, the method has the advantages that in the technique process, the temperature does not need to be heated to be higher than the melting point of soldering flux so as to melt the soldering flux, so that thermal damage to the device can be avoided, and the interconnection density and the reliability of the product can be improved by the solid bonding, the interface reaction is controllable, and organic matters such as scaling powder and the like are not needed, so that the technique process is simplified.

Owner:SHANGHAI JIAO TONG UNIV

Method for making printed circuit board (PCB)

InactiveCN102159034AThe production process is simpleShorten the production cyclePrinted circuit manufactureHigh densityInterconnection density

The invention discloses a method for making a printed circuit board (PCB) and belongs to an integrated high density interconnection (HDI) technology, in particular to a new high density interconnection technology which combines the present dry method, thick film technology, laser engraved technology and plasma cleaning technology of the PCB. In the method, processes of image transferring, soldering-resistant exposure developing, plating holes and electroplating are not required, so the production process is simplified and higher interconnection density can be obtained; the method can be used for chip level assembly and 3G products, thereby realizing energy saving and emission reduction and reducing cost.

Owner:HUIZHOU CITY GREEN MARK PHOTOELECTRIC TECH

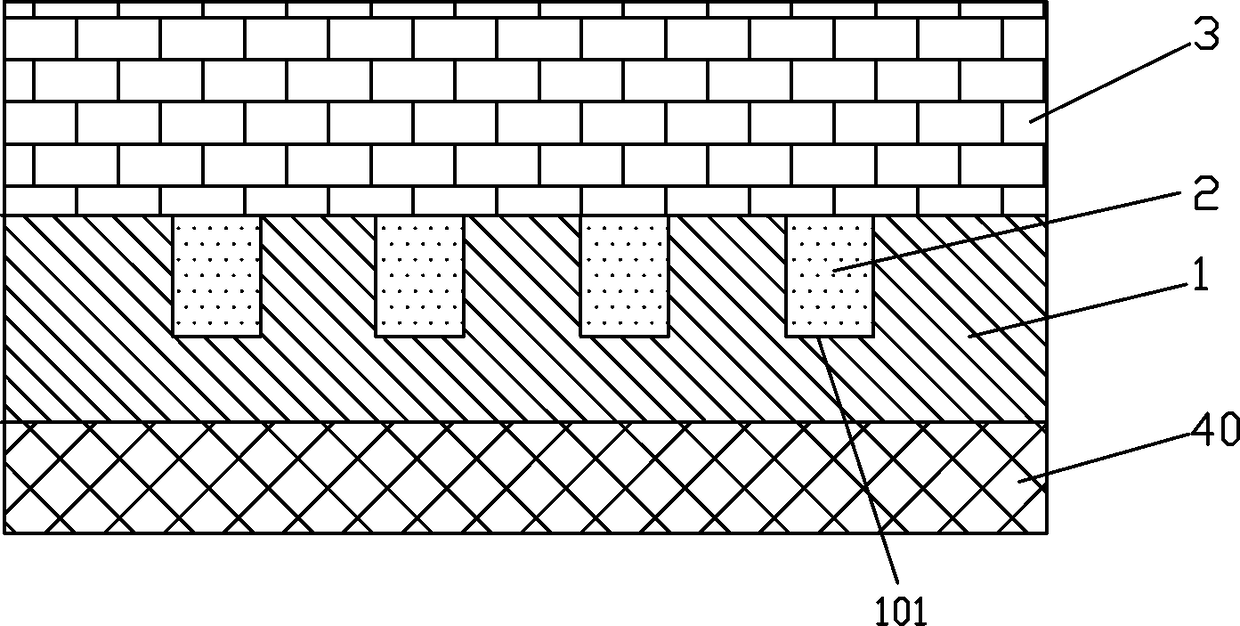

High-density optical waveguide structure, printing circuit board and preparation method thereof

PendingCN108415124ASmall line width/spacingImprove finenessCircuit optical detailsPrinted circuit manufactureHigh densityInterconnection density

The invention provides a high-density optical waveguide structure, a printing circuit board and a preparation method thereof. The high-density optical waveguide structure successively comprises a lower coating layer, a core layer and an upper coating layer; and a plurality of grooves are formed in the lower coating layer at intervals, and are filled with an optical waveguide materials to form thecore layer. Optical waveguide is integrated into a PCB to implement optoelectronic interconnection; high parallel interconnection density can be realized well, good signal integrity is maintained, andsizes of devices and equipment are reduced; meanwhile, power consumption is low, heat dissipation is facilitated, simple physical architecture and design can be realized, wiring space of the printingcircuit board is increased to a maximum extent, and manufacturing of an ultra-fine wire circuit board is facilitated; and moreover, wiring density of an existing preparation method can be improved, and the reliability is improved.

Owner:SHANGHAI MEADVILLE SCI & TECH

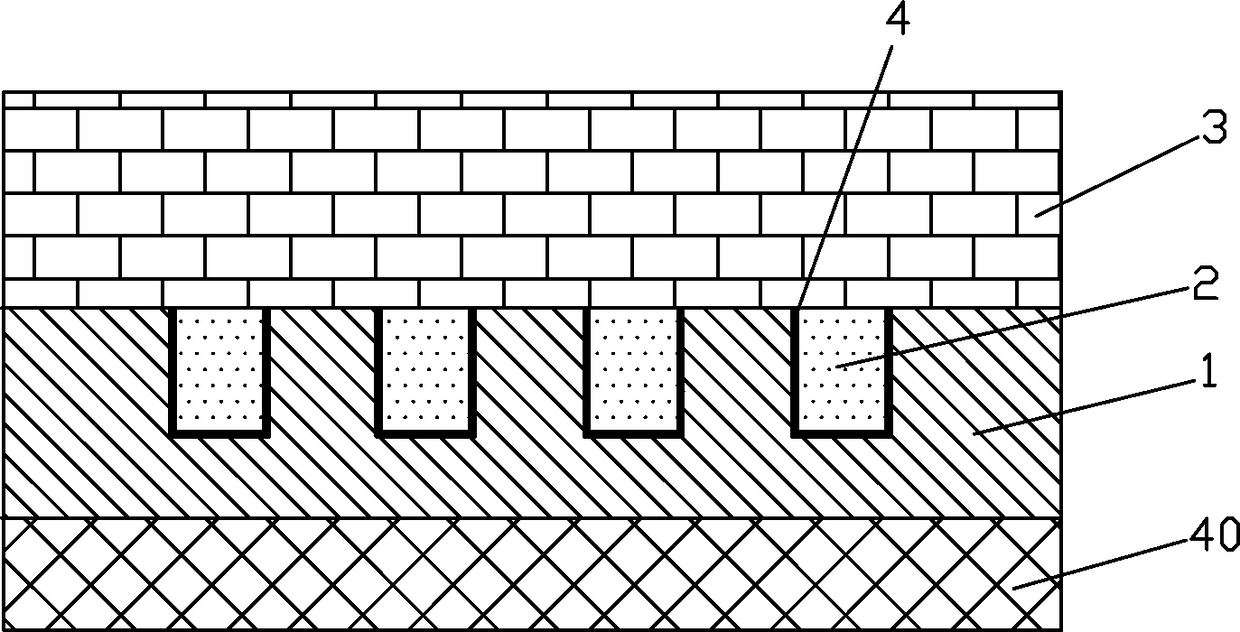

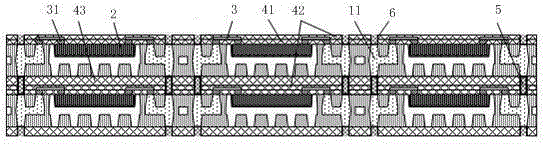

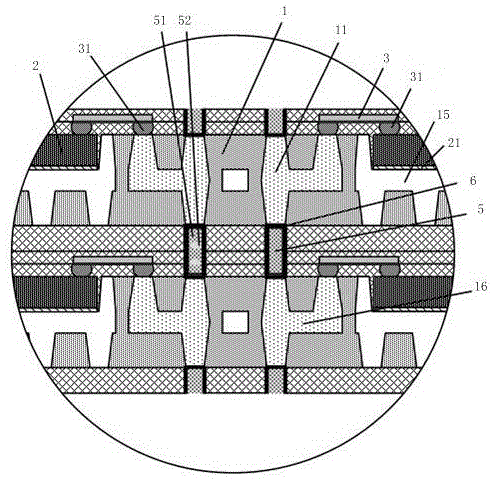

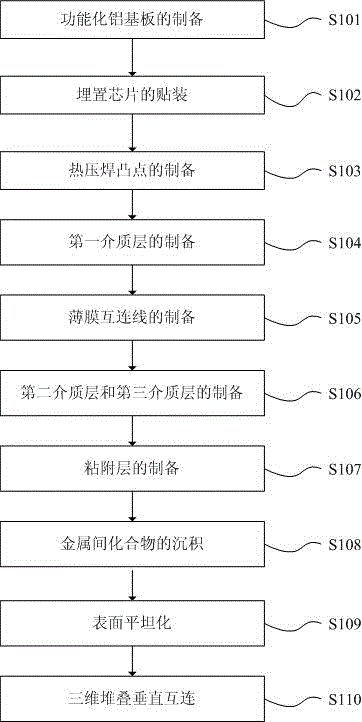

Vertical interconnection structure for three-dimensional package based on aluminum substrates and preparation method thereof

ActiveCN105118815AImprove packaging efficiencyIncrease packing densitySemiconductor/solid-state device detailsSolid-state devicesCrystallographySurface mounting

The present invention discloses a vertical interconnection structure for three-dimensional package based on aluminum substrates and a preparation method thereof. The structure comprises at least two layers of functionalized aluminum substrates. Each of the aluminum substrates comprises an aluminum through column, an aluminum semi-through column, a grounded aluminum column, a chip embedded cavity, an aluminum buried grounded layer and an aluminum embedded interconnection line. The vertical interconnection structure comprises embedded chips which are embedded in the chip embedded cavities of the functionalized aluminum substrates, film interconnection lines whose two ends are connected to the embedded chips and the aluminum through columns, intermetallic compound vertical interconnect lines whose two ends are connected to the aluminum through columns of two adjacent layers of functionalized aluminum substrates, and dielectric layers which are arranged at the surfaces of the functionalized aluminum substrates. The method comprises the preparation of the functionalized aluminum plate, the surface mounting of the embedded chips, the preparation of the film interconnection lines, the preparation of the dielectric layers, the deposition of the intermetallic compound, and the 3D stacked vertical interconnection. According to the vertical interconnection structure and the preparation method, the package efficiency and interconnection density are raised, and the intermetallic compound vertical interconnection is used to achieve the effect of 'low temperature preparation and high temperature use'.

Owner:SHANGHAI SPACEFLIGHT ELECTRONICS & COMM EQUIP RES INST

Method and apparatus for rapid thermal processing and bonding of materials using RF and microwaves

ActiveUS7569800B2Rapid and selective heatingUltra-high heating speedSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceInterconnection density

A method and apparatus for rapid and selective heating of materials using variable frequency RF and microwaves. The apparatus uses variable frequency solid state electronics as a microwave power source, a novel microwave heating head to couple microwave energy to the target materials and a match-up network to tune the frequency and impedance match between the microwave source and the load. An electronic and computer measurement and control system is employed to monitor and control the microwave heating process. The method teaches the use of inductive microwave coupling for thin conductive materials such as metal film and impurity doped silicon wafers. The method also teaches the use of capacitive microwave coupling for dielectric material such as glass and ceramics. The method further teaches the use of rapid and selective heating of heterostructure for bonding and sealing of mems and integrated circuits. The method and apparatus can provide ultra-high heating speed along with ultra-high heating temperatures for rapid thermal processing of semiconductors and other materials. It also allows the use of bonding materials with high melting temperature for strong bonding and sealing of mems and IC devices. The apparatus further provides for high interconnection density of integrated circuits as connections are made without the use of solder bumps.

Owner:TIAN YONGLAI +1

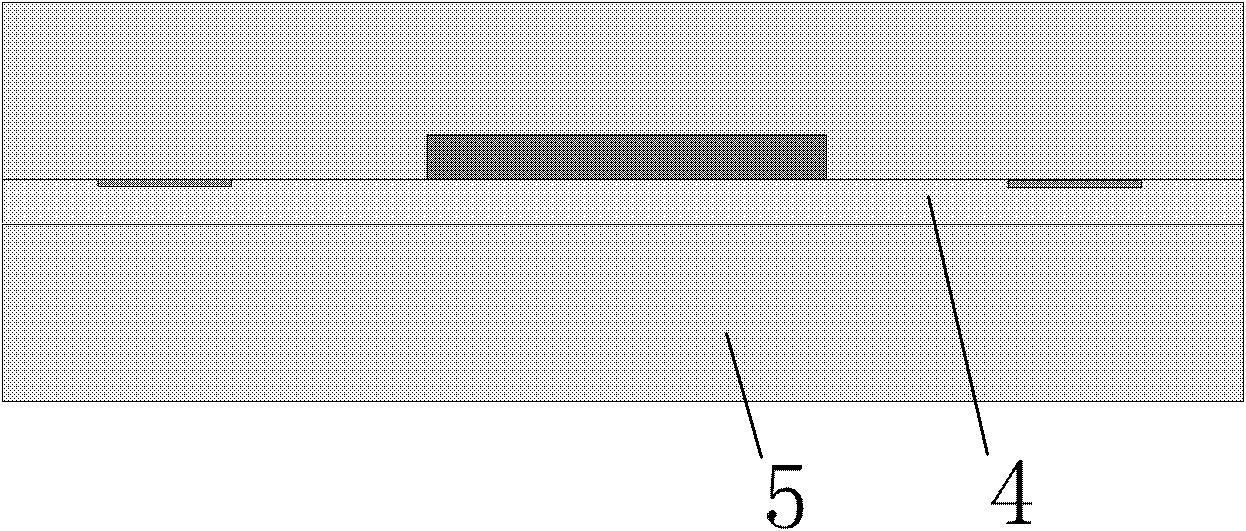

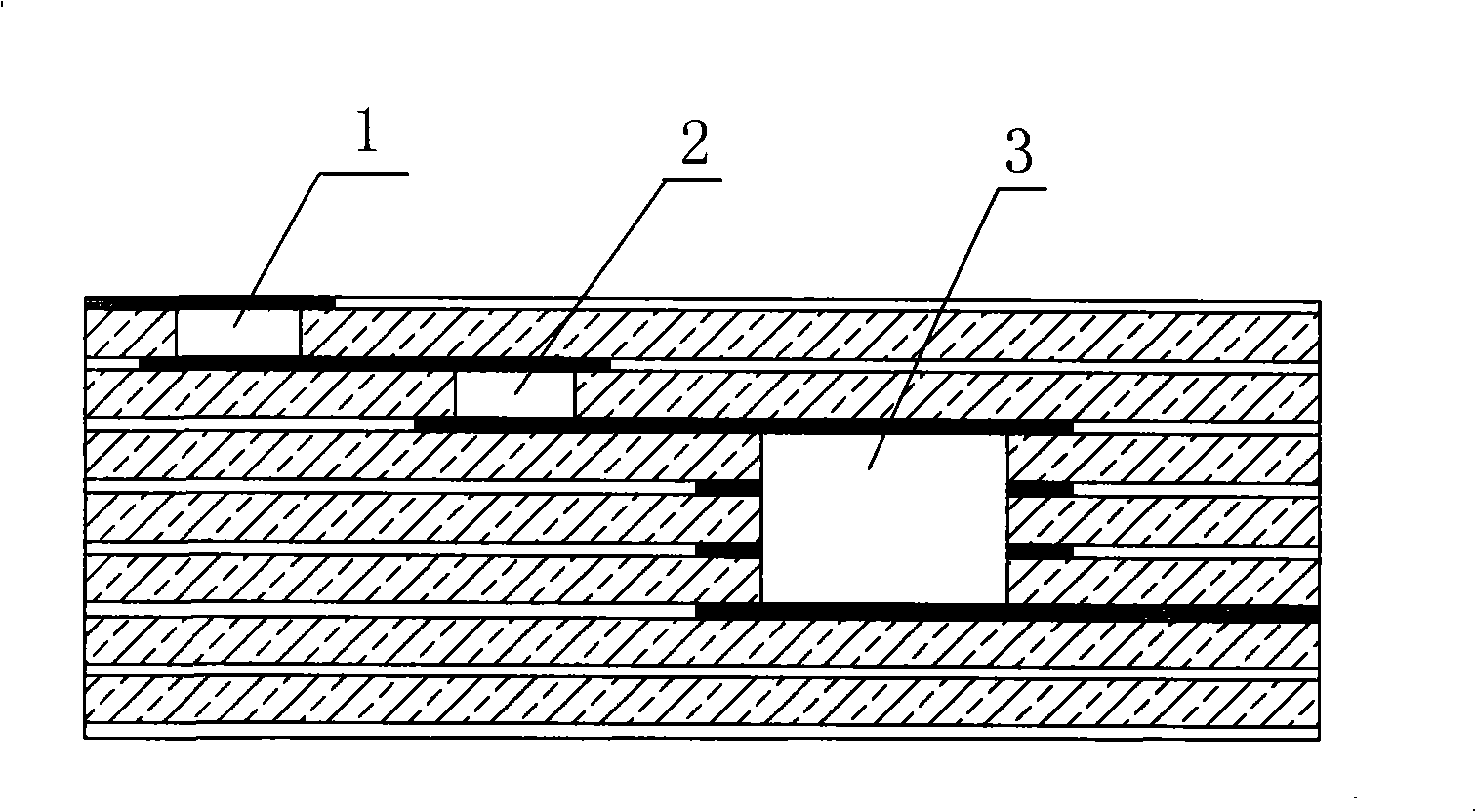

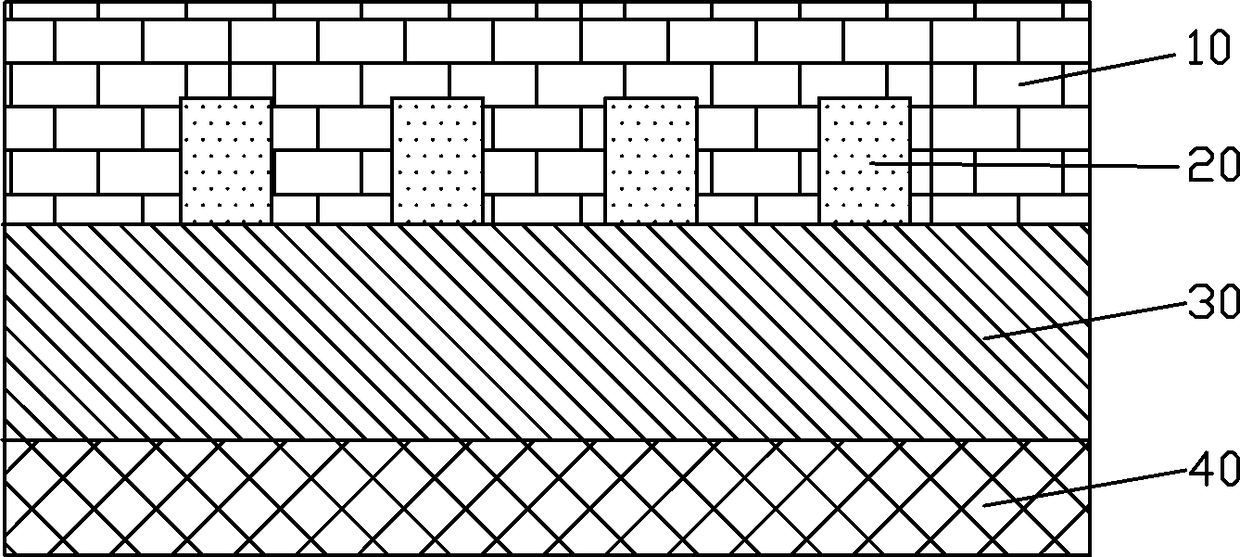

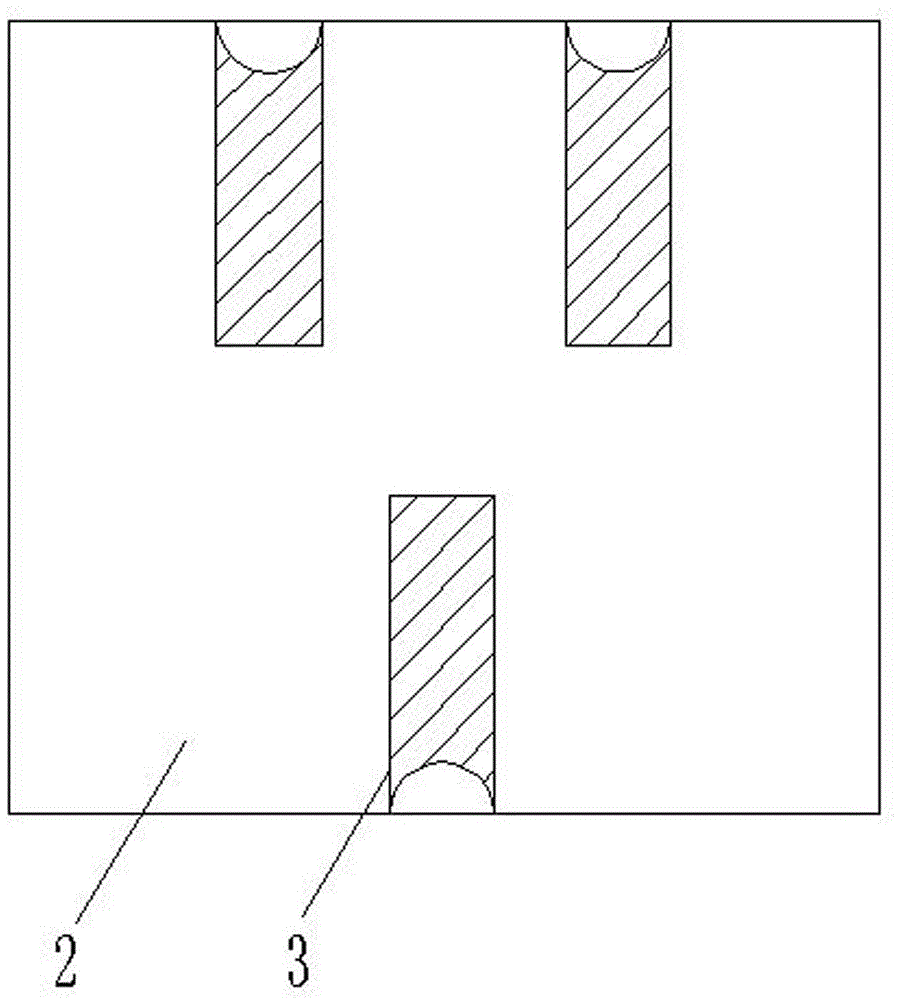

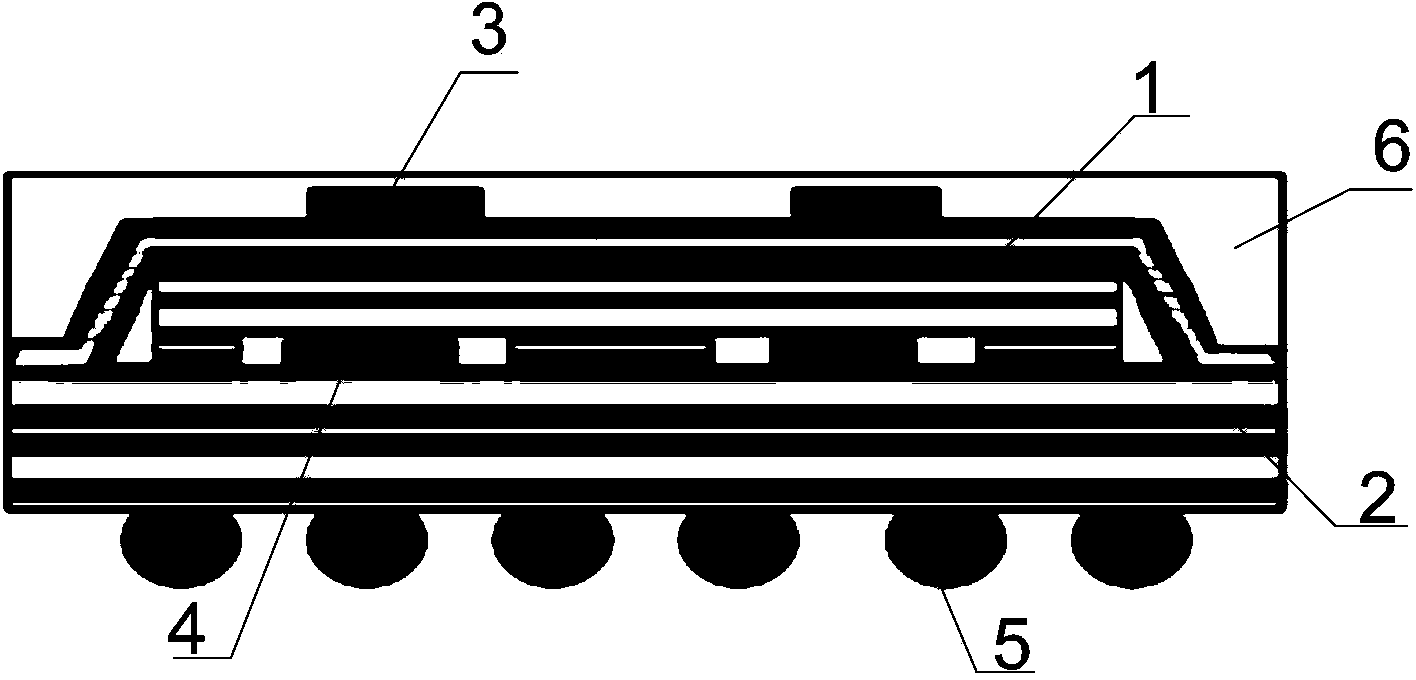

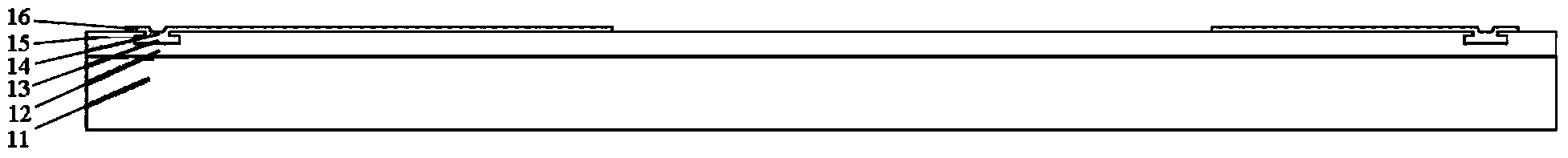

Wafer level packaging method and structure of image sensor

InactiveCN103247639AReduce volumeImprove package reliabilityRadiation controlled devicesPunchingInsulation layer

The invention relates to a wafer level packaging method and structure of an image sensor. The method comprises the following steps: an image sensor wafer (1) consisting of a plurality of chips is provided and bonded with a transparent substrate (5); back thinning is performed to the image sensor wafer (1); the punching is carried out at positions, corresponding to a bonding pad electrode (4), on the back of the image sensor wafer to form a plurality of first through holes; an insulation layers (8) is coated and solidified; inverted trapezoidal second through holes are further formed in the insulation layers in the first through holes to expose the bonding pad electrode (4), wherein the first through holes and the second through holes are coaxial; a metal seeding layer (10) is sputtered and a metal interconnection layer (11) is formed through electroplating sequentially; and a second passivation layer (12) and a solder ball bump (13) are prepared sequentially. According to the invention, the whole technological process is completed on wafer level, the interconnection density is relatively high on the basis of reducing the packaging cost, and meanwhile, the interconnection structure prepared has higher reliability.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Multifunctional base plate based on PCB technology and manufacturing method thereof

ActiveCN103762205AImprove interconnect densityLarge interconnect transmission capacitySemiconductor/solid-state device detailsSolid-state devicesManufacturing technologyInterconnection density

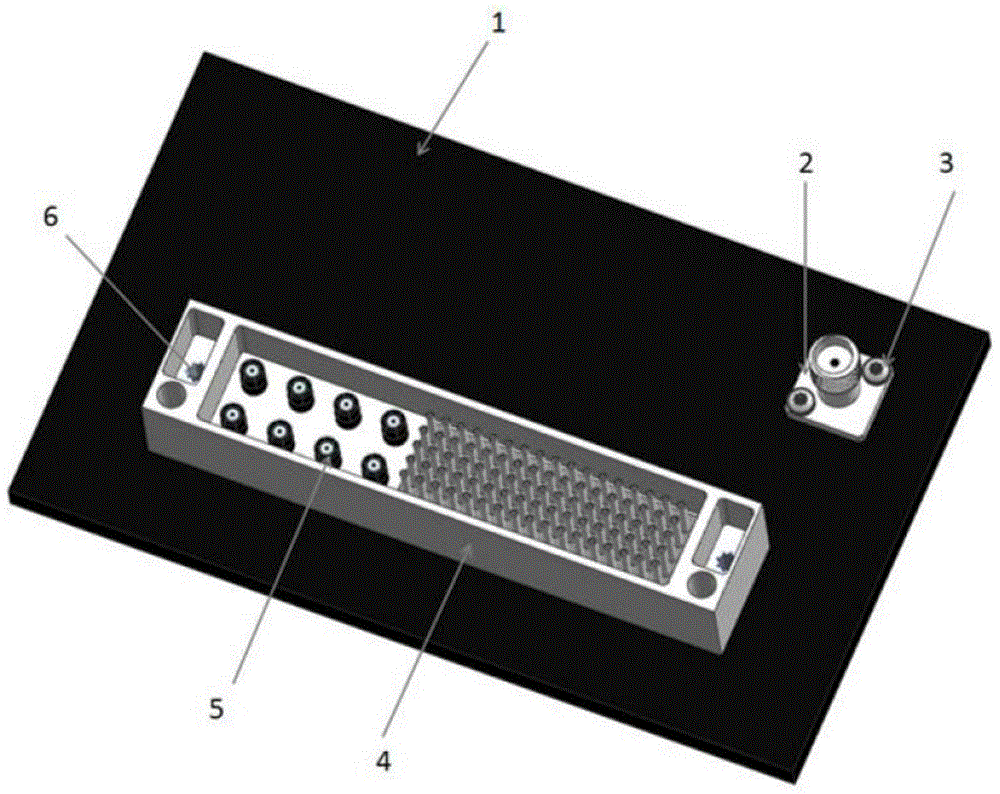

The invention discloses a multifunctional base plate based on the PCB technology and a manufacturing method thereof. The multifunctional base plate comprises a multilevel interconnection base plate, a glass base plate and an optical waveguide layer. An upper-layer graph is etched on the upper surface of the glass base plate, and a del-shaped reflector is arranged in the optical waveguide layer. A lower-layer graph is etched on the lower surface of the optical waveguide layer, and the upper-layer graph and the lower-layer graph are communicated with a transmission channel of the multilevel interconnection base plate through through holes vertically formed in the glass base plate, the multilevel interconnection base plate, and the optical waveguide layer in an embedded mode. The manufacturing method includes the steps of pressing the glass base plate and the optical waveguide layer, cutting the reflector, manufacturing the through holes, hole plating copper and face copper, etching the graphs and bonding pads and installing devices. The multifunctional base plate based on the PCB technology and the manufacturing method thereof can solve the problem of low losses of high-frequency transmission, so that the optical interconnection transmission capacity is high, the interconnection density is high, and the anti-electromagnetic interference capability is high; the multifunctional base plate based on the PCB technology and the manufacturing method thereof are suitable for millimeter wave interconnection, the manufacturing technology is simple, cost is low, and the multifunctional base plate based on the PCB technology and the manufacturing method thereof are also suitable for application with the sealing requirement.

Owner:NAT CENT FOR ADVANCED PACKAGING

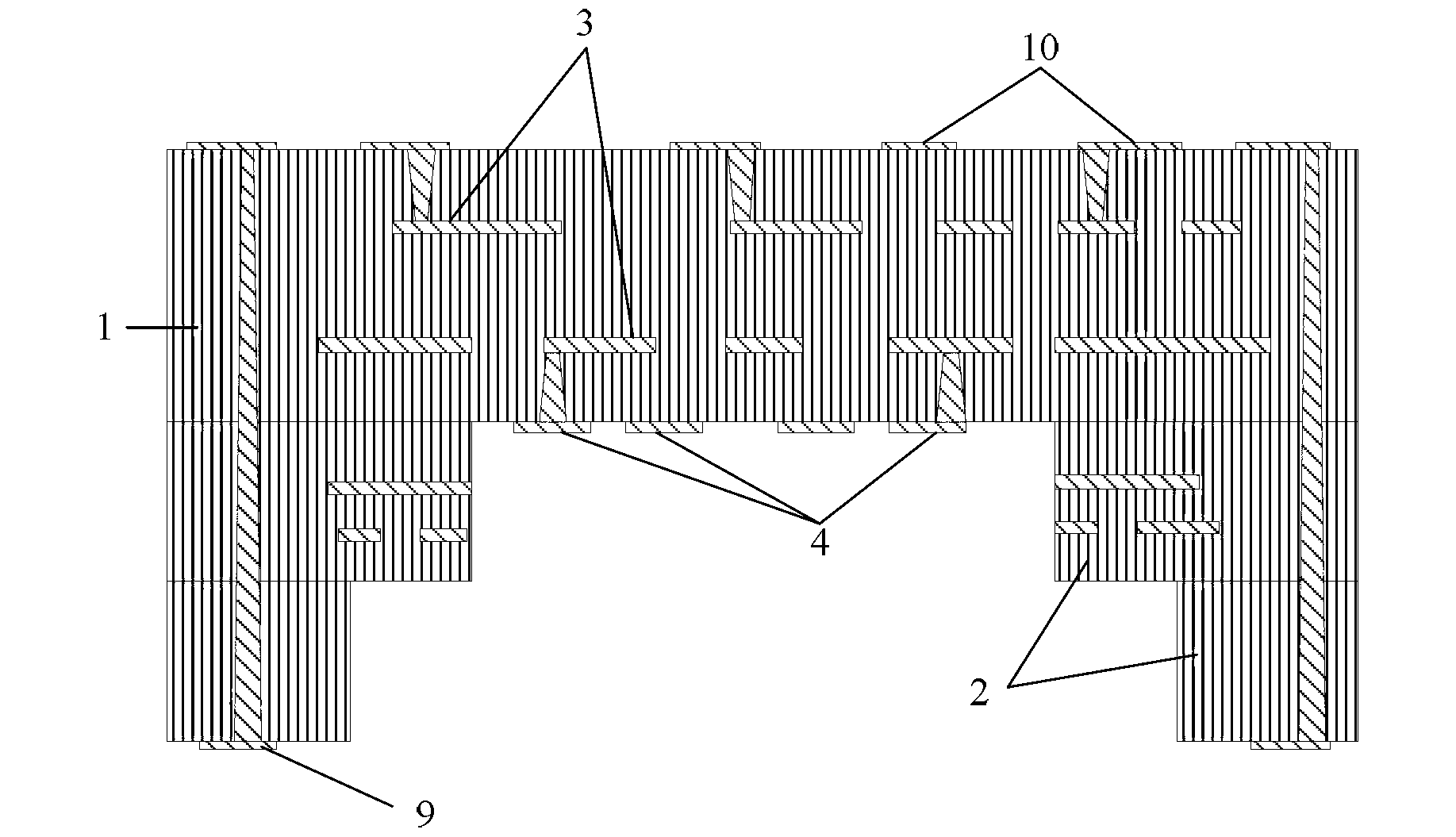

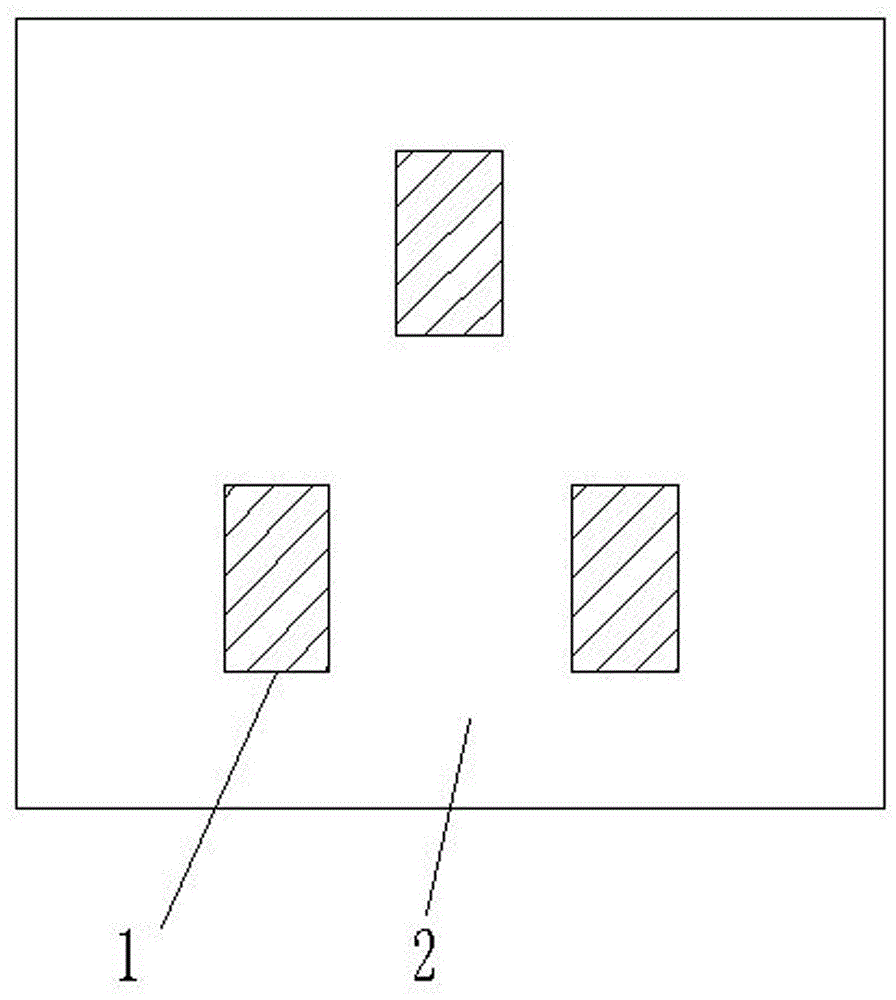

Base plate for stacked packaging

InactiveCN103311214AImprove interconnect densitySemiconductor/solid-state device detailsSolid-state devicesSolder ballInterconnection density

The invention discloses a base plate for stacked packaging. The surface of the base plate comprises more than one concave cavity. According to the base plate for stacked packaging provided by the invention, concave cavities are arranged on one side or both sides of the base plate, and the cavities are used for assembling chips. A certain difference in heights of the interior of each cavity and the edge of the base plate exists, interconnection solder balls are arranged on the edge of the base plate, and the interconnection solder balls with narrow pitches and small diameters can be allowed to be adopted, so that the interconnection density between two layers of packaging units can be improved.

Owner:NAT CENT FOR ADVANCED PACKAGING

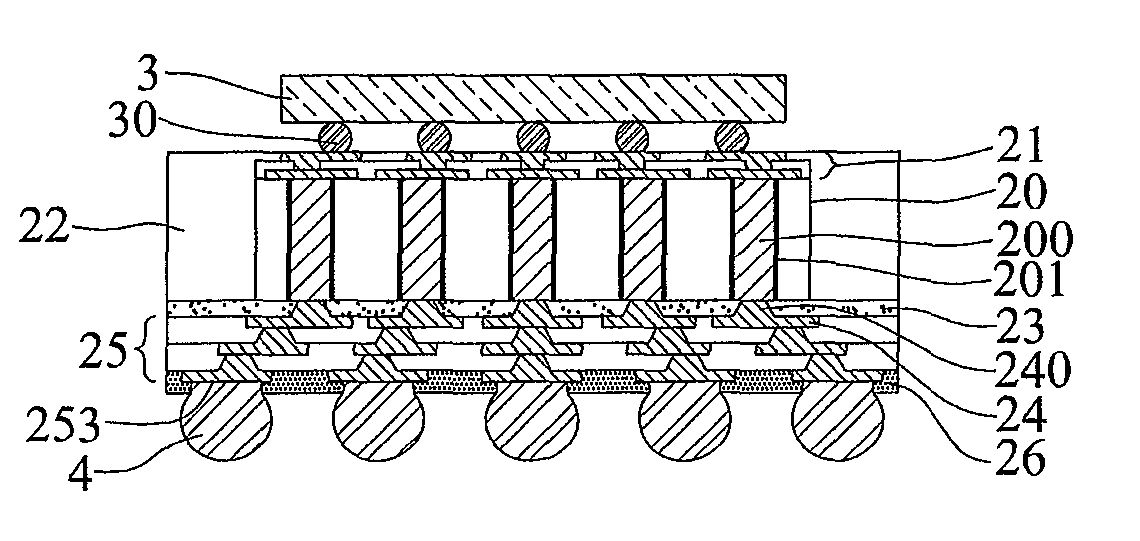

Package substrate having photo-sensitive dielectric layer and method of fabricating the same

ActiveUS9485874B2Semiconductor/solid-state device detailsSolid-state devicesLithography processInterposer

A package substrate and a method of fabricating the package substrate are provided. The package substrate may include an interposer having at least one conductive through via, a photo-sensitive dielectric layer formed on one side of the interposer, and at least one conductive via formed in the photo-sensitive dielectric layer and electrically connected to the conductive through via. By means of a photo lithography process with high alignment accuracy, at least one via with an extremely small diameter can be formed on the photo-sensitive dielectric layer and align with the conductive through via. Therefore, the conductive through via can have its diameter reduced as required, without considering the alignment with the at least one via. Accordingly, the interconnection density of the conductive through via on the interposer is increased.

Owner:IND TECH RES INST +1

Chip packaging structure and packaging method thereof

ActiveCN106129031AReduce warpageNot affectedSemiconductor/solid-state device detailsSolid-state devicesEnvironment effectPlastic packaging

The invention discloses a chip packaging structure and a packaging method thereof. Plastic packaging is carried out in a first opening corresponding to a bonding pad of a chip and on the back surface of the chip by adoption of a plastic packaging material, so that warpage of a chip wafer is reduced. Punching and penetrating a plastic package are carried out through processes of laser ablation and the like to form a small-size second opening for exposing the bonding pad, so that a high-density interconnected package can be achieved; and when the wafer is cut into the single chip after being packaged, the cutting interface is wrapped by a plastic packaging material and the chip can be protected from being affected by the external environment. The plastic packaging material itself is an insulating material, so that the passivation manufacturing process before a metal circuit is laid on a chip substrate in a commonly known wafer level packaging process is saved. According to the chip packaging structure and a manufacturing method, the cost is low and the interconnection density is high.

Owner:HUATIAN TECH KUNSHAN ELECTRONICS

Radio frequency and band-shaped wire interface assembly method

InactiveCN104916895AReduce space volumeReduce design difficultyWaveguide type devicesBand shapeInterconnection density

The invention discloses a radio frequency and band-shaped wire interface assembly method, which is high in transmission efficiency, small in loss, reliable in performance and high in integration interconnection density. The radio frequency and band shape wire interface assembly method can be realized through steps of integrating a high frequency signal member and a low frequency member through a broadband microwave backboard to form a motherboard, and placing a high frequency connector and an LAM connector on a same plane of a same plane layer, expanding into a stack of layers of a three-dimensional circuit toward a z direction through interlayer vertical interconnection by the planar circuit printed with the circuit graphs, in a radio frequency portion, adopting signals between Rogers RO6002 core board layers and performing radio frequency connection through metalized hole interconnection structure between the stack layers of the core plates, realizing signal transmission between the radio frequency layers through the layer pressure, realizing electric communication by a high frequency connector 2 and a high frequency connector 5 through a surface welding disc of a broadband microwave backboard 1 and manufacturing a three-dimensional non-interfering high density circuit through a corresponding prepreg sheet lamination layer.

Owner:10TH RES INST OF CETC

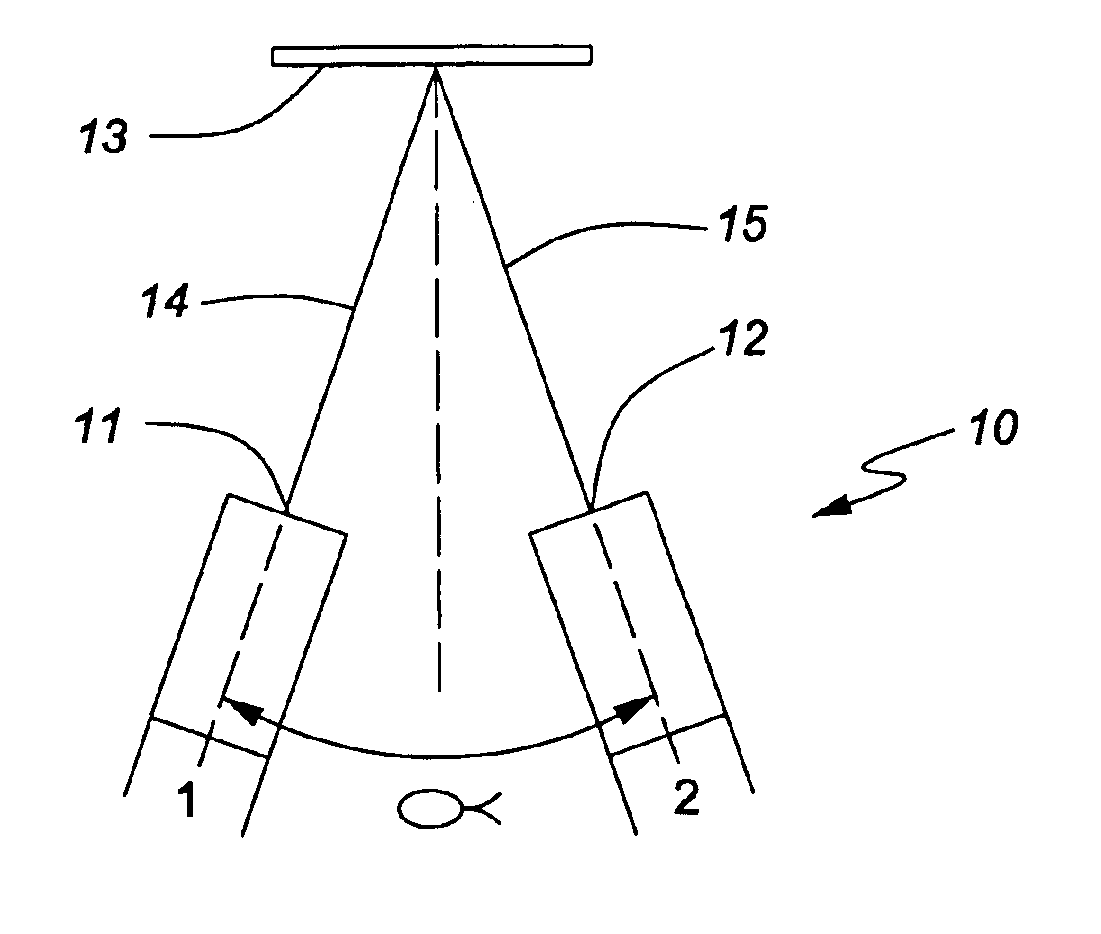

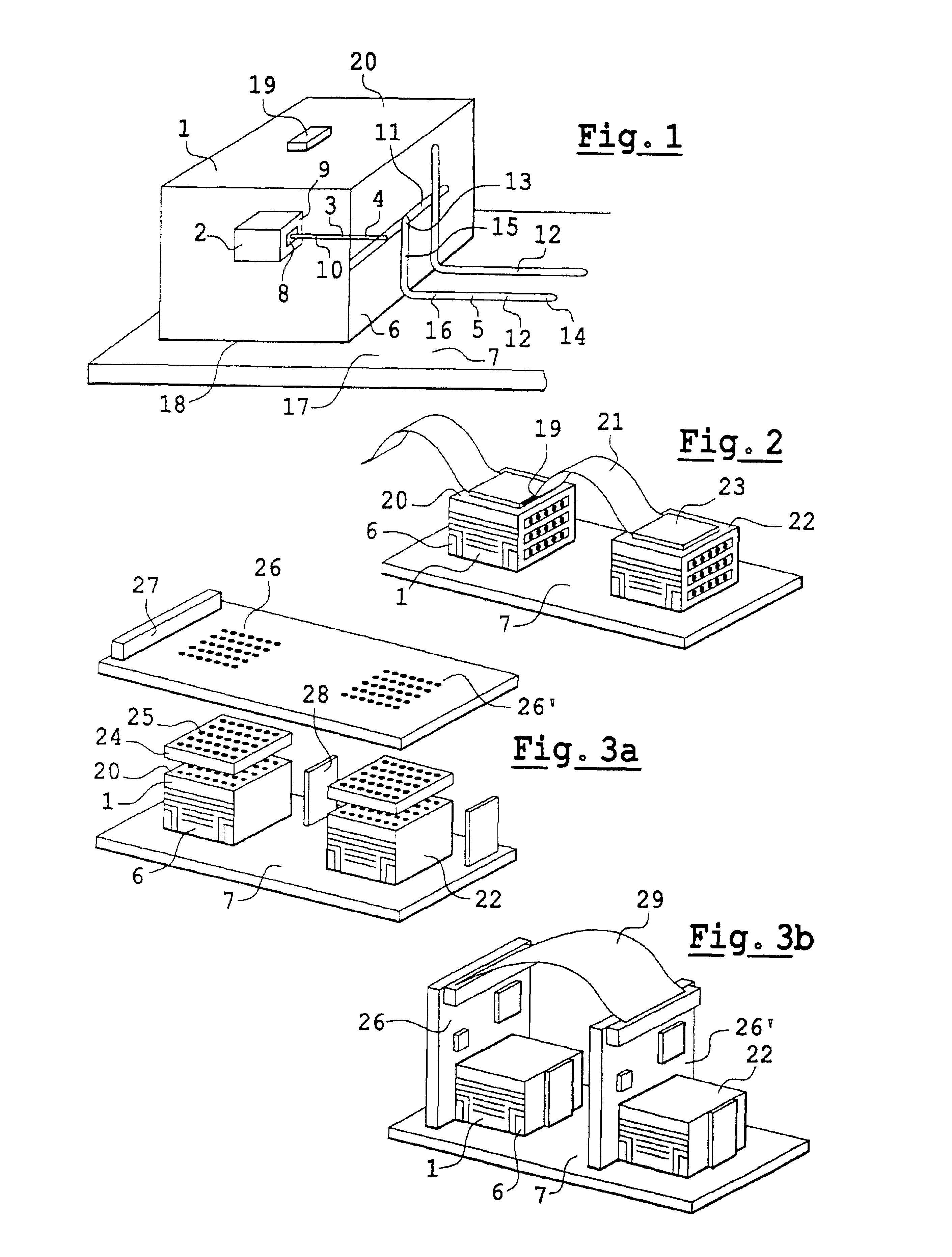

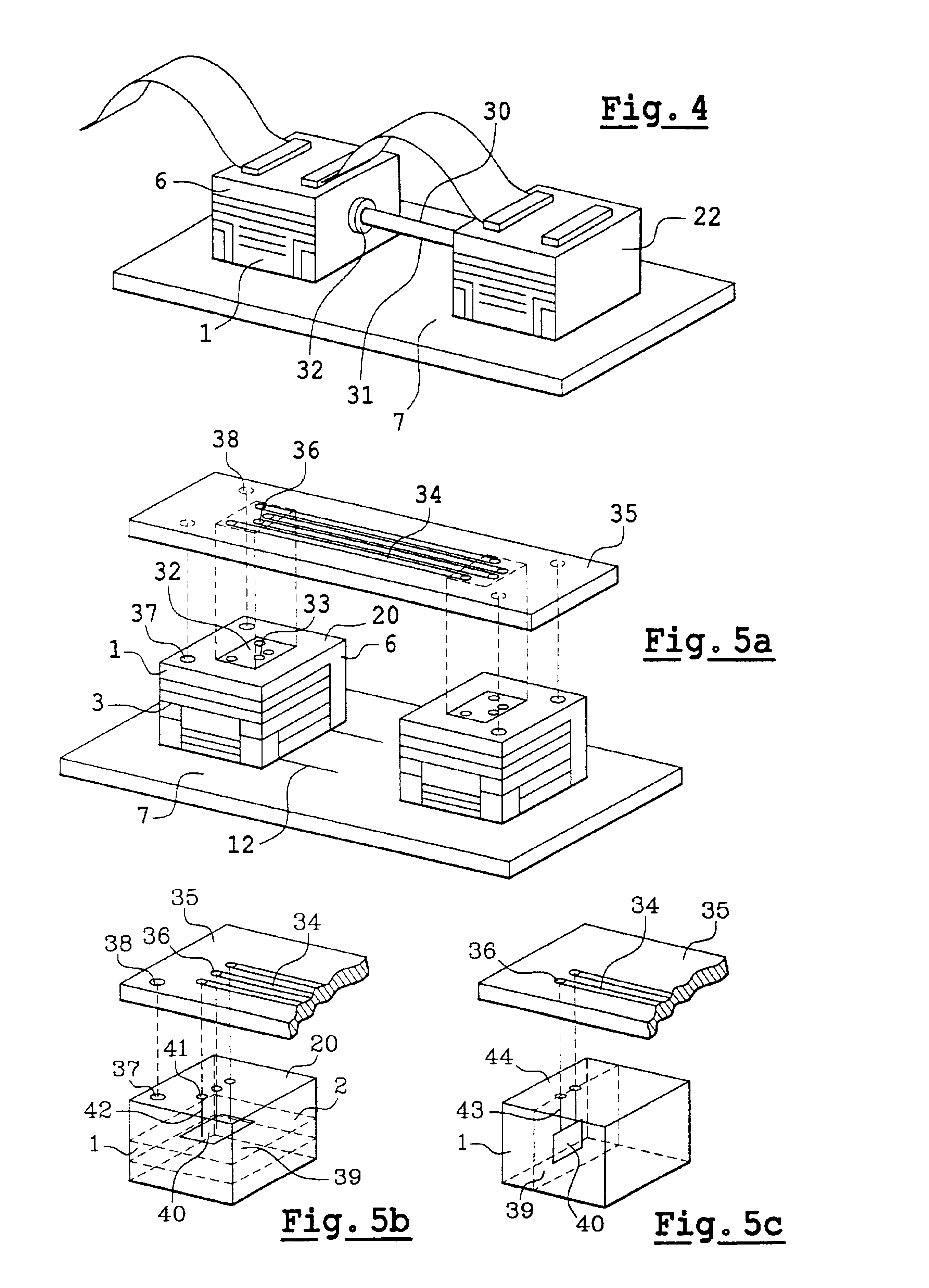

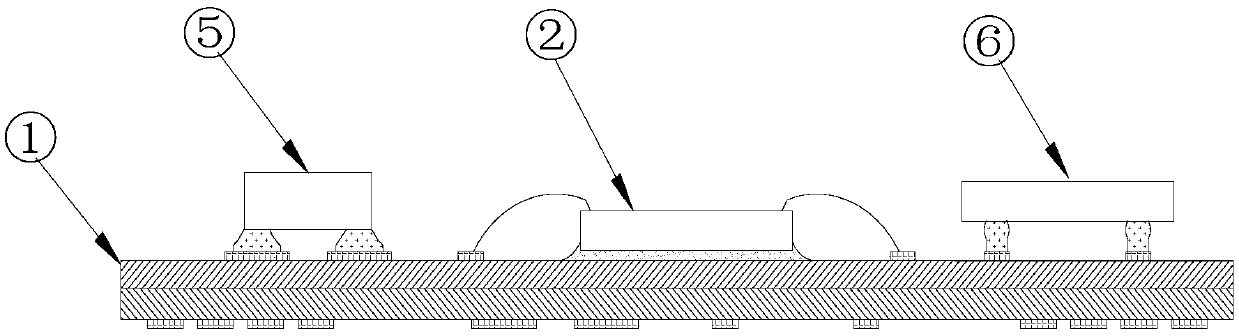

Electronic assembly having high interconnection density

InactiveUS20010050430A1Improve heat exchange effectLarge quantity of heatSemiconductor/solid-state device detailsSolid-state devicesInterconnection densityElectronic assemblies

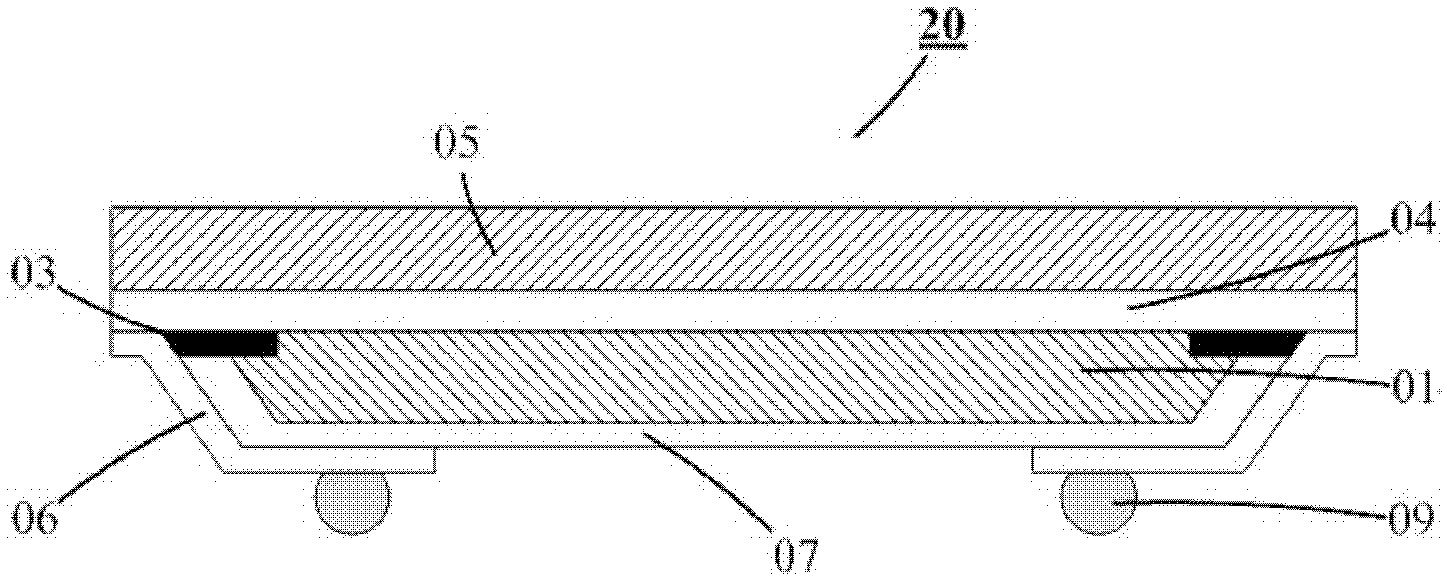

An electronic assembly comprising an electronic module provided with optical interconnection and heat removal means, the heat removal means comprising a soleplate dedicated to removing heat on which the module is mounted. The interconnection means is independent of the soleplate and preferably comprises a printed circuit and an optical fiber included in the printed circuit. The optical fiber has an end put accurately in register with an optical contact of the module by a BGA type mounting of the printed circuit on the module. A BGA type mounting consists in placing with precision firstly balls on the module and secondly areas on the circuit, and then in bringing the balls and areas face to face so that the balls center themselves automatically with the areas by capillarity.

Owner:ALCATEL LUCENT SAS

Vertical transition connector for chip package, substrate structure and fabrication method

ActiveCN105742274AImprove interconnect densityHigh transmission signal frequencySemiconductor/solid-state device detailsSolid-state devicesElectrical conductorMiniaturization

The invention discloses a vertical transition connector for chip package, a substrate structure and a fabrication method, and relates to the technical field of chip package. The vertical transition connector comprises an insulation connection substrate, wherein at least one conductor hole is formed in the insulation connection substrate in a vertical direction, a solid conductor post is fixedly arranged in the conductor hole, an upper bonding pad is arranged on the upper surface of the solid conductor post, and a lower bonding pad is arranged on the lower surface of the solid conductor post. The vertical transition connector has the characteristics of small size, low cost and high interconnection density, the assembly efficiency can be improved, the transmission signal frequency can be increased, and the fabrication method is simple and convenient and is suitable for automatic and miniature production application at a large scale.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

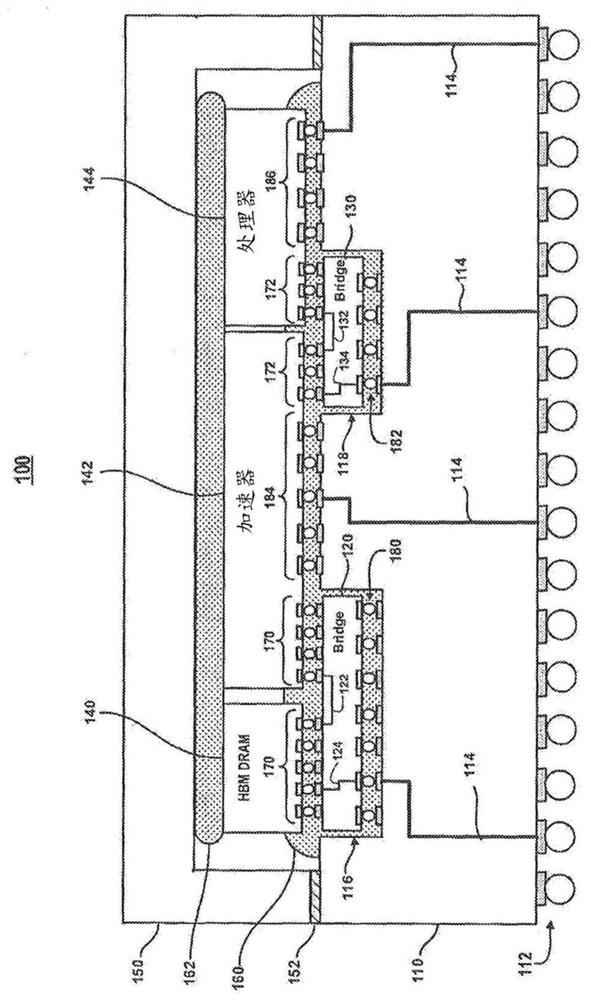

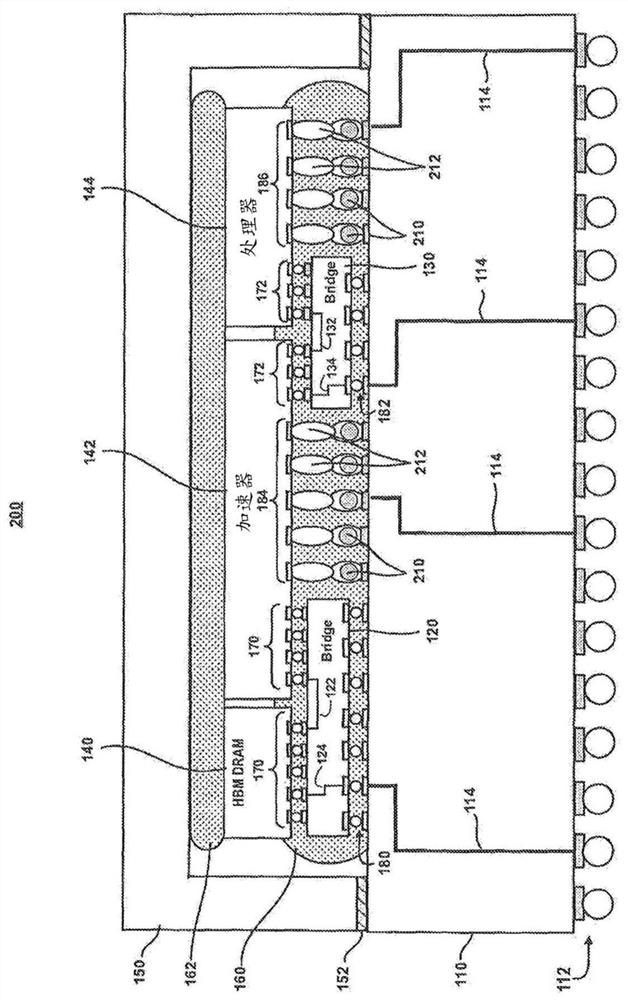

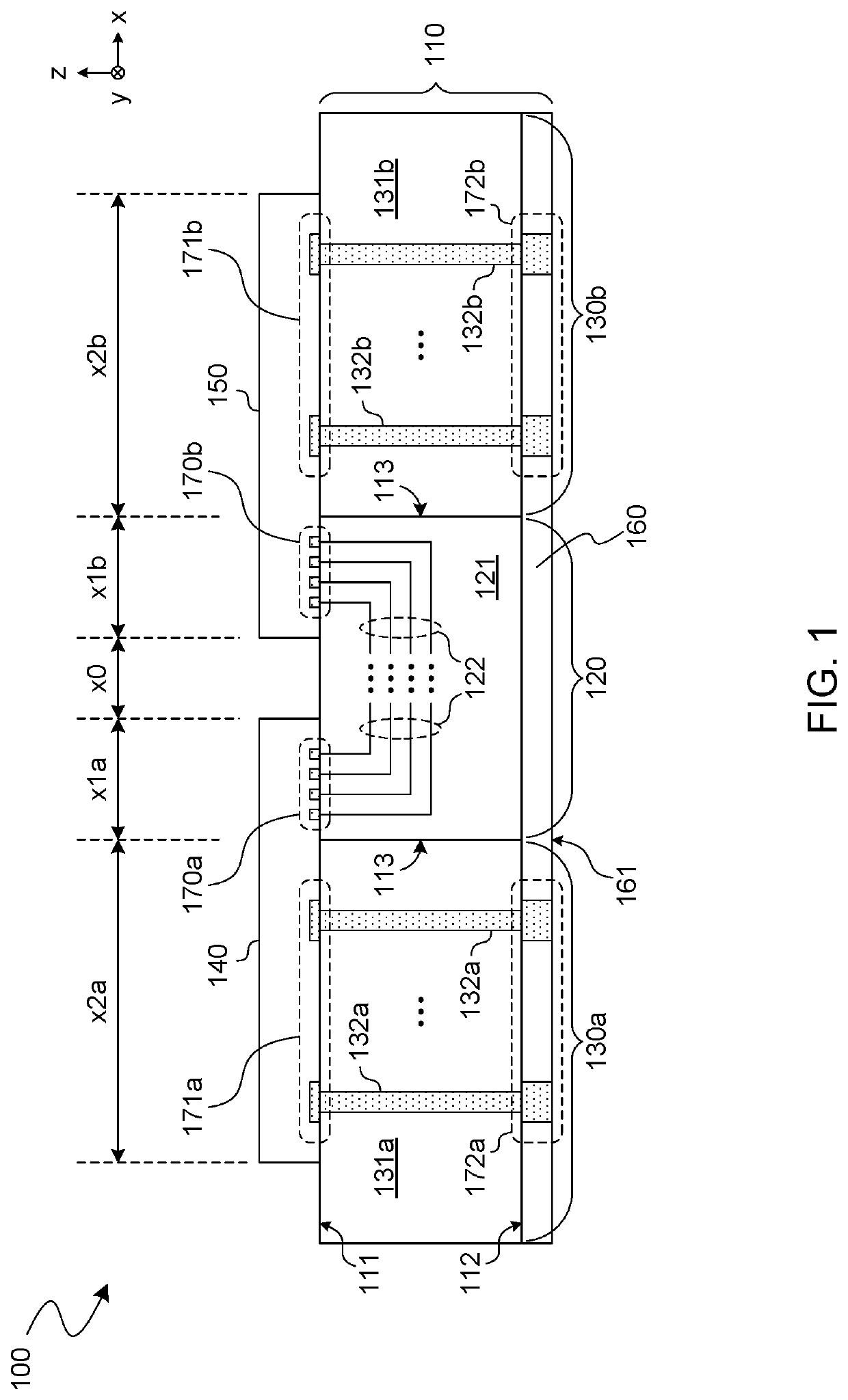

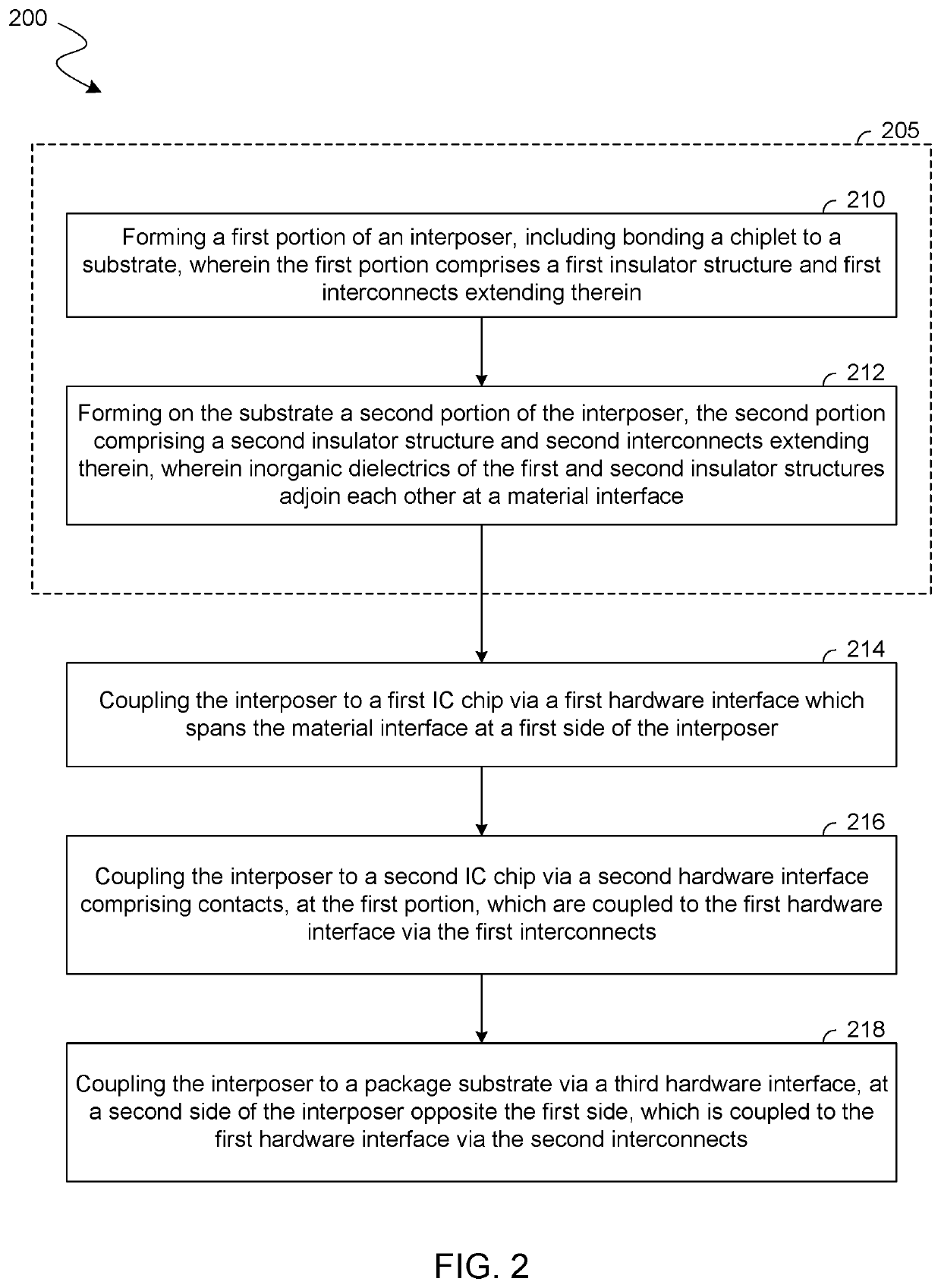

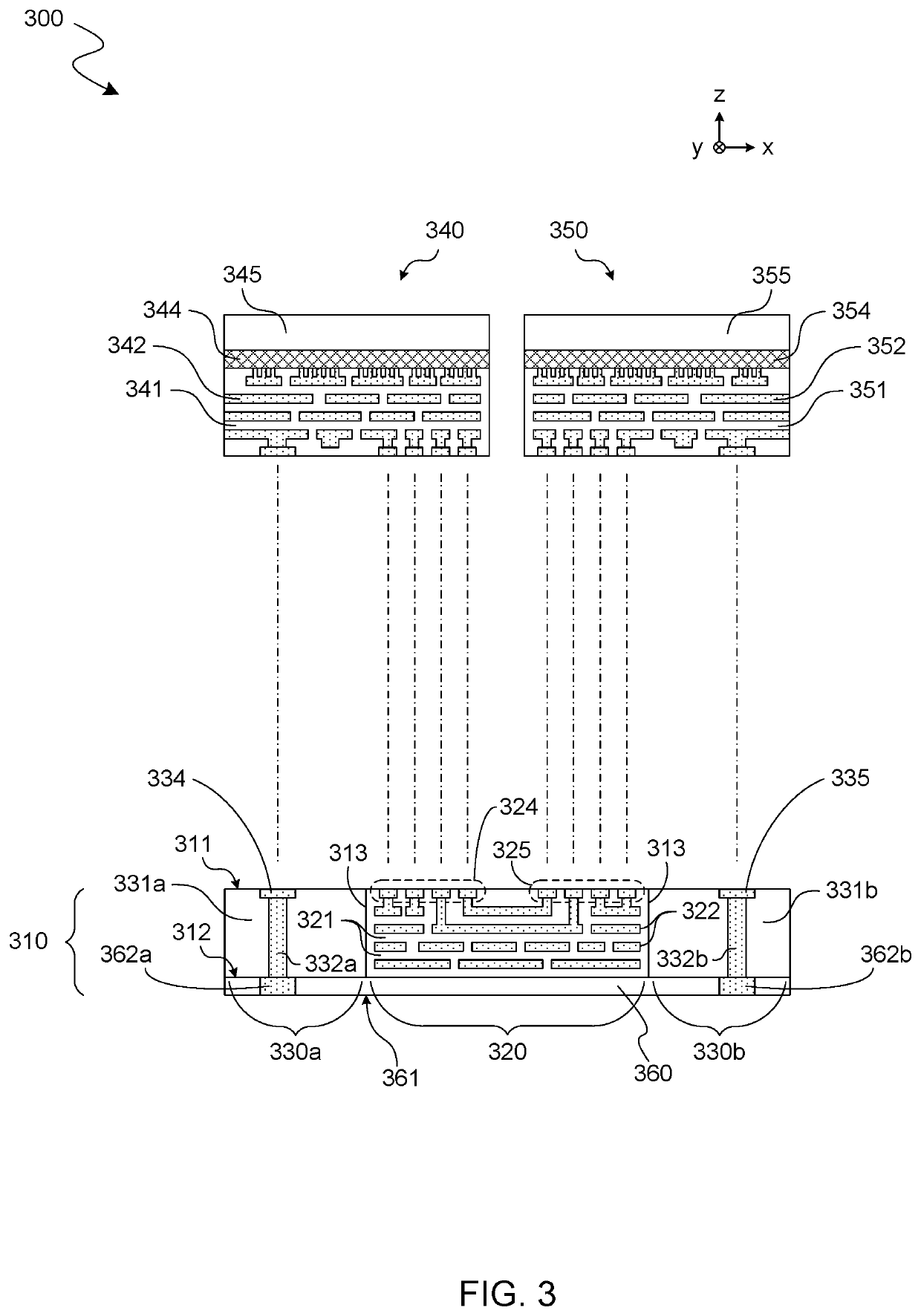

Multi-chip package structure having chip interconnection bridge which provides power connections between chip and package substrate

PendingCN112514062ASemiconductor/solid-state device detailsSolid-state devicesInterconnection densityMechanical engineering

Multi-chip package structures and methods for constructing multi-chip package structures are provided, which utilize chip interconnection bridge devices that are designed to provide high interconnectdensity between adjacent chips (or dies) in the package structure, as well as provide vertical power distribution traces through the chip interconnection bridge device to supply power (and ground) connections from a package substrate to the chips connected to the chip interconnection bridge device.

Owner:IBM CORP

Electronic assembly having high interconnection density

InactiveUS6754405B2High densityAvoid problemsSemiconductor/solid-state device detailsSolid-state devicesInterconnection densityEngineering

An electronic assembly comprising an electronic module provided with optical interconnection and heat removal means, the heat removal means comprising a soleplate dedicated to removing heat on which the module is mounted. The interconnection means is independent of the soleplate and preferably comprises a printed circuit and an optical fiber included in the printed circuit. The optical fiber has an end put accurately in register with an optical contact of the module by a BGA type mounting of the printed circuit on the module. A BGA type mounting consists in placing with precision firstly balls on the module and secondly areas on the circuit, and then in bringing the balls and areas face to face so that the balls center themselves automatically with the areas by capillarity.

Owner:ALCATEL LUCENT SAS

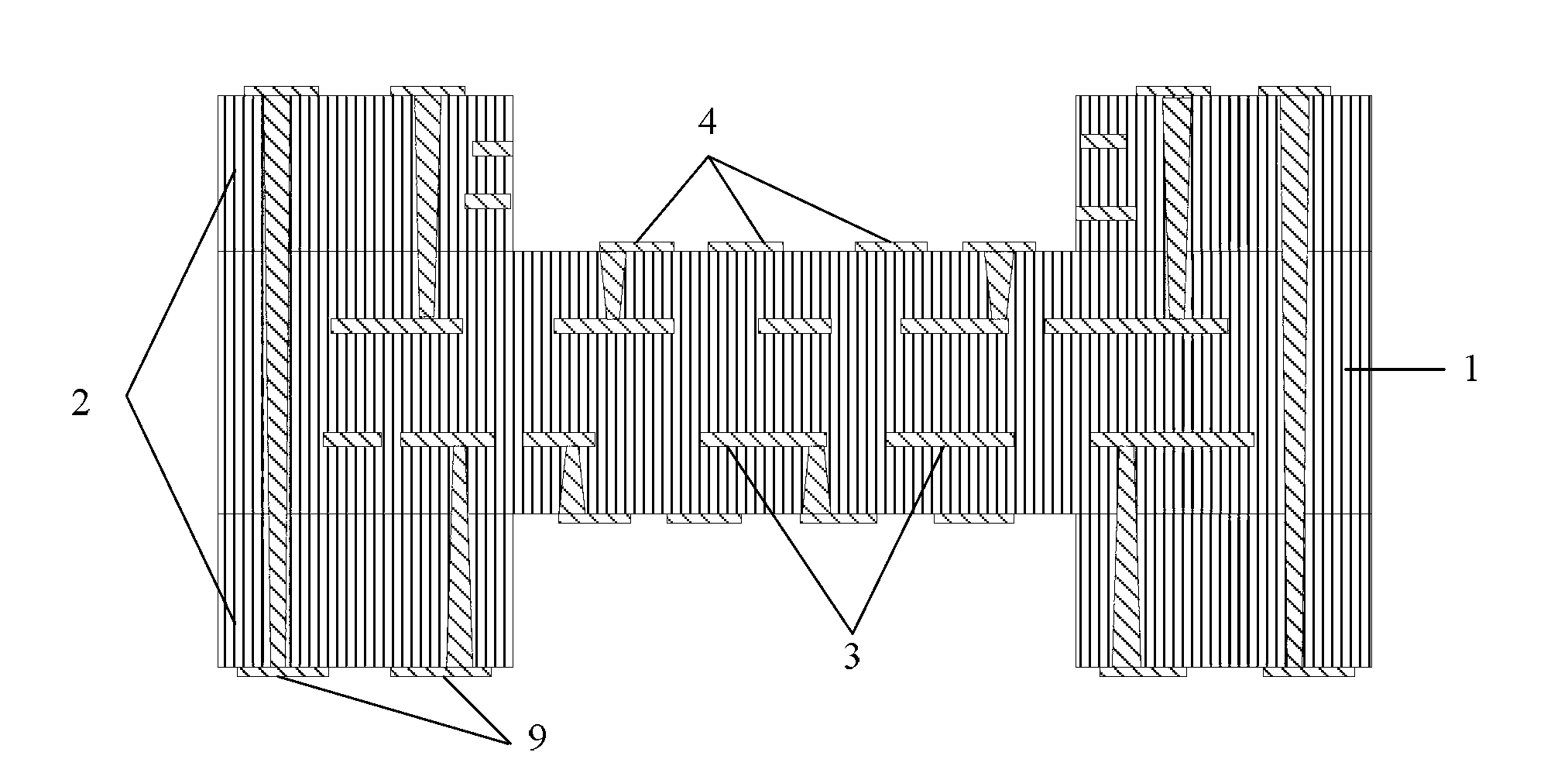

Structure with realization of 3D interlayer vertical interconnection by using flexible substrate and manufacturing method thereof

InactiveCN103887275AReduce crosstalkReduce continuitySemiconductor/solid-state device detailsSolid-state devicesHigh bandwidthInterconnection density

The invention relates to the technical field of electronic packaging and particularly relates to a structure with the realization of 3D interlayer vertical interconnection by using a flexible substrate and a manufacturing method thereof. The structure comprises a first printed circuit board, a second printed circuit board, a first device, a second device, a soldered ball and a lamination structure. The second device is installed above the second printed circuit board. The first printed circuit board is fixed above the second printed circuit board, and the second device is arranged in a groove. The first device is fixed above the first printed circuit board. The lamination layer covers the first printed circuit board, the second printed circuit board and the outer side of the first device. The soldered ball is arranged at the bottom of the second printed circuit board. The invention provides the structure with the realization of 3D interlayer vertical interconnection by using the flexible substrate and the manufacturing method, the discontinuity and impedance mismatching of signals can be reduced, thus the transmission rate of the signals is greatly improved, higher bandwidth is supported, and the interconnection density of the flexible substrate is higher.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +1

Packaging structure with supporting protection structure

InactiveCN103545264ASmall form factorImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesSignal-to-noise ratio (imaging)Interconnection density

The invention relates to a packaging structure with a supporting protection structure. The packaging structure at least comprises two layers of chips which are interconnected, external interfaces are led out in one layer of chip, the second layer of chip is stacked on the first layer of chip through a stacking structure, and a closed cavity is formed between the first layer of chip and the second layer of chip. The wafer-level stacked packaging of multiple layers of chips is achieved, reliability and stability of packaging are improved, multiple protection selections are added due to the closed cavity formed between the chips, the vertical connection shortens the wiring distance, a solution is provided for power chips and power management chips which are low in requirement for power consumption, the signal to noise ratio is reduced, the dimension of the multiple layers of chips is reduced, and higher space utilization rate and higher electric interconnection density are provided.

Owner:NINGBO CHIPEX SEMICON

Self-matching ultra-wideband microwave insulator

ActiveCN110011002AImproving ultra-wideband transmission performanceAvoid WeldingWaveguide type devicesUltra-widebandElectrical conductor

The invention discloses a self-matching ultra-wideband microwave insulator, which comprises a housing, a glass column, an inner conductor and a matching pad, wherein the glass column is arranged in the housing, and the inner conductor is arranged in the glass column; the inner conductor is provided with an upper bulge and a lower bulge which protrude from the glass column; the matching pad includes an upper pad and a lower pad which are plated with a gold layer and used for being bonded with a circuit wafer through a gold wire or gold strip, the upper pad and the lower pad are respectively welded with the upper bulge and the lower bulge, and the dimensions of the upper pad and the lower pad are determined by simulation design according to ultra-wideband microwave transmission requirements.The self-matching ultra-wideband microwave insulator is additionally provided with the matching pad at the end part of the inner conductor so as to improve the ultra-wideband transmission performanceof microwave signals; and the matching pad is plated with the gold layer so as to adapt to the bonding of the gold wire or gold strip, thereby avoiding the welding between the insulator and the circuit wafer, thus greatly reducing the size of the vertical interconnection structure, and improving the interconnection density and assembly reliability.

Owner:SOUTHWEST CHINA RES INST OF ELECTRONICS EQUIP

Fabrication method of 3D high-density interconnected PoP plastic package device

InactiveCN109559996AHigh feasibilityImprove interconnect densitySolid-state devicesSemiconductor/solid-state device manufacturingHigh densitySurface mounting

The invention belongs to the technical field of integrated circuit package, and relates to a fabrication method of a 3D high-density interconnected PoP plastic package device. The fabrication method comprises the steps of performing device surface-mounting on a front surface of an MCM substrate, and completing plastic package; completing SMT device surface-mounting and copper post surface-mountingin one time by a mode that tin paste is printed on a back surface of the substrate, and completing secondary plastic package of the back surface of the substrate; and thinning a plastic package bodyon the back surface of the substrate, exposing the copper post, and completing ball implantation at an exposure end of the copper post. The 3D high-density interconnected PoP plastic package device isin a way that on the basis of a PoP plastic device form, a conventional tin paste printing and copper post implantation process is used for substituting a vertical module through hole process, the process difficulty and cost can be reduced, the front-stage equipment investment is not needed, 3D stacking between devices is achieved, and meanwhile, the 3D direction interconnection density is further improved.

Owner:WUXI ZHONGWEI GAOKE ELECTRONICS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com