Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

38results about How to "Threshold Voltage Adjustment" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

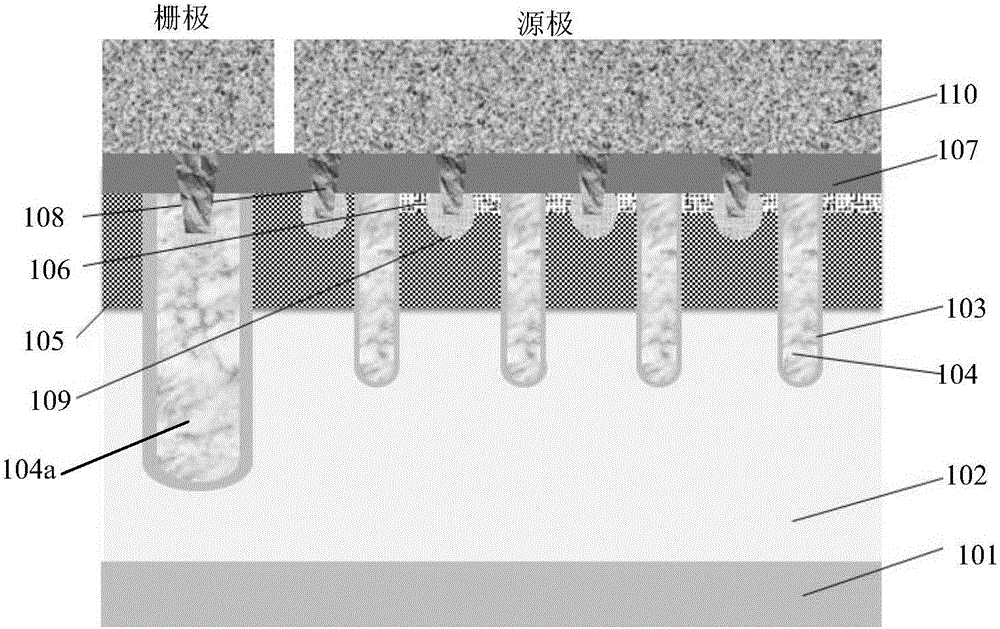

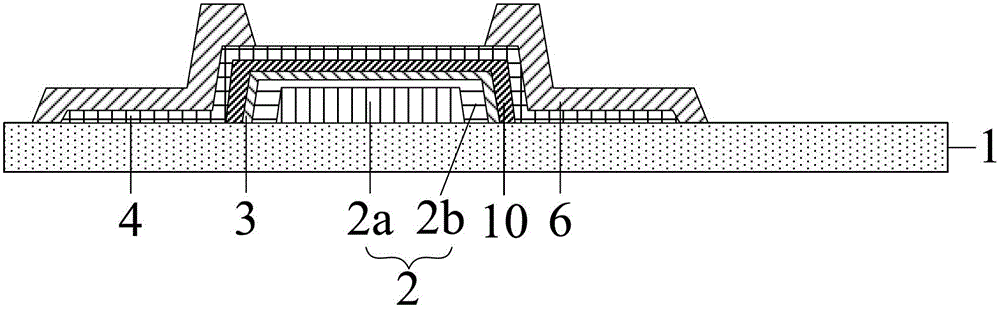

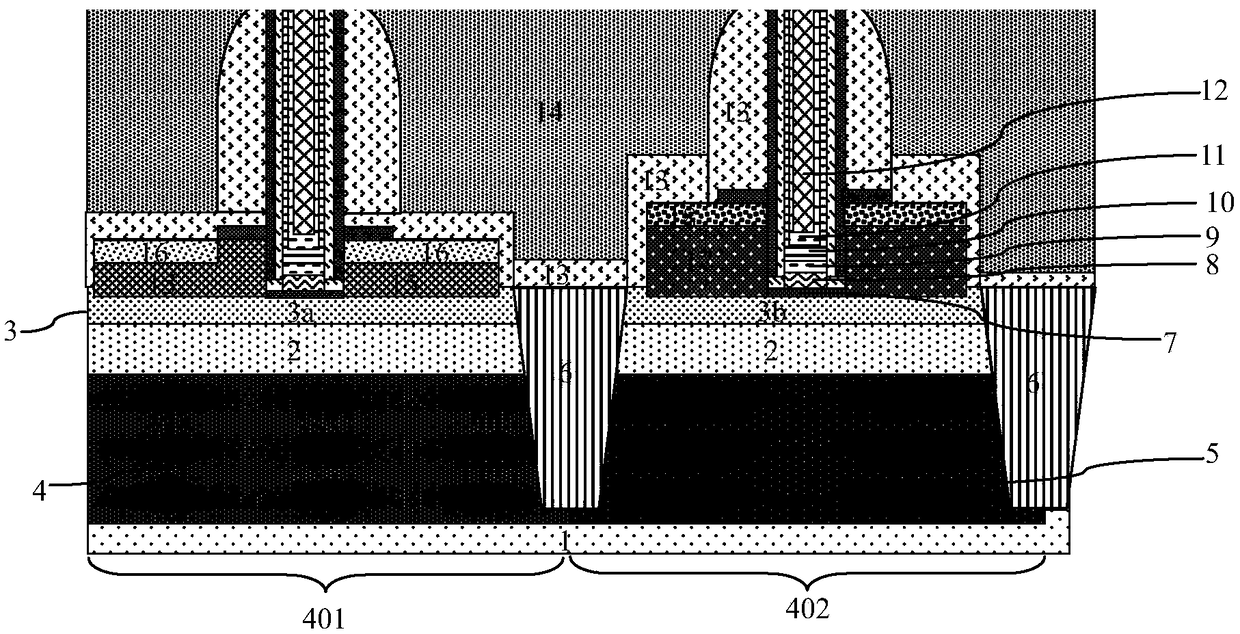

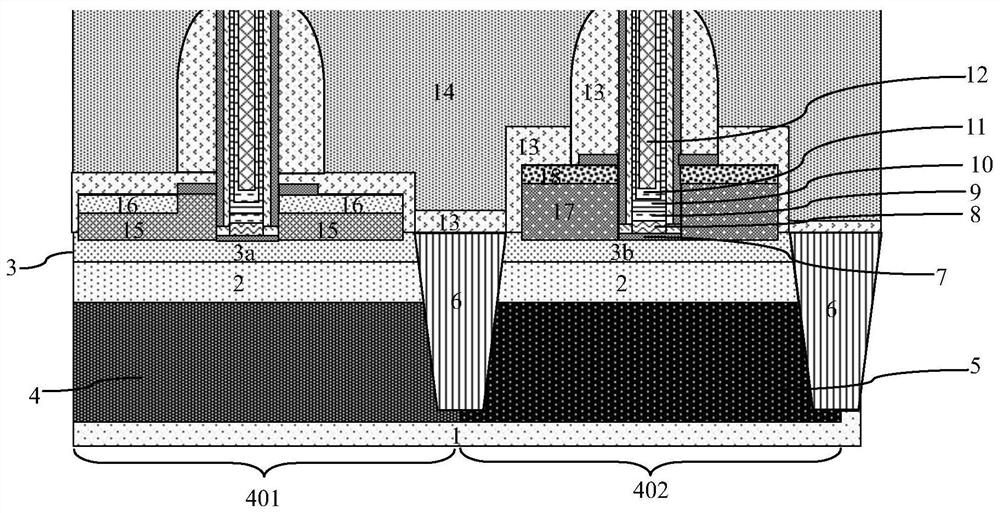

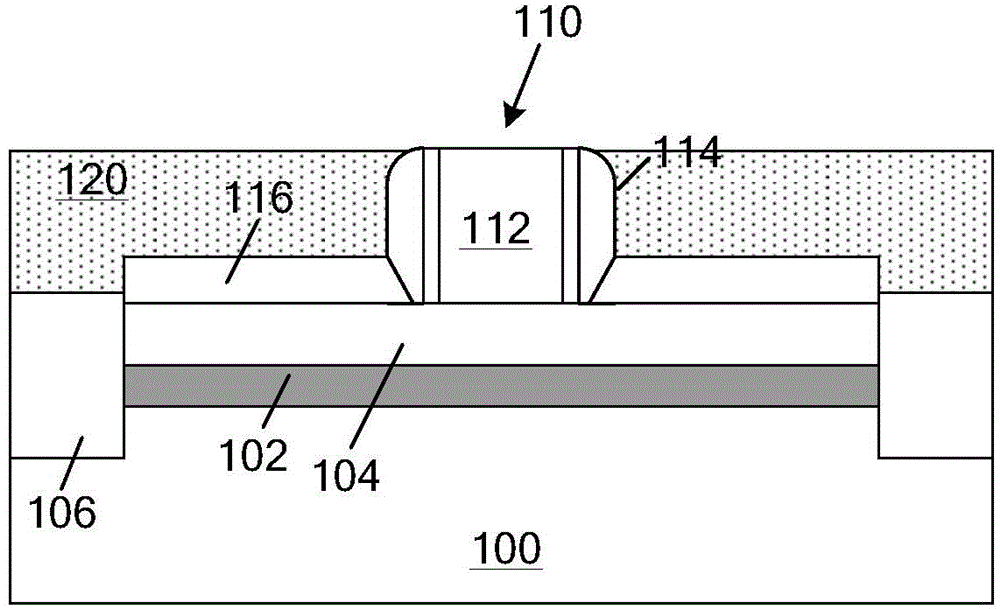

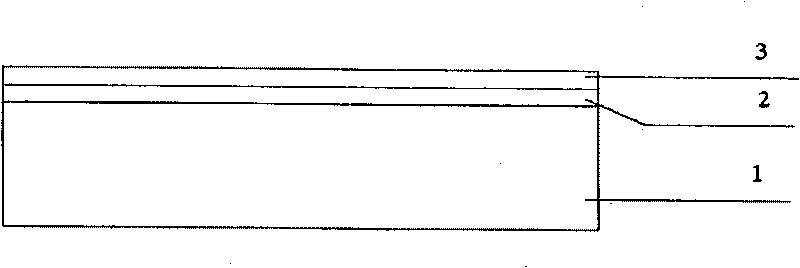

Shield gate trench MOSFET and manufacturing method thereof

InactiveCN108039369AElimination of sharp corner defectsEliminate leaksSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceTrench mosfet

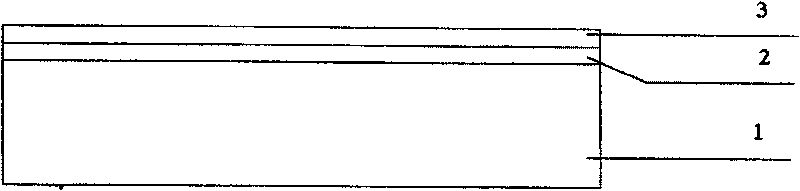

The invention discloses a shield gate trench MOSFET. A bottom oxide layer is formed on the side surface and the bottom surface of the trench of a gate structure, and shield polysilicon totally fills the trench; under self-alignment definition of the bottom oxide layer, the shield polysilicon is etched back to the bottom part of the trench in a self-alignment mode; the surface of the shield polysilicon after self-alignment etching back is oxidized to form an inter-polysilicon isolated oxide layer; after the inter-polysilicon isolated oxide layer is formed, the bottom oxide layer is etched backto the bottom part of the trench, the bottom oxide layer after etching back and the inter-polysilicon isolated oxide layer surround the shield polysilicon, and a top trench is formed at the top part of the trench; and the side surface of the top trench is provided with a gate oxide layer and is filled with polysilicon gate. The invention also discloses a manufacturing method for the shield gate trench MOSFET. Gate source electric leakage of the device can be reduced while the threshold voltage of the device is reduced, the thickness consistency of the inter-polysilicon isolated oxide layer canbe improved, and the capacitor corresponding to the inter-polysilicon isolated oxide layer is stable and controllable.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

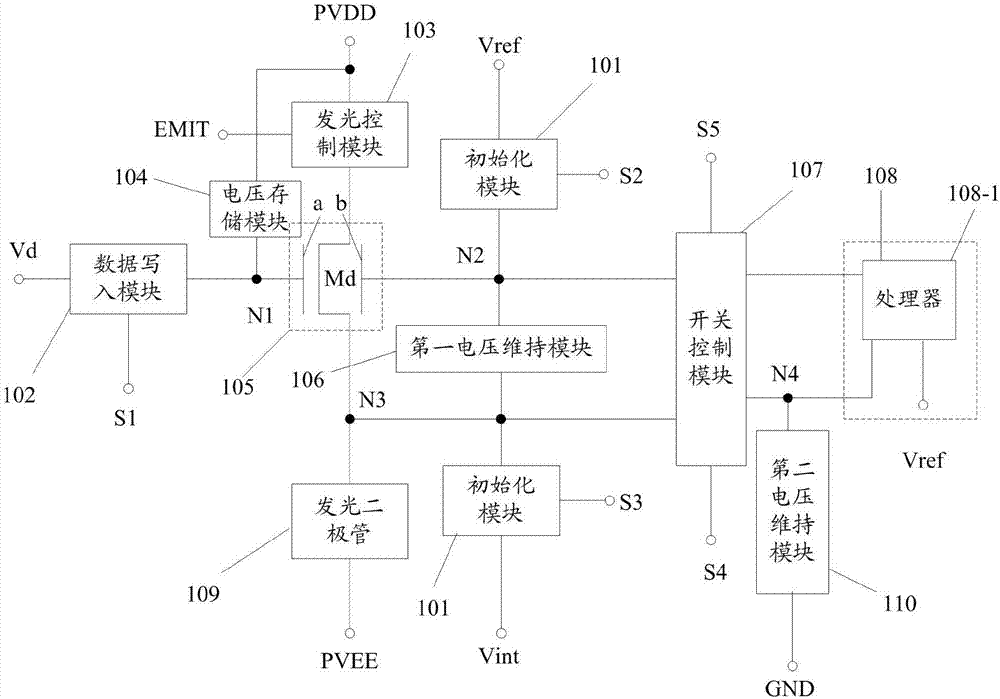

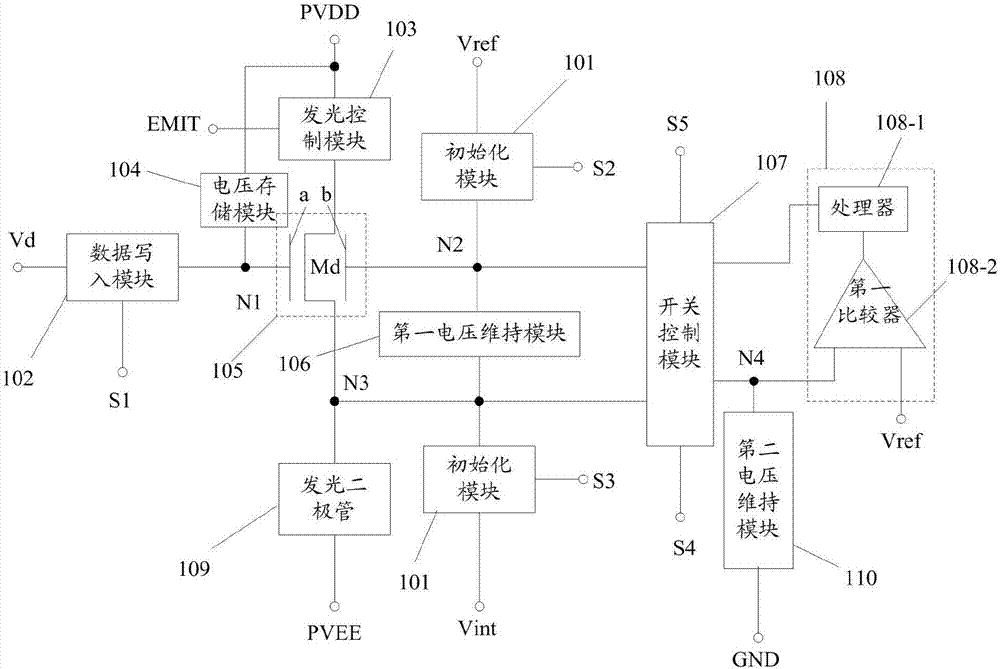

Pixel circuit and driving method thereof, electroluminescent display panel and display device

ActiveCN107358916AThreshold Voltage AdjustmentImpact sizeStatic indicating devicesSolid-state devicesDisplay deviceEngineering

The invention discloses a pixel circuit and a driving method thereof, an electroluminescent display panel and a display device. The pixel circuit comprises an initialization module, a data writing-in module, a light emitting control module, a voltage storage module, a driving transistor, a first voltage maintaining module, a switch control module, an external compensation module and a light-emitting diode. The driving transistor is a double-gate transistor; and a second gate of the double-gate transistor is electrically connected with the external compensation module through the switch control module. Under the control of the switch control module, the external compensation module collects the voltage of a third node and then provides a compensation voltage for a second node so as to realize adjustment of the threshold voltage of the dual-gate transistor, so that the threshold voltage of the dual-gate transistor is close to a standard threshold voltage and the current of the light-emitting diode during light emitting is be independent of the threshold voltage. Therefore, a phenomenon that the current is affected by the drift of the threshold voltage is avoided; and the residual image is eliminated to improve the quality of the displayed picture.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

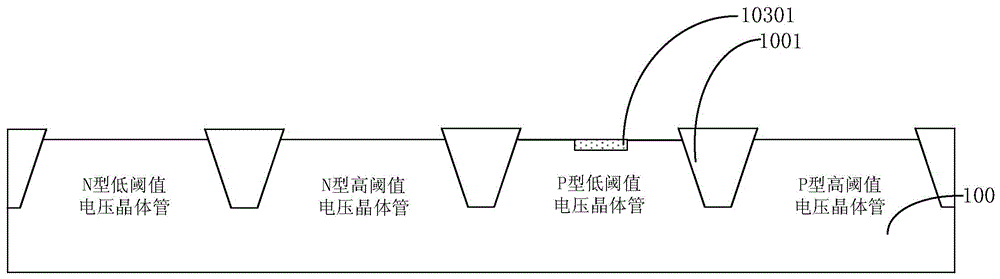

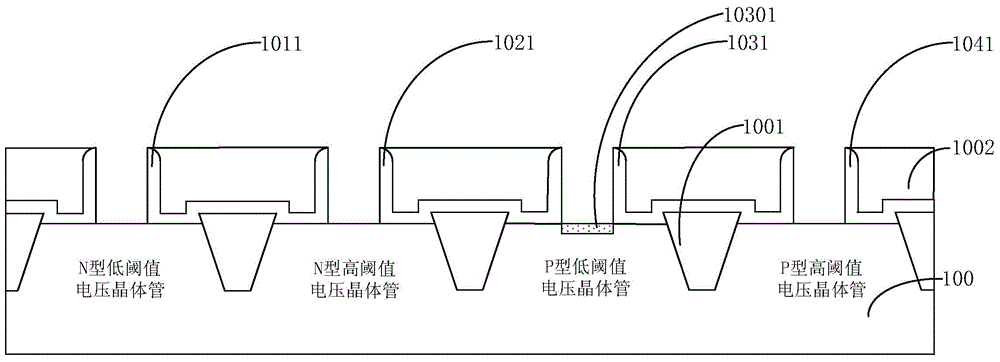

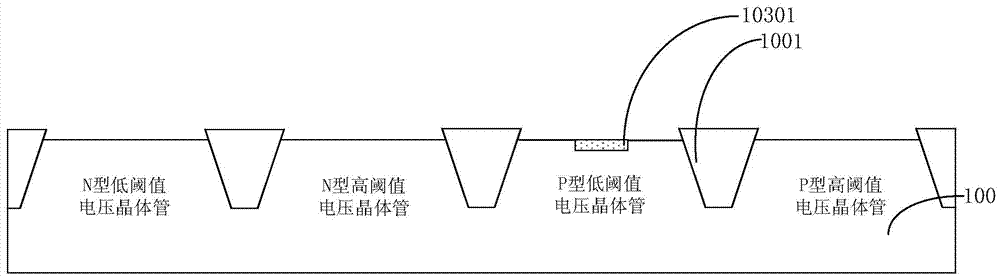

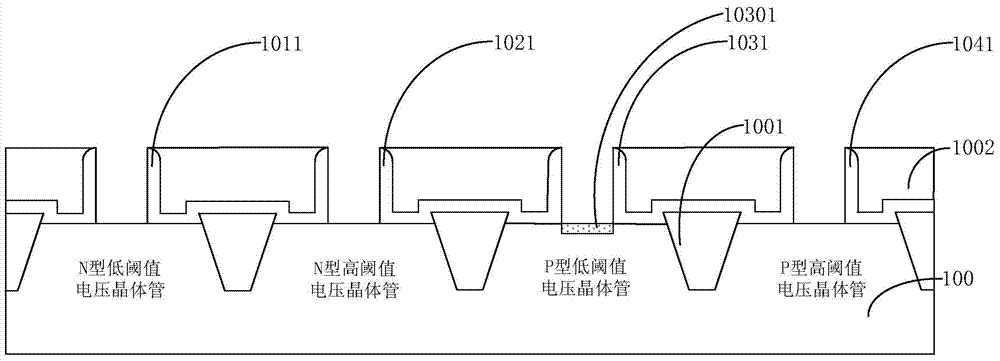

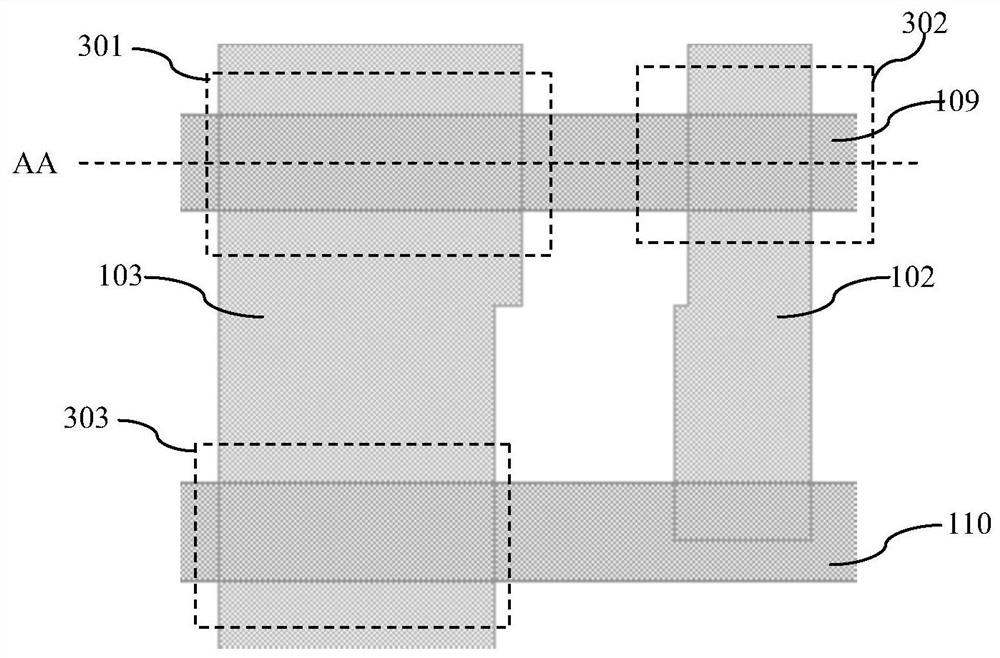

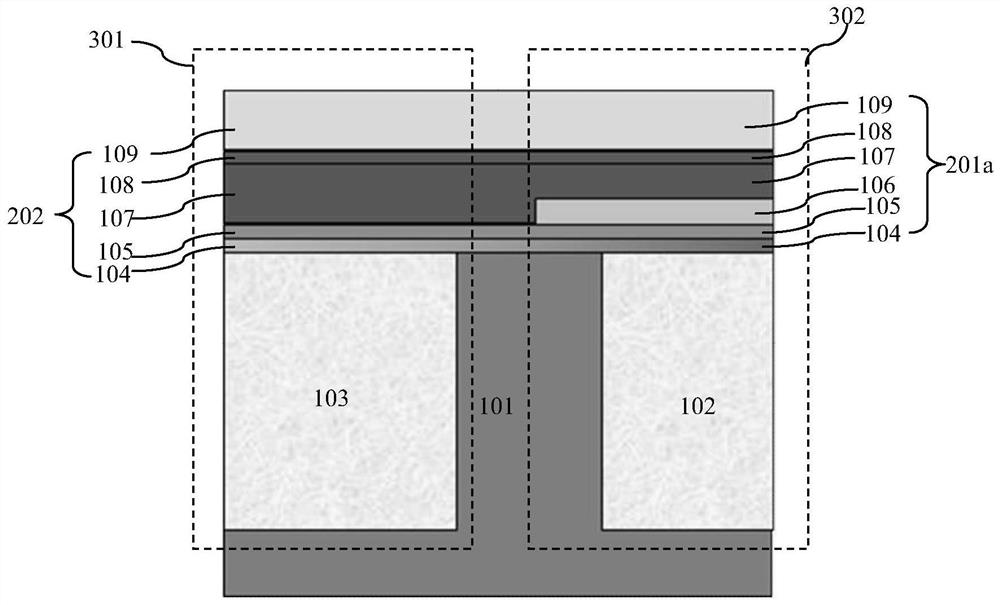

Semiconductor device and preparation method thereof

ActiveCN104425384AThreshold Voltage AdjustmentGood threshold voltage characteristicsTransistorSolid-state devicesSemiconductorThreshold voltage

The invention provides a semiconductor device and a preparation method thereof, relating to the technical field of semiconductors. The preparation method of the semiconductor device has the beneficial effect that regulation of threshold voltages of transistors is achieved by adding cap layers and barrier layers in a gate laminated structure, so that the semiconductor device with multiple threshold voltages can be better achieved. Regulation of the threshold voltages of the transistors can be achieved as the cap layers and the barrier layers are added in the gate laminated structure, so that the semiconductor device has better threshold voltage characteristics.

Owner:SEMICON MFG INT (SHANGHAI) CORP

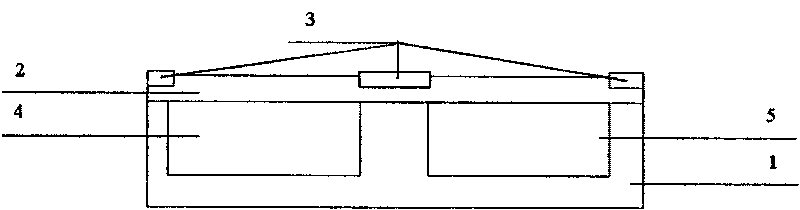

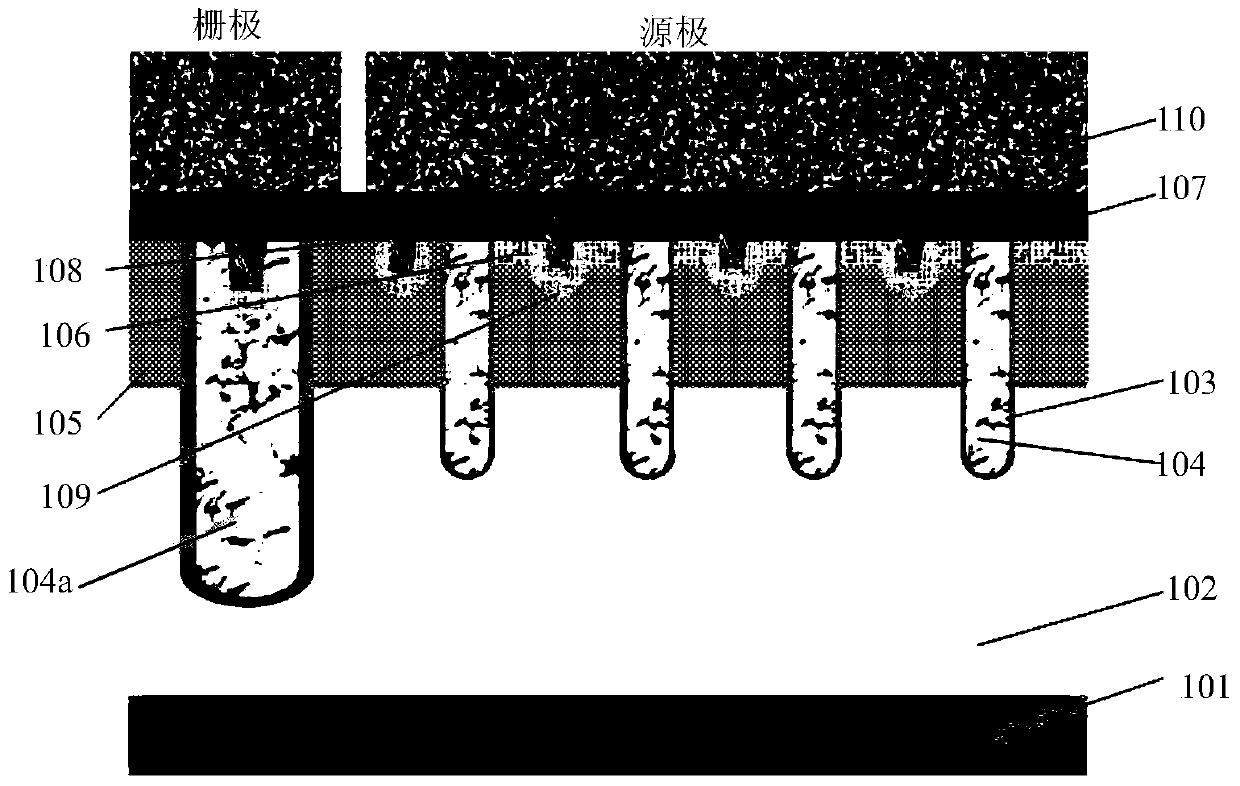

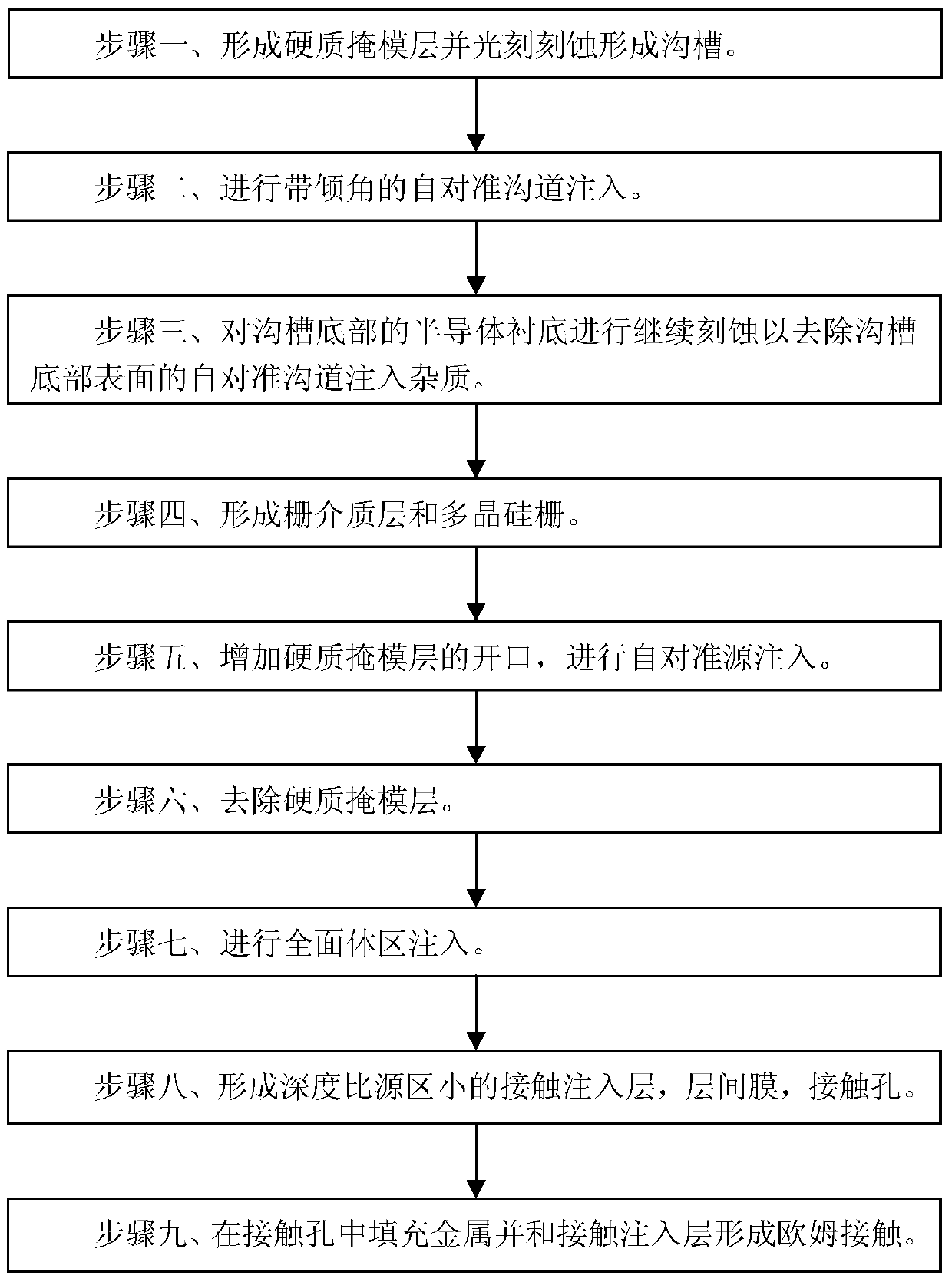

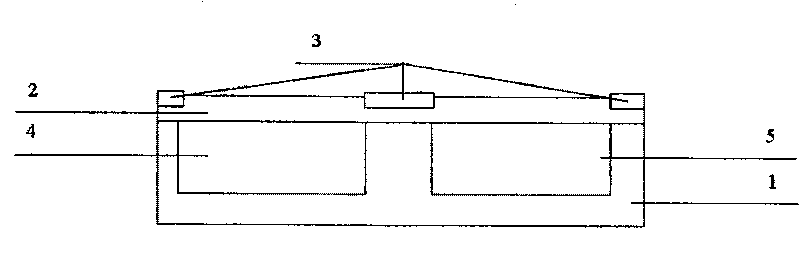

Trench gate power device manufacturing method and structure

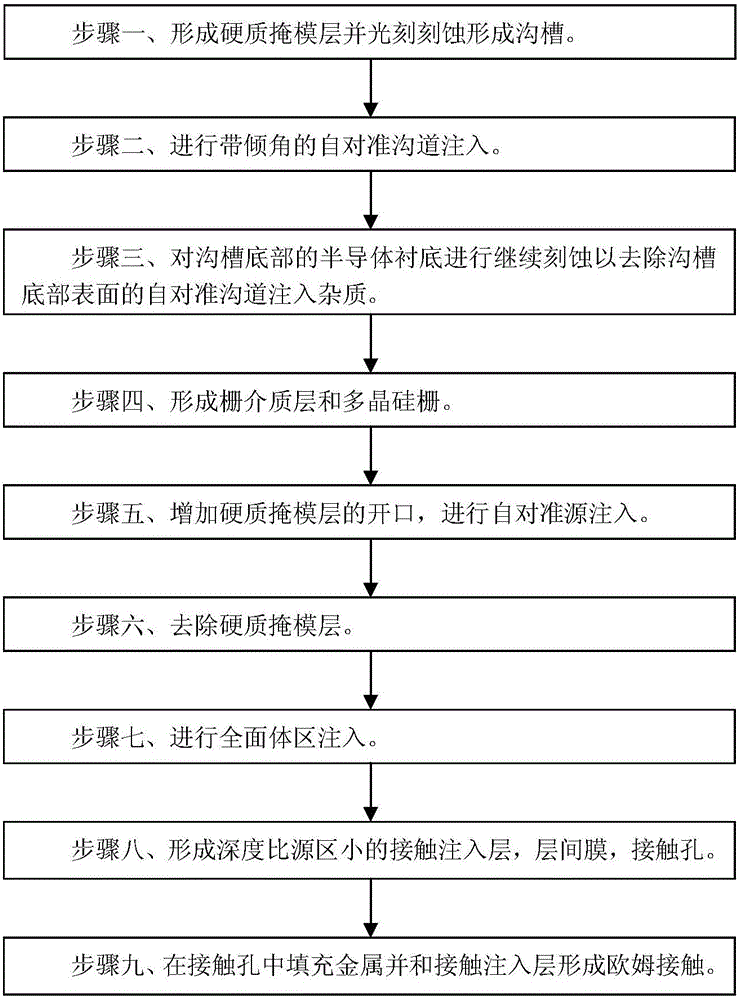

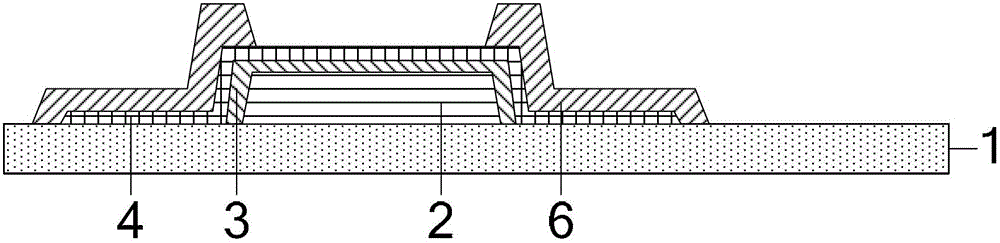

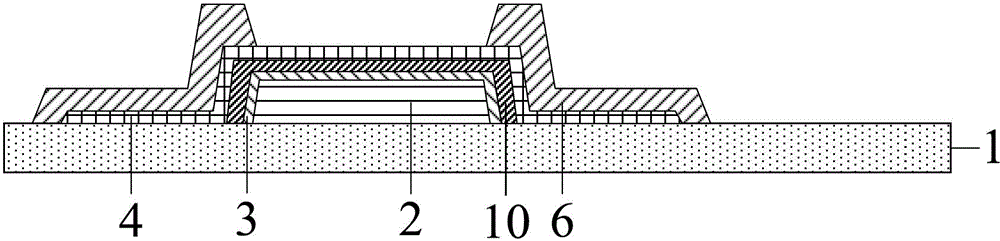

ActiveCN106024630AThreshold voltage is well regulatedThreshold Voltage AdjustmentSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionEtching

The invention discloses a trench gate power device manufacturing method, and the method comprises the steps: forming a hard mask layer, carrying out the photoetching and forming a trench; carrying out the self-aligning channel injection with an inclination angle; continuing the etching of a semiconductor substrate at the bottom of a trench, so as to remove the channel injection impurities on the surface of the bottom of the trench; forming a gate medium layer and a polysilicon gate; adding an opening of the hard mask layer, and carrying out the self-aligning source injection; removing the hard mask layer; carrying out the complete body region injection; forming a contact injection layer with the depth being less than the depth of a source region, and forming an interlayer film and a contact hole; carrying out the self-aligning contact injection formation after the contact injection layer is formed through complete contact injection before the interlayer film is formed or after the etching of the contact hole; placing metal in the contact hole, and forming ohmic contact with the contact injection layer. The invention also discloses a trench gate power device. The method can prevent the contact hole from passing through a source region, can improve the stability of a threshold voltage of the device, can reduce the size of a device unit, and can reduce the conduction resistance.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Thin-film transistor, manufacture method of thin-film transistor, array substrate and display device

ActiveCN102723359AImprove electrical performanceThreshold voltage adjustmentTransistorSolid-state devicesEtchingDisplay device

Owner:BOE TECH GRP CO LTD

Semiconductor device and preparation method thereof

ActiveCN104425283AThreshold Voltage AdjustmentGood threshold voltage characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorThreshold voltage

The invention provides a semiconductor device and a preparation method thereof, relating to the technical field of semiconductors. The preparation method has the beneficial effects that the threshold voltages of transistors can be effectively regulated by forming germanium-silicon layers in channel regions of the transistors, so that the prepared semiconductor device has different threshold voltages; the semiconductor device can be prepared by adopting the preparation method of the semiconductor device; as the channel regions have different concentrations of germanium-silicon layers, regulation of the threshold voltages of the transistors can be effectively achieved, and then the semiconductor device has good threshold voltage characteristics.

Owner:SEMICON MFG INT (SHANGHAI) CORP

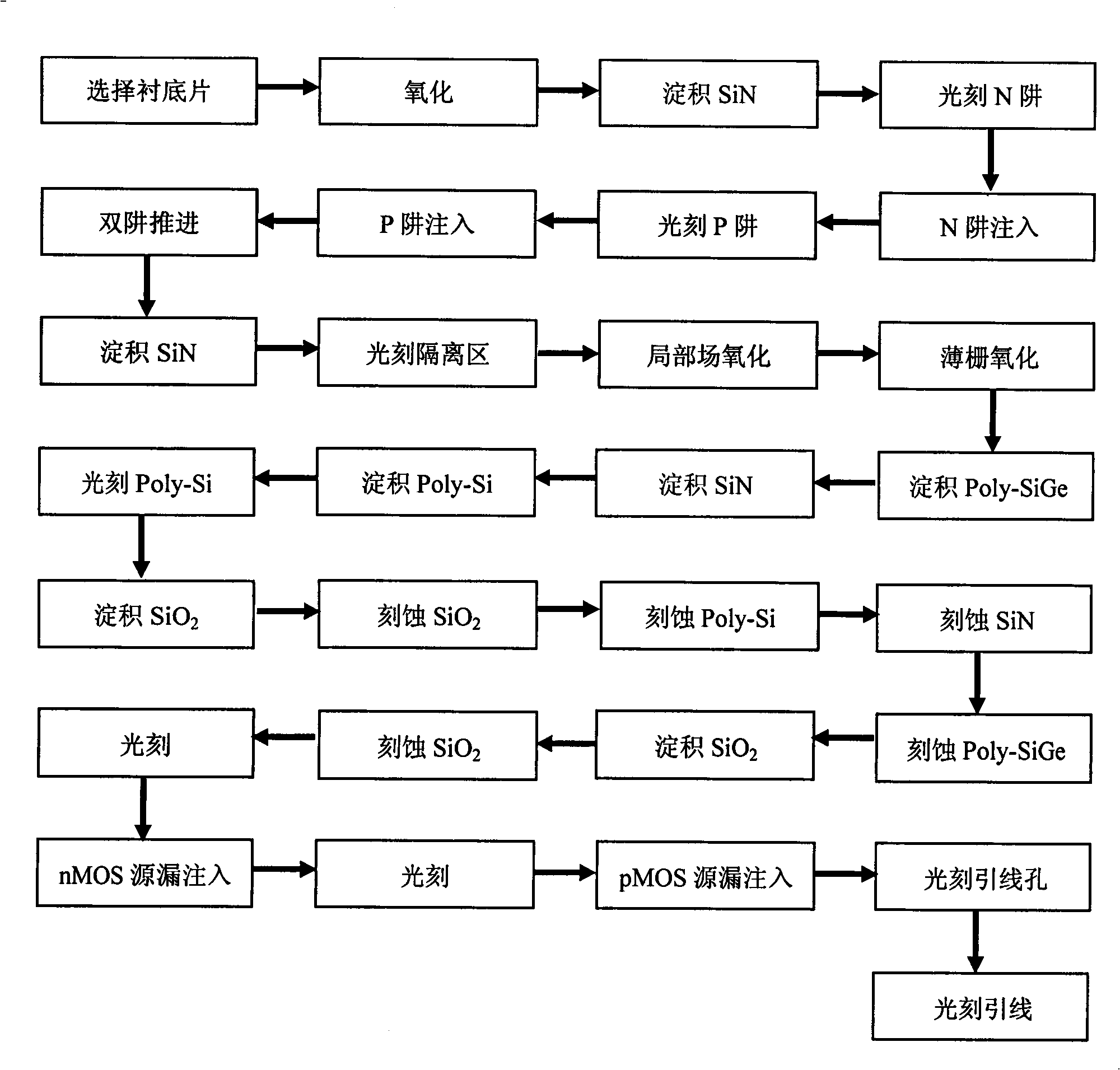

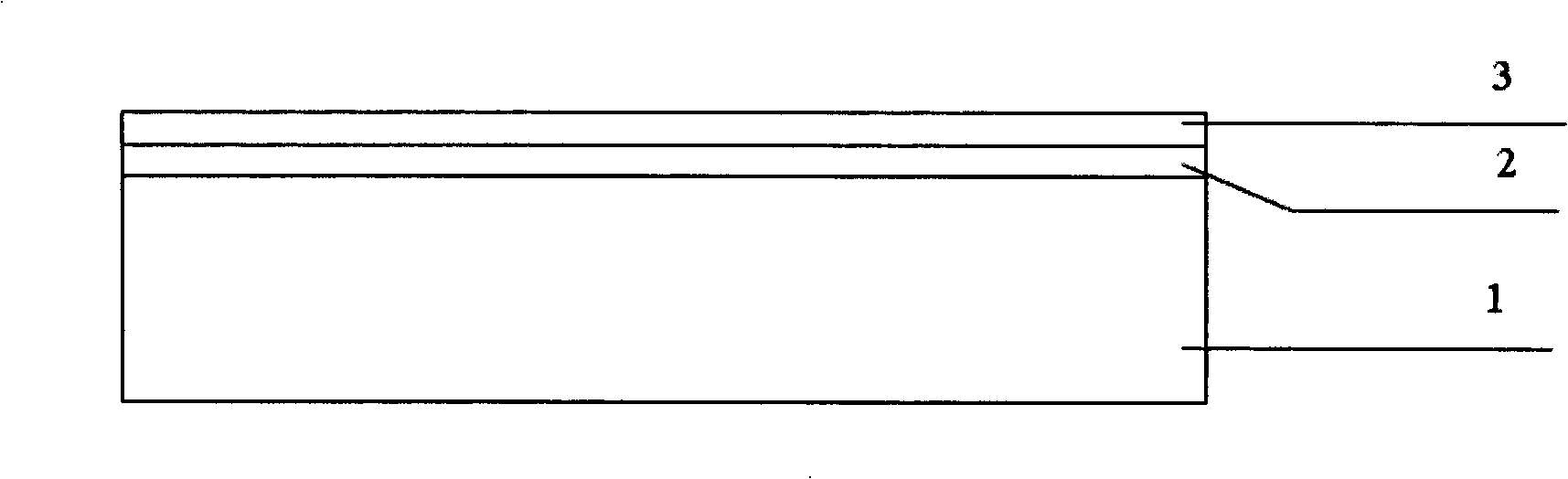

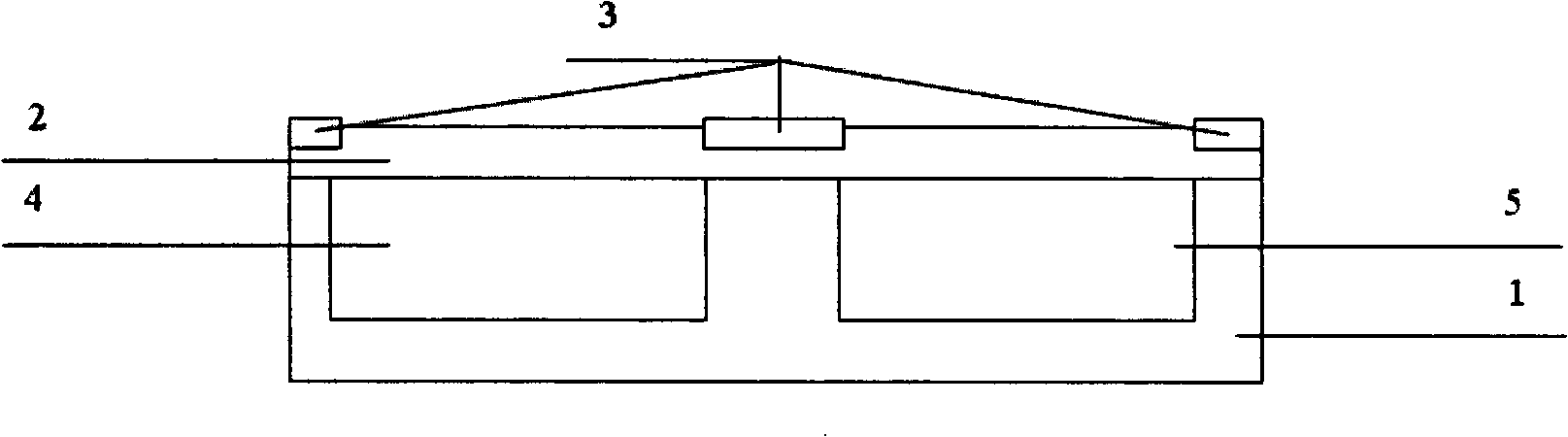

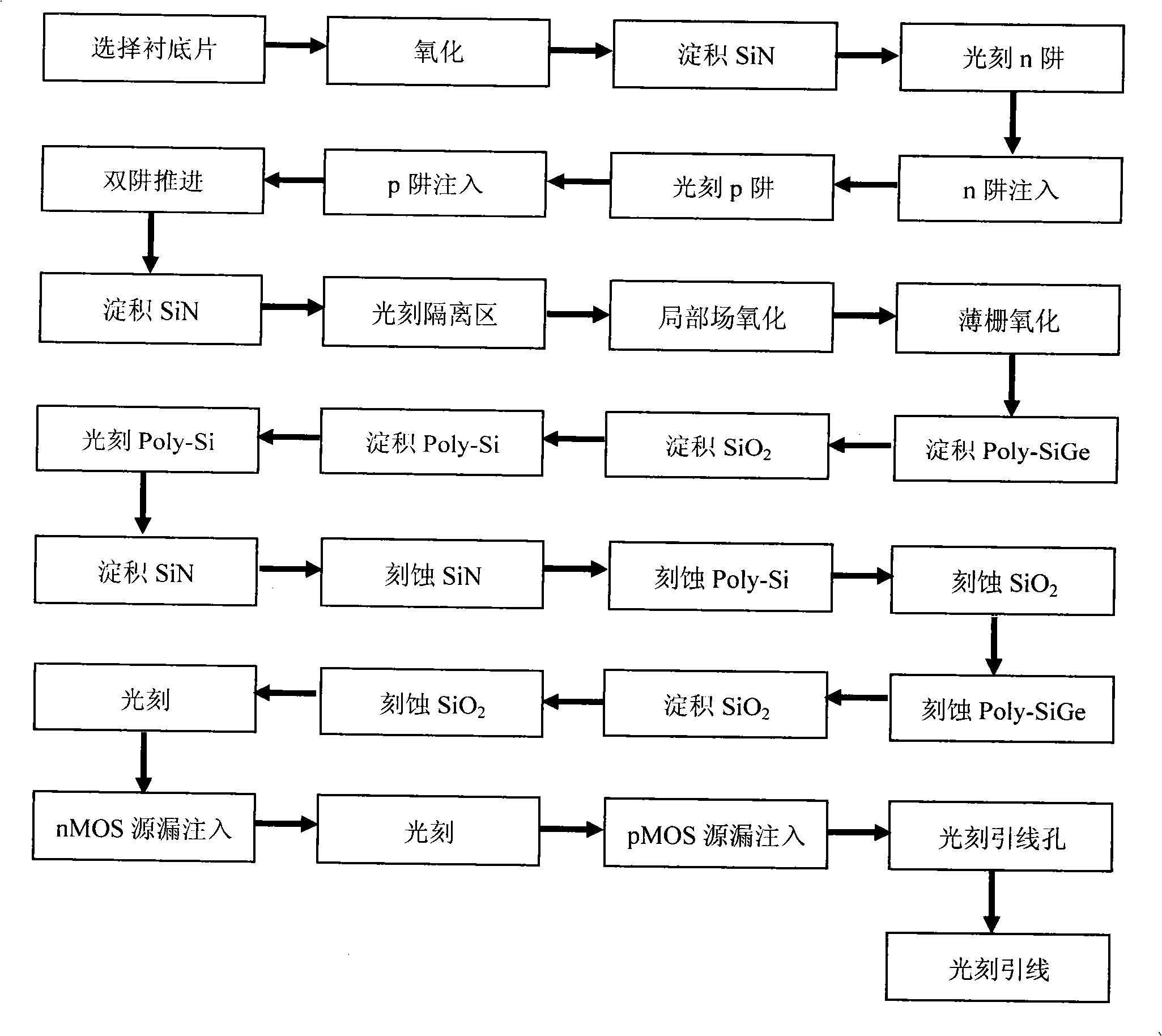

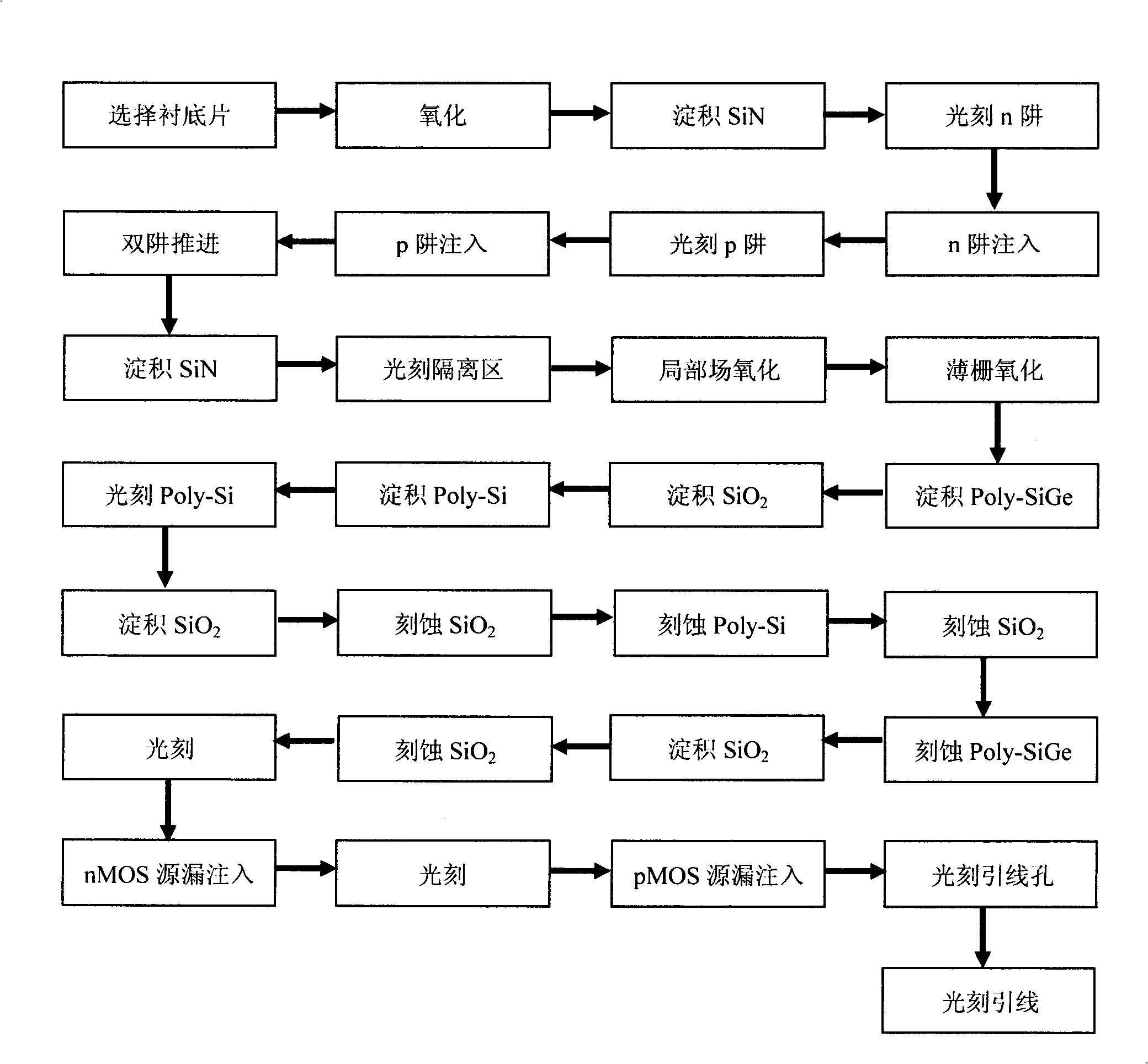

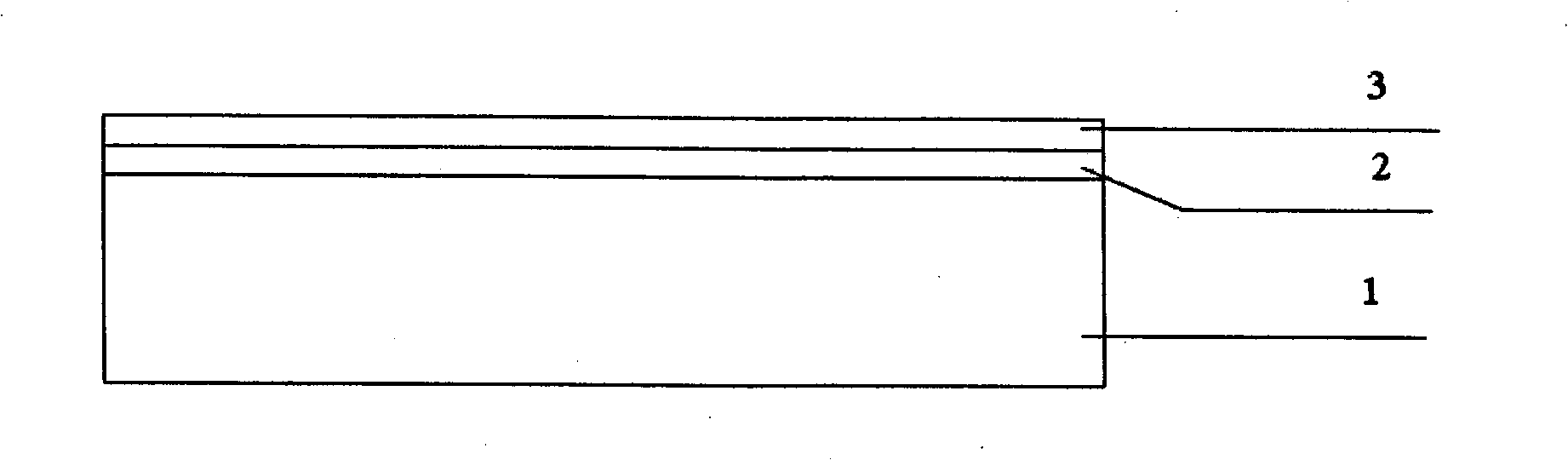

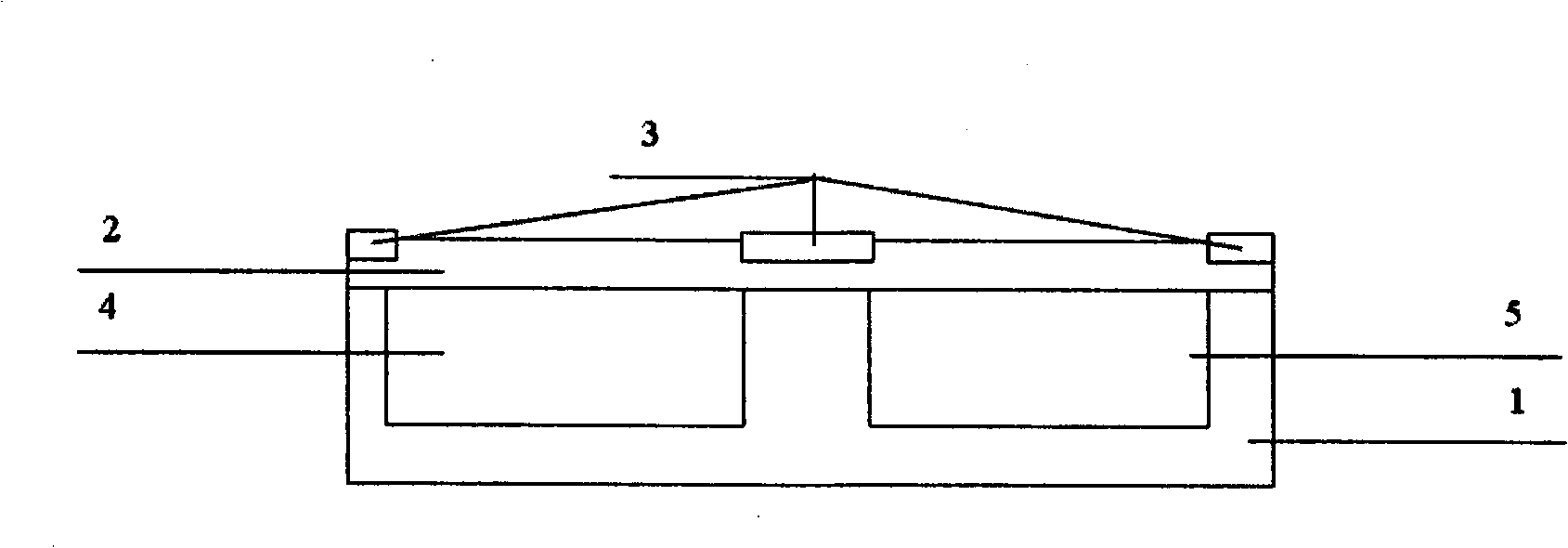

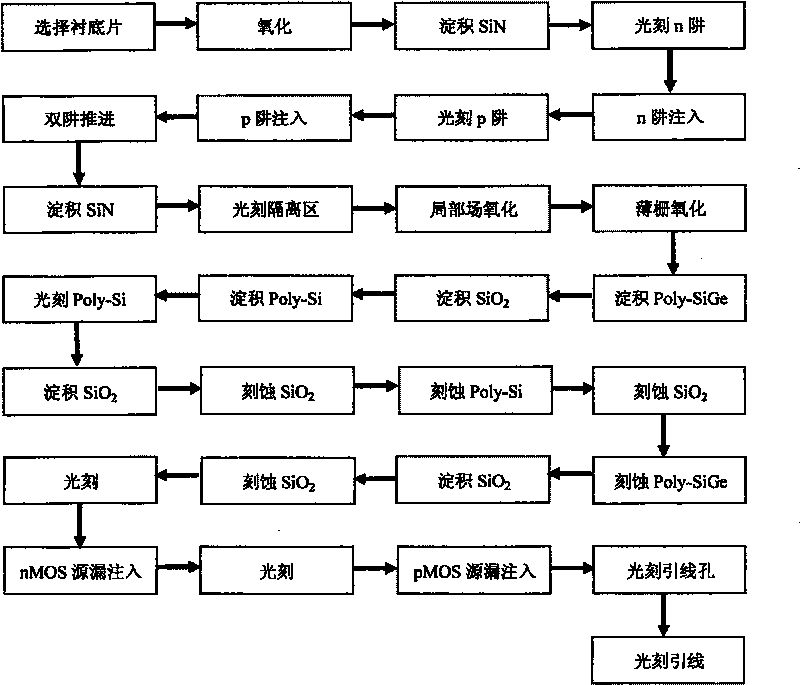

Method for preparing polycrystal SiGe gate nano CMOS integrated circuit by micro process

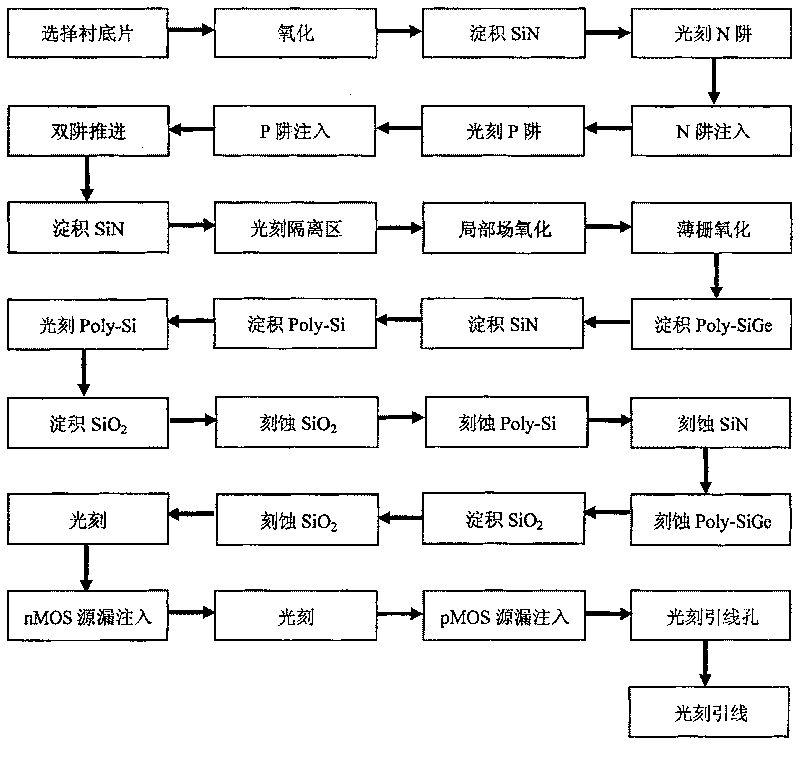

InactiveCN101359631AReduce process stepsReduce process difficultySemiconductor/solid-state device manufacturingMOSFETCMOS

The invention discloses a method based on micron-scale technique for fabricating a nano-scale CMOS integrated circuit which has a polycrystal SiGe grid. The process includes the following steps: fabricating an N / P well and growing a Poly- SiGe / SiN / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiO2; etching away the SiO2 layer on the surface of the substrate, except the SiO2 at the side wall of Poly-Si; based on the etching ratio of Poly-Si to SiN(11:1), etching the Poly-Si on the surface of SiN; based on the ratio of SiN to SiO2(2:1), etching the SiN, except the SiN in the protective area on the side wall of SiO2; based on the etching ratio of Poly-SiGe to SiO2(50:1), etching the Poly-SiGe, except the Poly-SiGe in the protective area on the side wall of SiO2 so as to form an n / p MOSFET grid; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form an n / p MOSFET device; and photoetching interconnection lines of the device so as to form a CMOS integrated circuit with a conducting channel at 45-90nm. The method can fabricate a CMOS integrated circuit which has a polycrystal SiGe grid on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

Method for preparing organic field effect transistor structure

InactiveCN102683591AImproved channel interfaceImprove mobilitySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricOrganic field-effect transistor

The invention discloses a method for preparing an organic field effect transistor structure. The method includes preparing a graphical gate electrode layer on an insulating substrate; depositing a gate dielectric layer on the gate electrode layer; preparing graphical source and drain metal electrodes on the surface of the gate dielectric layer; soaking samples with the prepared graphical source and drain metal electrodes into surface modification liquor to modify surfaces of the samples; and depositing organic semiconductor films on the modified surfaces of the samples to complete preparation of a device. The films with monomolecular layers can grow on surfaces of the metal electrodes and the surface of the gate dielectric layer simultaneously in a self-organized manner, a contact interface and a groove interface of the device are improved, and the device with a high mobility ratio is prepared.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

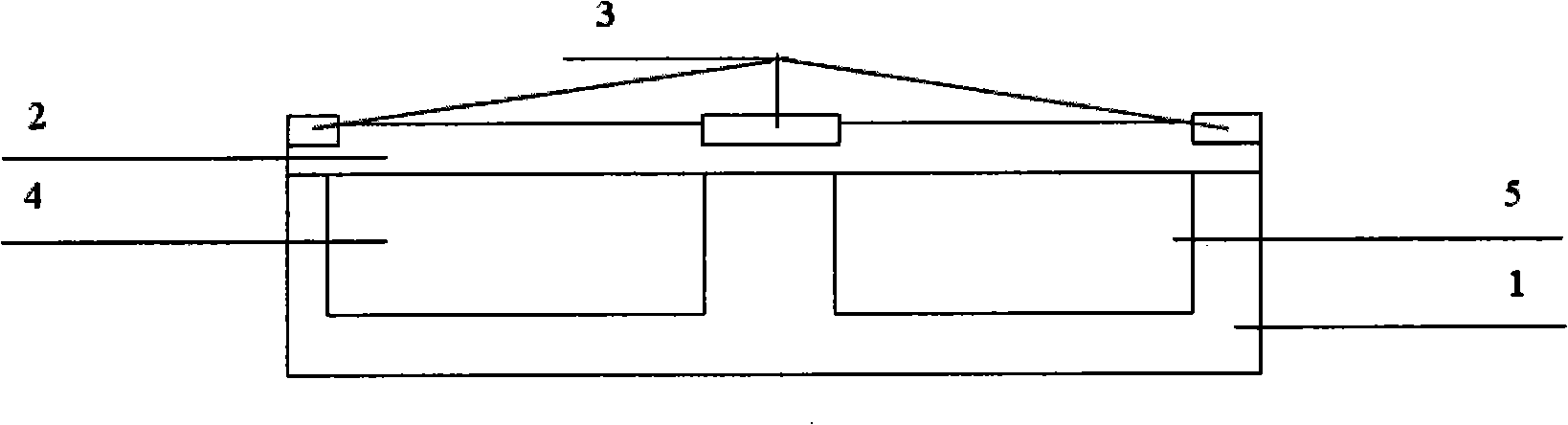

Novel GaN-base reinforced HEMT device and manufacturing method thereof

InactiveCN104393045AMeet the requirementsReduce design difficultySemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactAlloy

The invention discloses a novel GaN (gallium nitride)-base reinforced HEMT (high electron mobility transistor) device, and the device comprises: a GaN intrinsic layer and a GaN barrier layer both which are successively grown on a substrate; a high hole concentration structure layer is covered on the partial upper surface of the intrinsic layer; first and second metal electrodes are arranged on the partial upper surface of the intrinsic layer, and the partial upper surface isn't covered with the high hole concentration structure layer; a third metal electrode is covered on the upper surface of the high hole concentration structure layer; a passivation protection layer is covered on the upper surface of the intrinsic layer, and the upper surface isn't covered with the high hole concentration structure layer, and first and second metal electrodes; Ohmic contact is formed among the first and second metal electrodes and the intrinsic layer, and Schottky contact is formed between the third metal electrode and the high hole concentration structure layer. The invention further discloses a manufacturing method of the GaN-base reinforced HEMT device. The device has the advantages of high reliability and good repeatability, and the threshold voltage of the device can be adjusted by selecting different component scopes gradually changed, different nitride alloys and doping density and thickness, thus the manufactured device can satisfy different demands.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

GaN-based P-type grid-enhanced type HEMT device and preparation method thereof

InactiveCN105655388AImprove reliabilityEnhanced featuresSemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsDrain current

The invention provides a GaN-based P-type grid-enhanced type HEMT device and a preparation method thereof. The device comprises a substrate layer, a channel layer, a barrier layer, a grid electrode and a drain electrode; the channel layer is arranged on the substrate layer, the barrier layer is arranged on the channel layer, the grid electrode penetrates through the barrier layer, the drain electrode is arranged on the barrier layer, and P-type diamond is adopted as the grid electrode. The preparation method of the device comprises the following steps that 1, GaN deposition is performed on the substrate layer to form the channel layer; 2, an AlGaN layer grows on the channel layer; 3, a layer of the p-type diamond grows on the barrier layer to form the grid electrode; 4, a source electrode and the drain electrode are formed on the portions, on the two sides of the grid electrode, of the barrier layer respectively. According to the GaN-based P-type grid-enhanced type HEMT device and the preparation method thereof, the P-type diamond grid electrode is adopted, an energy band can be improved, the enhanced characteristic is achieved by using up channel electrons when the grid voltage is 0, regulation on threshold voltage of the device can be achieved, and small grid currents are kept while drain currents are increased.

Owner:SHANDONG INSPUR HUAGUANG OPTOELECTRONICS

P-type MOSFET and manufacturing method thereof

PendingCN111584636AEasy to dopeCompressive stress, compressive stress is conducive to the improvement of hole mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETImpurity diffusion

The invention discloses a P-type MOSFET. A channel region is composed of an N well covered by a gate structure, the N well comprises a superposition region composed of first to fourth injection regions, and the superposition region is subjected to annealing treatment; the injection impurities of the first to fourth injection regions are respectively phosphorus, germanium, xenon and arsenic, and the junction depths are sequentially reduced, wherein the doping concentration of the fourth injection region is used for adjusting the threshold voltage, the ion injection process of the fourth injection region is carried out after the ion injection process of the second injection region and the ion injection process of the third injection region are completed, and the second injection region and the third injection region form an amorphous layer in the semiconductor substrate to enable arsenic injection in the fourth injection region to be uniform, wherein the germanium impurities in the second injection region are used for providing pressure stress for the channel region; and the xenon impurities in the third injection region are used for preventing the germanium impurities from diffusinginto the fourth injection region so as to reduce defects caused by germanium diffusion. The invention further discloses a manufacturing method of the P-type MOSFET. According to the invention, the local fluctuation of the threshold voltage can be reduced, the channel carrier mobility can be improved, and the device performance and the product yield can be improved.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

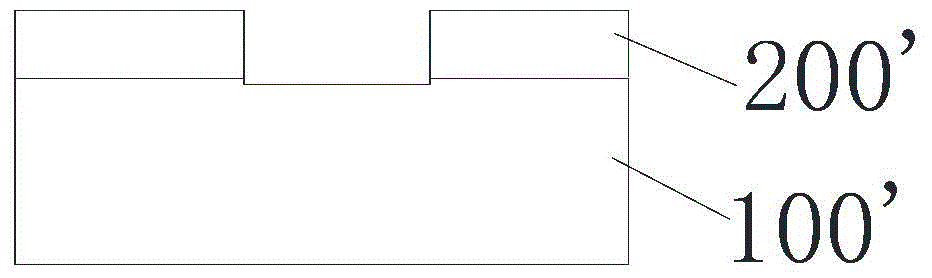

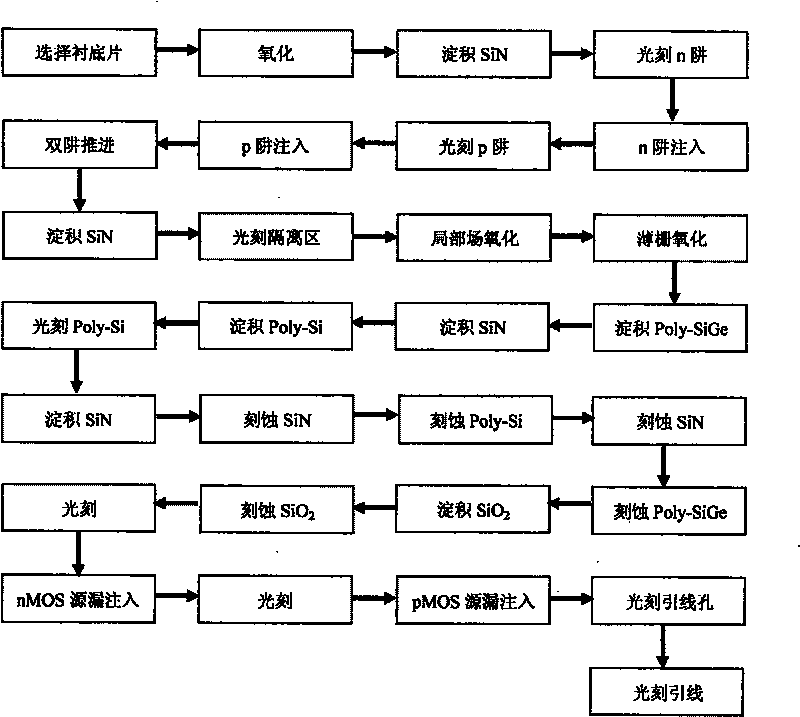

Method for preparing polycrystal SiGe gate nano-scale CMOS integrated circuit based on multilayered auxiliary structure

InactiveCN101359625AThreshold Voltage AdjustmentAchieve regulationSemiconductor/solid-state device manufacturingMOSFETMicron scale

The invention discloses a method for fabricating a nano-scale CMOS integrated circuit which has a polycrystal SiGe grid and is based on a multi-layer assistant structure. The method includes the following steps: fabricating an N / P well and growing a Poly-SiGe / SiO2 / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiN; etching the SiN layer on the surface, except the SiN at the side of the window; etching the SiN on the surface of the substrate; based on the etching ratio of Poly-Si to SiN (11:1), etching the Poly-Si at the surface of SiN; based on the etching ratio of SiO2 to SiN(4:1) and the etching ratio of Poly-SiGe to SiN, etching the SiO2 and Poly-SiGe on the surface except on the side wall of the SiN so as to form an n / p MOSFET grid; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form an n / p MOSFET device; and photoetching interconnection lines of the device so as to form a CMOS integrated circuit with a conducting channel at 65-90nm. The invention can fabricate a CMOS integrated circuit which is improved in performance by 3-5 generations on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

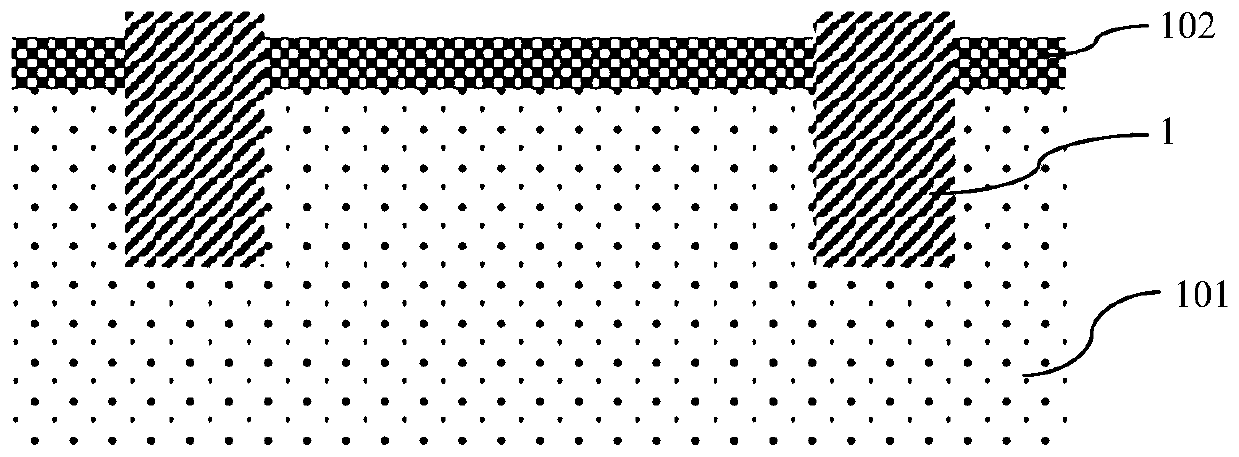

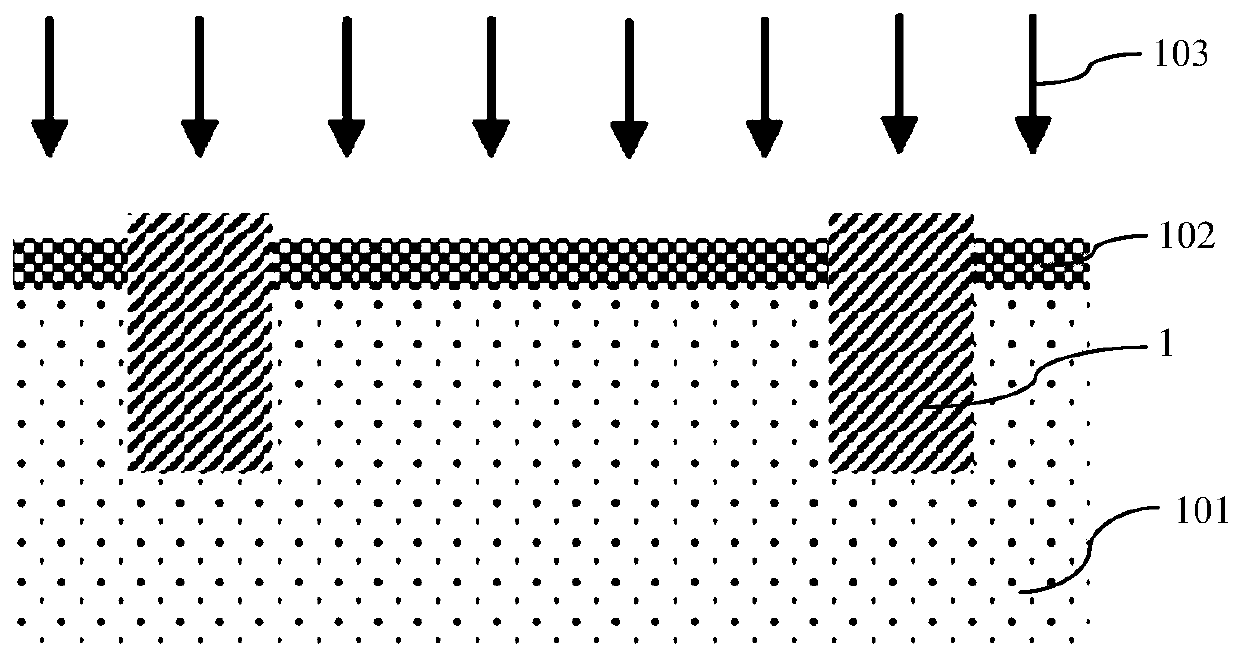

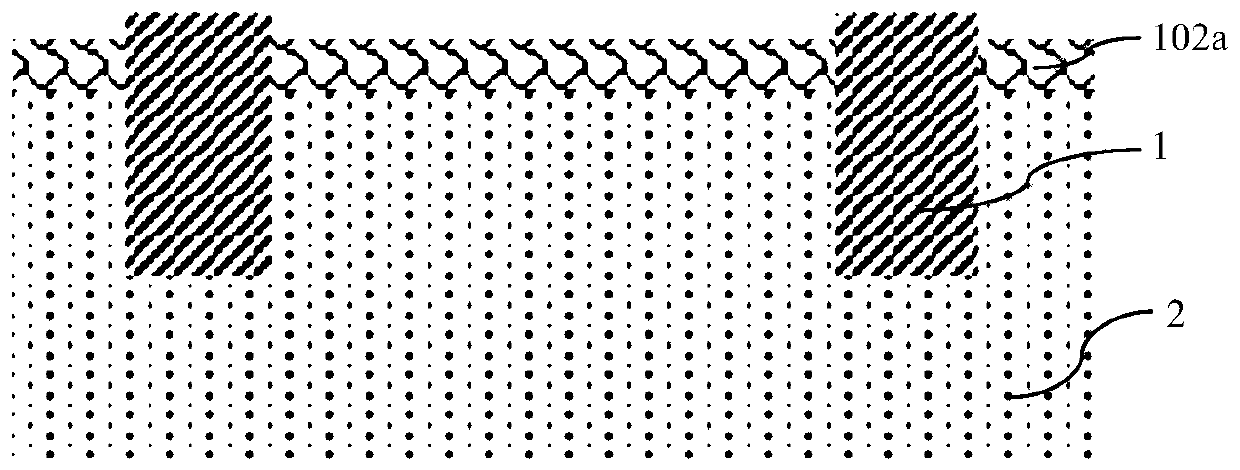

Method of forming gate oxide layer

InactiveCN105990110AThreshold Voltage AdjustmentThreshold voltage is effectively adjustedSemiconductor/solid-state device manufacturingSemiconductor devicesSurface oxidationGate oxide

The invention provides a method of forming a gate oxide layer. The method comprises the steps of S1, conducting the oxidation growth on the upper surface of a semiconductor substrate to form an oxide layer; S2, etching to remove the oxide layer located at a first position to expose the part of the semiconductor substrate that is corresponding to the first position; S3, conducting the oxidation growth on the exposed semiconductor substrate to form a first gate oxide layer of H1 in thickness; S4, etching to remove the first gate oxide layer at a second position to expose the part of the semiconductor substrate that is corresponding to the second position; S5, conducting the oxidation growth on the exposed semiconductor substrate to form a second gate oxide layer of H2 in thickness, wherein H2<H1; and S6, implanting ions into the semiconductor substrate below the first gate oxide layer and the second gate oxide layer. Through adjusting the manufacturing process of the first gate oxide layer and the second gate oxide layer, the process of implanting ions and adjusting the threshold voltage respectively is replaced. Therefore, the problems that the process is complicated and the cost is high can be solved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Semiconductor integrated circuit with HKMG

ActiveCN108807382AThreshold Voltage AdjustmentThreshold Voltage OffsetTransistorSolid-state devicesBoundary effectsWork function

The invention discloses a semiconductor integrated circuit with an HKMG. The semiconductor integrated circuit comprises a semiconductor device and an FDSOI substrate structure, wherein the semiconductor device is formed on the FDSOI substrate, and the magnitude of the work function of the HKMG work function layer trends to the intermediate value of forbidden bandwidth of a semiconductor layer on the top; and the FDSOI substrate structure is provided with an structure for adjusting the threshold voltage of the semiconductor device. The structure for adjusting the threshold voltage of the semiconductor device comprises an inversion channel doping structure and a substrate bias applying structure. The threshold voltage of the semiconductor device is adjusted through the structure for adjusting the threshold voltage of the semiconductor device, the influence of the power function layer on the threshold voltage of the semiconductor device is cancelled, and the semiconductor device of whichthe threshold voltage meets the requirement is formed. The HKMG structures of a PMOS tube and an NMOS tube can be uniform, and a metal gate boundary effect generated when the HKMG of the PMSO tube isdifferent from that of the NMOS tube can be eliminated.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

Polycrystal SiGe gate nano CMOS integrated circuit preparation based on SiO2 macking technique

InactiveCN101359629AThreshold Voltage AdjustmentAchieve regulationSemiconductor/solid-state device manufacturingMOSFETMicron scale

The invention discloses a method based on SiO2 masking technique for fabricating a nano-scale CMOS integrated circuit which has a polycrystal SiGe grid. The process includes the following steps: fabricating an N / P well and growing a Poly- SiGe / SiO2 / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiO2; etching the SiO2 layer on the surface, except the SiO2 at the side face of the window; based on the etching ratio of Poly-Si to SiO2 (50:1), etching the Poly-Si at the upper layer; based on the etching ratio of Poly-SiGe to SiO2 (50:1), etching the SiO2 and the Poly-SiGe, except the SiO2 and Poly-SiGe in the protective area at the side wall of the SiO2, preserving the SiO2 and Poly-SiGe below the side wall, forming a n / p MOSFET grid and depositing a layer of SiO2; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form an n / p MOSFET device; and photoetching interconnection lines of the device so as to form a CMOS integrated circuit with a conducting channel at 65-90nm. The method can fabricate a CMOS integrated circuit which is improved in performance by 3-5 generations on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

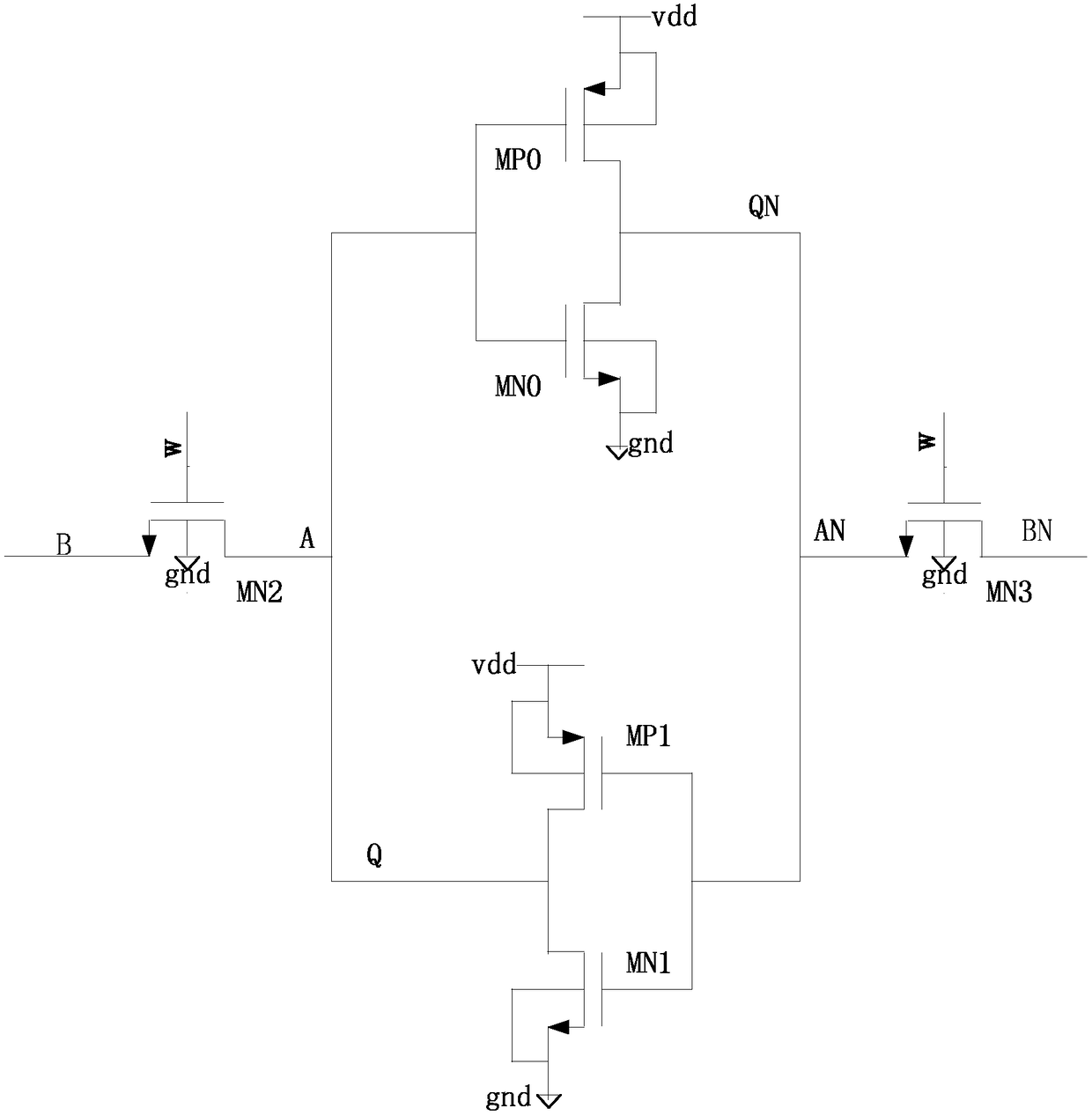

Method for outputting power-up constant value of six-tube SRAM (Static Random Access Memory) for single-threshold CMOS (Complementary Metal Oxide Semiconductor) device

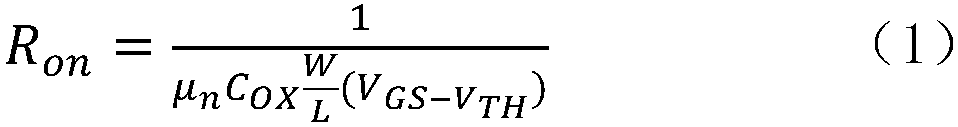

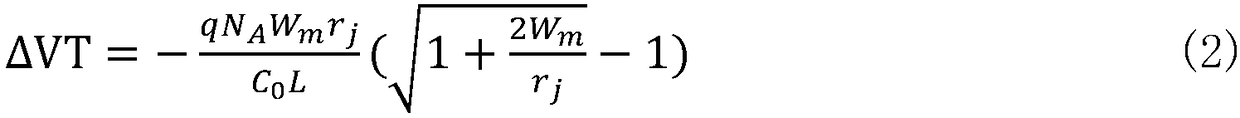

The invention relates to a method for outputting a power-up constant value of a six-tube SRAM (Static Random Access Memory) for a single-threshold CMOS (Complementary Metal Oxide Semiconductor) device. Through adjusting parameters of transistors, an initial value after powering up an SRAM unit is determined, the stability of a state of a circuit is ensured, and the design reliability of the circuit is enhanced. According to the method disclosed by the invention, an effect of powering up the SRAM unit with a six-tube structure of the CMOS device along with power to ensure a fixed initial stateis achieved, building of clear potentials on internal network of a large-scale integrated circuit with the SRAM unit is realized, and the reliability and the stability of the device are promoted.

Owner:NO 47 INST OF CHINA ELECTRONICS TECH GRP

A kind of semiconductor device and its manufacturing method

ActiveCN104425384BThreshold Voltage AdjustmentGood threshold voltage characteristicsTransistorSolid-state devicesEngineeringSemiconductor

The invention provides a semiconductor device and a preparation method thereof, relating to the technical field of semiconductors. The preparation method of the semiconductor device has the beneficial effect that regulation of threshold voltages of transistors is achieved by adding cap layers and barrier layers in a gate laminated structure, so that the semiconductor device with multiple threshold voltages can be better achieved. Regulation of the threshold voltages of the transistors can be achieved as the cap layers and the barrier layers are added in the gate laminated structure, so that the semiconductor device has better threshold voltage characteristics.

Owner:SEMICON MFG INT (SHANGHAI) CORP

semiconductor integrated circuit with hkmg

ActiveCN108807382BThreshold Voltage AdjustmentThreshold Voltage OffsetTransistorSolid-state devicesDevice materialCondensed matter physics

The invention discloses a semiconductor integrated circuit with HKMG, comprising: a semiconductor device is formed on an FDSOI substrate structure, the work function of the work function layer of HKMG tends to the middle value of the forbidden band width of the top semiconductor layer; the FDSOI substrate The bottom structure has an adjustment structure of the threshold voltage of the semiconductor device. The adjustment structure of the threshold voltage of the semiconductor device includes an inversion channel doping structure and a substrate bias application structure. The threshold voltage of the semiconductor device is adjusted by the threshold voltage adjustment structure of the semiconductor device, the influence of the work function layer on the threshold voltage of the semiconductor device is offset, and a semiconductor device with a threshold voltage meeting requirements is formed. The invention can unify the structure of the HKMG of the PMOS transistor and the NMOS transistor, and can eliminate the metal grid boundary effect produced when the HKMG of the PMOS transistor and the NMOS transistor are different.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

Formation method of semiconductor structure

ActiveCN108573921BReduce carbon contentChange work functionSemiconductor/solid-state device manufacturingChemical physicsSemiconductor structure

A method for forming a semiconductor structure, comprising: providing a substrate; forming a work function layer on the substrate, the step of forming the work function layer includes one or more steps of forming a work function film, and the step of forming the work function film includes: An initial work function film is formed on the substrate, and the initial work function film has carbon atoms; the carbon removal precursor is used to remove carbon from the initial work function film to form a work function film, and the carbon removal precursor is used to interact with The carbon atoms in the initial work function film react; a gate is formed on the work function layer. A gate is formed on the work function layer. After the initial work function film is formed, the carbon removal treatment is performed on the initial work function film through the carbon removal precursor. The carbon-removing precursor can react with the carbon atoms in the initial work function film, thereby reducing the carbon atom content in the initial work function film, thereby changing the work function of the work function layer, and then adjusting the threshold voltage of the formed transistor, so that all The threshold voltage of the formed transistor meets the design requirements.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

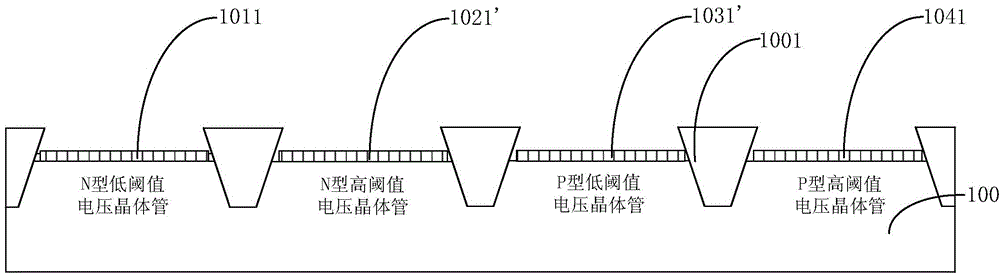

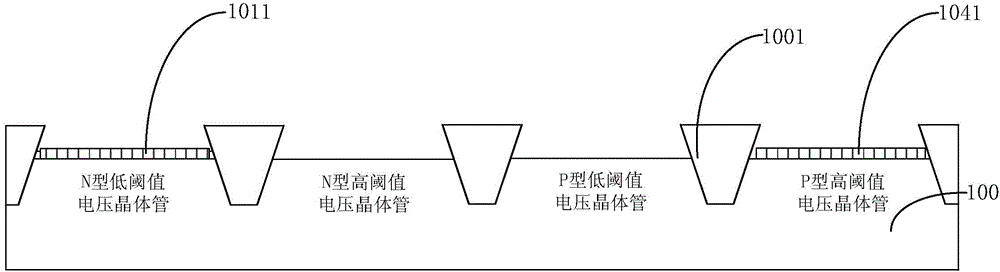

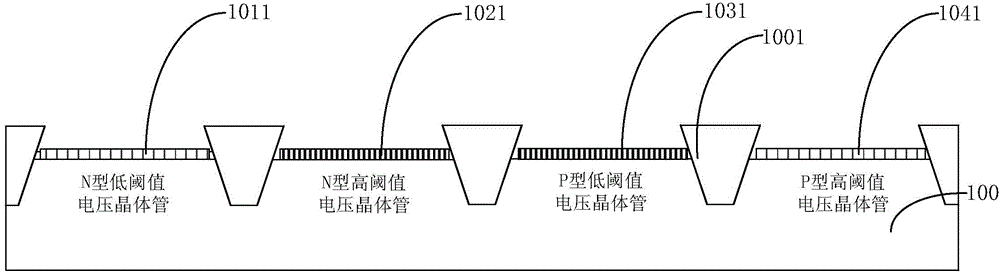

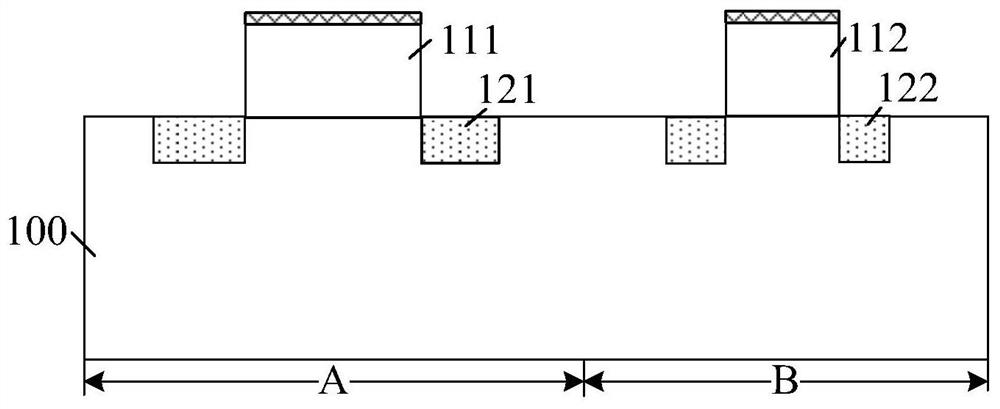

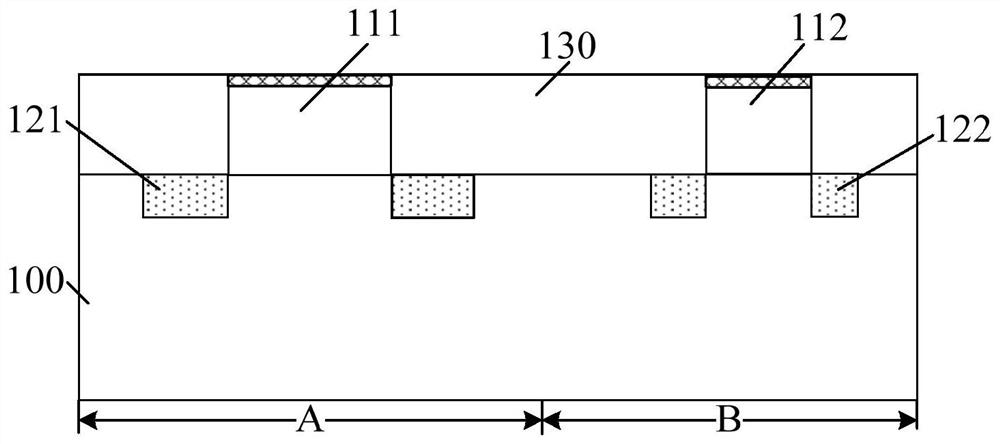

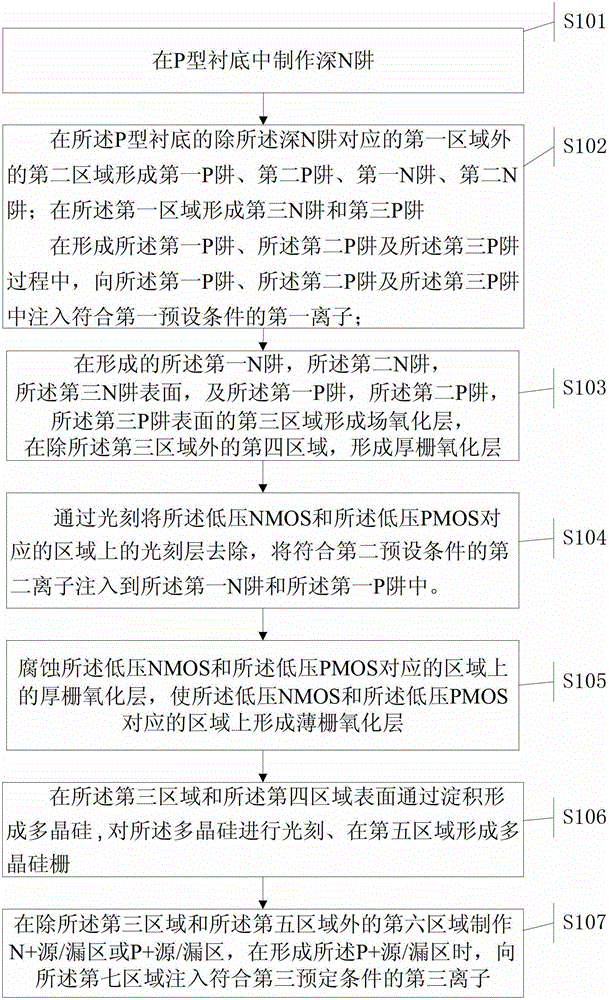

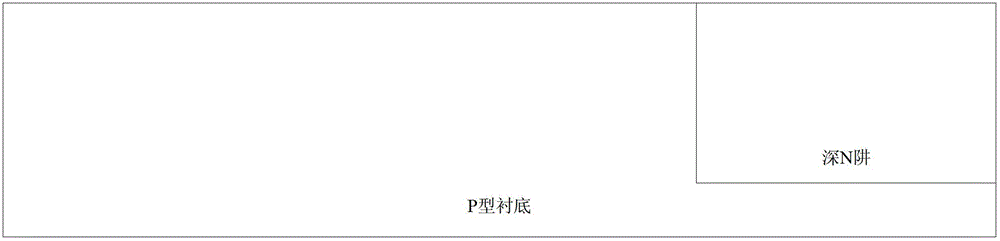

A threshold voltage adjustment method

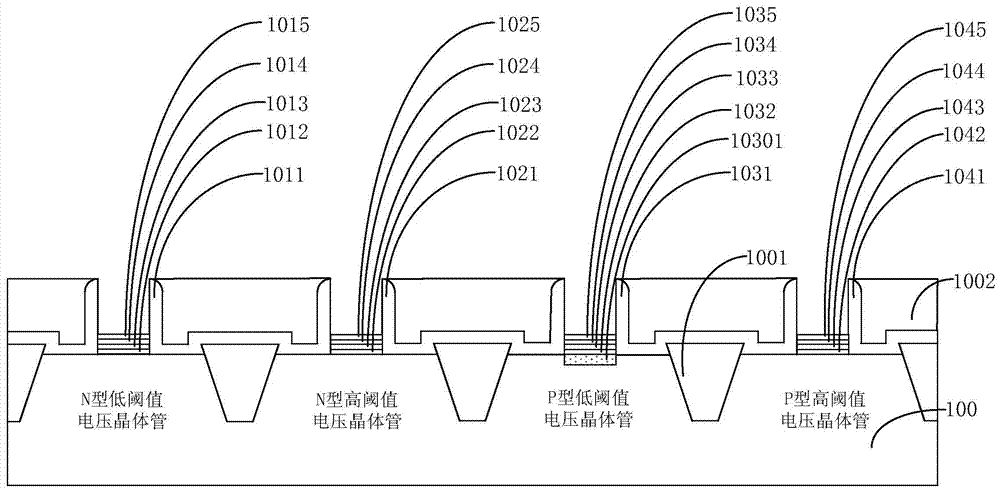

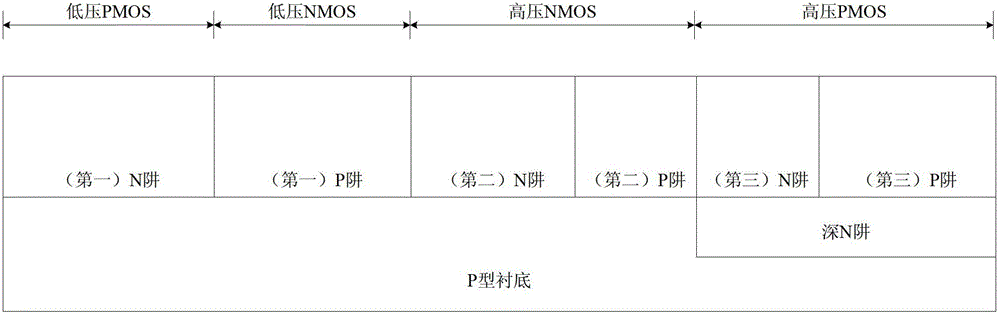

ActiveCN103730419BReasonable distributionGuaranteed source-drain breakdown voltageSemiconductor/solid-state device manufacturingCMOSEngineering

The invention discloses a threshold voltage adjusting method which is applied to a manufacturing process of a deep N-well high-voltage CMOS integrated circuit and can be used for adjusting threshold voltage of a high-voltage CMOS on the premise that a photoetching layer is not increased. The method includes the steps that when a first P well, a second P well and a third P well of the deep N-well high-voltage CMOS integrated circuit are formed, first ions according with first preset conditions are injected into the first P well, the second P well and the third P well, the first ions are injected in twice, and accordingly source drain breakdown voltage and threshold voltage of a high-voltage NMOS and source drain breakdown voltage and threshold voltage of a high-voltage PMOS are adjusted.

Owner:FOUNDER MICROELECTRONICS INT

Method for preparing polycrystal SiGe gate nano CMOS integrated circuit by micro process

InactiveCN101359631BThreshold Voltage AdjustmentAchieve regulationSemiconductor/solid-state device manufacturingMicron scaleMOSFET

The invention discloses a method based on micron-scale technique for fabricating a nano-scale CMOS integrated circuit which has a polycrystal SiGe grid. The process includes the following steps: fabricating an N / P well and growing a Poly- SiGe / SiN / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiO2; etching away the SiO2layer on the surface of the substrate, except the SiO2 at the side wall of Poly-Si; based on the etching ratio of Poly-Si to SiN(11:1), etching the Poly-Si on the surface of SiN; based on the ratio of SiN to SiO2(2:1), etching the SiN, except the SiN in the protective area on the side wall of SiO2; based on the etching ratio of Poly-SiGe to SiO2(50:1), etching the Poly-SiGe, except the Poly-SiGein the protective area on the side wall of SiO2 so as to form an n / p MOSFET grid; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form ann / p MOSFET device; and photoetching interconnection lines of the device so as to form a CMOS integrated circuit with a conducting channel at 45-90nm. The method can fabricate a CMOS integrated circuitwhich has a polycrystal SiGe grid on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

Method for preparing polycrystal SiGe gate nano CMOS integrated circuit by SiN masking technique

InactiveCN101359627BThreshold Voltage AdjustmentAchieve regulationSemiconductor/solid-state device manufacturingMicron scaleMOSFET

The invention discloses a method for fabricating a nano-scale CMOS integrated circuit which has a polycrystal SiGe grid through SiN masking technique. The process includes the following steps: fabricating an N / P well and growing a Poly- SiGe / SiN / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiN; etching the SiN layer onthe surface, except the SiN at the side face of the window; based on the etching ratio of Poly-Si to SiN (11:1), etching the Poly-Si at the surface of SiN and etching the SiN except on the side wallof SiN so as to expose the substrate of Poly-SiGe; based on the etching ratio of Poly-SiGe to SiN(11:1), etching the Poly-SiGe except on the side wall of the SiN so as to form an n / p MOSFET grid; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form an n / p MOSFET device; and photoetching interconnection lines of the device so as to forma CMOS integrated circuit with a conducting channel at 45-90nanometer. The method can fabricate a CMOS integrated circuit which is improved in performance by 3-5 generations on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

Manufacturing method and structure of trench gate power device

ActiveCN106024630BThreshold voltage is well regulatedThreshold Voltage AdjustmentSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingEngineering

The invention discloses a trench gate power device manufacturing method, and the method comprises the steps: forming a hard mask layer, carrying out the photoetching and forming a trench; carrying out the self-aligning channel injection with an inclination angle; continuing the etching of a semiconductor substrate at the bottom of a trench, so as to remove the channel injection impurities on the surface of the bottom of the trench; forming a gate medium layer and a polysilicon gate; adding an opening of the hard mask layer, and carrying out the self-aligning source injection; removing the hard mask layer; carrying out the complete body region injection; forming a contact injection layer with the depth being less than the depth of a source region, and forming an interlayer film and a contact hole; carrying out the self-aligning contact injection formation after the contact injection layer is formed through complete contact injection before the interlayer film is formed or after the etching of the contact hole; placing metal in the contact hole, and forming ohmic contact with the contact injection layer. The invention also discloses a trench gate power device. The method can prevent the contact hole from passing through a source region, can improve the stability of a threshold voltage of the device, can reduce the size of a device unit, and can reduce the conduction resistance.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

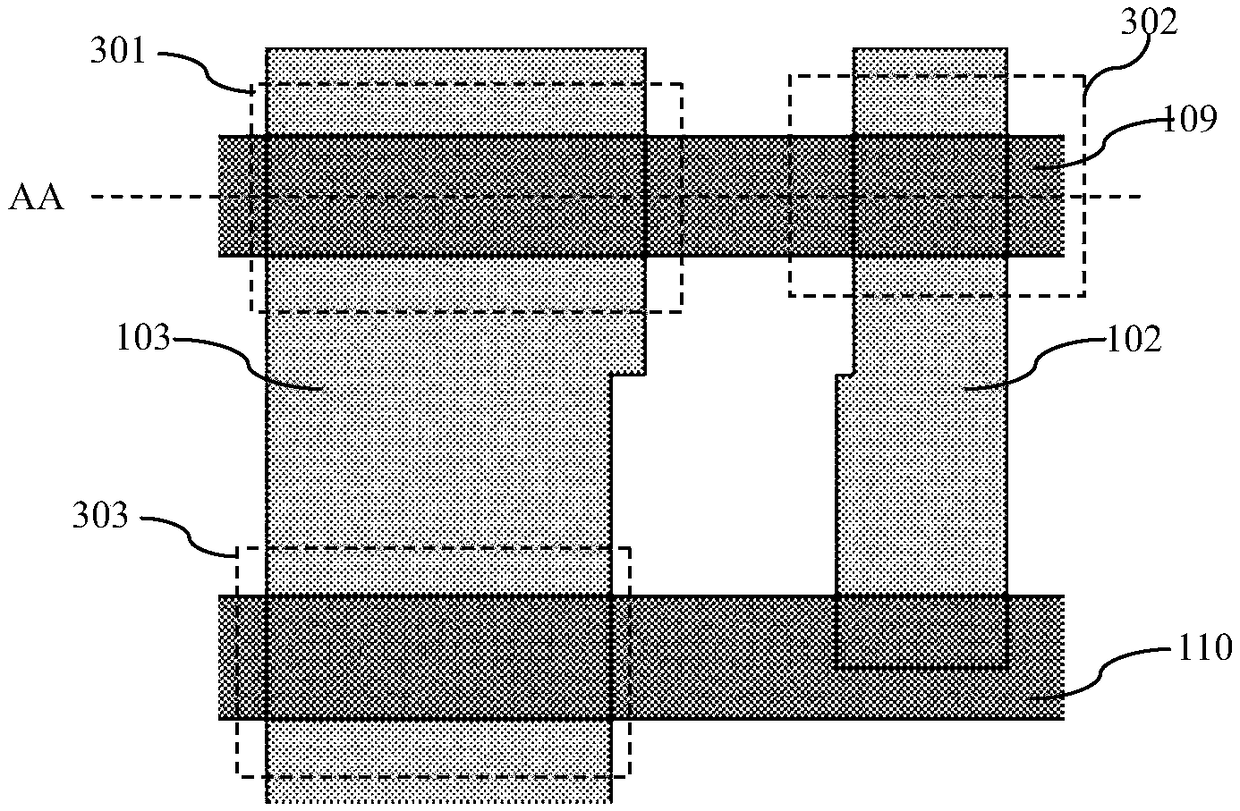

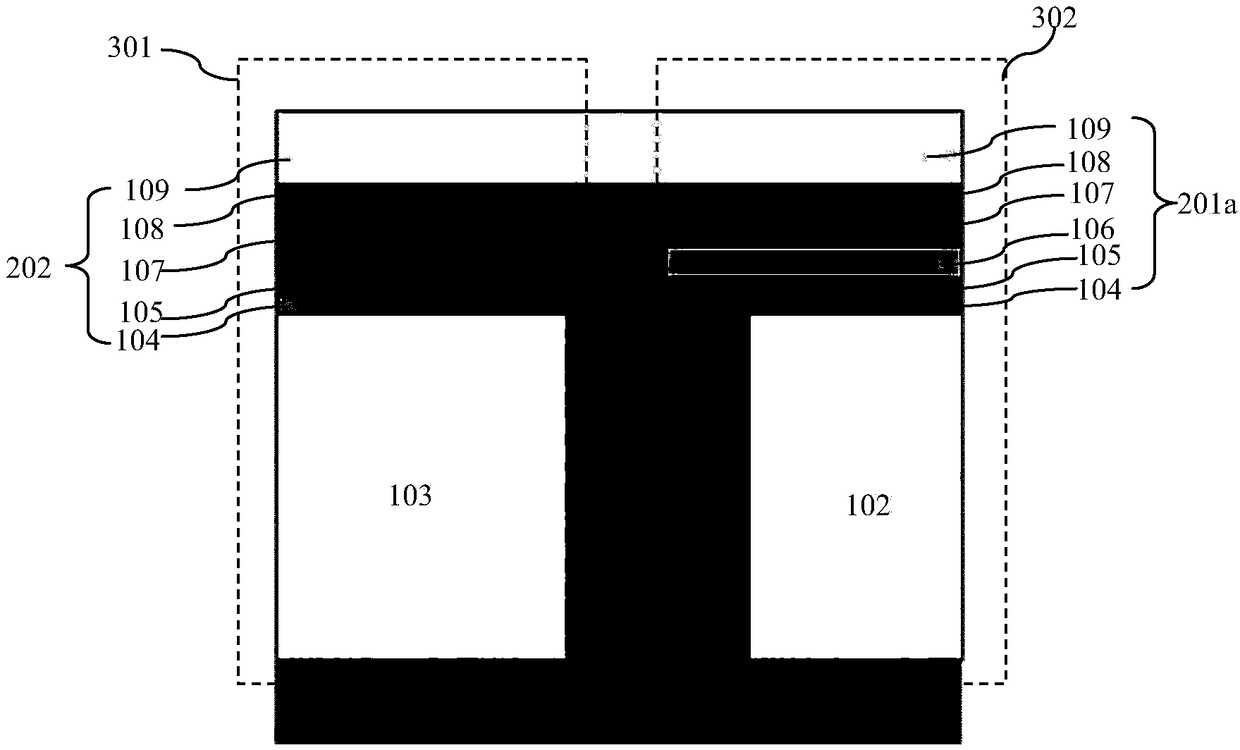

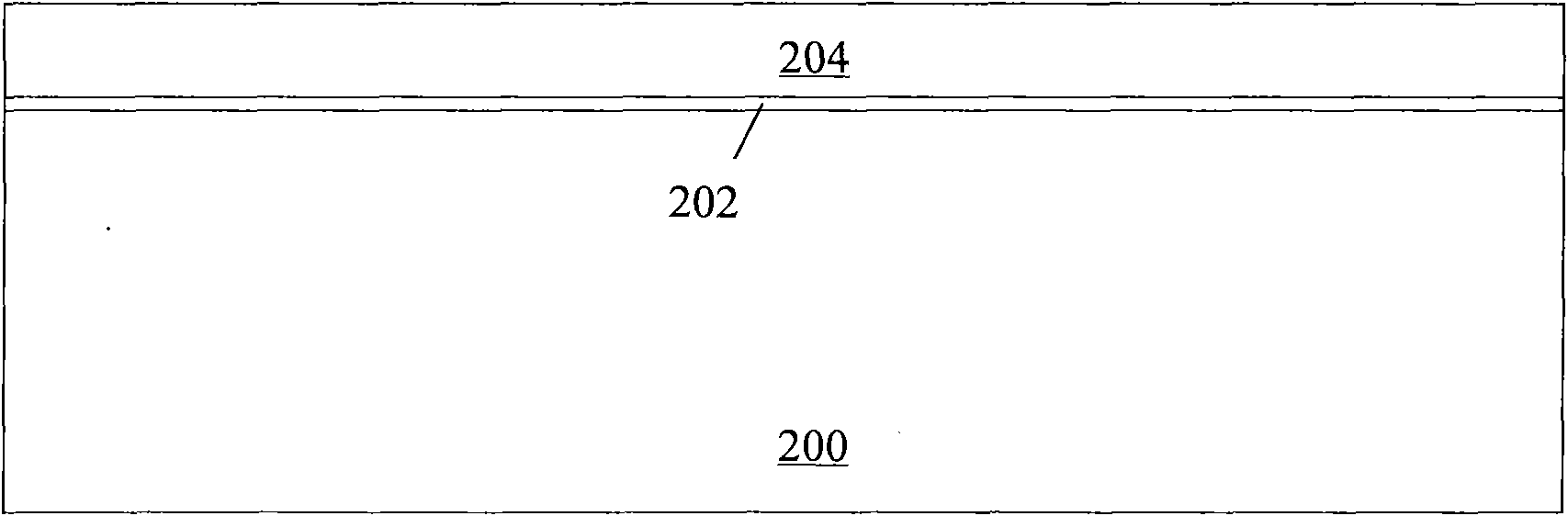

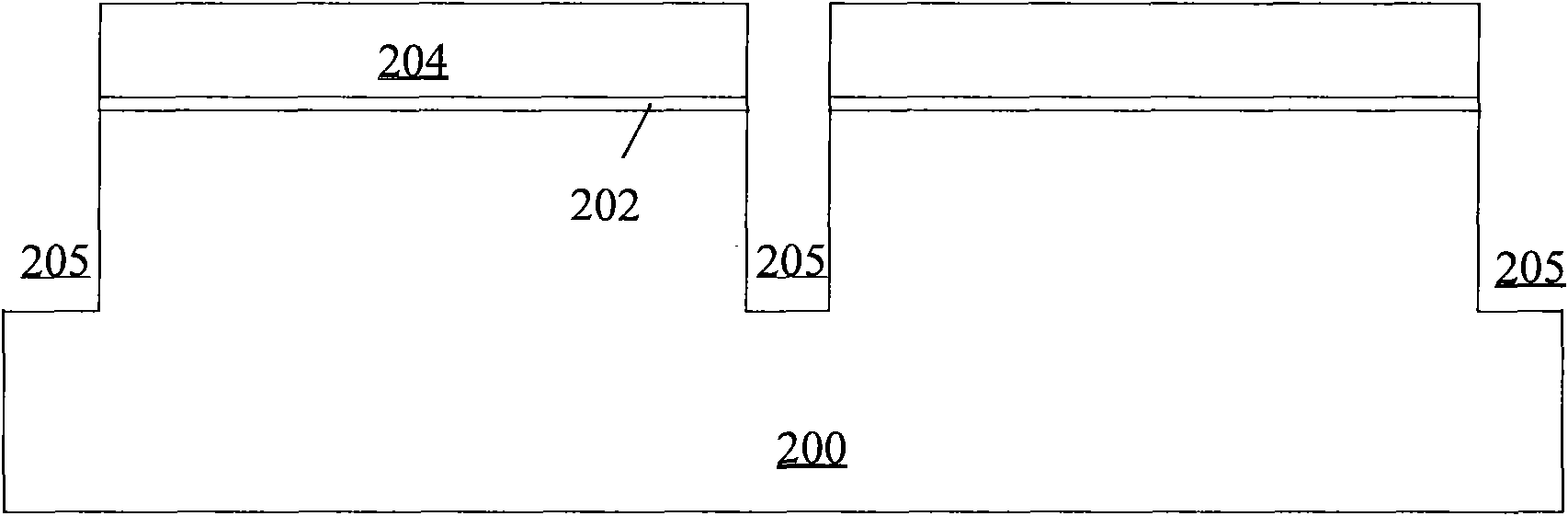

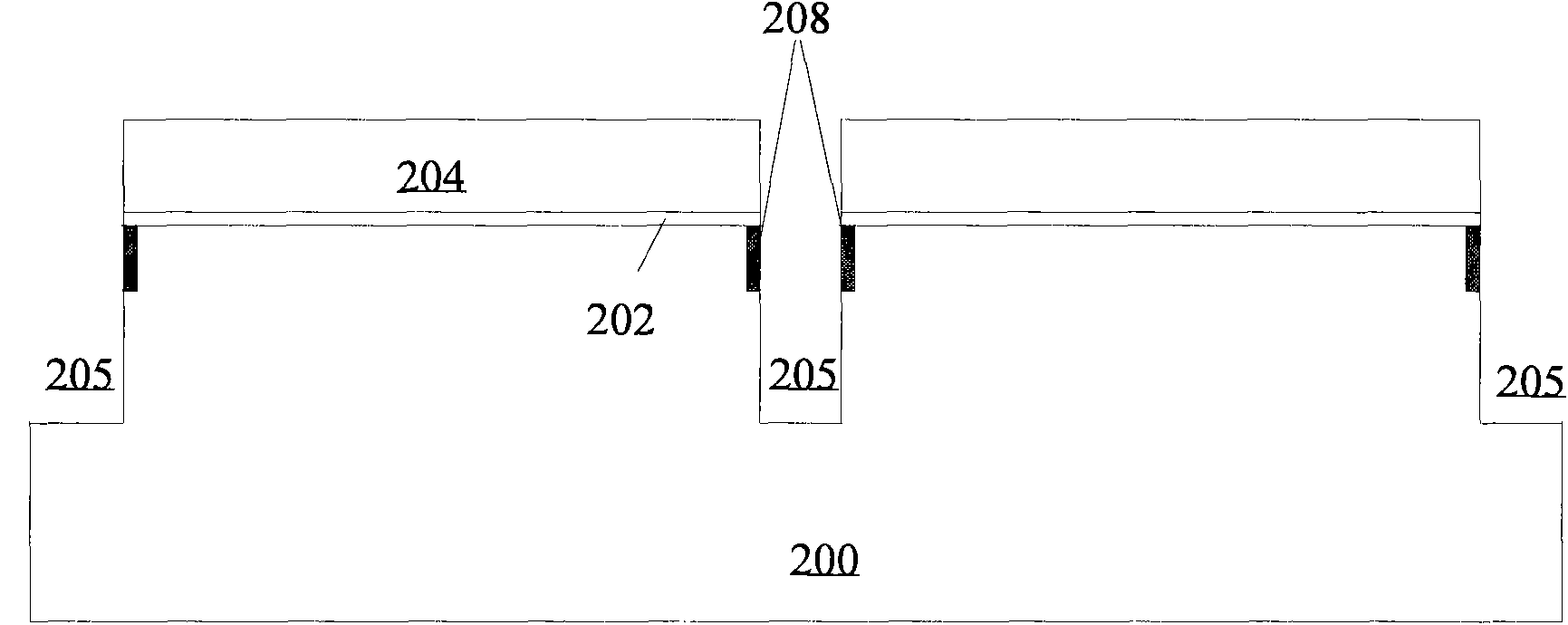

Isolation structure and manufacturing method, and semiconductor device with isolation structure

ActiveCN102468210BReduce the effect of effectivenessReduce usageTransistorSemiconductor/solid-state device manufacturingGate stackLanthanum

An isolation structure of a semiconductor device, a manufacturing method thereof and a semiconductor device including the same are provided. The isolation structure (209) comprises: a trench buried in a semiconductor substrate (200); an oxide layer (207) covering the bottom and the side walls of the trench; and isolation materials (210) positioned on the oxide layer in the trench; wherein, lanthanum enriched oxides (206) is included in the oxide layer on the upper portions of the side walls of the trench. By using the trench isolation structure, the metal lanthanum in the lanthanum enriched oxide may diffuse into the corner of the oxide layer of the gate stack (300), therefore, influence introduced by short-channel effects can be lowered, and meanwhile, threshold voltage can be adjusted.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Enhanced heterogeneous metal gate AlGaN/GaN MOS-HEMT device and preparation method thereof

ActiveCN110634946AIncrease areal densityImproved ability to limit 2DEGsSemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentCharge carrier mobility

The invention discloses an enhanced heterogeneous metal gate AlGaN / GaN MOS-HEMT device and a preparation method thereof. The enhanced heterogeneous metal gate AlGaN / GaN MOS-HEMT device comprises an AlN transition layer located on an Al2O3 substrate, a multi-layer buffer structure positioned on the AlN transition layer, an AlGaN barrier layer positioned on the multi-layer buffer structure, a GaN cap layer positioned on the AlGaN barrier layer, a source electrode and a drain electrode positioned on the first GaN layer and upwards penetrating through the AlGaN barrier layer and the GaN cap layer,a gate oxide layer positioned on the GaN cap layer, the source electrode and the drain electrode, and a heterogeneous gate structure positioned on the gate oxide layer. Thus, the channel driving current can be improved, the threshold voltage can be flexibly adjusted, and deterioration of the channel carrier mobility can be prevented.

Owner:博芯(重庆)半导体研究院有限公司

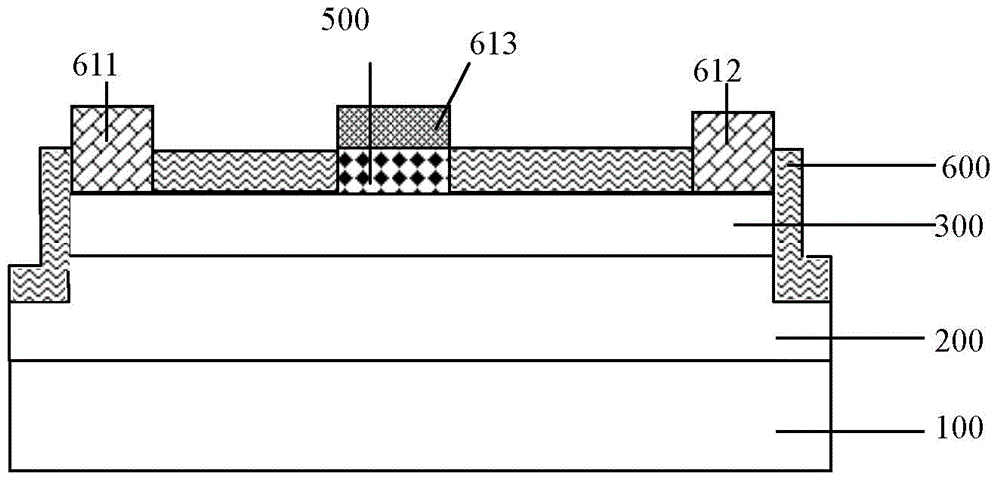

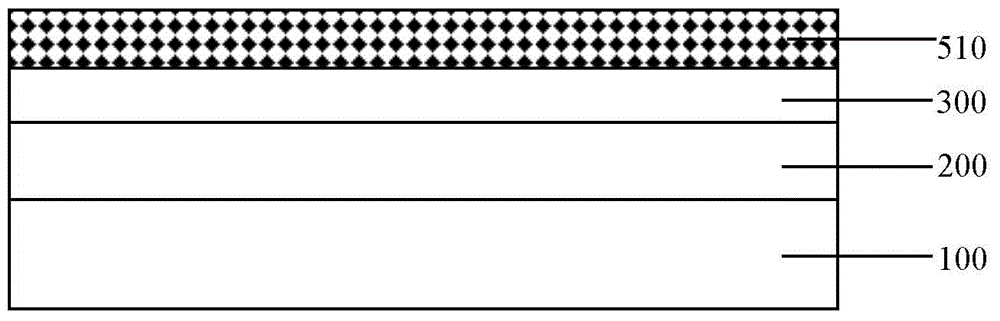

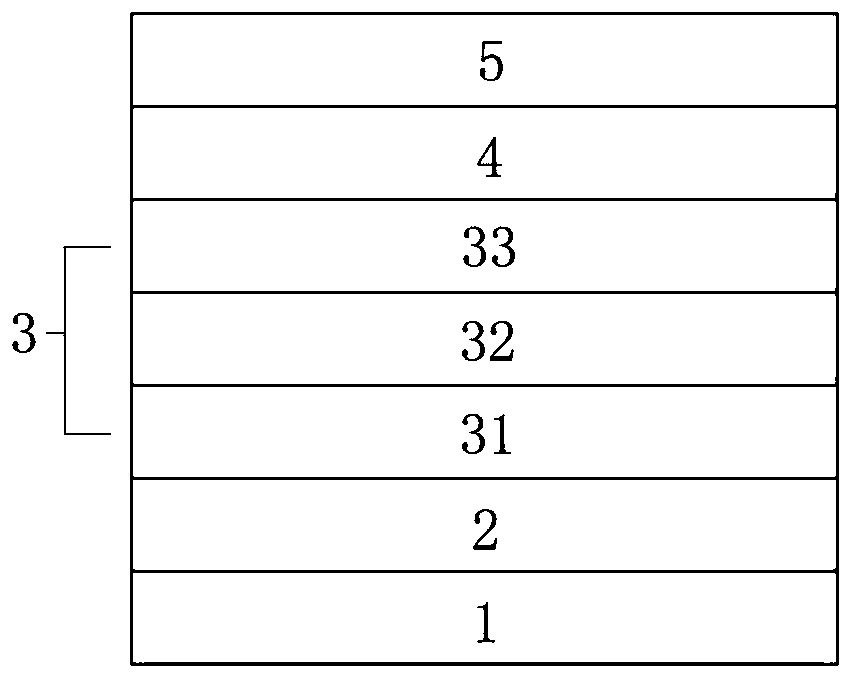

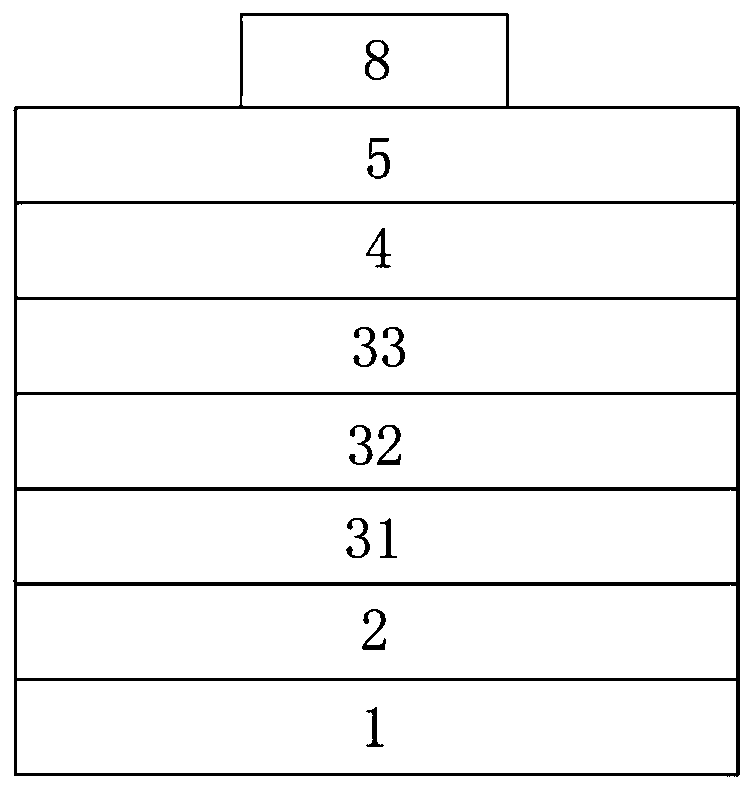

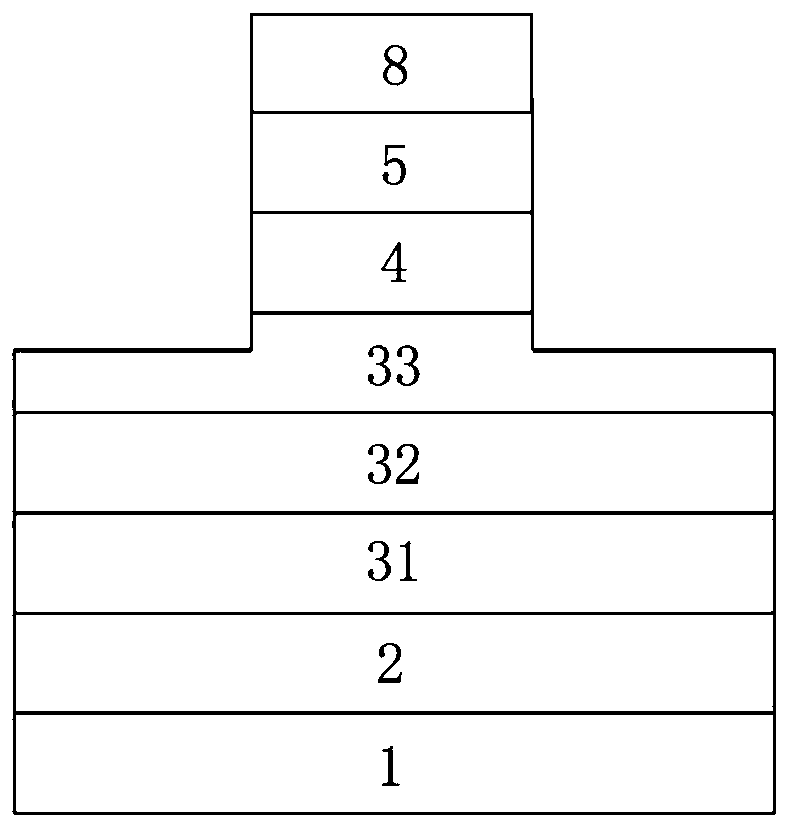

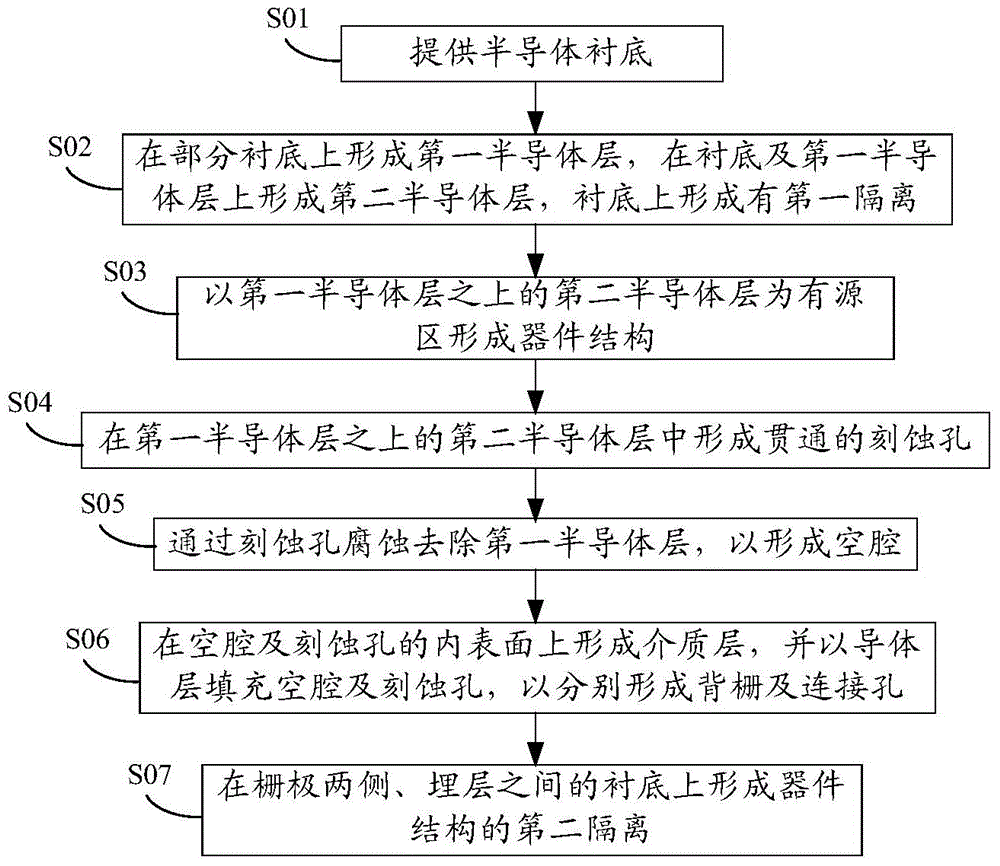

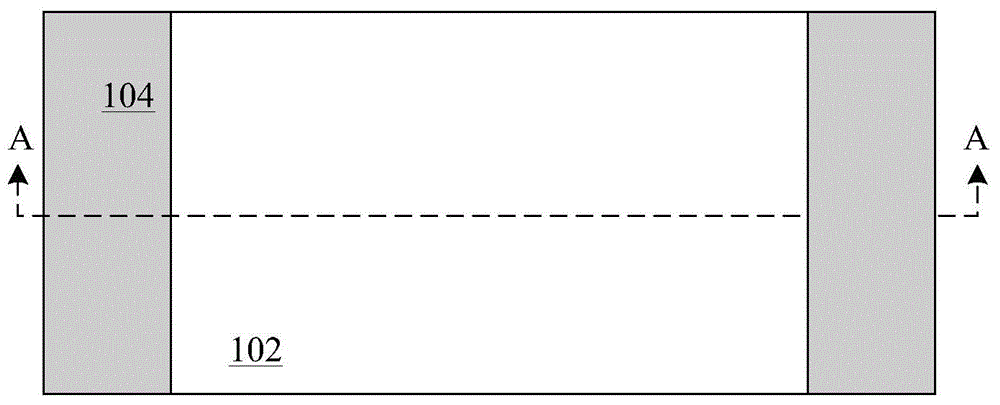

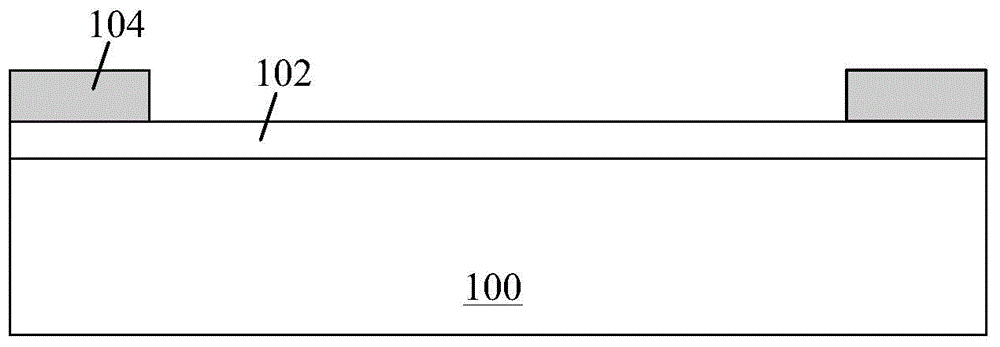

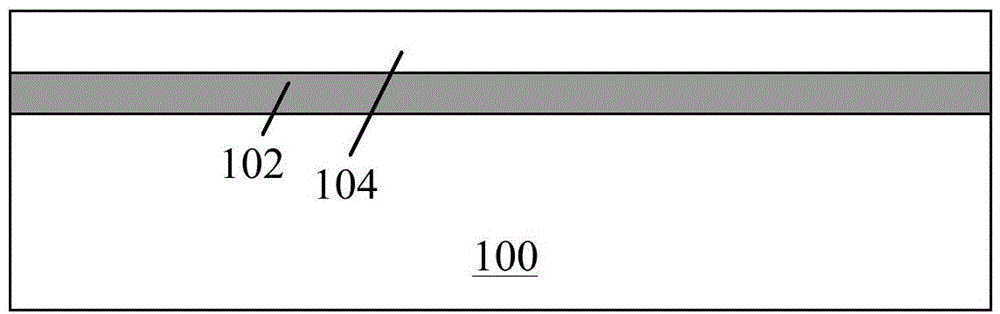

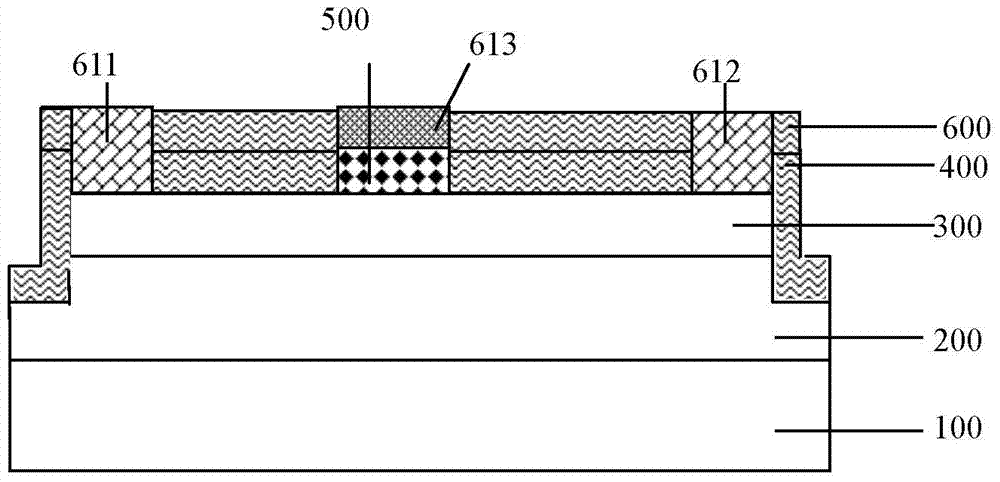

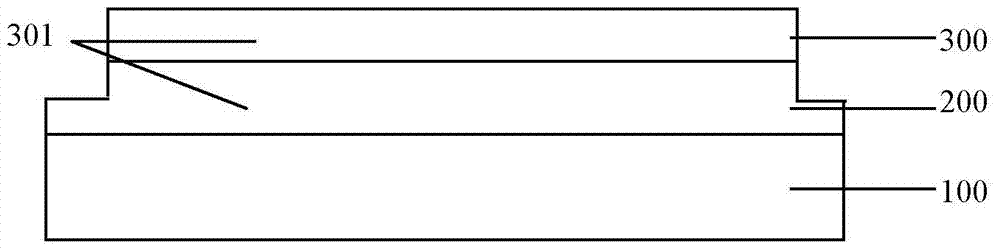

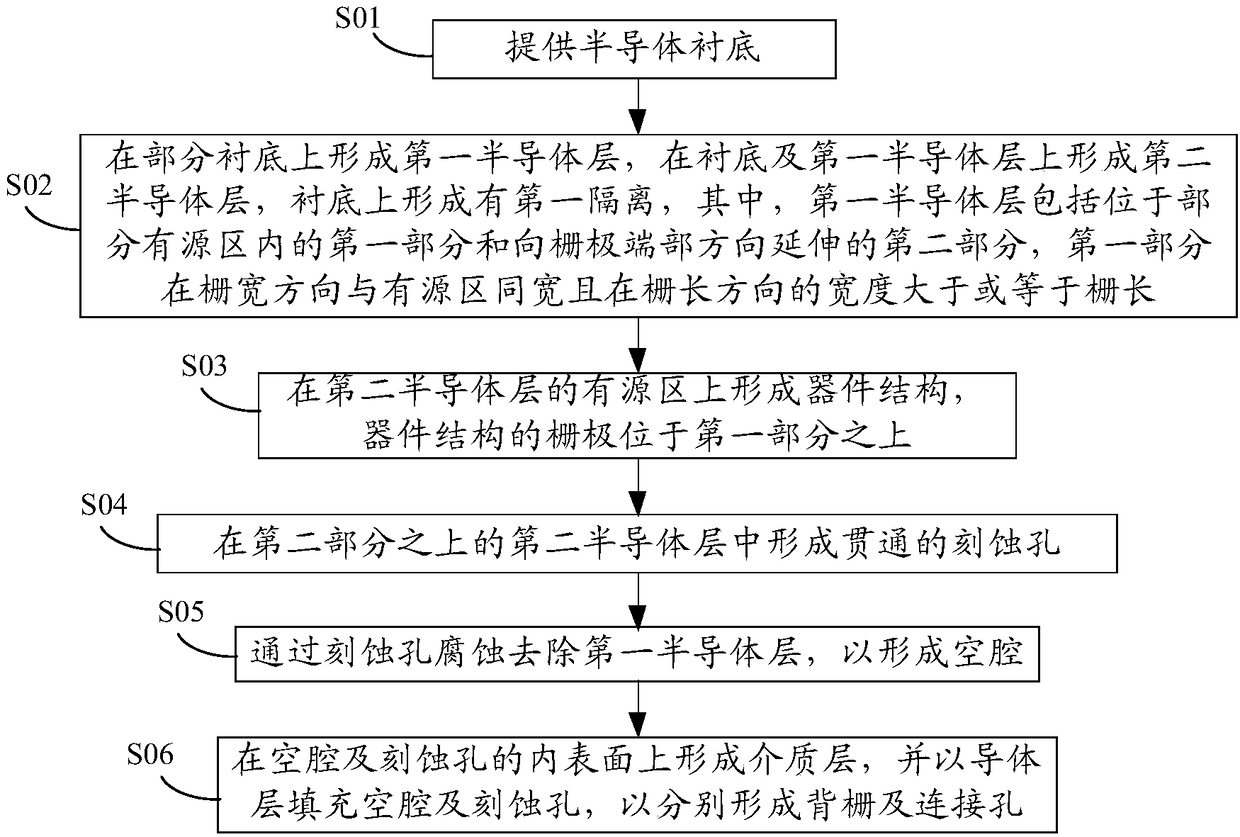

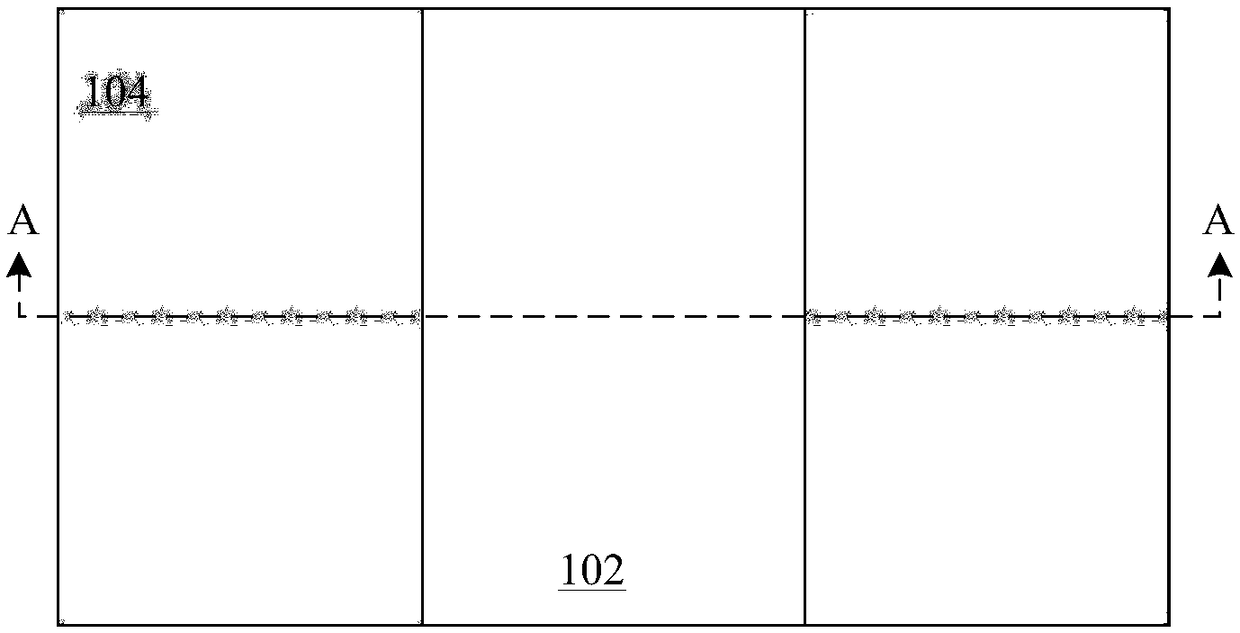

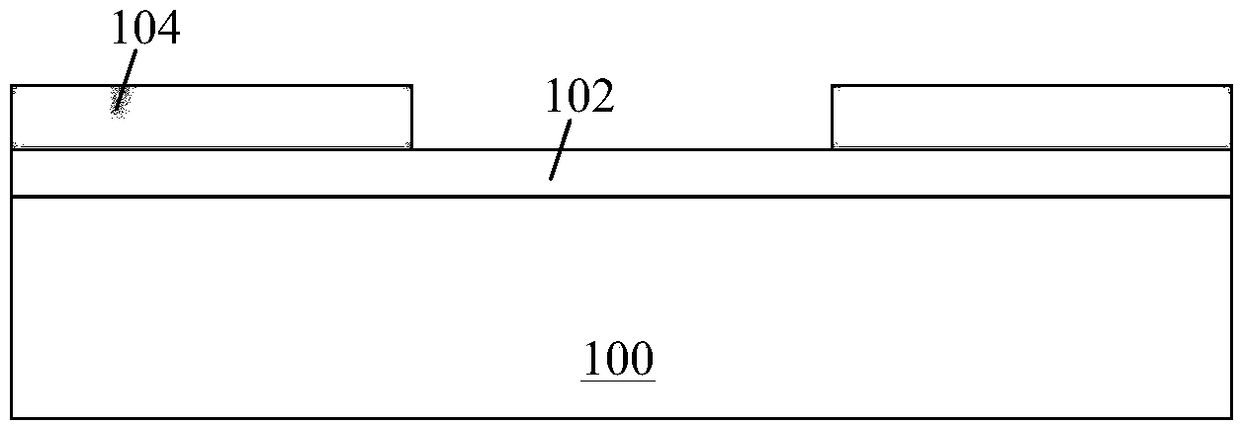

Semiconductor device and method for manufacturing same

InactiveCN105489650AThreshold Voltage AdjustmentSimple processSemiconductor devicesElectrical conductorDielectric layer

The invention discloses a method for manufacturing a semiconductor device. The method includes the following steps of: providing a semiconductor substrate; forming a first semiconductor layer on the substrate, and forming a second semiconductor layer on the substrate and the first semiconductor layer, wherein first isolations are formed on the substrate, and the second semiconductor layer on the first semiconductor layer is an active area for forming a device structure; forming through etching holes in the second semiconductor layer on the first semiconductor layer; etching and removing the first semiconductor layer through the etching holes to form a cavity; forming a dielectric layer on the inner surfaces of the cavity and the etching holes, and adding conductor layers into the cavity and the etching holes to respectively form a back gate and connection holes; and forming second isolations of the device structure on the substrate at two side of the gate and between the first isolations and the back gate. According to the method, an SOI device can be obtained through the substrate; and through the dielectric layer formed on the cavity and the etching holes and the back gate formed by adding the conductor layers, the threshold voltage of the device can be adjusted, and the process is simple and is easy to operate.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

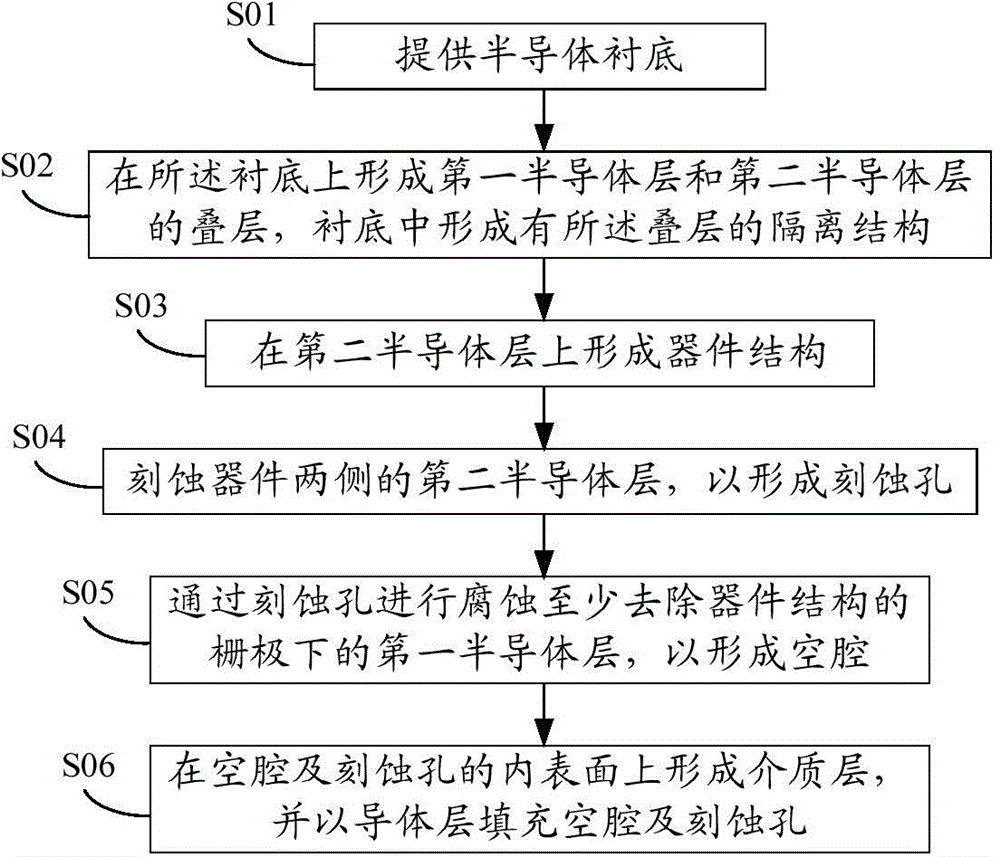

Semiconductor device and manufacturing method

ActiveCN105489546AThreshold Voltage AdjustmentSimple processSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorSemiconductor package

The invention discloses a semiconductor device and a manufacturing method. The manufacturing method comprises the steps of providing a semiconductor substrate; forming a laminated layer of a first semiconductor layer and a second semiconductor layer, and forming an isolating structure of the laminated layer in the substrate; forming a device structure on the second semiconductor layer; etching the second semiconductor layer on the two sides of the device to form etching holes; performing etching through the etching holes to remove at least the first semiconductor layer below a grid electrode of the device structure to form a cavity; and forming a dielectric layer on the inner surfaces of the cavity and the etching holes, and filling the cavity and the etching holes with a conductor layer. An SOI (silicon-on-insulator) device can be realized through the substrate; the dielectric layer is formed in the cavity and the etching hole, and the cavity and the etching hole are filled with the conductor layer to be used as back gates, so that regulation on the threshold value voltage of the device is realized; and in addition, the manufacturing process is simple and easy to implement.

Owner:北京中科微投资管理有限责任公司

A kind of gan-based enhanced hemt device and its preparation method

InactiveCN104465748BMeet the requirementsReduce design difficultySemiconductor/solid-state device manufacturingSemiconductor devicesAlloyMetal electrodes

The invention discloses a novel GaN-based enhanced HEMT device. The novel GaN-based enhanced HEMT device comprises a GaN intrinsic layer, a barrier layer, a high-hole-concentration structural layer, a first metal electrode, a second meta electrode, a third metal electrode, a passivating dielectric layer and a passivating protection layer, wherein the GaN intrinsic layer and the barrier layer sequentially grow on a substrate, the high-hole-concentration structural layer covers the partial area of the upper surface of the barrier layer, the first metal electrode and the second meta electrode are located in the partial area which is not covered by the high-hole-concentration structural layer, of the upper surface of the barrel layer, the third metal electrode covers the upper surface of the high-hole-concentration structural layer, the passivating dielectric layer covers the upper surface of the obtained substrate and forms a table top graph, and the passivating protection layer covers the upper surface of the passivating dielectric layer. The invention further discloses a manufacturing method of the novel GaN-based enhanced HEMT device. The novel GaN-based enhanced HEMT device is high in reliability and good in repeatability, adjustment of device threshold voltage can be achieved by selecting different component gradual change ranges, different nitride alloys and the dosage concentration and thickness of the different nitride alloys, and the manufactured device can meet different requirements.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

A kind of semiconductor device and its manufacturing method

ActiveCN105489492BThreshold Voltage AdjustmentSimple processSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingElectrical conductor

A structure and manufacturing method of a semiconductor device, comprising: providing a semiconductor substrate; forming a first semiconductor layer on part of the substrate, forming a second semiconductor layer on the substrate and the first semiconductor layer, and forming isolation on the substrate, wherein , the first semiconductor layer includes a first part located in part of the active region and a second part extending toward the end of the gate, the first part is as wide as the active region in the gate width direction and has a width greater than or equal to the gate length direction Long; form a device structure on the active region of the second semiconductor layer, the gate of the device structure is located above the first part; form a through etching hole in the second semiconductor layer above the second part; through the etching hole Etching and removing the first semiconductor layer to form a cavity; forming a dielectric layer on the inner surface of the cavity and the etching hole, and filling the cavity and the etching hole with the conductor layer. The invention can form the back gate structure by filling the dielectric layer and the conductor layer in the cavity and the etching hole, realize the adjustment of the threshold voltage of the device, and the process is simple and easy.

Owner:北京中科微投资管理有限责任公司

Polycrystal SiGe gate nano CMOS integrated circuit preparation based on SiO2 masking technique

InactiveCN101359629BThreshold Voltage AdjustmentAchieve regulationSemiconductor/solid-state device manufacturingMOSFETMicron scale

The invention discloses a method based on SiO2 masking technique for fabricating a nano-scale CMOS integrated circuit which has a polycrystal SiGe grid. The process includes the following steps: fabricating an N / P well and growing a Poly- SiGe / SiO2 / Poly-Si multi-layer structure on the N / P well; etching the top layer of Poly-Si into a window and then depositing a layer of SiO2; etching the SiO2 layer on the surface, except the SiO2 at the side face of the window; based on the etching ratio of Poly-Si to SiO2 (50:1), etching the Poly-Si at the upper layer; based on the etching ratio of Poly-SiGeto SiO2 (50:1), etching the SiO2 and the Poly-SiGe, except the SiO2 and Poly-SiGe in the protective area at the side wall of the SiO2, preserving the SiO2 and Poly-SiGe below the side wall, forming an / p MOSFET grid and depositing a layer of SiO2; injecting ions, self-aligning, and forming the source area and the drain area of the n / p MOSFET grid so as to form an n / p MOSFET device; and photoetching interconnection lines of the device so as to form a CMOS integrated circuit with a conducting channel at 65-90nm. The method can fabricate a CMOS integrated circuit which is improved in performanceby 3-5 generations on a micron-scale Si integrated circuit processing platform without adding any funds and equipment investment.

Owner:XIDIAN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com