Semiconductor integrated circuit with HKMG

A technology of integrated circuits and semiconductors, applied in the field of semiconductor integrated circuits, to achieve the effects of eliminating metal gate boundary effects, improving electrical performance and low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

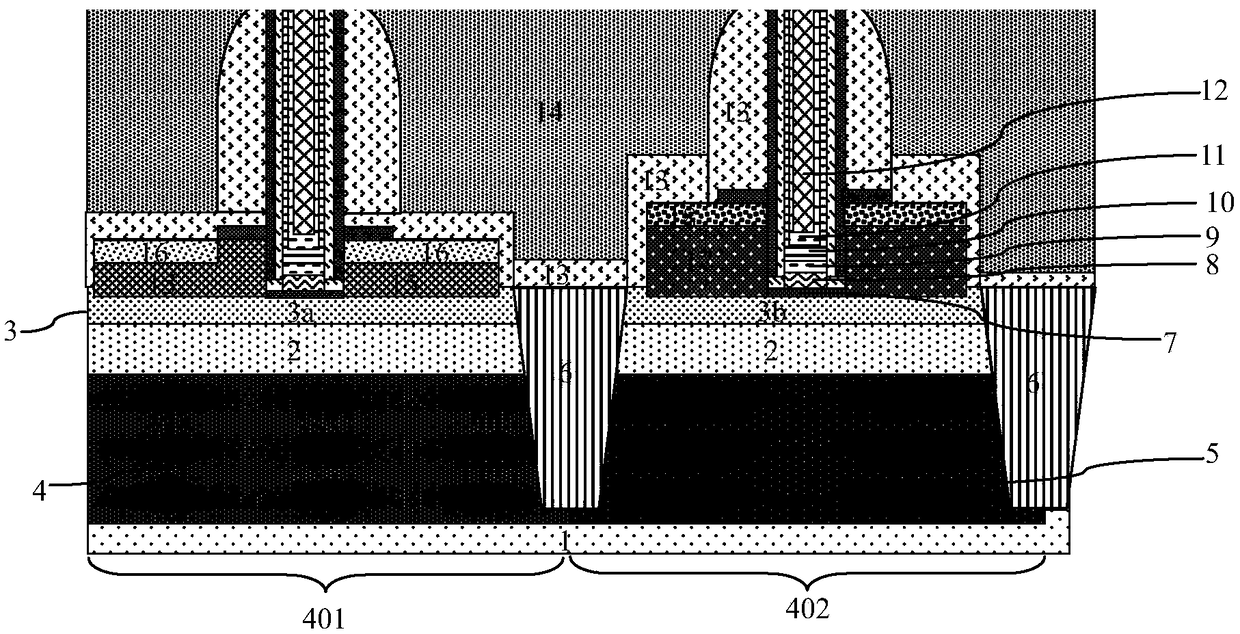

[0051] Such as image 3 Shown is the structural diagram of the semiconductor integrated circuit with HKMG in the embodiment of the present invention; the semiconductor integrated circuit with HKMG in the embodiment of the present invention includes:

[0052] FDSOI substrate structure, the FDSOI substrate comprises a bottom semiconductor layer 1, a buried oxide layer 2 and a top semiconductor layer 3, the buried oxide layer 2 is formed on the surface of the bottom semiconductor layer 1, and the top semiconductor layer 3 is formed on The surface of the buried oxide layer 2 . In the embodiment of the present invention, the bottom semiconductor layer 1 is a bottom silicon layer, the material of the buried oxide layer 2 is silicon oxide, and the top semiconductor layer 3 is a top silicon layer.

[0053] For the FDSOI process, it has the following typical characteristics: the wafer used, that is, the bottom semiconductor layer 1, has a layer of buried oxide (buried oxide, BOX), whi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com