A threshold voltage adjustment method

A technology of threshold voltage and adjustment method, which is applied in the manufacture of circuits, electrical components, semiconductors/solid-state devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

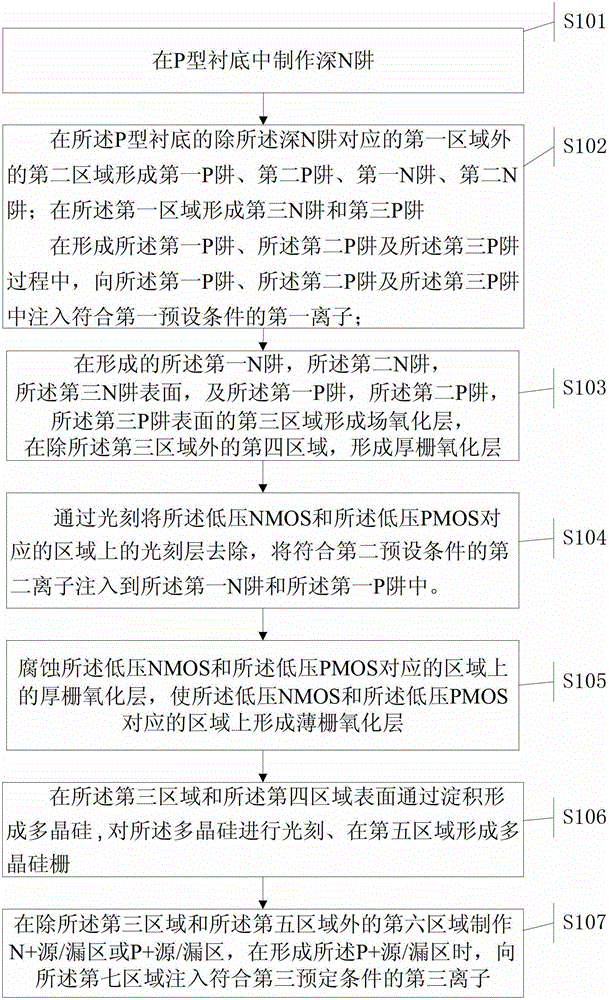

[0056] The embodiment of the application provides a threshold voltage adjustment method, which solves the need to add at least one photolithography layer in the deep N-well high-voltage CMOS integrated circuit manufacturing process to combine the four high-voltage NMOS, high-voltage PMOS, low-voltage NMOS, and low-voltage PMOS. The technical problem of adjusting the threshold voltage of the region to a predetermined range.

[0057] The technical solution of the embodiment of the present application is to solve the above-mentioned technical problem of adding at least one photolithography layer, and the general idea is as follows:

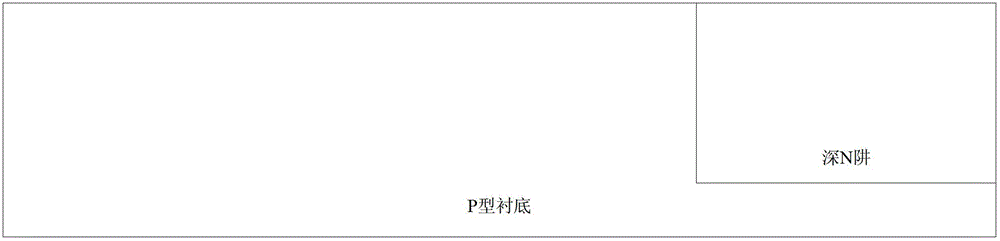

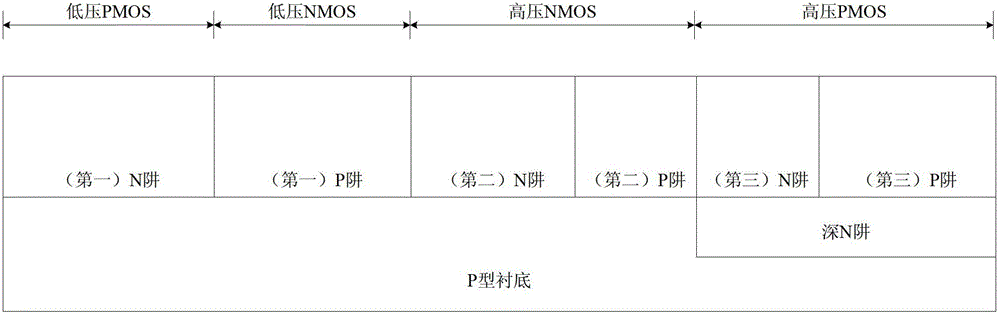

[0058] In the process of forming the first P-well, the second P-well, and the third P-well of the deep N-well high-voltage CMOS integrated circuit, implanting into the first P-well, the second P-well and the third P-well First ions that meet the first preset condition, the first ions are implanted twice to adjust the source-drain breakdown voltage and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com