Semiconductor device and preparation method thereof

A manufacturing method and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of random fluctuation of dopants, reduce device ion mobility, small device size, etc., and achieve good threshold voltage characteristics Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0047] An embodiment of the present invention provides a method for manufacturing a semiconductor device. The method realizes adjustment of the threshold voltage of the transistor by forming a silicon germanium layer in the channel region of the transistor, and can better realize a semiconductor device with multiple threshold voltages. Since the silicon germanium layer in the channel region can not only improve the carrier mobility, but also adjust the work function, the manufactured semiconductor device has better performance.

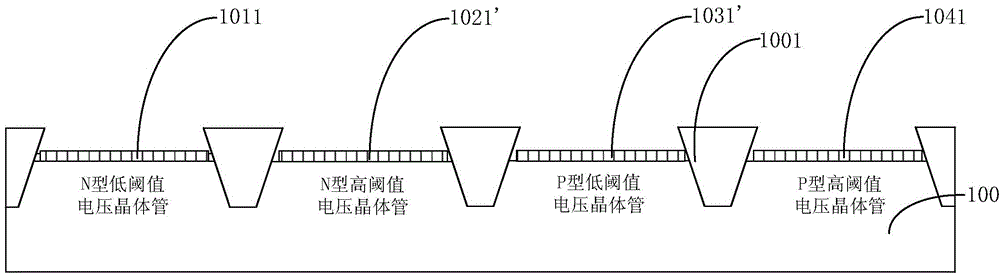

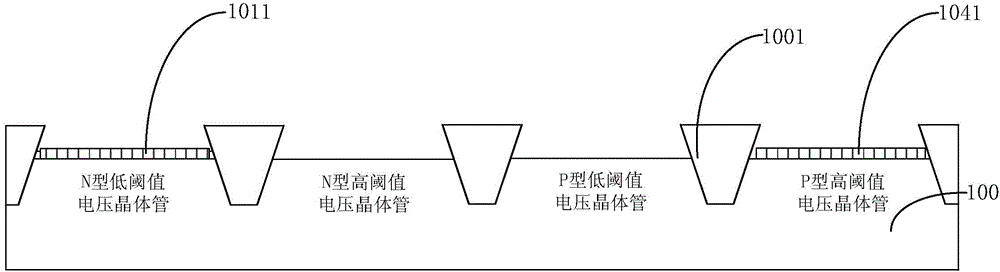

[0048] Below, refer to Figure 1A to Figure 1H as well as figure 2 A method for manufacturing a semiconductor device proposed in Embodiment 1 of the present invention will be described. in, Figure 1A to Figure 1H A schematic cross-sectional view of a structure formed in the relevant steps of a method for manufacturing a semiconductor device according to an embodiment of the present invention; figure 2 It is a typical flowchart of a manufacturing m...

Embodiment 2

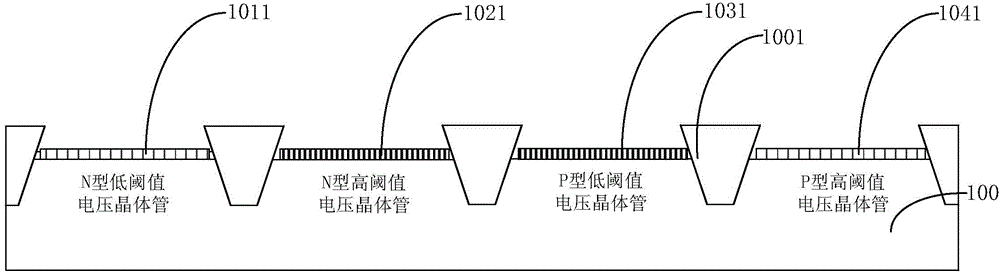

[0091] An embodiment of the present invention provides a semiconductor device, which can be manufactured by using the method for manufacturing the semiconductor device in the first embodiment above.

[0092] In the semiconductor device of this embodiment, the channel region of the transistor included has a silicon germanium layer, so the threshold voltage of the transistor can be effectively adjusted, so that the semiconductor device has different threshold voltages, that is, has good threshold voltage characteristics.

[0093] Below, refer to image 3 The structure of a semiconductor device proposed in Embodiment 2 of the present invention will be described. in, image 3 It is a schematic cross-sectional view of the structure of a semiconductor device according to an embodiment of the present invention.

[0094] Such as image 3 As shown, the semiconductor device of this embodiment includes: a semiconductor substrate 100 and an N-type low-threshold voltage transistor, an N...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com