Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1613 results about "Fin field effect transistor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A fin field-effect transistor ( FinFET) is a multigate device, a MOSFET (metal-oxide-semiconductor field-effect transistor) built on a substrate where the gate is placed on two, three, or four sides of the channel or wrapped around the channel, forming a double gate structure. These devices have been given...

Fin field-effect transistors

InactiveUS7667271B2TransistorSemiconductor/solid-state device detailsEngineeringField-effect transistor

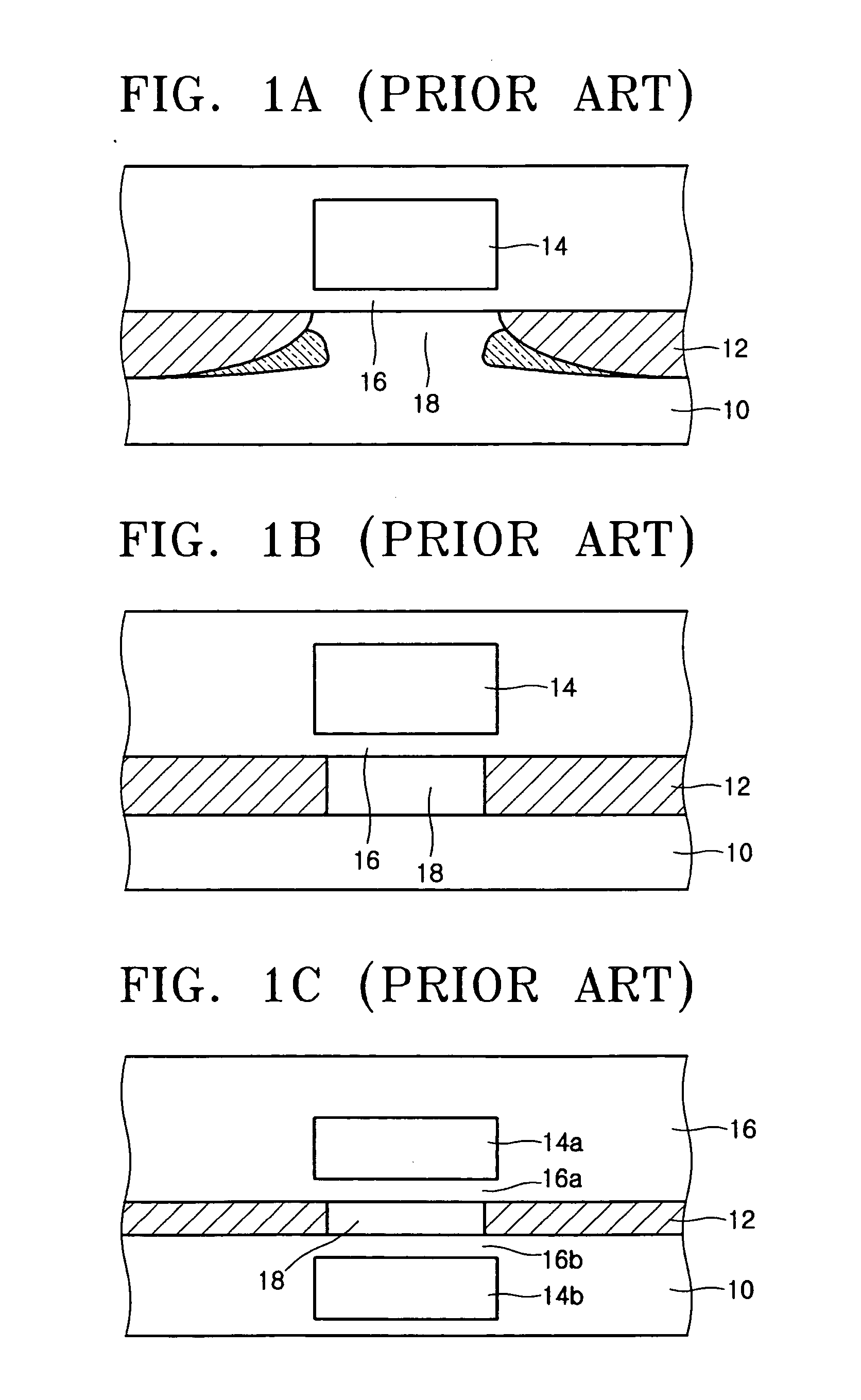

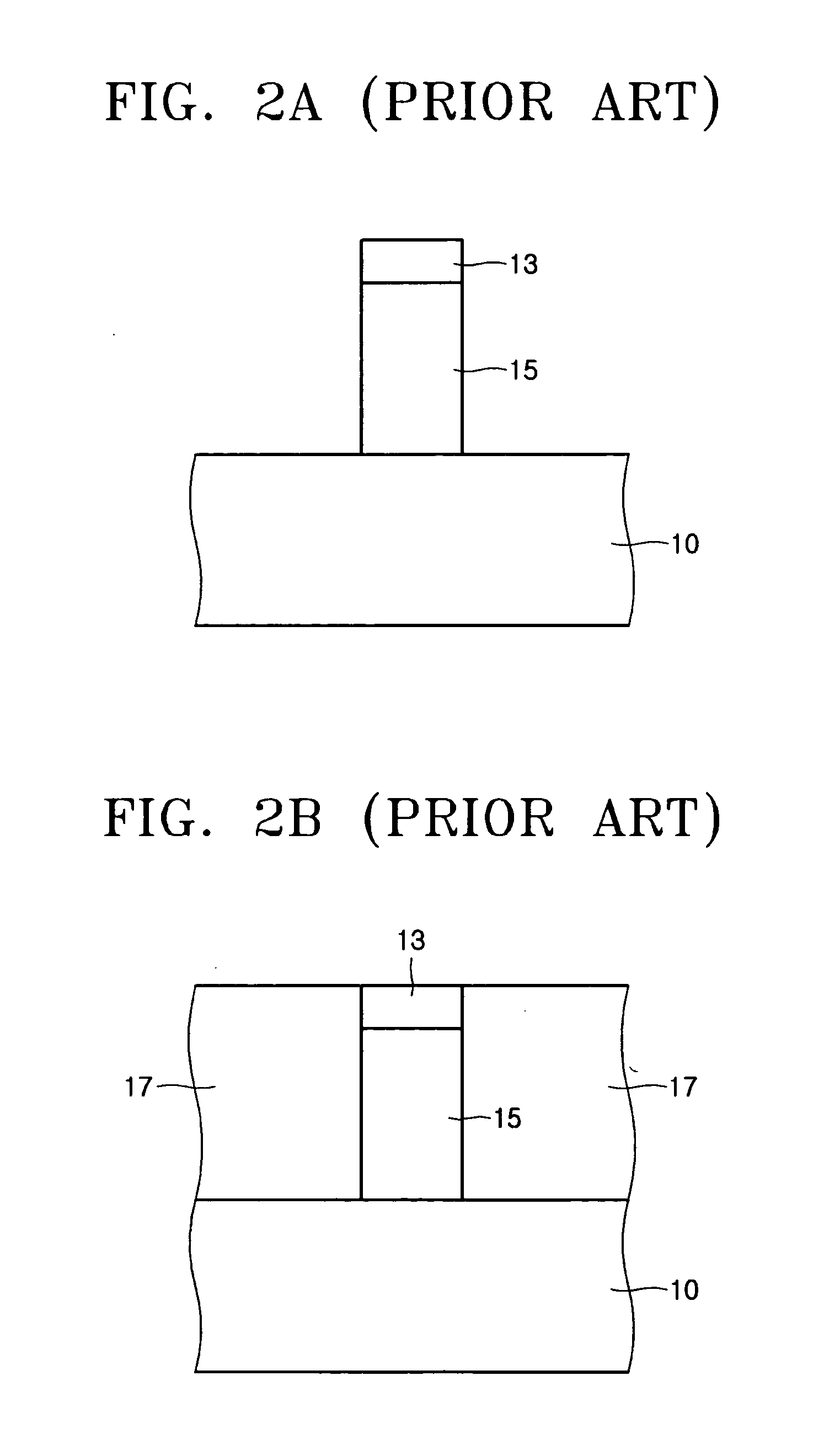

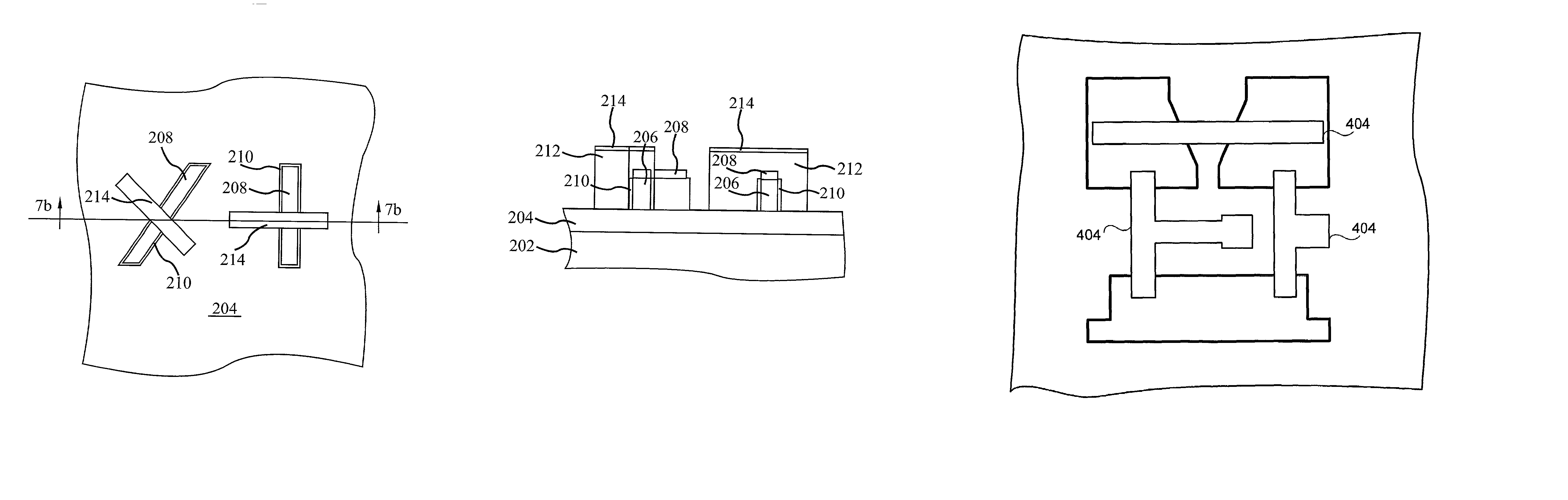

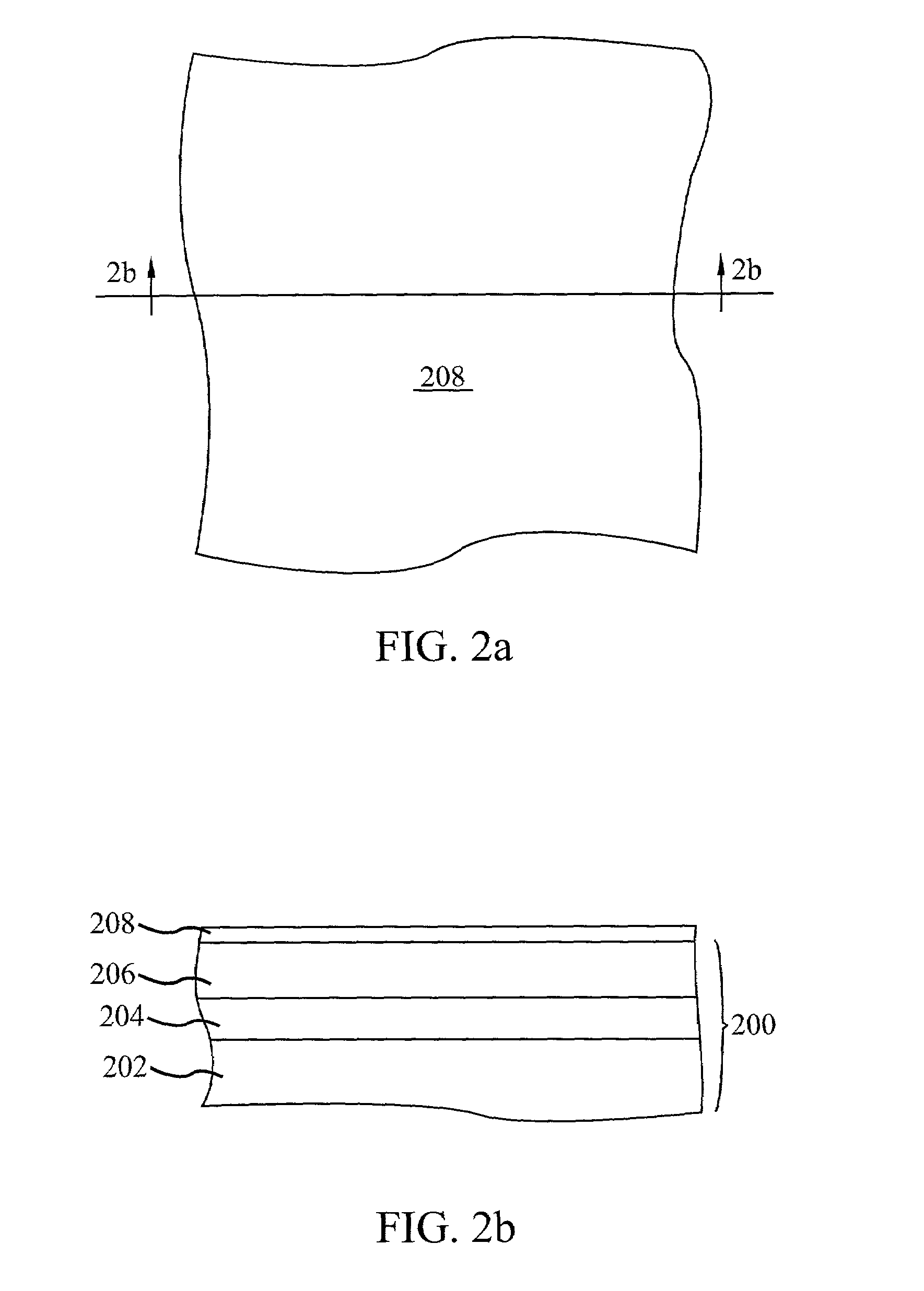

A fin field-effect transistor (finFET) with improved source / drain regions is provided. In an embodiment, the source / drain regions of the fin are removed while spacers adjacent to the fin remain. An angled implant is used to implant the source / drain regions near a gate electrode, thereby allowing for a more uniform lightly doped drain. The fin may be re-formed by either epitaxial growth or a metallization process. In another embodiment, the spacers adjacent the fin in the source / drain regions are removed and the fin is silicided along the sides and the top of the fin. In yet another embodiment, the fin and the spacers are removed in the source / drain regions. The fins are then re-formed via an epitaxial growth process or a metallization process. Combinations of these embodiments may also be used.

Owner:TAIWAN SEMICON MFG CO LTD

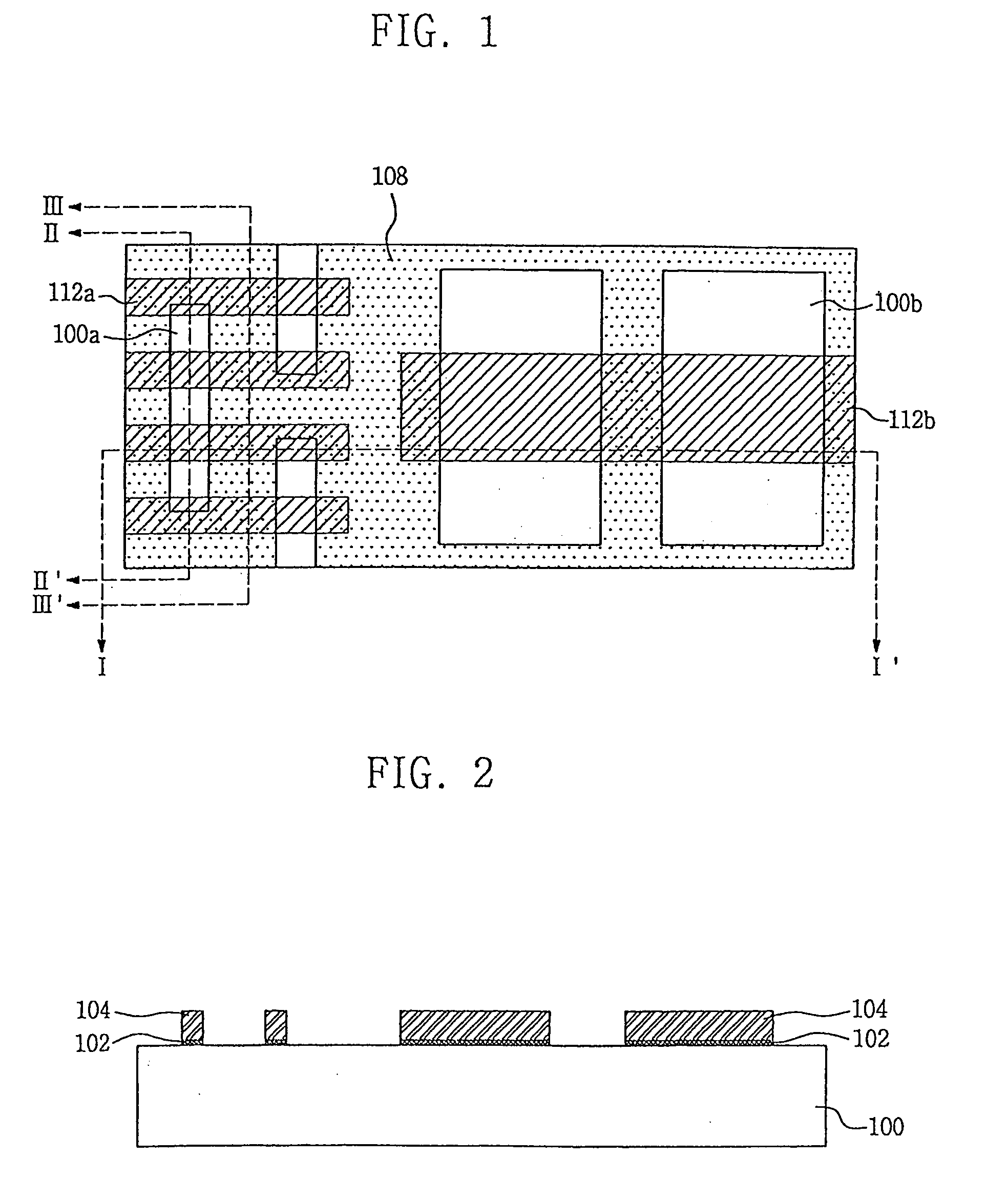

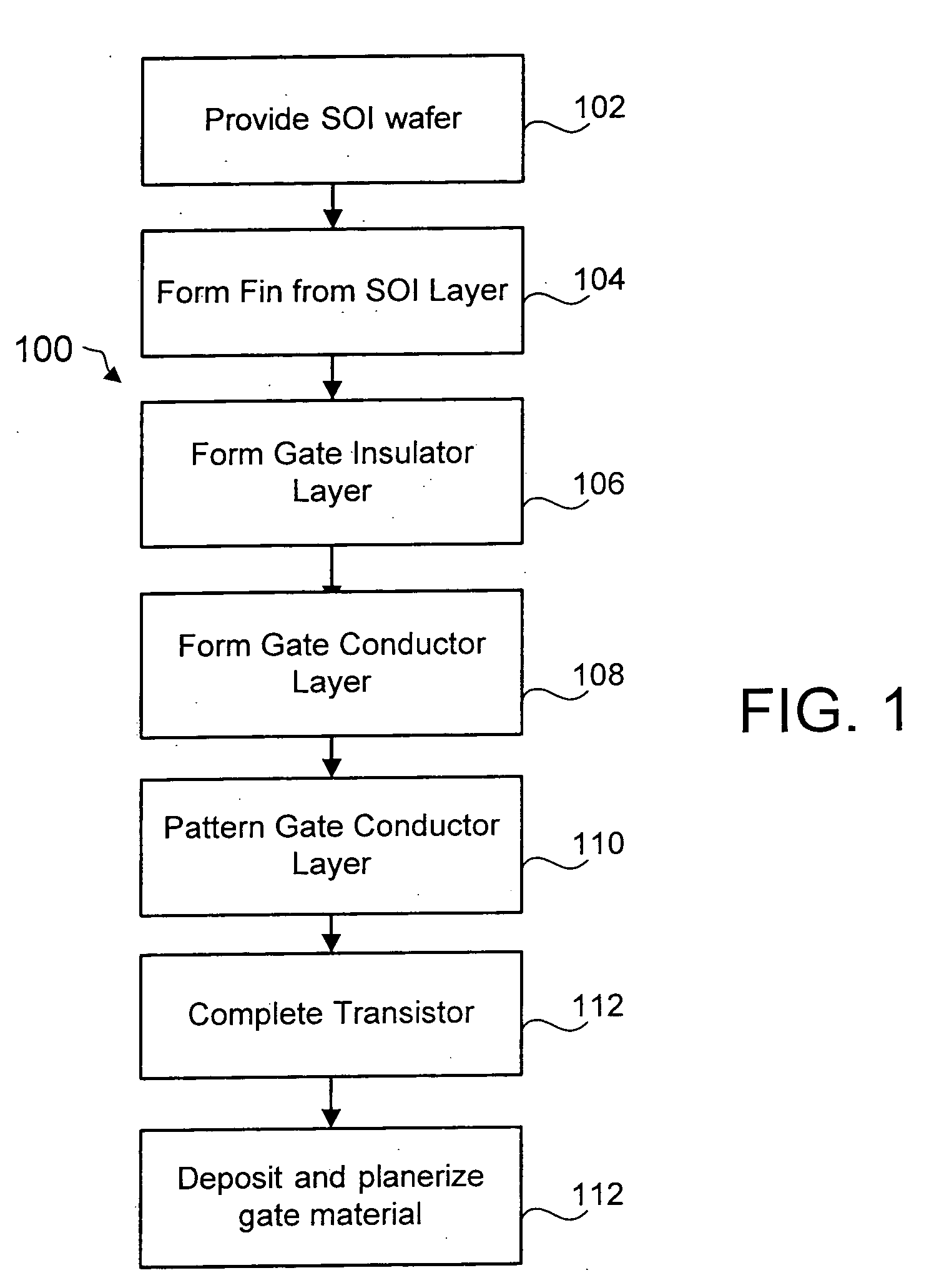

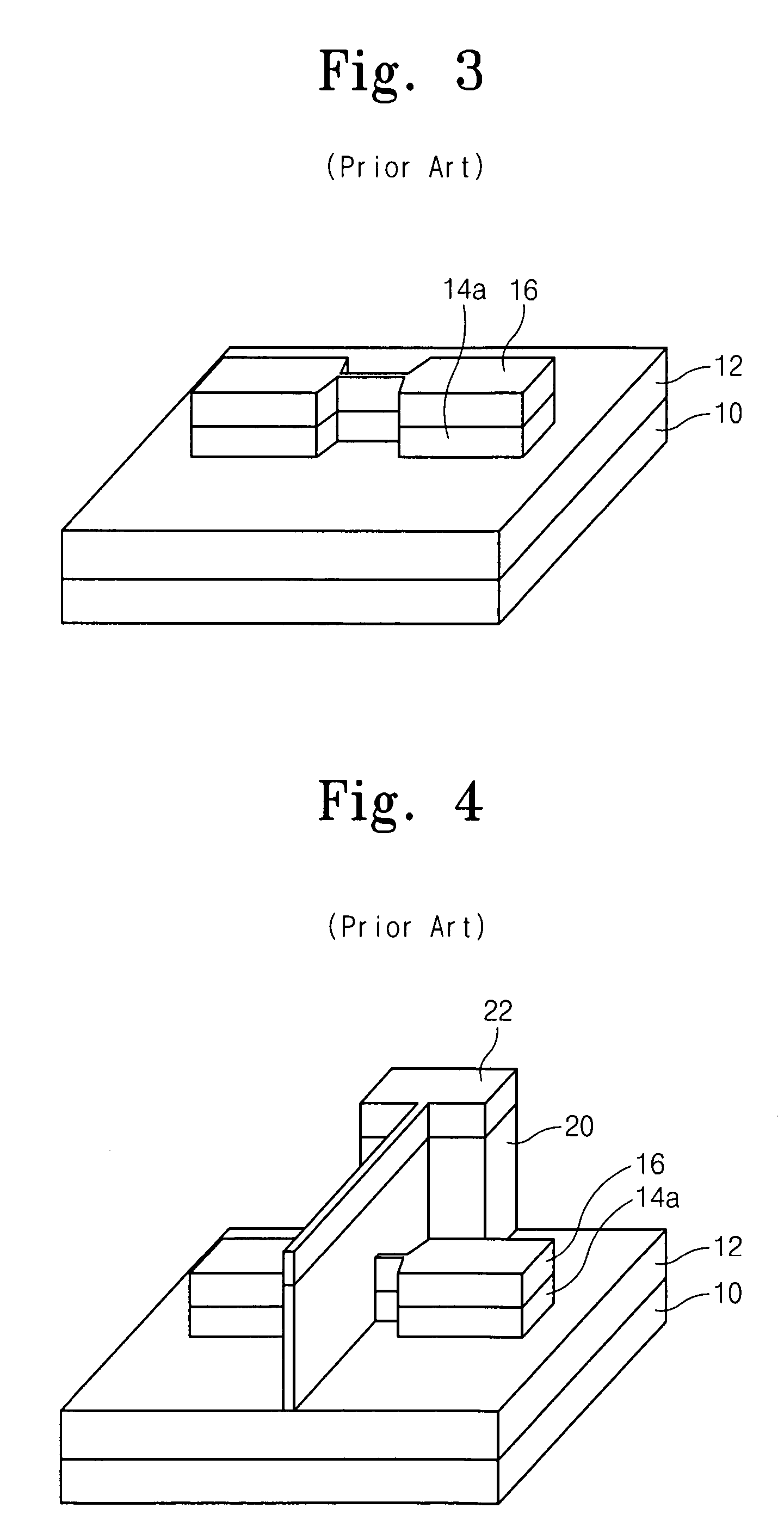

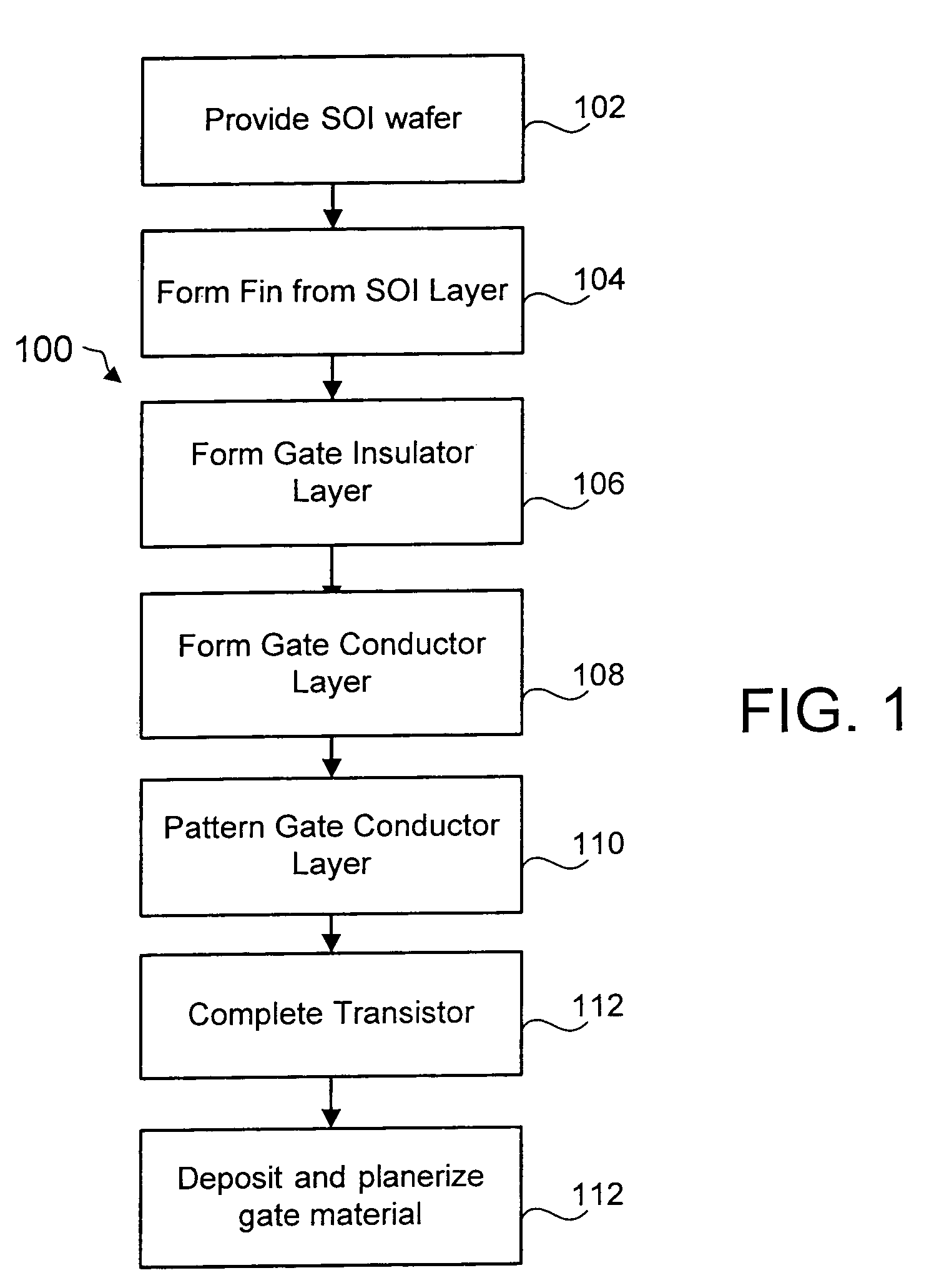

Method of forming fin field effect transistor

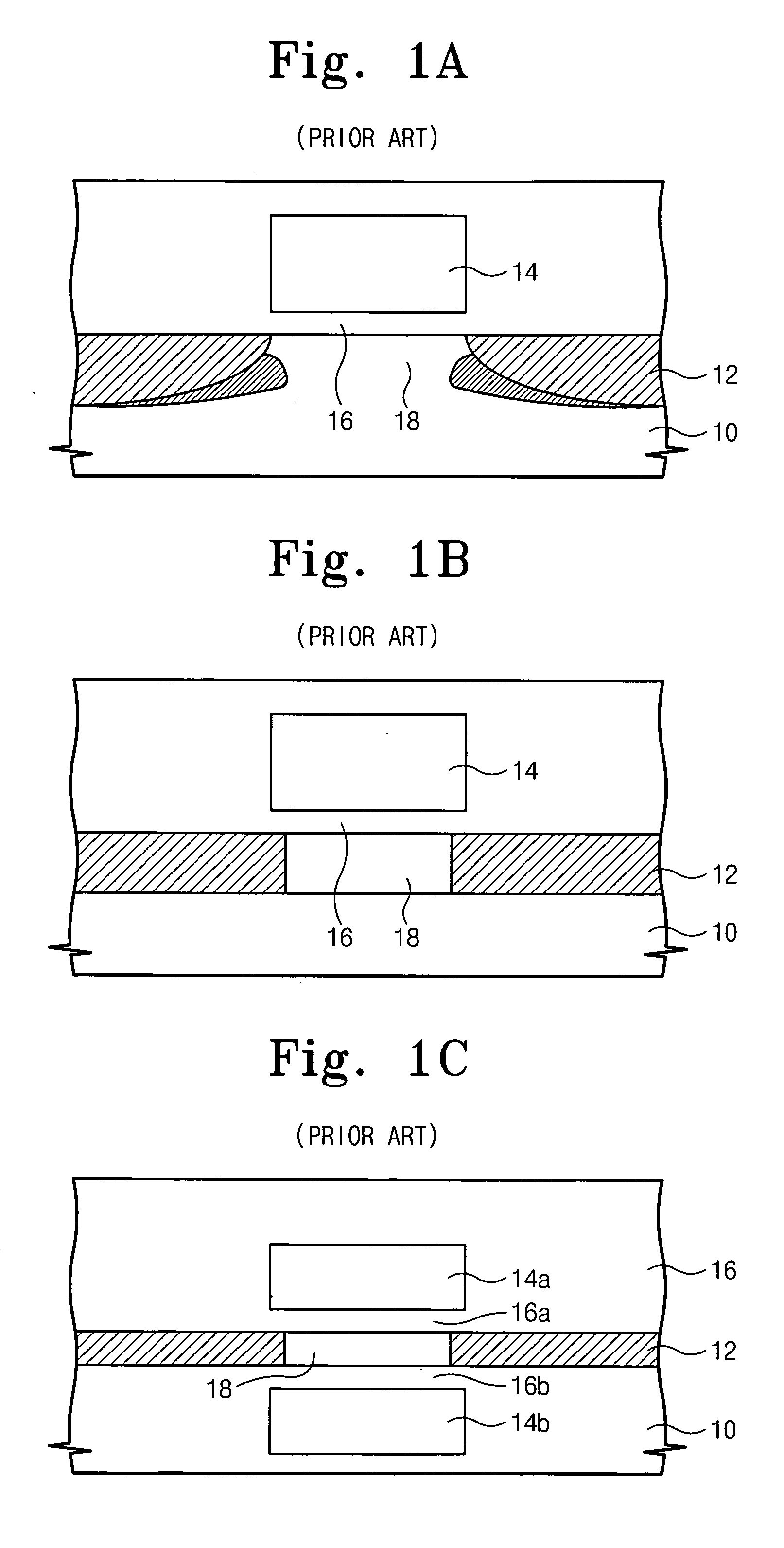

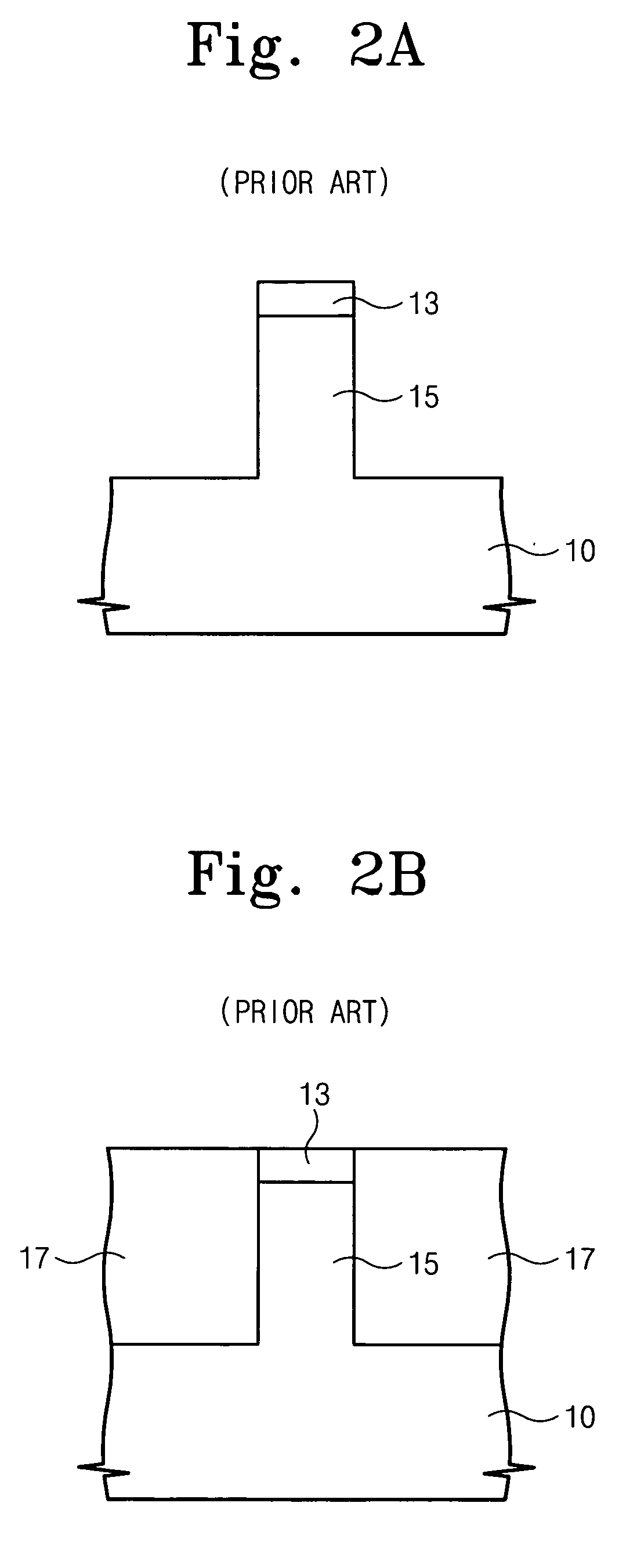

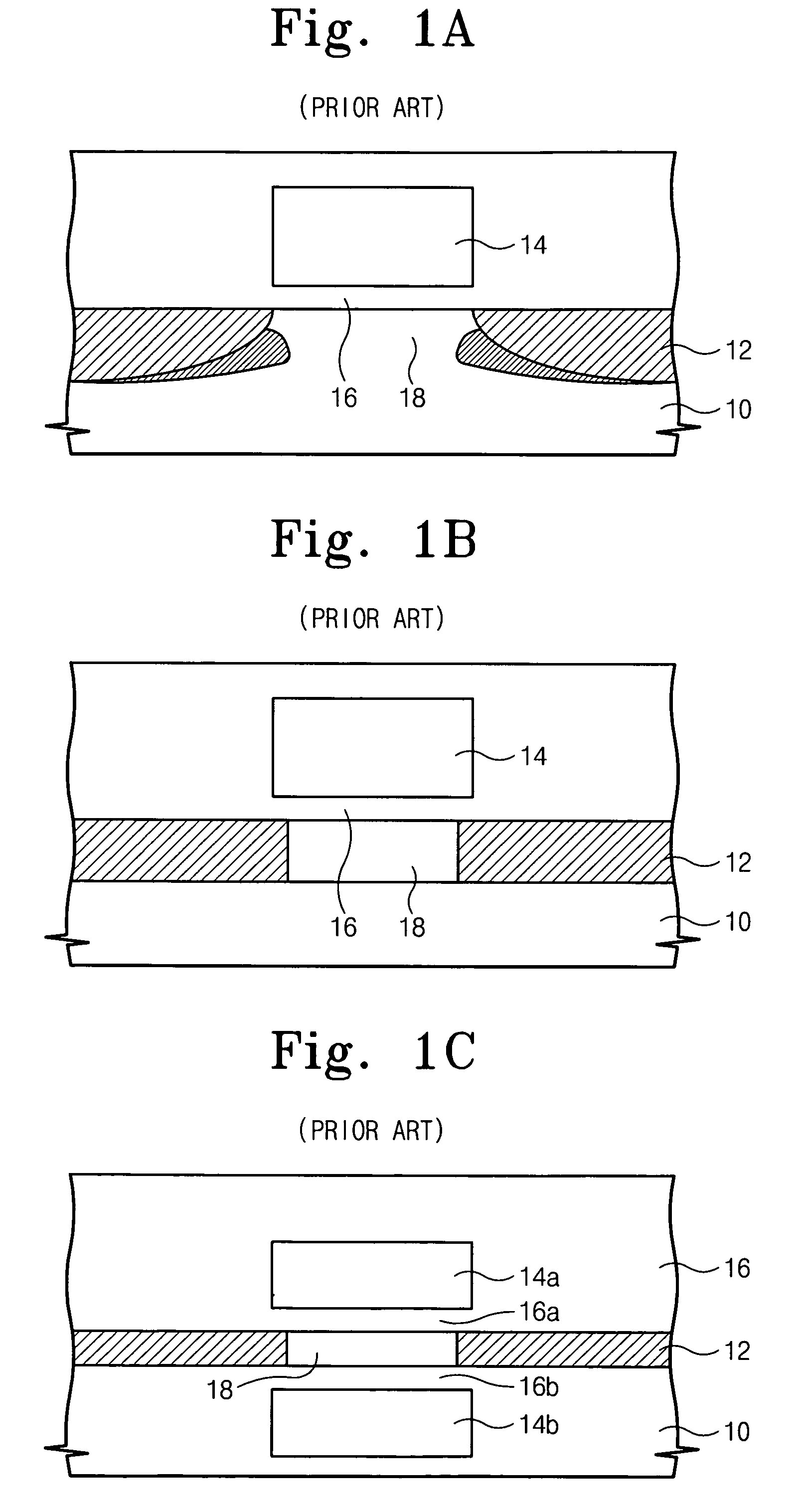

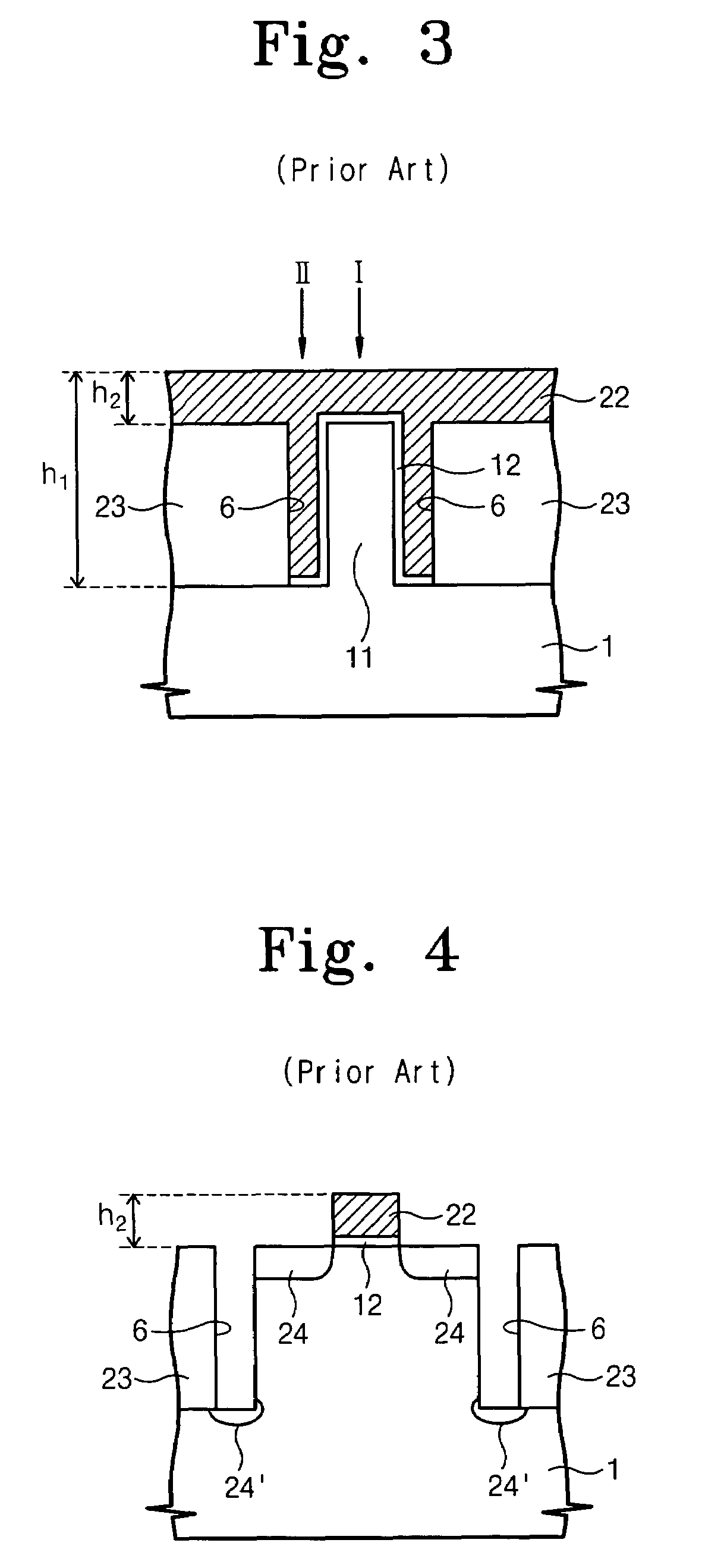

ActiveUS20050153490A1Prevent and substantially reduce leakage currentElectrode can be separatedTransistorSolid-state devicesInsulation layerDrain current

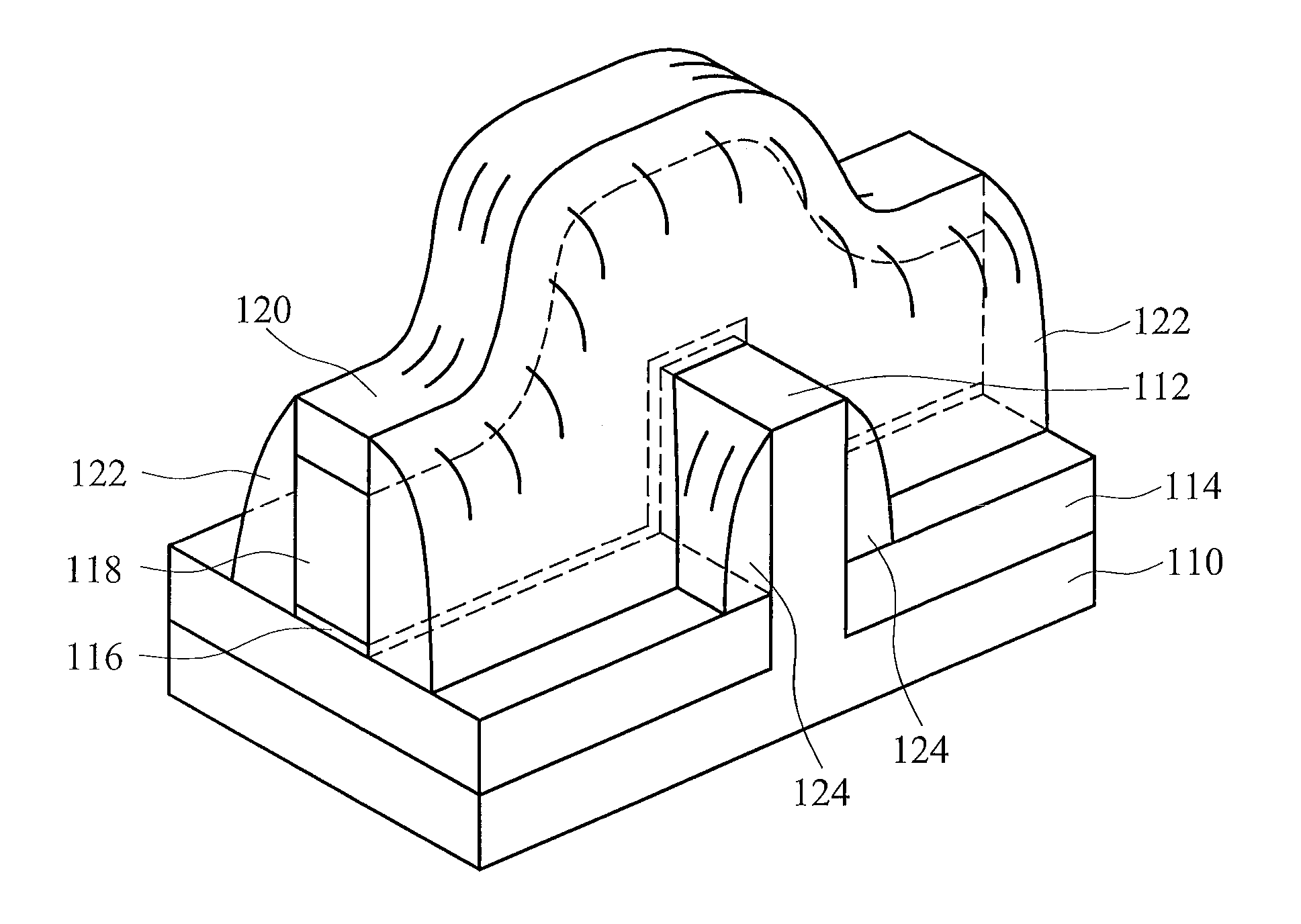

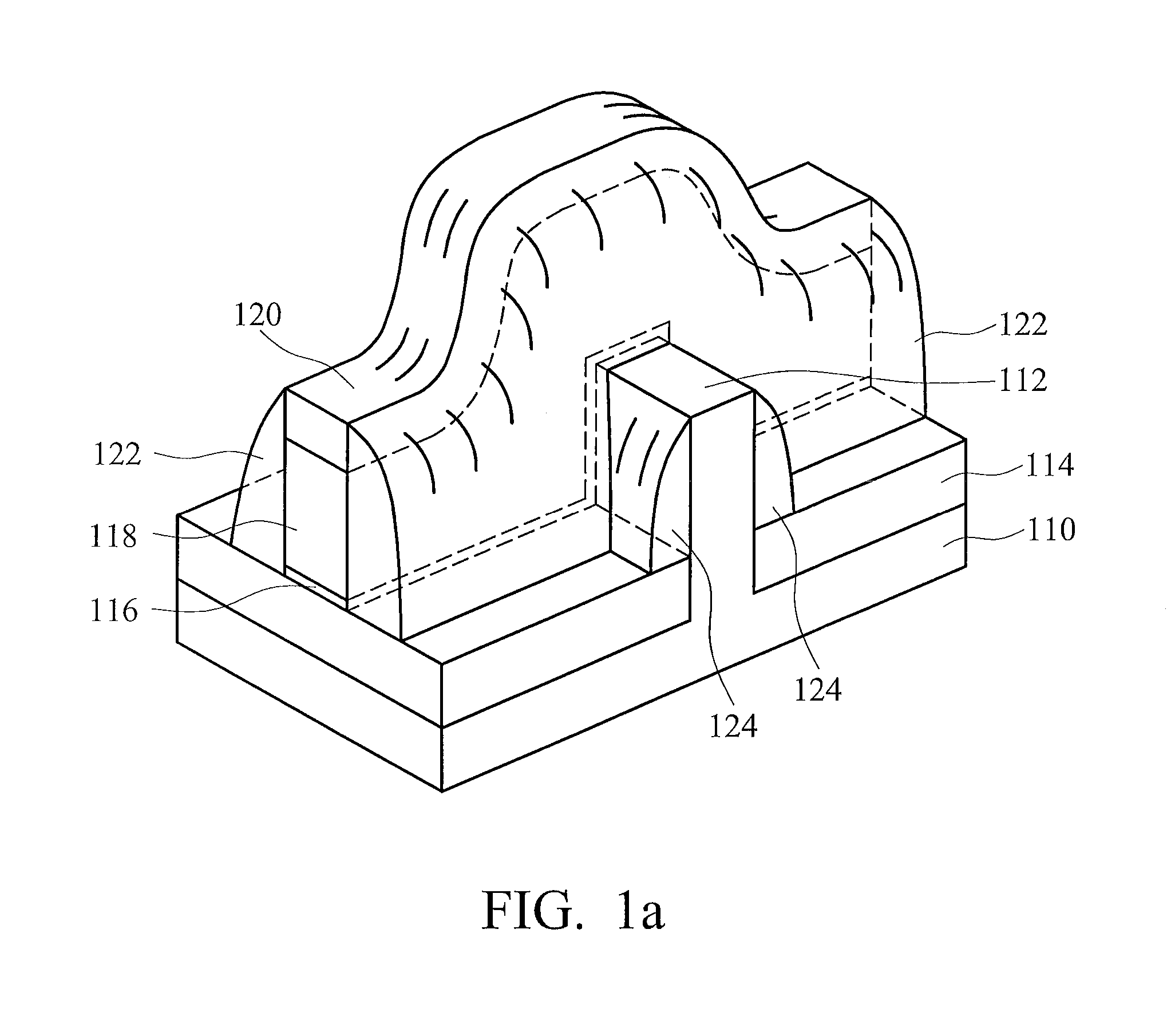

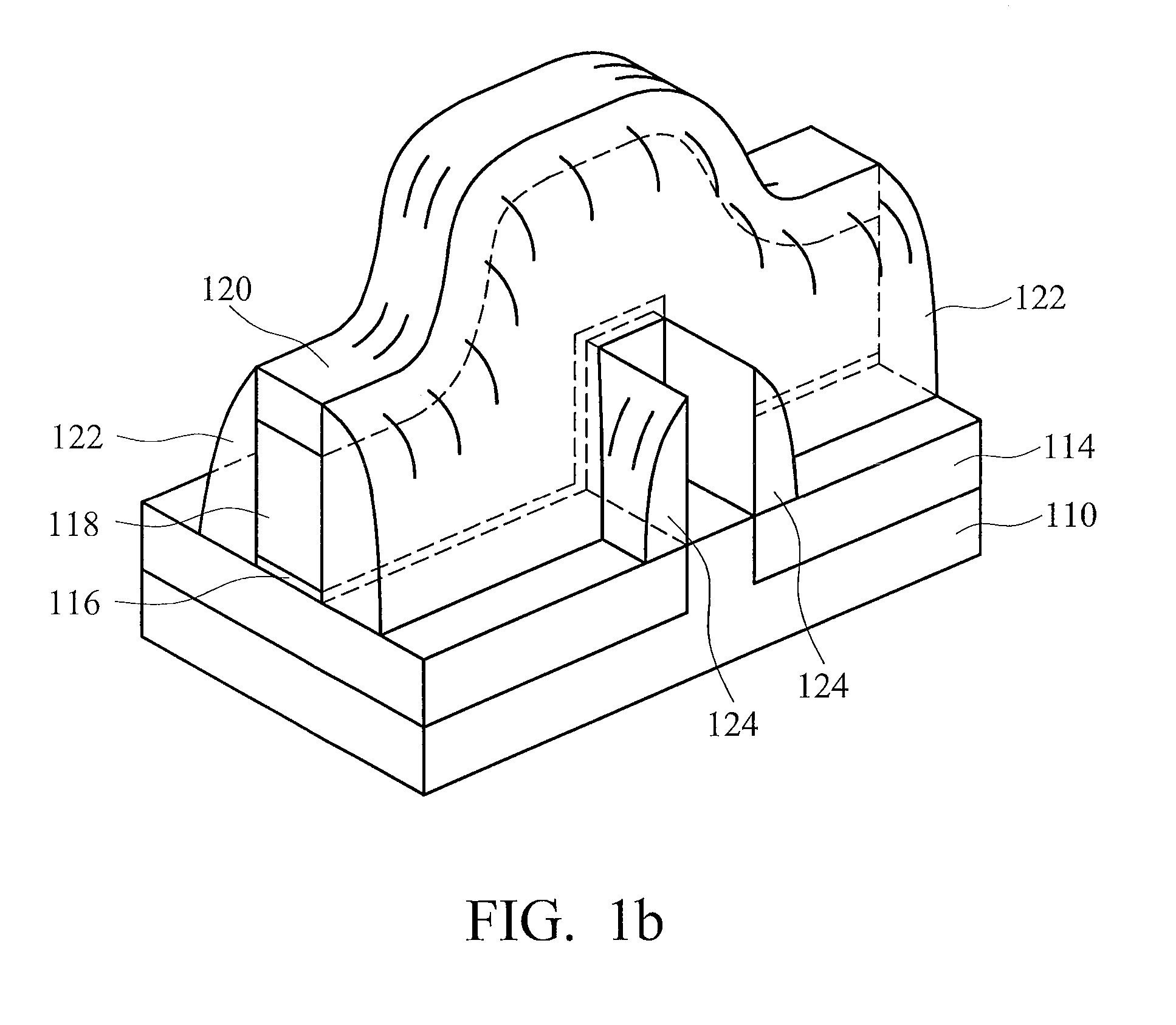

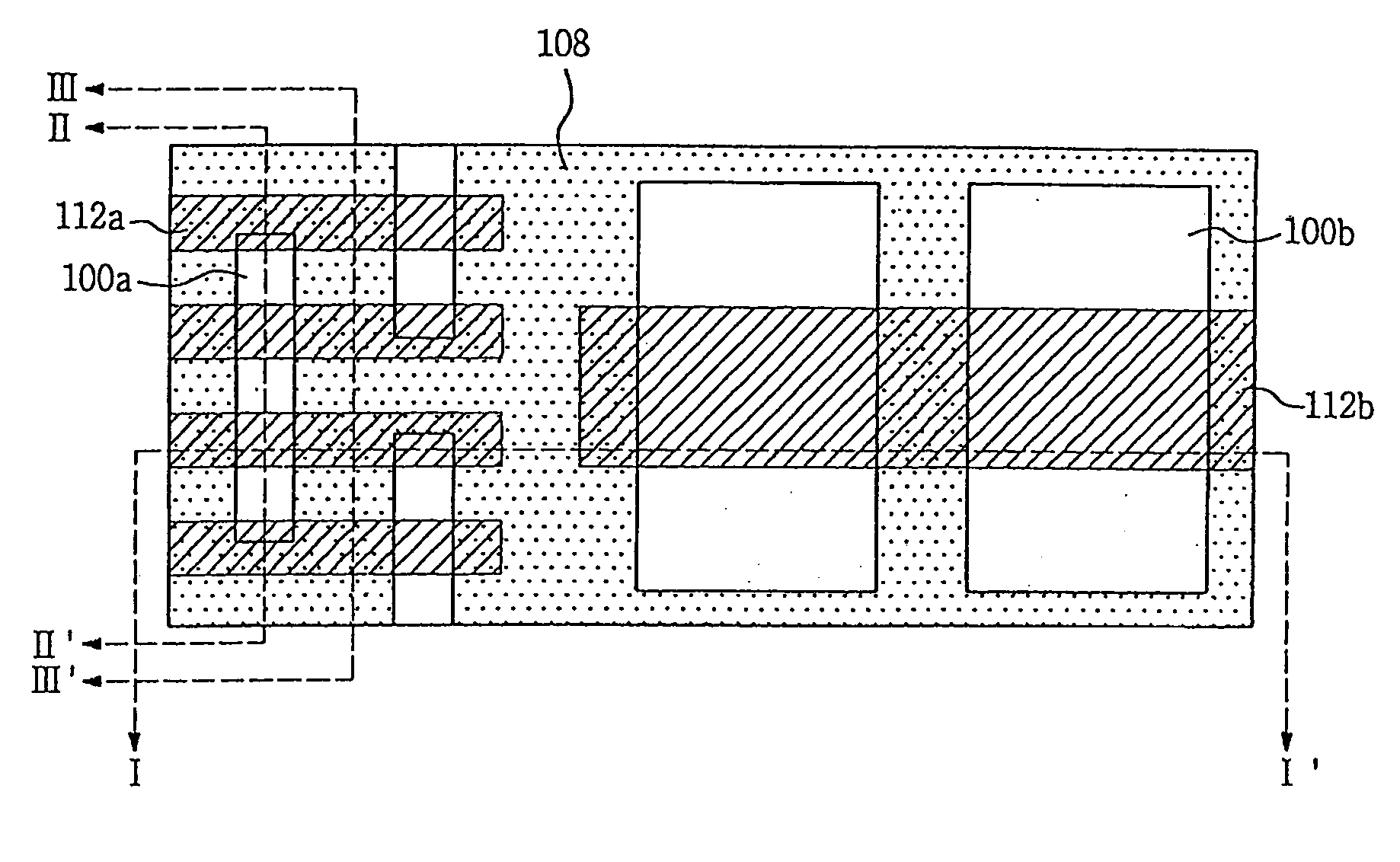

According to some embodiments, a fin type active region is formed under an exposure state of sidewalls on a semiconductor substrate. A gate insulation layer is formed on an upper part of the active region and on the sidewalls, and a device isolation film surrounds the active region to an upper height of the active region. The sidewalls are partially exposed by an opening part formed on the device isolation film. The opening part is filled with a conductive layer that partially covers the upper part of the active region, forming a gate electrode. Source and drain regions are on a portion of the active region where the gate electrode is not. The gate electrode may be easily separated and problems causable by etch by-product can be substantially reduced, and a leakage current of channel region and an electric field concentration onto an edge portion can be prevented.

Owner:SAMSUNG ELECTRONICS CO LTD

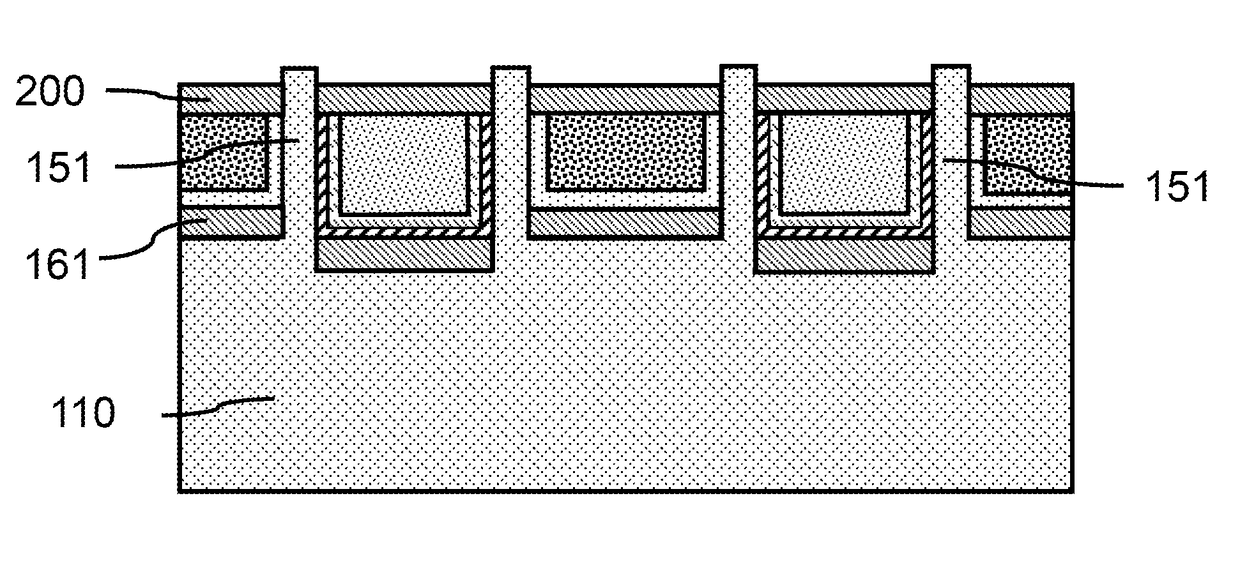

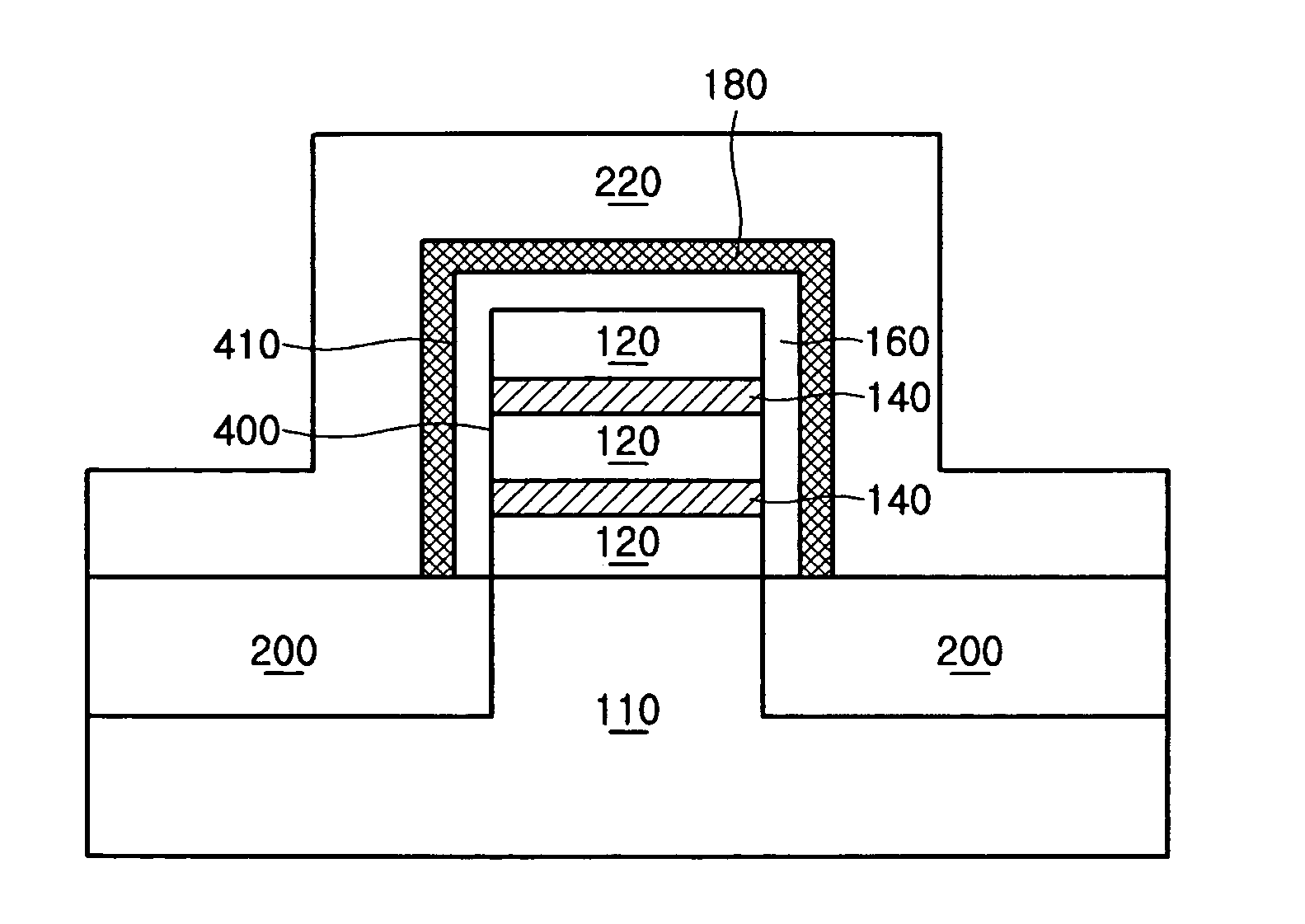

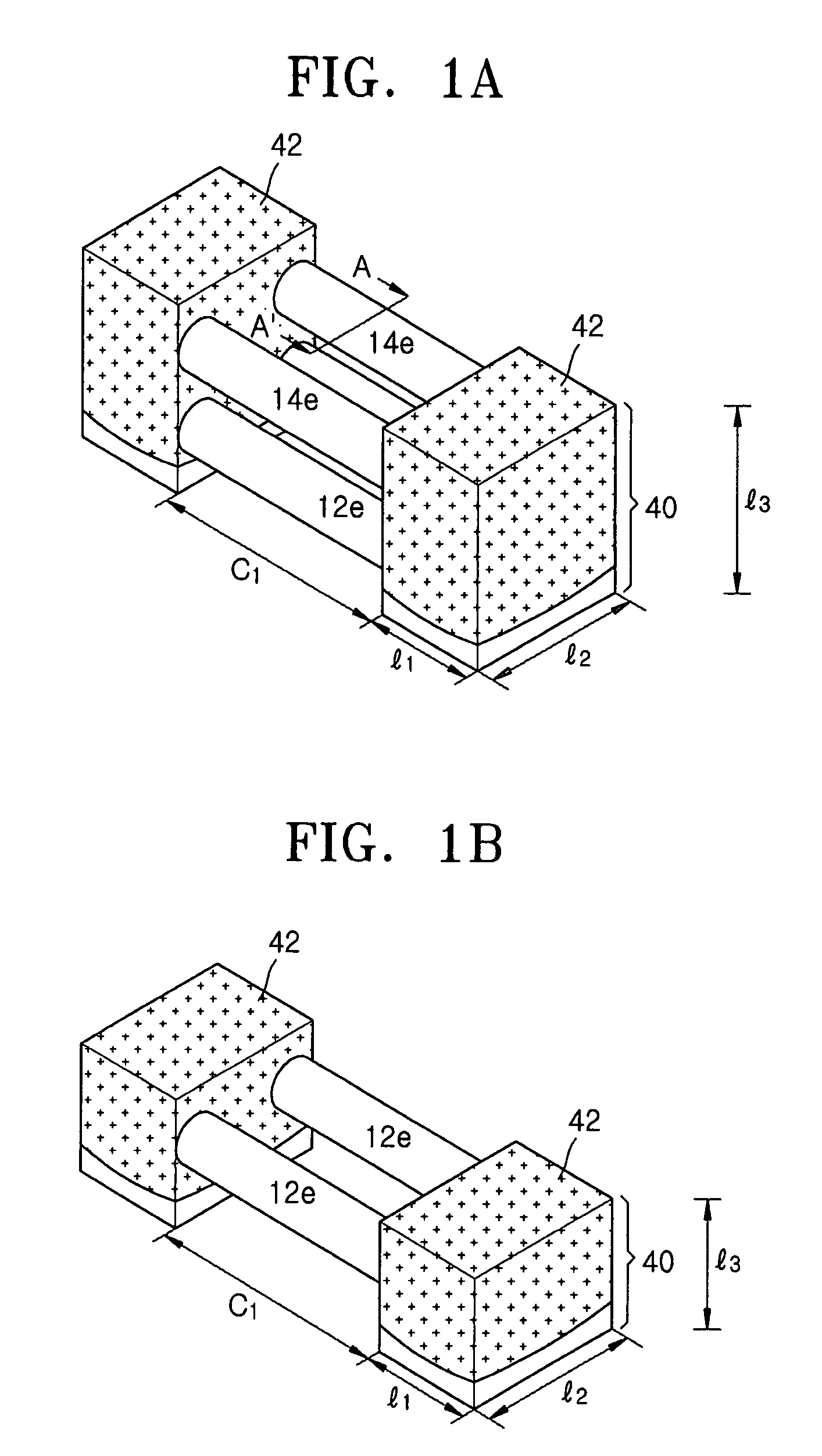

Fabrication of a vertical fin field effect transistor with an asymmetric gate structure

ActiveUS20170373188A1Reduce horizontal sizeSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringElectrical and Electronics engineering

A method of forming a vertical fin field effect transistor (vertical finFET) with two concentric gate structures, including forming one or more tubular vertical fins on a substrate, forming a first gate structure around an outer wall of at least one of the one or more tubular vertical fins, and forming a second gate structure within an inner wall of at least one of the one or more tubular vertical fins having the first gate structure around the outer wall.

Owner:SAMSUNG ELECTRONICS CO LTD

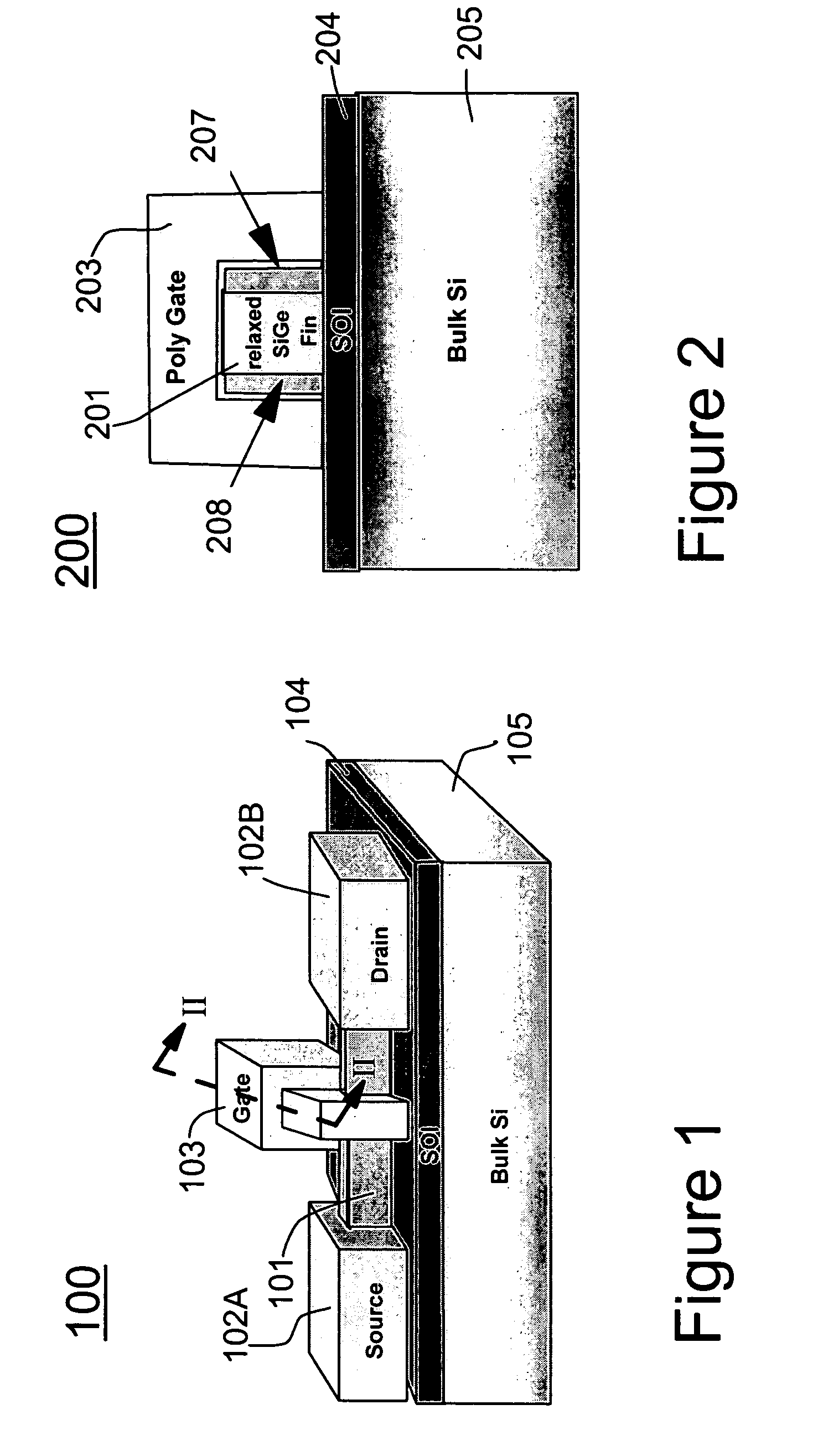

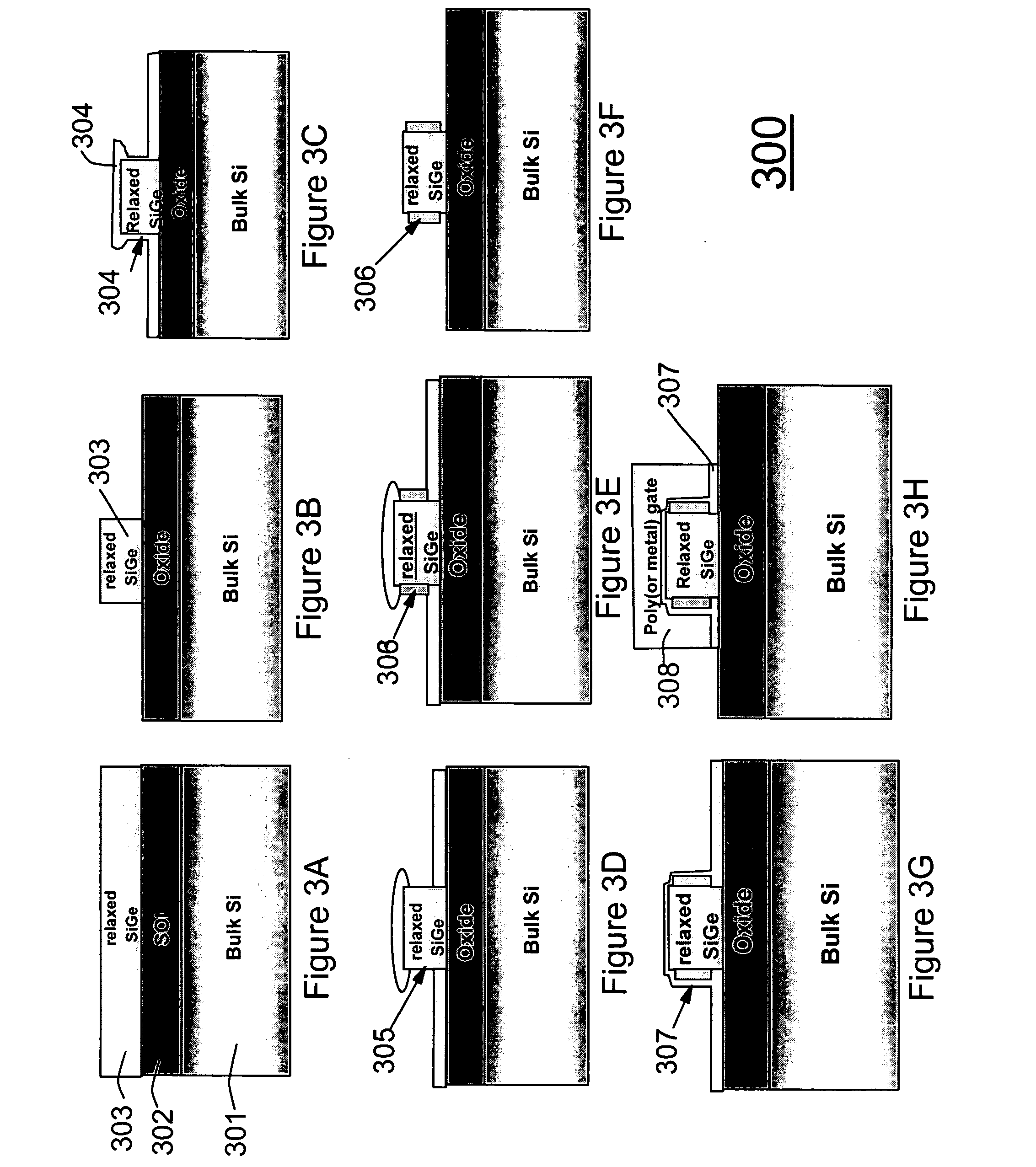

High performance strained silicon FinFETs device and method for forming same

ActiveUS20050145941A1Improve channel mobilityImprove device performanceTransistorSolid-state devicesSiliconMaterials science

A strained Fin Field Effect Transistor (FinFET) (and method for forming the same) includes a relaxed first material having a sidewall, and a strained second material formed on the sidewall of the first material. The relaxed first material and the strained second material form a fin of the FinFET.

Owner:GLOBALFOUNDRIES US INC

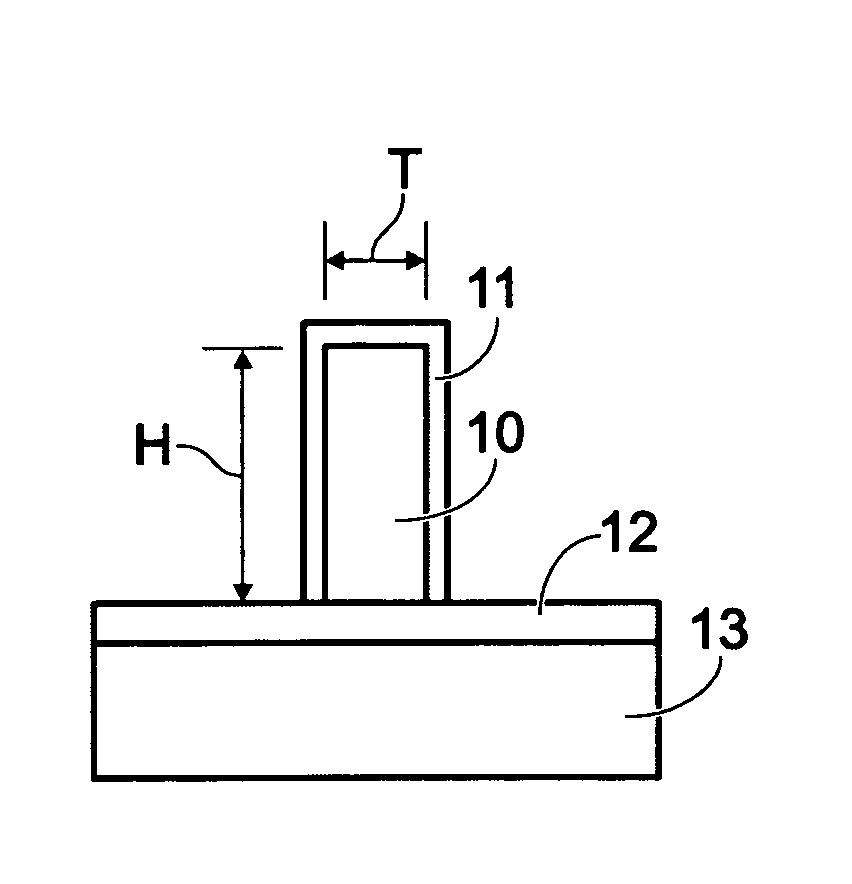

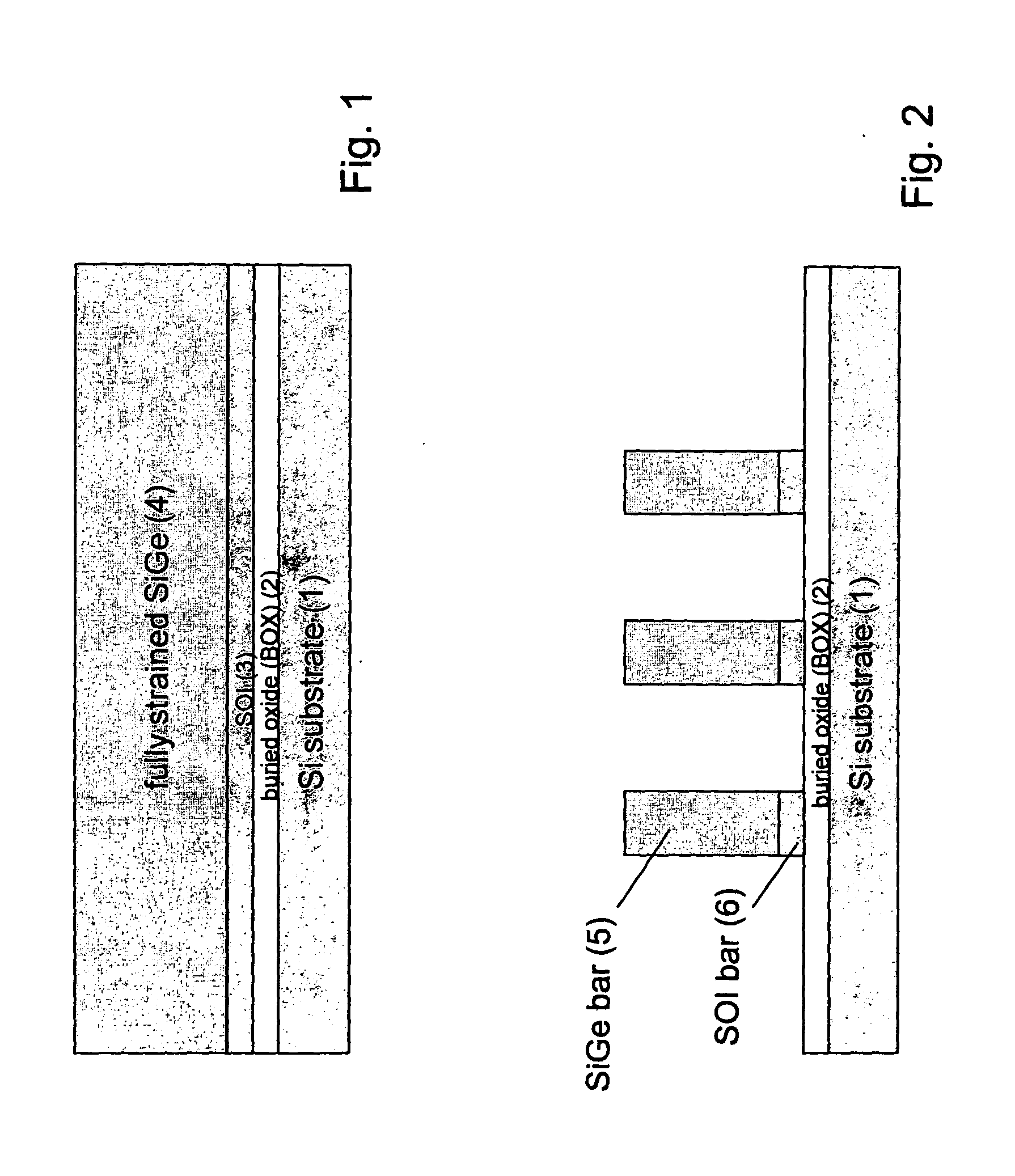

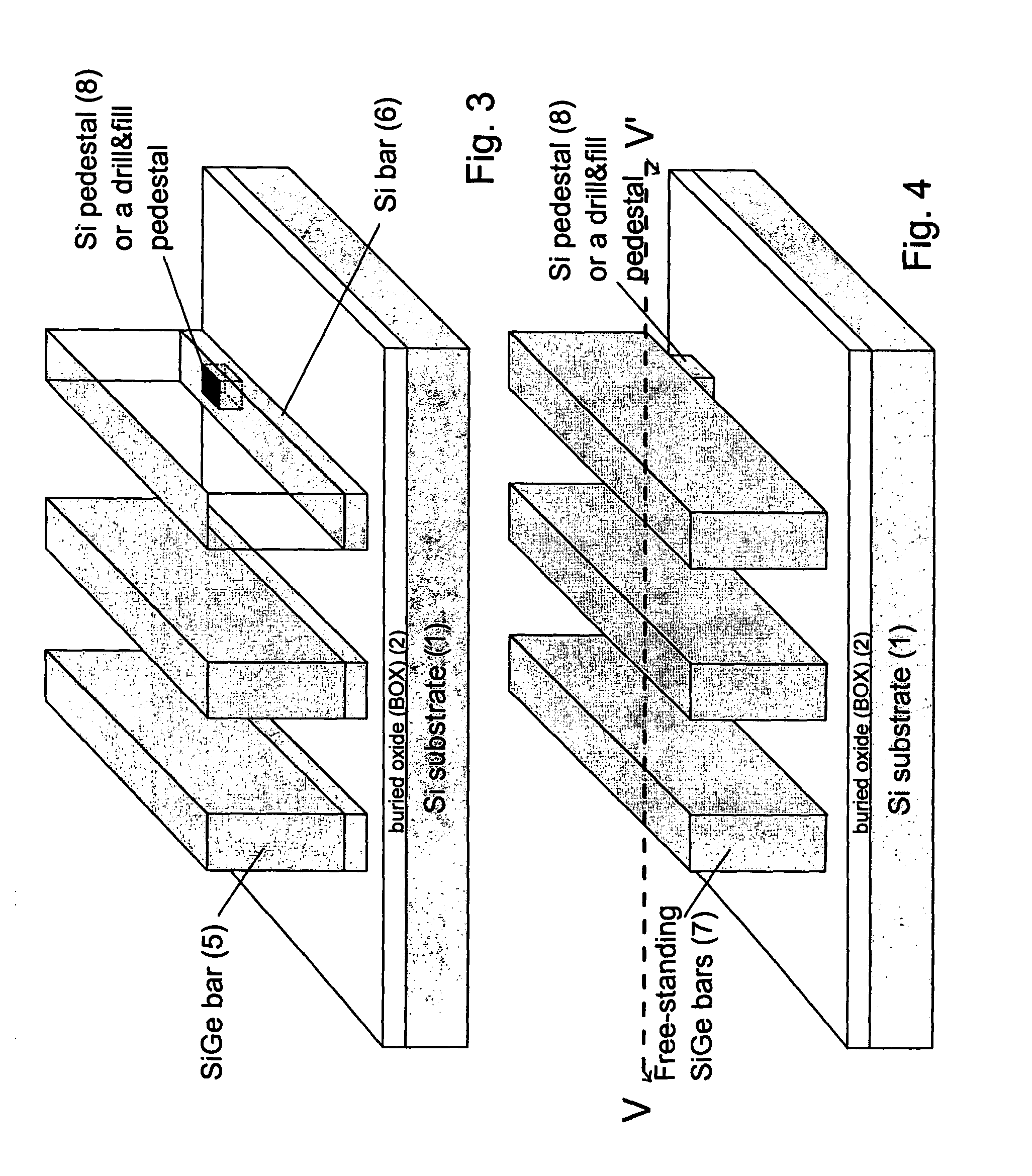

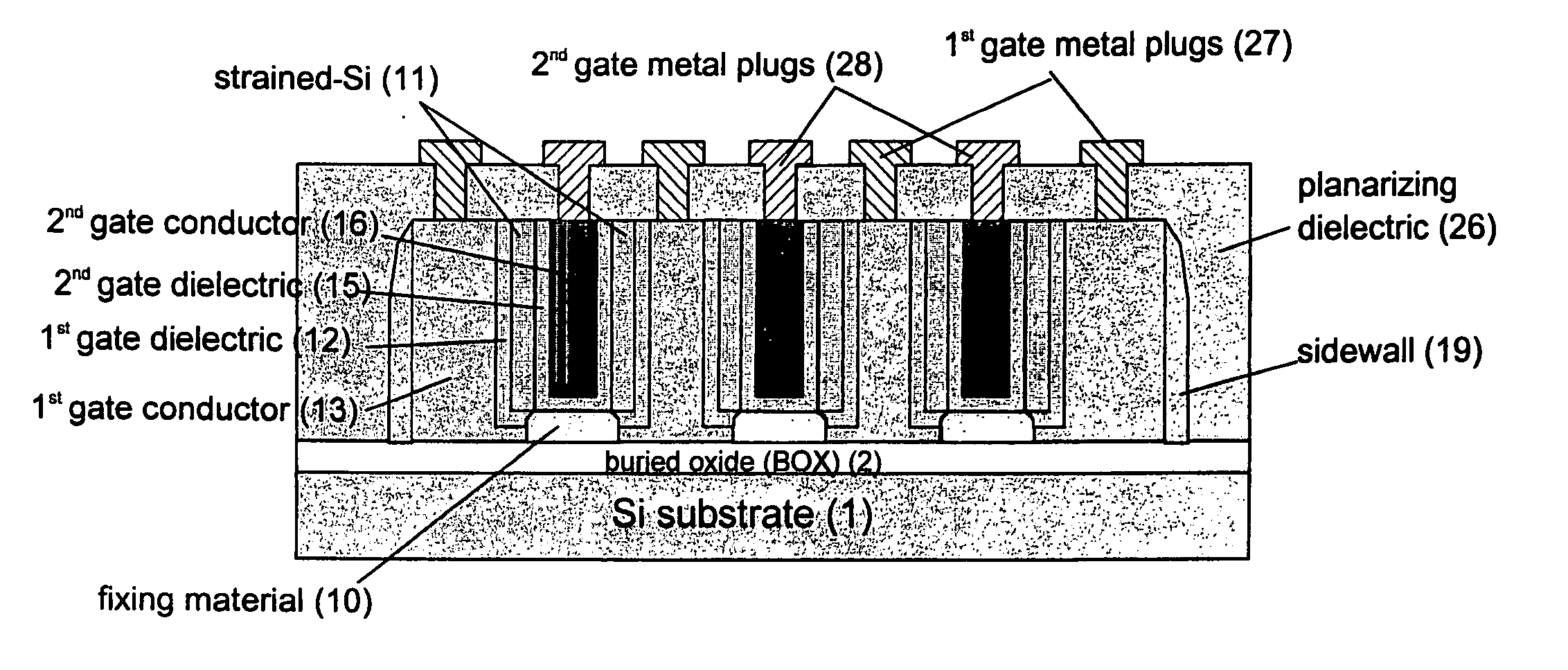

Strained silicon fin structure

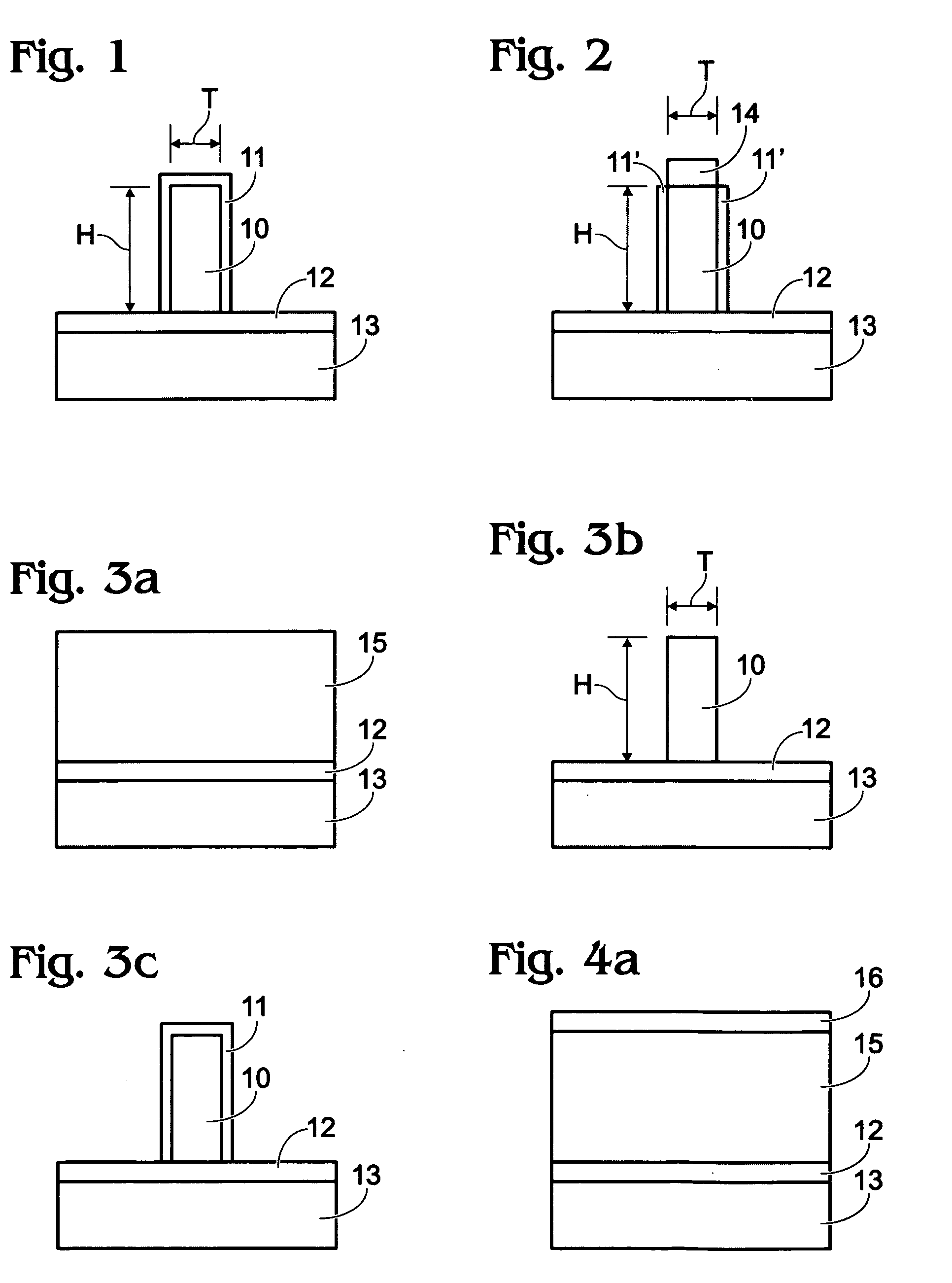

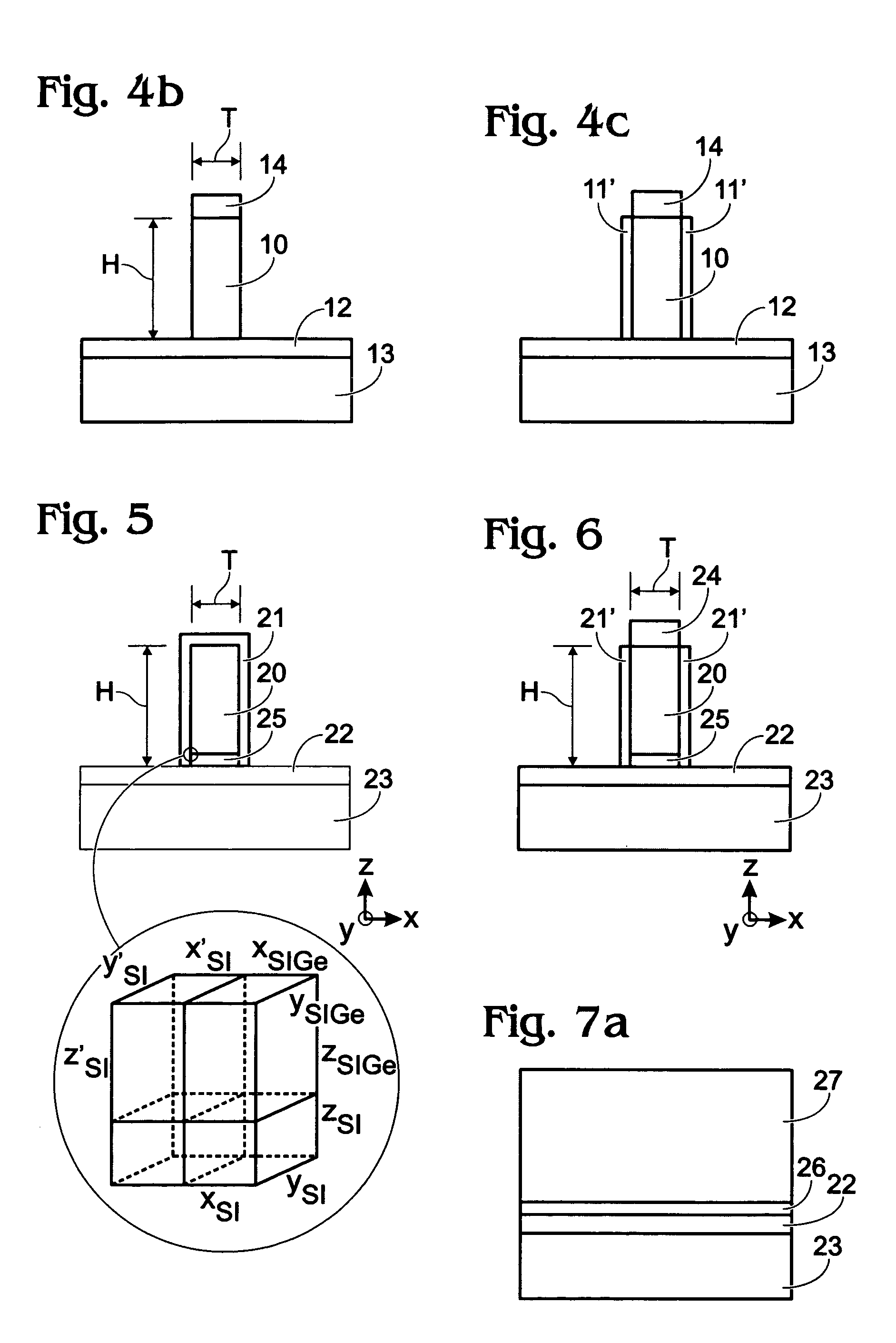

InactiveUS20060113522A1Suppression of short channel effectsIncrease currentTransistorSemiconductor/solid-state device manufacturingDriving currentLattice mismatch

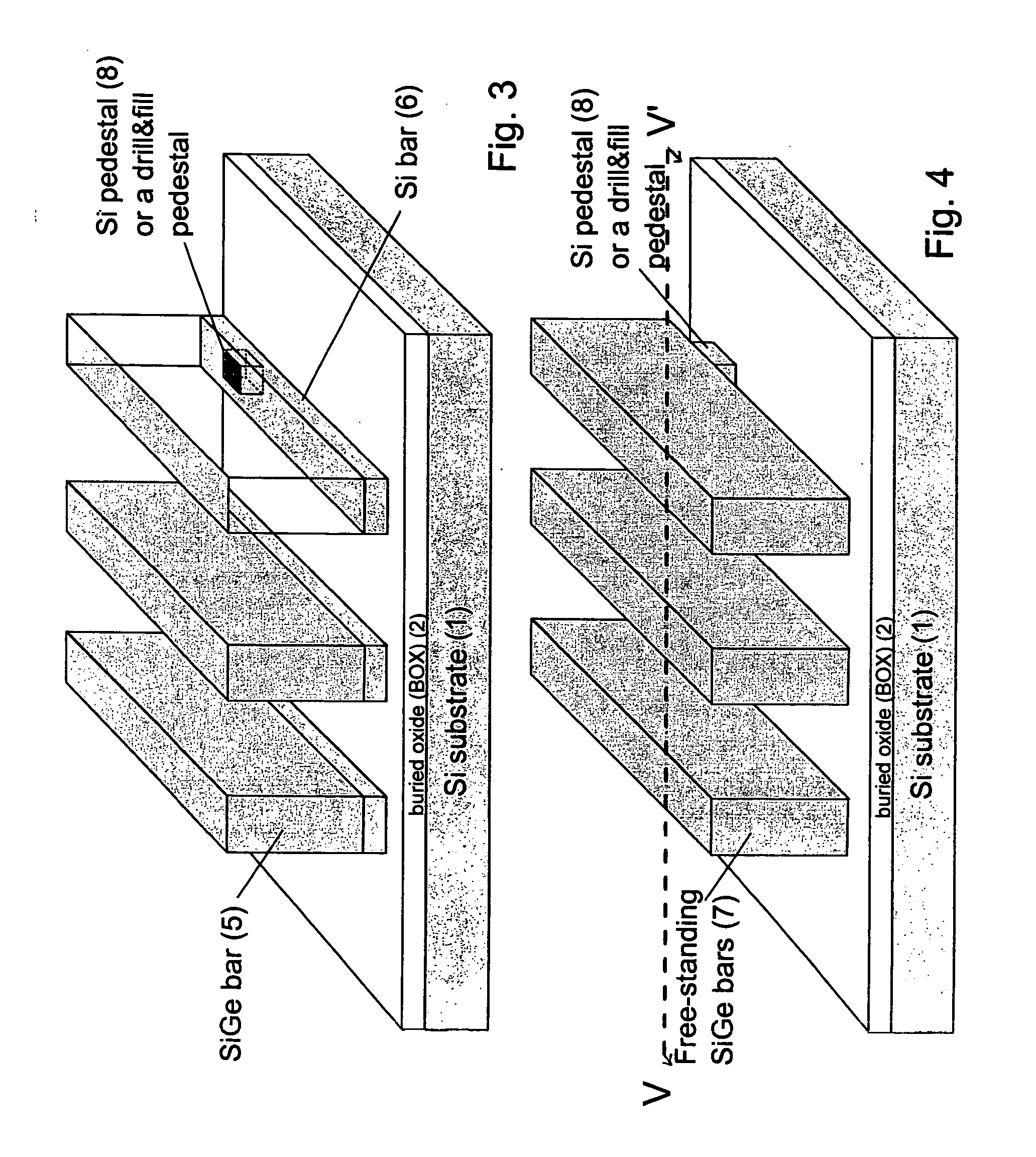

Disclosing is a strained silicon finFET device having a strained silicon fin channel in a double gate finFET structure. The disclosed finFET device is a double gate MOSFET consisting of a silicon fin channel controlled by a self-aligned double gate for suppressing short channel effect and enhancing drive current. The silicon fin channel of the disclosed finFET device is a strained silicon fin channel, comprising a strained silicon layer deposited on a seed fin having different lattice constant, for example, a silicon layer deposited on a silicon germanium seed fin, or a carbon doped silicon layer deposited on a silicon seed fin. The lattice mismatch between the silicon layer and the seed fin generates the strained silicon fin channel in the disclosed finFET device to improve hole and electron mobility enhancement, in addition to short channel effect reduction characteristic inherently in a finFET device.

Owner:MICROSOFT TECH LICENSING LLC +1

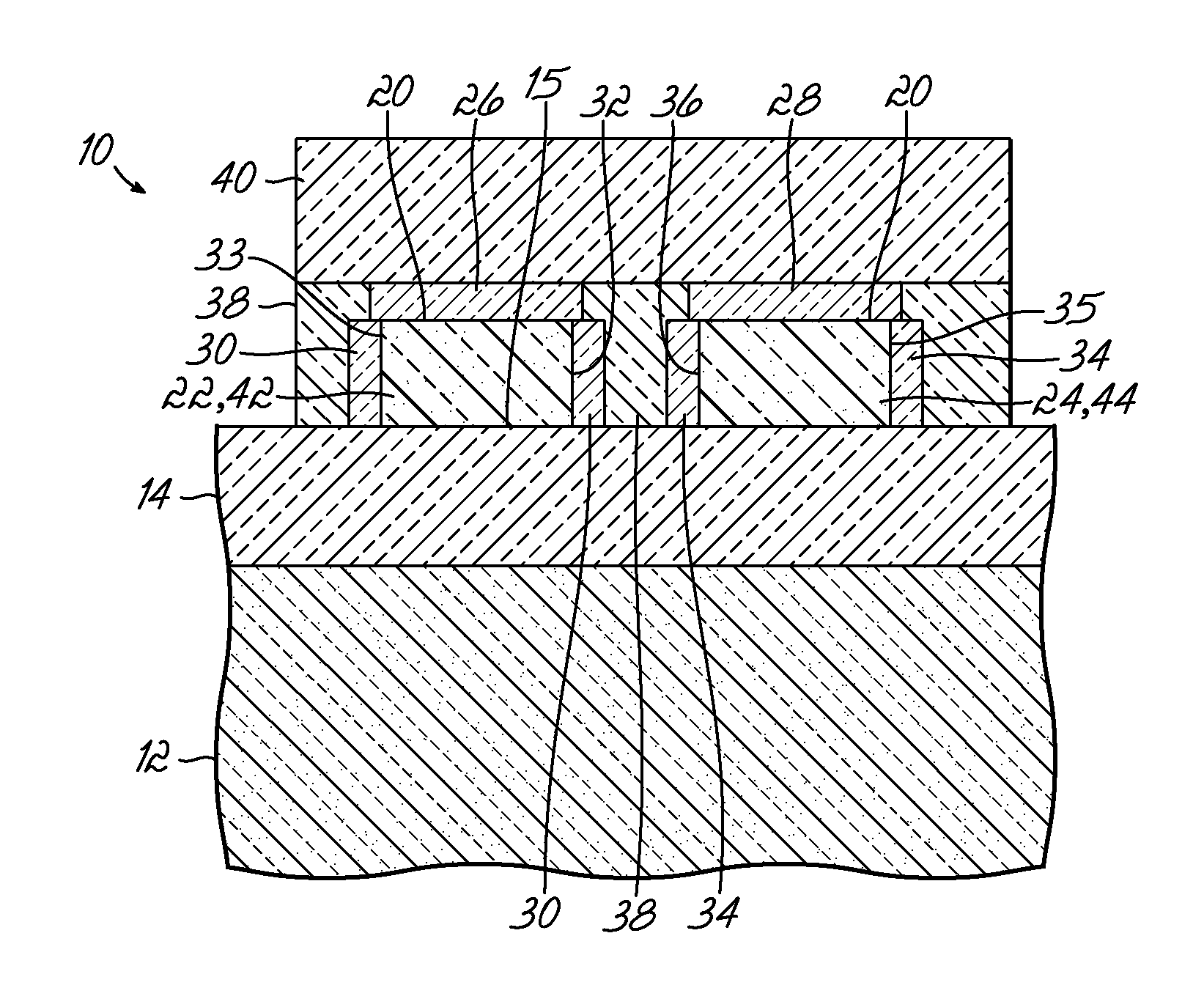

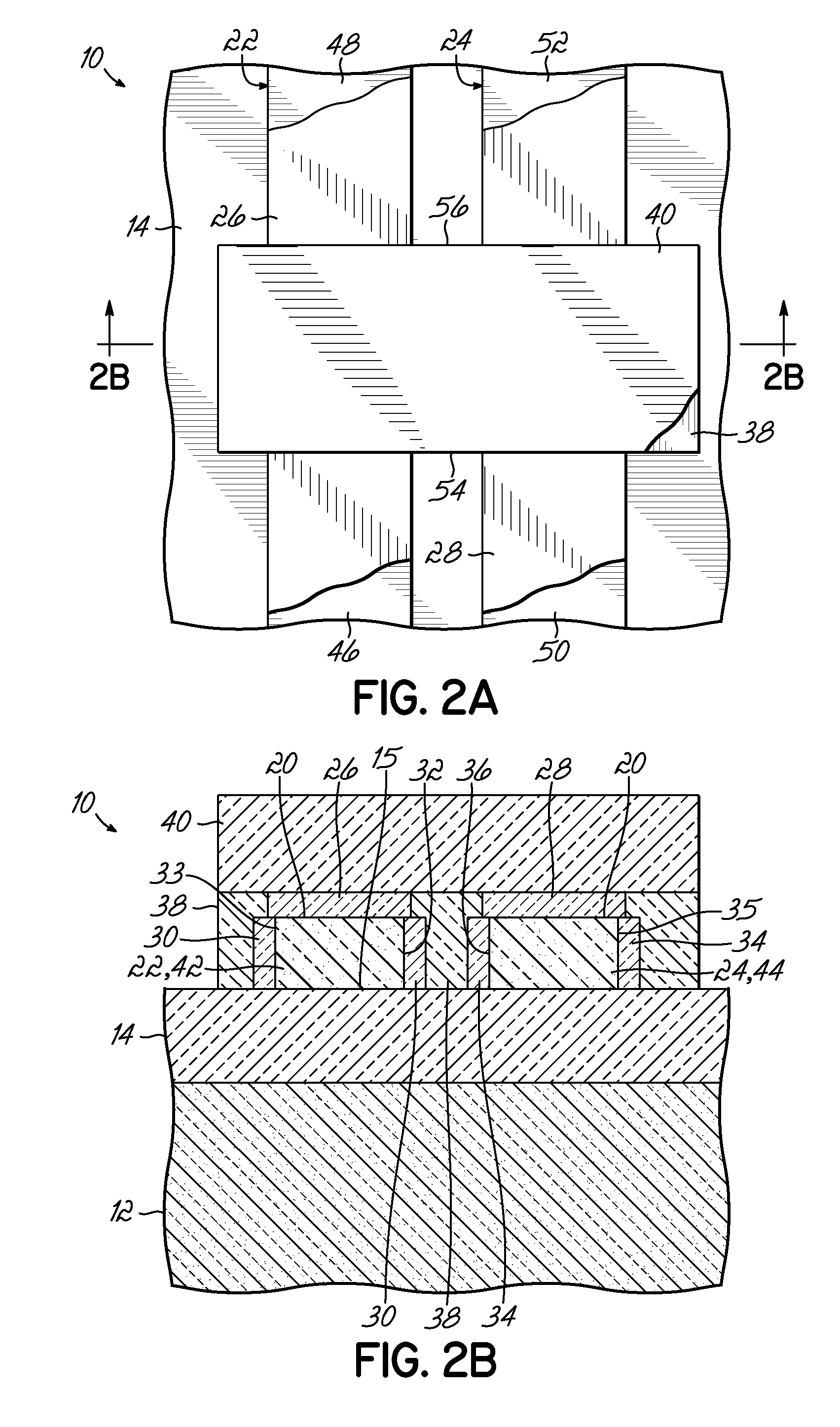

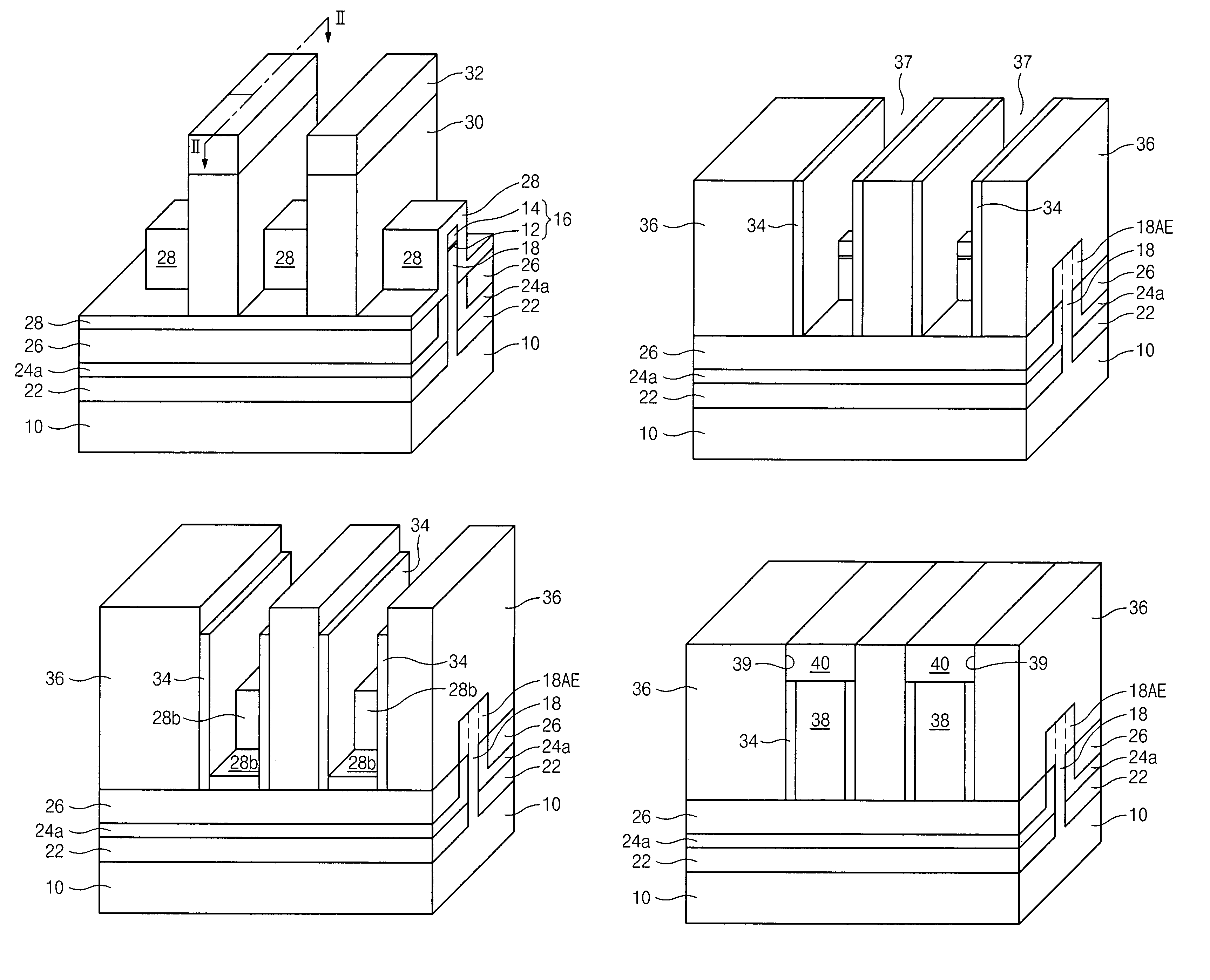

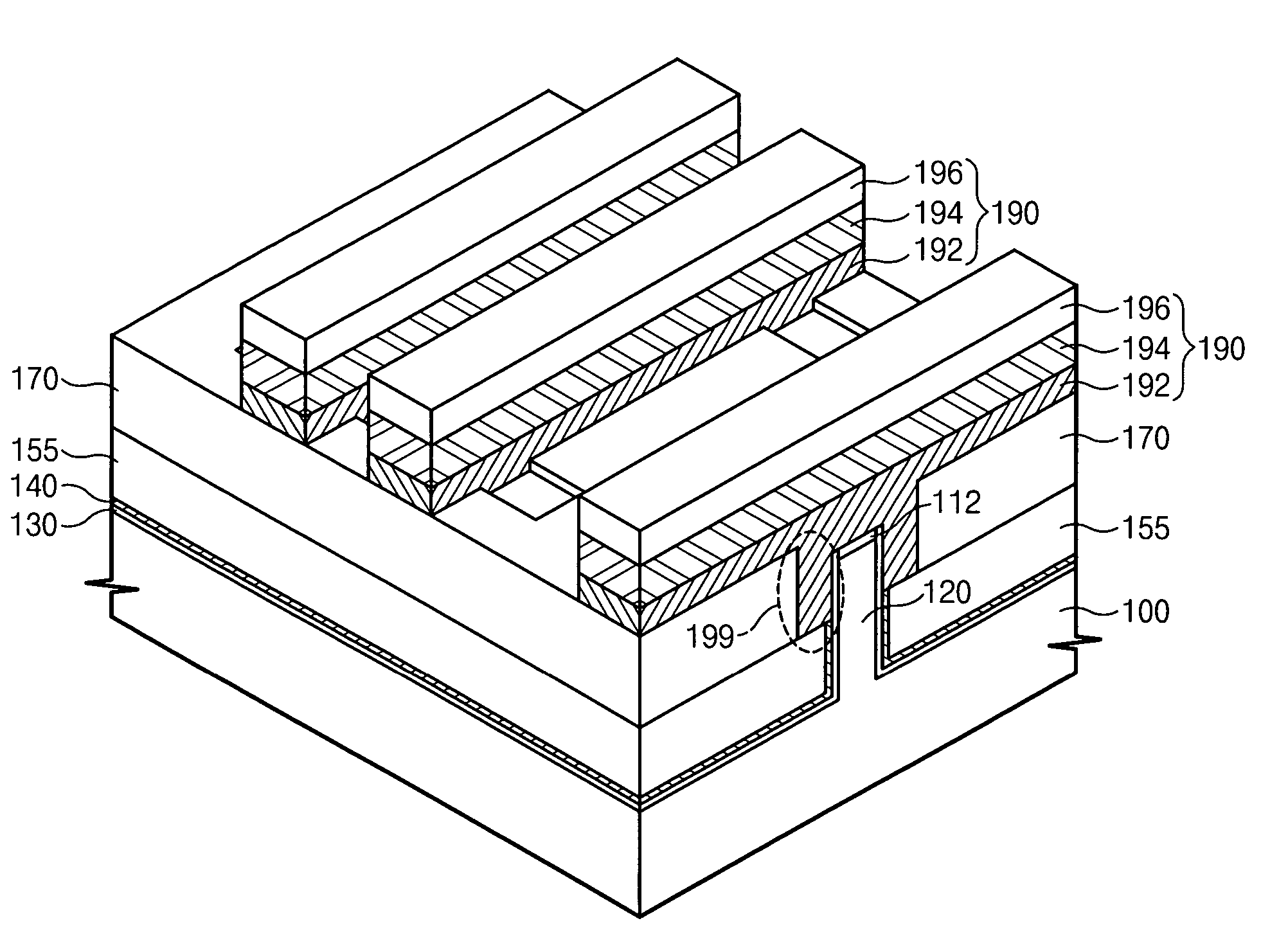

Fin Field Effect Transistor Devices with Self-Aligned Source and Drain Regions

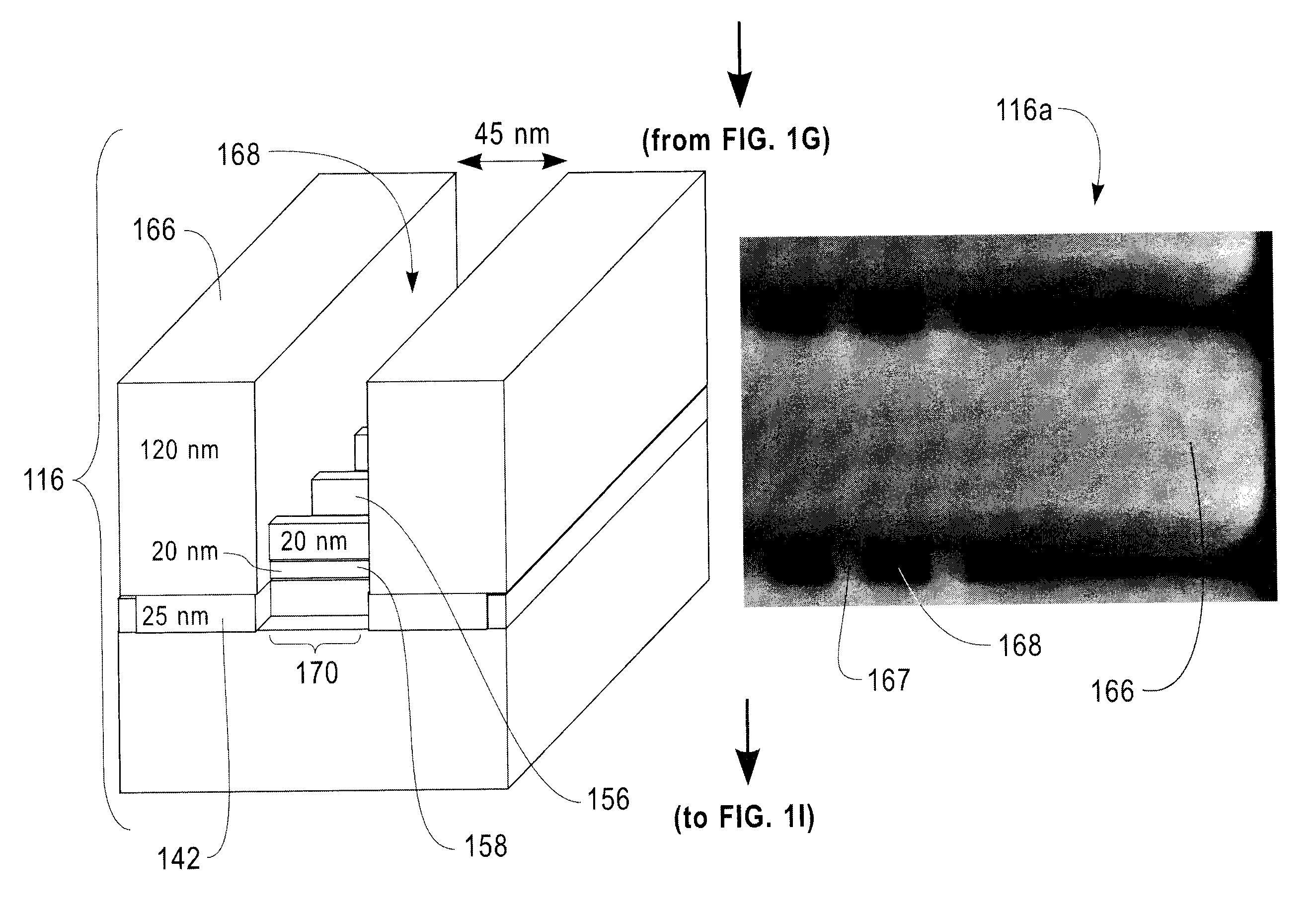

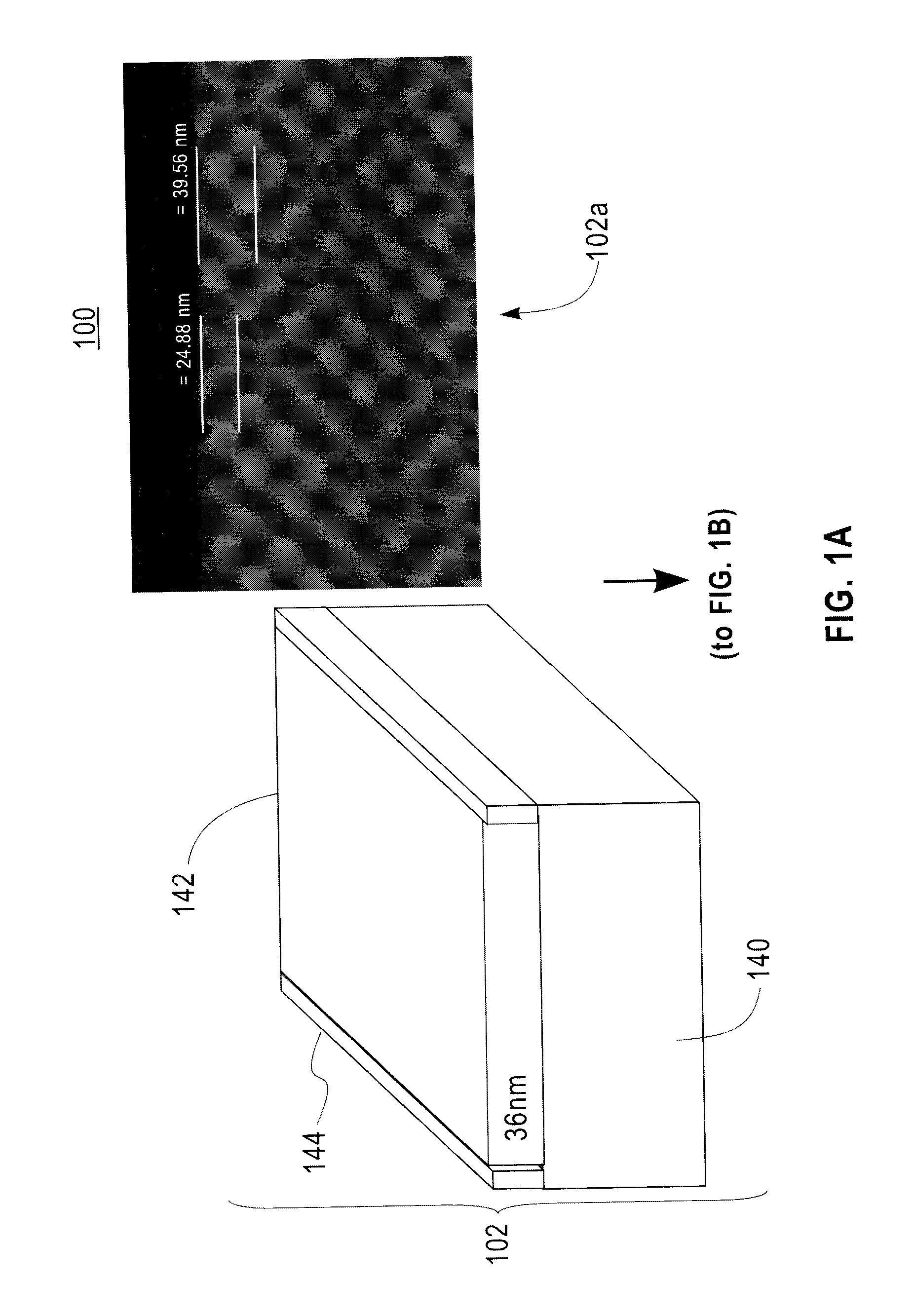

Improved fin field effect transistor (FinFET) devices and methods for the fabrication thereof are provided. In one aspect, a method for fabricating a field effect transistor device comprises the following steps. A substrate is provided having a silicon layer thereon. A fin lithography hardmask is patterned on the silicon layer. A dummy gate structure is placed over a central portion of the fin lithography hardmask. A filler layer is deposited around the dummy gate structure. The dummy gate structure is removed to reveal a trench in the filler layer, centered over the central portion of the fin lithography hardmask, that distinguishes a fin region of the device from source and drain regions of the device. The fin lithography hardmask in the fin region is used to etch a plurality of fins in the silicon layer. The trench is filled with a gate material to form a gate stack over the fins. The filler layer is removed to reveal the source and drain regions of the device, wherein the source and drain regions are intact and self-aligned with the gate stack.

Owner:GLOBALFOUNDRIES US INC

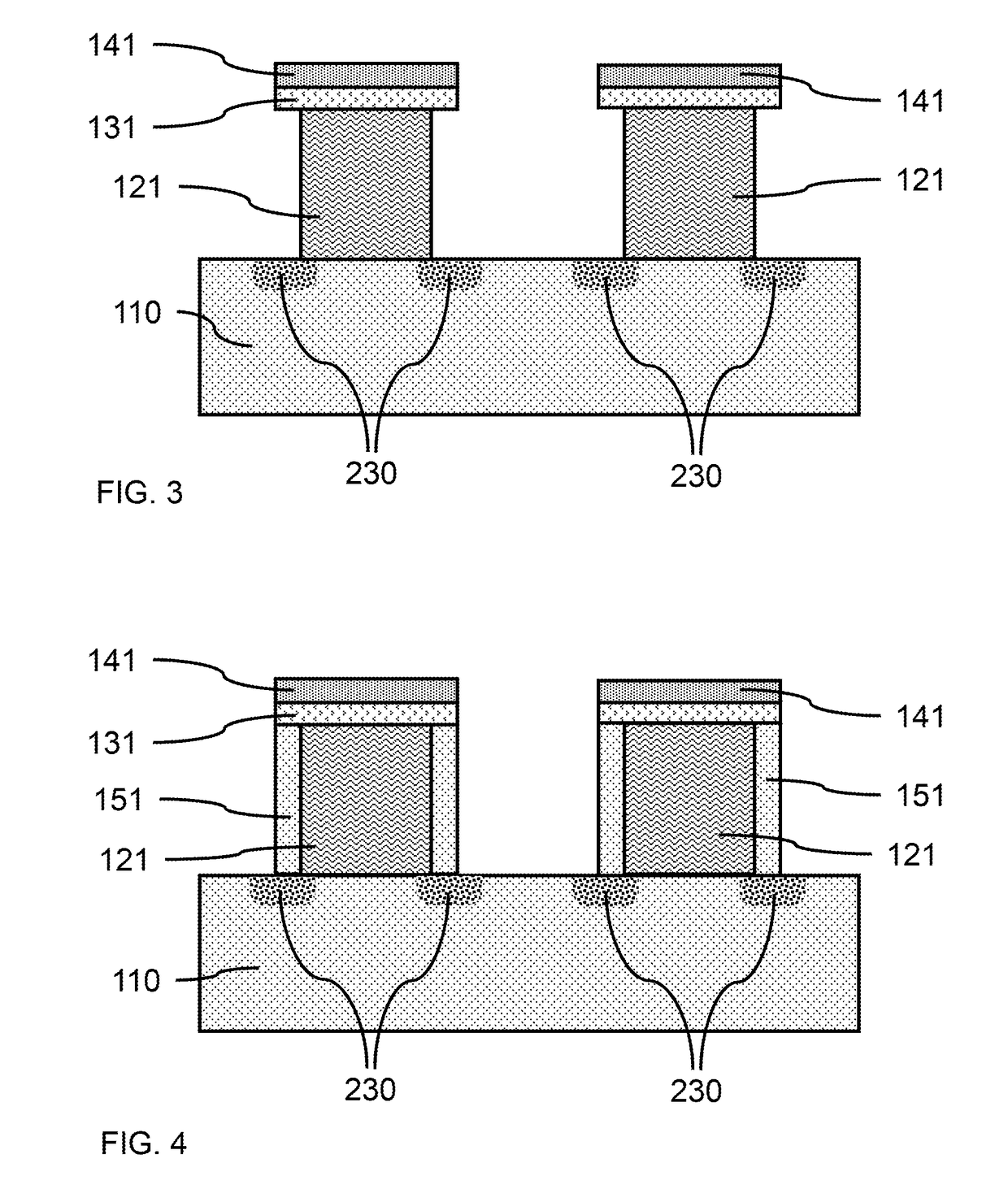

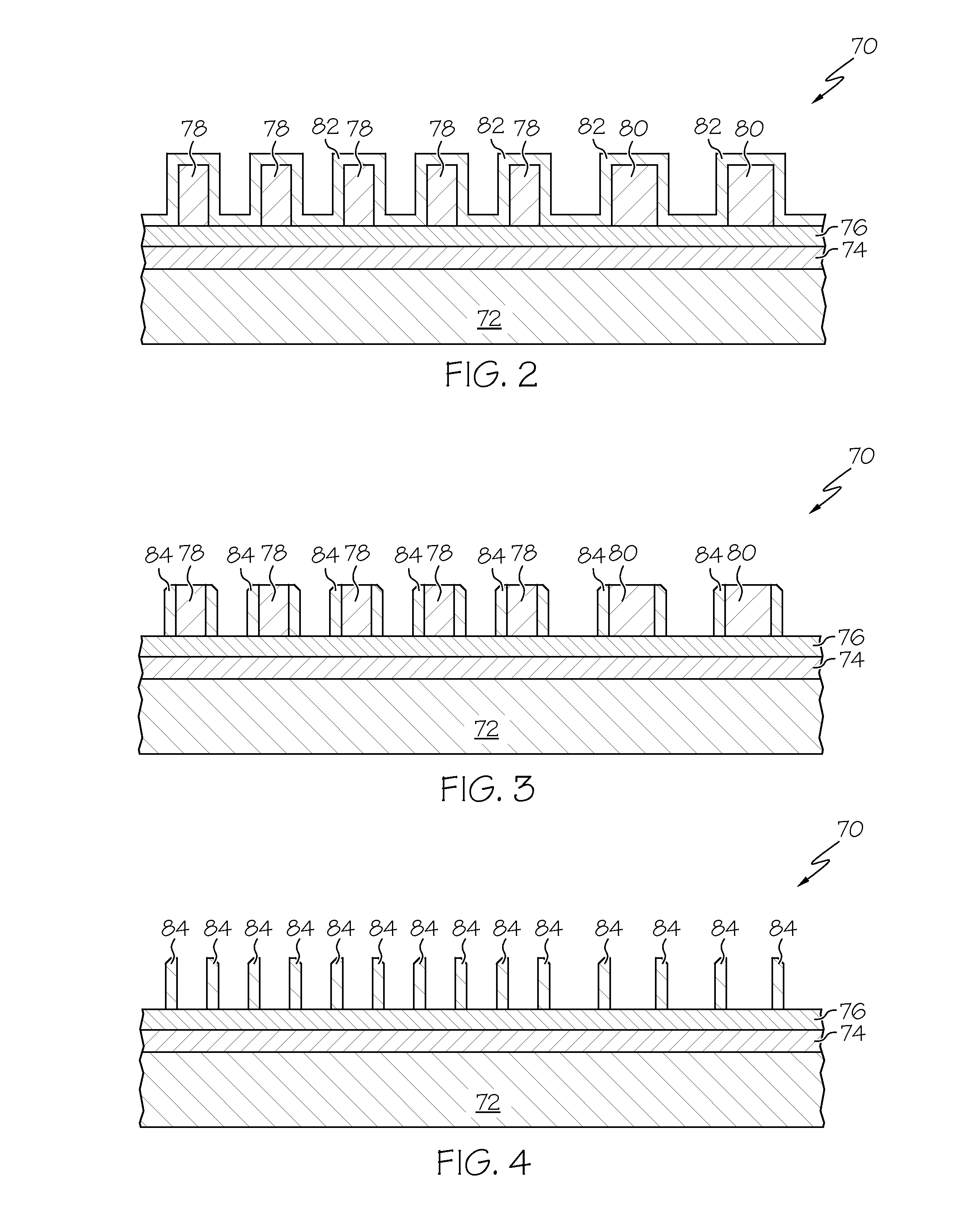

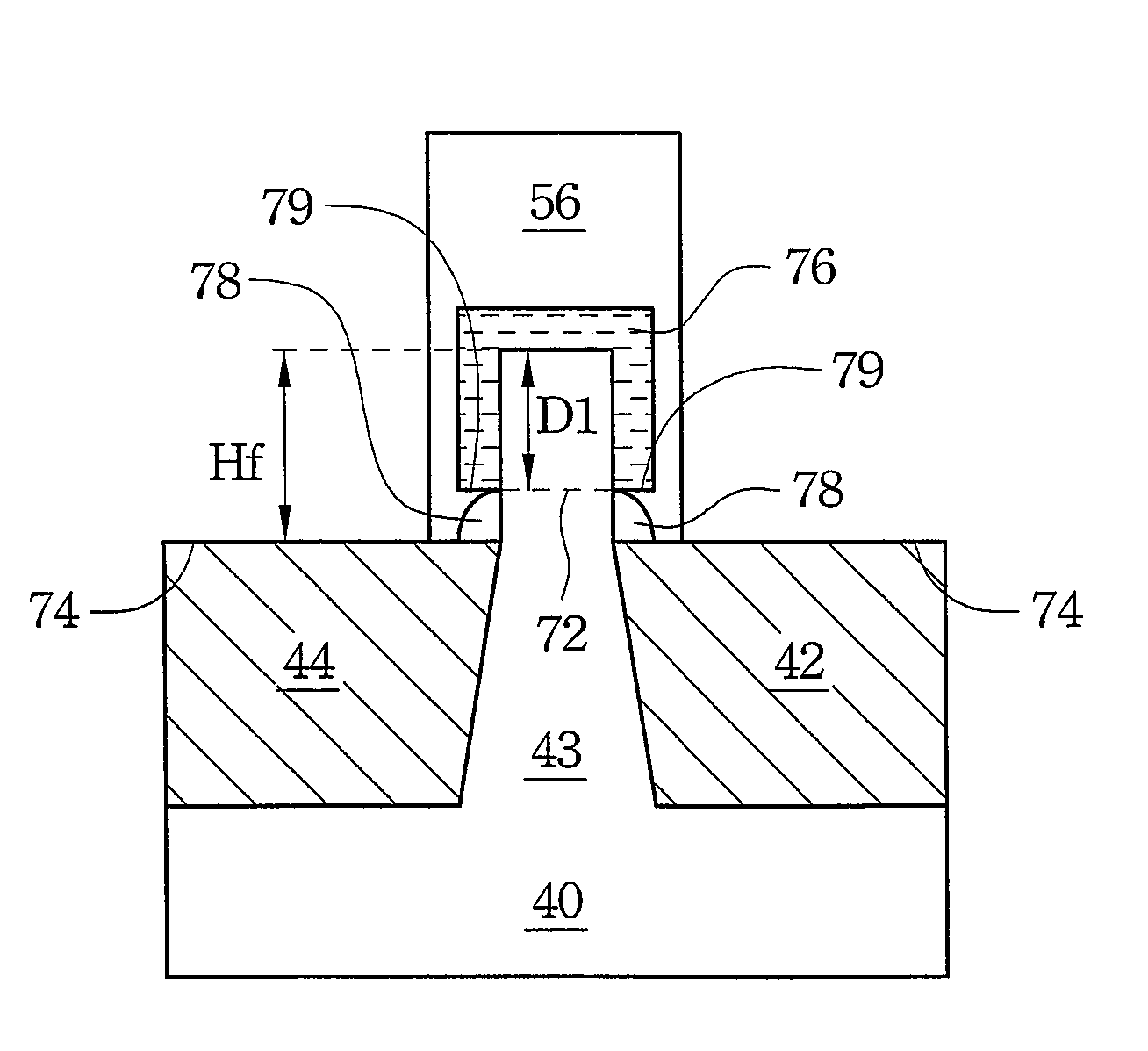

Dielectric Punch-Through Stoppers for Forming FinFETs Having Dual Fin Heights

ActiveUS20100163971A1Improved accuracy in formationTotal current dropTransistorSolid-state devicesDielectricSemiconductor structure

A semiconductor structure includes a semiconductor substrate having a first portion and a second portion. A first Fin field-effect transistor (FinFET) is formed over the first portion of the semiconductor substrate, wherein the first FinFET includes a first fin having a first fin height. A second FinFET is formed over the second portion of the semiconductor substrate, wherein the second FinFET includes a second fin having a second fin height different from the first fin height. A top surface of the first fin is substantially level with a top surface of the second fin. A punch-through stopper is underlying and adjoining the first FinFET, wherein the punch-through stopper isolates the first fin from the first portion of the semiconductor substrate.

Owner:TAIWAN SEMICON MFG CO LTD

FinFET SRAM cell using low mobility plane for cell stability and method for forming

InactiveUS20050121676A1High gainAccurate operationSolid-state devicesSemiconductor/solid-state device manufacturingStatic random-access memoryLow mobility

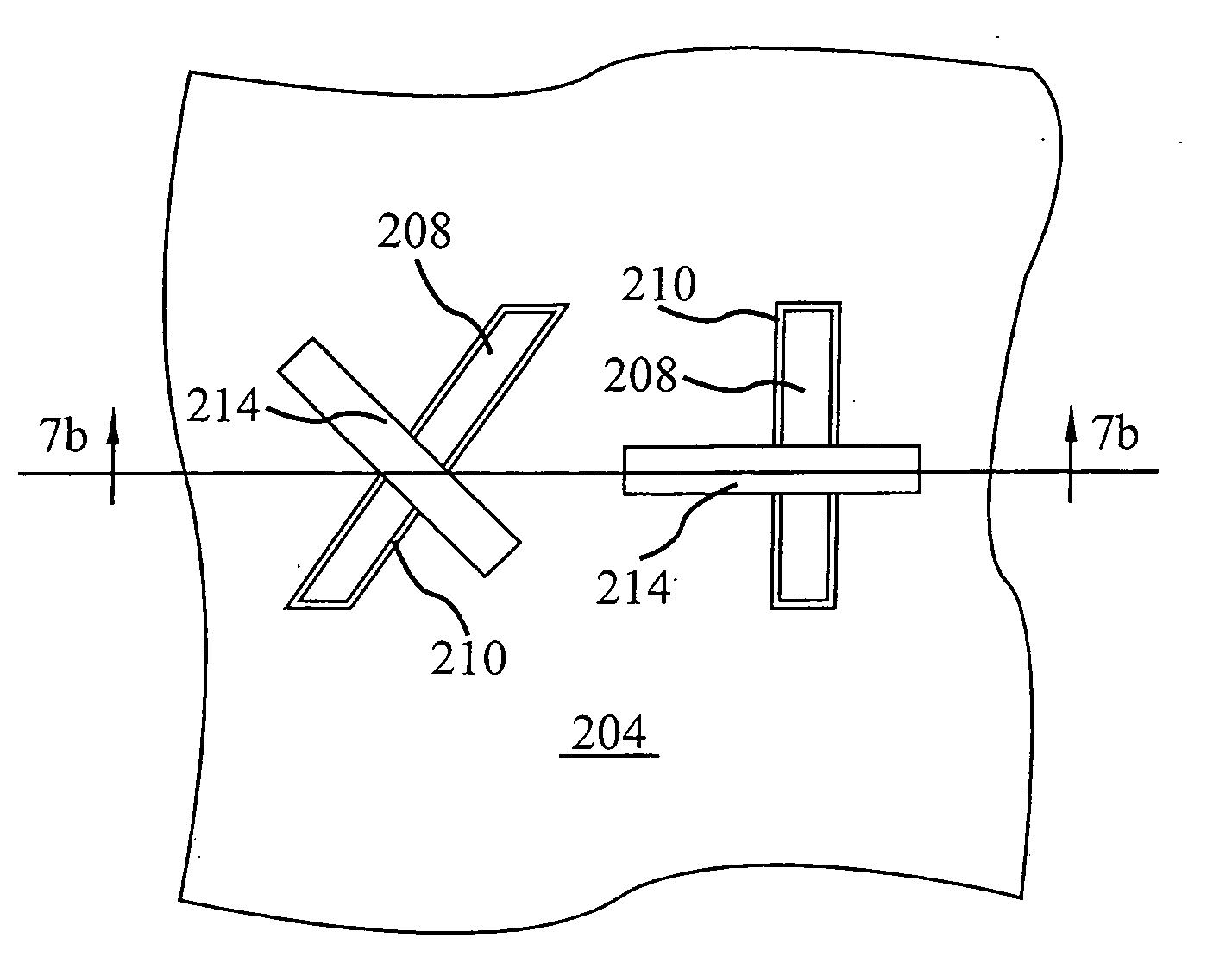

The present invention provides a device design and method for forming the same that results in Fin Field Effect Transistors having different gains without negatively impacting device density. The present invention forms relatively low gain FinFET transistors in a low carrier mobility plane and relatively high gain FinFET transistors in a high carrier mobility plane. Thus formed, the FinFETs formed in the high mobility plane have a relatively higher gain than the FinFETs formed in the low mobility plane. The embodiments are of particular application to the design and fabrication of a Static Random Access Memory (SRAM) cell. In this application, the bodies of the n-type FinFETs used as transfer devices are formed along the {110} plane. The bodies of the n-type FinFETs and p-type FinFETs used as the storage latch are formed along the {100}. Thus formed, the transfer devices will have a gain approximately half that of the n-type storage latch devices, facilitating proper SRAM operation

Owner:GLOBALFOUNDRIES INC

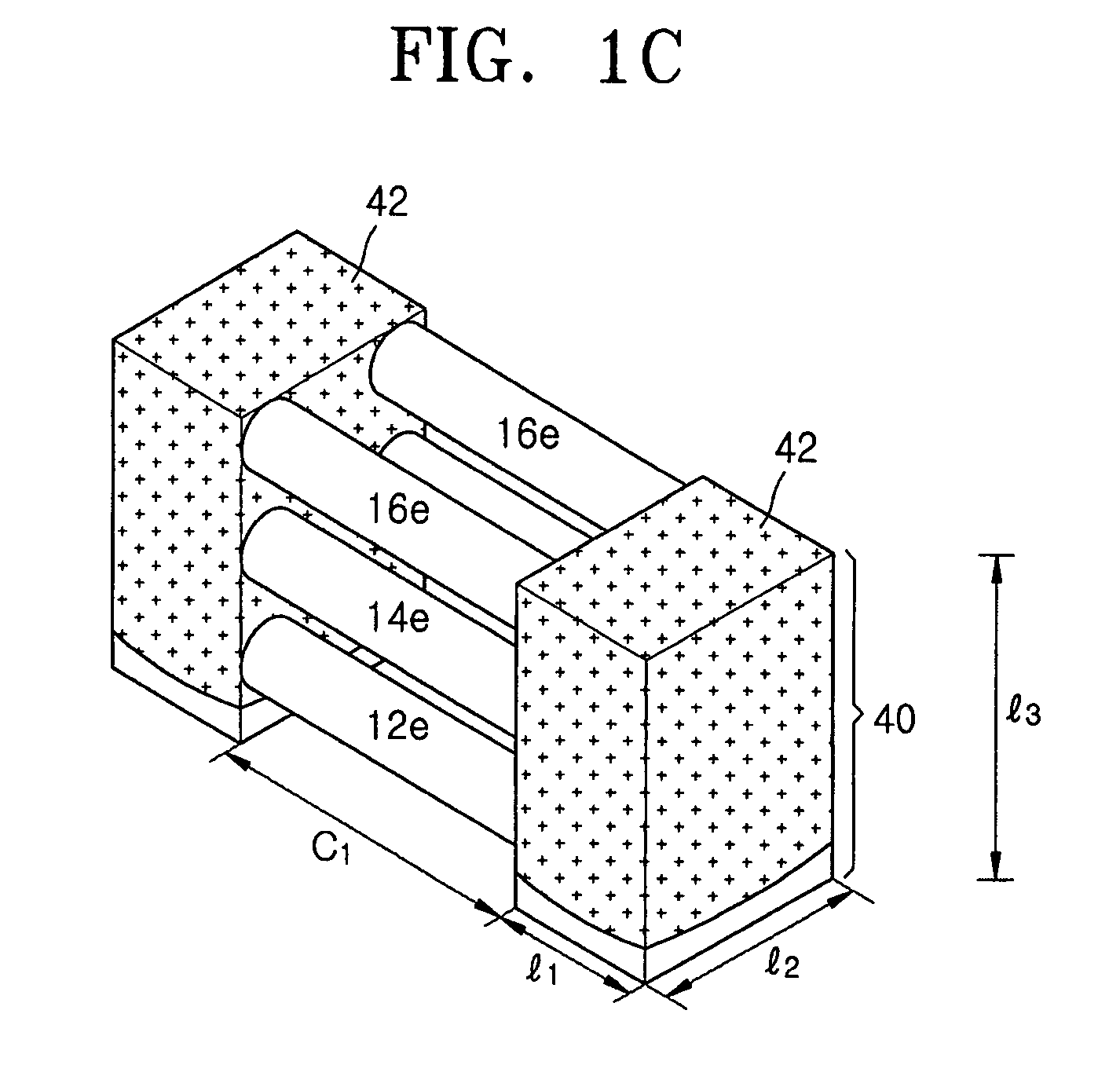

Strained-channel fin field effect transistor (FET) with a uniform channel thickness and separate gates

A semiconductor device (and method for making the same) includes a strained-silicon channel formed adjacent a source and a drain, a first gate formed over a first side of the channel, a second gate formed over a second side of the channel, a first gate dielectric formed between the first gate and the strained-silicon channel, and a second gate dielectric formed between the second gate and the strained-silicon channel. The strained-silicon channel is non-planar.

Owner:IBM CORP

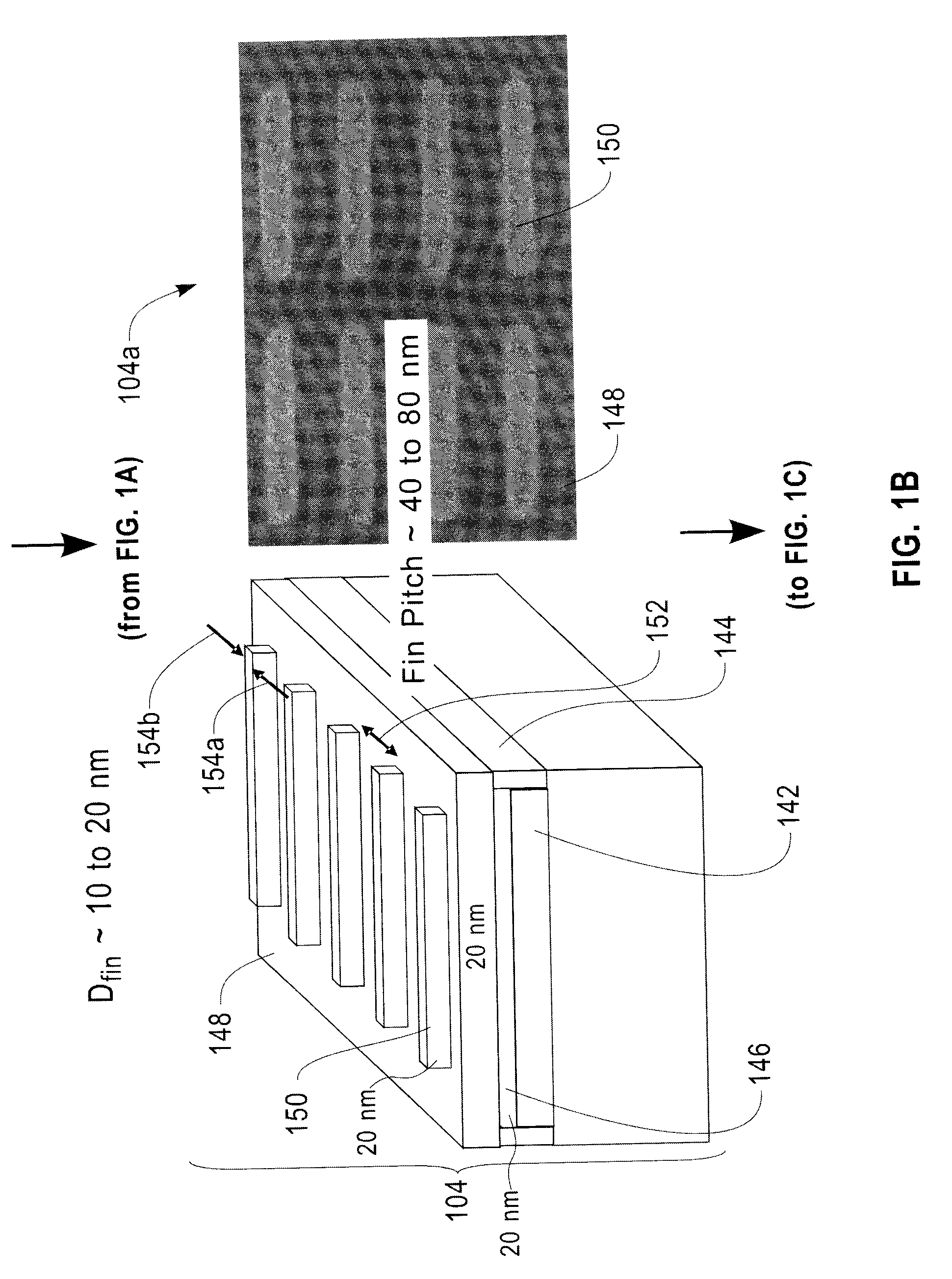

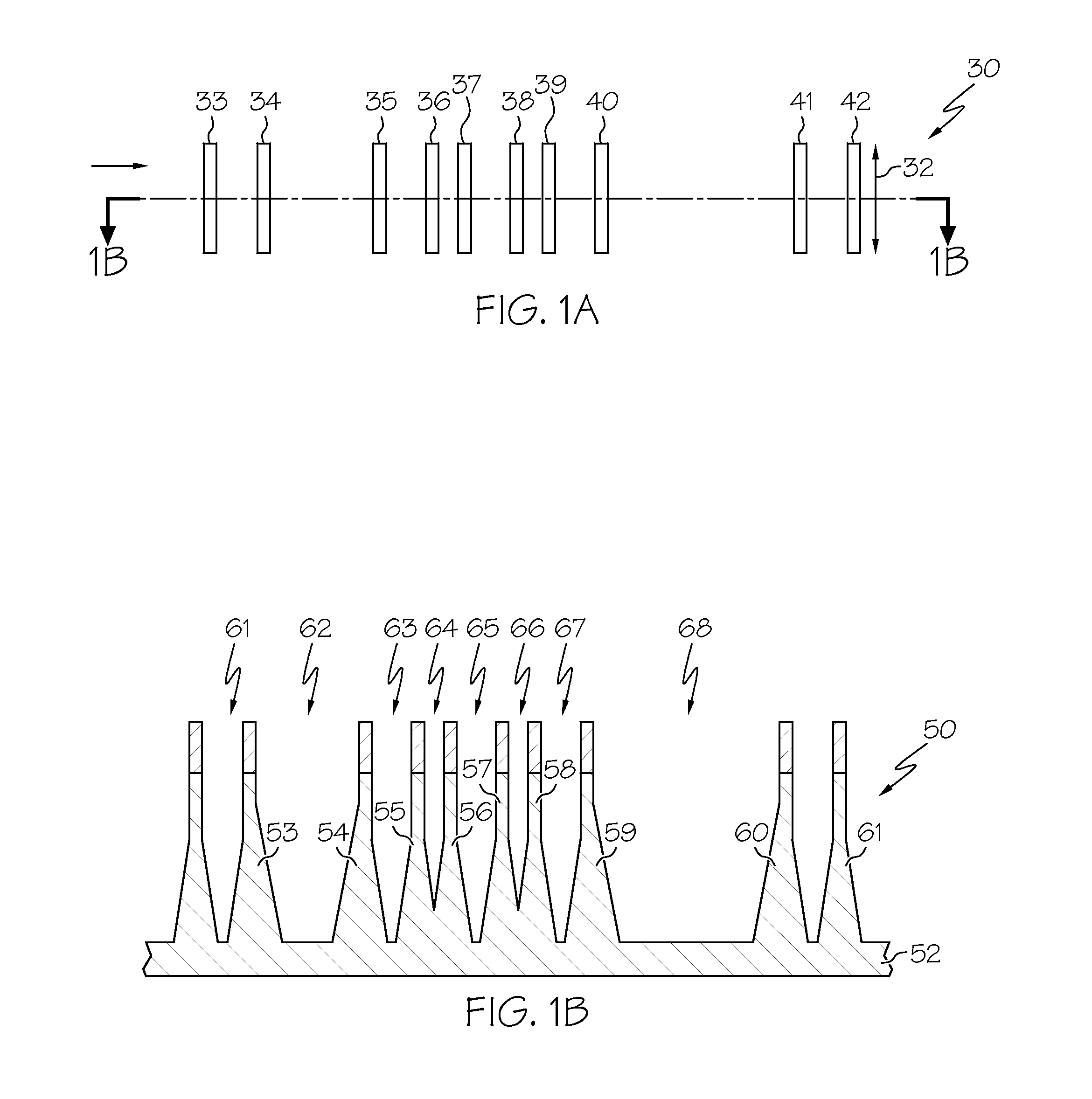

Methods for fabricating finfet integrated circuits on bulk semiconductor substrates

ActiveUS20130309838A1Reduce the overall heightSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

Methods are provided for fabricating FinFET integrated circuits on bulk semiconductor substrates. In accordance with one embodiment a patterned hard mask that defines locations of a regular array of a plurality of fins is formed overlying a semiconductor substrate. Portions of the patterned hard mask are removed using a cut mask to form a modified hard mask. The substrate is etched using the modified hard mask as an etch mask to form a plurality of fins extending upwardly from the substrate and separated by trenches. Selected ones of the plurality of fins are at least partially removed to form isolation regions and an insulating material is deposited to fill the trenches and to cover the at least partially removed selected ones of the plurality of fins.

Owner:GLOBALFOUNDRIES US INC

Field effect transistors having a strained silicon channel and methods of fabricating same

InactiveUS20060076625A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringField-effect transistor

Field effect transistors (FETs) and methods of fabricating FETs that include a channel layer on sidewalls of a structure on a semiconductor substrate and having at least a portion of the channel layer strained in a direction that the sidewalls of the structure extend from the semiconductor substrate are provided. The transistor may be a FinFET, the structure on the semiconductor substrate that includes a fin structure and the sidewalls may be sidewalls of the fin structure. The channel layer may be a Si epitaxial layer and may be on an inner fin structure that includes alternating layers of SiGe and Si. The channel layer may include strained and unstrained portions. The strained and unstrained portions may be sidewalls of the channel layer.

Owner:SAMSUNG ELECTRONICS CO LTD

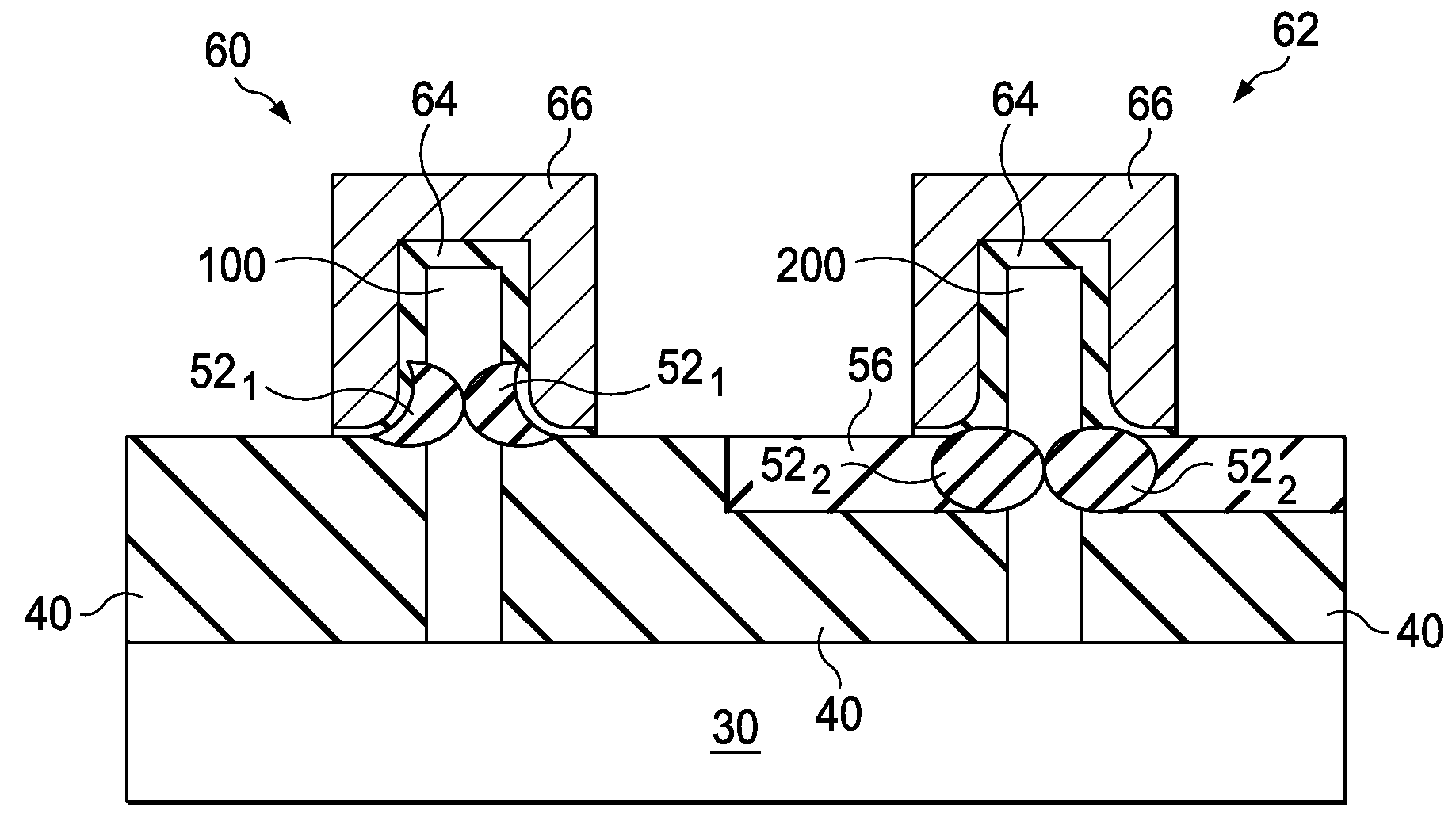

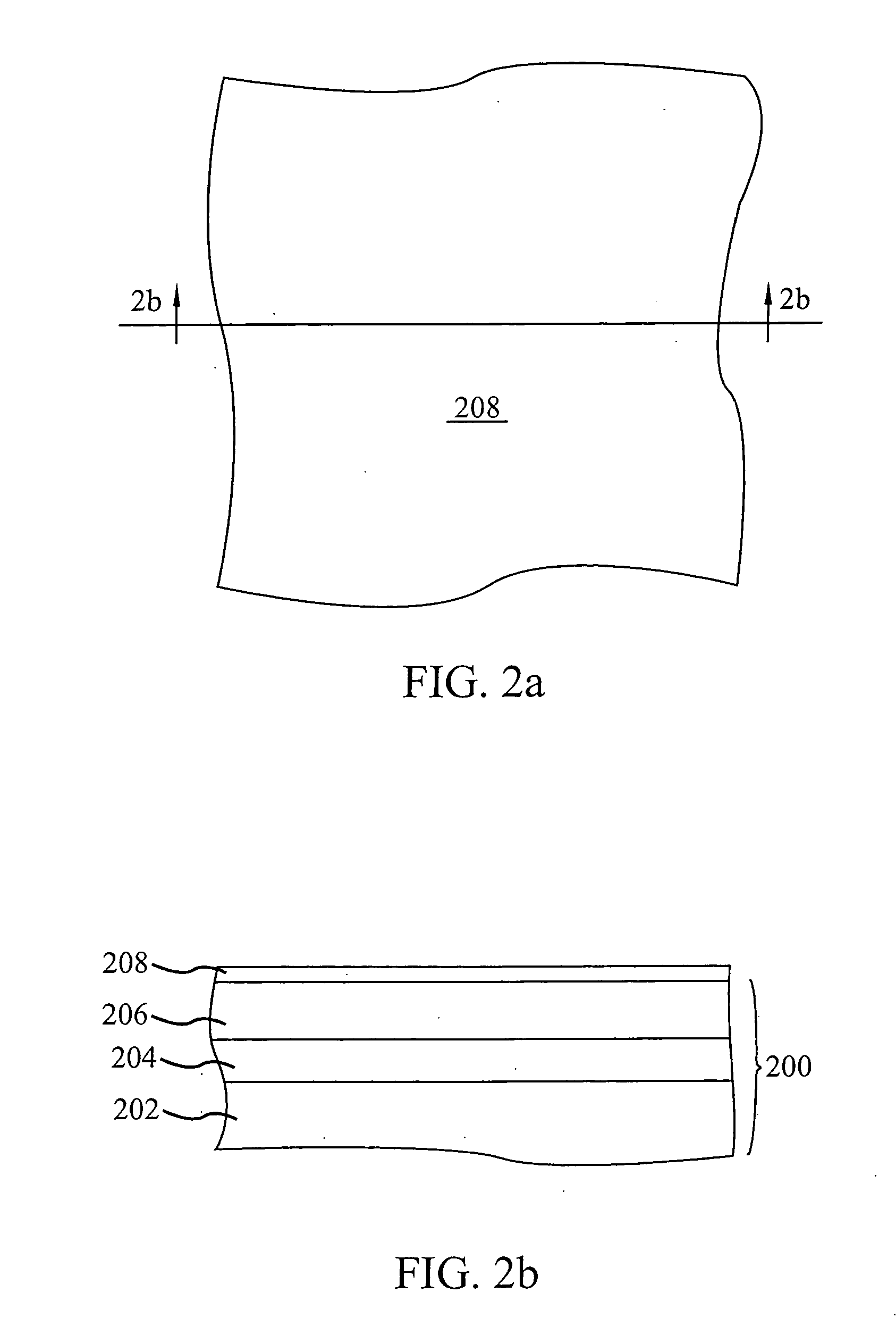

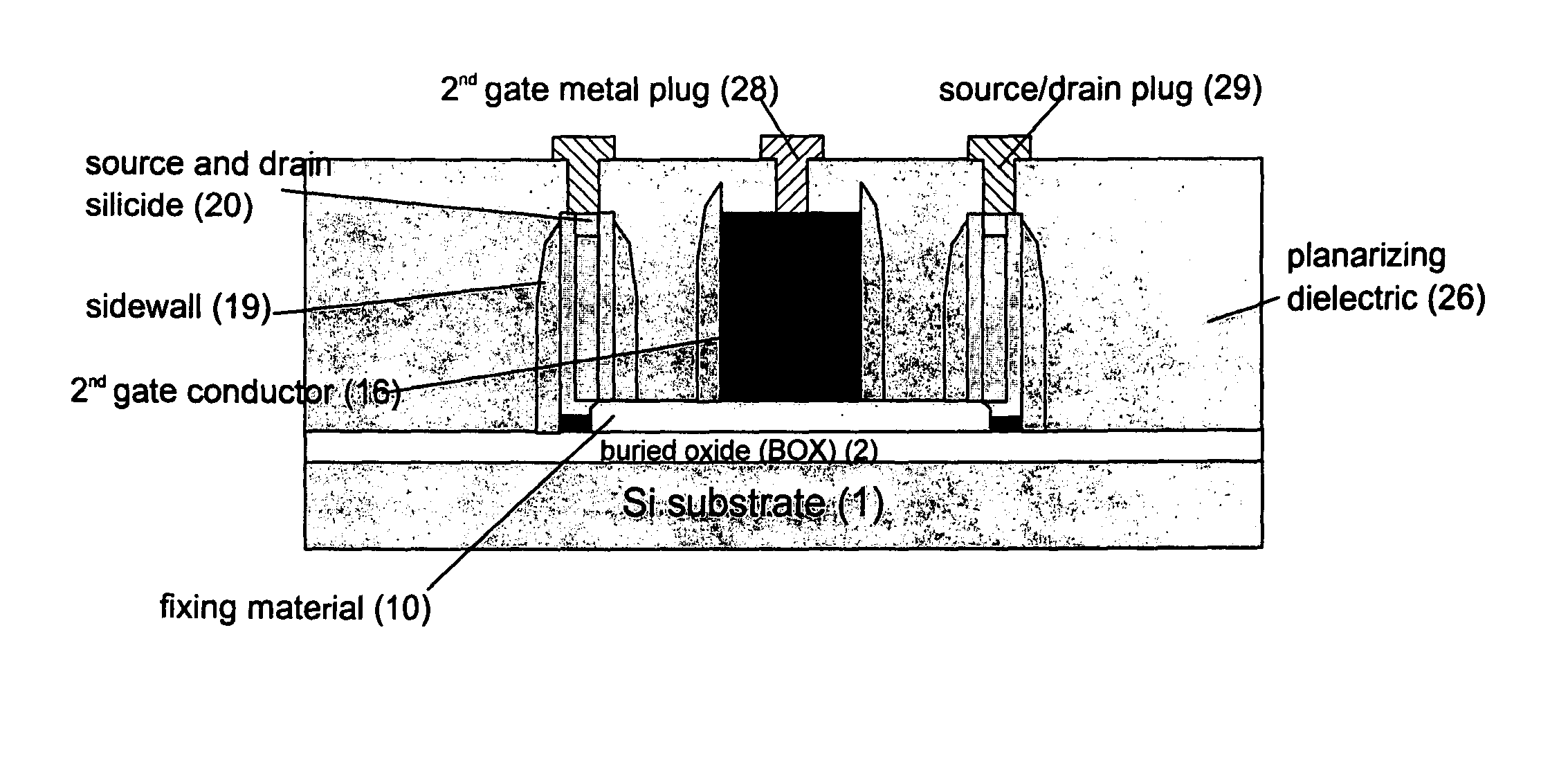

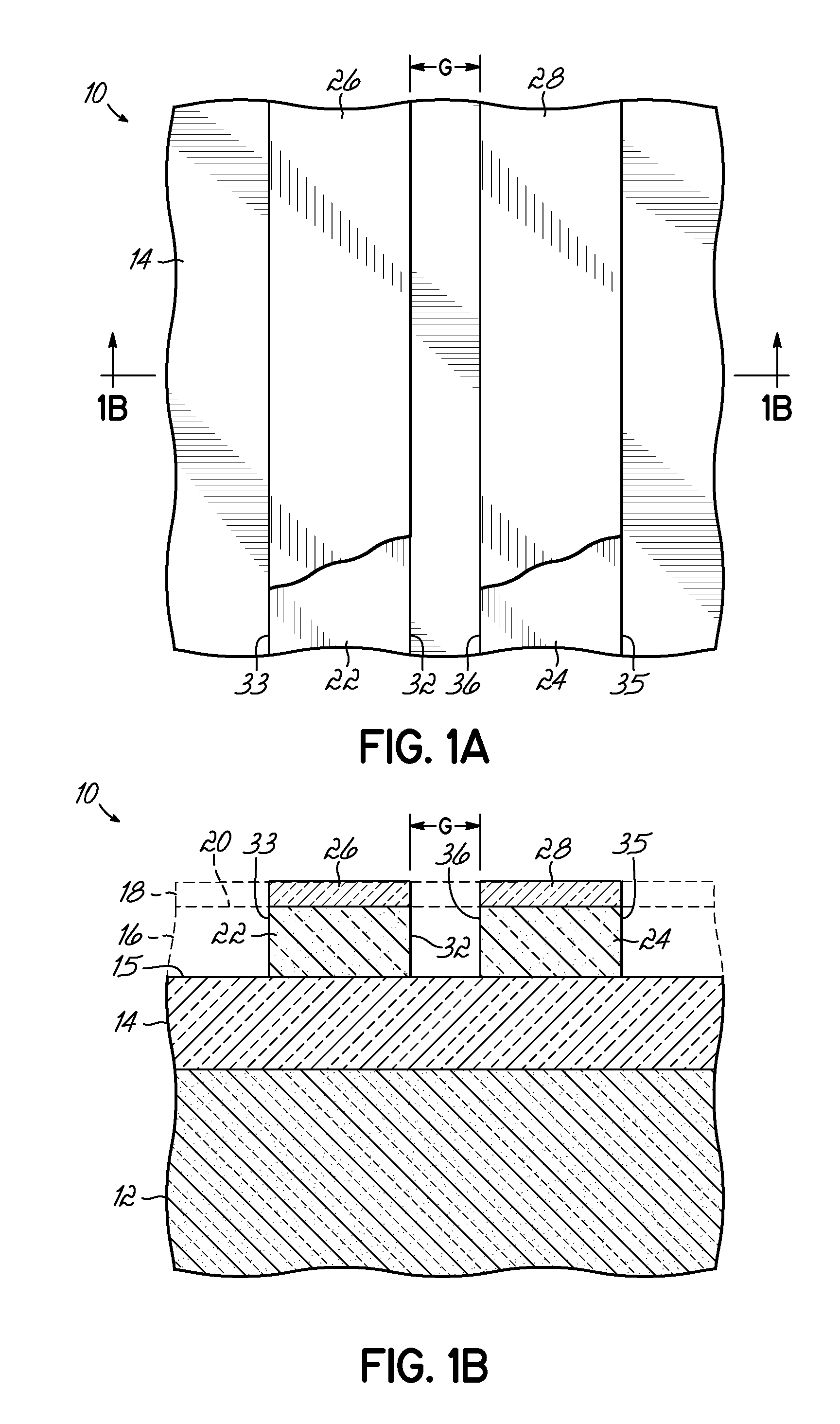

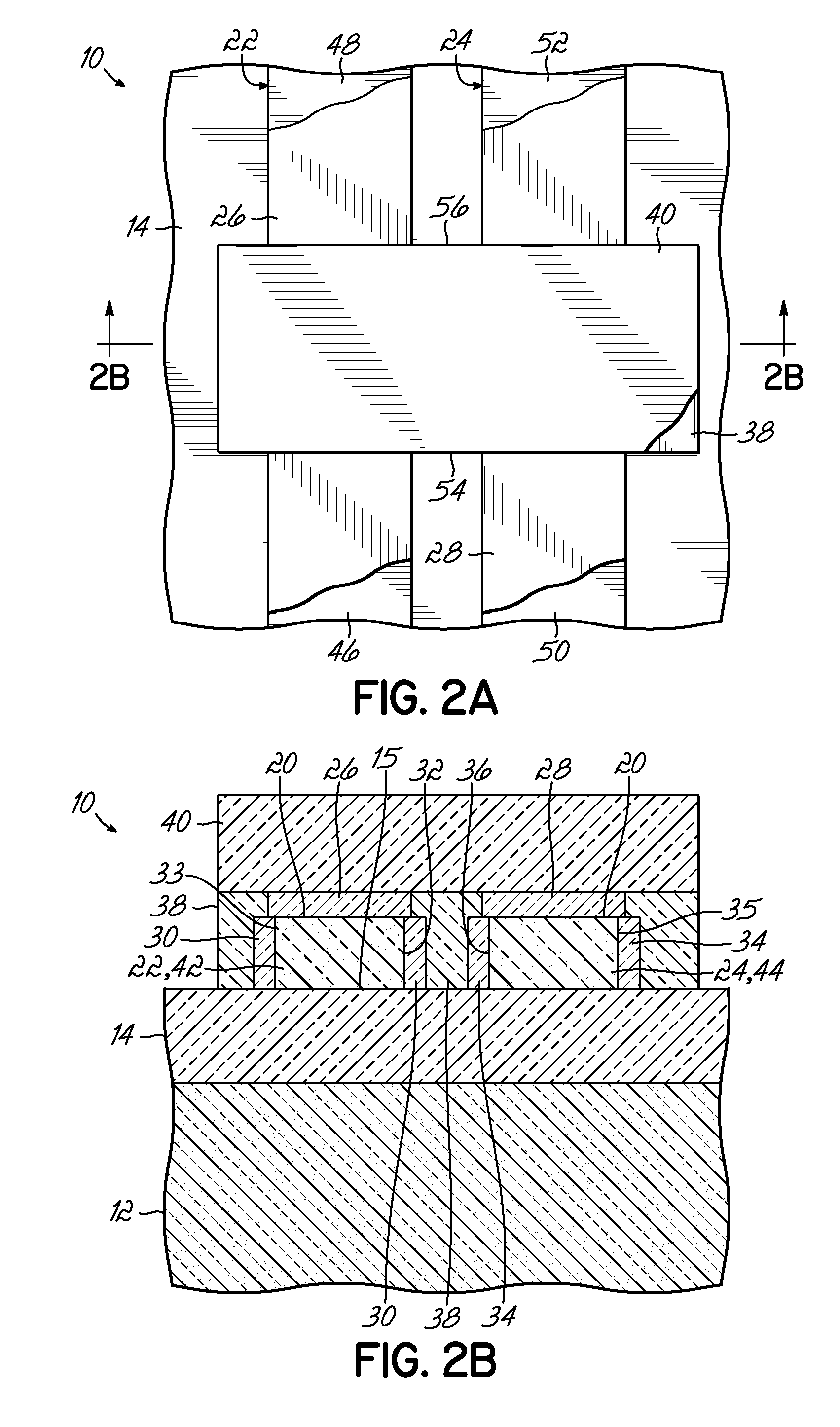

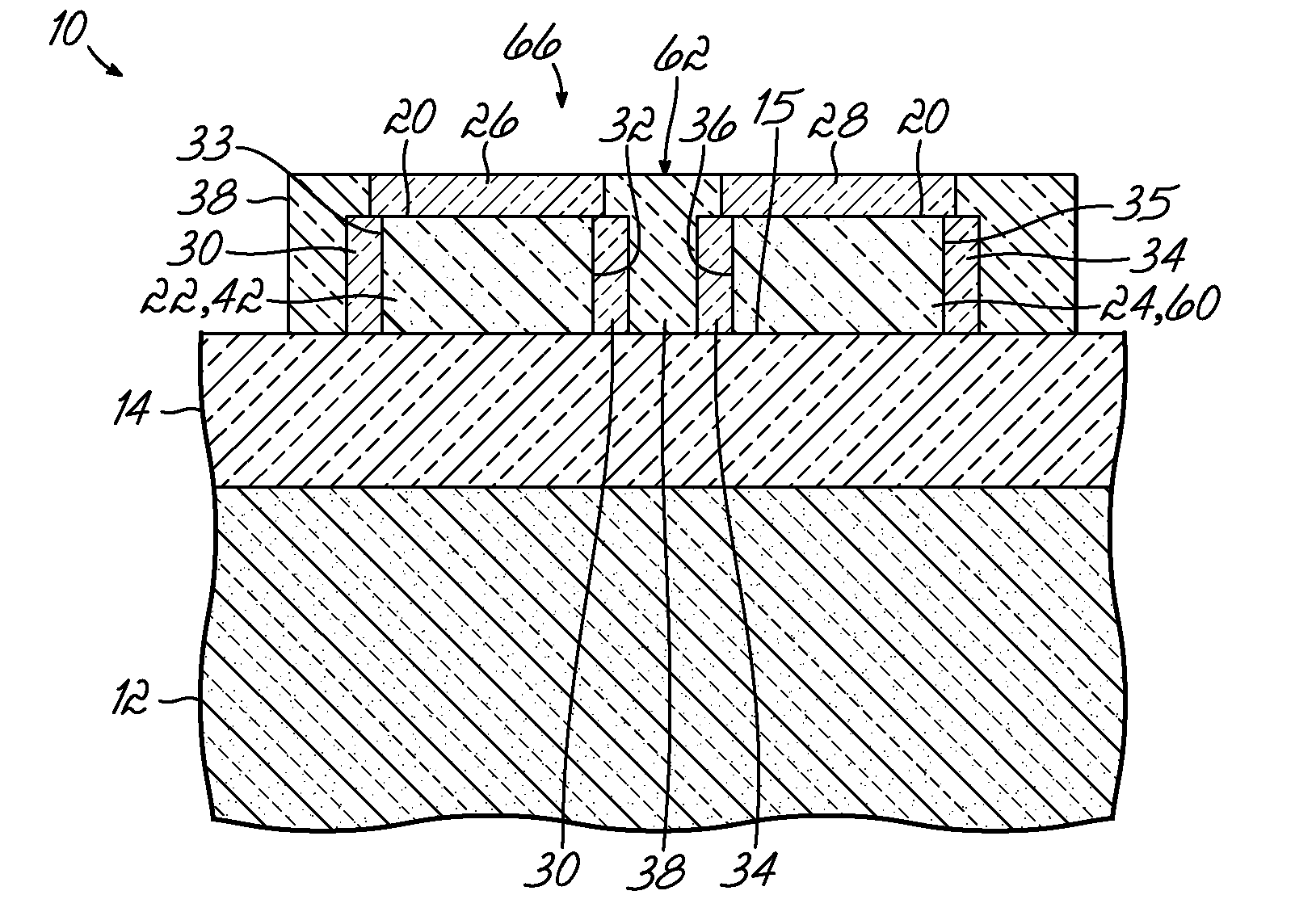

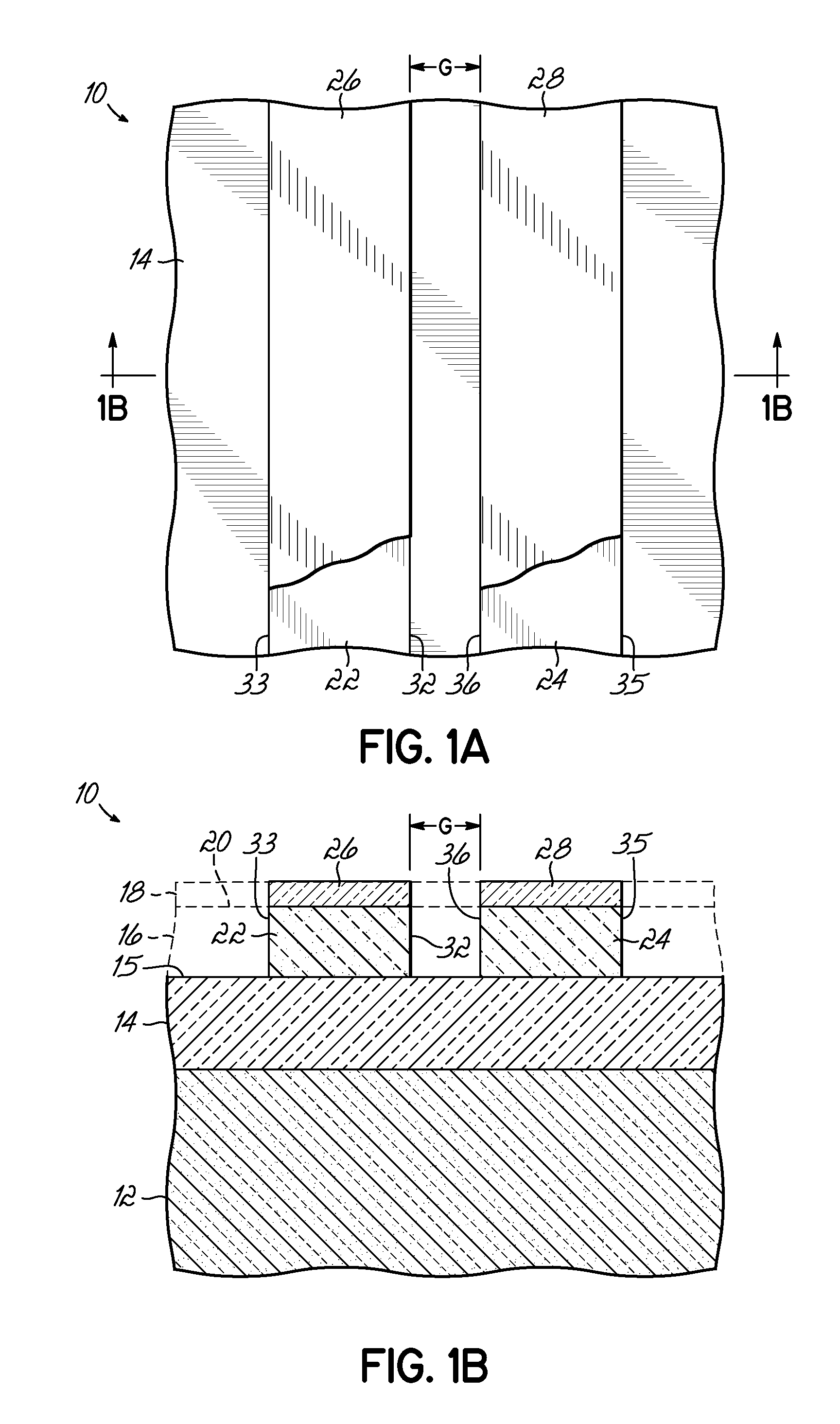

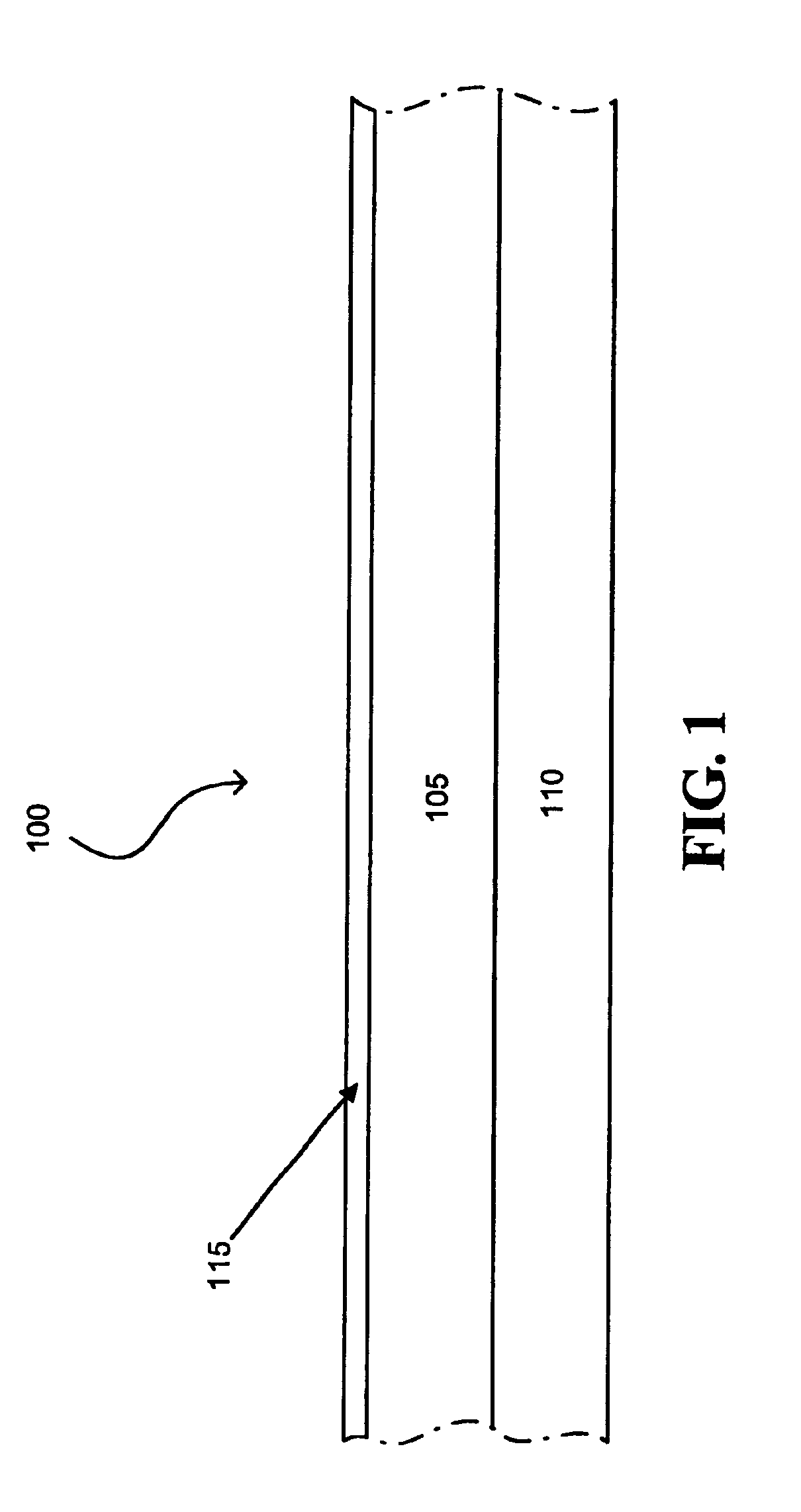

Device structures for a metal-oxide-semiconductor field effect transistor and methods of fabricating such device structures

InactiveUS7790543B2Solid-state devicesSemiconductor/solid-state device manufacturingMOSFETGate dielectric

Device structures for a metal-oxide-semiconductor field effect transistor (MOSFET) that is suitable for operation at relatively high voltages and methods of forming same. The MOSFET, which is formed using a semiconductor-on-insulator (SOI) substrate, includes a channel in a semiconductor body that is self-aligned with a gate electrode. The gate electrode and semiconductor body, which are both formed from the monocrystalline SOI layer of the SOI substrate, are separated by a gap that is filled by a gate dielectric layer. The gate dielectric layer may be composed of thermal oxide layers grown on adjacent sidewalls of the semiconductor body and gate electrode, in combination with an optional deposited dielectric material that fills the remaining gap between the thermal oxide layers.

Owner:GLOBALFOUNDRIES INC

Device structures for a metal-oxide-semiconductor field effect transistor and methods of fabricating such device structures

InactiveUS20090179266A1Solid-state devicesSemiconductor/solid-state device manufacturingMOSFETGate dielectric

Device structures for a metal-oxide-semiconductor field effect transistor (MOSFET) that is suitable for operation at relatively high voltages and methods of forming same. The MOSFET, which is formed using a semiconductor-on-insulator (SOI) substrate, includes a channel in a semiconductor body that is self-aligned with a gate electrode. The gate electrode and semiconductor body, which are both formed from the monocrystalline SOI layer of the SOI substrate, are separated by a gap that is filled by a gate dielectric layer. The gate dielectric layer may be composed of thermal oxide layers grown on adjacent sidewalls of the semiconductor body and gate electrode, in combination with an optional deposited dielectric material that fills the remaining gap between the thermal oxide layers.

Owner:GLOBALFOUNDRIES INC

Methods of forming fin field effect transistors using oxidation barrier layers and related devices

A method of forming a fin field effect transistor on a semiconductor substrate includes forming a fin-shaped active region vertically protruding from the substrate. An oxide layer is formed on a top surface and opposing sidewalls of the fin-shaped active region. An oxidation barrier layer is formed on the opposing sidewalls of the fin-shaped active region and is planarized to a height no greater than about a height of the oxide layer to form a fin structure. The fin structure is oxidized to form a capping oxide layer on the top surface of the fin-shaped active region and to form at least one curved sidewall portion proximate the top surface of the fin-shaped active region. The oxidation barrier layer has a height sufficient to reduce oxidation on the sidewalls of the fin-shaped active region about halfway between the top surface and a base of the fin-shaped active region. Related devices are also discussed.

Owner:SAMSUNG ELECTRONICS CO LTD

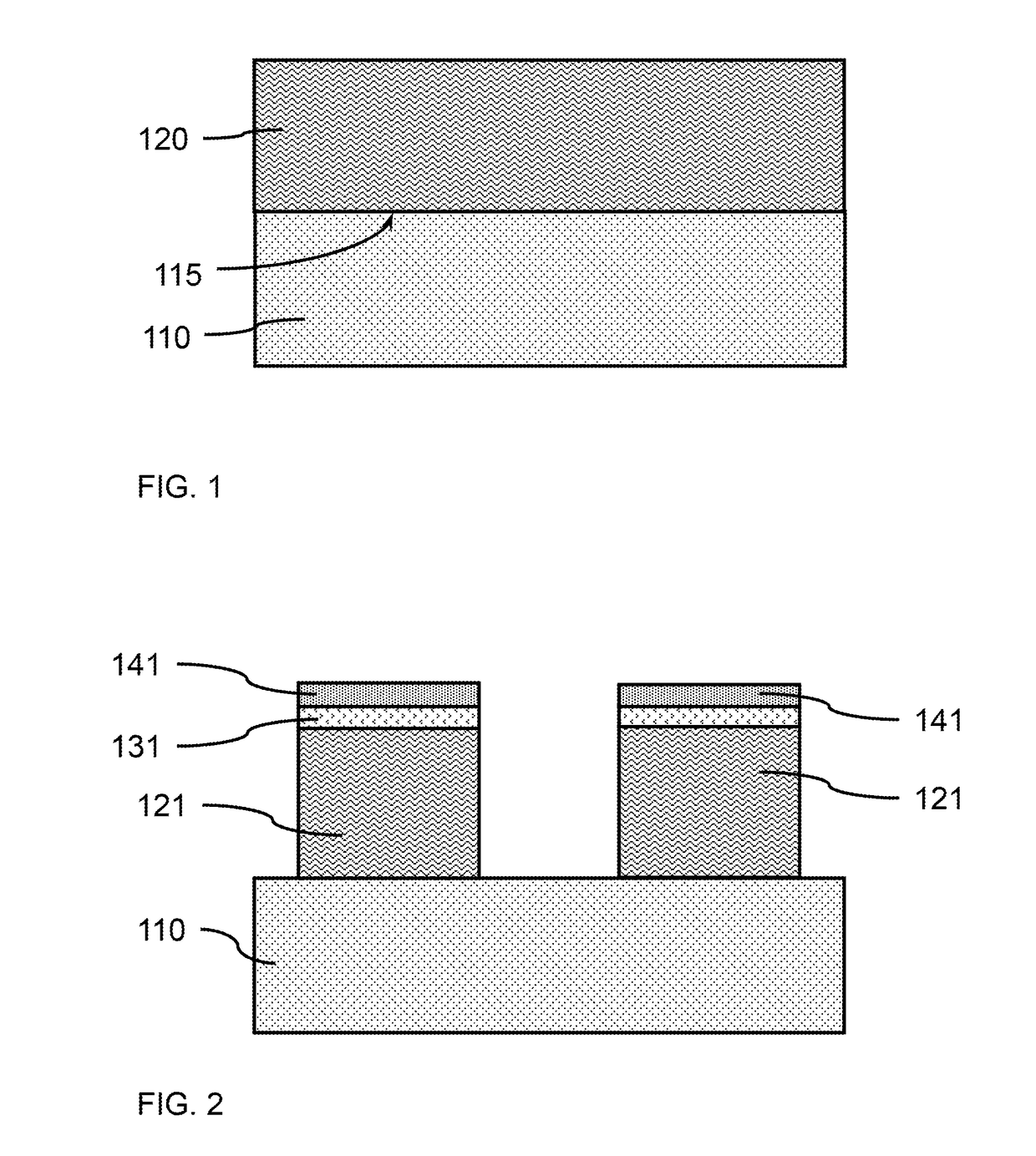

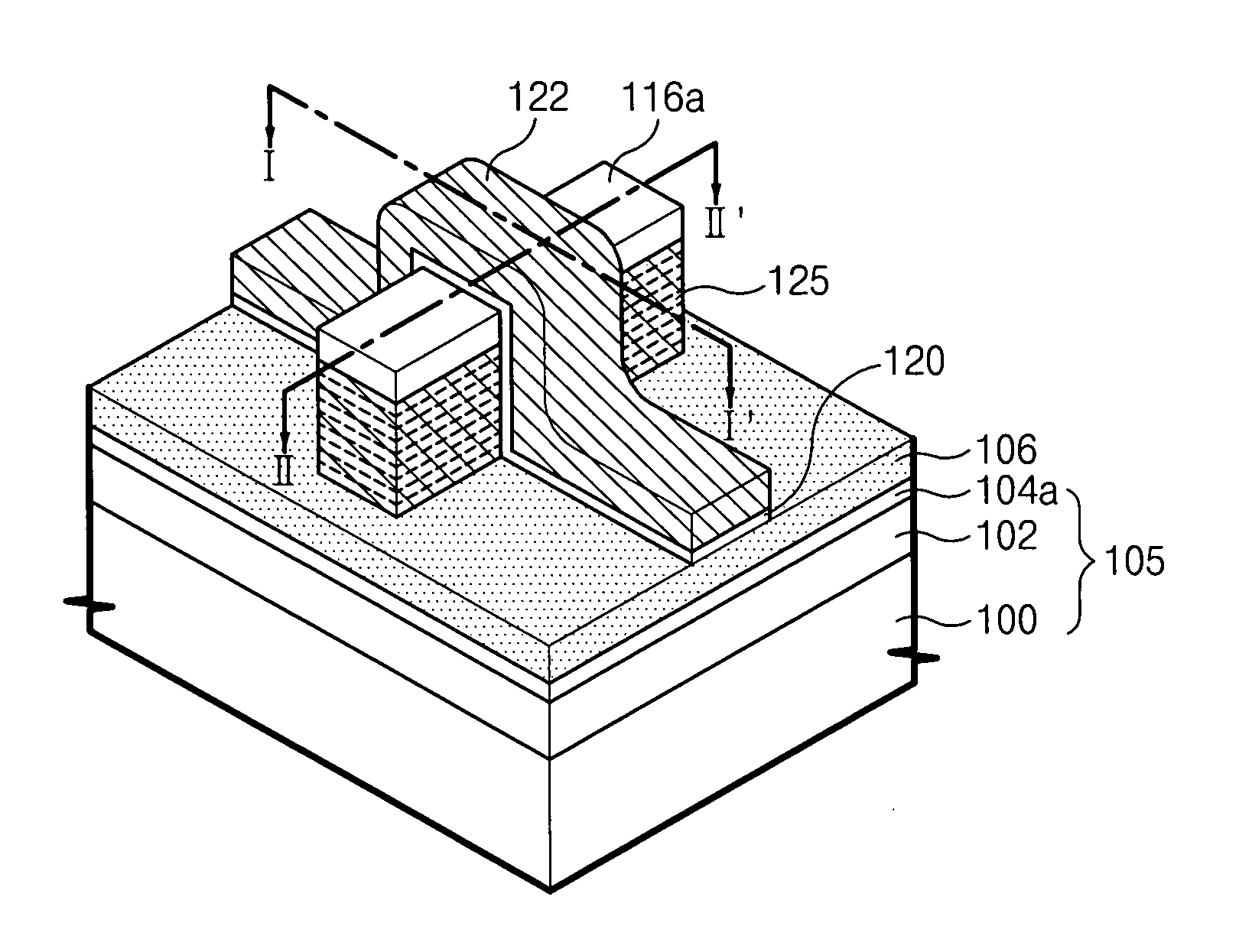

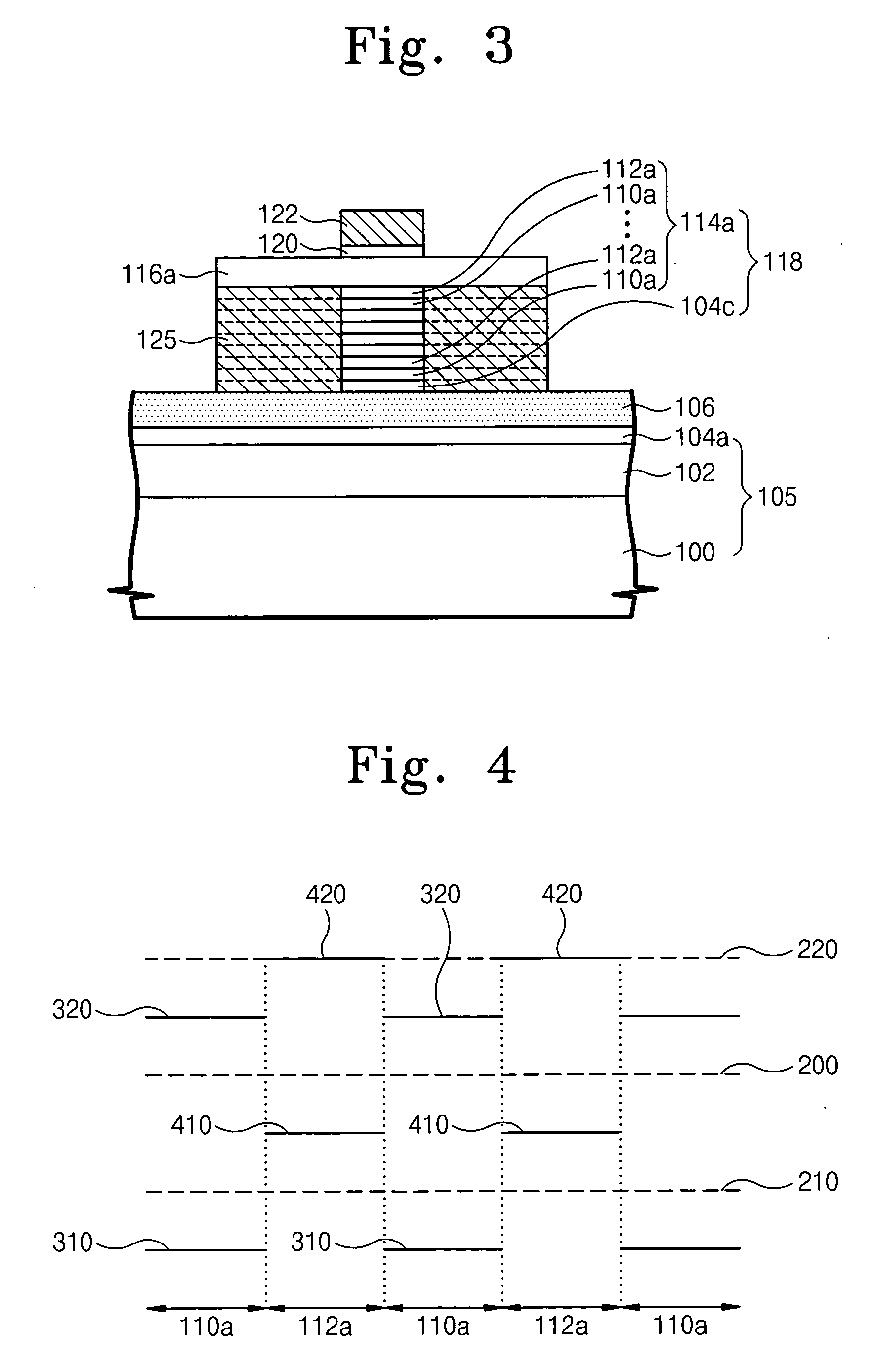

Fin field effect transistors having multi-layer fin patterns and methods of forming the same

ActiveUS20050184316A1Increase heightRelieve pressureTransistorSemiconductor/solid-state device manufacturingCarrier signalEngineering

A fin field effect transistor has a fin pattern protruding from a semiconductor substrate. The fin pattern includes first semiconductor patterns and second semiconductor patterns which are stacked. The first and second semiconductor patterns have lattice widths that are greater than a lattice width of the substrate in at least one direction. In addition, the first and second semiconductor patterns may be alternately stacked to increase the height of the fin pattern, such that one of the first and second patterns can reduce stress from the other of the first and second patterns. The first and second semiconductor patterns may be formed of strained silicon and silicon-germanium, where the silicon-germanium patterns can reduce stress from the strained silicon patterns. Therefore, both the number of carriers and the mobility of carriers in the transistor channel may be increased, improving performance of the fin field effect transistor. Related methods are also discussed.

Owner:SAMSUNG ELECTRONICS CO LTD

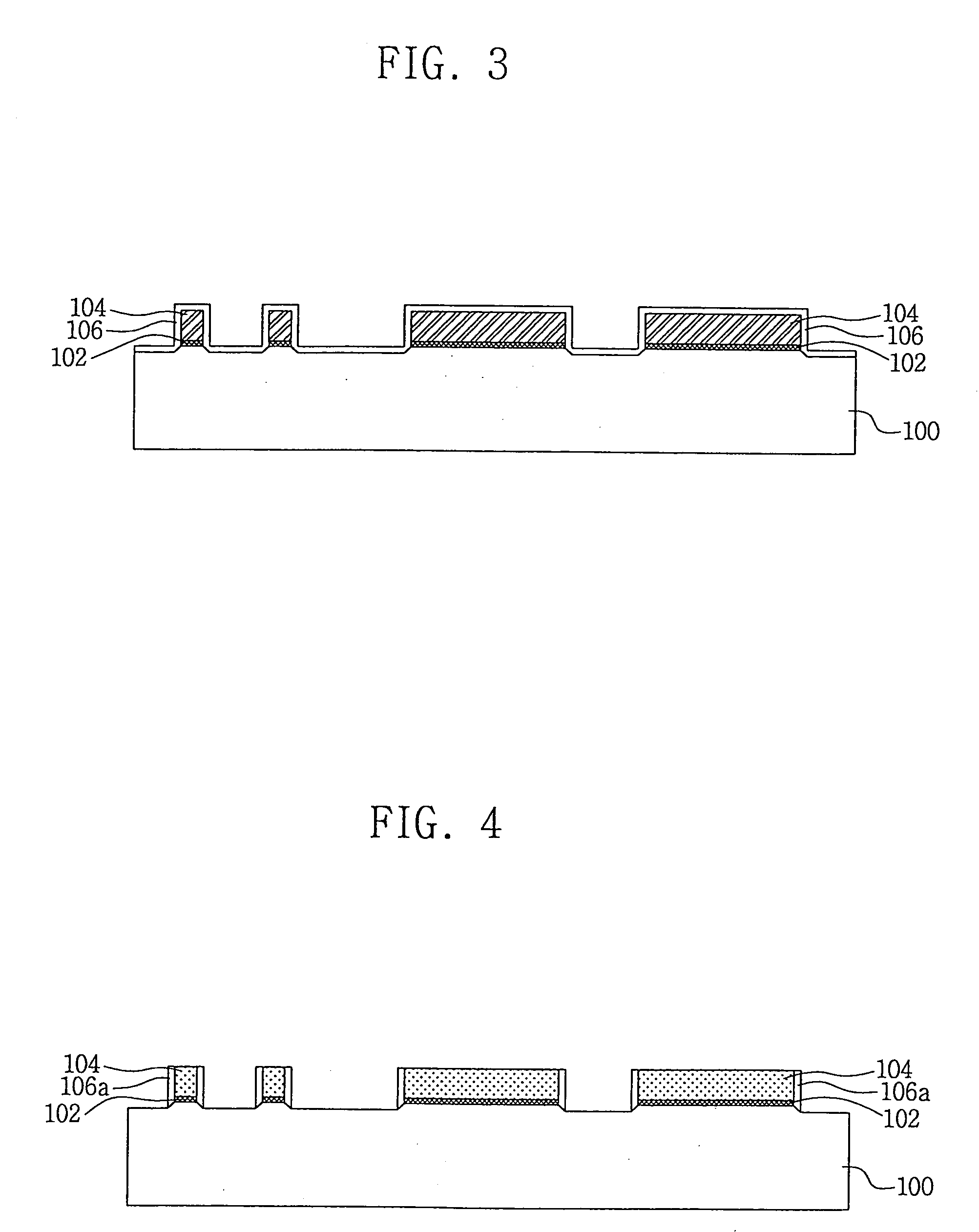

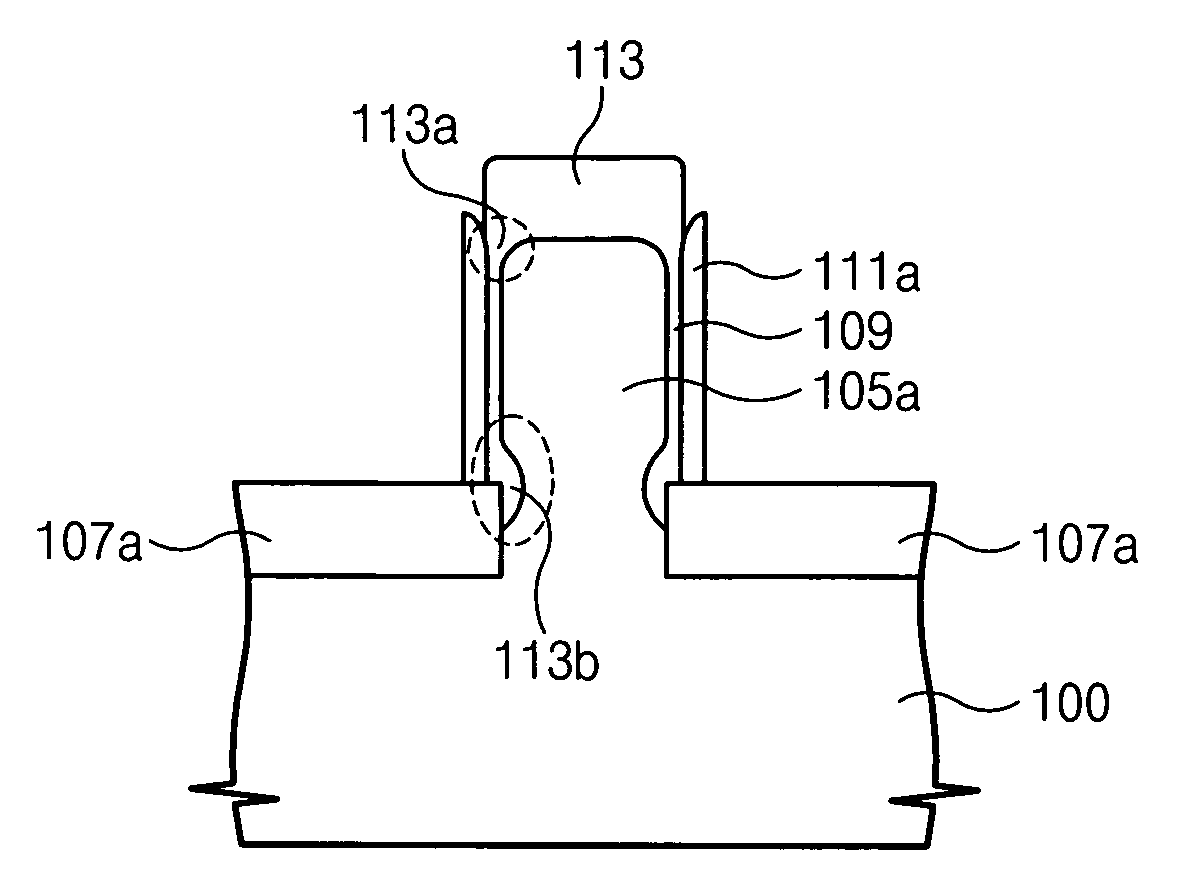

Methods for fabricating fin field effect transistors using a protective layer to reduce etching damage

A method of forming a fin field effect transistor on a semiconductor substrate includes forming a vertical fin protruding from the substrate. A buffer oxide liner is formed on a top surface and on sidewalls of the fin. A trench is then formed on the substrate, where at least a portion of the fin protrudes from a bottom surface of the trench. The trench may be formed by forming a dummy gate on at least a portion of the fin, forming an insulation layer on the fin surrounding the dummy gate, and then removing the dummy gate to expose the at least a portion of the fin, such that the trench is surrounded by the insulation layer. The buffer oxide liner is then removed from the protruding portion of the fin, and a gate is formed in the trench on the protruding portion of the fin.

Owner:SAMSUNG ELECTRONICS CO LTD

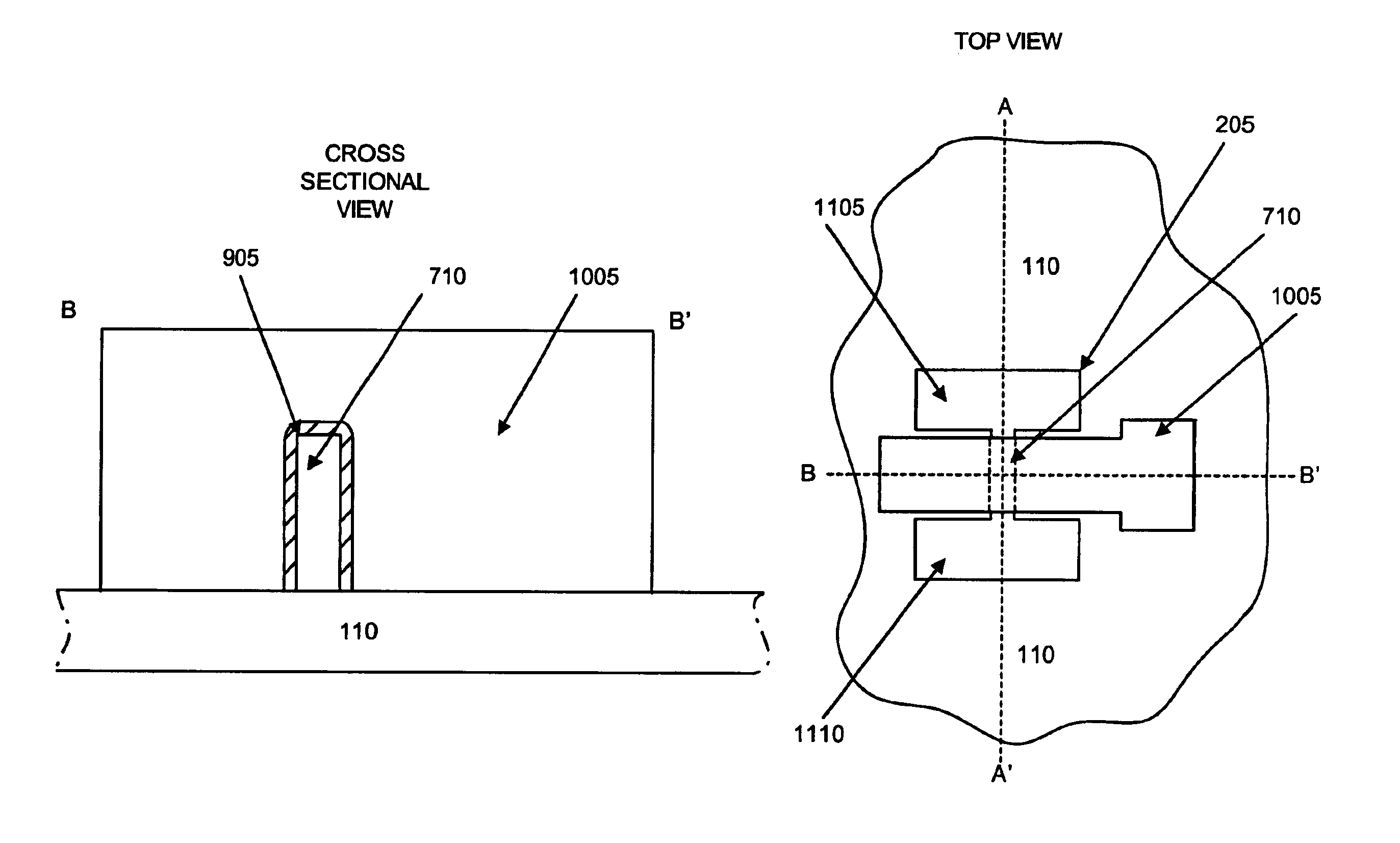

Fin Field-Effect Transistors

A fin field-effect transistor (finFET) with improved source / drain regions is provided. In an embodiment, the source / drain regions of the fin are removed while spacers adjacent to the fin remain. An angled implant is used to implant the source / drain regions near a gate electrode, thereby allowing for a more uniform lightly doped drain. The fin may be re-formed by either epitaxial growth or a metallization process. In another embodiment, the spacers adjacent the fin in the source / drain regions are removed and the fin is silicided along the sides and the top of the fin. In yet another embodiment, the fin and the spacers are removed in the source / drain regions. The fins are then re-formed via an epitaxial growth process or a metallization process. Combinations of these embodiments may also be used.

Owner:TAIWAN SEMICON MFG CO LTD

Methods of forming fin field effect transistors using oxidation barrier layers

Owner:SAMSUNG ELECTRONICS CO LTD

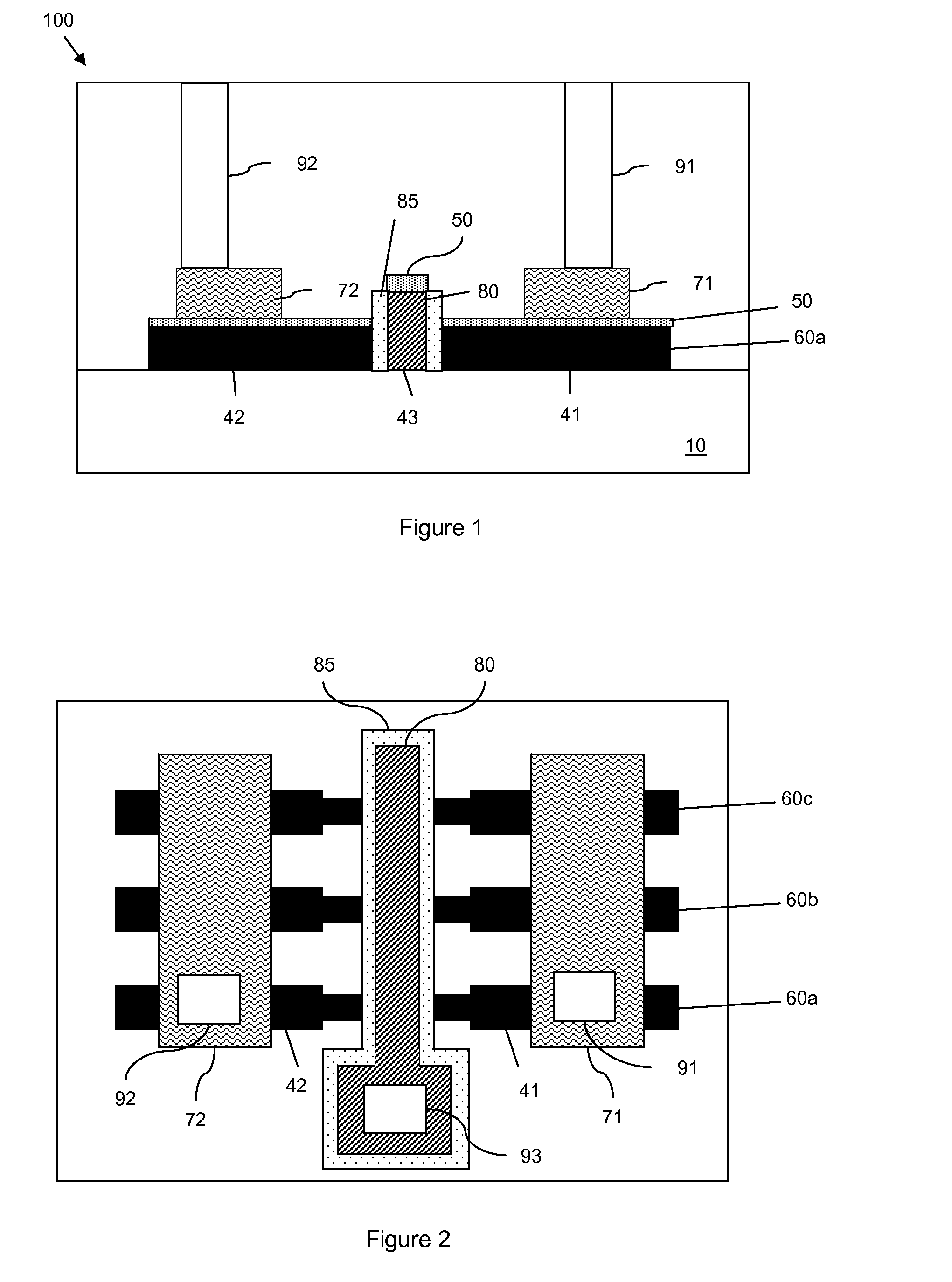

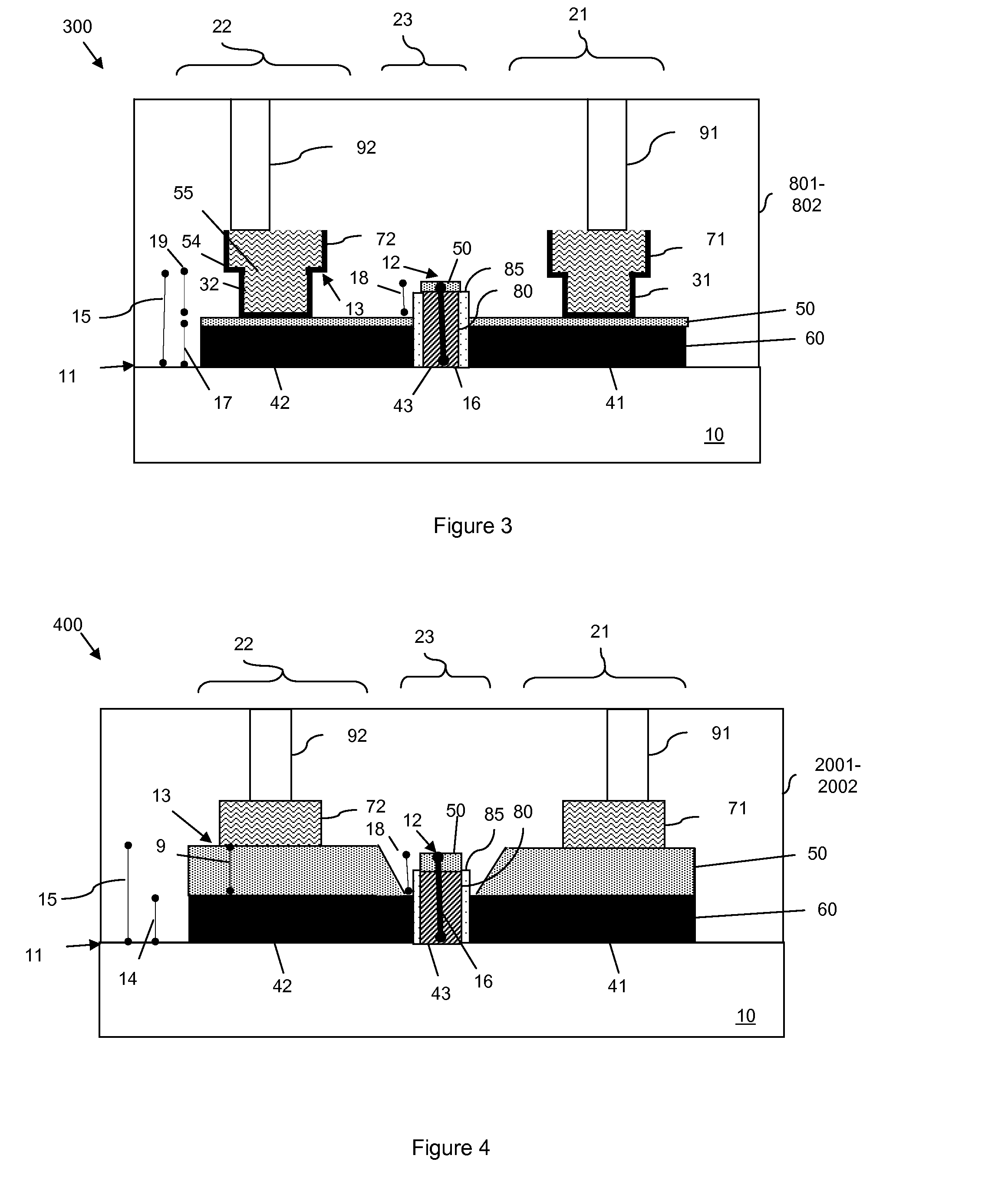

Integrated circuit structures with multiple FinFETs

ActiveUS20080296702A1Reduce resultReduce decreaseTransistorSolid-state devicesSemiconductor structureEngineering

A semiconductor structure includes a semiconductor substrate; and a first Fin field-effect transistor (FinFET) and a second FinFET at a surface of the semiconductor substrate. The first FinFET includes a first fin; and a first gate electrode over a top surface and sidewalls of the first fin. The second FinFET includes a second fin spaced apart from the first fin by a fin space; and a second gate electrode over a top surface and sidewalls of the second fin. The second gate electrode is electrically disconnected from the first gate electrode. The first and the second gate electrodes have a gate height greater than about one half of the fin space.

Owner:ADVANCED MFG INNOVATIONS INC

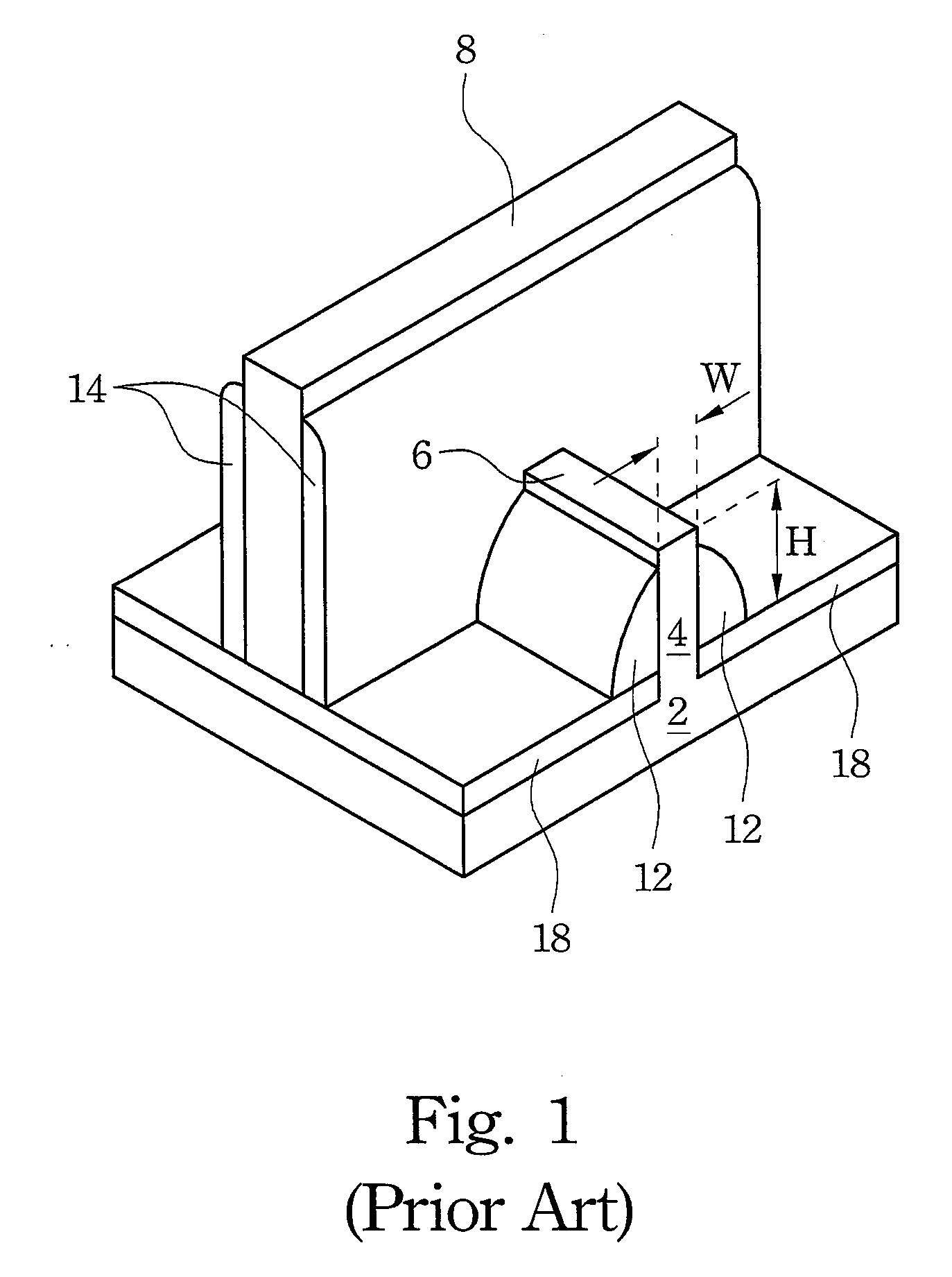

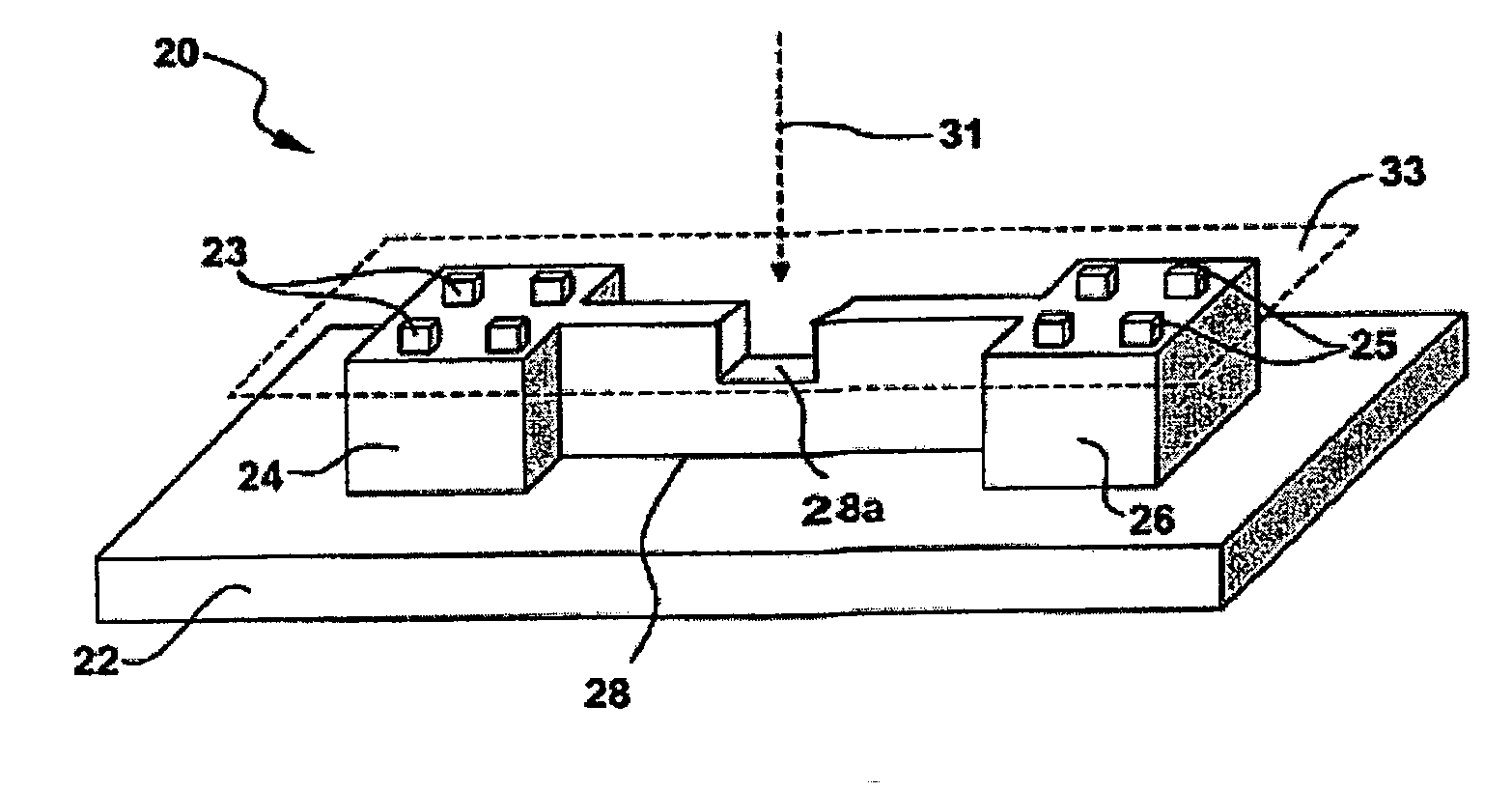

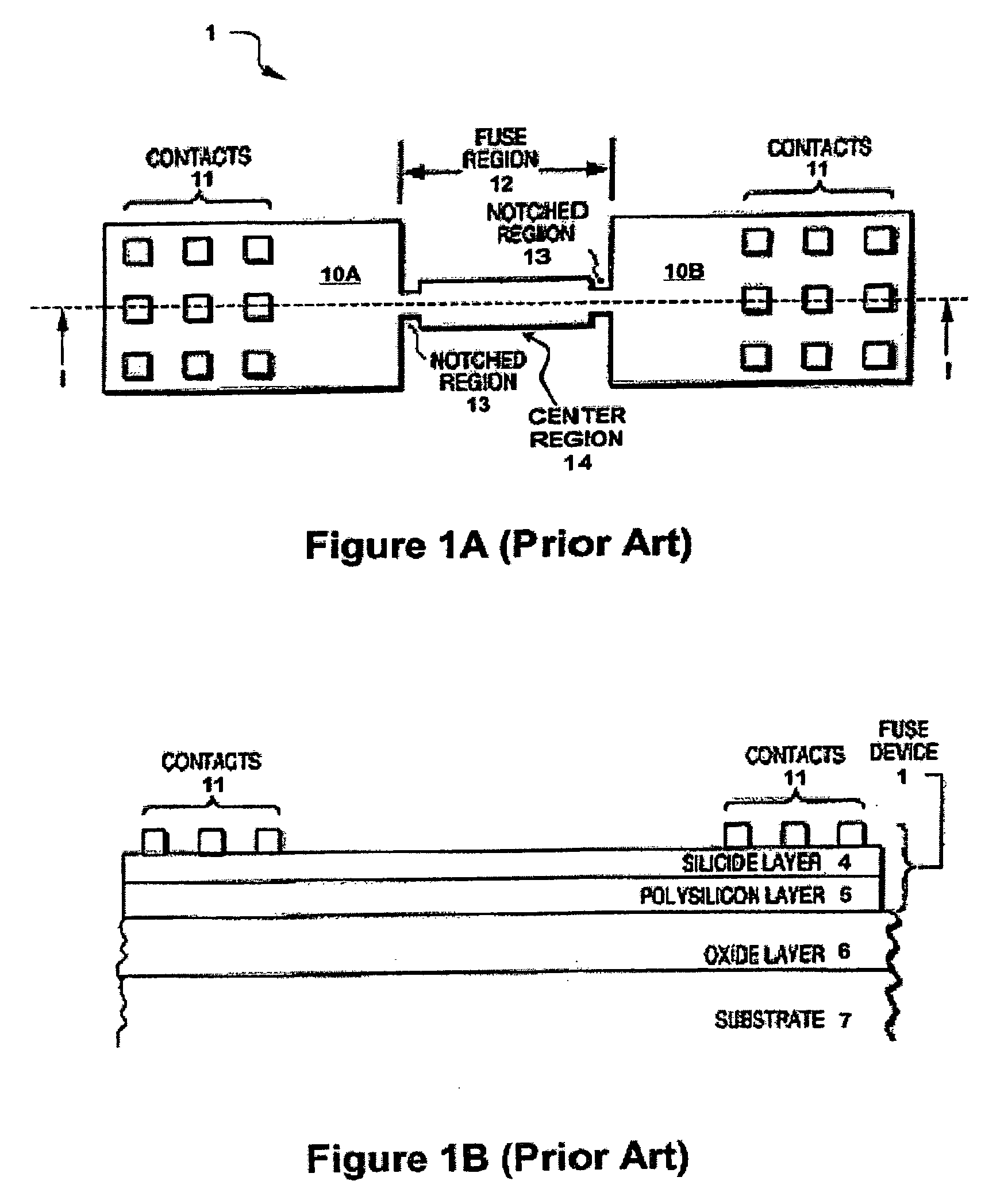

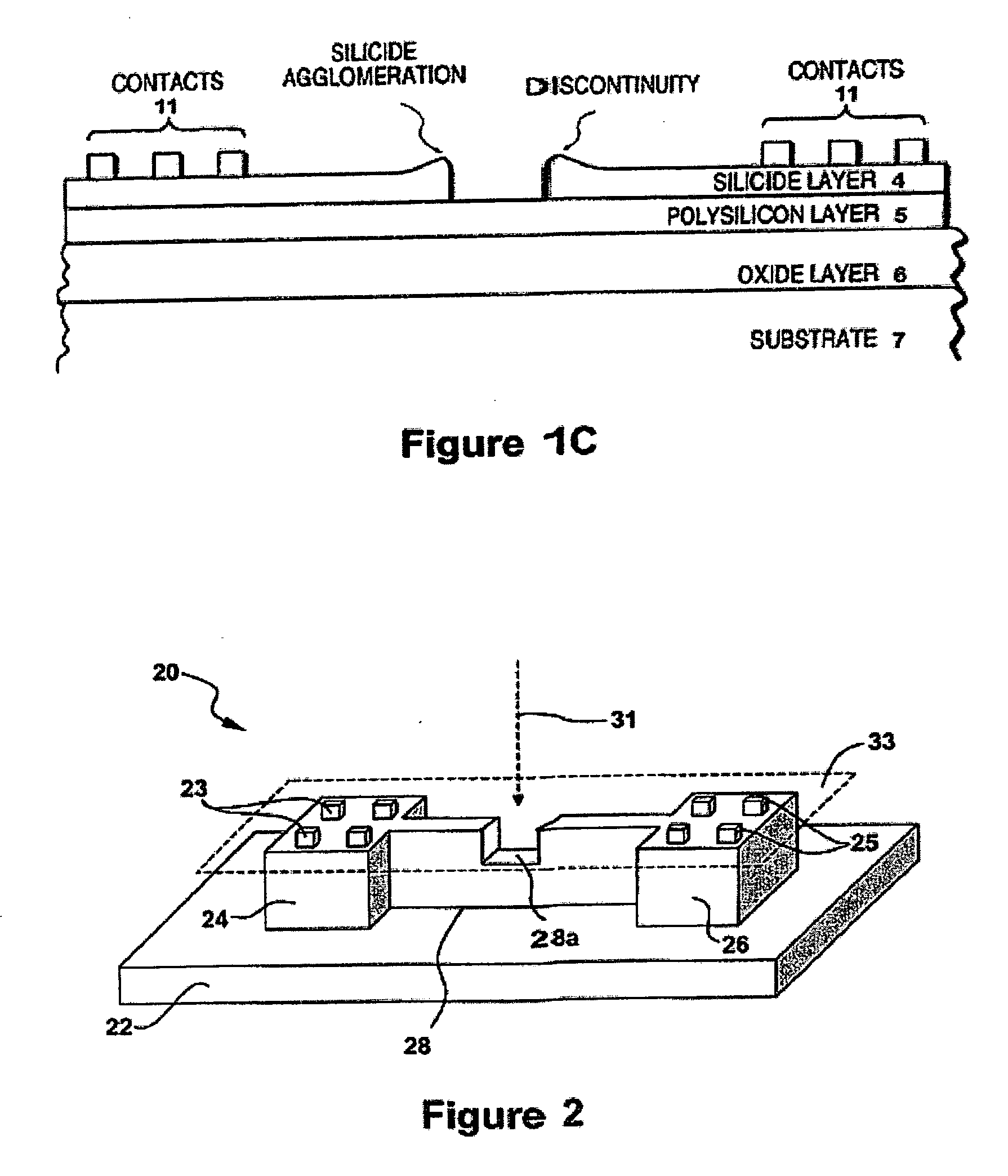

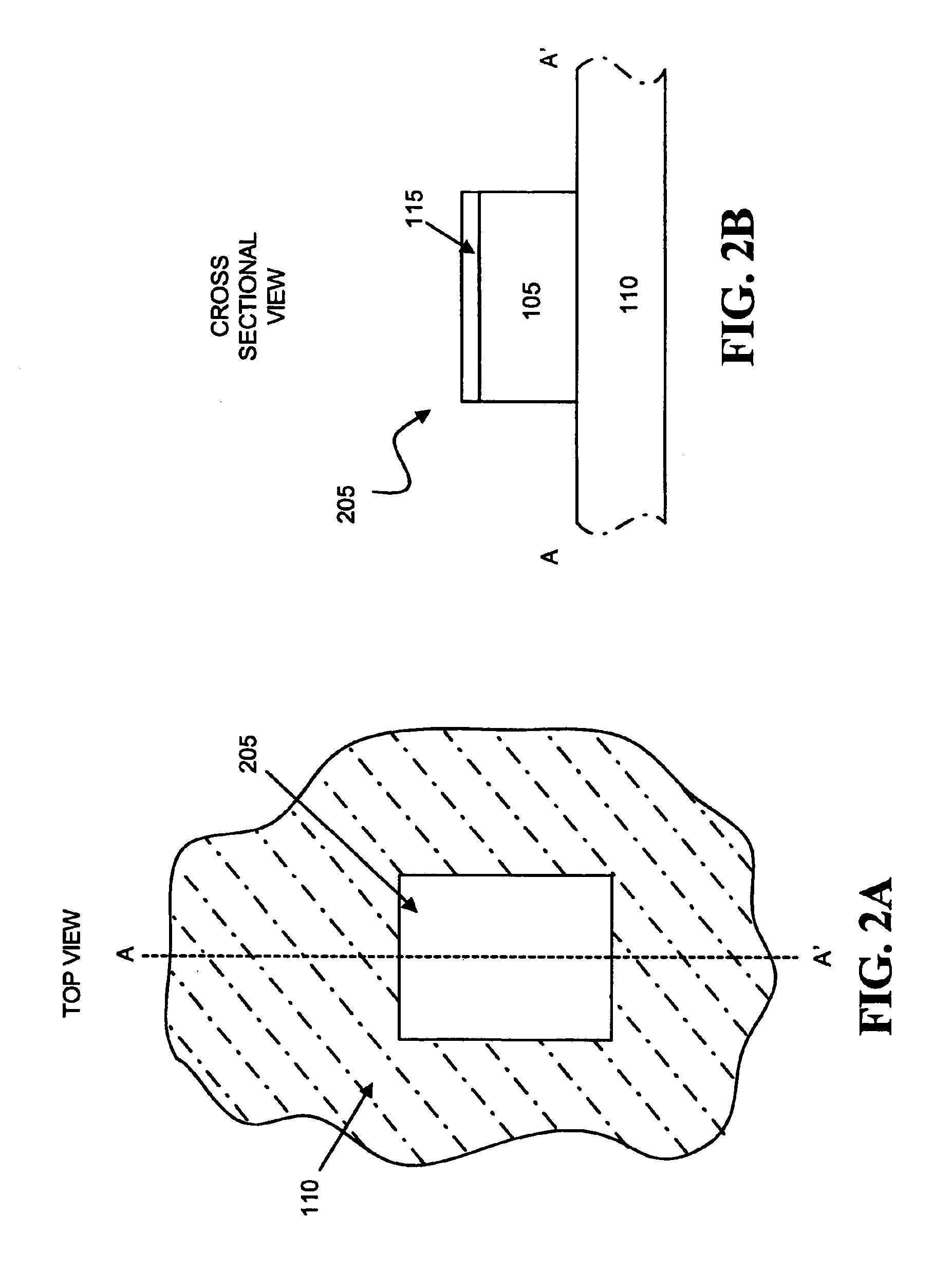

Programmable semiconductor device containing a vertically notched fusible link region and methods of making and using same

InactiveUS20070029576A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

The present invention relates to a programmable semiconductor device, preferably a FinFET or tri-gate structure, that contains a first contact element, a second contact element, and at least one fin-shaped fusible link region coupled between the first and second contact elements. The second contact element is laterally spaced apart from the first contact element, and the fin-shaped fusible link region has a vertically notched section. A programming current flowing through the fin-shaped fusible link region causes either significant resistance increase or formation of an electric discontinuity in the vertically notched section. Alternatively, the vertically notched section may contain a dielectric material, and application of a programming voltage between a gate electrode overlaying the vertically notched section and one of the contact elements breaks down the dielectric material and allows current flow between the gate electrode and the fin-shaped fusible link region.

Owner:IBM CORP

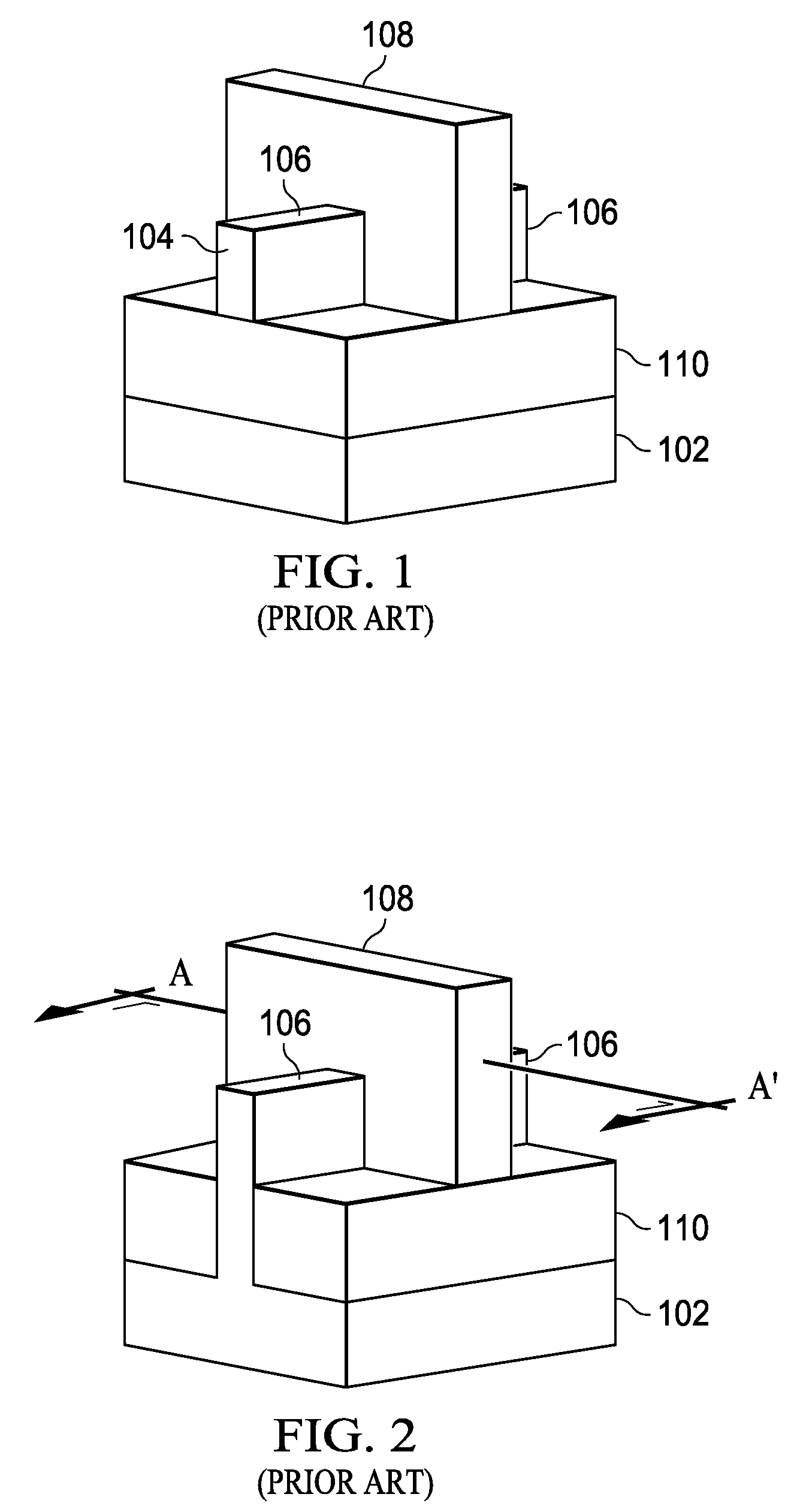

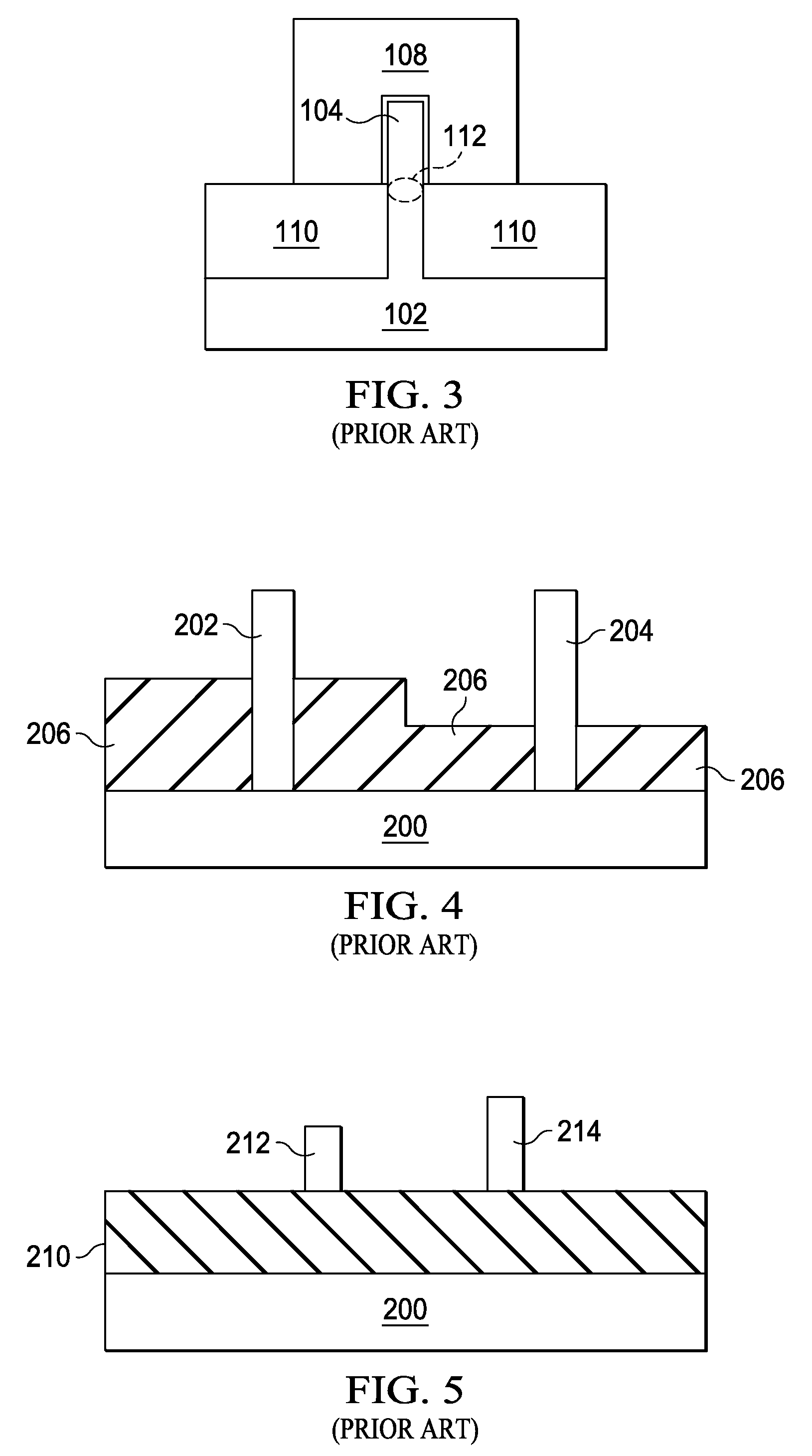

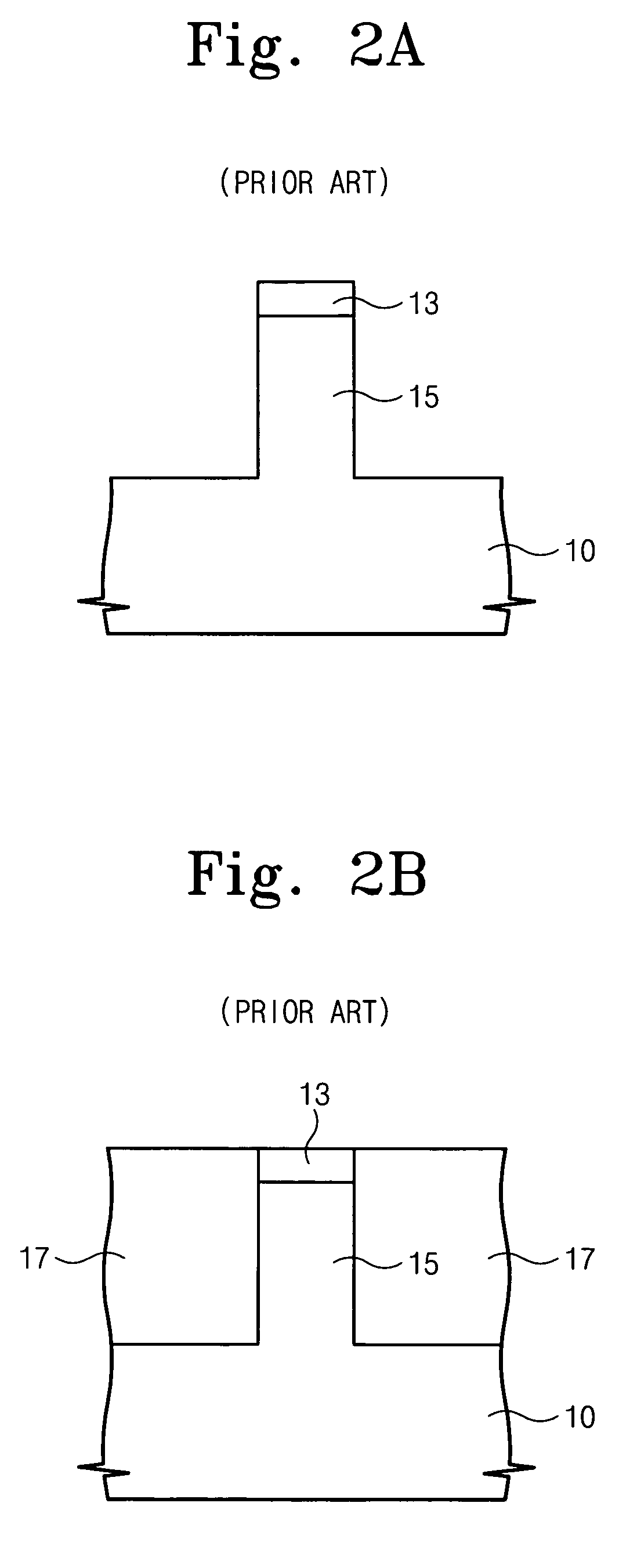

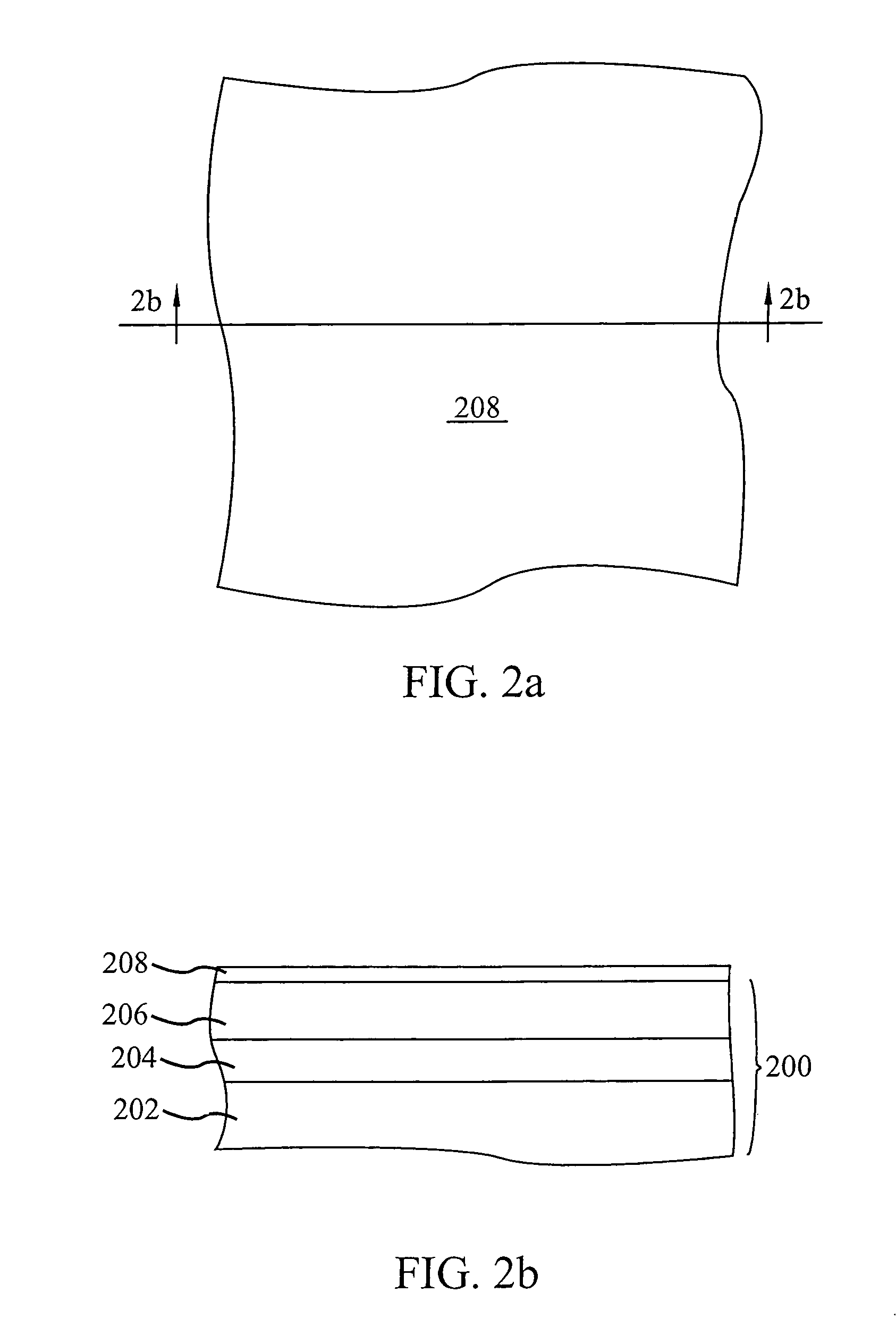

Method for forming tri-gate FinFET with mesa isolation

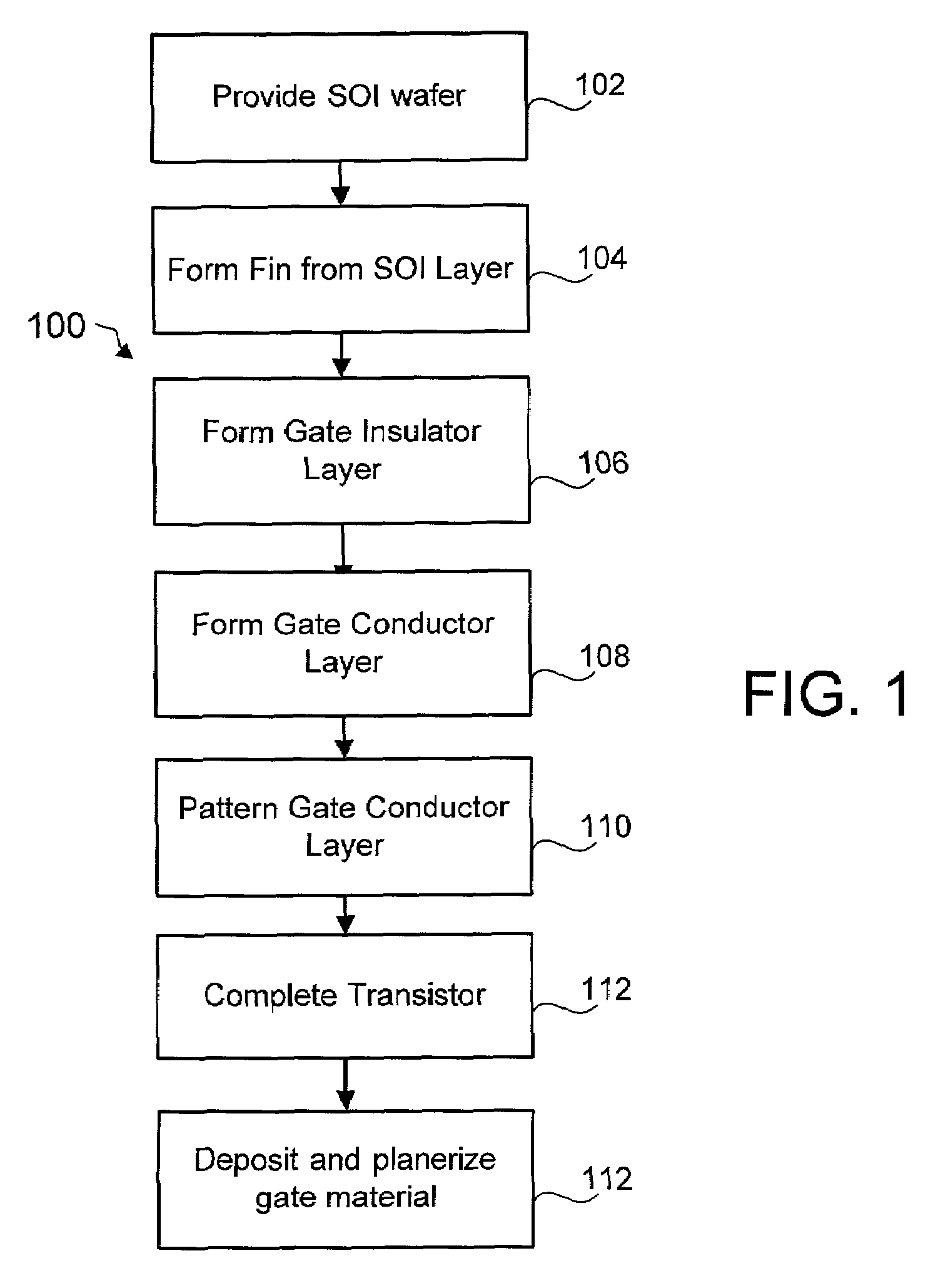

InactiveUS6855583B1TransistorSemiconductor/solid-state device manufacturingGate dielectricSilicon on insulator

A method forming a tri-gate fin field effect transistor includes forming an oxide layer over a silicon-on-insulator wafer comprising a silicon layer, and etching the silicon and oxide layers using a rectangular mask to form a mesa. The method further includes etching a portion of the mesa using a second mask to form a fin, forming a gate dielectric layer over the fin, and forming a tri-gate over the fin and the gate dielectric layer.

Owner:GLOBALFOUNDRIES INC

FinFET SRAM cell using low mobility plane for cell stability and method for forming

InactiveUS7087477B2Accurate operationSolid-state devicesSemiconductor/solid-state device manufacturingStatic random-access memoryLow mobility

The present invention provides a device design and method for forming the same that results in Fin Field Effect Transistors having different gains without negatively impacting device density. The present invention forms relatively low gain FinFET transistors in a low carrier mobility plane and relatively high gain FinFET transistors in a high carrier mobility plane. Thus formed, the FinFETs formed in the high mobility plane have a relatively higher gain than the FinFETs formed in the low mobility plane. The embodiments are of particular application to the design and fabrication of a Static Random Access Memory (SRAM) cell. In this application, the bodies of the n-type FinFETs used as transfer devices are formed along the {110} plane. The bodies of the n-type FinFETs and p-type FinFETs used as the storage latch are formed along the {100}. Thus formed, the transfer devices will have a gain approximately half that of the n-type storage latch devices, facilitating proper SRAM operation.

Owner:GLOBALFOUNDRIES INC

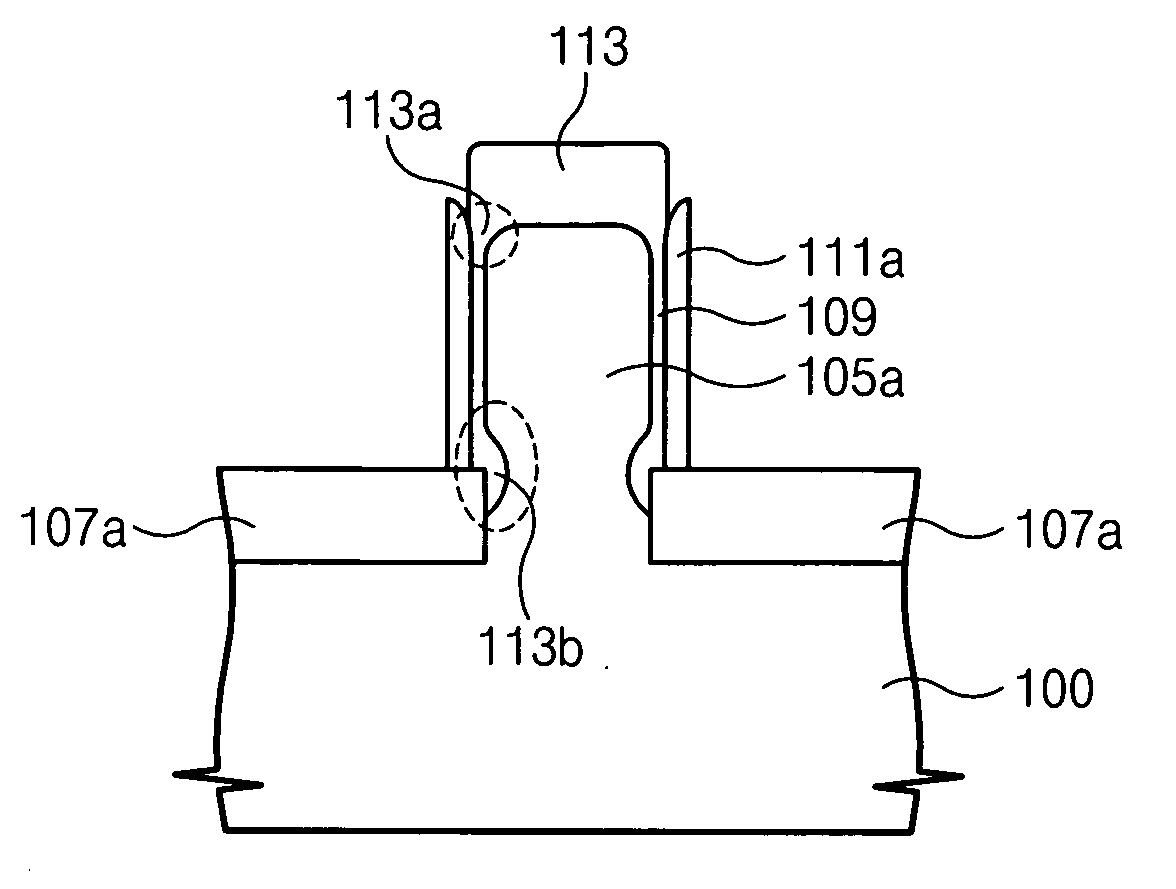

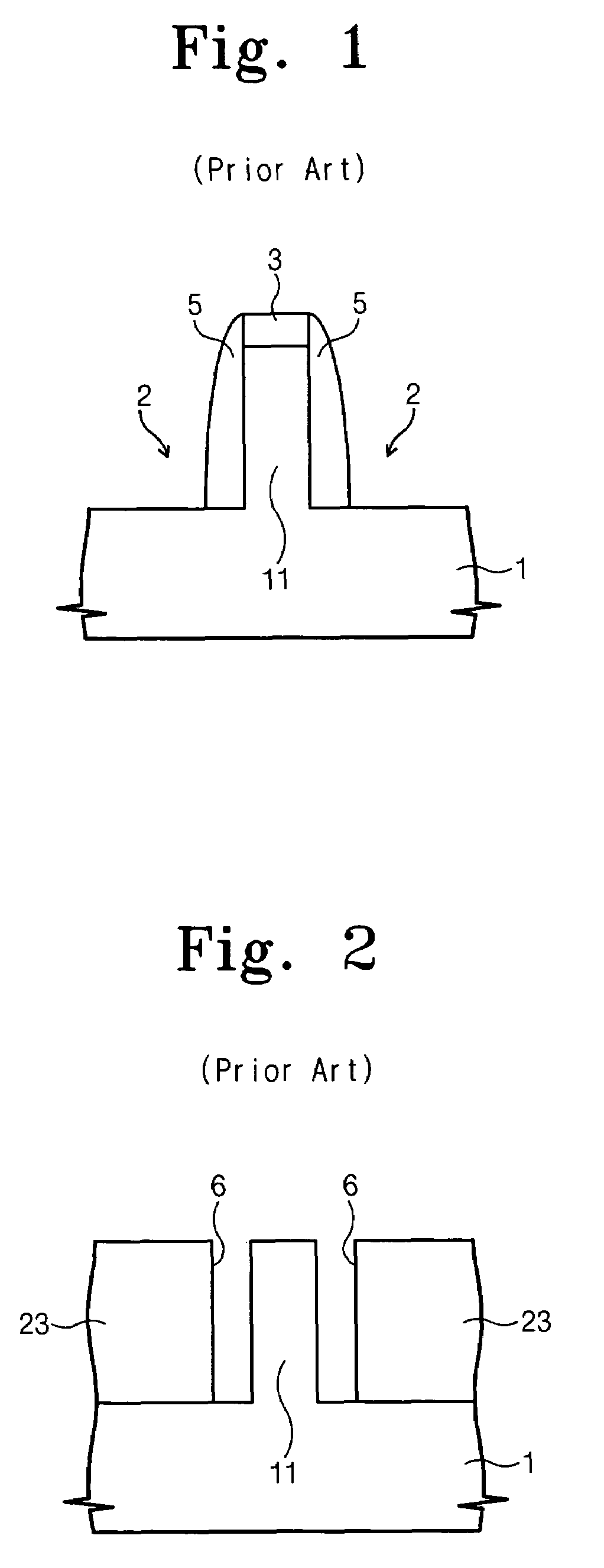

Fin field effect transistor device and method of fabricating the same

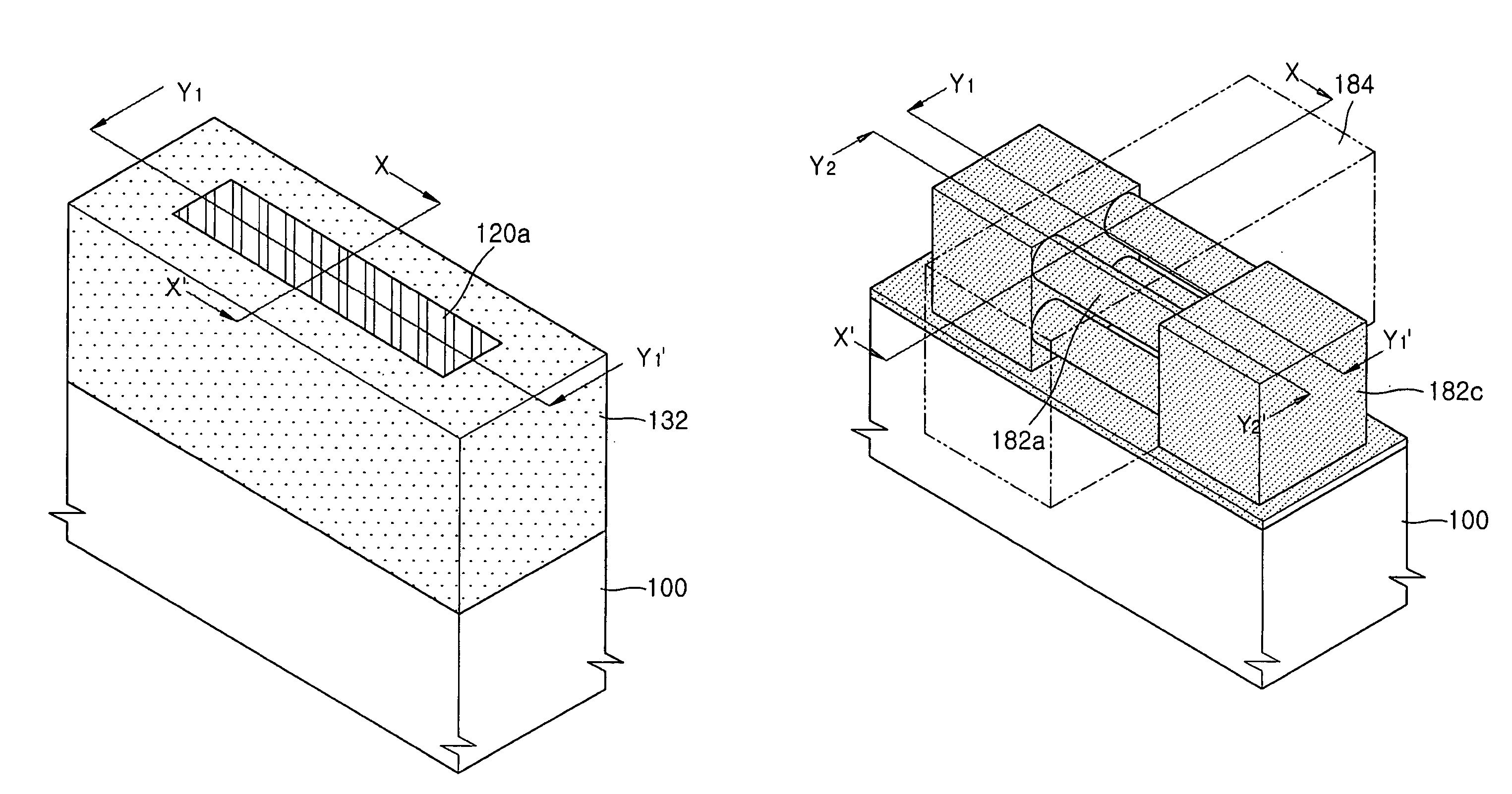

Methods of forming field effect transistors (FETs) having fin-shaped active regions include patterning a semiconductor substrate to define a fin-shaped semiconductor active region therein, which is surrounded by a trench. At least an upper portion of the fin-shaped semiconductor active region is covered with a sacrificial layer. This sacrificial layer is selectively etched-back to define sacrificial spacers on sidewalls of the fin-shaped semiconductor active region. The electrically insulating region is formed on the sacrificial spacers. The sacrificial spacers are then removed by selectively etching the sacrificial spacers using the electrically insulating region as an etching mask. An insulated gate electrode is then formed on the sidewalls of the fin-shaped semiconductor active region.

Owner:SAMSUNG ELECTRONICS CO LTD

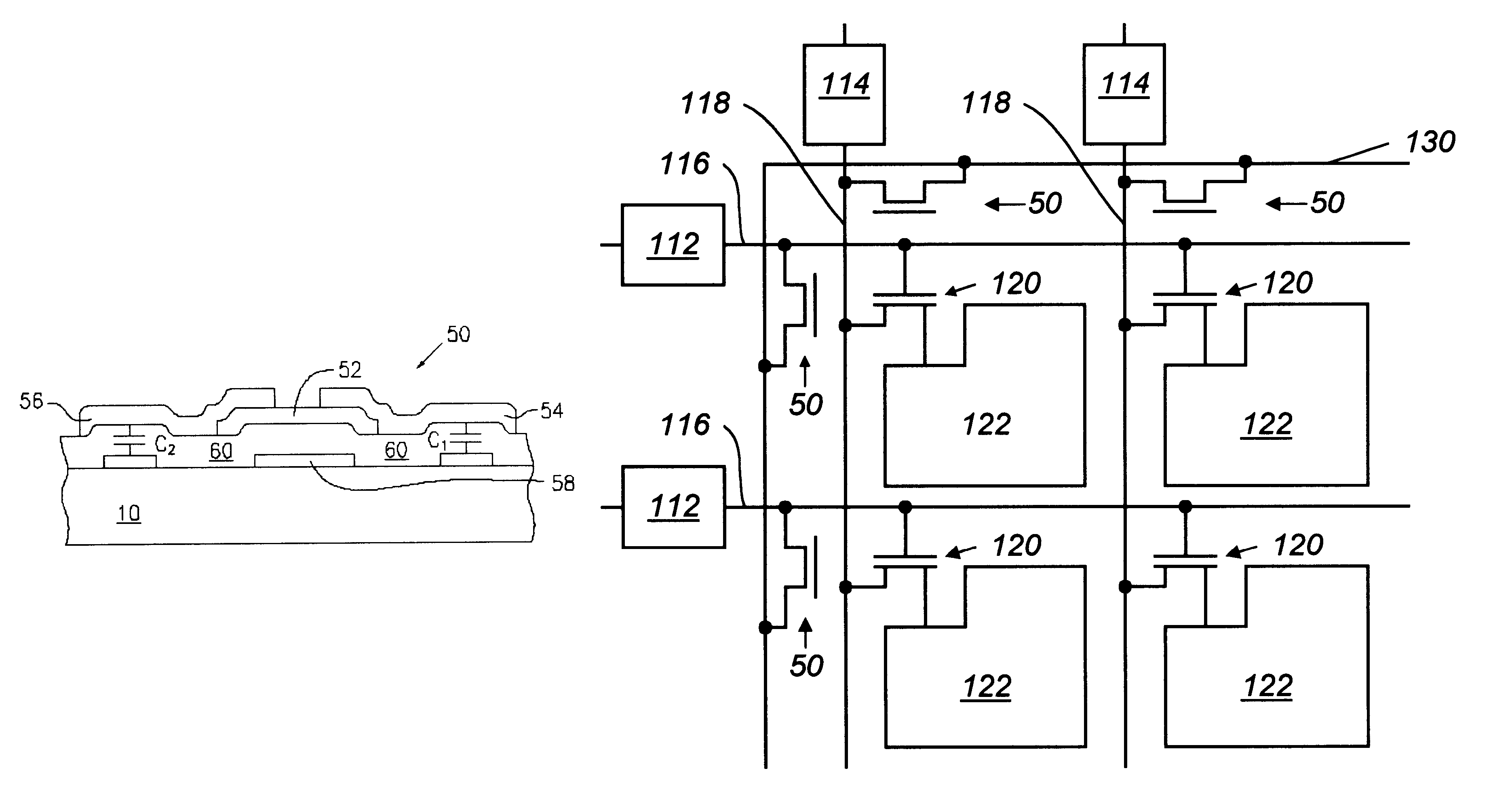

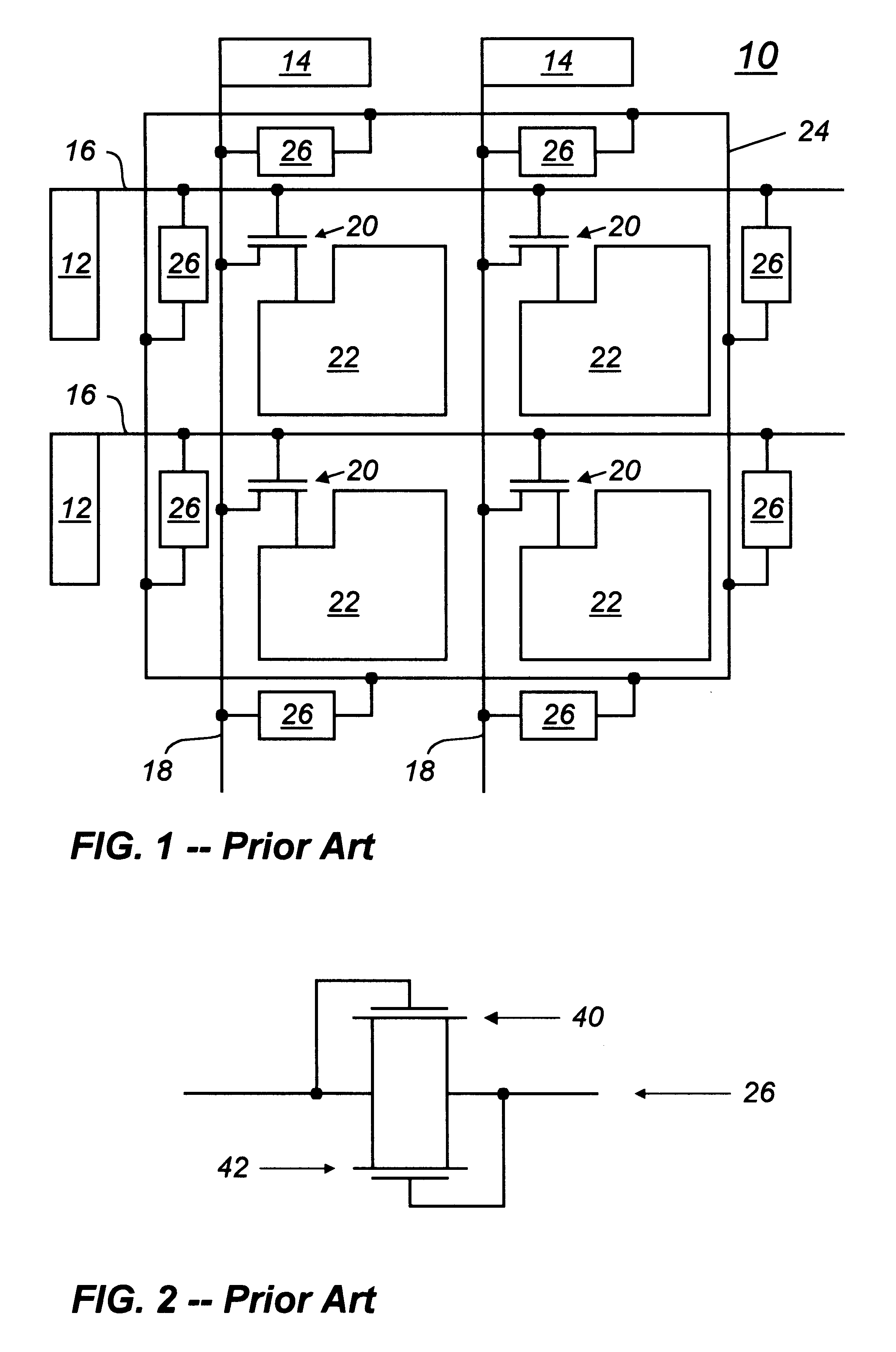

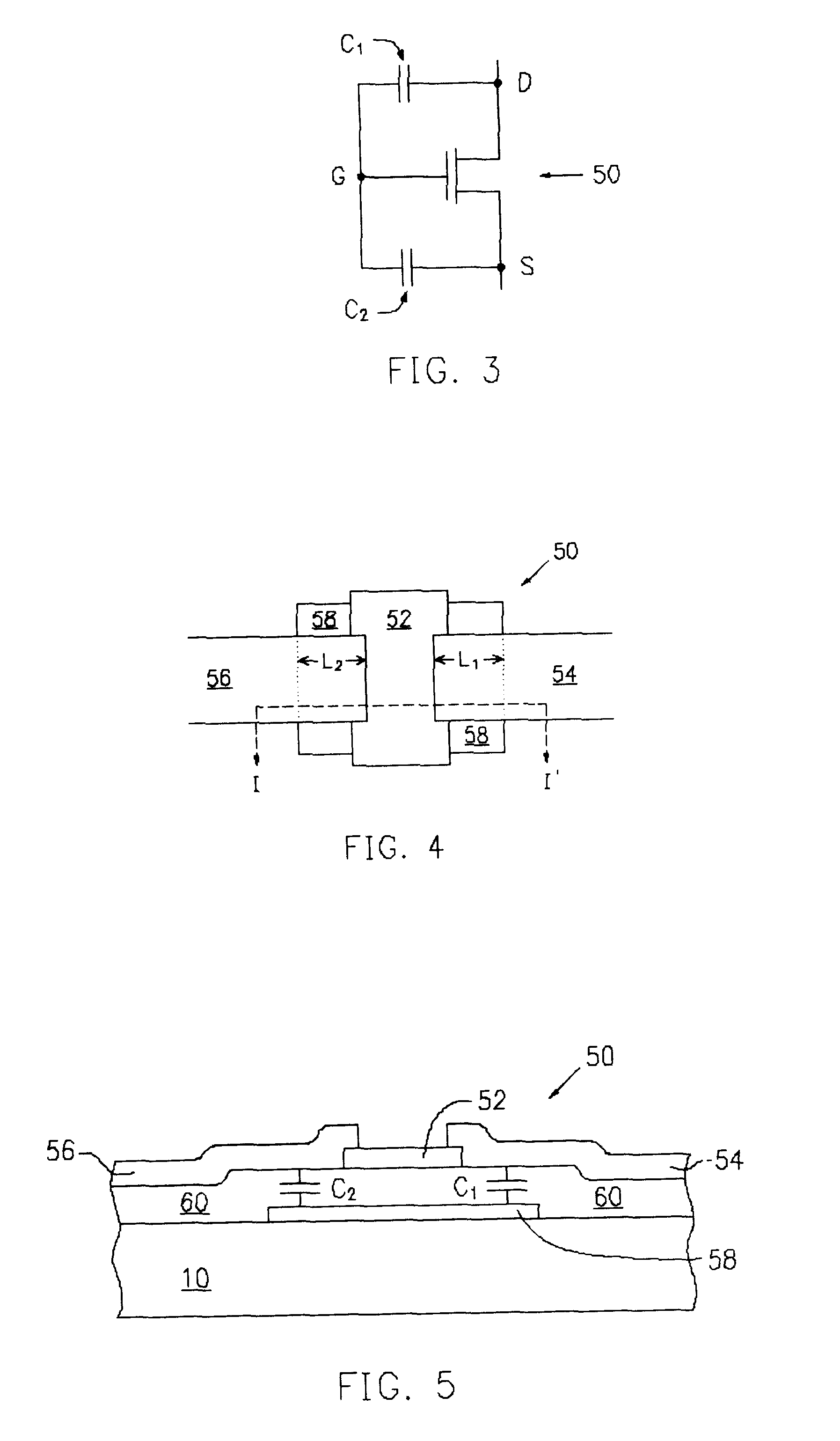

Capacitively coupled field effect transistors for electrostatic discharge protection in flat panel displays

A flat panel display includes a plurality of parallel row select lines and a plurality of column drive lines, with the row select lines and the column drive lines intersecting to define a matrix of pixel locations. Signals are provided to contact pads located on the periphery of the display and the signals flow over the row select lines and the column drive lines to thin film transistors located adjacent a pixel electrode at each of the pixel locations. The signals provided to each thin film transistor cause the transistor to charge a corresponding pixel electrode to control a pixel of the display. ESD protection for the display comprises a guard ring adjacent the contact pads. Capacitively coupled field effect transistors (CCFETs) connect the row select lines to the guard ring and connect the column drive lines to the guard ring. A CCFET is formed as a thin film transistor and typically has a floating gate capacitively coupled to the drain and source of the thin film transistor.

Owner:AU OPTRONICS CORP

Finfet SRAM cell using low mobility plane for cell stability and method for forming

InactiveUS6967351B2Accurate operationSolid-state devicesSemiconductor/solid-state device manufacturingStatic random-access memoryLow mobility

The present invention provides a device design and method for forming the same that results in Fin Field Effect Transistors having different gains without negatively impacting device density. The present invention forms relatively low gain FinFET transistors in a low carrier mobility plane and relatively high gain FinFET transistors in a high carrier mobility plane. Thus formed, the FinFETs formed in the high mobility plane have a relatively higher gain than the FinFETs formed in the low mobility plane. The embodiments are of particular application to the design and fabrication of a Static Random Access Memory (SRAM) cell. In this application, the bodies of the n-type FinFETs used as transfer devices are formed along the {110} plane. The bodies of the n-type FinFETs and p-type FinFETs used as the storage latch are formed along the {100}. Thus formed, the transfer devices will have a gain approximately half that of the n-type storage latch devices, facilitating proper SRAM operation.

Owner:GLOBALFOUNDRIES U S INC

Method of fabricating field effect transistor (FET) having wire channels

ActiveUS7374986B2Guaranteed generation effectHigh speedSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricOrganic field-effect transistor

In a field effect transistor (FET), and a method of fabricating the same, the FET includes a semiconductor substrate, source and drain regions formed on the semiconductor substrate, a plurality of wire channels electrically connecting the source and drain regions, the plurality of wire channels being arranged in two columns and at least two rows, and a gate dielectric layer surrounding each of the plurality of wire channels and a gate electrode surrounding the gate dielectric layer and each of the plurality of wire channels.

Owner:SAMSUNG ELECTRONICS CO LTD

Strained-channel Fin field effect transistor (FET) with a uniform channel thickness and separate gates

A semiconductor device (and method for making the same) includes a strained-silicon channel formed adjacent a source and a drain, a first gate formed over a first side of the channel, a second gate formed over a second side of the channel, a first gate dielectric formed between the first gate and the strained-silicon channel, and a second gate dielectric formed between the second gate and the strained-silicon channel. The strained-silicon channel is non-planar.

Owner:IBM CORP

Low power consumption MIS semiconductor device

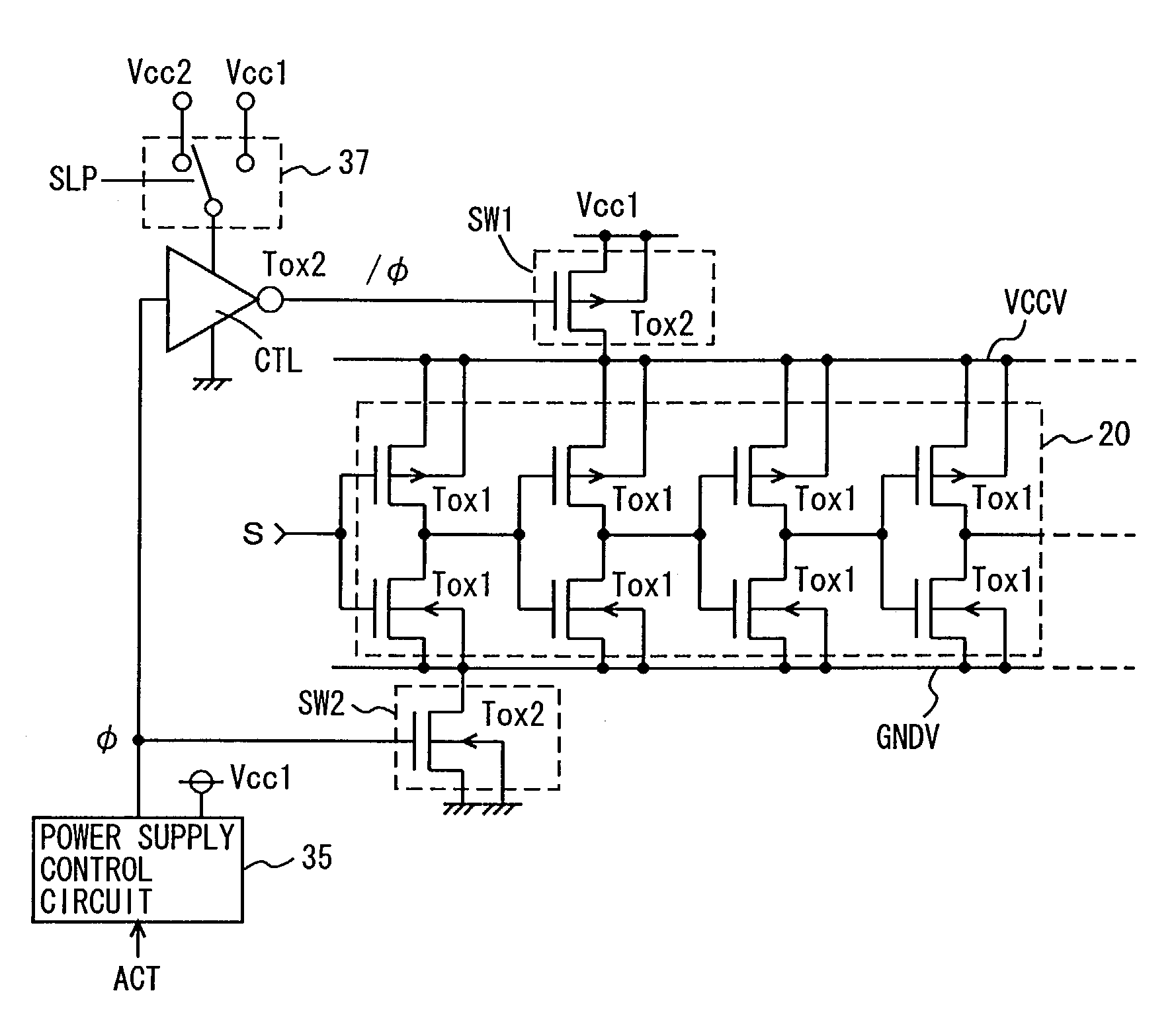

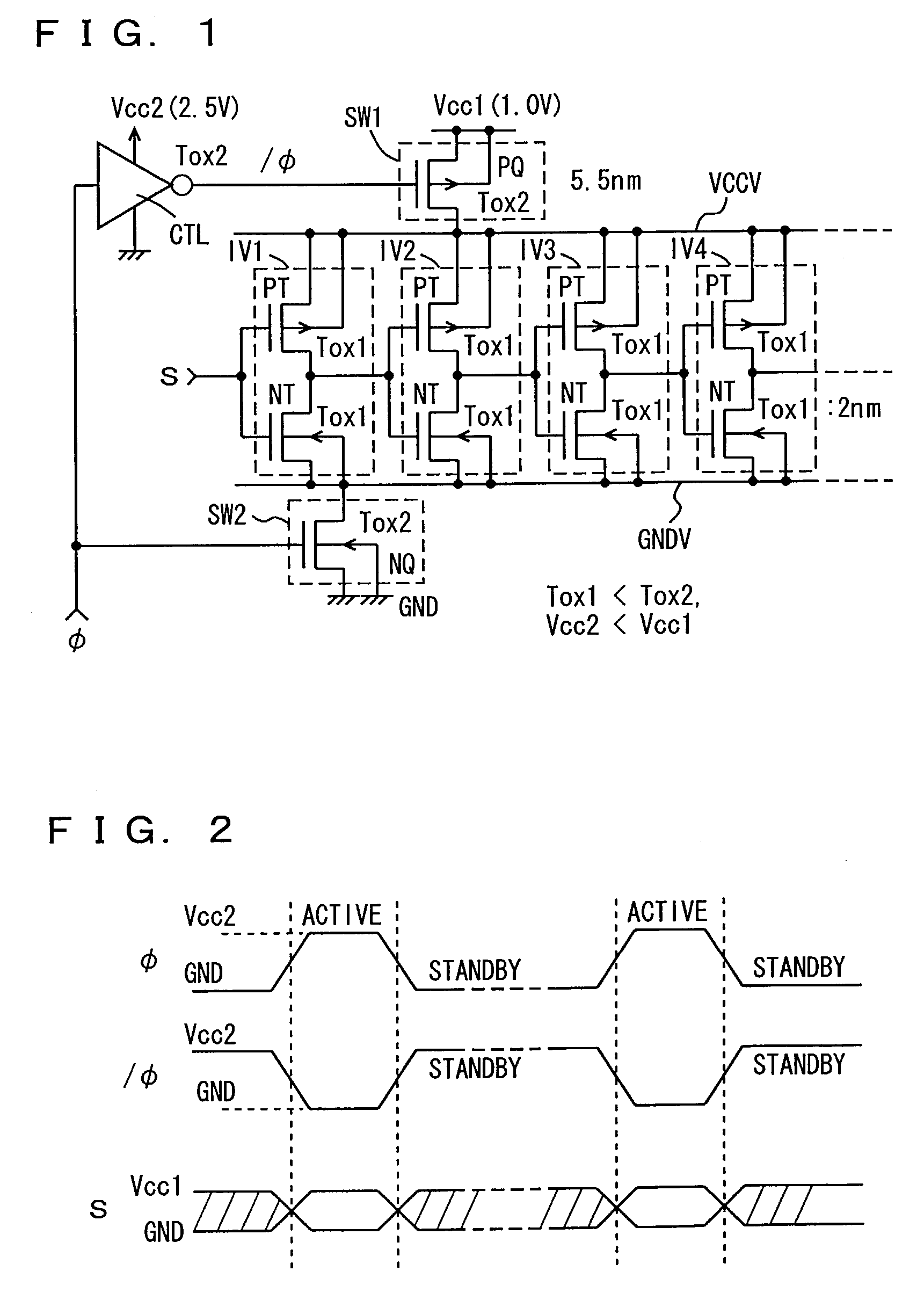

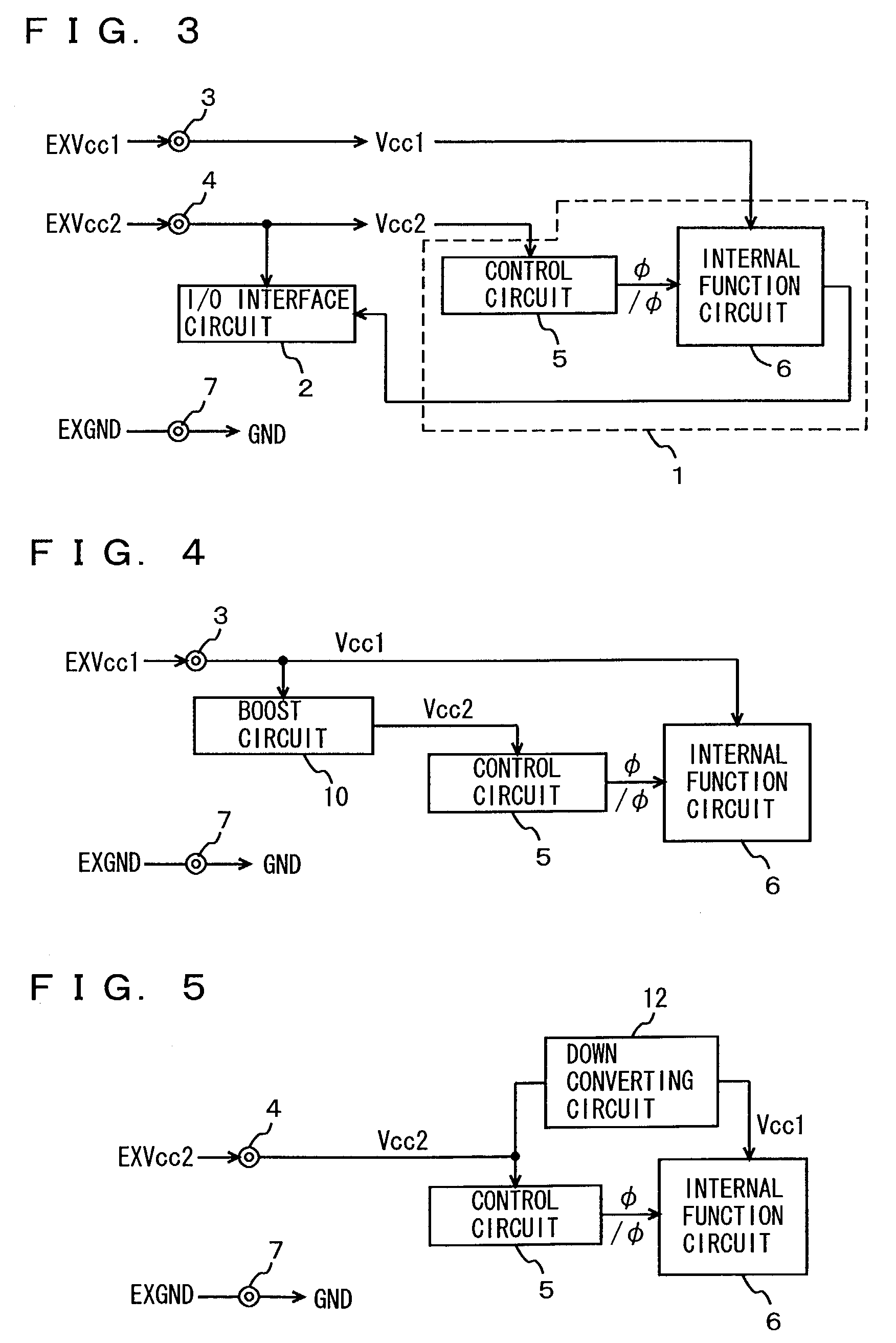

InactiveUS7042245B2Total current dropSimple circuit configurationTransistorReliability increasing modificationsCurrent consumptionLogic gate

A logic gate is constructed of an insulated gate field effect transistor (MIS transistor) having a thin gate insulation film. An operation power supply line to the logic gate is provided with an MIS transistor having a thick gate insulation film for switching the supply and stop of an operation power source voltage. A voltage of the gate of the power source switching transistor is made changing in an amplitude greater than an amplitude of an input and an output signal to the logic gate. Current consumption in a semiconductor device configured of MIS transistor of a thin gate insulation film can be reduced and an power source voltage thereof can be stabilized.

Owner:RENESAS ELECTRONICS CORP

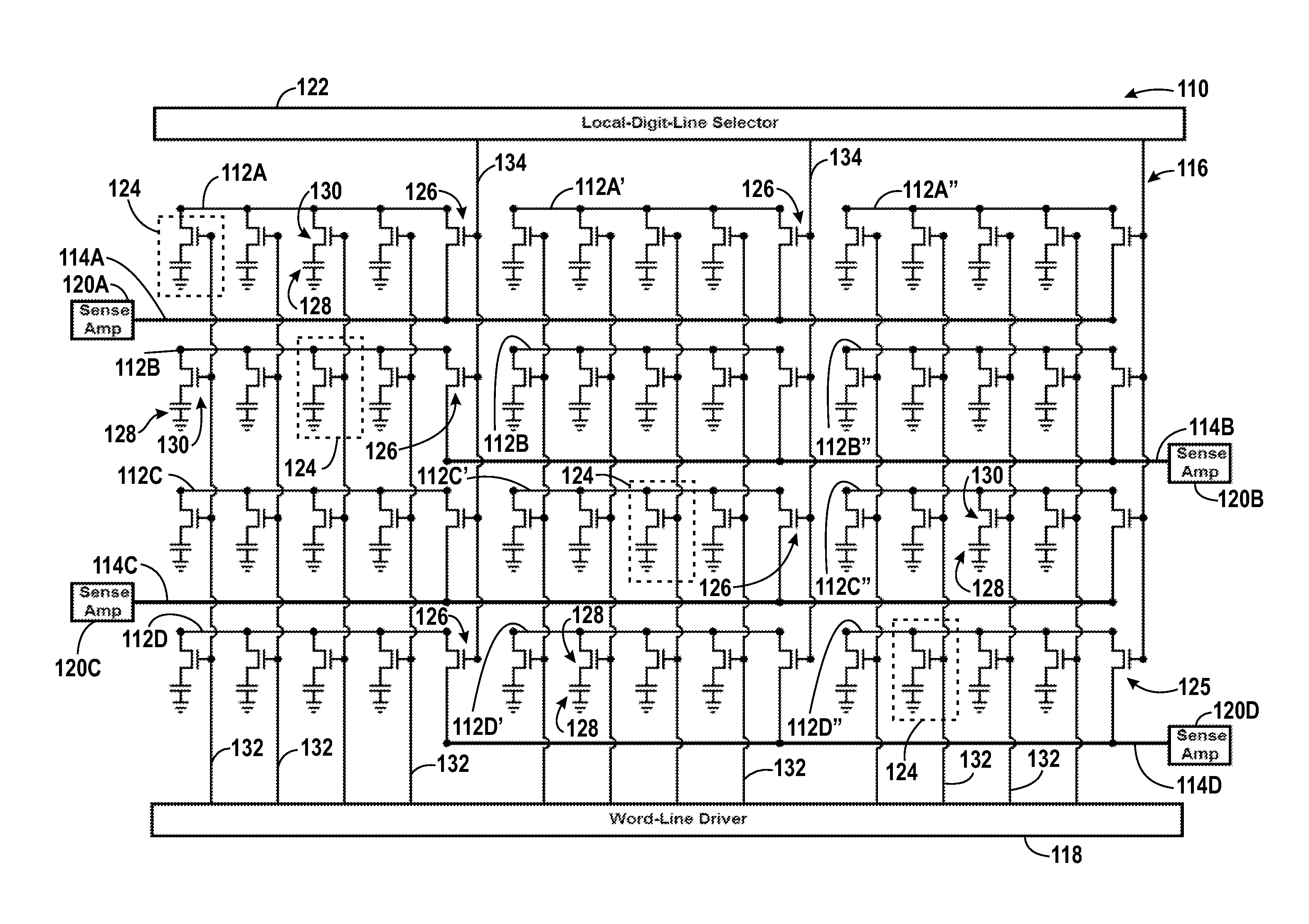

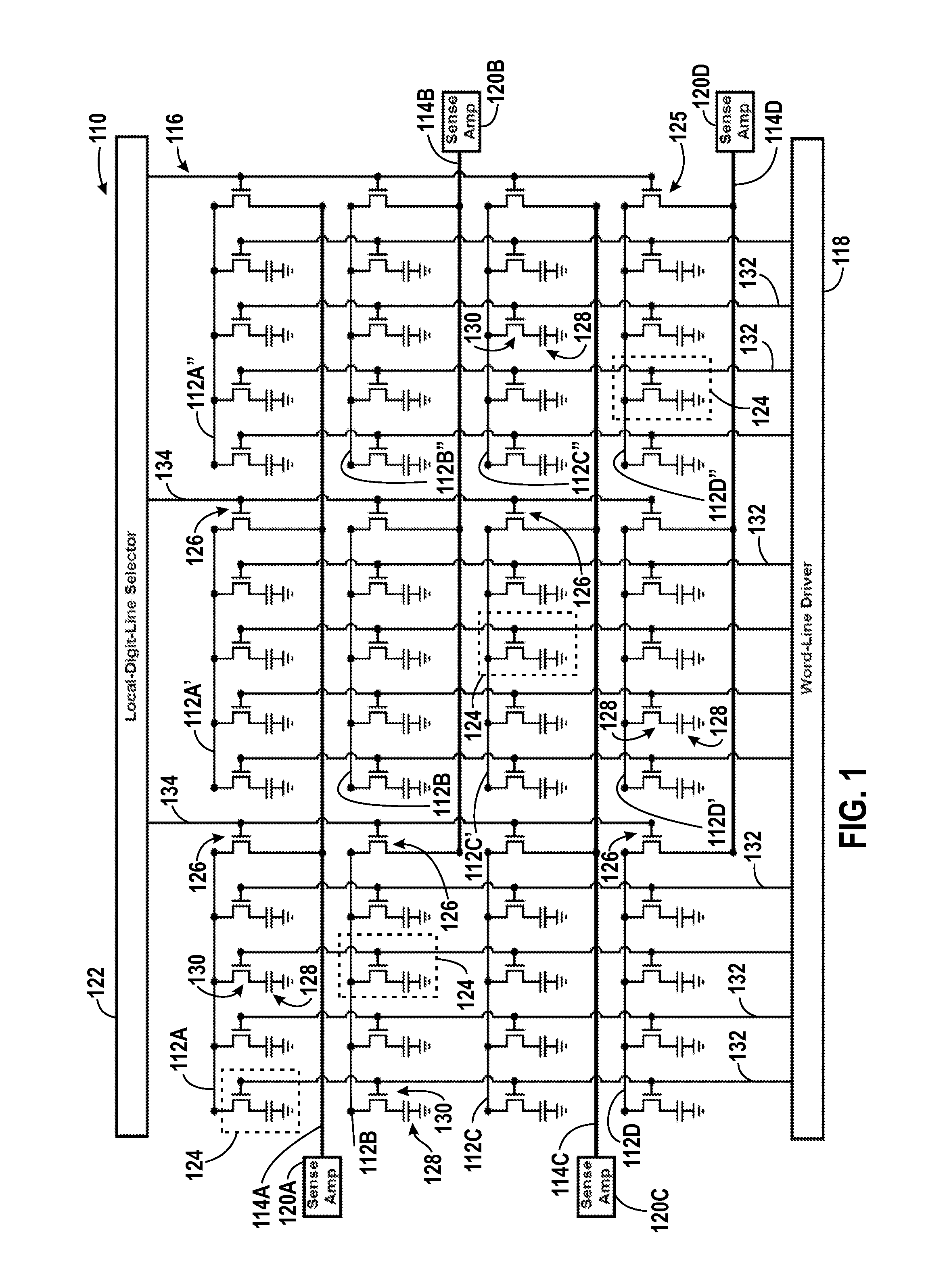

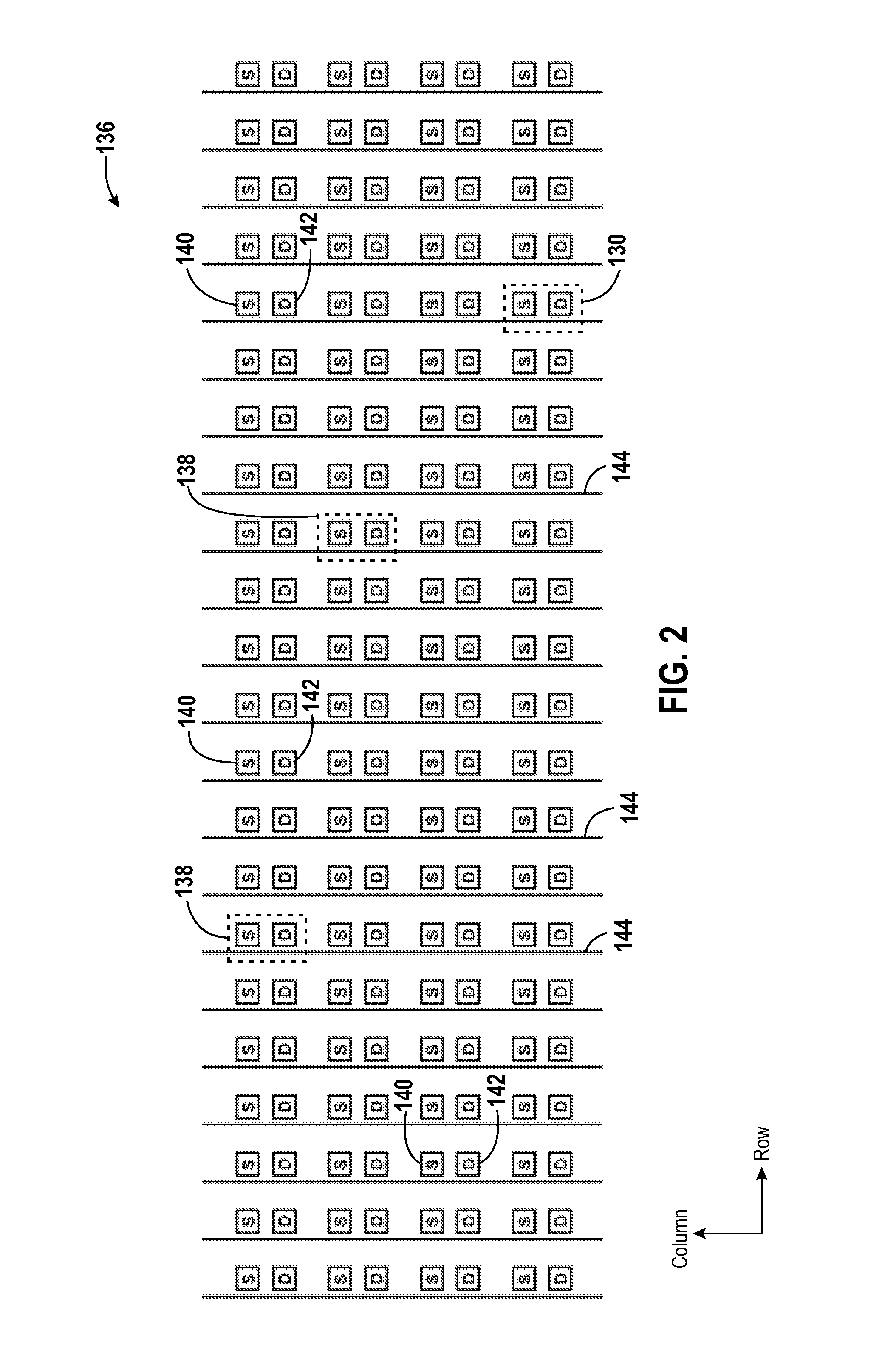

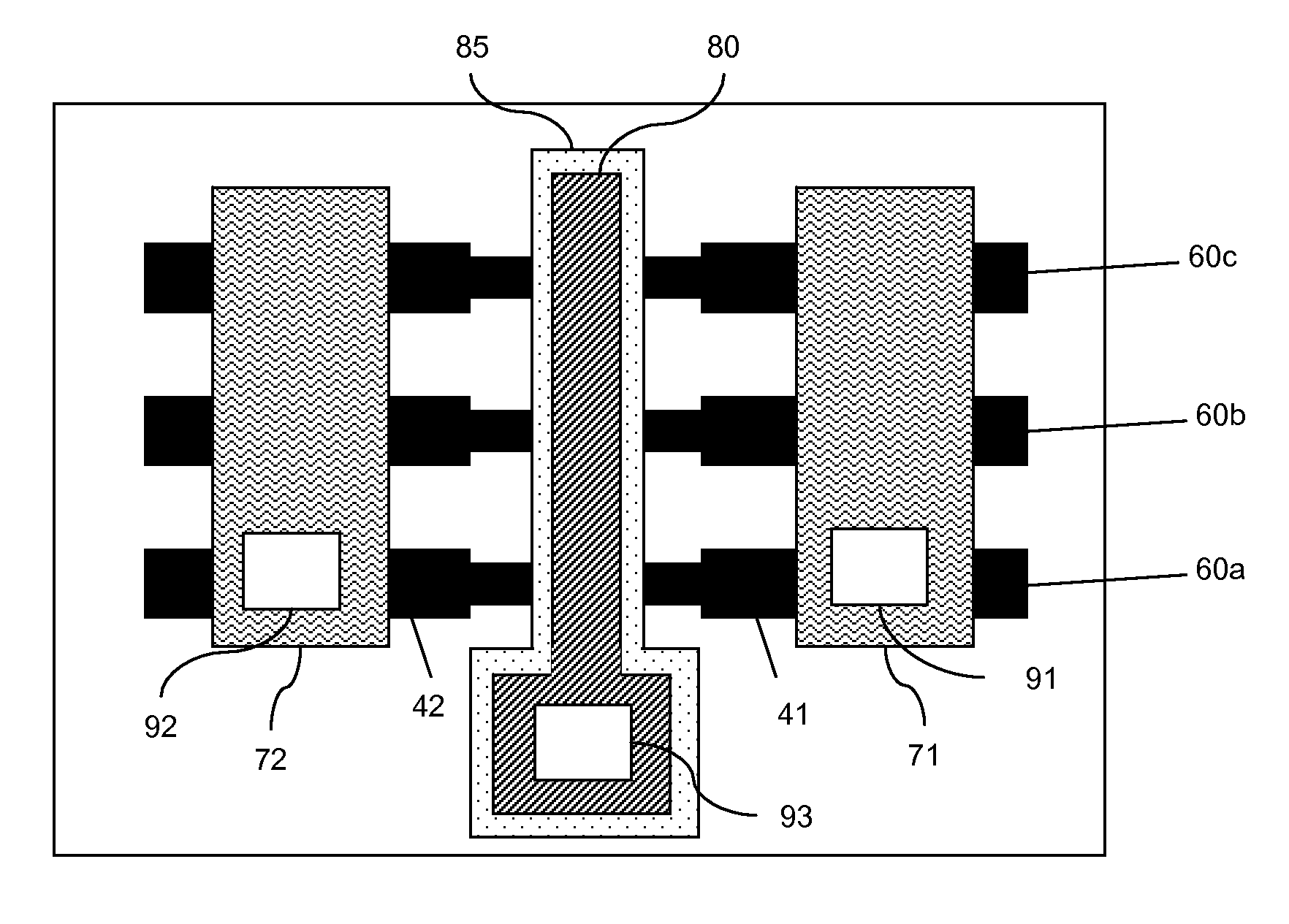

Systems and devices including local data lines and methods of using, making, and operating the same

Disclosed are methods, systems and devices, including a device having a fin field-effect transistor with a first terminal, a second terminal, and two gates. In some embodiments, the device includes a local data line connected to the first terminal, at least a portion of a capacitor plate connected to the second terminal, and a global data line connected to the local data line by the capacitor plate.

Owner:OVONYX MEMORY TECH LLC

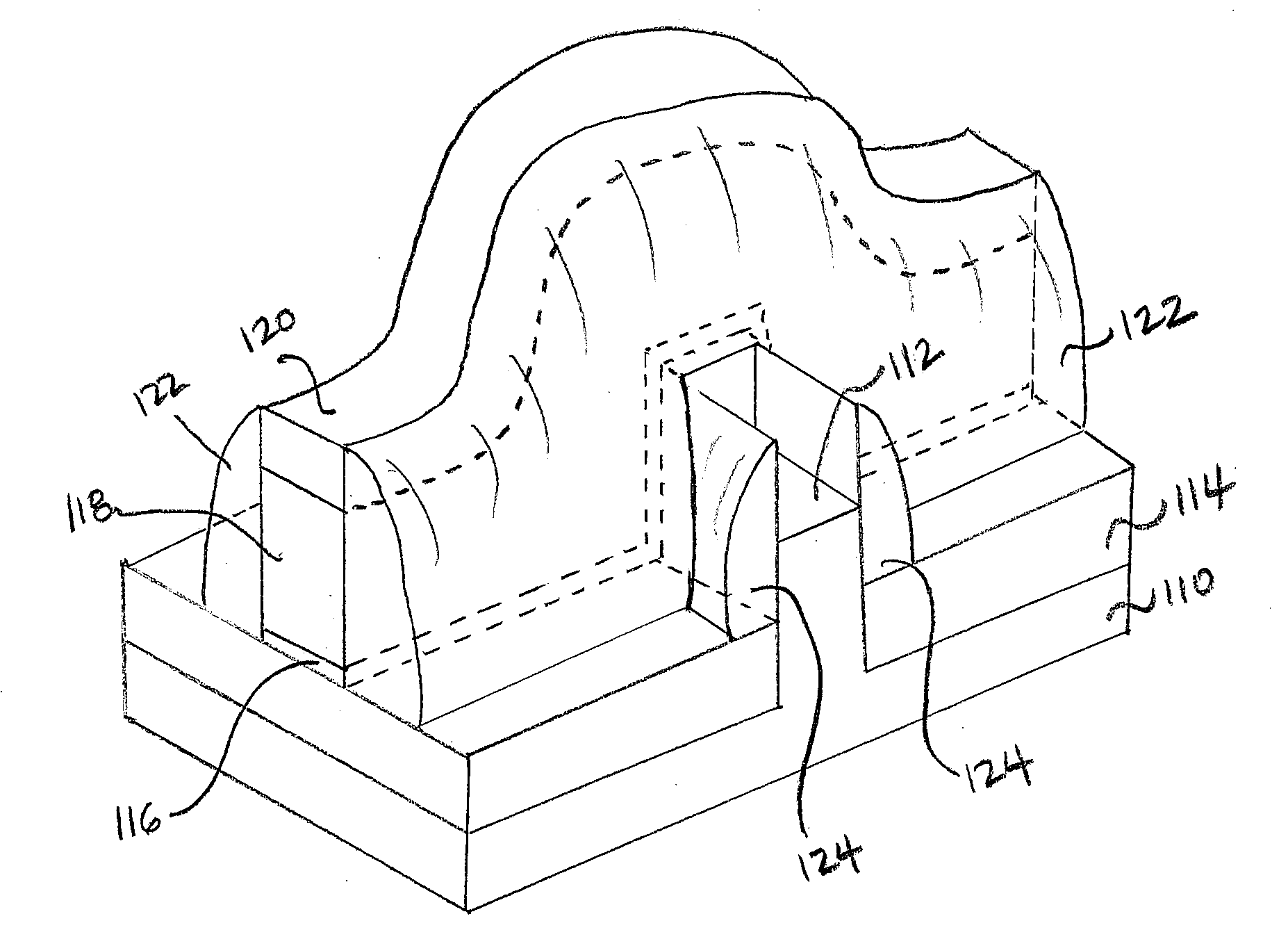

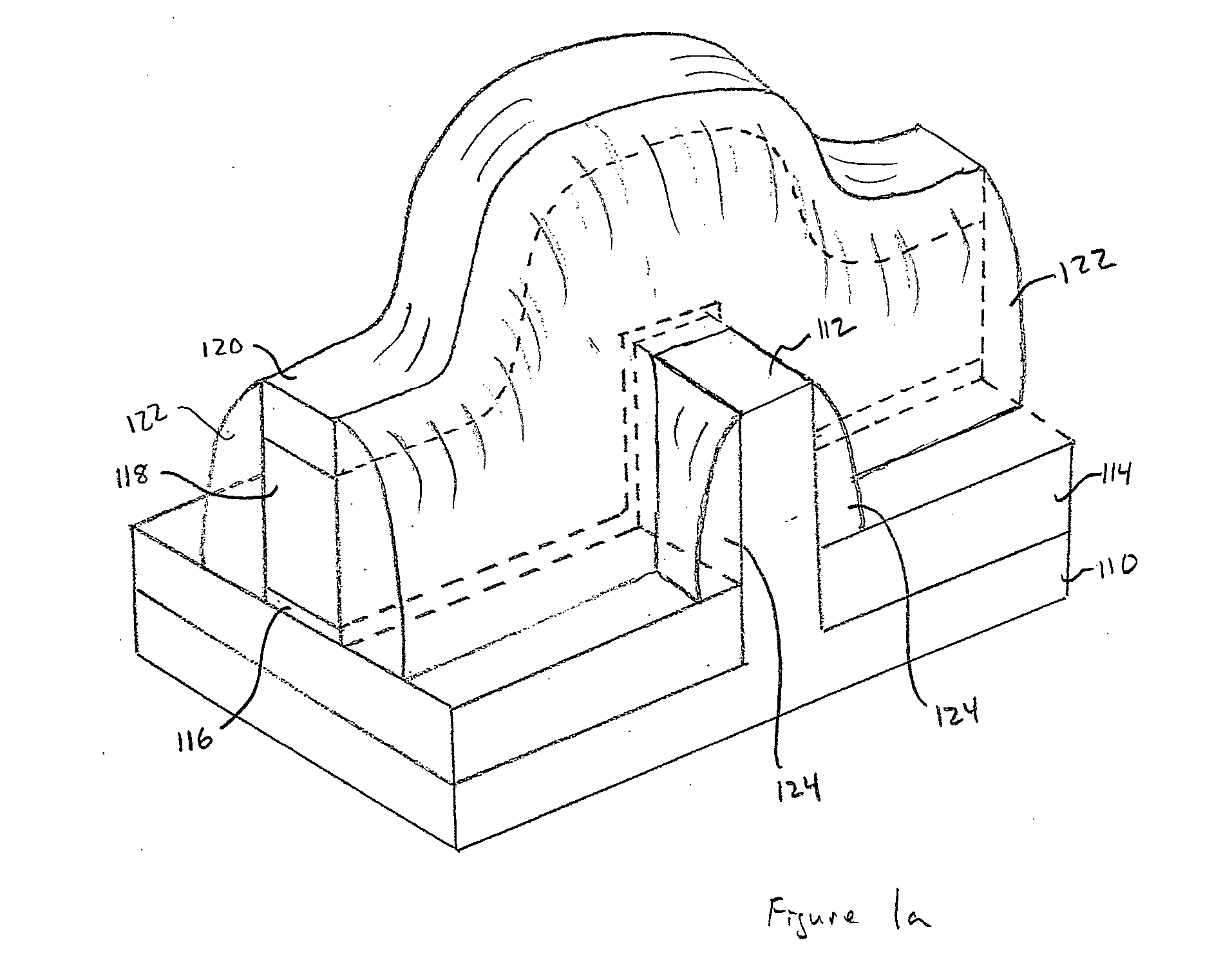

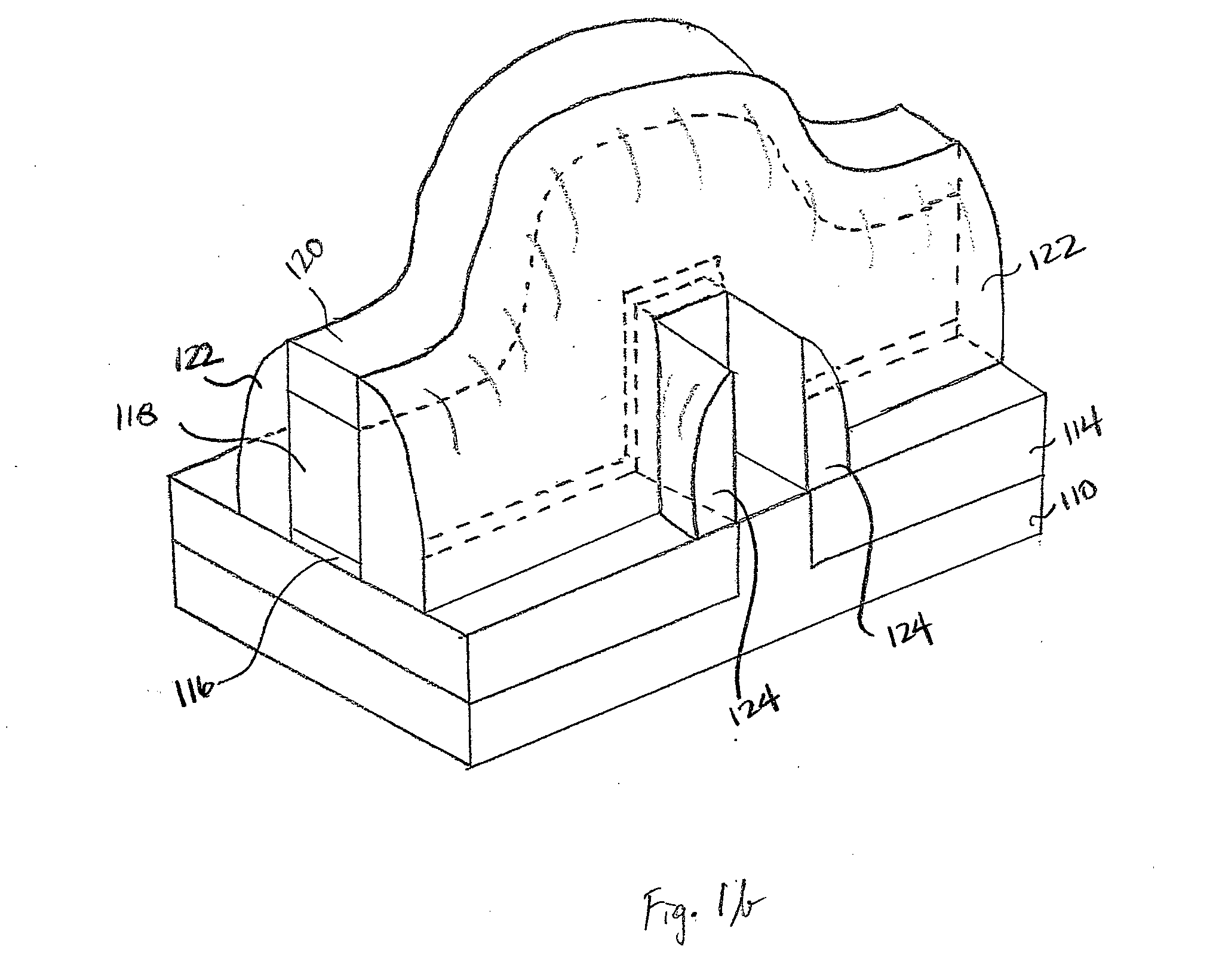

Field effect transistor with raised source/drain fin straps

ActiveUS20080067613A1Lower resistanceReduce capacitanceTransistorSolid-state devicesCapacitanceEngineering

Therefore, disclosed above are embodiments of a multi-fin field effect transistor structure (e.g., a multi-fin dual-gate FET or tri-gate FET) that provides low resistance strapping of the source / drain regions of the fins, while also maintaining low capacitance to the gate by raising the level of the straps above the level of the gate. Embodiments of the structure of the invention incorporate either conductive vias or taller source / drain regions in order to electrically connect the source / drain straps to the source / drain regions of each fin. Also, disclosed are embodiments of associated methods of forming these structures.

Owner:GLOBALFOUNDRIES US INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com