P-type MOSFET and manufacturing method thereof

A manufacturing method, N-type technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of large influence on device threshold voltage, inability to improve hole mobility, large fluctuations in phosphorus ion implantation depth, etc. , to improve mobility and improve device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

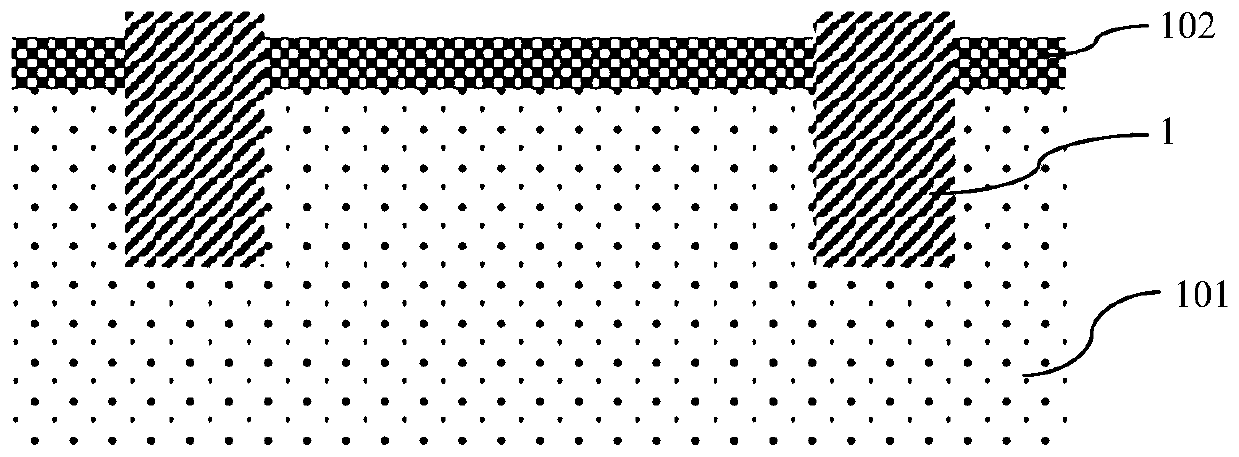

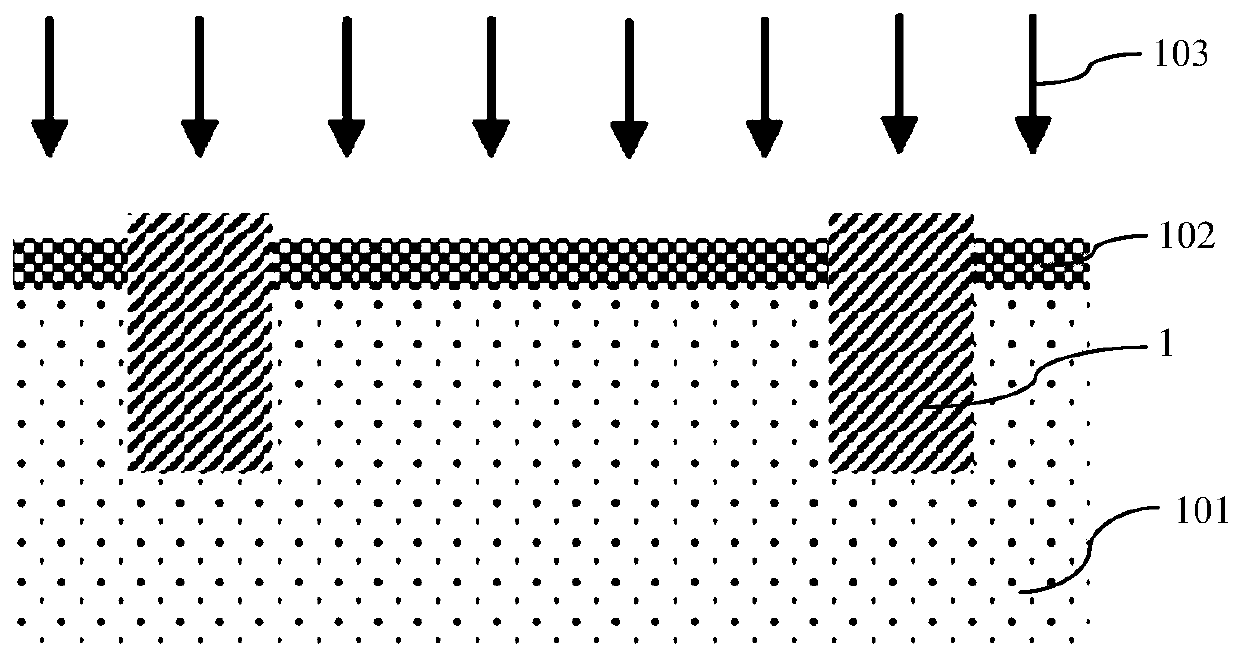

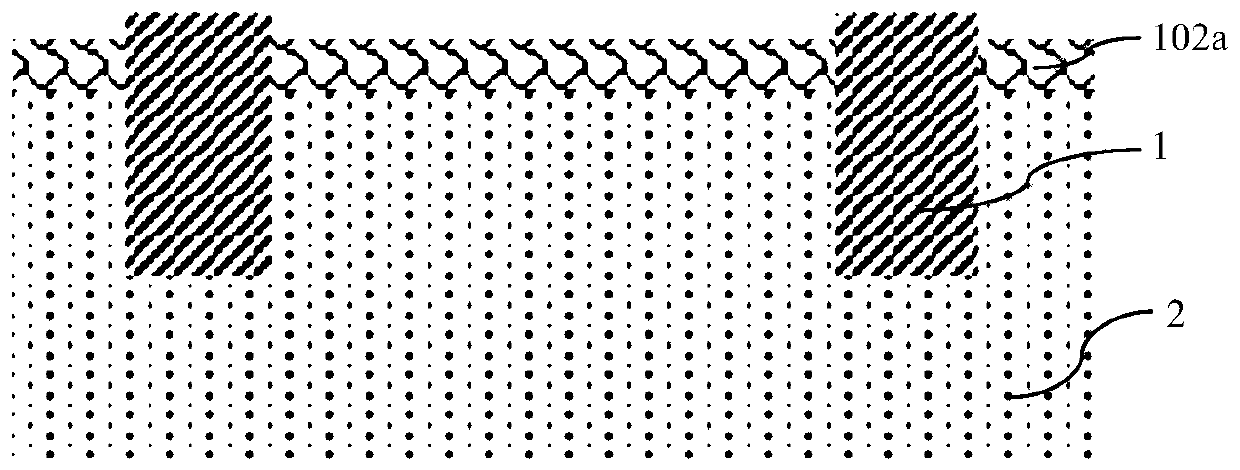

[0077] The structural reference of the channel region of the P-type MOSFET in the embodiment of the present invention Figure 1J and Figure 1K As shown, the channel region is composed of an N well 9 covered by a gate structure, and the N well 9 includes a first implantation region 4, a second implantation region 5, and a third implantation region 6 formed in a semiconductor substrate 101. The overlapping region 8 formed with the fourth implantation region 7 is annealed, that is, the N well 9 is formed after the overlapping region 8 is annealed. For the semiconductor substrate 101 please refer to Figure 1A as shown, Figure 1J Only the structure of the N-type deep well 2 formed in the semiconductor substrate 101 is illustrated in FIG.

[0078] In the embodiment of the present invention, the semiconductor substrate 101 includes a silicon substrate.

[0079] Preferably, a field oxide layer 1 is formed on the semiconductor substrate 101, and the active region is isolated by ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com