A charge-pump method for calculating stress-induced changes in interface state density in nano-cmos devices

A technology of interface state density and charge pump, which is applied in the direction of measuring electricity, measuring electrical variables, testing a single semiconductor device, etc., can solve problems that affect the accuracy of measurement results, and achieve the effect of promoting the development of research and high accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

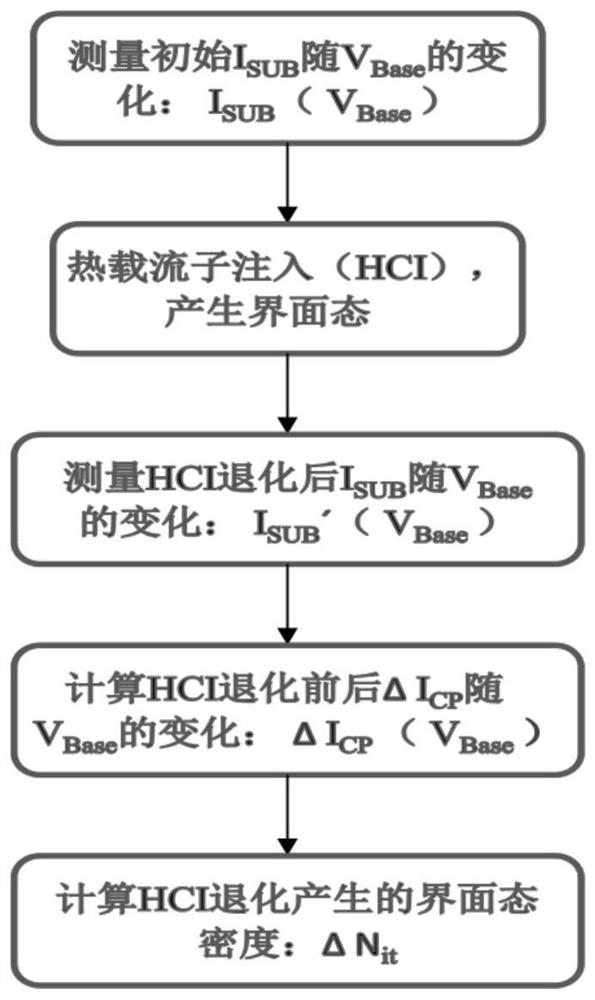

[0046] In the present embodiment, the CMOS device parameter used is that L (channel length) is 45nm, W (channel width)=10 μm, T OX (Oxide layer thickness) = 2.6nm, N A (Channel doping) = 1E20 / cm 3 . according to figure 1 As shown in the flow chart, the specific charge pump method for calculating the stress-induced interface state density change in the nanometer CMOS device in this embodiment is as follows:

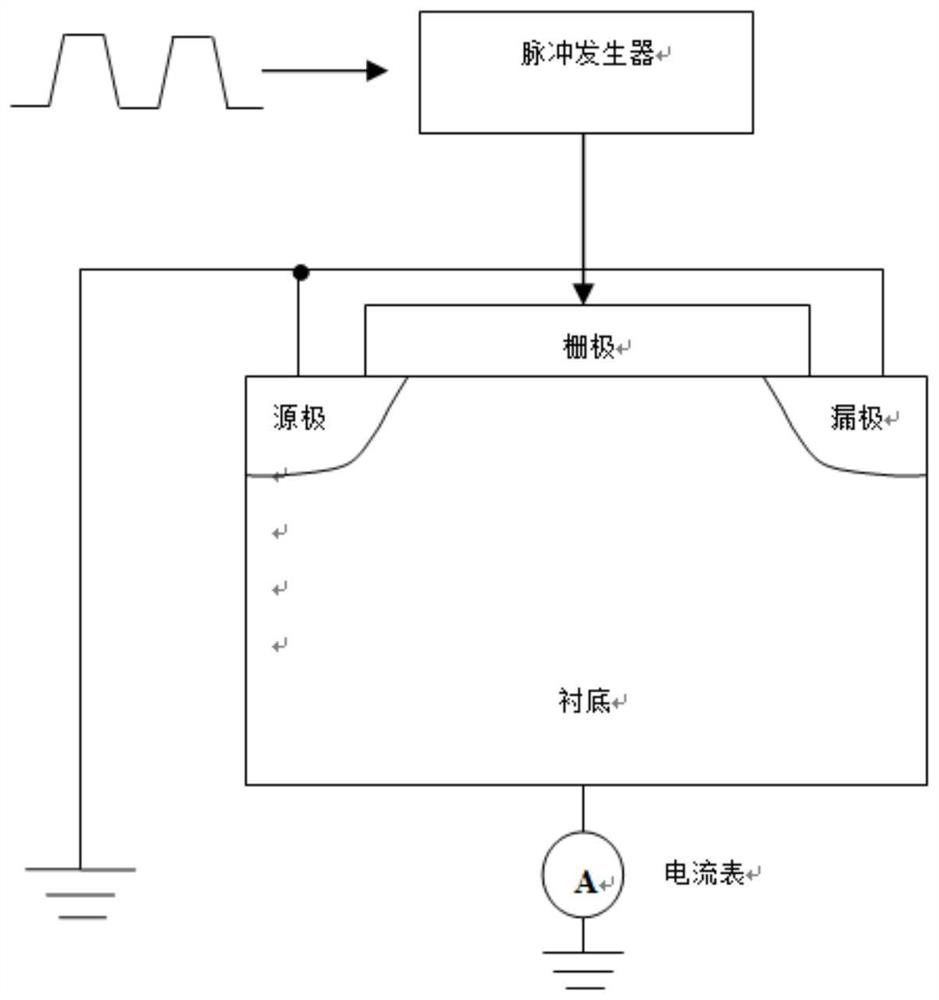

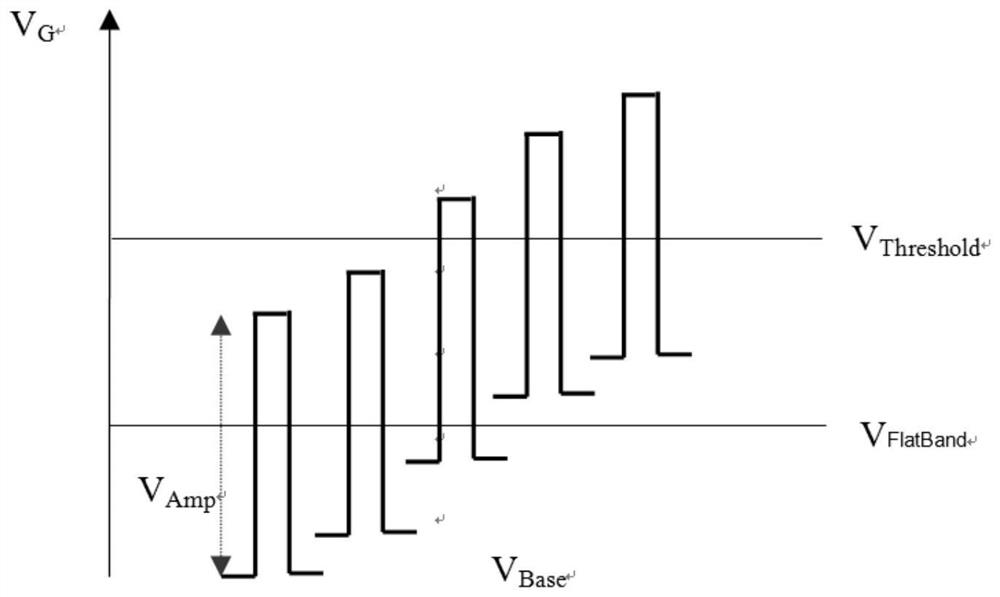

[0047] 1. In a CMOS device, measure the substrate current I SUB (I CP +I Leakage ) varies with substrate voltage V Base change curve. figure 2 The basic experimental setup of the charge pump test technology implemented in this implementation is given. For a CMOS device, the source, drain and substrate are grounded, and the substrate is connected to an ammeter at the same time to measure the current I from the gate to the substrate. SUB , the gate is connected to a voltage pulse generator. Apply voltage pulses to the grid for fixed-amplitude scanning, keep the pul...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com