Preparation method of p-GaN gate enhanced HEMTs device with stable threshold voltage

A threshold voltage and enhanced technology, which is applied in the field of preparation of p-GaN gate enhanced HEMTs devices, can solve problems such as circuit false conduction, device performance instability, burnout, etc., and achieve stable threshold voltage and high threshold voltage stability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

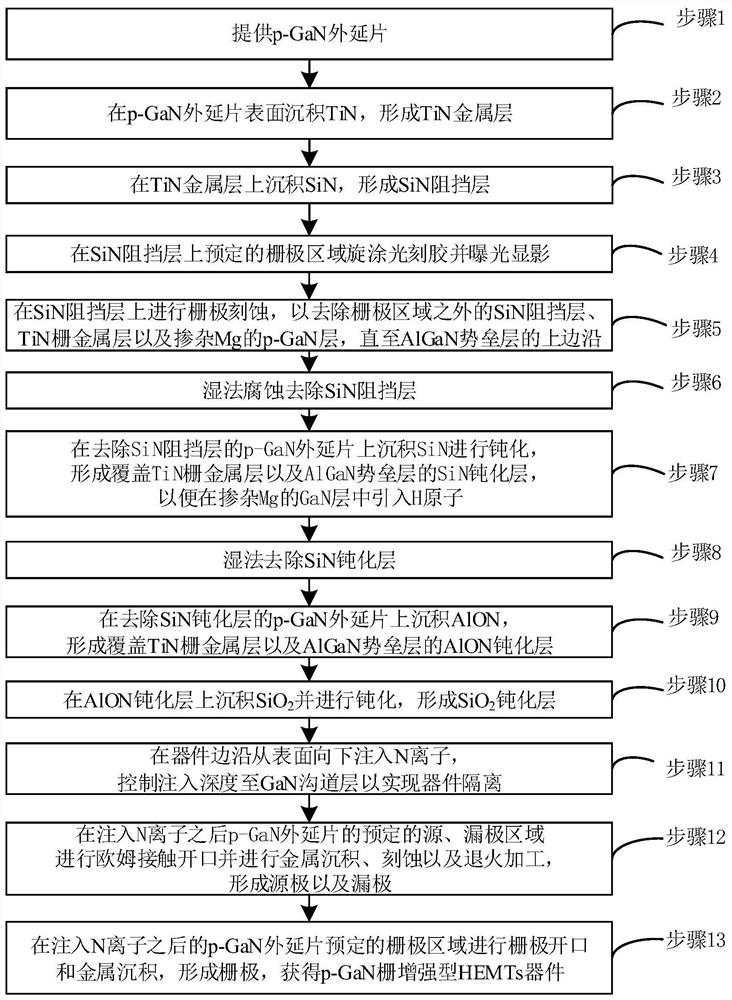

[0041] Such as figure 1 As shown, the preparation method of a p-GaN gate enhanced HEMTs device with stable threshold voltage provided by the present invention includes:

[0042] Step 1: Provide p-GaN epitaxial wafer;

[0043] Wherein, the p-GaN epitaxial wafer structure includes a substrate, an AlN nucleation layer, a (Al)GaN buffer layer, a GaN channel layer, an AlGaN barrier layer, and a Mg-doped p-GaN cap layer from bottom to top; The substrate is: SiC or sapphire or Si substrate.

[0044] Step 2: Depositing TiN on the surface of the p-GaN epitaxial wafer to form a TiN metal layer; Step 3: Depositing SiN on the TiN metal layer to form a SiN barrier layer;

[0045] refer to figure 2 , figure 2 is a schematic diagram after deposition on a p-GaN epiwafer. From bottom to top, there are substrate, AlN nucleation layer, (Al)GaN buffer layer, GaN channel layer, AlGaN barrier layer, Mg-doped p-GaN cap layer, TiN gate metal layer and SiN barrier layer.

[0046] Step 4: Spin-...

Embodiment approach

[0062] As an optional implementation manner of the present invention, the step 2 includes:

[0063] A layer of metal TiN with a thickness of 50 nm to 200 nm is sputtered on the Mg-doped p-GaN cap layer by physical vapor deposition method PVD to form a TiN metal layer.

[0064] As an optional implementation manner of the present invention, the step 6 includes:

[0065] Step 6.1: removing glue from the p-GaN epitaxial wafer after gate etching;

[0066] Step 6.2: Remove the SiN barrier layer by wet etching with BHF solution.

[0067] As an optional embodiment of the present invention, the SiN barrier layer has a thickness of 200 nm, the SiN passivation layer has a thickness of 5 nm to 20 nm, the AlON passivation layer has a thickness of 5 nm to 20 nm, and the SiO 2 The thickness of the passivation layer is 50nm-400nm.

[0068] As an optional implementation manner of the present invention, the step 7 includes:

[0069] Using the PEALD method, deposit SiN on the p-GaN epitaxial...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com