Semiconductor device and manufacturing method thereof

A technology of semiconductors and devices, which is applied in the field of power semiconductor devices and can solve problems such as complex processes, complex structures, and disadvantages

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

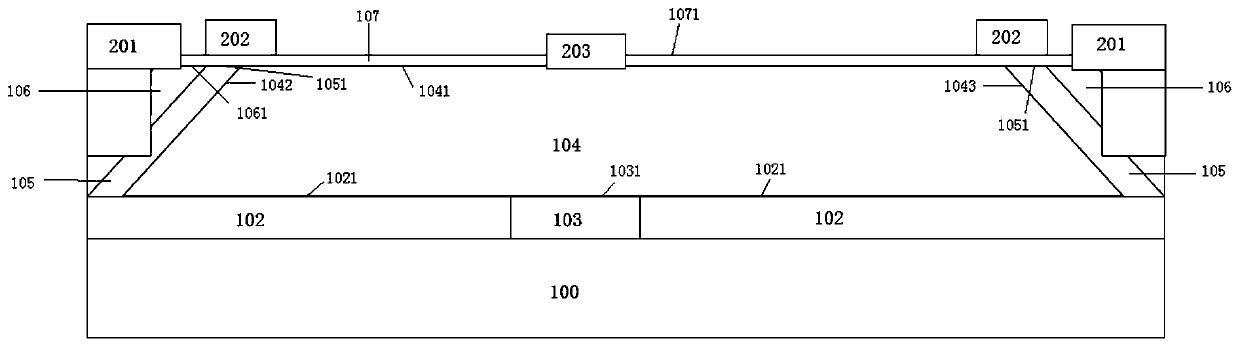

[0074] refer to Figure 1-Figure 2 A semiconductor device according to the first embodiment will be described.

[0075] Such as figure 1 As shown, in the first embodiment, the semiconductor device, an exemplary normally-off HEMT device, includes a substrate 100, and the material of the substrate 100 can be selected according to actual needs, which is not limited in this embodiment The specific form of the substrate 100. Optionally, the substrate 100 can be made of sapphire, ZnO, SiC, AlN, GaAs, LiAlO, GaAlLiO, GaN, Al 2 o 3or monocrystalline silicon etc.; further, the Al 2 o 3 The substrate can be (0001) Al 2 o 3 ; Further, the single crystal silicon substrate may be a (111) plane silicon substrate. There is a first insulating layer 102 on the first surface 1001 of the substrate 100. Exemplarily, the first insulating layer 102 is SiO 2 layer or Si 3 N 4 layer. The opening formed on the first insulating layer 102 exposes the substrate 100 , and a nucleation layer 1...

no. 2 approach

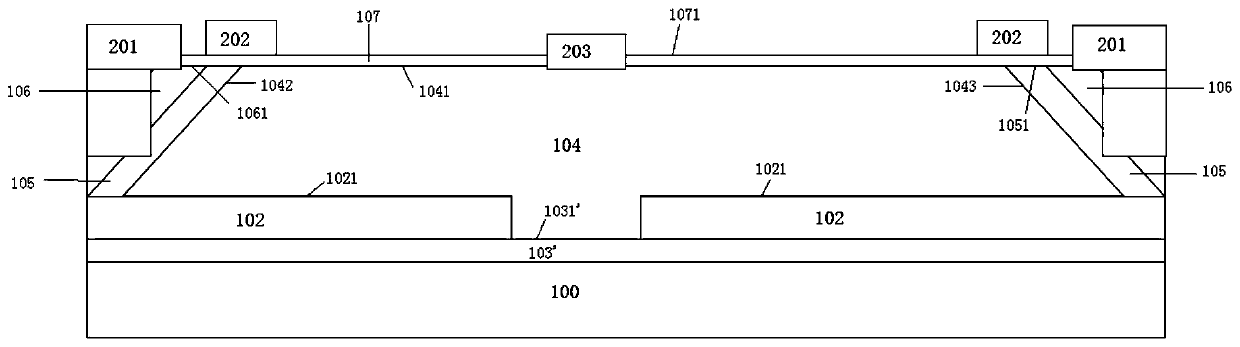

[0088] Such as image 3 As shown, in the second embodiment, the semiconductor device, exemplarily a normally-off HEMT device, includes a silicon substrate 100 . The first insulating layer 102 formed on the first surface of the substrate 100, for example, the first insulating layer 102 is SiO 2 layer or Si 3 N 4 . An opening is formed on the first insulating layer 102 at a position corresponding to the subsequent third electrode 203 or at a position corresponding to the subsequent first electrode 201 to expose the substrate 100 , preferably corresponding to the subsequent third electrode 203 . Then the exposed substrate 100 is etched to form a trench with a depth of 0.2-10 microns on the substrate 100, typically, the depth of the trench is about 1 micron. An insulating protection layer 1003 is formed on the sidewalls of both sides of the trench of the substrate 100 and the opening of the first insulating layer 102, such as SiO 2 Insulation protective layer. A nucleation l...

no. 3 approach

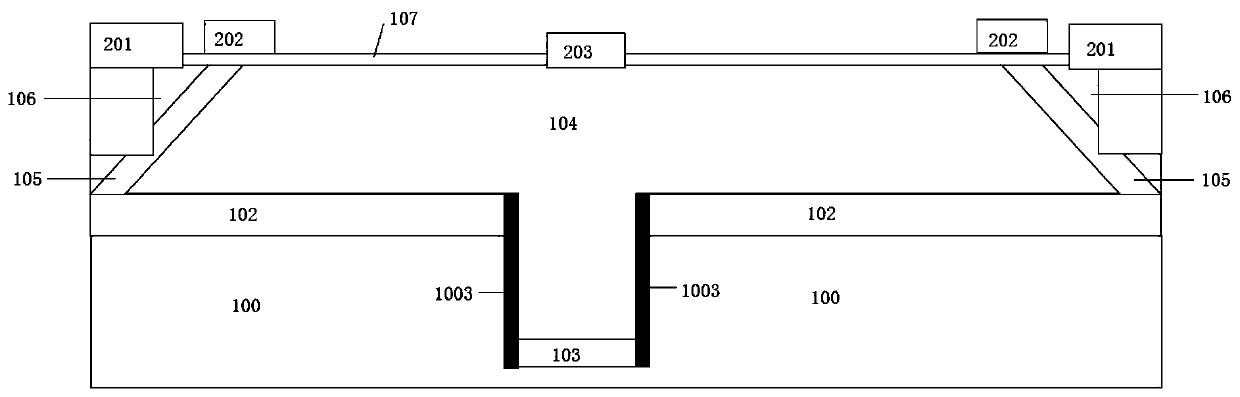

[0091] see Figure 4 , on the basis of the first embodiment or the second embodiment, there is also a fourth electrode 204, the fourth electrode 204 is a body electrode, which forms an ohmic contact with the second end of the second semiconductor layer 105 to control potential of the semiconductor device. The fourth electrode 204 can be an independent electrode to independently control the potential; or the fourth electrode 204 can be connected to the first electrode 201 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com