Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

302 results about "Resistive switching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

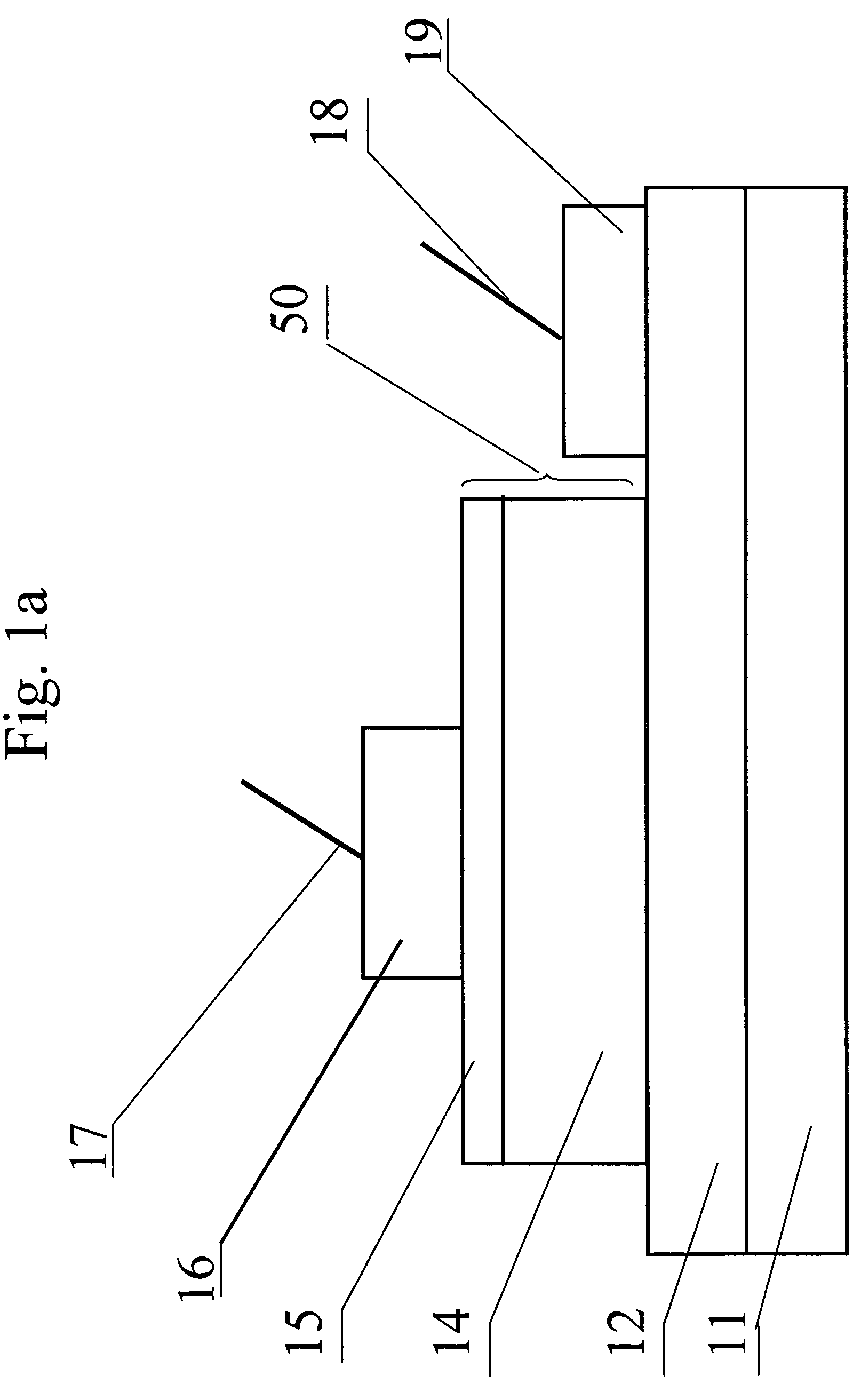

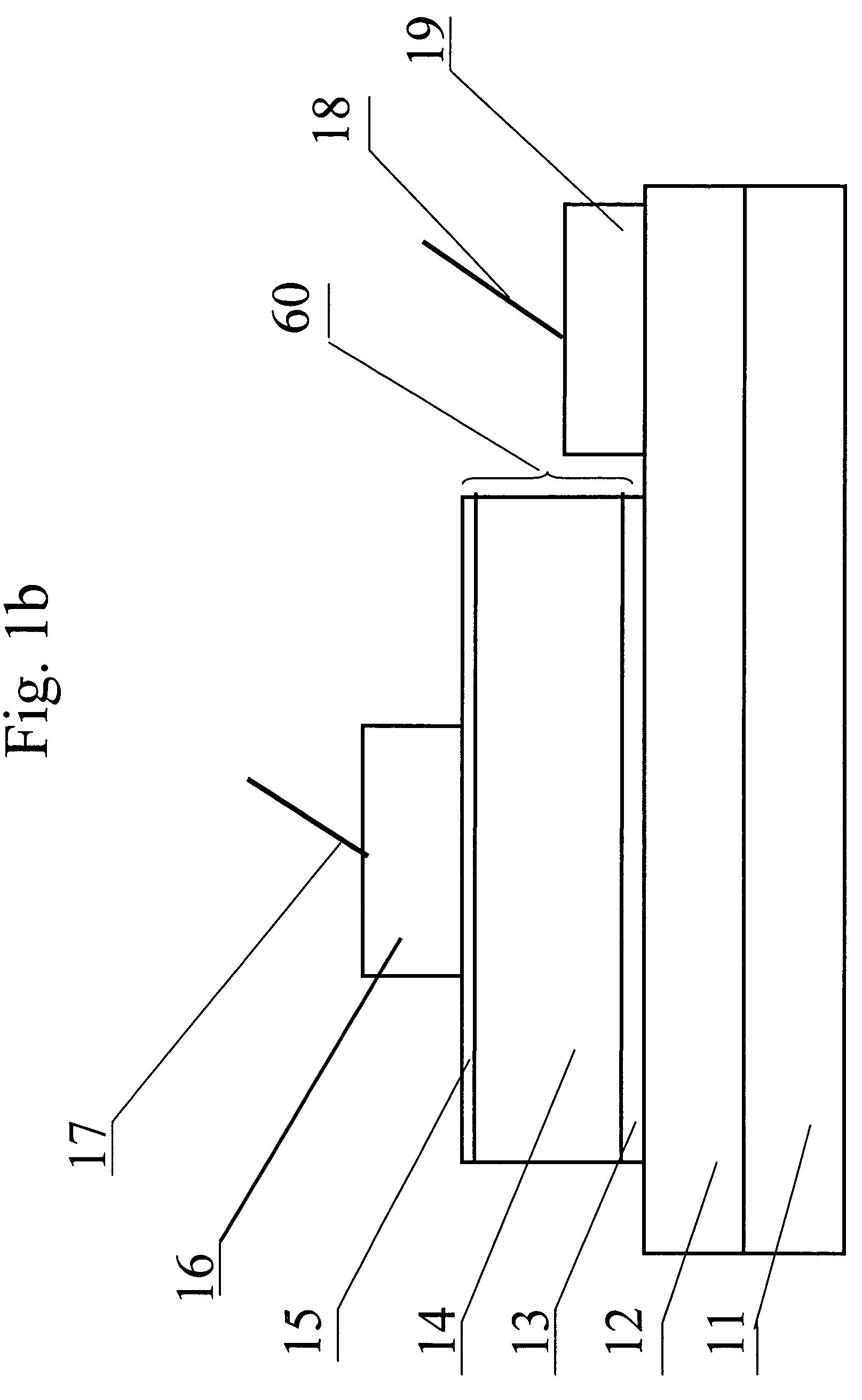

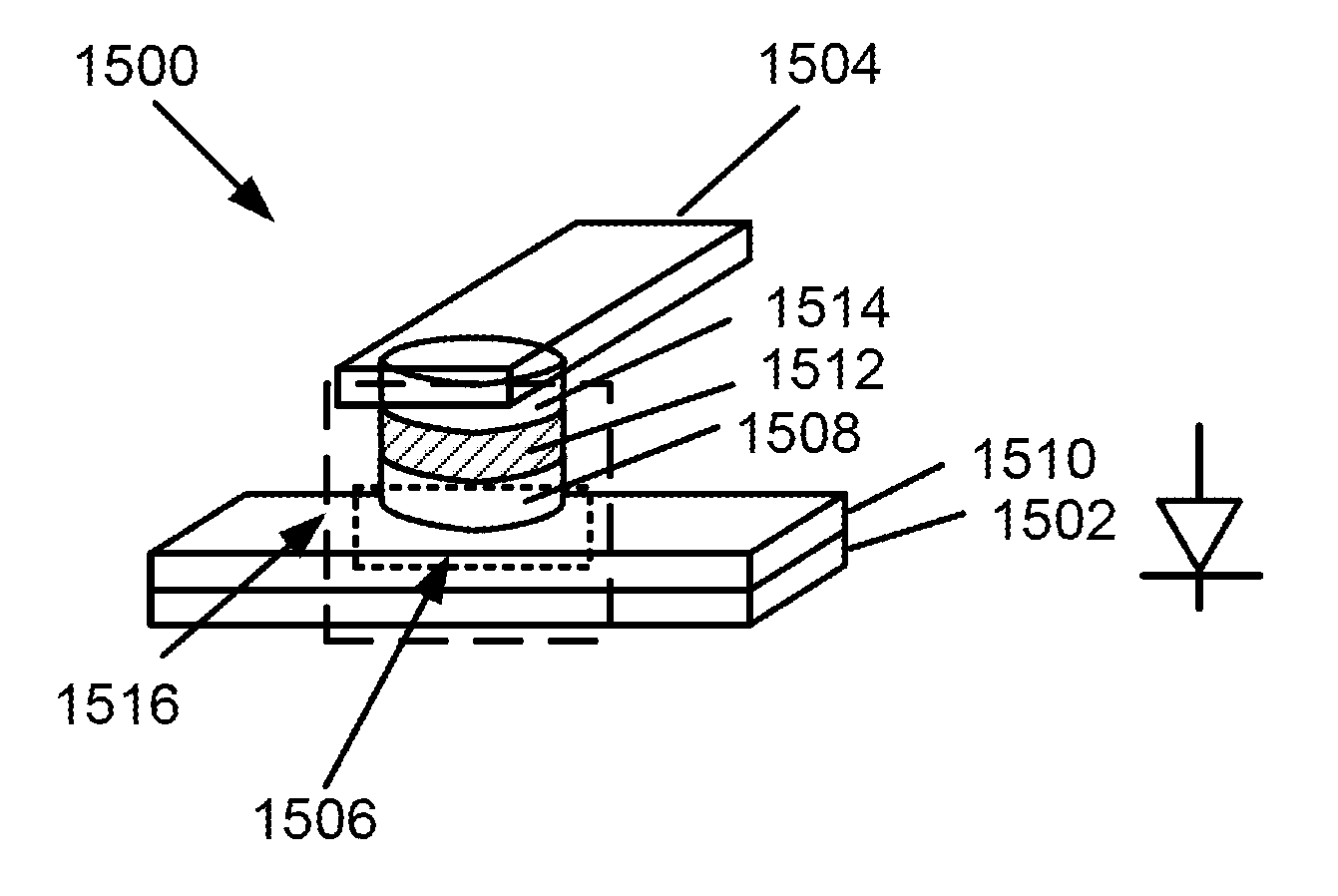

Rewriteable memory cell comprising a transistor and resistance-switching material in series

InactiveUS20060273298A1Solid-state devicesBulk negative resistance effect devicesHigh resistanceEngineering

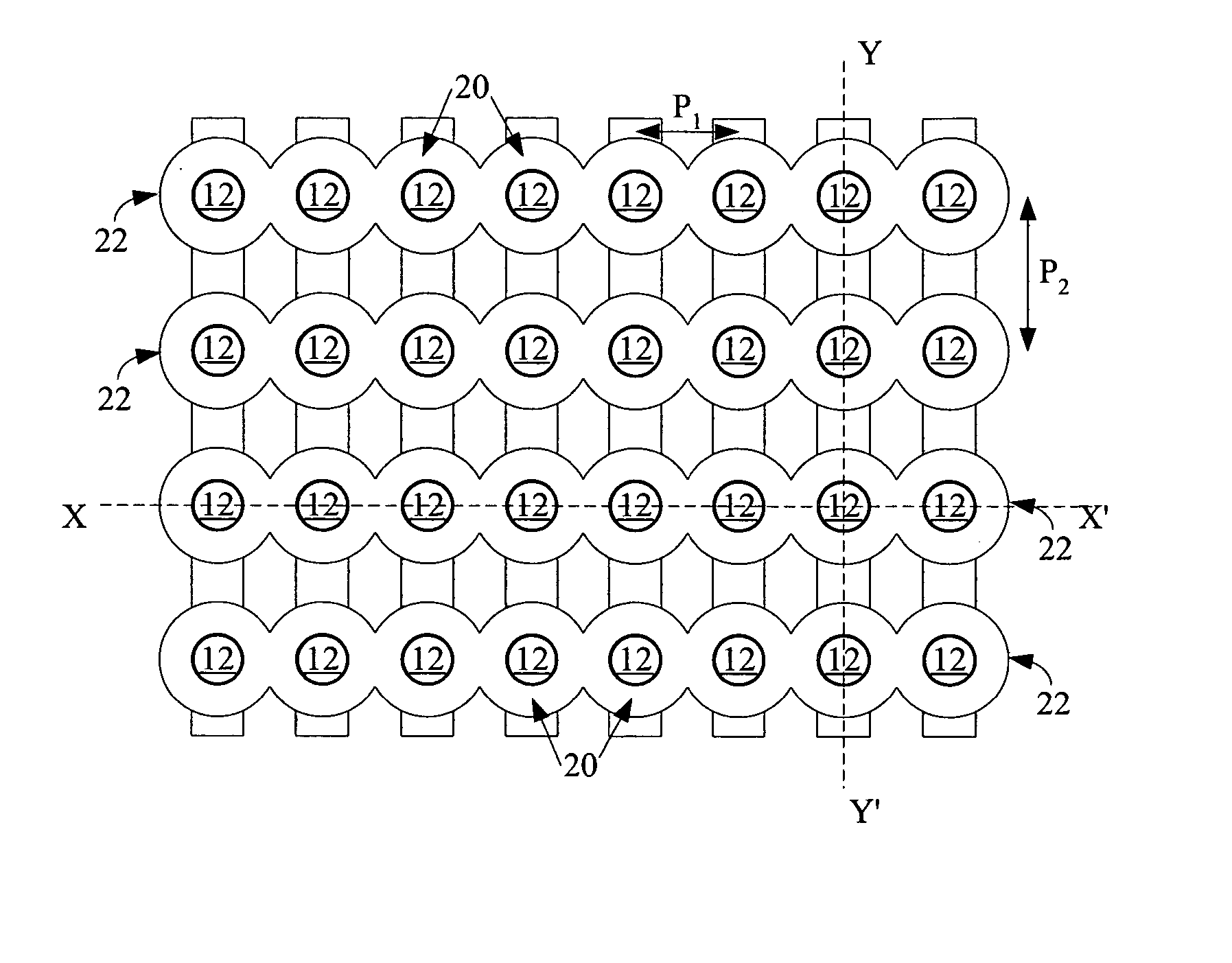

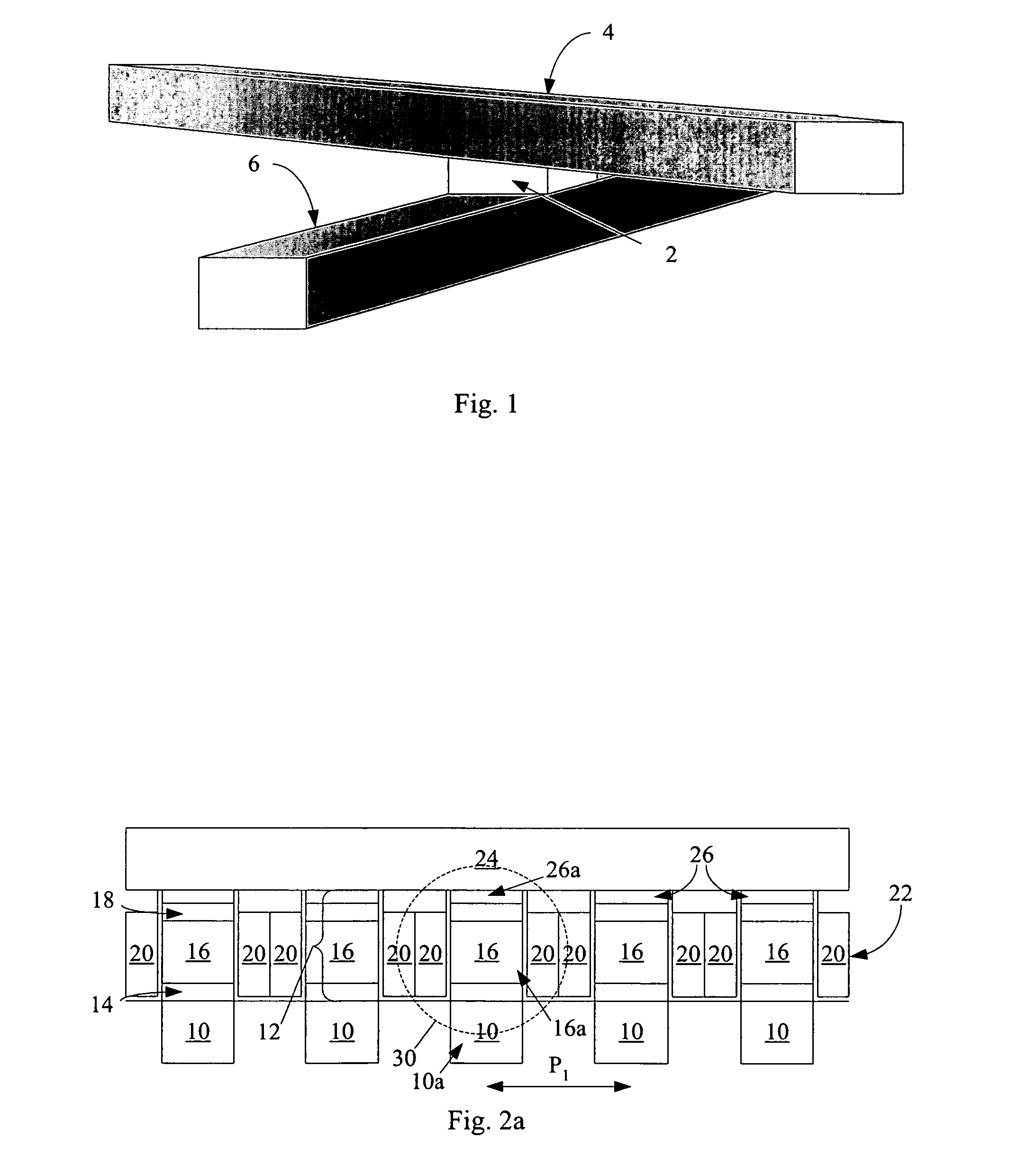

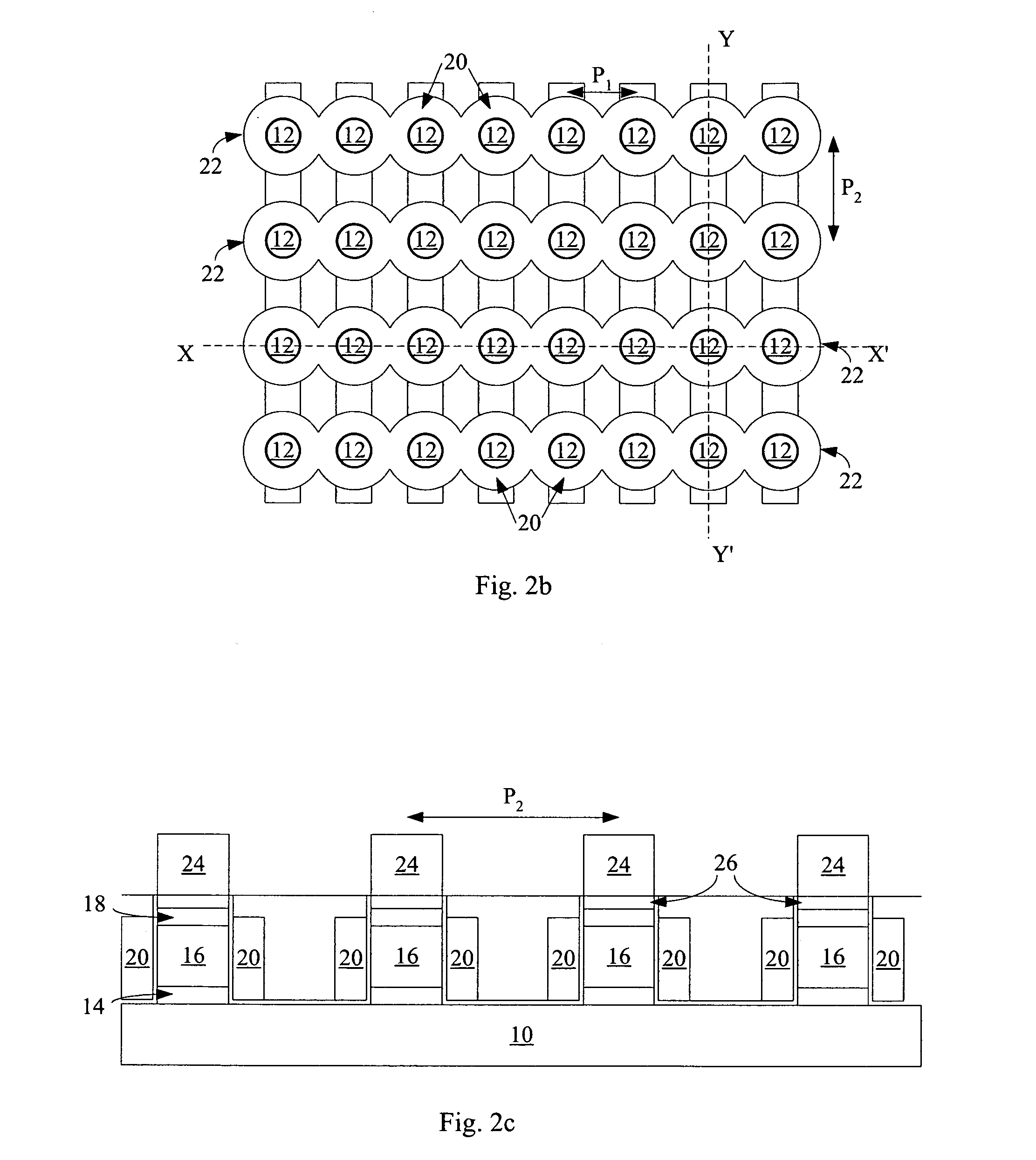

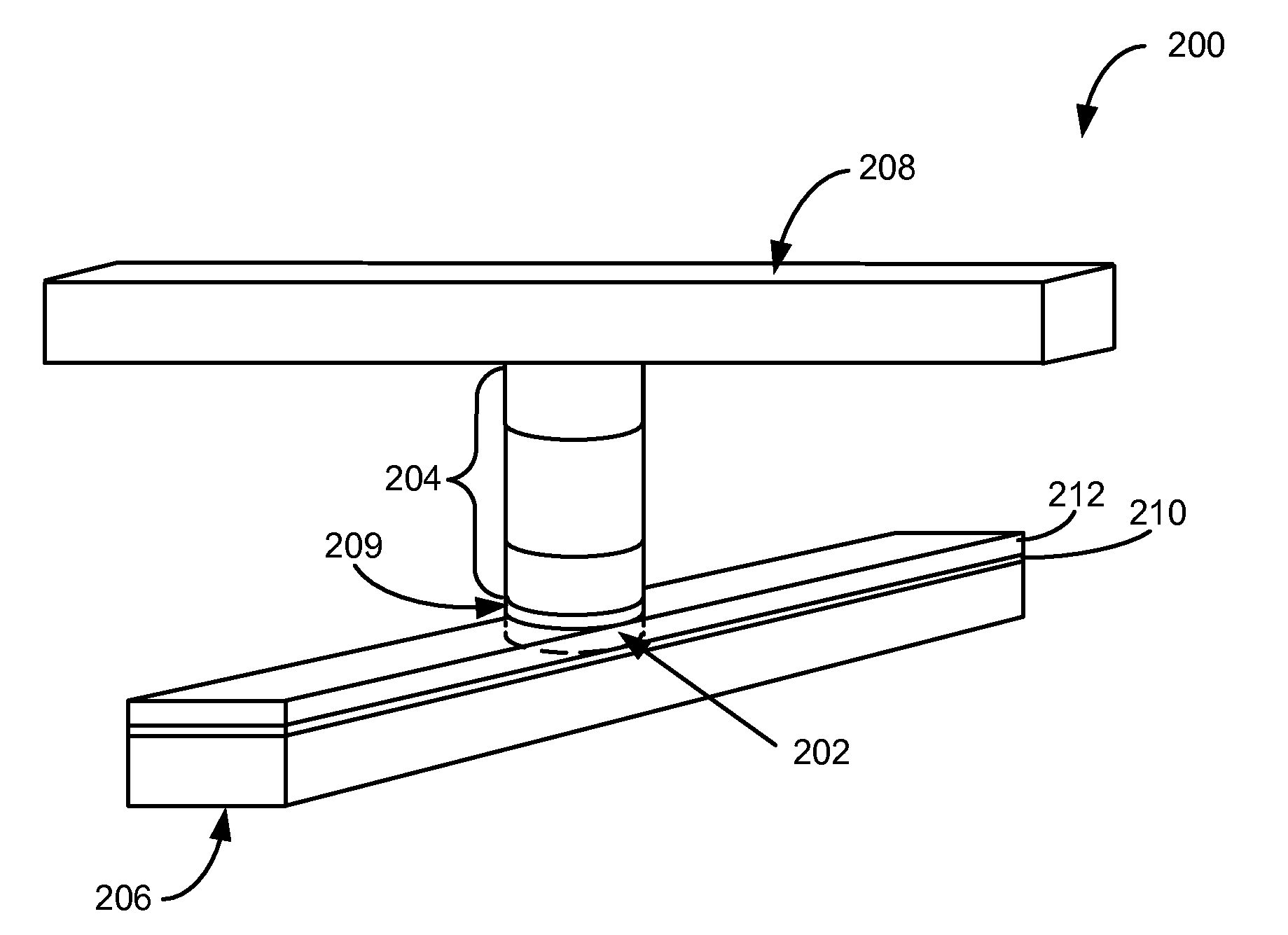

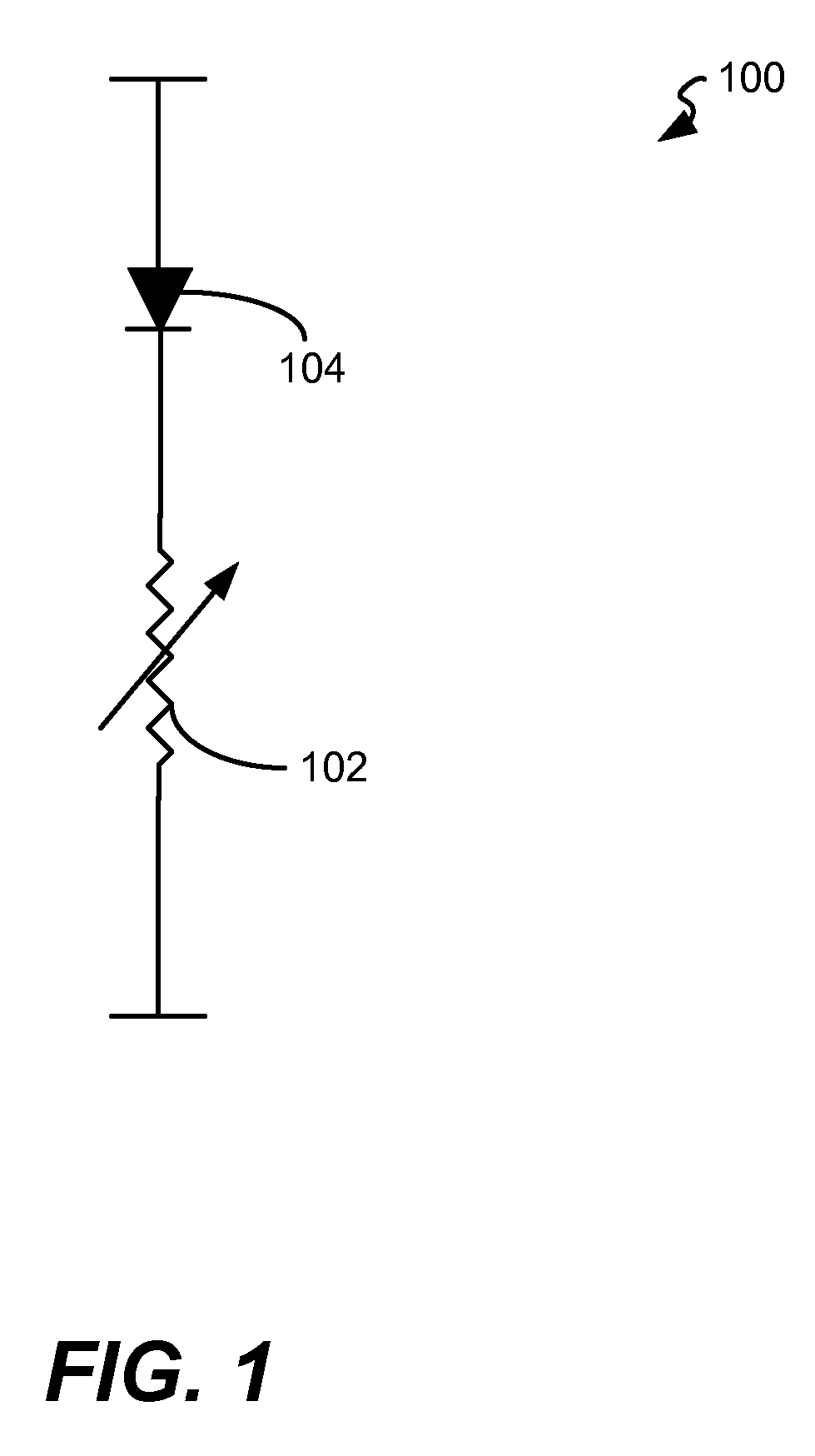

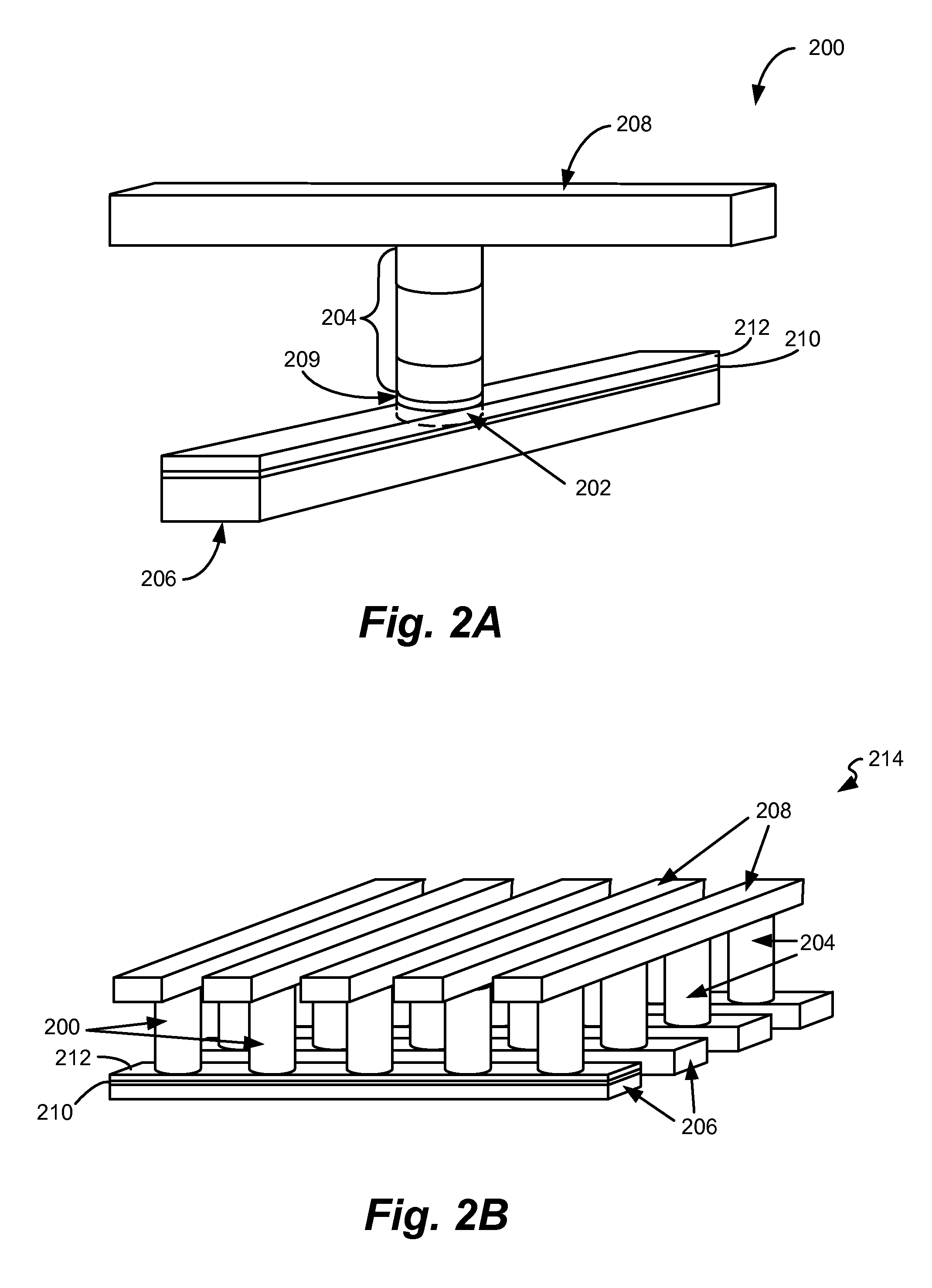

A nonvolatile memory cell is provided, the cell comprising a transistor in series with resistance-switching material, which can be switched between at least two stable resistance states, for example a high-resistance state and a low-resistance state. In preferred embodiments the transistor is a TFT, having a channel region not formed in a monocrystalline wafer substrate. In preferred embodiments the transistor may have either a vertically oriented channel or a laterally oriented channel. Either embodiment can be formed in a monolithic three dimensional memory array in which multiple memory levels can be formed above a single substrate, forming a highly dense nonvolatile memory array.

Owner:SANDISK TECH LLC

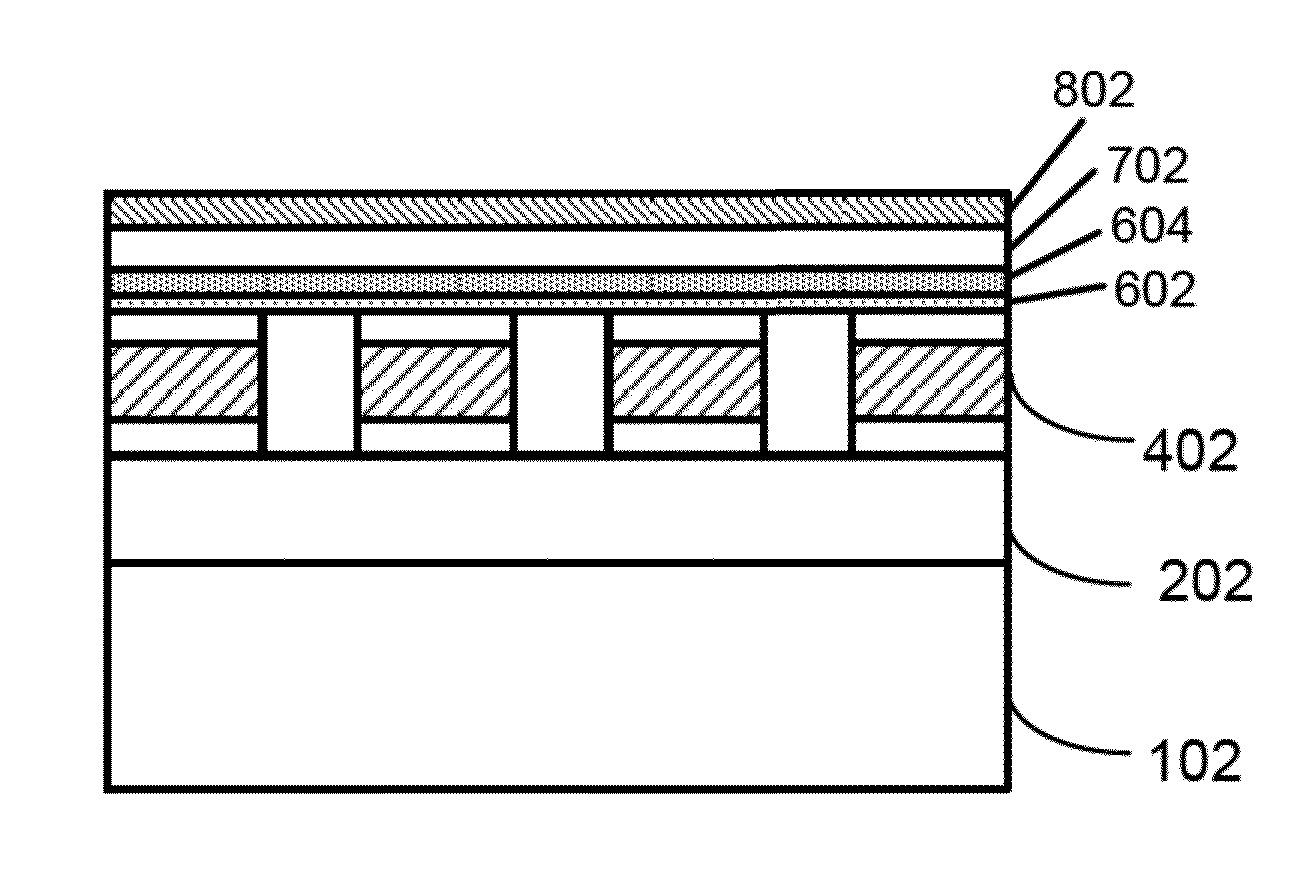

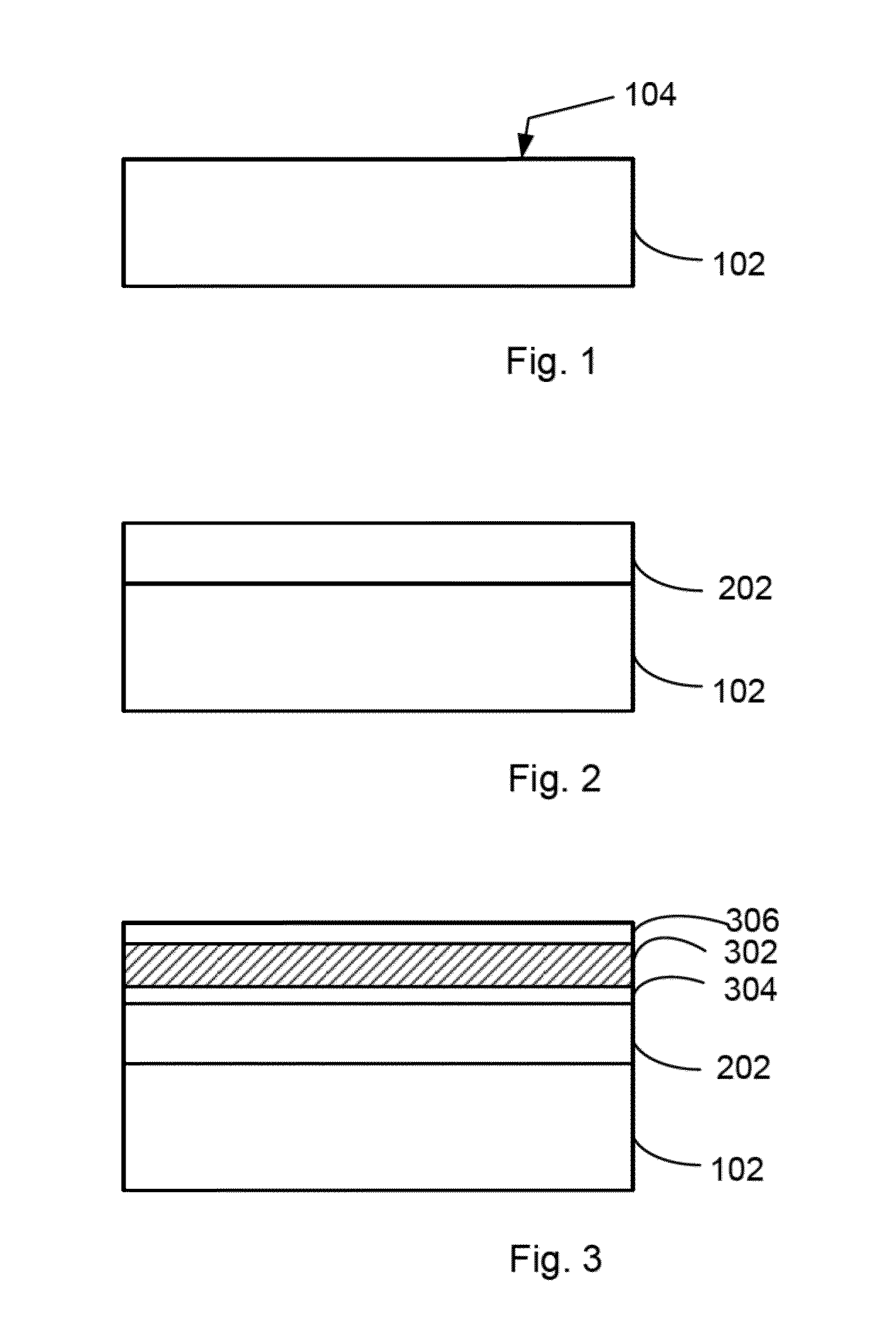

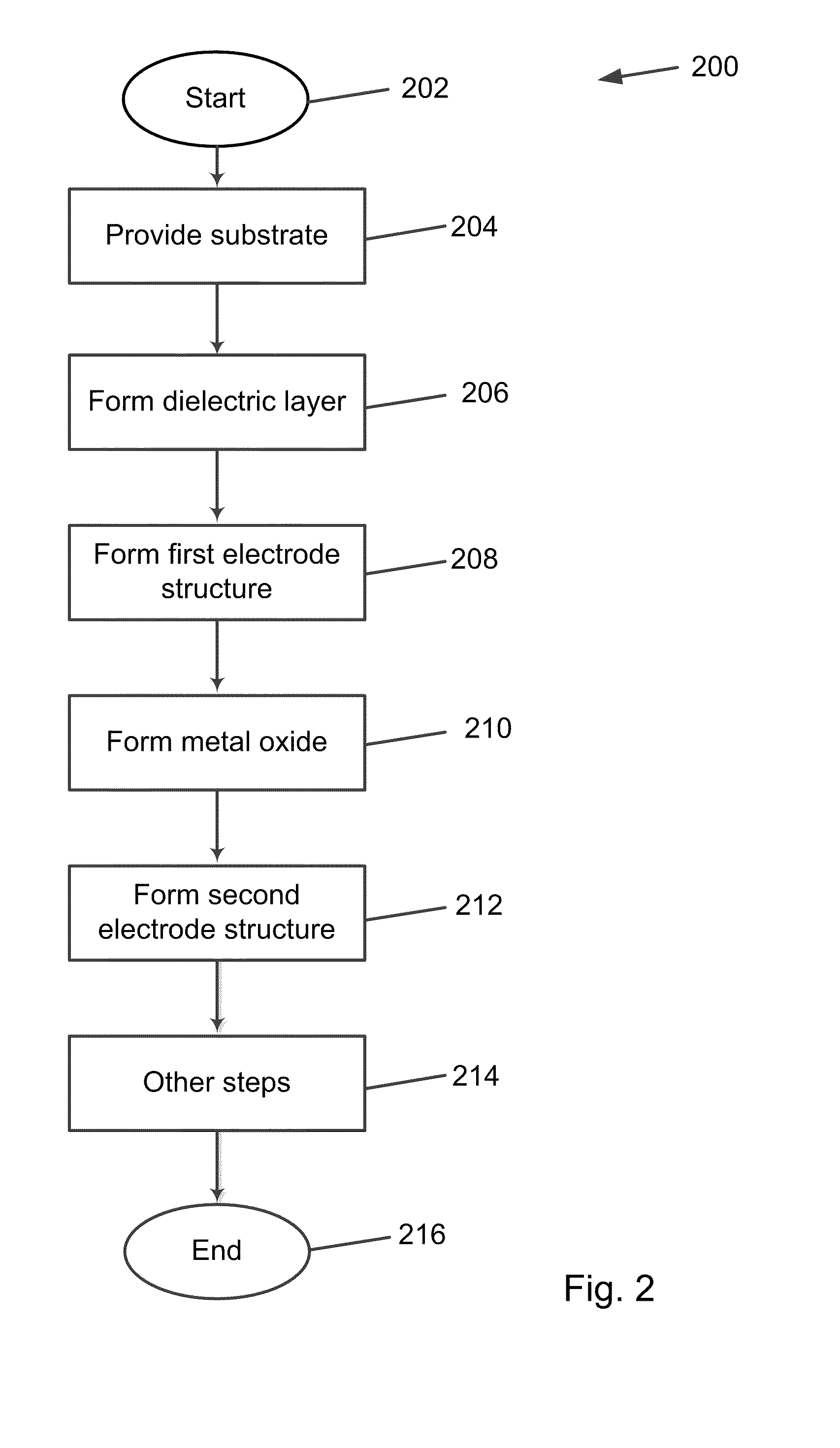

Methods of forming embedded resistors for resistive random access memory cells

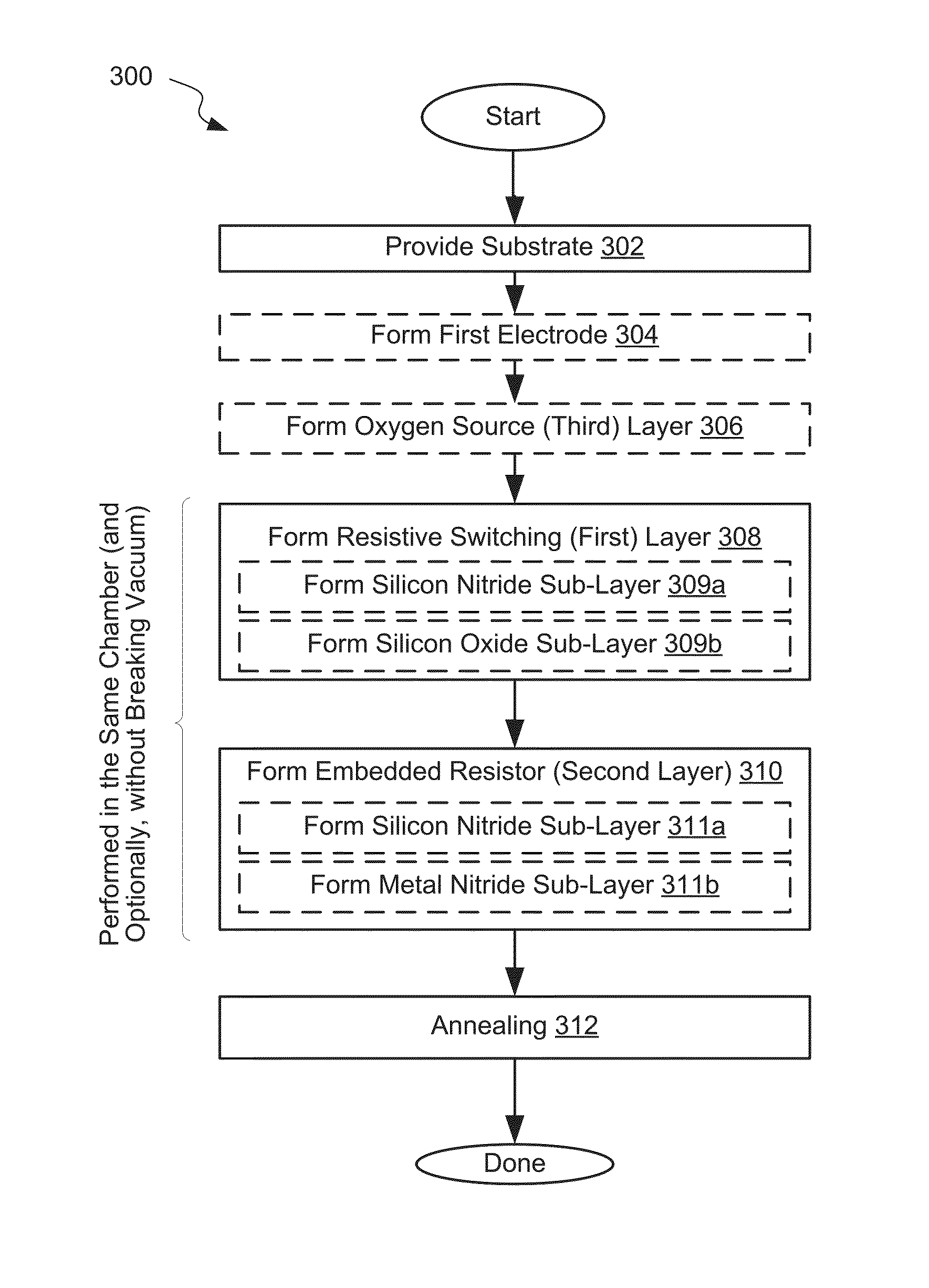

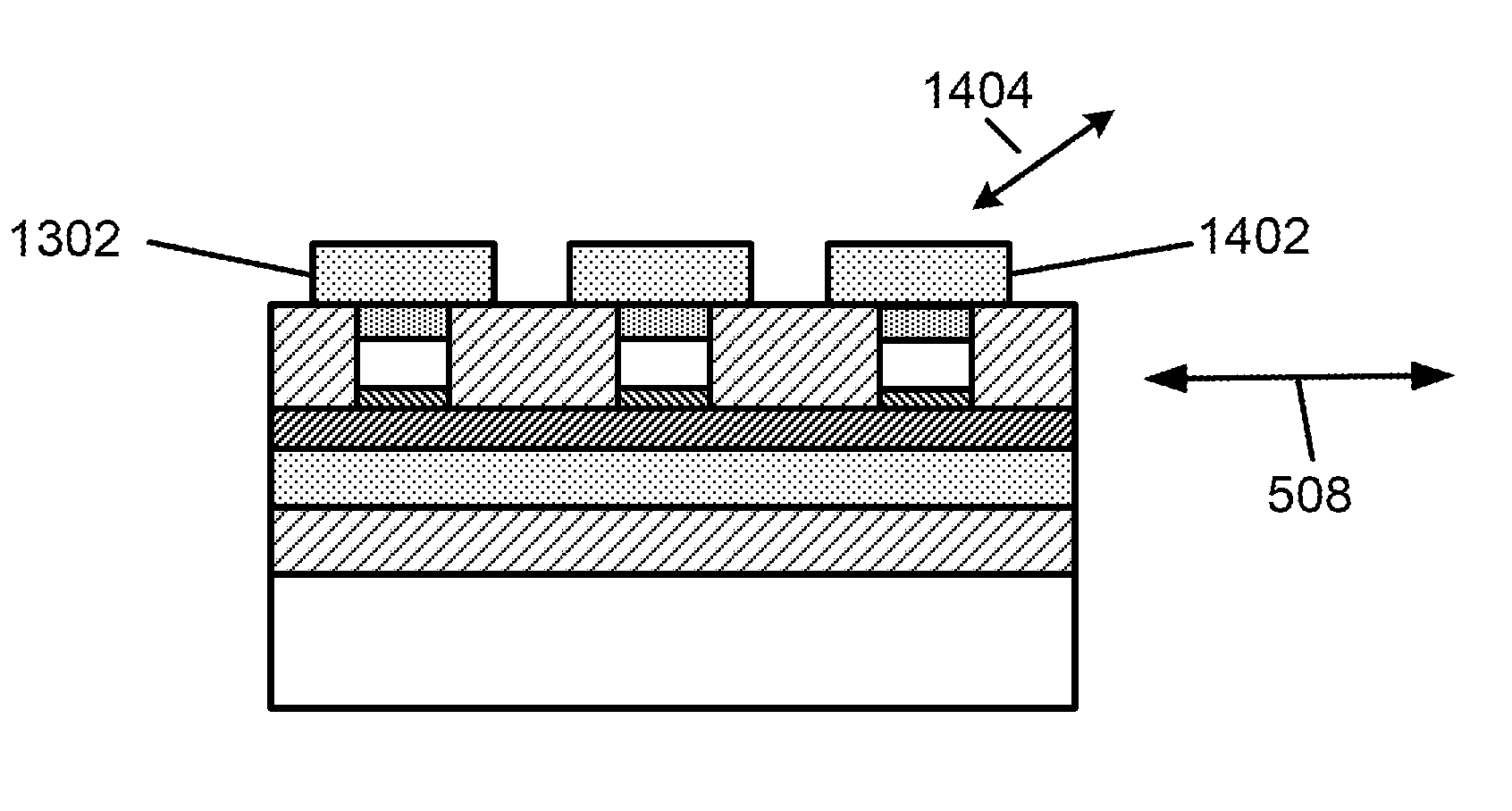

Provided are memory cells including resistive switching layers having silicon, oxygen, and nitrogen as well as embedded resistor layers having a metal, silicon, and nitrogen. In some embodiments, silicon may be partially or completely replaced with aluminum. The embedded resistor may also have oxygen. A resistive switching layer directly interfaces an embedded resistor layer of the same cell. A portion of each layer forming this interface may be formed substantially of silicon nitride and may be formed in the same deposition chamber without breaking vacuum. For example, these portions may be formed by sequential atomic layer deposition cycles. However, silicon concentrations in these portions may be different. Specifically, the silicon concentration of the embedded resistor portion may be less than the silicon concentration of the resistive switching layer portion. This variation may be achieved by varying one or more process conditions during fabrication of the memory cell.

Owner:INTERMOLECULAR

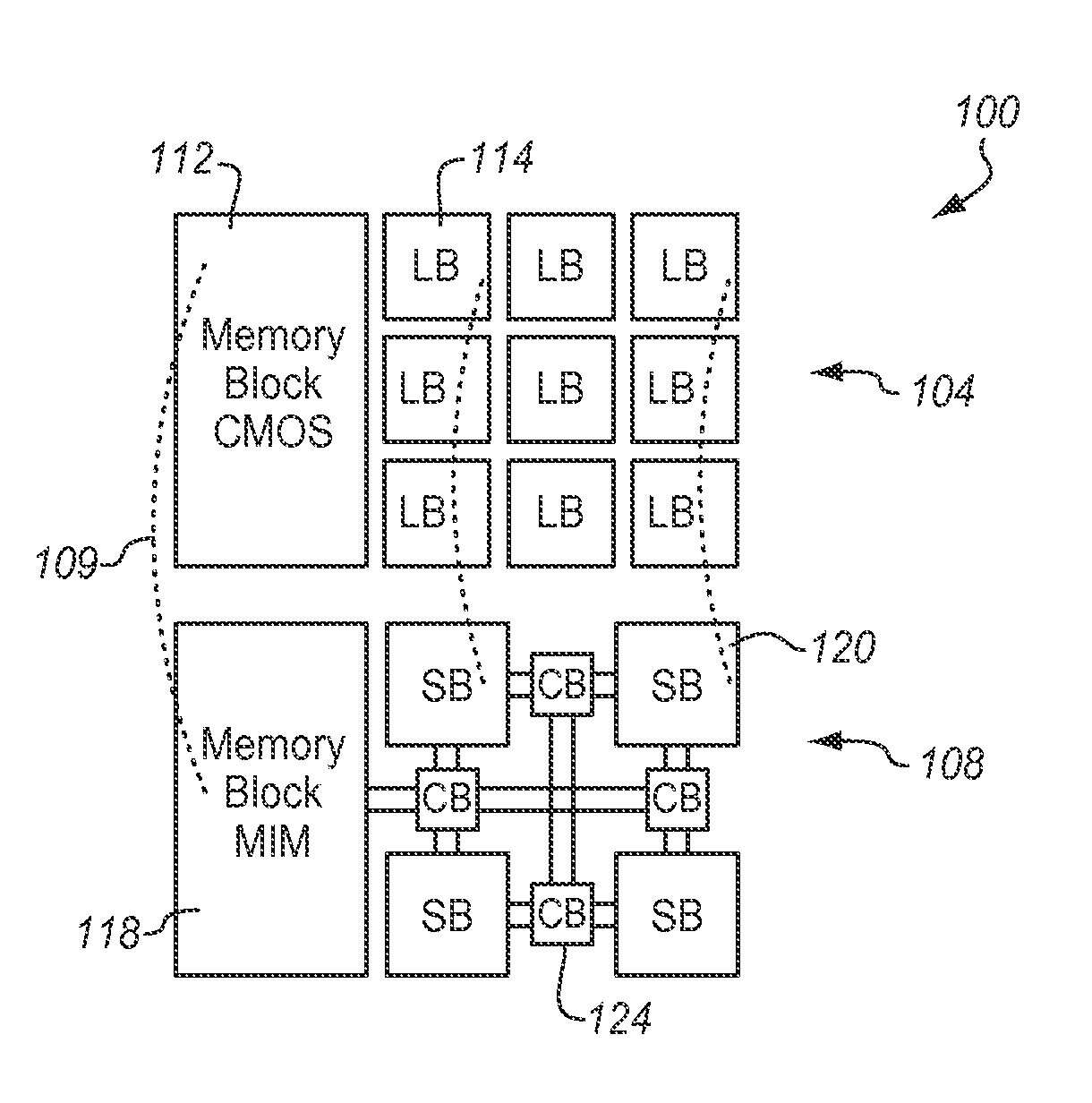

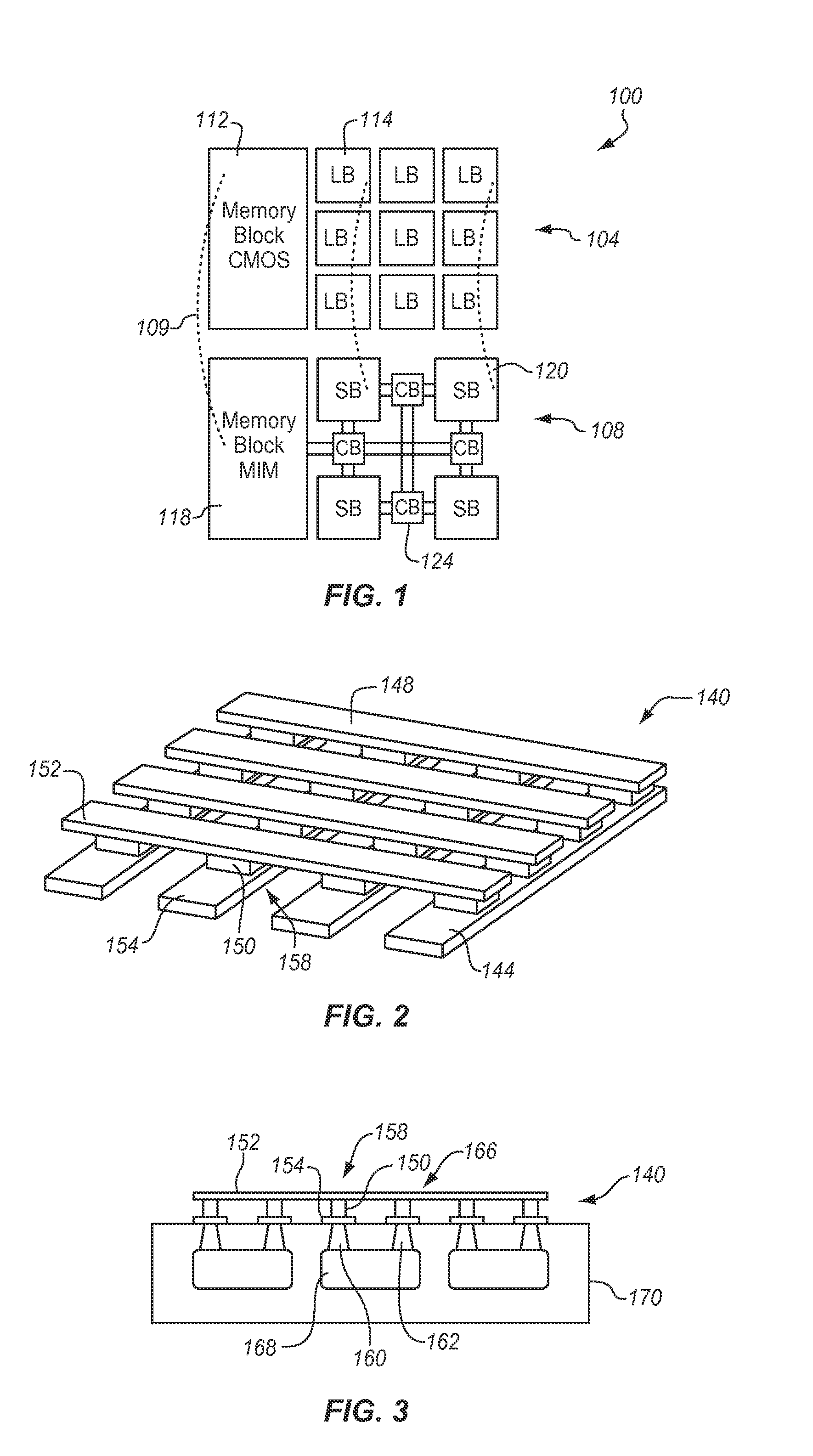

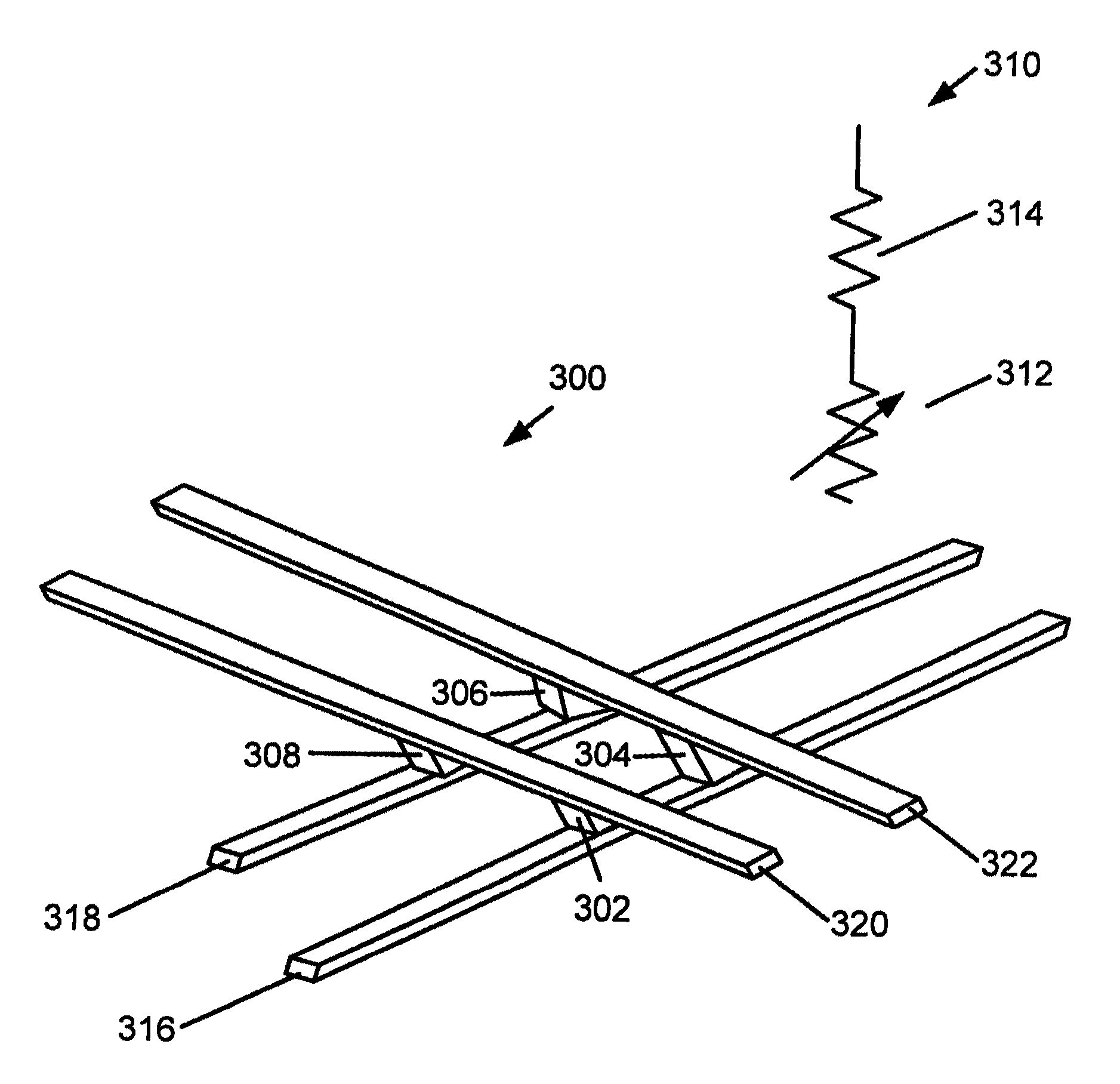

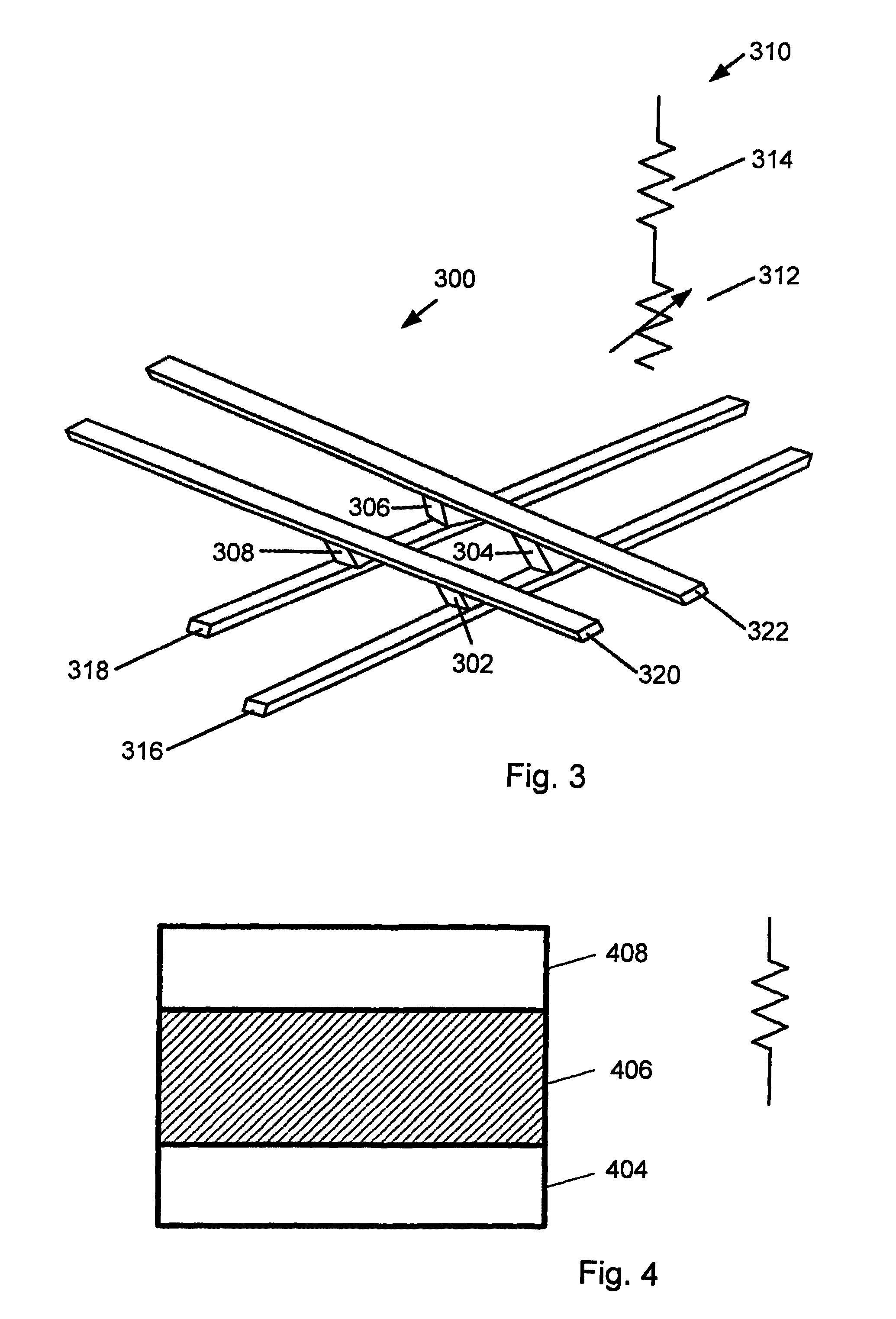

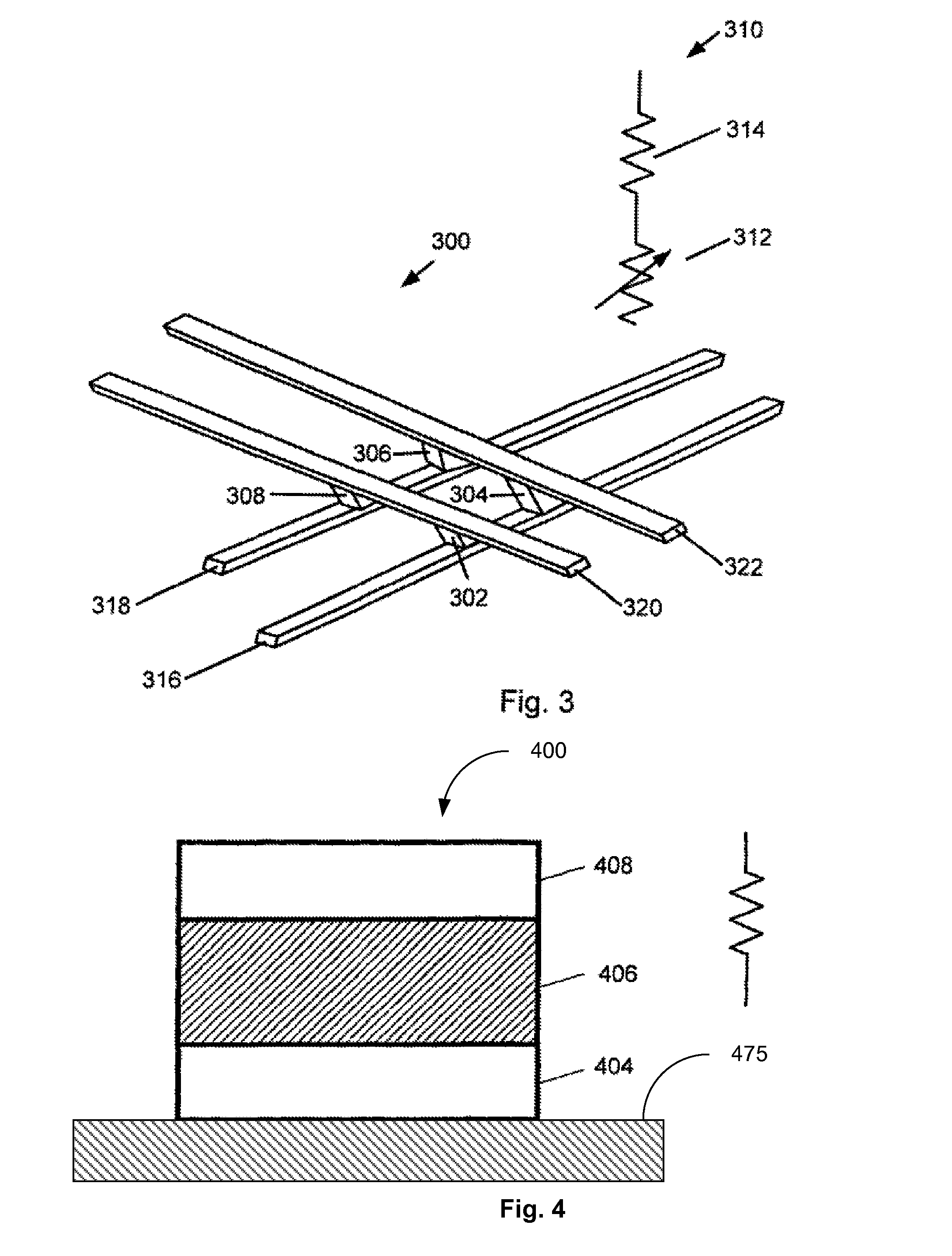

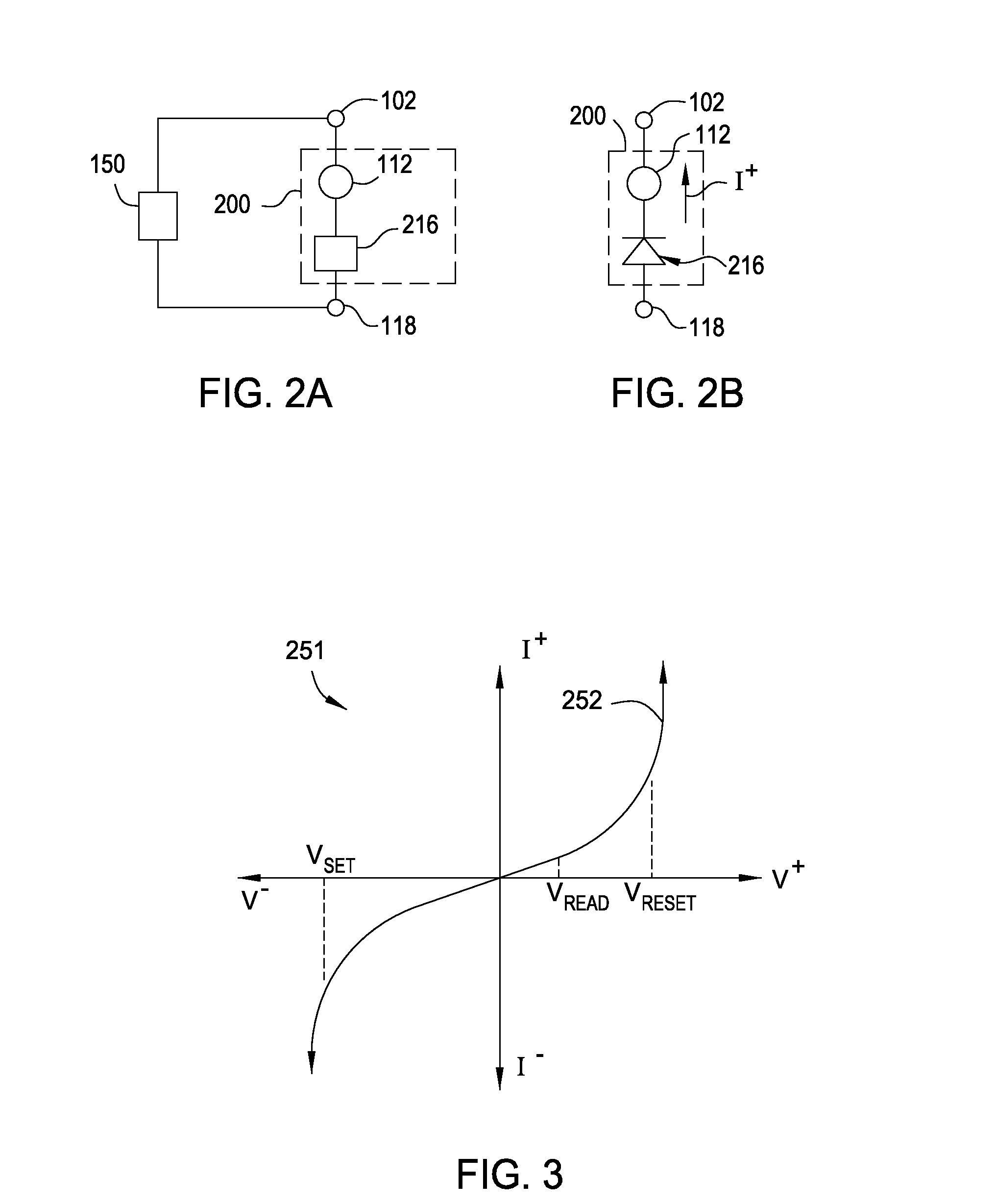

RE-PROGRAMMABLE ANTIFUSE FPGA UTILIZING RESISTIVE CeRAM ELEMENTS

ActiveUS20130285699A1Solid-state devicesRead-only memoriesElectrical resistance and conductanceResistive switching

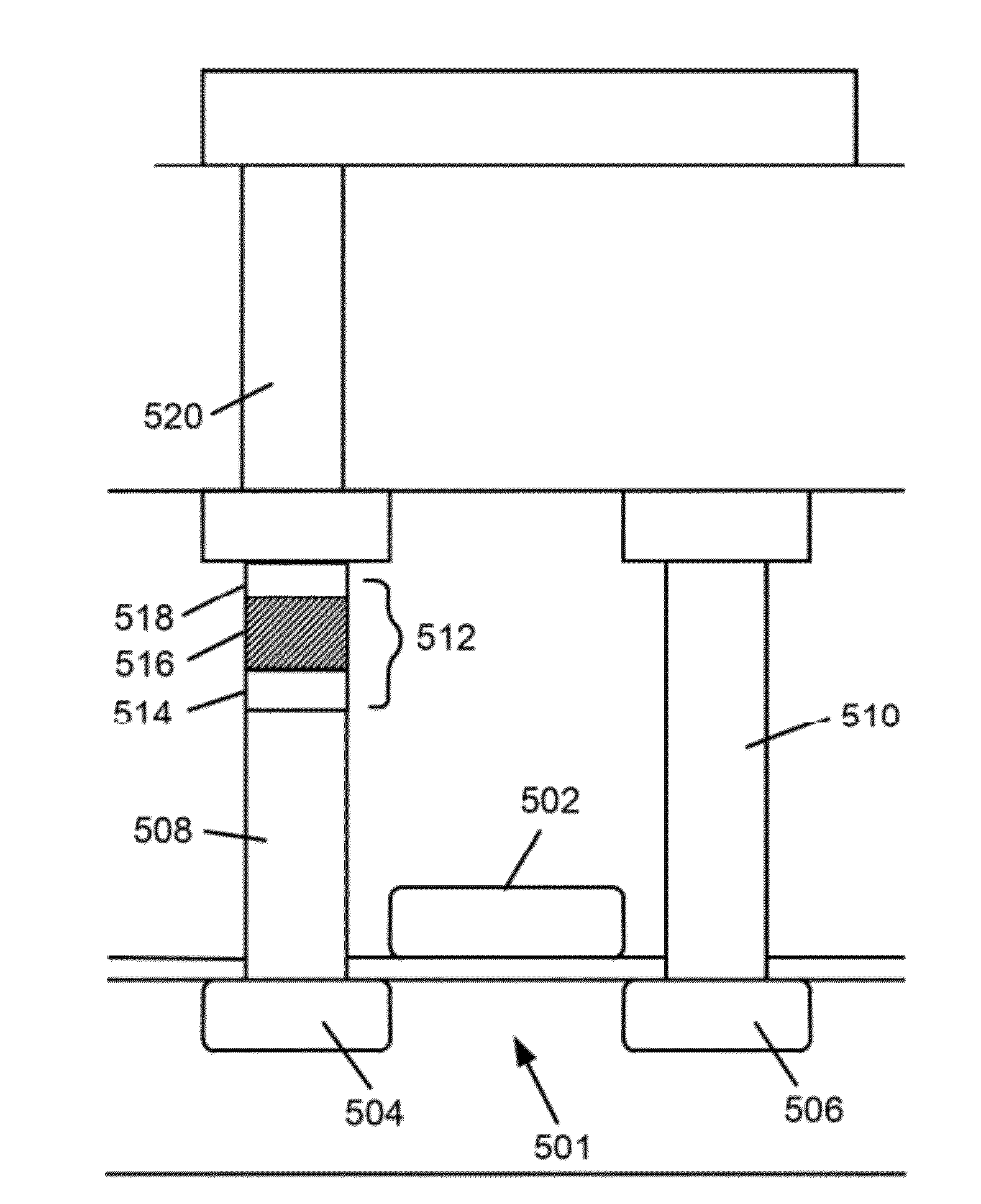

A re-programmable antifuse field programmable gate array (FPGA) integrated circuit, the FPGA comprising: a plurality of CeRAM resistive switching elements forming a connection block, the switching elements capable of being switched from a conductive (ON) state to a non-conductive (OFF) state and back to a conductive (ON) state; a plurality of logic elements forming a logic block; and a programming circuit for turning the CeRAM switching elements OFF and ON to connect the logic elements to form the FPGA.

Owner:SYMETRIX MEMORY

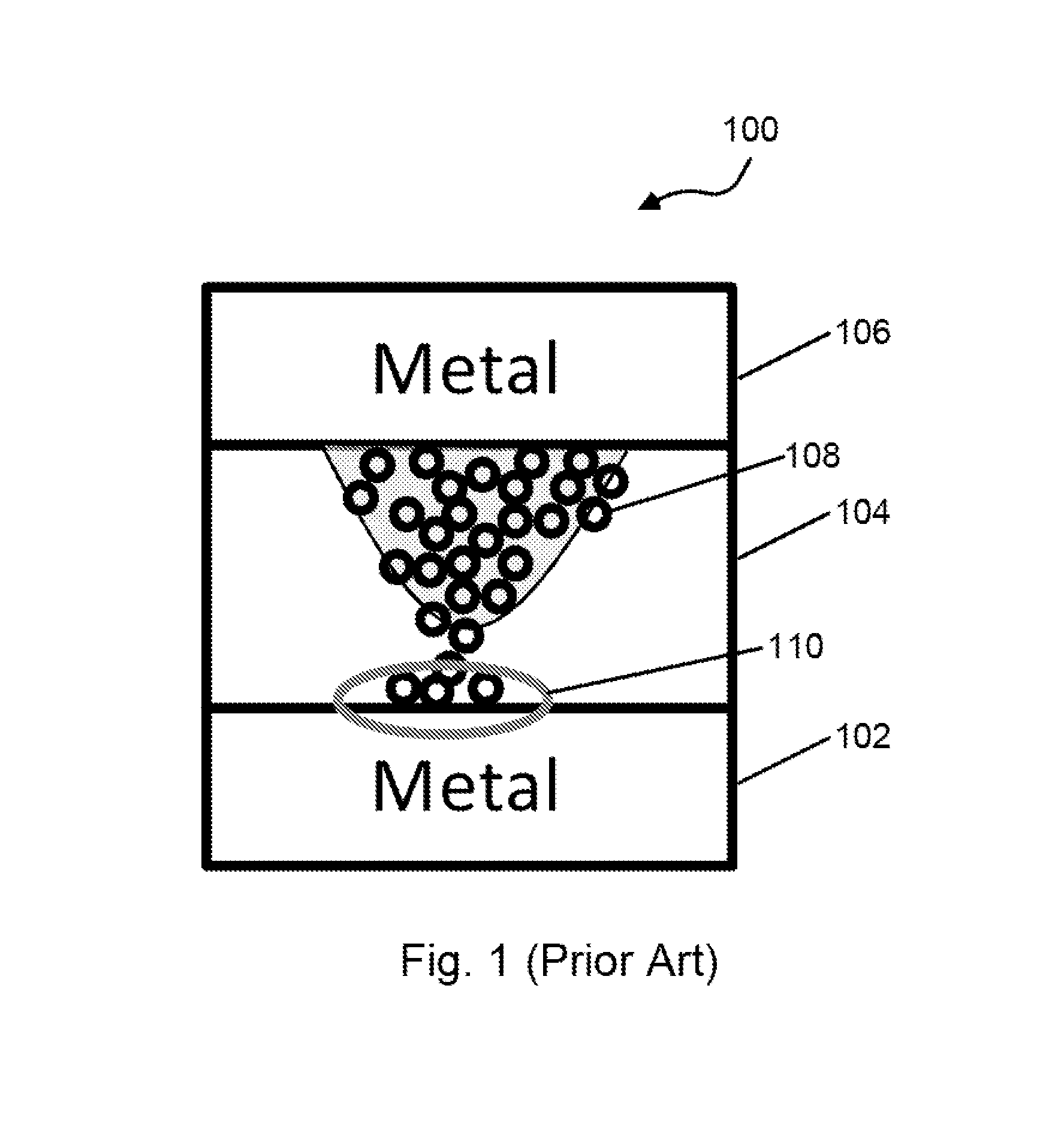

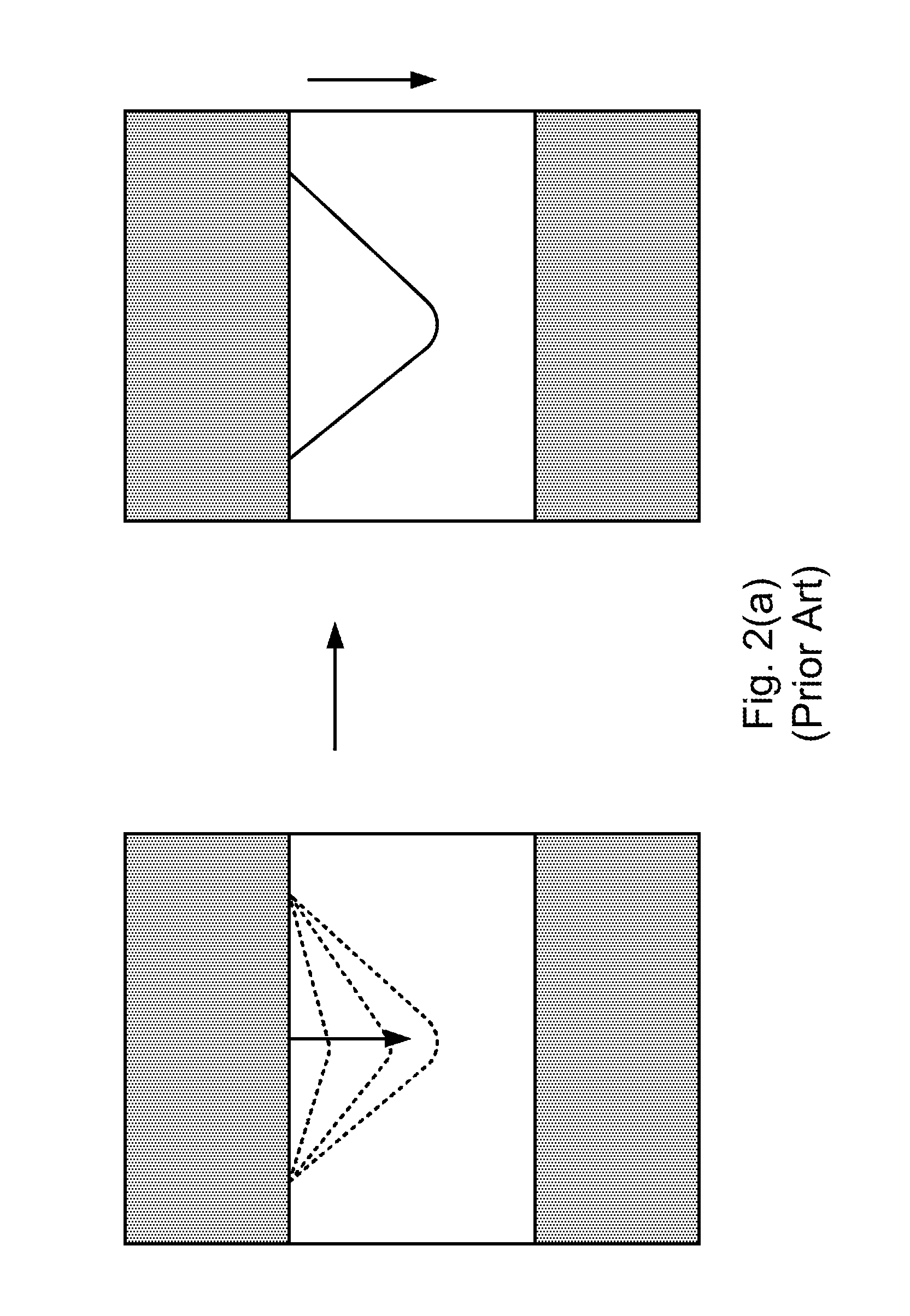

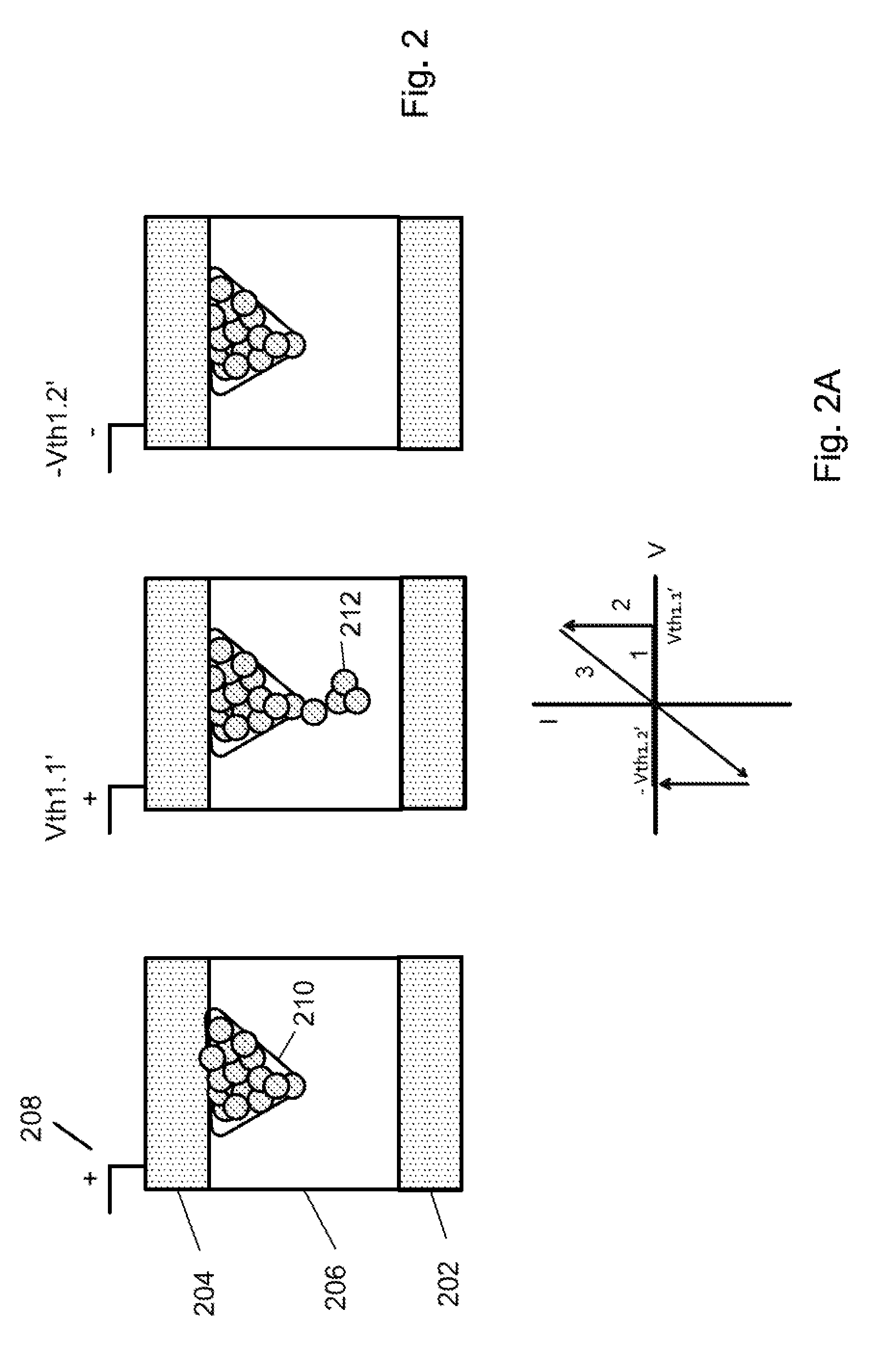

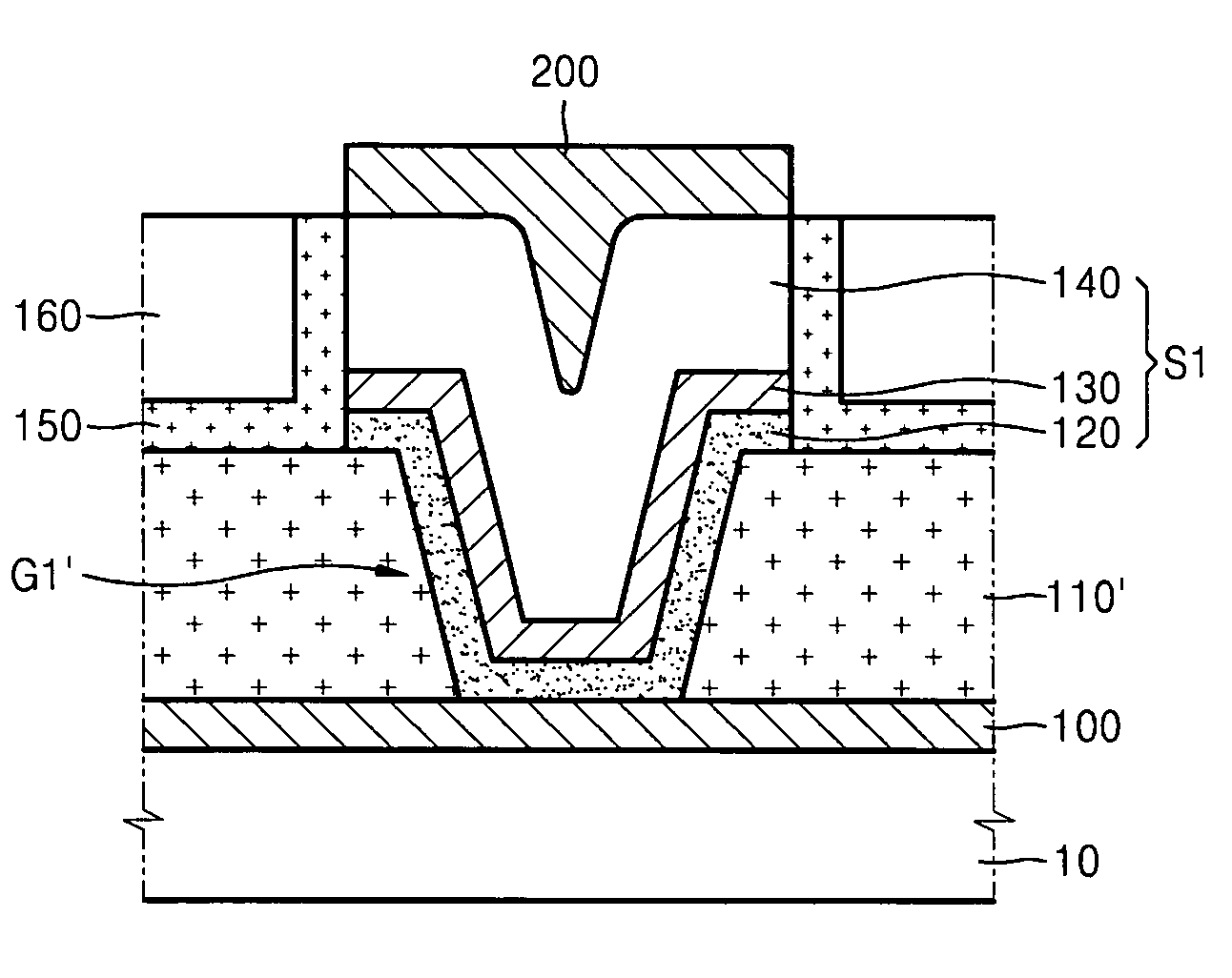

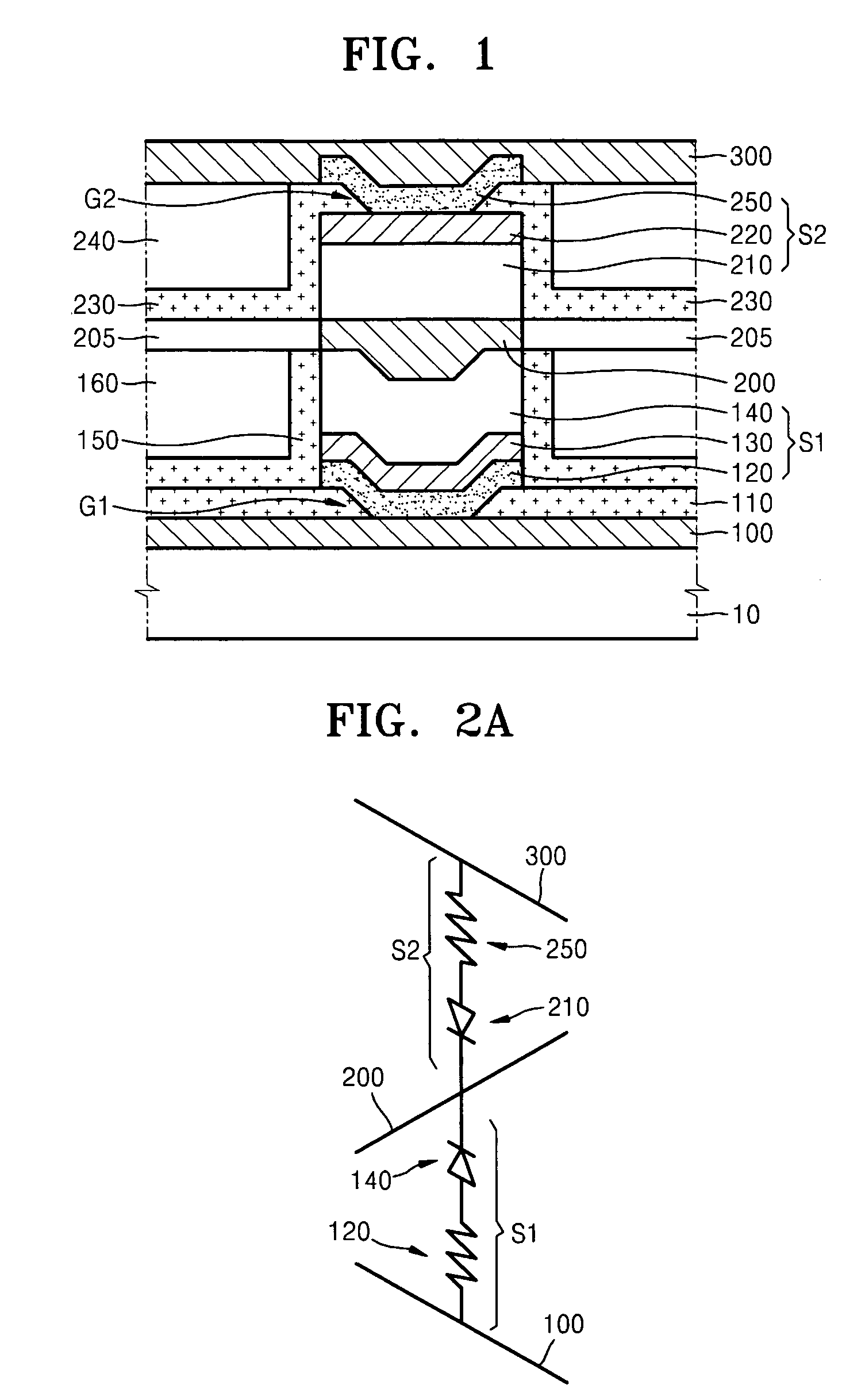

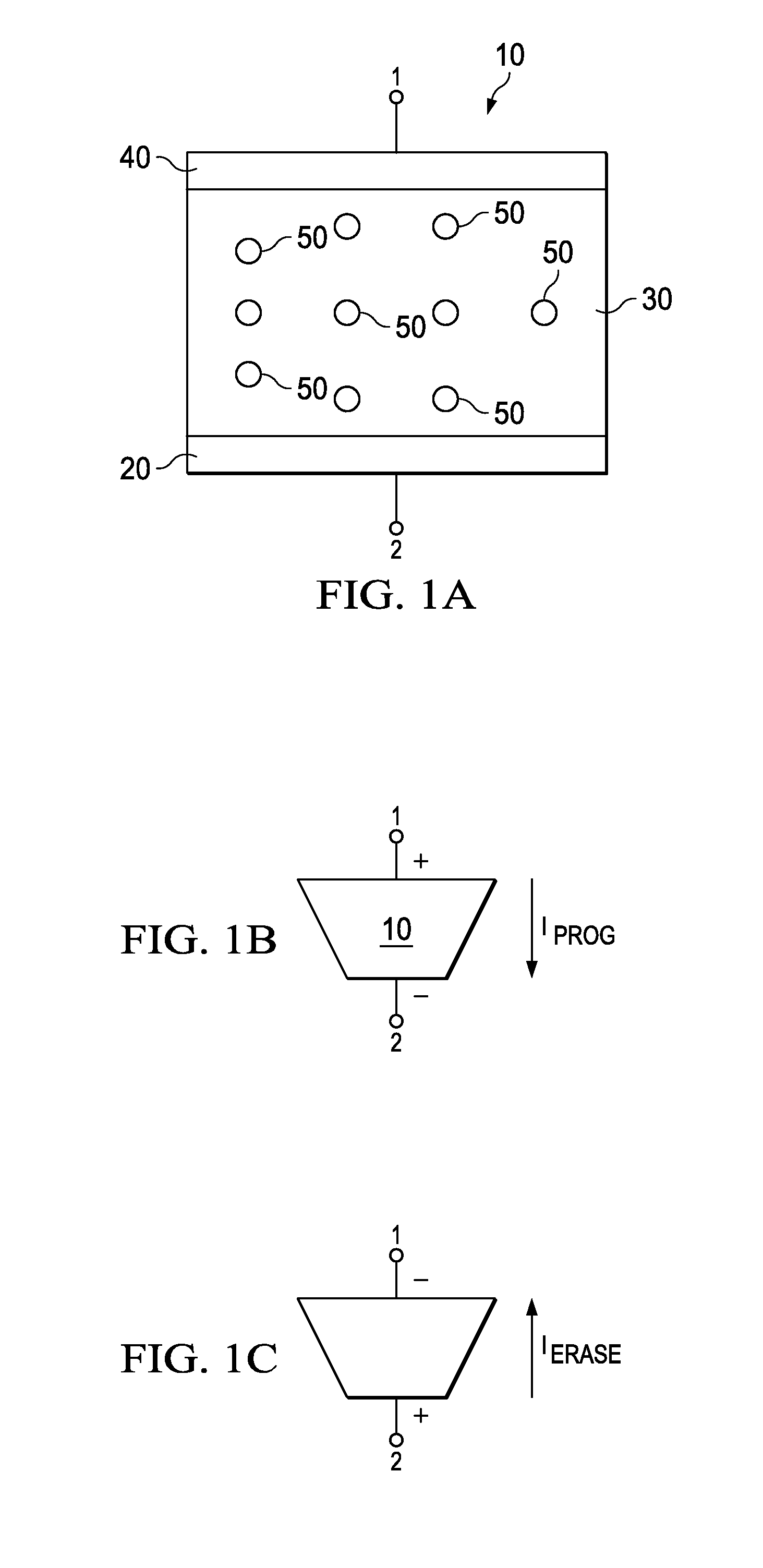

Rectification element and method for resistive switching for non volatile memory device

ActiveUS20110317470A1High densityFast switching speedSolid-state devicesDigital storageComputational physicsResistive switching

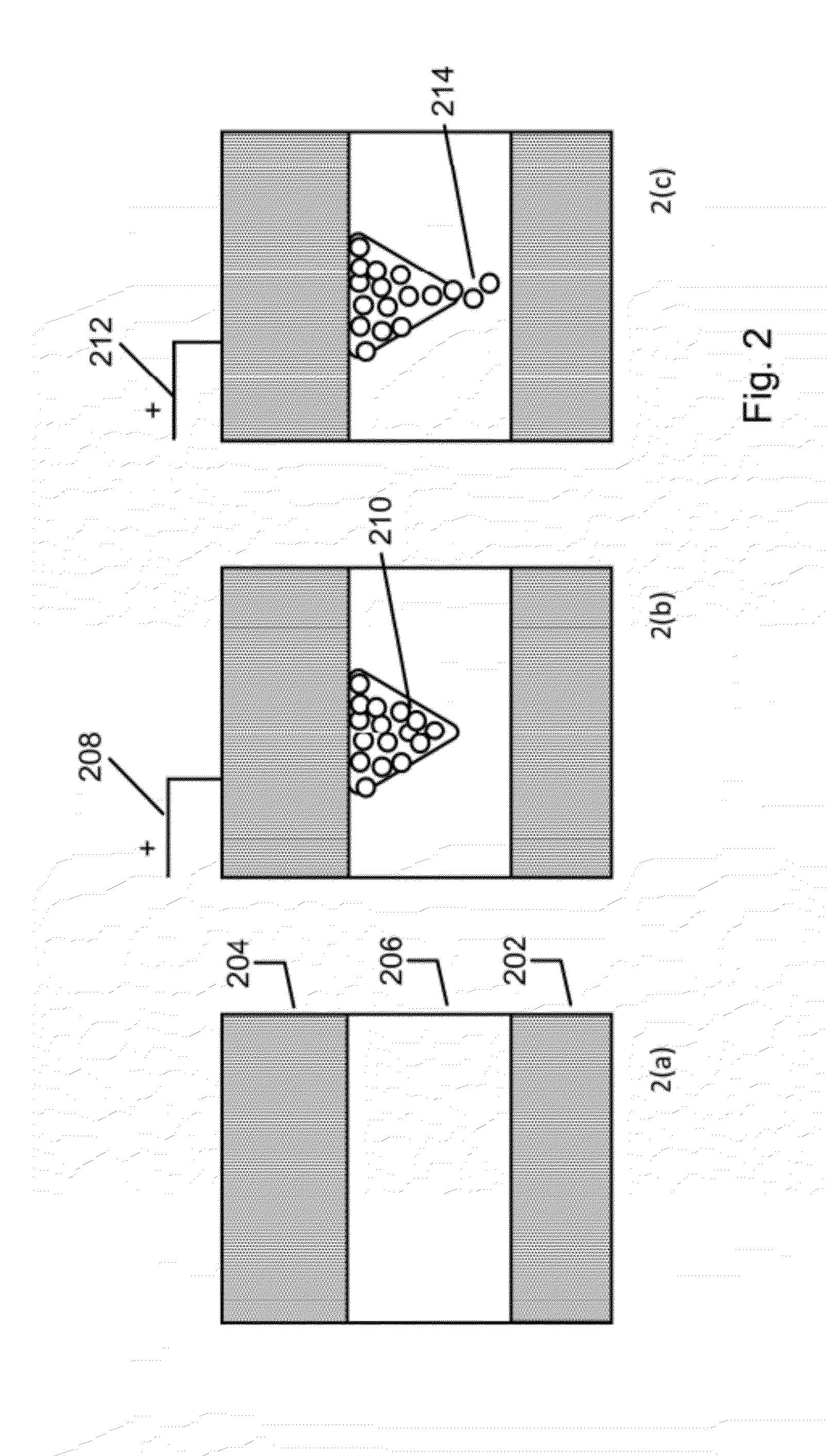

A method of suppressing propagation of leakage current in an array of switching devices. The method includes providing a dielectric breakdown element integrally and serially connected to a switching element within each of the switching device. A read voltage (for example) is applied to a selected cell. The propagation of leakage current is suppressed by each of the dielectric breakdown element in unselected cells in the array. The read voltage is sufficient to cause breakdown in the selected cells but insufficient to cause breakdown in the serially connected, unselected cells in a specific embodiment. Methods to fabricate of such devices and to program, to erase and to read the device are provided.

Owner:RGT UNIV OF MICHIGAN

Memory cell that employs a selectively fabricated carbon nano-tube reversible resistance-switching element formed over a bottom conductor and methods of forming the same

In some aspects, a method of fabricating a memory cell is provided that includes (1) fabricating a first conductor above a substrate; (2) selectively fabricating a carbon nano-tube (CNT) material above the first conductor; (3) fabricating a diode above the CNT material; and (4) fabricating a second conductor above the diode. Numerous other aspects are provided.

Owner:SANDISK TECH LLC

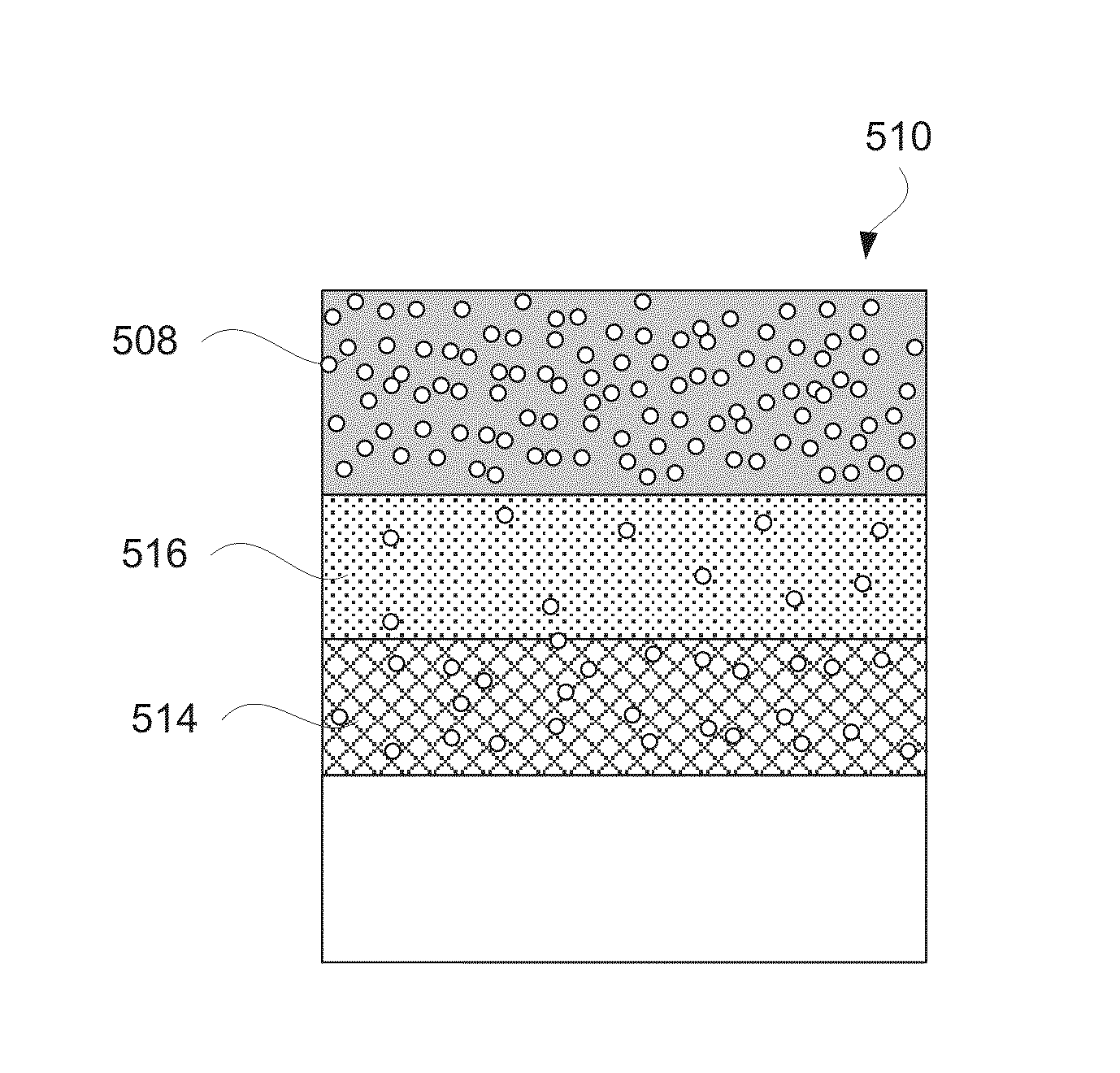

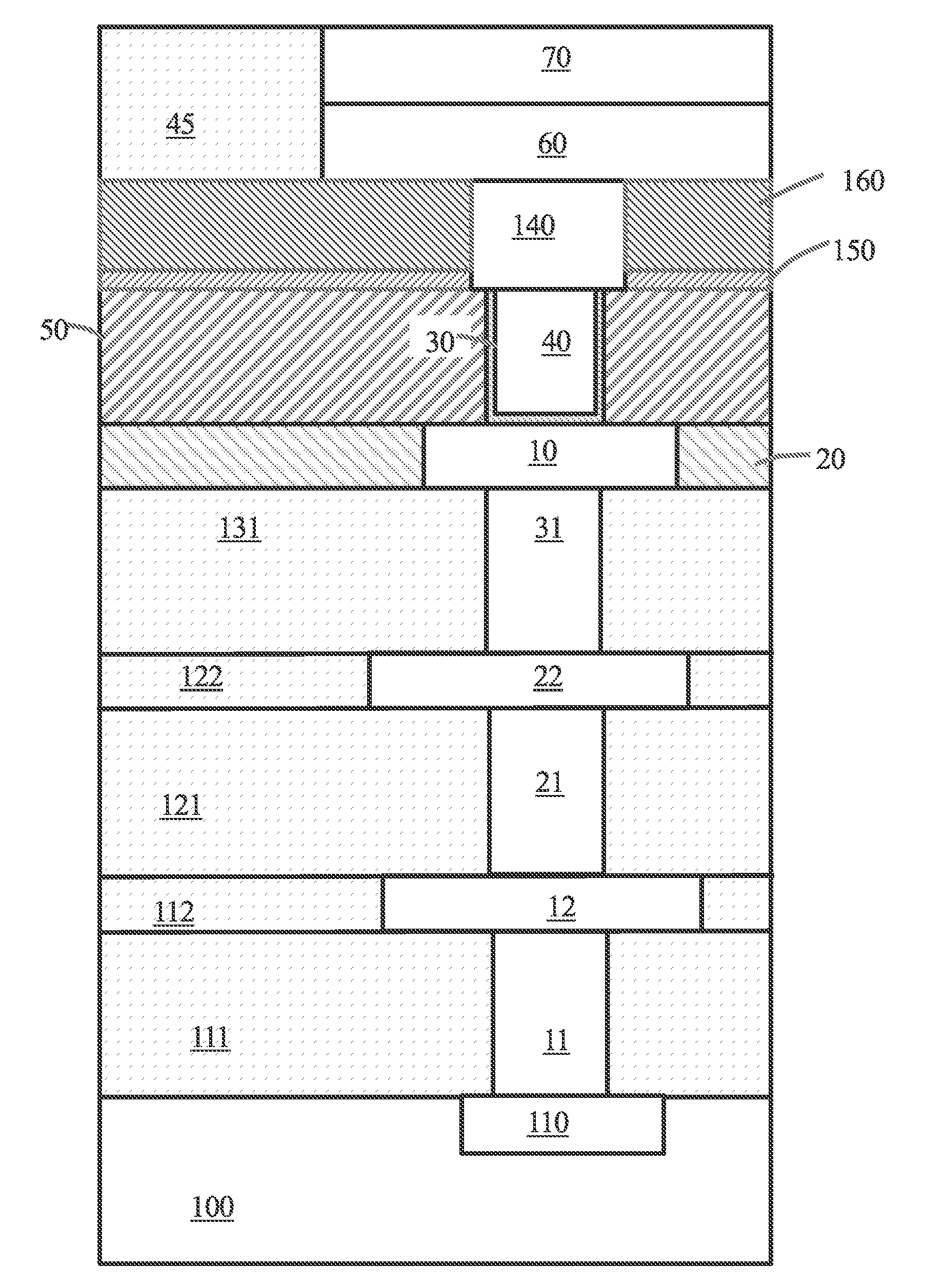

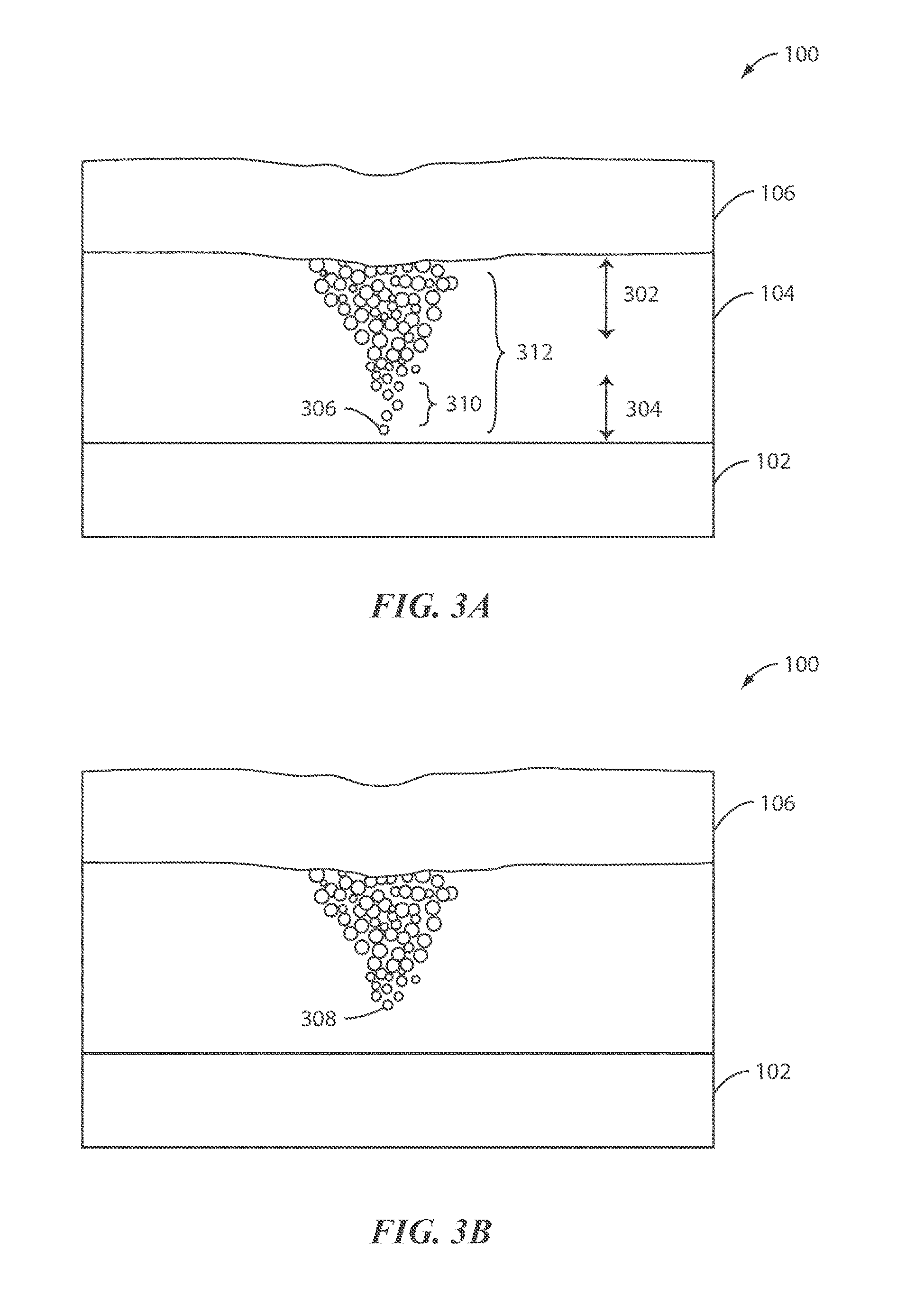

Confined Defect Profiling within Resistive Random Memory Access Cells

ActiveUS20150034898A1Improvement of resistive switching characteristicDigital storageBulk negative resistance effect devicesTitanium nitrideResistive switching

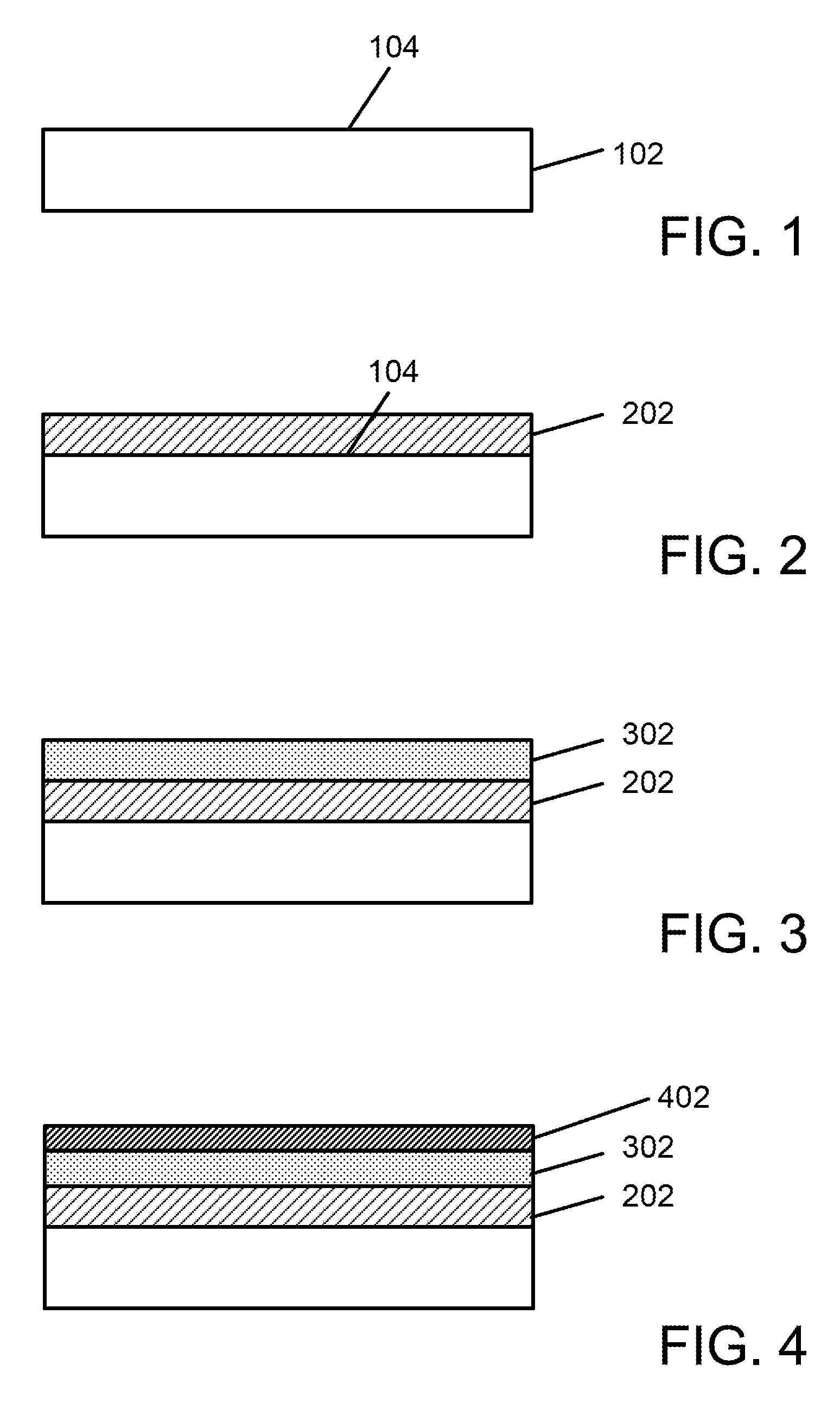

Provided are resistive random access memory (ReRAM) cells and methods of fabricating thereof. A stack including a defect source layer, a defect blocking layer, and a defect acceptor layer disposed between the defect source layer and the defect blocking layer may be subjected to annealing. During the annealing, defects are transferred in a controllable manner from the defect source layer to the defect acceptor layer. At the same time, the defects are not transferred into the defect blocking layer thereby creating a lowest concentration zone within the defect acceptor layer. This zone is responsible for resistive switching. The precise control over the size of the zone and the defect concentration within the zone allows substantially improvement of resistive switching characteristics of the ReRAM cell. In some embodiments, the defect source layer includes aluminum oxynitride, the defect blocking layer includes titanium nitride, and the defect acceptor layer includes aluminum oxide.

Owner:SANDISK TECH LLC

Intrinsic Programming Current Control for a RRAM

InactiveUS20120007035A1Improve staminaReduce the required powerSemiconductor/solid-state device manufacturingPower flowAmorphous silicon

A resistive switching device. The device includes a substrate and a first dielectric material overlying a surface region of the substrate. The device includes a first electrode overlying the first dielectric material and an optional buffer layer overlying the first electrode. The device includes a second electrode structure. The second electrode includes at least a silver material. In a specific embodiment, a switching material overlies the optional buffer layer and disposed between the first electrode and the second electrode. The switching material comprises an amorphous silicon material in a specific embodiment. The amorphous silicon material is characterized by a plurality of defect sites and a defect density. The defect density is configured to intrinsically control programming current for the device.

Owner:CROSSBAR INC

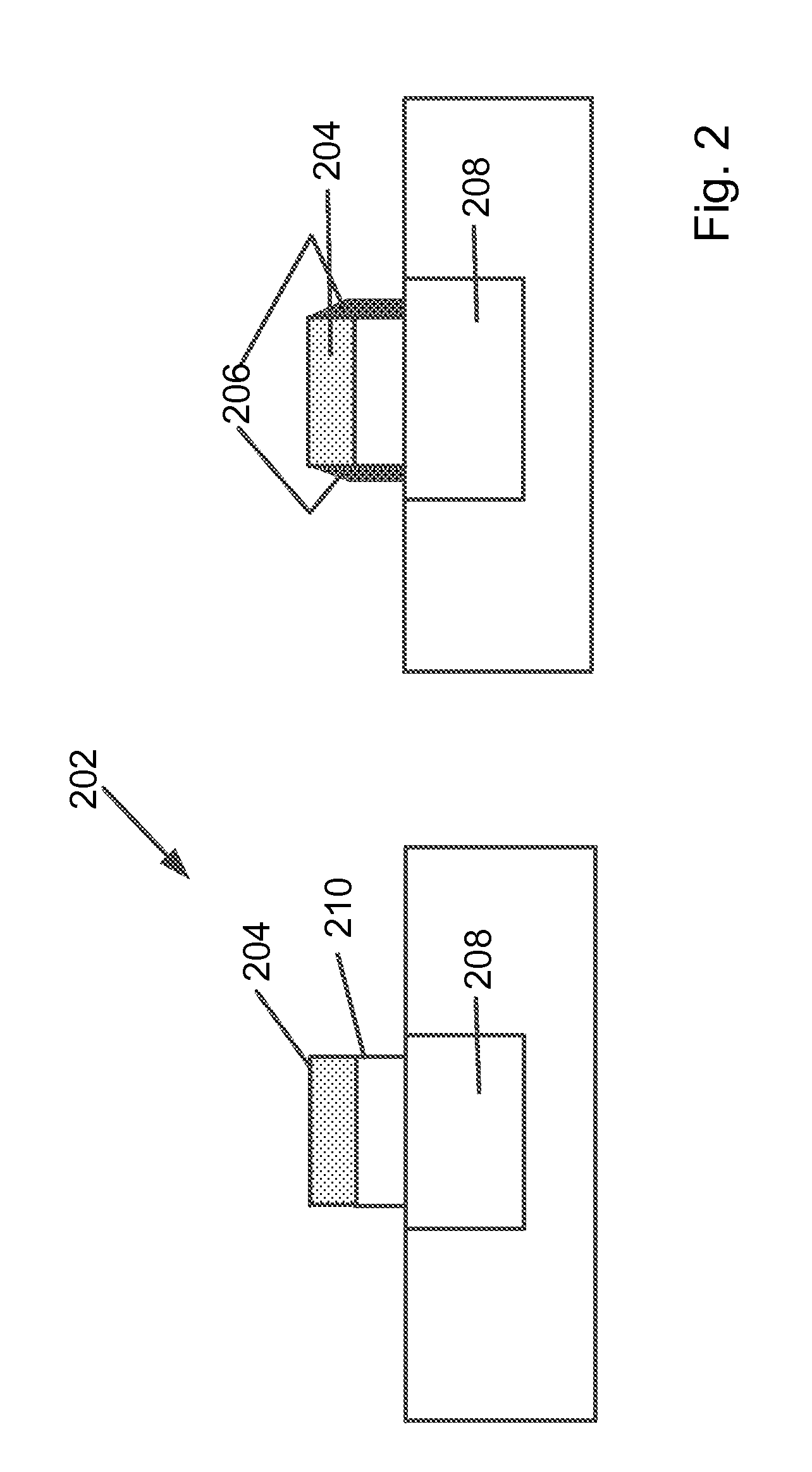

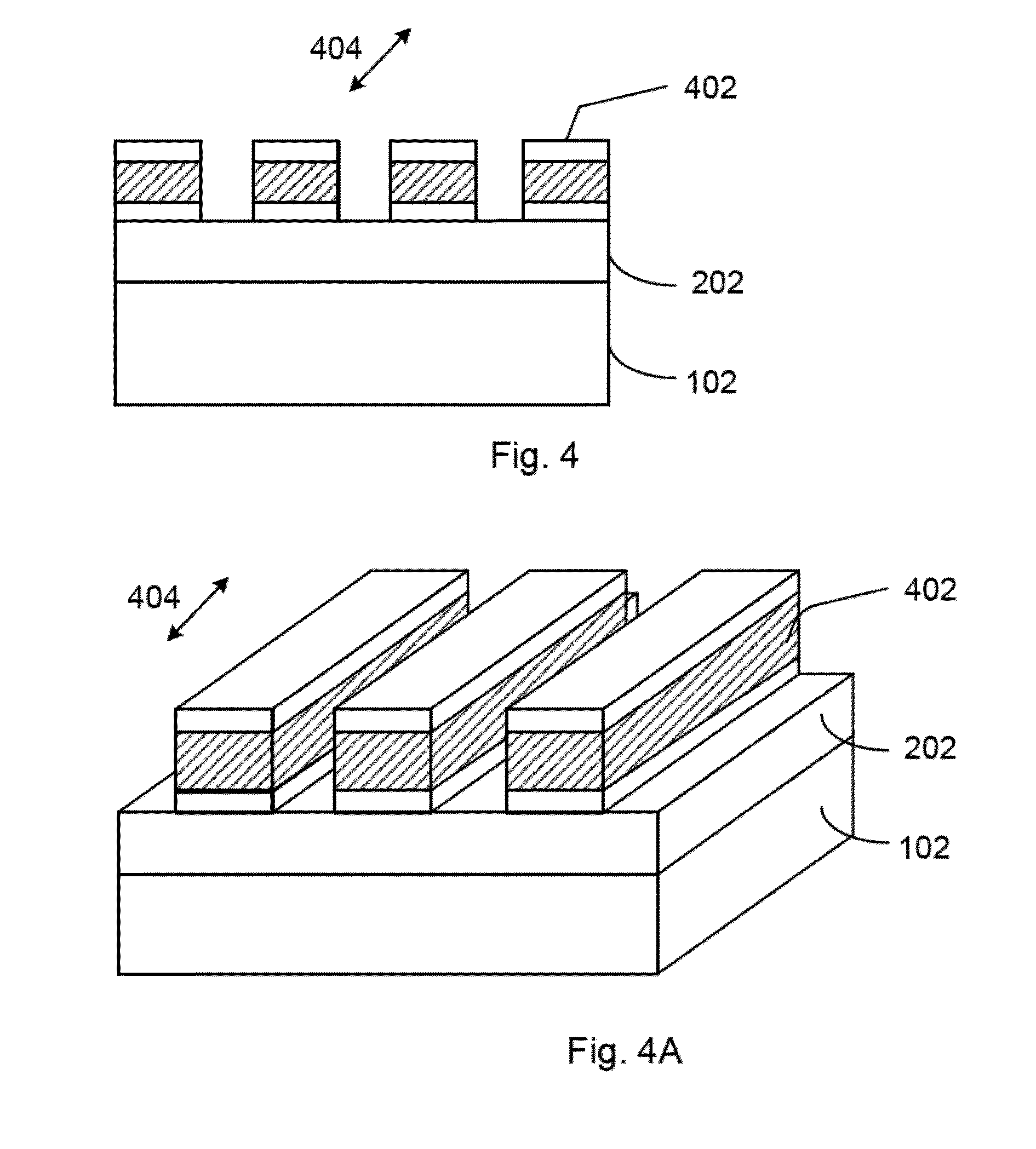

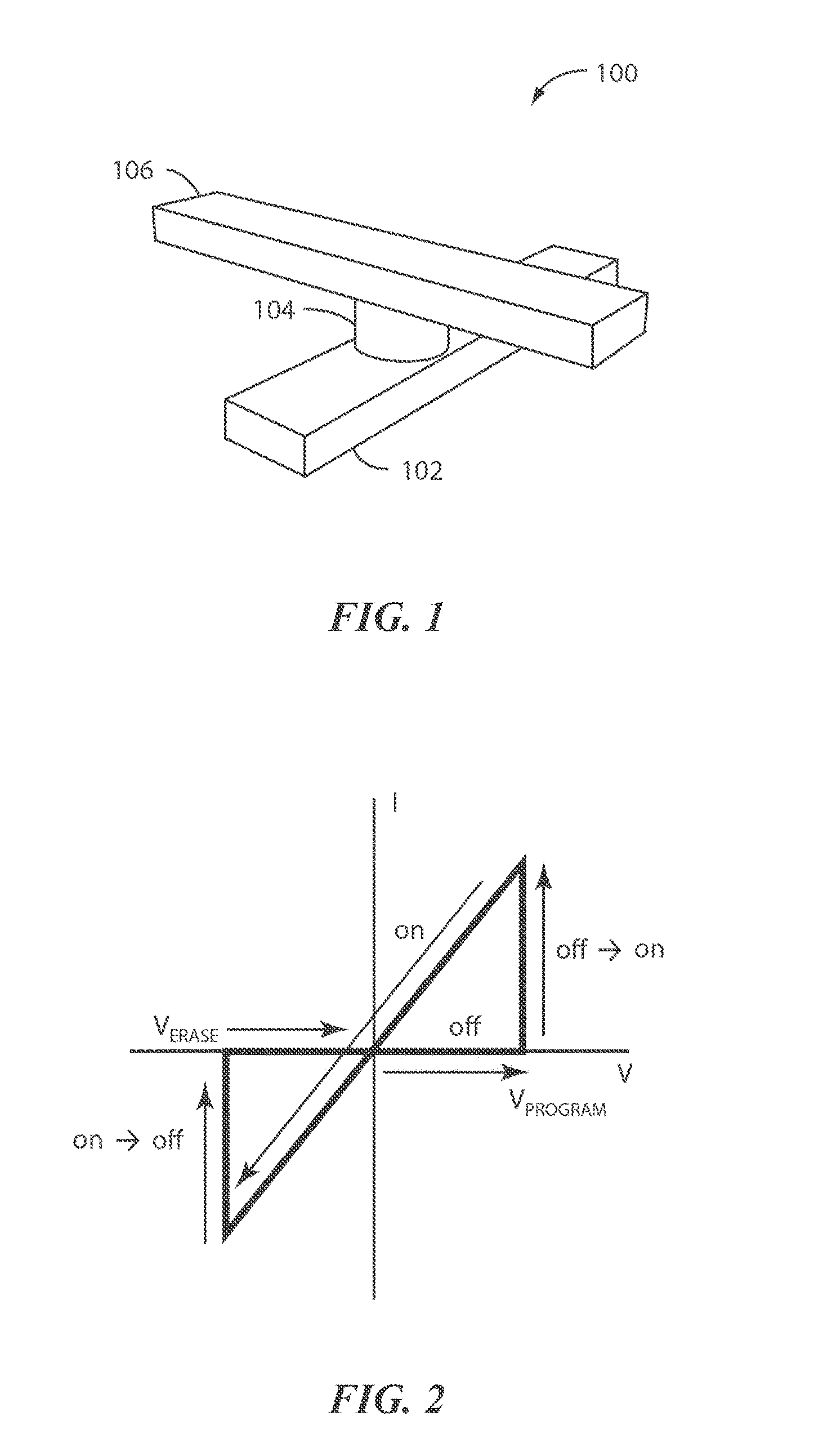

Two terminal resistive switching device structure and method of fabricating

ActiveUS20120015506A1Improve performanceHigh yieldSemiconductor/solid-state device manufacturingTerminal equipmentConductive materials

A method of forming a two terminal device. The method includes forming a first dielectric material overlying a surface region of a substrate. A bottom wiring material is formed overlying the first dielectric material and a switching material is deposited overlying the bottom wiring material. The bottom wiring material and the switching material is subjected to a first patterning and etching process to form a first structure having a top surface region and a side region. The first structure includes at least a bottom wiring structure and a switching element having a first side region, and a top surface region including an exposed region of the switching element. A second dielectric material is formed overlying at least the first structure including the exposed region of the switching element. The method forms an opening region in a portion of the second dielectric layer to expose a portion of the top surface region of the switching element. A top wiring material including a conductive material is formed overlying at lease the opening region such that the conductive material is in direct contact with the switching element. A second etching process is performed to form at least a top wiring structure. In a specific embodiment, the side region of the first structure including a first side region of the switching element is free from a contaminant conductive material from the second etching process.

Owner:CROSSBAR INC

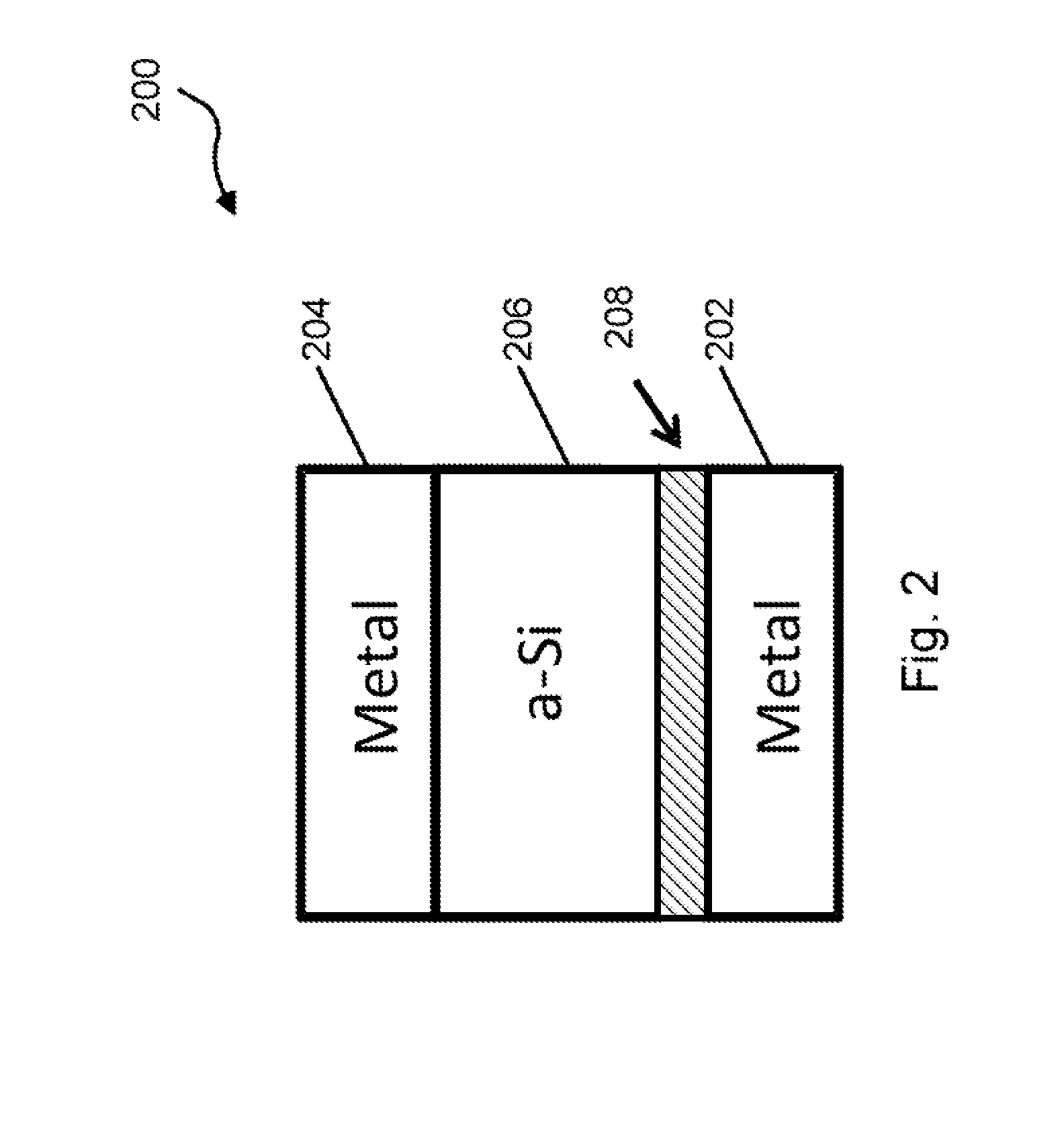

Device switching using layered device structure

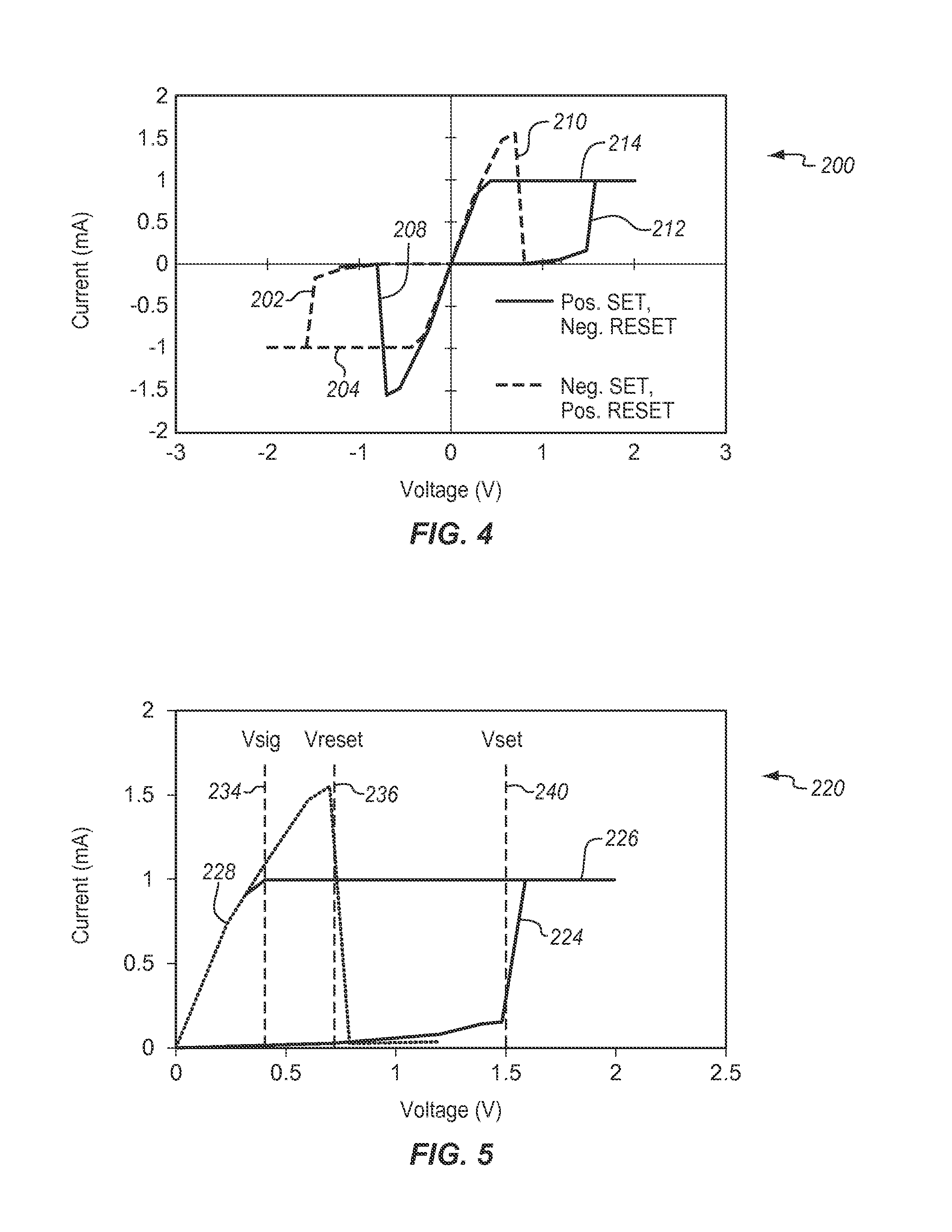

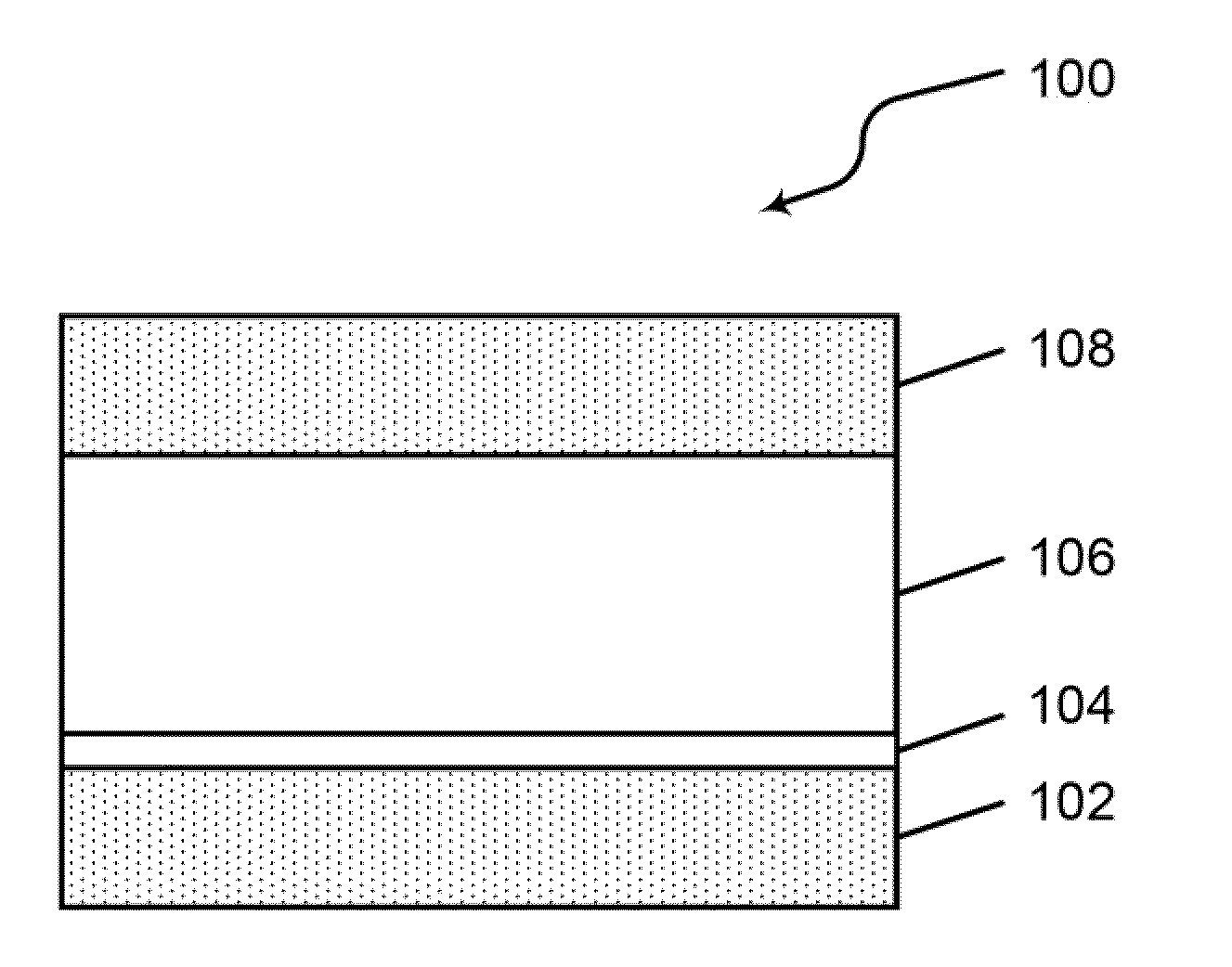

ActiveUS20120043519A1Total current dropImproved switchingSolid-state devicesDigital storageElectricityElectrical resistance and conductance

A resistive switching device. The device includes a first electrode comprising a first metal material overlying the first dielectric material and a switching material comprising an amorphous silicon material. The device includes a second electrode comprising at least a second metal material. In a specific embodiment, the device includes a buffer material disposed between the first electrode and the switching material. The buffer material provides a blocking region between the switching material and the first electrode so that the blocking region is substantially free from metal particles from the second metal material when a first voltage is applied to the second electrode.

Owner:CROSSBAR INC

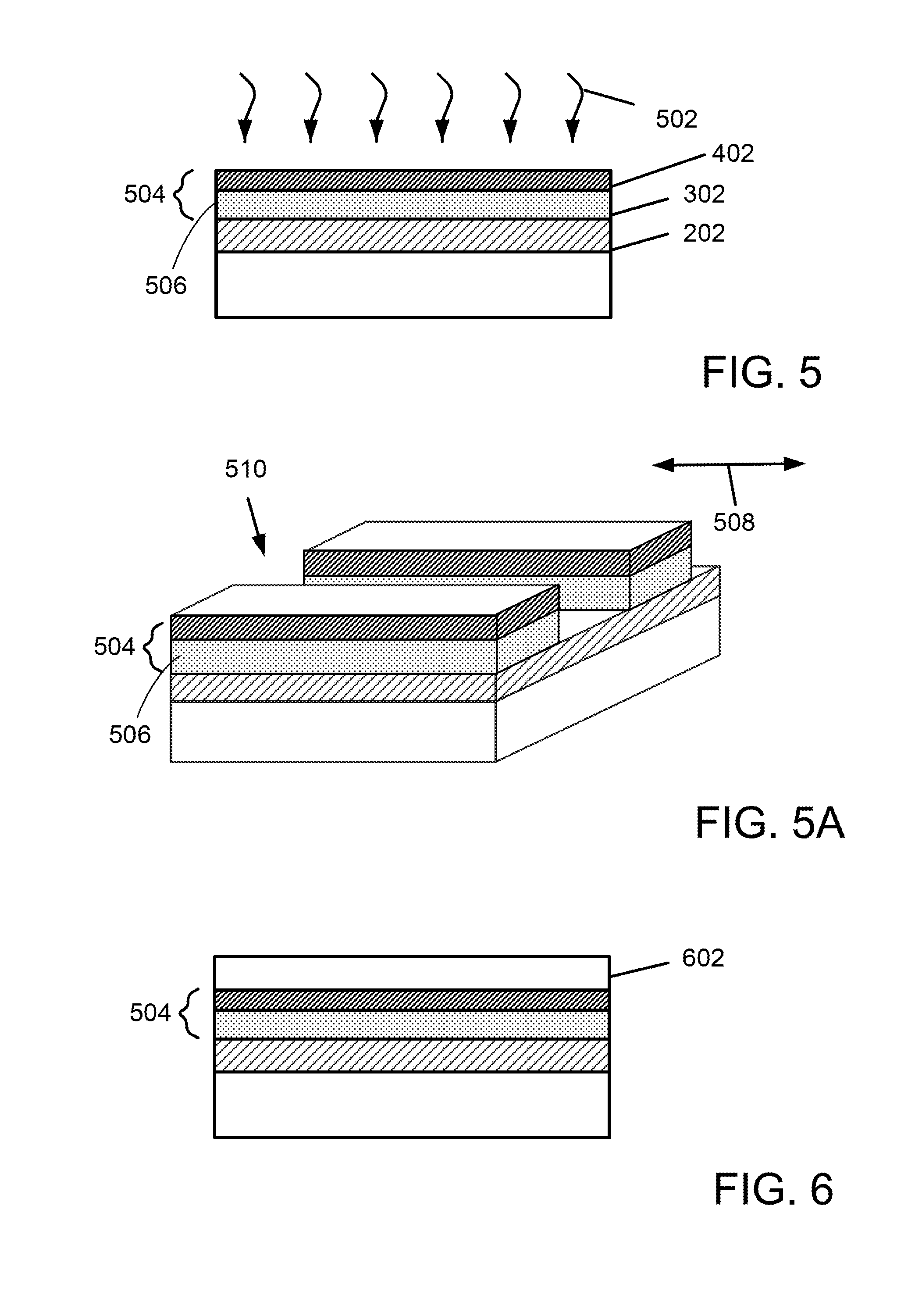

P+ polysilicon material on aluminum for non-volatile memory device and method

ActiveUS8088688B1Semiconductor/solid-state device detailsSolid-state devicesMetallic materialsAmorphous silicon

A method of forming a non-volatile memory device. The method includes providing a substrate having a surface region and forming a first dielectric material overlying the surface region. A first wiring material comprising at least an aluminum material is formed overlying the first dielectric material. The method forms a silicon material overlying the aluminum material and forms an intermix region consuming a portion of the silicon material and a portion of the aluminum material. The method includes an annealing process to cause formation of a first alloy material from the intermix region and a polycrystalline silicon material having a p+ impurity characteristic overlying the first alloy material. A first wiring structure is formed from at least a portion of the first wiring material. A resistive switching element comprising an amorphous silicon material is formed overlying the polycrystalline silicon material having the p+ impurity characteristic. A second wiring structure comprising at least a metal material is formed overlying the resistive switching element.

Owner:CROSSBAR INC

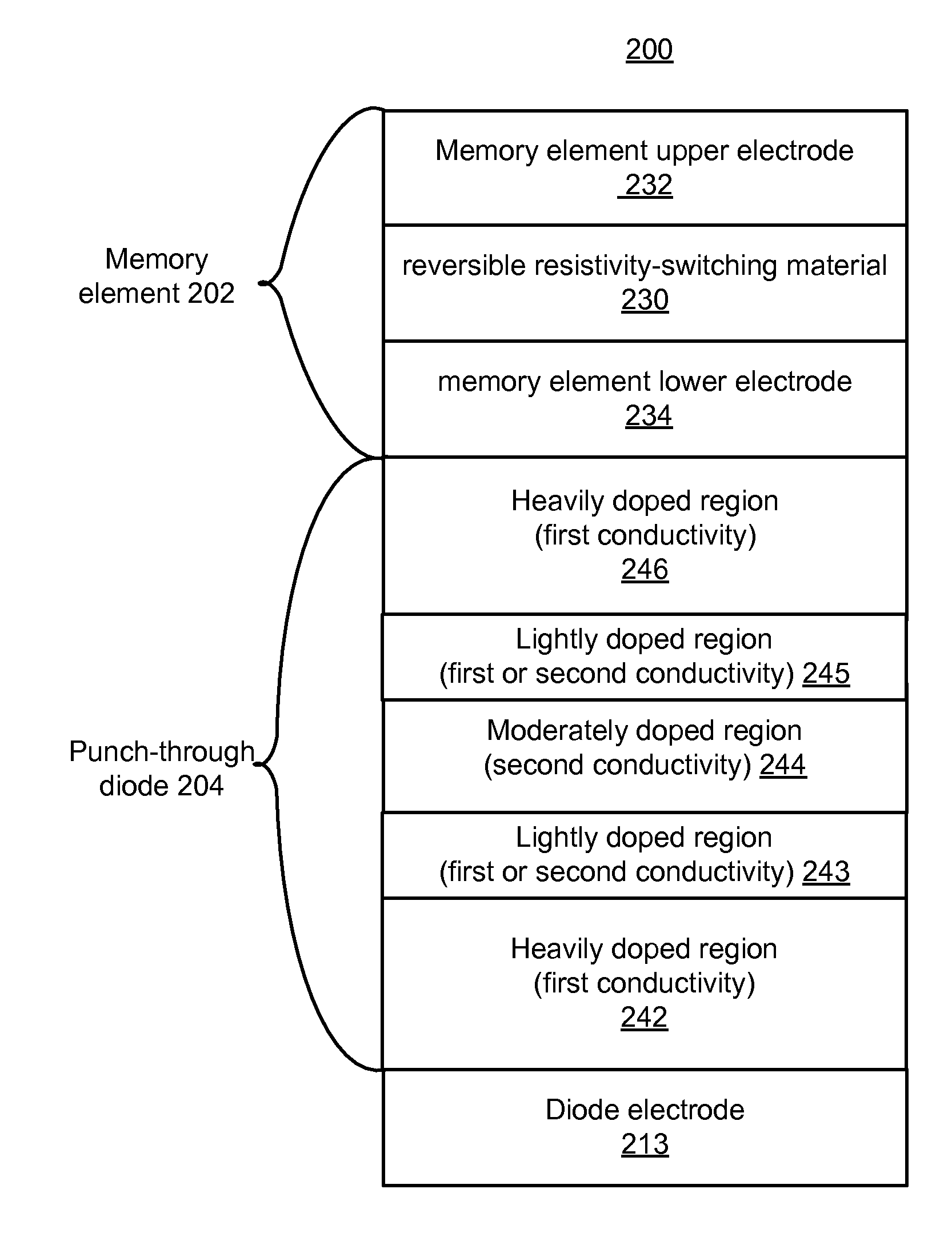

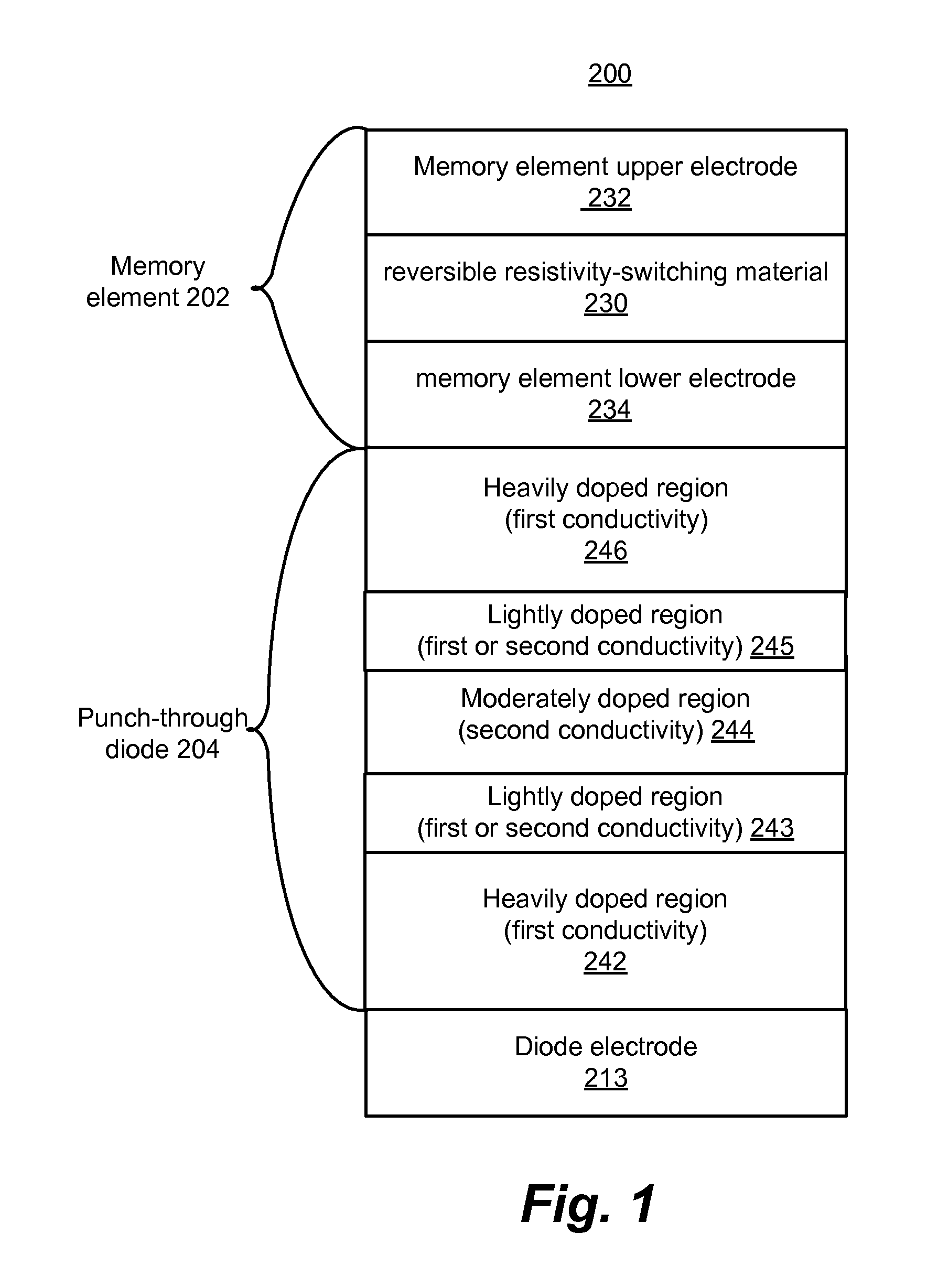

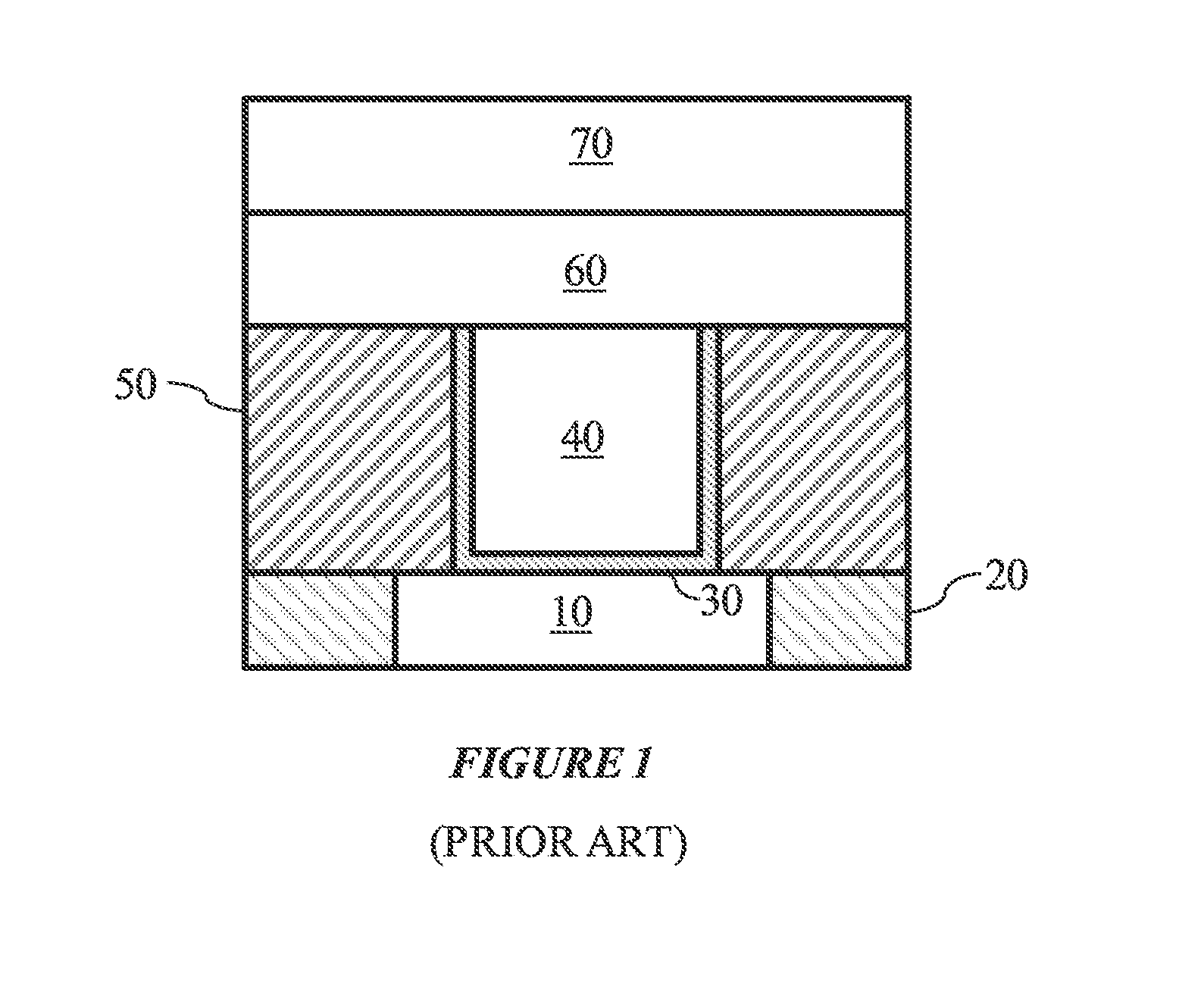

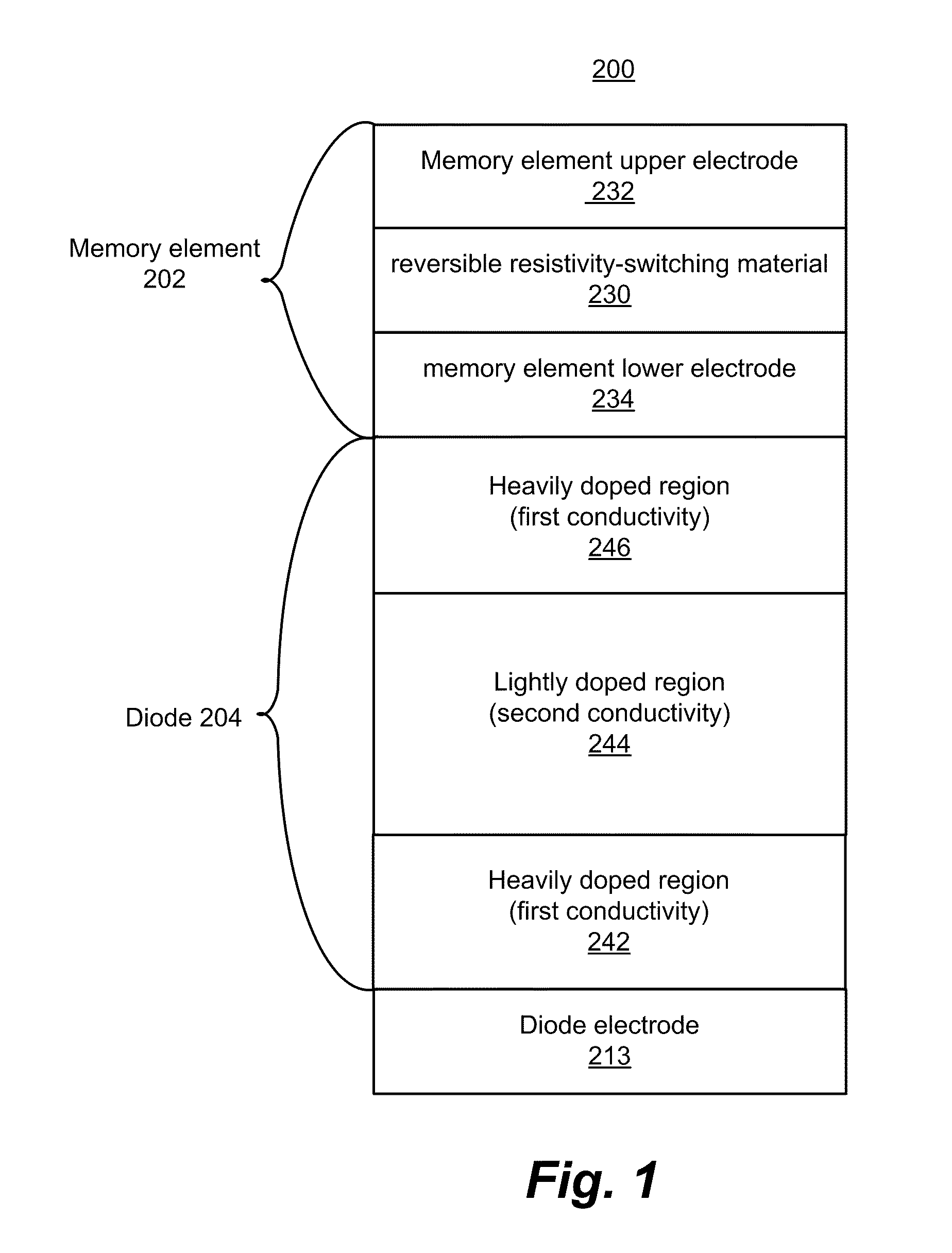

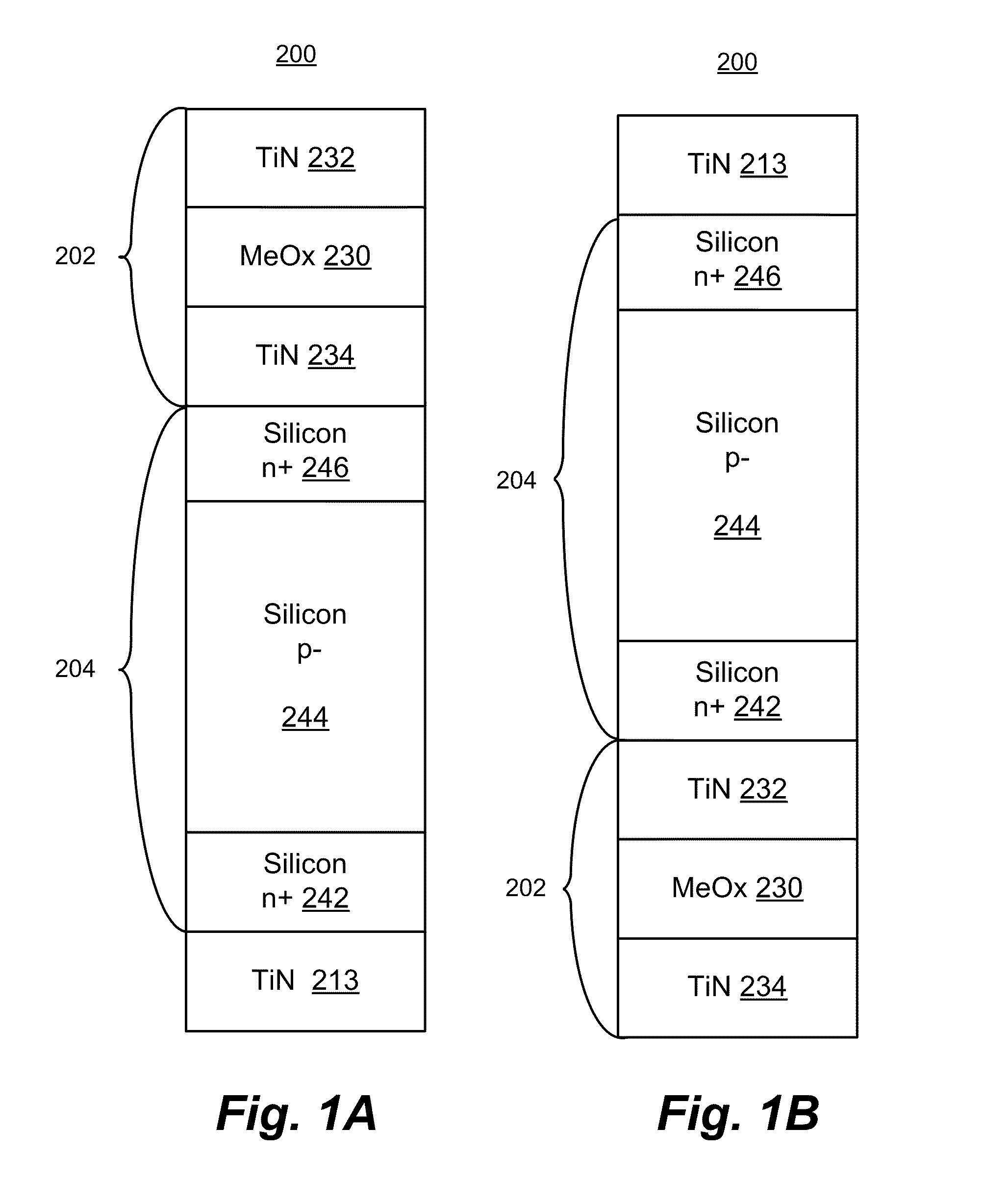

Punch-through diode

ActiveUS20120145984A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringLow leakage

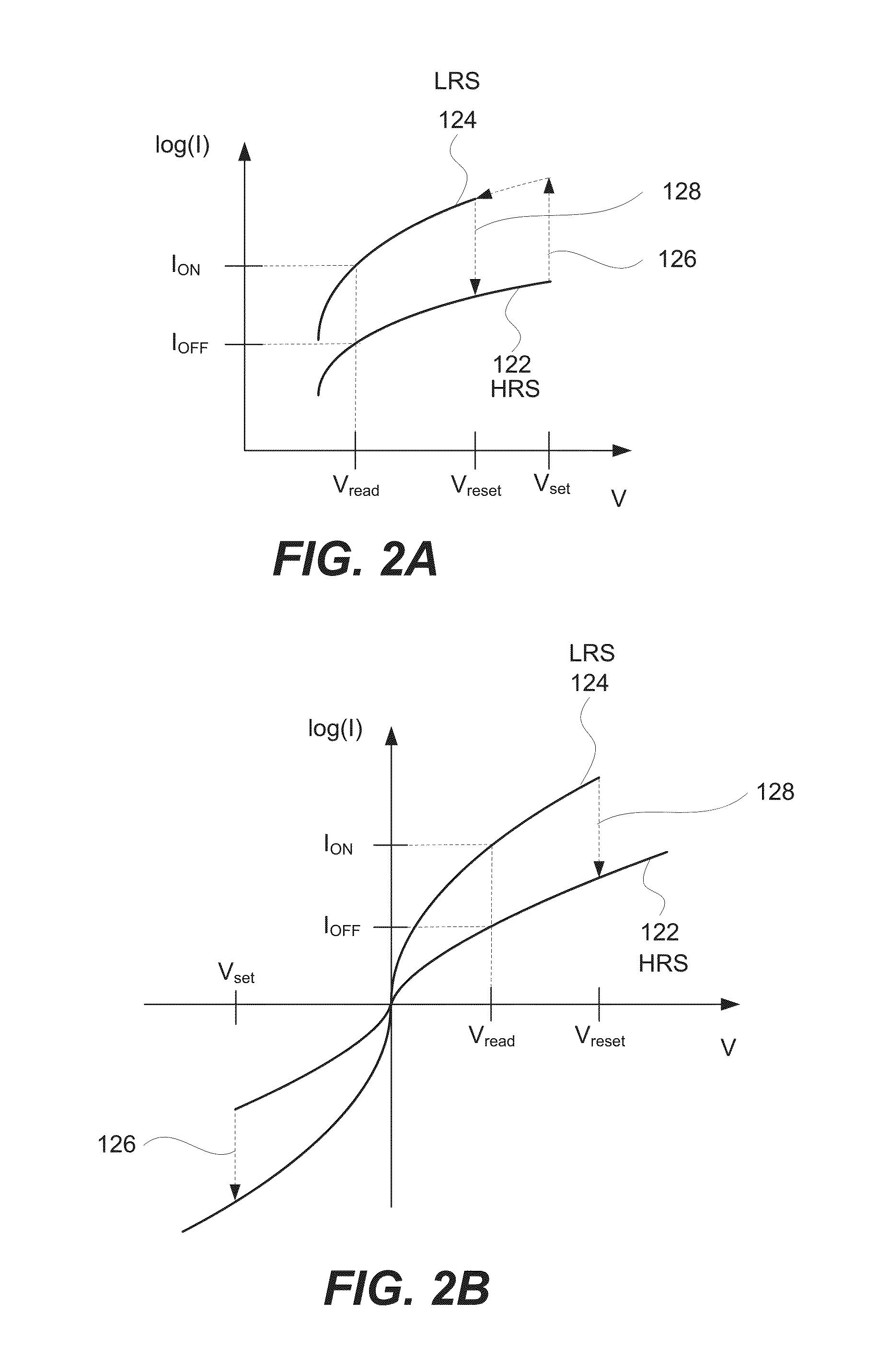

A punch-through diode and method of fabricating the same are disclosed herein. The punch-through diode may be used as a steering element in a memory device having a reversible resistivity-switching element. For example, a memory cell may include a reversible resistivity-switching element in series with a punch-through diode. The punch-through diode allows bipolar operation of a cross-point memory array. The punch-through diode may have a symmetrical non-linear current / voltage relationship. The punch-through diode has a high current at high bias for selected cells and a low leakage current at low bias for unselected cells. In other words, the ratio of Ion / Ioff is high. Therefore, the punch-through diode is compatible with bipolar switching in cross-point memory arrays having resistive switching elements.

Owner:SANDISK TECH LLC

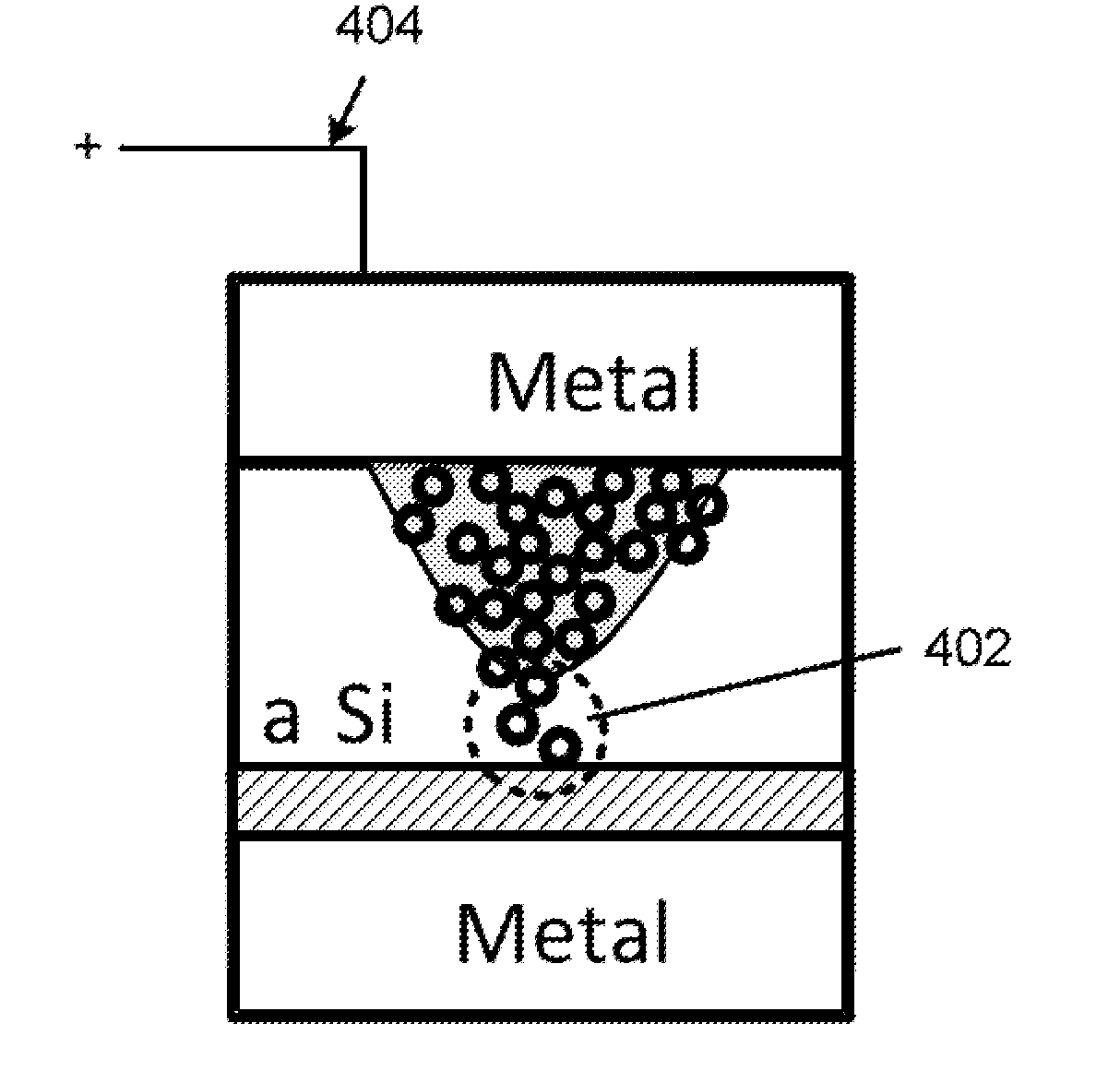

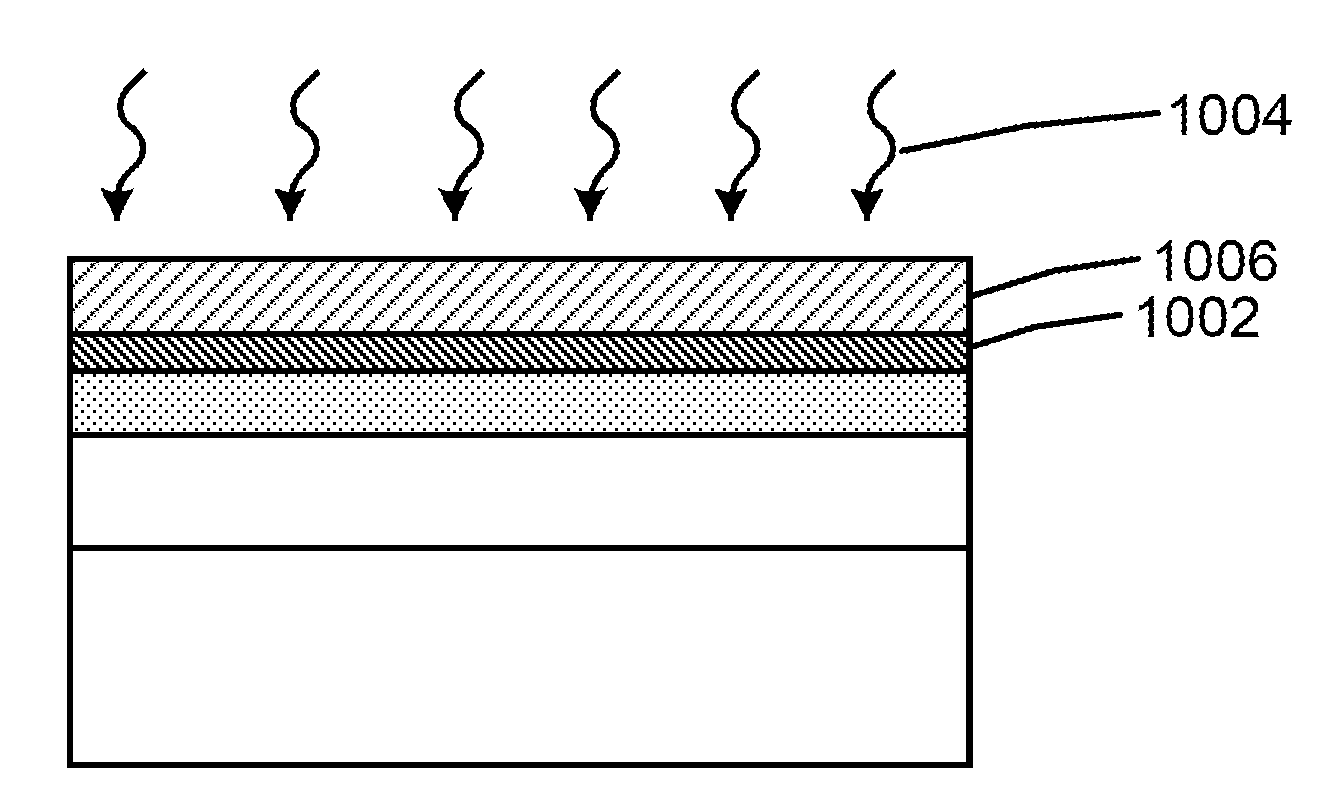

Conductive path in switching material in a resistive random access memory device and control

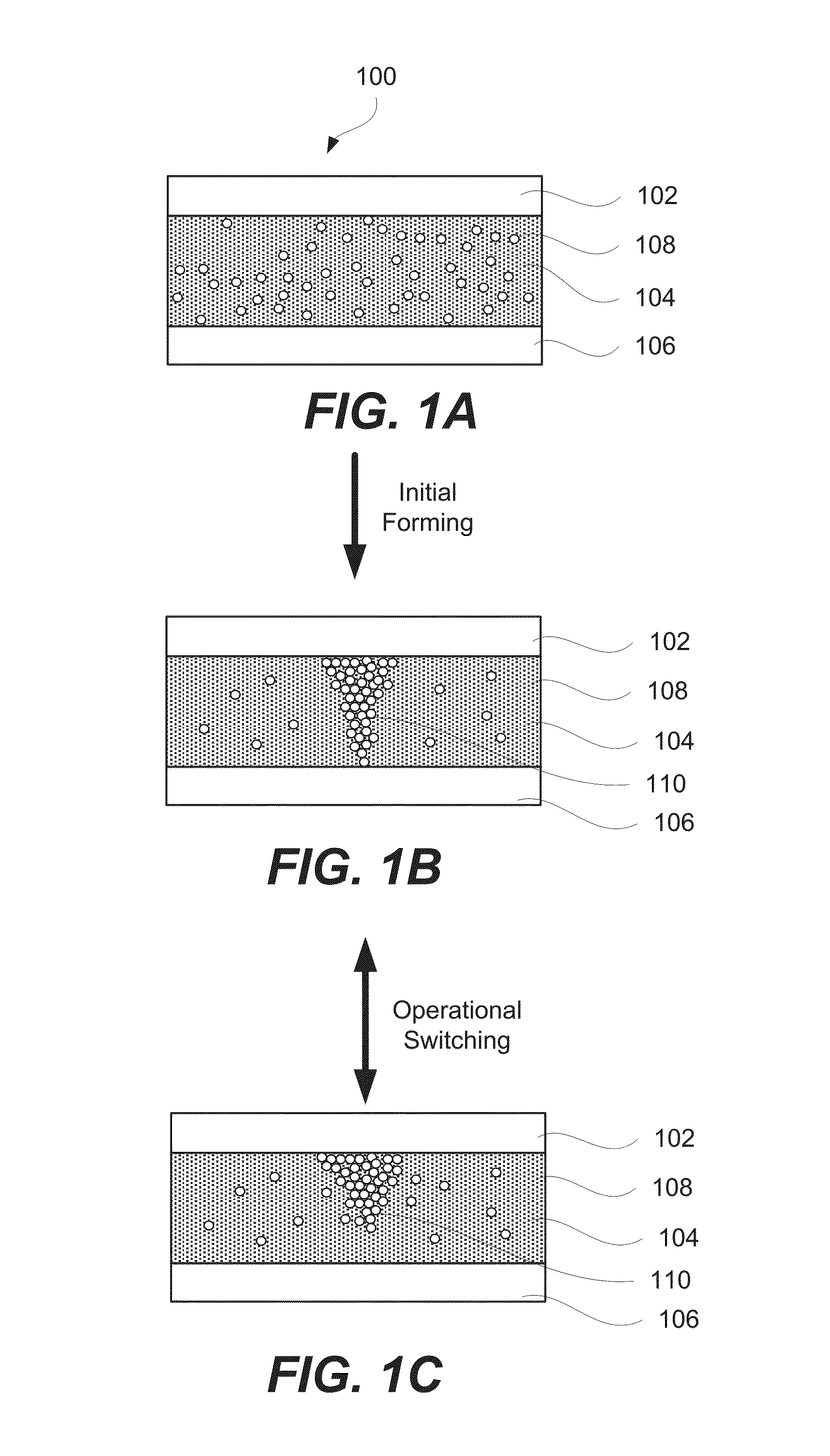

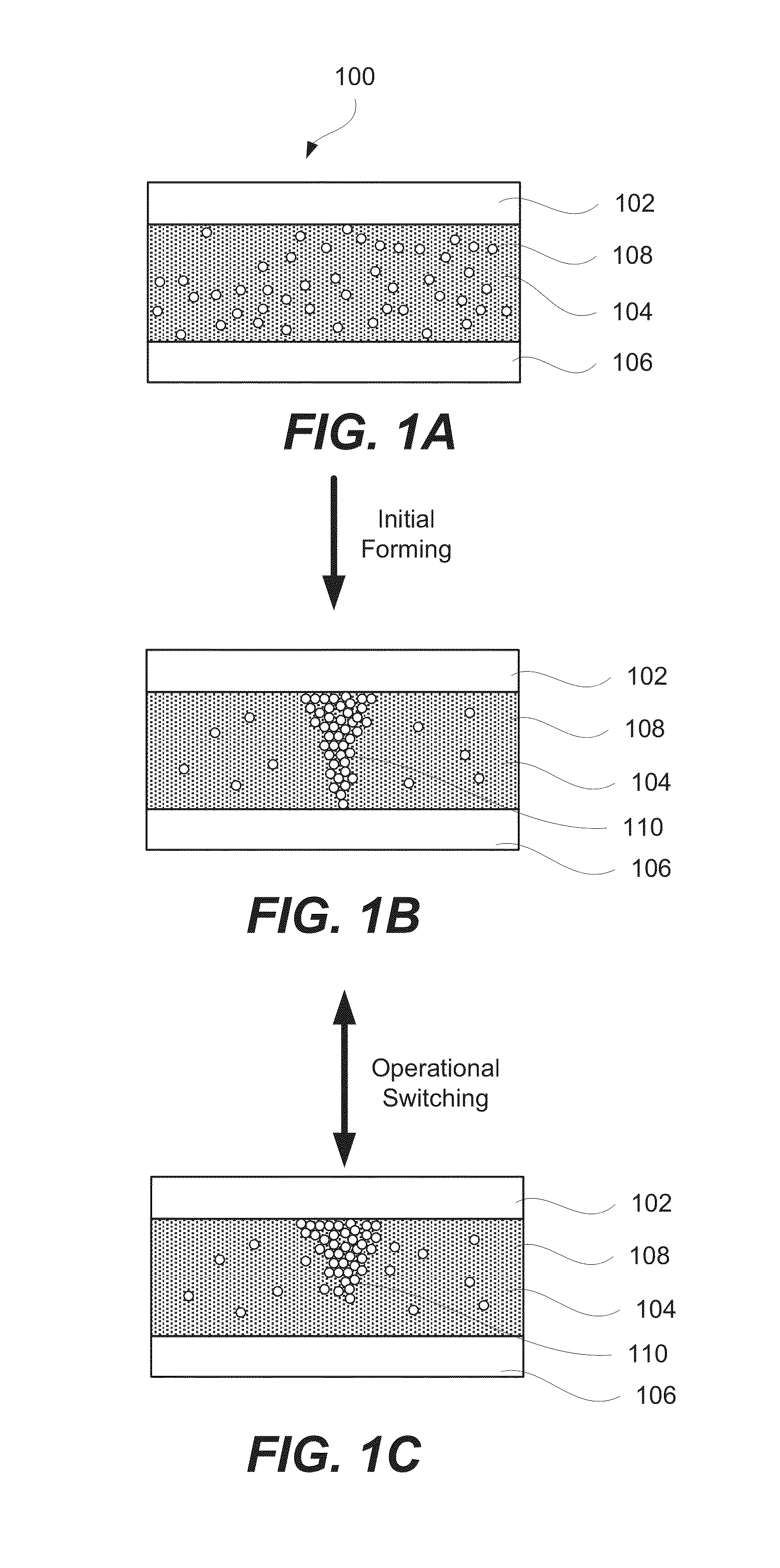

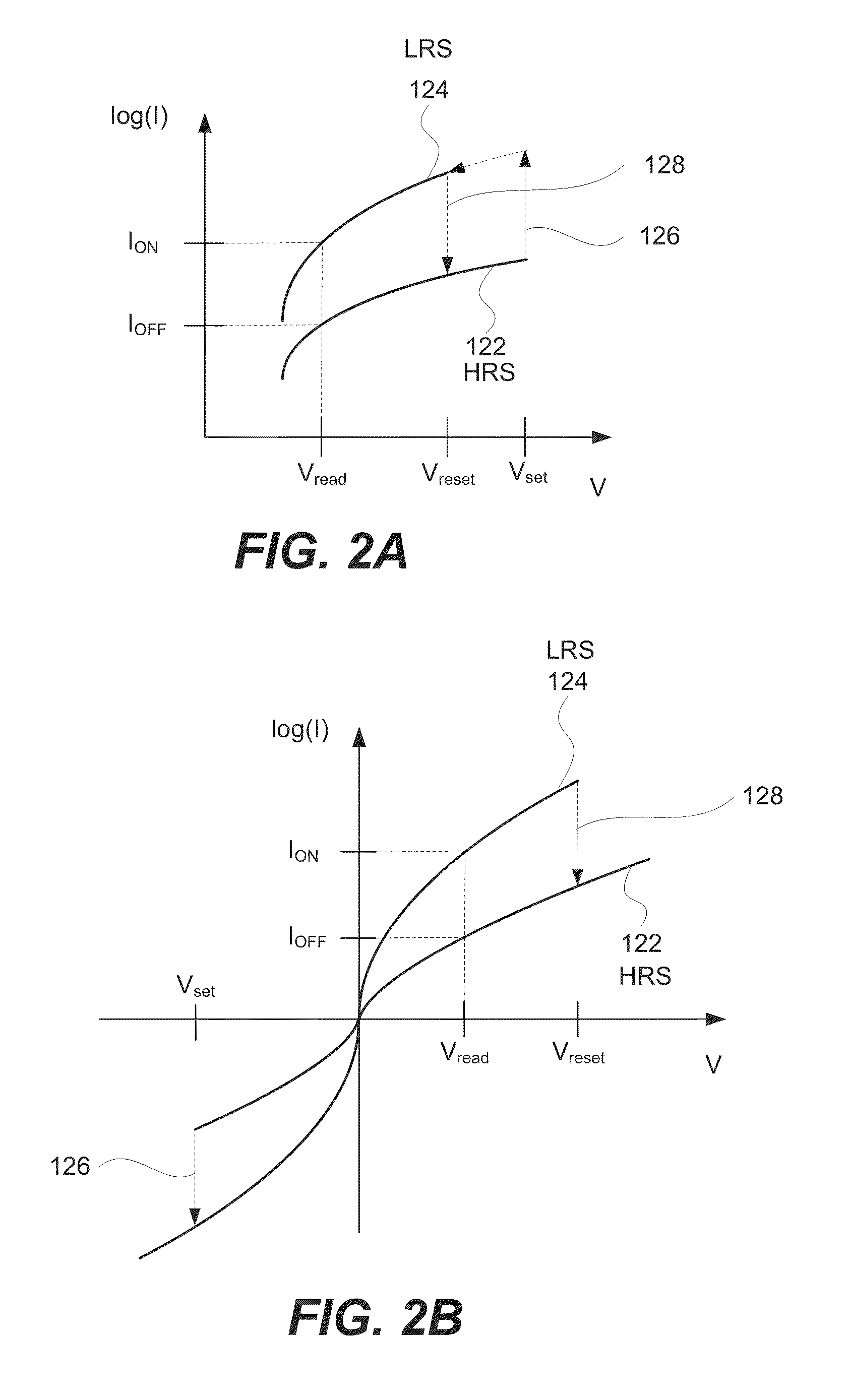

ActiveUS20120074374A1Low forming voltageReduce leakage currentSemiconductor/solid-state device manufacturingBulk negative resistance effect devicesAmorphous siliconResistive switching

A non-volatile memory device structure. The device structure includes a first electrode, a second electrode, a resistive switching material comprising an amorphous silicon material overlying the first electrode, and a thickness of dielectric material having a thickness ranging from 5 nm to 10 nm disposed between the second electrode and the resistive switching layer. The thickness of dielectric material is configured to electrically breakdown in a region upon application of an electroforming voltage to the second electrode. The electrical breakdown allows for a metal region having a dimension of less than about 10 nm by 10 nm to form in a portion of the resistive switching material.

Owner:INNOSTAR SEMICON SHANGHAI CO LTD

Resistive Switching Devices and Methods of Formation Thereof

ActiveUS20130214234A1Semiconductor/solid-state device manufacturingBulk negative resistance effect devicesFilling materialsResistive switching

In accordance with an embodiment of the present invention, a resistive switching device includes an opening disposed within a first dielectric layer, a conductive barrier layer disposed on sidewalls of the opening, a fill material including an inert material filling the opening. A solid electrolyte layer is disposed over the opening. The solid electrolyte contacts the fill material but not the conductive barrier layer. A top electrode is disposed over the solid electrolyte.

Owner:GLOBALFOUNDRIES US INC

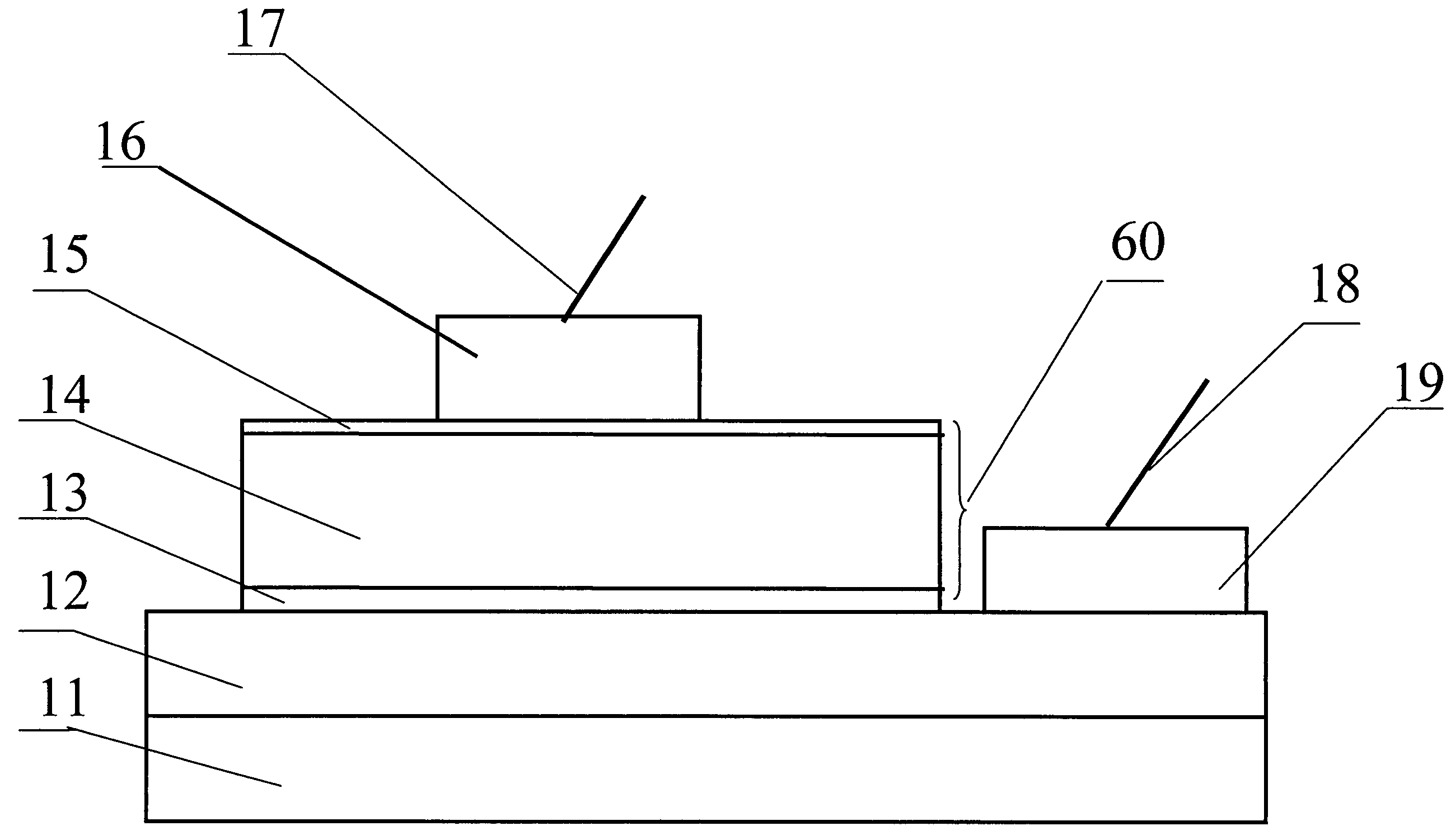

Integration of an amorphous silicon resistive switching device

InactiveUS20120074507A1Data stabilityImprove good performanceSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricElectrical conductor

An integrated circuit device. The integrated circuit device includes a semiconductor substrate having a surface region. A gate dielectric layer overlies the surface region of the substrate. The device includes a MOS device having a p+ active region. The p+ active region forms a first electrode for a resistive switching device. The resistive switching device includes an amorphous silicon switching material overlying the p+ active region and a metal electrode overlies the first metal conductor structure. The metal electrode includes a metal material, upon application of a positive bias to the metal electrode, forms a metal region in the amorphous silicon switching material. The MOS device provides for a select transistor for the integrated circuit device.

Owner:CROSSBAR INC

Vertical diodes for non-volatile memory device

A steering device. The steering device includes an n-type impurity region comprising a zinc oxide material and a p-type impurity region comprising a silicon germanium material. A pn junction region formed from the zinc oxide material and the silicon germanium material. The steering device is a serially coupled to a resistive switching device to provide rectification for the resistive switching device to form a non-volatile memory device.

Owner:INNOSTAR SEMICON SHANGHAI CO LTD

Hetero resistive switching material layer in RRAM device and method

ActiveUS8467227B1Improve performanceWide rangeSolid-state devicesDigital storageElectricityMetallic materials

A non-volatile memory device includes a first electrode, a resistive switching material stack overlying the first electrode. The resistive switching material stack comprising a first resistive switching material and a second resistive switching material. The second resistive switching material overlies the first electrode and the first resistive switching material overlying the second resistive switching material. The first resistive switching material is characterized by a first switching voltage having a first amplitude. The second resistive switching material is characterized by a second switching voltage having a second amplitude no greater than the first switching voltage. A second electrode comprising at least a metal material physically and electrically in contact with the first resistive switching material overlies the first resistive switching material.

Owner:CROSSBAR INC

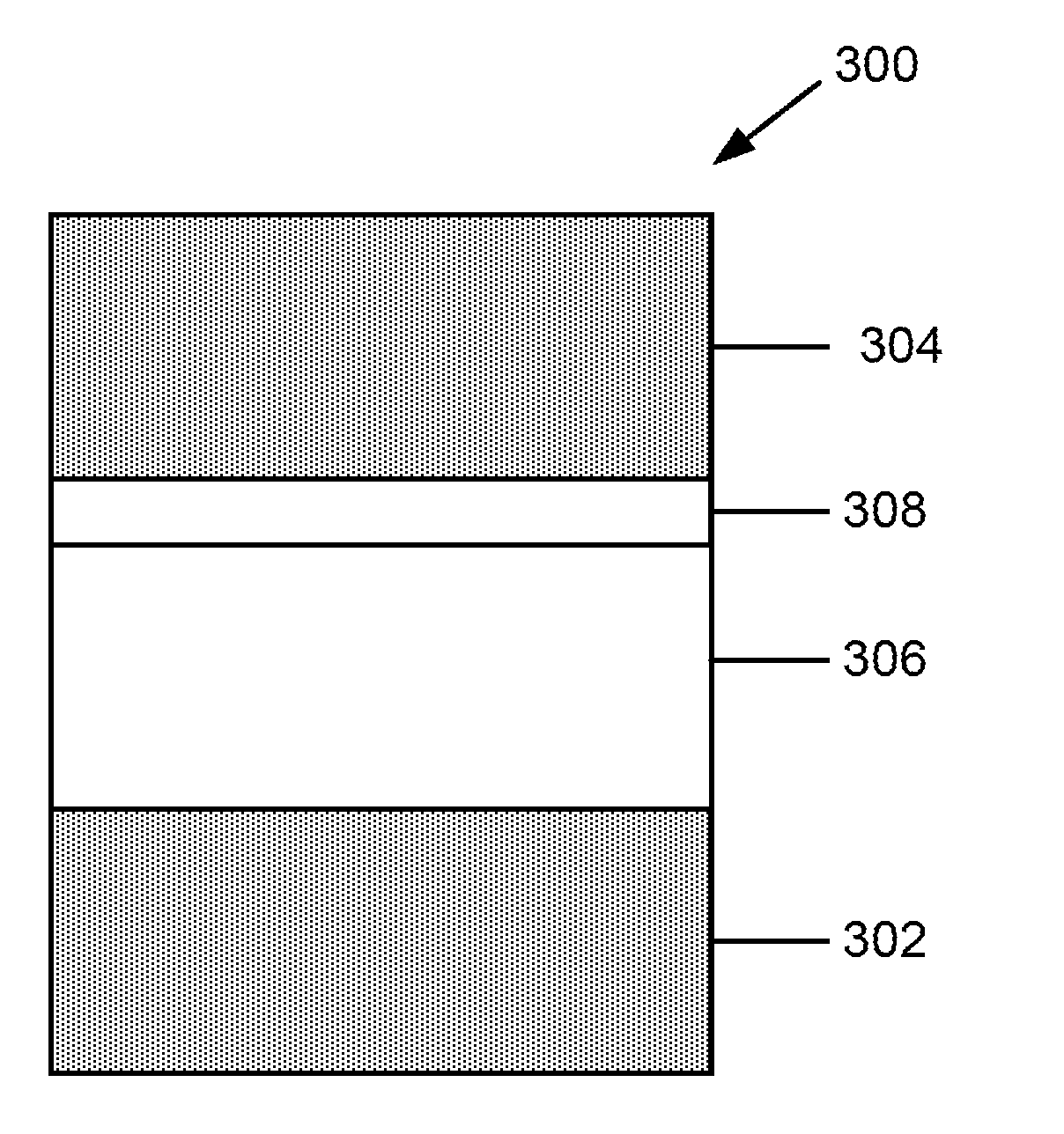

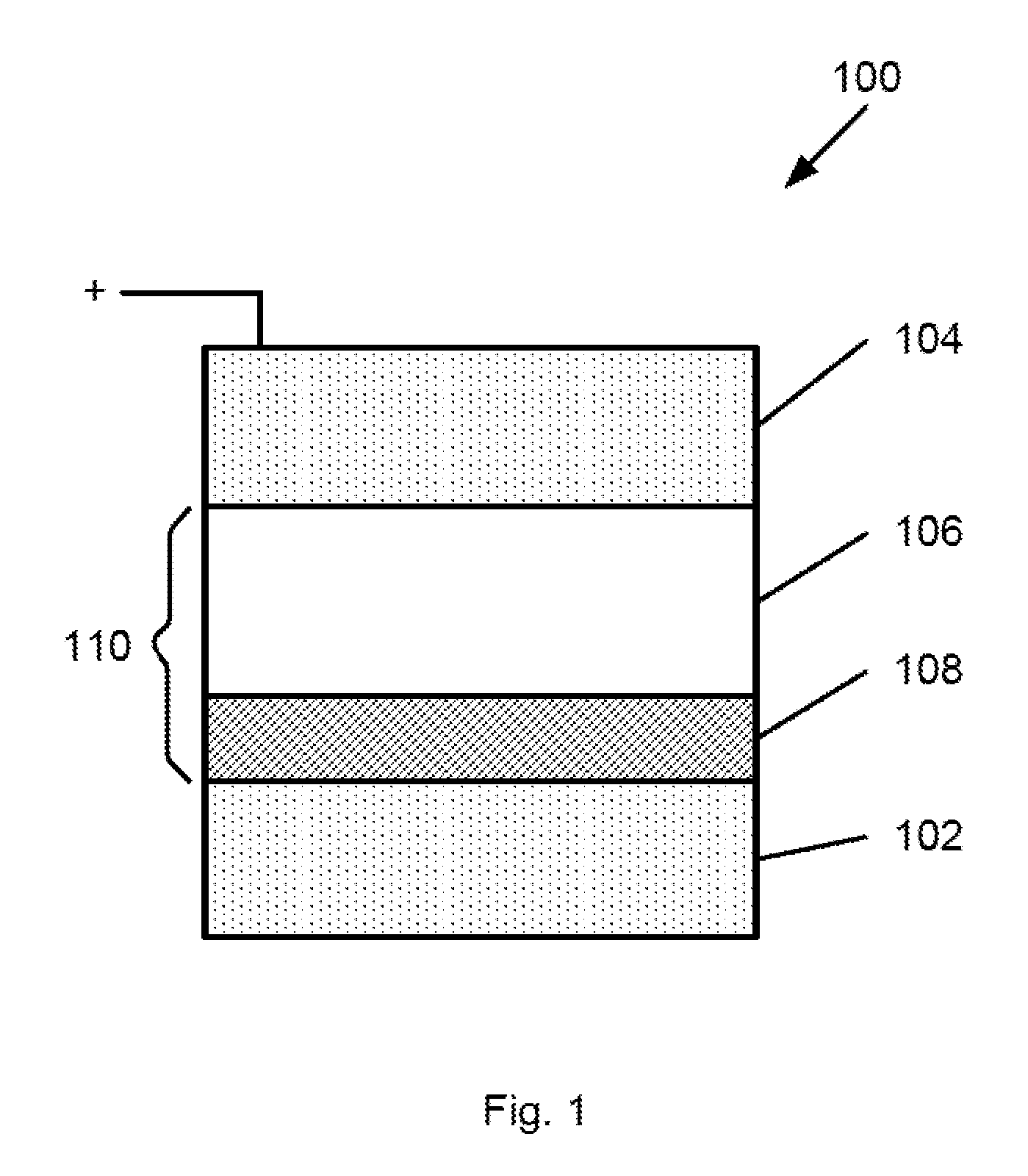

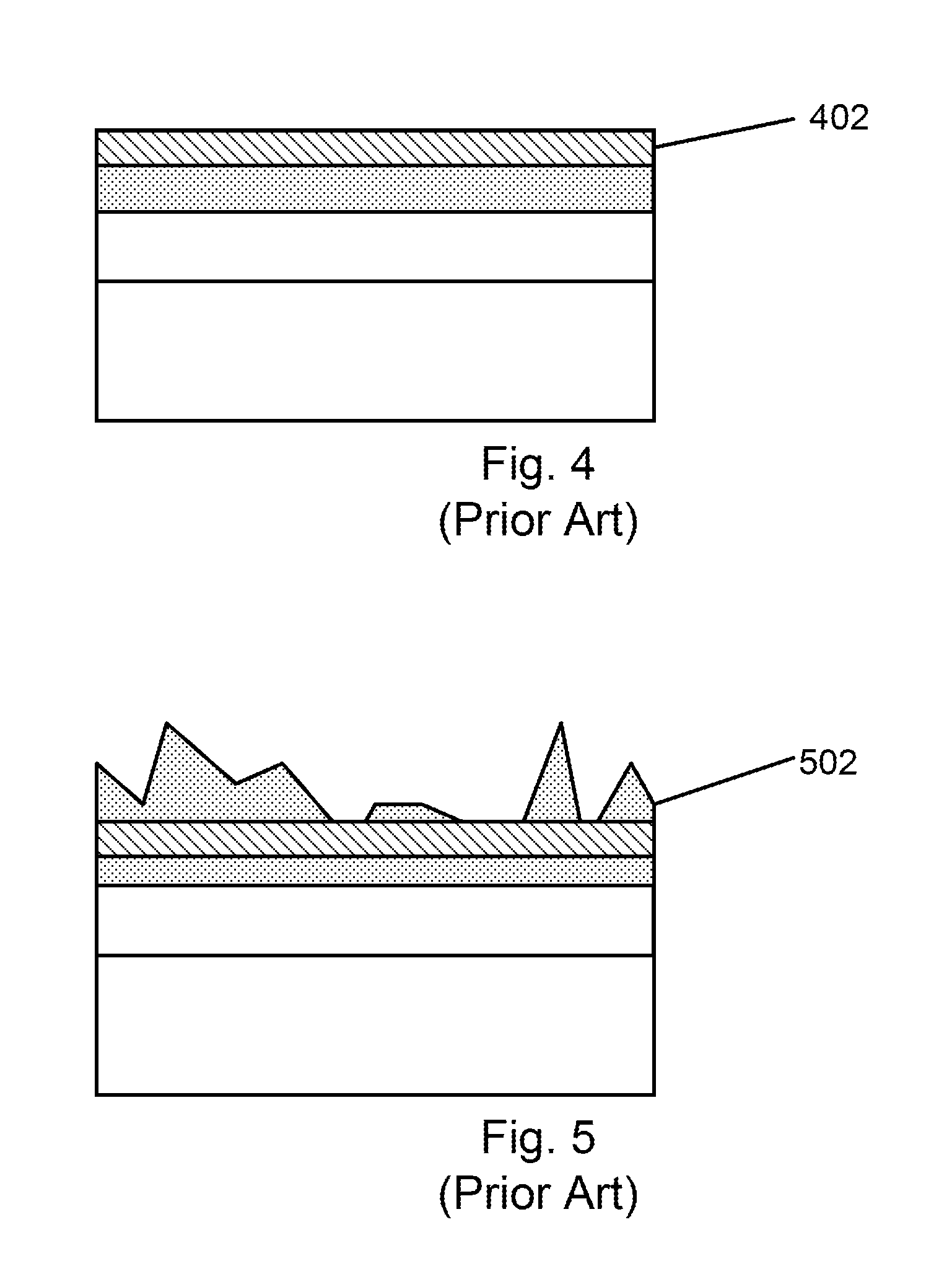

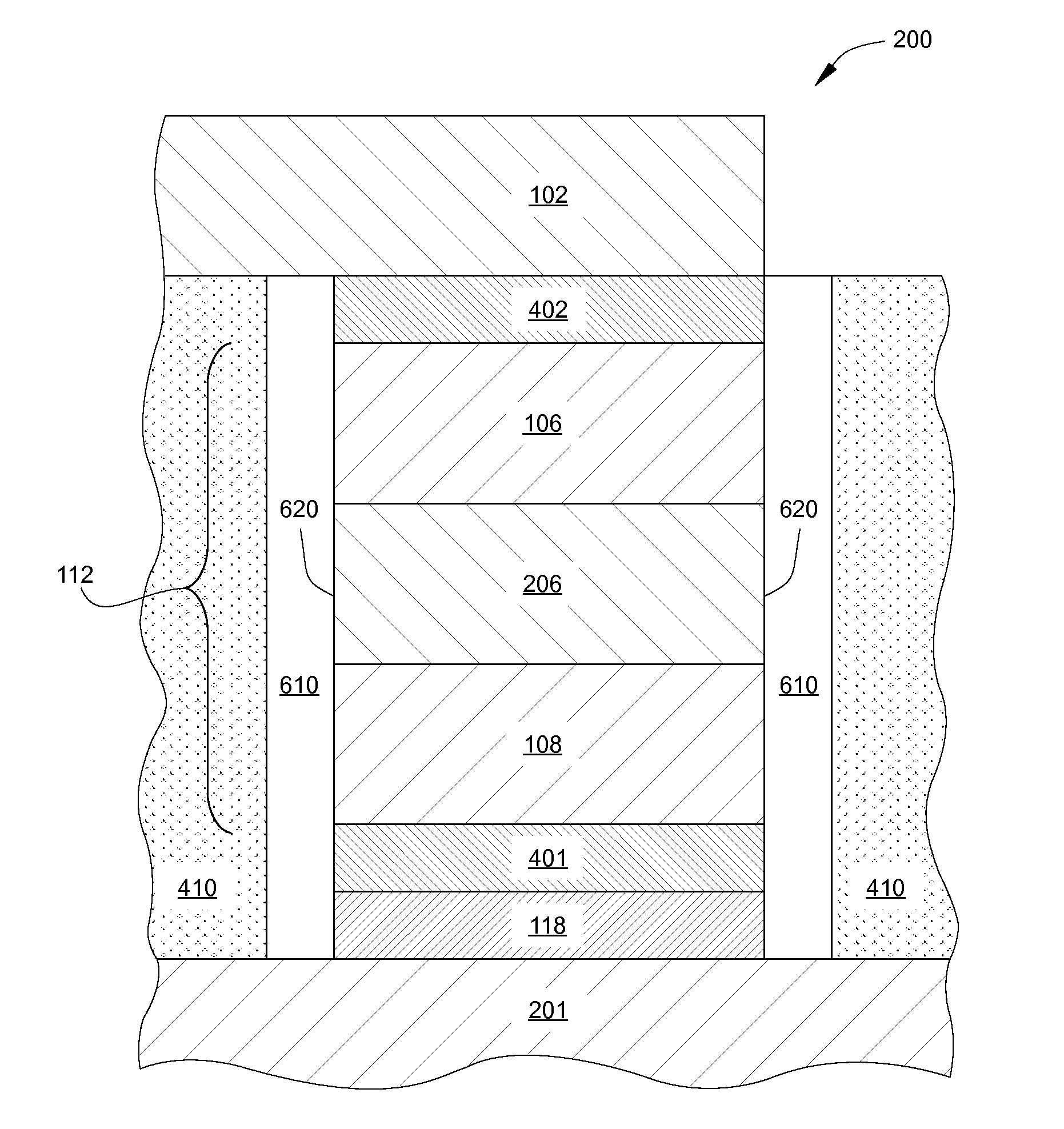

Switchable resistive perovskite microelectronic device with multi-layer thin film structure

ActiveUS7608467B2Reduce voltageImprove configurationSemiconductor/solid-state device manufacturingDigital storageElectrical resistance and conductanceMagnification

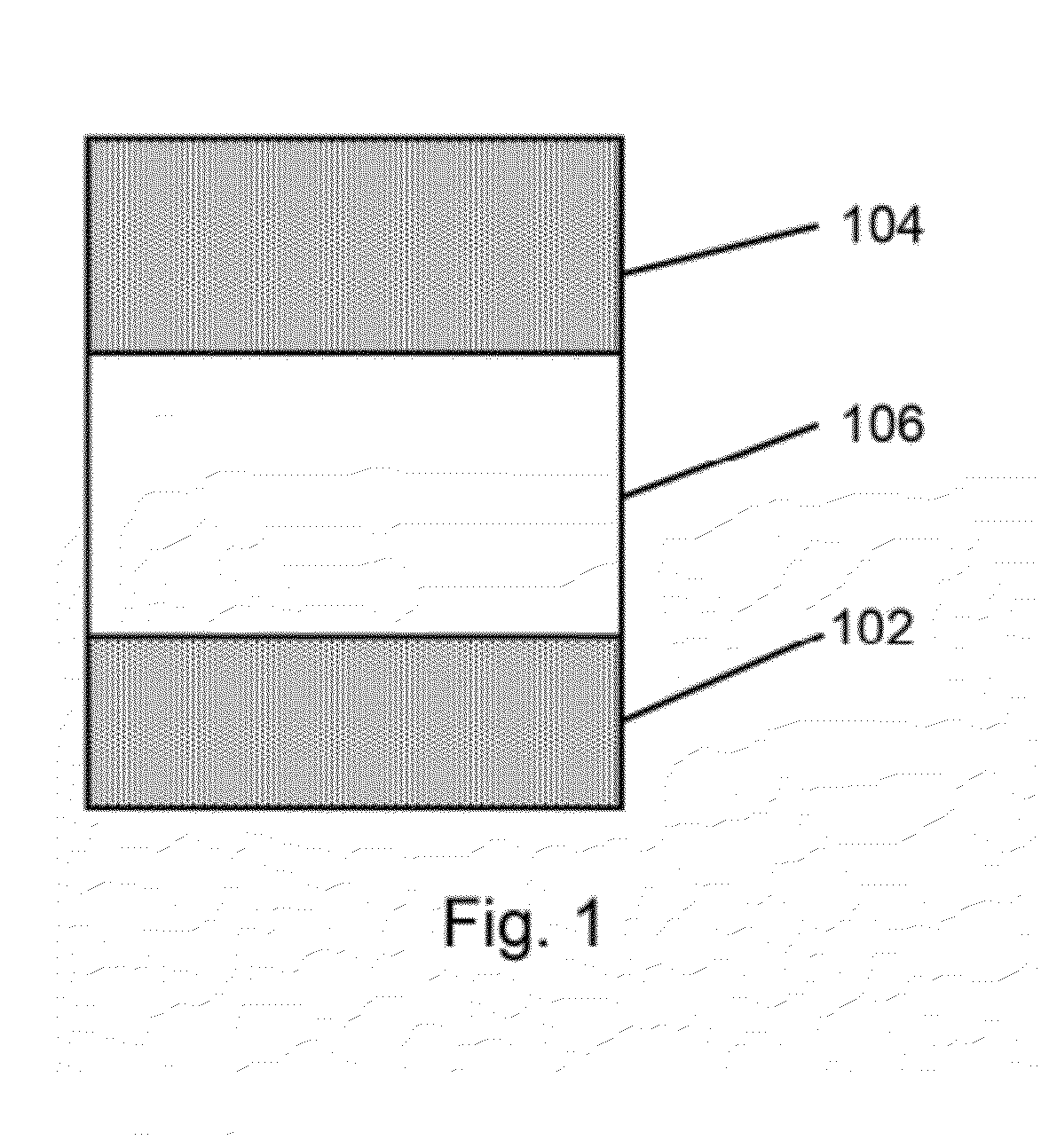

A switchable resistive device has a multi-layer thin film structure interposed between an upper conductive electrode and a lower conductive electrode. The multi-layer thin film structure comprises a perovskite layer with one buffer layer on one side of the perovskite layer, or a perovskite layer with buffer layers on both sides of the perovskite layer. Reversible resistance changes are induced in the device under applied electrical pulses. The resistance changes of the device are retained after applied electric pulses. The functions of the buffer layer(s) added to the device include magnification of the resistance switching region, reduction of the pulse voltage needed to switch the device, protection of the device from being damaged by a large pulse shock, improvement of the temperature and radiation properties, and increased stability of the device allowing for multivalued memory applications.

Owner:UNIV HOUSTON SYST

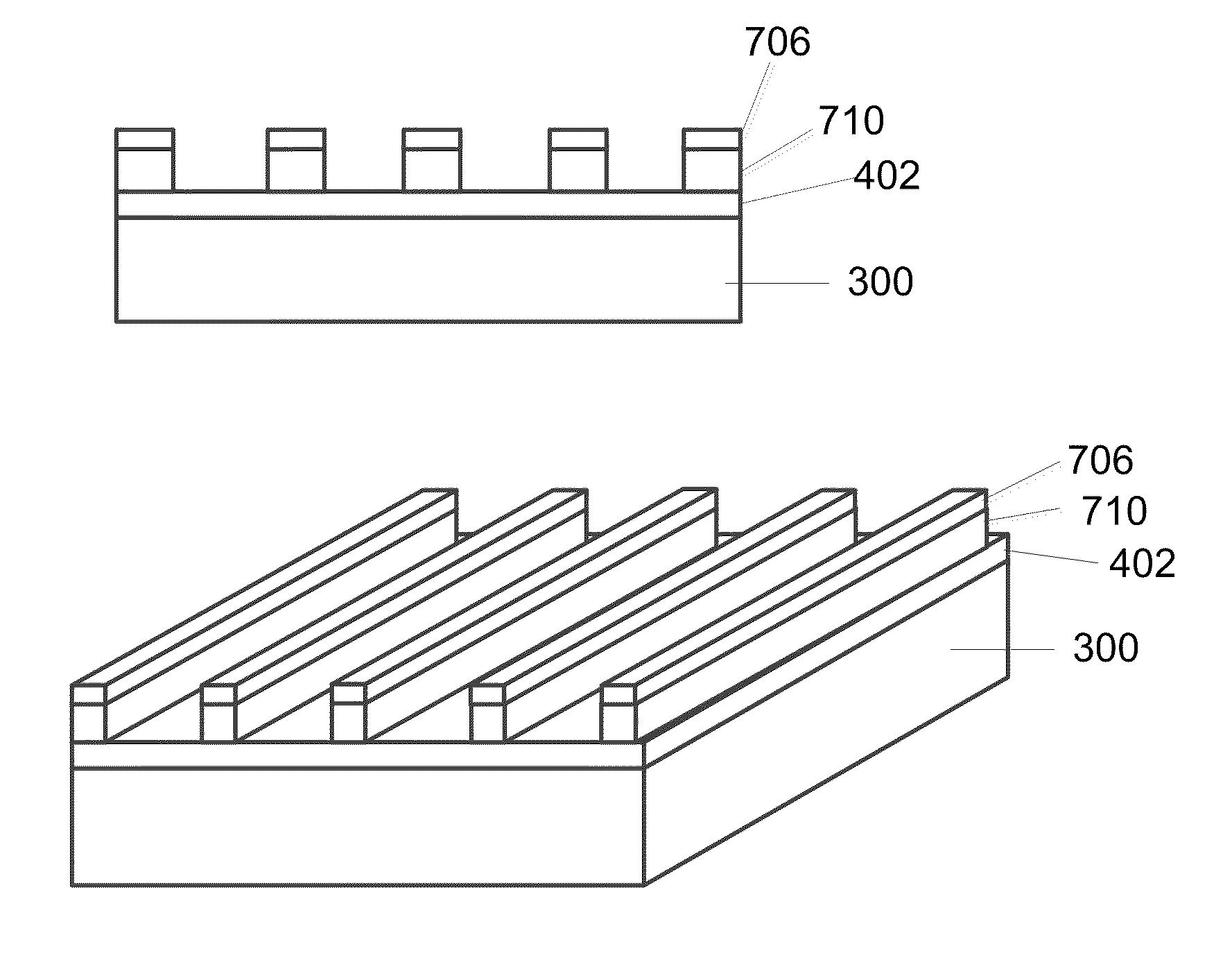

Low temperature P+ polycrystalline silicon material for non-volatile memory device

ActiveUS8658476B1Simplify the manufacturing processImprove device yieldSolid-state devicesSemiconductor/solid-state device manufacturingDeposition temperatureDegree Celsius

A method of forming a non-volatile memory device. The method includes providing a substrate having a surface region and forming a first dielectric material overlying the surface region of the substrate. A first electrode structure is formed overlying the first dielectric material and a p+ polycrystalline silicon germanium material is formed overlying the first electrode structure. A p+ polycrystalline silicon material is formed overlying the first electrode structure using the polycrystalline silicon germanium material as a seed layer at a deposition temperature ranging from about 430 Degree Celsius to about 475 Degree Celsius without further anneal. The method forms a resistive switching material overlying the polycrystalline silicon material, and a second electrode structure including an active metal material overlying the resistive switching material.

Owner:INNOSTAR SEMICON SHANGHAI CO LTD

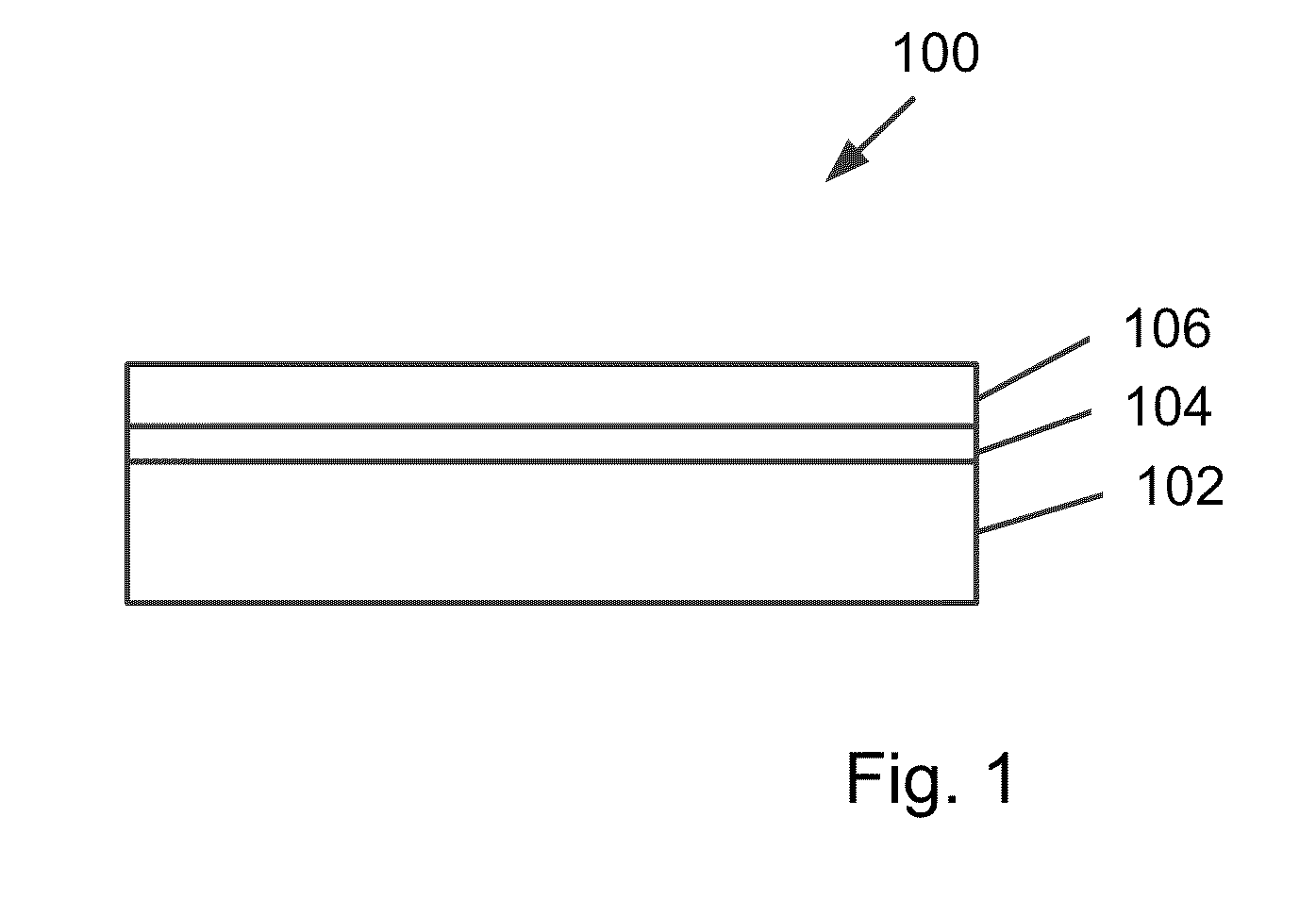

Nanoscale metal oxide resistive switching element

ActiveUS20120001146A1Flexible thermal budgetReduce power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingPhysical chemistryEngineering

A non-volatile memory device structure. The non-volatile memory device structure comprises a first electrode formed from a first metal material, a resistive switching element overlying the first electrode. The resistive switching element comprises a metal oxide material characterized by one or more oxygen deficient sites. The device includes a second electrode overlying the resistive switching layer, the second electrode being formed from a second metal material. The second electrode is made from a noble metal. The one or more oxygen deficient sites are caused to migrate from one of the first electrode or the second electrode towards the other electrode upon a voltage applied to the first electrode or the second electrode. The device can have a continuous change in resistance upon applying a continuous voltage ramp, suitable for an analog device. Alternatively, the device can have a sharp change in resistance upon applying the continuous voltage ramp, suitable for a digital device.

Owner:RGT UNIV OF MICHIGAN

Vertical Diodes for Non-Volatile Memory Device

A steering device. The steering device includes an n-type impurity region comprising a zinc oxide material and a p-type impurity region comprising a silicon germanium material. A pn junction region formed from the zinc oxide material and the silicon germanium material. The steering device is a serially coupled to a resistive switching device to provide rectification for the resistive switching device to form a non-volatile memory device.

Owner:INNOSTAR SEMICON SHANGHAI CO LTD

P+ polysilicon material on aluminum for non-volatile memory device and method

ActiveUS20120142163A1Solid-state devicesSemiconductor/solid-state device manufacturingDielectricMetallic materials

Owner:INNOSTAR SEMICON SHANGHAI CO LTD

Rectification element and method for resistive switching for non volatile memory device

ActiveUS8351241B2High densityFast switching speedSolid-state devicesDigital storageElectrical resistance and conductanceElectricity

Owner:RGT UNIV OF MICHIGAN

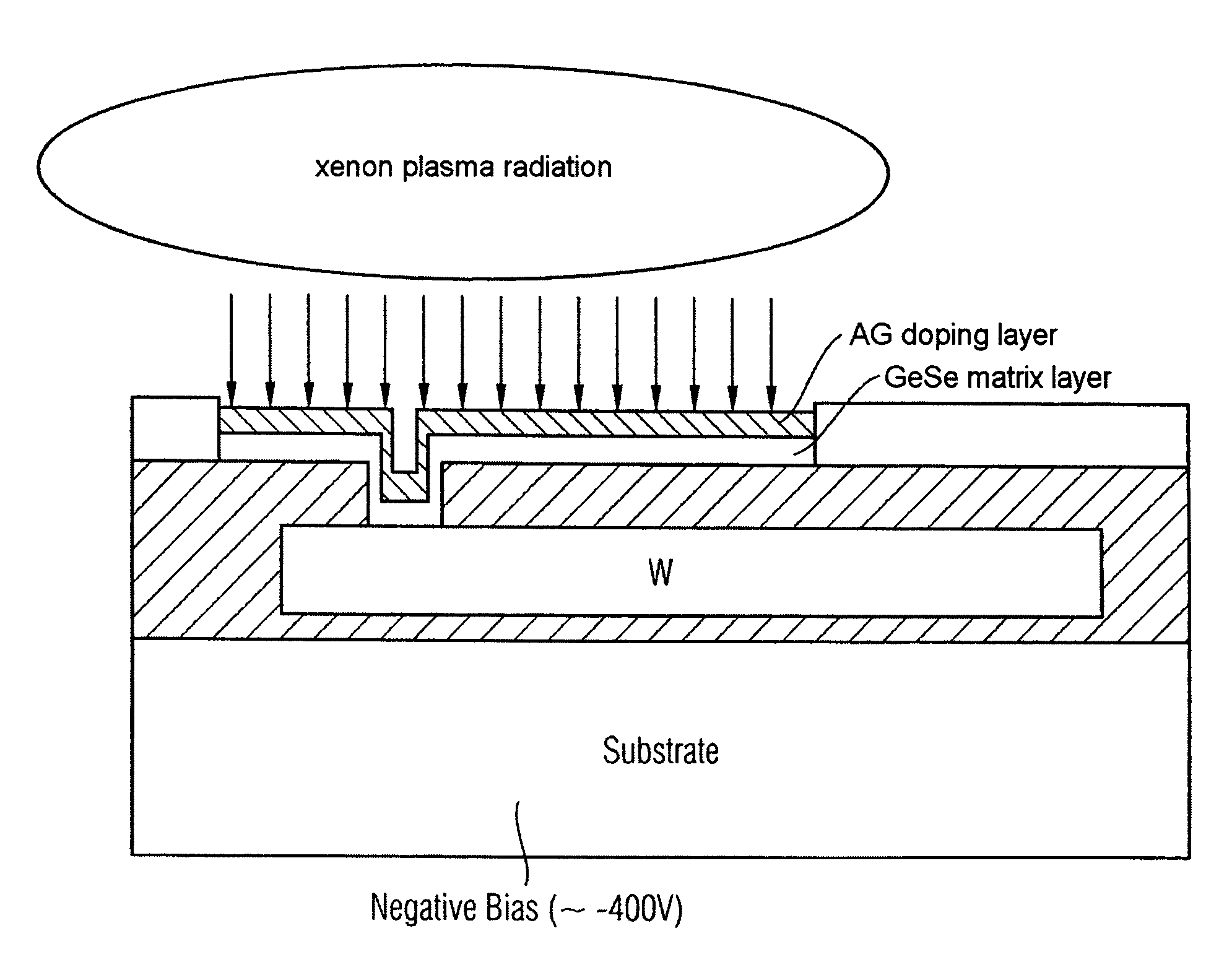

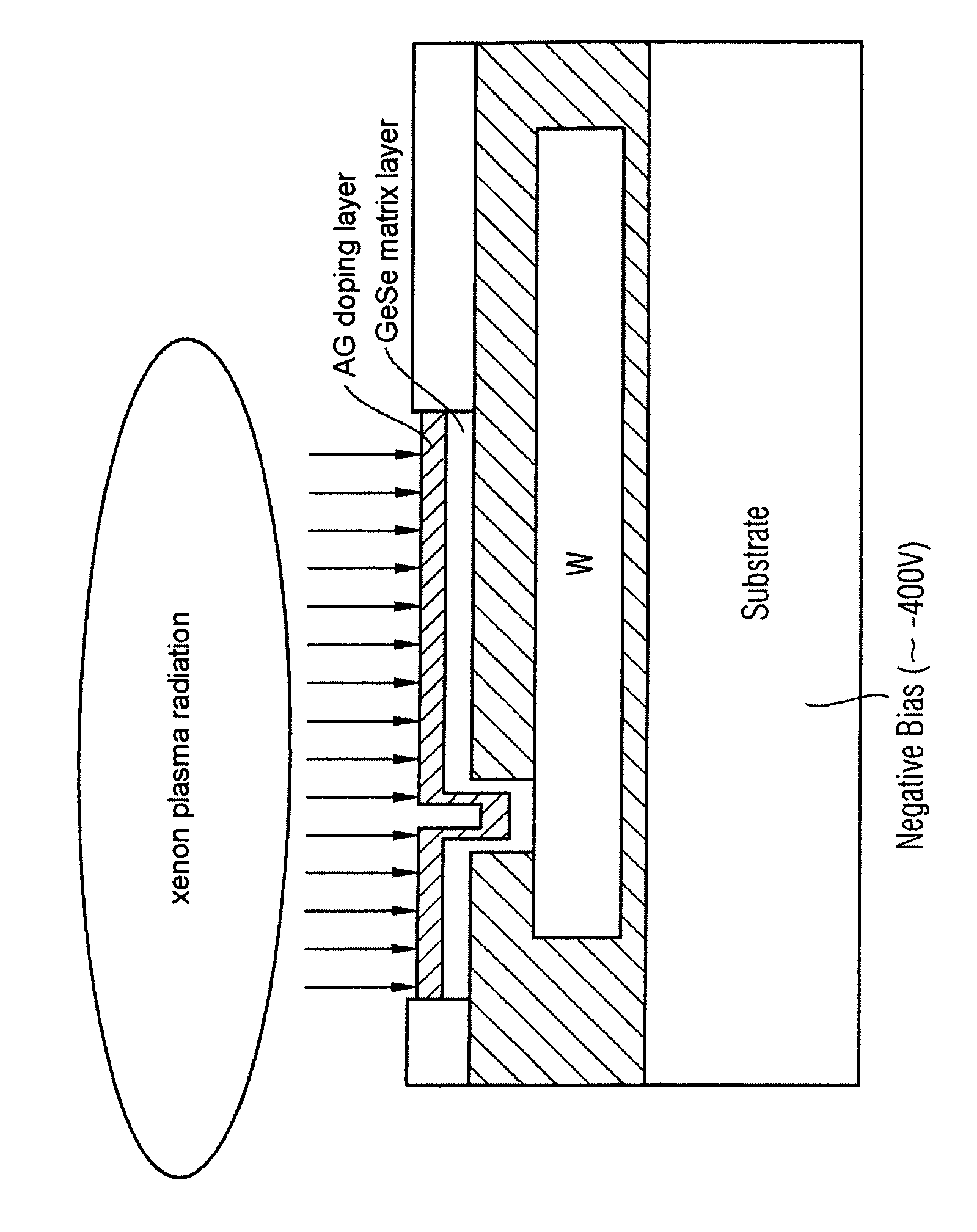

Method for fabricating a resistive memory

A method for fabricating a resistively switching memory cell is provided. The method includes the following steps: depositing a first electrode, applying a layer of a chalcogenide compound to the first electrode, applying a layer of silver or copper, and operating a noble gas plasma in a back-sputtering mode in order to effect silver or copper diffusion into the layer of the chalcogenide compound. Optionally, and if appropriate, further layers for the second electrode are then deposited.

Owner:ADESTO TECH

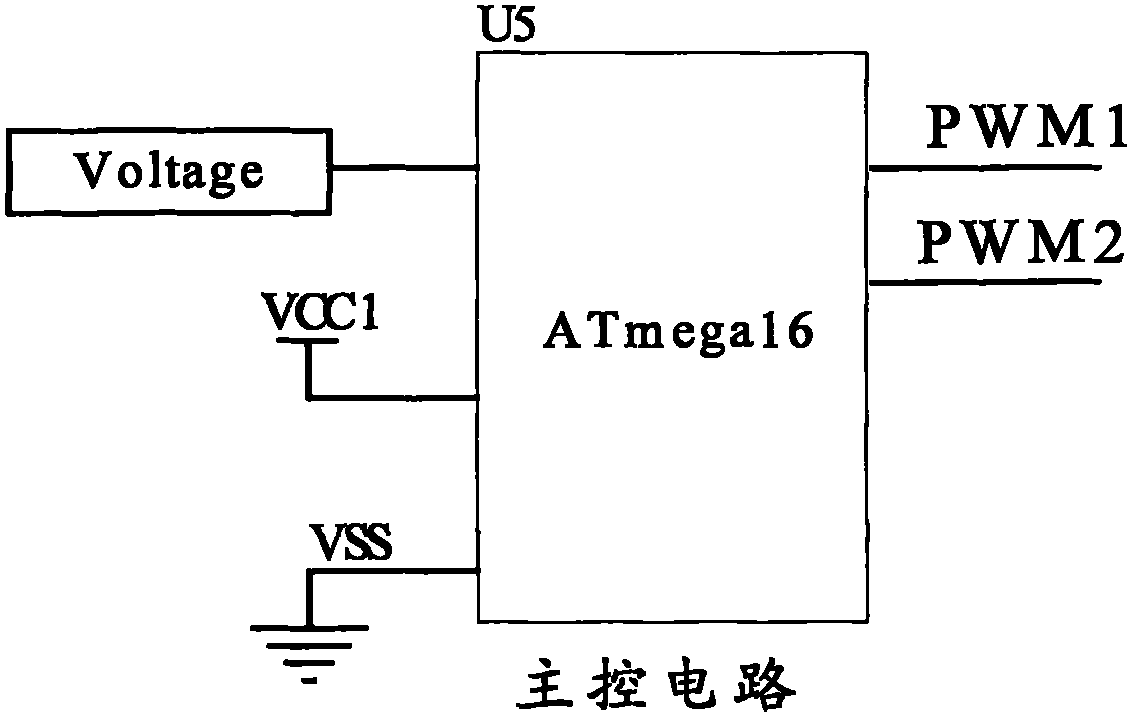

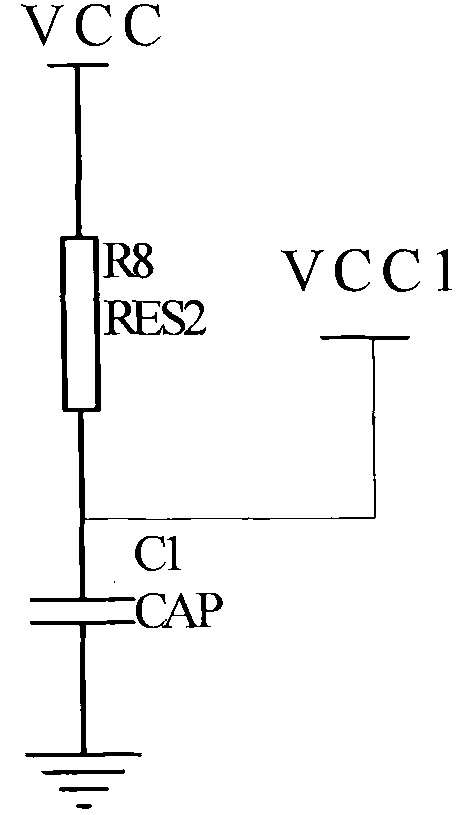

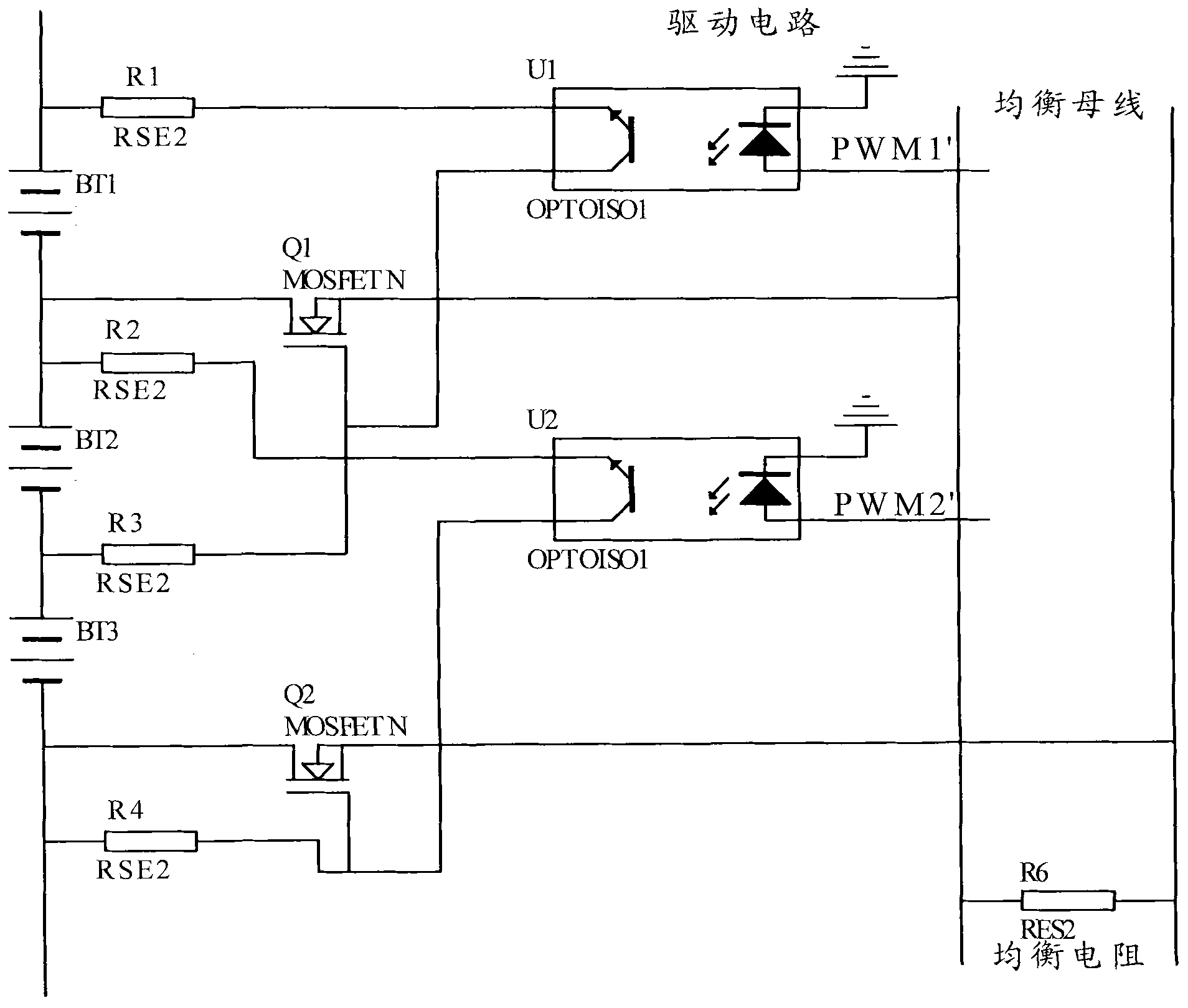

Battery equalizing device

ActiveCN101986508AReduce varianceBatteries circuit arrangementsElectric powerElectricityElectrical resistance and conductance

The invention discloses a battery equalizing device used for equalizing multiple battery units in a battery pack by utilizing an equalizing resistance, which comprises a controller, a resistance switching circuit and the equalizing resistance, wherein the resistance switching circuit is used for connecting the battery units specified by the equalizing resistance and the controller in parallel under the control of the controller; and the controller is used for collecting the voltage value of each battery unit in the multiple battery units, determining the residual electricity quantity of each battery unit according to the collected voltage and controlling the resistance switching circuit to connect the equalizing resistance with the battery unit in parallel under the circumstance that one battery unit meets the switching conditions, wherein the switching condition is as follows: the residual electricity quantity of the battery unit is higher than the specified value of the average residual electricity quantity of the multiple battery units. The battery equalizing device can intelligently equalize the battery units, effectively reduce the difference between the battery units and cansave the volume and the cost of equipment.

Owner:力高(山东)新能源技术股份有限公司

Resistive memory devices and methods of manufacturing the same

ActiveUS20090184305A1Solid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

A resistive memory device includes a first electrode and a first insulation layer arranged on the first electrode. A portion of the first electrode is exposed through a first hole in the first insulation layer. A first variable resistance layer contacts the exposed portion of the first electrode and extends on the first insulation layer around the first hole. A first switching device electrically connects to the first resistive switching layer.

Owner:SAMSUNG ELECTRONICS CO LTD

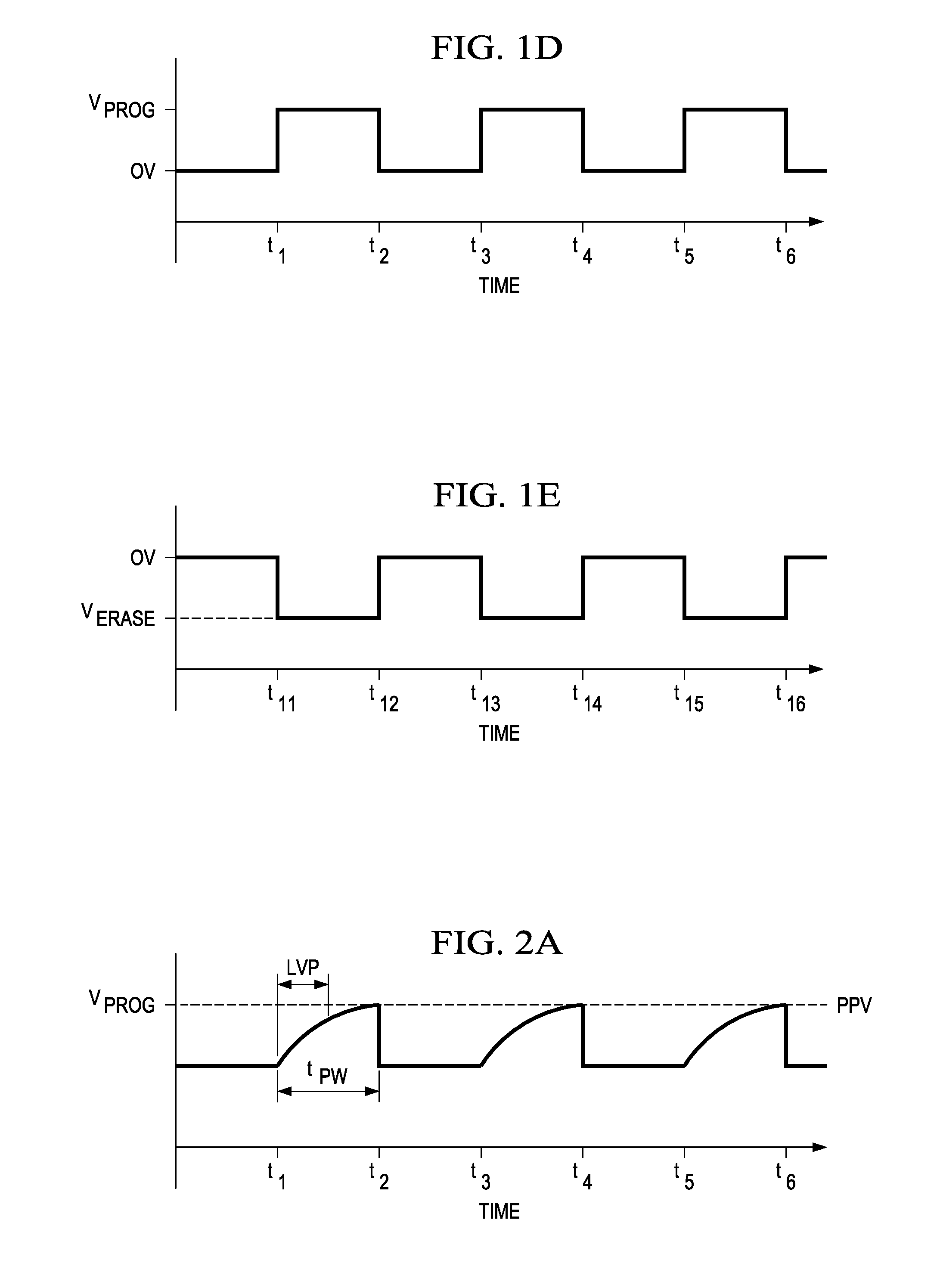

Resistive Devices and Methods of Operation Thereof

In one embodiment, a method of operating a resistive switching device includes applying a signal comprising a pulse on a first terminal of a two terminal resistive switching device having the first terminal and a second terminal. The resistive switching device has a first state and a second state. The pulse includes a first ramp from a first voltage to a second voltage over a first time period. The first time period is at least 0.1 times a total time period of the pulse.

Owner:GLOBALFOUNDRIES US INC

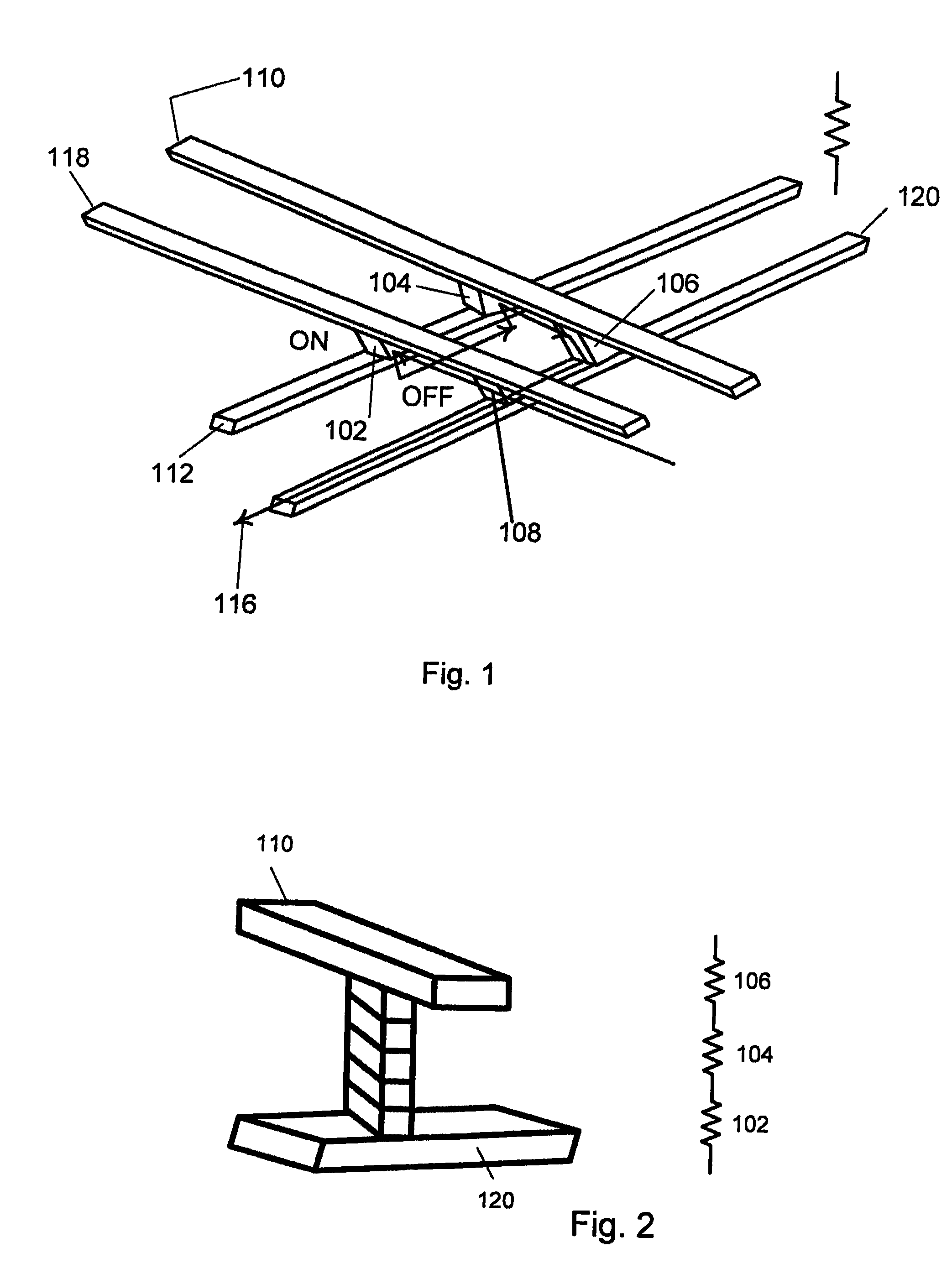

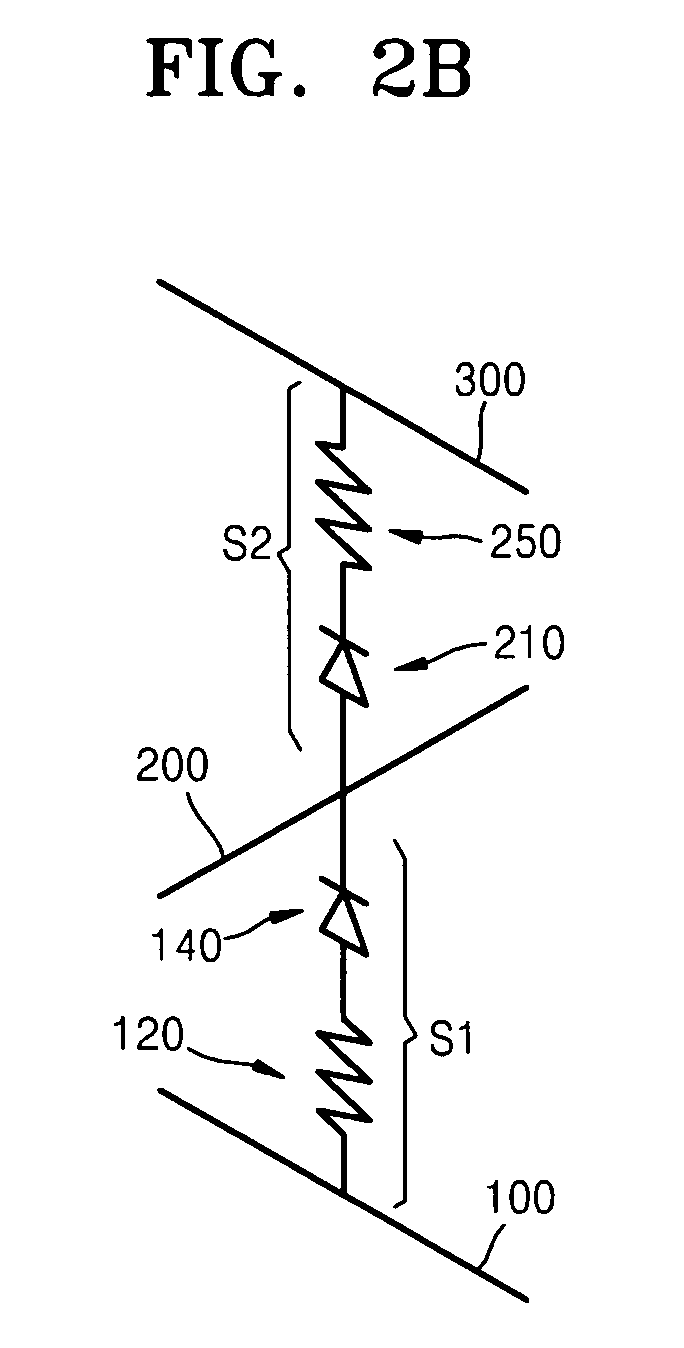

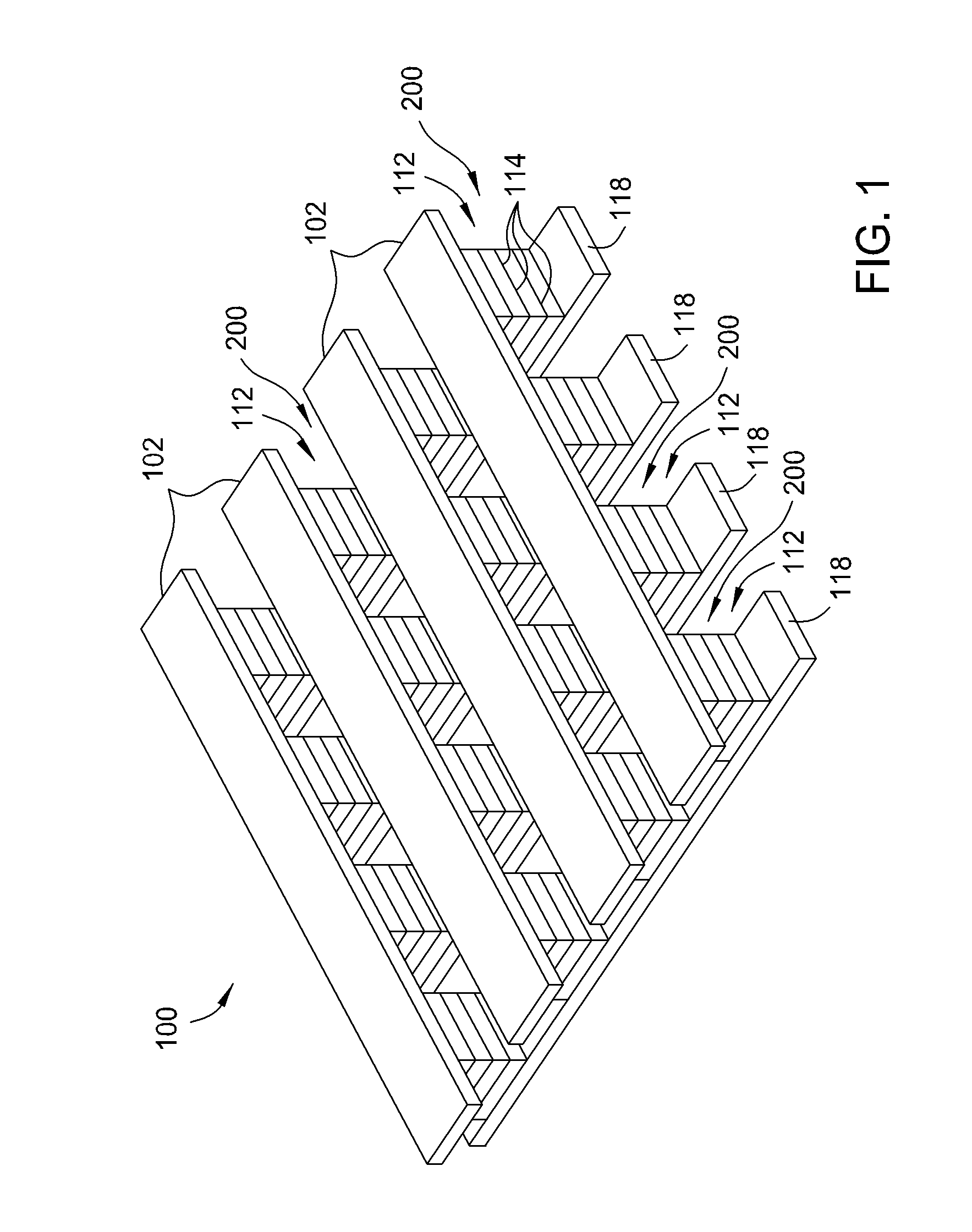

Punch-through diode steering element

ActiveUS8274130B2Semiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceEngineering

A storage system and method for forming a storage system that uses punch-through diodes as a steering element in series with a reversible resistivity-switching element is described. The punch-through diode allows bipolar operation of a cross-point memory array. The punch-through diode may have a symmetrical non-linear current / voltage relationship. The punch-through diode has a high current at high bias for selected cells and a low leakage current at low bias for unselected cells. Therefore, it is compatible with bipolar switching in cross-point memory arrays having resistive switching elements. The punch-through diode may be a N+ / P− / N+ device or a P+ / N− / P+ device.

Owner:SANDISK TECH LLC

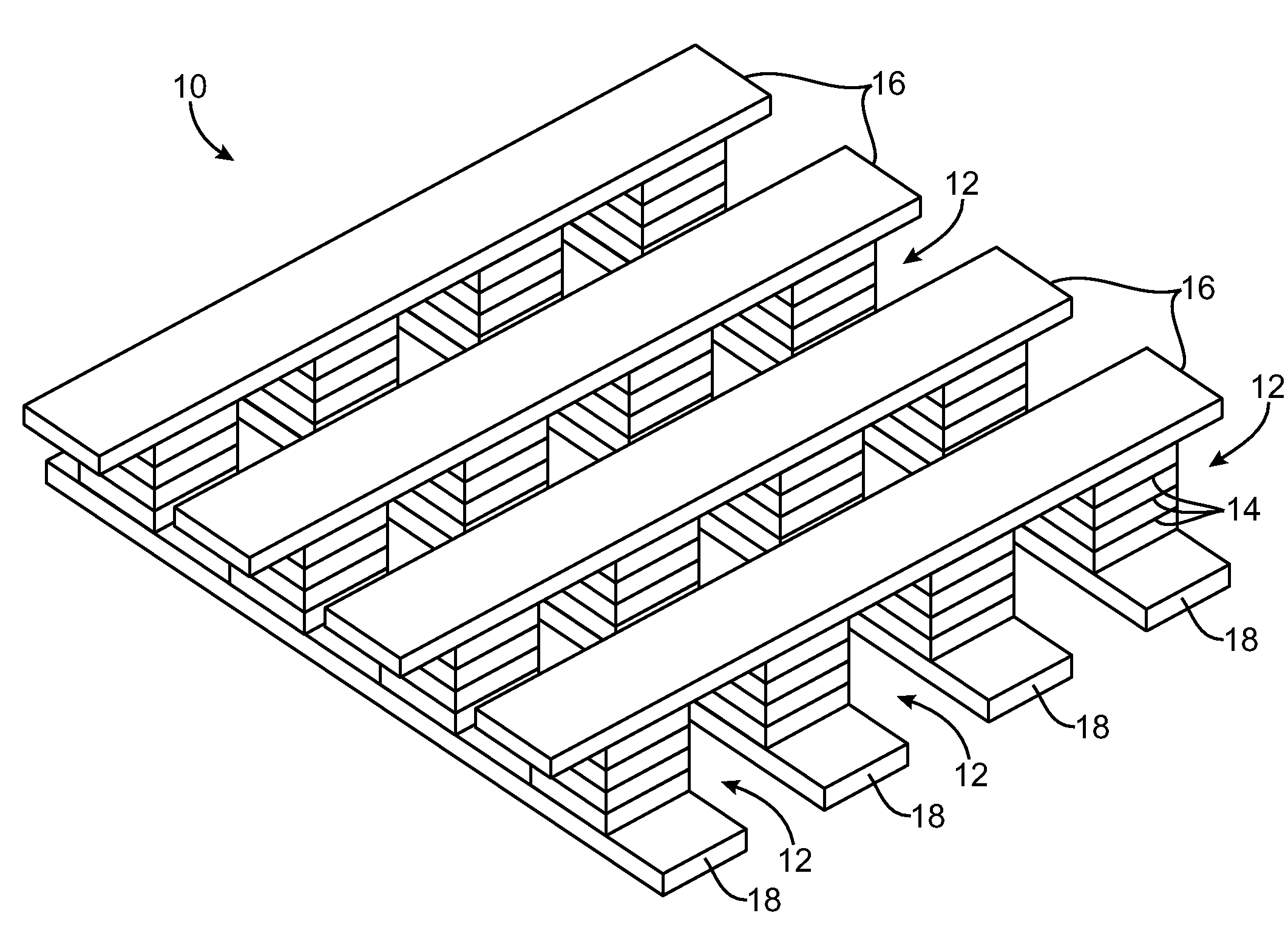

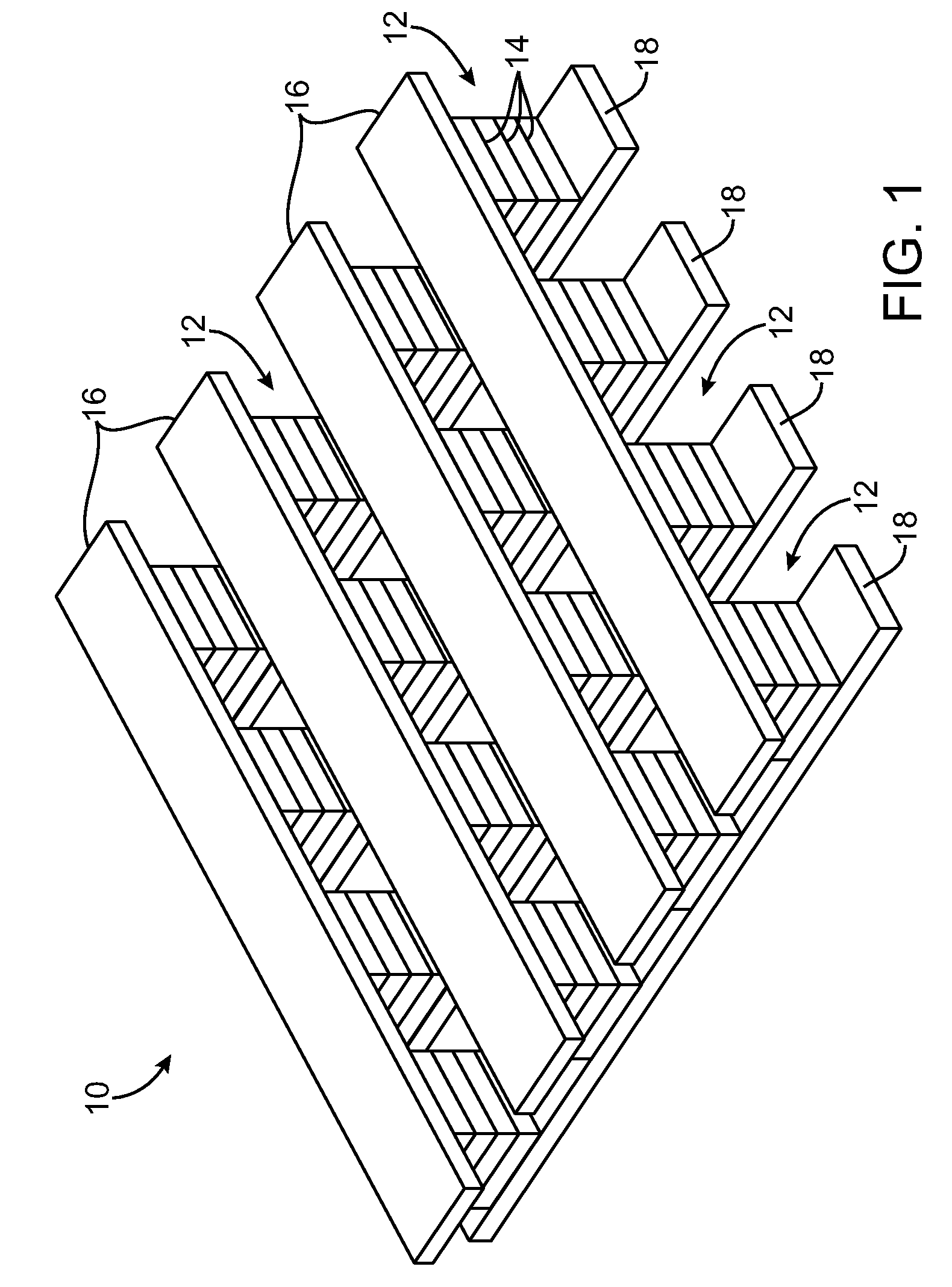

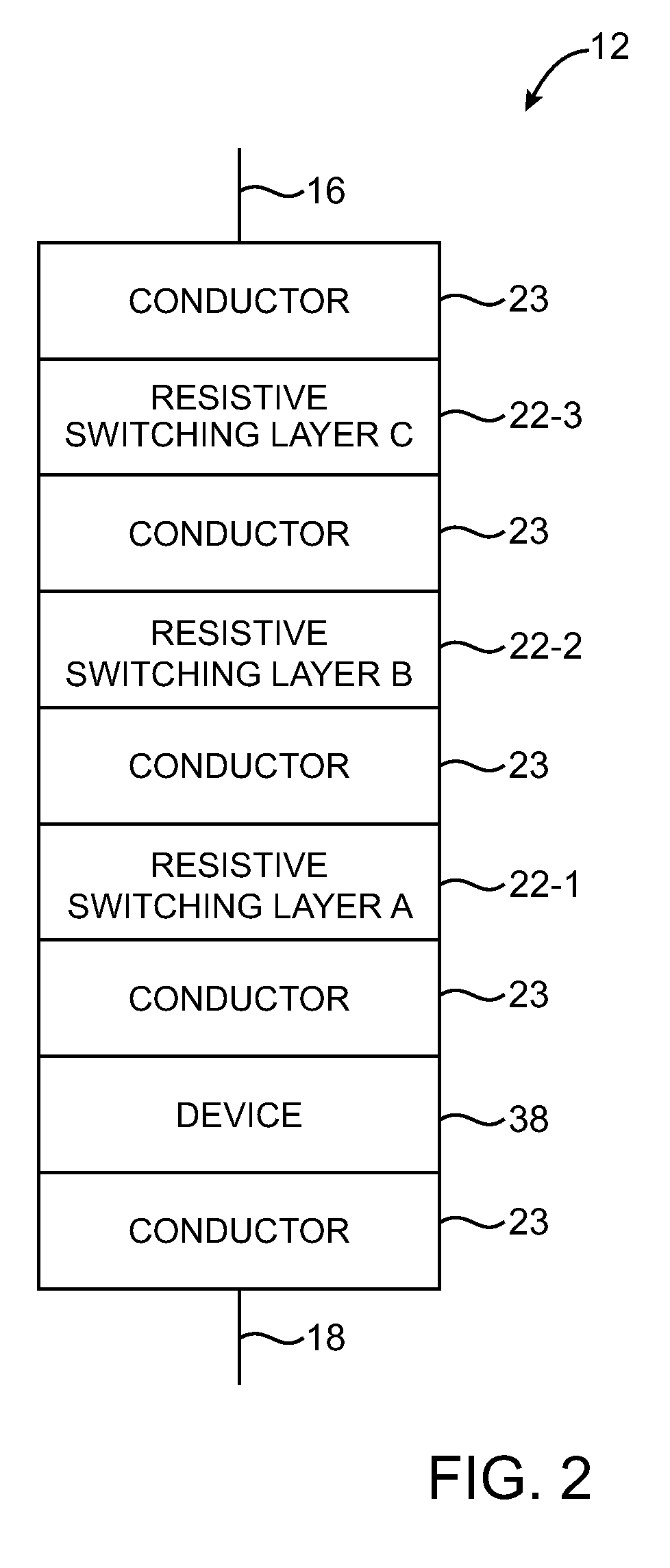

Multistate nonvolatile memory elements

ActiveUS20090026433A1Easy to switchDigital storageBulk negative resistance effect devicesElectrical conductorResistive switching

Multistate nonvolatile memory elements are provided. The multistate nonvolatile memory elements contain multiple layers. Each layer may be based on a different bistable material. The bistable materials may be resistive switching materials such as resistive switching metal oxides. Optional conductor layers and current steering elements may be connected in series with the bistable resistive switching metal oxide layers.

Owner:INTERMOLECULAR

Nonvolatile resistive memory element with an integrated oxygen isolation structure

InactiveUS20130221307A1Solid-state devicesBulk negative resistance effect devicesResistive switchingOxygen barrier

A nonvolatile resistive memory element includes one or more novel oxygen isolation structures that protect the resistive switching material of the memory element from oxygen migration. One such oxygen isolation structure comprises an oxygen barrier layer that isolates the resistive switching material from other portions of the resistive memory device during fabrication and / or operation of the memory device. Another such oxygen isolation structure comprises a sacrificial layer that reacts with unwanted oxygen migrating toward the resistive switching material during fabrication and / or operation of the memory device.

Owner:INTERMOLECULAR

Switching device having a non-linear element

ActiveUS20130308369A1High densityFast switching speedSolid-state devicesDigital storageLinear elementResistive switching

Method for a memory including a first, second, third and fourth cells include applying a read, program, or erase voltage, the first and second cells coupled to a first top interconnect, the third and fourth cells coupled to a second top interconnect, the first and third cells coupled to a first bottom interconnect, the second and fourth cells are to a second bottom interconnect, each cell includes a switching material overlying a non-linear element (NLE), the resistive switching material is associated with a first conductive threshold voltage, the NLE is associated with a lower, second conductive threshold voltage, comprising applying the read voltage between the first top and the first bottom electrode to switch the NLE of the first cell to conductive, while the NLEs of the second, third, and the fourth cells remain non-conductive, and detecting a read current across the first cell in response to the read voltage.

Owner:CROSSBAR INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com