Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

157results about How to "Improve device yield" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

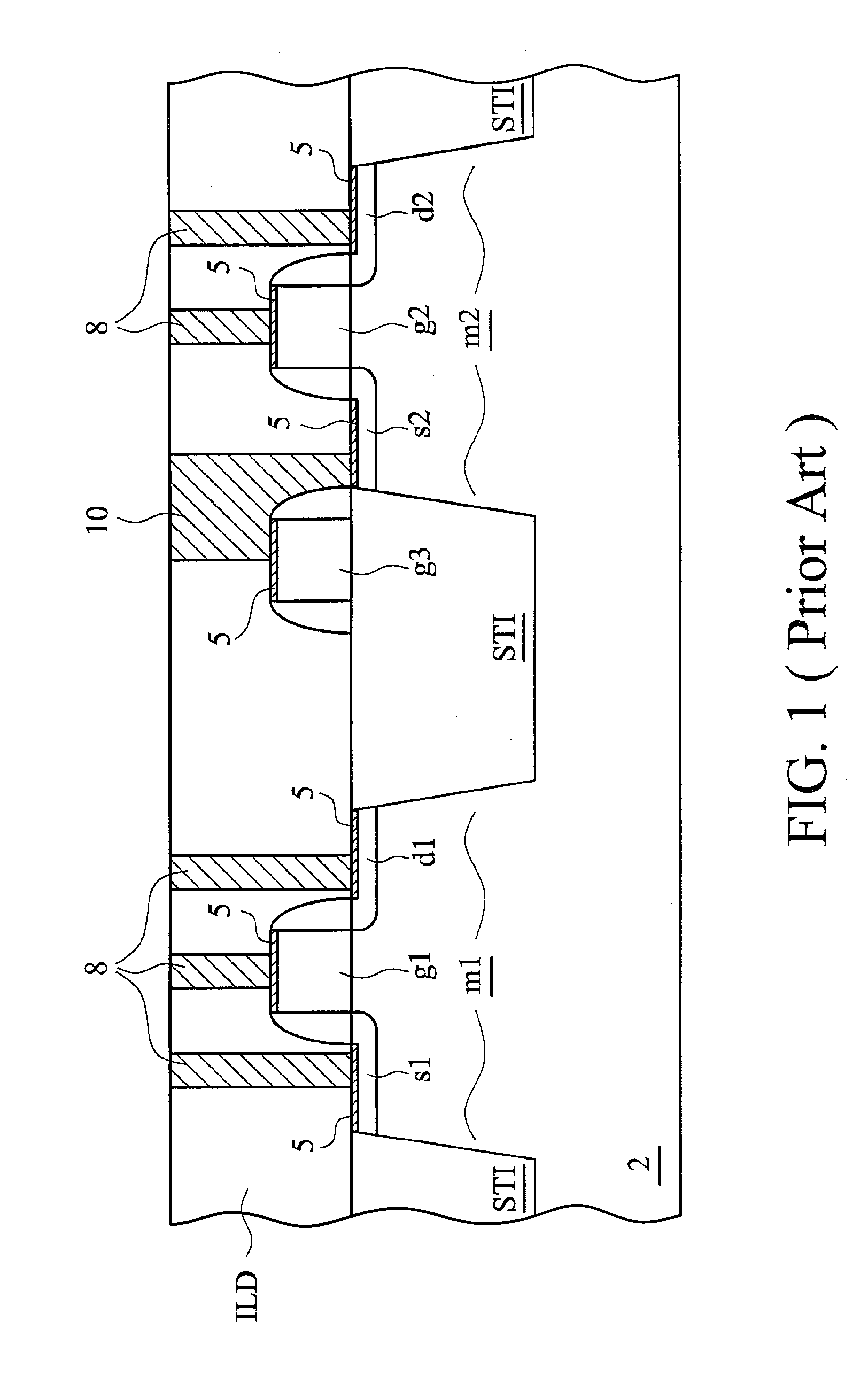

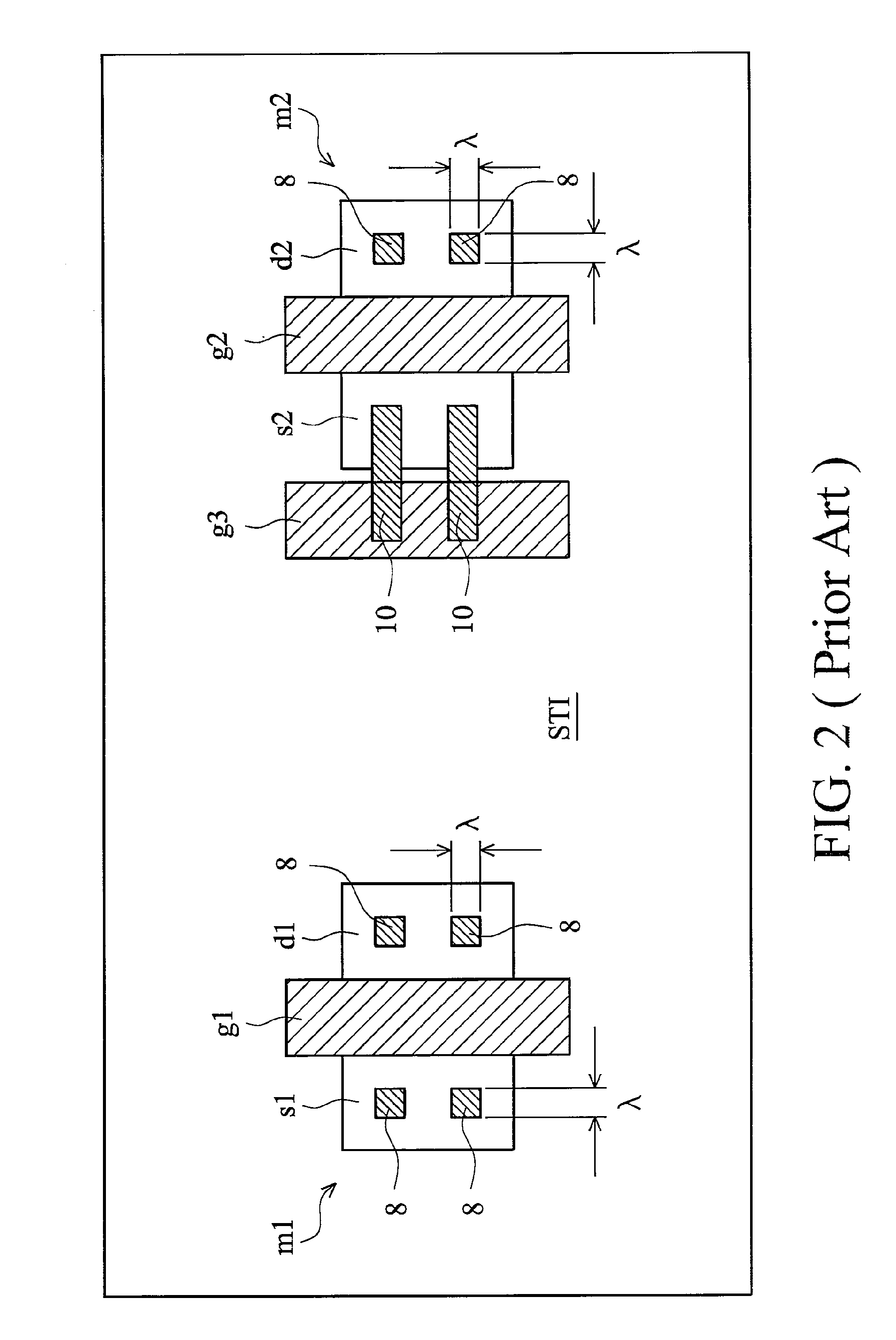

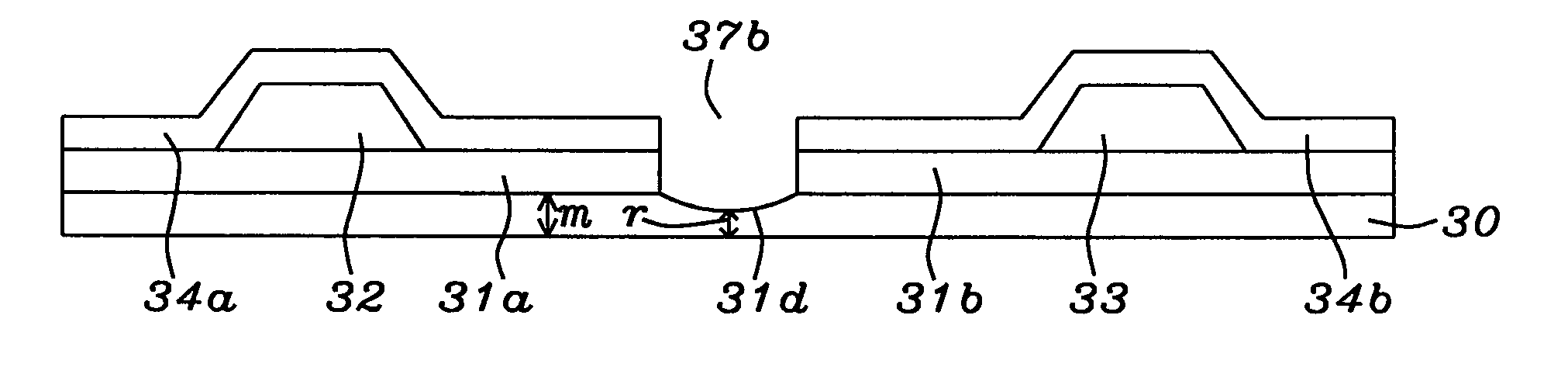

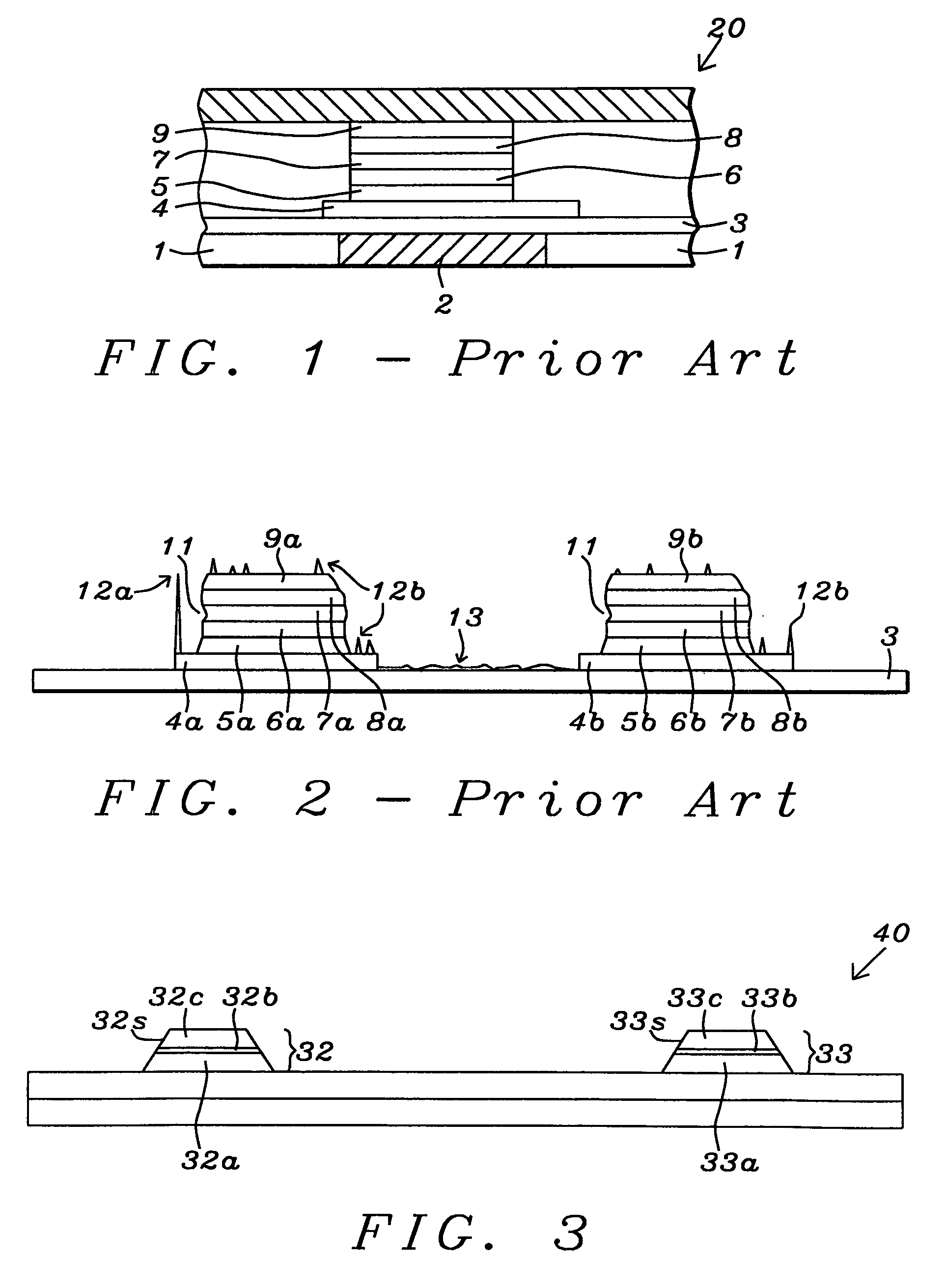

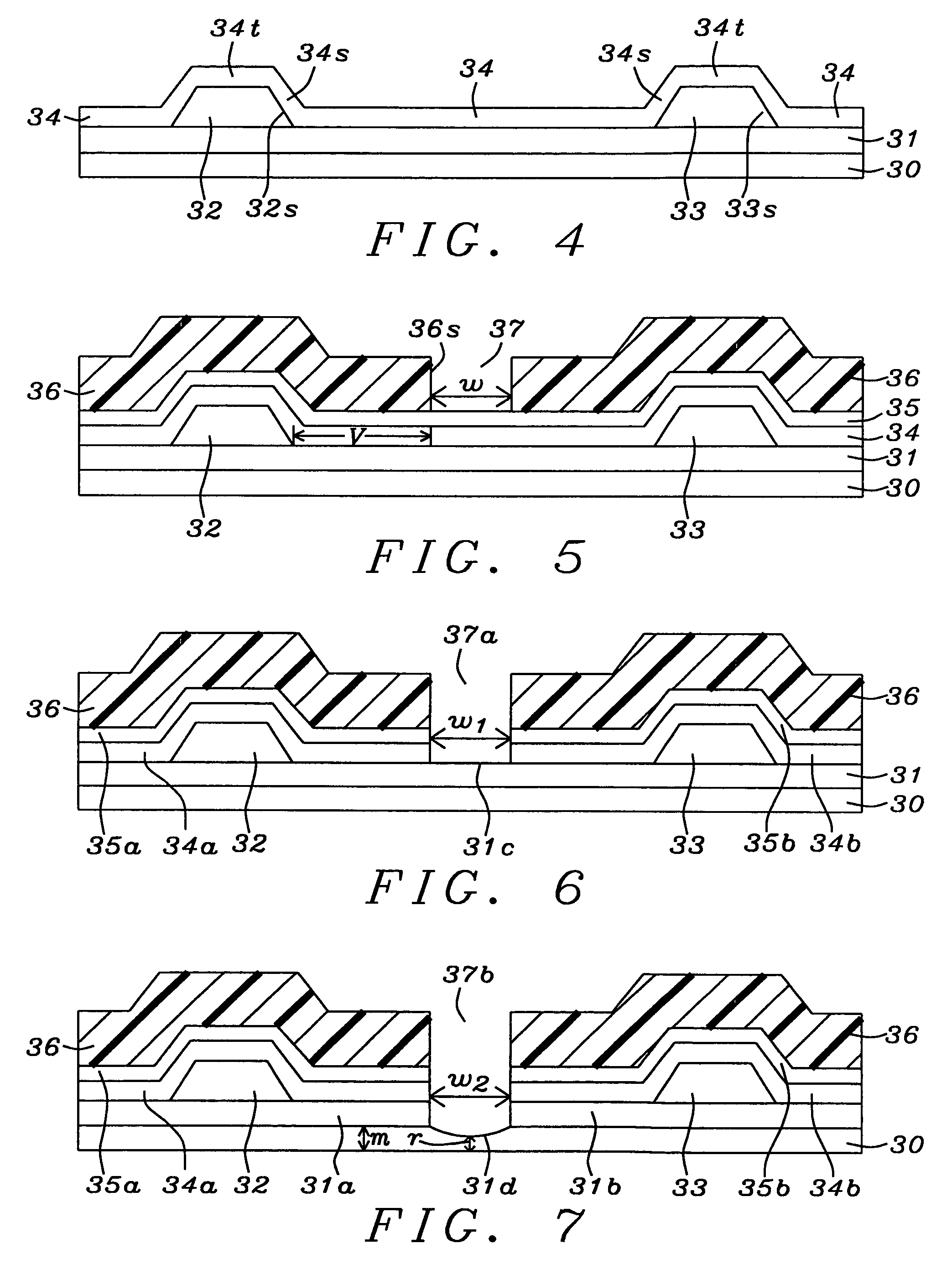

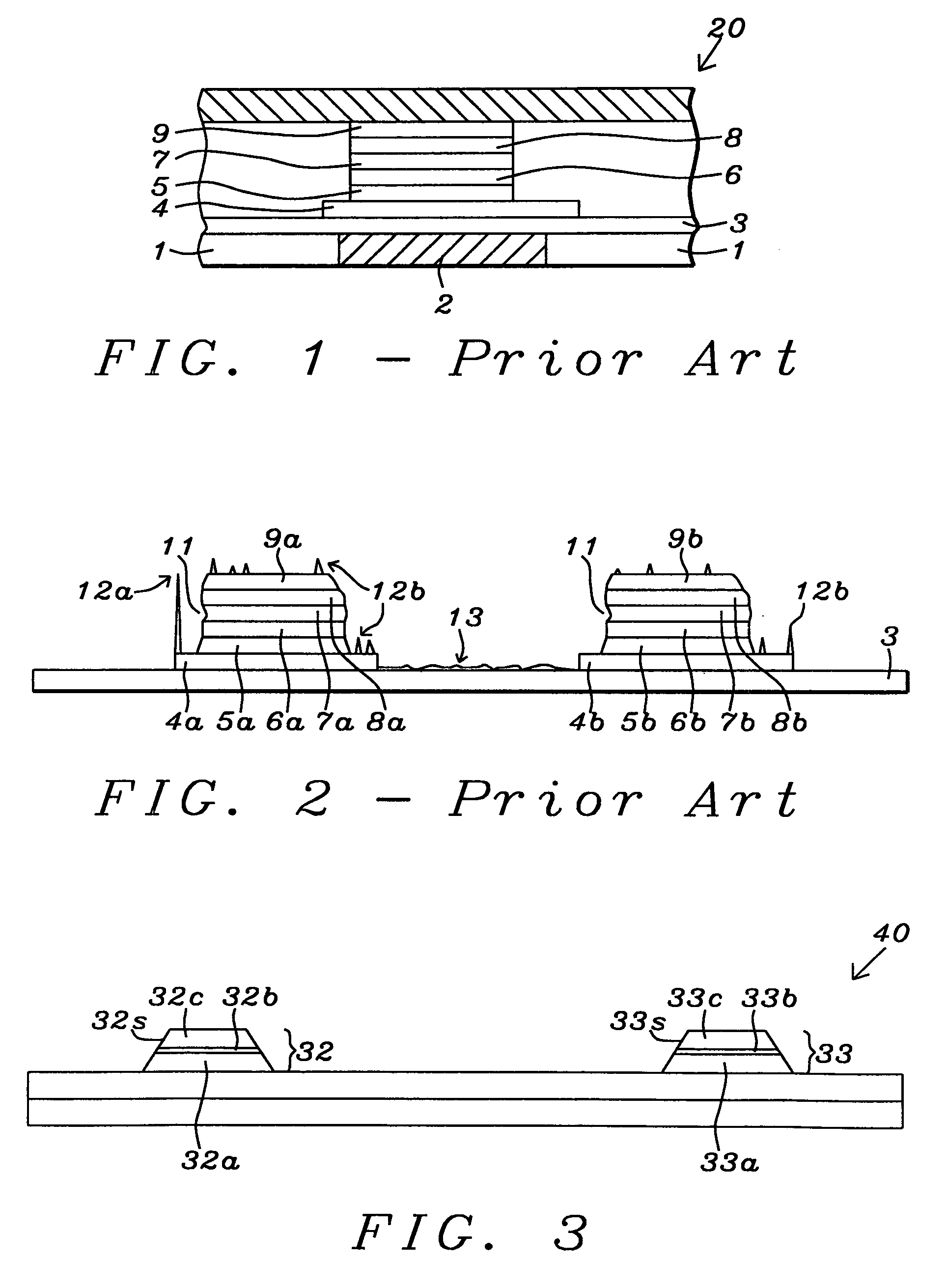

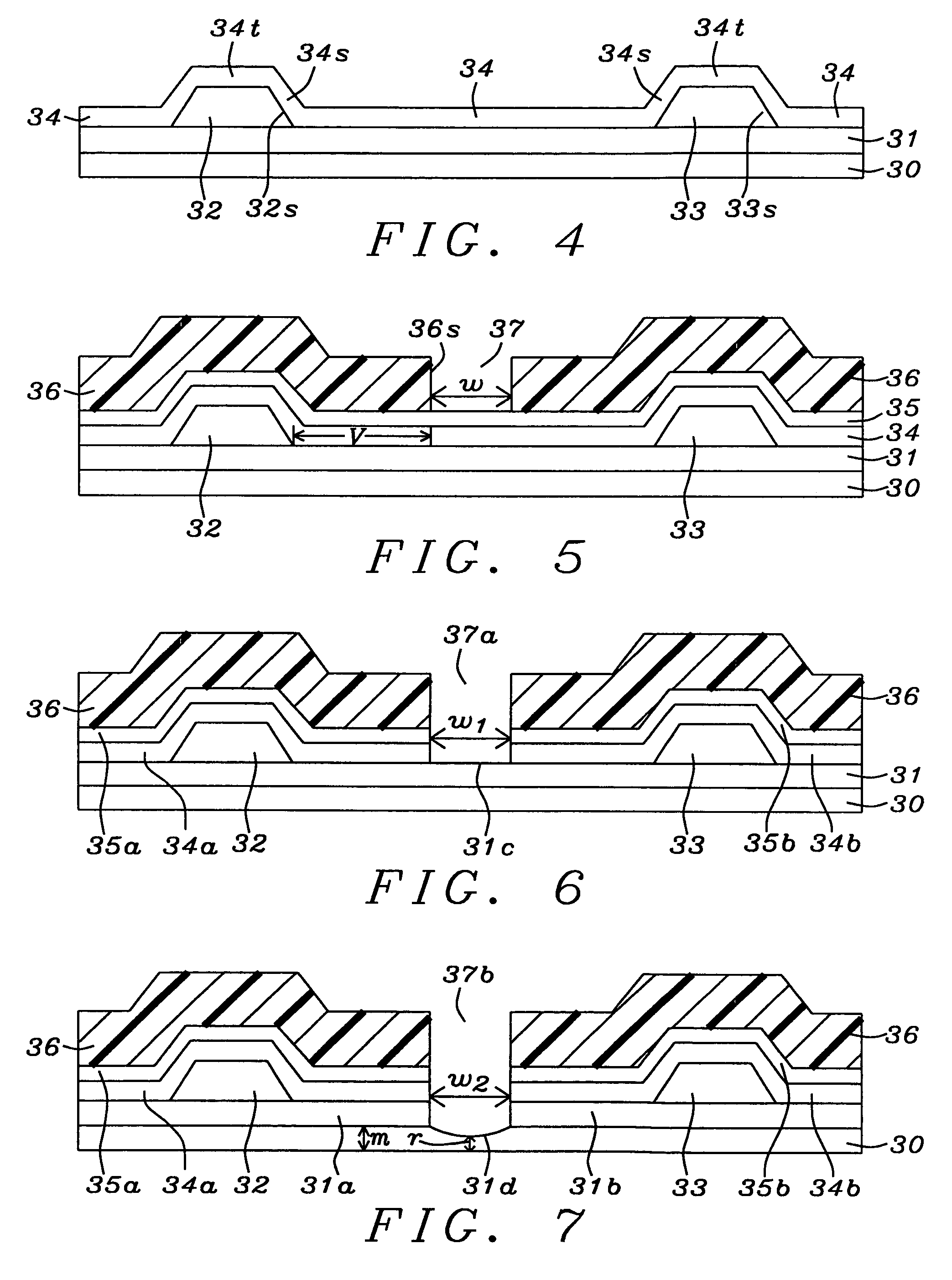

Interconnect layout method

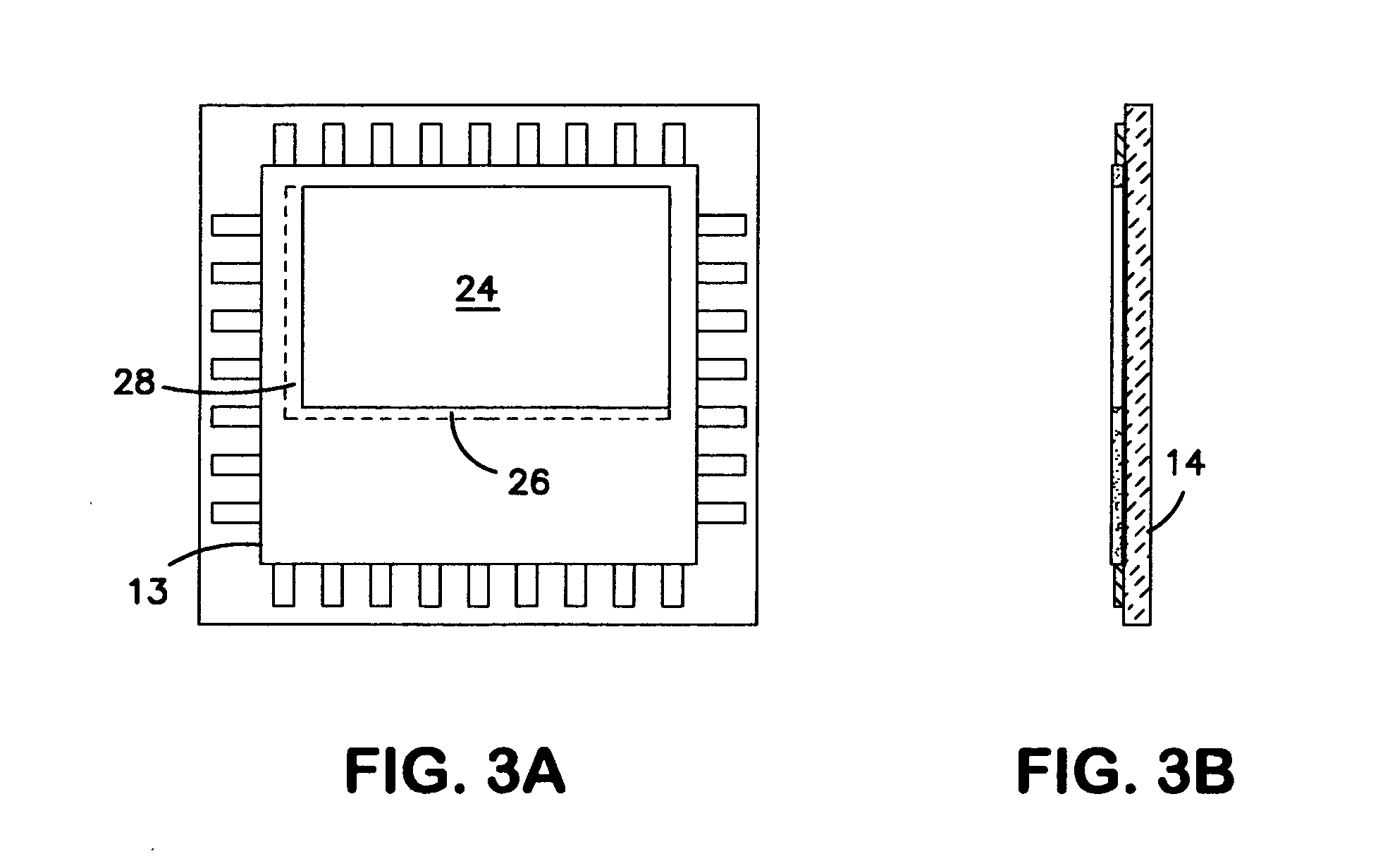

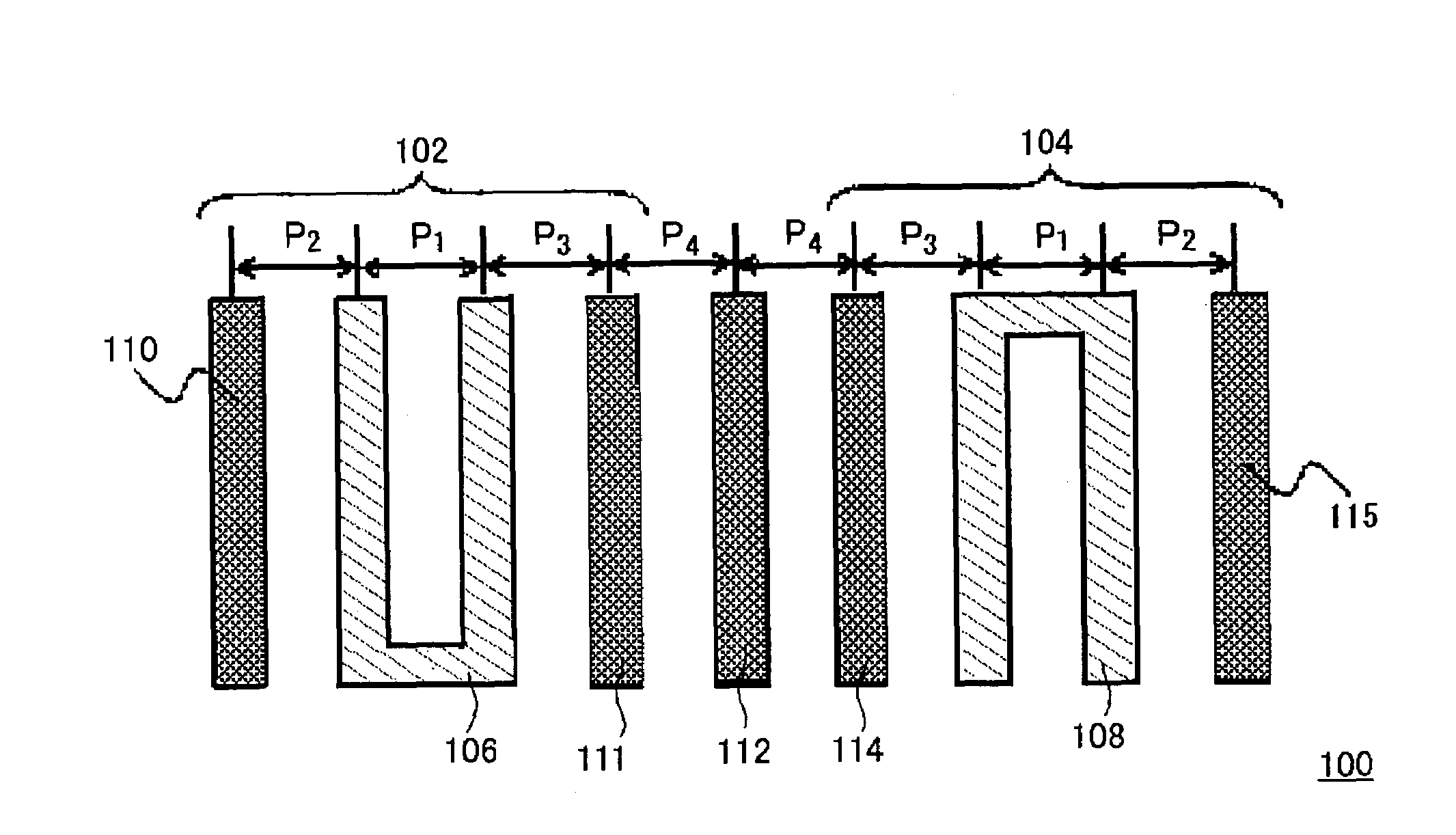

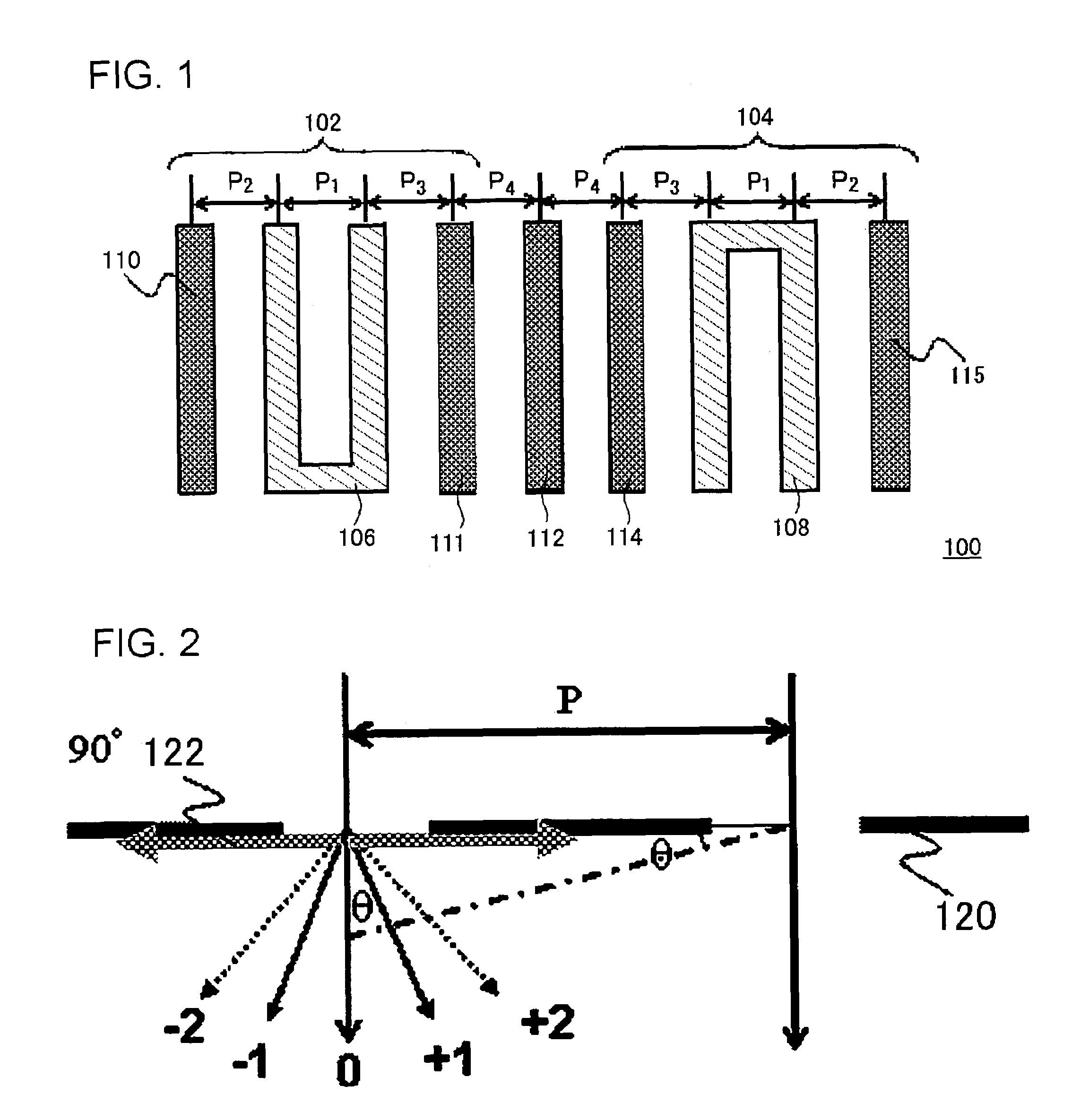

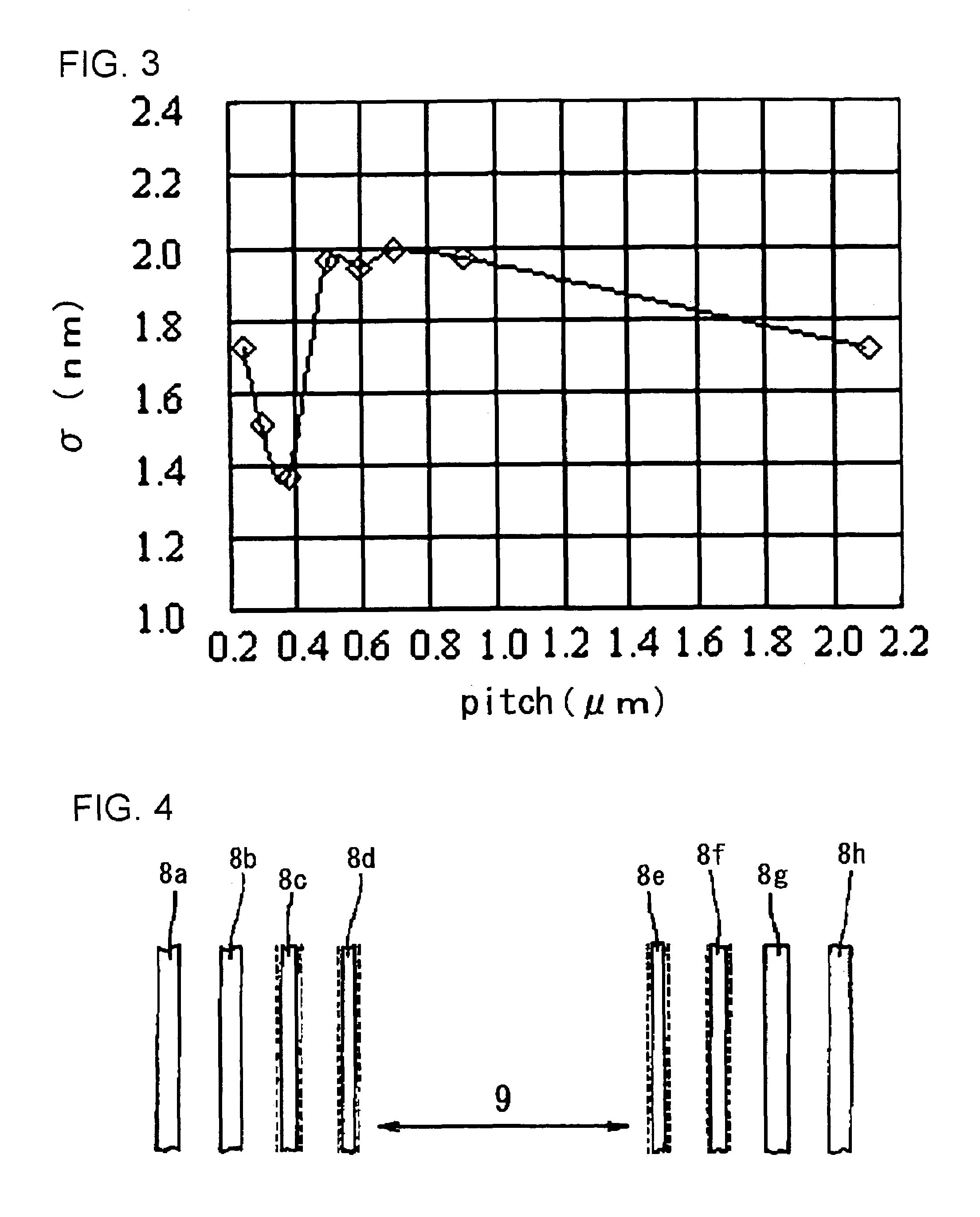

InactiveUS20060084261A1Image degradationReduce shapingSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

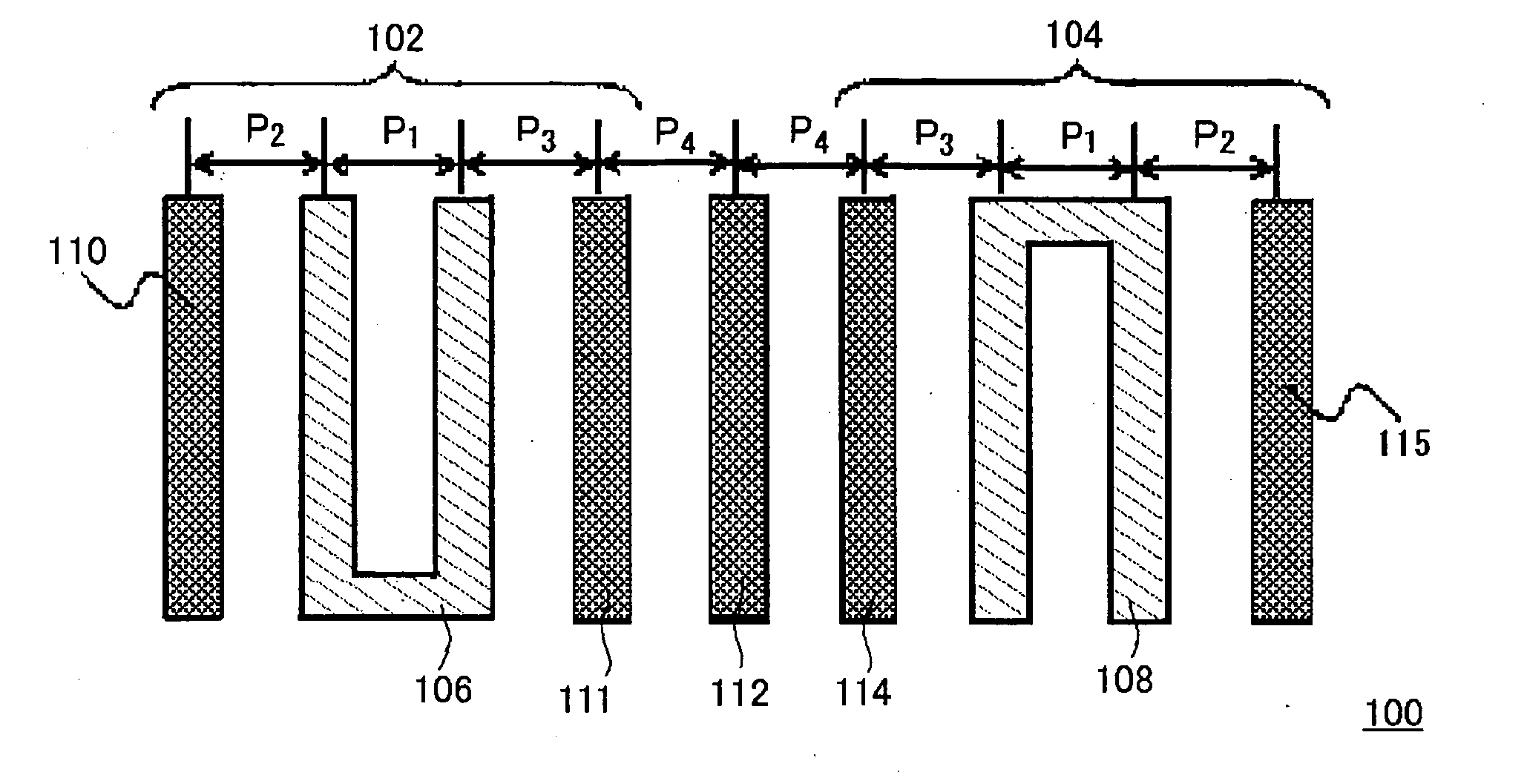

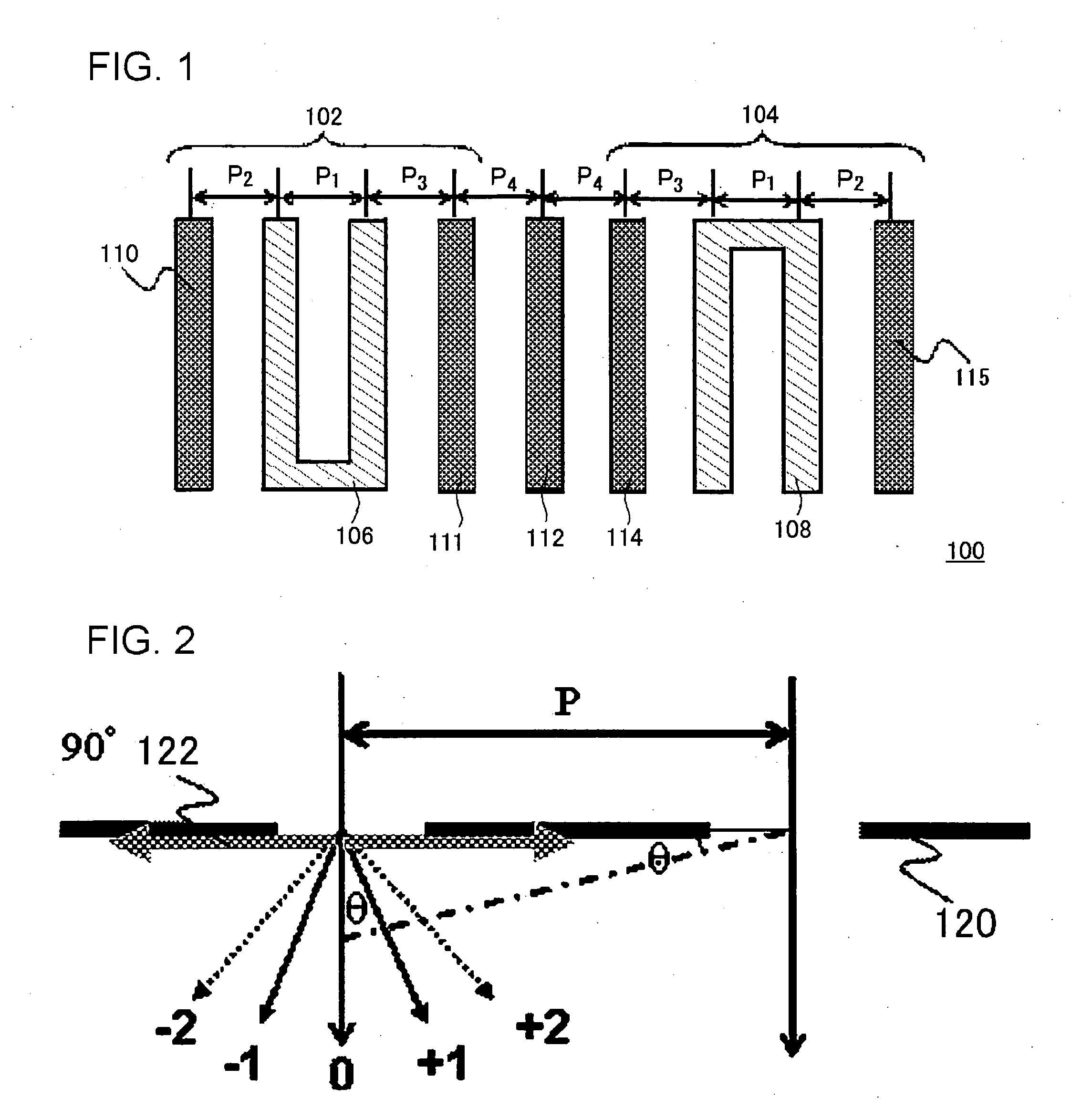

An interconnect layout method capable of reducing variations in shape of gate patterns and improving yield of a semiconductor device is provided. In an interconnect layout 100, the first gate pattern, the second gate pattern, the first dummy pattern, and the second dummy pattern are arranged so that, if a wavelength of a light used to expose the first gate pattern and the second gate pattern is λ, natural numbers are m1, m2, and m3, the first predetermined distance is P1, the second predetermined distance is P2, the third predetermined distance is P3, a design value of the first predetermined distance is P1′, a design value of the second predetermined distance is P2′, and a design value of the third predetermined distance is P3′, then the first predetermined distance satisfies relationships of P1=m1λ and P1′−0.1λ≦P1≦P1′+0.1λ, the second predetermined distance satisfies relationships of P2=m2λ and P2′−0.1λ≦P2≦P2′+0.1λ, and the third predetermined distance satisfies relationships of P3=m3λ and P3′−0.1λ≦P3≦P3′+0.1λ.

Owner:RENESAS ELECTRONICS CORP

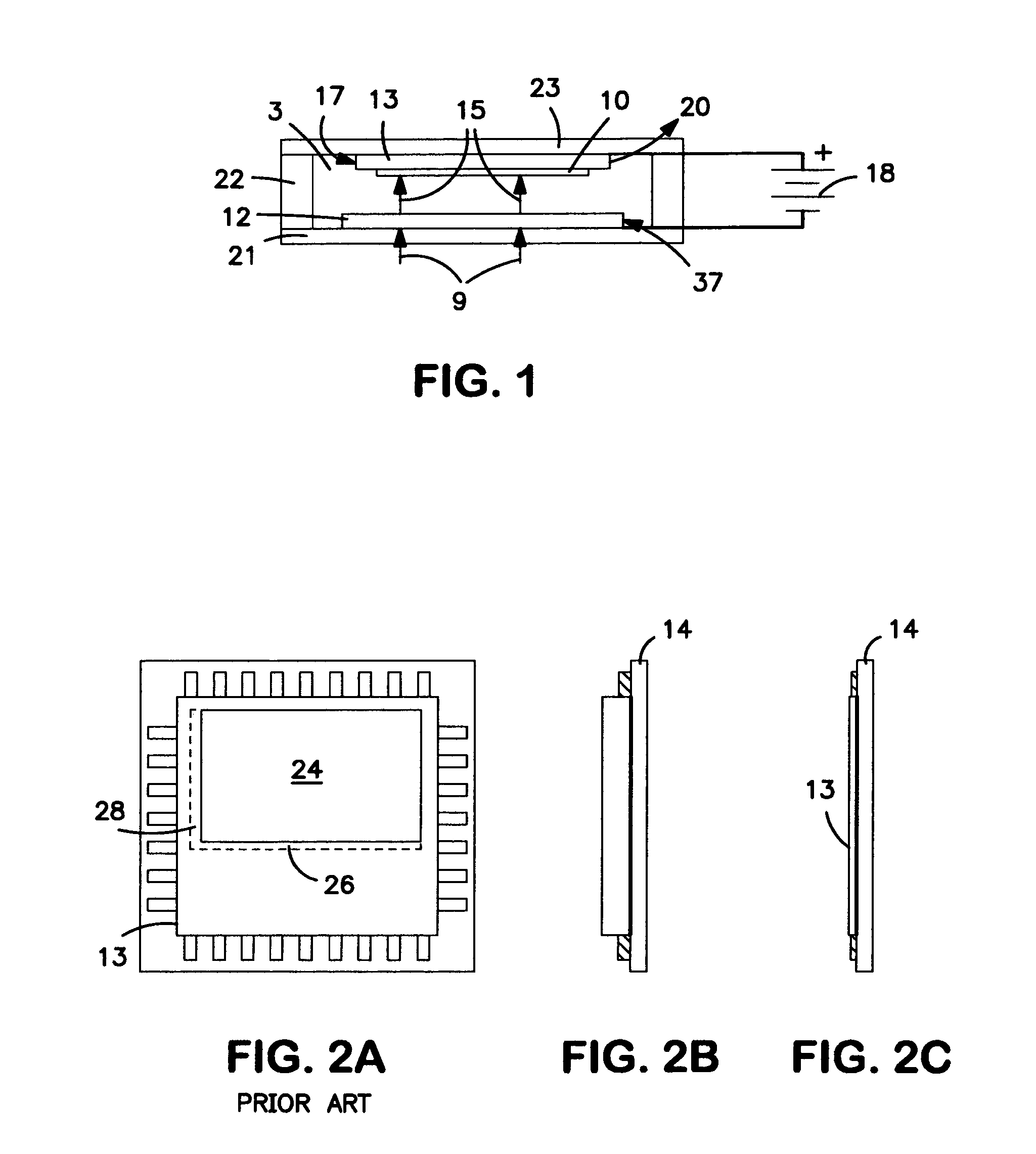

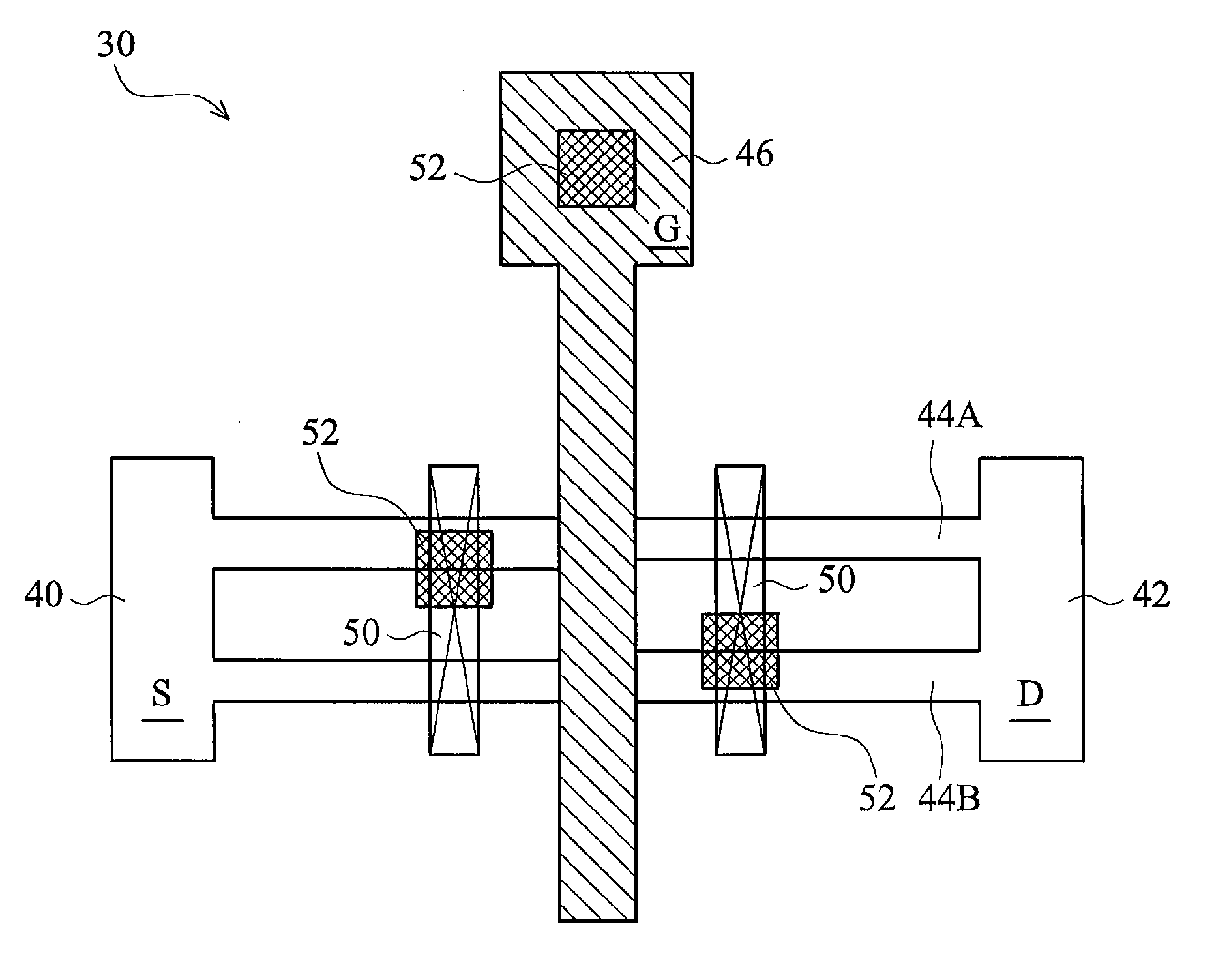

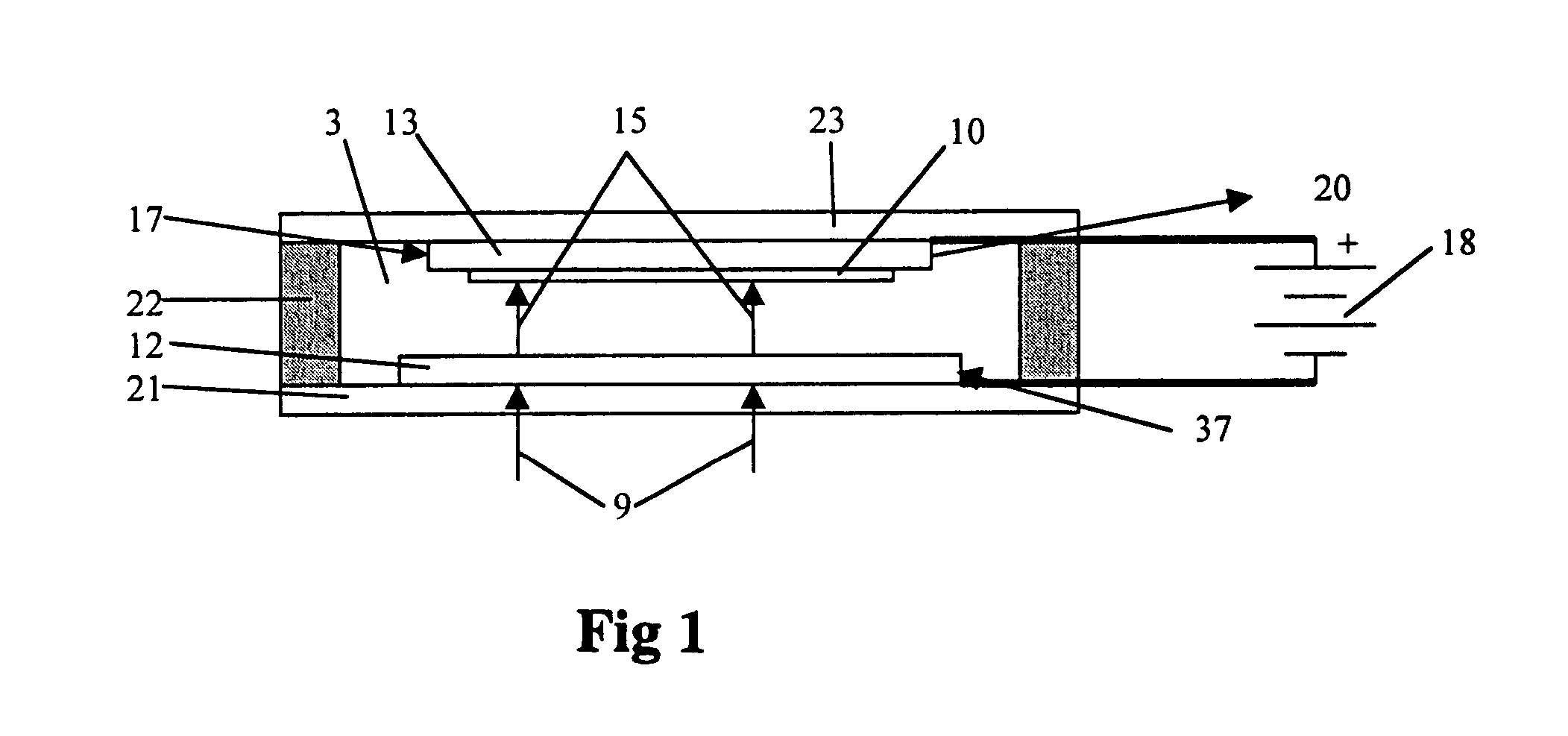

Backside imaging through a doped layer

ActiveUS20060138322A1Improve imaging effectImprove device yieldSolid-state devicesMaterial analysis by optical meansCMOSImage resolution

Backthinning in an area selective manner is applied to CMOS imaging sensors 12 for use in electron bombarded active pixel array devices. A further arrangement results in an array of collimators 51 aligned with pixels 42 or groups of pixels of an active pixel array providing improved image contrast of such image sensor. Provision of a thin P-doped layer 52 on the illuminated rear surface provides both a diffusion barrier resulting in improved resolution and a functional shield for reference pixels. A gradient in concentration of P-doped layer 52 optimizes electron collection at the pixel array.

Owner:EOTECH LLC

Interconnect layout method

InactiveUS7294534B2Image degradationReduce shapingSemiconductor/solid-state device detailsSolid-state devicesLength wavePhysics

In an interconnect layout 100, the first gate pattern, the second gate pattern, the first dummy pattern, and the second dummy pattern are arranged so that, if a wavelength of a light used to expose the first gate pattern and the second gate pattern is λ, natural numbers are m1, m2, and m3, the first predetermined distance is P1, the second predetermined distance is P2, the third predetermined distance is P3, a design value of the first predetermined distance is P1′, a design value of the second predetermined distance is P2′, and a design value of the third predetermined distance is P3′, then the first predetermined distance satisfies relationships of P1=m1λ and P1′−0.1λ≦P1≦P1′+0.1λ, the second predetermined distance satisfies relationships of P2=m2λ and P2′−0.1λ≦P2≦P2′+0.1λ, and the third predetermined distance satisfies relationships of P3=m3λ and P3′−0.1λ≦P3≦P3′+0.1λ.

Owner:RENESAS ELECTRONICS CORP

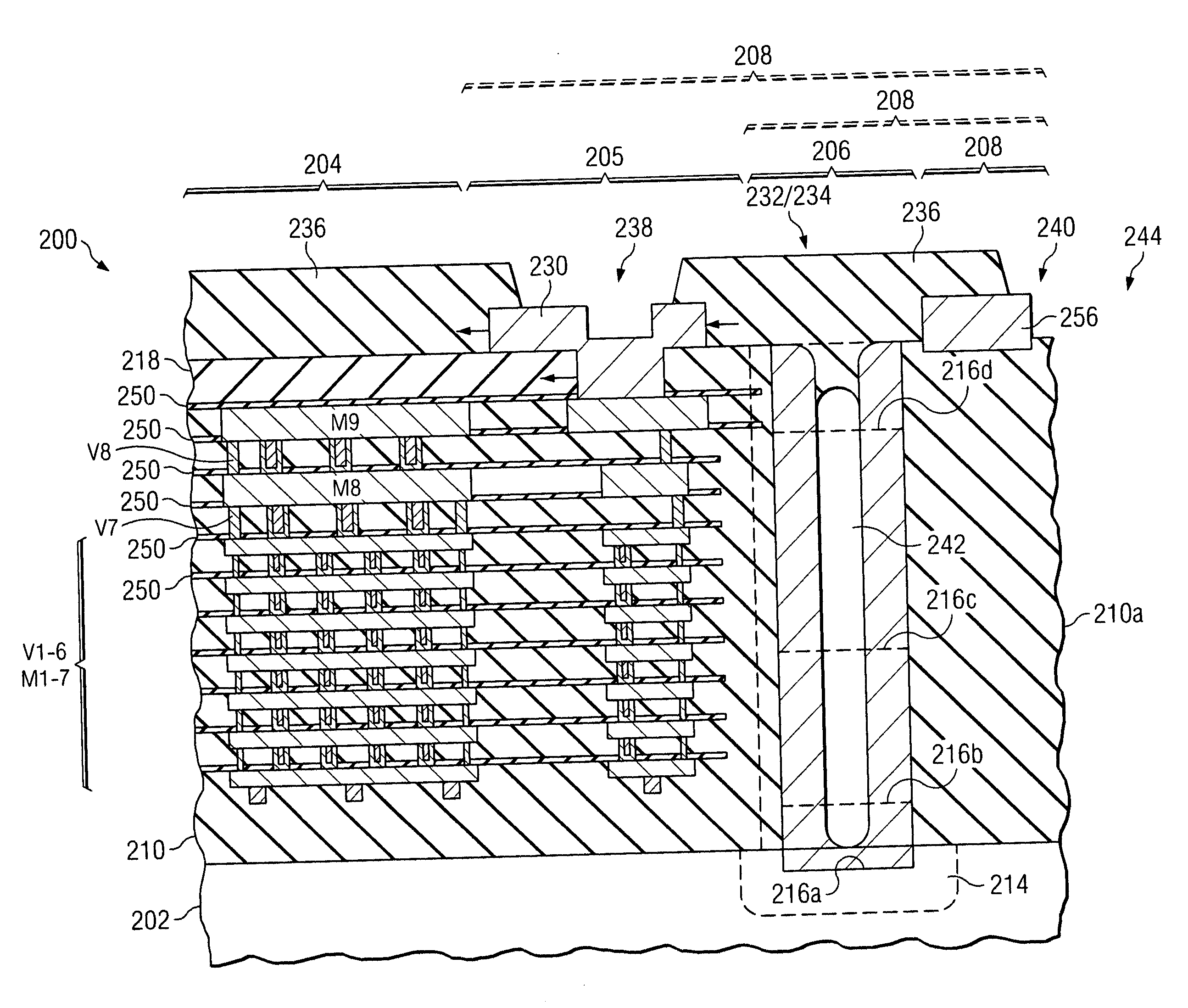

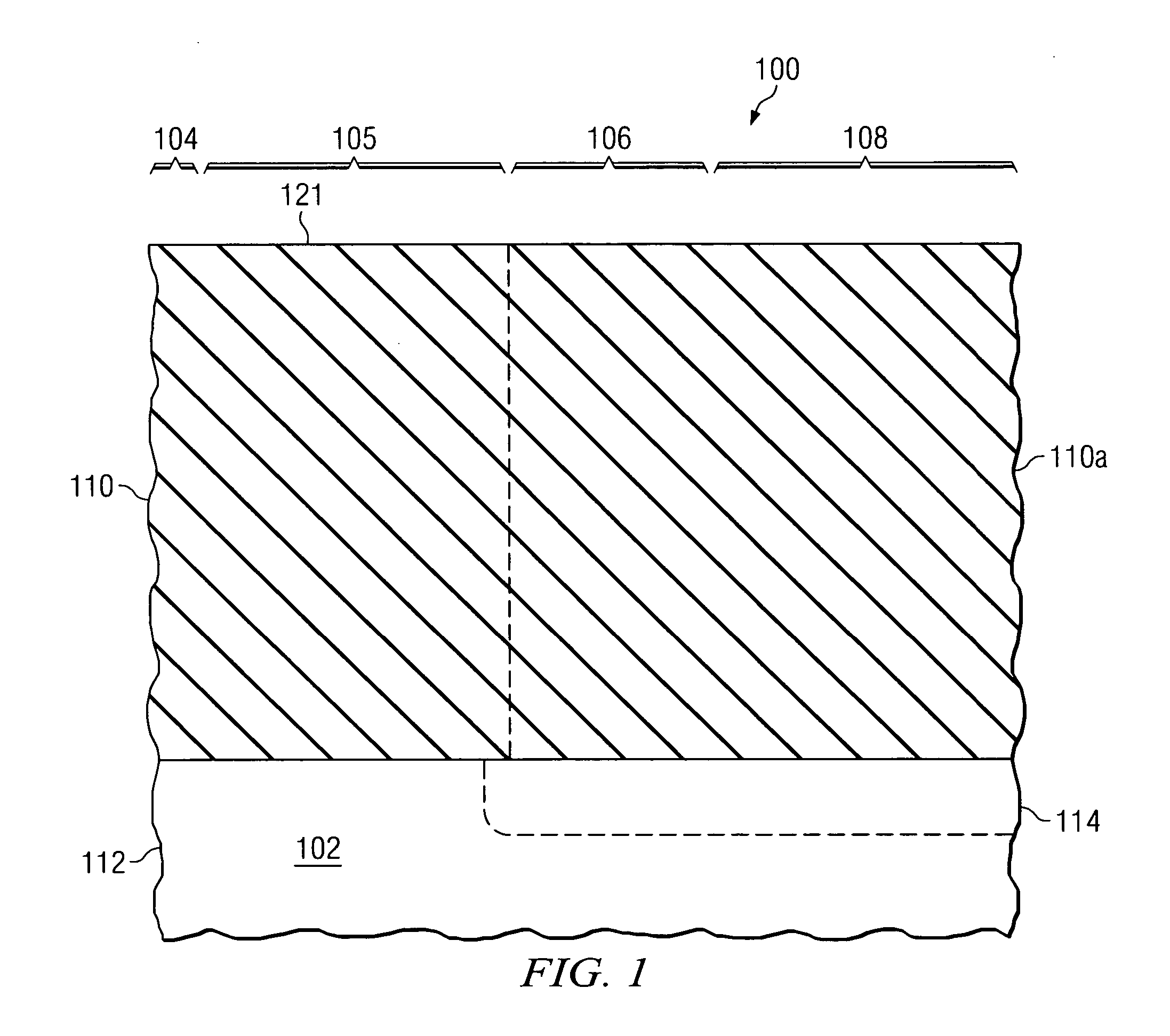

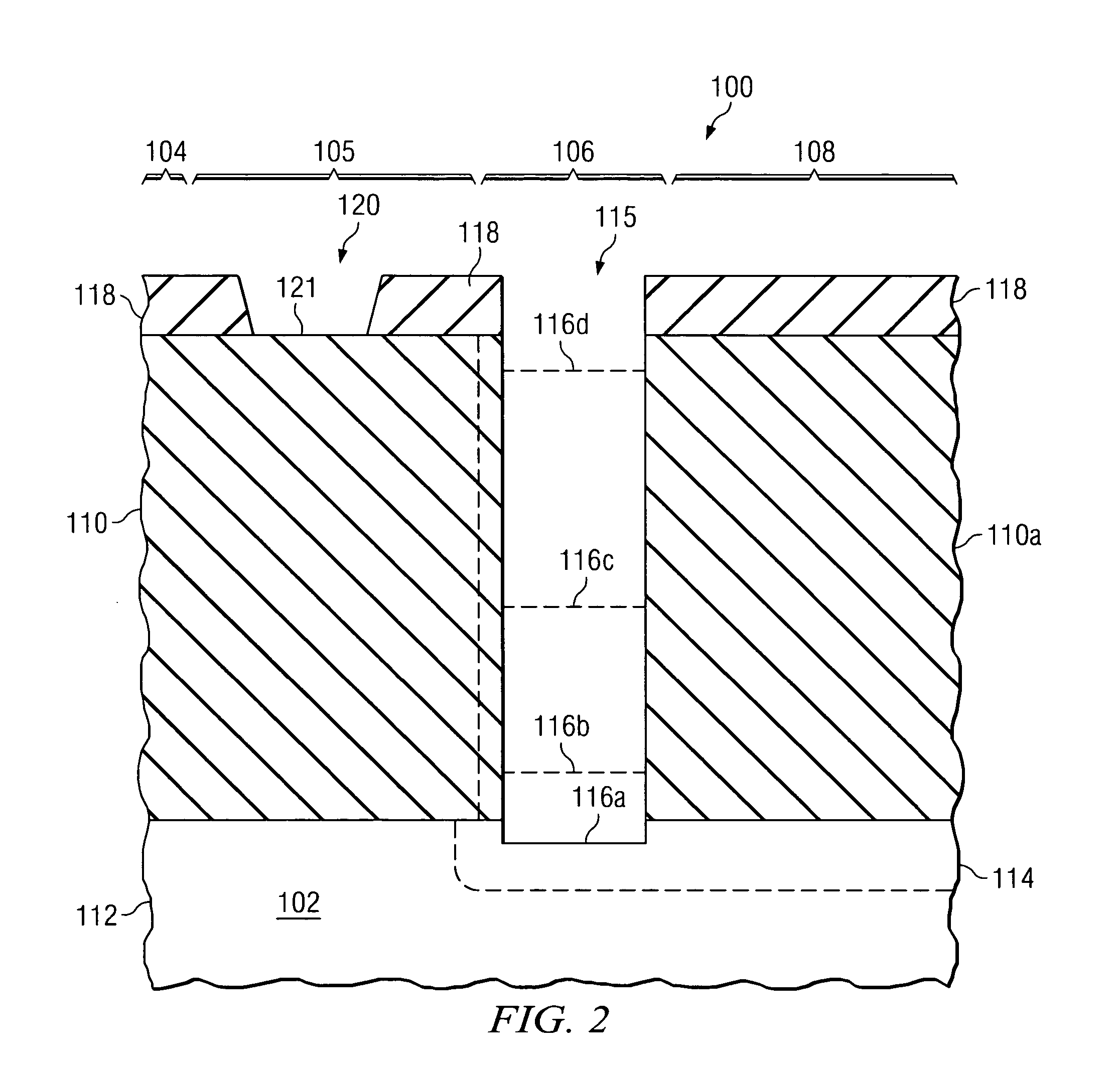

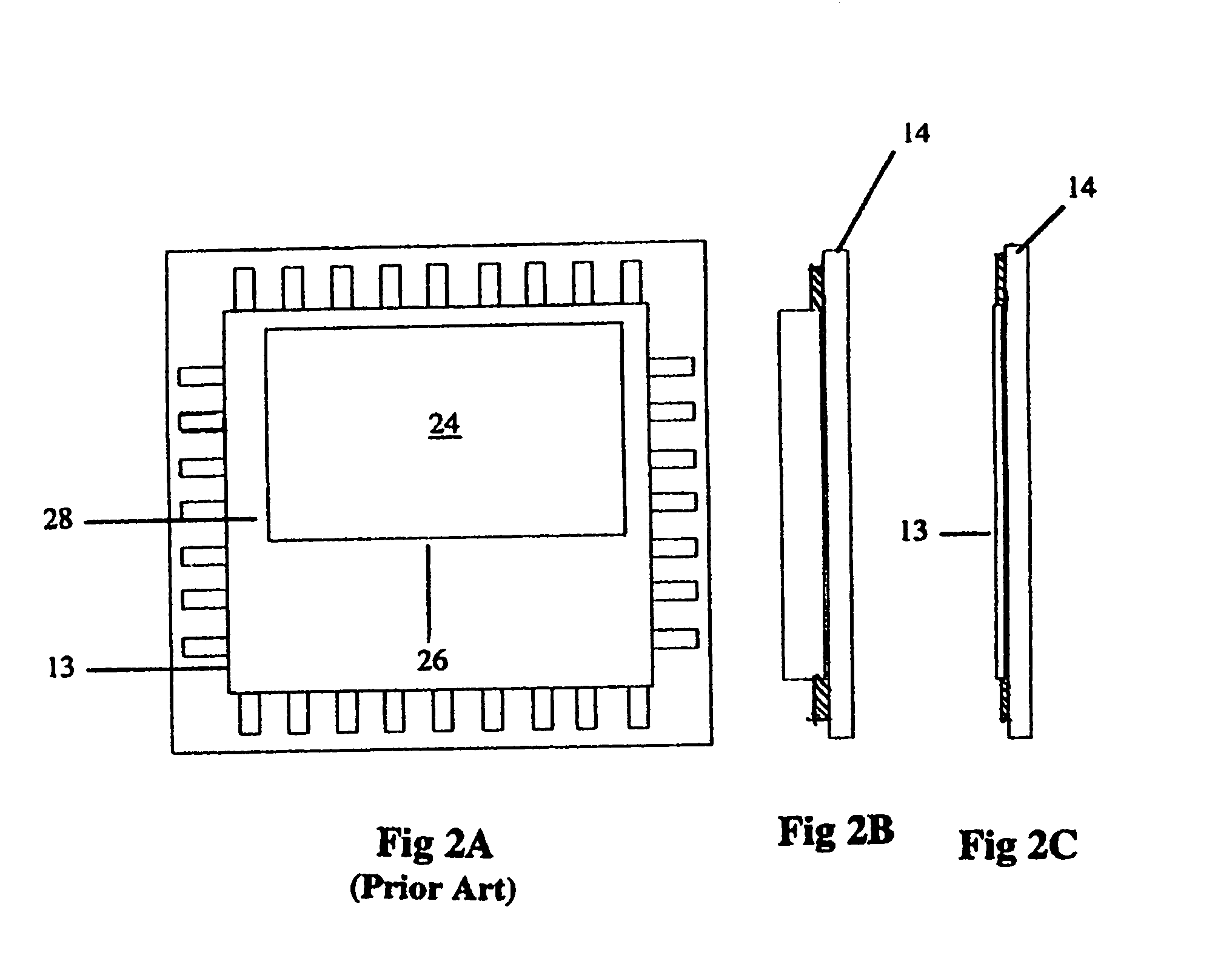

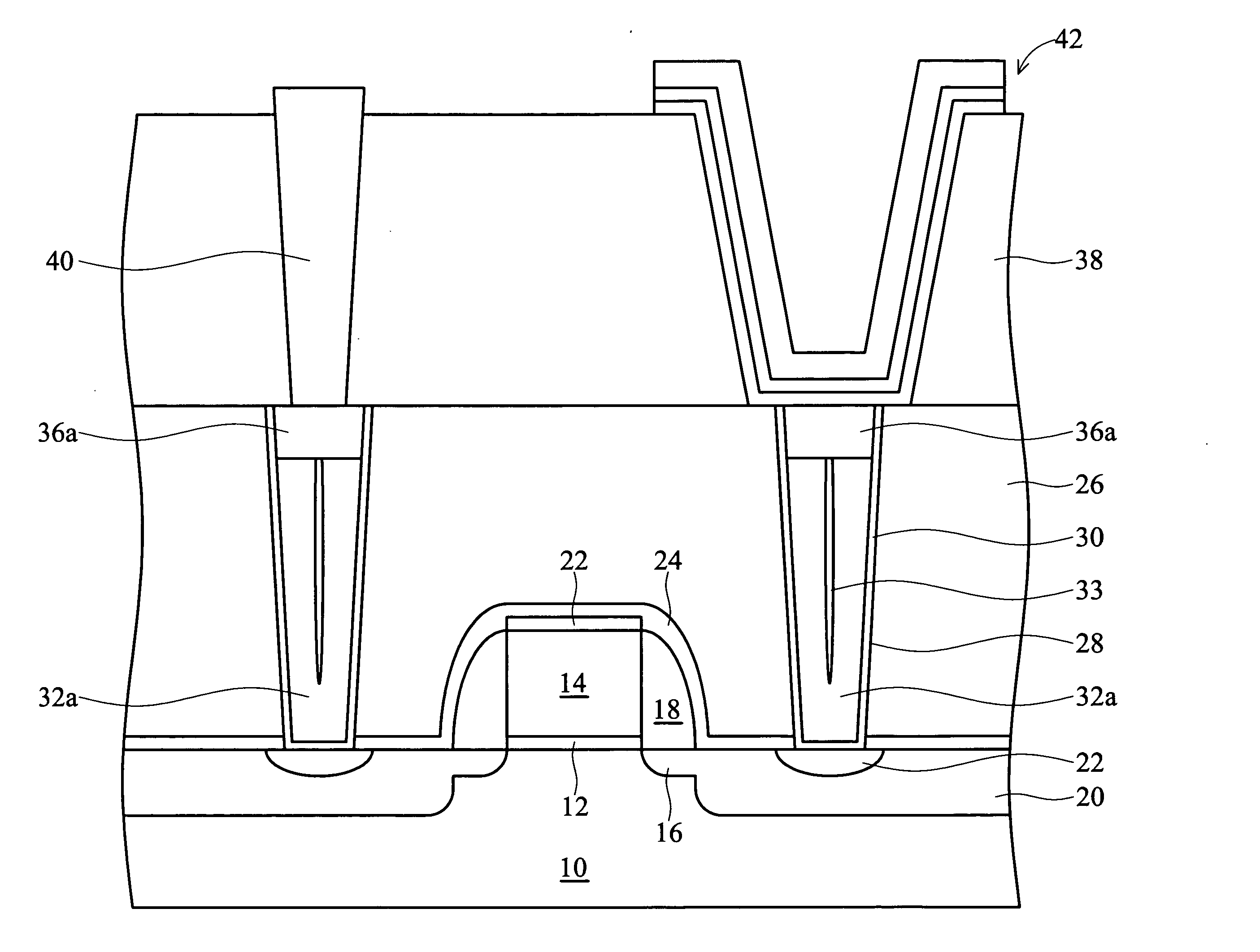

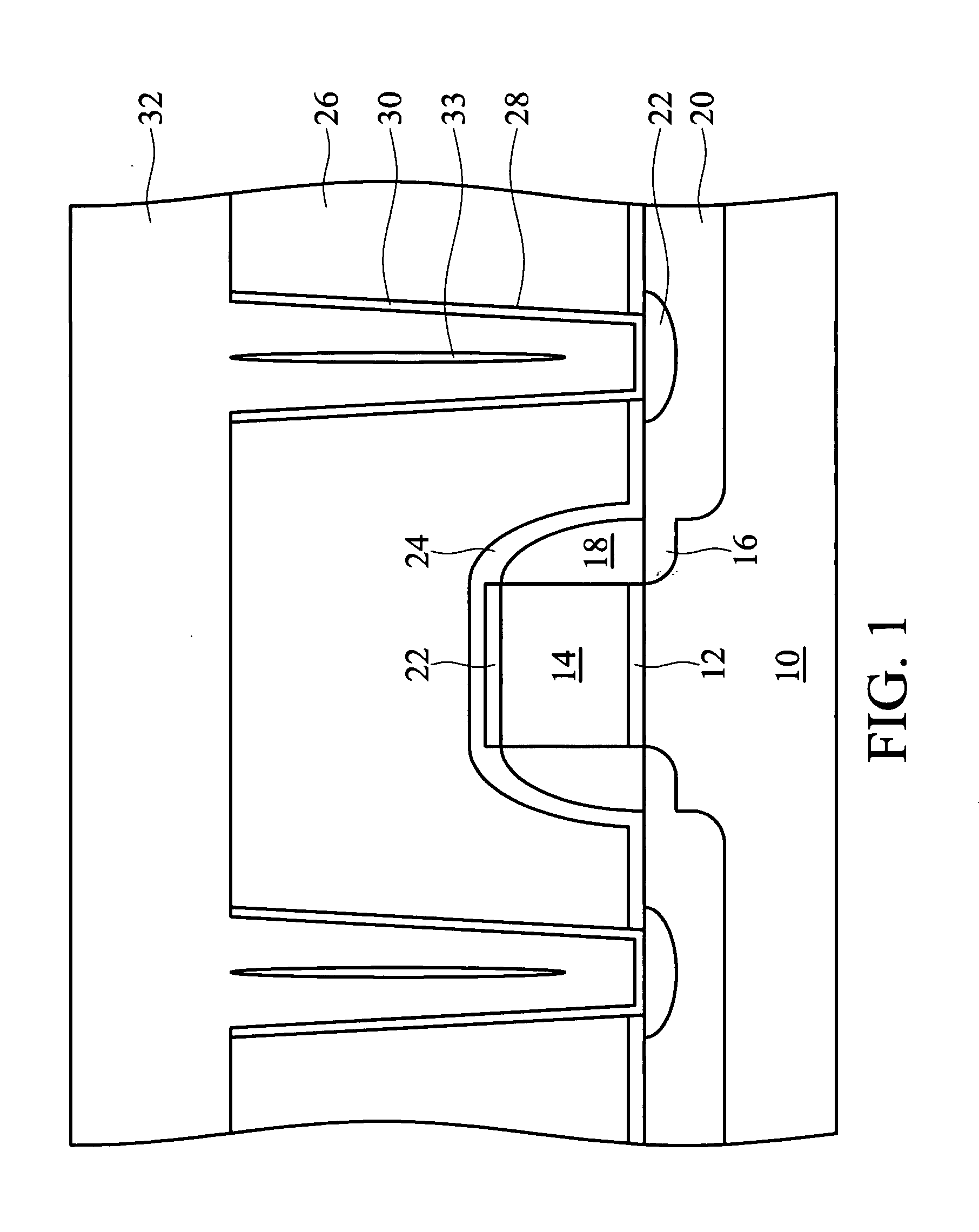

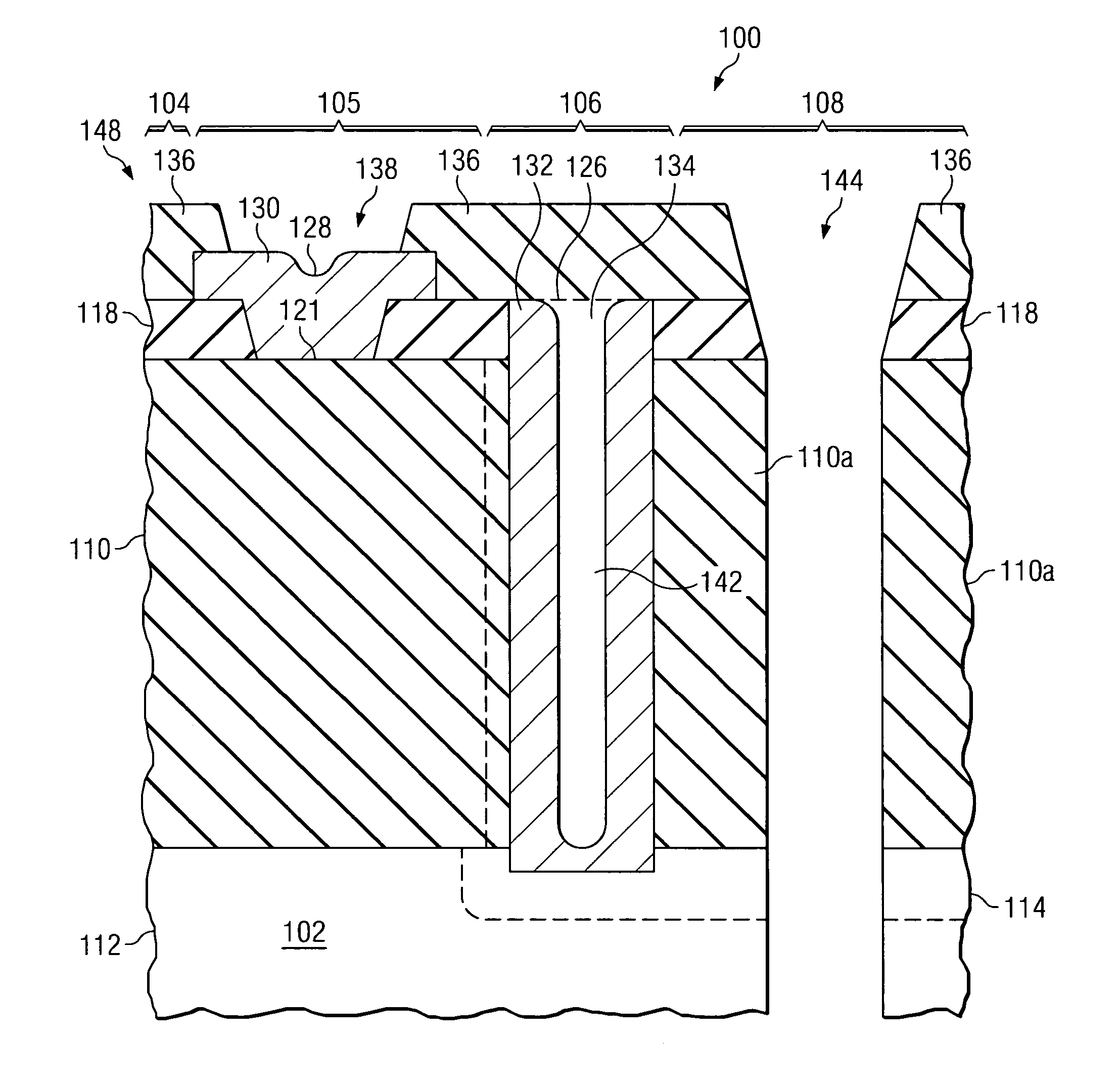

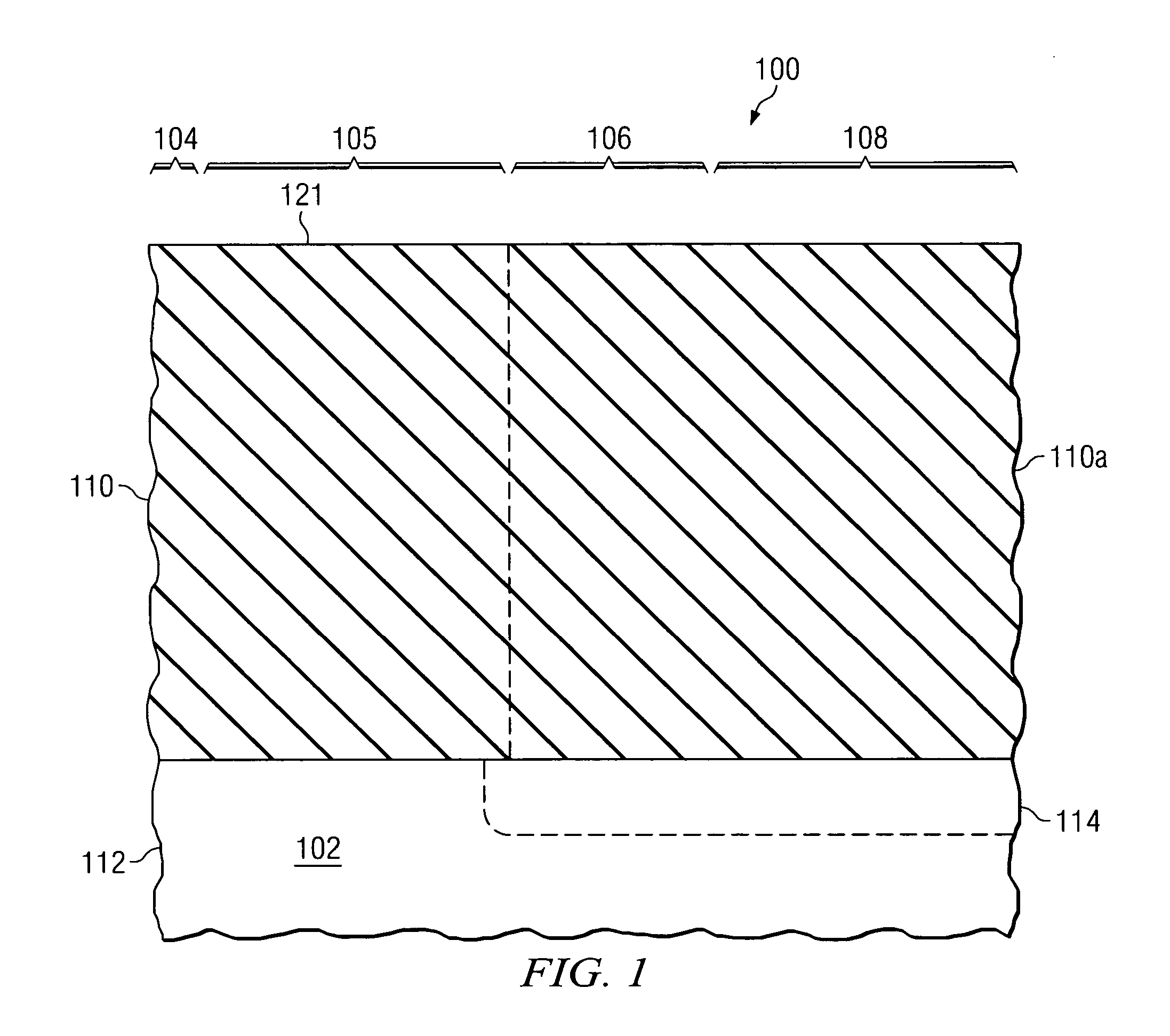

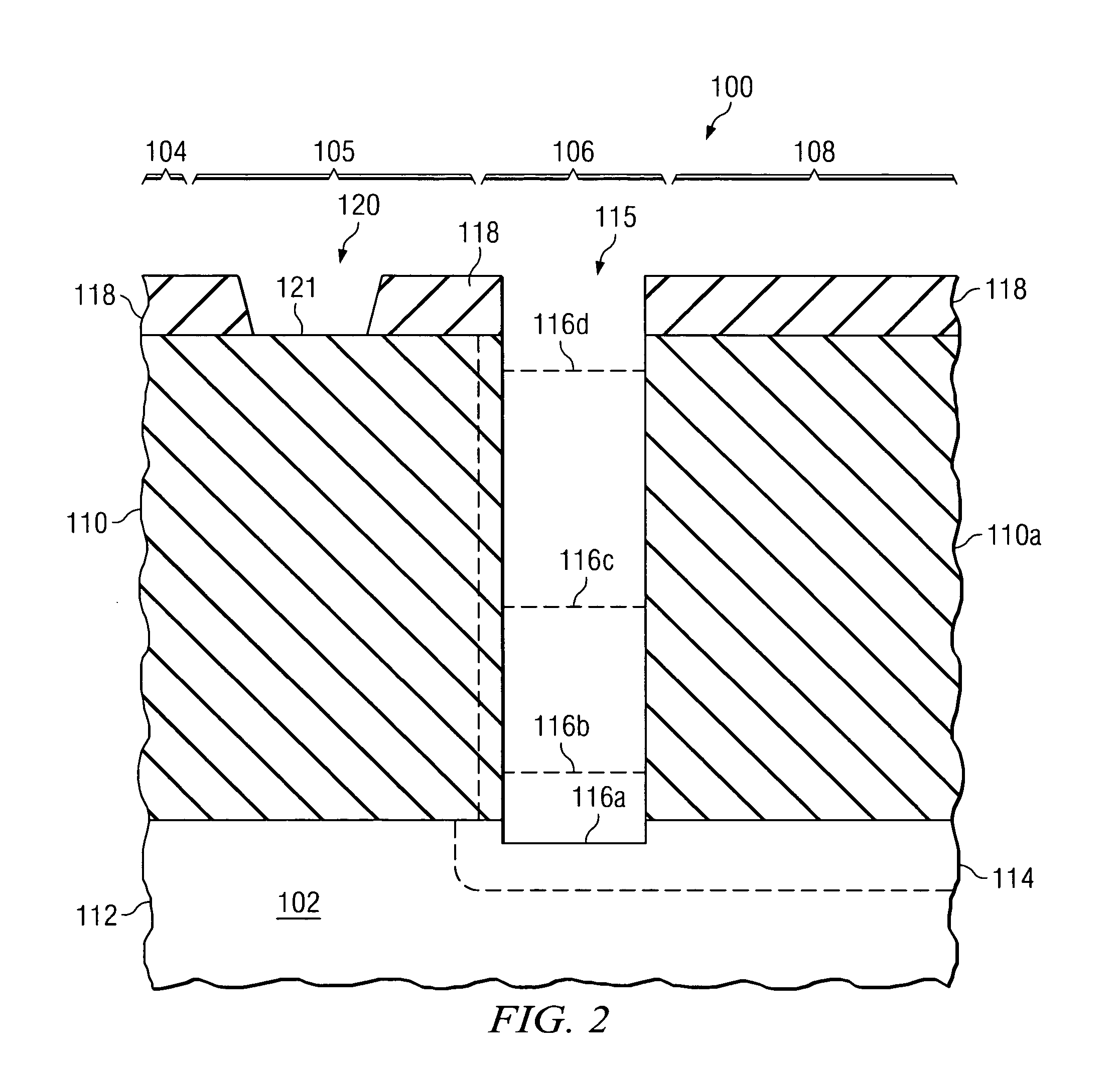

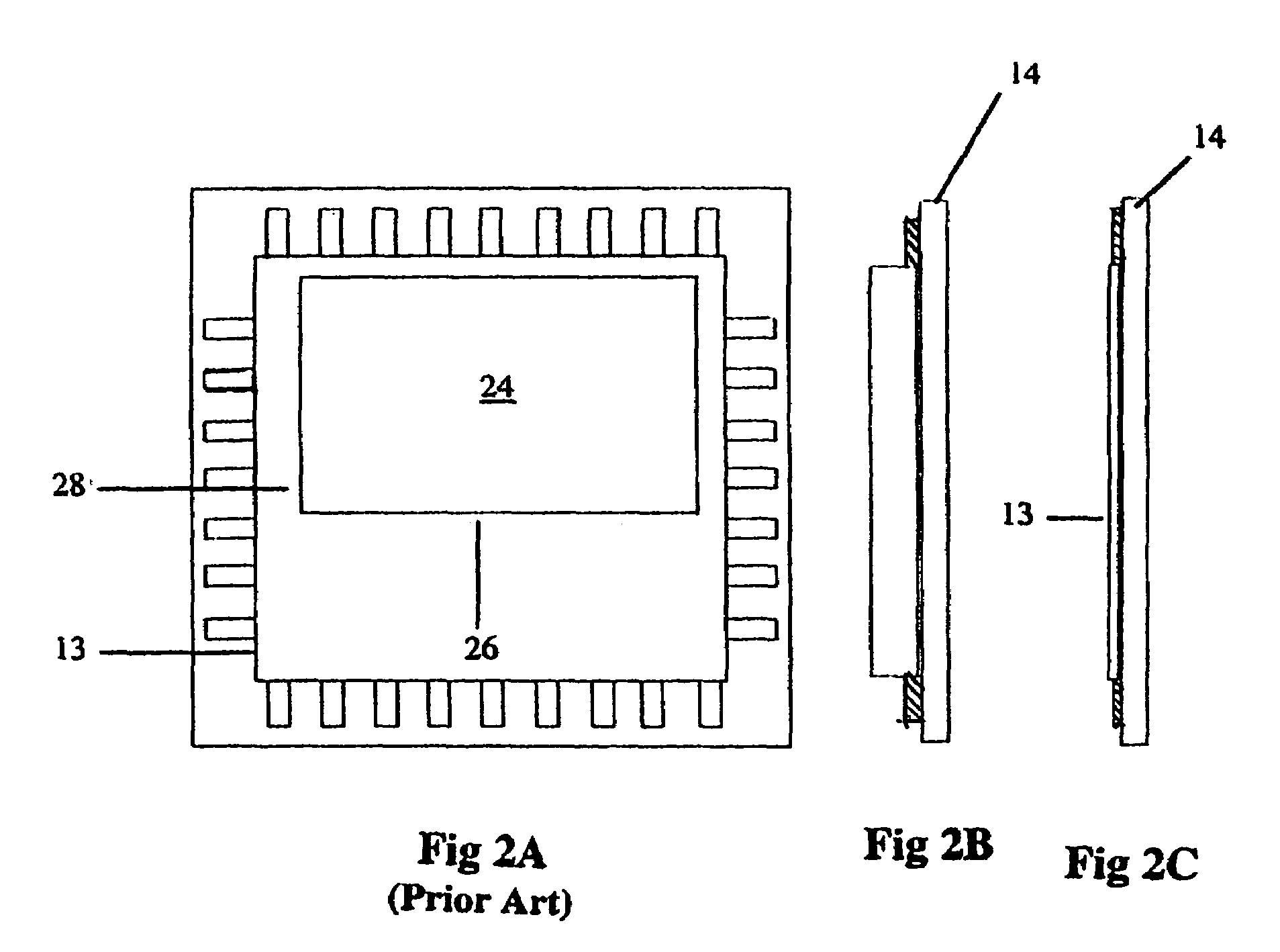

Semiconductor device with crack prevention ring and method of manufacture thereof

ActiveUS20060012012A1High mechanical strengthAvoid crackingSemiconductor/solid-state device detailsSolid-state devicesDevice materialConductive materials

A method of forming a crack prevention ring at the exterior edge of an integrated circuit to prevent delamination and cracking during the separation of the integrated circuits into individual die. The crack prevention ring extends vertically into a semiconductor workpiece to at least a metallization layer of the integrated circuit. The crack prevention ring may be formed simultaneously with the formation of test pads of the integrated circuits. The crack prevention ring may be partially or completely filled with conductive material. An air pocket may be formed within the crack prevention ring beneath a passivation layer of the integrated circuit. The crack prevention ring may be removed during the singulation process. An optional seal ring may be formed between the crack prevention ring and the integrated circuit.

Owner:TAIWAN SEMICON MFG CO LTD

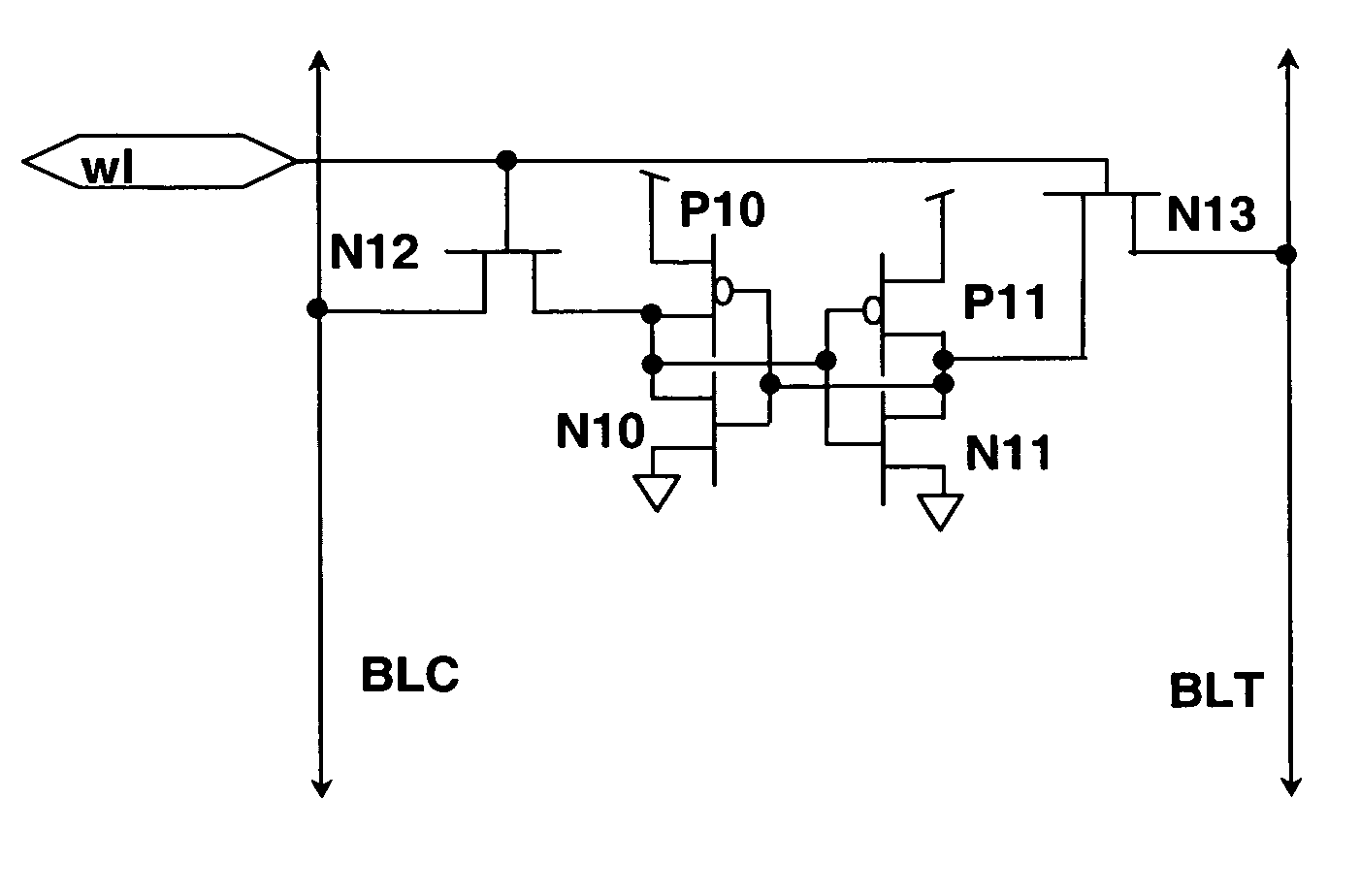

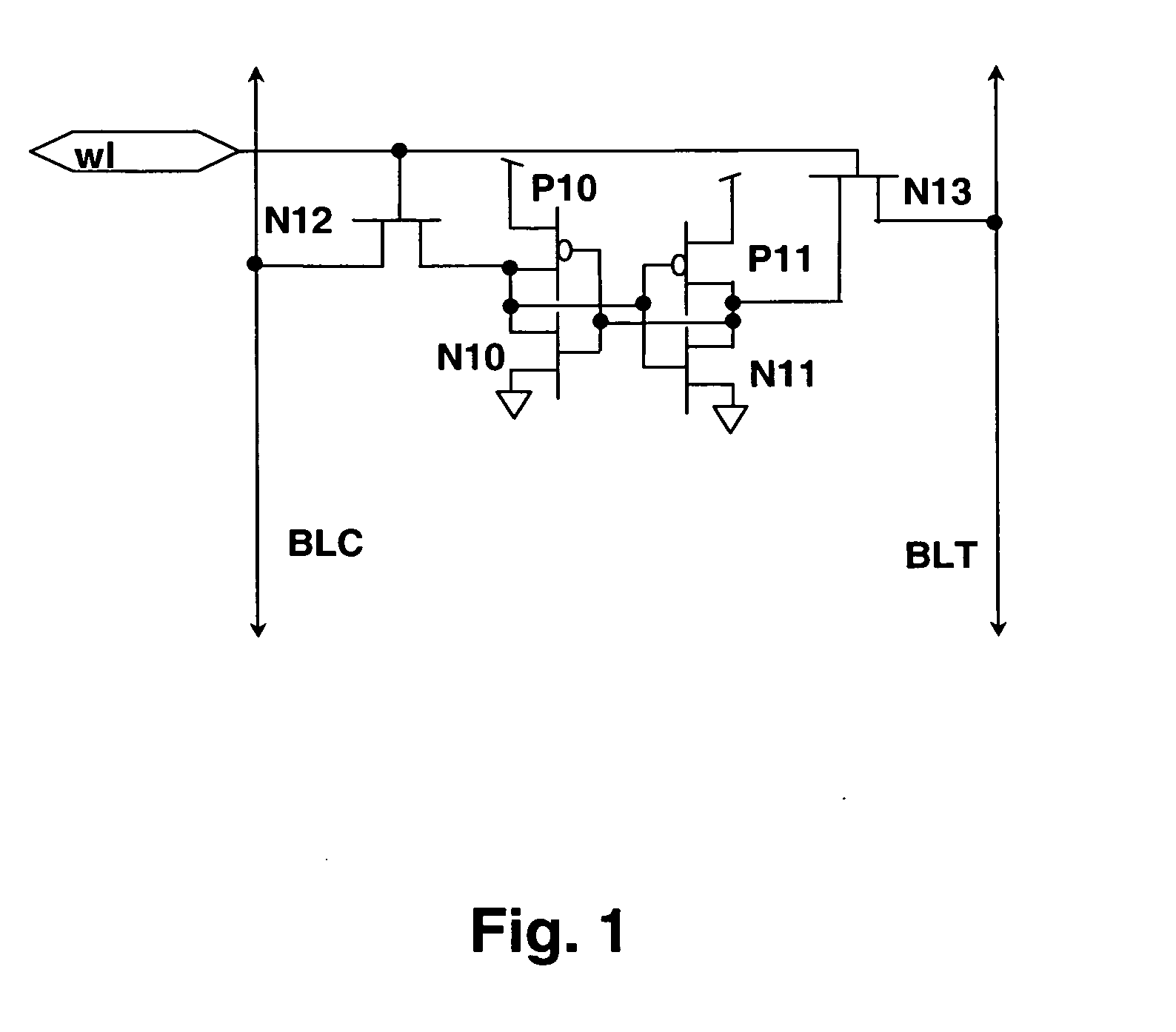

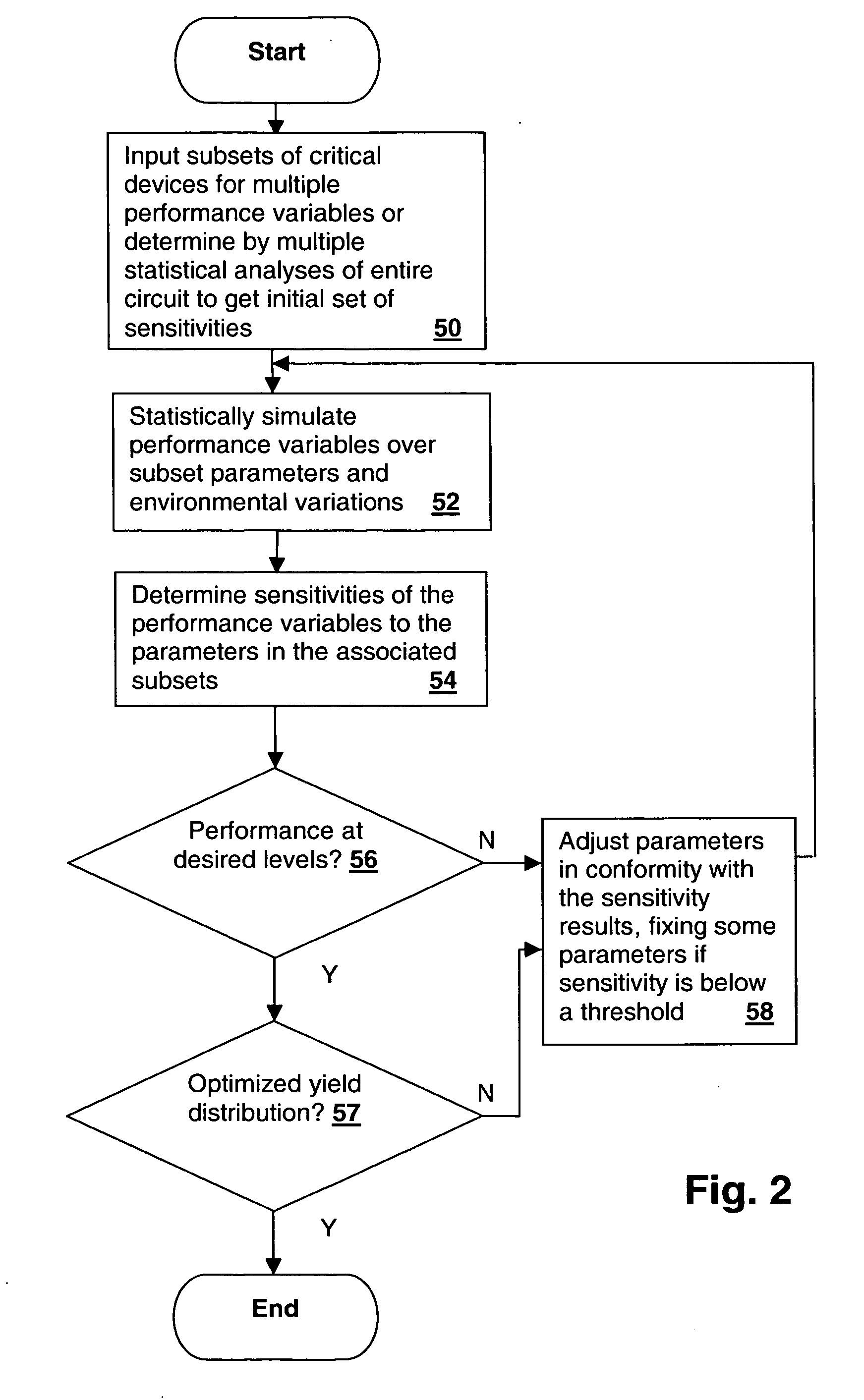

Efficient method and computer program for modeling and improving static memory performance across process variations and environmental conditions

InactiveUS20060203581A1Simple designImprove device yieldDigital storageCAD circuit designParallel computingCell design

An efficient method and computer program for modeling and improving stating memory performance across process variations and environmental conditions provides a mechanism for raising the performance of memory arrays beyond present levels / yields. Statistical (Monte-Carlo) analyses of subsets of circuit parameters are performed for each of several memory performance variables and then sensitivities of each performance variable to 15 each of the circuit parameters are determined. The memory cell design parameters and / or operating conditions of the memory cells are then adjusted in conformity with the sensitivities, resulting in improved memory yield and / or performance. Once a performance level is attained, the sensitivities can then be used to alter the probability distributions of the performance variables to achieve a higher yield. Multiple cell designs can be compared for performance, yield and sensitivity of performance variables to circuit parameters over particular environmental conditions in order to select the best cell design.

Owner:GLOBALFOUNDRIES INC

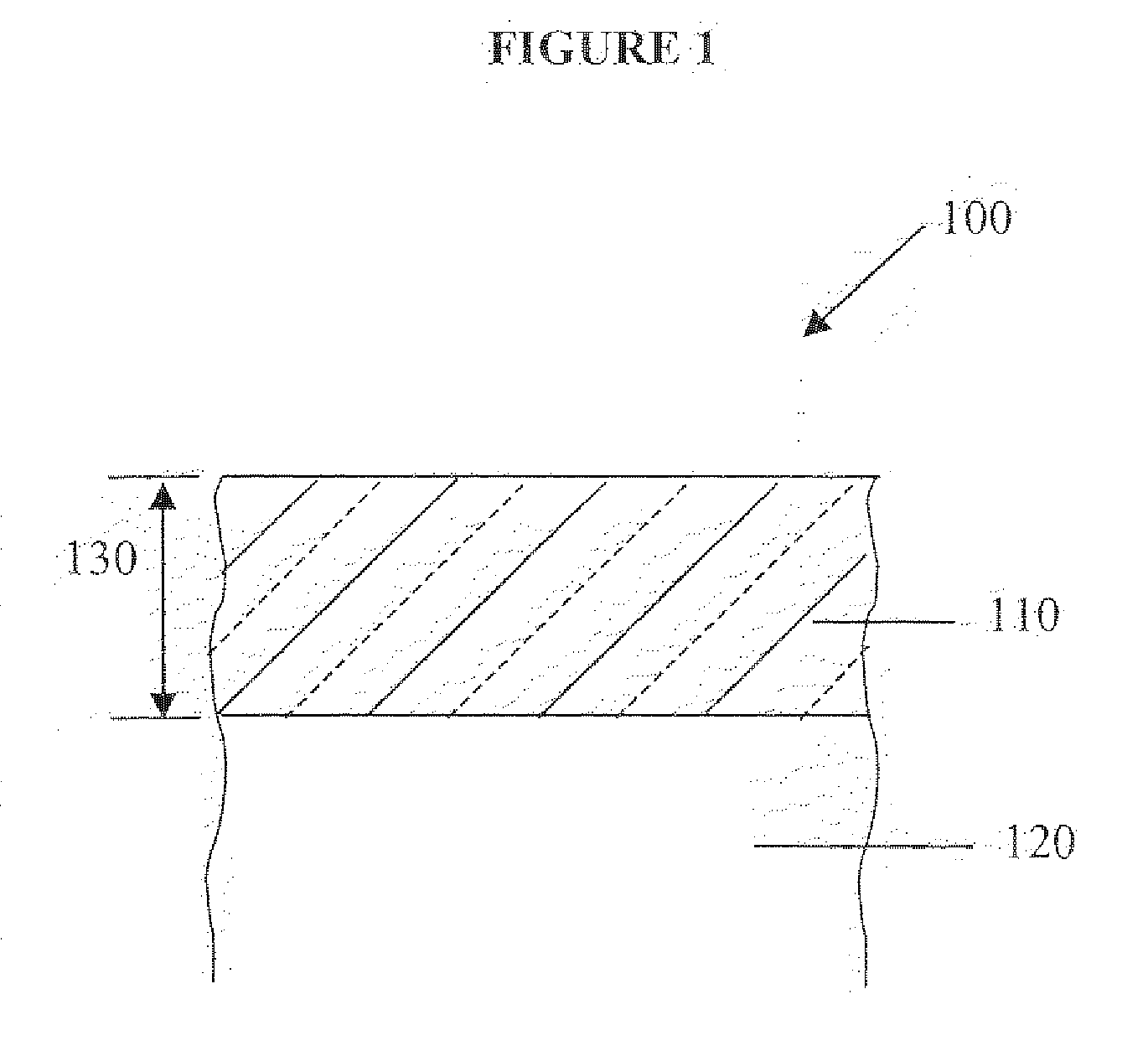

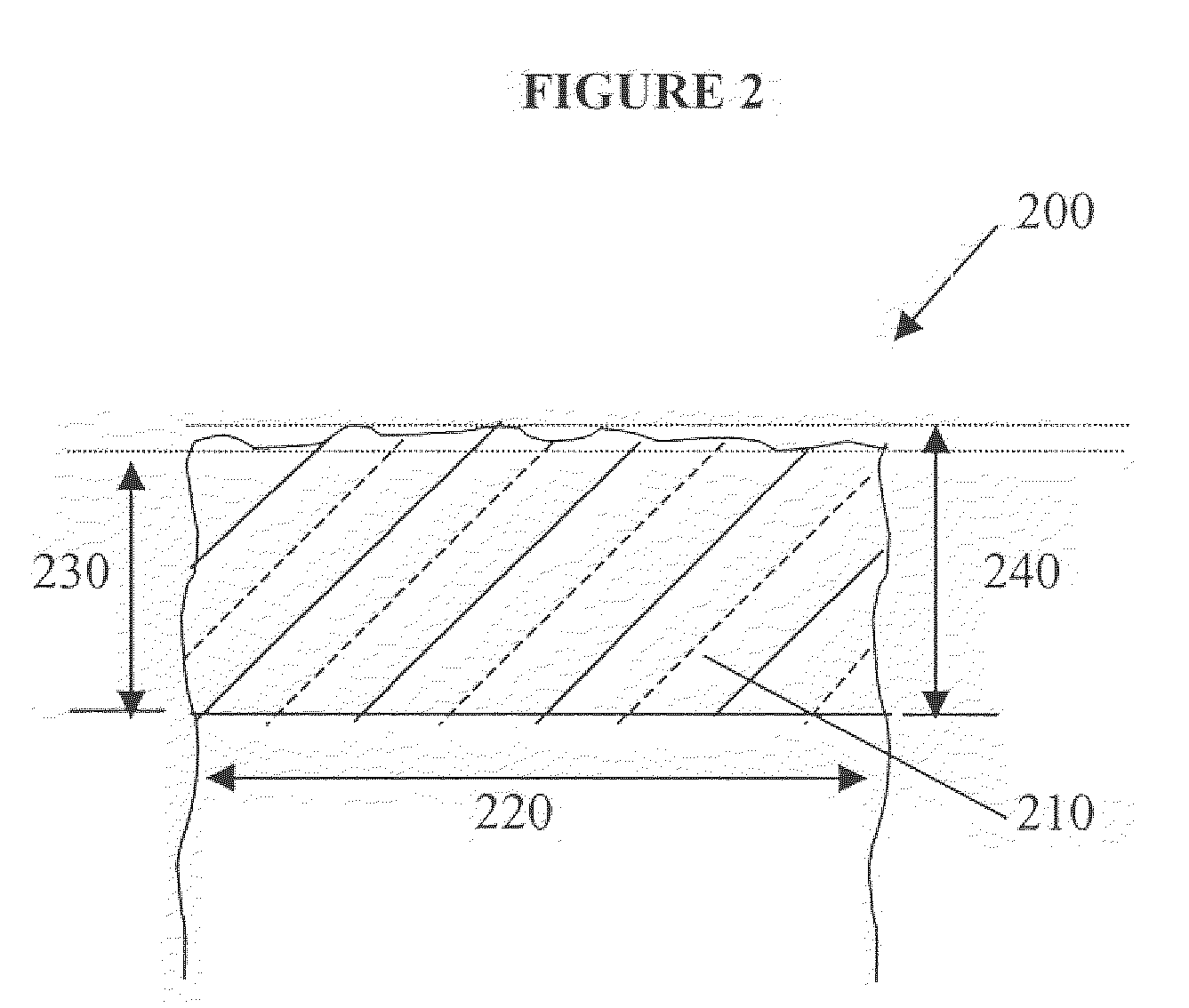

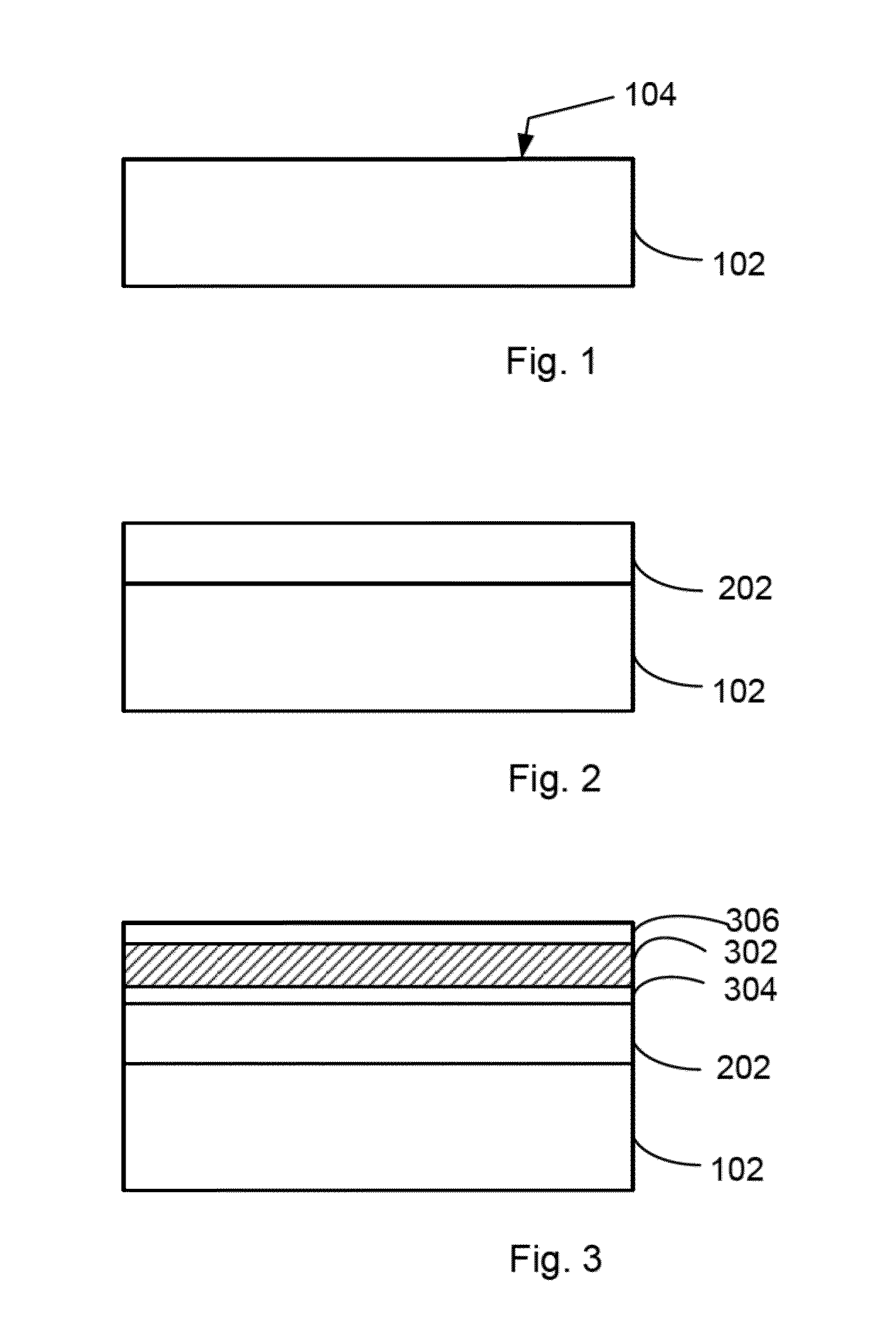

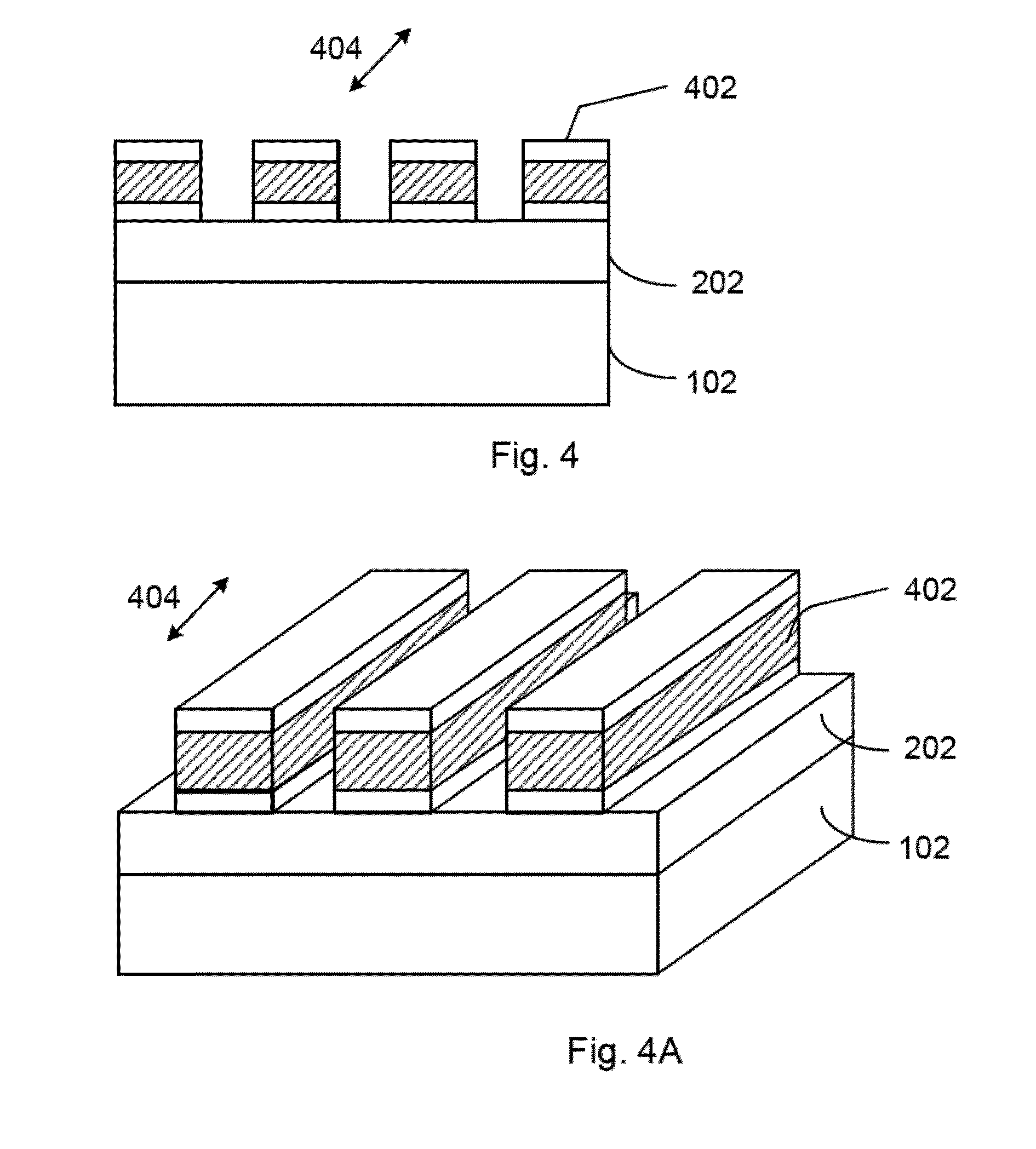

Thin Films and Methods of Making Them

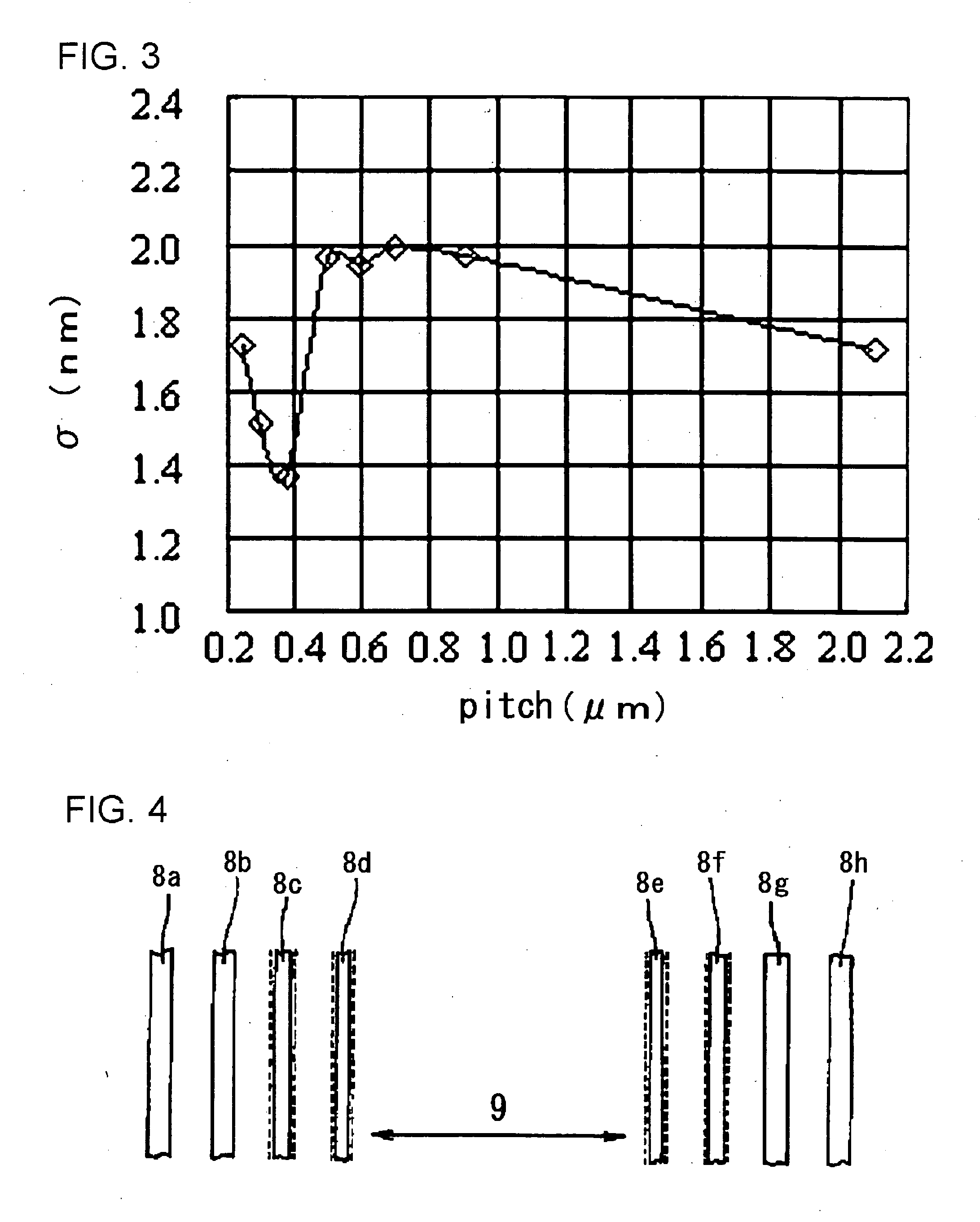

InactiveUS20020197831A1Increase productionImprove device yieldTransistorMaterial nanotechnologyAnti-reflective coatingSilicon membrane

<heading lvl="0">Abstract of Disclosure< / heading> Thin, smooth silicon-containing films are prepared by deposition methods that utilize a silicon-containing precursor. In preferred embodiments, the methods result in Si-containing films that are continuous and have a thickness of about 150 Åor less, a surface roughness of about 5 Å rms or less, and a thickness non-uniformity of about 20% or less. Preferred silicon-containing films display a high degree of compositional uniformity when doped or alloyed with other elements. Preferred deposition methods provide improved manufacturing efficiency and can be used to make various useful structures such as wetting layers, HSG silicon, quantum dots, dielectric layers, anti-reflective coatings (ARC s), gate electrodes and diffusion sources.

Owner:ASM IP HLDG BV

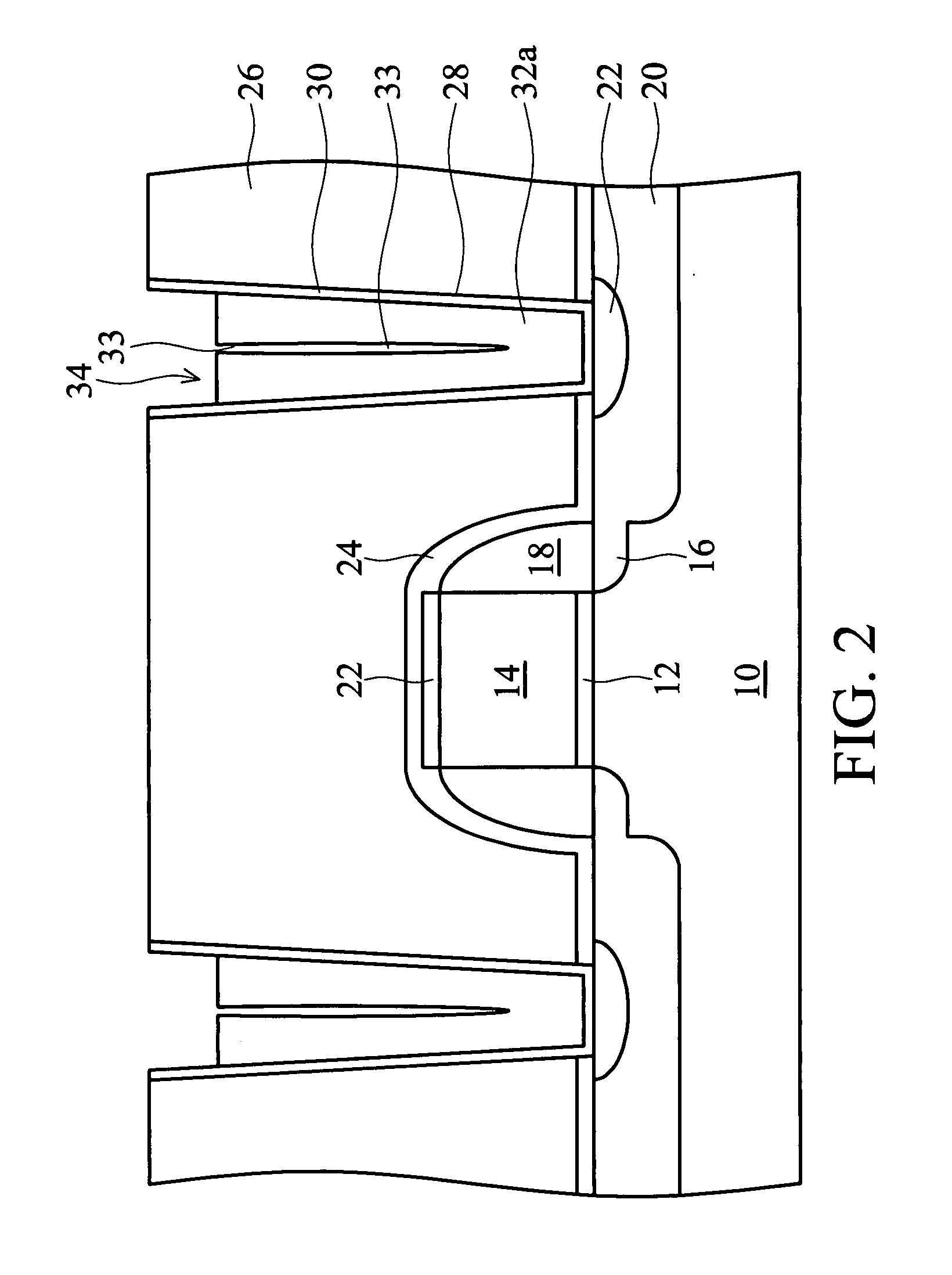

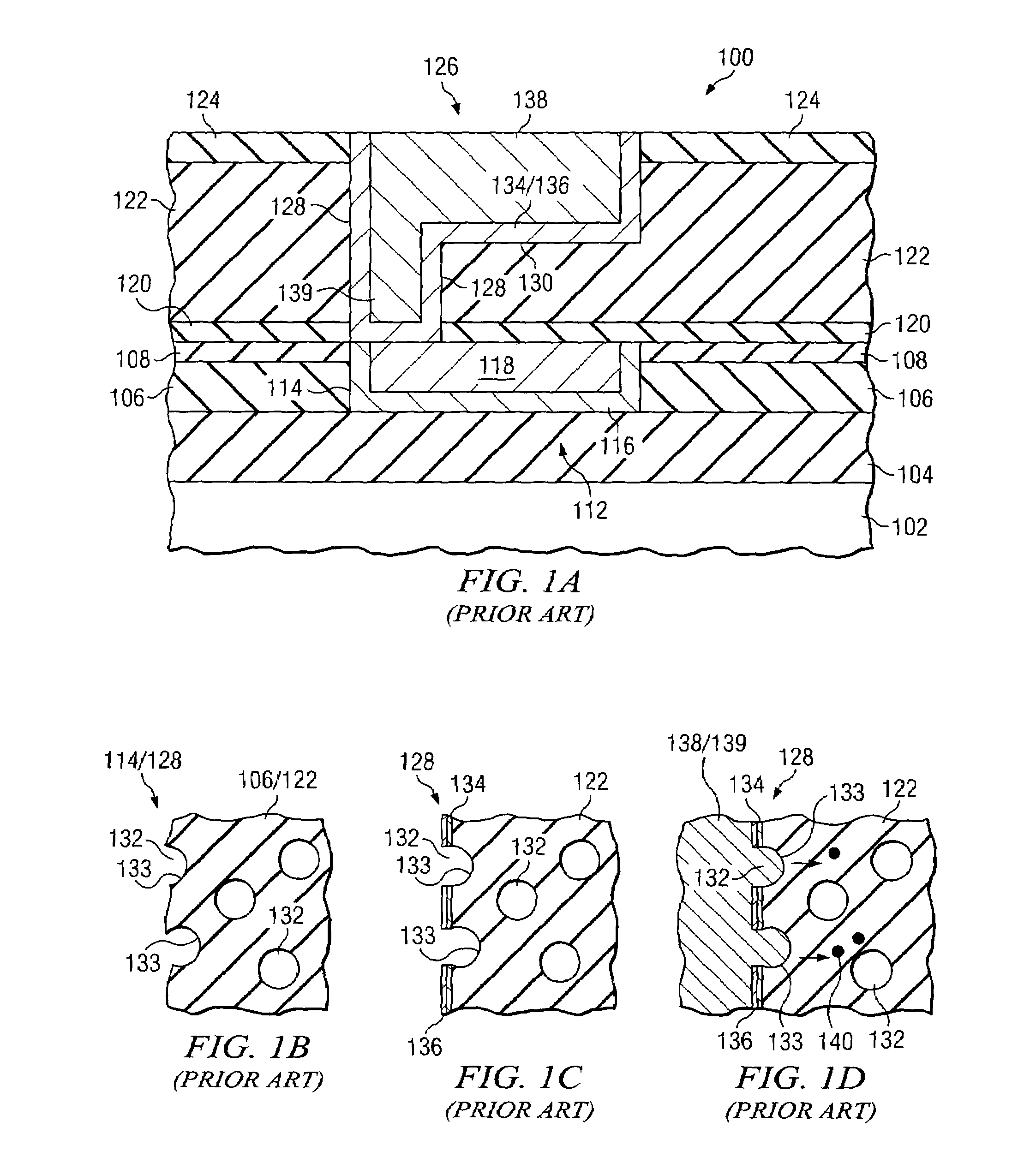

Semiconductor Device with Improved Contact Structure and Method of Forming Same

ActiveUS20090014796A1Reduce aspect ratioReduce contact densityTransistorSemiconductor/solid-state device detailsEngineeringDielectric layer

A contact structure includes a first contact formed in a first dielectric layer connecting to the source / drain region of a MOS transistor, and a second contact formed in a second dielectric layer connecting to a gate region of a MOS transistor or to a first contact. A butted contact structure abutting a source / drain region and a gate electrode includes a first contact formed in a first dielectric layer connecting to the source / drain region of a MOS transistor, and a second contact formed in a second dielectric layer with one end resting on the gate electrode and the other end in contact with the first contact.

Owner:MOSAID TECH

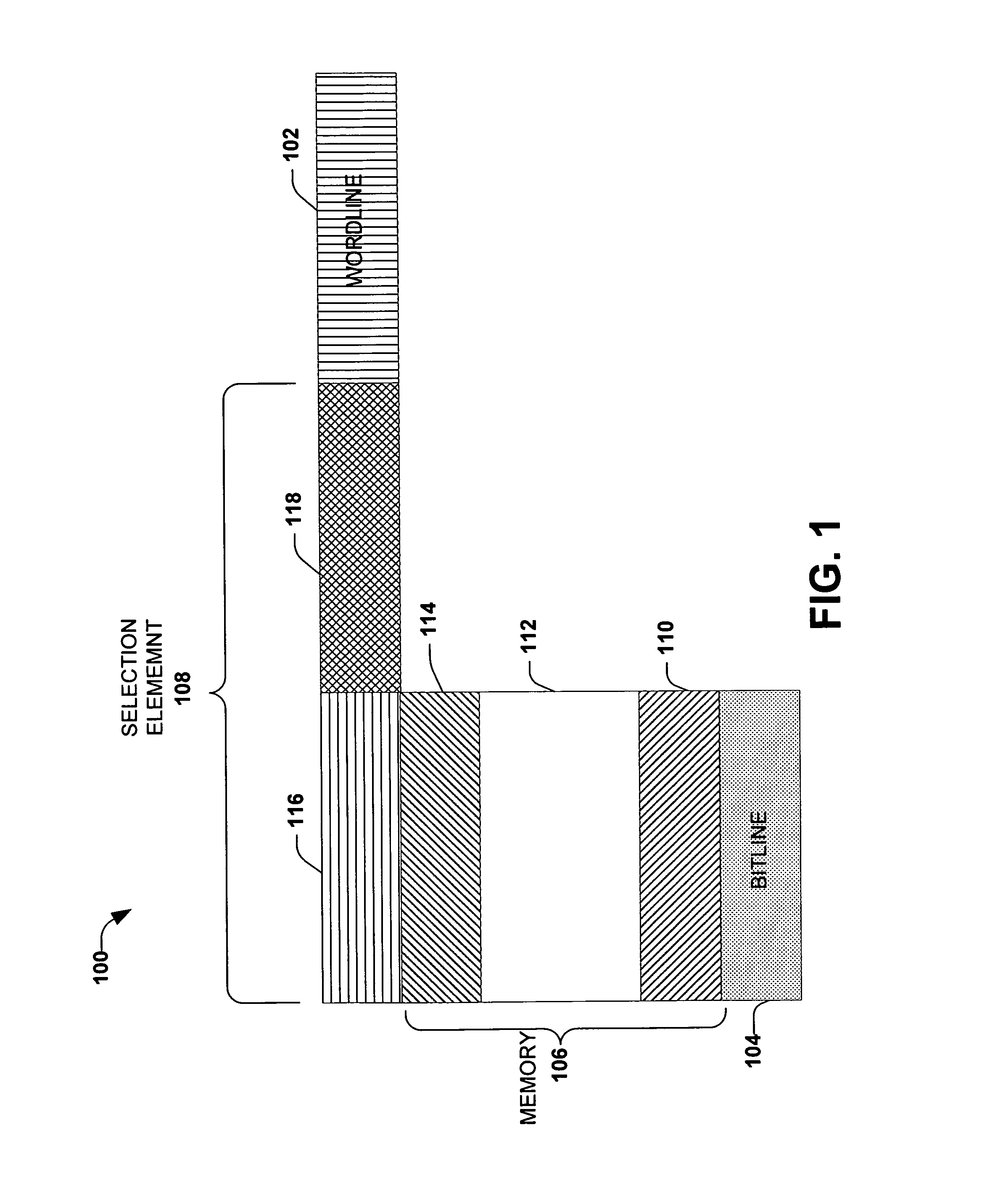

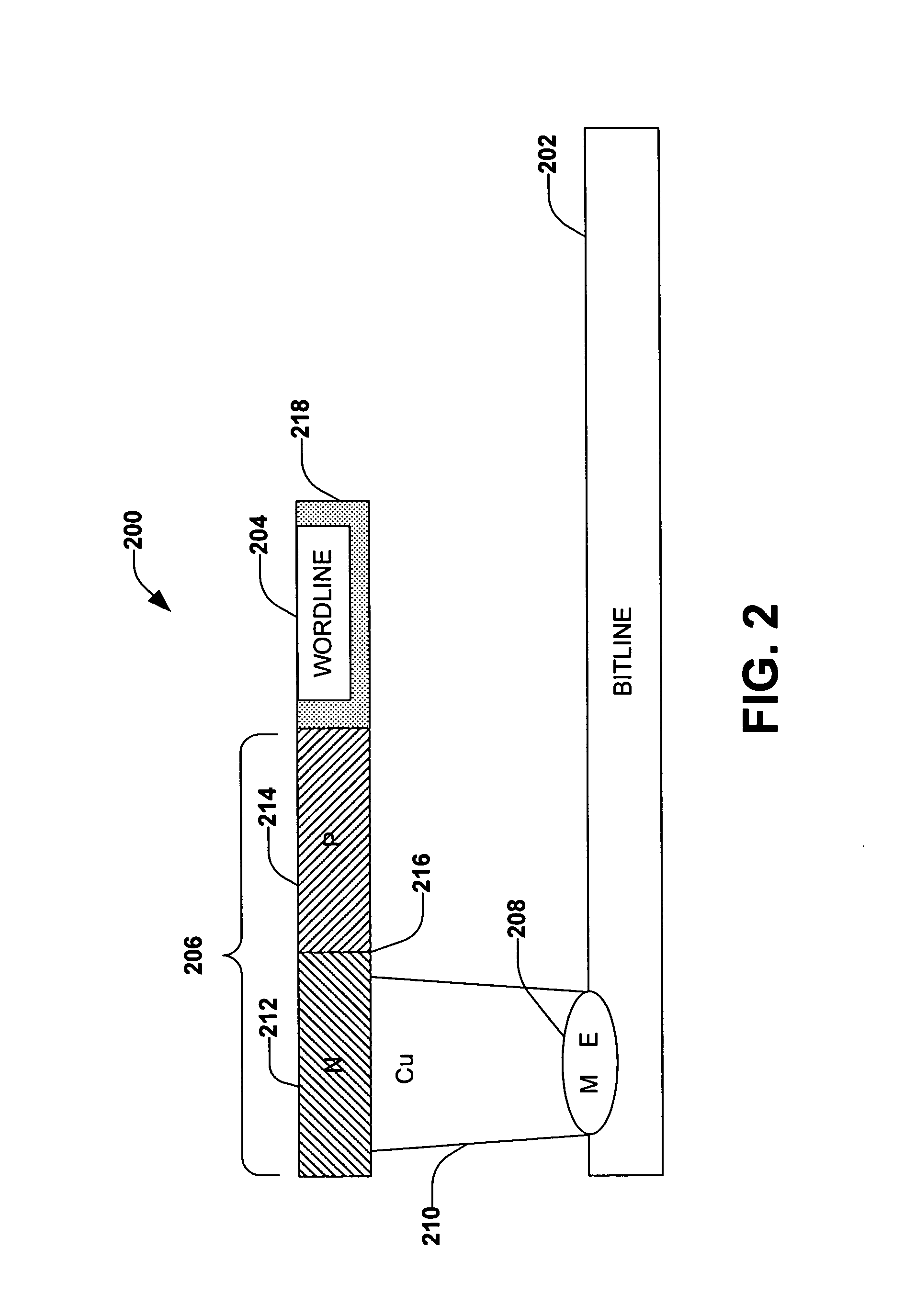

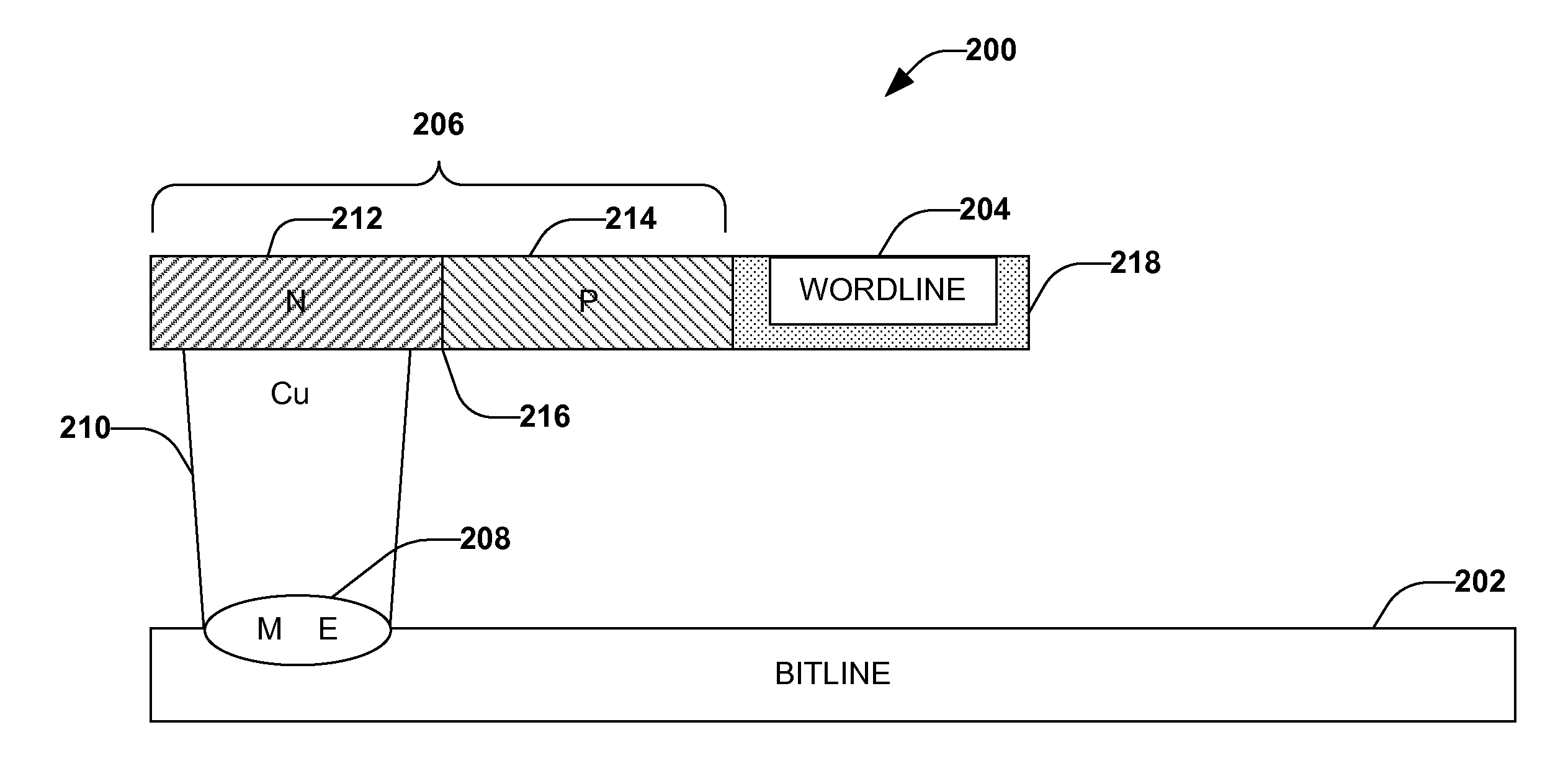

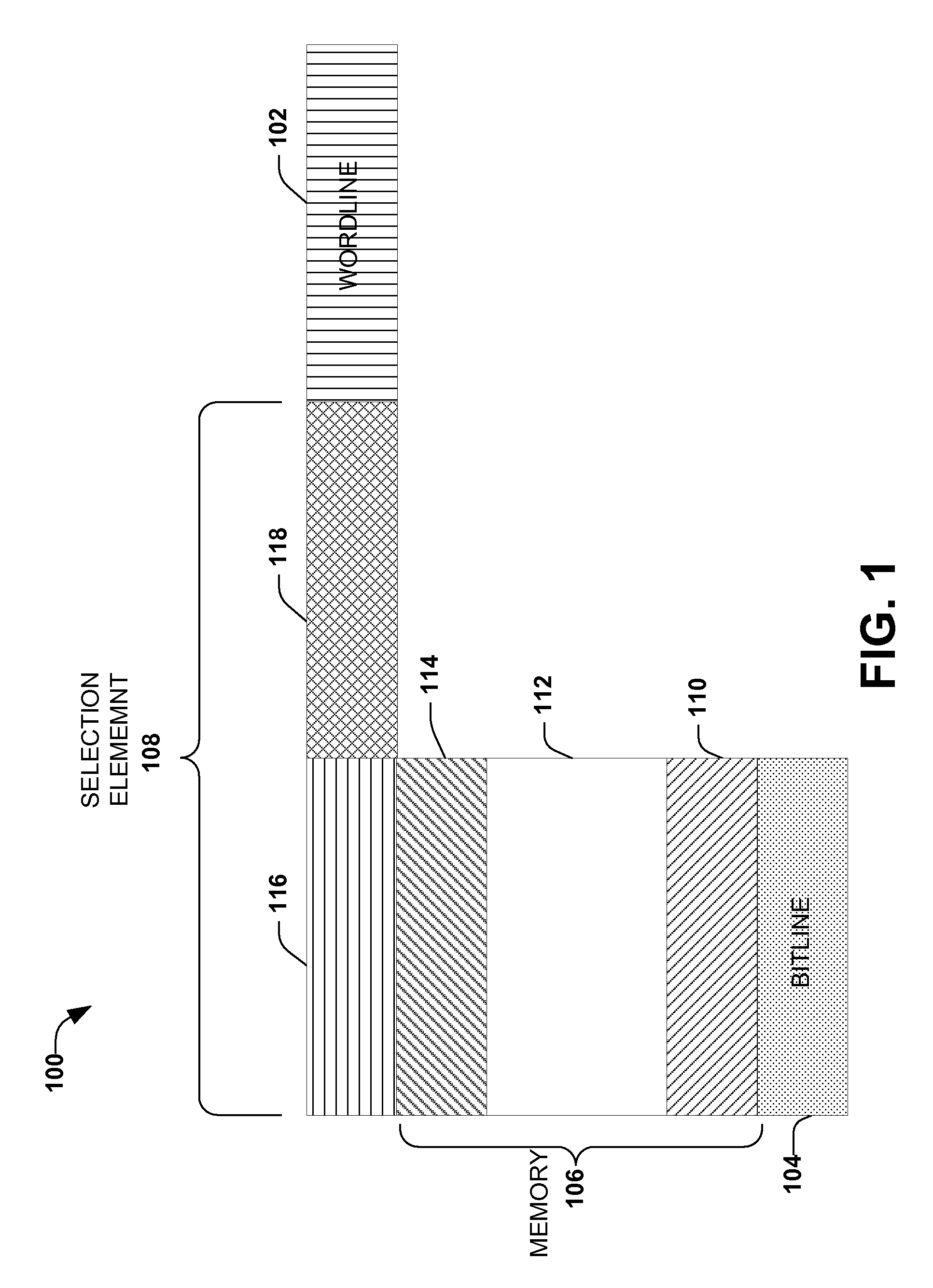

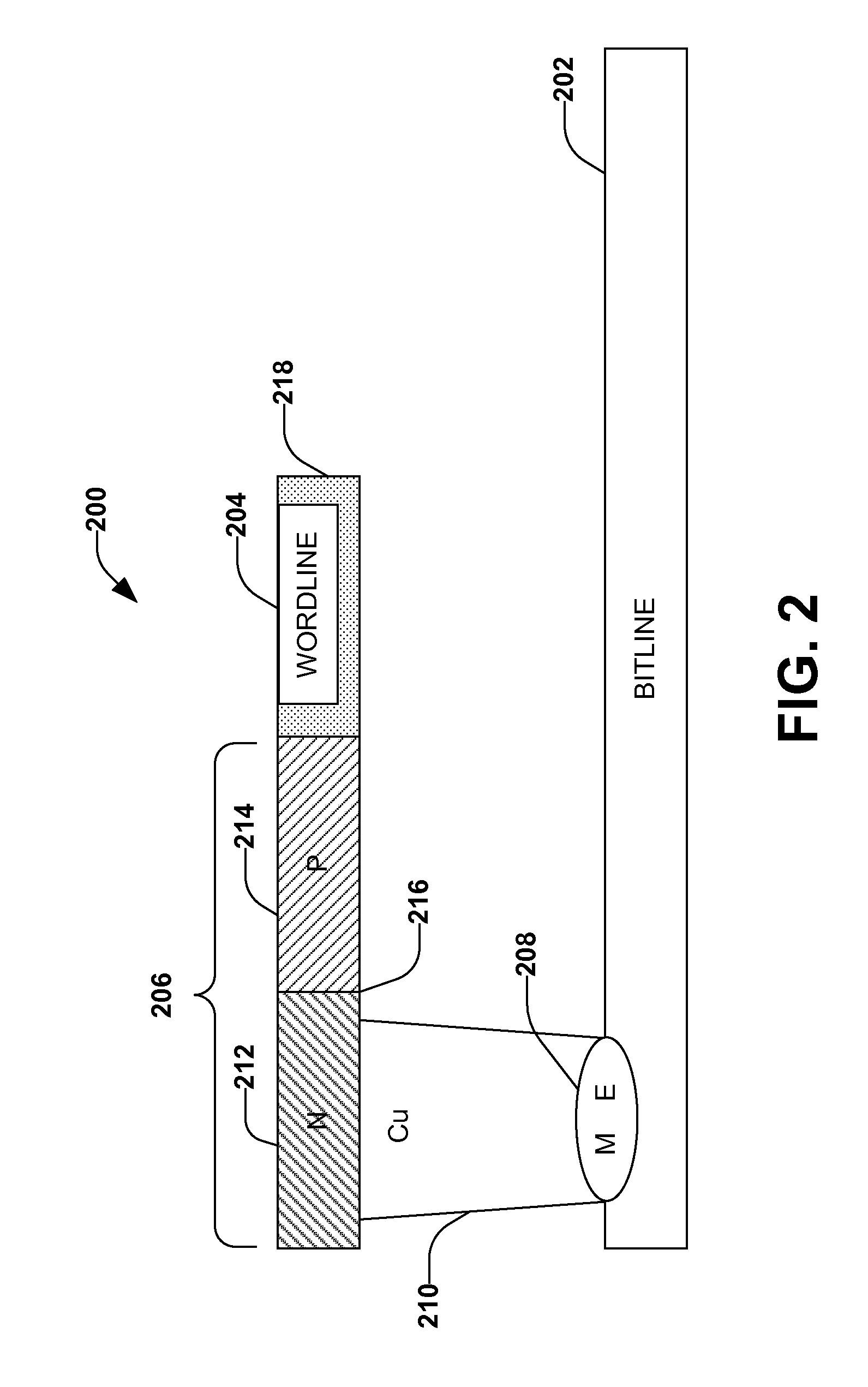

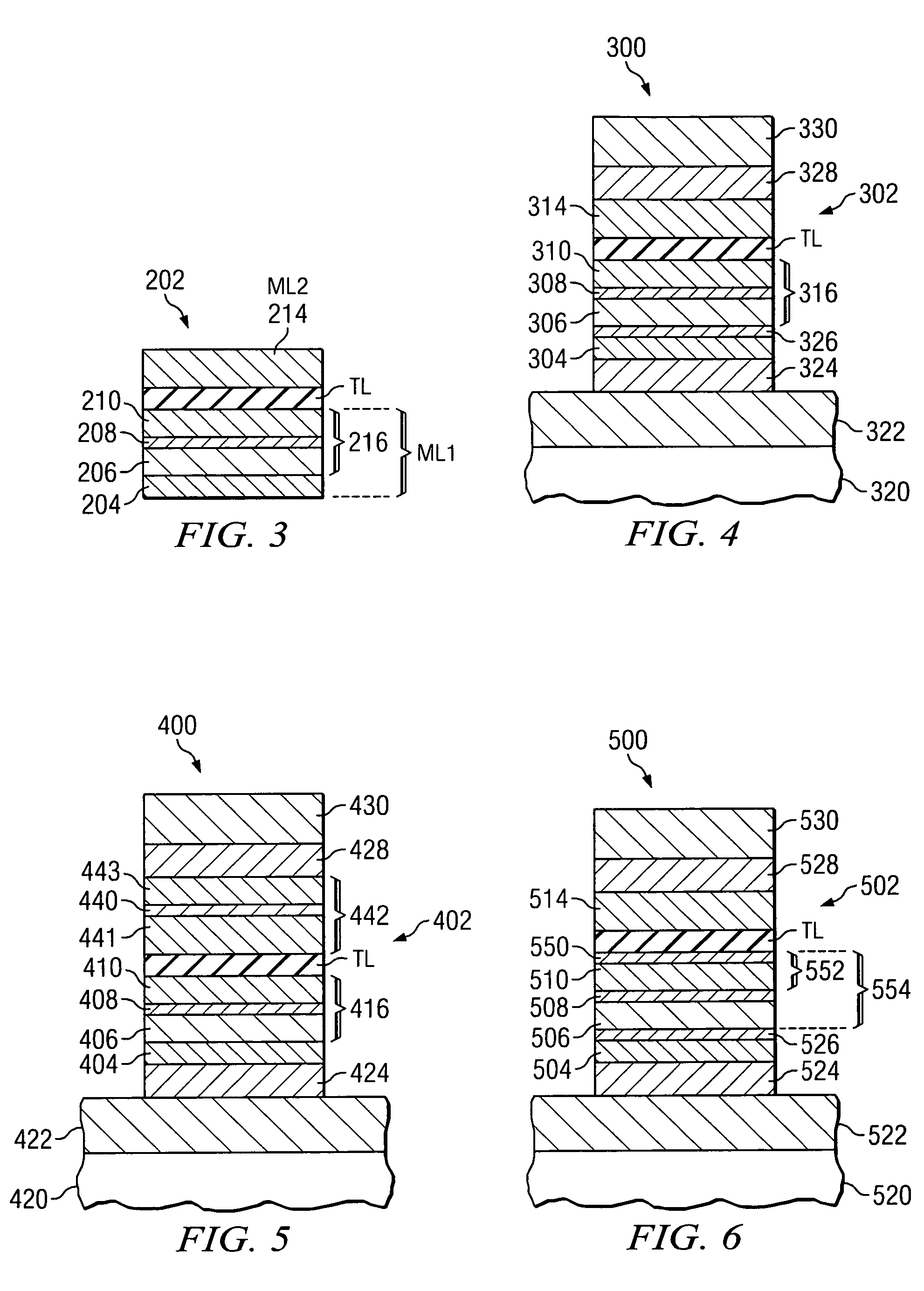

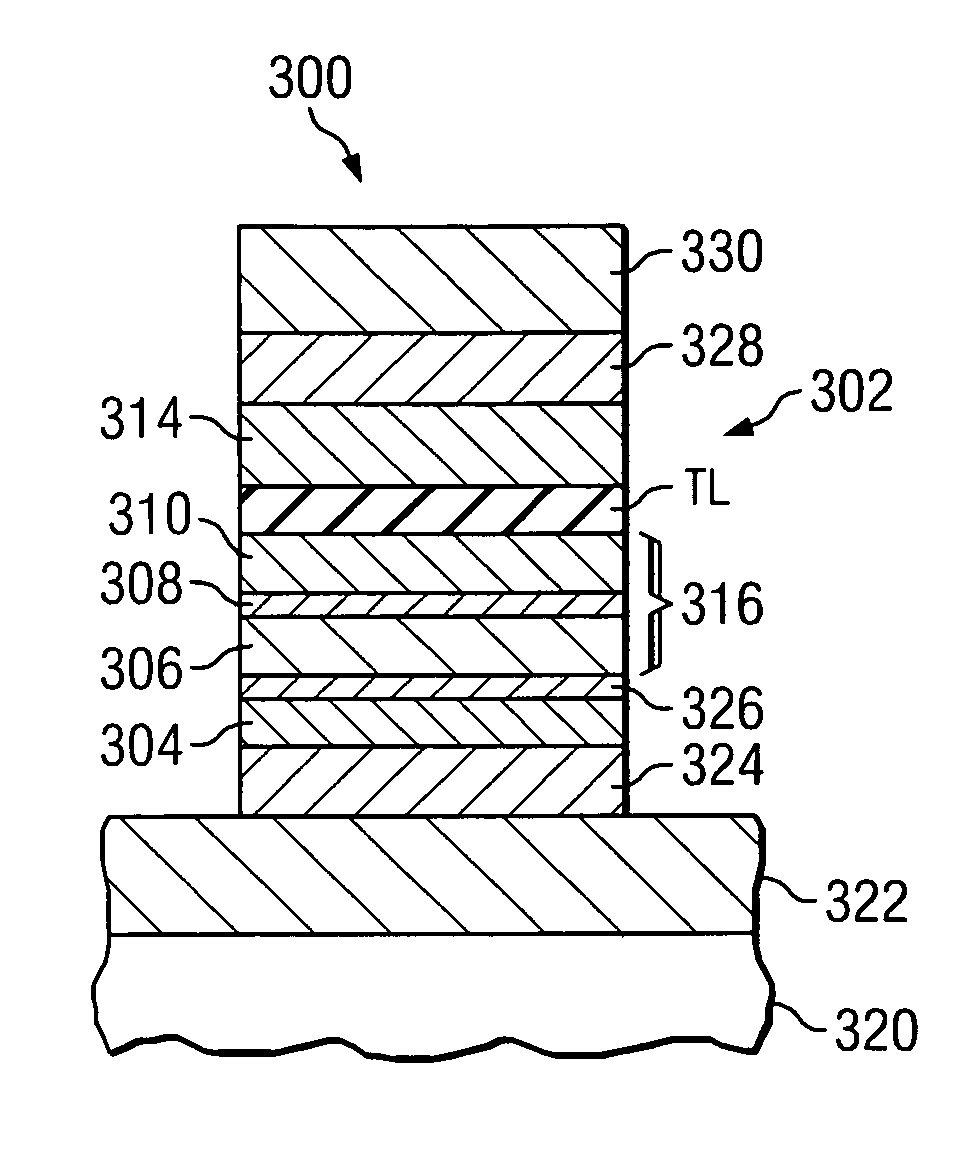

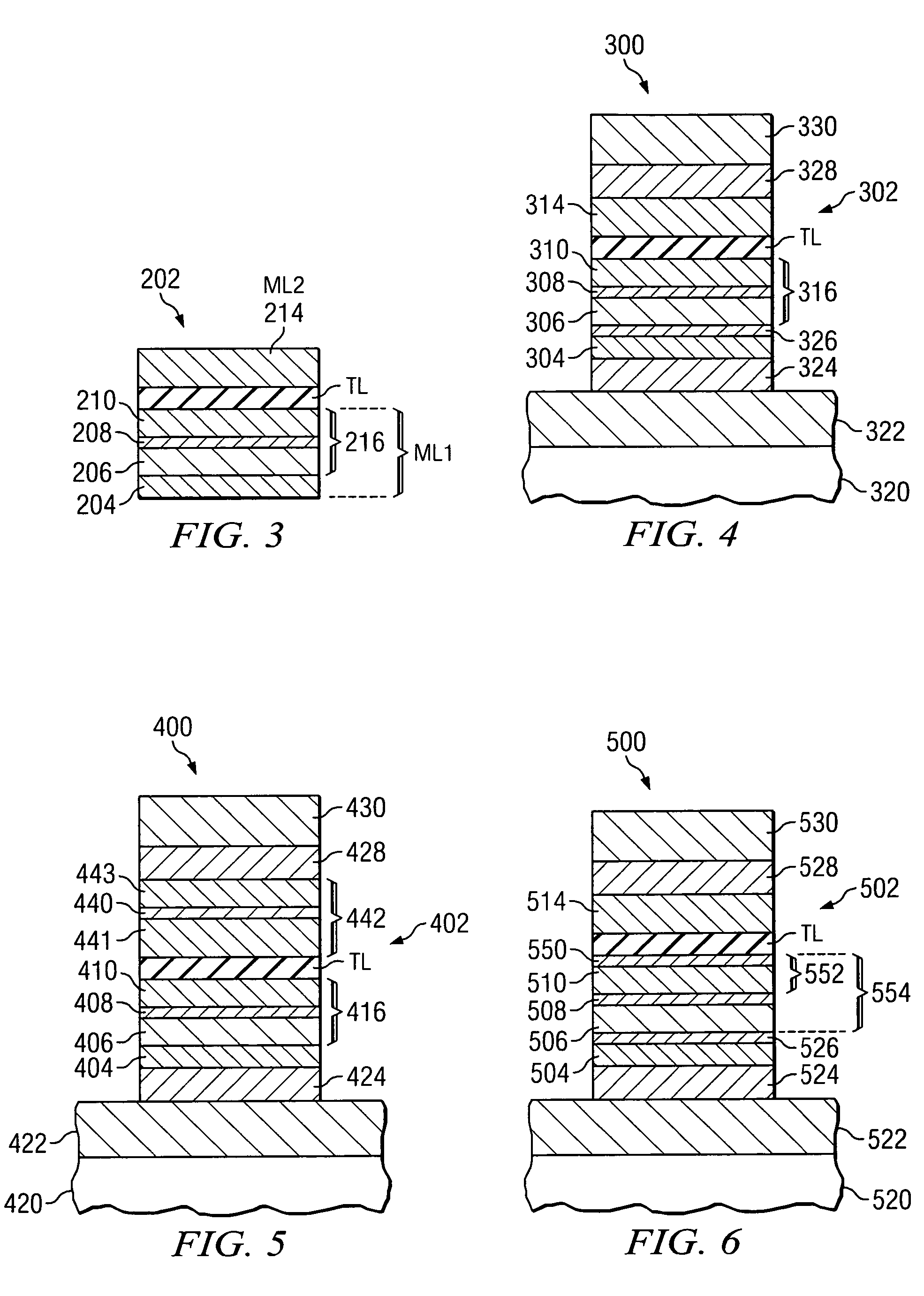

Memory device with a selection element and a control line in a substantially similar layer

ActiveUS7391064B1Reduce complexityMitigate vertical stacking issueTransistorSolid-state devicesControl lineSemiconductor

The invention facilitates manufacture of semiconductor memory components by reducing the number of layers required to implement a semiconductor memory device. The invention provides for a selection element to be formed in the same layer as one of the control lines (e.g. one of the wordline and bitline). In one embodiment of the invention, a diode is implemented as the selection element within the same layer as one of the control lines. Production of the selection element within the same layer as one of the wordline and bitline reduces problems associated with vertical stacking, increases device yield and reduces related production costs. The invention also provides an efficient method of producing memory devices with the selection element in the same layer as one of the control lines.

Owner:MONTEREY RES LLC

Bottom electrode etching process in MRAM cell

ActiveUS8334213B2Not to damageImprove device yieldDecorative surface effectsSolid-state devicesBit lineWater based

A BE patterning scheme in a MRAM is disclosed that avoids damage to the MTJ array and underlying ILD layer while reducing BE-BE shorts and BE-bit line shorts. A protective dielectric layer is coated over a MTJ array before a photoresist layer is coated and patterned on the dielectric layer. The photoresist pattern is transferred through the dielectric layer with a dielectric etch process and then through the BE layer with a metal etch that includes a certain amount of overetch to remove metal residues. The photoresist is stripped with a sequence involving immersion or spraying with an organic solution followed by oxygen ashing to remove any other organic materials. Finally, a second wet strip is performed with a water based solution to provide a residue free substrate. In another embodiment, a bottom anti-reflective coating (BARC) is inserted between the photoresist and dielectric layer for improved critical dimension control.

Owner:TAIWAN SEMICON MFG CO LTD

Memory device with a selection element and a control line in a substantially similar layer

ActiveUS7696017B1Reduce complexityMitigate vertical stacking issuesSolid-state devicesSemiconductor/solid-state device manufacturingControl lineEngineering

The invention facilitates manufacture of semiconductor memory components by reducing the number of layers required to implement a semiconductor memory device. The invention provides for a selection element to be formed in the same layer as one of the control lines (e.g. one of the wordline and bitline). In one embodiment of the invention, a diode is implemented as the selection element within the same layer as one of the control lines. Production of the selection element within the same layer as one of the wordline and bitline reduces problems associated with vertical stacking, increases device yield and reduces related production costs. The invention also provides an efficient method of producing memory devices with the selection element in the same layer as one of the control lines.

Owner:MONTEREY RES LLC

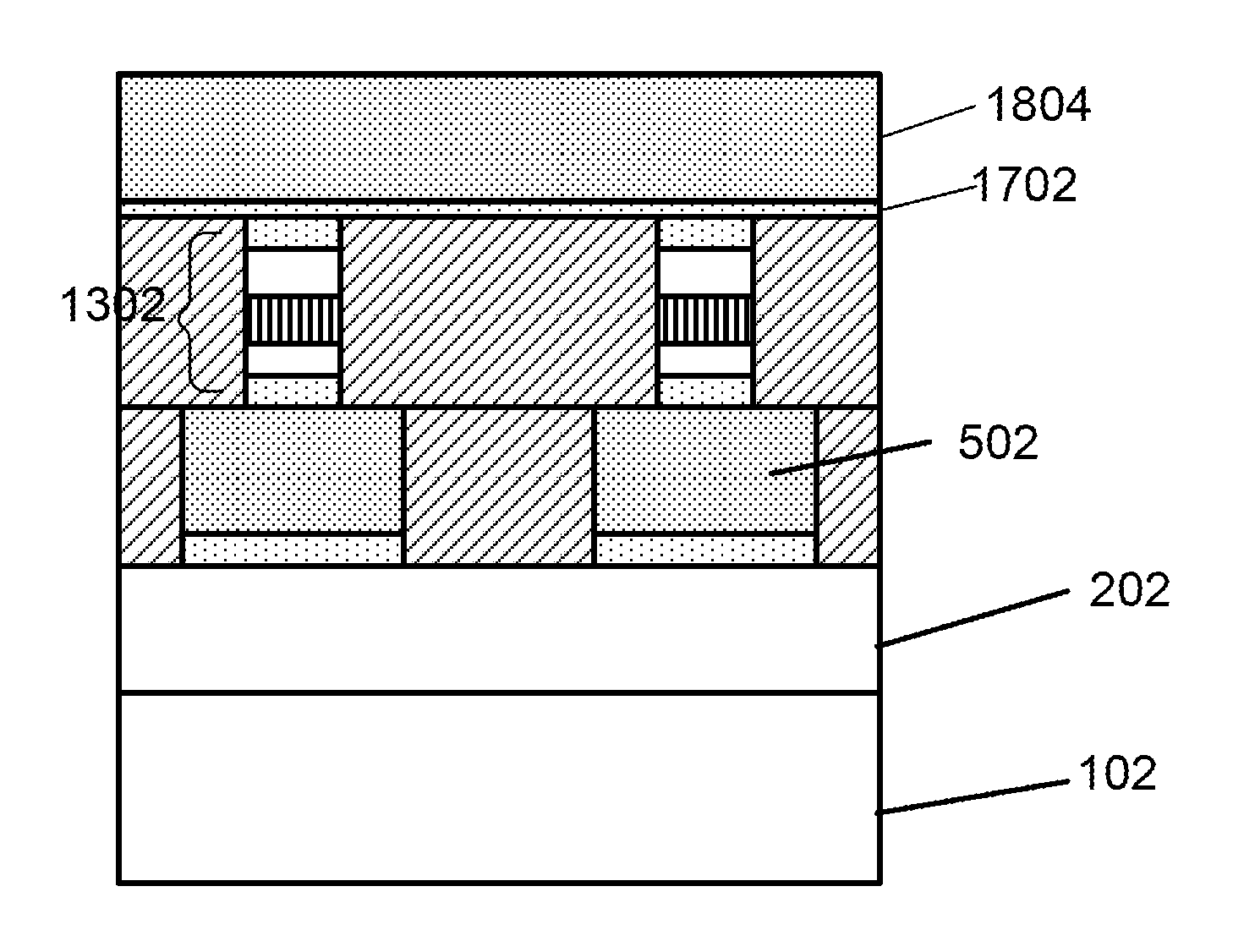

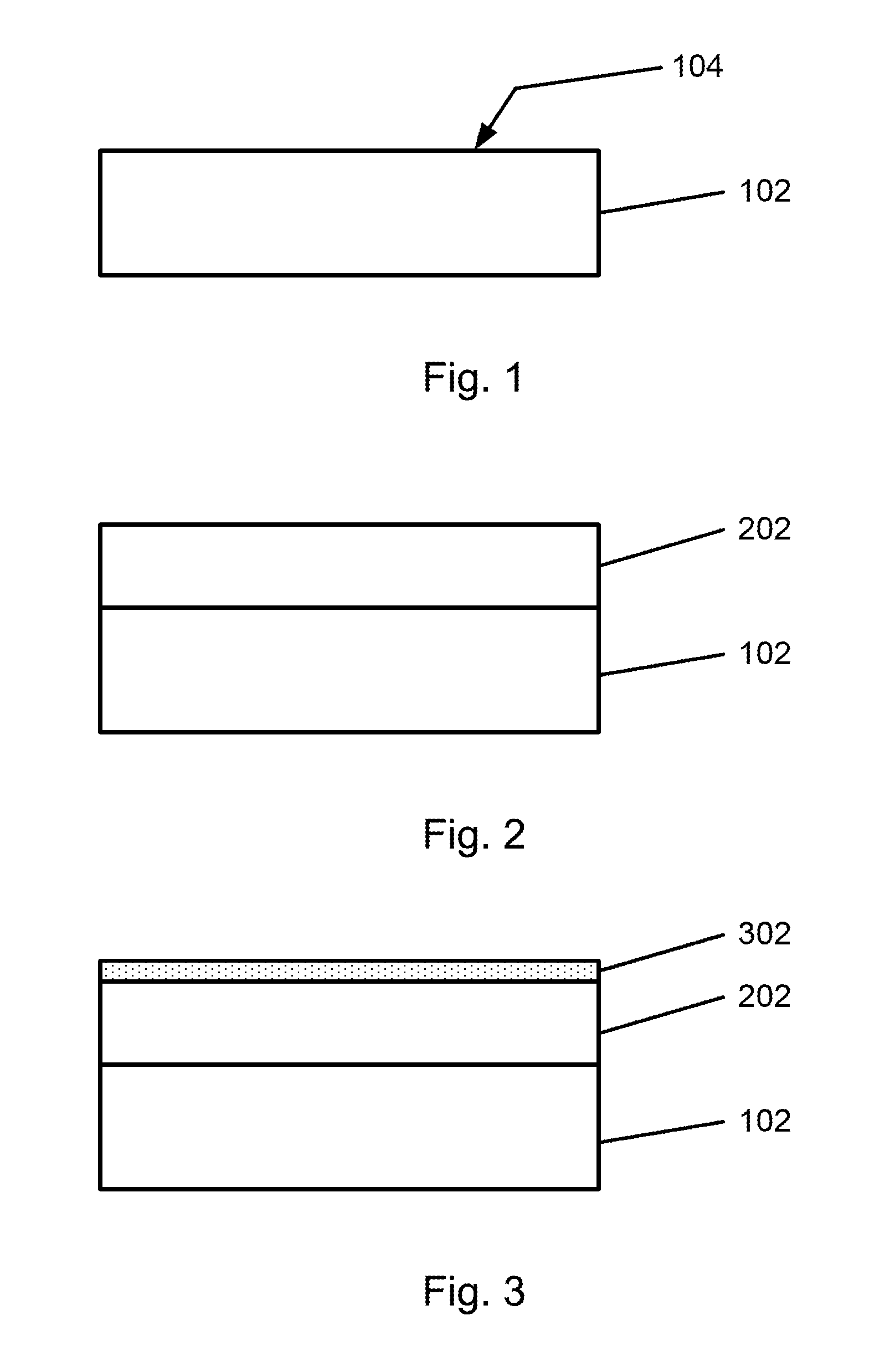

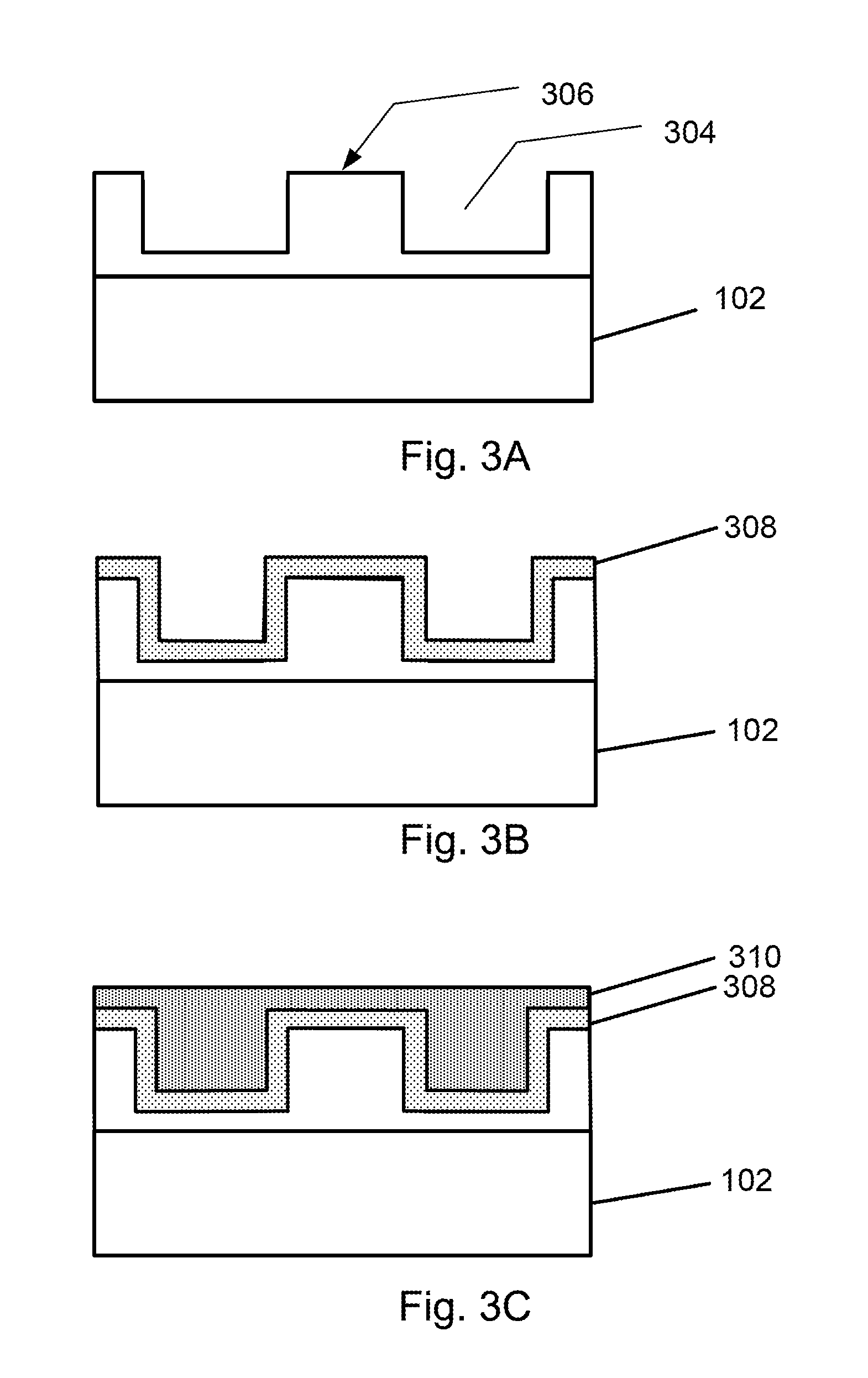

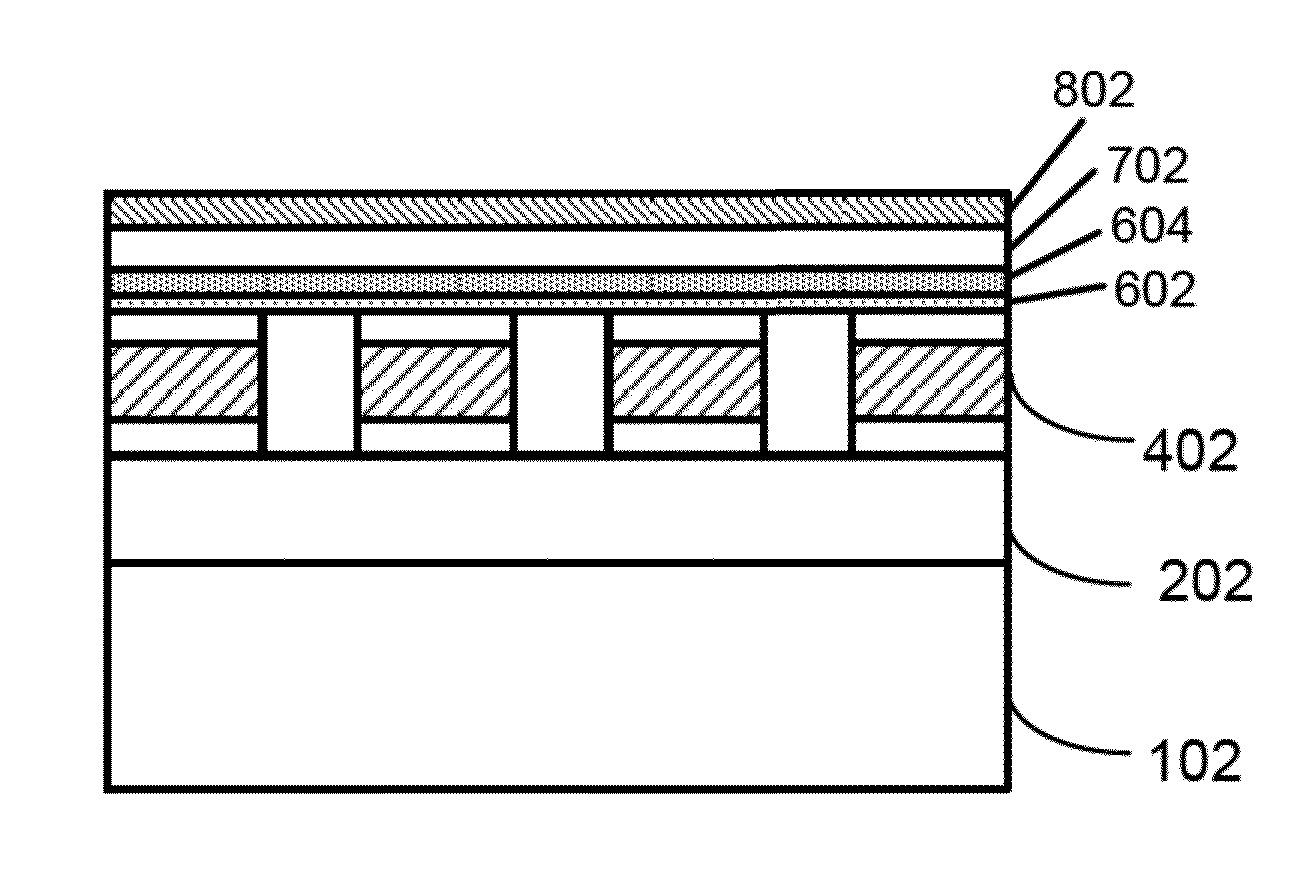

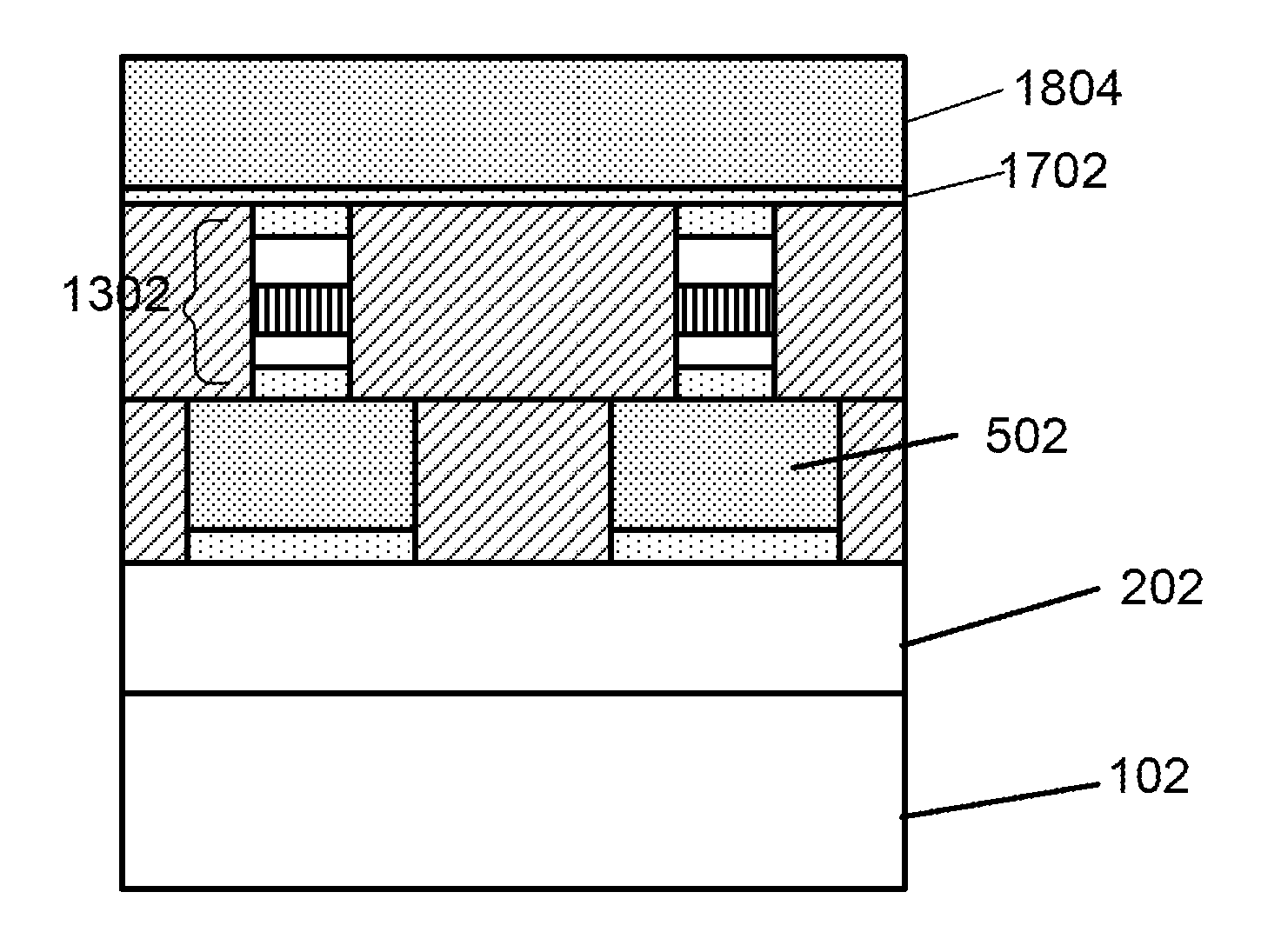

Pillar structure for memory device and method

ActiveUS20110312151A1High densityWide rangeSemiconductor/solid-state device manufacturingConductive materialsEngineering

A method of forming a memory device. The method provides a semiconductor substrate having a surface region. A first dielectric layer is formed overlying the surface region of the semiconductor substrate. A bottom wiring structure is formed overlying the first dielectric layer and a second dielectric material is formed overlying the top wiring structure. A bottom metal barrier material is formed to provide a metal-to-metal contact with the bottom wiring structure. The method forms a pillar structure by patterning and etching a material stack including the bottom metal barrier material, a contact material, a switching material, a conductive material, and a top barrier material. The pillar structure maintains a metal-to-metal contact with the bottom wiring structure regardless of the alignment of the pillar structure with the bottom wiring structure during etching. A top wiring structure is formed overlying the pillar structure at an angle to the bottom wiring structure.

Owner:CROSSBAR INC

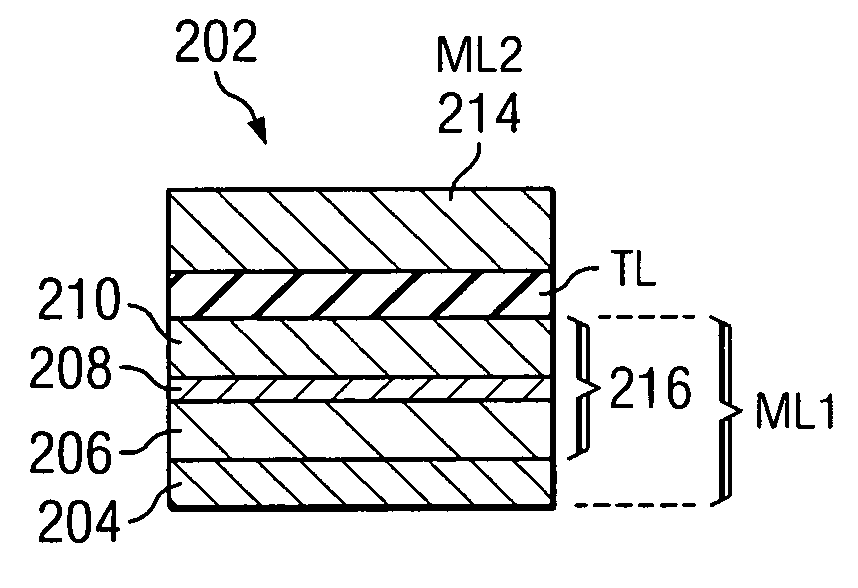

Magnetic tunnel junctions for MRAM devices

ActiveUS20050185454A1Reducing and eliminating Neel couplingImprove thermal stabilityMagnetic-field-controlled resistorsSolid-state devicesMagnetic layerMaterials science

Methods of manufacturing MTJ memory cells and structures thereof. A diffusion barrier is disposed between an anti-ferromagnetic layer and a pinned layer of an MTJ memory cell to improve thermal stability of the MTJ memory cell. The diffusion barrier may comprise an amorphous material or a NiFe alloy. An amorphous material may be disposed adjacent a bottom surface of a tunnel junction, within a free layer, or both. An MTJ memory cell with improved thermal stability and decreased Neel coupling is achieved.

Owner:IBM CORP +1

Bottom electrode etching process in MRAM cell

ActiveUS20100311243A1Not to damageImprove device yieldSolid-state devicesSemiconductor/solid-state device manufacturingWater basedResist

A BE patterning scheme in a MRAM is disclosed that avoids damage to the MTJ array and underlying ILD layer while reducing BE-BE shorts and BE-bit line shorts. A protective dielectric layer is coated over a MTJ array before a photoresist layer is coated and patterned on the dielectric layer. The photoresist pattern is transferred through the dielectric layer with a dielectric etch process and then through the BE layer with a metal etch that includes a certain amount of overetch to remove metal residues. The photoresist is stripped with a sequence involving immersion or spraying with an organic solution followed by oxygen ashing to remove any other organic materials. Finally, a second wet strip is performed with a water based solution to provide a residue free substrate. In another embodiment, a bottom anti-reflective coating (BARC) is inserted between the photoresist and dielectric layer for improved critical dimension control.

Owner:TAIWAN SEMICON MFG CO LTD

Stacked chip package using photosensitive polymer and manufacturing method thereof

ActiveUS20070048969A1Reduce decreaseImprove device reliabilitySemiconductor/solid-state device detailsSolid-state devicesMechanical reliabilityPhotosensitive polymer

In a stacked chip configuration, and manufacturing methods thereof, the gap between a lower and an upper chip is filled completely using a relatively simple process that eliminates voids between the lower and upper chips and the cracking and delamination problems associated with such voids. The present invention is applicable to both chip-level bonding and wafer-level bonding approaches. A photosensitive polymer layer is applied to a first chip, or wafer, prior to stacking the chips or stacking the wafers. The photosensitive polymer layer is partially cured, so that the photosensitive polymer layer is made to be structurally stable, while retaining its adhesive properties. The second chip, or wafer, is stacked, aligned, and bonded to the first chip, or wafer, and the photosensitive polymer layer is then cured to fully bond the first and second chips, or wafers. In this manner, adhesion between chips / wafers is greatly improved, while providing complete gap fill. In addition, mechanical reliability is improved, alleviating the problems associated with cracking and delamination, and leading to an improvement in device yield and device reliability.

Owner:SAMSUNG ELECTRONICS CO LTD

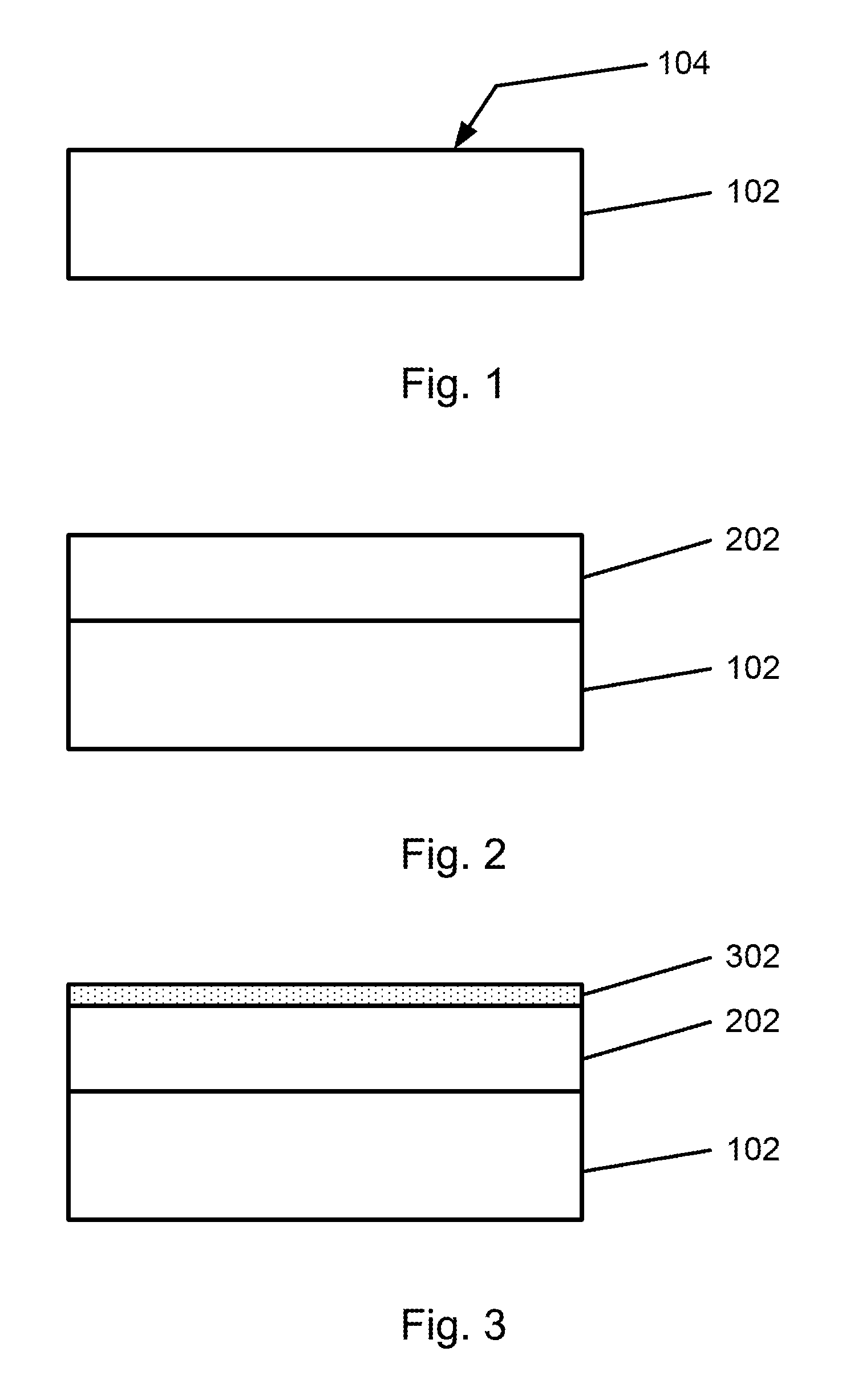

Low temperature P+ polycrystalline silicon material for non-volatile memory device

ActiveUS8658476B1Simplify the manufacturing processImprove device yieldSolid-state devicesSemiconductor/solid-state device manufacturingDeposition temperatureDegree Celsius

A method of forming a non-volatile memory device. The method includes providing a substrate having a surface region and forming a first dielectric material overlying the surface region of the substrate. A first electrode structure is formed overlying the first dielectric material and a p+ polycrystalline silicon germanium material is formed overlying the first electrode structure. A p+ polycrystalline silicon material is formed overlying the first electrode structure using the polycrystalline silicon germanium material as a seed layer at a deposition temperature ranging from about 430 Degree Celsius to about 475 Degree Celsius without further anneal. The method forms a resistive switching material overlying the polycrystalline silicon material, and a second electrode structure including an active metal material overlying the resistive switching material.

Owner:INNOSTAR SEMICON SHANGHAI CO LTD

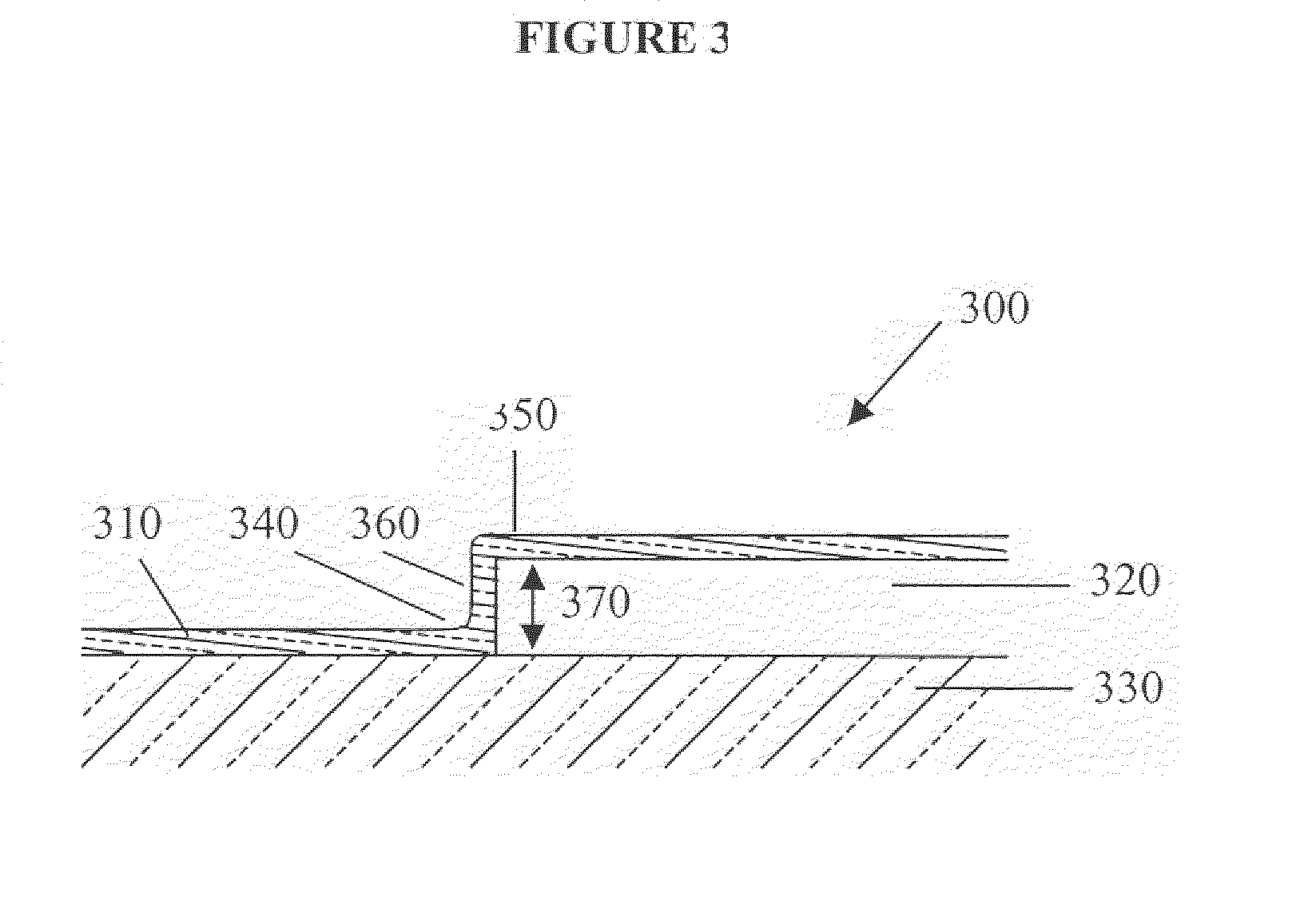

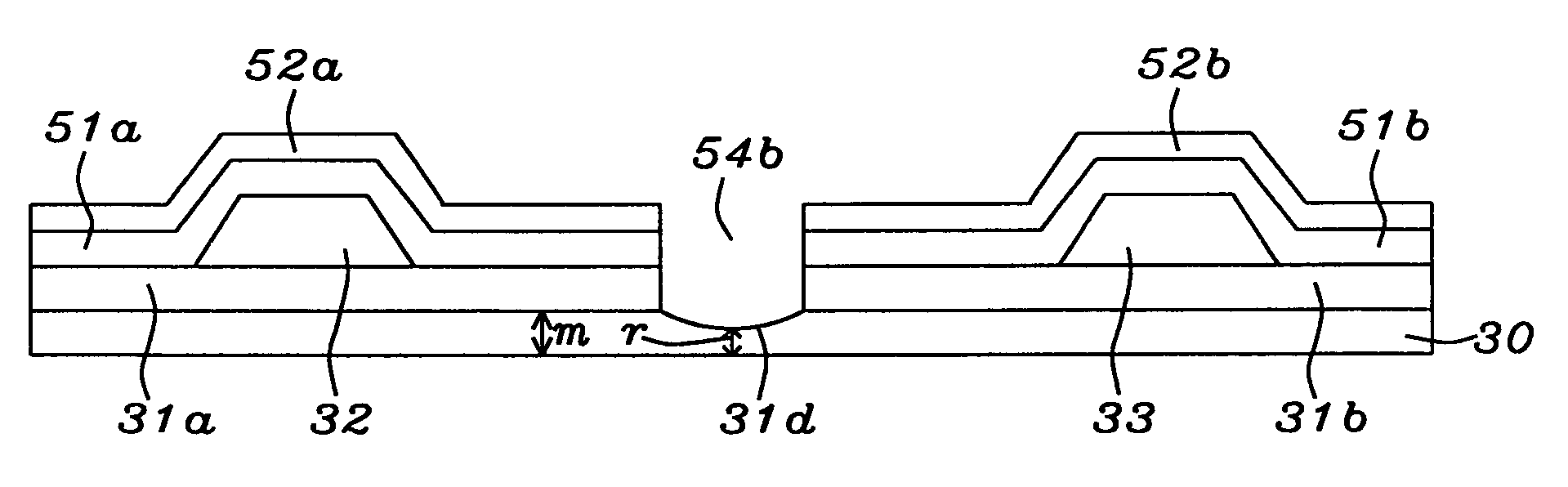

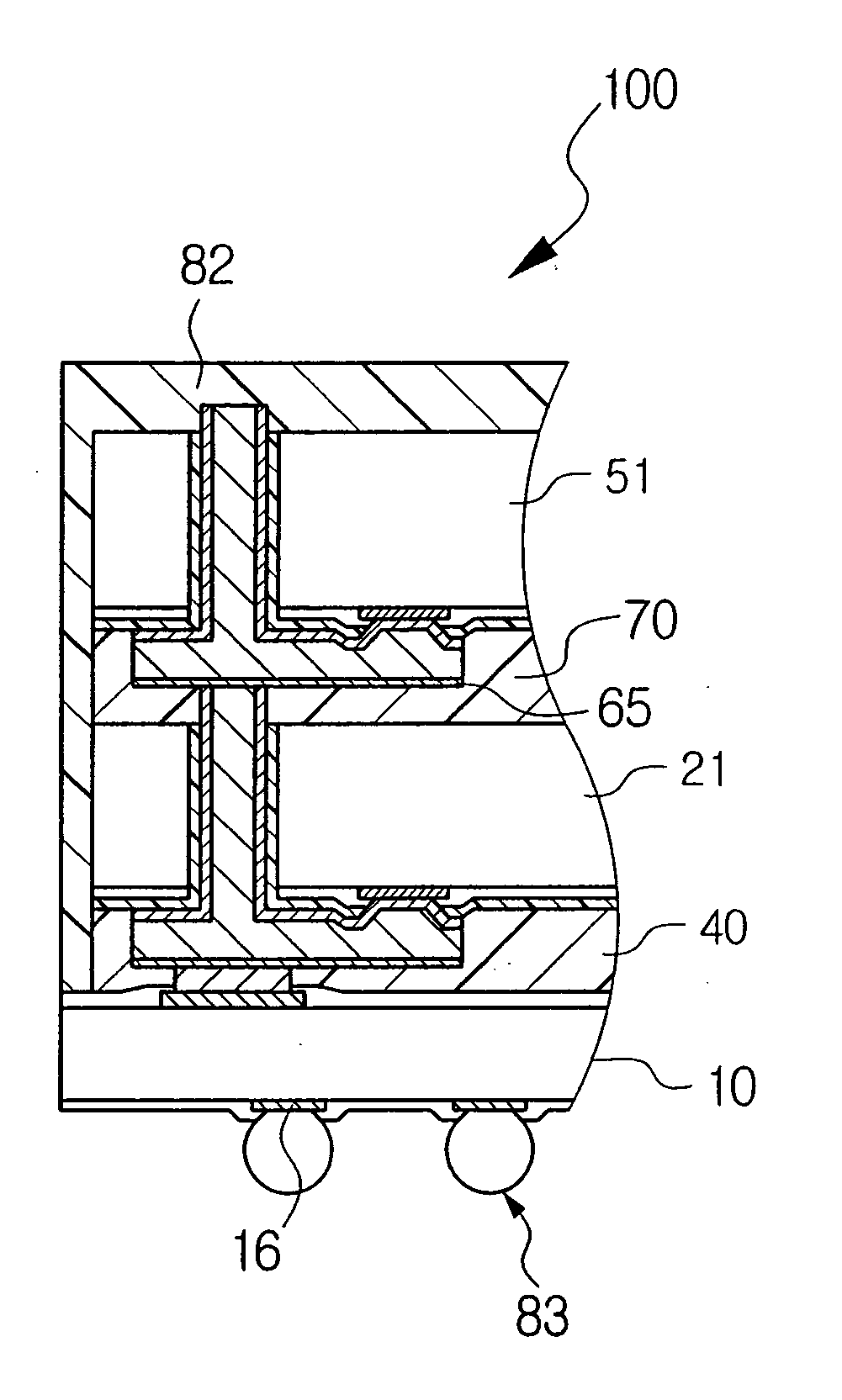

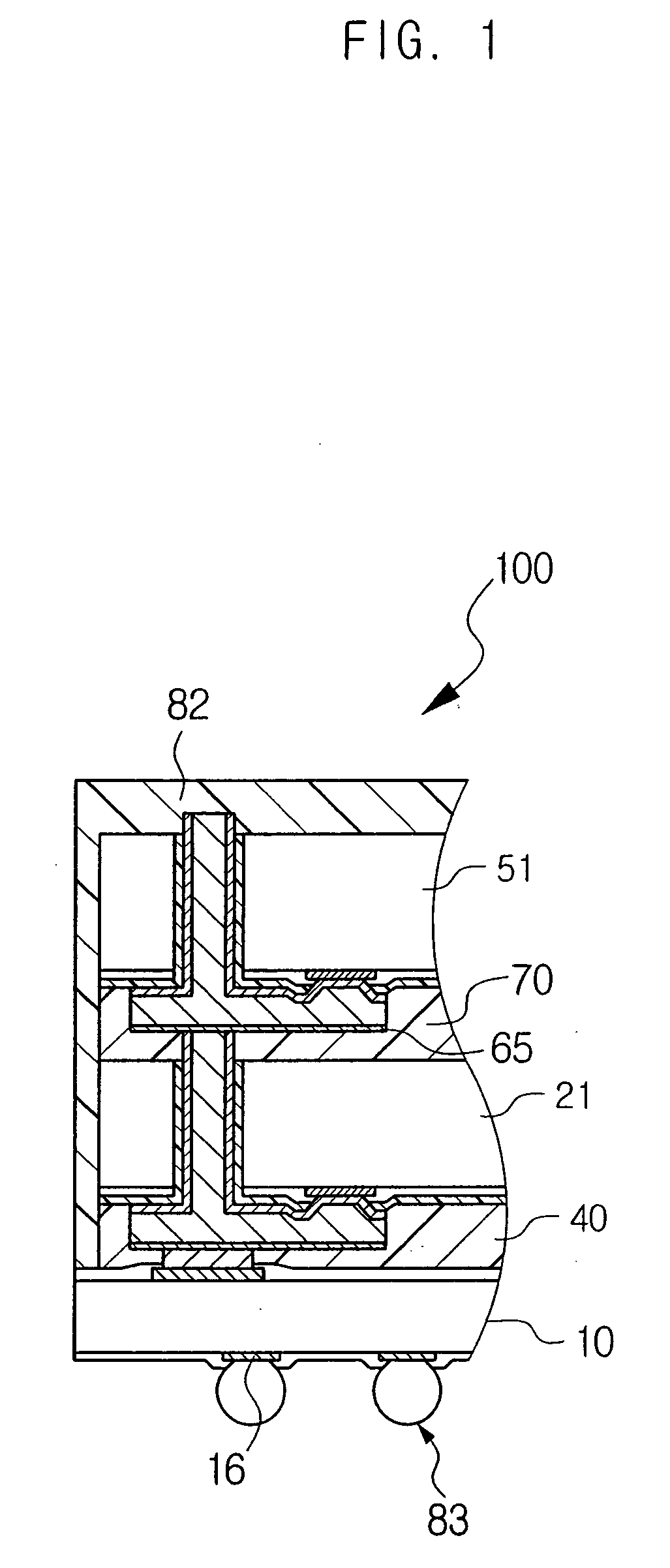

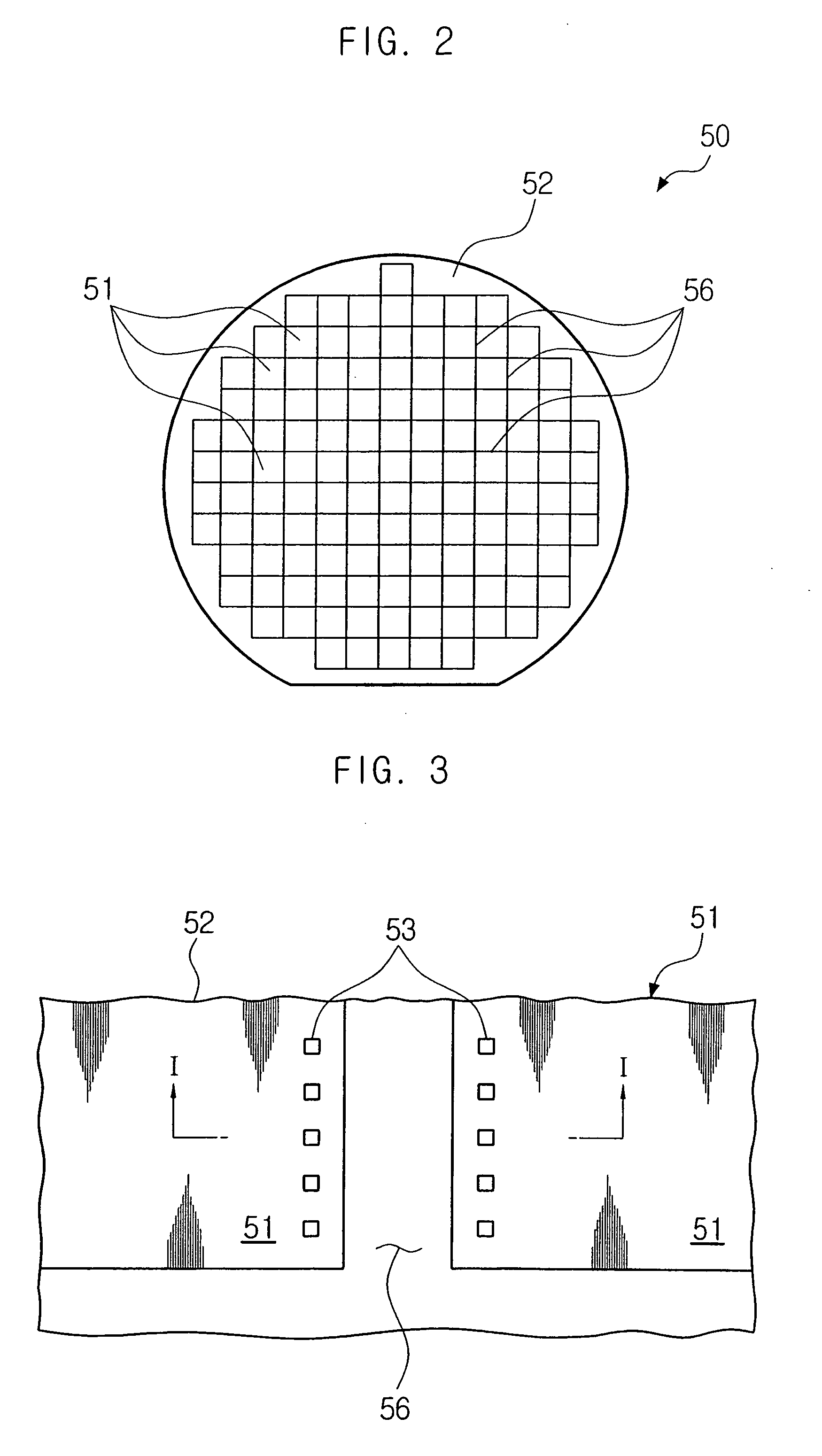

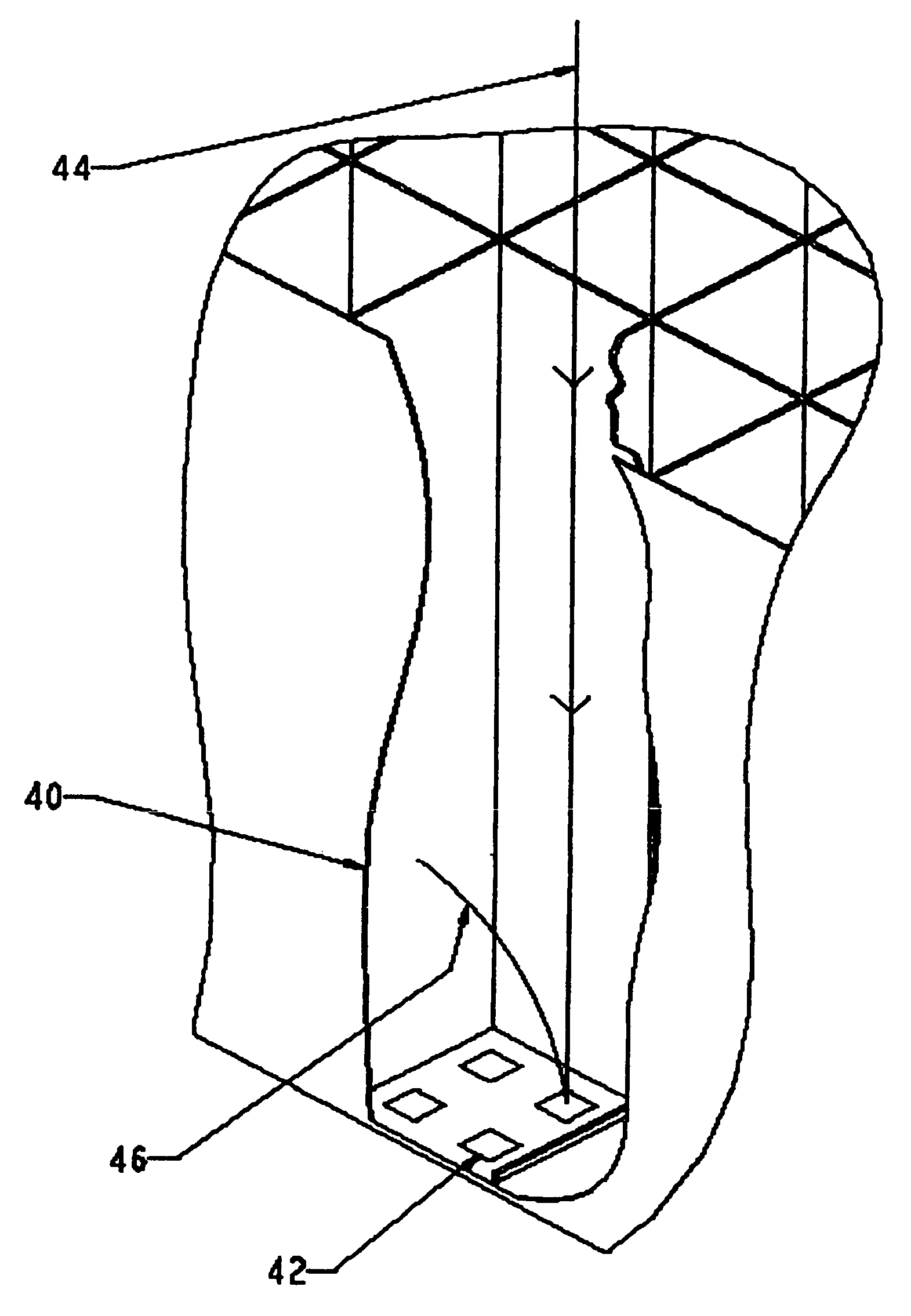

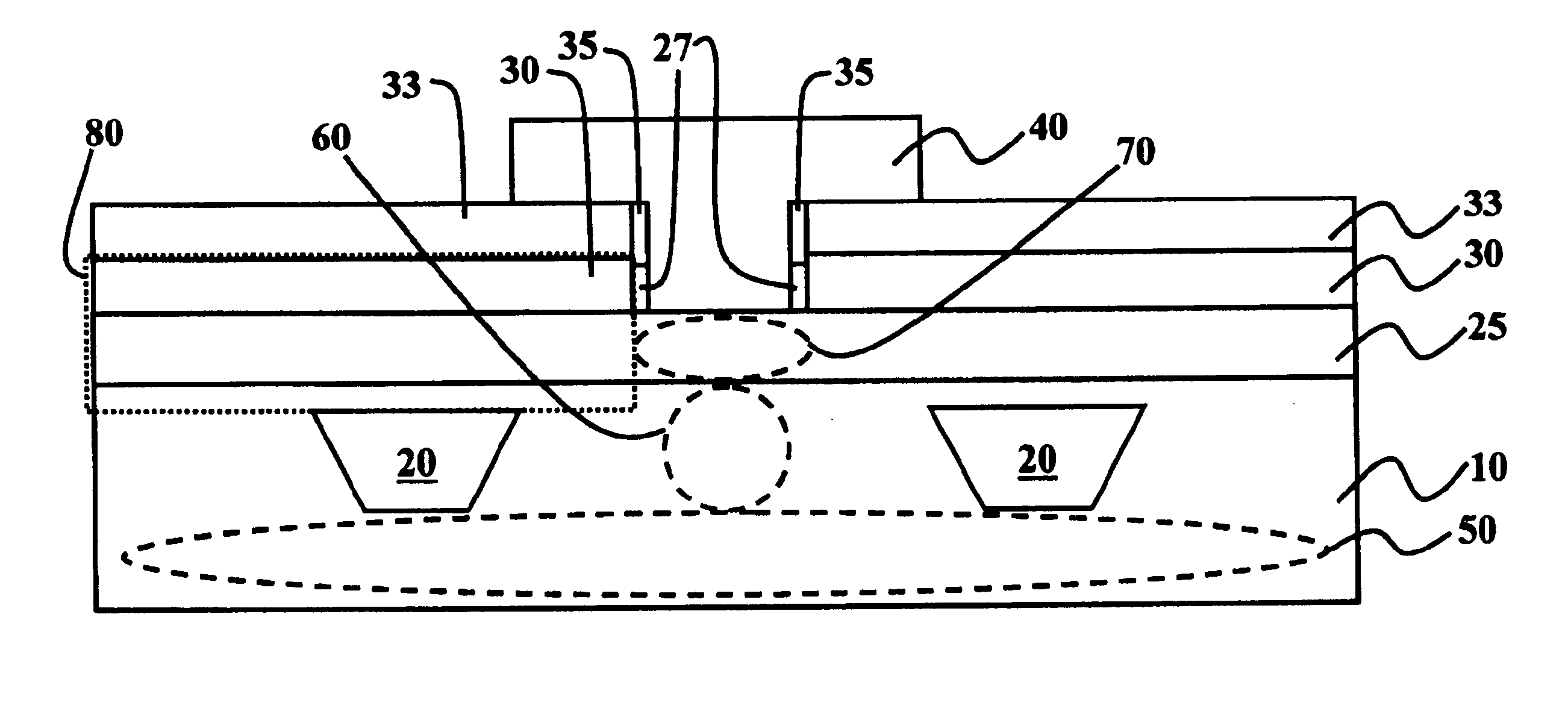

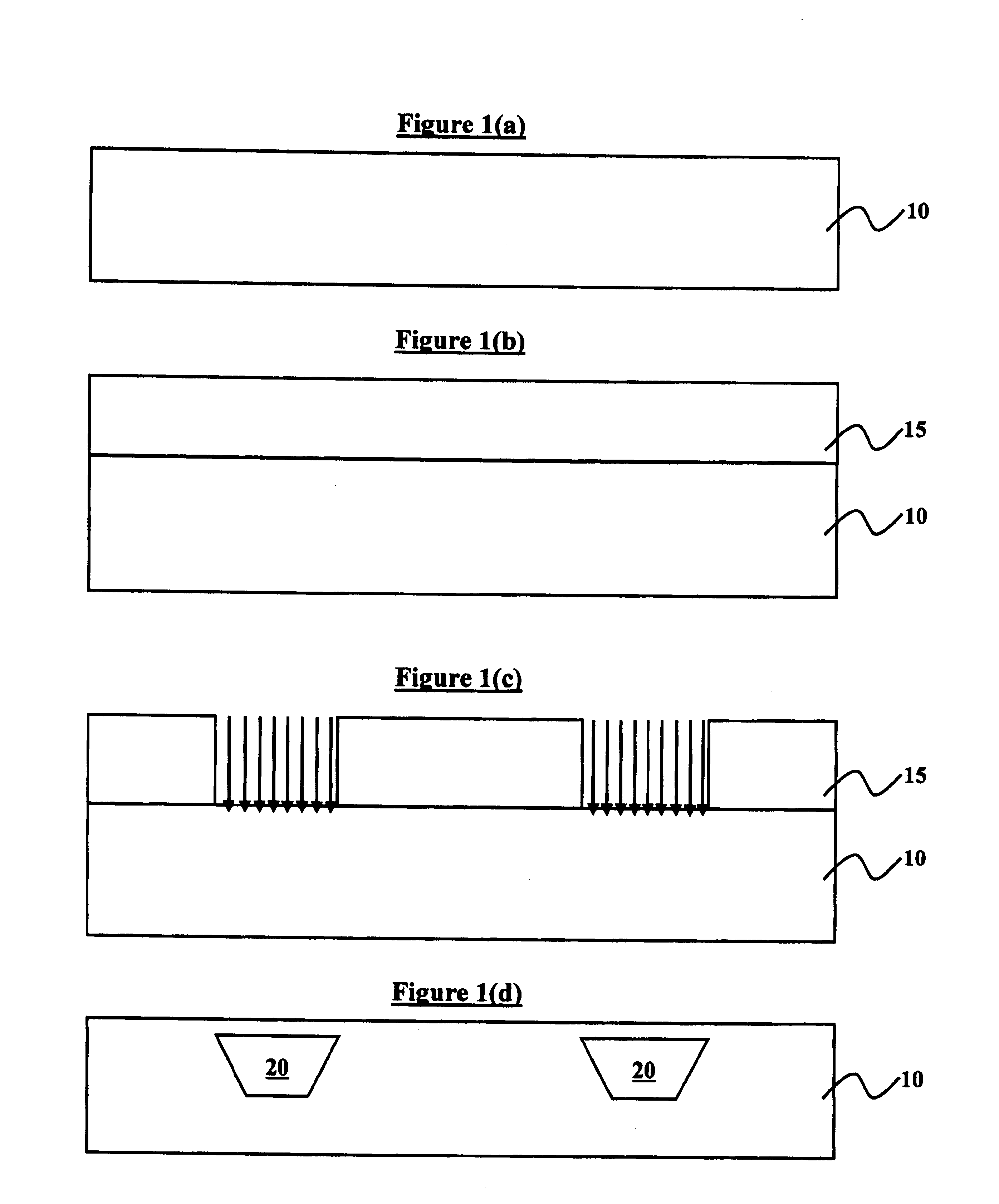

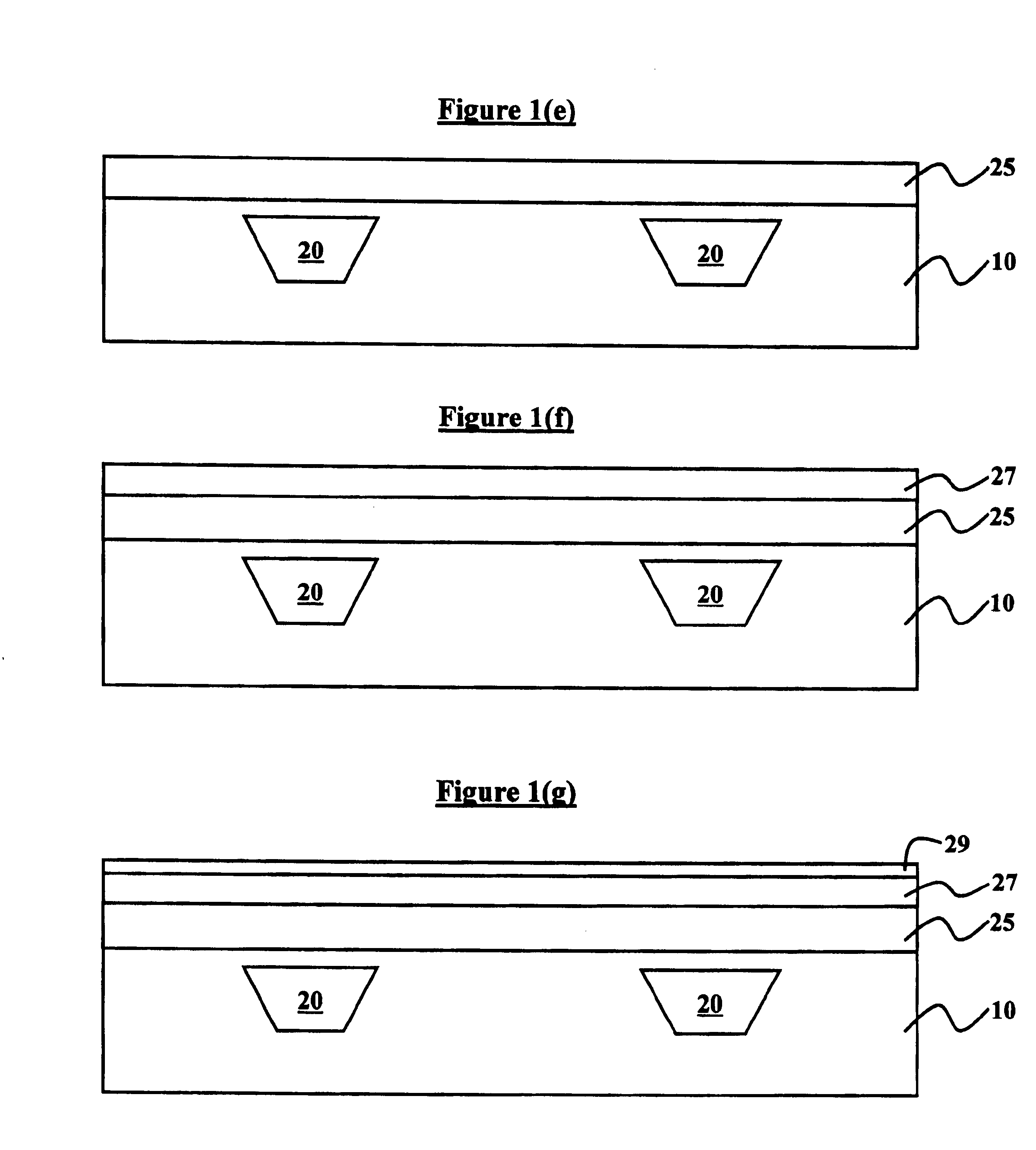

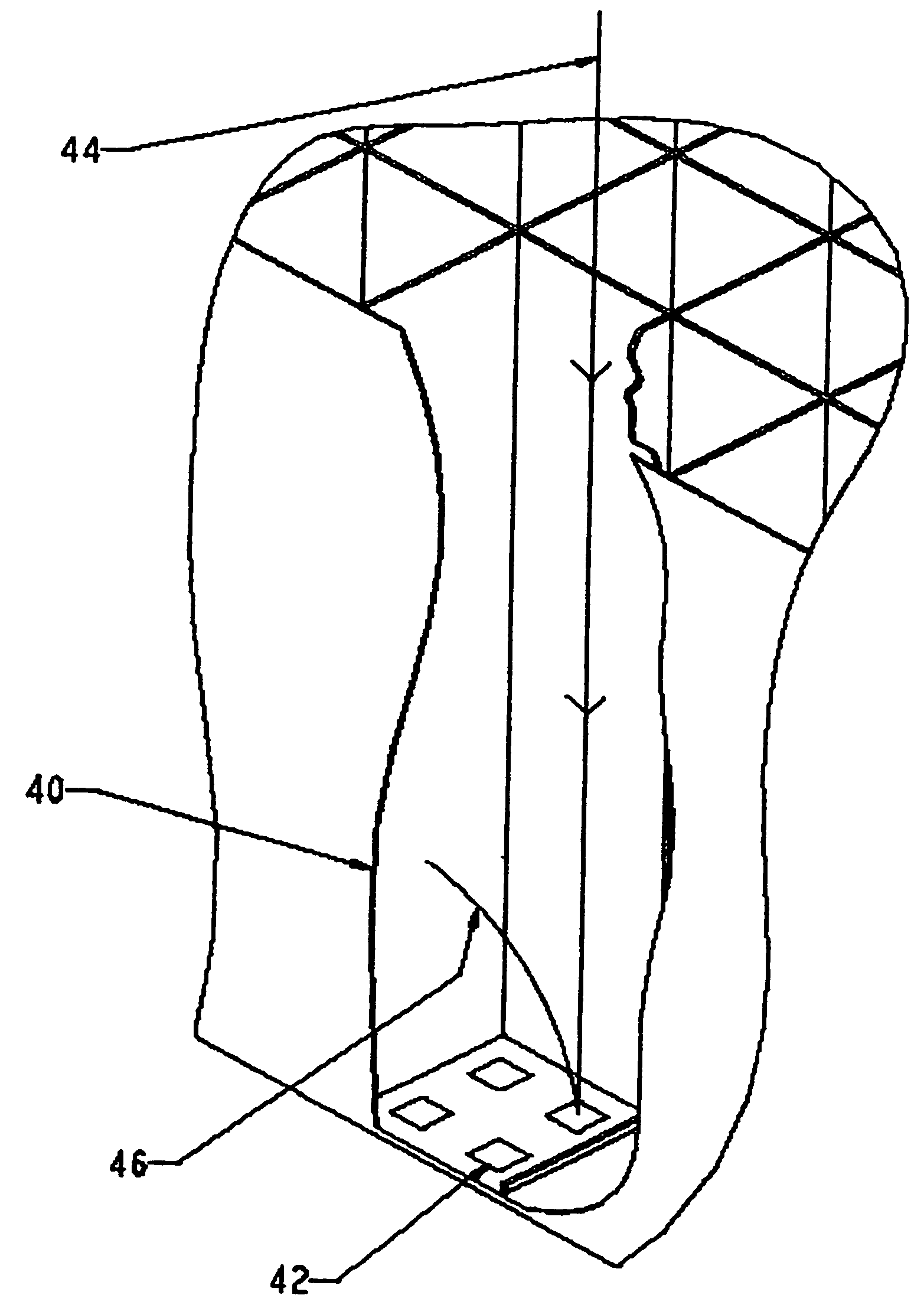

Backside thinning of image array devices

InactiveUS7005637B2Improve imaging effectImprove device yieldSolid-state devicesSemiconductor/solid-state device manufacturingImage resolutionImage contrast

Backthinning in an area selective manner is applied to imaging sensors 12 for use in electron bombarded devices. A further arrangement results in an array of collimators 51 aligned with pixels 42 or groups of pixels providing improved image contrast of such image sensor. Provision of a thin P-doped layer 52 on the illuminated rear surface provides both a diffusion barrier resulting in improved resolution and a functional shield for reference pixels. A gradient in concentration of P-doped layer 52 optimizes electron collection at the pixel array.

Owner:EOTECH LLC

Pillar structure for memory device and method

ActiveUS8198144B2High densityHigh yieldSemiconductor/solid-state device manufacturingConductive materialsDielectric layer

A method of forming a memory device. The method provides a semiconductor substrate having a surface region. A first dielectric layer is formed overlying the surface region of the semiconductor substrate. A bottom wiring structure is formed overlying the first dielectric layer and a second dielectric material is formed overlying the top wiring structure. A bottom metal barrier material is formed to provide a metal-to-metal contact with the bottom wiring structure. The method forms a pillar structure by patterning and etching a material stack including the bottom metal barrier material, a contact material, a switching material, a conductive material, and a top barrier material. The pillar structure maintains a metal-to-metal contact with the bottom wiring structure regardless of the alignment of the pillar structure with the bottom wiring structure during etching. A top wiring structure is formed overlying the pillar structure at an angle to the bottom wiring structure.

Owner:CROSSBAR INC

Magnetic tunnel junctions for MRAM devices

ActiveUS7149105B2Improve performanceReduce couplingMagnetic-field-controlled resistorsSolid-state devicesCouplingAlloy

Methods of manufacturing MTJ memory cells and structures thereof. A diffusion barrier is disposed between an anti-ferromagnetic layer and a pinned layer of an MTJ memory cell to improve thermal stability of the MTJ memory cell. The diffusion barrier may comprise an amorphous material or a NiFe alloy. An amorphous material may be disposed adjacent a bottom surface of a tunnel junction, within a free layer, or both. An MTJ memory cell with improved thermal stability and decreased Neel coupling is achieved.

Owner:IBM CORP +1

Method of forming contact plugs for eliminating tungsten seam issue

InactiveUS20080217775A1Decrease failure bit countImprove device yieldSemiconductor/solid-state device detailsSolid-state devicesDielectric layerTungsten

A method of forming a contact plug of an eDRAM device includes the following steps: forming a tungsten layer with tungsten seam on a dielectric layer to fill a contact hole; removing the tungsten layer from the top surface of the dielectric layer, recessing the tungsten layer in the contact hole to form a recess of about 600˜900 Angstroms in depth below the top surface of the dielectric layer, depositing a conductive layer on the dielectric layer and the recessed tungsten plug to fill the recess; and removing the conductive layer from the top surface of the dielectric layer to form a conductive plug on the recessed tungsten plug in the contact hole.

Owner:TAIWAN SEMICON MFG CO LTD

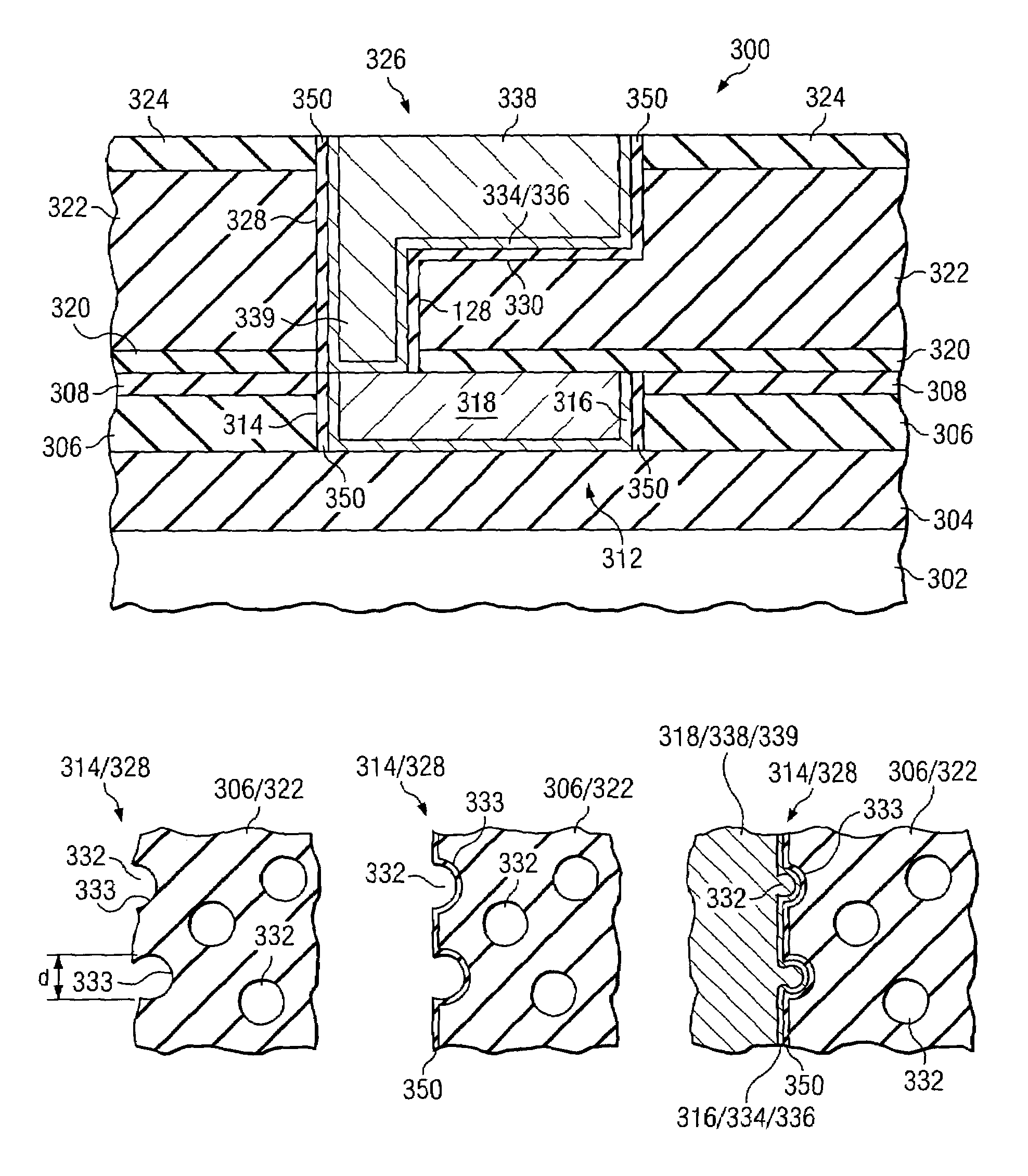

BICMOS technology on SIMOX wafers

InactiveUS6888221B1Reduce power consumptionImprove current drive capabilityTransistorSemiconductor/solid-state device manufacturingEngineeringSingle crystal

A method and structure for a bipolar transistor comprising a patterned isolation region formed below an upper surface of a semiconductor substrate and a single crystal extrinsic base formed on an upper surface of the isolation region. The single crystal extrinsic base comprises a portion of the semiconductor substrate located between the upper surface of the isolation region and the upper surface of the semiconductor substrate. The bipolar transistor further comprises a single crystal intrinsic base, wherein a portion of the single crystal extrinsic base merges with a portion of the single crystal intrinsic base. The isolation region electrically isolates the extrinsic base from a collector. The intrinsic and extrinsic bases separate the collector from an emitter. The extrinsic base comprises epitaxially-grown silicon. The isolation region comprises an insulator, which comprises oxide, and the isolation region comprises any of a shallow trench isolation region and a deep trench isolation region.

Owner:GLOBALFOUNDRIES INC

Method of manufacturing semiconductor device with crack prevention ring

ActiveUS7223673B2Avoid crackingPrevents cracking and delaminatingSemiconductor/solid-state device detailsSolid-state devicesConductive materialsSemiconductor

A method of forming a crack prevention ring at the exterior edge of an integrated circuit to prevent delamination and cracking during the separation of the integrated circuits into individual die. The crack prevention ring extends vertically into a semiconductor workpiece to at least a metallization layer of the integrated circuit. The crack prevention ring may be formed simultaneously with the formation of test pads of the integrated circuits. The crack prevention ring may be partially or completely filled with conductive material. An air pocket may be formed within the crack prevention ring beneath a passivation layer of the integrated circuit. The crack prevention ring may be removed during the singulation process. An optional seal ring may be formed between the crack prevention ring and the integrated circuit.

Owner:TAIWAN SEMICON MFG CO LTD

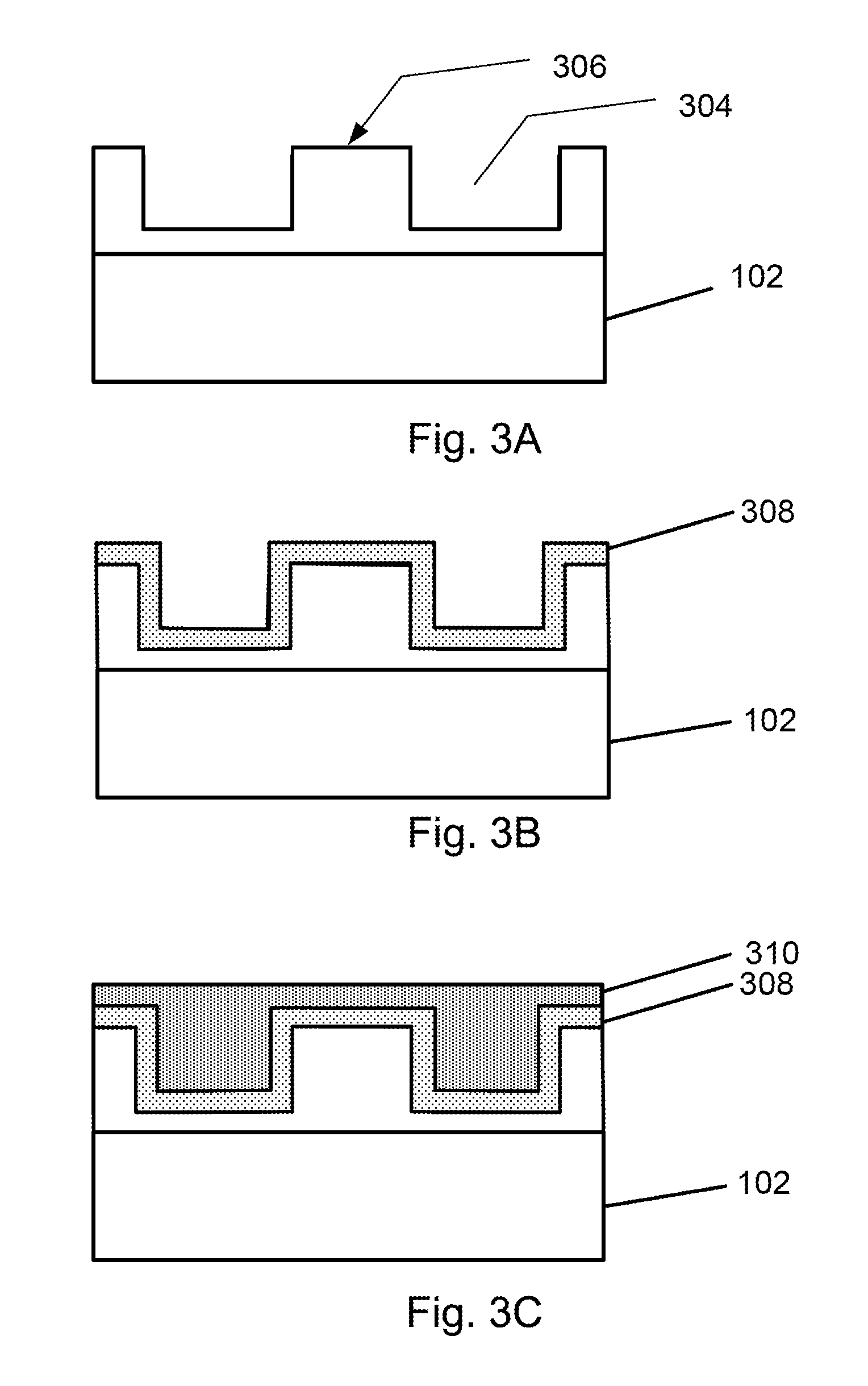

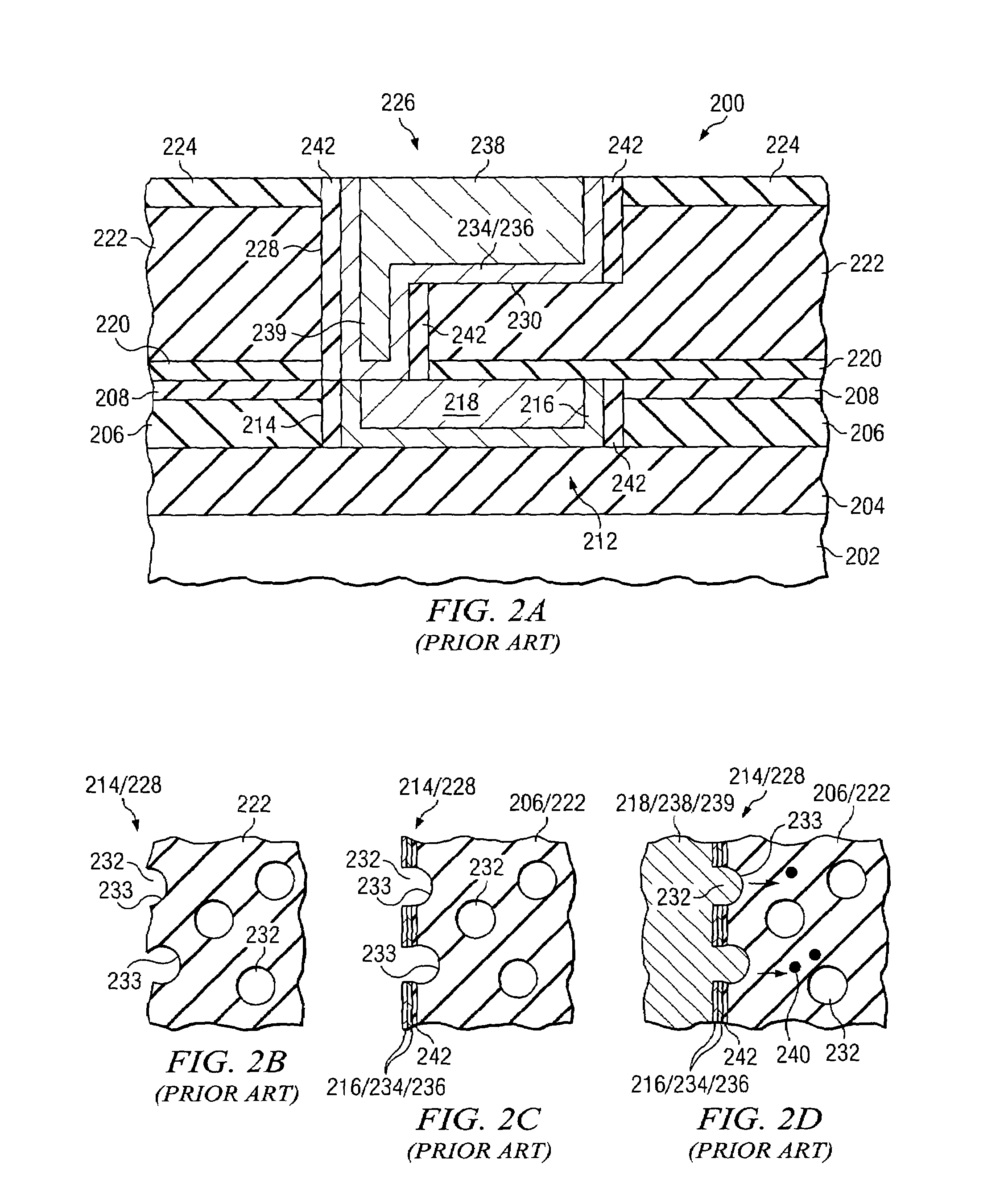

Sealed pores in low-k material damascene conductive structures

InactiveUS7052990B2Inhibit migrationImprove reliabilitySemiconductor/solid-state device manufacturingCopperAtomic layer deposition

An oxide layer is used to seal pores in porous low-dielectric constant materials, thus preventing the migration of subsequently deposited copper materials into the porous low-dielectric constant materials in damascene processes. The oxide layer is deposited over the inner surface of at least one pore along a sidewall of the patterned low-dielectric constant material. In one embodiment, the oxide layer is deposited using atomic layer deposition (ALD), and the oxide layer comprises SiO2.

Owner:INFINEON TECH AG

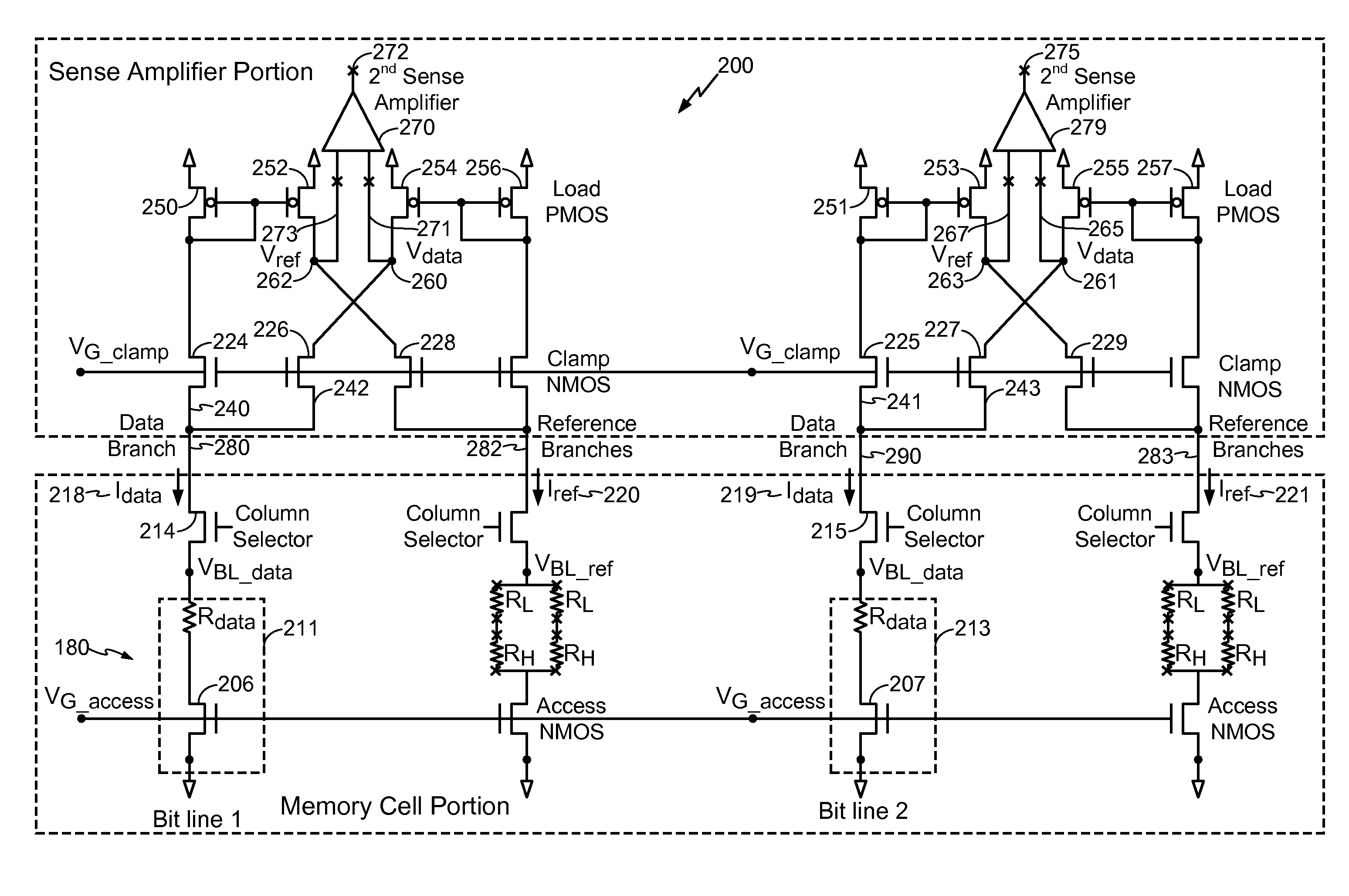

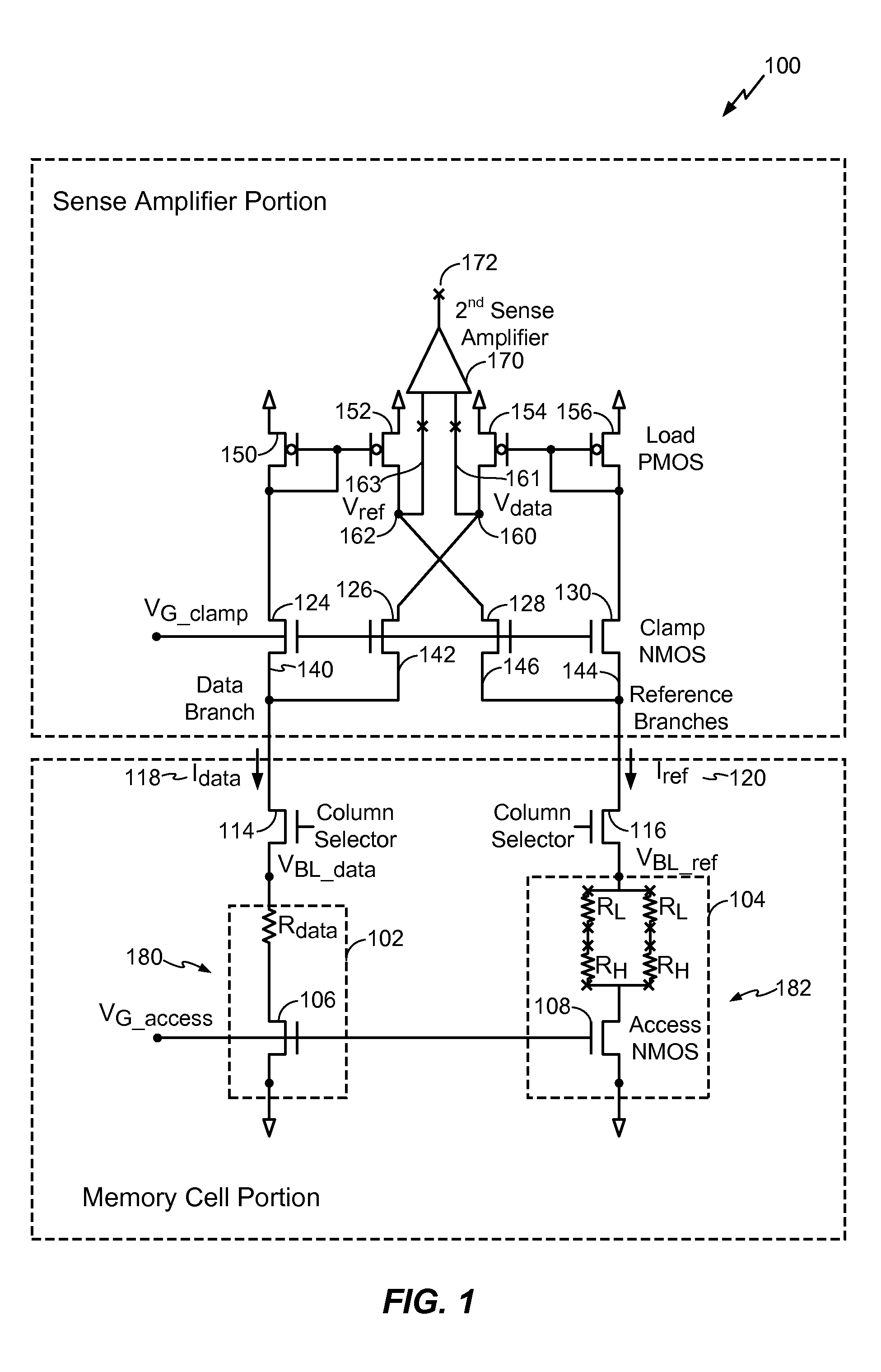

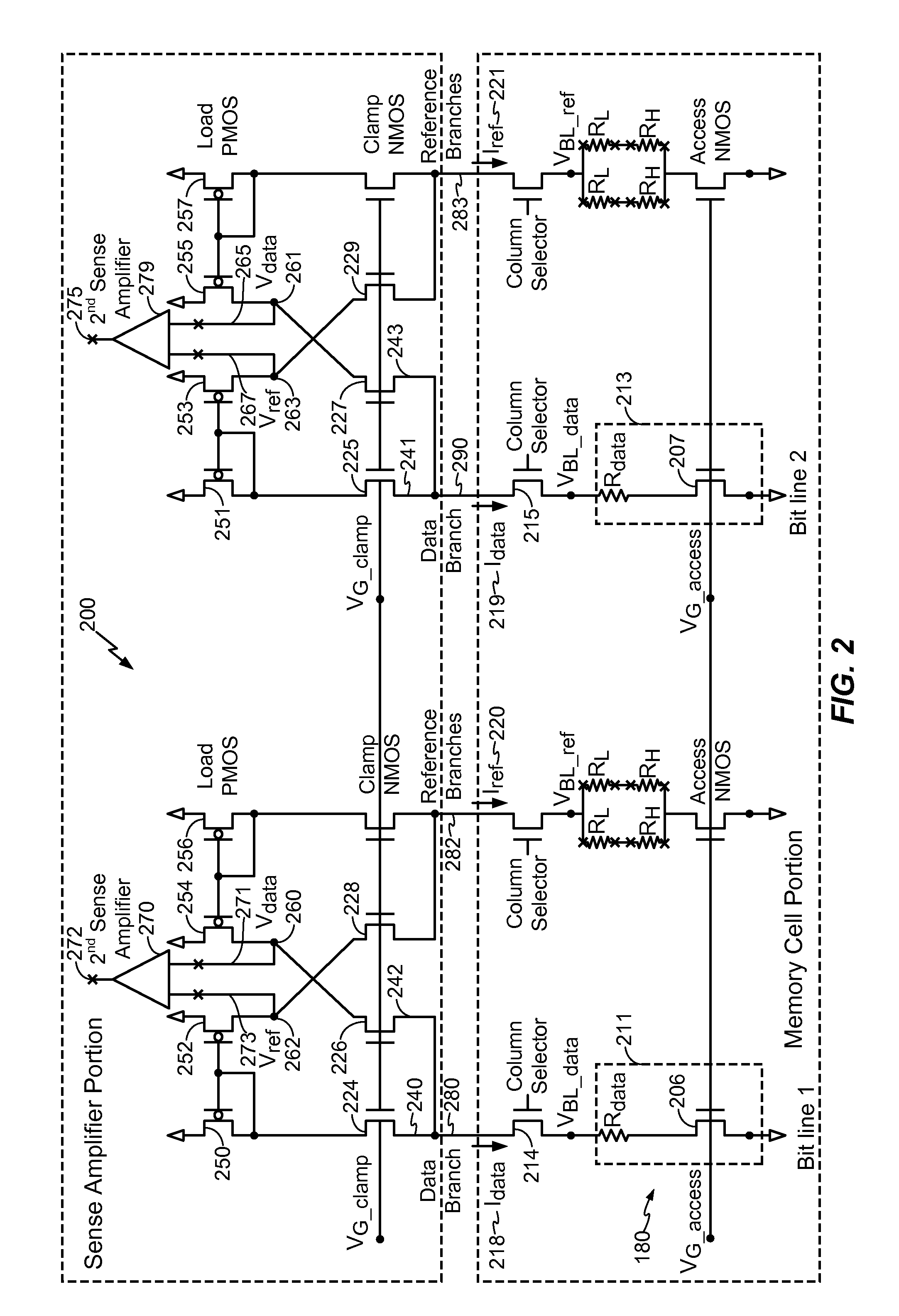

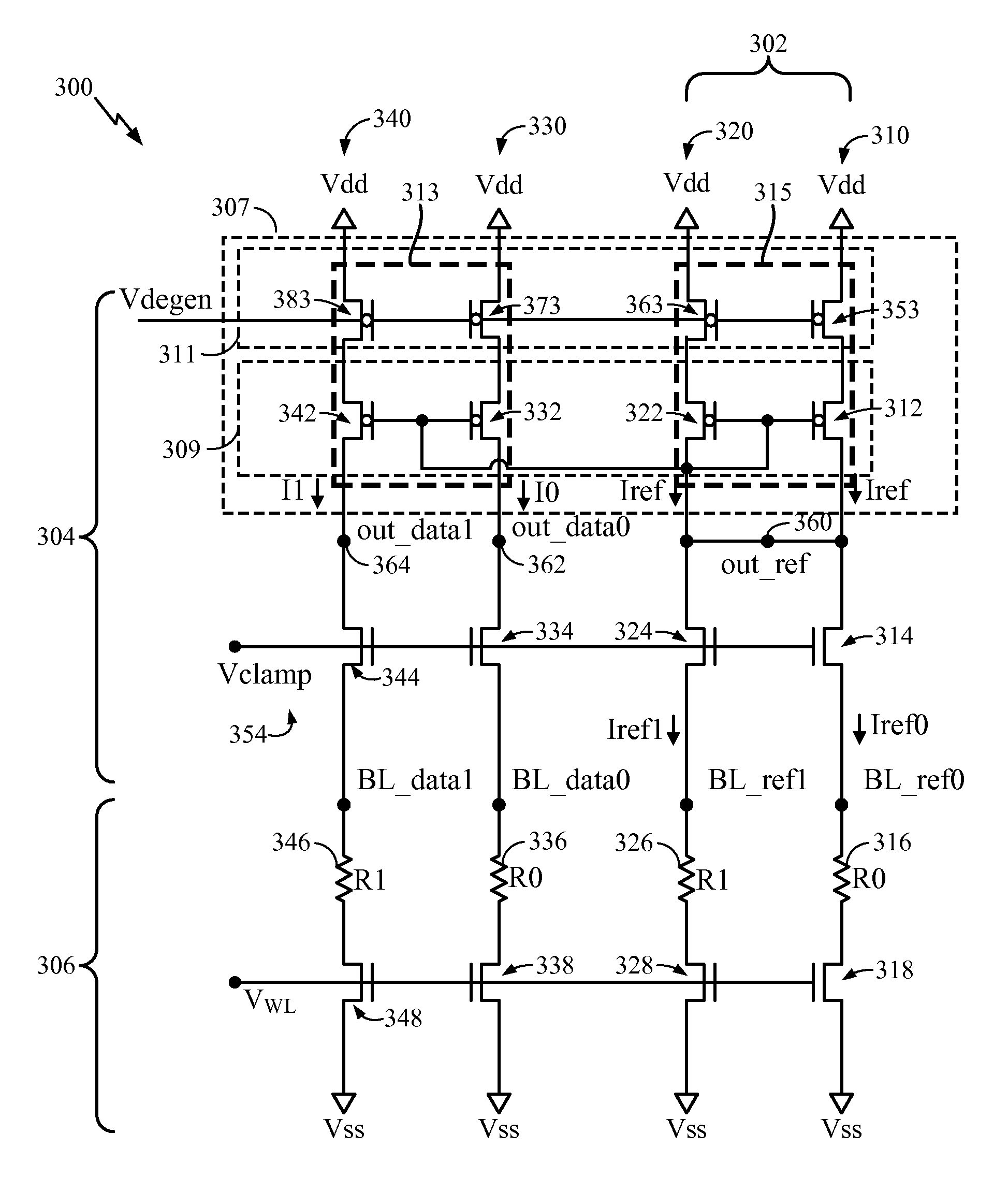

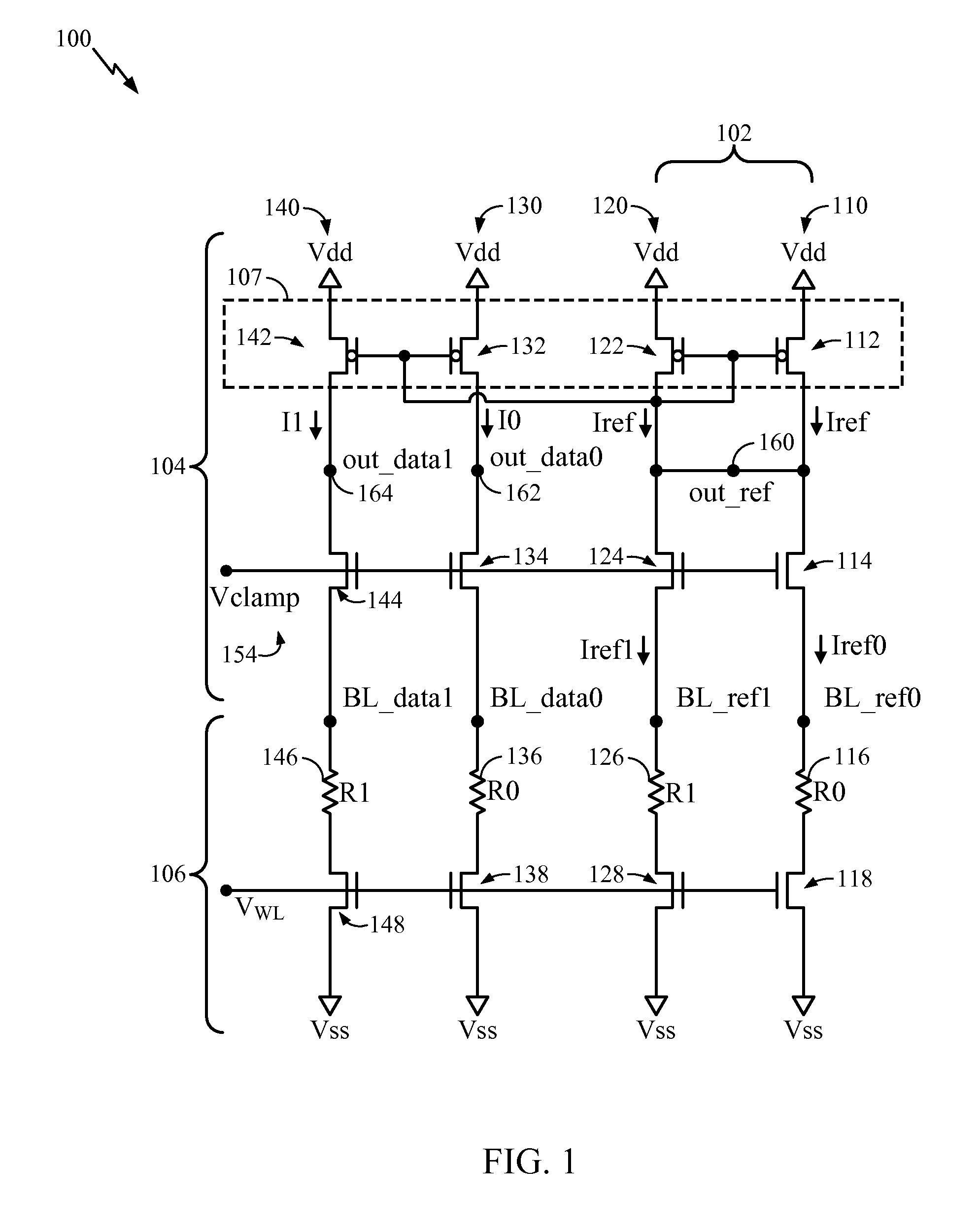

Split Path Sensing Circuit

A sensing circuit is disclosed. The sensing circuit includes a first path including a first resistive memory device and a second path including a reference resistive memory device. The first path is coupled to a first split path including a first load transistor and to a second split path including a second load transistor. The second path is coupled to a third split path including a third load transistor and to a fourth split path including a fourth load transistor.

Owner:QUALCOMM INC +1

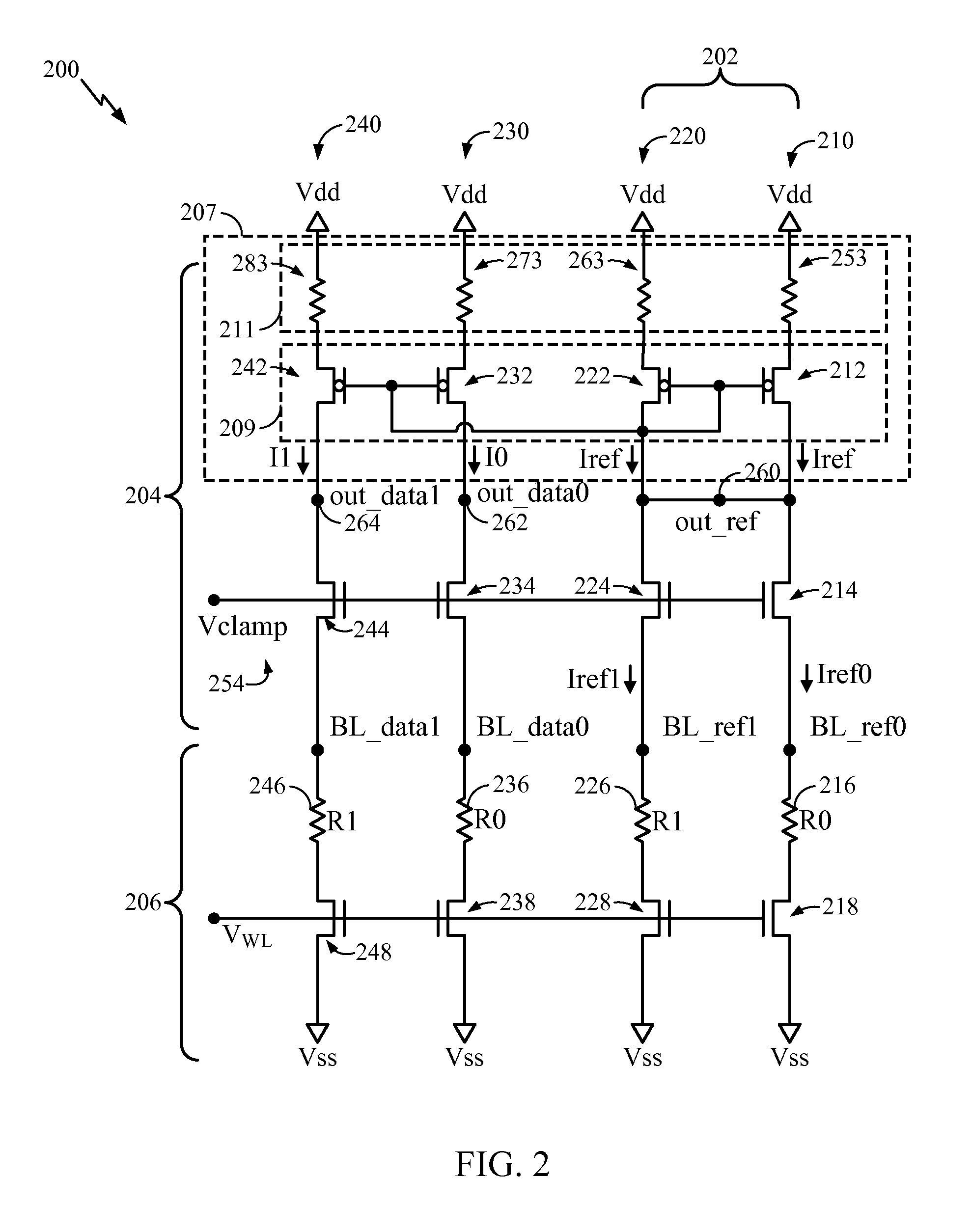

Balancing A Signal Margin Of A Resistance Based Memory Circuit

A resistance based memory circuit is disclosed. The circuit includes a first transistor load of a data cell and a bit line adapted to detect a first logic state. The bit line is coupled to the first transistor load and coupled to a data cell having a magnetic tunnel junction (MTJ) structure. The bit line is adapted to detect data having a logic one value when the bit line has a first voltage value, and to detect data having a logic zero value when the bit line has a second voltage value. The circuit further includes a second transistor load of a reference cell. The second transistor load is coupled to the first transistor load, and the second transistor load has an associated reference voltage value. A characteristic of the first transistor load, such as transistor width, is adjustable to modify the first voltage value and the second voltage value without substantially changing the reference voltage value.

Owner:QUALCOMM INC +1

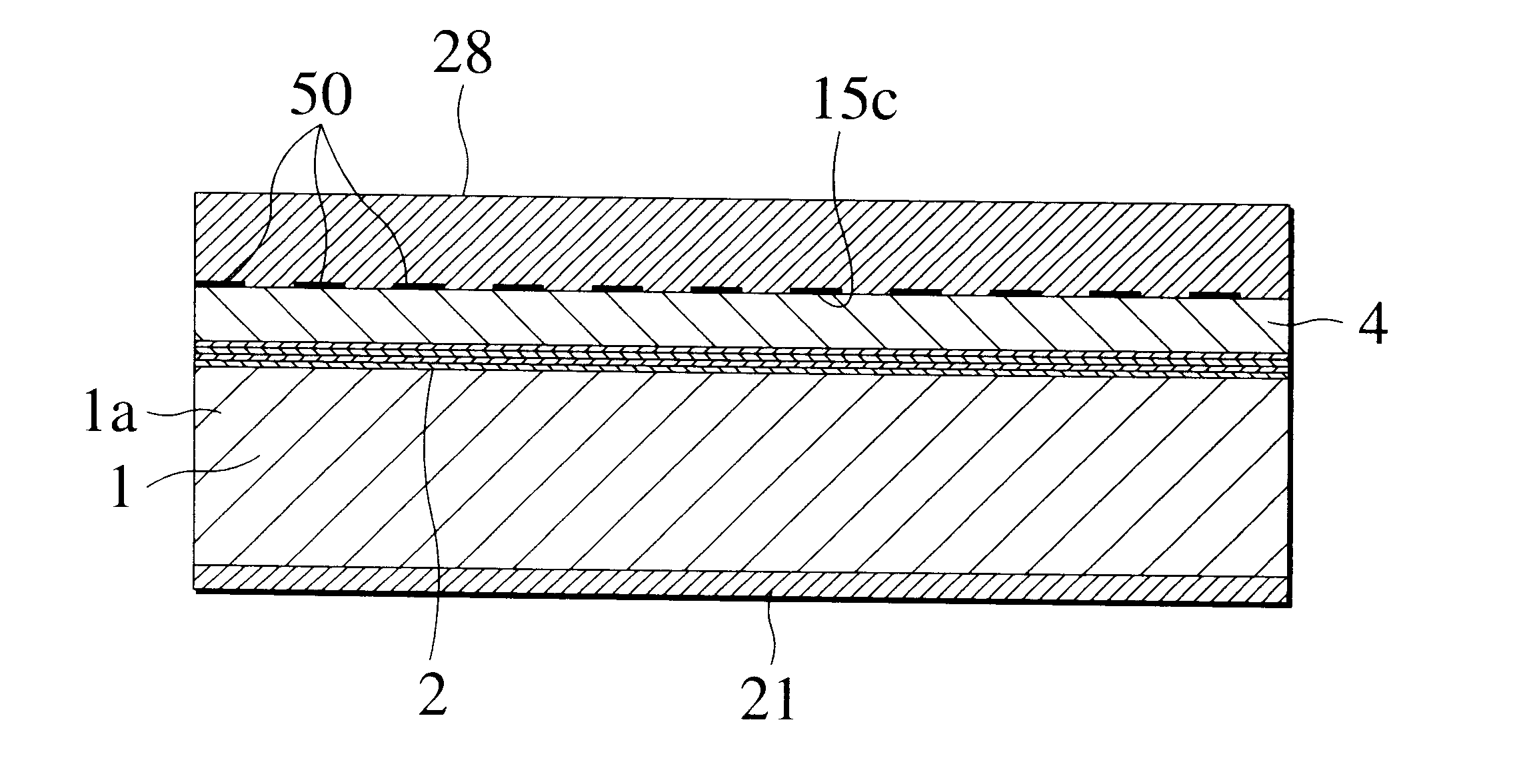

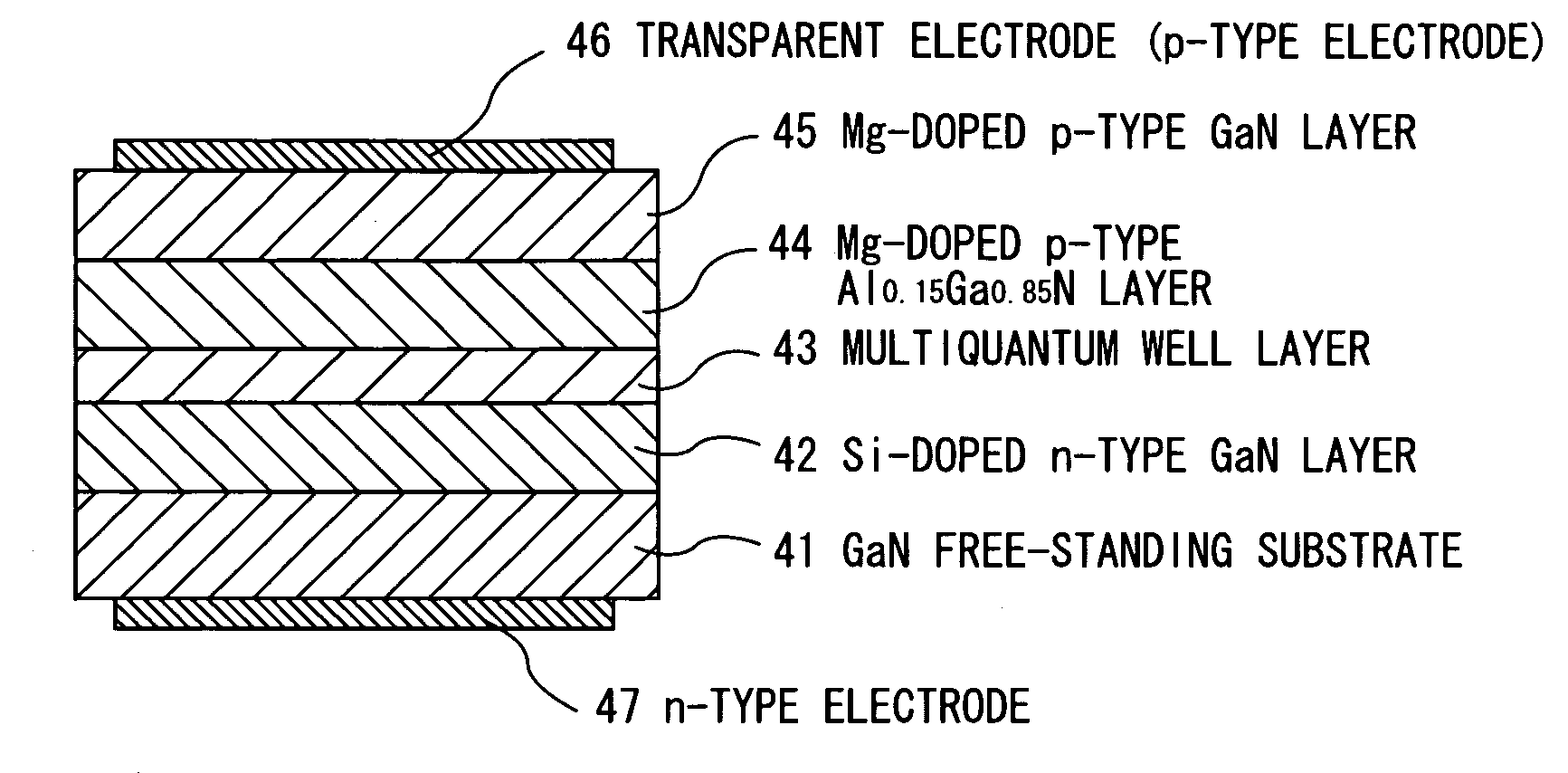

Optoelectronic device and laser diode

InactiveUS6327413B1Simple configurationReduce manufacturing stepsLaser detailsLaser optical resonator constructionWaveguideElectric field

Both an electric energy applying mechanism and an optical waveguide mechanism can be provided to an ITO layer (transparent electrode) by constituting an optical waveguide so as that the guided mode profile spread into the ITO layer. Also a bonding pad is provided to supply a power and apply an electric field onto the ITO layer. Accordingly, a device structure can be simplified and thus improvement in yield of the optoelectronic device having an optical waveguide and improvement in parameters of the optoelectronic device can be achieved.

Owner:KK TOSHIBA

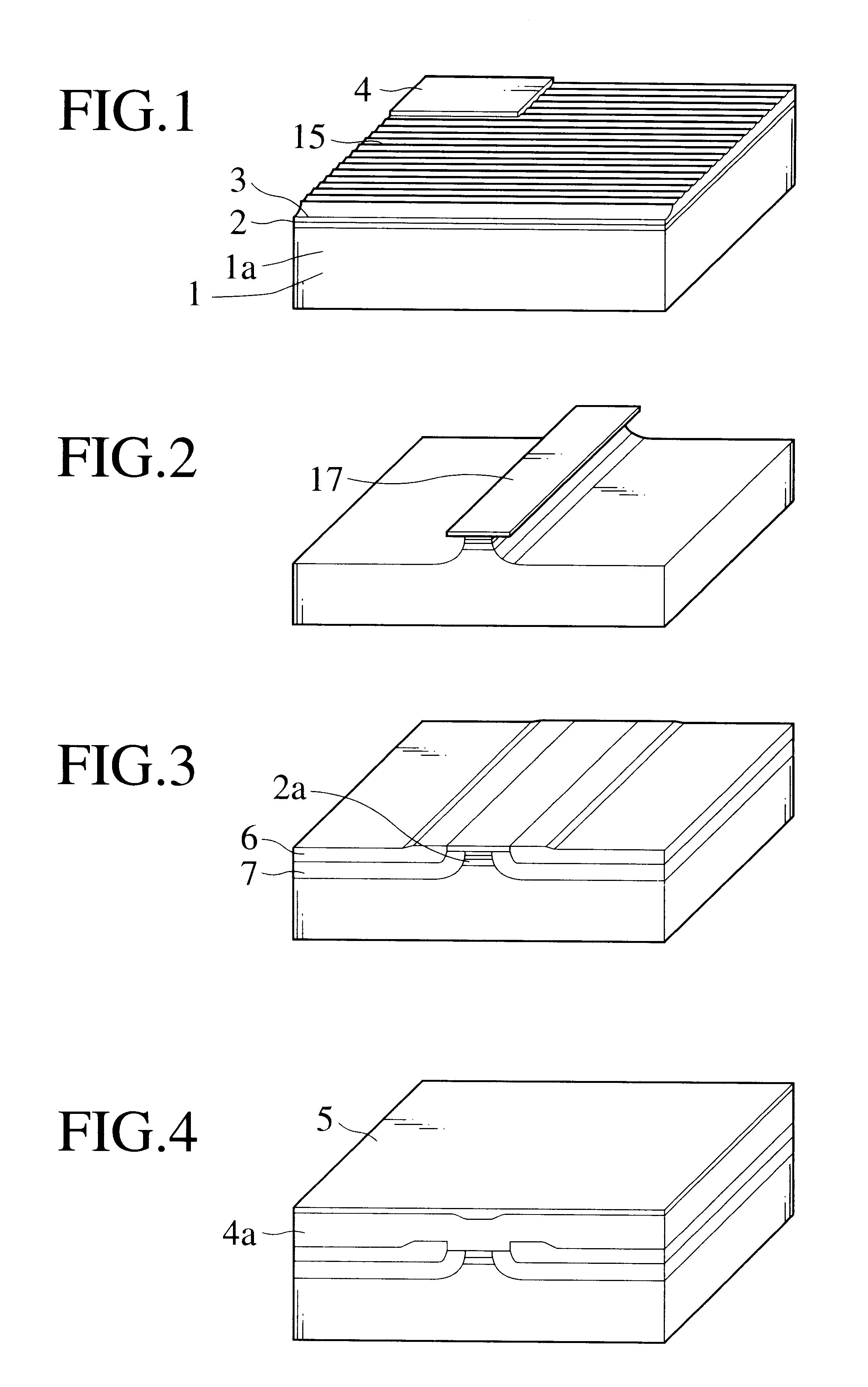

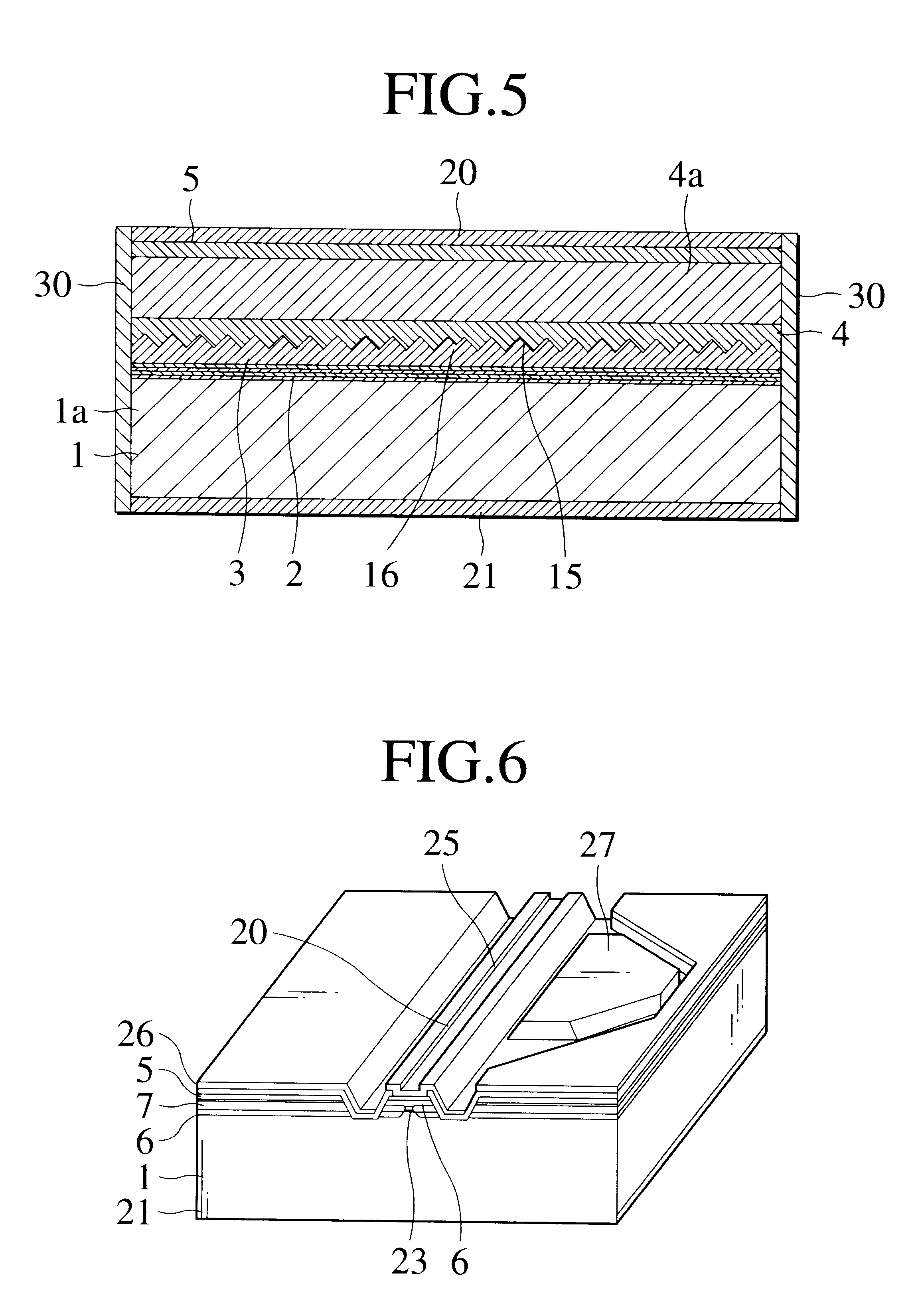

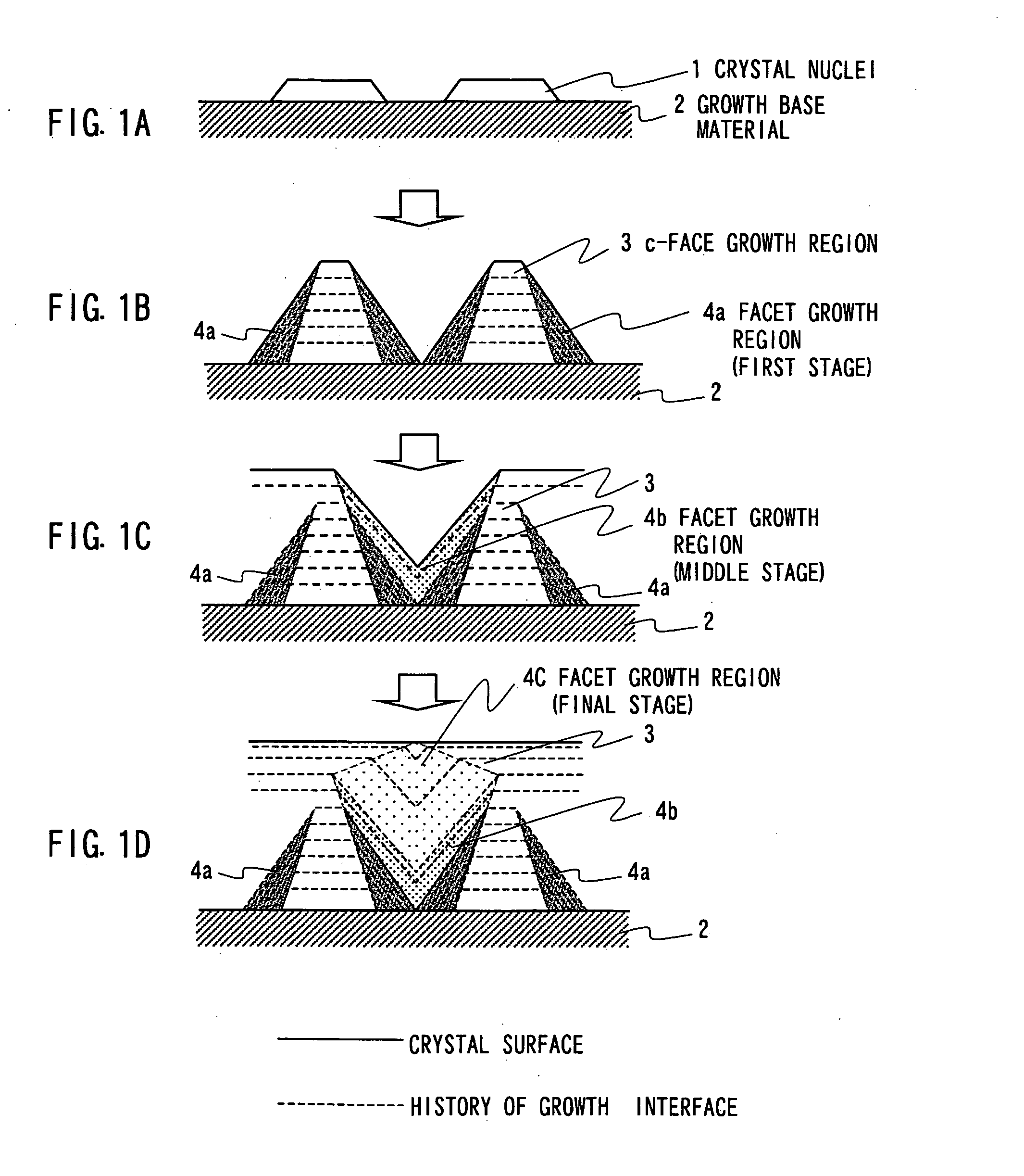

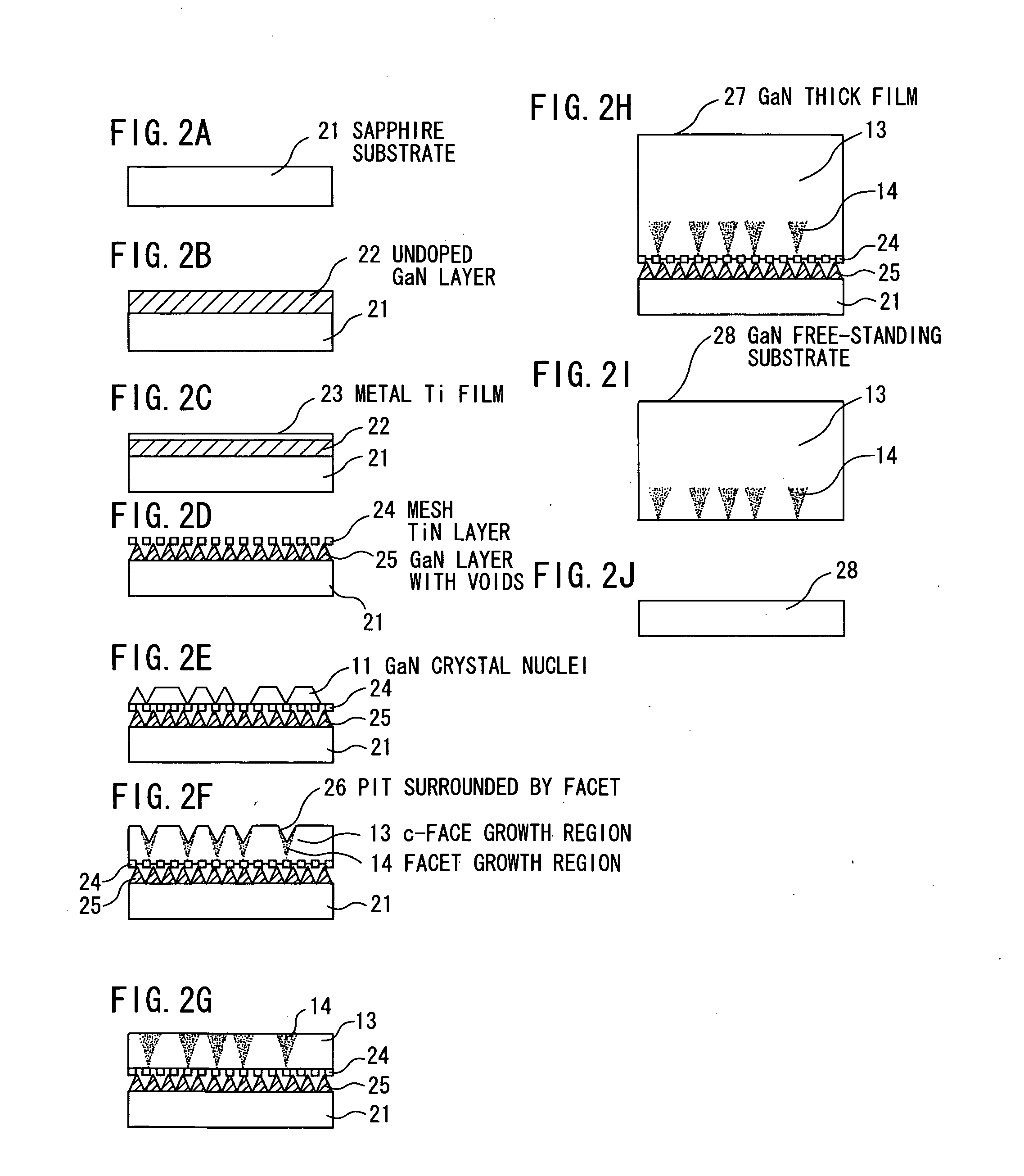

Nitride semiconductor free-standing substrate

ActiveUS20070290228A1Reduce variationImprove device yieldPolycrystalline material growthSolid-state devicesLattice constantNitride semiconductors

A nitride semiconductor free-standing substrate formed of a free-standing nitride-based compound semiconductor crystal that has a variation in lattice constant of ±12 ppm or less.

Owner:SUMITOMO CHEM CO LTD

Backside thinning of image array devices

InactiveUS7042060B2Poor resolutionMaximize fill factorSolid-state devicesDiodeImage resolutionImage contrast

Backthinning in an area selective manner is applied to imaging sensors 12 for use in electron bombarded devices. A further arrangement results in an array of collimators 51 aligned with pixels 42 or groups of pixels providing improved image contrast of such image sensor. Provision of a thin P-doped layer 52 on the illuminated rear surface provides both a diffusion barrier resulting in improved resolution and a functional shield for reference pixels. A gradient in concentration of P-doped layer 52 optimizes electron collection at the pixel array.

Owner:EOTECH LLC

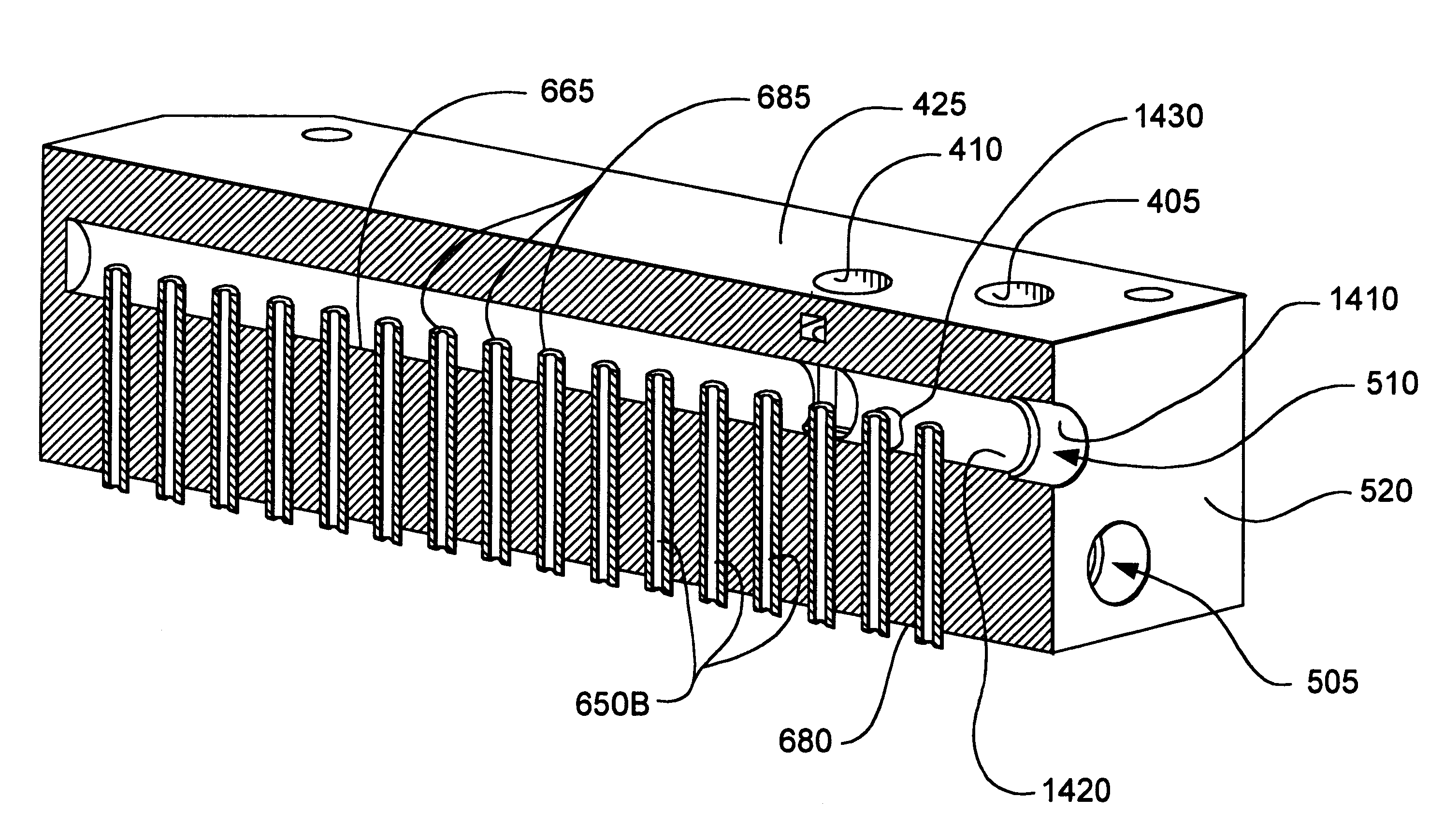

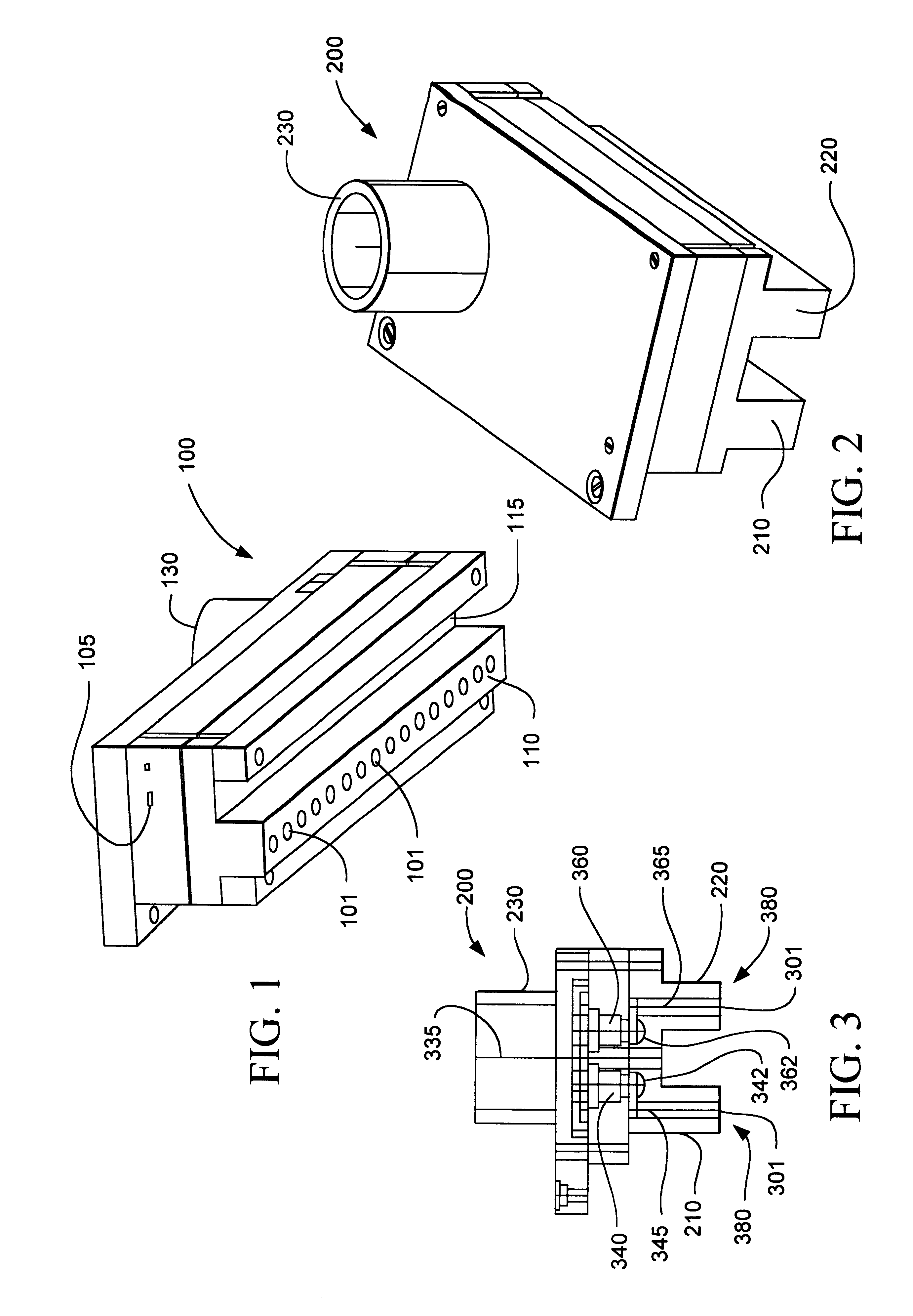

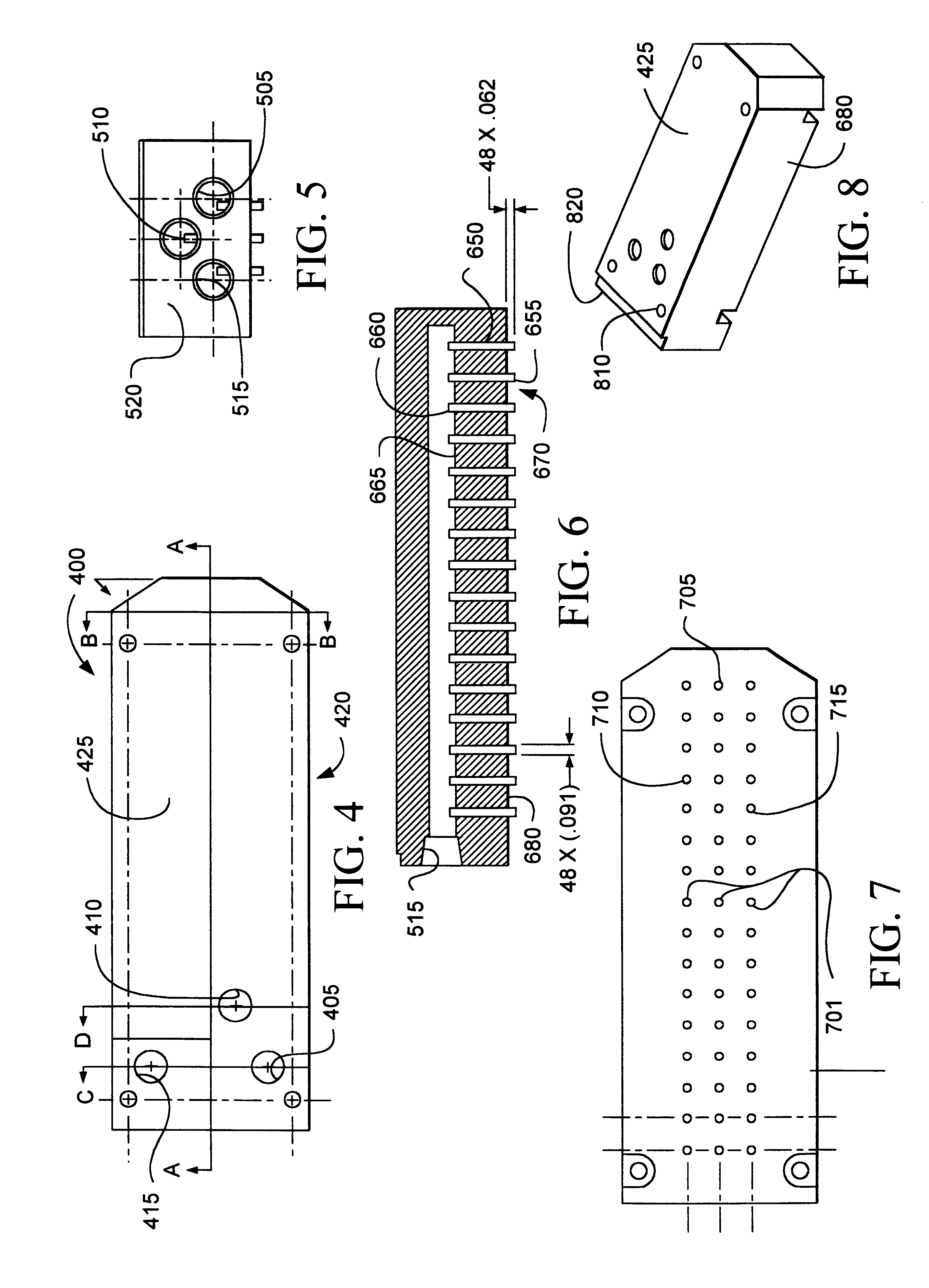

Yield and line width performance for liquid polymers and other materials

InactiveUS6248171B1Improves CD control capabilityIncrease productionLiquid surface applicatorsSemiconductor/solid-state device manufacturingEngineeringMechanical engineering

Systems and methods are described for improved yield and line width performance for liquid polymers and other materials. A method for minimizing precipitation of developing reactant by lowering a sudden change in pH includes: developing at least a portion of a polymer layer on a substrate with an initial charge of a developer fluid; then rinsing the polymer with an additional charge of the developer fluid so as to controllably minimize a subsequent sudden change in pH; and then rinsing the polymer with a charge of another fluid. An apparatus for minimizing fluid impingement force on a polymer layer to be developed on a substrate includes: a nozzle including: a developer manifold adapted to supply a developer fluid; a plurality of developer fluid conduits coupled to the developer manifold; a rinse manifold adapted to supply a rinse fluid; and a plurality of rinse fluid conduits coupled to the developer manifold. The developer manifold and the rinse manifold can be staggered so as to reduce an external width of the nozzle compared to a nominal external width of the nozzle achievable without either intersecting the fluid manifold and the another manifold or staggering the fluid manifold and the another manifold. The systems and methods provide advantages including improve yield via reduced process-induced defect and partial counts, and improved critical dimension (CD) control capability.

Owner:ASML HLDG NV

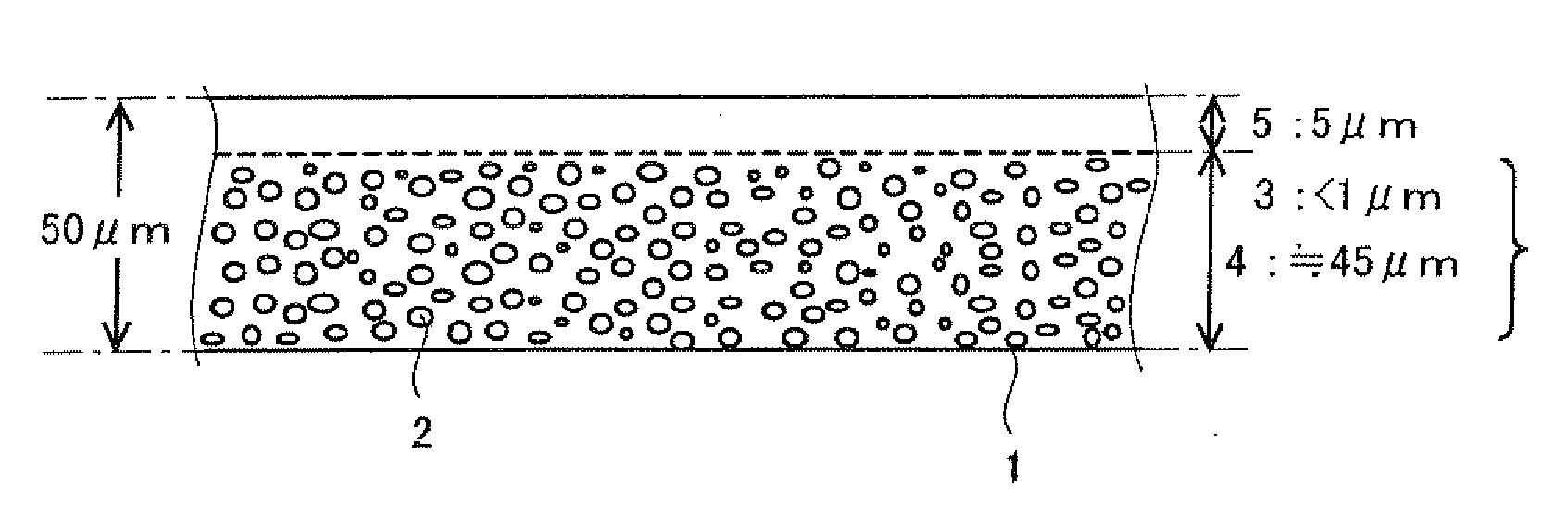

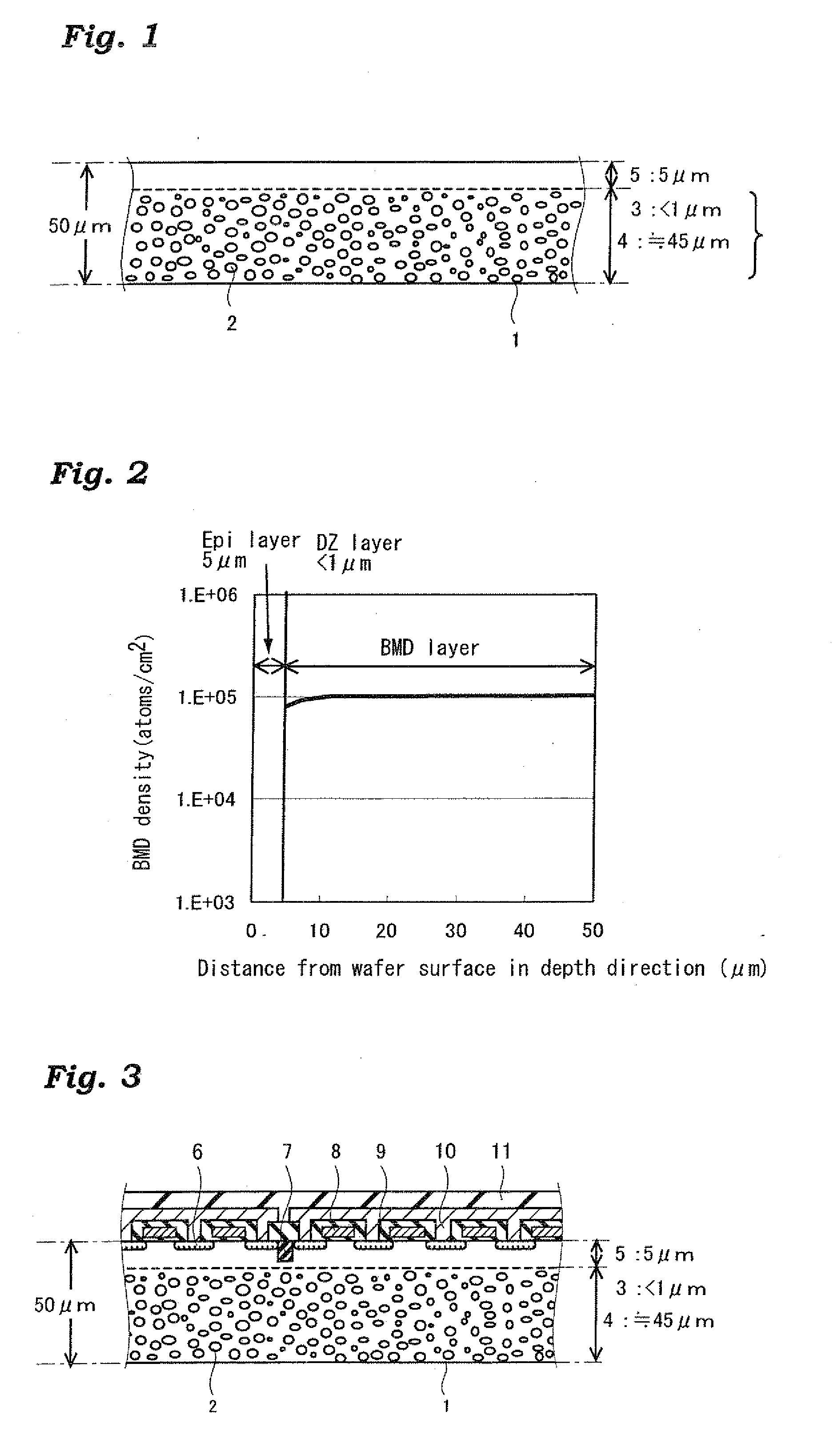

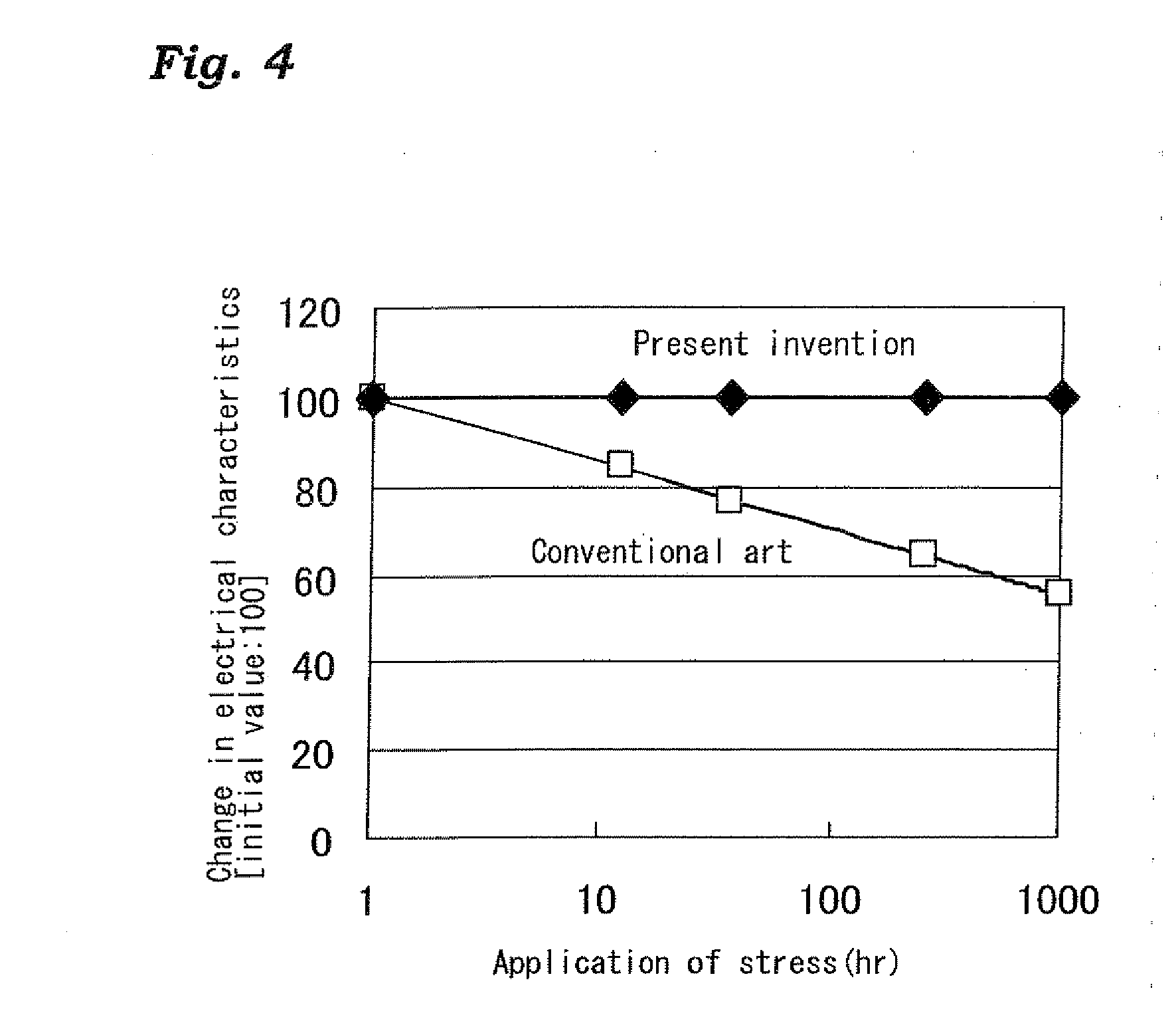

Semiconductor device and method for fabricating same

InactiveUS20090102024A1DegradationImprove device yieldSemiconductor/solid-state device detailsSolid-state devicesDevice formMetal impurities

A semiconductor device has an IC chip with a thickness of equal to or less than 100 μm and includes a semiconductor substrate. A device forming region is within the depth of approximately equal to or less than 5 μm from a surface of the semiconductor substrate, and a total thickness of the semiconductor substrate is from 5 μm to 100 μm. A BMD layer for carrying out gettering of metal impurities is provided immediately under the device forming region. Since a gettering site is provided immediately under the device forming region, in a device or the like of which extreme thinness is required, degradation of device characteristics and reliability due to contamination of metal impurities can be prevented, and stabilize and improve the device yield. The present invention inhibits degradation of device characteristics and reliability caused by contamination of metal impurities, in a device of which lamination of device chips is required or in a device of which extreme chip thinness for an IC card and the like is required, in an attempt to cope with an enlarged capacity of the device.

Owner:SHARP KK

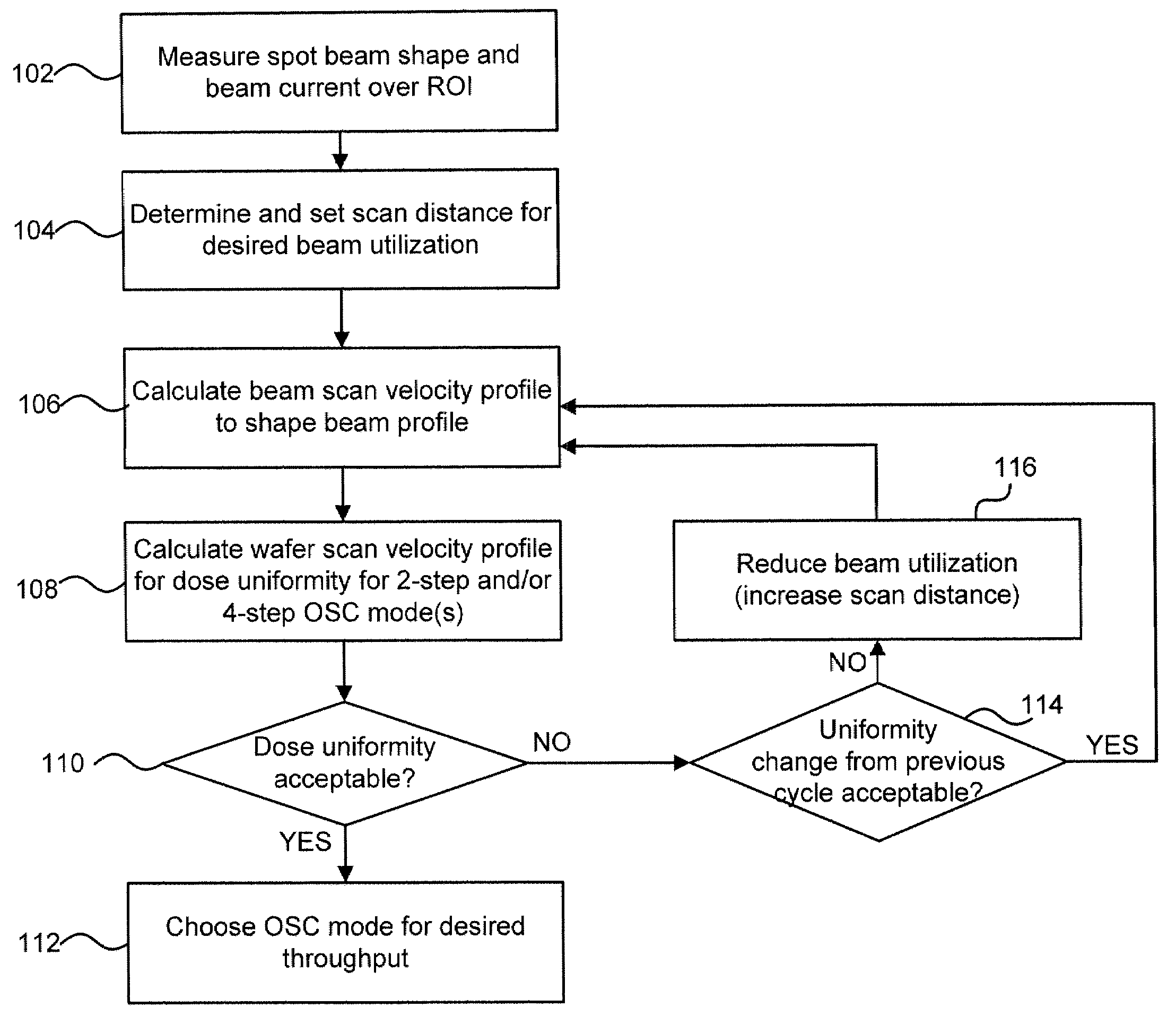

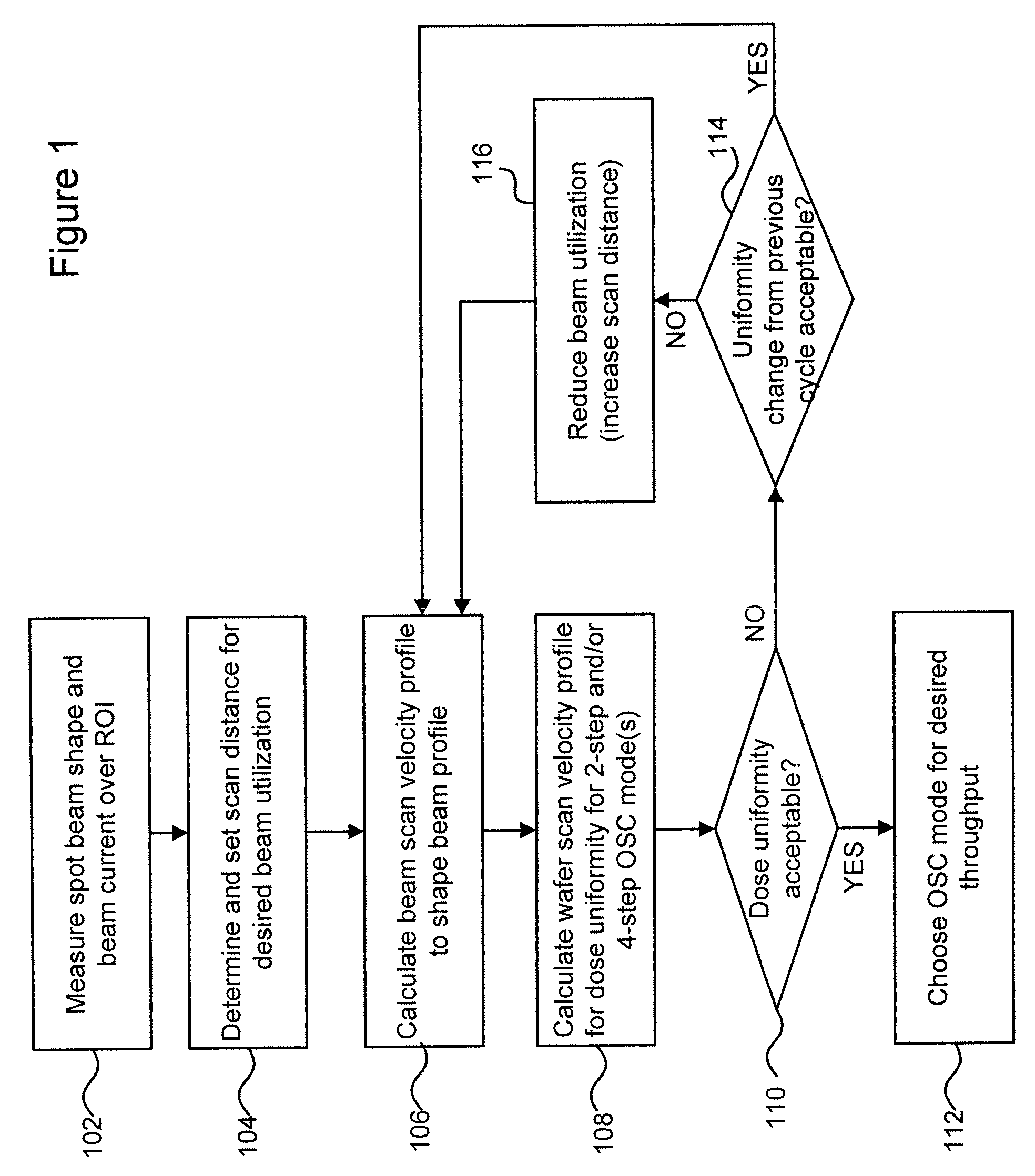

Technique for improving ion implantation throughput and dose uniformity

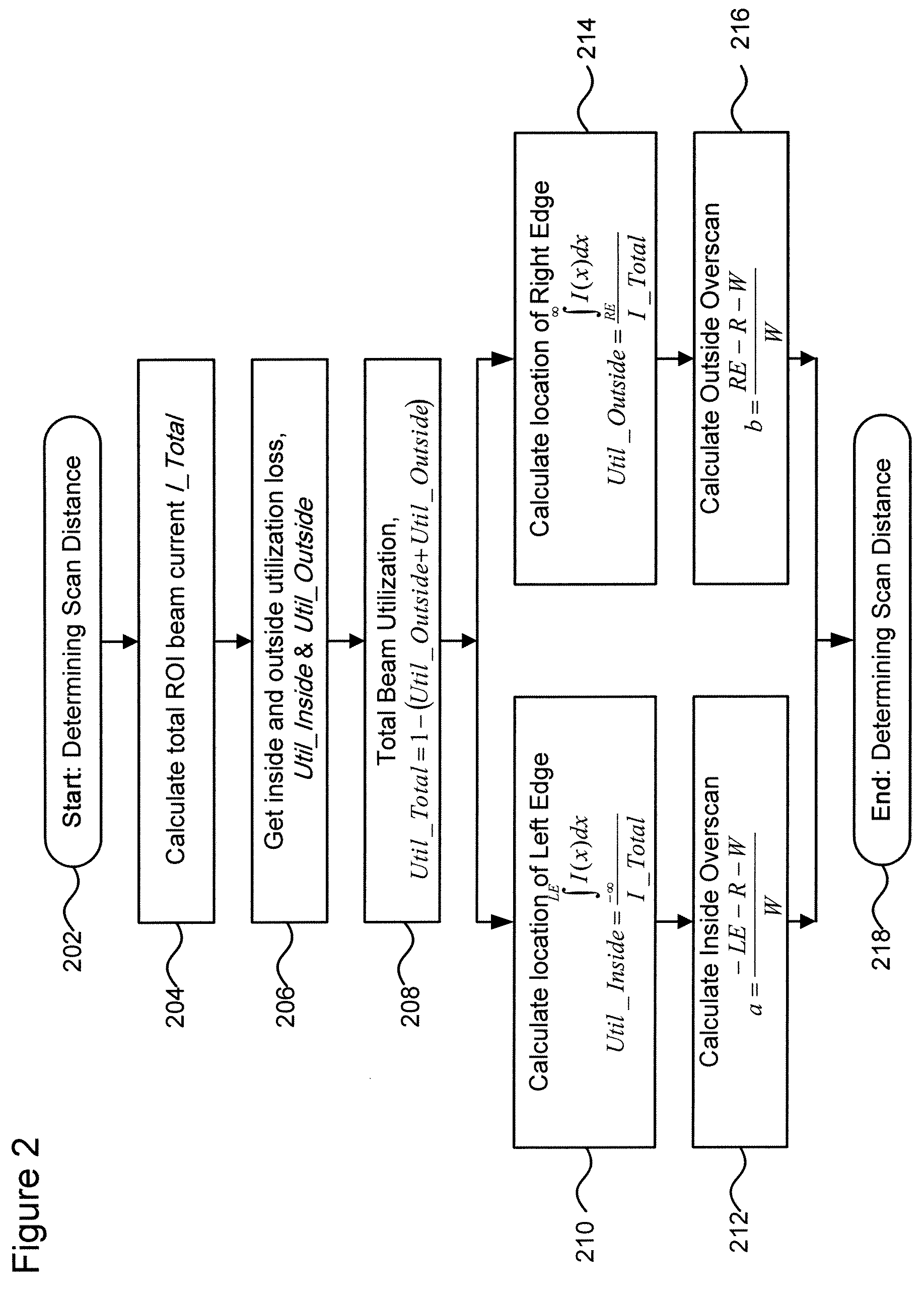

ActiveUS20080078953A1Improve device yieldImprove beam utilizationElectric discharge tubesIrradiation devicesDensity distributionDose uniformity

A technique for improving ion implantation throughput and dose uniformity is disclosed. In one exemplary embodiment, a method for improving ion implantation throughput and dose uniformity may comprise measuring an ion beam density distribution in an ion beam. The method may also comprise calculating an ion dose distribution across a predetermined region of a workpiece that results from a scan velocity profile, wherein the scan velocity profile comprises a first component and a second component that control a relative movement between the ion beam and the workpiece in a first direction and a second direction respectively, and wherein the ion dose distribution is based at least in part on the ion beam density distribution. The method may further comprise adjusting at least one of the first component and the second component of the scan velocity profile to achieve a desired ion dose distribution in the predetermined region of the workpiece.

Owner:VARIAN SEMICON EQUIP ASSOC INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com