Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

774results about How to "Image degradation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

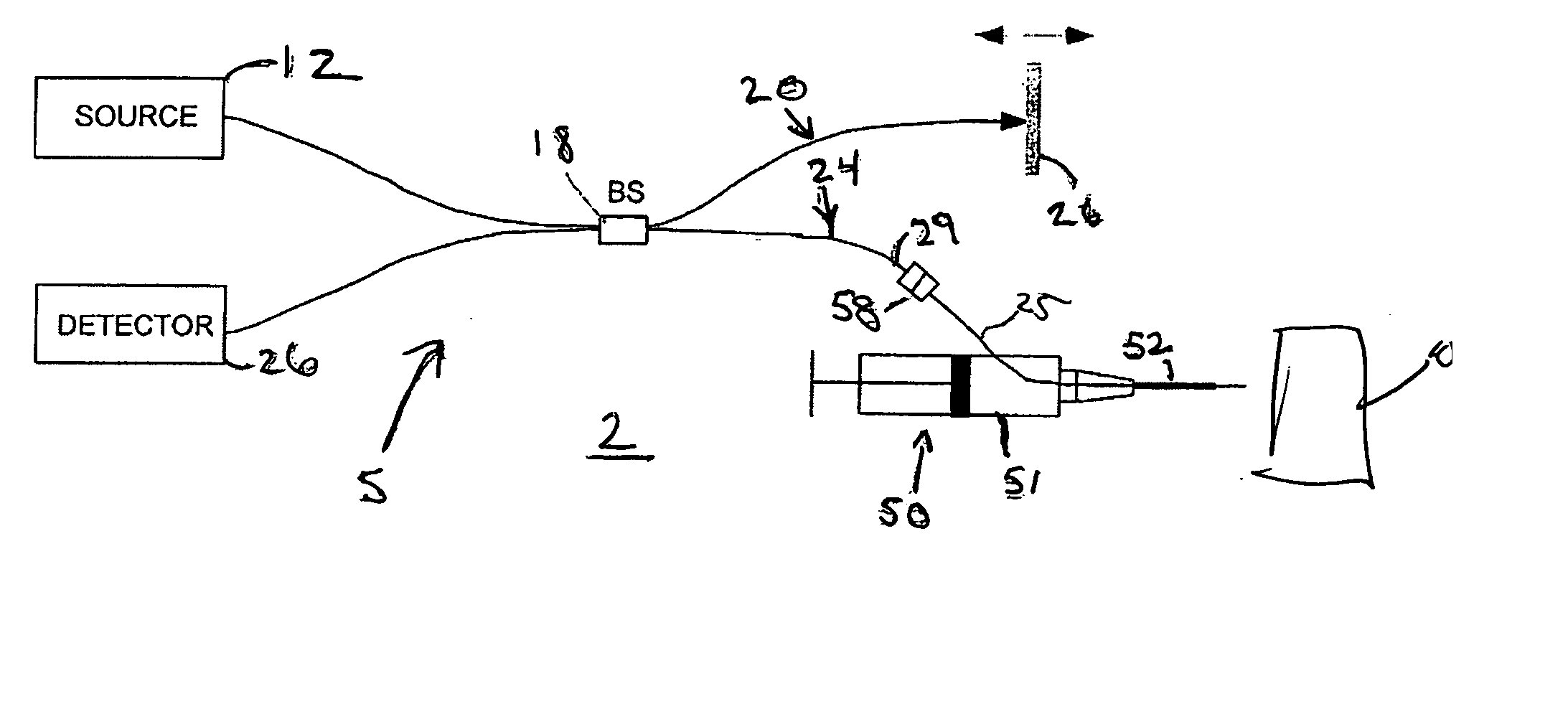

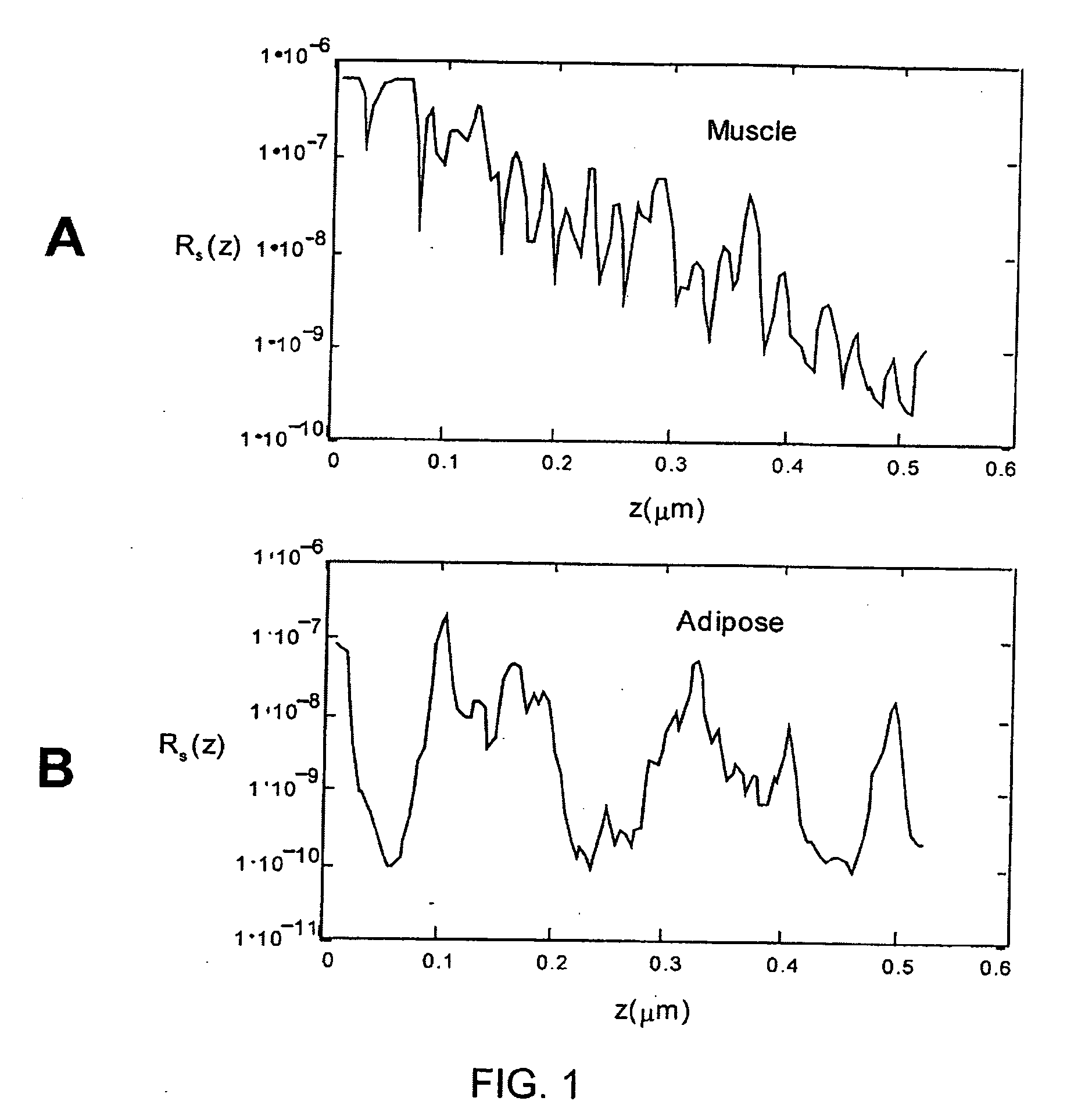

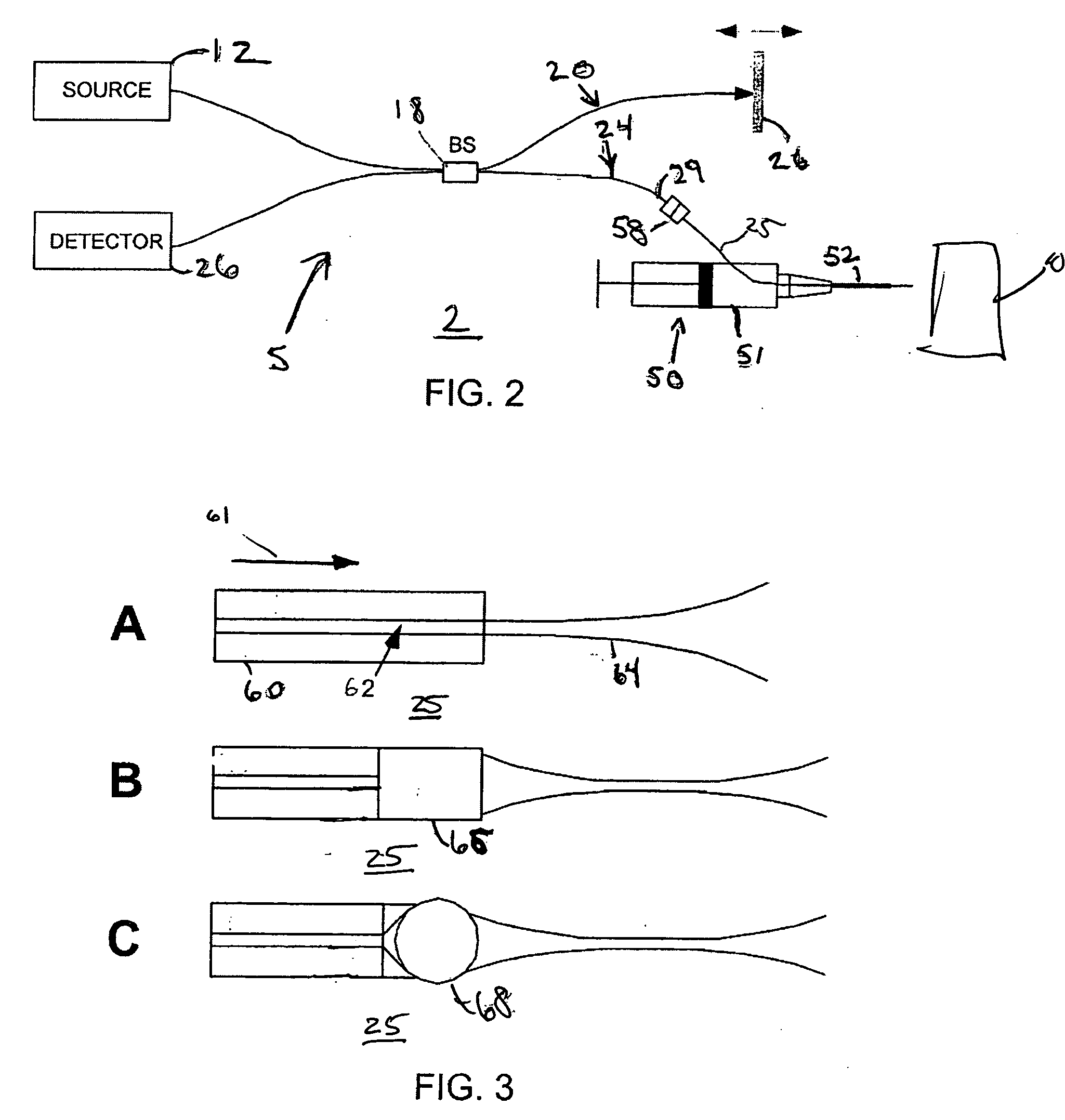

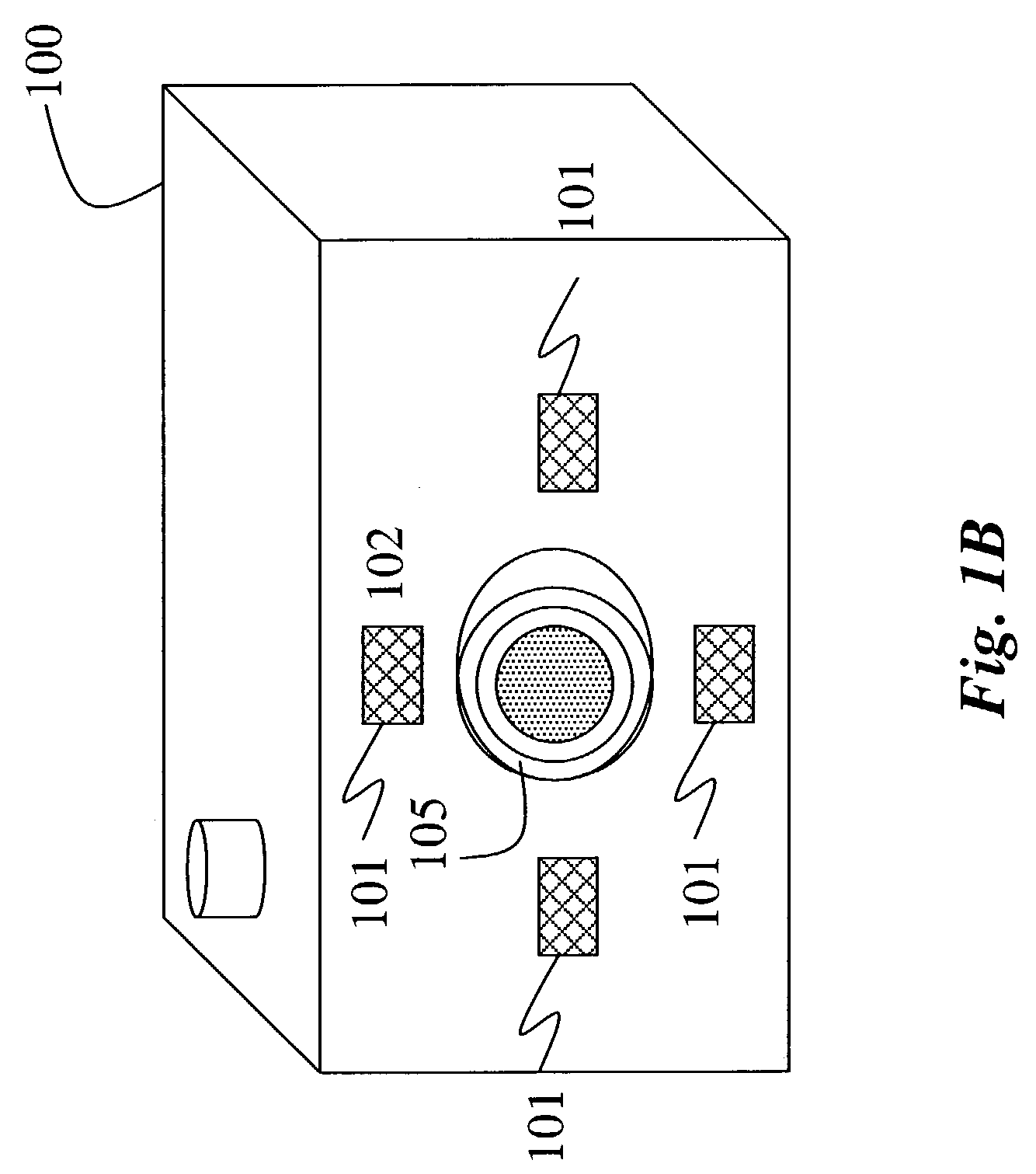

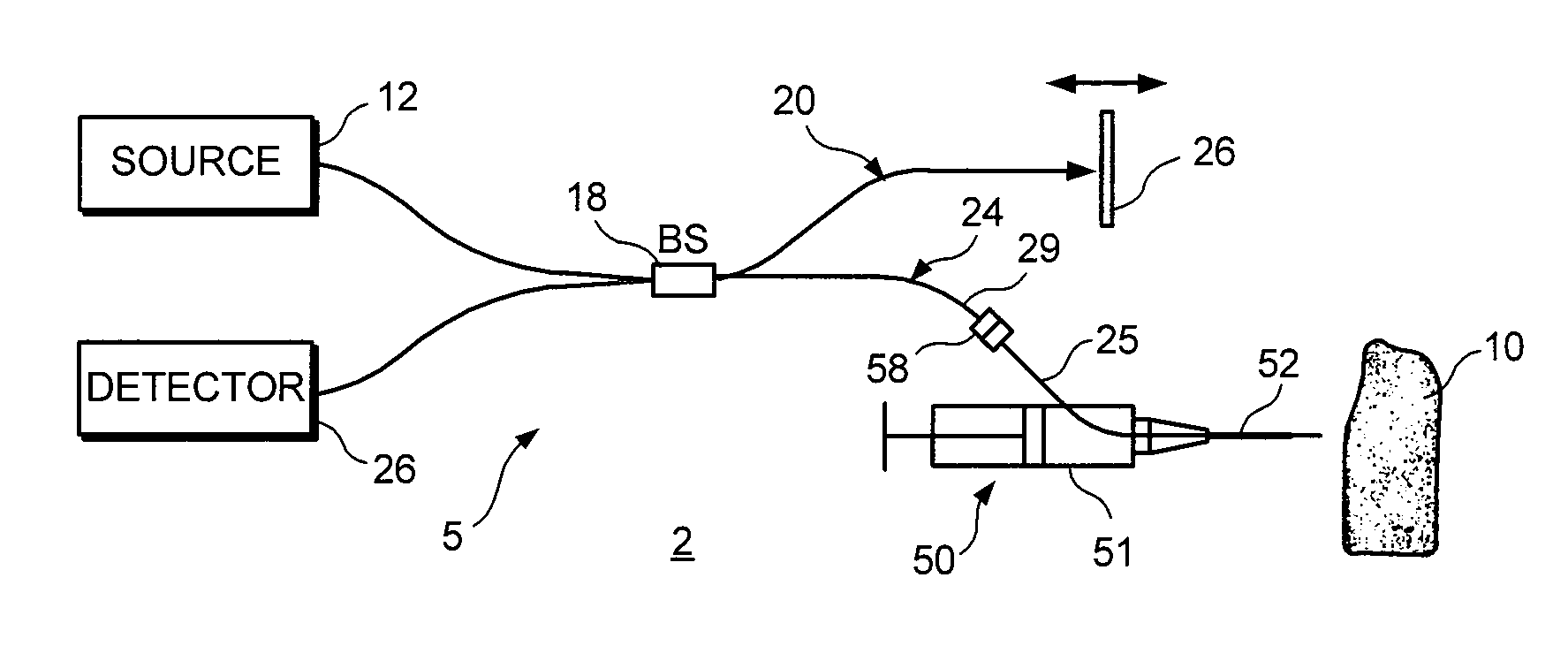

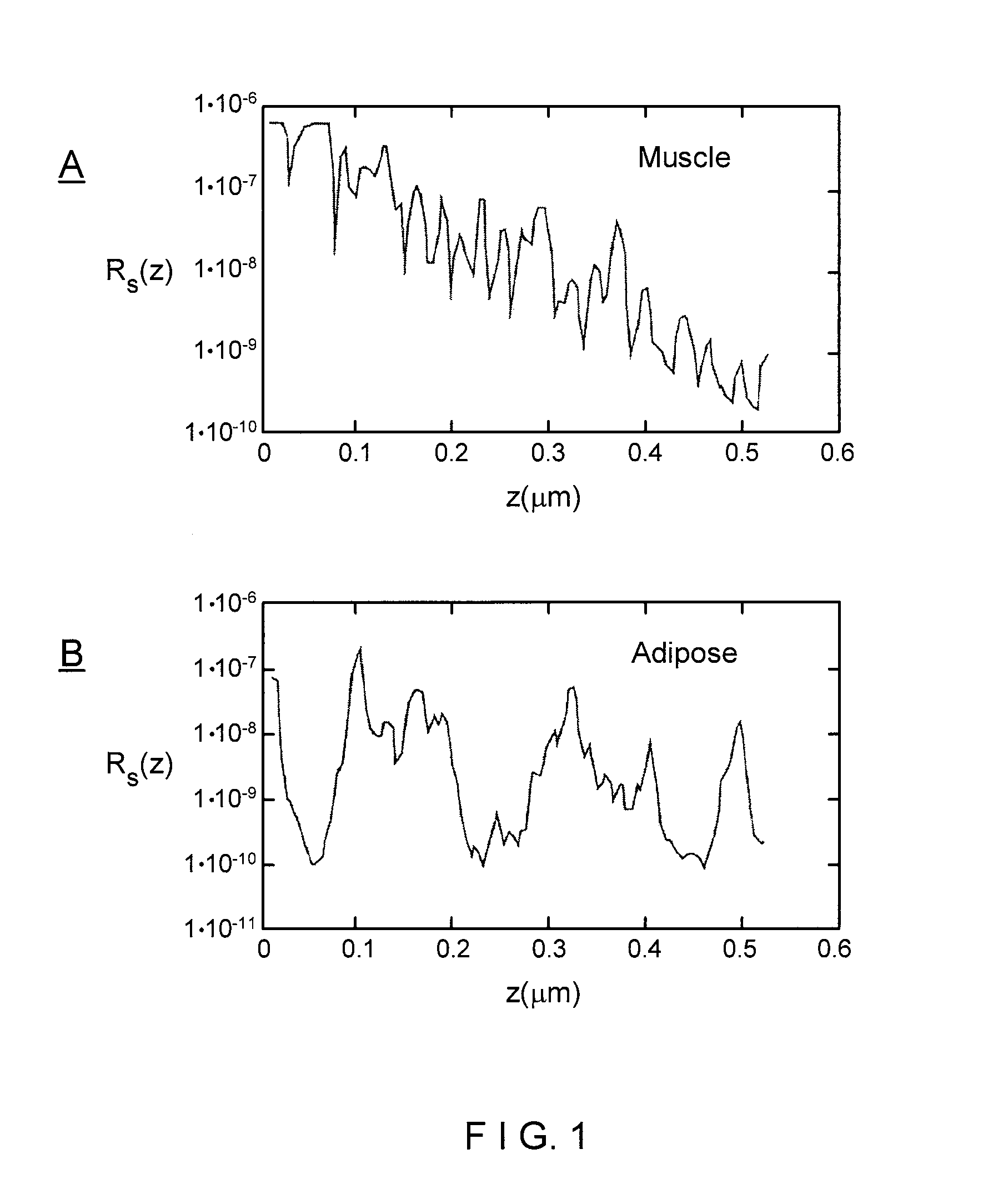

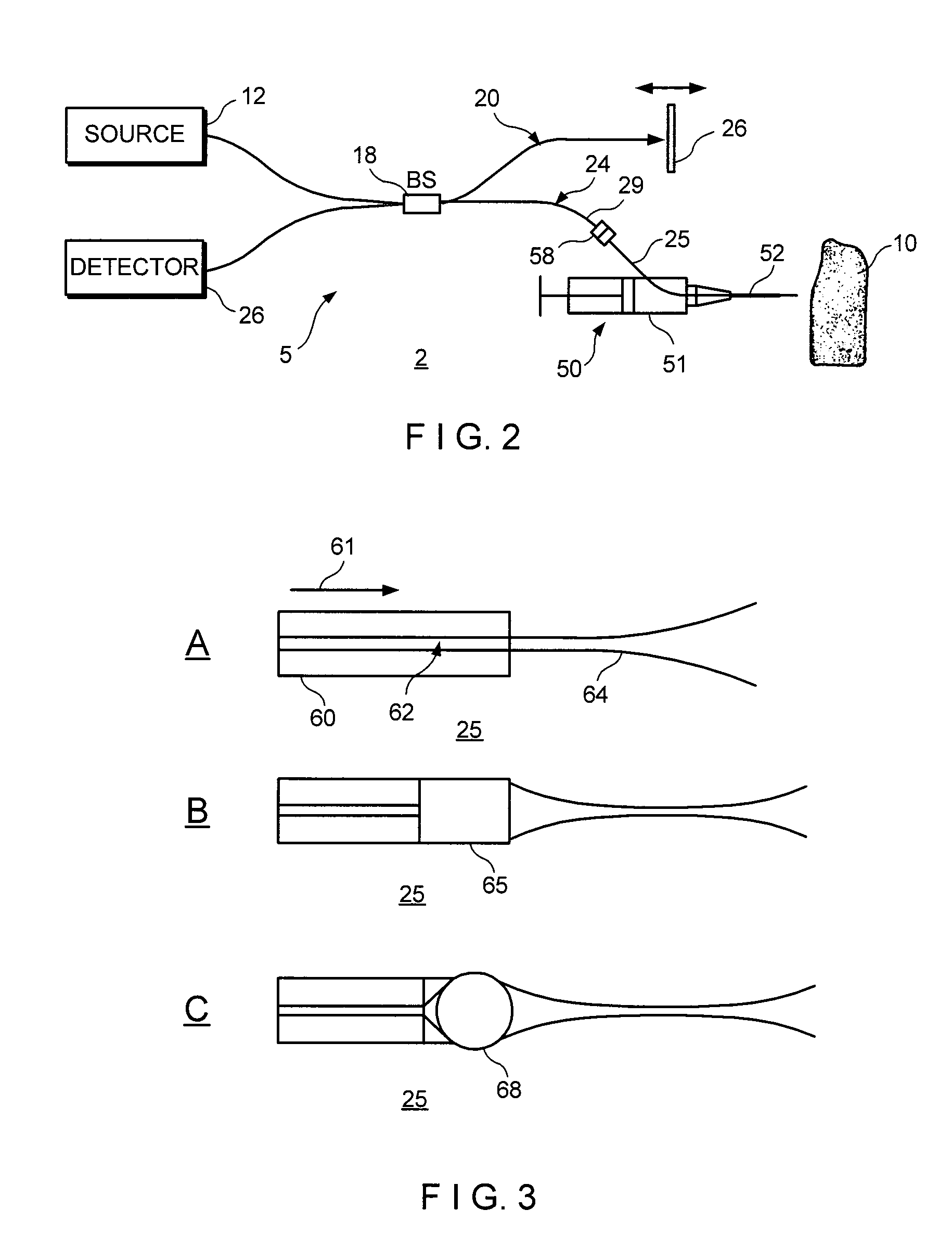

System and method for identifying tissue using low-coherence interferometry

ActiveUS20050004453A1Reduce requirementSimple and inexpensiveRadiation pyrometryCatheterNeedle biopsyTissue Differentiation

An apparatus for needle biopsy with real time tissue differentiation using one dimensional interferometric ranging imaging, comprising a biopsy device having a barrel and a needle, an optical fiber inserted in the needle, and a fiber optic imaging system connected to the optical fiber. The imaging system obtains images and compares the optical properties and patterns to a database of normalized tissue sample images to determine different tissue types. The physician performing the biopsy obtains feedback via a feedback unit associated with the biopsy device and which is connected to the imaging system. The feedback unit can provide visual, audible or vibratory feedback as to tissue type encountered when the needle is inserted toward the target tissue. The feedback unit can be programmed for different biopsy procedures so that the user can actuate a button to select a display or other feedback mechanism for the desired procedure and anticipated tissue to be encountered.

Owner:THE GENERAL HOSPITAL CORP

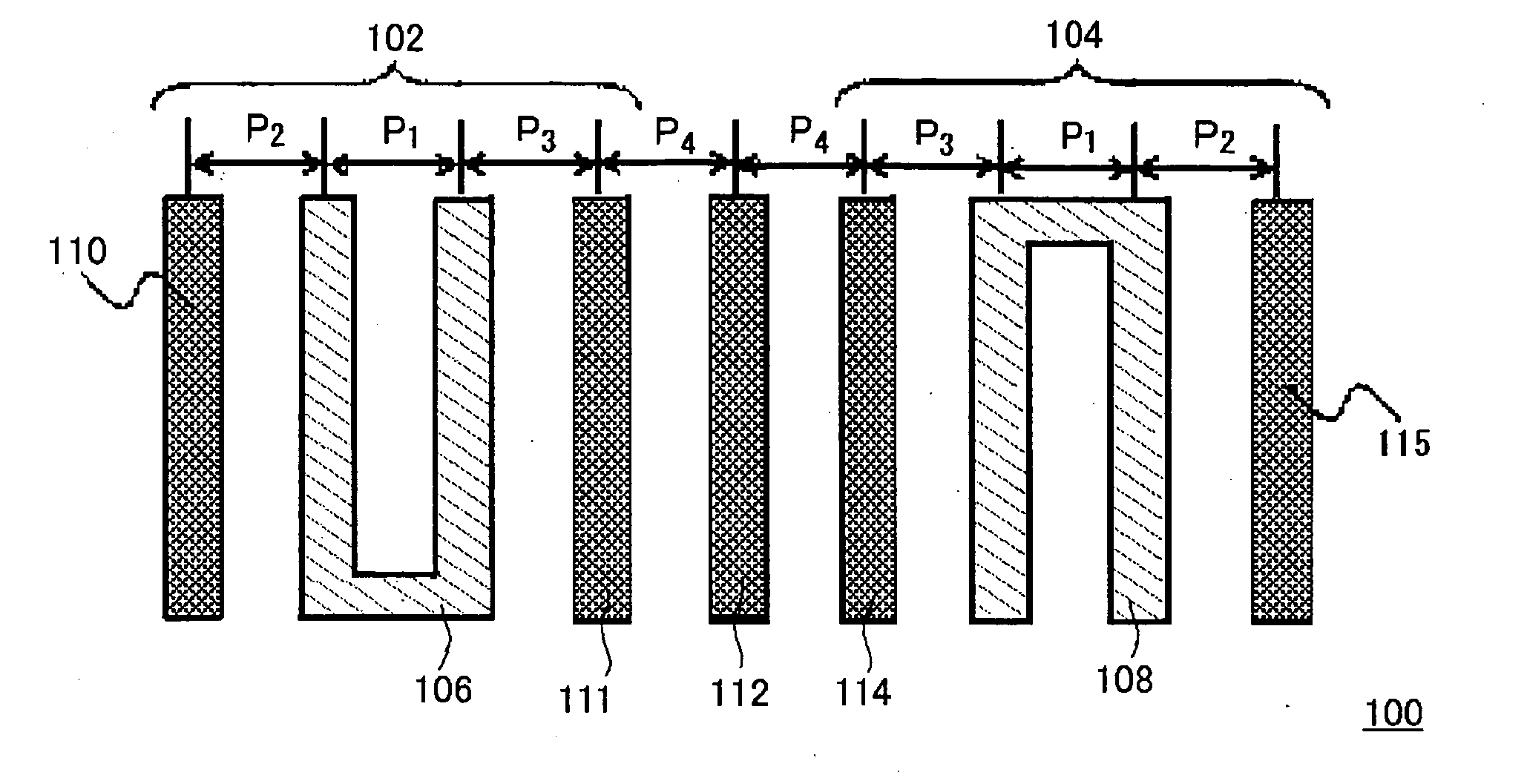

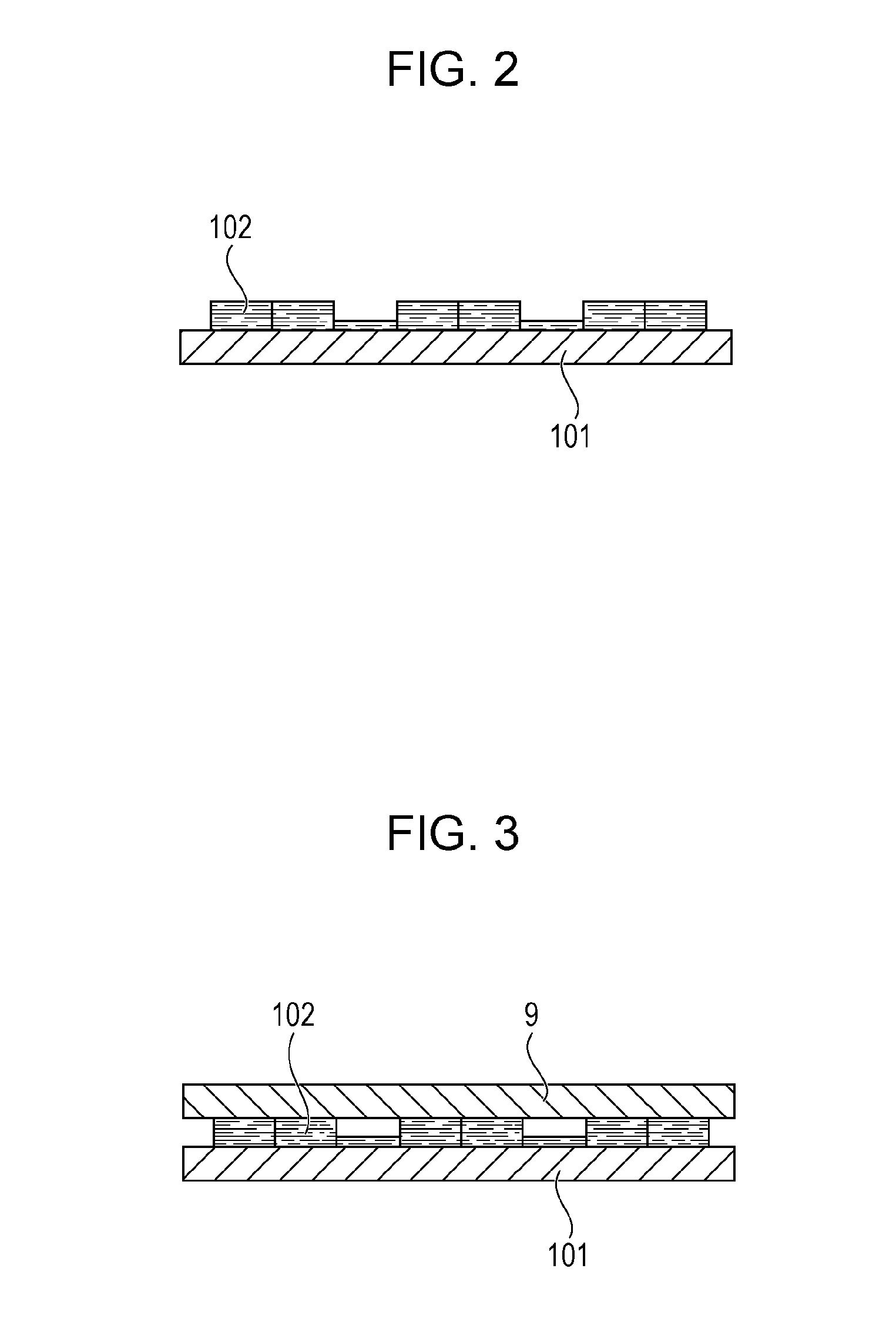

Interconnect layout method

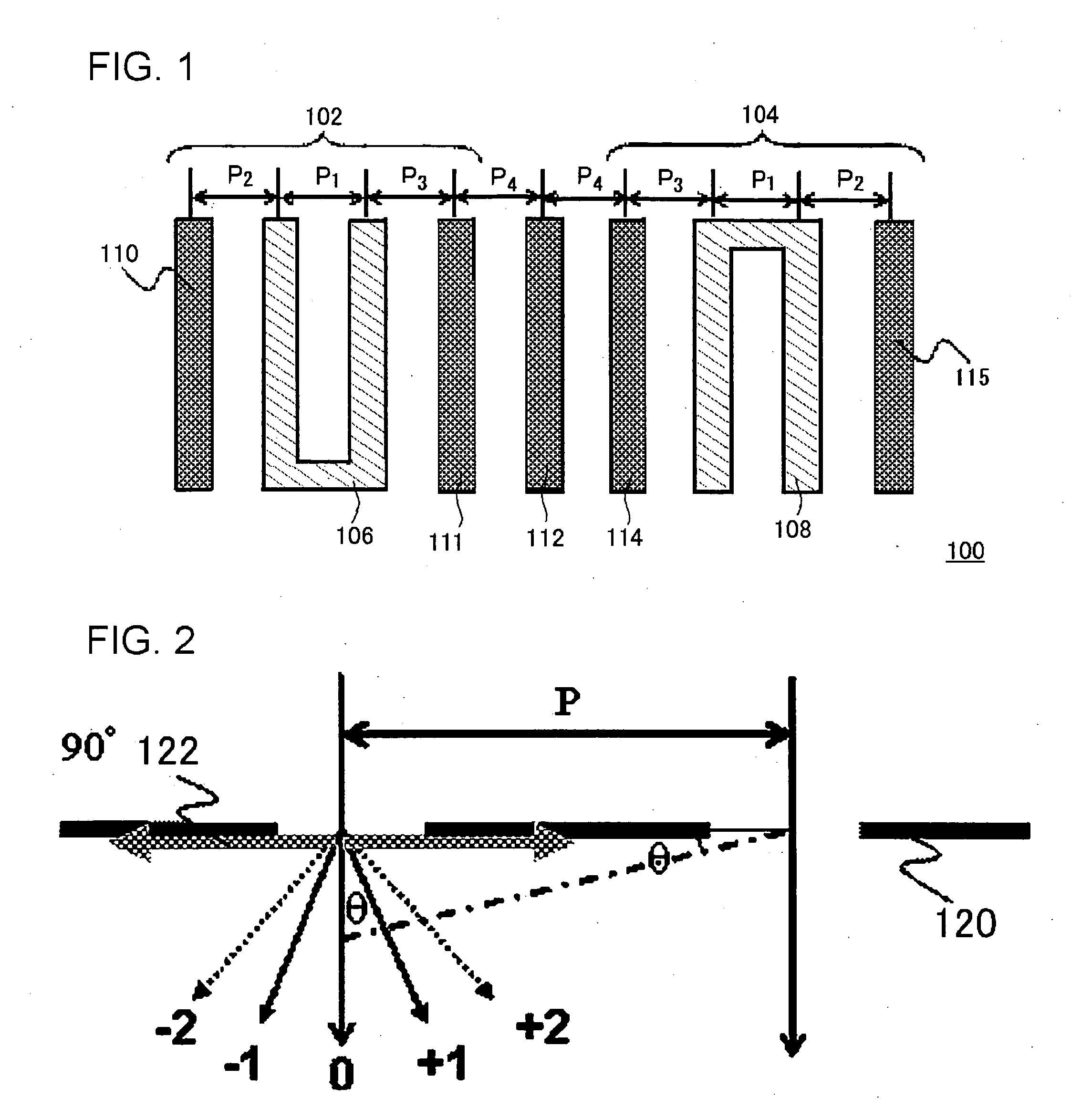

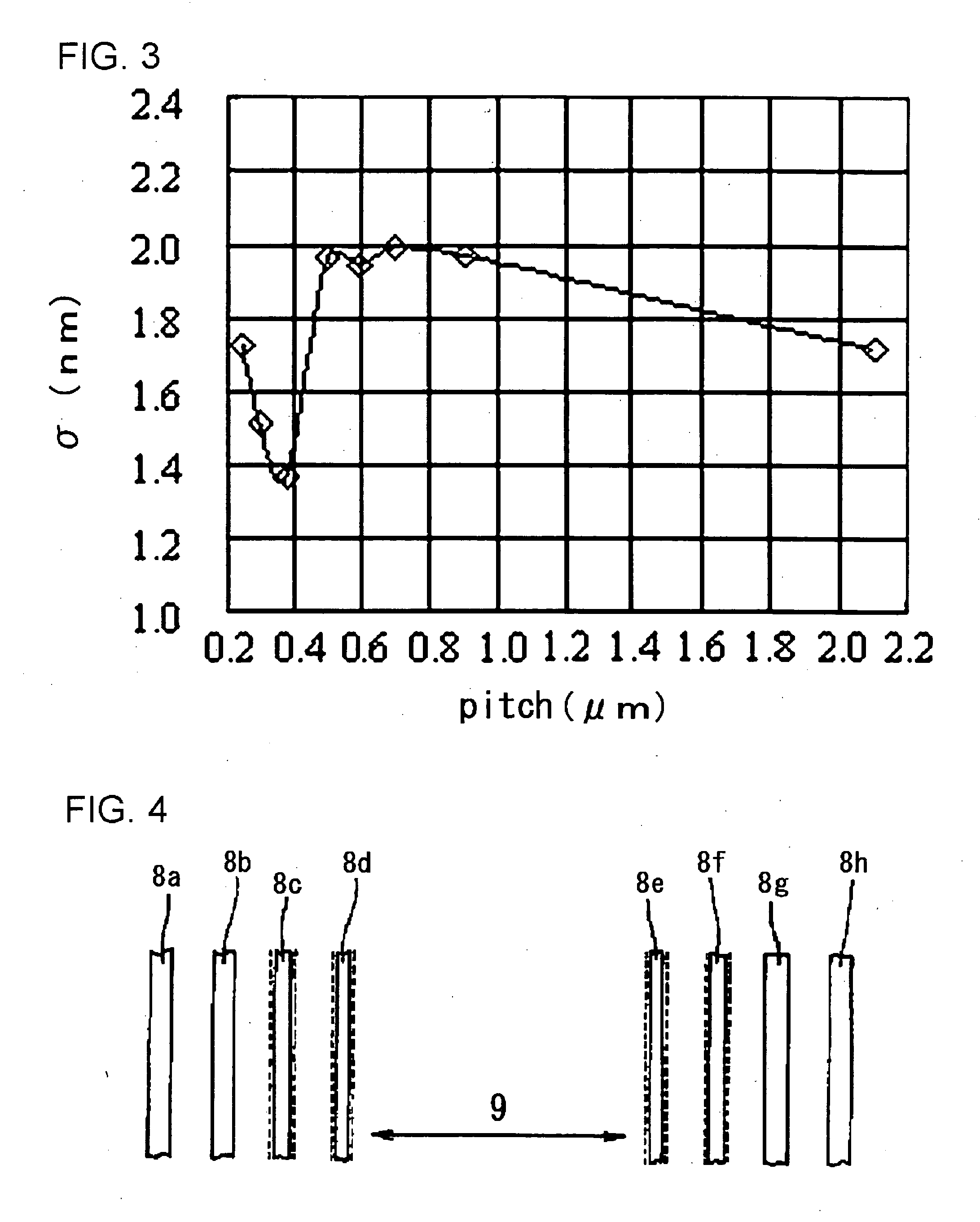

InactiveUS20060084261A1Image degradationReduce shapingSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

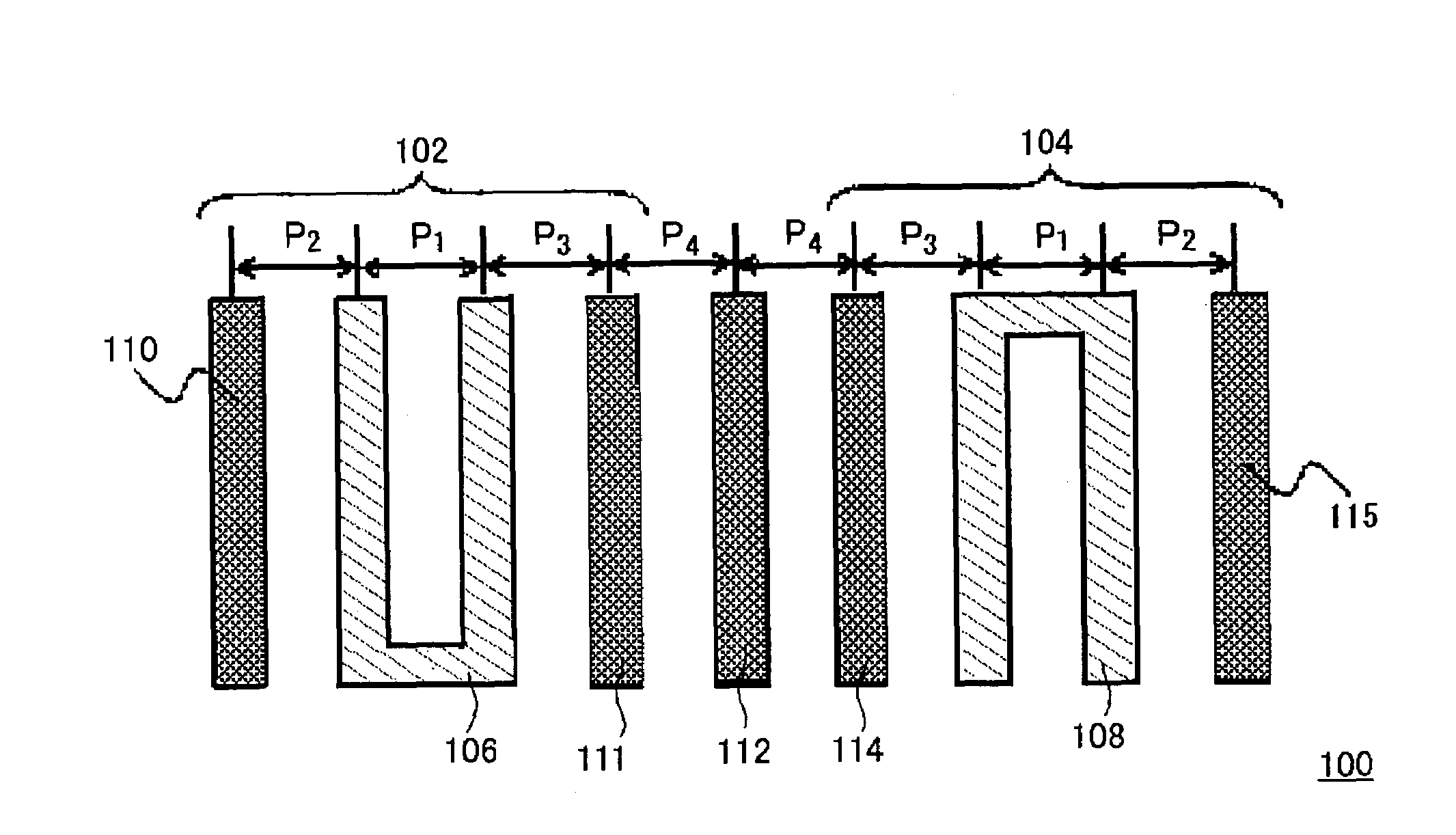

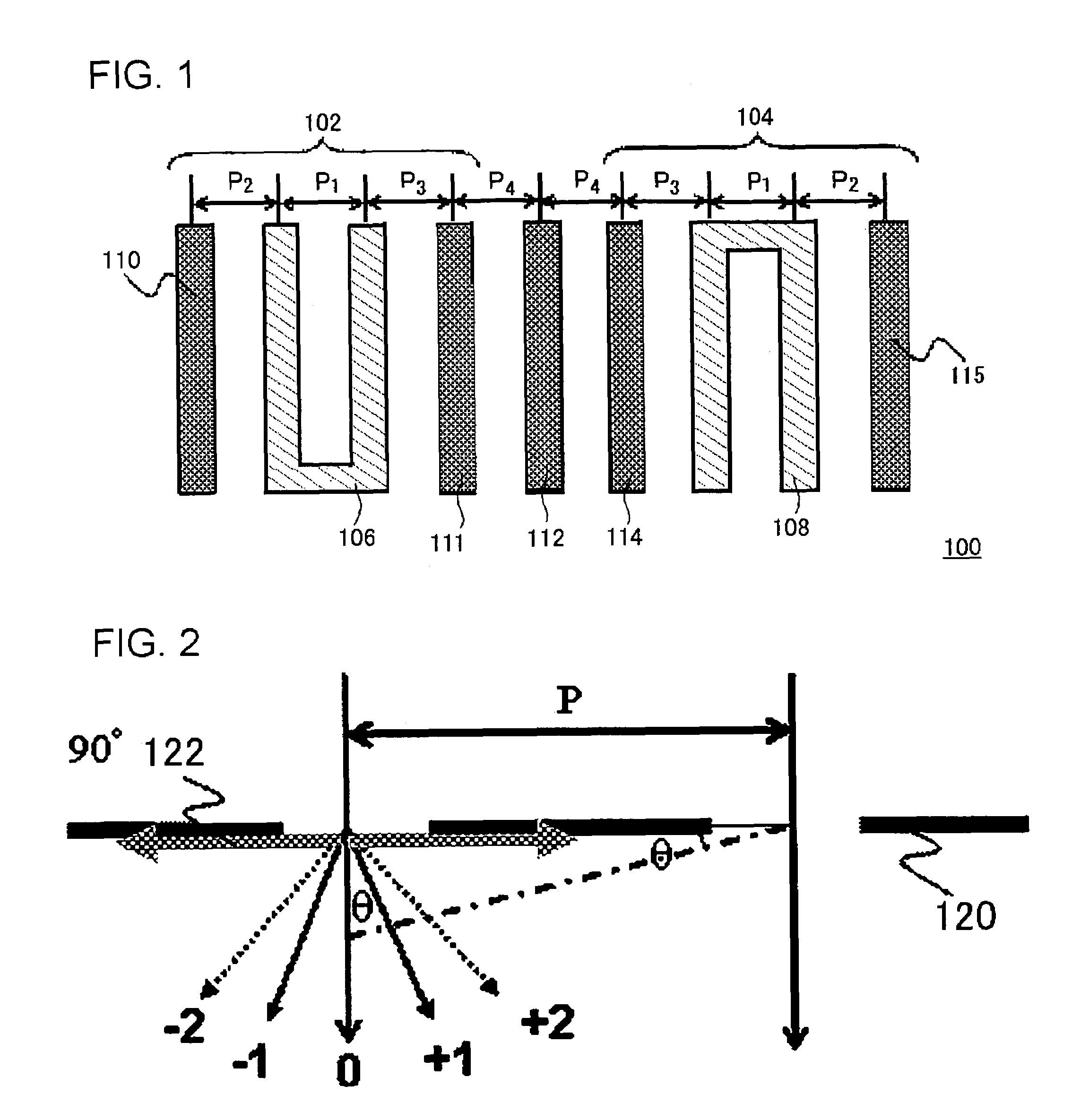

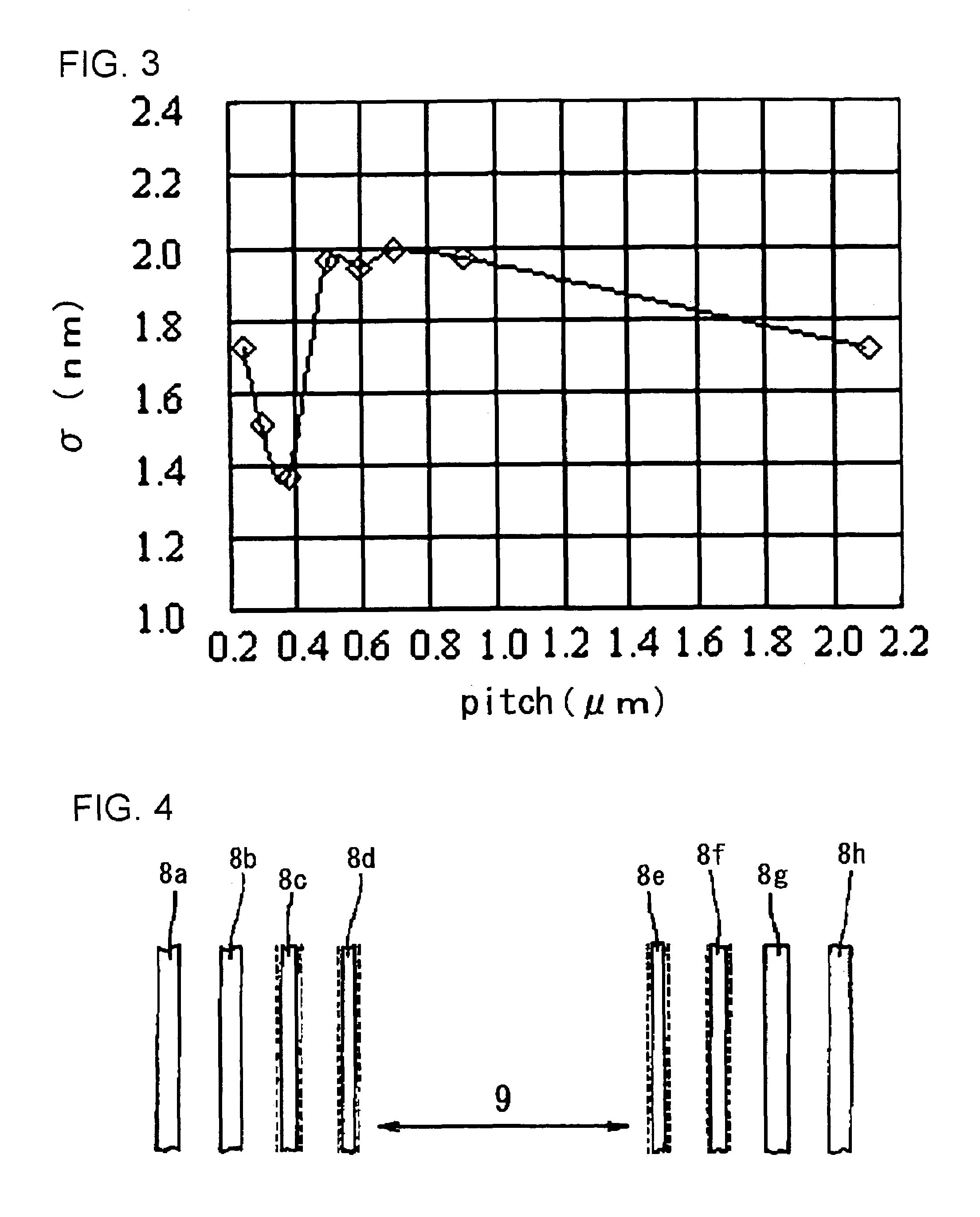

An interconnect layout method capable of reducing variations in shape of gate patterns and improving yield of a semiconductor device is provided. In an interconnect layout 100, the first gate pattern, the second gate pattern, the first dummy pattern, and the second dummy pattern are arranged so that, if a wavelength of a light used to expose the first gate pattern and the second gate pattern is λ, natural numbers are m1, m2, and m3, the first predetermined distance is P1, the second predetermined distance is P2, the third predetermined distance is P3, a design value of the first predetermined distance is P1′, a design value of the second predetermined distance is P2′, and a design value of the third predetermined distance is P3′, then the first predetermined distance satisfies relationships of P1=m1λ and P1′−0.1λ≦P1≦P1′+0.1λ, the second predetermined distance satisfies relationships of P2=m2λ and P2′−0.1λ≦P2≦P2′+0.1λ, and the third predetermined distance satisfies relationships of P3=m3λ and P3′−0.1λ≦P3≦P3′+0.1λ.

Owner:RENESAS ELECTRONICS CORP

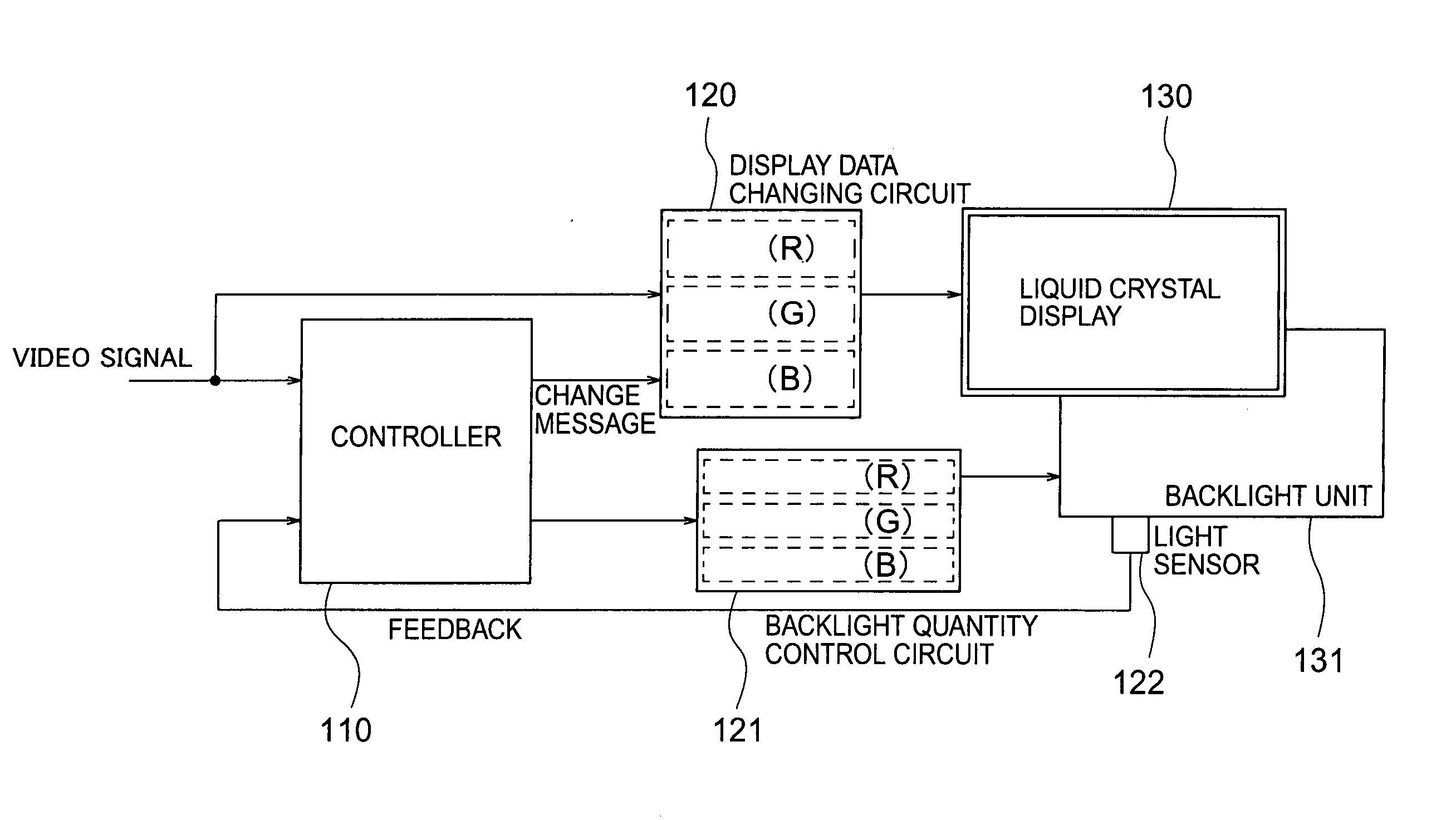

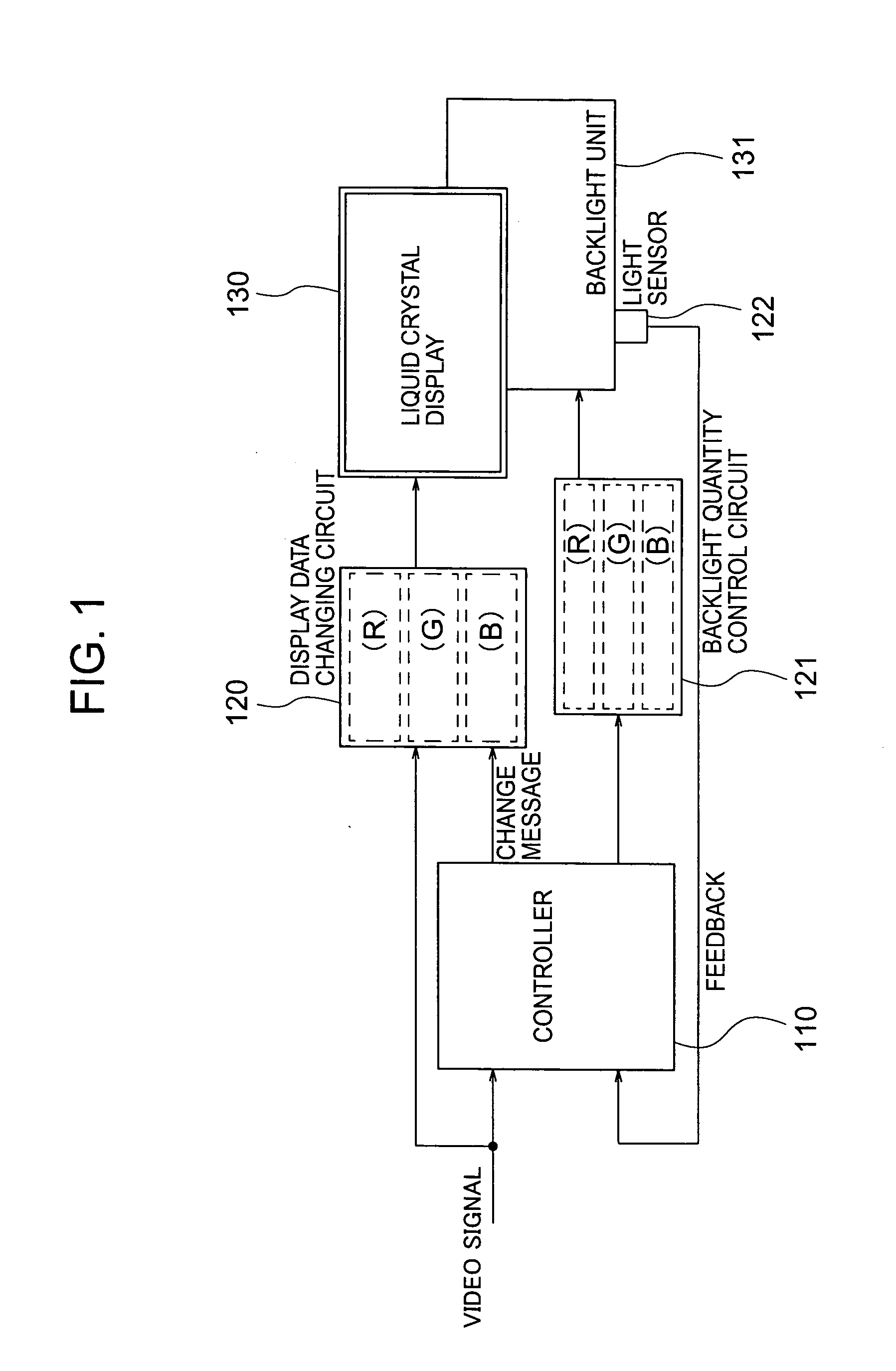

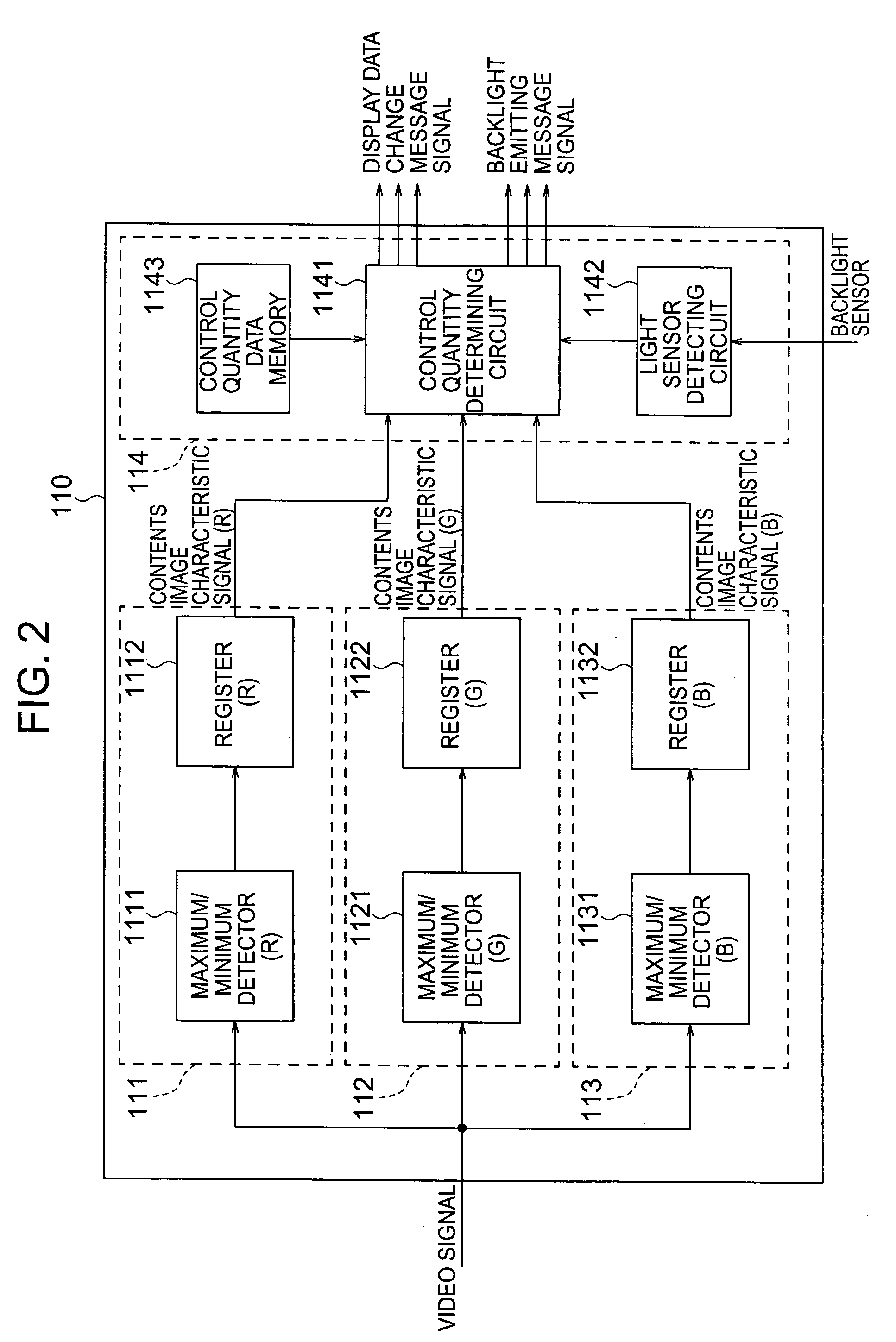

Liquid crystal display apparatus

ActiveUS20050231457A1Reduce in quantityQuality improvementTelevision system detailsStatic indicating devicesLiquid-crystal displayComputer science

The liquid crystal display apparatus includes a liquid crystal display, a backlight unit for emitting rays of light of three or more colors, the ray of each color being controlled, and applying these rays of light onto the liquid crystal display. A controller is further provided for controlling a change of display data of each color of the liquid crystal display and an emitted light quantity of each color of the backlight unit at a time, based on a video signal being inputted for displaying the corresponding image and an output signal sent from an ambient light sensor for sensing ambient light.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

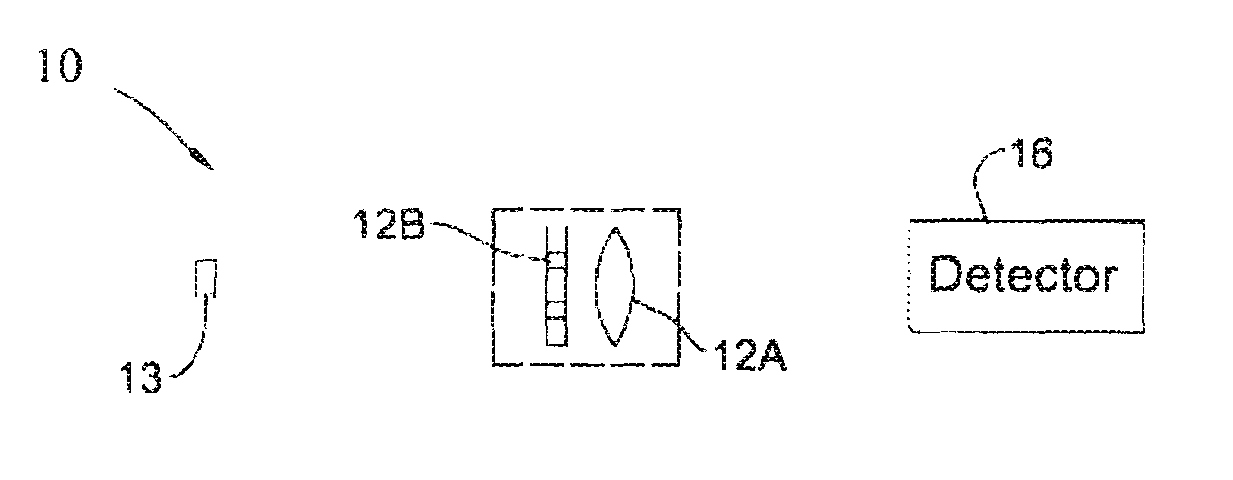

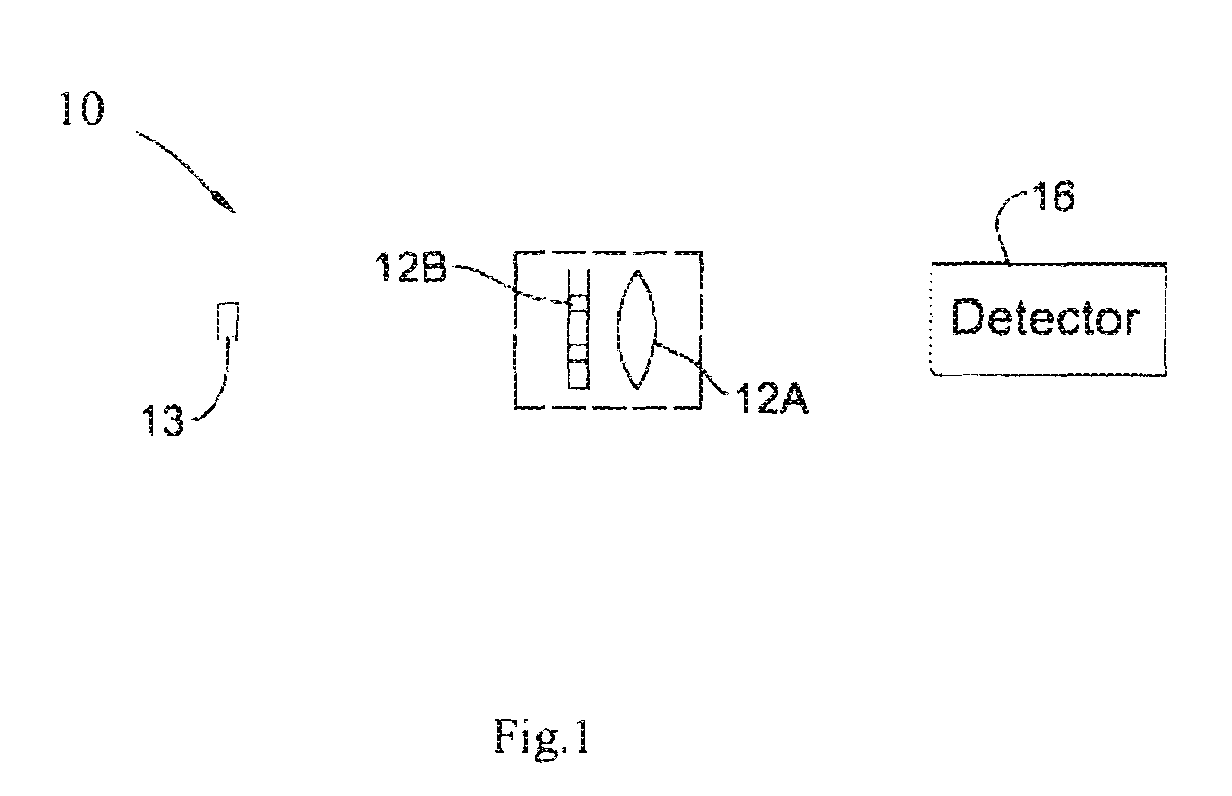

Imaging system and method for providing extended depth of focus, range extraction and super resolved imaging

InactiveUS7646549B2Improving geometrical resolutionIncrease depth of focusSemiconductor/solid-state device manufacturingDiffraction gratingsImaging lensField of view

An imaging system is presented for imaging objects within a field of view of the system. The imaging system comprises an imaging lens arrangement, a light detector unit at a certain distance from the imaging lens arrangement, and a control unit connectable to the output of the detection unit. The imaging lens arrangement comprises an imaging lens and an optical element located in the vicinity of the lens aperture, said optical element introducing aperture coding by an array of regions differently affecting a phase of light incident thereon which are randomly distributed within the lens aperture, thereby generating an axially-dependent randomized phase distribution in the Optical Transfer Function (OTF) of the imaging system resulting in an extended depth of focus of the imaging system. The control unit is configured to decode the sampled output of the detection unit by using the random aperture coding to thereby extract 3D information of the objects in the field of view of the light detector unit.

Owner:BRIEN HOLDEN VISION INST (AU)

Interconnect layout method

InactiveUS7294534B2Image degradationReduce shapingSemiconductor/solid-state device detailsSolid-state devicesLength wavePhysics

In an interconnect layout 100, the first gate pattern, the second gate pattern, the first dummy pattern, and the second dummy pattern are arranged so that, if a wavelength of a light used to expose the first gate pattern and the second gate pattern is λ, natural numbers are m1, m2, and m3, the first predetermined distance is P1, the second predetermined distance is P2, the third predetermined distance is P3, a design value of the first predetermined distance is P1′, a design value of the second predetermined distance is P2′, and a design value of the third predetermined distance is P3′, then the first predetermined distance satisfies relationships of P1=m1λ and P1′−0.1λ≦P1≦P1′+0.1λ, the second predetermined distance satisfies relationships of P2=m2λ and P2′−0.1λ≦P2≦P2′+0.1λ, and the third predetermined distance satisfies relationships of P3=m3λ and P3′−0.1λ≦P3≦P3′+0.1λ.

Owner:RENESAS ELECTRONICS CORP

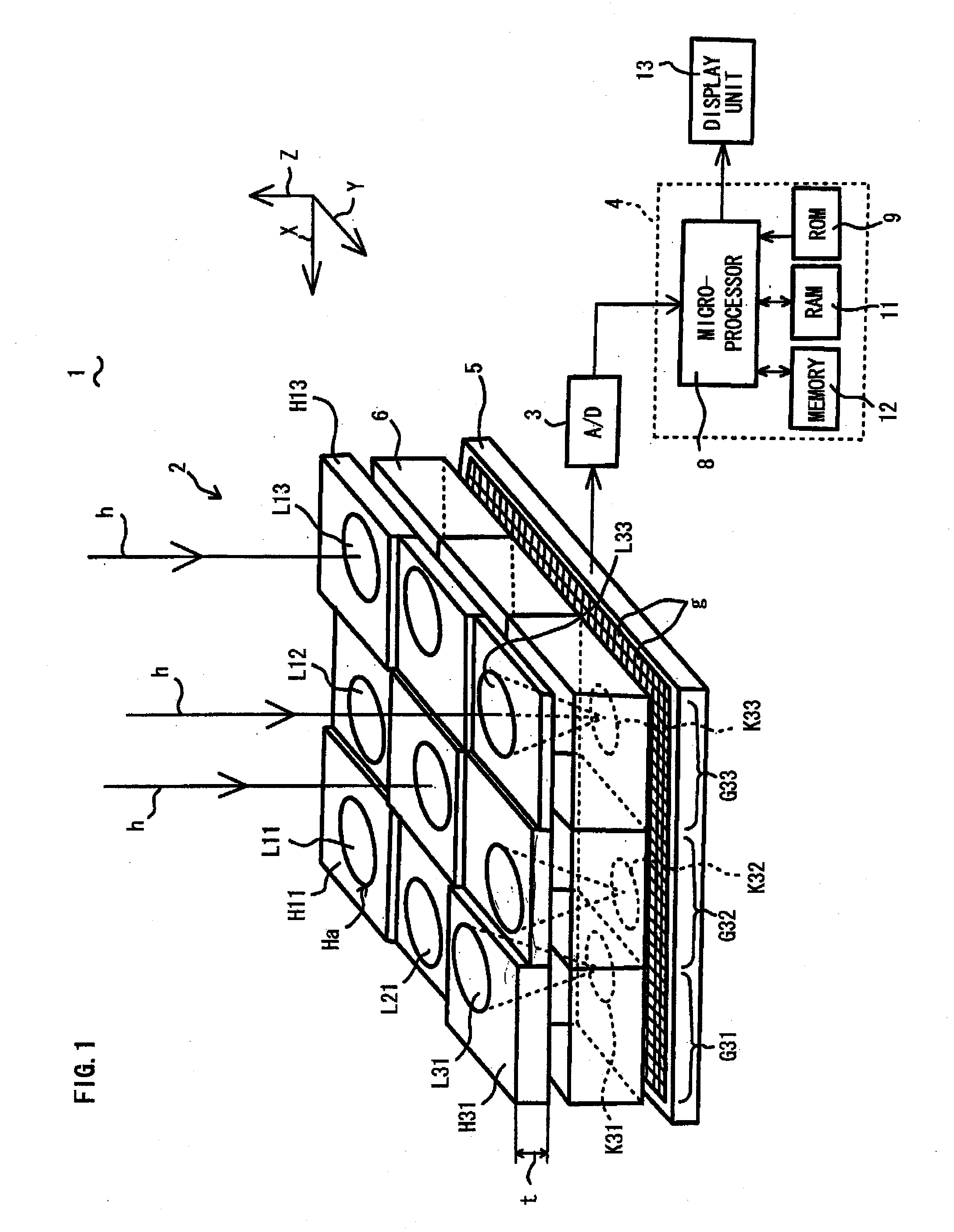

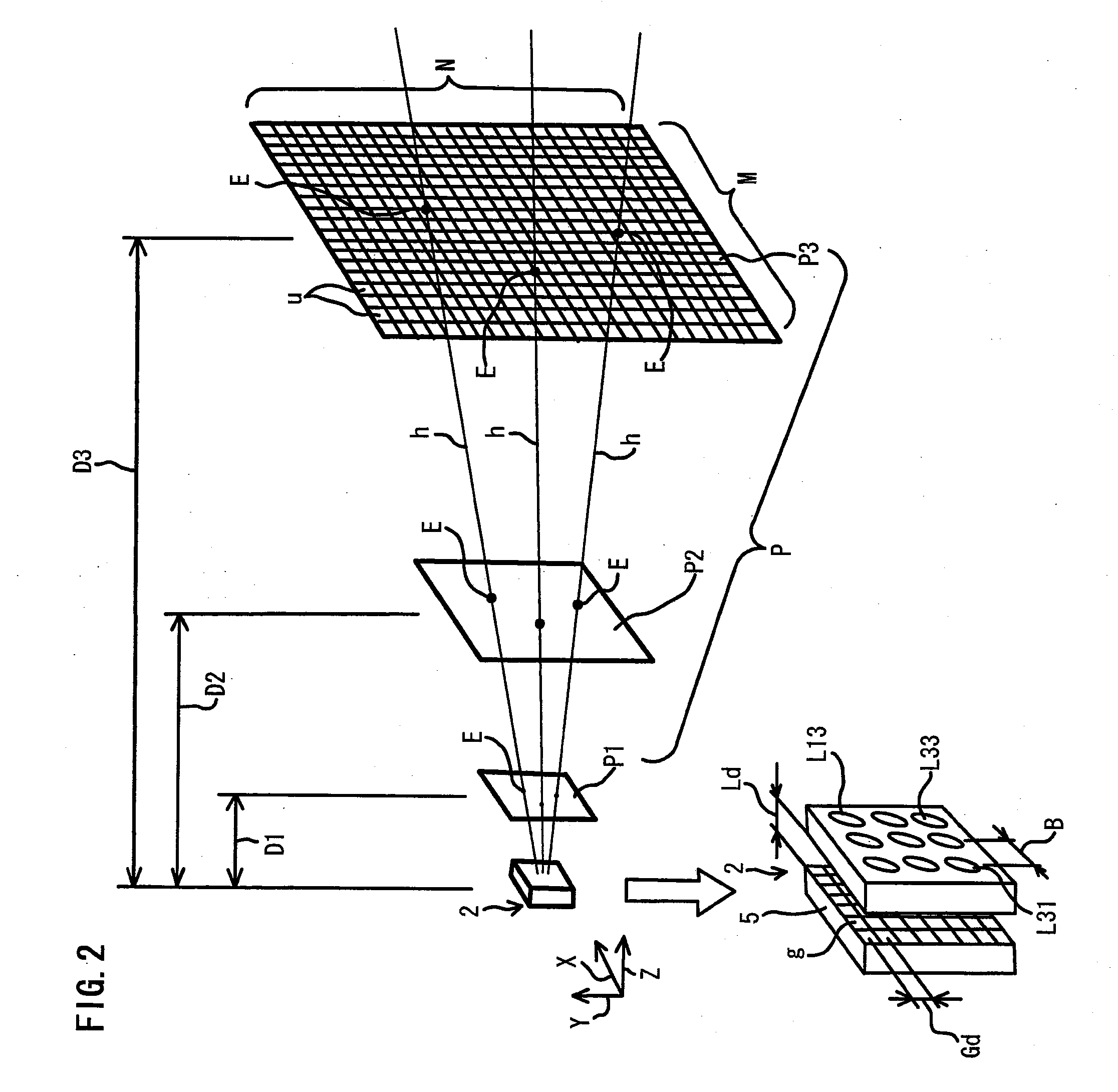

Optical Condition Design Method for a Compound-Eye Imaging Device

InactiveUS20100053600A1Cutting portionHigh definitionTelevision system detailsSolid-state devicesObservation pointHigh definition

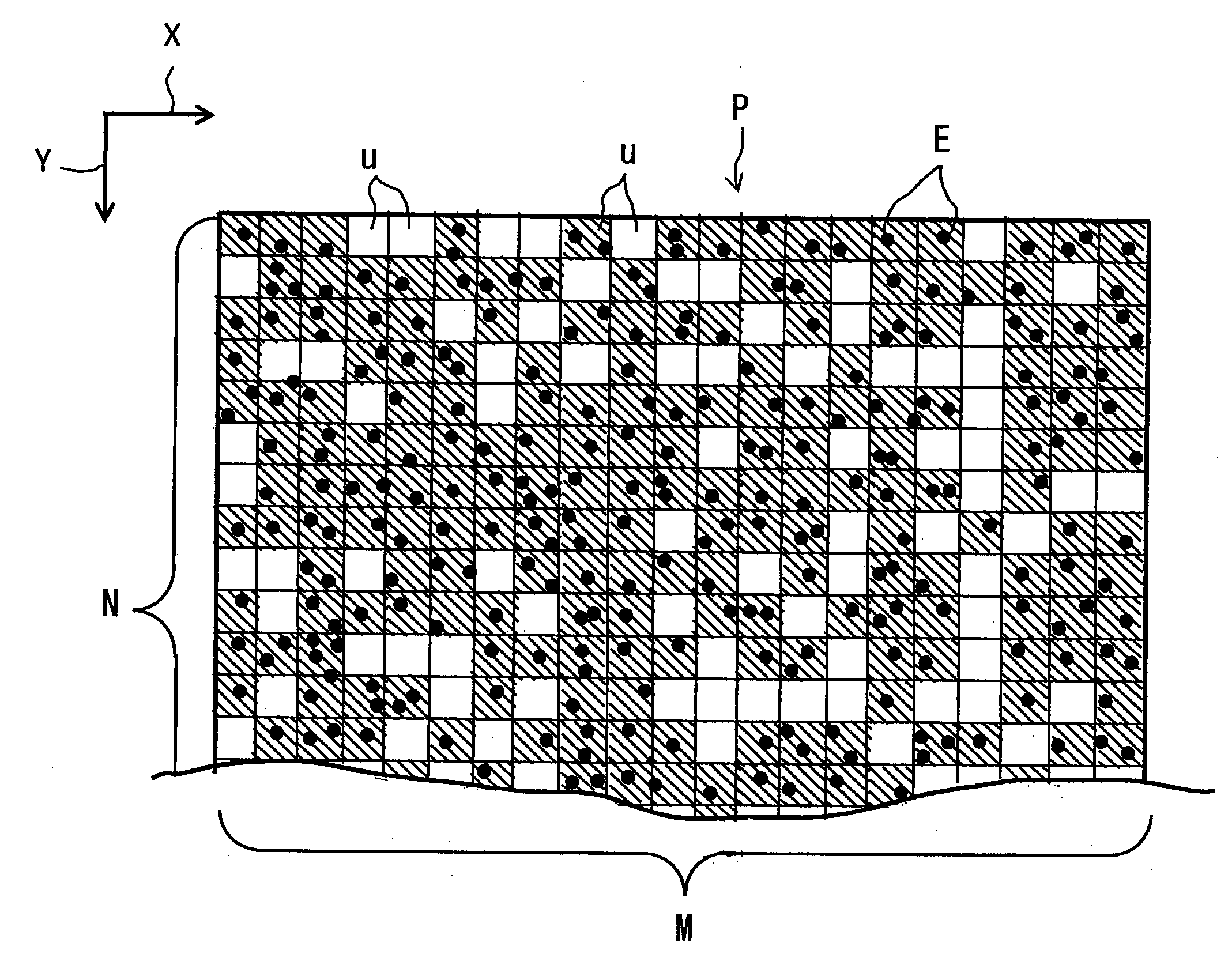

An imaginary object plane is set in front of an imaging device body (plane setting step). A part of optical conditions of optical lenses are changed as variables, and positions of points (pixel observation points) on the imaginary object plane where lights coming from pixels of a solid-state imaging element and back-projected through the optical lenses are calculated (pixel observation point calculating step). The dispersion in position of the calculated pixel observation points is evaluated (evaluating step). Finally, a set of values of the variables giving maximum evaluated dispersion of the calculated pixel observation points is determined as optimum optical condition of the optical lenses (condition determining step). This reduces the number of pixels which image the same portions of the target object, making it possible to reduce portions of the same image information in multiple unit images, and to stably obtain a reconstructed image having a high definition.

Owner:FUNAI ELECTRIC CO LTD +1

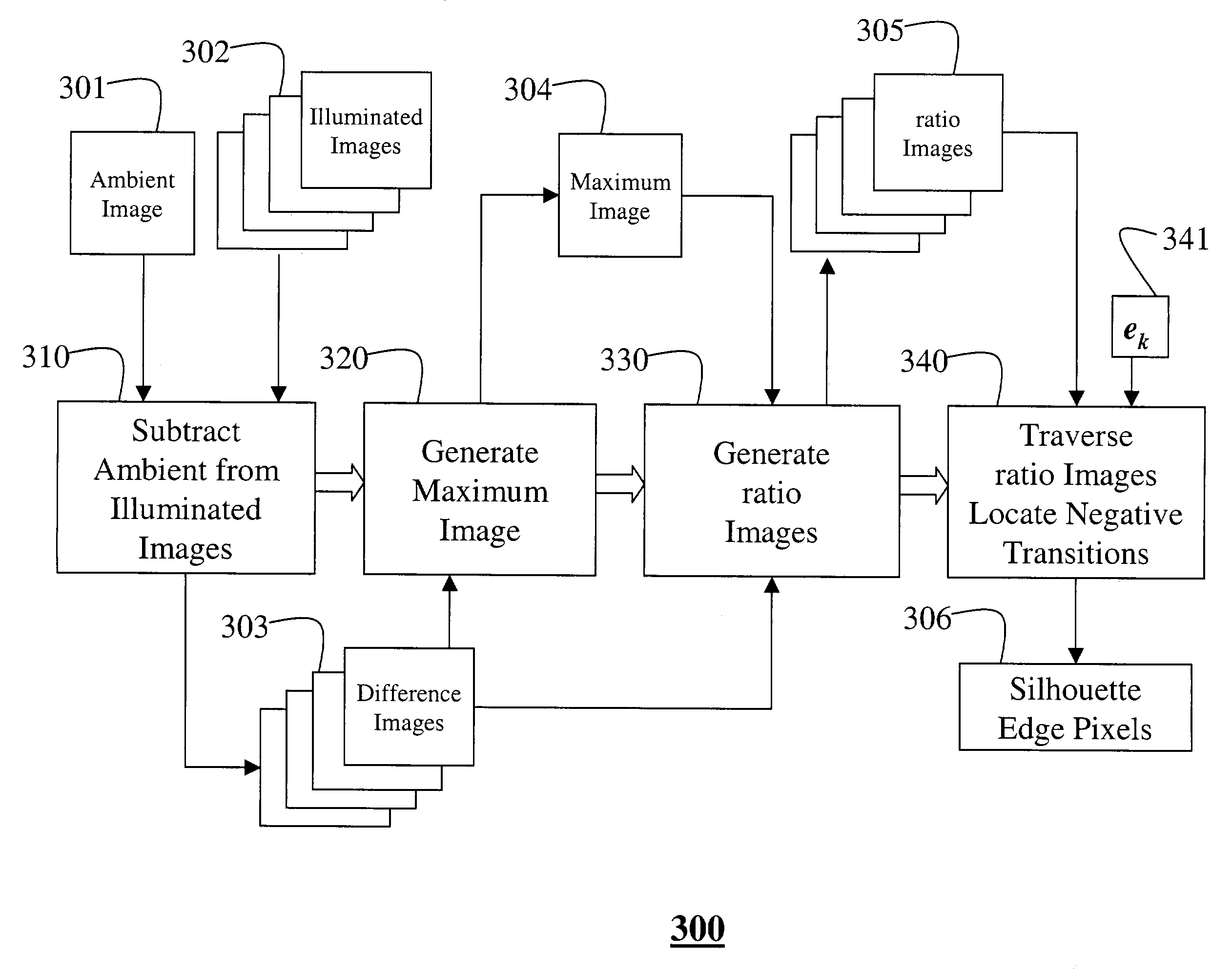

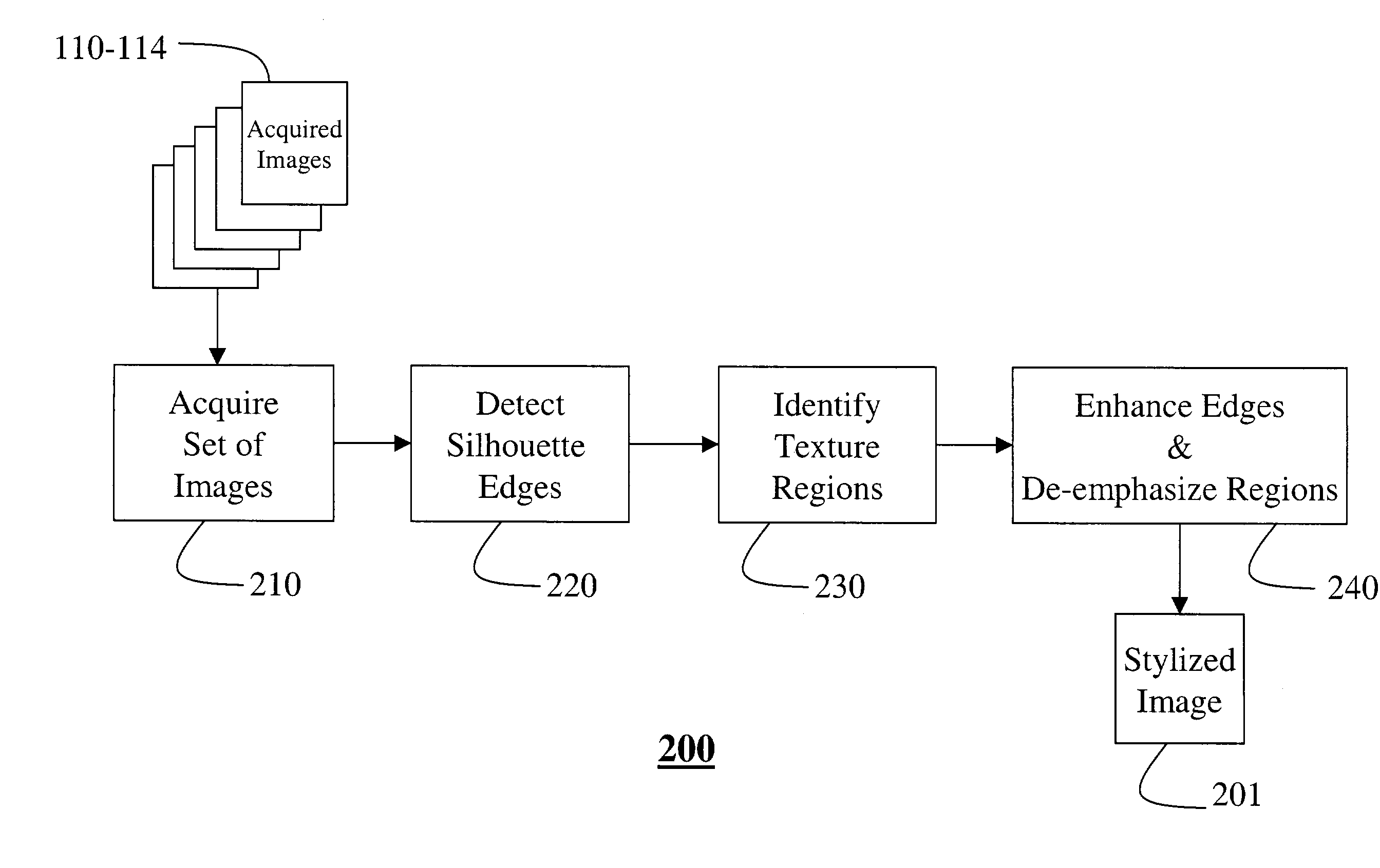

Detecting silhouette edges in images

InactiveUS7206449B2Good lookingReduce detailsImage enhancementImage analysisComputer visionSilhouette edge

A method detects silhouette edges in images. An ambient image is acquired of a scene with ambient light. A set of illuminated images is also acquired of the scene. Each illuminated image is acquired with a different light source illuminating the scene. The ambient image is combined with the set of illuminated to detect cast shadows, and silhouette edge pixels are located from the cast shadows.

Owner:MITSUBISHI ELECTRIC RES LAB INC

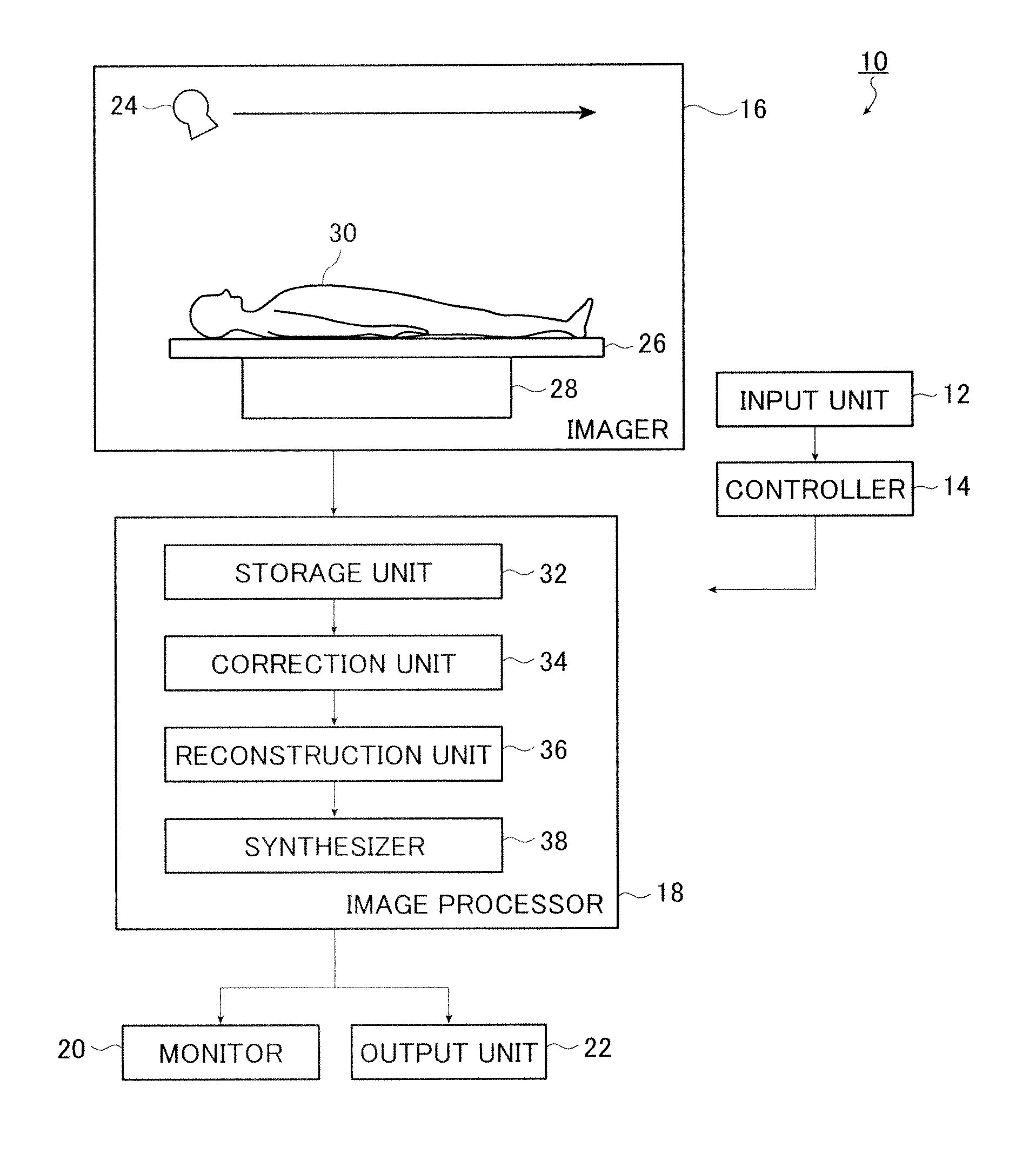

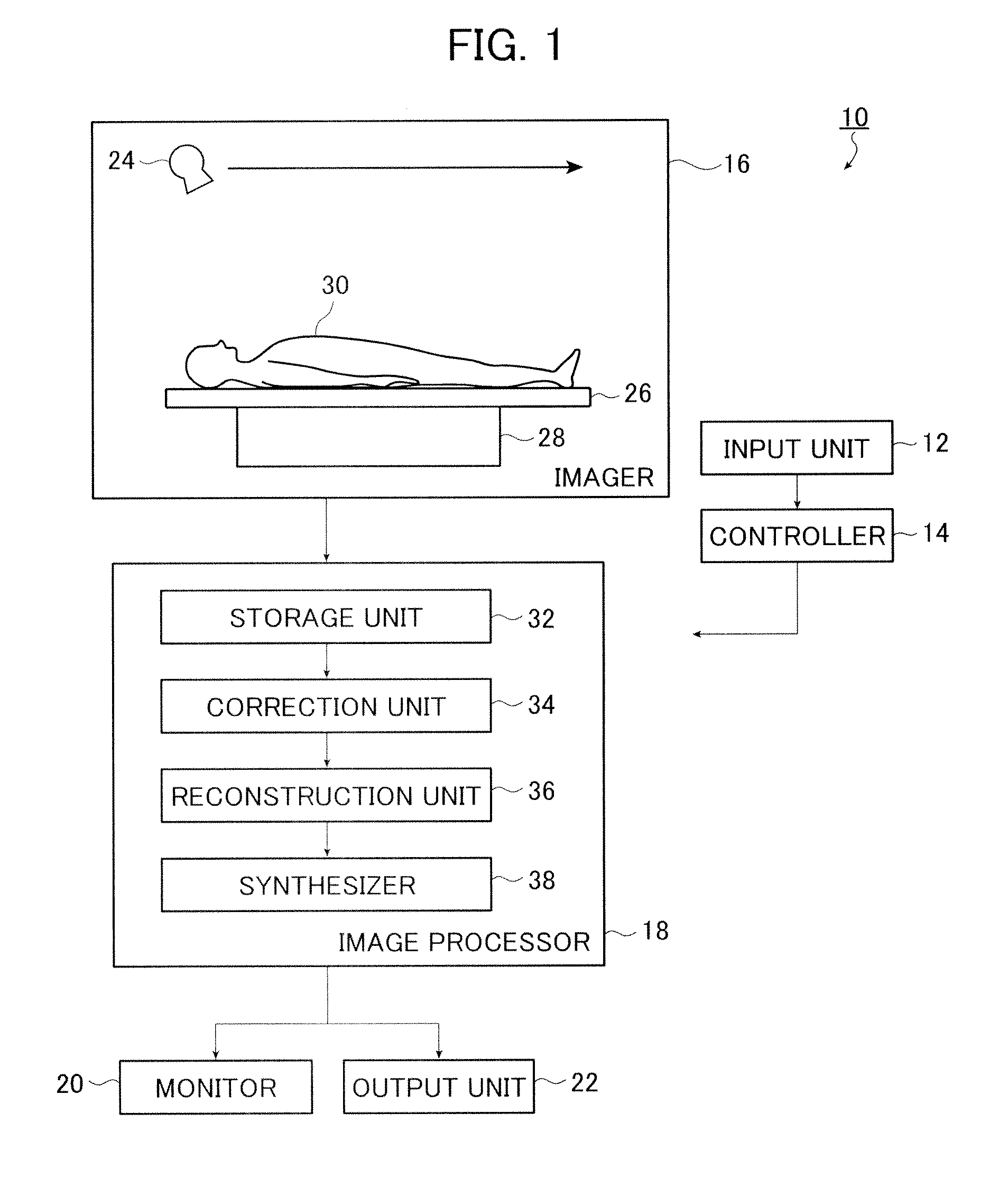

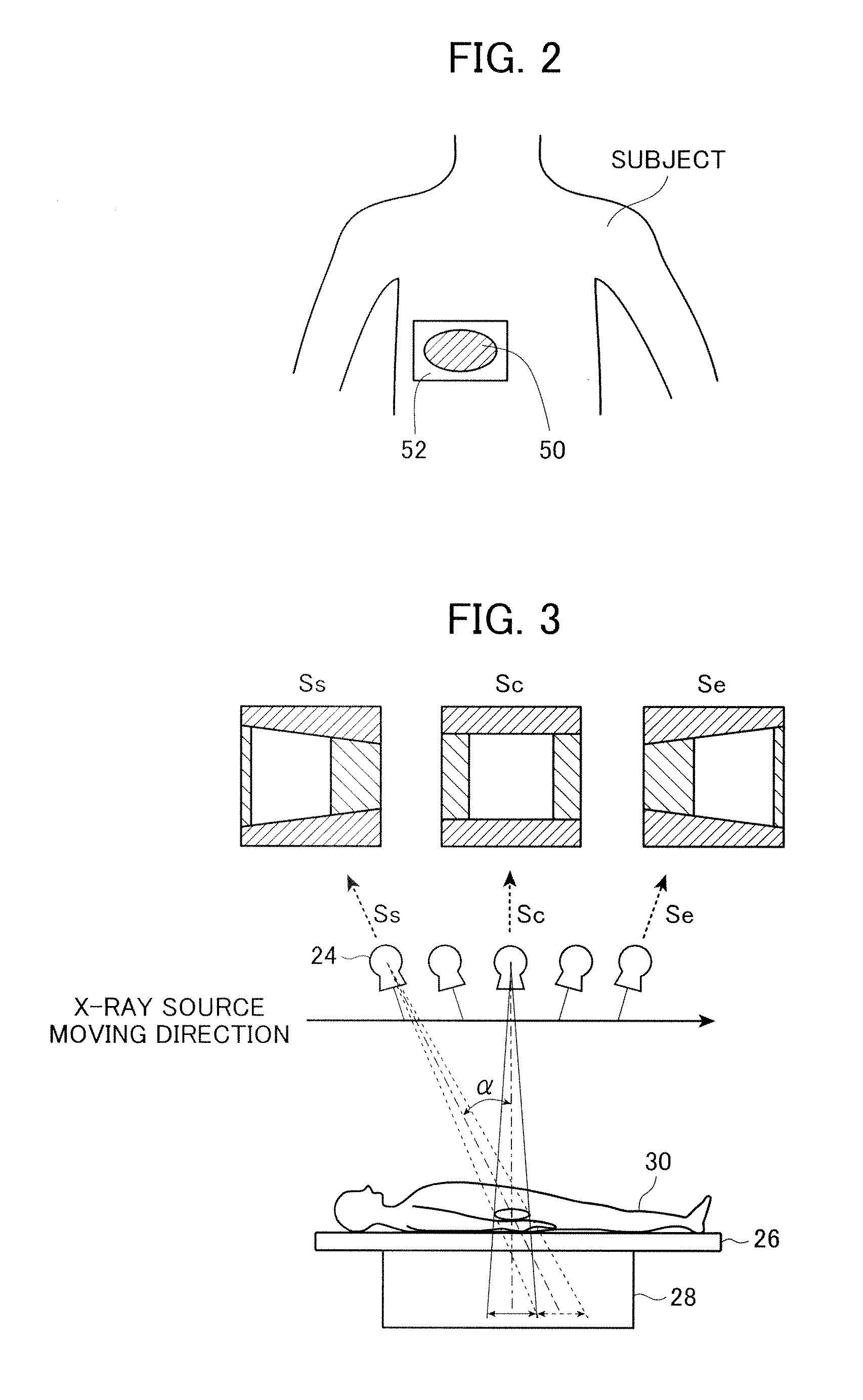

X-ray imaging system and x-ray imaging method

InactiveUS20120051498A1Reduce exposureReduced imaging timeReconstruction from projectionMaterial analysis using wave/particle radiationX-rayX ray image

An X-ray imaging system is for irradiating a subject with X ray from an X-ray source at a plurality of different angles to acquire X-ray images, and reconstructing an X-ray tomographic image from the X-ray images. The system comprising a region setting unit for setting a region of interest on a pre-shot image or a previously acquired X-ray tomographic image, an imaging control unit for continuously varying an aperture formed by collimator blades according to a position of the X-ray source to image the region of interest and acquiring projection data of the X-ray images in accordance with the position of the X-ray source, and an image reconstructing unit for reconstructing the X-ray tomographic image from the projection data of the X-ray images of the region of interest. The aperture formed by the collimator blades are varied so that all the X-ray images formed on the X-ray detector is rectangular regardless of the position of the X-ray source.

Owner:FUJIFILM CORP

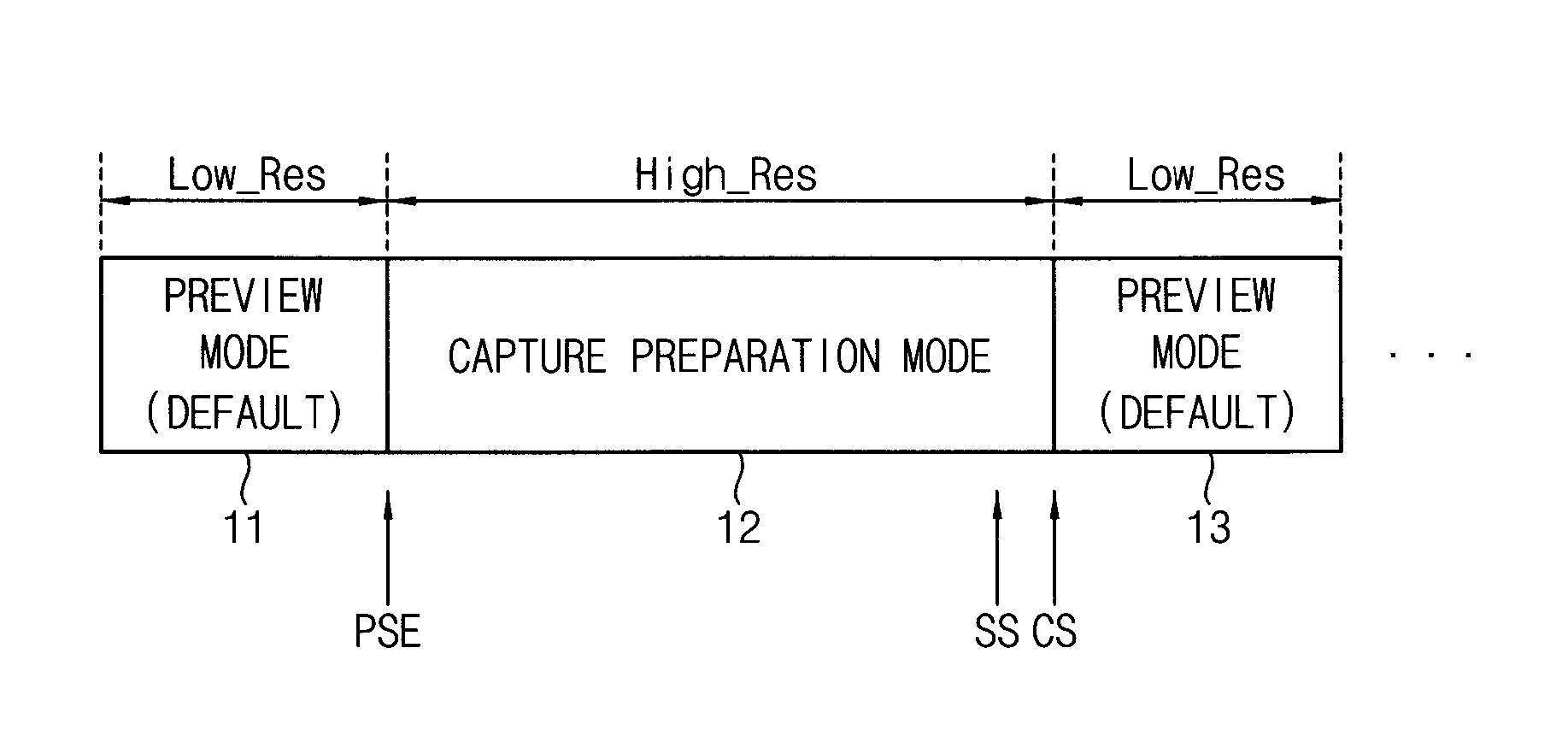

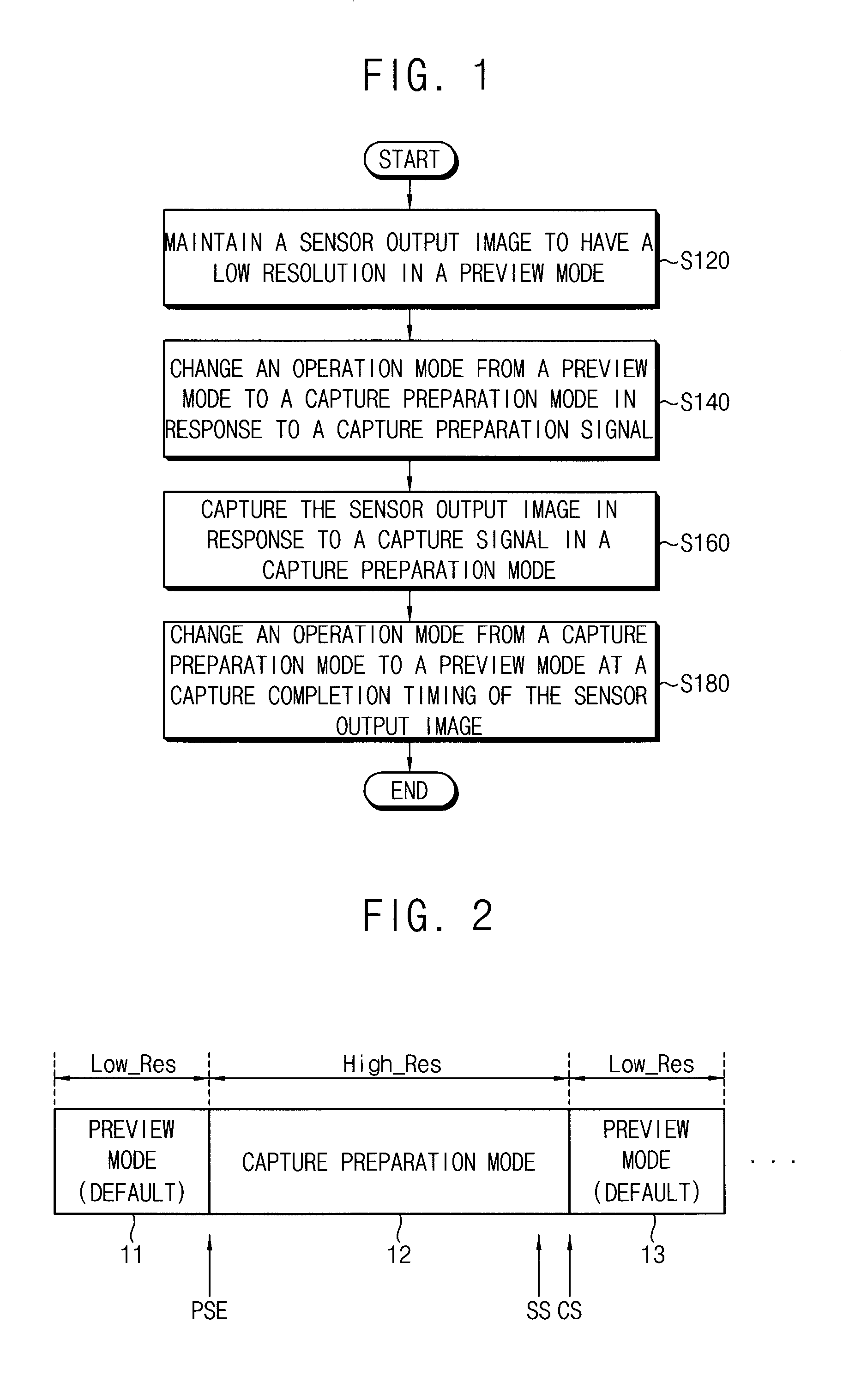

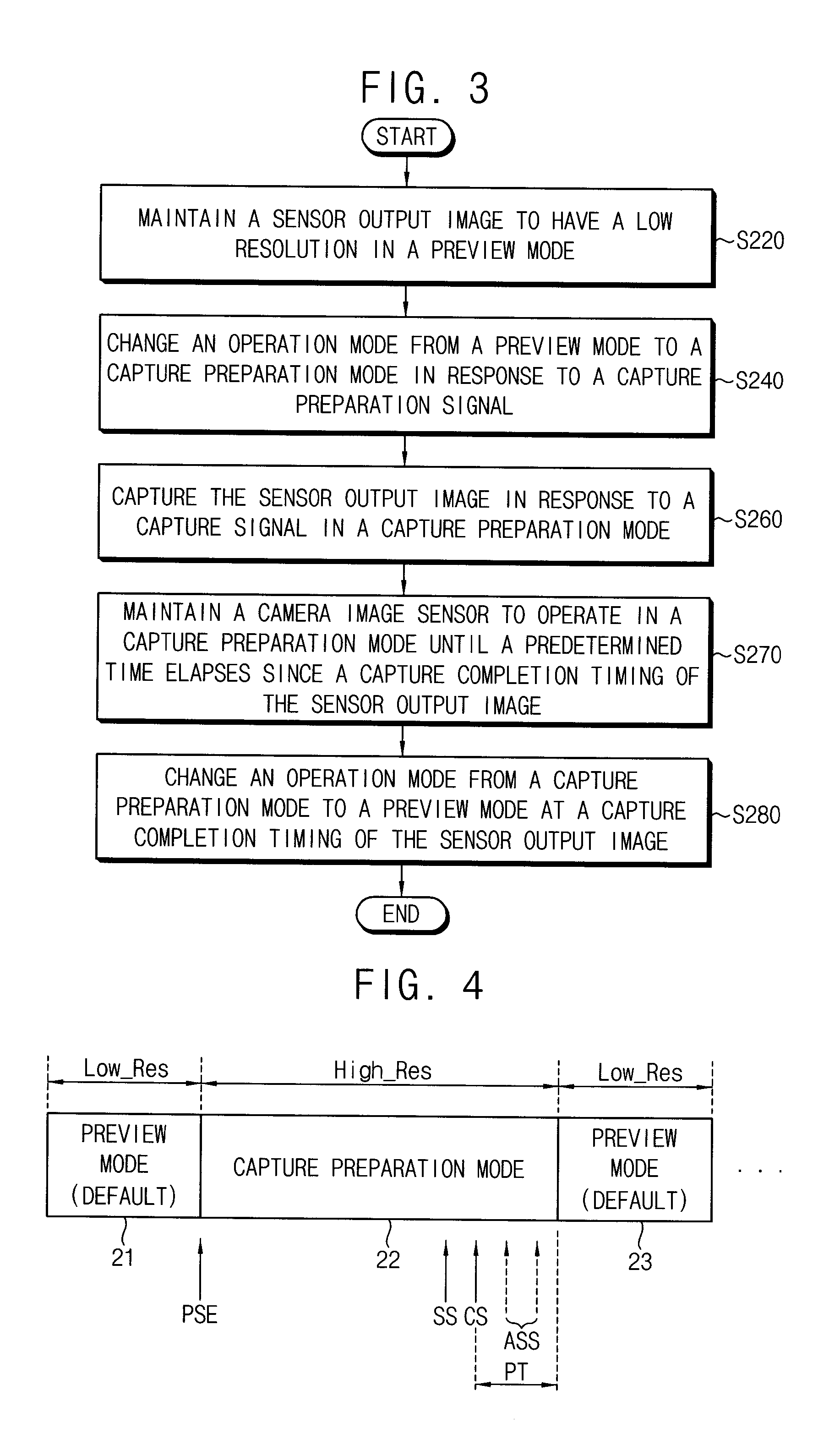

Method of eliminating a shutter-lag, camera module, and mobile device having the same

ActiveUS20130135499A1Prevent unnecessary power consumptionHigh resolutionTelevision system detailsColor television detailsImage resolutionImage sensor

A method of reducing shutter-lag in a camera image sensor may include maintaining a sensor output image to have a low resolution in a preview mode of a camera image sensor; changing a resolution of the sensor output image from a low resolution to a high resolution in response to a capture preparation signal to change an operation mode of the camera image sensor from a preview mode to a capture preparation mode, the low resolution being a resolution equal to or below a reference resolution, the high resolution being a resolution above the reference resolution; and capturing the sensor output image in response to a capture signal in the capture preparation mode of the camera image sensor.

Owner:SAMSUNG ELECTRONICS CO LTD

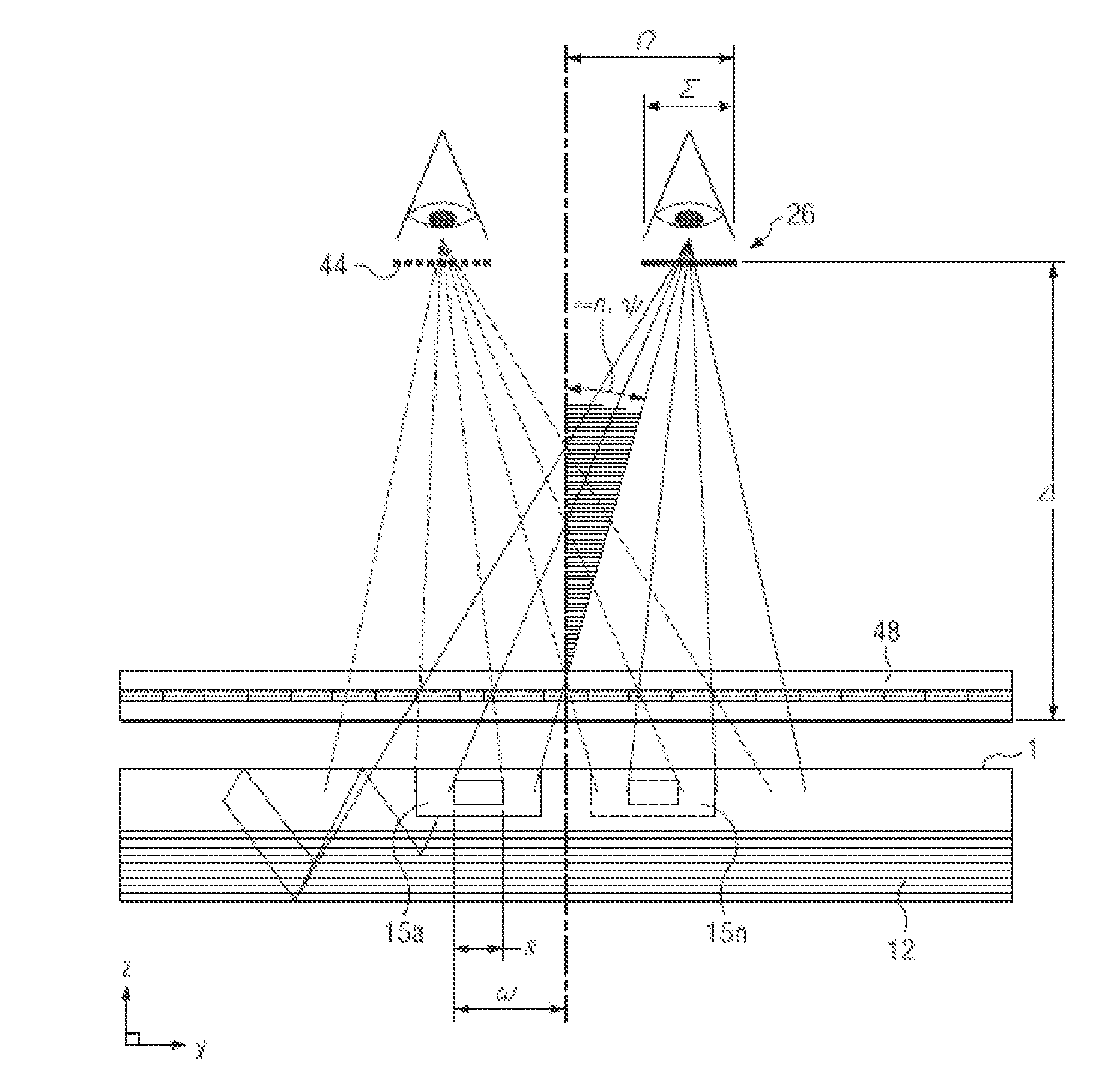

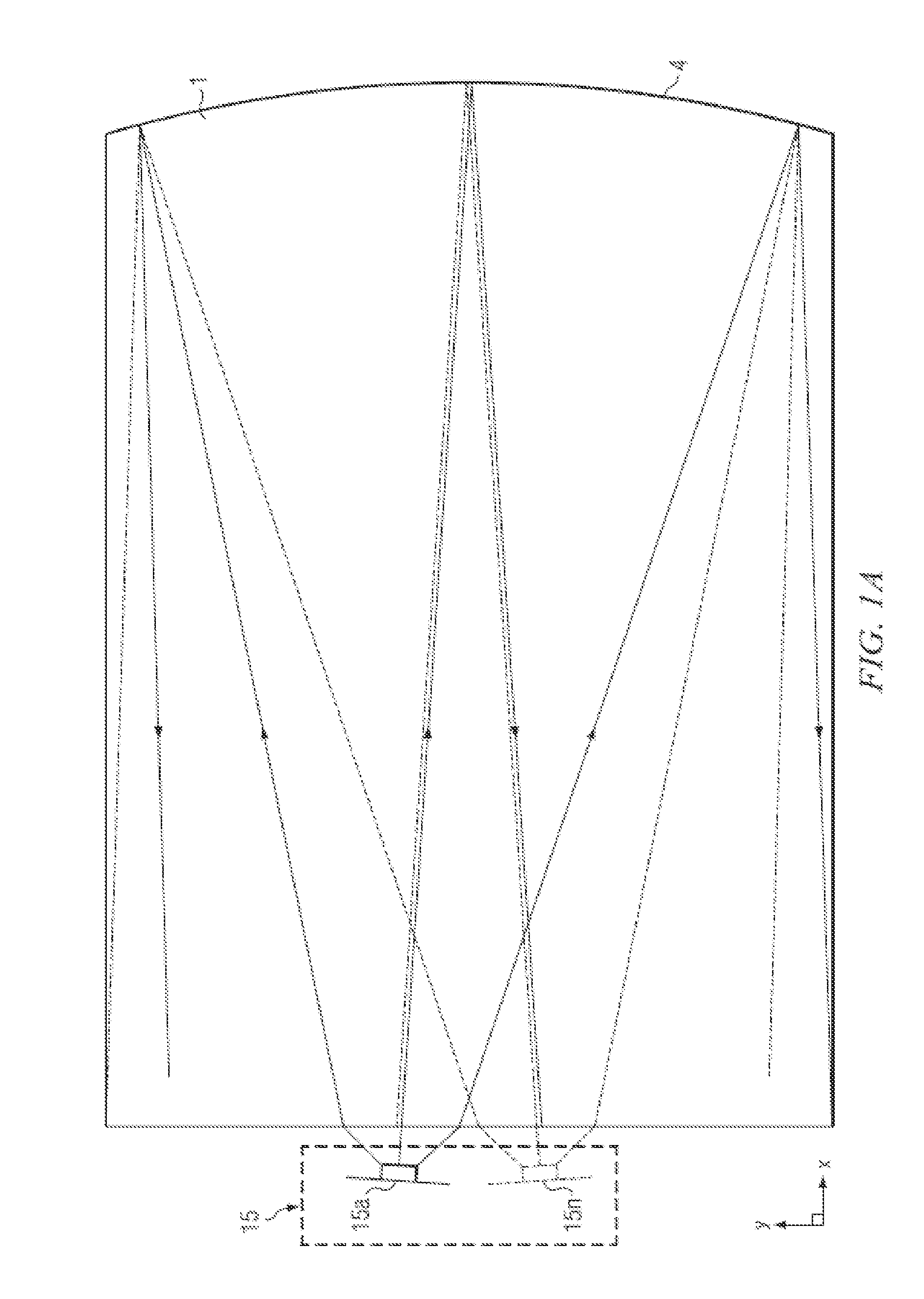

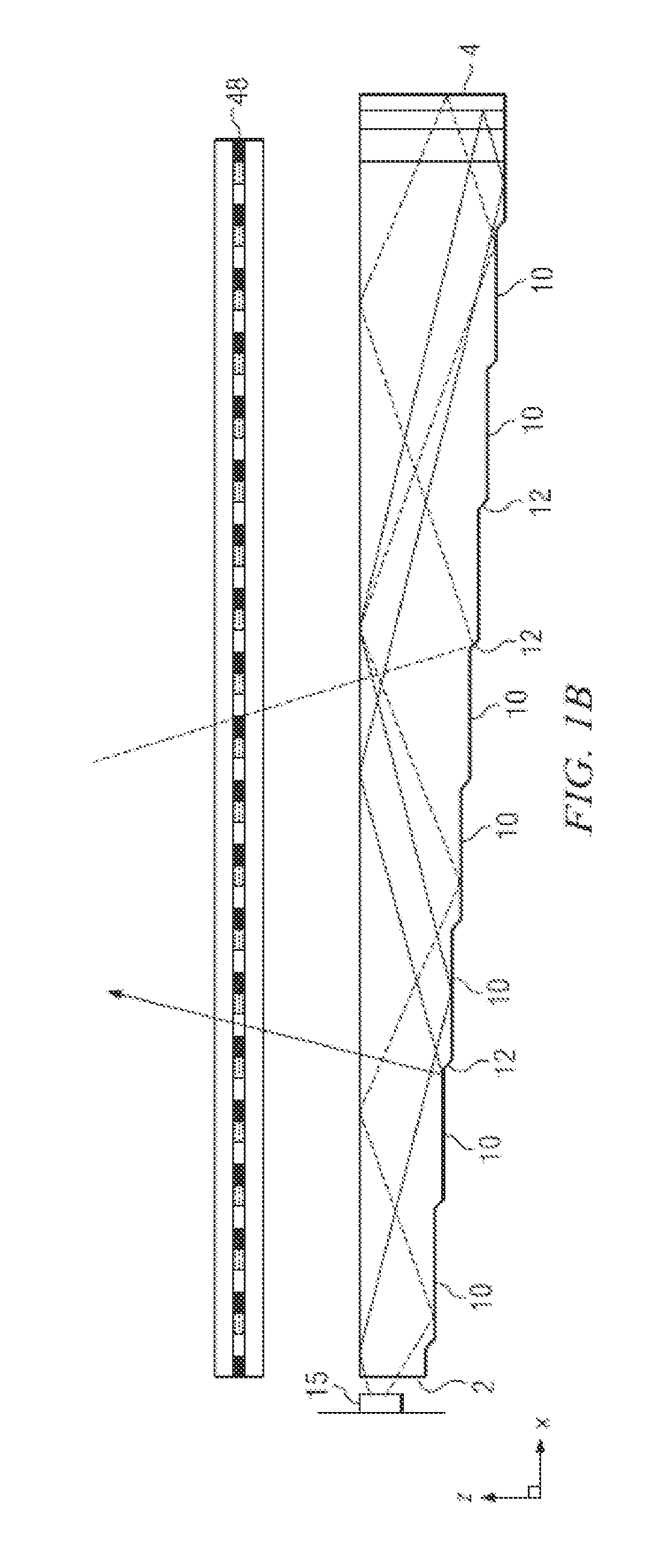

Directional backlight

InactiveUS20150268479A1High resolutionReduce thicknessSteroscopic systemsOptical light guidesParallaxSpatial light modulator

A directional display may include a waveguide. The waveguide may include light extraction features arranged to direct light from an array of light sources by total internal reflection to an array of viewing windows and a reflector arranged to direct light from the waveguide by transmission through extraction features of the waveguide to the same array of viewing windows. A further spatially multiplexed display device comprising a spatial light modulator and parallax element is arranged to cooperate with the illumination from the waveguide. An efficient and bright autostereoscopic display system with low cross talk and high resolution can be achieved.

Owner:REALD SPARK LLC

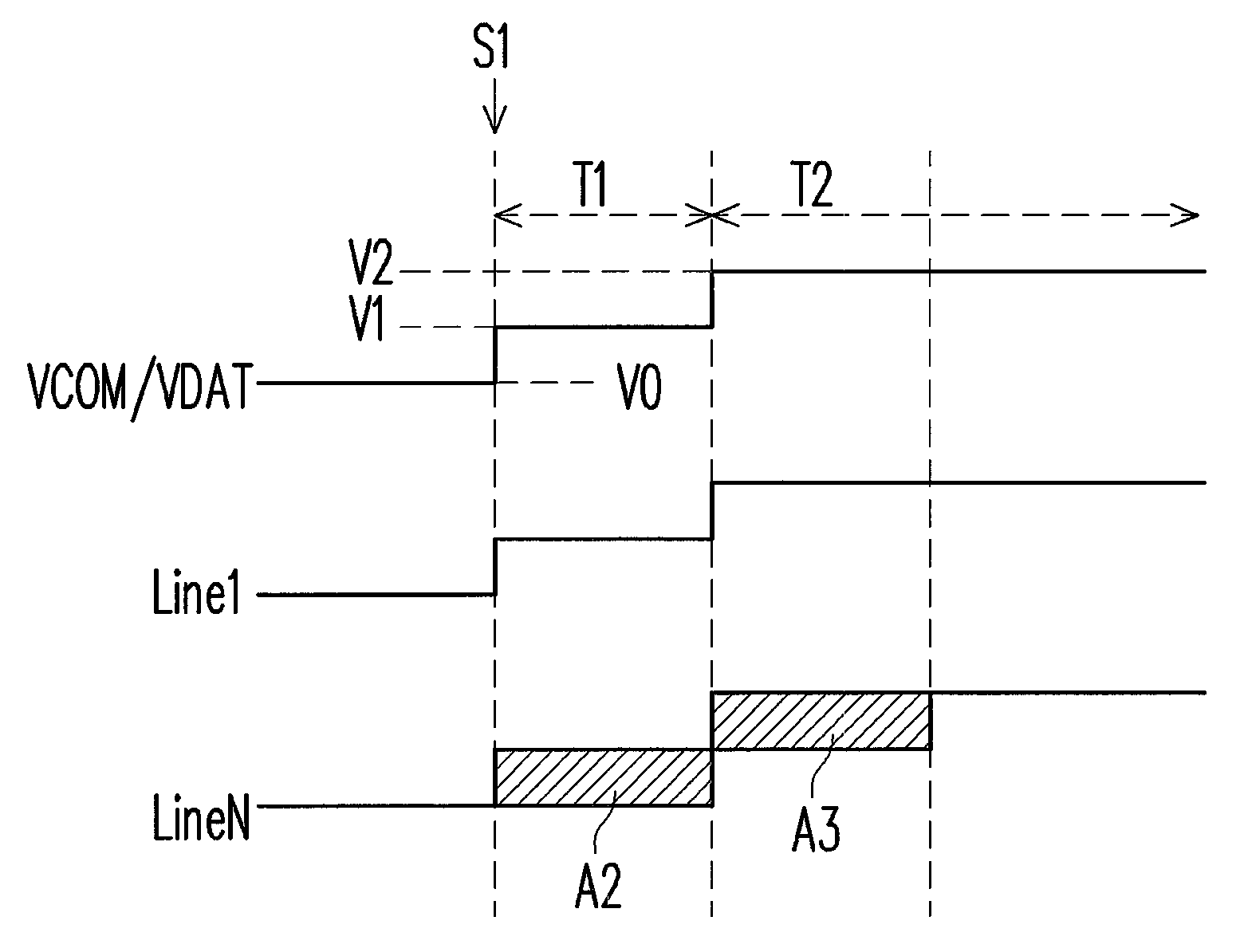

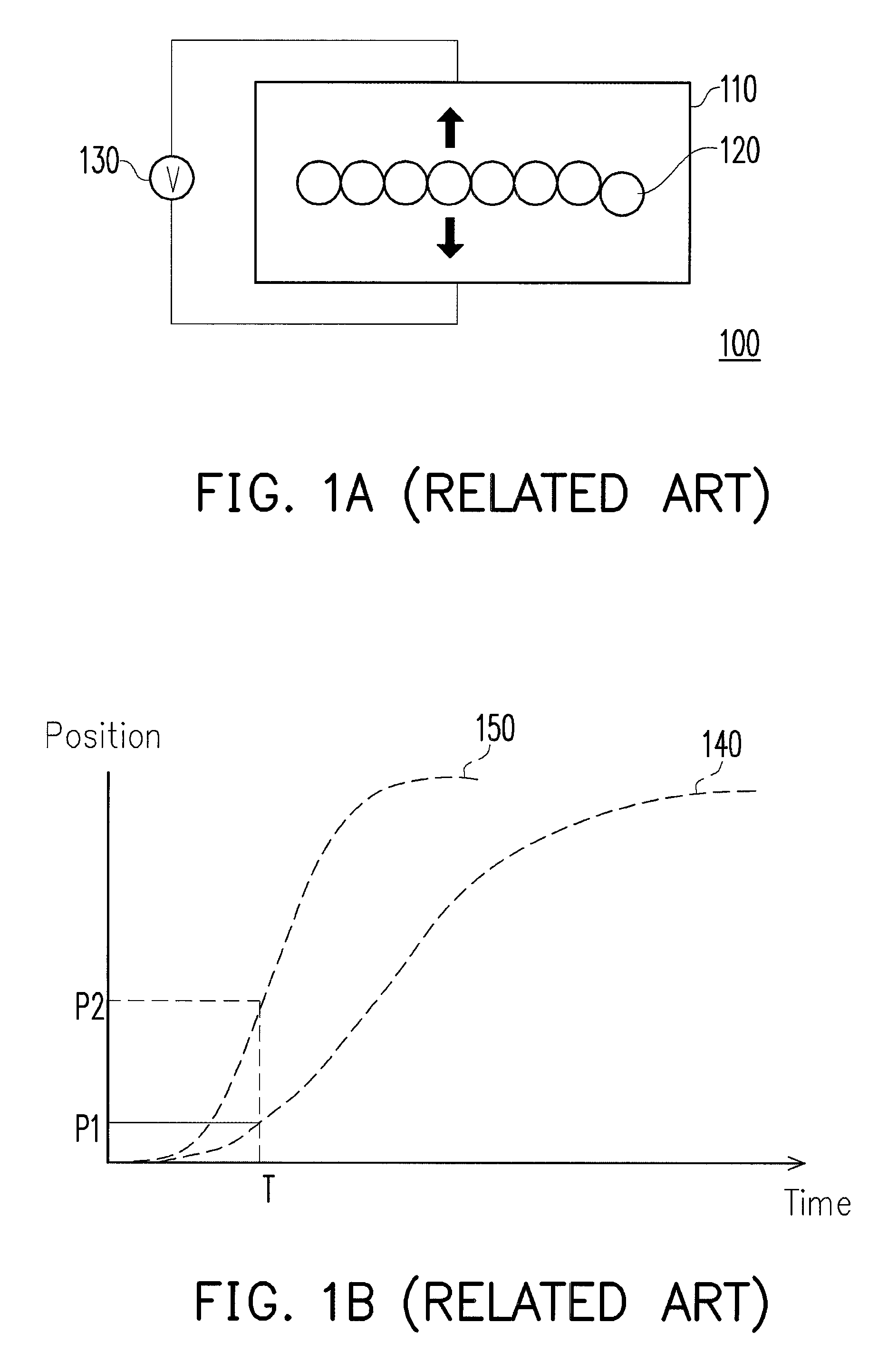

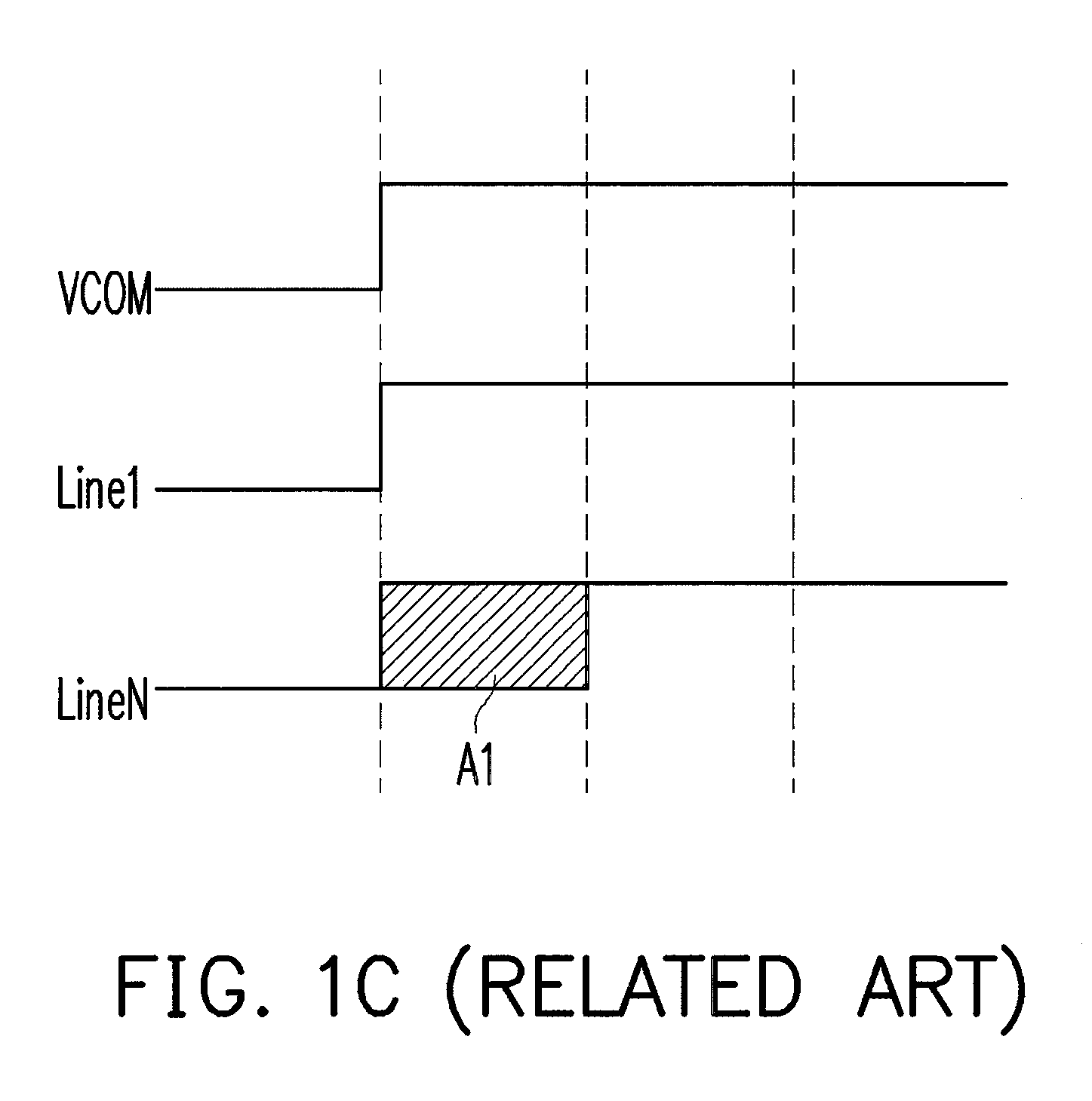

Electro-phoretic display apparatus and driving method thereof

ActiveUS9082352B2Effectively loweringImage degradationCathode-ray tube indicatorsInput/output processes for data processingVoltage generatorElectrophoresis

A driving method for an electro-phoretic display apparatus is disclosed. The method includes generating a common voltage by a common voltage generator held at a first voltage level before a polarity transfer, generating the common voltage held at a second voltage level when the polarity transfer starts during a first timing period, and generating the common voltage transfers held at a third voltage level during a second timing period after the first timing period, in which the second voltage level is between the first and the third voltageE levels.

Owner:YUANHAN MATERIALS INC

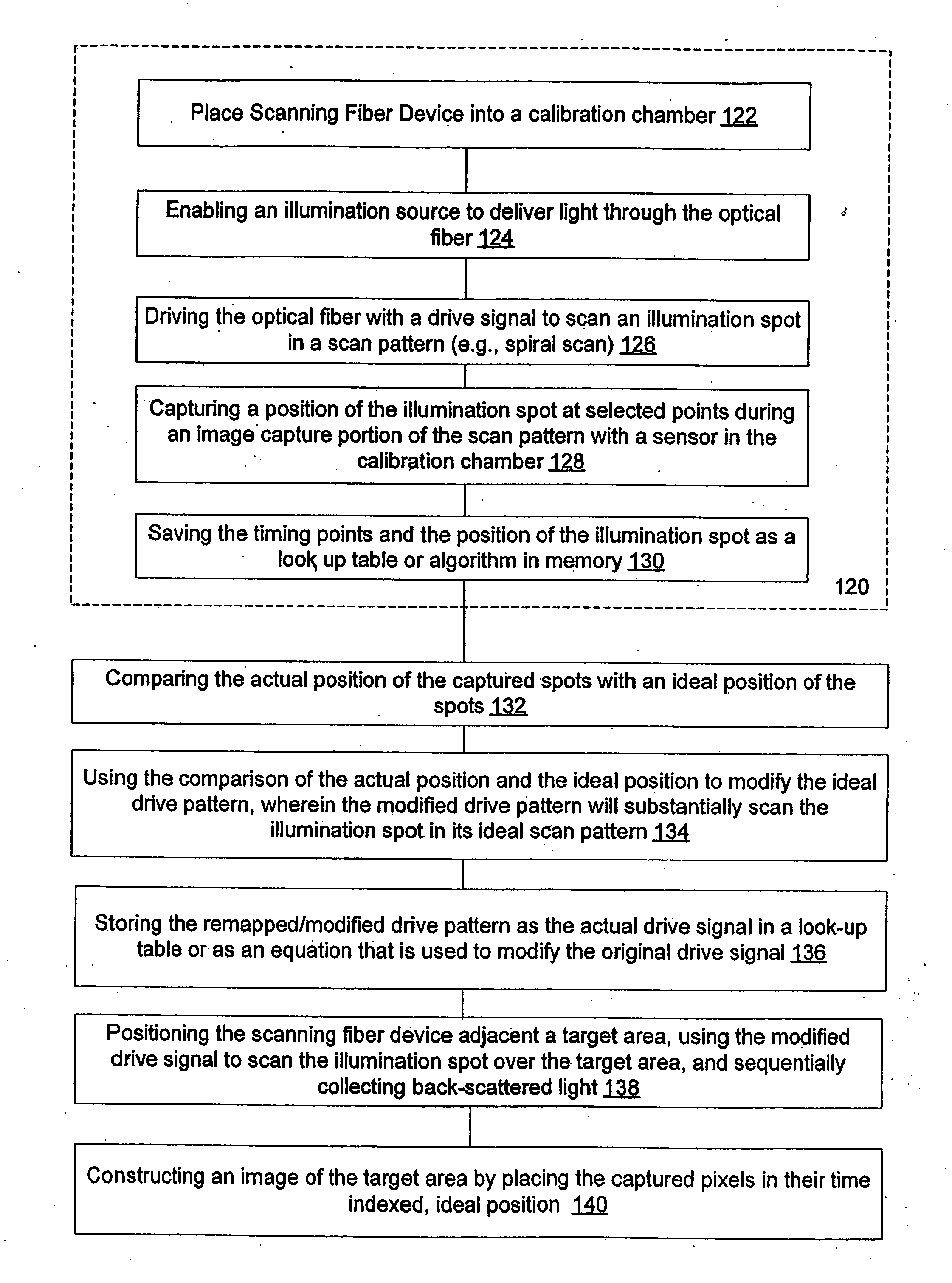

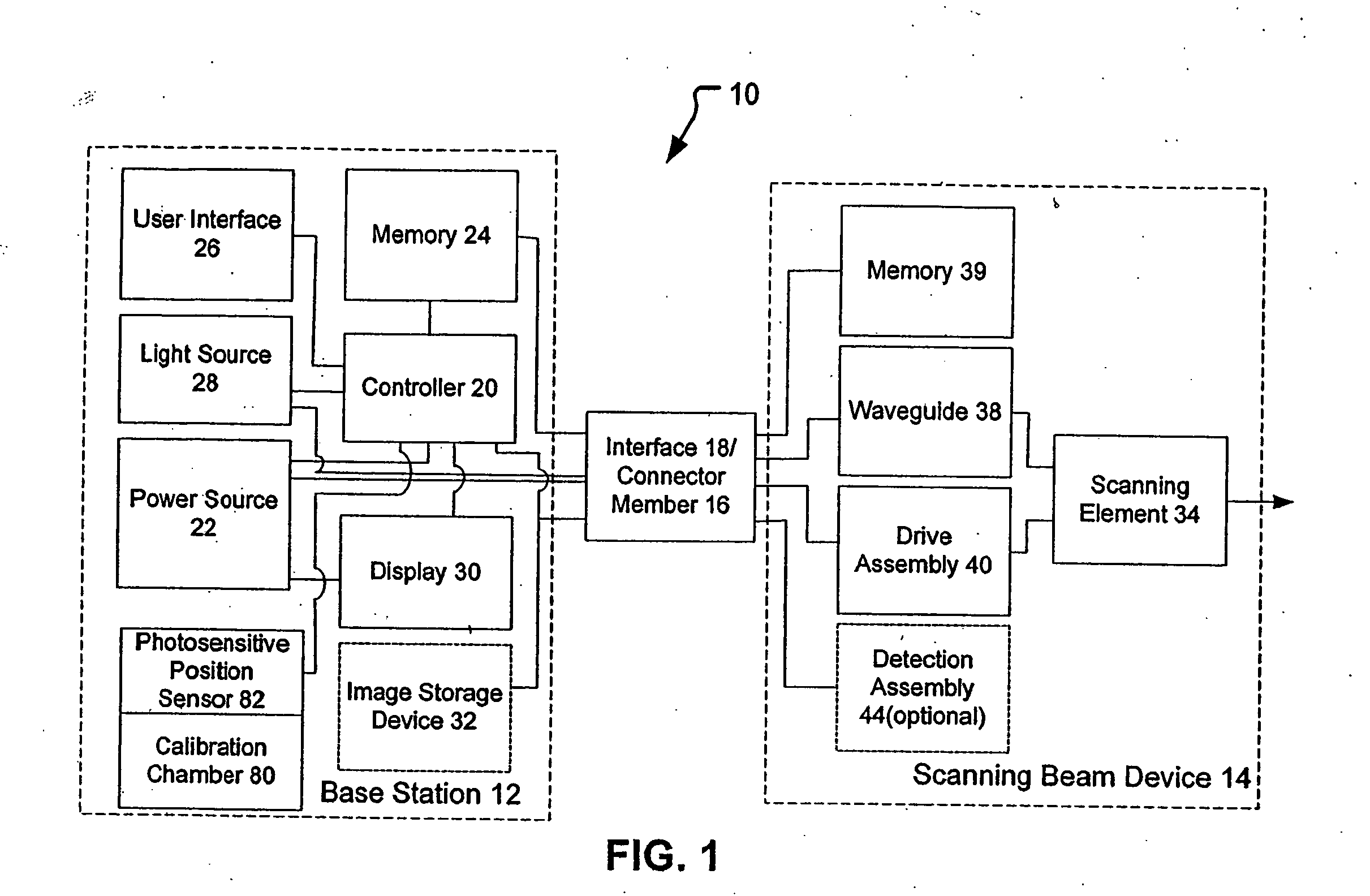

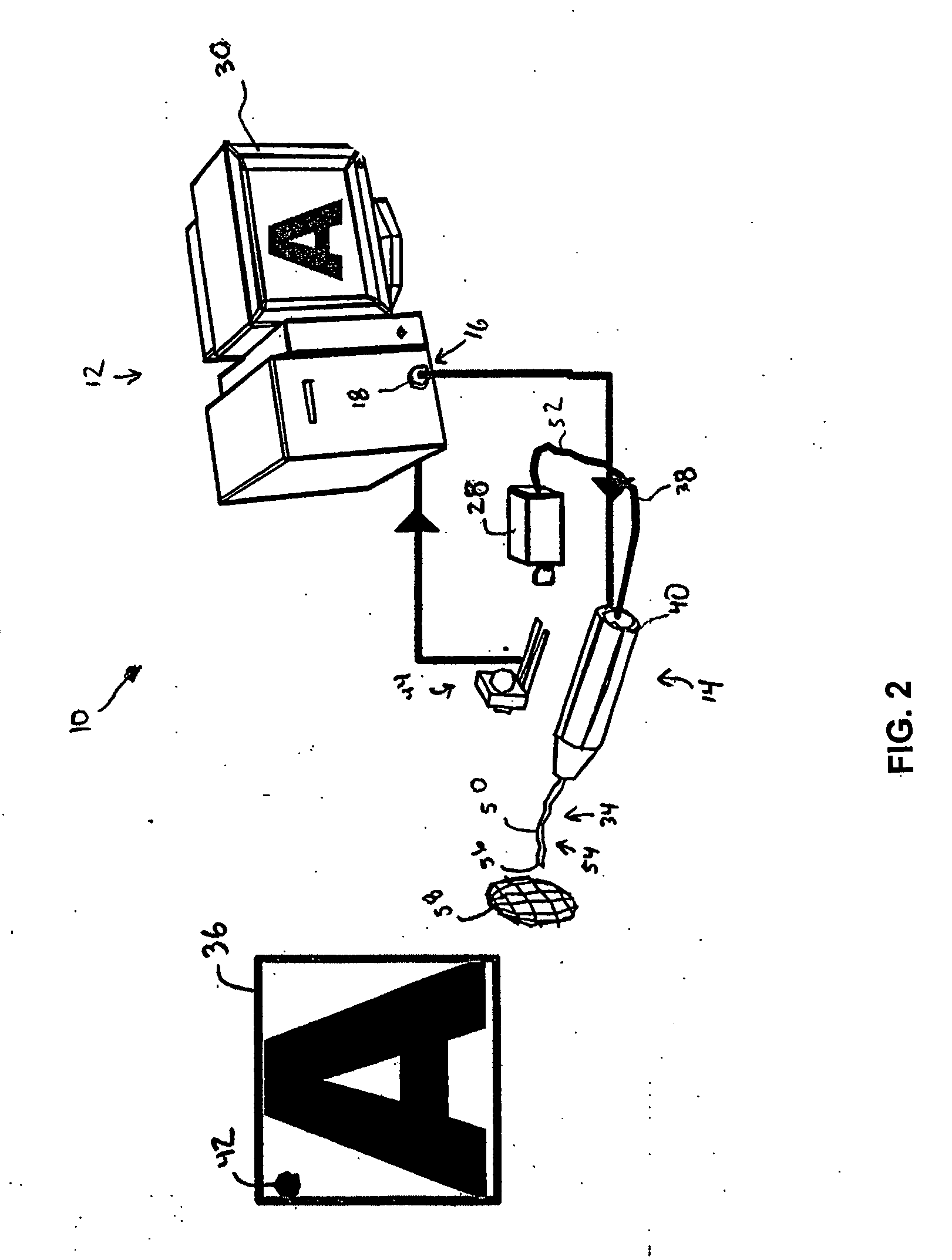

Remapping methods to reduce distortions in images

ActiveUS20060072843A1Reduce distortion problemsImage degradationCharacter and pattern recognitionClosed circuit television systemsPattern recognitionScanning beam

The present invention provides software, methods, and systems for characterizing an actual scan pattern of a scanning beam device. The characterization of the actual scan pattern may be used in an image remapping method and / or a drive signal remapping method to reduce distortions in an image.

Owner:UNIV OF WASHINGTON

System and method for identifying tissue using low-coherence interferometry

ActiveUS7761139B2Image degradationLower requirementCatheterDiagnostic recording/measuringFiberBiopsy procedure

Owner:THE GENERAL HOSPITAL CORP

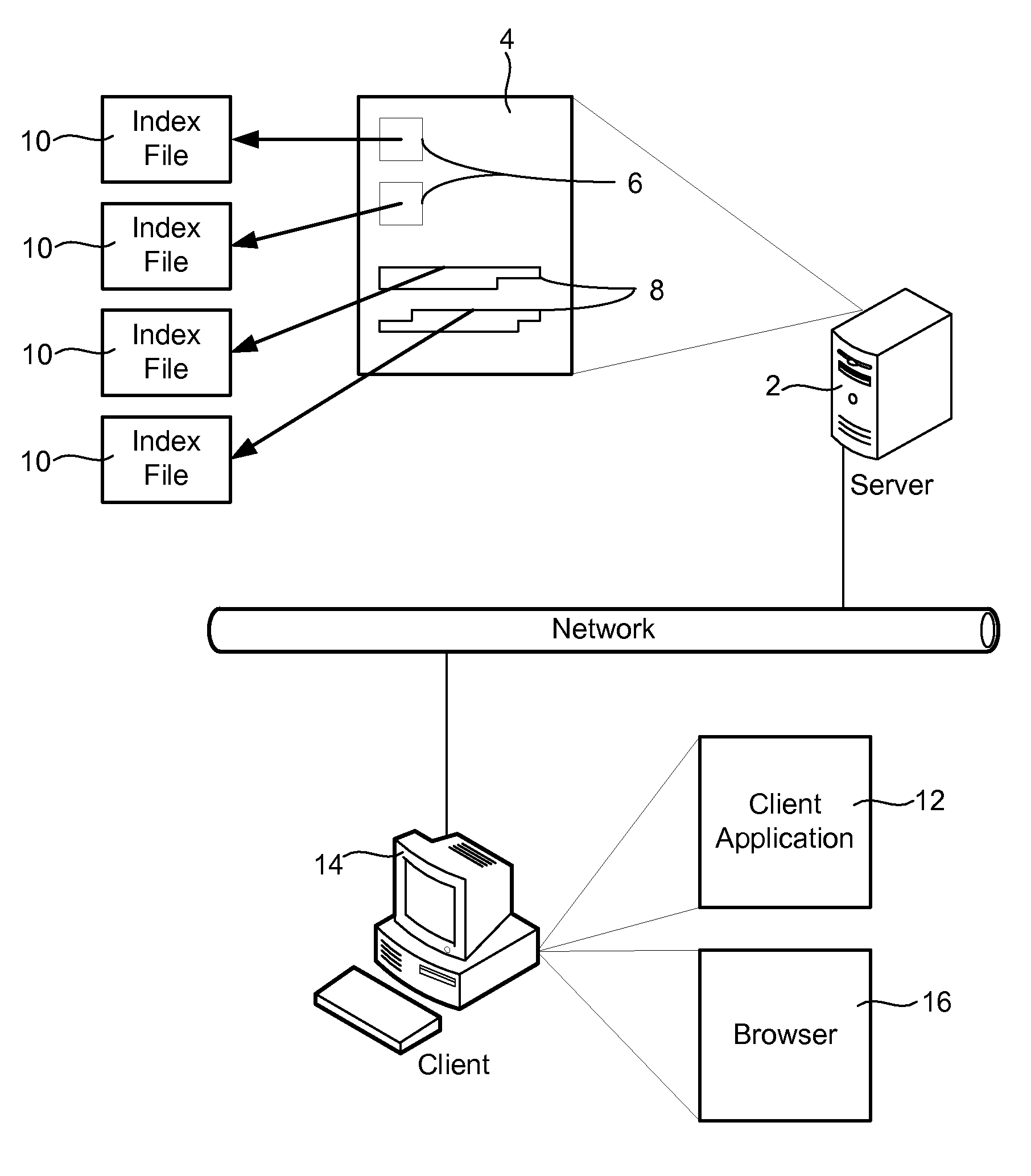

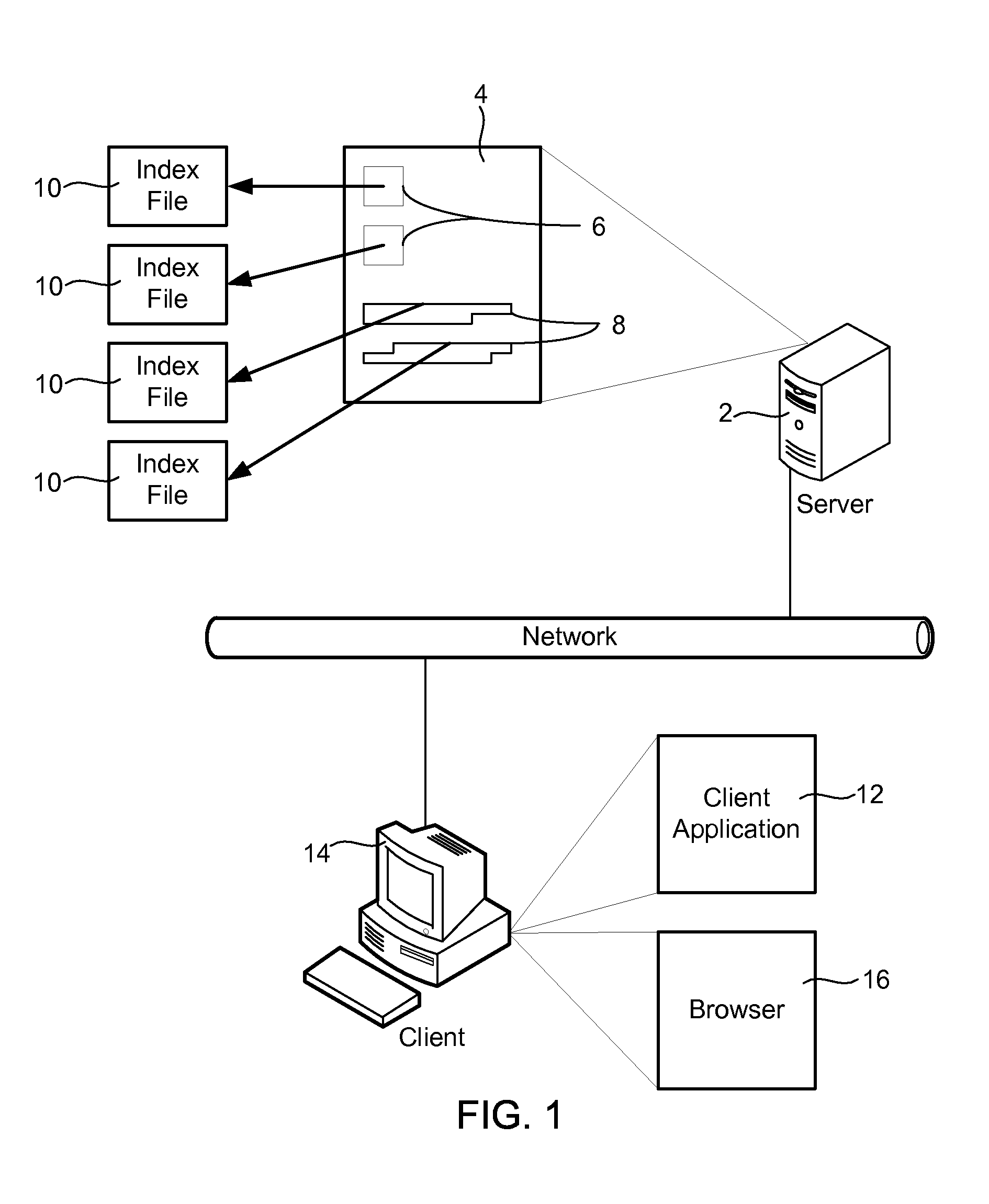

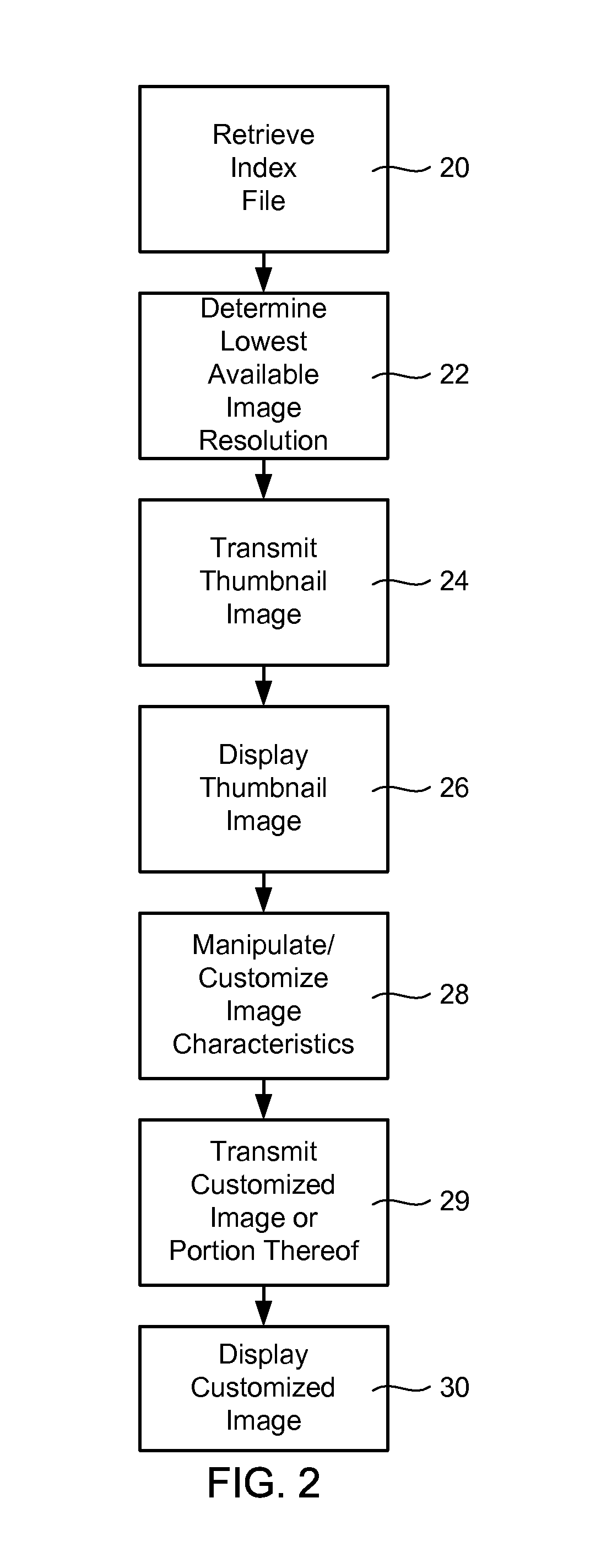

Methods and systems for transmitting digital images

InactiveUS7206804B1Lower latencyProcessing speedCharacter and pattern recognitionMultiple digital computer combinationsDigital imageMultimedia

Embodiments of the present invention comprise methods and systems for communicating a recipient-selected customization of a digital image using an index file. The index file associates a customization characteristic with the segments of the digital image required to construct a customized image that exhibits the customization characteristic.

Owner:SHARP KK

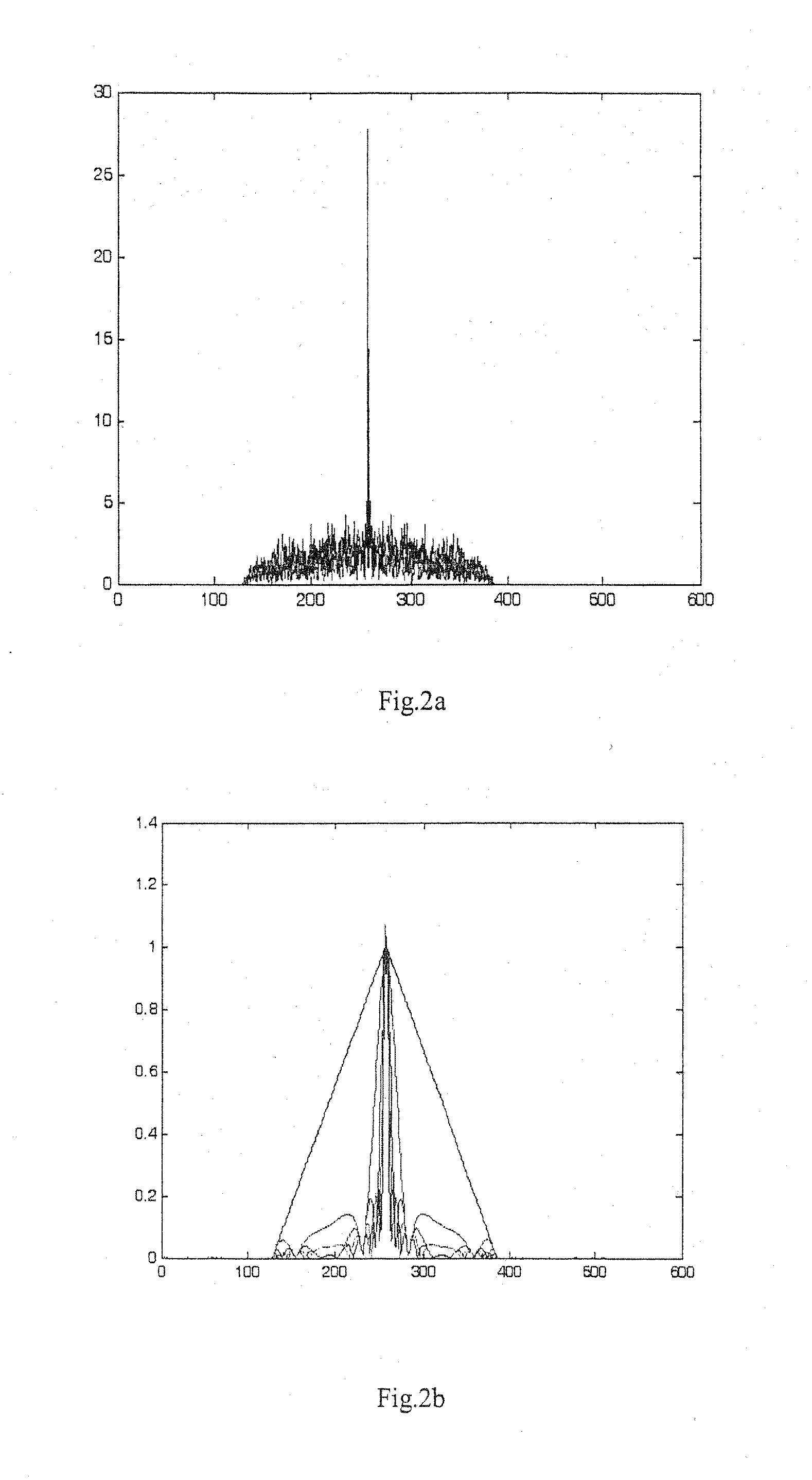

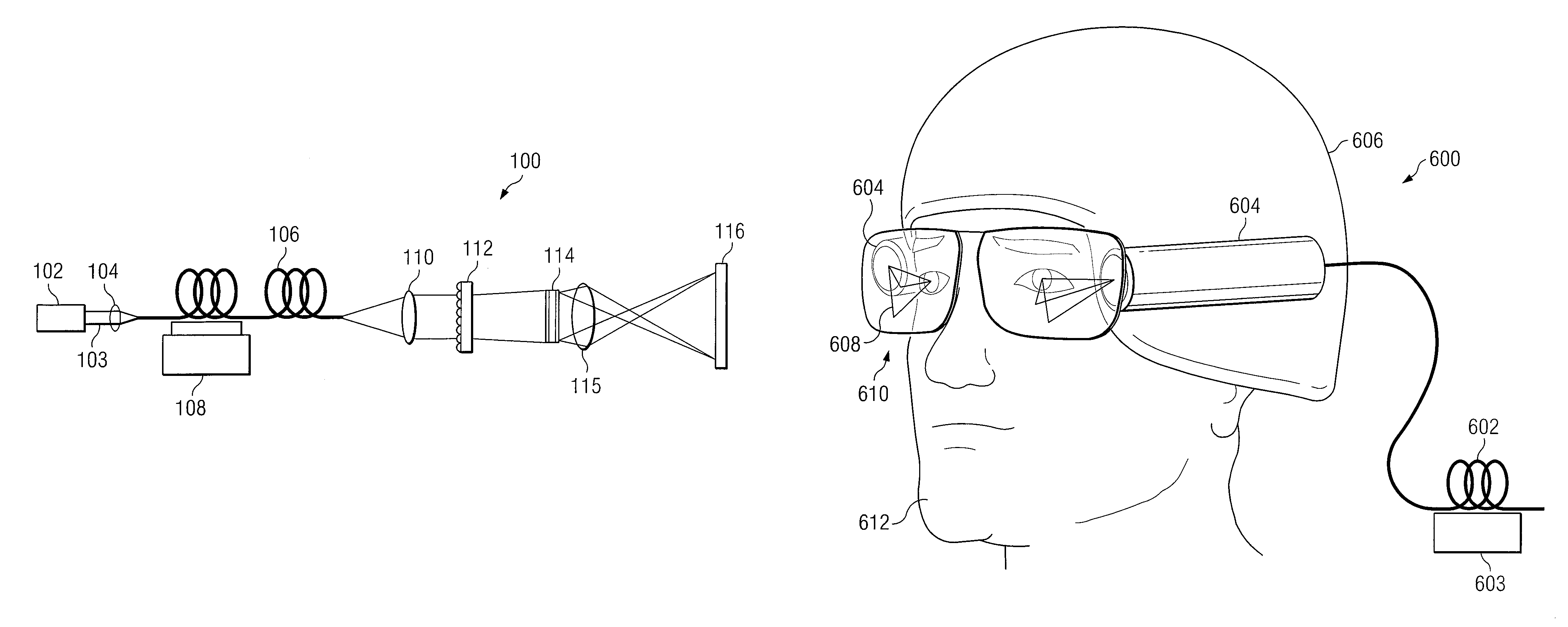

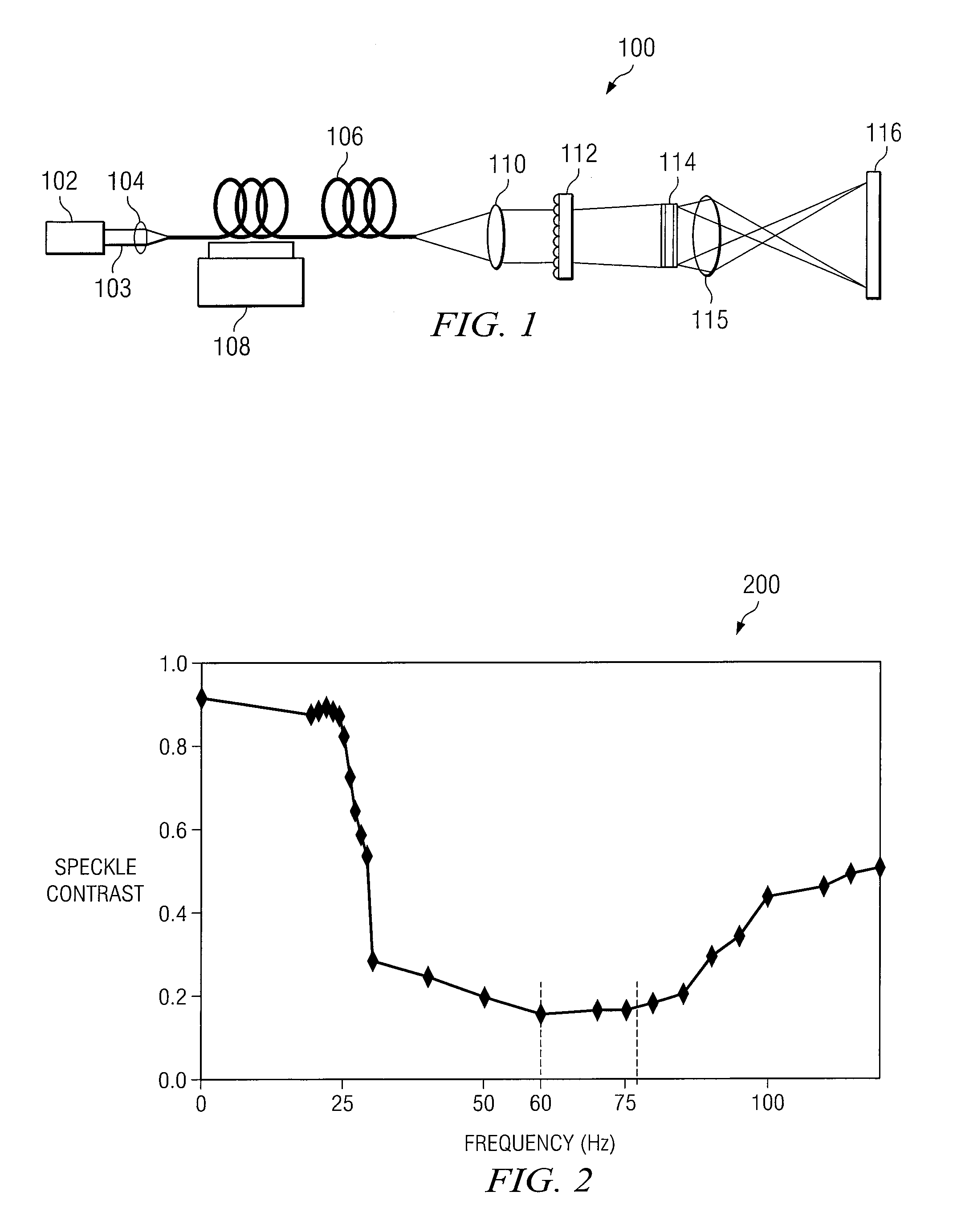

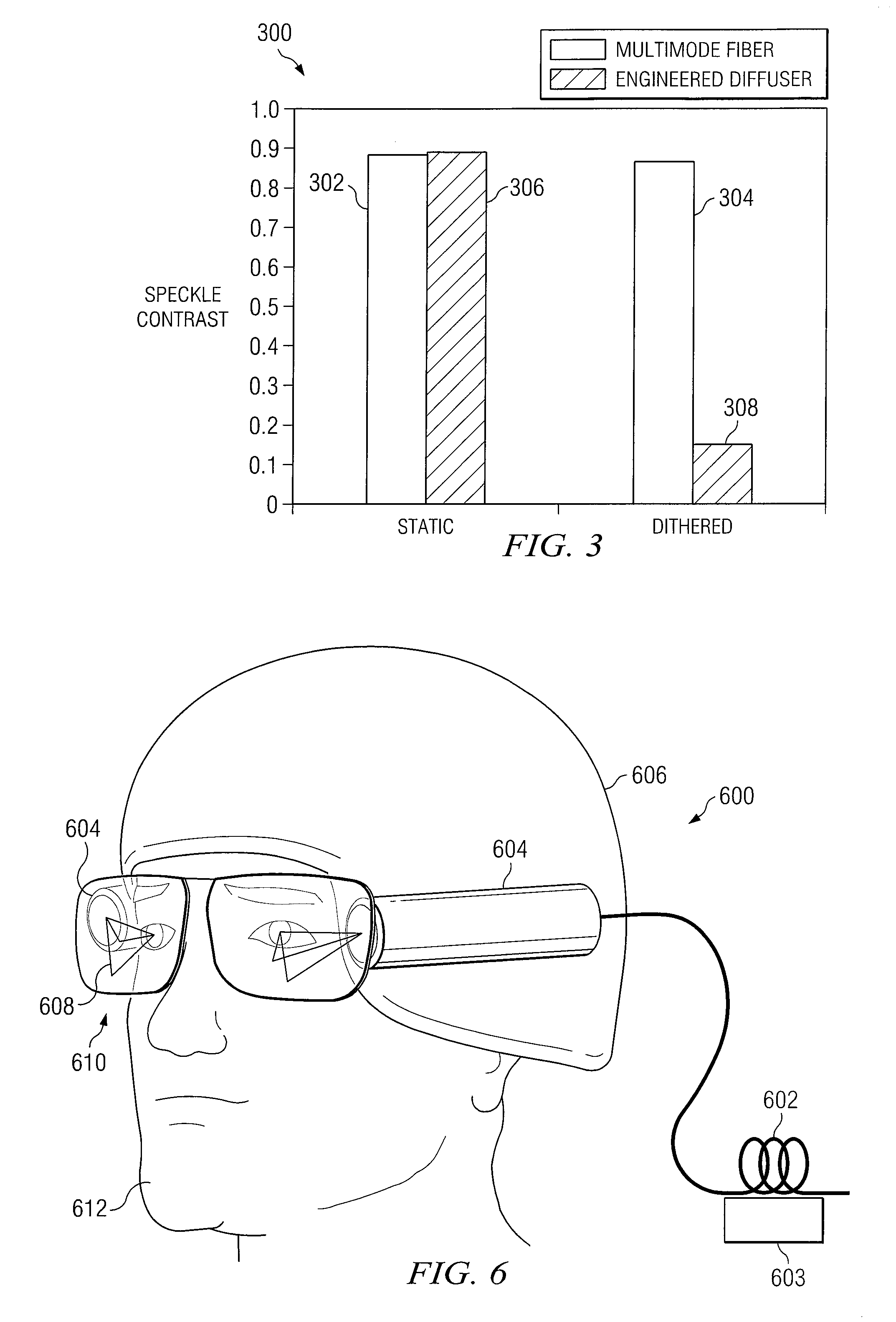

System and method for despeckling an image illuminated by a coherent light source

ActiveUS7969644B2Speckle reductionIncrease contrastCladded optical fibreColor television detailsFiberLight beam

A method and system for reducing speckle in an image produced from a coherent source of radiation is provided. The method includes coupling a source beam received from a coherent optical source into an optical fiber. A position of at least a portion of the fiber may be modulated using a ditherer. The source beam may be refracted by a lens after it is decoupled from the optical fiber, such that the source beam is aimed at a microlens diffuser. In accordance with a particular embodiment, the source beam may be projected from the microlens diffuser onto a spatial modulator. The spatial modulator may be positioned to project the source beam via an imaging lens, to a target.

Owner:ELBIT SYSTEMS OF AMERICA LLC

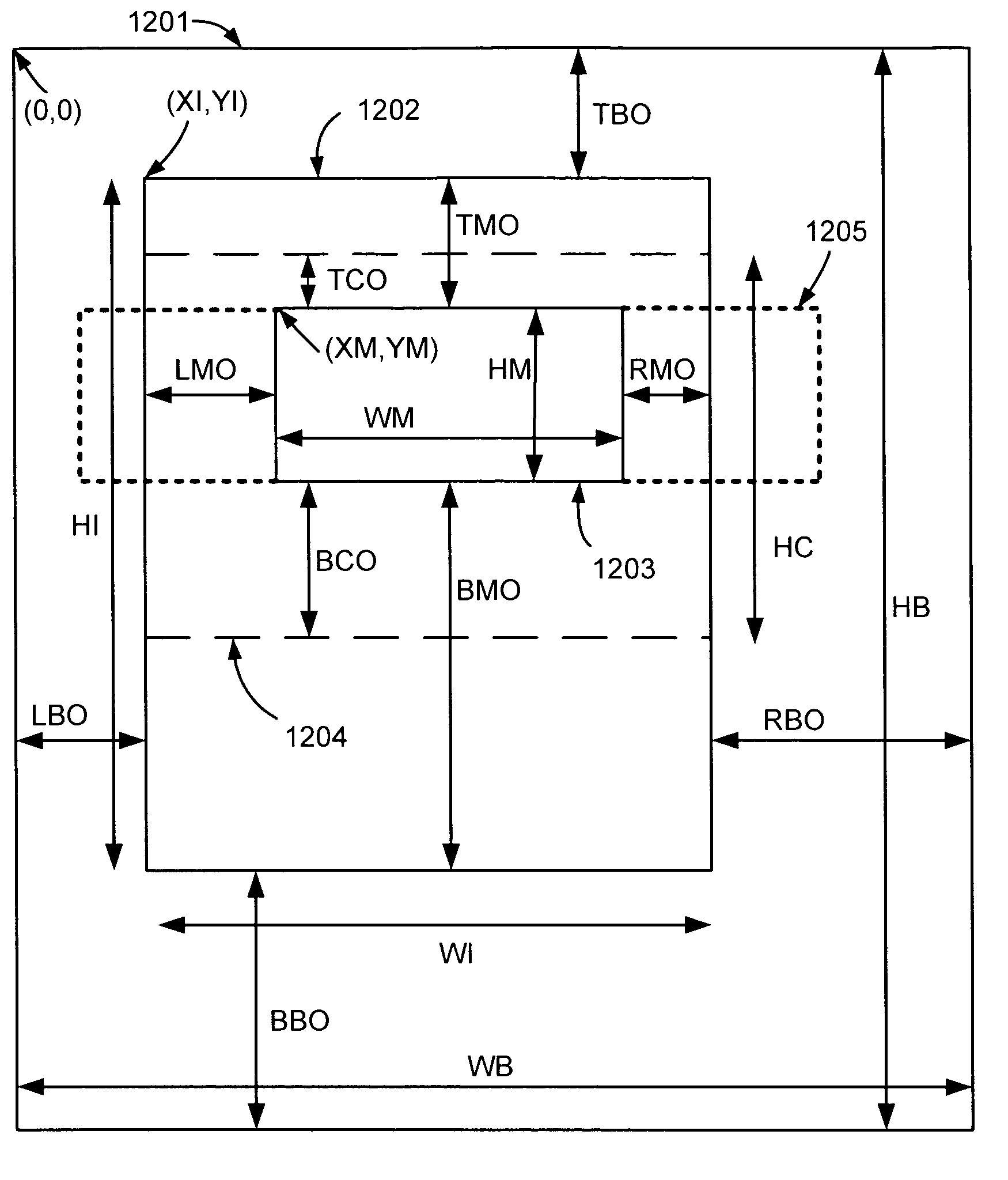

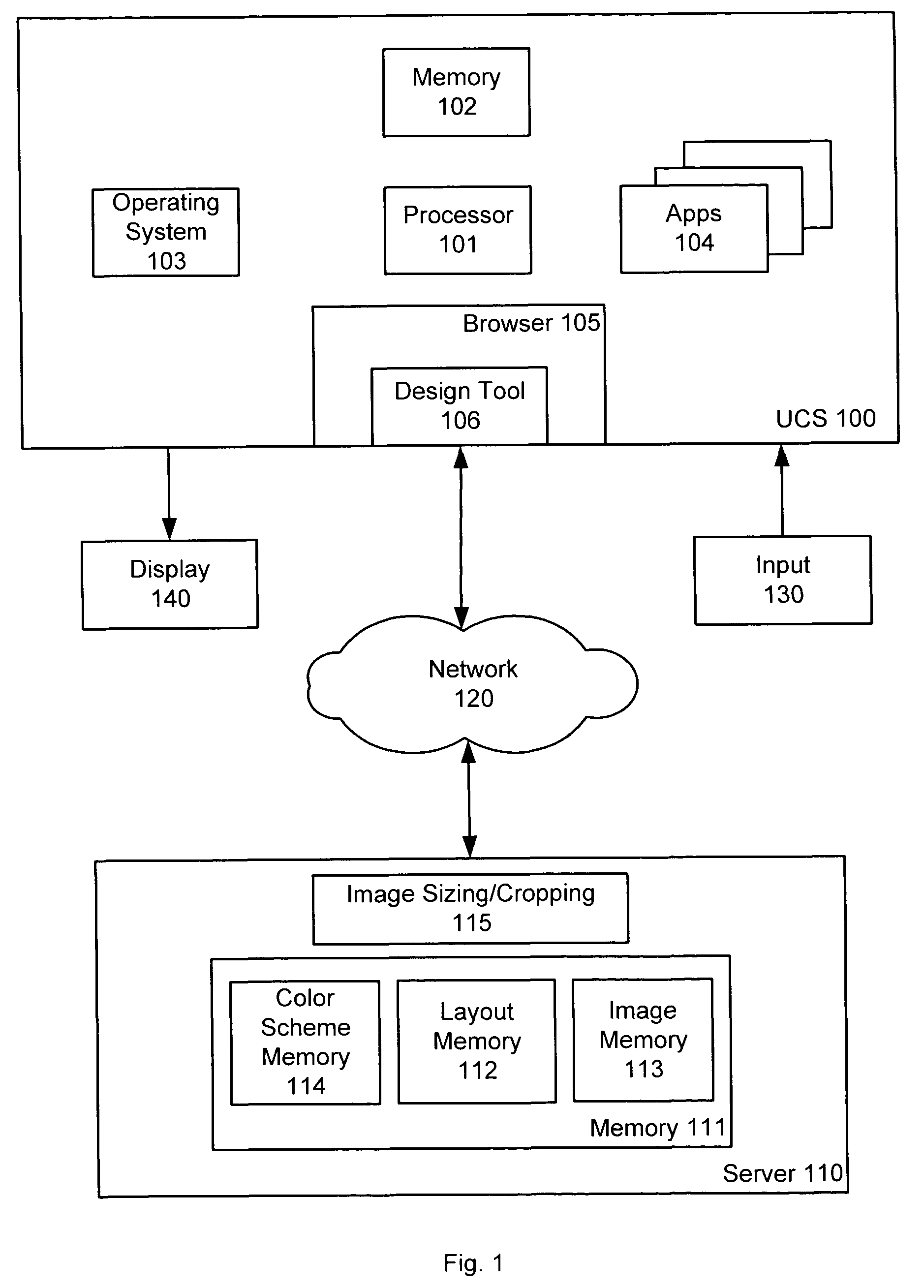

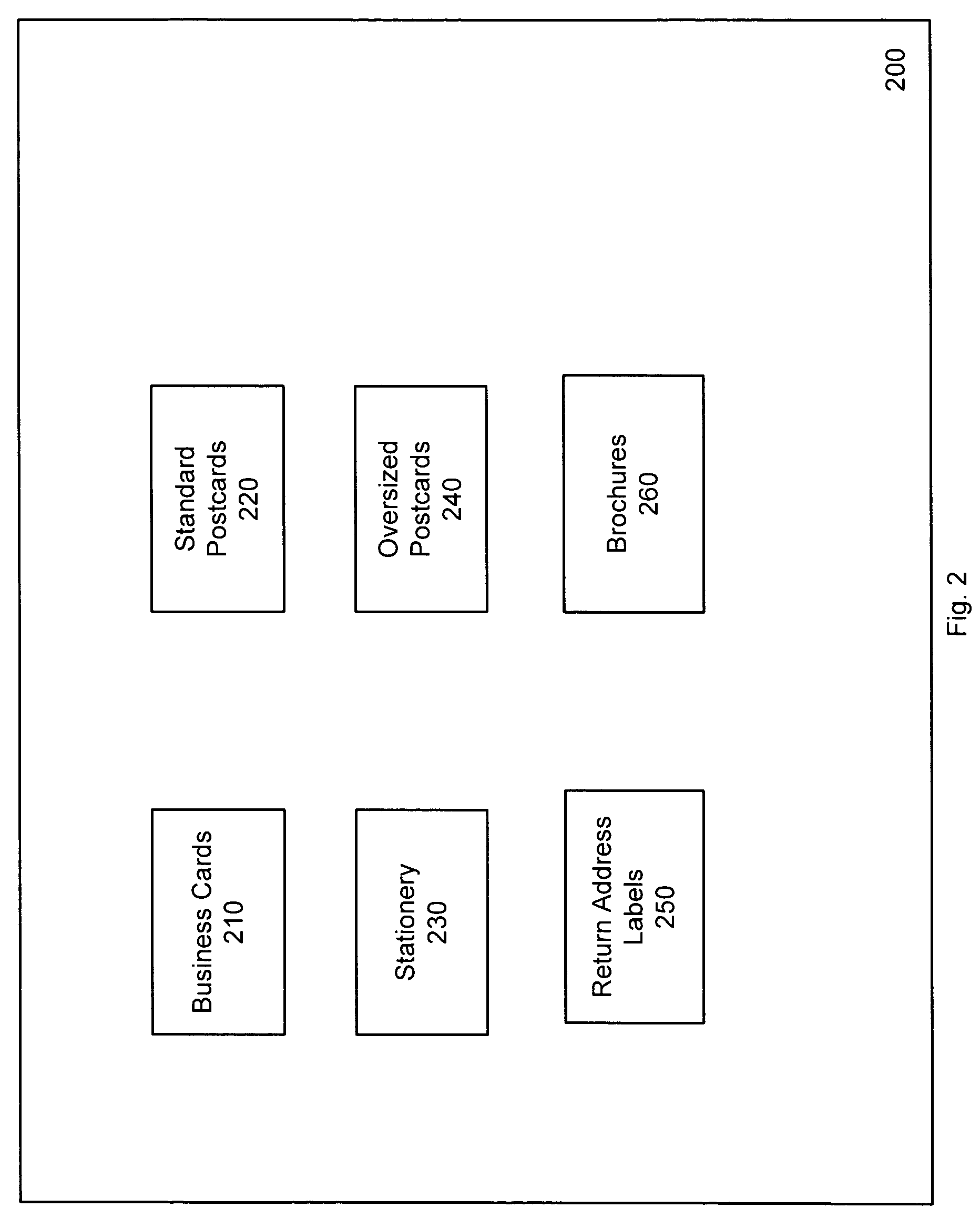

Automated image resizing and cropping

InactiveUS7133050B2Simple designGreat numberGeometric image transformationCathode-ray tube indicatorsProduct typeElectronic document

Automated electronic document design systems and methods for combining identified images and layouts into electronic product templates for displaying to a user. A plurality of images and a plurality of layouts are retained. Stored images are identified based on keyword input by the user. Stored layouts contain one or more image containers and are identified based on product type and number of layout images input by the user. Images are automatically sized and cropped to fit image containers. Sizing and cropping constraints are applying to control image quality.

Owner:CIMPRESS SCHWEIZ

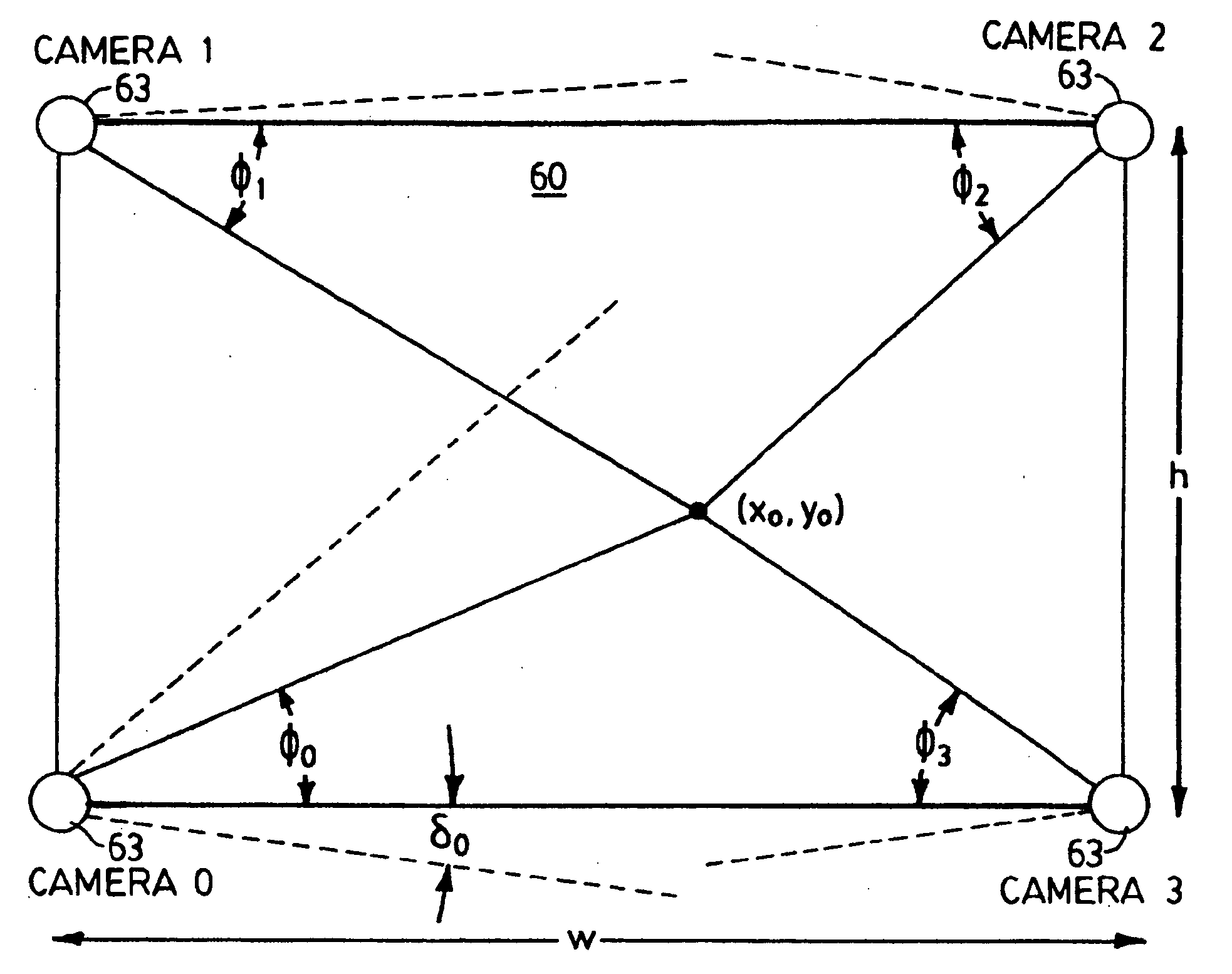

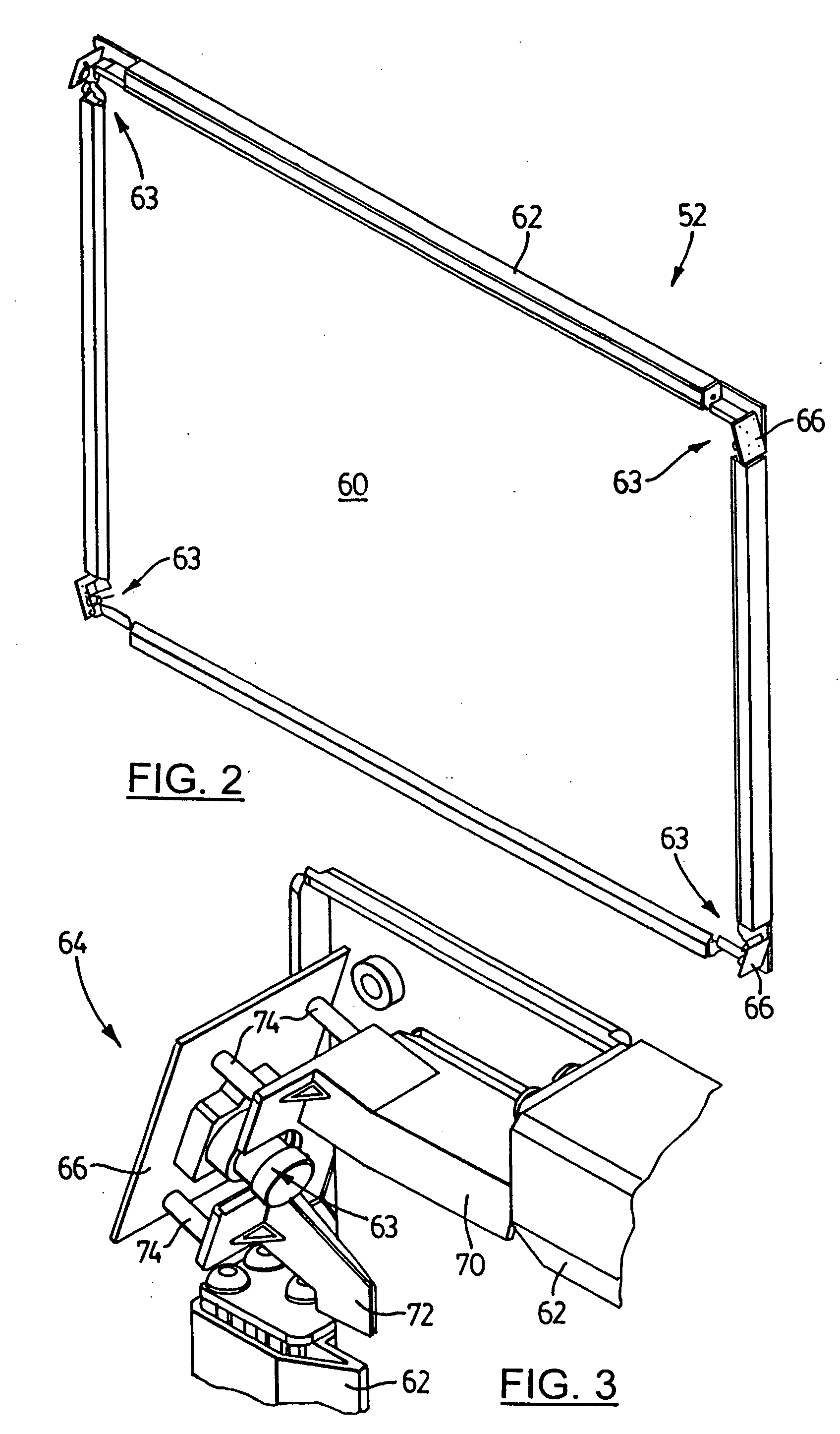

Size/scale and orientation determination of a pointer in a camera-based touch system

InactiveUS20060022962A1High measurement accuracyImage degradationCathode-ray tube indicatorsInput/output processes for data processingTriangulationField of view

A touch system includes a touch surface and at least two cameras associated with the touch surface. The at least two cameras acquire images of the touch surface from different locations and having overlapping fields of view. A digital signal processor is associated with each camera. The digital signal processors process pixel data acquired by selected pixel subsets of the at least two digital cameras to generate pointer characteristic data when a pointer exists in the acquired images. The pointer characteristic data identifies edges of the pointer. A master digital signal processor triangulates the edge information in the pointer characteristic data to determine a bounding area that represents a pointer perimeter.

Owner:SMART TECH INC (CA)

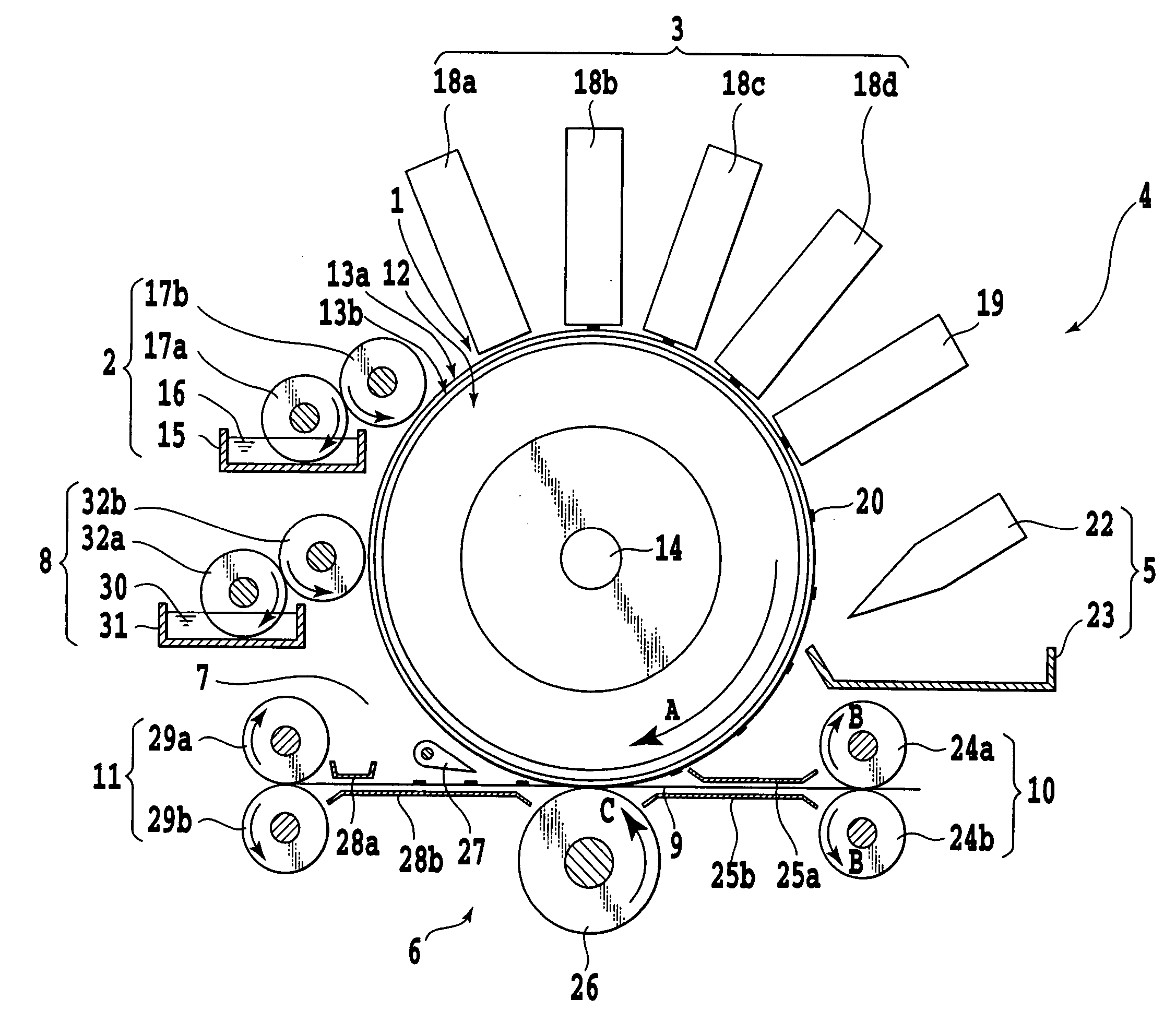

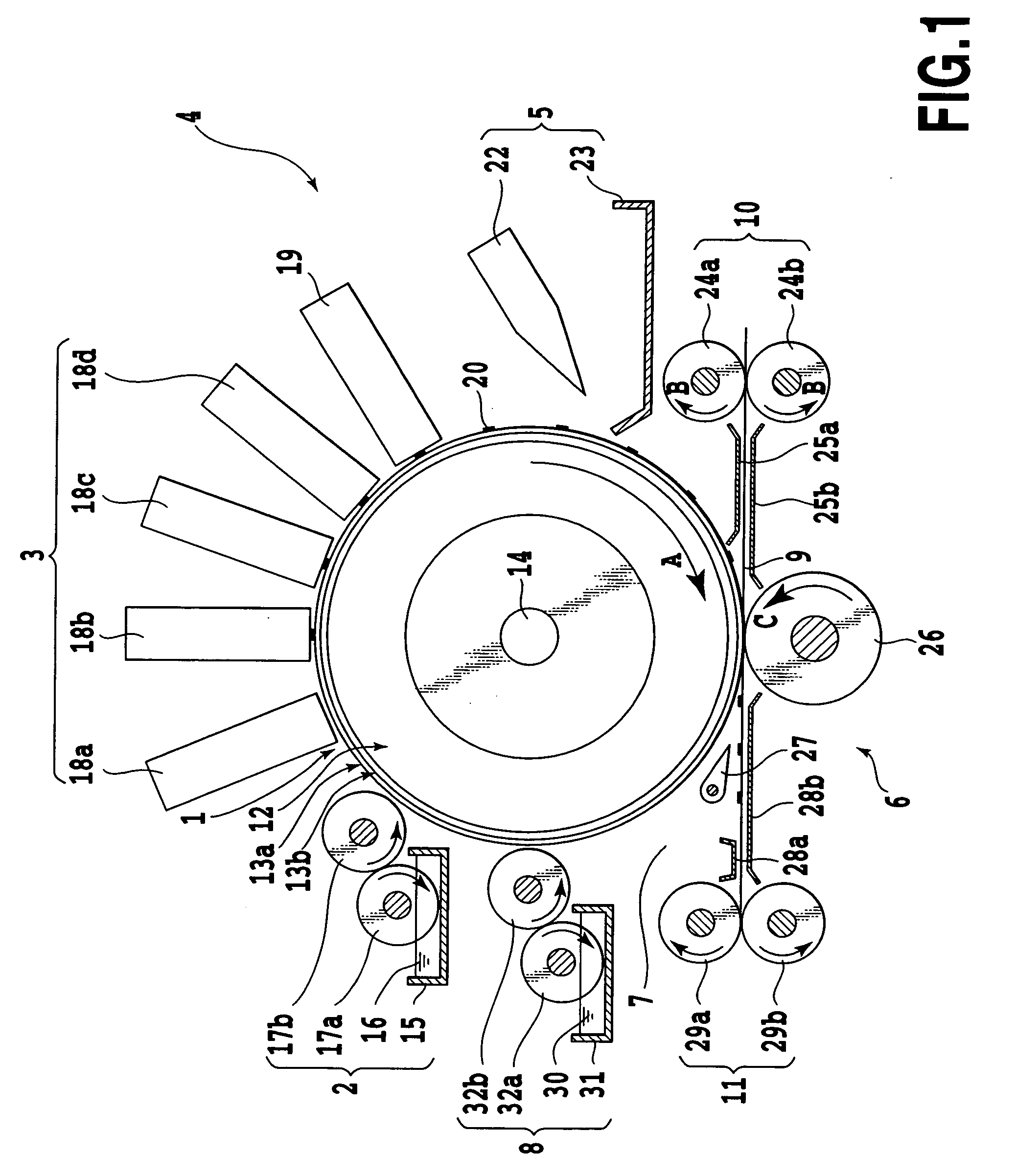

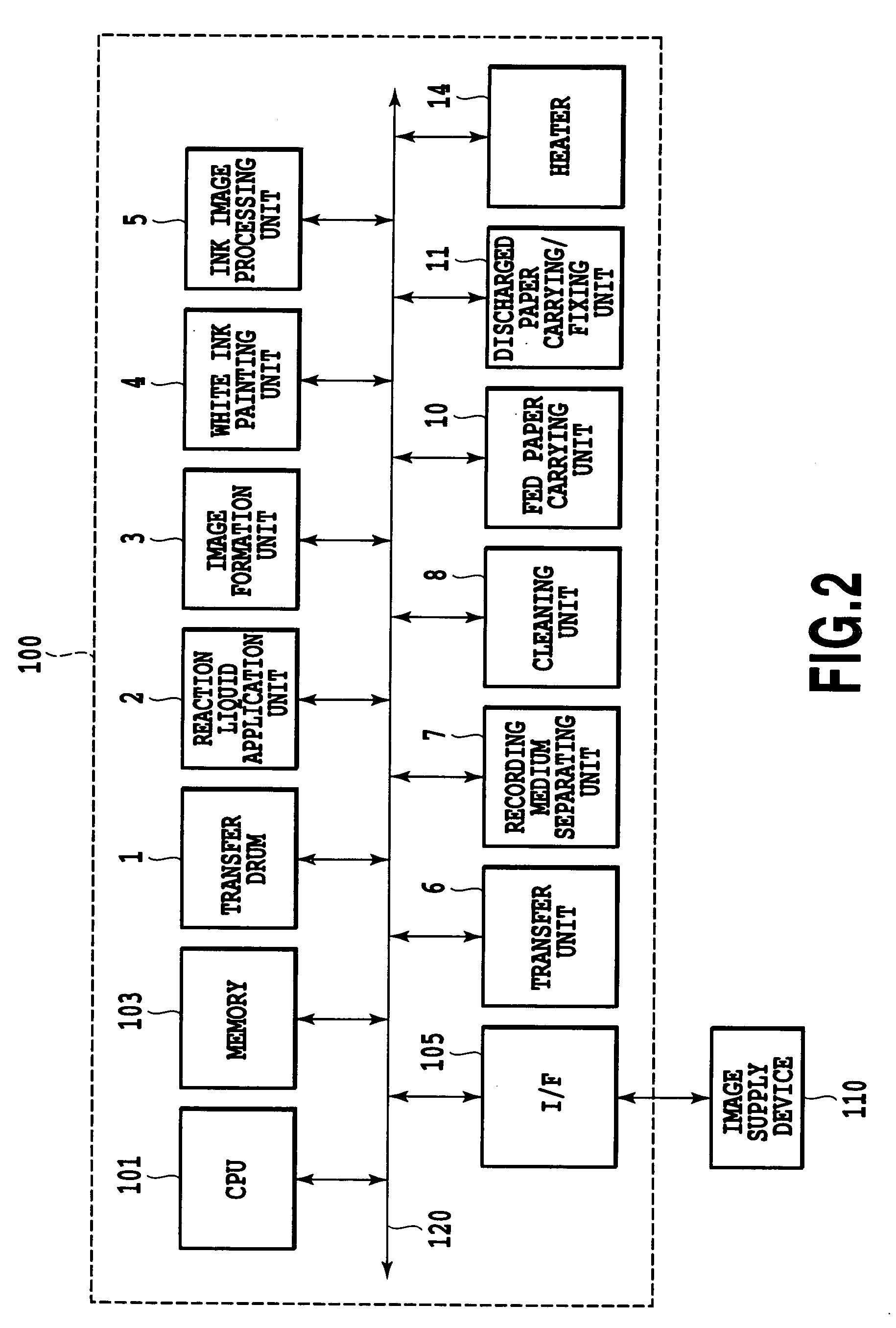

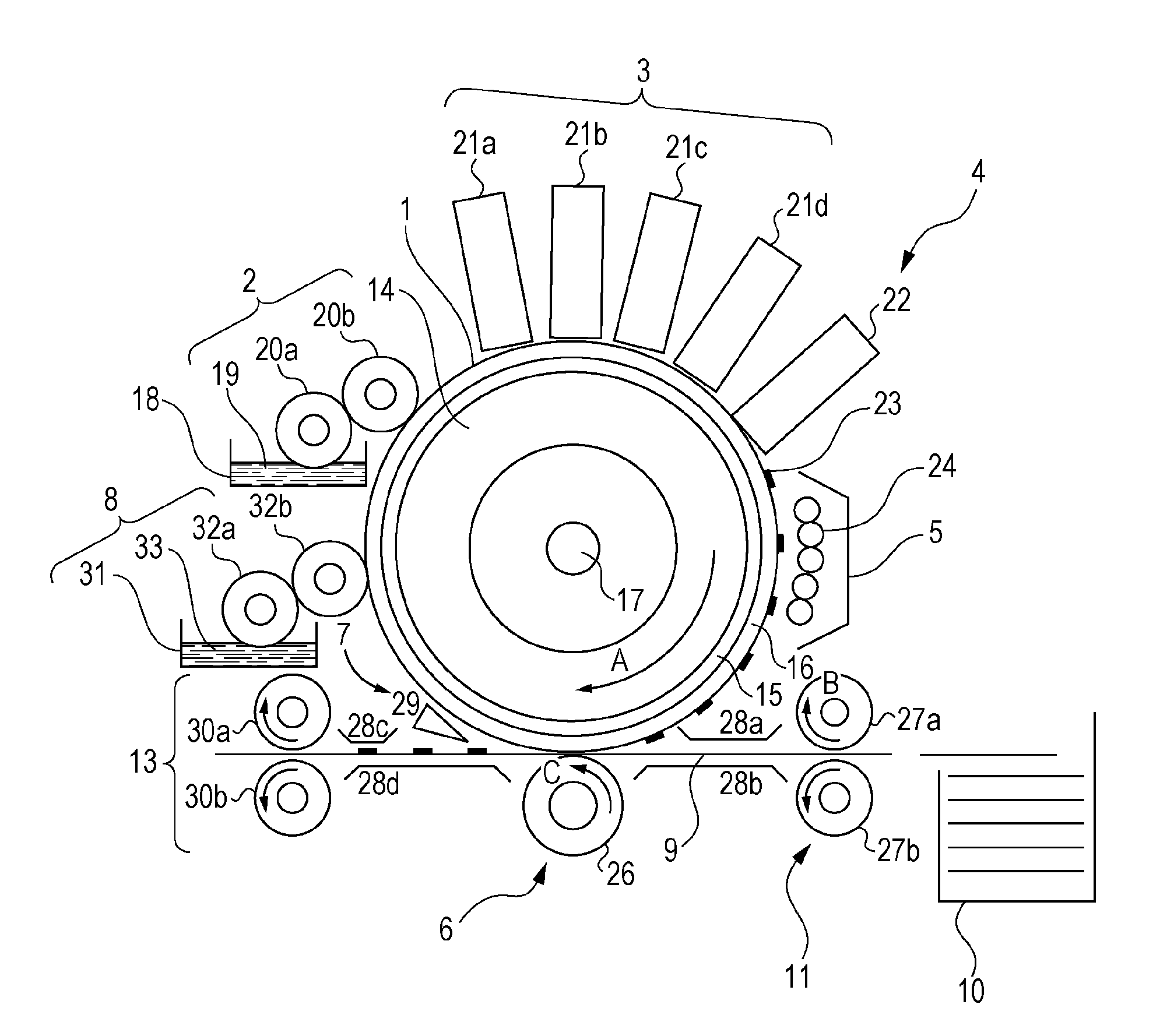

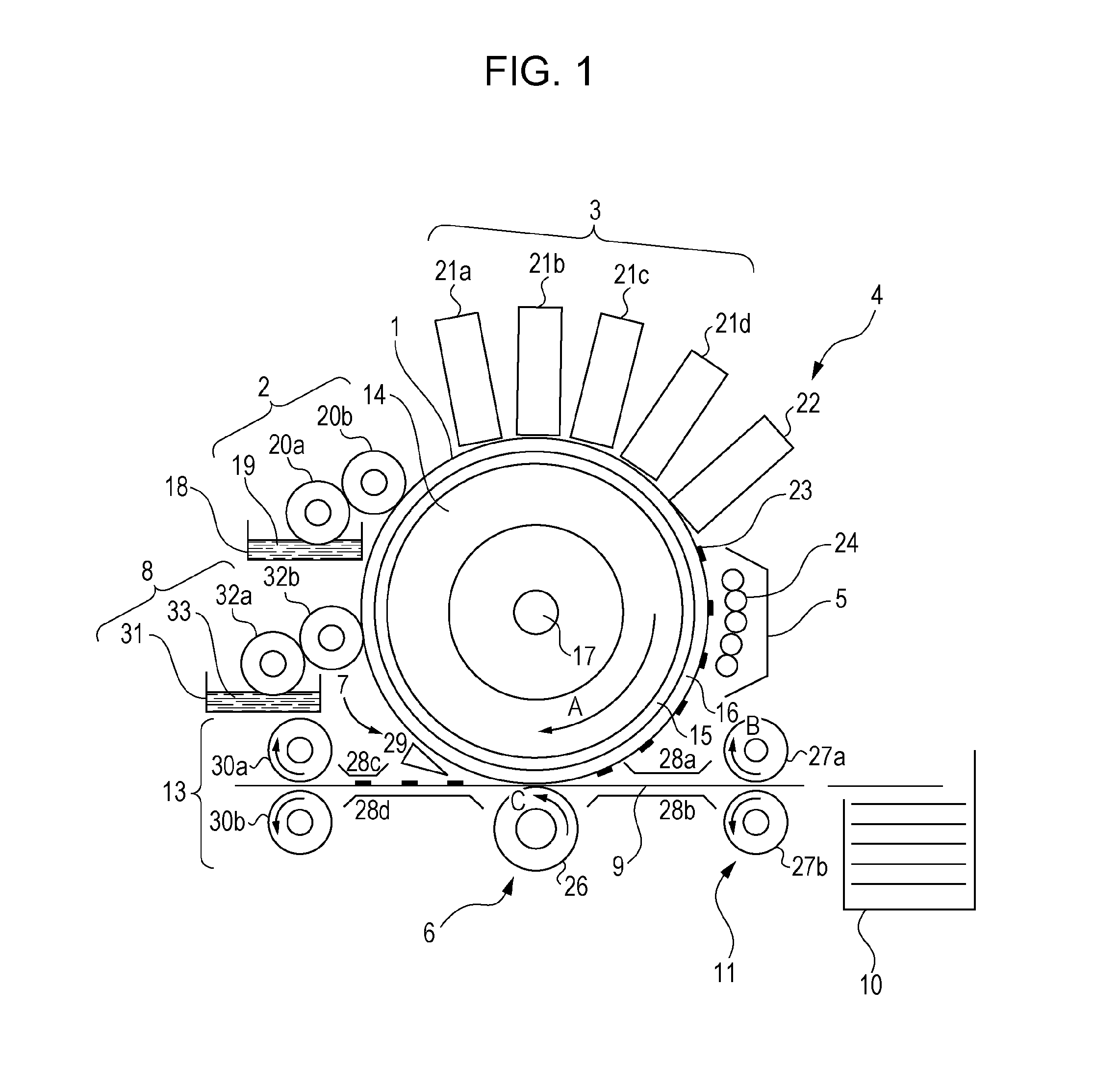

Ink jet recording method and ink jet recording apparatus

InactiveUS20050270351A1Reduce fluiditySuppressed in beadingNatural patternsRadiation applicationsImage formationEngineering

An ink jet recording method and an ink jet recording apparatus permitting image formation with a high degree of color reproducibility while alleviating the influences of the ink-absorbency of the recording medium and the base color is to be provided. A transfer drum is applied a reaction liquid, and inks of different colors are applied by recording heads to the area applied the reaction liquid to form a coagulated ink image on the transfer drum. Ahead of the step to transfer this coagulated ink image to the recording medium, white ink is applied to at least the area of the transfer drum to which ink dots are to be applied or at least the area to which ink dots are to be applied out of the area of the recording medium to which the coagulated ink image is to be transferred.

Owner:CANON KK

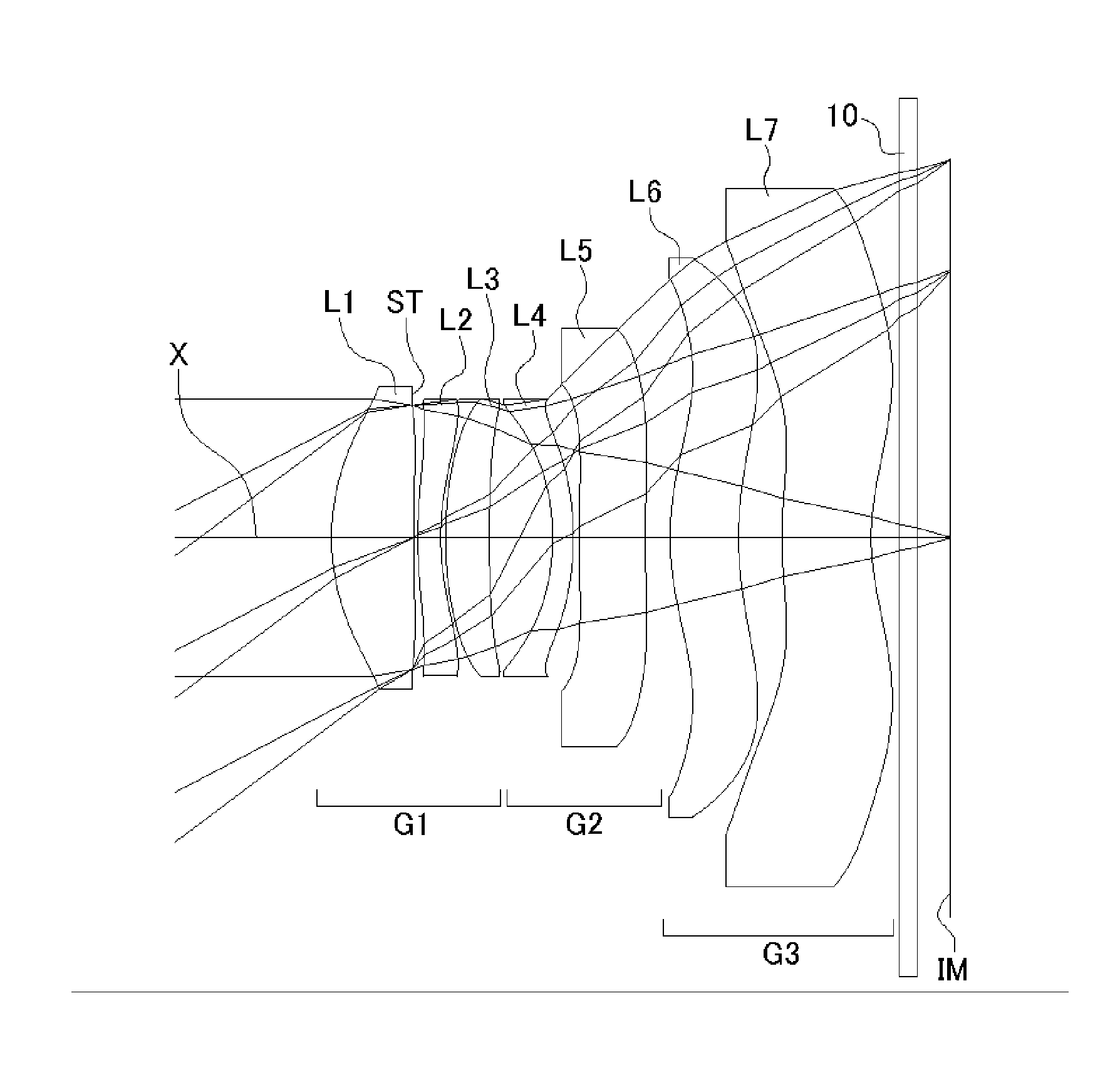

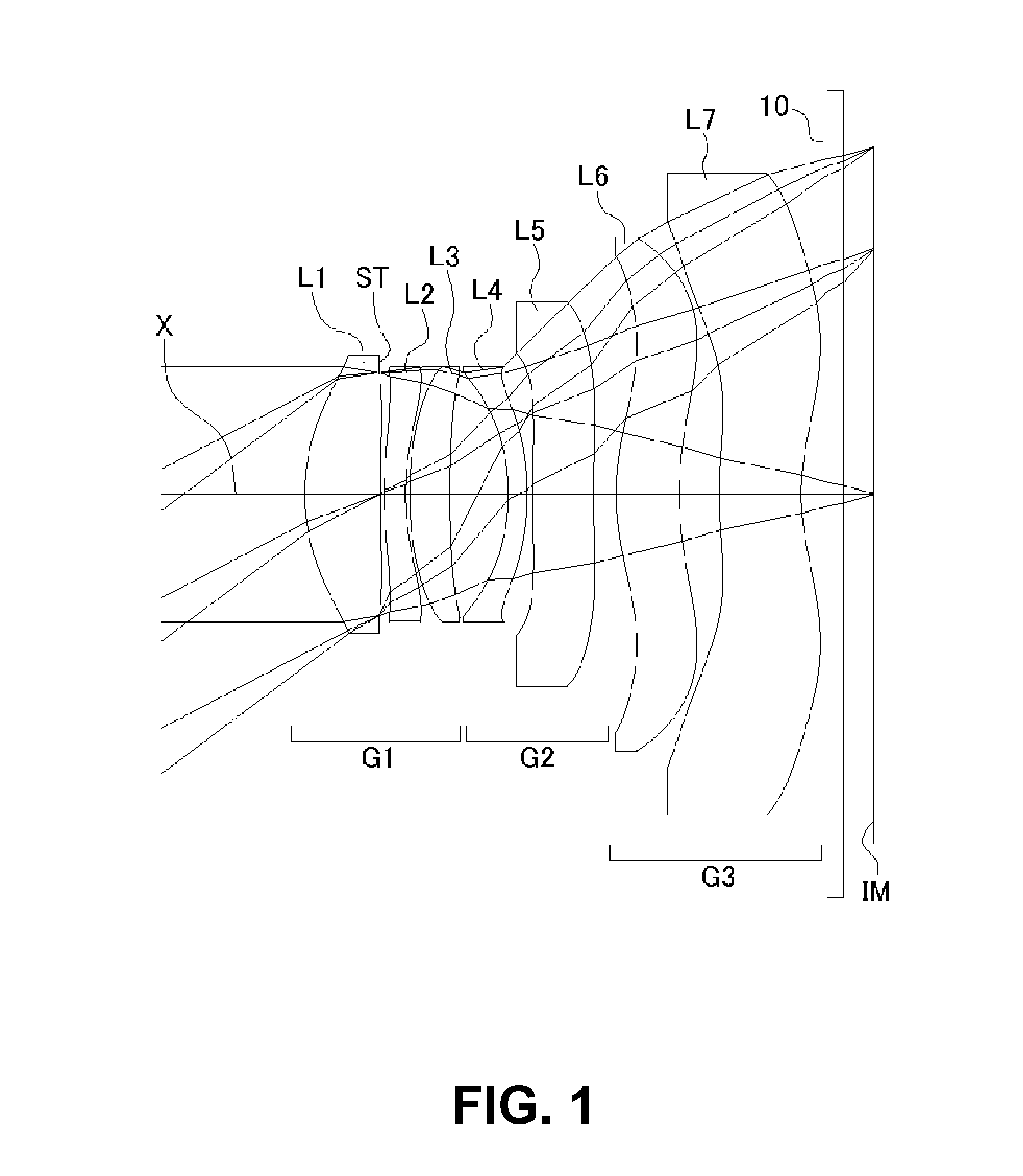

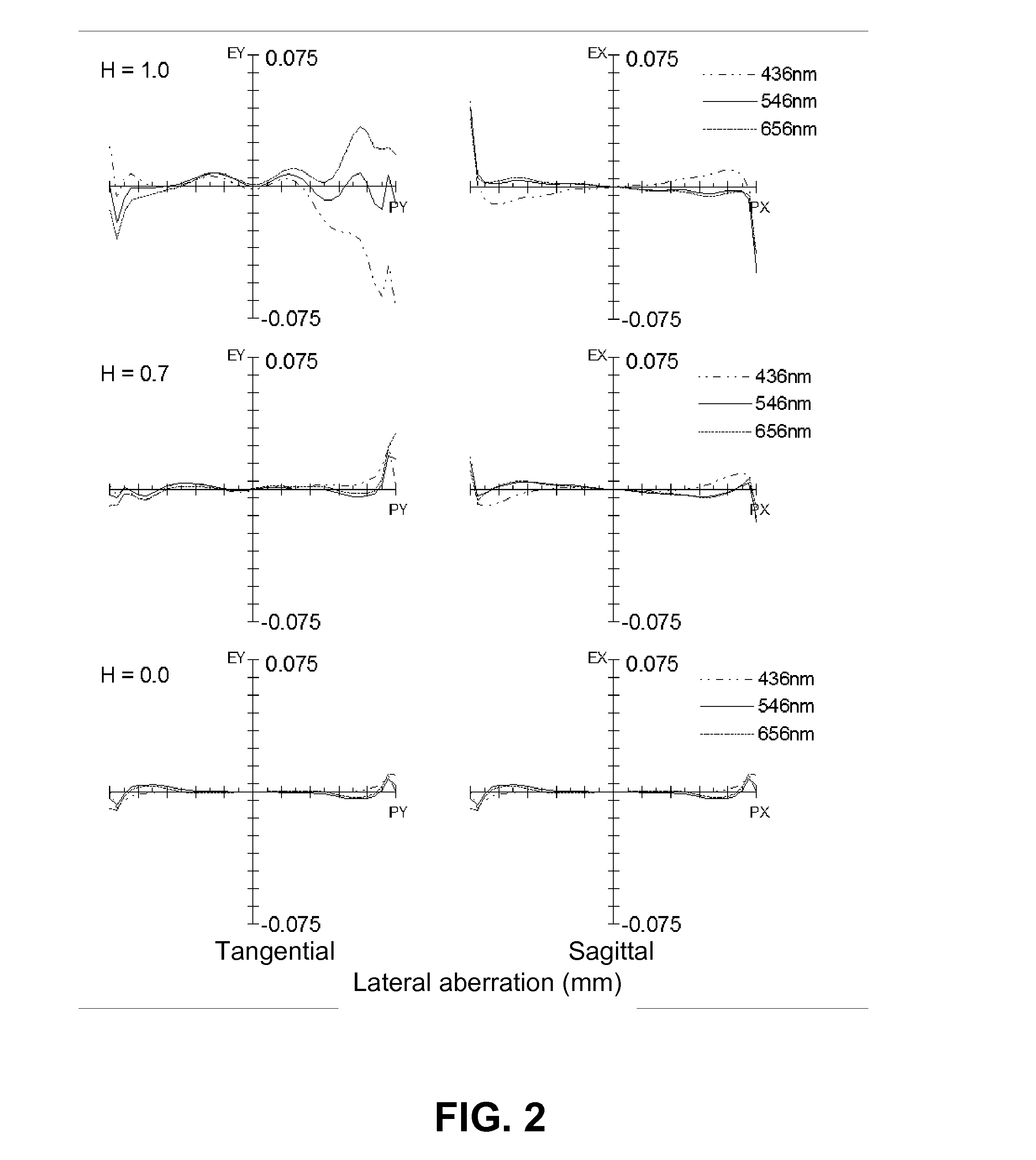

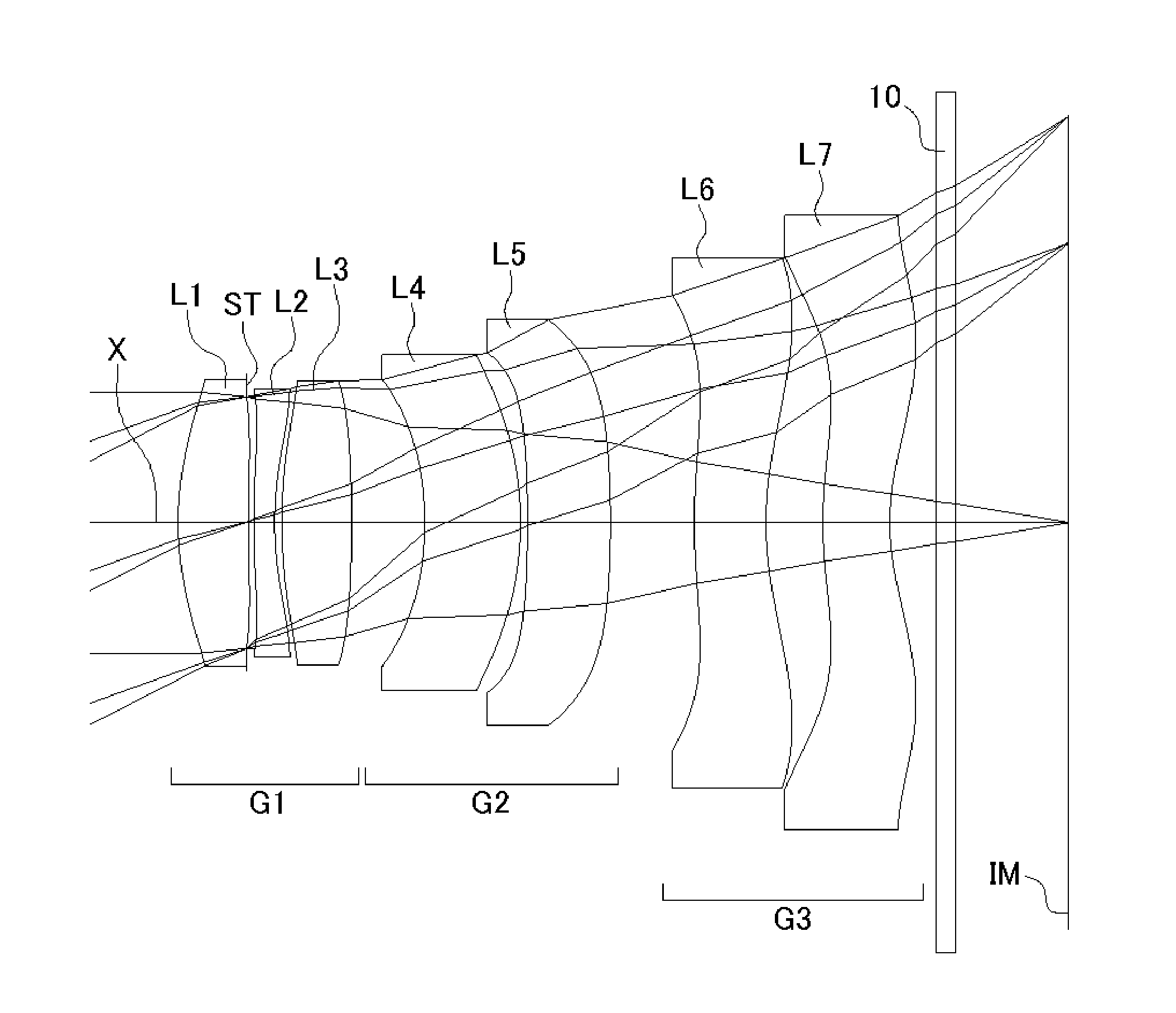

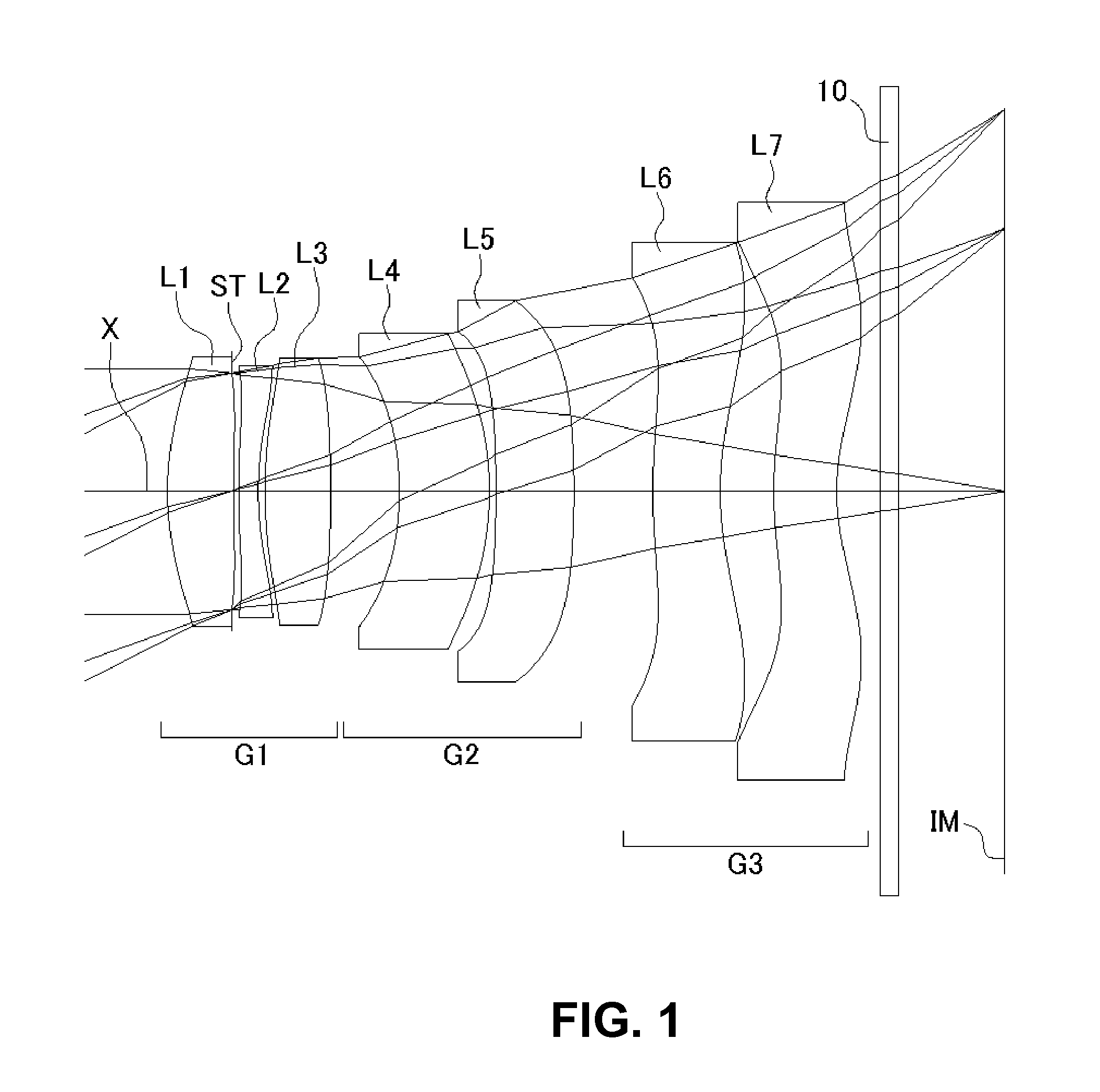

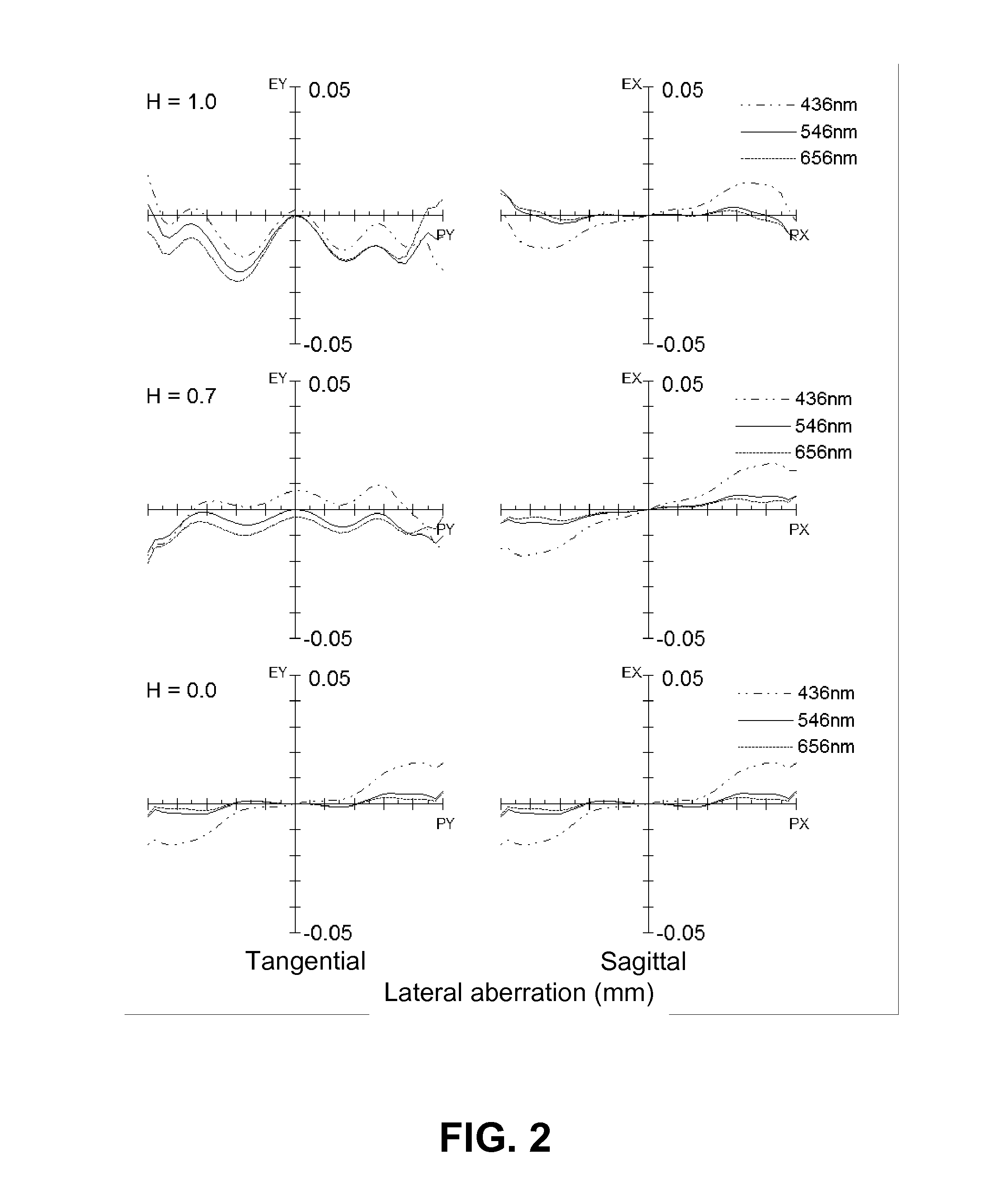

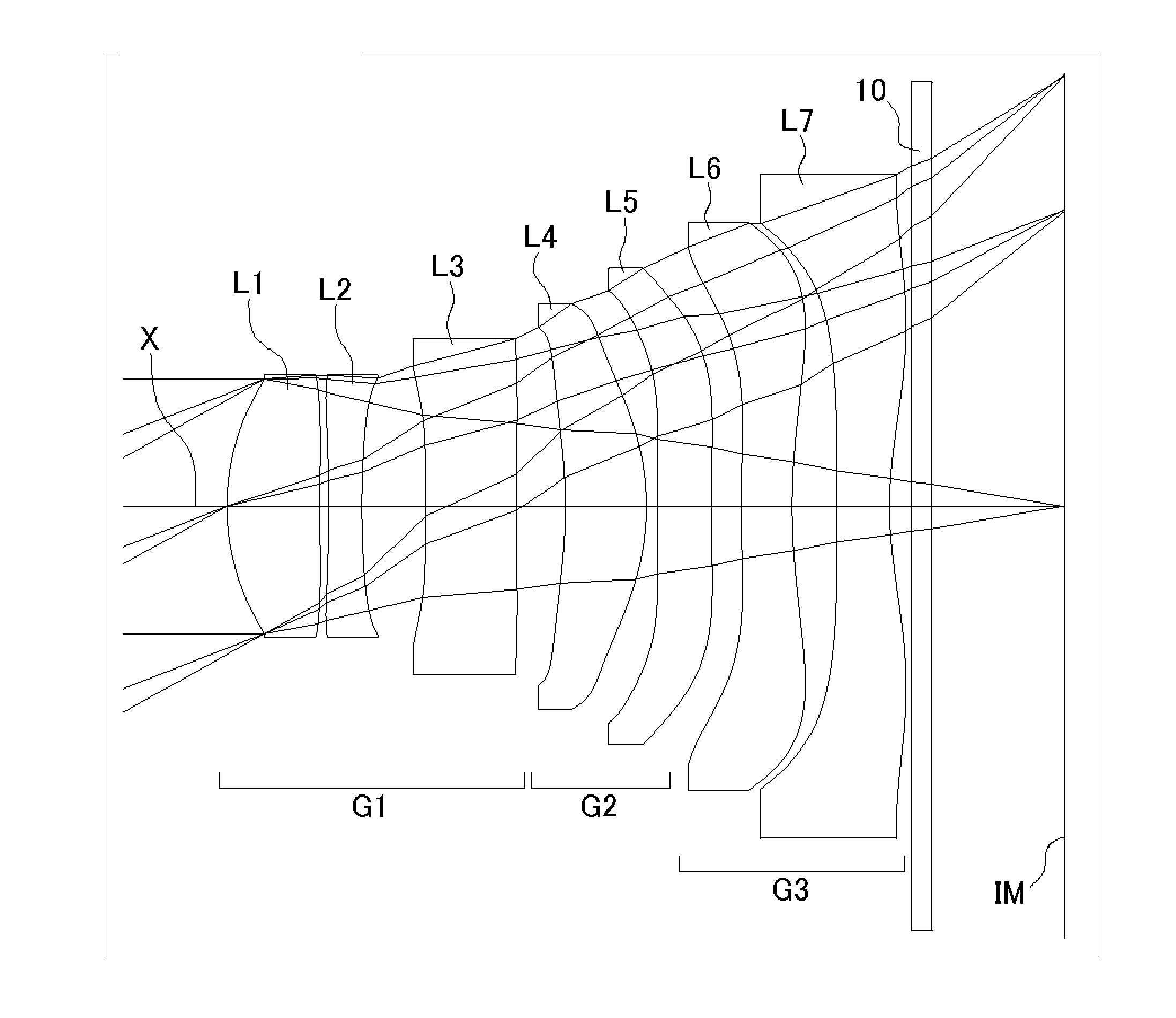

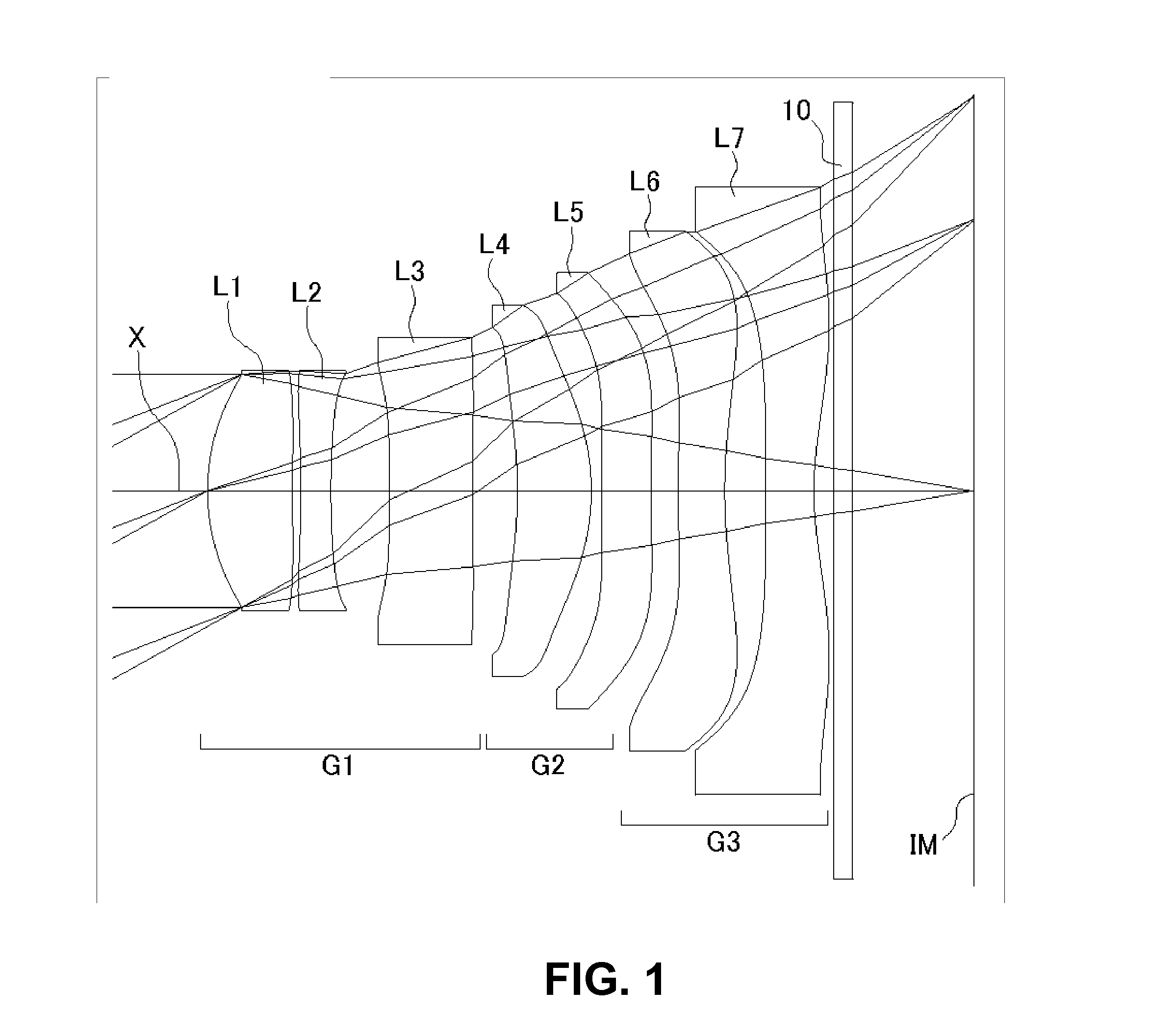

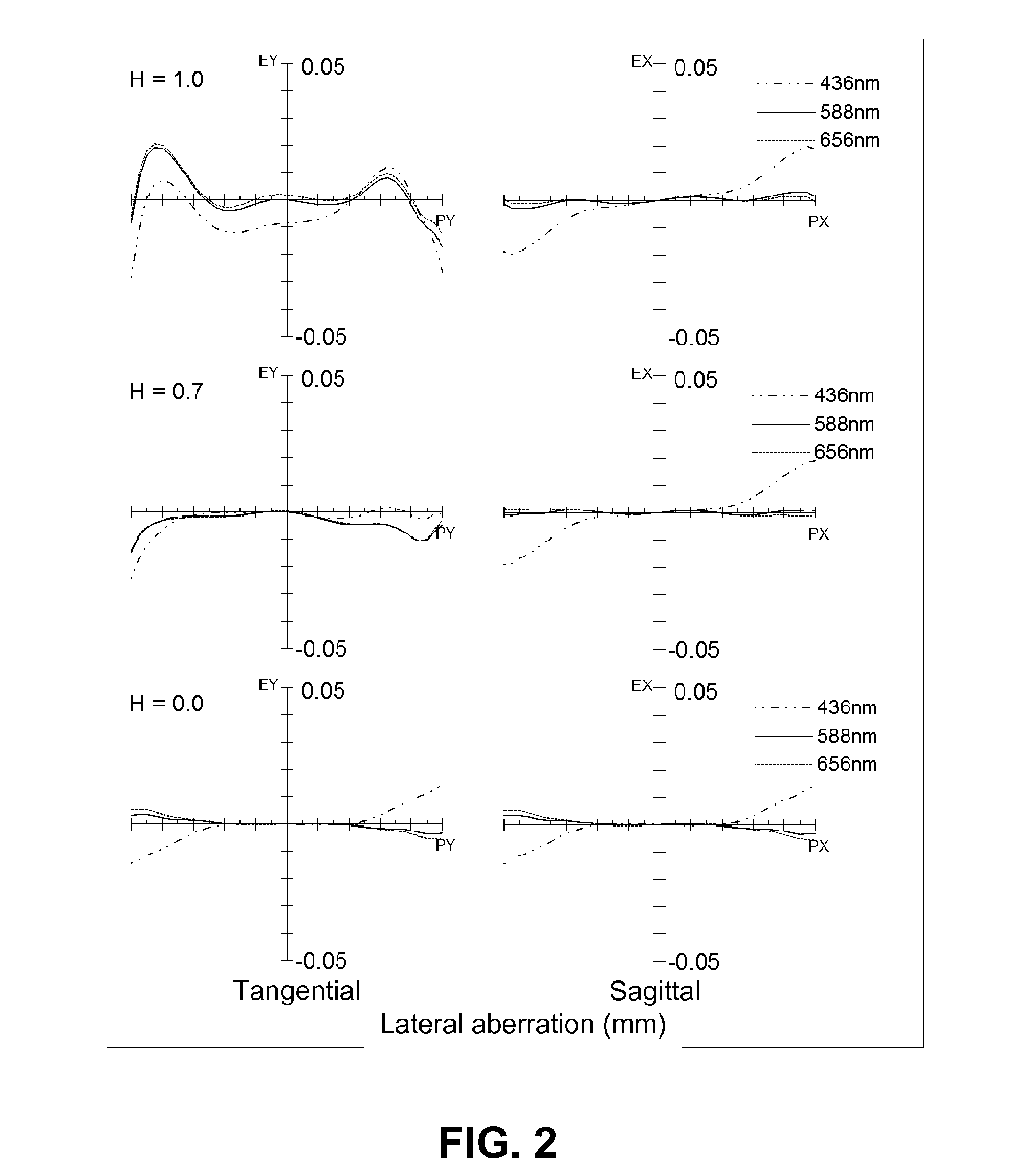

Imaging lens

ActiveUS20150198791A1Satisfactorily corrected aberrationHigh resolutionOptical elementsImaging lensImage plane

An imaging lens includes a first lens group having positive refractive power; a second lens group having negative refractive power; and a third lens group having negative refractive power, arranged in this order from an object side to an image plane side. The first lens group includes a first lens having positive refractive power, a second lens having negative refractive power, and a third lens having positive refractive power. The second lens group includes a fourth lens and a fifth lens. The third lens group includes a sixth lens having positive refractive power and a seventh lens having negative refractive power. The first to third lenses and the sixth to seventh lenses have specific Abbe's numbers.

Owner:TOKYO VISIONARY OPTICS CO LTD

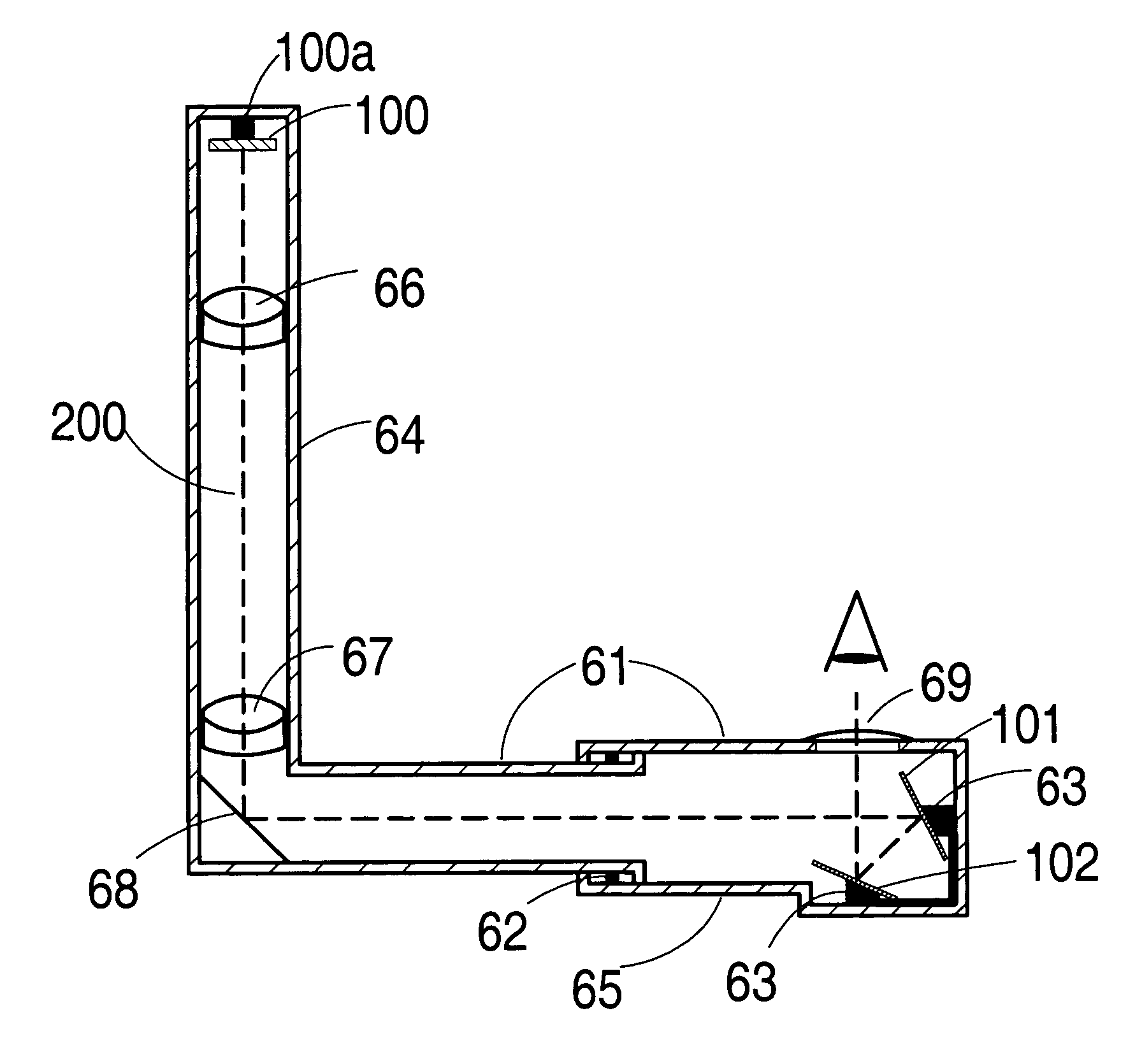

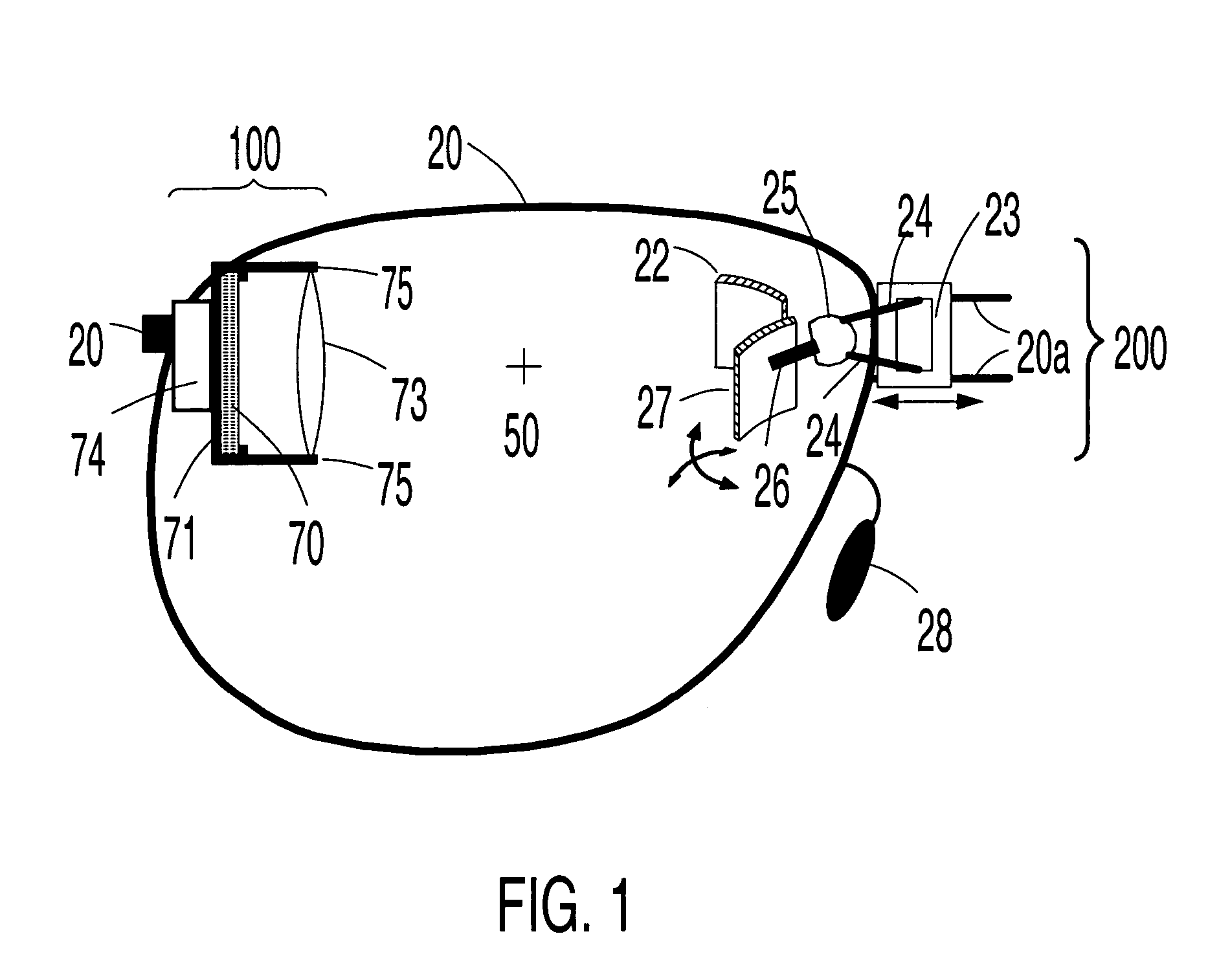

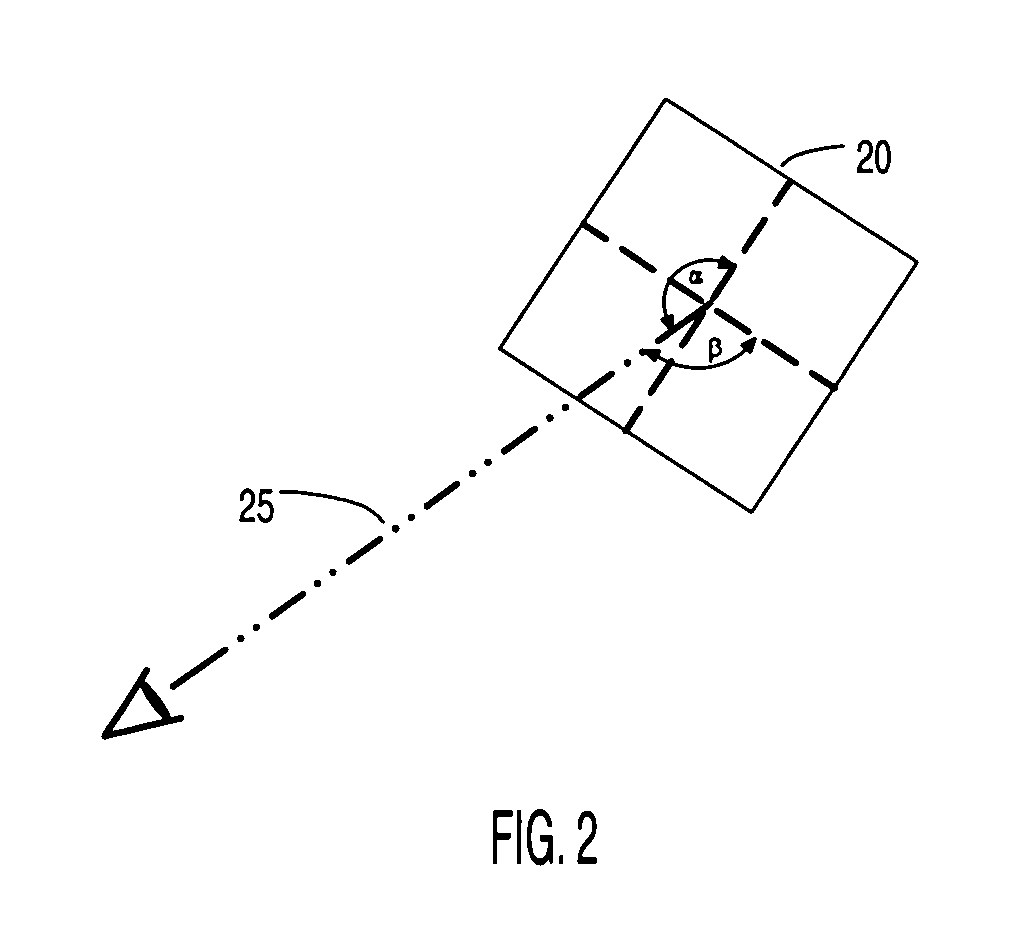

Head-mounted virtual display apparatus for mobile activities

InactiveUS7145726B2Minimize and eliminate geometric distortionPassively minimizing or eliminating image degrading factorsOperating means/releasing devices for valvesCathode-ray tube indicatorsOptical axisDisplay device

The present invention is a head-mounted virtual display apparatus based on a non-cross-cavity optical configuration, in which a near-eye light deflecting element (LDE) is located in the peripheral field of view. Positioning of the near-eye LDE in the peripheral field of view provides the user with simultaneous access to an inset magnified image of a miniature display and an unobstructed forward field of view of at least 35 degrees. Active and passive alignment means, including articulating connections and image warping electronics, allows for correction of geometric distortion arising from folding of the optical train, and orthogonal alignment of the virtual image plane with the optical axis between the user's eye and the virtual image plane.

Owner:GEIST RICHARD

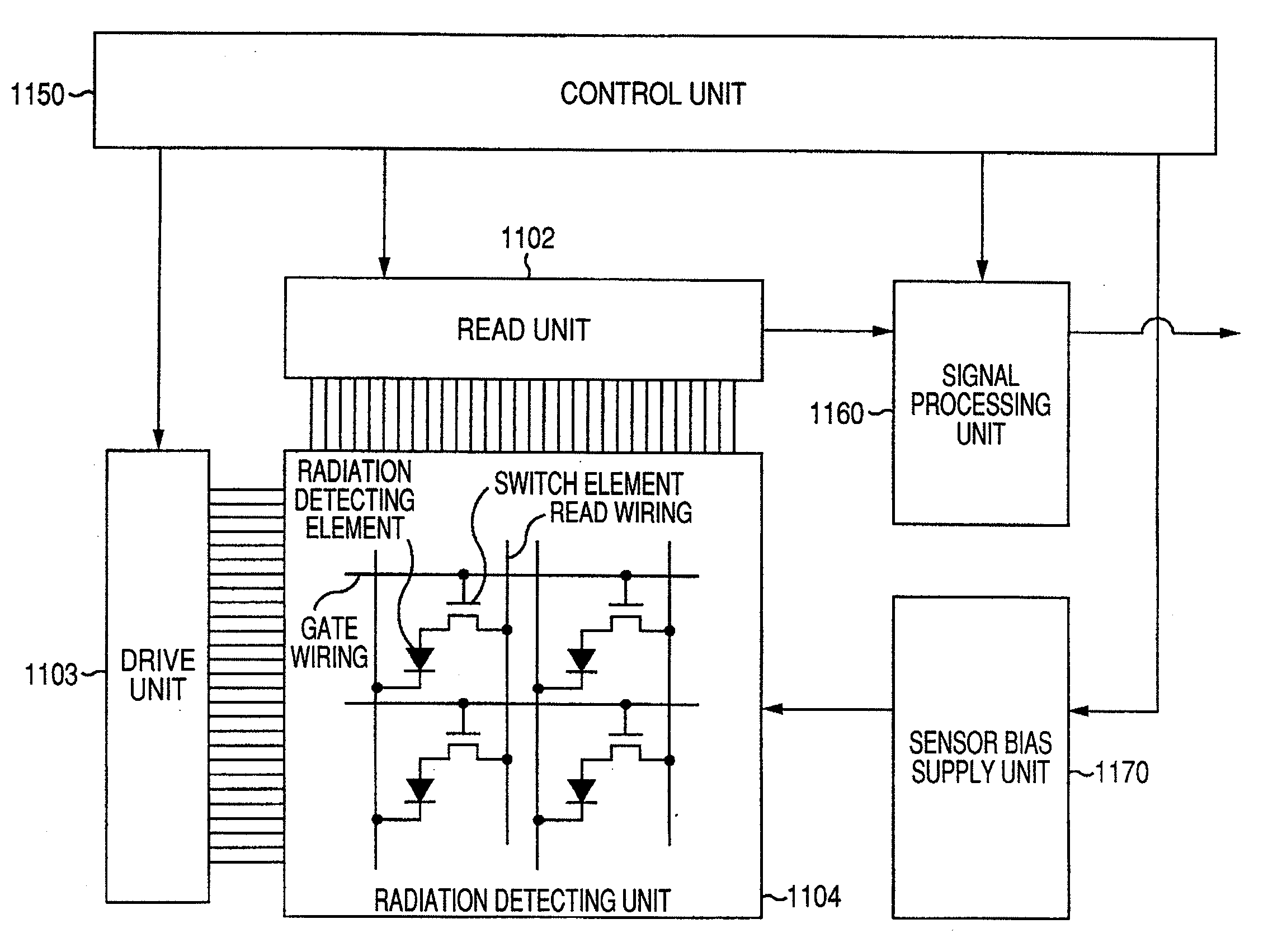

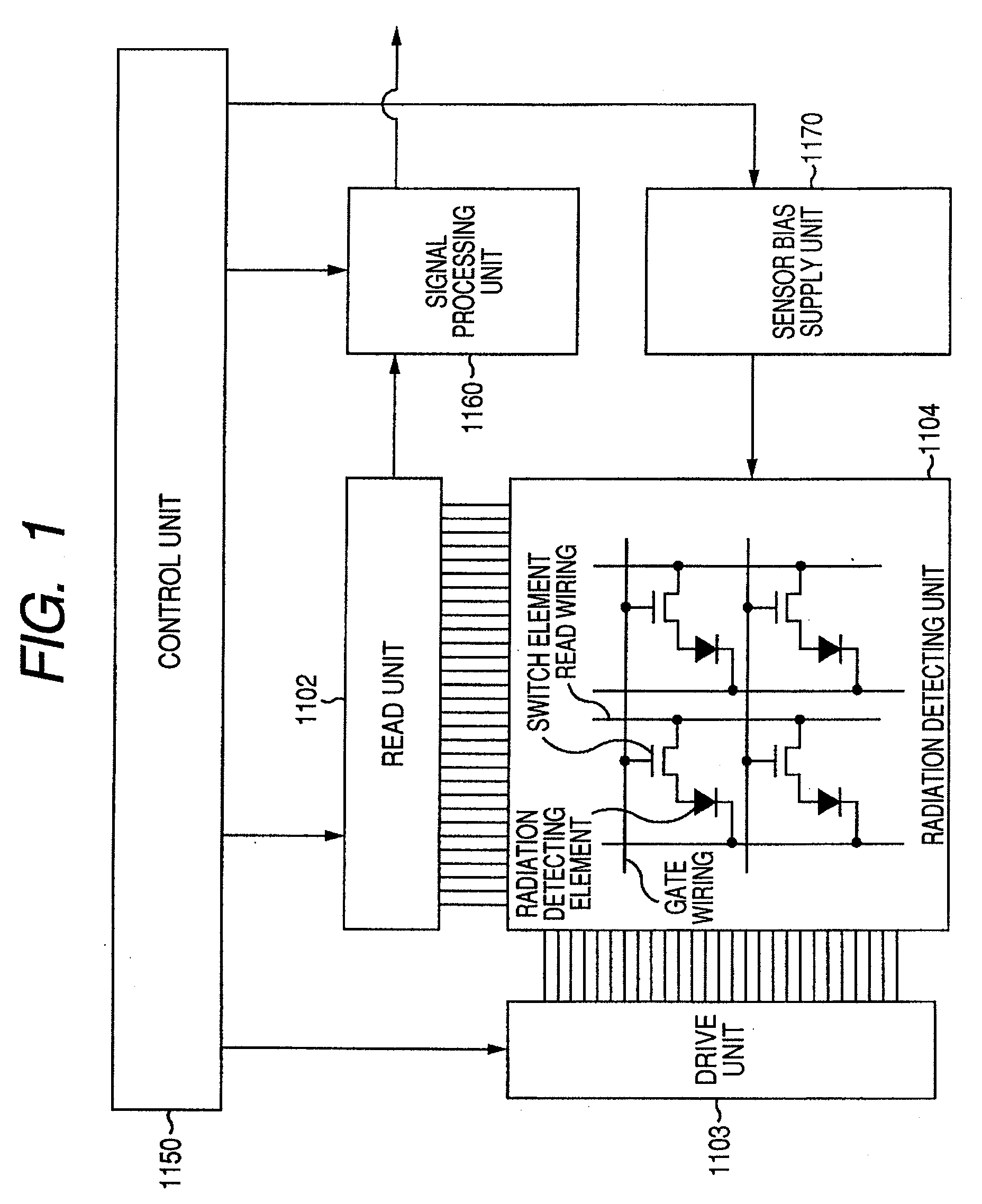

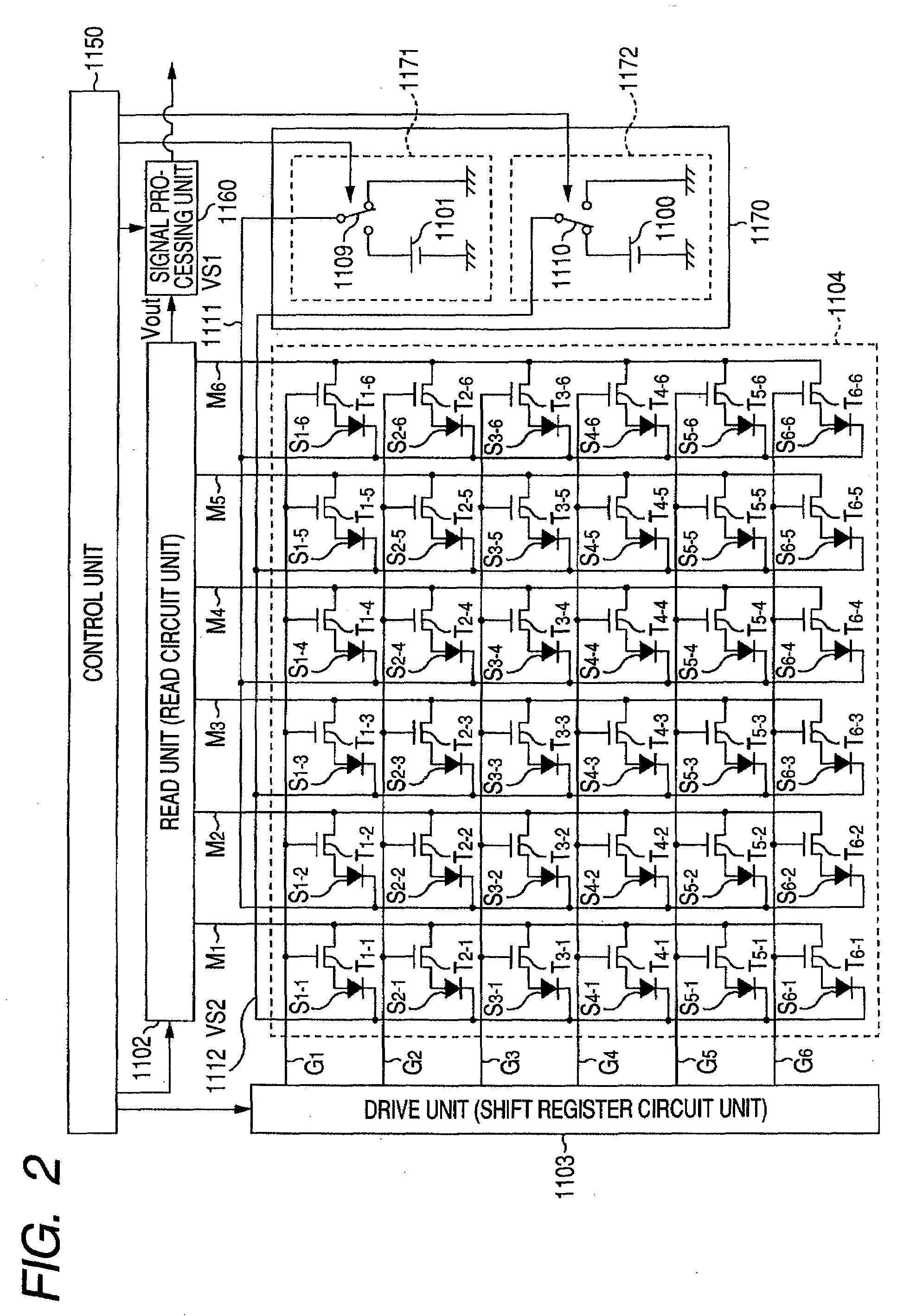

Radiation imaging apparatus and radiation imaging system

InactiveUS20070210258A1More time consumingReduce yieldTelevision system detailsSolid-state devicesRadiation imagingElectric signal

A radiation imaging apparatus comprises a read unit reading the electric signal in the radiation detecting elements in a radiation detecting unit comprises the radiation detecting elements converting incident radiation into electric signals arranged two-dimensionally, a control unit controlling the radiation detecting unit with such that a first radiation detecting element group is made senseless state and a second radiation detecting element group is made sensible state, and a signal processing unit performing a subtraction processing such that the electric signal in the radiation detecting elements made senseless state read by the read unit is subtracted from the electric signal in the radiation detecting elements made sensible state read by the read unit according to the state control by the control unit, to reduce conspicuous line noise in an image by a relatively simple configuration.

Owner:CANON KK

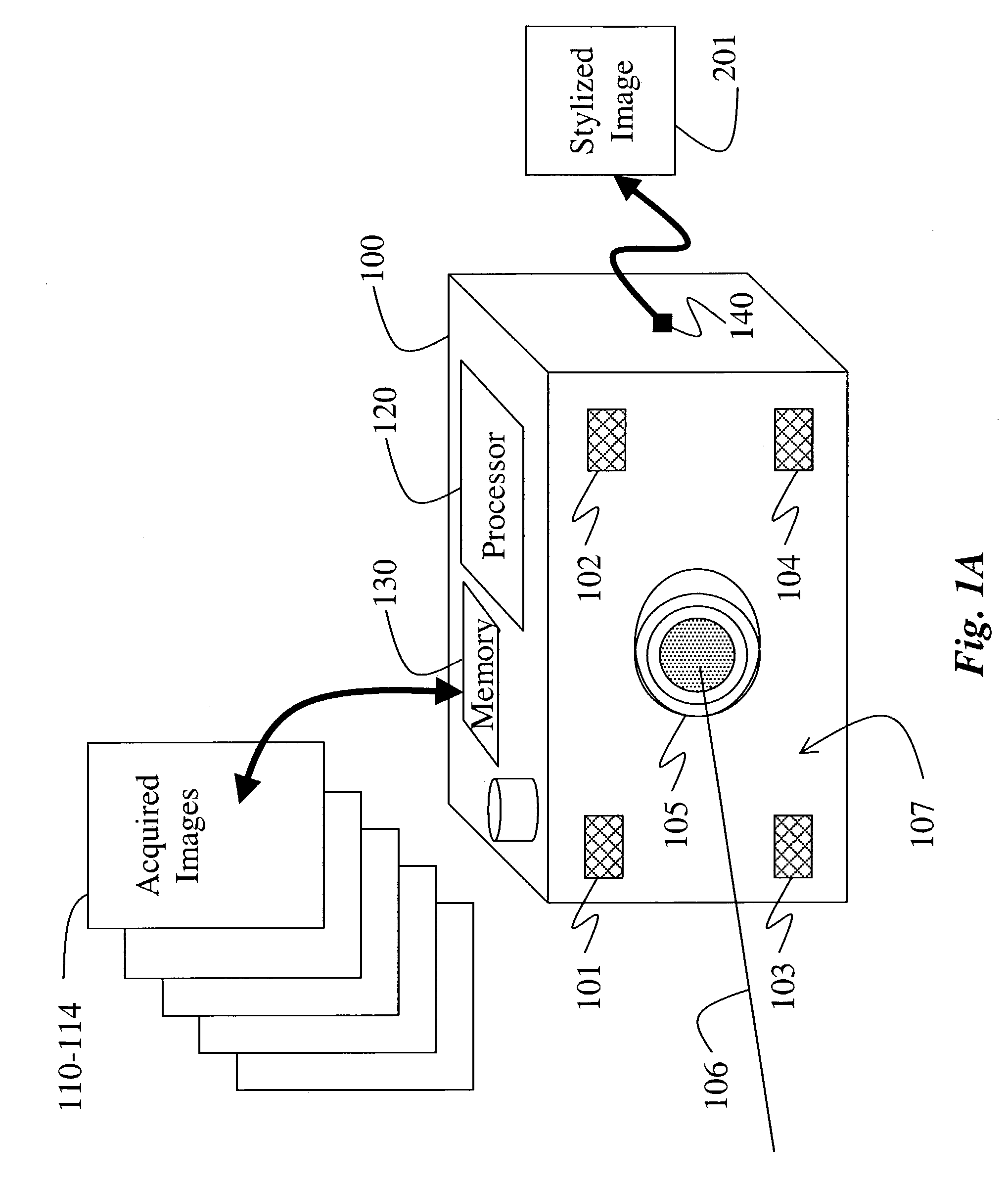

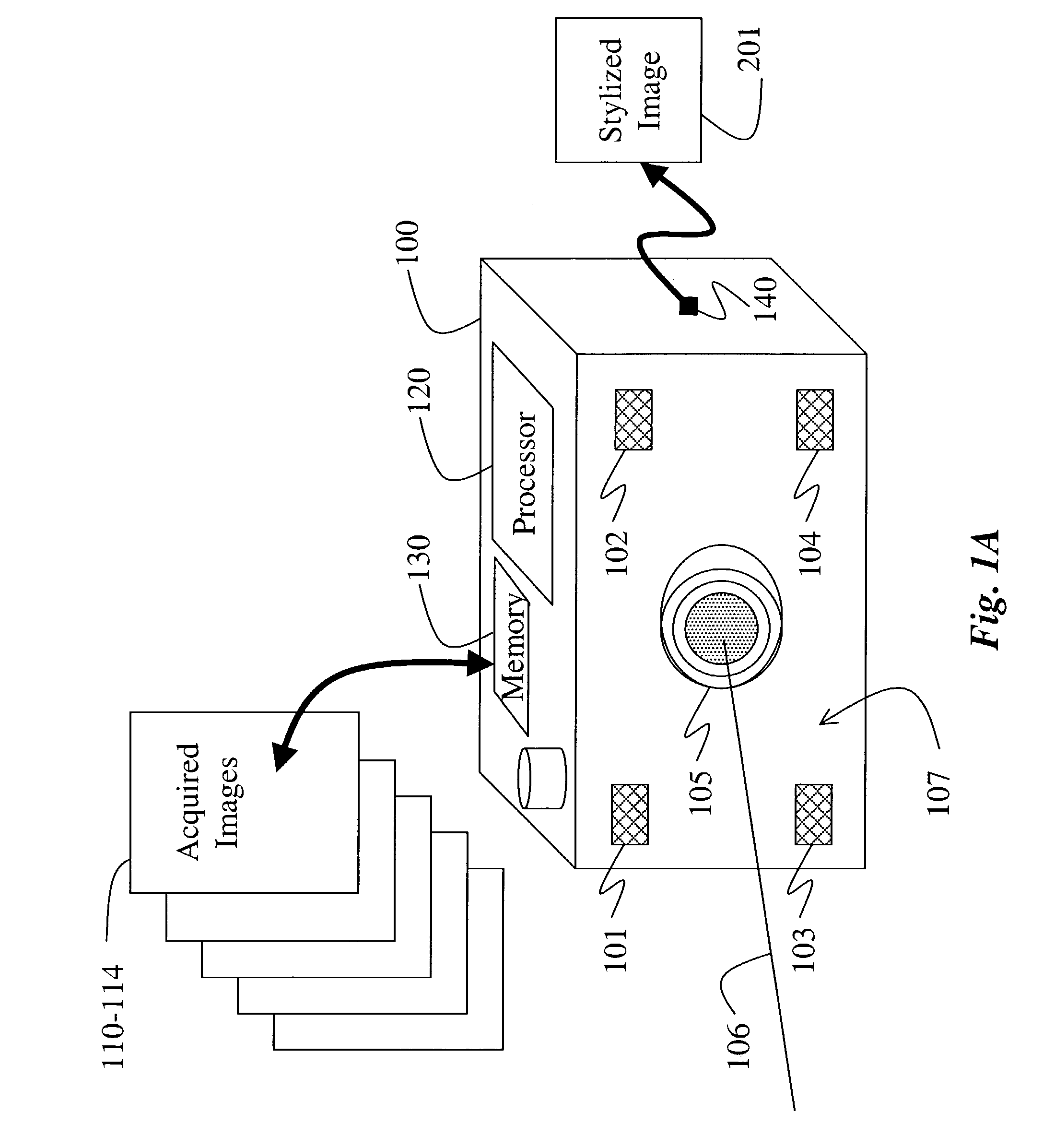

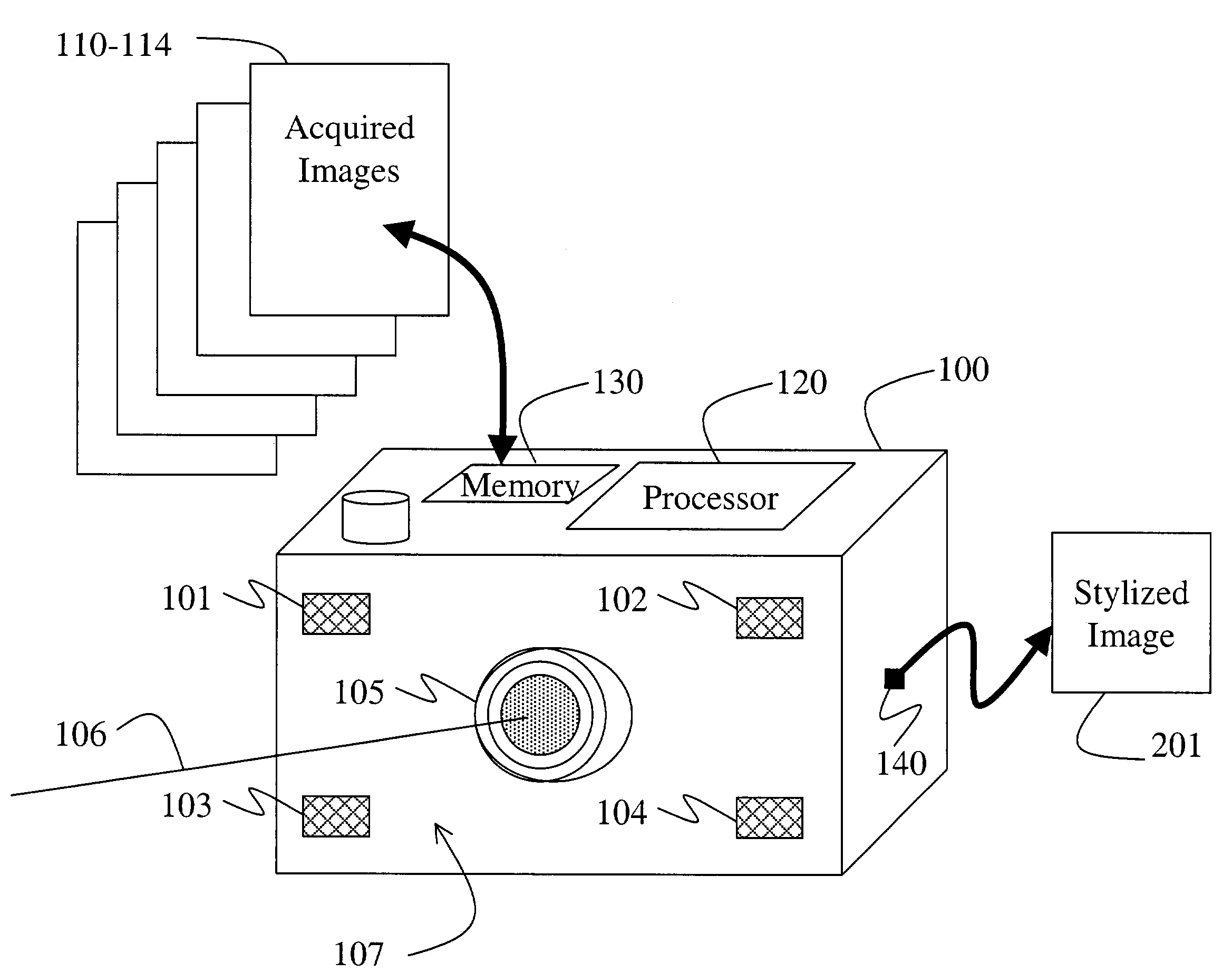

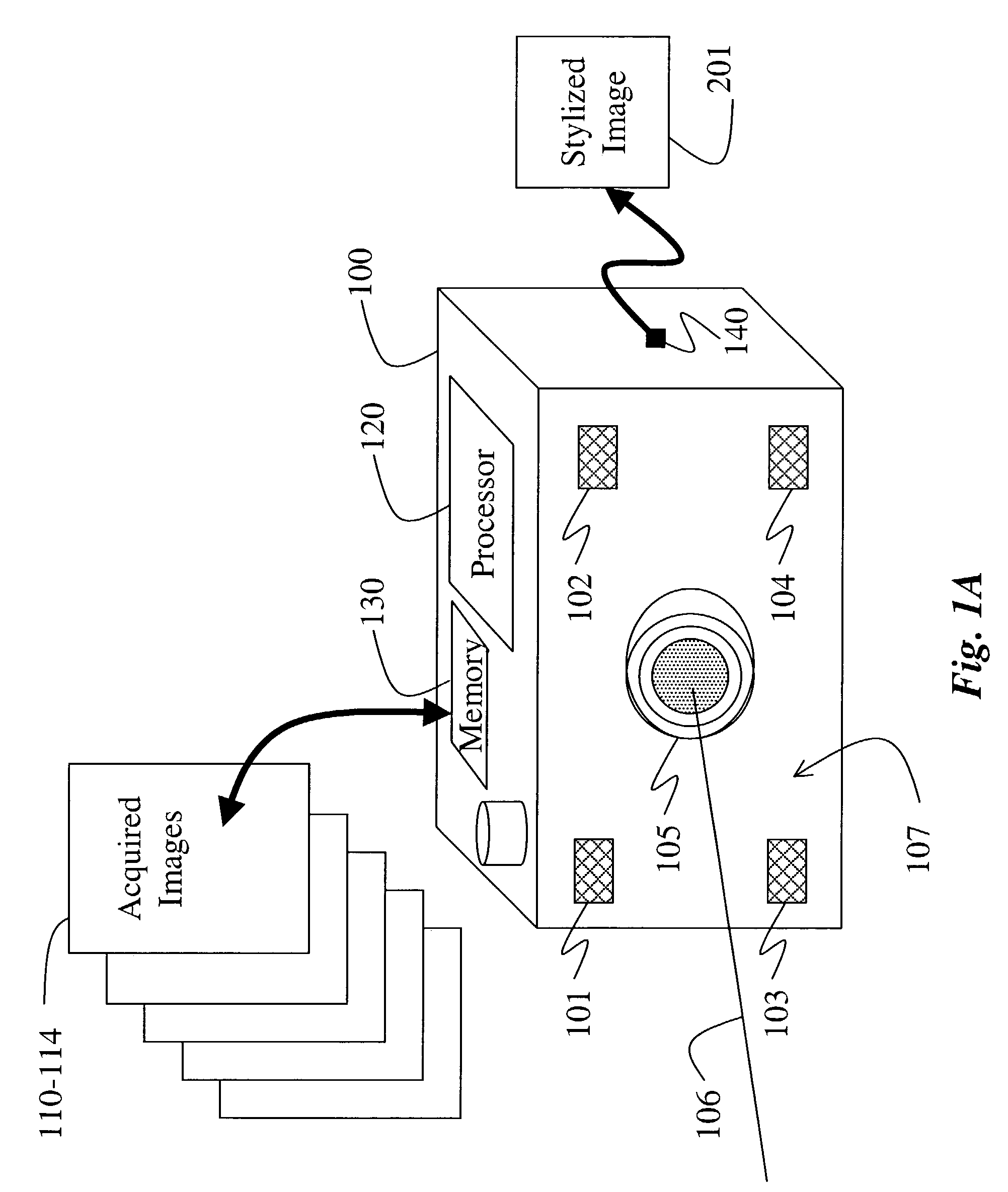

Stylized imaging using variable controlled illumination

InactiveUS7218792B2Good lookingReduce detailsTelevision system detailsGeometric image transformationEffect lightComputer vision

Owner:MITSUBISHI ELECTRIC RES LAB INC

Image forming method and image forming apparatus

InactiveUS20110141188A1Good transferabilityImage degradationOther printing apparatusControl mannerImage formation

Owner:CANON KK

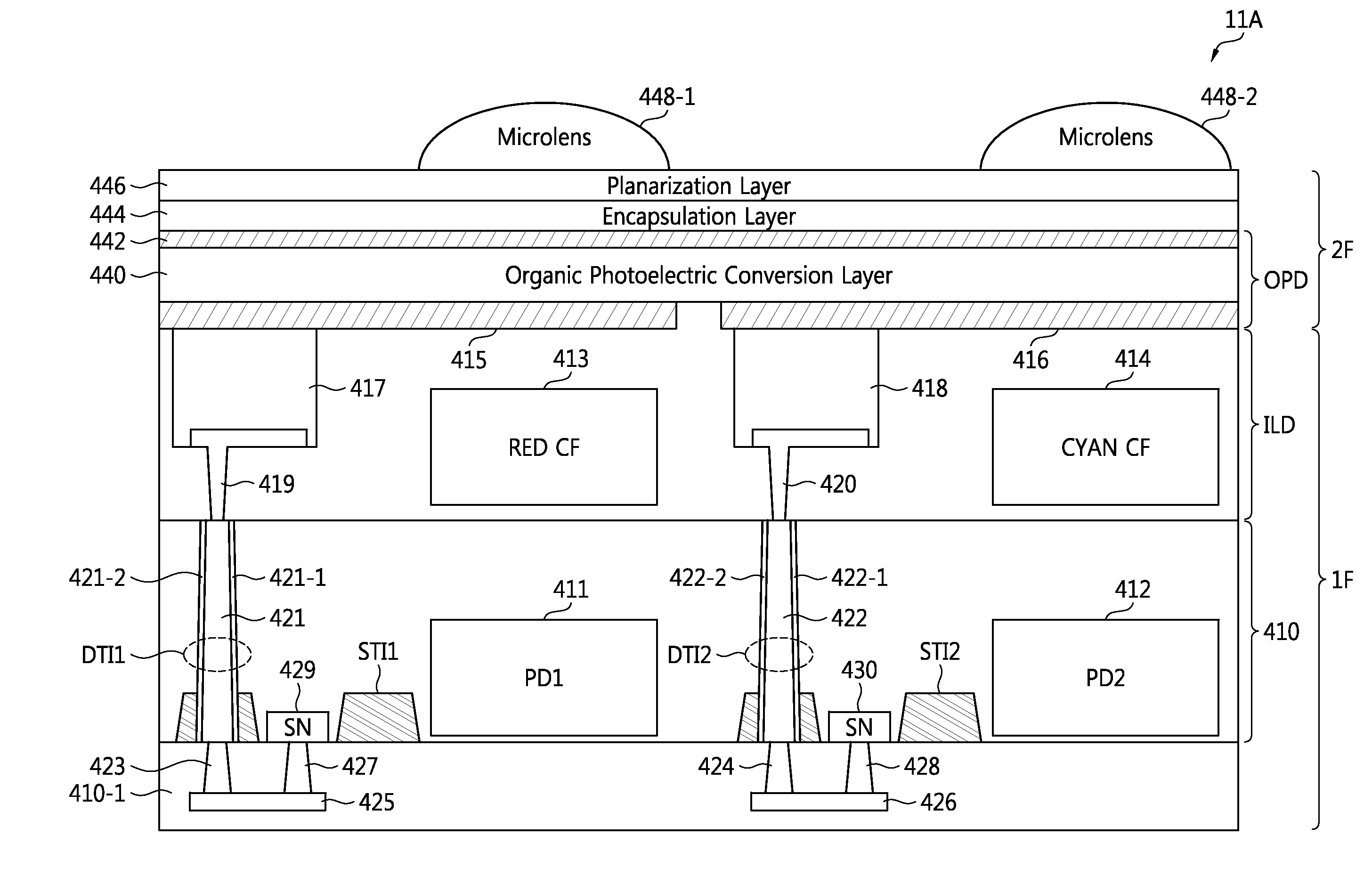

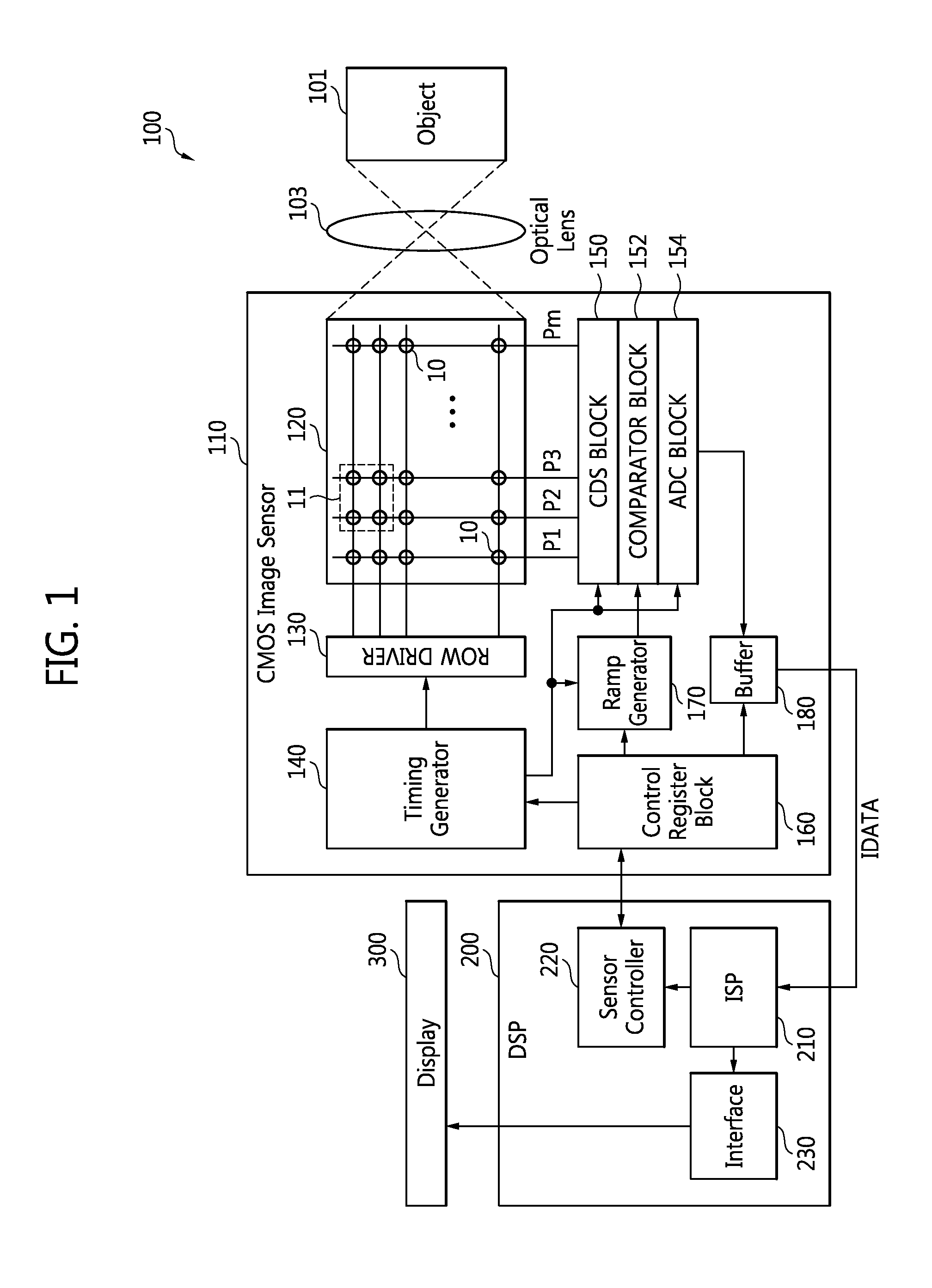

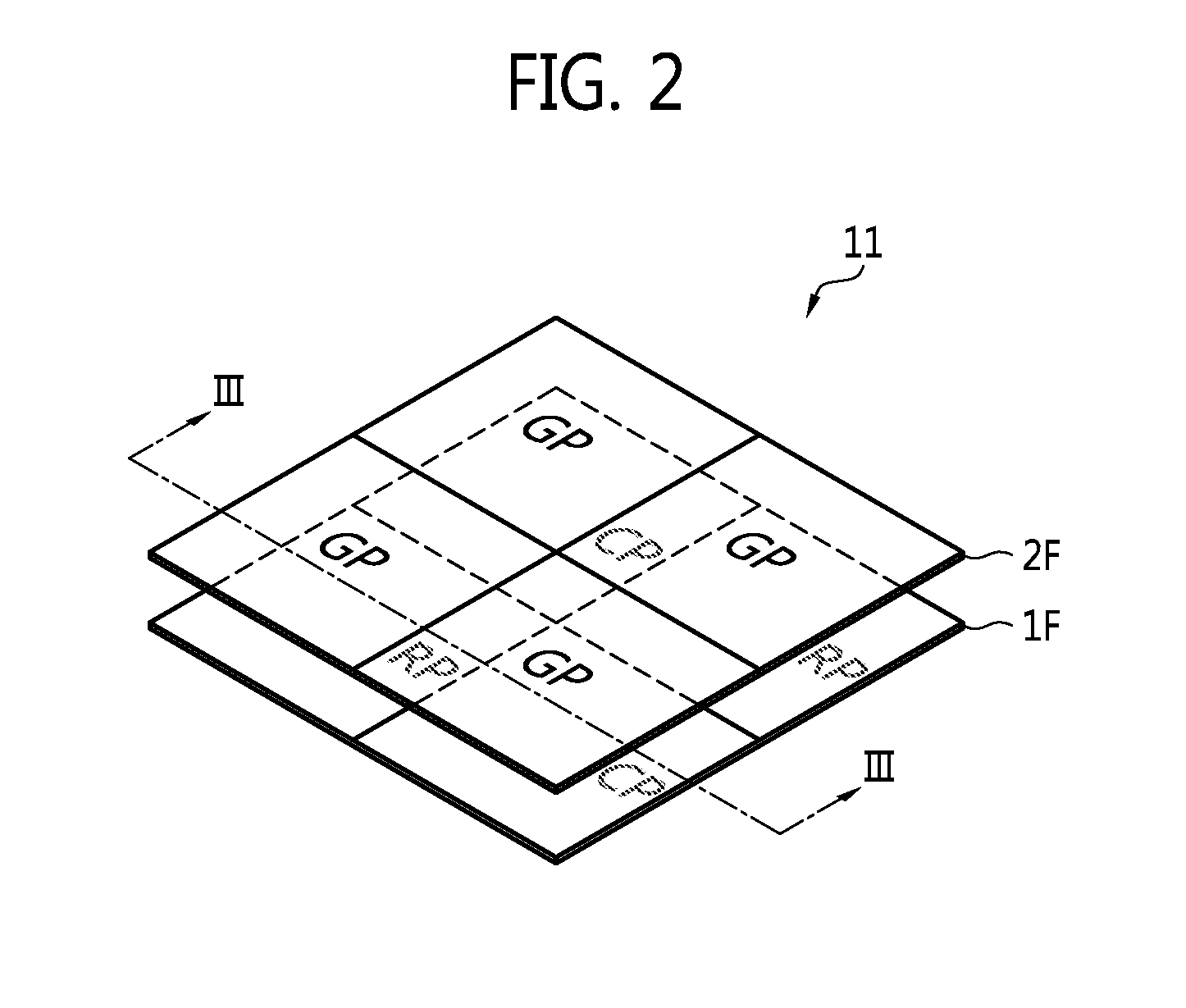

Image sensor and image processing system including the same

ActiveUS20150372036A1High sensitivityImage degradationTelevision system detailsTelevision system scanning detailsImaging processingPhotoelectric conversion

An image sensor is provided. The image sensor includes a first photoelectric conversion element and a second photoelectric conversion element, which are formed in a semiconductor substrate; a red color filter formed on the first photoelectric conversion element; a cyan color filter formed on the second photoelectric conversion element; and an organic photoelectric conversion layer formed on the red color filter and the cyan color filter, the organic photoelectric conversion layer configured to absorb wavelengths in a green range.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and apparatus for processing a micro sample

InactiveUS6927391B2Reduce resolutionGood for observationMaterial analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementHigh fluxIon beam

Owner:HITACHI LTD

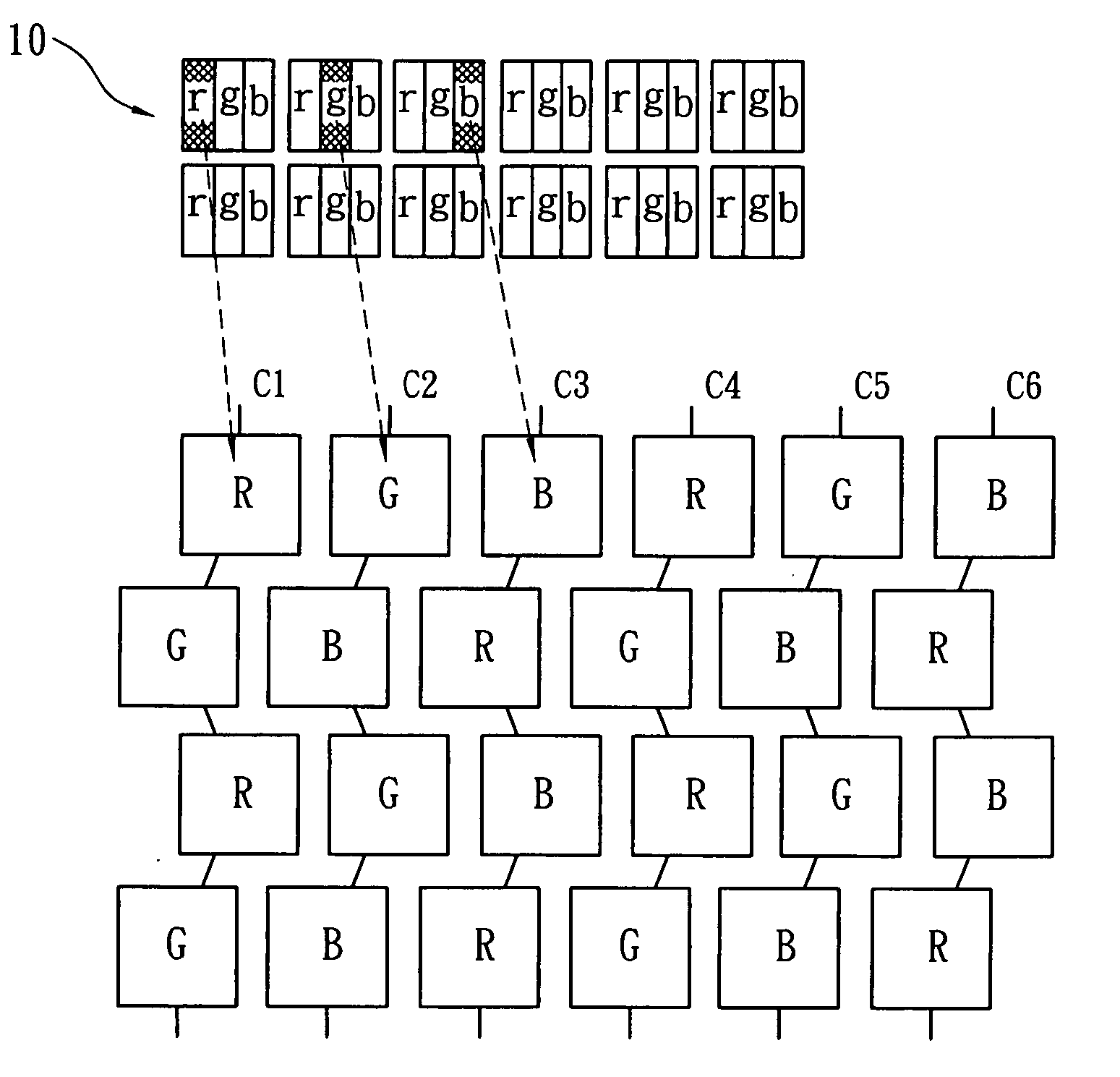

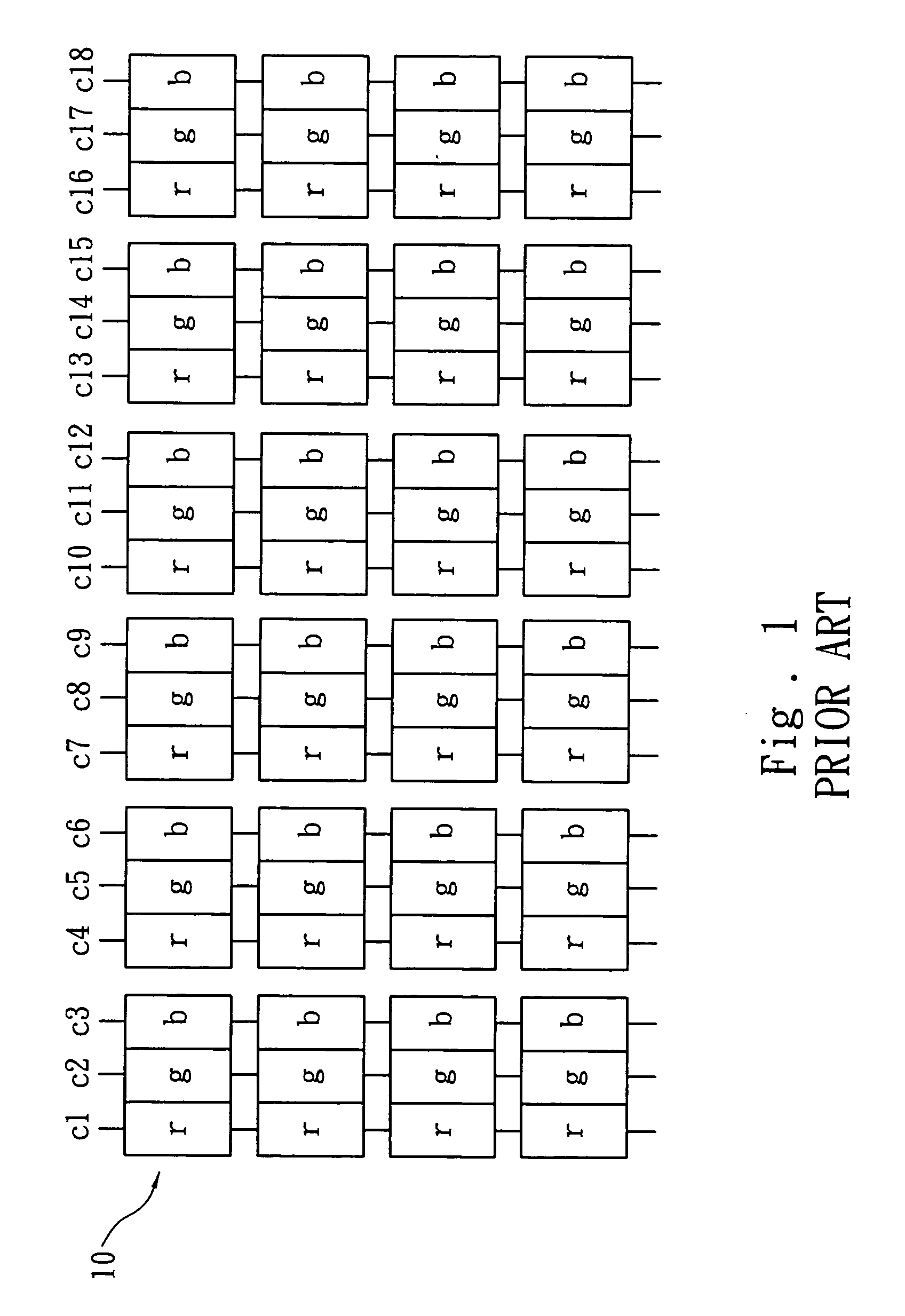

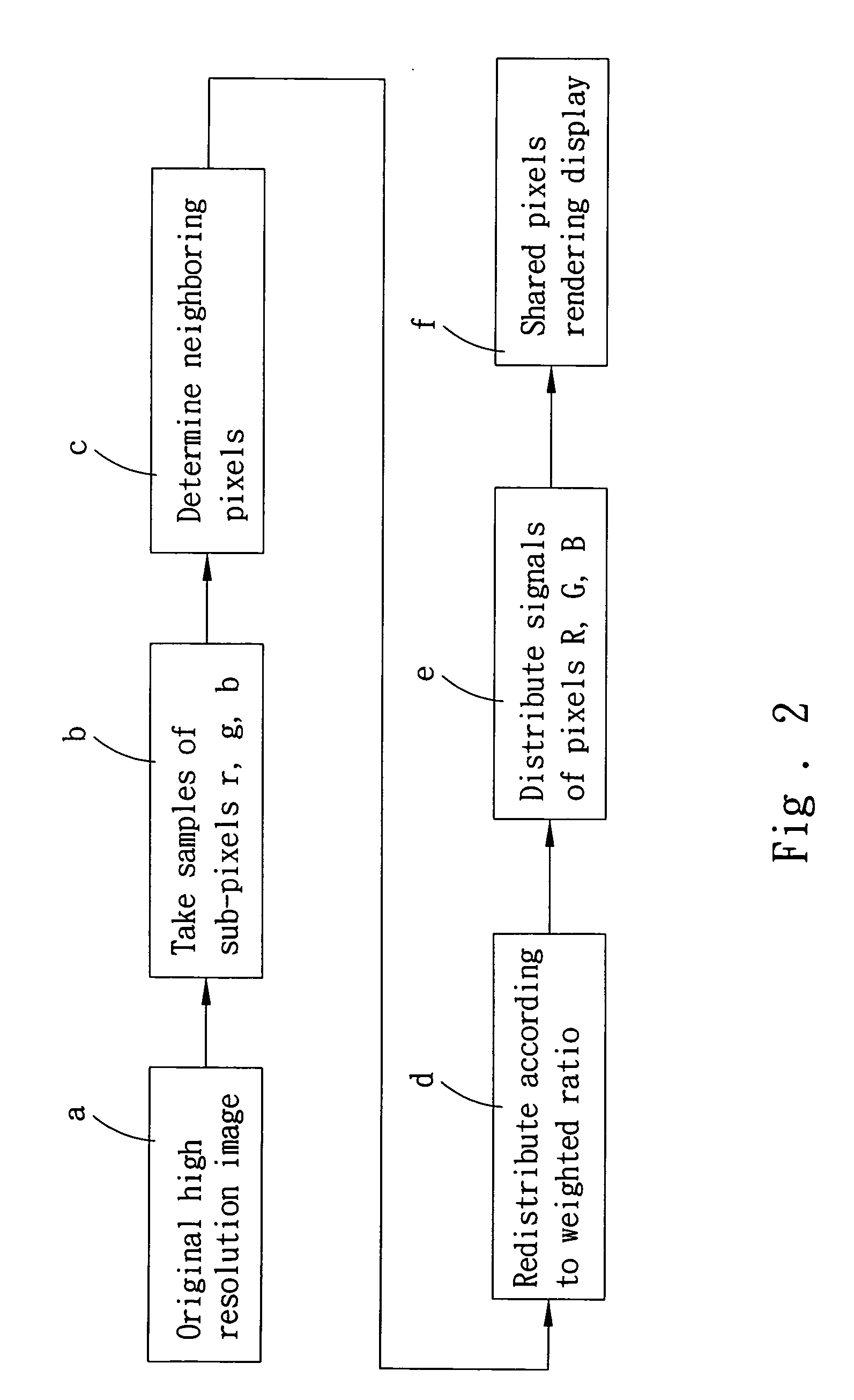

Shared pixels rendering display

InactiveUS20060158466A1Reduce usageReduce resolutionCathode-ray tube indicatorsInput/output processes for data processingColor gelVisual perception

A shared pixels rendering display includes the procedures of taking samples of sub-pixels (r, g, b) of original pixels that mate the pixel layout (R, G, B) of a color filter; determining content variations of neighboring pixels after sampling, and redistributing after a weighted ratio has been applied to the neighboring pixels of the same color; and a driving IC distributing pixel signals after sampling and weighted ratio redistributing to a mating color filter for displaying. By means of the sampling and weighted ratio redistribution, signal channels required for the display area may be reduced. Hence by using human eye vision error, unnecessary image pixels may be reduced, and the number of required driving IC decreases.

Owner:SITRONIX TECH CORP

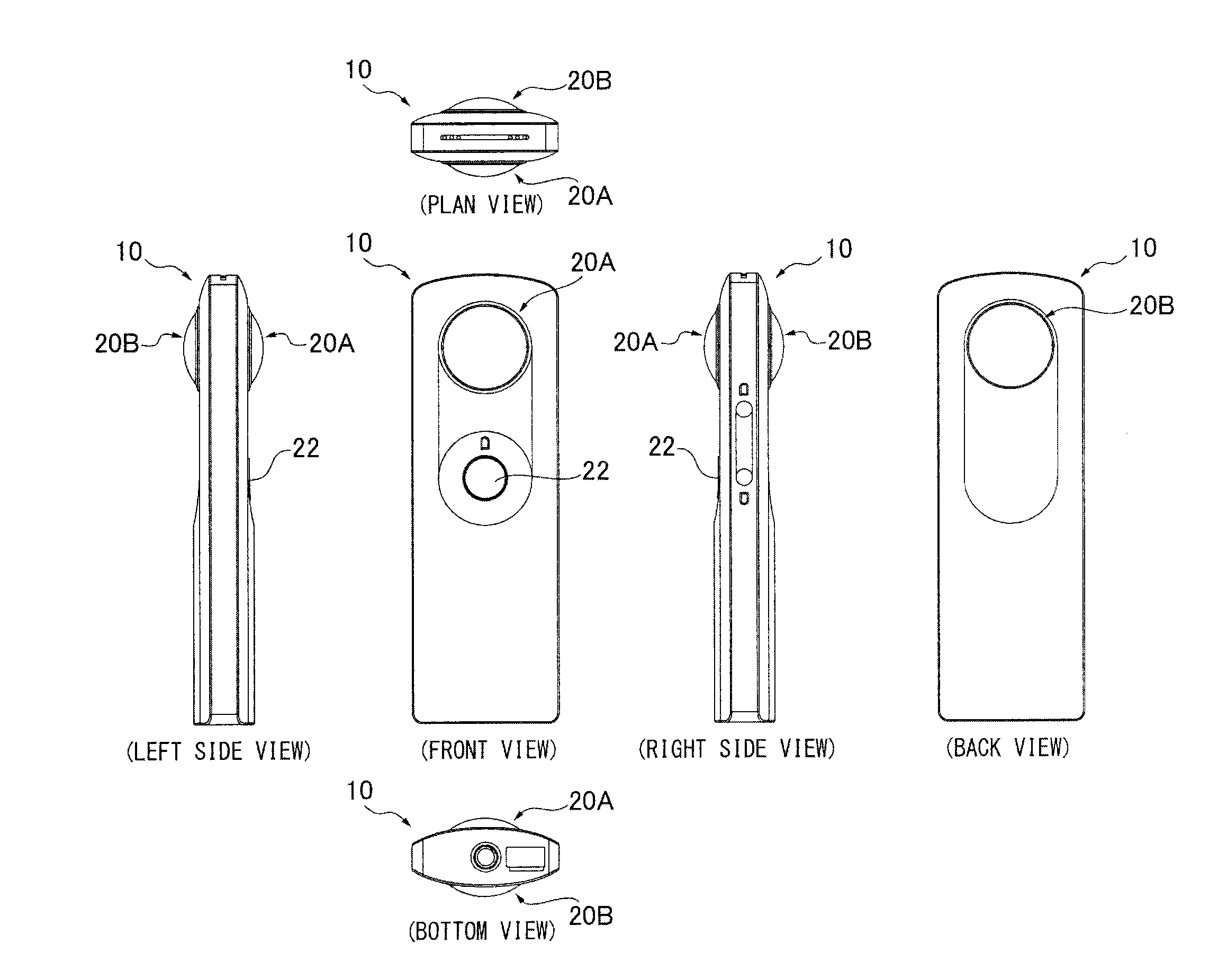

Imaging system

ActiveUS20130242040A1Improve balanceImage degradationTelevision system detailsPrismsGravity centerEngineering

An imaging system includes an imaging body having an optical system and an imaging element, a power supplier configured to supply power to the imaging element, and a housing configured to hold the imaging body and the power supplier, wherein the optical system includes at least one optical element projecting from the housing, and a distance AP between a gravity center A of a portion including the optical system and a gravity center P of the entire imaging system and a distance BP between a gravity center B of the power supplier and the gravity center P of the entire imaging system satisfy the following condition.AP>BP

Owner:RICOH KK

Imaging lens

ActiveUS20150247990A1Restrain incident angleCorrect chromatic aberrationOptical elementsImaging lensImage plane

An imaging lens includes a first lens group having positive refractive power; a second lens group having positive refractive power; and a third lens group having negative refractive power, arranged in this order from an object side to an image plane side. The first lens group includes a first lens having positive refractive power, a second lens having negative refractive power, and a third lens having positive refractive power. The second lens group includes a fourth lens having positive refractive power and a fifth lens having positive refractive power. The third lens group includes a sixth lens and a seventh lens. The first to fifth lenses have specific Abbe's numbers.

Owner:TOKYO VISIONARY OPTICS CO LTD

Non-photorealistic camera

ActiveUS7295720B2Good lookingReduce detailsTelevision system detailsColor signal processing circuitsCamera lensFlash light

A camera has a single lens and multiple flash units distributed around the lens. A set of images is acquired of a scene with different controlled lighting applied by the flash units, one at the time. The images are stored in a memory, and then combined to produce a single stylized image of the scene from the acquired images.

Owner:MITSUBISHI ELECTRIC RES LAB INC

Imaging lens

ActiveUS20150268448A1Correct chromatic aberrationSatisfactory performanceOptical elementsImaging lensImage plane

An imaging lens includes a first lens group having positive refractive power; a second lens group having positive refractive power; and a third lens group having negative refractive power, arranged in this order from an object side to an image plane side. The first lens group includes a first lens having positive refractive power, a second lens having negative refractive power, and a third lens having negative refractive power. The second lens group includes a fourth lens and a fifth lens. The third lens group includes a sixth lens and a seventh lens. The first to third lenses have specific Abbe's numbers.

Owner:UNIVERSITY OF PITTSBURGH +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com