Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

236results about How to "Increase the on-state current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

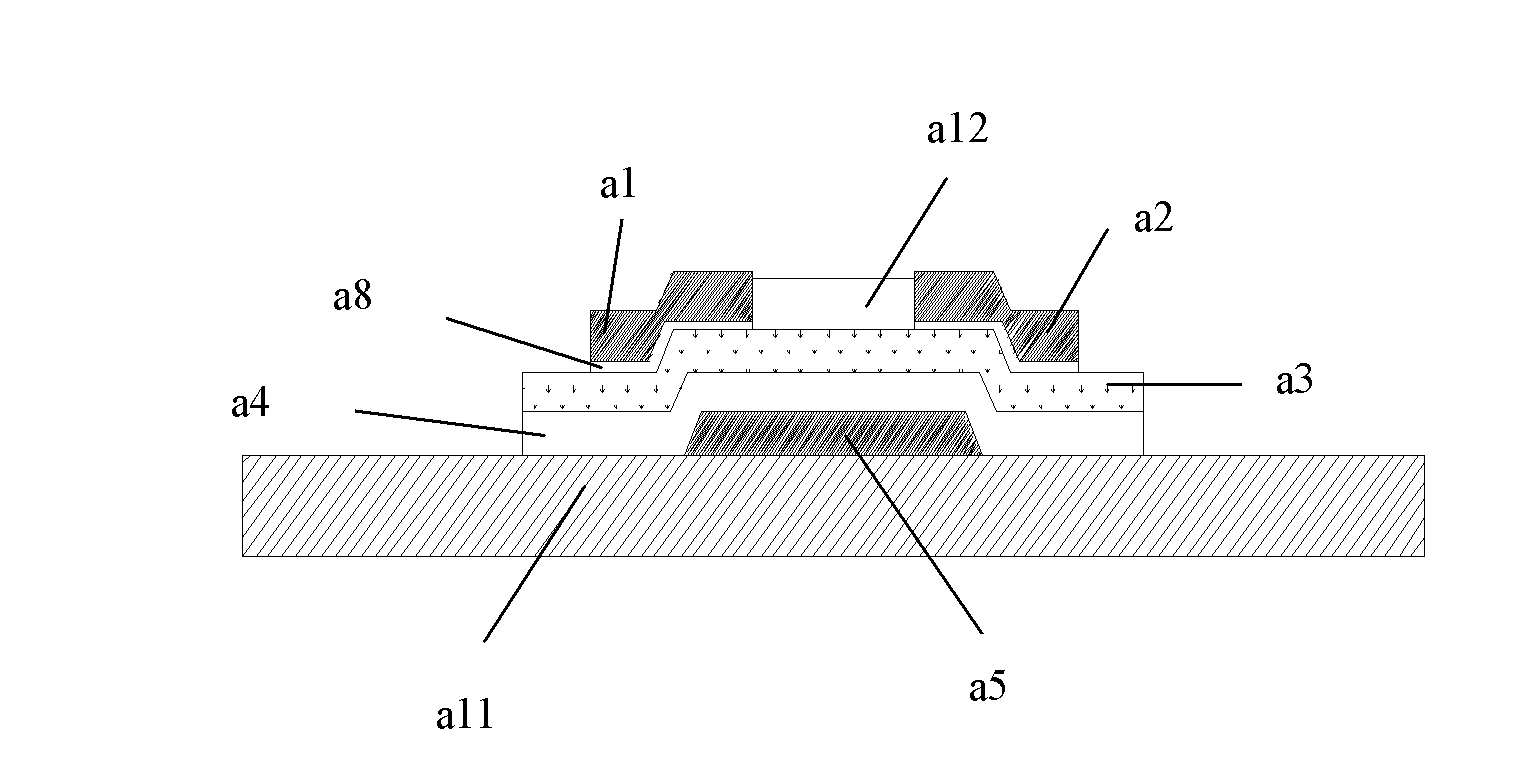

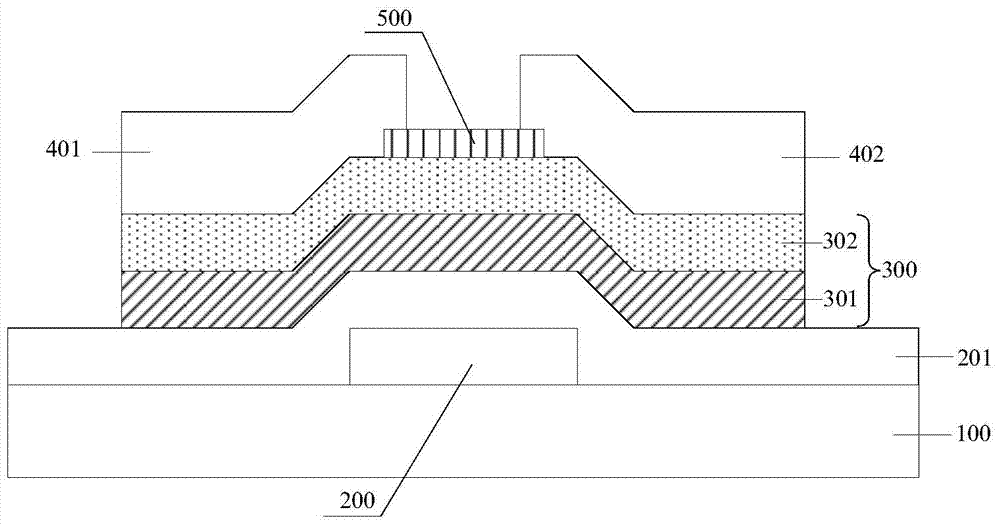

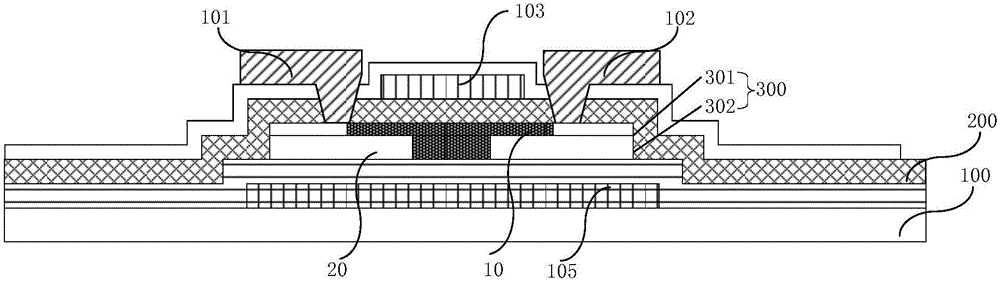

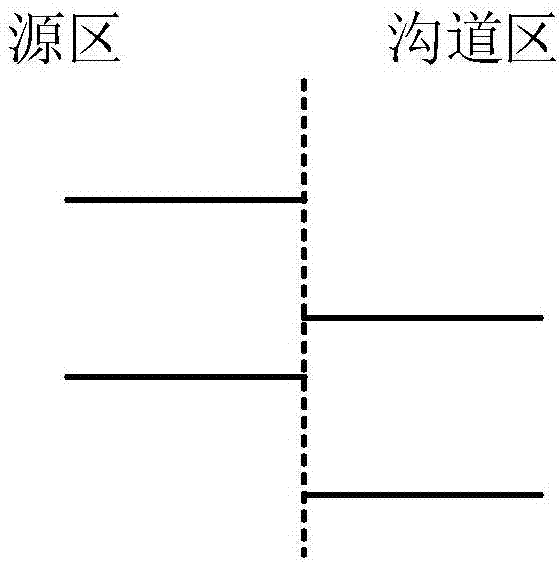

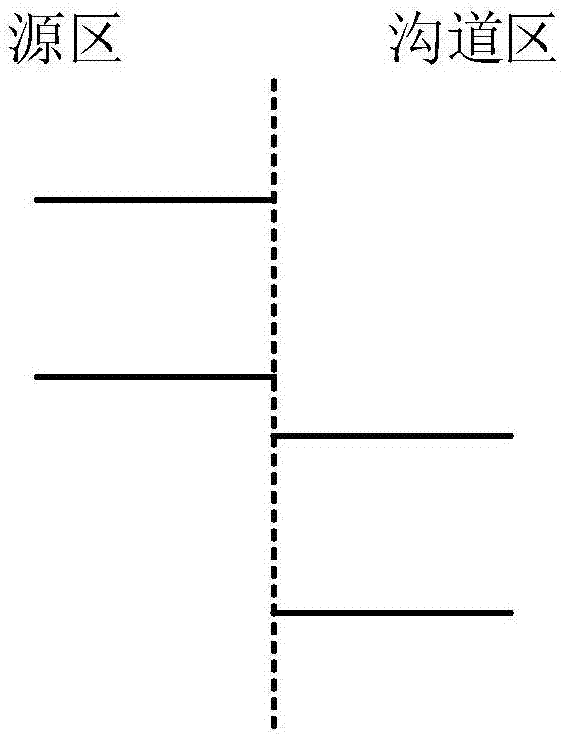

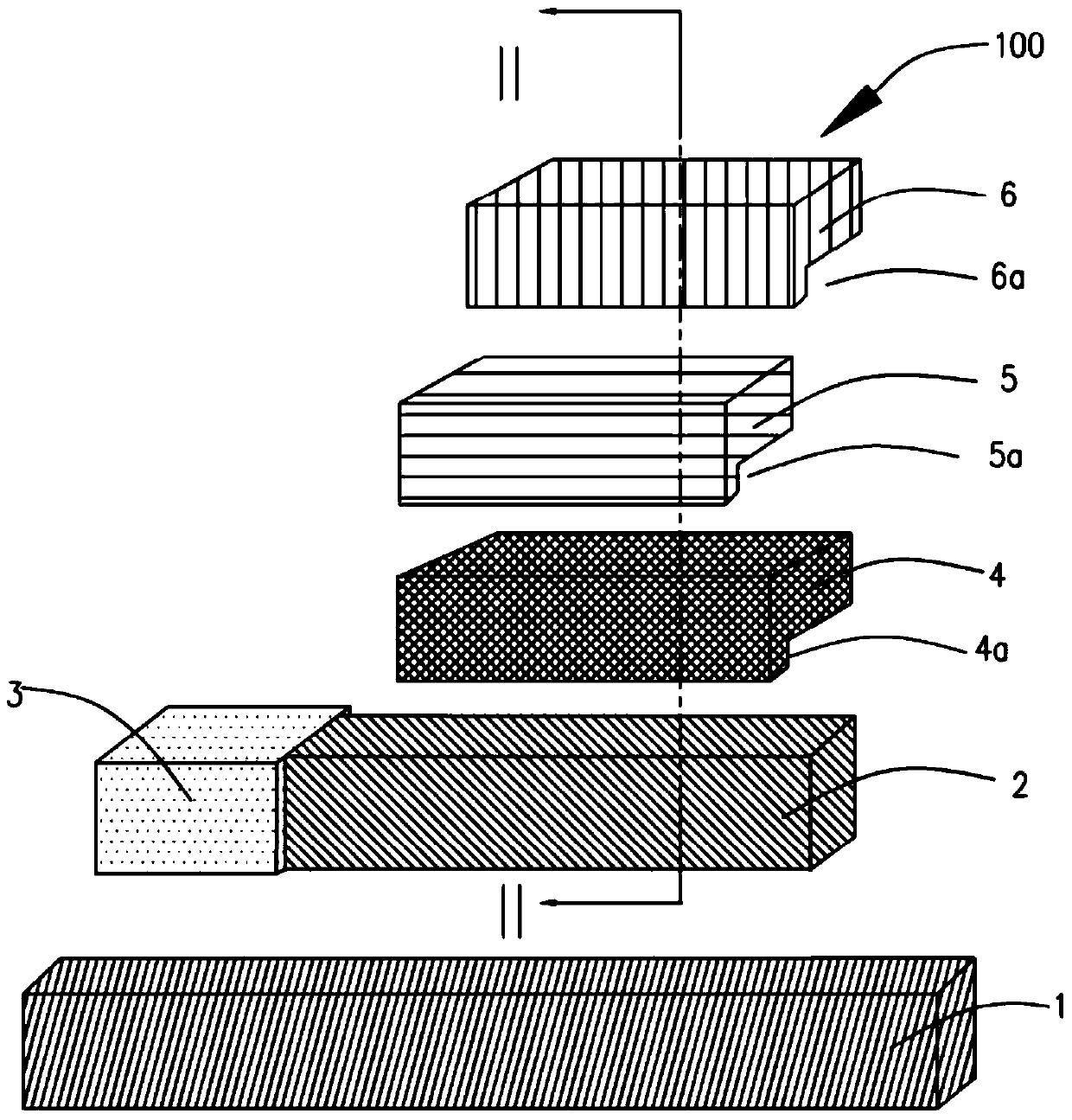

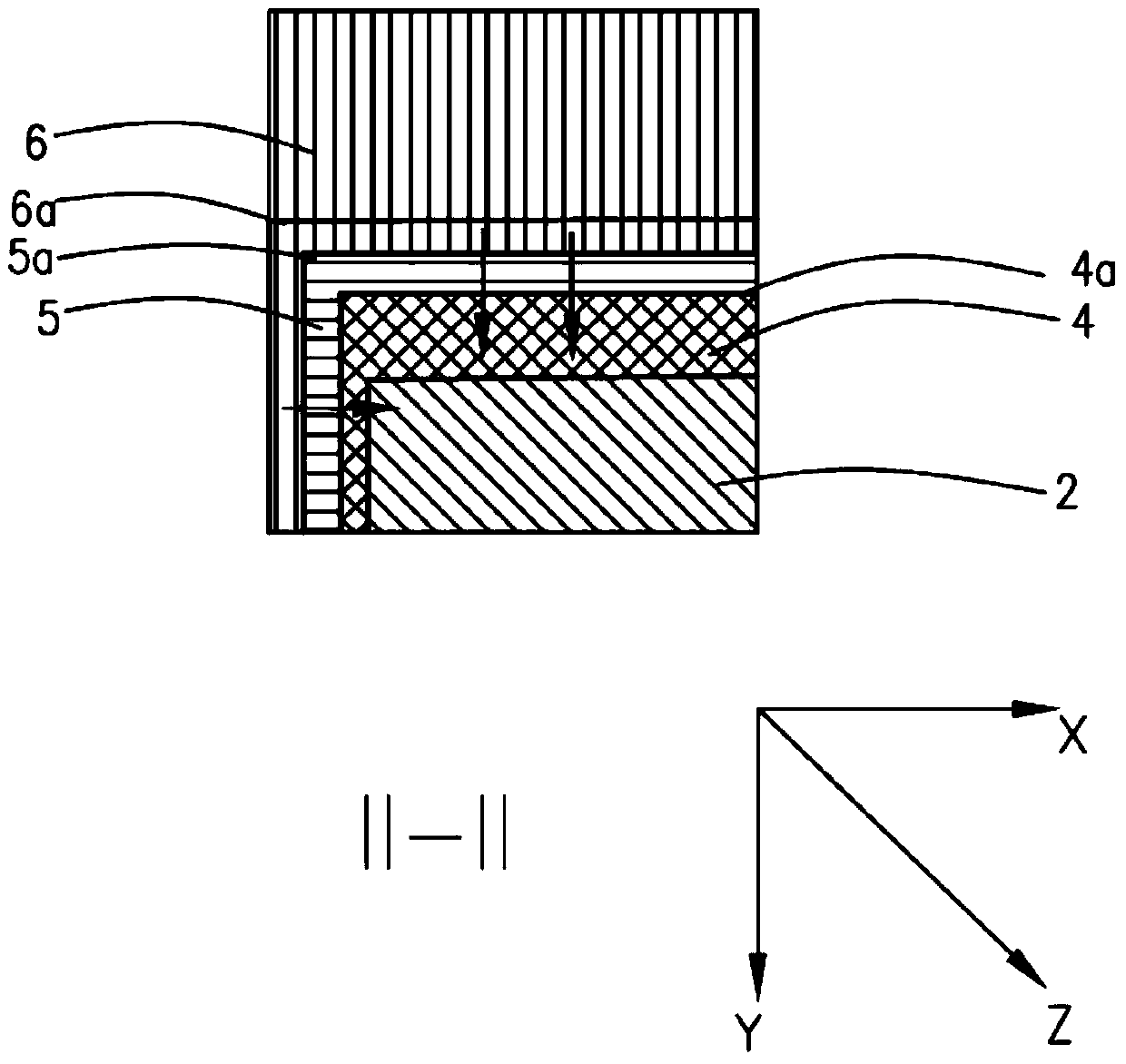

Thin film transistor with single-gate double-channel structure and manufacturing method thereof

ActiveCN102184968AIncrease the on-state currentImprove current drive capabilityTransistorSemiconductor/solid-state device manufacturingInsulation layerHemt circuits

The invention discloses a thin film transistor with a single-gate double-channel structure and a manufacturing method thereof. The manufacturing method comprises the steps of forming a first source electrode and a first drain electrode on a base plate; depositing a first active layer, wherein the edge of the active layer is overlapped with the edges of the first source electrode and the first drain electrode; then sequentially forming a first insulation layer, a gate electrode and a second insulation layer on the first active layer; forming a second active layer on the second insulation layerin a way of corresponding to the first active layer; and forming a second source electrode and a second drain electrode on the second active layer in a way of corresponding to the first source electrode and the first drain electrode to further form the thin film transistor with the single-gate double-channel structure. The thin film transistor with the single-gate double-channel structure has the advantages that: the thin film transistor can serve as a two-way switch device or a three-state device, can be used for controlling two circuit branches with a uniform circuit behavior, has a high on state current and can serve as an inverter.

Owner:王磊 +1

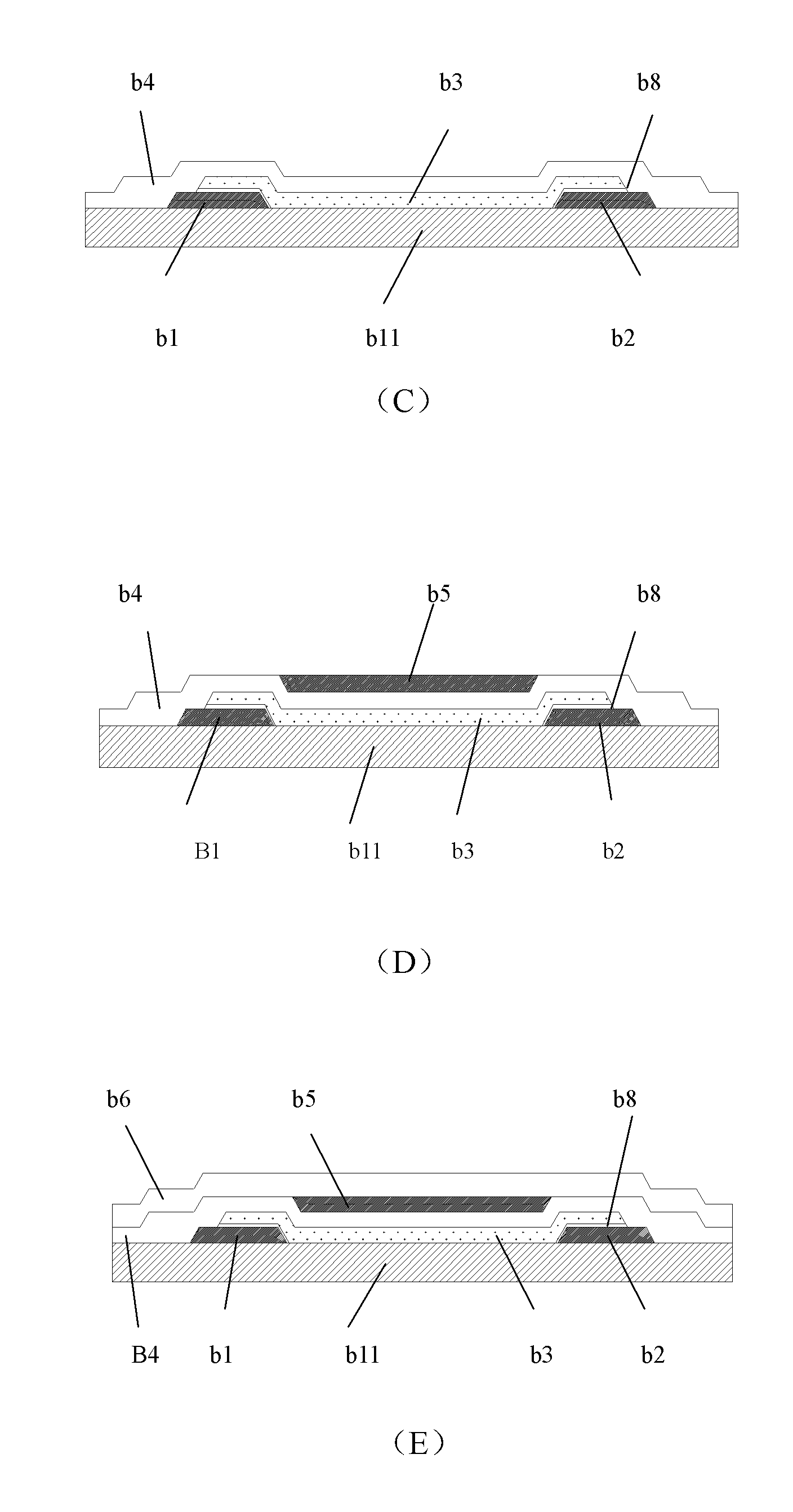

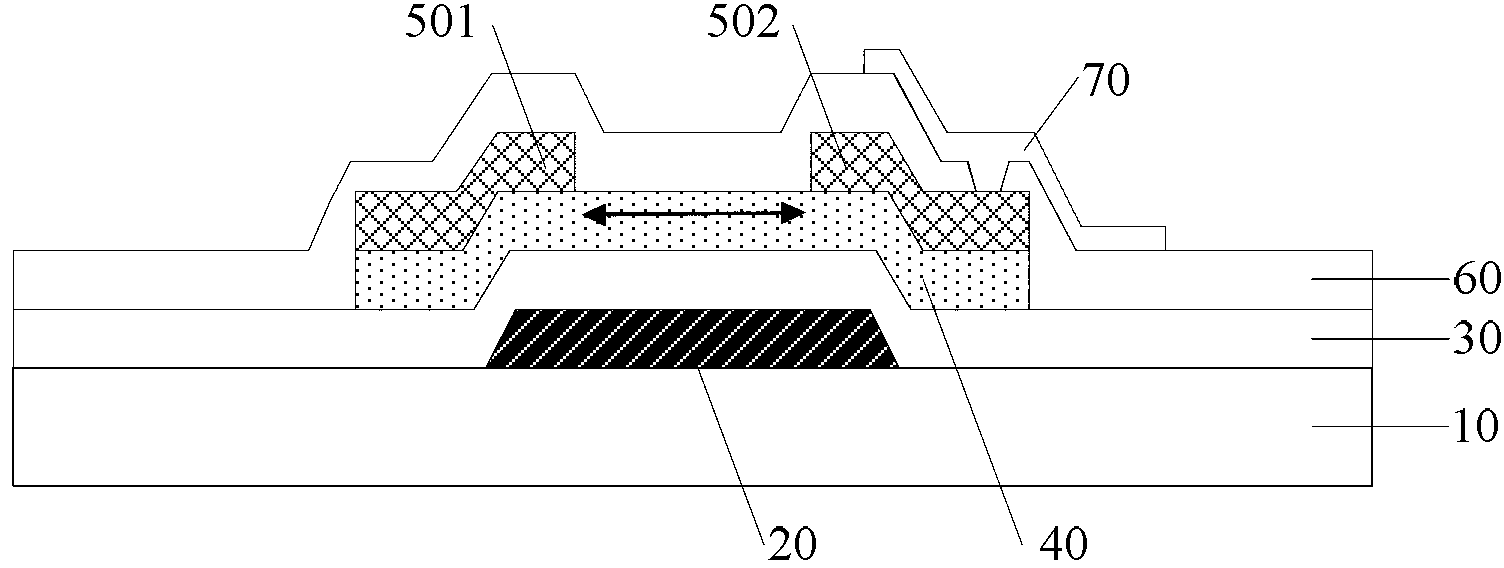

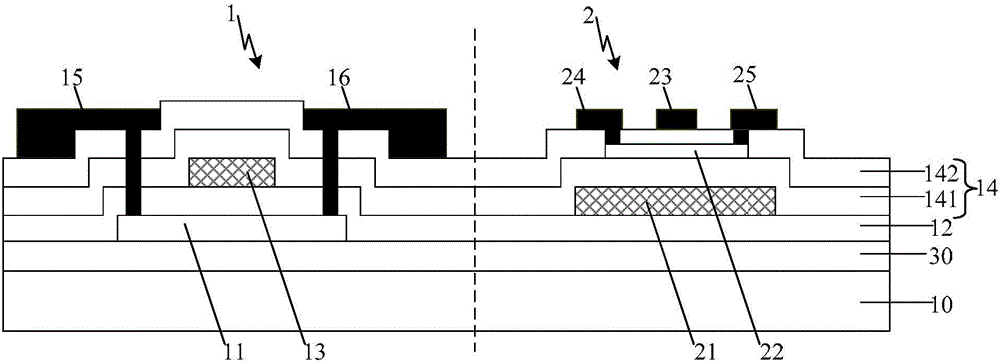

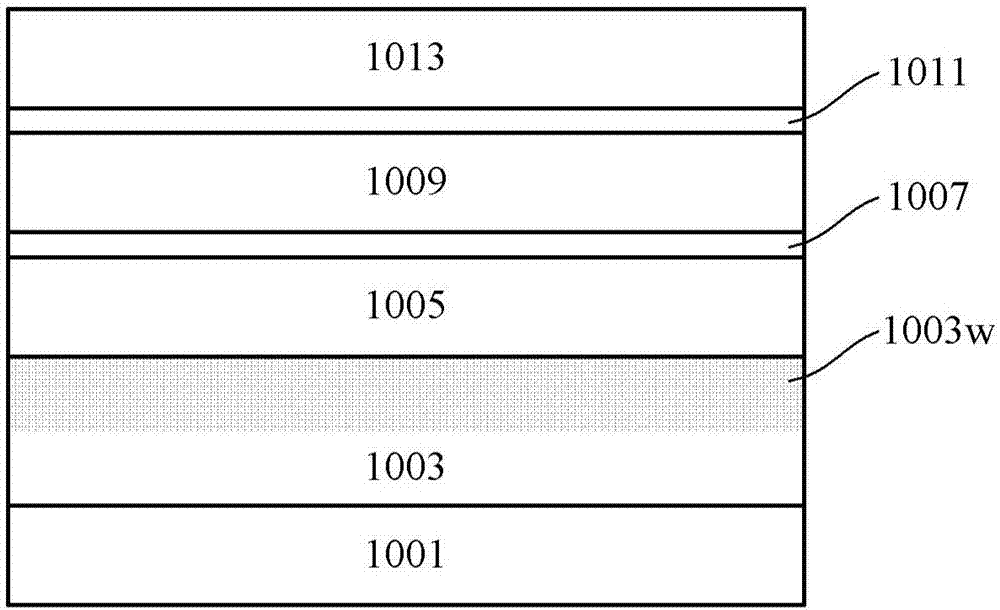

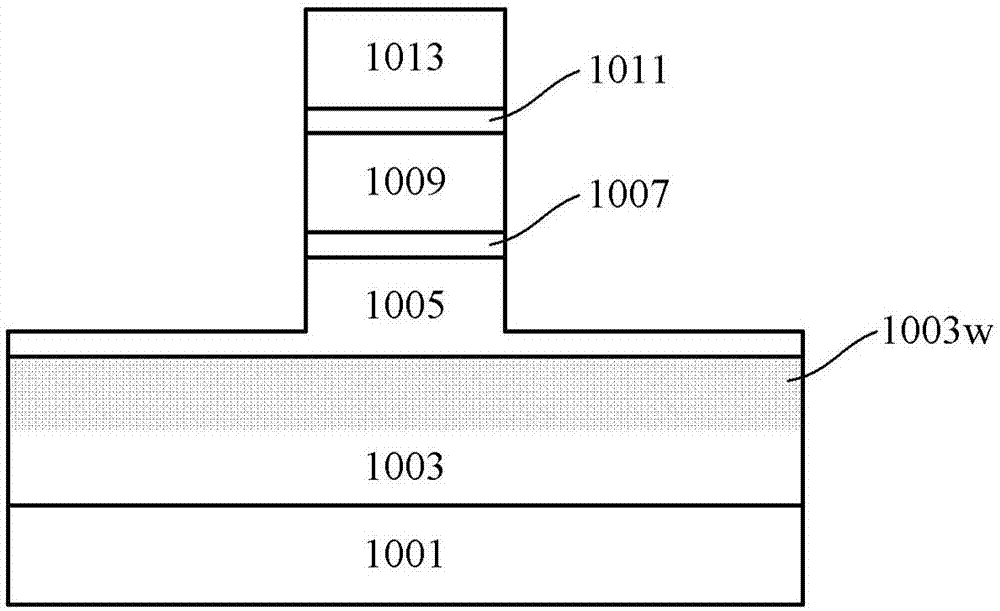

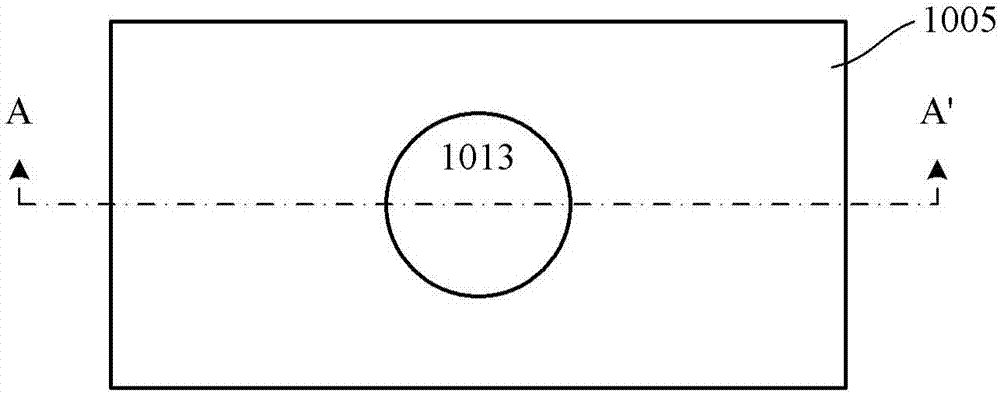

Thin-film transistor, and preparation method, array substrate and display thereof

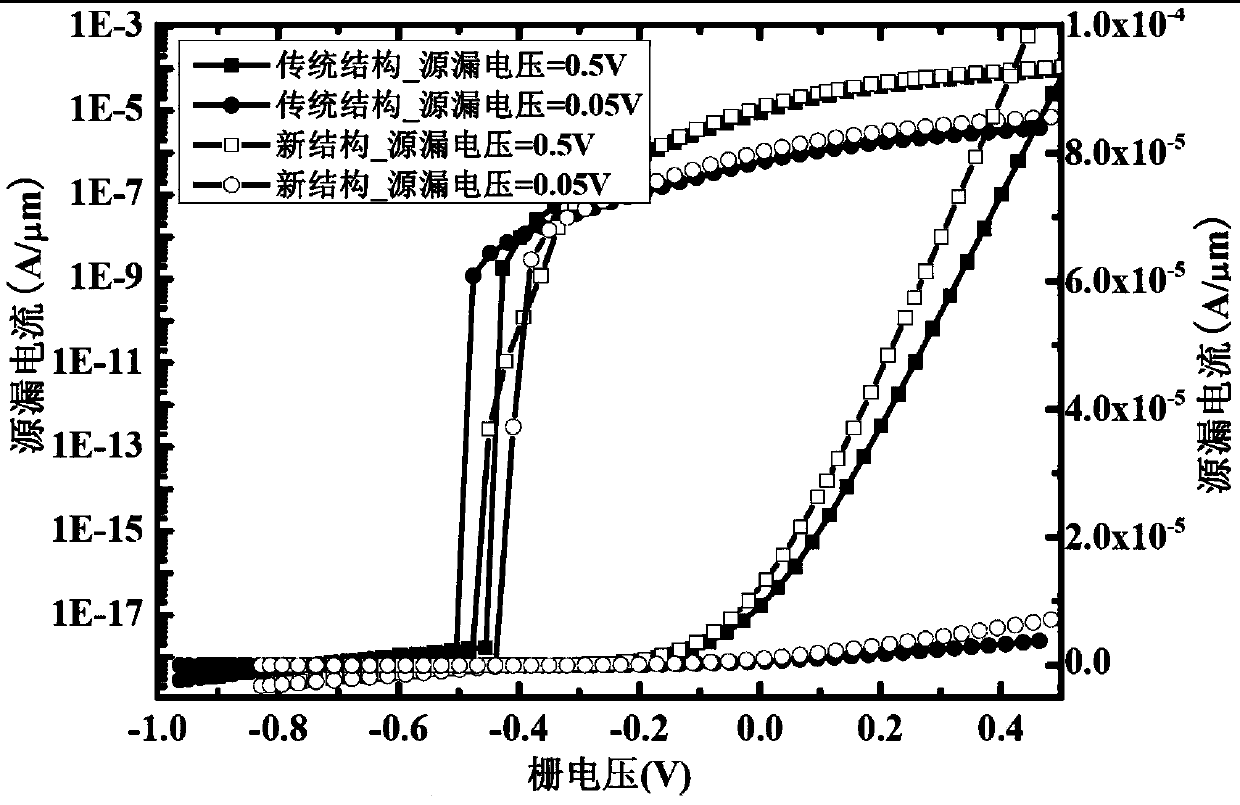

ActiveCN103500764AIncrease the on-state currentReduce leakage currentTransistorSolid-state devicesPower flowBiochemical engineering

The embodiment of the invention provides a thin-film transistor, and a preparation method, an array substrate and a display thereof, relating to the field of displaying technology and capable of reducing the current leakage and ensuring the performance reliability of the thin-film transistor while maintaining the high on-state current of the thin-film transistor. The thin-film transistor comprises a grid electrode, a grid insulating layer, an active layer, a source electrode and a drain electrode, wherein the active layer comprises a first active layer and a second active layer, the first active layer is arranged at one side close to the grid insulating layer, the second active layer is arranged at one side close to the source electrode and the drain electrode; the charge carrier mobility of the first active layer is higher than that of the second active layer. The invention provides the production method of the thin-film transistor capable of reducing the current leakage of the thin-film transistor while needing to maintain the high on-state current of the thin-film transistor, and a production method of the array substrate and the display of the thin-film transistor.

Owner:BOE TECH GRP CO LTD +1

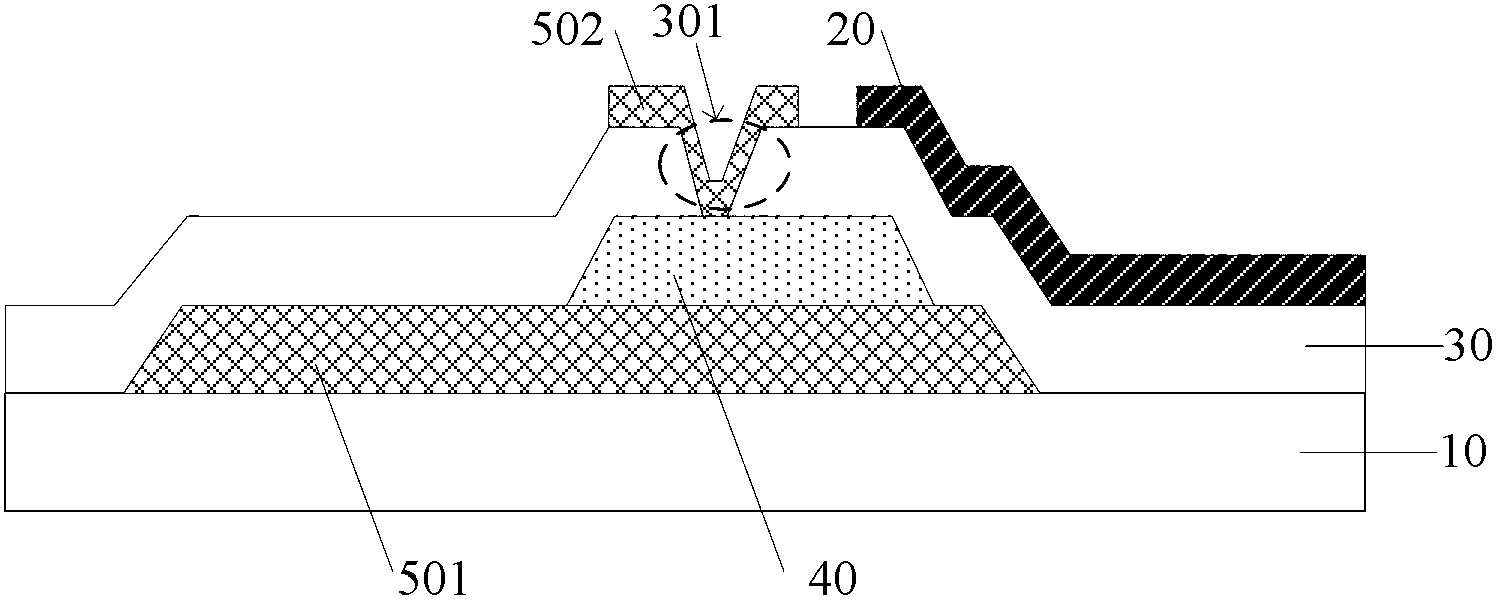

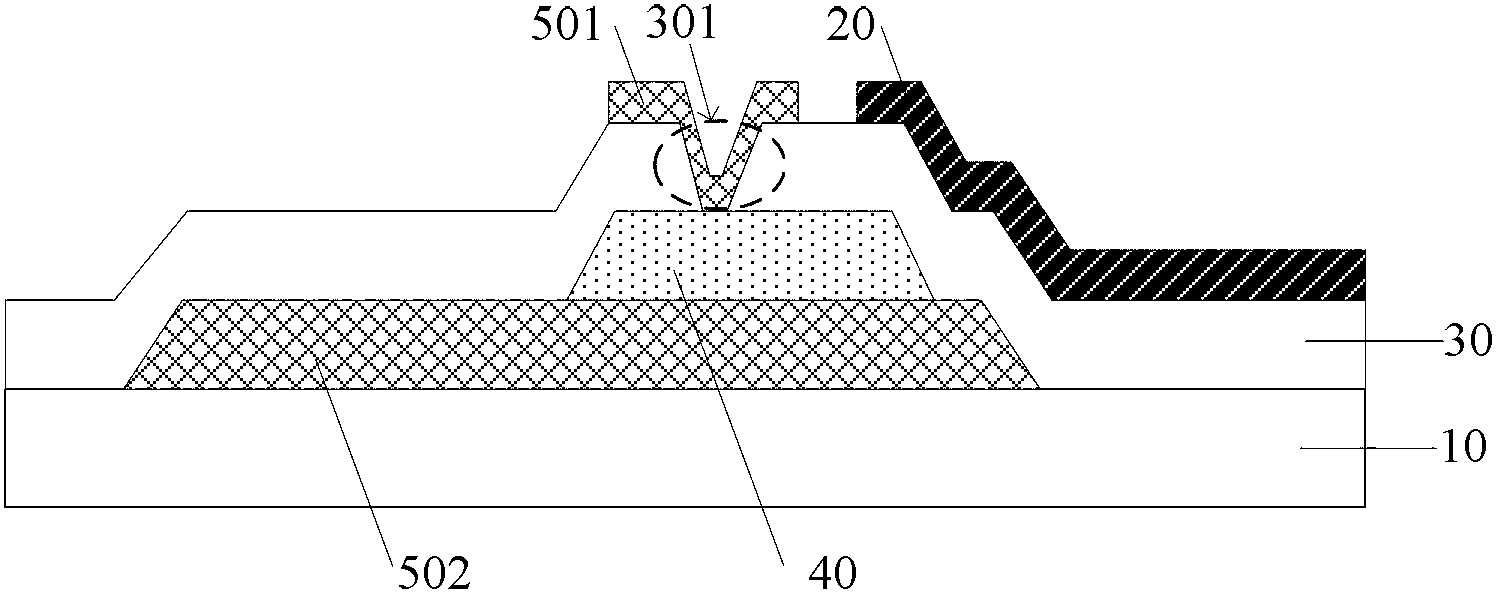

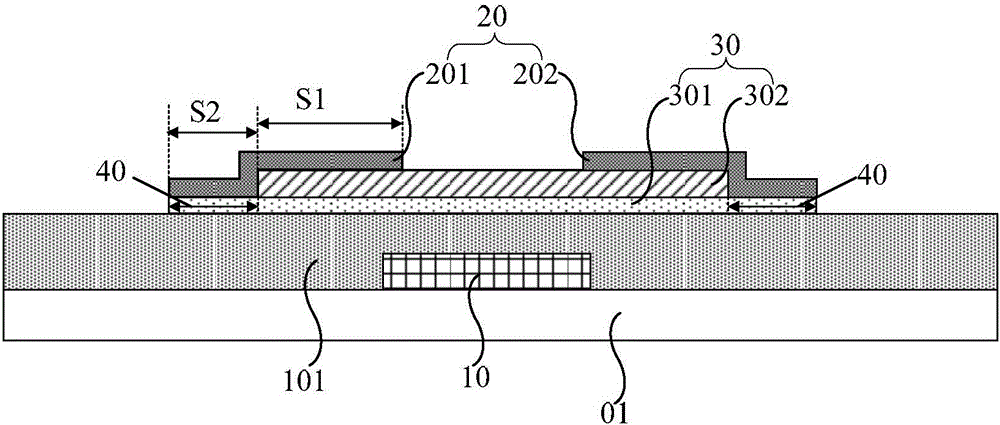

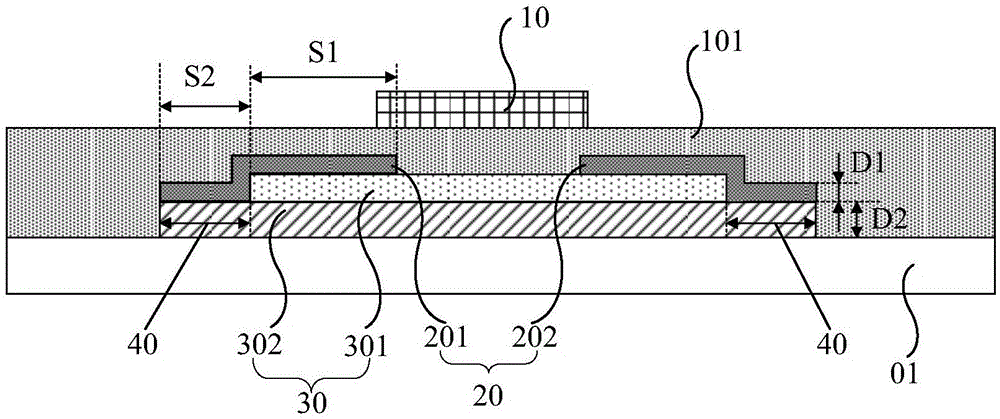

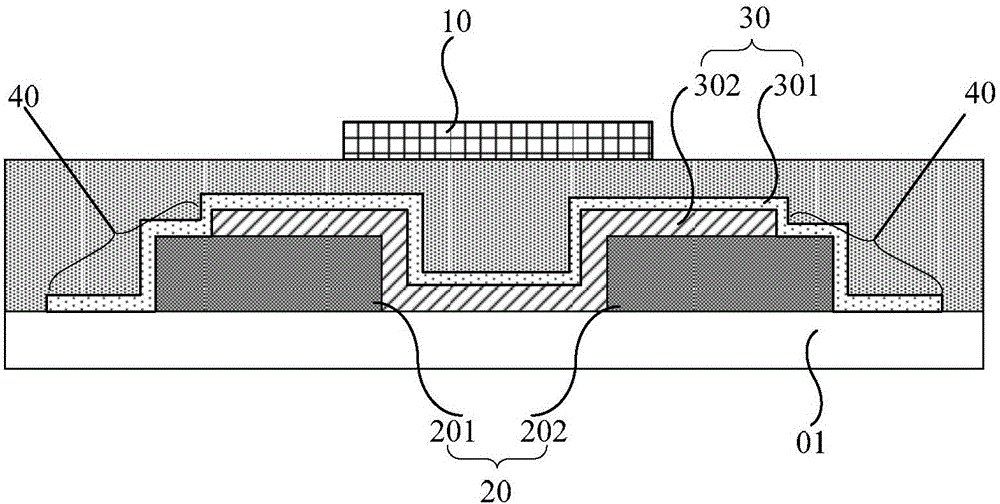

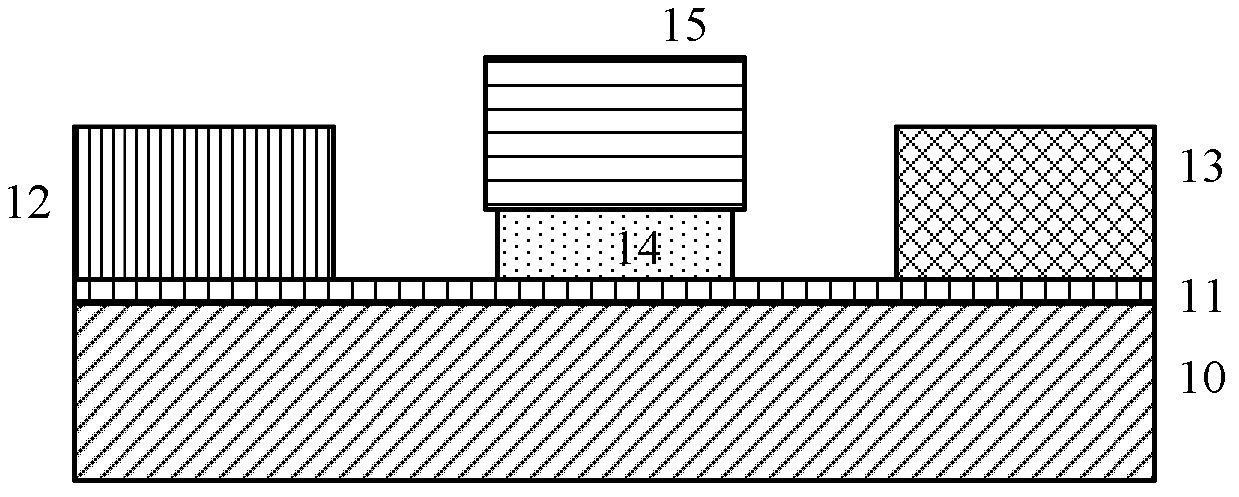

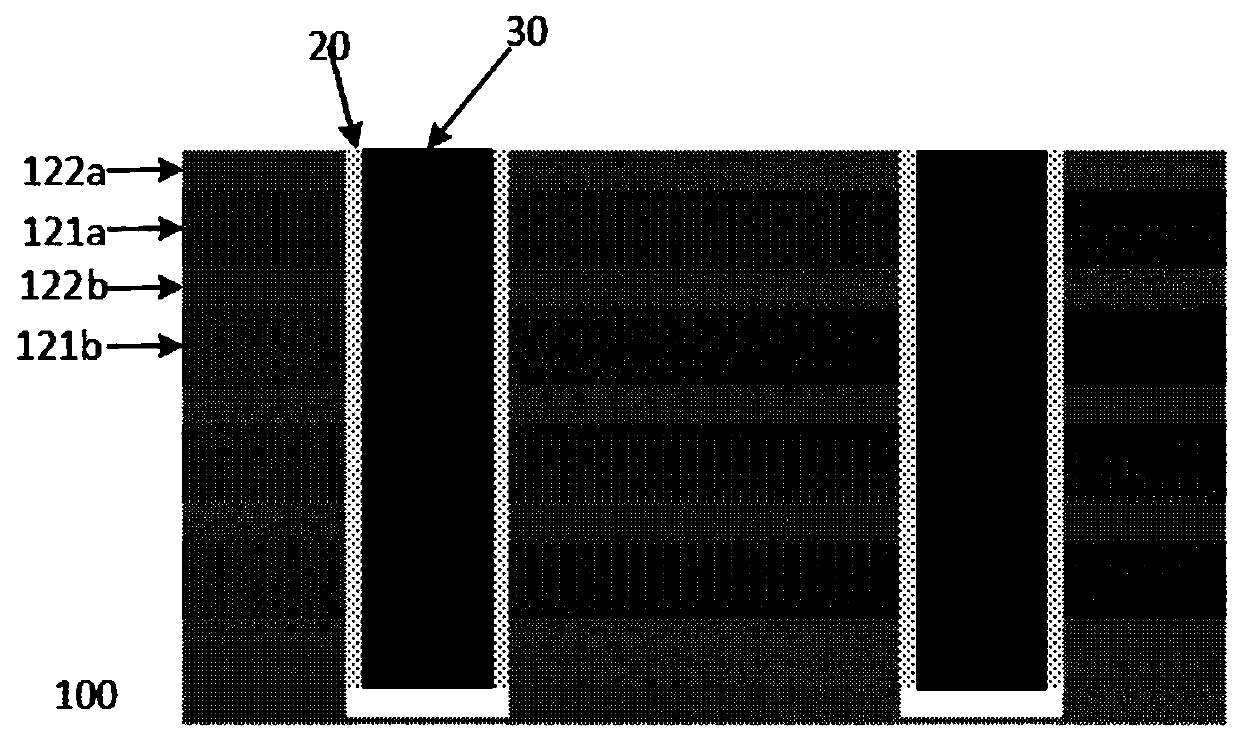

Thin film transistor, preparation method for same and array substrate

InactiveCN103311310AIncrease the on-state currentImprove featuresTransistorSolid-state devicesOxide thin-film transistorDisplay device

The invention provides a thin film transistor, a preparation method for the same and an array substrate, and relates to the technical field of display. The trench length of the thin film transistor can be reduced. The thin film transistor comprises a gate arranged on a substrate, a gate insulating layer, an active layer, a source and a drain, wherein the source and the drain are arranged on the two sides of the active layer along a direction perpendicular to the substrate respectively, and contact with the active layer. The thin film transistor, the preparation method for the same and the array substrate are used for manufacturing a display.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD

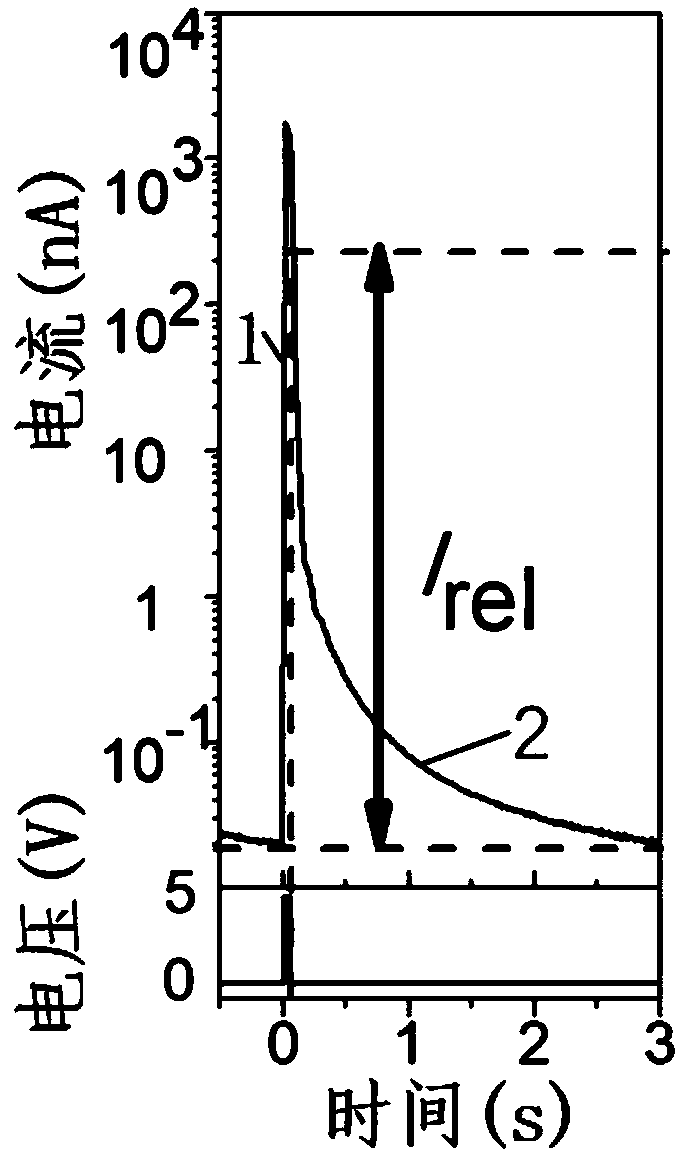

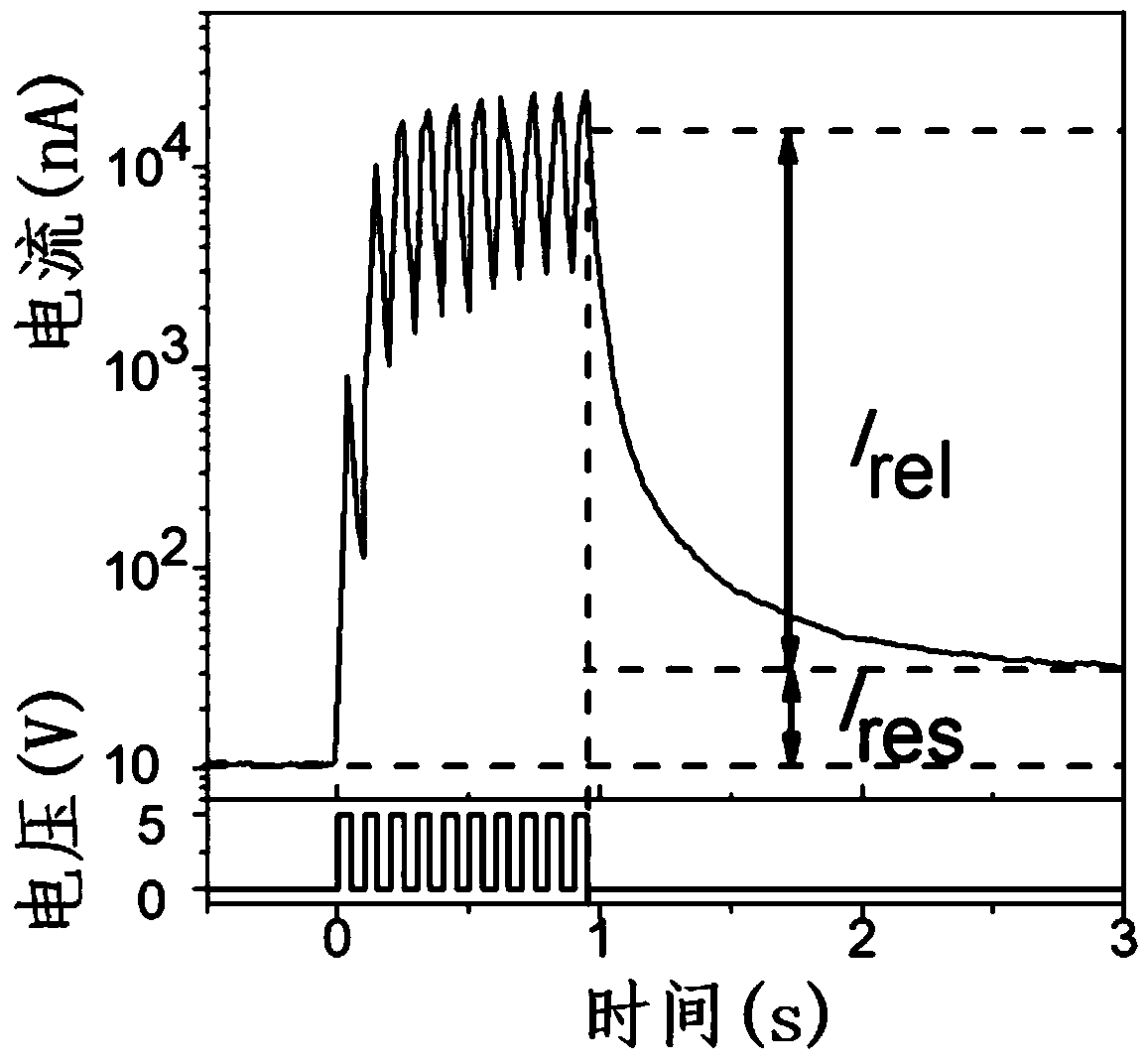

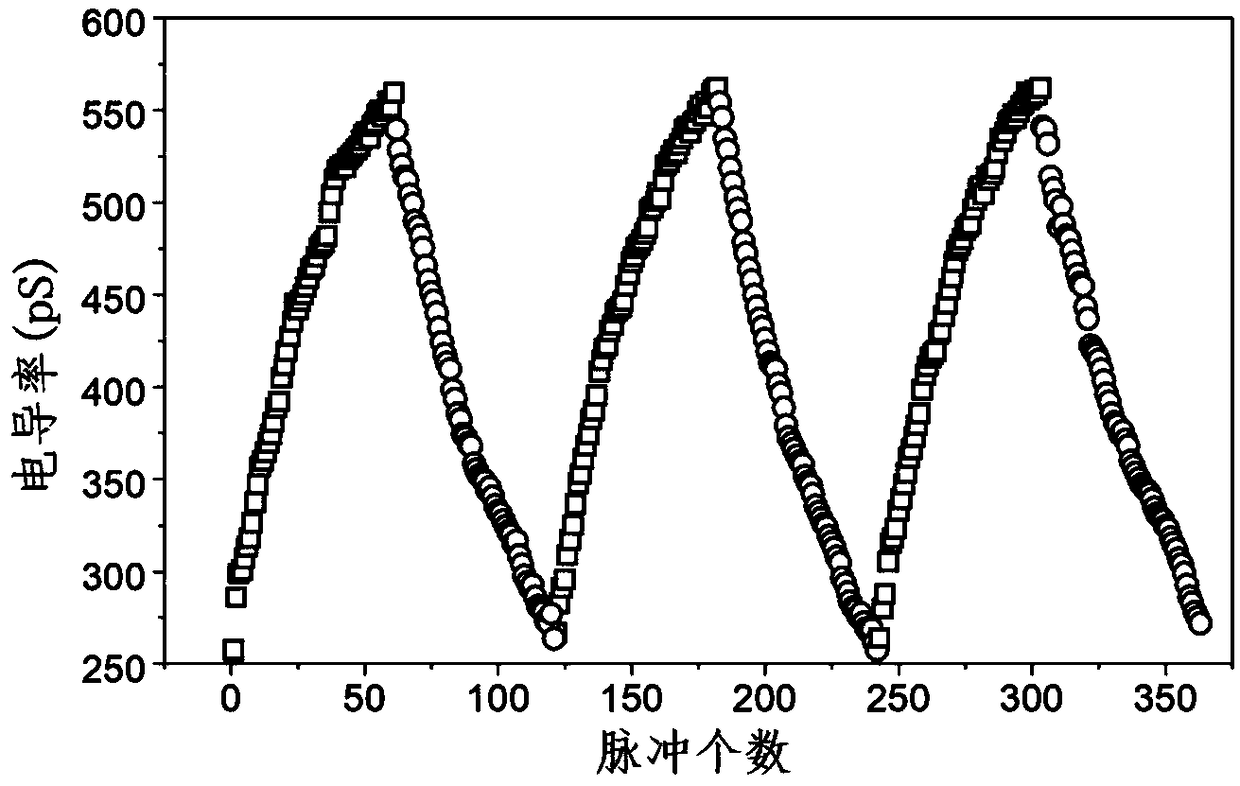

Synaptic transistor based on two-dimensional semiconductor material and preparation method of synaptic transistor

InactiveCN109473549AIncrease surface areaImprove linearitySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsOhmic contact

The invention discloses a synaptic transistor based on a two-dimensional semiconductor material and a preparation method of the synaptic transistor. The synaptic transistor comprises an insulating substrate, and a channel, a source electrode, a drain electrode and a gate electrode which are arranged on the substrate, wherein the channel is a two-dimensional semiconductor material; the source electrode and the drain electrode are arranged at the two ends of the channel respectively and form an ohmic contact with the channel material; the gate electrode and an electrical interconnection system formed by the channel, the source electrode and the drain electrode are kept in electronic insulation; an organic electrolyte covers a channel region and most of the gate electrode and comprises an organic carrier capable of being electrically insulated and ions capable of being migrated, and effective ion control of the gate to the channel material is formed. According to the synaptic transistor based on the two-dimensional semiconductor material and the preparation method of the synaptic transistor, an ion attachment-intercalation mechanism is utilized, and the characteristics of large surface area and adjustable resistance value of the two-dimensional material are combined, so that the device shows long-term and short-term synaptic plasticity, and the two characteristics can change witheach other along with the change of a gate signal. Meanwhile, the device has good linearity and ultralow operational power consumption, and the implementation and large-scale integration application of a high-precision neuromorphic device are facilitated.

Owner:PEKING UNIV

Method for producing liquid crystal display panel

ActiveCN102799014AEasy to controlSimple processSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceInsulation layer

The invention provides a method for producing a liquid crystal display panel, which comprises the following steps: 1, providing a substrate; 2, forming a black photoresist layer on the substrate, forming a preset pattern through a photomask process, and further producing a black matrix; 3, forming an isolating layer on the black photoresist layer; 4, producing a first metal layer on the isolating layer, forming a second metal layer on the first metal layer, forming the preset pattern through the photomask process, and furthermore, forming a source / drain electrode and a storage capacitor Com electrode; 5, forming an ohmic contact layer on the second metal layer, forming the preset pattern through the photomask process, and furthermore, forming a doped phosphorus film on a metal electrode; 6, arranging a channel layer on the ohmic contact layer, forming the preset pattern through the photomask process, and thus forming an island; 7, forming a gate insulation layer on the channel layer, arranging a third metal layer on the gate insulation layer, forming the preset pattern through the photomask process, furthermore, forming a grid and a storage capacitor counter electrode, and arranging a storage capacitor at the edge position of the black matrix; 8, forming a protective layer on the third metal layer; 9, forming right (R), green (G) and blue (B) pixels on the protective layer; 10, forming via holes in the positions of the R, G and B pixels, which correspond to the source electrode and the storage capacitor; 11, arranging a transparent electric conduction layer on the R, G and B pixels, forming the preset pattern through the photomask process, furthermore, forming a pixel electrode, and thus forming a color filter on array (COA) substrate; and 12, bonding the COA substrate with an upper substrate, filling liquid crystal into the COA substrate and the upper substrate, and thus forming the liquid crystal display panel.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

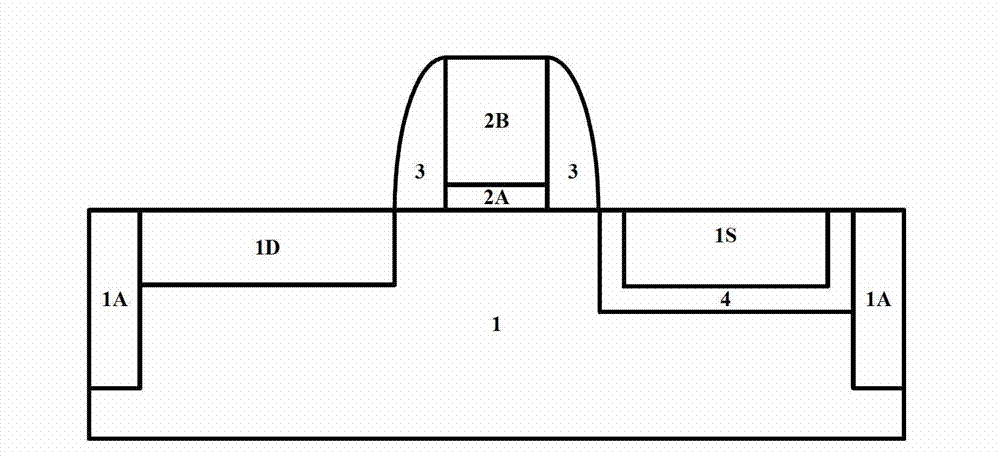

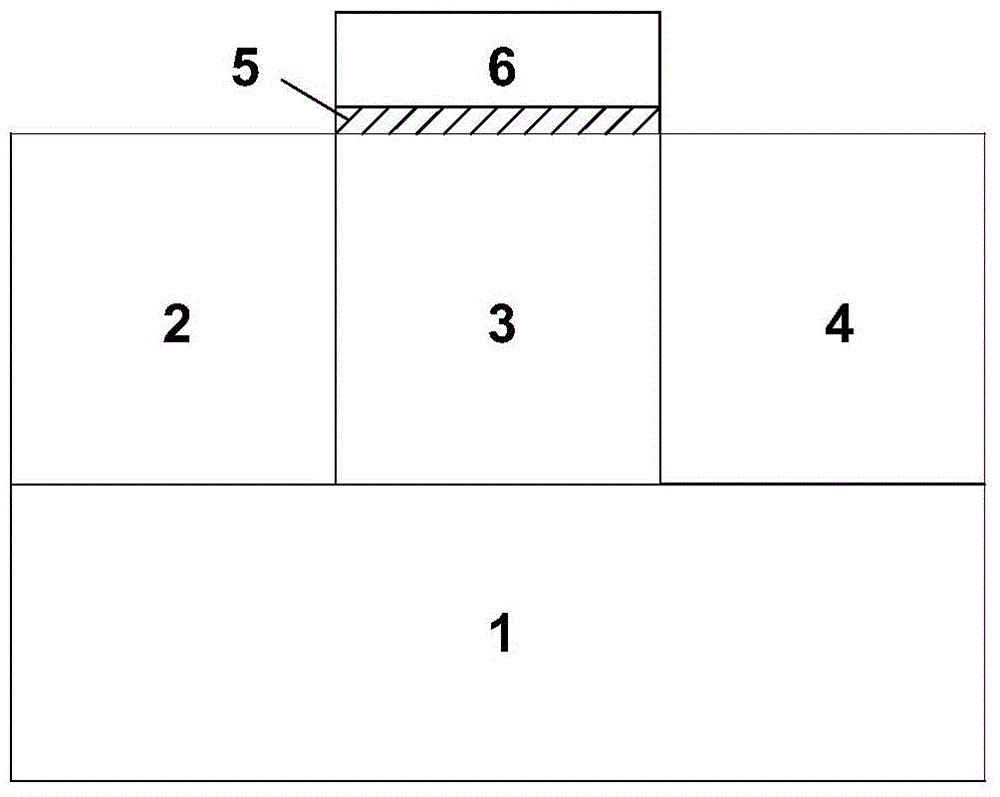

Semiconductor device and making method thereof

ActiveCN103594496AIncrease the on-state currentSemiconductor/solid-state device manufacturingDiodeAlloyGate stack

A semiconductor device is disclosed, and comprises a substrate, a gate stack structure on the substrate, source / drain regions in the substrate at two sides of the gate stack structure, and a channel region between the source / drain regions in the substrate. The source region in the source / drain region comprises a GeSn alloy, and a tunneling dielectric layer optionally exists between the GeSn alloy of the source region and the channel region. By using the semiconductor device and a manufacturing method thereof in the present invention, selective epitaxy is performed, or a precursor is injected and then rapid annealing is performed through laser, to form a GeSn alloy with a narrow band gap, thereby effectively increasing an on-state current of a TFET, and having an important application prospect in a high-performance low-consumption application.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

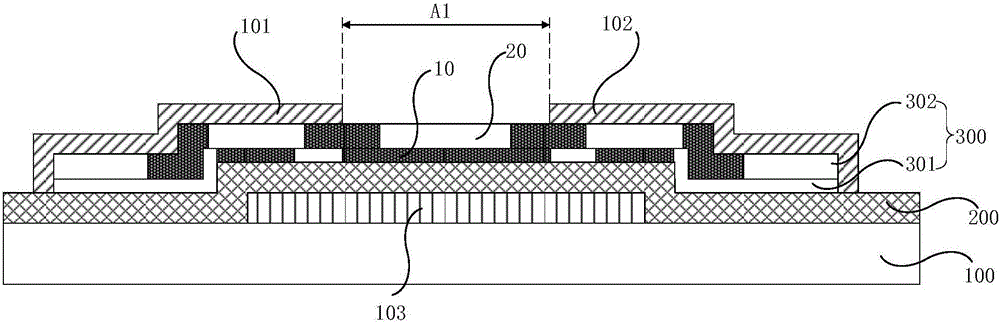

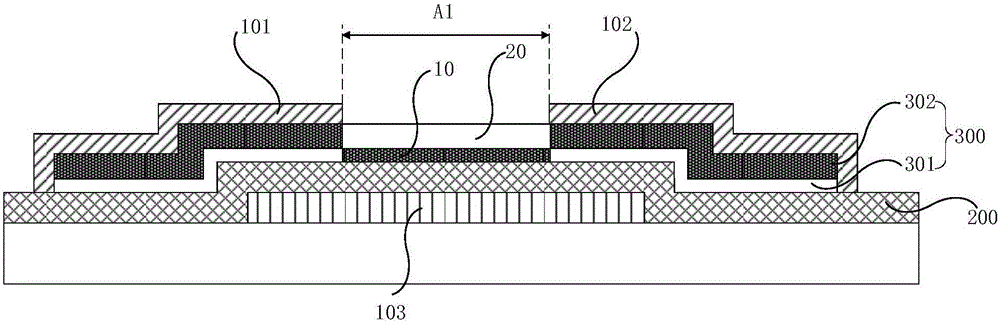

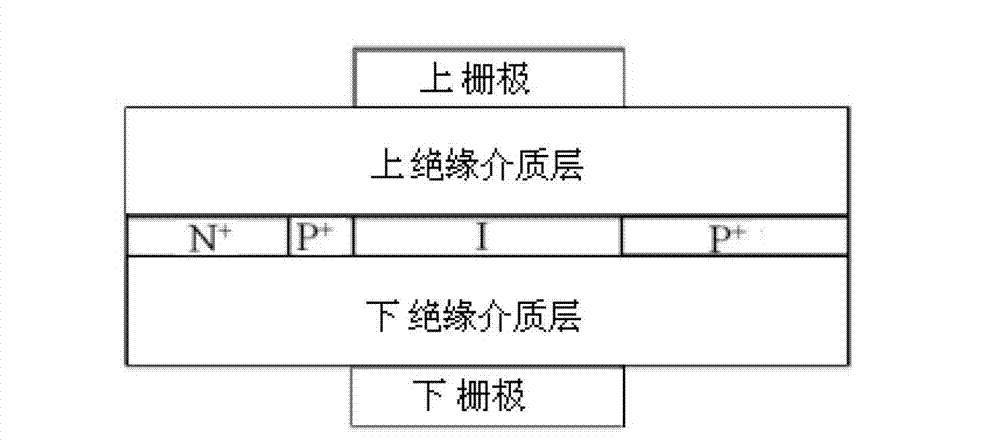

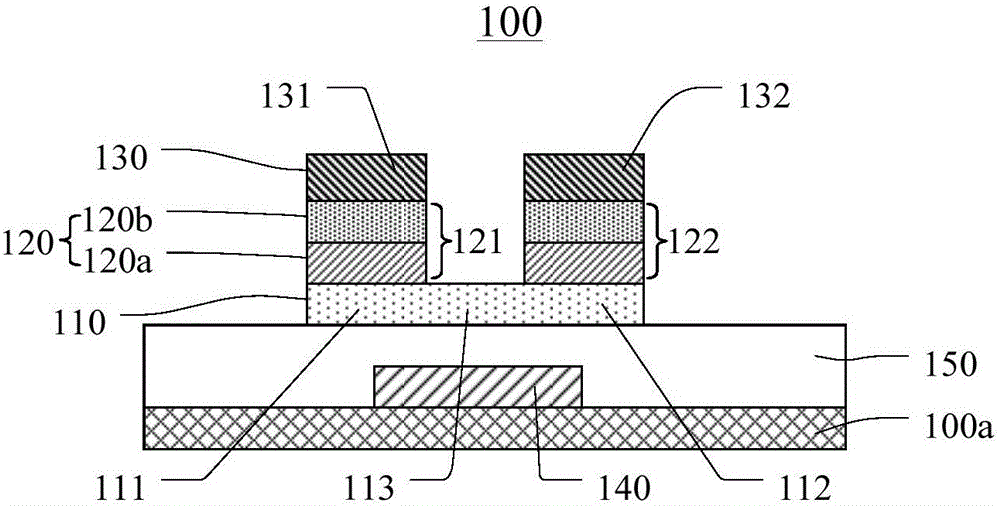

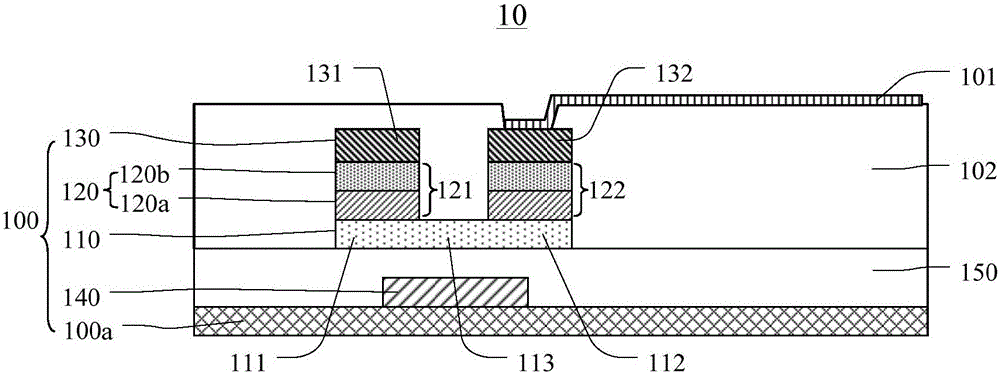

Array substrate and preparation method thereof and display panel

ActiveCN106847834AFast switching speedFast on state currentSolid-state devicesNon-linear opticsEngineeringDouble gate

The embodiment of the invention provides an array substrate and a preparation method thereof and a display panel and relates to the technical field of display. The display panel has good display performance by adopting two types of TFTs on the array substrate. The array substrate comprises a substrate, double-gate oxide TFTs, a display electrode and a polysilicon TFT arranged on the substrate, wherein one double-gate oxide TFT is arranged in each sub-pixel on the substrate; and a drain of each double-gate oxide TFT is electrically connected with the display electrode.

Owner:BOE TECH GRP CO LTD +1

Thin film transistor, manufacturing method thereof, array substrate and display device

ActiveCN105870203AIncrease movement speedReduce movement speedTransistorSolid-state devicesDisplay deviceActive layer

An embodiment of the invention provides a thin film transistor, a manufacturing method thereof, an array substrate and a display device and relates to the technical field of display. On-state current can be increased while leakage current is lowered. The thin film transistor comprises a source electrode, a drain electrode, a grid electrode and a semiconductor active layer, the semiconductor active layer comprises a first sub semiconductor layer and a second sub semiconductor layer, and the first sub semiconductor layer is close to the grid electrode; at least a portion corresponding to an area between the source electrode and the drain electrode in the first sub semiconductor layer is composed of polycrystalline silicon, and a portion corresponding to the area between the source electrode and the drain electrode in the second sub semiconductor layer at least comprises noncrystalline silicon.

Owner:BOE TECH GRP CO LTD

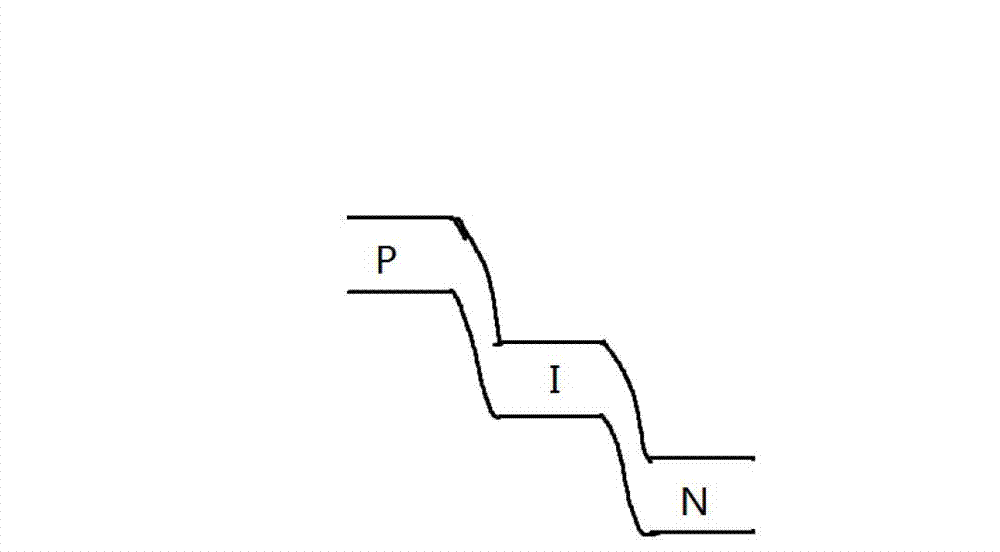

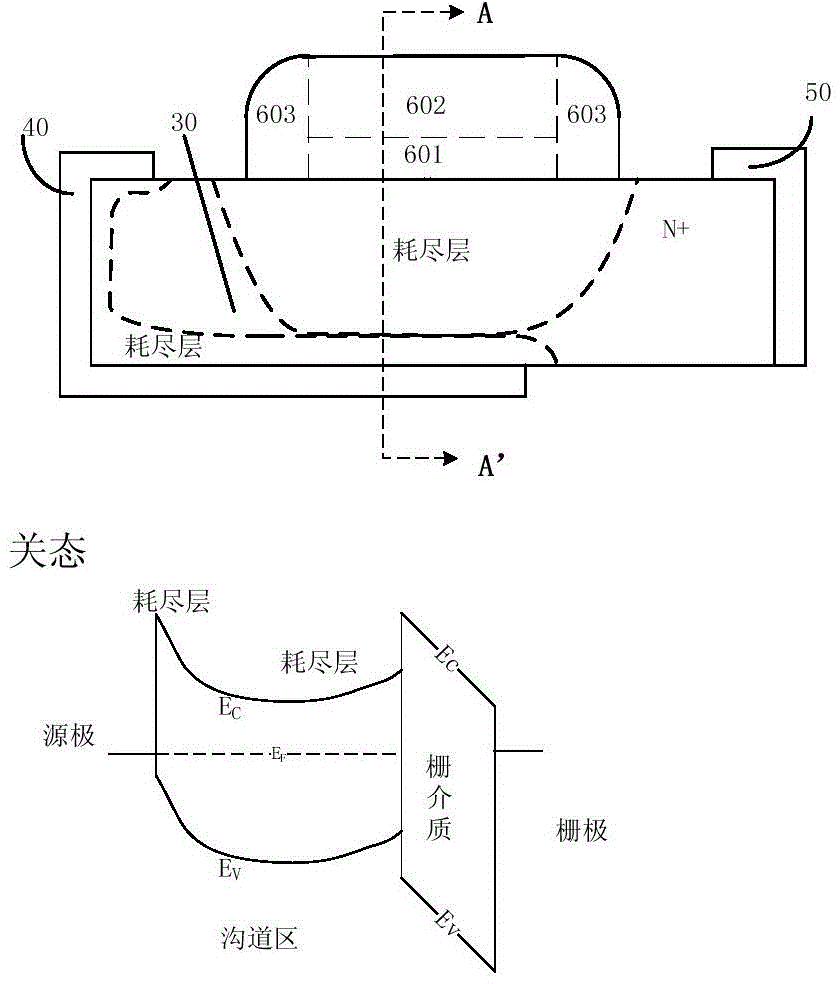

Tunneling field effect transistor

InactiveCN102832256AImprove performanceIncrease the on-state currentTransistorSub thresholdCondensed matter physics

The invention relates to the technical field of field effect transistors and discloses a tunneling field effect transistor. The tunneling field effect transistor comprises a source region, a channel region and a drain region, wherein the source region and the drain region are respectively formed on the two sides of the channel region, and a contact region between the source region and the channel region is made of extrinsic materials and different from the doping type of the source region. According to the invention, the contact area between the source region and the channel region is doped differently from the source region, so that the device is relatively narrow in a tunneling layer from the source end to the channel in an ON state, and the ON-state current is increased. As the thickness of a tunneling layer from the source end to the drain end in an OFF state is not changed with the method, a relatively low OFF-state current can be kept, as a result, a higher switch ratio and a relatively low sub-threshold slope can be acquired with the method, so that a better device performance can be acquired.

Owner:PEKING UNIV

Film transistor and the manufacturing method thereof, array substrate and display apparatus

ActiveCN106298957AIncrease movement speedReduce movement speedTransistorSolid-state devicesElectrical conductorEngineering

The embodiments of the present invention provide a film transistor and the manufacturing method thereof, an array substrate and a display apparatus, relating to the technical field of display and capable of effectively ensuring that while the on-state current is increased, the leakage current is reduced. The film transistor includes a gate electrode provided on a substrate, a source / drain pattern composed of a source electrode and a drain electrode, and an active layer, wherein the active layer comprises a first semiconductor layer and a second semiconductor layer arranged in layers, with the former having a larger electron mobility than the later and the former being closer to the gate electrode than the latter. The semiconductor layer at one side of the active layer and remote from the source / drain pattern has an extended part, compared with the semiconductor layer close to one side of the source / drain pattern, at a position corresponding to the source electrode and / or drain electrode. The source electrode and / or the drain electrode are in contact with the bottom surface of the semiconductor layer in the active layer close to one side of the source / drain pattern and extend to the extended part so that they are in contact with the extended part.

Owner:BOE TECH GRP CO LTD +1

Two-dimensional material/semiconductor hetero-junction tunneling transistor and preparation method thereof

ActiveCN107104140AEffective tunnelingDirect tunnelingSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsPower flow

The invention discloses a tunneling field effect transistor based on a two-dimensional material / semiconductor hetero-junction and a preparation method thereof. A device forms an interleaved energy band structure in the off state through the energy band design, namely, a tunneling window is inexistent between the two-dimensional material and the semiconductor material, and the ultra-low off-state current can be acquired; the grid voltage can be applied to regulate an energy band alignment way at the two-dimensional material / semiconductor hetero-junction so that the device can form the staggered energy band structure in the on-state, and the effective tunneling barrier height is a negative value; and meanwhile, the current carrier tunnels to a channel region from a source region to realize the direct tunneling, thereby acquiring large on-state current. The device adopts the highly-doped three-dimensional semiconductor material as the source region material, and the three-dimensional semiconductor material and the metal source electrode are unipotential; since the thickness of the two-dimensional material is ultra-thin, the grid voltage can regulate the two-dimensional material and the energy band at the two-dimensional material / semiconductor hetero-junction interface, thereby acquiring an ideal grid control capacity. The tunneling field effect transistor disclosed by the invention is simple in process, and large in compatibility with the traditional semiconductor process.

Owner:PEKING UNIV

Tunneling field effect transistor

ActiveCN103474459AIncrease contact areaIncrease chance of tunnelingSemiconductor devicesGate dielectricField effect

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

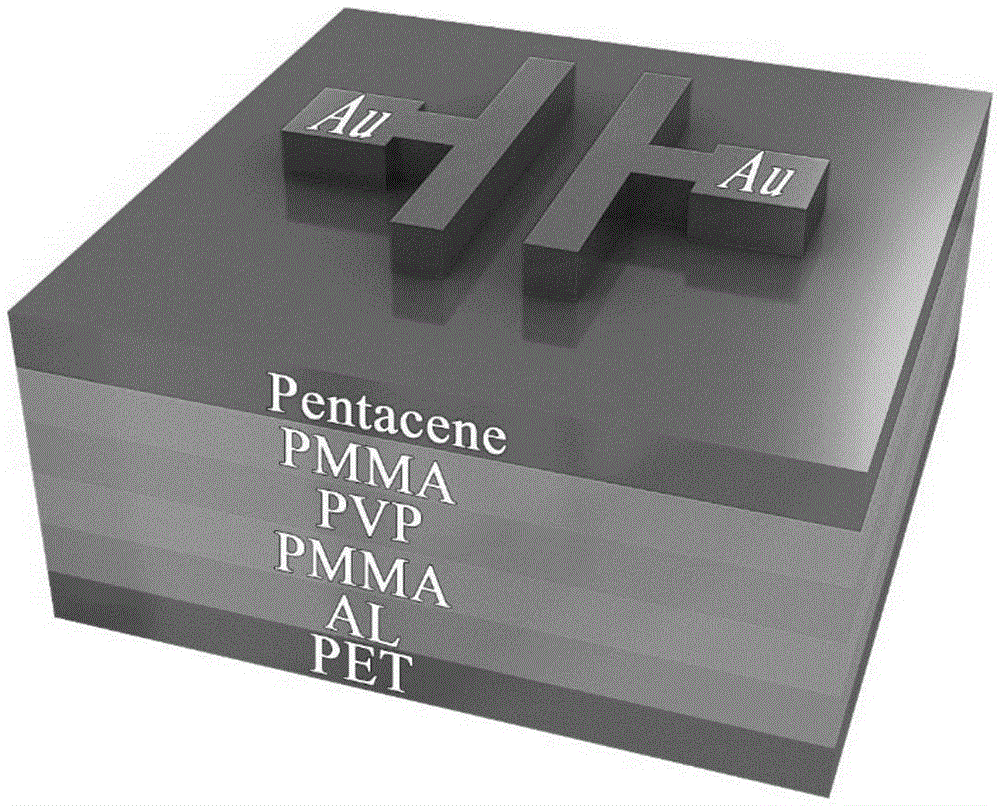

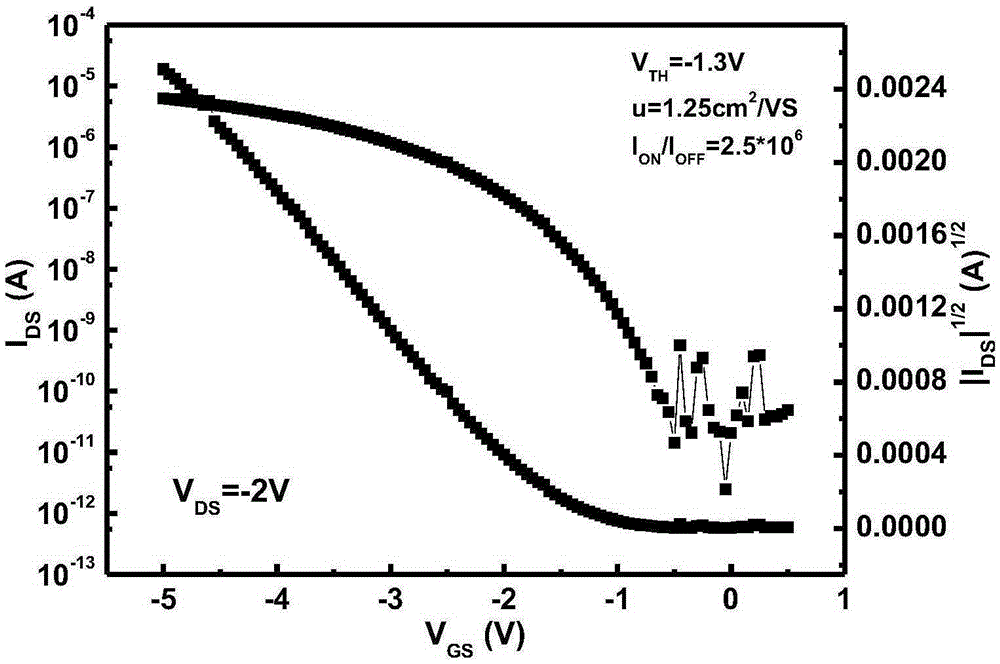

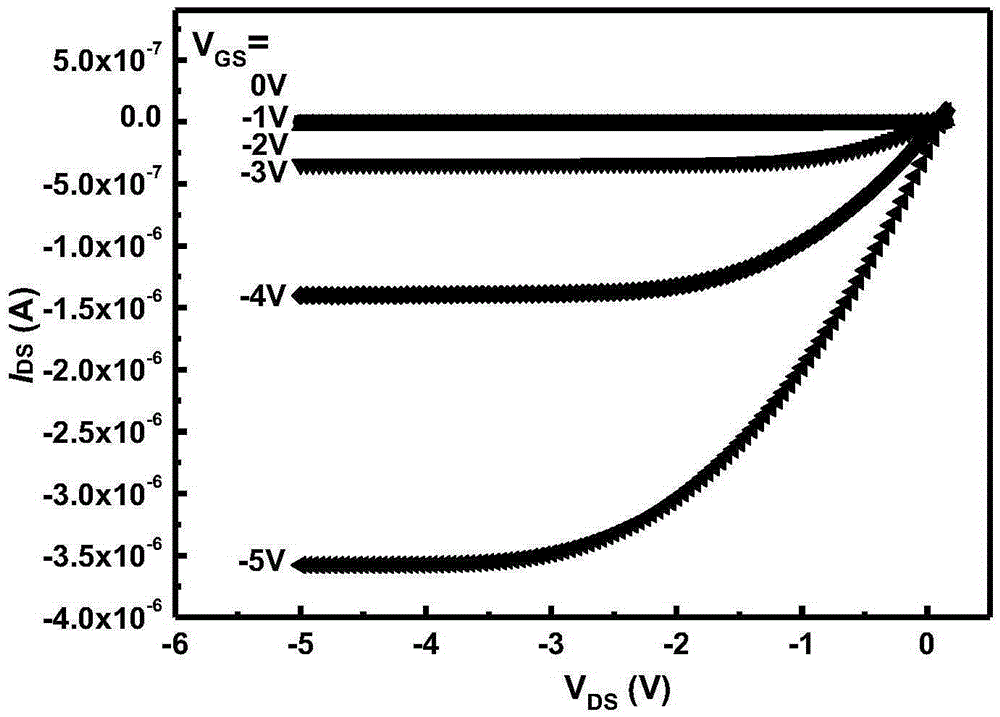

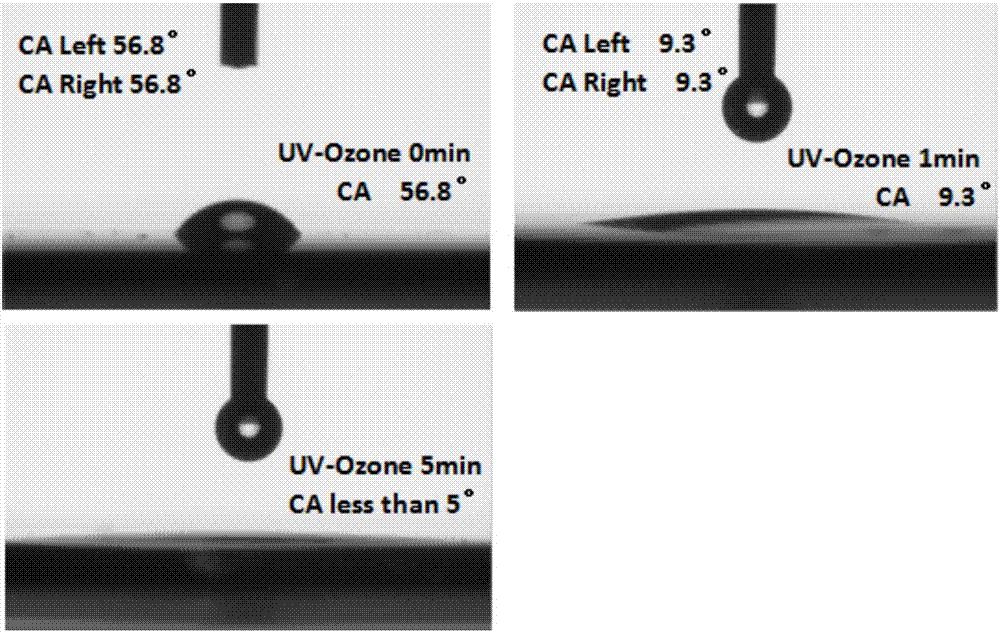

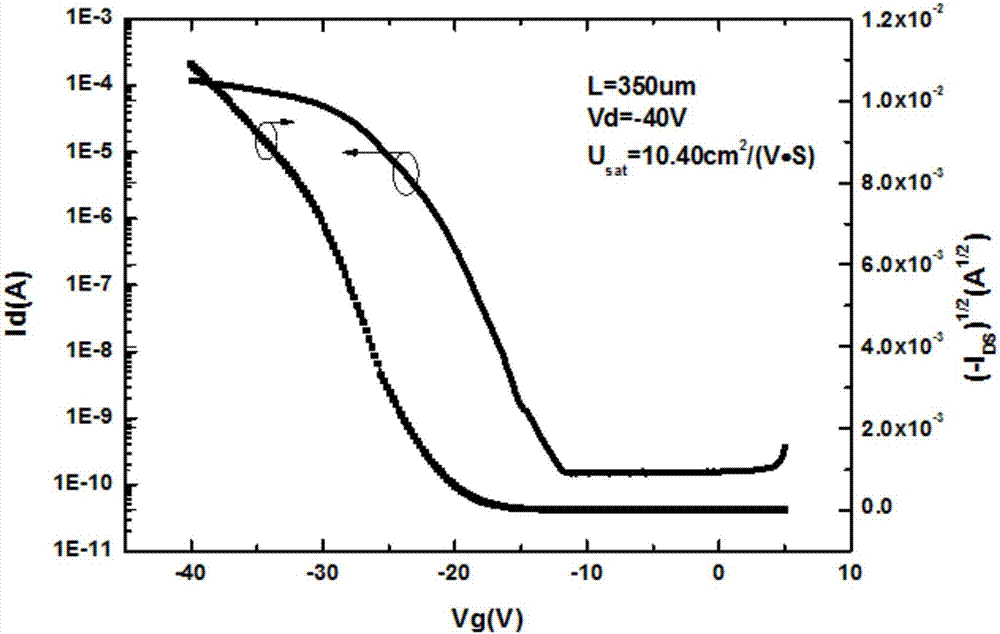

Flexible low-voltage organic field effect transistor and manufacturing method thereof

InactiveCN105336860AGood electrical propertiesImprove mobilitySolid-state devicesSemiconductor/solid-state device manufacturingOrganic field-effect transistorLow voltage

The invention discloses a flexible low-voltage organic field effect transistor and a manufacturing method thereof. Three layers of polymers are added between a gate and a semiconductor layer interface to serve as an insulated layer; the overall device comprises a source and drain electrode, a semiconductor, a high-insulation polymer, a high-dielectric constant material polymer, a high-insulation polymer, a gate, and a flexible transparent plastic substrate sequentially from top to bottom; and the dielectric layer with the structure has excellent insulation and good stability. Through measuring electrical properties and a semiconductor particle growth shape, whether the device is a flexible low-voltage organic field effect transistor can be judged. The organic field effect transistor has the advantages of realizing high mobility and large switch ratio under low voltage, maintaining good performance when bias voltage is applied and in a high temperature condition, and having good stability features in different bending modes.

Owner:NANJING UNIV OF POSTS & TELECOMM

Semiconductor device, manufacturing method thereof and electronic device comprising device

ActiveCN107887441AReduce parasitic capacitanceImprove performanceTransistorProgramme controlSemiconductor materialsGate stack

The invention relates to a semiconductor device, a manufacturing method thereof and an electronic device comprising the device. According to an embodiment, the semiconductor device may include a substrate, a first source / drain layer, a channel layer, a second source / drain layer and a gate stack, wherein the first source / drain layer, the channel layer and the second source / drain layer are sequentially stacked on the substrate, the channel layer contains a semiconductor material which can increase on-state current and / or decrease off-state current compared with Si material, and the gate stack isformed around the periphery of the channel layer.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

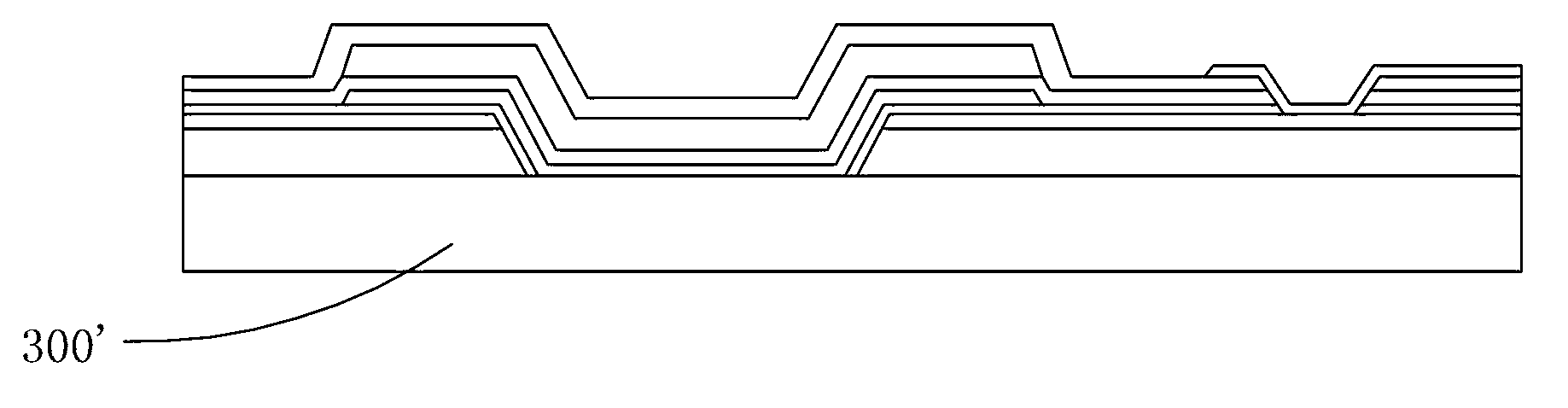

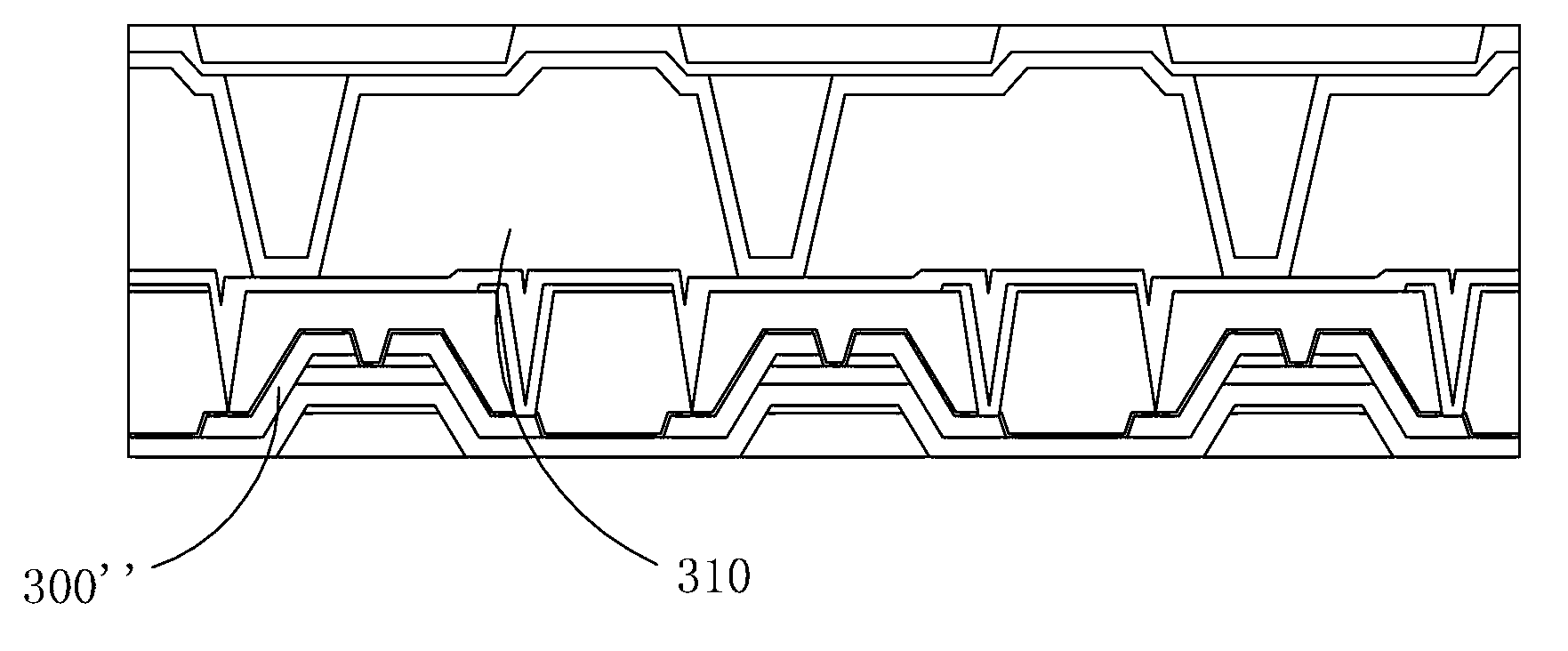

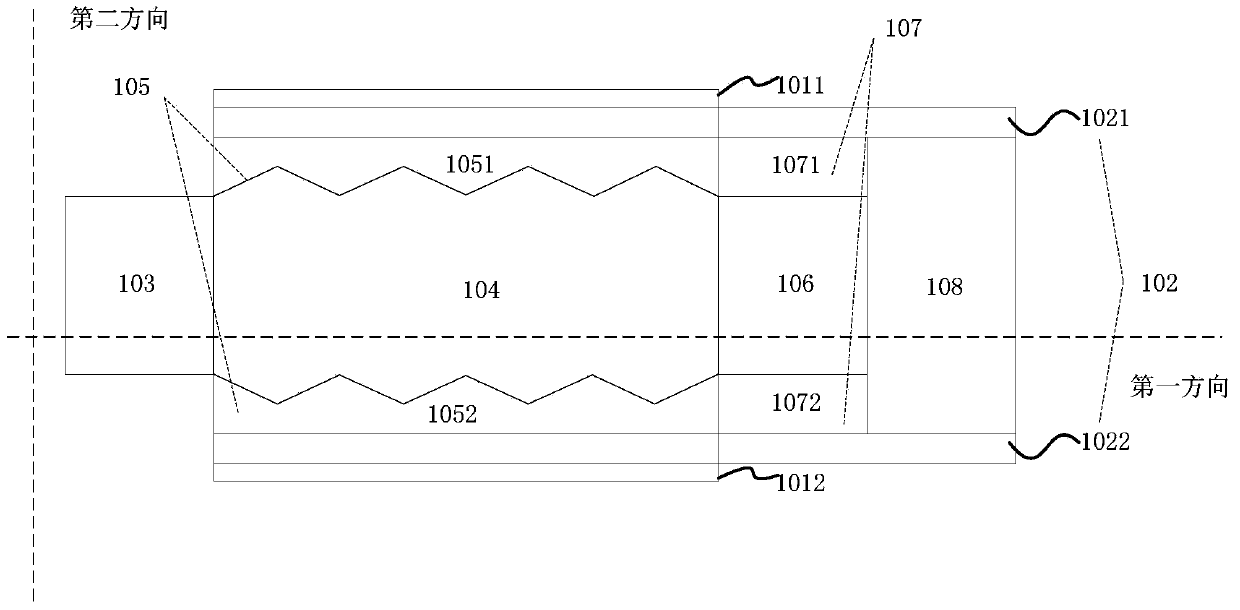

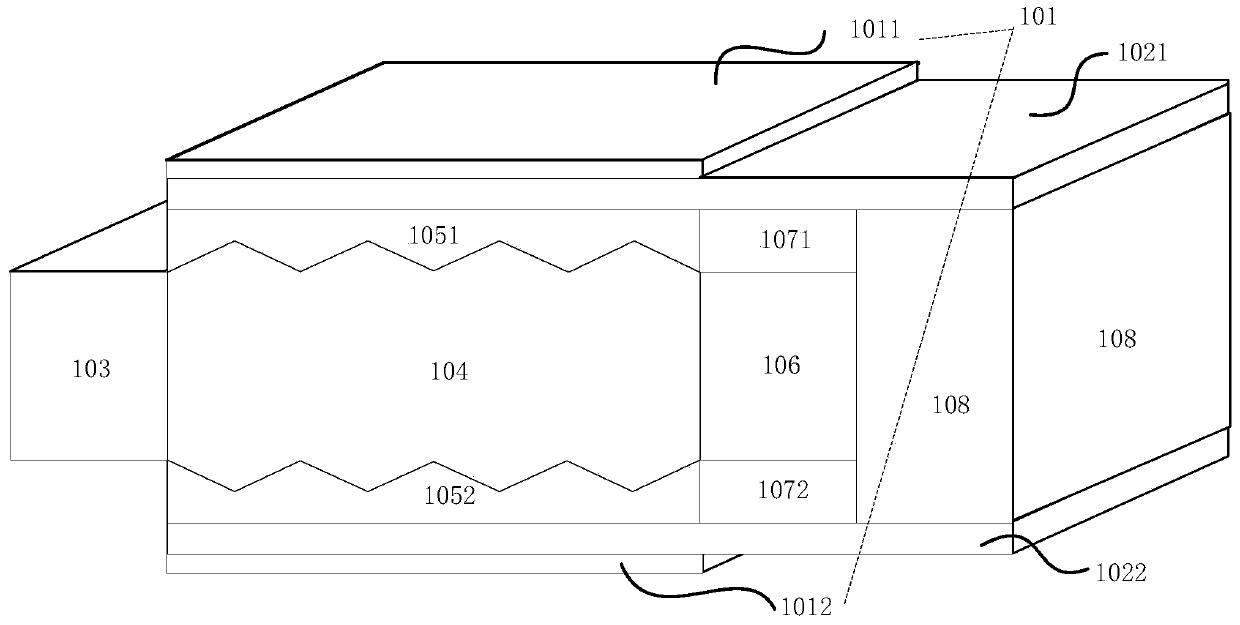

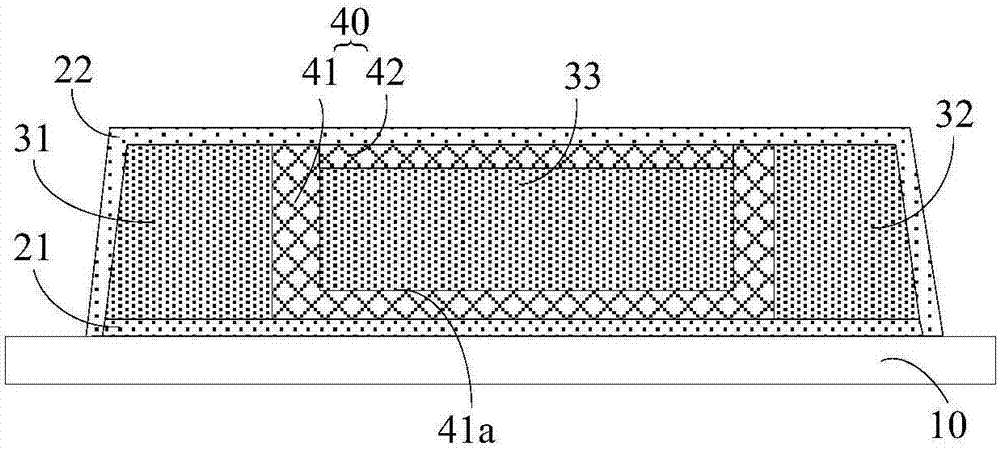

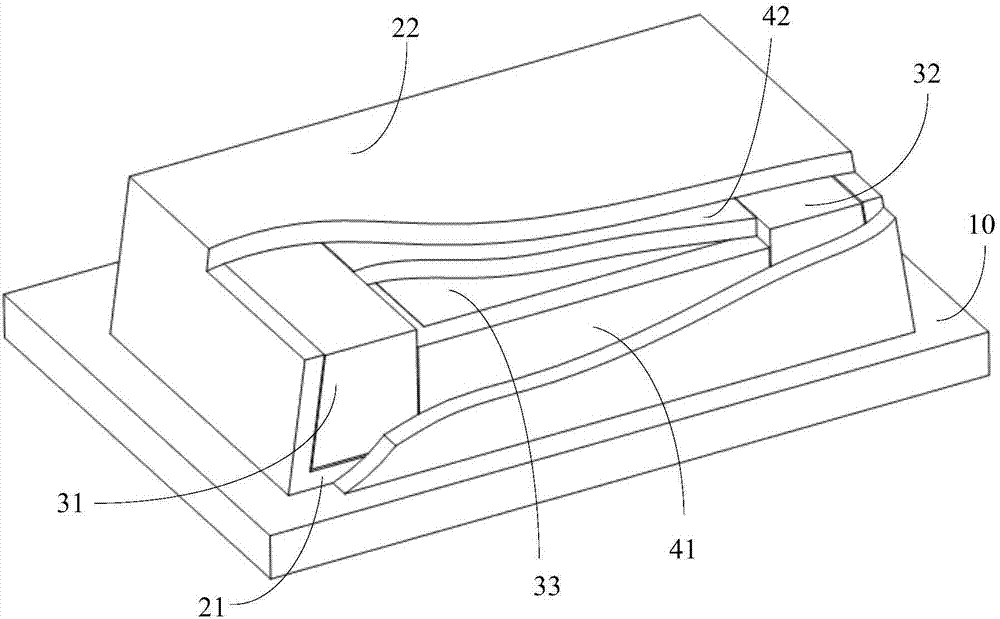

Film transistor array substrate, preparation method thereof and liquid crystal panel

InactiveCN105161542AHigh aspect ratioIncrease the on-state currentTransistorSolid-state devicesTransistor arrayEngineering

The invention discloses a film transistor array substrate which comprises a plurality of film transistors arranged on one glass substrate in an array manner. Each film transistor comprises a grid electrode formed on the glass substrate, a grid electrode insulating layer covering the grid electrode, an active layer arranged on the grid electrode insulating layer, and a source electrode and a drain electrode which are formed on the active layer, wherein the source electrode and the drain electrode are spaced in a first direction, and the region, corresponding to the interval between the source electrode and the drain electrode, of the active layer is a channel region; the surface, facing the active layer and at least corresponding to the channel region, of the grid electrode insulating layer is provided with a plurality of protruding structures, and a wrinkled surface with a plurality of grooves is formed; and the surface, facing the grid electrode insulating layer, of the active layer is totally engaged with the surface of the grid electrode insulating layer. The invention further discloses a preparation method of the film transistor array substrate and a liquid crystal panel comprising the film transistor array substrate.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

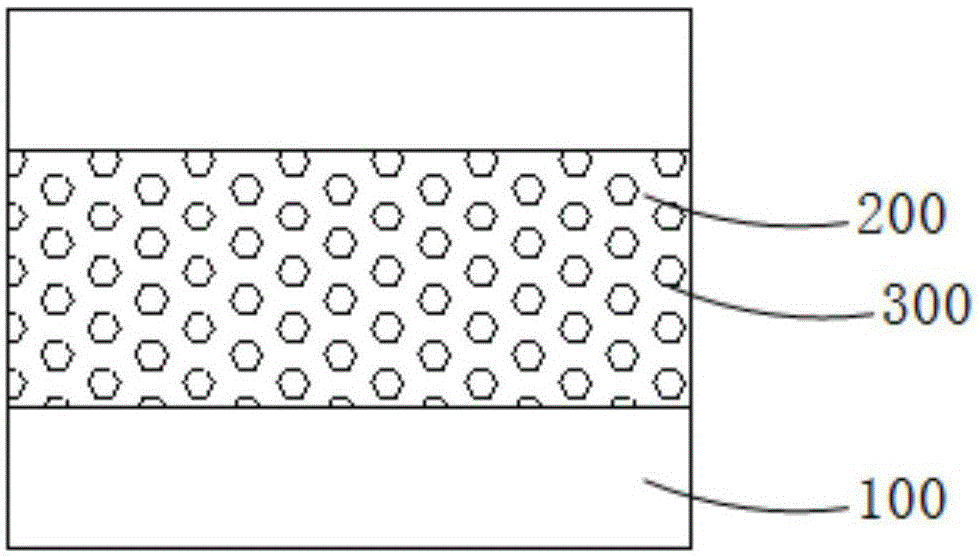

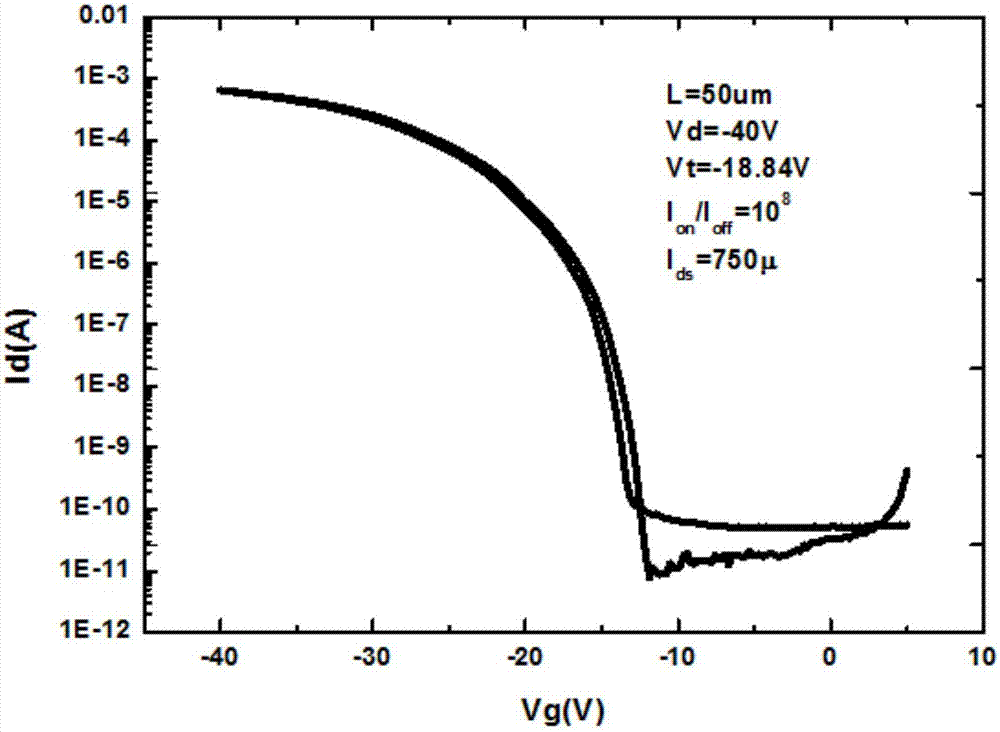

High-mobility transistor based on PMMA doped micro-molecule and preparation method thereof

ActiveCN107195781AImprove mobilityHigh on/off ratioSolid-state devicesSemiconductor/solid-state device manufacturingPower flowSpins

The invention relates to a preparation method of a high-mobility transistor based on PMMA doped micro-molecule. The preparation method comprises the following steps: S1, preparing a C8-BTBT and PMMA mixed solution; S2, cleaning a substrate: selecting a P-type heavily-doped silicon slice containing silicon dioxide, cleaning the P-type heavily-doped silicon slice after tailoring the same; S3, preparing a C8-BTBT active layer and a PMMA modification layer: overspreading the C8-BTBT and PMMA mixed solution configured through the step S1 on the substrate by using a dropper, spin-coating for 40s under the rotation speed of 2000-3000rpm; S4, thermally treating the spin-coated film; S5, preparing a molybdenum oxide buffer layer; and S6, preparing the source electrode and the drain electrode. The preparation method disclosed by the invention is simple, the prepared active layer is less in surface defect, the performance of the manufactured transistor device is improved.

Owner:SOUTH CHINA NORMAL UNIVERSITY

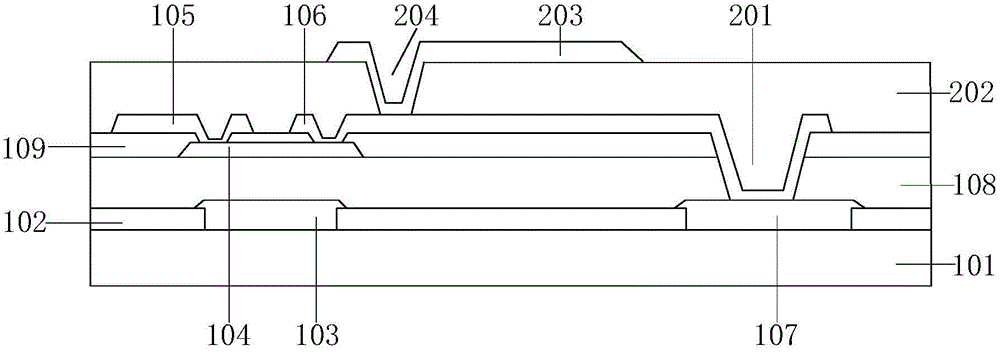

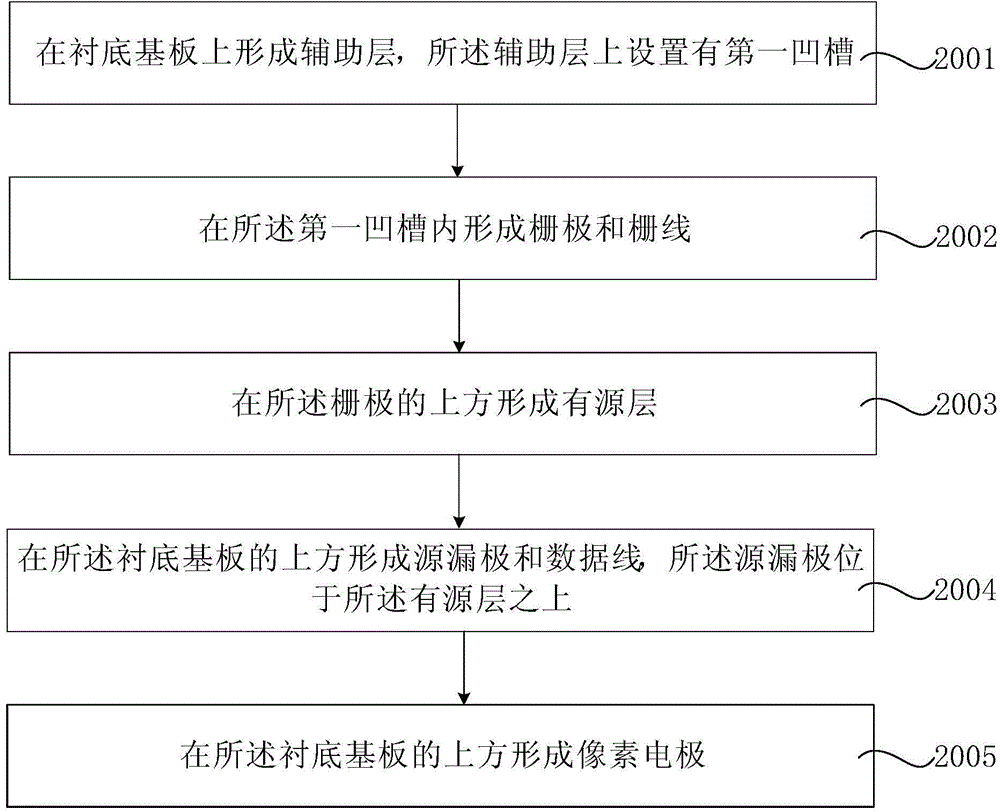

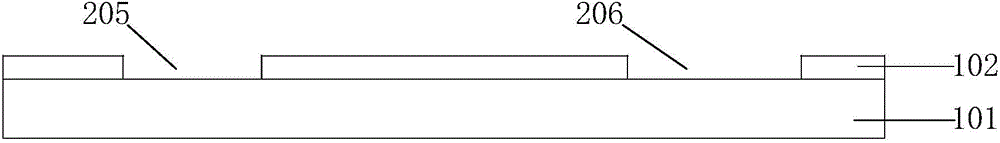

Display base plate and preparation method thereof, and display device

ActiveCN104393019AIncrease the on-state currentReduced characteristicsSolid-state devicesSemiconductor devicesDisplay deviceEngineering

The invention discloses a display base plate, a preparation method of the display base plate, and a display device. The display base plate comprises a substrate base plate, a grid line and a data wire, wherein the grid line and the data wire are positioned on the substrate base plate and used for limiting a pixel unit, wherein the pixel unit comprises a thin film transistor and a pixel electrode; the thin film transistor comprises a grid electrode, an active layer and a source / drain electrode; an assisting layer is also arranged on the substrate base plate; a first groove is arranged in the assisting layer; the grid electrode and the grid line are both positioned into the first groove. With the adoption of the display base plate, that the coverage characteristic of a grid insulating layer at the sidewall is lowered down as the thickness of the grid electrode layer increases and even the risk of wrinkling or breaking occurs can be reduced; moreover, a thin grid insulating layer can be adopted although a thick grid electrode layer is put into use because of the protection of the assisting layer, and therefore, the ON-state current of the thin film transistor can be improved.

Owner:BOE TECH GRP CO LTD

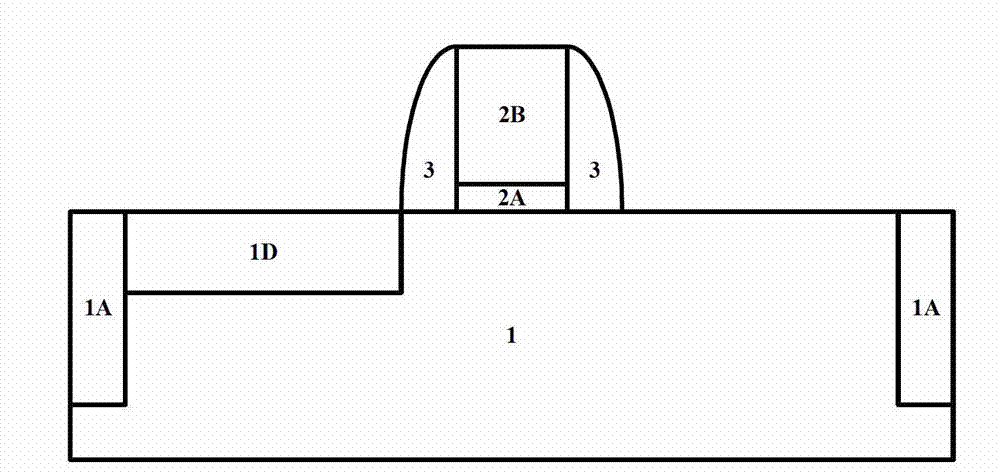

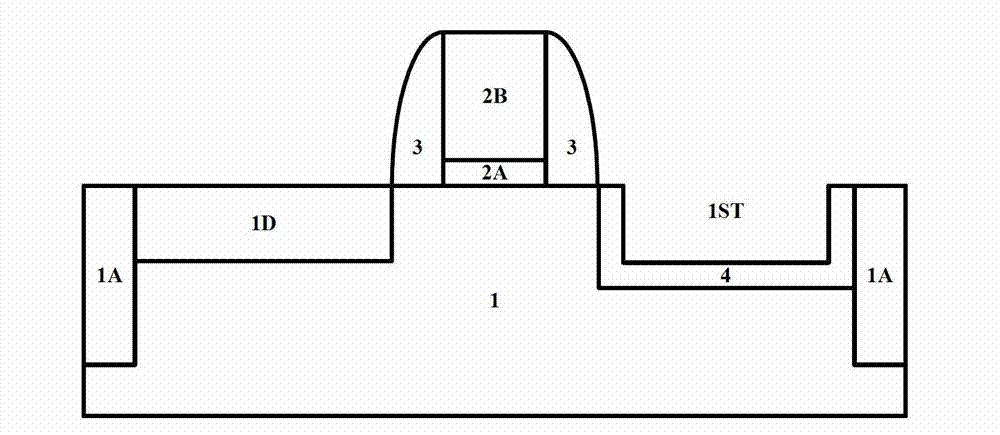

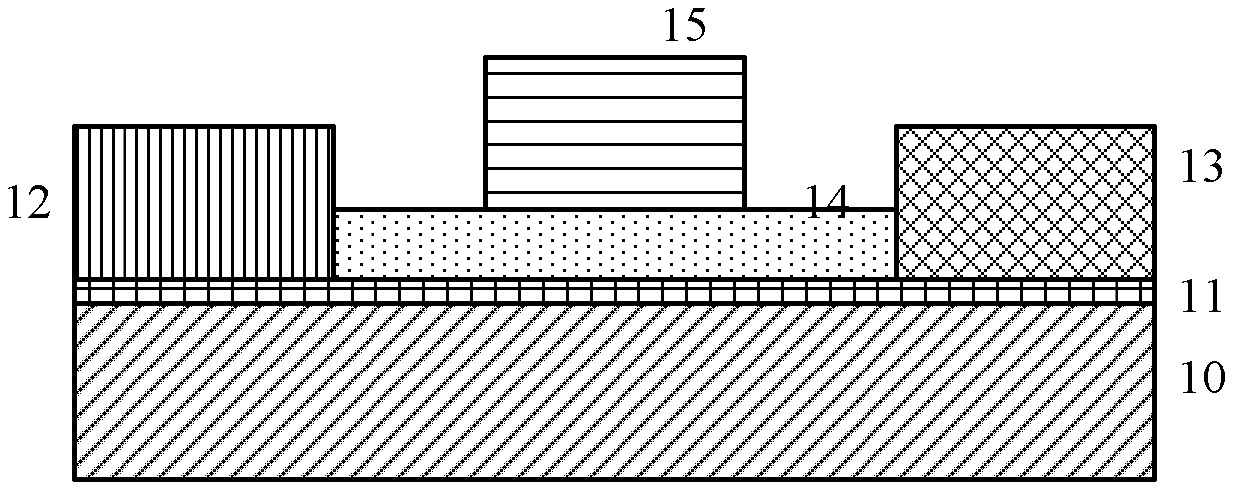

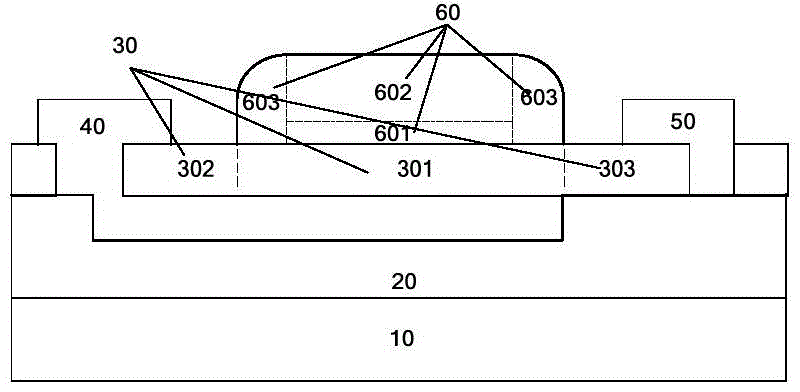

Tunneling transistor structure and manufacturing method thereof

ActiveCN104201198AIncrease the on-state currentLarge tunneling areaSemiconductor/solid-state device manufacturingDiodeGate dielectricDielectric layer

The invention provides a tunneling transistor structure. The tunneling transistor structure comprises a substrate, a silicon strip, a drain electrode area, a source electrode area, a gate dielectric layer and a grid electrode, wherein the silicone strip is formed on the substrate; the drain electrode area is formed at one side of the silicon strip; the source electrode area is equipped with a first groove in which the silicon strip is contained; the grate dielectric layer is formed on the source electrode area and partially covers the source electrode area; the grid electrode is equipped with a second groove in which the gate dielectric layer is contained; the cross section of the second groove is the same as that of the first groove; when in tunneling, the first groove tunnels under the effect of the second groove to form a tunneling current. The invention also provides a manufacturing method of the tunneling transistor structure. According to the tunneling transistor structure, the structures of the source electrode area and the grid electrode are changed; when in tunneling, the tunneling area of the source electrode area is expanded under the effect of the grid electrode, and point tunneling and line tunneling occur in the first groove; therefore, both the tunneling area and the tunneling portability are raised through the structure, and as a result, the on-state current of the whole device can be improved.

Owner:HUAWEI TECH CO LTD

Method for reducing parasitic resistance of graphene top gate FET device

InactiveCN103346088ALower resistanceIncrease the on-state currentSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowAccess resistance

The invention discloses a method for reducing parasitic resistance of a graphene top gate FET device. According to the method, top gate metal is used as a mask for protecting a gate medium below the top gate metal, corrosion is carried out on the graphene top gate FET device to remove the gate medium covering graphene channel regions among a gate source and gate drains, then graphene material among the gate source and the gate drains are covered by a layer of metal in an vapor deposition mode, therefore metal-graphene contact is formed, and channel access resistance introduced by the distance among the gate source and the gate drains is eliminated. An autocollimation technology is adopted for carrying out the vapor deposition on the source drain metal, the access parasitic resistance generated by the distance among the gate source and the gate drains is avoided, so that the ON-state current of the graphene top gate FET device is effectively increased, and transconductance frequency and cut-off frequency of the device are impoved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

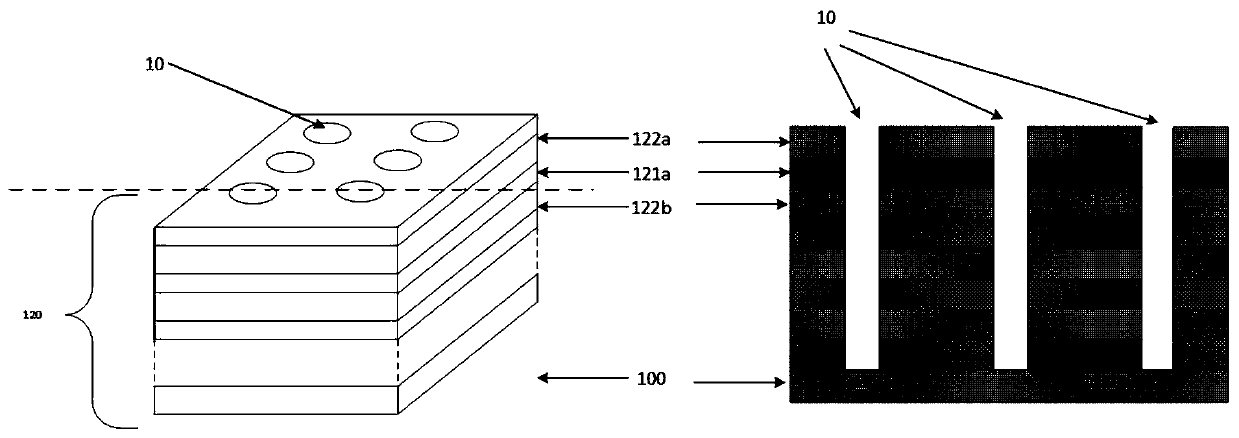

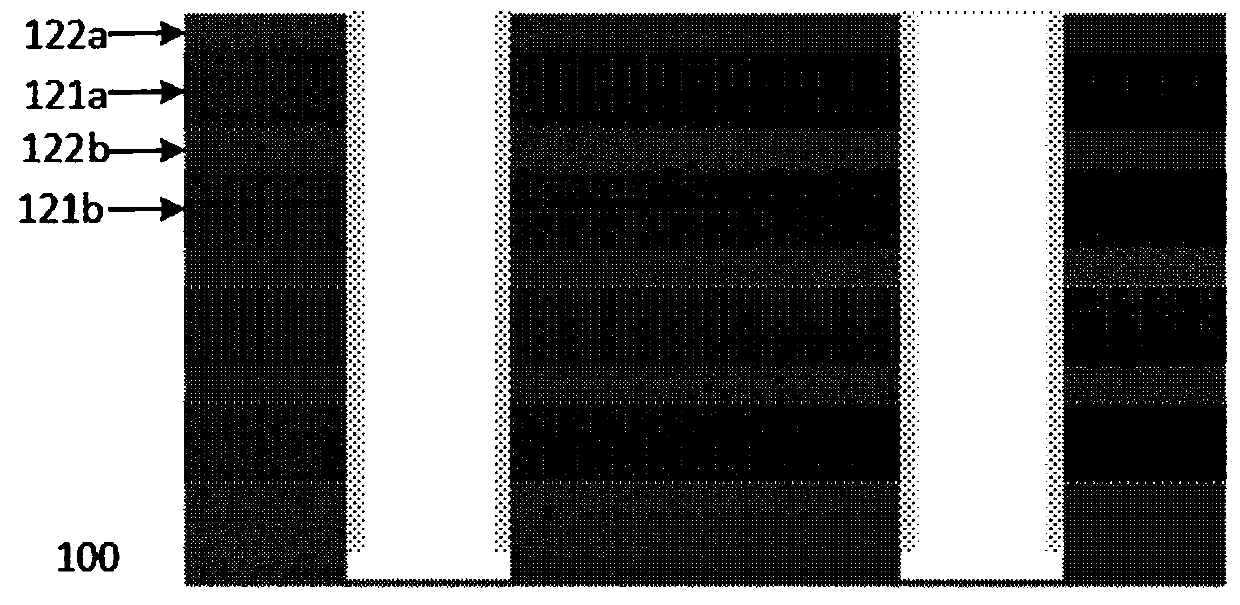

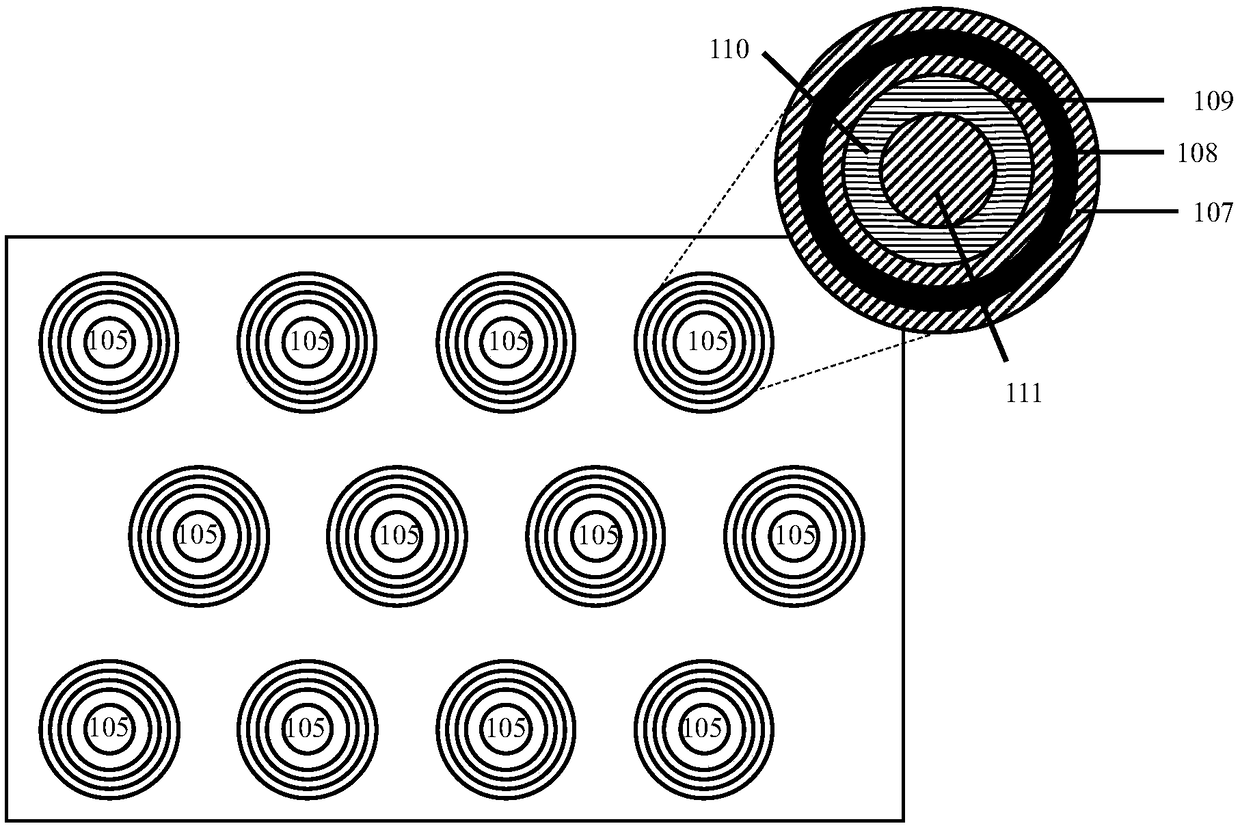

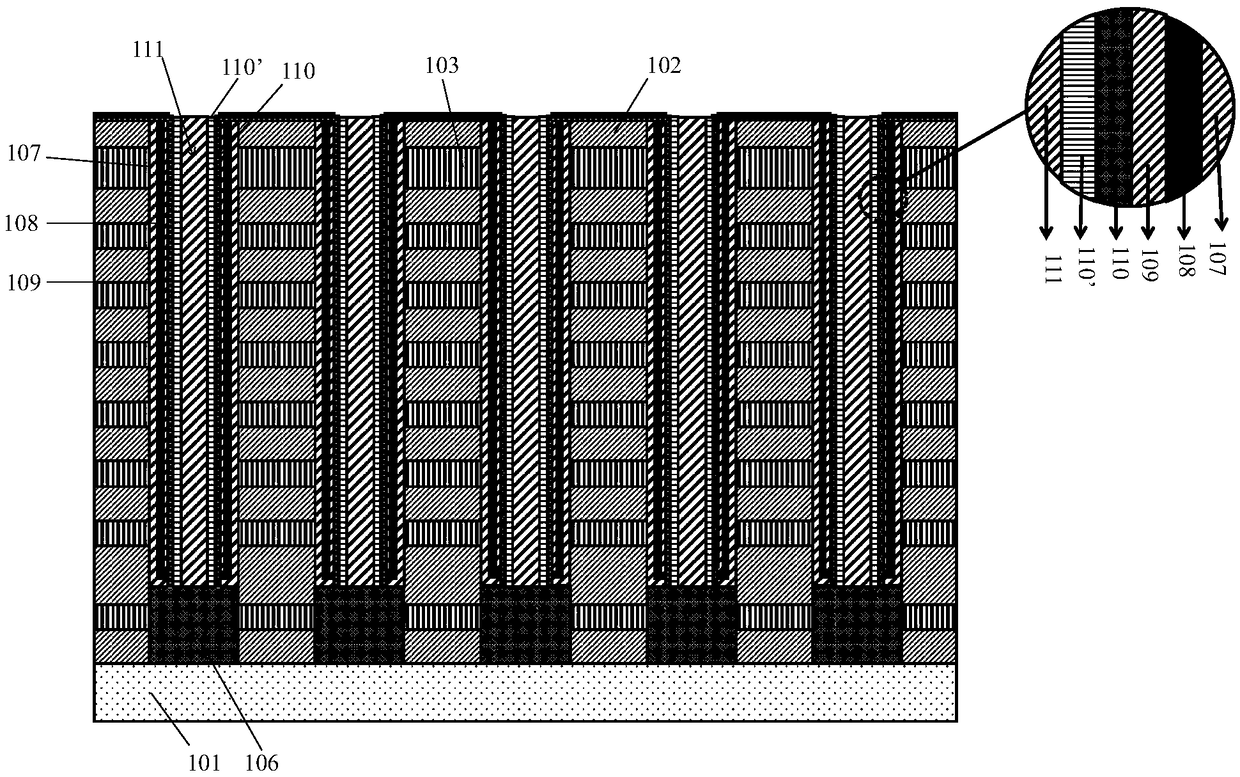

Three-dimensional flash memory based on vertical channels of two-dimensional semiconductor materials and preparation thereof

InactiveCN110148598AIncrease the on-state currentReduce operating voltage for reading and writingMaterial nanotechnologySolid-state devicesSemiconductor materialsCharge carrier mobility

The invention belongs to the field of semiconductor memory manufacturing and particularly relates to a three-dimensional semiconductor memory based on vertical channels of two-dimensional semiconductor materials and a preparation method thereof. The three-dimensional semiconductor memory comprises a plurality of three-dimensional storage strings in a vertical direction, and each three-dimensionalmemory string includes a semiconductor vertical channel whose length is determined by the number of layers of memory three-dimensional stack. The vertical channel materials comprise one or more two-dimensional semiconductor materials and protection layers on the surfaces of the two-dimensional semiconductor materials. The protection layers are used for supporting and protecting the two-dimensionalsemiconductor materials, and the carrier mobility of the two-dimensional semiconductor materials is higher than that of amorphous silicon. According to the invention, the two-dimensional materials are used as memory channels, higher memory cell on-state current can be provided, and therefore, the operational power consumption of the memory is reduced.

Owner:HUAZHONG UNIV OF SCI & TECH

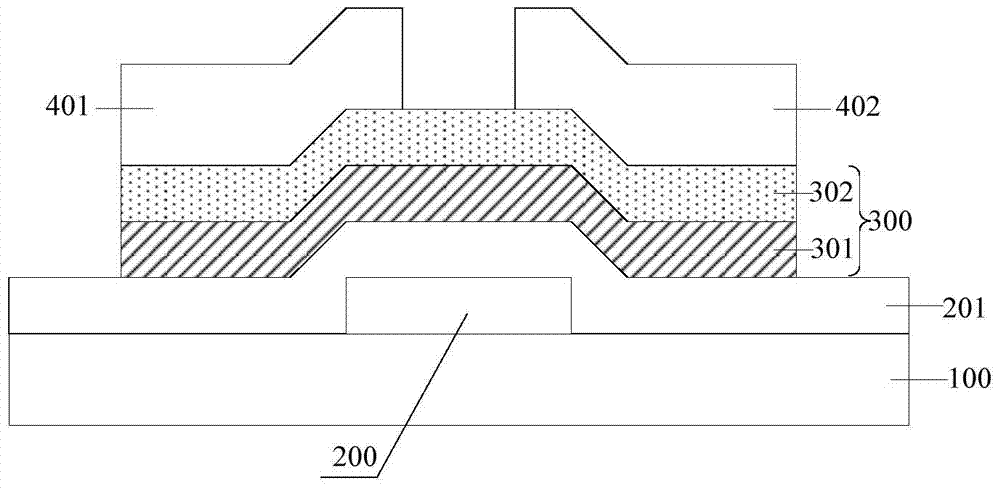

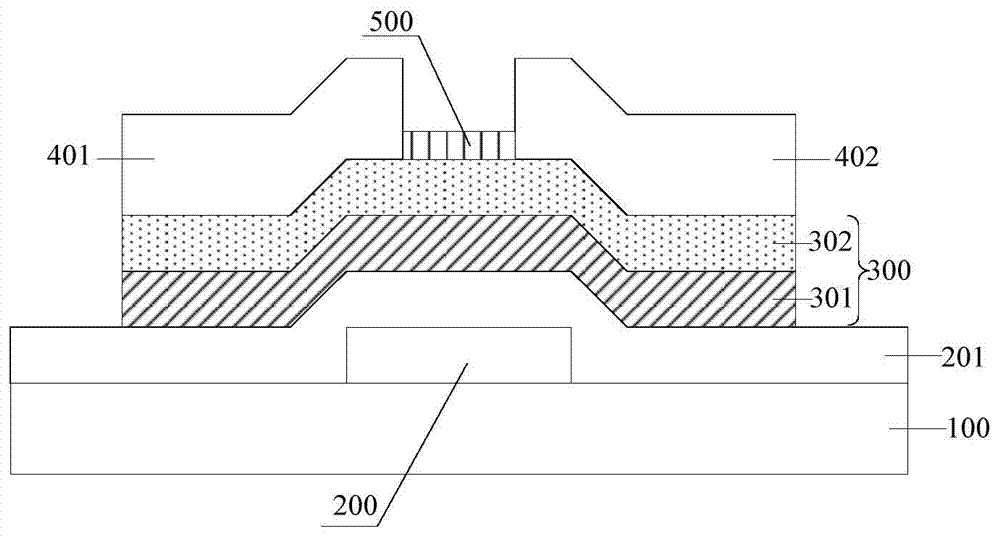

Thin film transistor and manufacturing method thereof, array substrate and manufacturing device thereof and display device

ActiveCN105870198AIncrease the on-state currentSimple manufacturing processTransistorSolid-state devicesDisplay deviceAmorphous silicon

Provided are a thin film transistor and a manufacturing method thereof, an array substrate and a manufacturing device thereof and a display device. The thin film transistor comprises an active layer, an amorphous silicon connecting layer and a source drain electrode layer. The active layer is provided with a groove area, a source electrode area and a drain electrode area. A forming material of the groove area comprises polycrystalline silicon. The amorphous silicon connecting layer is located at one side of the active layer and comprises a first connecting part and a second connecting part spaced from the first connecting part. The source drain electrode layer comprises a source electrode and a drain electrode spaced from the source electrode. The source electrode is electrically connected with the source electrode area through the first connecting part. The drain electrode is electrically connected with the drain electrode area through the second connecting part. According to the thin film transistor and the manufacturing method thereof, the array substrate and the manufacturing device thereof and the display device, the manufacturing process of the polycrystalline silicon thin film transistor can be simplified.

Owner:BOE TECH GRP CO LTD +1

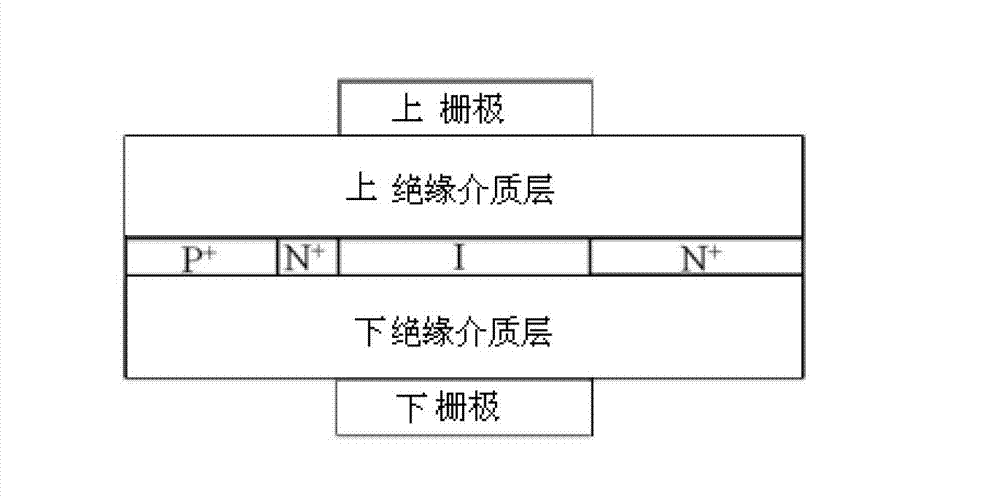

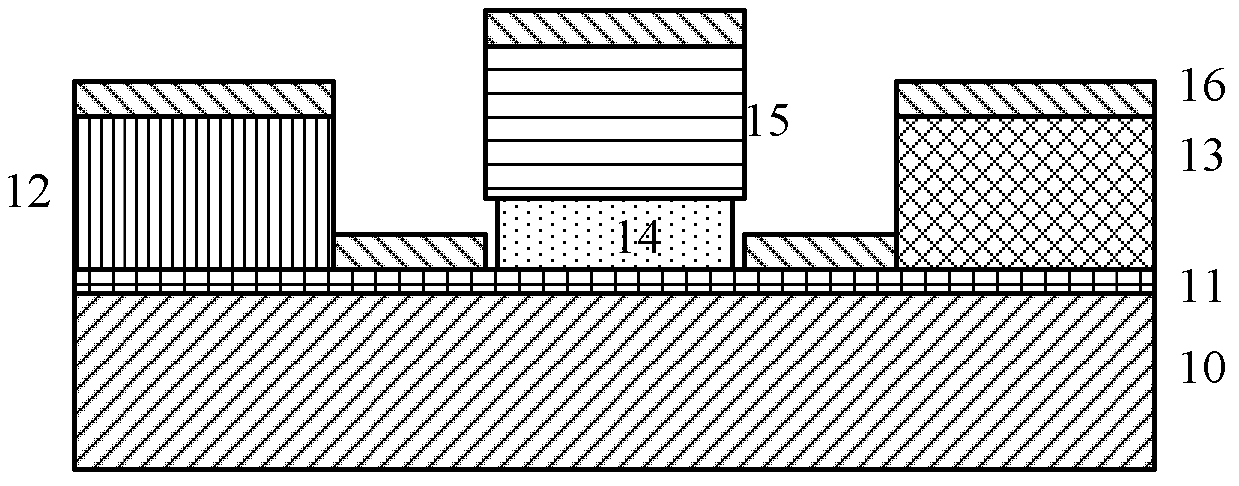

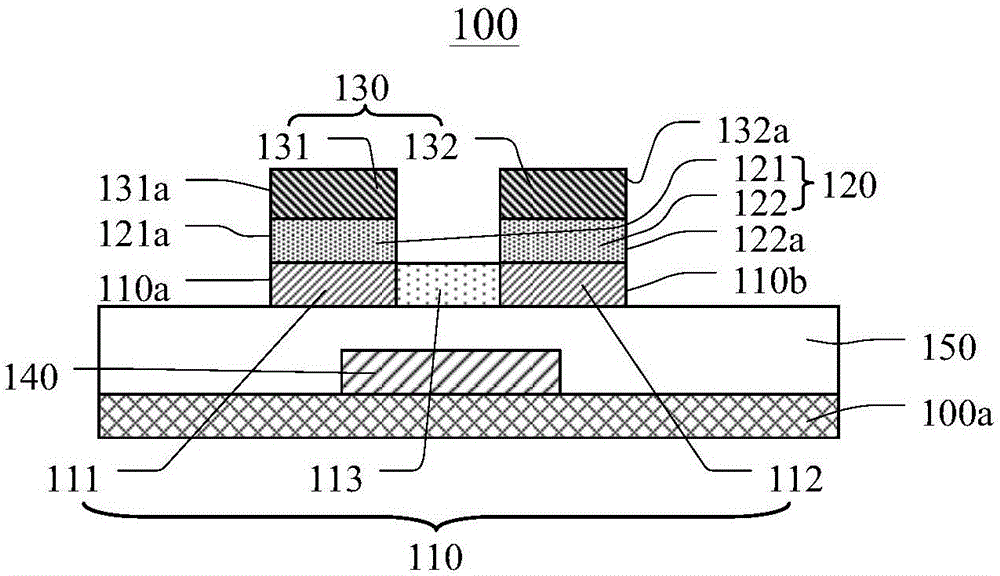

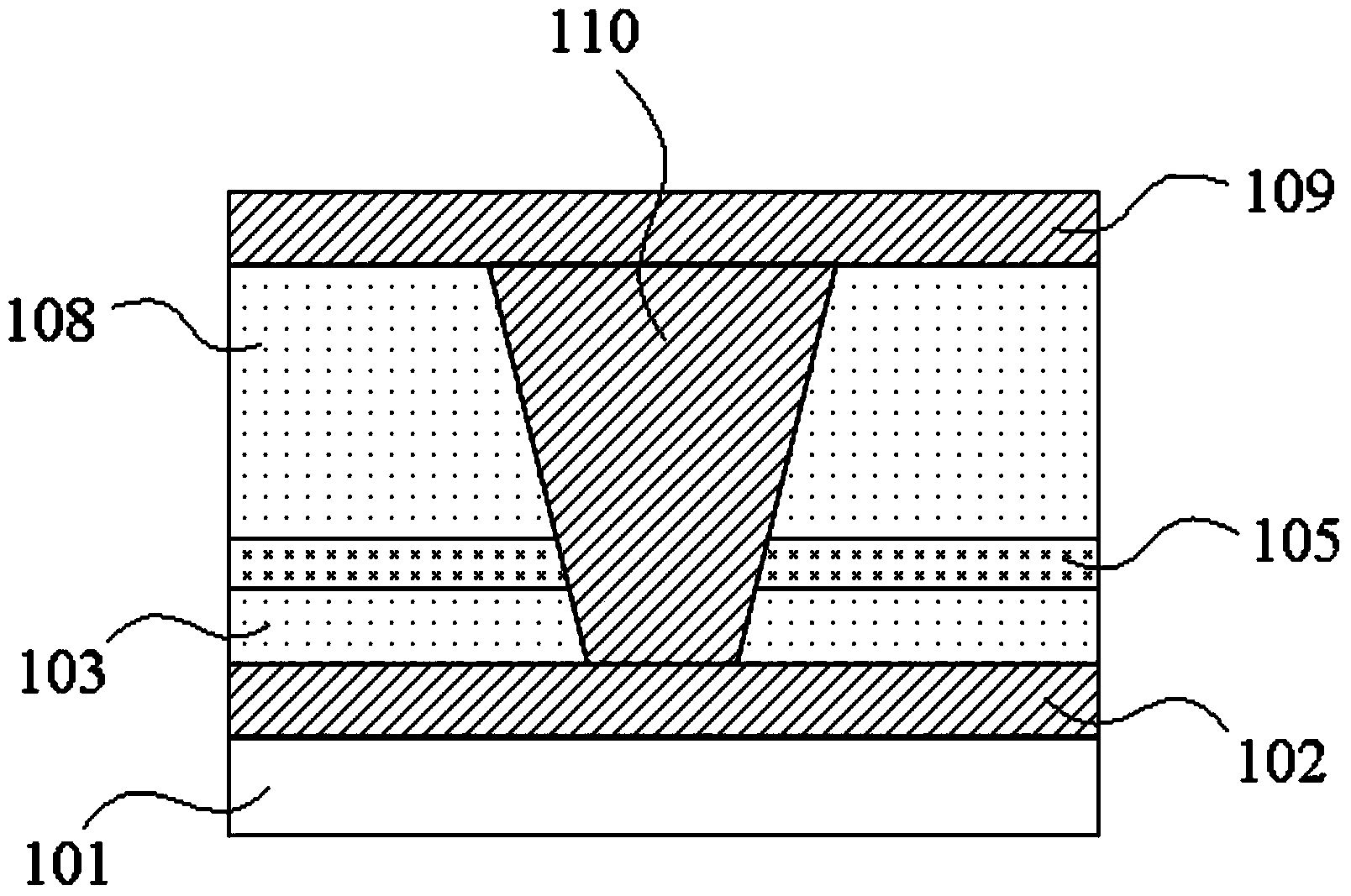

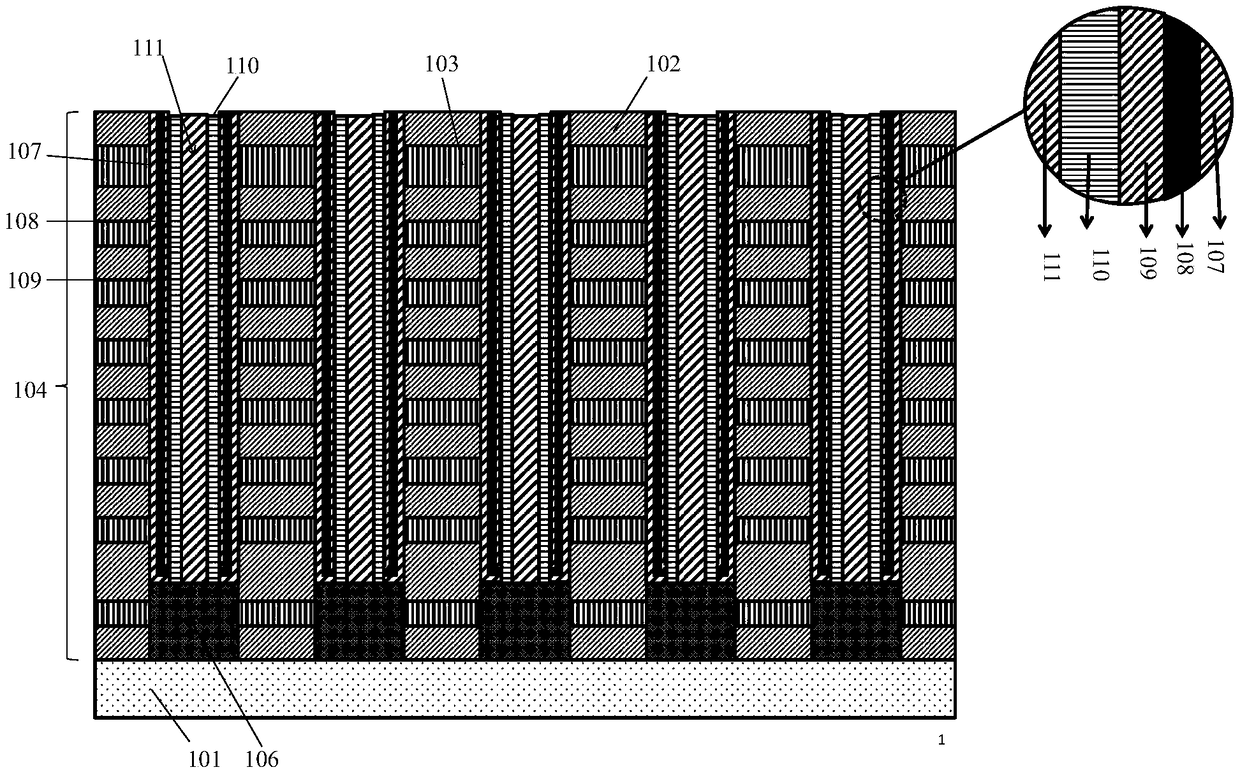

Array substrate, manufacturing method of array substrate and display device

ActiveCN104319279AReduces off-state leakage currentIncrease the on-state currentSolid-state devicesSemiconductor/solid-state device manufacturingLine resistanceDisplay device

The invention relates to the technical field of display, in particular to an array substrate, a manufacturing method of the array substrate and a display device. The array substrate comprises a first gate metal layer, a first gate insulating layer on the first gate metal layer, an active layer which is arranged on the first gate insulating layer and corresponds to the first gate metal layer, an etching barrier layer on the active layer, a source and drain metal layer comprising a source and a drain, a second gate insulating layer on the source and drain metal layer and a second gate metal layer on the second gate insulating layer, wherein the source and the drain are in contact with the two sides of the active layer respectively and are separated on the etching barrier layer. By means of the array substrate, the manufacturing method of the array substrate and the display device, the TFT characteristic can be optimized, the gate line resistance can be reduced, light irradiating the active layer can be shielded, IR Drop and TFT threshold voltage excursion and generation of the light leakage current of the active layer can be easily restrained, and the performance of the display device can be promoted.

Owner:BOE TECH GRP CO LTD

A 3D NAND memory and a method for manufacturing that same

InactiveCN108987408AGood electrical propertiesHigh electron mobilitySolid-state devicesSemiconductor devicesElectrical performanceElectron mobility

A 3D NAND memory and a method for manufacturing the same are disclosed. The channel layer in the 3D NAND memory includes a two-dimensional material layer. Because two-dimensional materials have higherelectron mobility, 3D NAND memories made of two-dimensional materials as channel layer materials can achieve better electrical performance.

Owner:YANGTZE MEMORY TECH CO LTD

Knot-free nanowire field effect transistor

InactiveCN102544073AImprove transconductance characteristicsHigh speedSemiconductor devicesNanowireLow voltage

The invention discloses a knot-free nanowire field effect transistor which comprises a channel, a source region and a drain region. The source region is arranged at one end of the channel, and the drain region is arranged at the other end of the channel; the outer surface of the channel is covered by a gate oxide layer which is covered by a grid electrode layer; and the grid electrode layer comprises a first grid electrode layer which is close to the source region and a second grid electrode layer which is close to the drain region. Compared with the prior art, the embodiment of the invention has the advantages that: by adopting a split gate structure, the speed of the charge carrier in the channel of the knot-free nanowire field effect transistor is increased, so the on-state current is increased, the off-state current of a device is reduced irrespective of the influence of the threshold voltage, the influence of the drain region on the device is screened, the drain induced barrier lowering effect is obviously weakened and the driving ability of the current is improved. Meanwhile, with the split gate, the transconductance feature of the knot-free nanowire field effect transistor under low voltage is obviously improved.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL +1

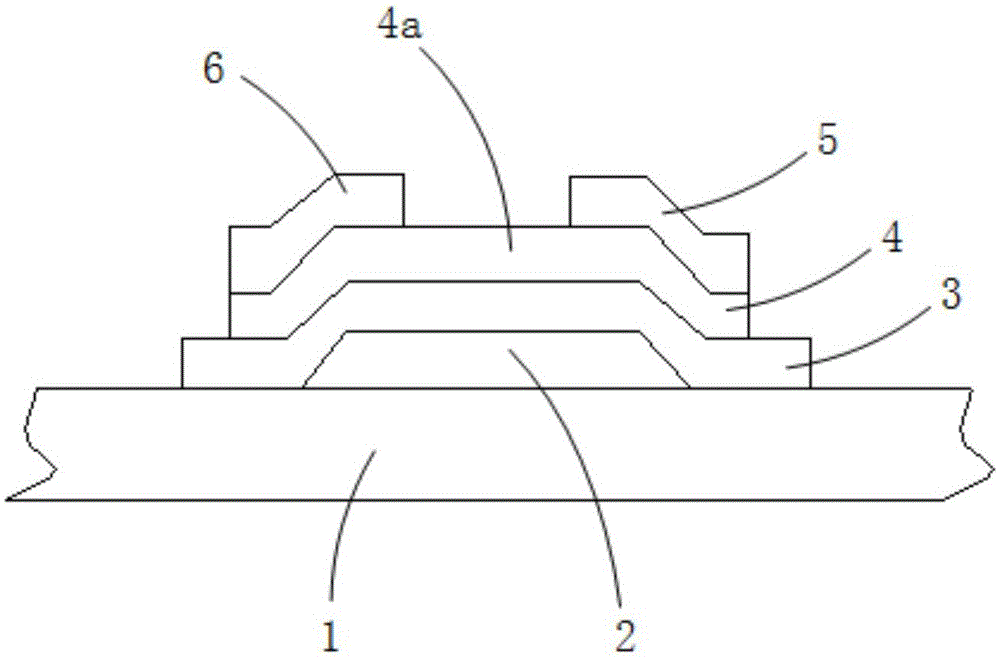

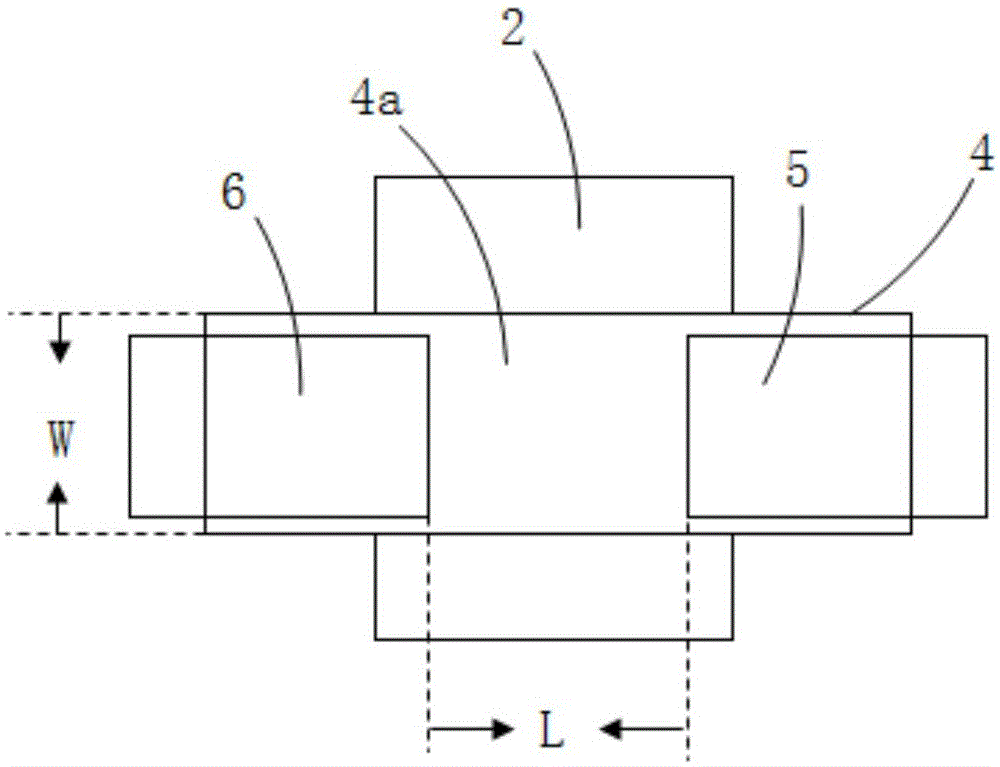

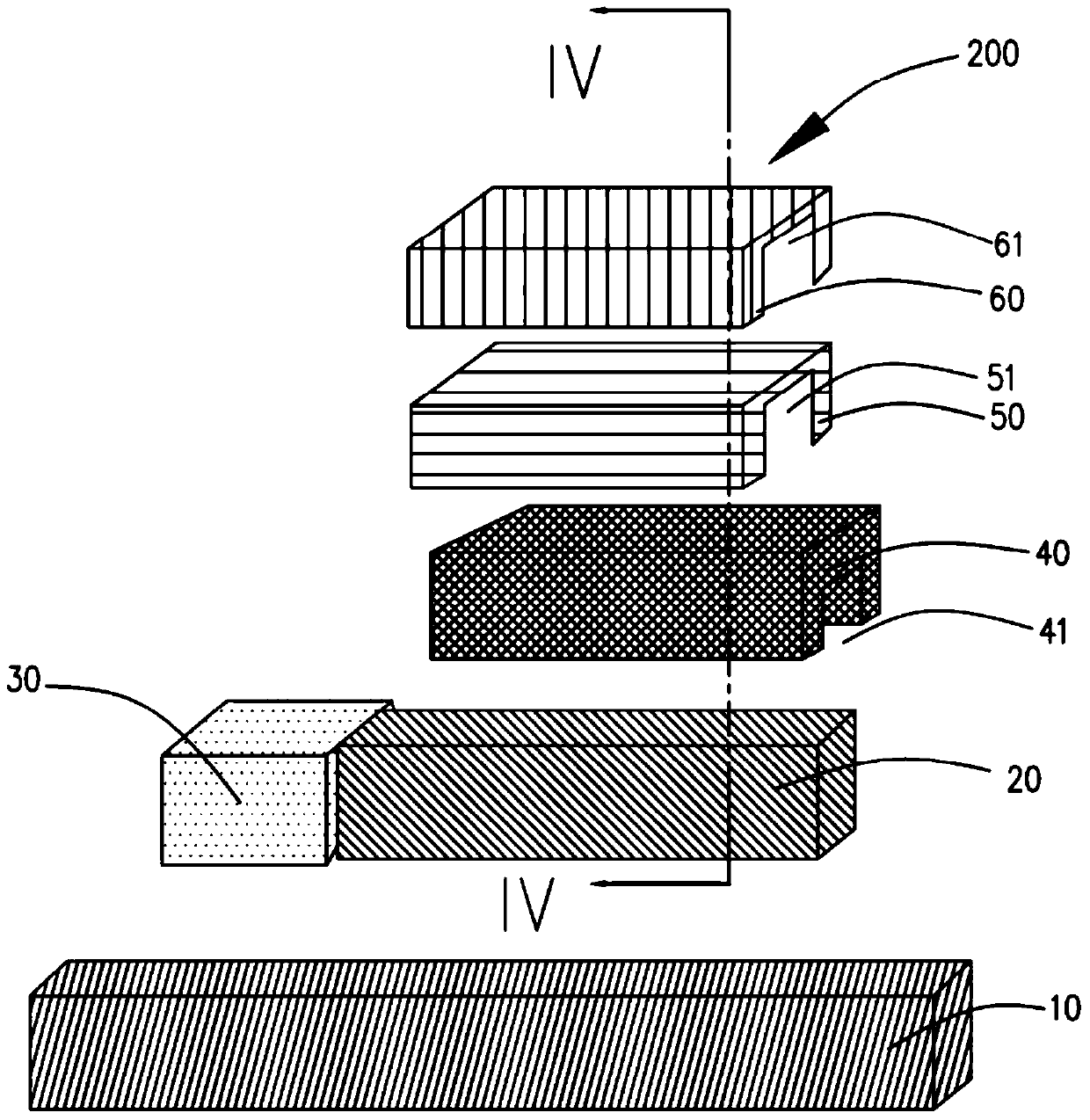

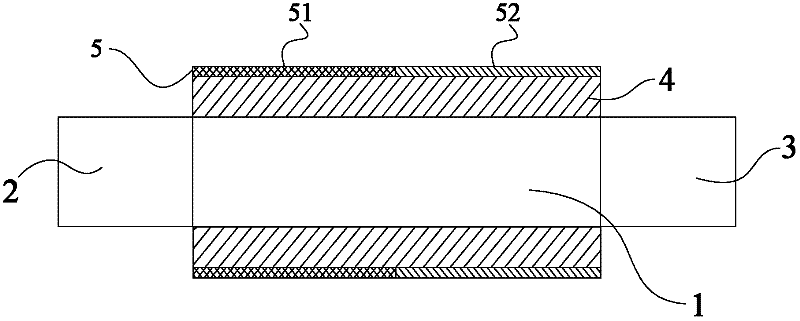

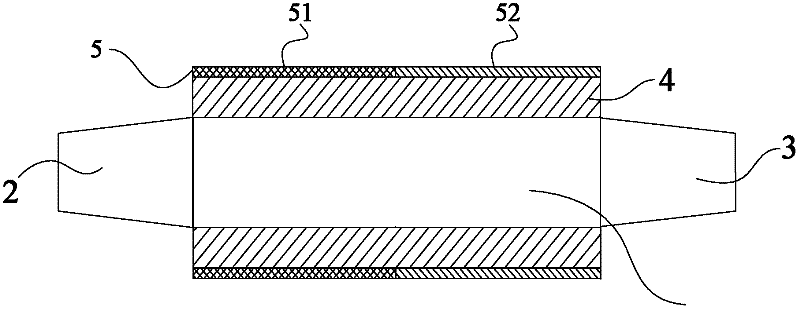

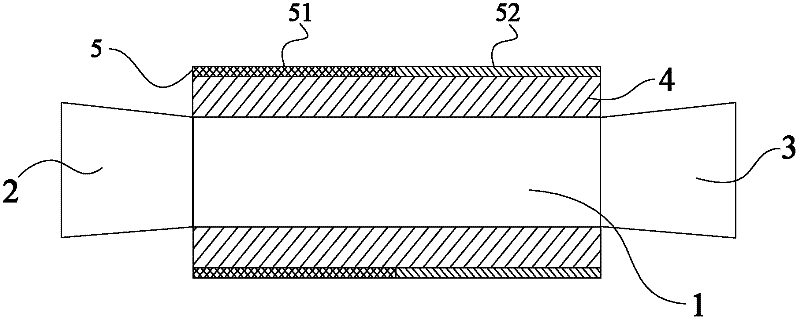

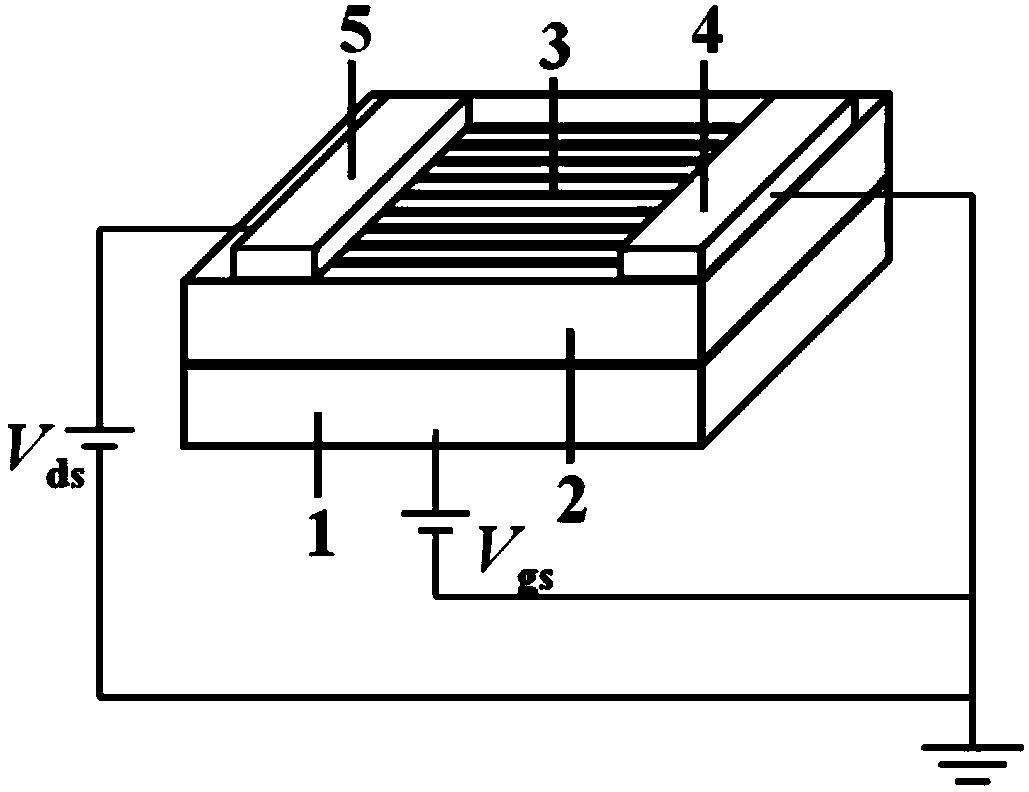

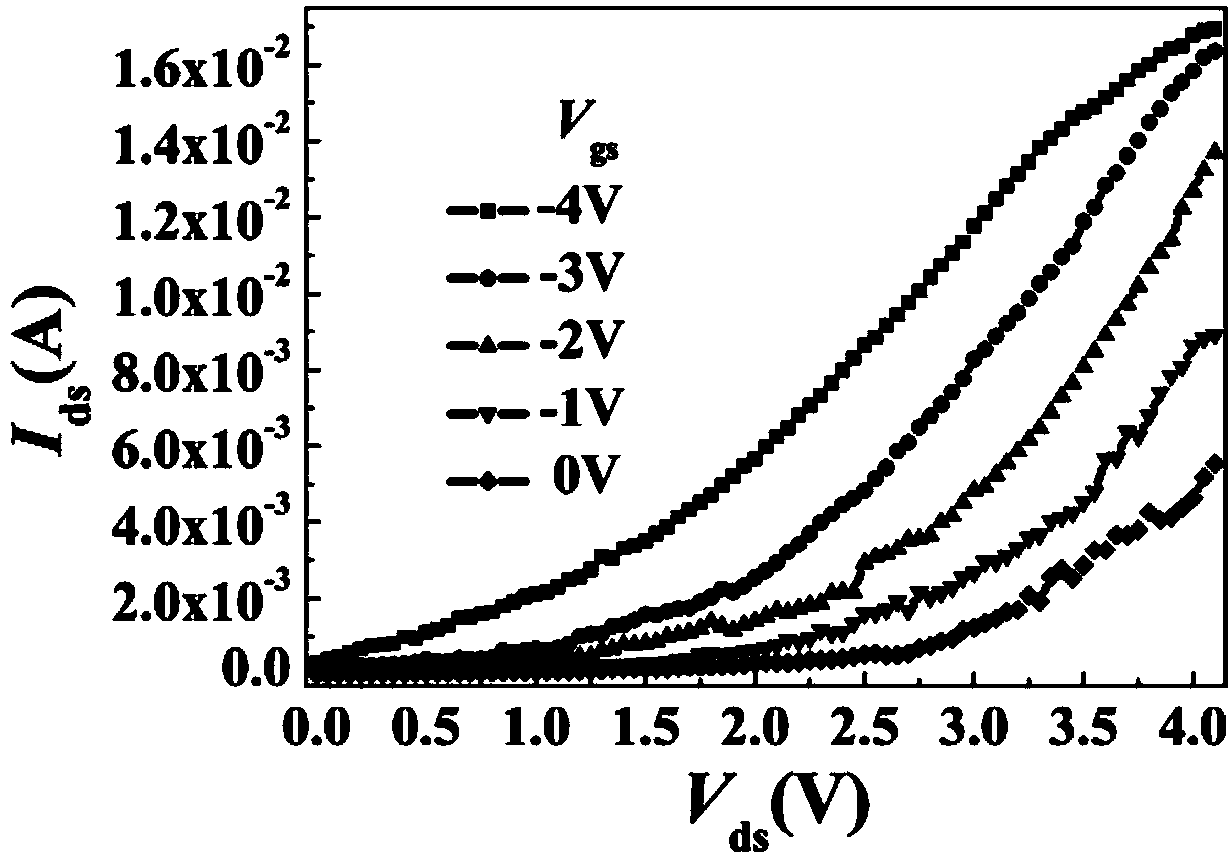

Ferro-electric field effect transistor based on structured carbon nano tube striped array and manufacturing method thereof

InactiveCN104009091AIncrease the on-state currentHigh switching ratioNanoinformaticsSemiconductor/solid-state device manufacturingOrganic field-effect transistorCharge carrier mobility

The invention discloses a ferro-electric field effect transistor based on a structured carbon nano tube striped array and a manufacturing method of the ferro-electric field effect transistor. According to the unit structure of the transistor, a bottom electrode layer (1) is arranged on the bottom layer, a ferro-electric film insulated gate layer (2) and a structured carbon nano tube striped array channel layer (3) are sequentially arranged on the middle layer, and a top layer is arranged on the structured carbon nano tube striped array channel layer (3) and comprises a transistor source electrode (4) and a transistor drain electrode (5); carbon nano tubes are single-walled carbon nano tubes, or double-walled carbon nano tubes or multi-walled carbon nano tubes. According to the ferro-electric field effect transistor, the on-state current and the switch ratio are large, carrier mobility is high, the starting voltage is small, the storage window is wide, and meanwhile the ferro-electric field effect transistor has the advantages of being simple in structure and a buffering layer is not needed, interface contact between a ferro-electric layer and a semiconductor layer is good, and large-area soft devices are easy to obtain. The manufacturing method is simple in technology, convenient to operate and low in cost and dispense with expensive equipment, and large-area and large-scale industrial production is easy to realize.

Owner:XIANGTAN UNIV

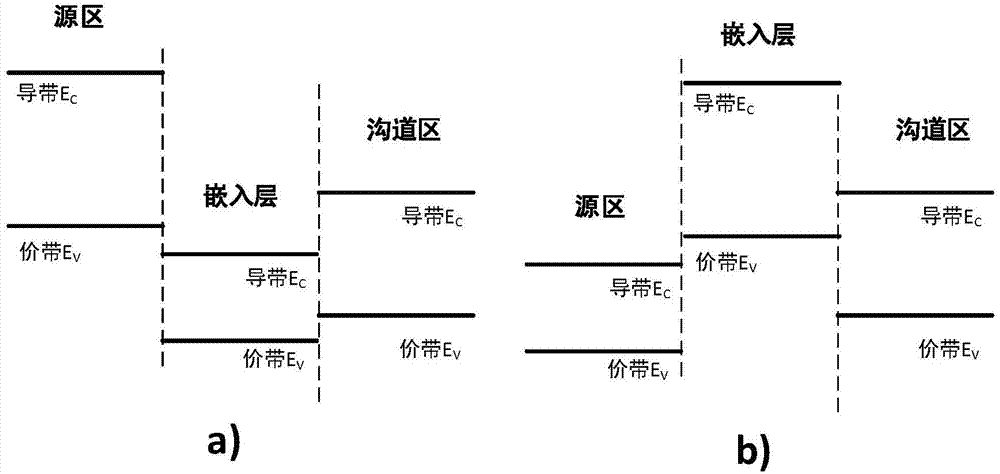

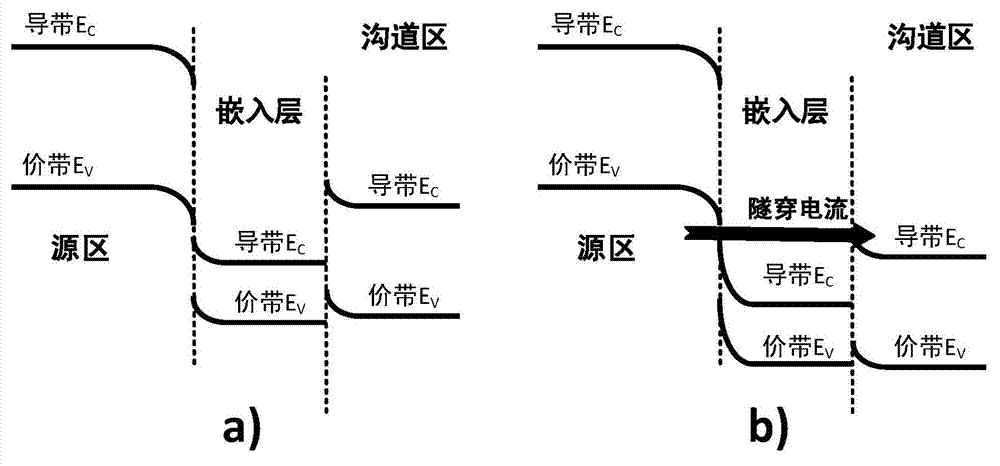

Embedding layer heterojunction tunneling field effect transistor and manufacturing method thereof

ActiveCN104269439AIncrease the on-state currentReduce off-state currentSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSIntegrated circuit

The invention discloses an embedding layer heterojunction tunneling field effect transistor and a manufacturing method of the embedding layer heterojunction tunneling field effect transistor, and belongs to the field of field effect transistor logic devices in the CMOS ultra large scale integration (ULSI). The two sides of a vertical channel region of the embedding layer heterojunction tunneling field effect transistor are provided with control gates respectively. The control gates are of an L-shaped structure. Gate medium layers are arranged between the two control gates and the vertical channel region. A tunneling source region is arranged above the vertical channel region. An embedding layer is arranged between the tunneling source region and the channel region. The thickness of the embedding layer is smaller than the width of a space charge region at a tunneling junction. A split-level heterojunction is formed on the interface position of the tunneling source region and the embedding layer. A staggered heterojunction is formed on the interface position of the embedding layer and the channel region. Compared with an existing TFET, by means of the embedding layer heterojunction tunneling field effect transistor, the device on-state current is increased remarkably, and the lower off-state current is kept.

Owner:PEKING UNIV

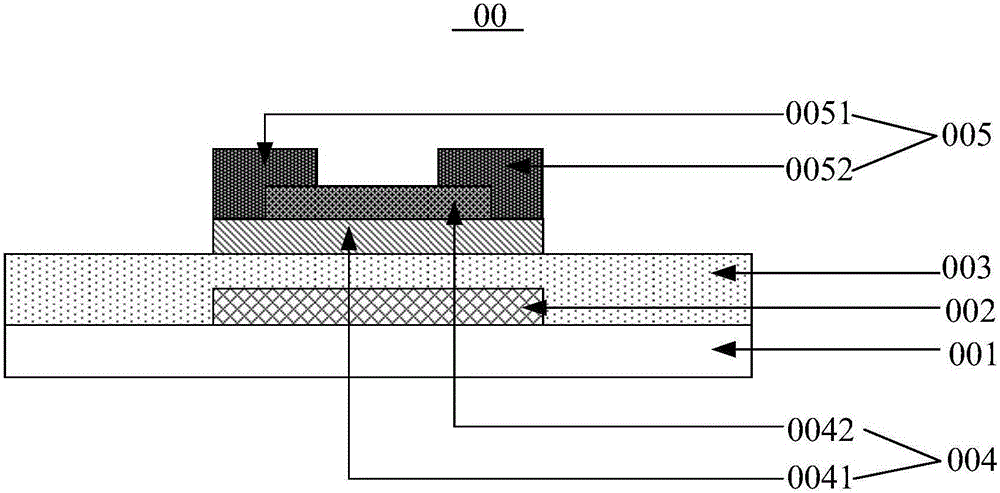

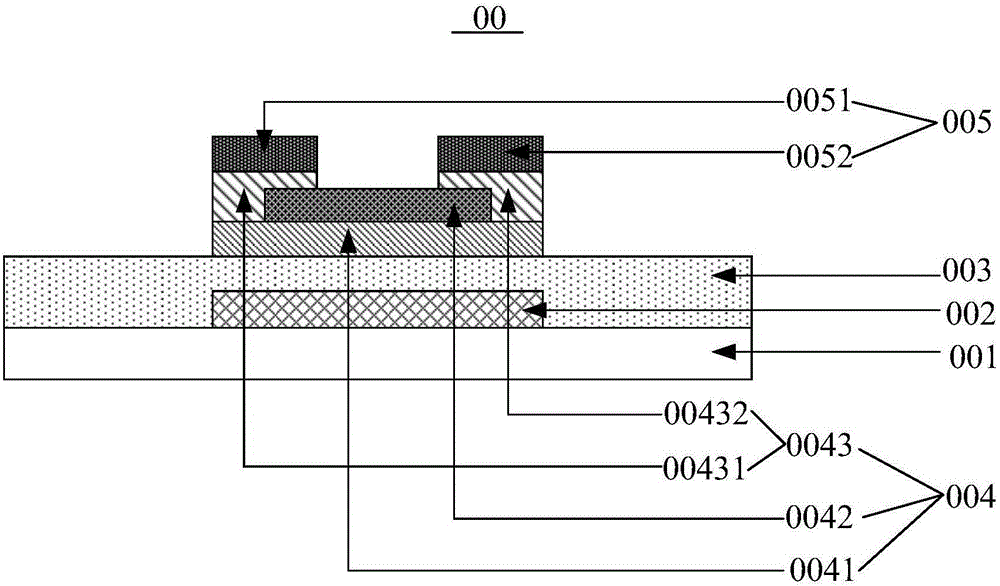

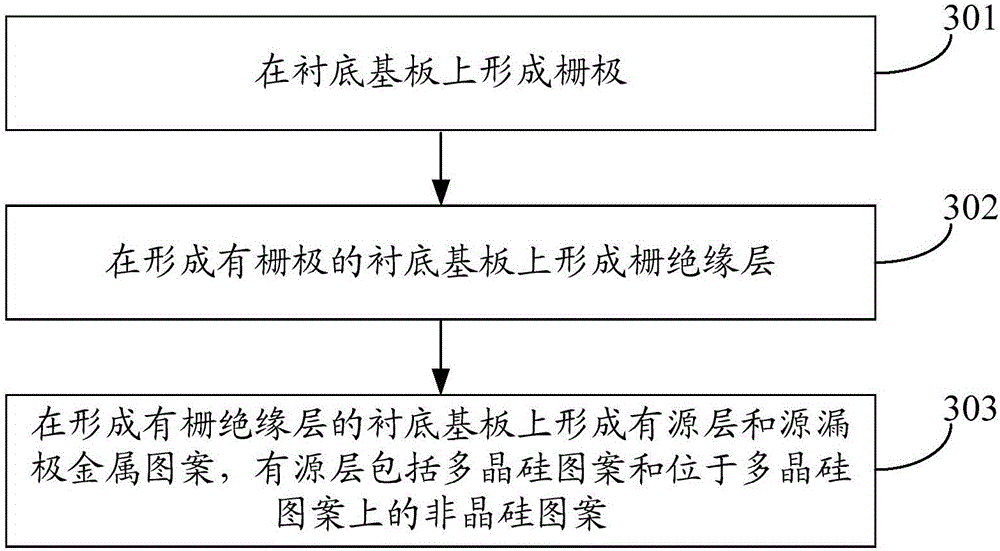

Thin film transistor, manufacture method thereof, array substrate and display device

ActiveCN105845737AIncrease the on-state currentIncrease charging rateTransistorSolid-state devicesOptoelectronicsPolycrystalline silicon

The invention discloses a thin film transistor, a manufacture method thereof, an array substrate and a display device, which belongs to the technical field of display. The thin film transistor comprises a substrate. A gate is formed on the substrate. A gate insulating layer is formed on the substrate with the gate. An active layer and a source drain metal pattern are formed on the substrate with the gate insulating layer. The active layer comprises a polysilicon pattern and an amorphous silicon pattern on the polysilicon pattern. The source drain metal pattern comprises a source and a drain. The source contacts the polysilicon pattern and the amorphous silicon pattern. The drain contacts the polysilicon pattern and the amorphous silicon pattern. According to the invention, the problems of small open current and low charging rate of the thin film transistor are solved; the open current of the thin film transistor is increased; and the charging rate is improved. The thin film transistor, the manufacture method thereof, the array substrate and the display device are applied to the array substrate.

Owner:BOE TECH GRP CO LTD +1

Junctionless tunneling field effect transistor and formation method thereof

ActiveCN103606563AIncreased tunneling currentIncrease the on-state currentTransistorSemiconductor/solid-state device manufacturingGate stackCondensed matter physics

The invention provides a junctionless tunneling field effect transistor and a formation method thereof. The junctionless tunneling field effect transistor includes the following components of: a substrate; a liner layer arranged on the substrate; a channel layer which is arranged on the liner layer and includes a channel region arranged in the middle as well as a source region and a drain region arranged at two sides of the channel region, wherein the channel region, the source region and the drain region have the same doping type; a source which coats on the upper surface, a side surface and the lower surface of the source region and coats the lower surface of the channel region, and is in Schottky contact with the channel region; a drain which coats the upper surface and a side surface of the drain region; and a gate stack structure which is located on the channel region. The junctionless tunneling field effect transistor has the advantages of simple structure, large tunneling current, capability of effectively suppressing a short channel effect and the like. The invention also provides a formation method of the junctionless tunneling field effect transistor.

Owner:TSINGHUA UNIV

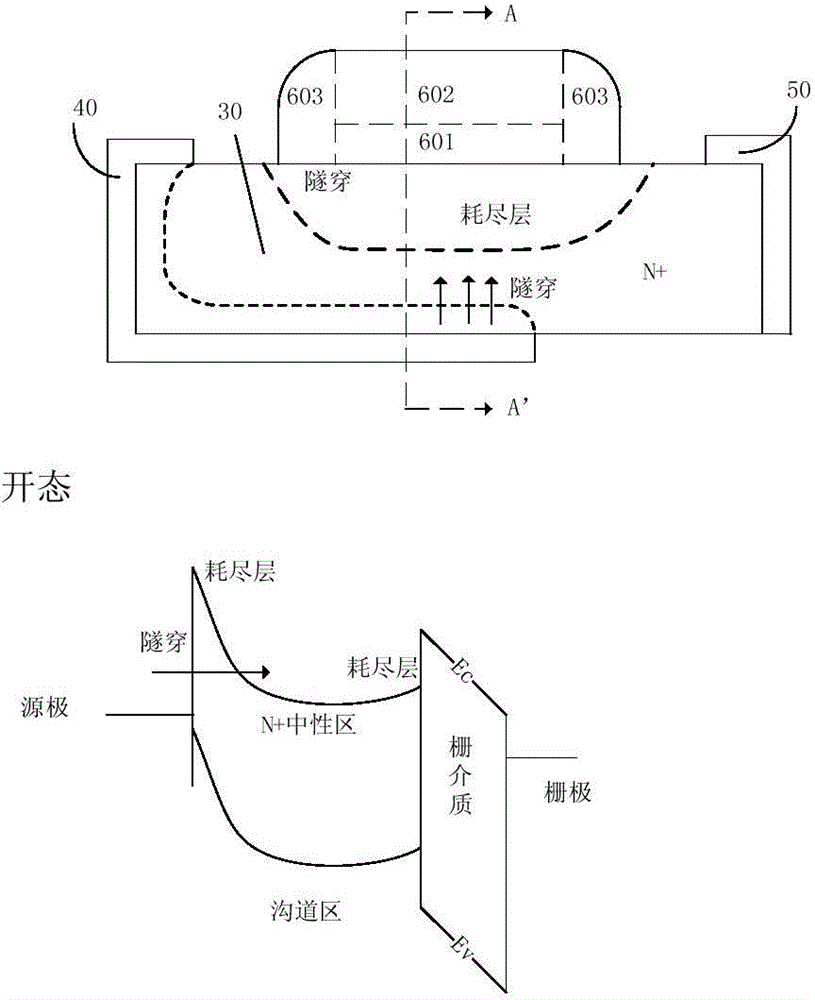

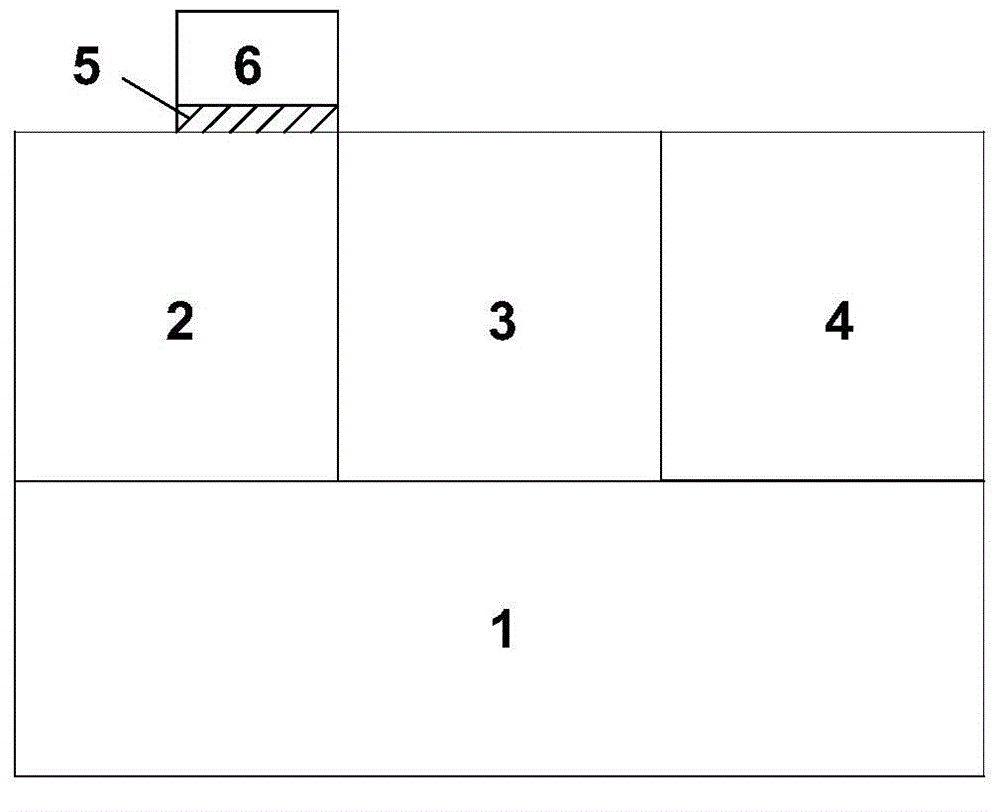

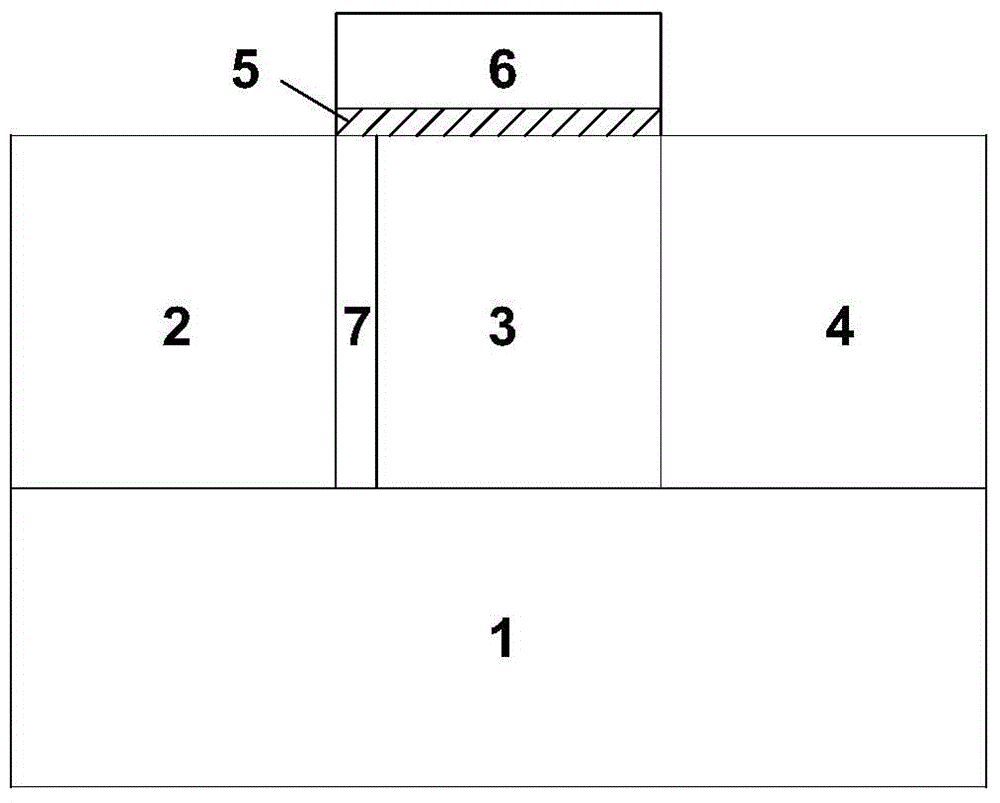

Tunneling field effect transistor with electric field concentration effect to enhance on state current

ActiveCN104576721ASteep bendIncrease the on-state currentSemiconductor devicesINCREASED EFFECTTunnel junction

The invention provides a tunneling field effect transistor with an electric field concentration effect to enhance the on state current and belongs to the field of semiconductor apparatuses. The tunneling field effect transistor provided by the invention comprises a semiconductor substrate 1, a source region 2, an intrinsic region 3, a drain region 4, a grid oxide layer 5, a metal grid 6 and a side wall 9 and further comprises a medium block 10 which is arranged in the intrinsic region, wherein the medium block 10 is arranged on an interface of the intrinsic region and the source region, and the medium block can be used for changing electric field distribution in a tunnel junction position, so that the electric field line at the tunnel junction is concentrated so as to enhance the on state current.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

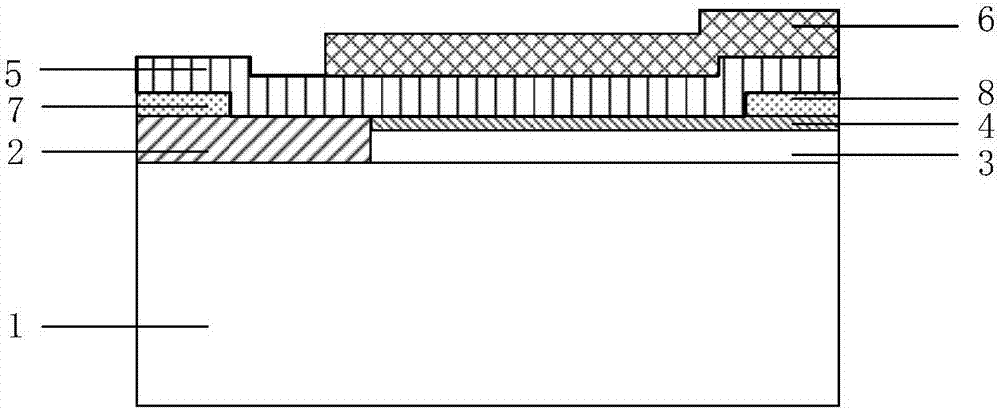

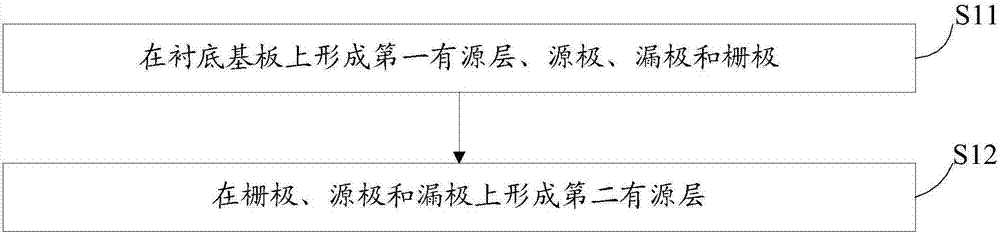

Thin film transistor and manufacturing method thereof and display device

ActiveCN106935657AIncrease the on-state currentSpeed up circulationTransistorSemiconductor/solid-state device manufacturingDisplay deviceEngineering

The invention discloses a thin film transistor and a manufacturing method thereof and a display device, and belongs to the field of a semiconductor. The thin film transistor comprises a first active layer, a source electrode, a drain electrode, a grid electrode and a second active layer, wherein the source electrode, the drain electrode and the grid electrode are arranged on the first active layer at intervals; the grid electrode is arranged between the source electrode and the drain electrode; the second active layer is arranged on the grid electrode, the source electrode and the drain electrode; the source electrode and the drain electrode are connected with the first active layer and the second active layer; the grid electrode is insulated from the first active layer, the second active layer, the source electrode and the drain electrode; when a voltage is applied to the grid electrode, the source electrode and the drain electrode can be conducted through the first active layer, and the source electrode and the drain electrode can also be conducted through the second active layer; and when the source electrode and the drain electrode are conducted in the thin film transistor, the source electrode and the drain electrode can be conducted through the first active layer and the second active layer simultaneously, so that higher current can flow between the source electrode and the drain electrode, and on-state current of the thin film transistor can be improved.

Owner:BOE TECH GRP CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com