Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

139results about How to "Reduce off-state current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

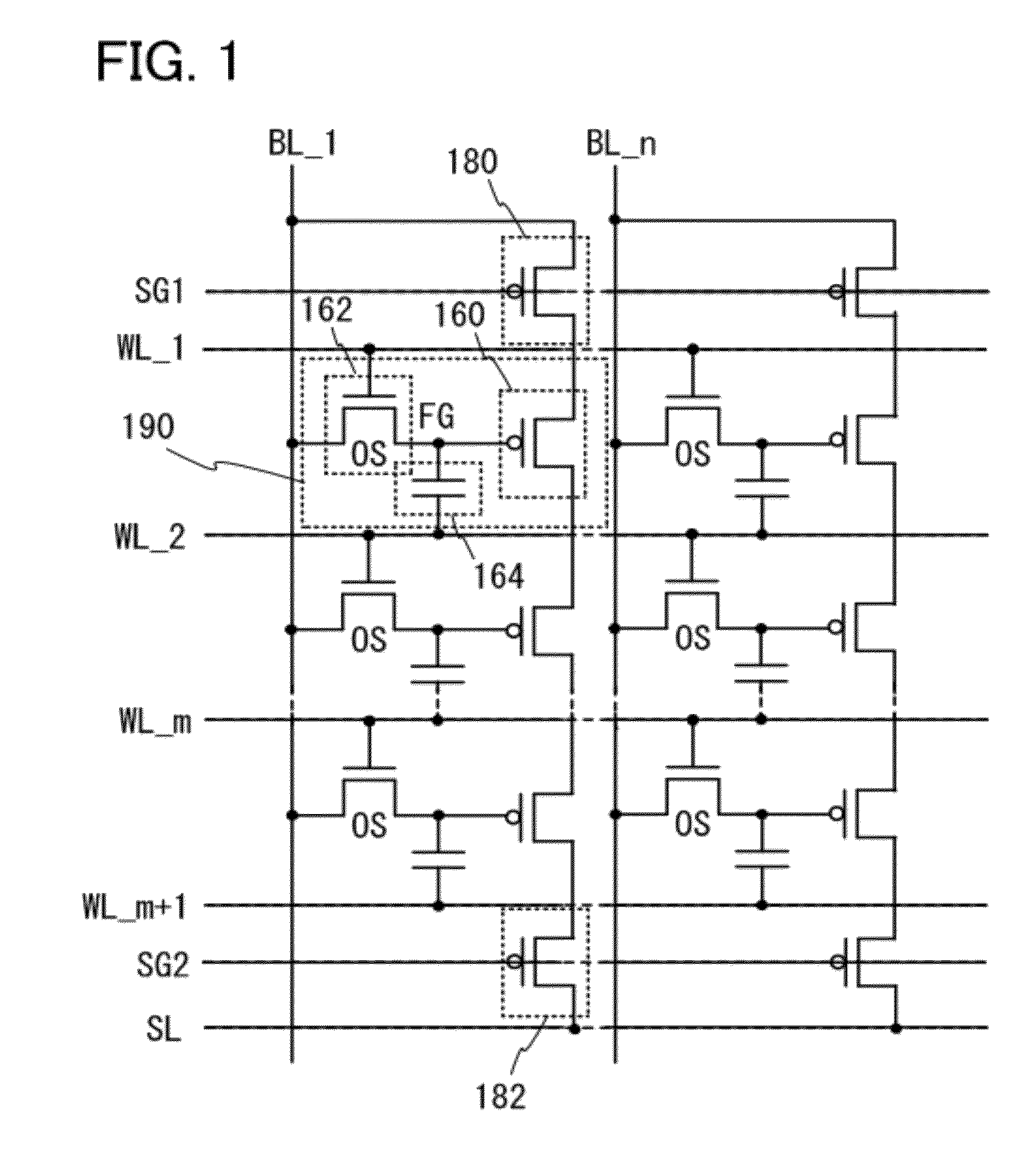

Semiconductor device and driving method thereof

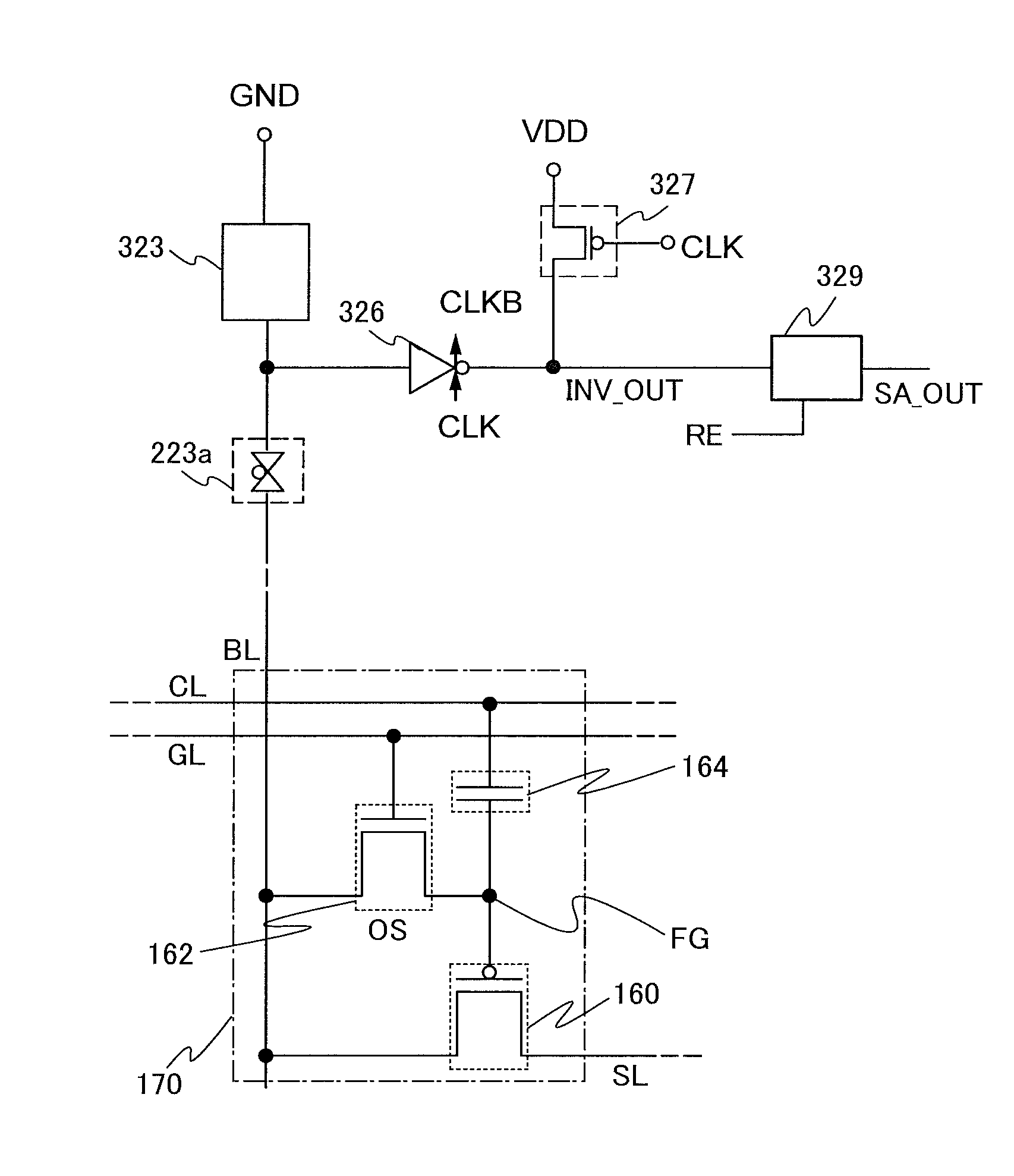

InactiveUS8614916B2Reduce off-state currentLonger heldSolid-state devicesRead-only memoriesPotential changeHemt circuits

Owner:SEMICON ENERGY LAB CO LTD

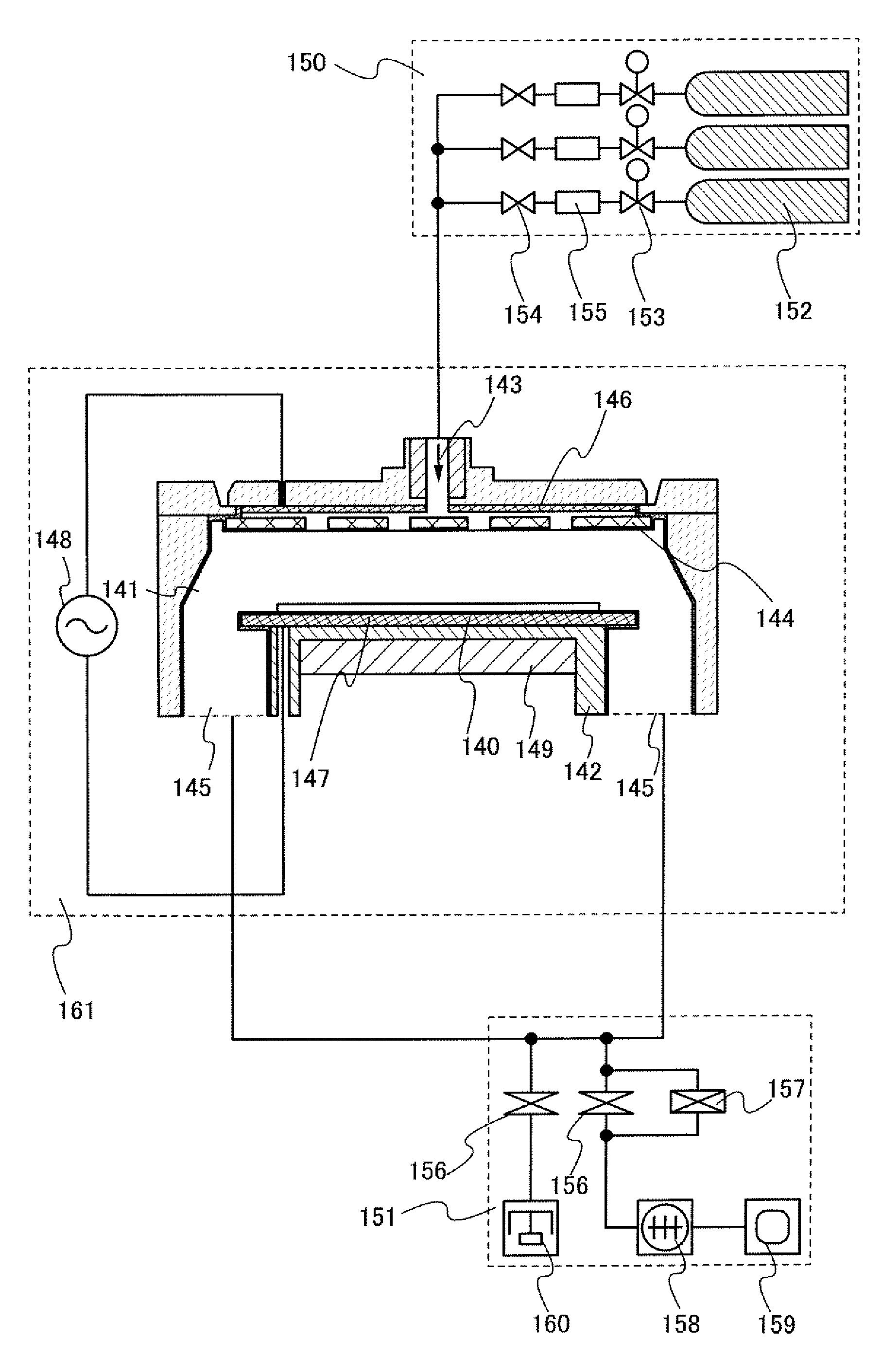

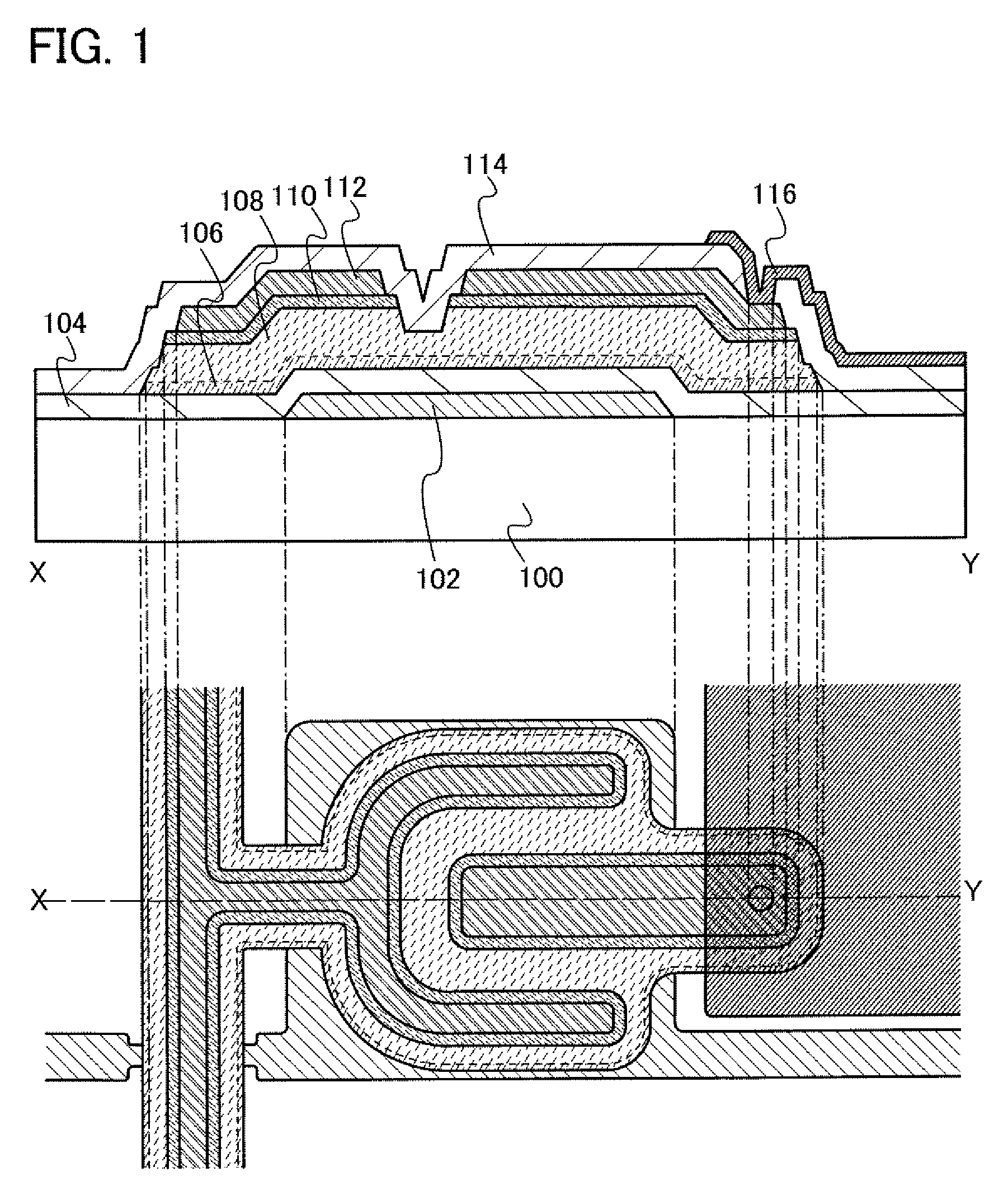

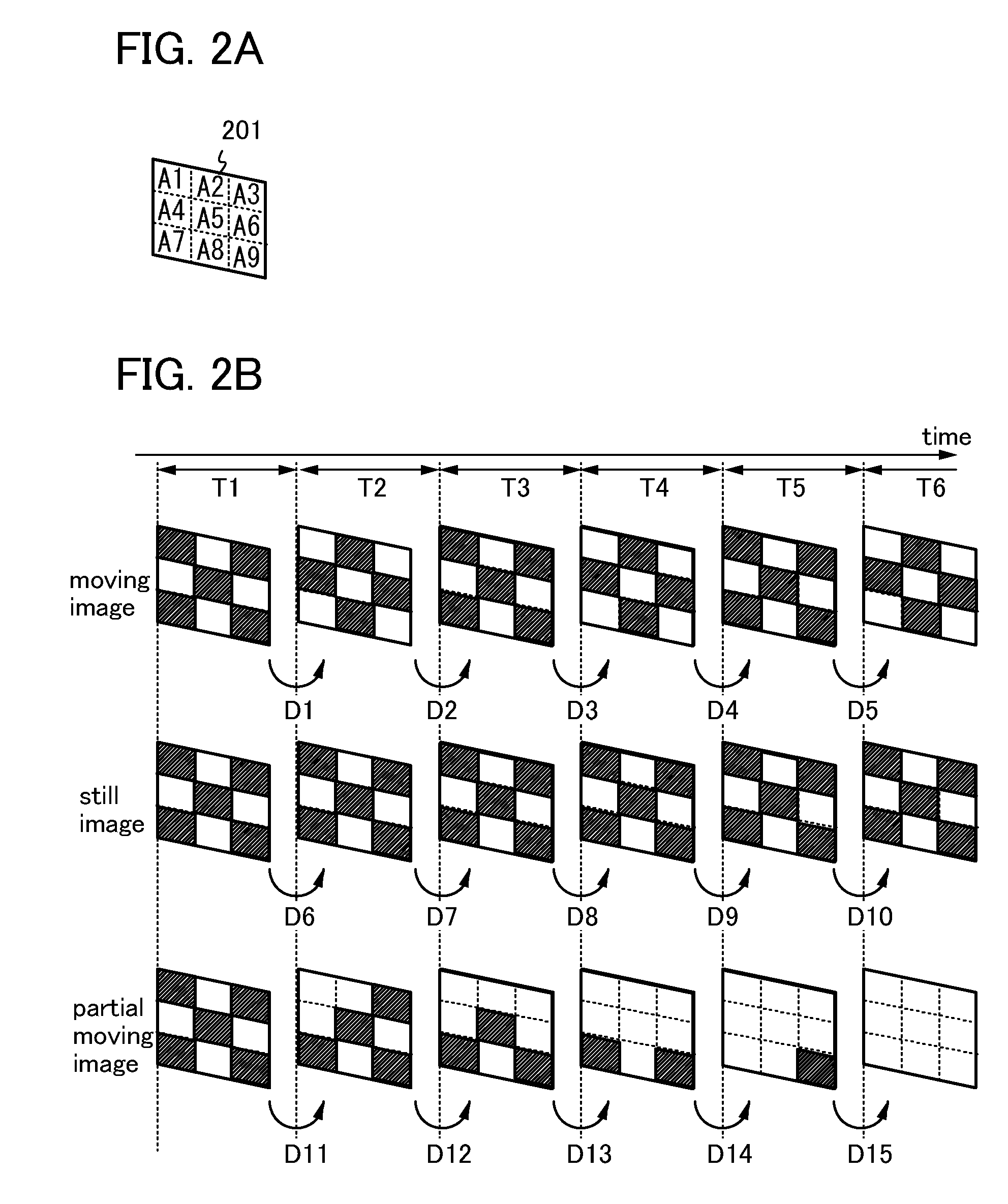

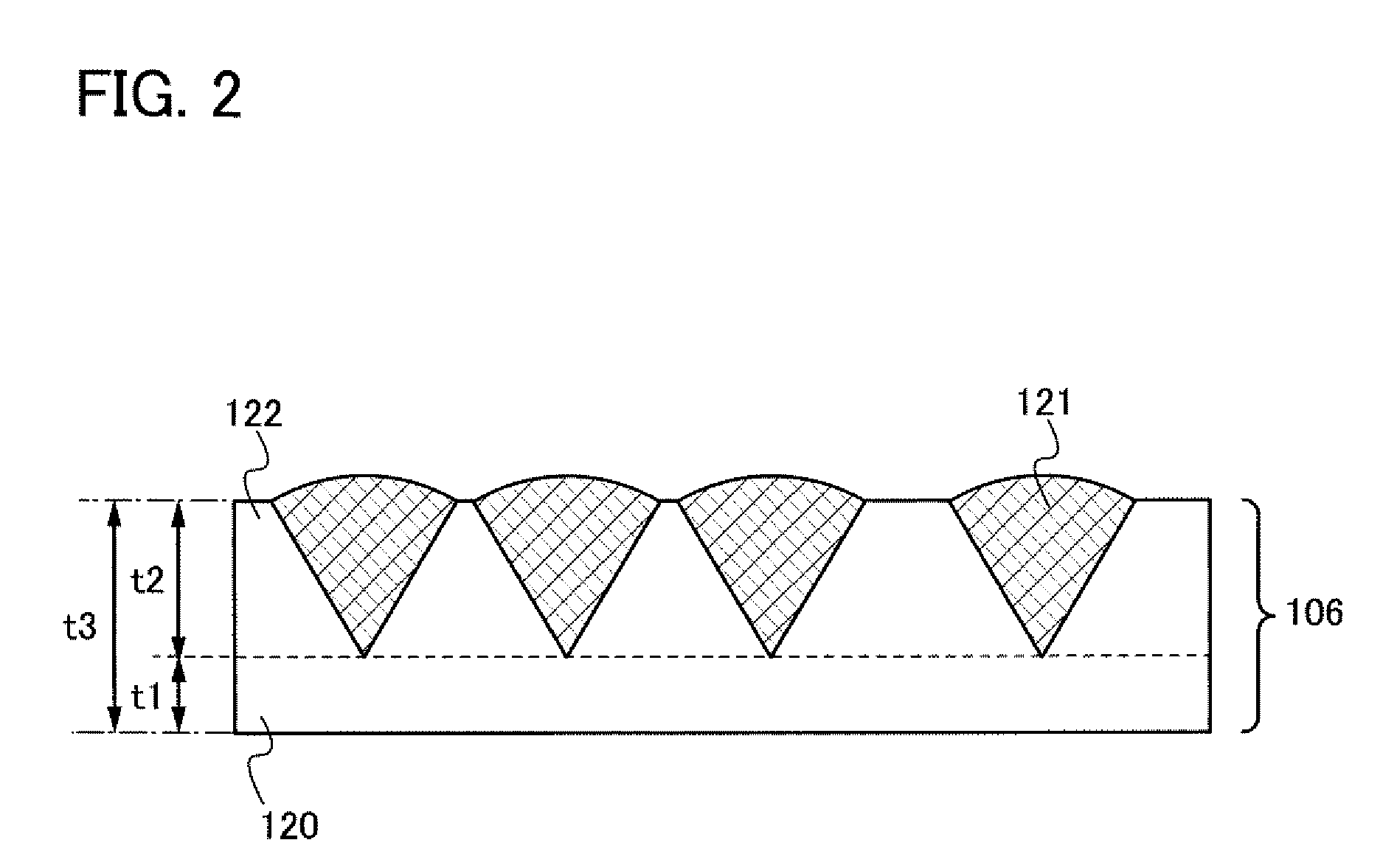

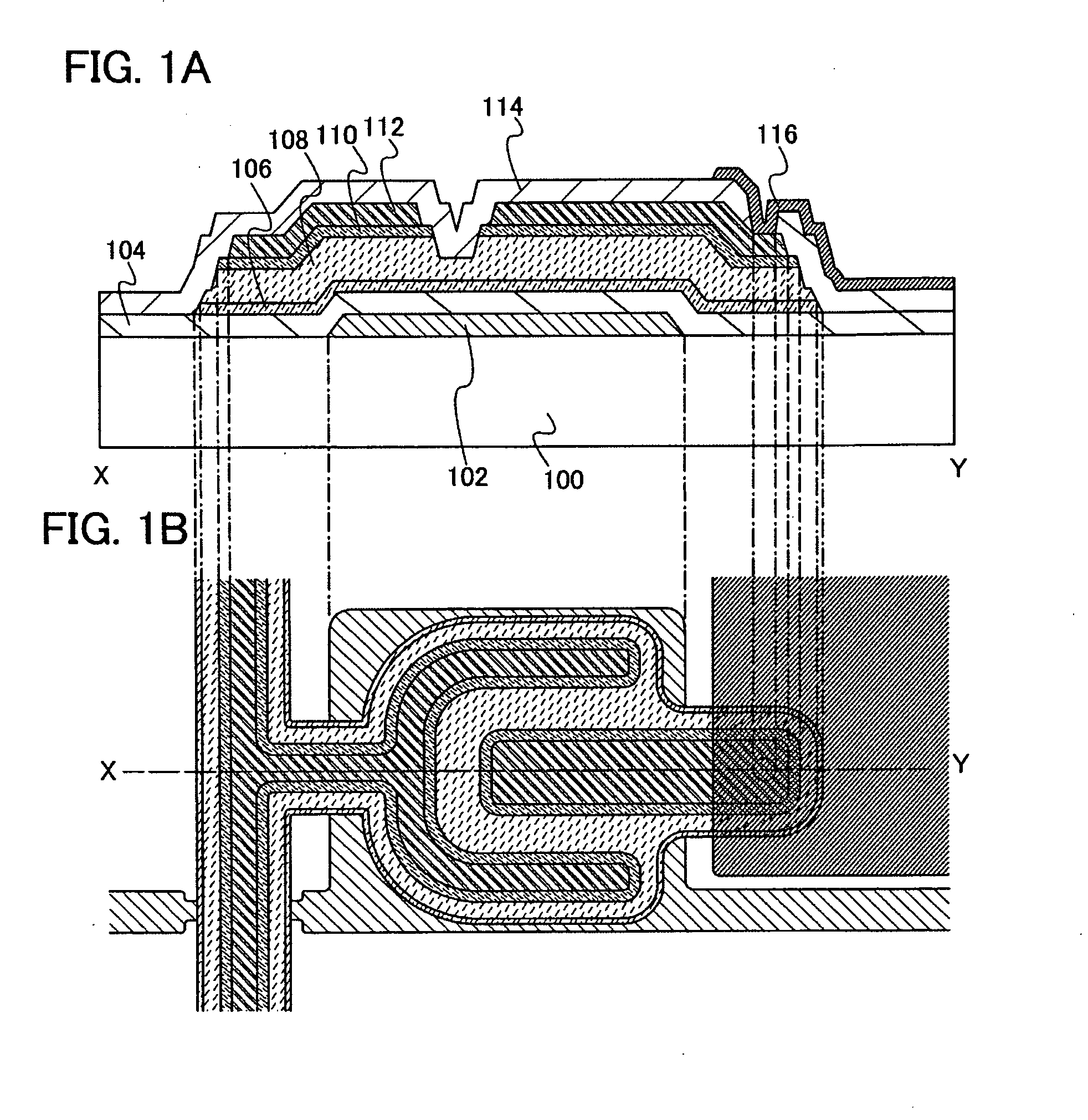

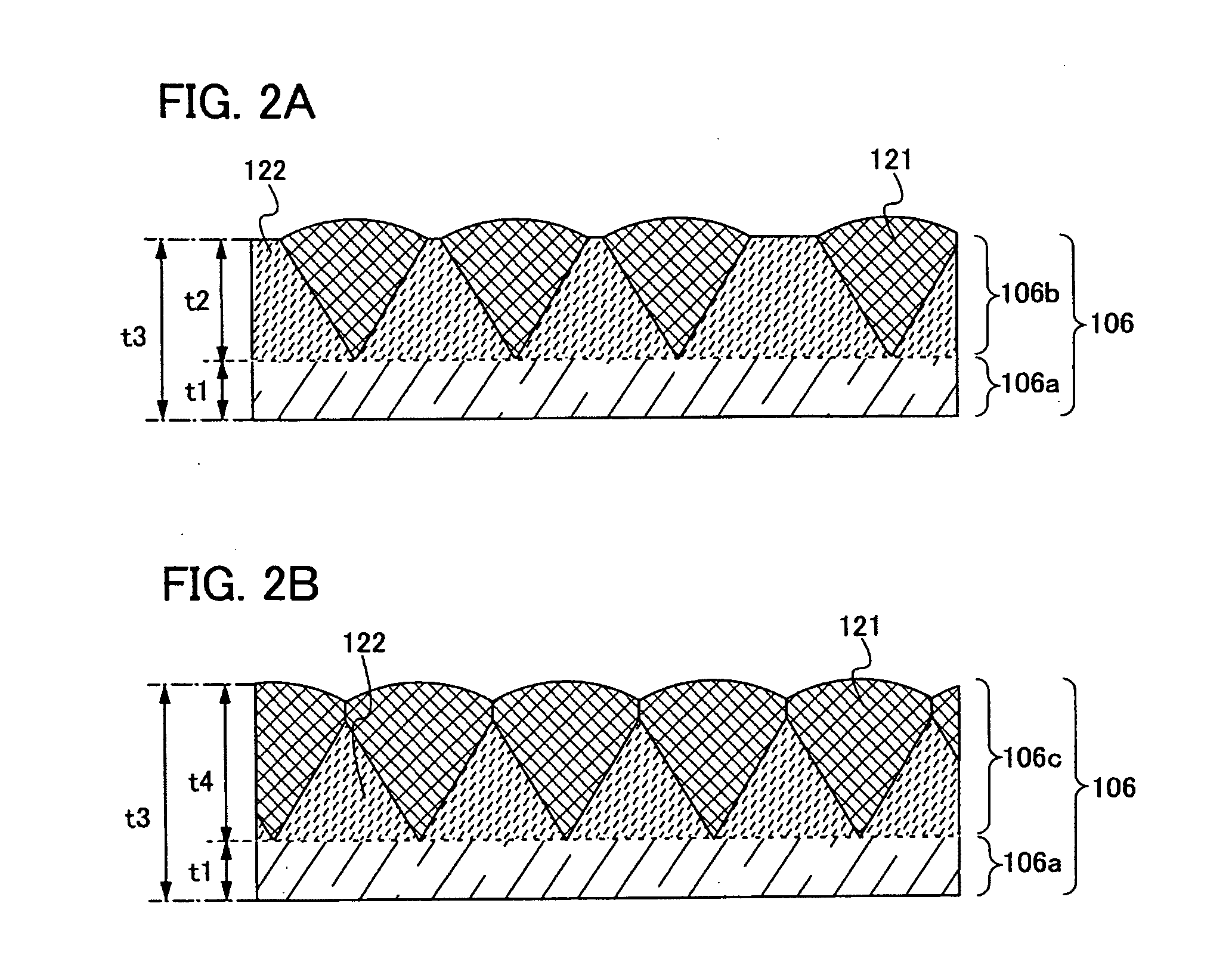

Method for manufacturing thin film transistor having microcrystalline semiconductor film

InactiveUS8138032B2Improve featuresIncrease the on-currentSolid-state devicesSemiconductor/solid-state device manufacturingImpuritySemiconductor

A thin film transistor includes, over a substrate having an insulating surface, a gate insulating layer covering a gate electrode; a semiconductor layer which includes a plurality of crystalline regions in an amorphous structure and which forms a channel formation region, in contact with the gate insulating layer; a semiconductor layer including an impurity element imparting one conductivity type, which forms source and drain regions; and a buffer layer including an amorphous semiconductor between the semiconductor layer and the semiconductor layer including an impurity element imparting one conductivity type. The crystalline regions have an inverted conical or inverted pyramidal crystal particle which grows approximately radially in a direction in which the semiconductor layer is deposited, from a position away from an interface between the gate insulating layer and the semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

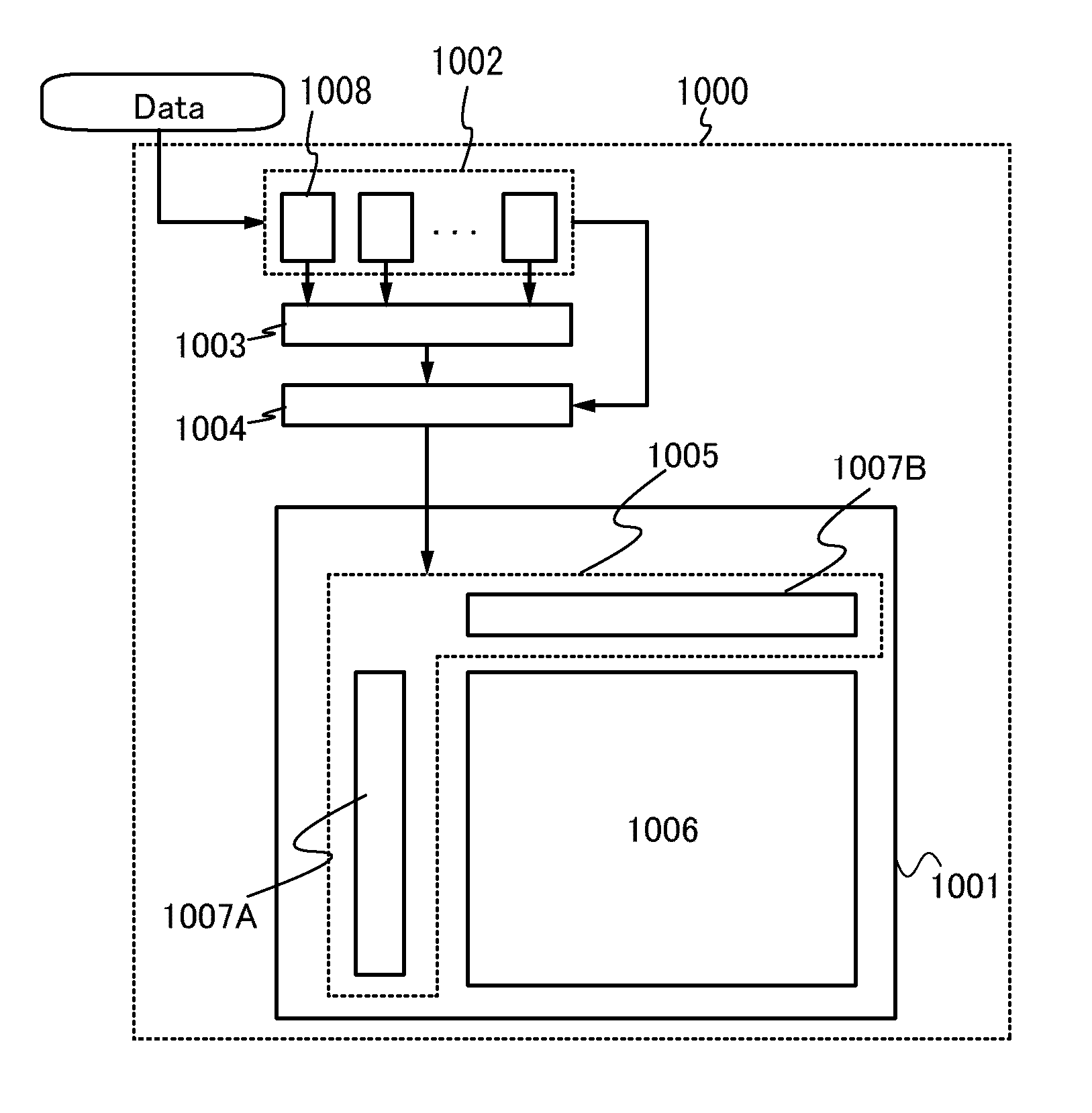

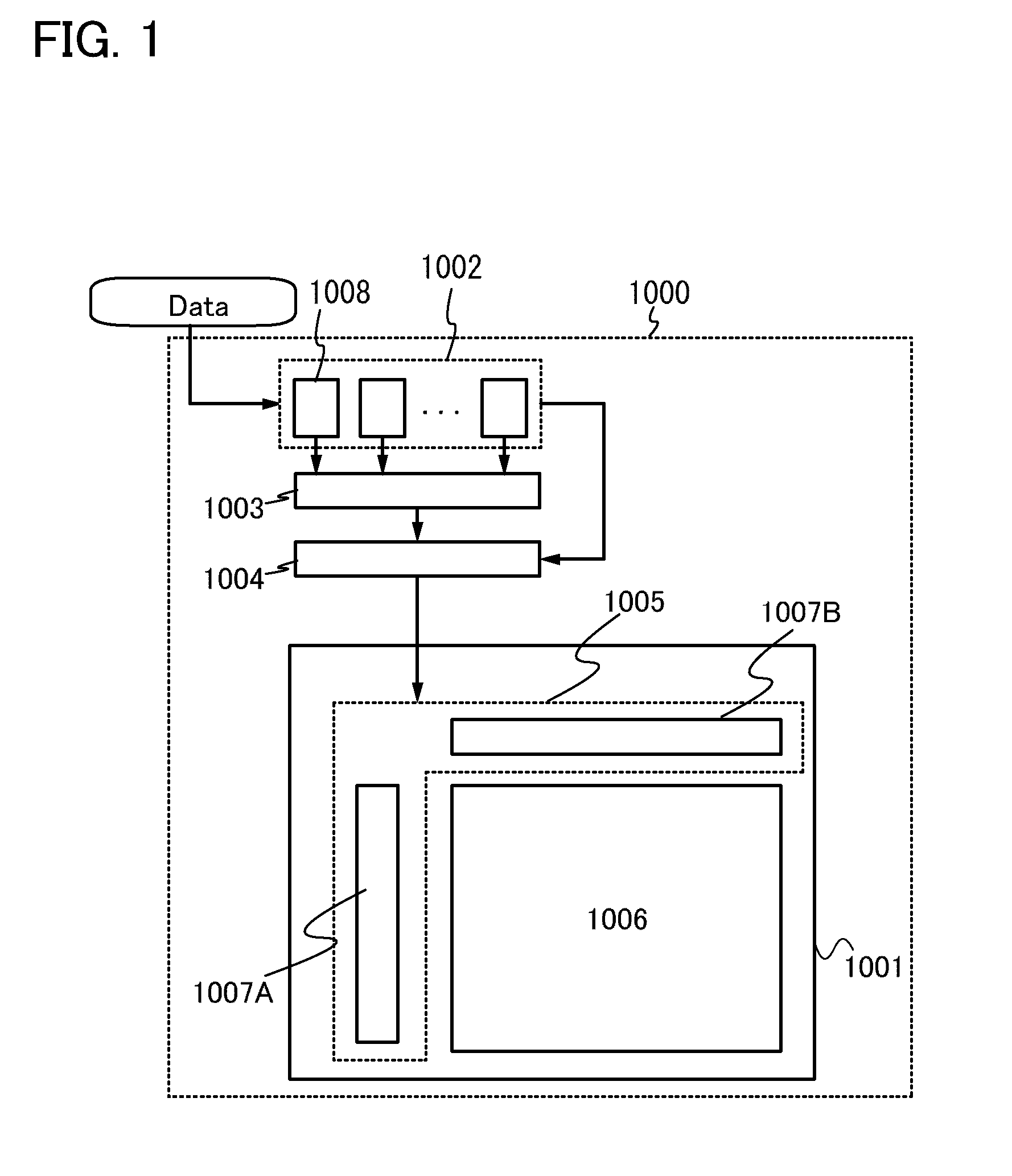

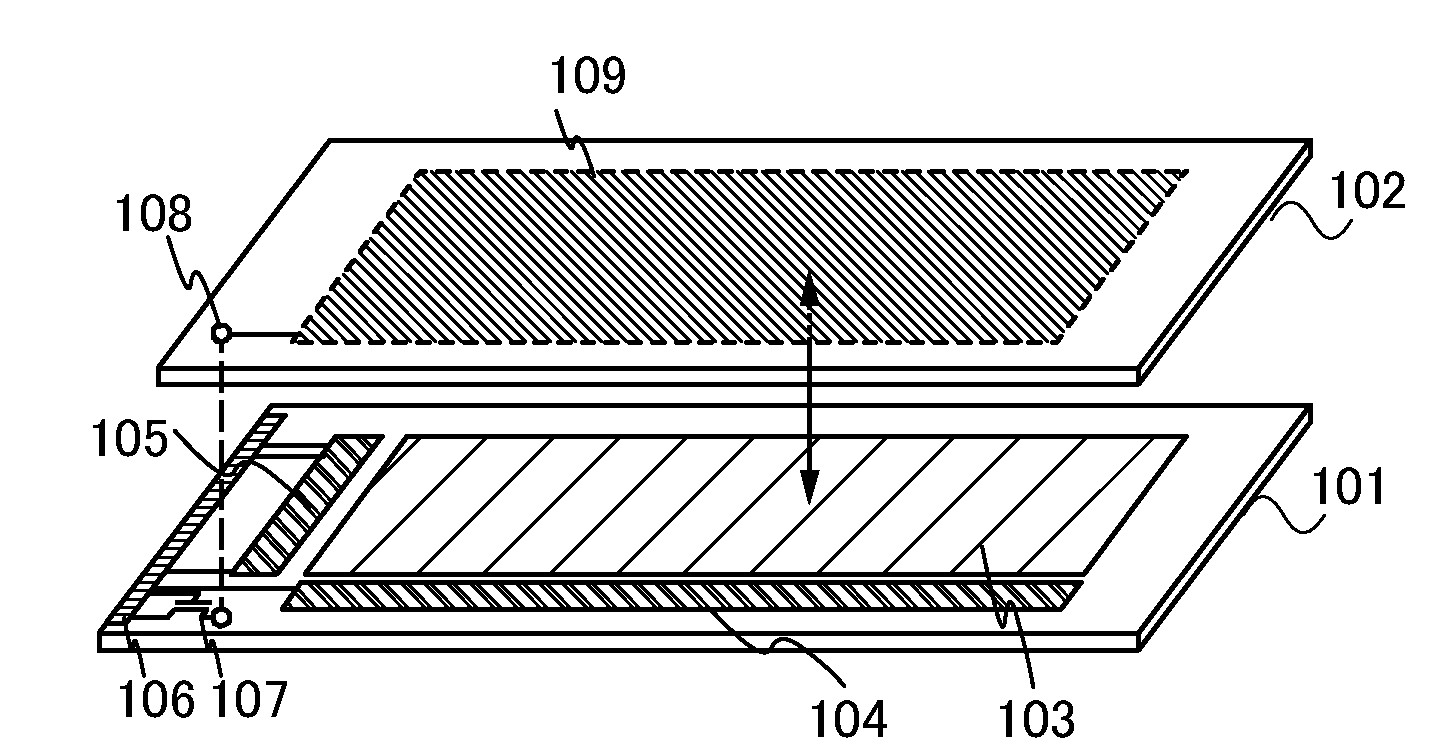

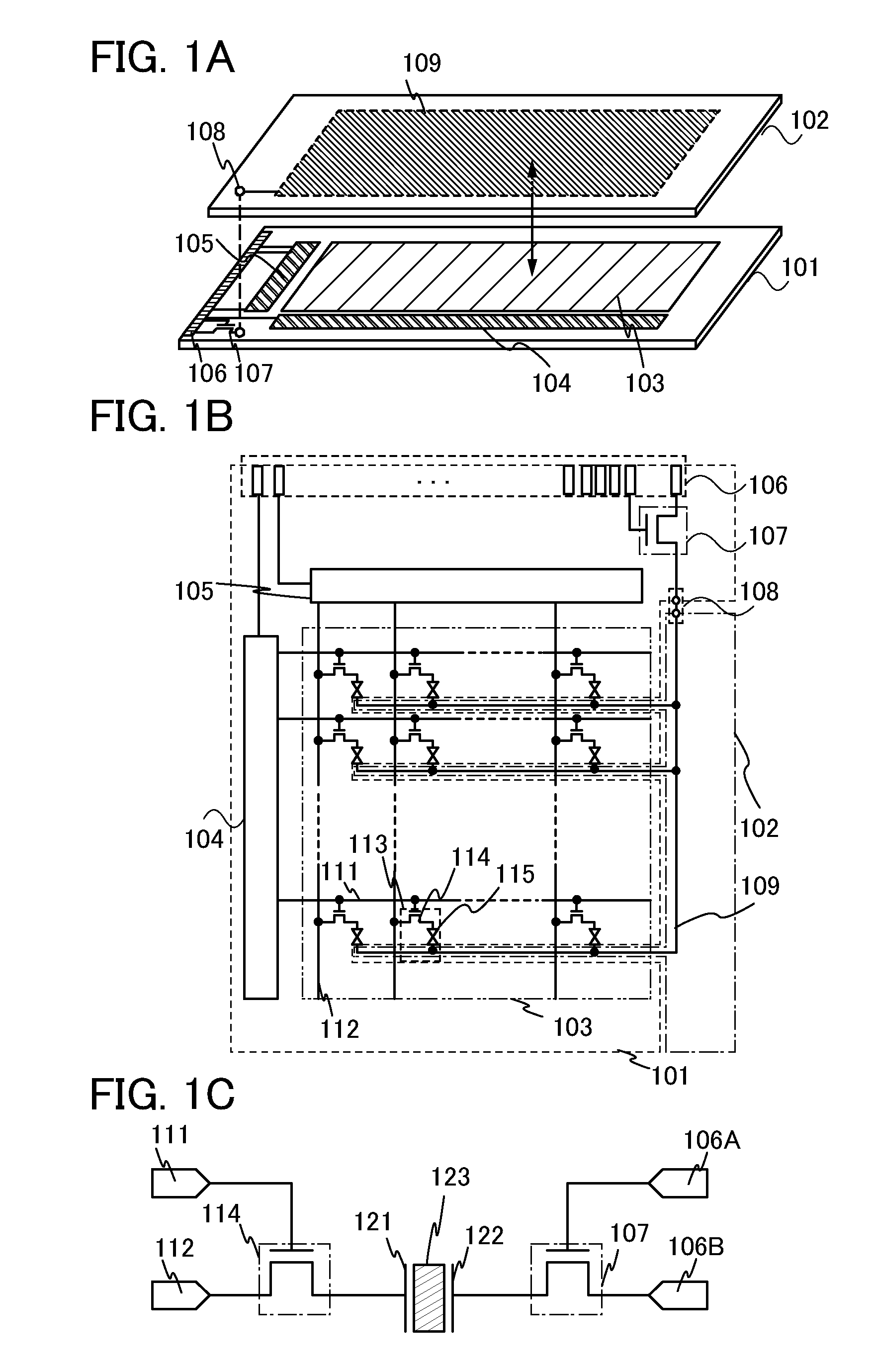

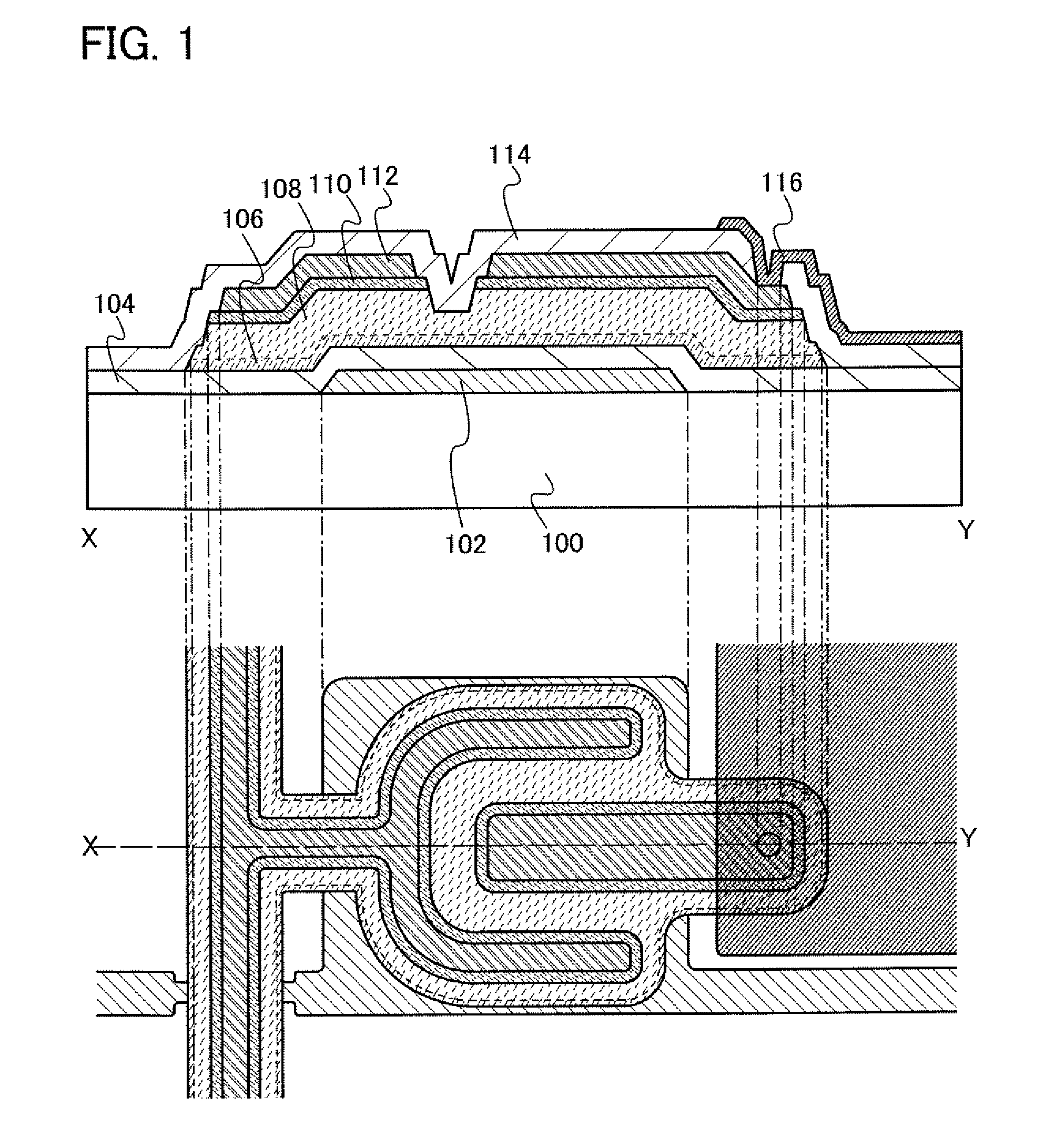

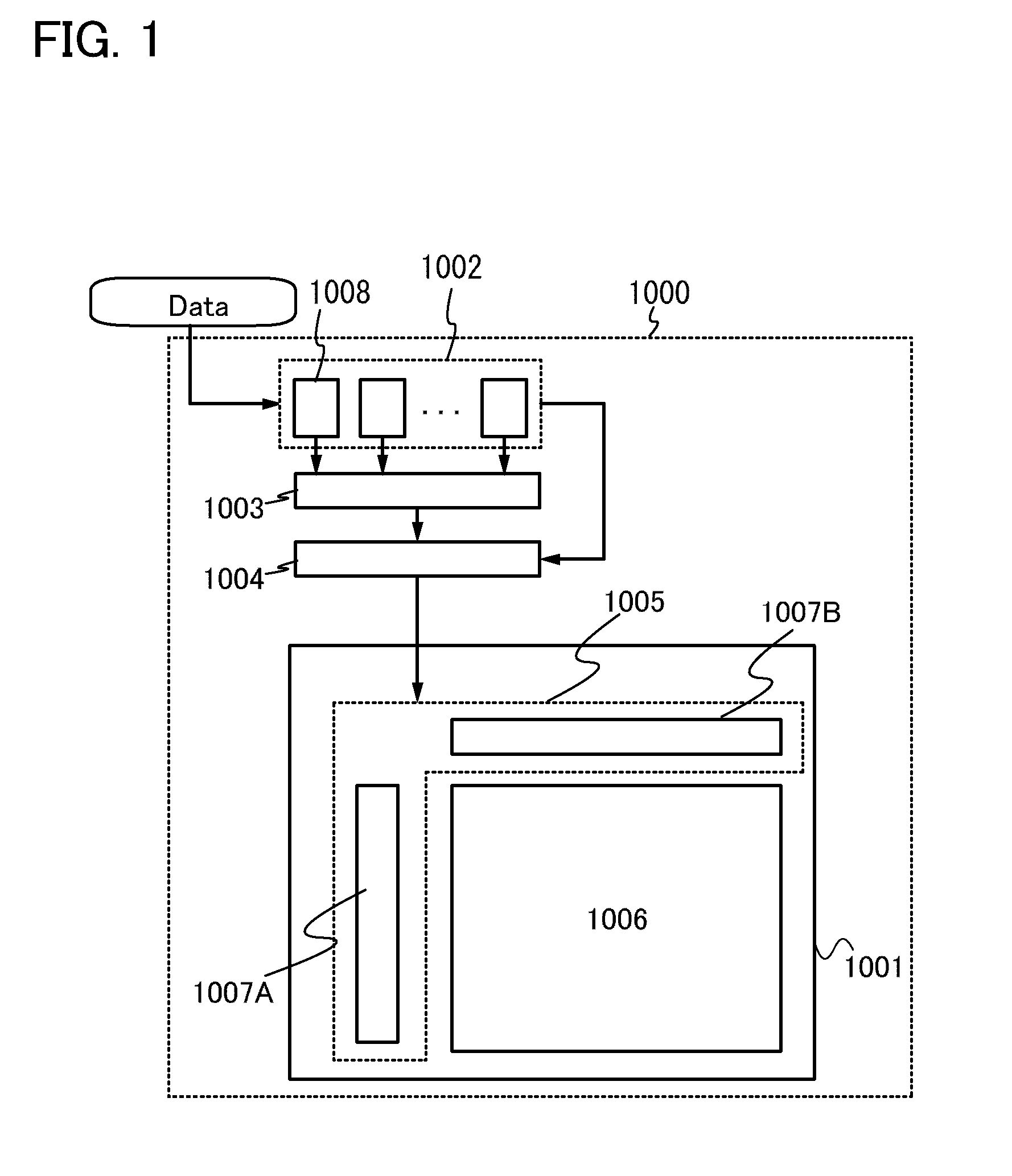

Liquid crystal display device, method for driving the same, and electronic device including the same

ActiveUS8531618B2Reduce leakageReduce off-state currentSolid-state devicesCathode-ray tube indicatorsDriver circuitLiquid-crystal display

The liquid crystal display device includes a pixel portion including a plurality of pixels to which image signals are supplied; a driver circuit including a signal line driver circuit which selectively controls a signal line and a gate line driver circuit which selectively controls a gate line; a memory circuit which stores the image signals; a comparison circuit which compares the image signals stored in the memory circuit in the pixels and detects a difference; and a display control circuit which controls the driver circuit and reads the image signal in accordance with the difference. The display control circuit supplies the image signal only to the pixel where the difference is detected. The pixel includes a thin film transistor including a semiconductor layer including an oxide semiconductor.

Owner:SEMICON ENERGY LAB CO LTD

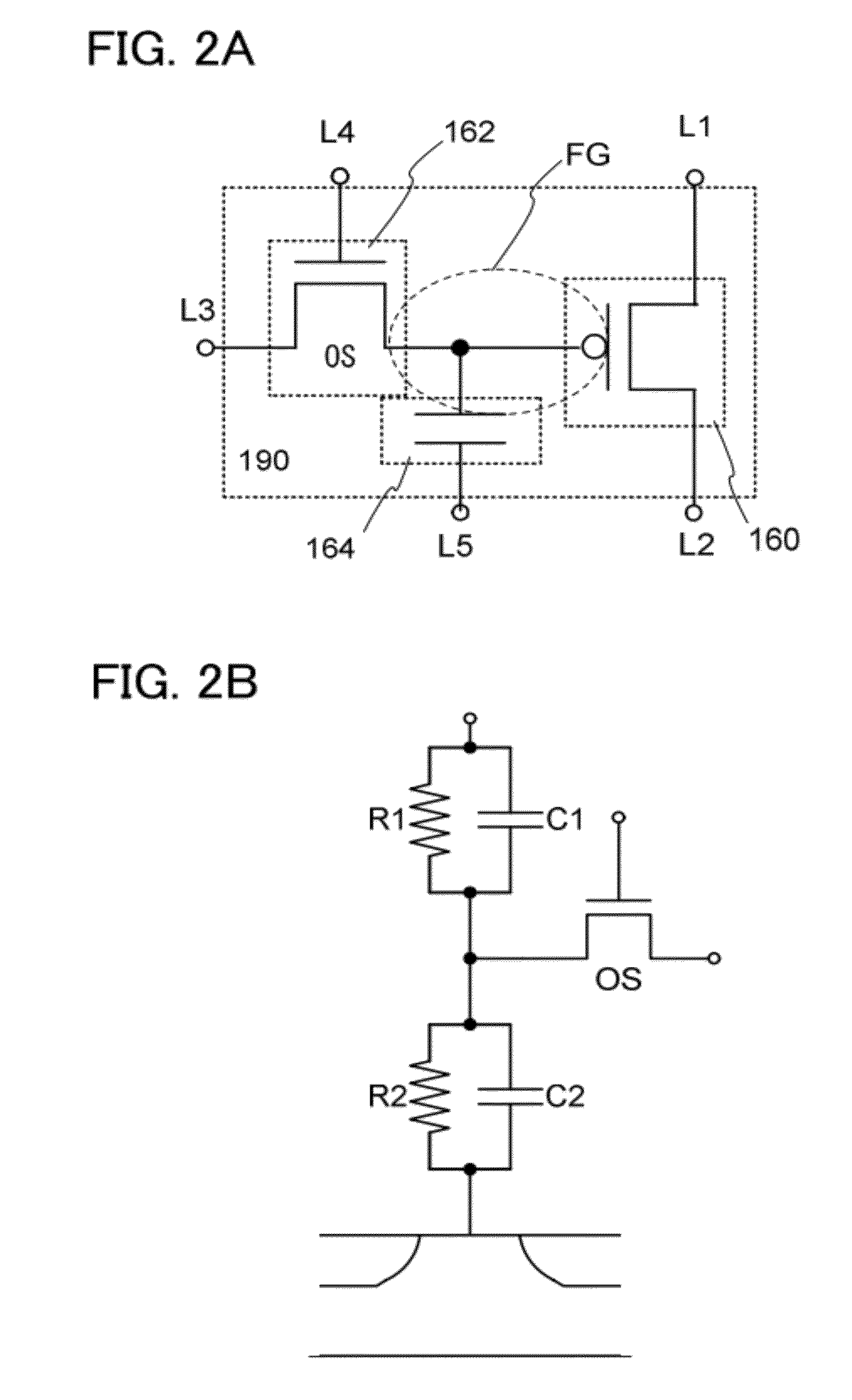

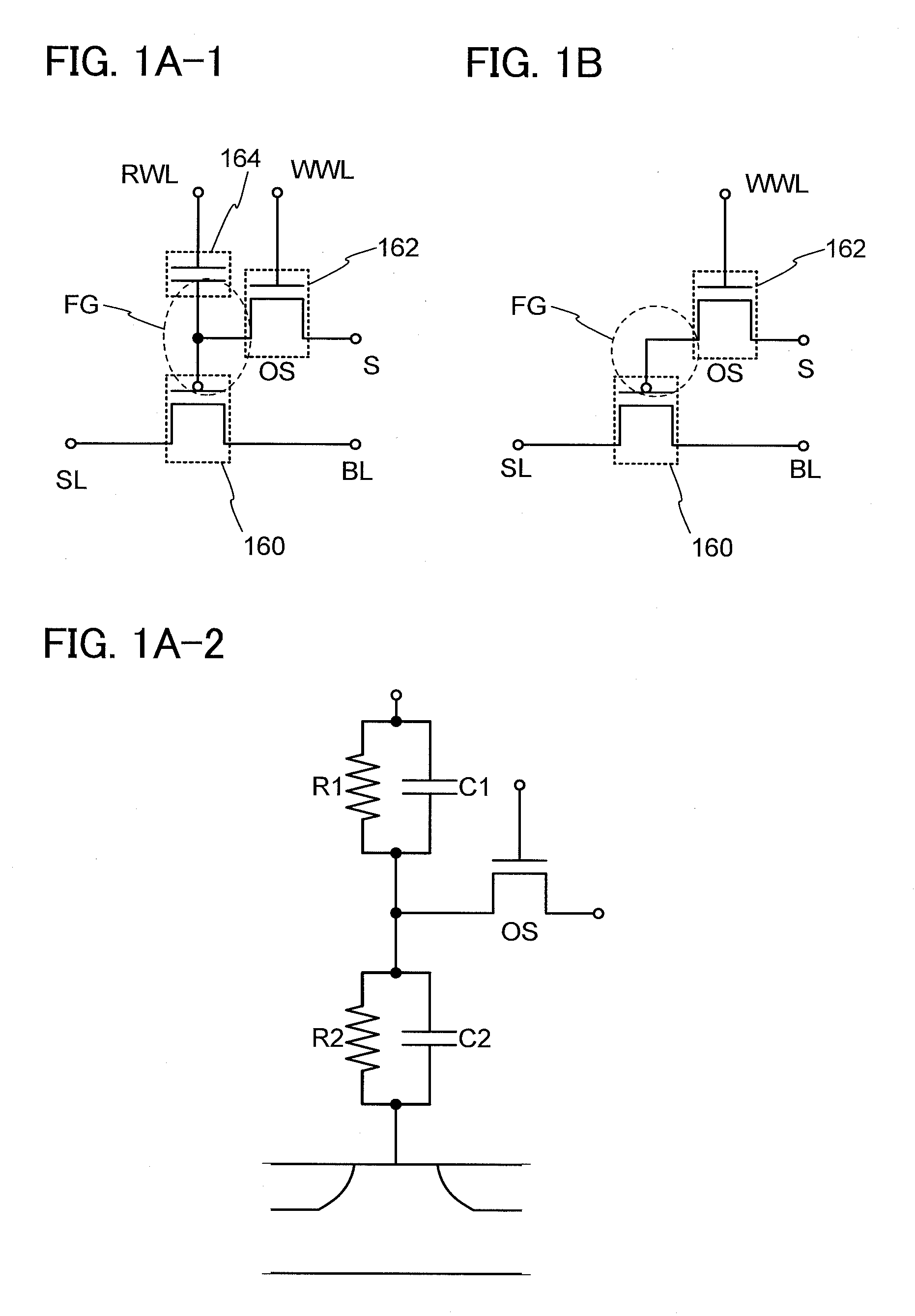

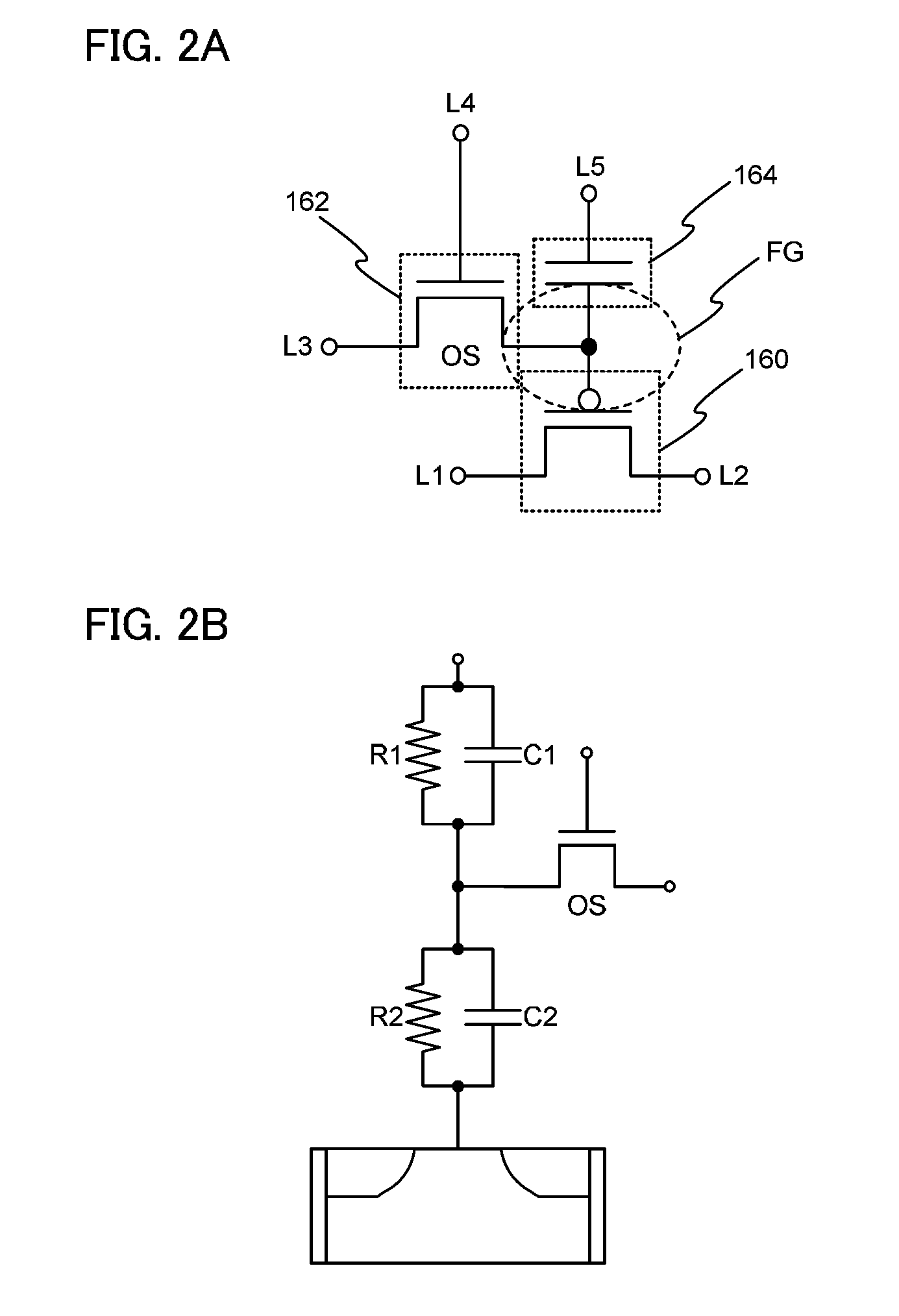

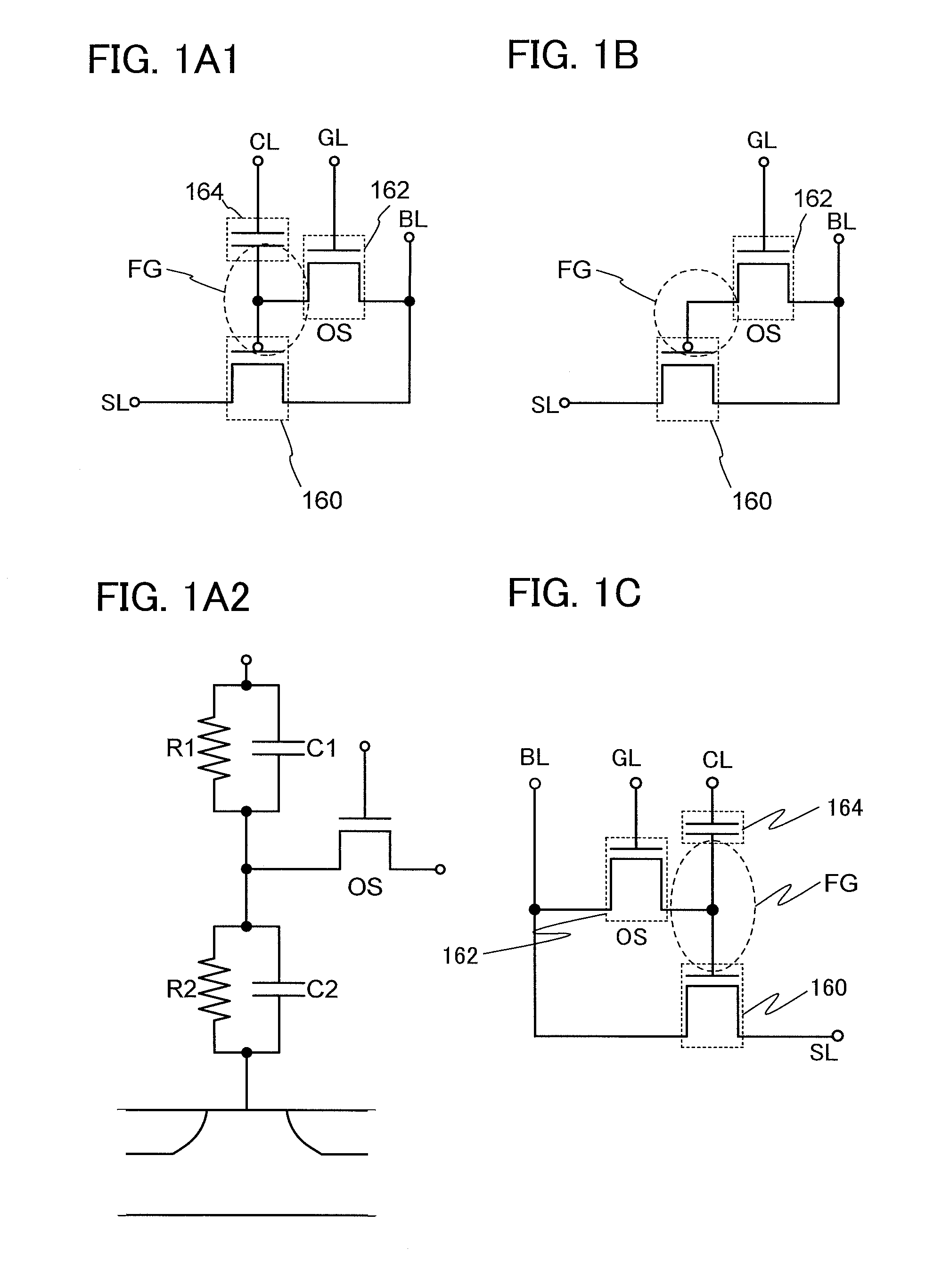

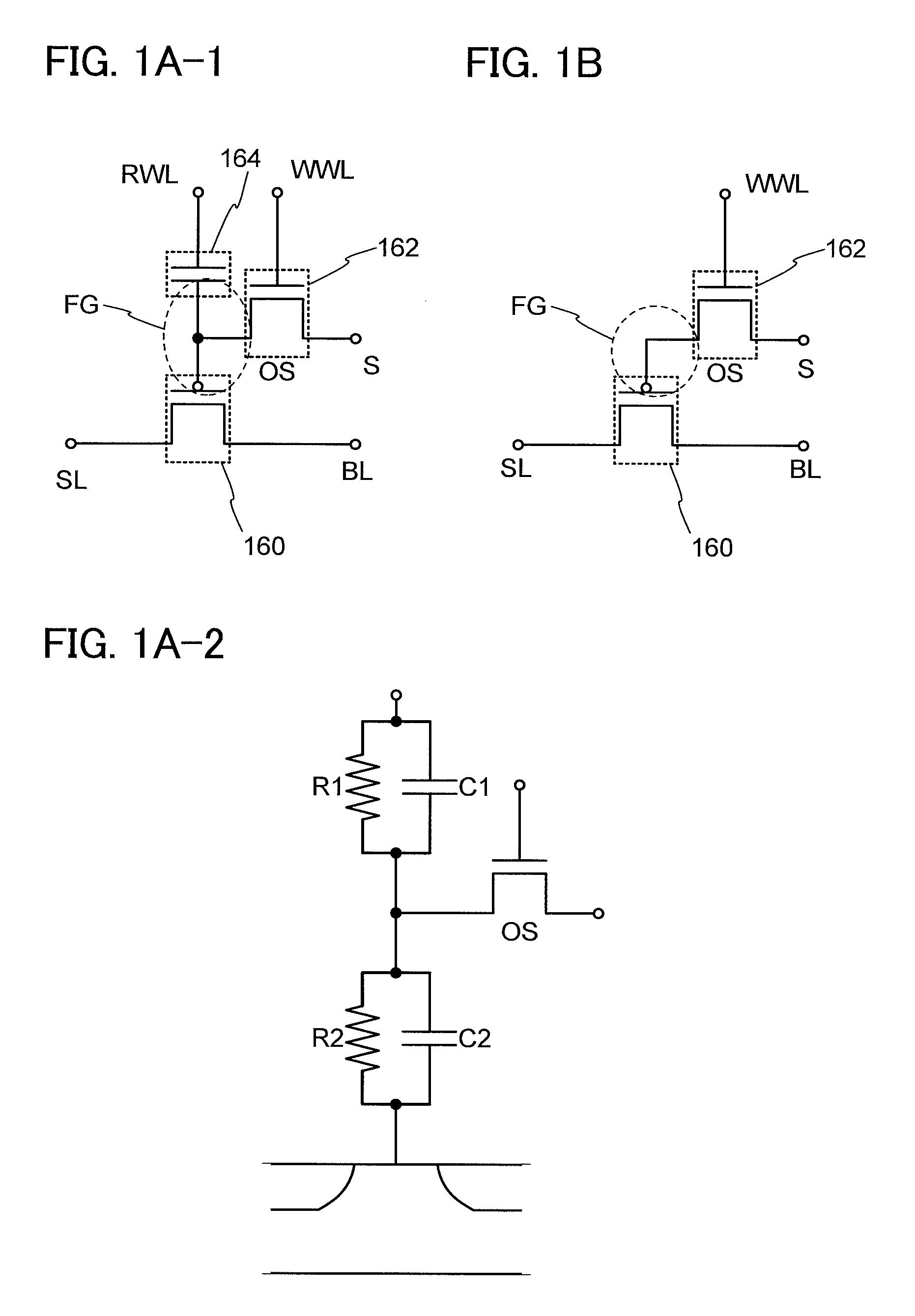

Semiconductor device and driving method thereof

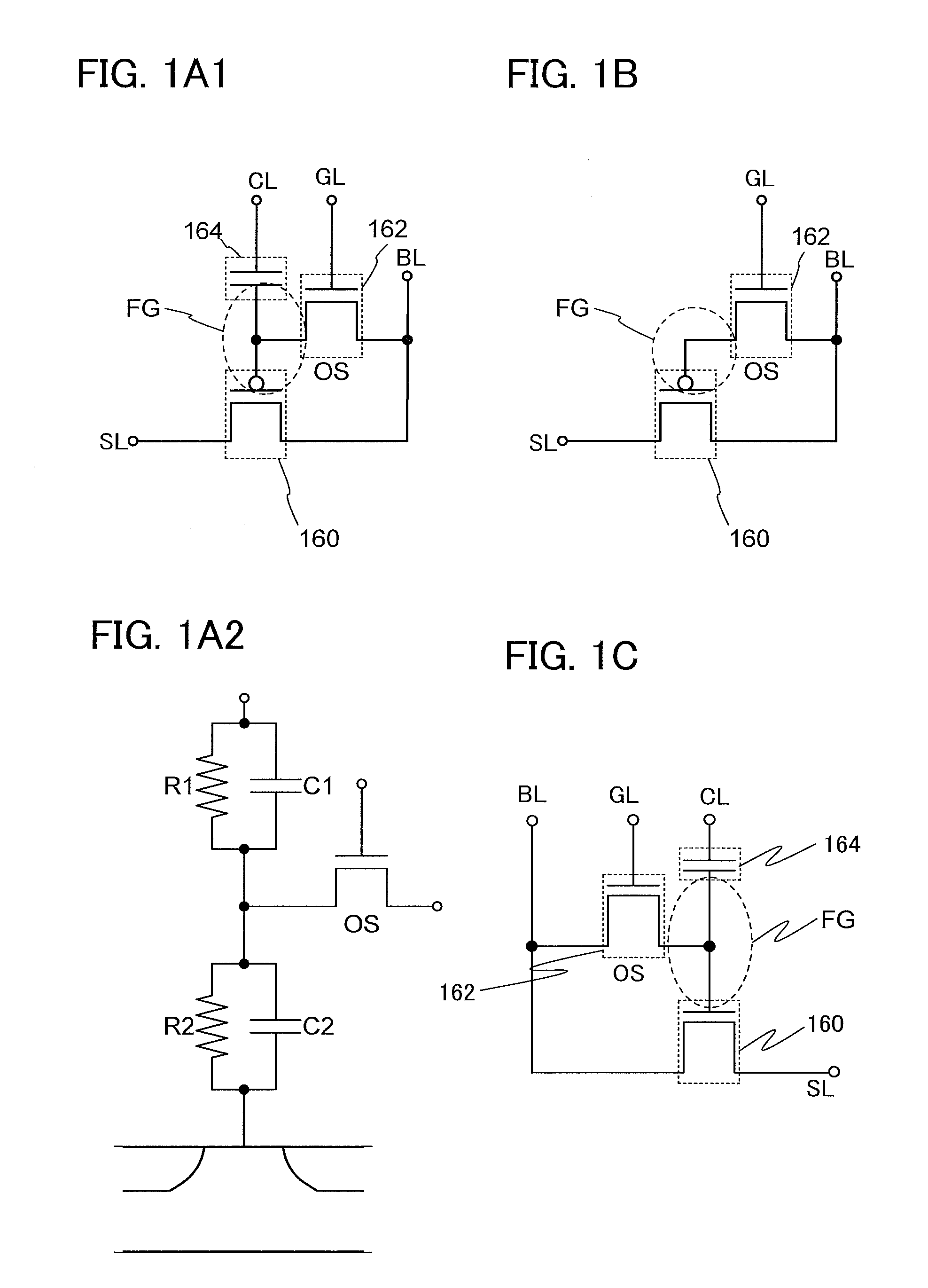

InactiveUS20120033488A1Reduce off-state currentLonger heldTransistorSolid-state devicesPotential changeEngineering

A semiconductor device including a memory cell formed using a wide bandgap semiconductor, for example, an oxide semiconductor is provided. The semiconductor device includes a potential change circuit having a function of outputting a potential lower than a reference potential for reading data from the memory cell. With the use of the wide bandgap semiconductor, an off-state current of a transistor included in the memory cell can be sufficiently reduced, and the semiconductor device which can hold data for a long period can be provided.

Owner:SEMICON ENERGY LAB CO LTD

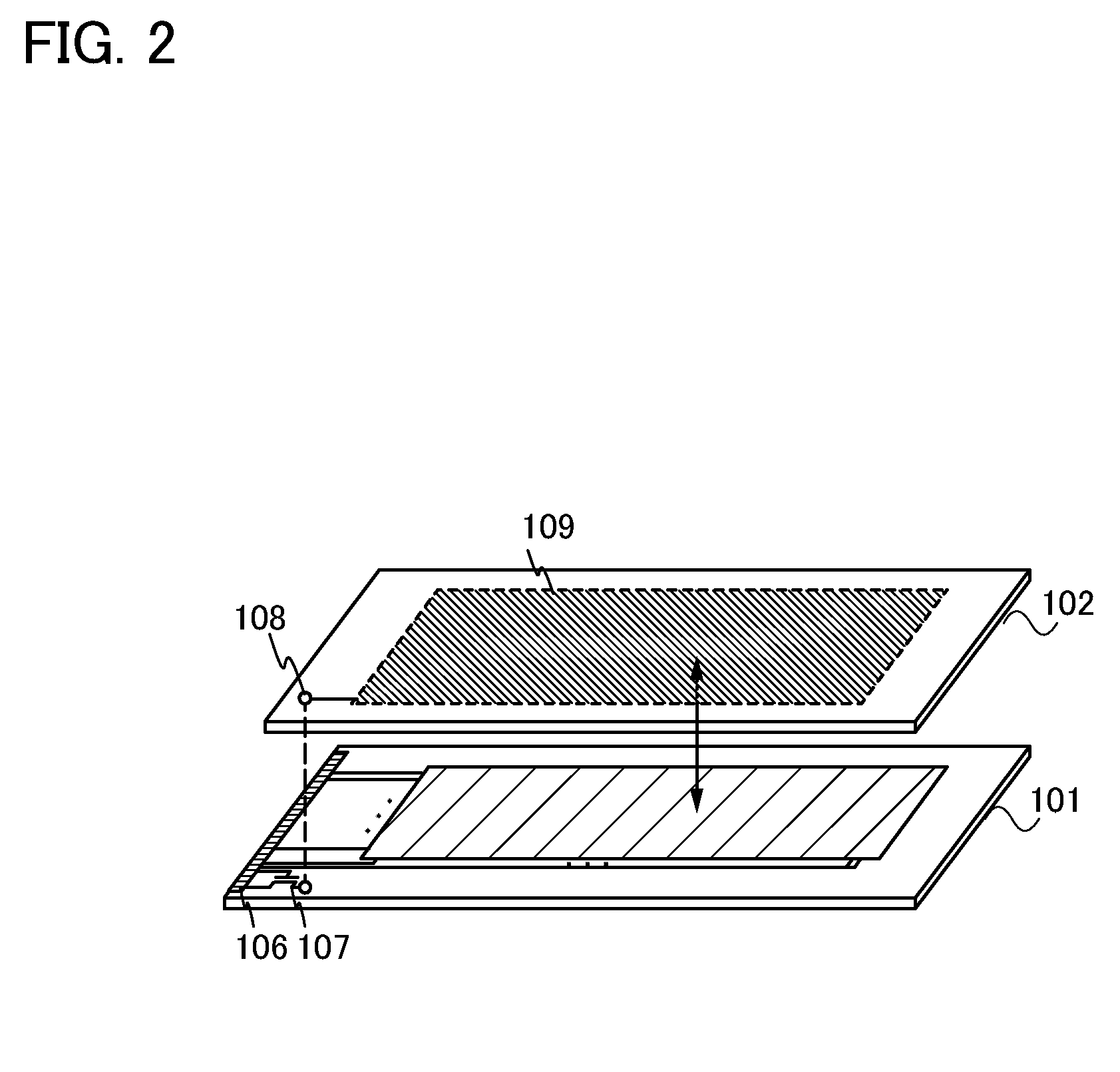

Liquid crystal display device, driving method of the same, and electronic appliance including the same

ActiveUS20110102696A1Reduce power consumptionTotal current dropStatic indicating devicesSolid-state devicesLiquid-crystal displayEngineering

An object is to provide a liquid crystal display device in which low power consumption can be achieved. A first substrate includes a terminal portion, a switching transistor, and a pixel circuit including a pixel electrode is provided. A second substrate includes a counter electrode. A liquid crystal element is interposed between the pixel electrode and the counter electrode. A potential to be input to the counter electrode is supplied from a terminal portion through the switching transistor. A semiconductor layer included in the switching transistor is an oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

Thin film transistor and method for manufacturing the same

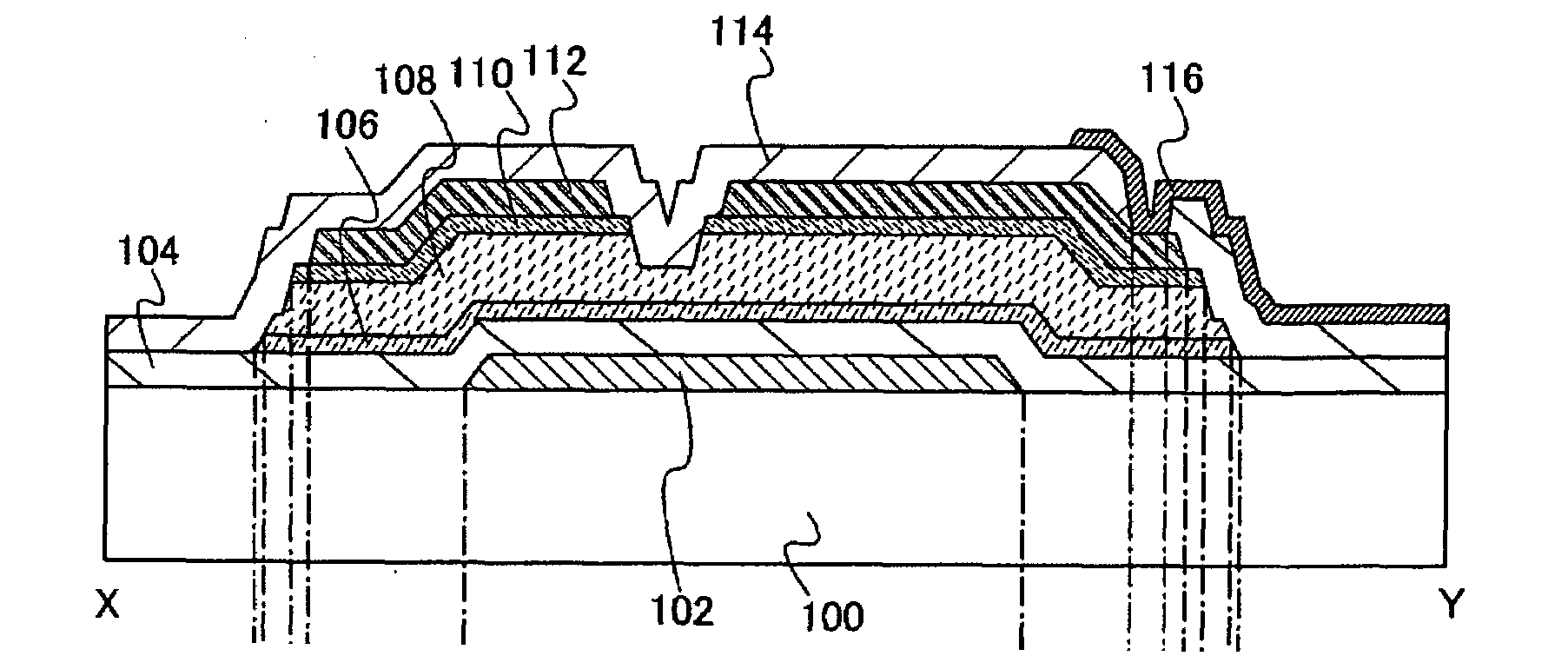

InactiveUS20100096631A1Increase currentTotal current dropTransistorSolid-state devicesSemiconductorImpurity

A thin film transistor includes, over a substrate having an insulating surface, a gate insulating layer covering a gate electrode; a semiconductor layer which includes a plurality of crystalline regions in an amorphous structure and which forms a channel formation region, in contact with the gate insulating layer; a semiconductor layer including an impurity element imparting one conductivity type, which forms source and drain regions; and a buffer layer including an amorphous semiconductor between the semiconductor layer and the semiconductor layer including an impurity element imparting one conductivity type. The crystalline regions have an inverted conical or inverted pyramidal crystal particle which grows approximately radially in a direction in which the semiconductor layer is deposited, from a position away from an interface between the gate insulating layer and the semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

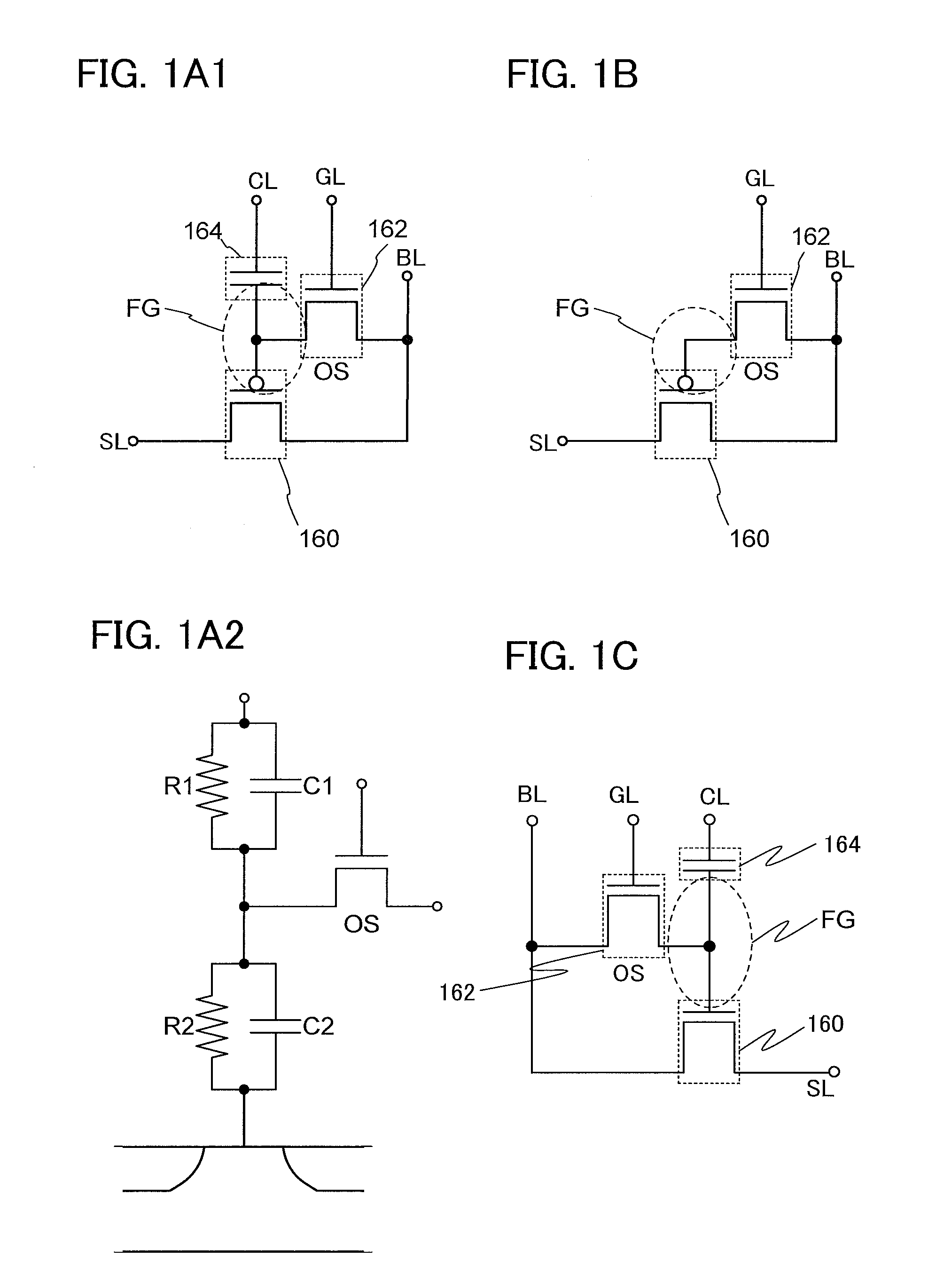

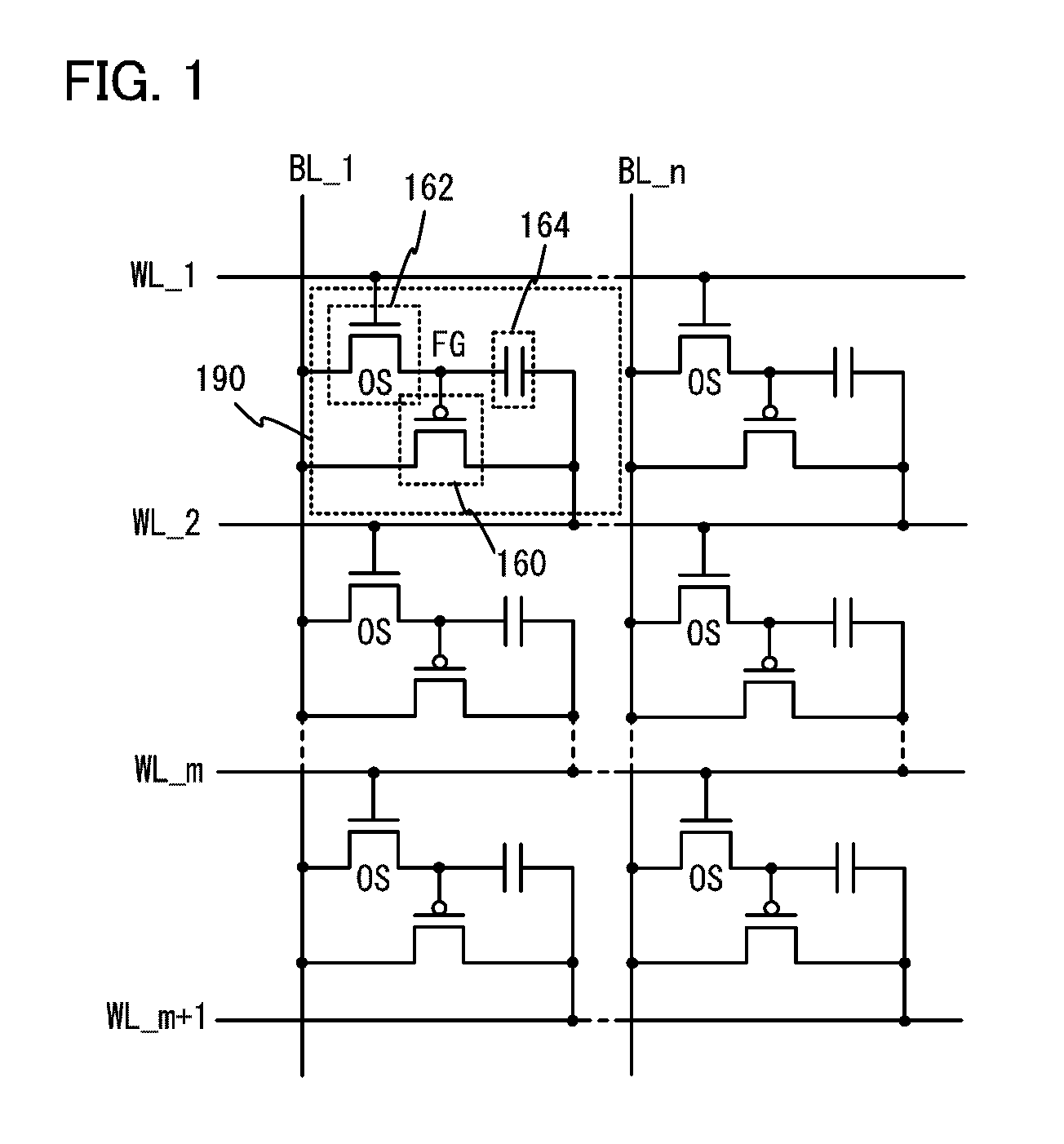

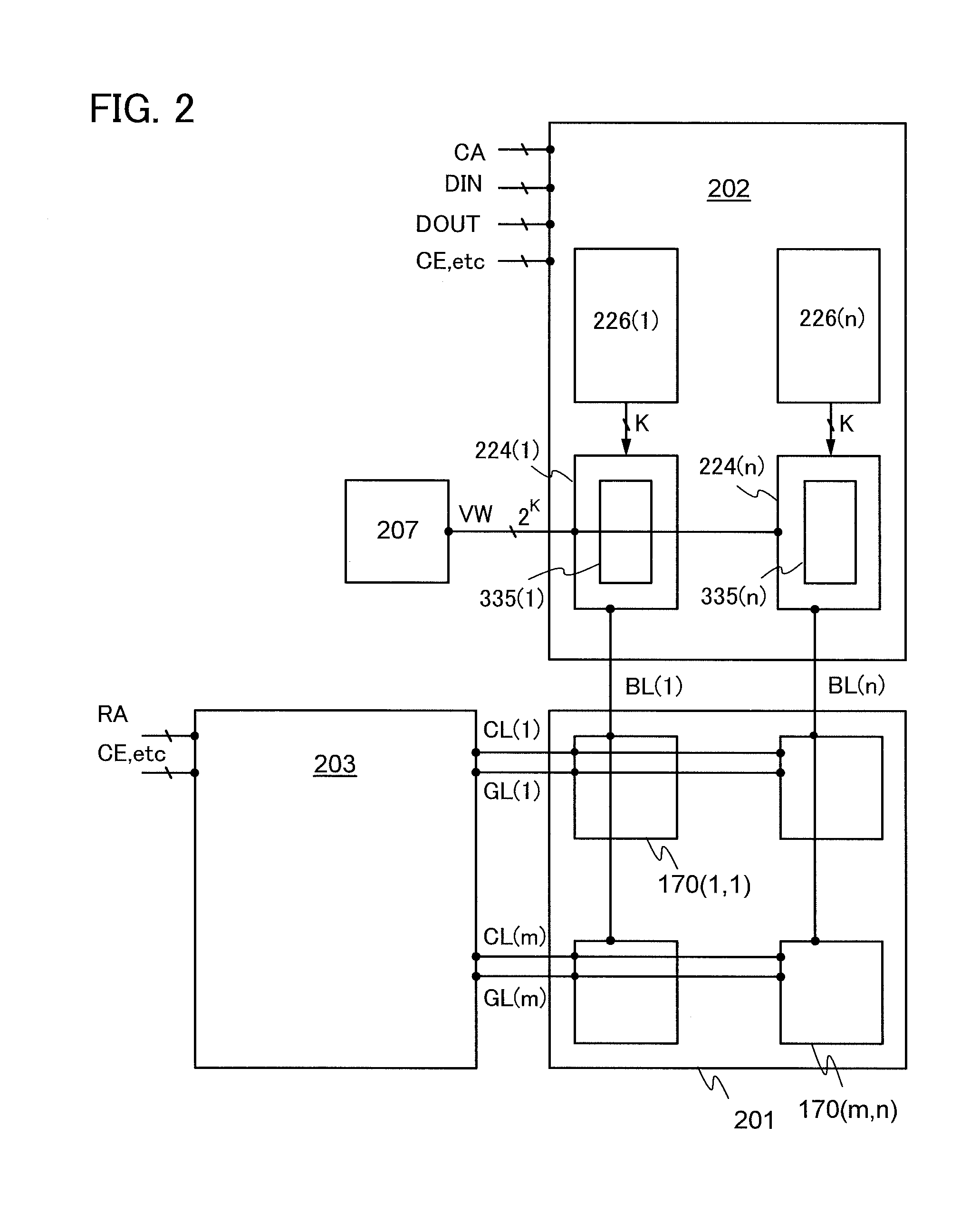

Semiconductor device

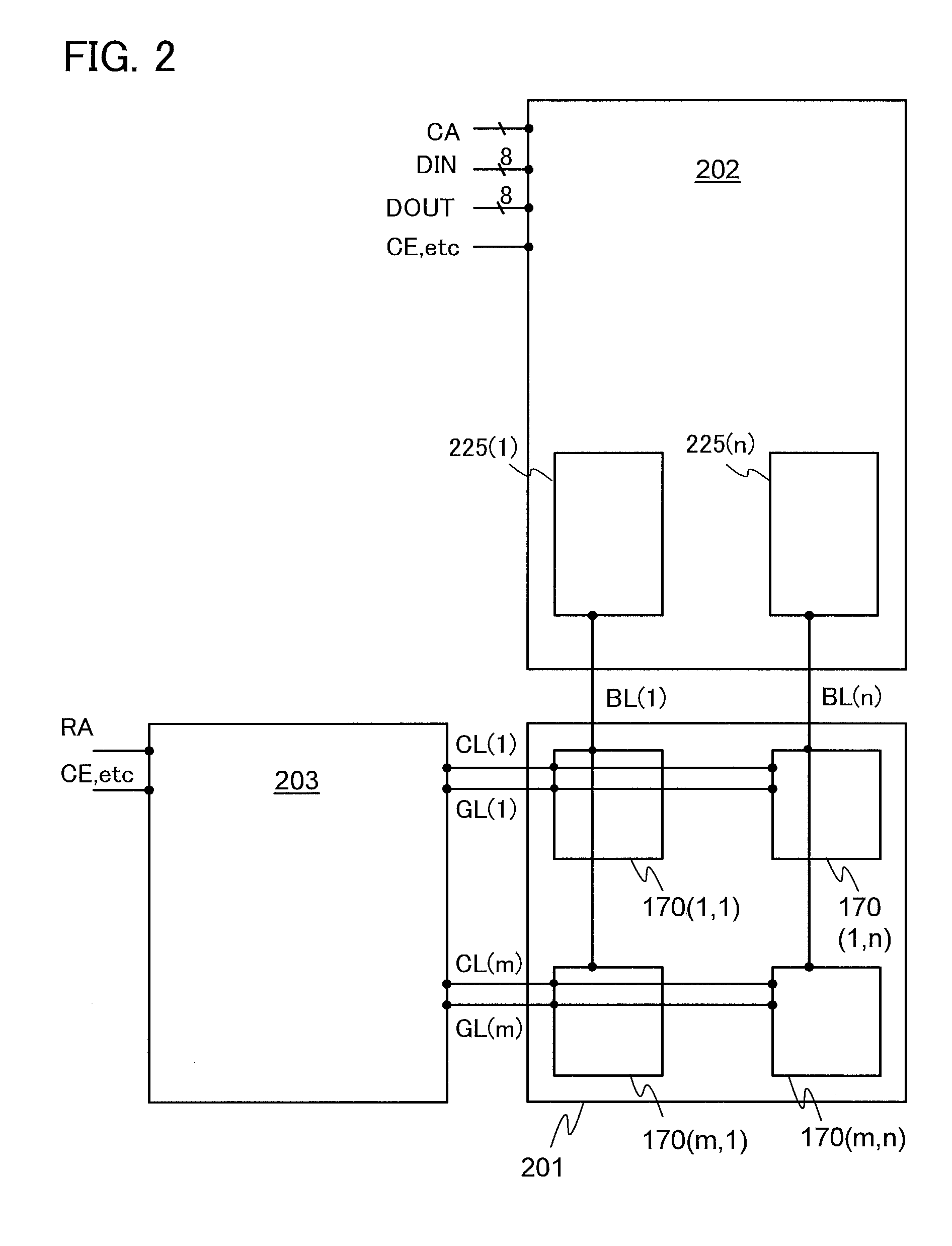

InactiveUS20120032162A1Sufficient reduction in power consumptionReduce the refresh rateTransistorSolid-state devicesBit lineSemiconductor materials

An object is to provide a semiconductor device which can hold stored data even when not powered and which achieves high integration by reduction of the number of wirings. The semiconductor device is formed using a material which can sufficiently reduce the off-state current of a transistor, e.g., an oxide semiconductor material which is a wide bandgap semiconductor. When a semiconductor material which allows a sufficient reduction in the off-state current of a transistor is used, data can be held for a long period. One line serves as the word line for writing and the word line for reading and one line serves as the bit line for writing and the bit line for reading, whereby the number of wirings is reduced. Accordingly, the storage capacity per unit area is increased.

Owner:SEMICON ENERGY LAB CO LTD

Liquid crystal display device, method for driving the same, and electronic device including the same

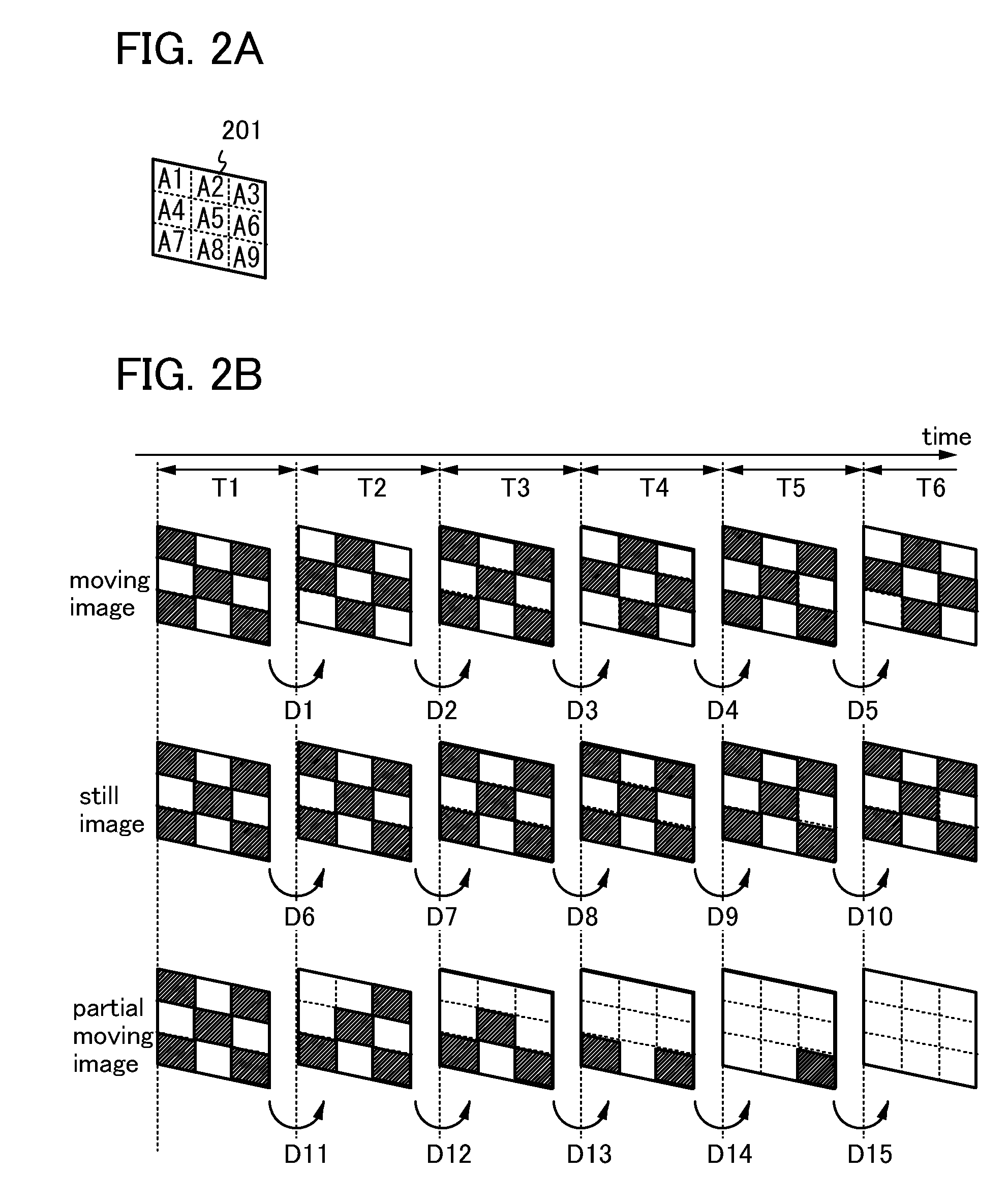

ActiveUS20110128461A1Reduce leakageReduce off-state currentSolid-state devicesCathode-ray tube indicatorsDriver circuitLiquid-crystal display

The liquid crystal display device includes a pixel portion including a plurality of pixels to which image signals are supplied; a driver circuit including a signal line driver circuit which selectively controls a signal line and a gate line driver circuit which selectively controls a gate line; a memory circuit which stores the image signals; a comparison circuit which compares the image signals stored in the memory circuit in the pixels and detects a difference; and a display control circuit which controls the driver circuit and reads the image signal in accordance with the difference. The display control circuit supplies the image signal only to the pixel where the difference is detected. The pixel includes a thin film transistor including a semiconductor layer including an oxide semiconductor.

Owner:SEMICON ENERGY LAB CO LTD

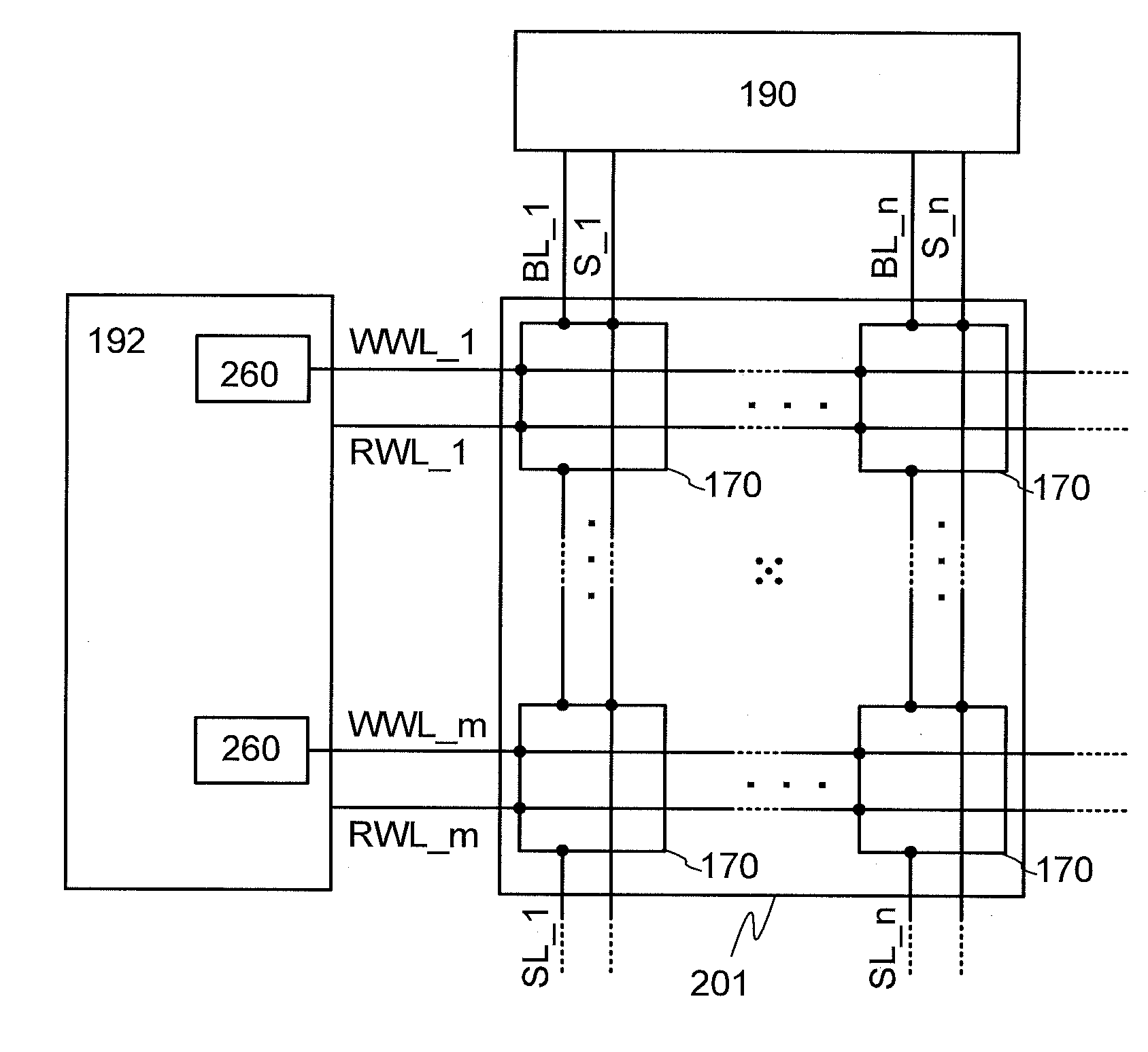

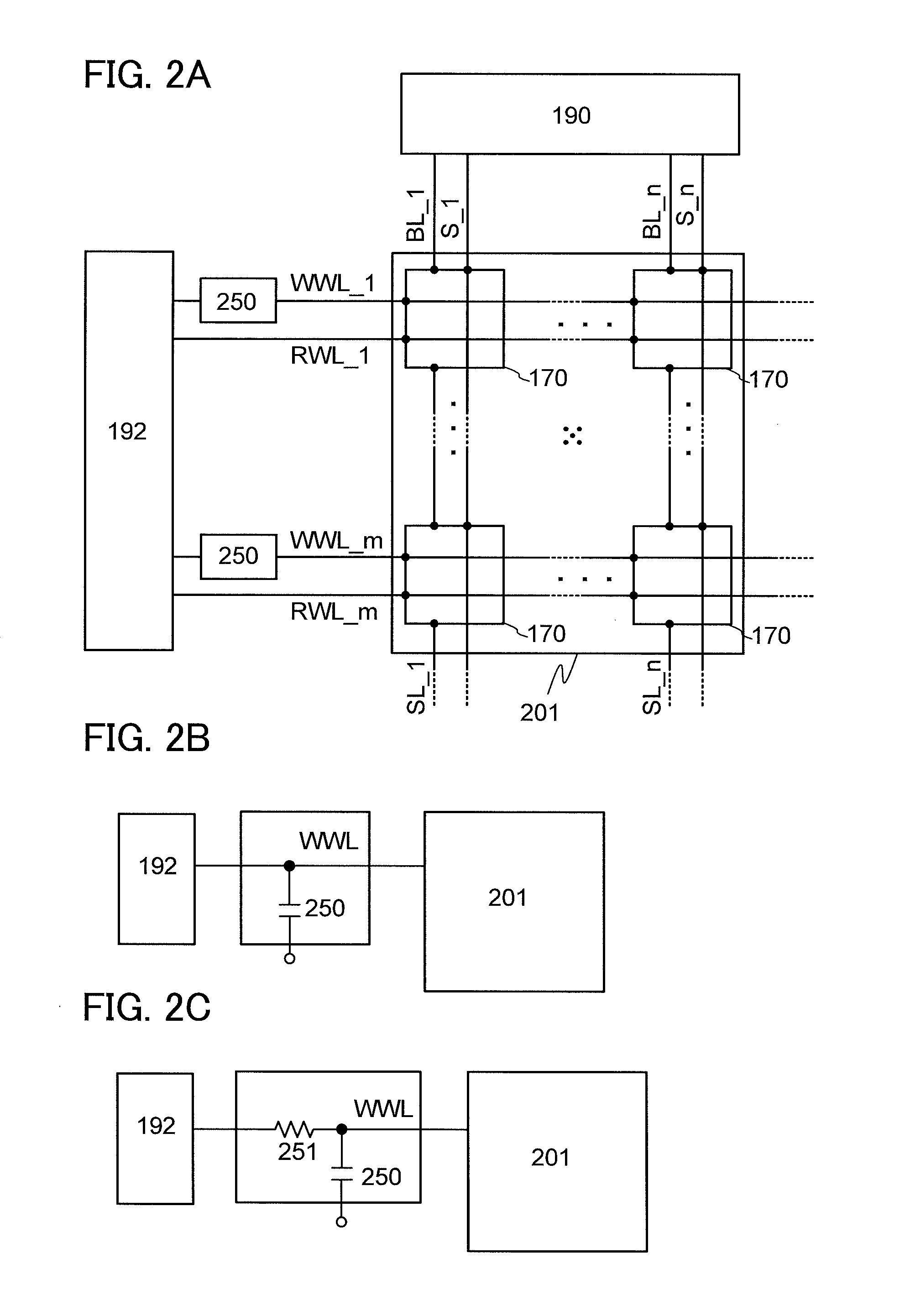

Semiconductor device

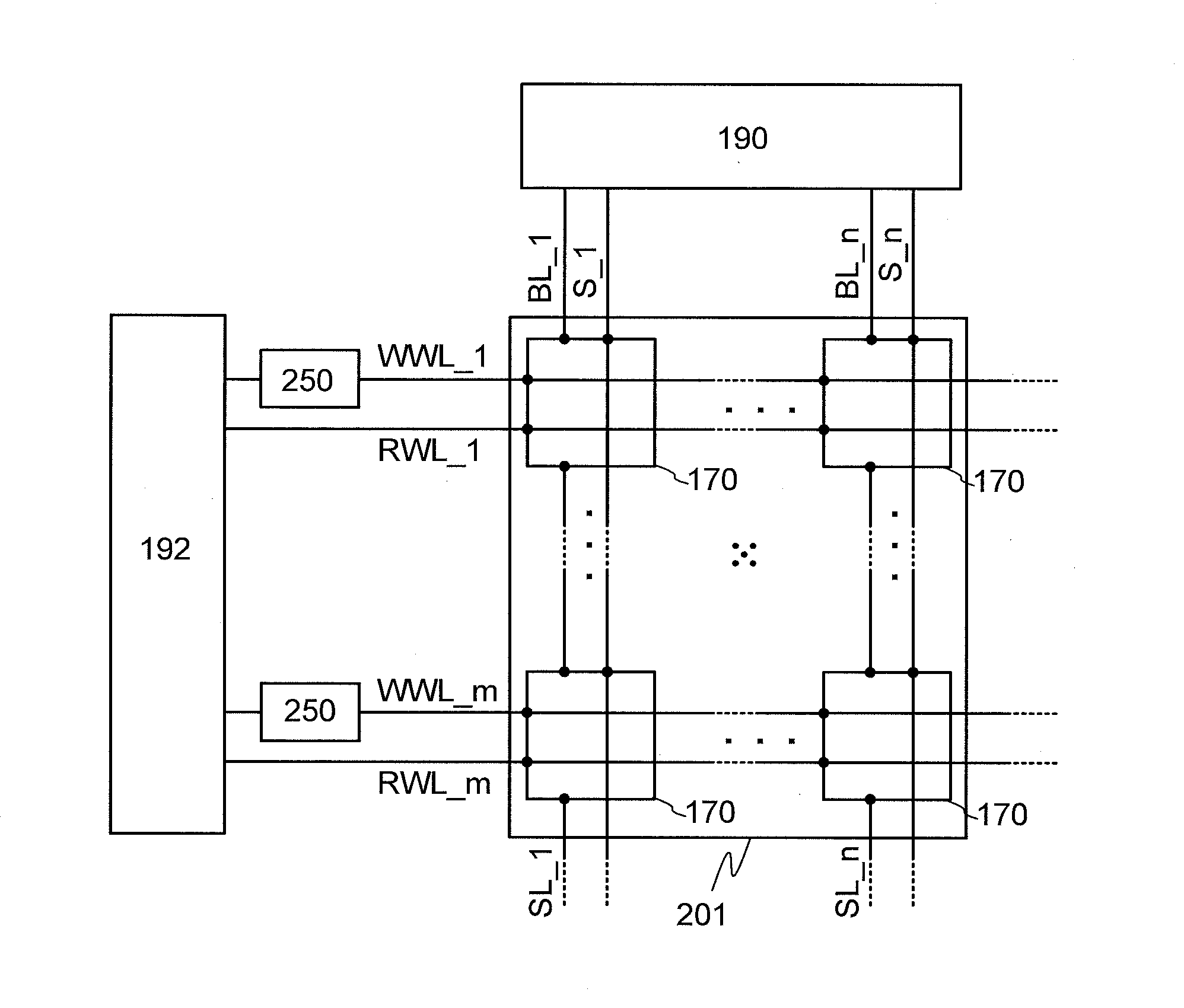

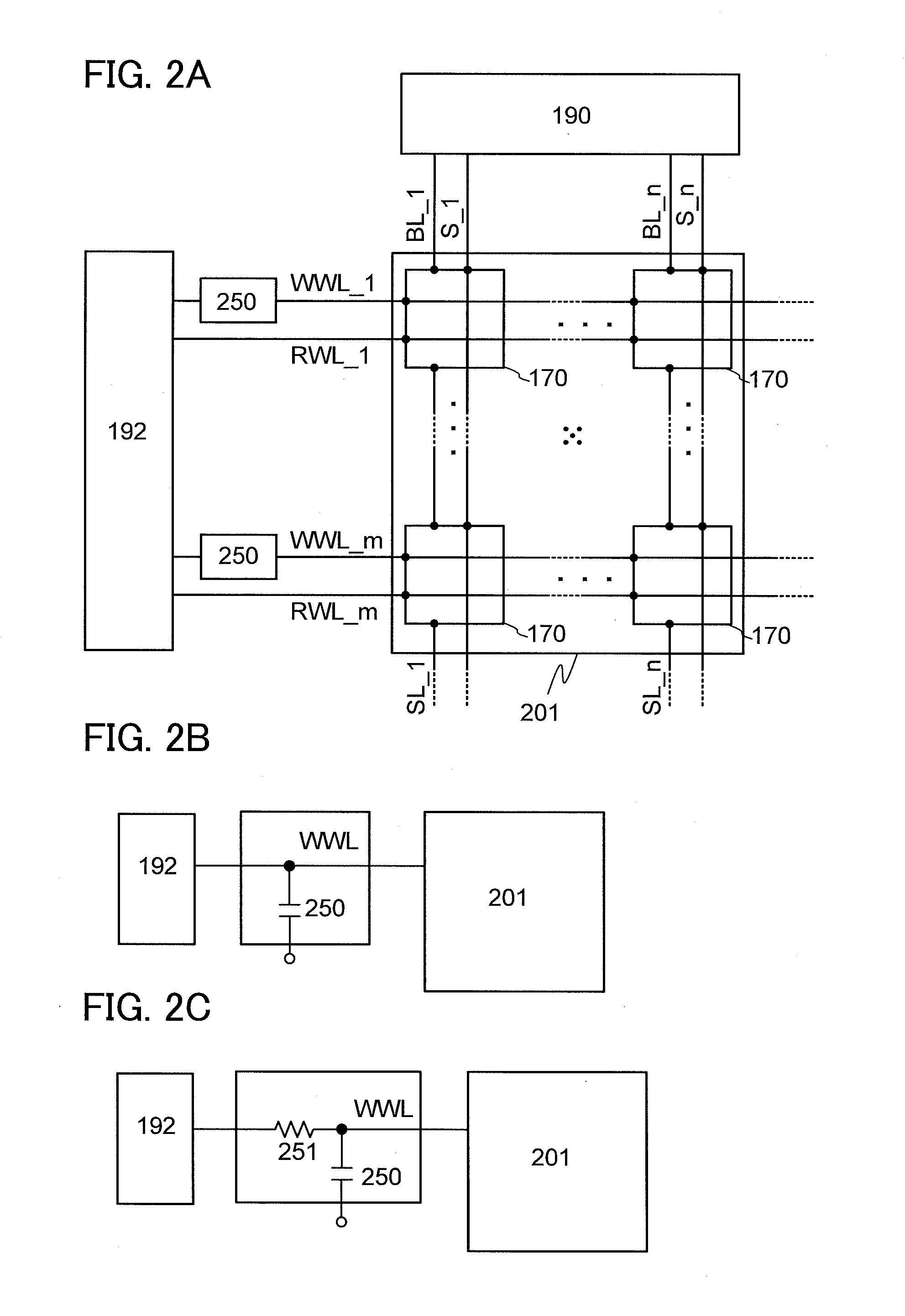

ActiveUS20120063205A1Novel structureReduce off-state currentSolid-state devicesRead-only memoriesOxide semiconductorOxide

A semiconductor device in which stored data can be held even when power is not supplied and there is no limitation on the number of writing operations is provided. A semiconductor device is formed using a material which can sufficiently reduce the off-state current of a transistor, such as an oxide semiconductor material that is a wide-gap semiconductor. When a semiconductor material which can sufficiently reduce the off-state current of a transistor is used, the semiconductor device can hold data for a long period. In addition, by providing a capacitor or a noise removal circuit electrically connected to a write word line, a signal such as a short pulse or a noise input to a memory cell can be reduced or removed. Accordingly, a malfunction in which data written into the memory cell is erased when a transistor in the memory cell is instantaneously turned on can be prevented.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

InactiveUS20120032161A1Sufficient reduction in power consumptionReduce the refresh rateTransistorSolid-state devicesBit lineSemiconductor materials

An object is to provide a semiconductor device which can hold stored data even when not powered and which achieves high integration by reduction of the number of wirings. The semiconductor device is formed using a material which can sufficiently reduce the off-state current of a transistor, e.g., an oxide semiconductor material which is a wide bandgap semiconductor. When a semiconductor material which allows a sufficient reduction in the off-state current of a transistor is used, data can be held for a long period. One line serves as the word line for writing and the word line for reading and one line serves as the bit line for writing and the bit line for reading, whereby the number of wirings is reduced. Further, by reducing the number of source lines, the storage capacity per unit area is increased.

Owner:SEMICON ENERGY LAB CO LTD

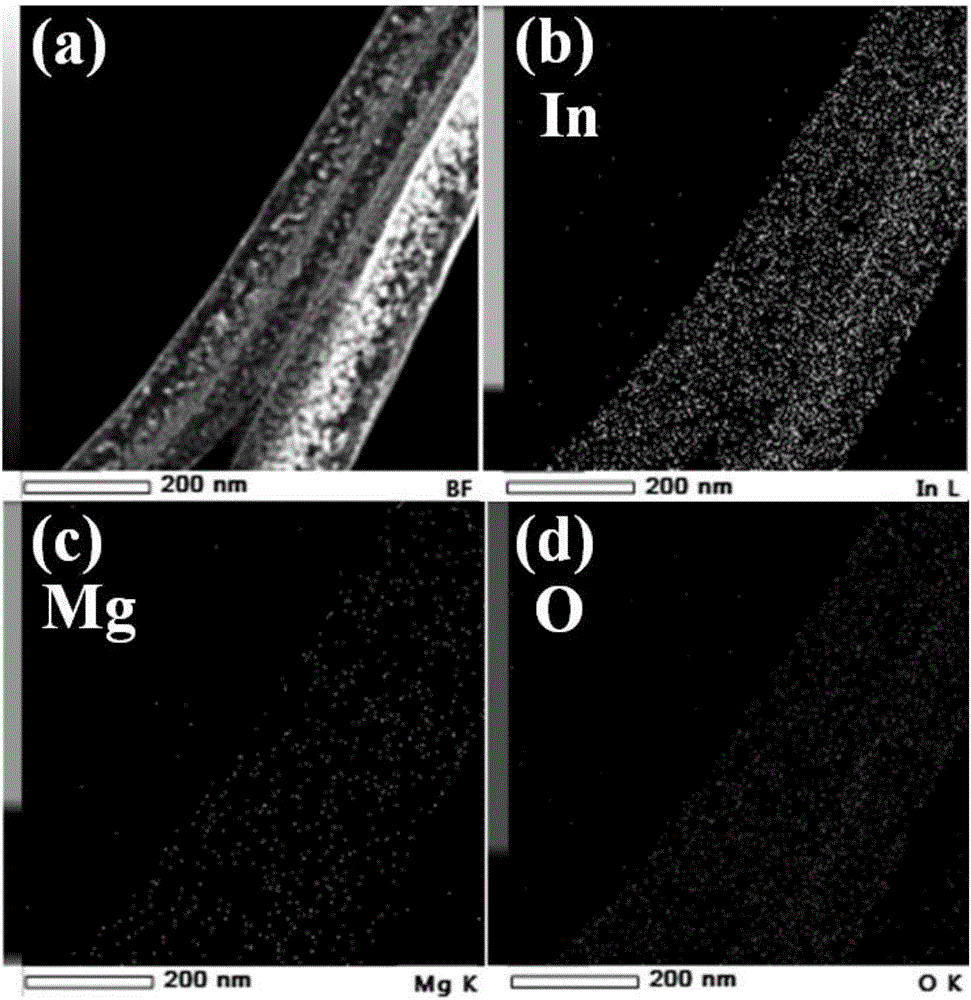

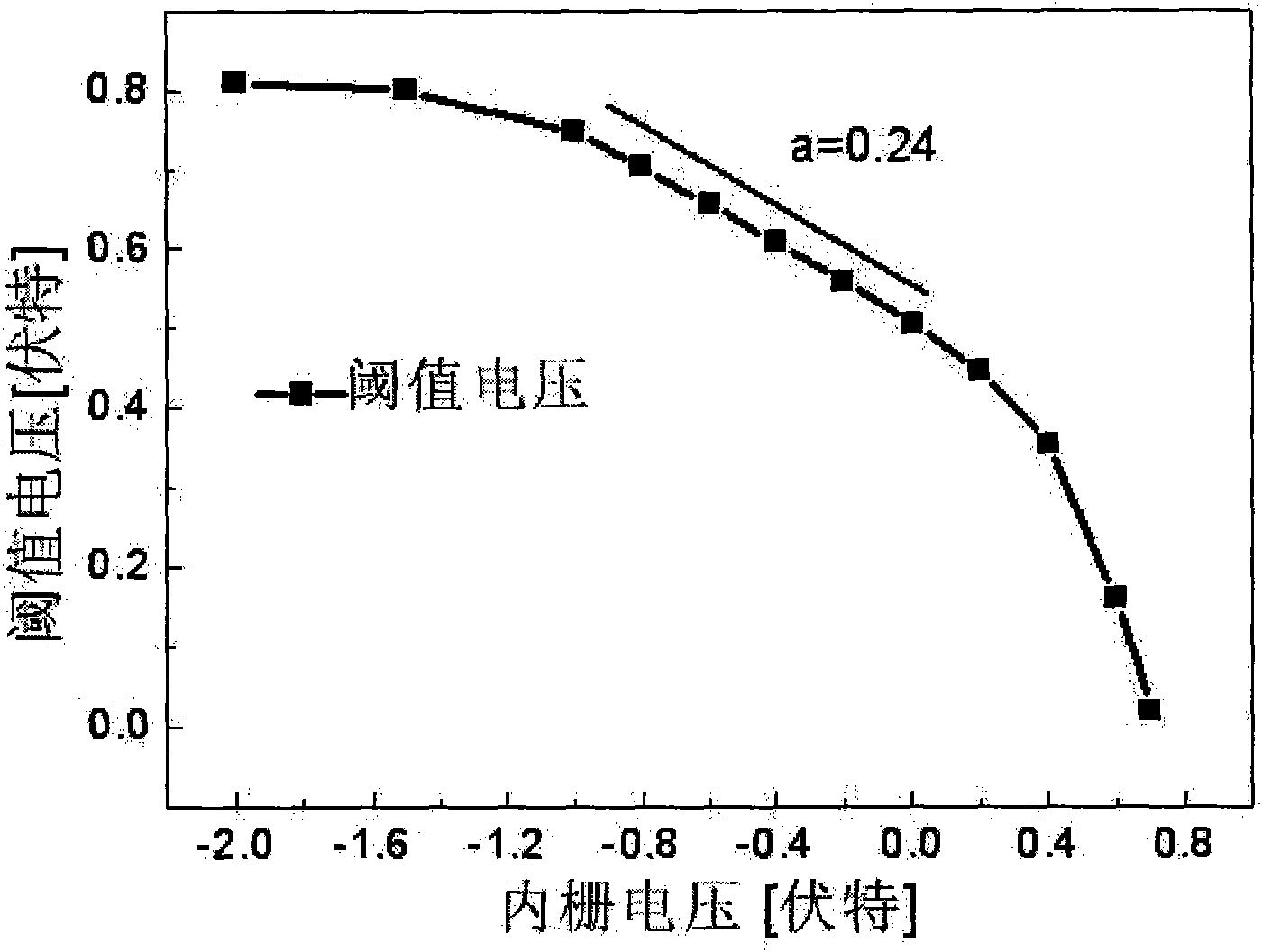

Regulation and control method for electrical property of indium oxide nanofiber field effect transistor

InactiveCN106486541ARegulation transmissionReduce concentrationInorganic material artificial filamentsNanoinformaticsIndiumElectrospinning

The invention belongs to the regulation and control technical field of electrical property of a transistor, and relates to a regulation and control method for electrical property of an indium oxide nanofiber field effect transistor. In<2>O<3> nanofibers are prepared through a simple, convenient and low-cost electrospinning technology; the electrical property of the In<2>O<3> nanofiber field effect transistor is regulated and controlled through simple and feasible metal doping so as to regulate and control the electrical property, such as a threshold voltage, an off-state current, a switching ratio and the like, of the In<2>O<3> nanofiber field effect transistor in a simple and convenient, efficient and low-cost manner, in order to obtain the excellent-performance and metal-doped In<2>O<3> nanofiber field effect transistor; the preparation process is simple, convenient, and safe, and the principle is reliable, and the production cost is low; and the prepared In<2>O<3> nanofibers and the metal-doped In<2>O<3> nanofibers have wide application prospect in the fields of an electronic switching device, a display, biological and chemical sensors and the like, and large-scale industrial production can be performed easily.

Owner:QINGDAO UNIV

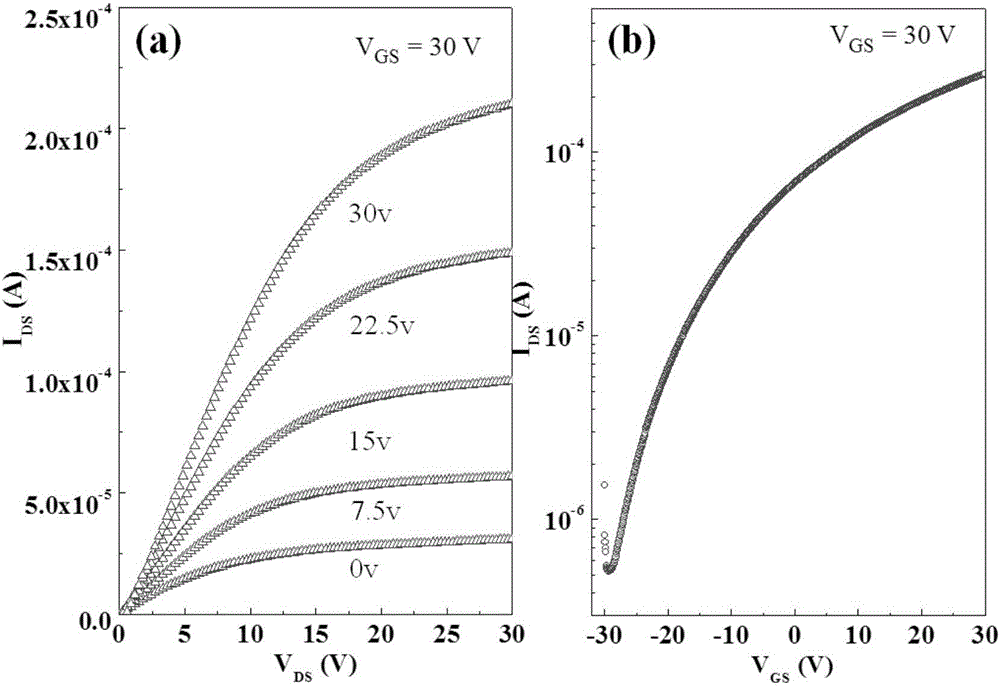

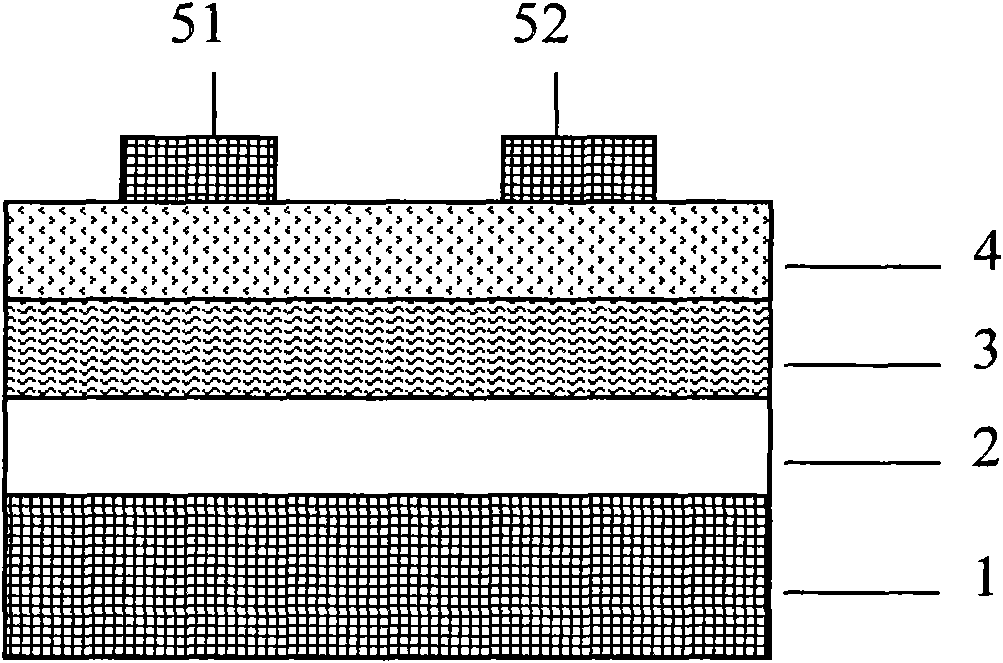

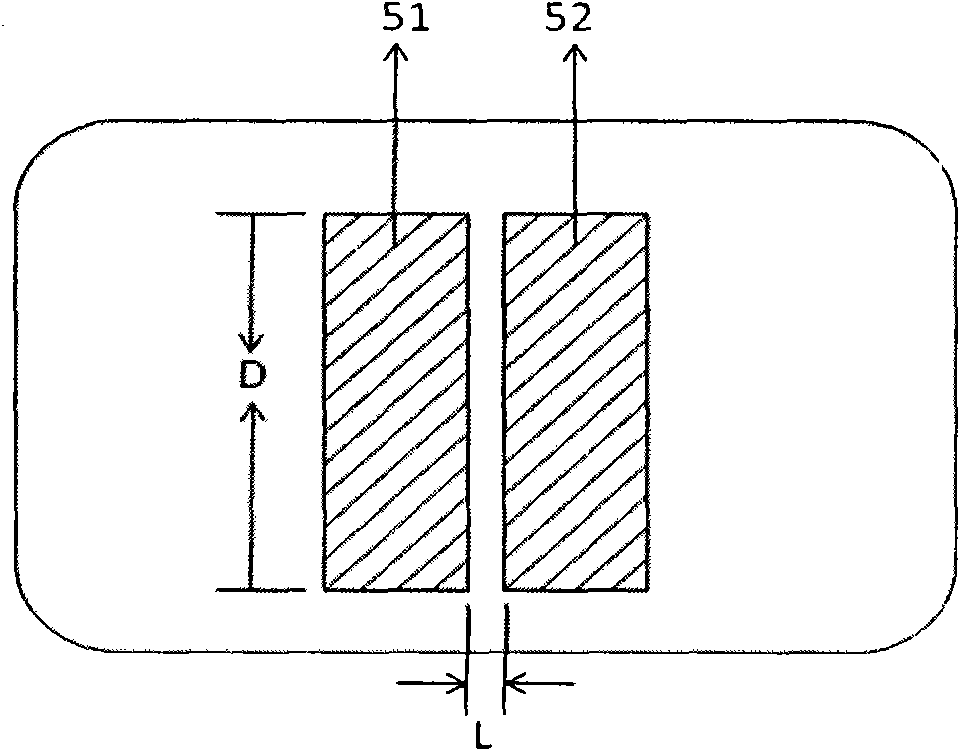

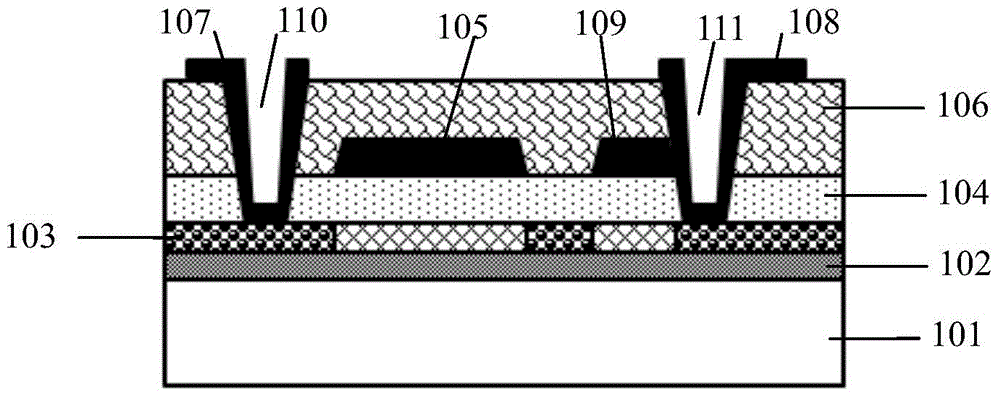

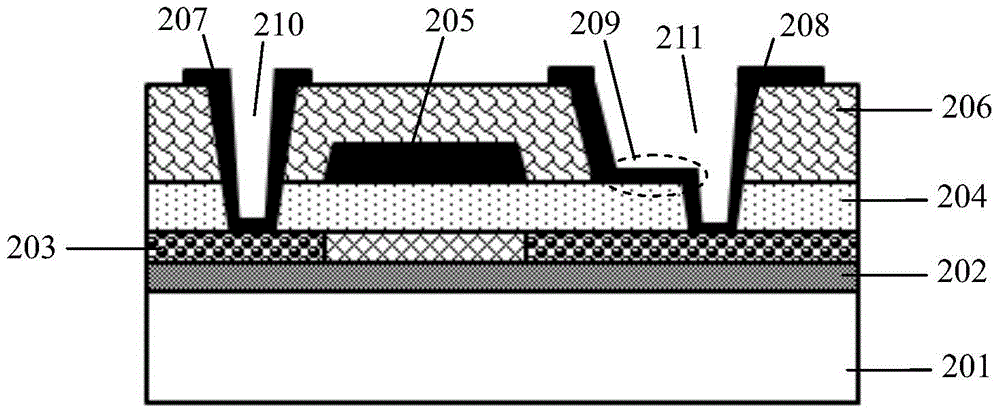

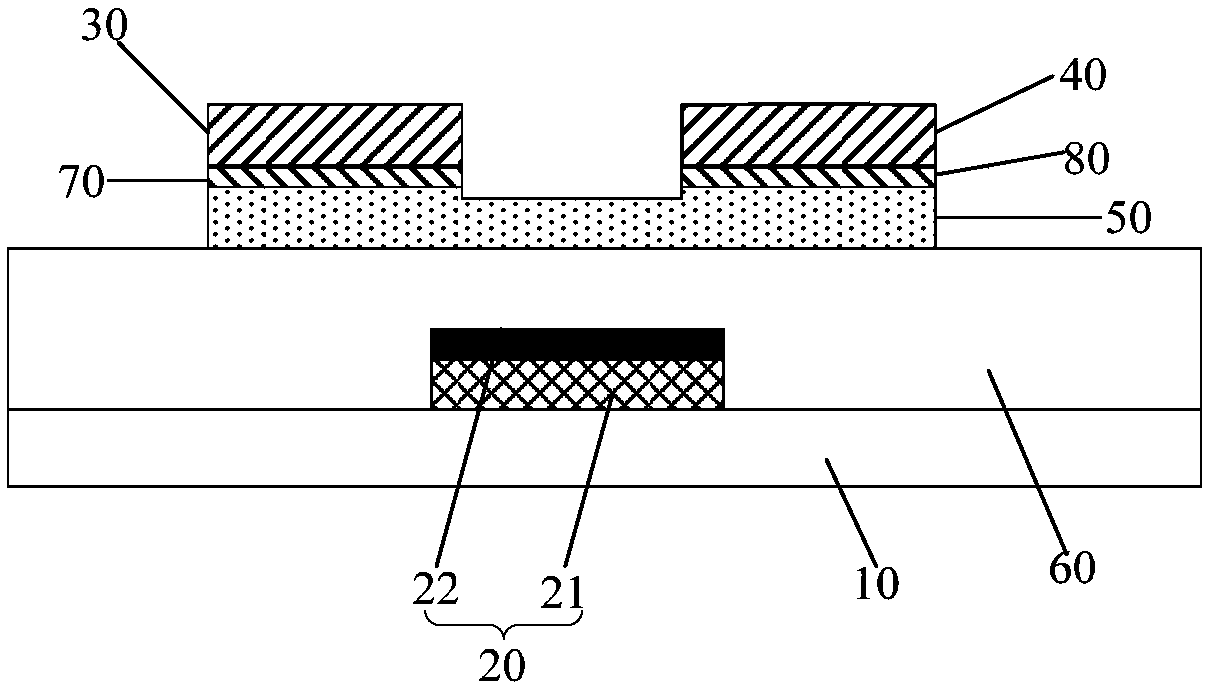

Metal oxide thin film transistor and preparation method thereof

InactiveCN101872787AReduce off-state currentImprove mobilityTransistorSemiconductor/solid-state device manufacturingElectrical stabilityOhmic contact

The invention discloses a metal oxide thin film transistor and a preparation method thereof. The metal oxide thin film transistor is composed of a grid electrode, an insulating layer, a transition layer, a semiconductor layer, a drain electrode and a source electrode, wherein the grid electrode, the insulating layer, the transition layer and the semiconductor layer are sequentially connected with each other from bottom to top; the drain electrode and the source electrode are positioned on the semiconductor layer; the transition layer and the semiconductor layer are prepared by means of sputtering with the same target being adopted in the process of sputtering, the material of the target is (In2O3)x(Ga2O3)y(ZnO)z, wherein x, y and z are not less than 0 but not more than 1, and x+y+z is equal to 1; and the transition layer and the insulating layer include excellent contact property so as to effectively lower carrier trap density between contact interfaces of the insulating layer and the transition layer as well as enhance output current of the transistor and improve electrical stability. The source electrode and the drain electrode can form outstanding ohmic contact with the semiconductor layer, thereby effectively reducing off-state current, raising on / off ratio of current and improving electronic carrier mobility.

Owner:SOUTH CHINA UNIV OF TECH

Semiconductor device

InactiveUS20120033510A1Reduce off-state currentLonger heldSolid-state devicesDigital storagePower semiconductor devicePower flow

An object is to provide a semiconductor device with a novel structure, which can hold stored data even when power is not supplied and which has an unlimited number of write cycles. The semiconductor device is formed using a memory cell including a wide band gap semiconductor such as an oxide semiconductor. The semiconductor device includes a potential change circuit having a function of outputting a potential lower than a reference potential for reading data from the memory cell. When the wide band gap semiconductor which allows a sufficient reduction in of state current of a transistor included in the memory cell is used, a semiconductor device which can hold data for a long period can be provided.

Owner:SEMICON ENERGY LAB CO LTD

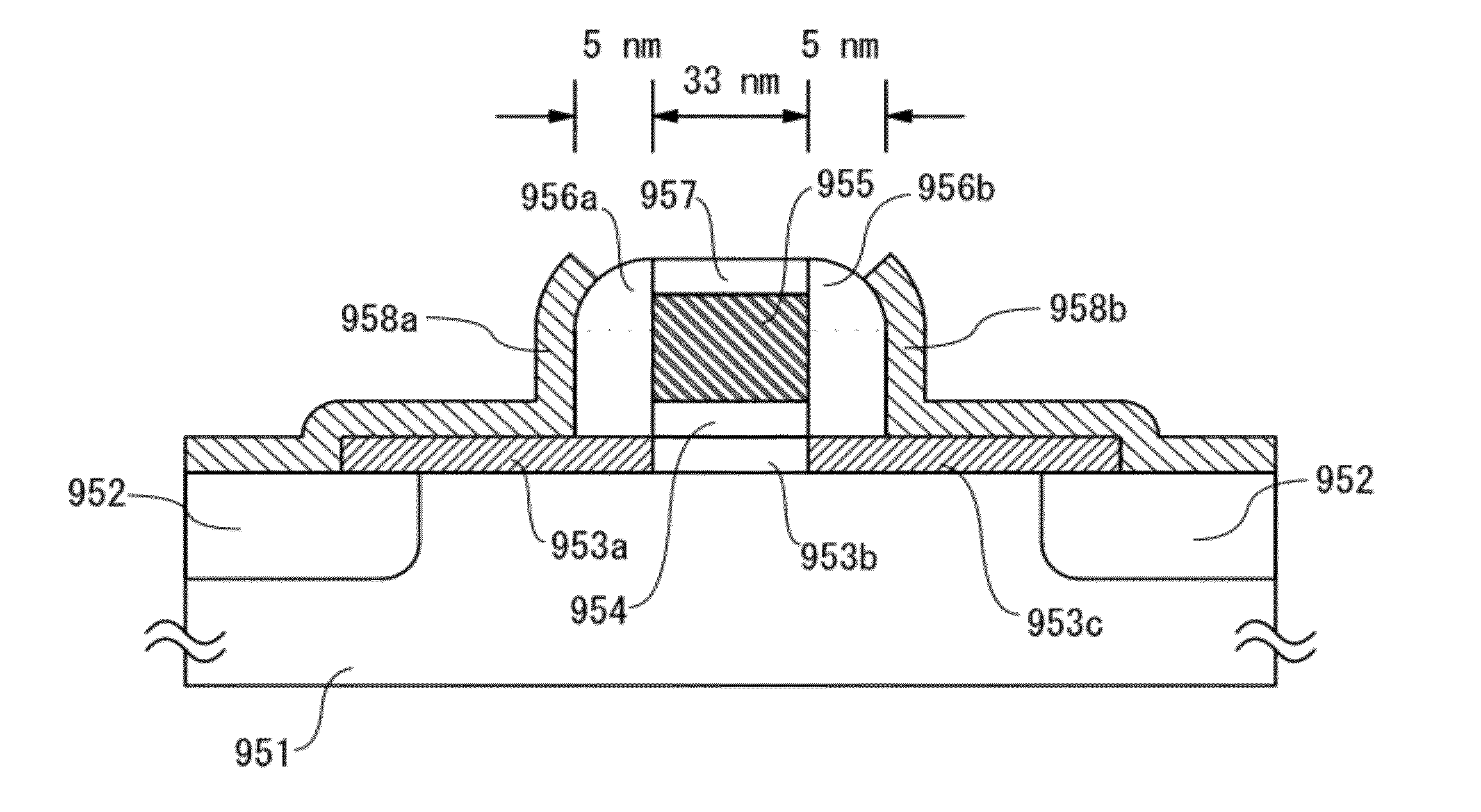

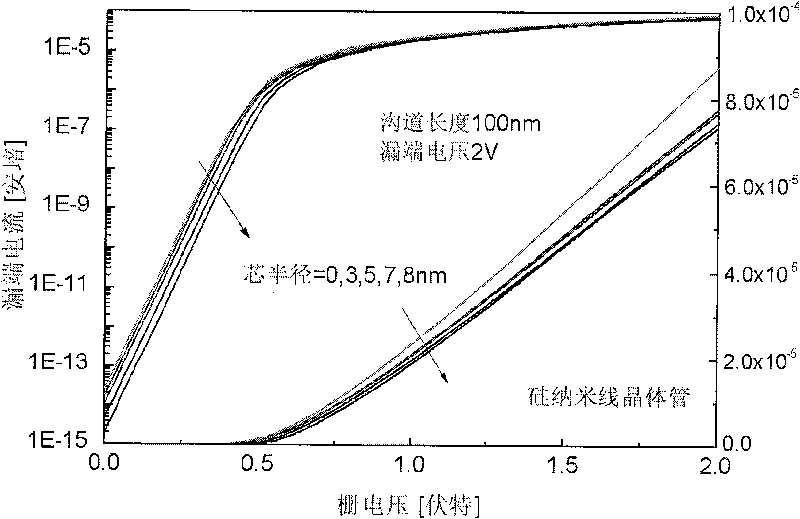

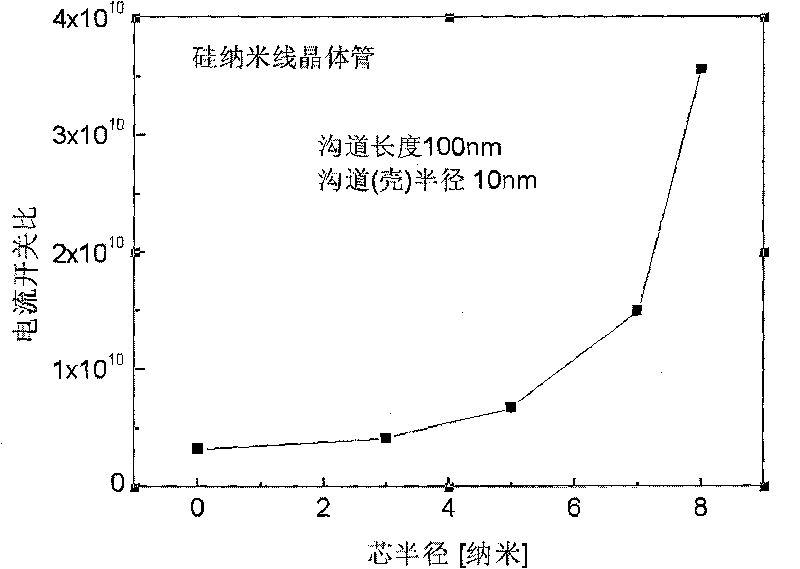

Nano-wire field effect transistor

ActiveCN101740619AReduce off-state currentReduce static power consumptionSemiconductor devicesGate dielectricNanowire

The invention discloses a nano-wire field effect transistor comprising a gate electrode, a source region, a drain region, a central region and a gate dielectric layer. The central region is in the core-shell structures which are coaxial; the gate dielectric layer fully surrounds the central region; the gate electrode fully surrounds the gate dielectric layer; the source region and the drain region are respectively arranged on two sides of the central region; the core structure of the central region is made from insulating material, and the shell structure of the central region is made from semiconductor material; the doping type and the doping concentration of the semiconductor material of the shell structure of the central region are adjustable; the lengths of both the core structure and the shell structure and the radii of both the core structure and the shell structure are adjustable; and the materials of the gate dielectric layer, the gate electrode, the source region and the drain region are adjustable. Due to the adoption of the insulating core structure, the off-current of the traditional nano-wire transistor can be reduced effectively, and the current on-off ratio of the devices can be increased. The threshold voltage shifting and the drain induced barrier lowering of the nano-wire field effect transistor are less affected by the short channel effect, and the size reducing performance of the nano-wire field effect transistor is more excellent.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

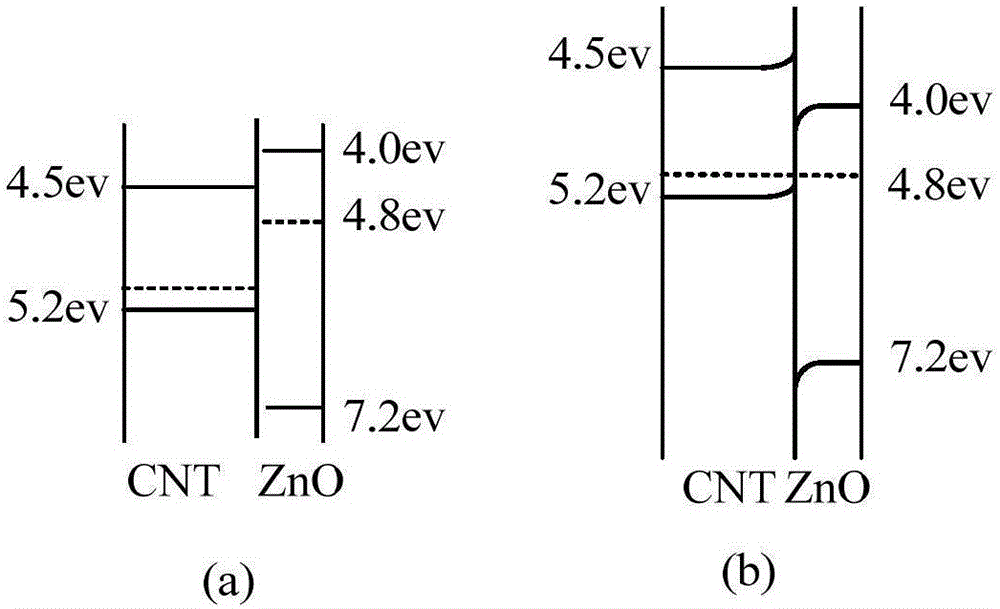

Two-dimensional material/semiconductor hetero-junction tunneling transistor and preparation method thereof

ActiveCN107104140AEffective tunnelingDirect tunnelingSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsPower flow

The invention discloses a tunneling field effect transistor based on a two-dimensional material / semiconductor hetero-junction and a preparation method thereof. A device forms an interleaved energy band structure in the off state through the energy band design, namely, a tunneling window is inexistent between the two-dimensional material and the semiconductor material, and the ultra-low off-state current can be acquired; the grid voltage can be applied to regulate an energy band alignment way at the two-dimensional material / semiconductor hetero-junction so that the device can form the staggered energy band structure in the on-state, and the effective tunneling barrier height is a negative value; and meanwhile, the current carrier tunnels to a channel region from a source region to realize the direct tunneling, thereby acquiring large on-state current. The device adopts the highly-doped three-dimensional semiconductor material as the source region material, and the three-dimensional semiconductor material and the metal source electrode are unipotential; since the thickness of the two-dimensional material is ultra-thin, the grid voltage can regulate the two-dimensional material and the energy band at the two-dimensional material / semiconductor hetero-junction interface, thereby acquiring an ideal grid control capacity. The tunneling field effect transistor disclosed by the invention is simple in process, and large in compatibility with the traditional semiconductor process.

Owner:PEKING UNIV

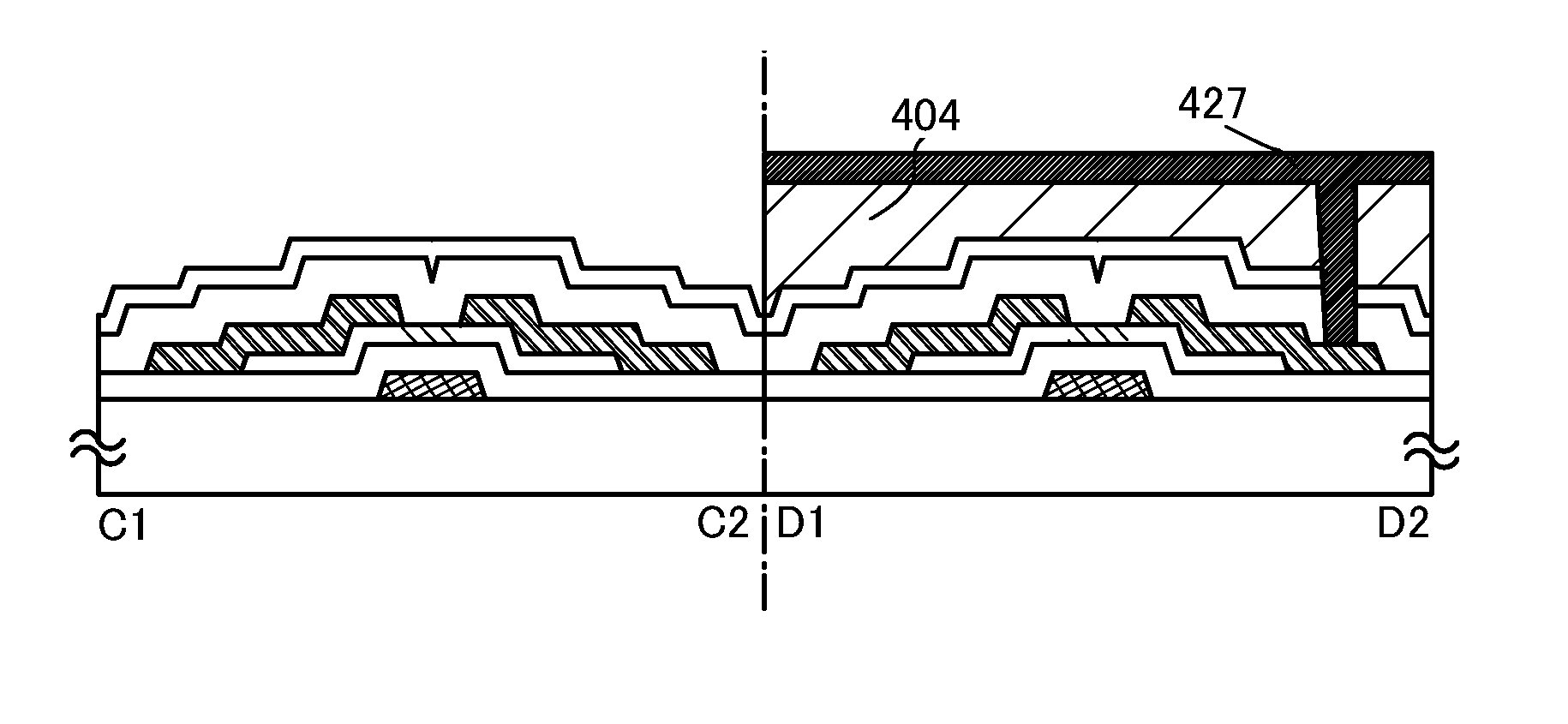

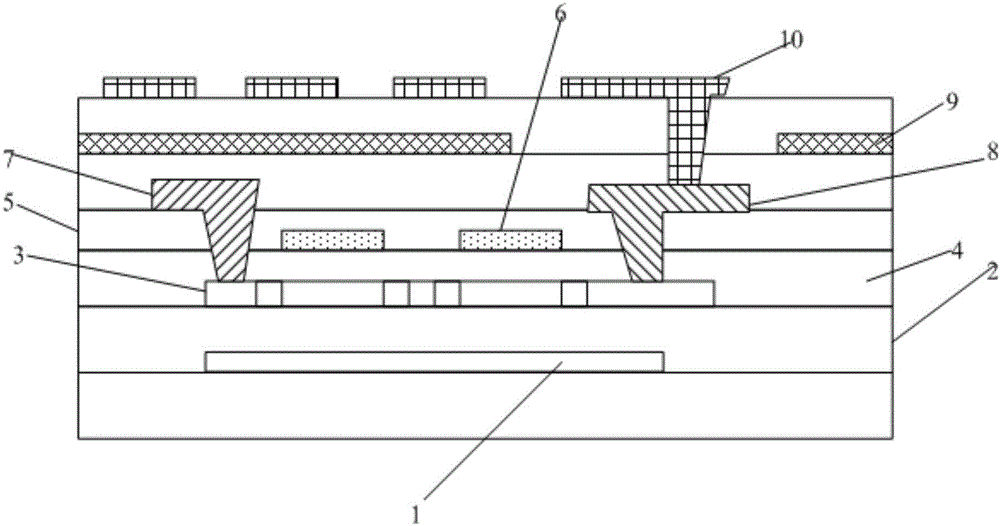

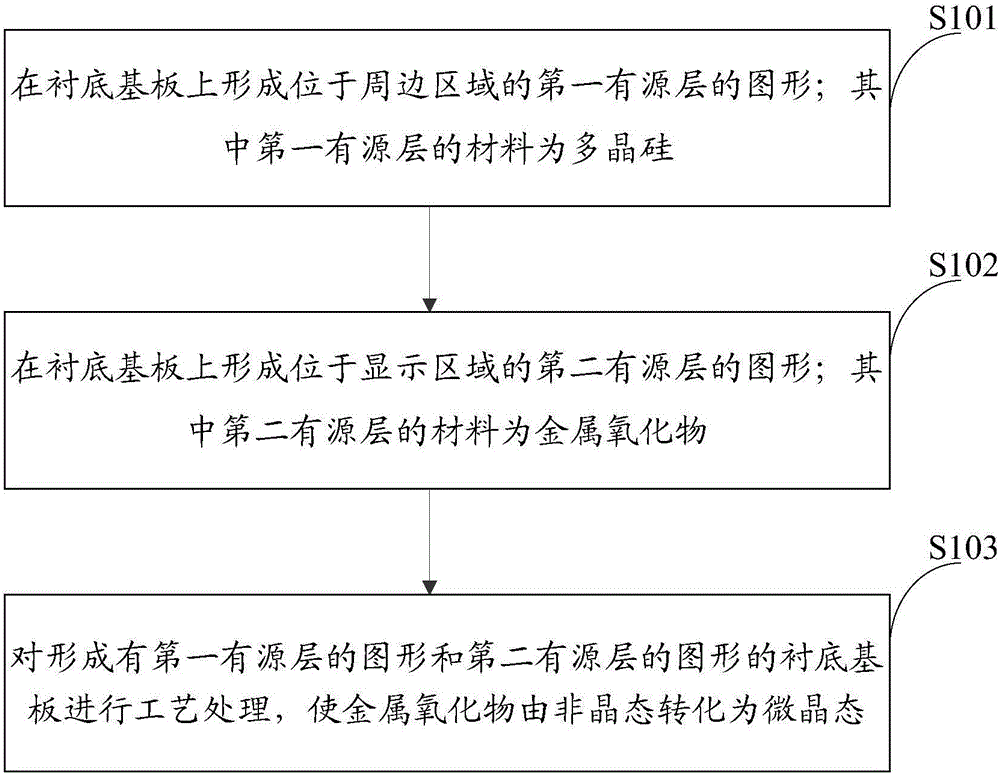

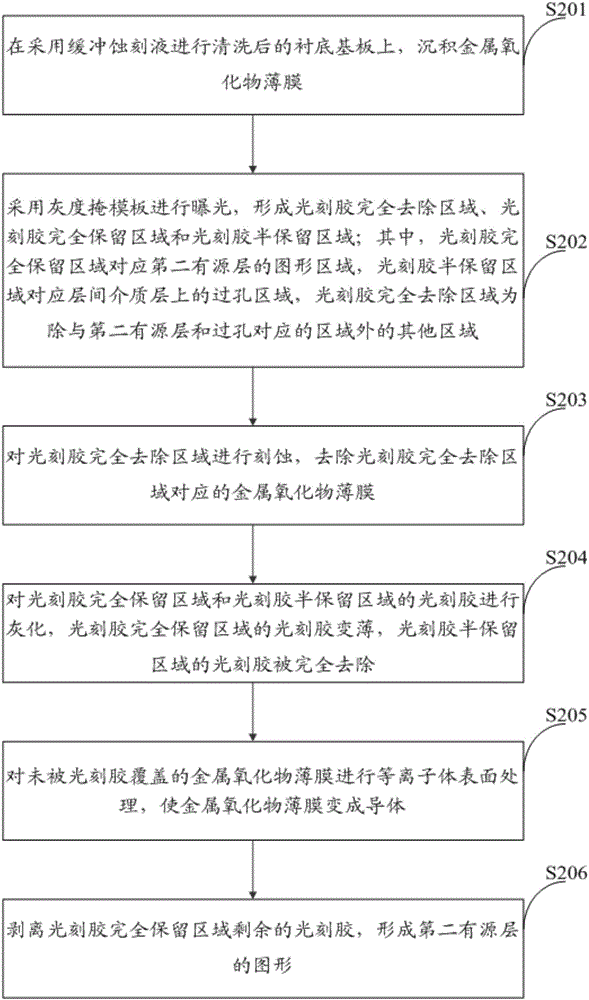

Array substrate, manufacturing method thereof, display panel and manufacturing method thereof

ActiveCN106098699AHigh electron mobilityImprove driving abilitySolid-state devicesSemiconductor/solid-state device manufacturingPower flowEngineering

The invention discloses an array substrate, a manufacturing method thereof, a display panel and a manufacturing method thereof. A first active layer manufactured from a metal oxide is used in a display area on the array substrate, so that the off-state current of a formed first switch transistor is relatively low, the metal oxide through fabrication processing can become into a microcrystal state from an amorphous state, and the stability of the first switch transistor is improved; and moreover, a second active layer manufactured from a polycrystalline silicon material is used in a surrounding area on the array substrate, so that a formed second switch transistor has relatively high electron mobility and relatively high drive capability and is applicable to constructing a drive circuit, and the requirement of an integrated drive circuit design in the surrounding area on the array substrate is met. In conclusion, the active layers of the switch transistors manufactured from the metal oxide and the polycrystalline silicon are used in the display area and the surrounding area on the array substrate respectively, so that the structural design of the array substrate is optimized, the display effect of the display product is guaranteed, and the product yield is improved.

Owner:BOE TECH GRP CO LTD

Thin film transistor and manufacturing method thereof

InactiveUS20090261330A1Increase currentTotal current dropTransistorSolid-state devicesEngineeringControl quality

It is an object to control quality of a microcrystalline semiconductor film or a semiconductor film including crystal grains so that operation characteristics of a semiconductor element typified by a TFT can be improved. It is another object to improve characteristics of a semiconductor element typified by a TFT by controlling a deposition process of a microcrystalline semiconductor film or a semiconductor film including crystal grains. In addition, it is another object to increase on-state current of a thin film transistor and to reduce off-state current of the thin film transistor. In a semiconductor layer including a plurality of crystalline regions in an amorphous structure, generation positions and generation density of crystal nuclei from which the crystalline regions start to grow are controlled, whereby quality of the semiconductor layer is controlled. In addition, after generation of crystal nuclei from which the crystalline regions start to grow in the semiconductor layer, an impurity element serving as a donor is added to the semiconductor layer, whereby crystallinity of the semiconductor layer is increased and the resistivity of the semiconductor layer is reduced.

Owner:SEMICON ENERGY LAB CO LTD

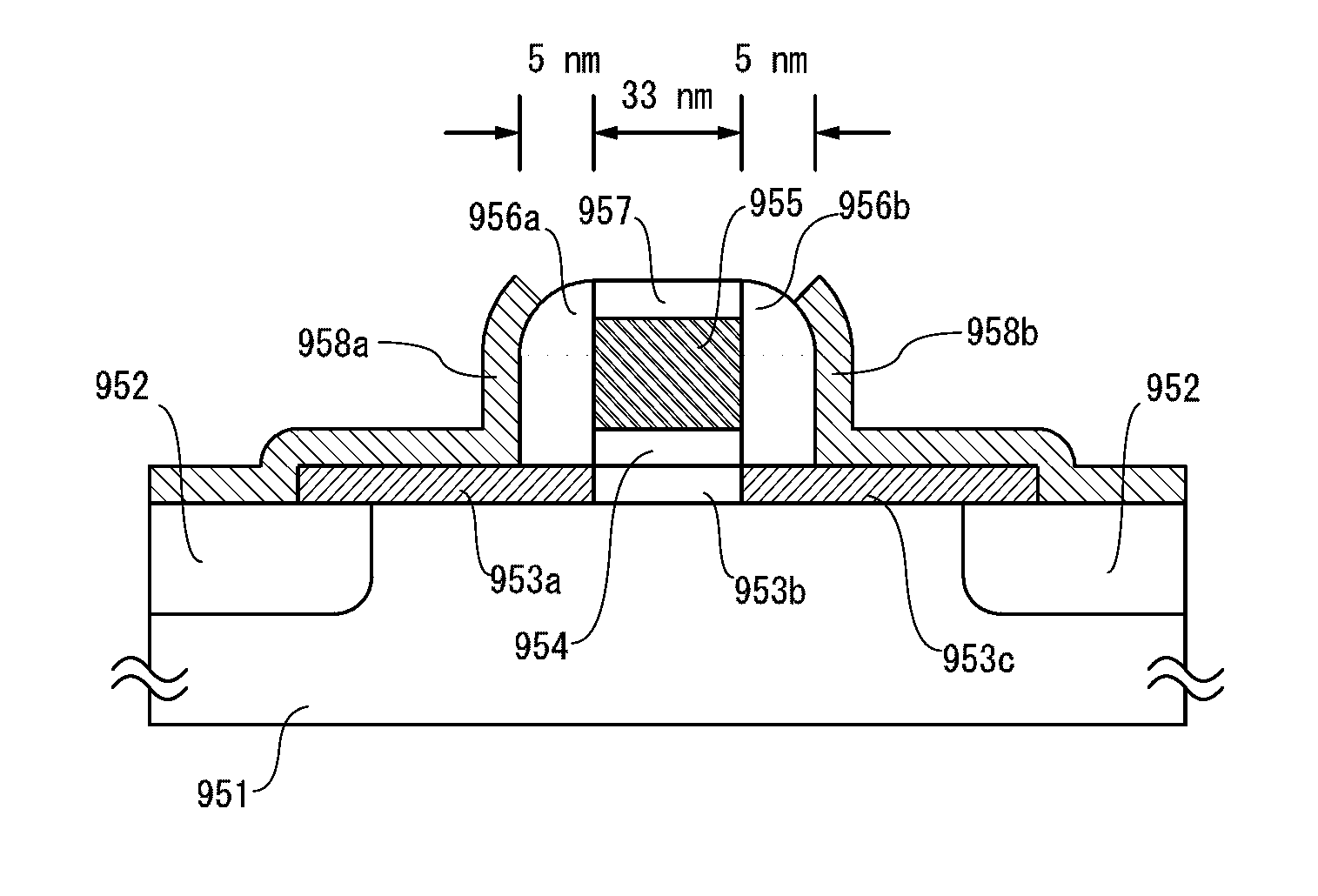

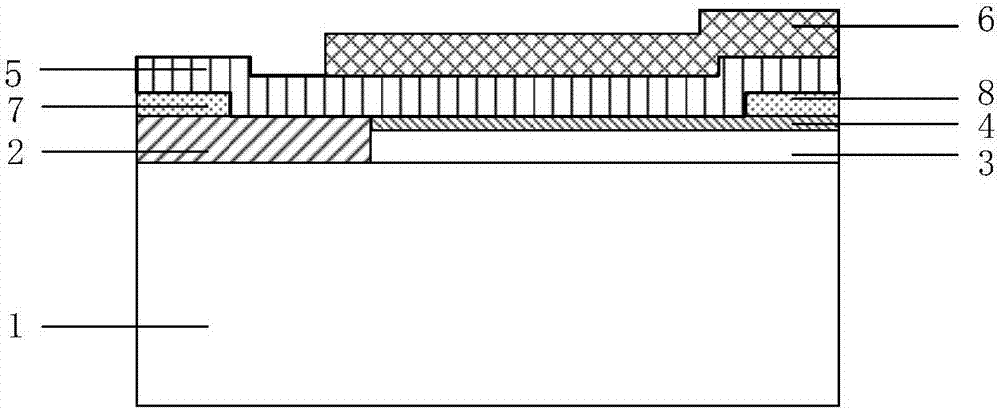

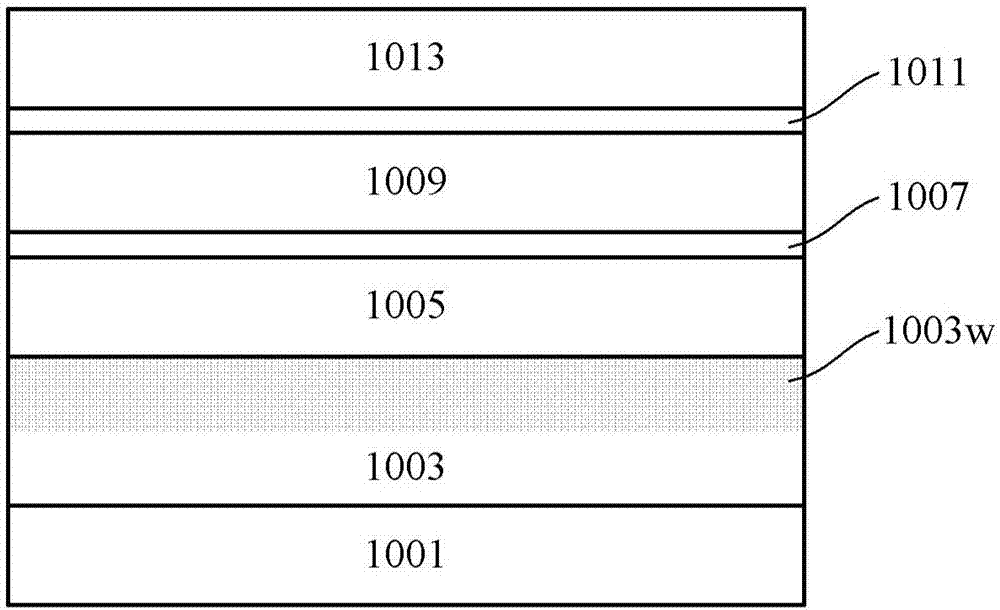

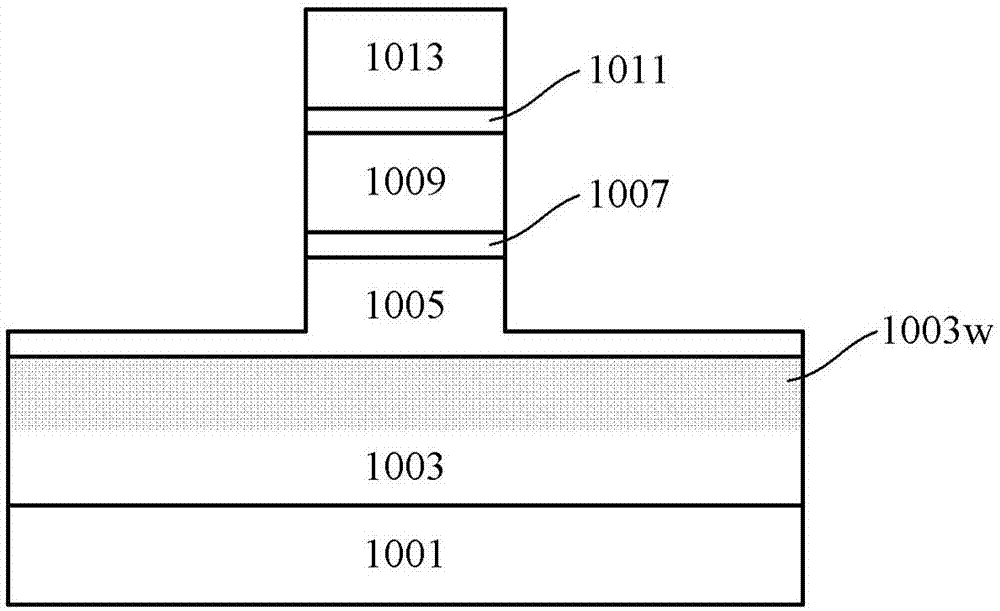

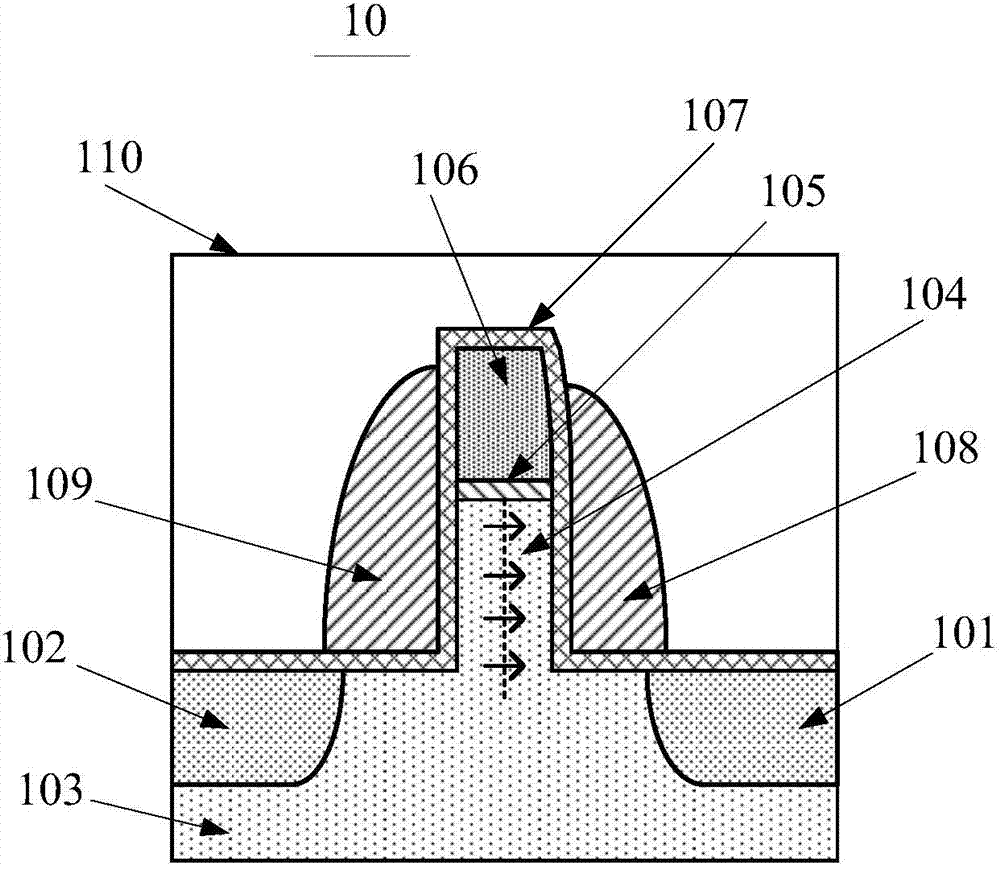

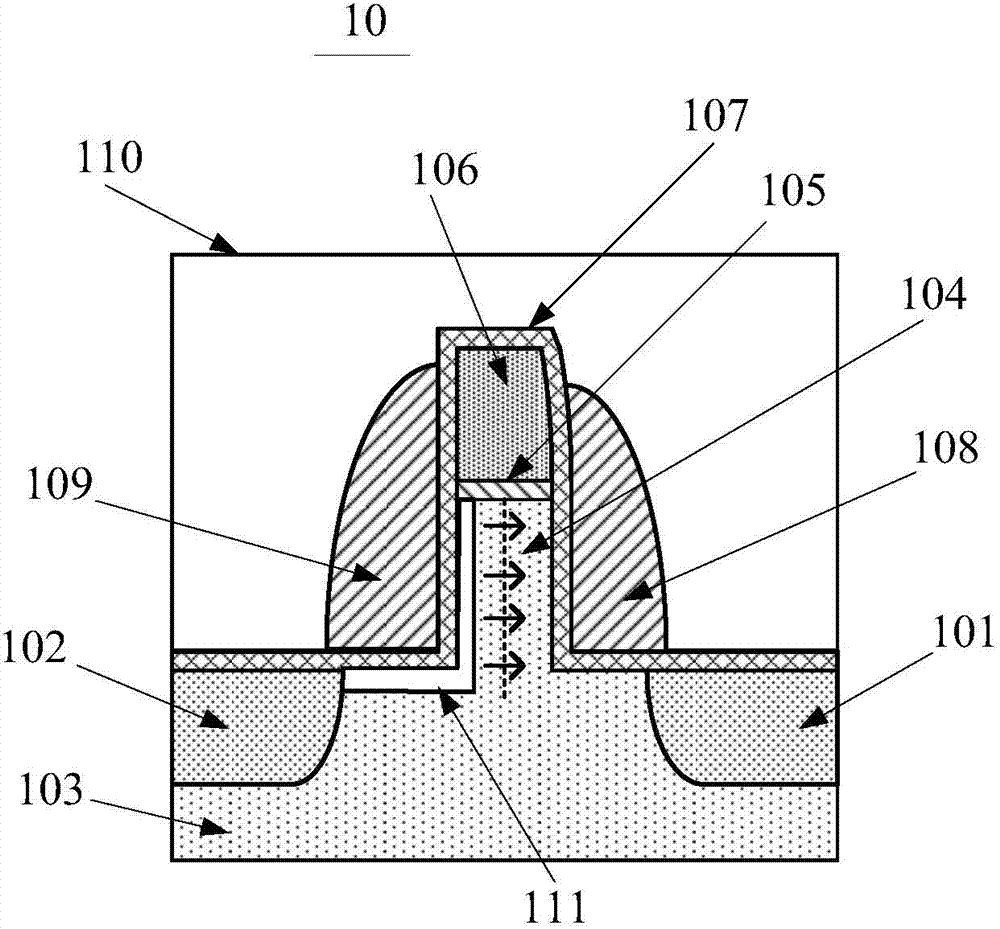

Semiconductor device, manufacturing method thereof and electronic device comprising device

ActiveCN107887441AReduce parasitic capacitanceImprove performanceTransistorProgramme controlSemiconductor materialsGate stack

The invention relates to a semiconductor device, a manufacturing method thereof and an electronic device comprising the device. According to an embodiment, the semiconductor device may include a substrate, a first source / drain layer, a channel layer, a second source / drain layer and a gate stack, wherein the first source / drain layer, the channel layer and the second source / drain layer are sequentially stacked on the substrate, the channel layer contains a semiconductor material which can increase on-state current and / or decrease off-state current compared with Si material, and the gate stack isformed around the periphery of the channel layer.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Tunnel field effect transistor and manufacturing method thereof

ActiveCN104779292AReduce off-state currentReduce static power consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesElectron holeMedia layer

The invention discloses a tunnel field effect transistor and a manufacturing method thereof, and belongs to the technical field of field effect transistors. The tunnel field effect transistor comprises a substrate provided with a first doped region and a second doped region at two ends respectively, wherein a fin-shaped raised channel region, a protective layer, a side wall-shaped channel etching hard mask layer structure and a grid insulation medium layer are formed on the substrate; a first grid and a second grid are formed on the substrate on which the grid insulation medium layer is formed; the first grid and the second grid are positioned on two sides of the channel region respectively; an insulation material filling layer is formed on the substrate on which the first grid and the second grid are formed; the first doped region and the second doped region are spaced a preset distance, and the preset distance is greater than the width of the channel region and smaller than the length of the substrate. The tunnel field effect transistor solves a problem of relatively poor universality of an EHB-TFET (electron hole bilayer-tunnel field effect transistor) structure, achieves an effect of improving the universality, and is used for controlling the on and off of devices.

Owner:湖州优研知识产权服务有限公司

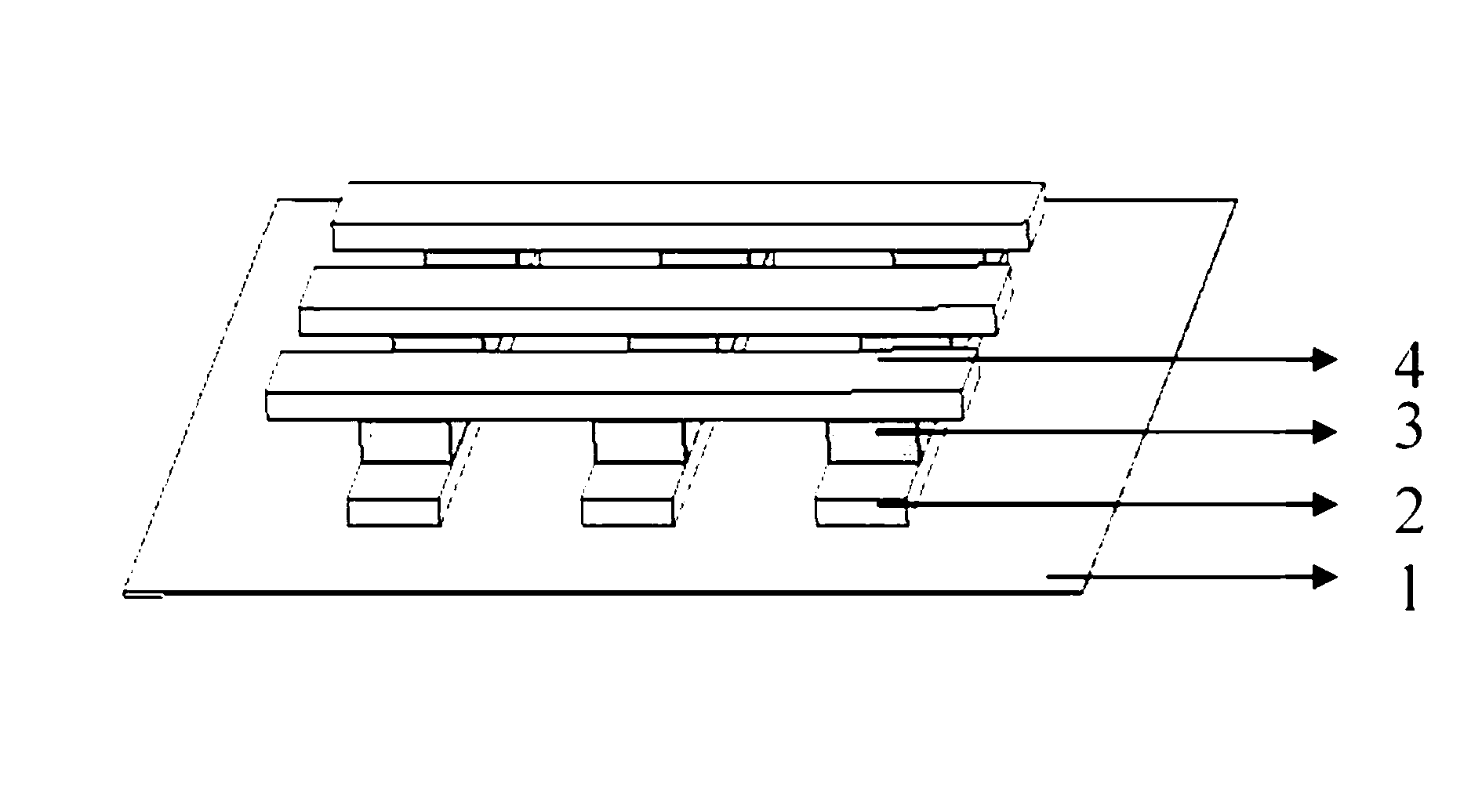

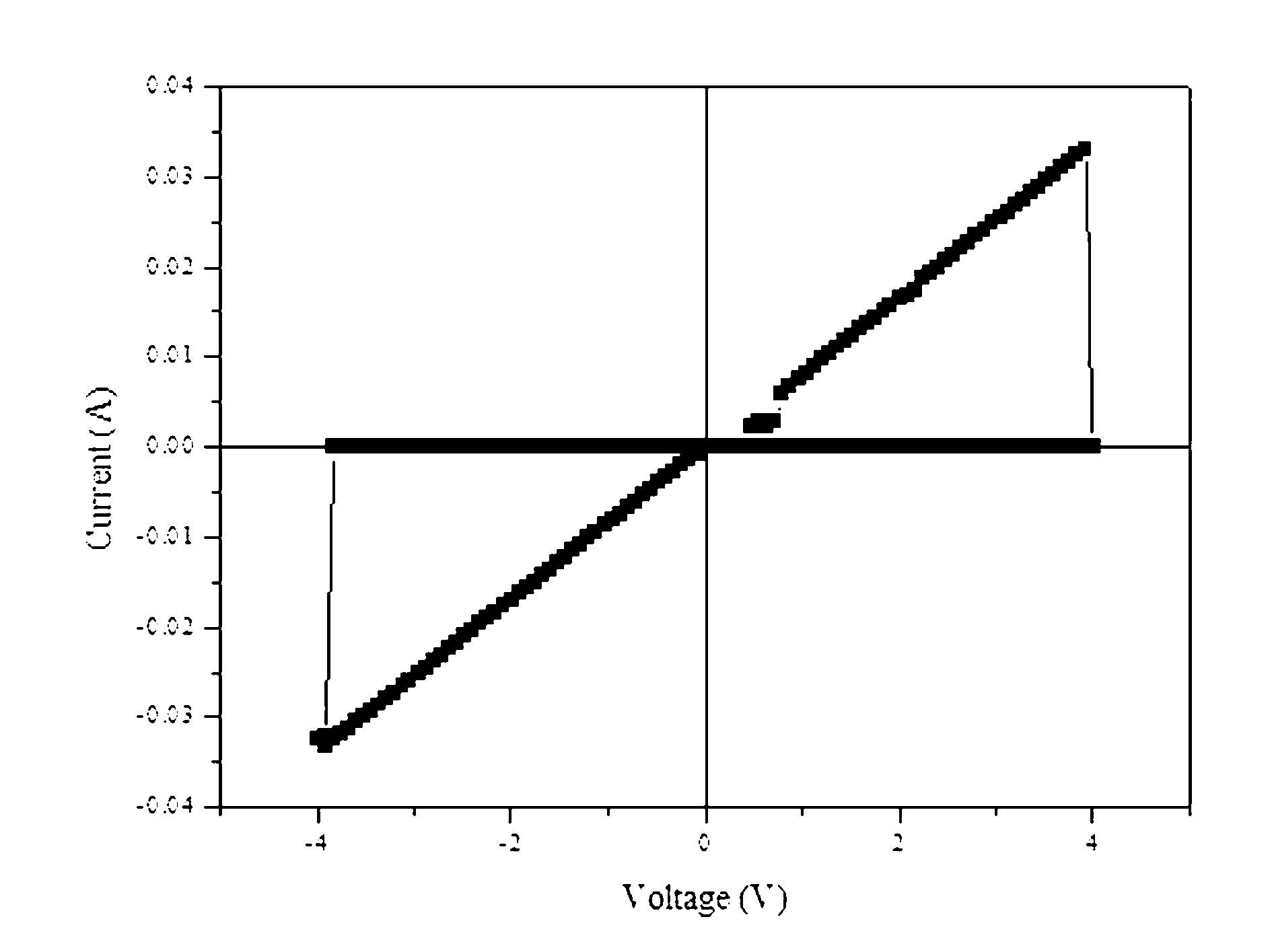

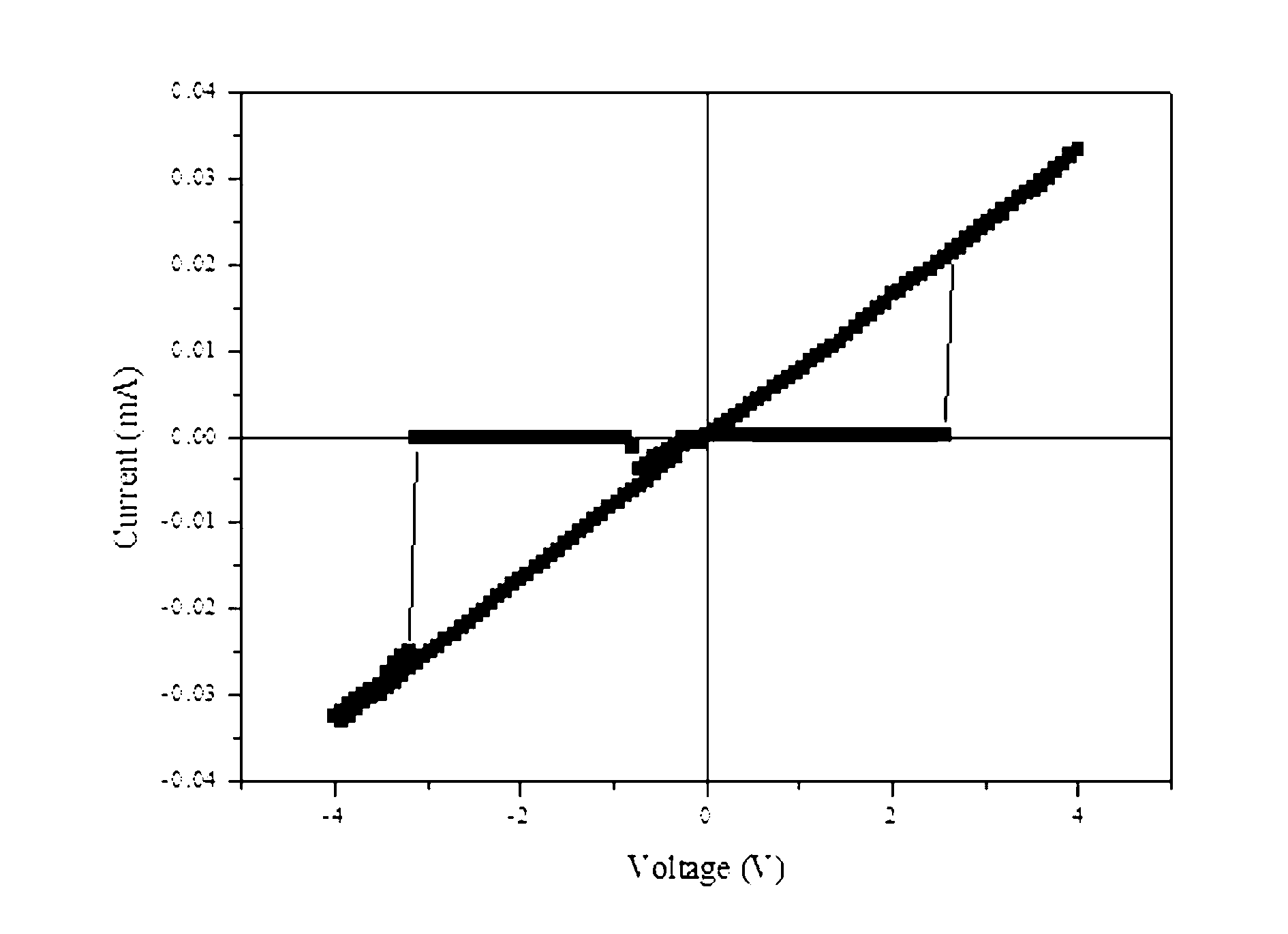

Organic resistive random access memory and preparation method thereof

InactiveCN103219466AImprove thermoplasticityImprove thermal stabilitySolid-state devicesSemiconductor/solid-state device manufacturingImidePolyetherimide

The invention provides an organic resistive random access memory and a preparation method thereof. The memory comprises a substrate, bottom electrodes, resistive change layers and top electrodes which are overlapped and connected from bottom to top. The memory is characterized in that the storage structure is an array structure; and an organic resistive change transition material of the resistive change layer is a blend of polymethyl methacrylate (PMMA) and polyetherimide (PEI). In preparation, firstly, the strip bottom electrodes are prepared on the substrate, then the organic resistive change layer films are coated on the strip bottom electrodes, and after low-temperature setting, the crossed strip electrodes are prepared on the surfaces of the resistive change layer films to form the array storage structure. According to the invention, the organic resistive random access memory has the advantages of high switch ratio, stable memory property, extremely small switch current, and relatively low preparation temperature.

Owner:GUILIN UNIV OF ELECTRONIC TECH

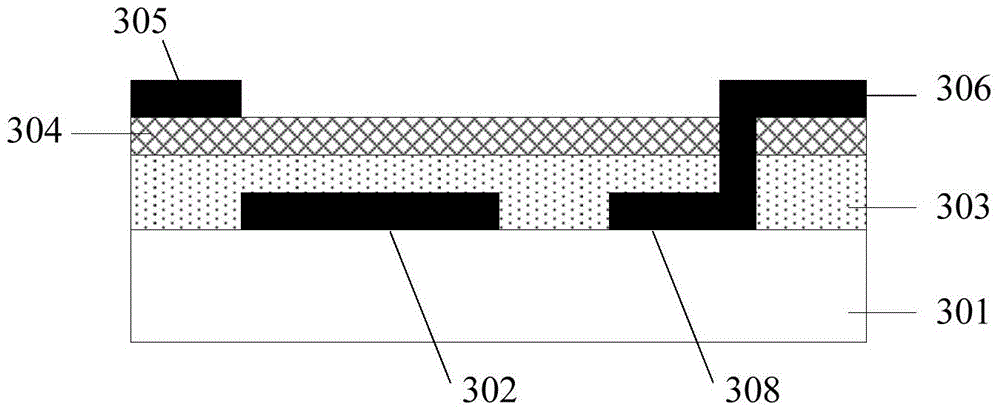

Thin film transistor and manufacturing method thereof as well as array substrate and display device

ActiveCN104681631AReduce off-state currentTransistorSolid-state devicesInsulation layerDisplay device

The invention relates to the technical field of display and discloses a thin film transistor. The thin film transistor comprises a gate, a source, a drain, an active layer and a gate insulation layer which are formed on a substrate, and further comprises an auxiliary gate connected with the drain, wherein the gate insulation layer is arranged between the auxiliary gate and the active layer. The invention further relates to a manufacturing method for the thin film transistor, an array substrate and a display device. The thin film transistor can effectively reduce off-state current.

Owner:BOE TECH GRP CO LTD

Thin film transistor, manufacturing method thereof, array substrate and display apparatus

InactiveCN108110060AAvoid reflectionsReduce reflectionTransistorSolid-state devicesDisplay deviceActive layer

The invention provides a thin film transistor which comprises a grid electrode, a source electrode and a drain electrode arranged on a substrate and an active layer, the source electrode and the drainelectrode are electrically connected with the active layer, and at least one of the grid electrode, the source electrode and the drain electrode is a light absorption electrode. The light absorptionelectrode comprises an electrode body and a light absorption layer, the light absorption layer is arranged on one side, facing the active layer, of the electrode body. Correspondingly, the invention further provides a manufacturing method of the thin film transistor, an array substrate and a display device. The light irradiated on the active layer can be reduced, and the stability of the thin filmtransistor can be improved.

Owner:HEFEI BOE DISPLAY TECH CO LTD +1

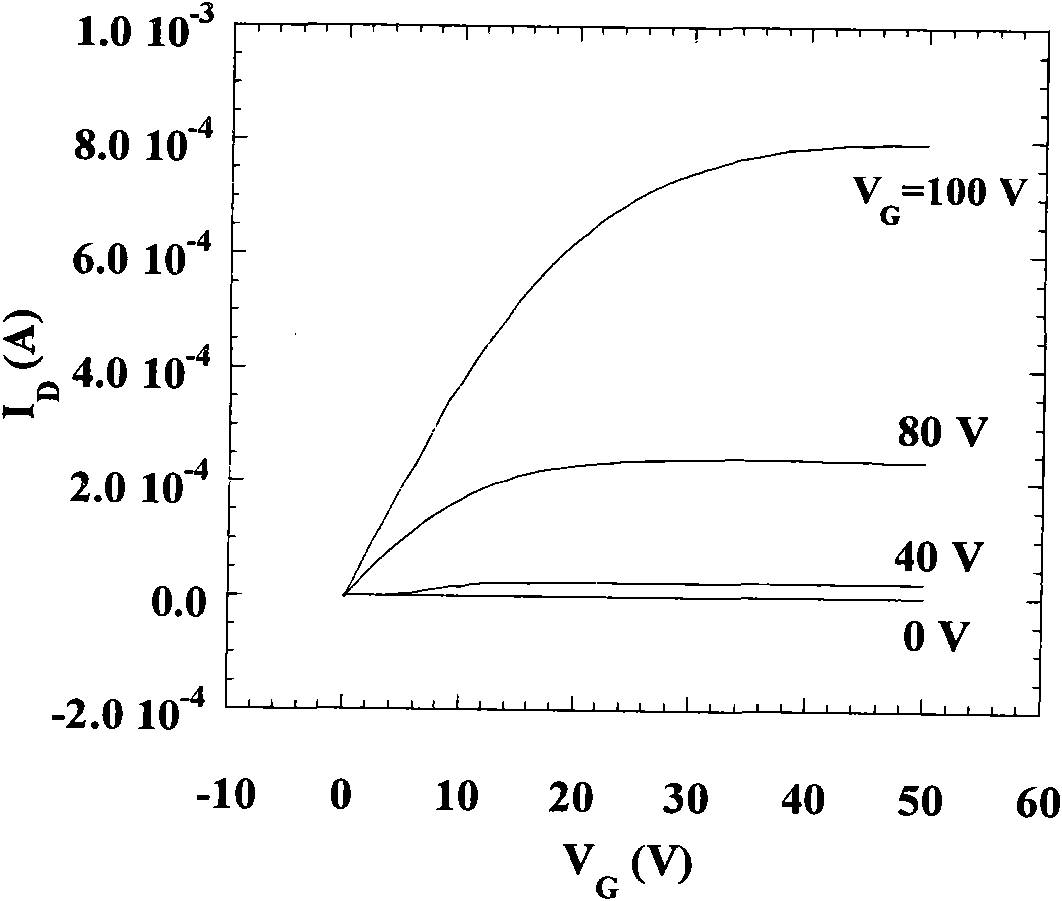

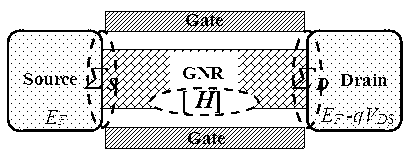

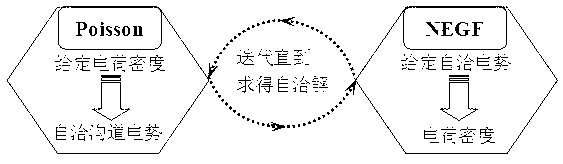

Graphene nanoribbon field-effect tube (GNRFET) with asymmetric HALO-lightly-doped drain (HALO-LDD) structure

InactiveCN103077968AReduce off-state currentGood gating abilitySemiconductor devicesPower flowSwitched current

The invention discloses a graphene nanoribbon field-effect tube (GNRFET) with an asymmetric HALO-lightly-doped drain (HALO-LDD) structure. A transport model which is suitable for a non-uniformly-doped GNRFET is constructed on the basis of a quantum mechanics non-balance Green function theoretical frame under an open boundary condition through self-consistent solution of 3D-Poisson and Schr.dinger equations, and the influence of an asymmetric HALO-LDD doping strategy on the electrical properties of the GNRFET is analyzed and calculated by using the model. As proved by comparison and analysis of the electric properties such as the output properties, transfer properties, switch current ratios, sub-threshold amplitudes and threshold voltage drifts of GNRFETs for which other doping strategies are adopted, the GNRFET with the doping structure has a higher switch current ratio, lower drain current, a smaller sub-threshold amplitude and a smaller threshold voltage drift, i.e., the GNRFET for which the asymmetric HALO-LDD doping strategy is adopted has a better grid control capability, and a short-groove effect and a hot carrier effect can be effectively restrained.

Owner:NANJING UNIV OF POSTS & TELECOMM

Knot-free nanowire field effect transistor

InactiveCN102544073AImprove transconductance characteristicsHigh speedSemiconductor devicesNanowireLow voltage

The invention discloses a knot-free nanowire field effect transistor which comprises a channel, a source region and a drain region. The source region is arranged at one end of the channel, and the drain region is arranged at the other end of the channel; the outer surface of the channel is covered by a gate oxide layer which is covered by a grid electrode layer; and the grid electrode layer comprises a first grid electrode layer which is close to the source region and a second grid electrode layer which is close to the drain region. Compared with the prior art, the embodiment of the invention has the advantages that: by adopting a split gate structure, the speed of the charge carrier in the channel of the knot-free nanowire field effect transistor is increased, so the on-state current is increased, the off-state current of a device is reduced irrespective of the influence of the threshold voltage, the influence of the drain region on the device is screened, the drain induced barrier lowering effect is obviously weakened and the driving ability of the current is improved. Meanwhile, with the split gate, the transconductance feature of the knot-free nanowire field effect transistor under low voltage is obviously improved.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL +1

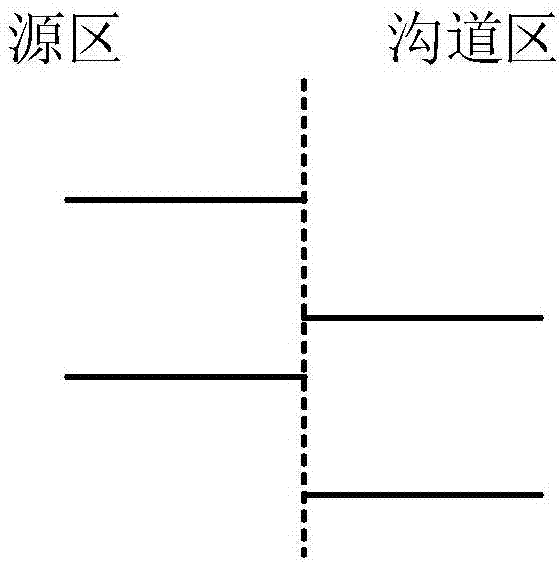

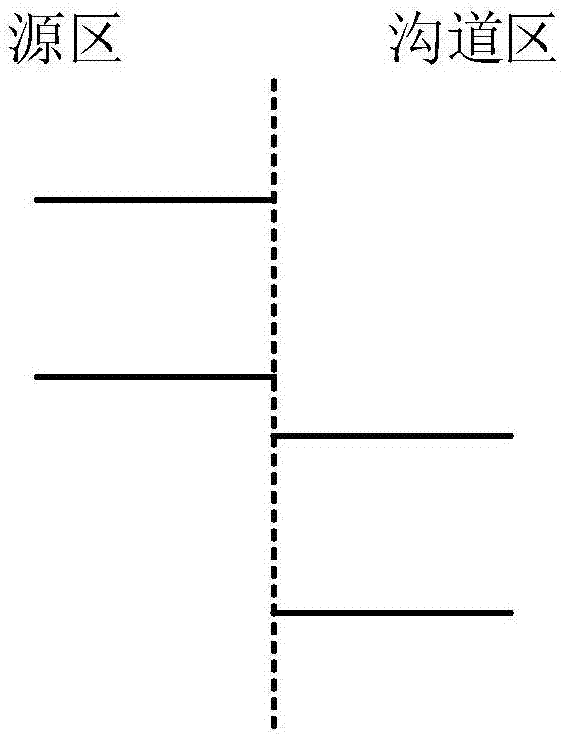

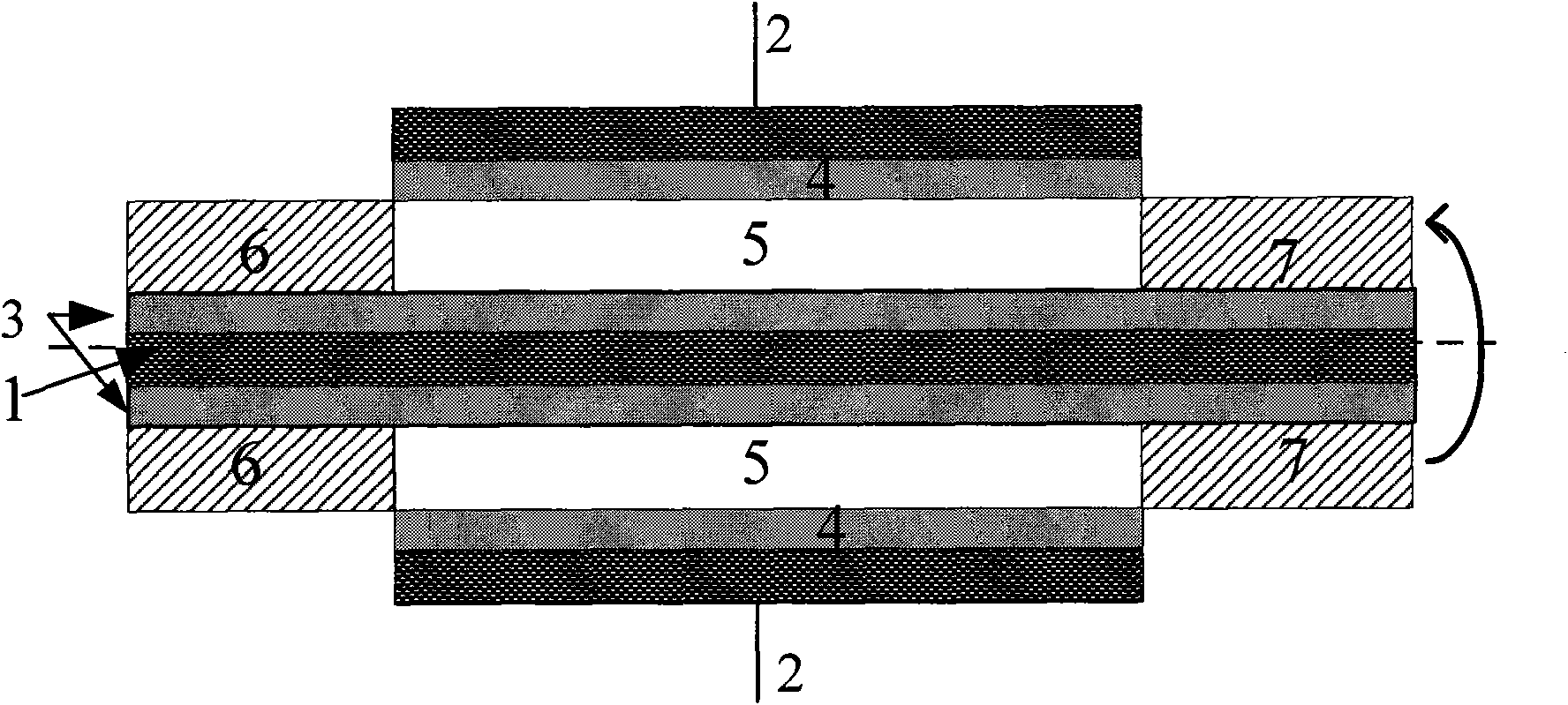

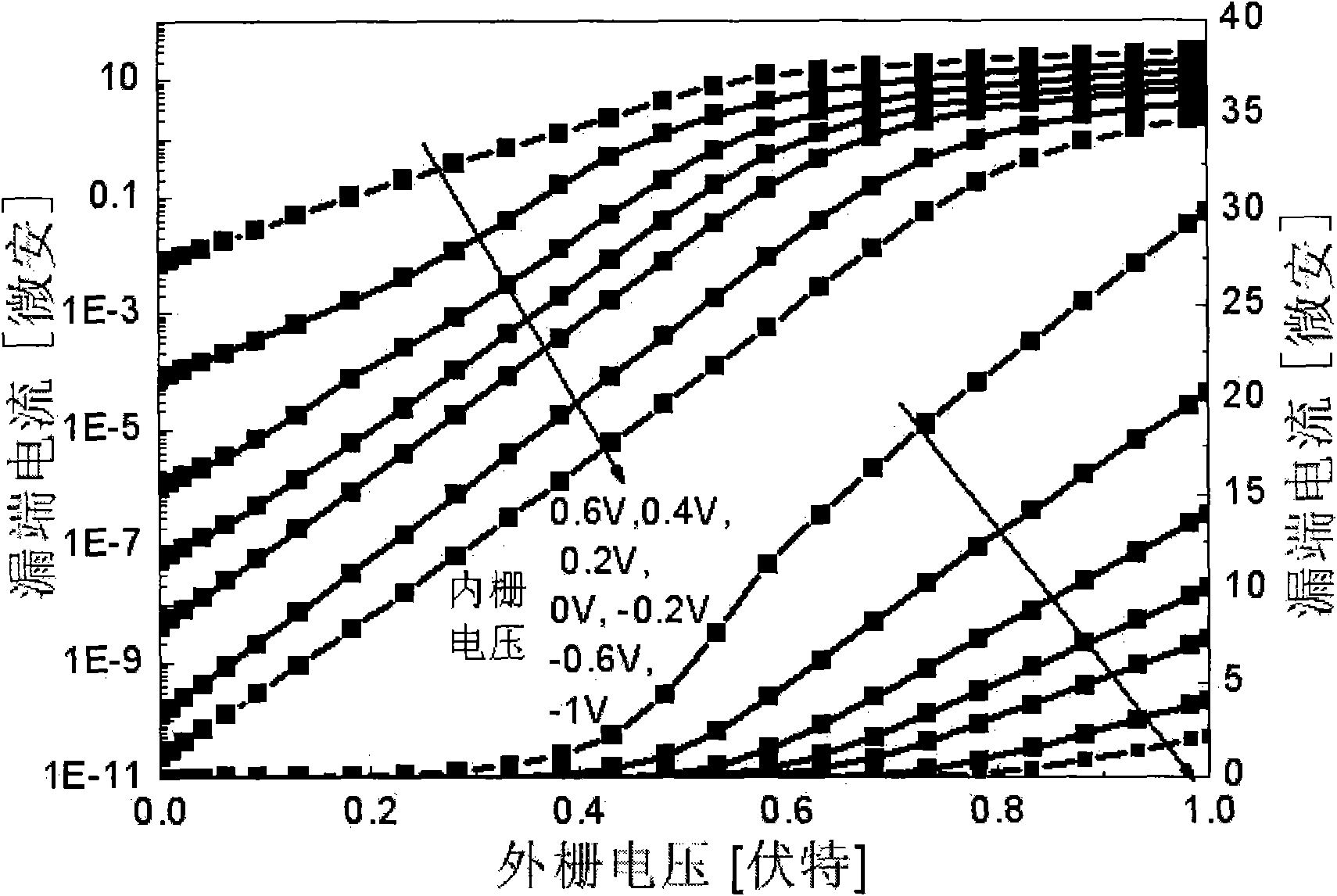

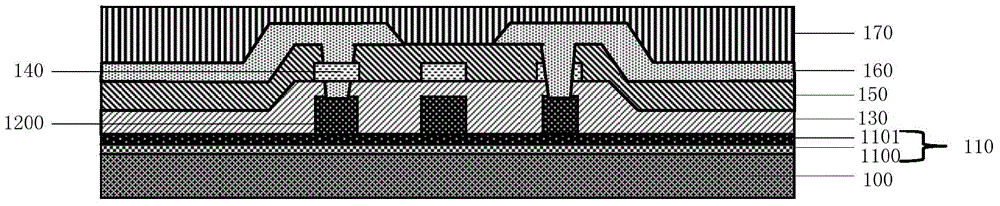

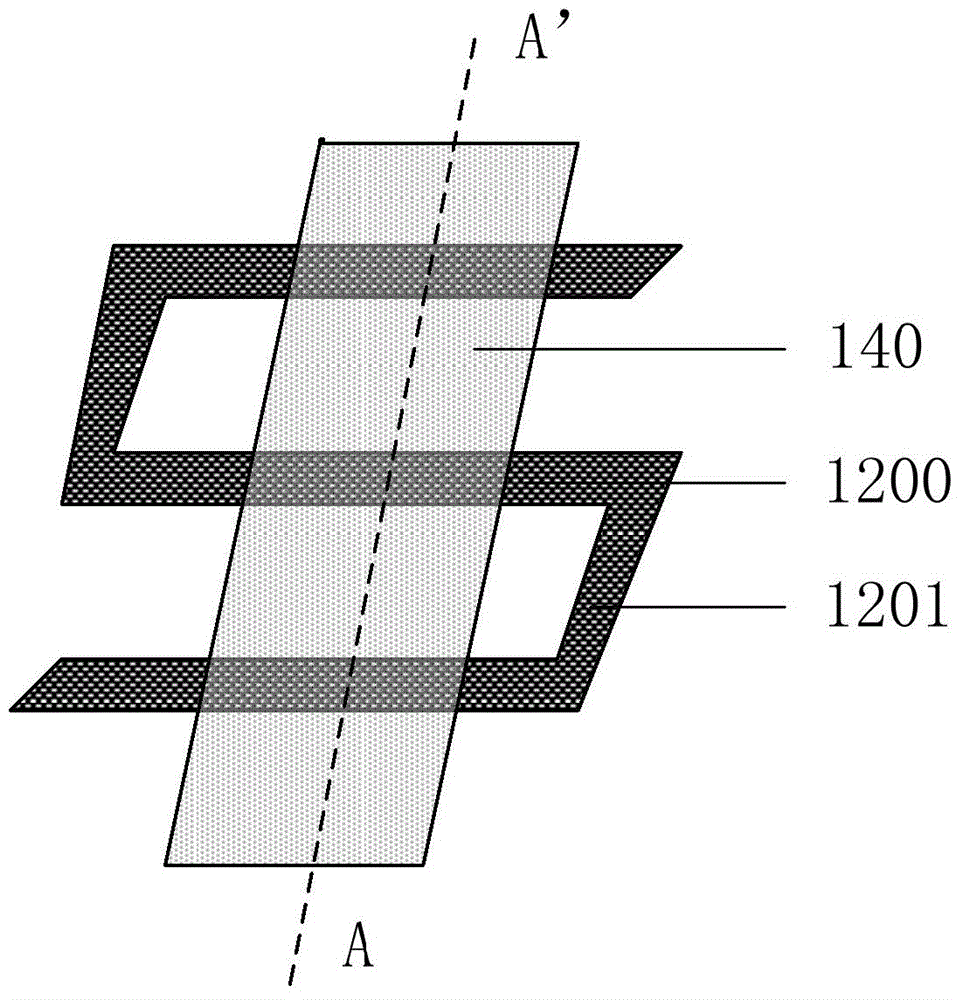

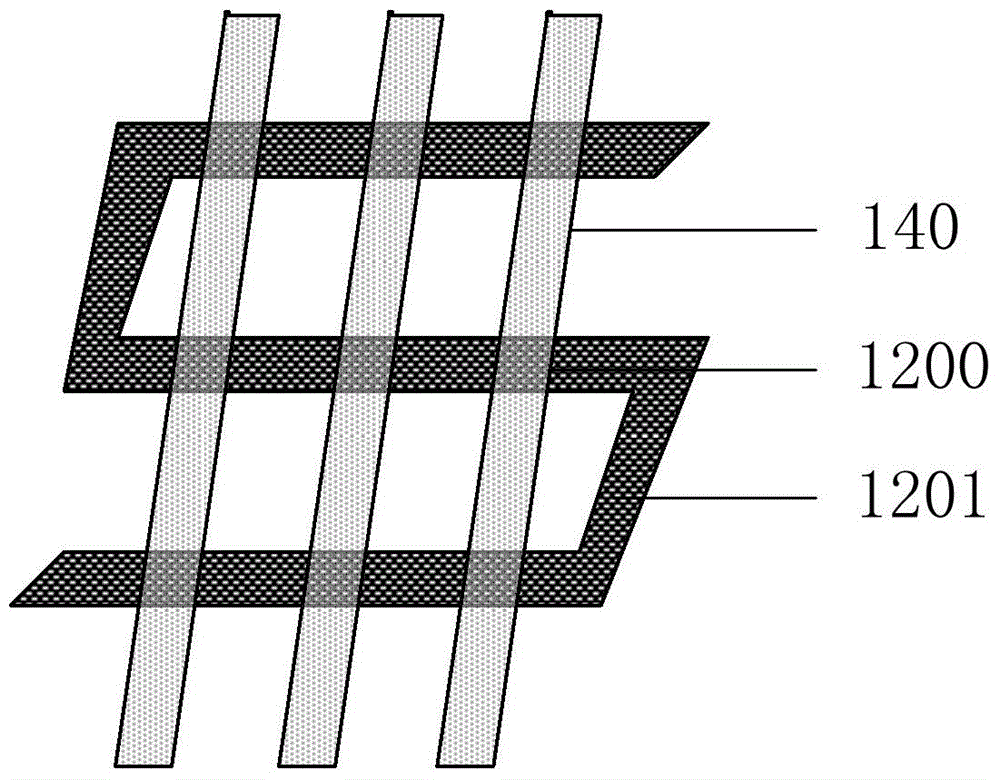

Independent grid-controlled nano line field effect transistor

ActiveCN101944539ASmall driving currentReduce off-state currentSemiconductor devicesPhysicsDielectric

The invention discloses an independent grid-controlled nano line field effect transistor which comprises an inner grid electrode, an outer grid electrode, inner and outer grid dielectric layers, a channel region, a source region and a drain region, wherein the inner grid electrode is positioned at the center of the whole device structure; and the inner grid dielectric, the channel region, the outer dielectric and the outer grid electrode are coaxially arranged from inside to outside to completely enclose the inner-layer region. The arrangement of the inner grid electrode can enable the nano line device to work under the condition of independent grid control so as to provide a selection scheme for the design of a low power consumption circuit, and the threshold voltage is more sensitive to the adjustment of the controlled electrode. When the device works under the common grid condition, the electrical performance of the device is superior to that of the conventional nano circular grid device and double grid device. For a silicon film thickness of 10nm, the independent grid-controlled nano line transistor device can shorten the grid length to 20nm.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

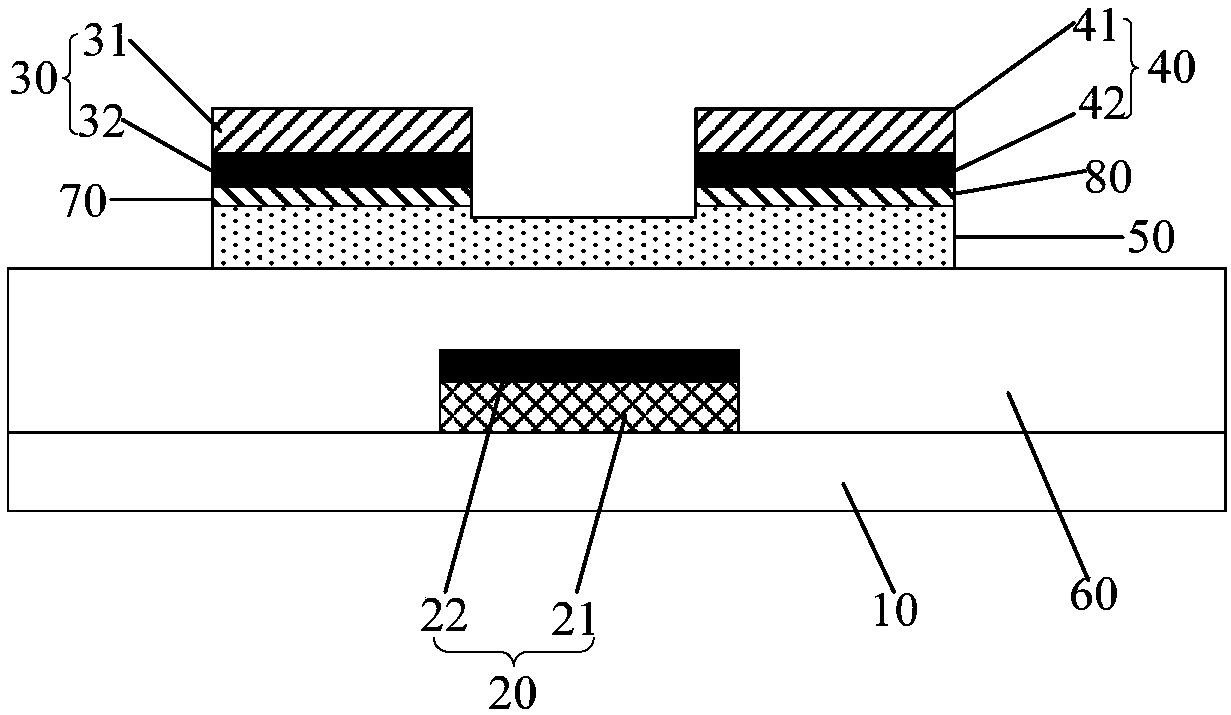

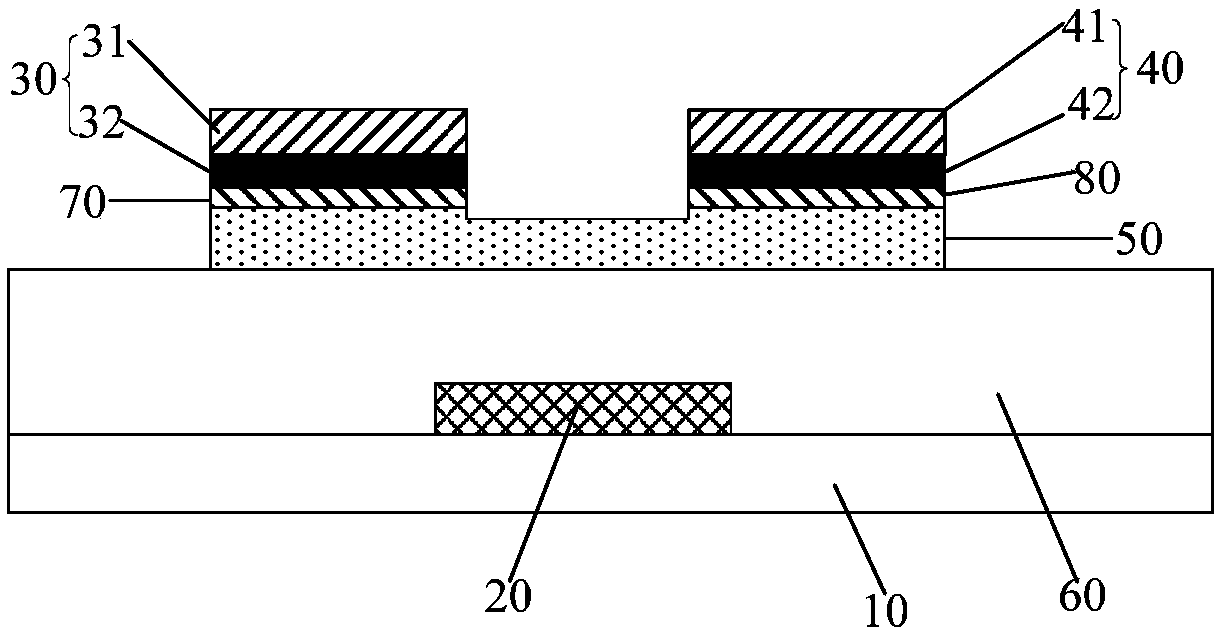

Thin film transistor device and preparation method therefor

InactiveCN105789317ASolve the problem of long length in one directionReduce off-state currentTransistorSemiconductor/solid-state device manufacturingPower flowInstability

The invention provides a thin film transistor device and a preparation method therefor. The thin film transistor device comprises a substrate, a buffer layer, a channel layer, a gate insulating layer, gate electrodes, an interlayer insulating layer, and a source electrode and a drain electrode in sequence, wherein the channel layer is bent, so that influence on the pixel of the device from the overlong length of the channel can be avoided; the length and the width of the channel layer can be both adjusted according to needs, so that the problem of relatively long channel layer in a single direction is well solved; in addition, the channel region in a non-doping region is arranged in a region which is covered with the gate electrodes; the channel layer in a doping region is arranged outside the region which is covered with the gate electrodes, so that a PN junction is formed in the contact interface between the channel layer in the non-doping region and the channel layer in the doping region; therefore, the off-state current of the thin film transistor device is lowered consequently; the performance of the device is improved to a large extent; and meanwhile, the device instability caused by an electric field effect between the source electrode and the drain electrode can be well avoided.

Owner:KUNSHAN GO VISIONOX OPTO ELECTRONICS CO LTD

Thin film transistor, production method thereof, array substrate and display device

InactiveCN106298815AReduce off-state currentIncrease display contrastTransistorSolid-state devicesDisplay deviceEngineering

The invention provides a thin film transistor, a production method thereof, an array substrate and a display device, and belongs to the technical field of display. The thin film transistor comprises a grid, a grid insulating layer, a source, a drain and an active layer which are positioned on a substrate; a one-way conducting device is arranged between the active layer and the drain, so that an electric signal is transmitted from the active layer to the drain through the one-way conducting device. According to the technical scheme of the invention, the off-state current of the thin film transistor can be effectively reduced, and the display effect of the display device can be improved.

Owner:BOE TECH GRP CO LTD

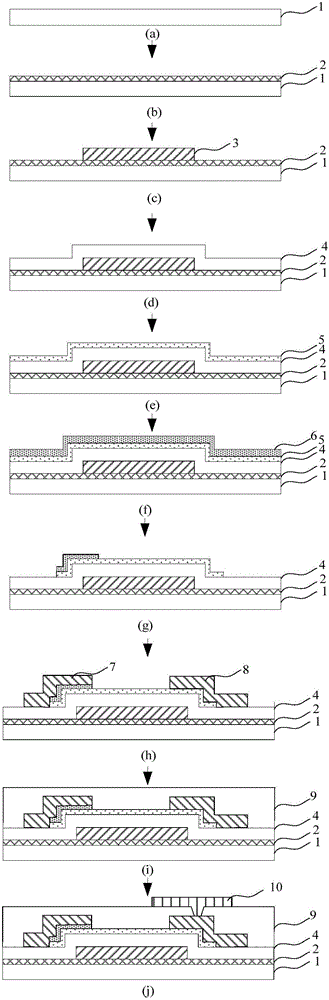

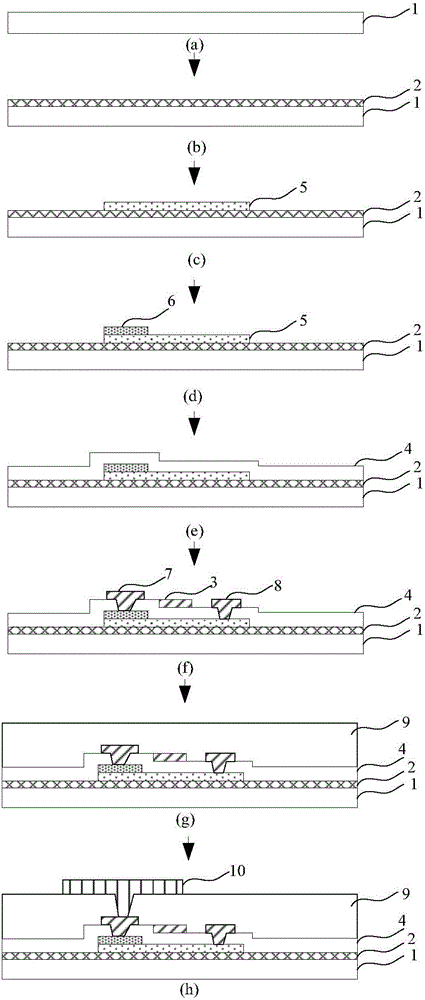

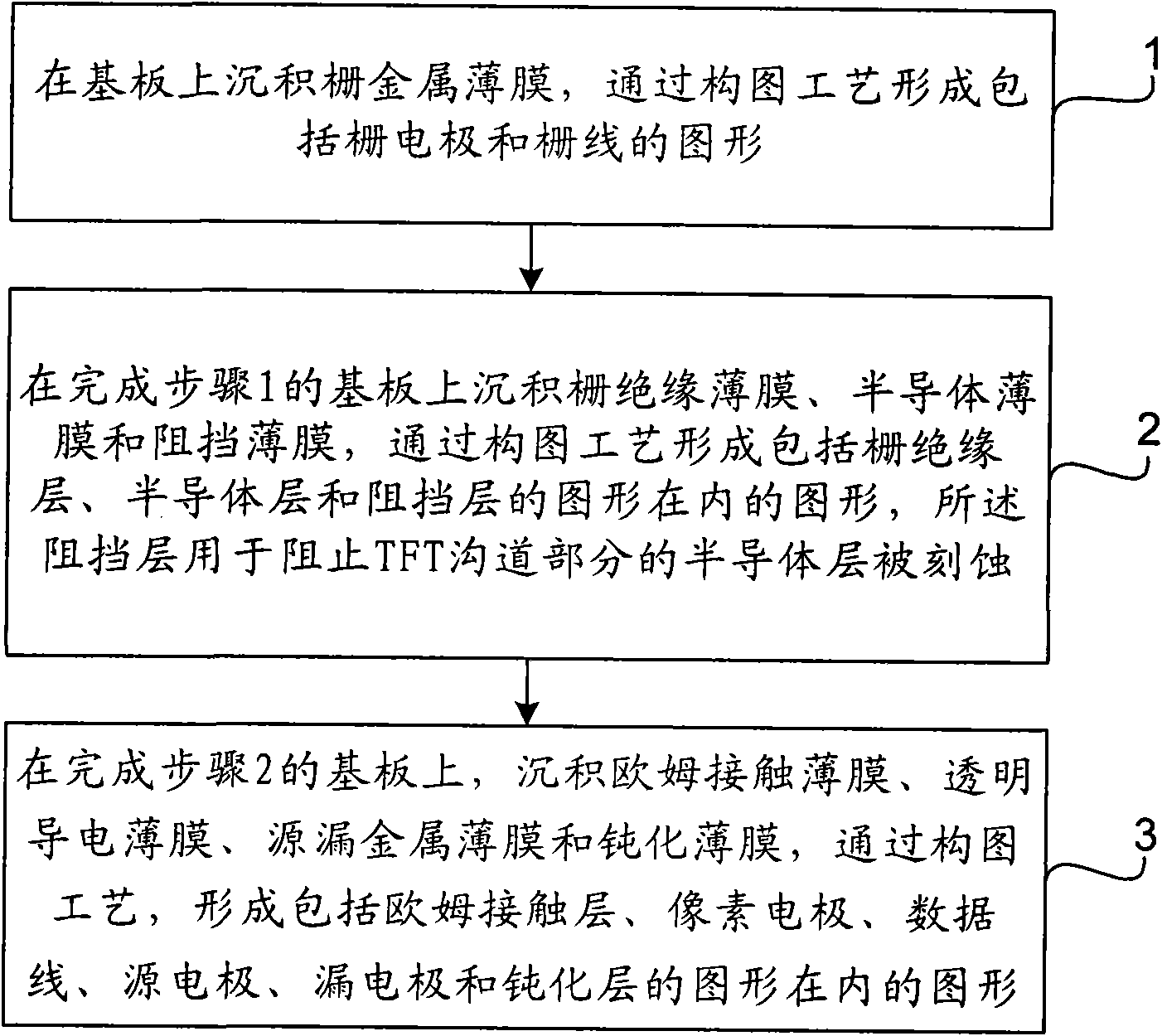

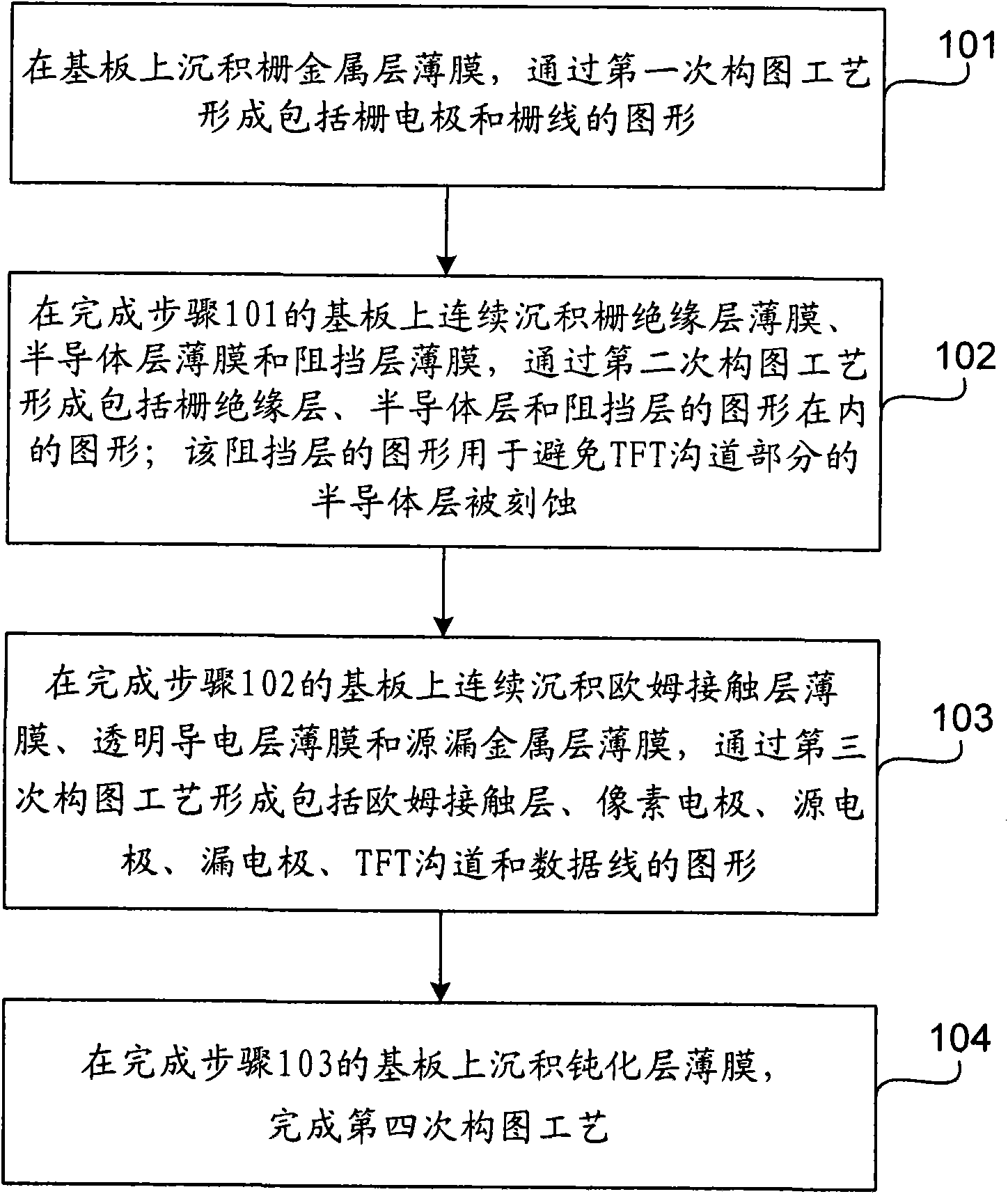

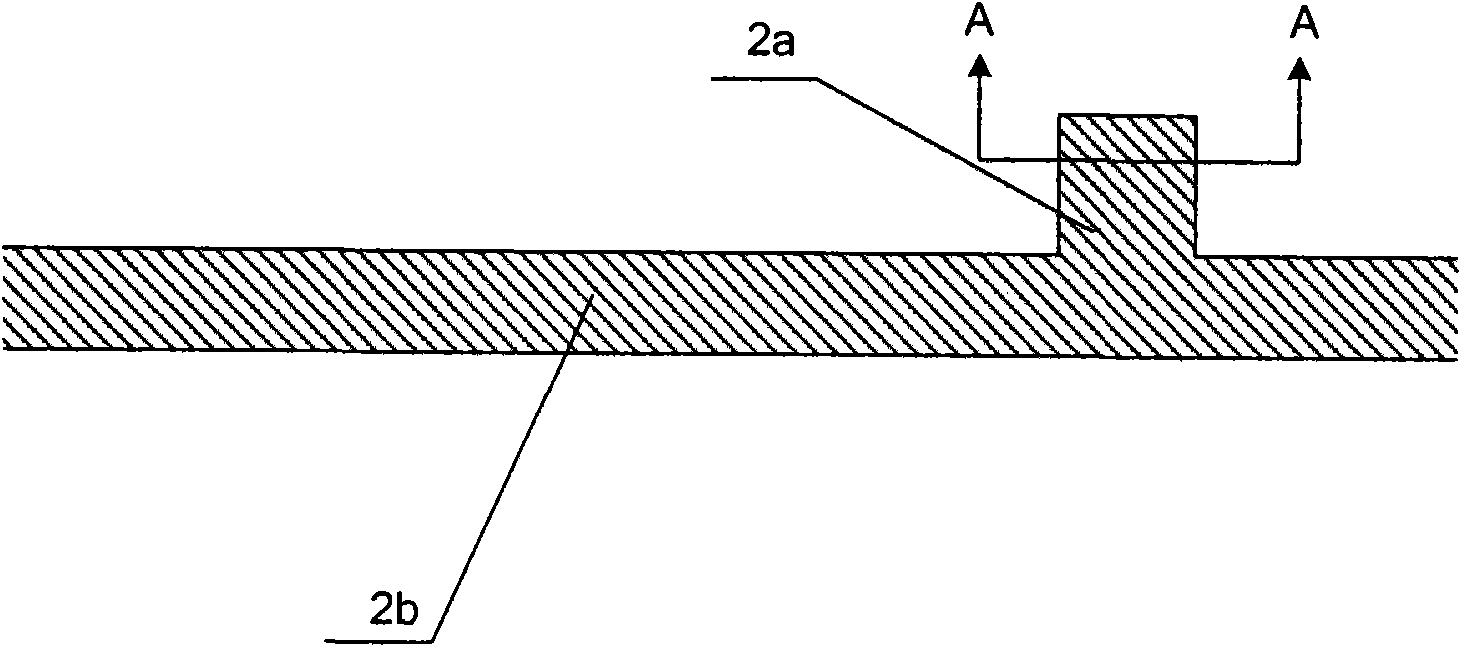

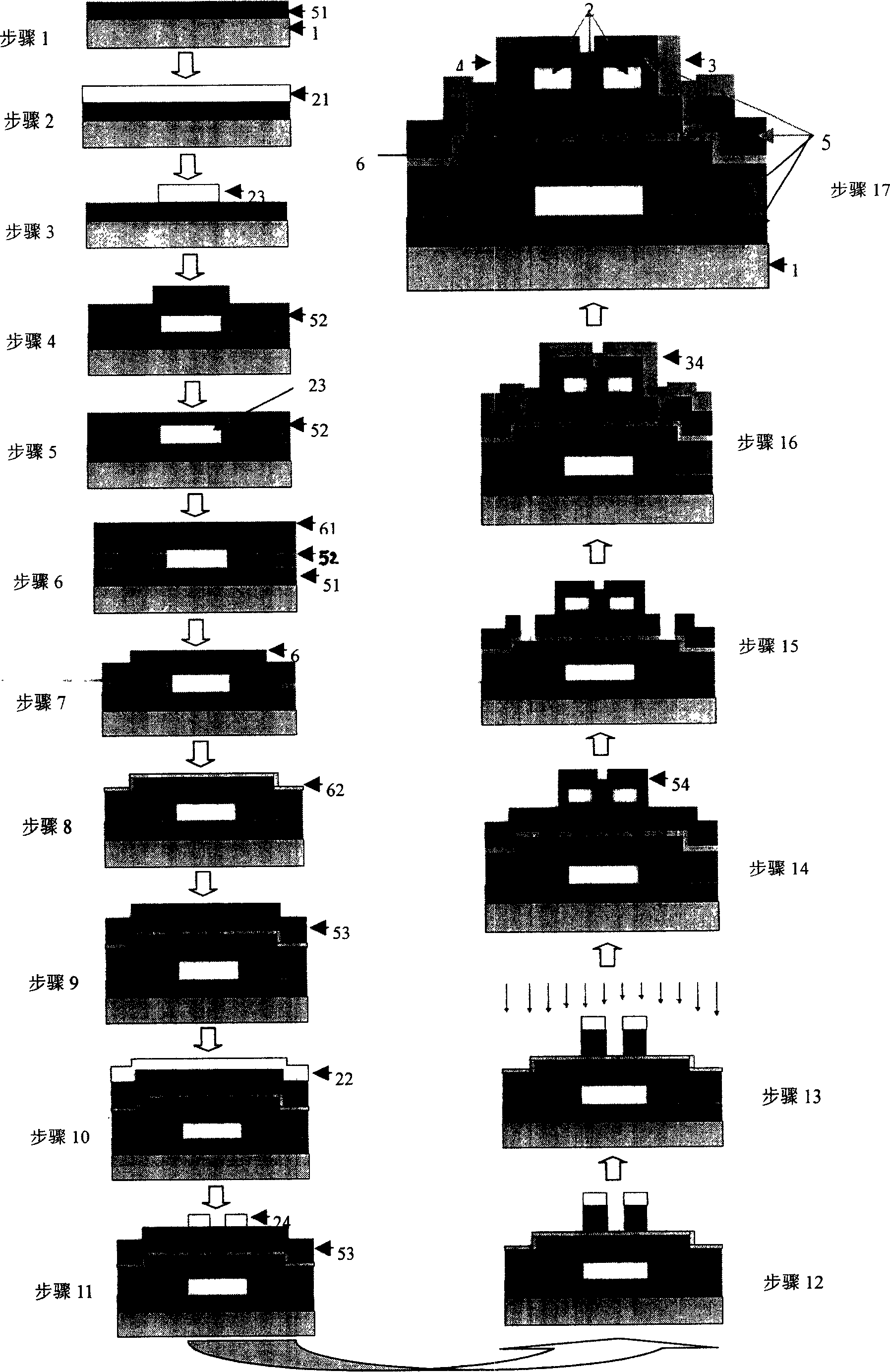

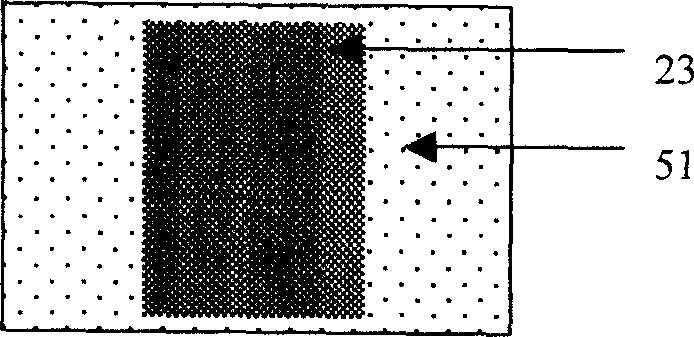

Thin film transistor liquid crystal display (TFT-LCD) array substrate and manufacturing method thereof

ActiveCN101770124AImprove performanceReduce thicknessSolid-state devicesSemiconductor/solid-state device manufacturingOhmic contactComposition process

The invention relates to a thin film transistor liquid crystal display (TFT-LCD) array substrate and a manufacturing method thereof, wherein the manufacturing method comprises the following steps of: 1, depositing a gate metal-layer thin film on a substrate, forming a figure comprising a gate electrode and a gate line; 2, depositing a gate insulating layer thin film, a semiconductor layer thin film and a barrier layer thin film on the on the substrate subjected to the step 1, forming a figure comprising figures of a gate insulating layer, a semiconductor layer and a barrier layer, wherein the barrier layer is used for preventing the semiconductor layer of a thin film transistor (TFT) channel from being etched; and 3, depositing an ohmic contact layer thin film, a transparent conductive layer thin film, a source-drain metal layer thin film and a passivation layer thin film on the substrate subjected to the step 2, and forming a figure comprising figures of an ohmic contact layer, a pixel electrode, a data line, a source electrode, a drain electrode and a passivation layer. The invention can reduce the thickness of the semiconductor layer under the condition without increasing composition processes and enhance the performance of a thin film transistor (TFT) by arranging the barrier layer between the semiconductor layer and the ohmic contact layer in a clamping way.

Owner:K TRONICS (SUZHOU) TECH CO LTD +1

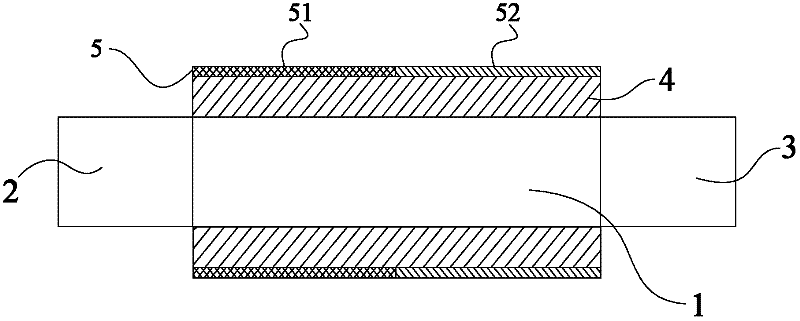

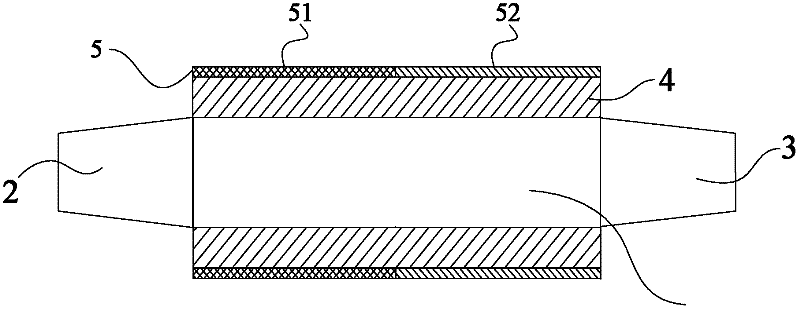

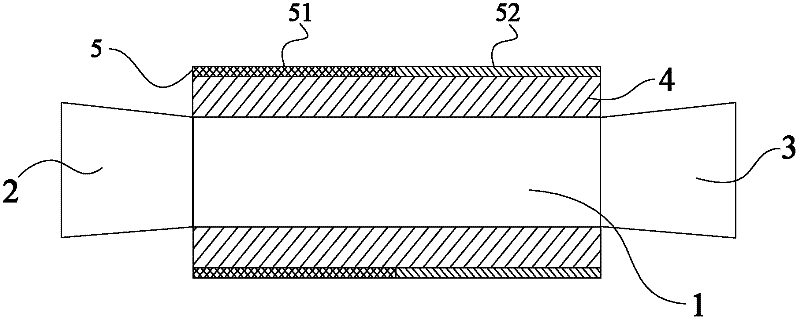

Polycrystalline SiTFT of multi-grid double-channel structure

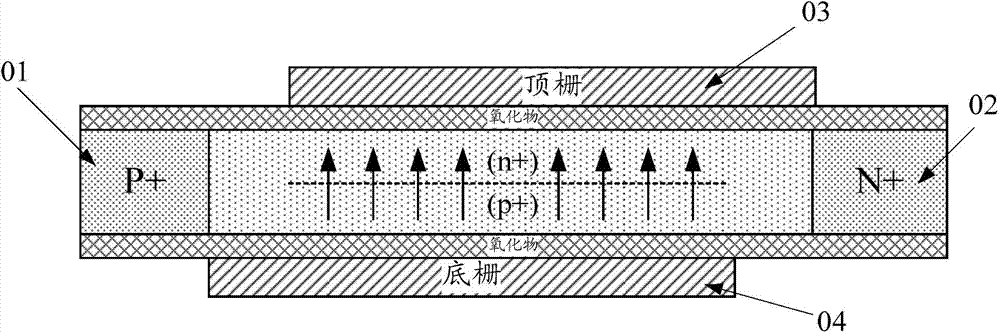

The invention relates to silicon polycrystal film transistor with multi-gate tow-channel structure, comprising insulating substrate (1) , SiO2 cushion layer (51), gate electrode insulating layer (53), two top gate electrodes (24) in gate electrode insulating layer (53) , drain region (3) and source region (4), gate electrode insulating layer (52) on SiO2 cushion layer (51), bottom gate electrode (23) on gate electrode insulating layer (52), bottom gate electrode (23) and top gate electrode (24) are connected by linking hole of gate electrode (25), and channel (6) formed by silicon polycrystal film on gate electrode insulating layer (52). The invention of TFT component has the same extent of close drain current of TFT made in the same condition, besides, it has more advantages such as open current increased by one time, better drive capability for load than TFT which has the same ratio of width and length, smaller area in integration matrix when supplies the same current, and increasing opening rate.

Owner:JILIN UNIV

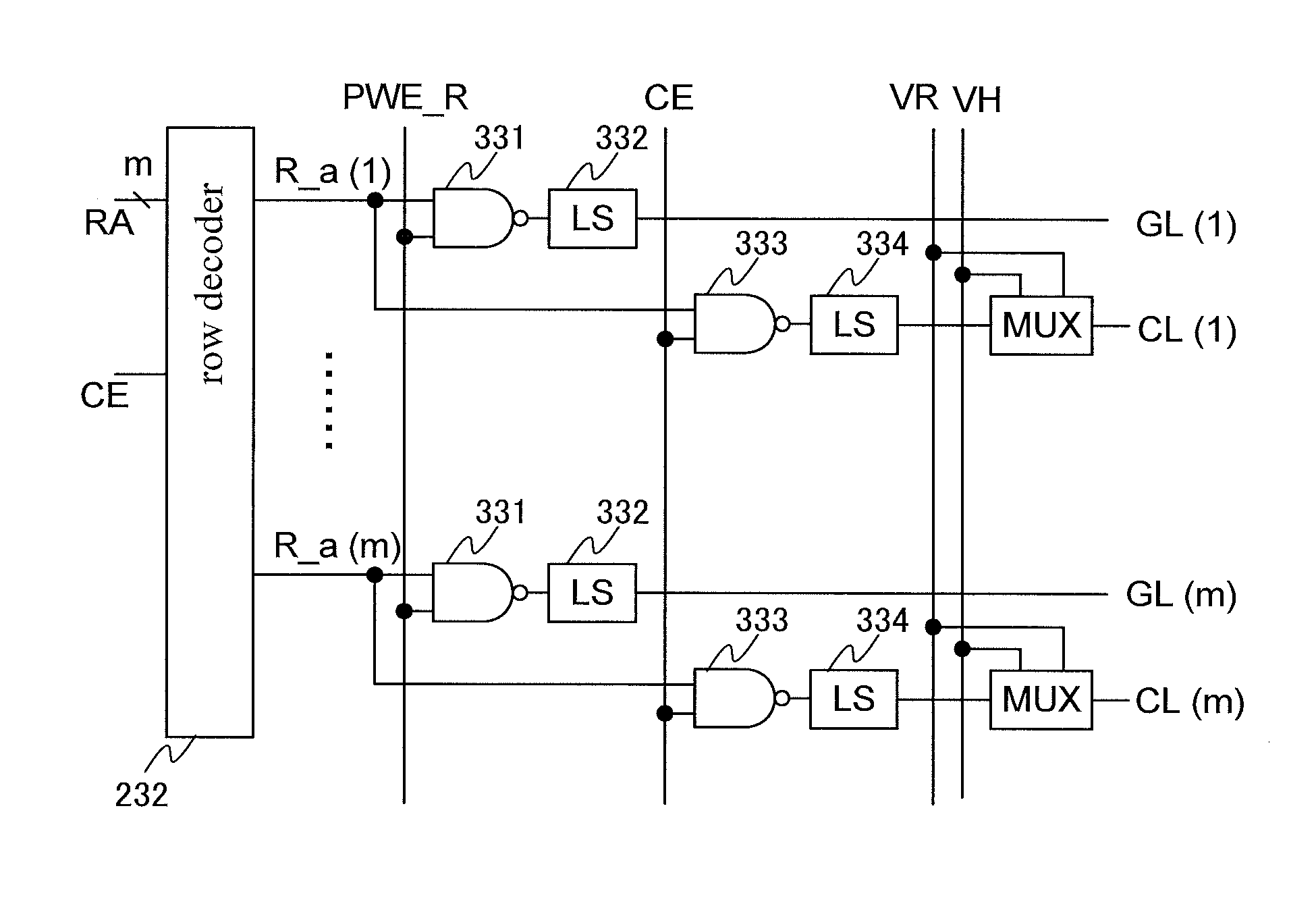

Semiconductor device including memory cell array

ActiveUS8767442B2Reduce off-state currentTotal current dropSolid-state devicesRead-only memoriesElectricityPower semiconductor device

A semiconductor device in which stored data can be held even when power is not supplied and there is no limitation on the number of writing operations is provided. A semiconductor device is formed using a material which can sufficiently reduce the off-state current of a transistor, such as an oxide semiconductor material that is a wide-gap semiconductor. When a semiconductor material which can sufficiently reduce the off-state current of a transistor is used, the semiconductor device can hold data for a long period. In addition, by providing a capacitor or a noise removal circuit electrically connected to a write word line, a signal such as a short pulse or a noise input to a memory cell can be reduced or removed. Accordingly, a malfunction in which data written into the memory cell is erased when a transistor in the memory cell is instantaneously turned on can be prevented.

Owner:SEMICON ENERGY LAB CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com