Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

293 results about "Tunnel field-effect transistor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

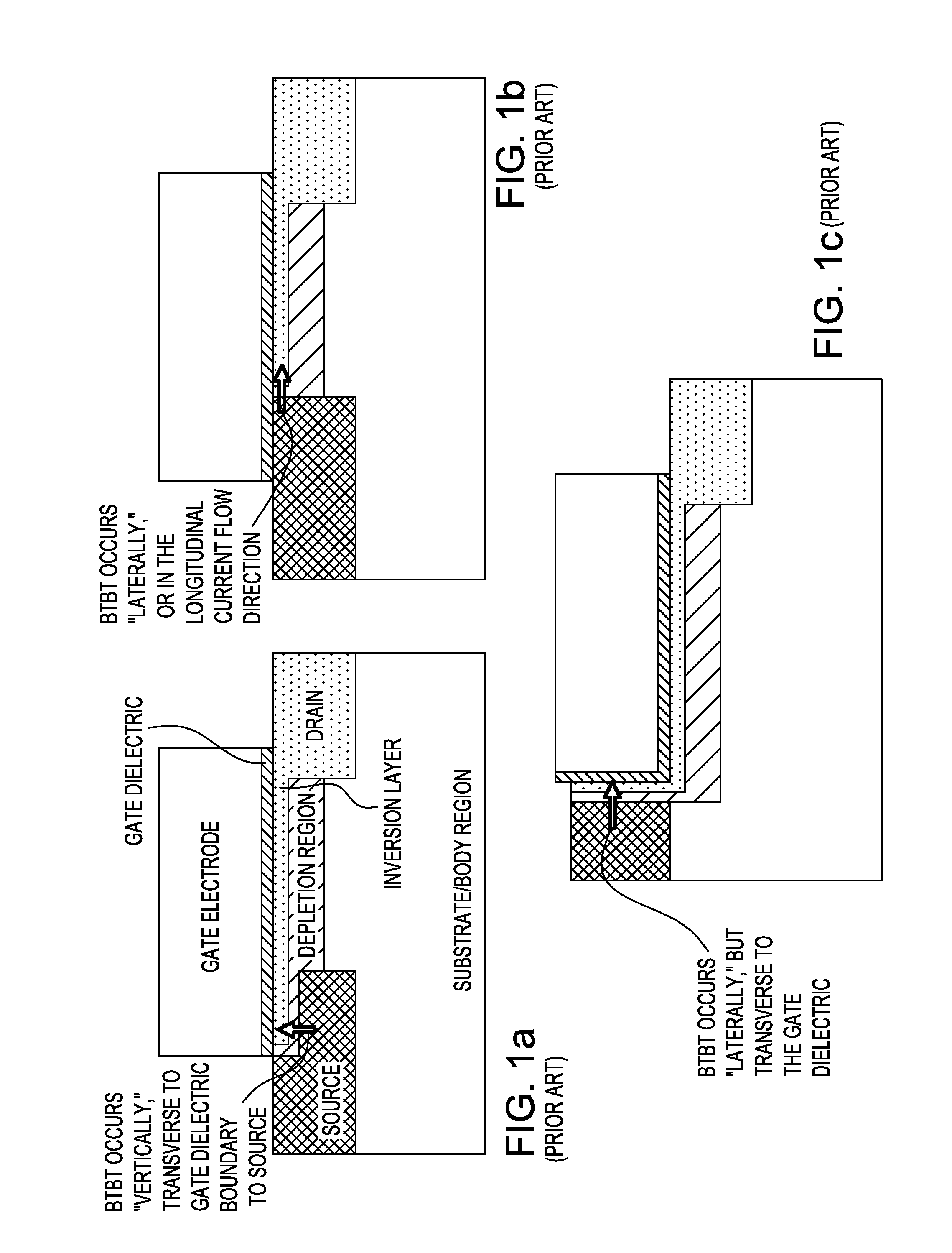

The tunnel field-effect transistor (TFET) is an experimental type of transistor. Even though its structure is very similar to a metal-oxide-semiconductor field-effect transistor (MOSFET), the fundamental switching mechanism differs, making this device a promising candidate for low power electronics. TFETs switch by modulating quantum tunneling through a barrier instead of modulating thermionic emission over a barrier as in traditional MOSFETs.

Tunnel effect transistors based on silicon nanowires

InactiveUS20080067495A1Optimize architectureReduce power consumptionTransistorNanoinformaticsMOSFETLattice mismatch

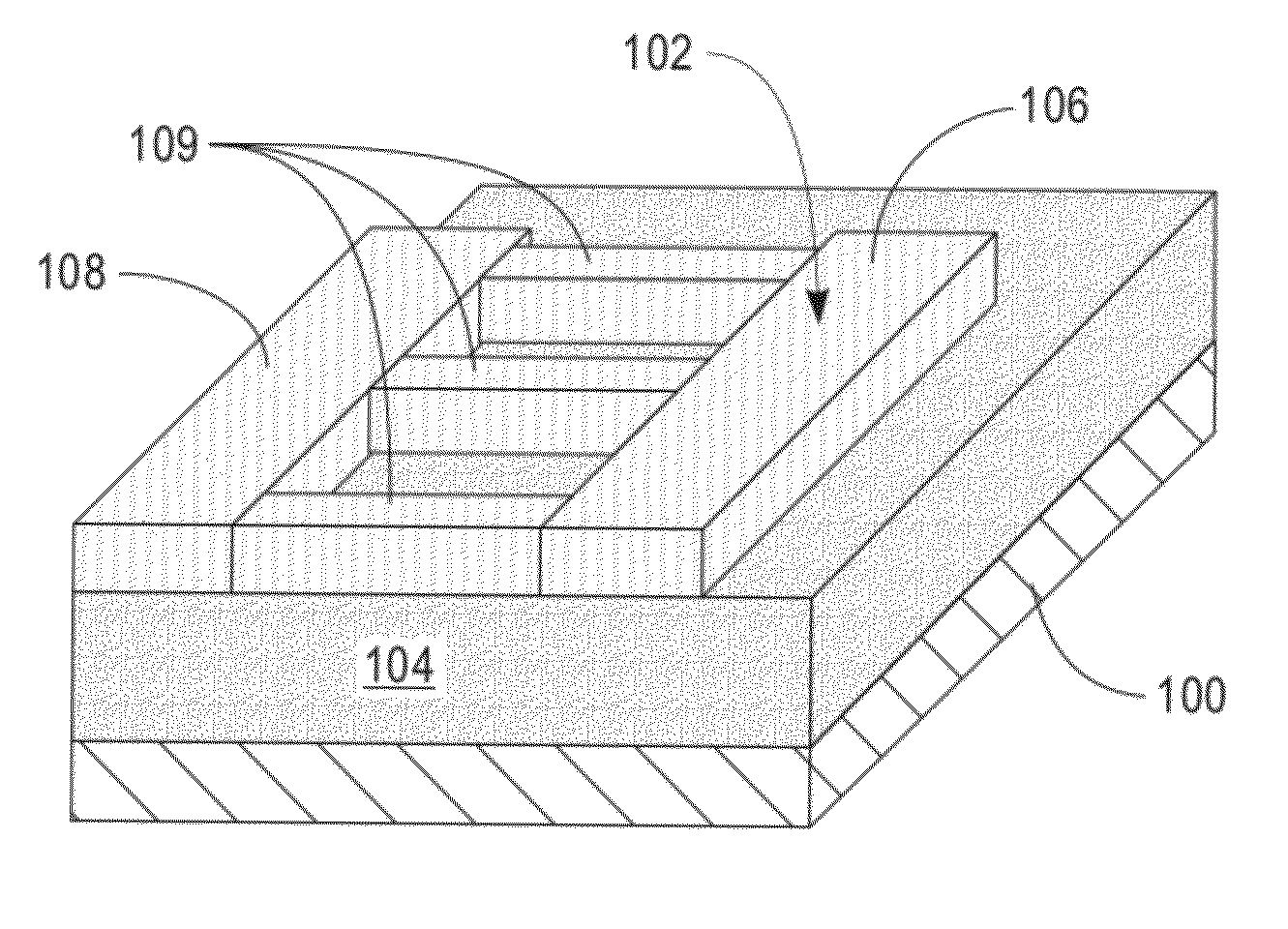

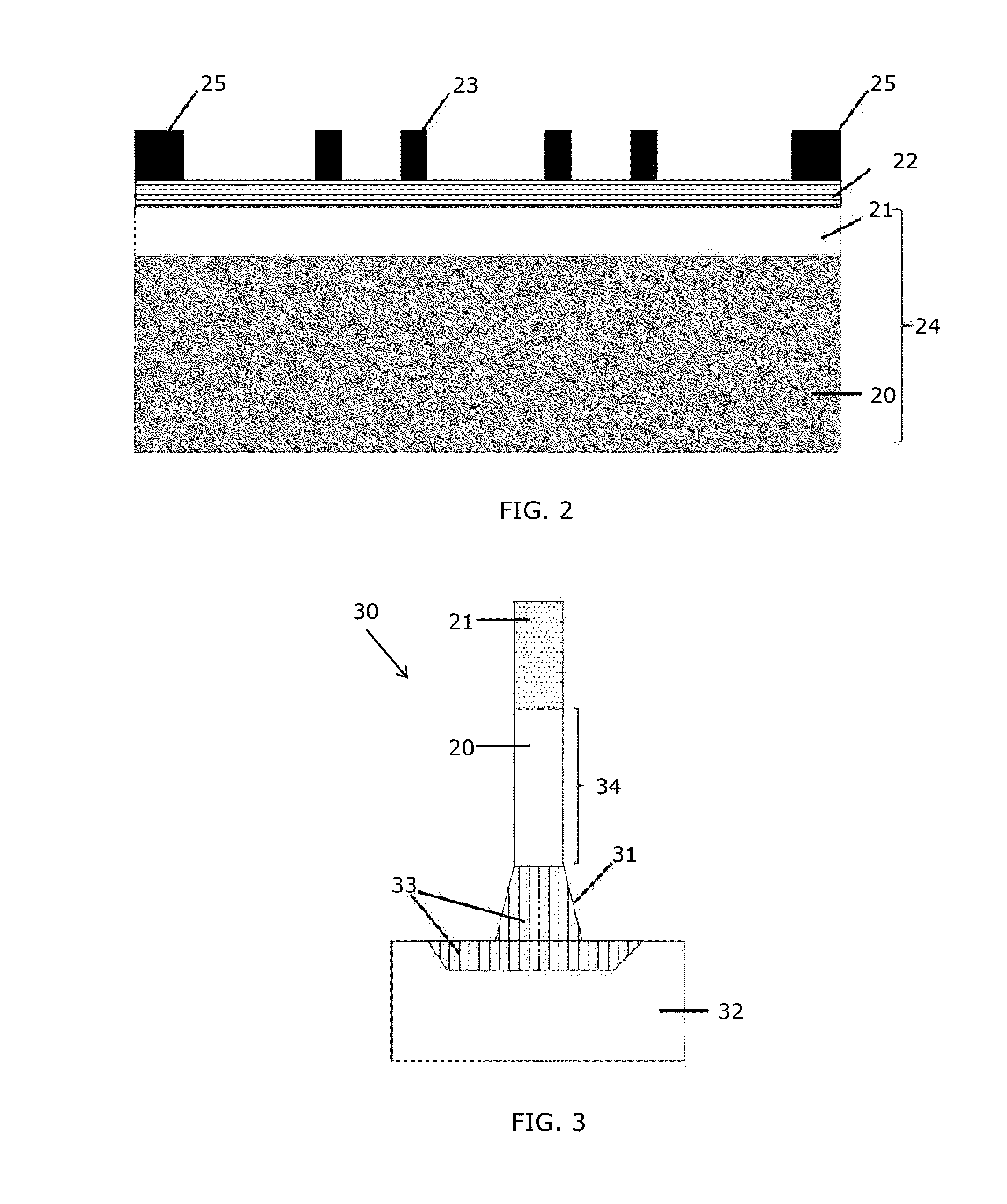

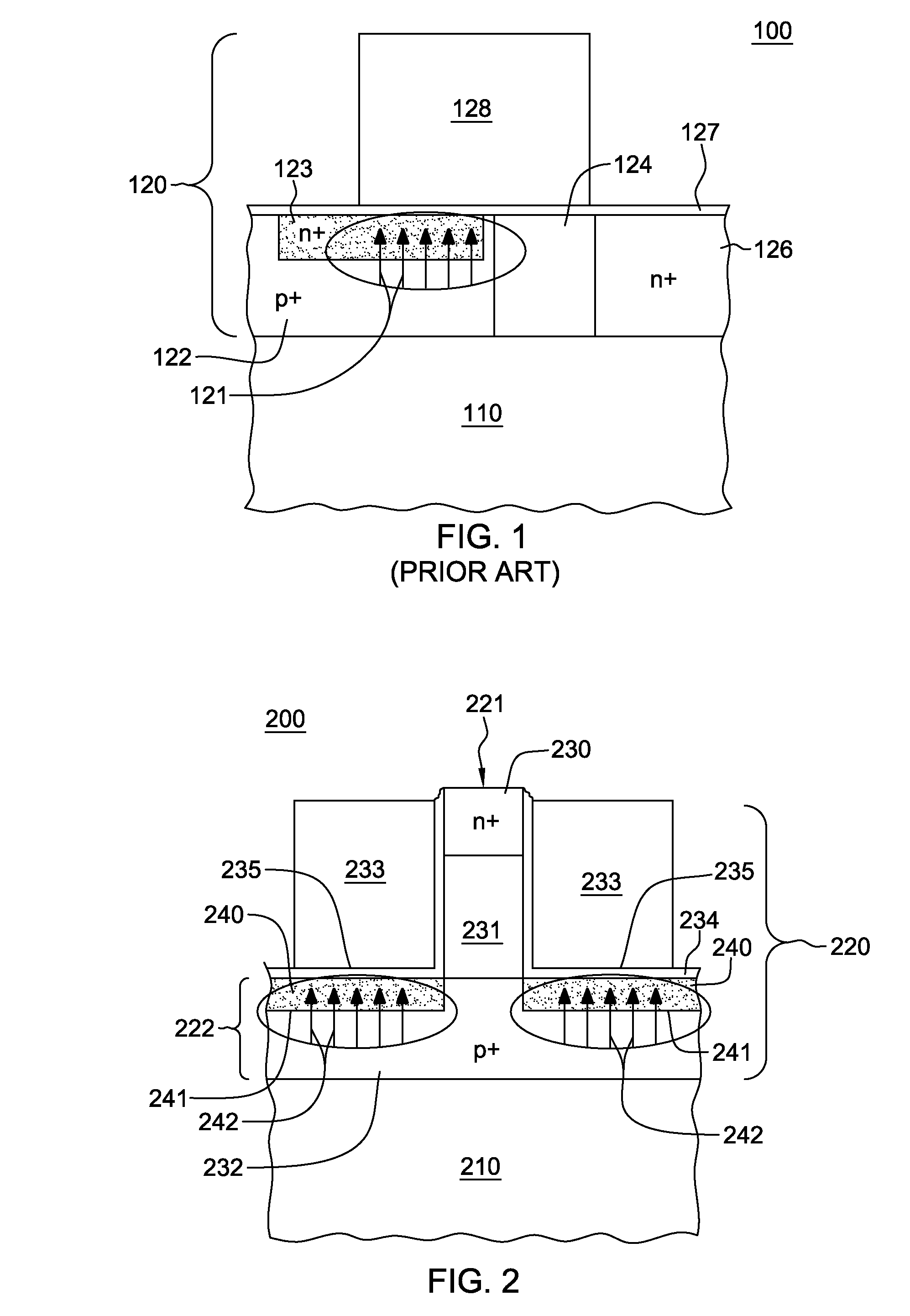

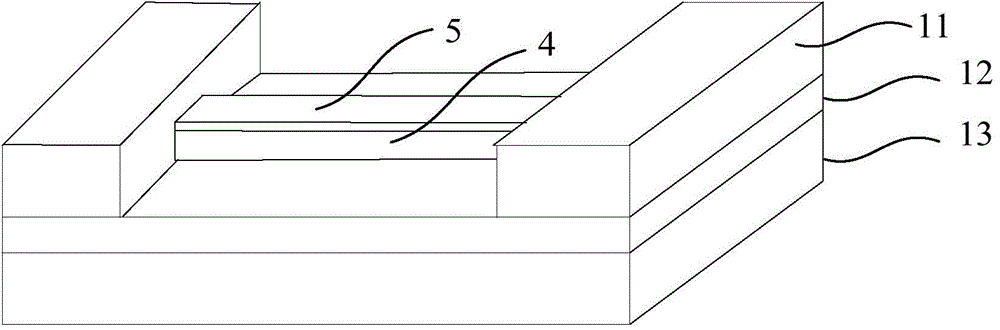

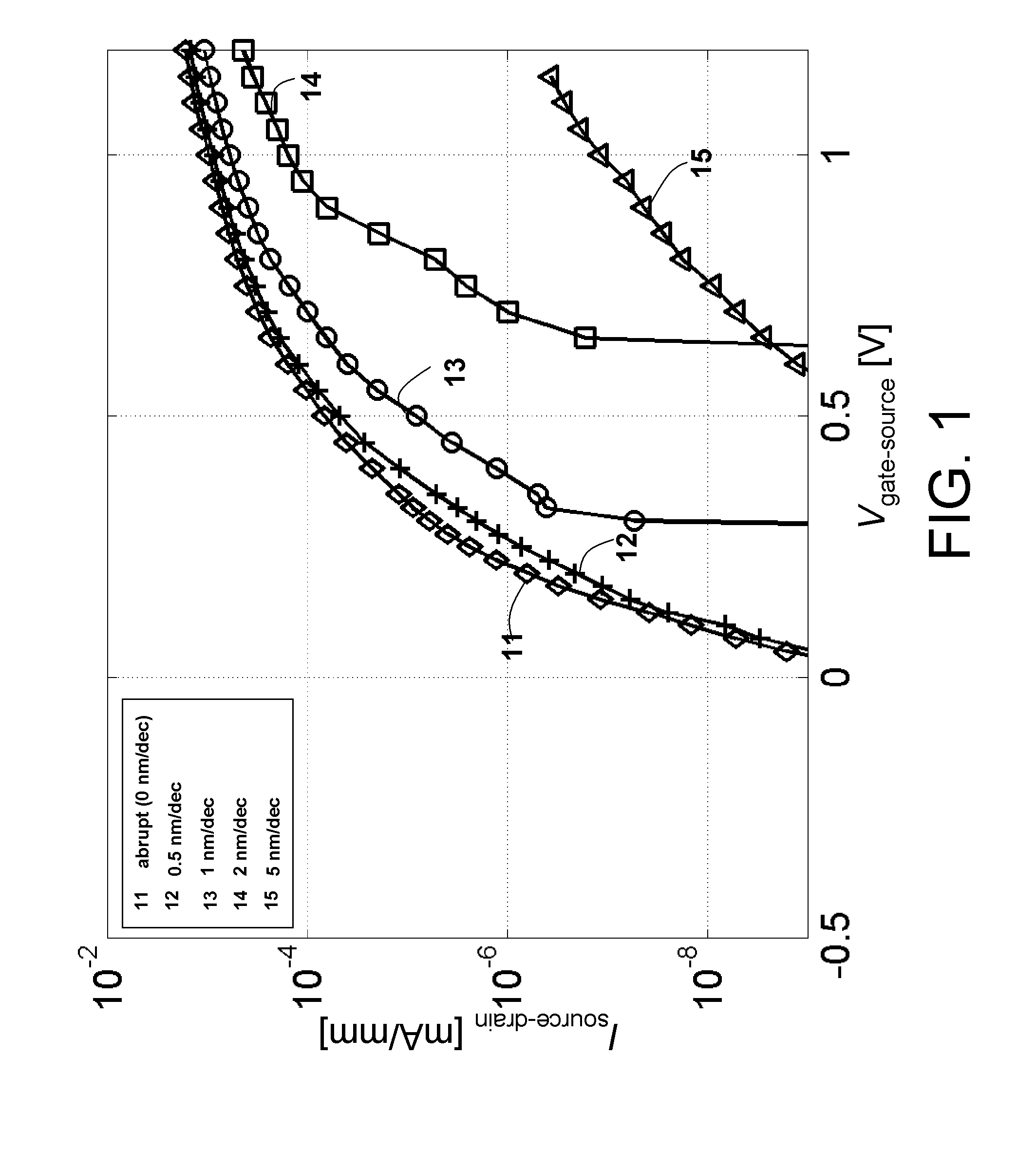

Tunnel field-effect transistors (TFETs) are regarded as successors of metal-oxide semiconductor field-effect transistors (MOSFETs), but silicon-based TFETs typically suffer from low on-currents, a drawback related to the large resistance of the tunnel barrier. To achieve higher on-currents a nanowire-based TFET with a germanium (Ge) tunnel barrier in an otherwise silicon (Si) channel is used. A nanowire is introduced such that the lattice mismatch between silicon and germanium does not result in a highly defective interface. A dynamic power reduction as well as a static power reduction can result, compared to conventional MOSFET configurations. Multiple layers of logic can therefore be envisioned with these nanowire Si / Ge TFETs resulting in ultra-high on-chip transistor densities.

Owner:KATHOLIEKE UNIV LEUVEN

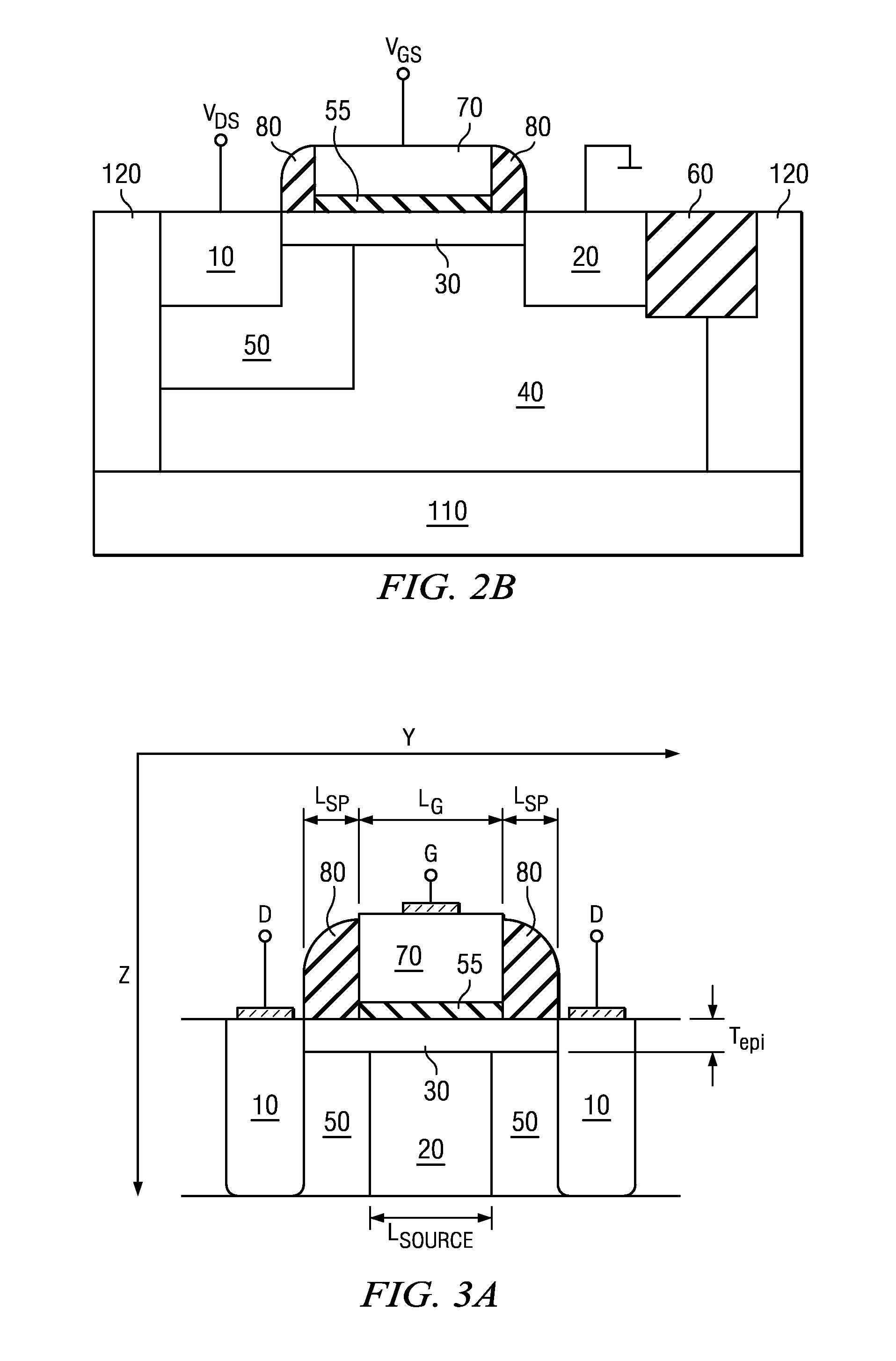

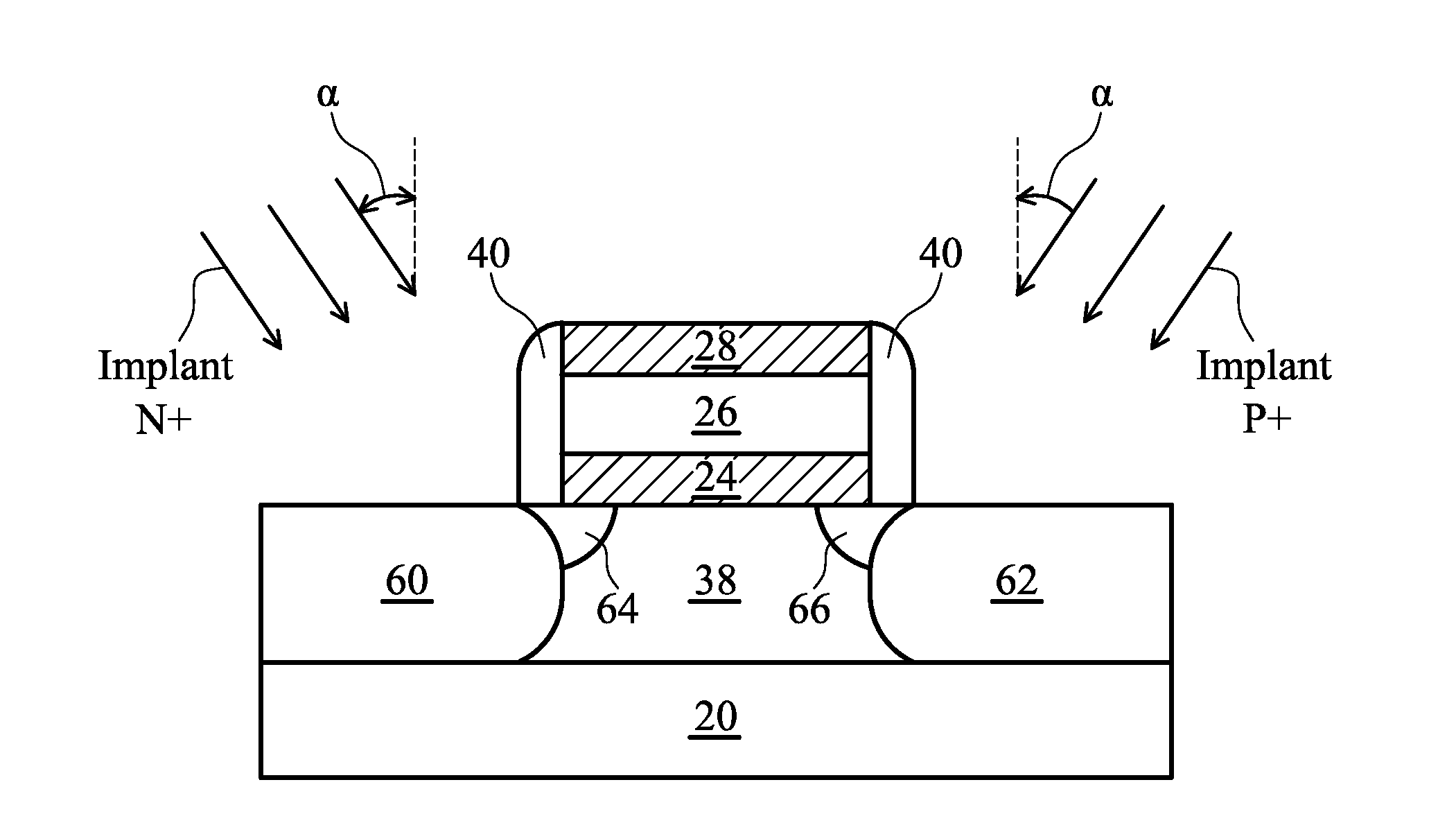

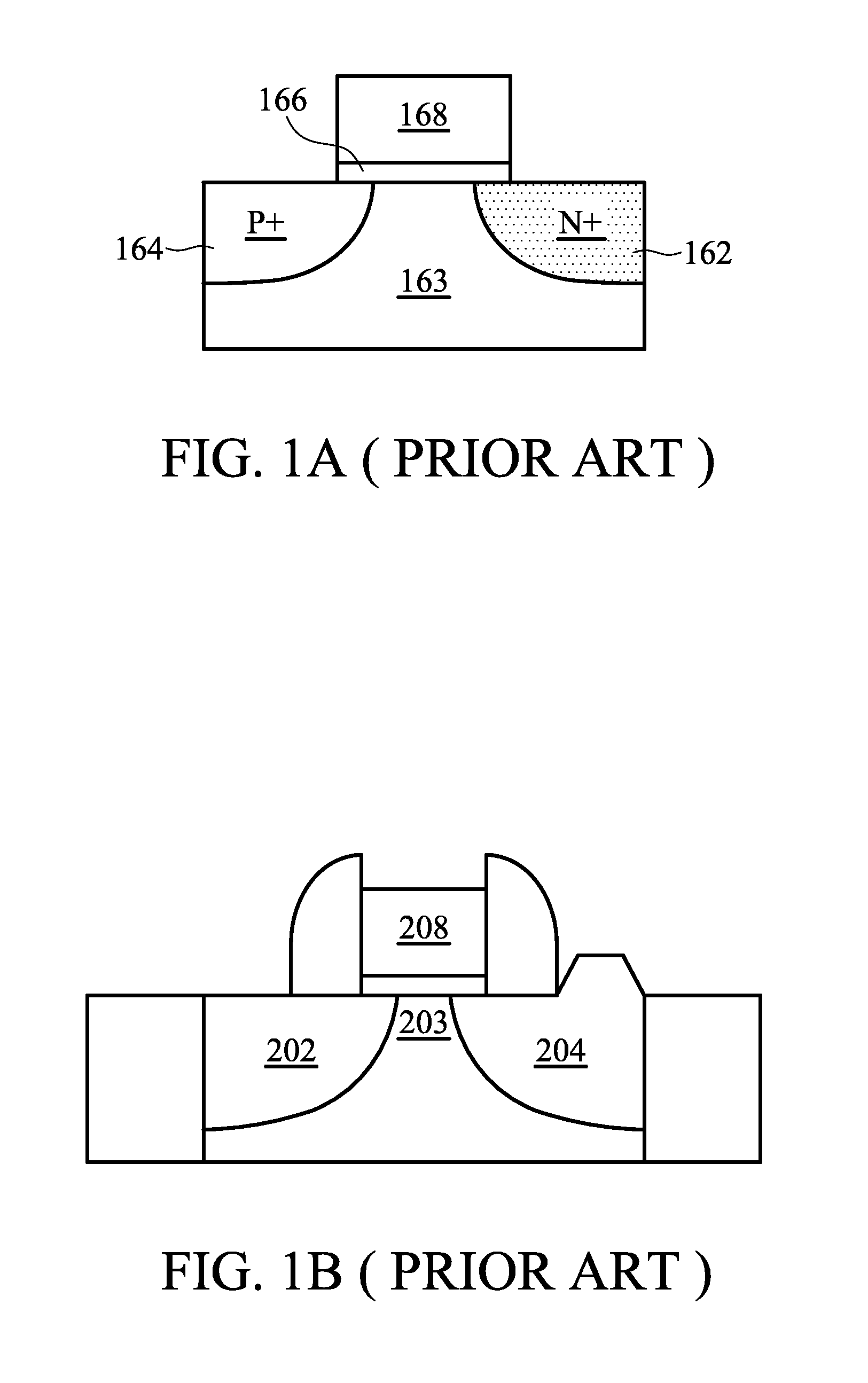

Tunneling field effect transistor using angled implants for forming asymmetric source/drain regions

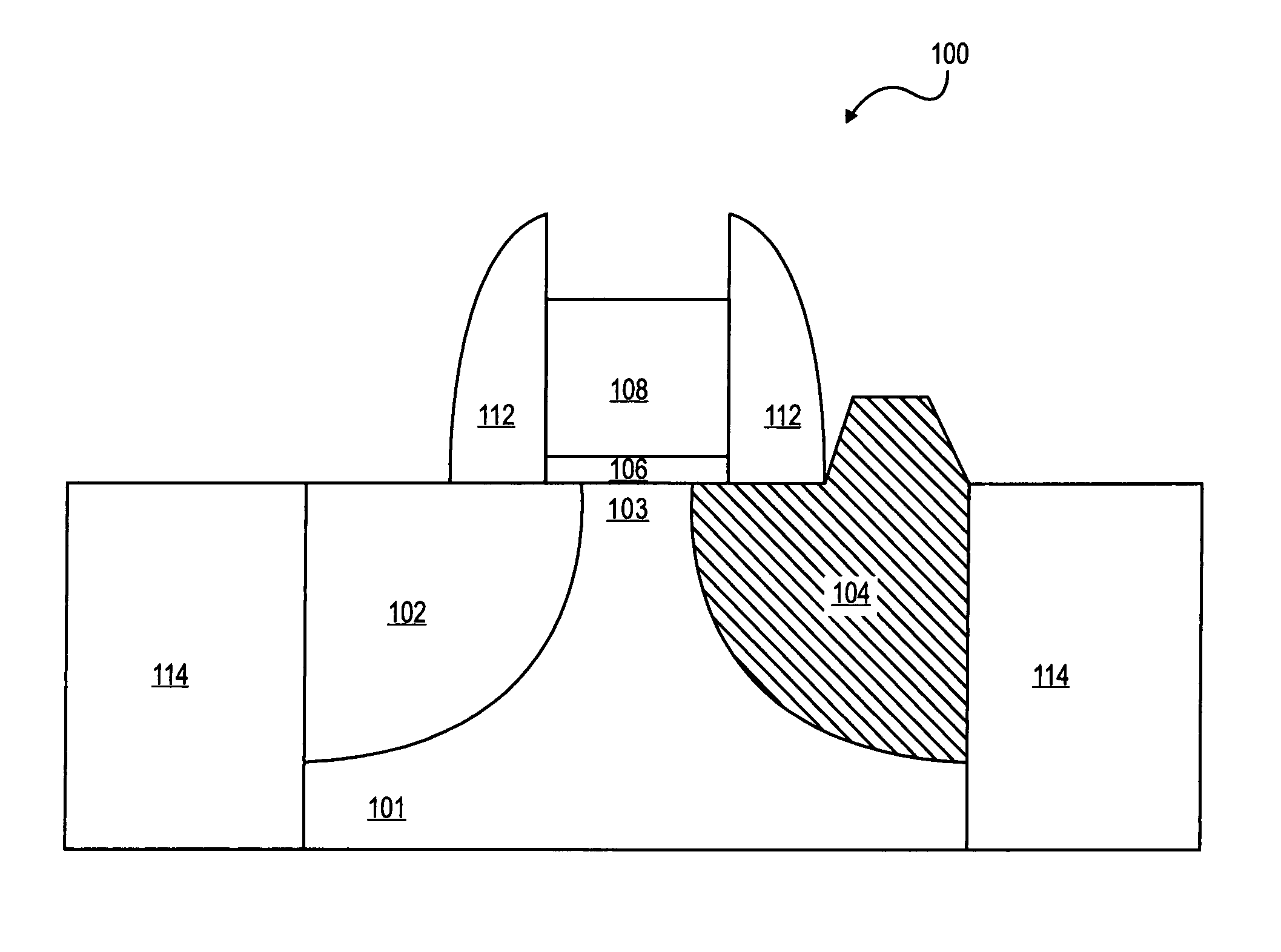

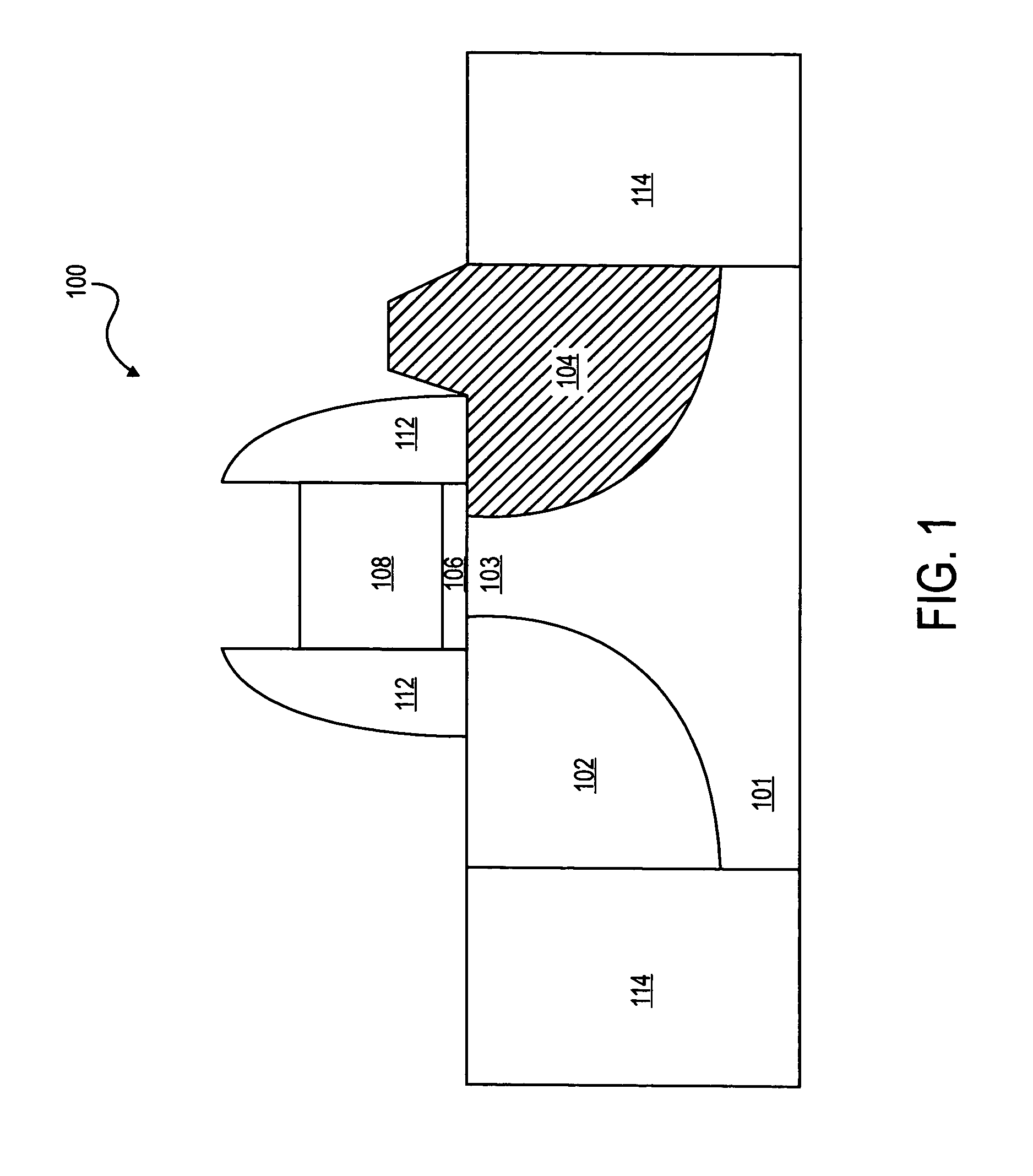

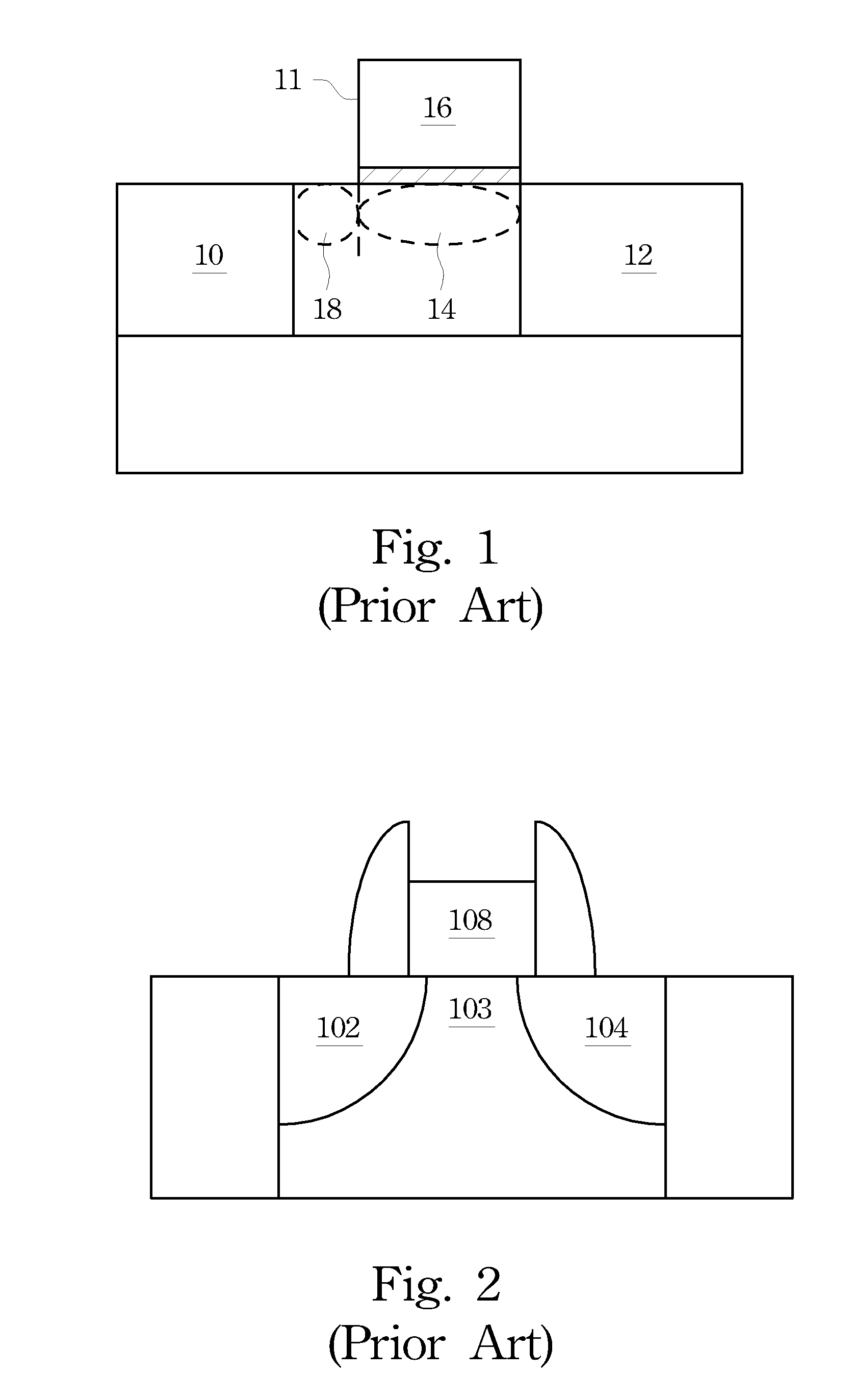

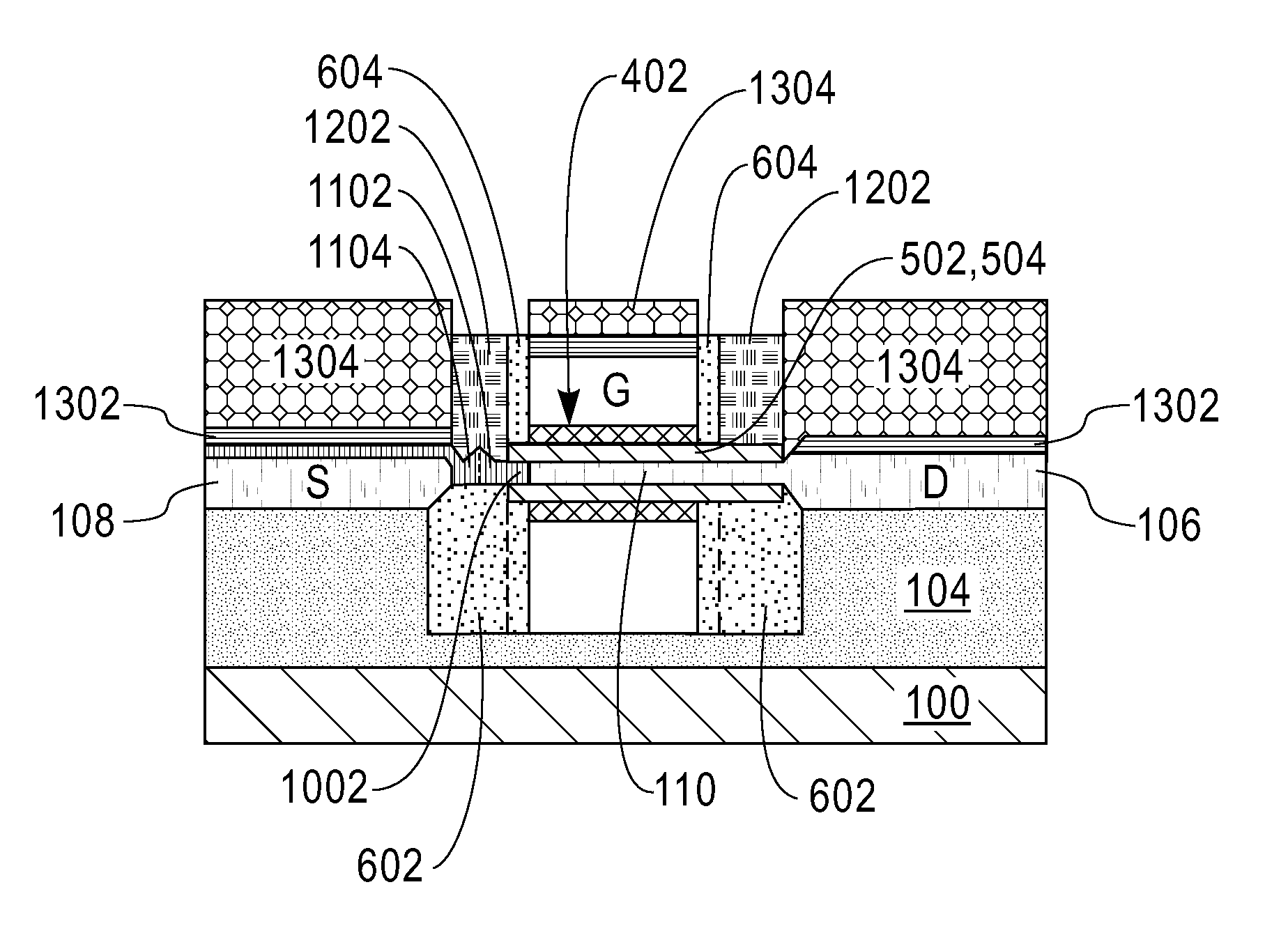

The present invention relates to a Tunnel Field Effect Transistor (TFET), which utilizes angle implantation and amorphization to form asymmetric source and drain regions. The TFET further comprises a silicon germanium alloy epitaxial source region with a conductivity opposite that of the drain.

Owner:INTEL CORP

Tunnel Field-Effect Transistor with Narrow Band-Gap Channel and Strong Gate Coupling

InactiveUS20090026553A1Reduce leakage currentImproved sub-threshold swingSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSemiconductor materials

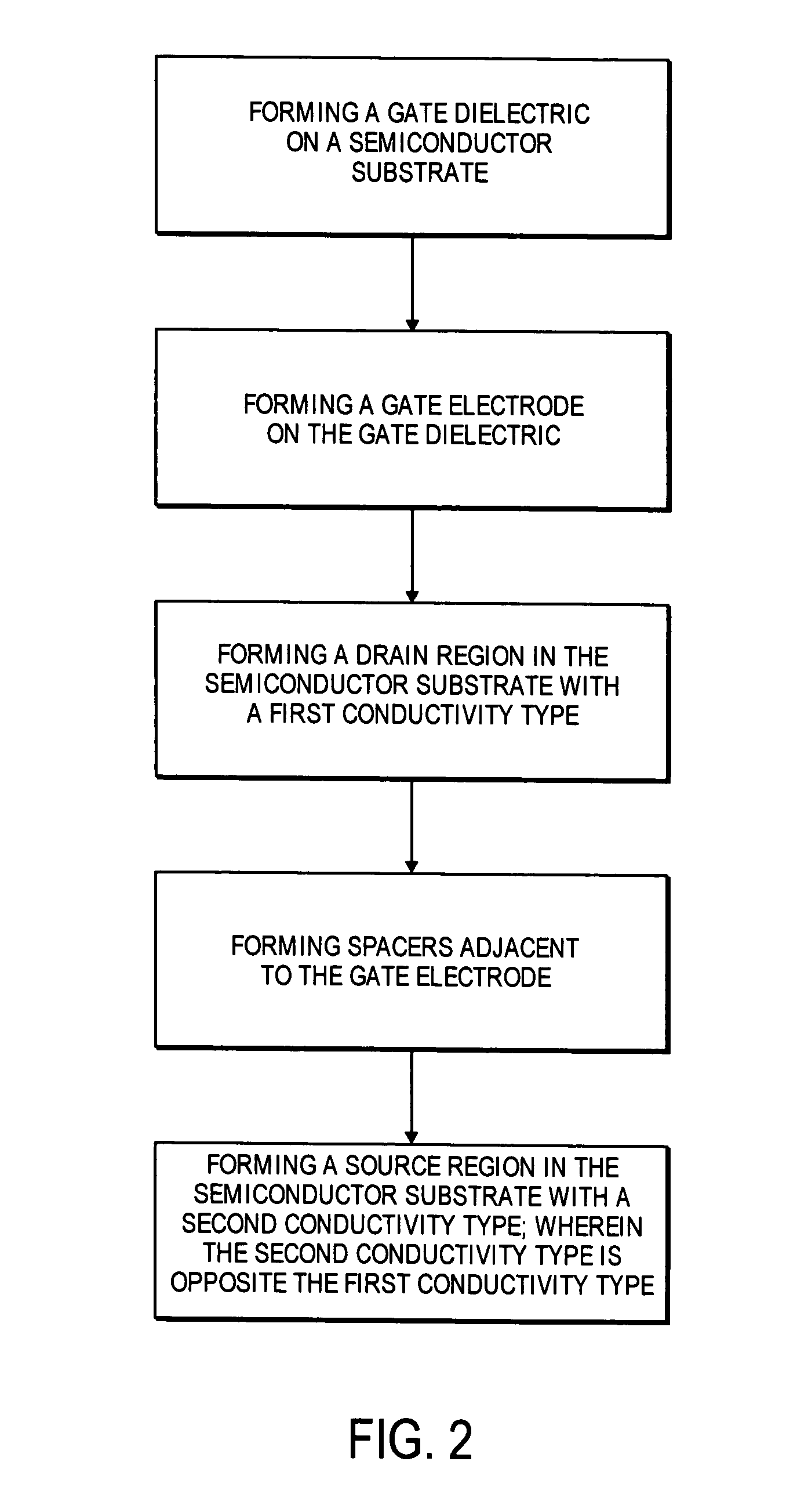

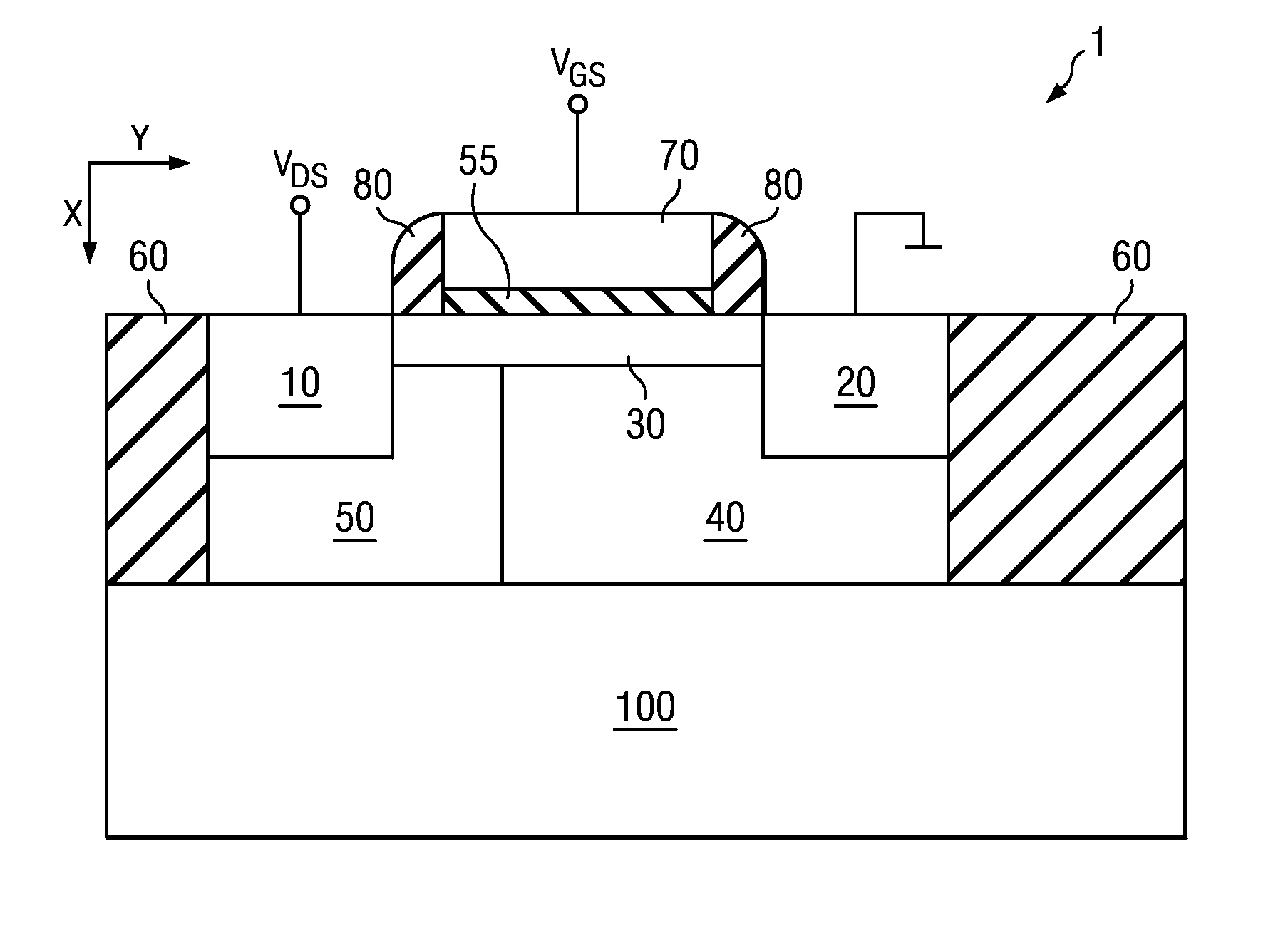

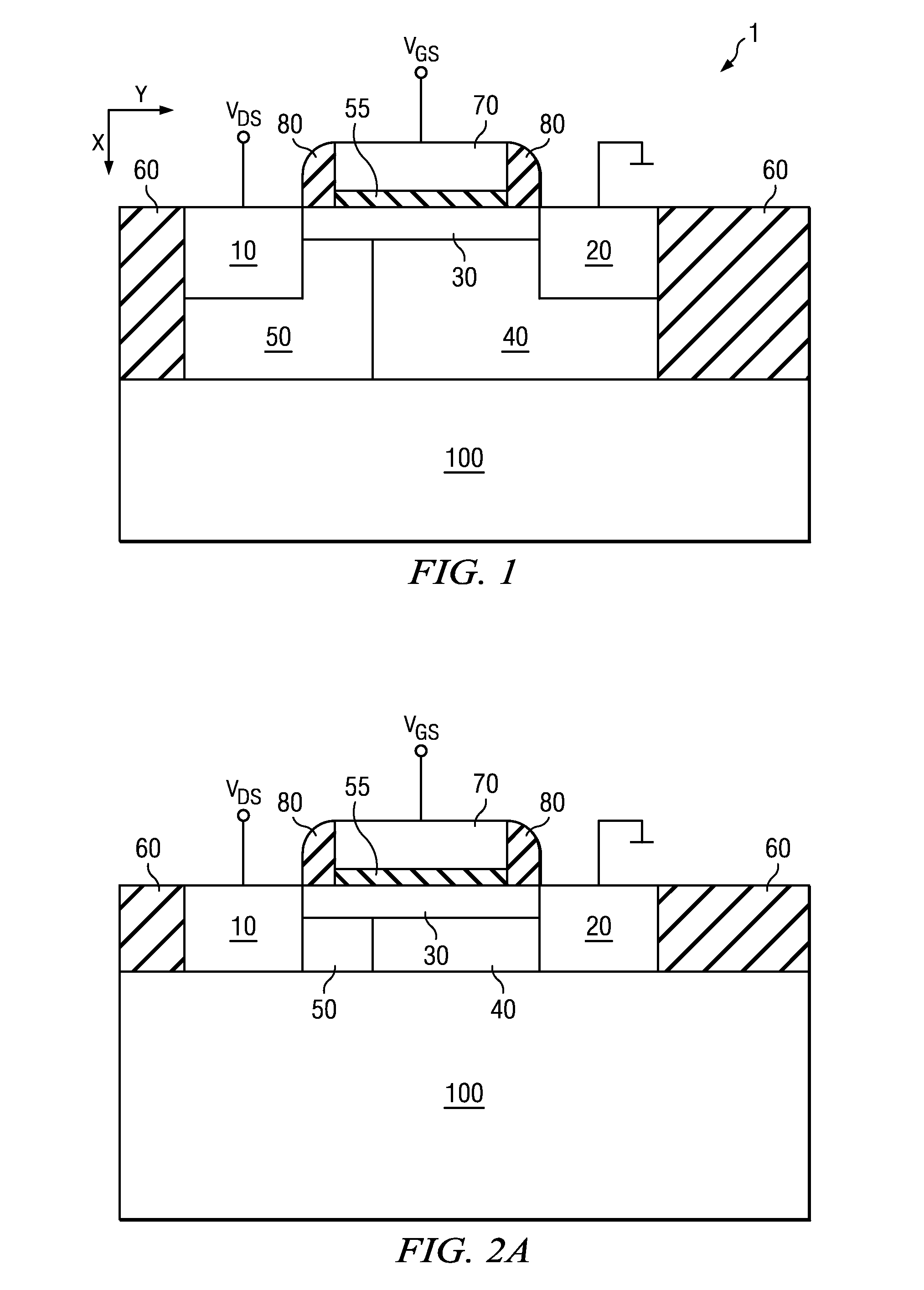

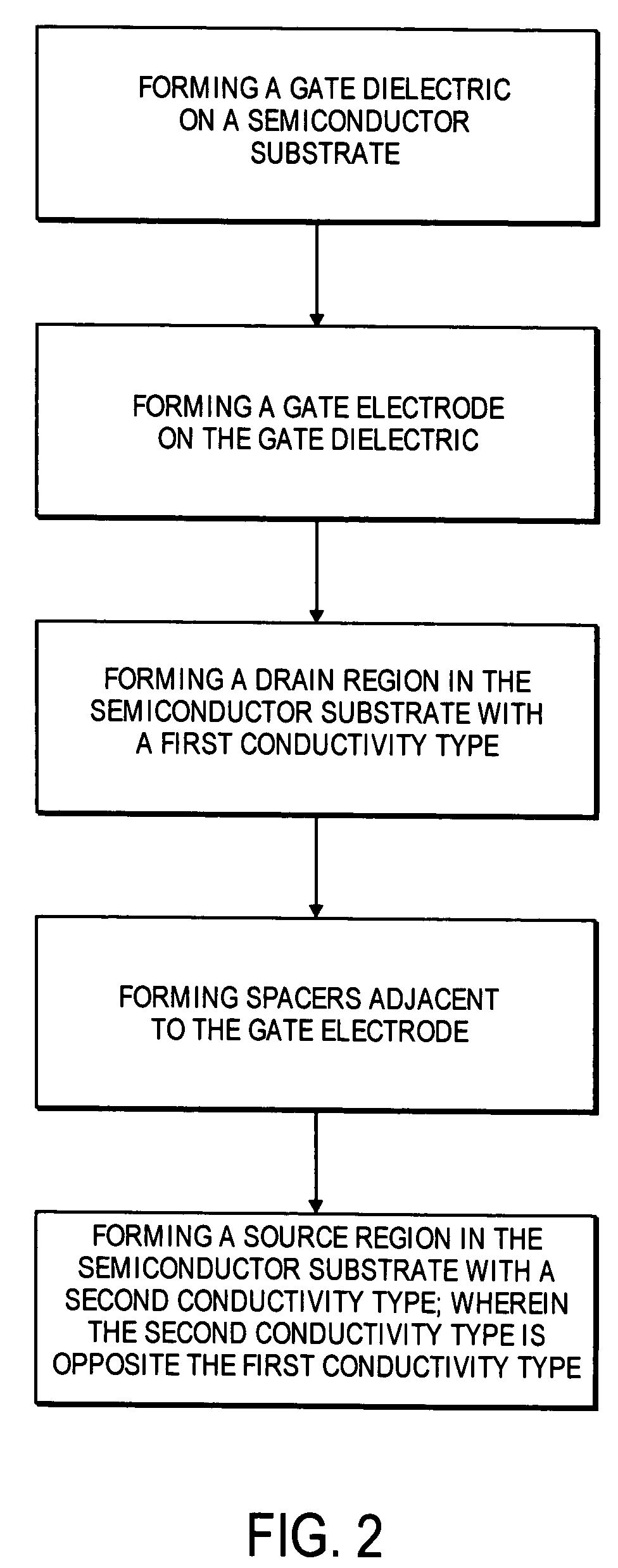

A semiconductor device and the methods of forming the same are provided. The semiconductor device includes a low energy band-gap layer comprising a semiconductor material; a gate dielectric on the low energy band-gap layer; a gate electrode over the gate dielectric; a first source / drain region adjacent the gate dielectric, wherein the first source / drain region is of a first conductivity type; and a second source / drain region adjacent the gate dielectric. The second source / drain region is of a second conductivity type opposite the first conductivity type. The low energy band-gap layer is located between the first and the second source / drain regions.

Owner:TAIWAN SEMICON MFG CO LTD

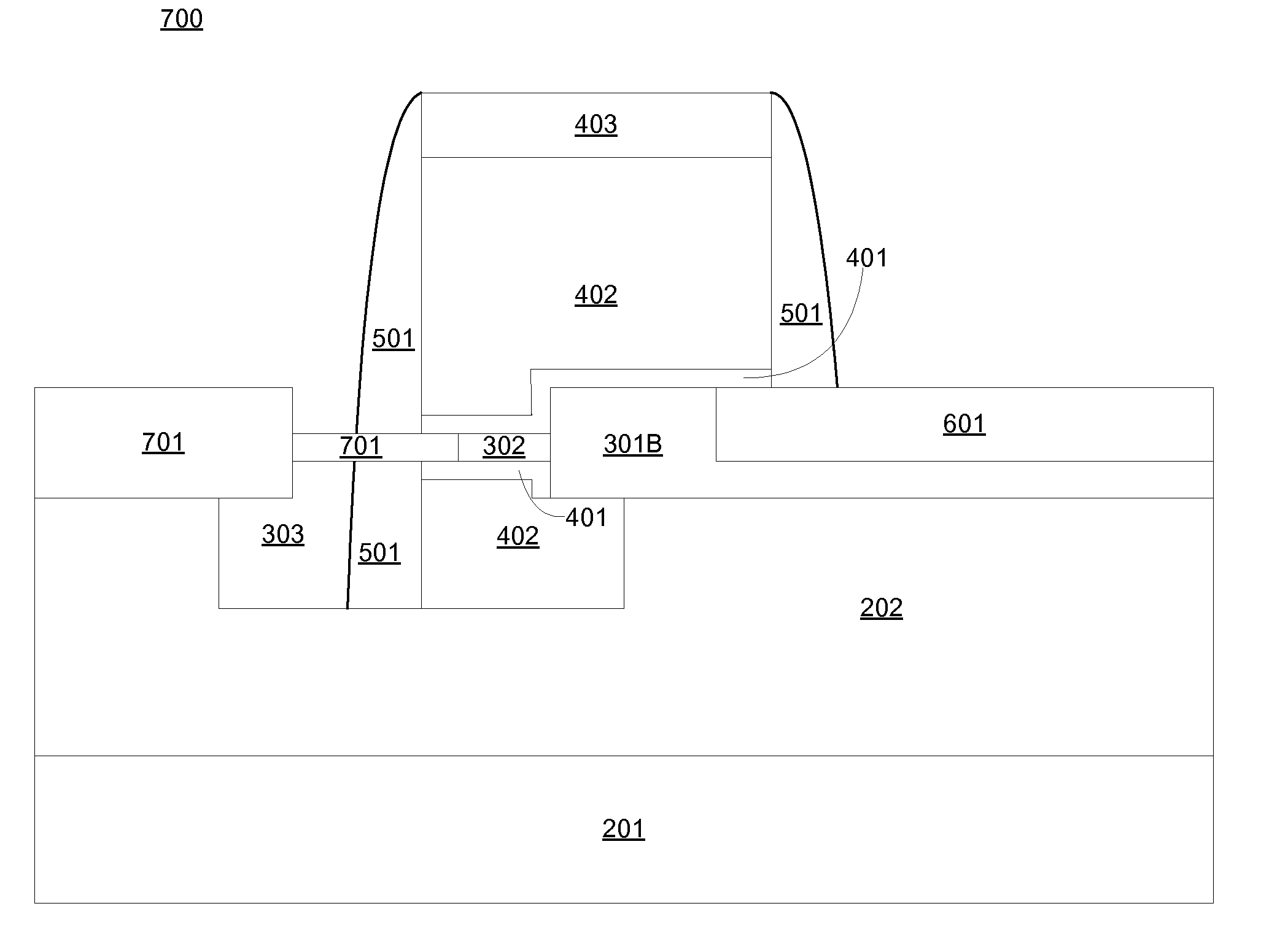

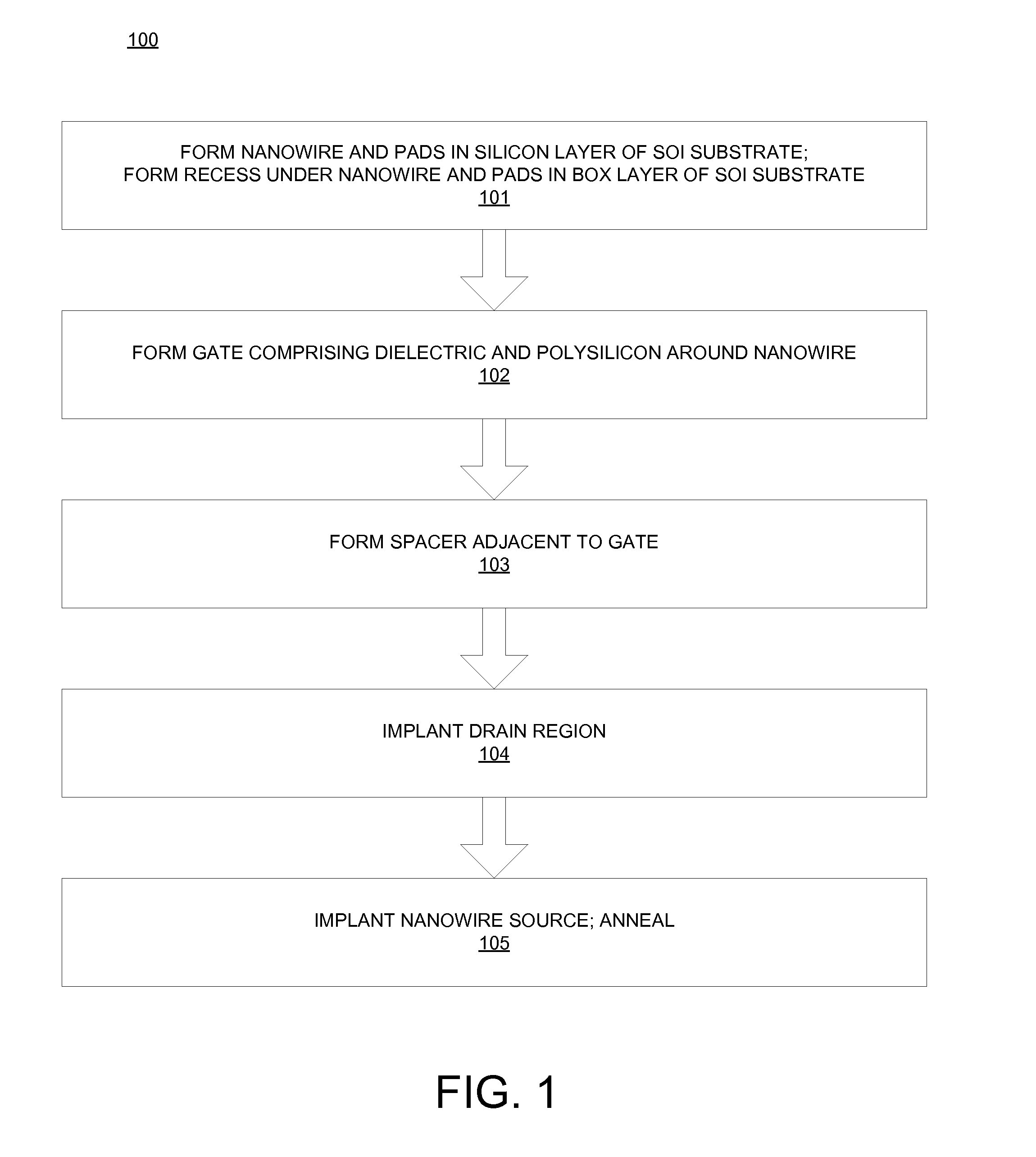

Gate-All-Around Nanowire Tunnel Field Effect Transistors

ActiveUS20110133169A1NanoinformaticsSemiconductor/solid-state device manufacturingNanowireSemiconductor materials

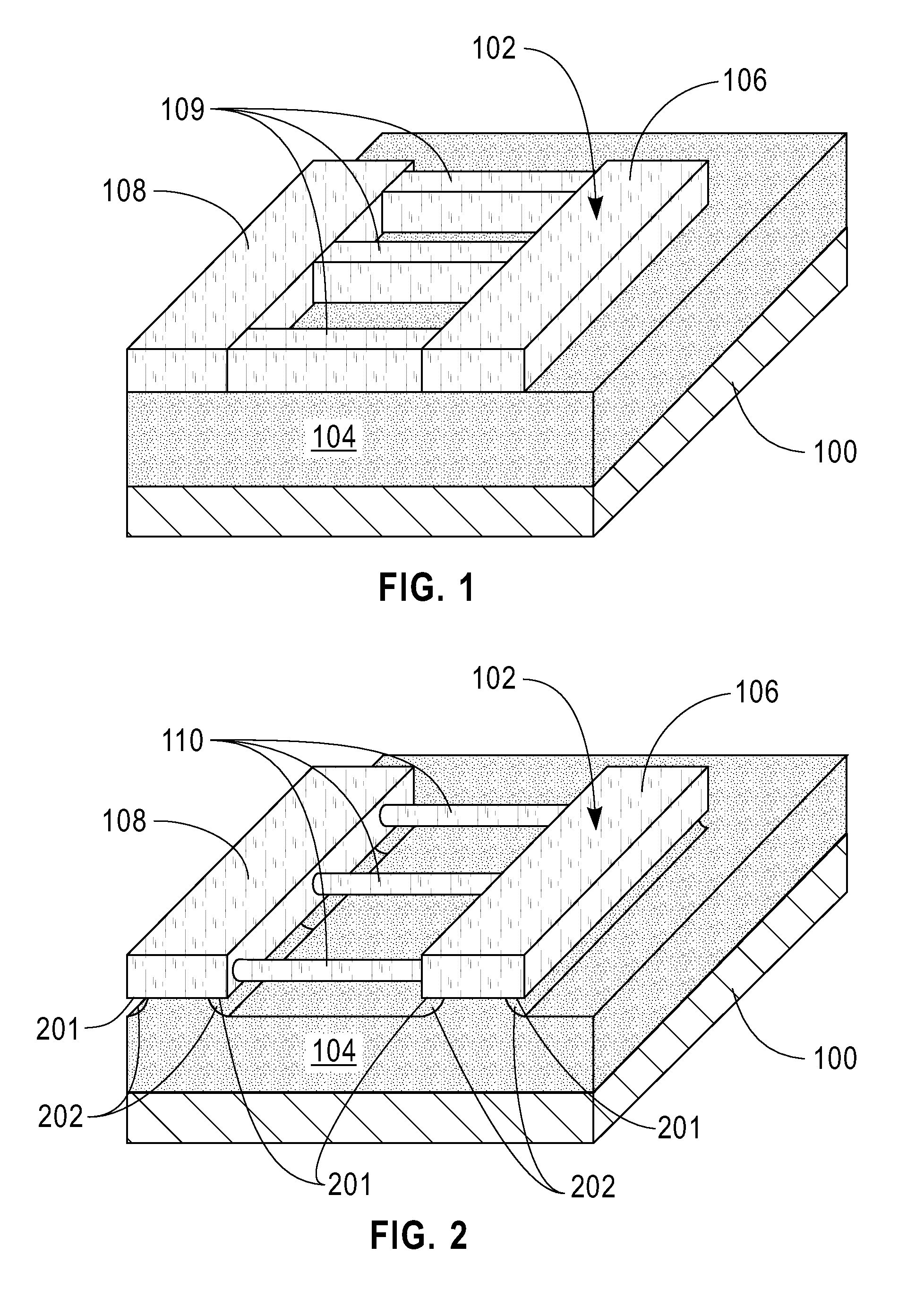

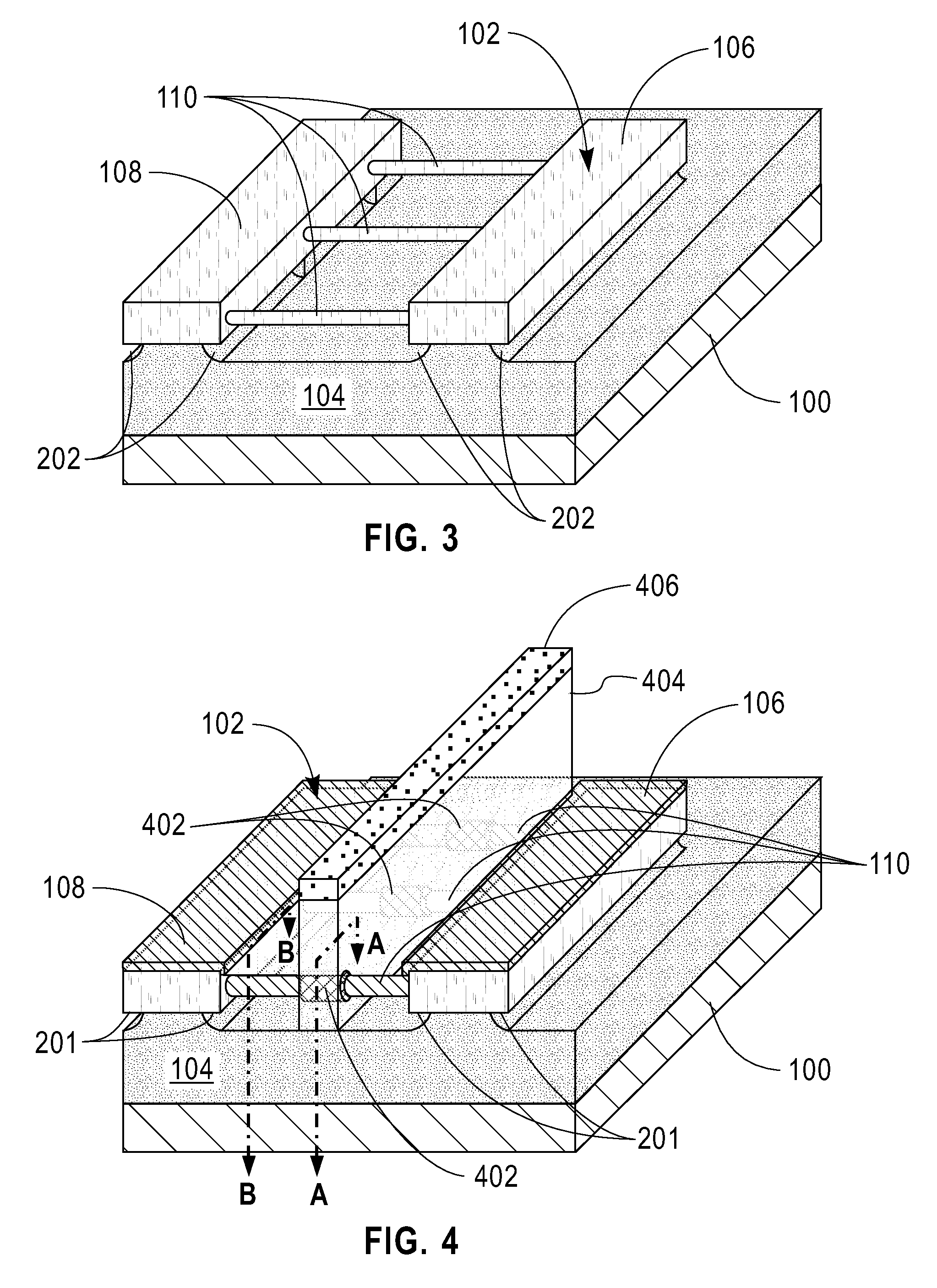

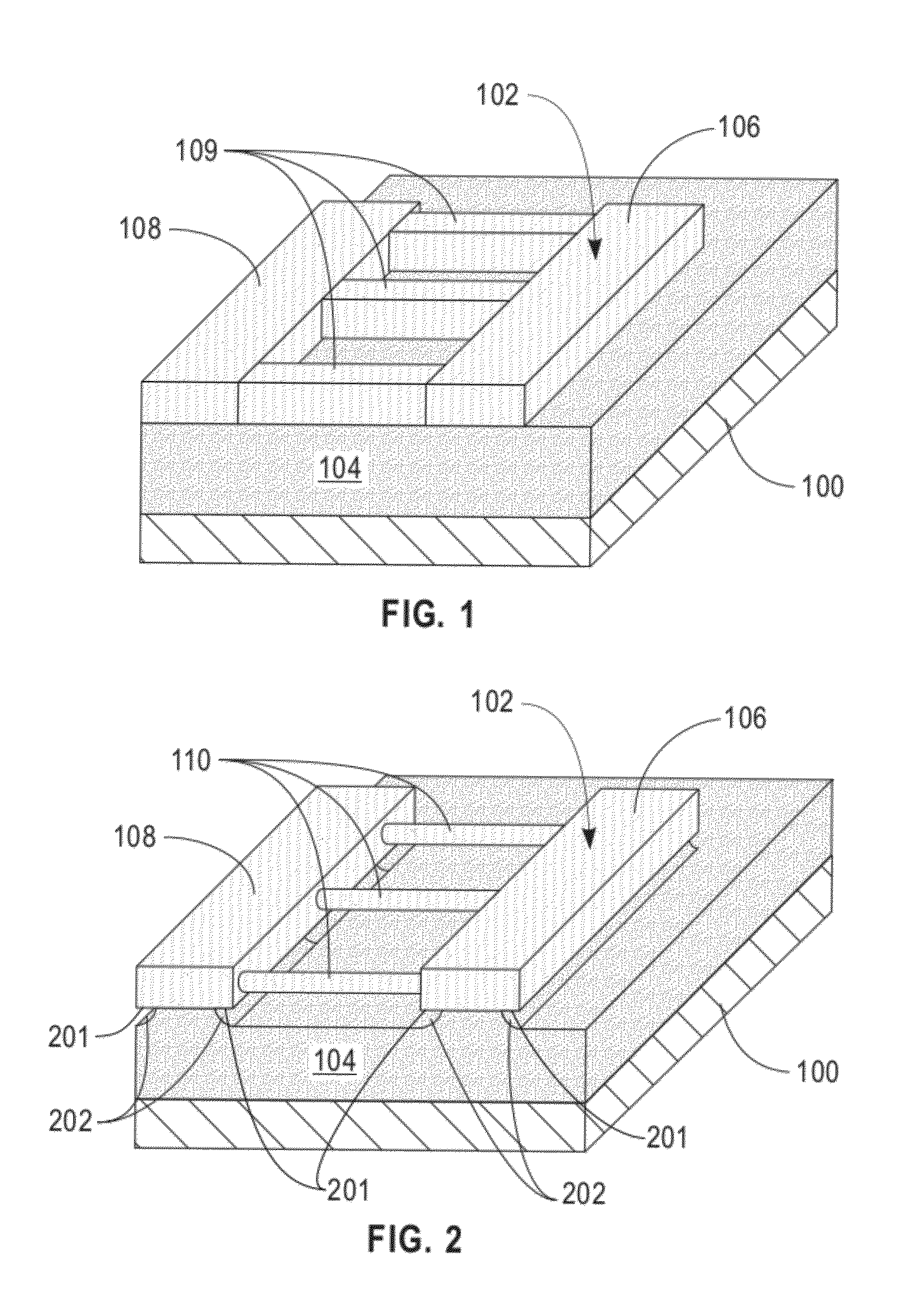

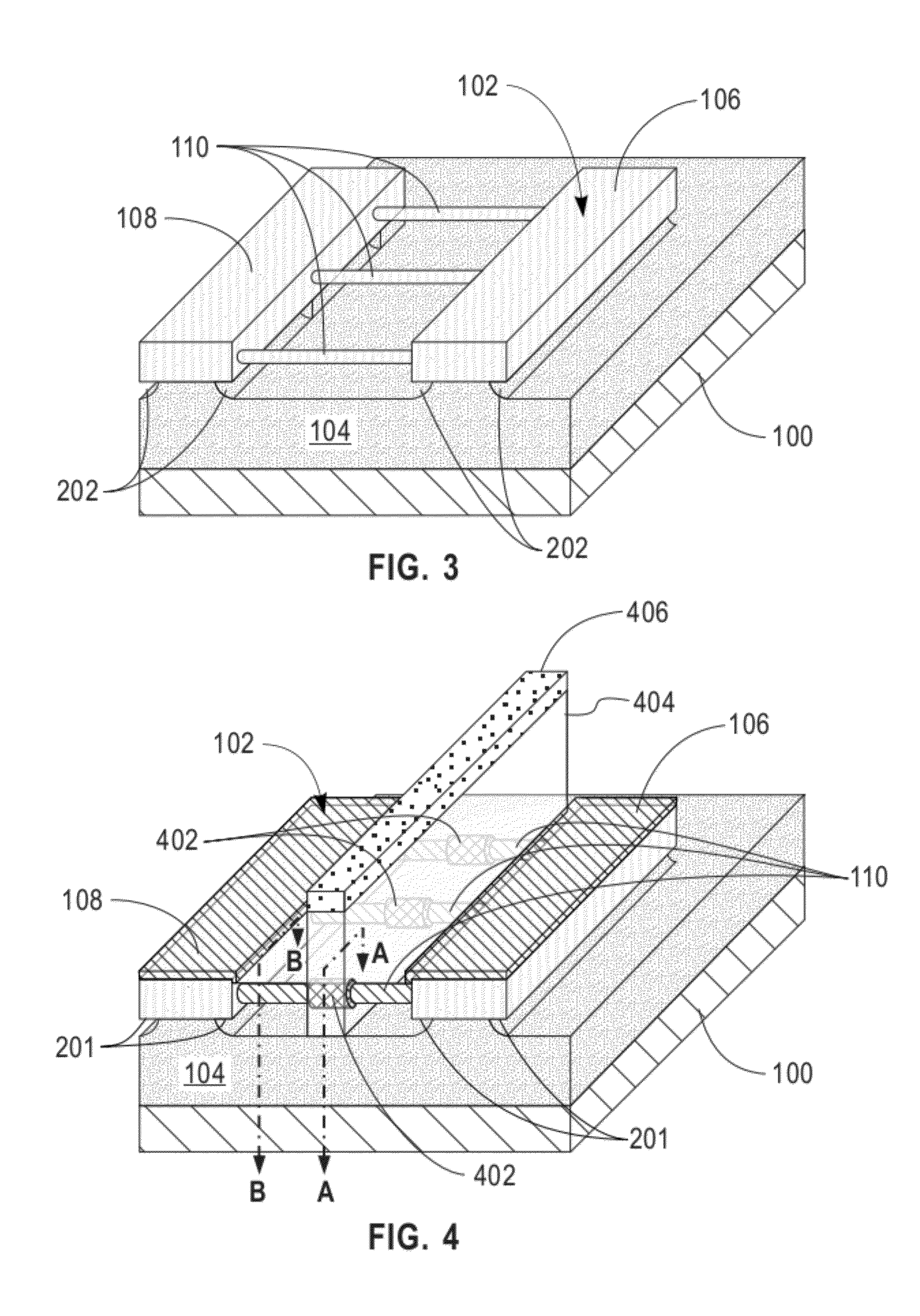

A method for forming a nanowire tunnel field effect transistor (FET) device includes forming a nanowire suspended by first and second pad regions over a semiconductor substrate, the nanowire including a core portion and a dielectric layer, forming a gate structure around a portion of the dielectric layer, forming a first spacer around portions of the nanowire extending from the gate structure, implanting ions in a first portion of the nanowire, implanting ions in the dielectric layer of a second portion of the nanowire, removing the dielectric layer from the second portion of the nanowire, removing the core portion of the second portion of the exposed nanowire to form a cavity, and epitaxially growing a doped semiconductor material in the cavity from exposed cross sections of the nanowire and the second pad region to connect the exposed cross sections of the nanowire to the second pad region.

Owner:GLOBALFOUNDRIES US INC

Tunnel effect transistors based on elongate monocrystalline nanostructures having a heterostructure

ActiveUS20080067607A1Optimize architectureReduce power consumptionTransistorNanoinformaticsMOSFETSemiconductor materials

Tunnel field-effect transistors (TFETs) are regarded as successors of metal-oxide semiconductor field-effect transistors (MOSFETs), but silicon-based TFETs typically suffer from low on-currents, a drawback related to the large resistance of the tunnel barrier. To achieve higher on-currents an elongate monocrystalline nanostructure-based TFET with a heterostructure made of a different semiconducting material (e.g. germanium (Ge)) is used. An elongate monocrystalline nanostructure made of a different semiconducting material is introduced which acts as source (or alternatively drain) region of the TFET. The introduction of the heterosection is such that the lattice mismatch between silicon and germanium does not result in a highly defective interface. A dynamic power reduction as well as a static power reduction can result, compared to conventional MOSFET configurations. Multiple layers of logic can therefore be envisioned with these elongate monocrystalline nanostructure Si / Ge TFETs resulting in ultra-high on-chip transistor densities.

Owner:KATHOLIEKE UNIV LEUVEN +1

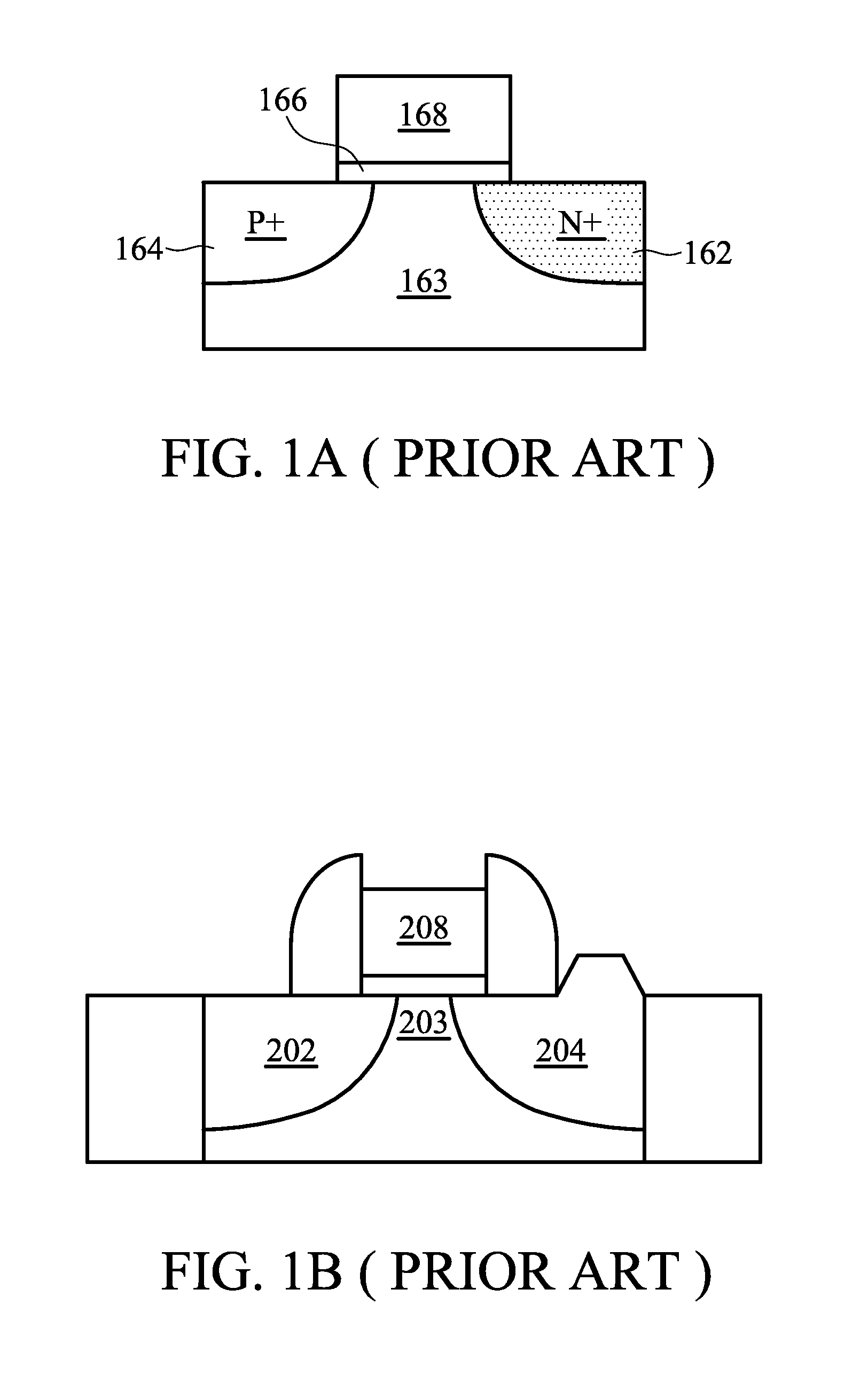

Tunnel Field Effect Transistors

ActiveUS20110147838A1Semiconductor/solid-state device manufacturingDiodeGate stackCondensed matter physics

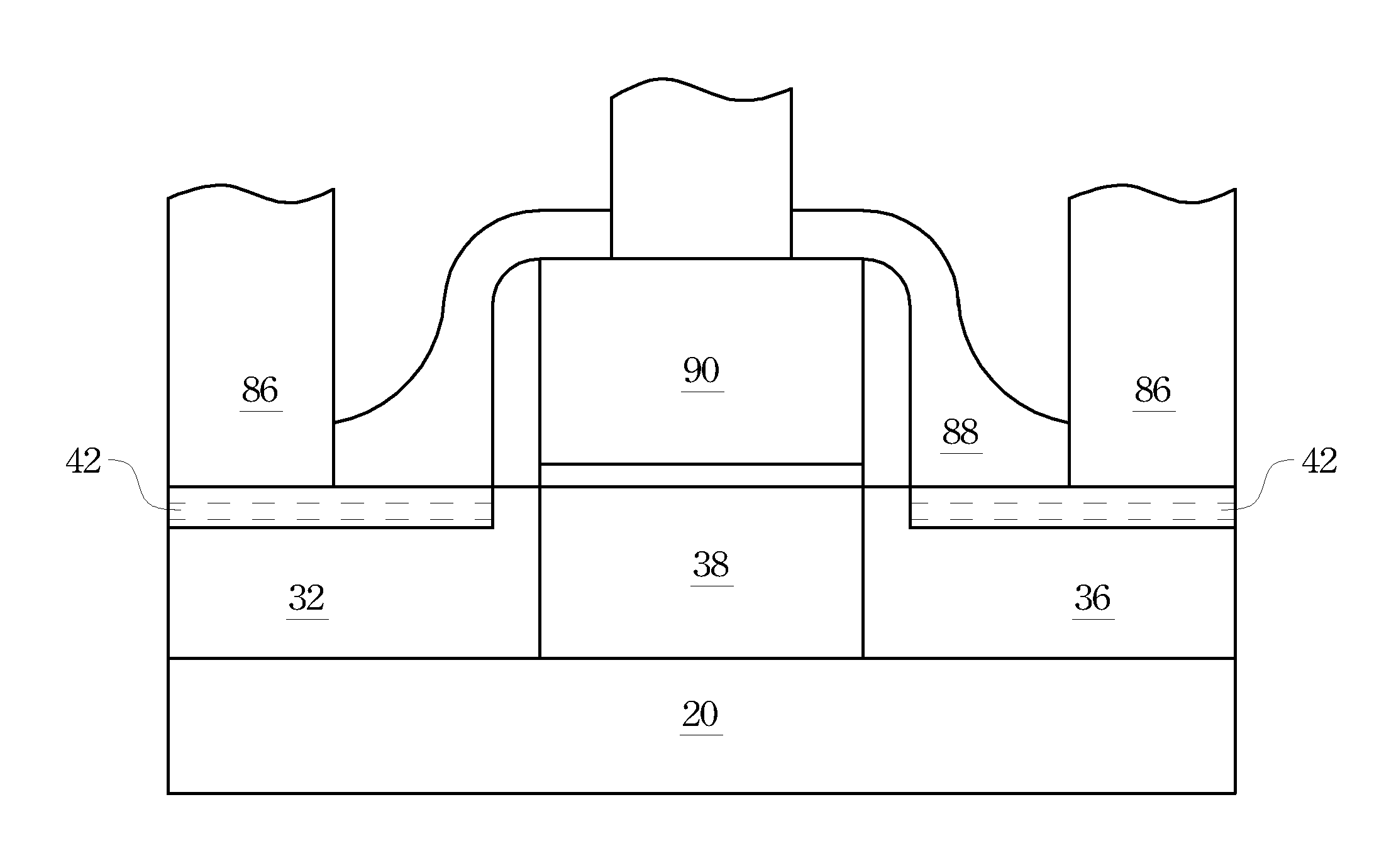

Tunnel field effect devices and methods of fabricating tunnel field effect devices are described. In one embodiment, the semiconductor device includes a first drain region of a first conductivity type disposed in a first region of a substrate, a first source region of a second conductivity type disposed in the substrate, the second conductivity type being opposite the first conductivity type, a first channel region electrically coupled between the first source region and the first drain region, the first source region underlying a least a portion of the first channel region, and a first gate stack overlying the first channel region.

Owner:INFINEON TECH AG +1

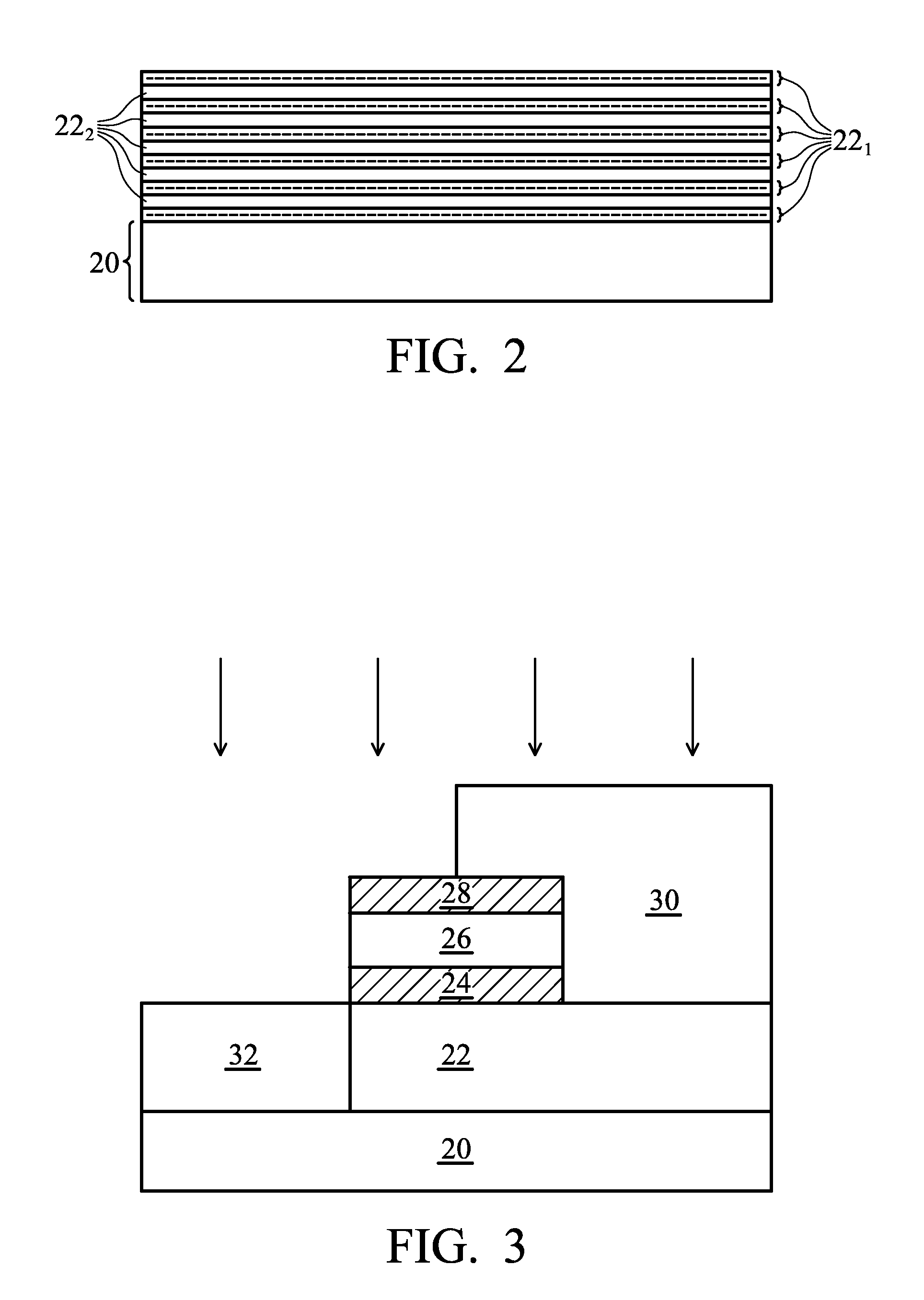

Tunnel field-effect transistors with superlattice channels

InactiveUS7834345B2Increase the on-currentReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor

A semiconductor device includes a channel region; a gate dielectric over the channel region; a gate electrode over the gate dielectric; and a first source / drain region adjacent the gate dielectric. The first source / drain region is of a first conductivity type. At least one of the channel region and the first source / drain region includes a superlattice structure. The semiconductor device further includes a second source / drain region on an opposite side of the channel region than the first source / drain region. The second source / drain region is of a second conductivity type opposite the first conductivity type. At most, one of the first source / drain region and the second source / drain region comprises an additional superlattice structure.

Owner:TAIWAN SEMICON MFG CO LTD

Tunnel Field-Effect Transistors with Superlattice Channels

InactiveUS20100059737A1Increase the on-currentSacrificing source-drain leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor

A semiconductor device includes a channel region; a gate dielectric over the channel region; a gate electrode over the gate dielectric; and a first source / drain region adjacent the gate dielectric. The first source / drain region is of a first conductivity type. At least one of the channel region and the first source / drain region includes a superlattice structure. The semiconductor device further includes a second source / drain region on an opposite side of the channel region than the first source / drain region. The second source / drain region is of a second conductivity type opposite the first conductivity type. At most, one of the first source / drain region and the second source / drain region comprises an additional superlattice structure.

Owner:TAIWAN SEMICON MFG CO LTD

Tunnel field-effect transistor with narrow band-gap channel and strong gate coupling

InactiveUS7812370B2Reduce leakage currentImproved sub-threshold swing and on-currentSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSemiconductor materials

A semiconductor device and the methods of forming the same are provided. The semiconductor device includes a low energy band-gap layer comprising a semiconductor material; a gate dielectric on the low energy band-gap layer; a gate electrode over the gate dielectric; a first source / drain region adjacent the gate dielectric, wherein the first source / drain region is of a first conductivity type; and a second source / drain region adjacent the gate dielectric. The second source / drain region is of a second conductivity type opposite the first conductivity type. The low energy band-gap layer is located between the first and the second source / drain regions.

Owner:TAIWAN SEMICON MFG CO LTD

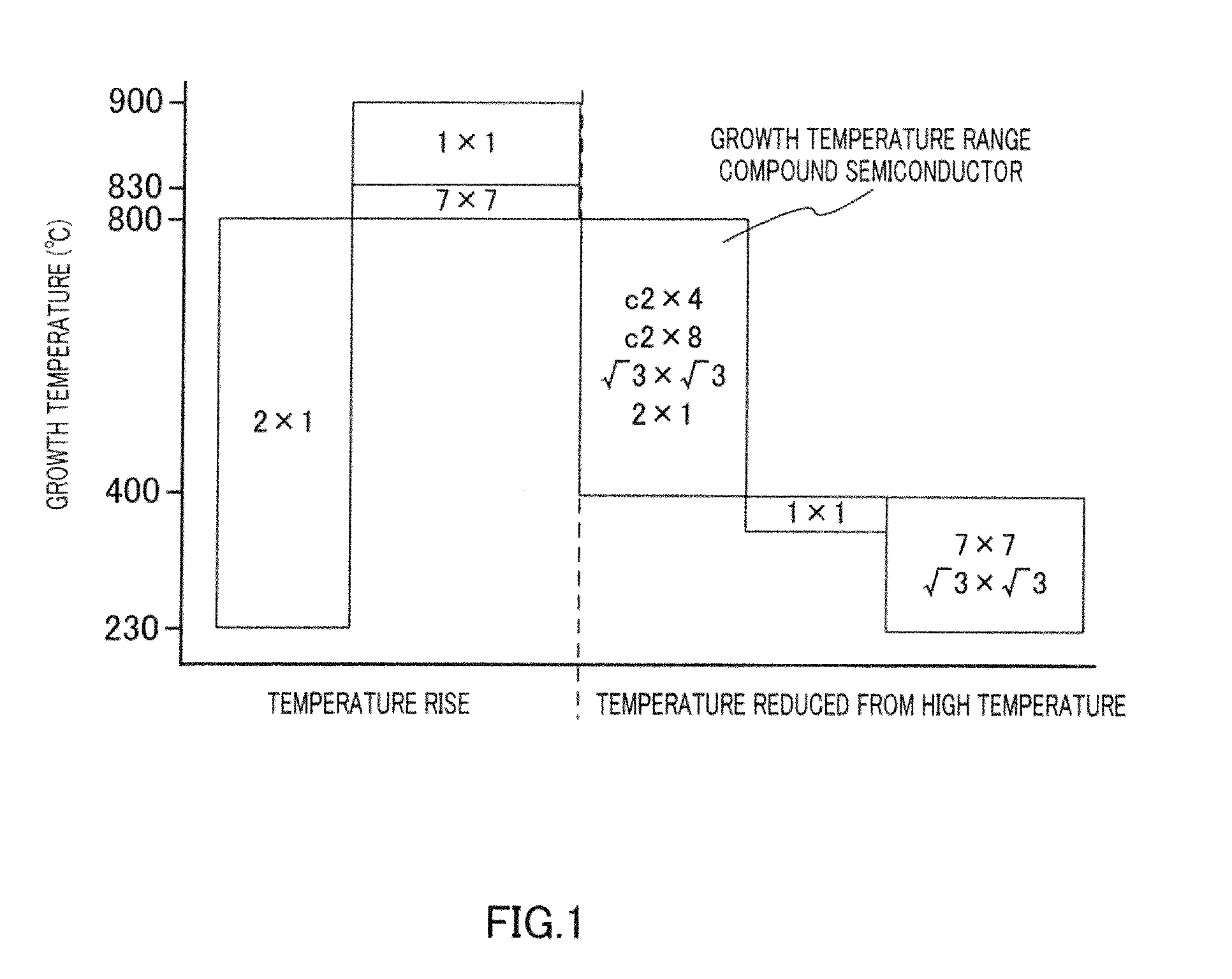

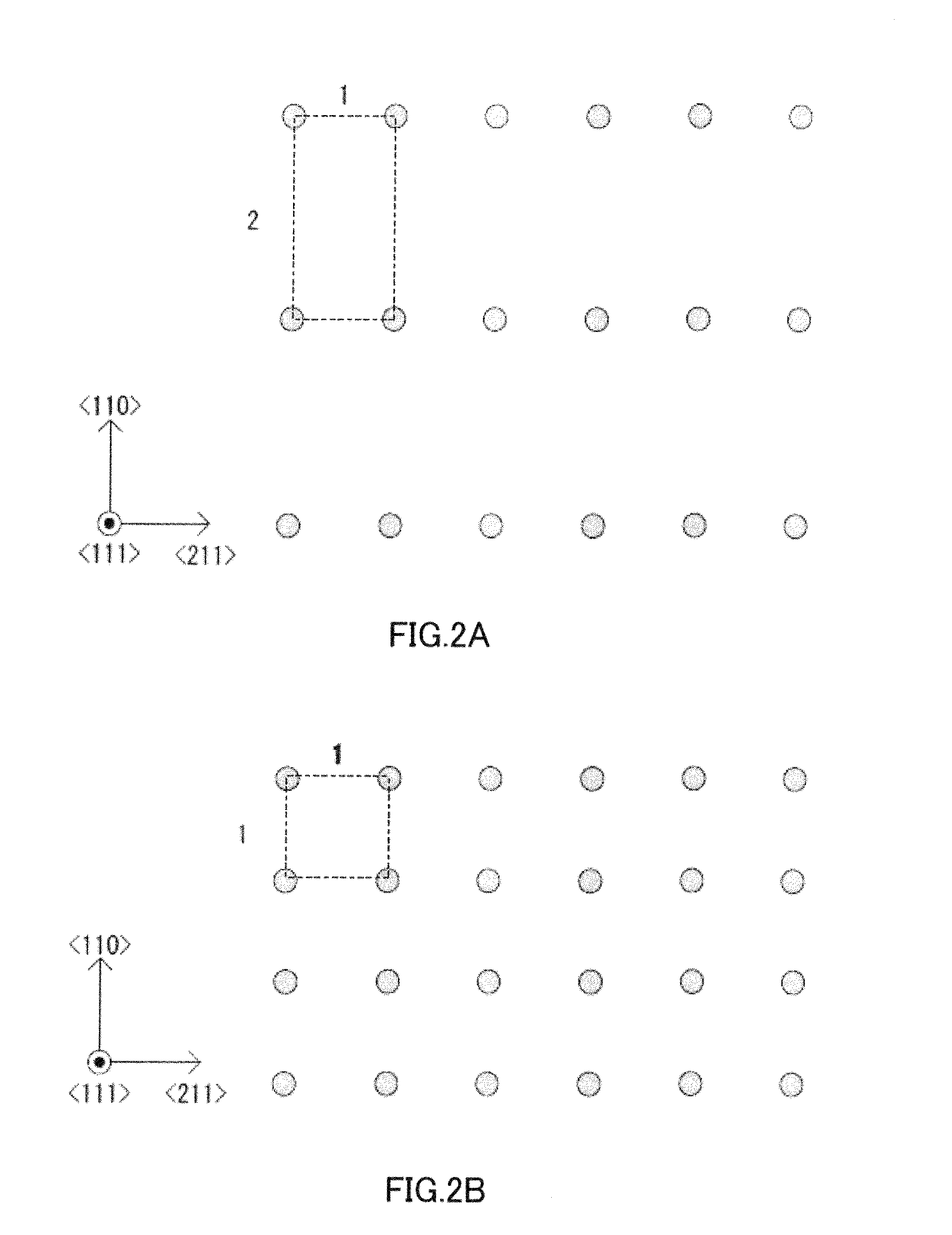

Tunnel field effect transistor and method for manufacturing same

ActiveUS20120187376A1Easy to manufactureHigh degree of integrationPolycrystalline material growthNanoinformaticsNanowireCondensed matter physics

A tunnel field effect transistor is capable of operating at a low subthreshold and is able to be manufactured easily. The tunnel field effect transistor includes a group IV semiconductor substrate having a (111) surface and doped so as to have a first conductivity type, a group III-V compound semiconductor nanowire arranged on the (111) surface and containing a first region connected to the (111) surface and a second region doped so as to have a second conductivity type, a source electrode connected to the group IV semiconductor substrate; a drain electrode connected to the second region, and a gate electrode for applying an electric field to an interface between the (111) surface and the group III-V compound semiconductor nanowire, or an interface between the first region and the second region.

Owner:HOKKAIDO UNIVERSITY

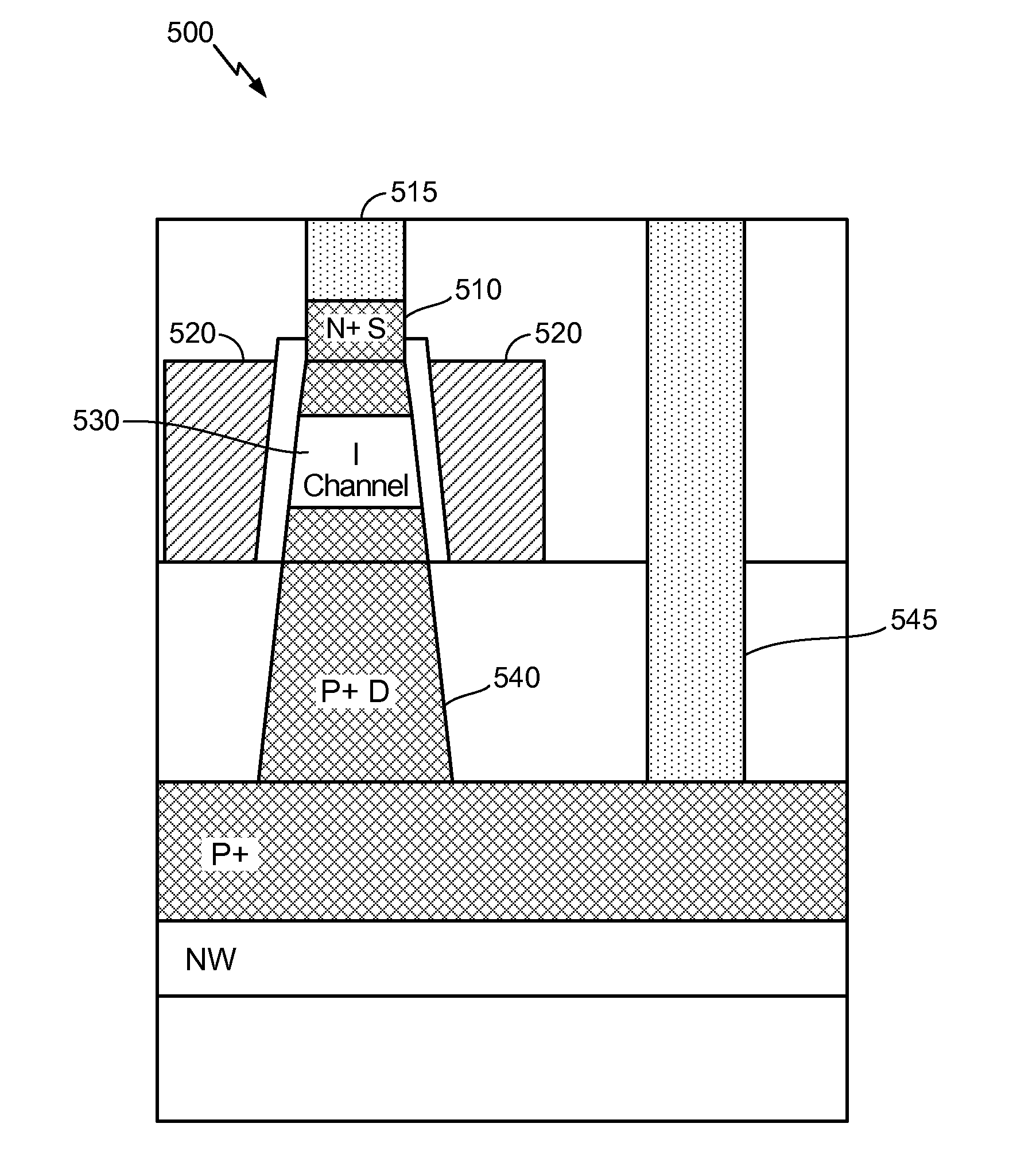

Tunnel field effect transistor and method for making thereof

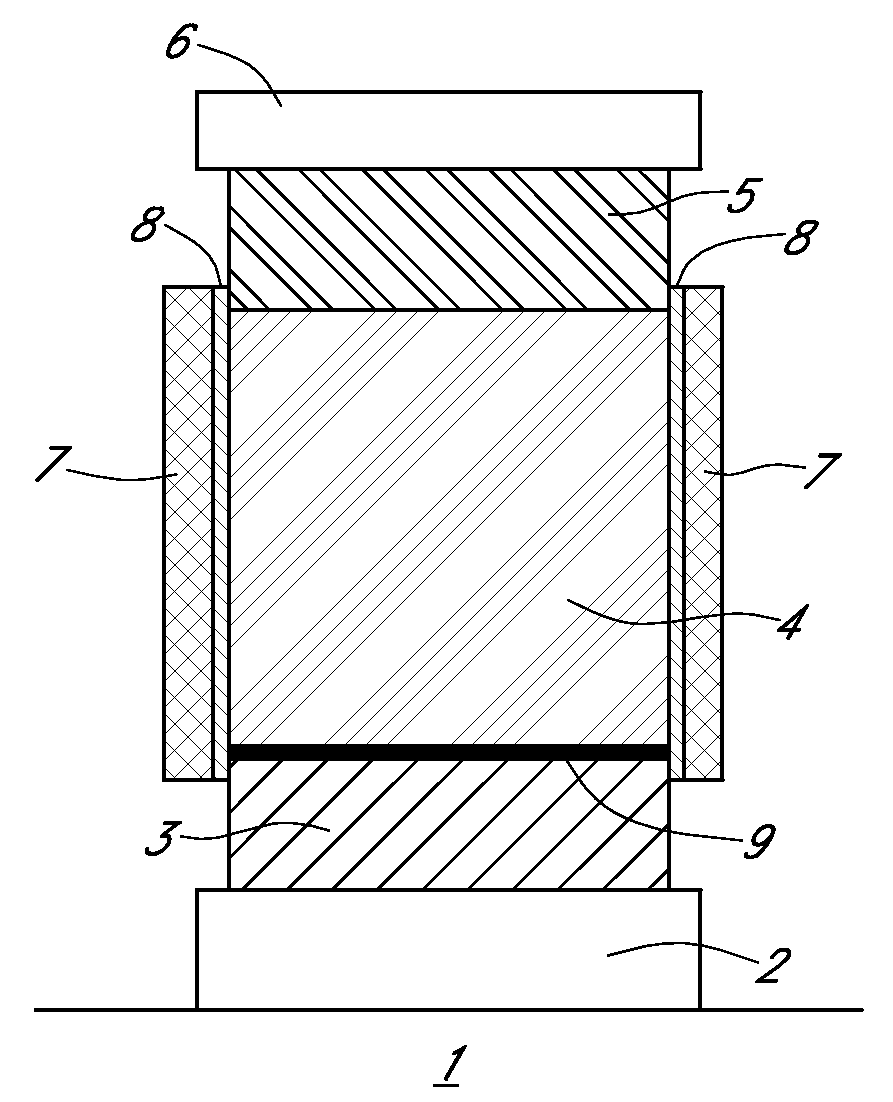

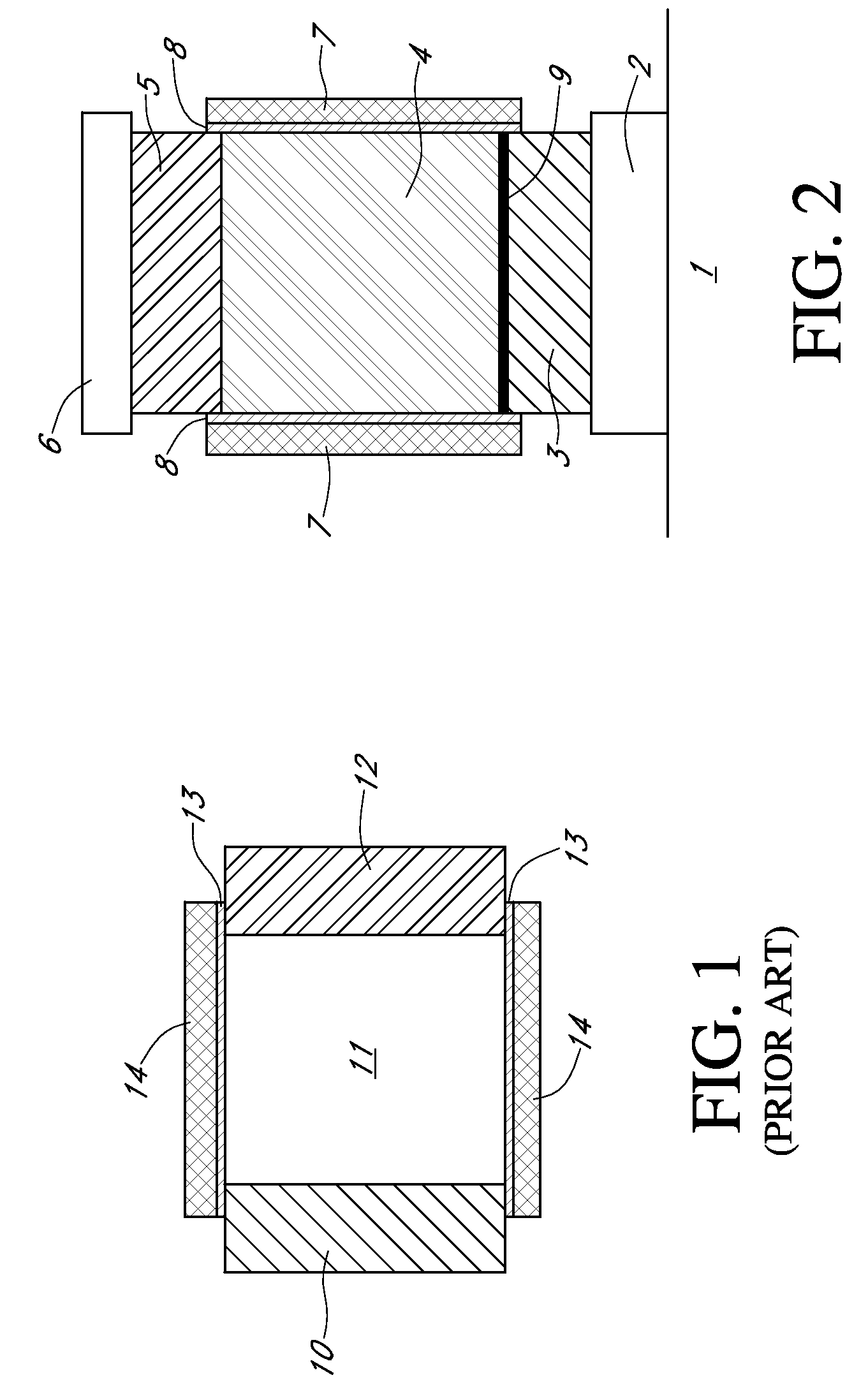

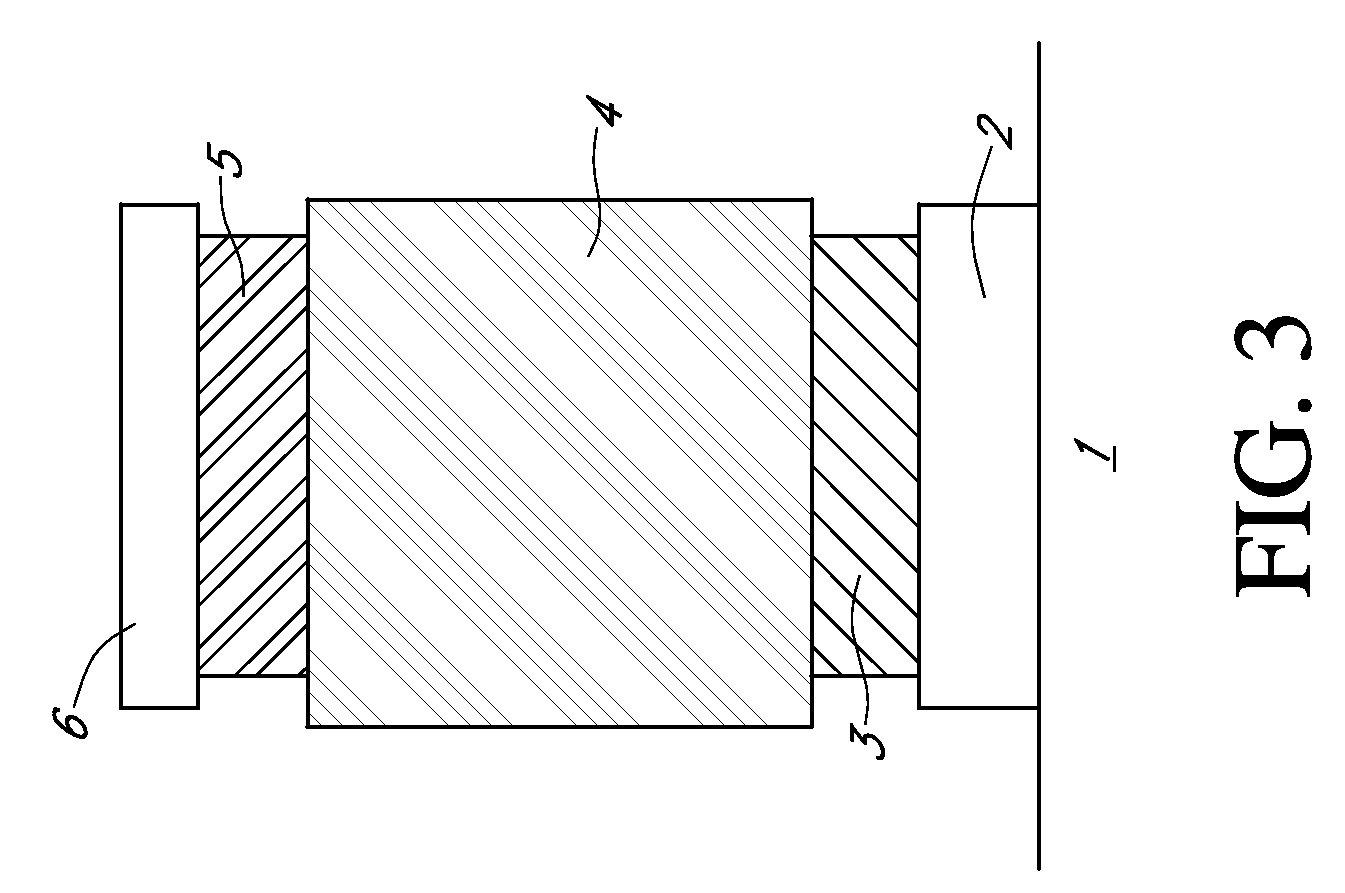

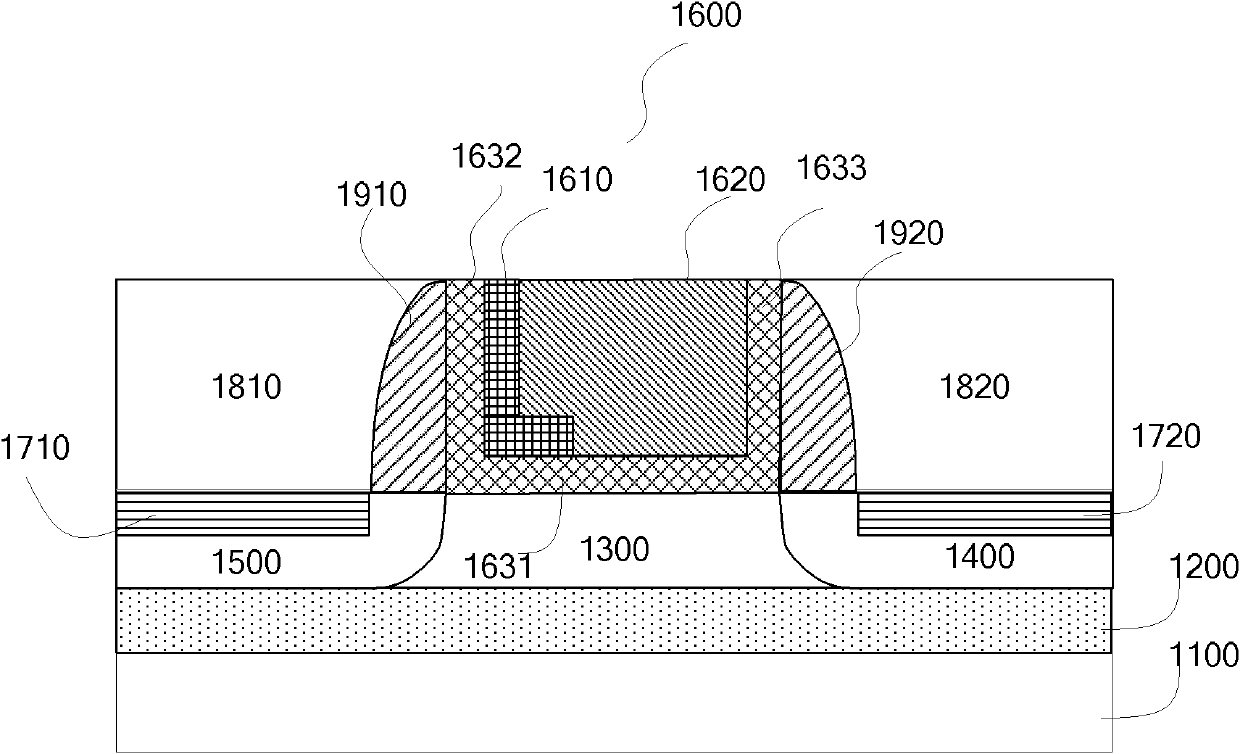

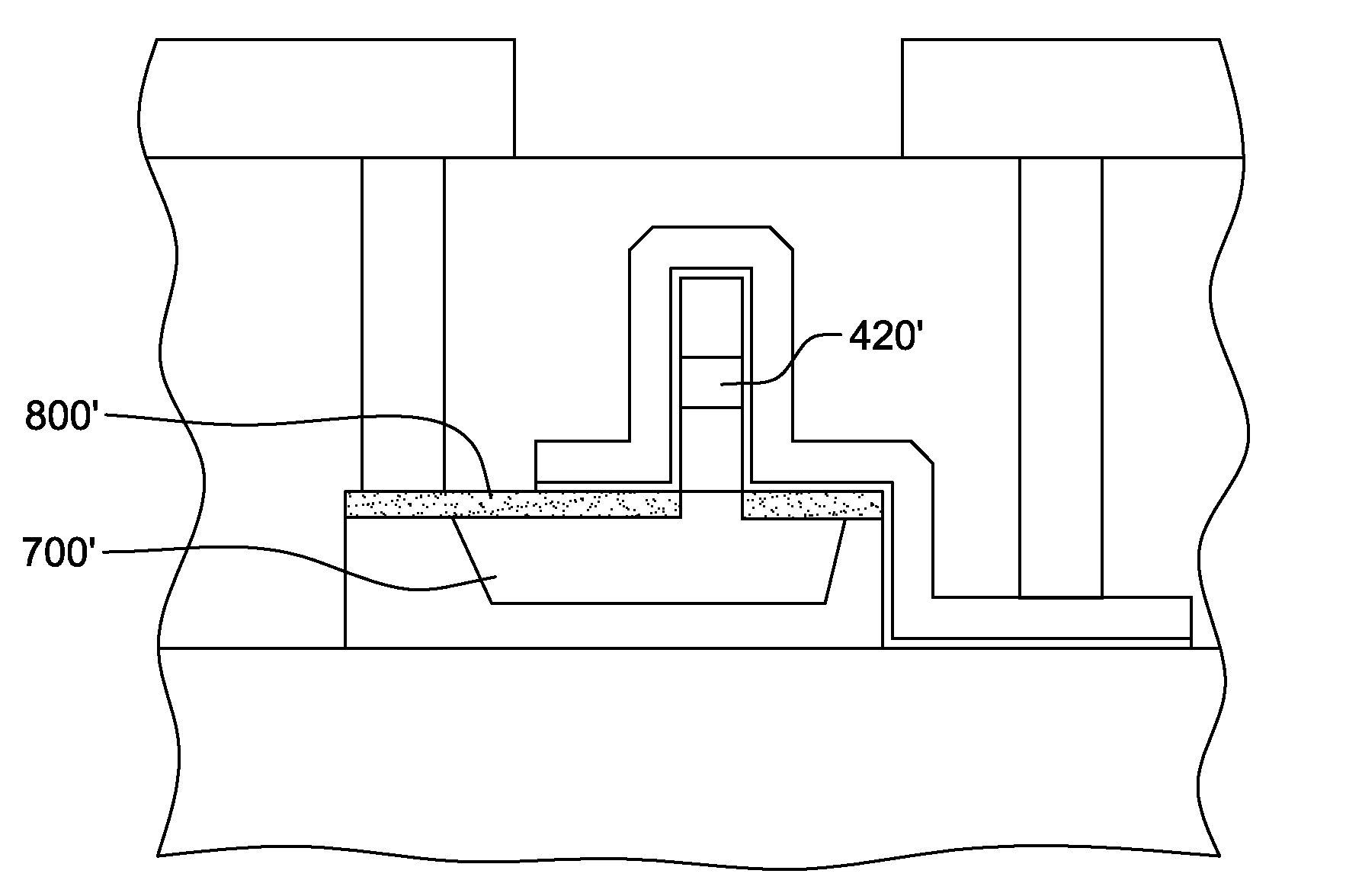

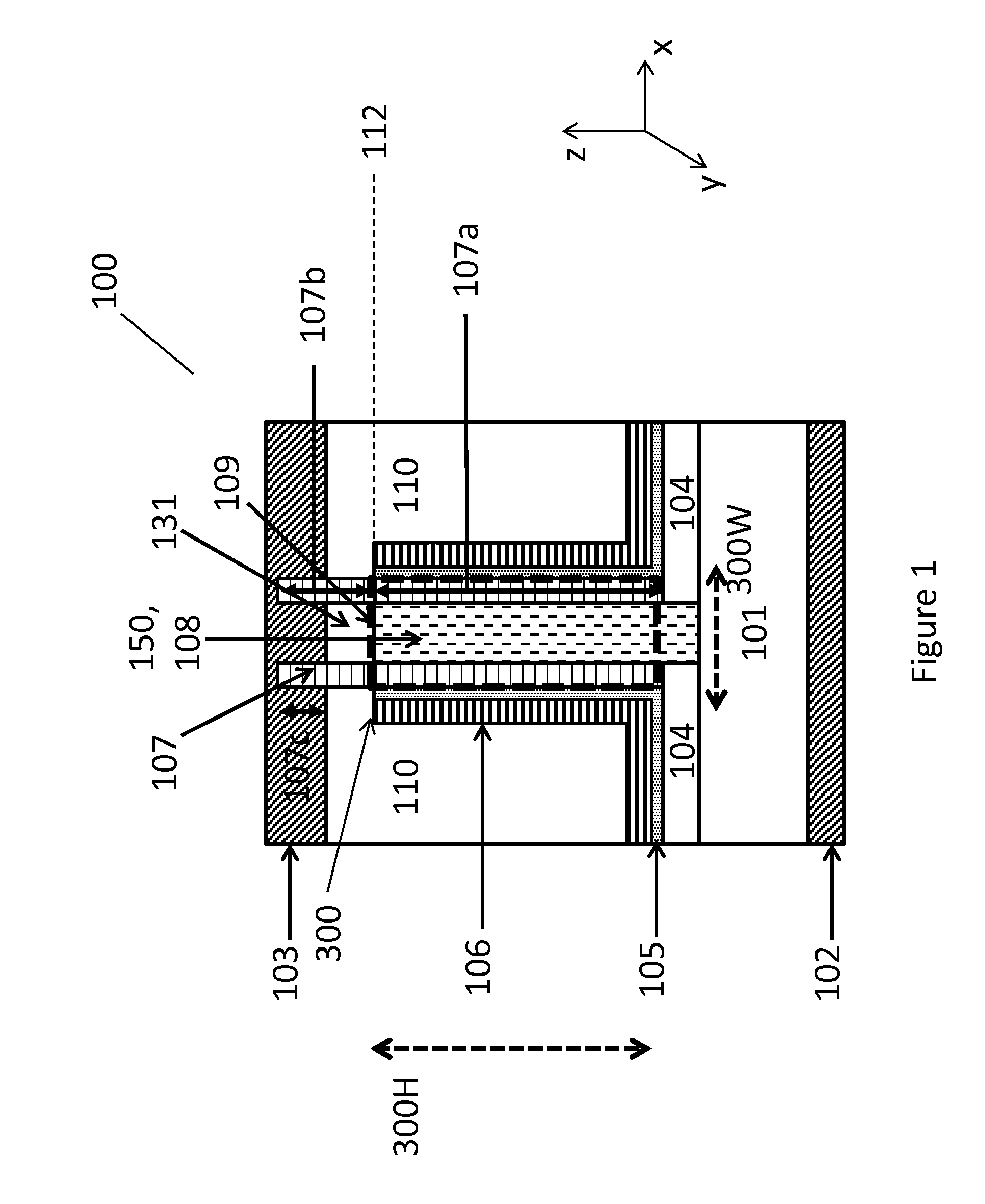

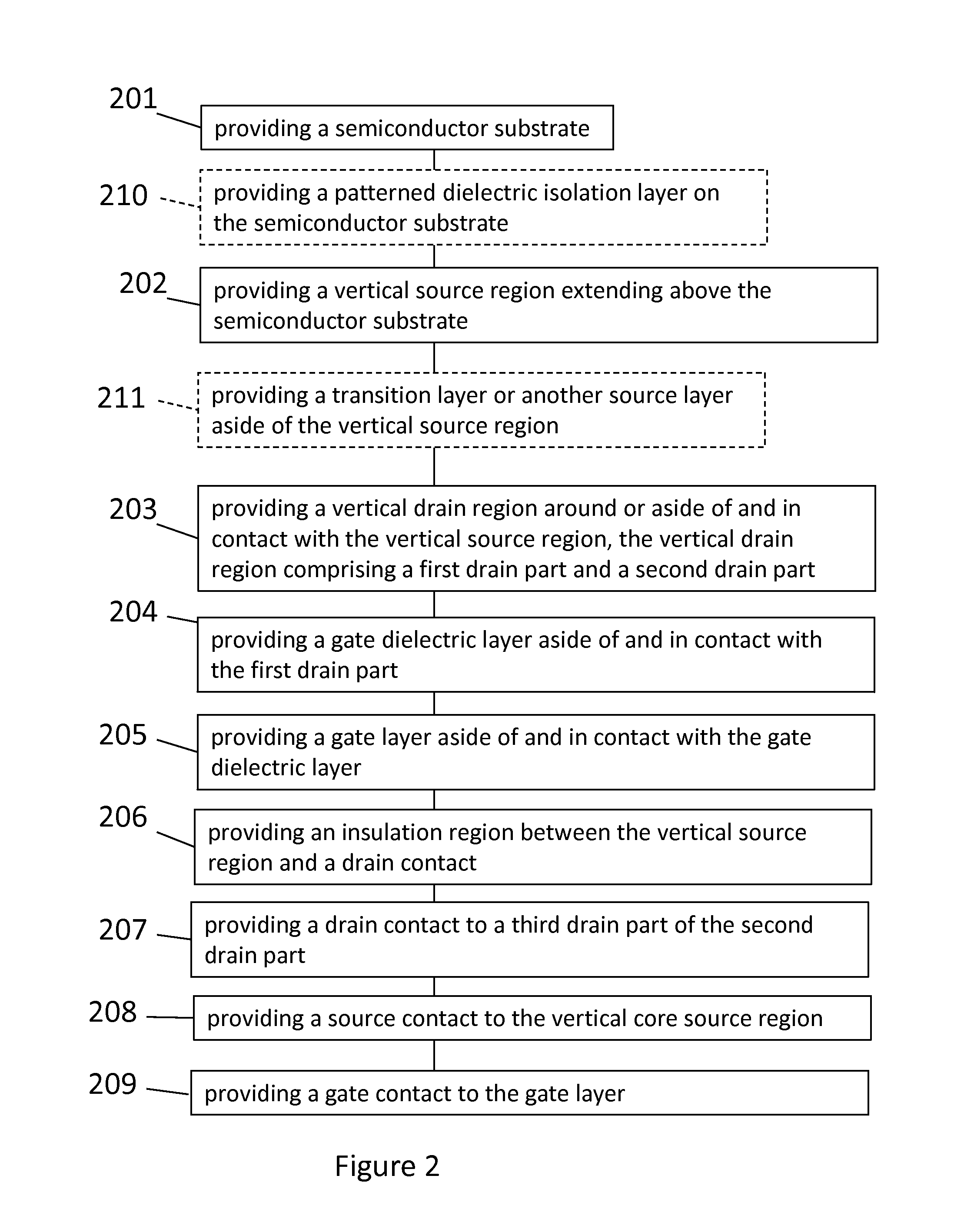

ActiveUS20140353593A1Enlarge tunnelEasy to integrateSemiconductor/solid-state device manufacturingDiodeGate dielectricDielectric layer

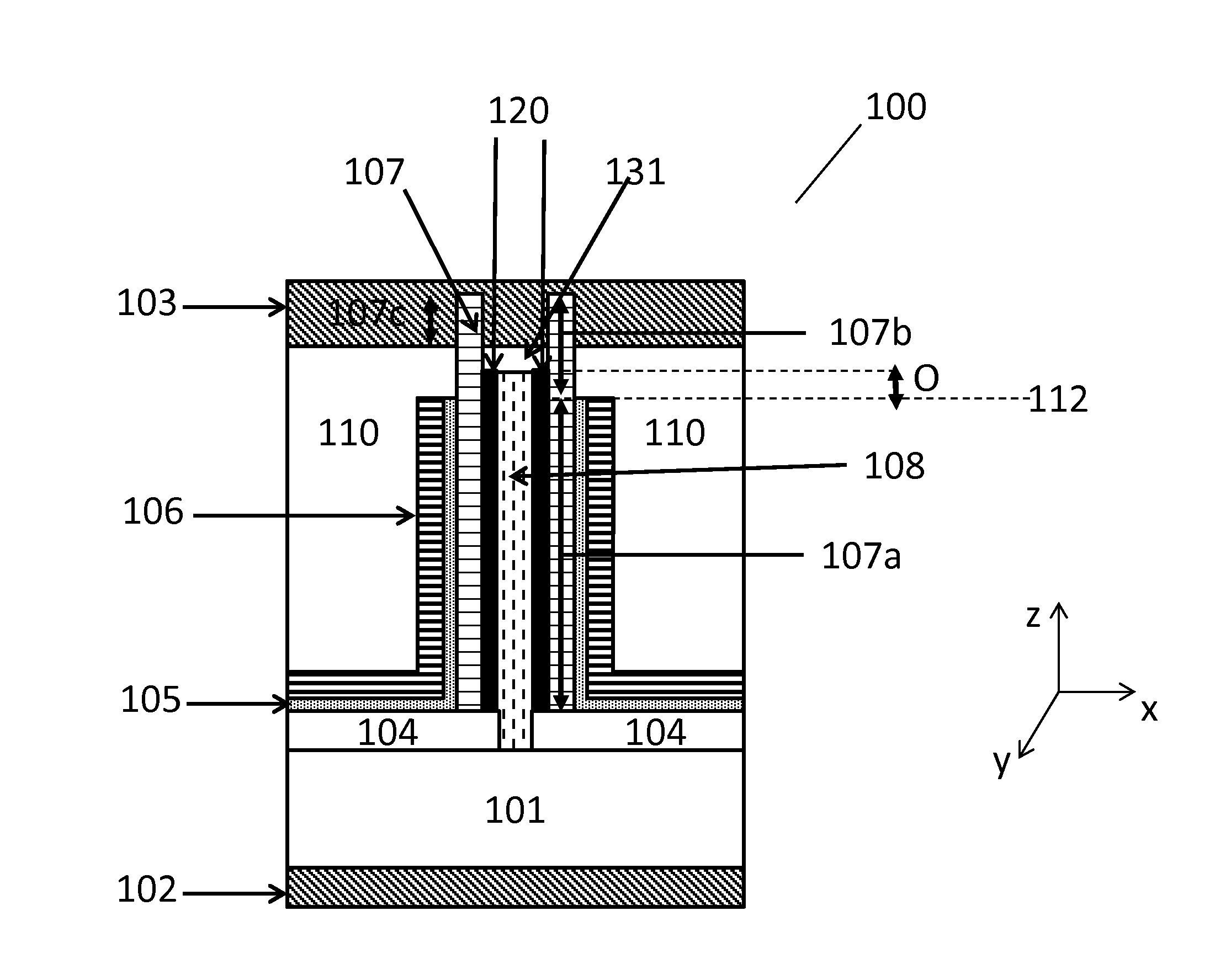

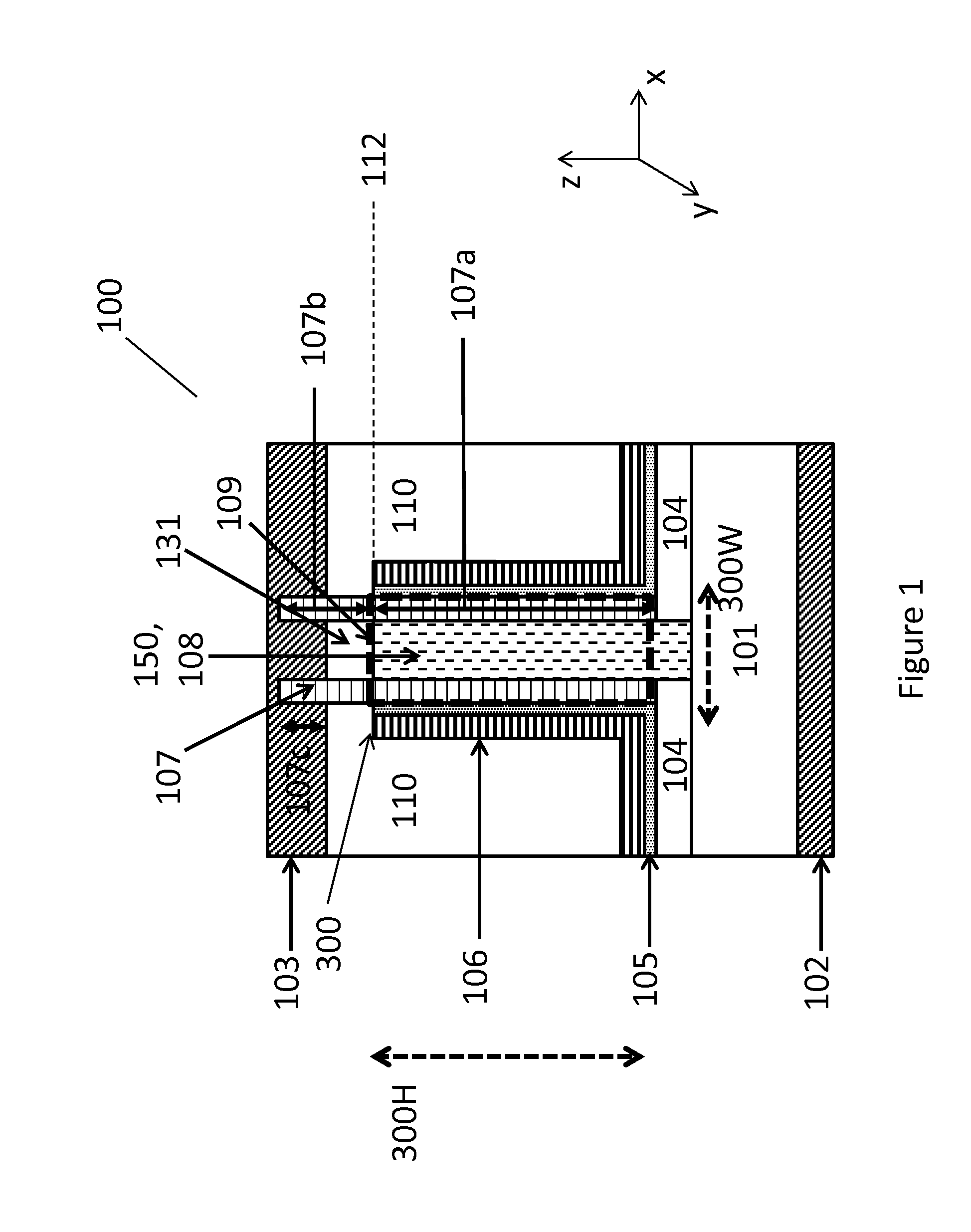

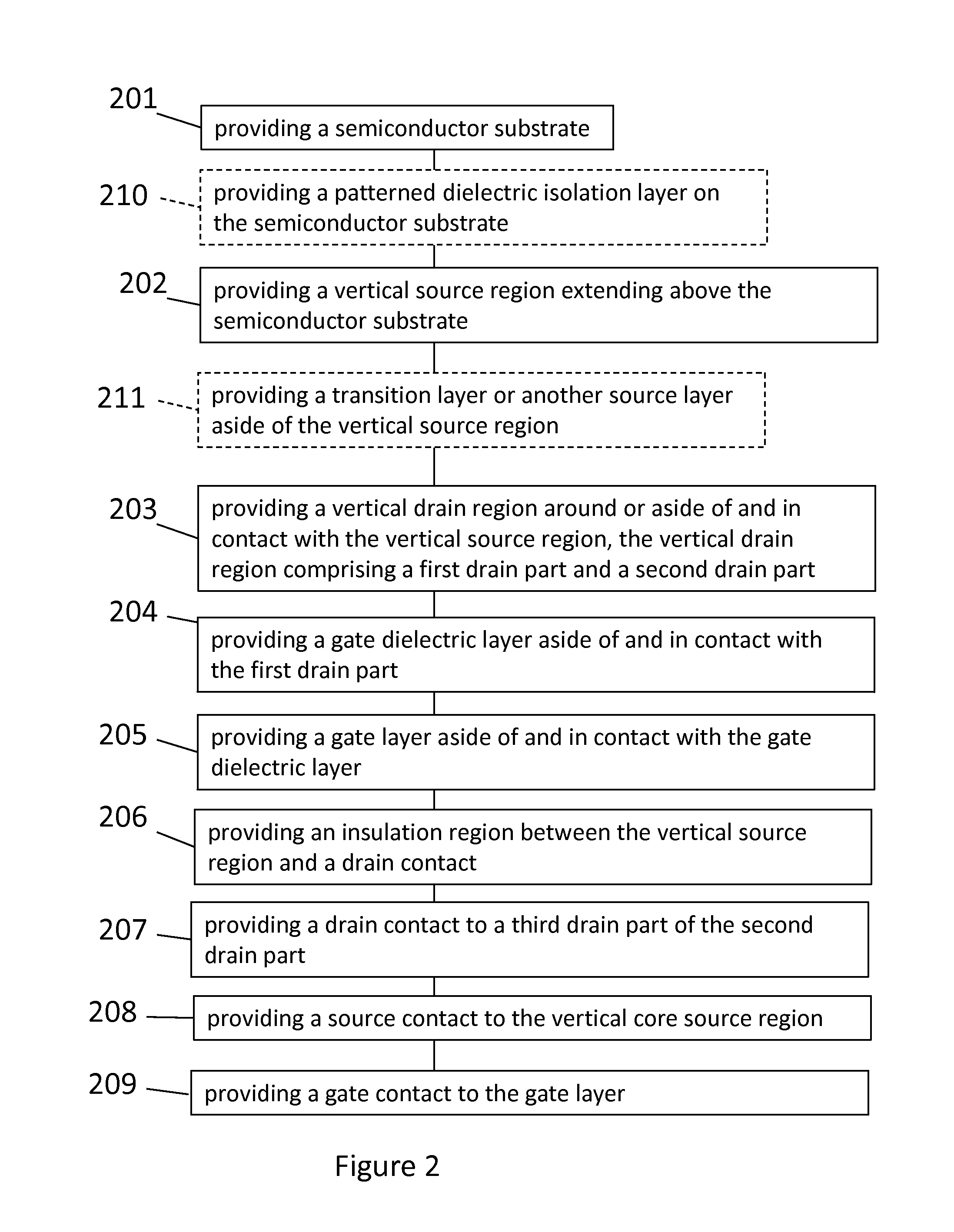

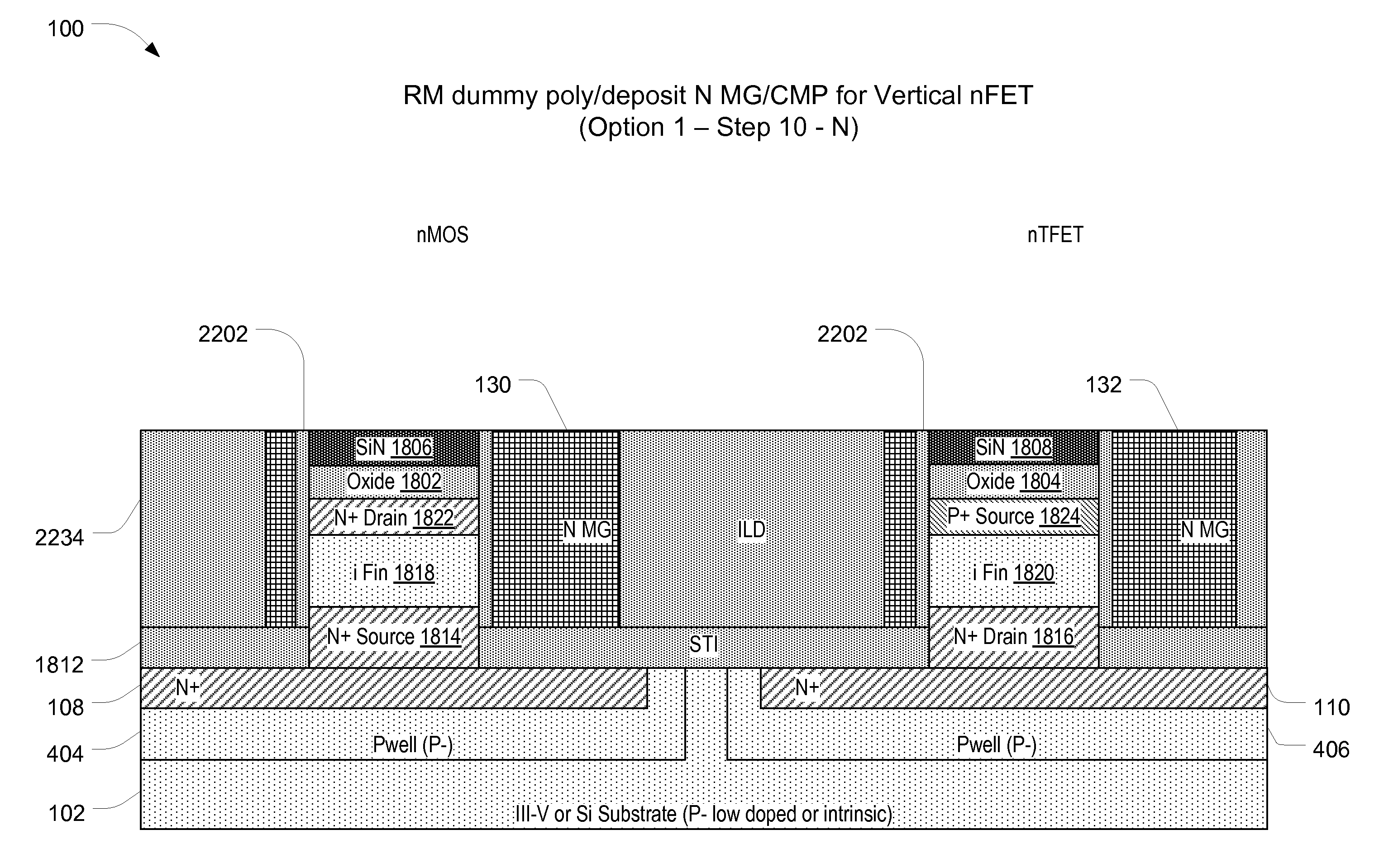

A vertical tunneling field effect transistor (TFET) and method for forming a vertical tunneling field effect transistor (TFET) is disclosed. The vertical tunneling field effect transistor TFET comprises a vertical core region, a vertical source region, a vertical drain region and a gate structure. The vertical core region is extending perpendicularly from a semiconductor substrate, having a top surface, consisting of a doped outer part and a middle part. The vertical source region of semiconducting core material comprises the doped outer part of the vertical core region. The vertical drain region of semiconducting drain material comprises along its longitudinal direction a first drain part and a second drain part, the first drain part either directly surrounding said vertical source region or directly sandwiching said vertical source region between two sub-parts of said first drain part, the second drain part located directly above and in contact with the first drain part. The gate structure comprises a gate dielectric layer directly aside of the first drain part of the vertical drain region and a gate layer directly aside of the gate dielectric layer. The second drain part is extending above the gate layer and gate dielectric layer. The vertical tunneling field effect transistor TFET further comprises a drain contact directly connected to a third drain part, the third drain part being an upper part of the second drain part of the vertical drain region. The vertical tunneling field effect transistor TFET further comprises a source contact electrically connected to the vertical source region. The vertical tunneling field effect transistor TFET further comprises a gate contact electrically connected to the gate layer

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +1

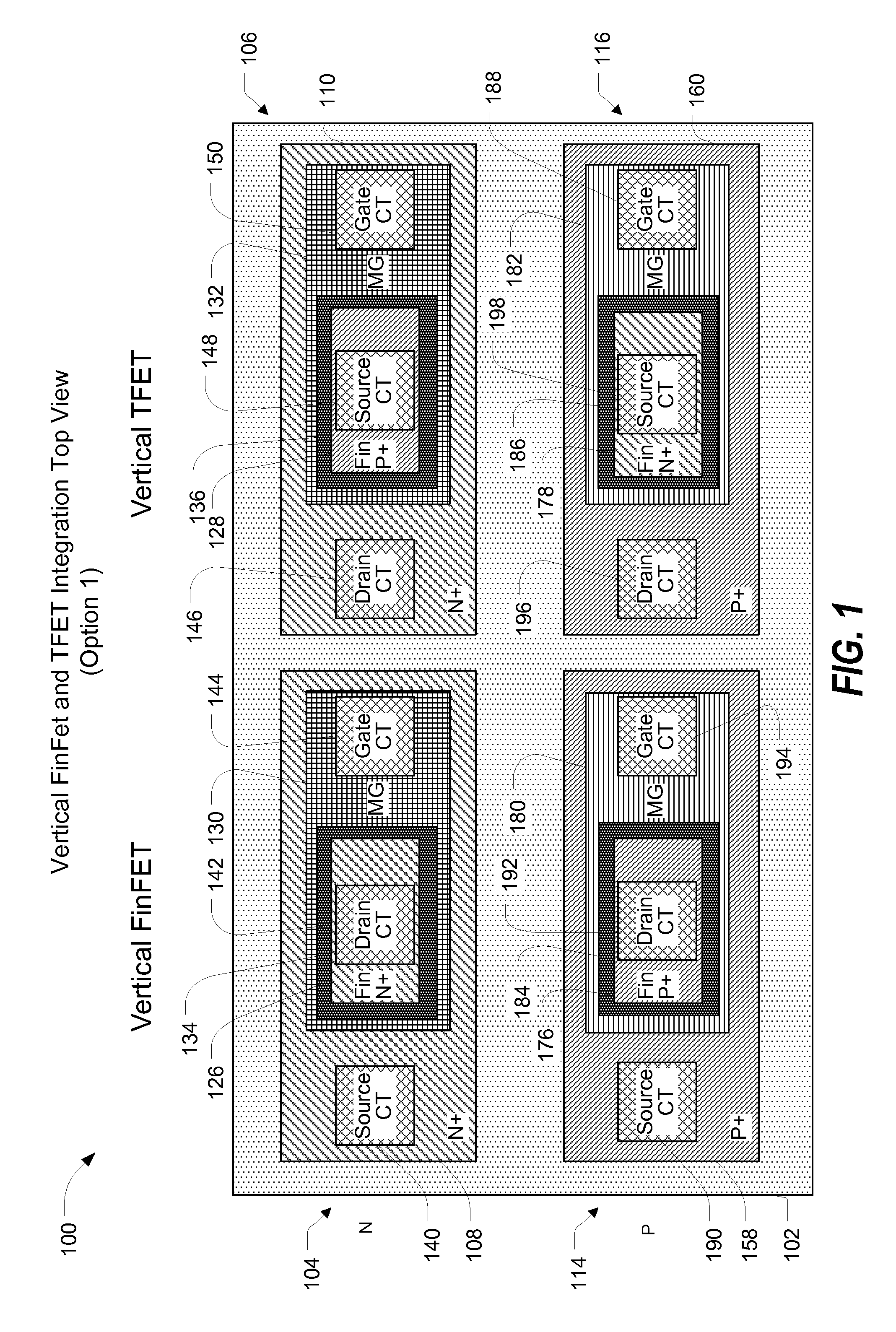

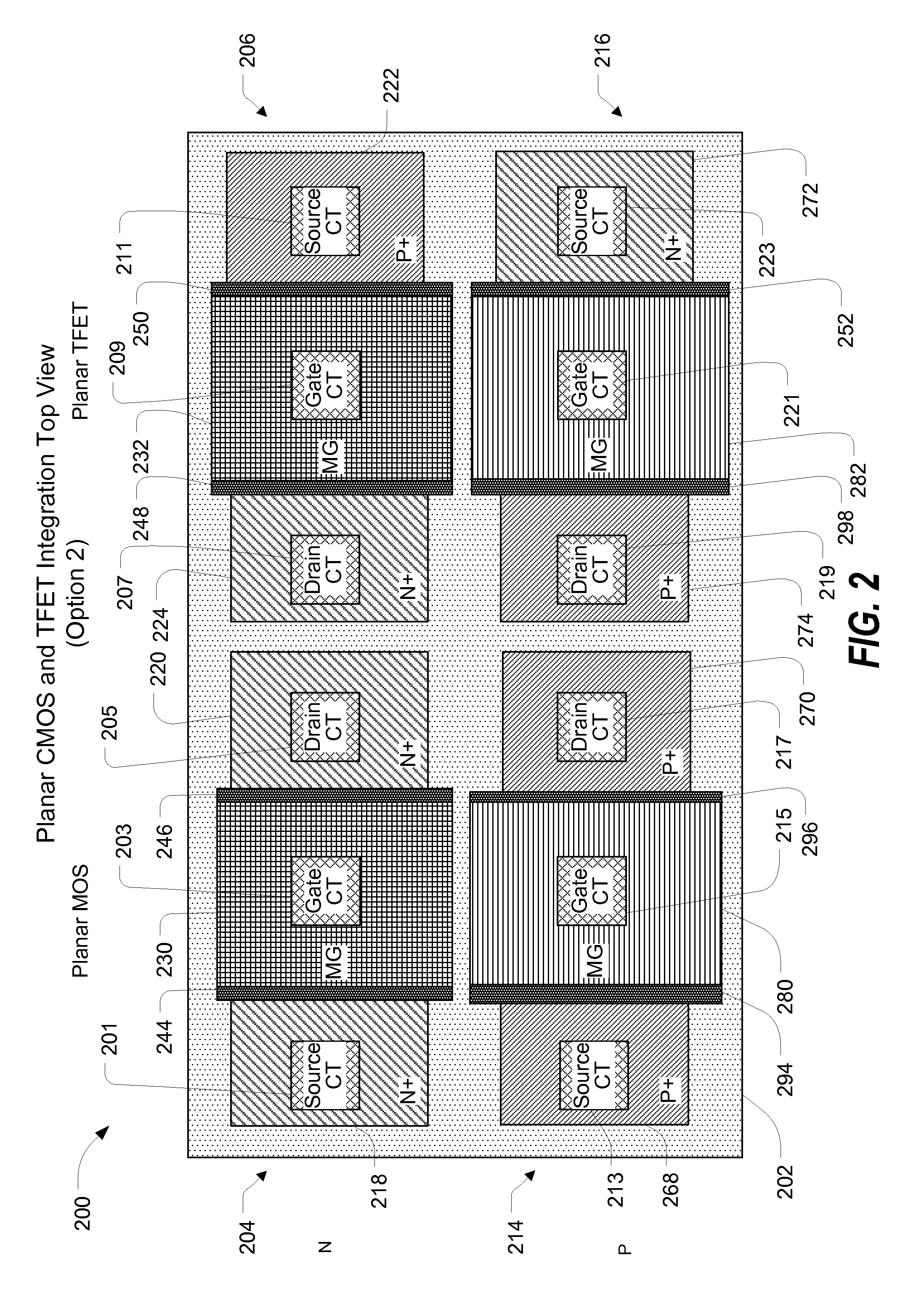

Complementary metal-oxide semiconductor (CMOS) transistor and tunnel field-effect transistor (TFET) on a single substrate

An apparatus includes a structure that includes a single substrate, a planar complementary metal-oxide semiconductor (CMOS) transistor formed on the single substrate, a planar tunnel field-effect transistor (TFET) formed on the single substrate, and a mobility enhancement strength layer included in the planar CMOS transistor or included in the planar TFET.

Owner:QUALCOMM INC

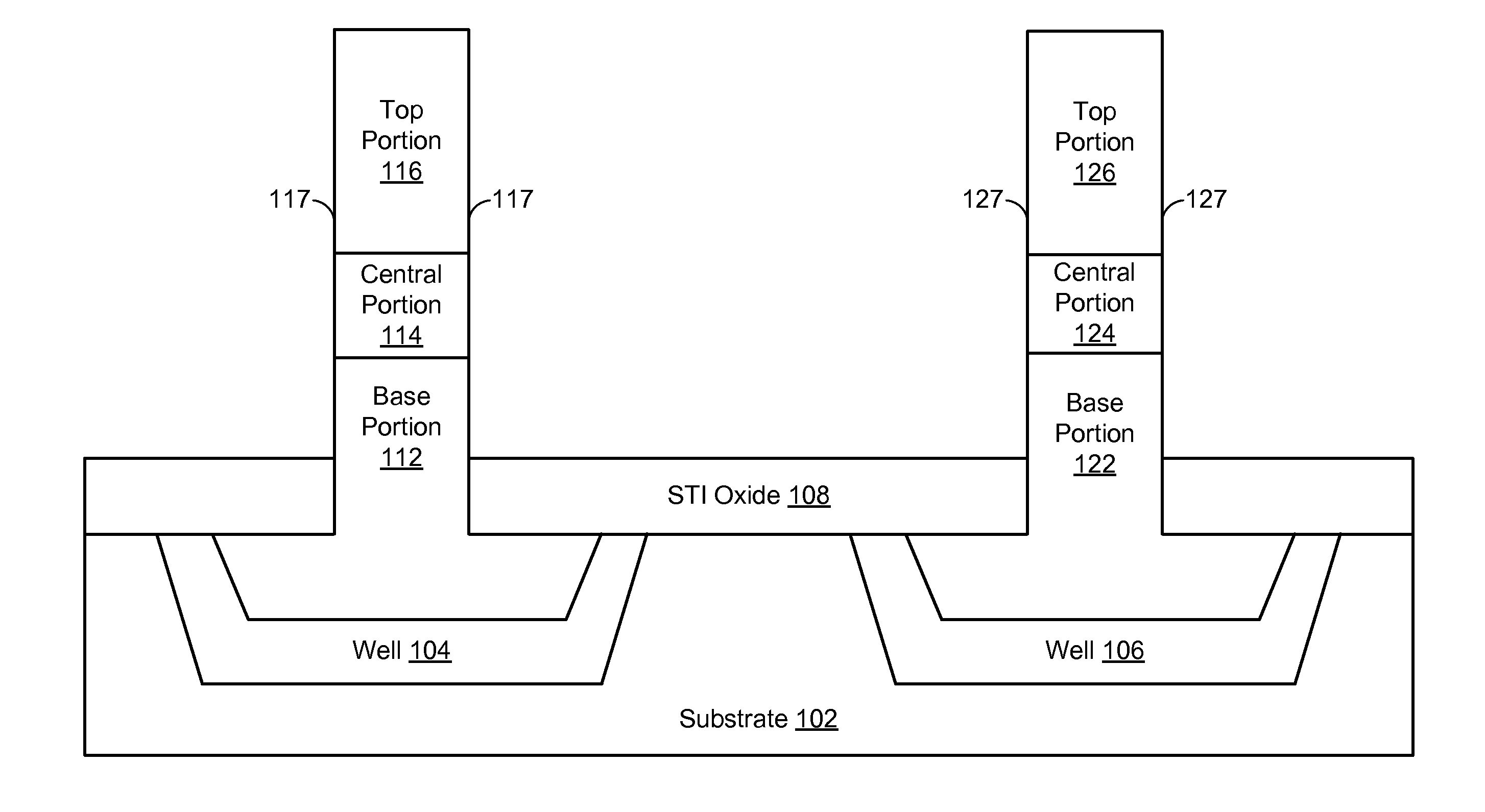

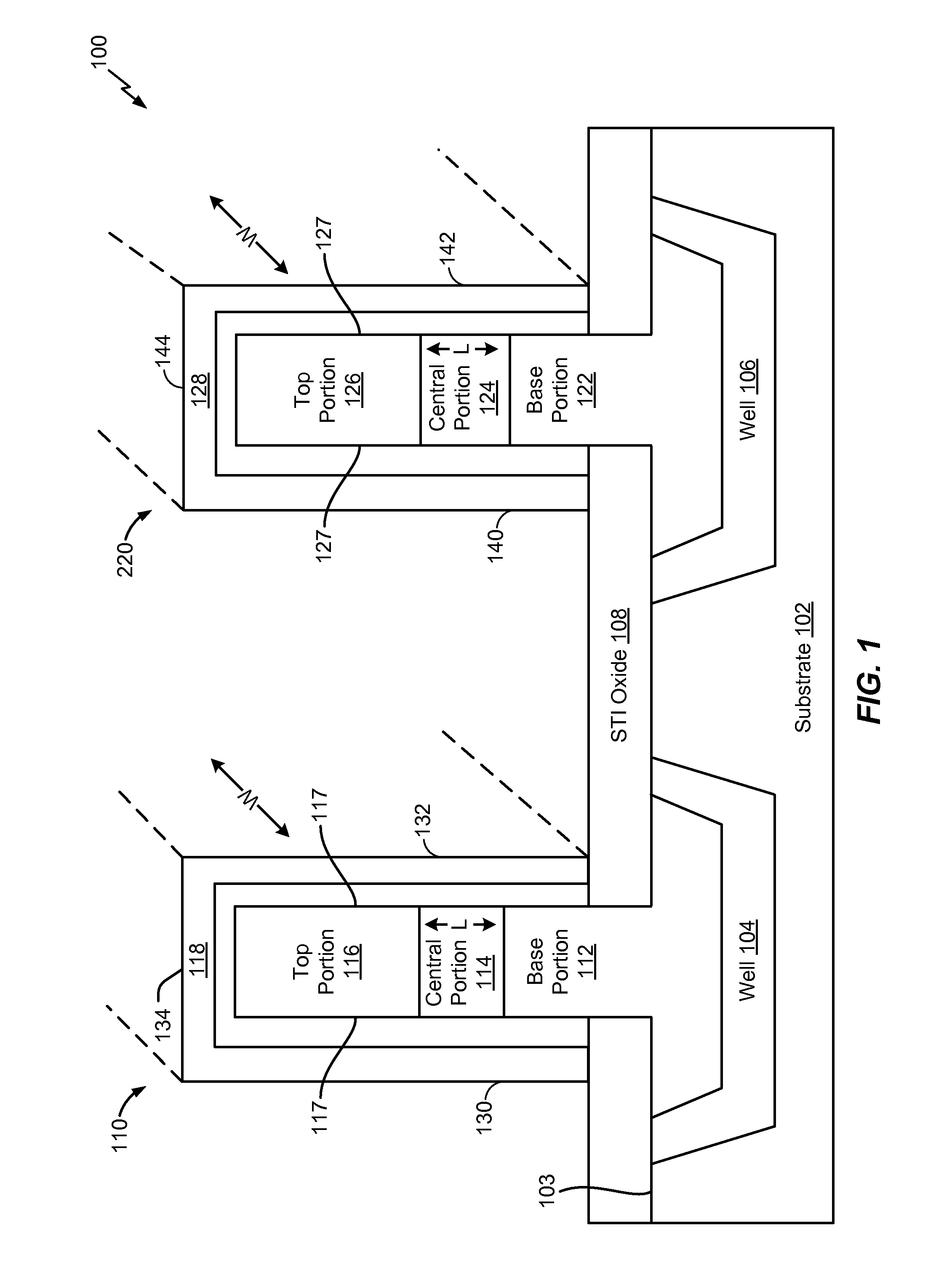

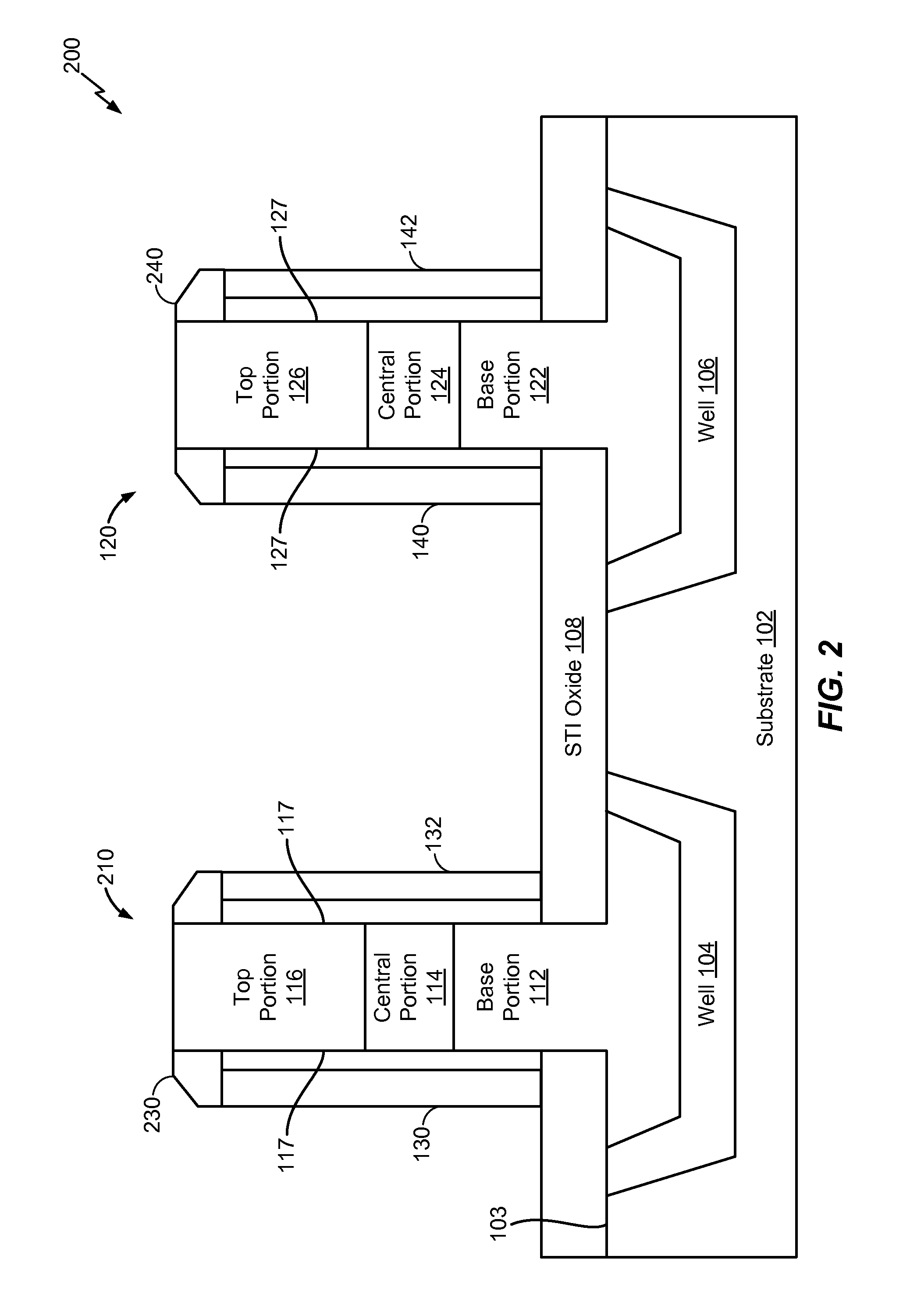

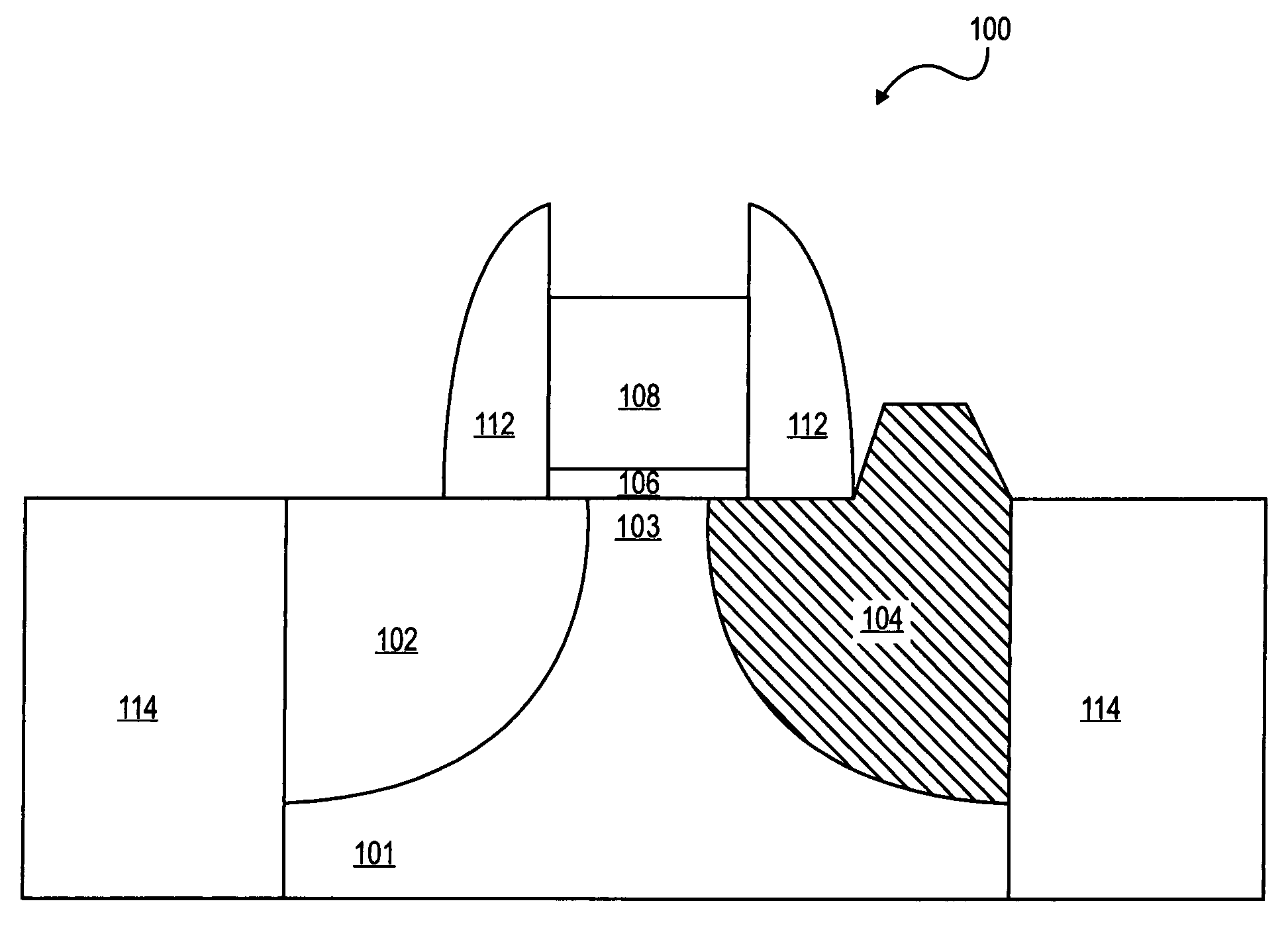

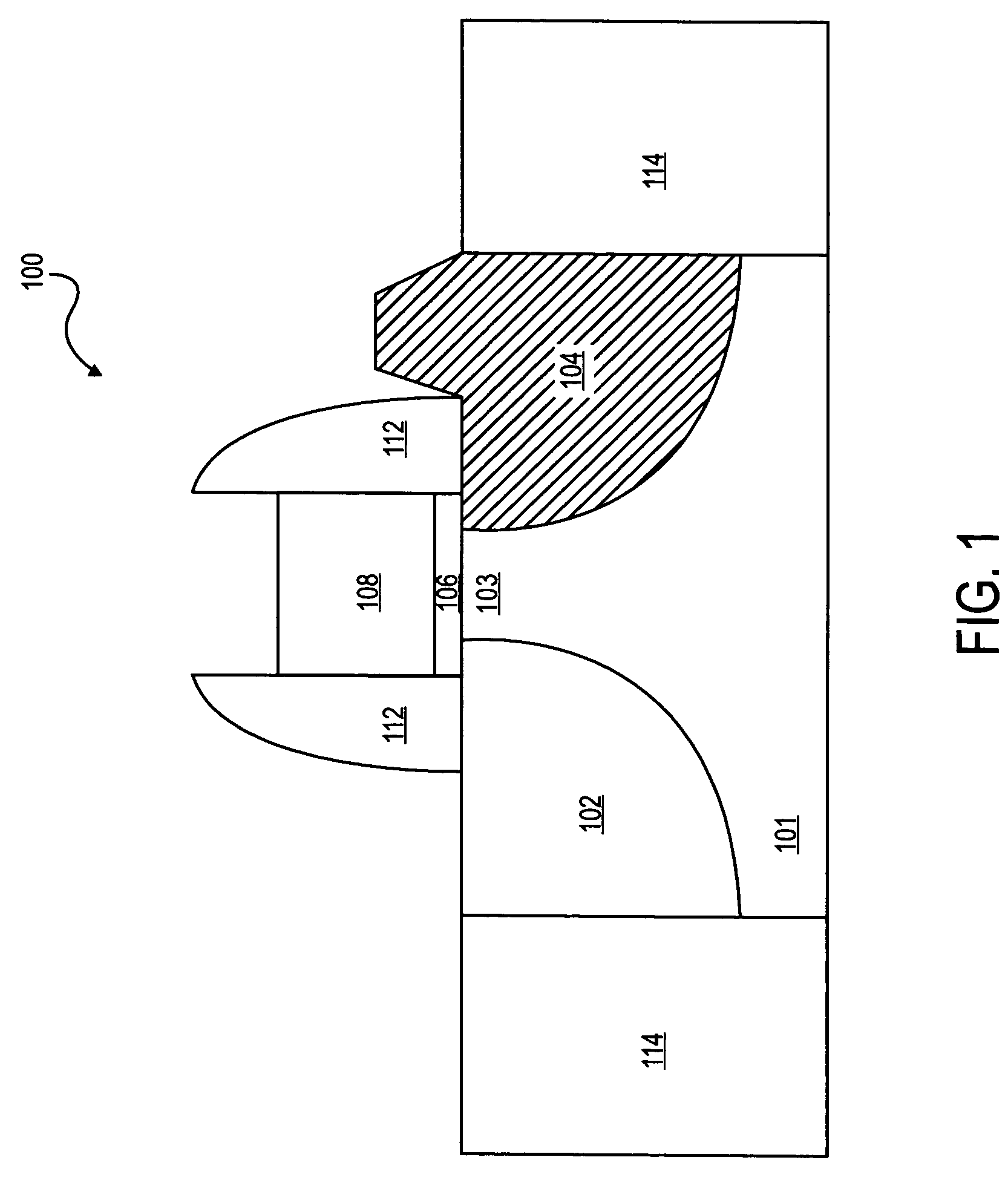

Vertical tunnel field effect transistor

A tunnel field transistor (TFET) device includes a fin structure that protrudes from a substrate surface. The fin structure includes a base portion proximate to the substrate surface, a top portion, and a first pair of sidewalls extending from the base portion to the top portion. The first pair of sidewalls has a length corresponding to a length of the fin structure. The fin structure also includes a first doped region having a first dopant concentration at the base portion of the fin structure. The fin structure also includes a second doped region having a second dopant concentration at the top portion of the fin structure. The TFET device further includes a gate including a first conductive structure neighboring a first sidewall of the first pair of sidewalls. A dielectric layer electrically isolates the first conductive structure from the first sidewall.

Owner:QUALCOMM INC

Tunneling field effect transistor using angled implants for forming asymmetric source/drain regions

The present invention relates to a Tunnel Field Effect Transistor (TFET). which utilizes angle implantation and amorphization to form asymmetric source and drain regions. The IFET further includes a silicon germanium alloy epitaxial source region with a conductivity opposite that of the drain.

Owner:INTEL CORP

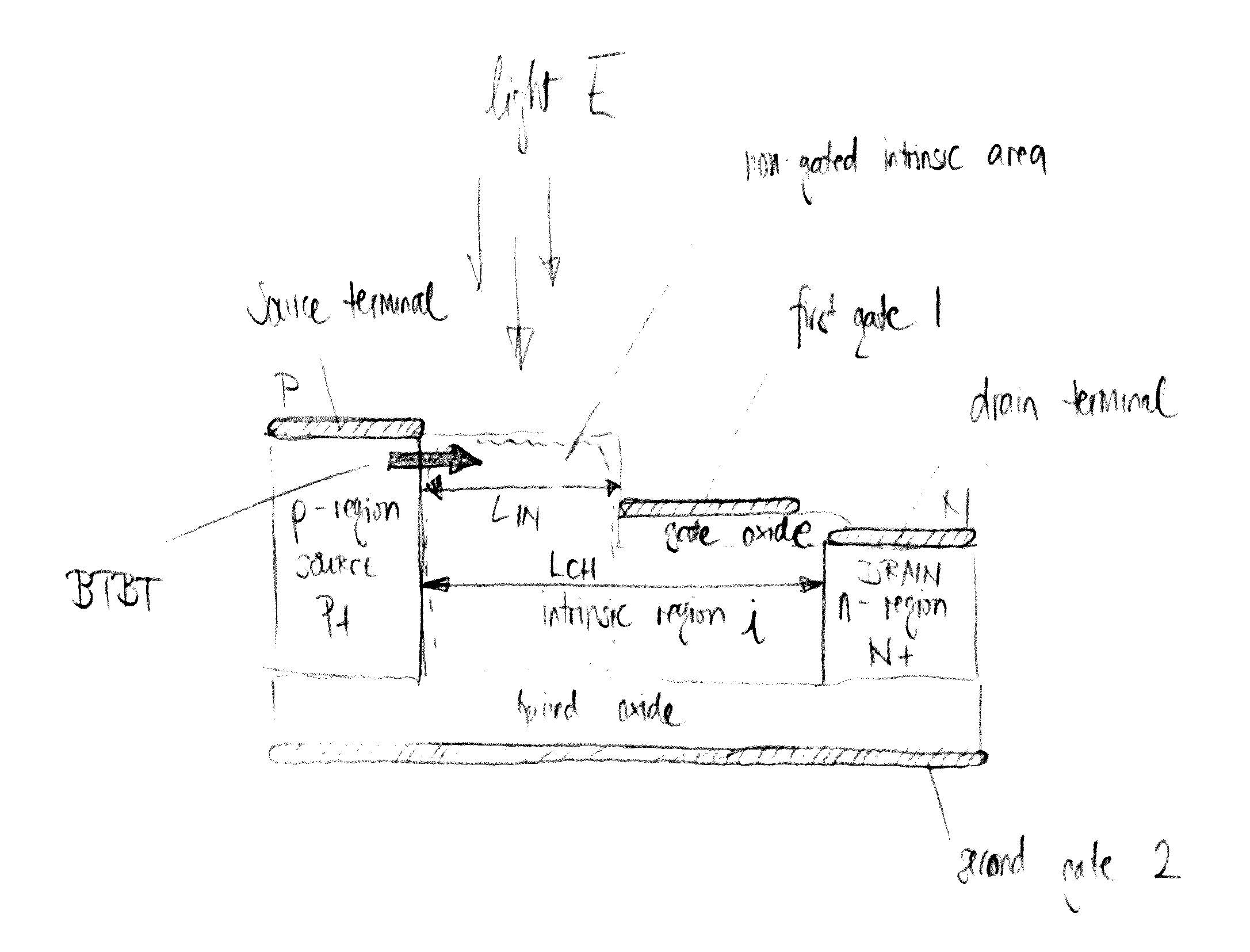

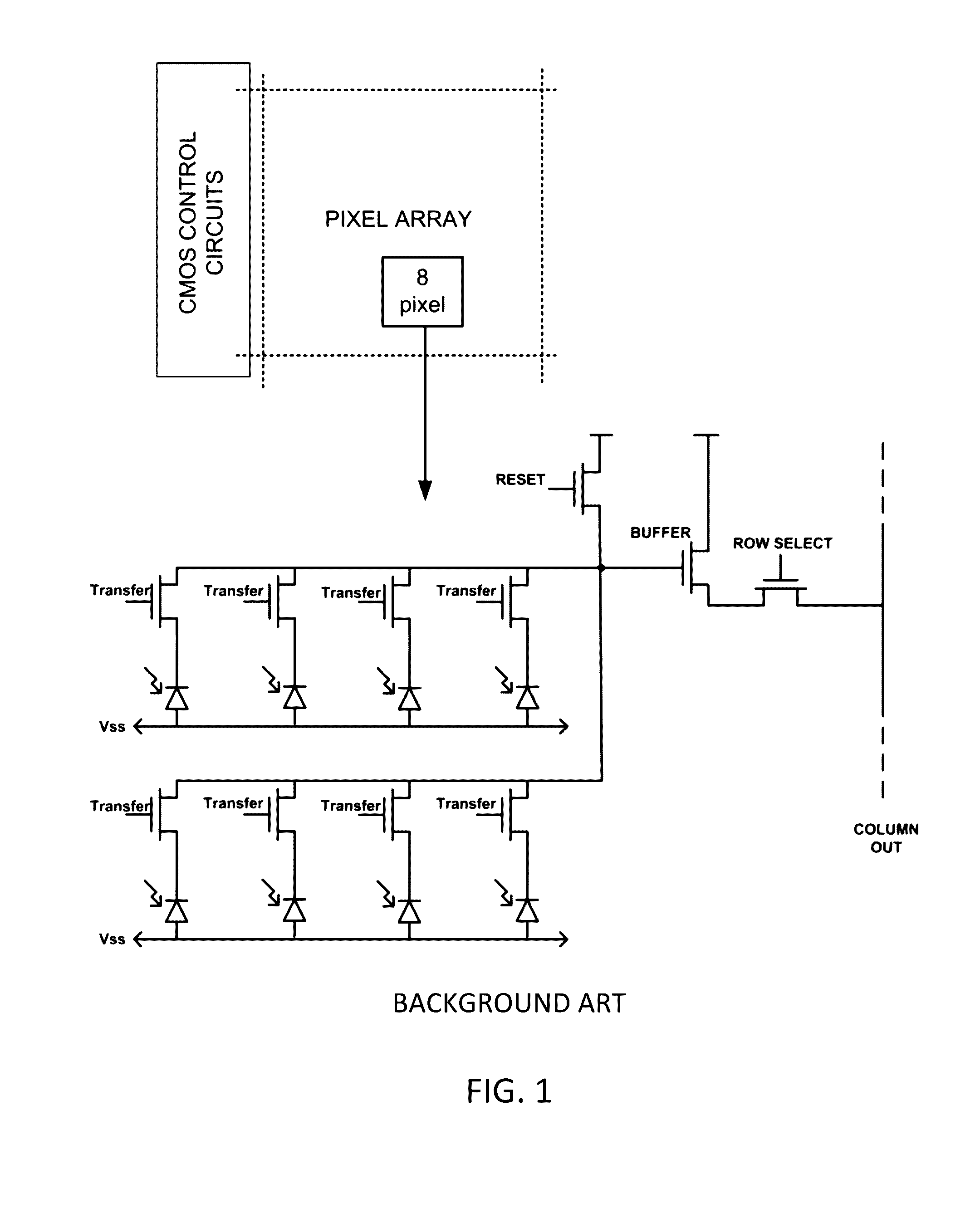

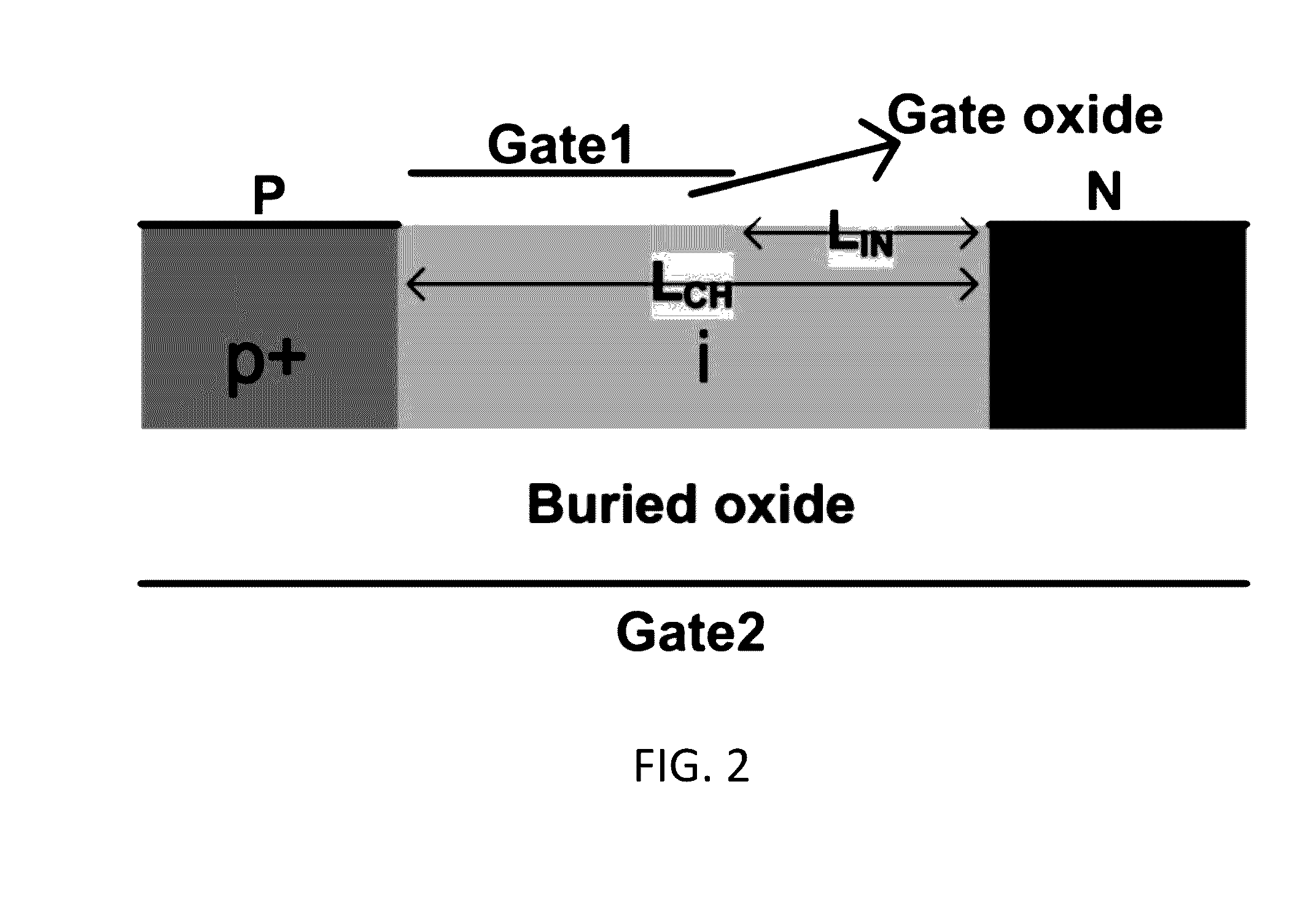

One Transistor Active Pixel Sensor with Tunnel FET

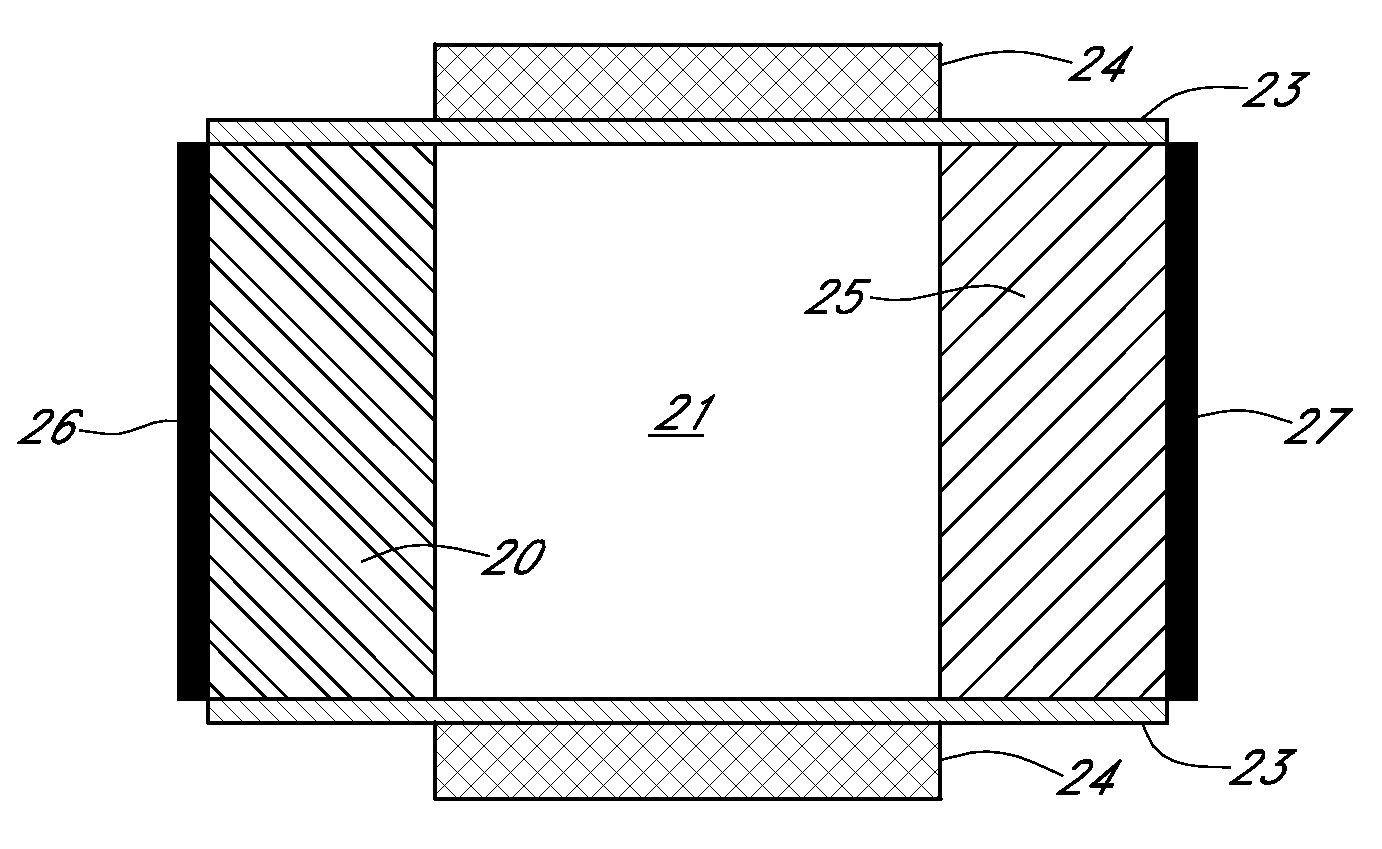

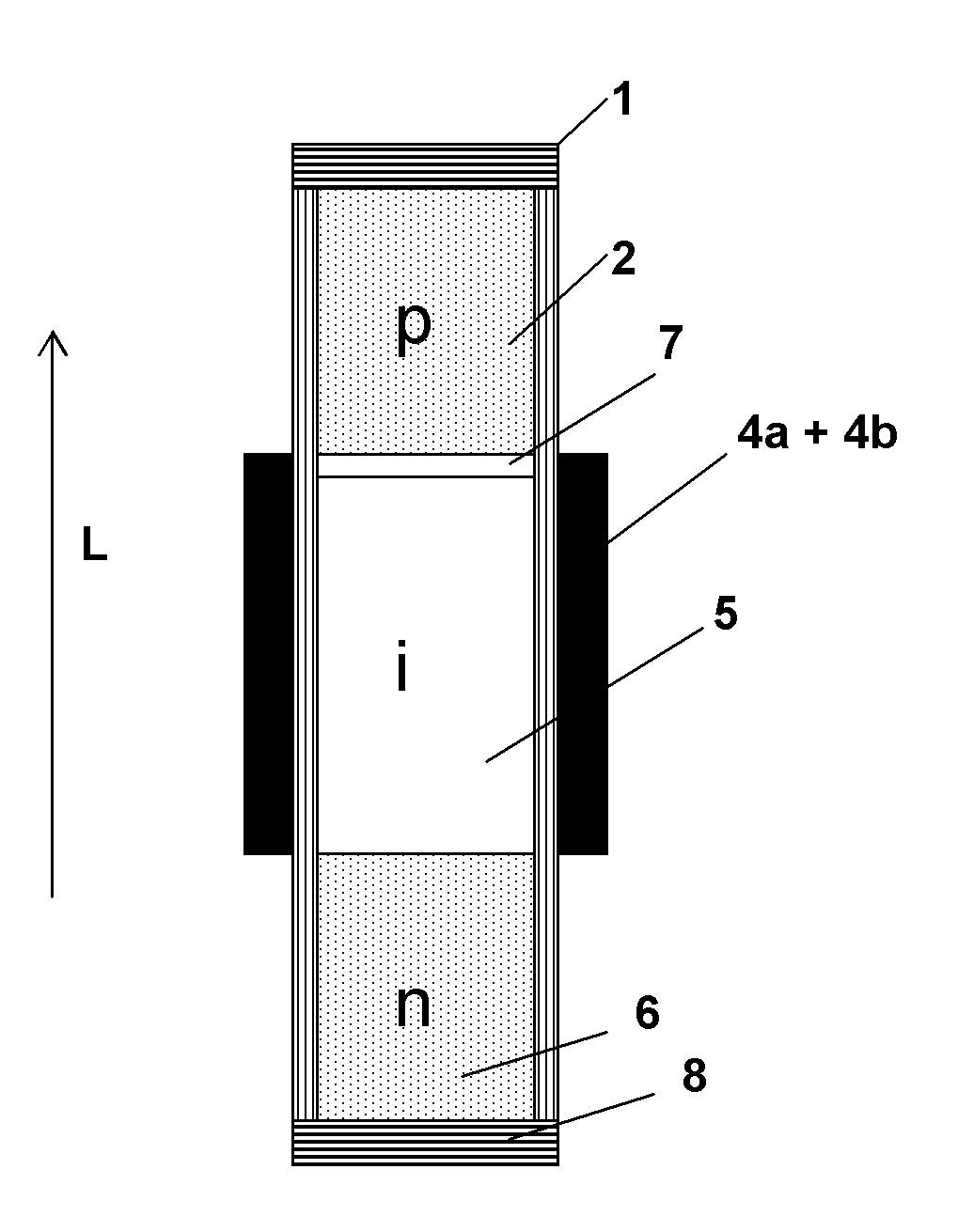

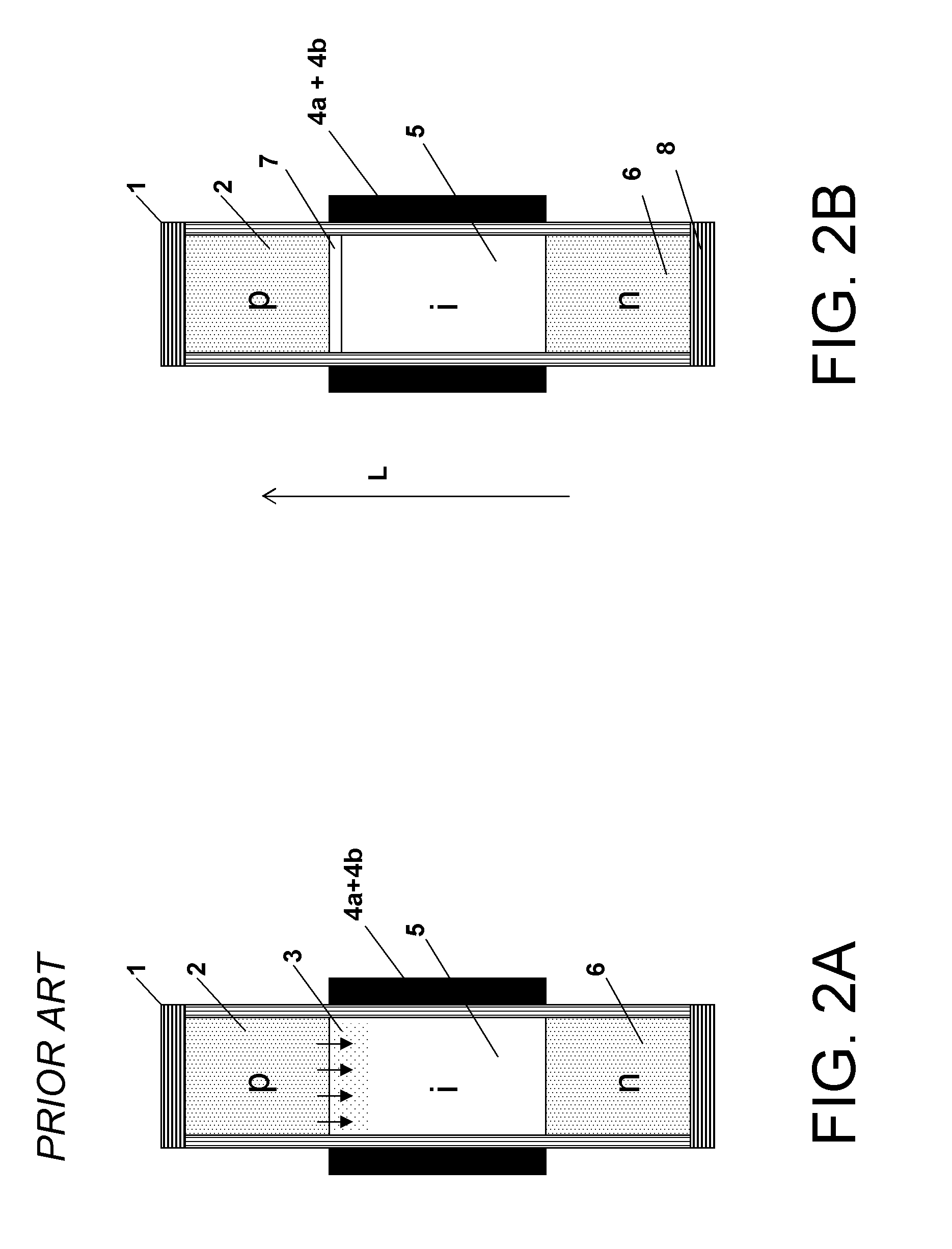

A tunneling field effect transistor for light detection, including a p-type region connected to a source terminal, a n-type region connected to a drain terminal, an intrinsic region located between the p-type region and the n-type region to form a P-I junction or an N-I junction with the n-type region or the p-type region, respectively, a first insulating layer and a first gate electrode, the first gate electrode covering a portion of the intrinsic region on one side, and a second insulating layer and a second gate electrode, the second insulating layer and the second gate electrode covering an entire other side of the intrinsic region opposite to the one side, wherein an area of the intrinsic region that is not covered by the first gate electrode forms a non-gated intrinsic area configured for light absorption.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

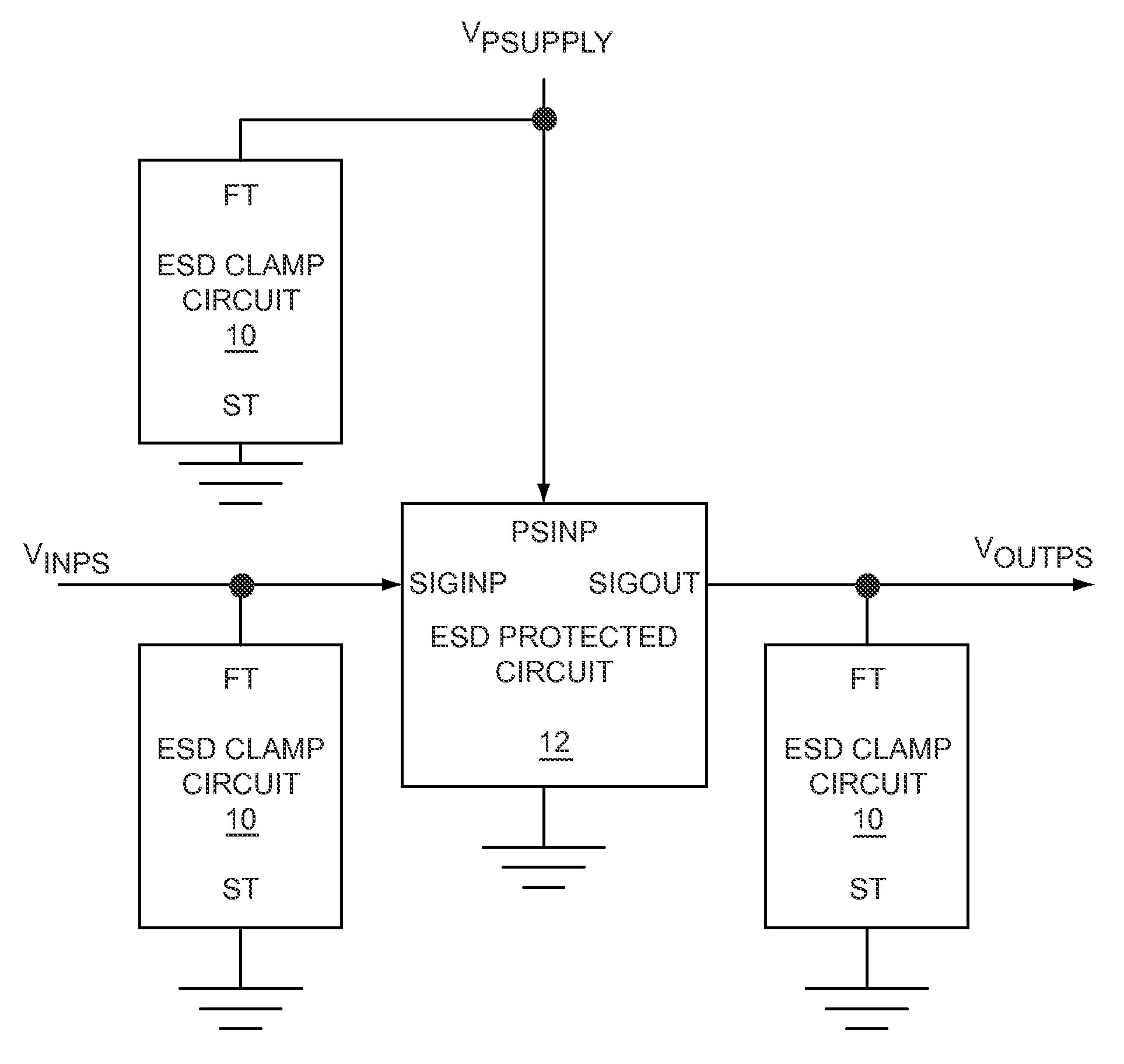

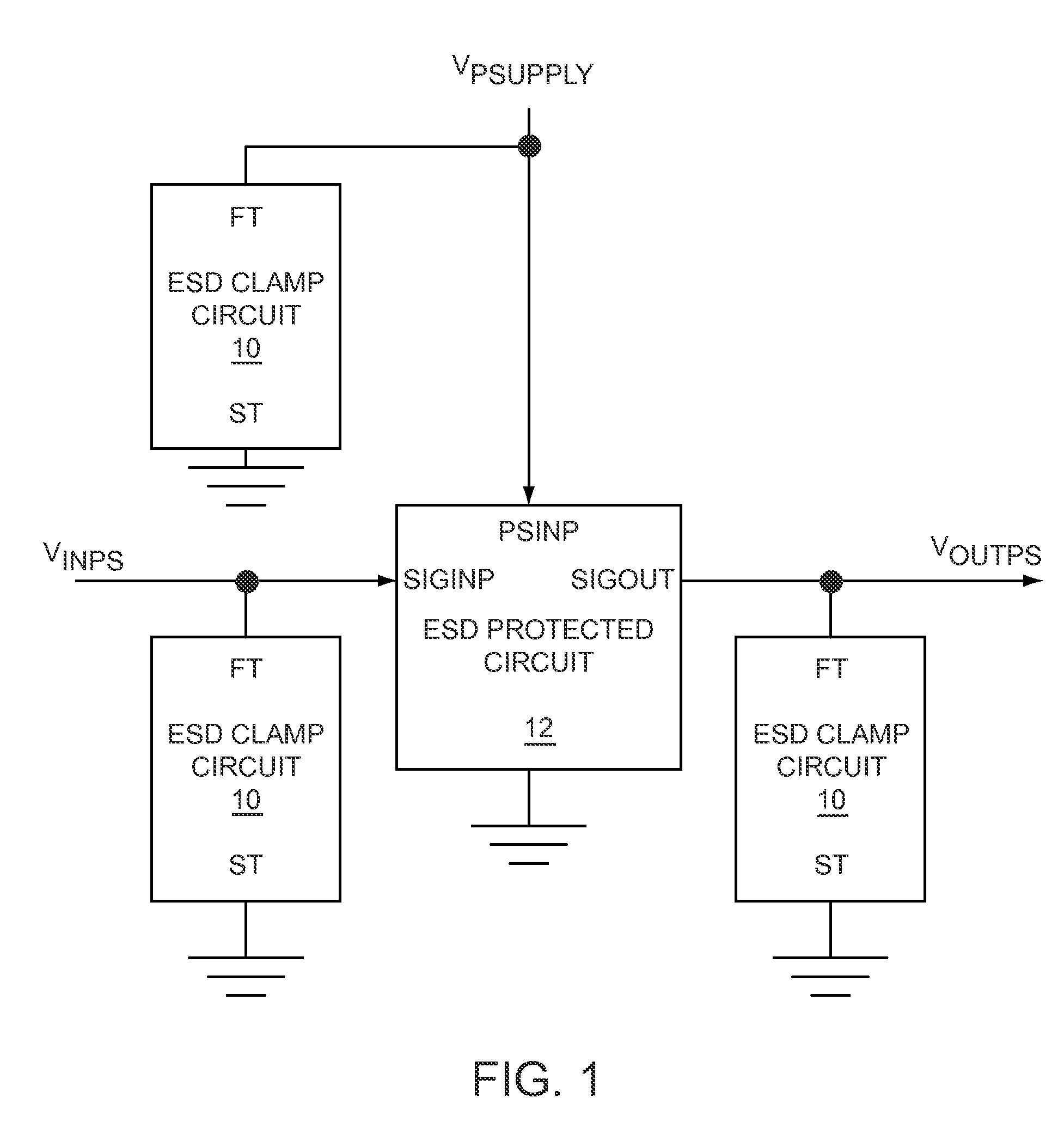

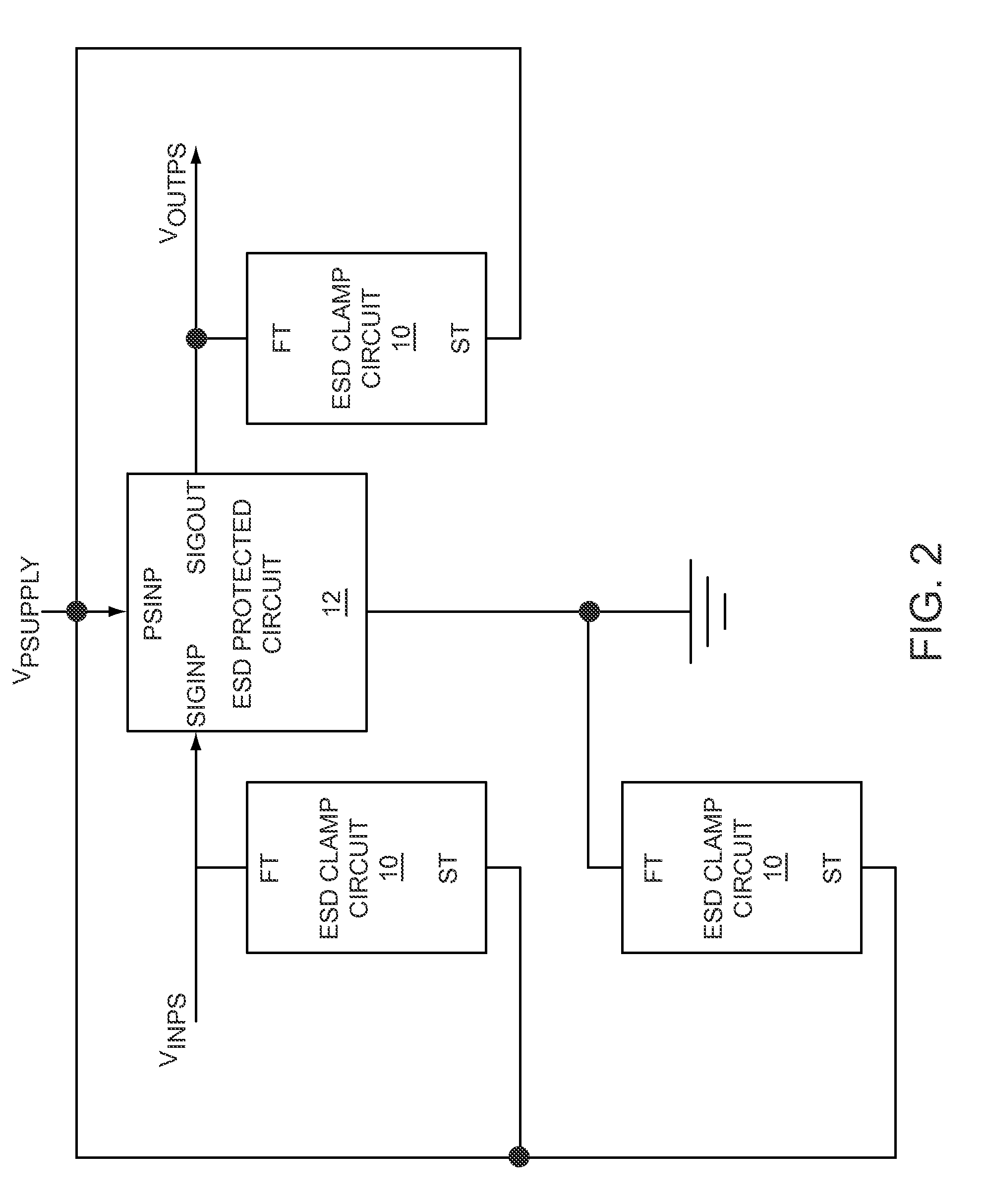

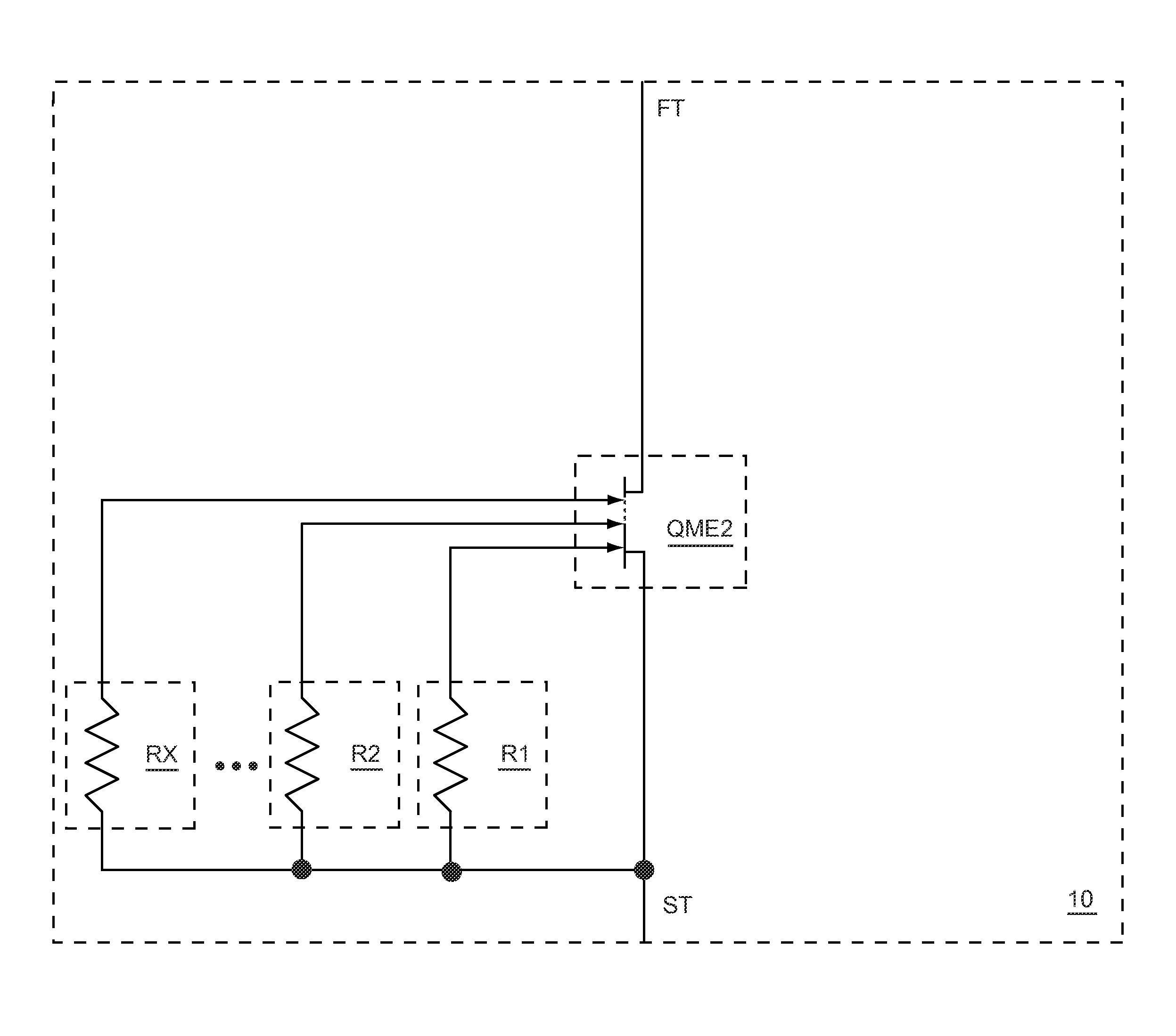

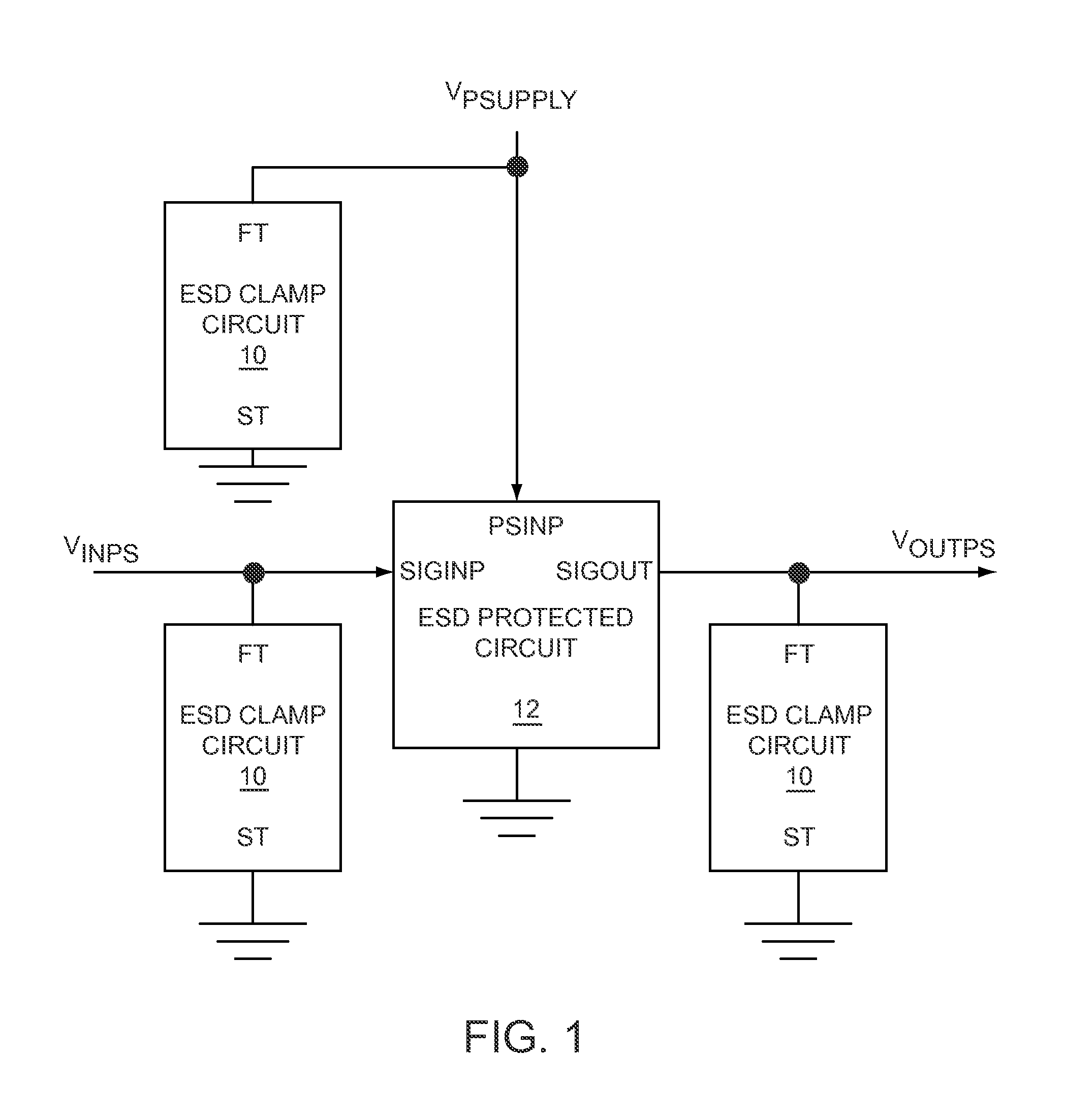

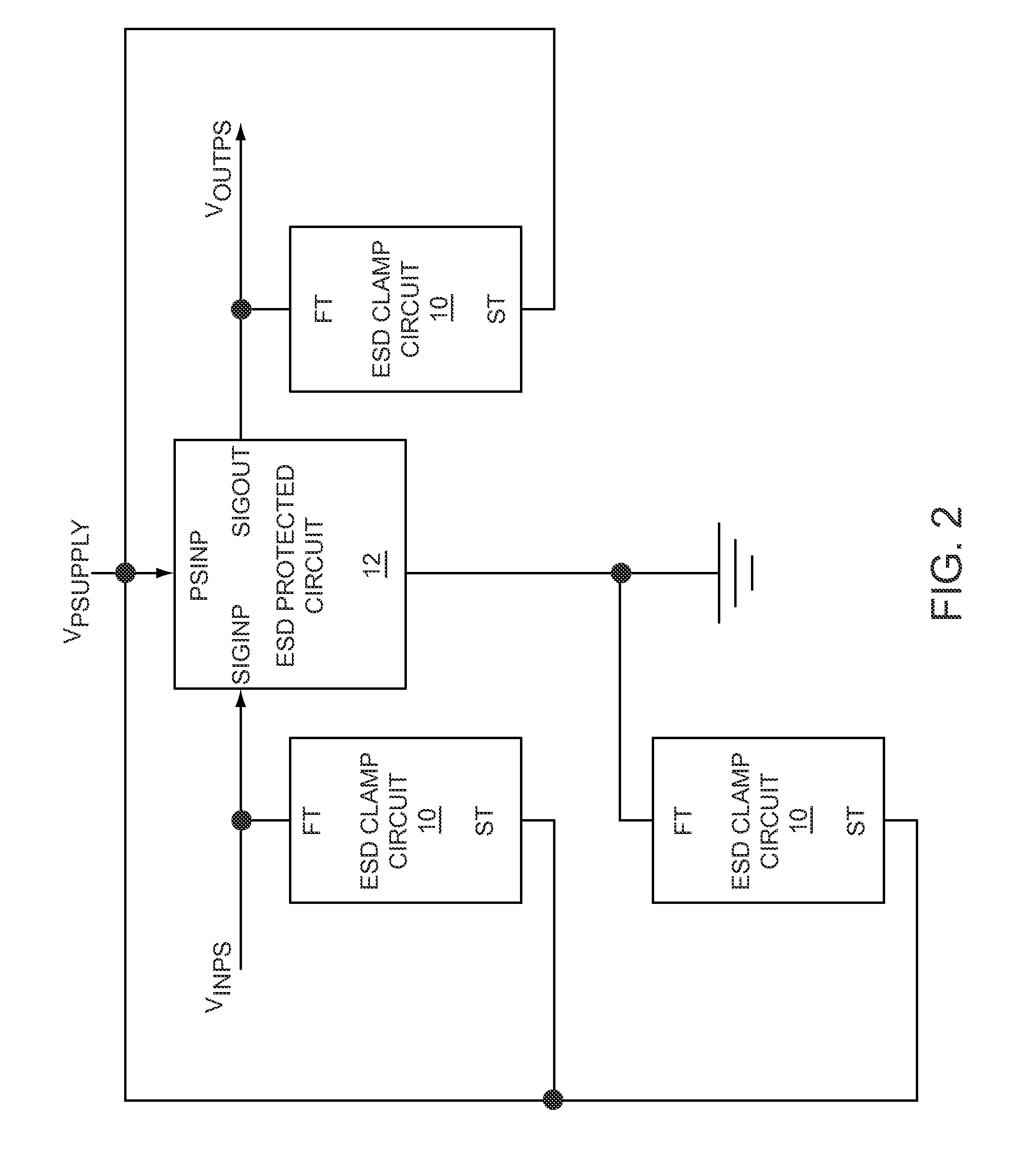

Depletion-mode field effect transistor based electrostatic discharge protection circuit

InactiveUS7881029B1Minimize parasitic capacitanceMaximize linearityAntennas earthing switches associationAmplifier protection circuit arrangementsLevel shiftingEngineering

The present invention relates to an electrostatic discharge (ESD) clamp circuit that is used to protect other circuitry from high voltage ESD events. The ESD clamp circuit may include a field effect transistor (FET) element as a clamping element, which is triggered by using a drain-to-gate capacitance and a drain-to-gate resistance of the FET element and a resistive element as a voltage divider to divide down an ESD voltage to provide a triggering gate voltage of the FET element. In its simplest embodiment, the ESD clamp circuit includes only an FET element, a resistive element, a source-coupled level shifting diode, and a reverse protection diode. Therefore, the ESD clamp circuit may be small compared to other ESD protection circuits. The simplicity of the ESD clamp circuit may minimize parasitic capacitances, thereby maximizing linearity of the ESD clamp circuit over a wide frequency range.

Owner:QORVO US INC

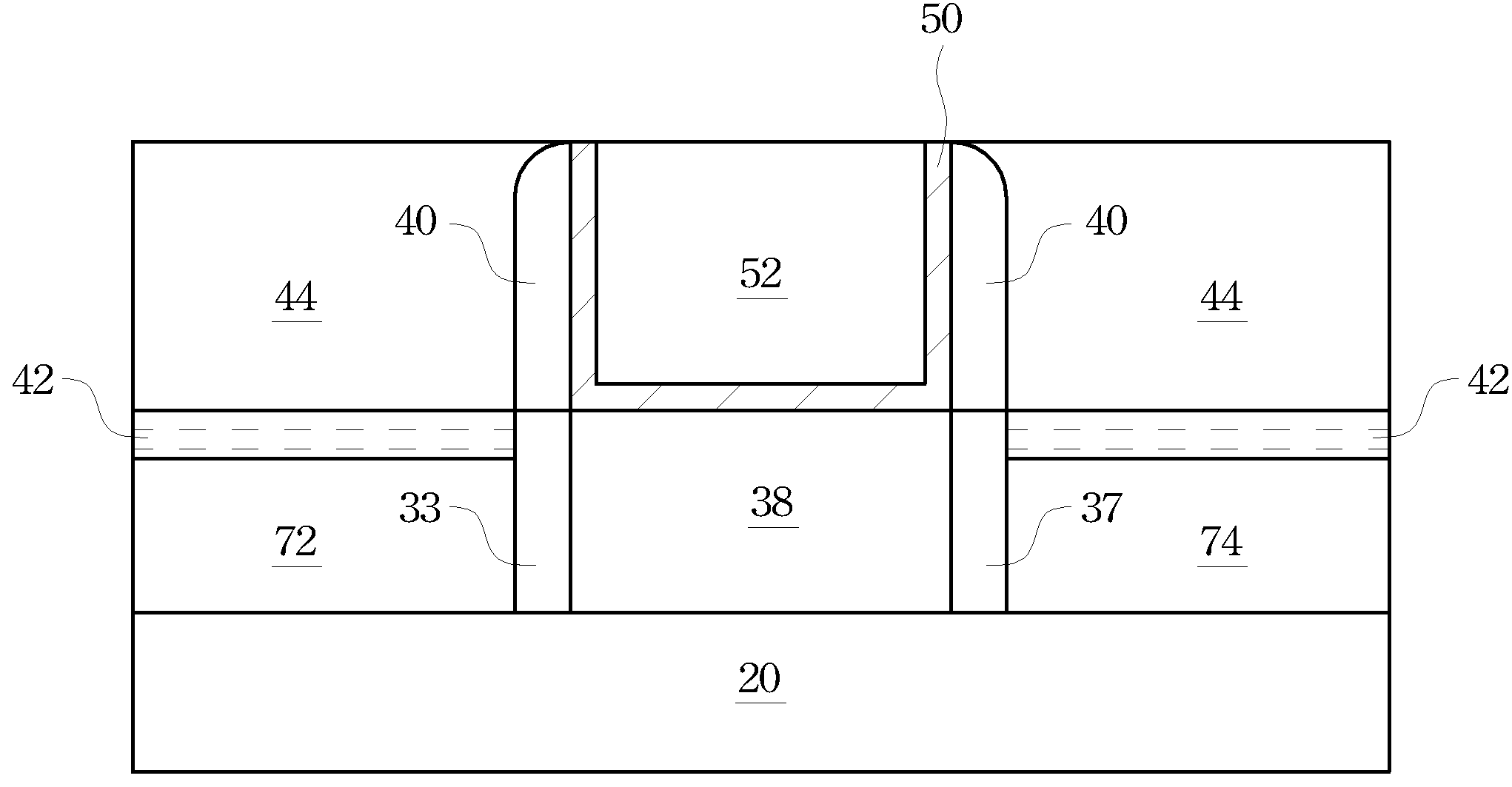

Tunnelling field effect transistor based on work function of heterogeneous gate and forming method of tunnelling field effect transistor

ActiveCN102169900ASmall subthreshold slopeIncrease drive currentSemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentGate dielectric

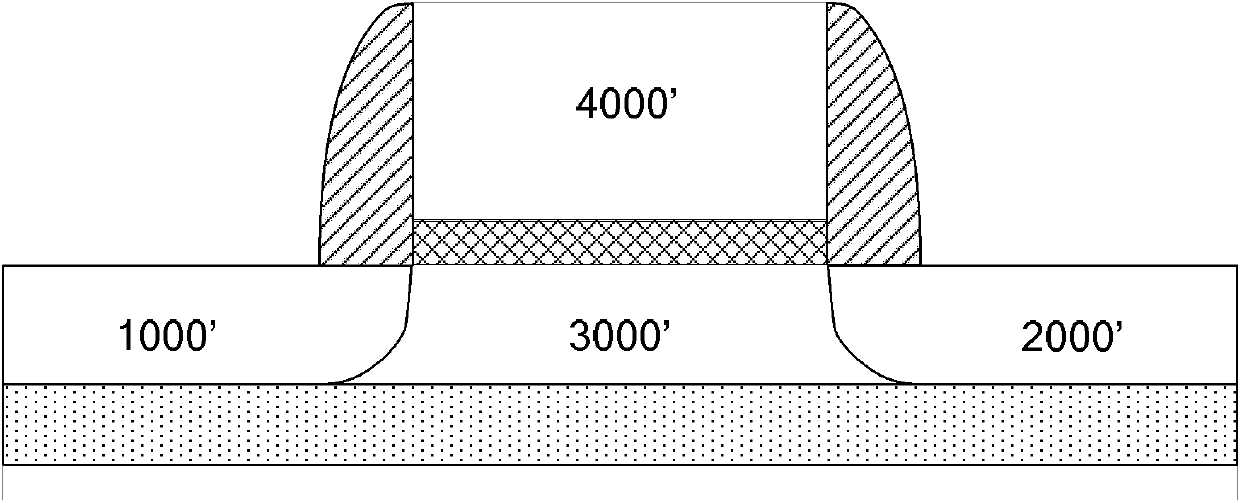

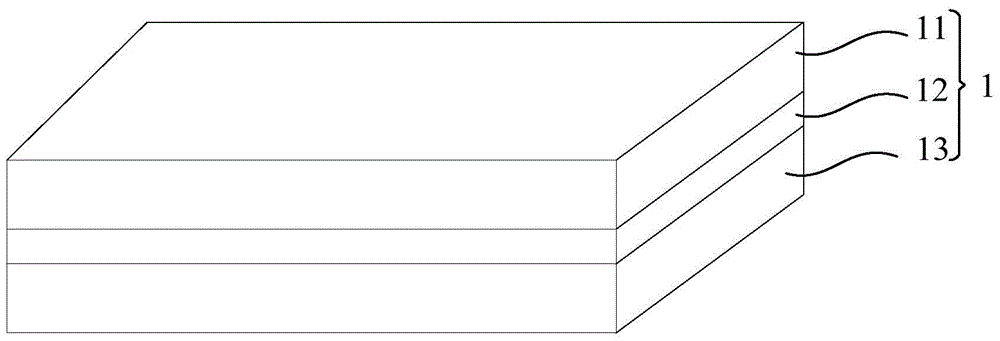

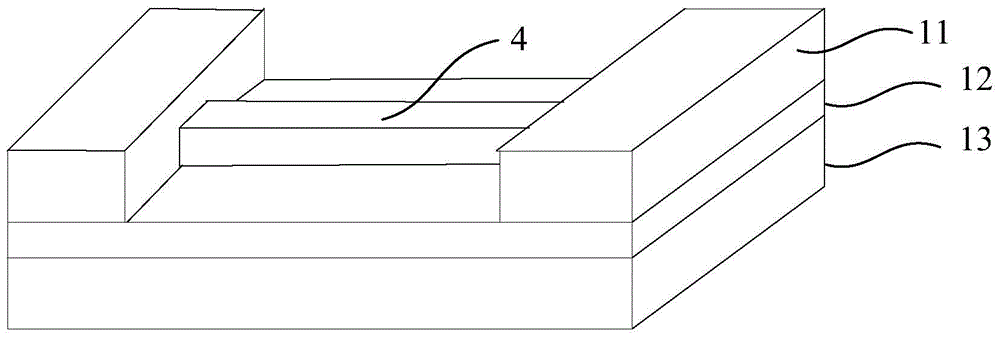

The invention provides a tunnelling field effect transistor based on a work function of a heterogeneous gate. The tunnelling field effect transistor comprises a substrate, a channel region, a source region, a drain region, a gate stack and side walls, wherein the channel region is formed in the substrate; the source region and the drain region are formed on two sides of the channel region; the drain region is in a first doping type; the source region is in a second doping type; the gate stack is formed on the channel region; the side walls are formed on the two sides of the gate stack; the gate stack comprises a first gate dielectric layer and at least comprises a first gate electrode and a second gate electrode; the first gate electrode and the second gate electrode are distributed alongdirection from the source region to the drain region and formed on the gate dielectric layer; and the first gate electrode and the second gate electrode have different work functions. In the embodiment of the invention, a lateral heterogeneous gate work function structure is introduced into the tunnelling field effect transistor, so that the distribution of energy bands of the channel region is modulated, the sub-threshold slope of the transistor is remarkably reduced, and a driving current is improved greatly at the same time.

Owner:TSINGHUA UNIV

Low Power Nanoelectronics

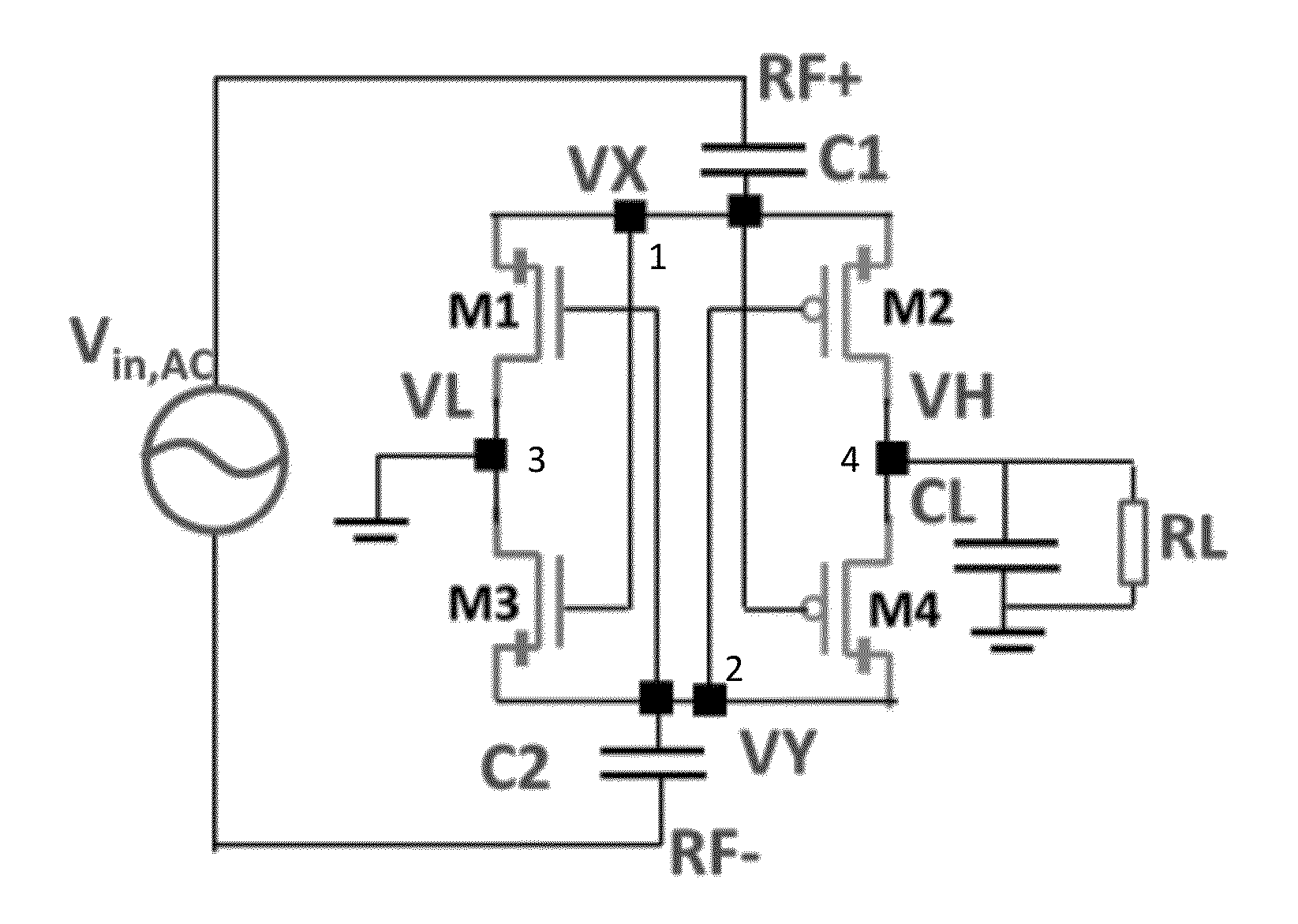

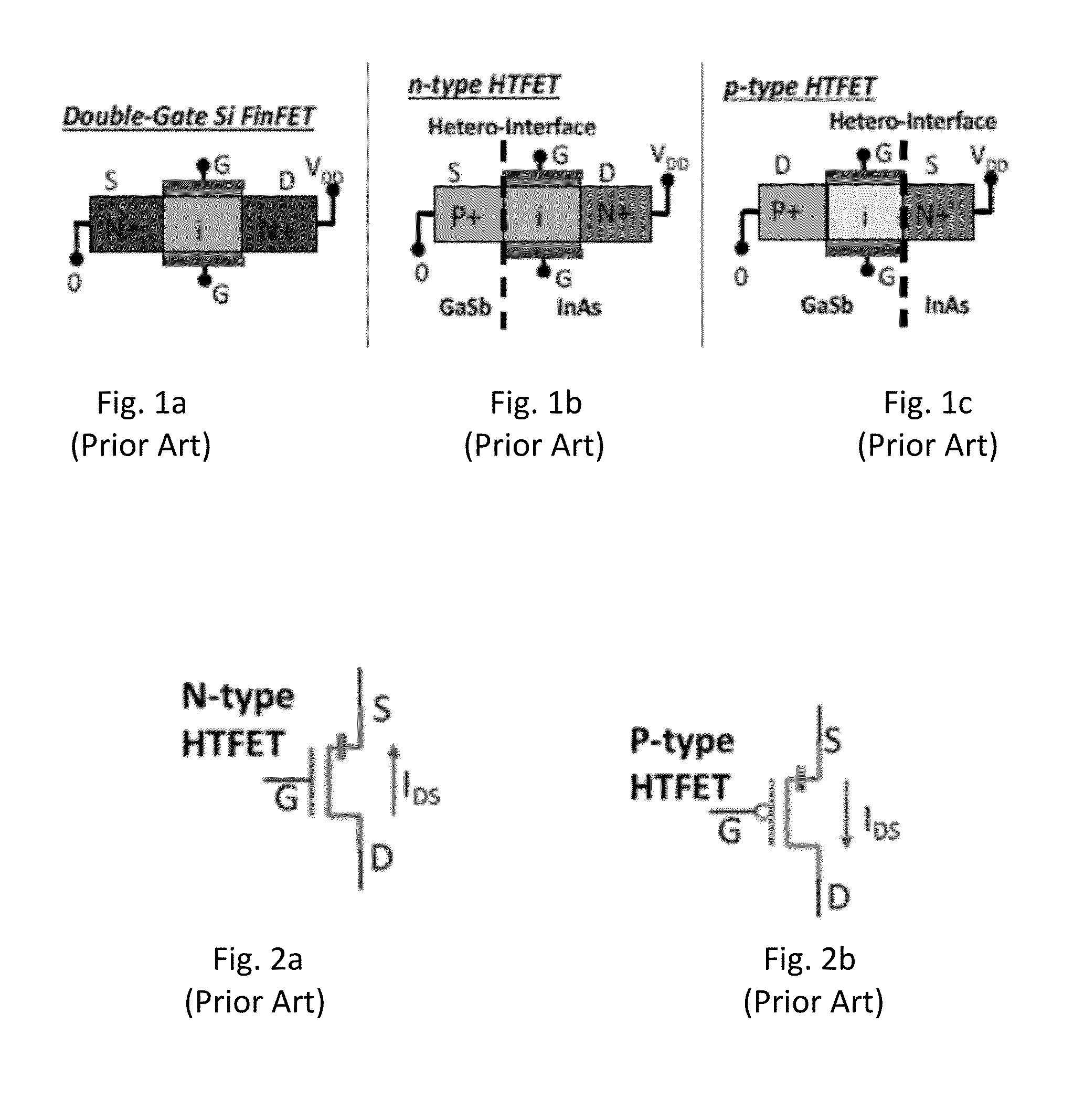

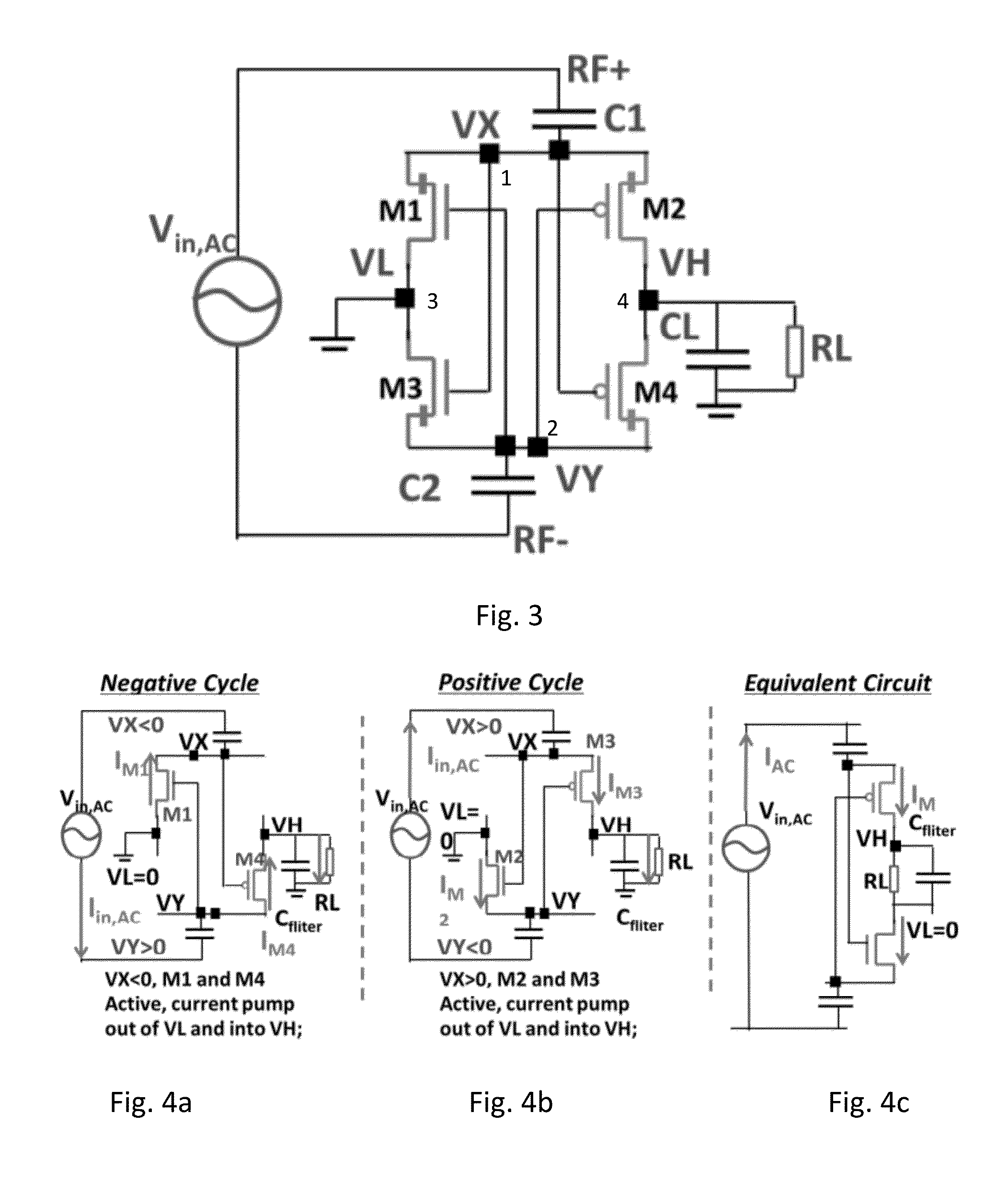

ActiveUS20150333534A1Improve power efficiencyReduce channel resistanceTransformersCircuit arrangementsLow voltageElectric power system

Disclosed are low power electronic devices configured to exploit the sub-threshold swing, unidirectional tunneling, and low-voltage operation of steep slope-tunnel tunnel field-effect transistors (TFET) to improve power-conversion efficiency and power-efficiency of electrical systems incorporating the TFET as an electrical component to perform energy harvesting, signal processing, and related operations. The devices include a HTFET-based rectifier having various topologies, a HTFET-based DC-DC charge pump converter, a HTFET-based amplifier having an amplifier circuit including a telescopic operational transconductance amplifier, and a HTFET-based SAR A / D converter having a HTFET-based transmission gate DFF. Any one of the devices may be used to generate a RF-powered system with improved power conversion efficiencies of power harvesters and power efficiencies of processing components within the system.

Owner:PENN STATE RES FOUND

Gate-all-around nanowire tunnel field effect transistors

ActiveUS8173993B2NanoinformaticsSemiconductor/solid-state device manufacturingNanowireSemiconductor materials

A method for forming a nanowire tunnel field effect transistor (FET) device includes forming a nanowire suspended by first and second pad regions over a semiconductor substrate, the nanowire including a core portion and a dielectric layer, forming a gate structure around a portion of the dielectric layer, forming a first spacer around portions of the nanowire extending from the gate structure, implanting ions in a first portion of the nanowire, implanting ions in the dielectric layer of a second portion of the nanowire, removing the dielectric layer from the second portion of the nanowire, removing the core portion of the second portion of the exposed nanowire to form a cavity, and epitaxially growing a doped semiconductor material in the cavity from exposed cross sections of the nanowire and the second pad region to connect the exposed cross sections of the nanowire to the second pad region.

Owner:GLOBALFOUNDRIES US INC

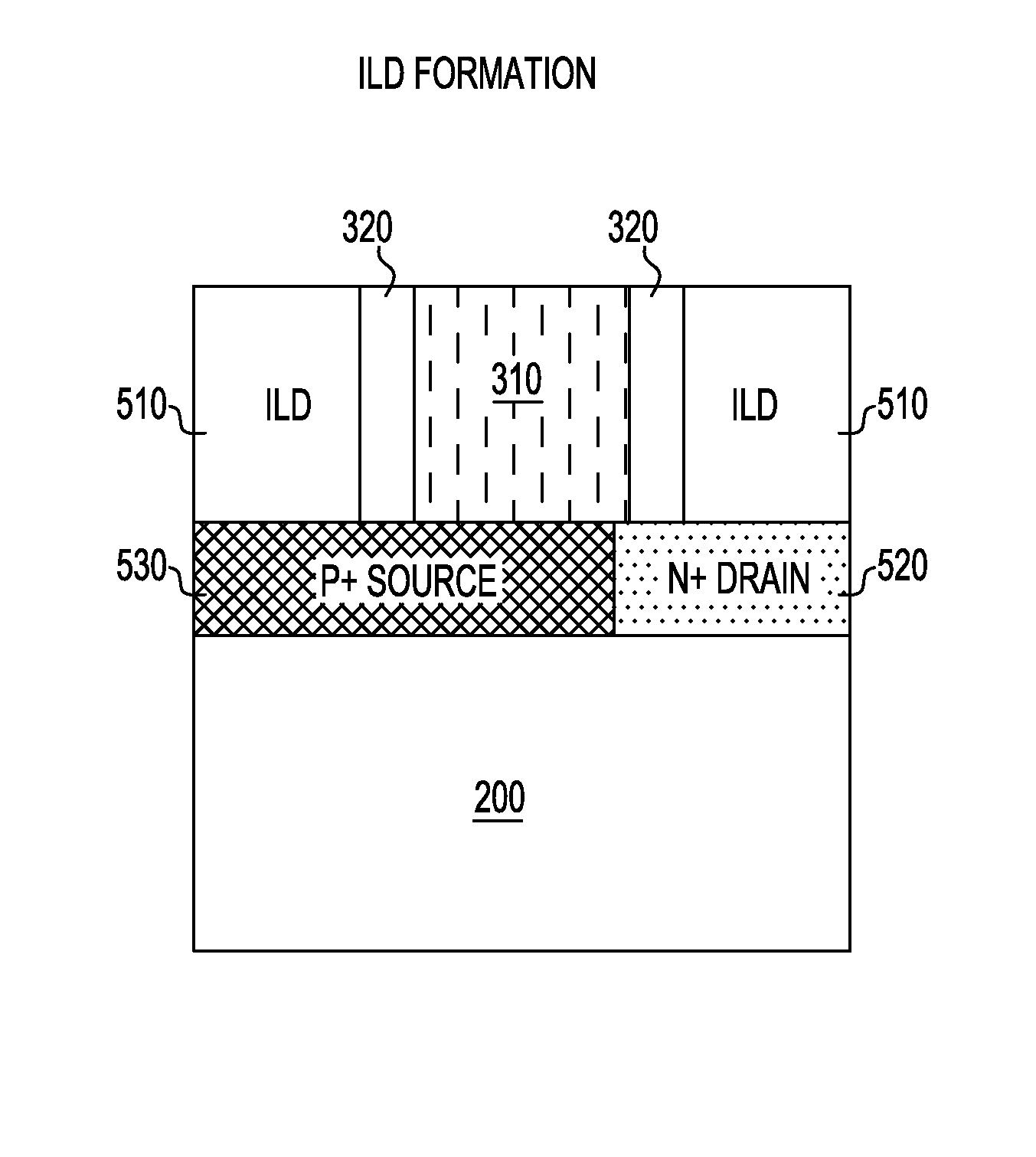

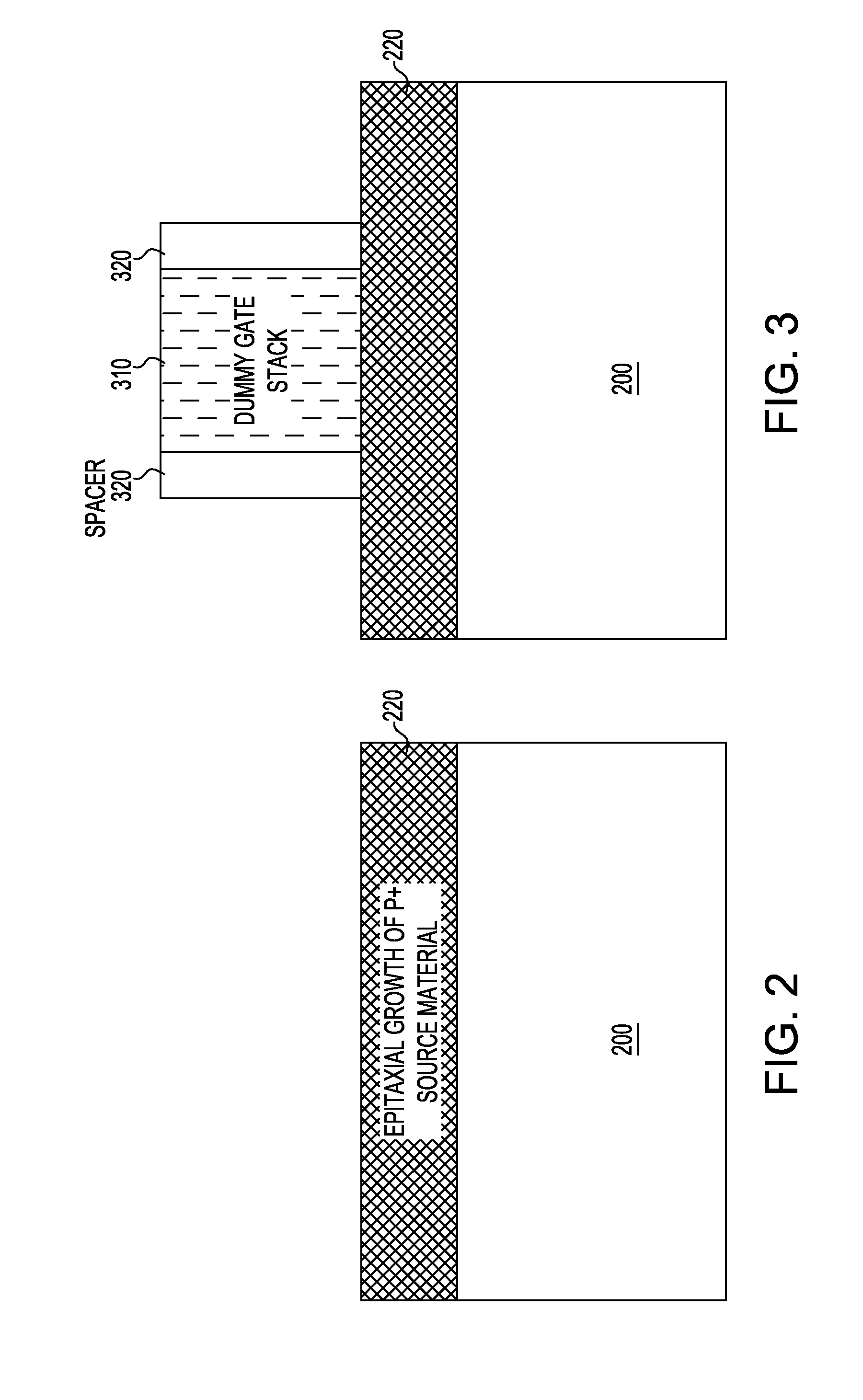

Method of Fabricating Tunnel Transistors With Abrupt Junctions

A method of manufacturing a tunnel field effect transistor (TFET) includes forming on a substrate covered by an epitaxially grown source material a dummy gate stack surrounded by sidewall spacers; forming doped source and drain regions followed by forming an inter-layer dielectric surrounding the sidewall spacers; removing the dummy gate stack, etching a self-aligned cavity; epitaxially growing a thin channel region within the self-aligned etch cavity; conformally depositing gate dielectric and metal gate materials within the self-aligned etch cavity; and planarizing the top surface of the replacement metal gate stack to remove the residues of the gate dielectric and metal gate materials.

Owner:IBM CORP

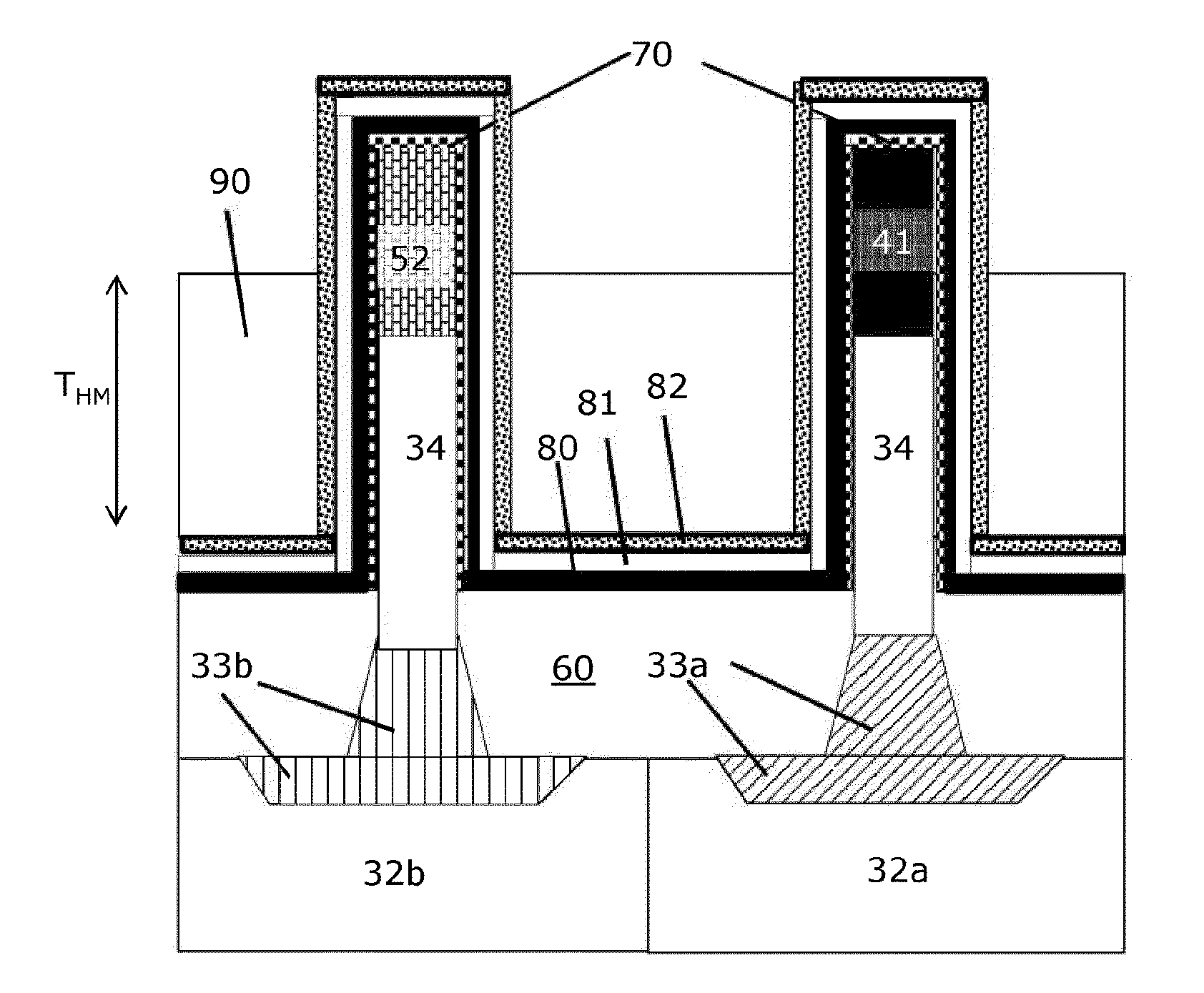

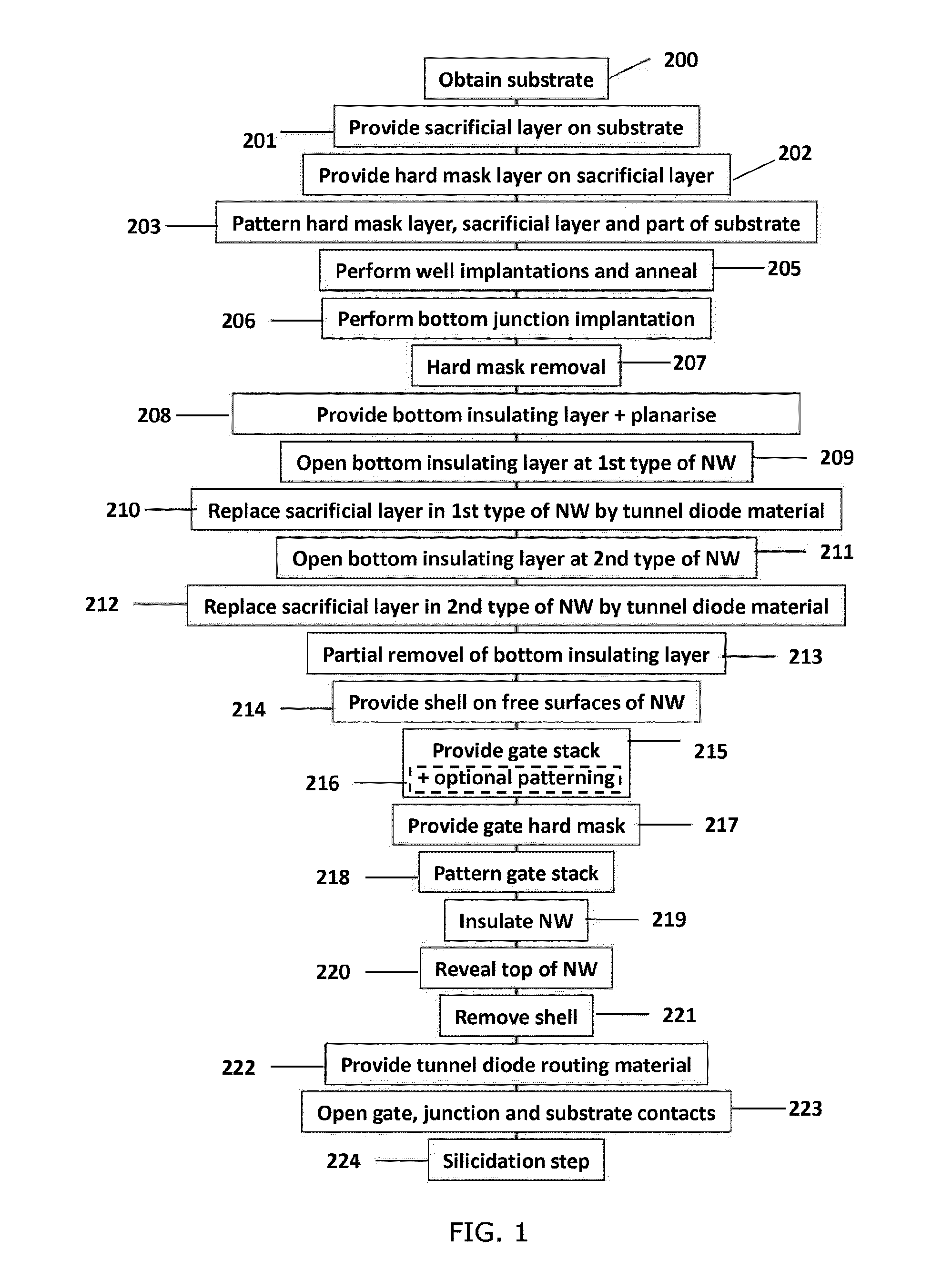

Method of manufacturing a complementary nanowire tunnel field effect transistor semiconductor device

ActiveUS8415209B2Easy to manufactureEnlarge tunnelNanoinformaticsSemiconductor/solid-state device manufacturingHeterojunctionNanowire

The present disclosure provides a method for manufacturing at least one nanowire Tunnel Field Effect Transistor (TFET) semiconductor device. The method comprises providing a stack comprising a layer of channel material with on top thereof a layer of sacrificial material, removing material from the stack so as to form at least one nanowire from the layer of channel material and the layer of sacrificial material, and replacing the sacrificial material in the at least one nanowire by heterojunction material. A method according to embodiments of the present disclosure is advantageous as it enables easy manufacturing of complementary TFETs.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +1

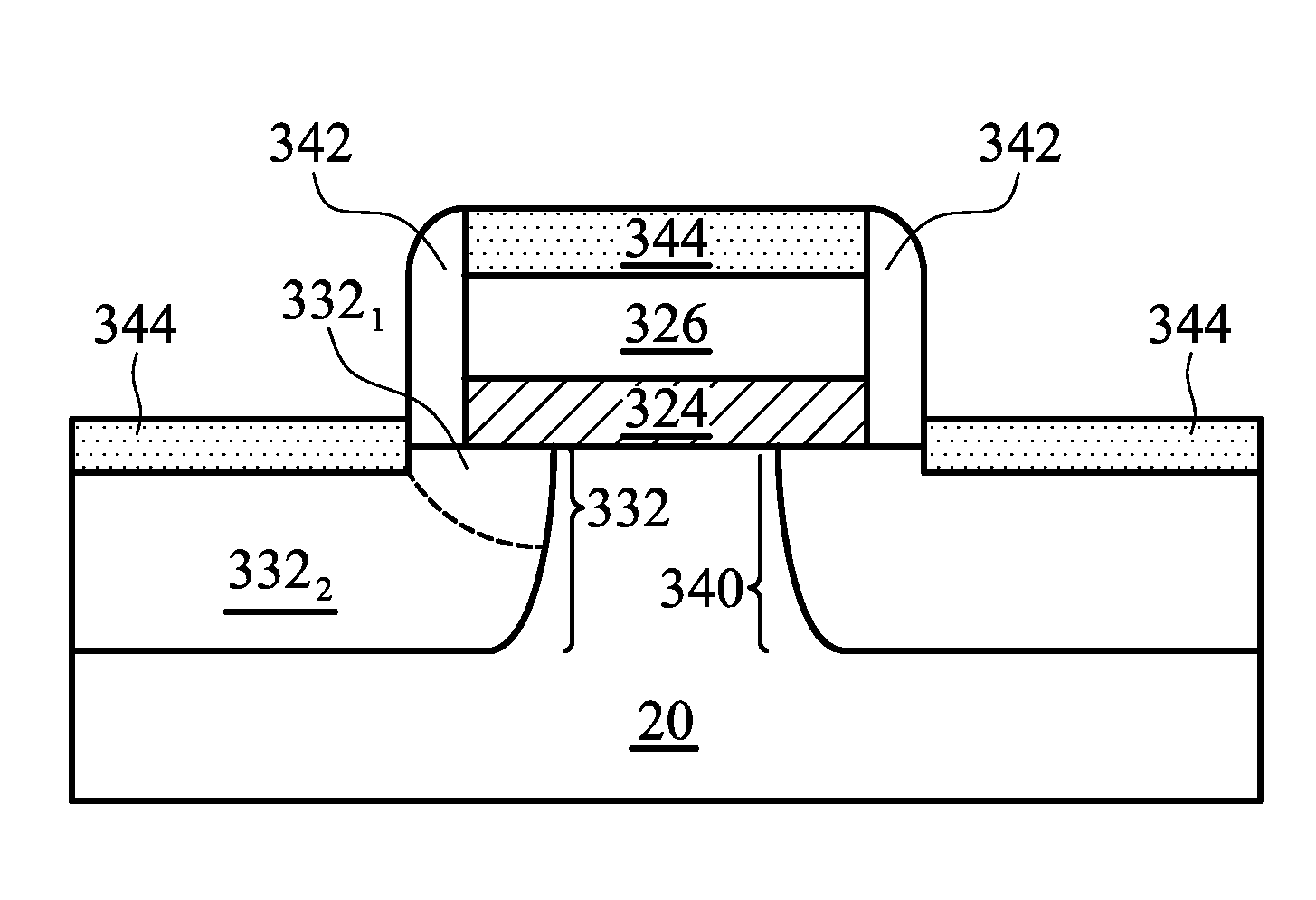

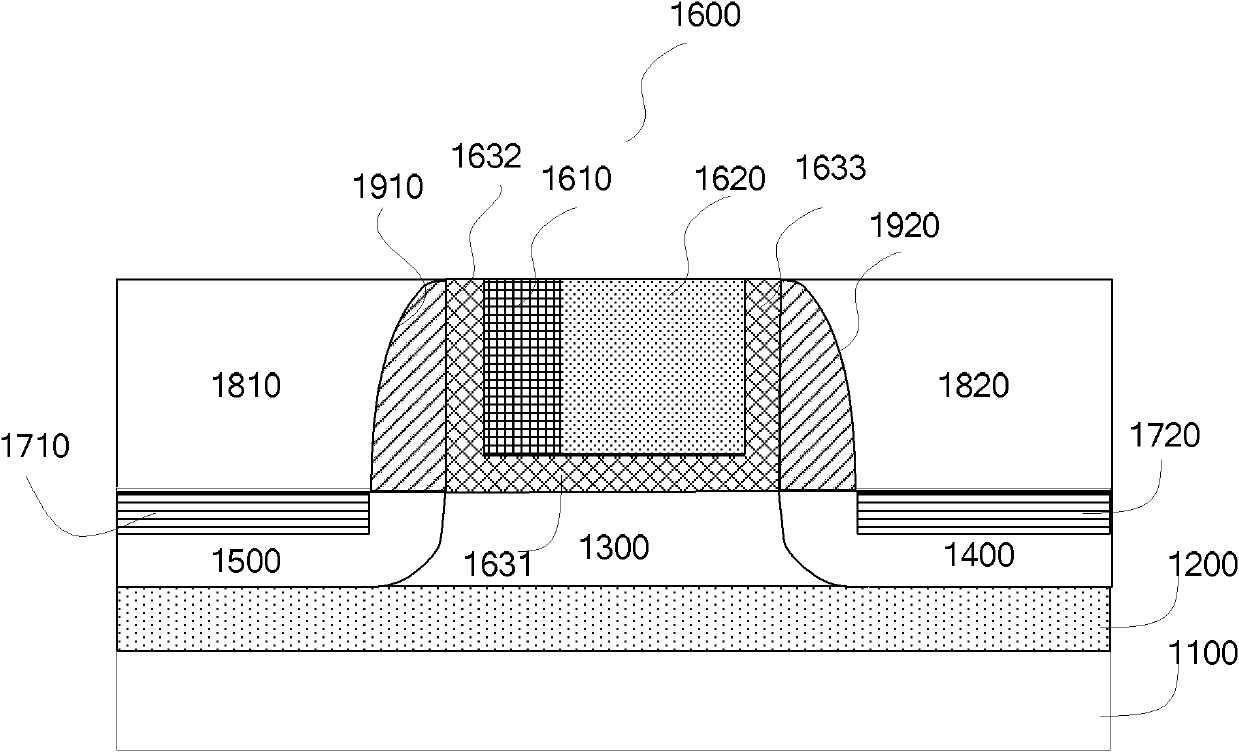

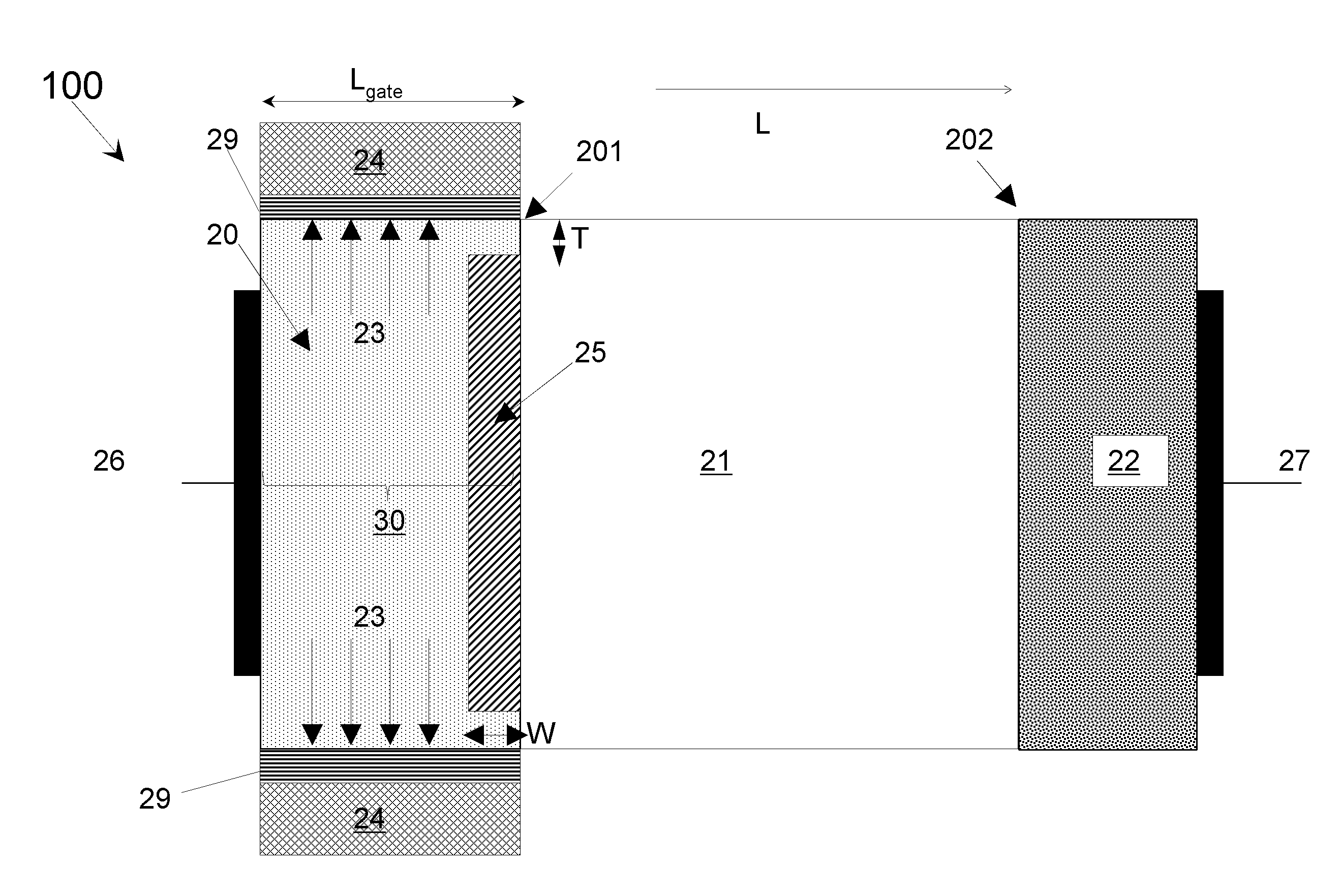

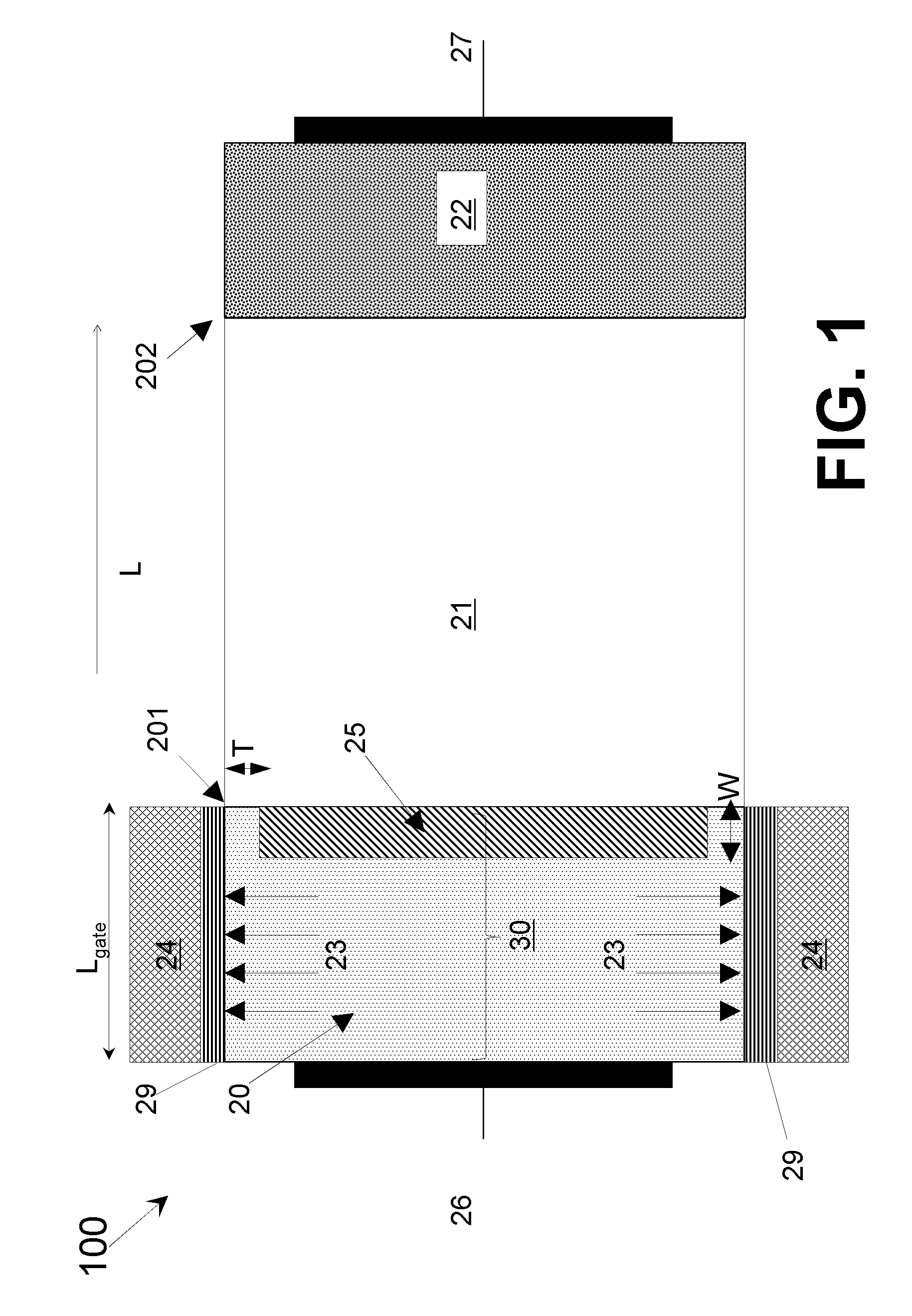

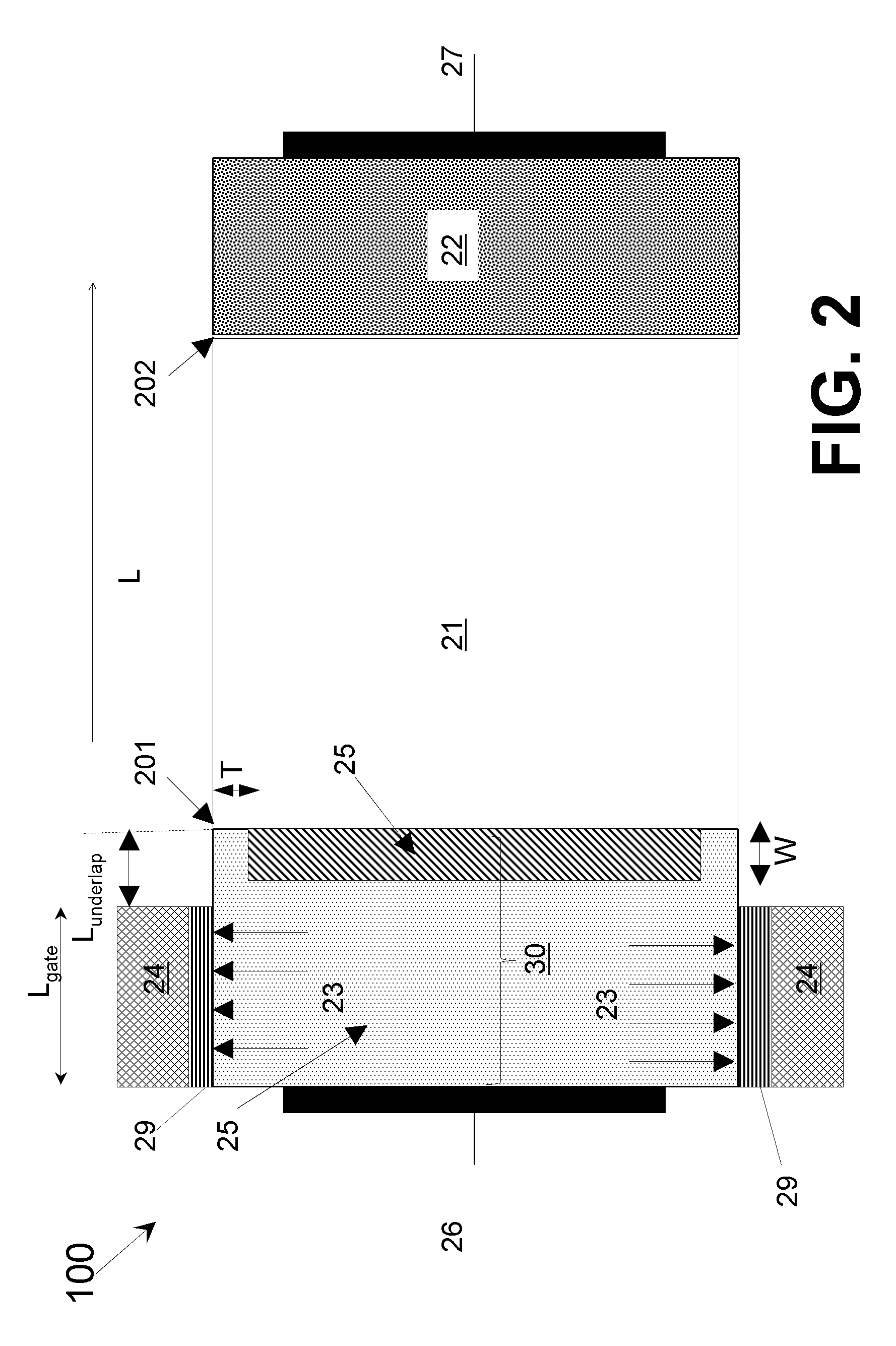

Line-tunneling tunnel field-effect transistor (TFET) and manufacturing method

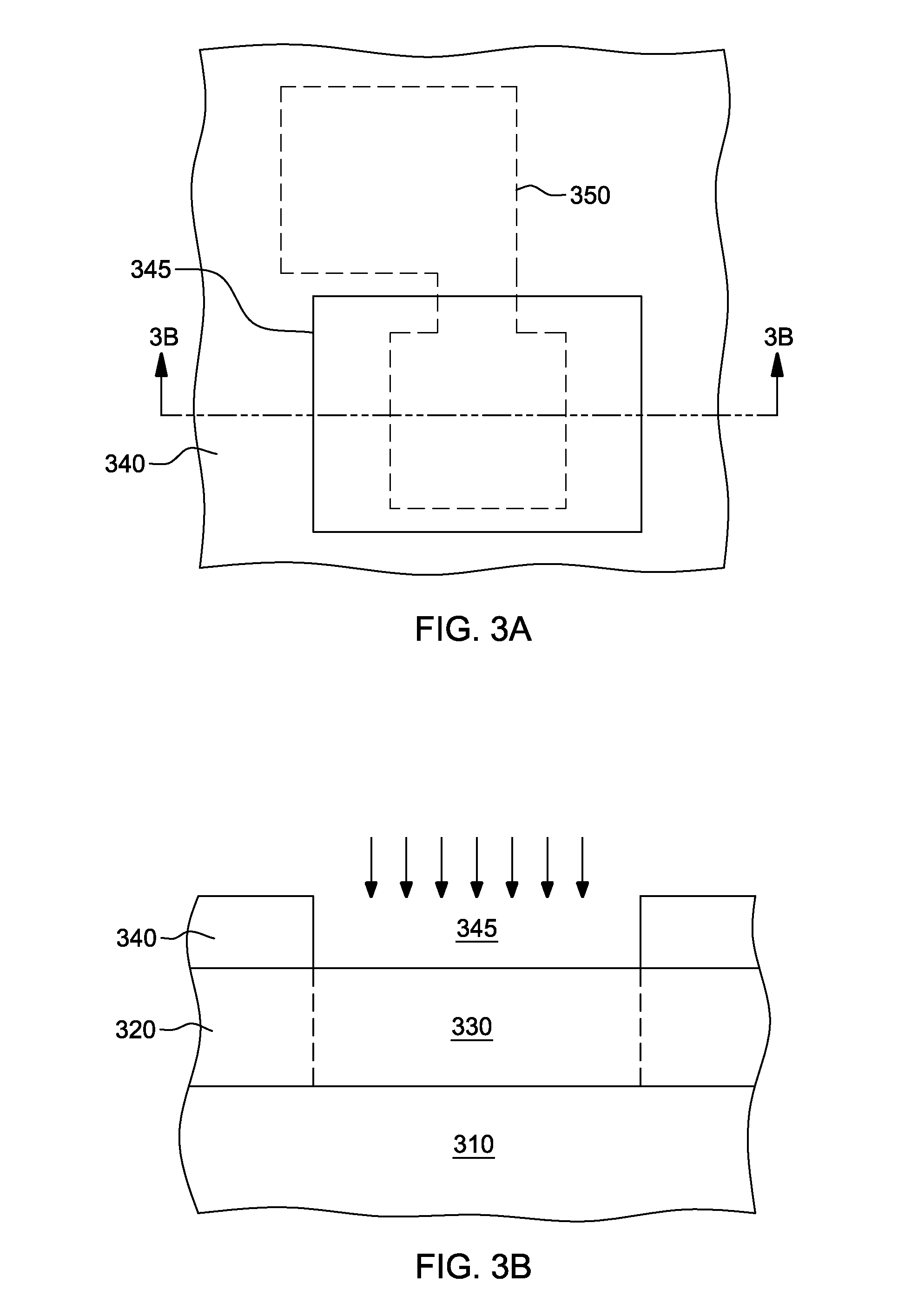

InactiveUS20120298959A1Reduce variationNanoinformaticsSemiconductor/solid-state device manufacturingPeak concentrationCondensed matter physics

A tunnel field effect transistor (TFET) and method of making the same is provided. The TFET comprises a source-channel-drain structure and a gat electrode. The source region comprises a first source sub-region which is doped with a first doping profile with a dopant element of a first doping type having a first peak concentration and a second source sub-region close to a source-channel interface which is doped with a second doping profile with a second dopant element with the same doping type as the first dopant element and having a second peak concentration. The second peak concentration of the second doping profile is substantially higher than the maximum doping level of the first doping profile close to an interface between the first and the second source sub-regions.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +2

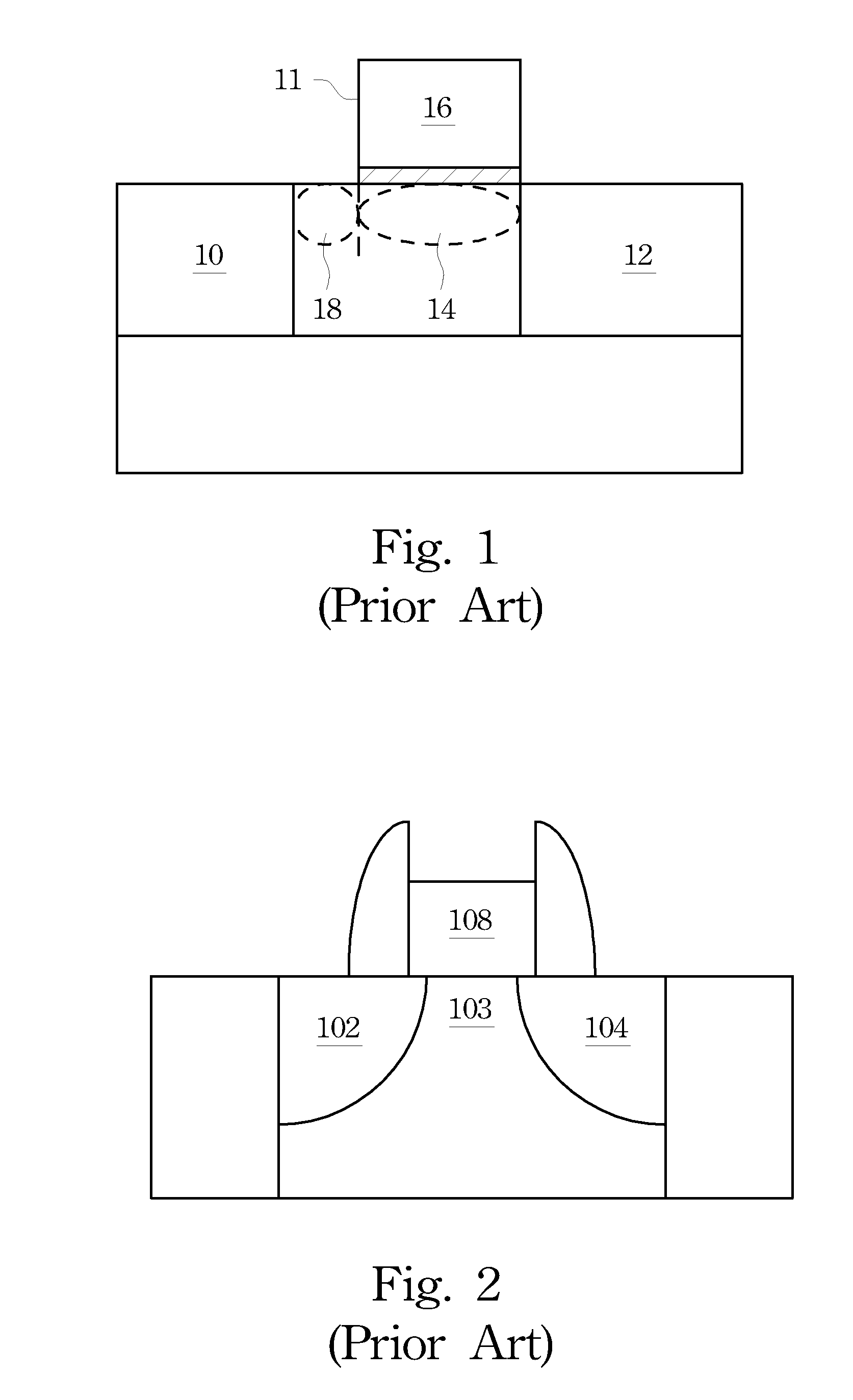

Gated circuit structure with self-aligned tunneling region

InactiveUS20130320427A1Semiconductor/solid-state device manufacturingDiodeEngineeringTunnel field-effect transistor

A tunnel field-effect transistor is provided, which includes a fin-shaped, source-drain circuit structure with a source region and a drain region. The circuit structure is angled in cross-sectional elevation, and includes a first portion and a second portion. The first portion extends away from the second portion, and the source region is disposed in the first or second portion, and the drain region is disposed in the other of the first or second portion. The transistor further includes a gate electrode for gating the circuit structure and a self-aligned tunneling region. The tunneling region is self-aligned to at least a portion of the circuit structure and extends between the gate electrode and the first or second portion of the fin-shaped circuit structure, and the self-aligned tunneling region is at least partially disposed in parallel, spaced opposing relation to a control surface of the gate electrode.

Owner:INTEL CORP

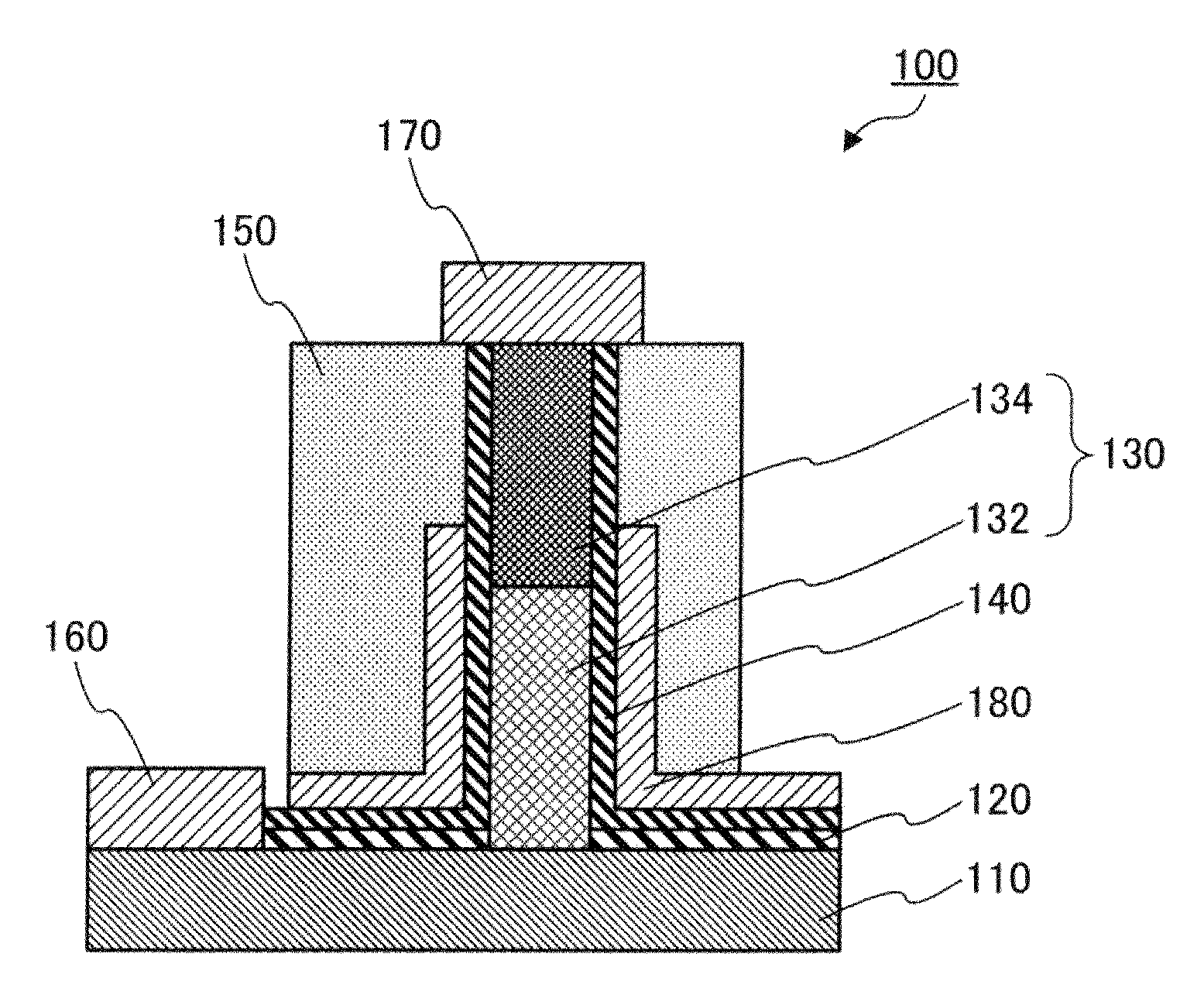

Tunnel field effect transistor and method for making thereof

A vertical tunneling field effect transistor (TFET) and method for forming a vertical tunneling field effect transistor (TFET) is disclosed. The vertical tunneling field effect transistor TFET comprises a vertical core region, a vertical source region, a vertical drain region and a gate structure. The vertical core region is extending perpendicularly from a semiconductor substrate, having a top surface, consisting of a doped outer part and a middle part. The vertical source region of semiconducting core material comprises the doped outer part of the vertical core region. The vertical drain region of semiconducting drain material comprises along its longitudinal direction a first drain part and a second drain part, the first drain part either directly surrounding said vertical source region or directly sandwiching said vertical source region between two sub-parts of said first drain part, the second drain part located directly above and in contact with the first drain part. The gate structure comprises a gate dielectric layer directly aside of the first drain part of the vertical drain region and a gate layer directly aside of the gate dielectric layer. The second drain part is extending above the gate layer and gate dielectric layer. The vertical tunneling field effect transistor TFET further comprises a drain contact directly connected to a third drain part, the third drain part being an upper part of the second drain part of the vertical drain region. The vertical tunneling field effect transistor TFET further comprises a source contact electrically connected to the vertical source region. The vertical tunneling field effect transistor TFET further comprises a gate contact electrically connected to the gate layer.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +1

Biosensor based on tunneling field effect transistor and preparation method of biosensor

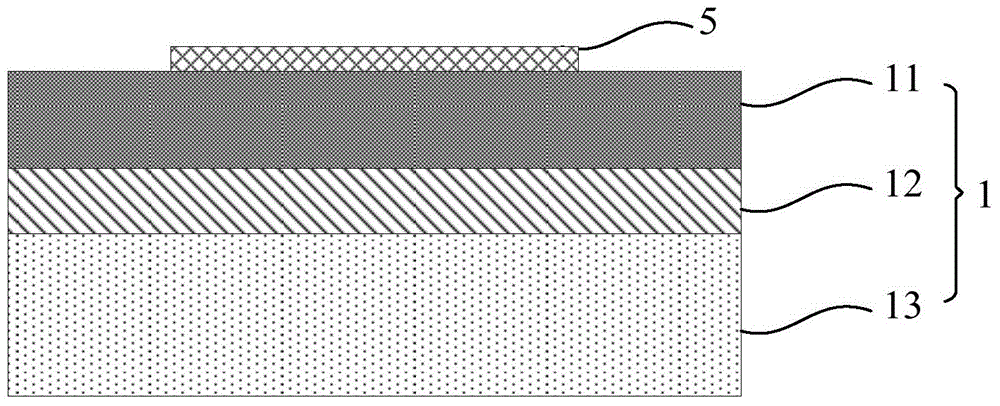

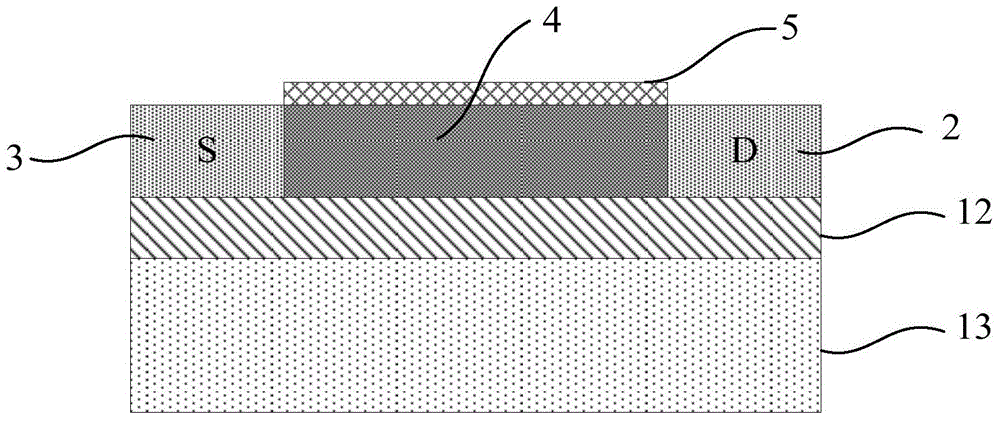

InactiveCN103558280ASteep subthreshold slopeSensitiveMaterial analysis by electric/magnetic meansGate dielectricOxygen

The invention provides a biosensor based on a tunneling field effect transistor and a preparation method of the biosensor. The preparation method of the biosensor at least comprises the steps of firstly, preparing a tunneling field effect transistor as a converter; and then carrying out activated modification on the surface of a channel in the tunneling field effect transistor by adopting a surface modification agent, wherein the step of preparing the tunneling field effect transistor specifically comprises the procedures of providing an SOI (Silicon On Insulator) substrate, wherein the SOI substrate comprises a top layer silicon, a buried oxygen layer and a bottom layer silicon; forming a gate dielectric layer on the surface of the top layer silicon; carrying out ion injection on the top layer silicon at two sides of the gate dielectric layer by adopting an ion injection process to form a source electrode and a leak electrode, defining the top layer silicon of the gate dielectric layer, which is not subjected to the ion injection, as a channel; and forming a back gate on the surface of the bottom layer silicon. The tunneling field effect transistor provided by the invention is abrupt in sub-threshold slope, and is sensitive in change of charges on the surface of the channel, thereby enabling the biosensor to be capable of detecting a biomolecule at high sensitivity.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Enhancement-mode field effect transistor based electrostatic discharge protection circuit

ActiveUS7881030B1Maximize linearityMinimizes parasitic capacitanceAntennas earthing switches associationAmplifier protection circuit arrangementsParasitic capacitanceGate voltage

The present invention relates to an electrostatic discharge (ESD) clamp circuit that is used to protect other circuitry from high voltage ESD events. The ESD clamp circuit may include a field effect transistor (FET) element as a clamping element, which is triggered by using a drain-to-gate capacitance, a drain-to-gate resistance, or both of the FET element, and a resistive element as a voltage divider to divide down an ESD voltage to provide a triggering gate voltage of the FET element. In its simplest embodiment, the ESD clamp circuit includes only an FET element and a resistive element. Therefore, the single FET element ESD clamp circuit may be small compared to other ESD protection circuits. The simplicity of the ESD clamp circuit may minimize parasitic capacitances, thereby maximizing linearity of the ESD clamp circuit over a wide frequency range.

Owner:QORVO US INC

Tunnel field effect transistor and method of making the same

InactiveUS20160336324A1Large horizontal widthImprove drivabilityTransistorSolid-state devicesEngineeringTunnel field-effect transistor

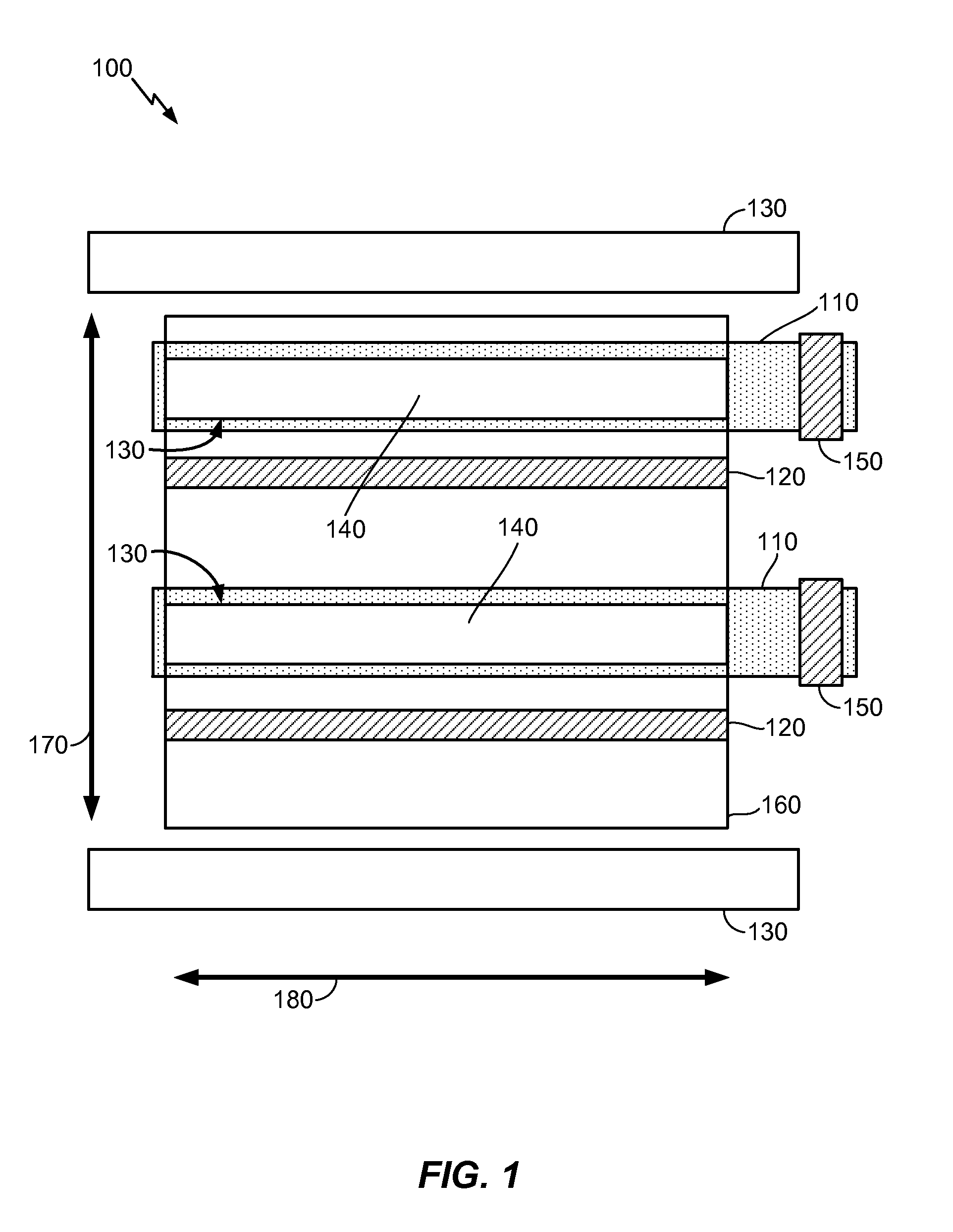

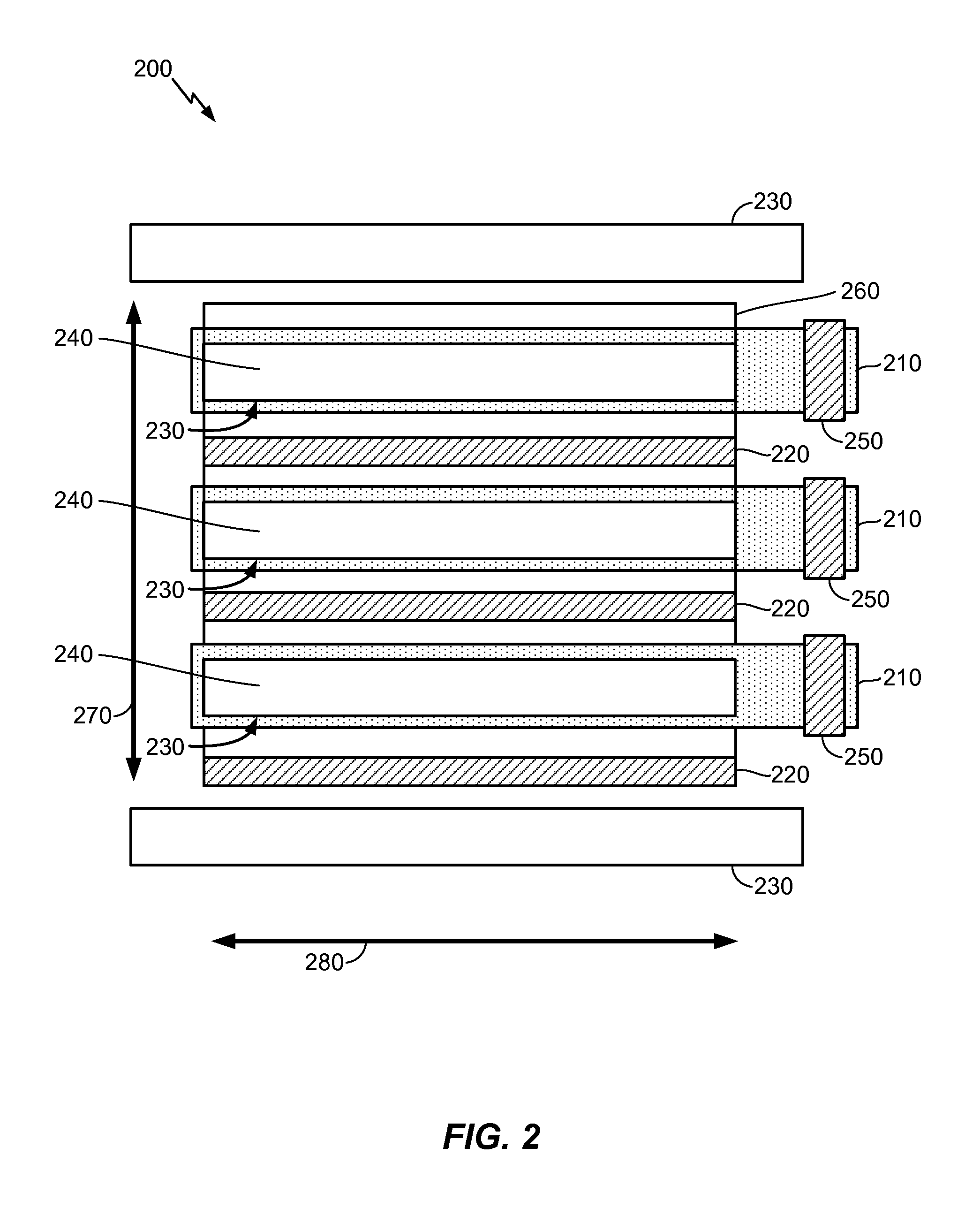

A vertically integrated transistor device increases the effective active area of the device to improve the performance characteristics of the device. The transistor device may include a plurality of gate elements, a plurality of source-drain elements extending parallel to the plurality of gate elements and horizontally spaced therefrom; and a plurality of fin elements extending parallel to the plurality of gate elements and vertically spaced therefrom, wherein each of the plurality of fin elements is horizontally spaced a first distance from each of the other ones of the plurality of fin elements.

Owner:QUALCOMM INC

Biosensor based on silicon nanowire tunneling field effect transistor and manufacturing method of biosensor

ActiveCN103558279ASensitiveSensitive detectionMaterial analysis by electric/magnetic meansOxygenIon implantation

The invention provides a biosensor based on a silicon nanowire tunneling field effect transistor and manufacturing method of the biosensor. The method comprises the following steps: step one, manufacturing a tunneling field effect transistor with a silicon nanowire channel as a converter; and step two, carrying out activated modification on the surface of the silicon nanowire channel by adopting a surface modifier; the specific step of preparing the silicon nanowire tunneling field effect transistor in the step one comprises the substeps: providing an SOI (silicon on insulator) substrate comprising a top silicon layer, an oxygen-burying layer and a bottom silicon layer; etching the top silicon layer to form the silicon nanowire channel, depositing a gate medium layer on the surface of the channel, performing ion injection on the top silicon layer by adopting an ion injection process, forming a source electrode and a drain electrode at two ends of the channel, and forming a back gate on the back of the bottom silicon. The tunneling field effect transistor based on the silicon nanowire has a steeper sub-threshold slope, and is more sensitive to the change of the surface charge of the channel, so that the biosensor is capable of detecting the biomolecules with high sensitivity.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

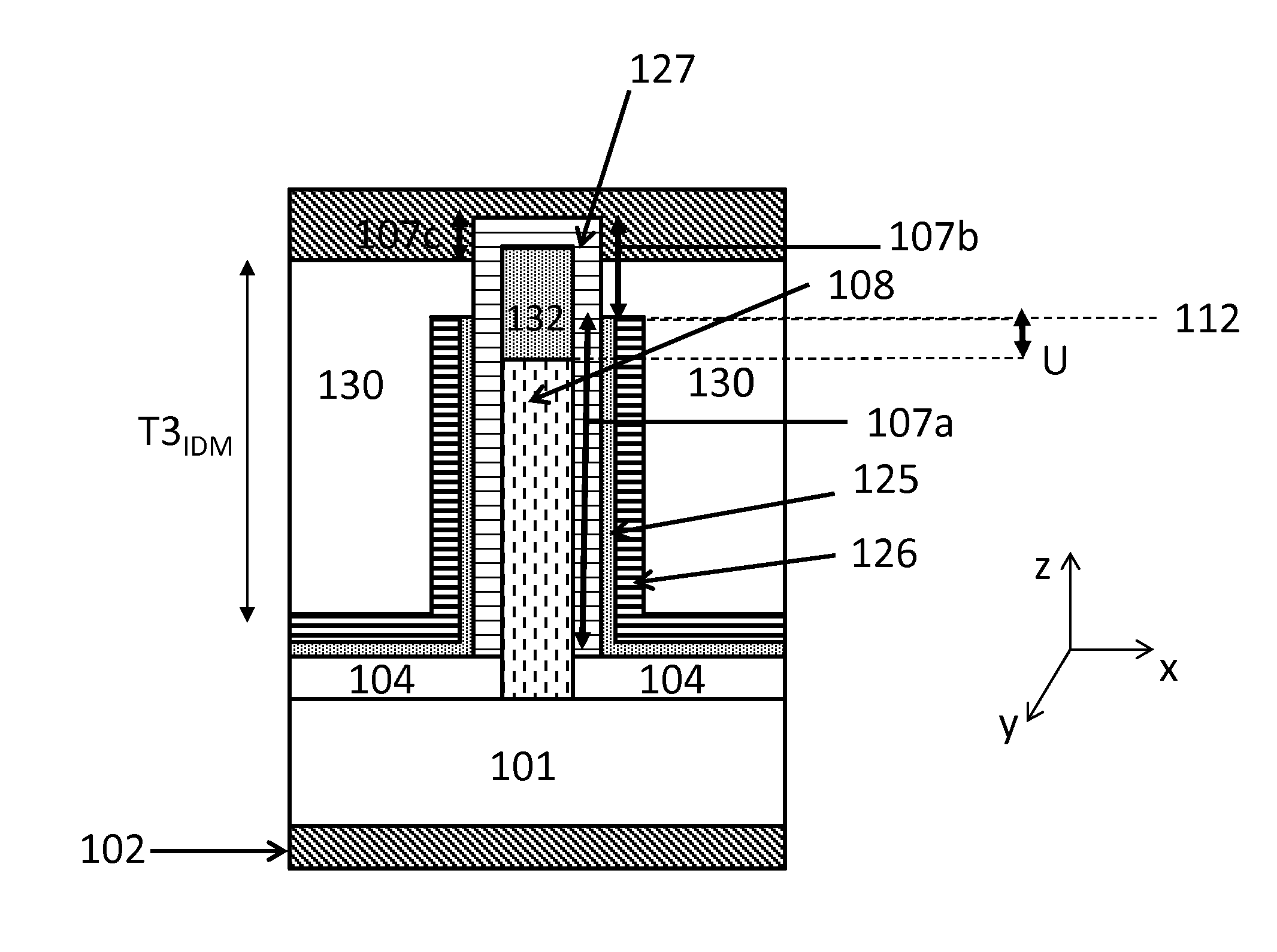

Control of tunneling junction in a hetero tunnel field effect transistor

ActiveUS20100327319A1Reducing drastically the out-diffusion of the dopantsMaintain good propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesDopantTunnel junction

Embodiments of the present disclosure provide a method to fabricate a hetero-junction in a Tunnel Field Effect Transistor (TFET) device configuration (e.g. in a segmented nanowire TFET). Since in prior art devices the highly doped source is in direct contact with the lowly doped or undoped channel, some amount of dopants will diffuse from the source to the channel which cannot be avoided due to the source deposition thermal budget. This out-diffusion reduces the steepness of the doping profile and hence deteriorates the device operation. Particular embodiments comprise the insertion of a thin transition layer in between the source region and channel region such that the out-diffusion is within a very limited region of a few nm, guaranteeing extremely good doping abruptness thanks to the lower diffusion of the dopants in the transition layer. The transition layer avoids the direct contact between the highly doped (e.g. Ge or SiGe) source region and the lowly doped or undoped (e.g. Si) channel and allows to contain the whole doping (e.g. B atoms) entirely within the source region and transition layer. The thickness of the transition layer can be engineered such that the transition layer coincides with the steep transition step from the highly doped source region to the intrinsic region (channel), and hence maximizing the tunneling current.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

TFET with Nanowire Source

A tunnel field effect transistor (TFET) includes a source region, the source region comprising a first portion of a nanowire; a channel region, the channel region comprising a second portion of the nanowire; a drain region, the drain region comprising a portion of a silicon pad, the silicon pad being located adjacent to the channel region; and a gate configured such that the gate surrounds the channel region and at least a portion of the source region.

Owner:GLOBALFOUNDRIES INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com