Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

329 results about "Doping profile" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

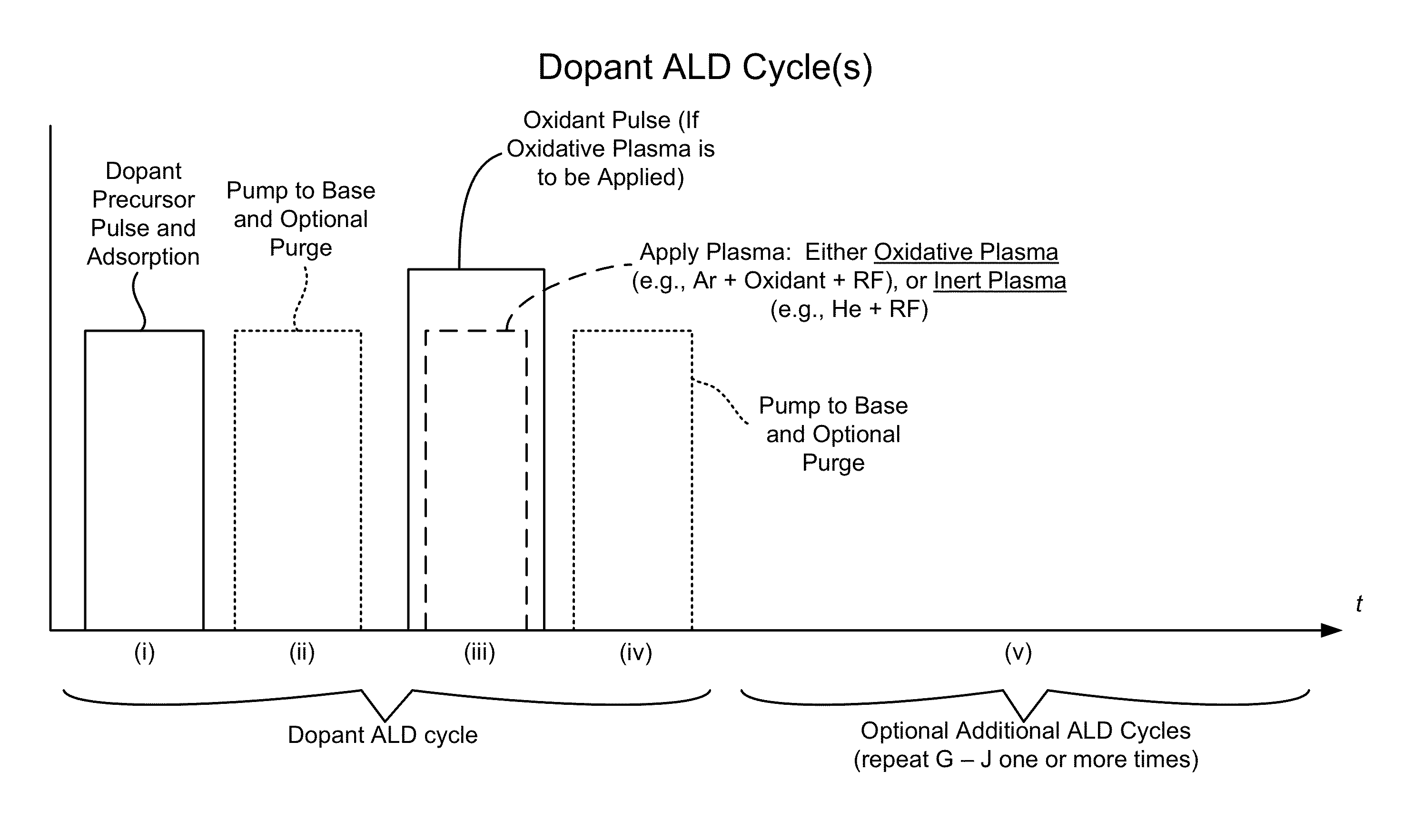

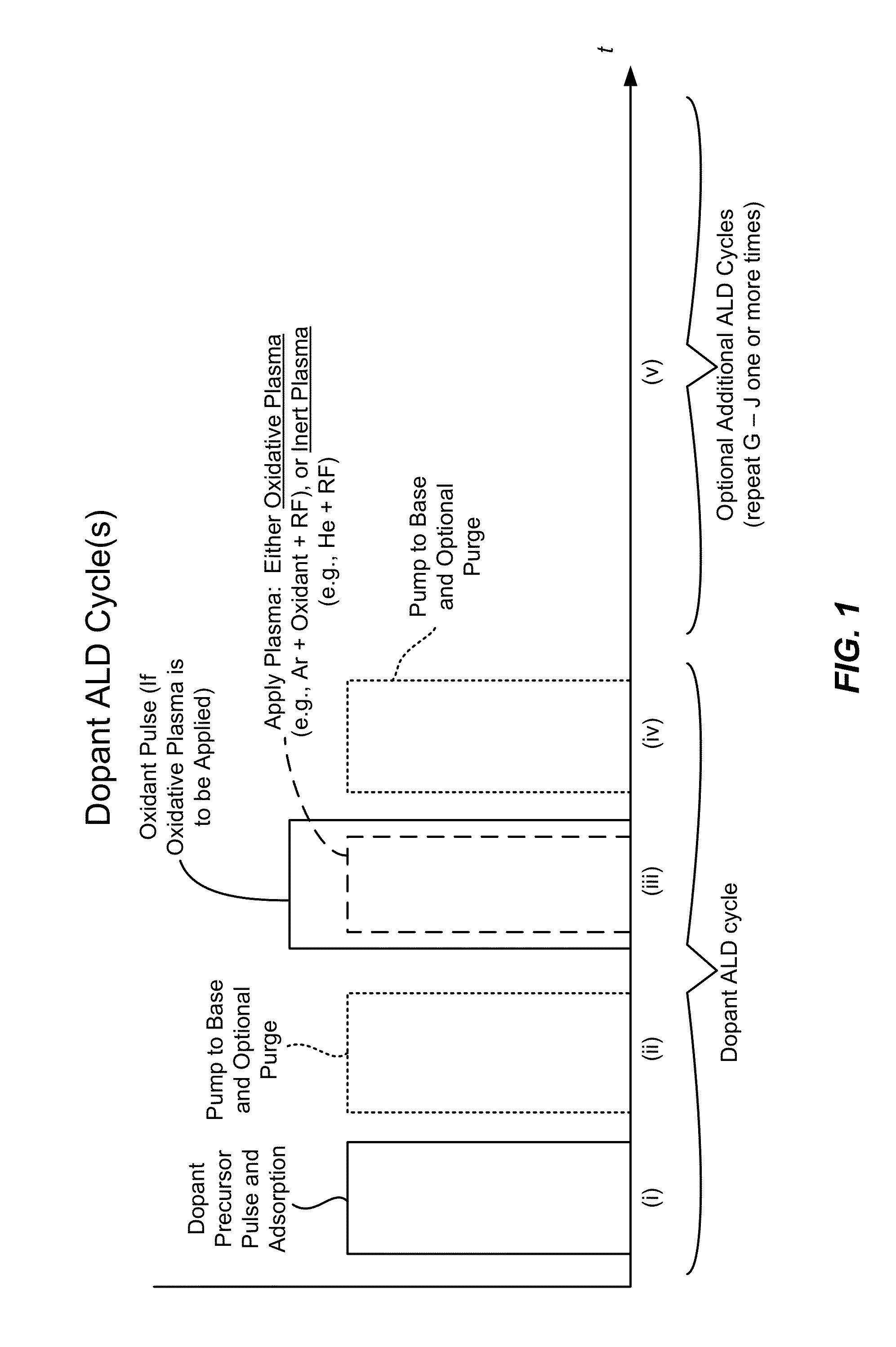

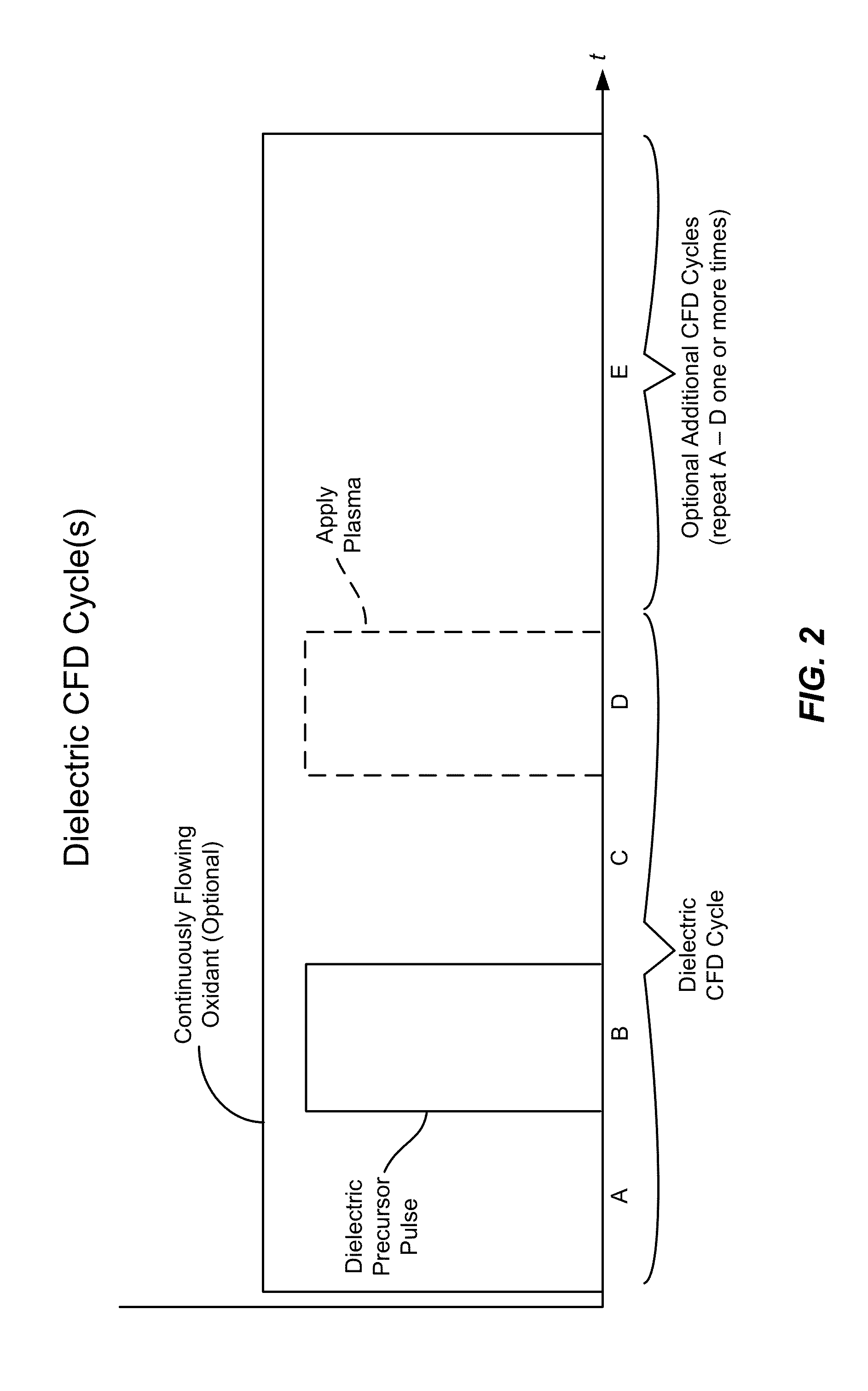

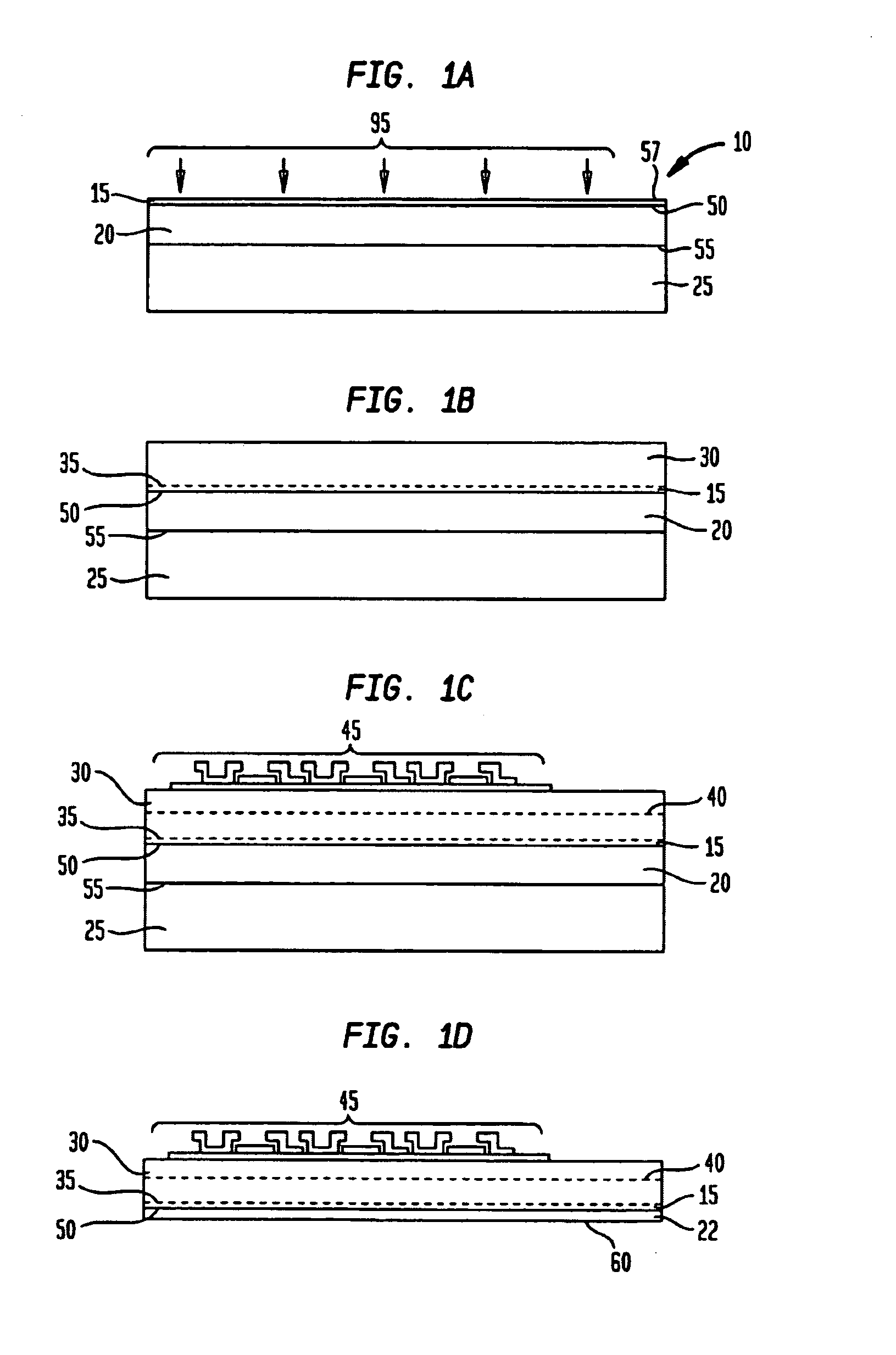

Conformal doping via plasma activated atomic layer deposition and conformal film deposition

ActiveUS8956983B2Liquid surface applicatorsSemiconductor/solid-state device manufacturingDopantPatterned substrate

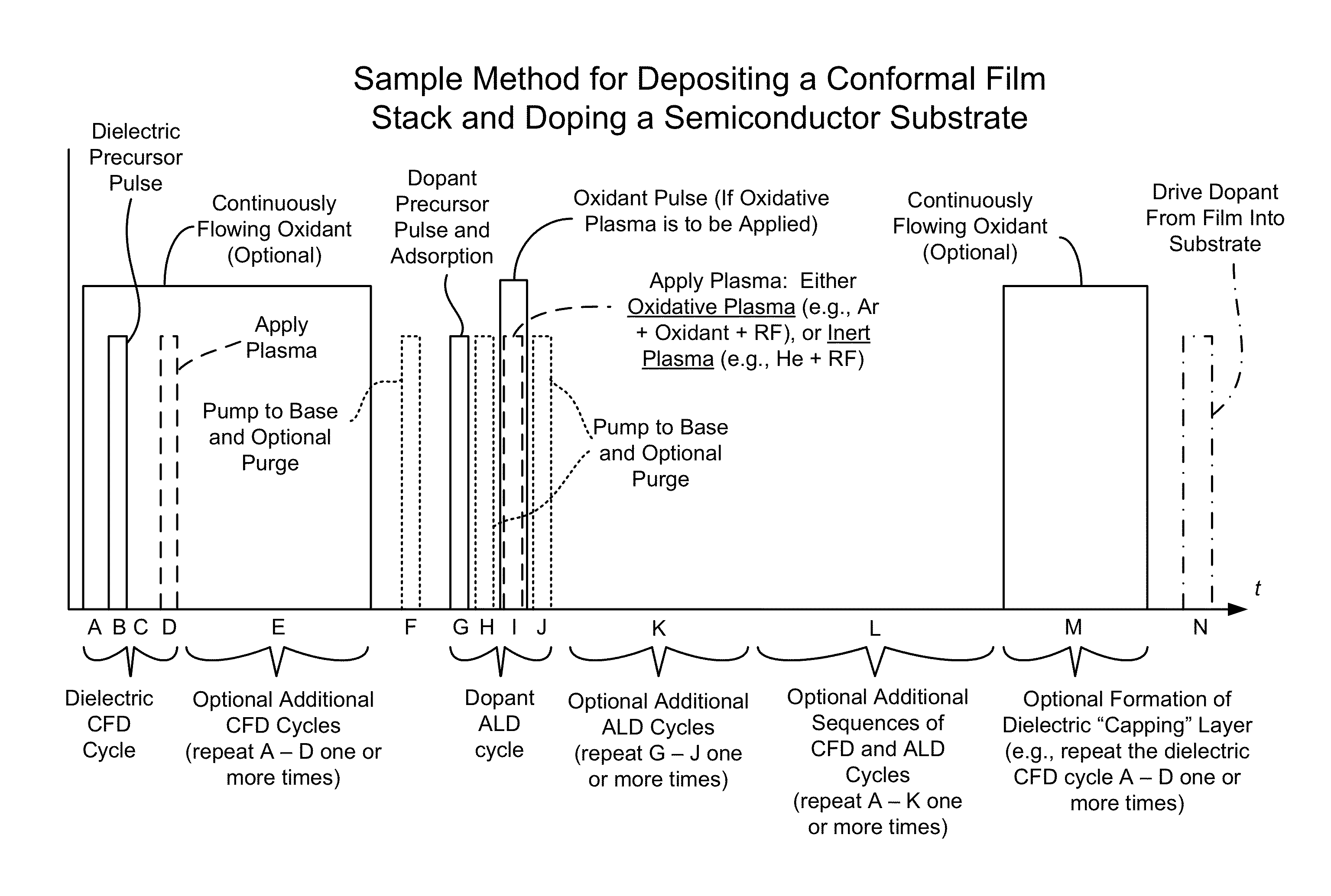

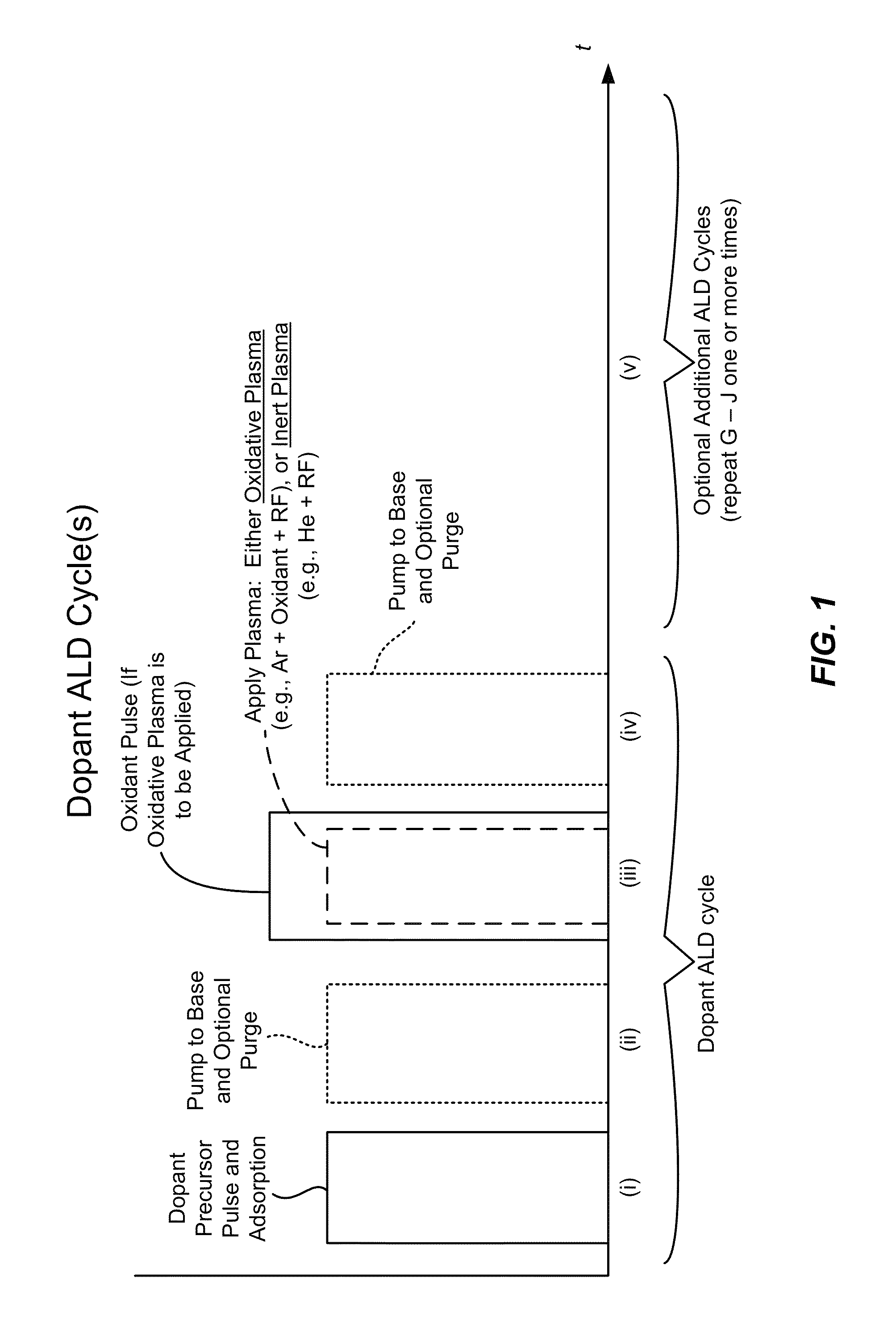

Disclosed herein are methods of doping a patterned substrate in a reaction chamber. The methods may include forming a first conformal film layer which has a dopant source including a dopant, and driving some of the dopant into the substrate to form a conformal doping profile. In some embodiments, forming the first film layer may include introducing a dopant precursor into the reaction chamber, adsorbing the dopant precursor under conditions whereby it forms an adsorption-limited layer, and reacting the adsorbed dopant precursor to form the dopant source. Also disclosed herein are apparatuses for doping a substrate which may include a reaction chamber, a gas inlet, and a controller having machine readable code including instructions for operating the gas inlet to introduce dopant precursor into the reaction chamber so that it is adsorbed, and instructions for reacting the adsorbed dopant precursor to form a film layer containing a dopant source.

Owner:NOVELLUS SYSTEMS

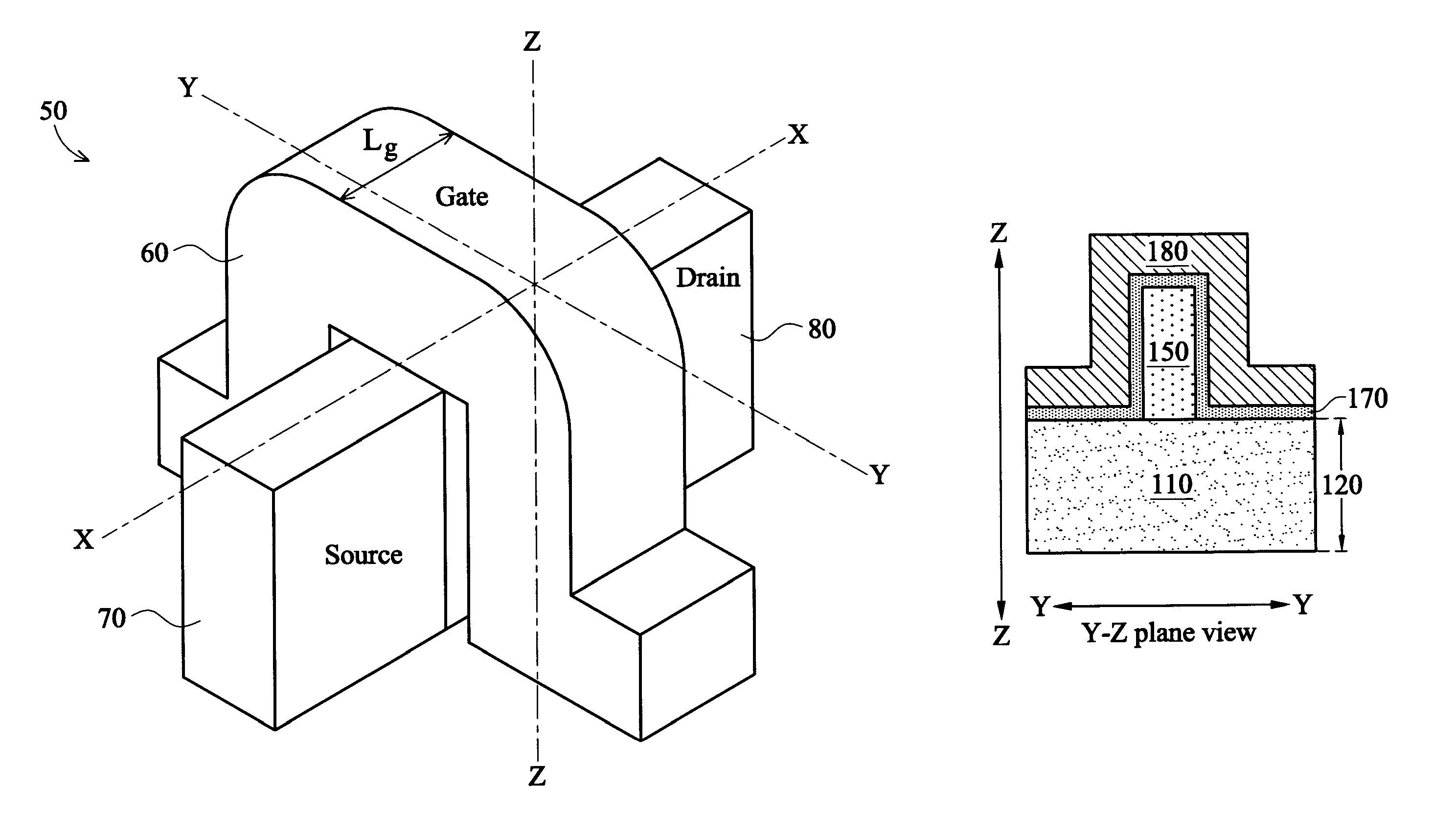

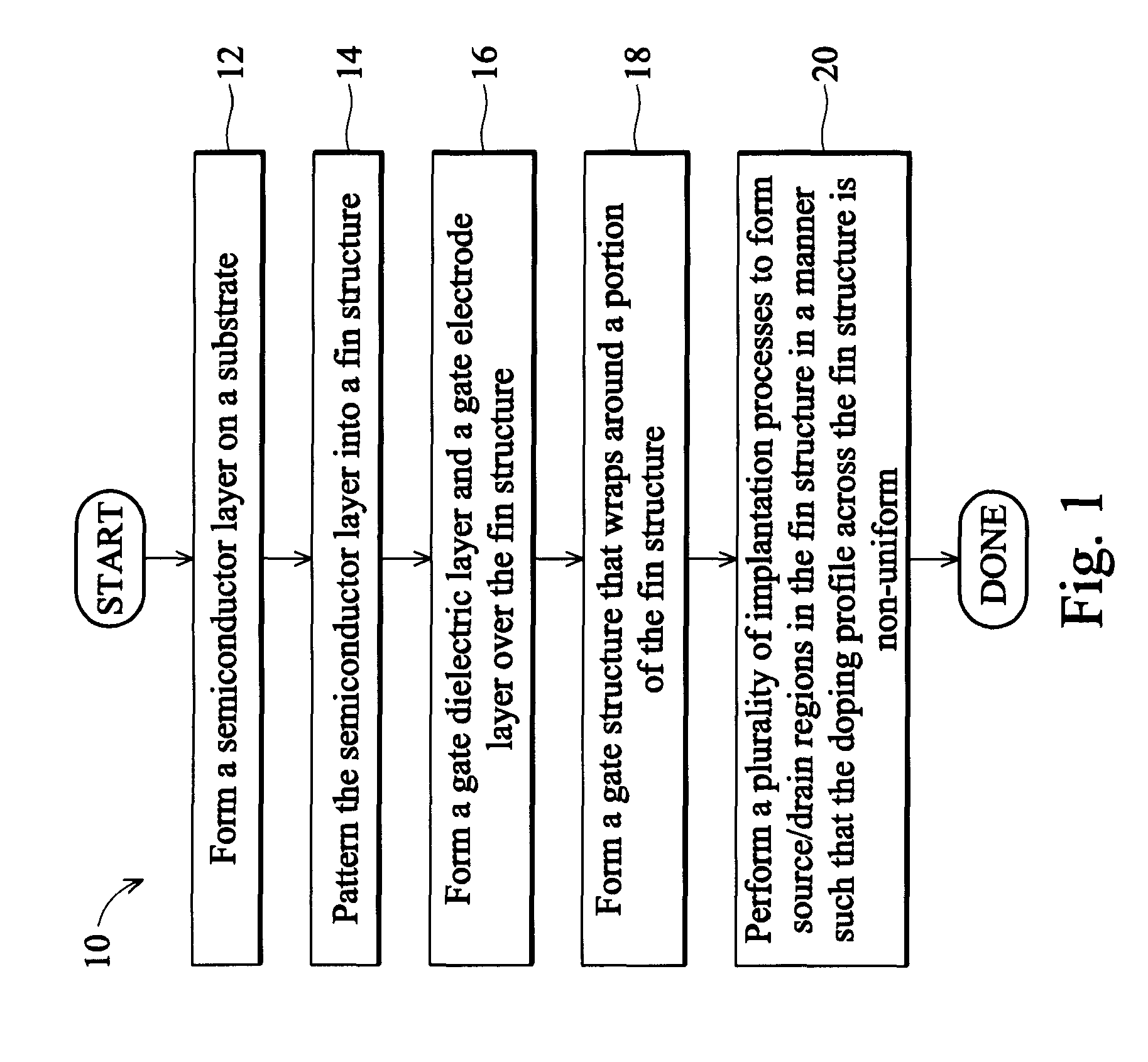

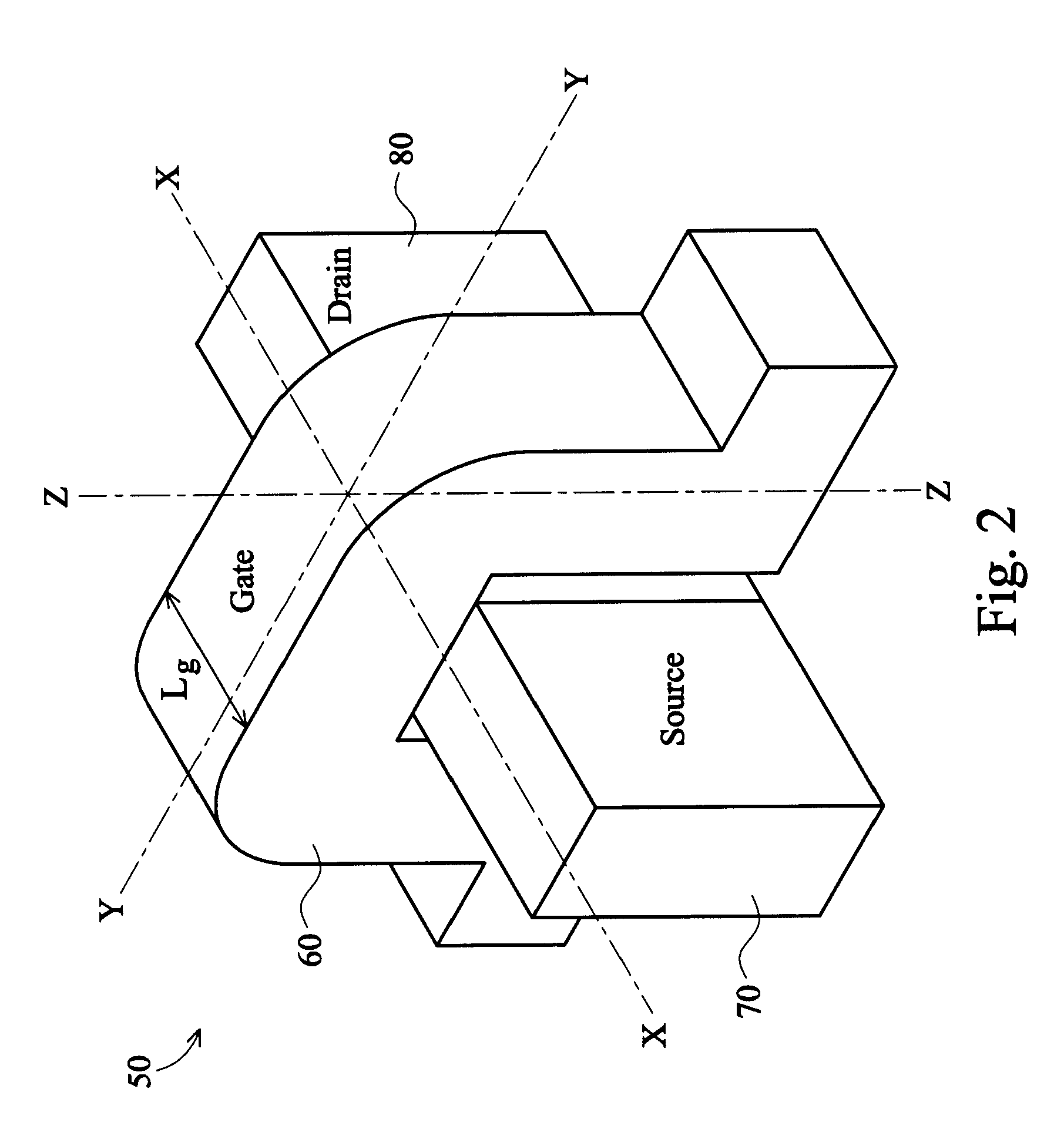

Non-uniform channel junction-less transistor

ActiveUS8487378B2Easy to controlImprove device densitySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSemiconductor

Owner:TAIWAN SEMICON MFG CO LTD

Conformal doping via plasma activated atomic layer deposition and conformal film deposition

ActiveUS20130040447A1Liquid surface applicatorsSemiconductor/solid-state device manufacturingDopantPatterned substrate

Disclosed herein are methods of doping a patterned substrate in a reaction chamber. The methods may include forming a first conformal film layer which has a dopant source including a dopant, and driving some of the dopant into the substrate to form a conformal doping profile. In some embodiments, forming the first film layer may include introducing a dopant precursor into the reaction chamber, adsorbing the dopant precursor under conditions whereby it forms an adsorption-limited layer, and reacting the adsorbed dopant precursor to form the dopant source. Also disclosed herein are apparatuses for doping a substrate which may include a reaction chamber, a gas inlet, and a controller having machine readable code including instructions for operating the gas inlet to introduce dopant precursor into the reaction chamber so that it is adsorbed, and instructions for reacting the adsorbed dopant precursor to form a film layer containing a dopant source.

Owner:NOVELLUS SYSTEMS

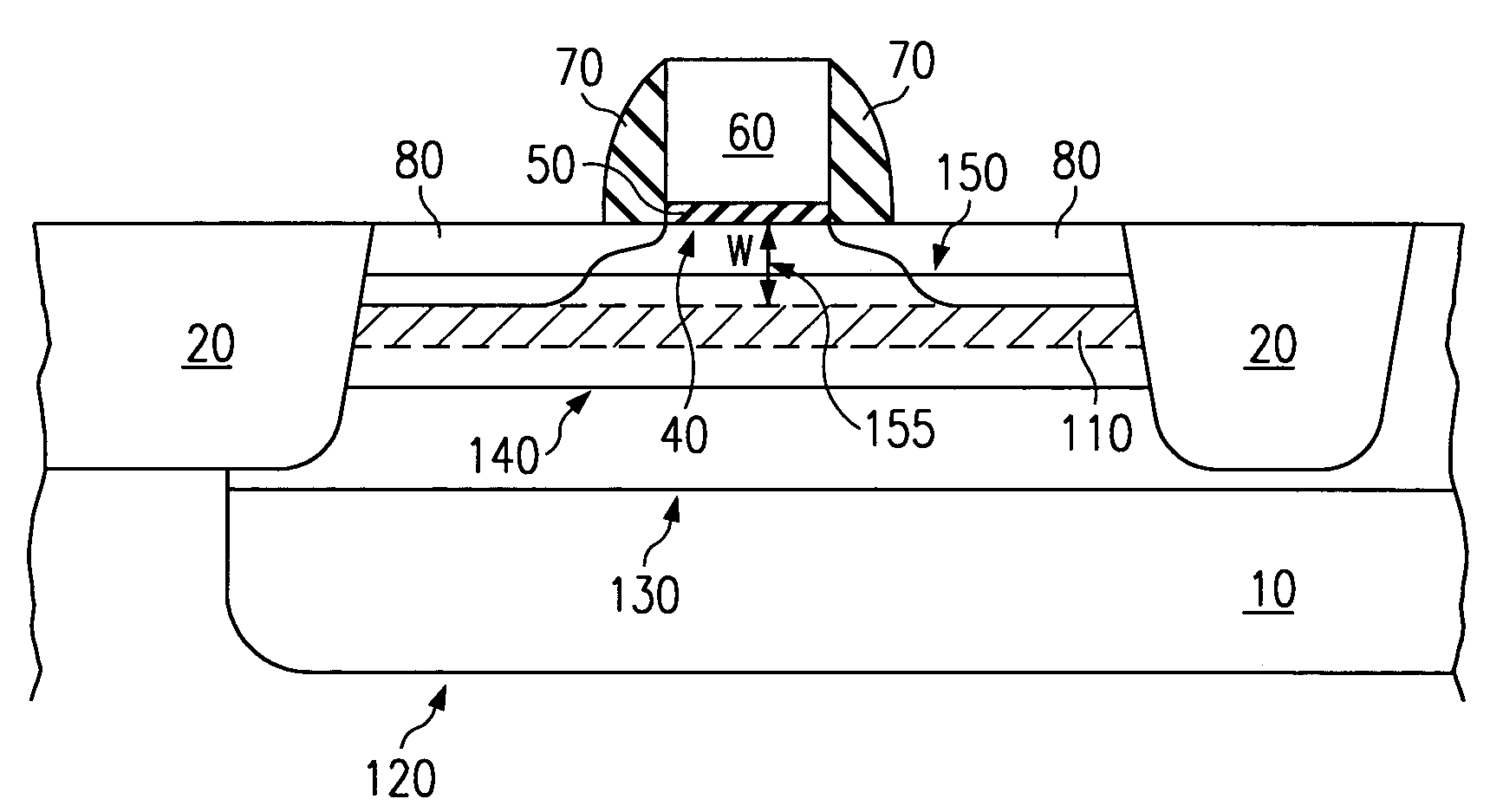

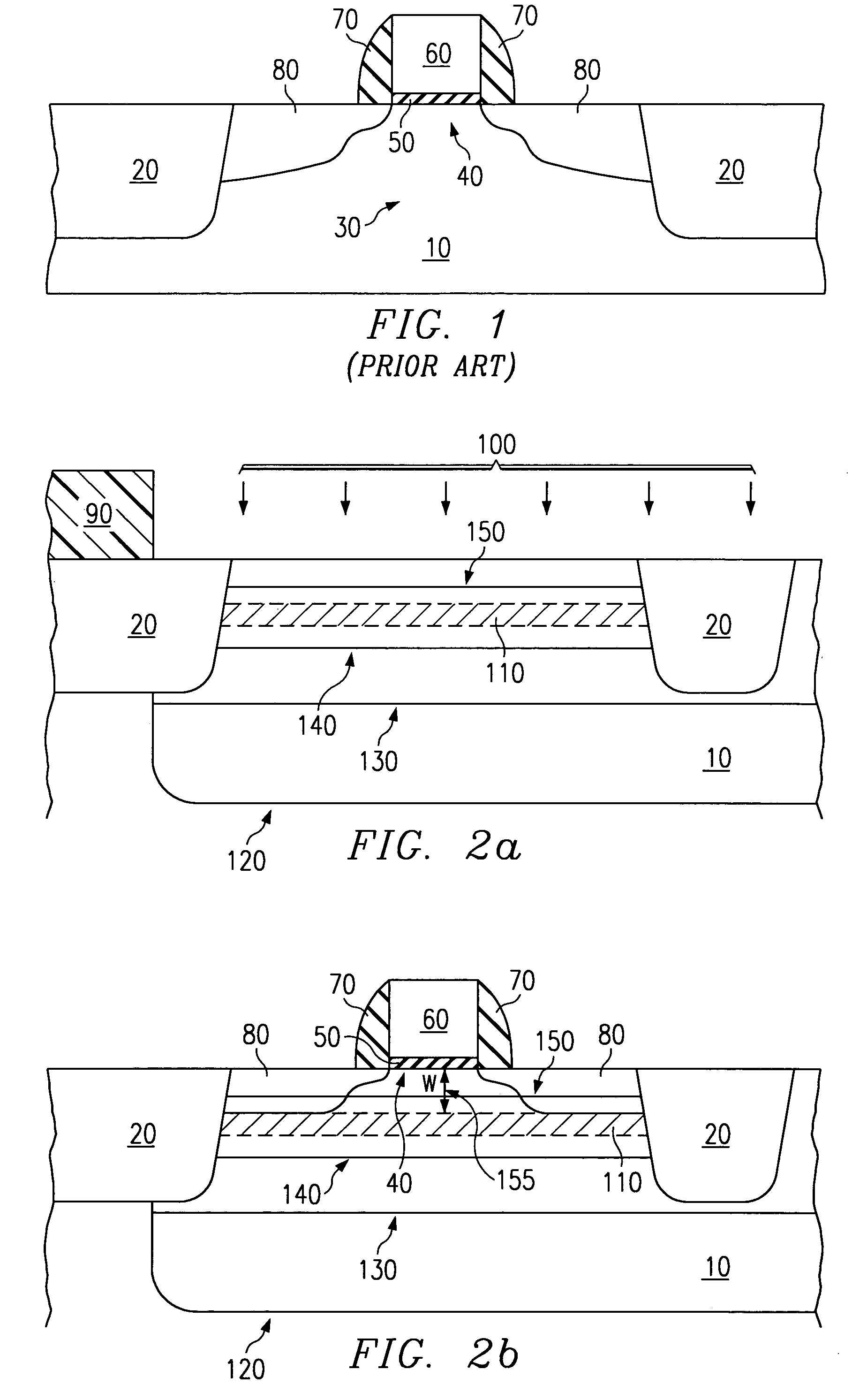

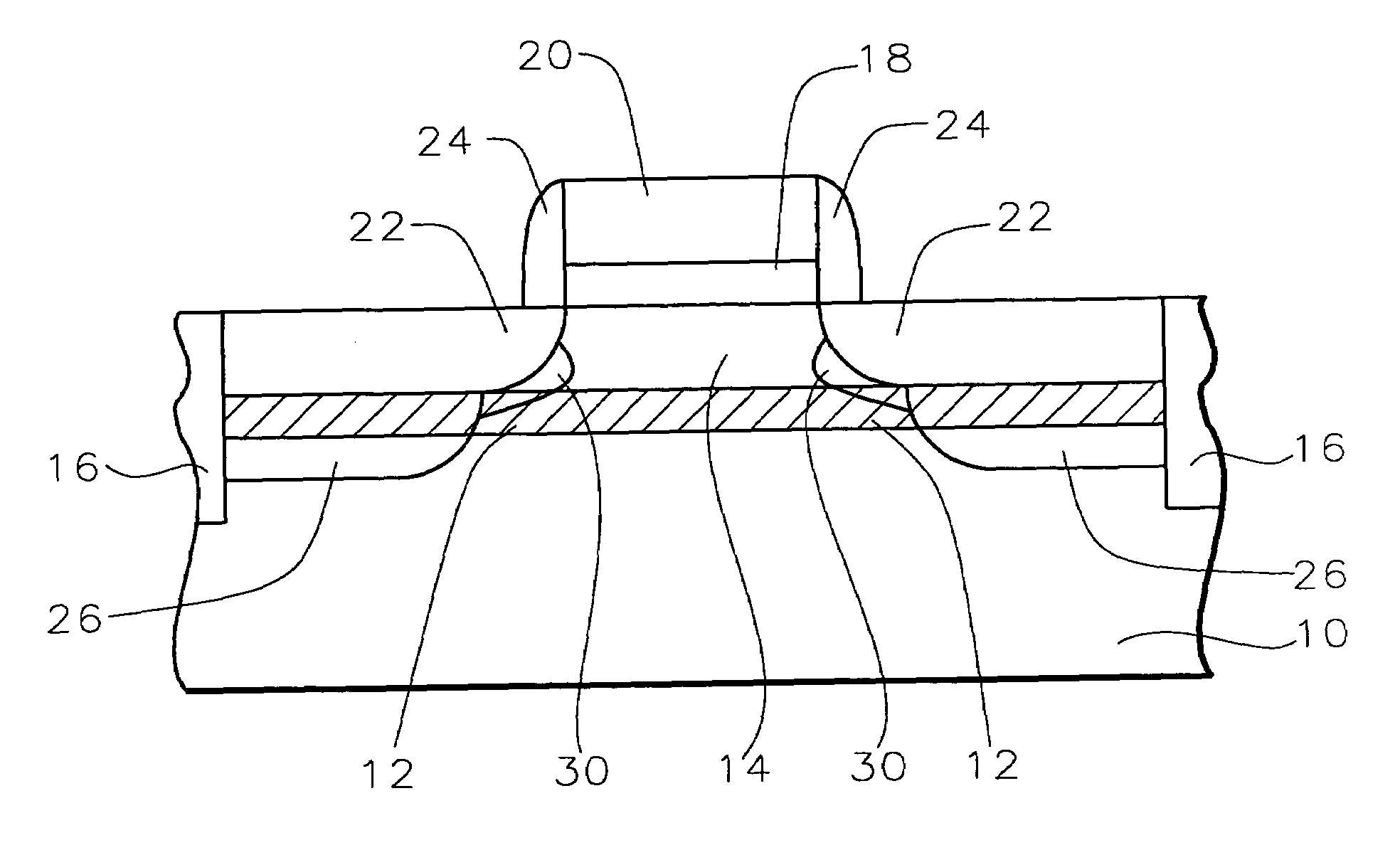

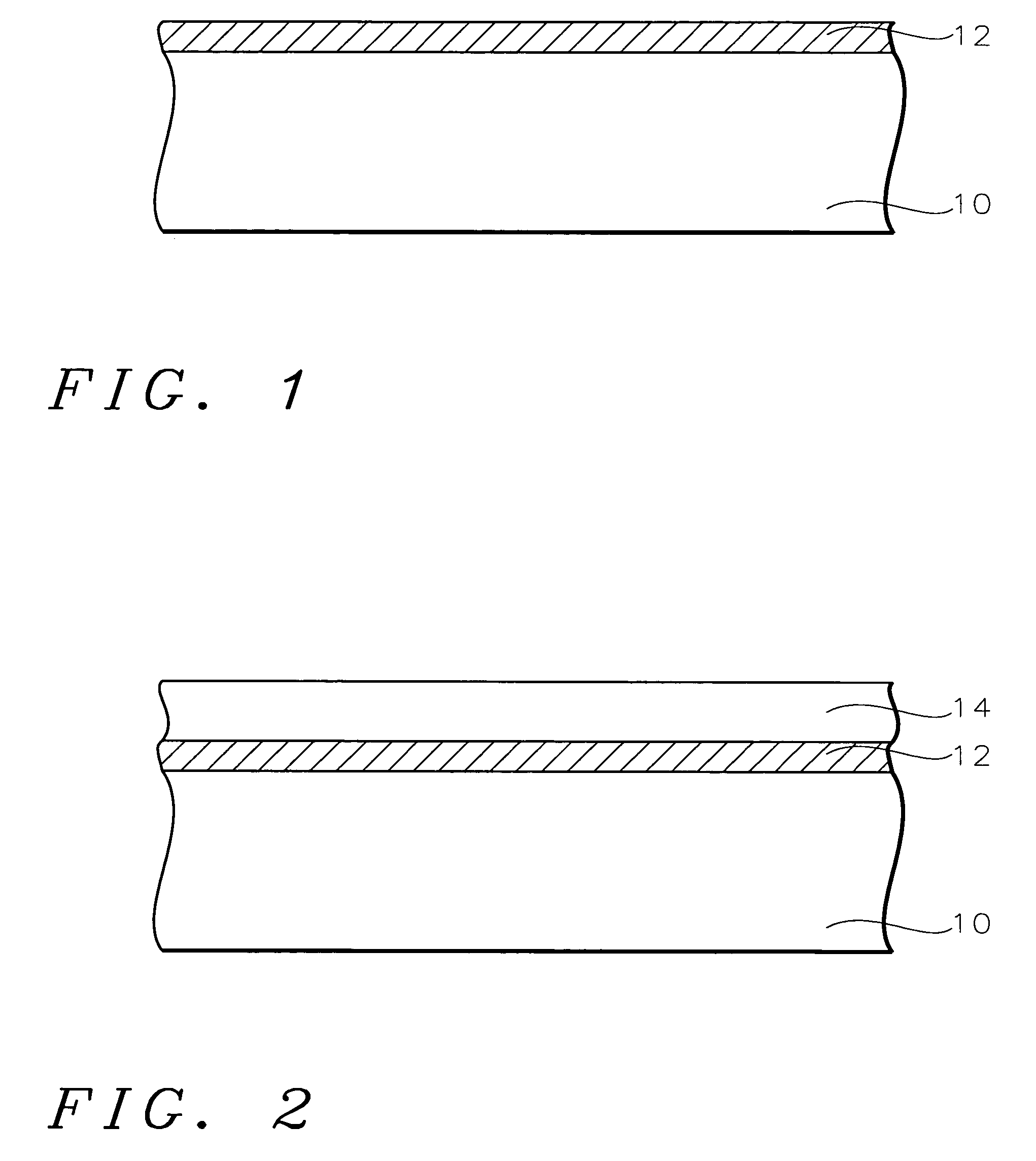

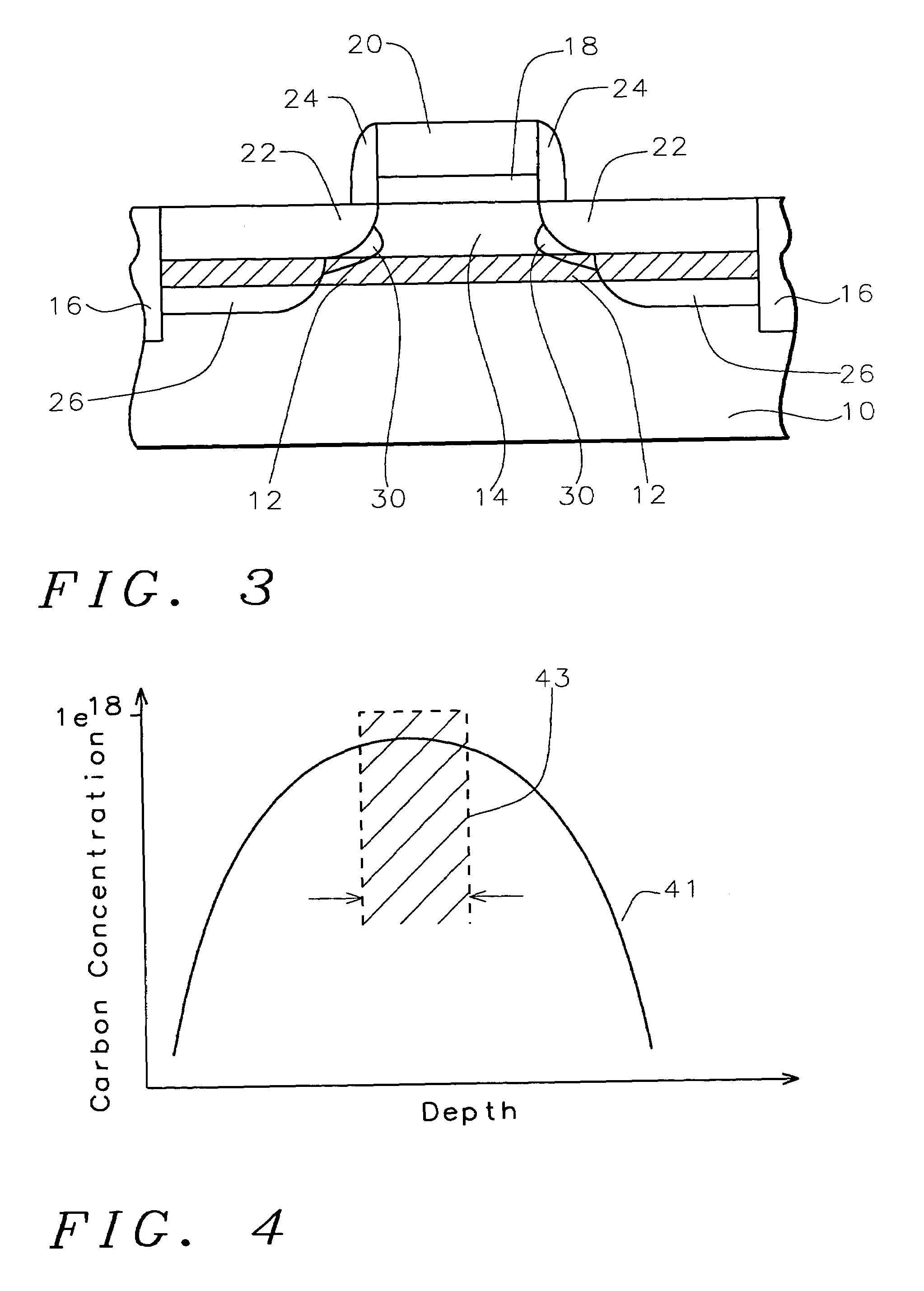

Advanced CMOS using super steep retrograde wells

InactiveUS7064399B2High thermal budgetIncrease dopant activationTransistorSemiconductor/solid-state device detailsDopantCMOS

The present invention is a method for forming super steep doping profiles in MOS transistor structures. The method comprises forming a carbon containing layer (110) beneath the gate dielectric (50) and source and drain regions (80) of a MOS transistor. The carbon containing layer (110) will prevent the diffusion of dopants into the region (40) directly beneath the gate dielectric layer (50).

Owner:TEXAS INSTR INC

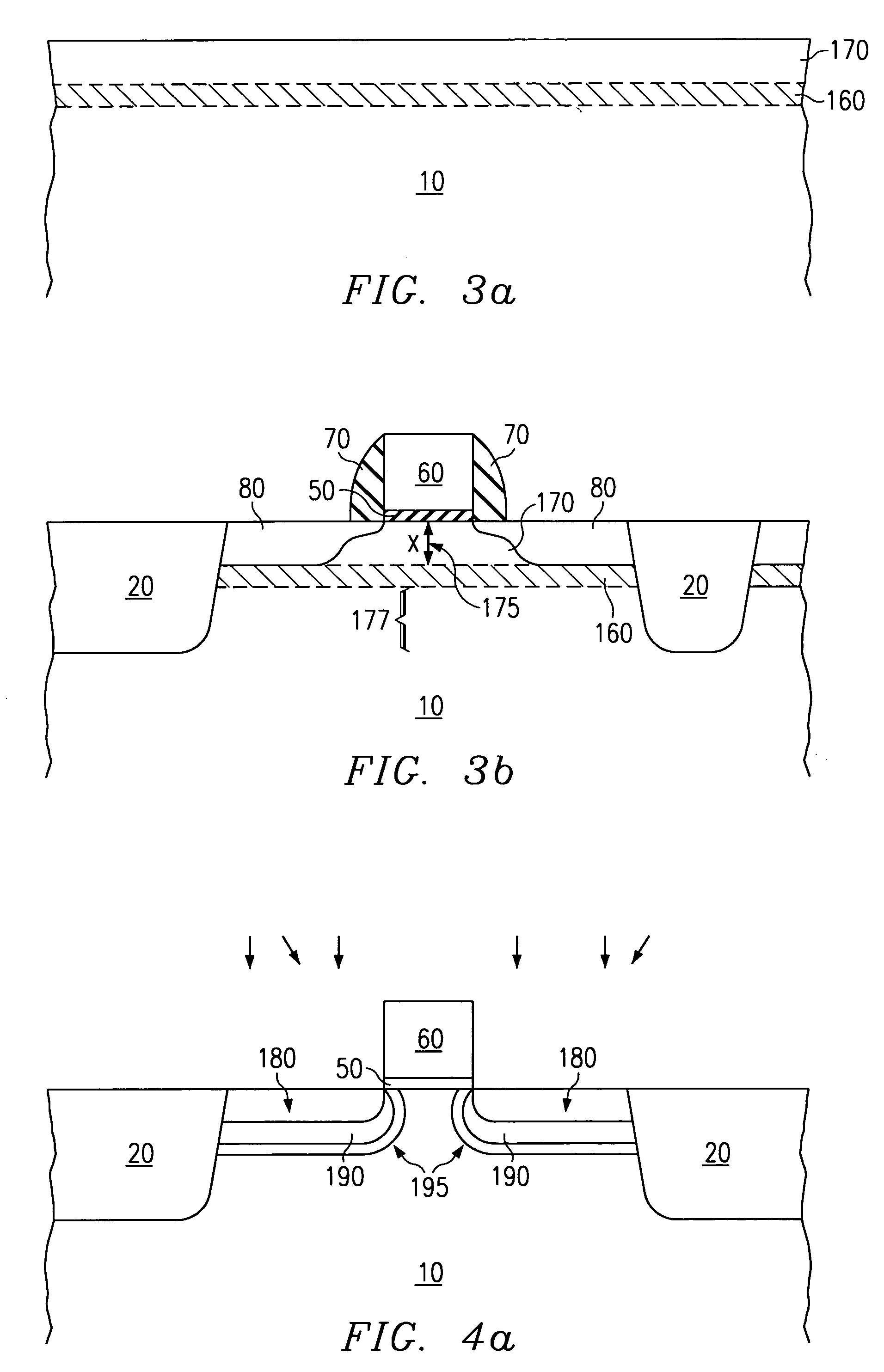

Abrupt “delta-like” doping in Si and SiGe films by UHV-CVD

InactiveUS7906413B2Eliminating the slow transient behaviorEliminate the effects ofTransistorPolycrystalline material growthCMOSSemiconductor structure

A structure and method of forming an abrupt doping profile is described incorporating a substrate, a first epitaxial layer of Ge less than the critical thickness having a P or As concentration greater than 5×1019 atoms / cc, and a second epitaxial layer having a change in concentration in its first 40 from the first layer of greater than 1×1019 P atoms / cc. Alternatively, a layer of SiGe having a Ge content greater than 0.5 may be selectively amorphized and recrystalized with respect to other layers in a layered structure. The invention overcomes the problem of forming abrupt phosphorus profiles in Si and SiGe layers or films in semiconductor structures such as CMOS, MODFET's, and HBT's.

Owner:GLOBALFOUNDRIES INC

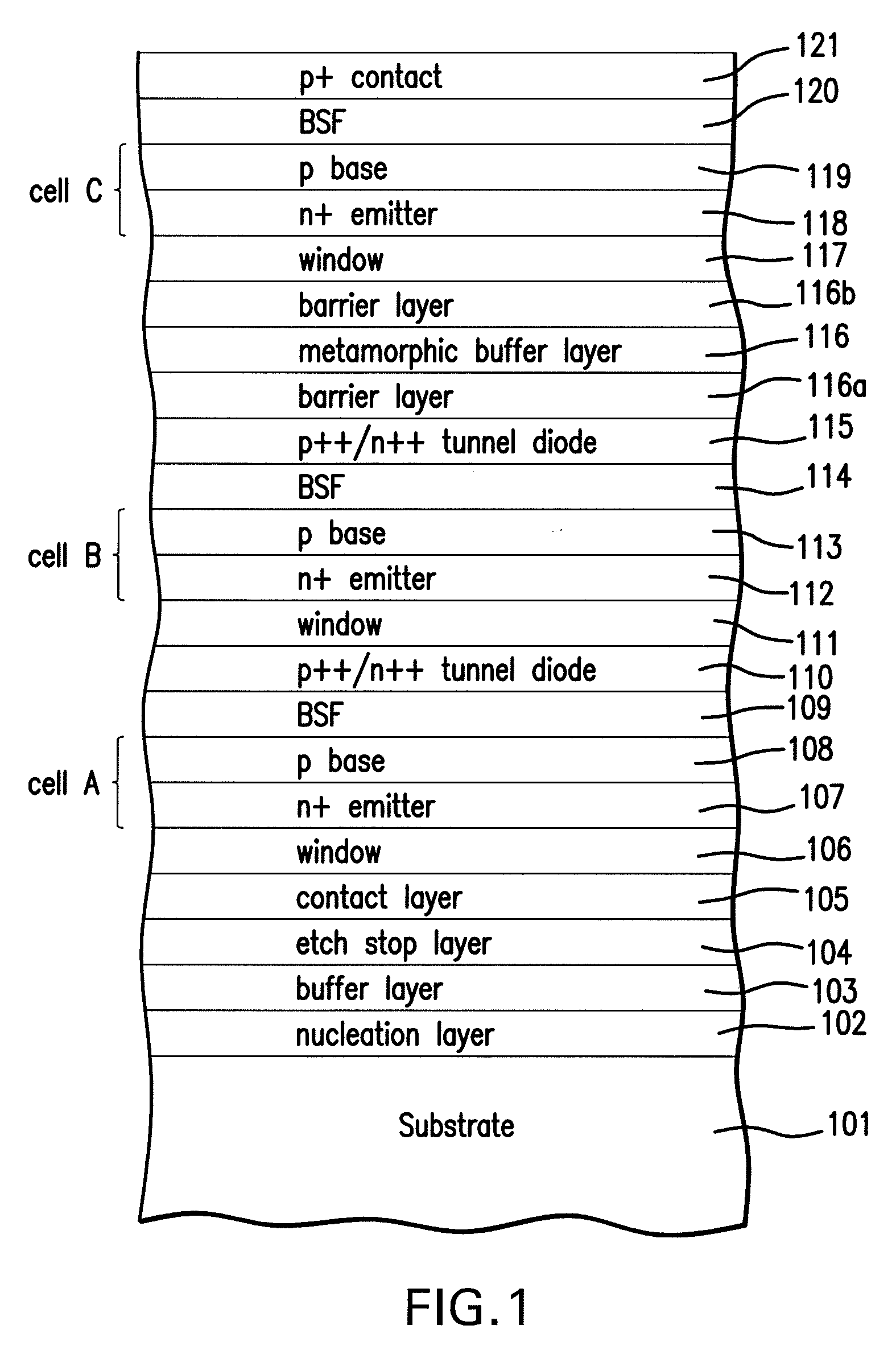

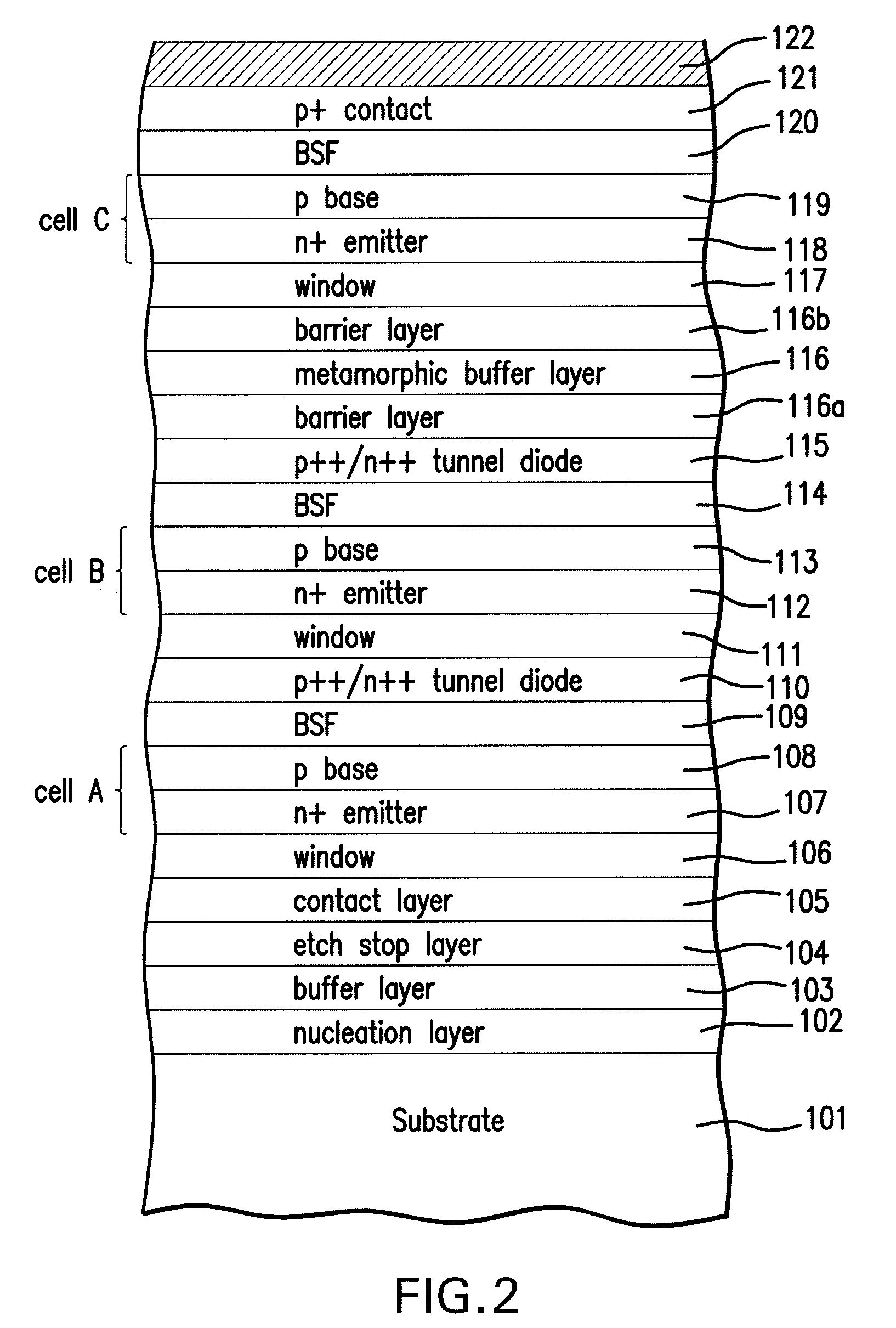

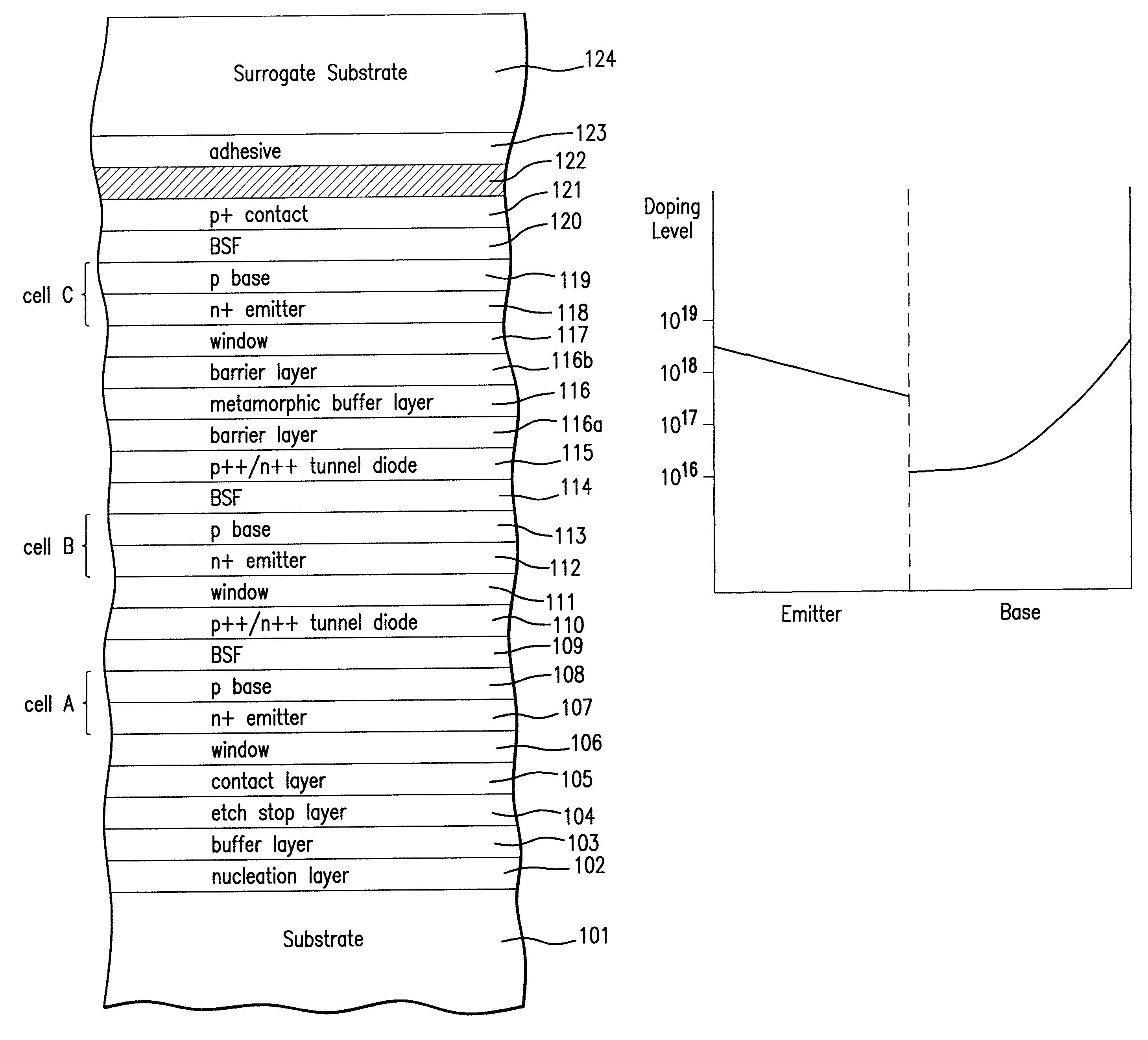

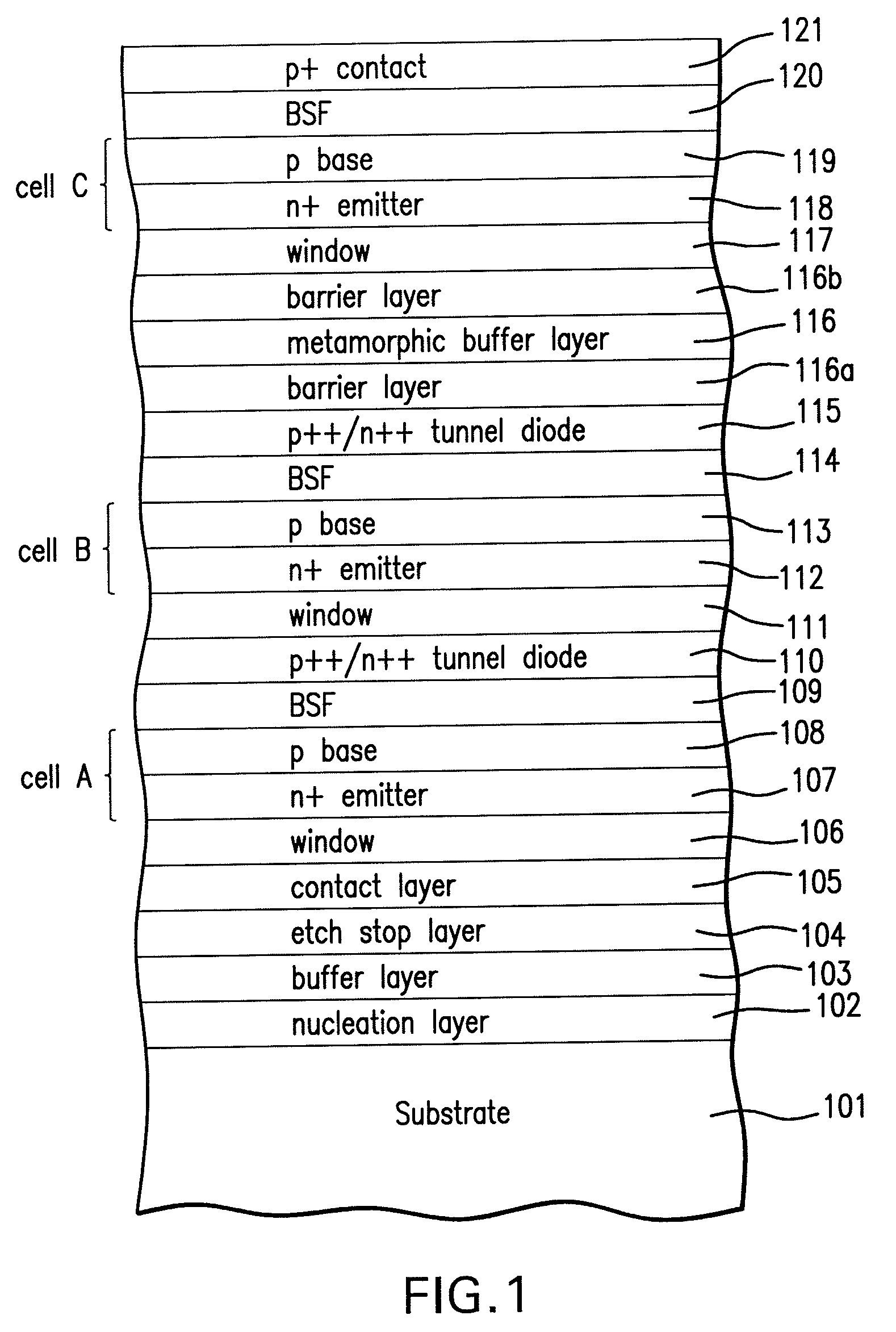

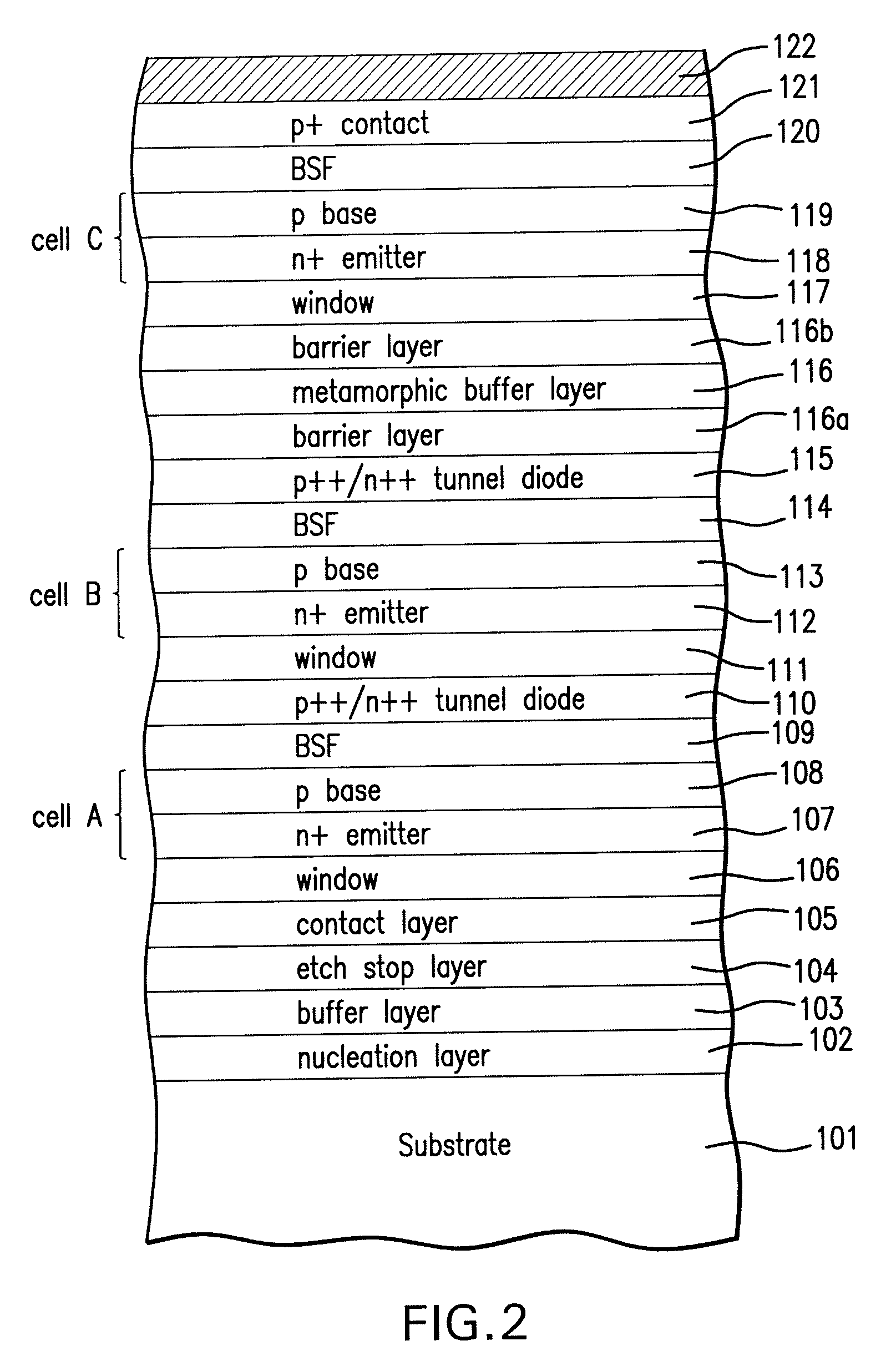

Exponentially Doped Layers In Inverted Metamorphic Multijunction Solar Cells

InactiveUS20090155952A1Increase currentFinal product manufactureSemiconductor/solid-state device manufacturingSemiconductor materialsLattice mismatch

A method of forming a multifunction solar cell including an upper subcell, a middle subcell, and a lower subcell, including providing first substrate for the epitaxial growth of semiconductor material; forming a first solar subcell on the substrate having a first band gap; forming a second solar subcell over the first solar subcell having a second band gap smaller than the first band gap; forming a grading interlayer over the second subcell, the grading interlayer having a third band gap greater than the second band gap; and forming a third solar subcell over the grading interlayer having a fourth band gap smaller than the second band gap such that the third subcell is lattice mismatched with respect to the second subcell, wherein at least one of the bases of a solar subcell has an exponentially doped profile.

Owner:EMCORE SOLAR POWER

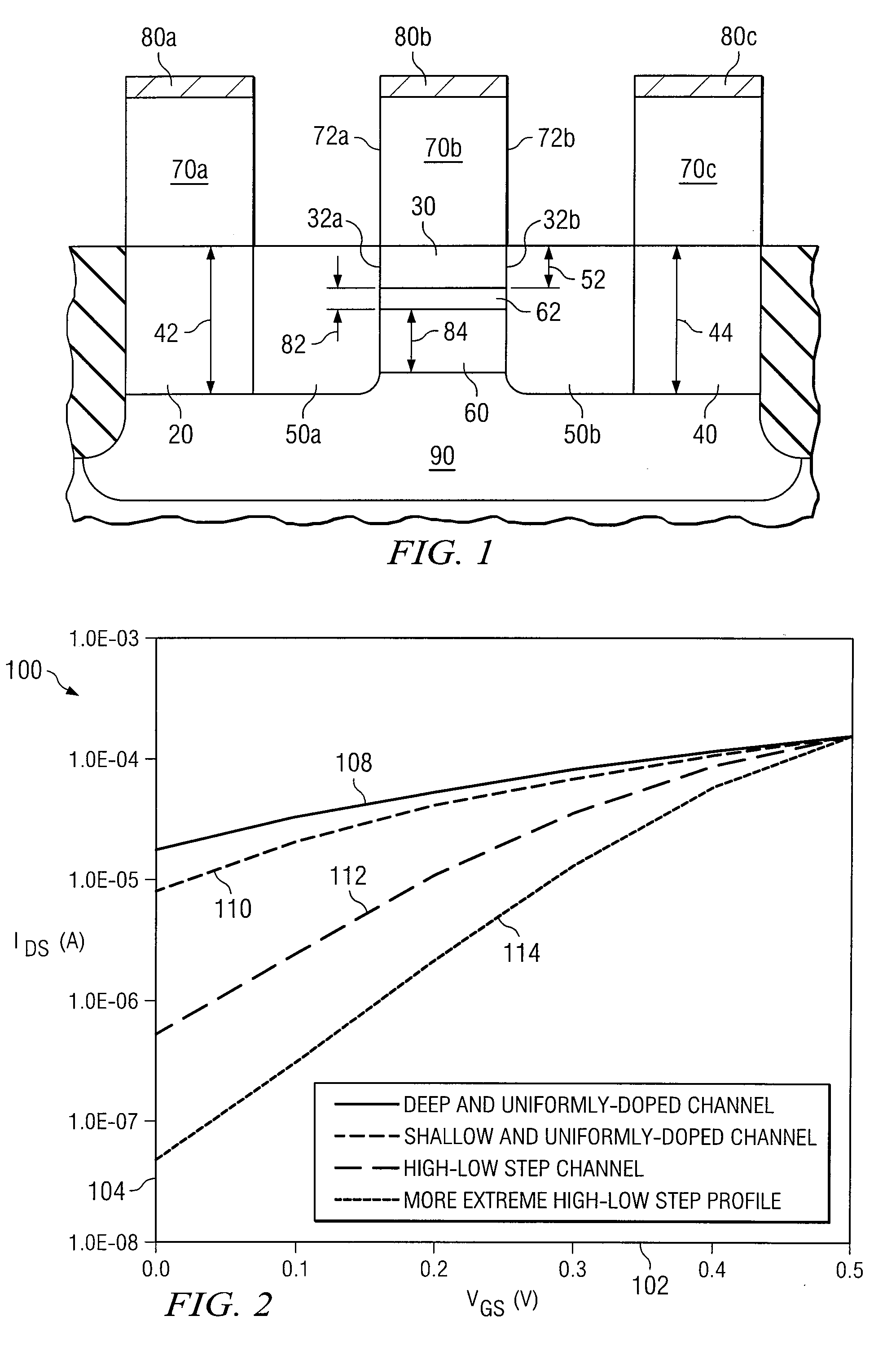

JFET Having a Step Channel Doping Profile and Method of Fabrication

InactiveUS20080272409A1Disadvantages and reduced eliminatedEffect reduced eliminatedTransistorSemiconductor/solid-state device manufacturingHigh concentrationJFET

A junction field effect transistor comprises a semiconductor substrate, a source region formed in the substrate, a drain region formed in the substrate and spaced apart from the source region, and a gate region formed in the substrate. The transistor further comprises a first channel region formed in the substrate and spaced apart from the gate region, and a second channel region formed in the substrate and between the first channel region and the gate region. The second channel region has a higher concentration of doped impurities than the first channel region.

Owner:DSM SOLUTIONS

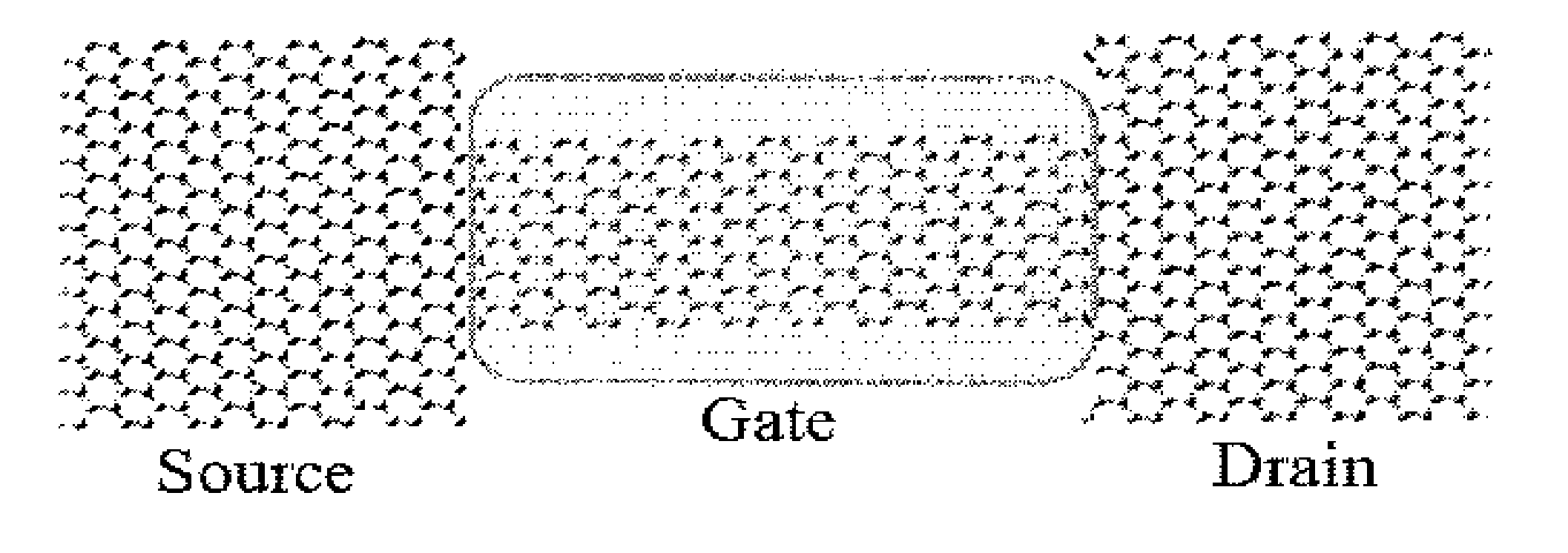

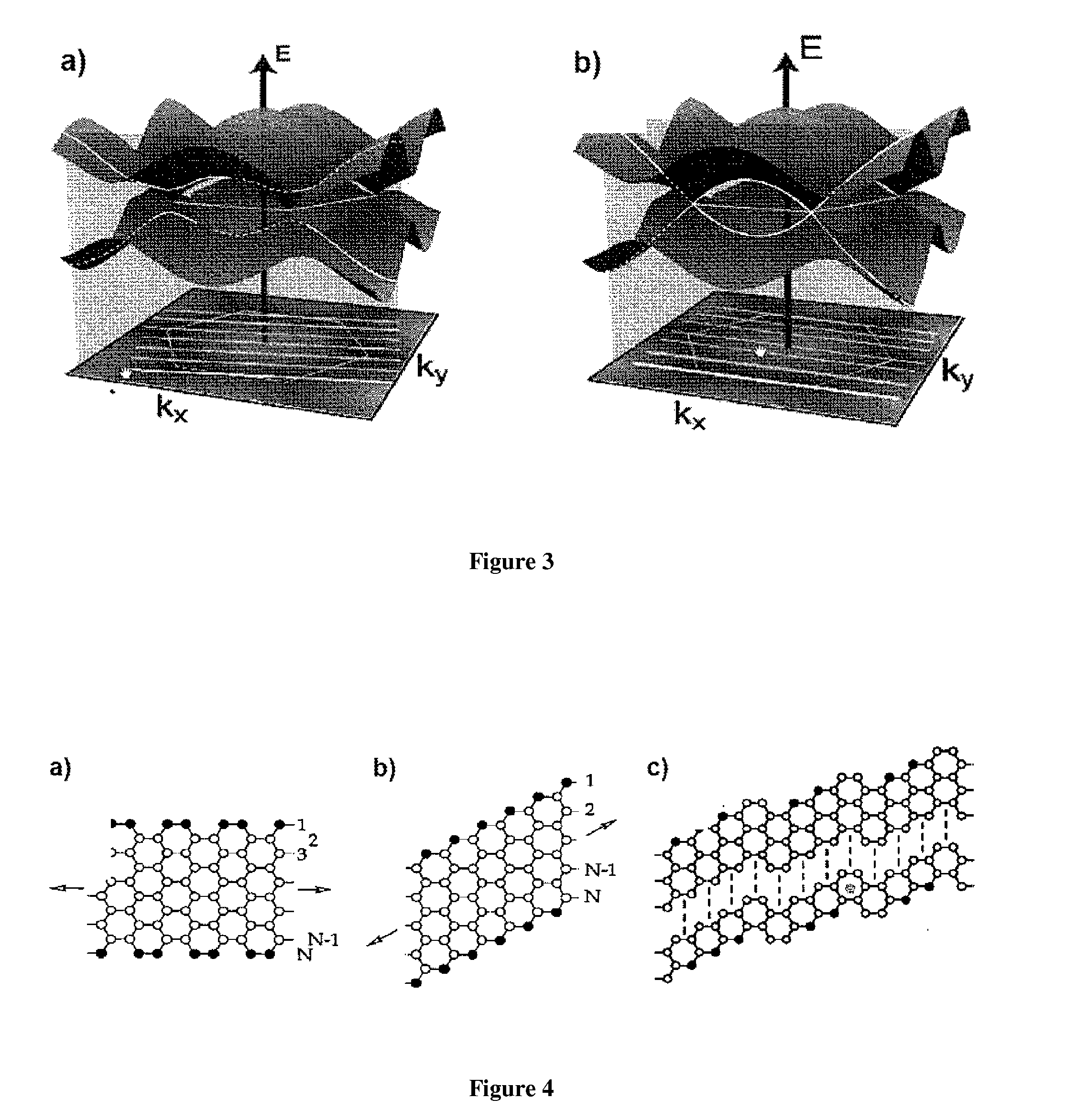

Monolithically-Integrated Graphene-Nano-Ribbon (GNR) Devices, Interconnects and Circuits

InactiveUS20090174435A1Logic circuits characterised by logic functionNanoinformaticsGraphene nanoribbonsElectronic component

The invention discloses new and advantageous uses for carbon / graphene nanoribbons (GNRs), which includes, but is not limited to, electronic components for integrated circuits such as NOT gates, OR gates, AND gates, nano-capacitors, and other transistors. More specifically, the manipulation of the shapes, sizes, patterns, and edges, including doping profiles, of GNRs to optimize their use in various electronic devices is disclosed.

Owner:UNIV OF VIRGINIA

ESD protection apparatus and circuit thereof

ActiveUS20080067601A1Improve electrical contact characteristicsTransistorSemiconductor/solid-state device detailsEngineeringDoping profile

The present invention provides several embodiments with layout patterns for ESD protection. An apparatus with a layout pattern may be configured to protect I / O pads or the power rail. The layout pattern may designed to increase the current paths for ESD stress currents. For example, more rings may be applied. The present invention also provides circuit embodiments for ESD protection. According to one embodiment, an ESD protection circuit comprising four parasitic BJTs may be configured to protect the I / O pads or the power rail. More BJTs or resistors may be used to increase the current paths for ESD stress currents. Several variations and modifications may be made by changing the doping profiles of the doped regions.

Owner:HIMAX TECH LTD

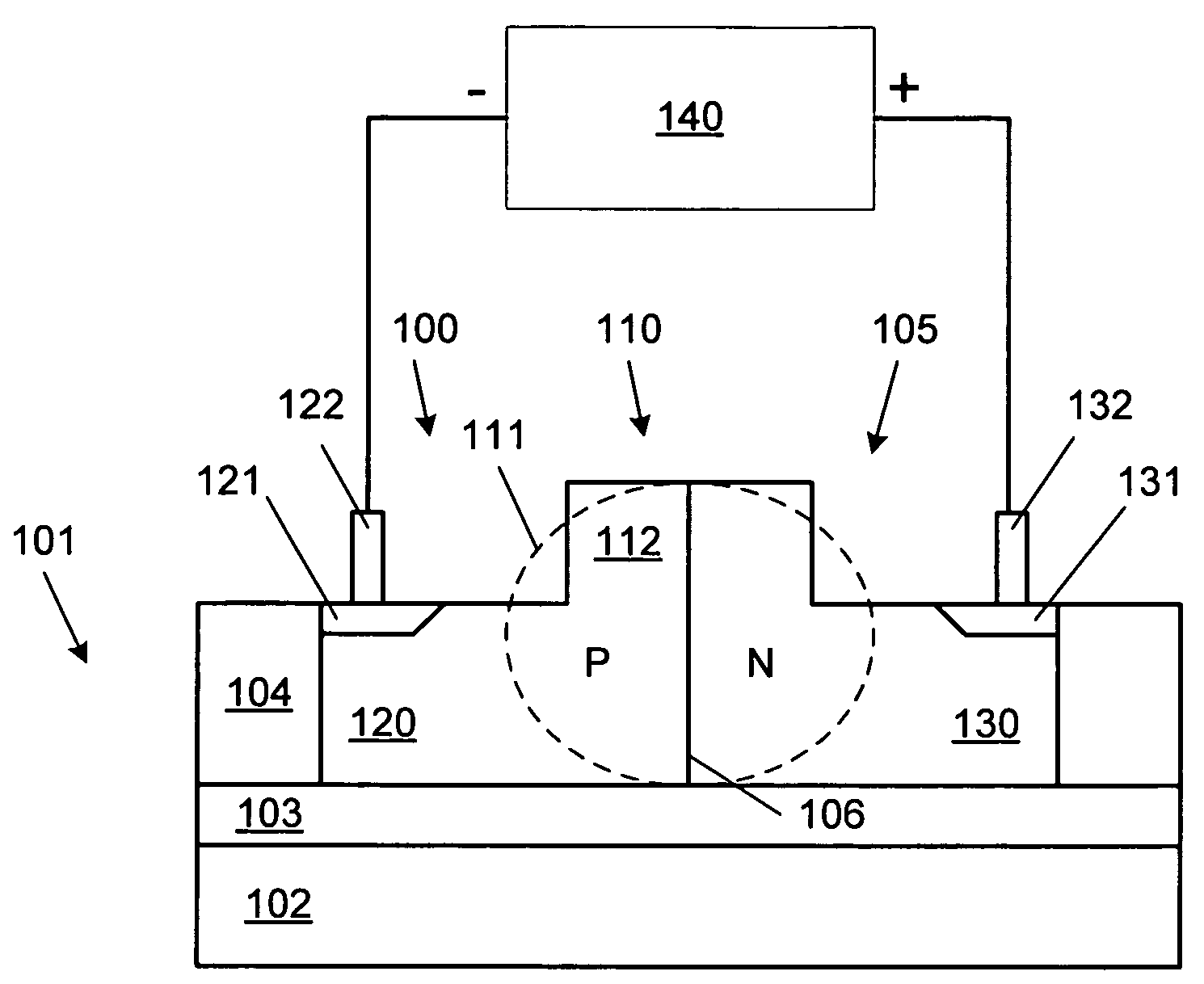

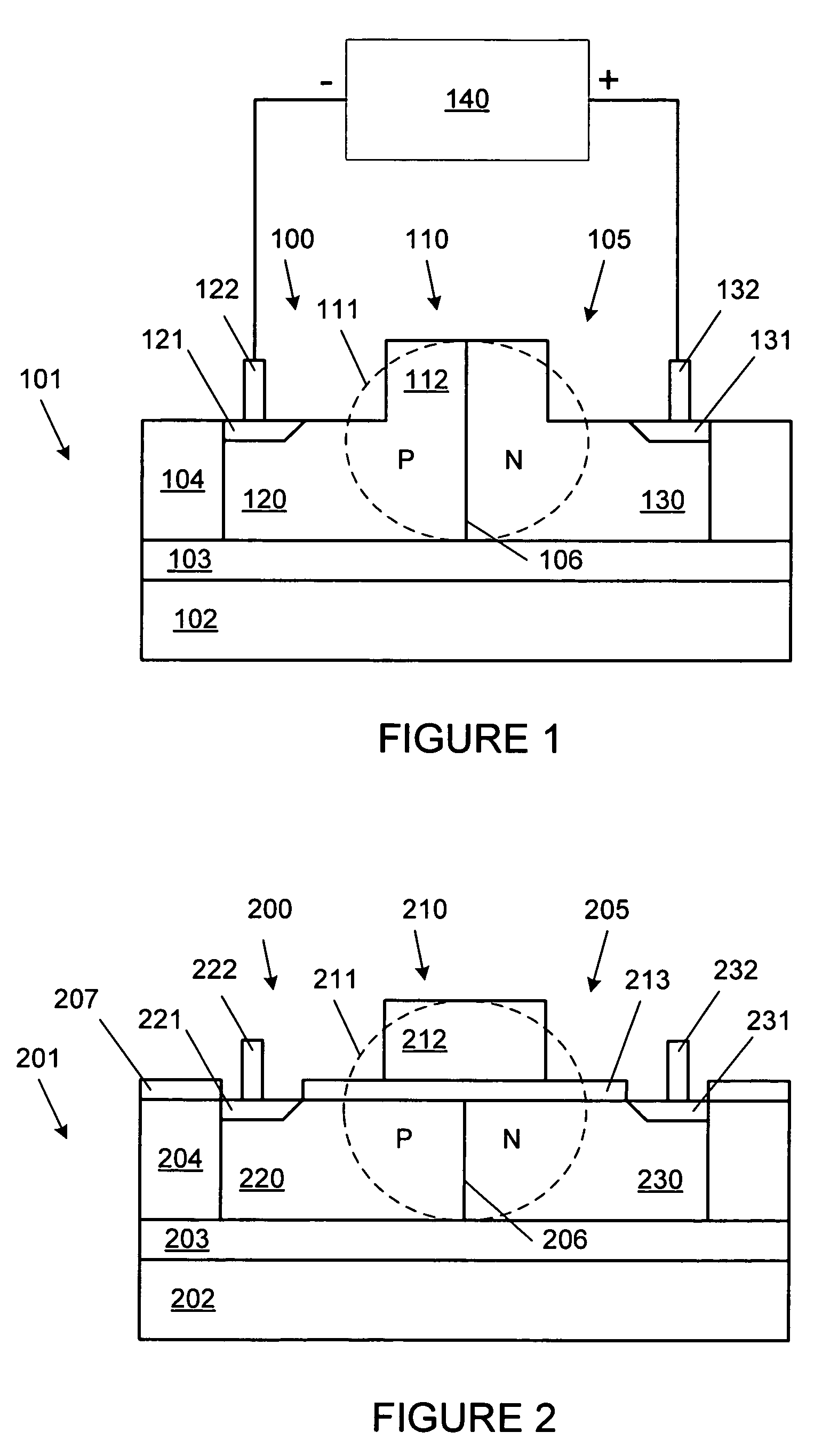

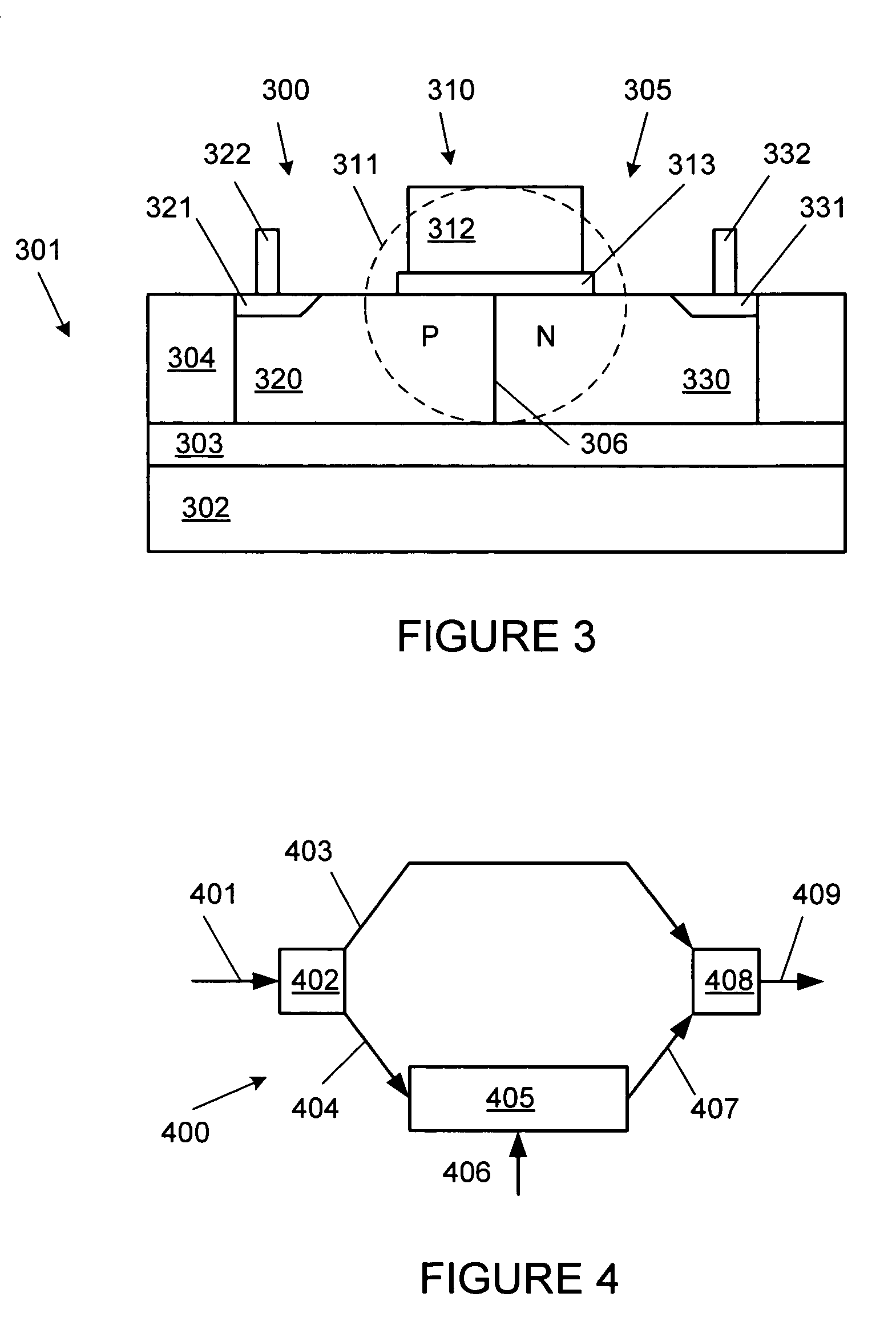

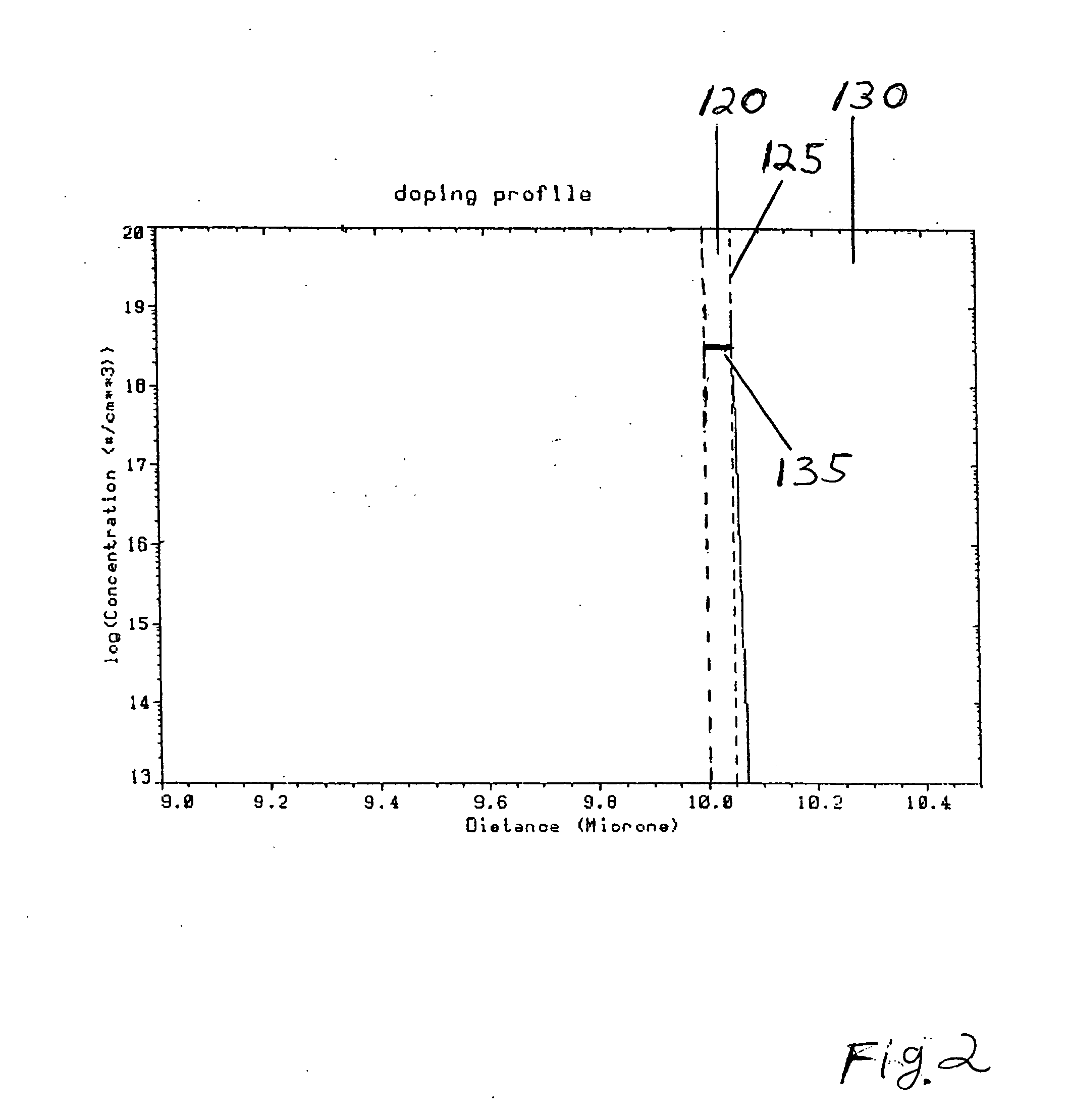

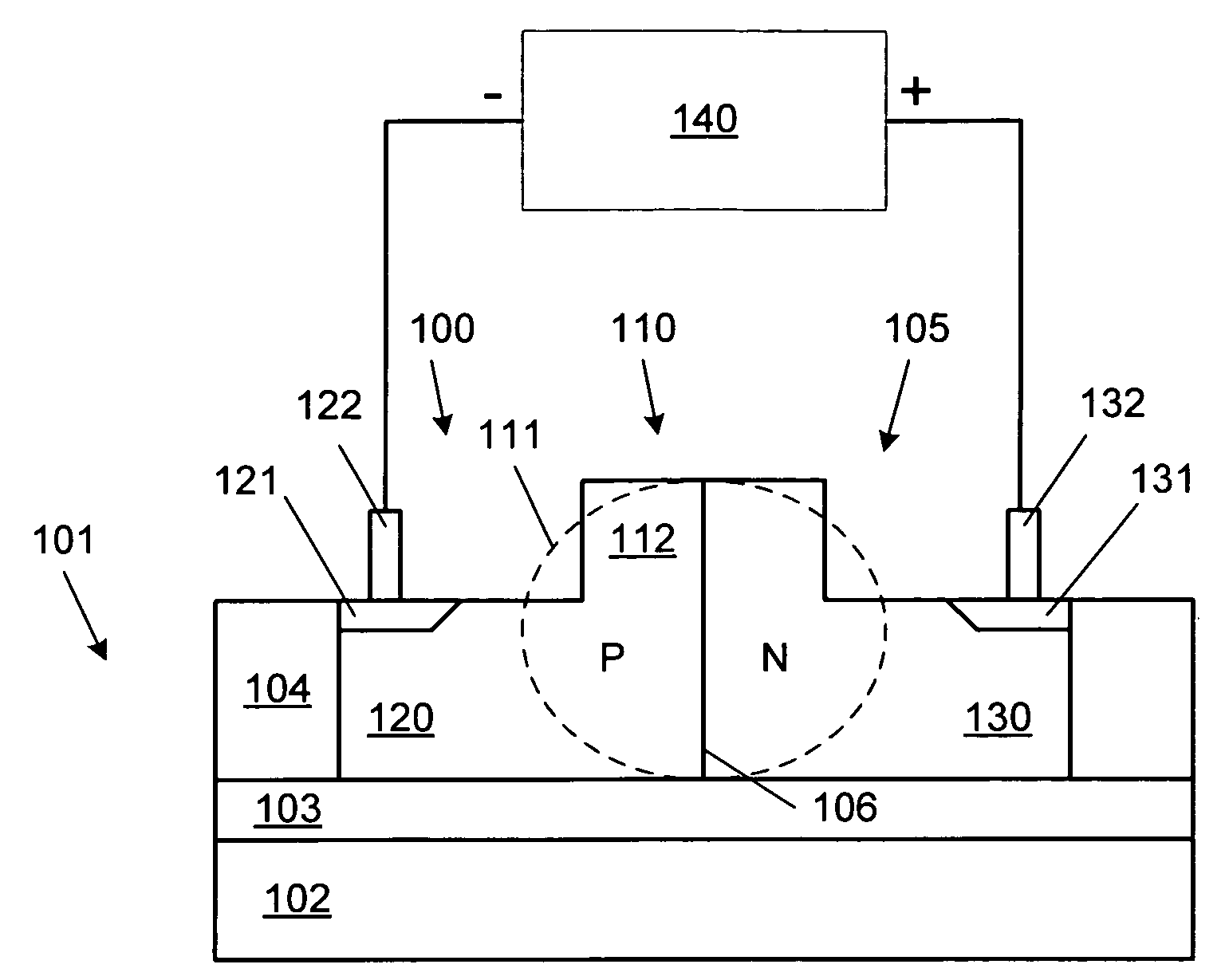

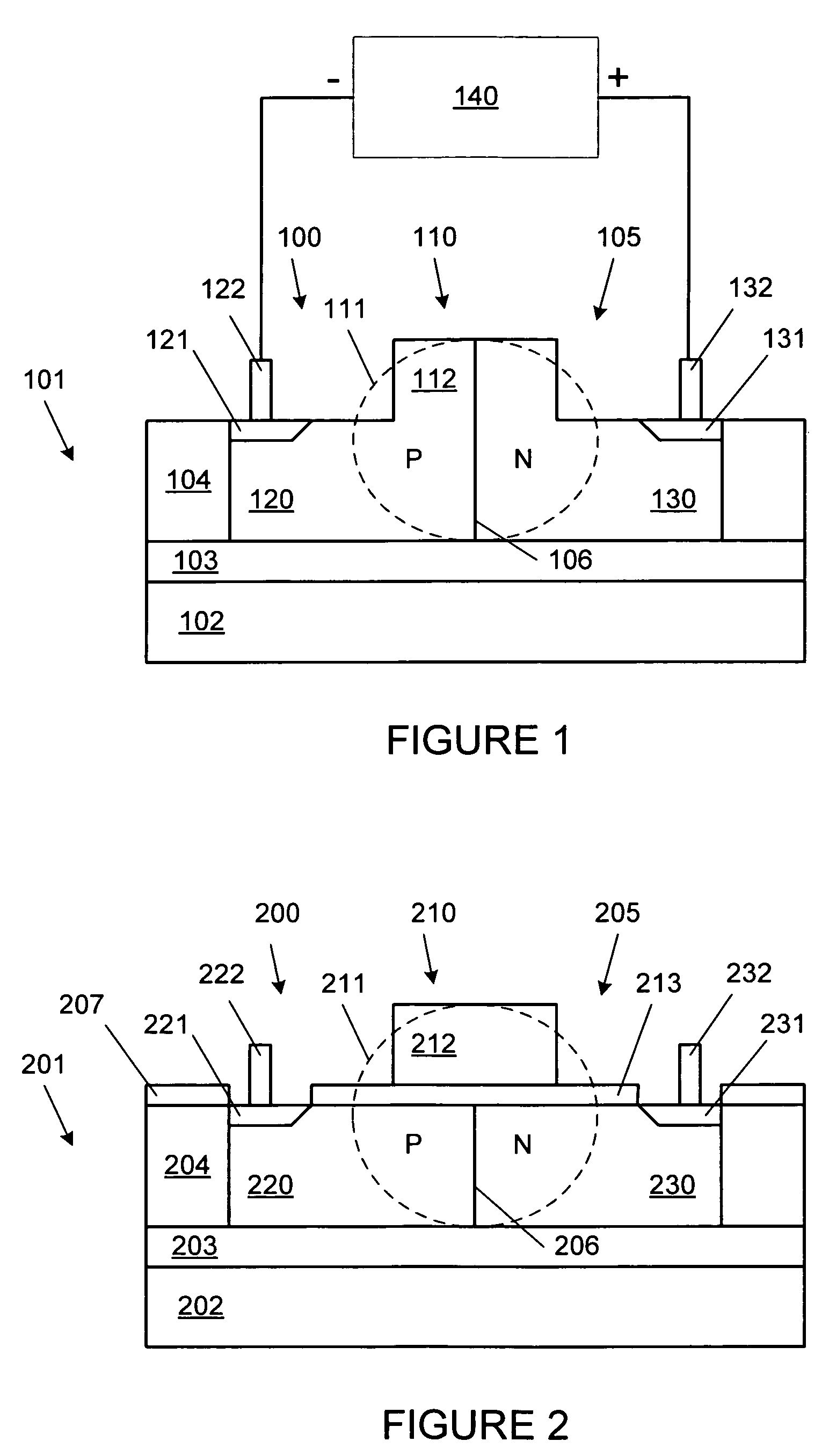

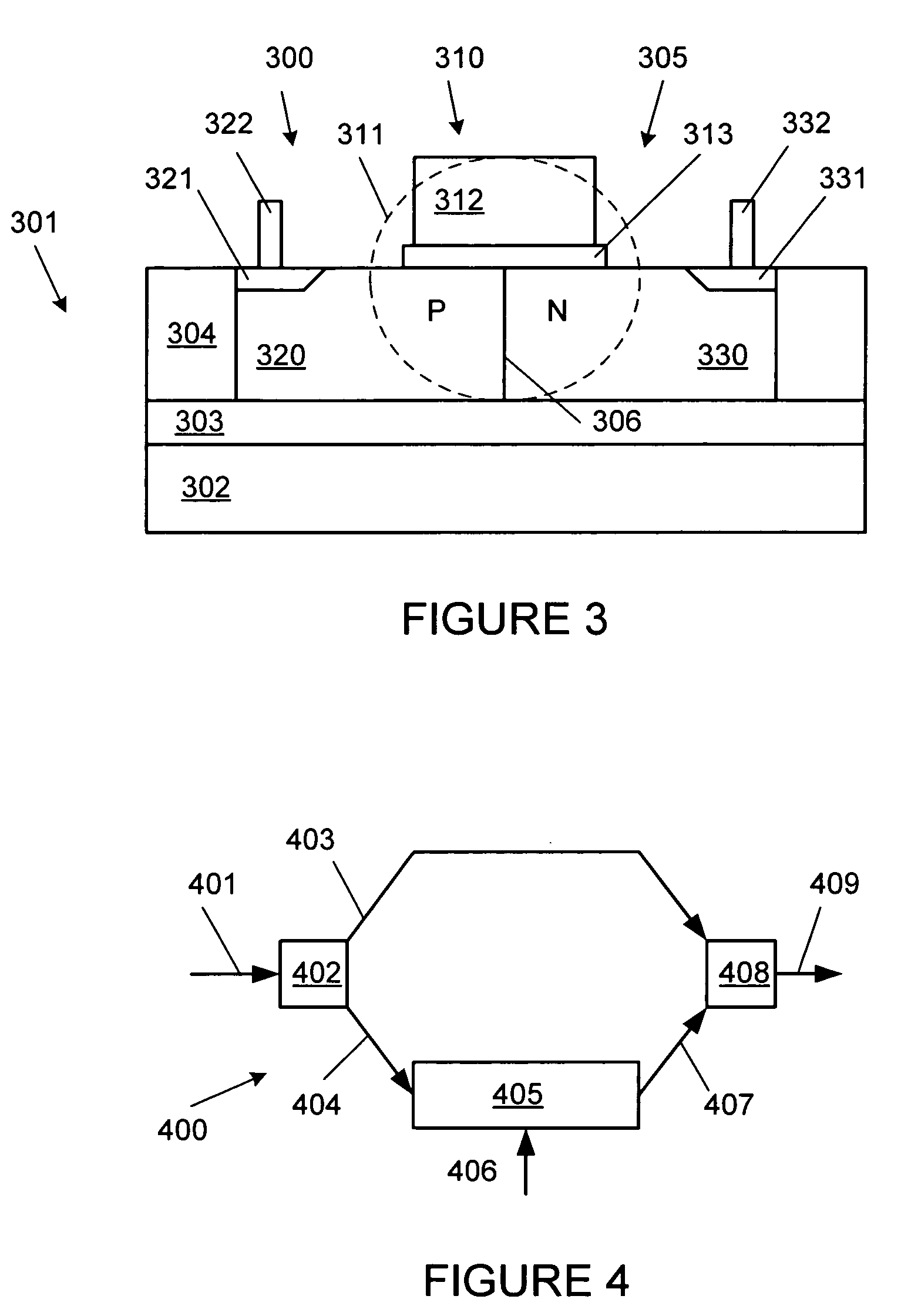

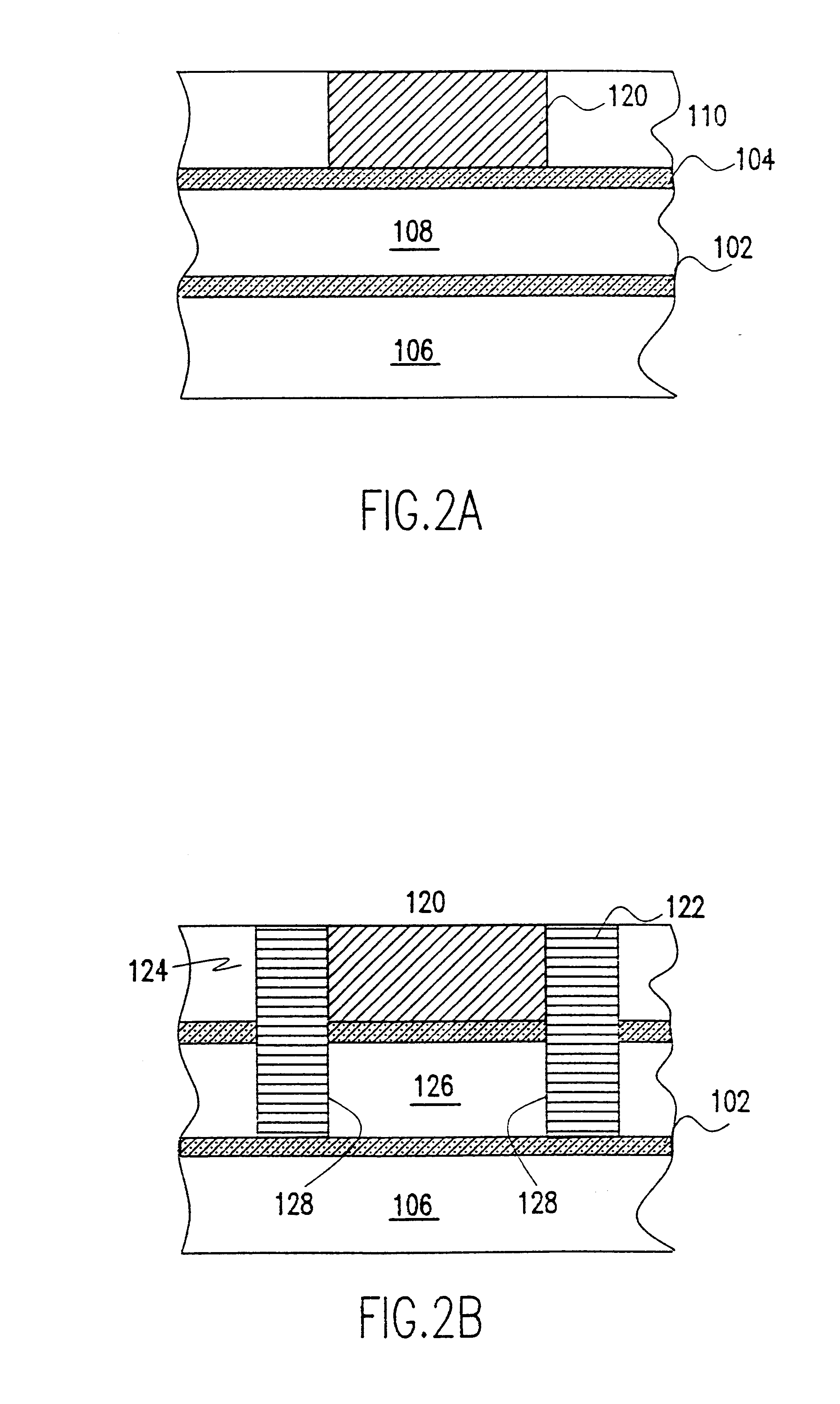

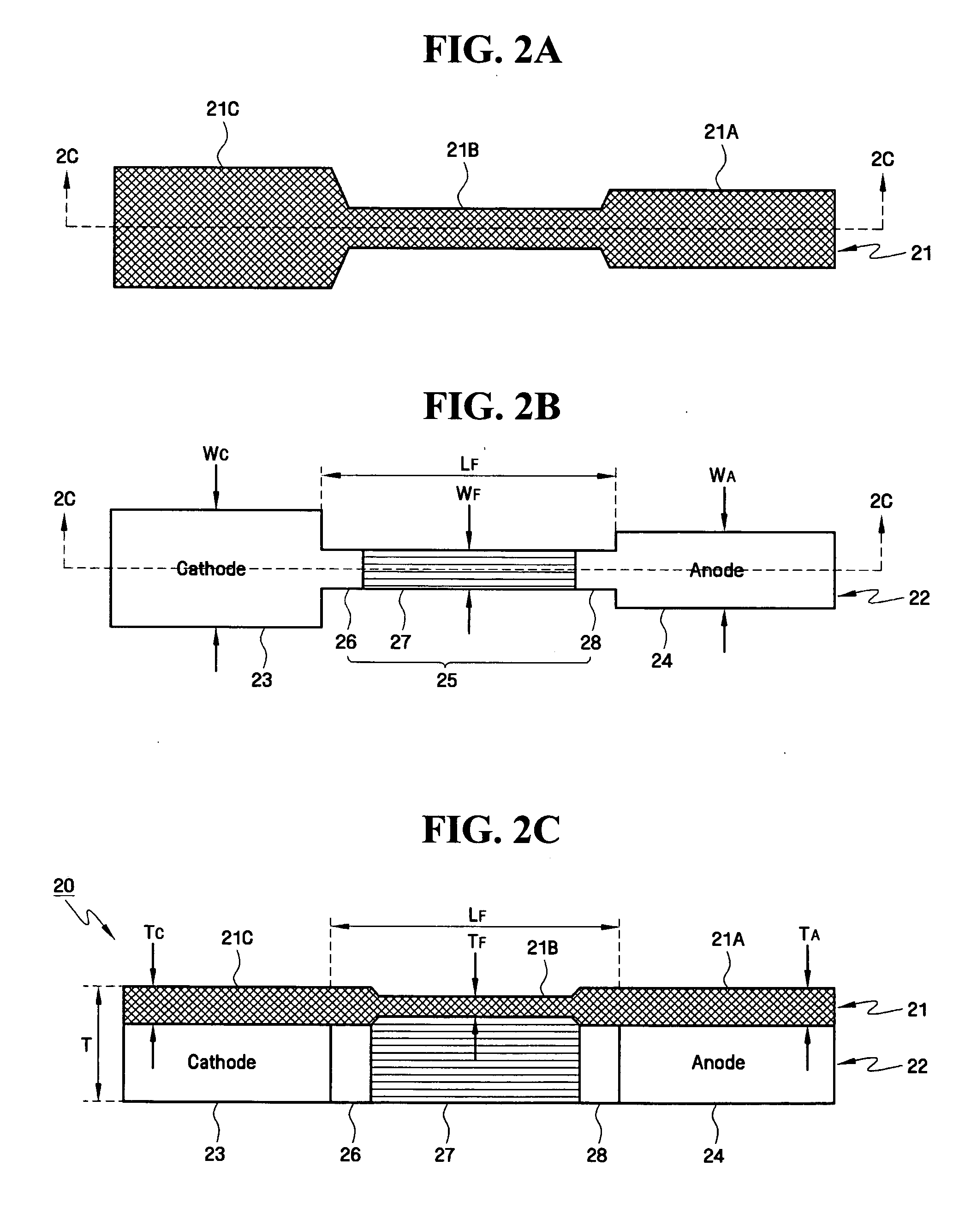

Doping profiles in PN diode optical modulators

ActiveUS7085443B1Coupling light guidesOptical waveguide light guideElectrical resistance and conductanceDopant

High speed optical modulators can be made of a lateral PN diode formed in a silicon optical waveguide, disposed on a SOI or other silicon based substrate. A PN junction is formed at the boundary of the P and N doped regions. The depletion region at the PN junction overlaps with the center of a guided optical mode propagating through the waveguide. Electrically modulating a lateral PN diode causes a phase shift in an optical wave propagating through the waveguide. Each of the doped regions can have a stepped or gradient doping profile within it or several doped sections with different doping concentrations. Forming the doped regions of a PN diode modulator with stepped or gradient doping profiles can optimize the trade off between the series resistance of the PN diode and the optical loss in the center of the waveguide due to the presence of dopants.

Owner:CISCO TECH INC

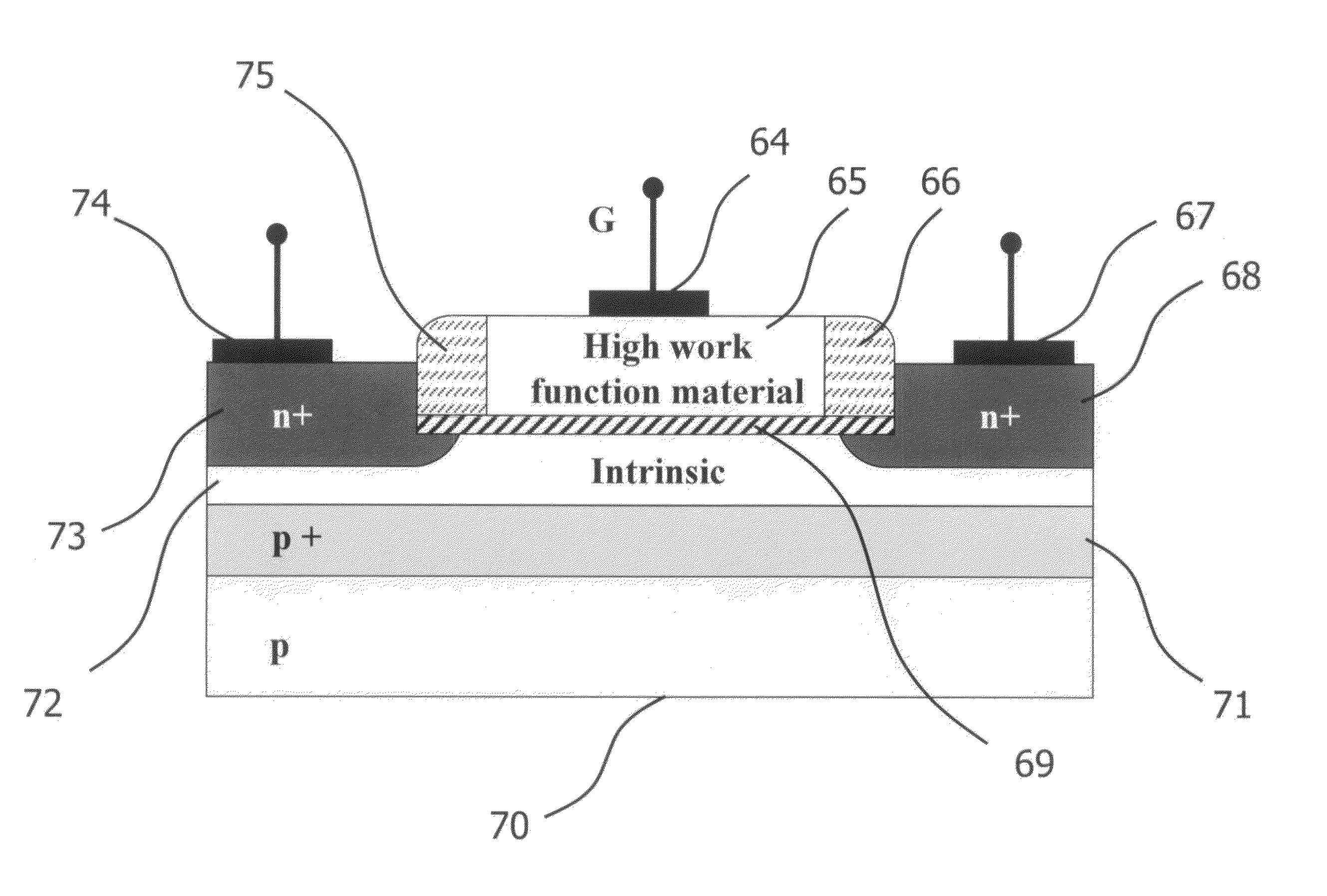

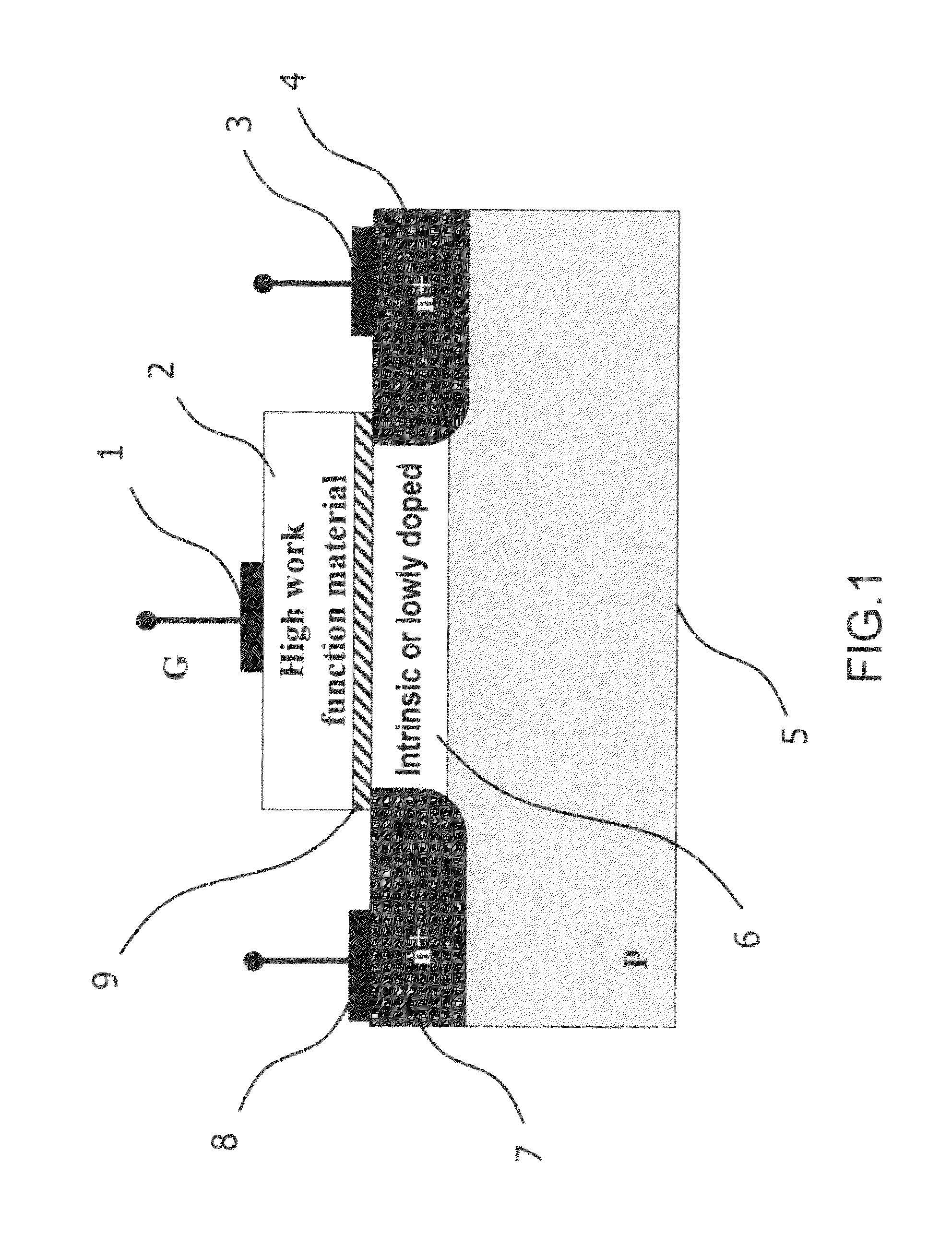

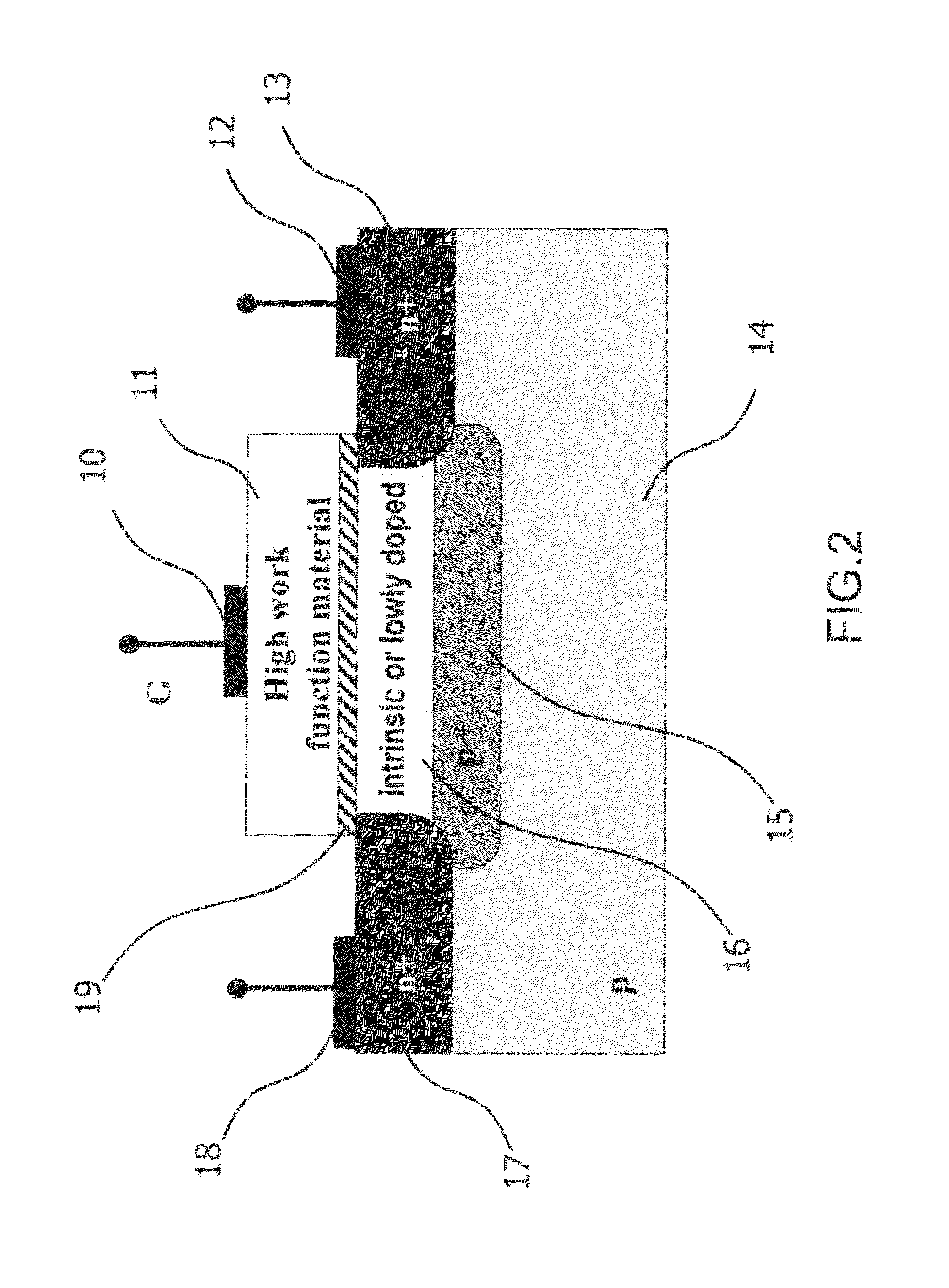

High mobility enhancement mode FET

ActiveUS8803242B2Reduce variationReduce impurityTransistorSolid-state devicesMOSFETSemiconductor structure

A novel semiconductor transistor is presented. The semiconductor structure has a MOSFET like structure, with the difference that the device channel is formed in an intrinsic region, so as to effectively decrease the impurity and surface scattering phenomena deriving from a high doping profile typical of conventional MOS devices. Due to the presence of the un-doped channel region, the proposed structure greatly reduces Random Doping Fluctuation (RDF) phenomena decreasing the threshold voltage variation between different devices. In order to control the threshold voltage of the device, a heavily doped poly-silicon or metallic gate is used. However, differently from standard CMOS devices, a high work-function metallic material, or a heavily p-doped poly-silicon layer, is used for a n-channel device and a low work-function metallic material, or heavily n-doped poly-silicon layer, is used for a p-channel FET.

Owner:QUALCOMM INC

Exponentially doped layers in inverted metamorphic multijunction solar cells

ActiveUS7727795B2Increase currentDischarge tube luminescnet screensFinal product manufactureSemiconductor materialsDoping profile

A method of forming a multijunction solar cell including an upper subcell, a middle subcell, and a lower subcell, including providing first substrate for the epitaxial growth of semiconductor material; forming a first solar subcell on the substrate having a first band gap; forming a second solar subcell over the first solar subcell having a second band gap smaller than the first band gap; forming a grading interlayer over the second subcell, the grading interlayer having a third band gap greater than the second band gap; and forming a third solar subcell over the grading interlayer having a fourth band gap smaller than the second band gap such that the third subcell is lattice mis-matched with respect to the second subcell, wherein at least one of the bases of a solar subcell has an exponentially doped profile.

Owner:SOLAERO TECH CORP

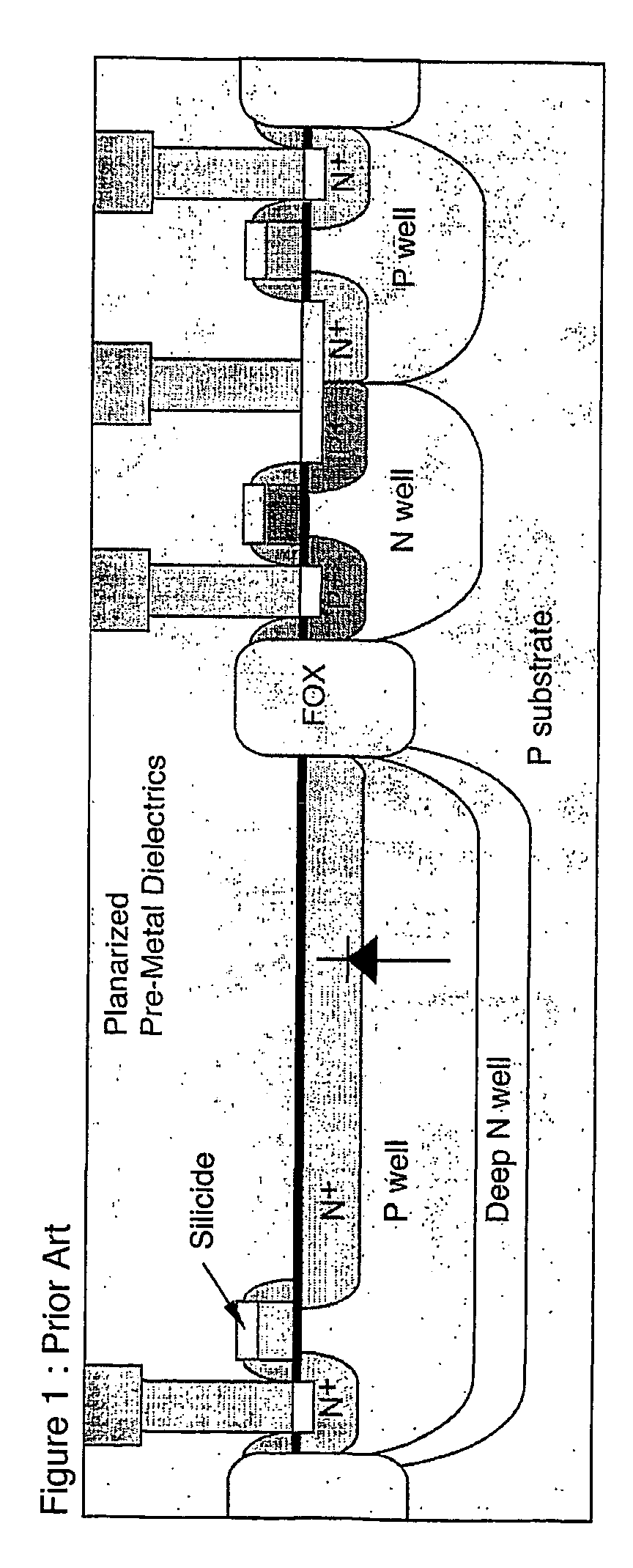

End of range (EOR) secondary defect engineering using substitutional carbon doping

A method for incorporating carbon into a wafer at the interstitial a-c silicon interface of the halo doping profile is achieved. A bulk silicon substrate is provided. A carbon-doped silicon layer is deposited on the bulk silicon substrate. An epitaxial silicon layer is grown overlying the carbon-doped silicon layer to provide a starting wafer for the integrated circuit device fabrication. An integrated circuit device is fabricated on the starting wafer by the following steps. A gate electrode is formed on the starting wafer. LDD and source and drain regions are implanted in the starting wafer adjacent to the gate electrode. Indium is implanted to form halo implants adjacent to the LDD regions and underlying the gate electrode wherein the halo implants extend to an interface between the epitaxial silicon layer and the carbon-doped silicon layer wherein carbon ions in the carbon-doped silicon layer act as a silicon interstitial sink for silicon interstitials formed by the halo implants to prevent end of range secondary defect formation.

Owner:TAIWAN SEMICON MFG CO LTD

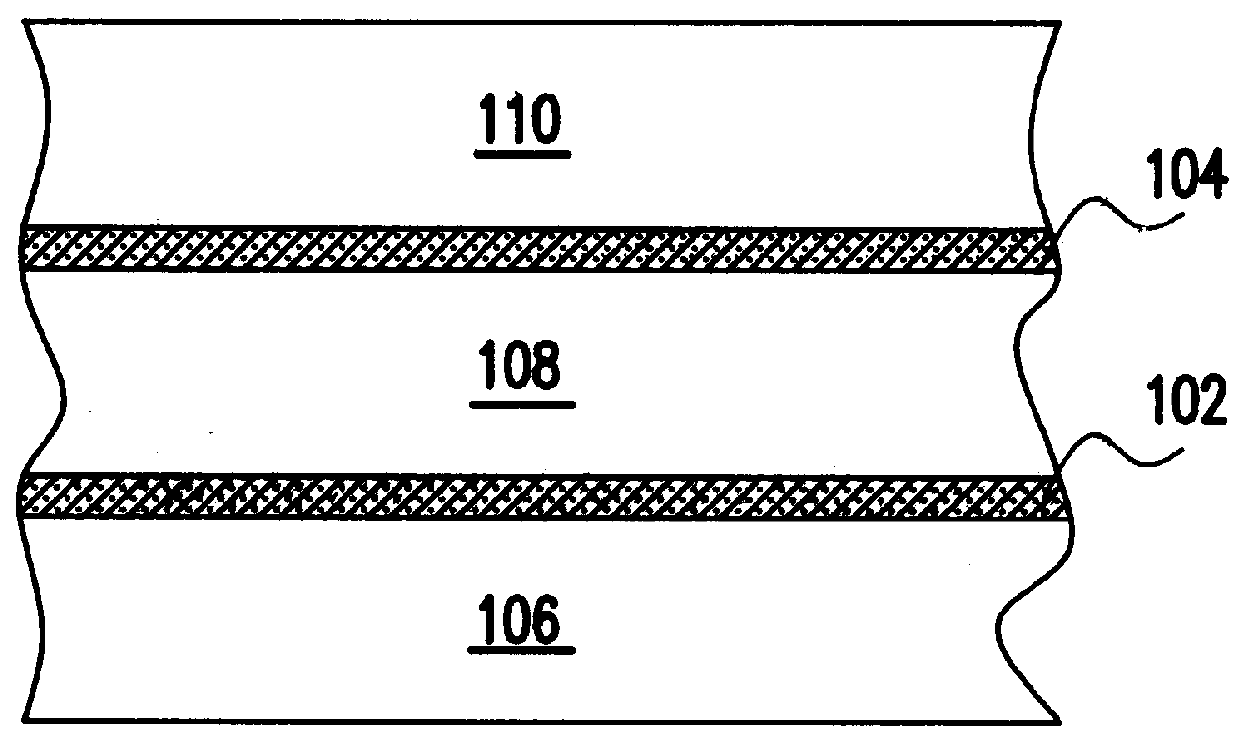

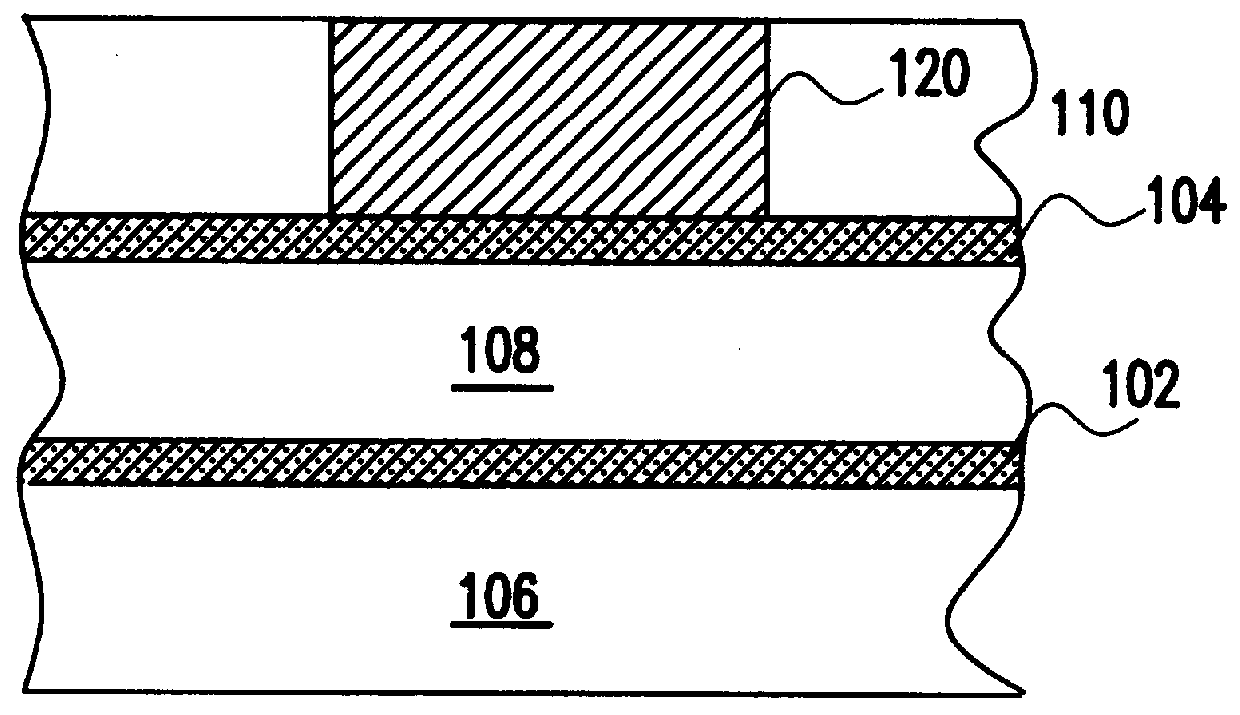

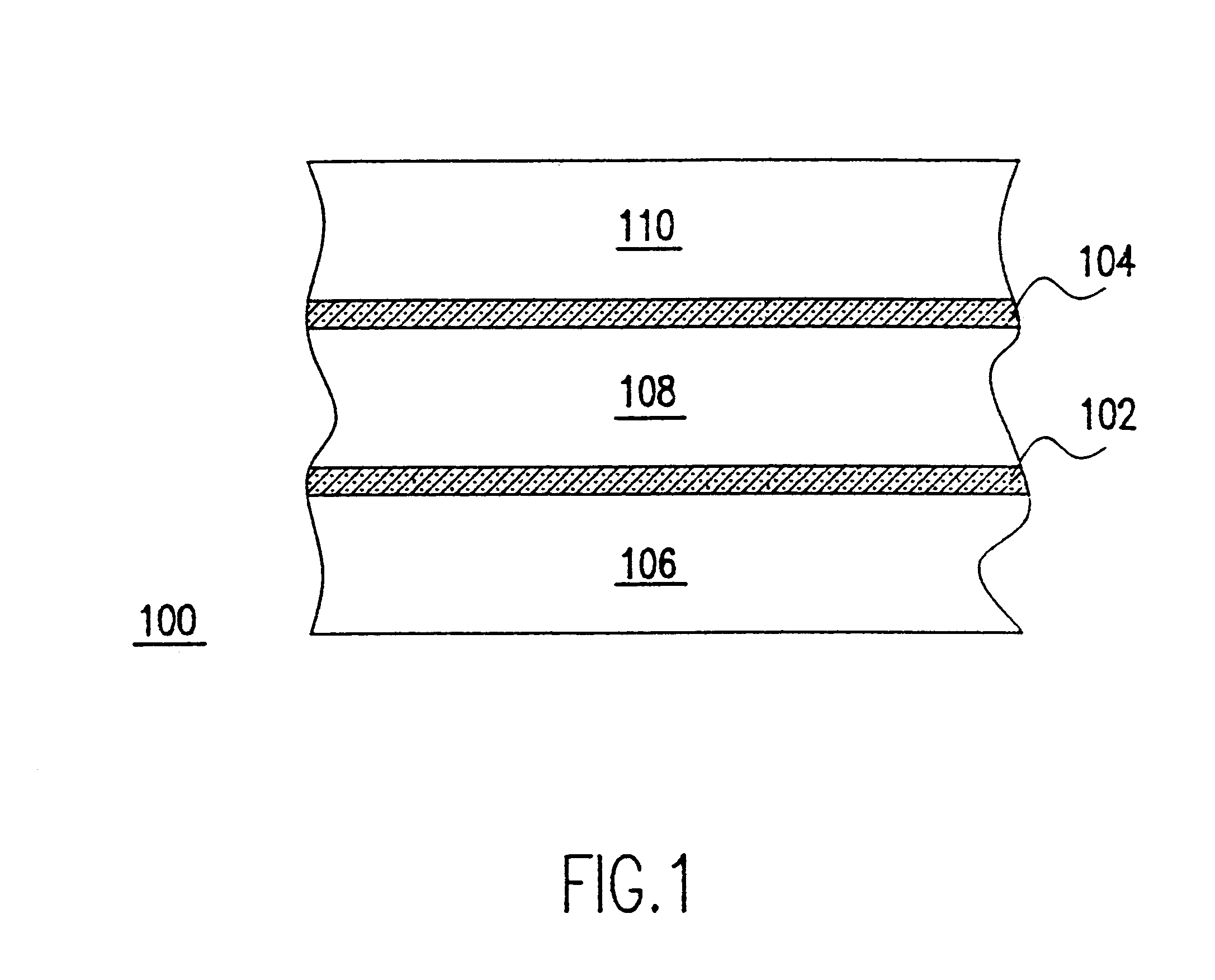

Double silicon-on-insulator device and method therefor

InactiveUS6013936ATransistorSemiconductor/solid-state device detailsDevice materialField-effect transistor

An integrated circuit chip wherein one or more semiconductor devices are completely isolated from bulk effects of other semiconductor devices in the same circuit and a method of making the integrated circuit chip. The devices may be passive devices such as resistors, or active devices such as diodes, bipolar transistors or field effect transistors (FETs). A multi-layer semiconductor body is formed of, preferably silicon and silicon dioxide. A conducting region or channel is formed in one or more of the layers. For the FET, silicon above and below the channel region provides controllable gates with vertically symmetrical device characteristics. Buried insulator layers may be added to isolate the lower gate of individual devices from each other and to create multiple vertically stacked isolated devices. Both PFET and NFET devices can be made with independent doping profiles in both depletion and accumulation modes.

Owner:GLOBALFOUNDRIES INC

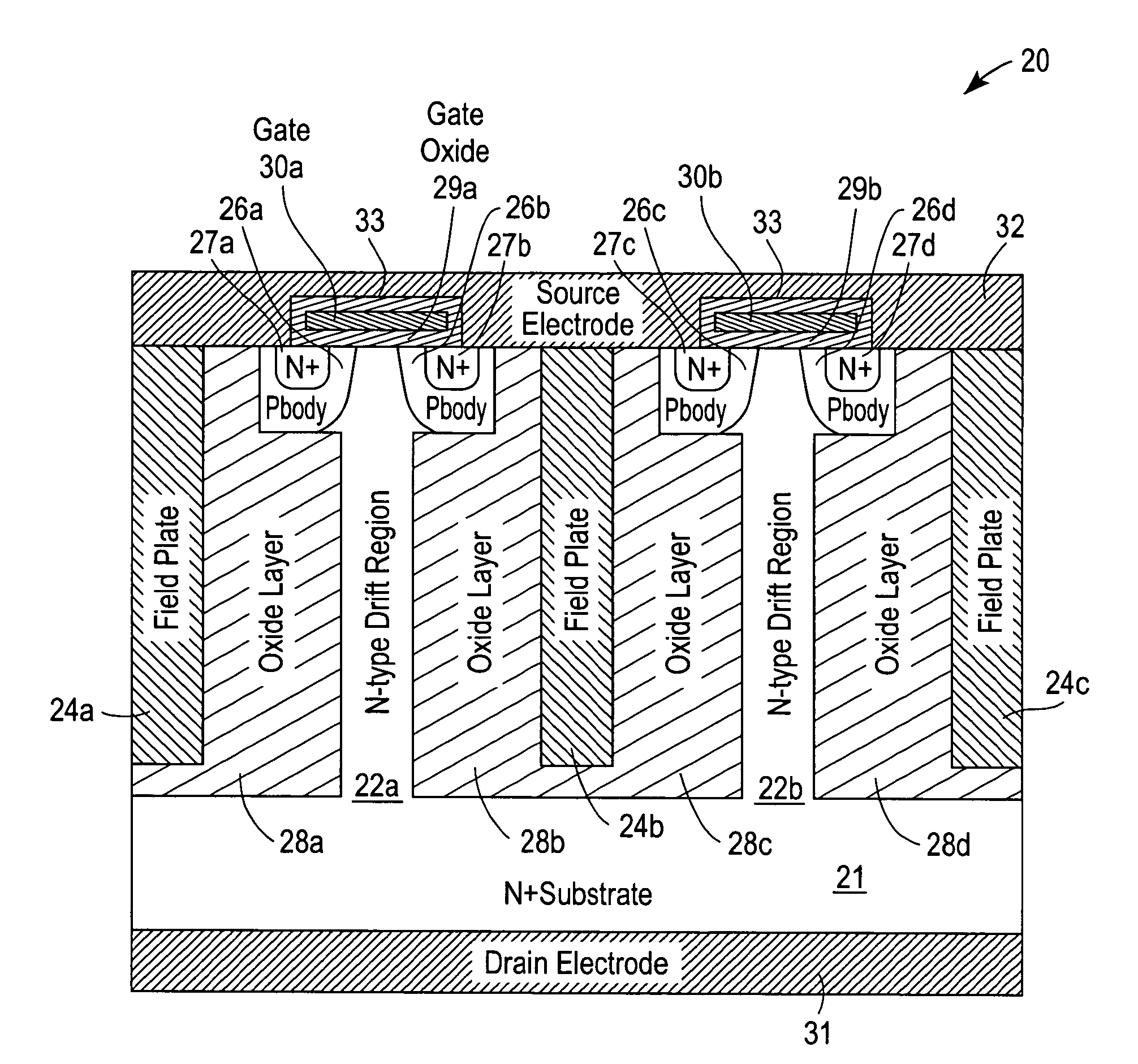

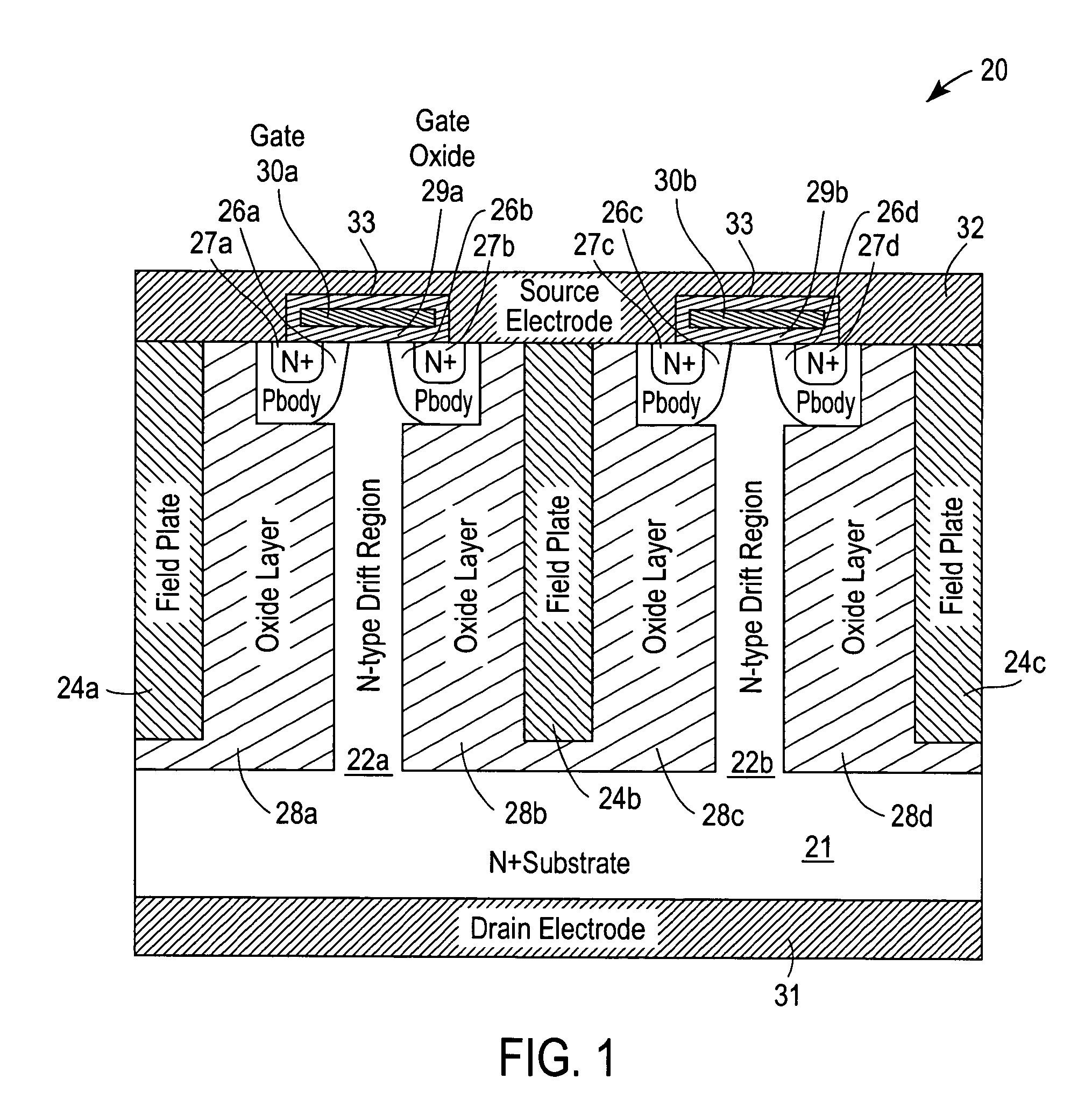

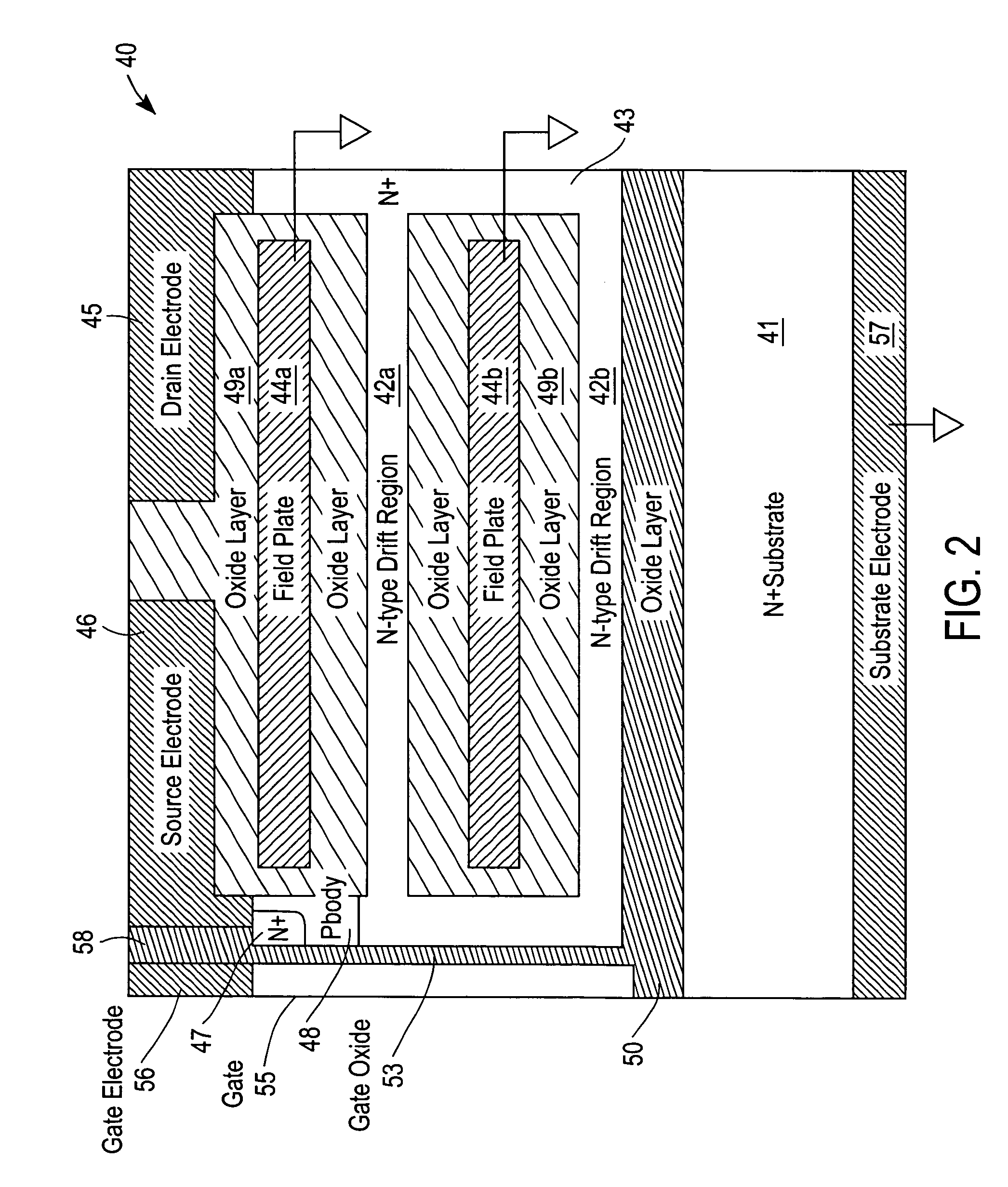

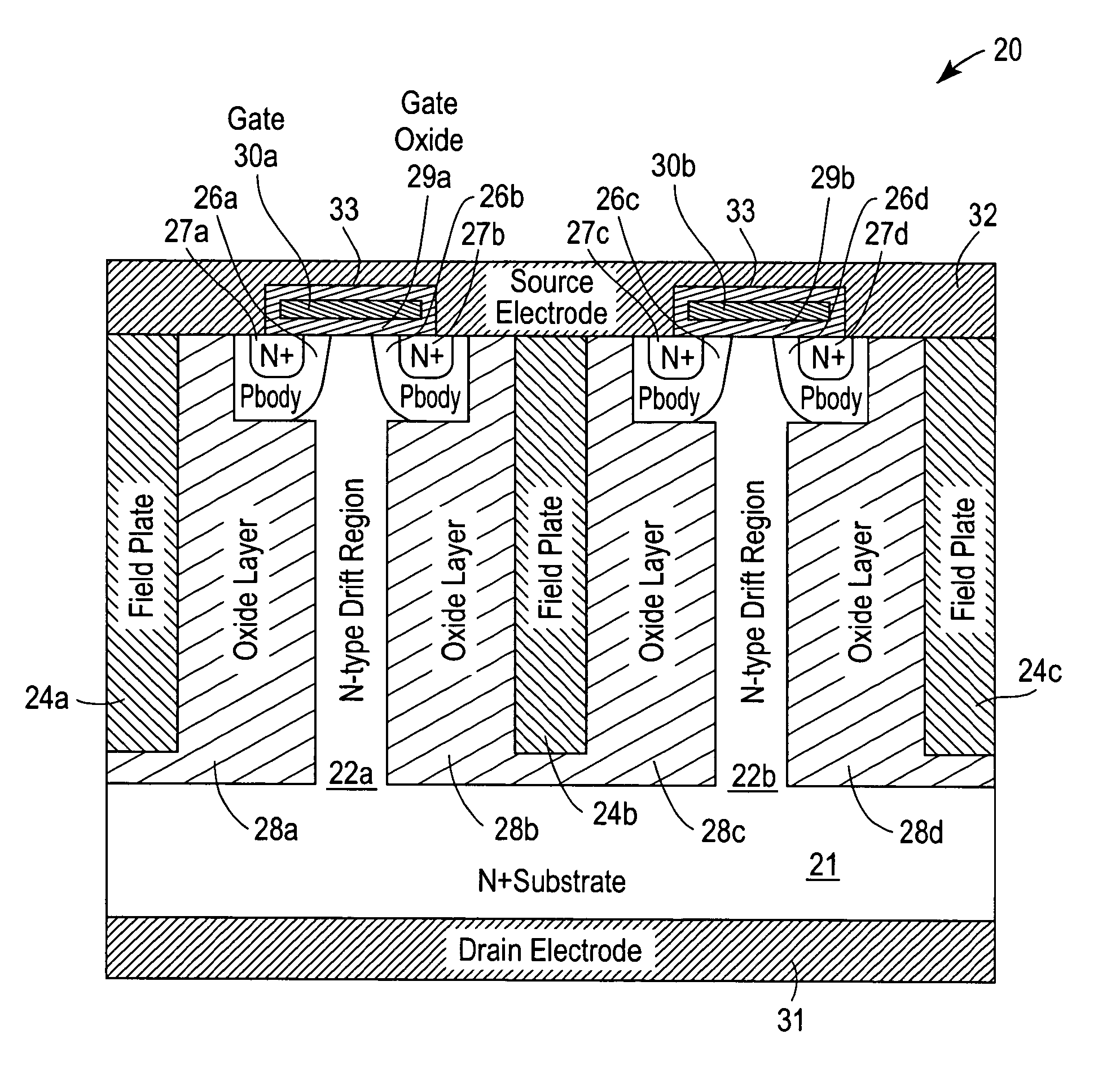

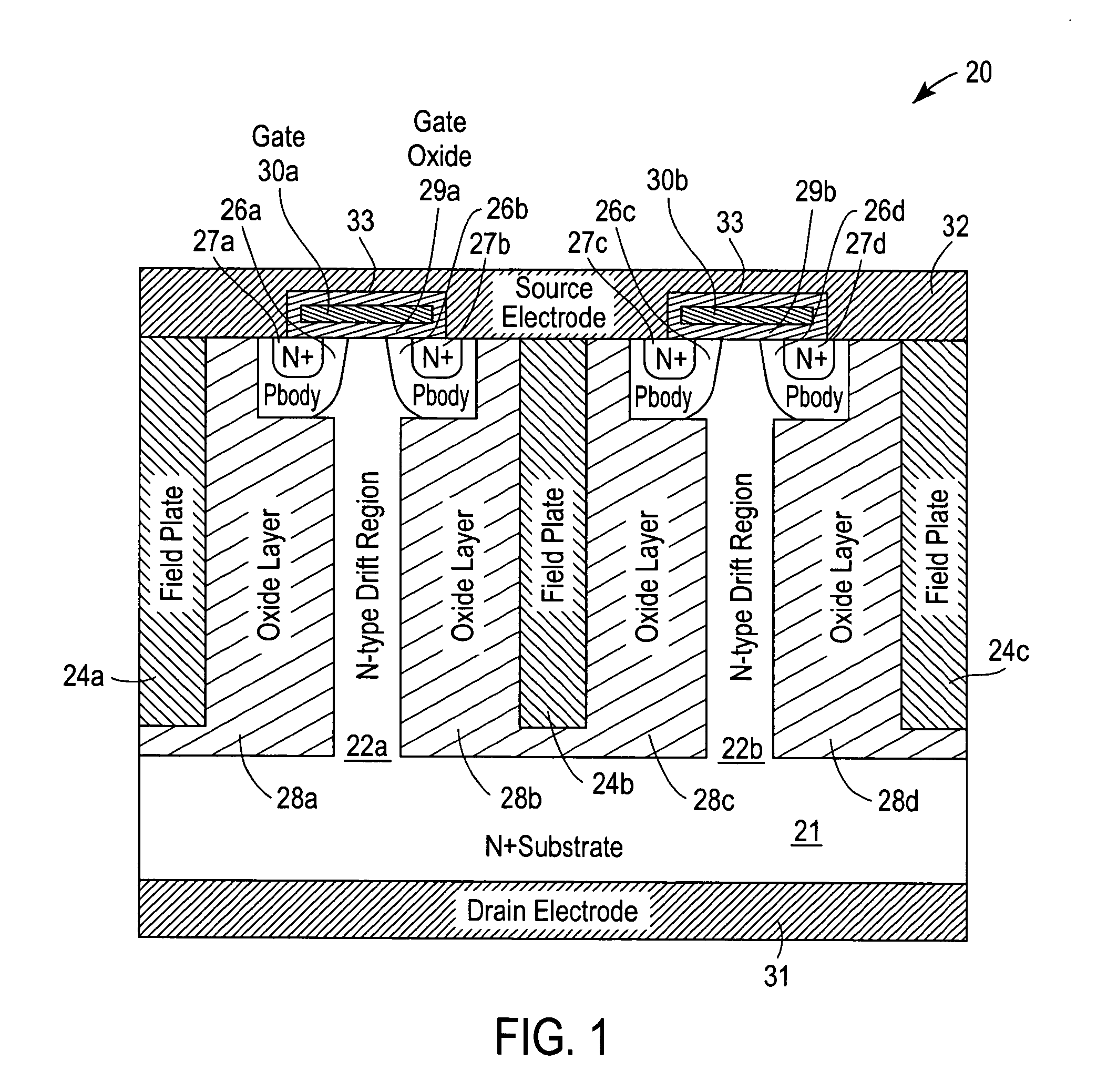

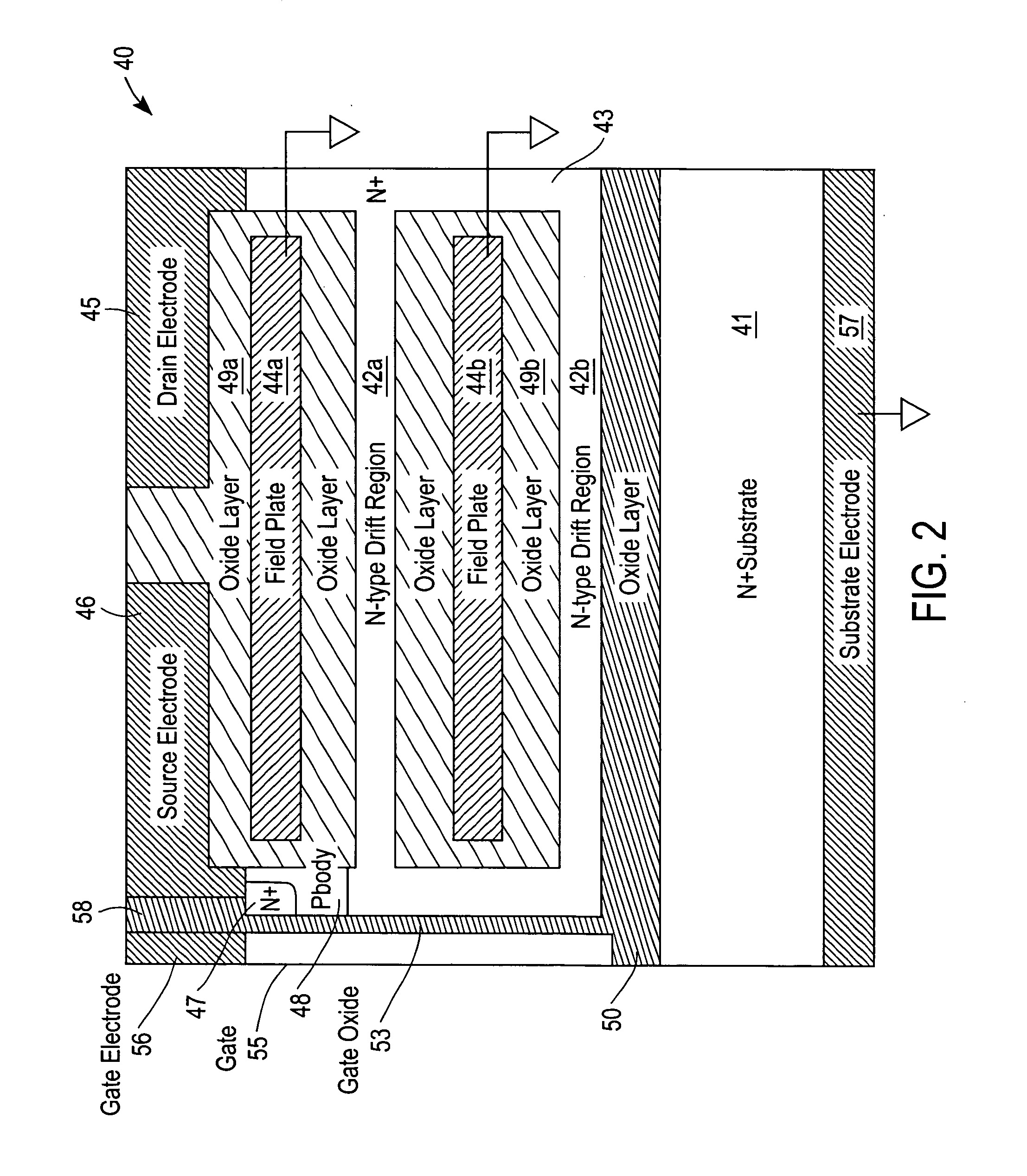

High-voltage vertical transistor with a multi-gradient drain doping profile

InactiveUS7221011B2Semiconductor/solid-state device manufacturingSemiconductor devicesHigh voltage transistorsSubject matter

A high-voltage transistor includes first and second trenches that define a mesa in a semiconductor substrate. First and second field plate members are respectively disposed in the first and second trenches, with each of the first and second field plate members being separated from the mesa by a dielectric layer. The mesa includes a plurality of sections, each section having a substantially constant doping concentration gradient, the gradient of one section being at least 10% greater than the gradient of another section. It is emphasized that this abstract is provided to comply with the rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims. 37 CFR 1.72(b).

Owner:POWER INTEGRATIONS INC

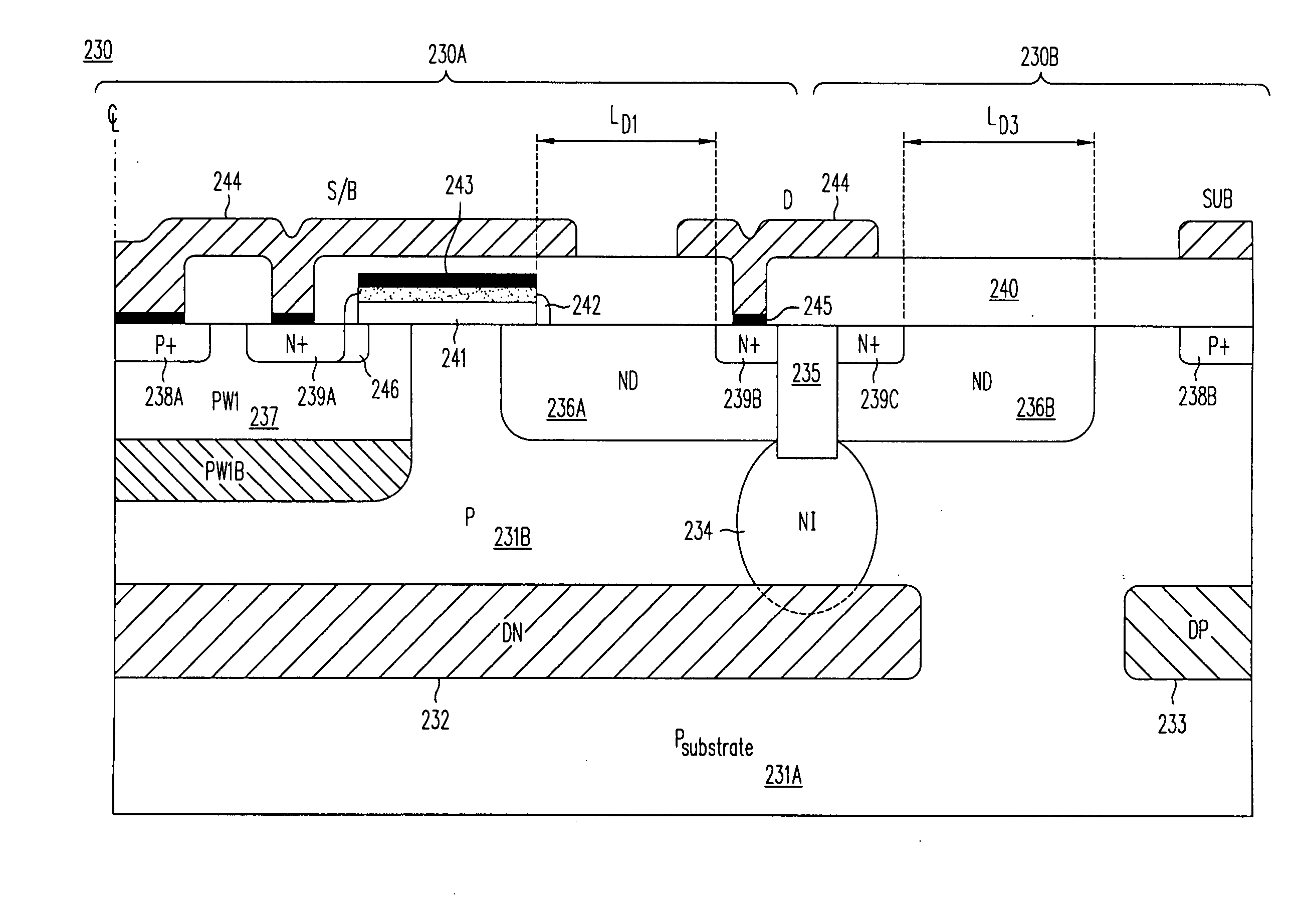

Lateral MOSFET

A lateral MOSFET formed in a substrate of a first conductivity type includes a gate formed atop a gate dielectric layer over a surface of the substrate, a drain region of a second conductivity type, a source region of a second conductivity type, and a body region of the first conductivity type which extends under the gate. The body region may have a non-monotonic vertical doping profile with a portion located deeper in the substrate having a higher doping concentration than a portion located shallower in the substrate. The lateral MOSFET may be drain-centric, with the source region and an optional dielectric-filled trench surrounding the drain region.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED +1

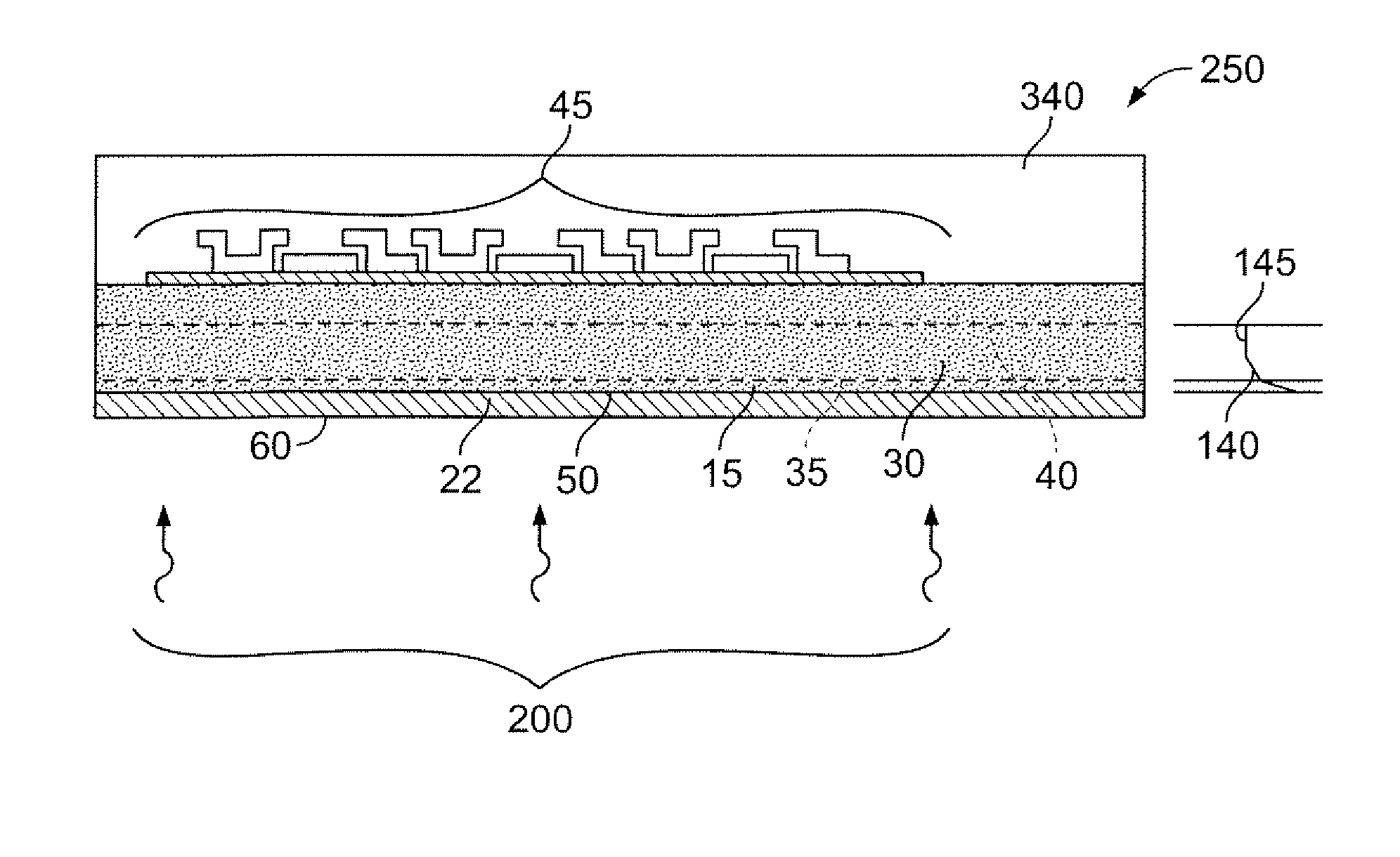

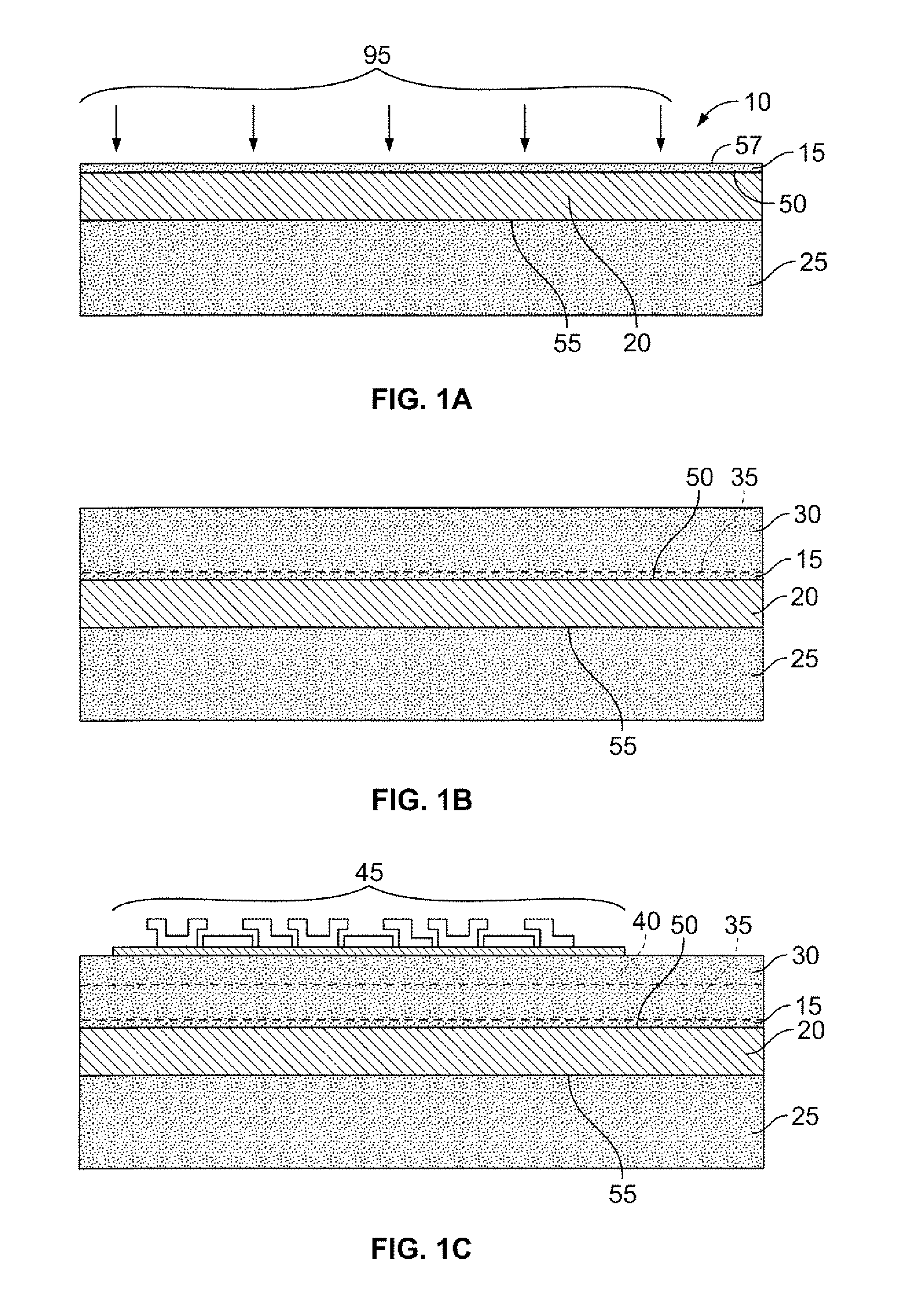

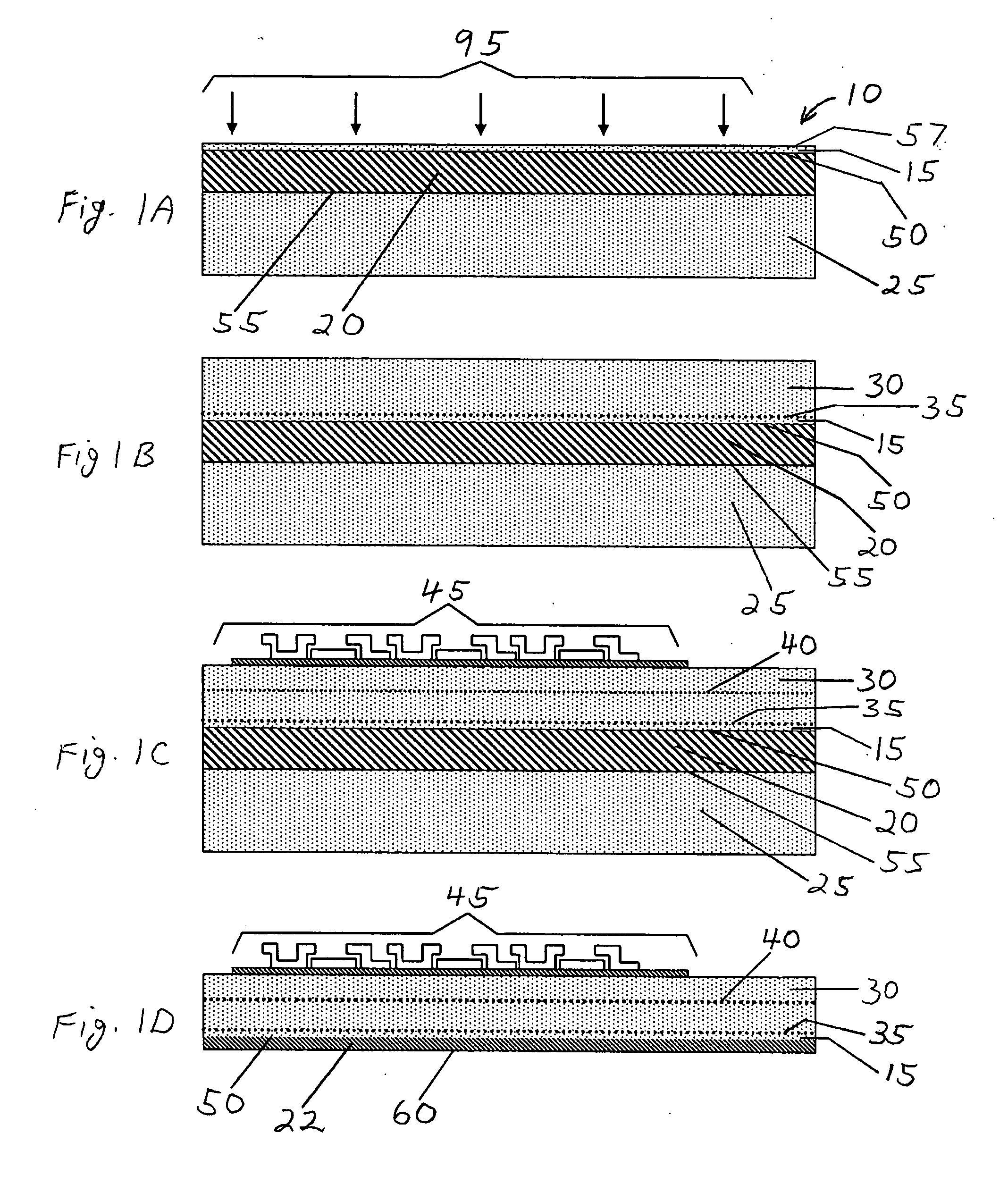

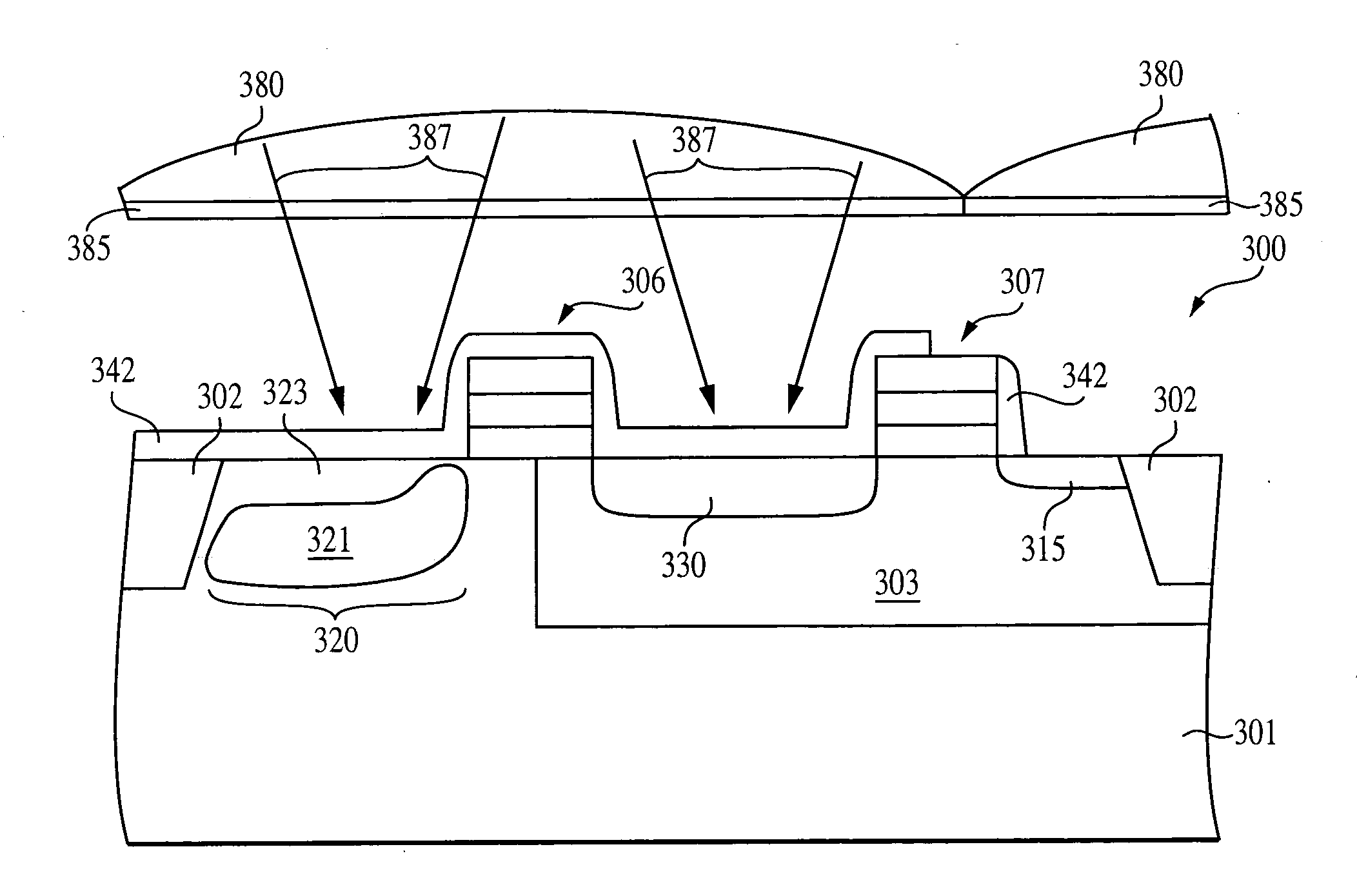

Dark Current Reduction in Back-Illuminated Imaging Sensors and Method of Fabricating Same

ActiveUS20070235829A1Reduces and eliminates dark currentSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerOptoelectronics

A method for fabricating a back-illuminated semiconductor imaging device on a semiconductor-on-insulator substrate, and resulting imaging device is disclosed. The device includes an insulator layer; a semiconductor substrate, having an interface with the insulator layer; an epitaxial layer grown on the semiconductor substrate by epitaxial growth; and one or more imaging components in the epitaxial layer in proximity to a face of the epitaxial layer, the face being opposite the interface of the semiconductor substrate and the insulator layer, the imaging components comprising junctions within the epitaxial layer; wherein the semiconductor substrate and the epitaxial layer exhibit a net doping concentration having a maximum value at a predetermined distance from the interface of the insulating layer and the semiconductor substrate and which decreases monotonically on both sides of the profile from the maximum value within a portion of the semiconductor substrate and the epitaxial layer. The doping profile between the interface with the insulation layer and the peak of the doping profile functions as a “dead band” to prevent dark current carriers from penetrating to the front side of the device.

Owner:SRI INTERNATIONAL

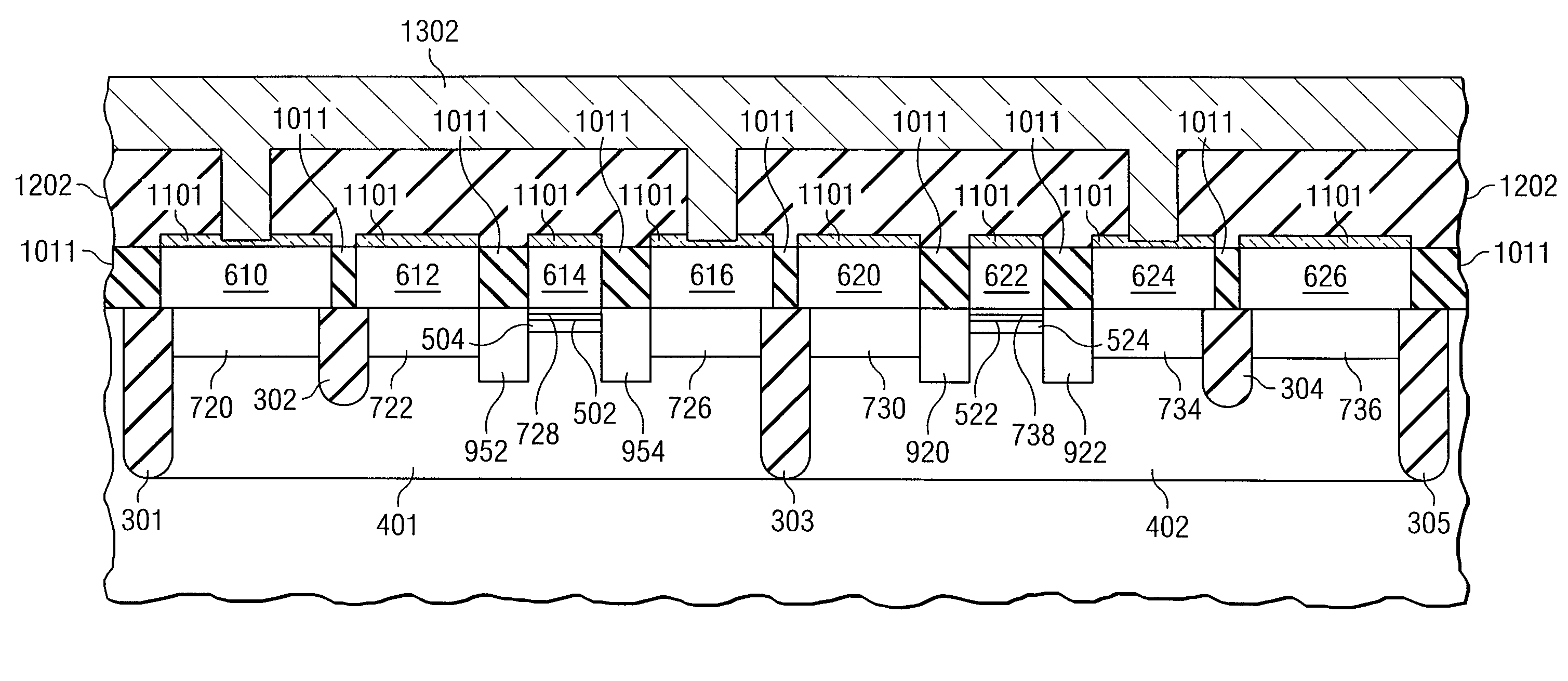

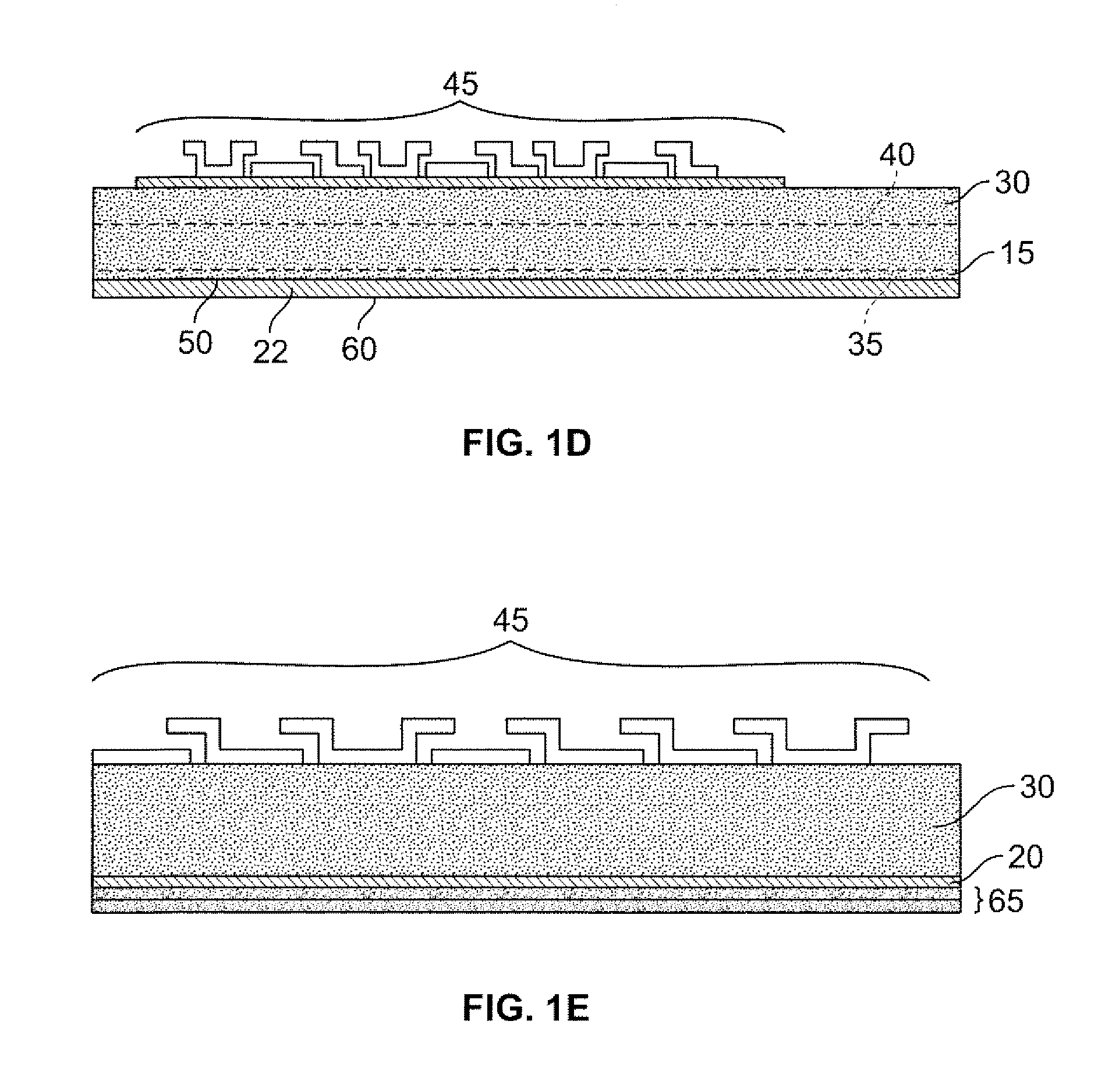

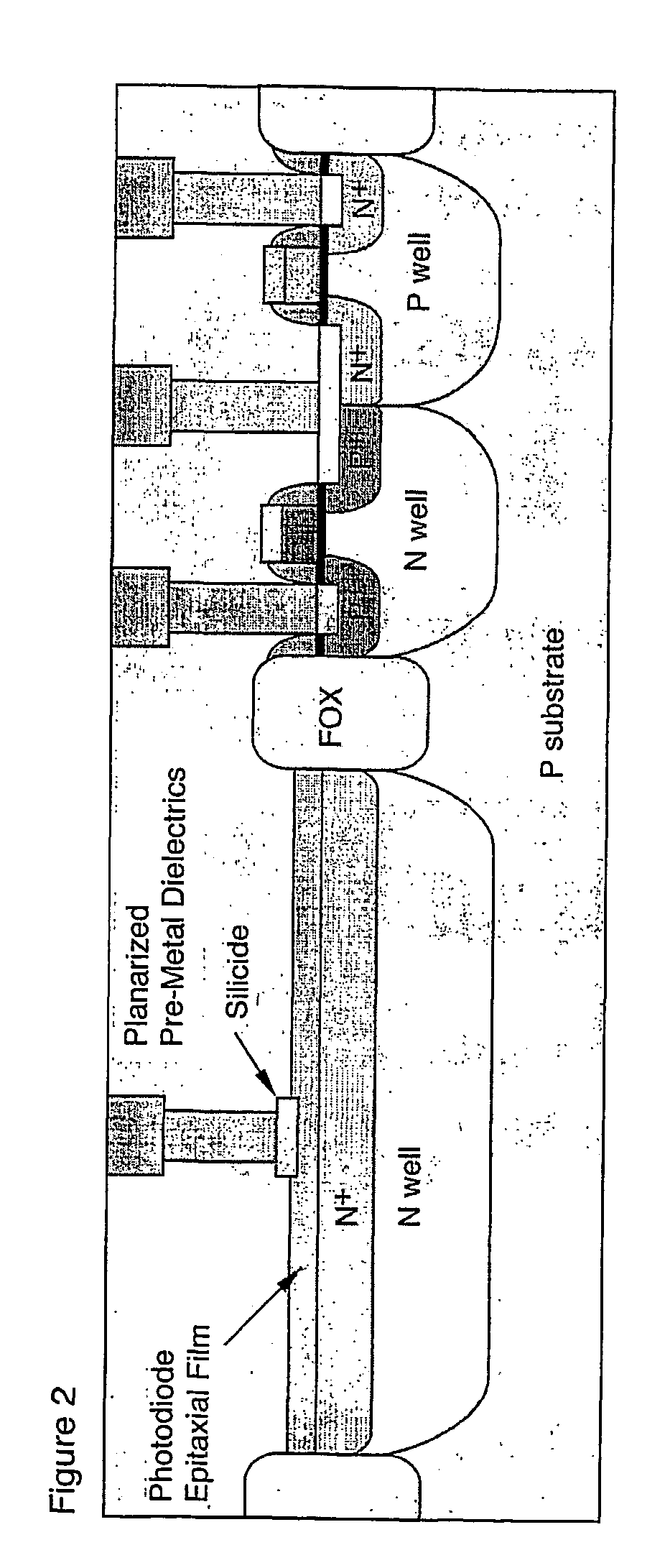

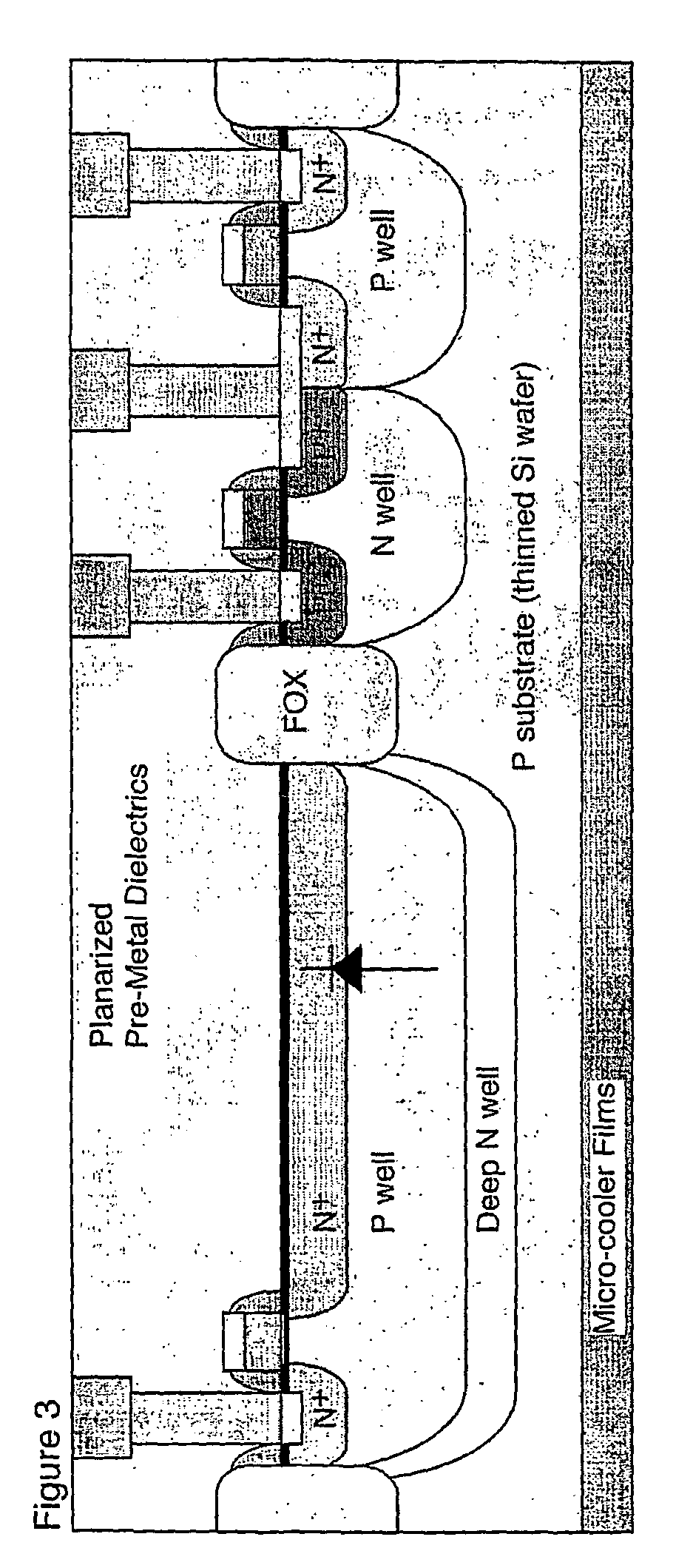

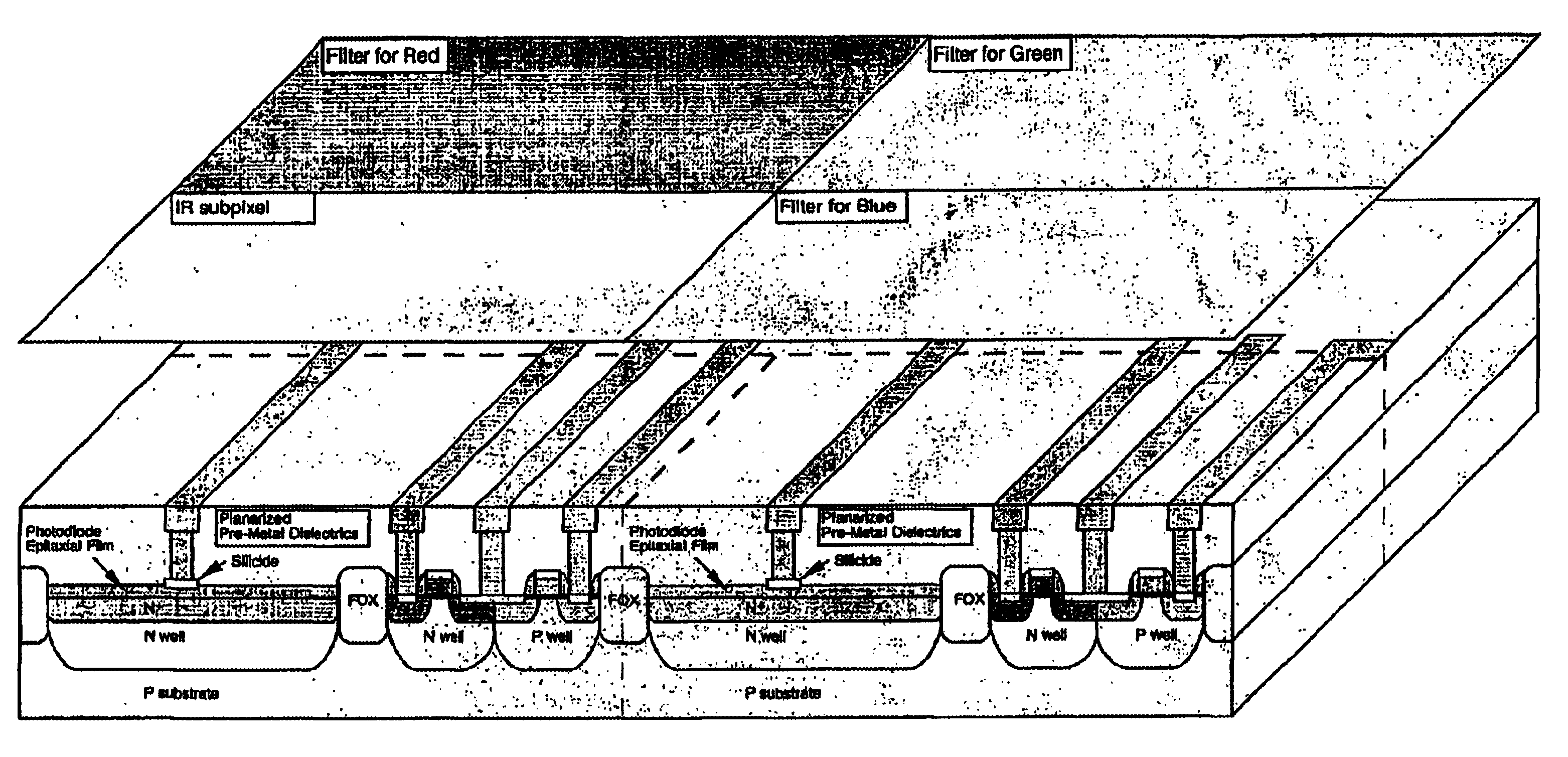

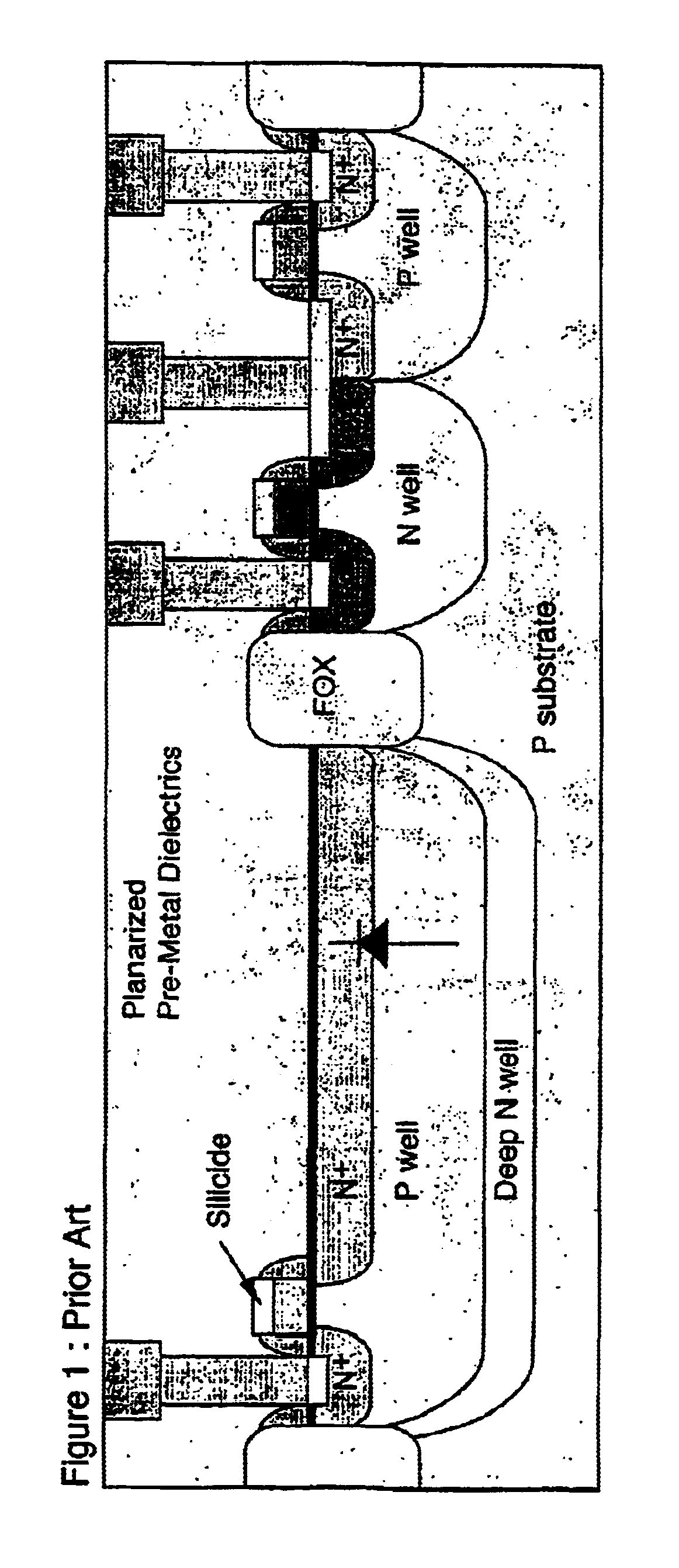

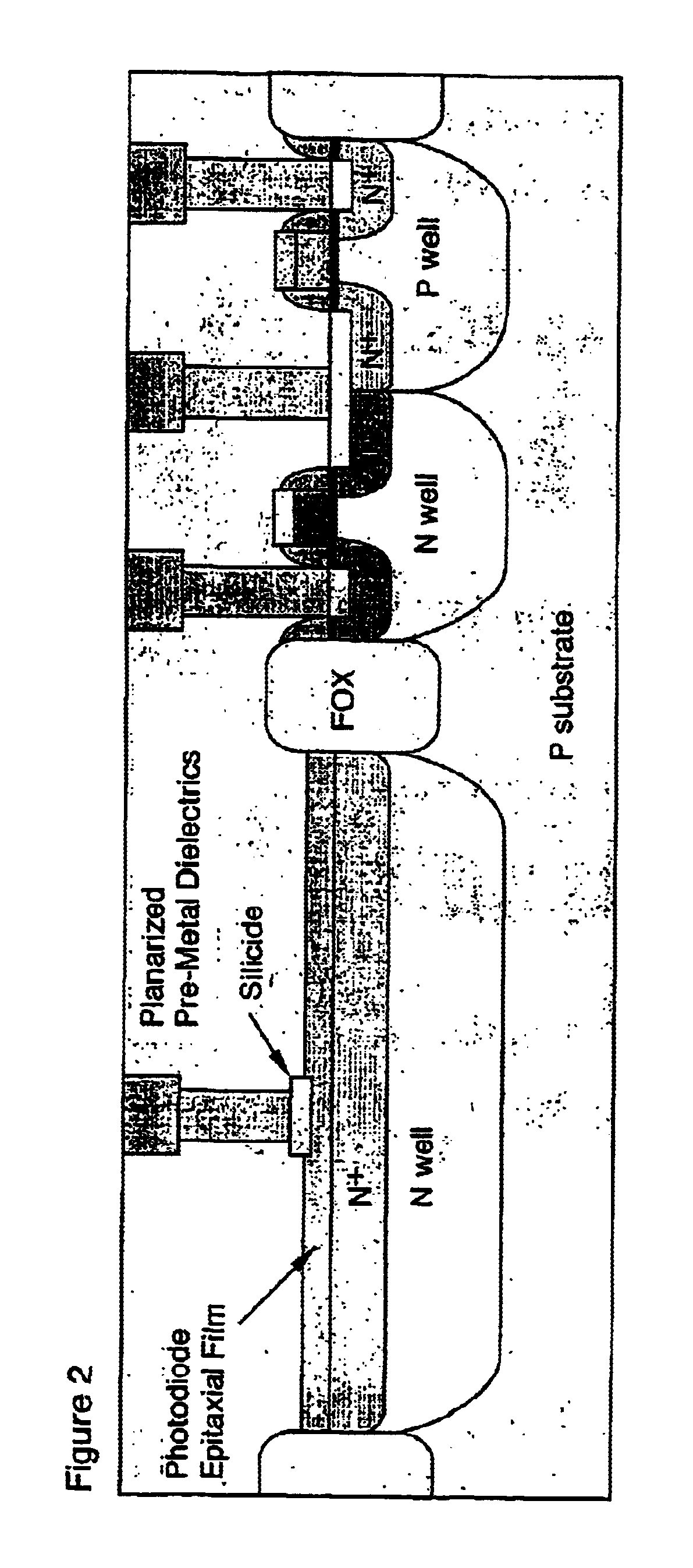

Method of fabricating heterojunction photodiodes integrated with cmos

A method in which thin-film p-i-n heterojunction photodiodes are formed by selective epitaxial growth / deposition on pre-designated active-area regions of standard CMOS devices. The thin-film p-i-n photodiodes are formed on active areas (for example n<+>-doped), and these are contacted at the bottom (substrate) side by the "well contact" corresponding to that particular active area. There is no actual potential well since that particular active area has only one type of doping. The top of each photodiode has a separate contact formed thereon. The selective epitaxial growth of the p-i-n photodiodes is modular, in the sense that there is no need to change any of the steps developed for the "pure" CMOS process flow. Since the active region is epitaxially deposited, there is the possibility of forming sharp doping profiles and band-gap engineering during the epitaxial process, thereby optimizing several device parameters for higher performance. This new type of light sensor architecture, monolithically integrated with CMOS, decouples the photo-absorption active region from the MOSFETs, hence the bias applied to the photodiode can be independent from the bias between the source, drain, gate and substrate (well) of the MOSFETs.

Owner:QUANTUM SEMICON

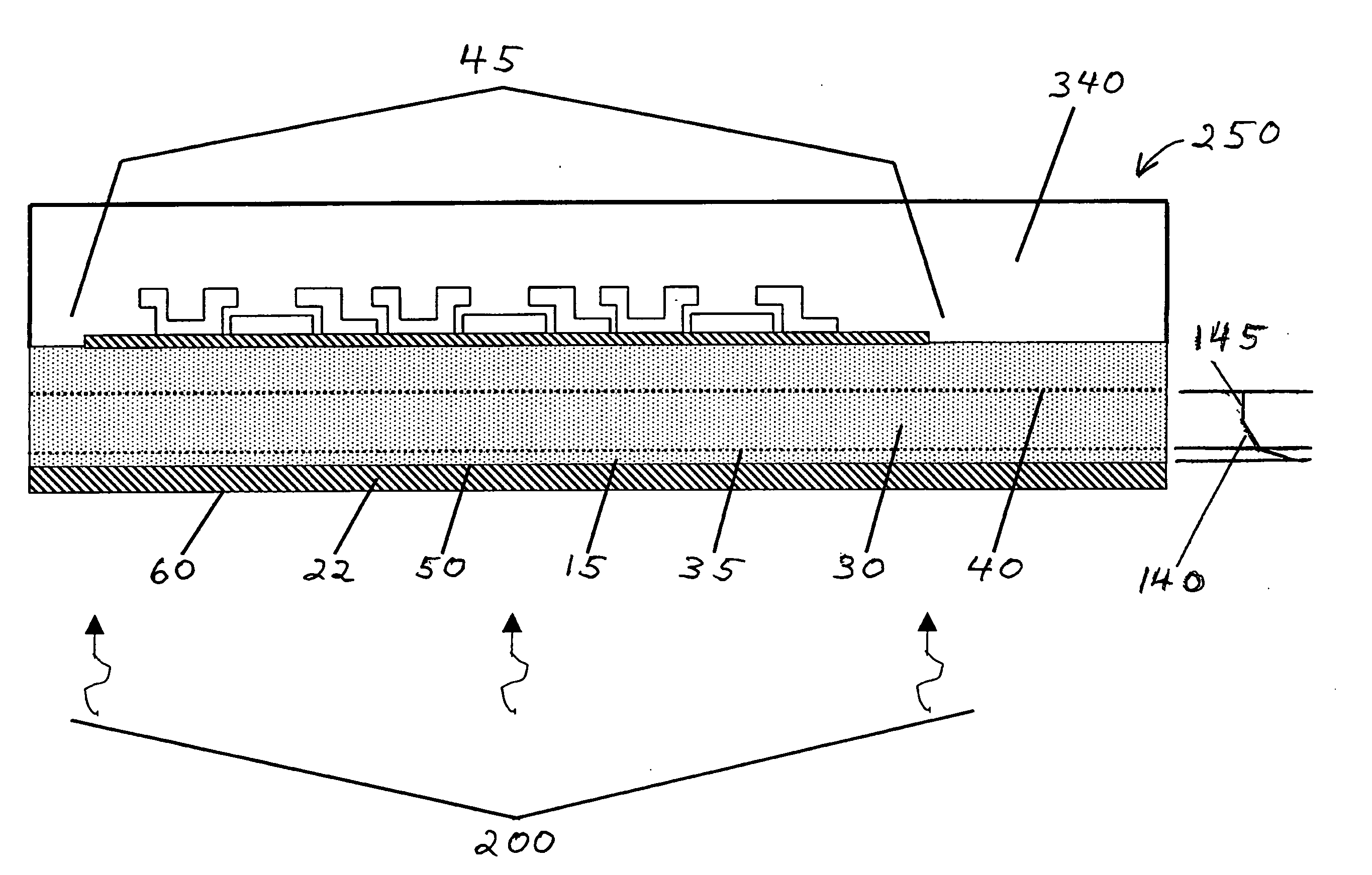

Back-illuminated imaging device and method of fabricating same

ActiveUS20060186560A1Effectively eliminate a backside dead bandSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorCondensed matter physics

A method for fabricating a back-illuminated semiconductor imaging device on a thin semiconductor-on-insulator substrate, and resulting imaging device. Resulting device has a monotonically varying doping profile which provides a desired electric field and eliminates a dead band proximate to the backside surface.

Owner:SRI INTERNATIONAL

Doping profiles in PN diode optical modulators

ActiveUS7251408B1Coupling light guidesOptical waveguide light guideDopantElectrical resistance and conductance

High speed optical modulators can be made of a lateral PN diode formed in a silicon optical rib waveguide, disposed on a SOI or other silicon based substrate. A PN junction is formed at the boundary of the P and N doped regions. The depletion region at the PN junction overlaps with the center of a guided optical mode propagating through the waveguide. Electrically modulating a lateral PN diode causes a phase shift in an optical wave propagating through the waveguide. Each of the doped regions can have a stepped or gradient doping profile within it or several doped sections with different doping concentrations. Forming the doped regions of a PN diode modulator with stepped or gradient doping profiles can optimize the trade off between the series resistance of the PN diode and the optical loss in the center of the waveguide due to the presence of dopants.

Owner:CISCO TECH INC

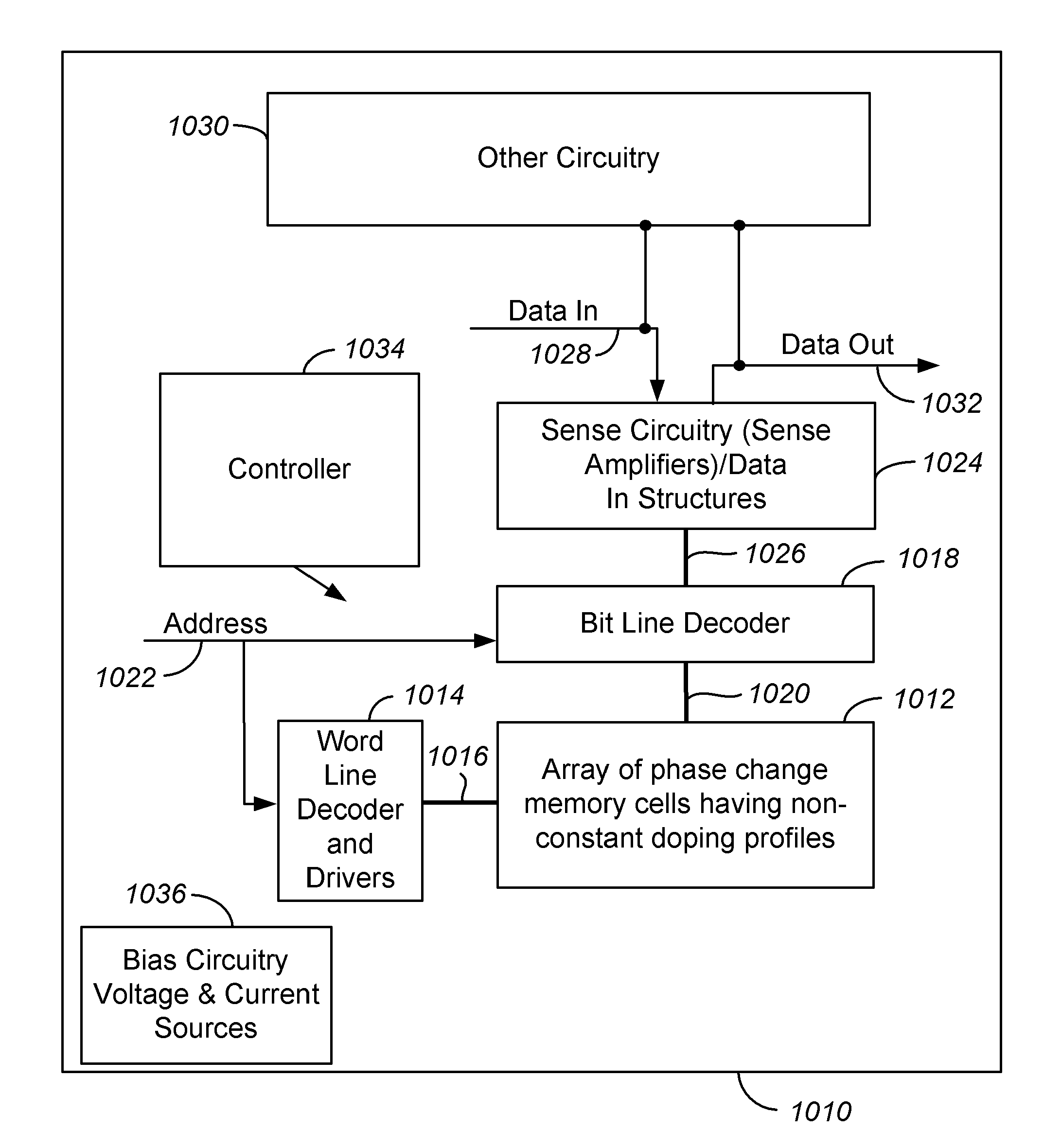

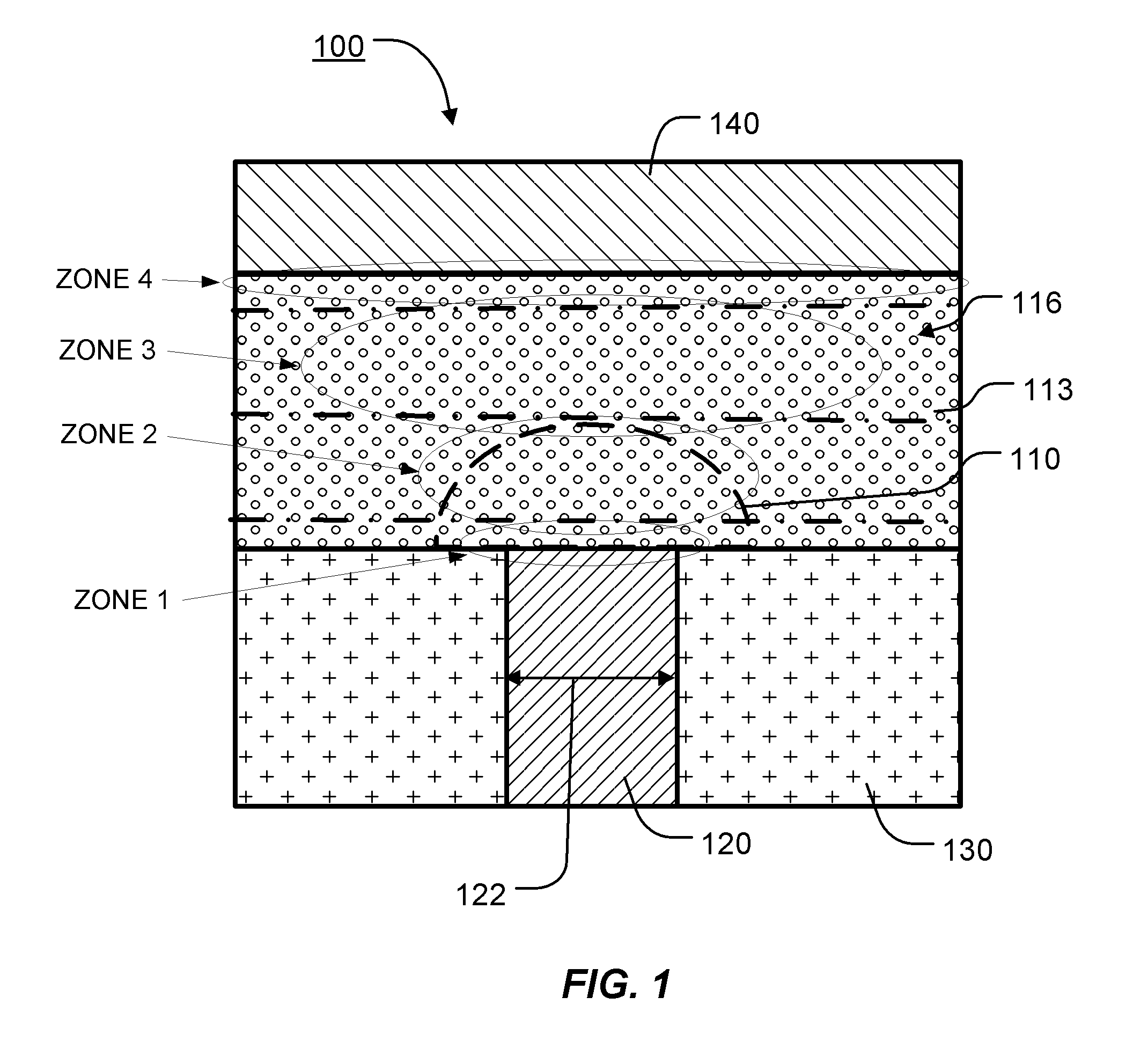

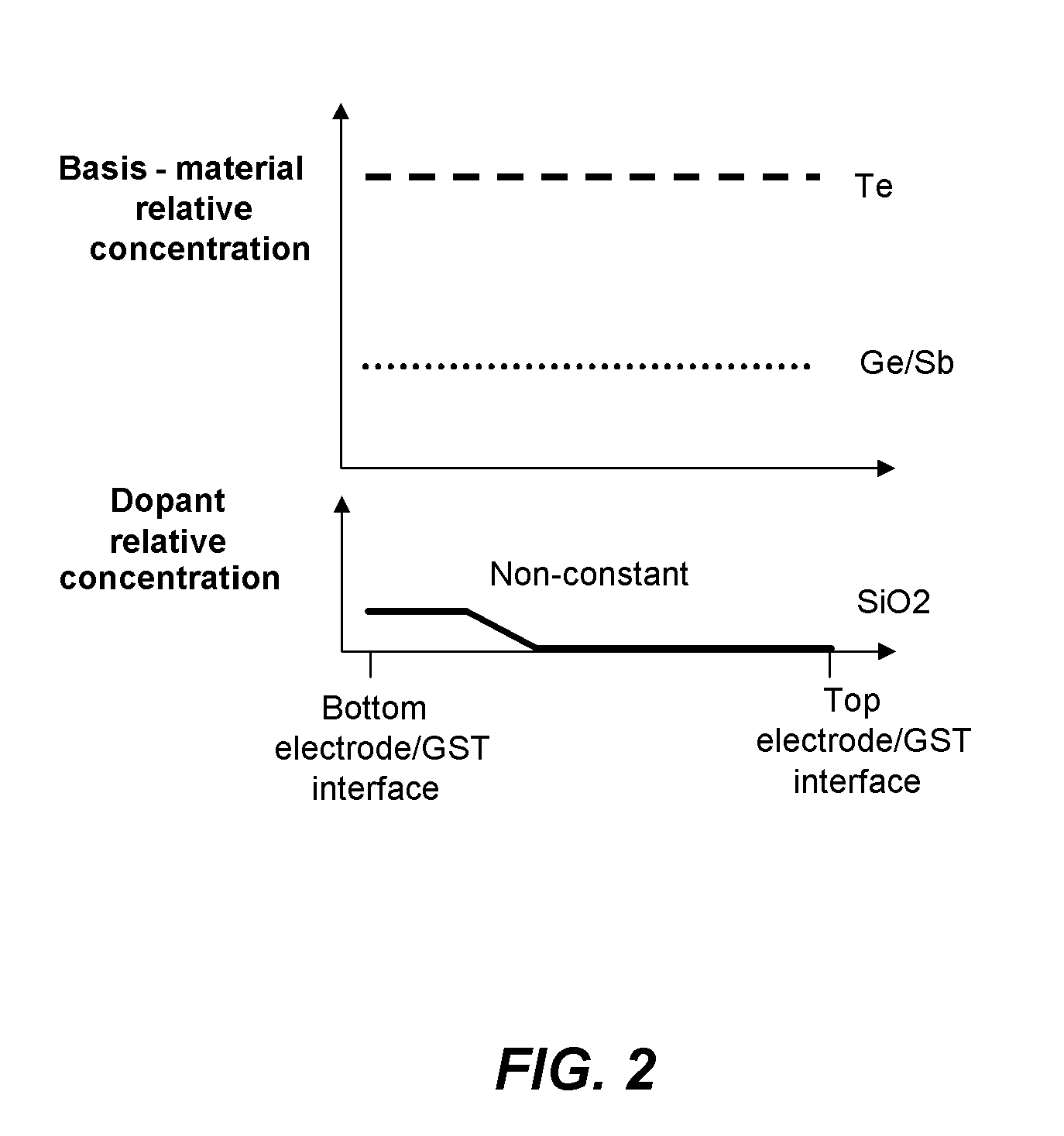

Phase change memory having one or more non-constant doping profiles

ActiveUS20100328996A1Improve stabilityImproved Impedance StabilityDigital storageBulk negative resistance effect devicesPhase-change memoryPhase-change material

A phase change memory device with a memory element including a basis phase change material, such as a chalcogenide, and one or more additives, where the additive or additives have a non-constant concentration profile along an inter-electrode current path through a memory element. The use of “non-constant” concentration profiles for additives enables doping the different zones with different materials and concentrations, according to the different crystallographic, thermal and electrical conditions, and different phase transition conditions.

Owner:IBM CORP +1

Double silicon-on-insulator device and method thereof

InactiveUS6383892B1TransistorSemiconductor/solid-state device detailsEngineeringField-effect transistor

An integrated circuit chip wherein one or more semiconductor devices are completely isolated from bulk effects of other semiconductor devices in the same circuit and a method of making the integrated circuit chip. The devices may be passive devices such as resistors, or active devices such as diodes, bipolar transistors or field effect transistors (FETs). A multi-layer semiconductor body is formed of, preferably silicon and silicon dioxide. A conducting region or channel is formed in one or more of the layers. For the FET, silicon above and below the channel region provides controllable gates with vertically symmetrical device characteristics. Buried insulator layers may be added to isolate the lower gate of individual devices from each other and to create multiple vertically stacked isolated devices. Both PFET and NFET devices can be made with independent doping profiles in both depletion and accumulation modes.

Owner:GLOBALFOUNDRIES INC

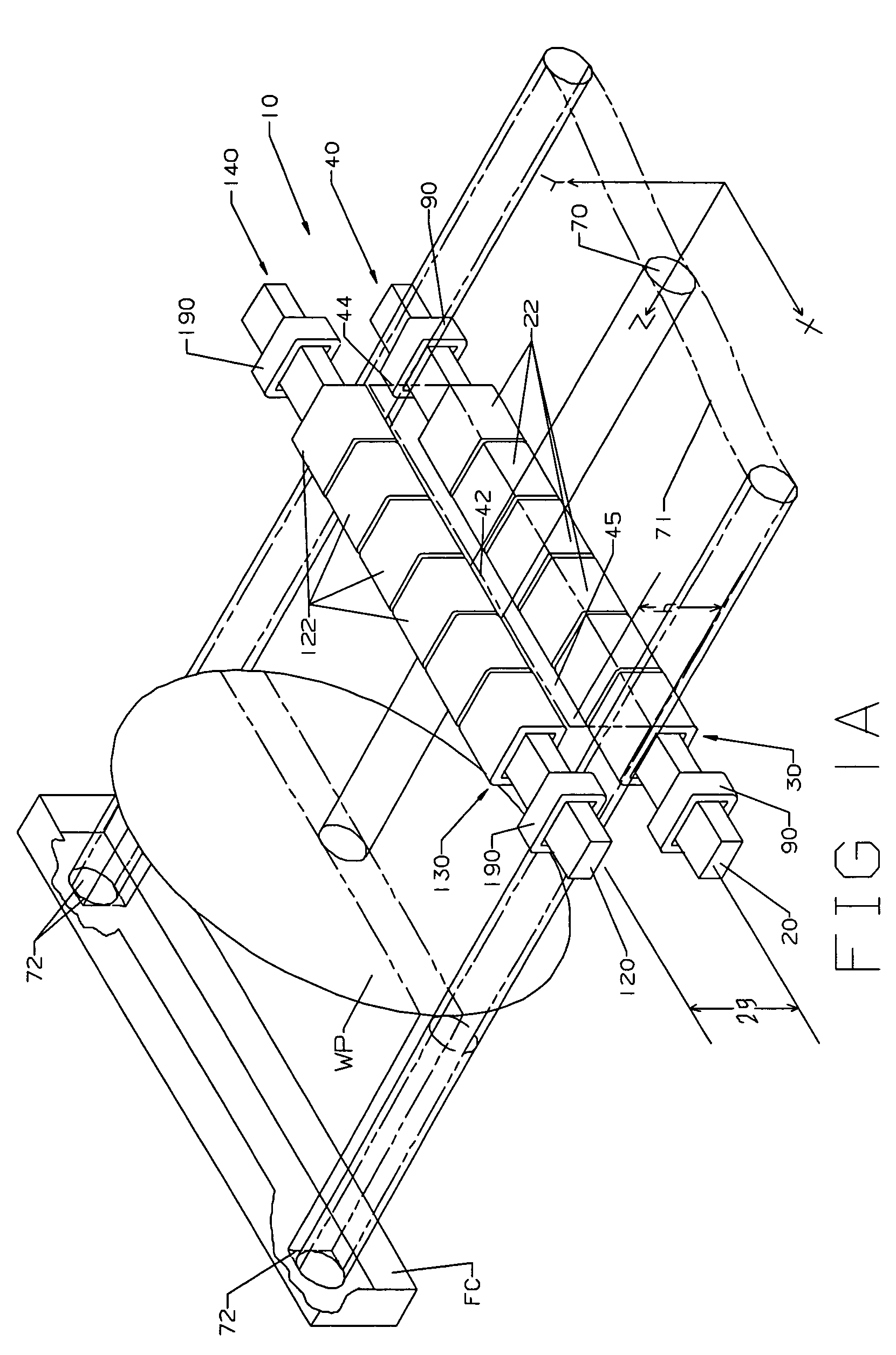

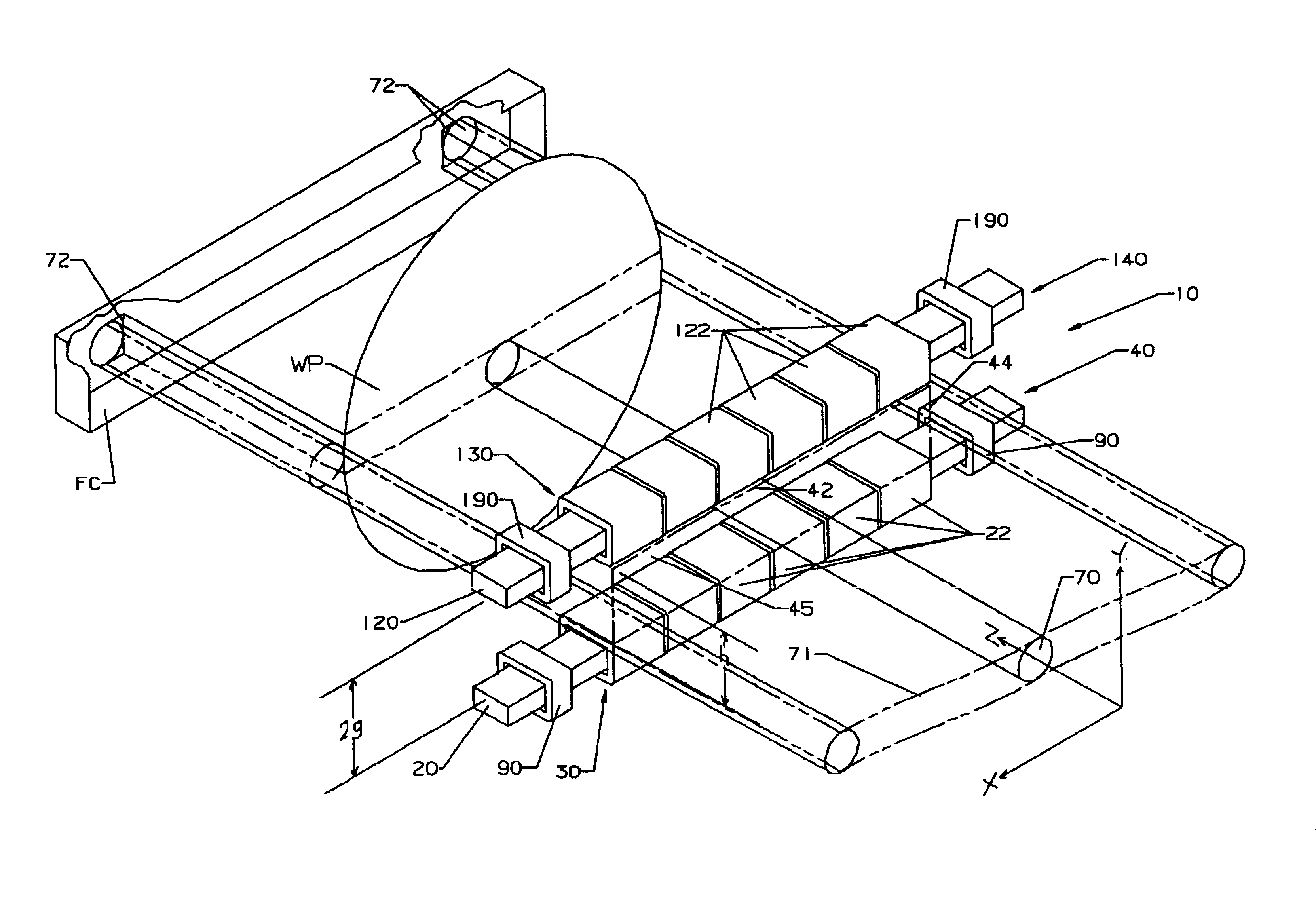

Method and fine-control collimator for accurate collimation and precise parallel alignment of scanned ion beams

InactiveUS20050082498A1Easy to controlMore accurateIsotope separationStatic spectrometersWave shapeBand shape

In a system for implanting workpieces with an accurately parallel scanned ion beam, a fine-control collimator construct is used to reduce the deviation of the scanned ion beam from a specified axis of parallelism and thereby improve its collimation. The shape of the fine-control collimator matches the ribbon shape of the beam and correction of parallelism in two orthogonal directions is possible. Measurement of the non-parallelism is accomplished by sampling the scanned beam in two planes and comparing timing information; and such measurement is calibrated to the orientation of the workpiece in the plane where ion implantation occurs. Measurement of non-uniformity in the doping profile is accomplished using the same means; and the scan waveform is adjusted to substantially remove any non-uniformity in the doping profile.

Owner:WHITE NICHOLAS R

Method of fabricating heterojunction photodiodes integrated with CMOS

Owner:QUANTUM SEMICON

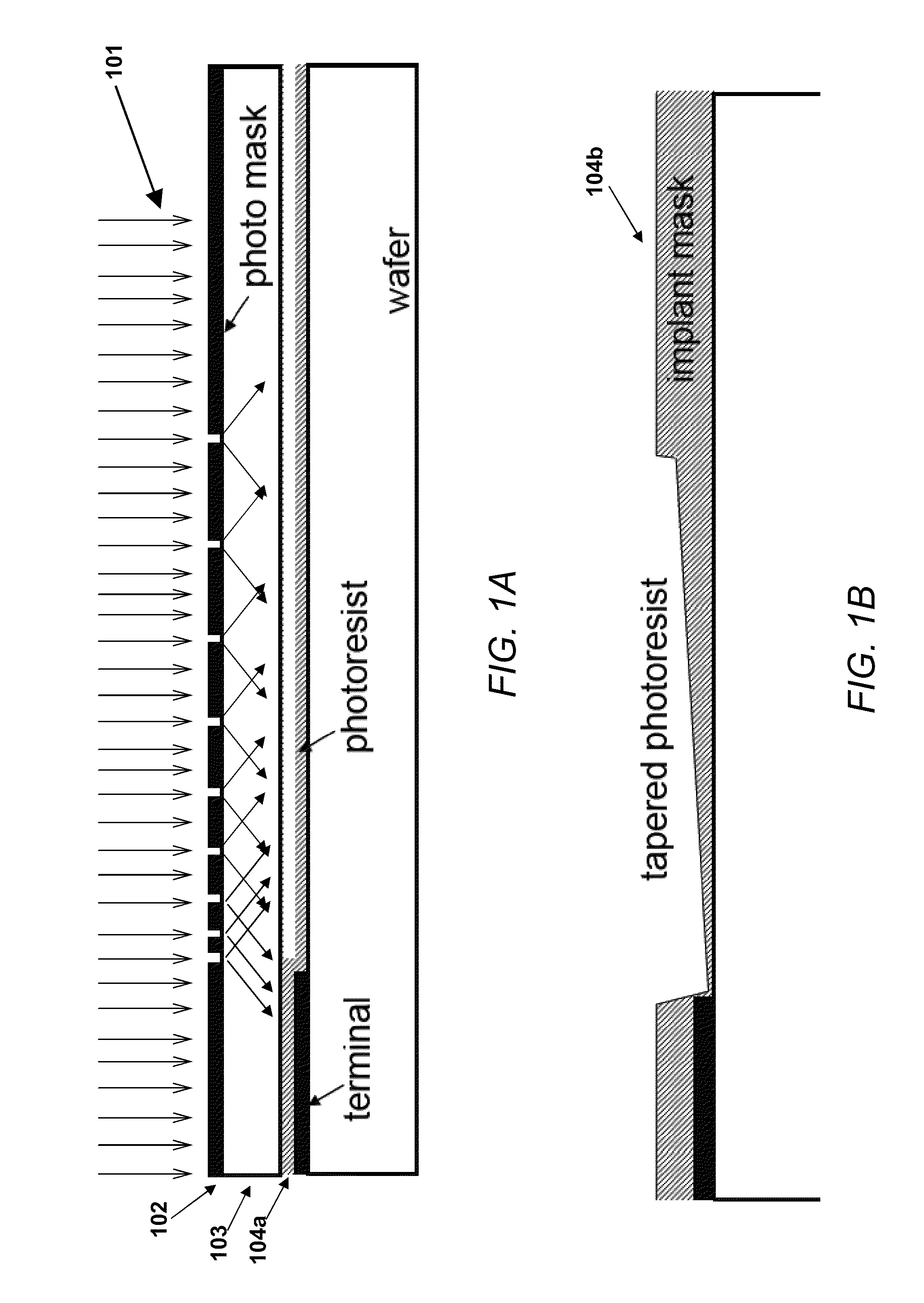

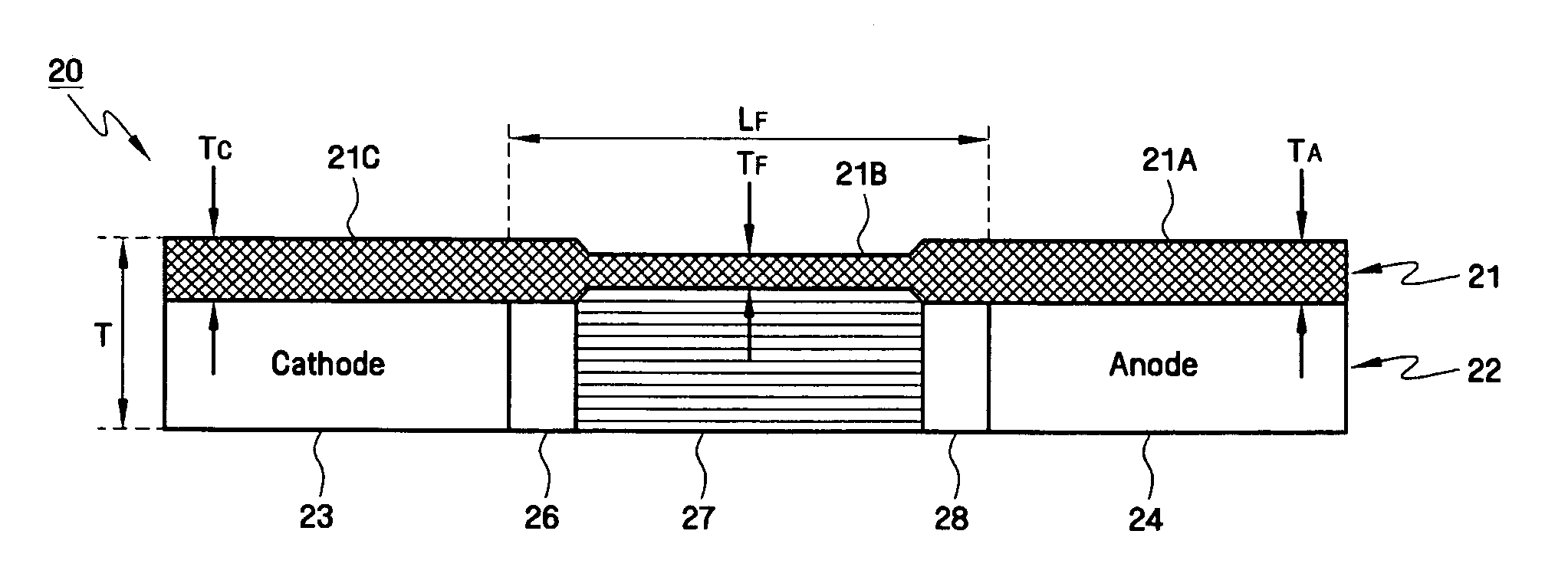

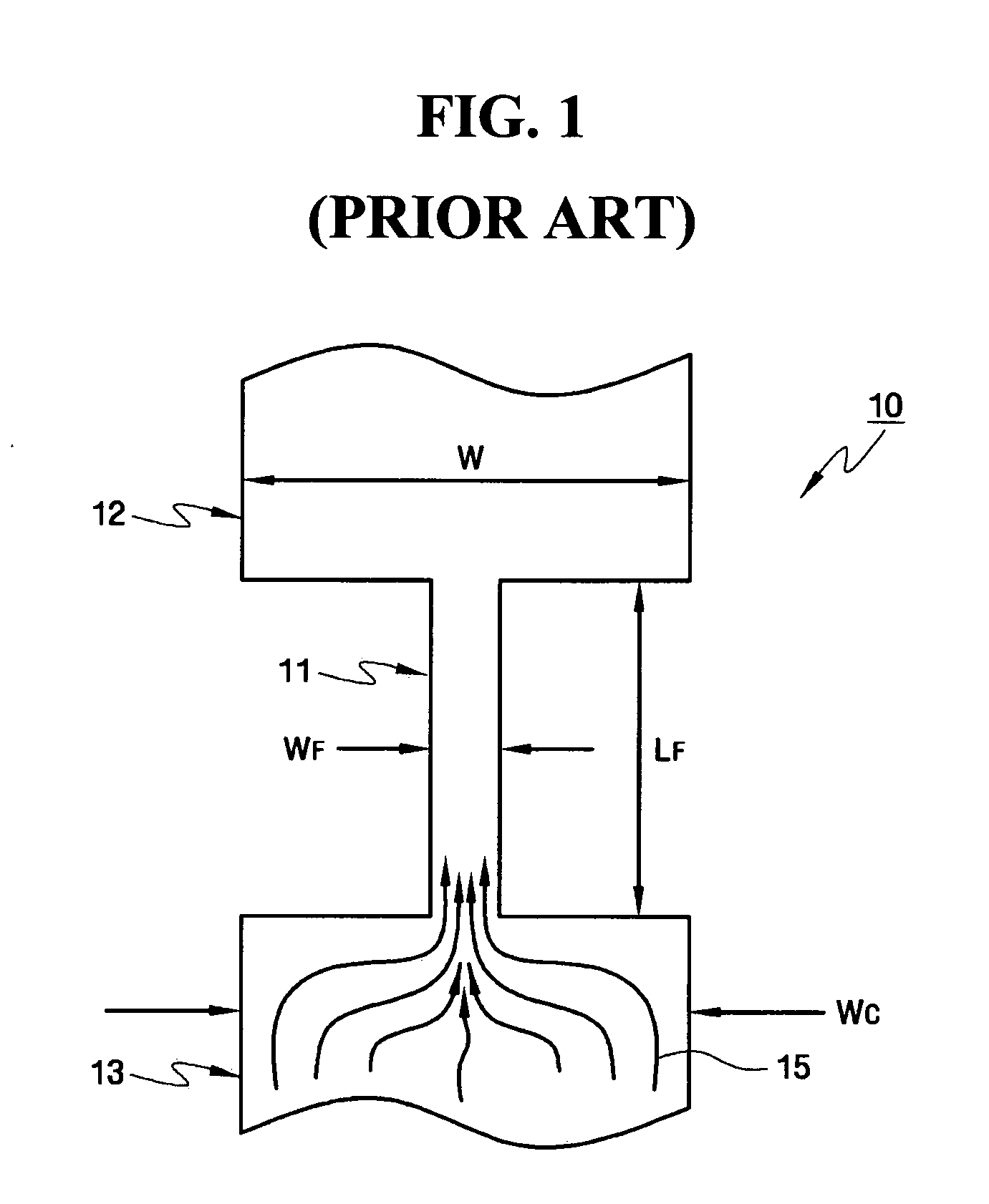

Junction Termination Extension with Controllable Doping Profile and Controllable Width for High-Voltage Electronic Devices

ActiveUS20100055882A1Semiconductor/solid-state device manufacturingSemiconductor devicesDopantSemiconductor materials

Methods for producing a junction termination extension surrounding the edge of a cathode or anode junction in a semiconductor substrate, where the junction termination extension has a controlled arbitrary lateral doping profile and a controlled arbitrary lateral width, are provided. A photosensitive material is illuminated through a photomask having a pattern of opaque and clear spaces therein, the photomask being separated from the photosensitive material so that the light diffuses before striking the photosensitive material. After processing, the photosensitive material so exposed produces a laterally tapered implant mask. Dopants are introduced into the semiconductor material and follow a shape of the laterally tapered implant mask to create a controlled arbitrary lateral doping profile and a controlled lateral width in the junction termination extension in the semiconductor.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

High-voltage vertical transistor with a multi-gradient drain doping profile

InactiveUS20050133858A1Semiconductor/solid-state device manufacturingSemiconductor devicesHigh voltage transistorsSubject matter

A high-voltage transistor includes first and second trenches that define a mesa in a semiconductor substrate. First and second field plate members are respectively disposed in the first and second trenches, with each of the first and second field plate members being separated from the mesa by a dielectric layer. The mesa includes a plurality of sections, each section having a substantially constant doping concentration gradient, the gradient of one section being at least 10% greater than the gradient of another section. It is emphasized that this abstract is provided to comply with the rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims.

Owner:POWER INTEGRATIONS INC

Devices and methods for constructing electrically programmable integrated fuses for low power applications

ActiveUS20070252237A1Increase resistanceImprove consistencySemiconductor/solid-state device detailsSolid-state devicesPower applicationEngineering

Electrically programmable integrated fuses are provided for low power applications. Integrated fuse devices have stacked structures with a polysilicon layer and a conductive layer formed on the polysilicon layer. The integrated fuses have structural features that enable the fuses to be reliably and efficiently programmed using low programming currents / voltages, while achieving consistency in fusing locations. For example, programming reliability and consistency is achieved by forming the conductive layers with varied thickness and forming the polysilicon layers with varied doping profiles, to provide more precise localized regions in which fusing events readily occur.

Owner:INFINEON TECH AG +1

Back-illuminated imaging device and method of fabricating same

ActiveUS7238583B2Effectively eliminate a backside dead bandSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorCondensed matter physics

Owner:SRI INTERNATIONAL

Method and fine-control collimator for accurate collimation and precise parallel alignment of scanned ion beams

InactiveUS7105839B2Easy to controlMore accurateStability-of-path spectrometersBeam/ray focussing/reflecting arrangementsBand shapeWave shape

In system for implanting workpieces with an accurately parallel scanned ion beam, a fine-control collimator construct is used to reduce the deviation of the scanned ion beam from a specified axis of parallelism and thereby improve its collimation. The shape of the fine-control collimator matches the ribbon shape of the beam and correction of parallelism in two orthogonal directions is possible. Measurement of the non-parallelism is accomplished by sampling the scanned beam in two planes and comparing timing information; and such measurement is calibrated to the orientation of the workpiece in the plane where ion implantation occurs. Measurement of non-uniformity in the doping profile is accomplished using the same means; and the scan waveform is adjusted to substantially remove any non-uniformity in the doping profile.

Owner:WHITE NICHOLAS R

CMOS imaging for ALC and CDS

ActiveUS20050001143A1Television system detailsTelevision system scanning detailsFloating diffusionPhoto conversion

Embodiments of the invention provide pixel cells that allow both automatic light control and correlated double sampling operations. The pixel cell includes first and second photo-conversion devices that can be separately read out. For example, the second photo-conversion device can be the pixel cells' floating diffusion region, with an area and doping profile suitable for photo-conversion. An image sensor may include an array of pixel cells, some or all of which have two photo-conversion devices, and peripheral circuitry for reading out signals from the pixel cells. The image sensor's readout circuitry may monitor charge generated by the second photo-conversion devices to determine when to read out signals from the first photo-conversion devices.

Owner:APTINA IMAGING CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com