Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

166 results about "Hot carrier effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

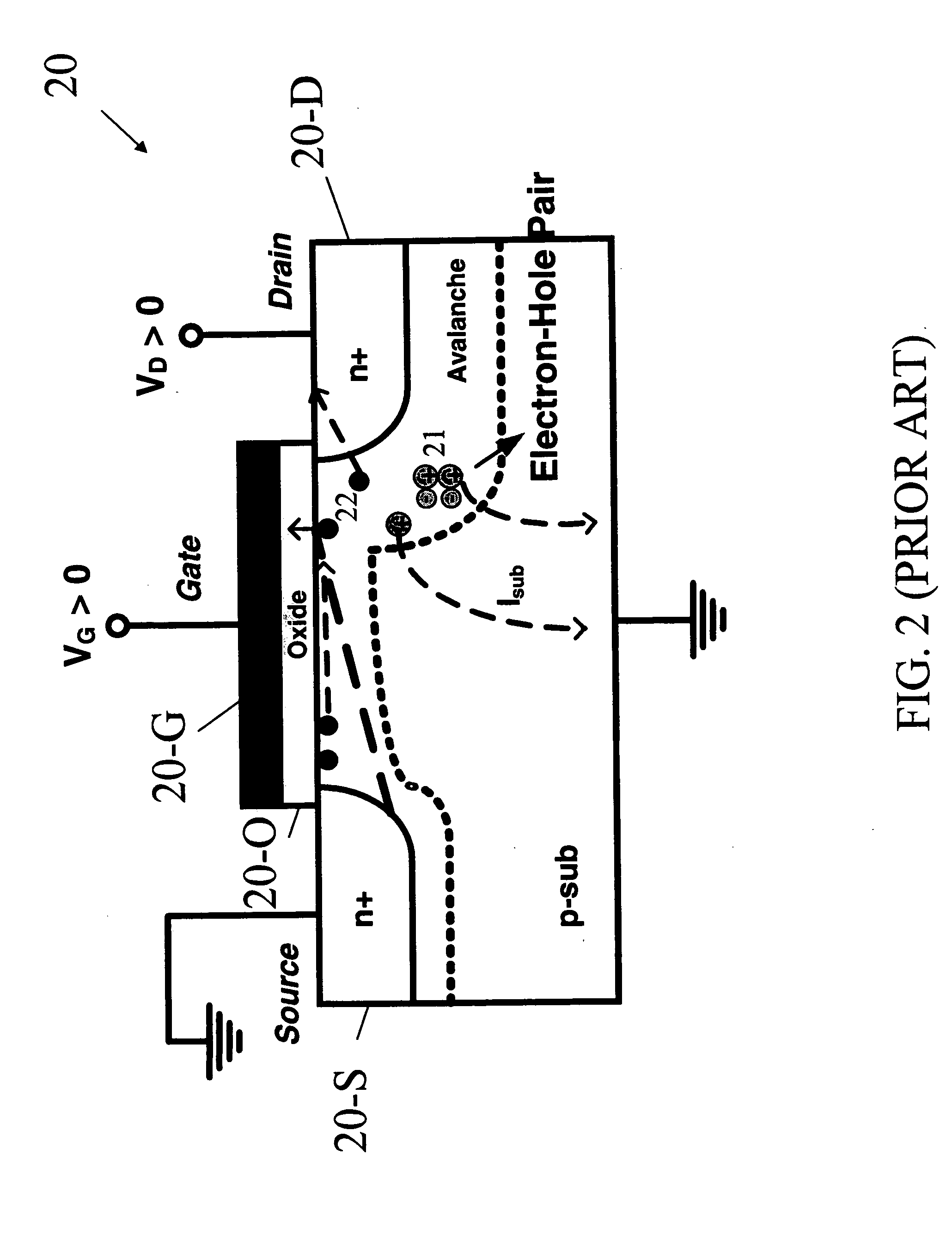

Hot carrier effects are brought about or aggravated by reductions in device dimensions without corresponding reductions in operating voltages, resulting in higher electric fields internal to the device. Problems due to hot carrier injection therefore constitute a major obstacle towards higher circuit densities.

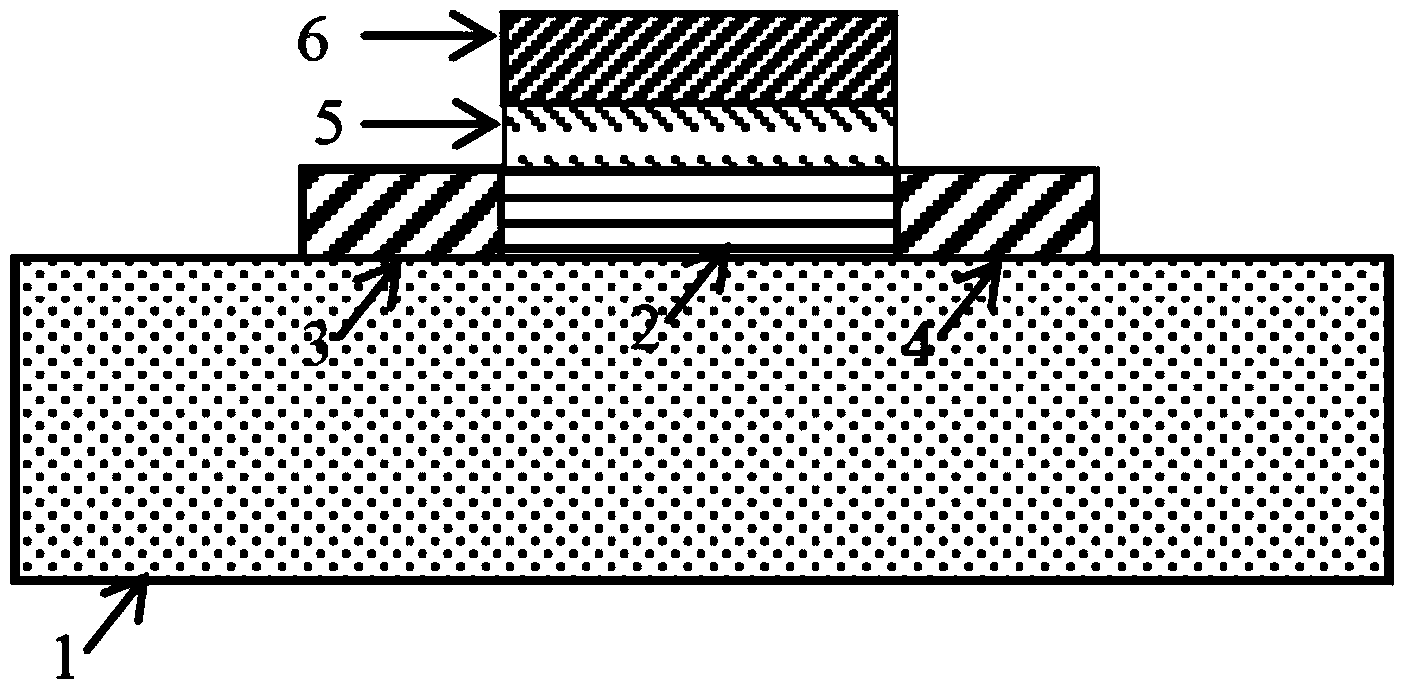

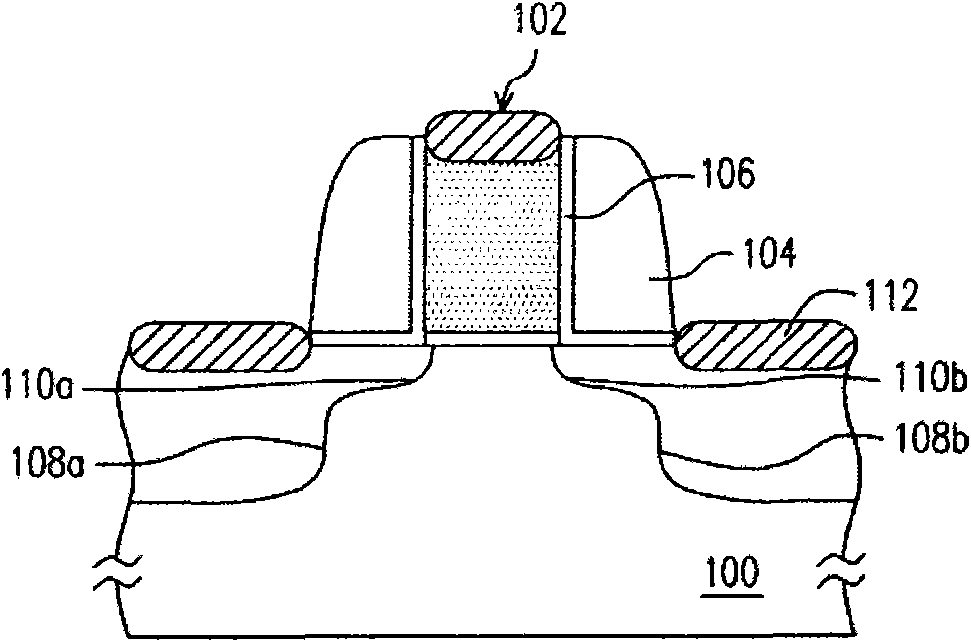

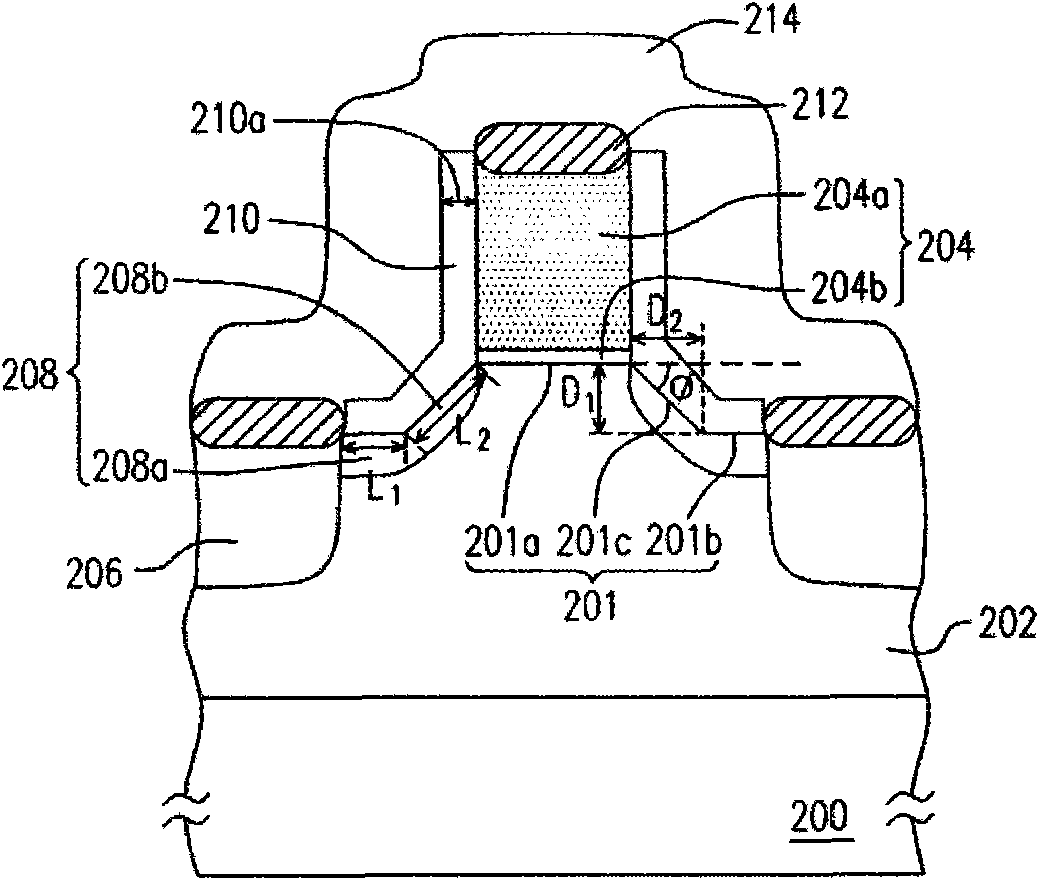

High Voltage LDMOS Transistor and Method

InactiveUS20090273029A1Easy to solveTransistorSemiconductor/solid-state device manufacturingLDMOSDielectric

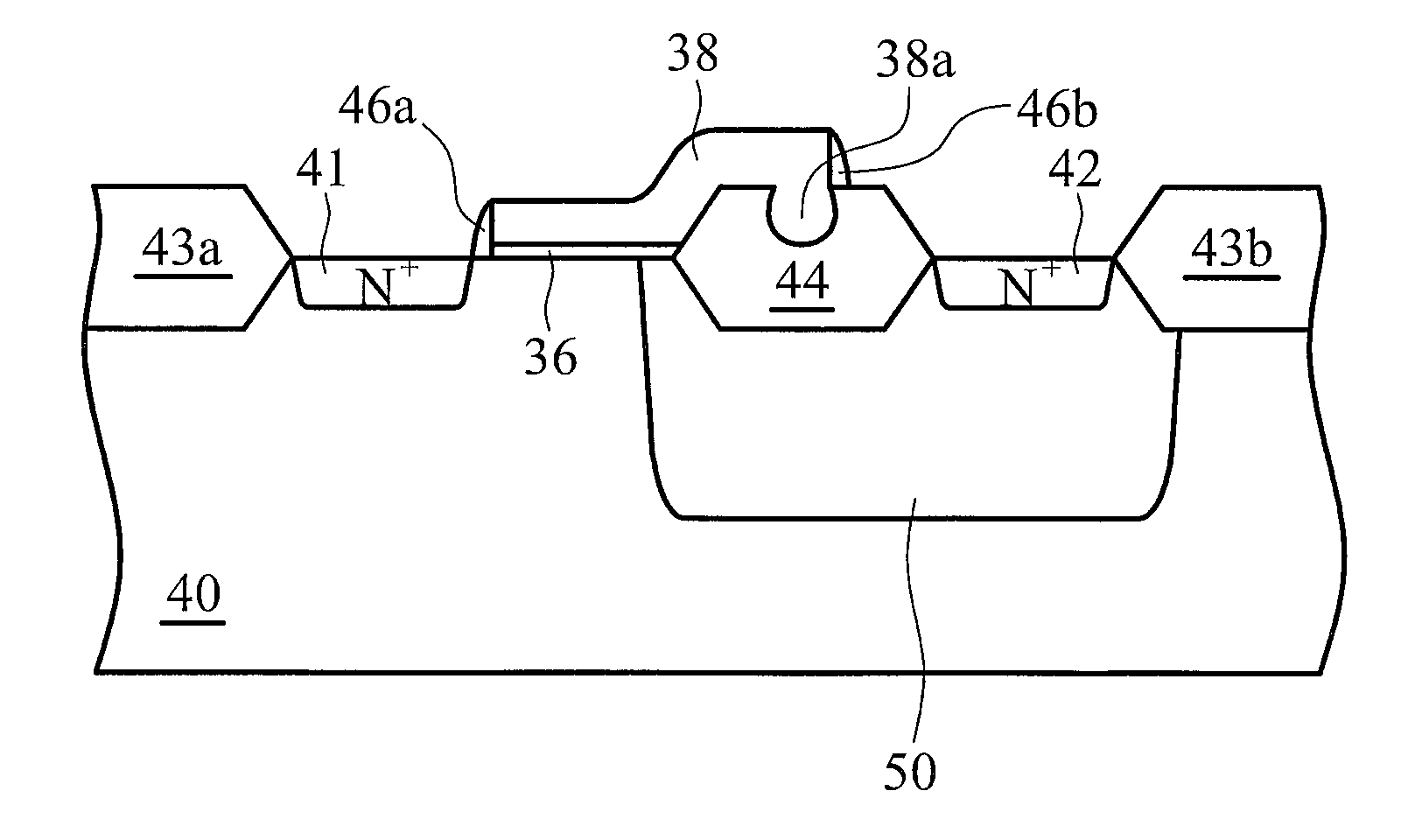

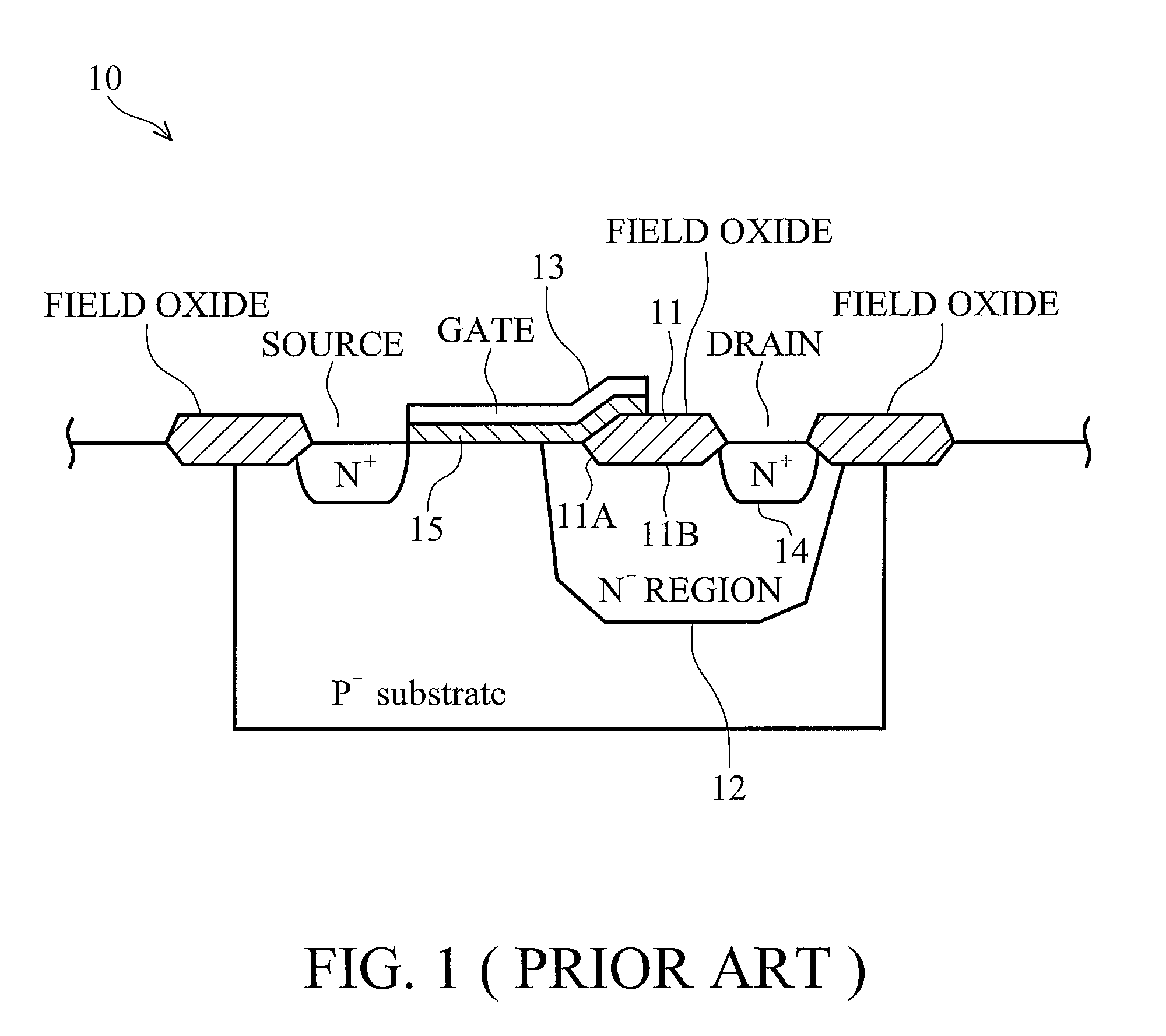

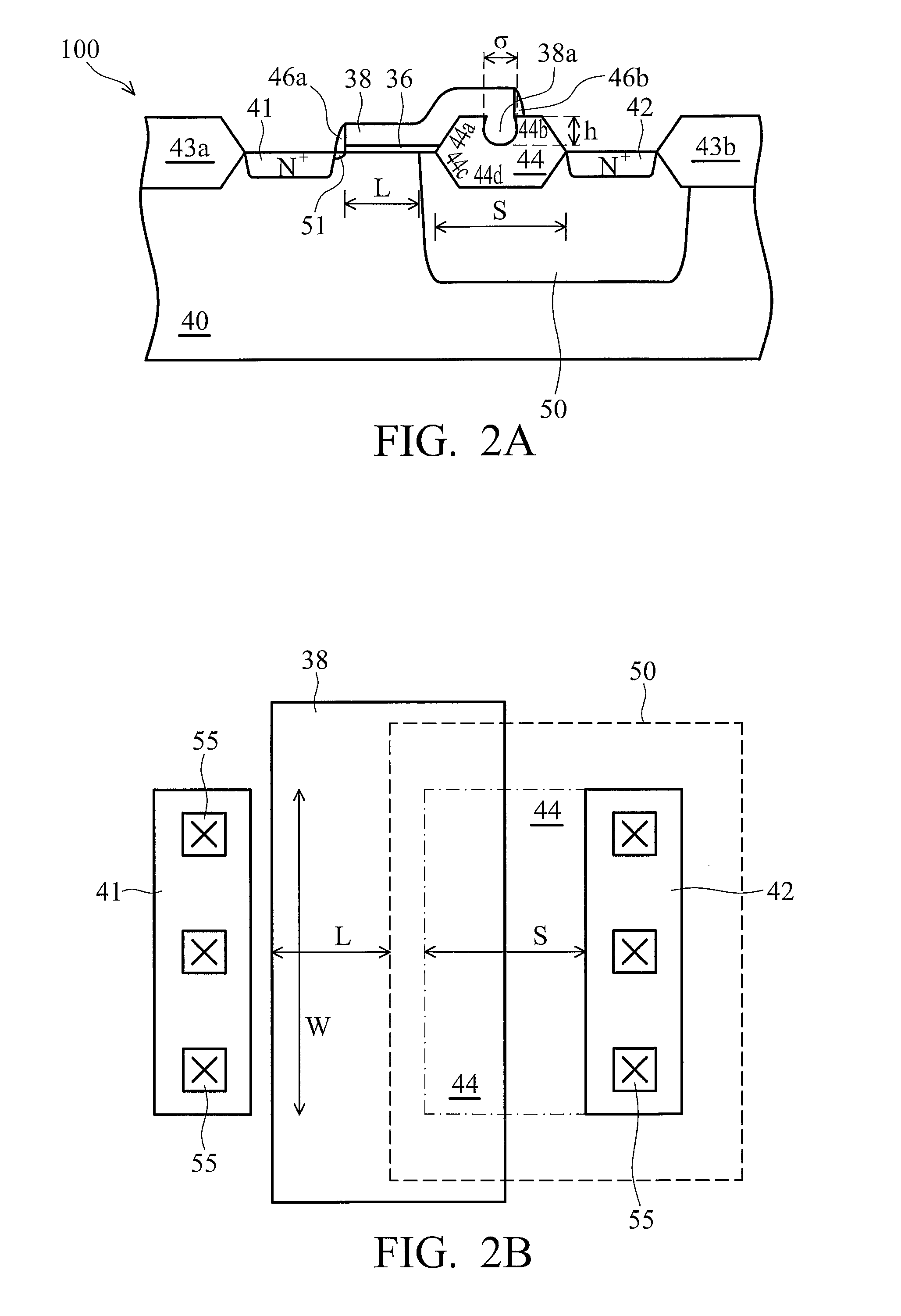

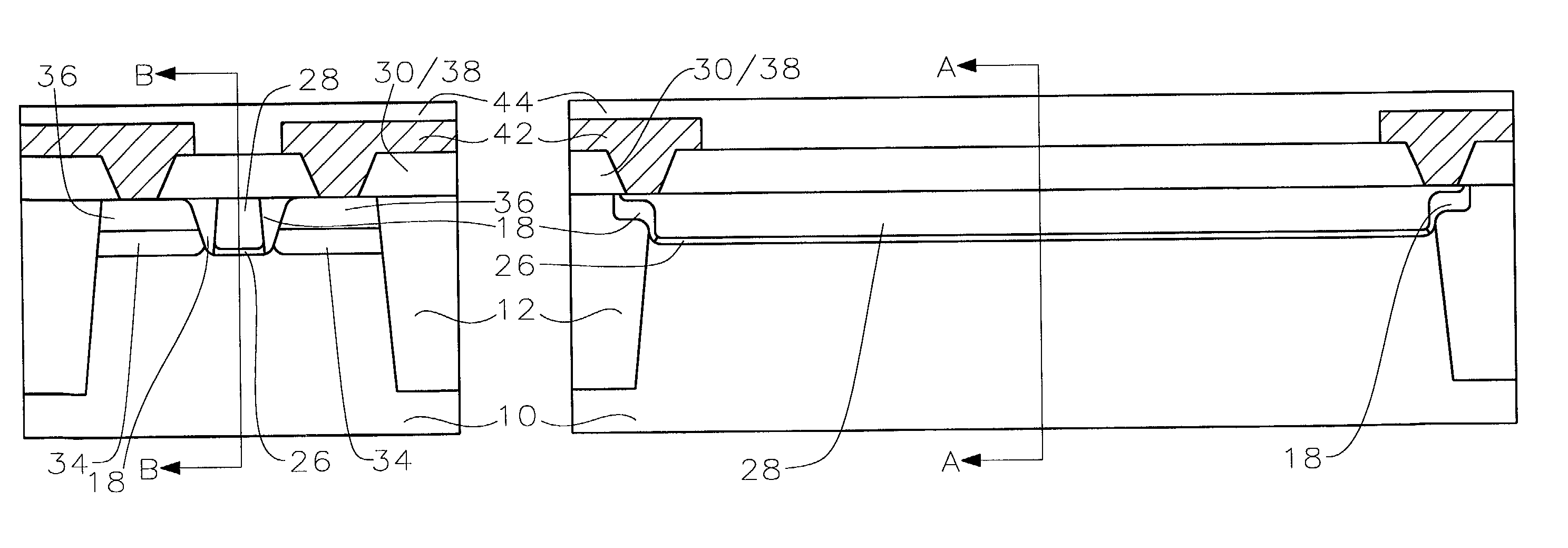

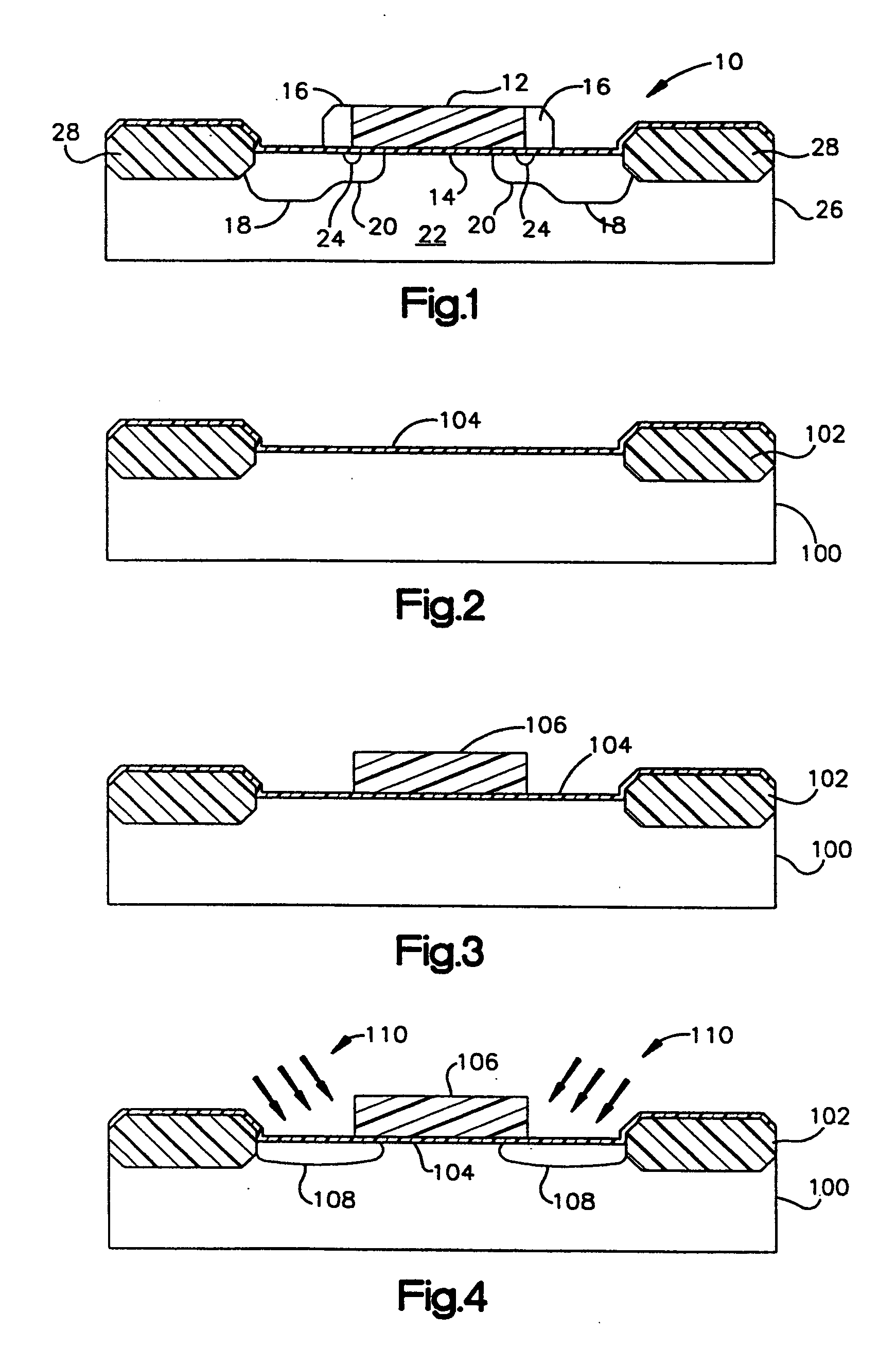

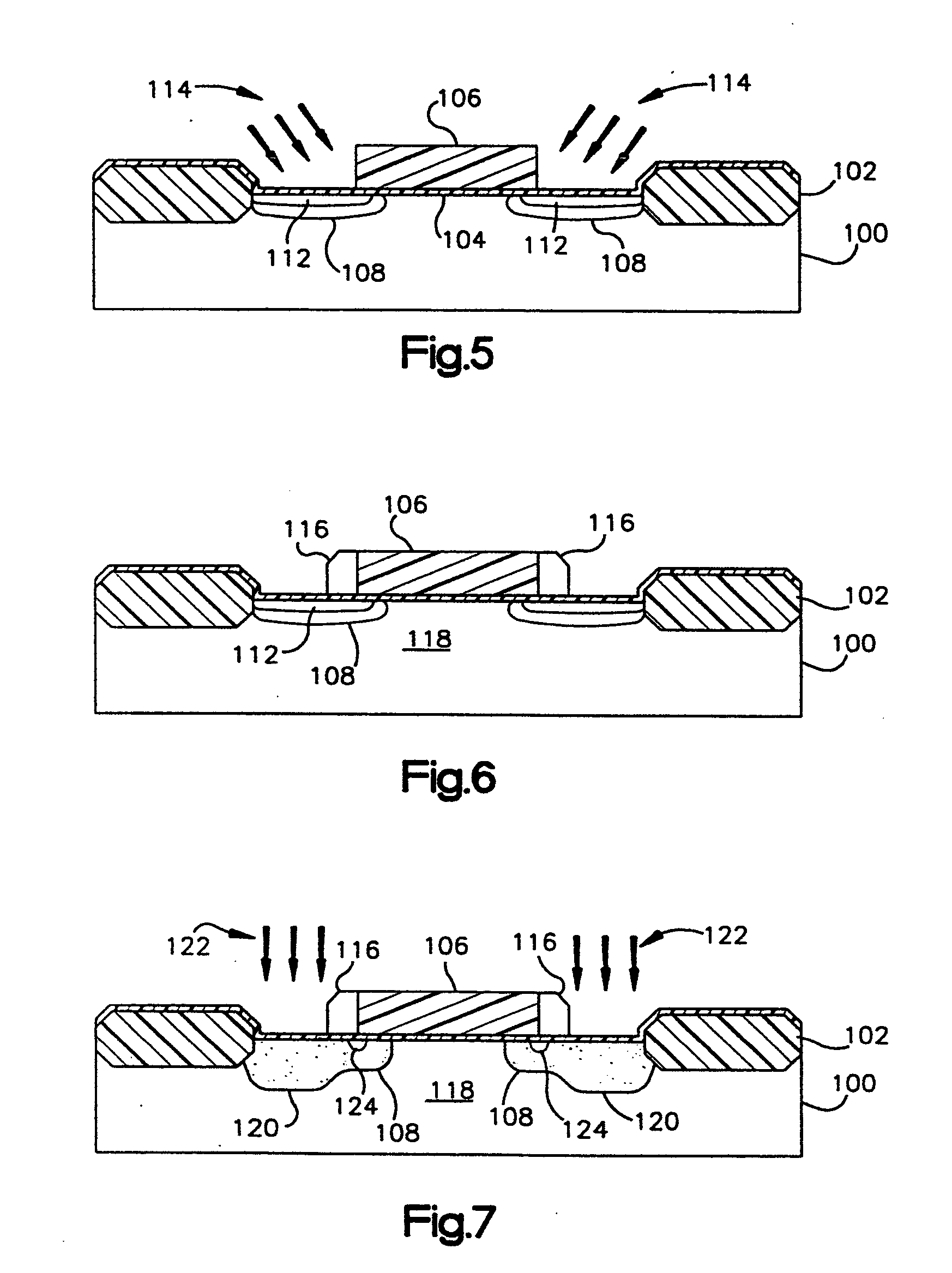

An LDMOS transistor structure and methods of making the same are provided. The structure includes a gate electrode extended on an upper boundary of an extension dielectric region that separates the gate electrode from the drain region of the LDMOS transistor. Moreover, at an area close to an edge of the extended gate electrode portion, the gate electrode further projects downwards into a convex-shaped recess or groove in the upper boundary of the extension dielectric region, forming a tongue. LDMOS transistors with this structure may provide improved suppression of hot carrier effects.

Owner:TAIWAN SEMICON MFG CO LTD

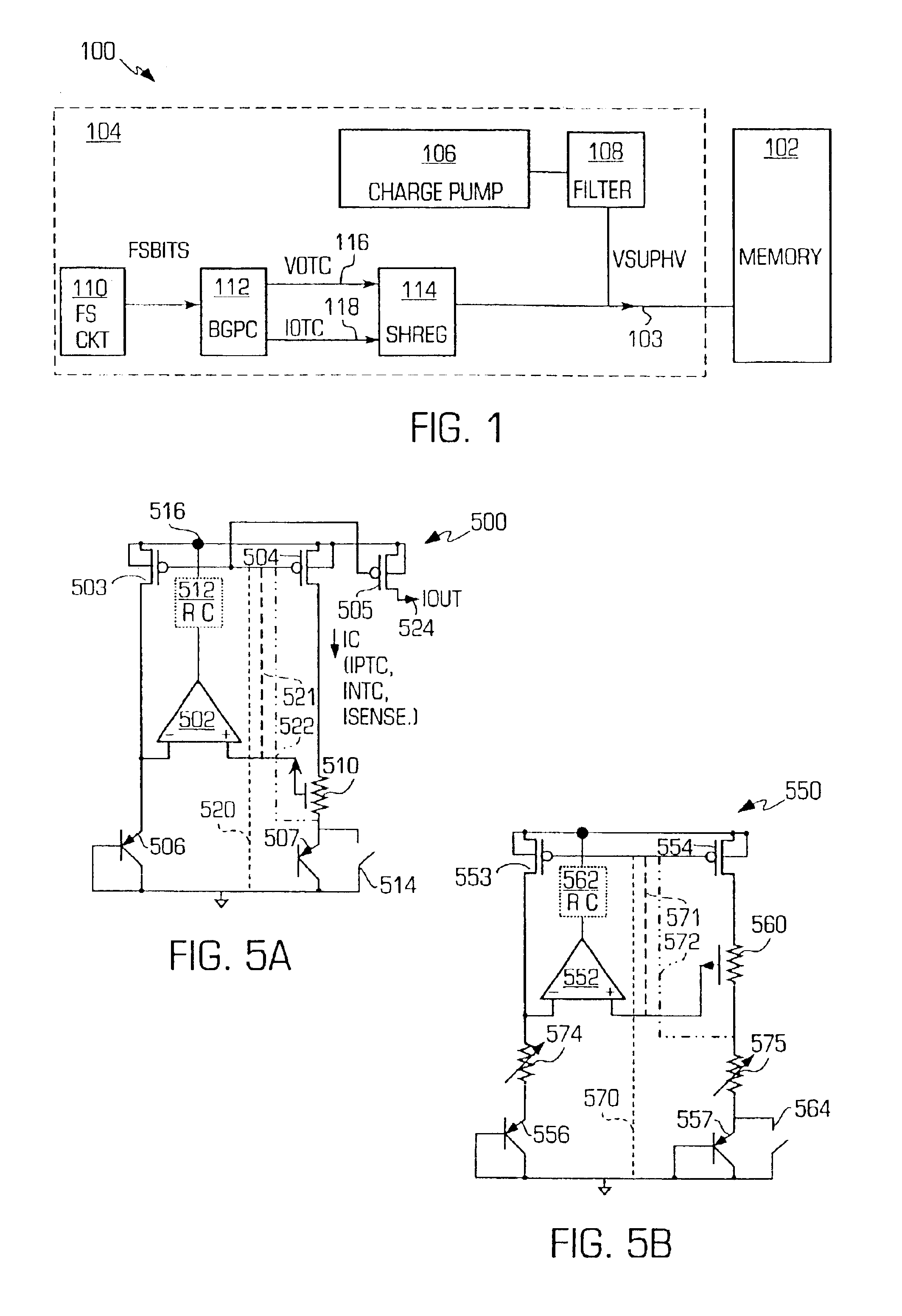

Curved fractional CMOS bandgap reference

InactiveUS6841982B2Voltage is accurateArea minimizationElectric variable regulationEngineeringDigital control

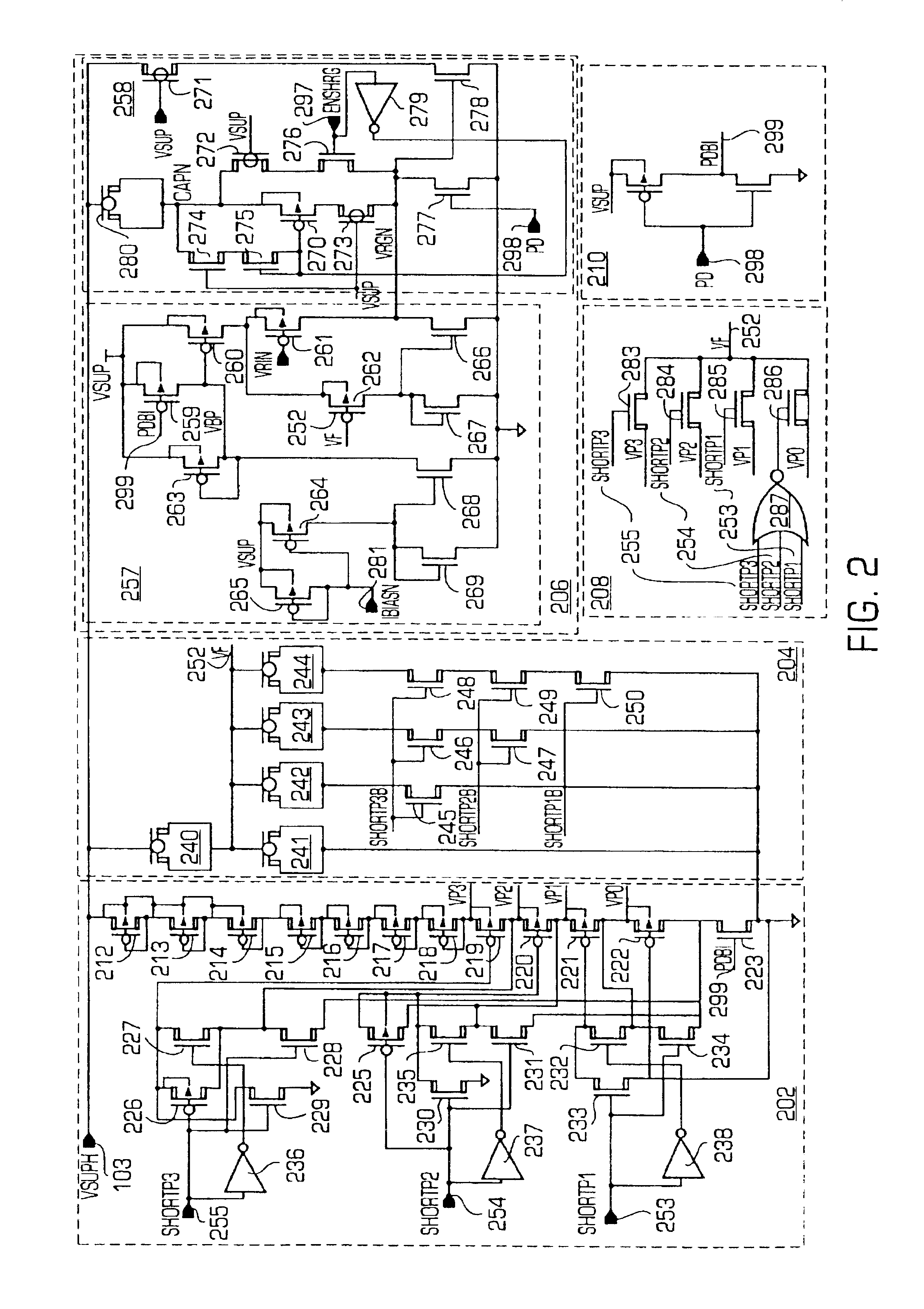

A high shunt regulator provides precise voltage over process, temperature, power supply, and foundries. The HV level is settable by a digital control bits such as fuse bits. A filter network filters out the ripple noise and charge transient. A tracking capacitor divider network speeds up response time. A fractional band gap reference provides fractional bandgap voltage and current, and operates at low power supply and has superior power supply rejection. It is unsusceptible to substrate hot carrier effect. It exposes very little to drain induced barrier lowering effect. The bandgap core has better than conventional transient response and stability. One embodiment has adjustable level control. Complementary TC (temperature coefficient) trimming allows efficient realization of zero temperature coefficients of current and voltage. Higher order curvature correction of voltage and current is integrated. Replica bias for the control loop is presented. A Binary and Approximation Complementary TC search trimming is described. A zero TC fractional voltage less than the theoretical bandgap voltage (<<−1.2. Volt) is realizable. The bandgap core has a filtering mechanism to reject high frequency noise. A low power startup circuit powers up the band gap. The band gap also has variable impedance.

Owner:SILICON STORAGE TECHNOLOGY

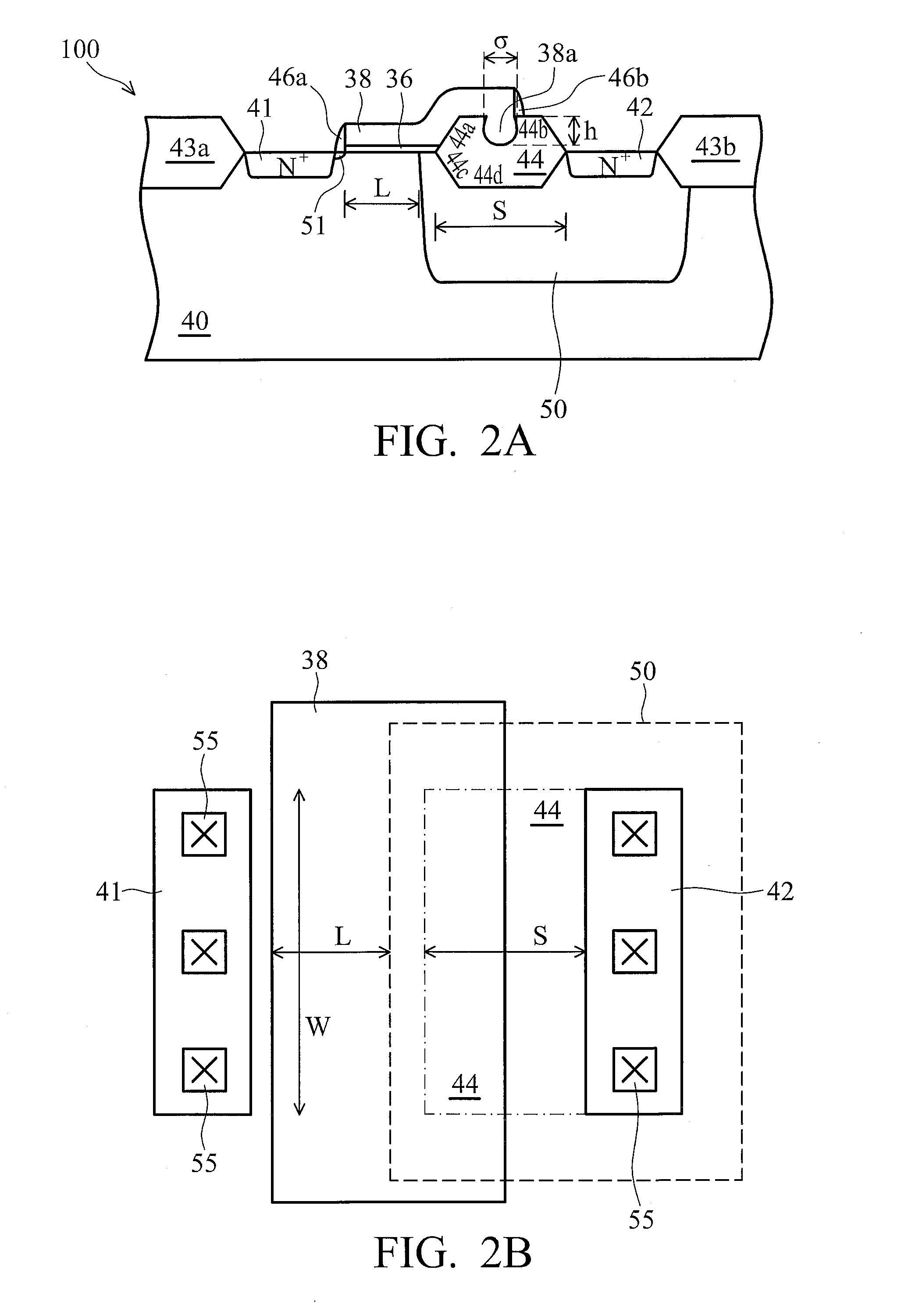

High voltage LDMOS transistor

InactiveUS8174071B2Easy to solveTransistorSemiconductor/solid-state device manufacturingLDMOSDielectric

An LDMOS transistor structure and methods of making the same are provided. The structure includes a gate electrode extended on an upper boundary of an extension dielectric region that separates the gate electrode from the drain region of the LDMOS transistor. Moreover, at an area close to an edge of the extended gate electrode portion, the gate electrode further projects downwards into a convex-shaped recess or groove in the upper boundary of the extension dielectric region, forming a tongue. LDMOS transistors with this structure may provide improved suppression of hot carrier effects.

Owner:TAIWAN SEMICON MFG CO LTD

Process flow for a performance enhanced MOSFET with self-aligned, recessed channel

ActiveUS7091092B2Reduce decreaseIncrease capacitanceTransistorSolid-state devicesCapacitanceGate dielectric

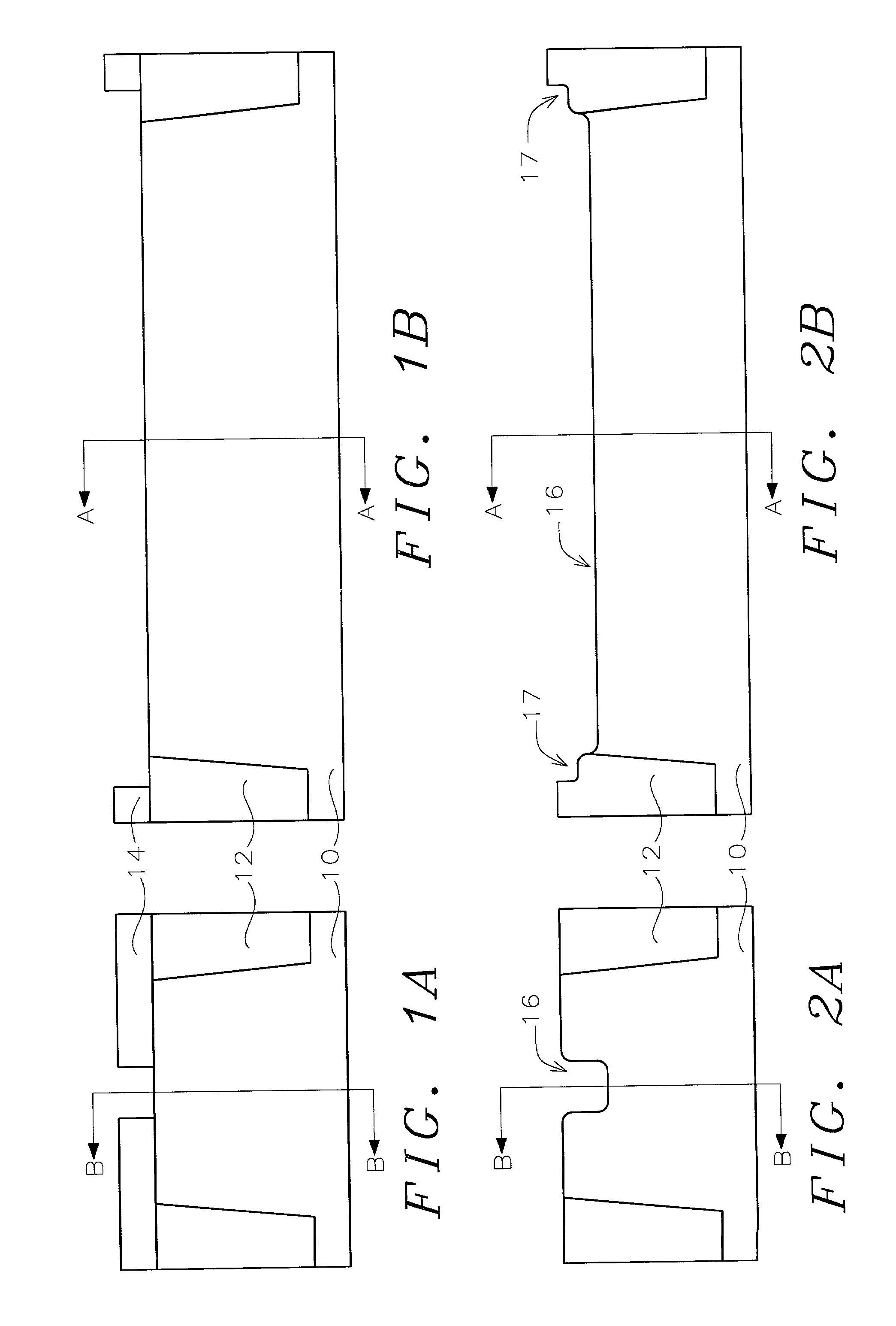

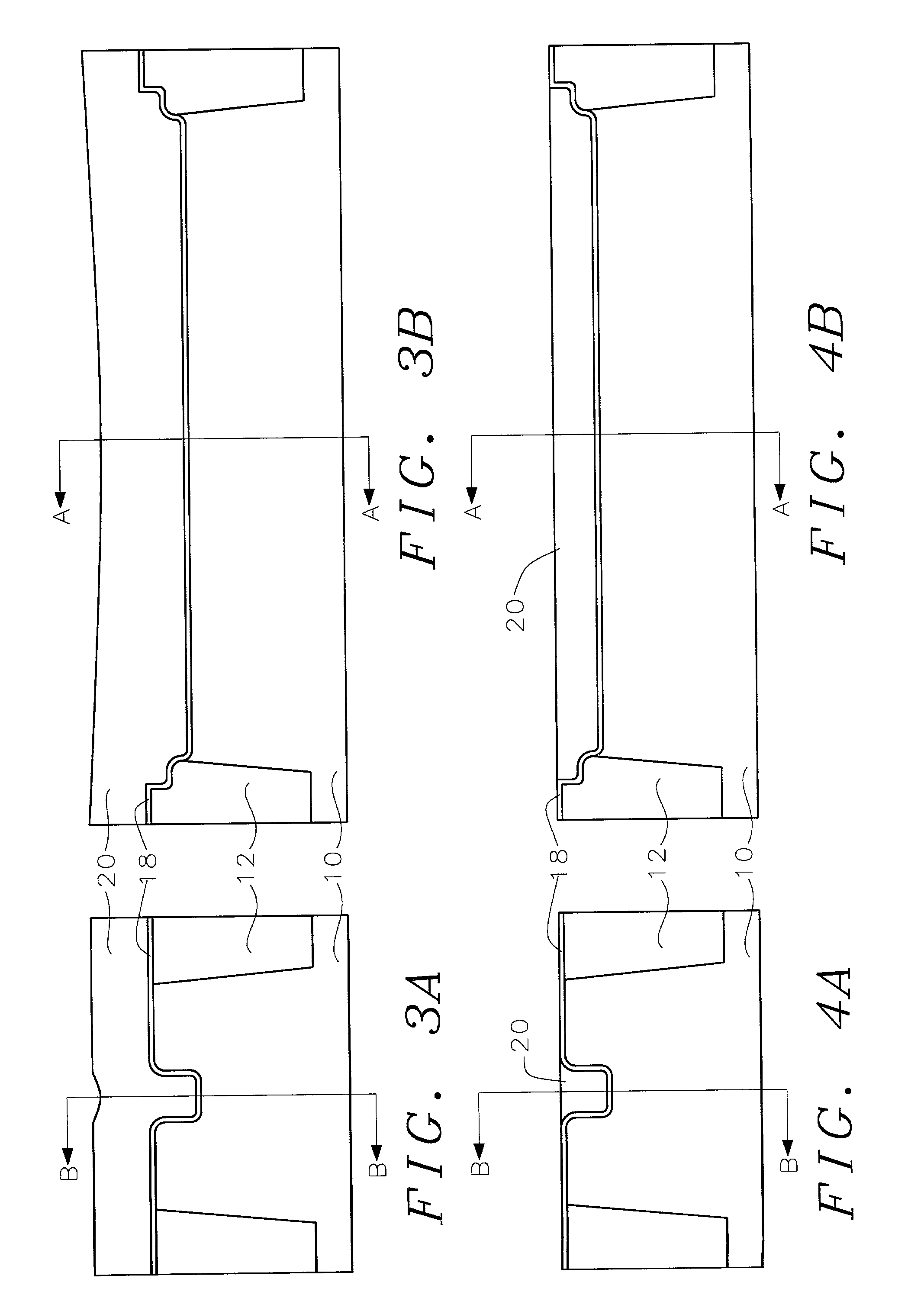

A method for forming a self-aligned, recessed channel, MOSFET device that alleviates problems due to short channel and hot carrier effects while reducing inter-electrode capacitance is described. A thin pad oxide layer is grown overlying the substrate and a gate recess, followed by deposition of a thick silicon nitride layer filling the gate recess. The top surface is planarized exposing the pad oxide layer. An additional oxide layer is grown, thickening the pad oxide layer. A portion of the silicon nitride layer is etched away and additional oxide layer is again grown. This forms a tapered oxide layer along the sidewalls of the gate recess. The remaining silicon nitride layer is removed. The oxide layer at the bottom of the gate recess is removed and a gate dielectric layer is grown. Gate polysilicon is deposited filling the gate recess. S / D implantations, metallization, and passivation complete fabrication of the device.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING +1

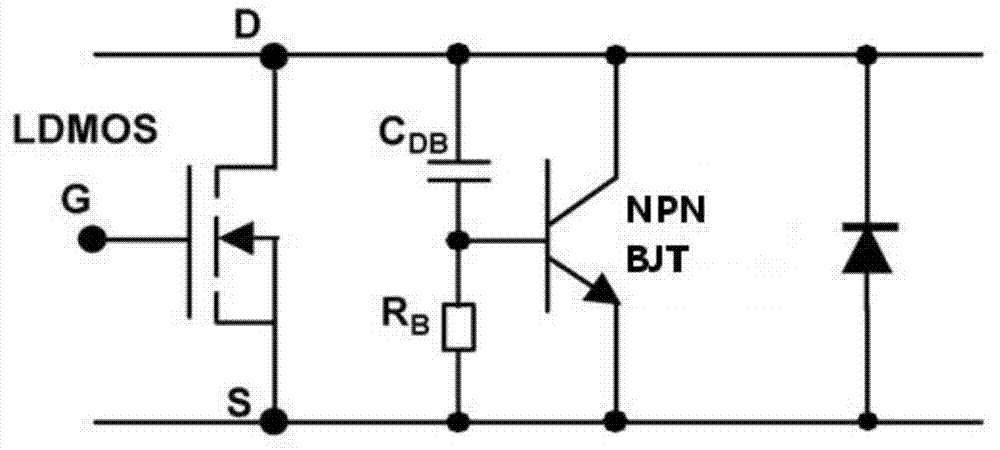

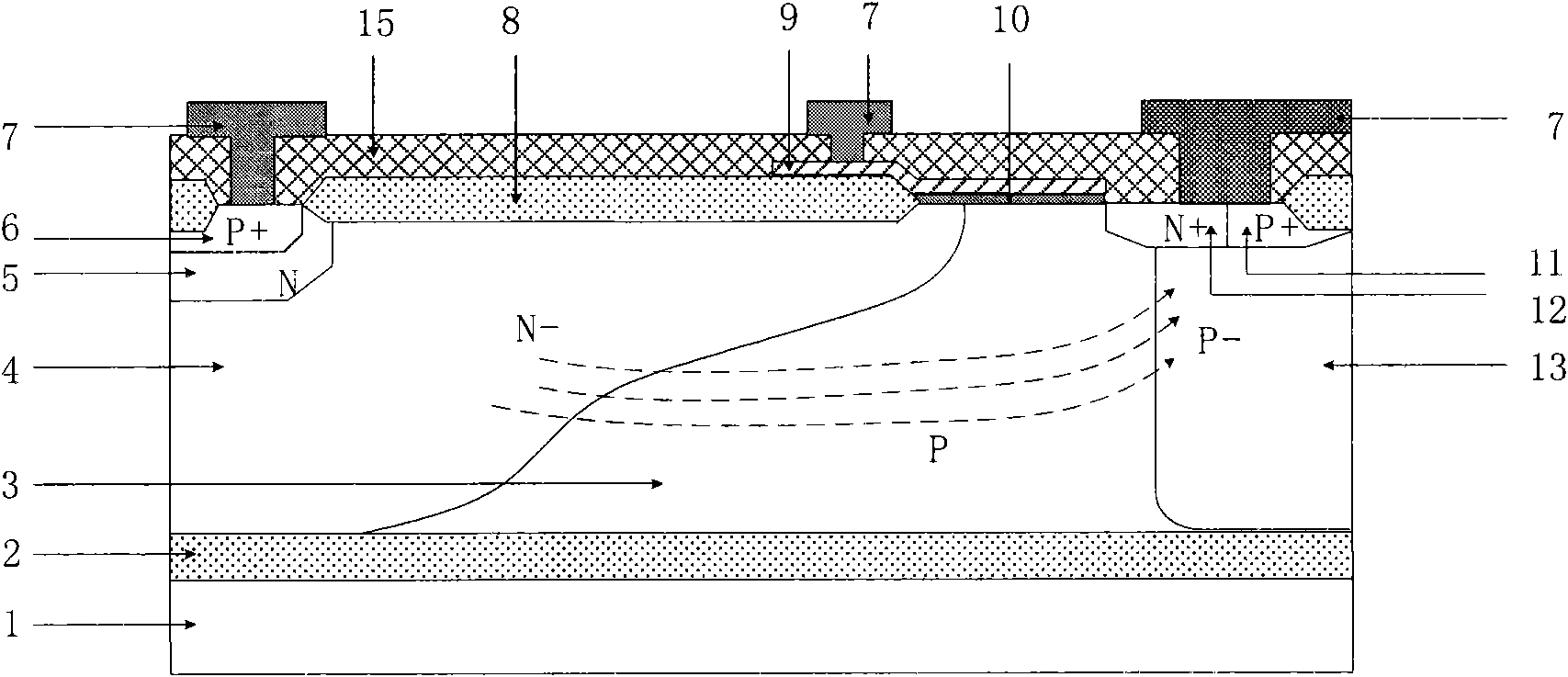

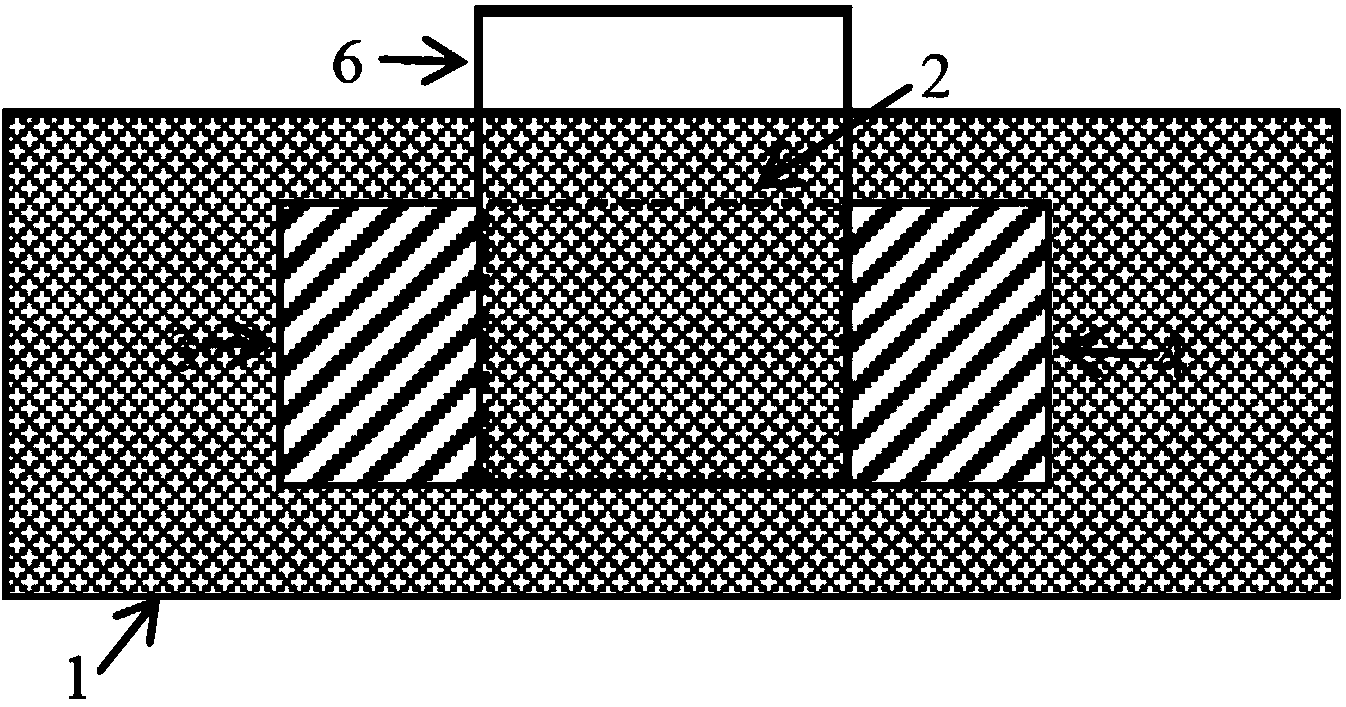

Radio frequency (RF) laterally diffused metal oxide semiconductor (LDMOS) component and manufacture method

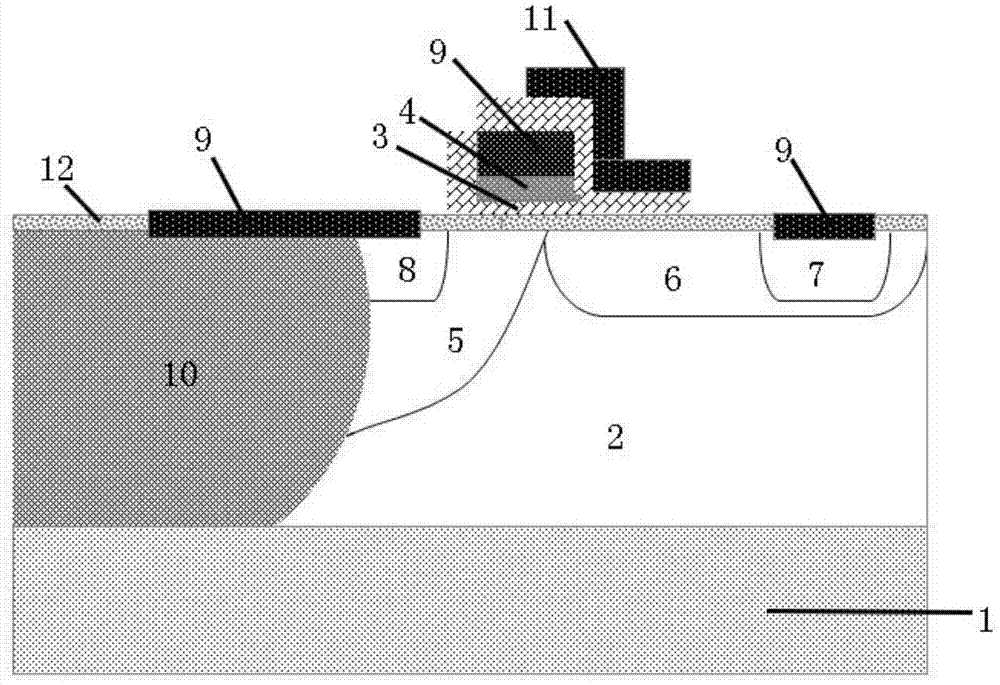

ActiveCN103035727AImprove transconductanceLower base resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesRadio frequencyTransconductance

The invention discloses a radio frequency (RF) laterally diffused metal oxide semiconductor (LDMOS) component. A light dope P type buried layer and a middle dope buried layer in the light dope P type buried layer are additionally arranged under a P type channel region. The base electrode resistance of a parasitic non-protein nitrogen (NPN) pipe can be reduced, so that snapback effect is not prone to be generated. A reversed diode formed by a source electrode, the channel and the buried layer can strangulate drain-source voltage of an LDMOS and can sink extra current on a substrate. Thick gate oxide at the drain electrode end can reduce hot carrier effect, and thin gate oxide at the source electrode end can improve transconductance of the component. The invention further discloses a manufacture method of the RF LDMOS component. In process realization, the manufacture method only adds two photoetching steps in an existing process so as to be easy to implement.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

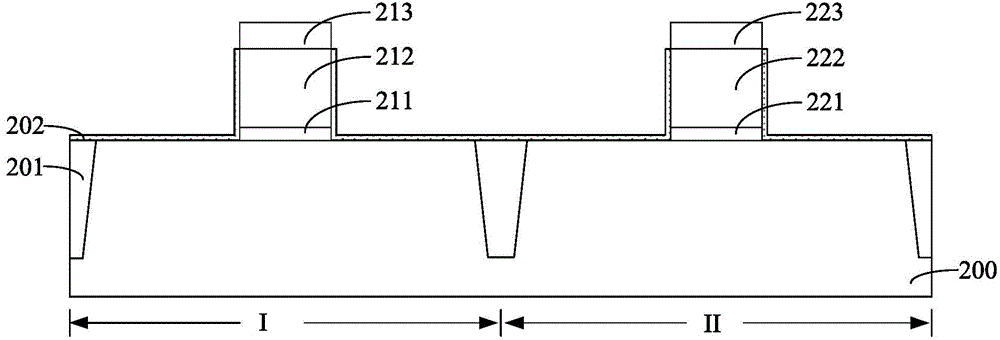

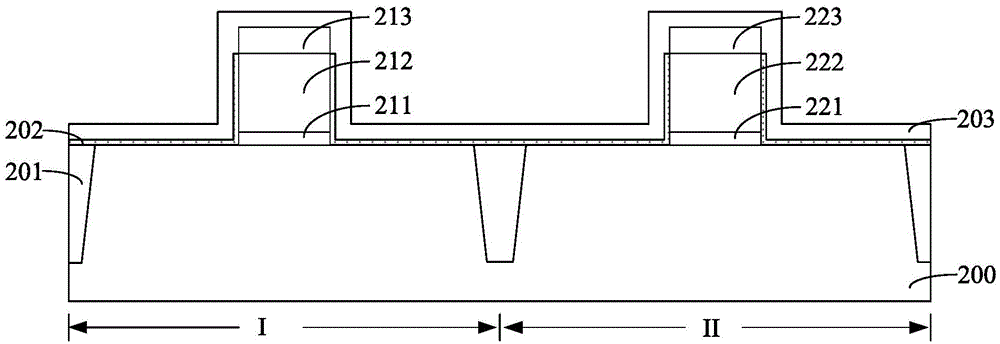

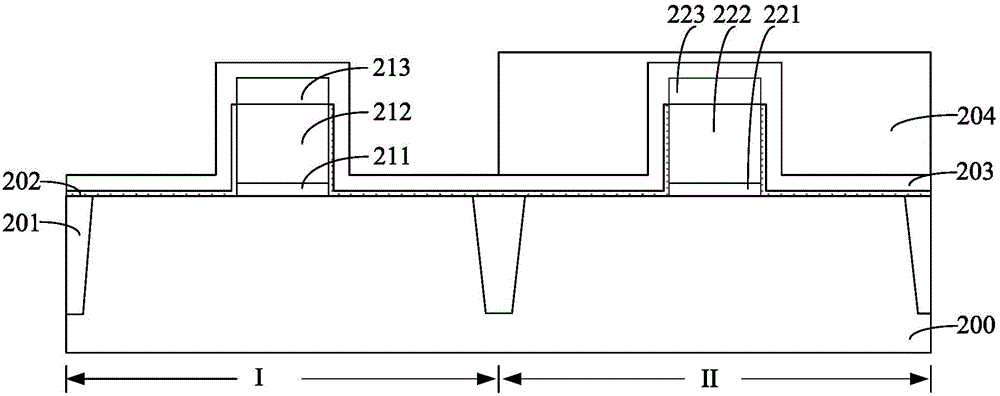

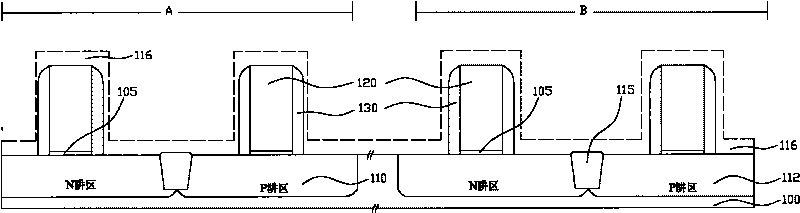

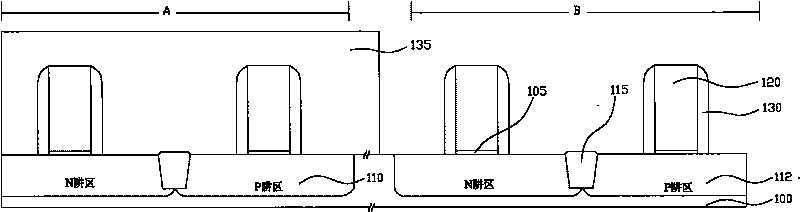

Semiconductor device forming method

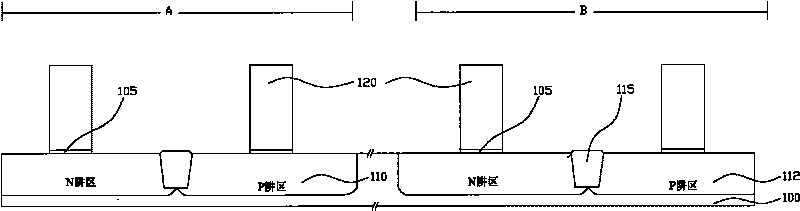

ActiveCN105448679AIncrease stressReduce distanceSemiconductor/solid-state device manufacturingCharge carrier mobilityElectrical performance

The invention discloses a semiconductor device forming method, and the method comprises the steps: providing a substrate, forming a first grid structure and a second grid structure on the surface of the substrate, and forming first mask layers on the surface of the substrate, the surface of the first grid structure and the surface of the second grid structure; Etching the parts, at two sides of the first grid structure, of the substrate to form a first groove, and forming a first offset side wall through the remaining first mask layer in a first region; forming a light-doped region in the substrate below the first offset side wall; forming a first stress layer which is filled in the first groove; forming a second mask layer; etching the parts, at two sides of the second grid structure, of the substrate to form a second groove, and forming a second offset side wall through the remaining first and second mask layers in a second region; forming a second light-doped region in the substrate below the second offset side wall; and forming a second stress layer filled in the second groove. The method effectively alleviates the hot carrier effect while improving the carrier mobility of a semiconductor device, and optimizes the electrical performances of the semiconductor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method for manufacturing silicon oxynitride gate oxide layer

ActiveCN102122614ALow densityImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSilicon oxideDangling bond

The invention provides a method for manufacturing a silicon oxynitride gate oxide layer of an MOS (metal oxide semiconductor) device, and the method comprises the following steps: firstly nitridizing on a provided silicon substrate for forming silicon oxynitride, then performing thermal oxidization for forming a first silicon oxide layer between the silicon oxynitride and the silicon substrate and a second silicon oxide layer on the silicon oxynitride, and then depositing polysilicon on the second silicon oxide layer after secondly annealing the silicon substrate; and etching for forming a gate and the silicon oxynitride gate oxide layer. The silicon oxide layer is introduced between the silicon substrate and the silicon oxynitride, thereby reducing dangling bonds between the silicon oxynitride gate oxide layer and the silicon substrate, further reducing the interface state charge density between the silicon oxynitride gate oxide layer and the substrate and improving certain properties of the MOS device, such as improving the stability of threshold voltage of the device, reducing the hot-carrier effect and the flicker noise of the device and the like.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Lightly doped drain forming method and semiconductor device

InactiveCN101740517AEasy to driveHigh speedTransistorSemiconductor/solid-state device manufacturingCapacitanceEngineering

The invention provides a lightly doped drain forming method and a semiconductor device. The method comprises the following steps of: providing a semiconductor substrate, wherein the semiconductor substrate comprises a core device area and an input / output device area, and the side of a grid is provided with a first side wall; forming a masking layer on the semiconductor substrate to cover the core device area; removing the first side wall outside the side wall of the grid in the input / output device area; removing the masking layer covered on the core device area; forming lightly doped drains in the core device area and the input / output device area by a ion implantation method, wherein the first side wall outside the side wall of the grid in the core device area blocks the ions from being implanted into the lower area. The lightly doped drain forming method can improve the overlapping capacitance of the grid and source / drain, avoid generating hot carrier effect, and improve the property and reliability of the input / output device.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

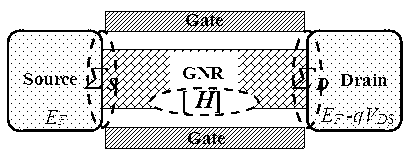

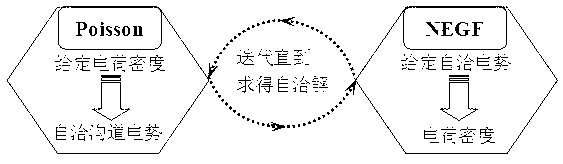

Graphene nanoribbon field-effect tube (GNRFET) with asymmetric HALO-lightly-doped drain (HALO-LDD) structure

InactiveCN103077968AReduce off-state currentGood gating abilitySemiconductor devicesPower flowSwitched current

The invention discloses a graphene nanoribbon field-effect tube (GNRFET) with an asymmetric HALO-lightly-doped drain (HALO-LDD) structure. A transport model which is suitable for a non-uniformly-doped GNRFET is constructed on the basis of a quantum mechanics non-balance Green function theoretical frame under an open boundary condition through self-consistent solution of 3D-Poisson and Schr.dinger equations, and the influence of an asymmetric HALO-LDD doping strategy on the electrical properties of the GNRFET is analyzed and calculated by using the model. As proved by comparison and analysis of the electric properties such as the output properties, transfer properties, switch current ratios, sub-threshold amplitudes and threshold voltage drifts of GNRFETs for which other doping strategies are adopted, the GNRFET with the doping structure has a higher switch current ratio, lower drain current, a smaller sub-threshold amplitude and a smaller threshold voltage drift, i.e., the GNRFET for which the asymmetric HALO-LDD doping strategy is adopted has a better grid control capability, and a short-groove effect and a hot carrier effect can be effectively restrained.

Owner:NANJING UNIV OF POSTS & TELECOMM

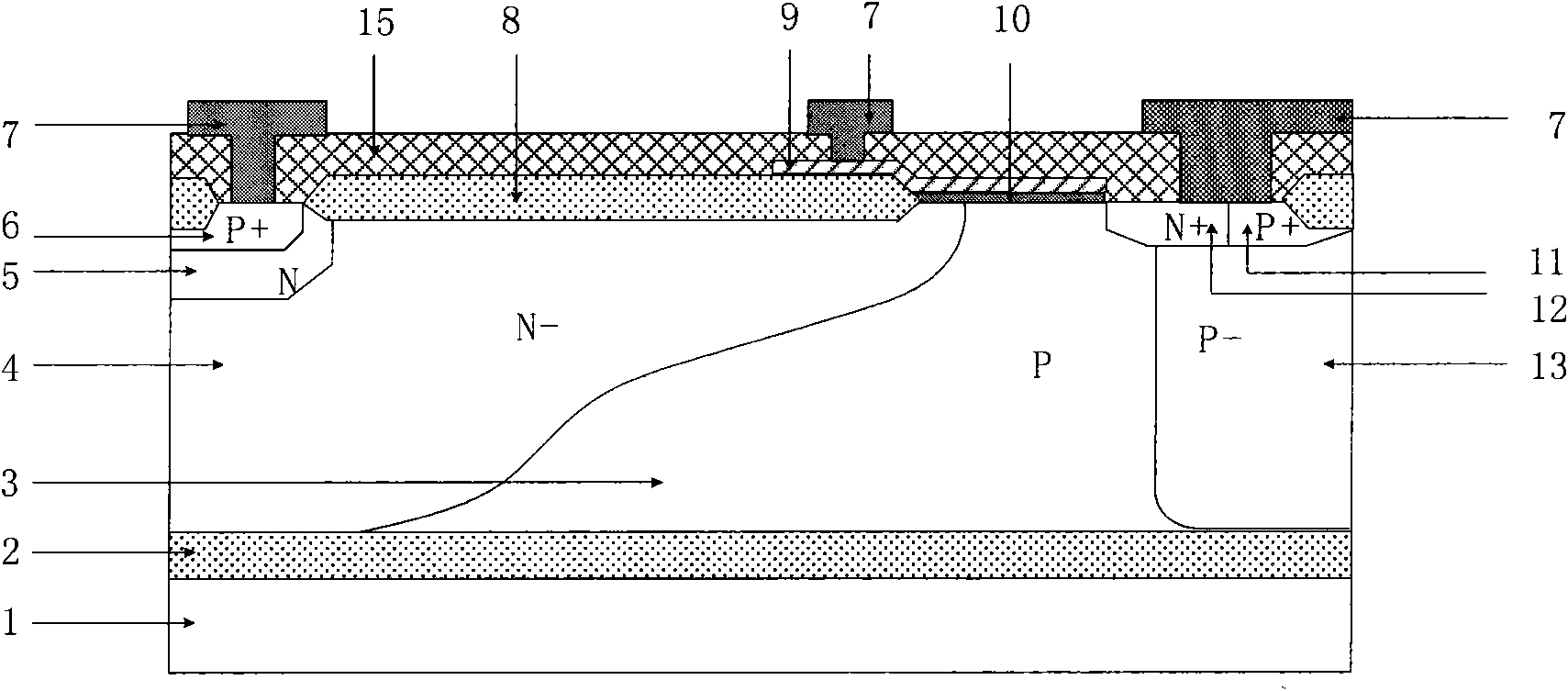

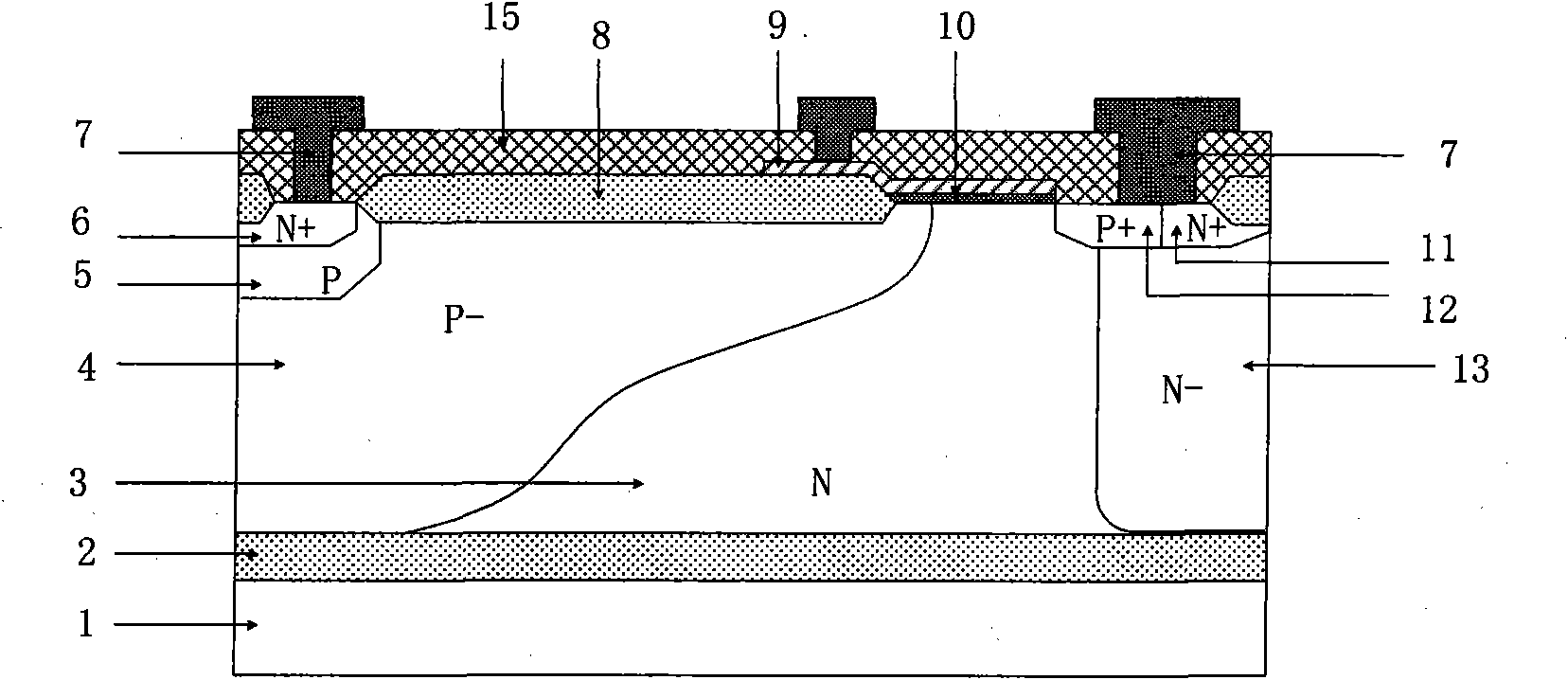

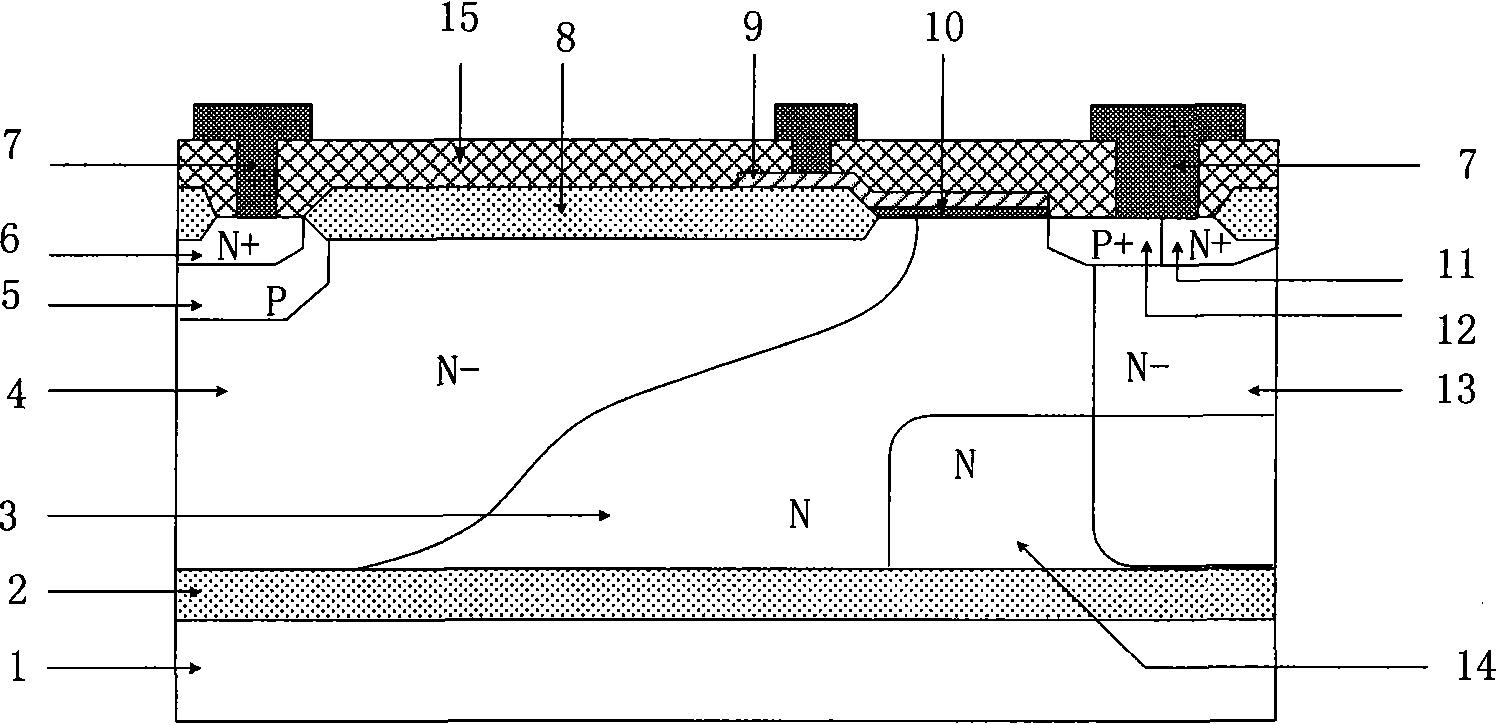

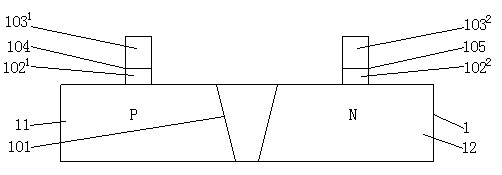

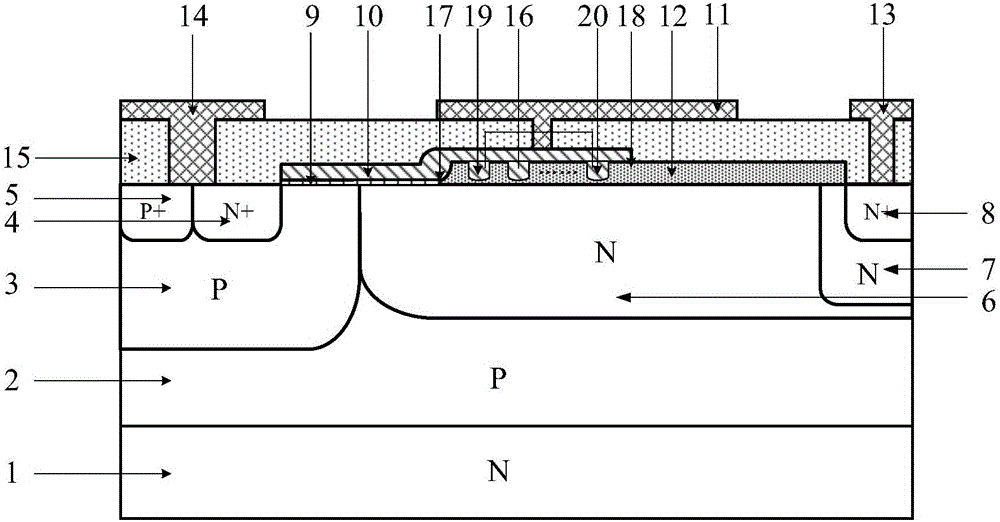

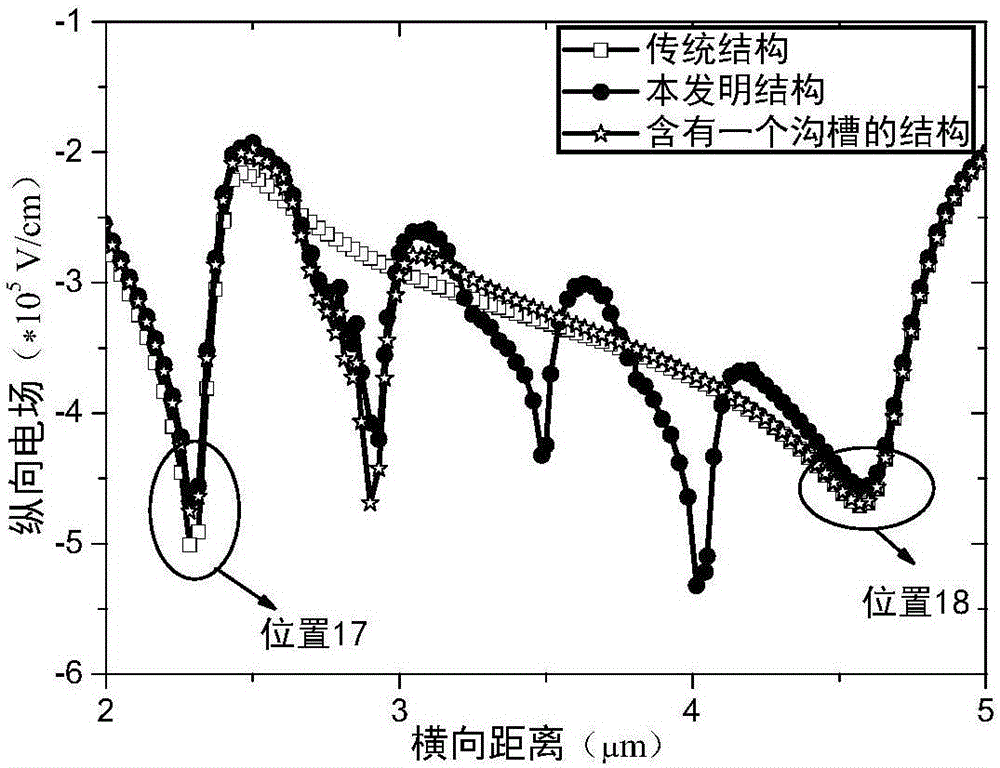

N-type lateral insulated gate bipolar device capable of reducing hot carrier effect

The invention relates to an N-type lateral insulated gate bipolar device capable of reducing hot carrier effect. The N-type lateral insulated gate bipolar device capable of reducing the hot carrier effect comprises a P-type substrate; buried oxide is arranged on the P-type substrate, and is provided with a P-type epitaxial layer; the P-type epitaxial layer is provided with an N-type well and a P-well area, the N-type well is provided with an N-type buffering well which is provided with a P-type positive area, and the P-well area is provided with an N-type negative area and a P-type body contact area; and a field oxide layer, a metal layer, a gate oxide layer, a polysilicon gate and an oxide layer are arranged on the upper surface of the device. The device is characterized in that a P-type buried layer is arranged below the P-well area and above the buried oxide and is inserted into part of the P-type epitaxial layer to form a reversed L-type P-area together with the whole P-well area, and the structure can lead the hole current of the device to the bottom part so as to reduce the iron generation rate and longitudinal electric field in the channel area of the device and lower the temperature of thermion, thereby effectively inhibiting the hot carrier effect of the device.

Owner:SOUTHEAST UNIV

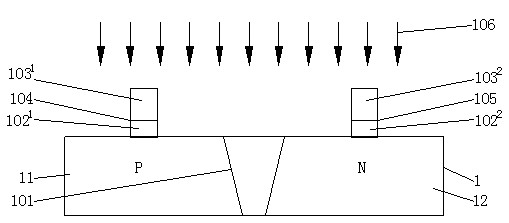

Wafer-level method of hot-carrier reliability test for semiconductor wafers

A wafer-level method is provided for hot-carrier reliability testing a plurality of MOS transistors formed in a semiconductor wafer. The MOS transistors in the semiconductor wafer are divided into at least three groups, including a first group, a second group, and a third group. A built-in multi-voltage supplier is integrally formed along with the MOS transistors undergoing testing in the same semiconductor wafer. This built-in multi-voltage supplier is devised in such a manner as to divide an input voltage into at least four testing voltages, including a first drain voltage, a second drain voltage, a third drain voltage, and a gate voltage. The gate voltage is connected to all of the MOS transistors undergoing testing, while the first drain voltage is connected to the drain of all of the first group of MOS transistors, the second drain voltage is connected to the drain of all of the second group of MOS transistors, and the third drain voltage is connected to the drain of all of the third group of MOS transistors. After this, the electrical characteristics under influence of the hot-carrier effects are measured. The method allows for a wafer-level testing procedure that can be performed immediately after the fabrication of the semiconductor wafer is completed. The testing procedure is also efficient and cost-effective to perform.

Owner:WINBOND ELECTRONICS CORP

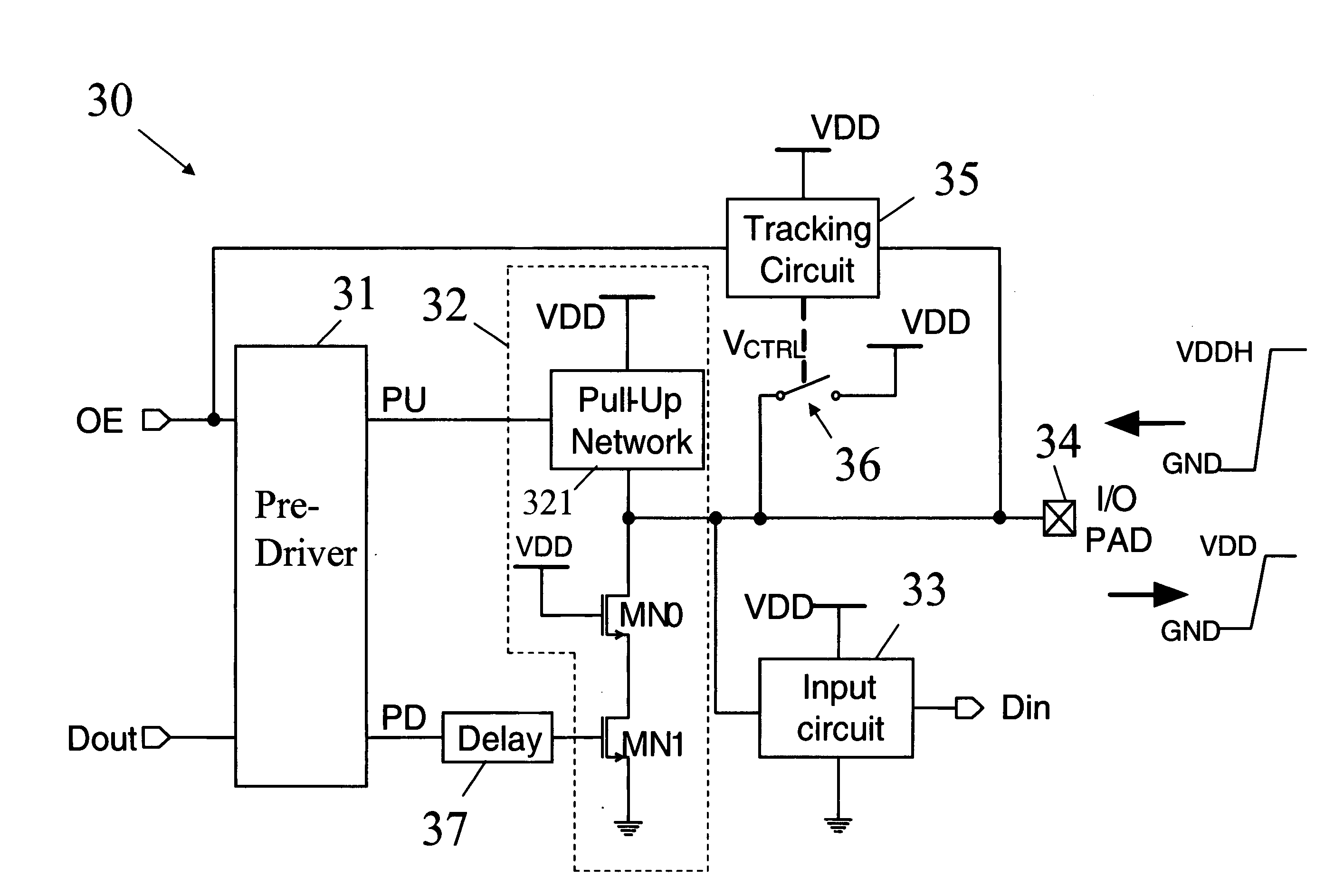

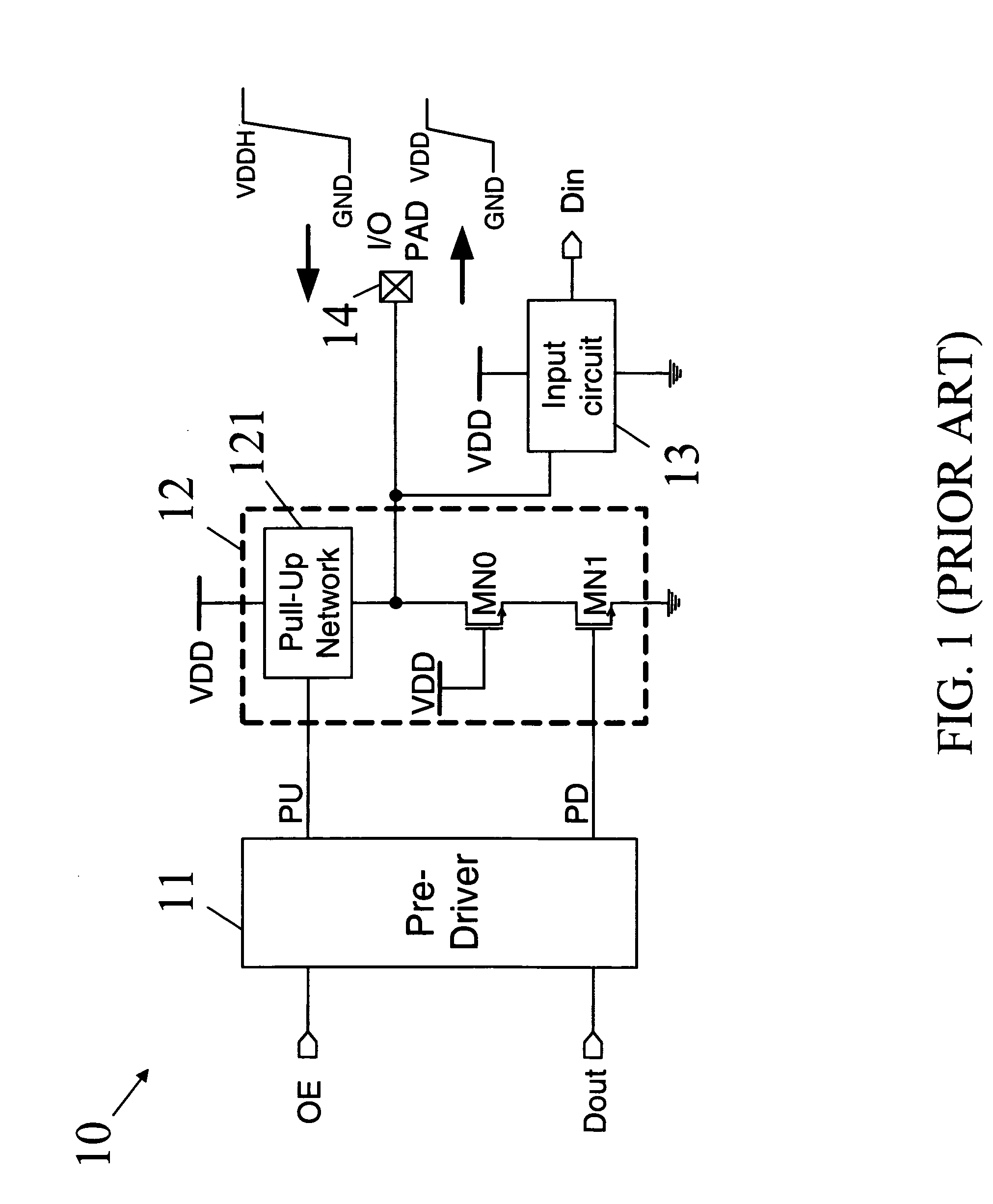

Protection circuits and methods of protecting circuits

InactiveUS20080061832A1Good effectVoltage/current interference eliminationLogic circuit coupling/interface arrangementsVoltage referenceEngineering

A circuit configured for providing hot-carrier effect protection, the circuit comprising a first transistor including a first terminal and a second terminal, the first terminal being coupled to a conductive pad, a switch device including a terminal coupled to the conductive pad, and a control circuit configured for keeping the switch at an off state during a receiving mode at which a signal of a first voltage level or a reference level is received at the conductive pad, keeping the switch at the off state during a transmitting mode from which a signal of a second voltage level or the reference level is transmitted at the conductive pad, and keeping the switch at an on state during a transition from the receiving mode when receiving a signal of the first voltage level to the transmitting mode when transmitting a signal having the reference voltage level, wherein during the transition a voltage across the first terminal and the second terminal of the first transistor is maintained at a level below approximately the first voltage level minus the second voltage level.

Owner:IND TECH RES INST

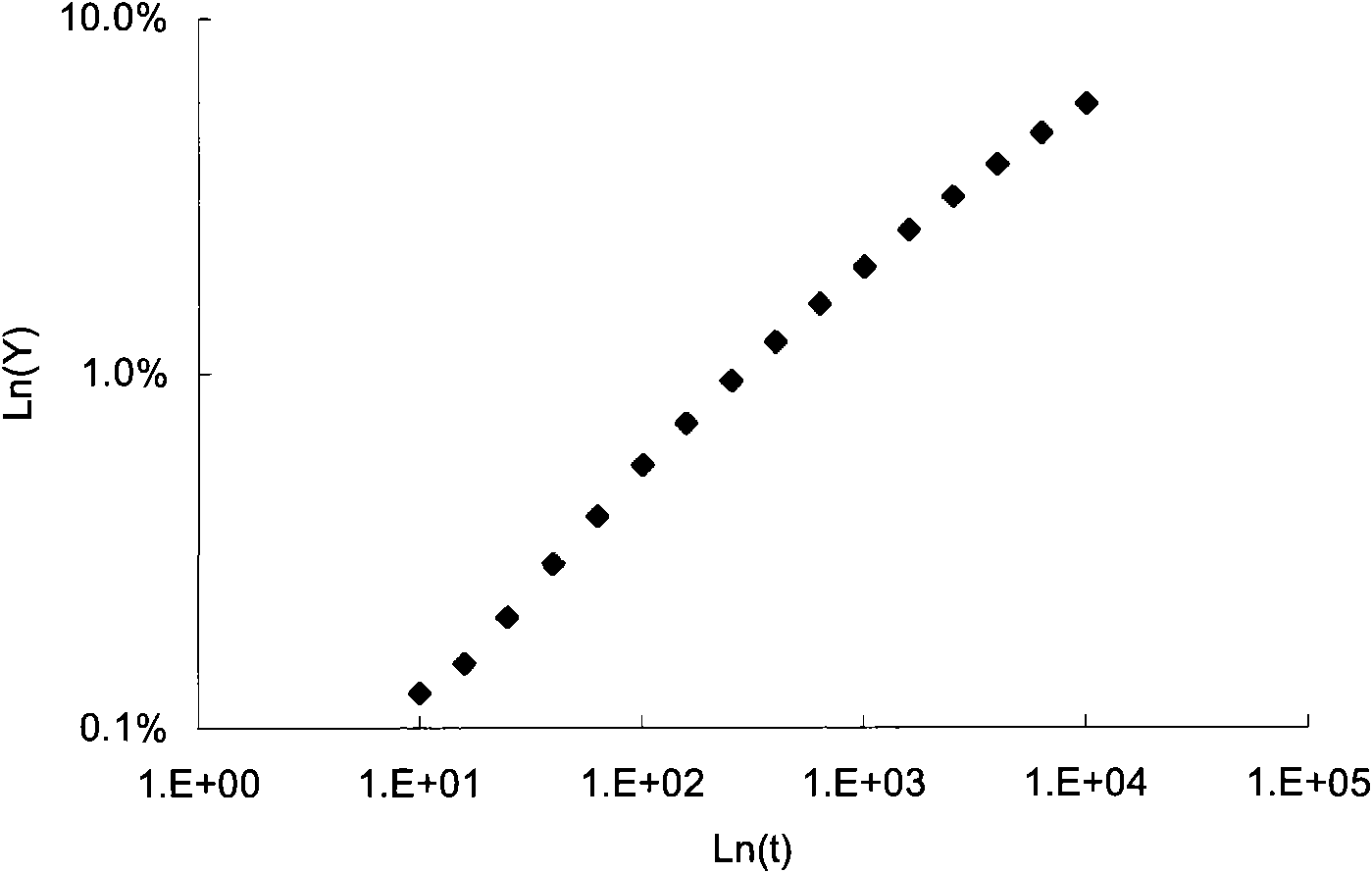

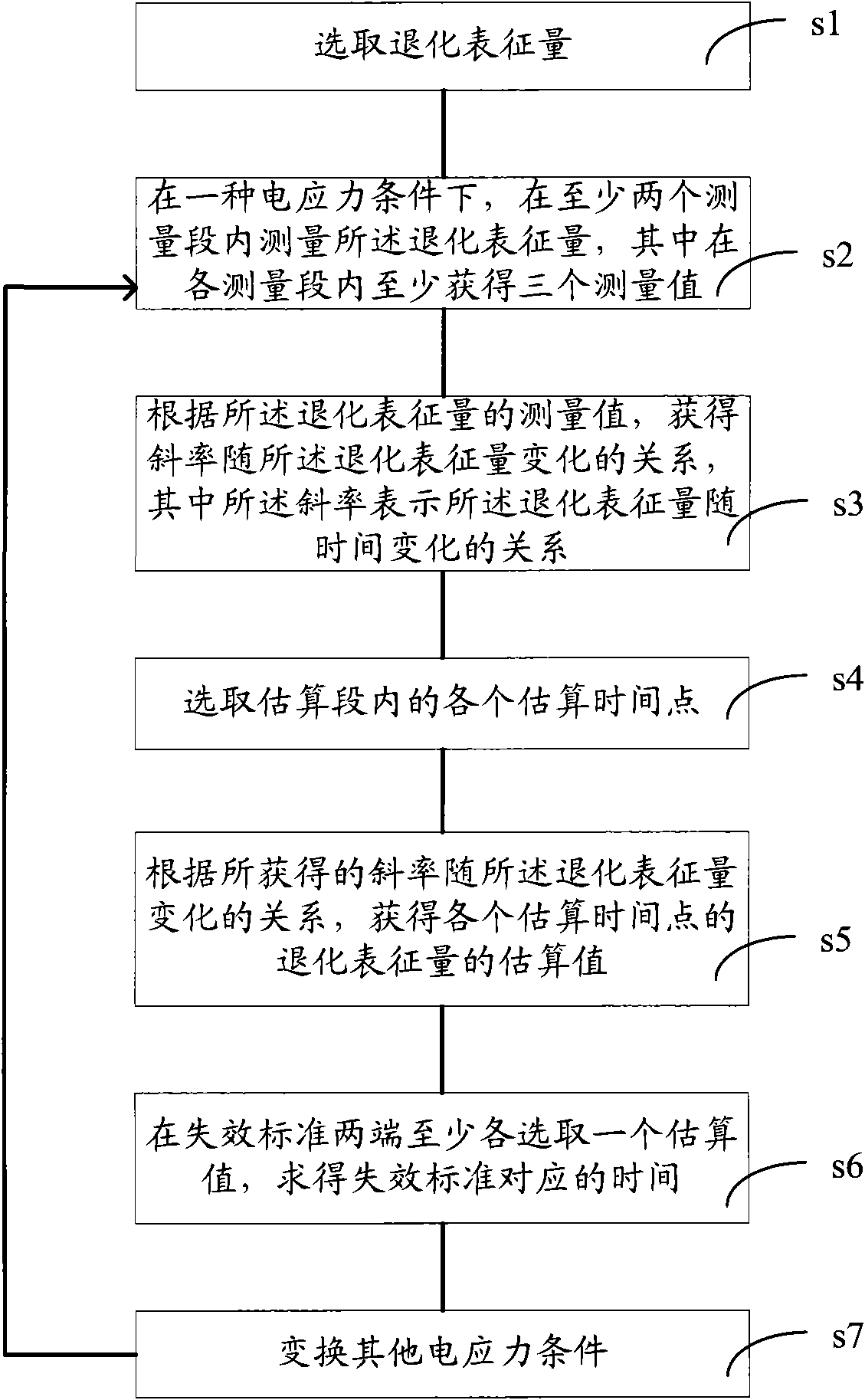

Method for detecting hot carrier effect of semiconductor device

InactiveCN101587162AAccurate estimateThe test result is accurateIndividual semiconductor device testingImputed TimeElectric stress

The invention relates to a method for detecting hot carrier effect of a semiconductor device, which comprises the following steps: selecting degradation characterizing quantity; under the condition of various electric stress, measuring the degradation characterizing quantity in at least two measuring sections, wherein at least three measuring values are acquired in each measuring section; obtaining the relation of the slope changing along with the degradation characterizing quantity according to the measuring values of the degradation characterizing quantity, wherein the slope represents the relation of the degradation characterizing quantity changing along with the time; selecting various estimate time points in an estimate section; according to the obtained relation of slope changing along with the degradation characterizing quantity, acquiring estimate values of the degradation characterizing quantity of various estimate time points; and at least respectively selecting one estimate value at two ends of failure criteria to obtain the time corresponding to the failure criteria. The detecting result for estimating the service life of the device by the method is more accurate.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

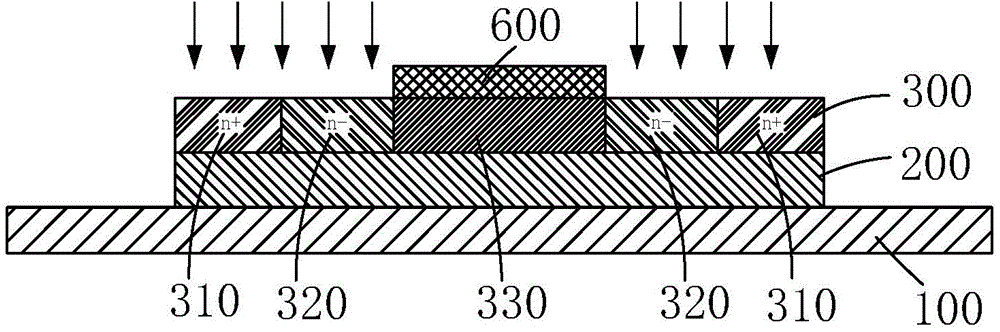

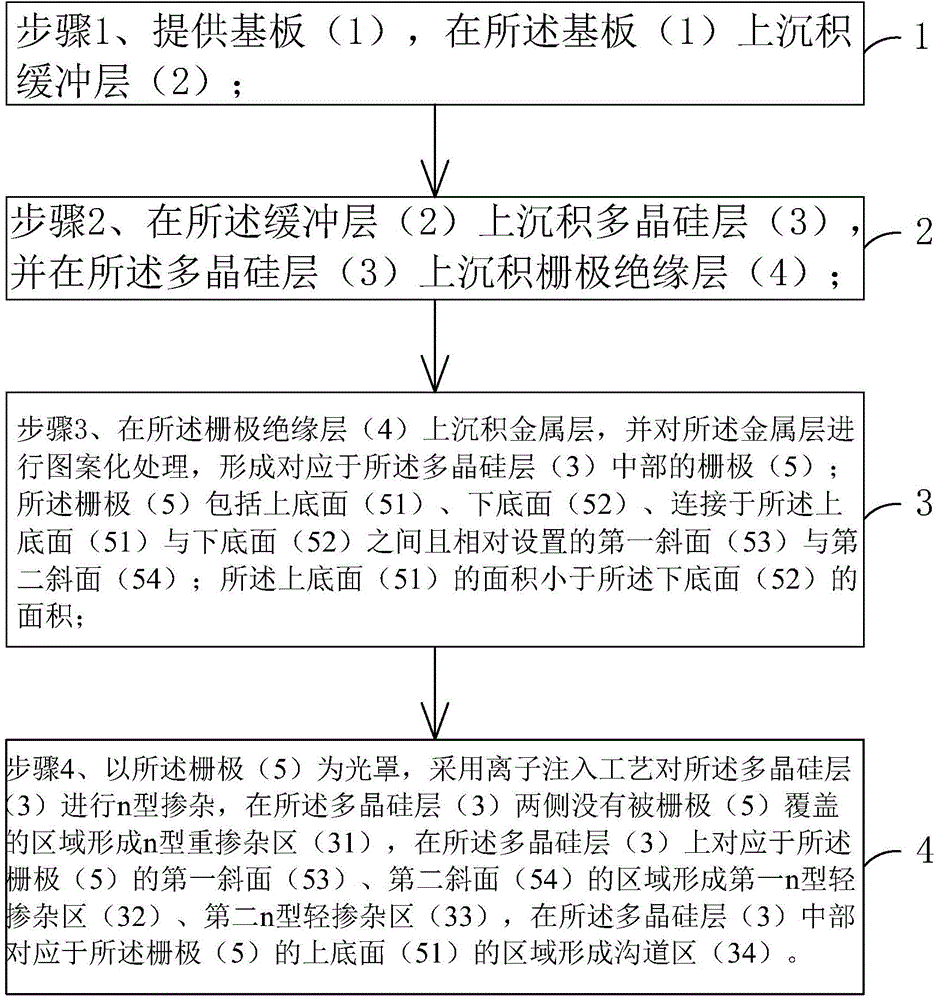

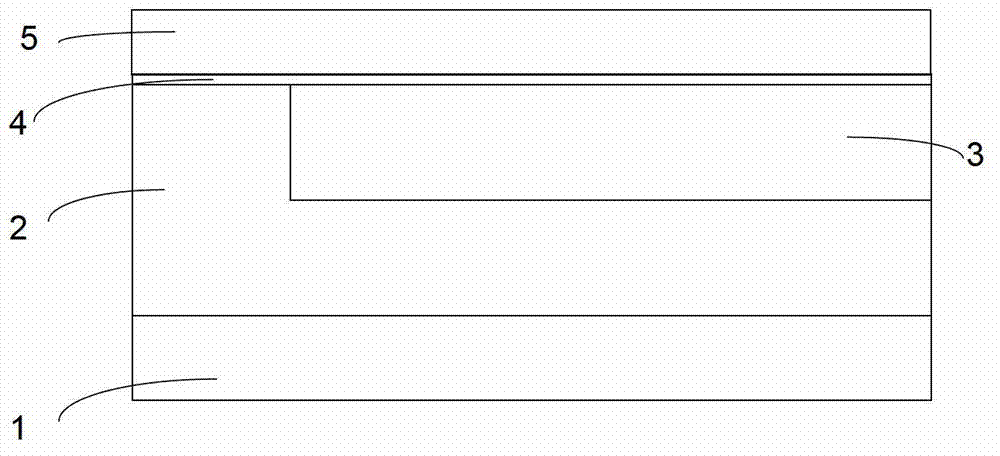

TFT substrate structure manufacturing method and TFT substrate structure thereof

InactiveCN104900712AReduce processFeature eliminationTransistorSolid-state devicesIon implantationMaterials science

The invention provides a TFT substrate manufacturing method and a TFT substrate structure thereof. According to the TFT substrate structure manufacturing method, through an etching parameter in manufacturing a gate, oblique surfaces are formed at two sides of the gate. Furthermore the gate is used as an optical cover. Ion implantation is performed on a polysilicon layer. Simultaneously n-type heavily doped regions and n-type lightly doped regions are formed on the polysilicon layer. The TFT substrate manufacturing method and the TFT substrate structure have functions of enlarging a resistance, dispersing a strong electric field next to electrodes, preventing device characteristic reduction by a hot carrier effect caused by existence of a partial strong electric field, saving a process for singly forming the n-type lightly doped region, improving generation efficiency and reducing production cost. According to the TFT substrate structure, the polysilicon layer comprises the n-type heavily doped regions at two sides and the n-type lightly doped regions between the channel region of the polysilicon layer and the n-type heavily doped regions, thereby preventing generation of the partial strong electric field, and eliminating the effect of a hot carrier to the characteristic of the device.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

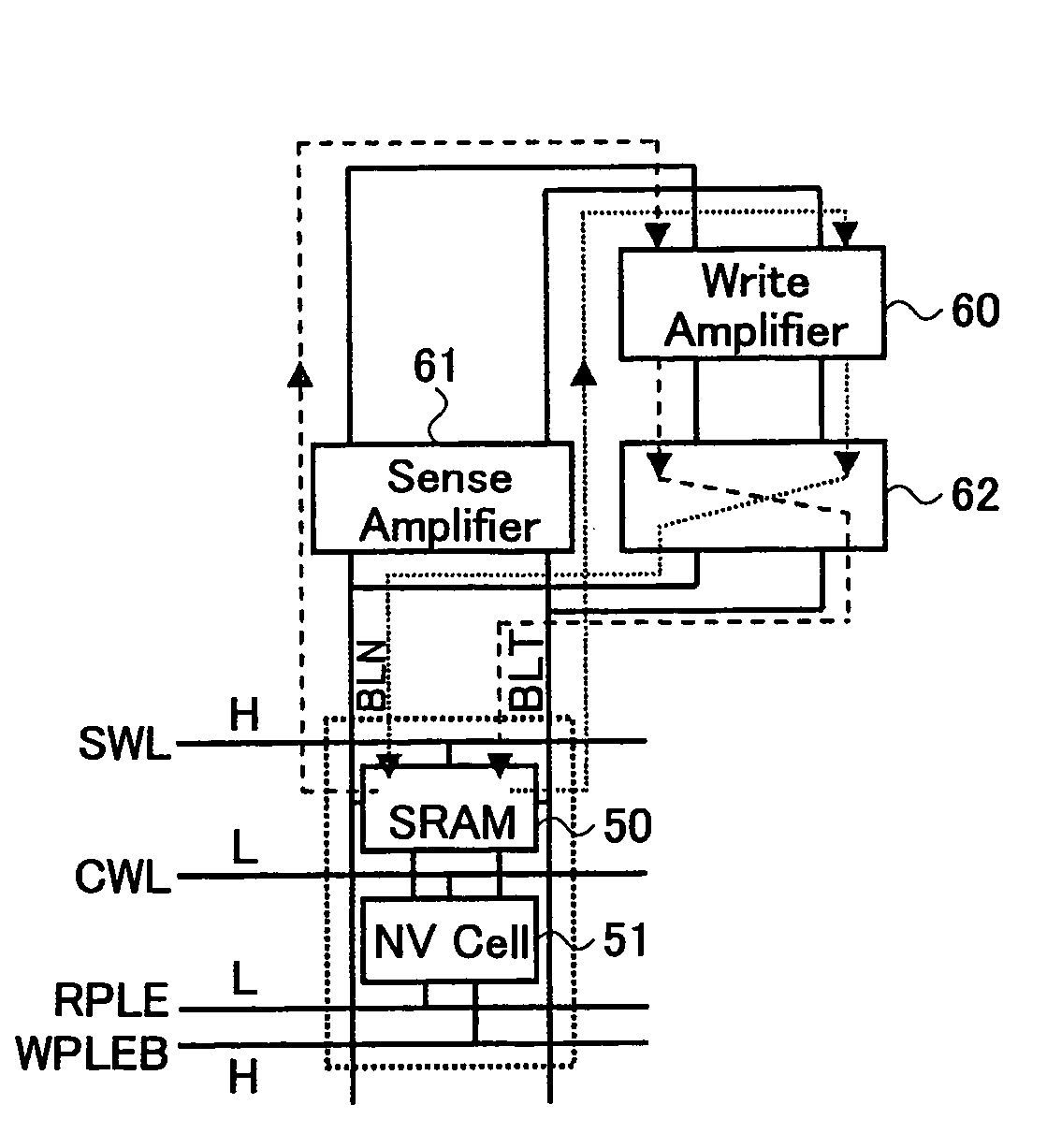

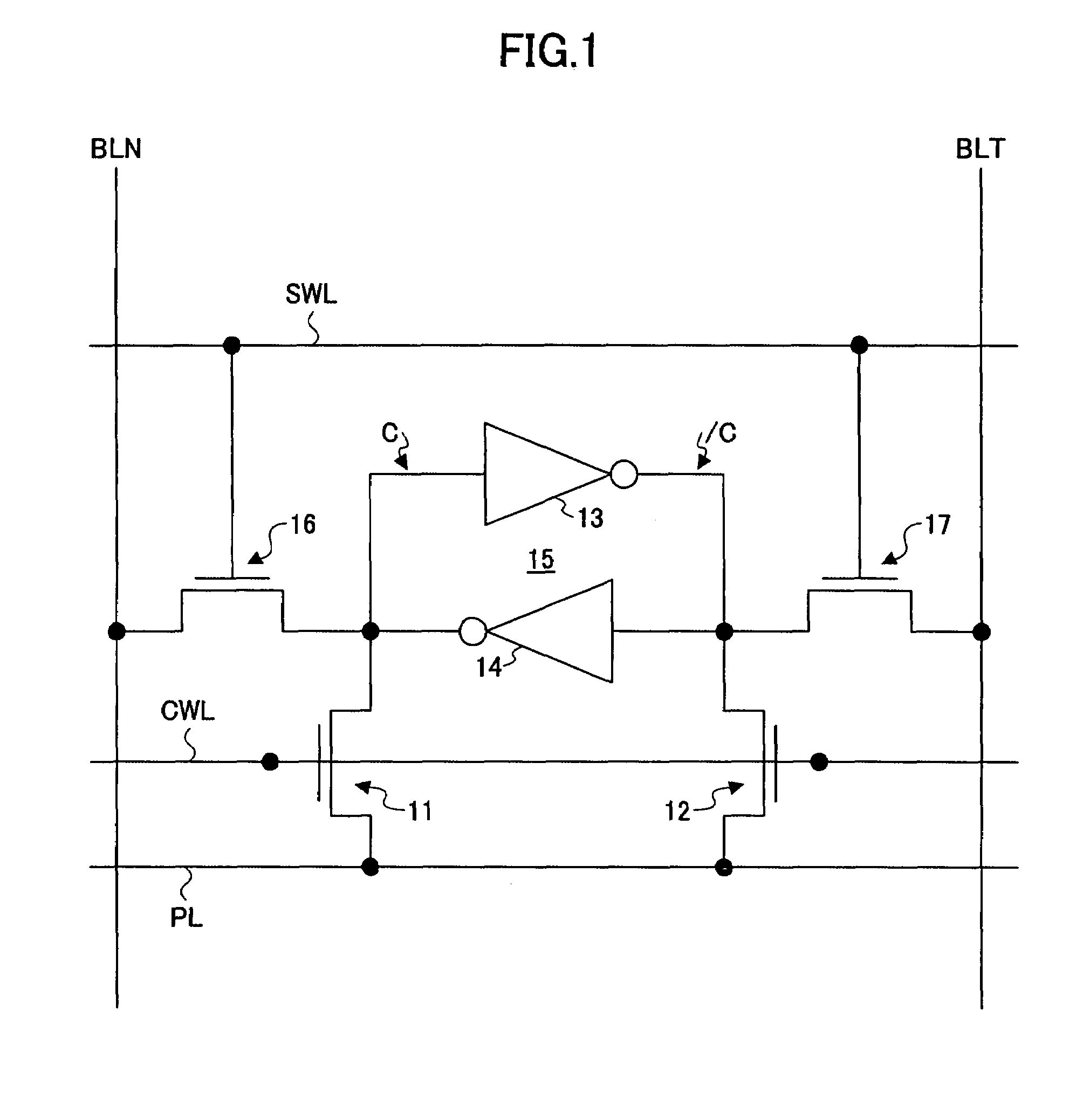

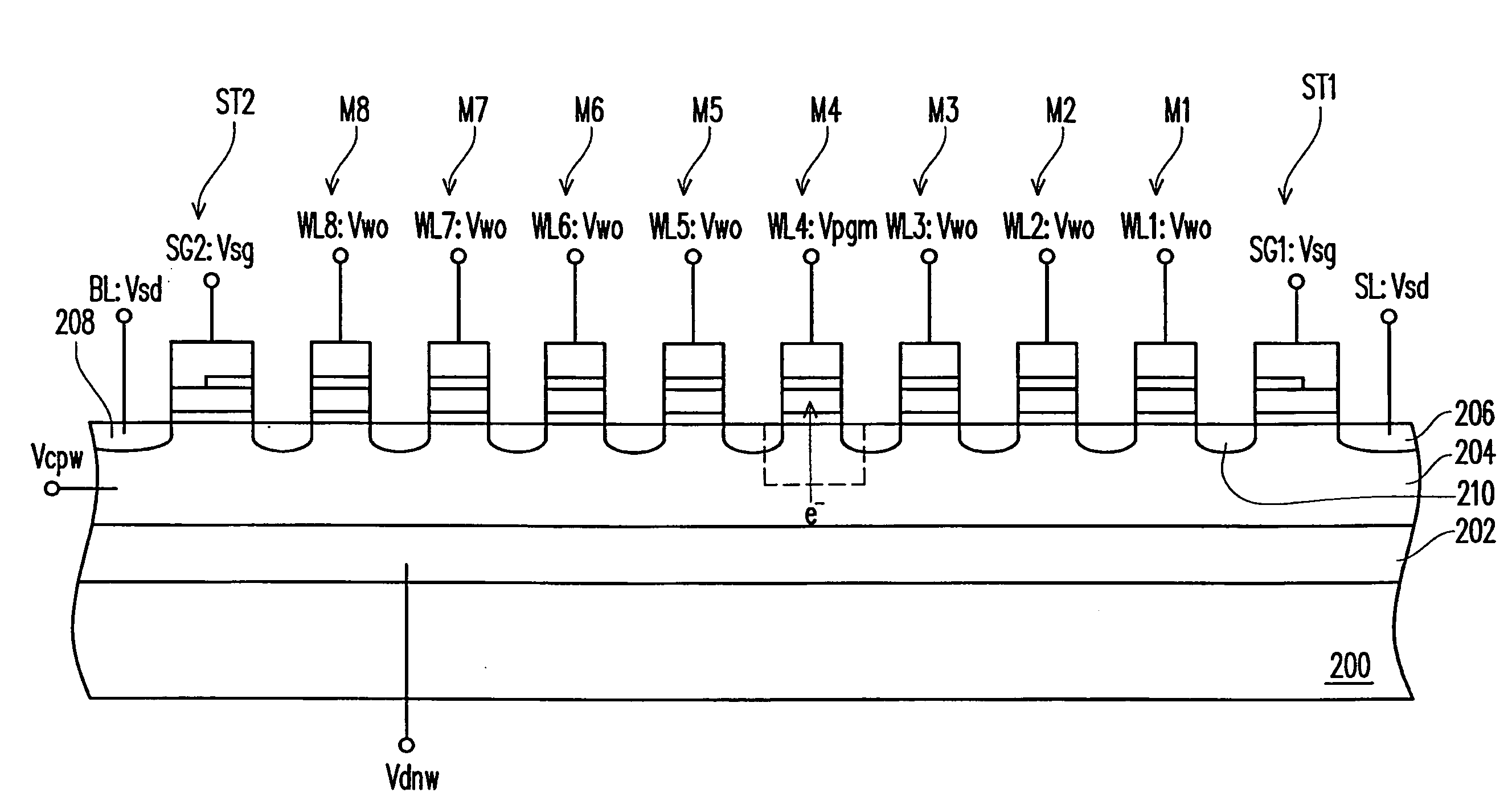

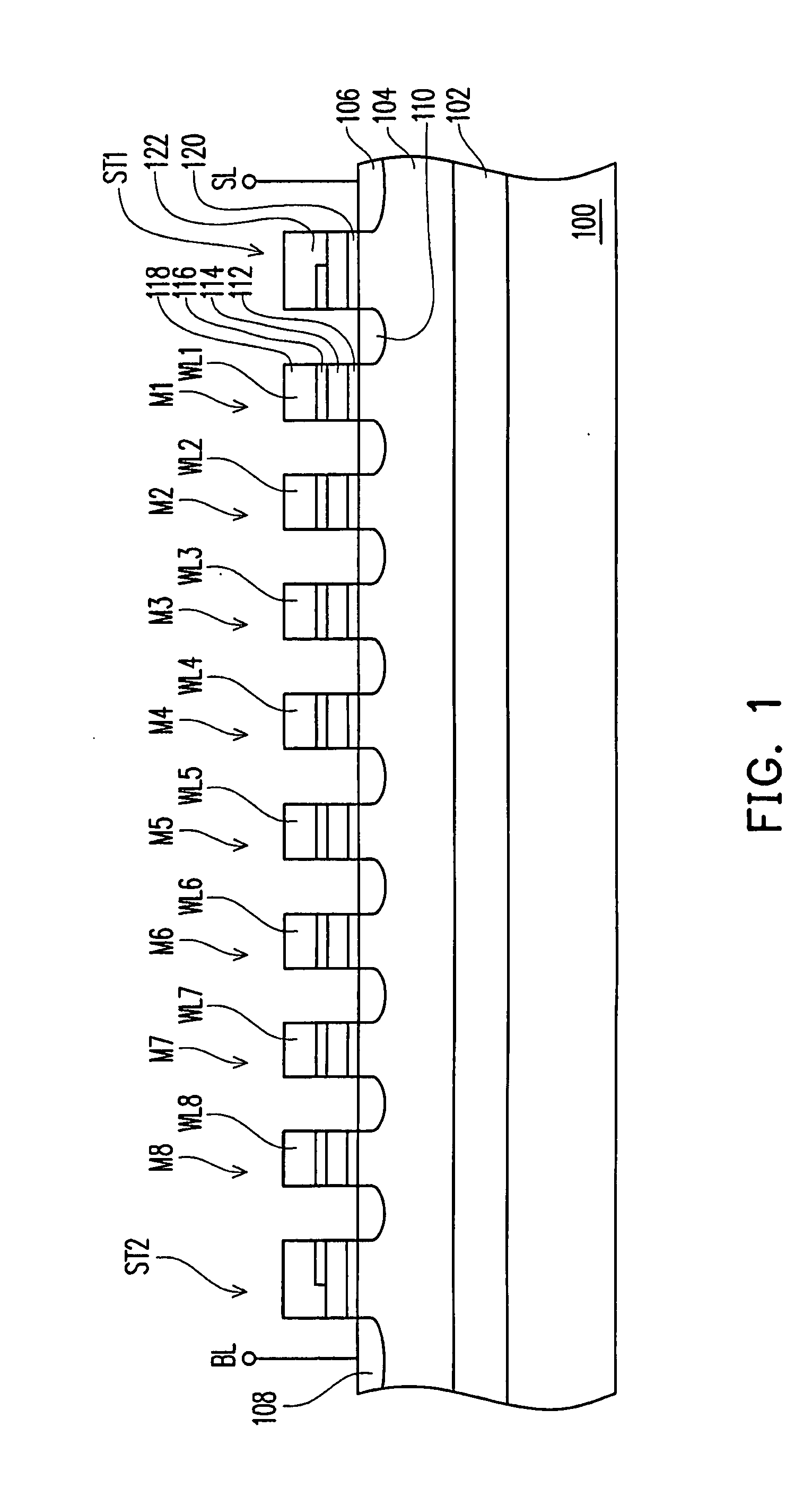

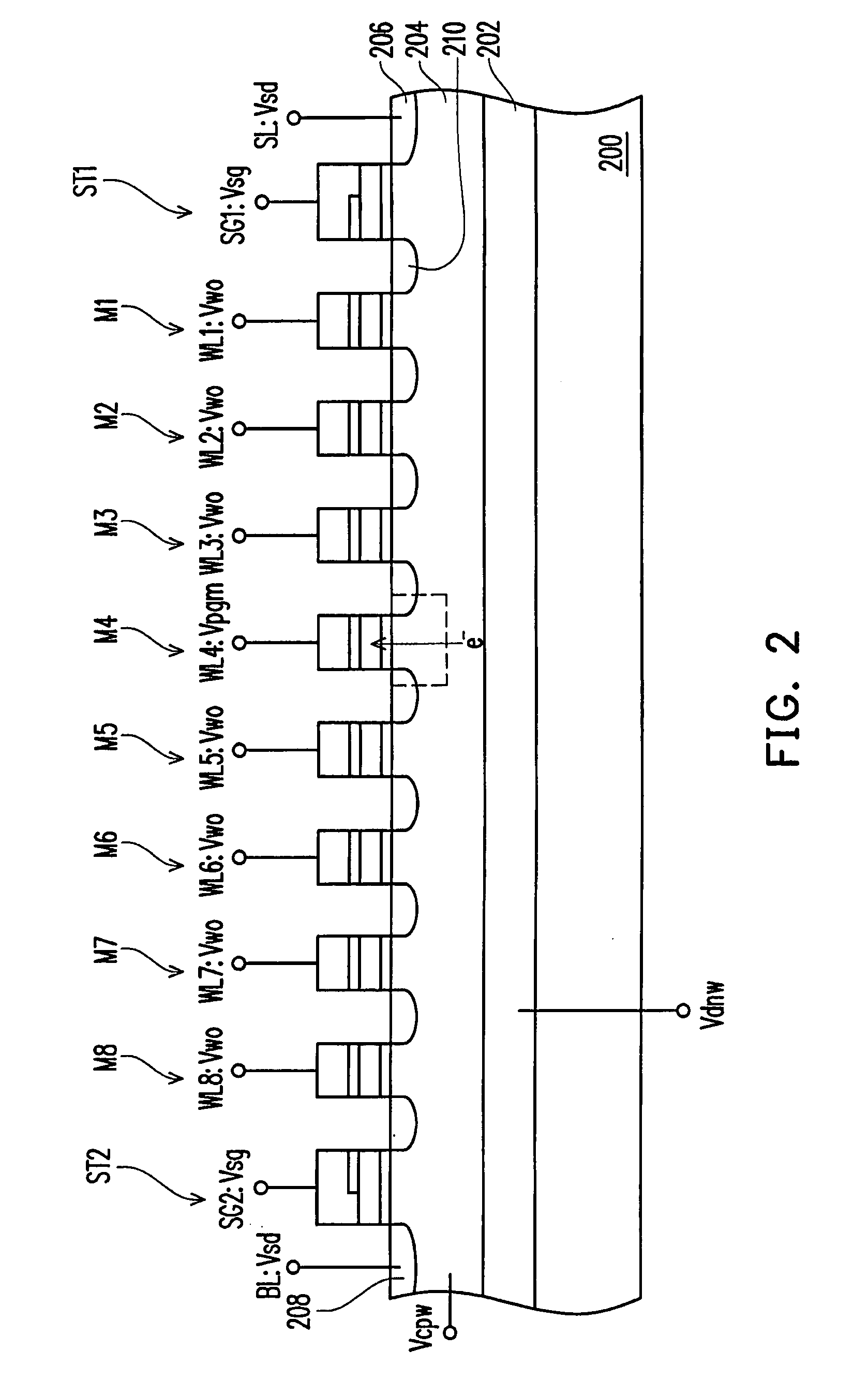

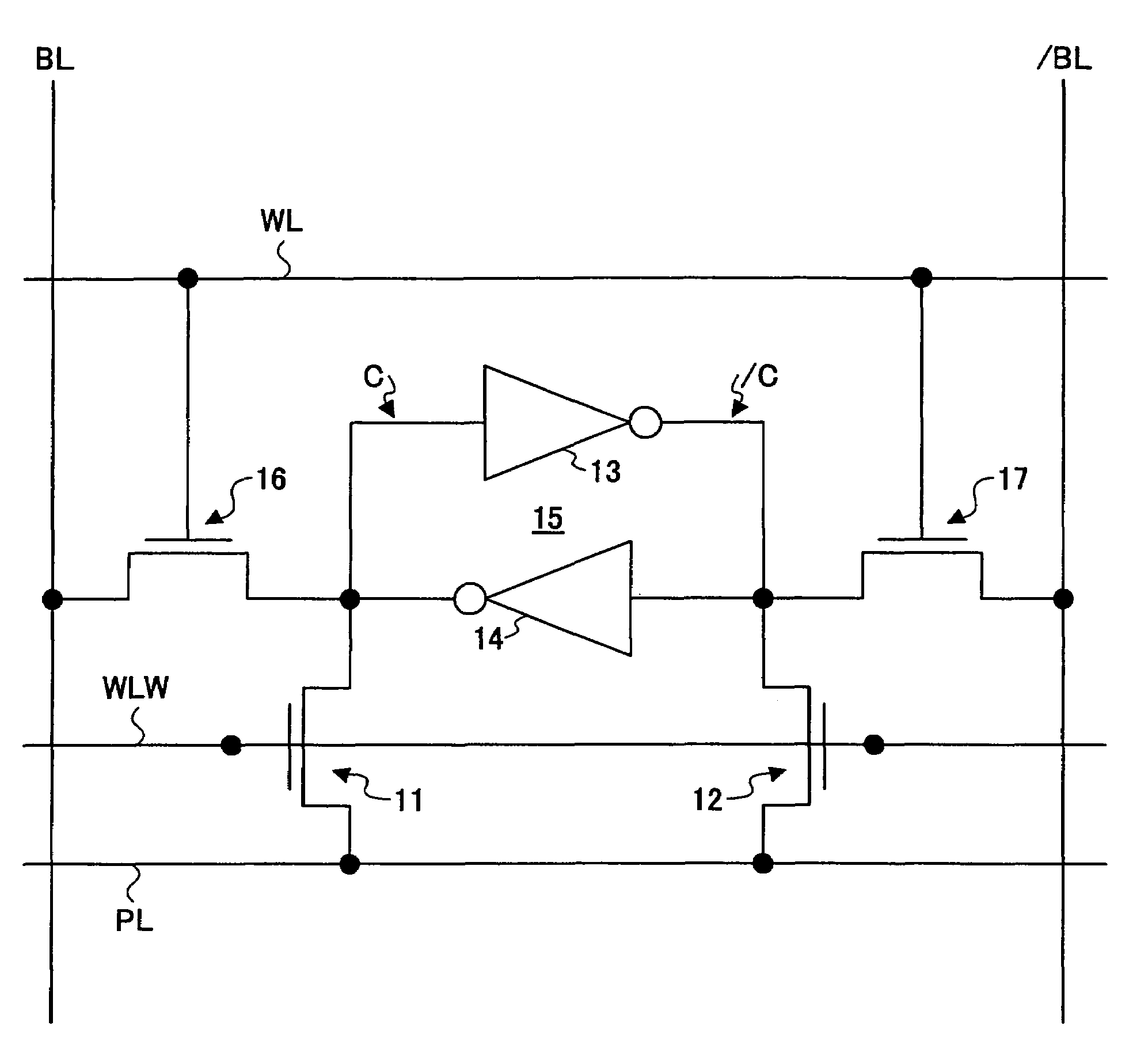

Method for programming non-volatile memory

InactiveUS20090109762A1Save power consumptionImprove programming efficiencyRead-only memoriesDigital storageElectronHot carrier effect

A method for programming non-volatile memory utilizes substrate hot carrier effect to conduct programming operations. A forward bias voltage is applied between an N-type well region and a P-type well region so as to inject electrons in the N-type well region into the P-type well region. After that, the electrons are accelerated by a depletion region established by a voltage applied to a source region and a drain region, and a vertical electrical field established between a control gate and the P-type well region further forces the electrons to be injected into a charge storage layer. Since the present invention adopts the substrate hot carrier effect to inject carriers into the charge storage layer, the required program operation voltage is low, which benefits to save power consumption and enhance the reliability of the device.

Owner:POWERCHIP SEMICON CORP

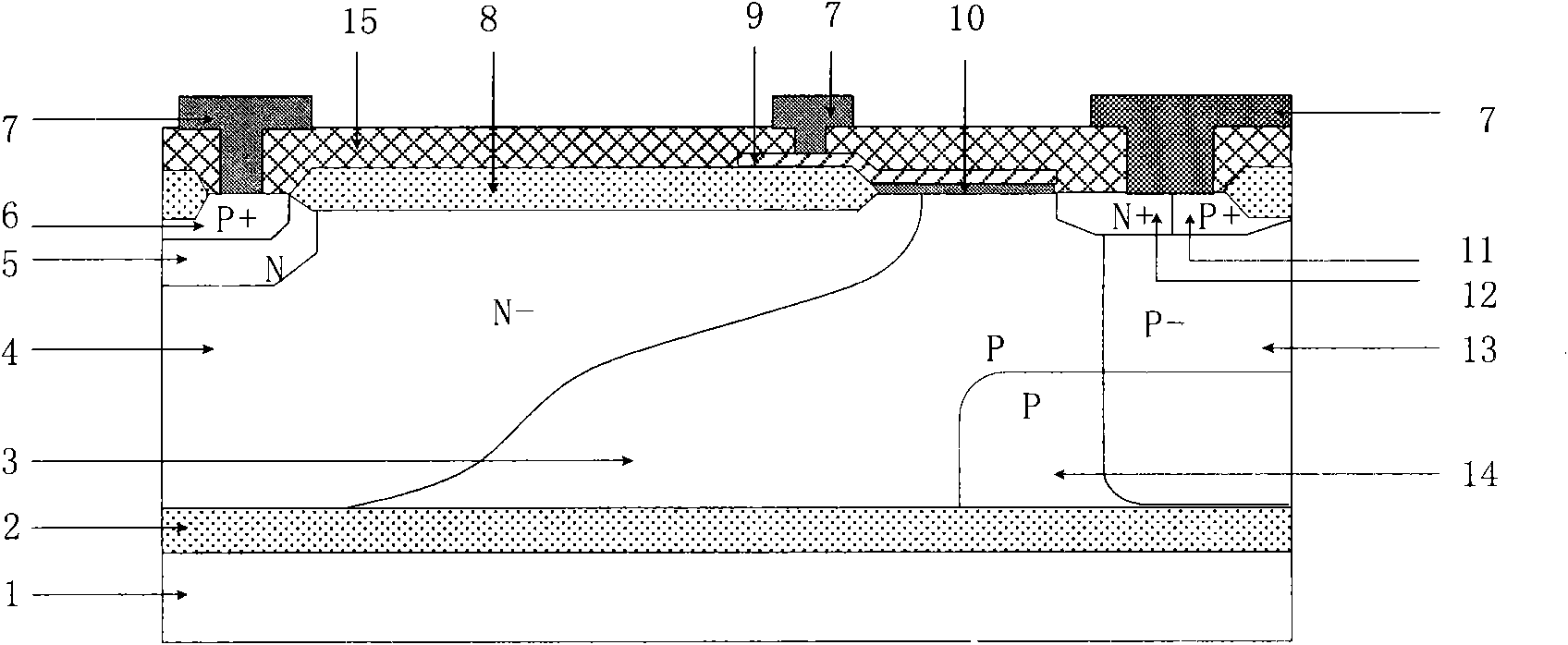

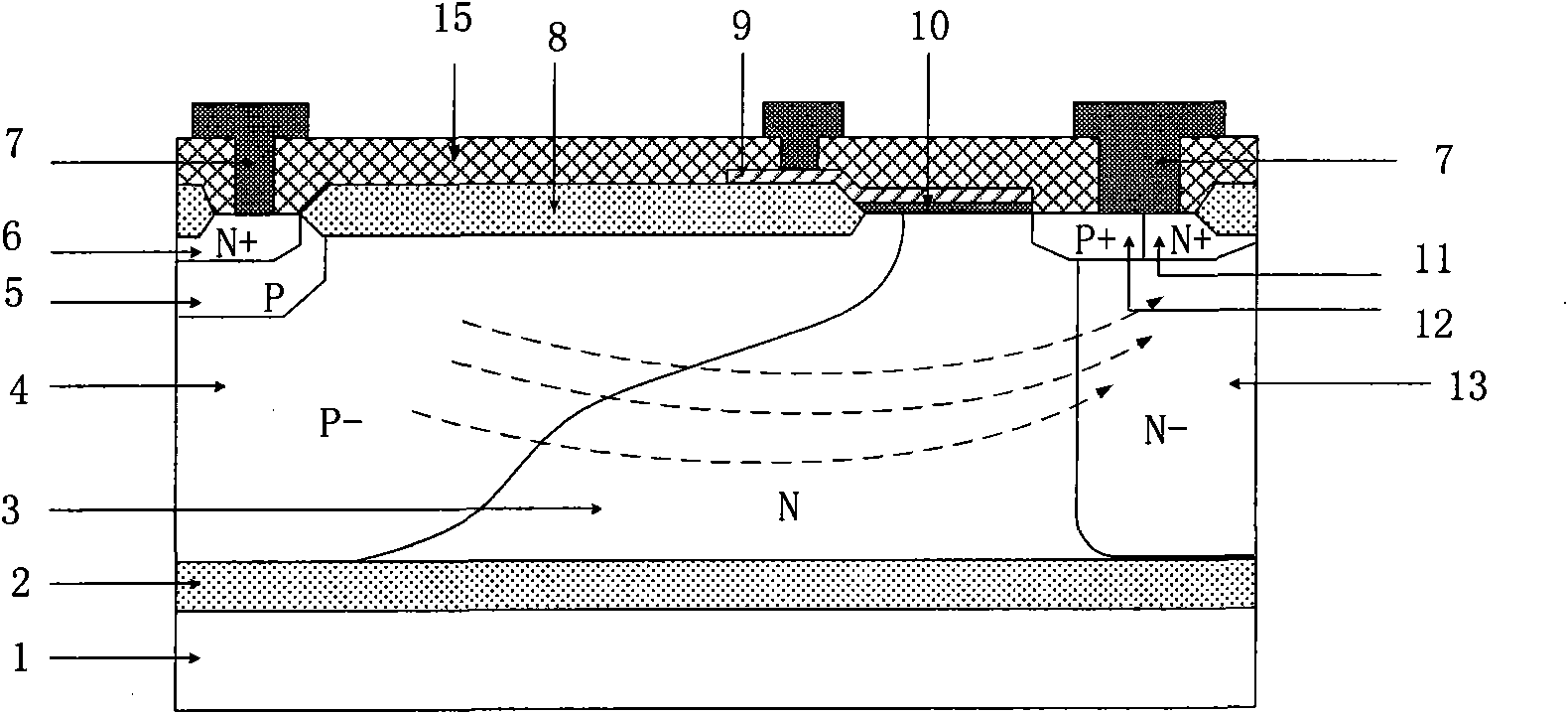

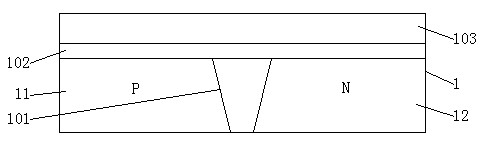

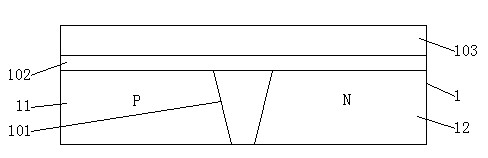

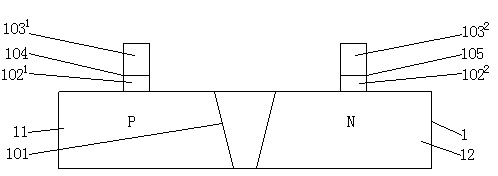

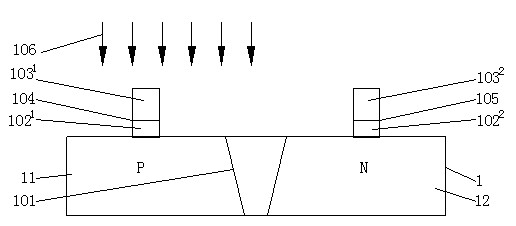

P type lateral insulated gate bipolar device for reducing hot carrier effect

InactiveCN101819993ASmall doseReduce incidenceSemiconductor devicesGeneration rateLongitudinal field

The invention relates to a P type lateral insulated gate bipolar device for reducing the hot carrier effect, comprising an N type substrate. Buried oxide is arranged on the N type substrate, an N type epitaxial layer is arranged on the buried oxide, a P type well and an N well region are arranged on the N type epitaxial layer, a P type buffer well is arranged on the P type well, an N type positive region is arranged on the P type buffer well, a P type negative region and an N type physical contact region are arranged on the N well region, and a field oxide, a metal layer, a gate oxide, a polysilicon gate and an oxide layer arranged on the surface of the device. The P type lateral insulated gate bipolar device for reducing the hot carrier effect is characterized in that N type buried layers are arranged at the lower part of the N well region and on the buried oxide, and the N type buried layers are partially inserted into the N type epitaxial layer to integrally form a reverse L type N region with the N well region. The structure can introduce the electronic current of the device to the bottom, reduce ion generation rate and longitudinal field of a channel region of the device, and lower the thermionic temperature, thereby effectively restraining the hot carrier effect of the device.

Owner:SOUTHEAST UNIV

Radio frequency LDMOS (laterally diffused metal oxide semiconductor) device and manufacture method thereof

ActiveCN103050536AReduce doping concentrationDoping concentration unchangedSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSGate oxide

The invention discloses a radio frequency LDMOS (laterally diffused metal oxide semiconductor) device. The side surface of a channel doping region and the side surface of a drift region of the radio frequency LDMOS device are contacted; a gate oxide and a grid electrode are successively arranged above the channel doping region and the drift region; and the doping density of the part of the drift region, which is below the channel doping region, is smaller than the doping density of rest parts. The invention also discloses a manufacture method for the radio frequency LDMOS device. Because the doping density of the drift region is unevenly distributed, the hot carrier effect can be lowered while the low-conduction resistance is obtained.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

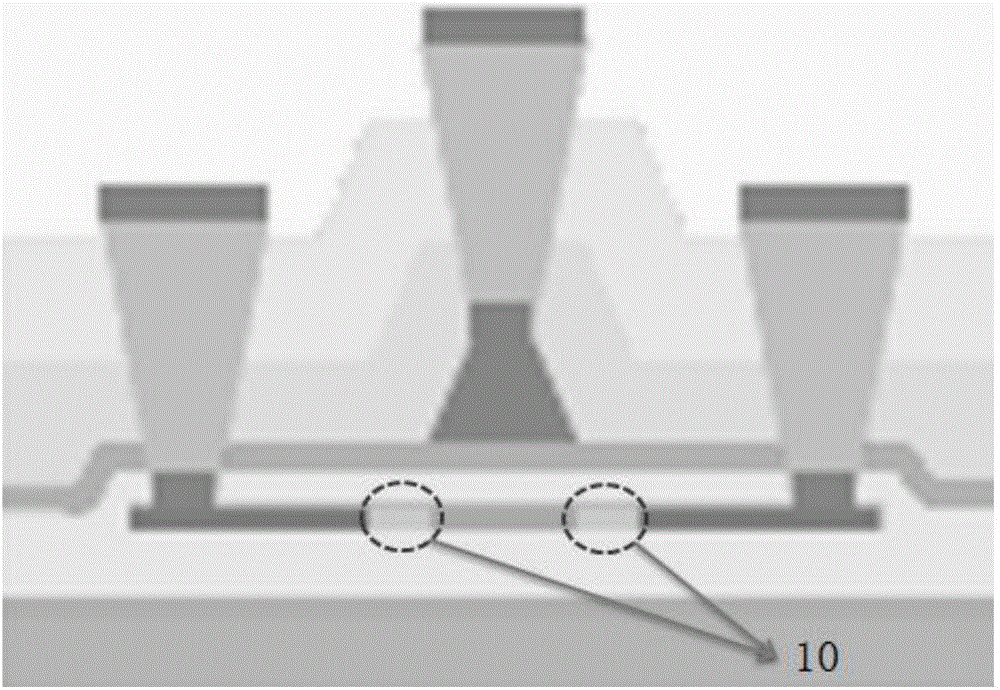

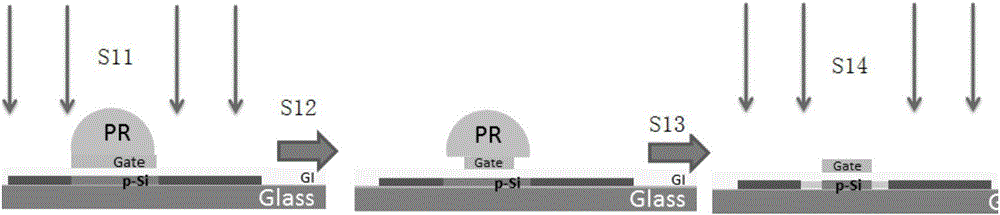

Preparation method of drain electrode lightly-offset structure

ActiveCN106847702AEasy to control the sizeGood repeatabilitySemiconductor/solid-state device manufacturingSemiconductor devicesEtchingInsulation layer

The invention provides a preparation method of a drain electrode lightly-offset structure. The preparation method comprises the steps of glass substrate crystallization, P-Si substrate imaging, gate insulation layer film formation and gate layer film formation. The drain electrode lightly-offset structure is formed through the following steps of a gumming step, a half-tone exposure step, a developing step, a first-time metal etching step, a first-time ion implantation step, a photoresist-ashing step, a second-time metal etching step, a demoulding step and a second-time ion implantation step, wherein photoresist is subjected to half-tone exposure and developing, and two times of heavily doped and lightly doped ion implantation steps, the photoresist-ashing step and the two times of metal etching steps are combined, so that a source electrode or drain electrode heavily doped region, a gate lightly doped region and a drain electrode lightly doped region are formed, a drain electrode lightly offset (LDO) structure is formed, a hot carrier effect is effectively relieved, a leakage current is reduced, the drain electrode lightly-doped structure has an easy-to-control size and better processing repeatability and uniformity, the production cost and the bad product rate are reduced, and the reliability of a TFT (Thin Film Transistor) product is improved.

Owner:TRULY HUIZHOU SMART DISPLAY

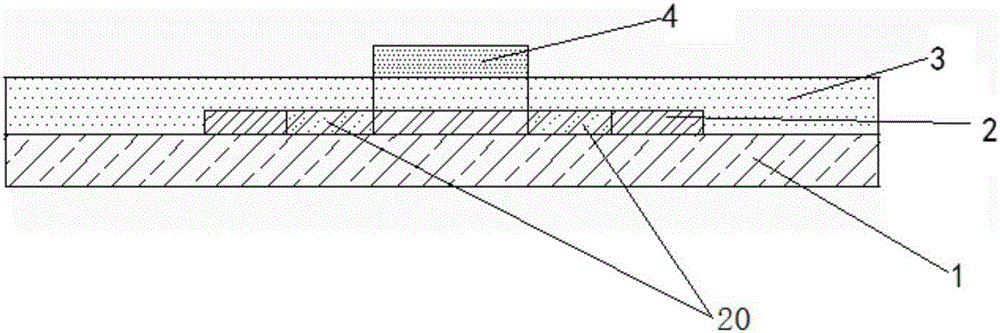

Thin film transistor

ActiveCN103730514AReduce processing difficultyNo effect on normal workTransistorCircuit reliabilityCharge carrier

The invention discloses a thin film transistor. The thin film transistor comprises a substrate, a semiconductor channel region, a gate insulating layer, a source region, a leakage region, a source electrode, a leakage electrode and a gate electrode. The thin film transistor further comprises a current carrier injection structure. The thin film transistor can remarkably reduce device degradation and threshold voltage drift, the device and circuit reliability of the thin film transistor is improved, the complexity of the threshold voltage compensating circuit design is simplified. In addition, the thin film transistor is low in process difficulty and does not influence normal work of devices.

Owner:SUZHOU UNIV

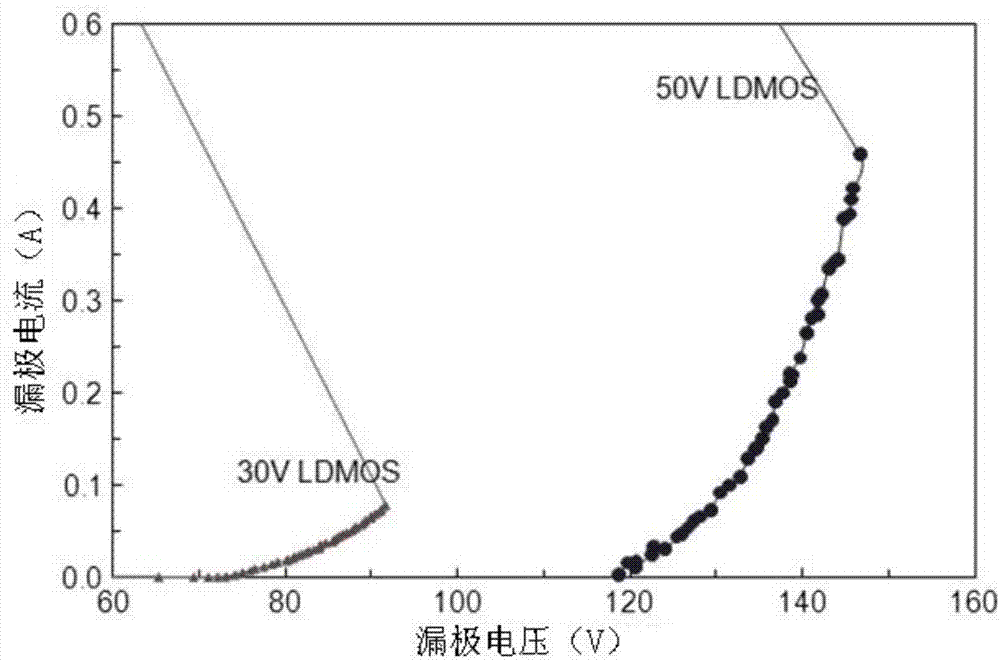

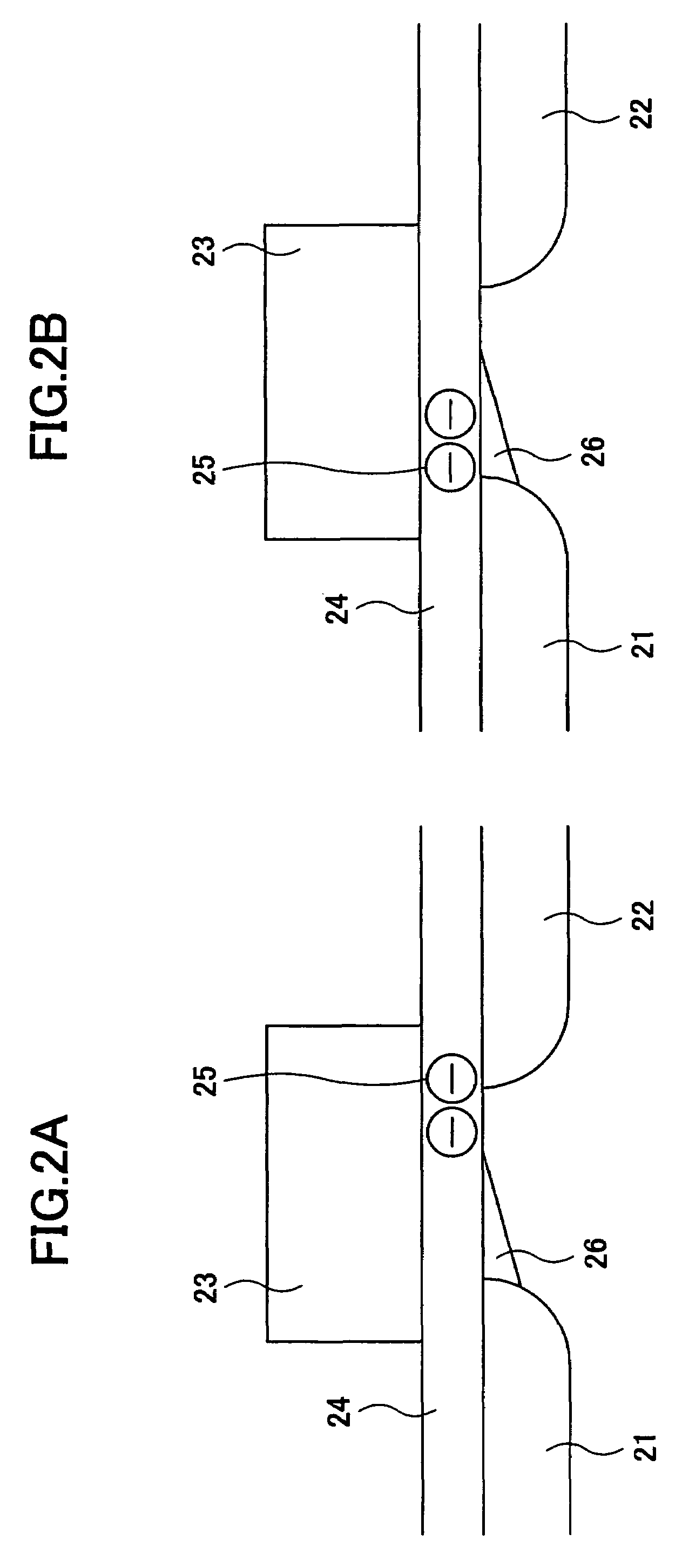

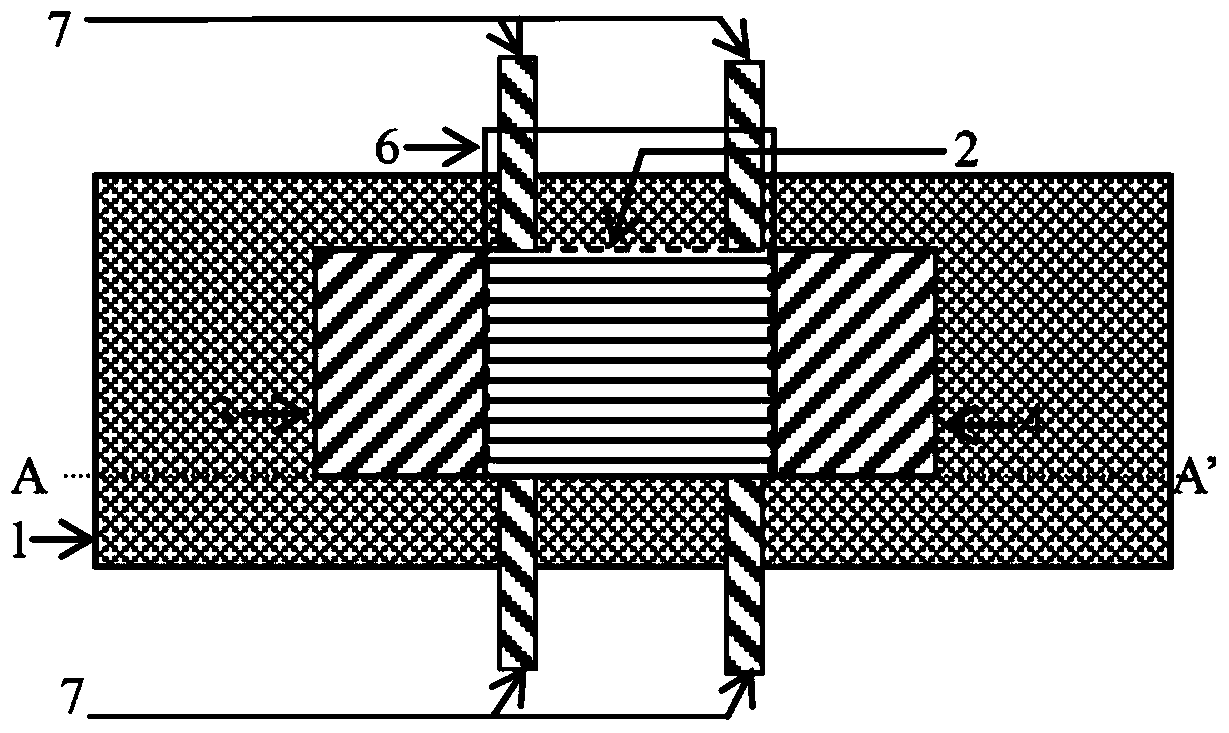

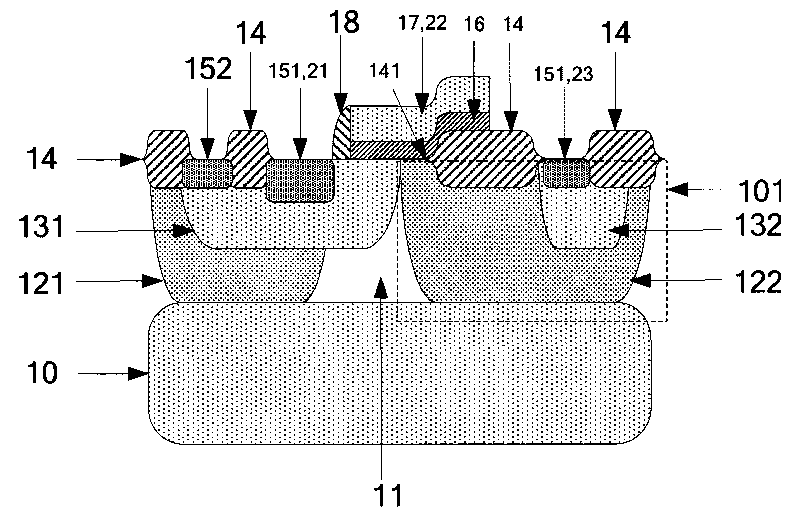

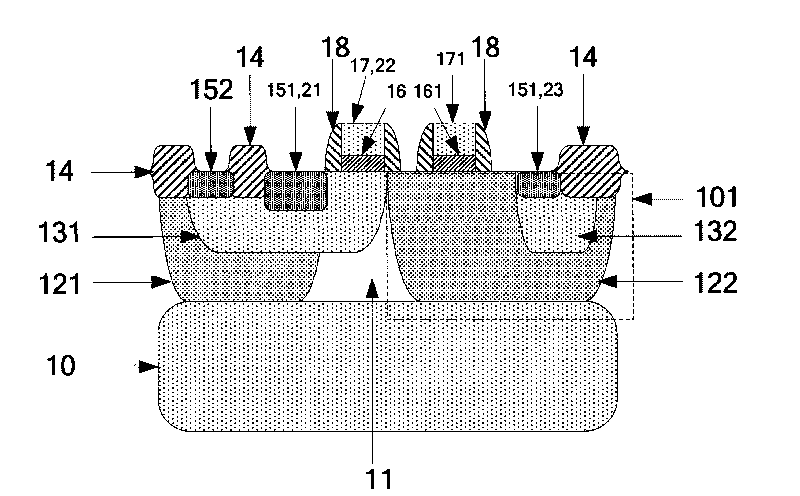

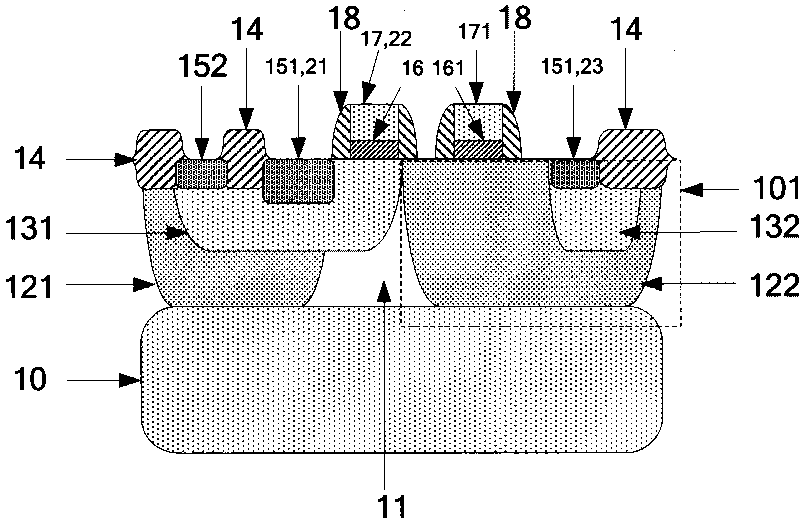

High-voltage LDMOS device

InactiveCN101752416APrevent breakdownReduce electric field strengthSemiconductor devicesLDMOSLow voltage

The invention discloses a high-voltage LDMOS device. The high-voltage LDMOS device comprises a grid (22) and a drain (23), wherein the drain (23) is arranged in a low-voltage N well (132) and the low-voltage N well (132) is arranged in a high-voltage N well (122); a part, above the high-voltage N well (122), between the grid (22) and the drain (23) is provided with silicon oxide (161); polycrystalline silicon (171) is arranged above the silicon oxide (161); and the two sidewalls of each of the silicon oxide (161) and the polycrystalline silicon (171) are provided with a silicon nitride sidewall (18) respectively. On one hand, the high-voltage LDMOS device can avoid the poor hot carrier effect and the Snapback breakdown of the device caused by a 'bird beak' structure of the conventional high-voltage LDMOS device; and on the other hand, 'field plate effect' can be achieved and electric field strength in the vicinity of a PN junction of the drain (23) is reduced, so that high breakdown voltage can be satisfied.

Owner:SHANGHAI HUA HONG NEC ELECTRONICS

MOS (Metal Oxide Semiconductor) transistor and forming method thereof

InactiveCN101740389AIncrease the lengthImprove stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

The invention provides a forming method of an MOS transistor, which comprises the steps of: sequentially forming a gate dielectric layer and a grid electrode on a semiconductor substrate, wherein the gate dielectric layer and the grid electrode form a grid electrode structure; forming offset side walls at two sides of the grid electrode structure, wherein the width of each offset side wall is 8-9 nanometers; forming source / drain extension areas in the grid electrode structure and the semiconductor substrate at the two sides of the offset side walls; forming interstitial walls on the offset side walls; and forming source / drain extension areas in the semiconductor substrate at the interstitial walls and the two sides of the grid electrode structure. The invention improves the stability of a hot carrier and reduces hot carrier effect.

Owner:SEMICON MFG INT (SHANGHAI) CORP

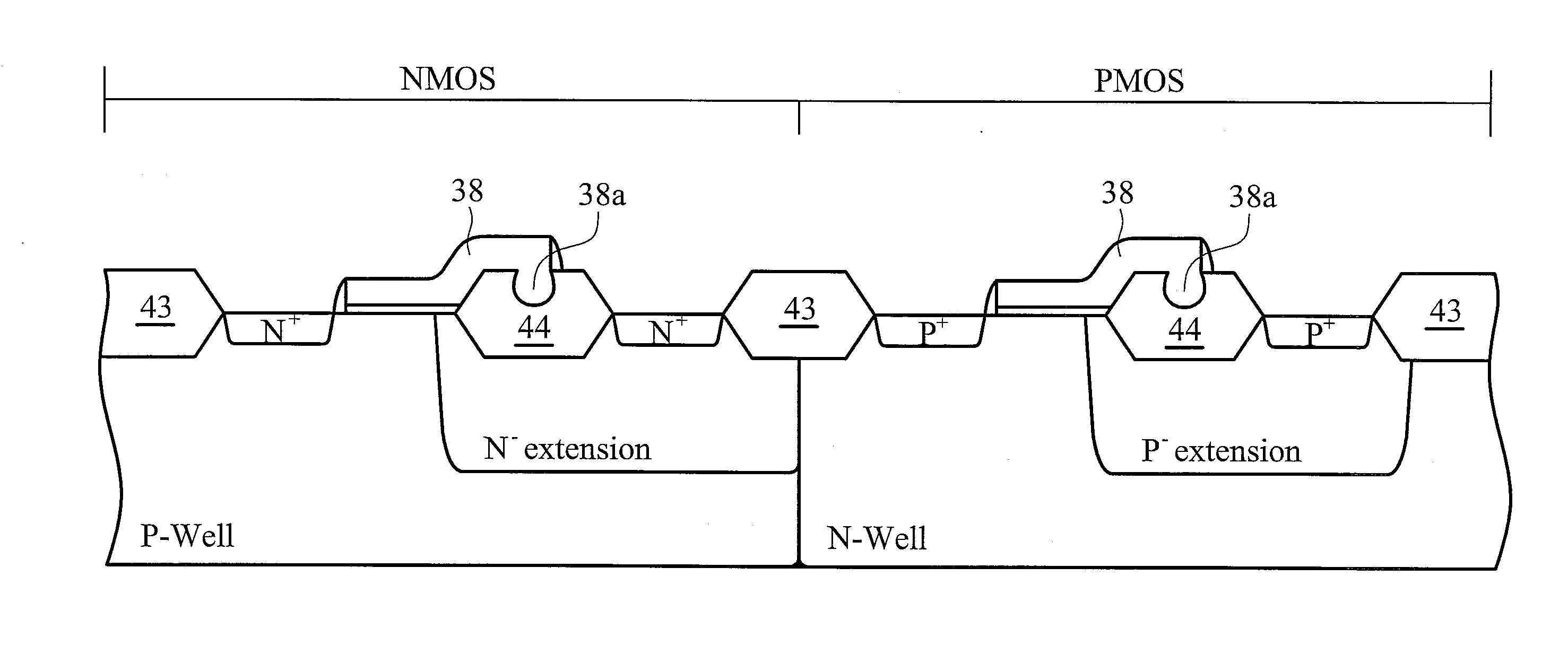

Method for improving reliability of under-gate technology high-K gate dielectric medium CMOS (complementary metal oxide semiconductor)

ActiveCN102420189AImproving the performance of PMOS devices against NBTI effectImproved performance against NBTI effectsSemiconductor/solid-state device manufacturingGate dielectricEngineering

The invention generally relates to a method for improving an NMOS (N-channel metal oxide semiconductor) hot carrier injection effect and a PMOS (P-channel metal oxide semiconductor) negative bias temperature instability effect in the field of semiconductor manufacturing, and in particular relates to a method for improving the NMOS hot carrier injection effect and PMOS negative bias temperature instability effect of an under-gate-technology high-K gate dielectric medium CMOS (complementary metal oxide semiconductor). The invention discloses a method for improving the reliability of the high-K gate dielectric medium CMOS in the under-gate-technology. According to the invention, in the under-gate technology manufacture process, fluorine ions are injected in NMOS and PMOS device regions through an ion injection process after a sample gate is formed, and a stable chemical bond is formed at the interface by virtue of a thermal treatment process, thereby effectively improving the HCI (hot carrier injection) effect resistance performance of the NMOS device and the NBTI (negative bias temperature instability) effect resistance performance of the PMOS device.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

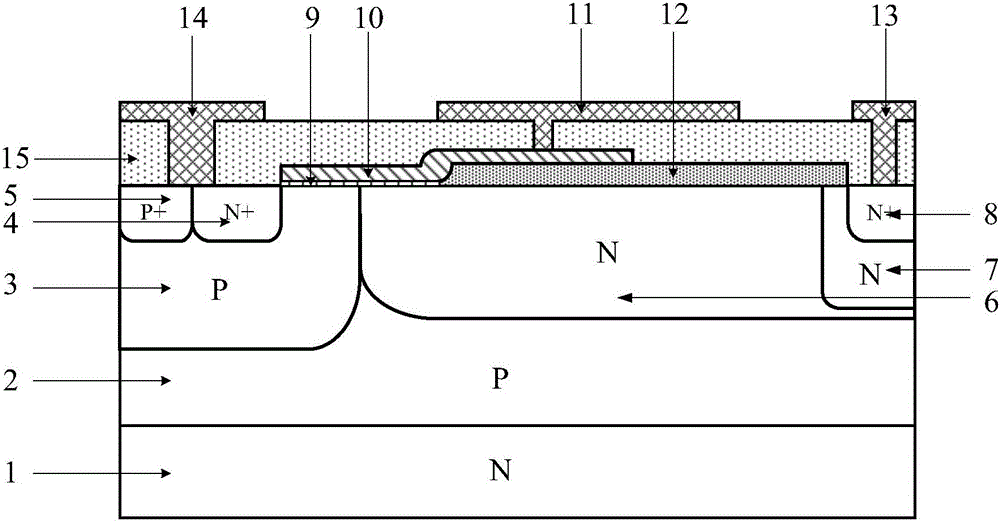

High-reliability lateral double-diffusion metal oxide semiconductor tube

InactiveCN106129117APrevent degradationExtend your lifeSemiconductor devicesDouble diffusionBody contact

A high-reliability lateral double-diffused metal oxide semiconductor tube, comprising: an N-type substrate, a P-type epitaxial layer is arranged on the N-type substrate, and a P-type body region and an N-type body region are arranged inside the P-type epitaxial layer. In the P-type body region, an N-type source region and a P-type body contact region are arranged, an N-type buffer layer is arranged in the N-type drift region, and an N-type drain region is arranged in the N-type buffer layer. The surface of the P-type epitaxial layer is provided with a gate oxide layer and a field oxide layer, and a polysilicon gate is provided on the surface of the gate oxide layer and extends to the upper surface of the field oxide layer. The structure that can reduce the hot carrier effect is composed of multiple The trench array formed by the trench is located in the field oxide layer region under the polysilicon gate, and the trench array is filled with polysilicon and connected with the polysilicon gate. The introduced groove array can effectively reduce the impact ionization peak at the junction of the gate oxide layer and the field oxide layer, reduce the hot carrier degradation of the device, and improve the reliability of the device.

Owner:SOUTHEAST UNIV

Semiconductor element and manufacturing method thereof

ActiveCN101908560ANo need to reduce dopant concentrationReduce Overlap CapacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEngineering

Owner:MACRONIX INT CO LTD

Method for improving HCI (Hot Carrier Injection) effect of high-K gate dielectric NMOS (N-Mental-Oxide-Semiconductor) by adopting gate-last process

InactiveCN102420143AImproved performance against HCI effectsSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

The invention generally relates to a method for improving the HCI (Hot Carrier Injection) effect of an NMOS (N-Mental-Oxide-Semiconductor) in the field of semiconductor manufacture, in particular to a method for improving the hot carrier effect of a high-K gate dielectric NMOS by adopting a gate-last process. In the processing procedure of the gate-last process, after a dummy gate is formed, fluorine ions are implanted in an NMOS device region through an ion injection process; and a stable chemical bond is formed at the interface by a heat treatment process, so that the performance of the NMOS resisting the HCI effect is effectively improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

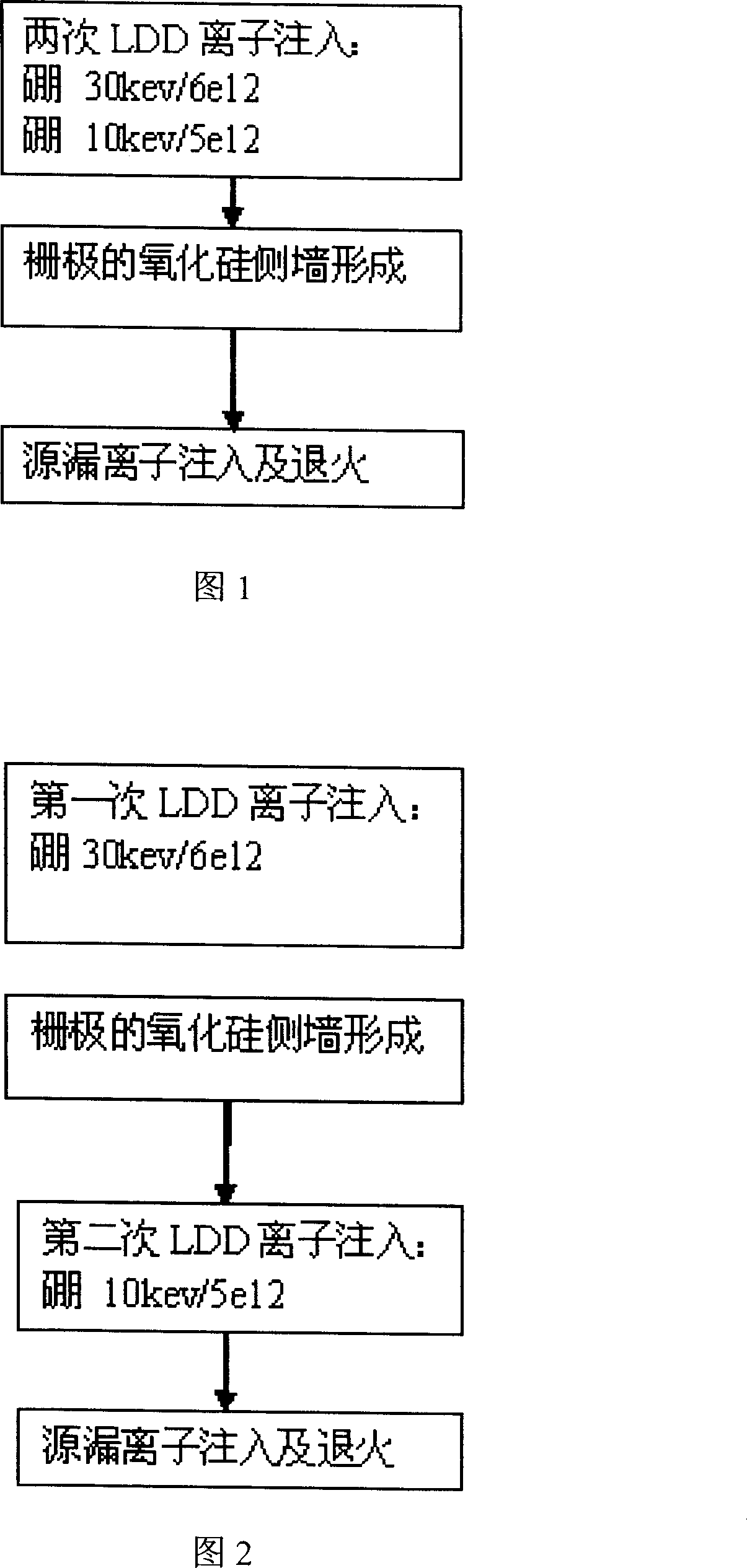

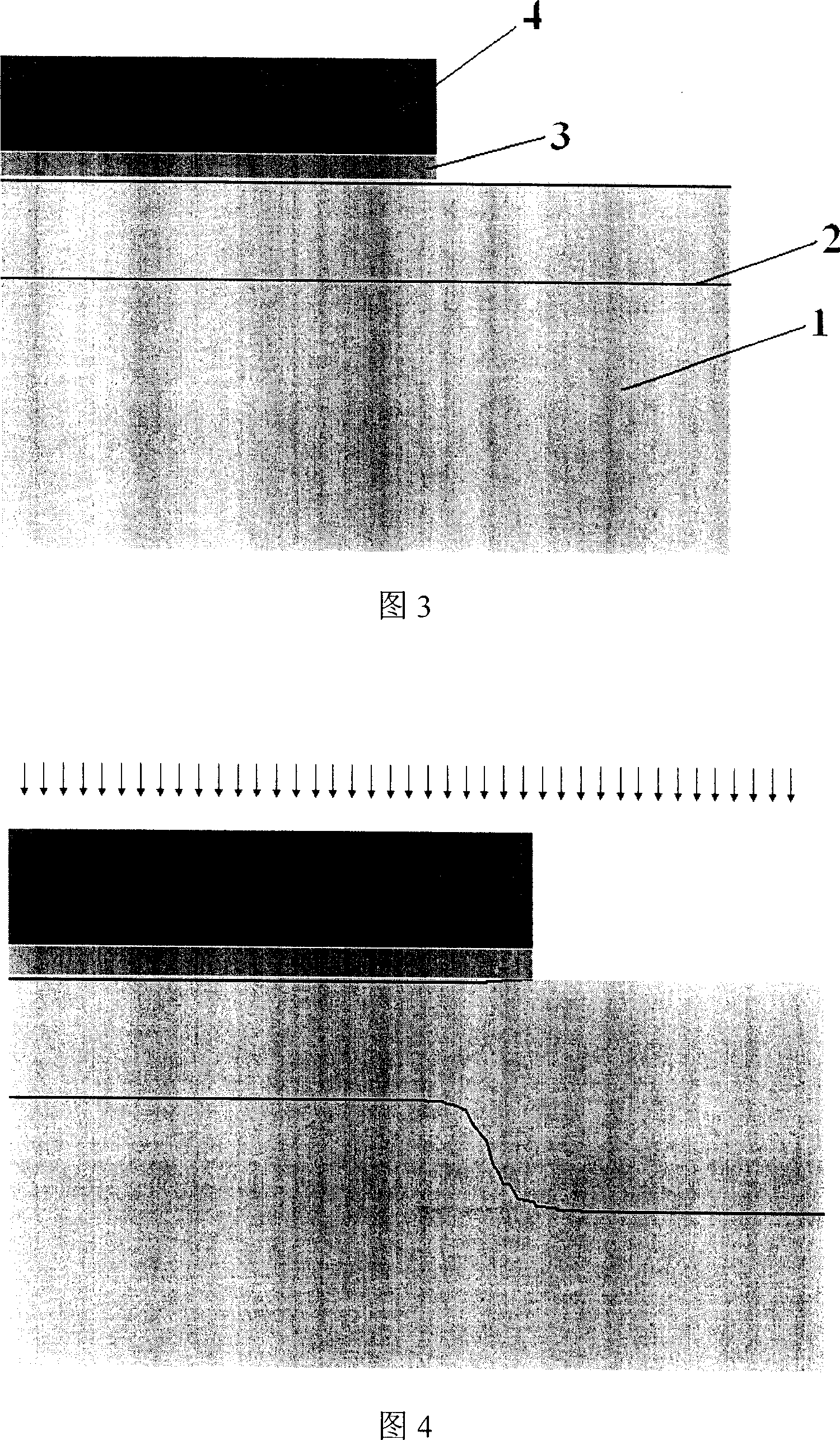

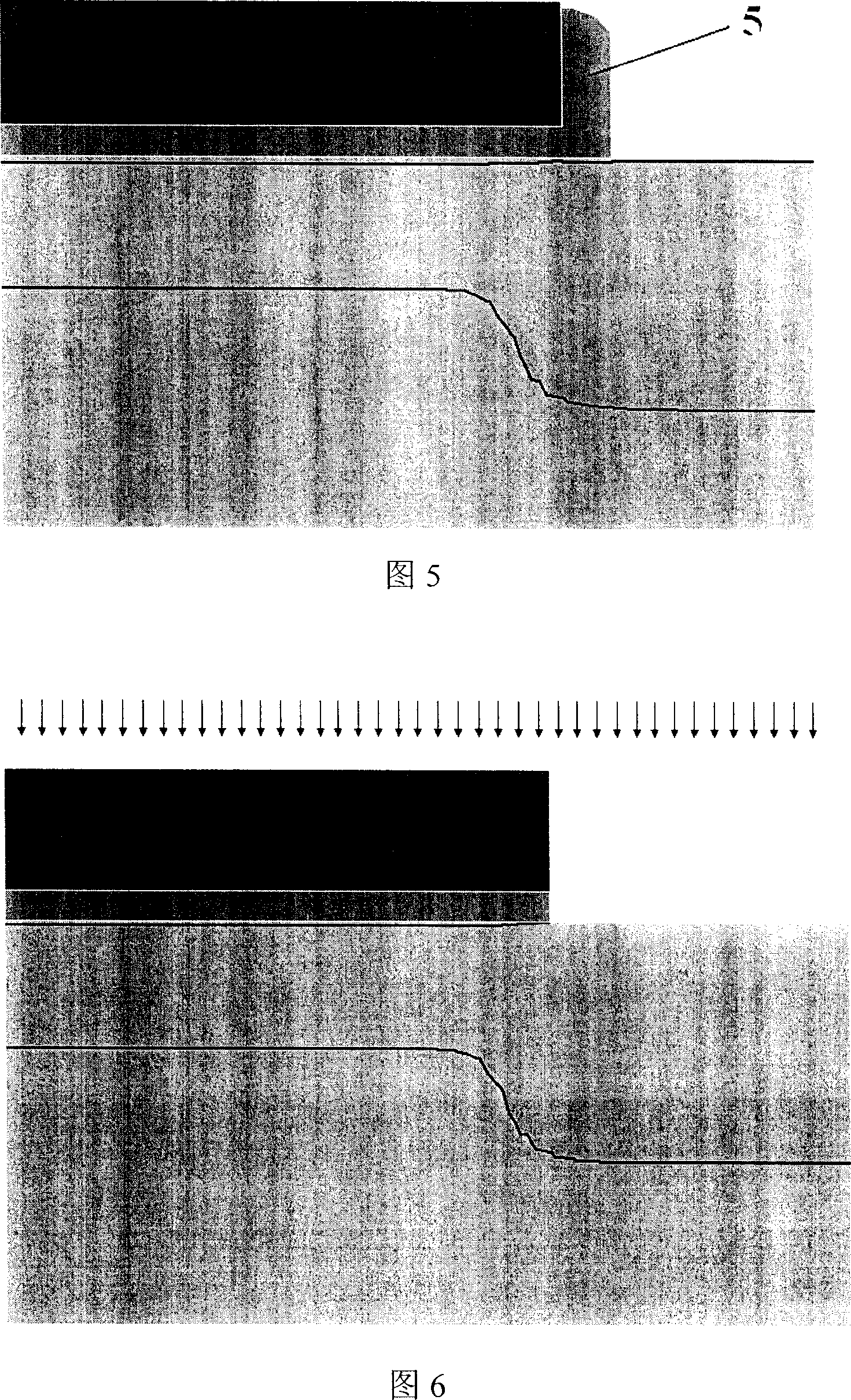

Method for ion implantation of high-voltage transistor LDD

InactiveCN1983529AImprove breakdown voltageImprove reliabilitySemiconductor/solid-state device manufacturingHeat carrierHigh voltage transistors

The invention is concerned with the method of high-pressured transistor LDD ion implantation, it is: separates the multi-times LDD ion implantation during the high-pressured parts technics, processes the high-energy ion implantation before forming the silicon oxidation sidewall of the grid, the low-energy ion implantation finishes after the silicon oxidation sidewall of the grid, in order that the fold area of the LDD and the grid adulterates slightly, increases the breakdown potential of the LDD knot, decreases heat carrier effect, improves the reliability of the parts, the threshold value voltage and saturation current of the parts maintains steadily because the adulterating thickness between the sidewall and the active leaking is steadiness.

Owner:SHANGHAI HUA HONG NEC ELECTRONICS

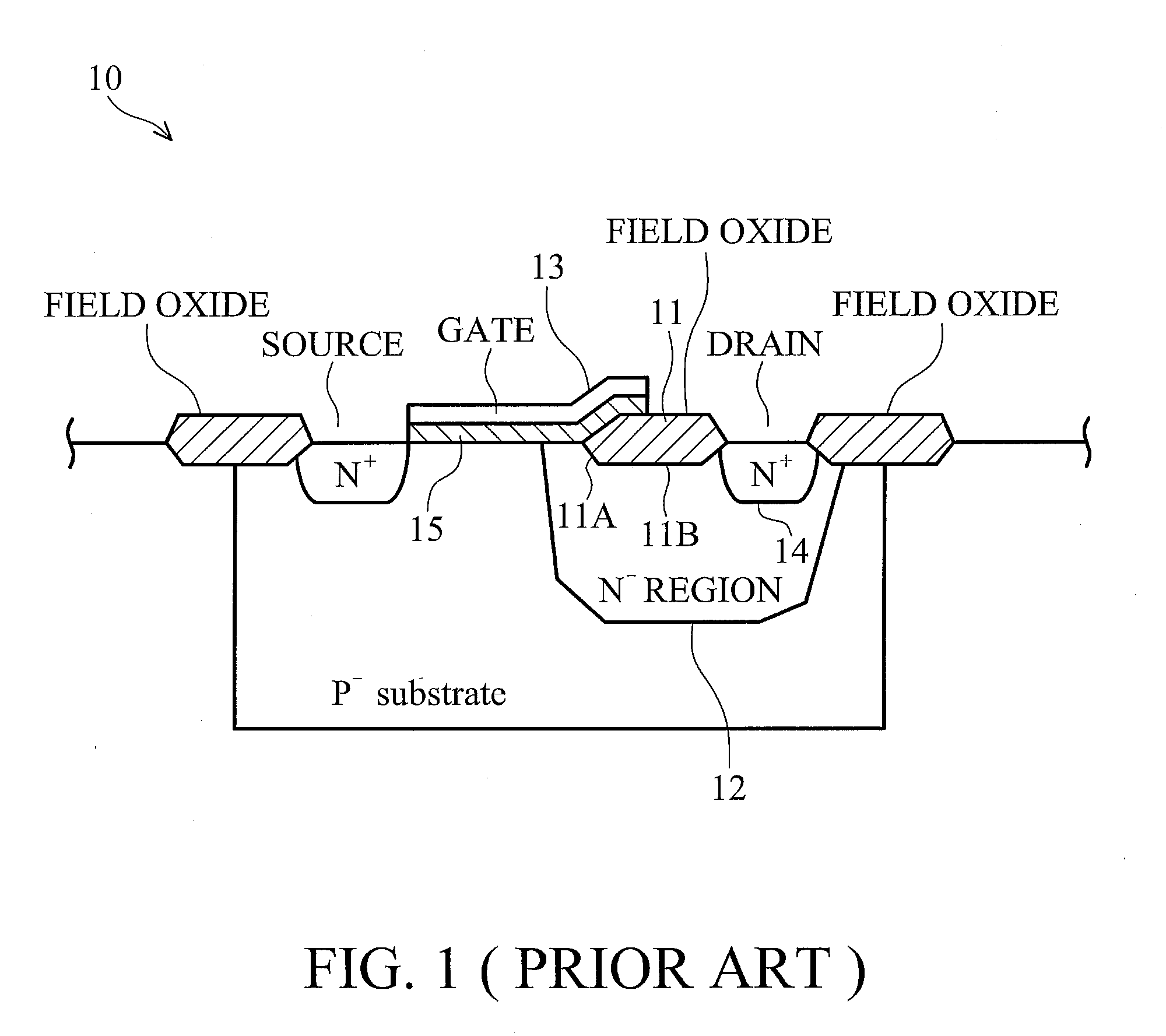

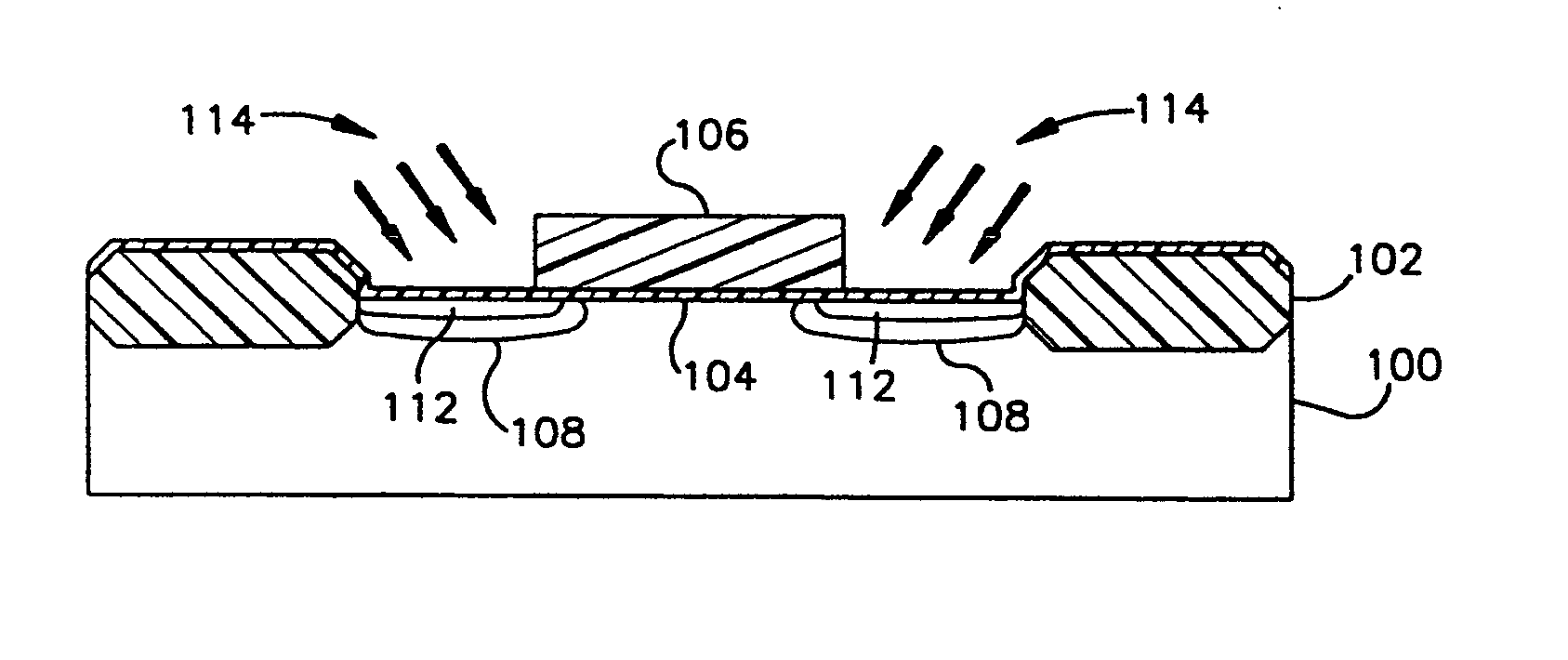

Reduction of channel hot carrier effects in transistor devices

A transistor can be fabricated to exhibit reduced channel hot carrier effects. According to one aspect of the present invention, a method for fabricating a transistor structure includes implanting a first dopant into a lightly doped drain (LDD) region to form a shallow region therein. The first dopant penetrates the substrate to a depth that is less than the LDD junction depth. A second dopant is implanted into the substrate beyond the LDD junction depth to form a source / drain region. The implantation of the second dopant overpowers a substantial portion of the first dopant to define a floating ring in the LDD region that mitigates channel hot carrier effects.

Owner:TEXAS INSTR INC

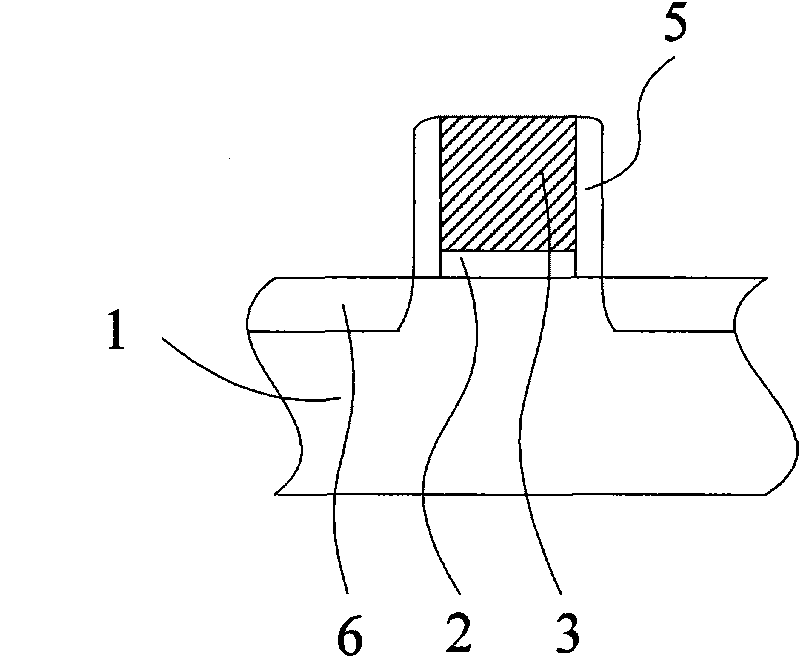

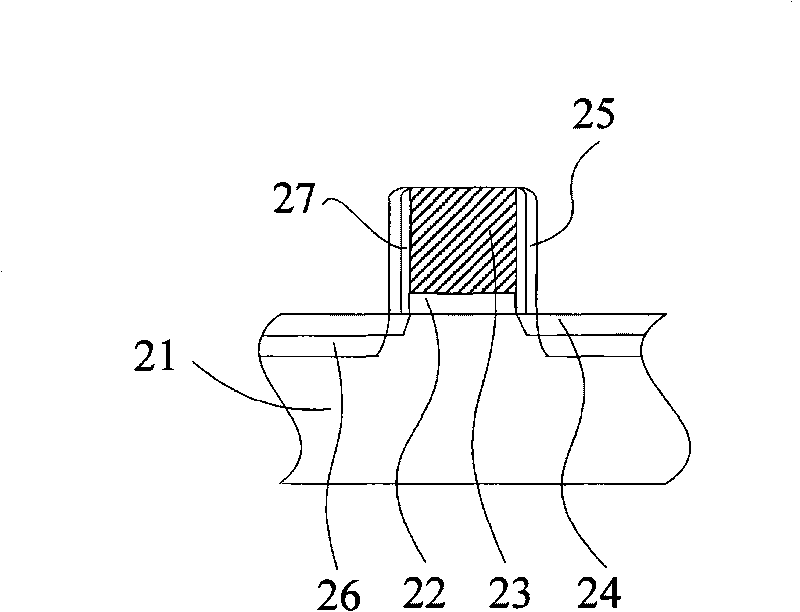

RF-LDMOS (radio frequency laterally diffused metal oxide semiconductor) self-alignment drain terminal field plate structure and fabrication method thereof

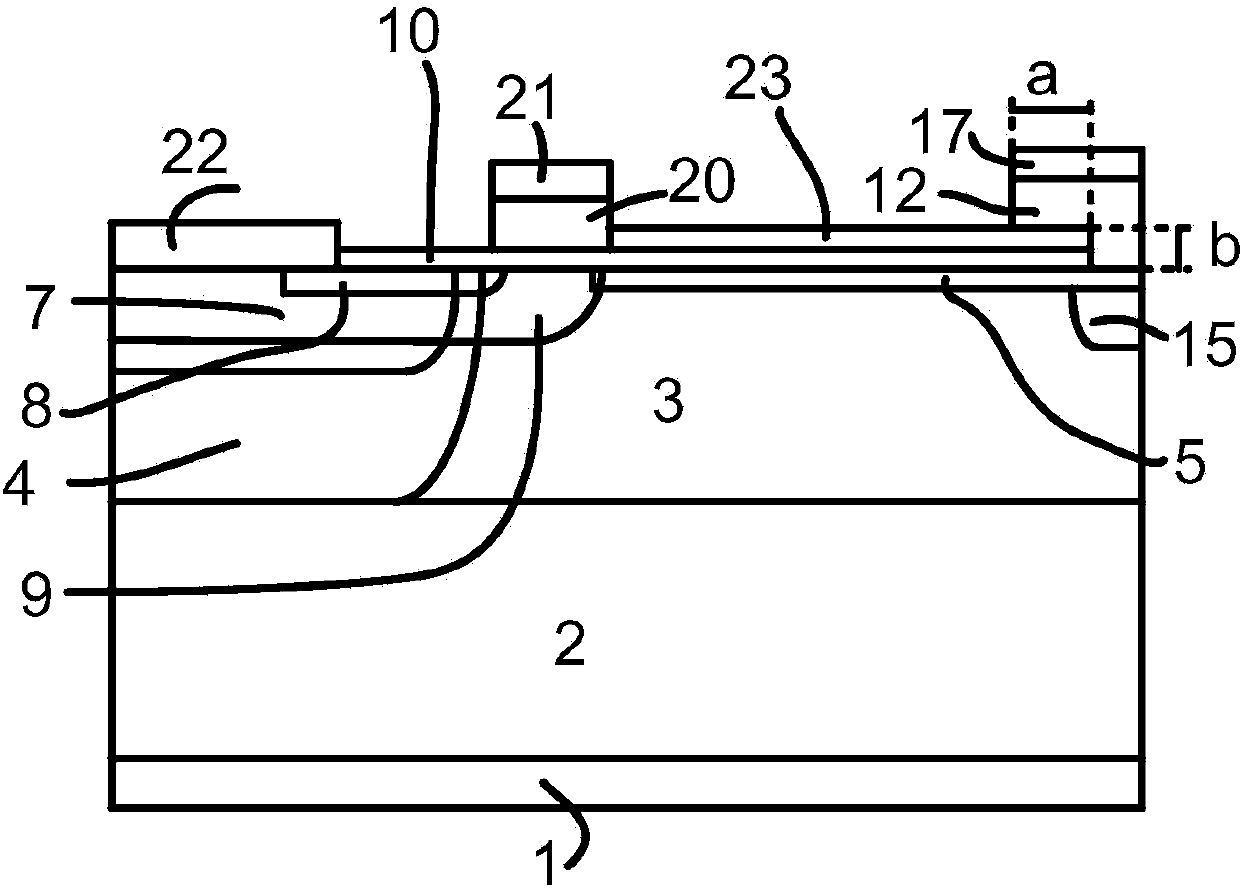

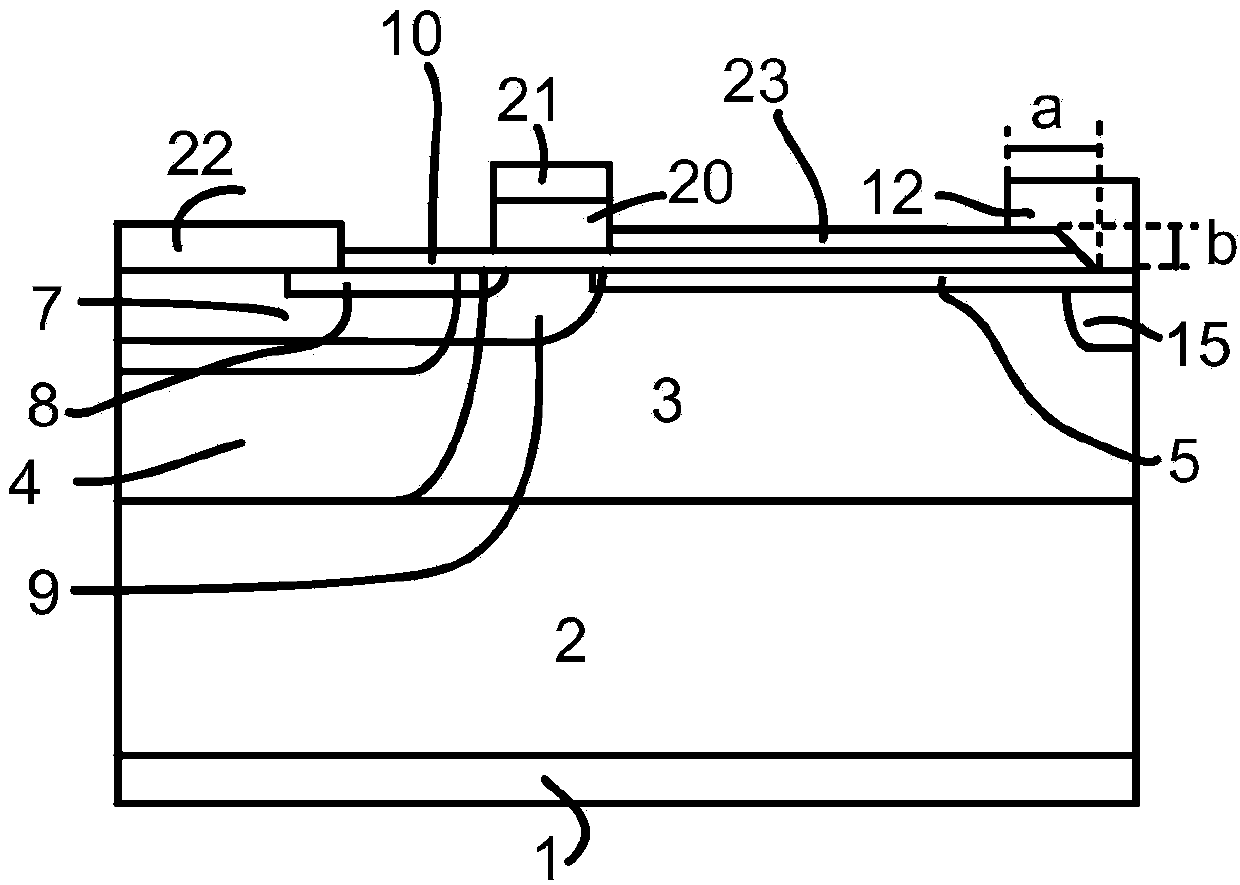

ActiveCN104183632AIncrease the electric field strengthImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceMetal silicide

The invention discloses an RF-LDMOS (radio frequency laterally diffused metal oxide semiconductor) self-alignment drain terminal field plate structure, which comprises an electrode layer (1), a substrate (2), an epitaxial layer (3), a source electrode-substrate connecting layer (4), a drift region (5), a fixed potential region (7), a source electrode (8), a channel (9), a drain electrode (15), an insulating layer (10), a grid electrode (20), a grid electrode metal silicide (21), and a source electrode-channel connecting region (22), and further comprises an SiO2 layer (23), amorphous silicon (12) and a metal silicide (17), wherein the amorphous silicon (12) comprises a transversely extending structure and a longitudinally extending structure, the longitudinally extending structure is contacted with the drift region (5), and the transversely extending structure is arranged on the SiO2 layer (23); and the metal silicide (17) is arranged on the amorphous silicon (12). The RF-LDMOS self-alignment drain terminal field plate structure can improve breakdown voltage of devices, reduces the hot carrier effect, reduces drifting of quiescent current, and obviously reduces Cds capacitance.

Owner:KUNSHAN HUATAI ELECTRONICS TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com